Patents

Literature

49 results about "Differential nonlinearity" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

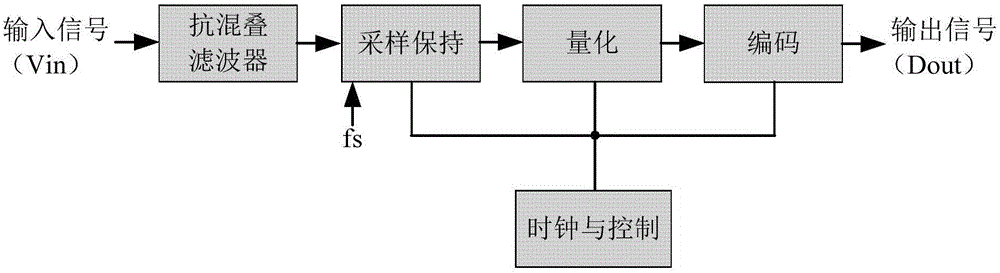

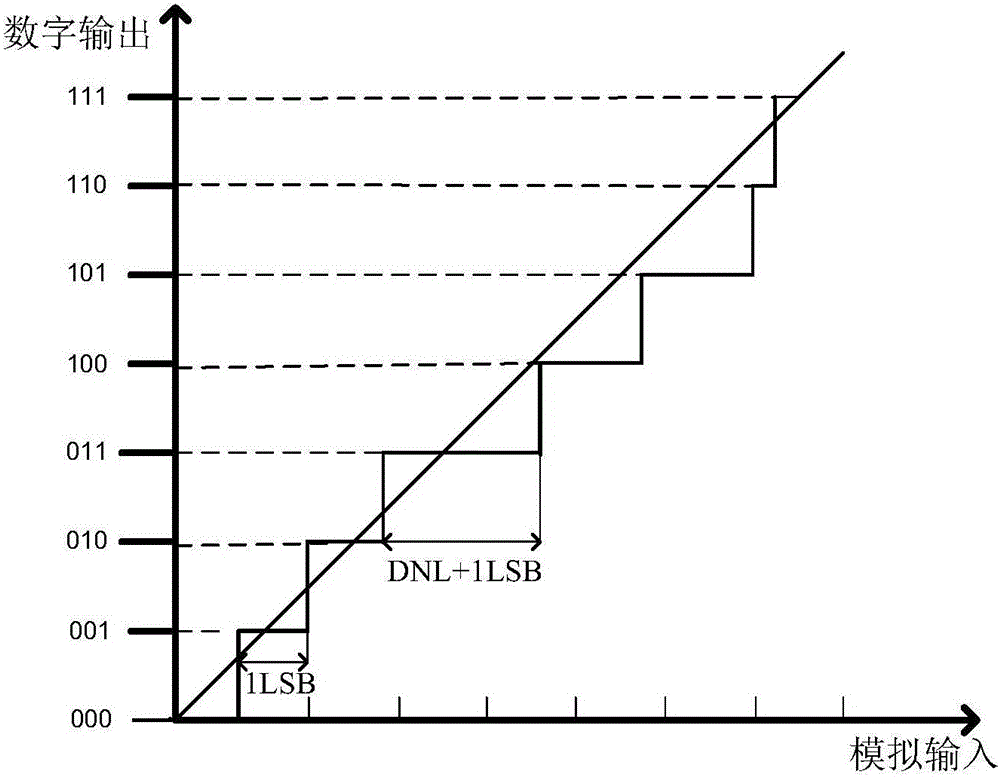

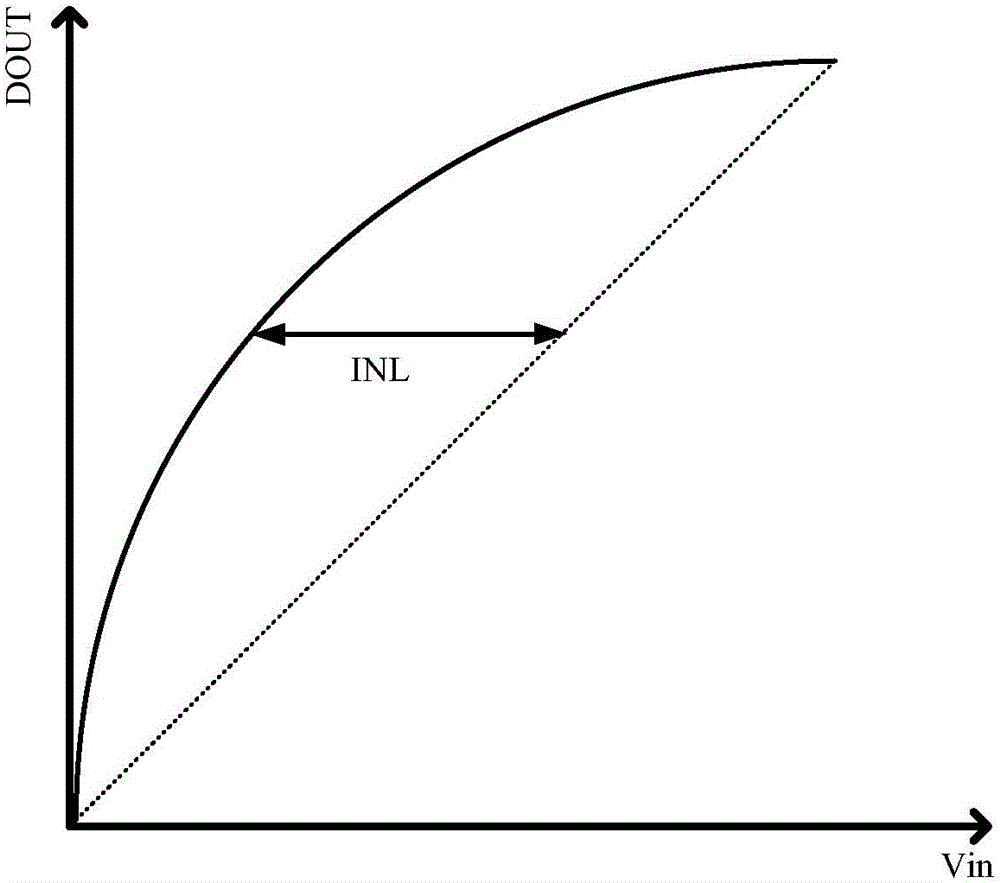

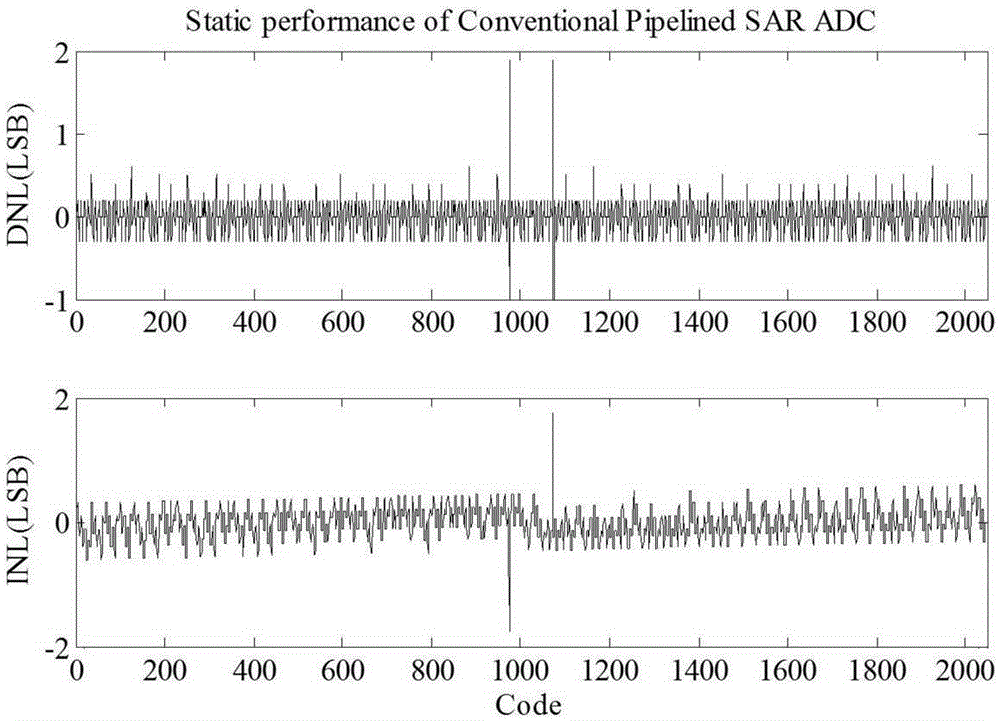

Differential nonlinearity (acronym DNL) is a term describing the deviation between two analog values corresponding to adjacent input digital values. It is an important specification for measuring error in a digital-to-analog converter (DAC); the accuracy of a DAC is mainly determined by this specification. Ideally, any two adjacent digital codes correspond to output analog voltages that are exactly one Least Significant Bit (LSB) apart. Differential non-linearity is a measure of the worst case deviation from the ideal 1 LSB step. For example, a DAC with a 1.5 LSB output change for a 1 LSB digital code change exhibits 1⁄2 LSB differential non-linearity. Differential non-linearity may be expressed in fractional bits or as a percentage of full scale. A differential non-linearity greater than 1 LSB may lead to a non-monotonic transfer function in a DAC. It is also known as a missing code.

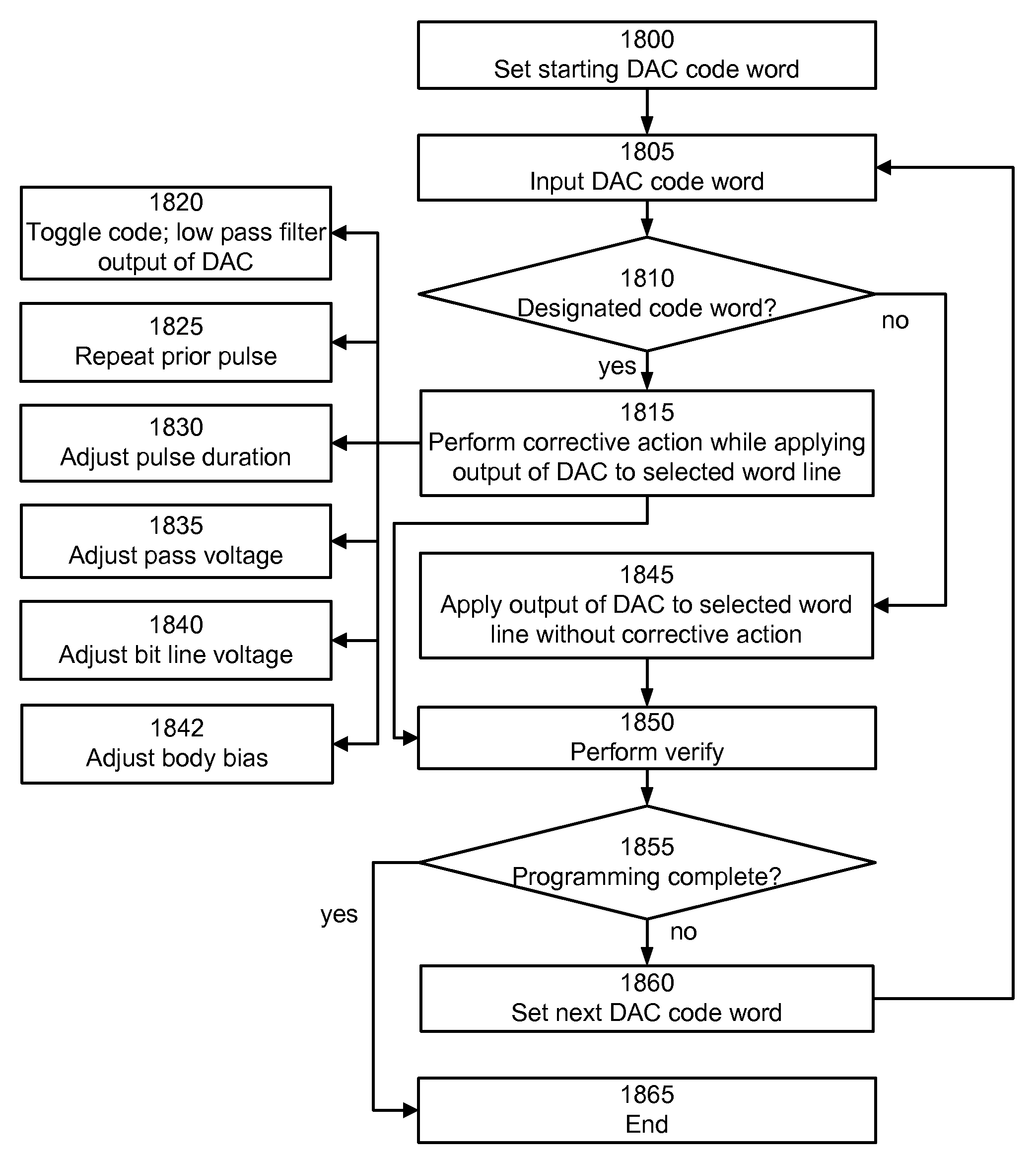

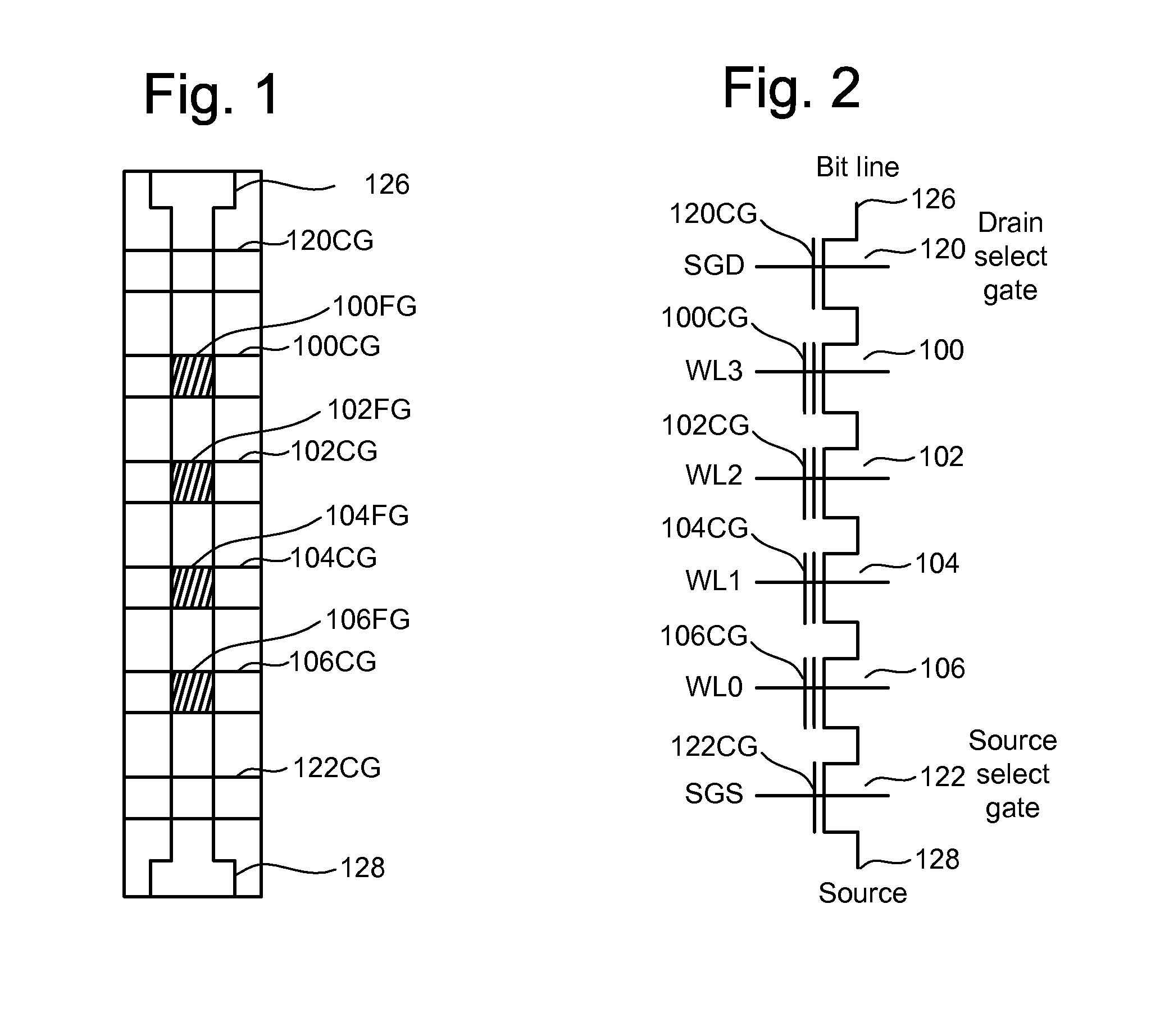

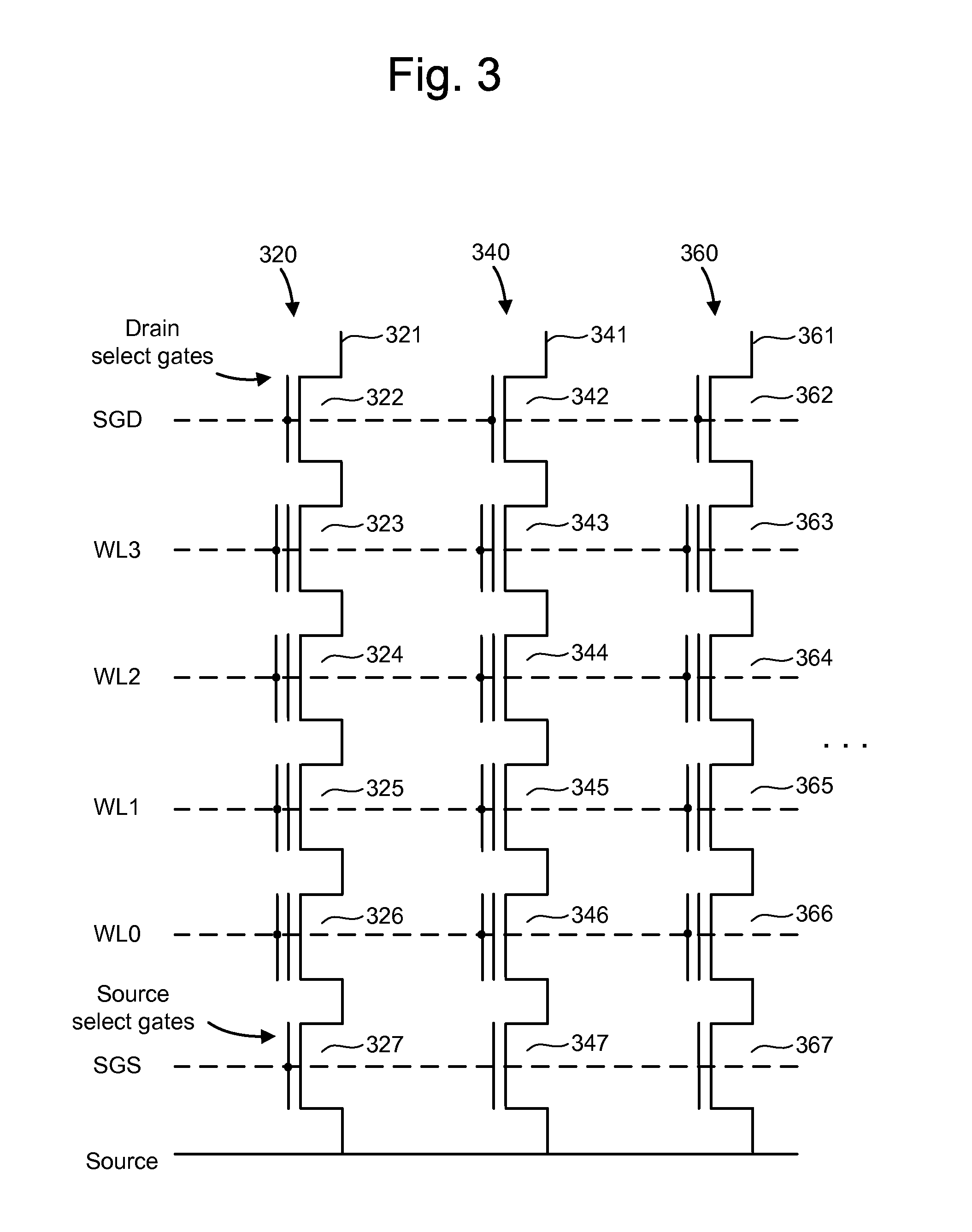

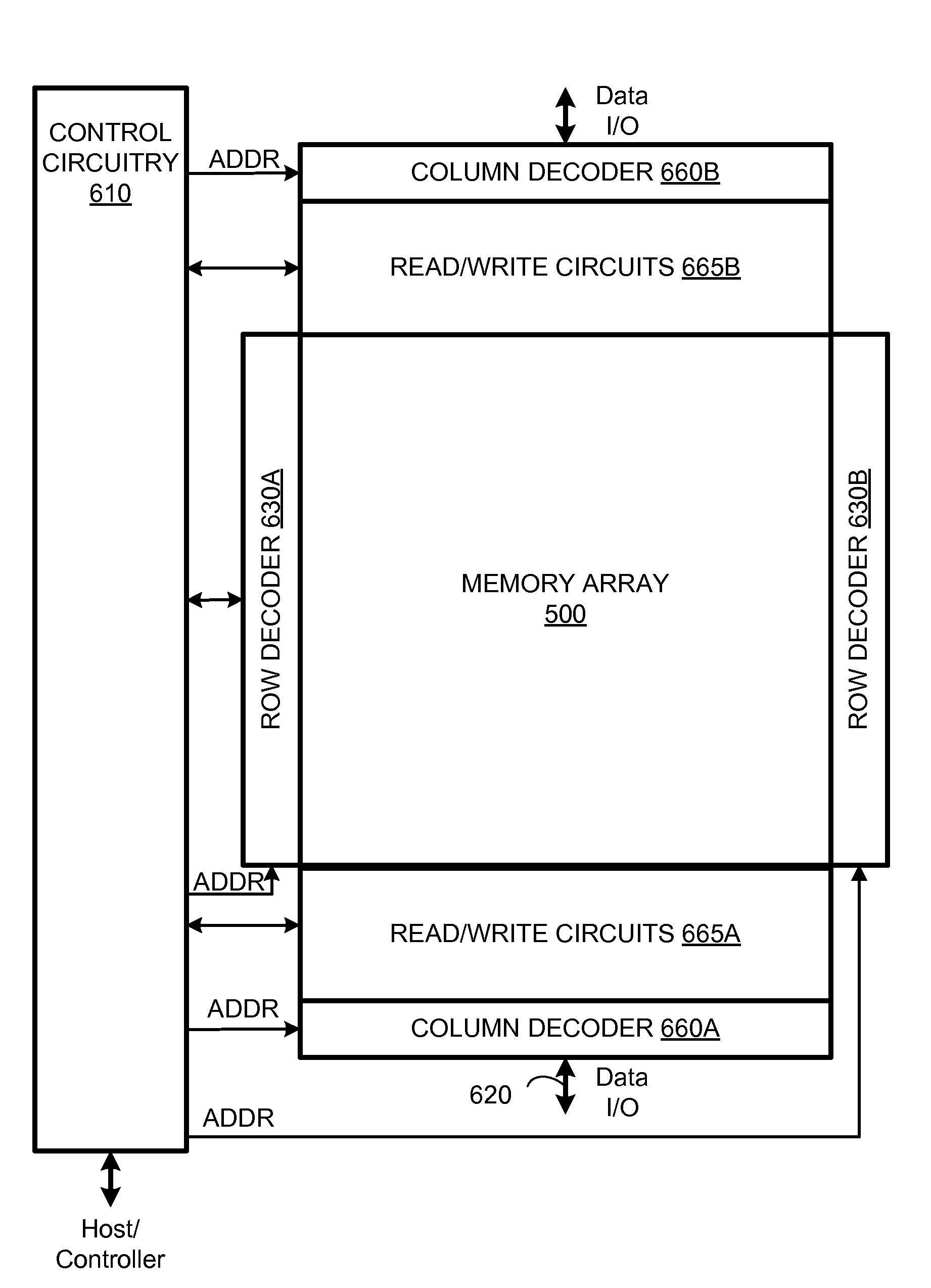

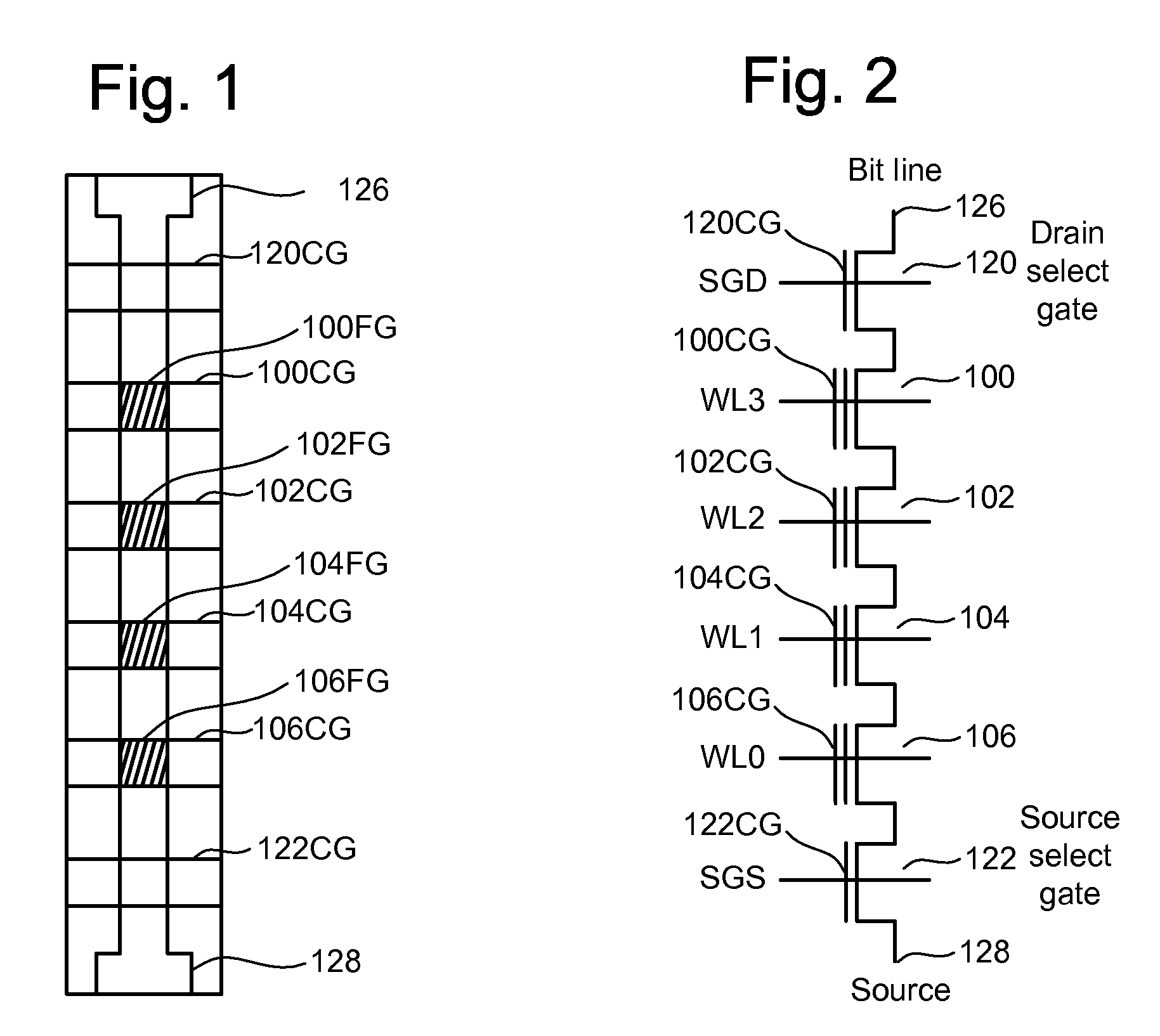

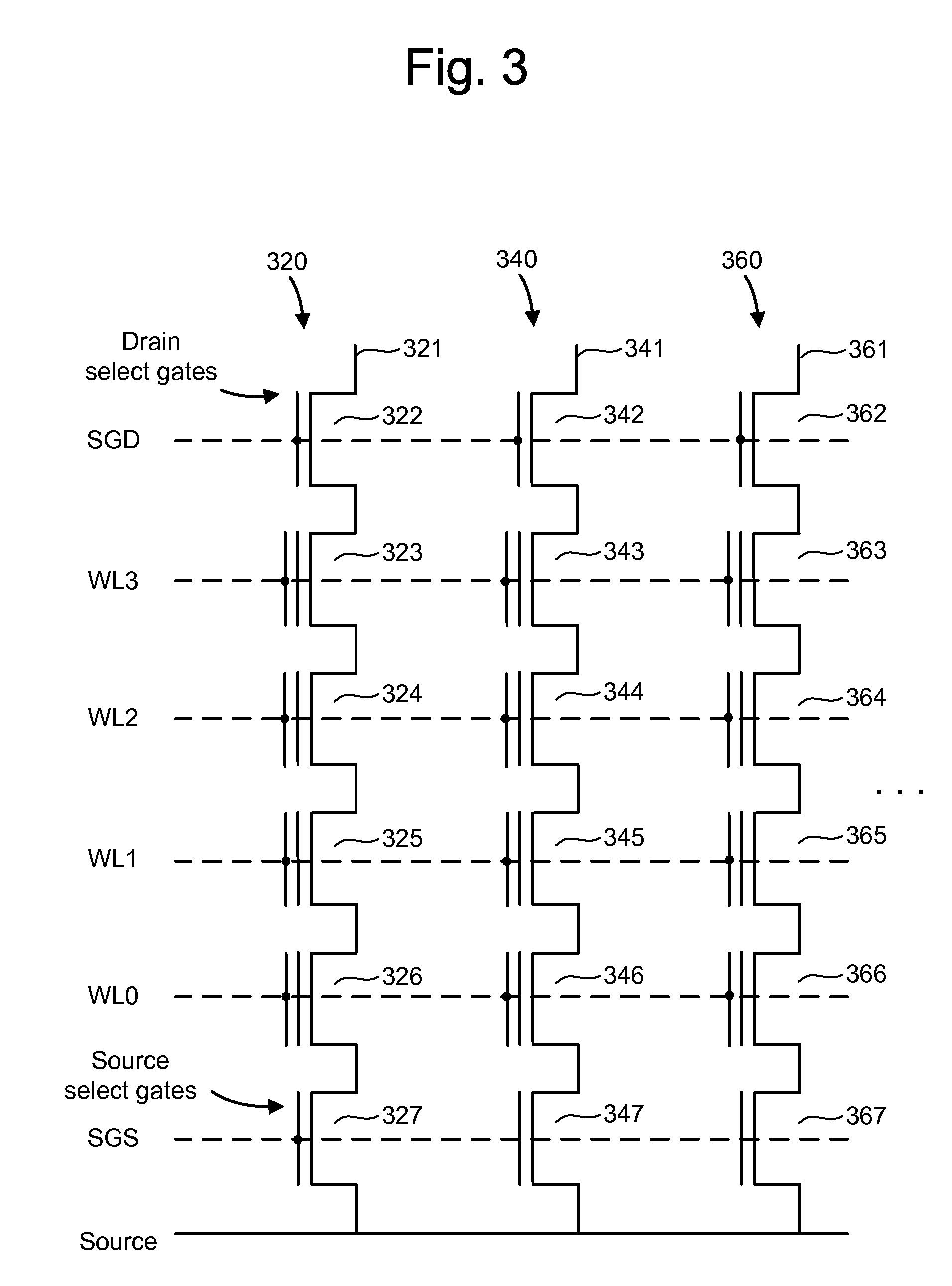

Reducing programming voltage differential nonlinearity in non-volatile storage

A corrective action is taken to adjust for nonlinearities in a program voltage which is applied to a selected word line in a memory device. The nonlinearities result in a non-uniform program voltage step size which can cause over programming or slow programming. A digital to analog converter (DAC) which provides the program voltages can have a nonlinear output, such as when certain code words are input to the DAC. The memory device can be tested beforehand to determine where the nonlinearities occur, and configured to take corrective action when the corresponding code words are input. For example, the DAC may have a nonlinear output when a rollover code word is input, e.g., a when a string of least significant bits in successive code words change from 1's to 0's. The corrective action can include repeating a prior program pulse or adjusting a duration of a program pulse.

Owner:SANDISK TECH LLC

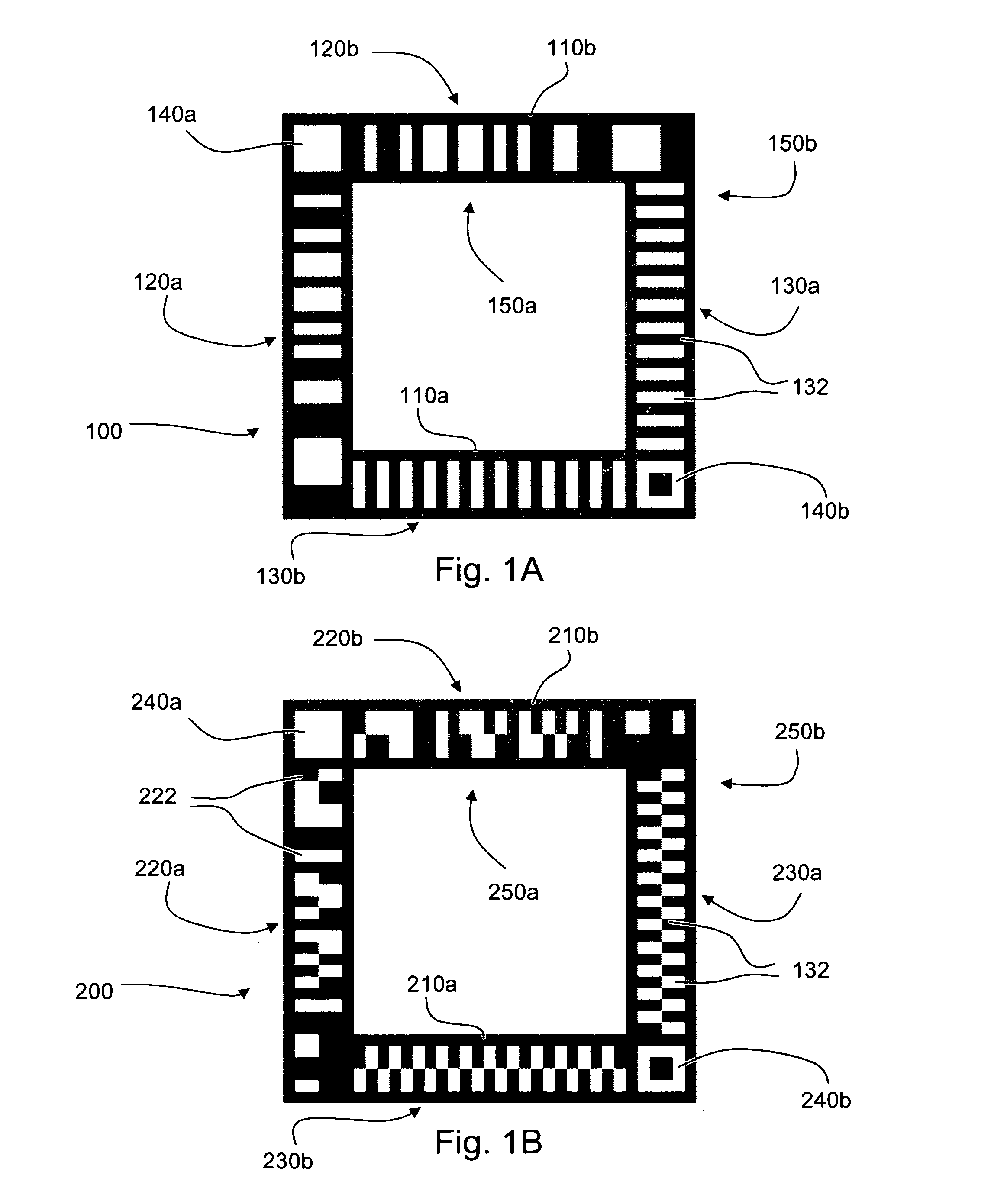

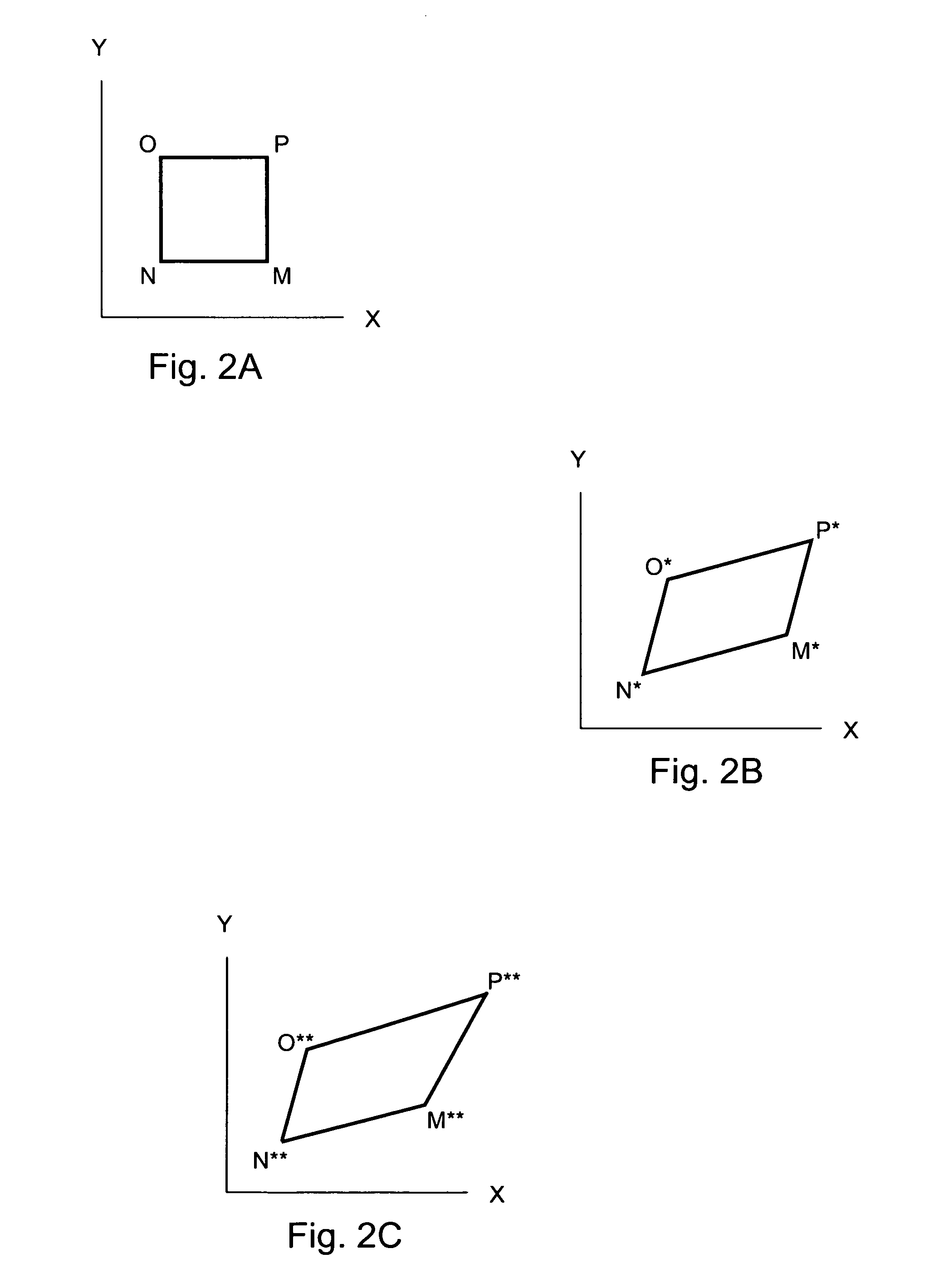

Differential non-linear strain measurement using binary code symbol

InactiveUS8245578B2Force measurement by measuring optical property variationUsing electrical meansDifferential nonlinearityStrain measurement

The bands and corners of rectangular or other geometric shapes for binary code symbols are used to measure non-linear and non-uniform strain in a material with an anomaly such as a crack in the area of strain measurement. In particular, they can be used to evaluate differential strains in the regions of the bands and corners; and the external and internal boundaries can be used to measure differentials in strain between the external boundaries and internal boundaries.

Owner:GENERAL ELECTRIC CO

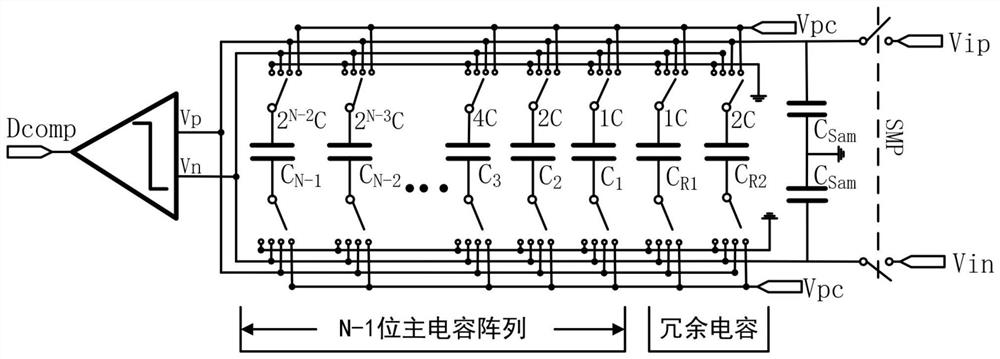

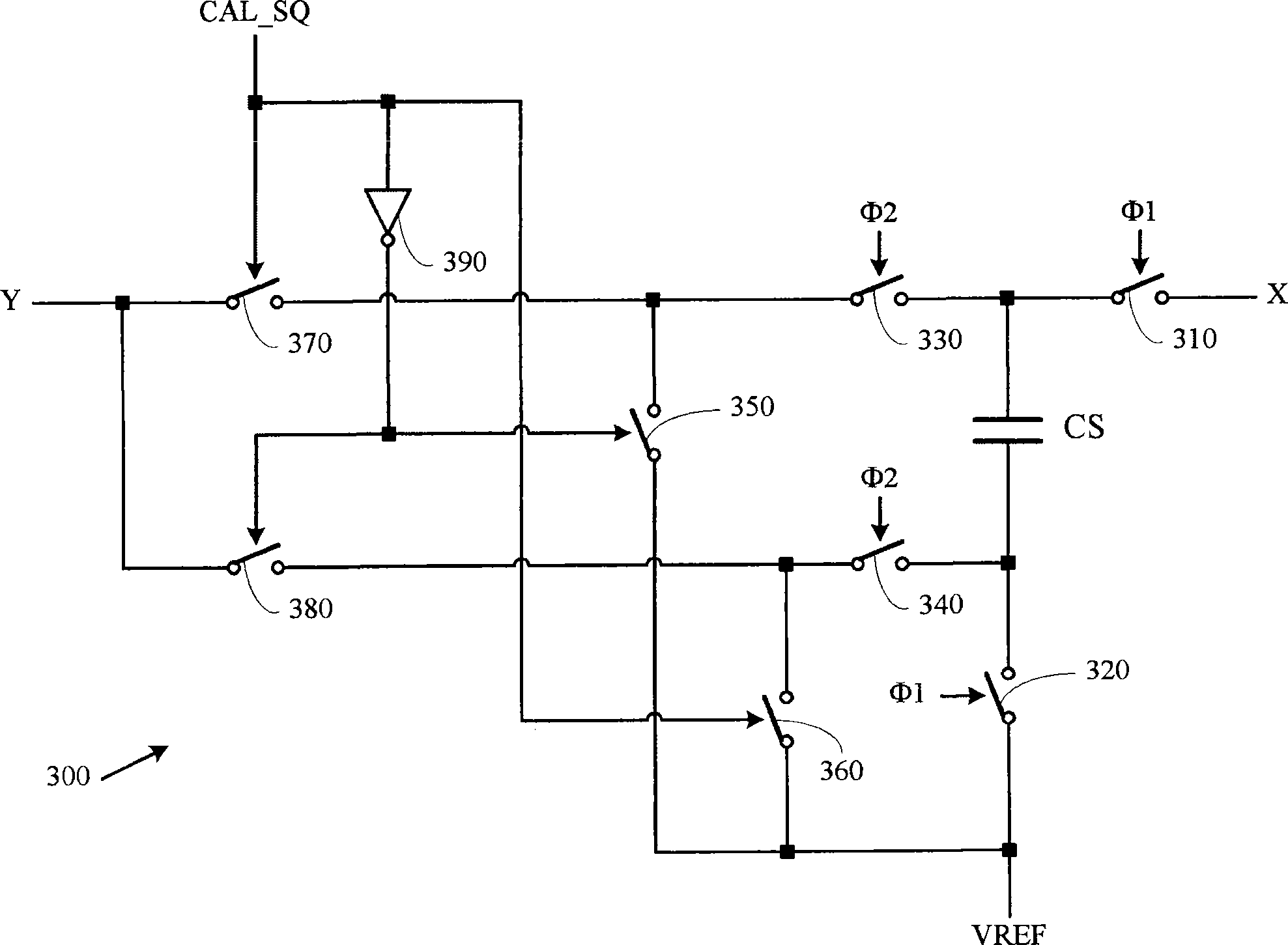

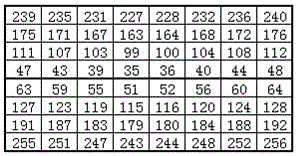

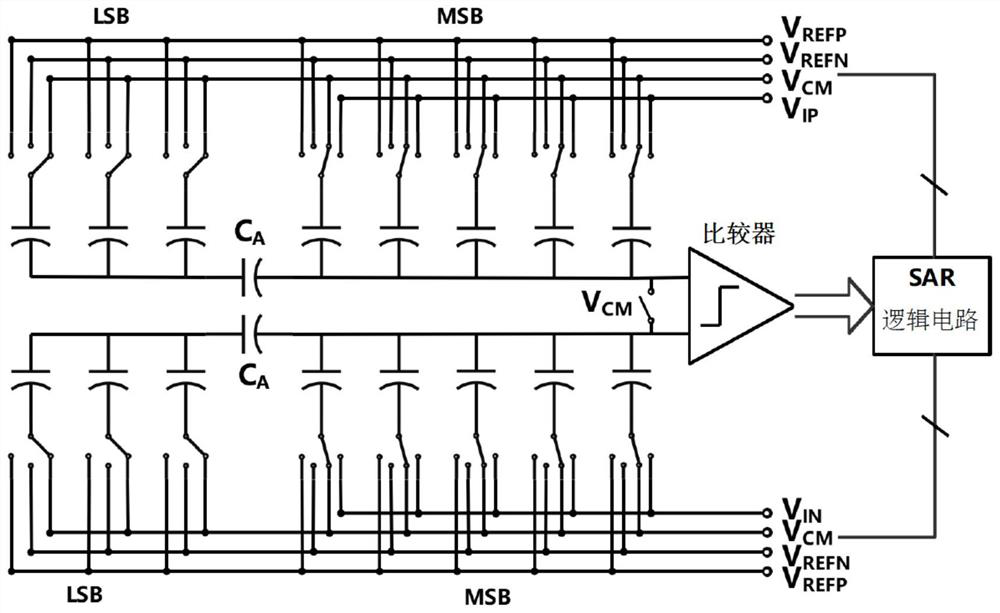

Capacitor exchange method for improving DNL (Differential Nonlinearity)/INL (Integral Nonlinearity) of successive approximation analog to digital converter

InactiveCN105049049AReduce areaSimple structureAnalogue/digital conversionElectric signal transmission systemsCapacitanceCorrection algorithm

The invention discloses a capacitor exchange method for improving the DNL (Differential Nonlinearity) / INL (Integral Nonlinearity) of a successive approximation analog to digital converter (ADC), and relates to the fields of microelectronics and solid-state electronics, in particular to the field of high-performance ADCs. The DNL / INL error caused by judgment of a secondary high order can be offset by exchange of a secondary high-order capacitor with all subsequent capacitors between two conversions without introduction of any extra ADC, introduction of any correction algorithm or splitting of any capacitor. Compared with a conventional correction method for improving the DNL / INL with dependence on an auxiliary ADC, a correction algorithm or capacitor splitting, the capacitor exchange method has the effects of simpler structure, smaller chip occupation area and higher easiness in on-chip implementation.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Reducing programming voltage differential nonlinearity in non-volatile storage

A corrective action is taken to adjust for nonlinearities in a program voltage which is applied to a selected word line in a memory device. The nonlinearities result in a non-uniform program voltage step size which can cause over programming or slow programming. A digital to analog converter (DAC) which provides the program voltages can have a nonlinear output, such as when certain code words are input to the DAC. The memory device can be tested beforehand to determine where the nonlinearities occur, and configured to take corrective action when the corresponding code words are input. For example, the DAC may have a nonlinear output when a rollover code word is input, e.g., a when a string of least significant bits in successive code words change from 1's to 0's. The corrective action can include repeating a prior program pulse or adjusting a duration of a program pulse.

Owner:SANDISK TECH LLC

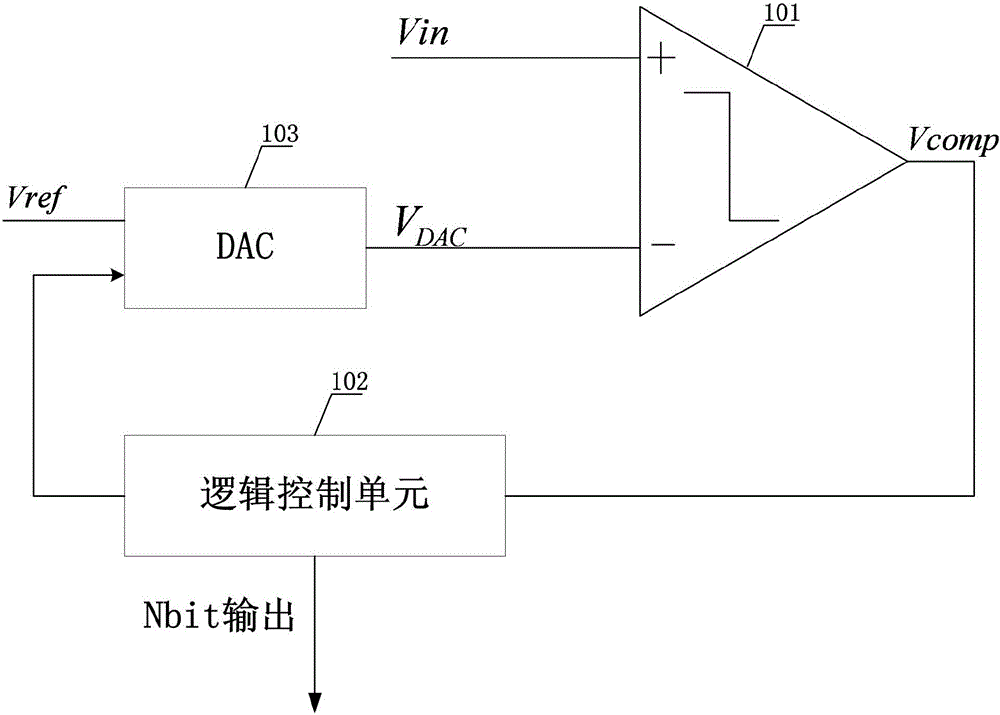

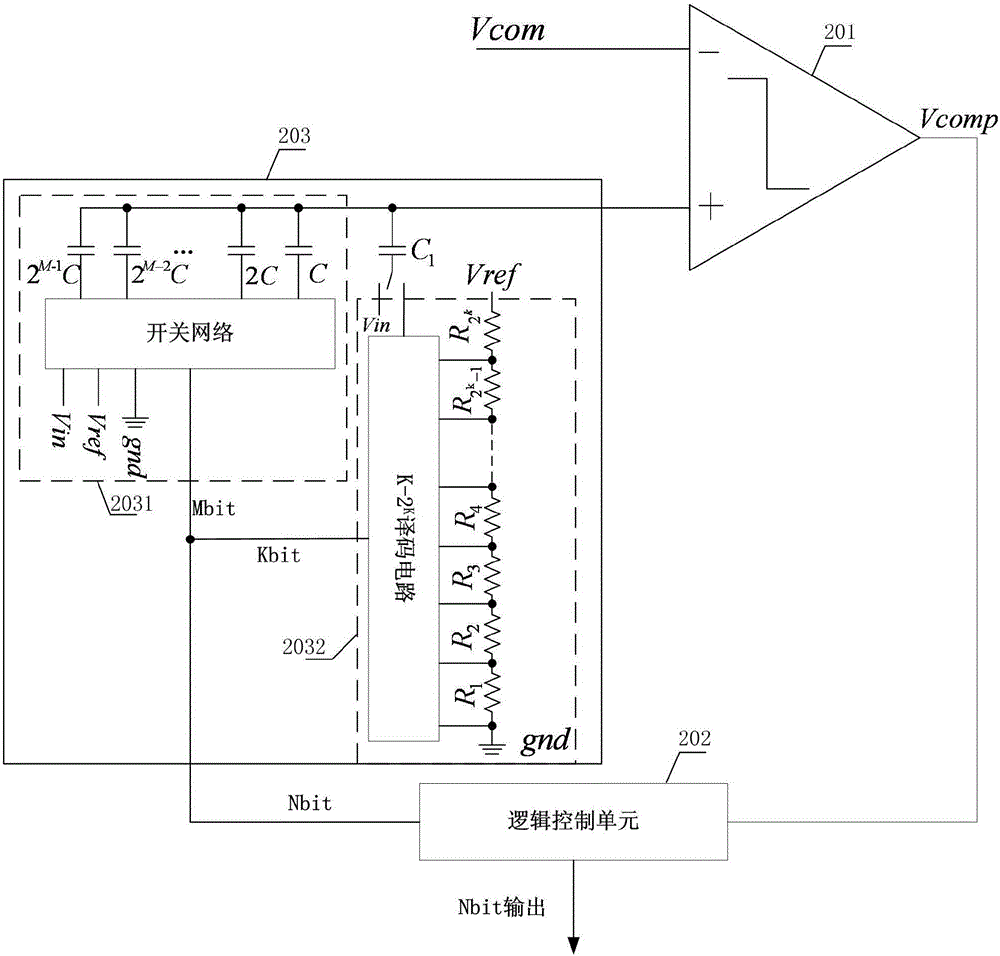

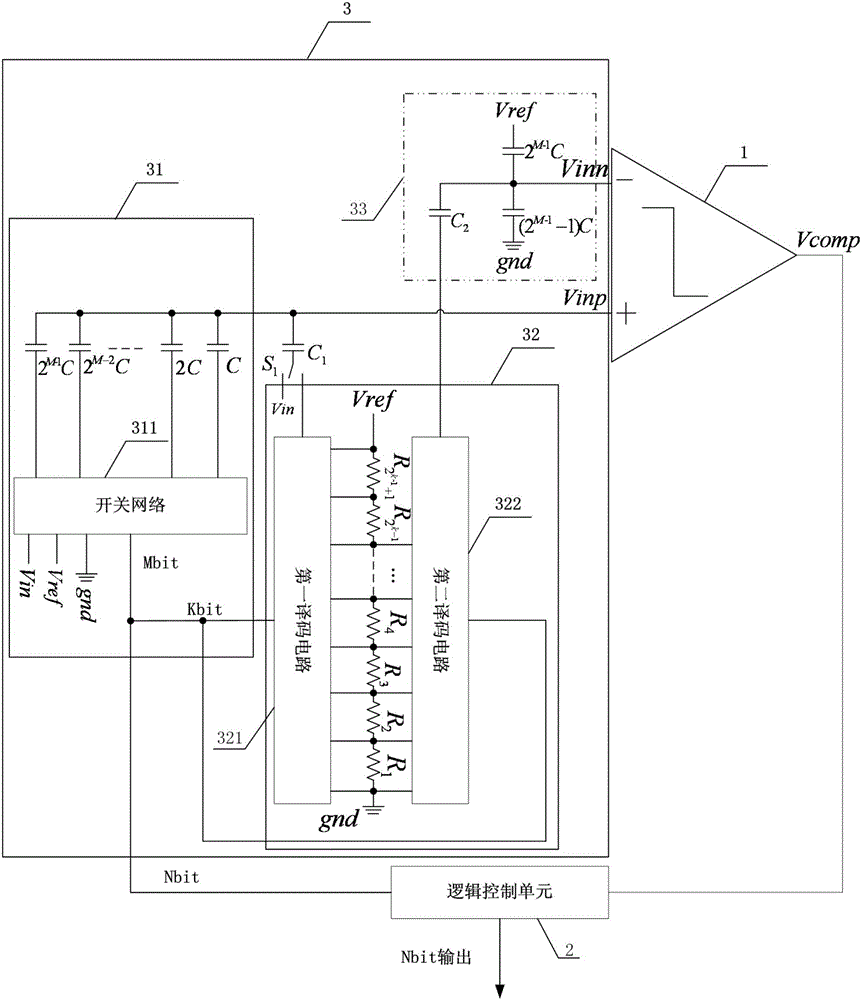

Successive approximation type analog-to-digital converter structure

ActiveCN105827245AReduce Integral NonlinearityReduce differential nonlinearityElectric signal transmission systemsAnalogue-digital convertersCapacitanceDifferential nonlinearity

The invention relates to a successive approximation type analog-to-digital converter (ADC) structure which comprises a comparator, a logic control unit and a digital to analog converter (DAC). The DAC comprises a capacitive sub DA structure, a resistive sub DA structure and an input common-mode setting circuit; and the resistive sub DA structure comprises a first decoding circuit, a second decoding circuit and a resistor string. The resistor string is formed by connecting 2<k-1>+1 resistors in series, the lower end of the resistor string is connected with reference ground level, the upper end of the resistor string is connected with a reference level, a lower-end tapping of each resistor of the resistor string is led out and connected with the first decoding circuit, an upper-end tapping of a (2<k-1>+1)th resistor is led out and connected with the first decoding circuit, lower-end tappings of the first to (2<k-1>)th resistors are led out and connected with the second decoding circuit, the first decoding circuit is connected to the positive input end of the comparator via a first switch, and the second decoding circuit is connected with the input common-mode setting circuit via a second capacitor. The resistor string multiplexing structure is used to reduce integral and differential nonlinearity caused by mismatching of resistors.

Owner:58TH RES INST OF CETC

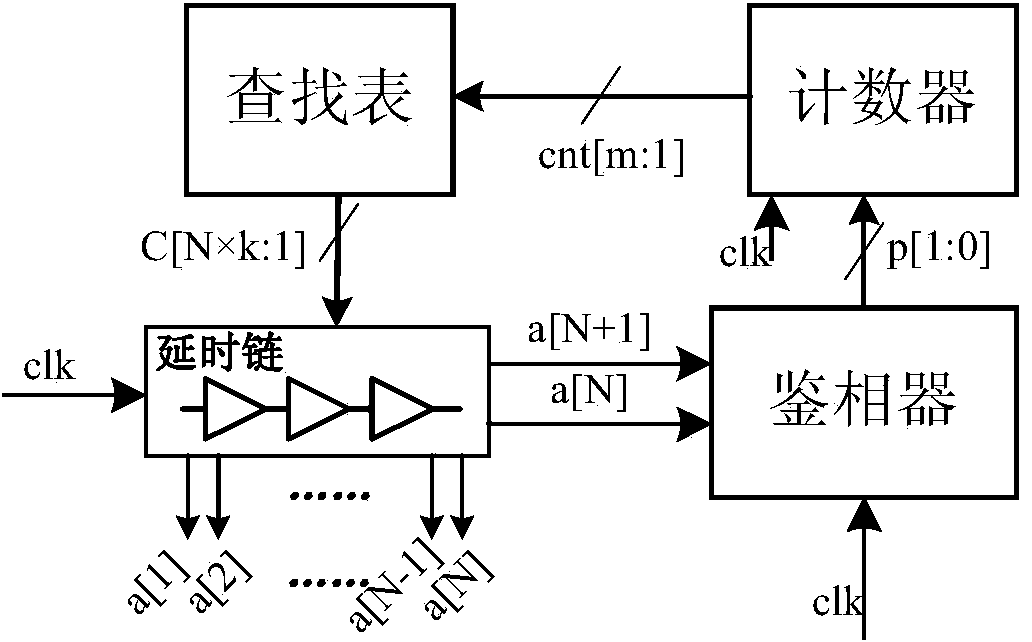

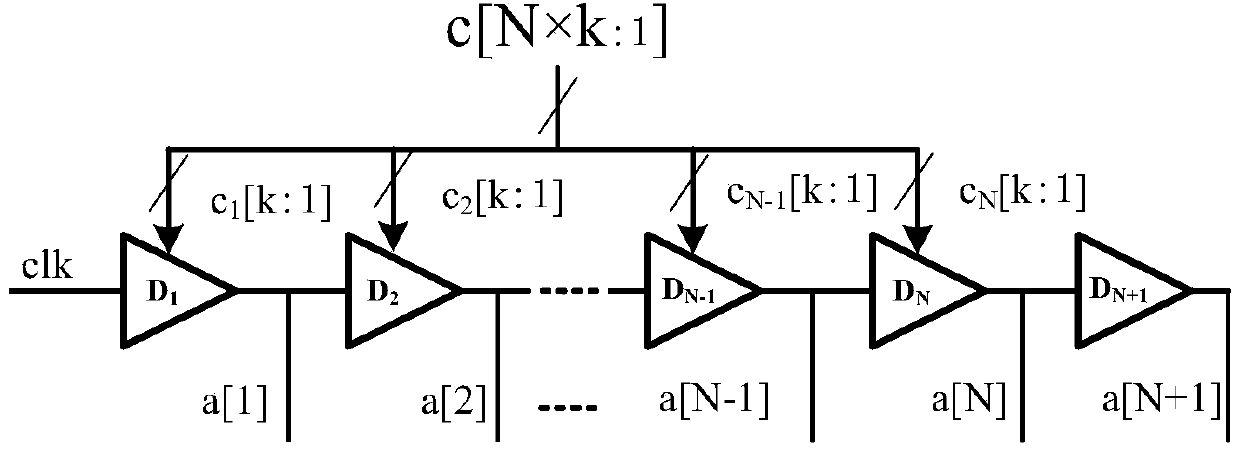

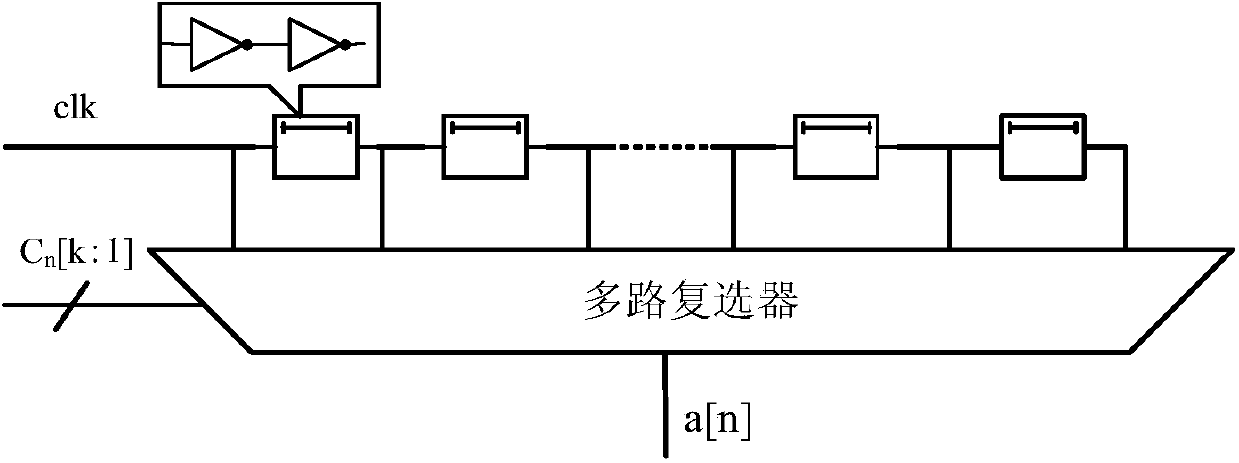

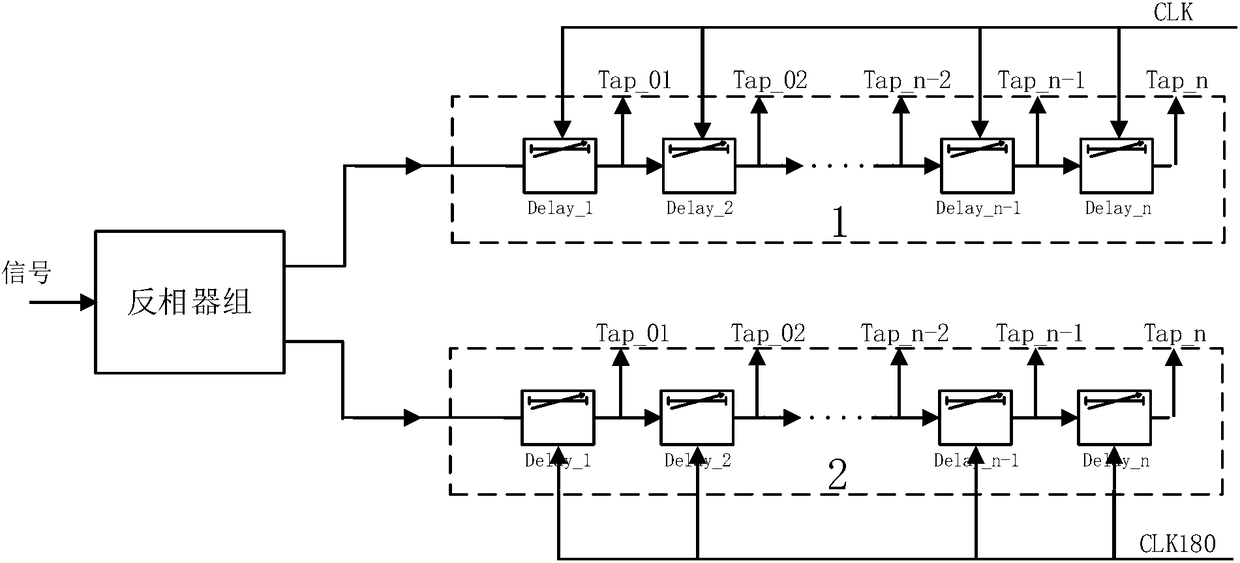

Multiphase clock generation circuit

InactiveCN103427798AEvenly distributed phase differenceSimple structureElectric pulse generator circuitsPhase detectorDiscriminator

The invention discloses a multiphase clock generation circuit, and belongs to the technical field of electronics. The multiphase clock generation circuit comprises a delay chain, a phase discriminator, a counter and a lookup table module. The phase discriminator judges whether delay of the delay chain is equal to a reference clock period or not, and the delay of delay units of the delay chain is adjusted according to output results of the phase discriminator, so that the delay of the delay chain is equal to the reference clock period. In the adjusting process and N delay units, the delay of k delay units is smaller than an ideal value, the delay of N-k delay units is larger than the ideal value, and both N and k are integers. The delay units are divided into 2*min [k, (N-k)] +1 groups, and the difference of control codes of the delay units in adjacent groups is 1, so that an optimized linearity result is obtained. The multiphase clock generation circuit has the advantages of simple structure, high reliability, low differential nonlinearity and integral nonlinearity and the like.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

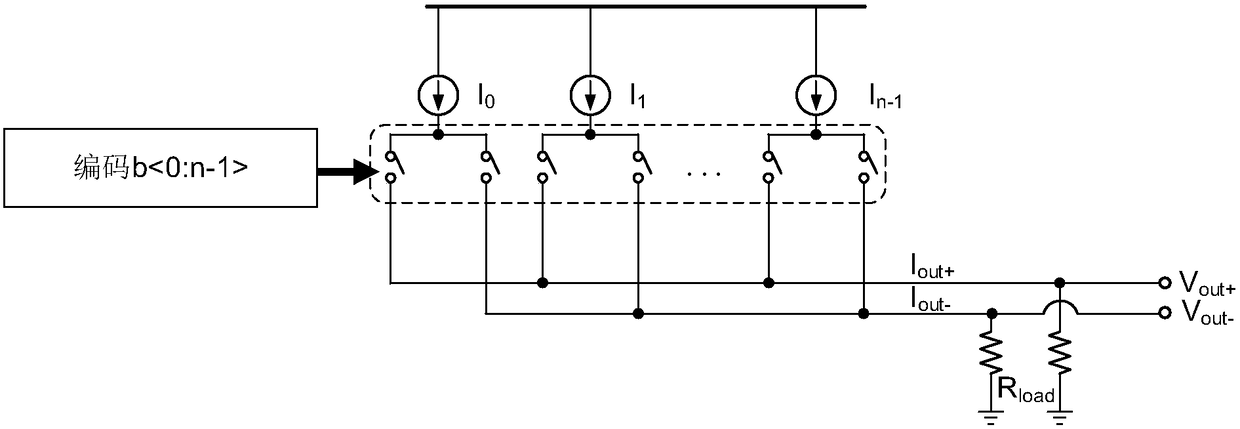

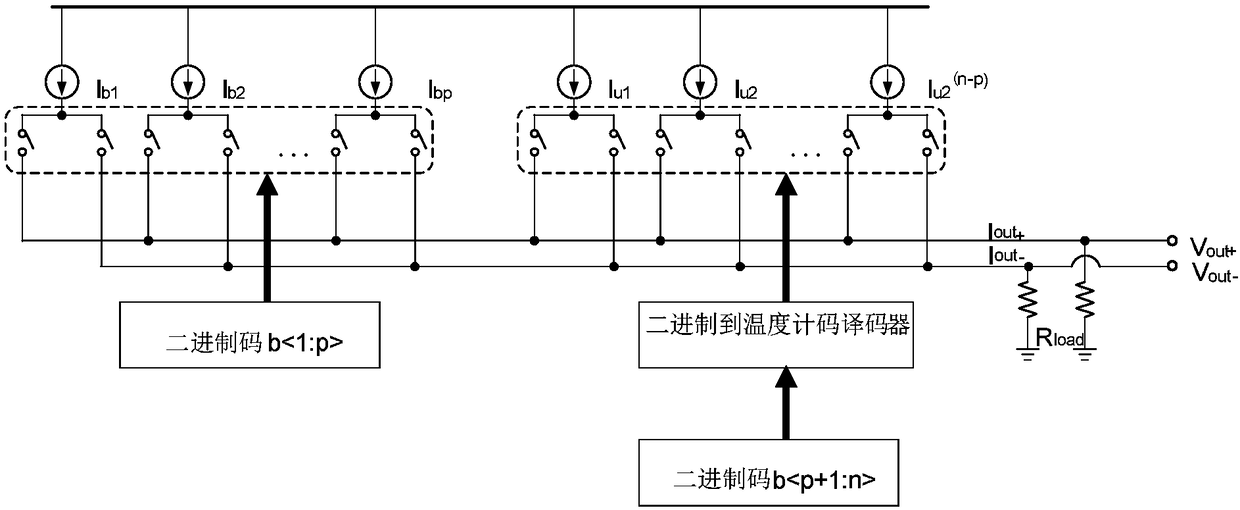

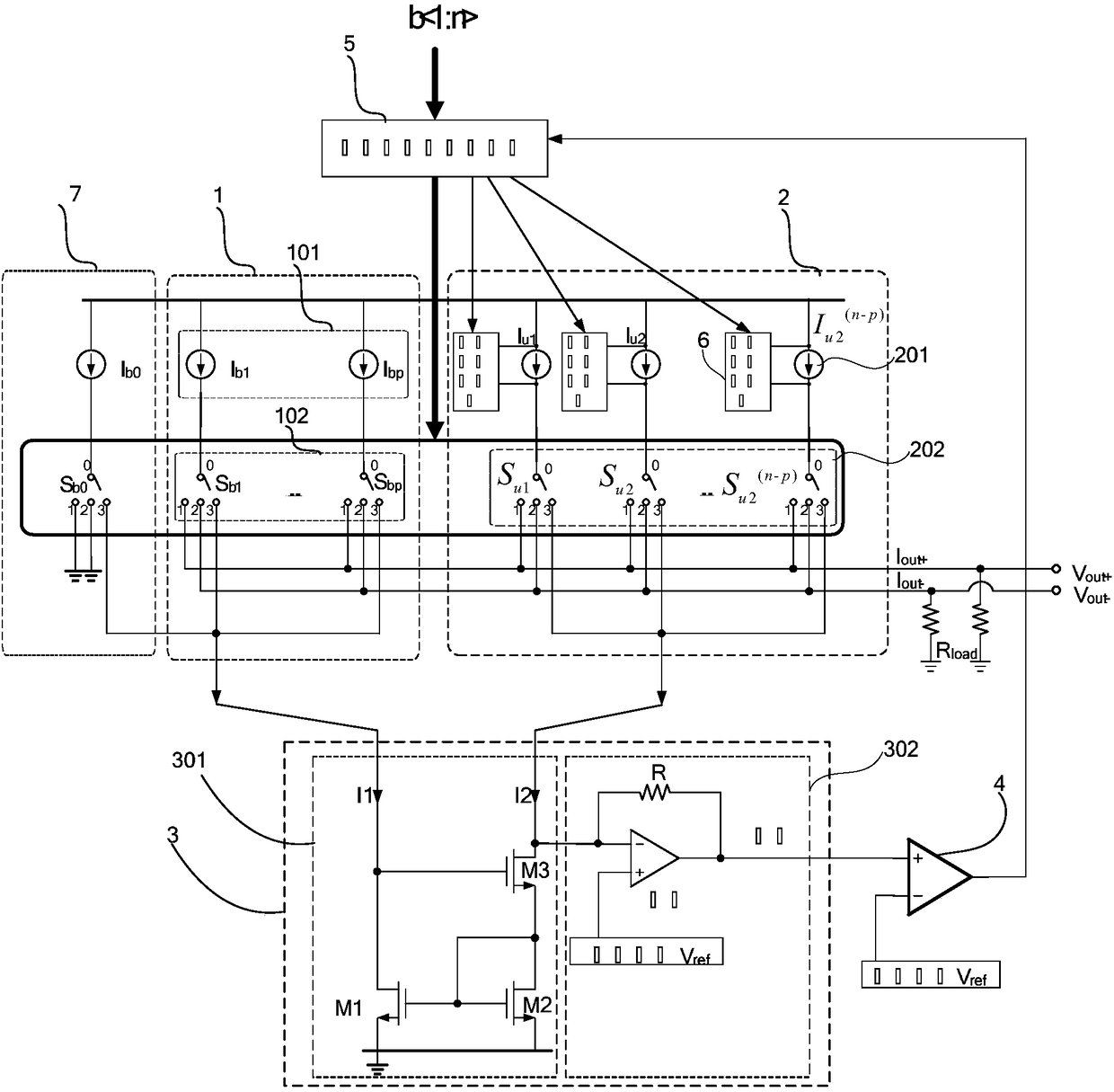

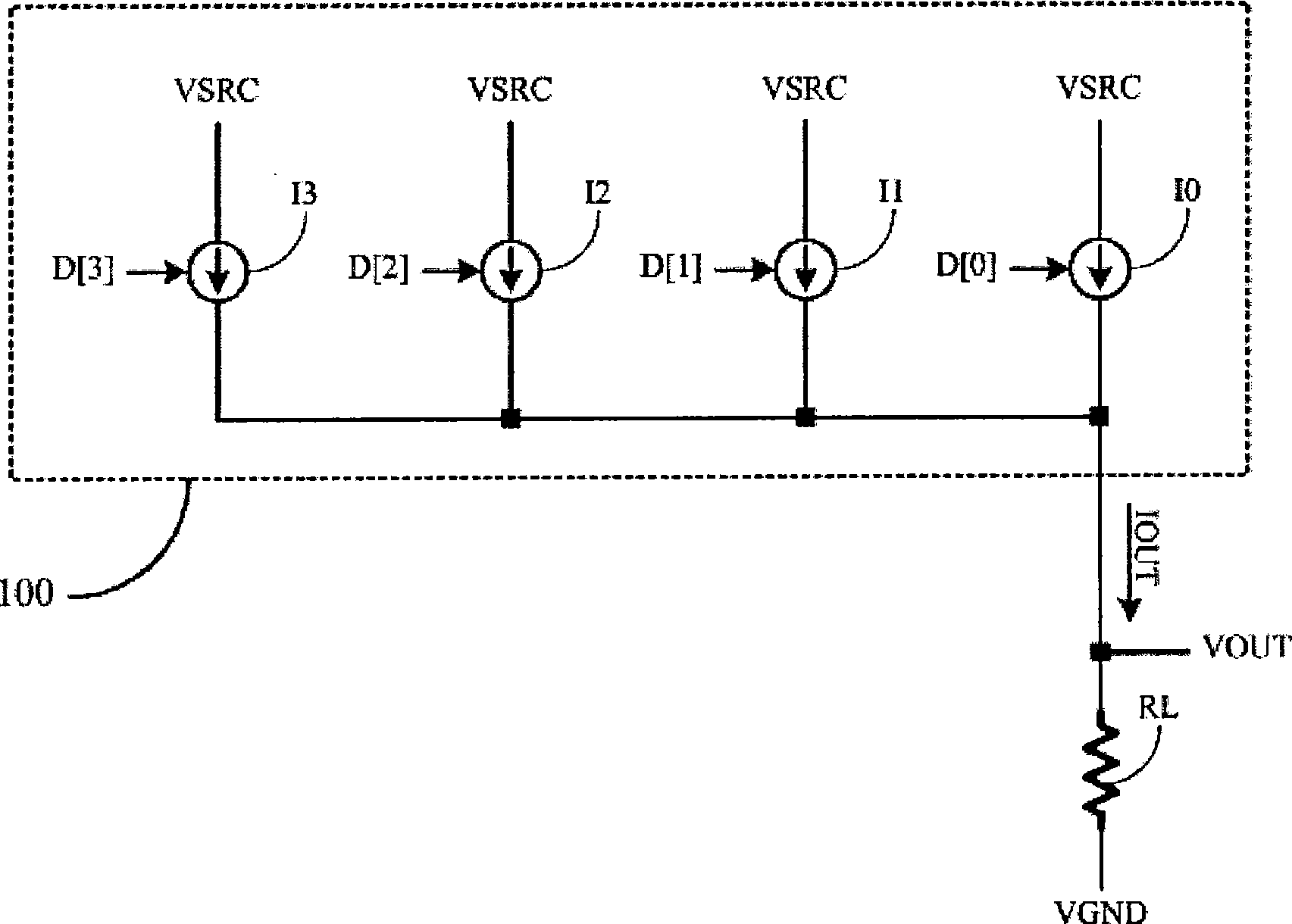

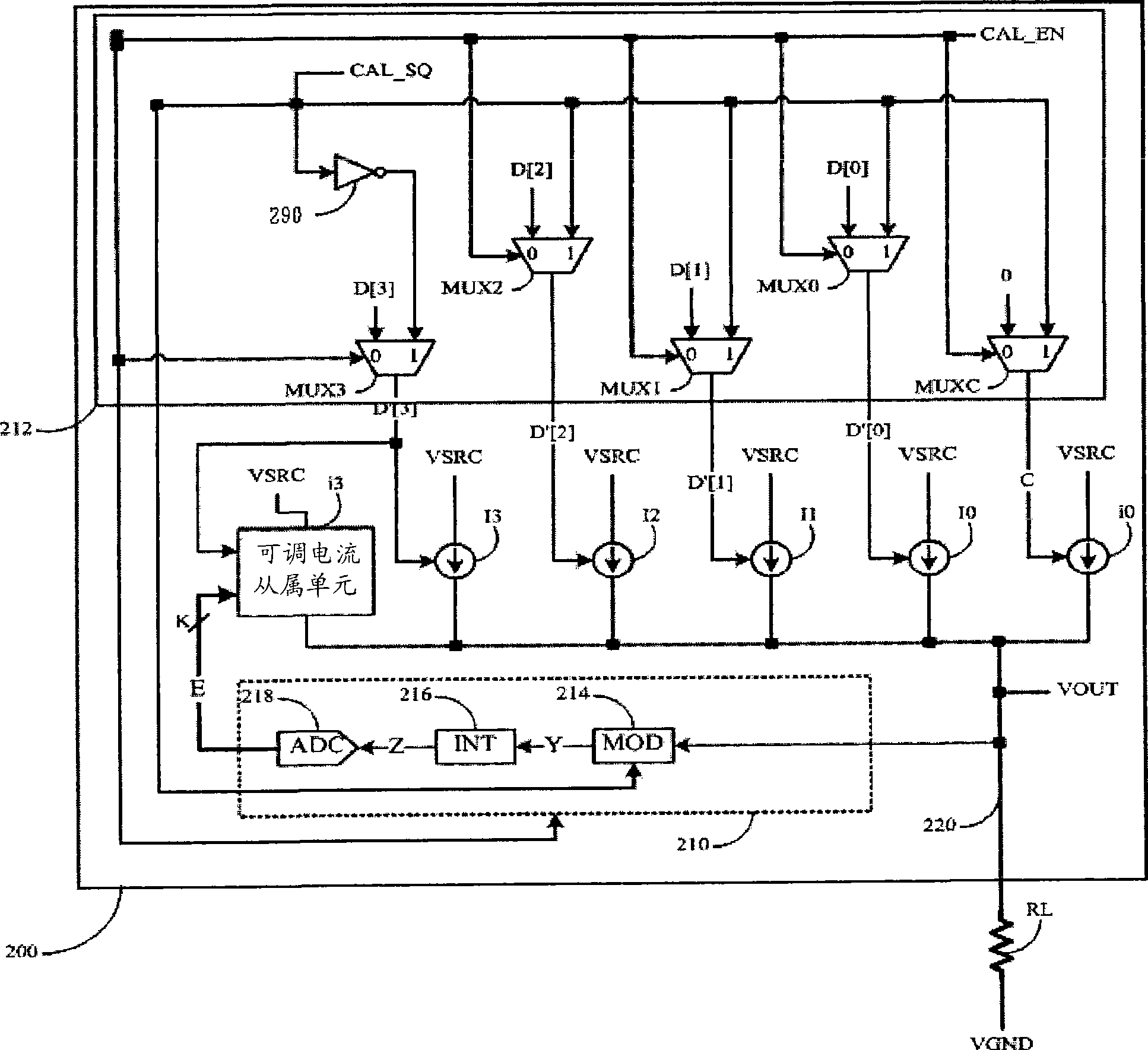

Current steering type digital-to-analog converter for achieving digitization calibration, chip and communication terminal

InactiveCN108449089AReduce differential nonlinearityImprove linearityDigital-analogue convertorsElectric variable regulationHybrid typeDifferential nonlinearity

The invention discloses a current steering type digital-to-analog converter for achieving digitization calibration. The current steering type digital-to-analog converter separately compares a receivedcurrent output bit-by-bit by a thermometer coding module with the sum of currents output by a binary coding module and a reference power source circuit via a current subtractor circuit; a comparisonresult is transmitted to a control and calibration logic circuit via a comparator; the control and calibration logic circuit controls the magnitude of a calibration current output by a corresponding calibration current source until the output of the comparator turns over, and thus the calibration process of the current output bit-by-bit by the thermometer coding module is completed. According to the current steering type digital-to-analog converter, the differential nonlinearity of the piecewise hybrid coded current steering type digital-to-analog converter can be reduced, and the linearity ofthe current steering type digital-to-analog converter can be improved under the premise of not increasing too much chip area, power consumption and size of the unit current source.

Owner:SHANGHAI VANCHIP ELECTRONICS TECH CO LTD

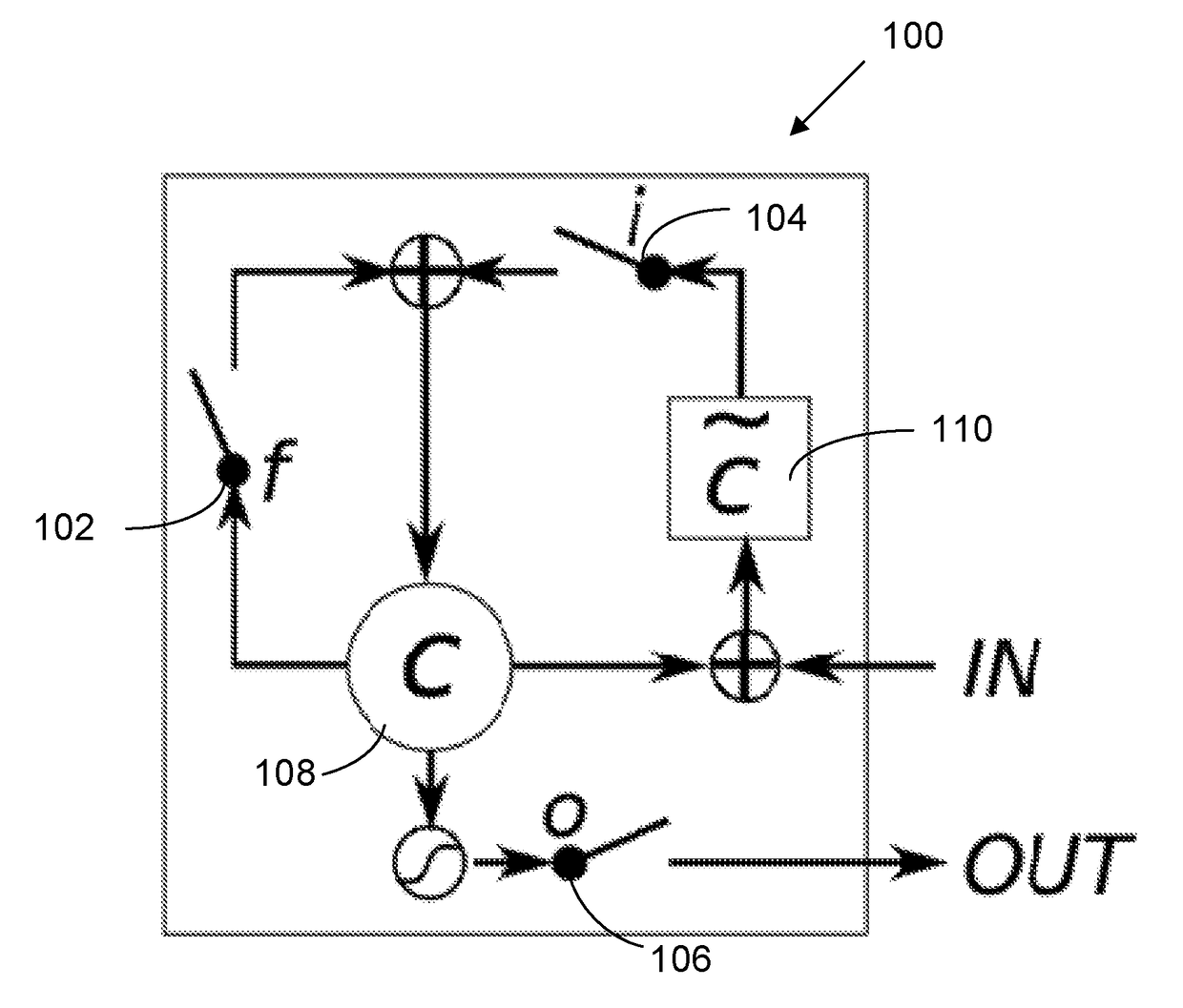

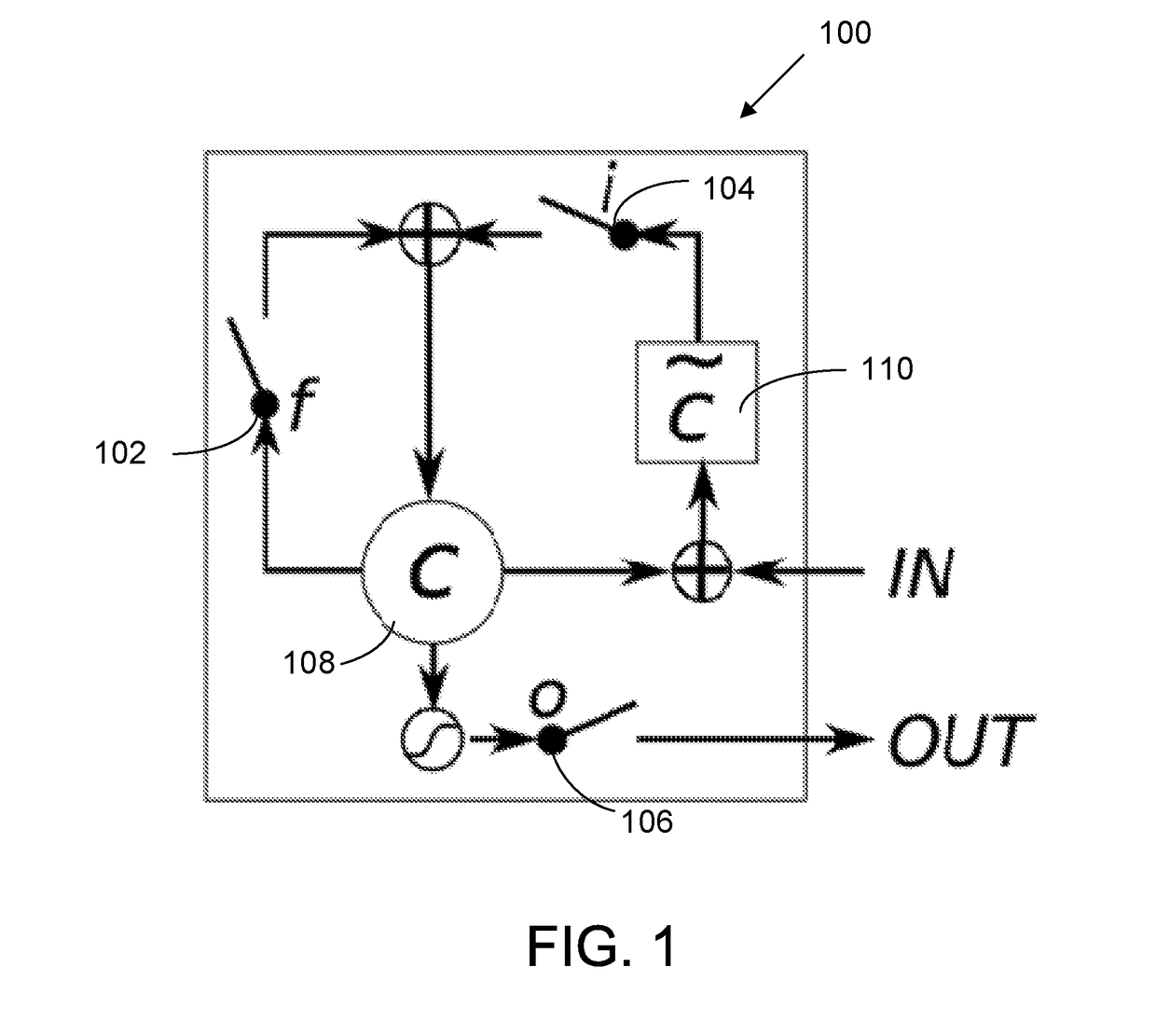

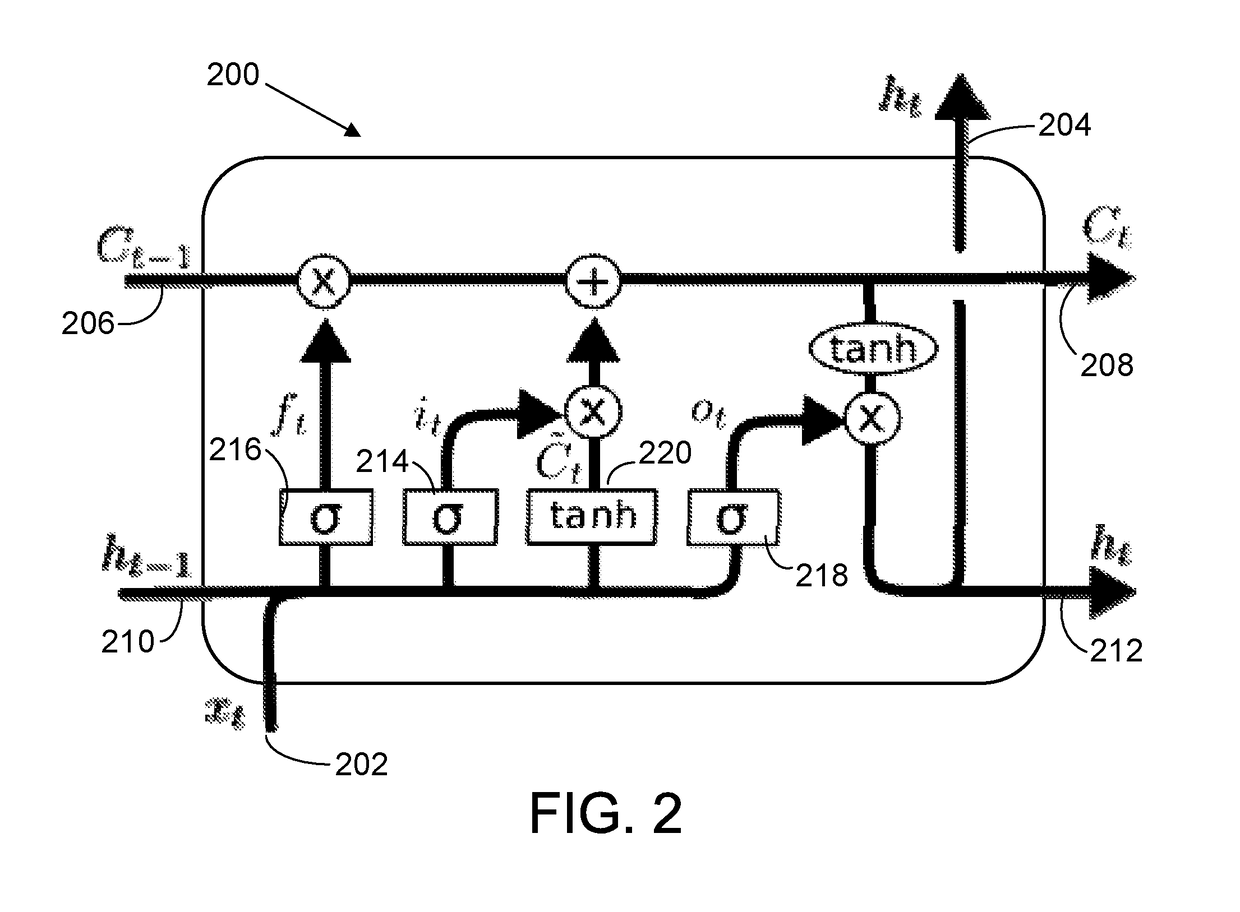

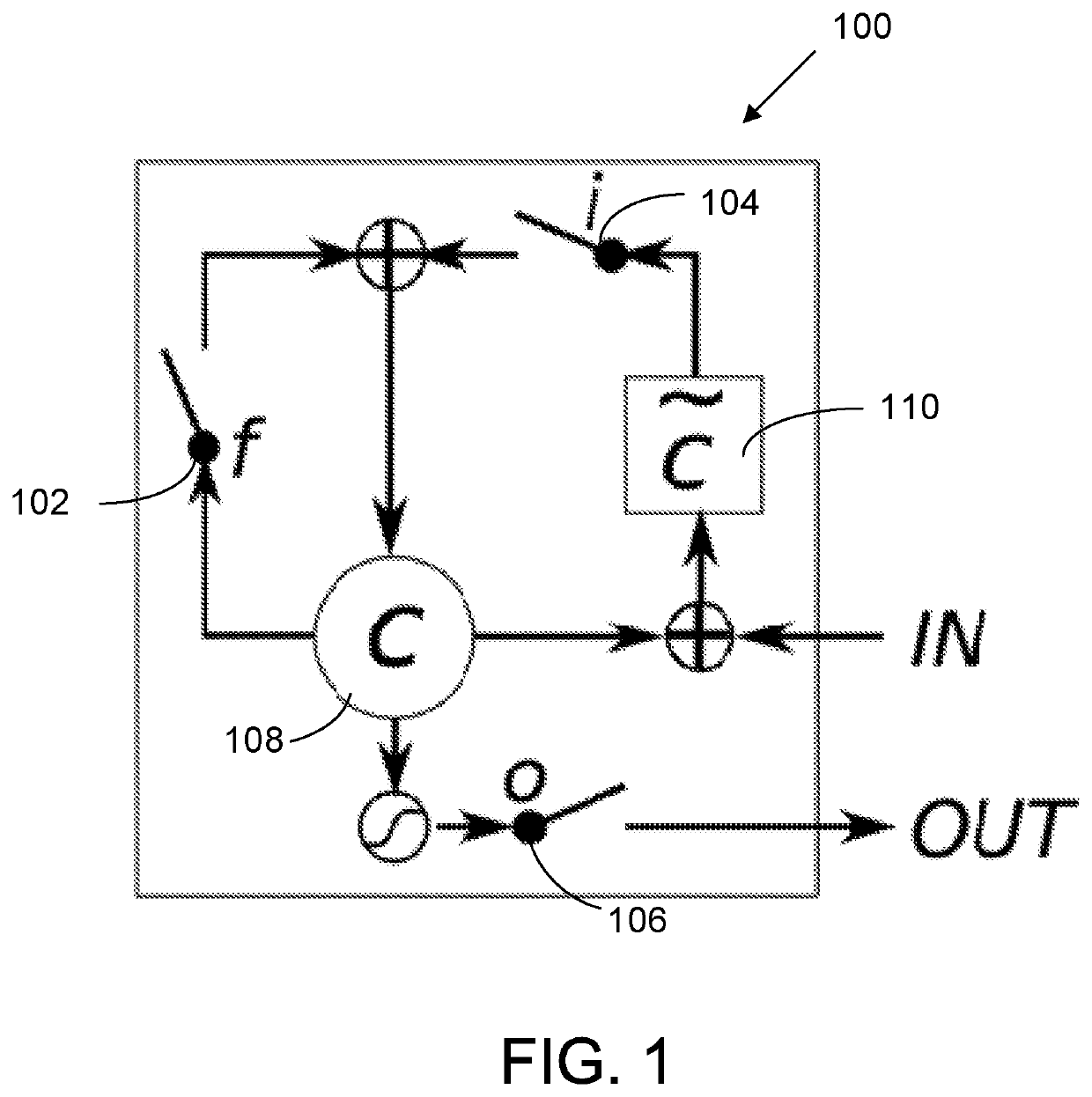

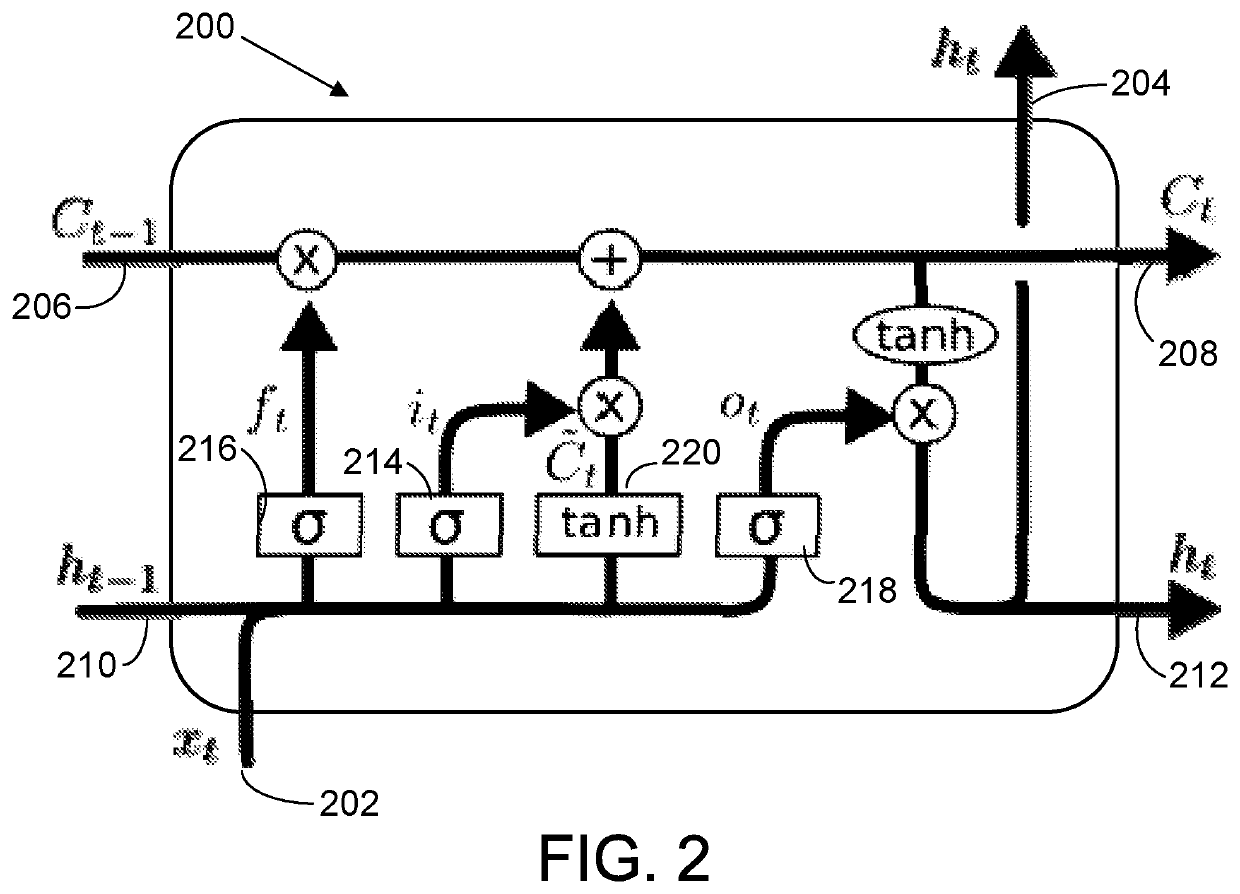

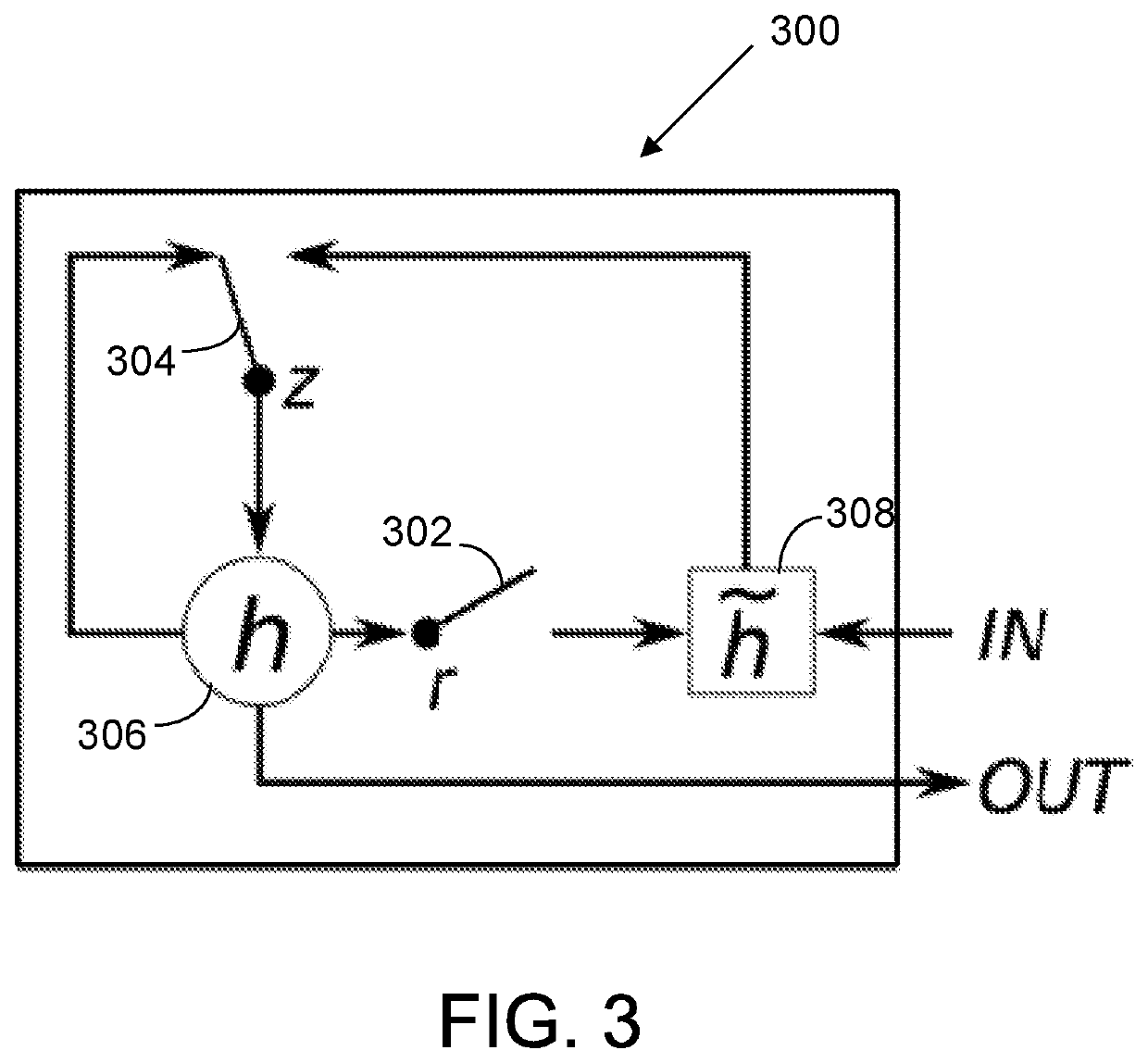

Differential recurrent neural network

ActiveUS20180144245A1Fast convergenceIncreasing the curvature of the HessianNeural architecturesNeural learning methodsNerve networkDifferential nonlinearity

A differential recurrent neural network (RNN) is described that handles dependencies that go arbitrarily far in time by allowing the network system to store states using recurrent loops without adversely affecting training. The differential RNN includes a state component for storing states, and a trainable transition and differential non-linearity component which includes a neural network. The trainable transition and differential non-linearity component takes as input, an output of the previous stored states from the state component along with an input vector, and produces positive and negative contribution vectors which are employed to produce a state contribution vector. The state contribution vector is input into the state component to create a set of current states. In one implementation, the current states are simply output. In another implementation, the differential RNN includes a trainable OUT component which includes a neural network that performs post-processing on the current states before outputting them.

Owner:MICROSOFT TECH LICENSING LLC

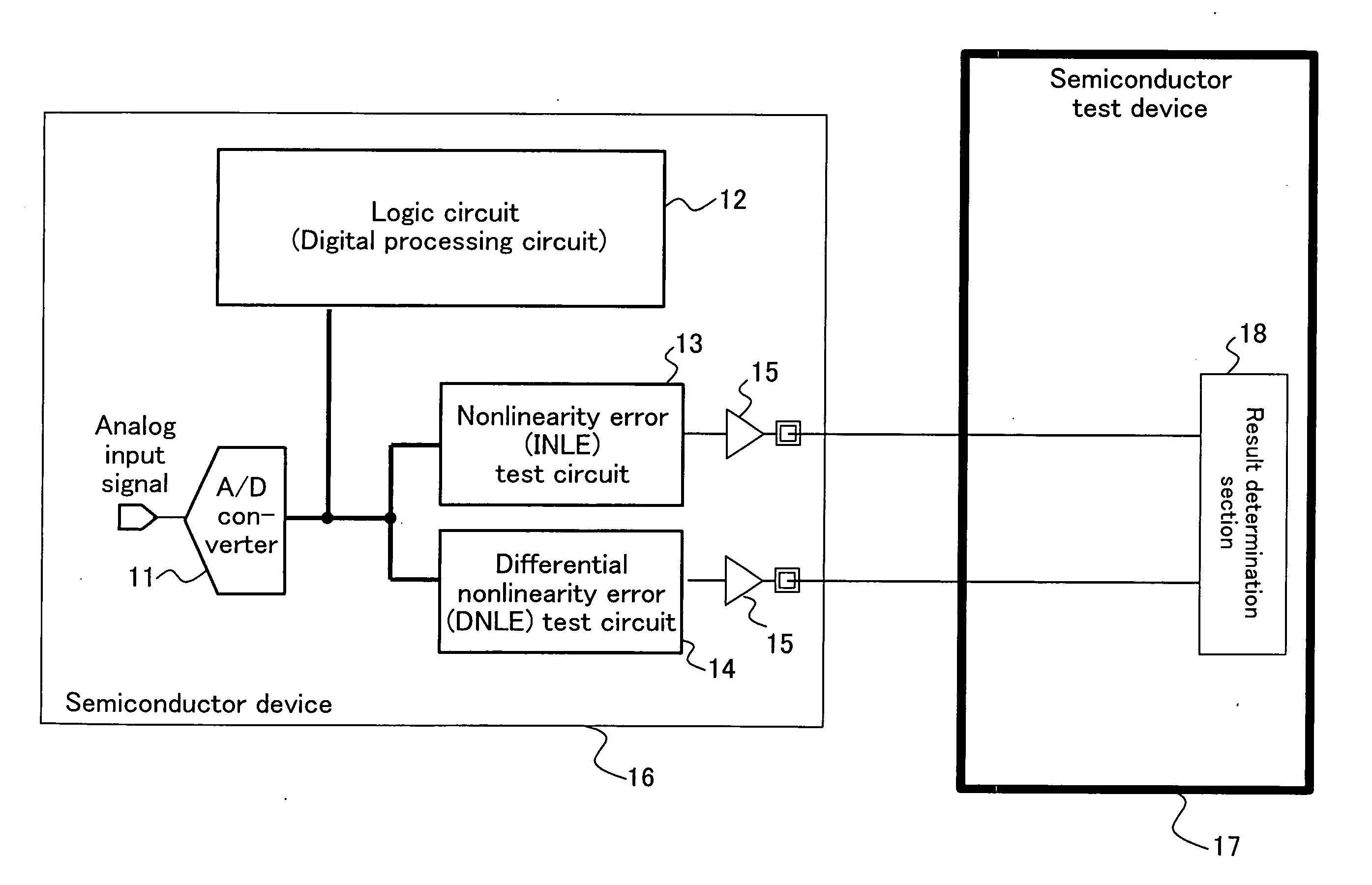

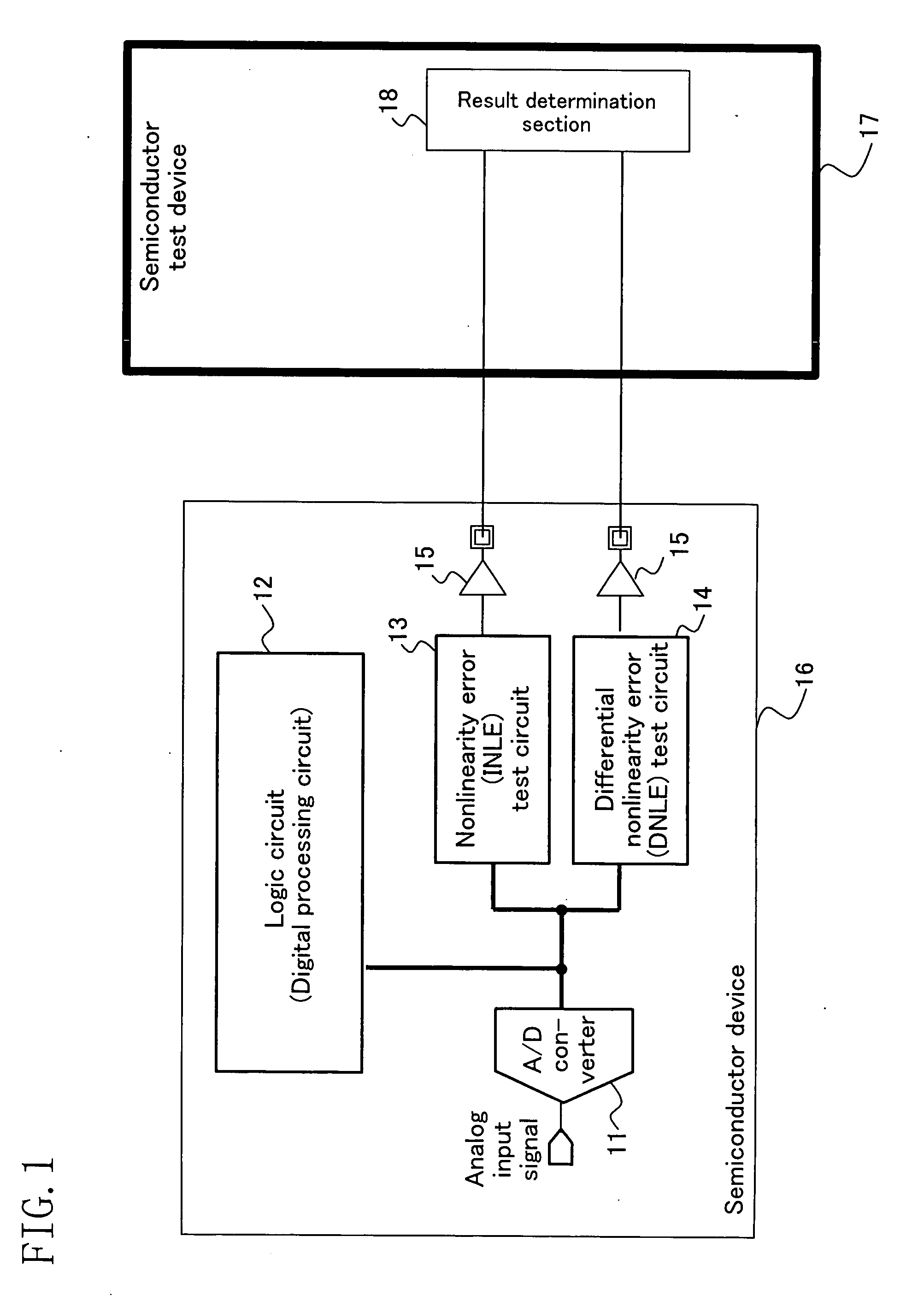

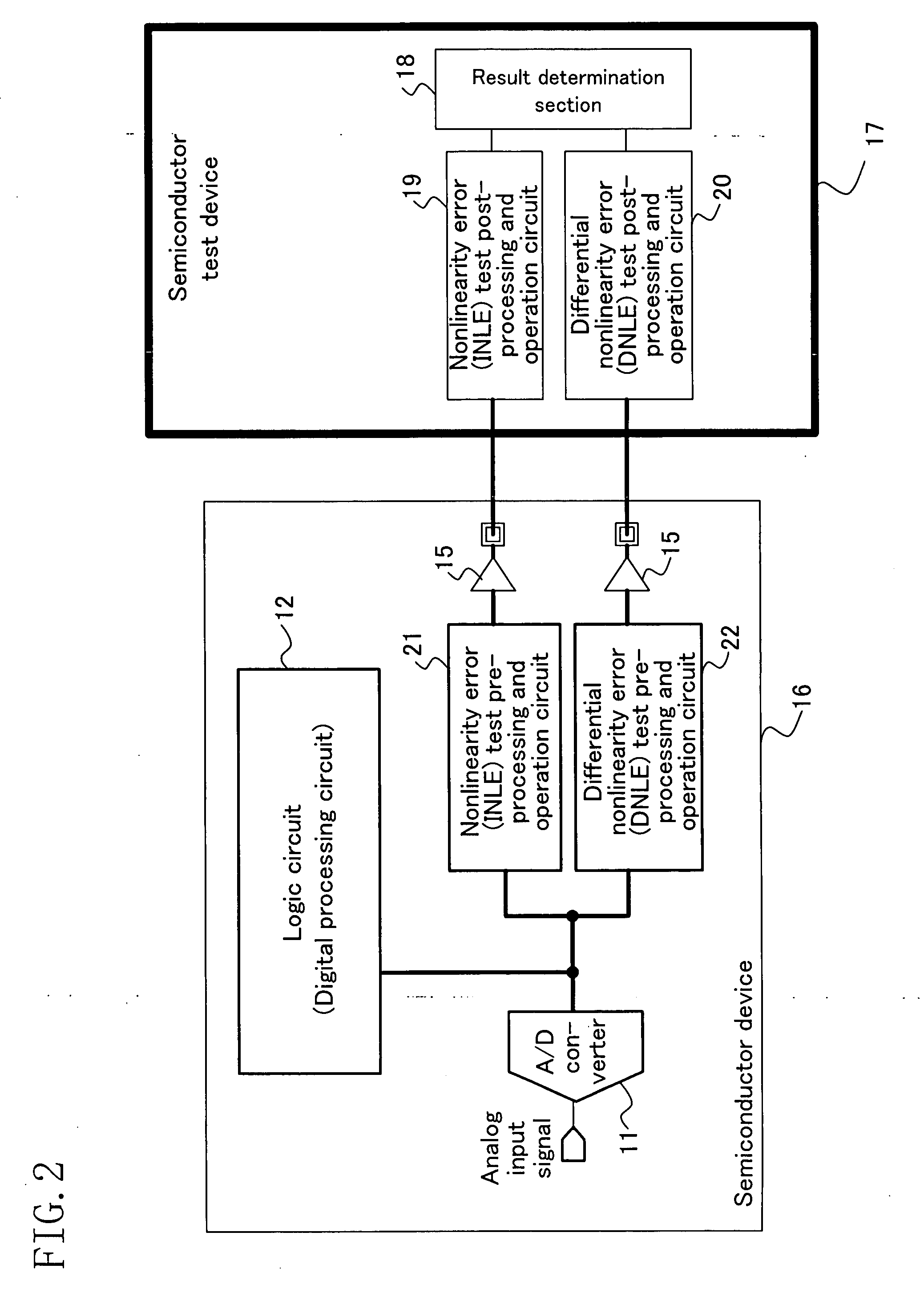

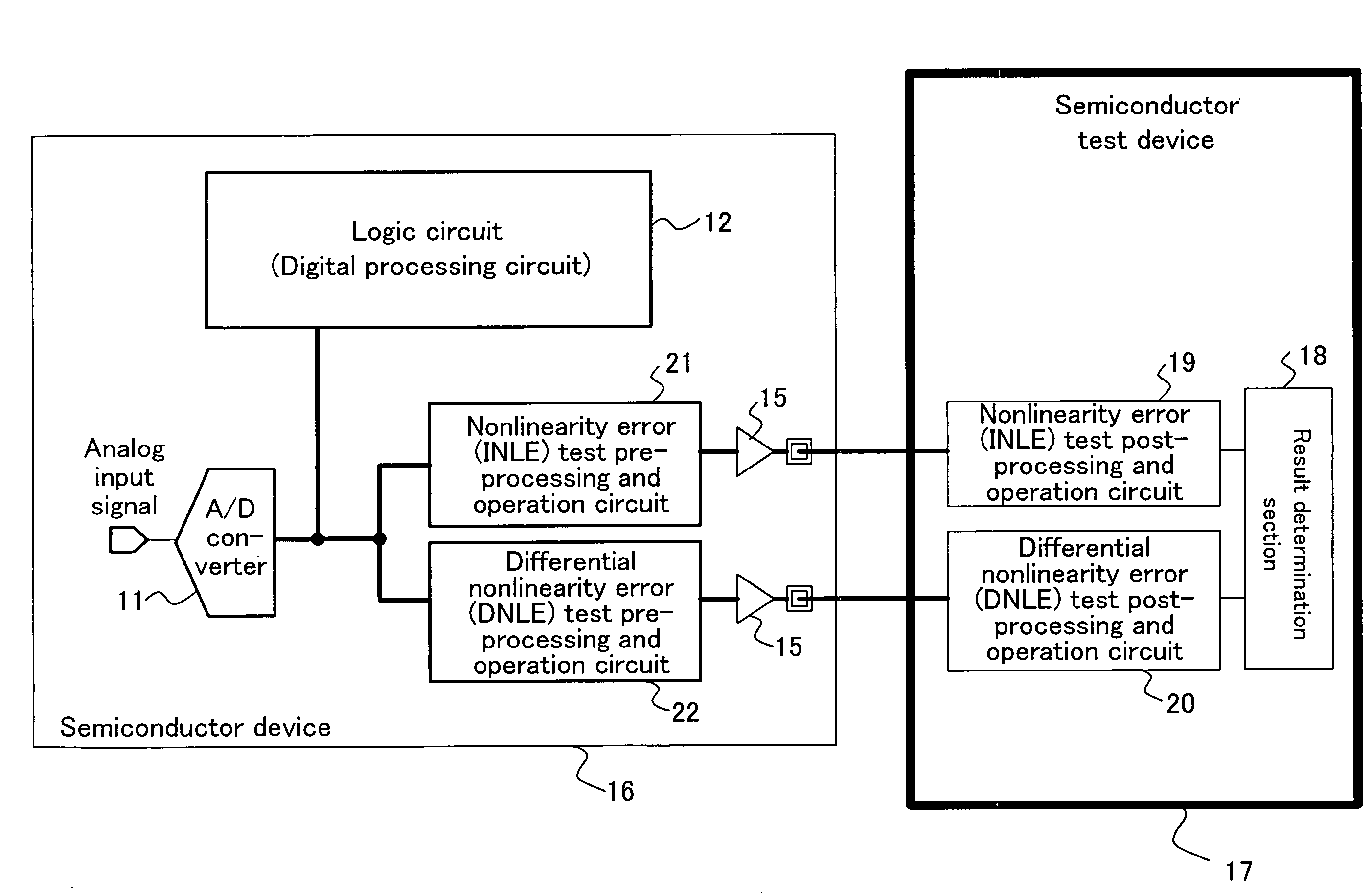

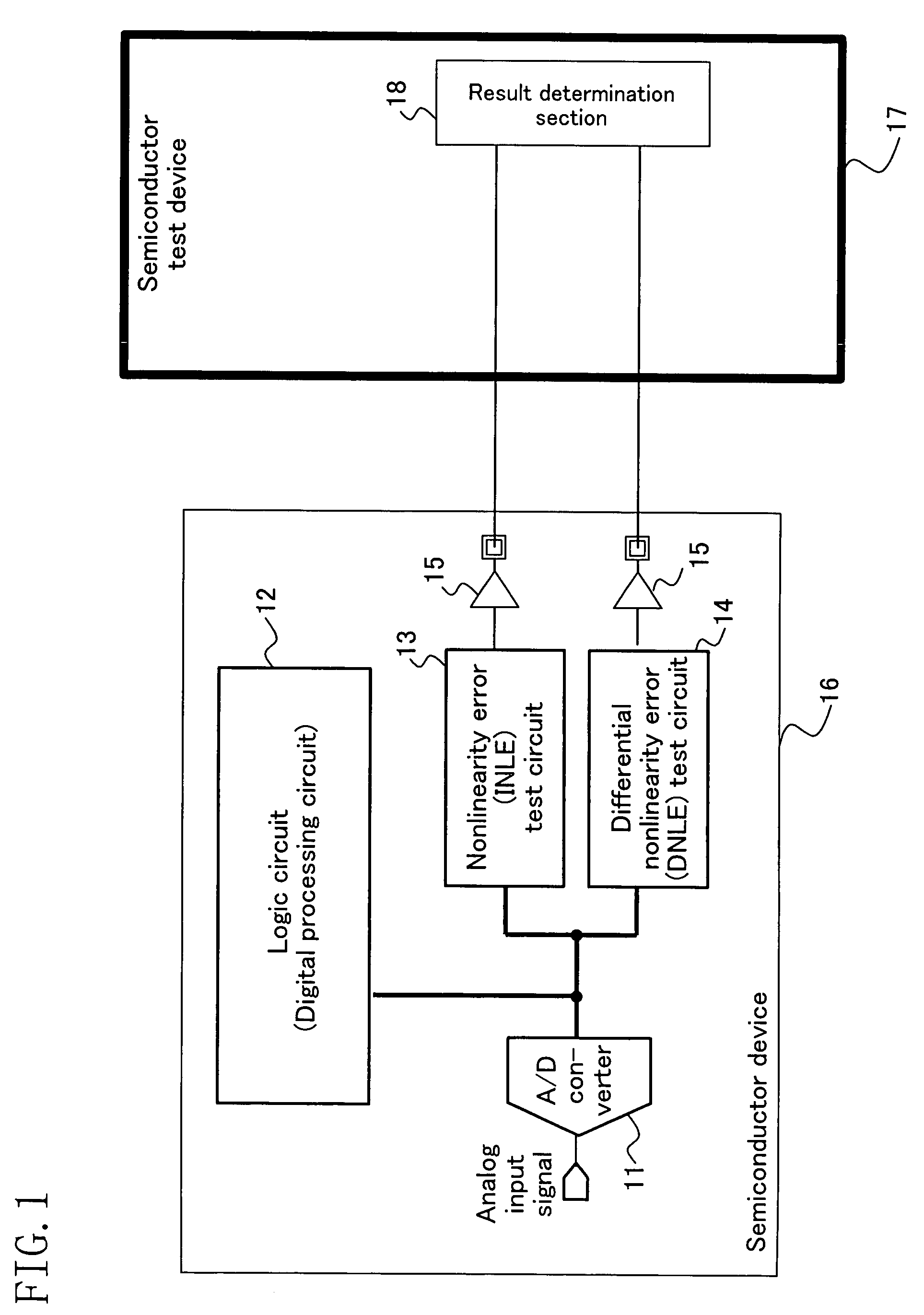

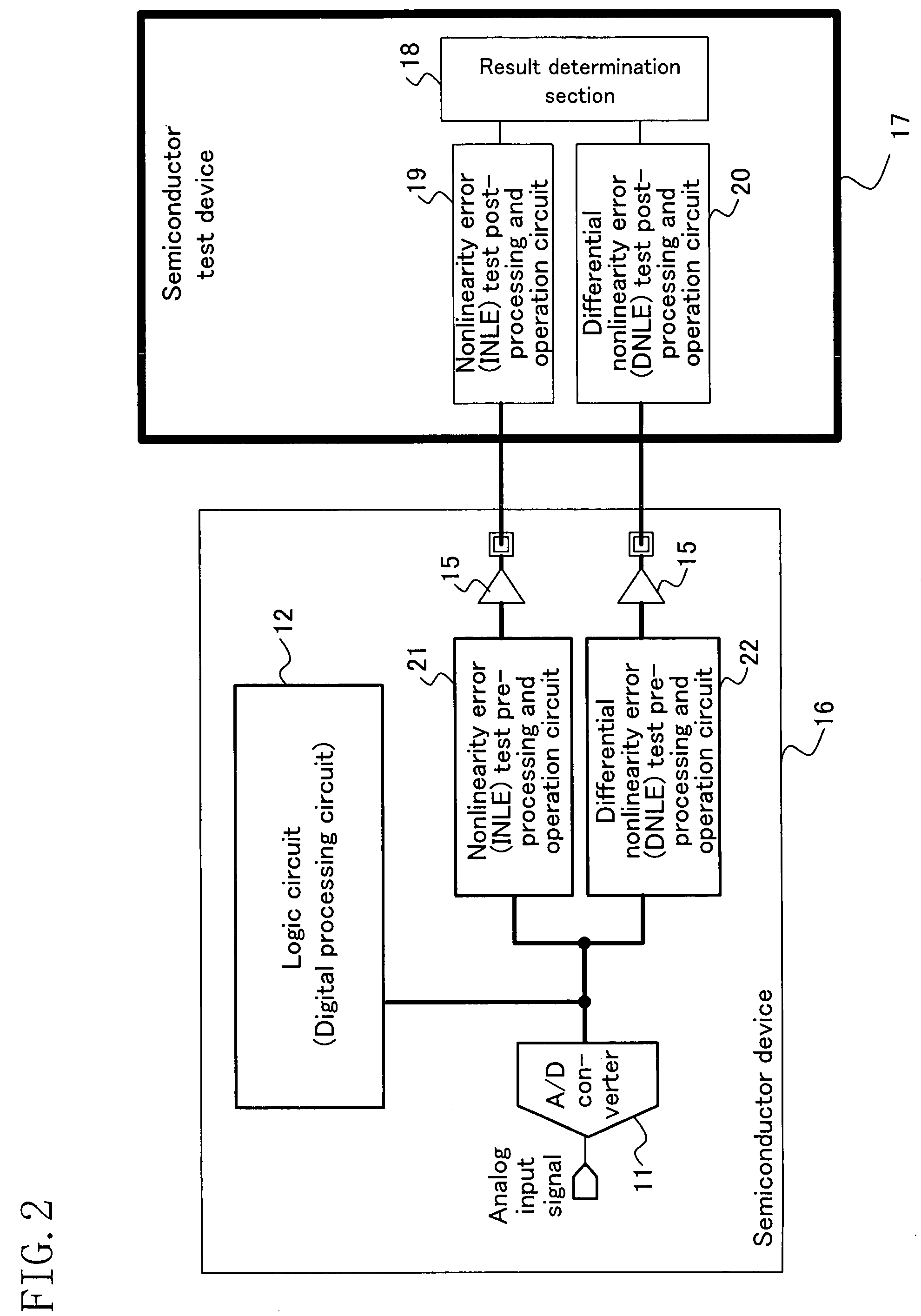

Semiconductor device including A/D converter

InactiveUS20080007439A1Easy to implementLower the volumeElectric signal transmission systemsAnalogue/digital conversion calibration/testingDifferential nonlinearityBuck converter

A semiconductor device includes: an A / D converter; a digital processing circuit for performing processing based on conversion results from the A / D converter; a first test circuit for performing operation processing for checking a nonlinearity error (INLE) of the conversion results from the A / D converter; and a second test circuit for performing operation processing for checking a differential nonlinearity error (DNLE) of the conversion results from the A / D converter. The first test circuit performs only part of the operation processing for checking the nonlinearity error (INLE) of the conversion results from the A / D converter. The second test circuit performs only part of the operation processing for checking the differential nonlinearity error (DNLE) of the conversion results from the A / D converter. An operation processing section for performing the rest of the operation processing for checking the nonlinearity error (INLE) and the rest of the operation processing for checking the differential nonlinearity error (DNLE) is in a semiconductor test device.

Owner:SOCIONEXT INC

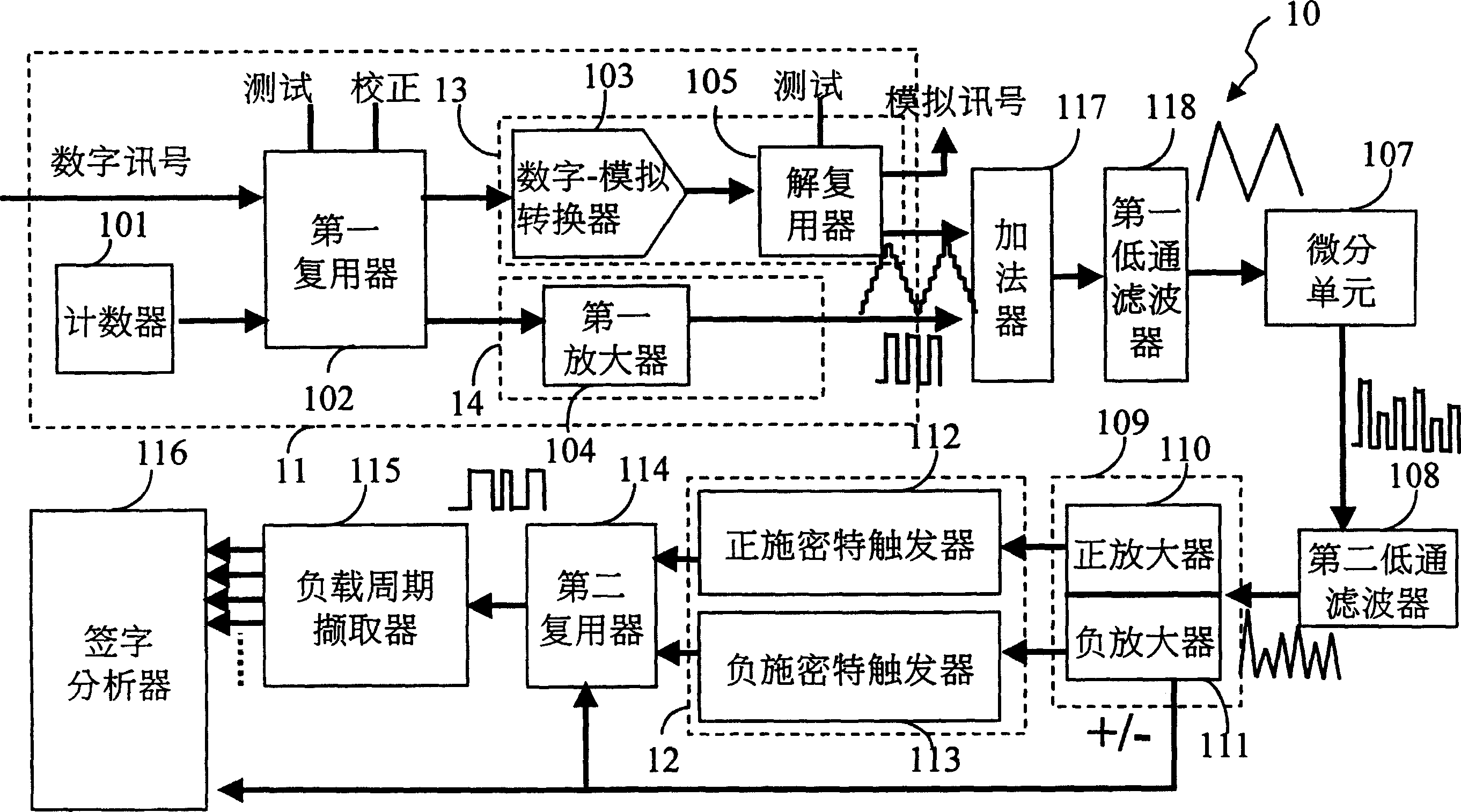

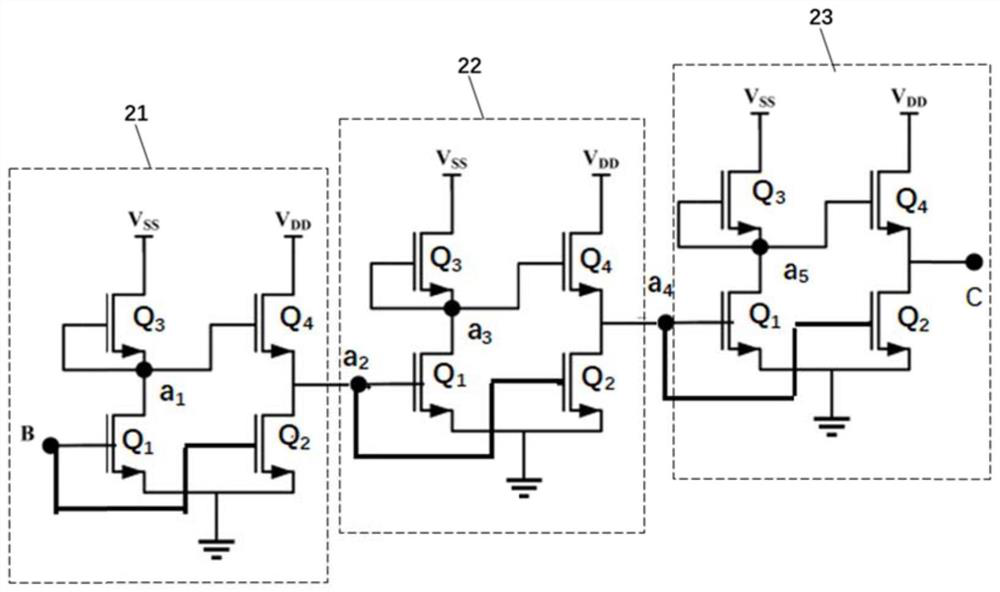

Built self testing unit and method inside D/A converter

InactiveCN1728559AReduce complexityReduce difficultyDigital-analogue convertorsAnalogue/digital conversion calibration/testingDifferential nonlinearityEngineering

D / A signal is differentiated through a differential element in order to obtain difference between pulses of analog signals. Based on a threshold voltage, Schmidt triggering unit converts the analog signals to digital signals. Using a duty cycle picker calculates duty cycle of the digital signal, which is sent to a signature analyzer to calculate degree of non-linearity of differential in order to carry out error analysis. In order to treat D / A signal in high speed, a combined circuit including a pattern test unit, a sample-and-hold circuit and a logic circuit is adopted as front-end circuit of differential element to lower speed of D / A signal.

Owner:NASOFORM INC

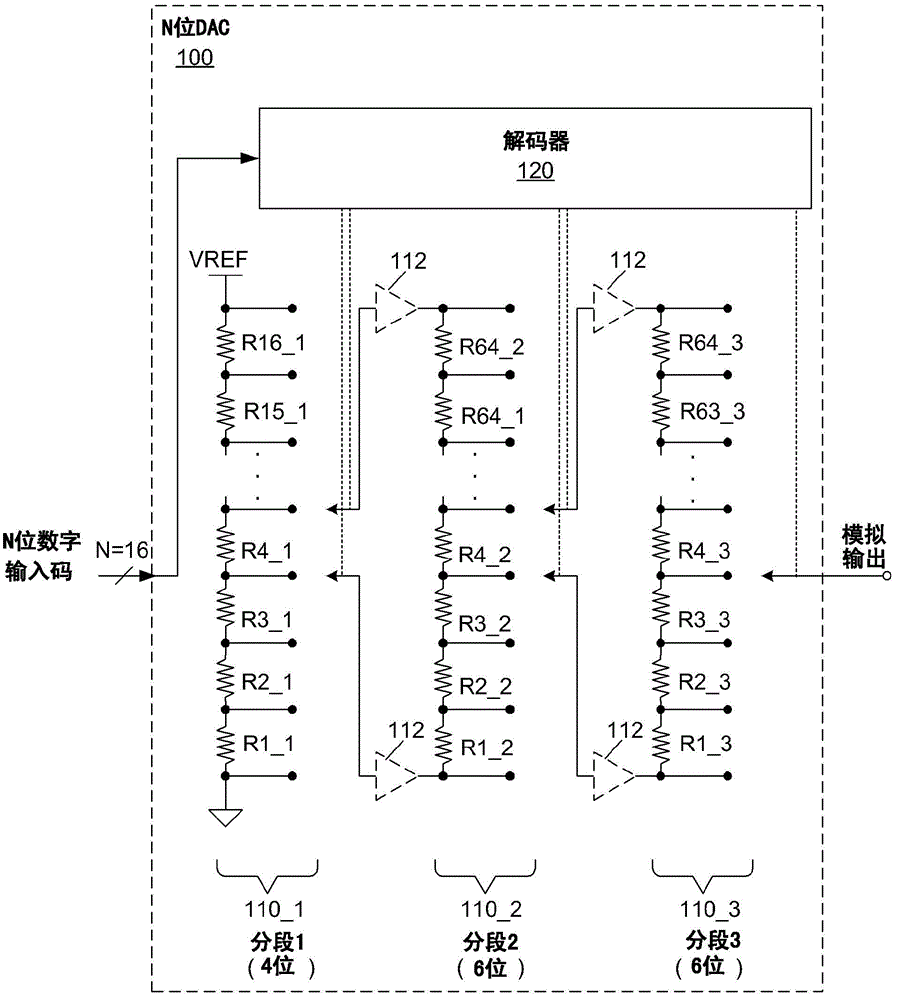

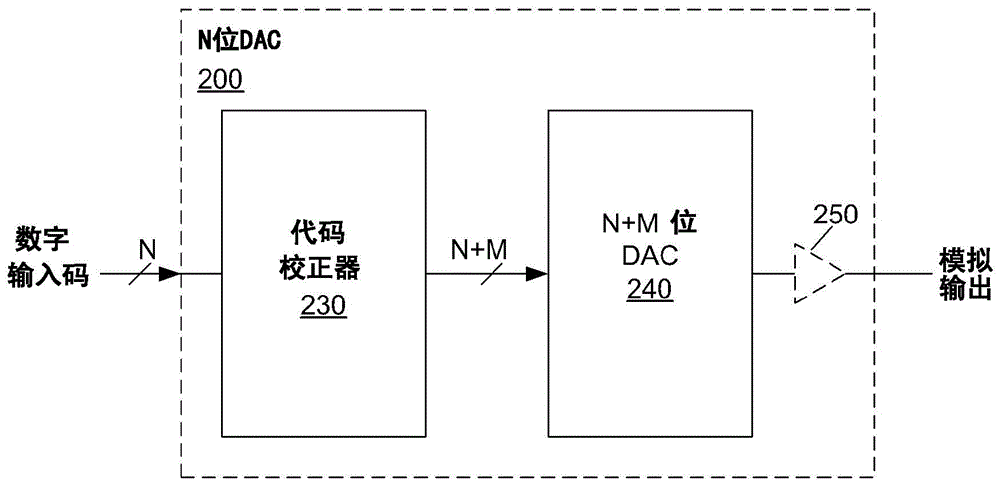

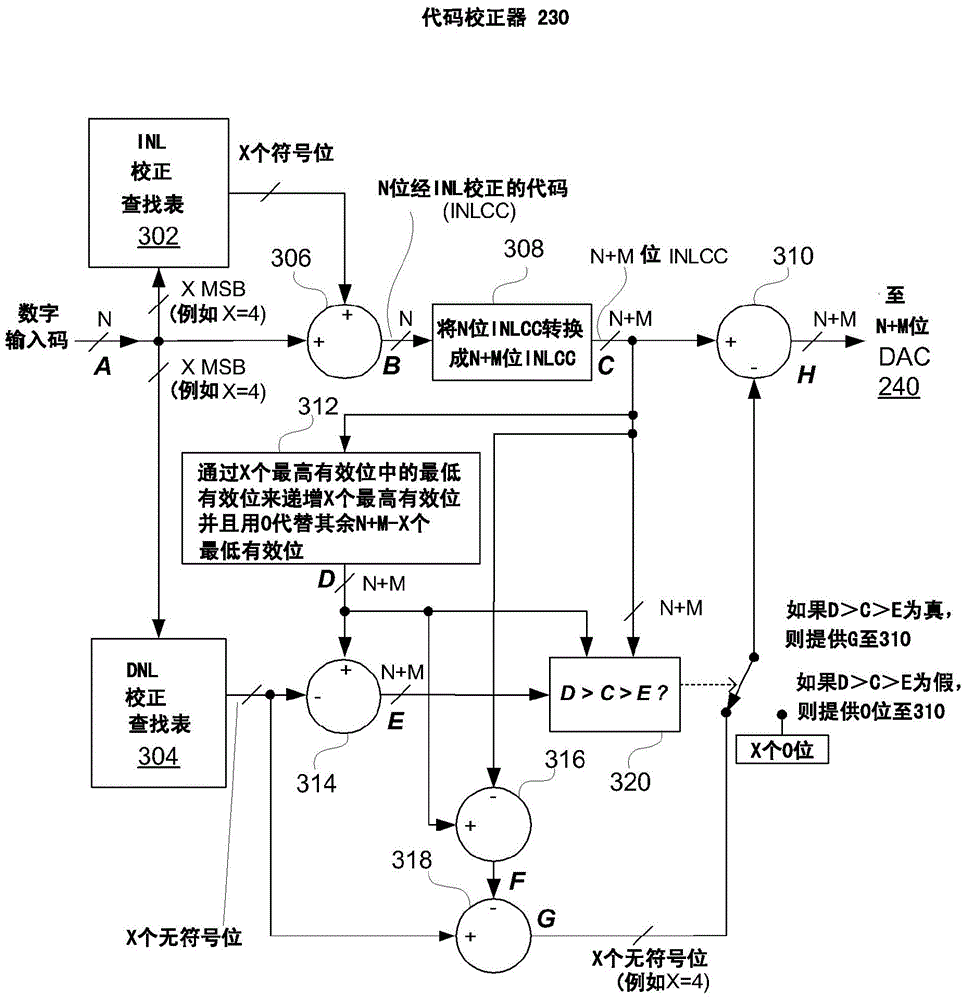

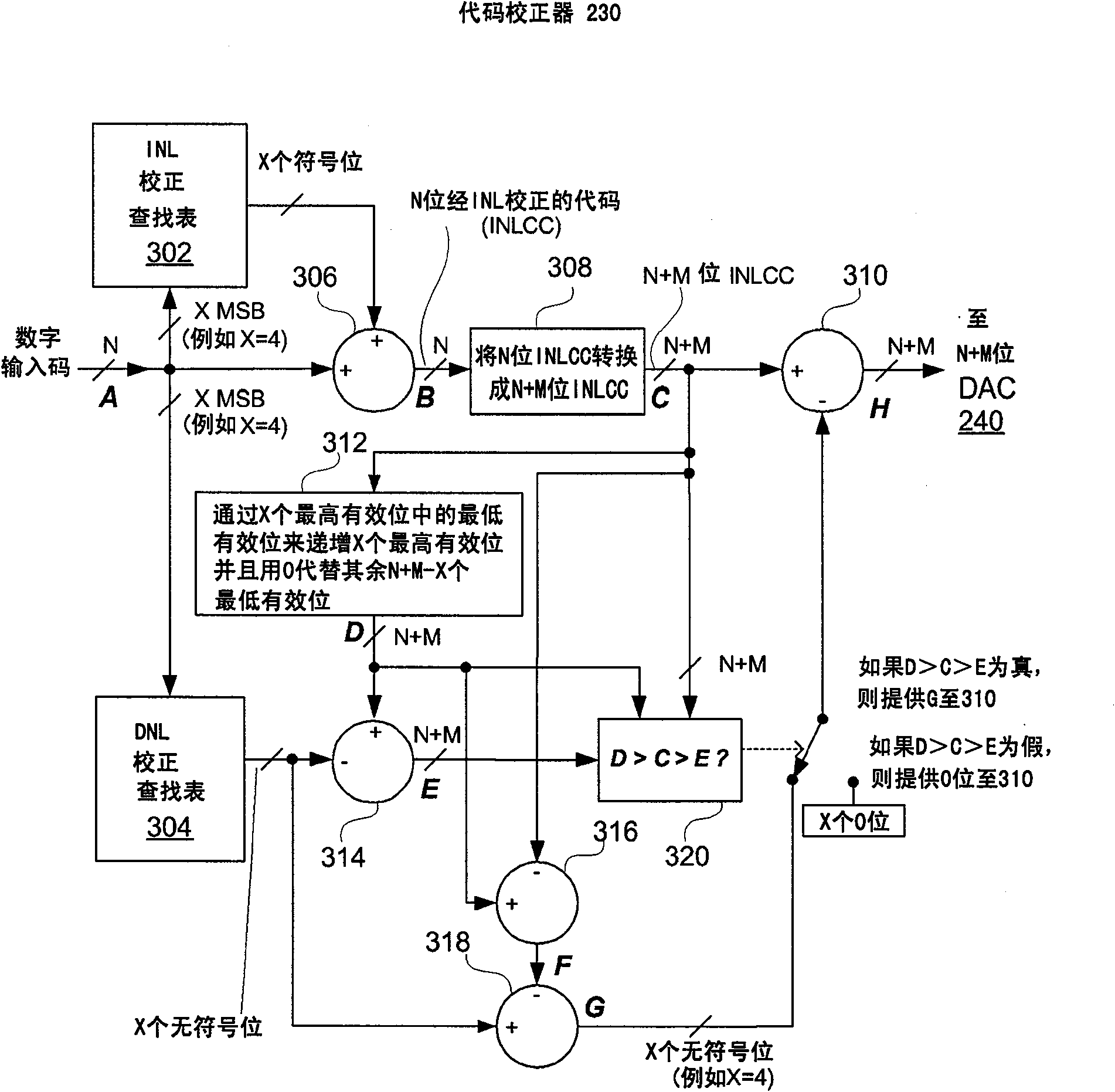

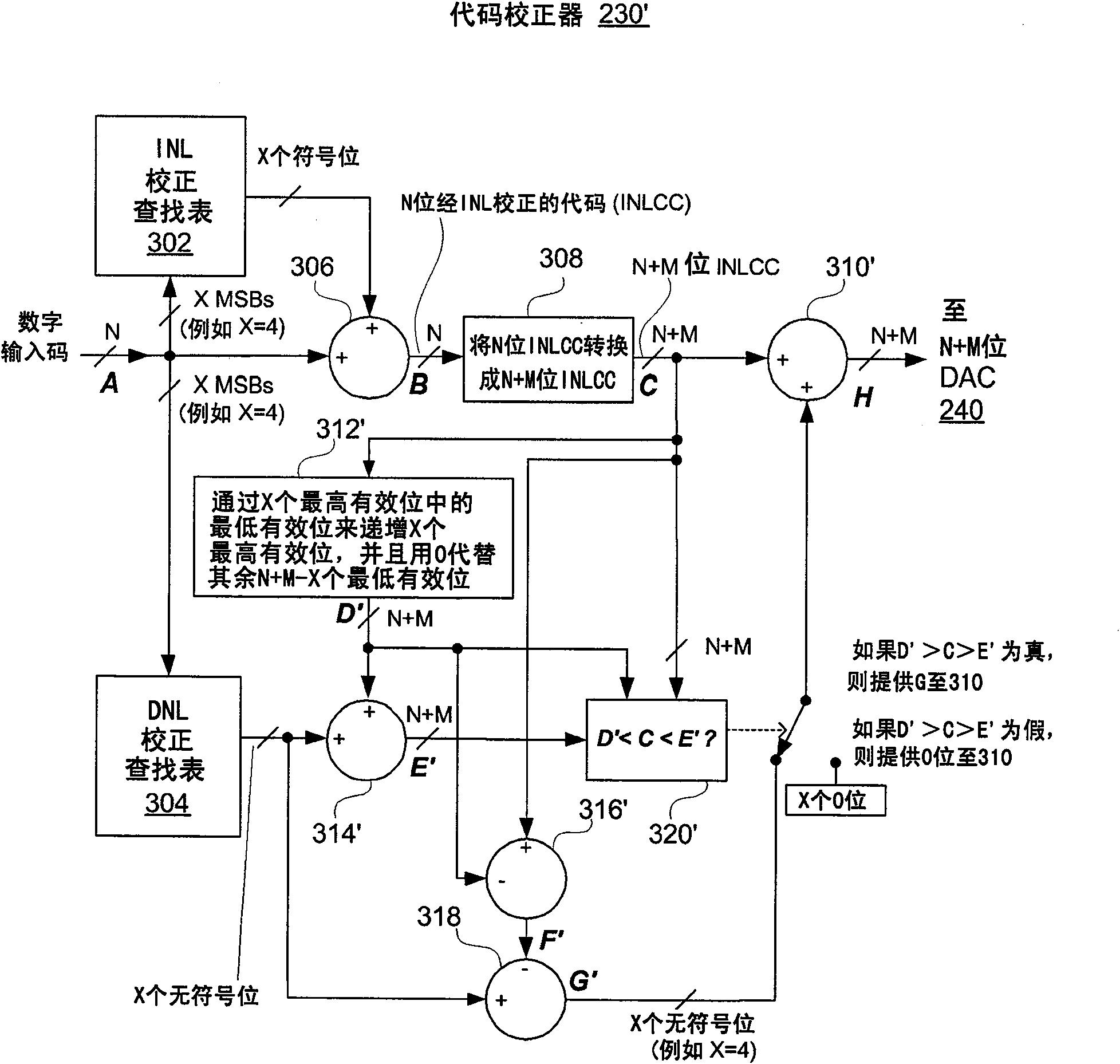

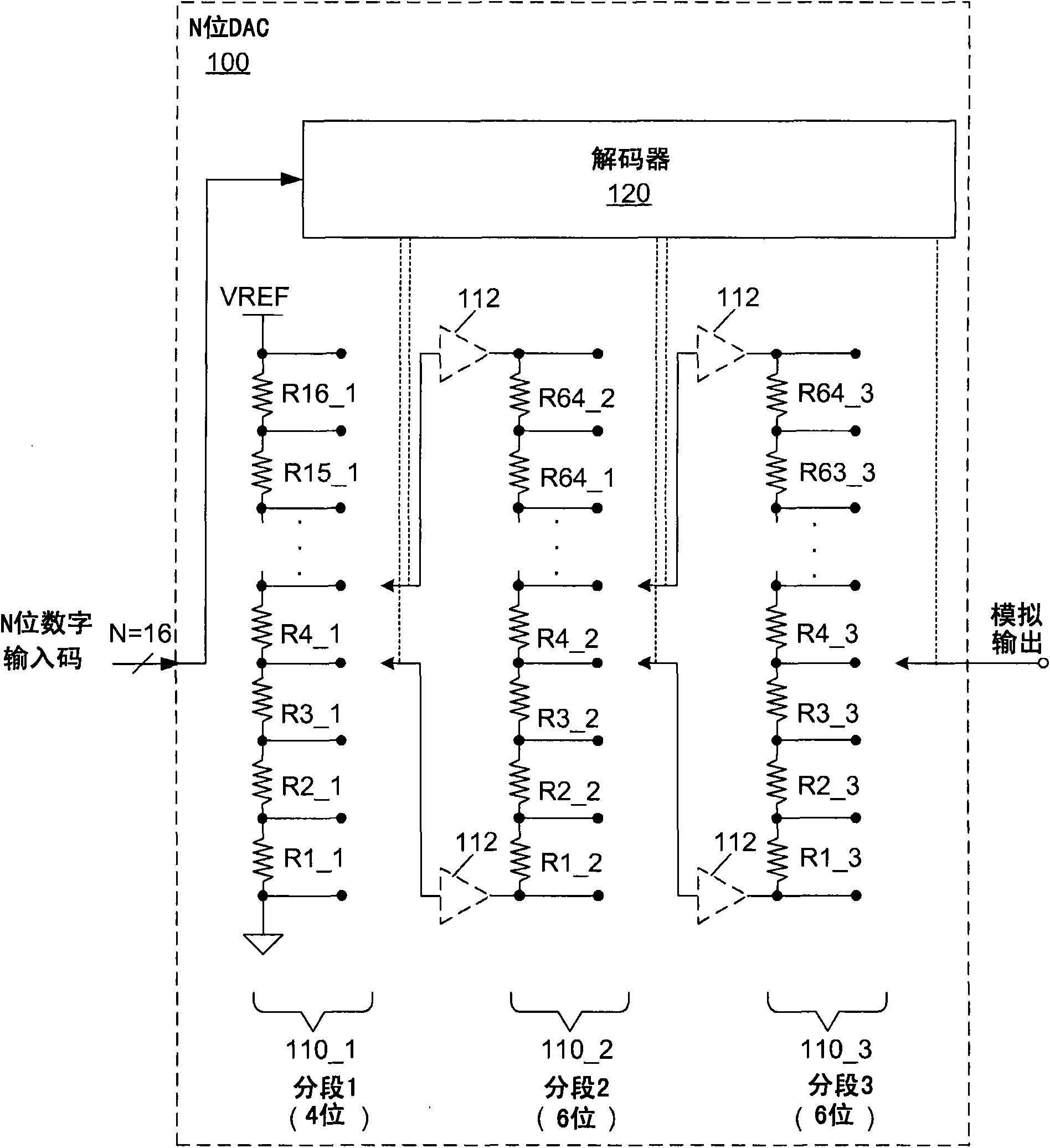

Integrated non-linearity (INL) and differential non-linearity (DNL) correction techniques for digital-to-analog converters (DACS)

ActiveCN103986471ADigital-analogue convertorsAnalogue/digital conversion calibration/testingDifferential nonlinearityImage resolution

INL values are determined for a plurality of sub-segments of a DAC that is adapted to accept N bit digital input codes, and a first set of correction codes that can be used to reduce to a range of INL values (to thereby improve linearity of the DAC) are determined and stored. Additionally, DNL values are determined for the plurality of sub-segments for which INL values were determined, and a second set of correction codes that can be used to ensure that all values of DNL >-1 (to thereby ensure that the DAC is monotonic) are determined and stored. This can include using one or more extra bits of resolution to remap at least some of the 2N possible digital input codes (that can be accepted by the DAC) to more than 2N possible digital output codes, to ensure that all values of DNL >-1. Such stored first and second sets are thereafter used when performing digital to analog conversions.

Owner:INTERSIL INC

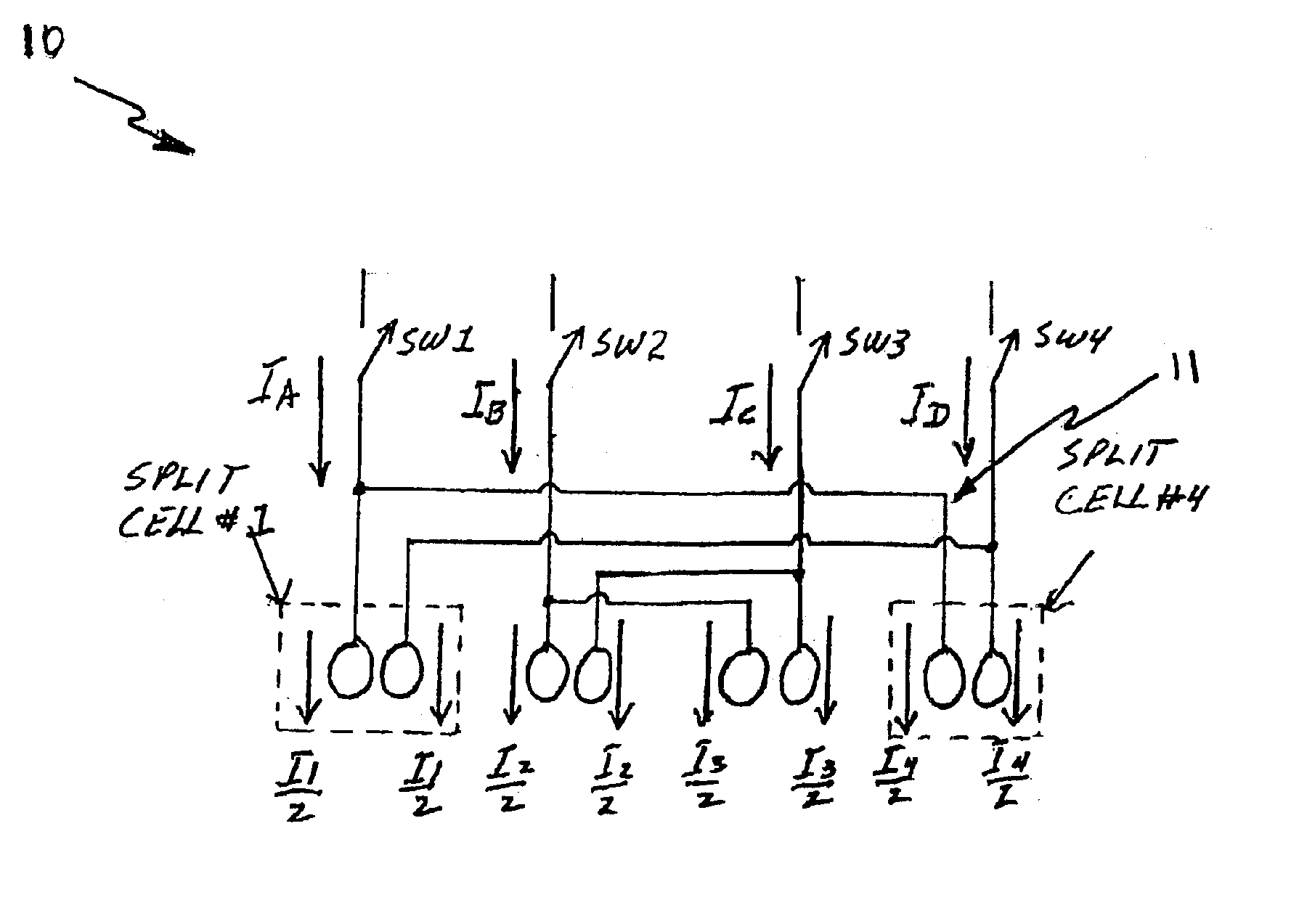

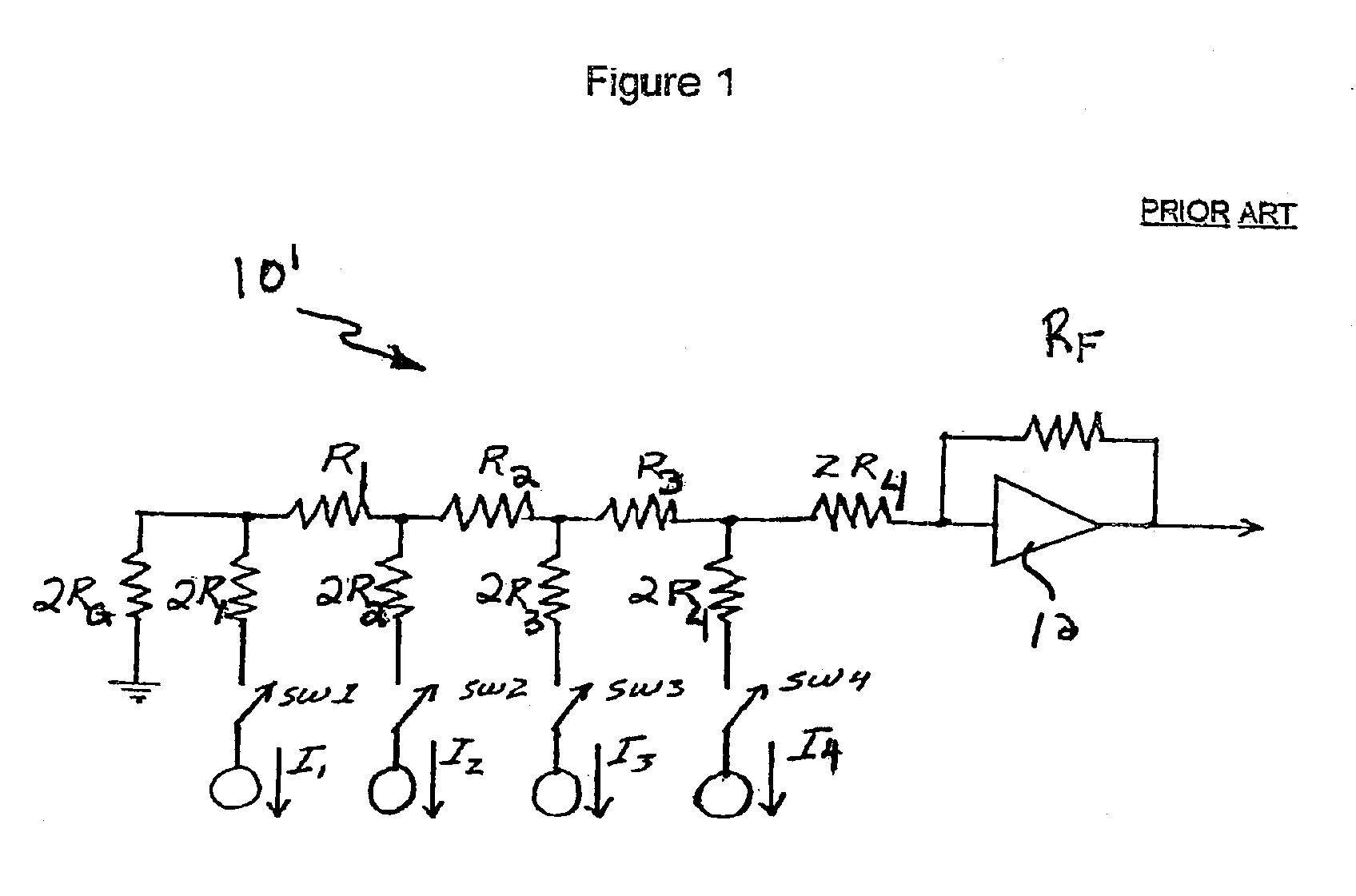

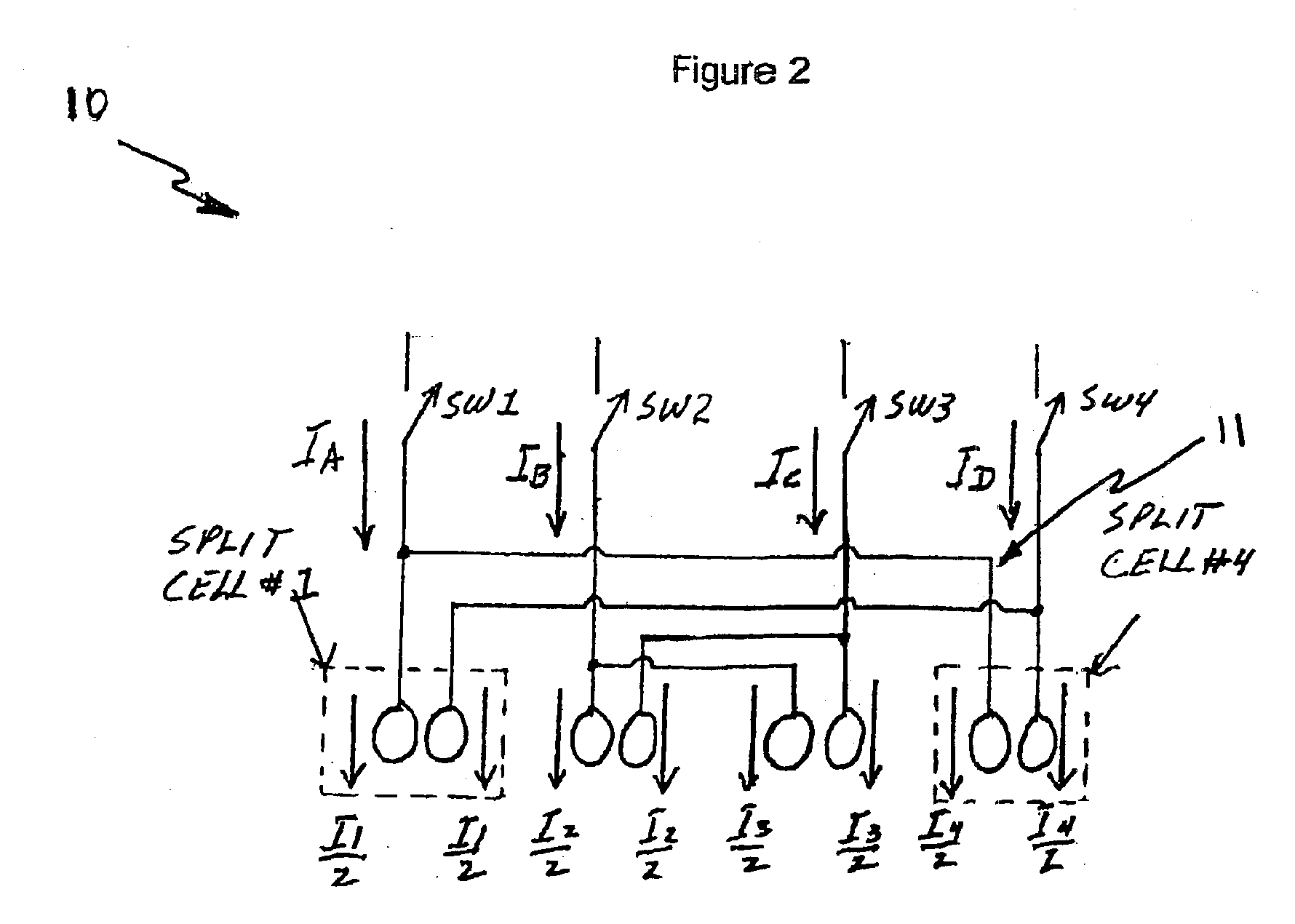

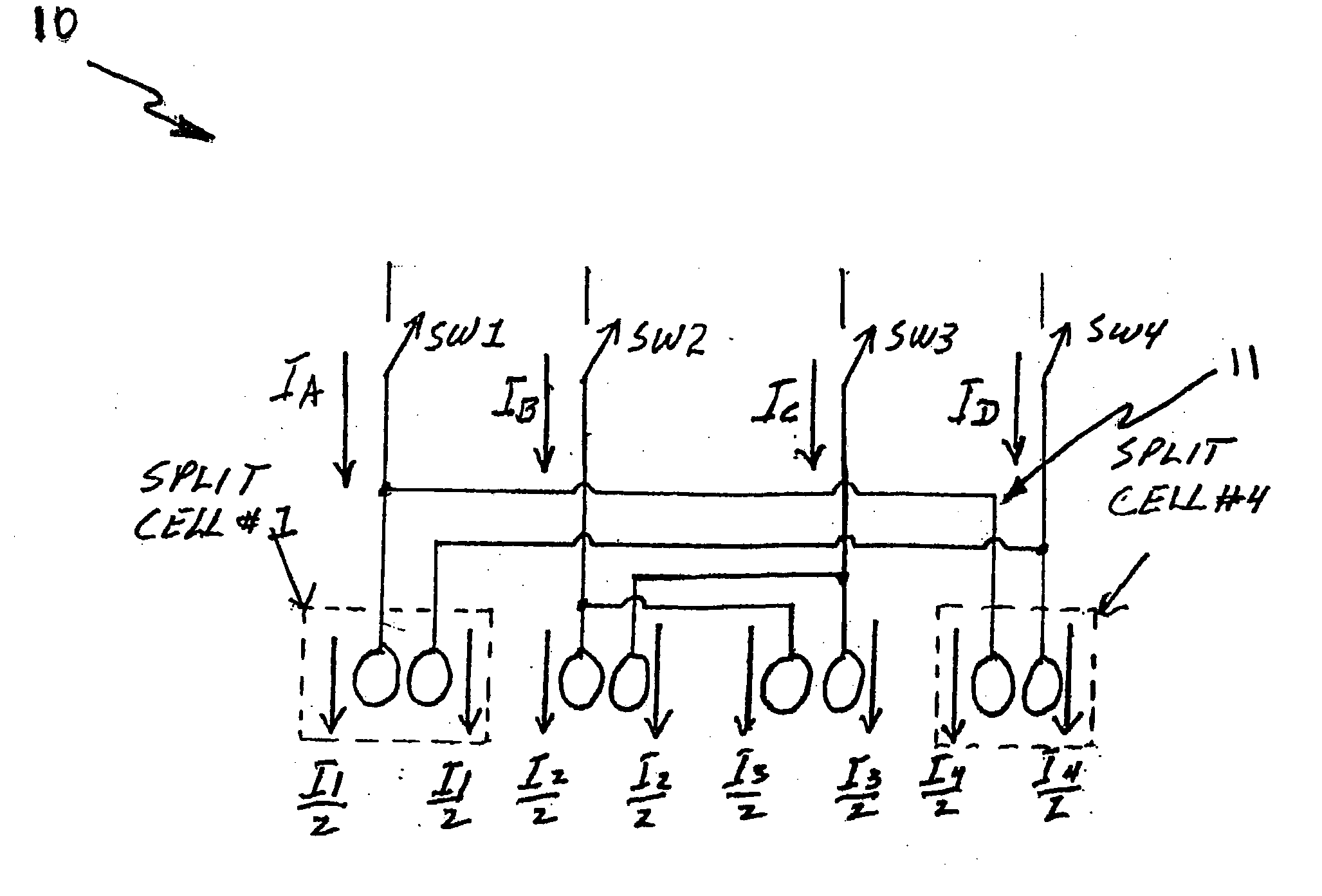

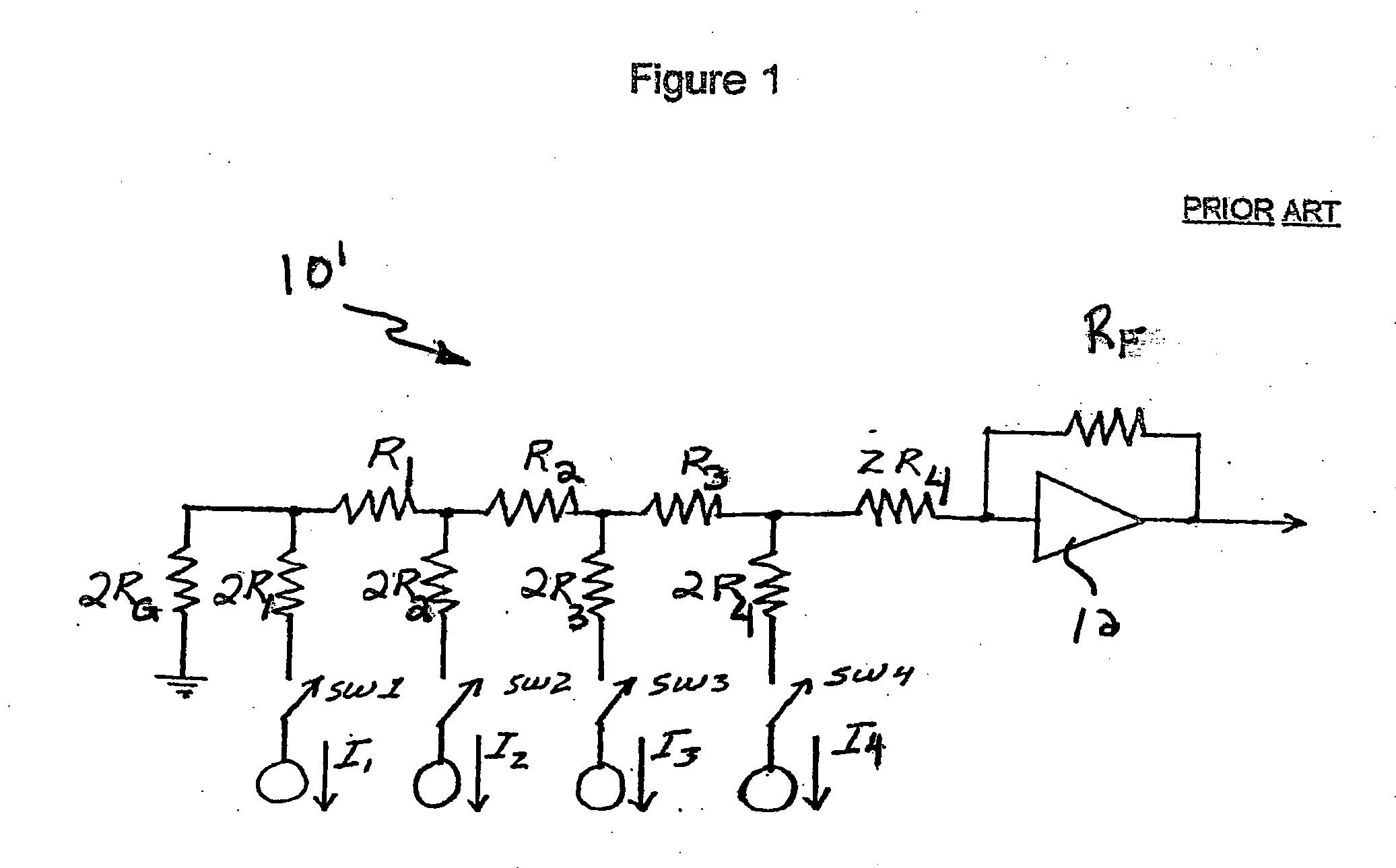

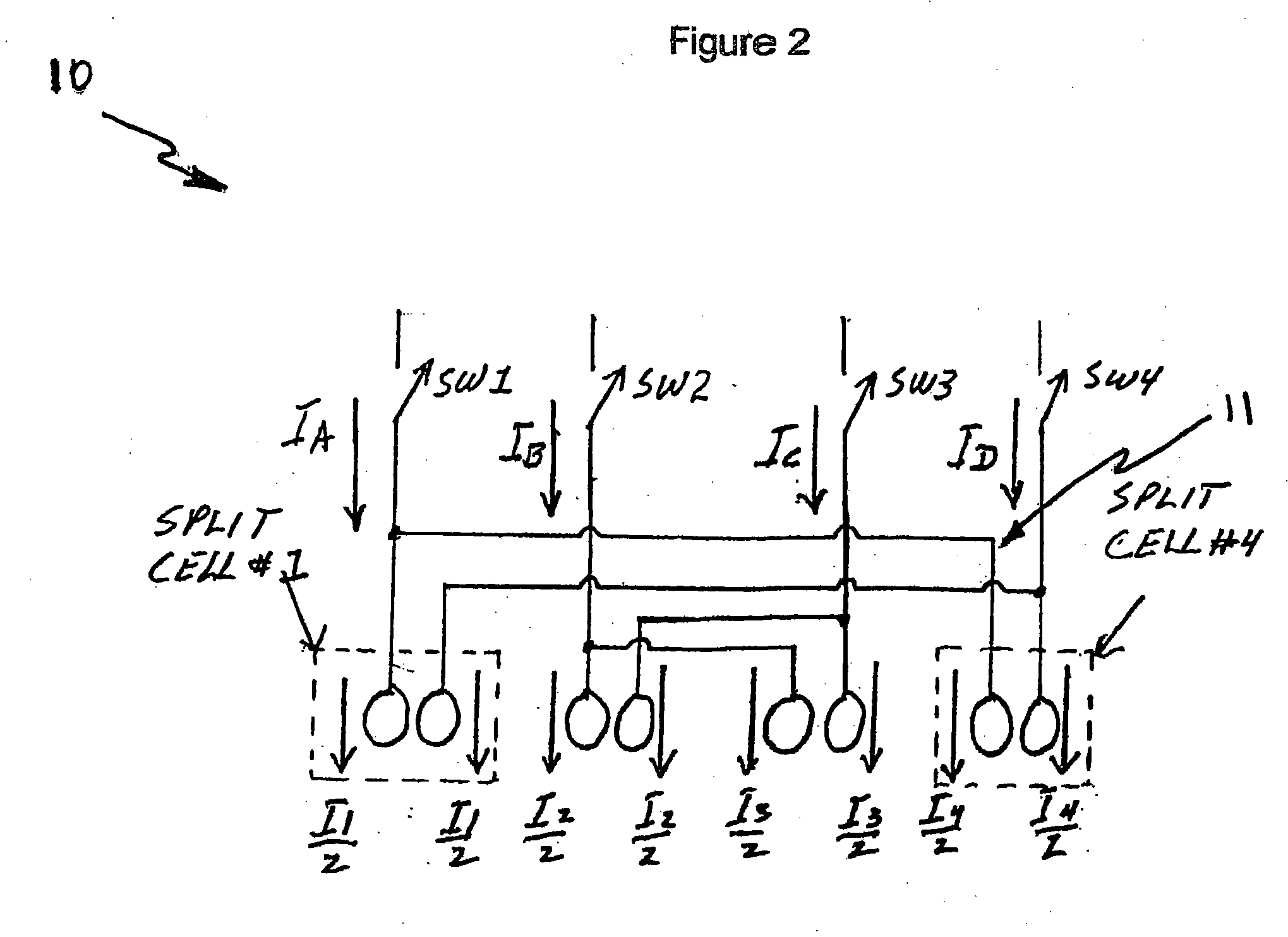

Split cell bowtie digital to analog converter and method

ActiveUS6879276B2Promote lowerElectric signal transmission systemsDigital-analogue convertorsAudio power amplifierDifferential nonlinearity

A DAC (10) including an operational amplifier (12) having an input terminal; a plurality of current paths coupled to the input terminal; a plurality of current sources (I1 / 2 -I4 / 2); and an arrangement (11) for switchably coupling current from at least two of the cells to a respective one of the paths in response to an input signal. In a specific embodiment, the inventive DAC (10) further includes a first resistive element (2R1-2R4) disposed in each of the current paths, a second resistive element (R1-R4) disposed between the current paths, and a feedback resistor (RF) disposed between an output terminal of the amplifier and the input terminal thereof. In the illustrative embodiment, the coupling arrangement includes a plurality of switches (SW1-SW4); each of the switches is adapted to switch half of the current from a first source and half of the current from a second source into a respective one of the paths. The invention is adapted to lower the distortion of digital to analog converters by improving differential nonlinearities and integral nonlinearities, caused primarily by current source gradient errors, without the need for trimming.

Owner:MICROELECTRONICS TECH INC

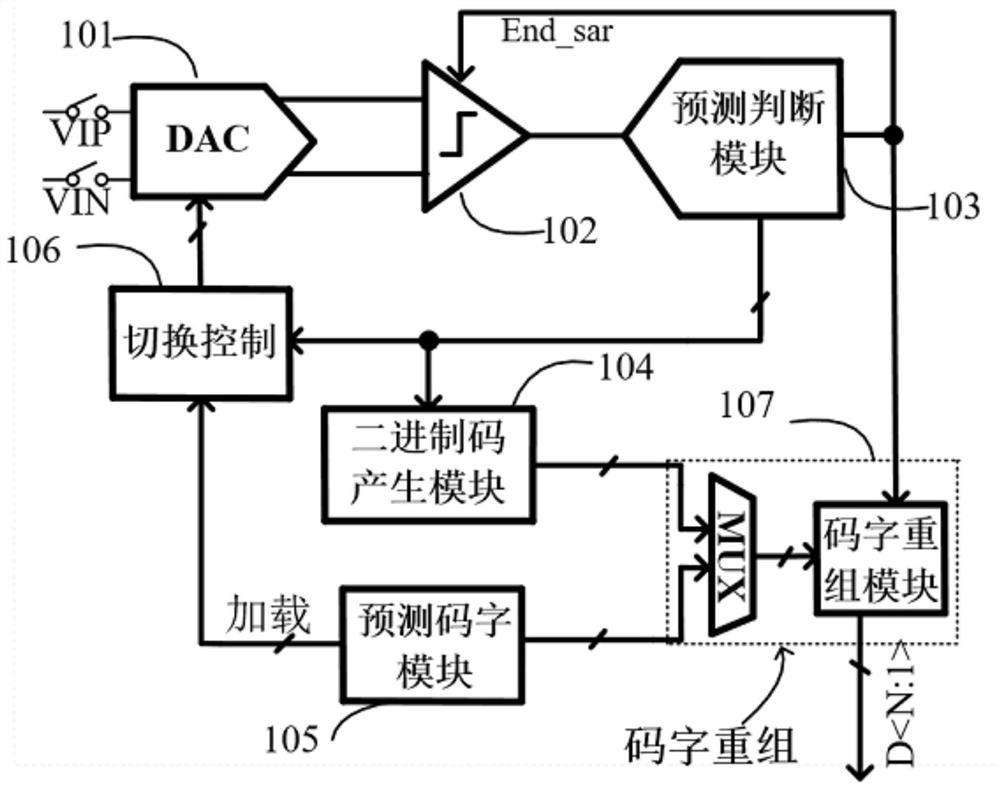

Charge sharing type analog-to-digital converter quantification method based on dynamic tracking

ActiveCN111786675AReduce the number of comparisonsReduce power consumptionElectric signal transmission systemsAnalogue-digital convertersCapacitanceDifferential nonlinearity

The invention discloses a charge sharing type analog-to-digital converter quantification method based on dynamic tracking. According to the method, the difference of code words between two sampling points is quantified, the capacitor switching direction is judged according to the comparison result of a comparator, the interval where the sampling points are located is searched in a binary increasing or decreasing mode until the comparison result is reversed, the interval where the sampling points are located is determined, and new prediction code words and final output code words are obtained;the DAC module adopts a charge sharing switching mode, only one group of capacitor array is needed, the capacitor array is simplified, and the power consumption is reduced; two groups of capacitor substitution arrays are introduced when prediction is inaccurate, and 1-2 capacitors are used for switching at most except the capacitor substitution arrays in the quantization process, so that differential nonlinear DNL can be improved, and the power consumption of the analog-to-digital converter is reduced on the whole. The method is particularly suitable for temperature sensor signals which are slow in sensor signal amplitude change and do not change suddenly, and the comparison frequency of the comparator and the capacitor array switching frequency of the DAC can be greatly reduced.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA +1

Self-calibrating digital-to-analog converter and method thereof

ActiveCN101388667ABest practiceAnalogue/digital conversion calibration/testingDifferential nonlinearityEngineering

A digital-to-analog converter improves differential non-linearity by performing a calibration of at least one weighted cell in response to a calibration command. The digital-to-analog converter includes a group of weighted cells, a tunable cell having a tunable weight controlled by a tuning word, and a calibration cell to generate a combined output signal in response to a digital input word, the calibration command, and a calibration sequence. The digital-to-analog converter also includes a calibration circuit configured to sample and subsequently process the combined output signal to establish the tuning word in accordance with the calibration command and the calibration sequence.

Owner:REALTEK SEMICON CORP

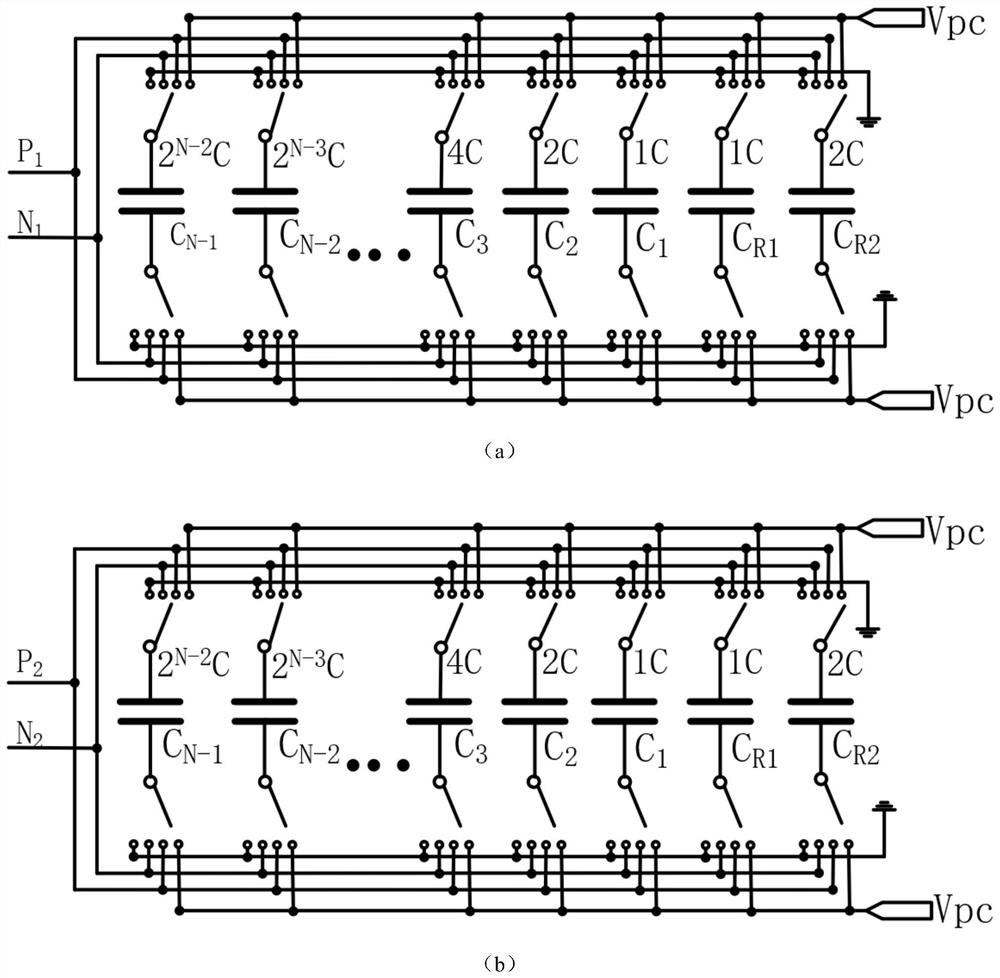

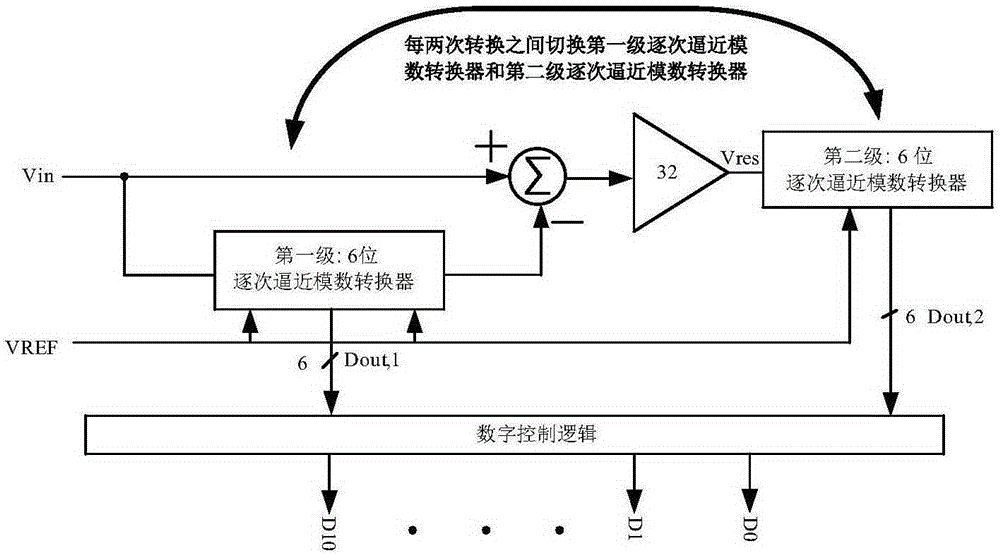

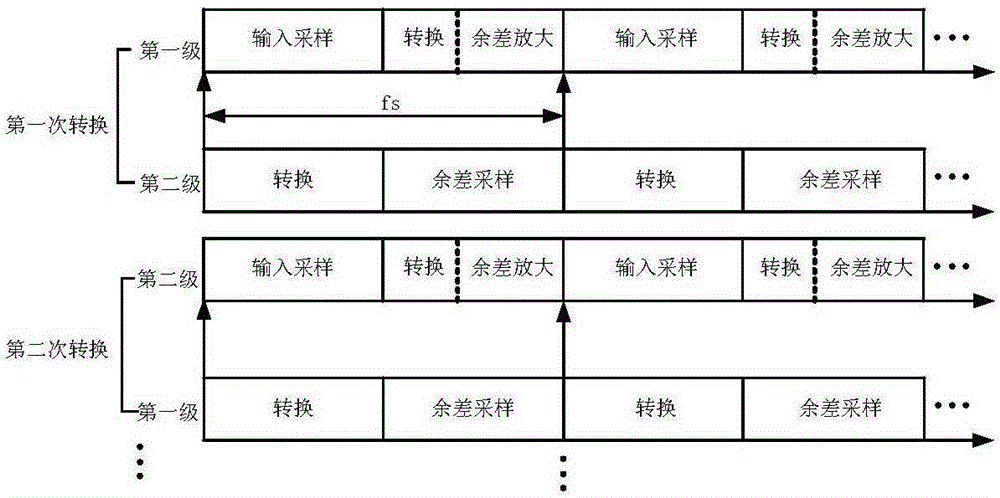

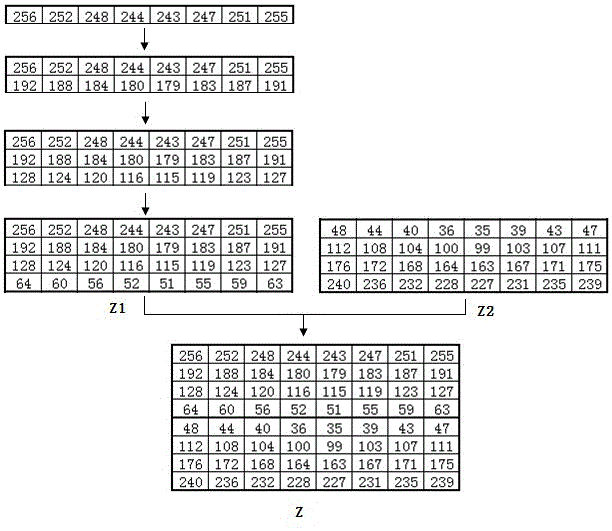

Forward stage and backward stage switching method for pipelined successive approximation analog-to-digital converter

ActiveCN105245231ASimple structureOccupies a small chip areaAnalogue/digital conversionElectric signal transmission systemsCapacitanceCorrection algorithm

The invention discloses a forward stage and backward stage switching method for a pipelined successive approximation analog-to-digital converter, and relates to the fields of microelectronics and solid-state electronics, in particular to the pipelined successive approximation analog-to-digital converter. An additional operational amplifier does not need to be introduced to perform noise shaping, any correction algorithm does not need to be introduced, and Dither does not need to be introduced. Accumulation of errors of capacitor mismatch on the same code word can be avoided only by exchange of a first successive approximation analog-to-digital converter and a second successive approximation analog-to-digital converter between two conversions. Compared with a conventional correction method for increasing DNL / INL (Differential Nonlinearity / Integral Nonlinearity) based on the noise shaping, the correction algorithm or the Dither, the forward stage and backward stage switching method has the effects of simpler structure, smaller chip occupation area and higher easiness in on-chip implementation.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA

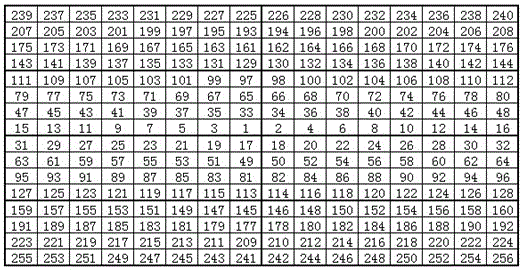

8-bit high-precision DAC current source array and layout method thereof

ActiveCN105897274AReduce dependencyReduce mismatchDigital-analogue convertorsSignal-to-noise ratio (imaging)Differential nonlinearity

The invention provides an 8-bit high-precision DAC current source array and a layout method thereof. Dependence between adjacent elements in a DAC current source array is reduced, and accumulation of second-order gradient errors is prevented; gradient errors are allocated to each element uniformly, and thus linearity of a circuit can be improved very well; and the co-gravity-center layout can offset influence of first-order gradient errors. High conversion accuracy and high speed are guaranteed, and meanwhile, mismatching of the current source array due to systematic errors and random errors can be reduced, so that the DAC circuit is allowed to have good monotonicity, offset error, differential nonlinearity error (DNL), integral nonlinearity error (INL), spurious-free dynamic range (SFDR) and signal-to-noise ratio (SNR).

Owner:南京德睿智芯电子科技有限公司

Split cell bowtie digital to analog converter and method

ActiveUS20050035892A1Promote lowerImprove errorElectric signal transmission systemsDigital-analogue convertorsDifferential nonlinearityEngineering

A DAC (10) including an operational amplifier (12) having an input terminal; a plurality of current paths coupled to the input terminal; a plurality of current sources (I1 / 2-I4 / 2); and an arrangement (11) for switchably coupling current from at least two of the cells to a respective one of the paths in response to an input signal. In a specific embodiment, the inventive DAC (10) further includes a first resistive element (2R1-2R4) disposed in each of the current paths, a second resistive element (R1-R4) disposed between the current paths, and a feedback resistor (RF) disposed between an output terminal of the amplifier and the input terminal thereof. In the illustrative embodiment, the coupling arrangement includes a plurality of switches (SW1-SW4); each of the switches is adapted to switch half of the current from a first source and half of the current from a second source into a respective one of the paths. The invention is adapted to lower the distortion of digital to analog converters by improving differential nonlinearities and integral nonlinearities, caused primarily by current source gradient errors, without the need for trimming.

Owner:MICROELECTRONICS TECH INC

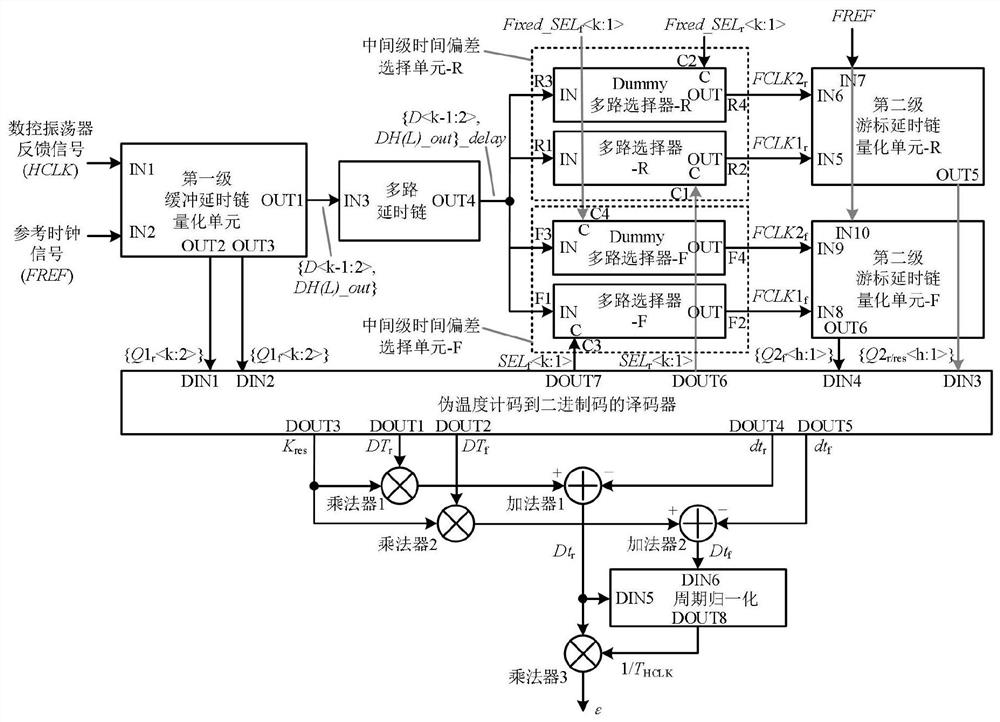

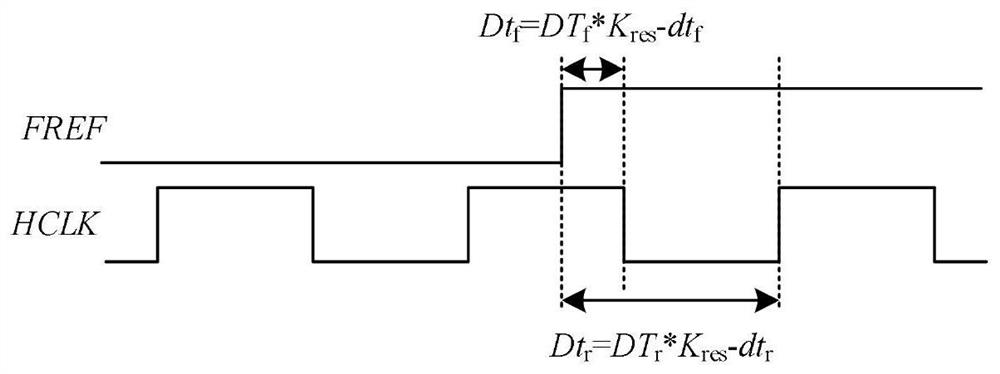

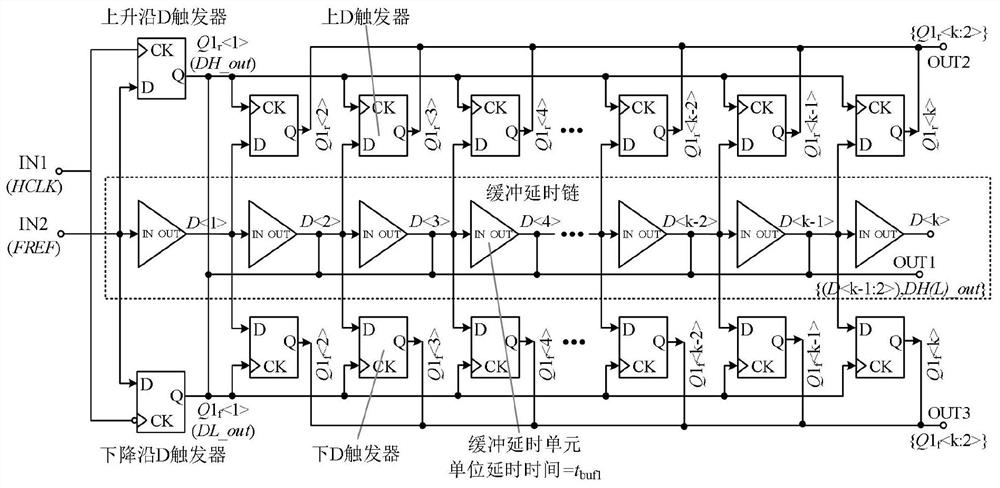

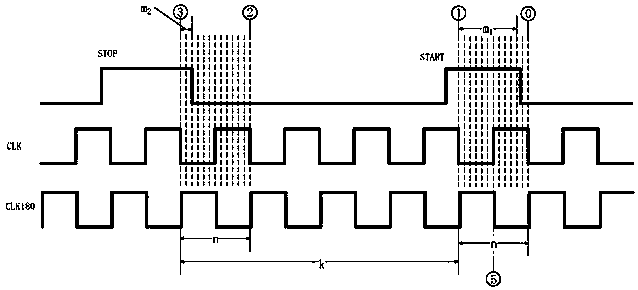

Time-to-digital converter for measuring decimal phase error of all-digital phase-locked loop

ActiveCN113179100AHigh precisionWide measurement rangePulse automatic controlDifferential nonlinearityNumerically controlled oscillator

The invention discloses a time-to-digital converter for measuring a decimal phase error of an all-digital phase-locked loop, which is based on a cascade structure of a buffer delay chain and a vernier delay chain, adopts a time window technology, delays a reference clock signal with lower frequency, and extracts a rising / falling edge of a single clock signal for signal detection; a circuit multiplexing technology is adopted, a rising / falling edge detection delay chain of the first-stage quantization unit is multiplexed, and meanwhile, a coarse quantization time error detection circuit and a two-stage resolution ratio scale factor detection circuit of the second-stage quantization unit are multiplexed; meanwhile, coarse quantization and fine quantization are carried out on the time deviation between the rising edge of the reference clock signal FREF and the nearest rising edge and falling edge of the feedback signal HCLK of the numerically controlled oscillator, so that a high-precision quantization result of the HCLK signal period is obtained. The measurement range is larger than 1.6 ns, the resolution ratio is higher than 2.8 ps, and the differential nonlinearity is smaller than 0.31 LSB.

Owner:SOUTHEAST UNIV

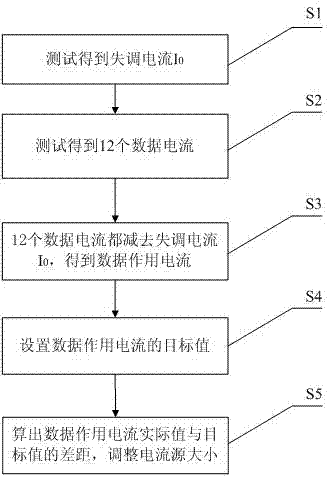

Current-steering DAC (digital-to-analog converter) calibration method

InactiveCN104333382AAnalogue/digital conversion calibration/testingDifferential nonlinearityStatic performance

The invention provides a current-steering DAC (digital-to-analog converter) calibration method, and belongs to the field of integrated circuits. A current-steering DAC is a 12-bit current-steering DAC and implemented in a binary coding mode. The current-steering DAC firstly acquires an offset current value I0 by testing, secondly acquires 12 data currents by testing, thirdly subtracts the offset current value I0 from the 12 data currents to obtain a data action current, fourthly sets a target value of the data action current and finally calculates the difference between an actual value and the target value of the data action current to respectively adjust current sources corresponding to data. The current-steering DAC calibration method effectively solves the problem of poor static performances such as DAC INL (integral non-linearity) and DNL (differential non-linearity) caused by process mismatch and the like, and the performance of the DAC is greatly improved. Moreover, the calibration method is simple to operate and low in implementation cost and can be effectively applied to calibrating the current-steering DAC.

Owner:长沙瑞达星微电子有限公司

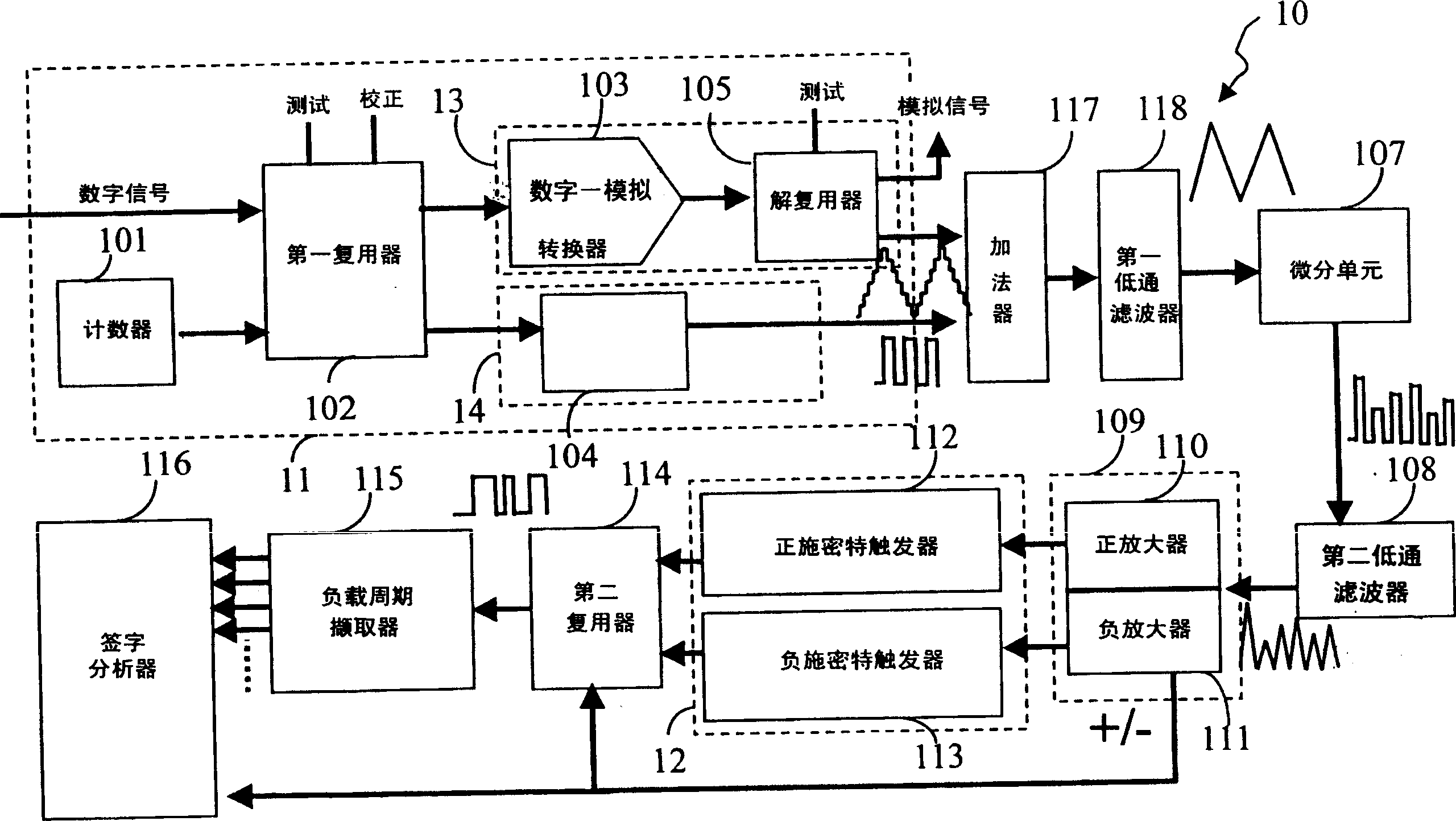

Built-in self testing device and method of digital analog converter

InactiveCN1599256AReduce complexityReduce difficultyDigital-analogue convertorsDifferential coefficientDigital down converter

The invention discloses built-in self-detecting device of the digital / analog convertor and the manufacturing method. It mainly differentiates the digital / analog signal with a differential coefficient unit to get the difference between the pulses of analog signal and transforms the analog signal into the digital signal with a Schmidt burst unit according to a critical voltage. Then, it calculates the loading cycle of the digital signal with a load cycle collector and sends it in signature analyzer to calculate the differential coefficient nonlinearity in order to analysis the error.

Owner:NASOFORM INC

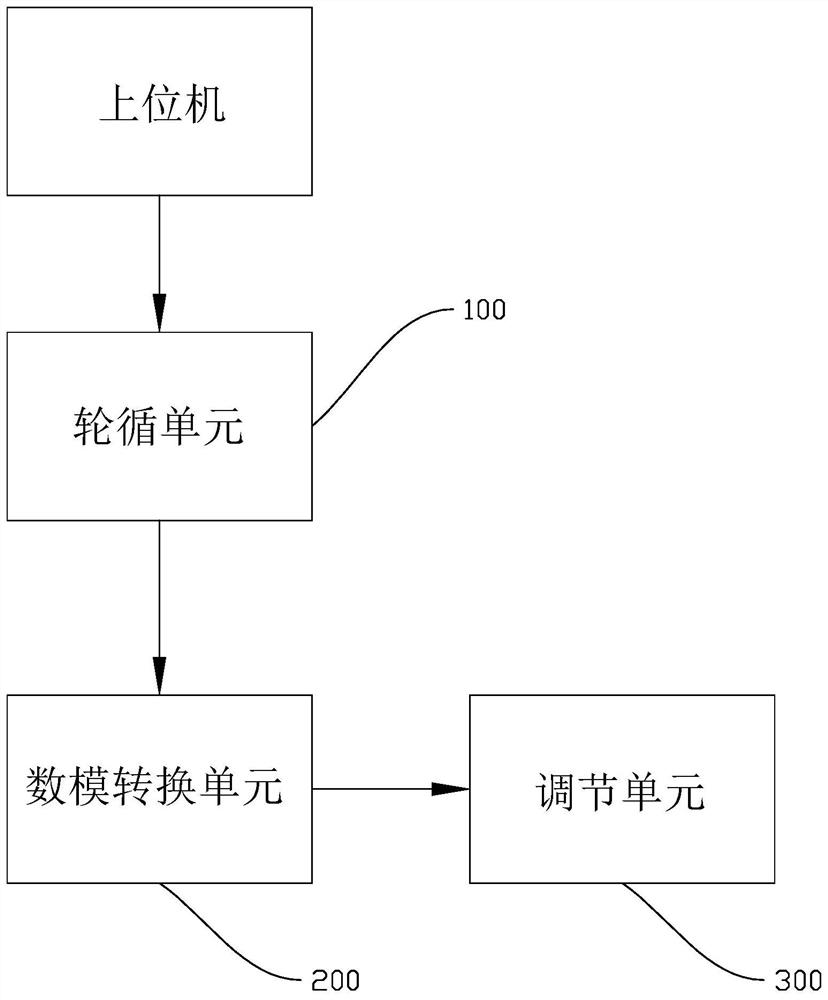

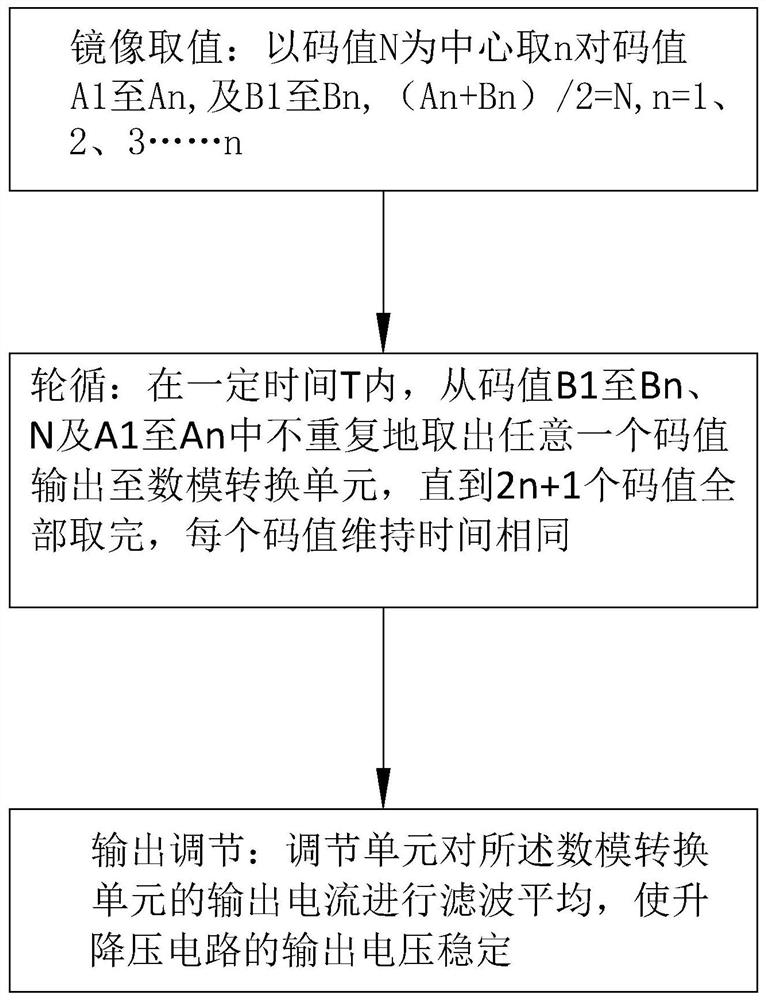

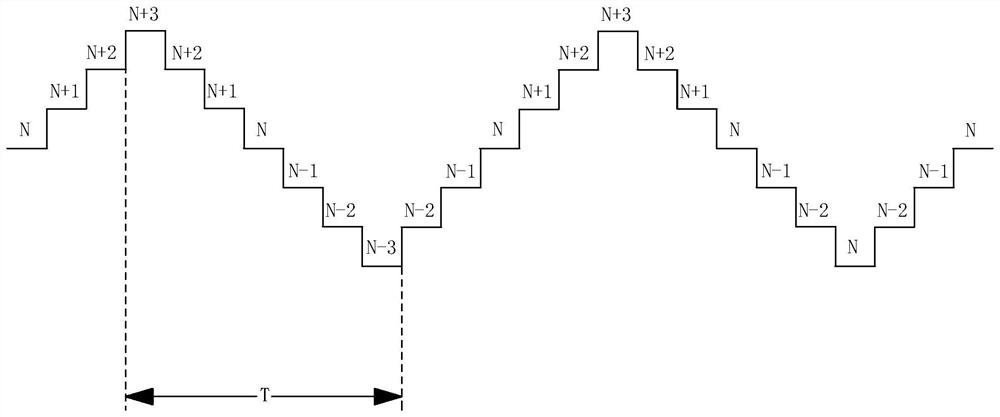

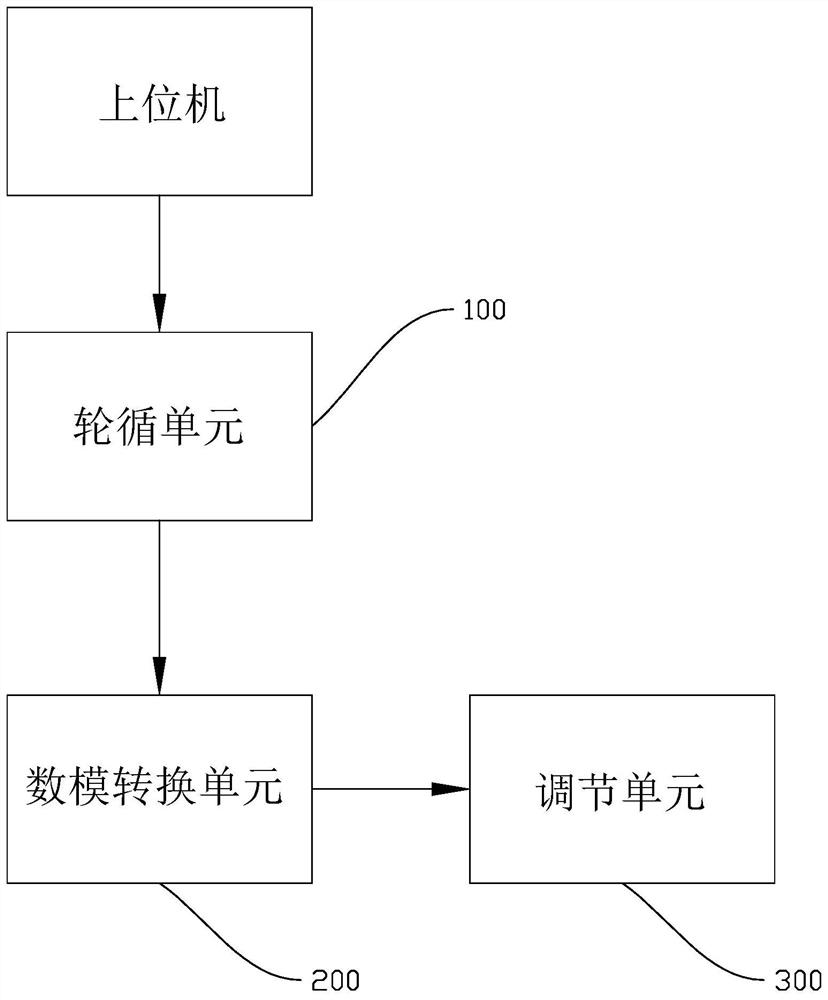

Current steering DAC buck-boost correction method and circuit

ActiveCN111835350ALow Differential NonlinearityGood pressure regulation monotonicityPhysical parameters compensation/preventionAlgorithmDifferential nonlinearity

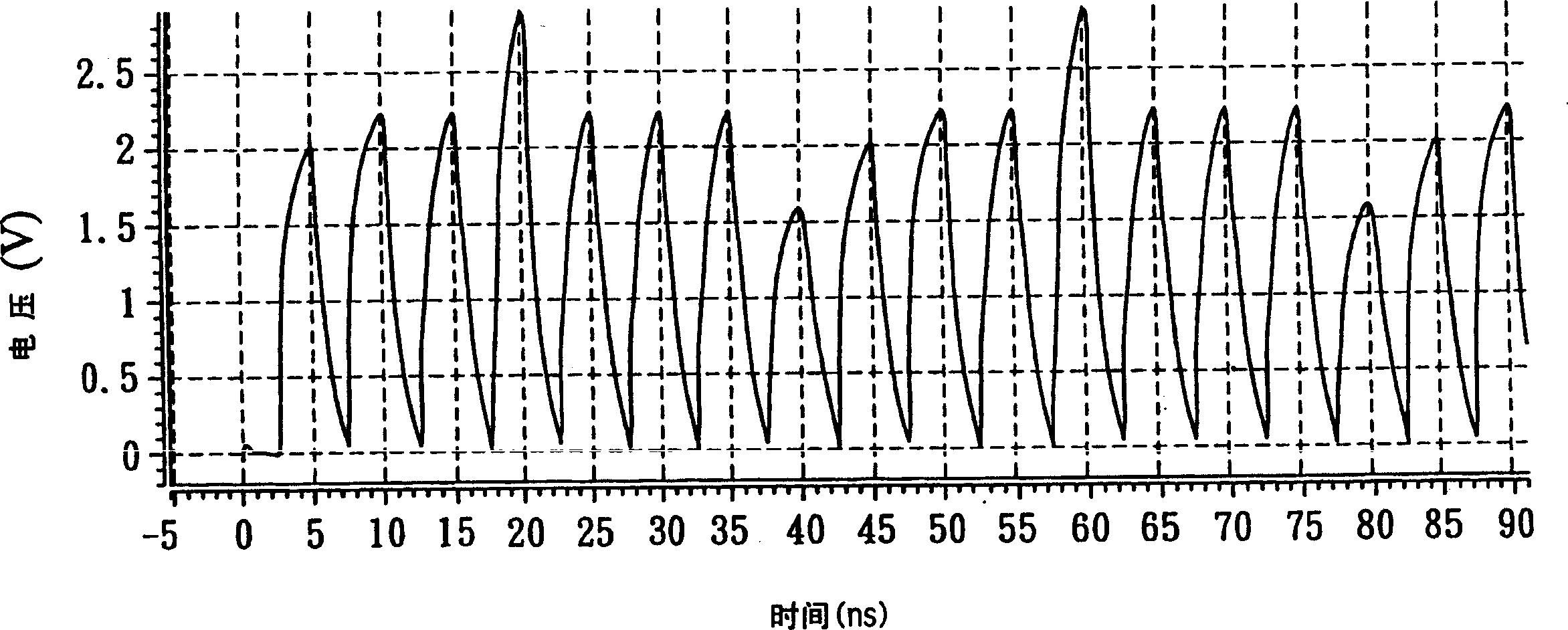

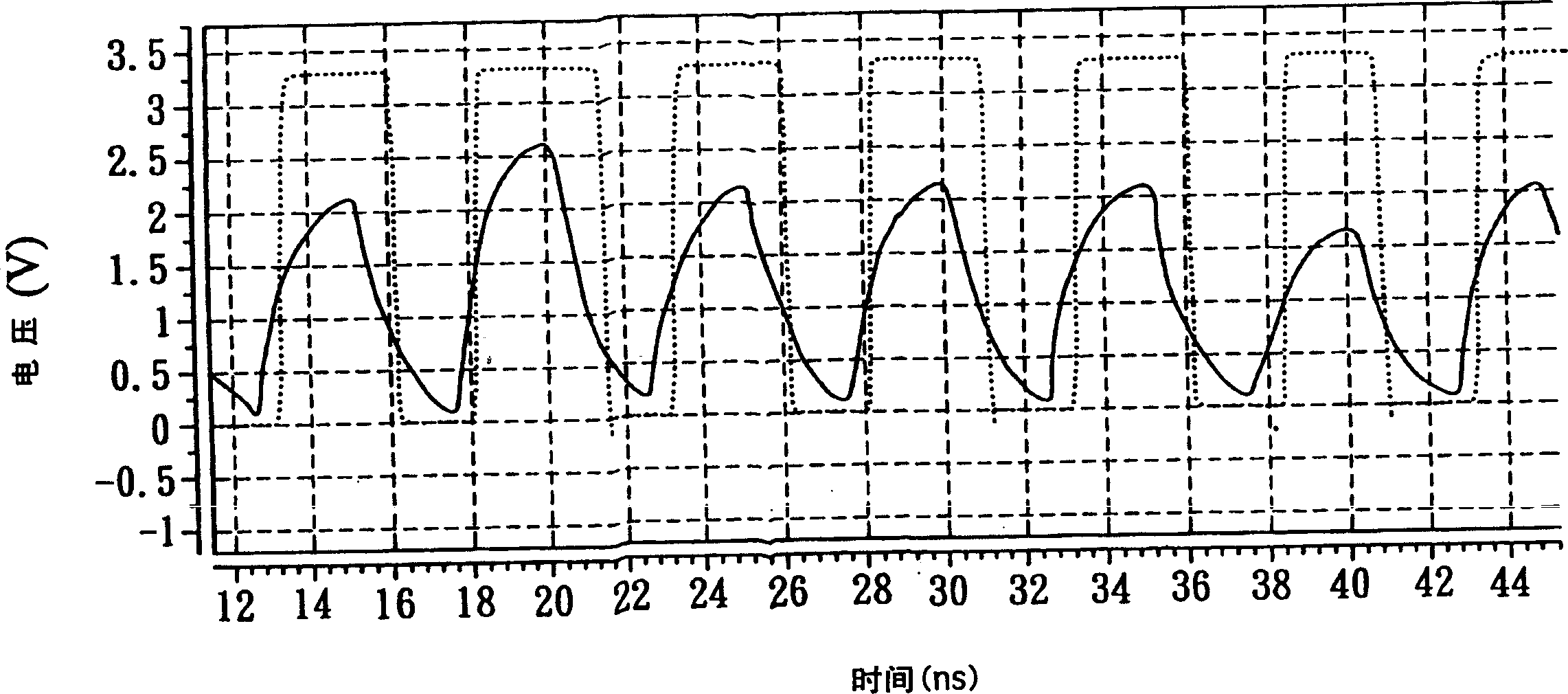

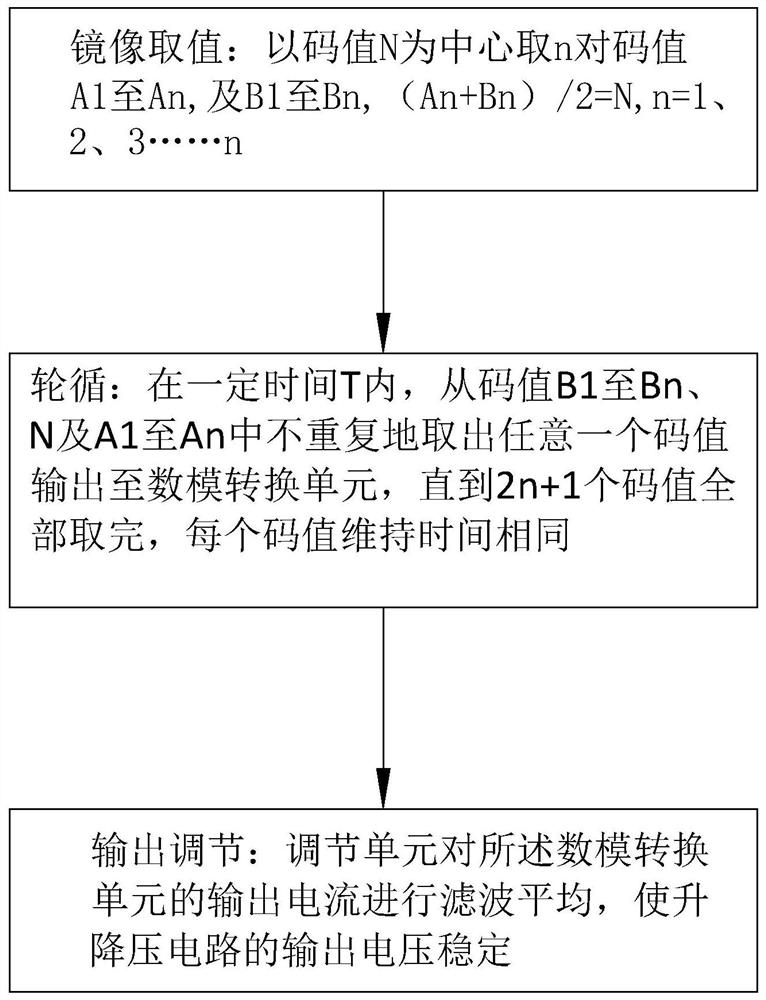

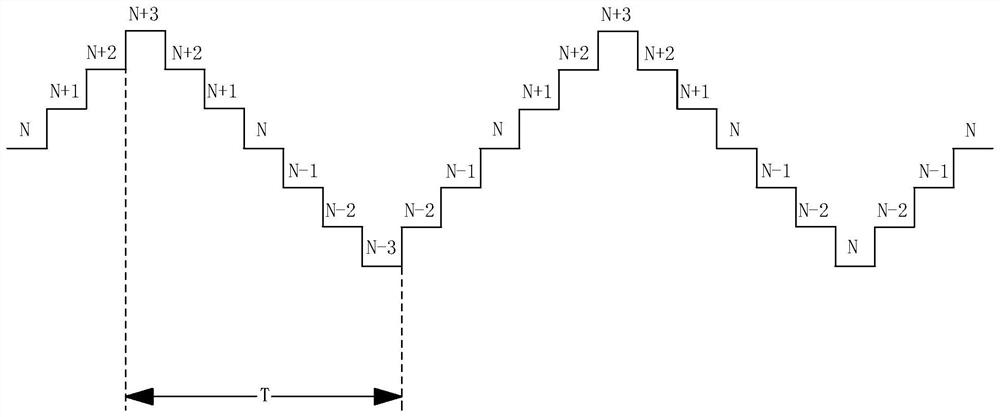

The invention discloses a current steering DAC buck-boost correction method and circuit. The method comprises the steps that: mirror image value: n pairs of code values are taken with a code value N to be converted as a center value, the n pairs of code values are A1 to An and B1 to Bn, the code values A1 to An are larger than the code value N, the code values B1 to Bn are smaller than the code value N, n is a positive integer, and the mean value of each pair of code values is N; within a certain time T, any code value is extracted from the code values B1 to Bn, N and A1 to An in a non-repeated mode and output to a digital-to-analog conversion unit until all (2n+1) code values are extracted, and the maintaining time of each code value is the same; and output adjustment: the adjusting unitadjusts the output of the digital-to-analog conversion unit, so that the output voltage of the buck-boost circuit is stable. According to the current steering DAC buck-boost correction method in the technical scheme, the influence caused by mismatch of a single code value is reduced through round robin of the mirror image code value, the differential nonlinearity of digital-to-analog conversion isreduced, and the monotonicity of buck-boost voltage regulation output is improved.

Owner:ZHUHAI ISMARTWARE TECH CO LTD

FPGA-based TDC realization method

InactiveCN108389225ASolving Differential Nonlinear ProblemsLow costProgramme controlMultiple input and output pulse circuitsPhase shiftedDifferential nonlinearity

Owner:BEIJING INSTITUTE OF TECHNOLOGYGY

Integrated non-linearity (INL) and differential non-linearity (DNL) correction techniques for digital-to-analog converters (DACs)

ActiveCN102064829ADigital-analogue convertorsAnalogue/digital conversion calibration/testingDigital analog converterDifferential nonlinearity

INL values are determined for a plurality of sub-segments of a DAC that is adapted to accept N bit digital input codes, and a first set of correction codes that can be used to reduce to a range of INL values (to thereby improve linearity of the DAC) are determined and stored. Additionally, DNL values are determined for the plurality of sub-segments for which INL values were determined, and a second set of correction codes that can be used to ensure that all values of DNL >-1 (to thereby ensure that the DAC is monotonic) are determined and stored. This can include using one or more extra bits of resolution to remap at least some of the 2 possible digital input codes (that can be accepted by the DAC) to more than 2 possible digital output codes, to ensure that all values of DNL >-1. Such stored first and second sets are thereafter used when performing digital to analog conversions.

Owner:INTERSIL INC

Semiconductor device including A/D converter

InactiveUS7479908B2Increased cost of testingLower the volumeElectric signal transmission systemsAnalogue/digital conversion calibration/testingDifferential nonlinearityBuck converter

A semiconductor device includes: an A / D converter; a digital processing circuit for performing processing based on conversion results from the A / D converter; a first test circuit for performing operation processing for checking a nonlinearity error (INLE) of the conversion results from the A / D converter; and a second test circuit for performing operation processing for checking a differential nonlinearity error (DNLE) of the conversion results from the A / D converter. The first test circuit performs only part of the operation processing for checking the nonlinearity error (INLE) of the conversion results from the A / D converter. The second test circuit performs only part of the operation processing for checking the differential nonlinearity error (DNLE) of the conversion results from the A / D converter. An operation processing section for performing the rest of the operation processing for checking the nonlinearity error (INLE) and the rest of the operation processing for checking the differential nonlinearity error (DNLE) is in a semiconductor test device.

Owner:SOCIONEXT INC

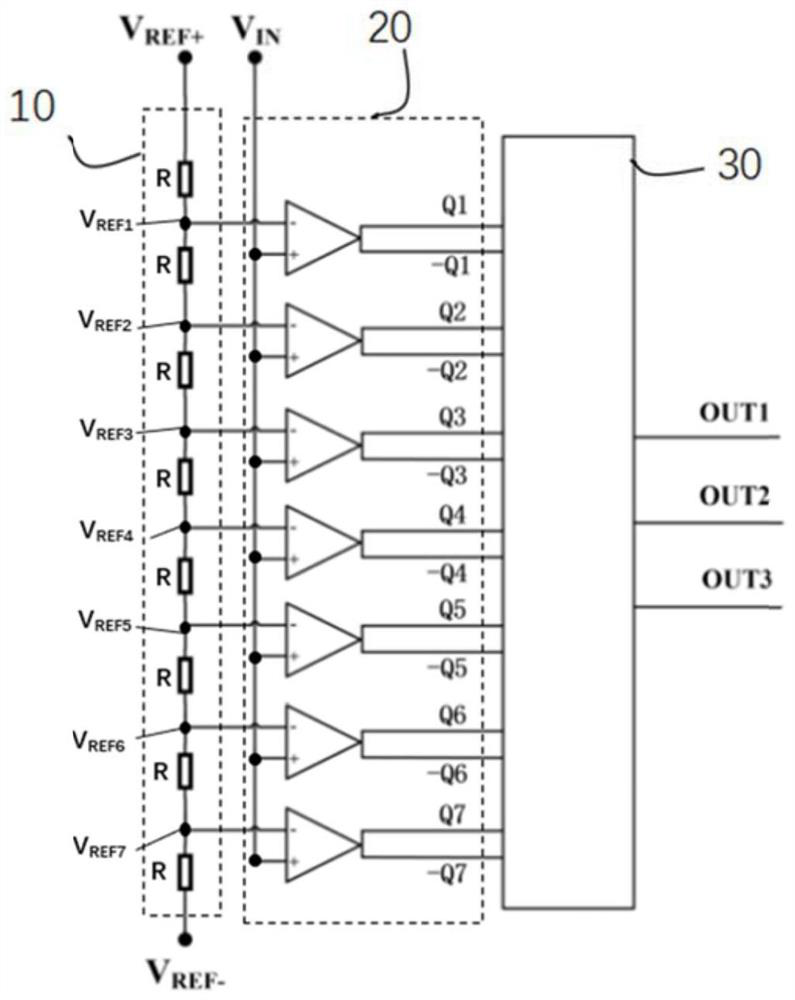

Analog-to-digital converter based on thin film transistor, chip and control method

ActiveCN111786678AHigh-resolutionImprove output swingElectric signal transmission systemsAnalogue-digital convertersDifferential nonlinearityHemt circuits

The invention discloses an analog-to-digital converter based on a thin film transistor, a chip and a control method. A reference voltage is provided for a comparator module through a reference level module, a comparison unit compares the reference voltage with an analog signal input quantity to output a first comparison quantity, then a pseudo CMOS inverter unit processes the first comparison quantity to obtain a second comparison quantity, and a decoder module decodes the second comparison quantity to obtain an output digital quantity; the pseudo CMOS inverter unit is arranged to process thefirst comparison quantity; the output swing and the direct current gain of the circuit are increased by utilizing the characteristic that the pseudo CMOS inverter unit has a shaping effect on the waveform; and due to the improvement of the direct current gain, the obtained second comparison quantity is a value obtained by further amplifying the first comparison quantity, so that the overall resolution of the comparator module can be improved, and the differential nonlinear error and the integral nonlinear error of the analog-to-digital converter are reduced. The analog-to-digital converter canbe widely applied to the technical field of integrated circuits.

Owner:SOUTH CHINA UNIV OF TECH

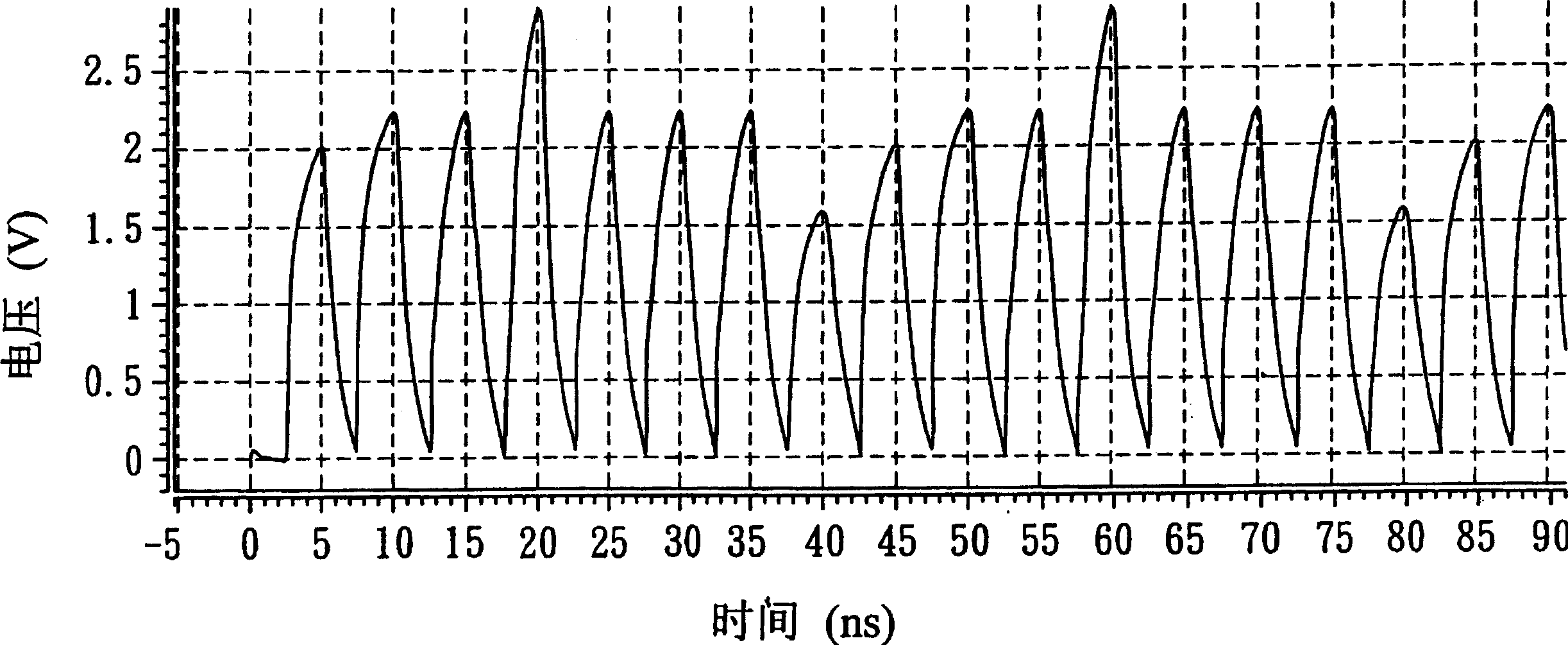

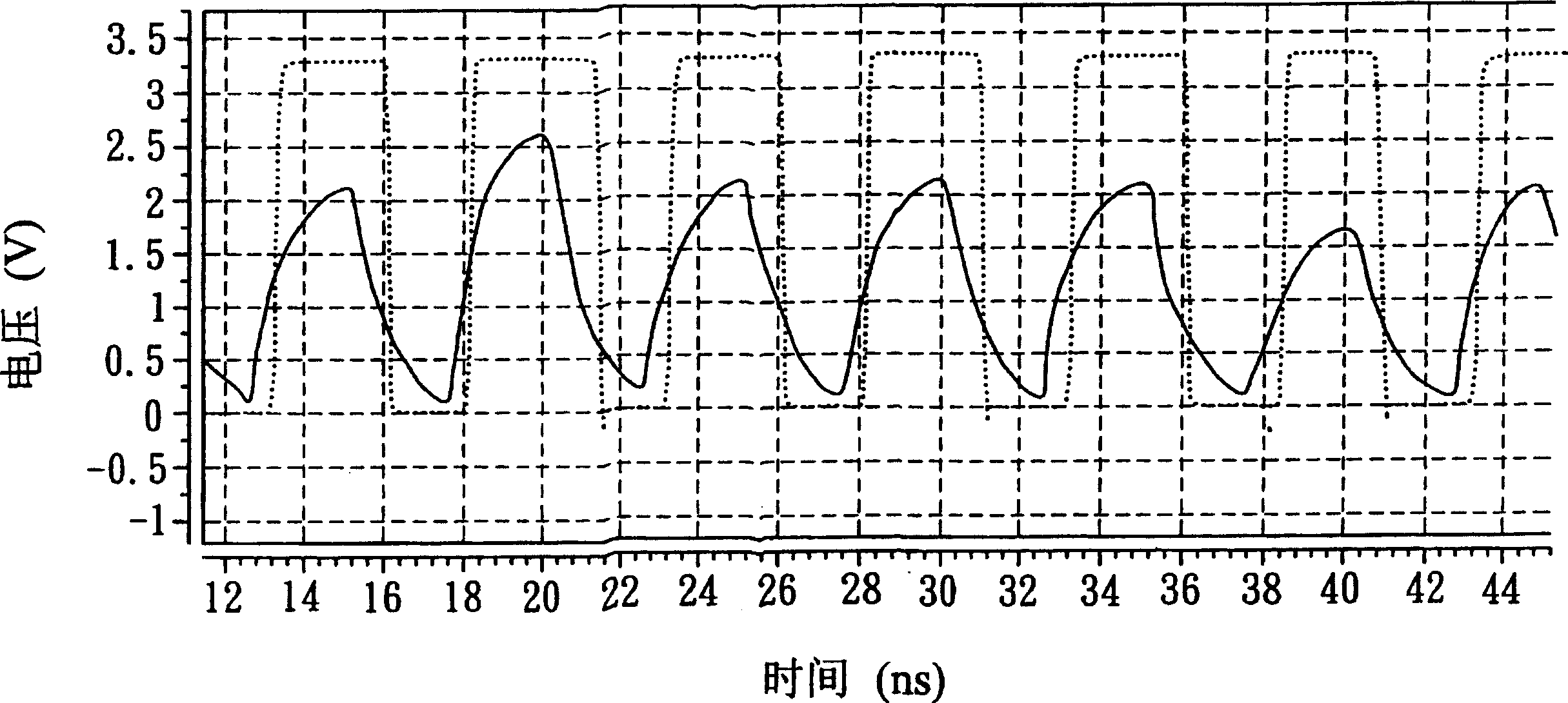

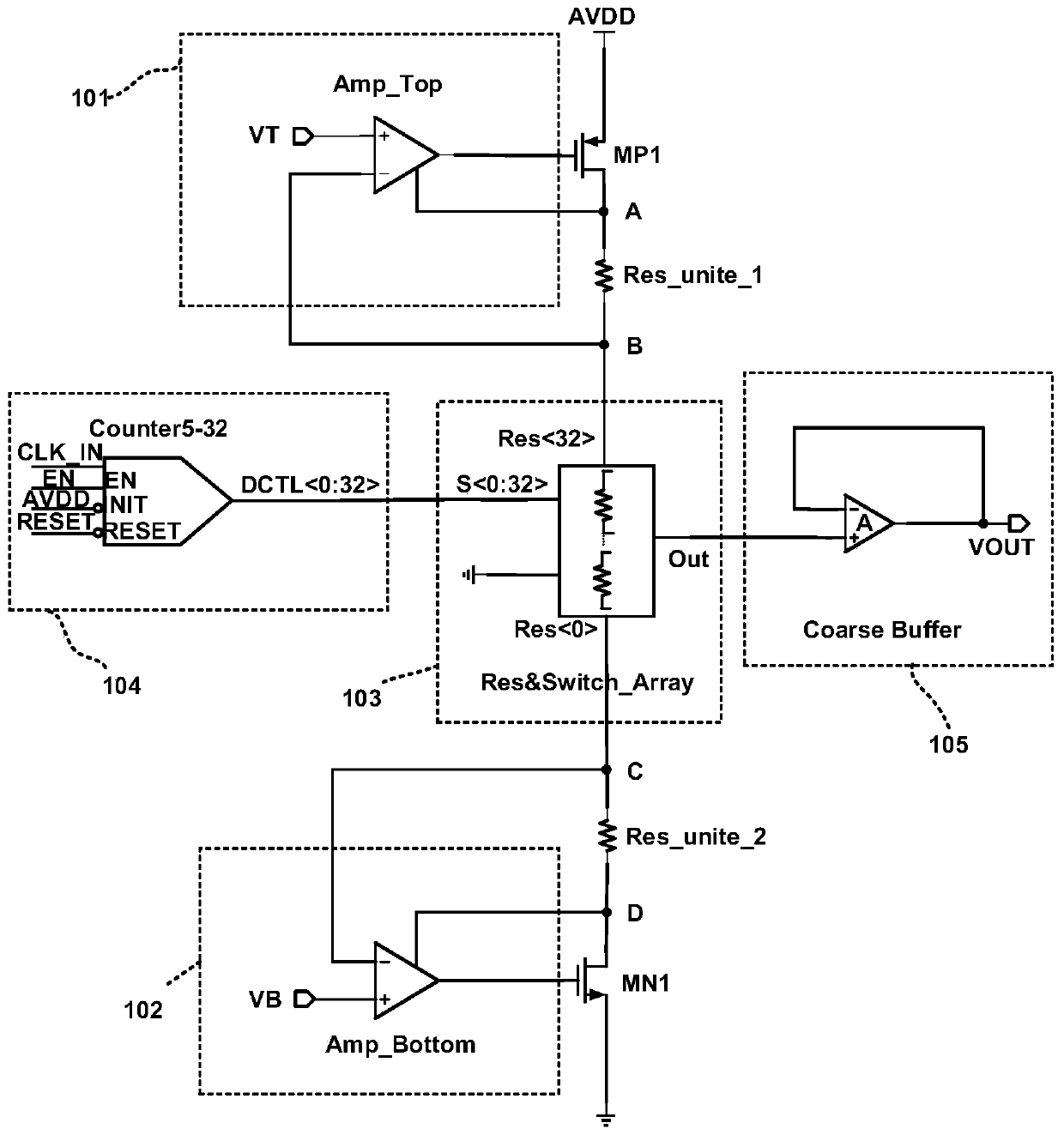

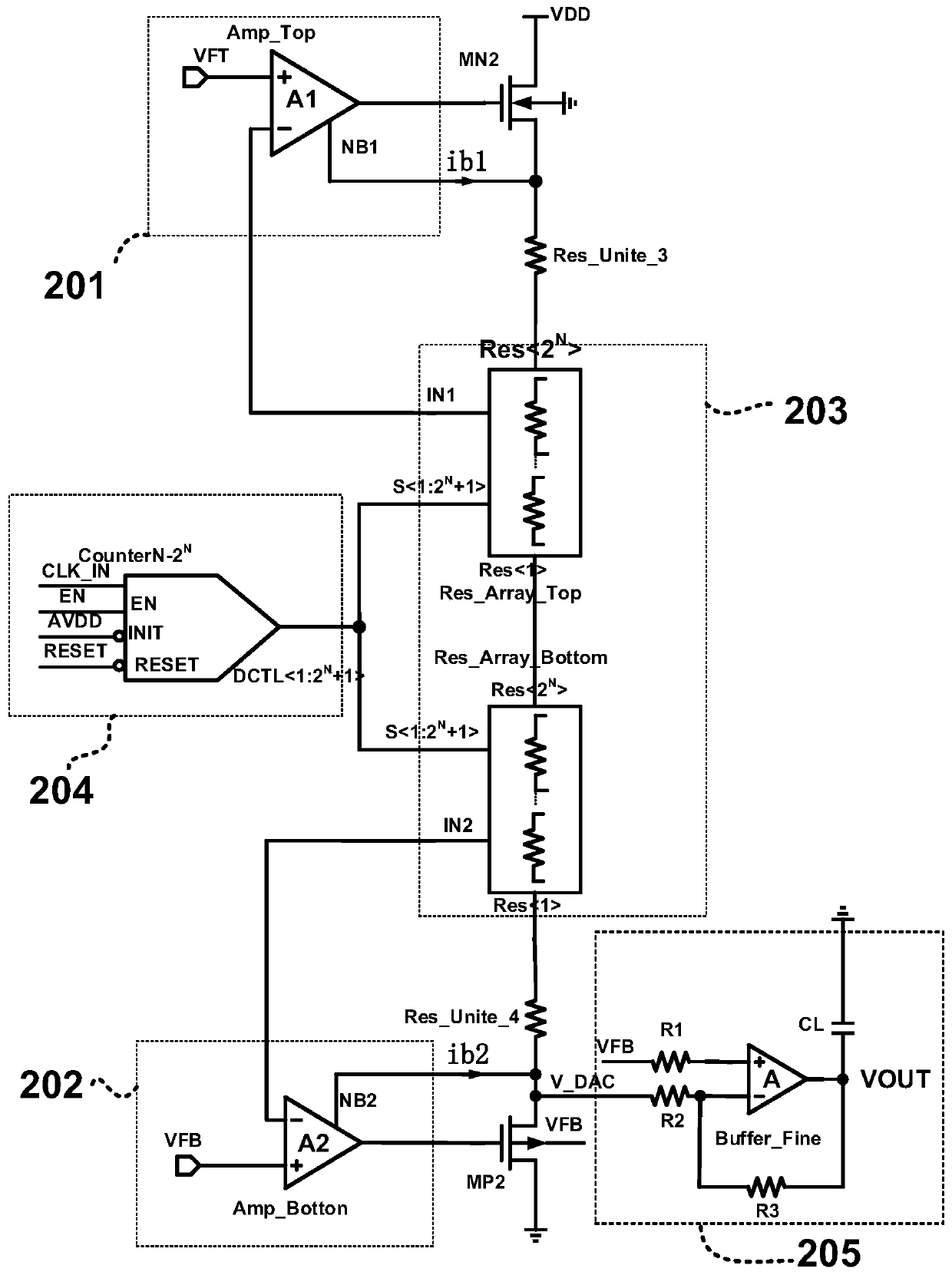

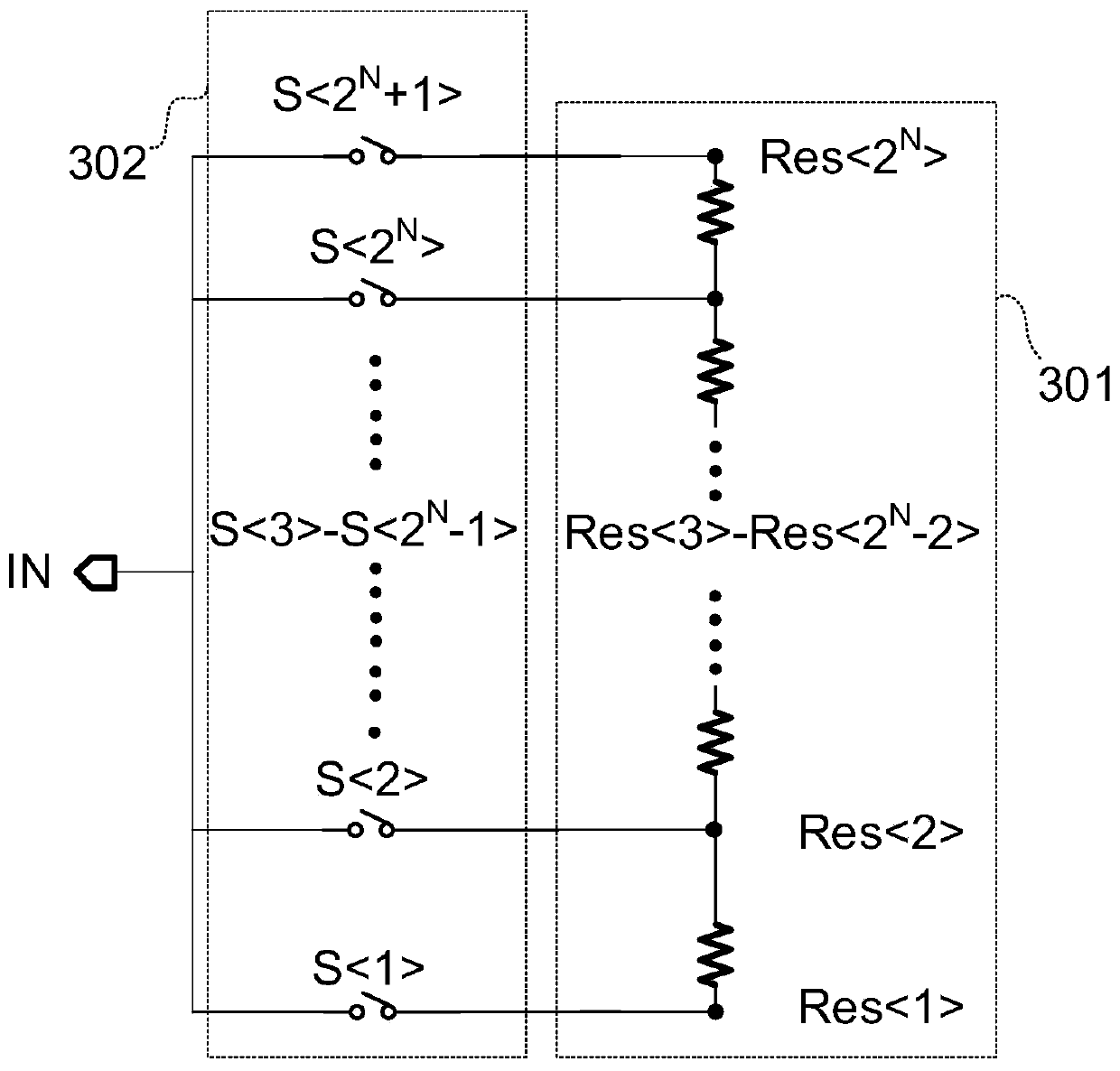

Fine quantization ramp generator for two-step monoclinic analog-to-digital converter

ActiveCN111224667ASolve Integral Nonlinearity (INL)Solving Differential Nonlinearity (DNL)Analogue-digital convertersDifferential nonlinearityEngineering

The invention belongs to the technical field of analog-to-digital conversion, and particularly relates to a fine quantization ramp generator for a two-step monoclinic analog-to-digital converter. According to the fine quantization ramp generator, an output buffer module 205 adopts a common-mode invariant mode, so that the problem that the performances such as integral nonlinearity (INL), differential nonlinearity (DNL) and spurious-free dynamic range (SFDR) of the slope generator become poor due to the change of the common-mode level of the output buffer of the slope generator in the establishing process is solved; meanwhile, the problem that substrate parasitic capacitance is introduced into a loop by adopting substrate source short circuit is avoided, and a good effect of improving the linearity of an output signal of the ramp generator is achieved; in addition, a feedforward transconductance path structure and a resistance-capacitance compensation structure are adopted, so that thepurpose of zero-pole cancellation of an operational amplifier of the output buffer module 205 of the fine-quantization ramp generator is achieved, and the linearity, the loop stability and the establishing stabilization time of the output buffer module 205 of the fine quantization ramp generator are optimized.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

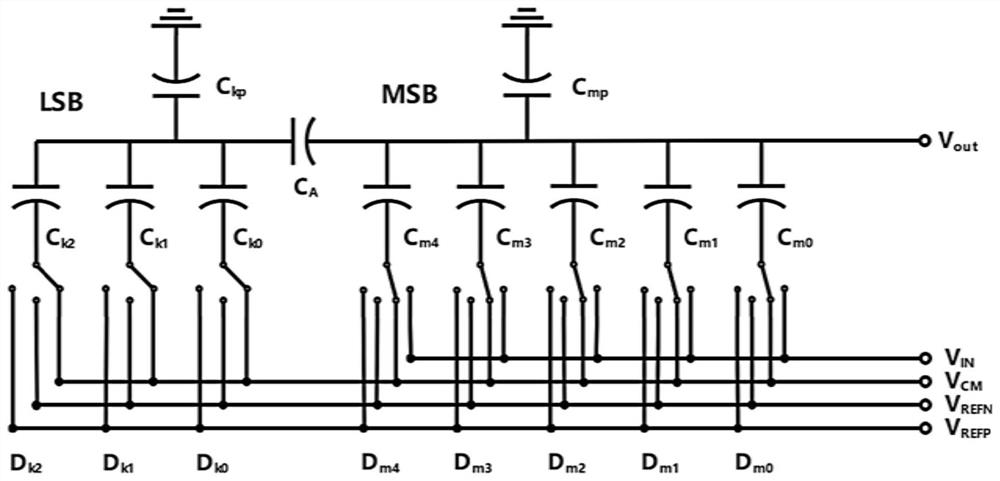

Successive approximation analog-to-digital conversion transpose

PendingCN114244369AReduce areaReduce power consumptionPower saving provisionsElectric signal transmission systemsDifferential nonlinearityControl theory

The invention discloses a successive approximation type analog-to-digital conversion device which comprises a comparison device, a successive approximation register logic circuit and two digital-to-analog conversion devices. The digital-to-analog conversion device comprises a capacitor array and a plurality of multipath selection devices; the capacitor array comprises a bridge capacitor, and an LSB array and an MSB array which are connected through the bridge capacitor; each of the LSB array and the MSB array comprises at least one first capacitor; each first capacitor is correspondingly connected with one multi-path selection device; the comparison device and each multi-path selection device are respectively connected with the successive approximation register logic circuit; and the two digital-to-analog conversion devices are respectively connected with the positive input end and the negative input end of the comparison device. According to the successive approximation type analog-to-digital conversion device, the capacitor array is divided into the LSB array and the MSB array, differential nonlinearity can be improved, exponential increase of the number of capacitors is reduced, and therefore the total area and power consumption of the capacitor array are greatly reduced.

Owner:TSINGHUA UNIV +1

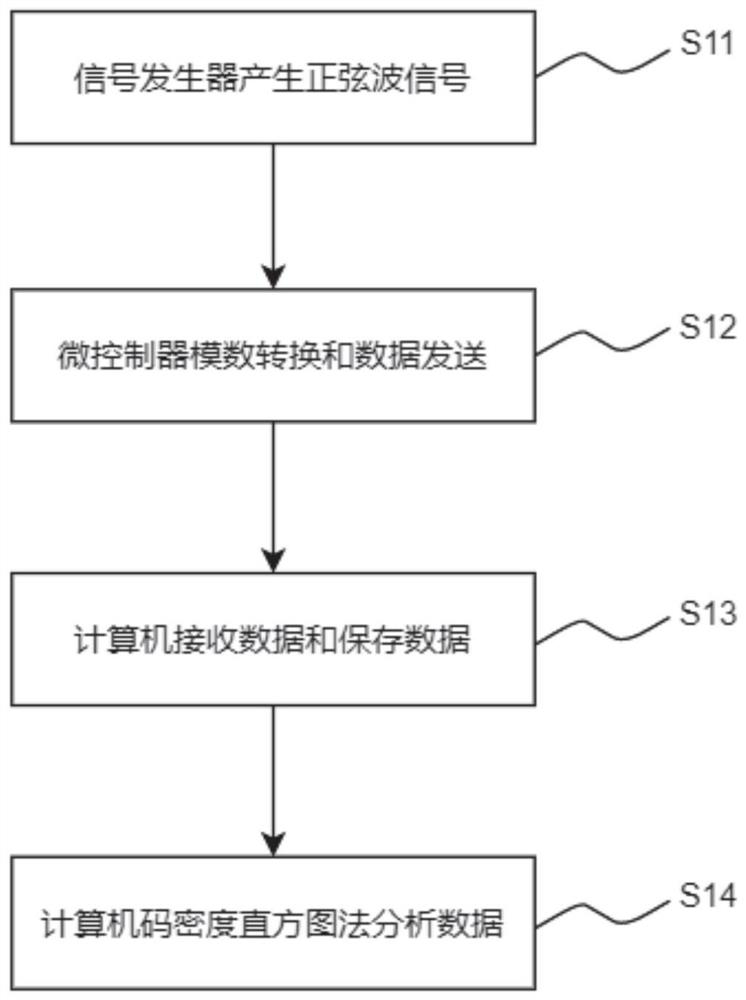

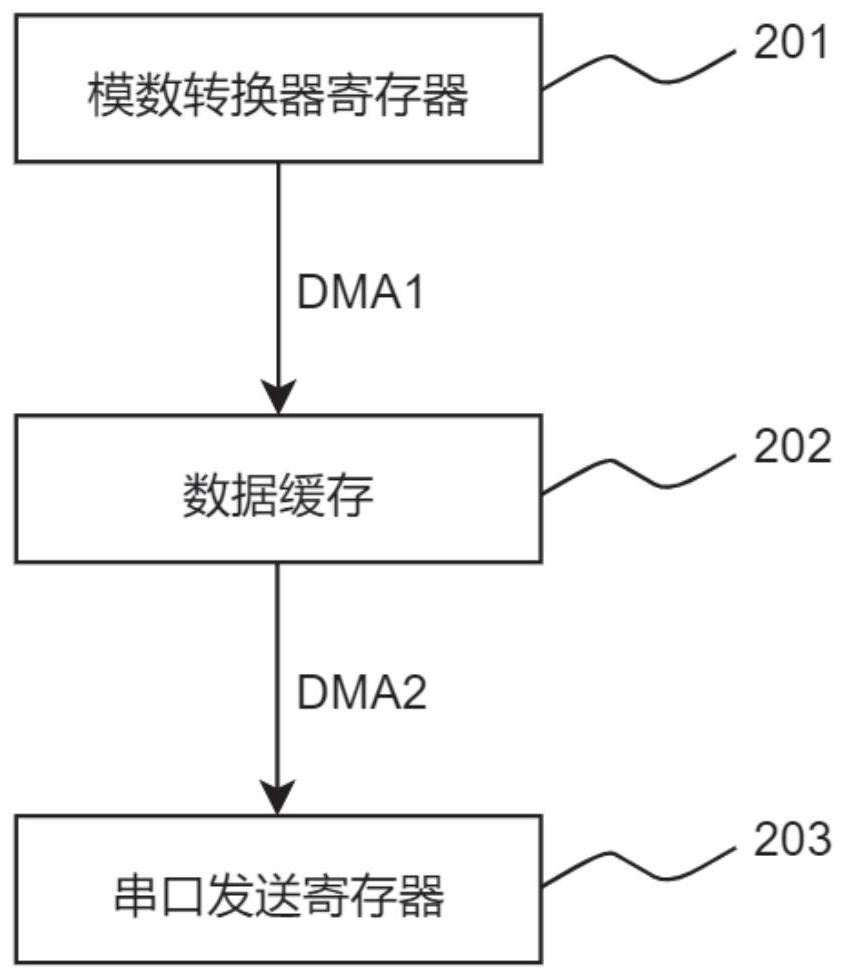

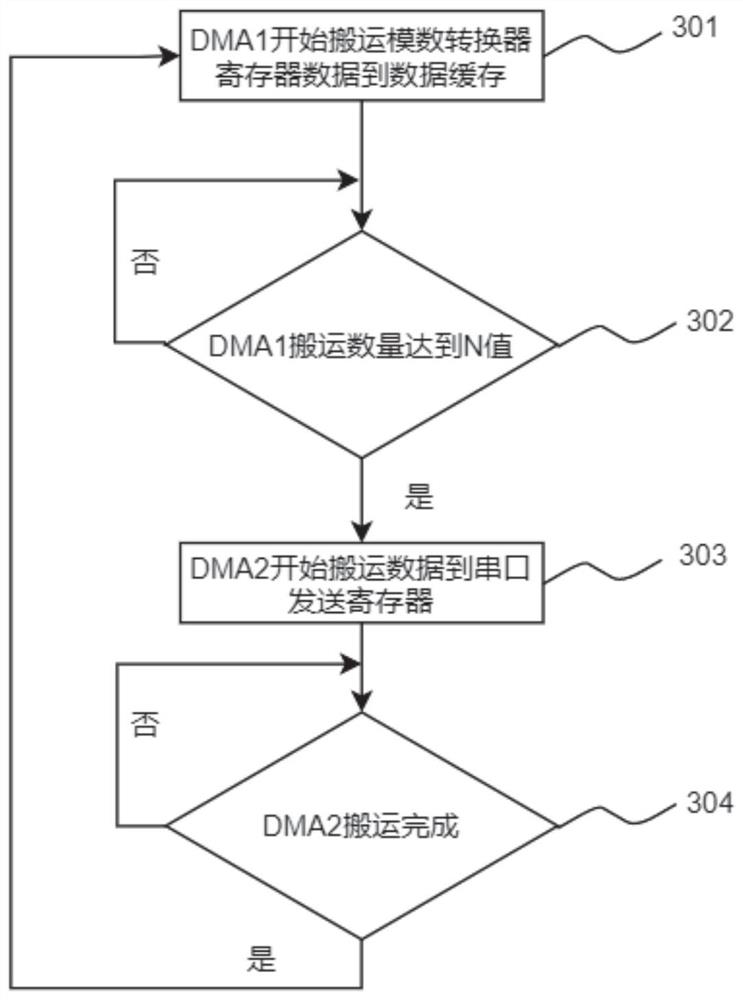

Method for testing differential nonlinearity and integral nonlinearity of microcontroller analog-to-digital converter

PendingCN112526973ALow costSimple wayElectric testing/monitoringAnalogue/digital conversion calibration/testingMicrocontrollerDifferential nonlinearity

The invention provides a method for testing differential nonlinearity and integral nonlinearity of a microcontroller analog-to-digital converter. The method comprises the following steps that S1, a signal generator generates a sine wave with a preset frequency as a test signal; S2, a microcontroller samples the test signal by adopting an analog-to-digital conversion sampling frequency at a presetrate; S3, the microcontroller adopts a serial port to send sampling data; S4, a computer terminal receives the sampling data and stores the sampling data as a file; and S5, the computer analyzes the data of the file by adopting a code density histogram method to obtain a test result. According to the invention, a performance test of important parameter differential nonlinearity and integral nonlinearity of a built-in analog-to-digital converter can be completed in a low-cost and convenient manner under the condition that the microcontroller only has a low-speed input / output interface.

Owner:SHANGHAI AISINOCHIP ELECTRONICS TECH

Differential recurrent neural network

ActiveUS10671908B2Fast convergenceIncreasing the curvature of the HessianCharacter and pattern recognitionNeural architecturesDifferential nonlinearityNetworked system

Owner:MICROSOFT TECH LICENSING LLC

Correction method and circuit for current rudder DAC buck-boost

ActiveCN111835350BLow Differential NonlinearityGood pressure regulation monotonicityPhysical parameters compensation/preventionDifferential nonlinearityVoltage regulation

The invention discloses a current rudder DAC buck-boost correction method and circuit, wherein the method includes: image value acquisition: taking the code value N to be converted as the central value to obtain n pairs of code values, and the n pair of code values are A1 to An and B1 to Bn, wherein, the code value A1 to An is greater than the code value N, the code value B1 to Bn is less than the code value N, n is a positive integer, and the mean value of every pair of code values is N; within a certain time T, from the code value B1 To Bn, N, and A1 to An, take out any code value without repetition and output it to the digital-to-analog conversion unit until all 2n+1 code values are taken, and each code value maintains the same time; output adjustment: the adjustment unit adjusts all The output of the digital-to-analog conversion unit is adjusted to stabilize the output voltage of the buck-boost circuit. According to the current rudder DAC buck-boost correction method of the above-mentioned technical solution, the influence caused by the mismatch of a single code value is reduced through the round-robin of the mirror code value, the differential nonlinearity of the digital-to-analog conversion is reduced, and the monotonicity of the buck-boost voltage regulation output is improved. sex.

Owner:ZHUHAI ISMARTWARE TECH CO LTD