Multiphase clock generation circuit

A multi-phase clock and circuit generation technology, which is applied in the electronic field, can solve the problems affecting the accuracy of the circuit and the phase uniformity of the output clock, and achieve the effect of high reliability, simple structure and uniform distribution of phase difference

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

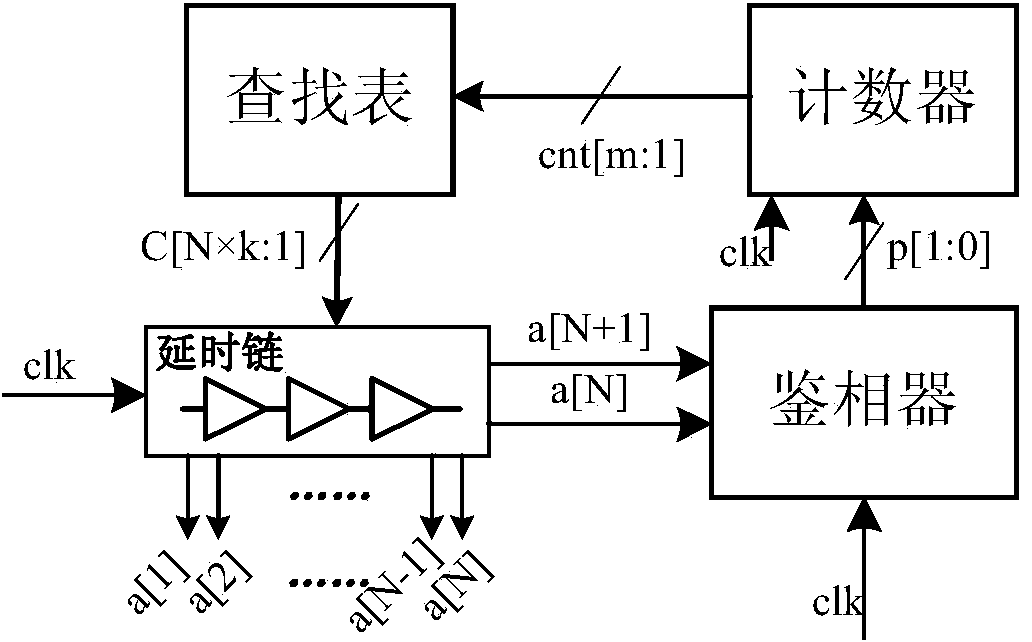

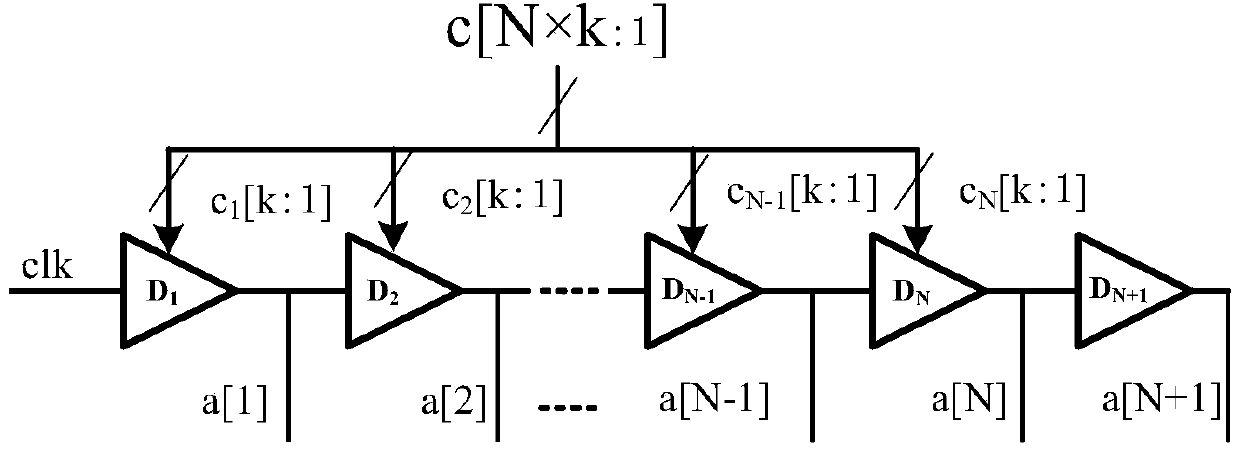

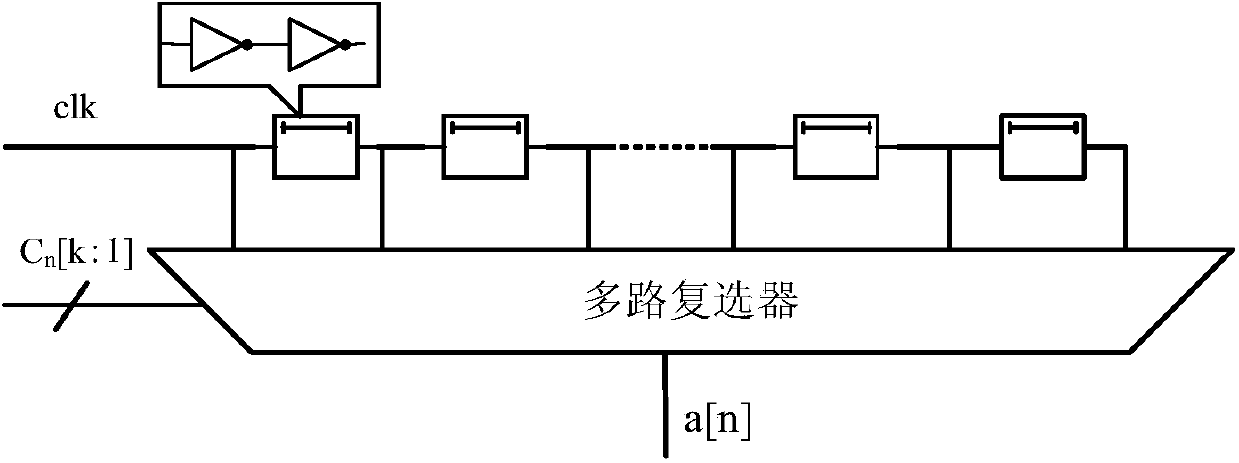

[0040] A multi-phase clock generation circuit, its structure is as follows figure 1 , 2 As shown, it includes a delay chain, a phase detector, a counter and a look-up table module; the delay chain is formed by (N+1) delay units connected in series, wherein the input terminal of the first delay unit As the input terminal of the entire delay chain, it is connected to a fixed-frequency reference clock clk; N k-bit control signals c[k:1] are recorded as c[n×k:1], n=1,2,…,N,N is a natural number, where the first k-bit control signal c 1 [k:1] controls the first delay unit, the second k-bit control signal c 2 [k:1] controls the second delay unit, the nth k-bit control signal c n [k:1] Control the nth delay unit until the Nth k-bit control signal c N [k:1] controls the Nth delay unit; the first N delay units are respectively in the corresponding k-bit control signal c n Under the control of [k:1], corresponding N clocks a[1]~a[N] with the same frequency and different phases are ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More