Patents

Literature

114results about How to "Occupies a small chip area" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

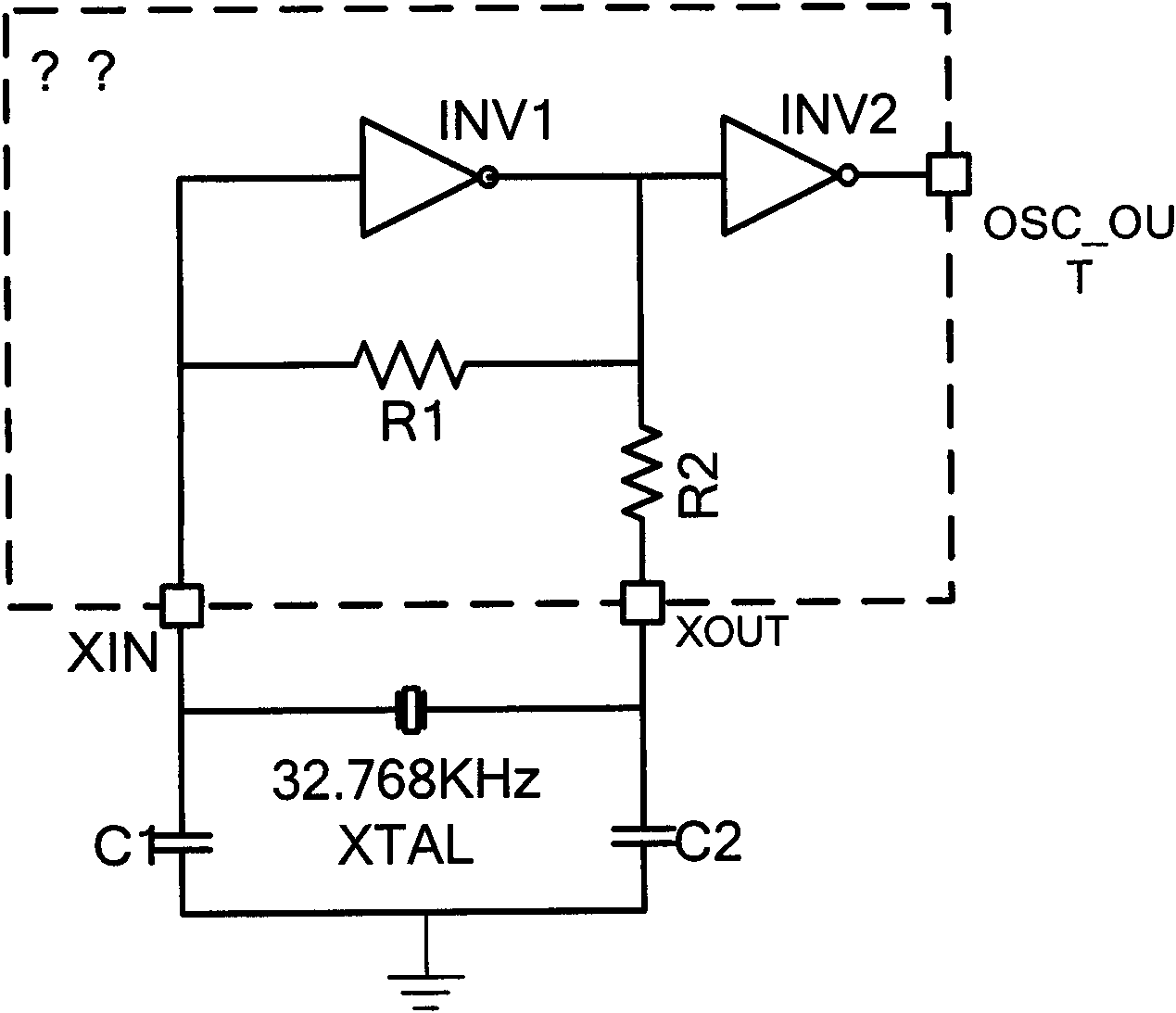

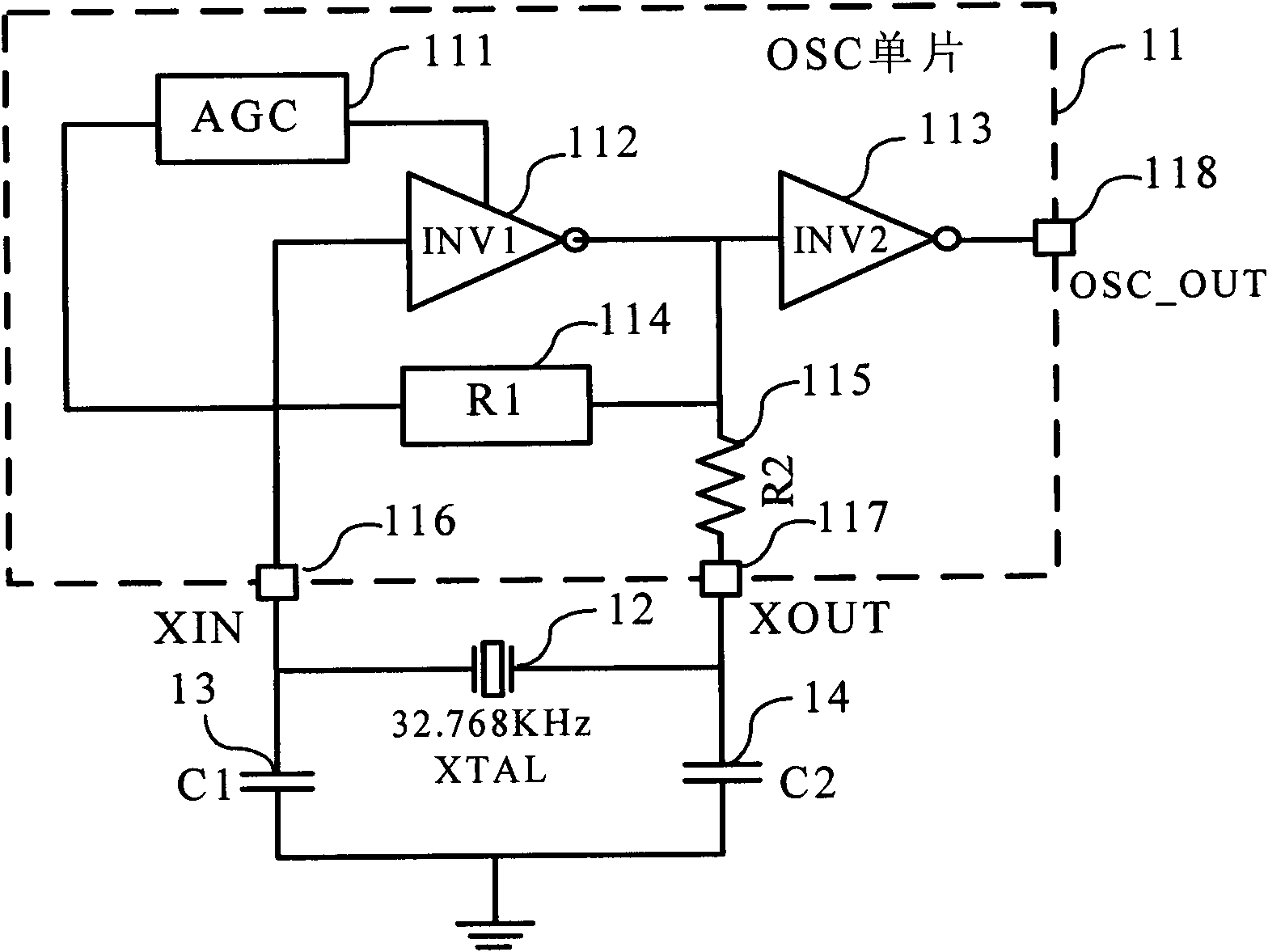

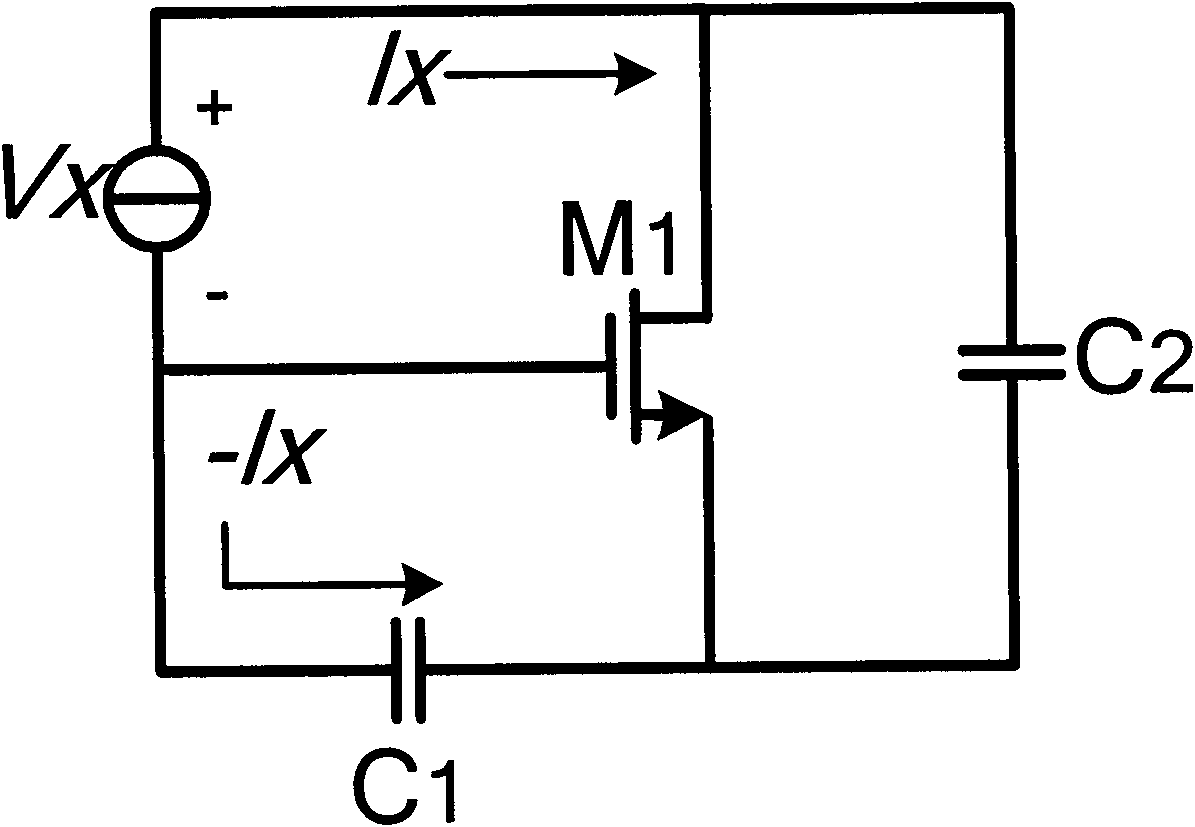

Low power consumption and rapid oscillation starting crystal oscillator module with programmable adjusting start-oscillation condition

The invention discloses a low power consumption and rapid oscillation starting crystal oscillator module with a transposable start oscillation condition, which consists of an inverting amplifier, an inverting reshaper chain, an automatic gain control loop (AGC), a feedback resistor, a power limitation resistor, and an external passive crystal oscillator and an external load capacitor. The inverting amplifier is provided with a transposable feedback resistor R1, and the transposable start oscillation condition of the crystal oscillator is realized; and the automatic gain control loop (AGC) is inserted between an input end and a bias end of the inverting amplifier, and the contradiction between the oscillation starting time and power consumption is solved. The invention also provides a highresistor realizing IC (integrated circuit) by adopting a transconductance amplifier of micro current source, and a transposable feedback resistor R1 for the oscillator amplifier branch circuit and a high resistor in a pi-shaped filter. The resistance value of the high resistance can be controlled by programming, the start oscillation condition of the oscillator can be adjusted through adjusting the feedback resistance R1, and reliable and quick start oscillation of the oscillator can be realized; and lower phase noise can be realized through adjusting the high resistor in the pi-shaped filter. The crystal oscillator circuit has the characteristics of low power consumption and rapid start oscillation, and can be used for the digital integrated circuit, such as a base band of various of satellite navigation allocation receptors, real time clocks (RTC).

Owner:杭州中科微电子有限公司

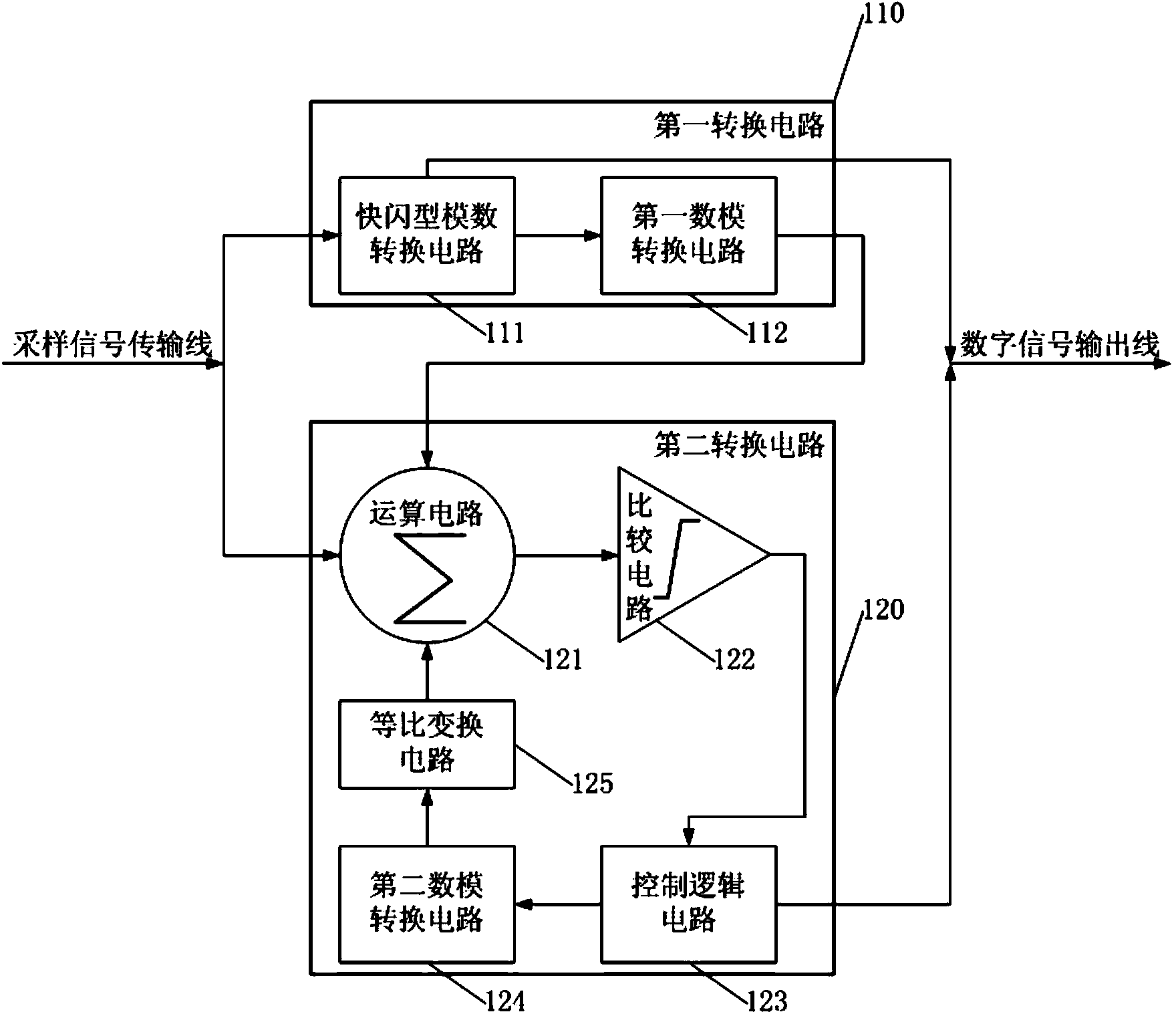

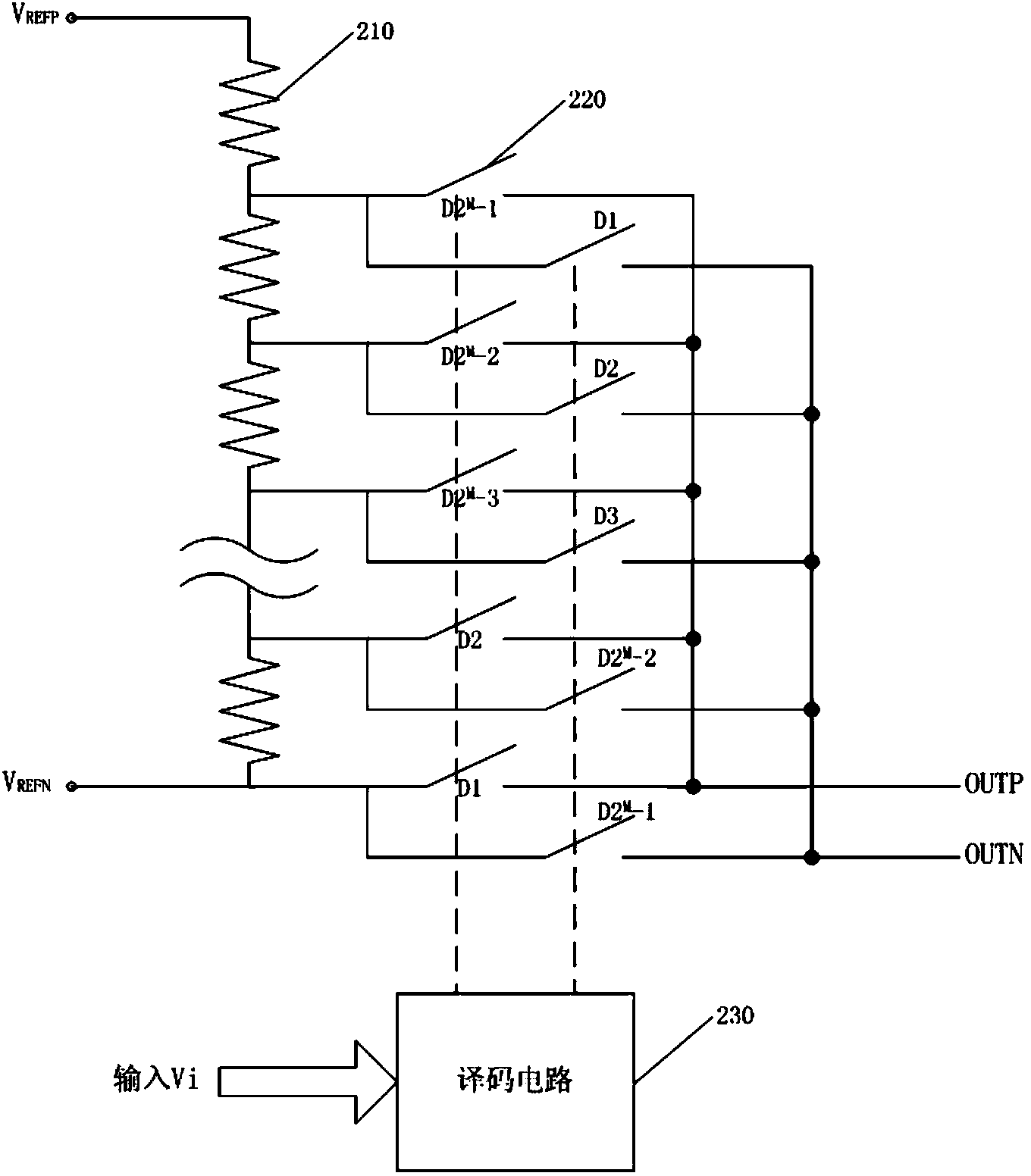

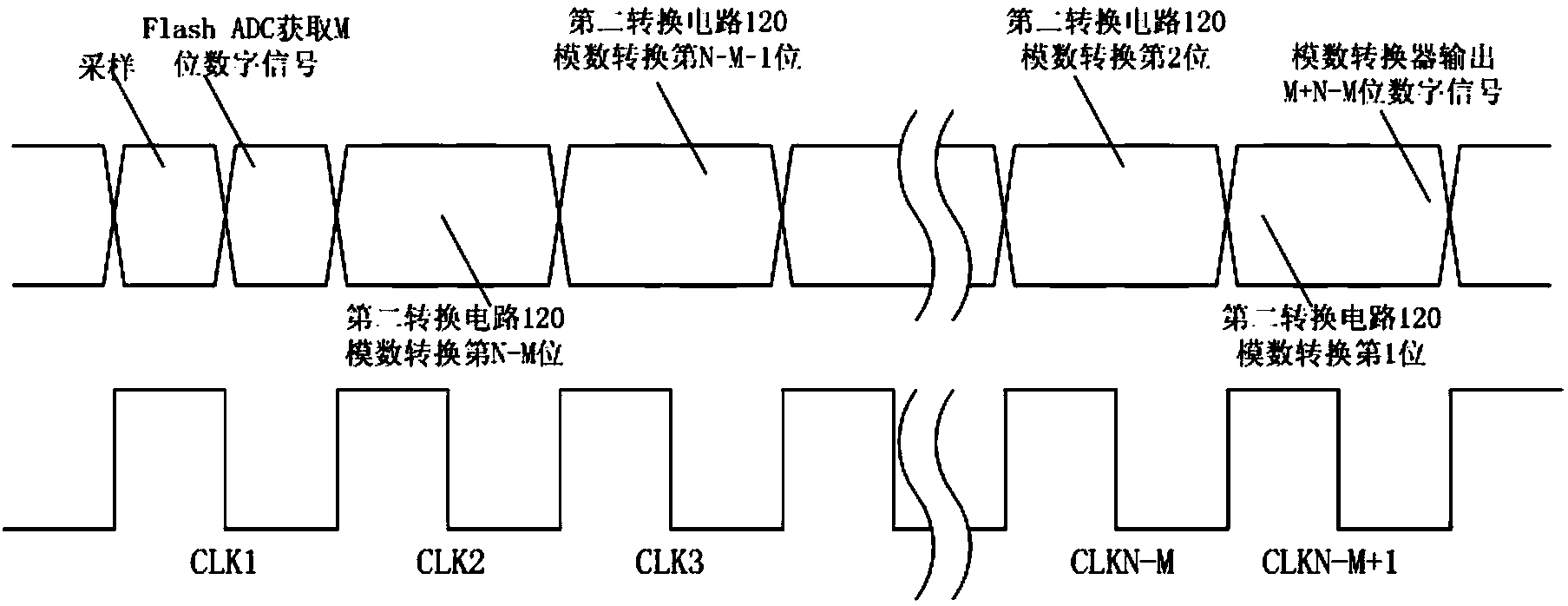

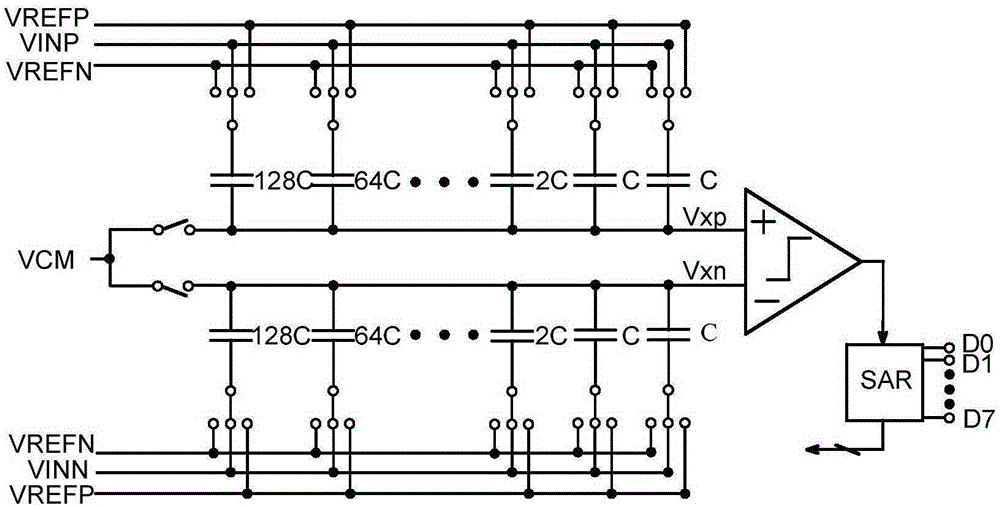

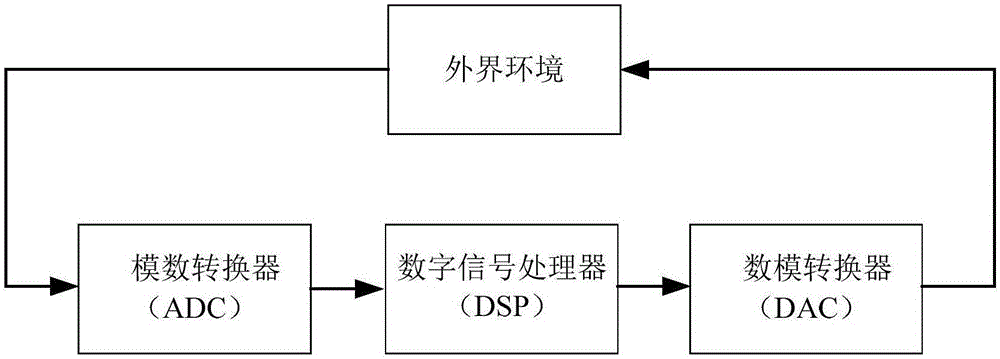

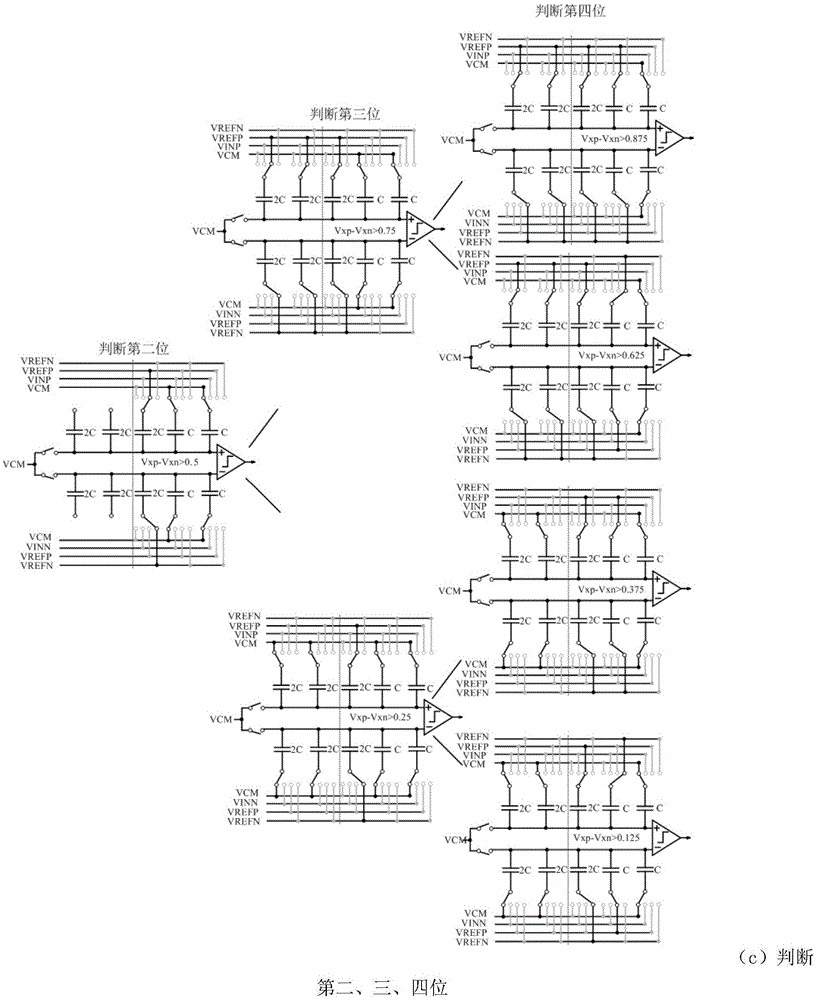

Analog-digital converter and analog-digital conversion method

ActiveCN104300984AReduce power consumptionOccupies a small chip areaAnalogue/digital conversionElectric signal transmission systemsDigital down converterAnalog-to-digital converter

Owner:ZHANGJIAGANG KANGDE XIN OPTRONICS MATERIAL

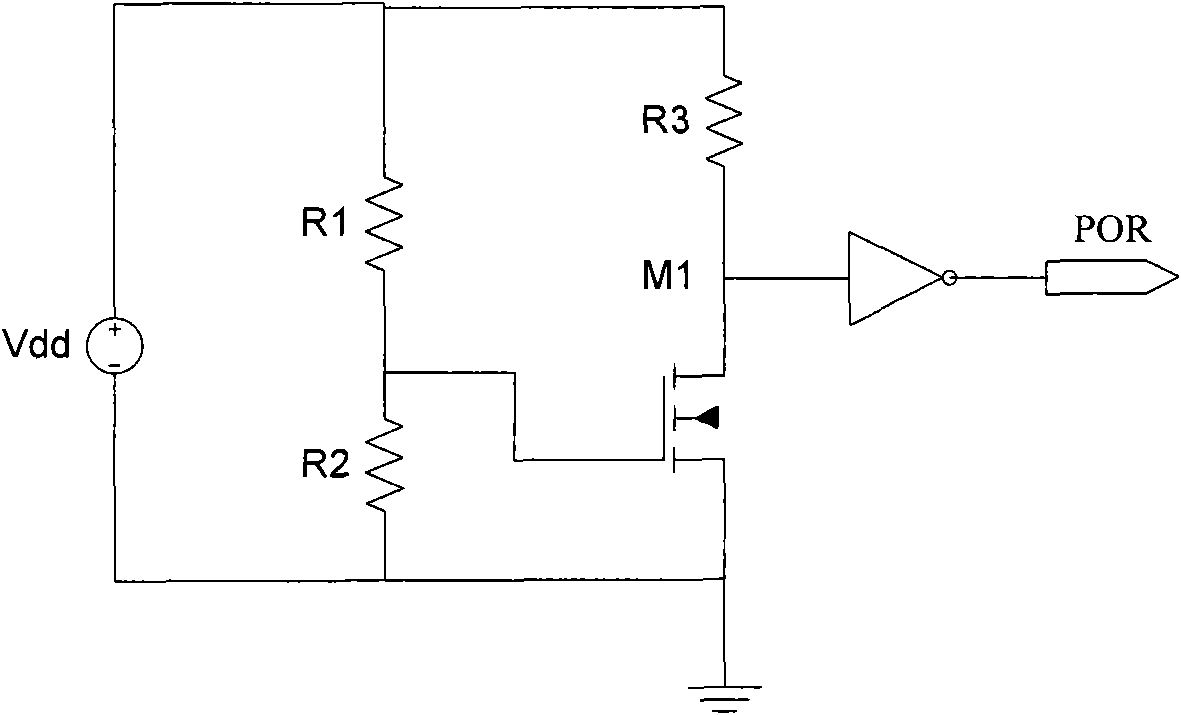

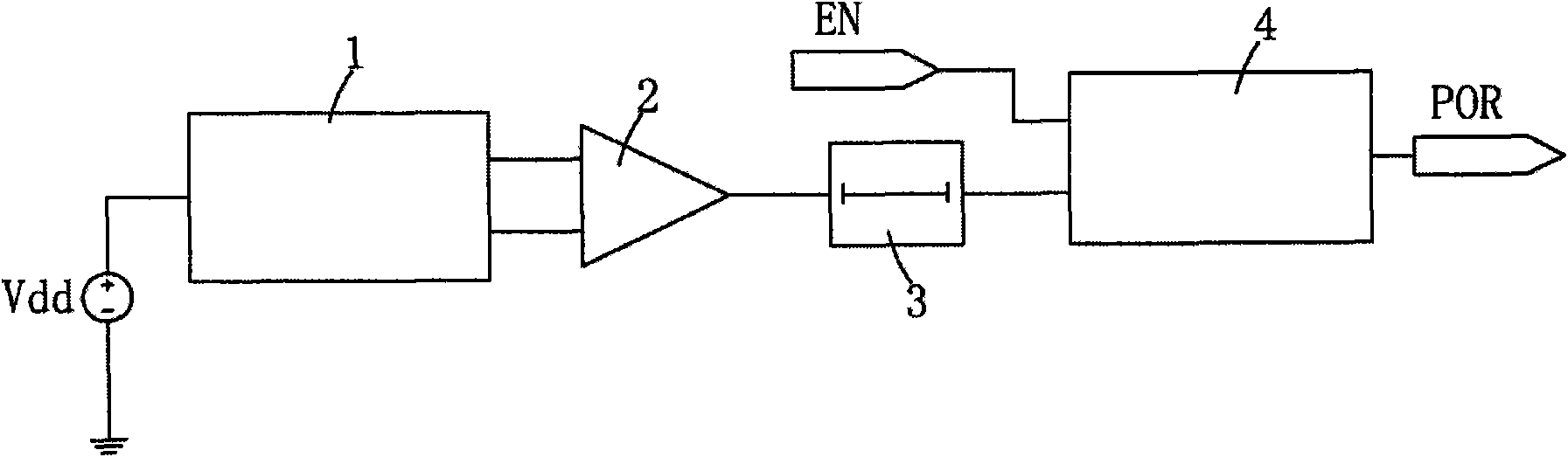

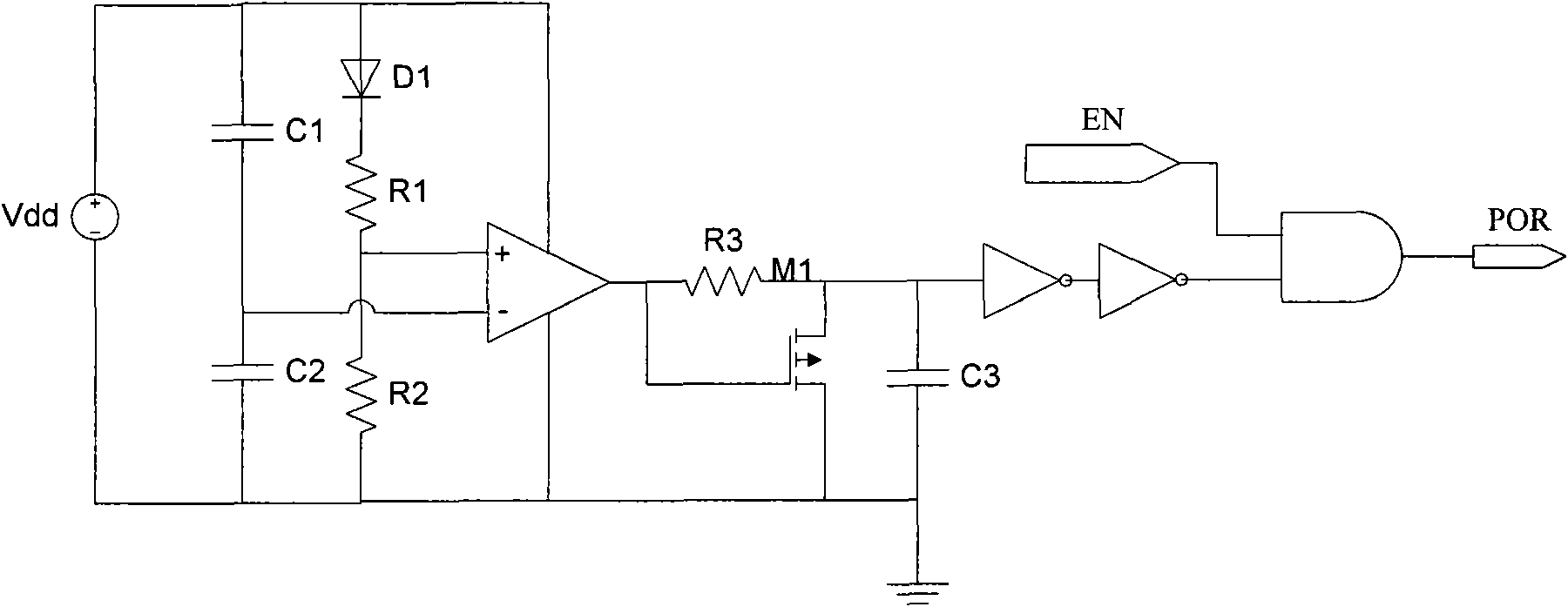

Electrifying reset and undervoltage turnoff circuit

ActiveCN101588167AReduce power consumptionReduce areaElectronic switchingData resettingElectricityPower-on reset

The invention discloses an electrifying reset and undervoltage turnoff circuit, including a partial pressure following circuit (1), a voltage comparator (2), a delay buffer circuit (3) and a reset turnoff circuit (4). The partial pressure following circuit (1) generates two outputs by two detection circuits to compare by the voltage comparator (2), an output of the voltage comparator (2) after delaying and reshaping of the delay buffer circuit (3) generates an electrifying reset signal to output, the reset turnoff circuit may input EN to decide a reset opportunity. The structure of the circuit is simple and novel, an area of a chip occupied by circuit is small, and a power consumption is low. It is capable of providing a electrifying reset and undervoltage turnoff function on a on-chip system, and the circuit is capable of operating on various technique angles and in a wider temperature range by a small current reliably.

Owner:GUANGZHOU RUNXIN INFORMATION TECH

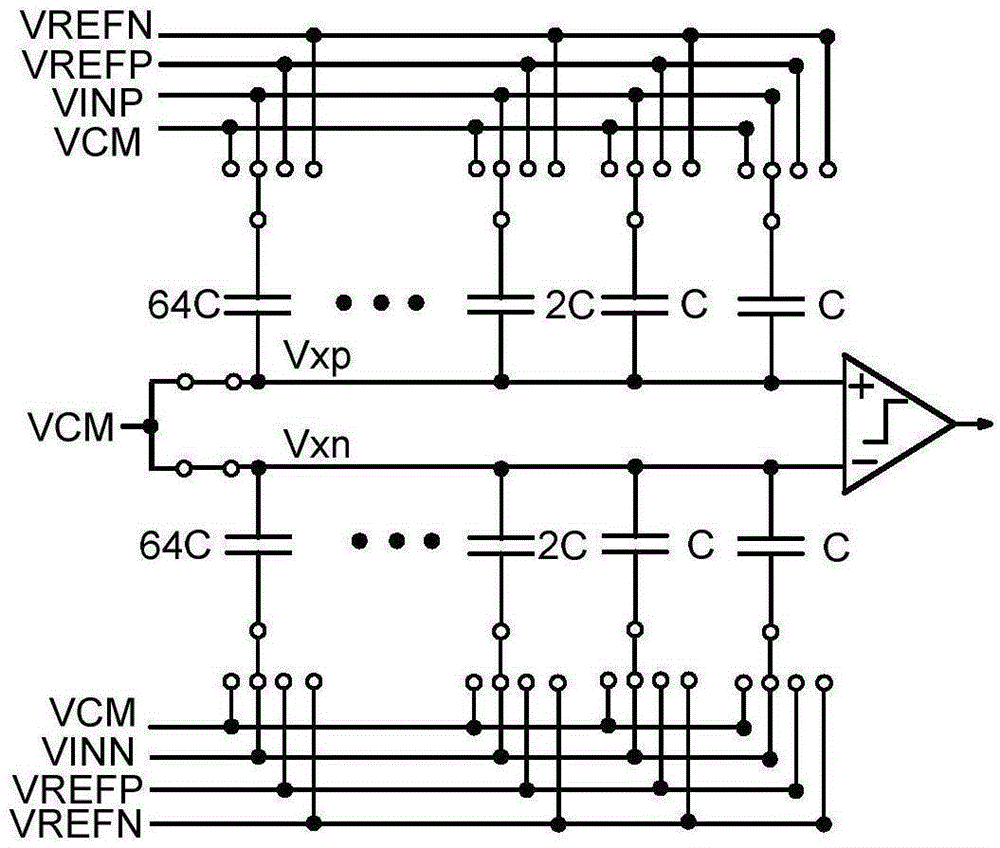

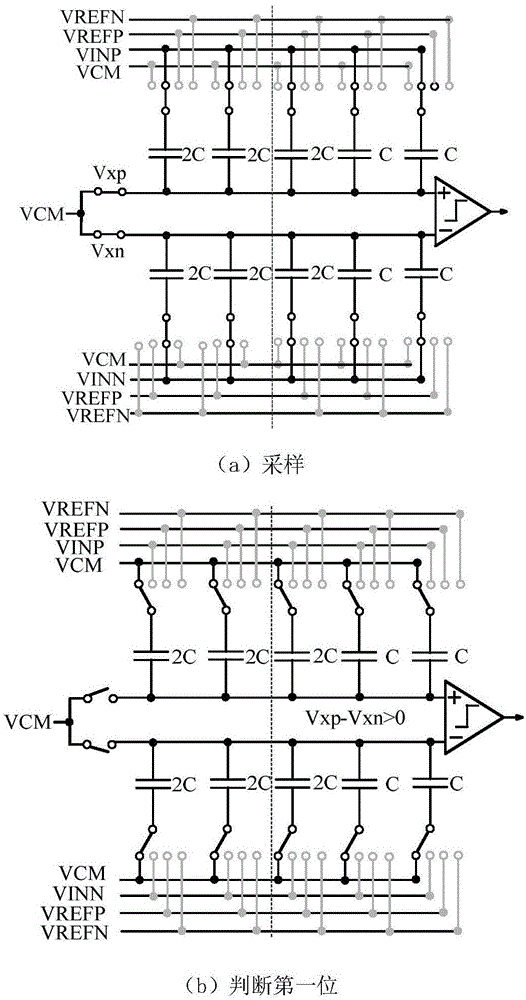

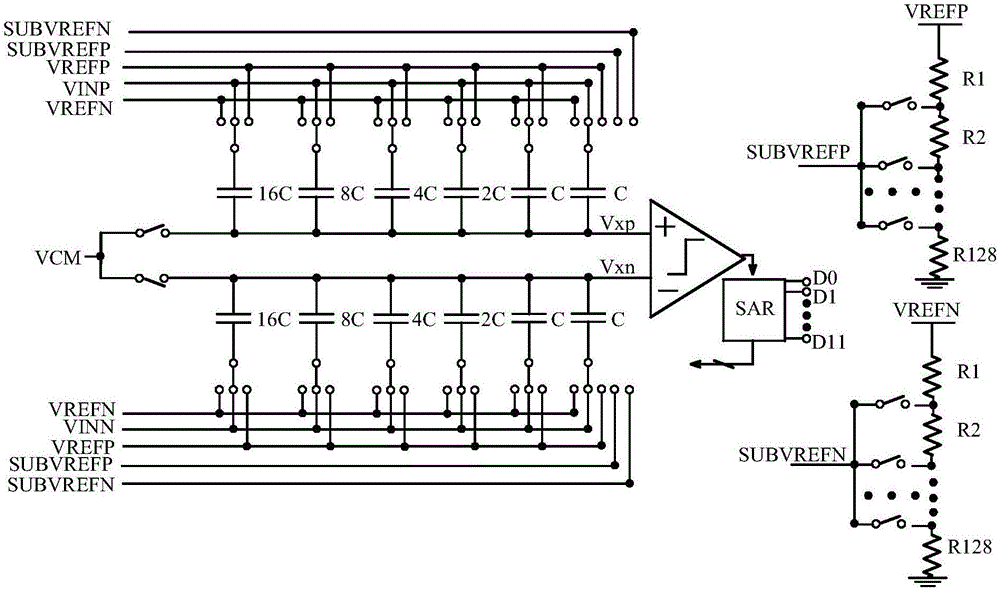

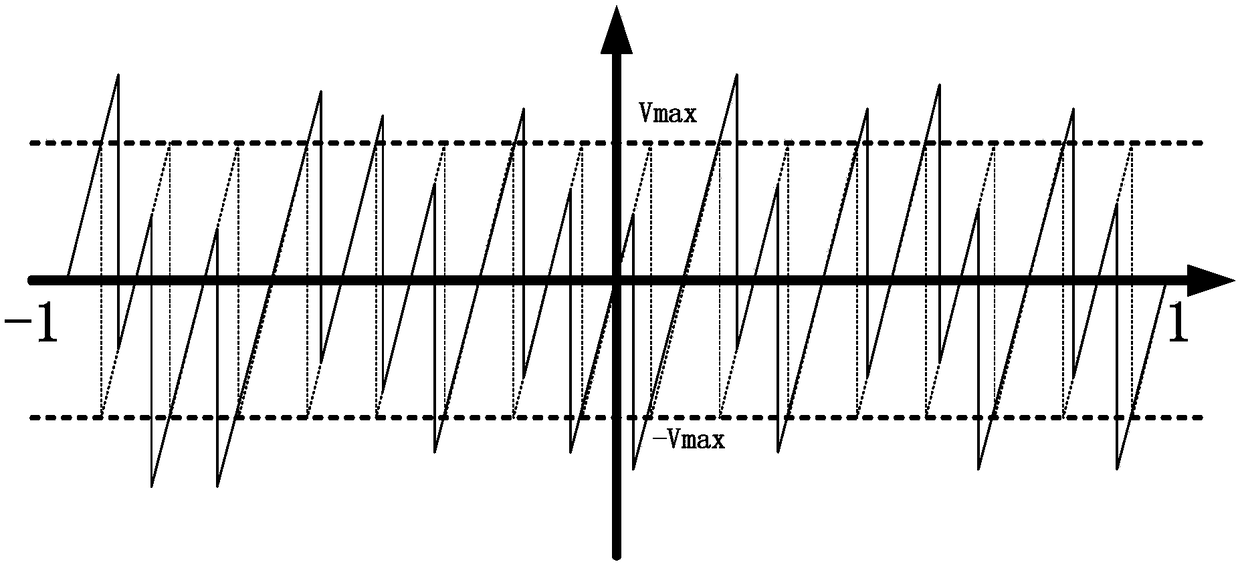

Capacitor switching and averaging method for improving linearity of successive approximation analog-digital converter

InactiveCN105322966ASimple structureOccupies a small chip areaAnalogue/digital conversionElectric signal transmission systemsCapacitanceCorrection algorithm

The invention discloses a capacitor switching and averaging method for improving the linearity of a successive approximation analog-digital converter, and relates to the field of microelectronics and solid state electronics, and in particular to successive approximation analog-digital converters. No correction algorithm needs to be introduced, the capacitance does not need to be split, high capacitance DAC and low capacitance DAC only need to be exchanged between two transformations, bit circulation is carried out on remaining bits for twice, and two transformation results are averaged to obtain a final output codeword. The capacitor switching and averaging method provided by the invention can be used for avoiding accumulating errors of capacitor mismatch at the same codeword, therefore, compared with a traditional correction method of improving the linearity by a correction algorithm, the capacitor switching and averaging method has the advantages that the structure is simpler, a smaller chip area is occupied and on-chip implementation is easier.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

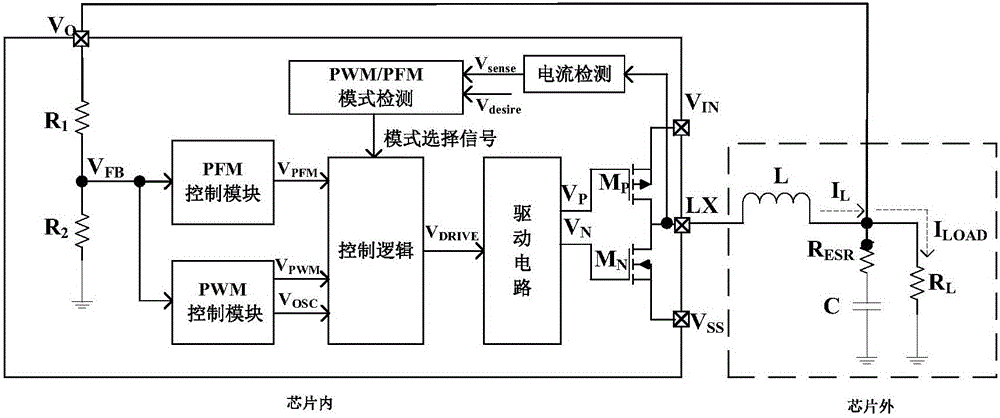

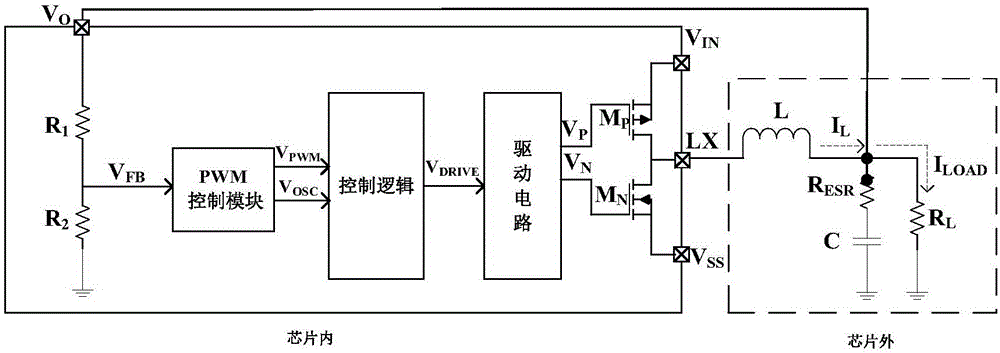

PWM/PFM dual mode automatically-switched step-down DC-DC converter

ActiveCN106787719ASimple structureOccupies a small chip areaEfficient power electronics conversionDc-dc conversionDc dc converterDual mode

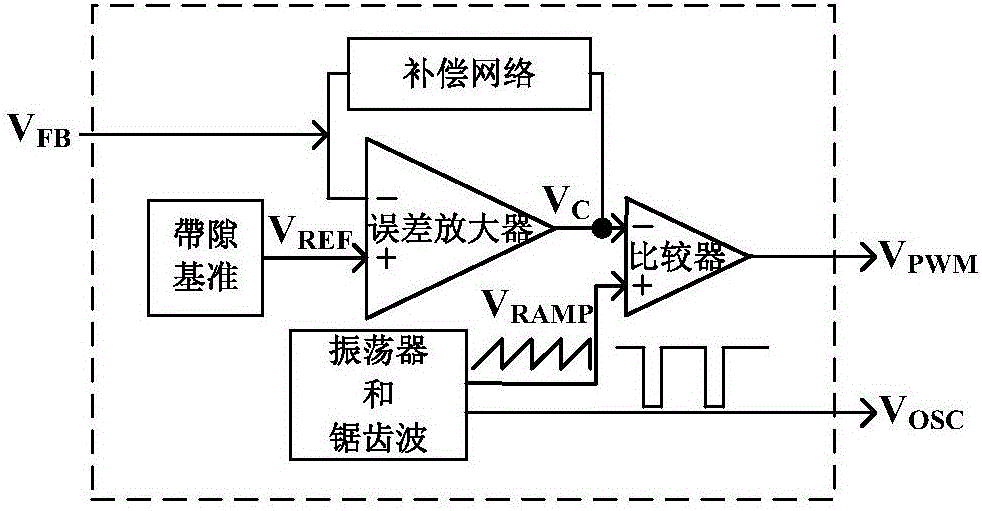

The invention discloses a PWM / PFM dual mode automatically-switched step-down DC-DC converter, comprising a conversion circuit and a control circuit, wherein the control circuit comprises an output voltage sampling circuit, a PWM control module, a control logic module and a driving module; two output ends of the driving module are connected with the control end of a main switch tube and the control end of a freewheeling switch tube; the PWM control module comprises an error amplifier, a comparator, an oscillator and a sawtooth wave generation circuit; the first input end of the error amplifier is connected with the output end of the output voltage sampling circuit, and the second input end of the error amplifier is connected with the reference voltage; the first input end of the comparator is connected with the output end of the error amplifier, and the second input end of the comparator is connected with the output end of the sawtooth wave generation circuit; the output end of the comparator is connected with the first input end of the control logic module, and the output end of the oscillator is connected with the second input end of the control logic module; and the output end of the control logic module is connected with the input end of the driving module. In summary, the PWM / PFM dual mode automatically-switched step-down DC-DC converter disclosed by the invention determines the switching points by using the delay of the comparator, and is simple in structure and small in occupied chip area.

Owner:SHENZHEN INSTITUTE OF INFORMATION TECHNOLOGY

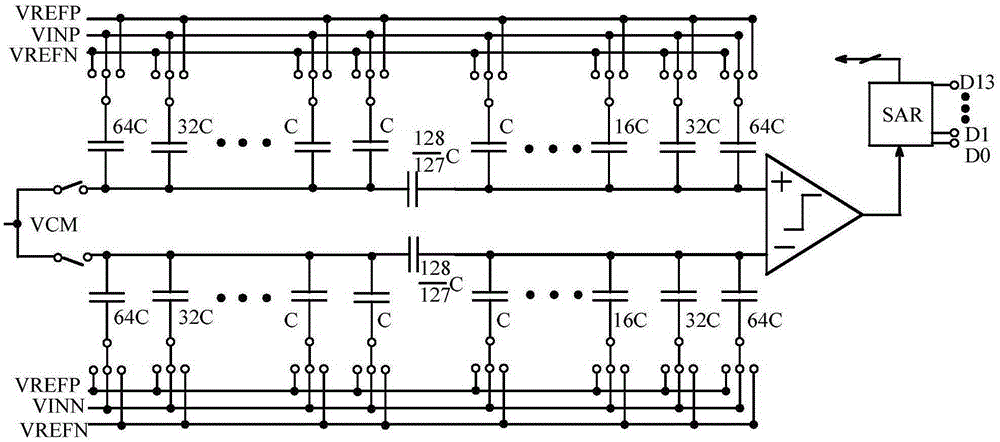

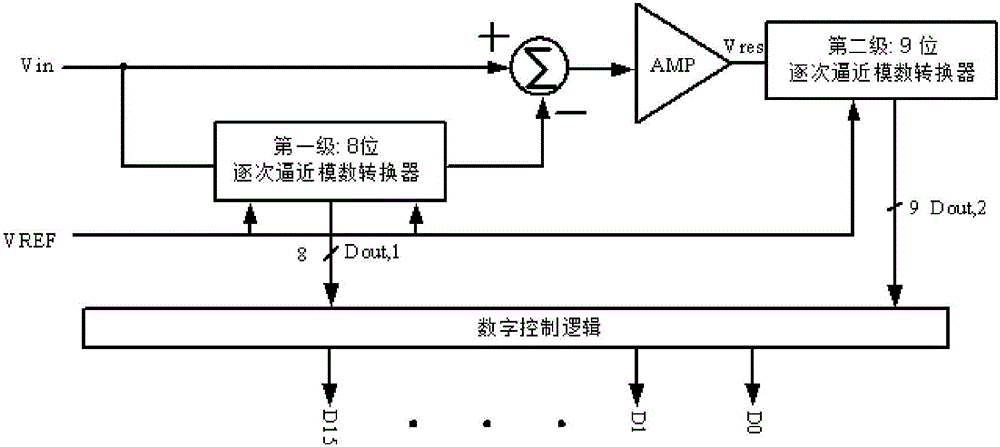

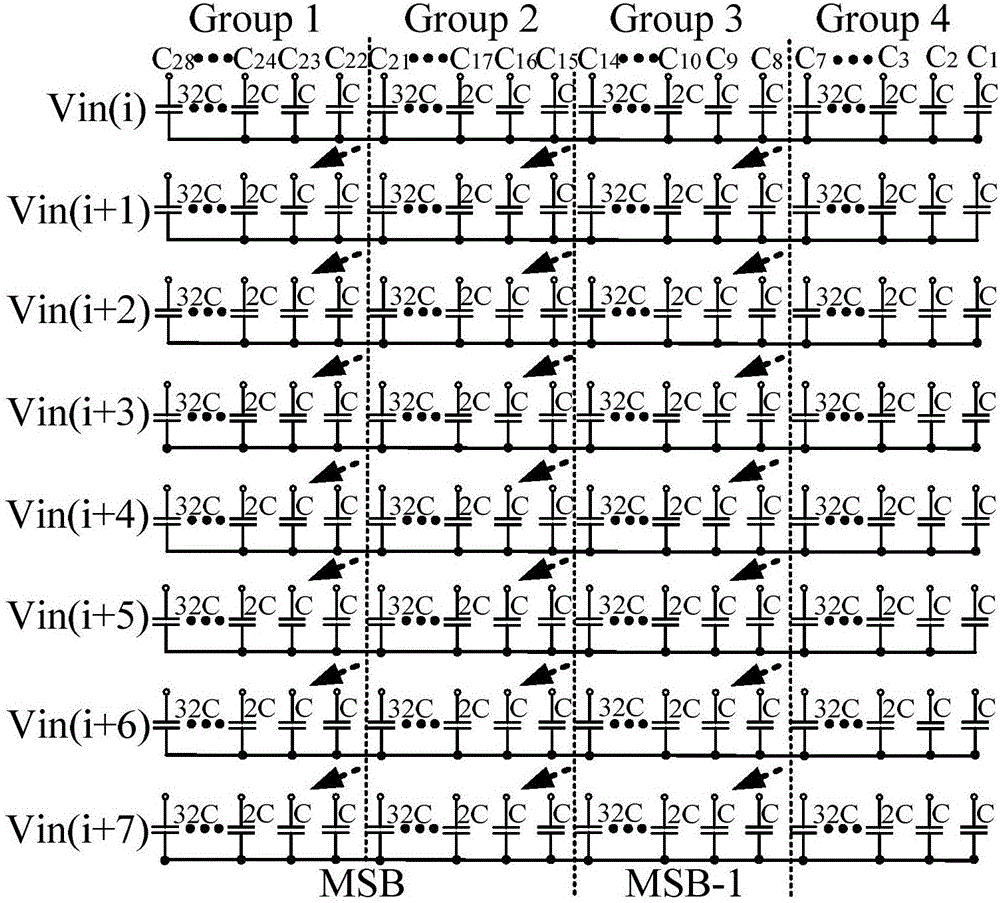

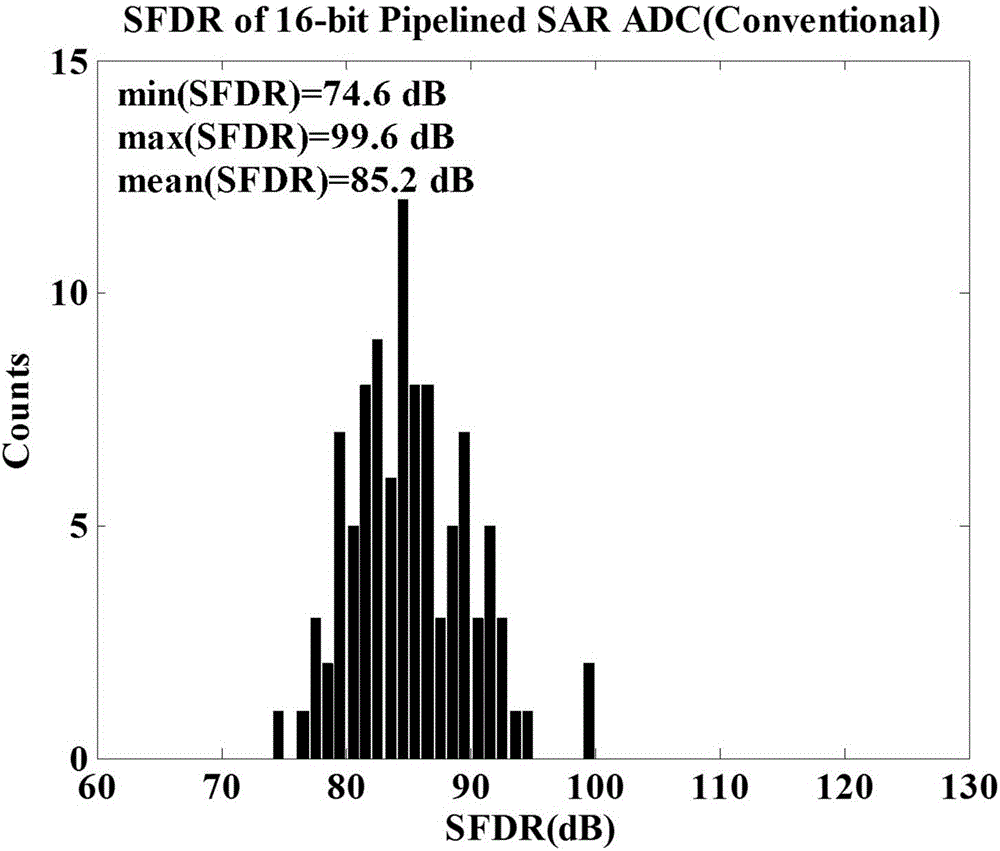

Method for improving linearity of pipelined successive-approximation analog-to-digital converter

ActiveCN106230439AAvoid accumulationReduce areaAnalogue/digital conversionElectric signal transmission systemsCapacitanceCorrection algorithm

The invention discloses a method for improving a linearity of a pipelined successive-approximation analog-to-digital converter. The method is applied to a high-performance analog-to-digital converter in the field of microelectronics and solid-state electronics. The method is characterized in that an ADC sampling rate does not need to be sacrificed; an additional operational amplifier does not need to be introduced to carry out noise shaping; an auxiliary DAC or a slow and accurate ADC does not need to be introduced; a Dither also does not need to be introduced; only capacitors of a first-stage capacitor array of the pipelined successive-approximation analog-to-digital converter need to be grouped; and different capacitor combinations are adopted for each conversion, so that accumulation of errors of capacitor mismatch at the same codon can be avoided. Therefore, compared with a conventional DAC foreground correction method, LMS correction algorithm or correction method for improving a linearity by slow and accurate auxiliary ADC correction, the method disclosed by the invention has effects of no sacrifice of the sampling rate, simpler structure, smaller occupied area of a chip and higher easiness for implementing on a chip.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

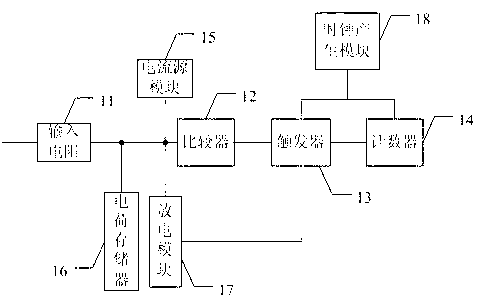

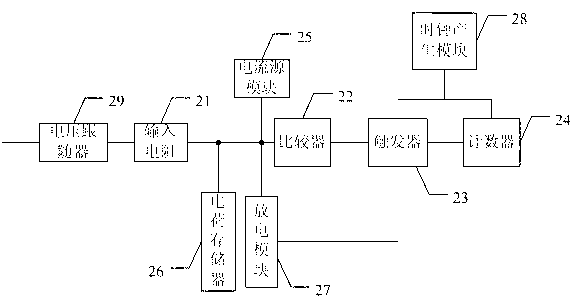

Modulus switching circuit

ActiveCN102957430AOccupies a small chip areaLow costAnalogue/digital conversionElectric signal transmission systemsInterference resistanceComputer module

The invention provides a modulus switching circuit and belongs to the field of integrated circuits. The modulus switching circuit comprises a charge storage, a current source module, an input resistor, a comparator, a trigger, a counter and a discharging module. Simulation voltage signals to be switched is connected with a first input end of the comparator through the input resistor, a second input end of the comparator is connected with a reference voltage, an input end of the trigger is connected with an output end of the comparator, an output end of the trigger is connected with an input end of the counter and the discharging module, and the charge storage is connected between the first input end of the comparator and a first fixed level. The current source module is connected with the first input end of the comparator, and the discharging module is connected between the first input end of the comparator and a second fixed level. The modulus switching circuit is high in interference resistance, adjustable in switching accuracy and low in manufacturing cost.

Owner:BYD SEMICON CO LTD

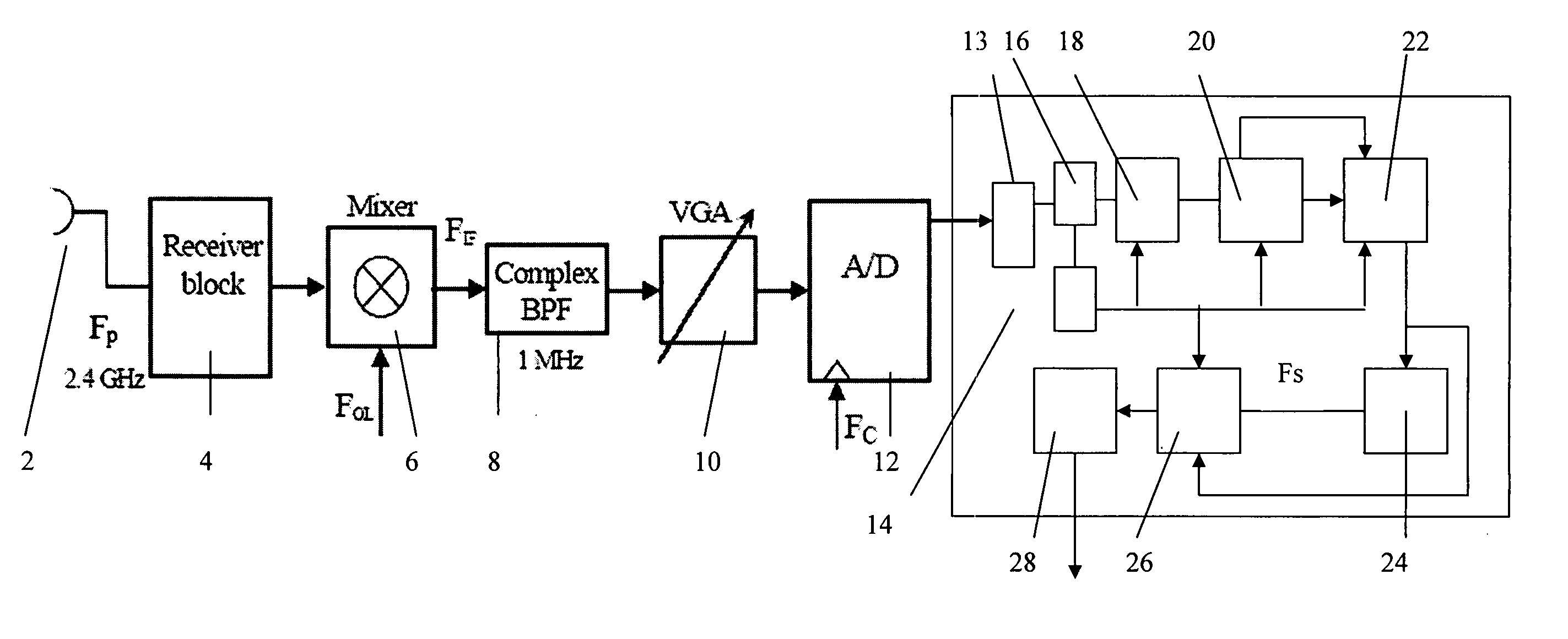

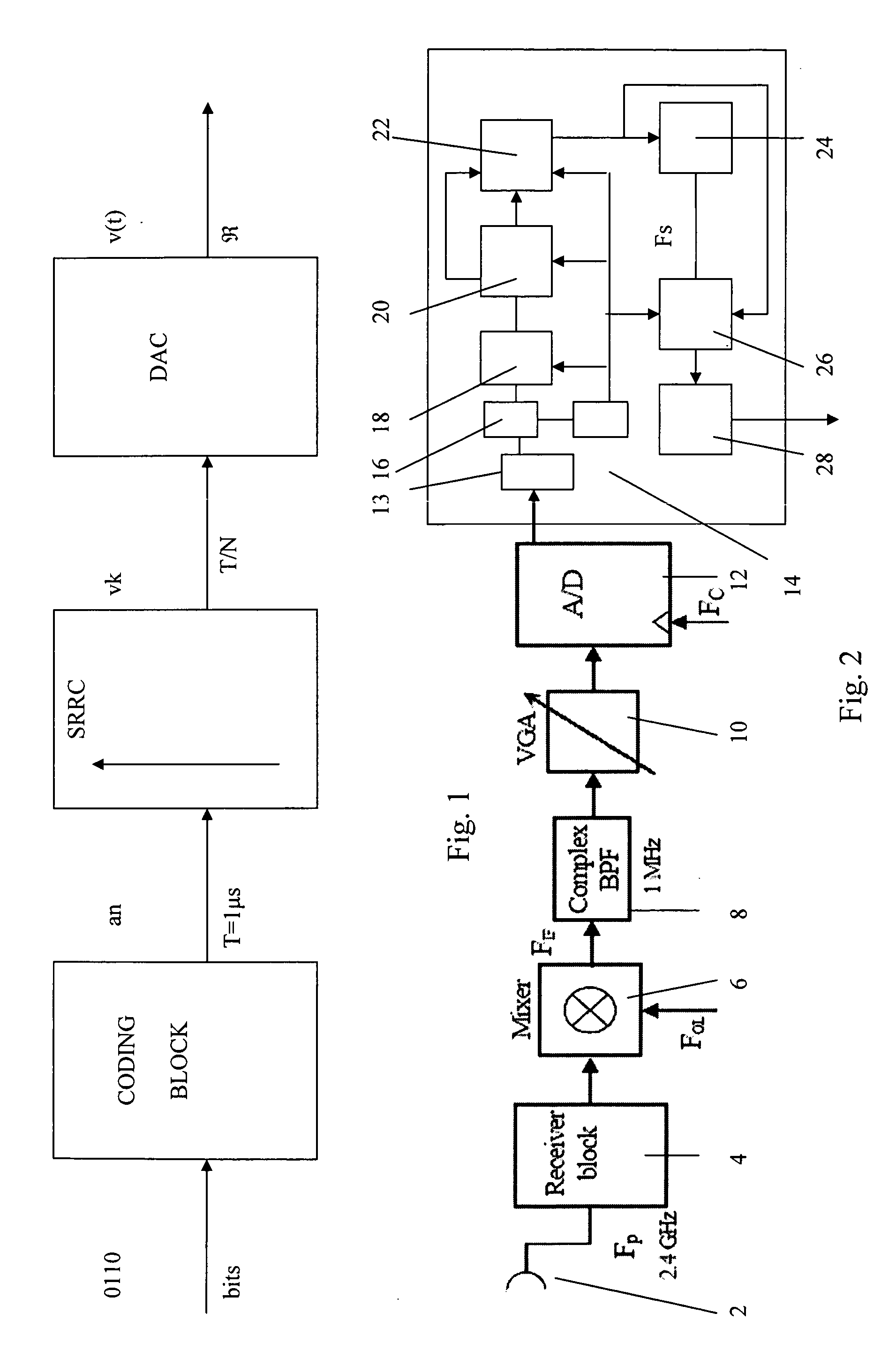

Enhanced data rate receiver

ActiveUS20070037511A1Reduce processing stepsSimple circuitElectric signal transmission systemsModulated-carrier systemsData rateAnalog signal

A receiver having circuitry for generating first digitized samples from a received analog signal at a first sampling rate, e.g. an ADC. An interpolating filter is used to generate second digitized samples which are estimates of samples obtainable by sampling the received analog signal at a second sample rate lower than the first sampling rate, second digitized samples being output at the first sampling rate and including at least one unusable sample. A circuit is provided for generating a signal for controlling components of the receive path downstream of the interpolation filter to prevent processing of the unusable second digitized samples.

Owner:TELEFON AB LM ERICSSON (PUBL)

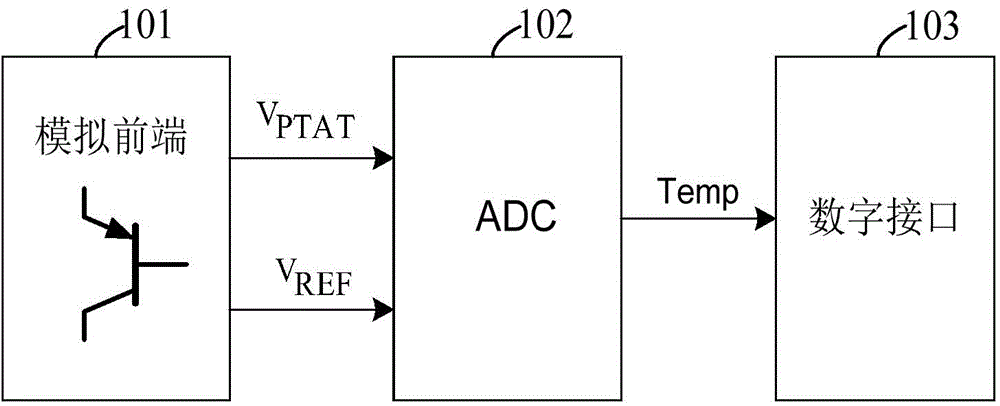

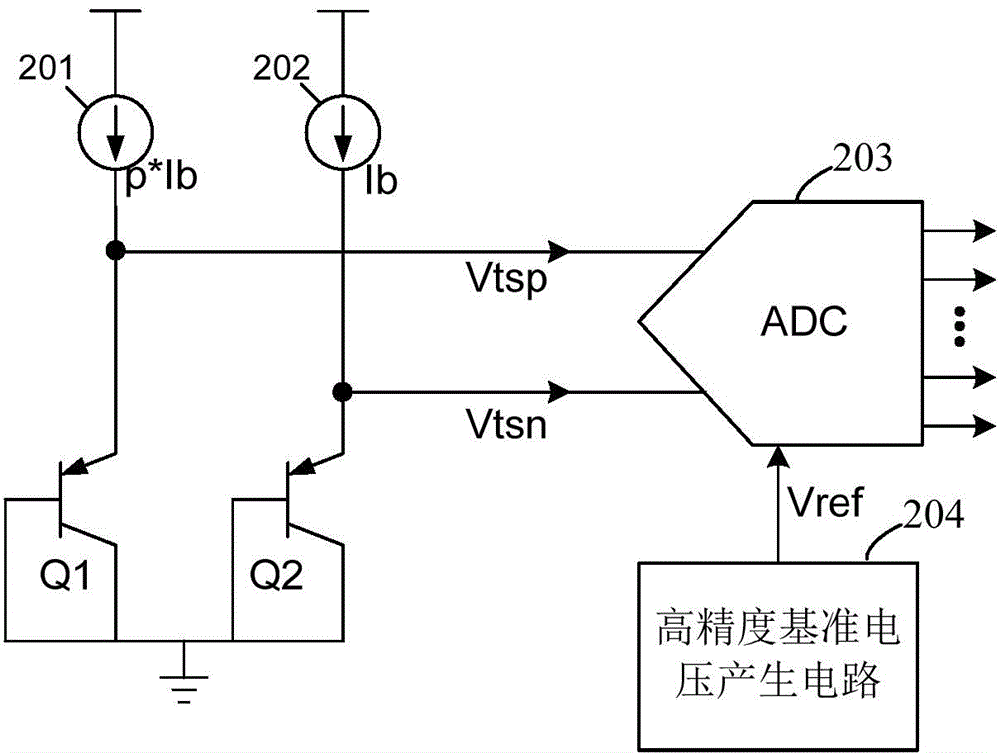

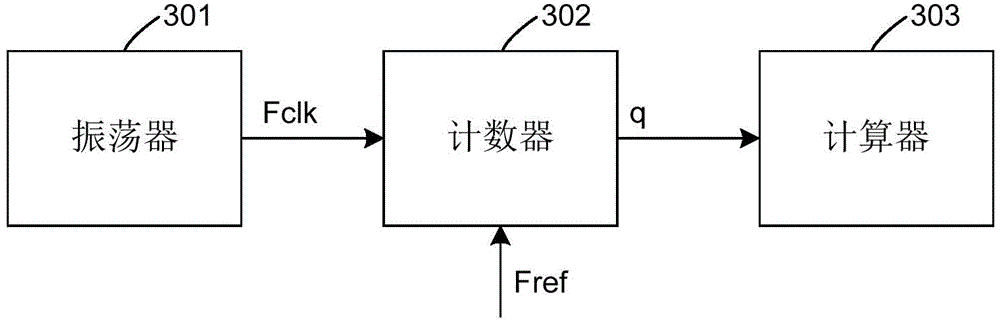

Temperature sensor and temperature measurement method

ActiveCN104132738ASimple structureSimplify complexityThermometers using electric/magnetic elementsUsing electrical meansAnalog-to-digital converterCalculator

The invention relates to the technical field of temperature measurement, and provides a temperature sensor and a temperature measurement method. The temperature sensor comprises an oscillator, a counter and a calculator. The oscillator is used for outputting periodic signals at a certain frequency to the counter, the counter is used for counting the periodic signals and sending a count value of the signals and total time duration of the signals to the calculator, and the calculator is used for calculating a temperature value according to the count value of the signals and the total time duration of the signals. Compared with the prior art, the quantization function of an analog-to-digital converter in the prior art is completed through the simple counter, and due to the fact that the counter is quite easy to implement, the complexity of the link of converting analog quantity to digital quantity in the prior art is simplified; the temperature sensor and the temperature measurement method have the advantages of being simple in structure, easy to implement, small in occupied chip area and low in power dissipation.

Owner:SHENZHEN RENERGY TECH

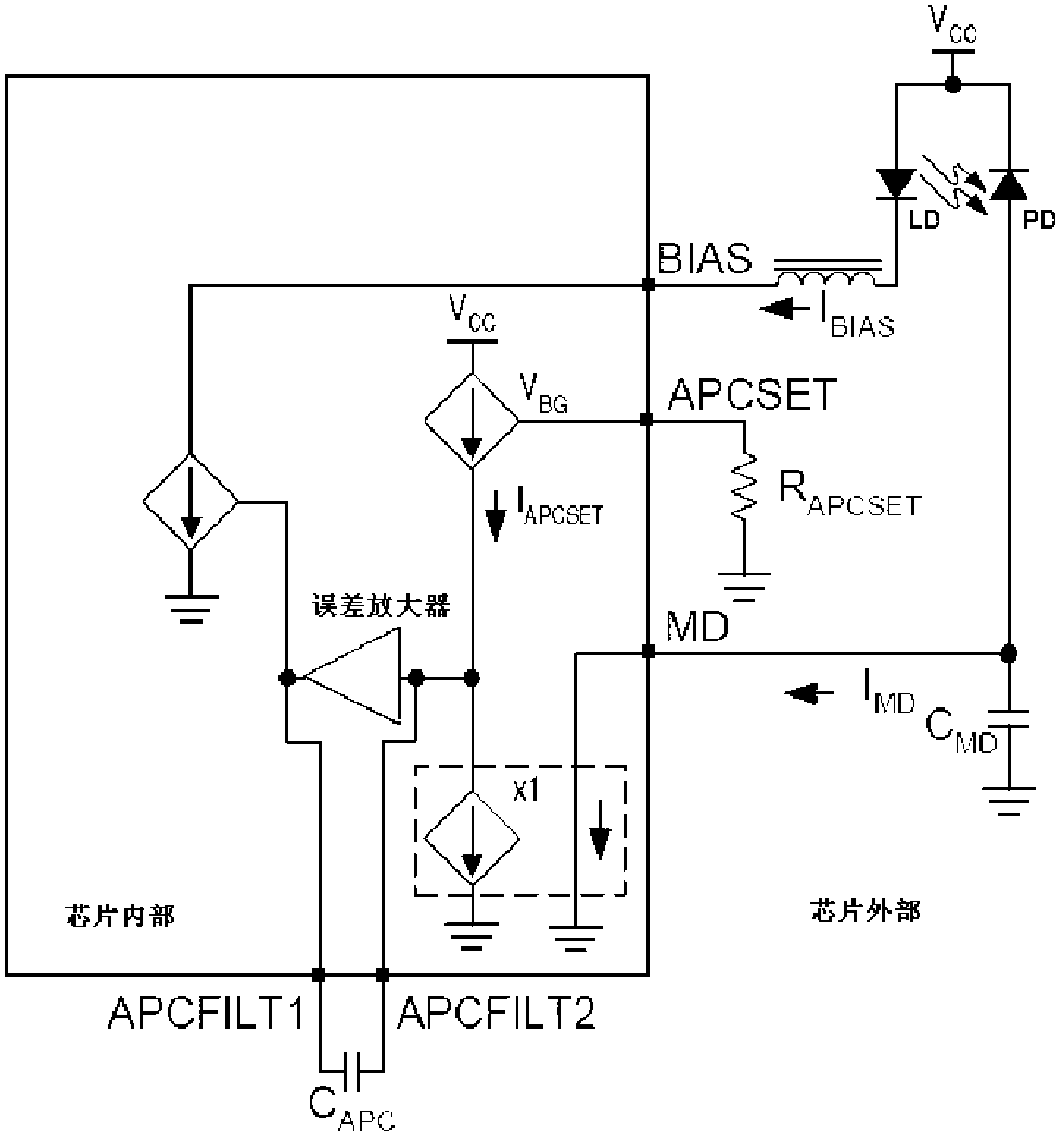

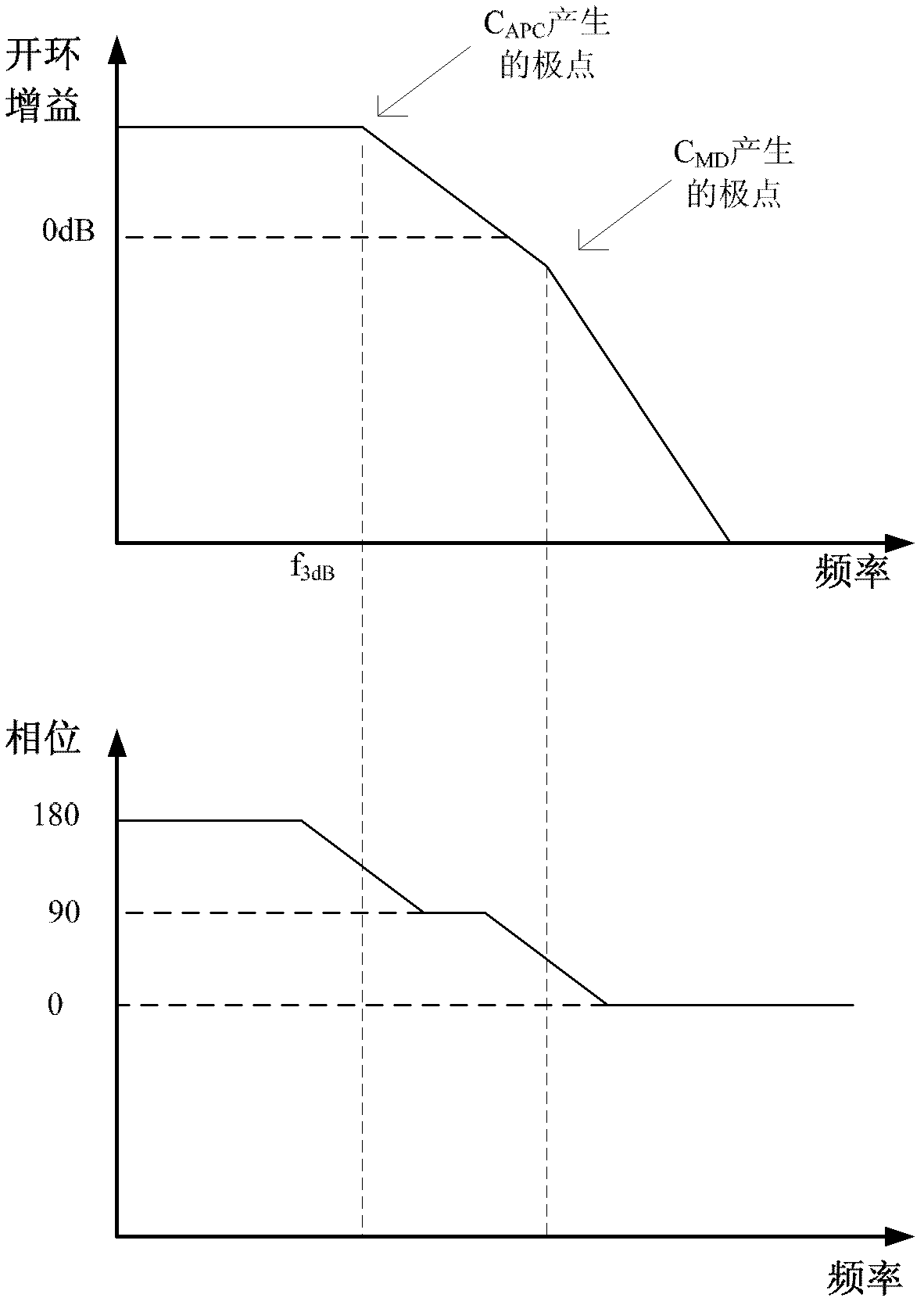

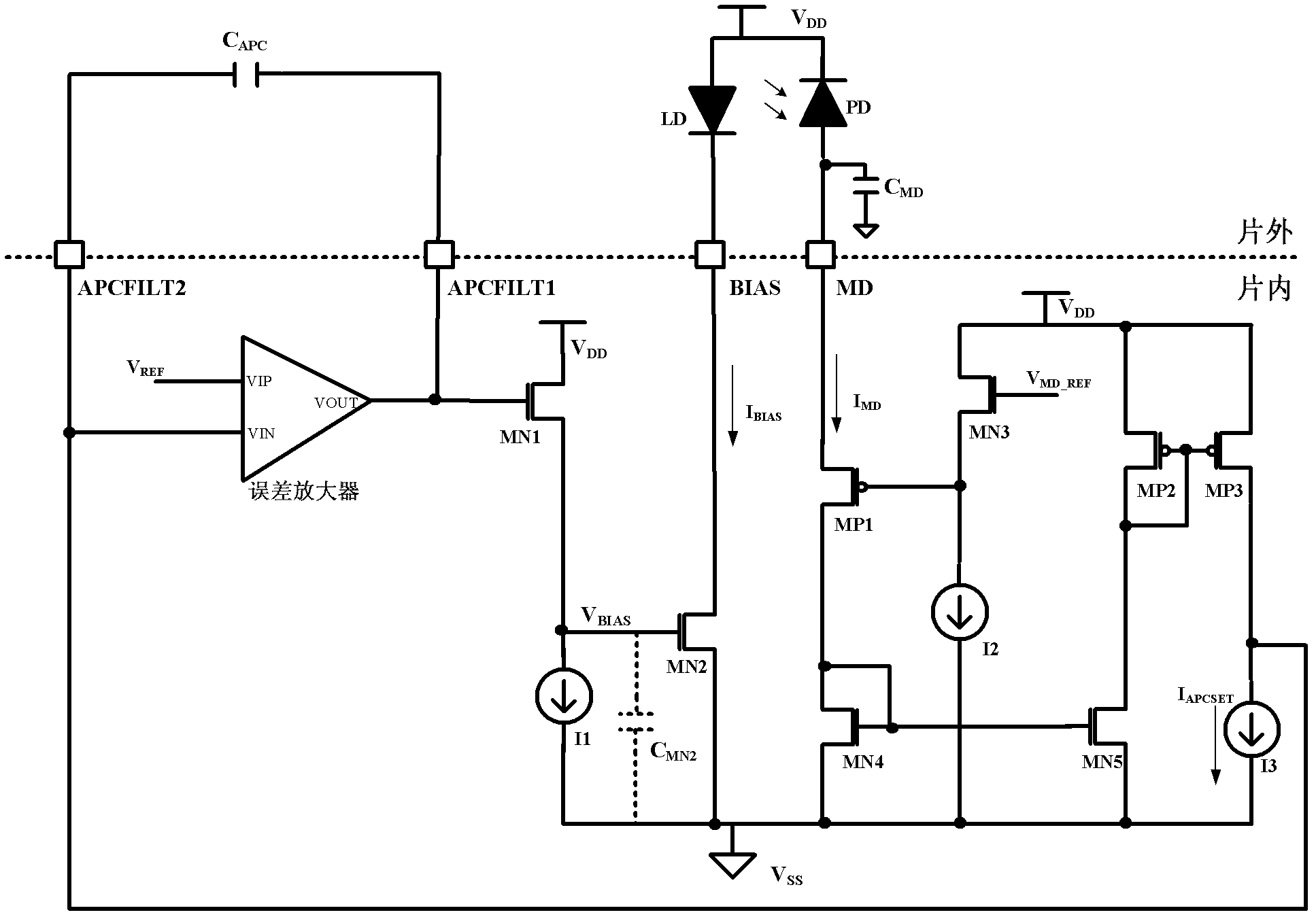

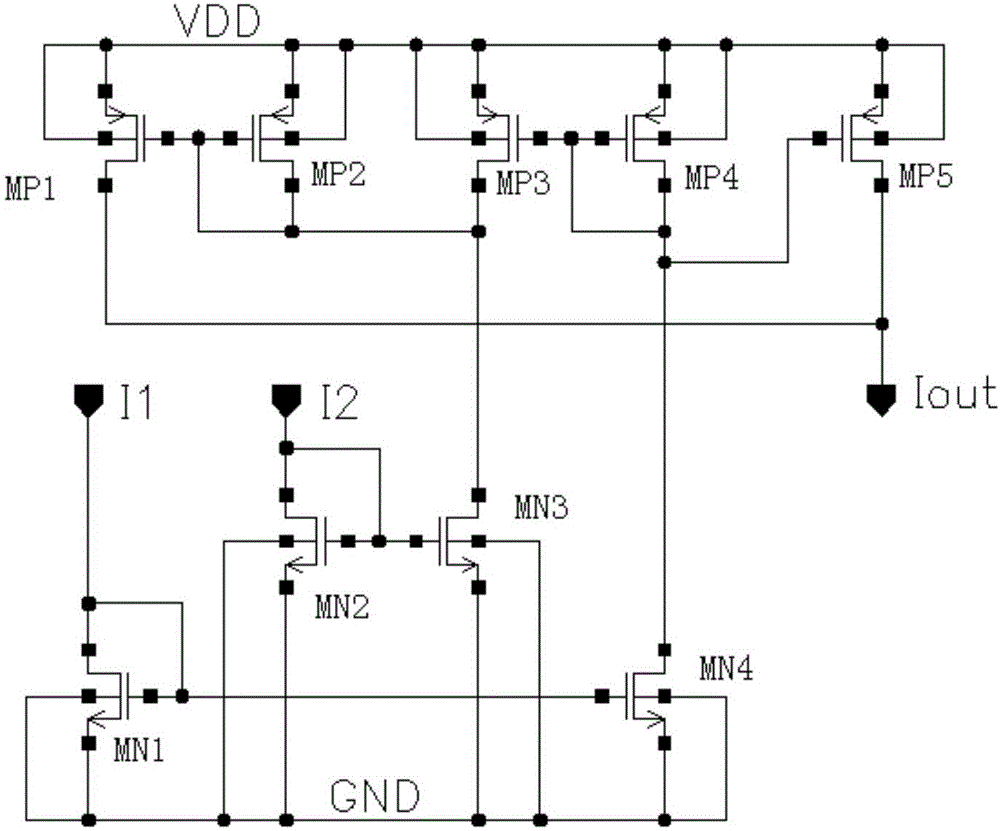

Automatic power control circuit for driving optical communication laser

ActiveCN102437507AStable DC Voltage BiasImprove work performanceLaser detailsDifferential amplifiersWork performanceEngineering

The invention relates to an automatic power control circuit for driving an optical communication laser. The circuit comprises an error amplifier, wherein the VIP end of the error amplifier is connected with a direct current reference stabilized voltage VREF, and the VIN end of the error amplifier is connected with a node APCFILT2; the VOUT end of the error amplifier is connected to a node APCFILT1; a transistor MN1 and a current source I1 form a source follower; a direct current reference stabilized voltage VMD_REF is connected to the gate of an N-channel metal oxide semiconductor (NMOS) transistor MN3; the transistor MN3 and a current source I2 form a source follower; transistors MN4 and MN5 form a pair of current mirrors; and transistors MP3 and MP2 form a pair of current mirrors. By the automatic power control circuit for the driving of the optical communication laser, the influence of other poles in the circuit on circuit stability is effectively eliminated, stable direct current voltage offset is provided for a photo diode at the same time, the working performance of the photo diode is improved, a circuit structure is simple and a small chip area is occupied.

Owner:FENGHUO COMM SCI & TECH CO LTD +1

Electric charge reallocation method for successive approximation analog-digital converter

InactiveCN105049050ASimple structureOccupies a small chip areaAnalogue/digital conversionElectric signal transmission systemsCorrection methodCorrection algorithm

The invention discloses an electric charge reallocation method for a successive approximation analog-digital converter, relating to the field of microelectronics and solid electronics and more particularly to the electric charge reallocation method for the successive approximation analog-digital converter. No extra correction digital-analog converter (DAC) is introduced, and no correction algorithm is introduced. It only needs to disassemble a maximum capacitor into two capacitors, and a first capacitor and a third capacitor are exchanged during two conversions, so as to offset the maximum error of differential non linearity (DNL) / integral non linearity (INL). Compared with a traditional correction method for improving DNL / INL by relying on the correction DAC or the correction algorithm, the electric charge reallocation method makes the structure of the successive approximation analog-digital converter simpler, allows the successive approximation analog-digital converter to occupy a smaller chip area, and makes realization of the successive approximation analog-digital converter on a chip easier.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA

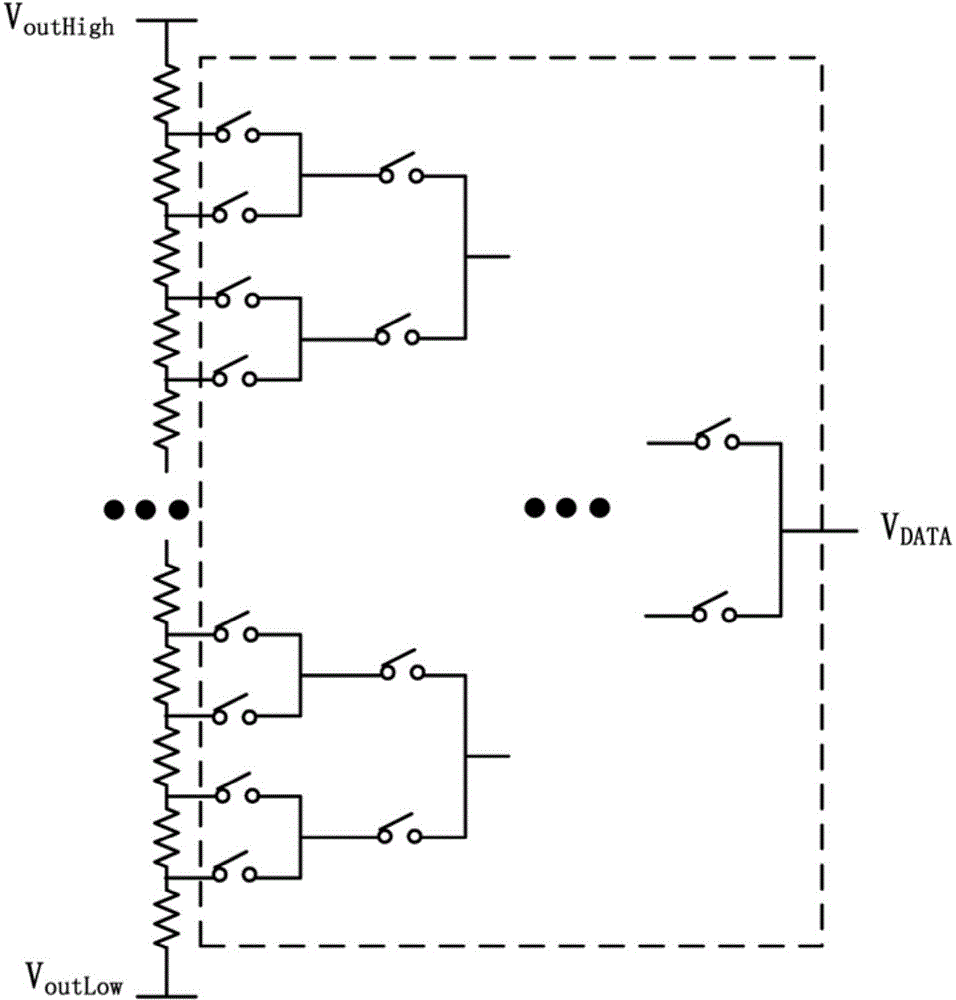

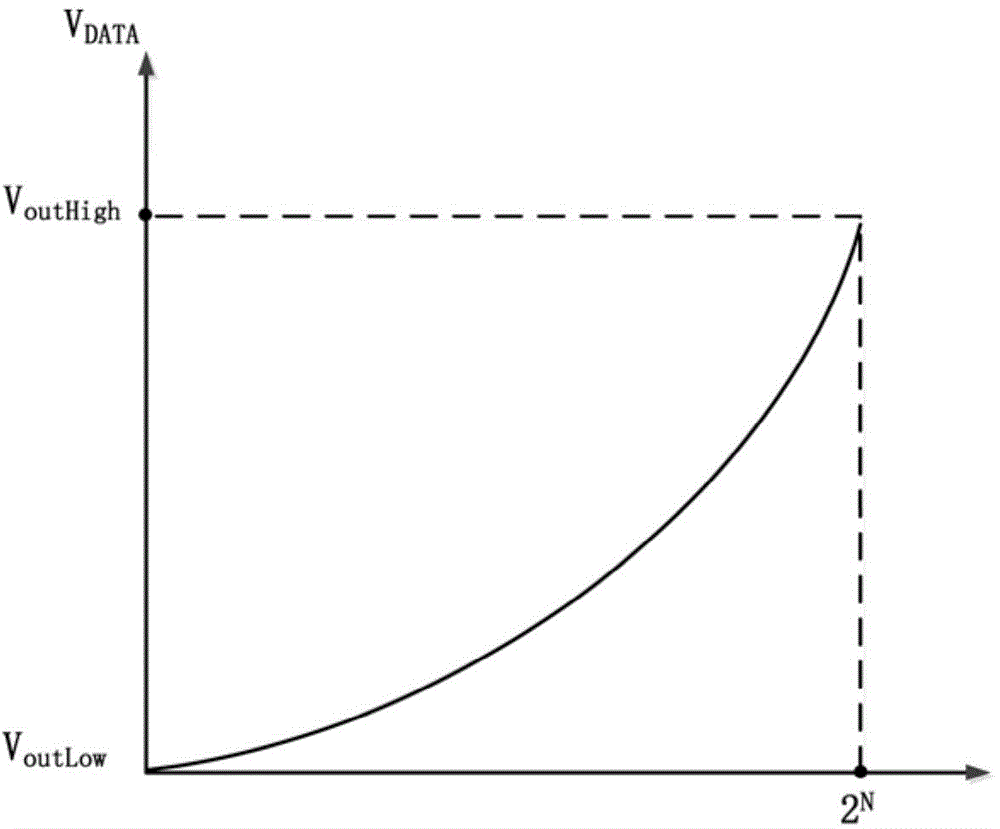

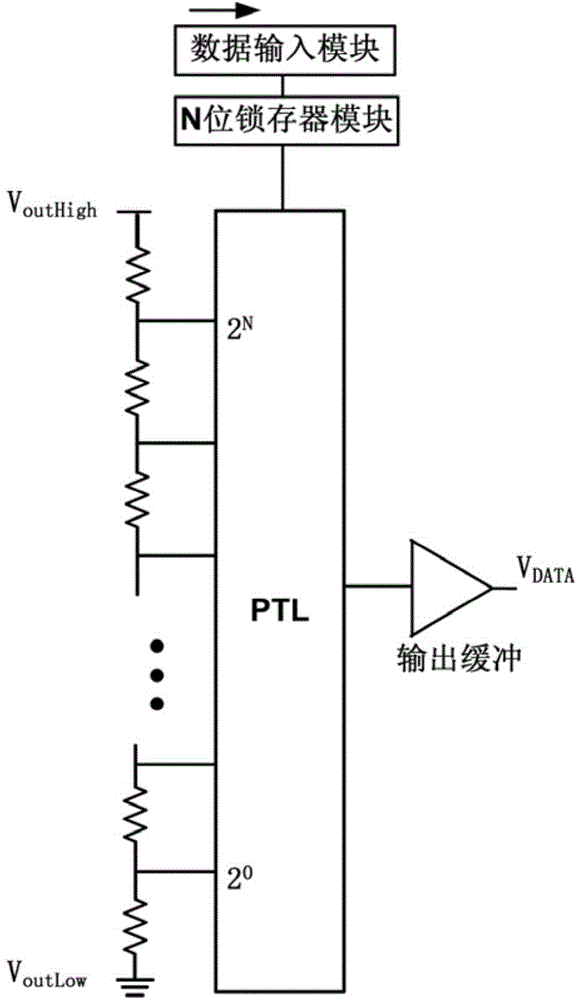

Low-voltage digital-to-analog signal converting circuit, data driving circuit and display system

ActiveCN104821828AReduce power consumptionOccupies a small chip areaStatic indicating devicesDigital-analogue convertorsLower limitLow voltage

The invention discloses a low-voltage digital-to-analog signal converting circuit, a data driving circuit and a display system. The low-voltage digital-to-analog signal converting circuit comprises at least one voltage-dividing unit (10); the voltage-dividing unit (10) includes a plurality of resistors which are connected in series between low-limit voltage and high-limit voltage, and voltage-dividing output ends which are led out from series connection nodes of the resistors and high-limit voltage connection ends. According to the low-voltage digital and analog signal converting circuit, the data driving circuit and the display system of the invention, the voltage-dividing units (10) are adopted, so that the low-voltage digital-to-analog signal converting circuit, the data driving circuit and the display system can be low-voltage devices, and the power consumption of the low-voltage digital-to-analog signal converting circuit, the data driving circuit and the display system are low, and the low-voltage digital-to-analog signal converting circuit occupies a small area of a chip.

Owner:PEKING UNIV SHENZHEN GRADUATE SCHOOL

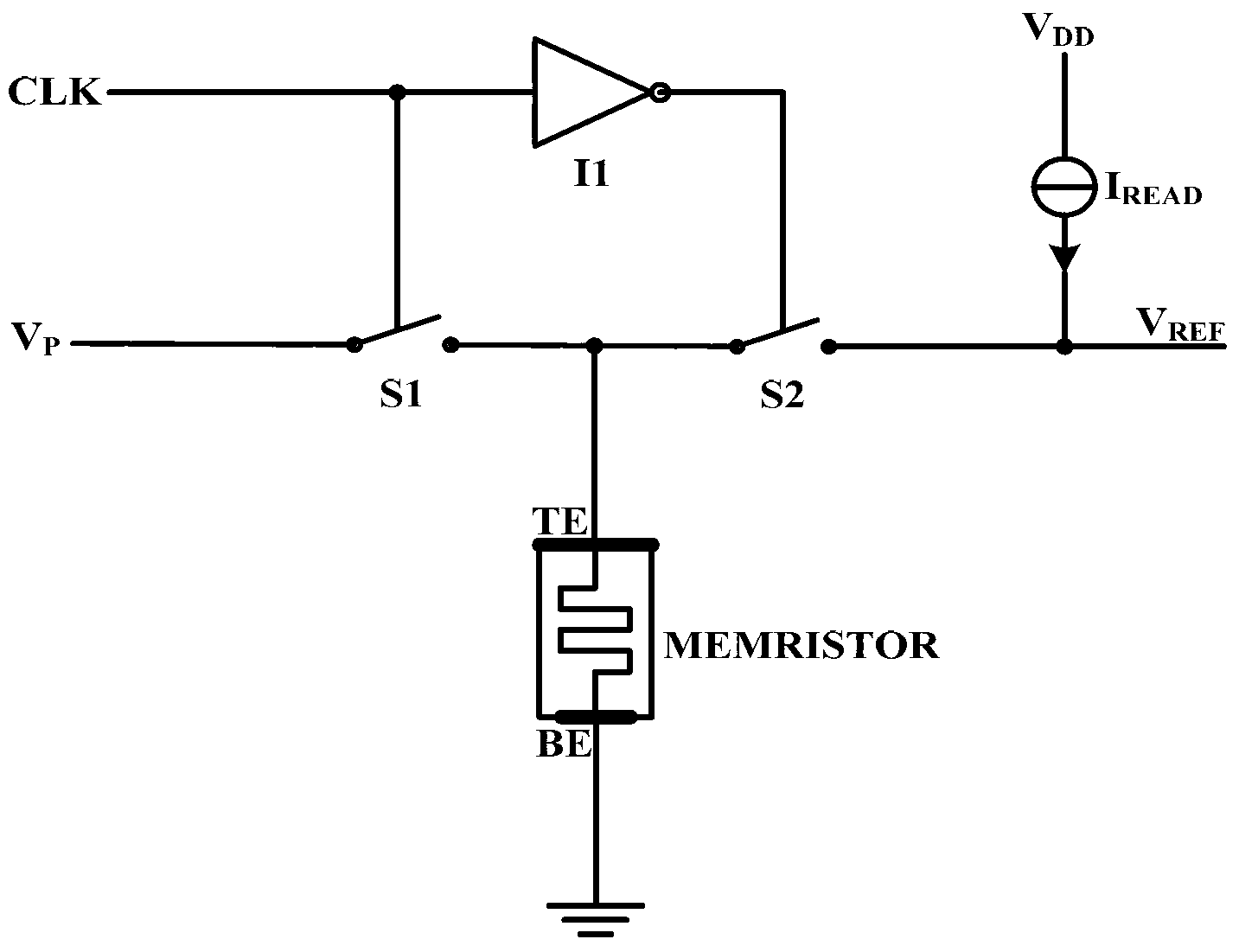

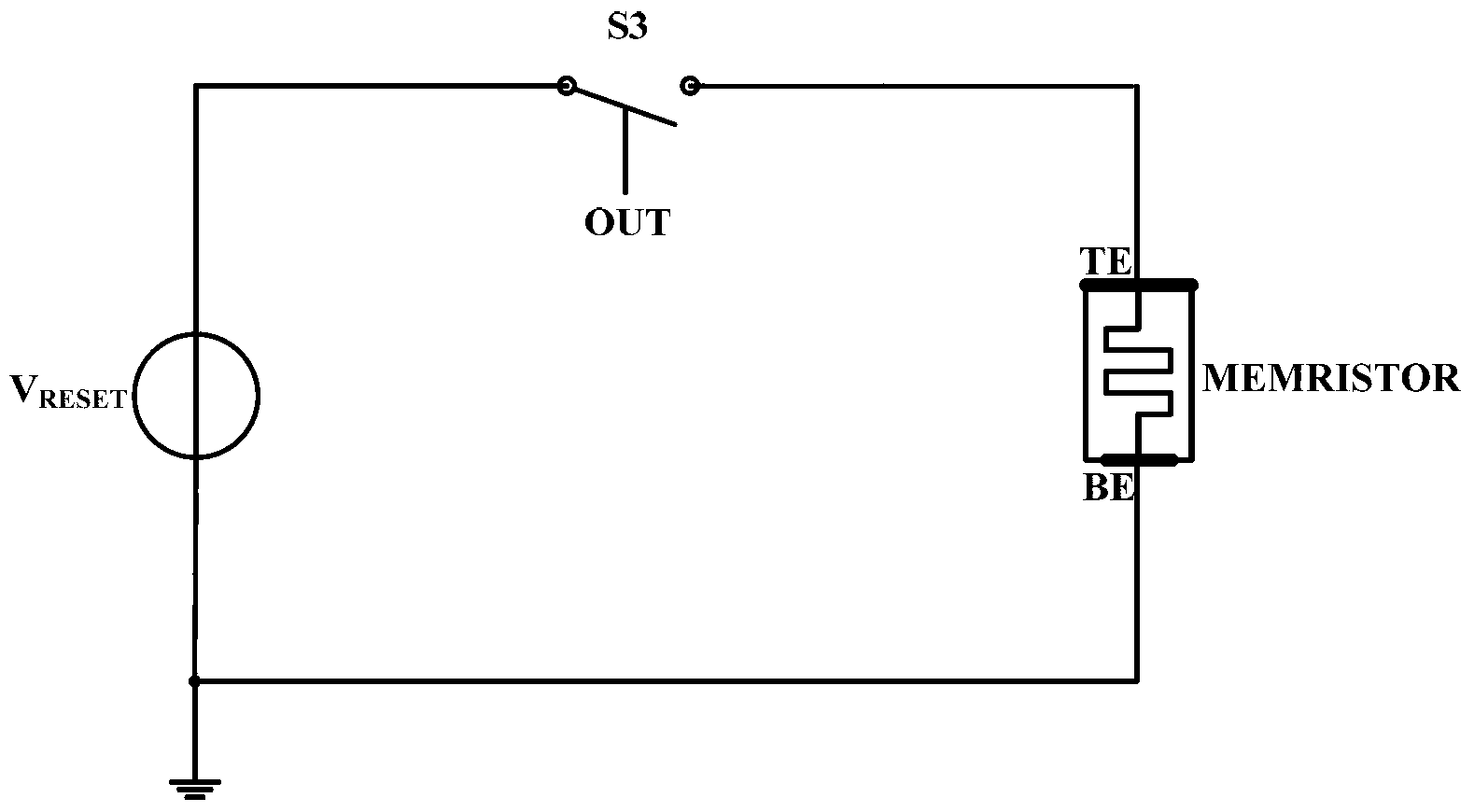

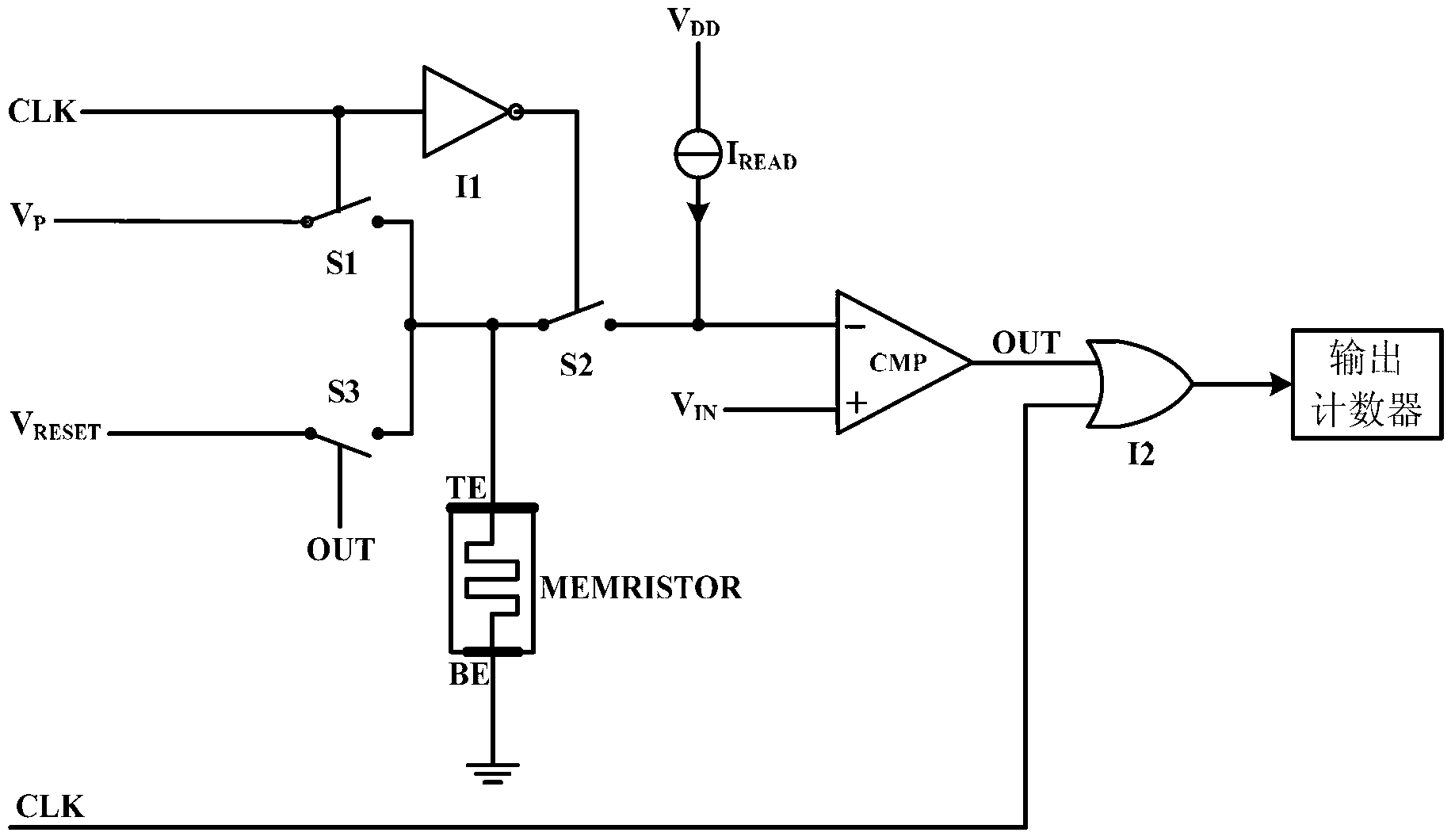

Analog-digital converter based on memristor

ActiveCN103312331AHigh precisionReduce power consumptionAnalogue-digital convertersVoltage referenceAnalog-to-digital converter

The invention relates to the field of a semiconductor integrated circuit, and discloses a novel analog-digital converter based on a memristor, which is high in precision, low in power consumption and small in occupied chip area. The analog-digital converter comprises a reference voltage production circuit, a comparator, a counter which can produce output codons and a reset circuit, wherein the reference voltage production circuit is connected with the antiphase end of the comparator; voltage is input to the in-phase end of the comparator; the output end of the comparator is connected with the counter which can produce the output codans through an OR gate; and the reset circuit is connected with the reference voltage production circuit. The analog-digital converter based on the memristor has the advantages that the precision is high, the power consumption is low, the occupied chip area is small, the structure is simple, the control is easy, and the analog-digital converter is suitable for low power consumption analog-digital conversion.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

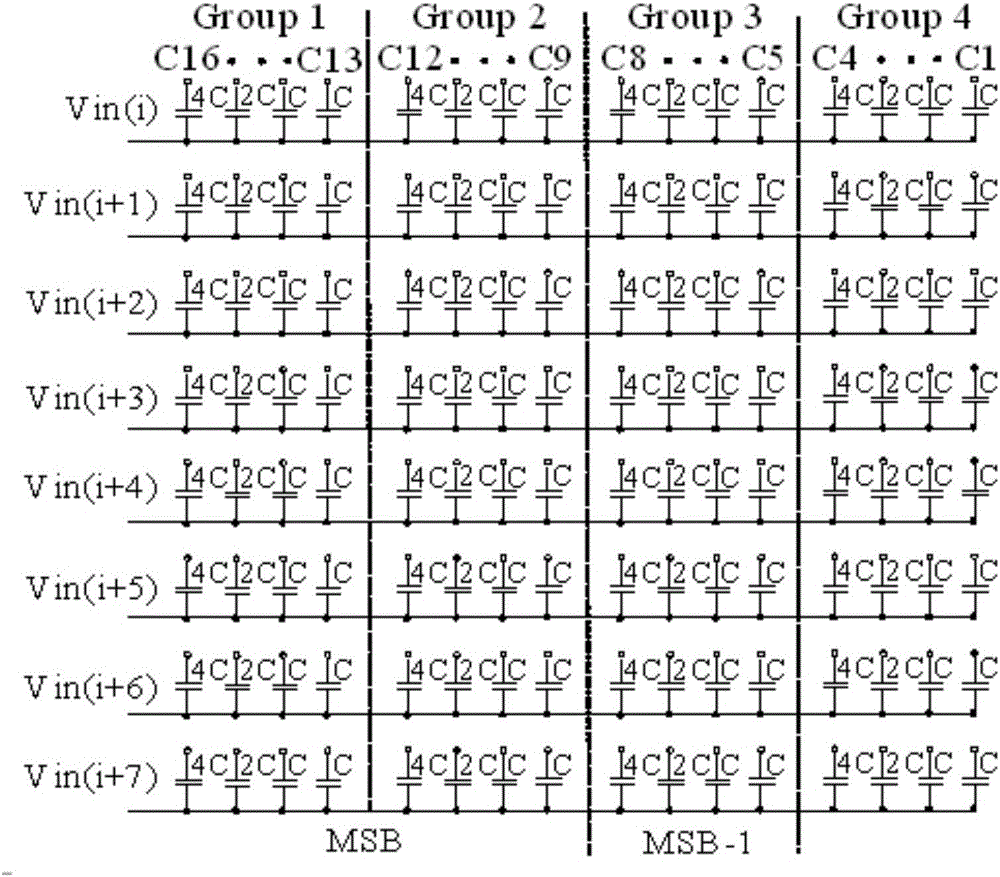

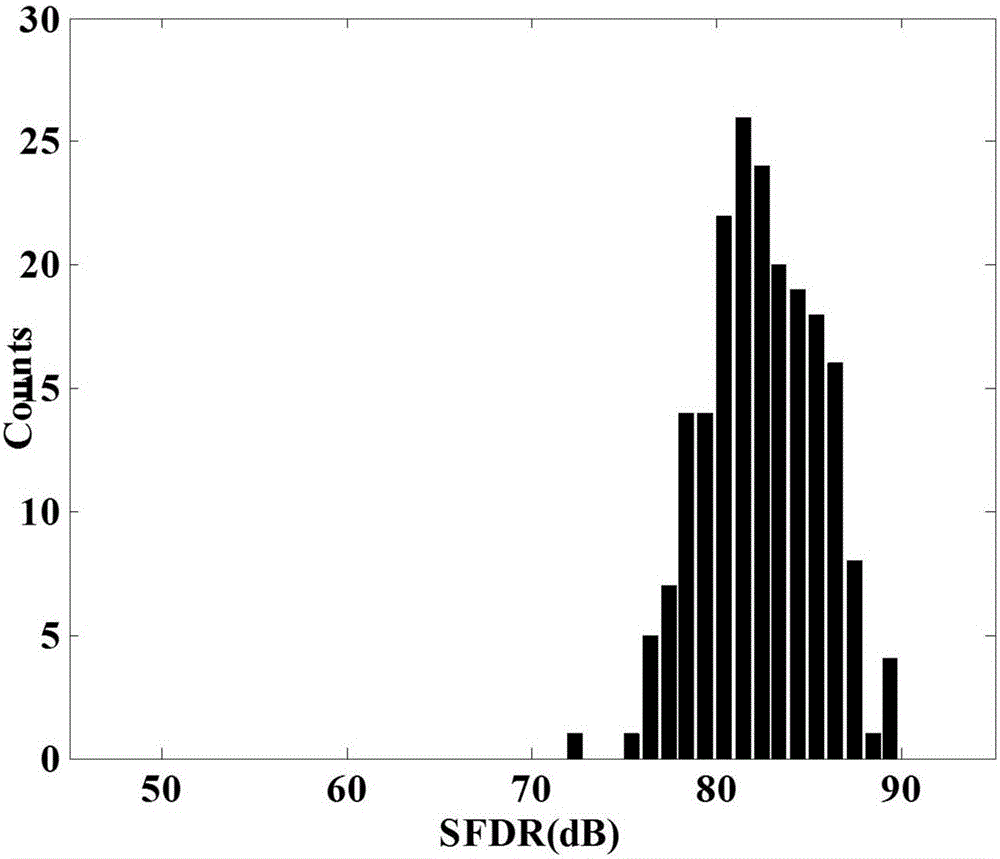

Bit cycle method for improving dynamic performance of hybrid resistance and capacitance type analog to digital converter

ActiveCN106209106AReduce areaSimple structureAnalogue/digital conversionElectric signal transmission systemsCorrection algorithmCapacitance

The invention discloses a bit cycle method for improving the dynamic performance of a hybrid resistance and capacitance type analog to digital converter. The applied technical field is a high-precision analog to digital converter in the field of microelectronics and solid state electronics. The bit cycle method provided by the invention is applicable to successive approximation analog to digital converter of any structure, the core idea is to split a most significant bit (MSB) capacitance and secondary most significant bit (MSB-capacitance), a capacitance array is divided into four groups, and the capacitance order is changed in each bit cycle to a dynamic averaging effect of capacitance errors is realized. The bit cycle method is characterized in that no correction algorithm needs to be introduced, no correction DAC needs to be introduced, the sampling rate of the analog to digital converter is not sacrificed, and the normal operation of the analog to digital converter is not interrupted. The bit cycle method provided by the invention can be used for carrying out dynamic averaging on the capacitance errors, therefore compared with the traditional correction method that depends on the correction DAC and the correction algorithm to improve the linearity, the structure is simpler, the occupied chip area is smaller, and a on-chip effect is realize more easily.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

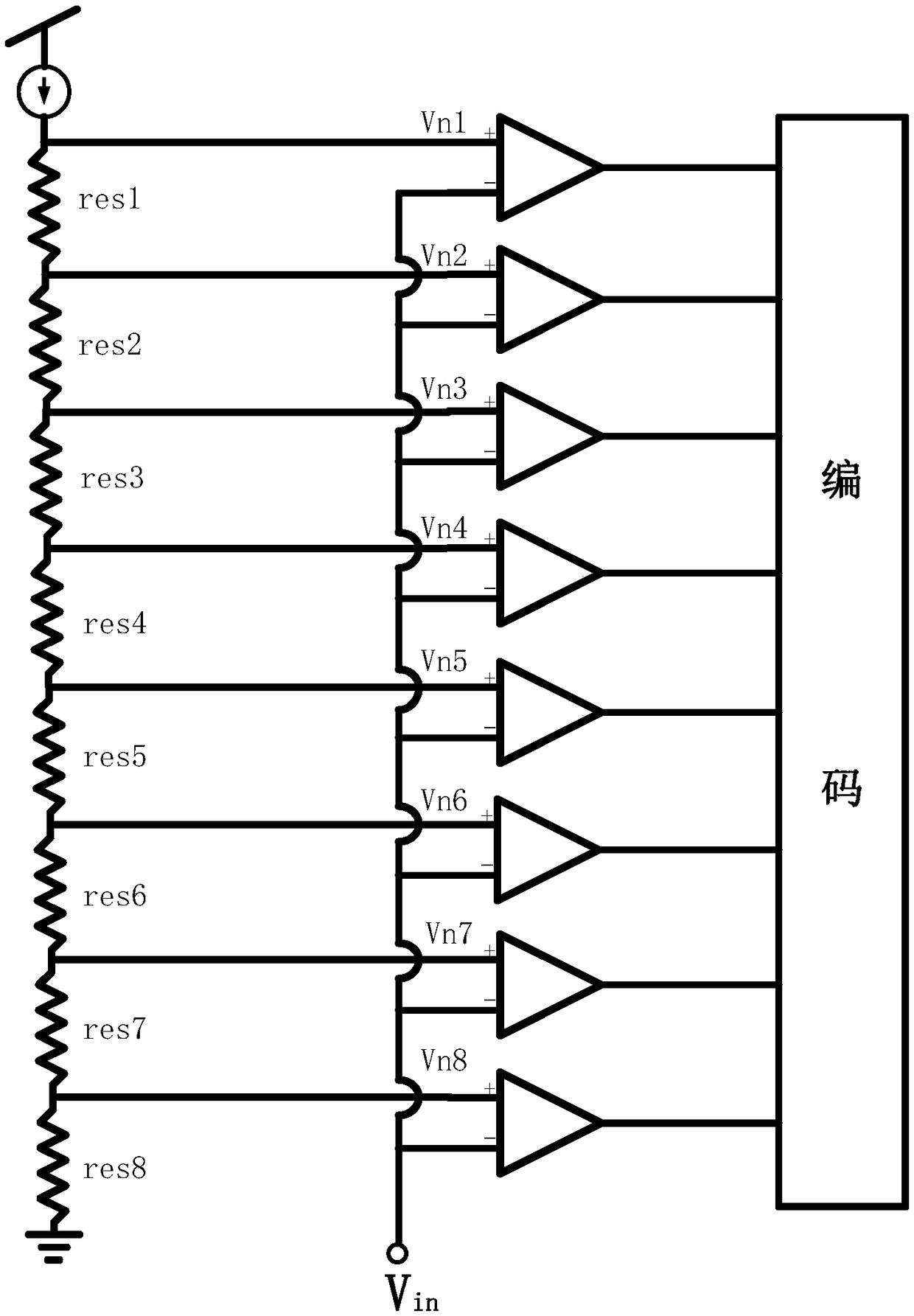

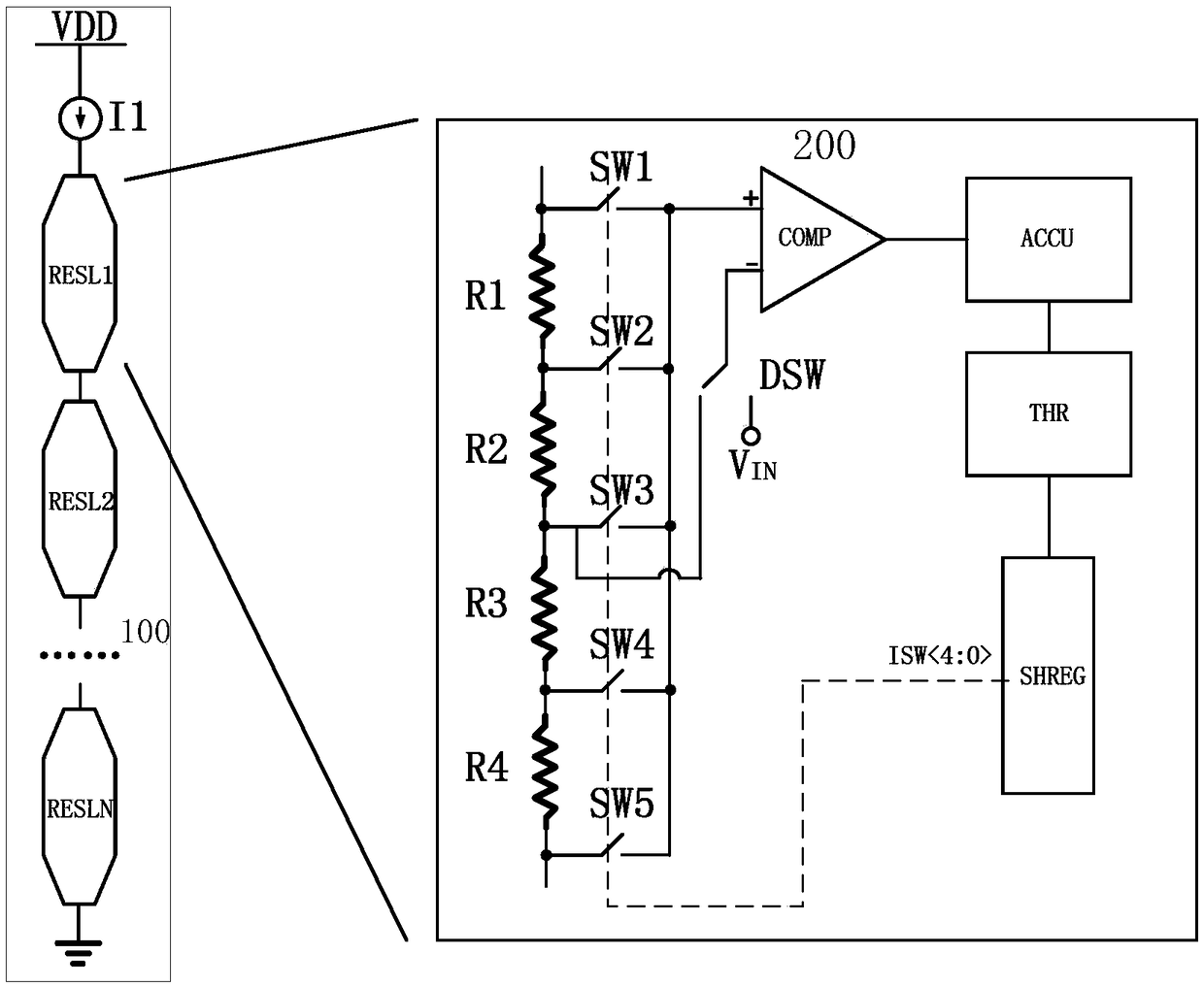

Pipelined analog-to-digit converter comparator offset foreground calibration circuit and method

ActiveCN108880545ACalibrating Static Offset ErrorCalibrate Dynamic Offset ErrorAnalogue/digital conversion calibration/testingShift registerElectrical resistance and conductance

The invention discloses a pipelined analog-to-digit converter comparator offset foreground calibration circuit and method. The circuit comprises a current source I1 and an adjustable resistor string unit array, wherein the adjustable resistor string unit array comprises N adjustable resistor string units RESL1 to RESLN; the current source I1 and the adjustable resistor string units RESL1 to RESLNare connected in series between a power supply VDD and the ground in sequence; the structures of the adjustable resistor string units RESL1 to RESLN are the same, and have adjustable resistance values; and each adjustable resistor string unit comprises 4 fine adjustment resistors R1 to R4, 5 switches SW1 to SW5, 1 two-for-one switch DSW, a comparator COMP, an accumulator ACCU, a threshold value judger THR and a bidirectional shift register SHREG. The pipelined analog-to-digit converter comparator offset foreground calibration circuit disclosed by the invention divides a traditional voltage sharing resistor into four parts so as to finely adjust the offset voltage of a comparator without introducing extra static power consumption, and is particularly applicable to low-power-consumption design.

Owner:BEIJING MXTRONICS CORP +1

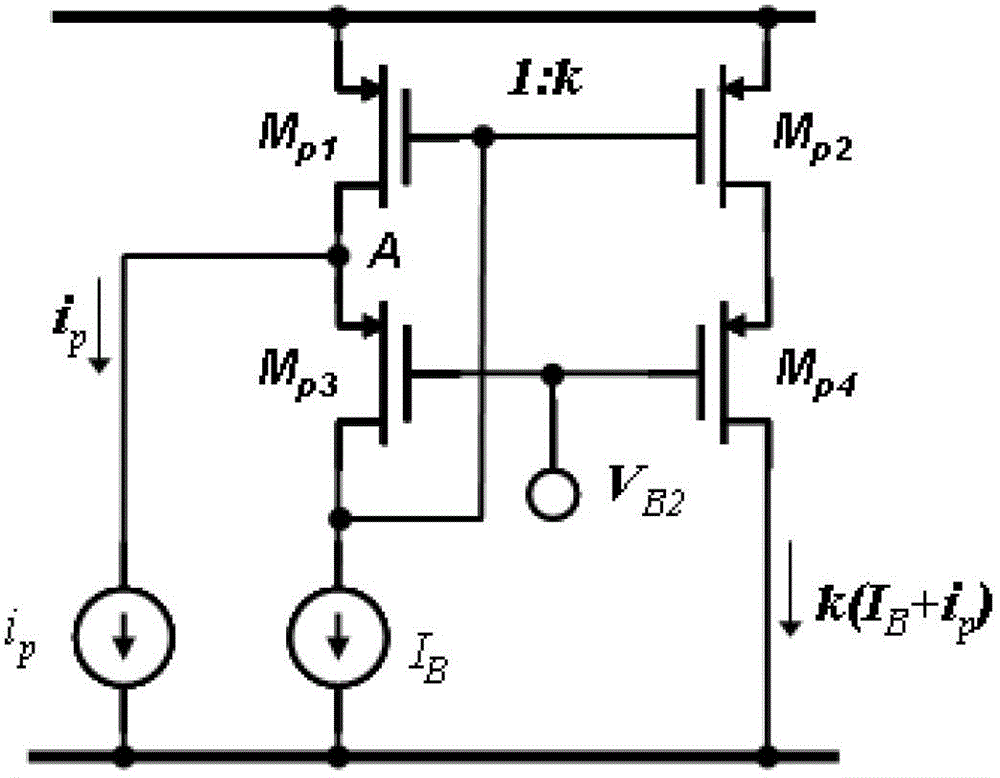

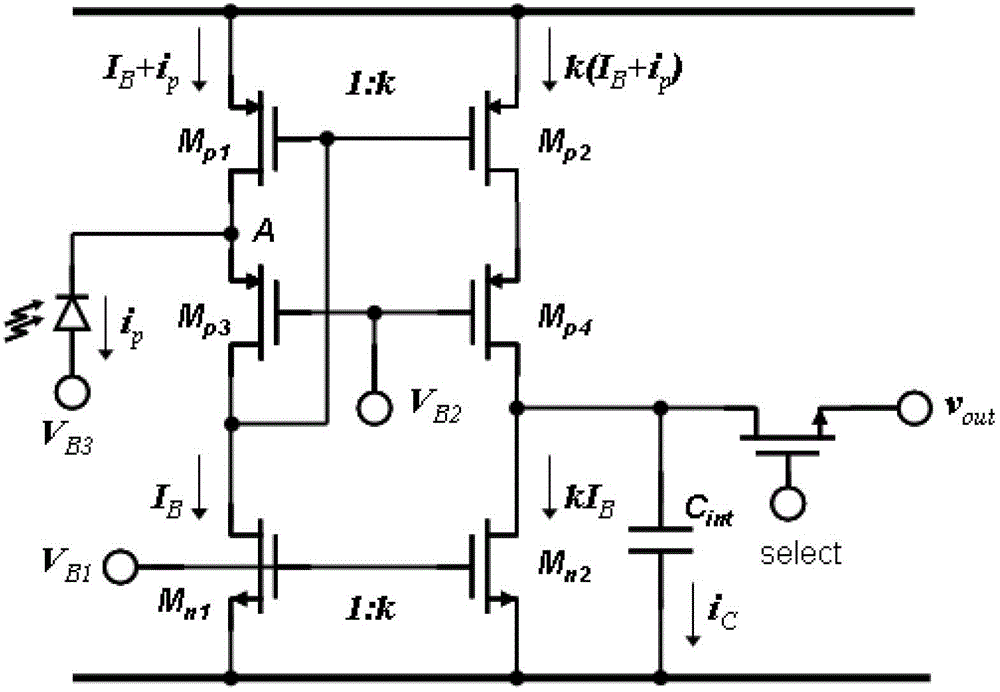

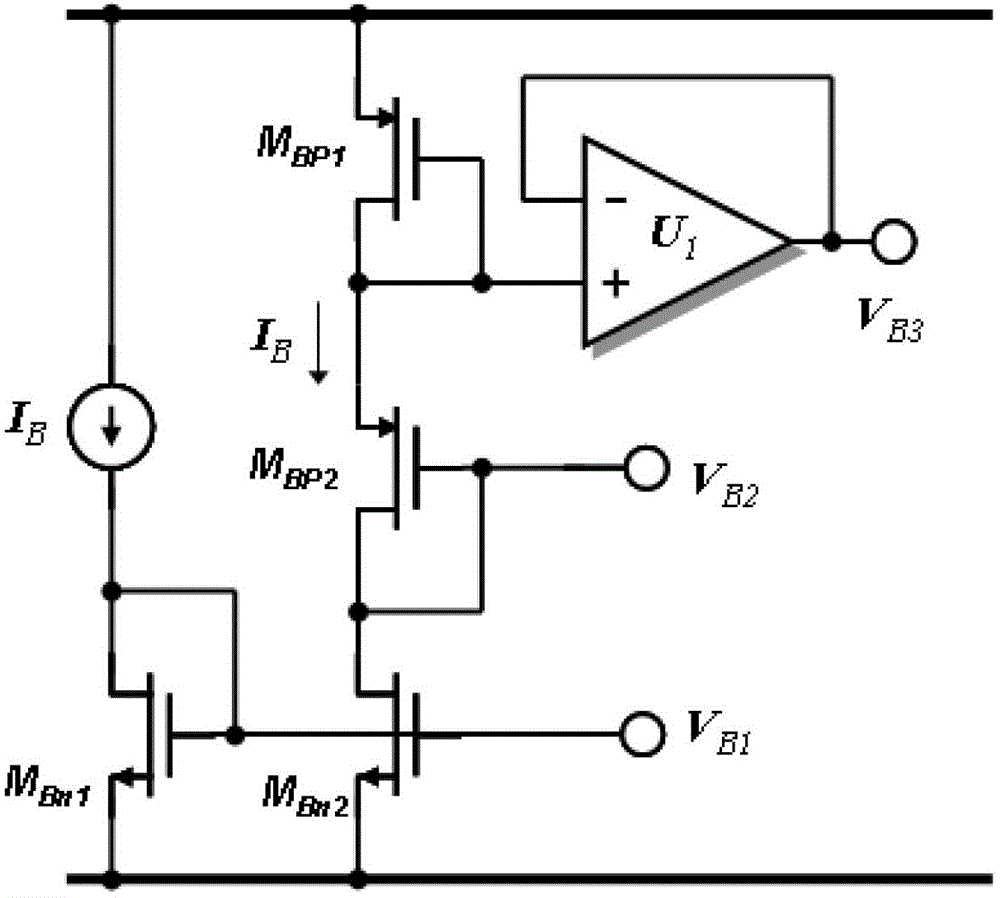

Photovoltaic detector read-out unit circuit applying inverted voltage follower

InactiveCN102722213AReduce power consumptionConstant bias voltageElectric variable regulationCapacitanceWilson current mirror

The invention relates to a photovoltaic detector read-out unit circuit applying an inverted voltage follower. The photovoltaic detector read-out unit circuit comprises a cascade current mirror circuit, a current integrating circuit and a bias voltage generating circuit, wherein transistors (Mp1 and Mp3) and transistors (Mp2 and Mp4) form the cascade current mirror circuit; transistors (Mp2, Mp4 and Mn2) and an integrating capacitor (Cint) form the current integrating circuit; and transistors (MBn1, MBn2, MBp1 and MBp2) form the bias voltage generating circuit. According to the circuit, an amplifier is not needed, the power loss is low, lower input resistance is realized and is unrelated to current of a detector, and the constant injection efficiency can be realized; bias voltage of the detector can be controlled accurately, and constant bias voltage of the detector can be provided; current gain of the read-out unit circuit can be changed through a dimension ratio of the transistors of a current mirror; a background current deduction circuit can be conveniently added, background suppression is realized, and the dynamic range of the circuit is enlarged; and the dynamic range is large, and input light current higher than bias current can be processed.

Owner:KUNMING INST OF PHYSICS

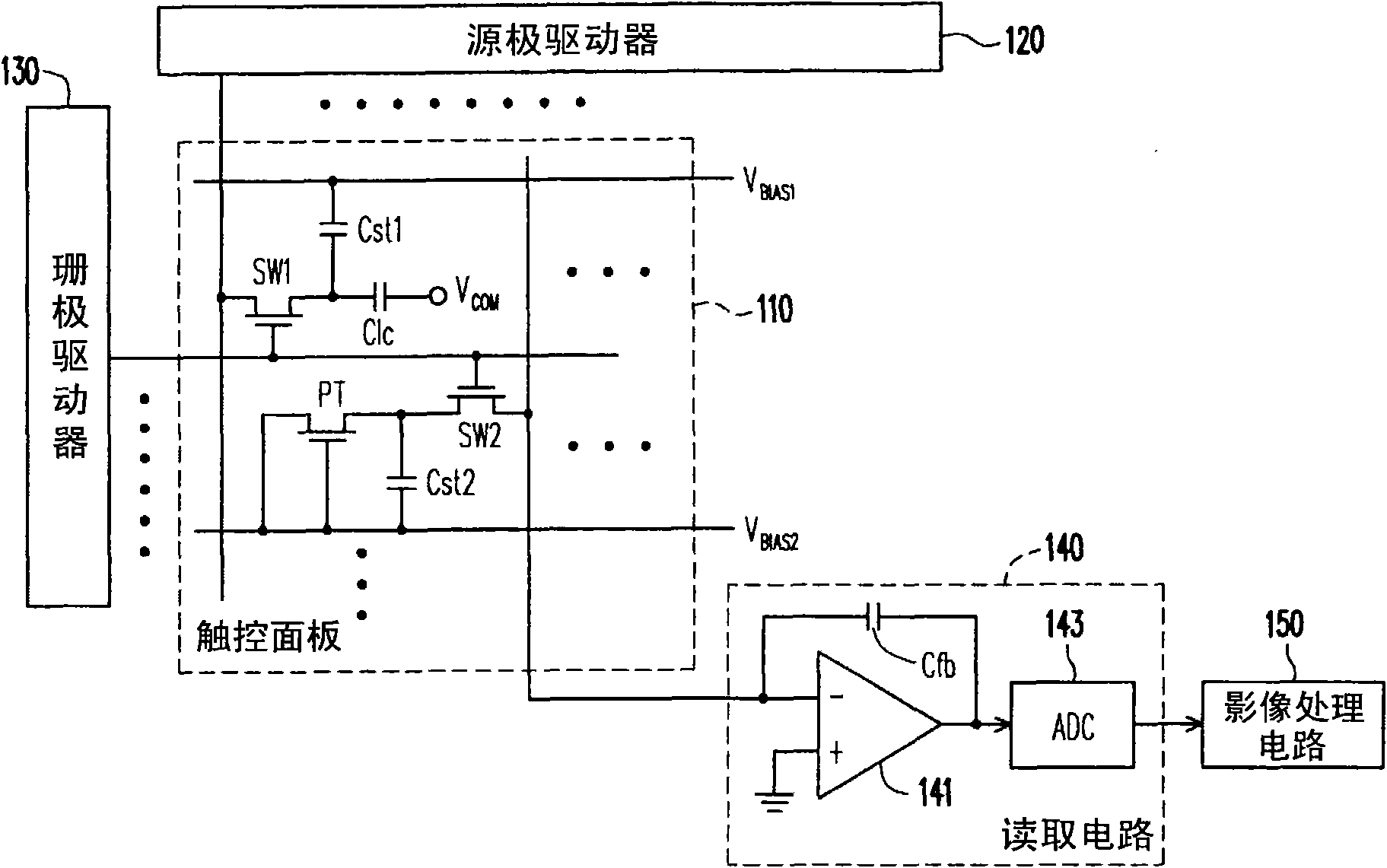

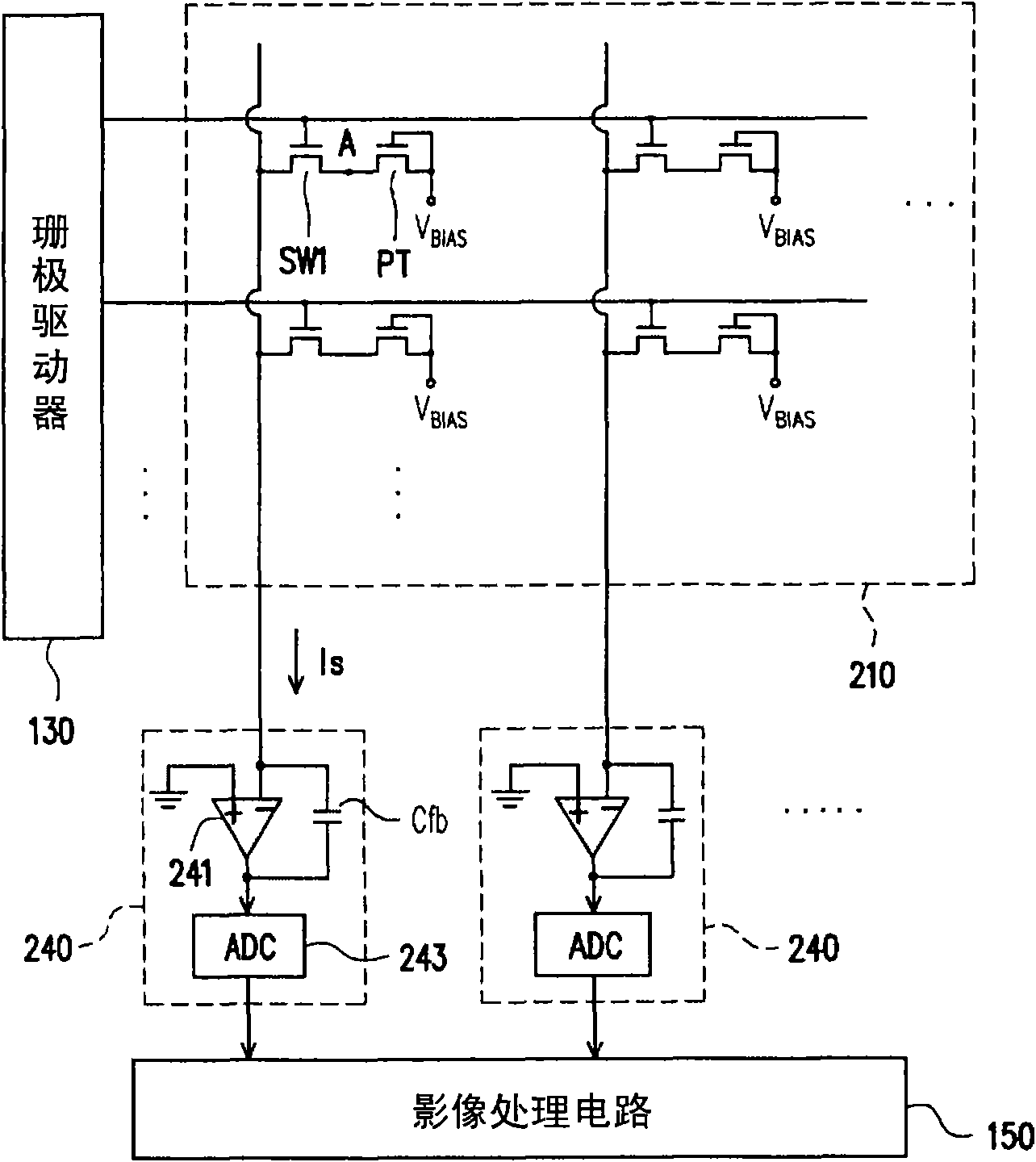

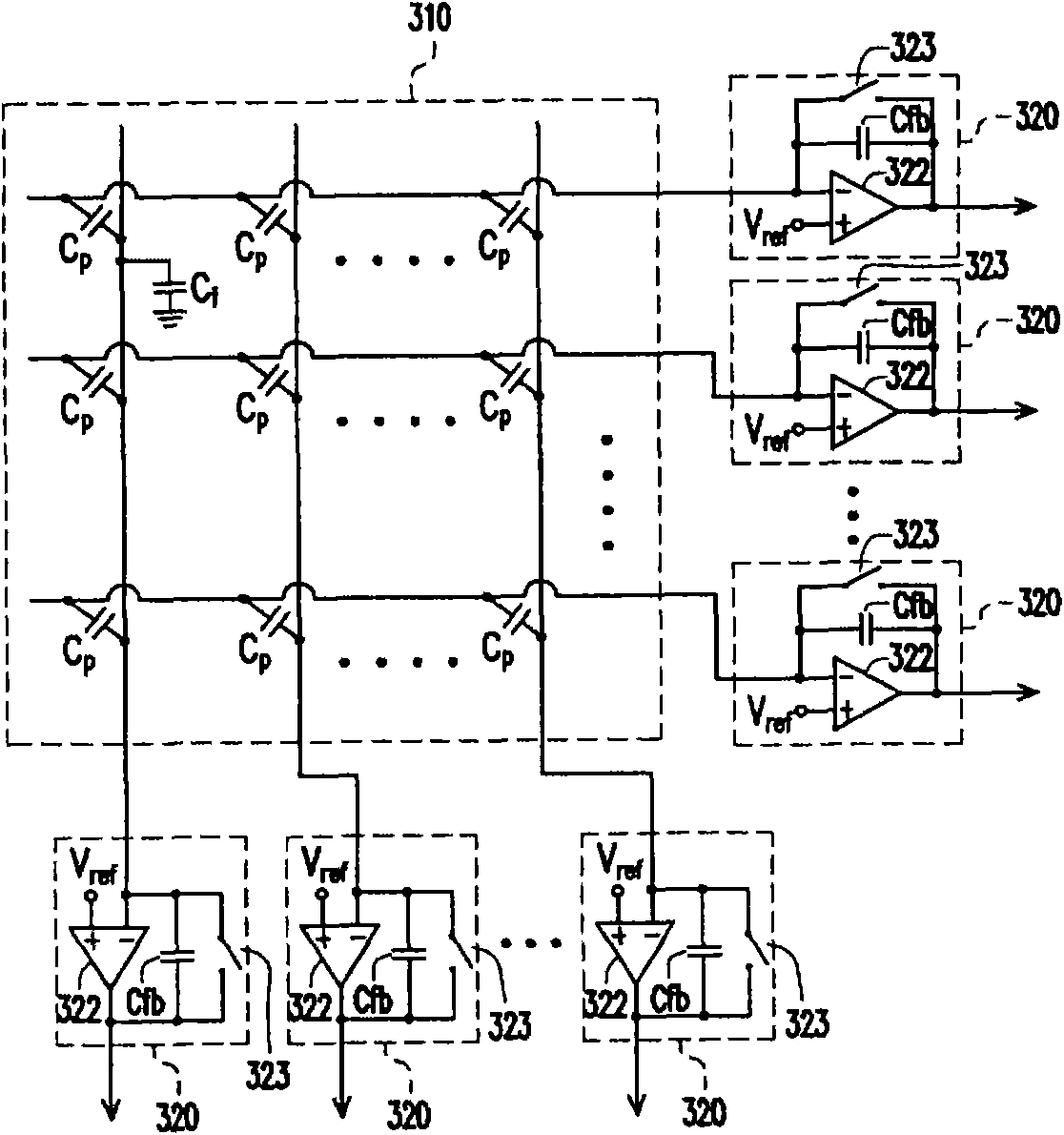

Reading device and multichannel reading device for touch-control panel

InactiveCN102043503AOccupies a small chip areaReduce areaInput/output processes for data processingCapacitanceIntegrator

The invention relates to a reading device and a multichannel reading device for a touch-control panel, which are used for integrating reading circuits of different types. A reading device in a first mode reads a touch-control panel with few quantity of electric charge by utilizing an integrator; a reading device in a second mode reads the sensing current of a current touch-control panel by utilizing a current-to-voltage conversion unit and an inverting amplifier to save the area of chips; and a multichannel reading device in a third mode shares a group of integrators with large-capacitance (or area) feedback capacitors (integral capacitors) in turn by a plurality of channels, so that the number of the large-area feedback capacitors can be reduced substantially. Therefore, the embodiment of the invention can be suitable for touch-control panels of different types except for fulfilling the aim of reducing the area of the chips.

Owner:HIMAX TECH LTD

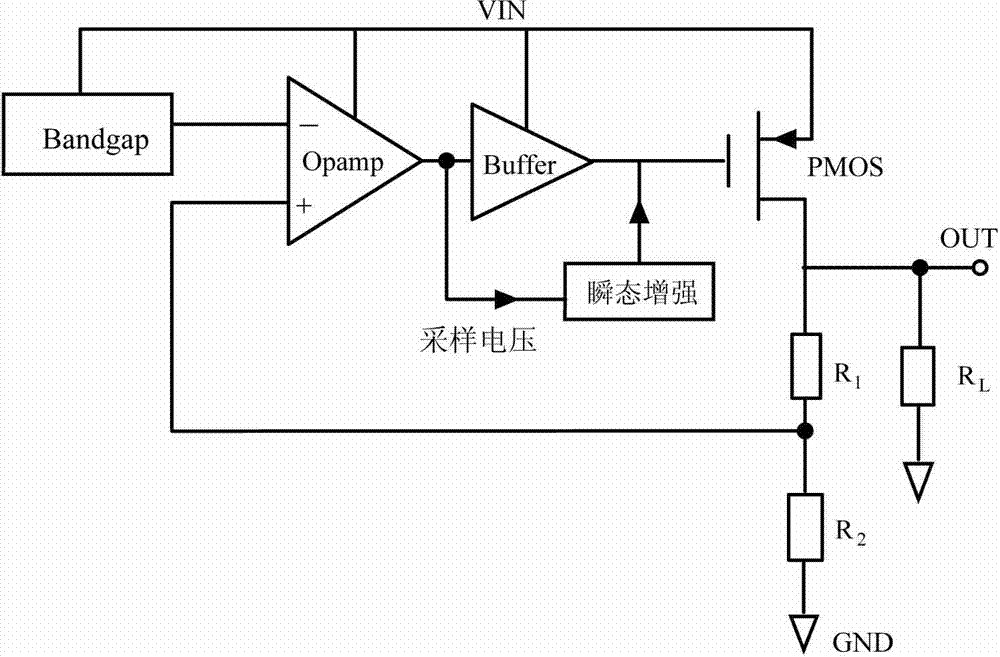

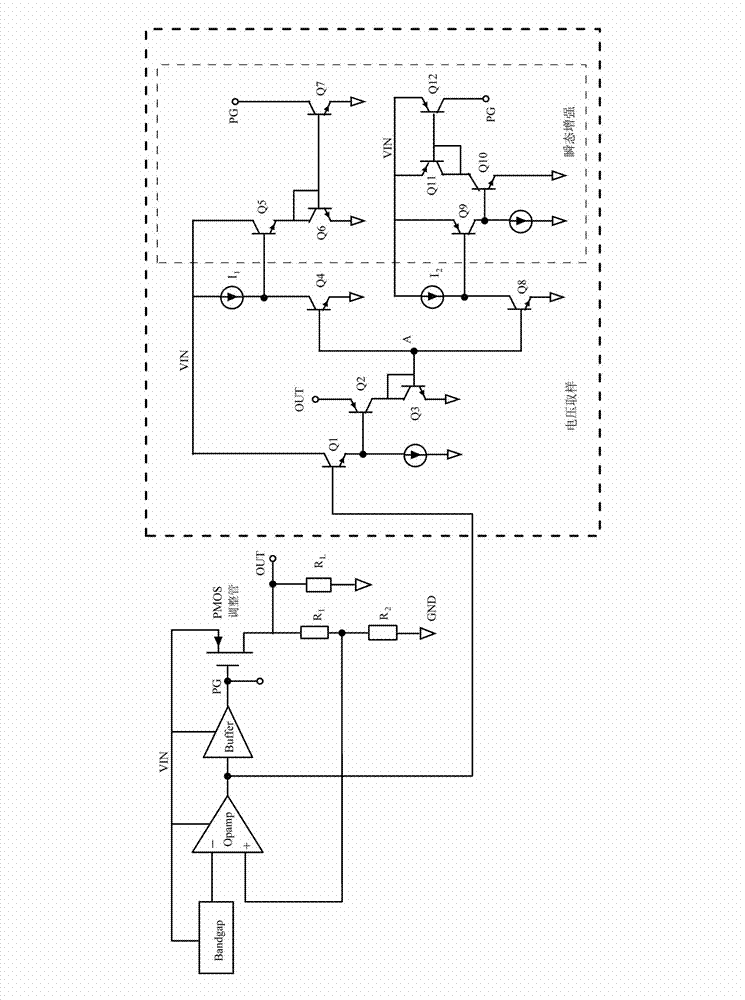

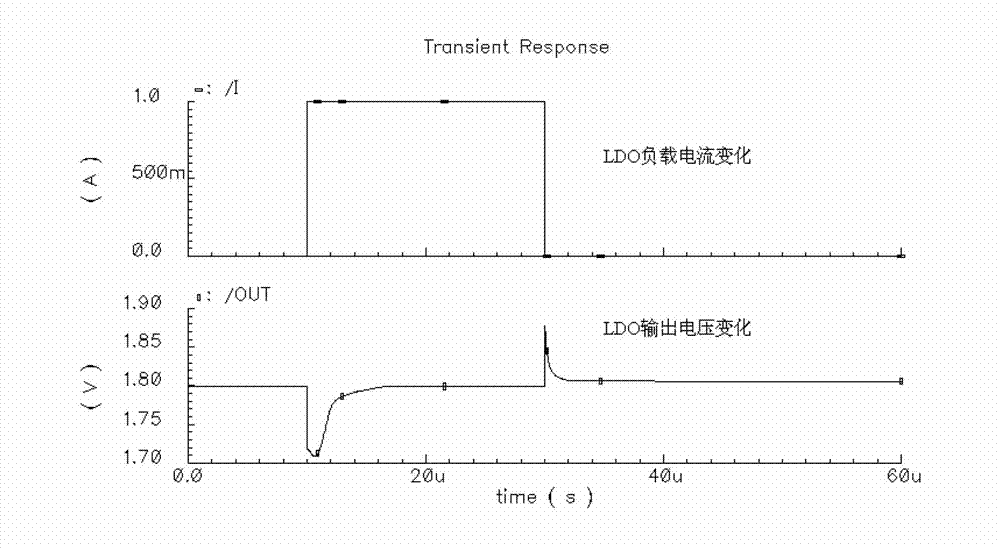

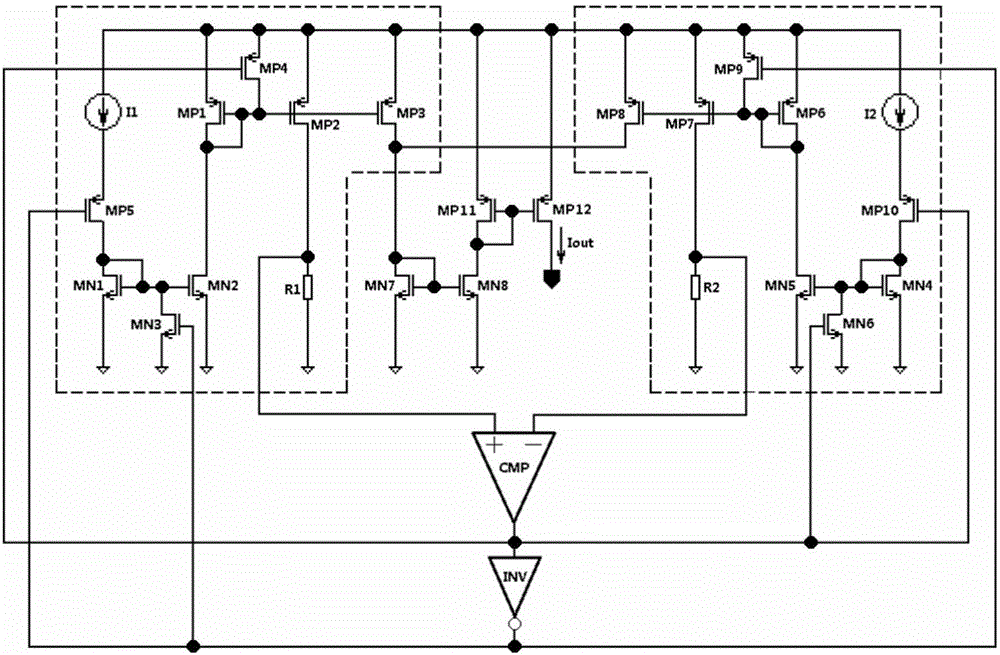

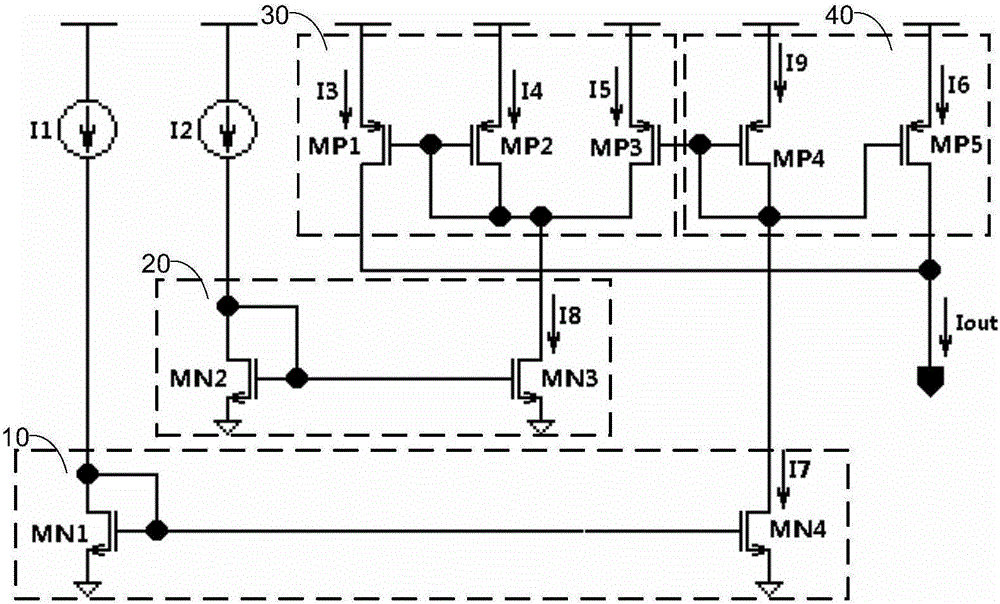

Transient state intensifier circuit applicable for capacitance-free large power low voltage difference linear voltage regulator

ActiveCN102759942ASimple structureOccupies a small chip areaElectric variable regulationCapacitanceTransient state

The invention relates to a transient state intensifier circuit applicable for a capacitance-free large power low voltage difference linear voltage regulator. The low voltage difference linear voltage regulator comprises a power adjusting tube; the transient state intensifier circuit comprises a voltage sampling part and a transient state intensifying part; the voltage sampling part is connected with an output end of the low voltage difference linear voltage regulator; an input end of the transient state intensifying part is connected with the voltage sampling part; an output end of the transient state intensifying part is connected with the grid of the power adjusting tube; when the low voltage difference linear voltage regulator changes from the light load to the heavy load, the level of the grid of the power adjusting tube is pulled down by the transient state intensifying part and an output voltage of the lowered low voltage difference linear voltage regulator is recovered; and when the low voltage difference linear voltage regulator changes from the heavy load to the light load, the level of the grid of the power adjusting tube is risen by the transient state intensifying part and the output voltage of the risen low voltage difference linear voltage regulator is recovered. The transient state intensifier circuit is simple in structure; a static power consumption current of the low voltage difference linear voltage regulator is hardly increased; and the rapid response of the low voltage difference linear voltage regulator is realized.

Owner:EAST CHINA INST OF OPTOELECTRONICS INTEGRATEDDEVICE

Current mode circuit of maximum current value

InactiveCN106200755ASimple structureReduce power consumptionElectric variable regulationEngineeringElectrical current

The invention discloses a current mode circuit of a maximum current value. The current mode circuit comprises a first current mirror, a second current mirror, an operation unit and a third current mirror, wherein the first current mirror is used for converting first input current into first current sink; the second current mirror is used for converting second input current into second current sink; the operation unit is used for generating an operation result according to relative sizes of the first current sink and the second current sink; the third current mirror is used for converting the first current sink into current source output; the current source output of the operation unit and the current source output of the third current mirror are summed to be used as final current output; and the current mode circuit of the maximum current value, which is simple in structure, low in power consumption and small in occupied chip area is realized.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

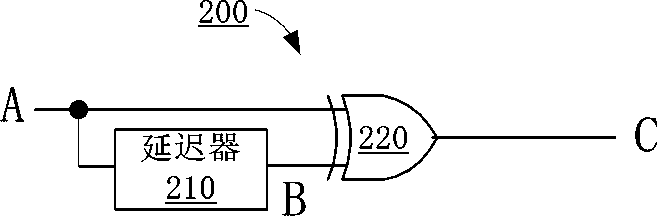

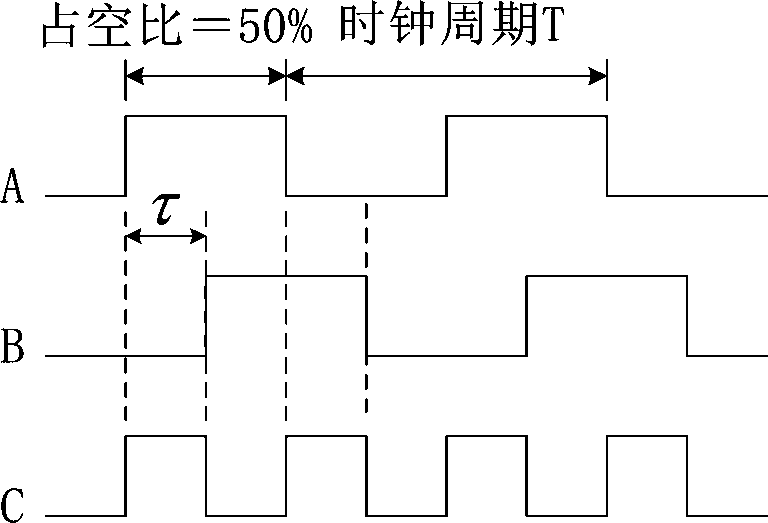

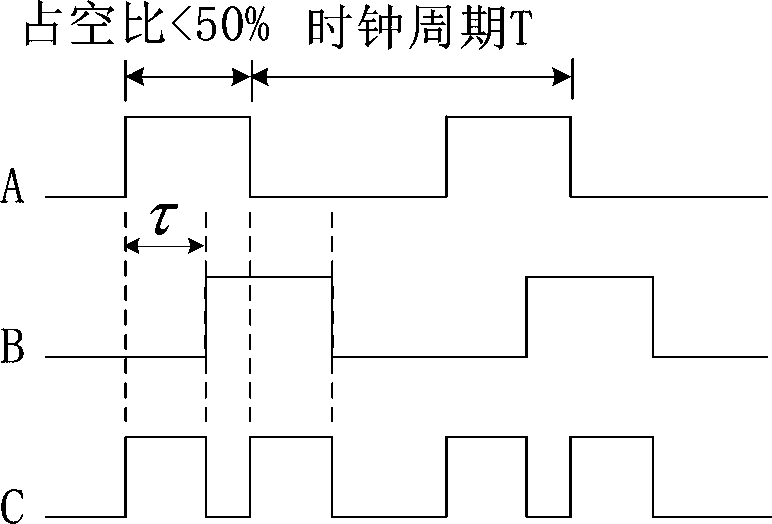

Circuit for accurately correcting duty ratio of clock signal

ActiveCN110957998ADuty cycle controlFew modulesContinuous to patterned pulse manipulationCMOSLow-pass filter

The invention discloses a circuit for accurately correcting the duty ratio of a clock signal. The circuit comprises an inverter chain, a delay unit, a phase detection unit and a low-pass filter. The inverter chain adopts one CMOS inverter or adopts a plurality of cascaded CMOS inverters. An input signal enters the input end of the inverter chain. The duty ratio of the input signal is adjusted through the change of the grid bias voltage of the first CMOS inverter in the inverter chain, and the inverter chain outputs an output signal subjected to duty ratio correction. And the output signal passes through the time delay unit to obtain a time delay signal. The output signal and the delay signal are used as input of the phase detection unit together, and the phase detection unit outputs an indication signal representing whether the duty ratio of the output signal reaches a target value or not. After high-frequency components of the indication signals are filtered out through a low-pass filter, the remaining low-frequency and direct-current components serve as grid direct-current bias voltage of a first CMOS inverter in the inverter chain. The duty ratio of the output signal can be accurately controlled.

Owner:ASR SMART TECH CO LTD

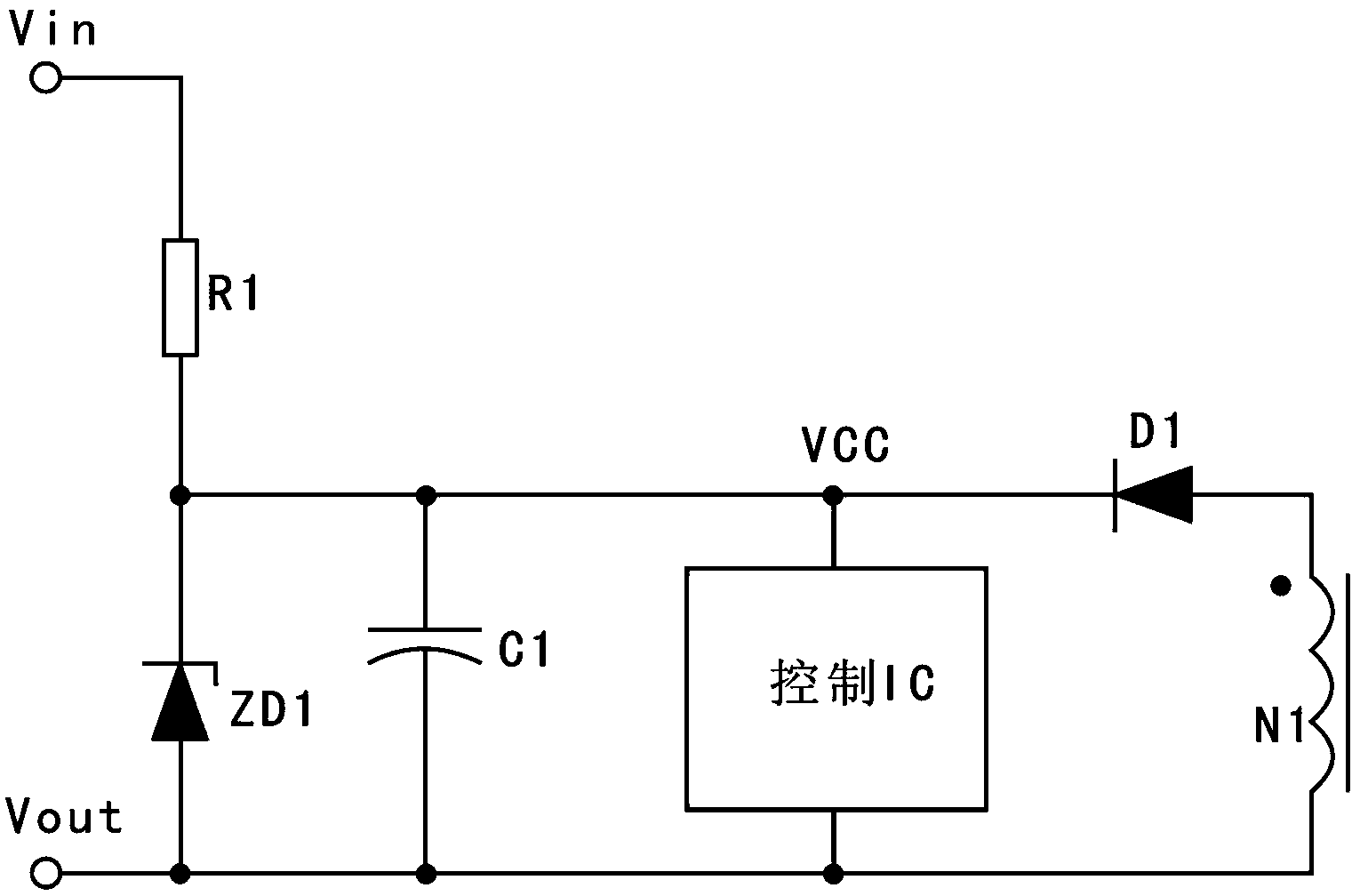

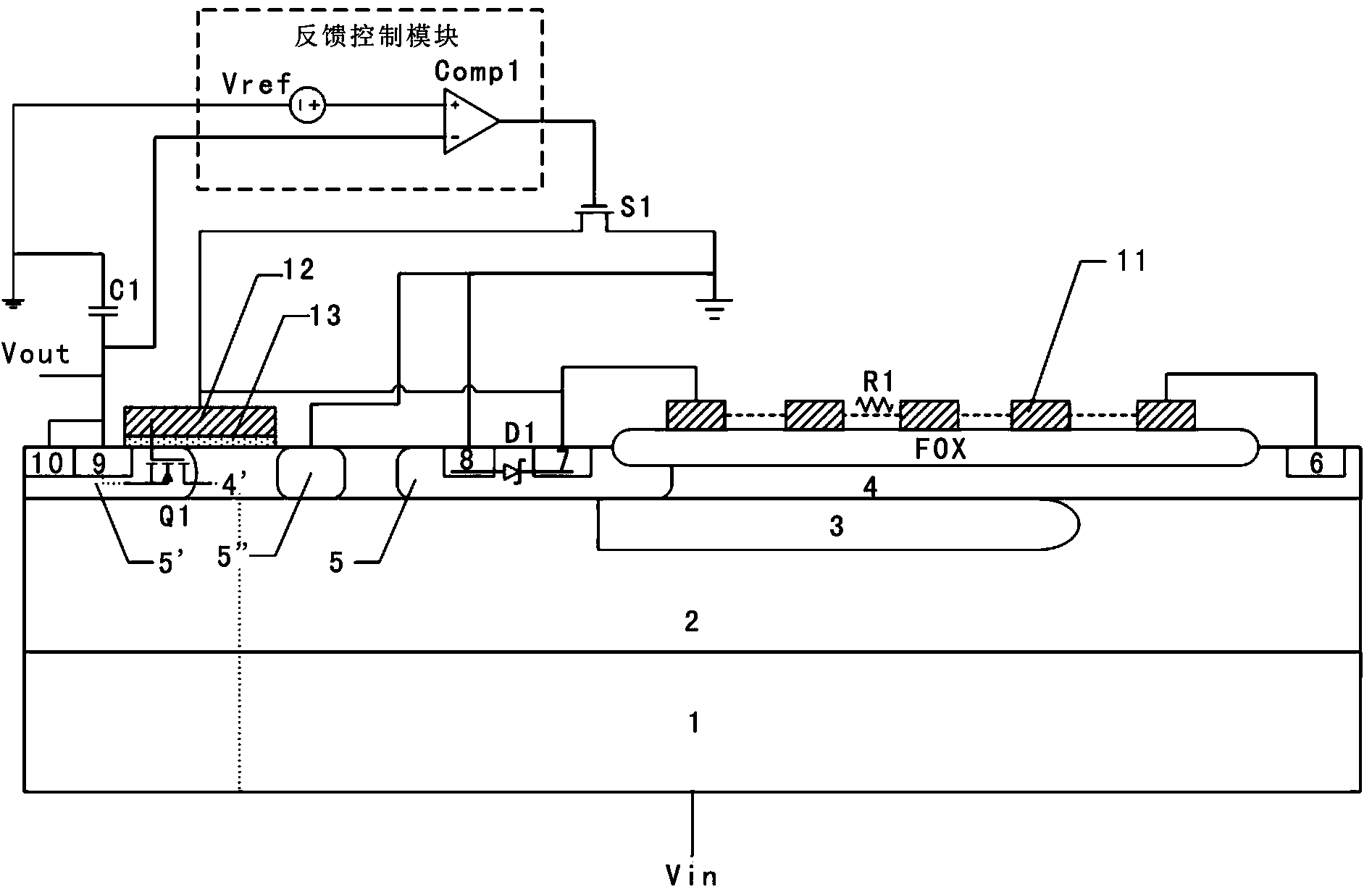

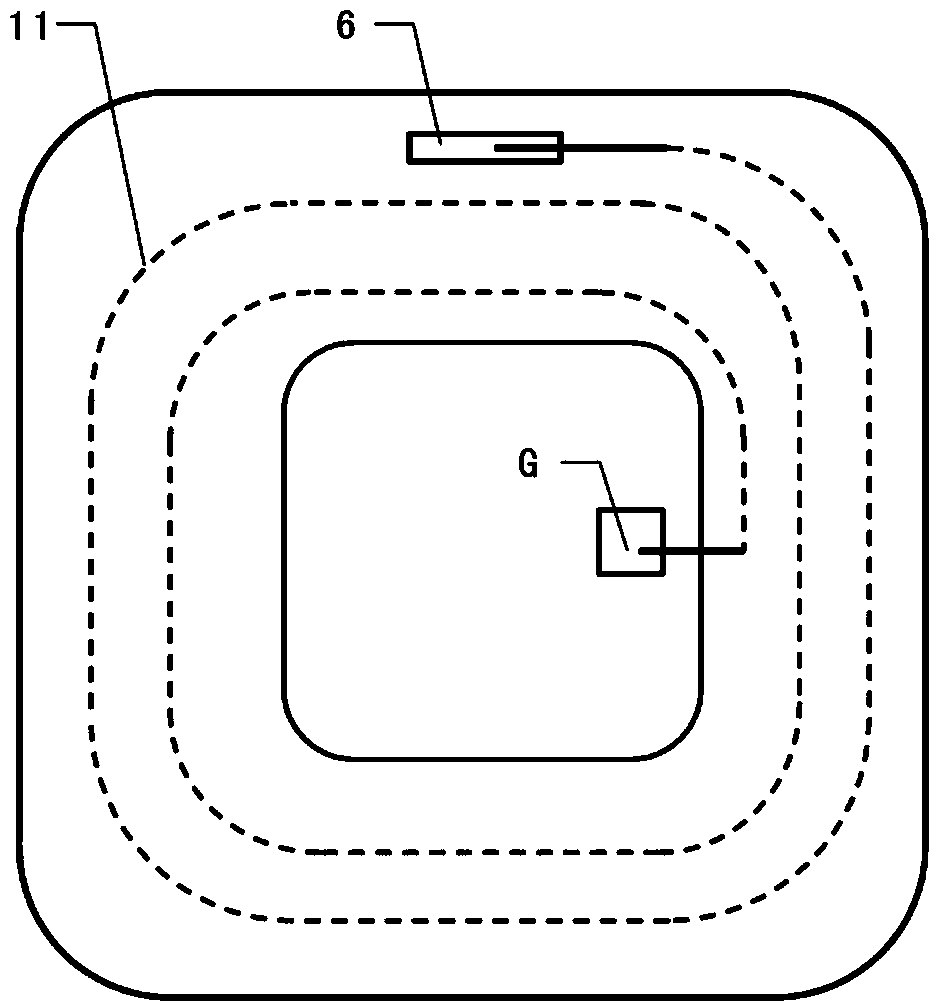

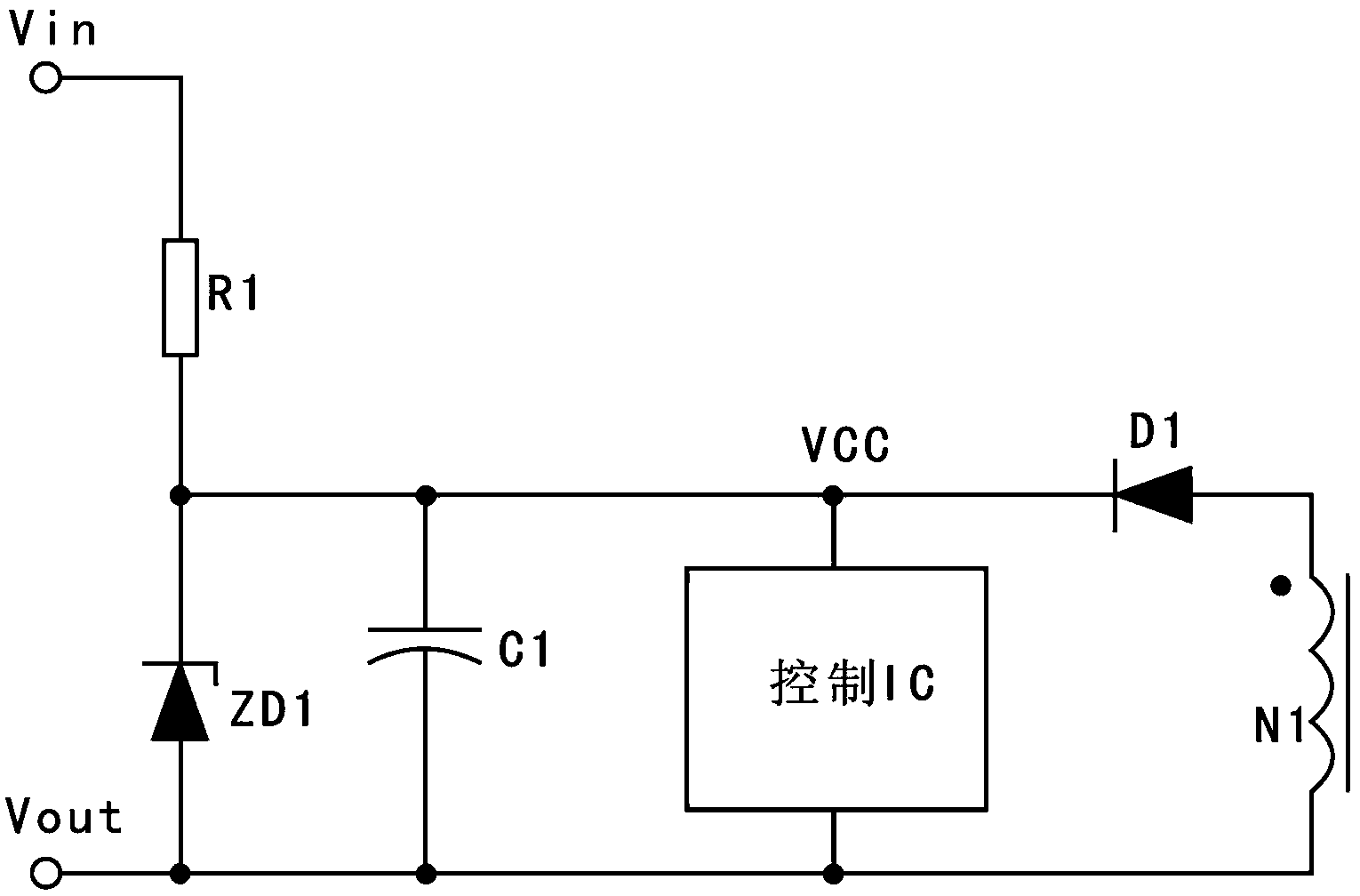

Semiconductor starting device based on spiral polycrystalline silicon field effect transistor charging and manufacturing process of semiconductor starting device

InactiveCN104362149AImprove efficiencyReduce areaSolid-state devicesSemiconductor/solid-state device manufacturingCapacitanceElectronic switch

The invention discloses a semiconductor starting device based on spiral polycrystalline silicon field effect transistor charging. The semiconductor starting device is characterized in that the first end of a resistor is connected with the drain of a field effect transistor to serve as an input end, the second end of the resistor, the grid of the field effect transistor and the first end of an electronic switch are connected with the cathode of a diode, the source of the field effect transistor and the cathode signal input end of a feedback control module are connected with the first end of a capacitor to serve as an output end, the output end of the feedback control module is connected with the control input end of the electronic switch, and the anode signal input end of the feedback control module, the second end of the capacitor, the second end of the electronic switch and the anode of a voltage stabilizing diode are grounded. The invention further discloses a manufacturing process of the semiconductor starting device. The manufacturing process uses the field effect transistor integrated by a BCD process, the resistor and the voltage stabilizing diode. The semiconductor starting device has the advantages that the integrated field effect transistor is used to directly charge the capacitor, and due to the fact the integrated field effect transistor is low in resistance and power consumption when the field effect transistor is on, high power efficiency, low loss and low heating value are achieved.

Owner:CHENGDU SMET TECH

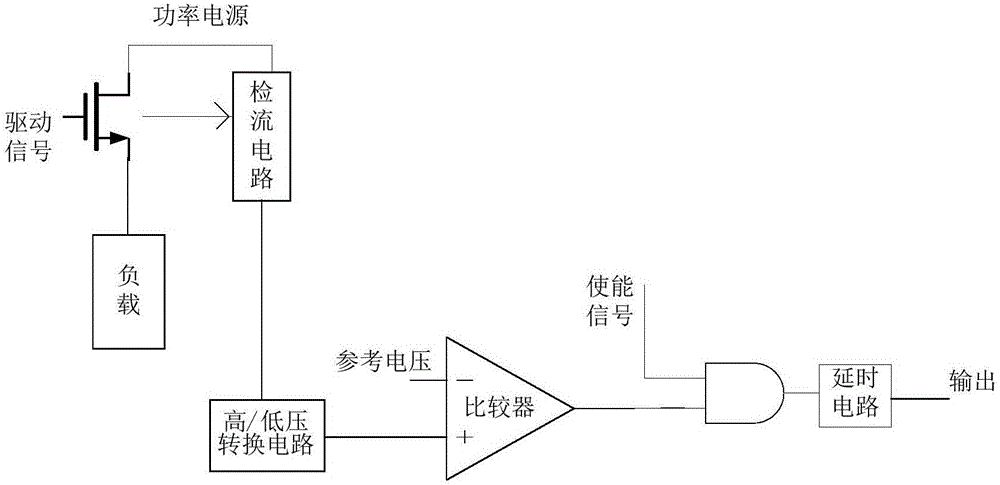

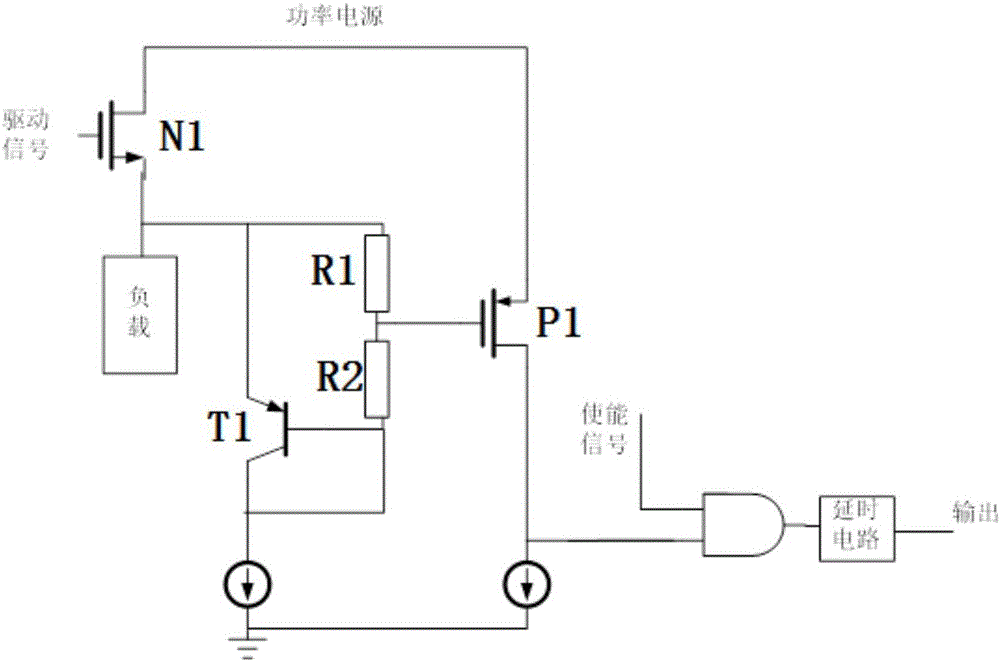

Simplified over-current detection circuit for high-side power tube

ActiveCN105954570ASimple structureEasy to transplantCurrent/voltage measurementElectrical resistance and conductancePower flow

The invention discloses a simplified over-current detection circuit for a high-side power tube. The simplified over-current detection circuit comprises a high-side power tube, a load, a transistor, a voltage-dividing resistor, a switching tube, a first tail current source and a second tail current source, a logic circuit and a delay circuit. The logic circuit is used for introducing an enabling signal. The high-side power tube is an NMOS tube; the triode is a PNP tube or an NPN tube; and the switching tube is a PMOS tube. The triode is configured to have a translation voltage; the logic circuit is an AND gate. When the switching tube is in conduction, a drain terminal high level is converted into a low level that is provided for the logic circuit. The load is an inductive load, a resistive load or a short-circuit grounding unit. The resistance proportion of the first resistor to the second resistor can be adjusted. The enabling signal and a drive signal of the high-side power tube are synchronous. According to the invention, detection of the current detection circuit becomes direct; no auxiliary device is needed; and the detection precision is high. Under the circumstance that the current detection precision is improved, the circuit structure become simple; easy adjusting is realized; the occupied chip area is small; the domain layout becomes convenient; the chip cost is saved; and easy transplanting is realized.

Owner:杭州中科微电子有限公司

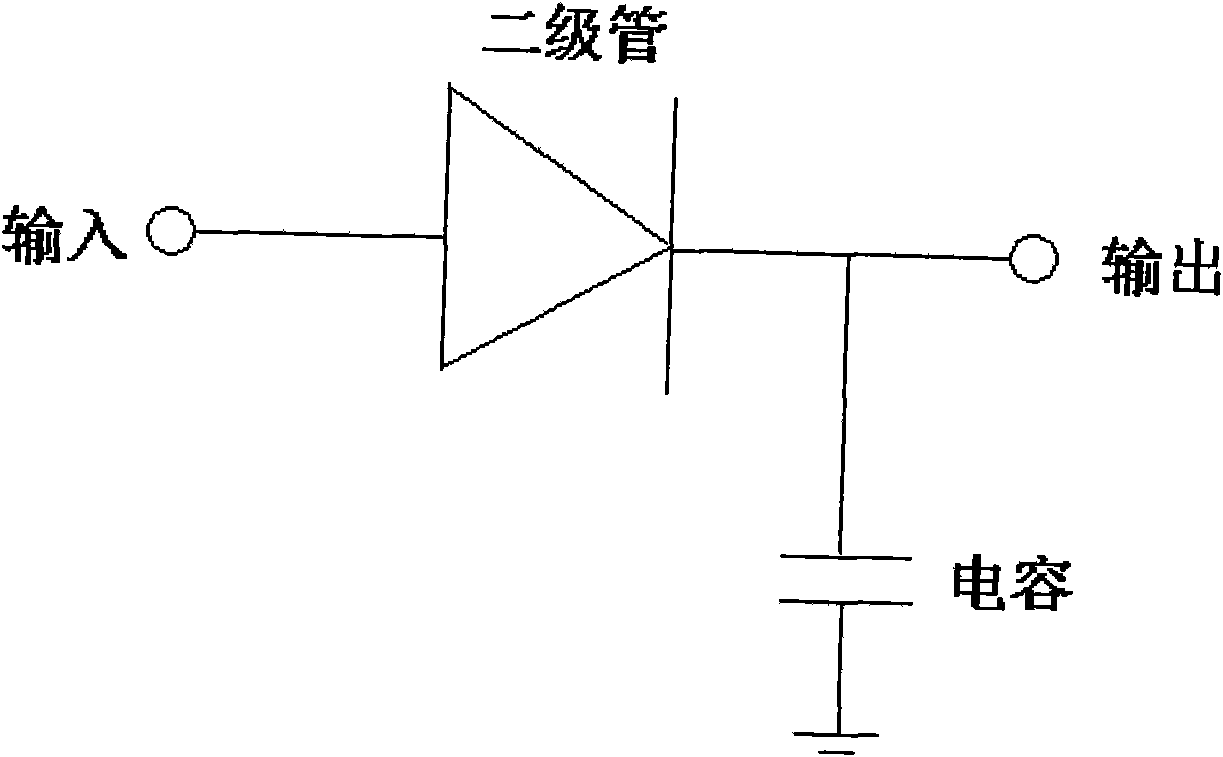

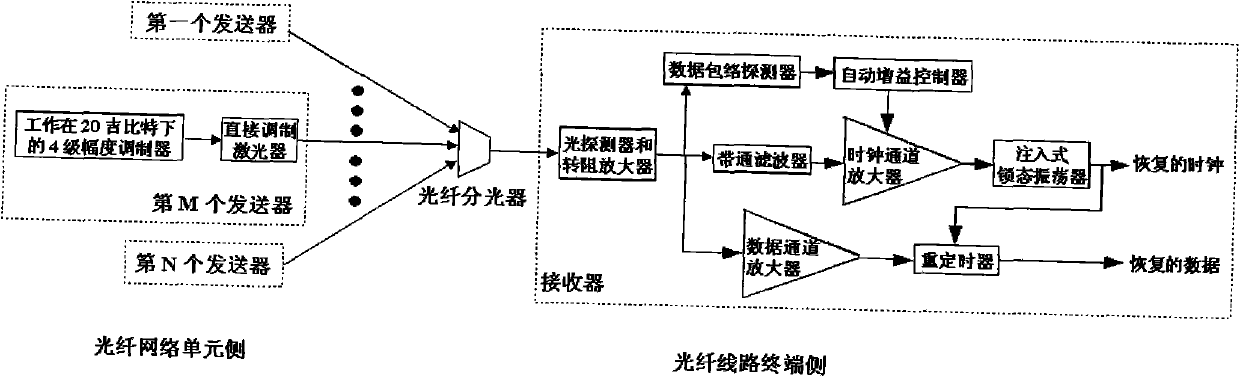

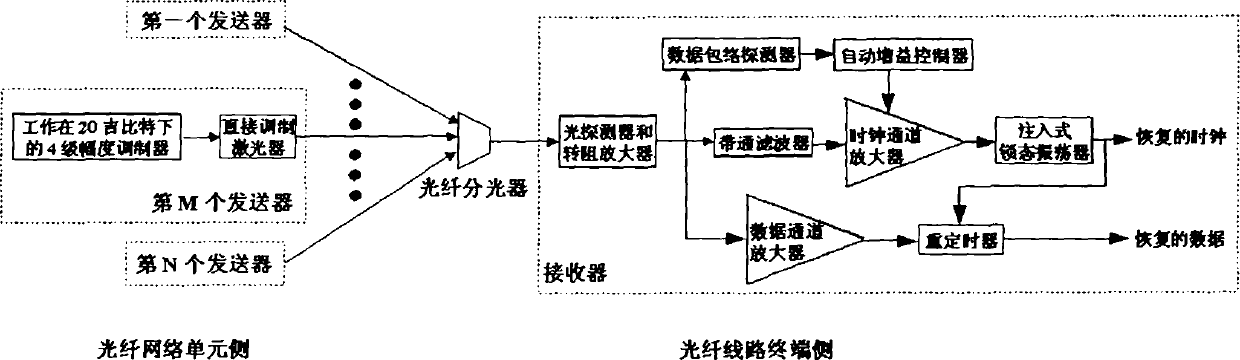

Sudden clock recovery method for dynamic optimal regulation at receiver in passive optical network

InactiveCN101951311ASimple structureReduce power consumptionElectromagnetic receiversSynchronising arrangementInjection lockedTransimpedance amplifier

The invention discloses a sudden clock recovery method for the dynamic optimal regulation at a receiver in a passive optical network when multistage amplitude modulation is used. The method is as follows: a received optical signal in an optical receiver positioned in an optical line terminal is converted into an electric signal by an optical detector and a transimpedance amplifier; and the electric signal is the inputs of subsequent 3 circuit links, wherein 2 circuit links generate a clock signal through an injection locked oscillator, and the injection intensity of the two circuit links are regulated automatically and dynamically. Compared with other clock recovery schemes under a condition of adopting non-return-to-zero-codes for multistage amplitude modulation, the scheme with a simplestructure has the advantages of low power consumption and small occupation of chip area. The distinctive dynamic regulation function of the method can achieve short locking time and light after-locking clock vibration at the same time.

Owner:SHANGHAI MARITIME UNIVERSITY

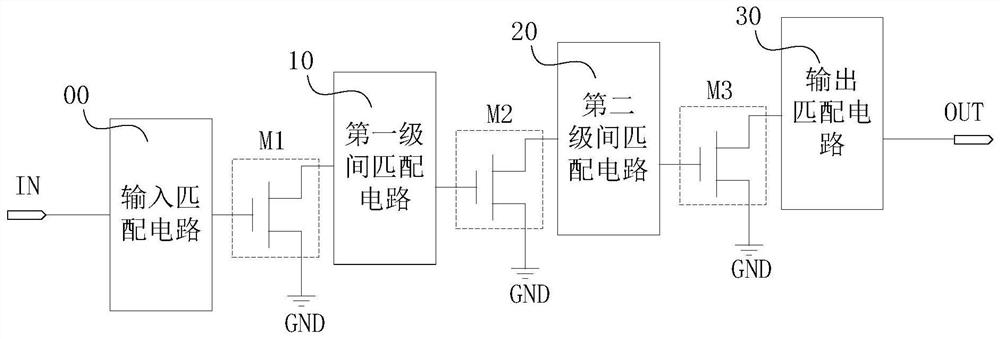

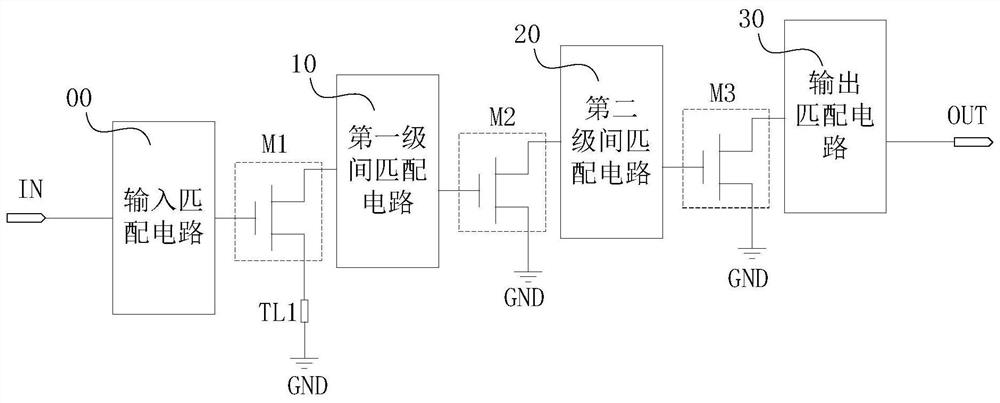

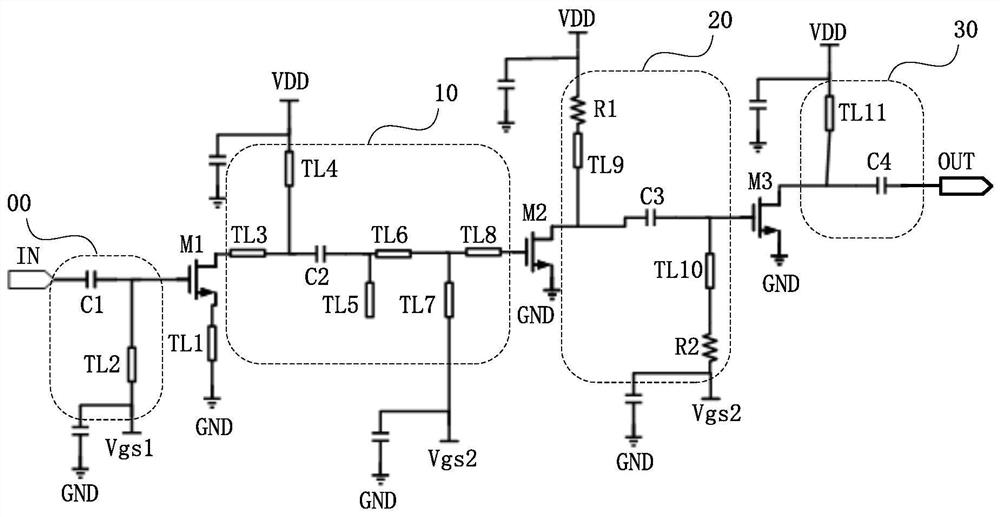

Low noise amplifier and radio frequency front-end circuit

PendingCN113067552AImprove flatnessHigh bandwidthAmplifier modifications to reduce noise influenceHigh frequency amplifiersLow noiseNoise (radio)

The invention provides a low-noise amplifier and a radio frequency front-end circuit. The low-noise amplifier comprises an input matching circuit, a first-stage amplification transistor, a first inter-stage matching circuit, a second-stage amplification transistor, a second inter-stage matching circuit, a third-stage amplification transistor and an output matching circuit which are sequentially cascaded; the first-stage amplification transistor, the second-stage amplification transistor and the third-stage amplification transistor are used for amplifying signals input by grid electrodes; the input matching circuit, the first inter-stage matching circuit, the second inter-stage matching circuit and the output matching circuit are used for realizing impedance matching; wherein the matching frequency point of the first-stage matching circuit is a secondary high frequency point; and the matching frequency point of the second-stage matching circuit is a high-frequency point. Therefore, on the basis of ensuring high gain, the flatness of the circuit is increased, the bandwidth of the circuit is increased, and the broadband low-noise amplifier is realized. Moreover, the low-noise amplifier provided by the invention is relatively simple in circuit structure, relatively small in occupied chip area and relatively low in power consumption.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

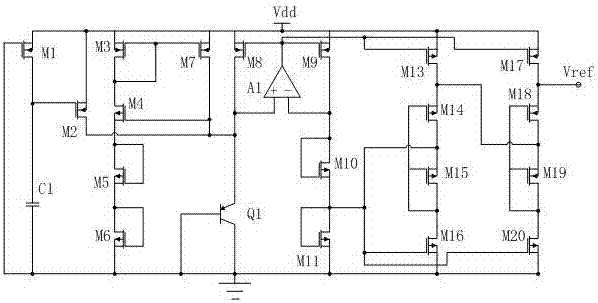

Low power consumption auto-bias reference voltage source

ActiveCN106959720ASimple structureInhibition of working effectsElectric variable regulationHemt circuitsCascode

The invention provides a low power consumption auto-bias reference voltage source which comprises a starting circuit, a bias compensation circuit and a common source and common barrier band gap circuit, wherein the starting circuit provides starting current to the reference voltage source; the bias compensation circuit provides bias voltage to the reference voltage source and achieves temperature curvature compensation of the circuit; the influence of power supply voltage fluctuation and ambient temperature change on the circuit is avoided; precise, stable and undistorted operation of the reference voltage source is ensured; the bias compensation circuit achieves a bias function via balance between transistor junction voltage and MOS (metal oxide semiconductor) grid source voltage; a bias resistor is not required; the power consumption of the circuit is effectively reduced; the common source and common barrier band gap circuit is used for generating and outputting reference voltage and can operate only with very low power supply voltage; and the power consumption of the reference voltage source is further reduced. According to the low power consumption auto-bias reference voltage source, no resistor is used in a circuit structure design; the working current is small; a circuit structure is simple; the occupied chip area is small; and the power consumption is very low.

Owner:XUCHANG UNIV

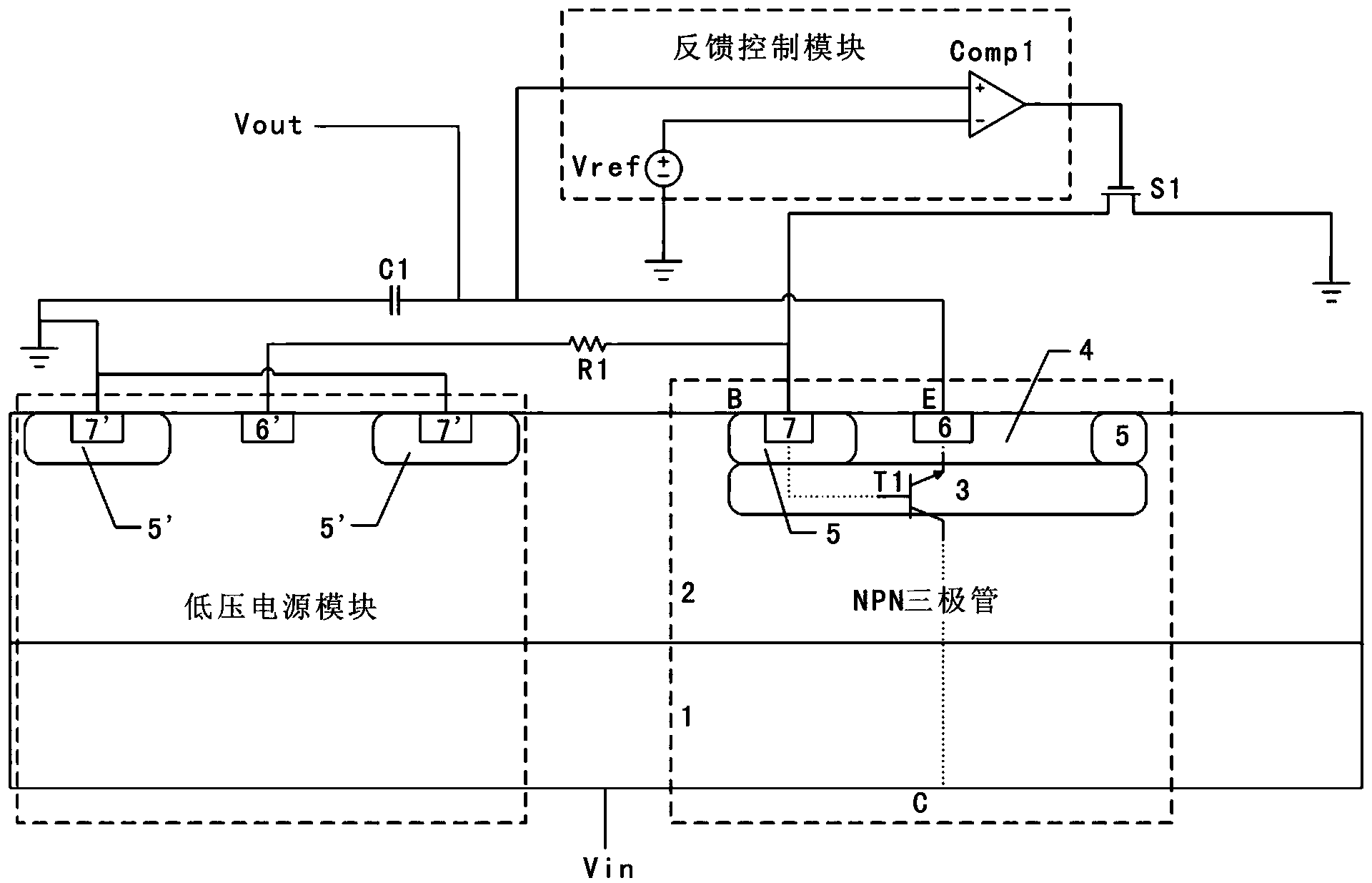

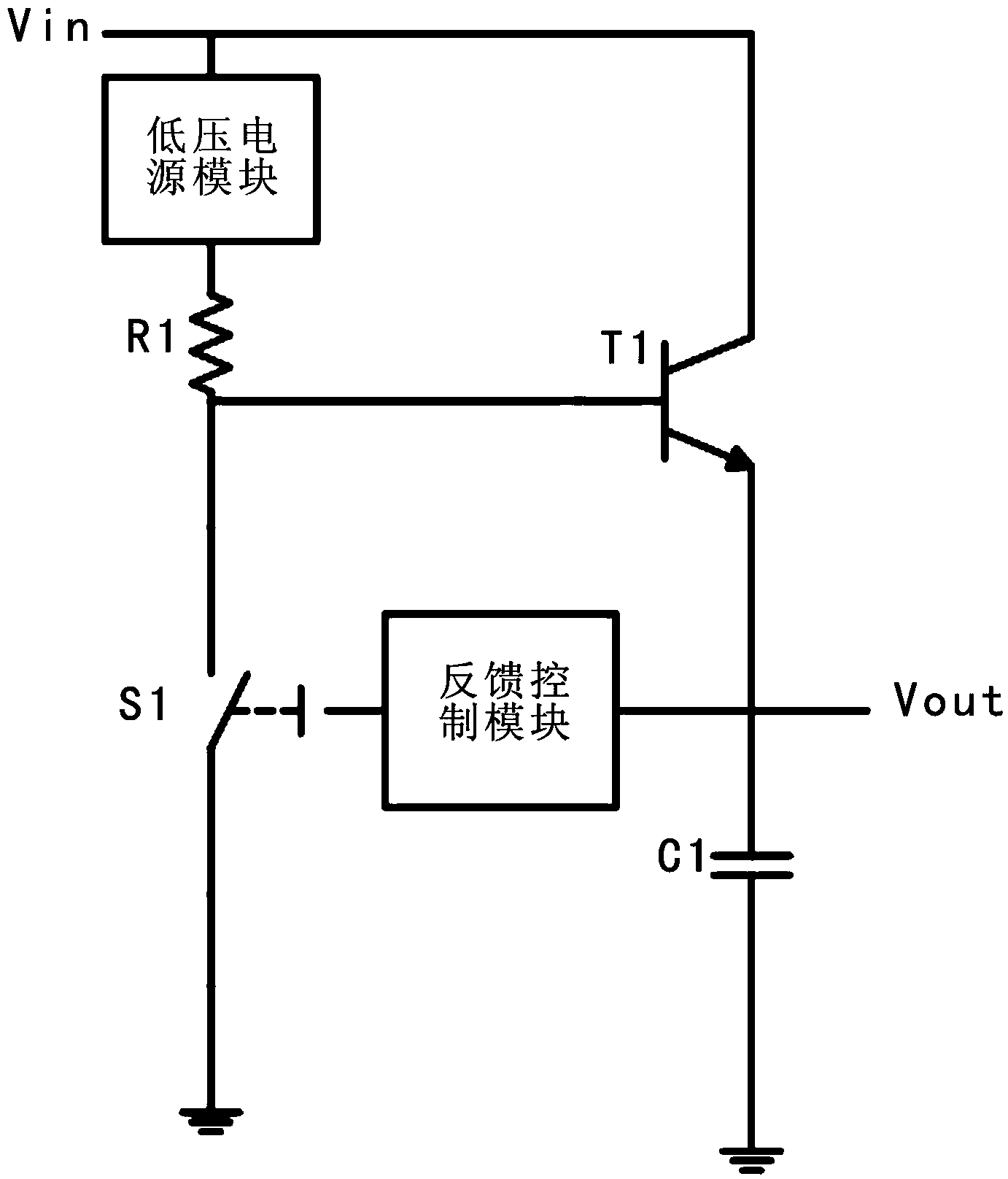

Semiconductor starting device based on triode charging and manufacturing process of semiconductor starting device

InactiveCN104362148AImprove efficiencyReduce power consumptionSolid-state devicesSemiconductor/solid-state device manufacturingCapacitanceLow voltage

The invention discloses a semiconductor starting device based on triode charging and a manufacturing process of the semiconductor starting device. The semiconductor starting device is characterized in that one end of a low-voltage power module is connected with one end of a resistor, the other end of the resistor is connected the base of an NPN triode and one end of an electronic switch, the anode input end of a feedback control module, the transmitter of the NPN triode and the first end of a capacitor are connected to serve as a power output end, the other end of the low-voltage power module is connected with the collector of the NPN triode to serve as a power input end, and the second end of the capacitor, the second end of the electronic switch and the cathode input end of the feedback control module are grounded. The invention further discloses a manufacturing process of the semiconductor starting device. The manufacturing process uses a BCD process to integrate the NPN triode. The semiconductor starting device has the advantages that the integrated NPN triode is used to directly charge the capacitor, high power efficiency, low loss and low heating value are achieved due to the fact that the NPN triode is low in resistance and low in power consumption when the triode is on, the circuit can be automatically disconnected after charging, and low energy consumption is achieved.

Owner:CHENGDU SMET TECH

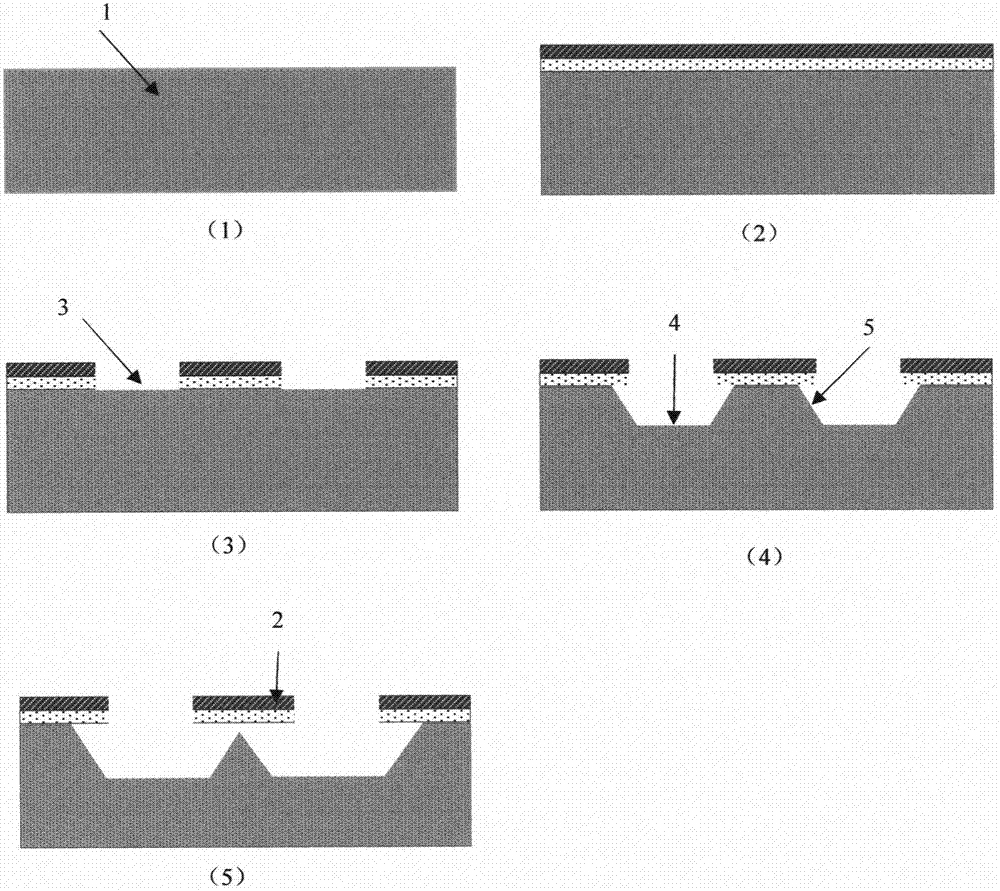

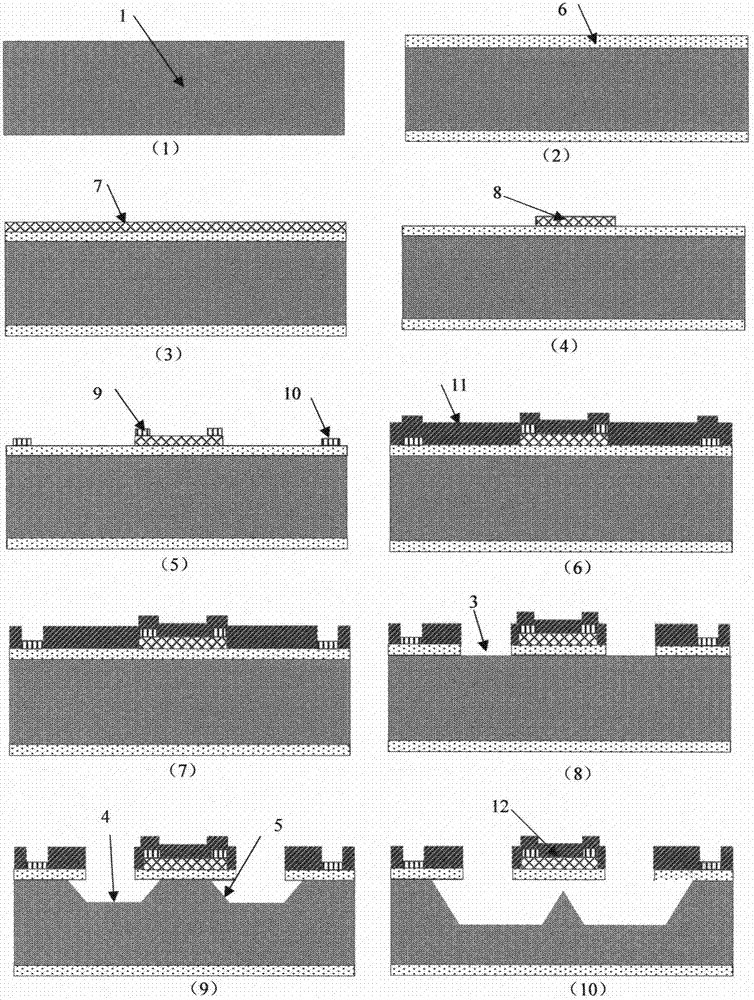

Front face release technique of suspended microstructure

ActiveCN107265394AReduce areaOccupies a small chip areaTelevision system detailsImpedence networksAnisotropic etchingMaterials science

The invention discloses a front face release technique of a suspended microstructure. A thin film structure of a microstructure (2) is formed by using a heavily doped silicon wafer (1) as a substrate, a corrosion window (3) is formed by lithography and etching, and finally front face corrosion is performed in an anisotropic etching solution, and the microstructure (2) is cut longitudinal corroded along a surface (4) and is cut along a surface (5), so that the microstructure (2). The front face release technique of the suspended microstructure (2) requires no double-faced registration or lithography and occupies a small chip area, and the suspended microstructure (2) is not adhered with the substrate, and the design of the microstructure (2) is not limited by the crystal direction.

Owner:CHINA JILIANG UNIV

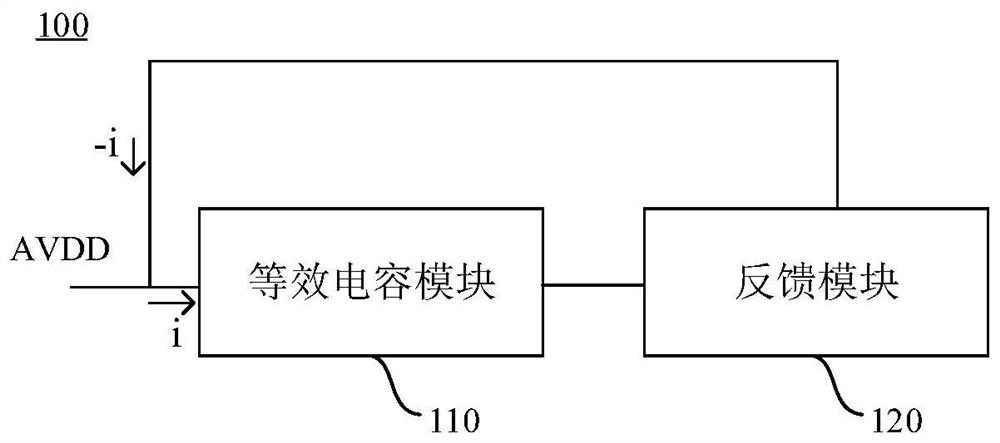

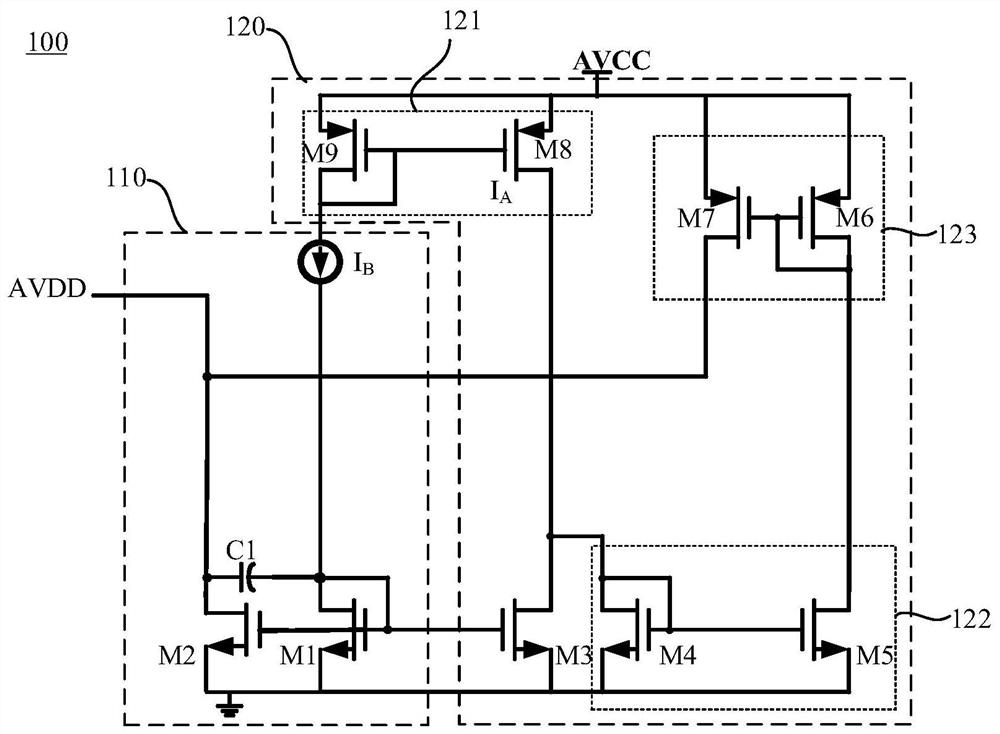

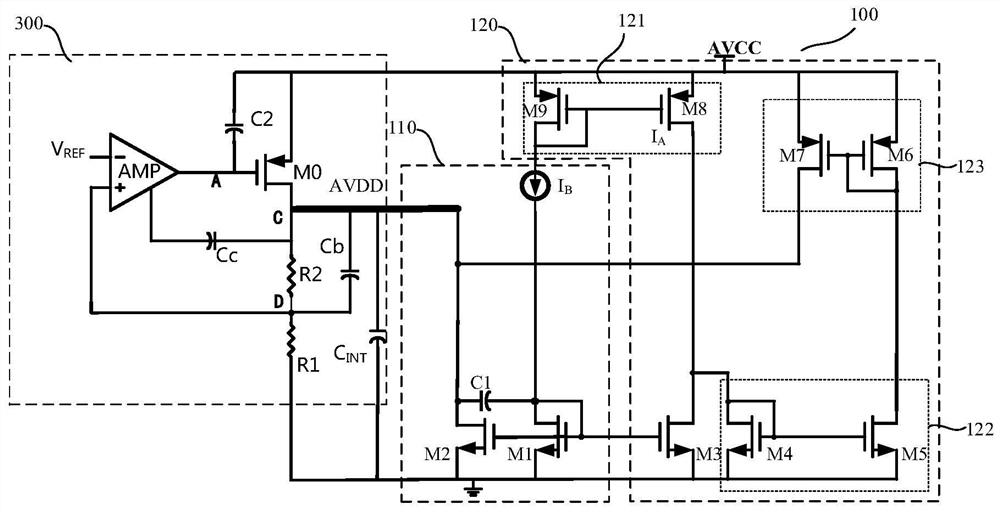

Capacitance multiplication circuit and linear voltage regulator

ActiveCN111736652AImprove stabilitySuppression of transient spike effectsElectric variable regulationCapacitanceHemt circuits

The invention discloses a capacitance multiplication circuit and a linear voltage regulator. The capacitance multiplication circuit comprises an equivalent capacitance module, wherein the equivalent module comprises an on-chip capacitor, the equivalent capacitance module is used for providing equivalent capacitance for a voltage stabilization node, and the capacitance value of the equivalent capacitance is multiple times of the capacitance value of the on-chip capacitor; and a negative feedback module connected to the equivalent capacitance module and the voltage stabilization node and used for feeding back compensation current to the voltage stabilization node when the voltage of the voltage stabilization node overshoots or undershoots, wherein the compensation current and transient current generated at the voltage stabilization node are the same in magnitude and opposite in direction. The capacitance multiplication circuit is simple in structure and easy to integrate.

Owner:SHANGHAI AWINIC TECH CO LTD

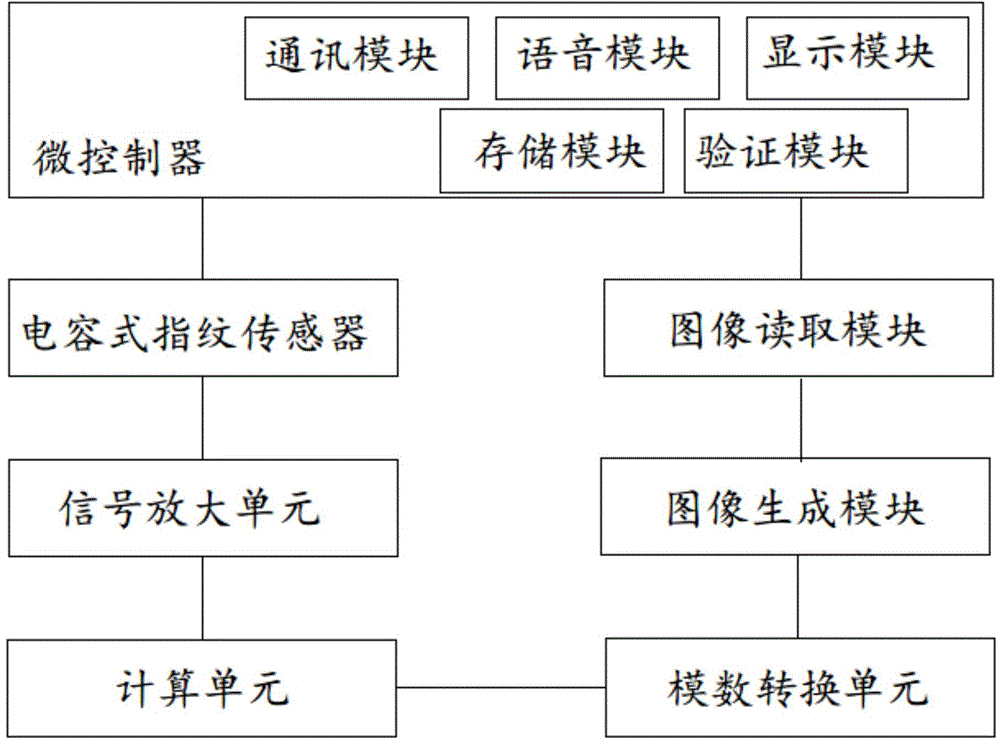

Fingerprint detector

InactiveCN104657715AHigh precisionReduce power consumptionPrint image acquisitionMicrocontrollerCapacitance

The invention discloses a fingerprint detector. The fingerprint detector comprises a power supply assembly, a capacitance type fingerprint sensor, a microcontroller and a signal processor, wherein the power supply assembly is electrically connected with the capacitance type fingerprint sensor, the microcontroller and the signal processor respectively; the microcontroller is connected with one end of the capacitance type fingerprint sensor, and the signal processor is connected with the other end of the capacitance type fingerprint sensor; the capacitance type fingerprint sensor comprises a plurality of sensing units arranged in an array manner and used for acquiring fingerprint information and transmitting the fingerprint information to the signal processor; the signal processor is used for processing the fingerprint information; the microcontroller is used for controlling the capacitance type fingerprint sensor and the signal processor according to the processing result of the signal processor. According to the fingerprint detector disclosed by the invention, when the capacitance type fingerprint sensor acquires the fingerprint information, a high-precision fingerprint image is acquired by enabling the fingerprint to form a capacitance array and then enabling the capacitance array to be combined with the sensing units to form a plurality of micro-capacitors.

Owner:柳州市金旭节能科技有限公司

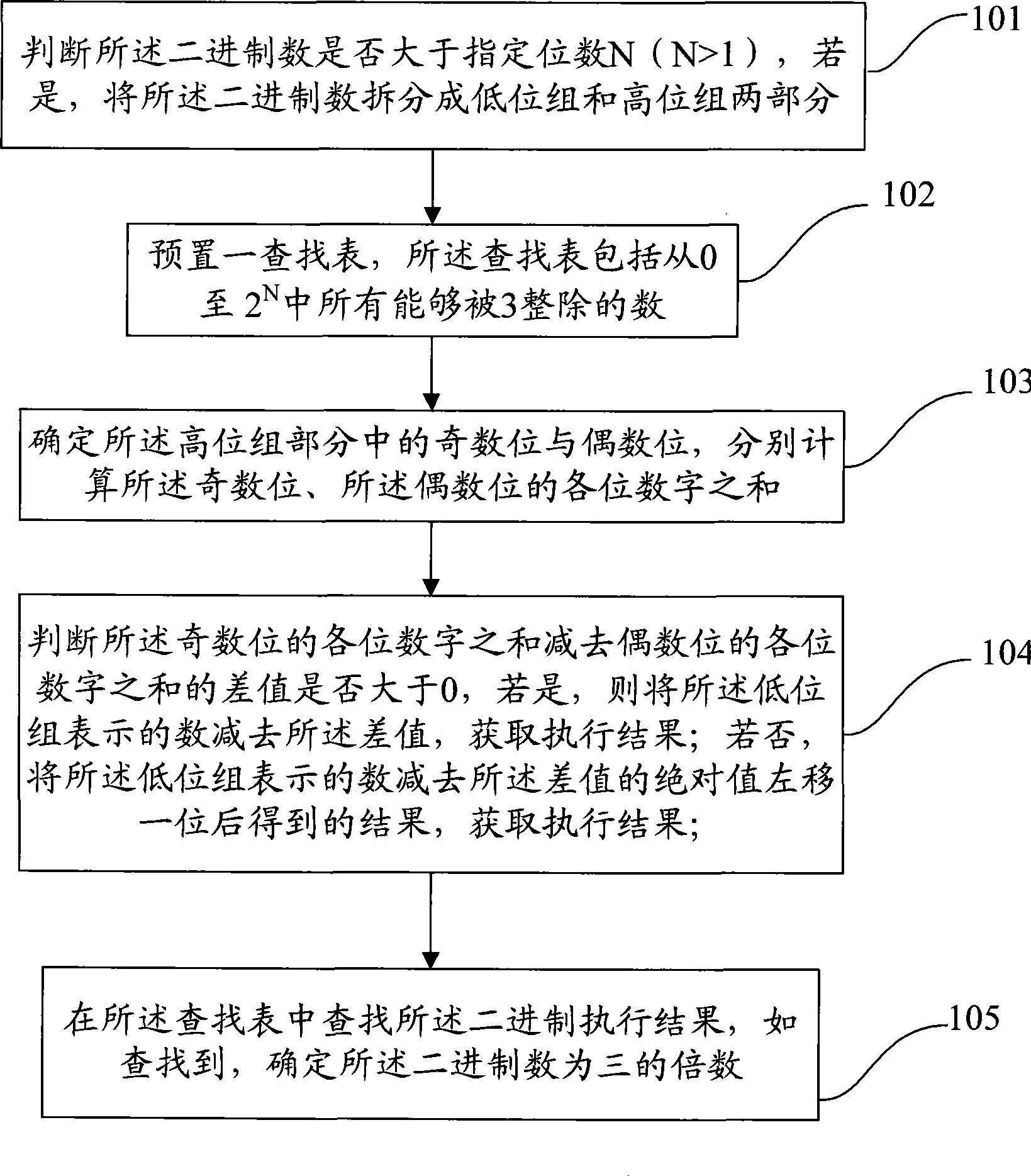

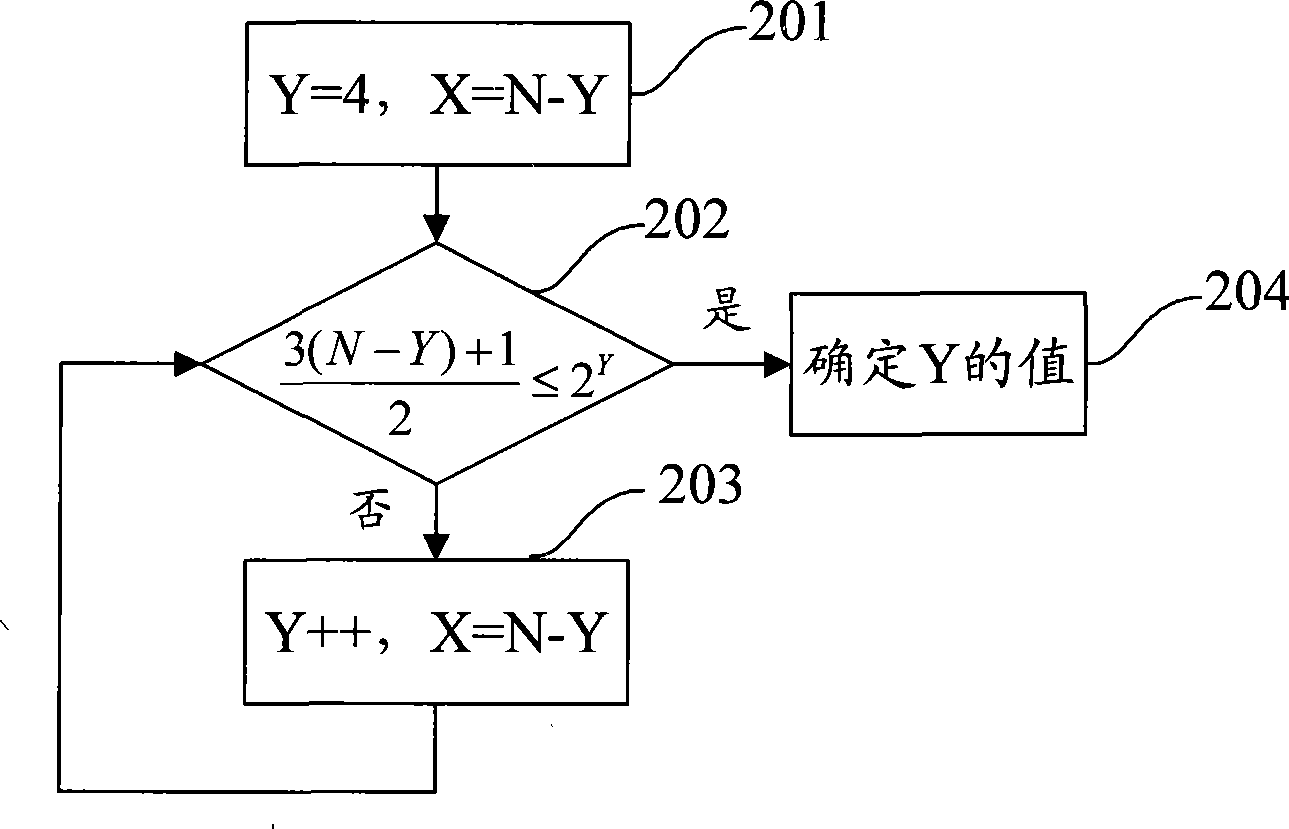

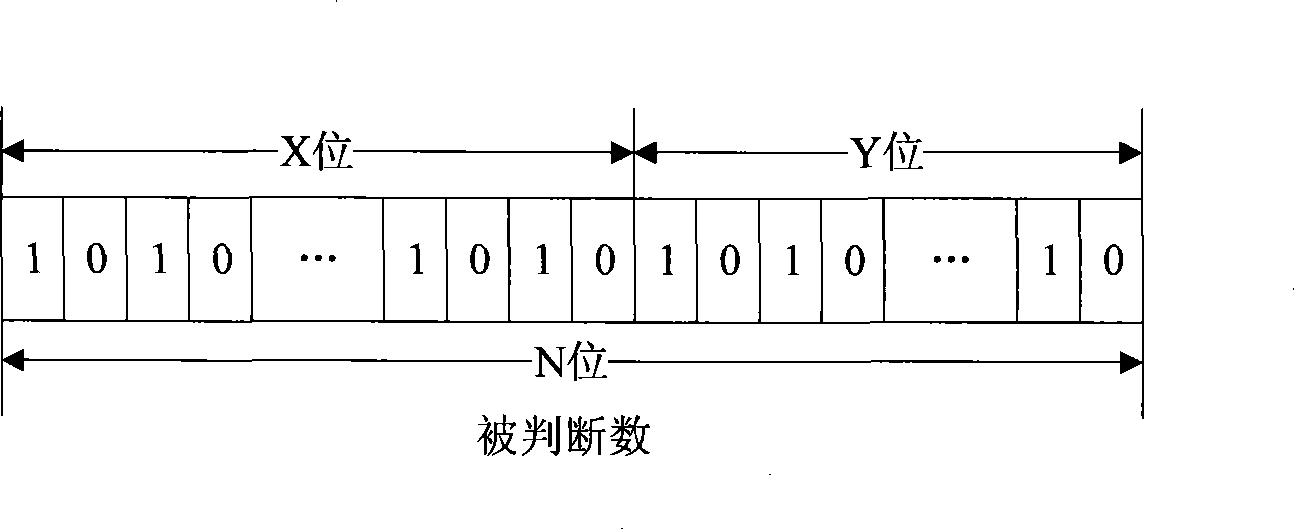

Method and device for checking whether binary number is multiple of three, and checking chip thereof

InactiveCN101464788AAvoid the defect of too wide bit widthAvoid the defect that the number of iterations is too large to meet the timing requirementsDigital function generatorsComputation using denominational number representationNumbering systemLookup table

The invention provides a method for testing whether a binary digit is a mulriple of three. The method comprises the following steps: whether the binary digit is larger than the specified digit of N (N is larger than one) is determined, if yes, the binary digit is split into two parts of a low byte and a high byte; a lookup table which consists of all the numbers from 0 to 2<N> which can be divided by three is preset; if the difference value between the sum of all the numbers at the odd number position and the sum of all the numbers at the even number position is larger than zero, the number represented by the low byte minus the difference to obtain an execution result; if the execution result is smaller than zero, the number represented by the low byte is taken as a minuend, the absolute value of the difference is moved leftwards for one digit, and the execution result of the binary digit is obtained; the execution result of the binary digit is looked up in the lookup table, if so, the binary digit is determined as the mulriple of three. The method of the invention avoids the shortcomings of complicated numbering system conversion, longer subtracter bitwidth and multiple times of interations, when determining whether the binary digit is the mulriple of three in the prior art. Therefore, the determination can be realized with the least resource and the highest efficiency.

Owner:WUXI ZGMICRO ELECTRONICS CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com