Method for improving linearity of pipelined successive-approximation analog-to-digital converter

An analog-to-digital converter and successive approximation technology, applied in the direction of analog/digital conversion, code conversion, instrumentation, etc., can solve the problems of large power consumption and area, high algorithm complexity, and difficult on-chip implementation, etc., to achieve small chip area occupation , without sacrificing the sampling rate, easy-to-achieve effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

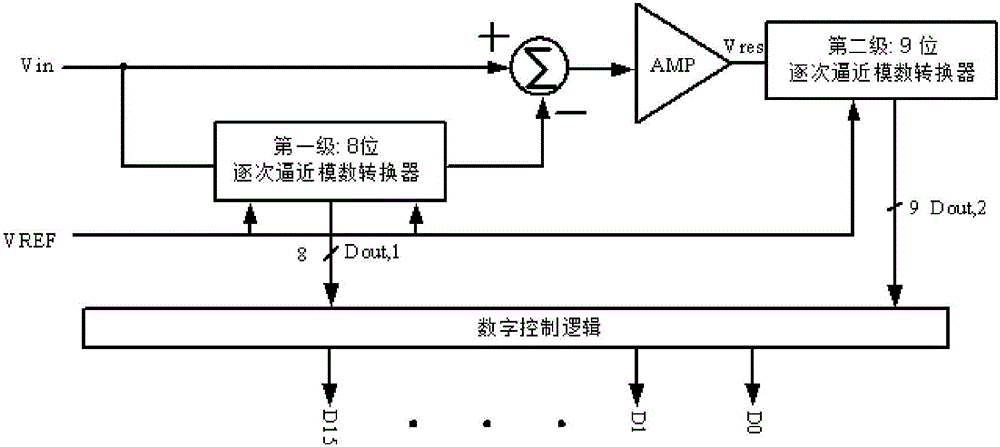

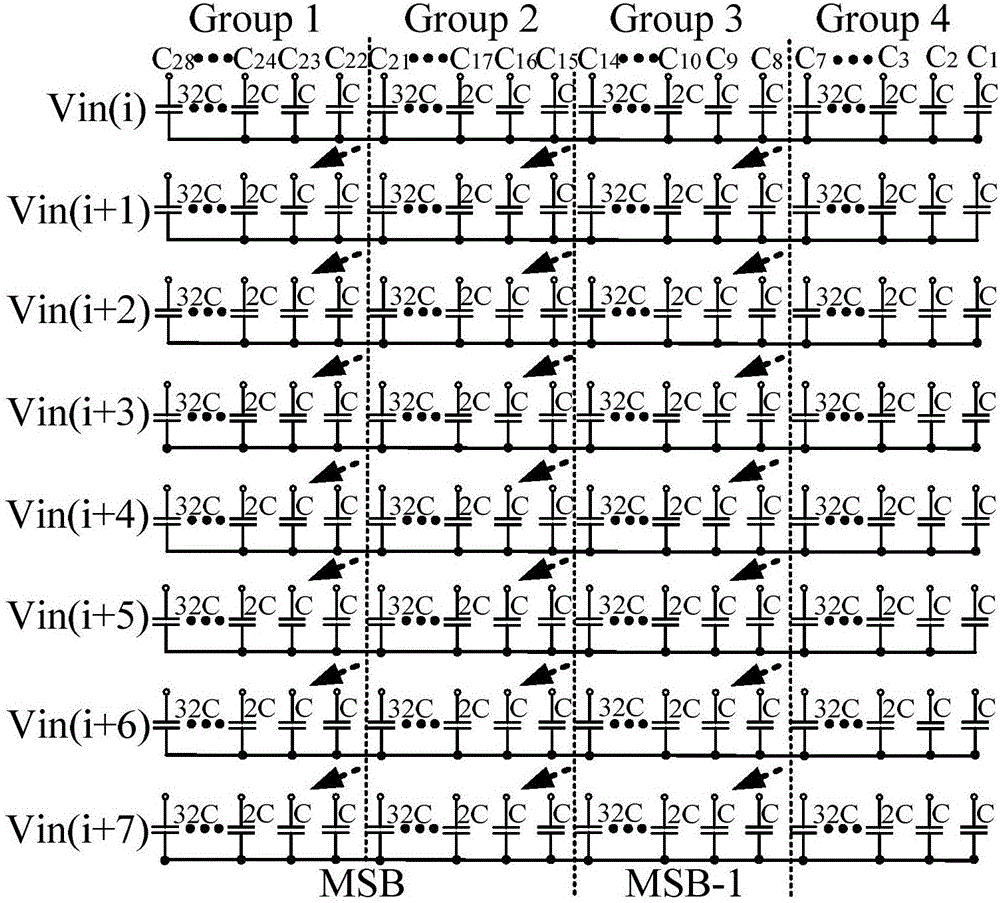

[0020]The invention proposes a capacitance grouping and circulation method capable of improving the linearity of the line-type successive approximation analog-to-digital converter, and each bit circulation changes the order of the capacitance array, thereby achieving the purpose of improving the linearity. The following takes a 16-bit pipeline successive approximation analog-to-digital converter as an example to describe in detail. The system structure of the 16-bit pipeline successive approximation analog-to-digital converter proposed by the present invention is as follows figure 1 shown. Using the idea of a pipelined ADC, a 16-bit pipelined successive approximation analog-to-digital converter is divided into two stages, and the first-stage 8-bit successive approximation analog-to-digital converter and residual amplifier together form a gain digital-to-analog converter ( Multiplier Digital to Analog Converter, MDAC), the capacitor 256C of the binary capacitor array of the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com