Pipelined analog-to-digit converter comparator offset foreground calibration circuit and method

A technology of analog-to-digital converter and calibration circuit, which is applied in the directions of analog/digital conversion calibration/test, analog/digital conversion, code conversion, etc., which can solve the problem that the dynamic offset error of the comparator cannot be solved, and achieve strong technical portability , The effect of occupying a small chip area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

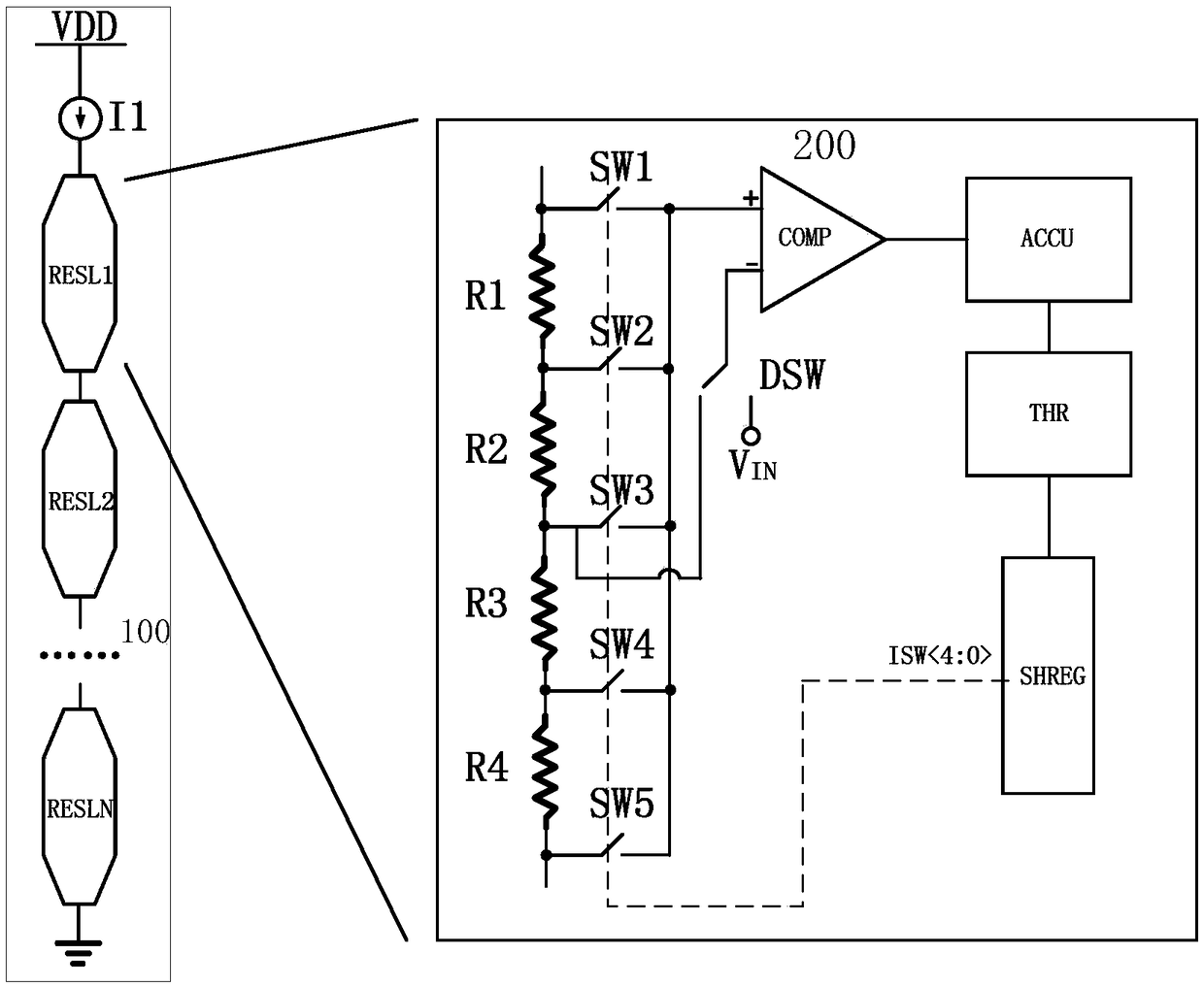

[0057] The circuit and method provided by the invention are calibrated for the key module comparator in the pipeline analog-to-digital converter, which can greatly reduce the offset error of the comparator without introducing excessive power consumption. This technology has been successfully used in the first and second pipeline stages of a certain 16-bit pipeline analog-to-digital converter. The maximum absolute value of the offset voltage of the original comparator is about ±60mV. After using this calibration technique to set the number of cycle comparisons to 65536, the maximum absolute value of the offset voltage drops to about ±1mV. When this calibration method is not used, the integral error INL of the converter can reach a maximum value of about 20LSB, such as Figure 5 shown. After using this calibration method, the maximum value is only about 2LSB, such as Figure 6 shown. Compared with other inventions, the invention does not introduce static power consumption dur...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com