Bit cycle method for improving dynamic performance of hybrid resistance and capacitance type analog to digital converter

A technology of analog-to-digital converters and mixed resistors, which is applied in the field of high-precision analog-to-digital converters, can solve the problems of interrupting the normal operation of analog-to-digital converters, increasing algorithm complexity, and difficulty in on-chip implementation, achieving the sacrifice of sampling rate and structure Simple, easy-to-achieve effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

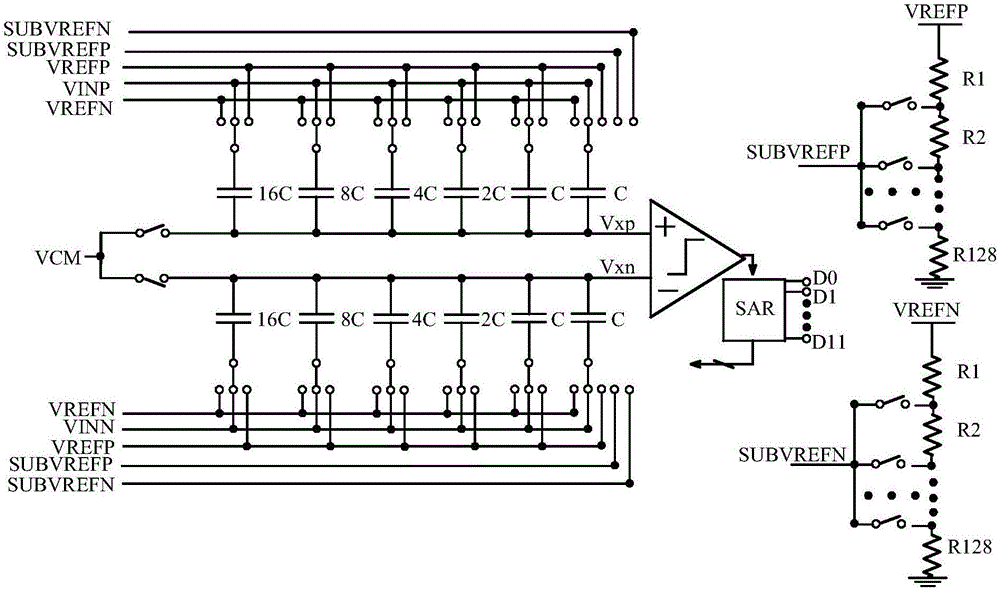

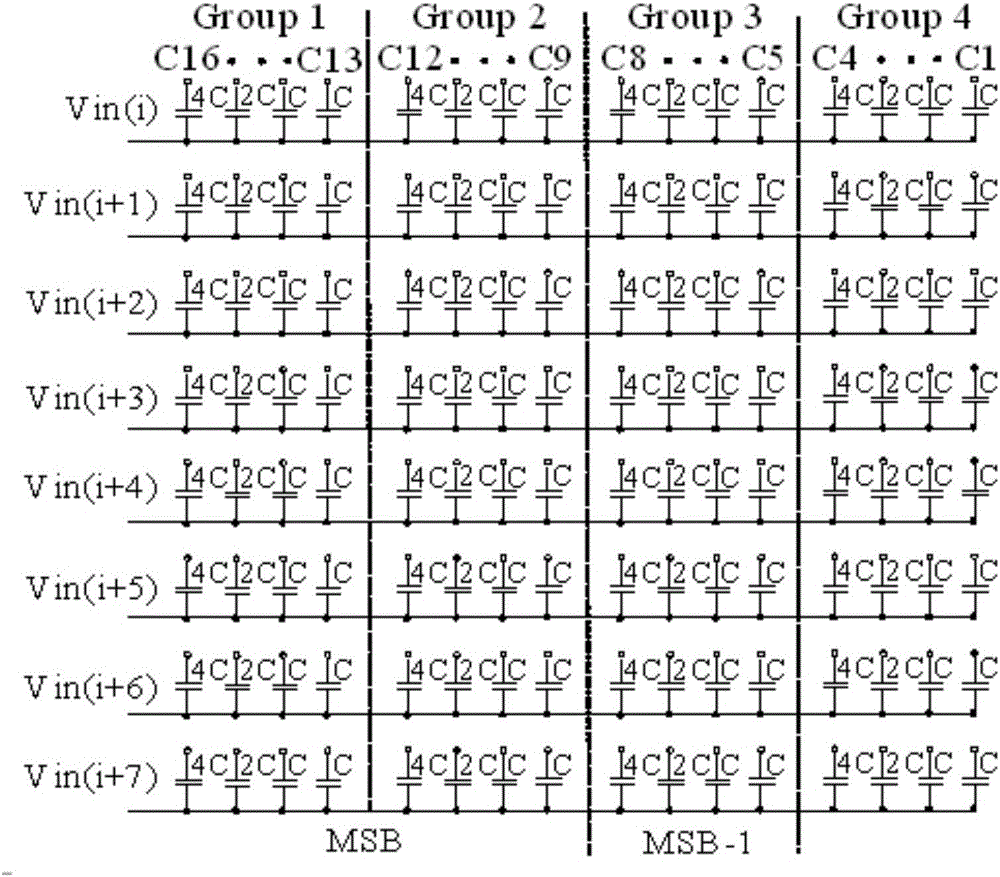

[0022] The present invention proposes a bit cycle method that can improve the dynamic performance of successive approximation analog-to-digital converters, such as figure 2 As shown, will figure 1 The highest bit (MSB) capacitor 16C is split into 4C, 2C, C, C, 4C, 2C, C, and C, and the second highest bit (MSB-1) capacitor 8C is split into 4C, 2C, C, and C. figure 1 The total capacitance 32C of the medium and high 5-bit capacitor DAC is divided into four groups, and these four groups of capacitors are in figure 2 The first group of capacitors C13-C16 is represented by black, the second group of capacitors C9-C12 is represented by purple, the third group of capacitors C5-C8 is represented by red, and the fourth group of capacitors C1-C4 is represented by blue It means that each group contains 8 unit capacitors, namely 4C, 2C, C, and C. Each bit cycle uses a different combination of capacitors to achieve dynamic averaging of capacitance errors, thereby achieving the purpose of...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com