Capacitor switching and averaging method for improving linearity of successive approximation analog-digital converter

An analog-to-digital converter and successive approximation technology, which is applied in the field of microelectronics and solid-state electronics, can solve problems such as difficult on-chip implementation, increased algorithm complexity, and growth, and achieves a small chip area, easy implementation, and simple structure. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

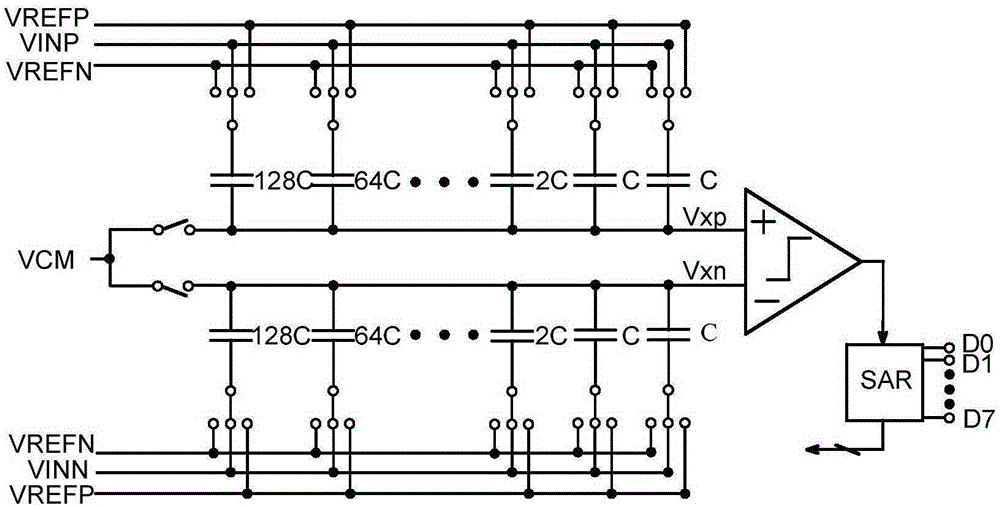

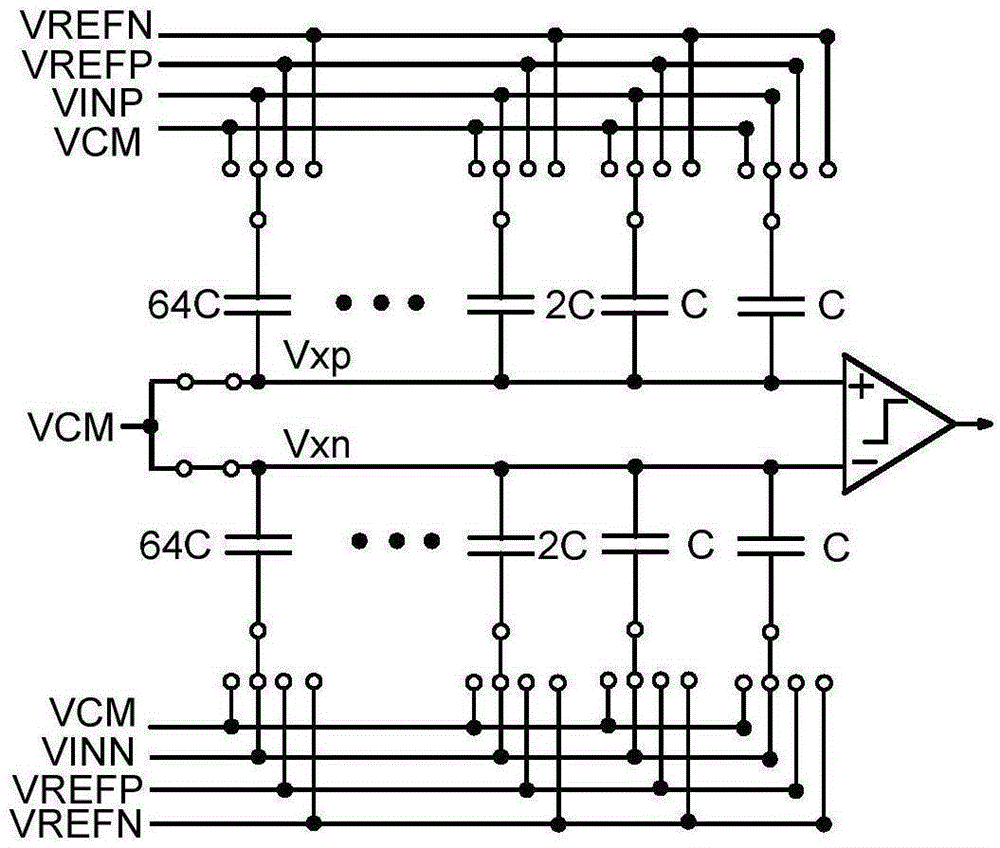

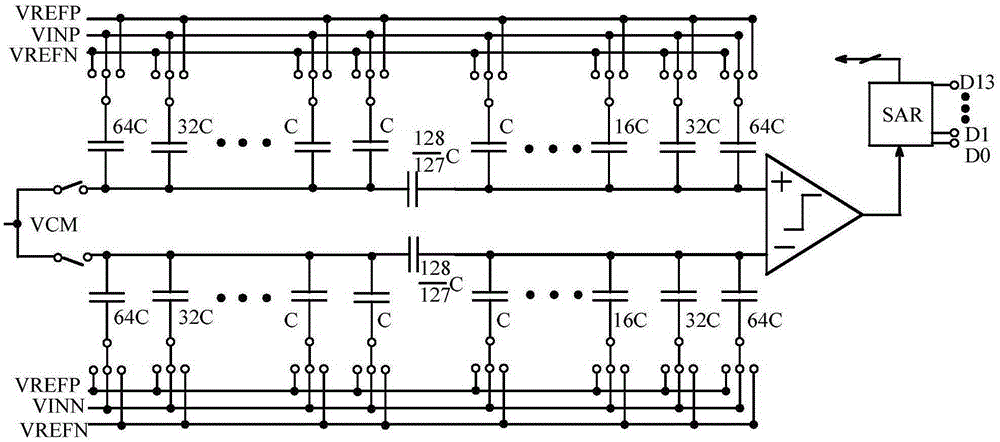

[0023] The invention proposes a capacitance exchange and averaging method that can improve the linearity of a segmented capacitance type successive approximation analog-to-digital converter. The high-order capacitance DAC and the low-order capacitance DAC are switched between every two conversions, and the bits of the lower 4 bits are cyclically performed. Twice, the final results are averaged, so as to achieve the purpose of improving the linearity. The following is an example of a 14-bit segmented capacitive successive approximation analog-to-digital converter. The system structure of the 14-bit segmented capacitance type successive approximation analog-to-digital converter proposed by the present invention is as follows: Figure 4 As shown, it consists of the upper 7-bit capacitance DAC and the lower 7-bit capacitance DAC and a comparator. The upper 7-bit capacitance DAC and the lower 7-bit capacitance DAC simultaneously sample the input voltage Vin(i) and enter the bit lo...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com