Integrated non-linearity (INL) and differential non-linearity (DNL) correction techniques for digital-to-analog converters (DACs)

A digital-to-analog converter, integral nonlinear technology, applied in the direction of digital-to-analog converter, analog/digital conversion calibration/test, analog/digital conversion, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

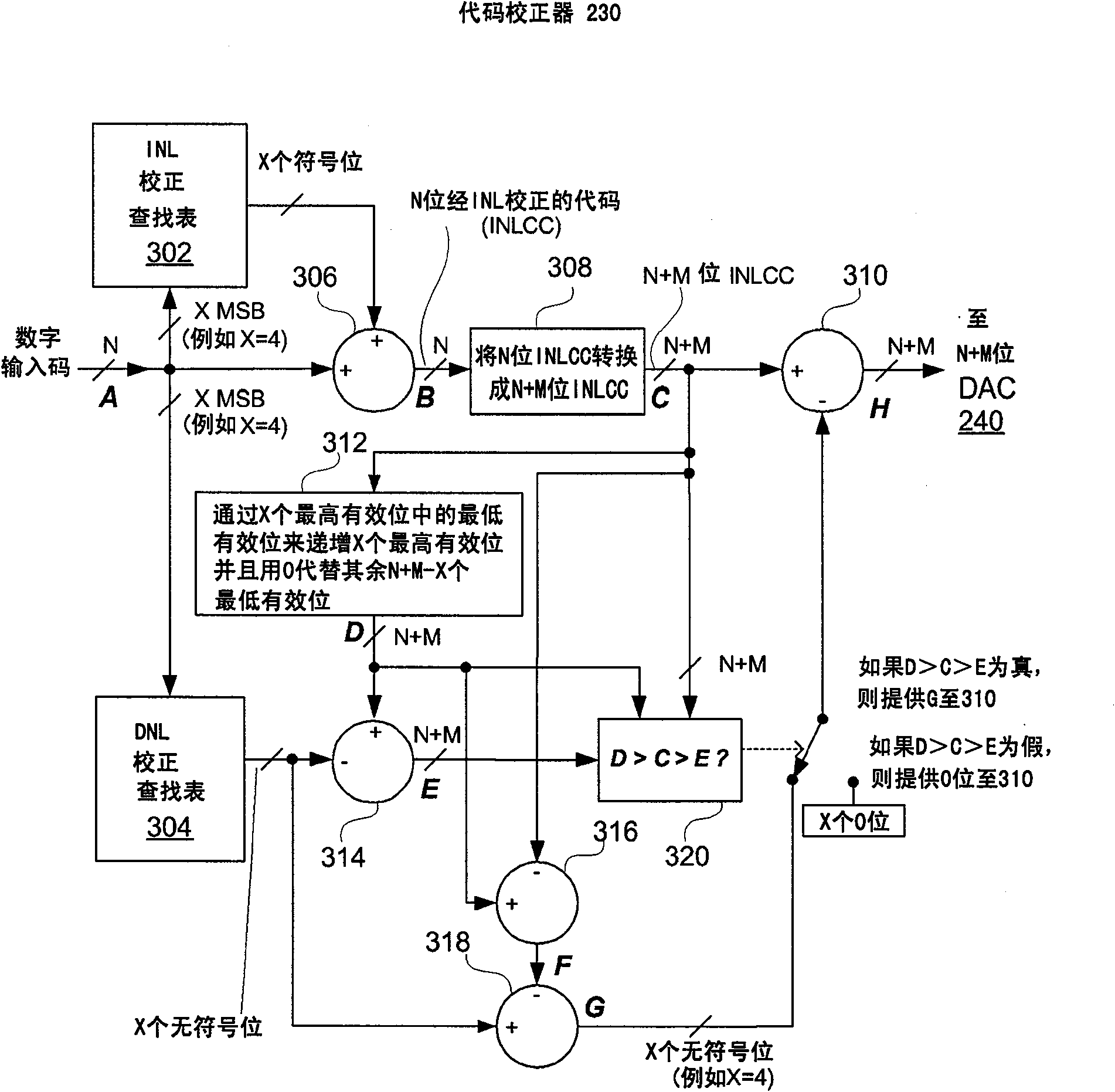

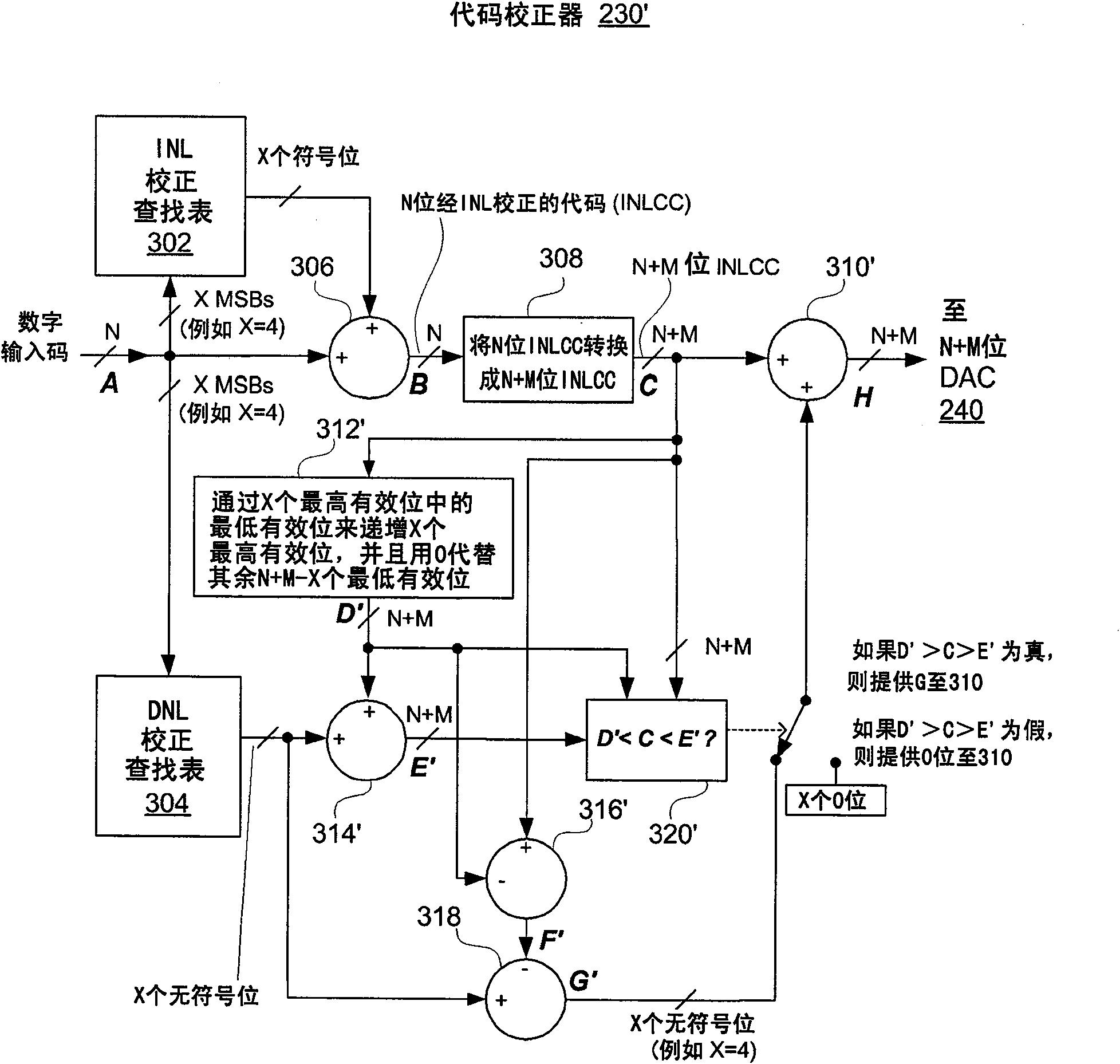

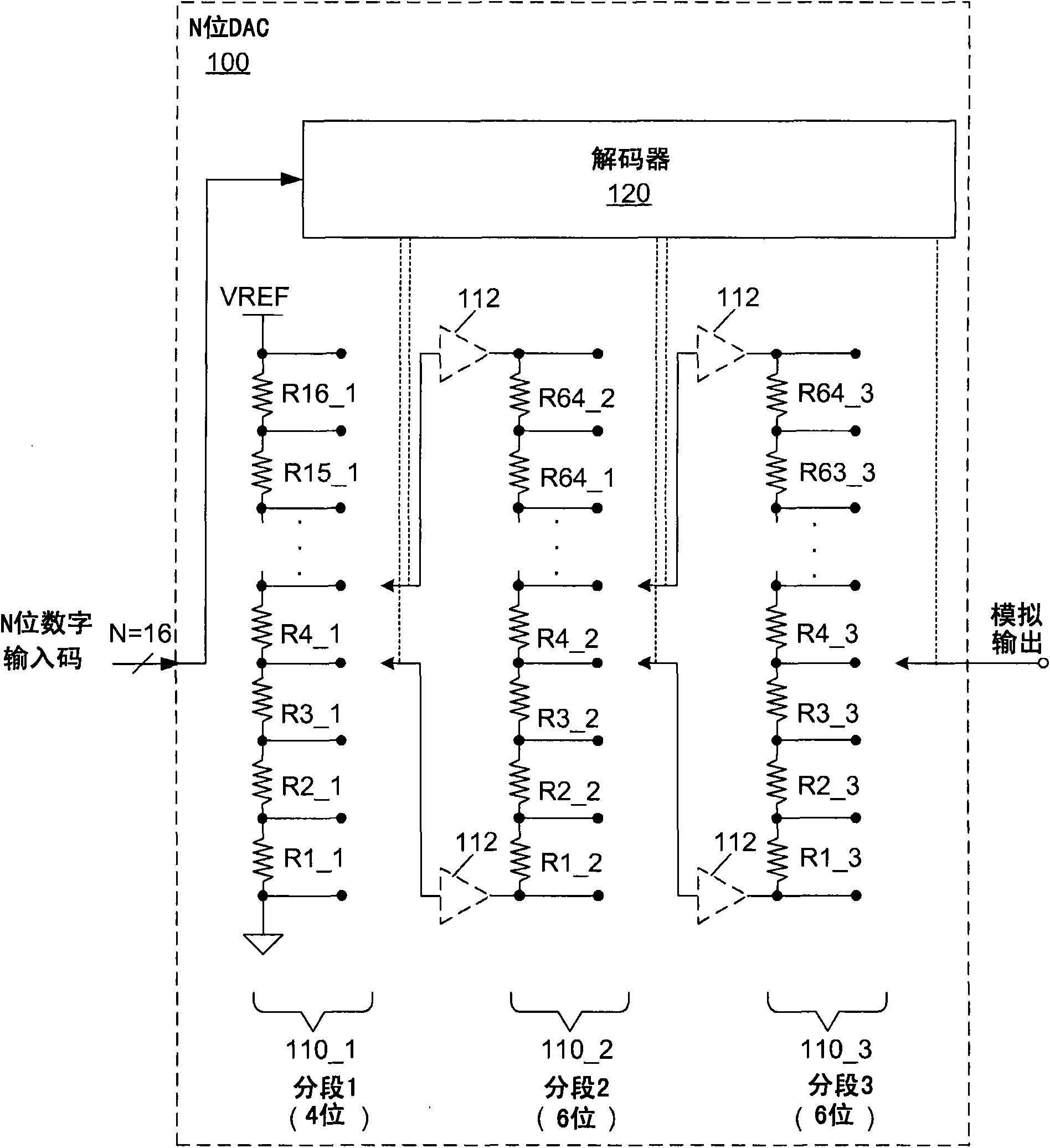

[0033] For INL correction, various techniques for reducing the effect of INL can be used, resulting in different trade-offs as they involve computational requirements and on-chip storage. As described in more detail below, in one embodiment, the most efficient segment of the DAC (e.g., figure 1 Each sub-segment of the middle segment 110_1) (except the end sub-segment, which is used to eliminate the unintentional gain error caused by INL correction) determines a correction code. Various correction techniques can be used including, but not limited to, zero-order correction (essentially INL offset correction), or first-order correction (linear fit between major inflection points in the INL curve).

[0034] Particular embodiments of the present invention relate to systems, devices, and methods that use a look-up table to reduce the INL of a DAC without modifying the DAC output voltage range, while still providing a monotonic DAC. In some embodiments, the size of the lookup table...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More