Patents

Literature

151results about How to "Prevent display quality degradation" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Display device

InactiveUS20090115942A1Avoid display qualityPrevent display quality degradationSolid-state devicesNon-linear opticsLiquid-crystal displayAdhesive

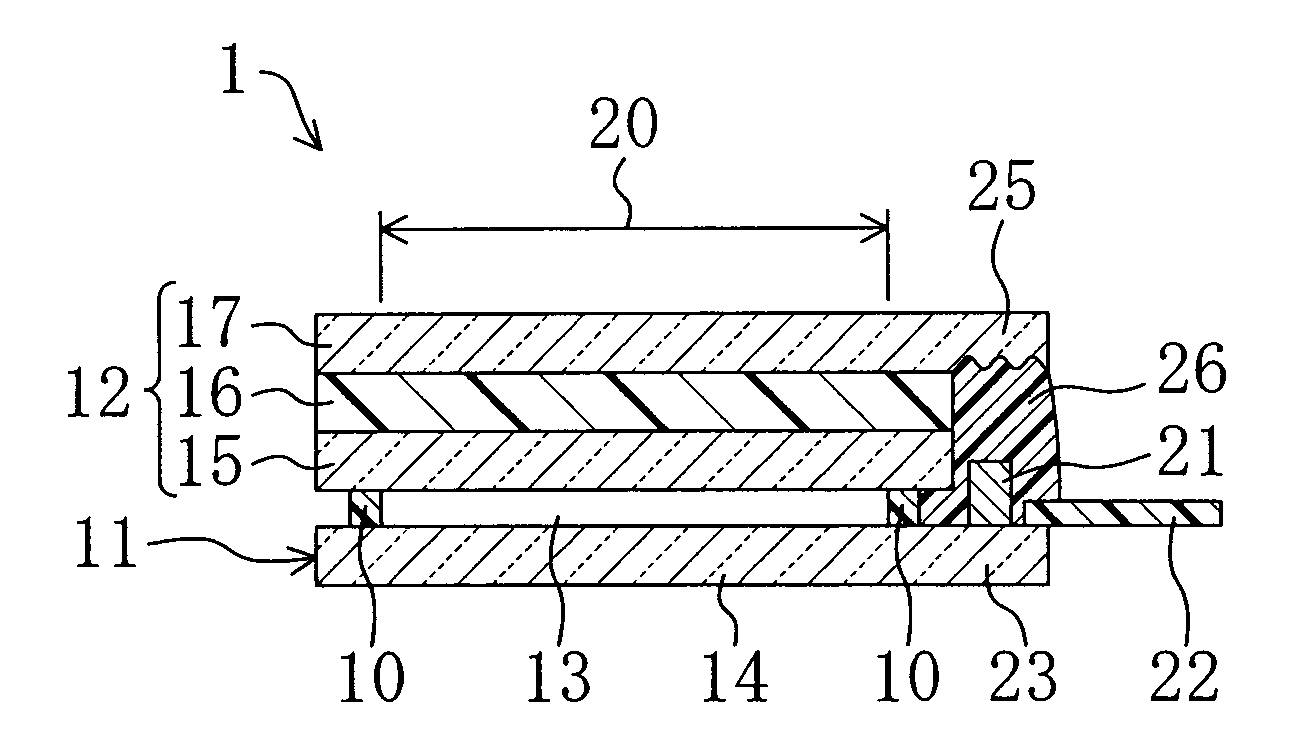

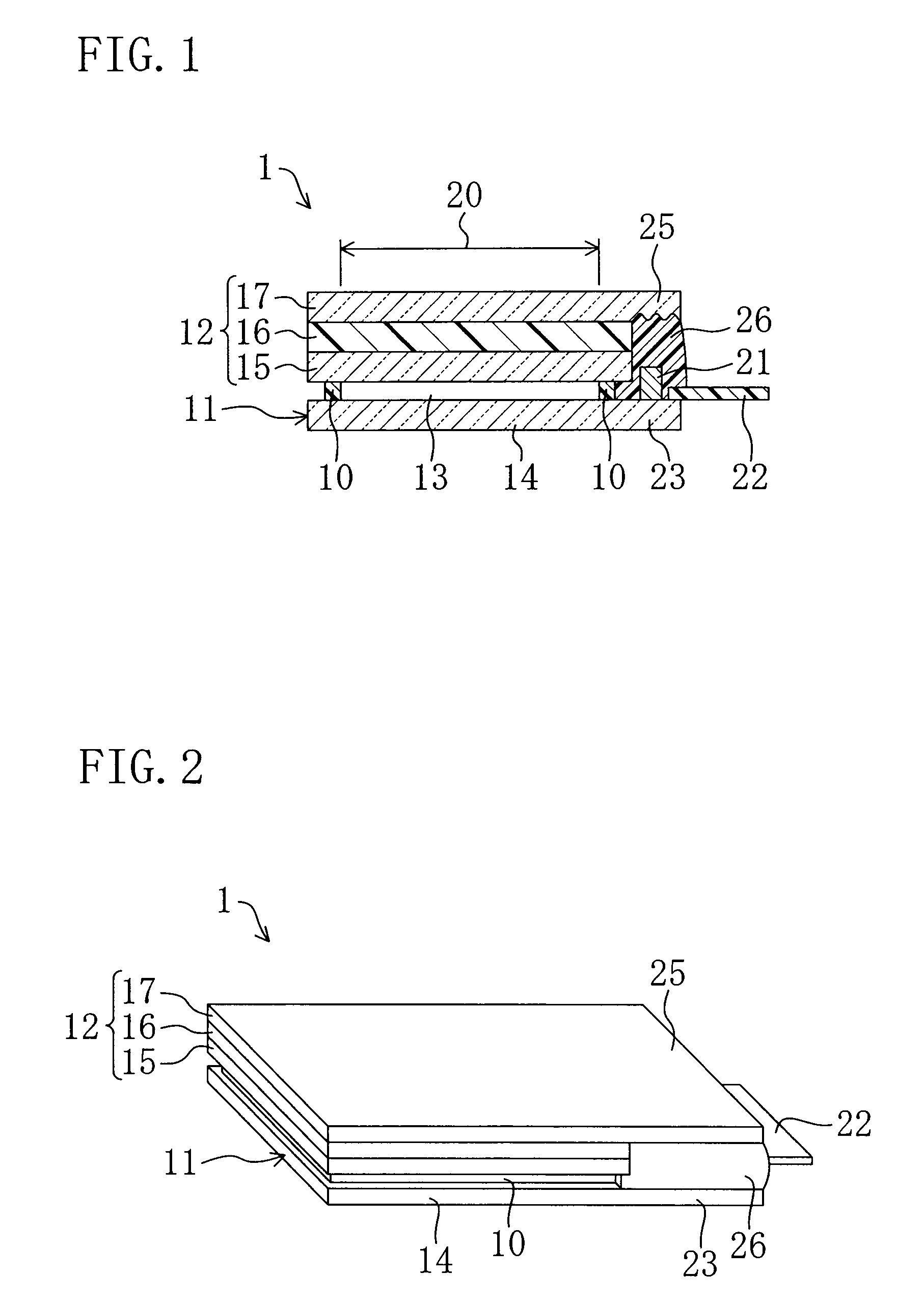

A display device is provided with a sealing member for sealing a liquid crystal layer between a flexible first substrate and a second substrate, a mounting region provided in a portion of the first substrate outside a display area in which the liquid crystal layer is sealed, the mounting region mounting a circuit component on at least a portion thereof, wherein the second substrate includes an extending region extending to face the mounting region and an adhesive arranged to bond the extending region and the mounting region is provided in at least a portion of a space between the extending region and the mounting region.

Owner:SHARP KK

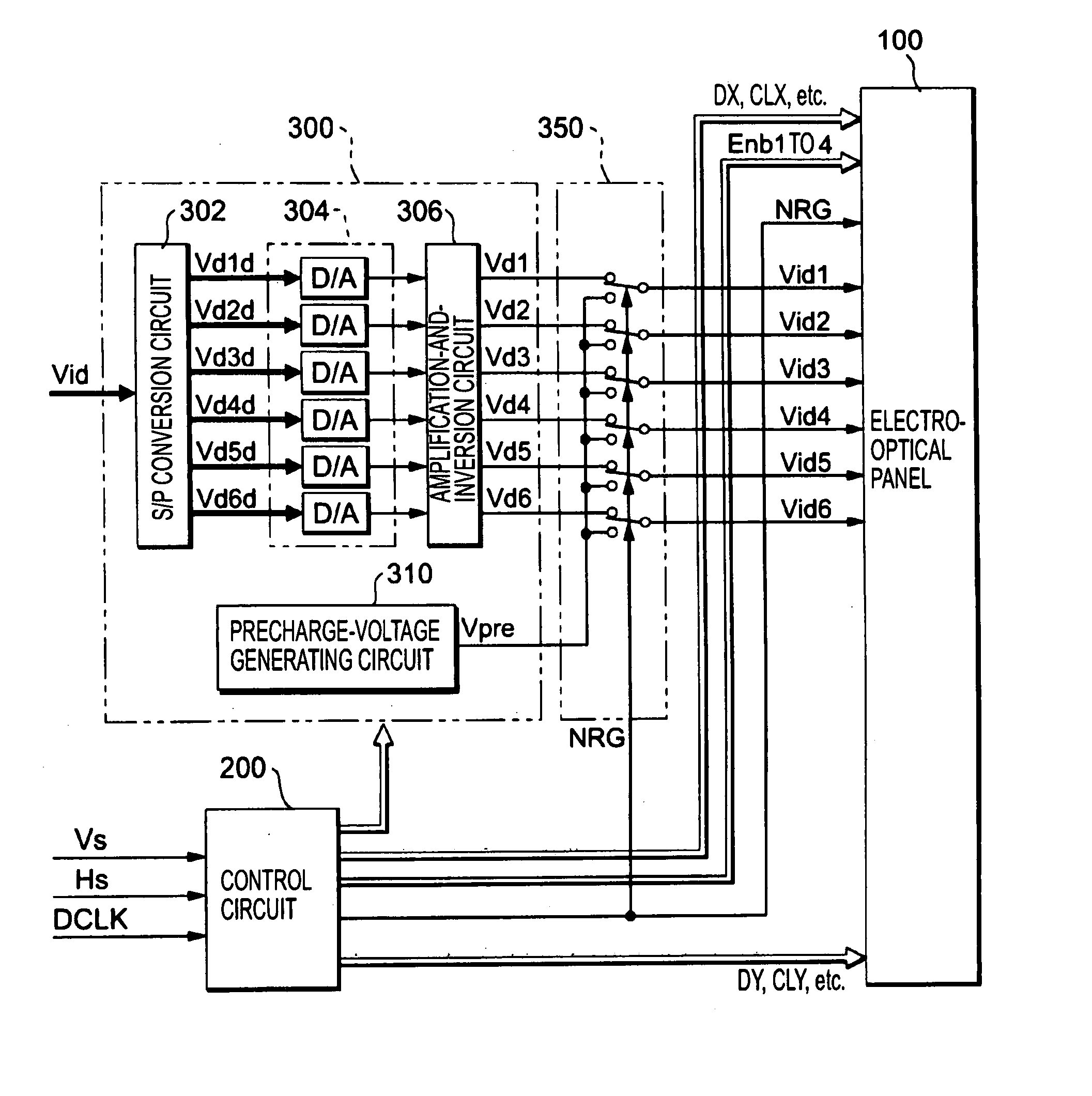

Data driving circuit and organic light emitting display comprising the same

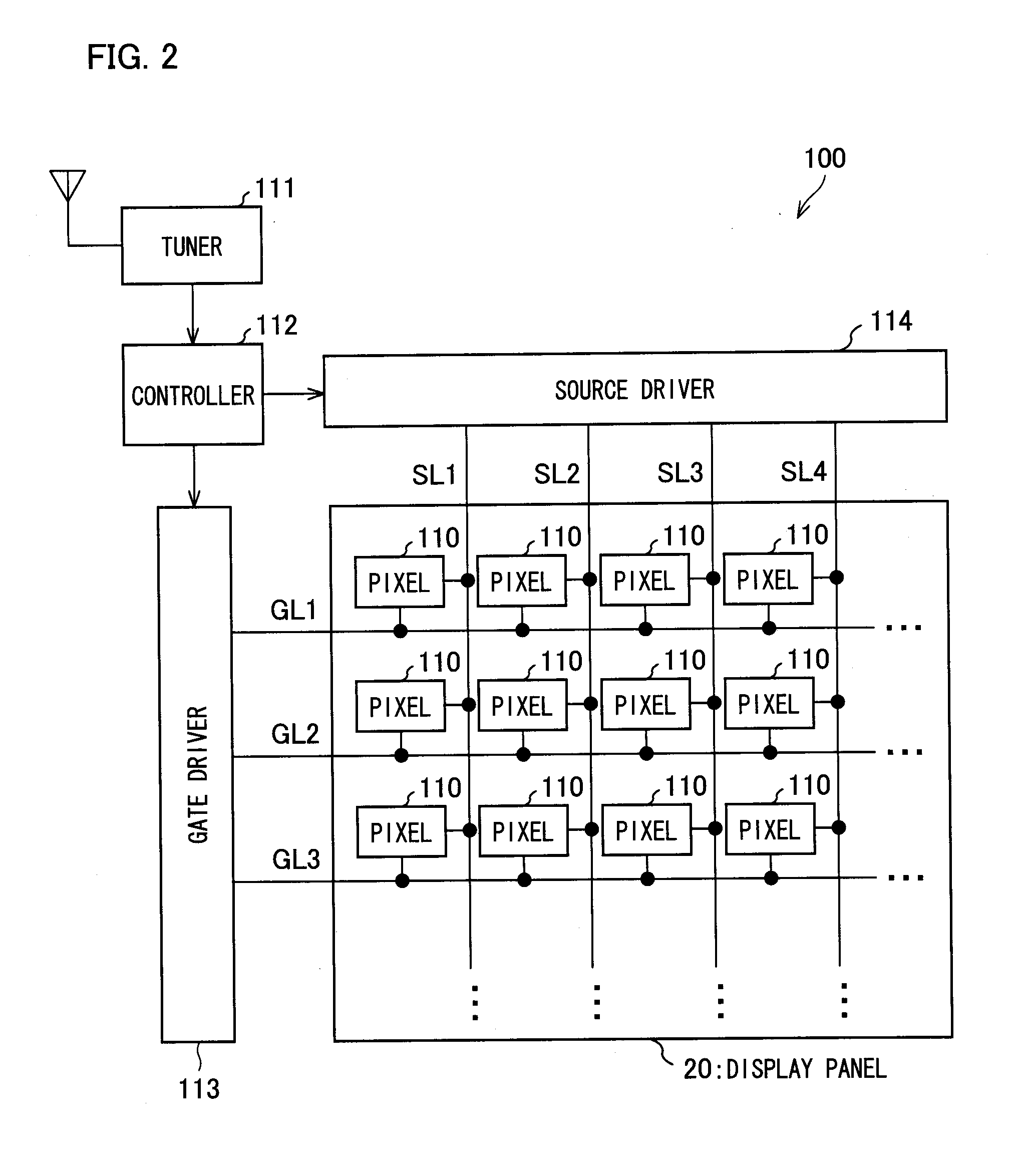

InactiveUS20080122819A1Improve display qualityPrevent display quality degradationCathode-ray tube indicatorsDigital-analogue convertorsDigital analog converterReference current

Provided are a data driving circuit of an organic light emitting display and an organic light emitting display comprising the same. The organic light emitting display comprises a reference pixel controller, a data driver, and a display panel. The reference pixel controller comprises a light detector for detecting an amount of light emission of a reference pixel and outputting a first control signal thereof and a reference current controller for outputting a second control signal controlling an amount of a reference current according to the first control signal. The data driver comprises a current source for outputting a current having the same amount as the reference current according to the second control signal and a digital-analog converter for outputting a data current by scaling the current having the same amount as the reference signal to be proportioned to a data signal. The display panel formed of pixels, each of which comprises an organic light emitting device that emits light in accordance with the data current.

Owner:IKAIST CO LTD

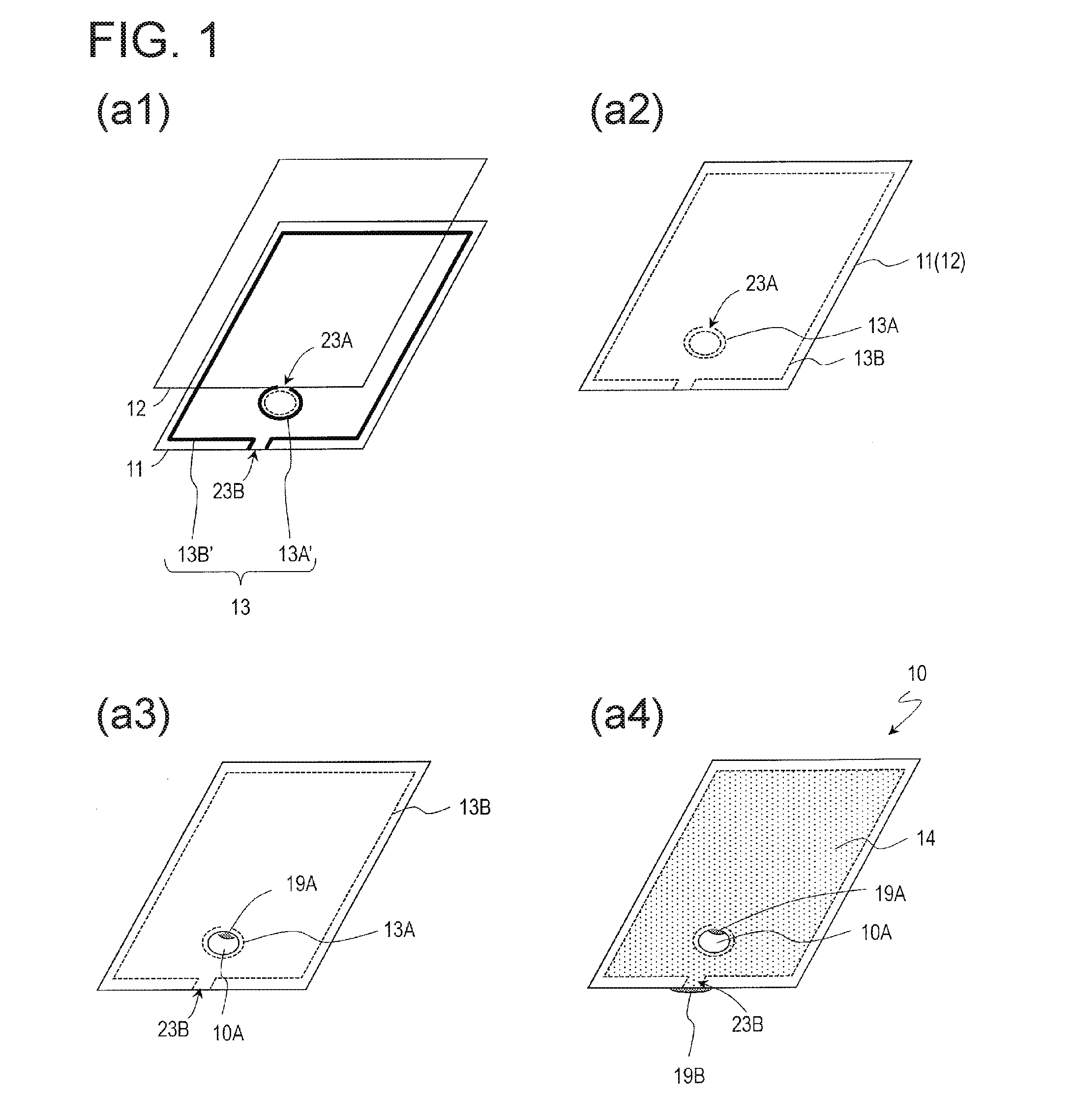

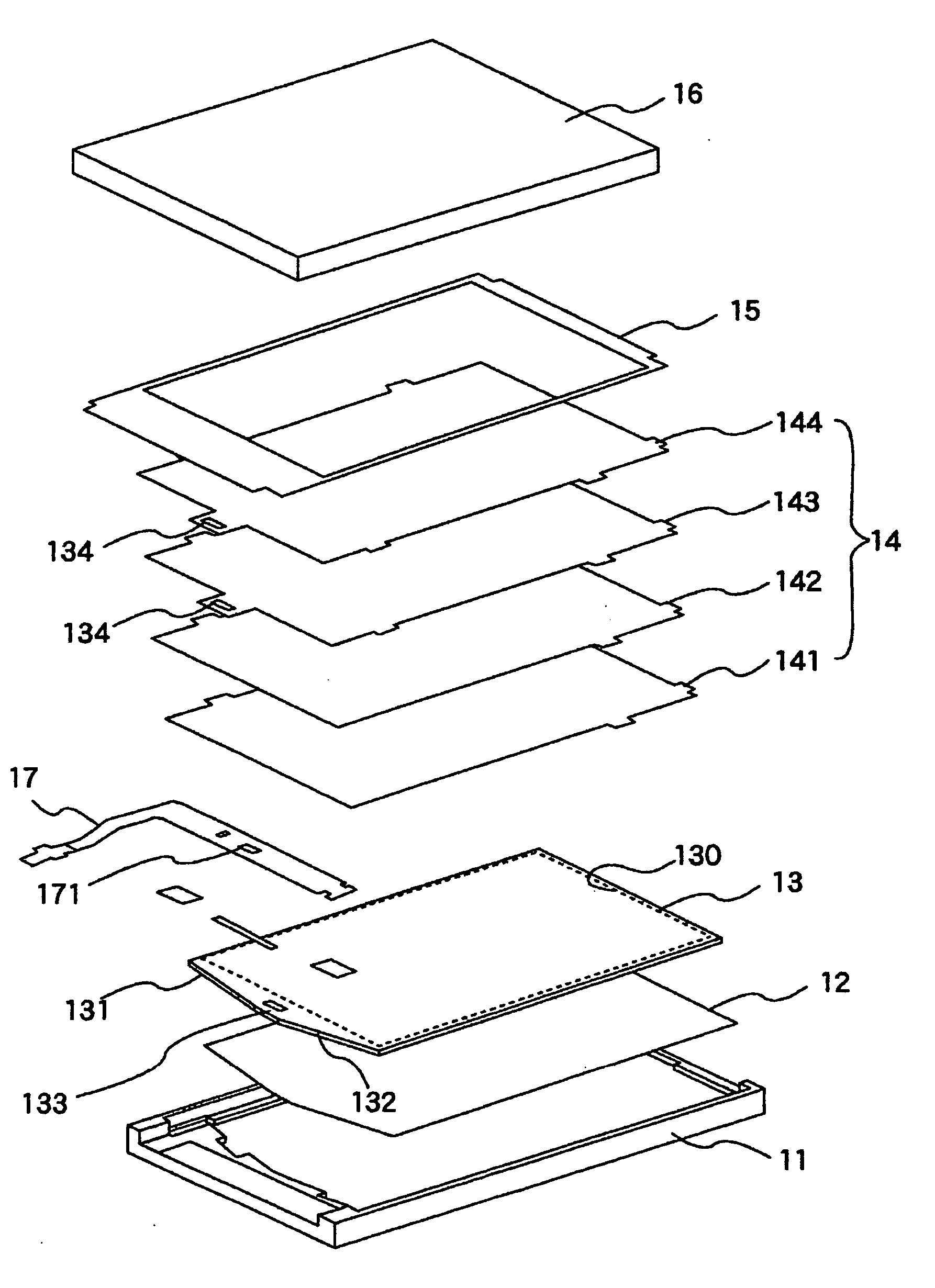

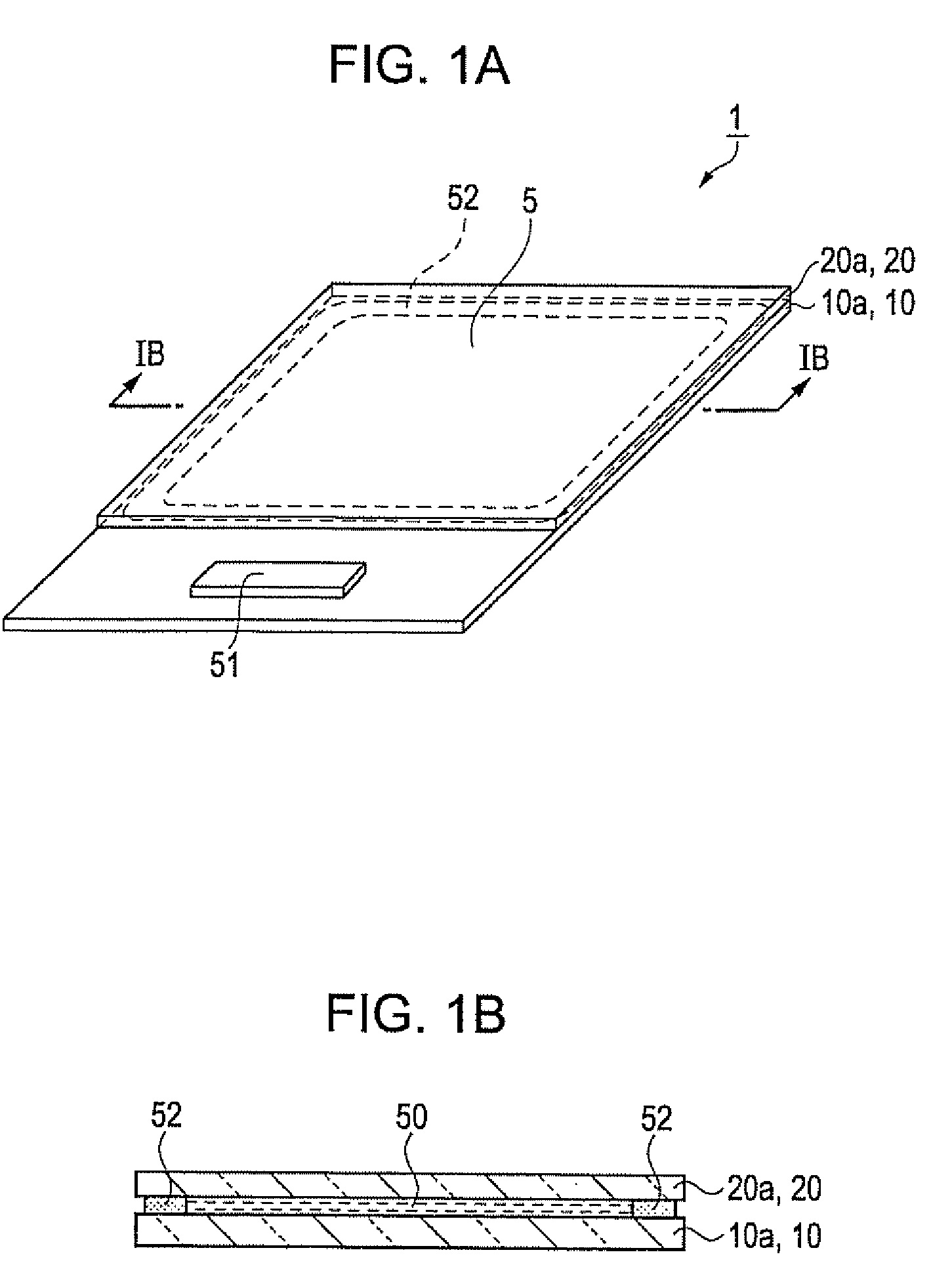

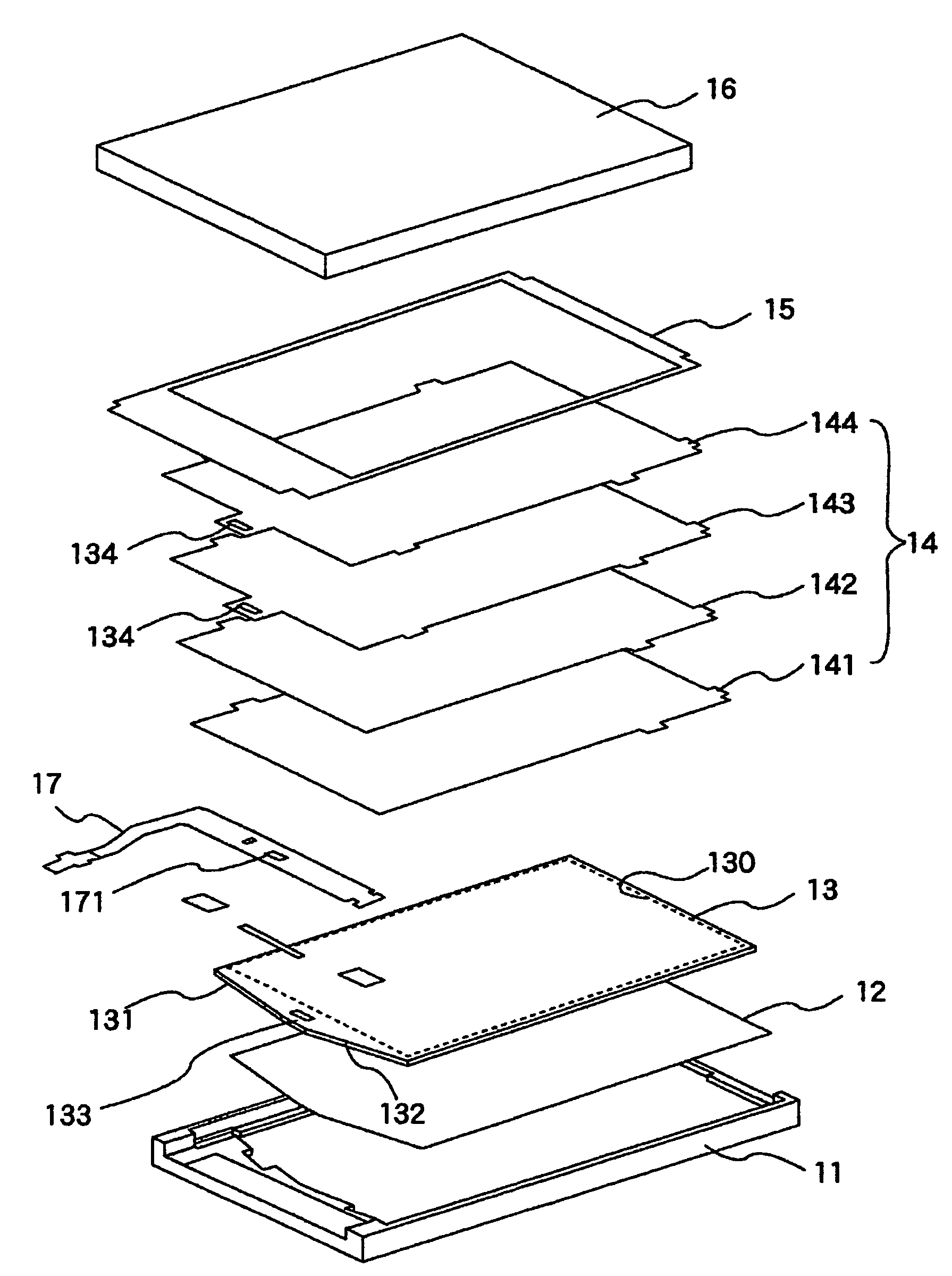

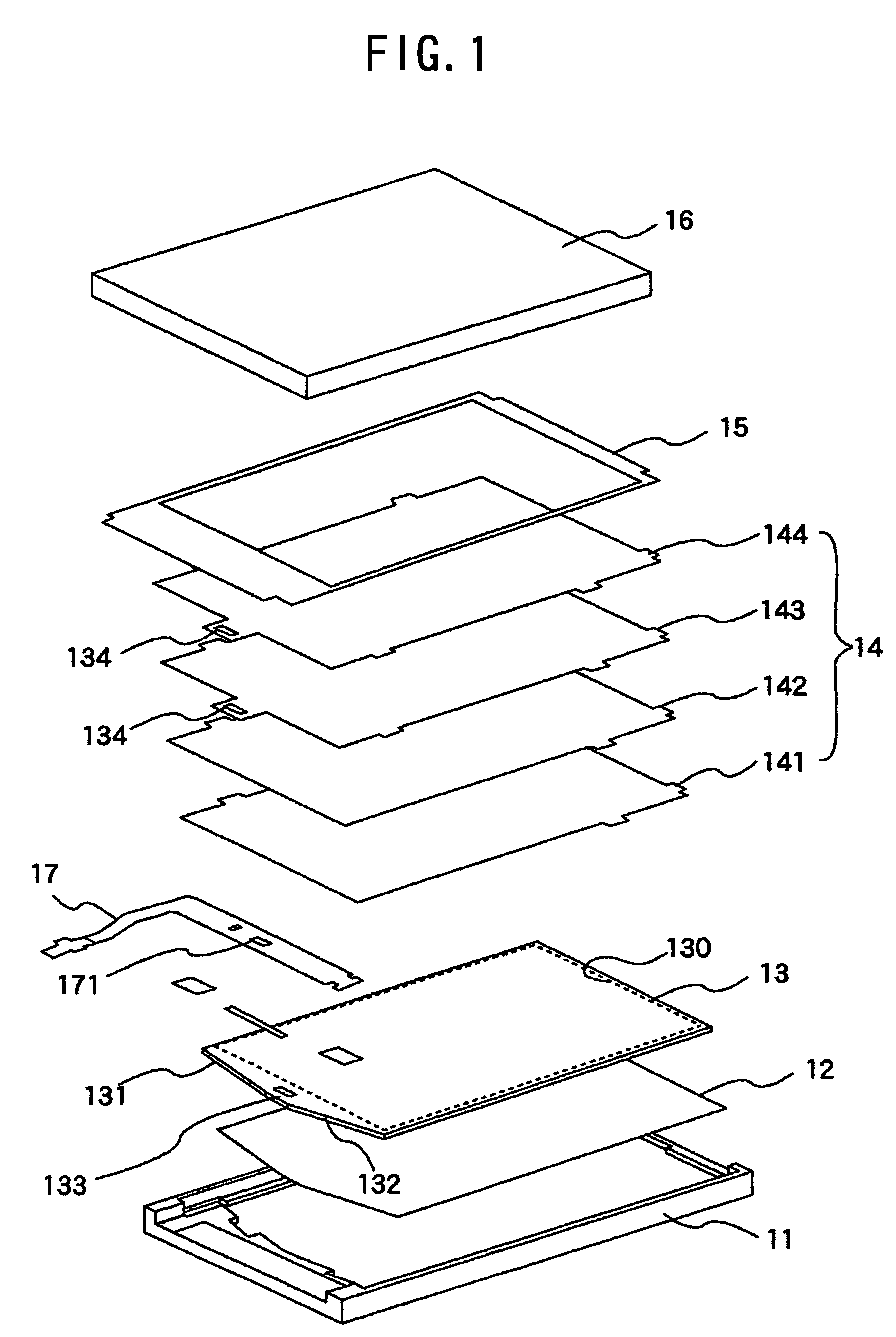

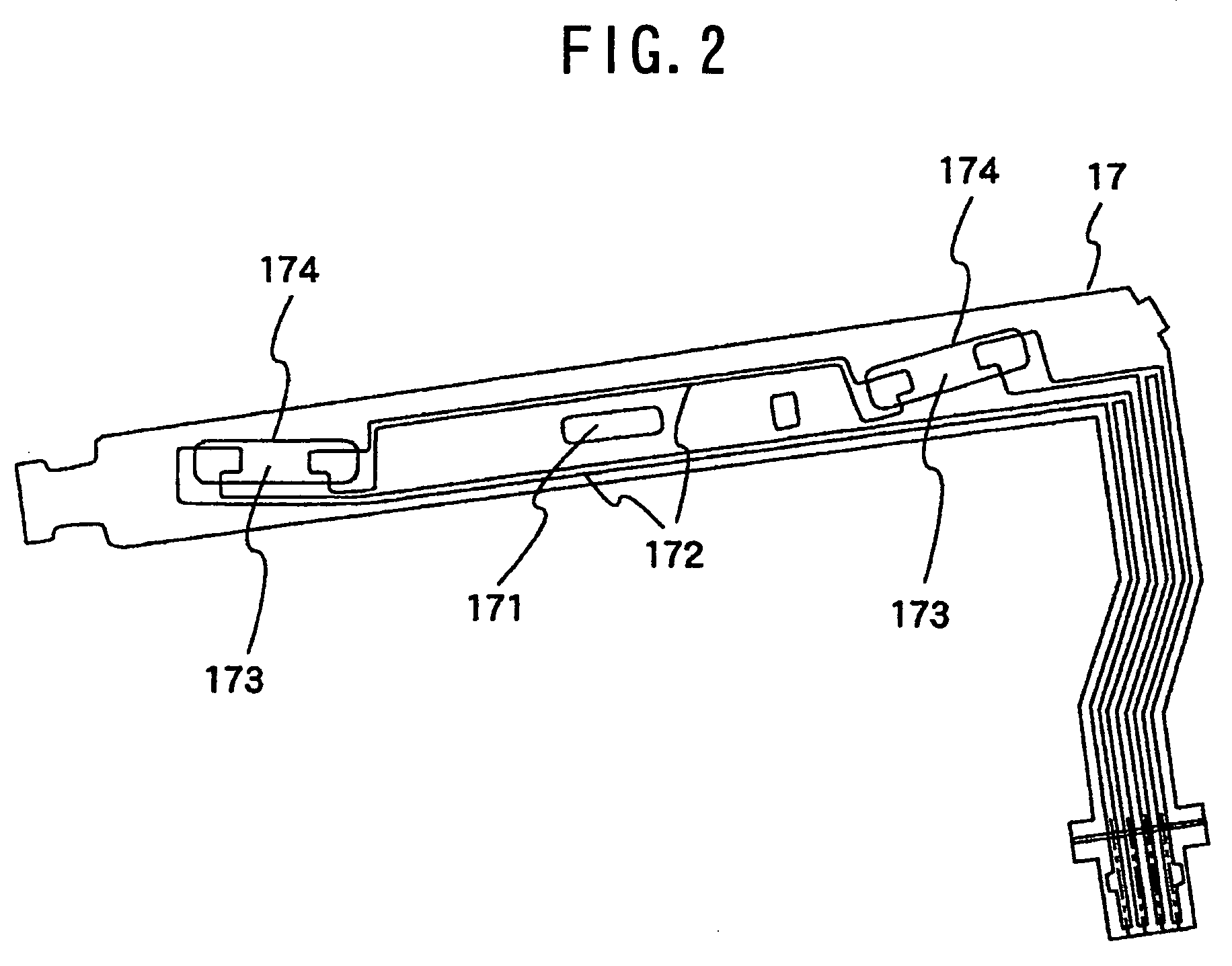

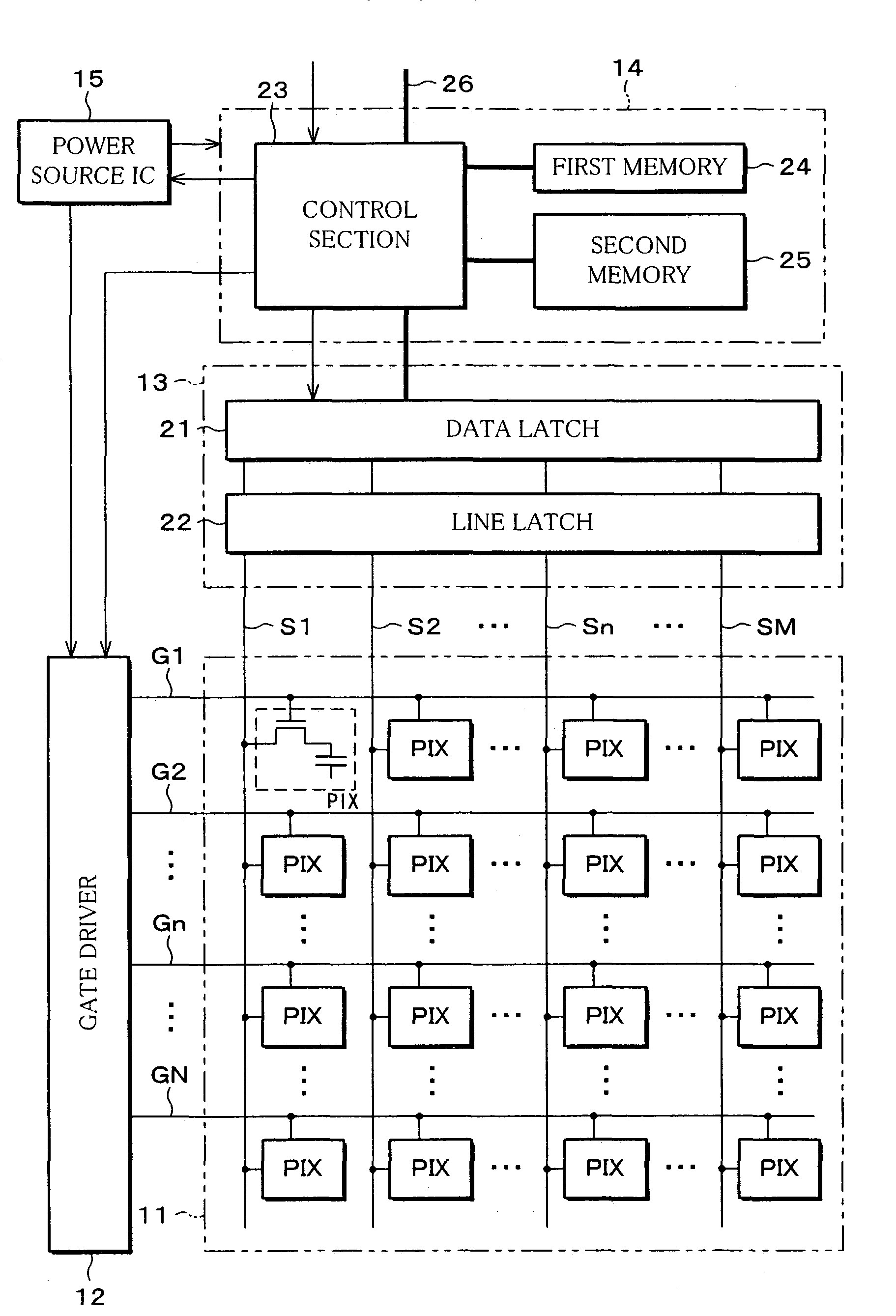

Display device and method of manufacturing thereof

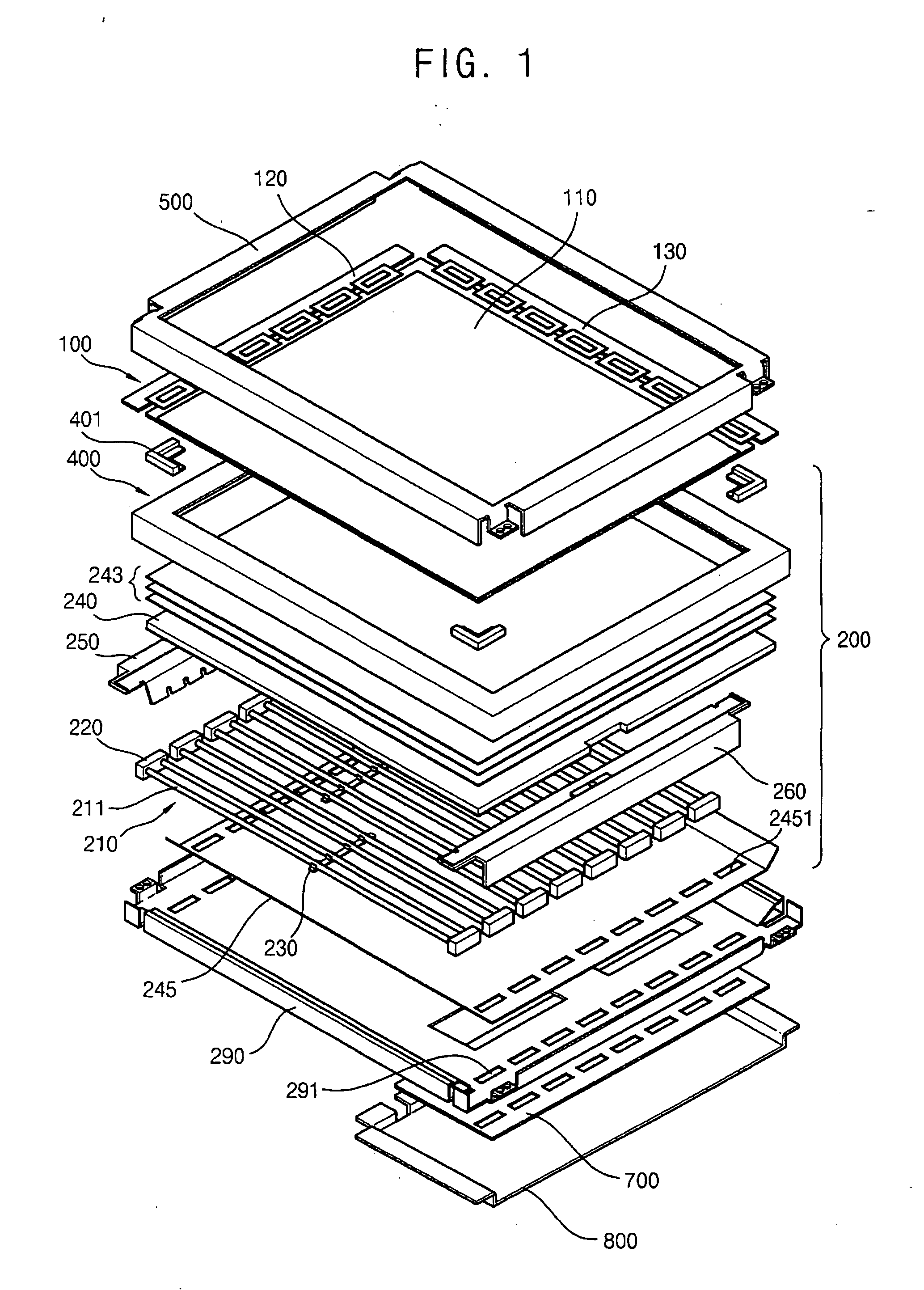

InactiveUS20060103774A1Prevent display quality degradationInhibit deteriorationElongate light sourcesElectrical apparatus contructional detailsDisplay deviceEngineering

Owner:SAMSUNG DISPLAY CO LTD

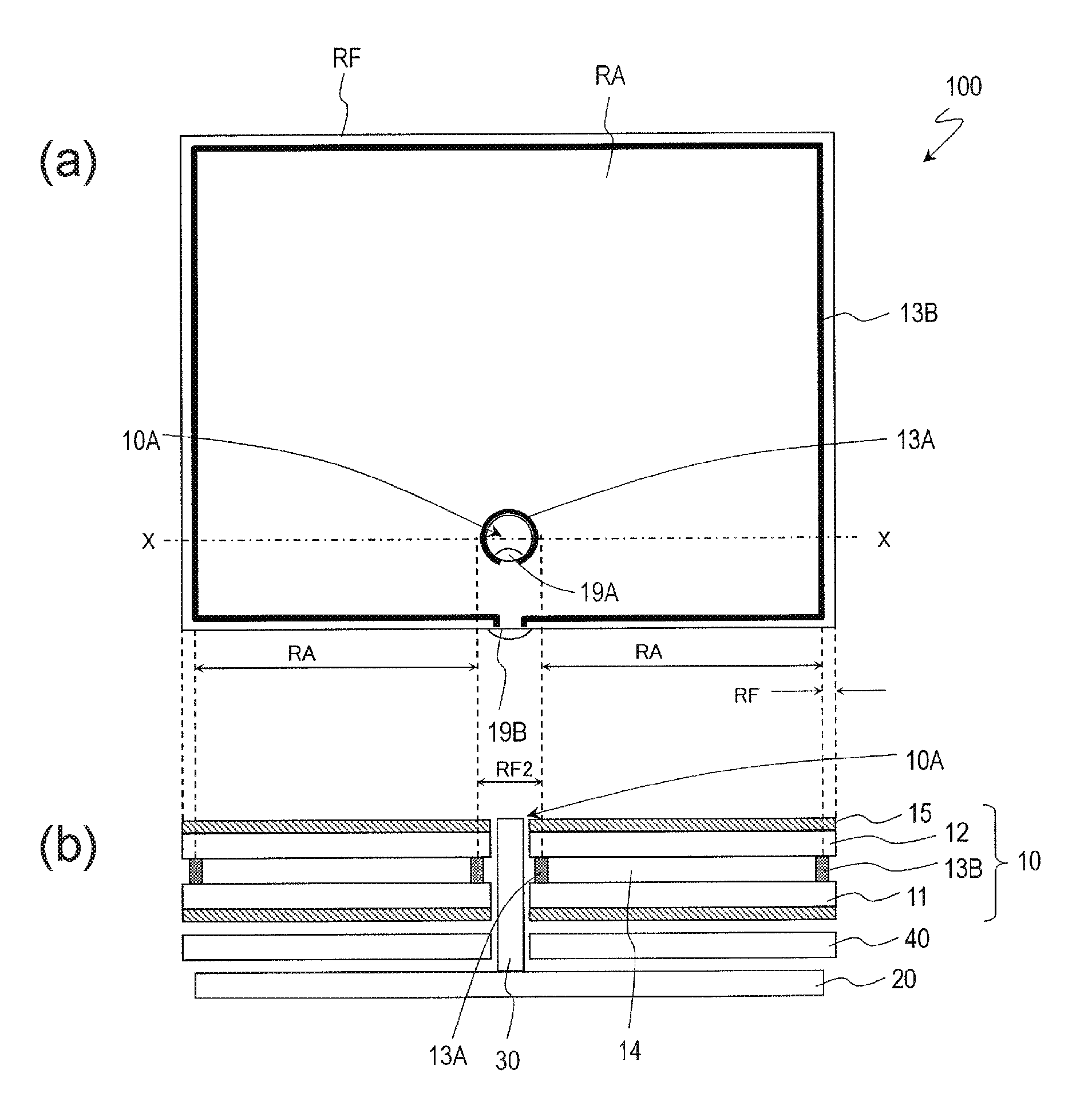

Display panel

ActiveUS20160202515A1Prevent display quality degradationDetails for portable computersNon-linear opticsMedia layerMechanical engineering

Owner:SHARP KK

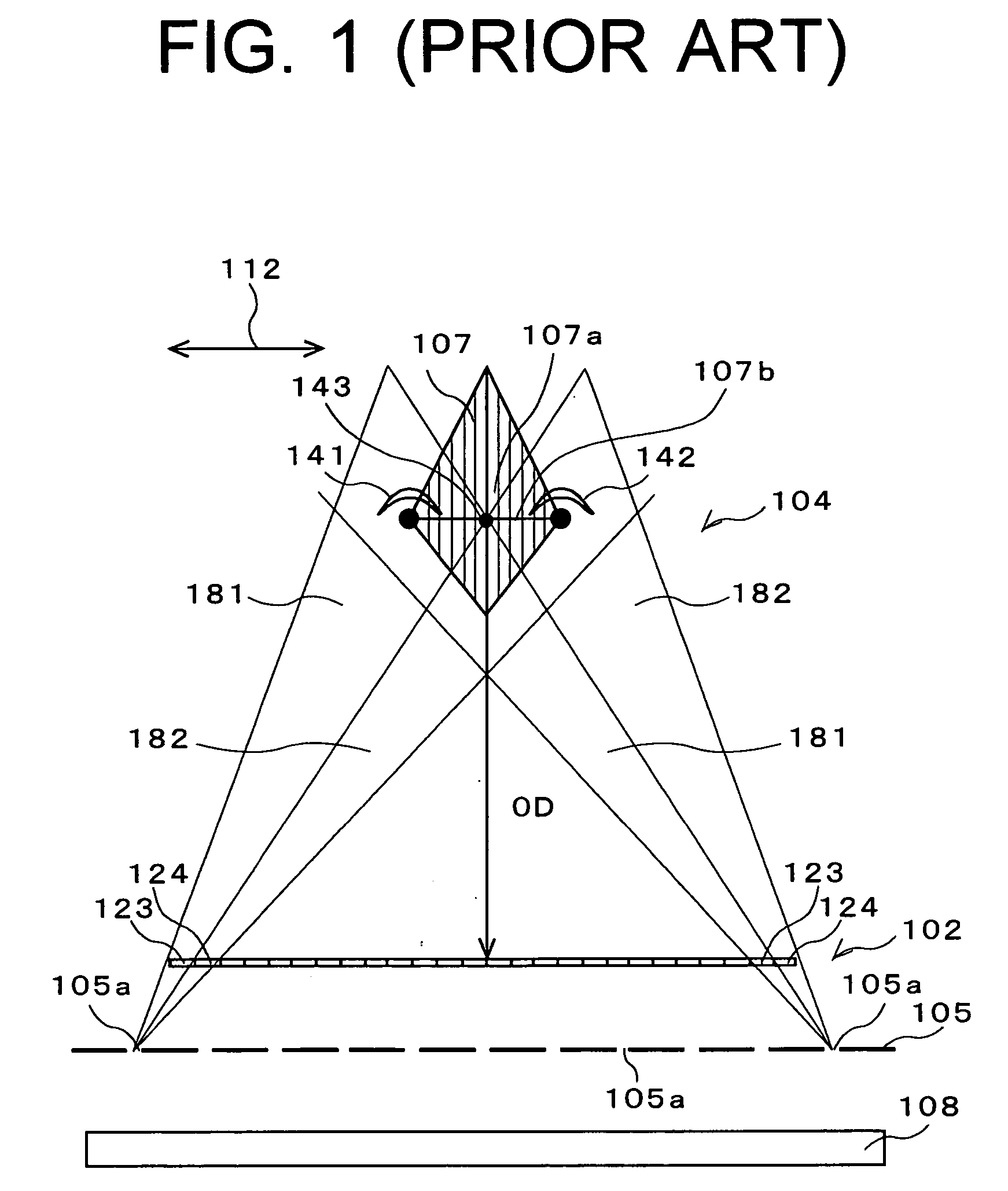

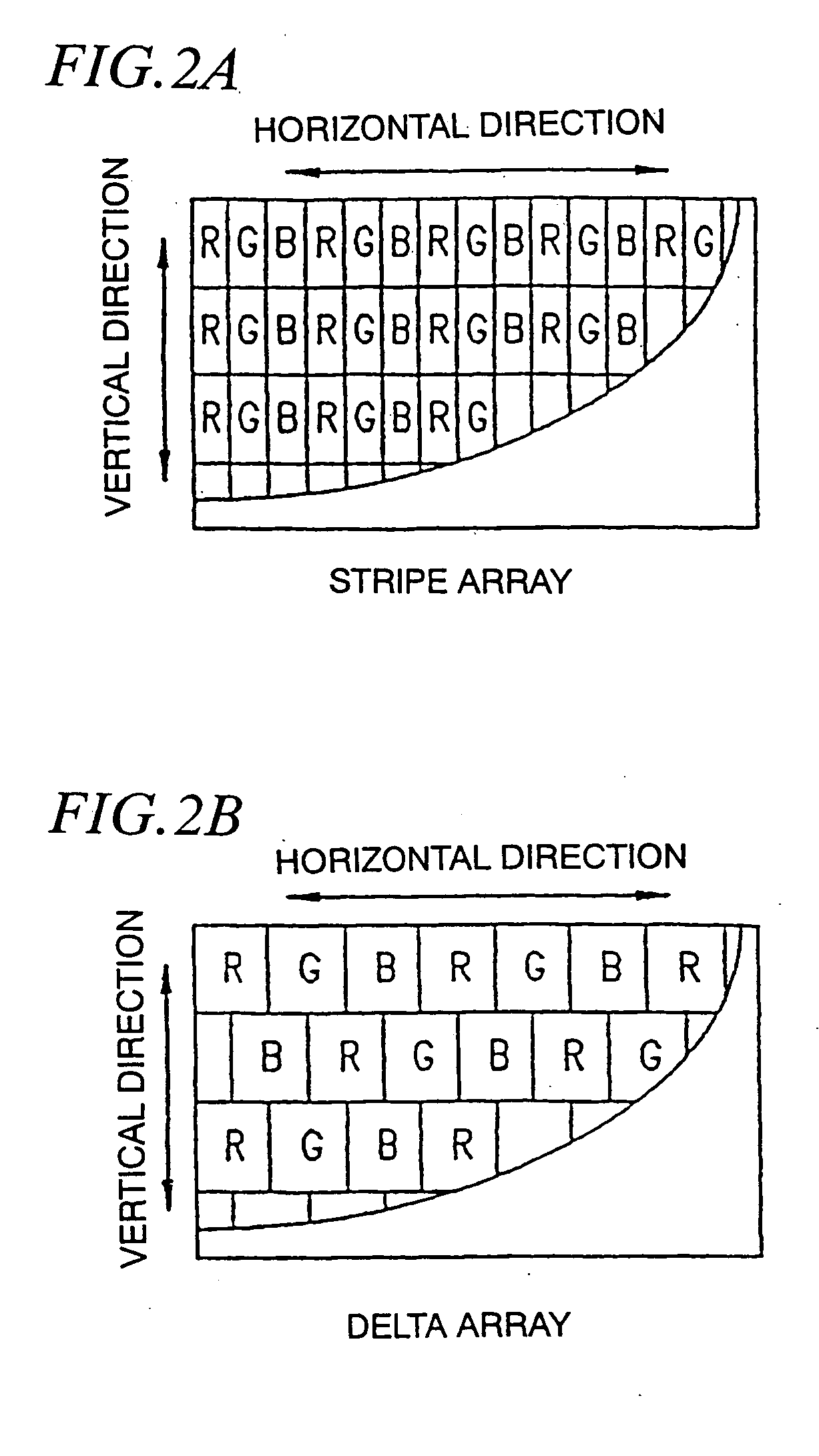

Image display device, portable terminal, display panel, and lens

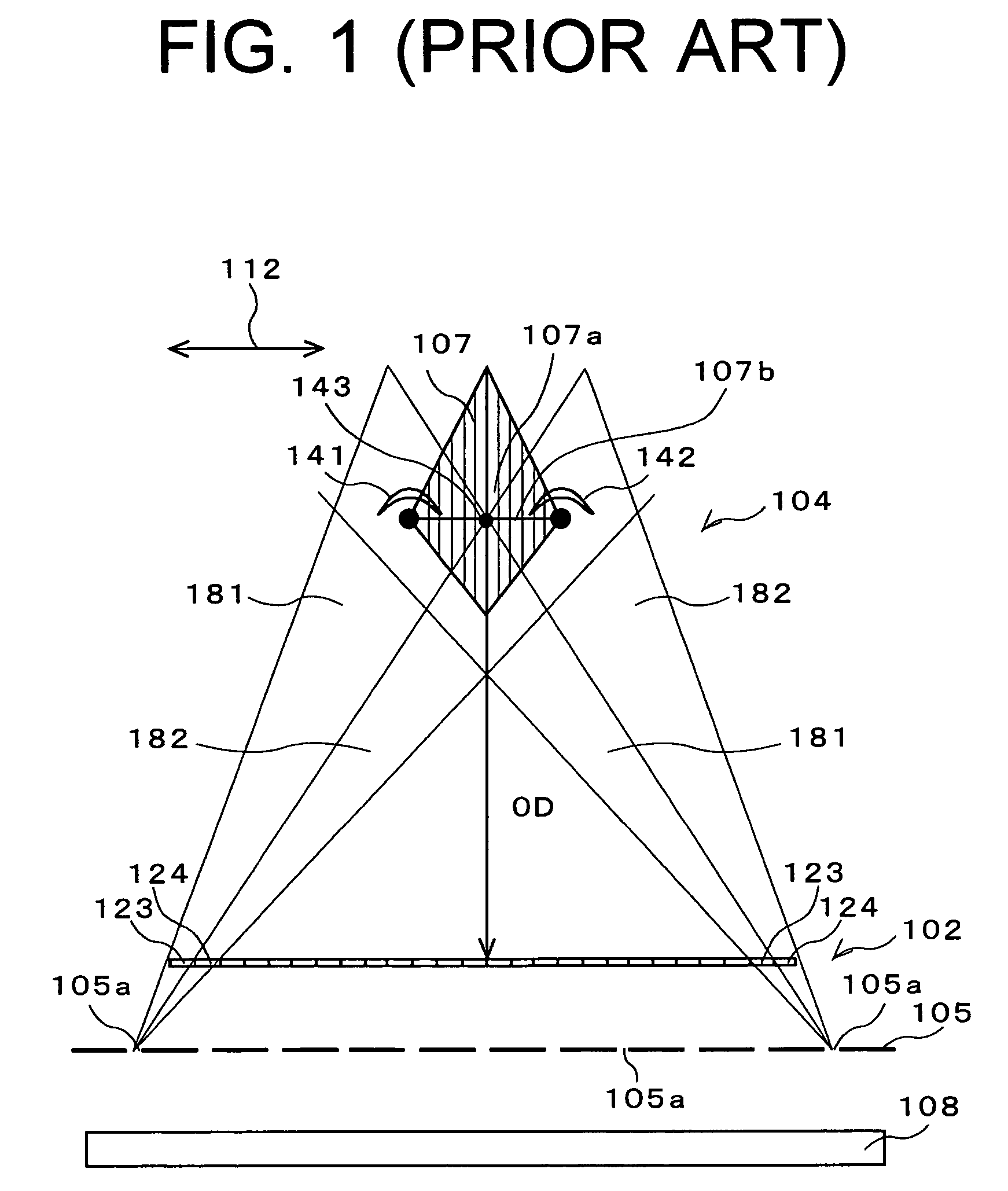

ActiveUS20060050385A1Prevent display quality degradationSteroscopic systemsLensLenticular lensCylindrical lens

In an image display device where a lenticular lens, a display panel, and a light source are provided in order from a viewer side, when cylindrical lenses of the lenticular lens are arrayed in a horizontal direction, in first-viewpoint pixels and second-viewpoint pixels of the display panel, openings whose sides which intersect with straight lines in the horizontal direction are not parallel to a vertical direction are formed. And, a shape of the openings of a pair of pixels mutually adjacent in the vertical direction is made line-symmetric with respect to edges of the pixels extending in the horizontal direction as an axis.

Owner:NEC LCD TECH CORP

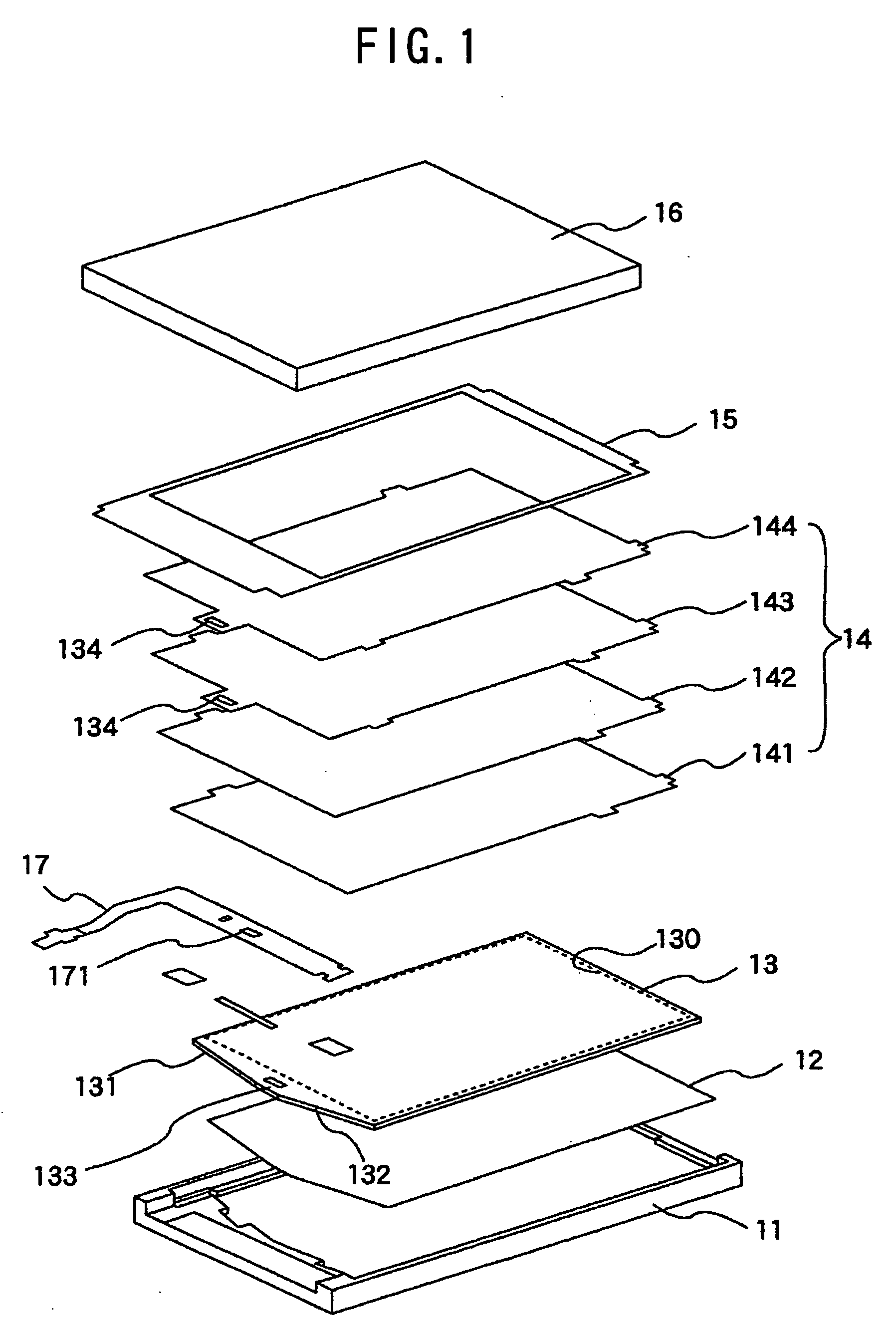

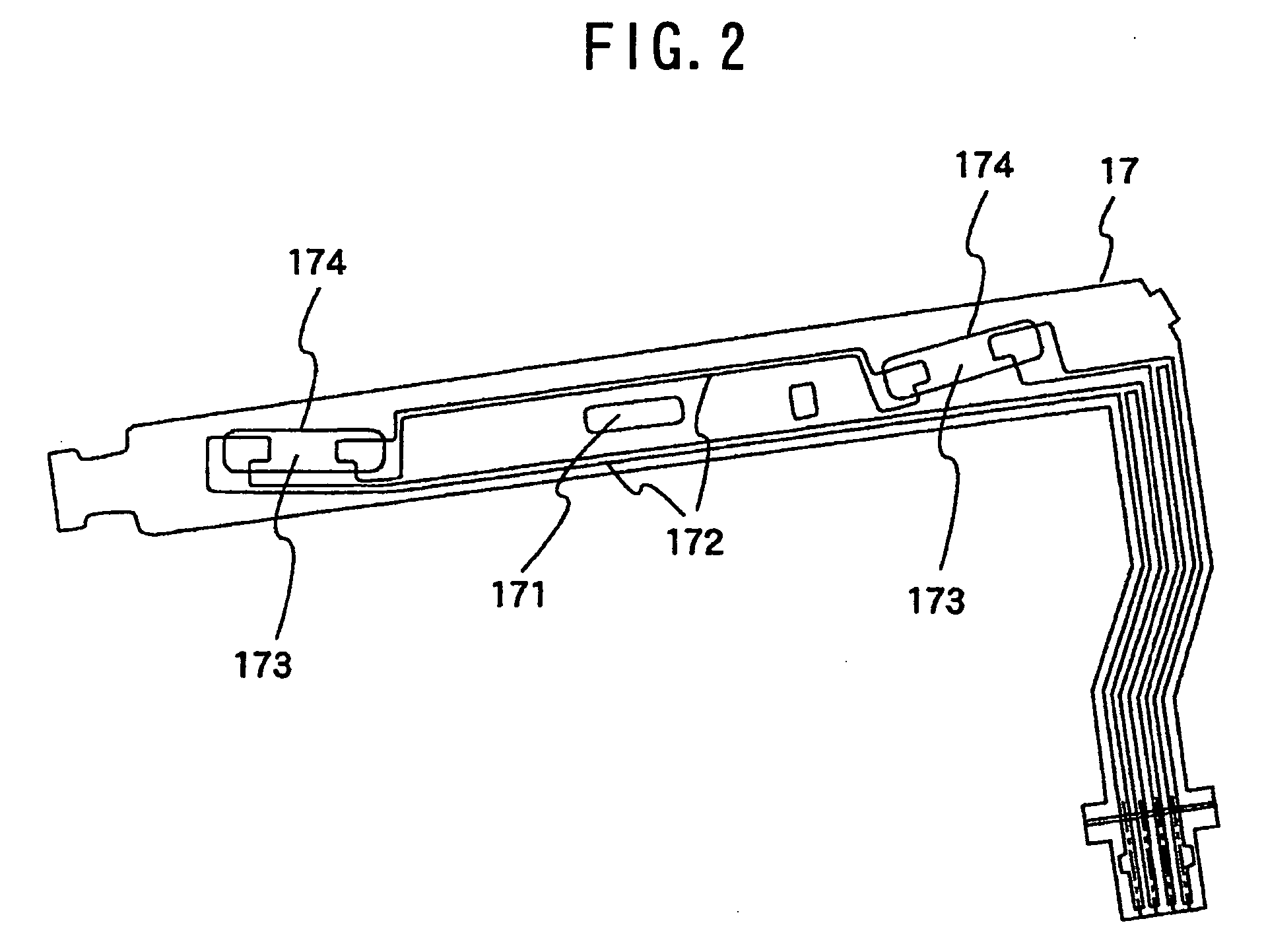

Liquid crystal display device and backlight

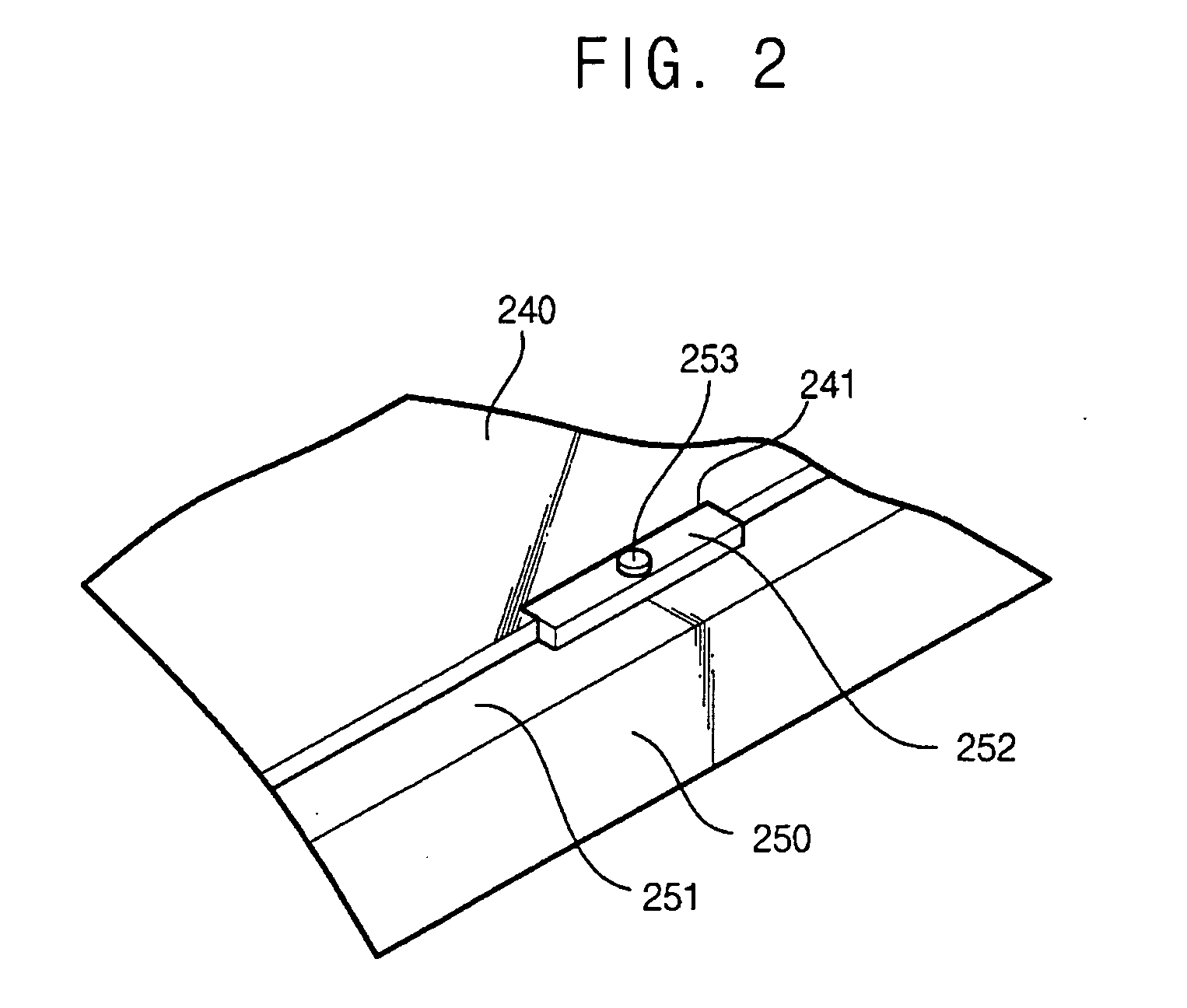

ActiveUS20070008457A1Prevent display quality degradationLow costPlanar/plate-like light guidesPrinted circuitsFlexible electronicsLiquid-crystal display

A liquid crystal display device having includes a light guide plate having a surface thereof serving as an illuminating surface region opposite to a liquid crystal display panel, light sources mounted on a flexible printed-circuit board and provided on a side face of the light guide plate, an optical sheet member interposed between the liquid crystal display panel and the light guide plate. The side surfaces of the light guide plate with the light sources provided thereon have a ridge-like inclined surface formed thereon, when viewed from the illuminating surface, and the ridge-like inclined surfaces serve as a light-receiving surface with the light source arranged thereon.

Owner:PANASONIC LIQUID CRYSTAL DISPLAY CO LTD

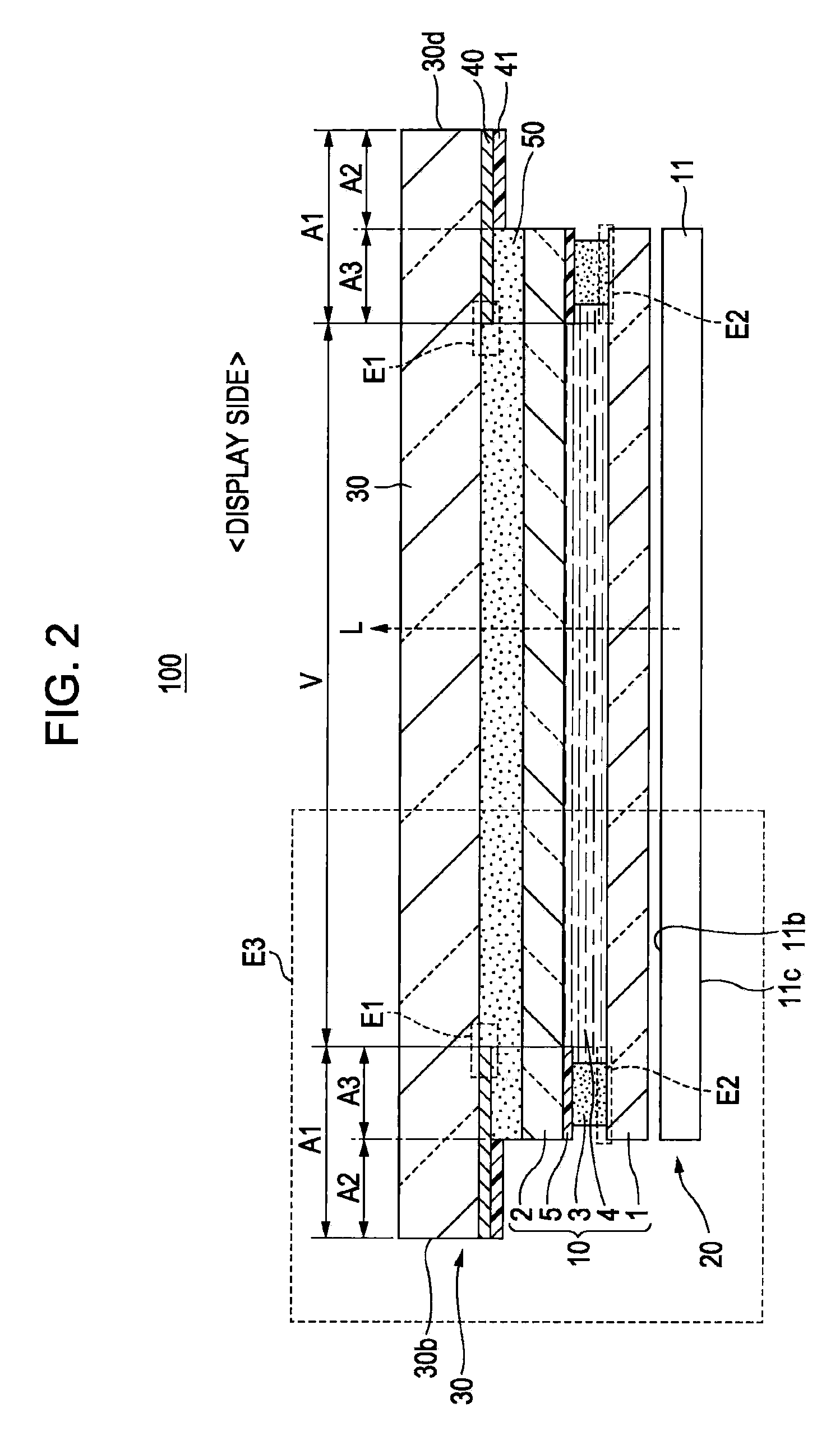

Electro-optical device, input device, and electronic apparatus

ActiveUS20090257010A1Prevent display quality degradationImprove design qualityOptical light guidesNon-linear opticsEngineeringOpto electronic

An electro-optical device includes: an electro-optical panel; a light-transmissive member that overlaps the electro-optical panel and has a protruding part that protrudes so as to be positioned outside an edge of the electro-optical panel, the light-transmissive member having a first area and a second area that is located outside the first area; a coloration layer that is formed on a surface of the light-transmissive member at the second area; an adhesive material that is provided between a part of the coloration layer and a corresponding part of the electro-optical panel as well as between the part of the light-transmissive member and a corresponding part of the electro-optical panel; and a first light-shielding layer formed over one surface of the light-transmissive member, and the first light-shielding layer being formed at an area where the coloration layer does not overlap the adhesive material in a plan view.

Owner:JAPAN DISPLAY WEST

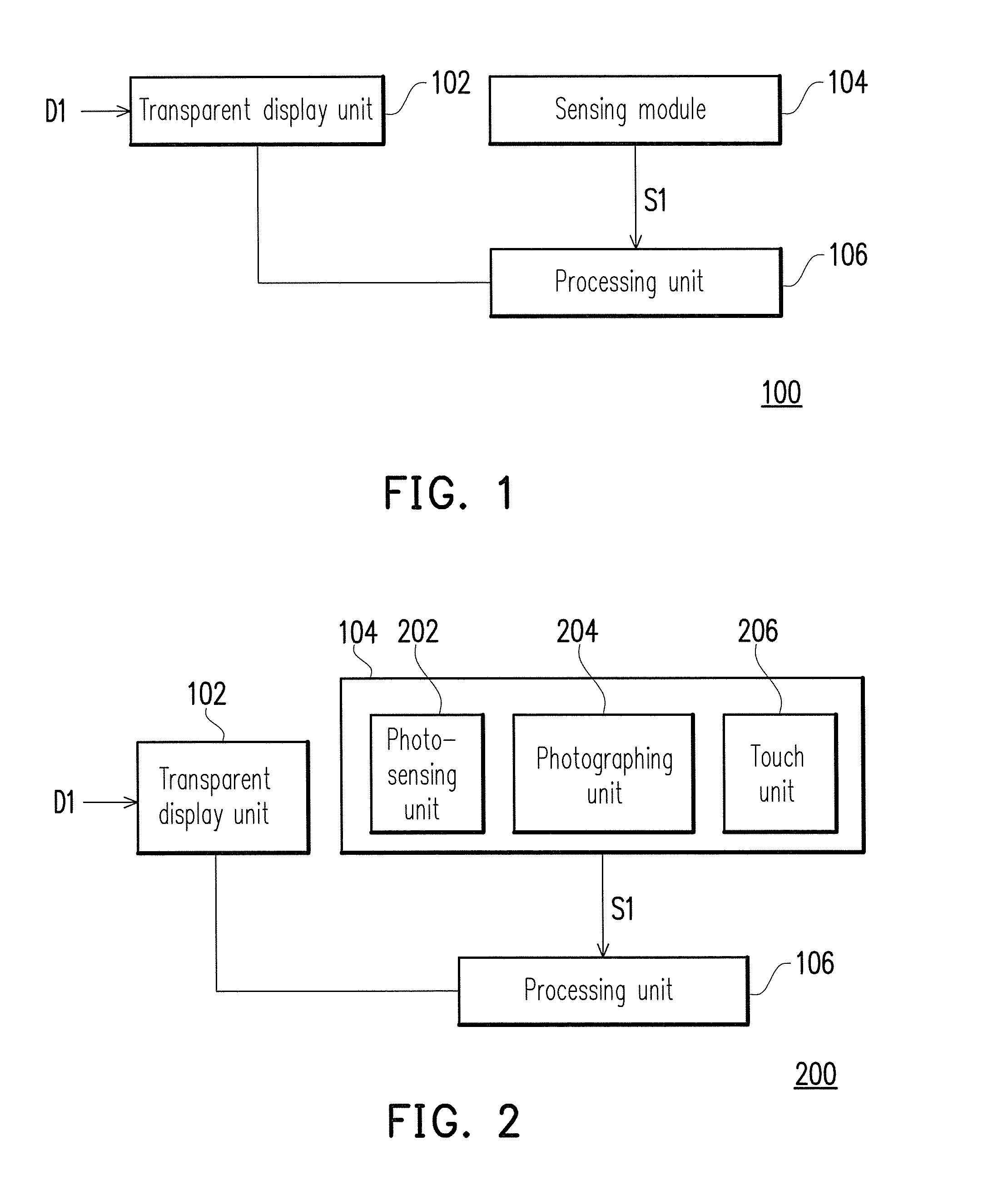

Transparent display device and transparency adjustment method thereof

ActiveUS20130314433A1Improve display qualityPrevent display quality degradationCathode-ray tube indicatorsInput/output processes for data processingComputer scienceTransparent display

A transparent display device and a transparency adjustment method thereof are provided. The transparent display device includes a transparent display unit, a sensing module and a processing unit. The sensing module detects at least one of conditions of the environmental background of the transparent display device and a user's input. The processing unit determines if it is necessary to adjust the transparent degree of a transparent image displayed by the transparent display unit or not according to a sensing result detected by the sensing module.

Owner:ACER INC

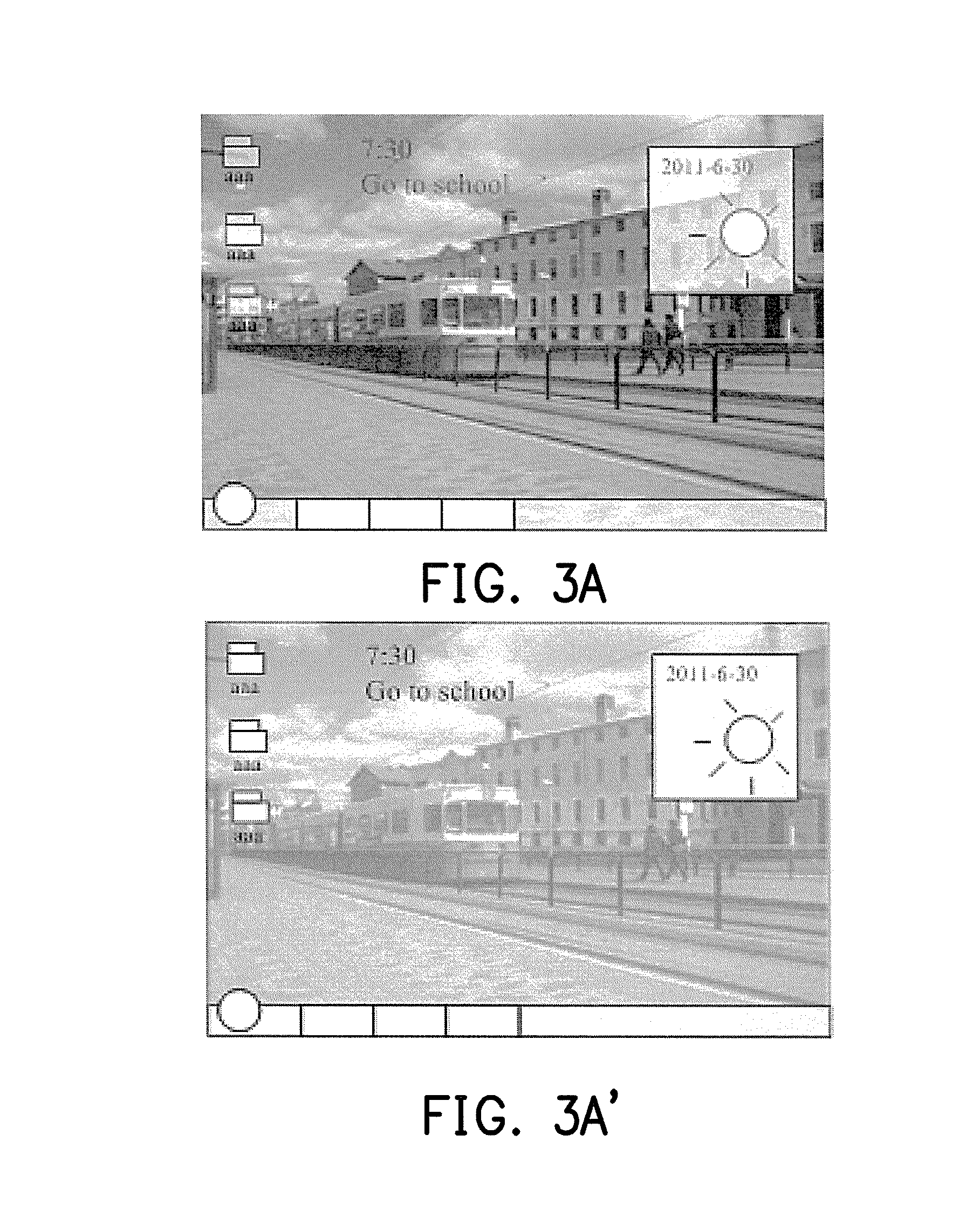

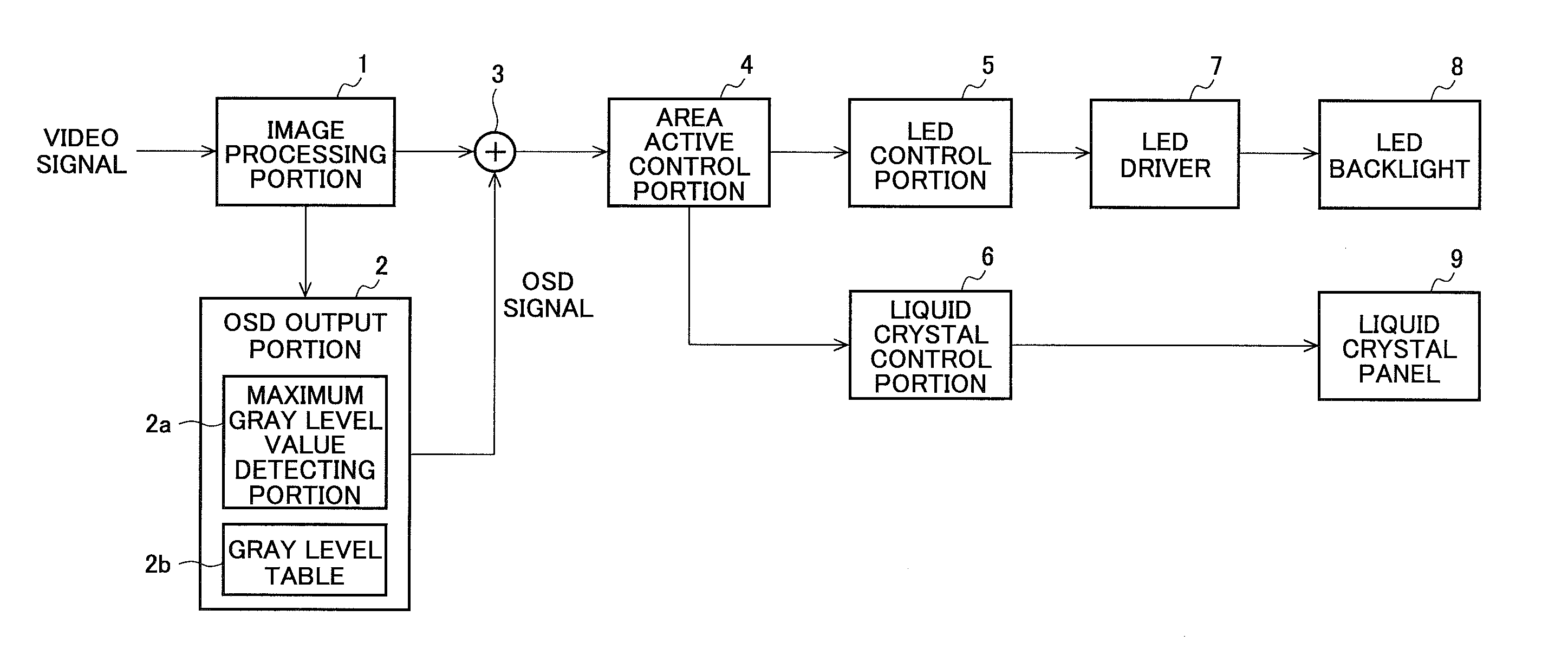

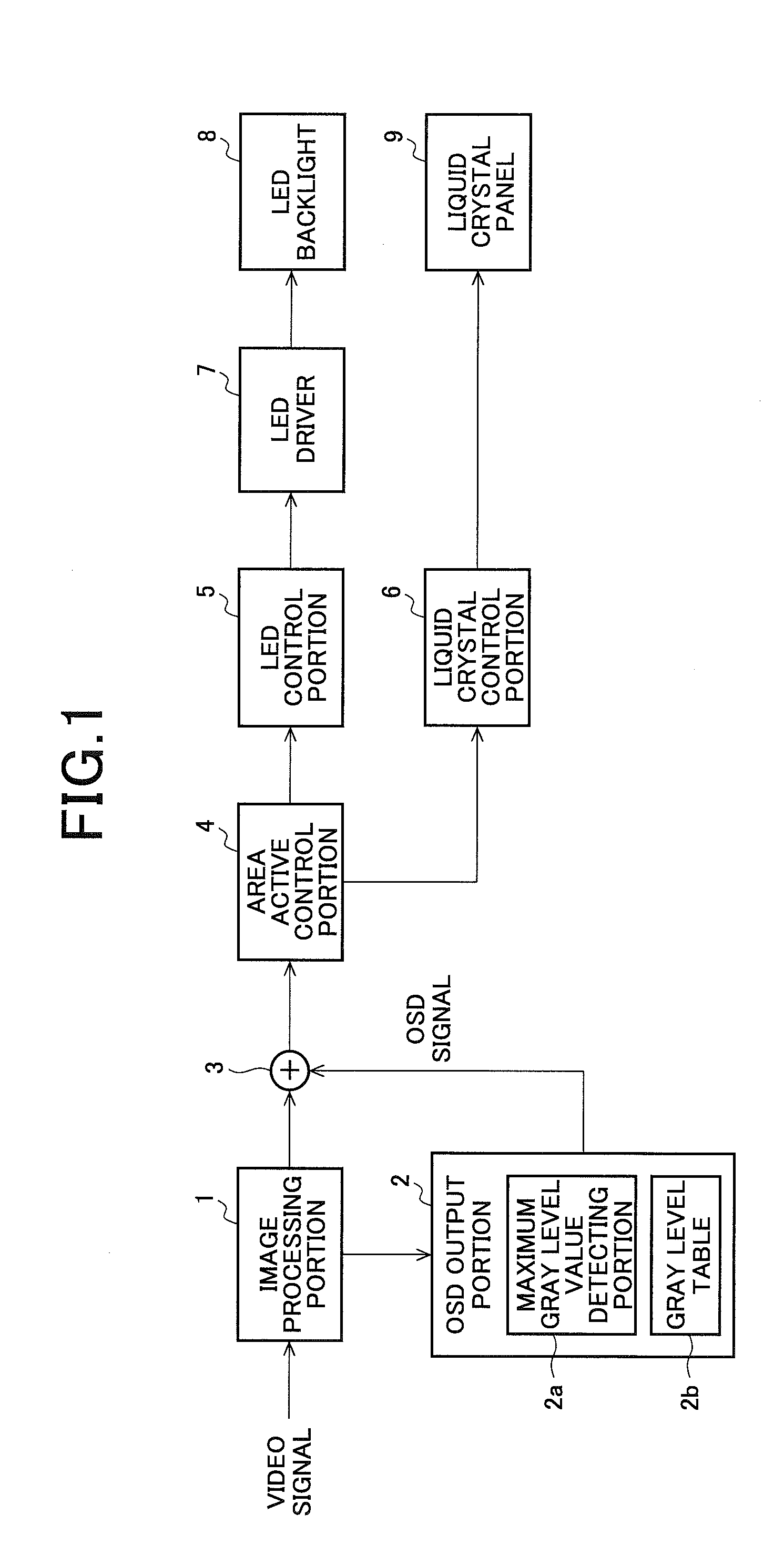

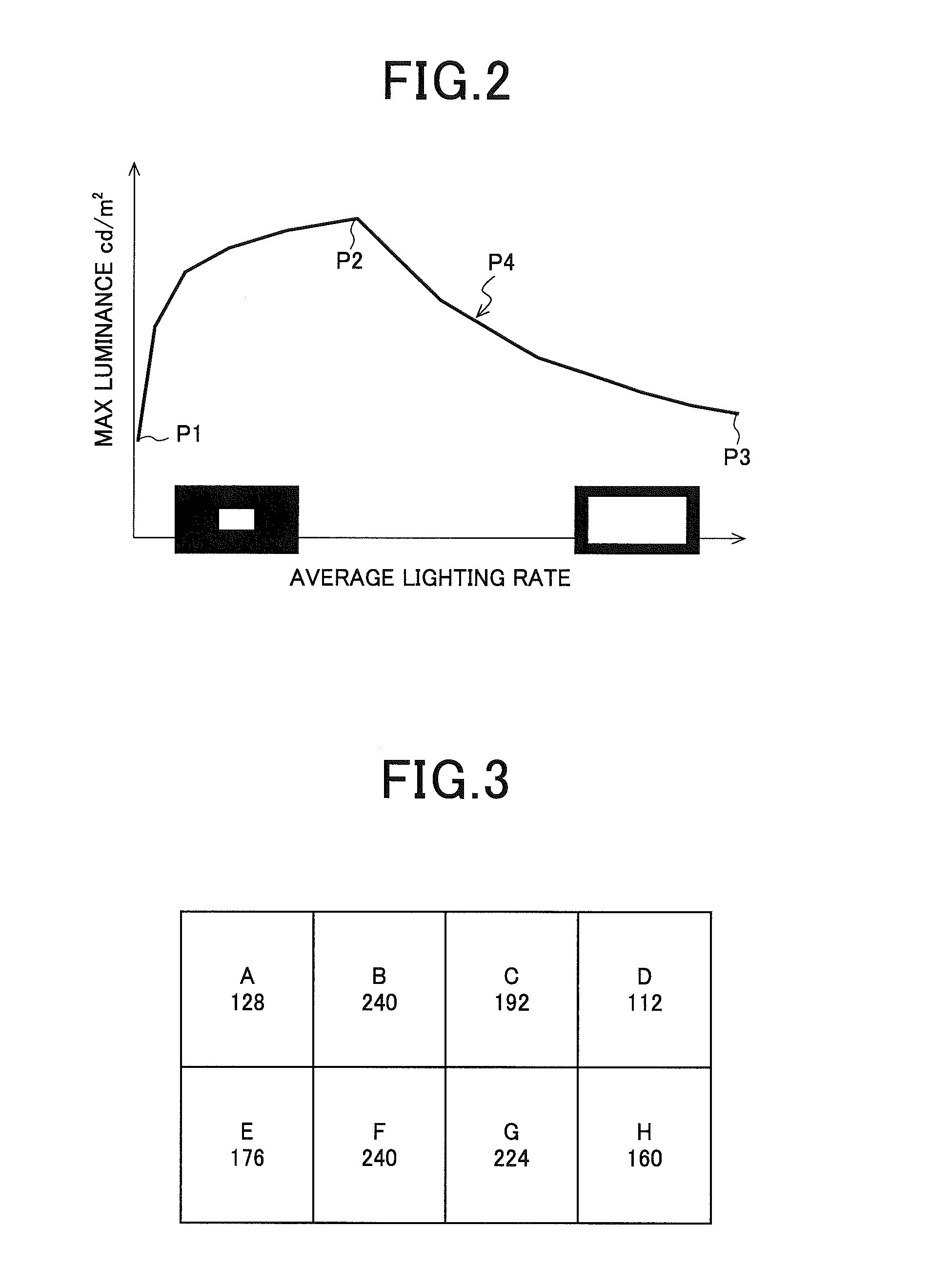

Video display device and television receiving device

InactiveUS20150009249A1Increase contrastFeel goodTelevision system detailsImage enhancementDriving currentComputer graphics (images)

Provided is a video display device wherein a light emission luminance control is performed in accordance with a video signal corresponding to each of a plurality of divisional areas of a backlight. In the video display device: while power limiting control is being performed, the contrast can be improved and further the feeling of brightness for a high-luminance video can be increased; and even when an OSD image is displayed, display quality can be prevented from being degraded. A backlight control portion of the video display device defines a first luminance of LED for each divisional areas according to a first feature amount for a video indicated by a video signal after synthesizing of an OSD signal to be displayed in a display area corresponding to the divisional area, and controls the LED light emission by uniformly multiplying the first luminance by constant scale factor in a range where a total value of the LED drive current is equal to or less than a predetermined allowable current value. An OSD output portion (2) determines and outputs the OSD signal by use of gray scale data that is associated with a second feature amount of the video indicated by an input video signal to be displayed in a display area of the OSD image (or by an input video signal to be displayed in a display area corresponding to the divisional area including the display area of the OSD image).

Owner:SHARP KK

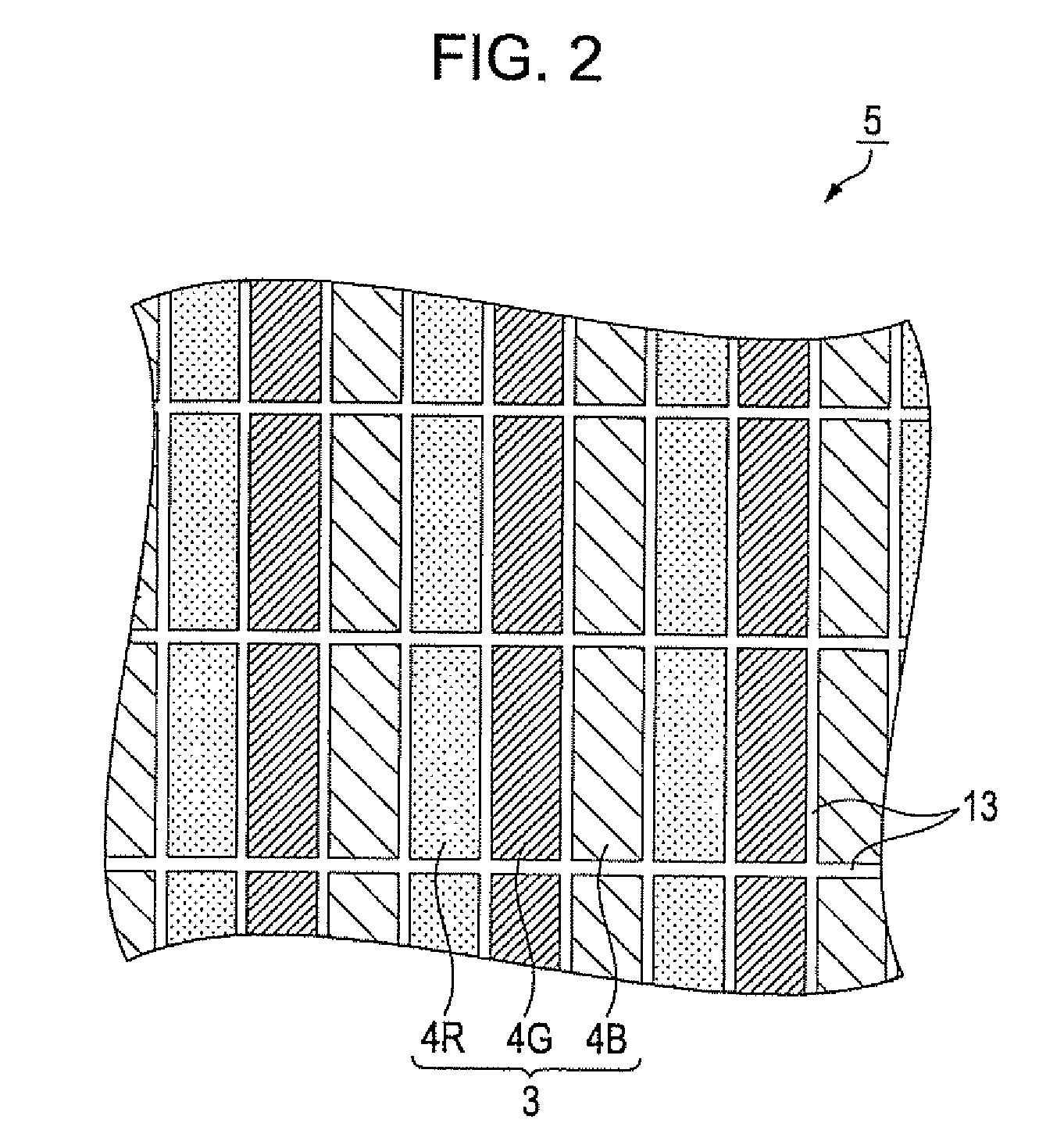

Electric field driving device and electronic apparatus

ActiveUS20080225217A1High light transmittanceHigh quality displayNon-linear opticsPotential differenceOptoelectronics

An electric field driving device, in which a plurality of pixels, each of which is formed of two or more sub-pixels that respectively correspond to different colors from one another, are arranged in a matrix in a pixel region on a substrate, includes pixel electrodes, a common electrode, an insulating layer, and a material. Each of the pixel electrodes is formed in correspondence with the sub-pixel on the substrate. The common electrode is formed above the pixel electrodes on the substrate so that at least part of the common electrode overlaps each of the pixel electrodes in plan view. The insulating layer is formed on the substrate between the pixel electrodes and the common electrode. The material is driven by an electric field that is generated on the basis of a difference in electric potential between each of the pixel electrodes and the common electrode. The common electrode has a plurality of slits that at least partly overlap the pixel electrodes in plan view. At least a portion of the slits are respectively provided continuously over a plurality of the sub-pixels. Each of the sub-pixels corresponding to the same color includes the same numbers of end portions of the plurality of slits.

Owner:SEIKO EPSON CORP

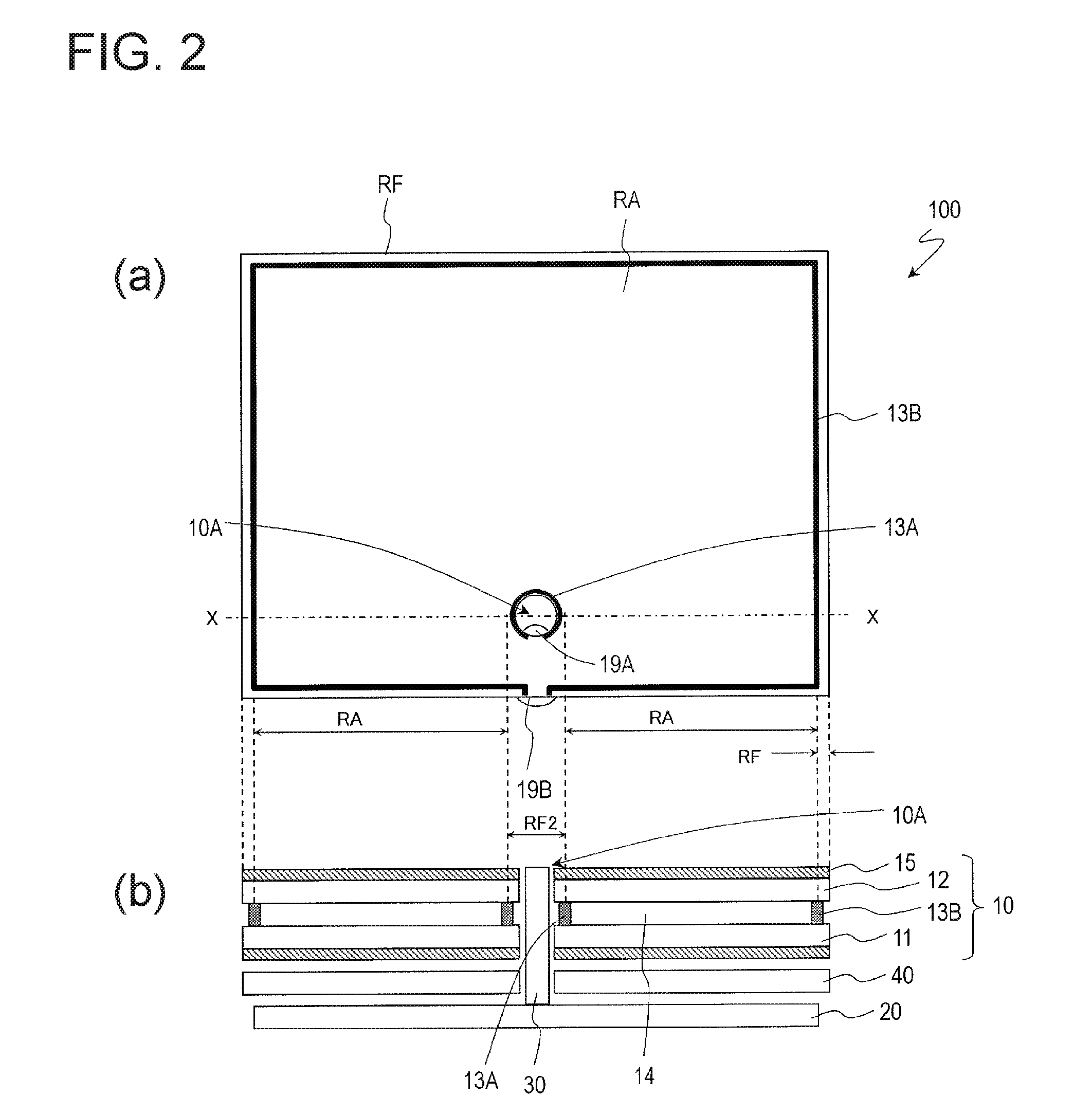

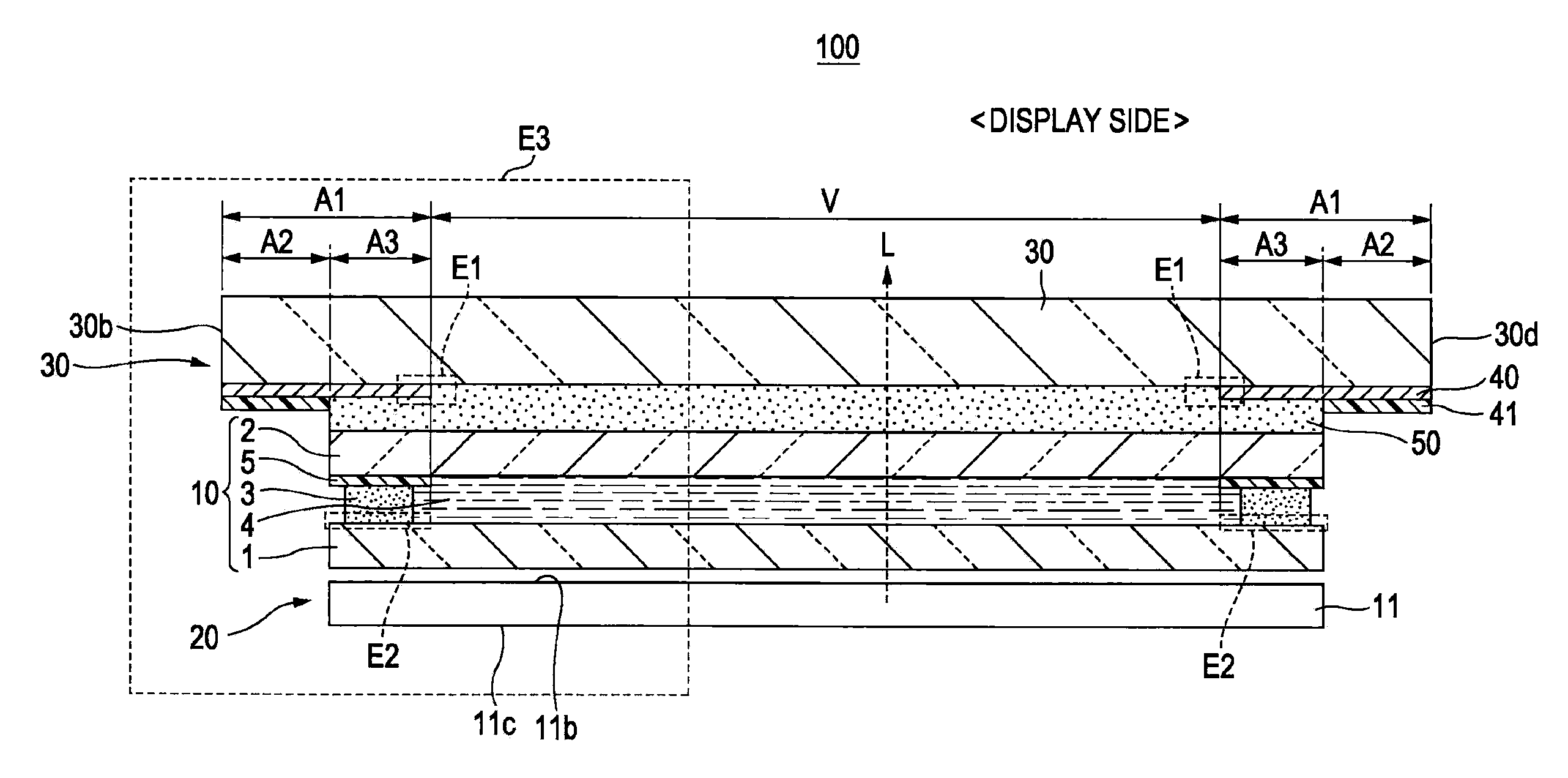

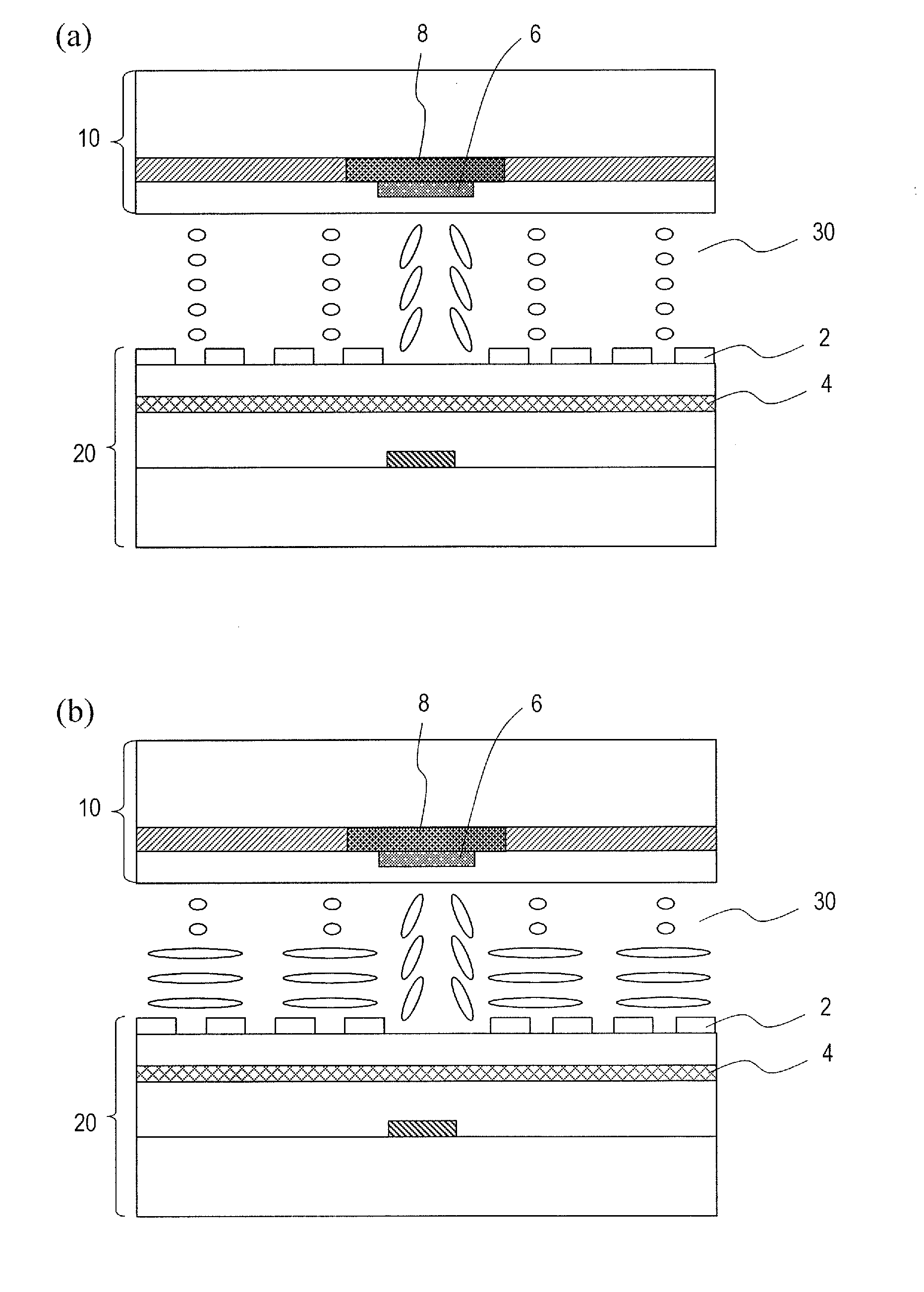

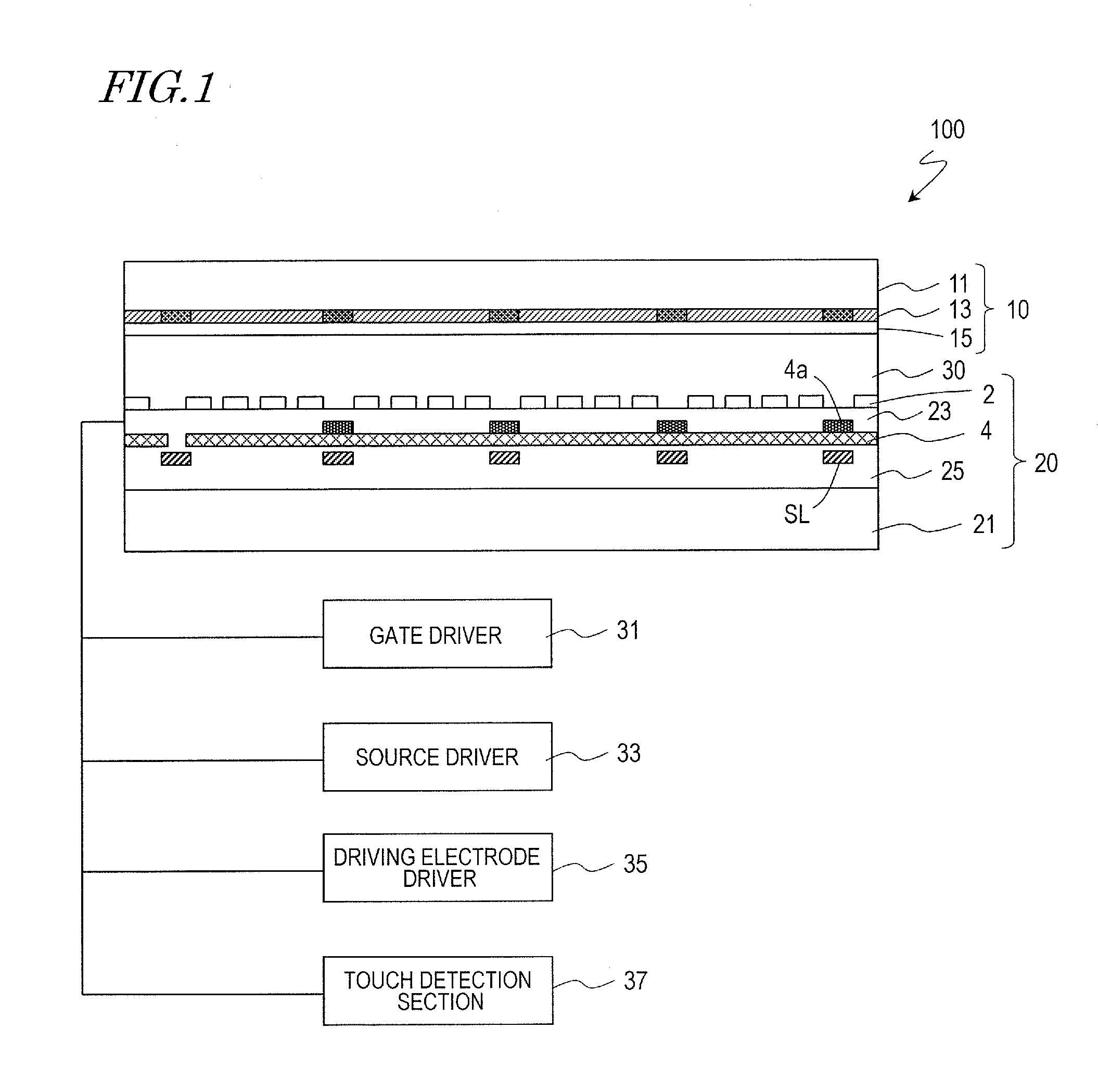

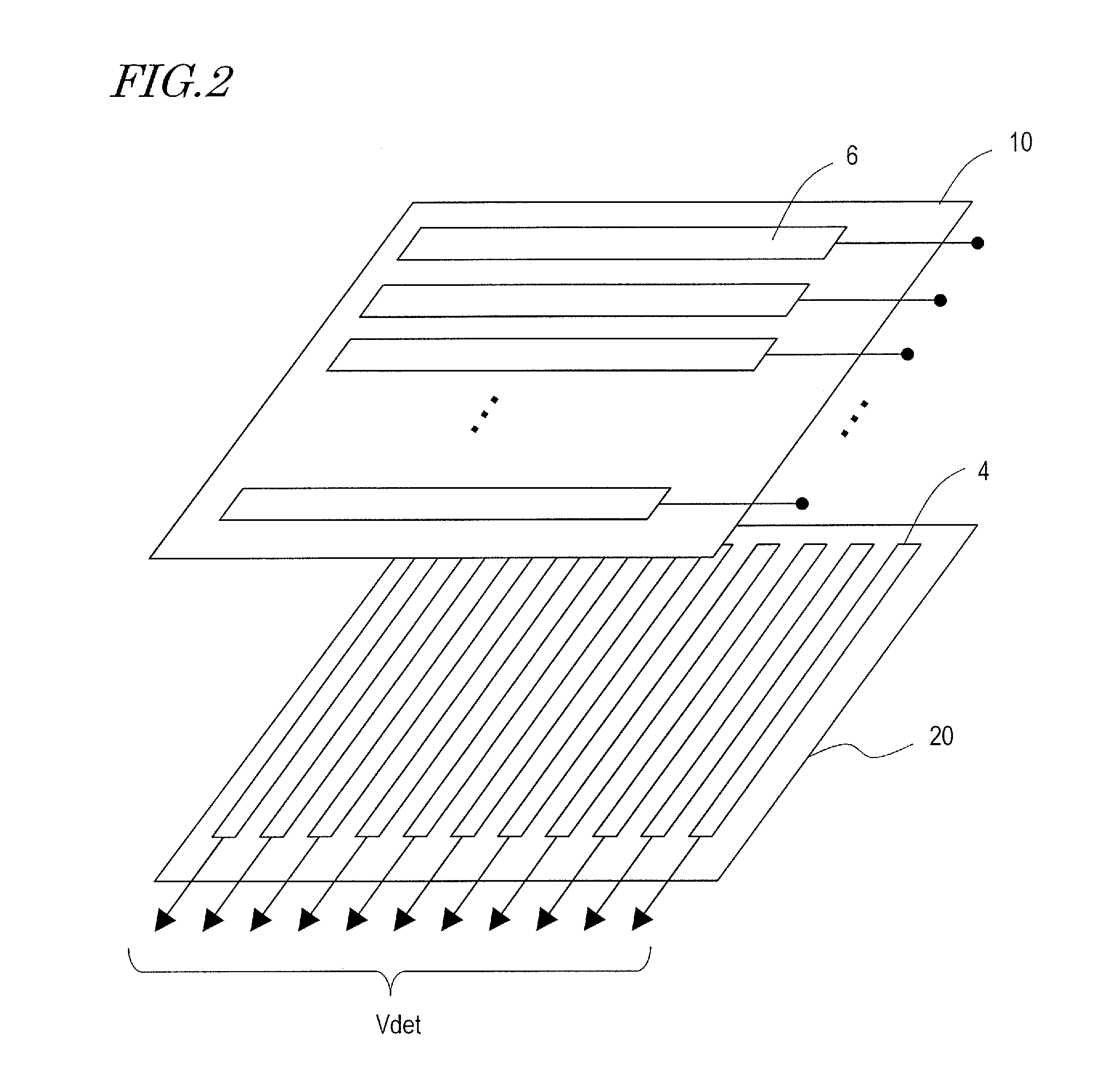

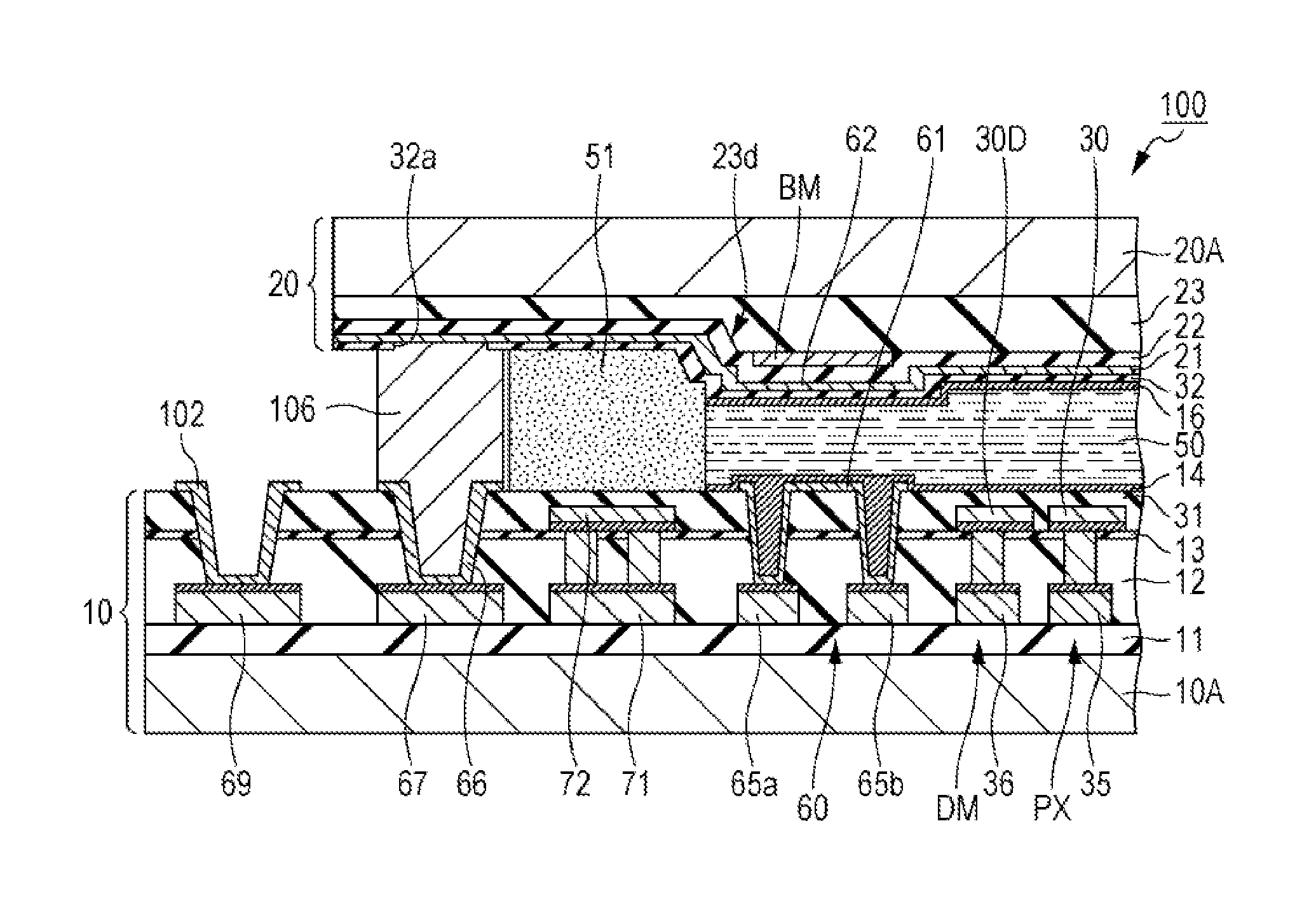

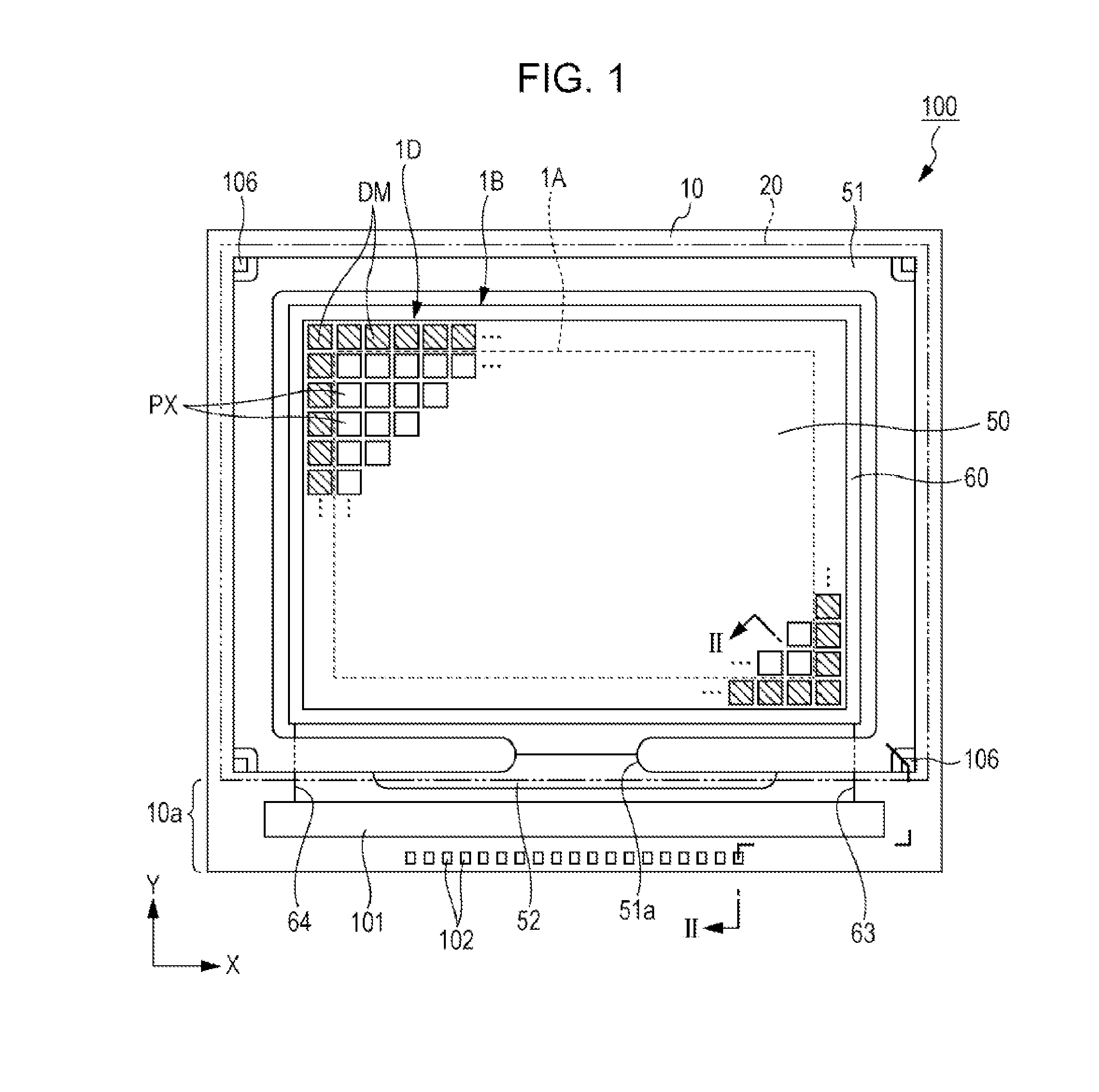

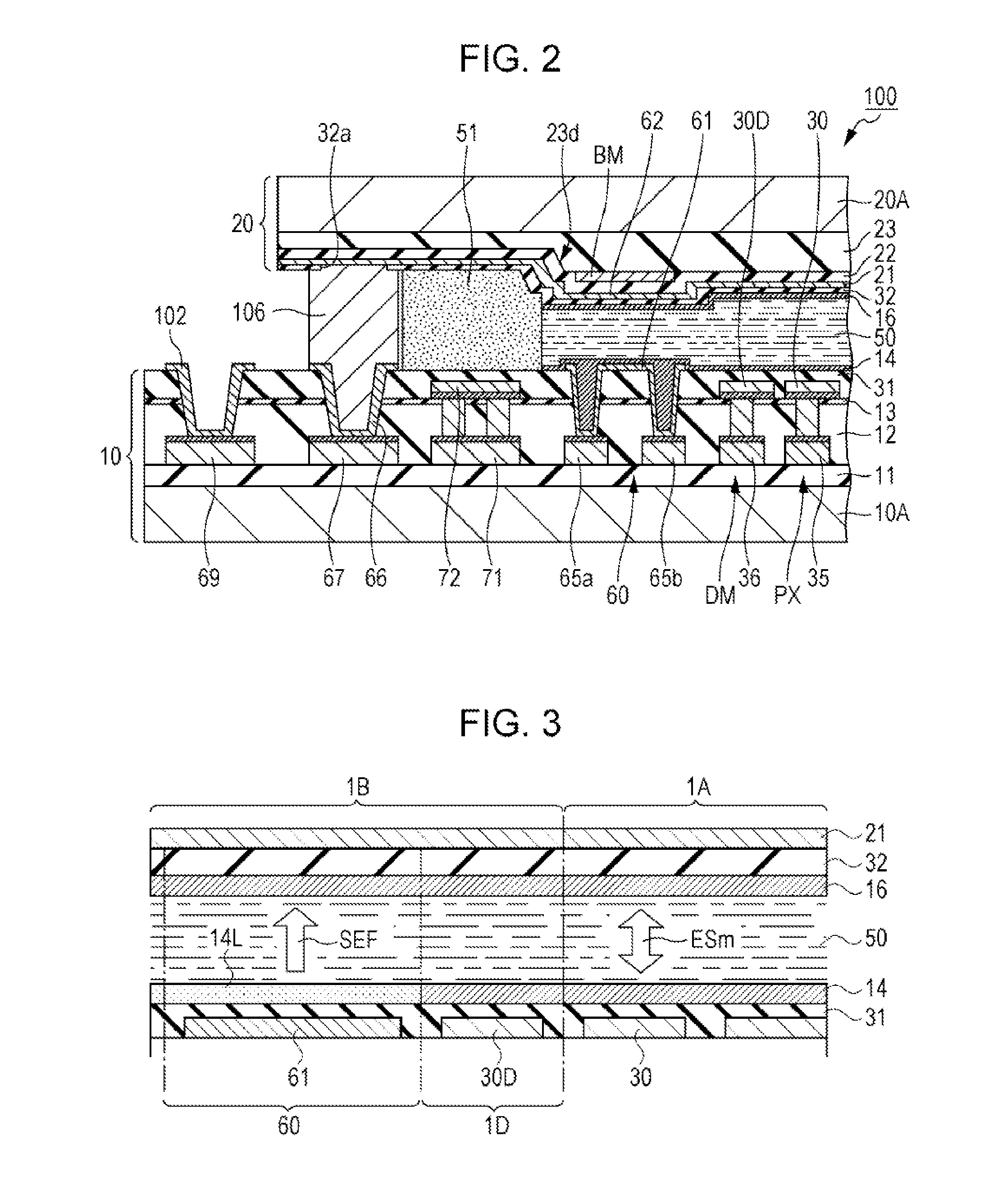

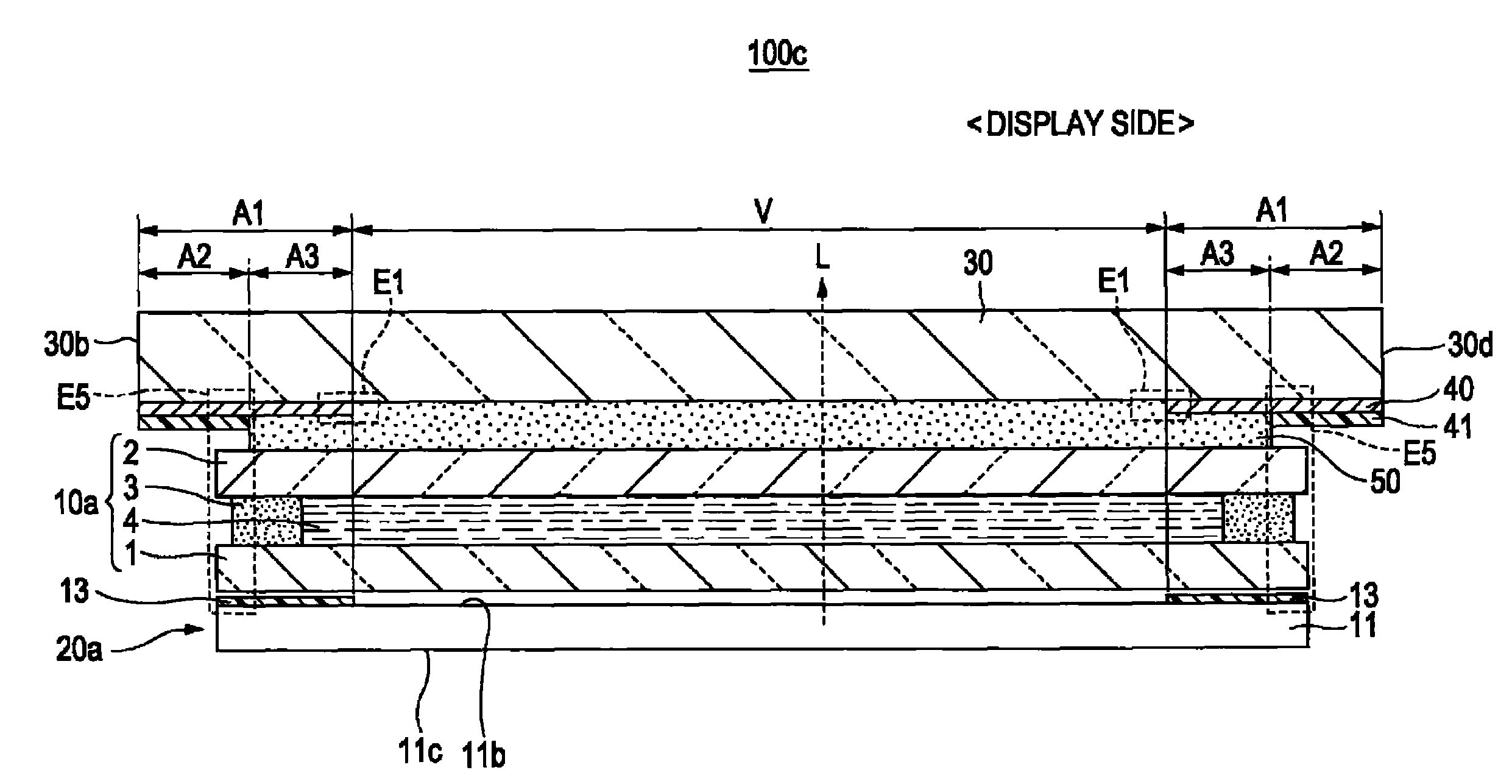

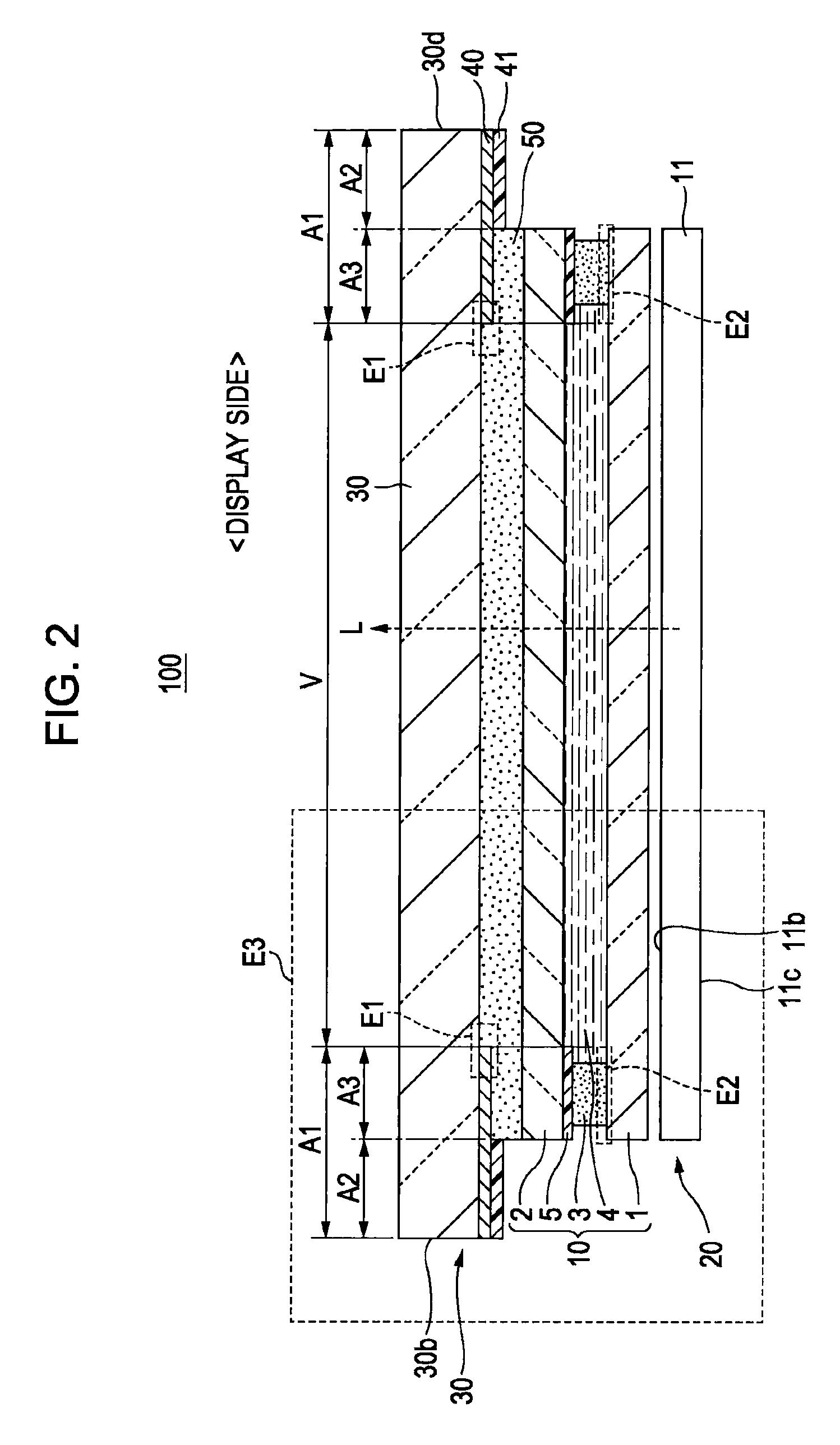

Display device with touch sensor

InactiveUS20160253030A1Improve accuracyPrevent display quality degradationNon-linear opticsInput/output processes for data processingDisplay deviceEngineering

A display device with a touch sensor (100) according to an embodiment of the present invention includes: a pixel substrate (20) including a plurality of pixel electrodes (2); a counter substrate (10) opposing the pixel substrate (20); a black matrix (8) extending in a first direction and in a second direction different from the first direction; and a touch sensor electrode (6) extending in the first direction. In a plan view where the counter substrate (10) is seen from a direction vertical to a planar direction of the counter substrate (10), a width in the second direction of a line of the black matrix (8) extending in the first direction is larger than a width in the first direction of a line of the black matrix (8) extending in the second direction; a width (W1) in the second direction of a line of the touch sensor electrode (6) extending in the first direction is smaller than a width (W2) in the second direction of the line of the black matrix (8) extending in the first direction; and the line of the touch sensor electrode (6) extending in the first direction and the line of the black matrix (8) extending in the first direction overlap each other.

Owner:SHARP KK

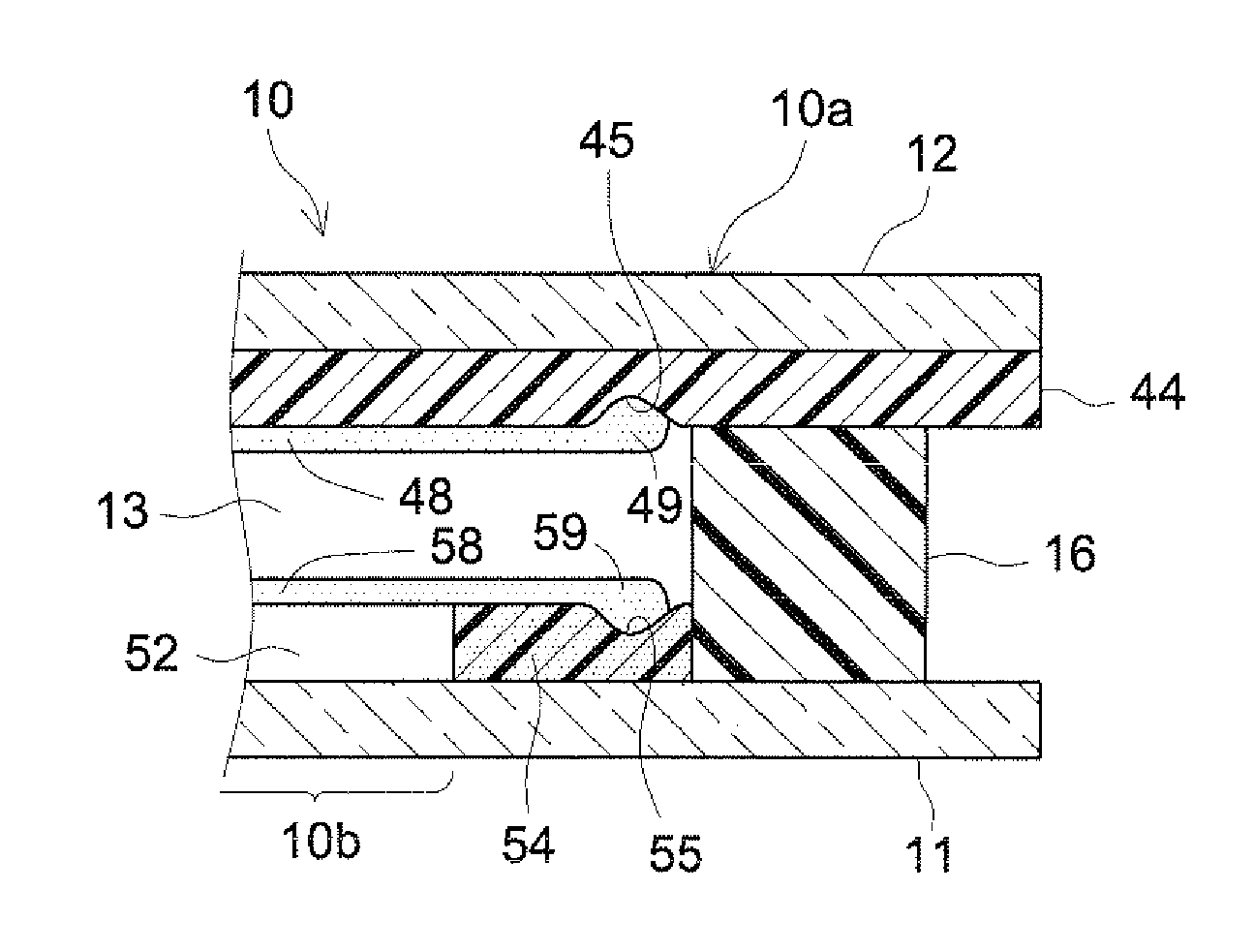

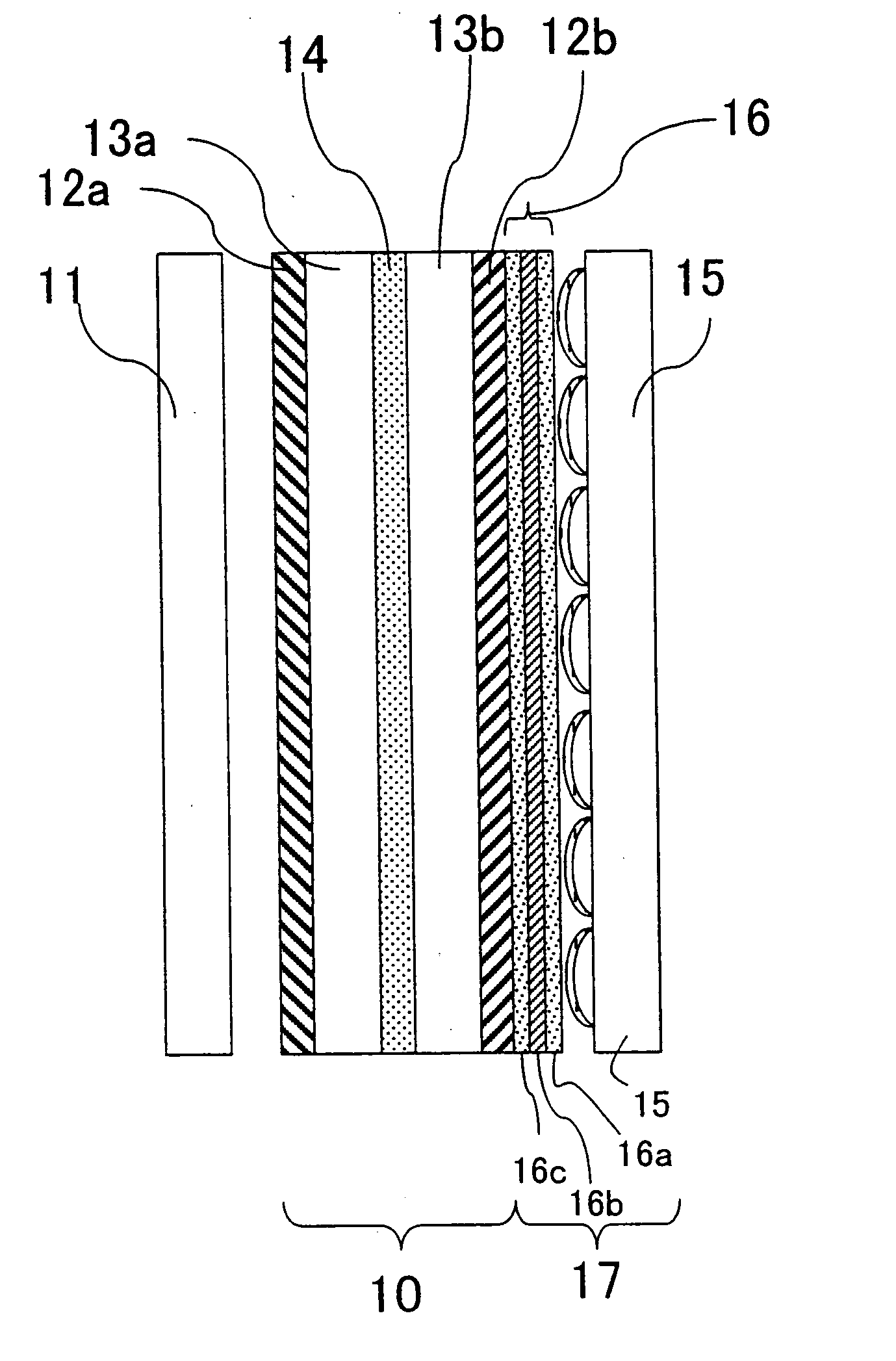

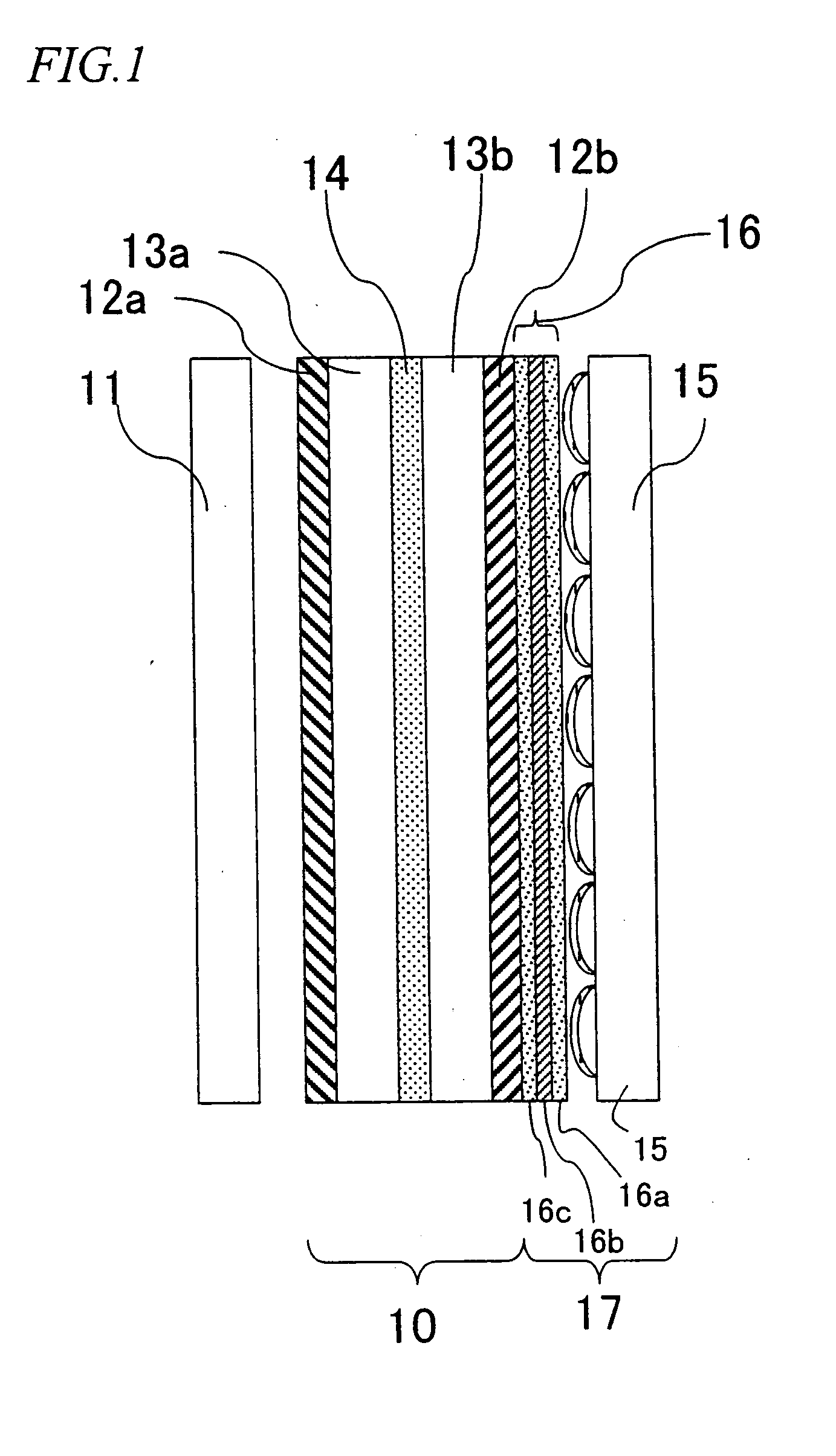

Liquid crystal panel and liquid crystal display device

InactiveUS20110255041A1Avoid display qualityPrevent display quality degradationNon-linear opticsLiquid-crystal displayEngineering

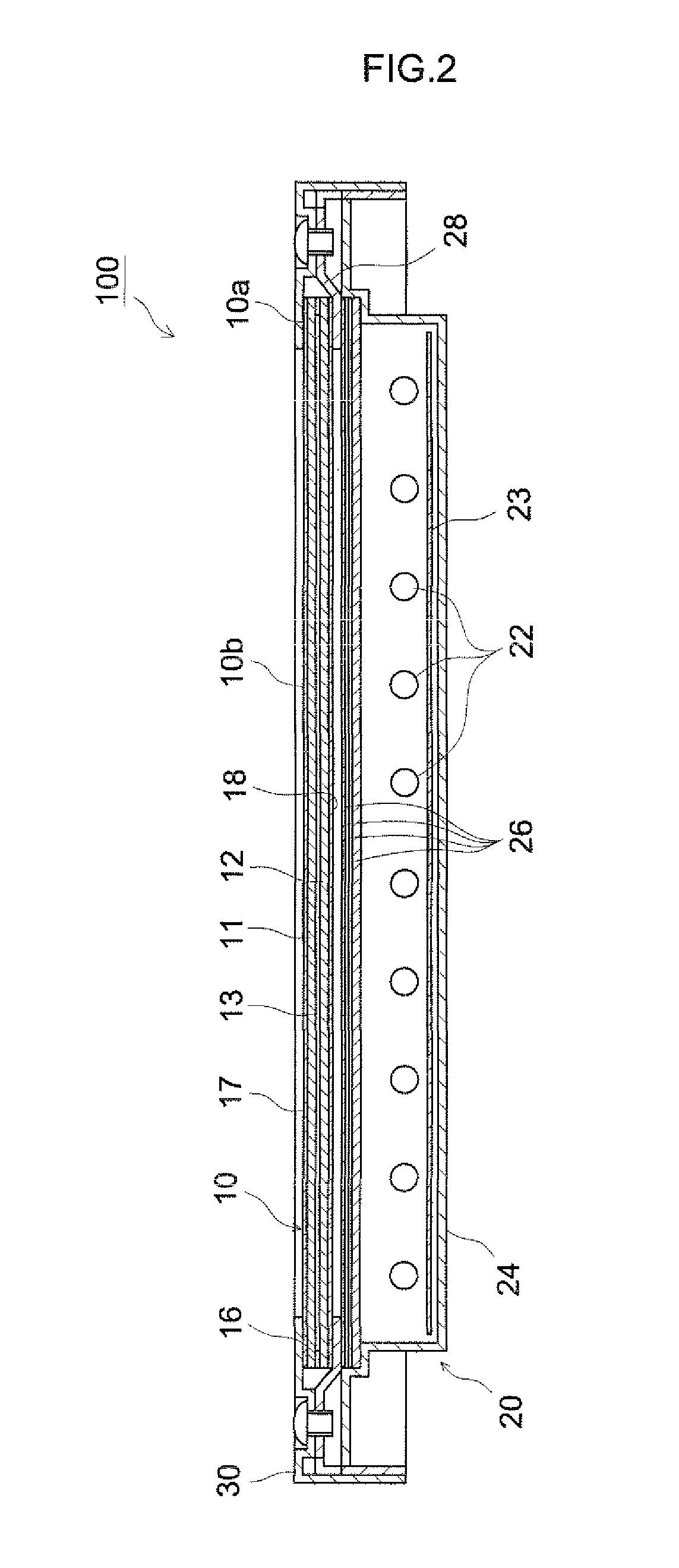

According to a liquid crystal panel 10 provided by the present invention, in the vicinity of an inner surface of a sealing portion 16 located on a peripheral portion 10a between a pair of substrates 11 and 12 in order to hold a liquid crystal layer 13 between the substrates 11 and 12, barrier portions 49 and 59 formed of a material for forming alignment films 48 and 58 are formed to be thicker than the alignment films 48 and 58.

Owner:SHARP KK

Illumination device for display device, display device, and television receiver

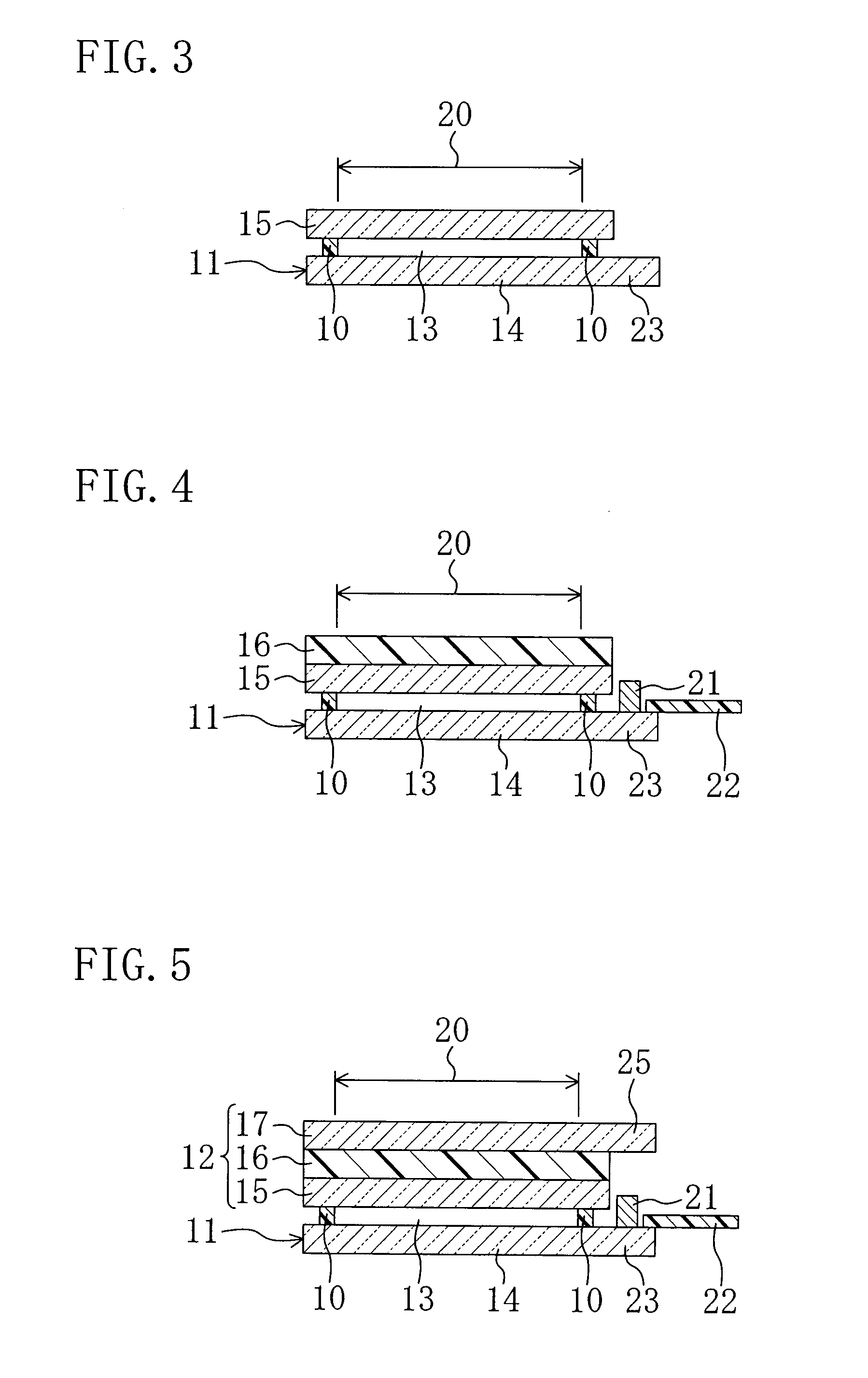

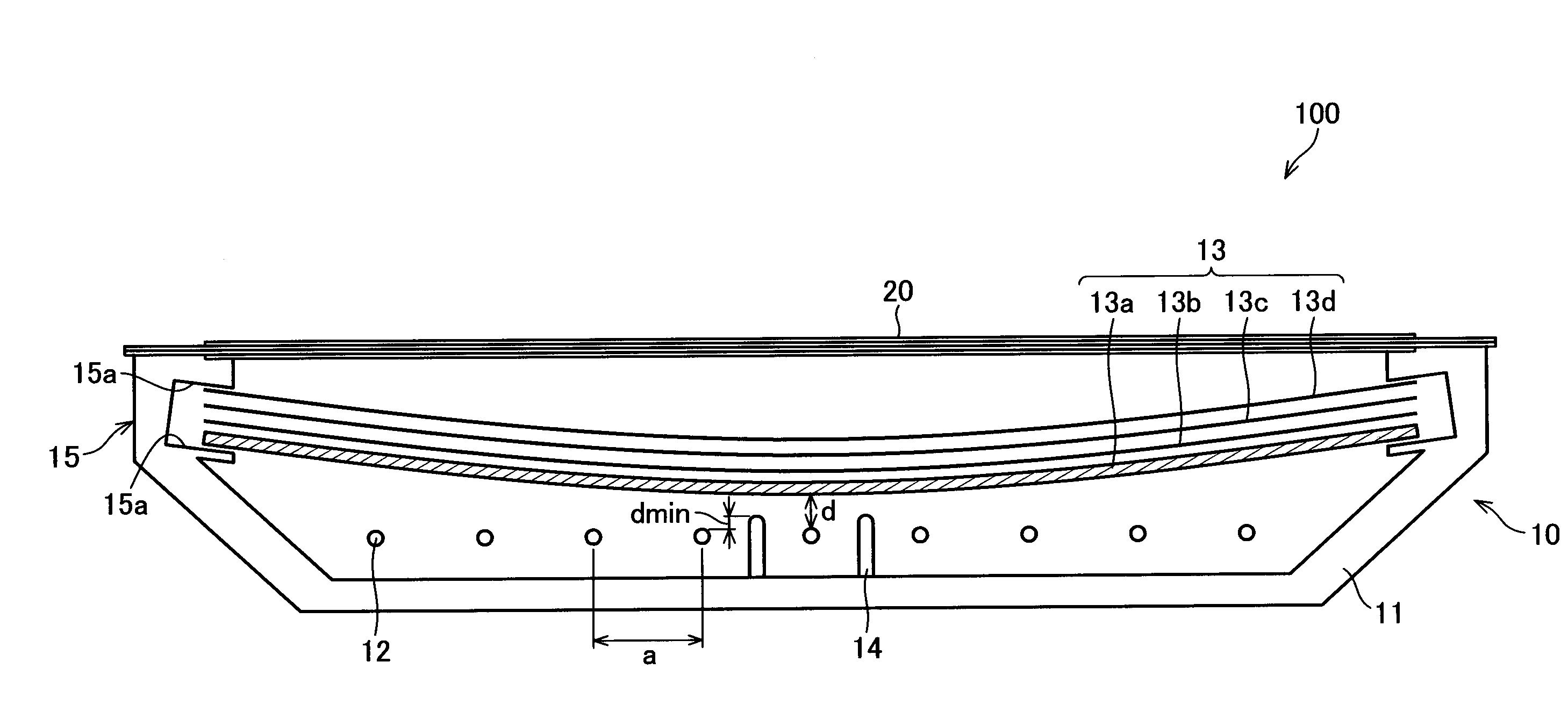

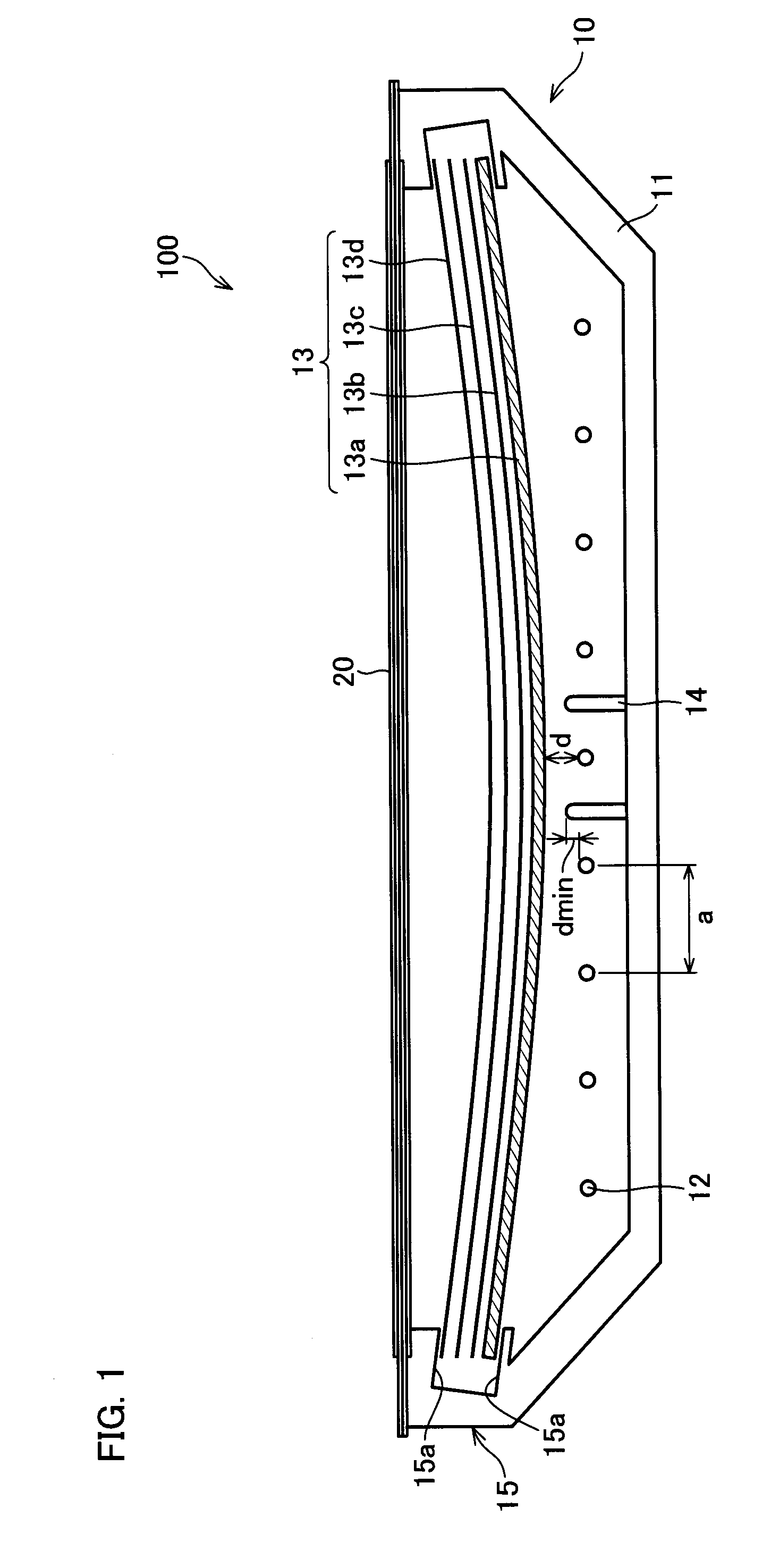

InactiveUS20090059563A1Prevent display quality degradationAvoid wrinklesIlluminated signsNon-linear opticsTelevision receiversDisplay device

In a display device having a liquid crystal panel and a backlight unit, an optical sheet group provided on a surface of the backlight unit facing the liquid crystal panel is curved so as to form a convex shape in a direction opposite to the liquid crystal panel. In this way, a wrinkle on the optical sheet provided in the display device is prevented while avoiding deterioration in the displaying quality.

Owner:SHARP KK

Method of driving electro-optic device and electro-optic device

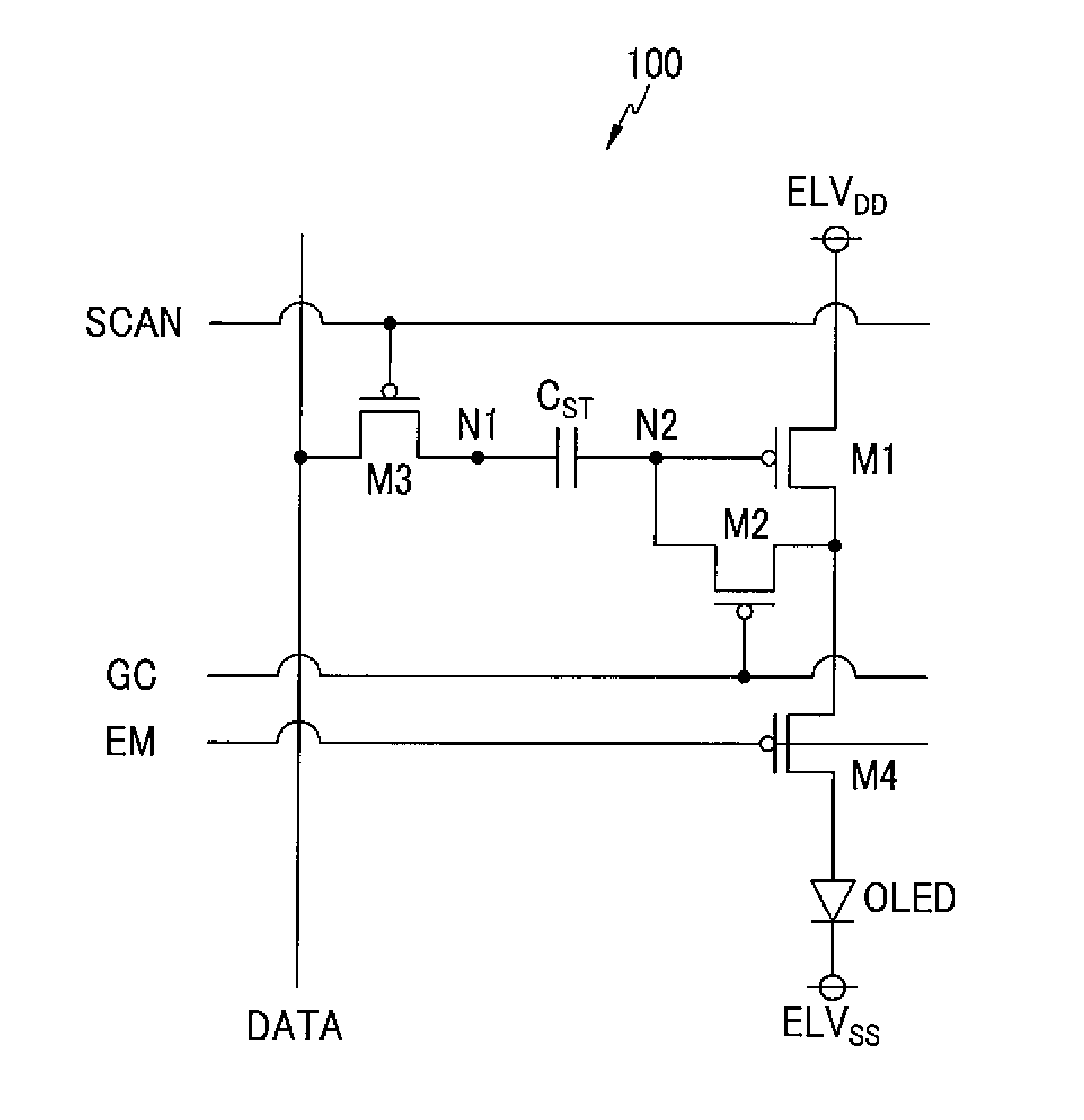

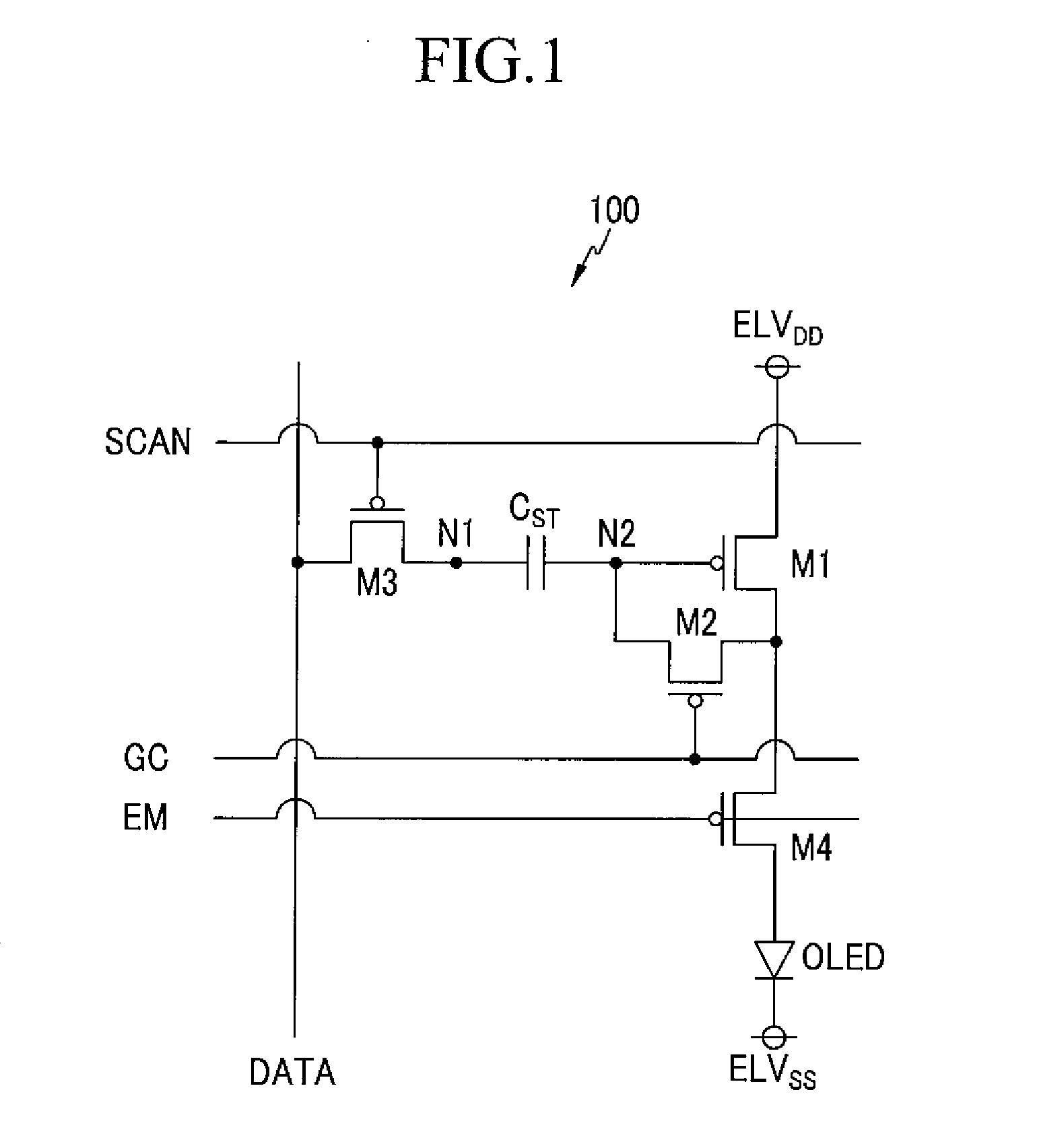

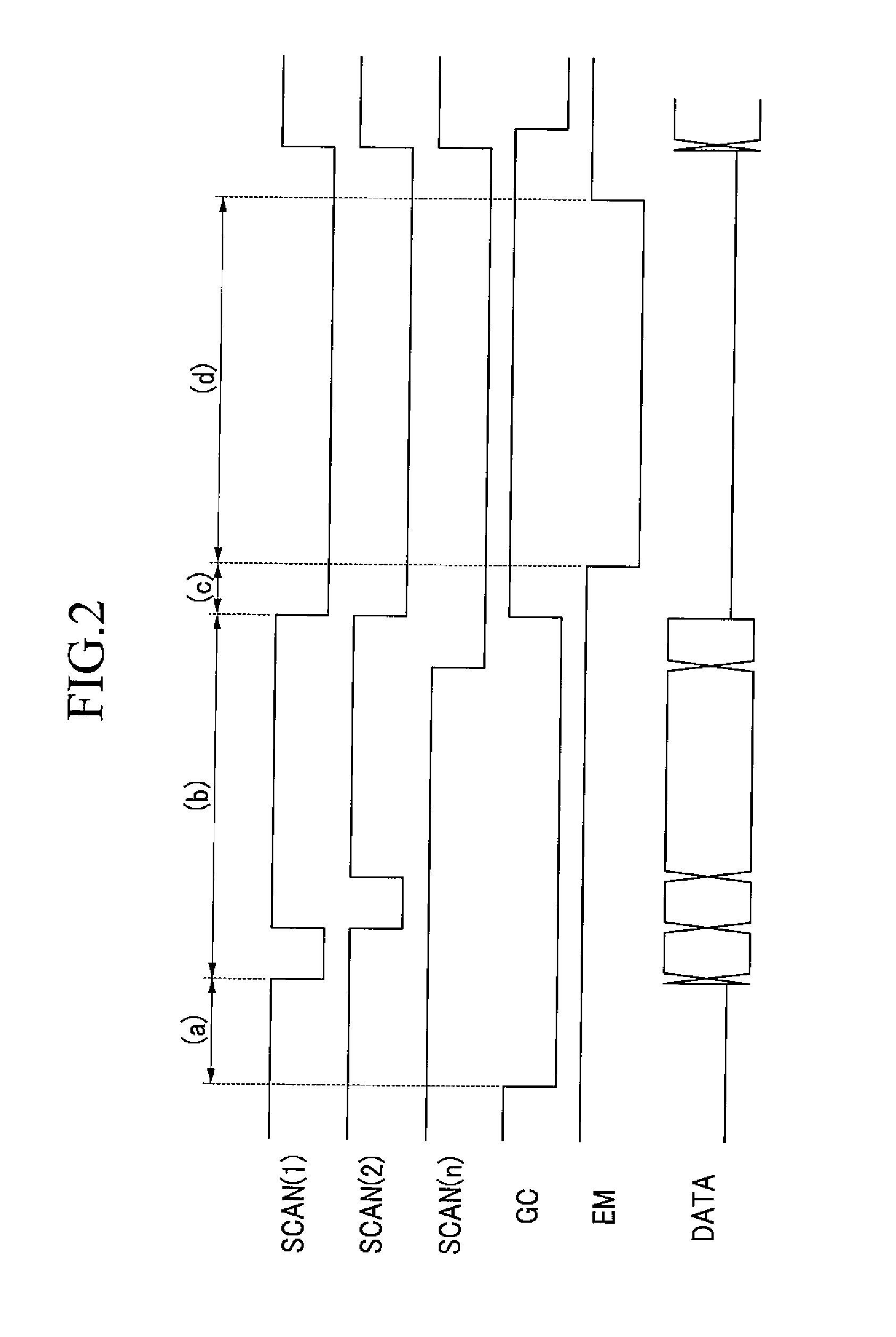

ActiveUS20130113690A1Reduce in quantityPrevent display quality degradationStatic indicating devicesScan lineThreshold voltage

A driving method of an electro-optic device is capable of sufficiently providing a threshold voltage compensation time of a driving transistor and a data writing time. A driving method of an electro-optic device including a first power source, a second power source, data lines, scan lines, signal lines, and pixel circuits, includes: a first step in which a light emitting element is in a non-light-emitting state, and a second transistor is turned on by a change of a pulse applied to a signal line; and a second step in which the scan line is sequentially and exclusively selected after the second transistor is turned on, a third transistor including a gate connected to a selected scan line is turned on, and a corresponding data voltage is written to a first node from the data line through the third transistor.

Owner:SAMSUNG DISPLAY CO LTD

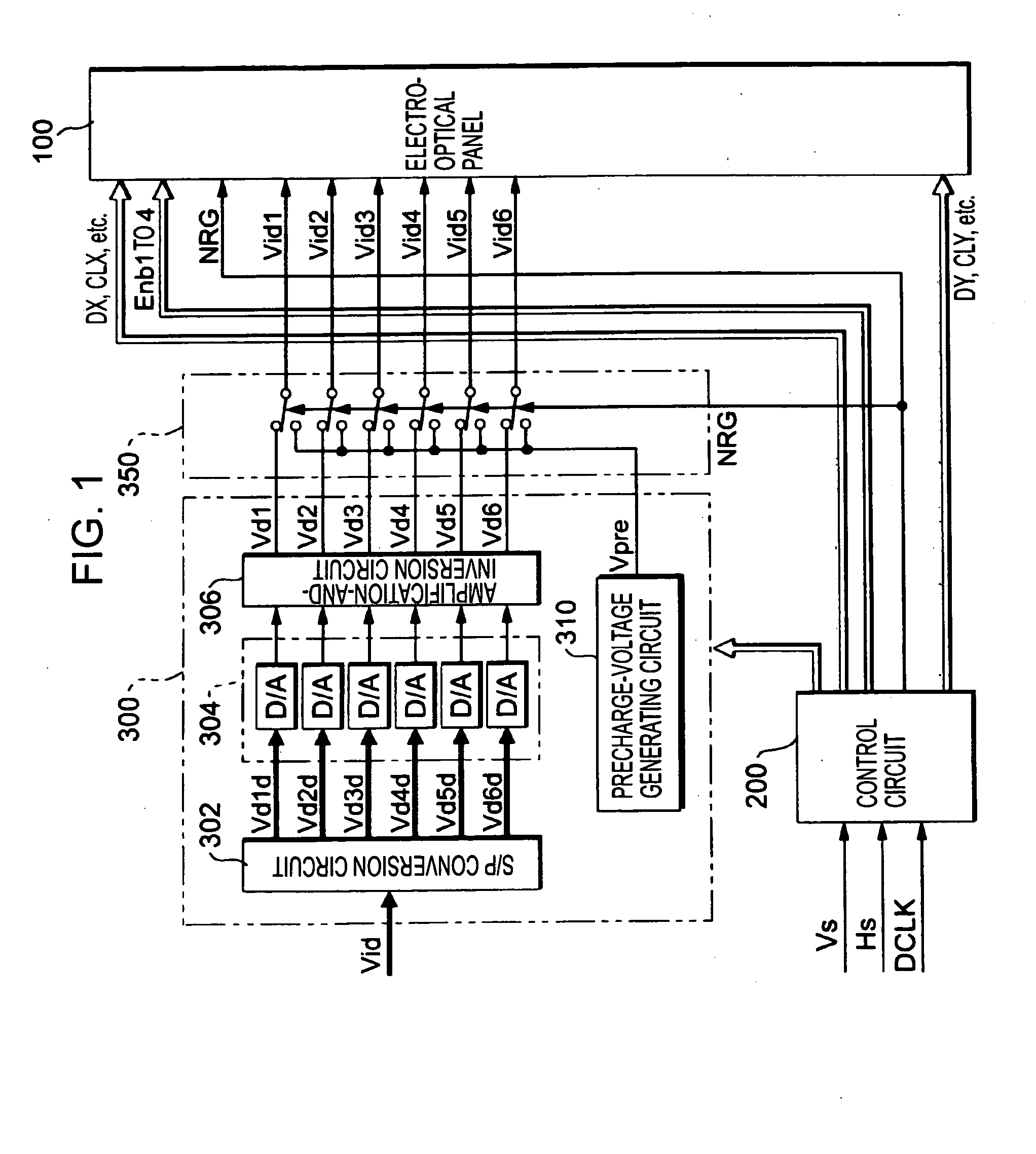

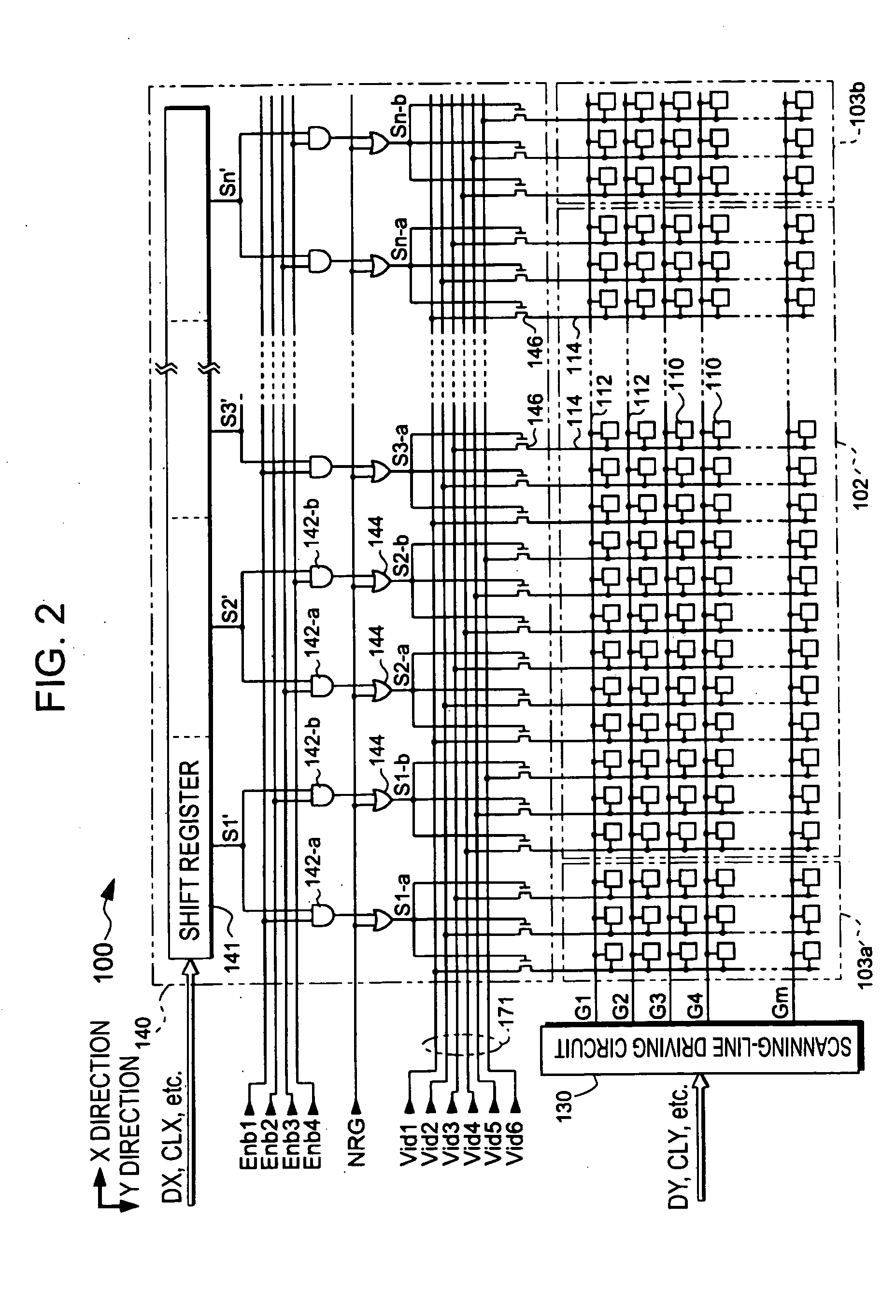

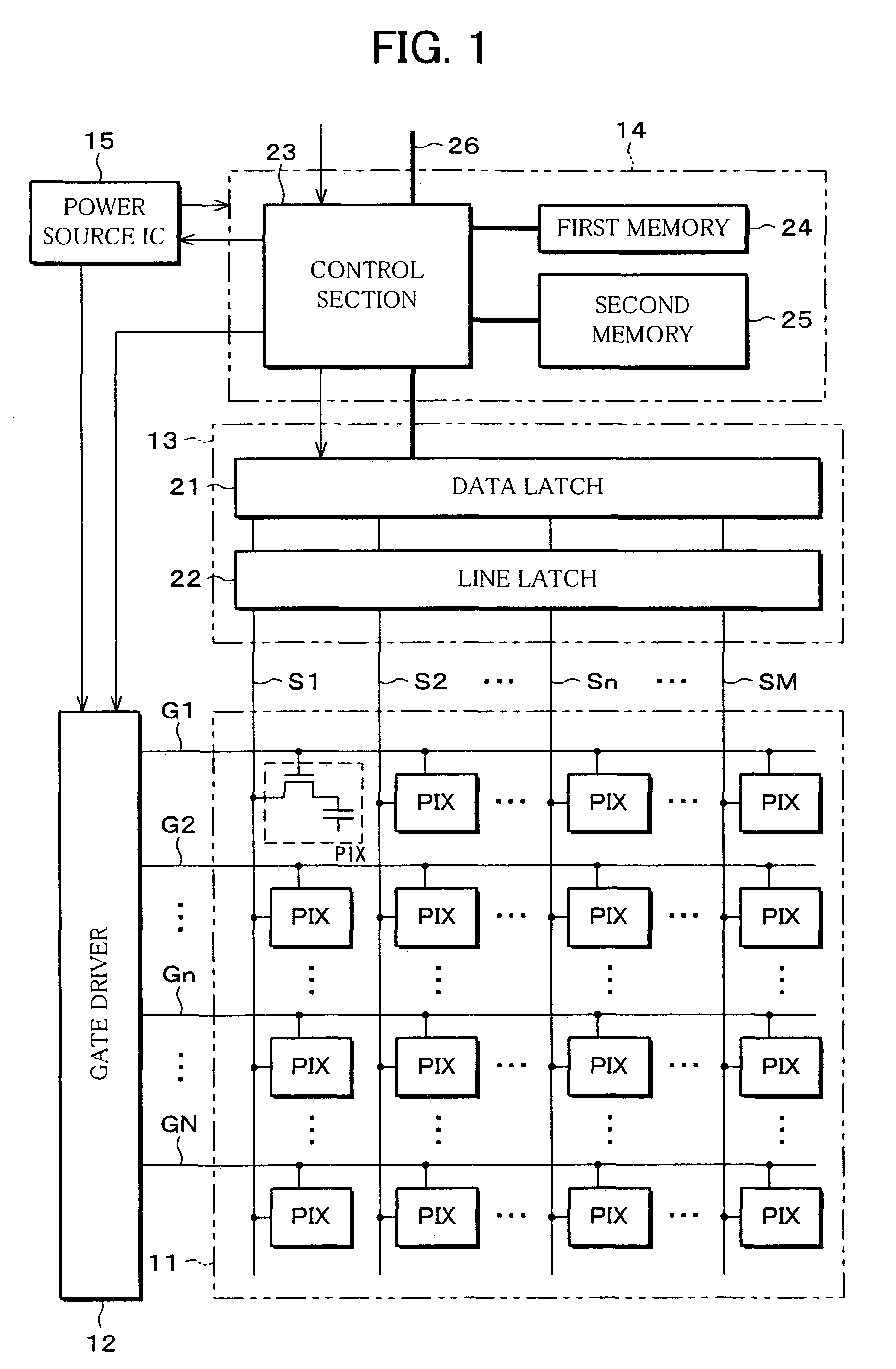

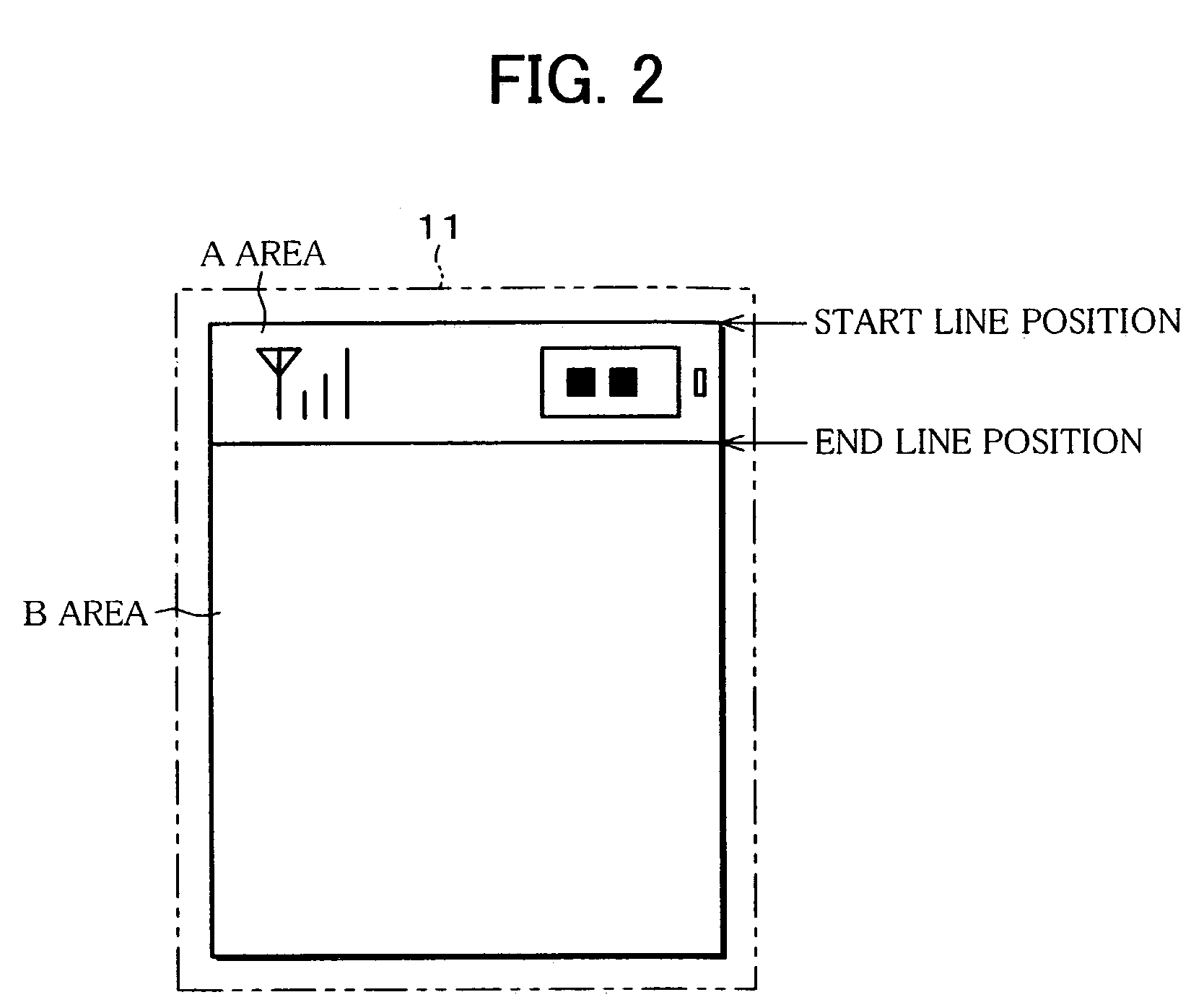

Electro-optical device, method for driving electro-optical device, driving circuit, and electronic apparatus

InactiveUS20050206597A1Prevent display quality degradationExtension of timeStatic indicating devicesProjectorsComputer scienceImage signal

According to exemplary embodiments, three data lines are selected in a horizontal scanning period during which a scanning line is selected. Image signals according to the gradation of pixels corresponding to the intersections of the selected scanning line and the selected data lines are sampled for the selected data lines. While the three data lines are selected, the subsequent three data lines are also selected. Then, image signals according to the gradation of pixels corresponding to the intersections of the selected scanning line and the subsequent three data lines are sampled for the subsequent three data lines. The pixels corresponding to the three data lines selected at the beginning of the horizontal scanning period are included in a non-display area so that they do not contribute to display.

Owner:SEIKO EPSON CORP

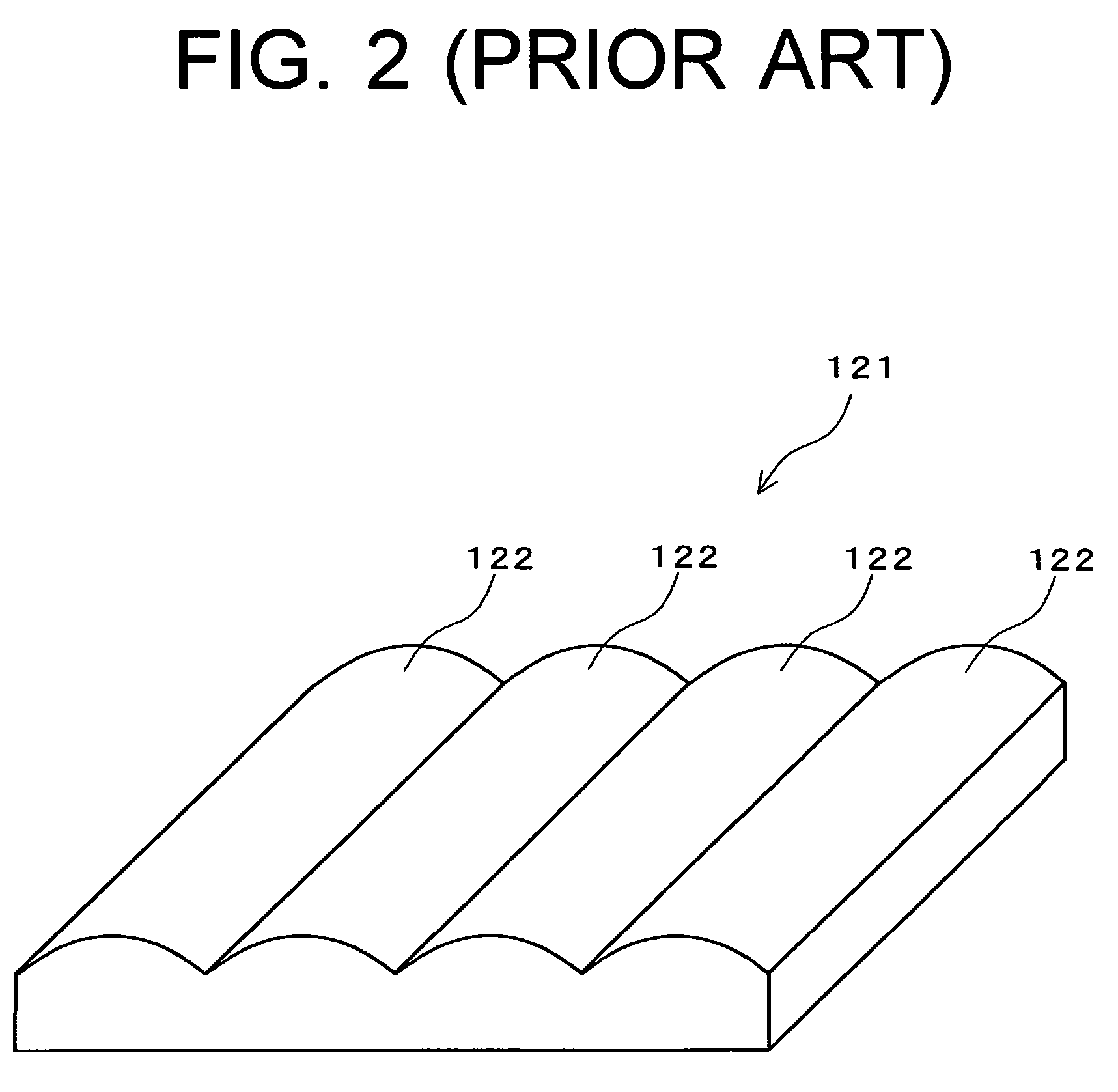

Method for fabricating a laminate film, laminate film, and method for fabricating a display device

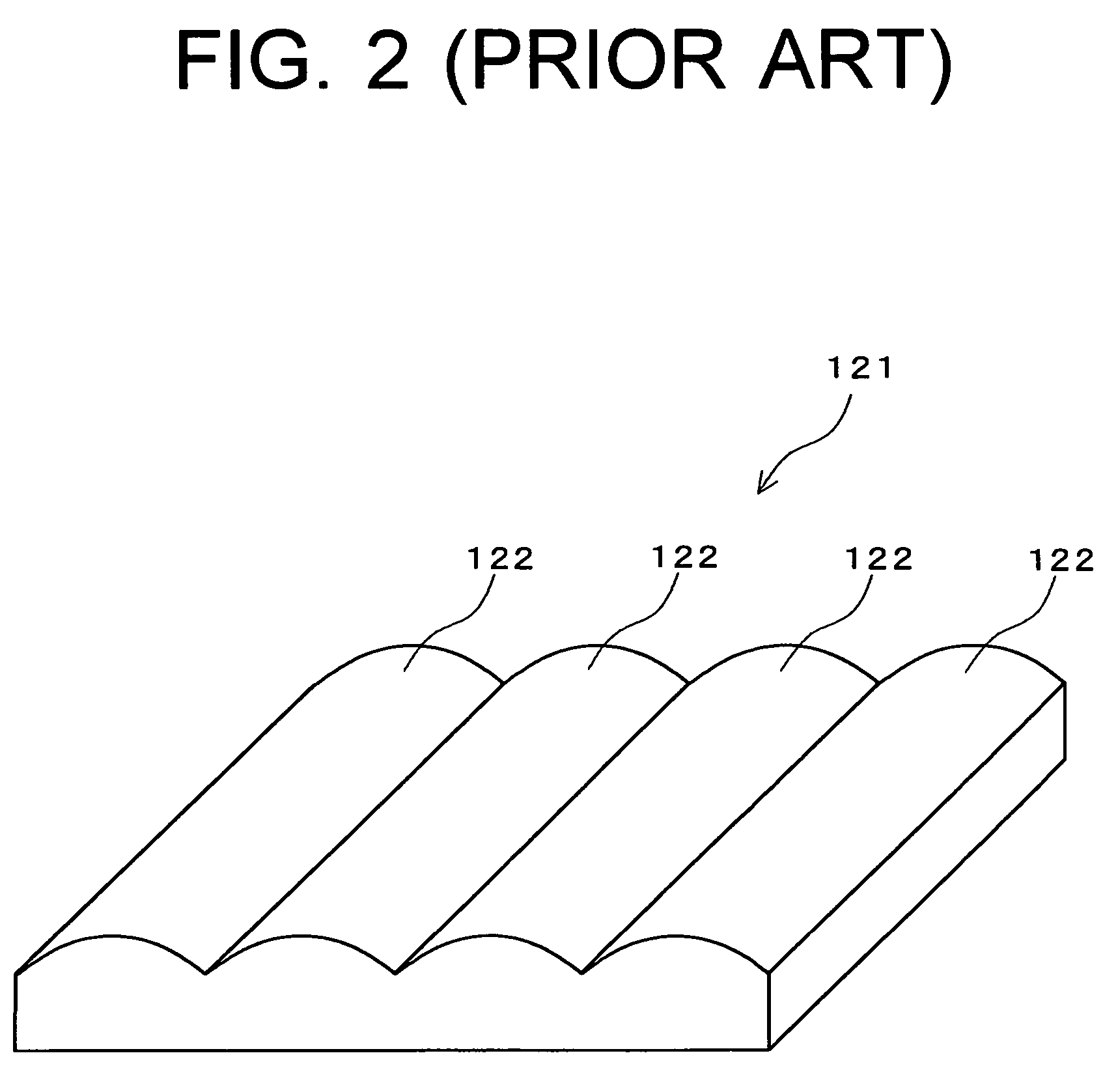

InactiveUS20050003108A1Good adhesionEasily fixed togetherLiquid crystal compositionsDiffusing elementsLiquid-crystal displayDisplay device

Adhesive layers are formed on the two opposing surfaces of a transparent support. At least one of the adhesive layers is made of a material of which the cured state may be changed. The adhesive layer is irradiated with light and a lens sheet is then pressed against the adhesive layer. The adhesive layer is cured. In this illustrative way, a laminate film of the lens sheet fixed to the transparent support via the adhesive layer may be obtained. The laminate film may be bonded to a polarizing plate on the viewer's side of a liquid crystal display element via the other adhesive layer.

Owner:SHARP KK

Planar light source device and liquid crystal display apparatus having the same

InactiveUS20050180172A1Improve brightness uniformityPrevent channelingStatic indicating devicesSensing record carriersDriver circuitElectricity

An LCD apparatus includes a light source generating light, a driver circuit and an LCD panel. The driver circuit includes a driving voltage control section and a driving voltage generating section. The driving voltage control section senses an environmental temperature and outputs a control signal having a level which is adjusted based on a comparison of the environmental temperature to a reference temperature. The driving voltage generating section is electrically connected to the driving voltage control and generates a driving voltage based on the control signal. The LCD panel displays an image by using the light generated from the light source. Channeling that induces deterioration of display quality is prevented by adjusting an operating frequency of the light source according to the environmental temperature.

Owner:SAMSUNG DISPLAY CO LTD

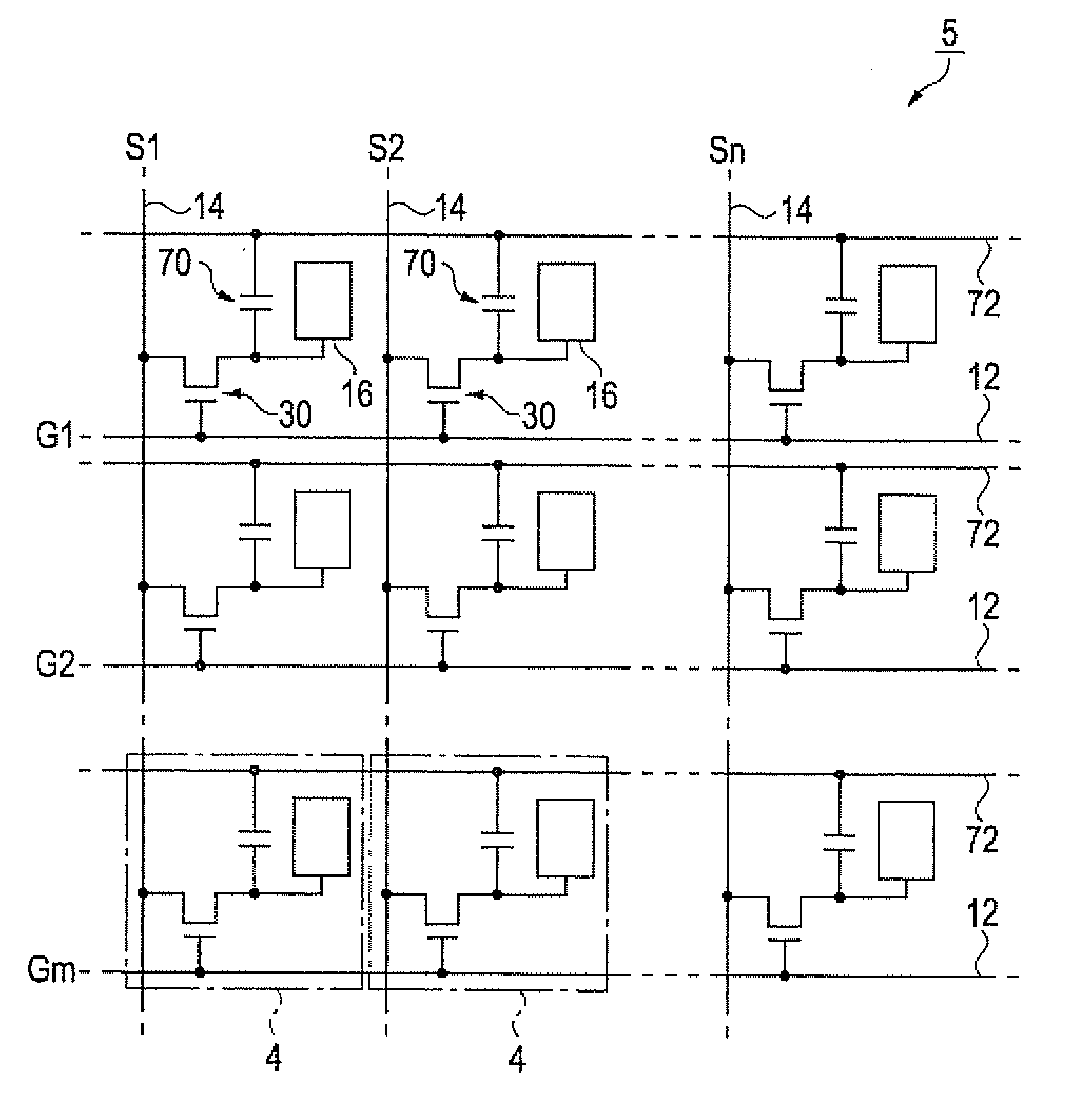

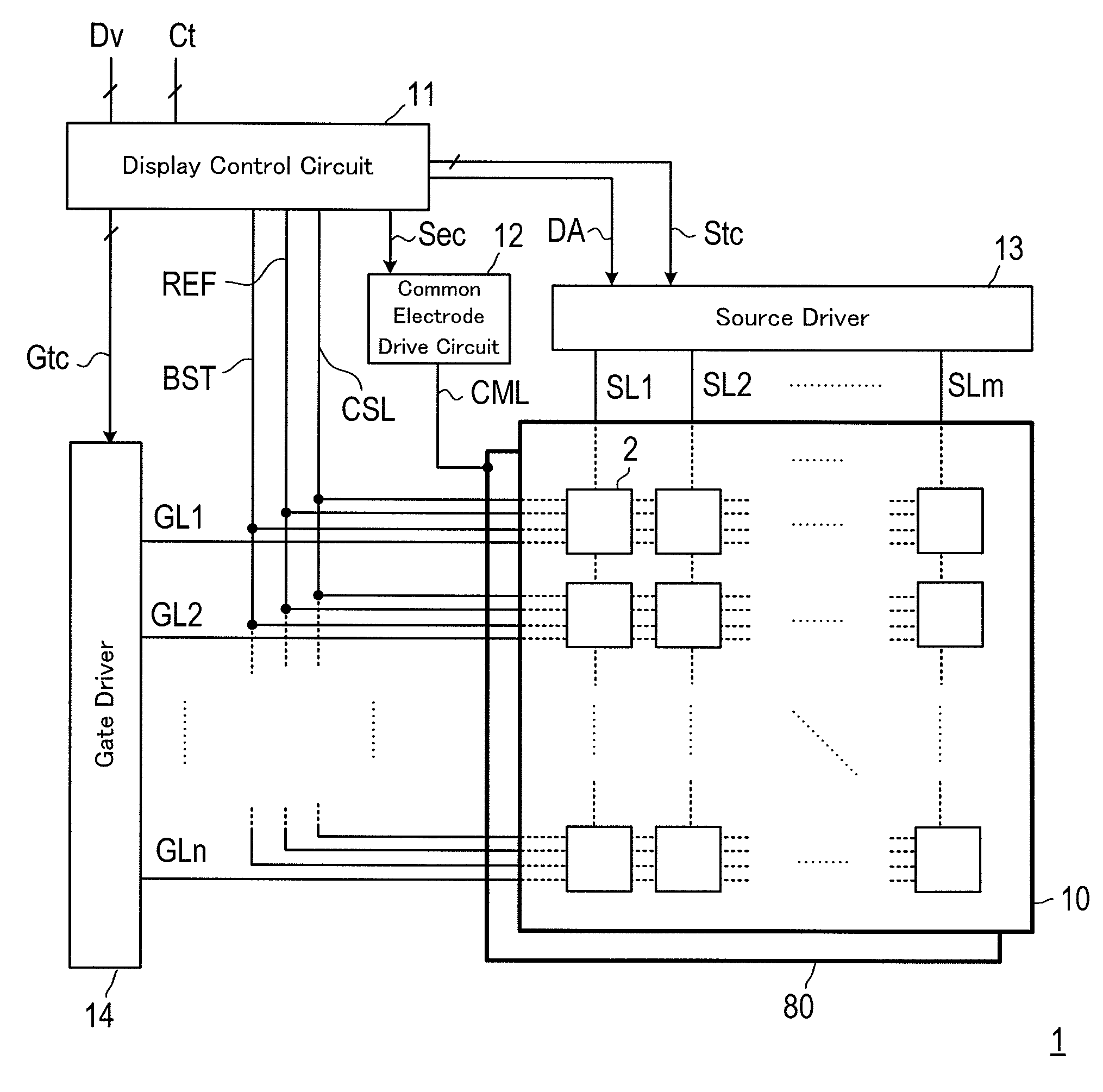

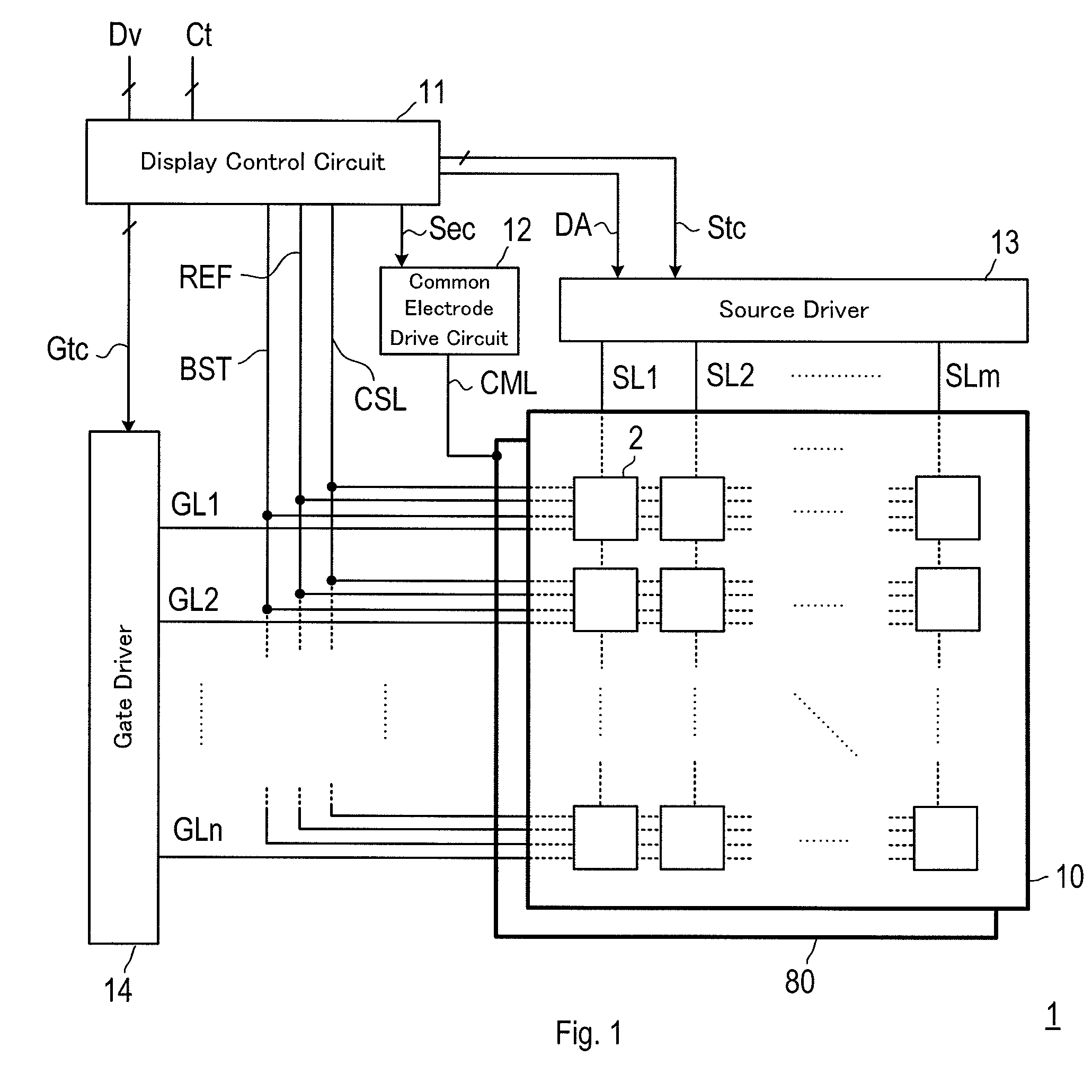

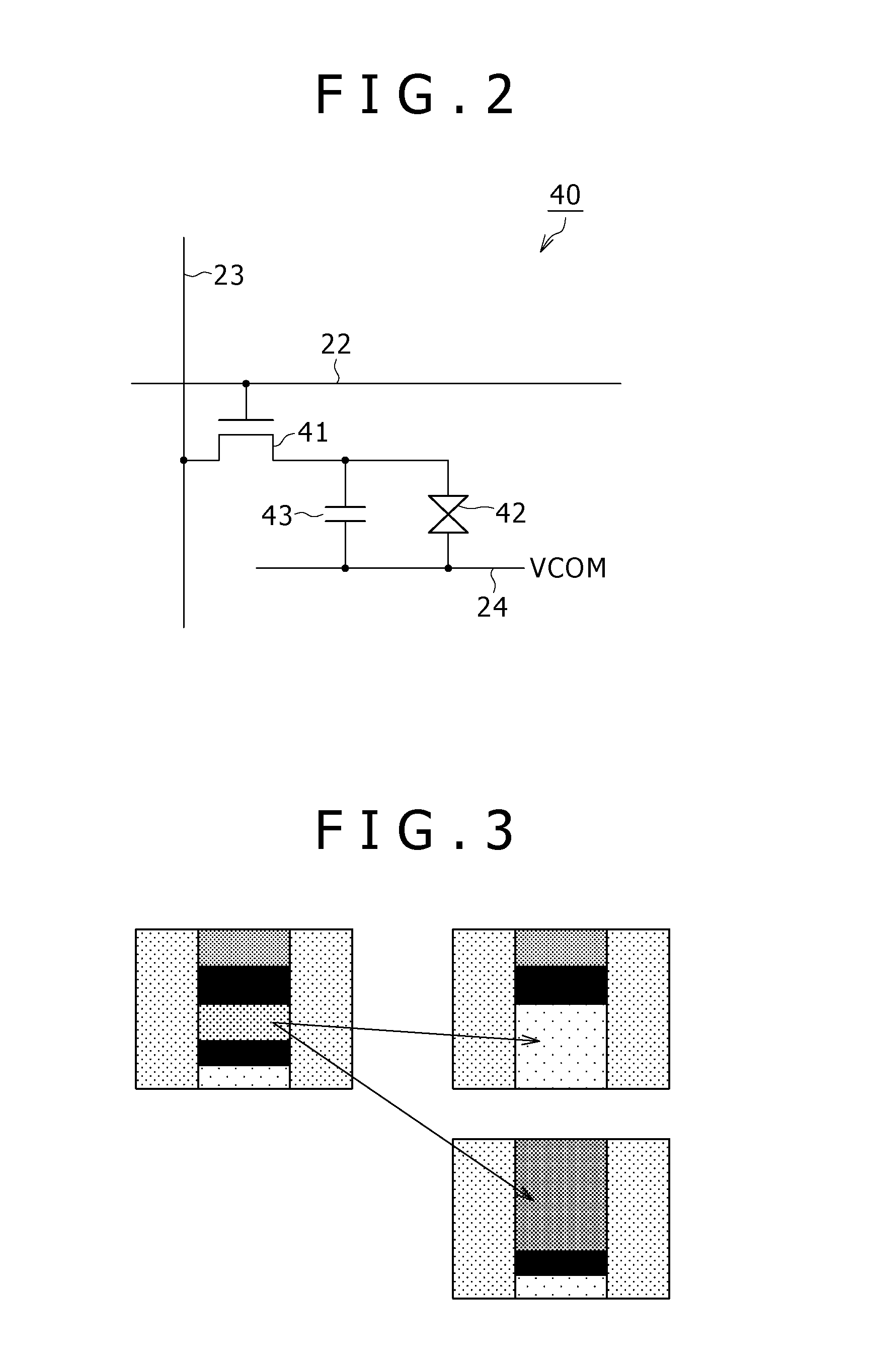

Pixel circuit and display device

ActiveUS20120218246A1Reduce power consumptionShorten the timeCathode-ray tube indicatorsNon-linear opticsCapacitanceDisplay device

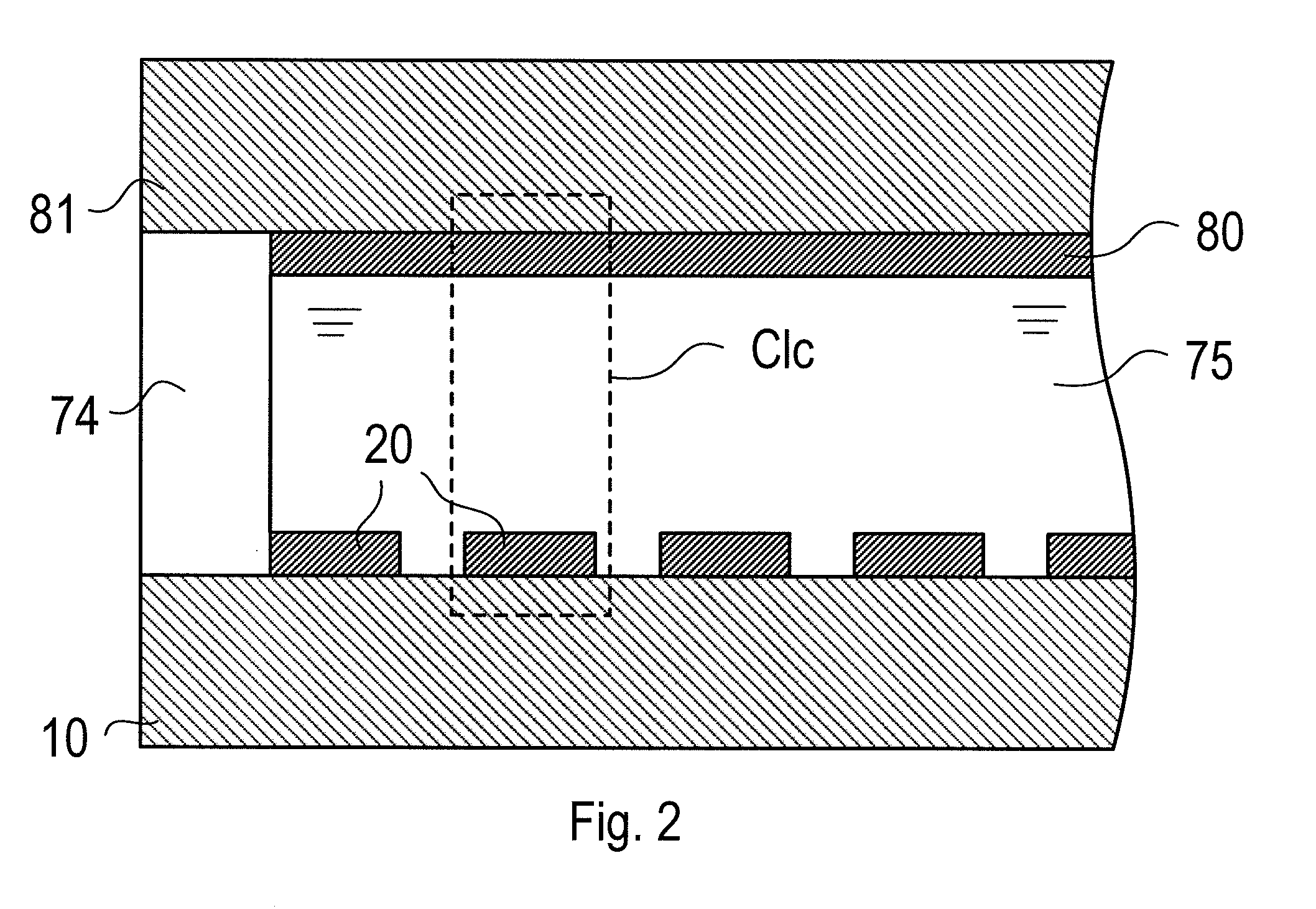

A display device in which low power consumption is realized without lowering an aperture ratio is provided. A liquid crystal capacitive element Clc is sandwiched between a pixel electrode 20 and an opposite electrode 80. The pixel electrode 20, one end of a first switch circuit 22, one end of a second switch circuit 23 and a first terminal of a second transistor T2 form an internal node N1. The other terminals of the first switch circuit 22 and the second switch circuit 23 are connected to a source line SL. The second switch circuit 23 is a series circuit composed of a first transistor T1 and a diode D1. A control terminal of the first transistor T1, a second terminal of the second transistor T2 and one end of a boost capacitive element Cbst form an output node N2. The other end of the boost capacitive element Cbst and the control terminal of the second transistor T2 are connected to a boost line BST and a reference line REF, respectively. The diode D1 has a rectifying function from the source line SL to the internal node N1.

Owner:SHARP KK

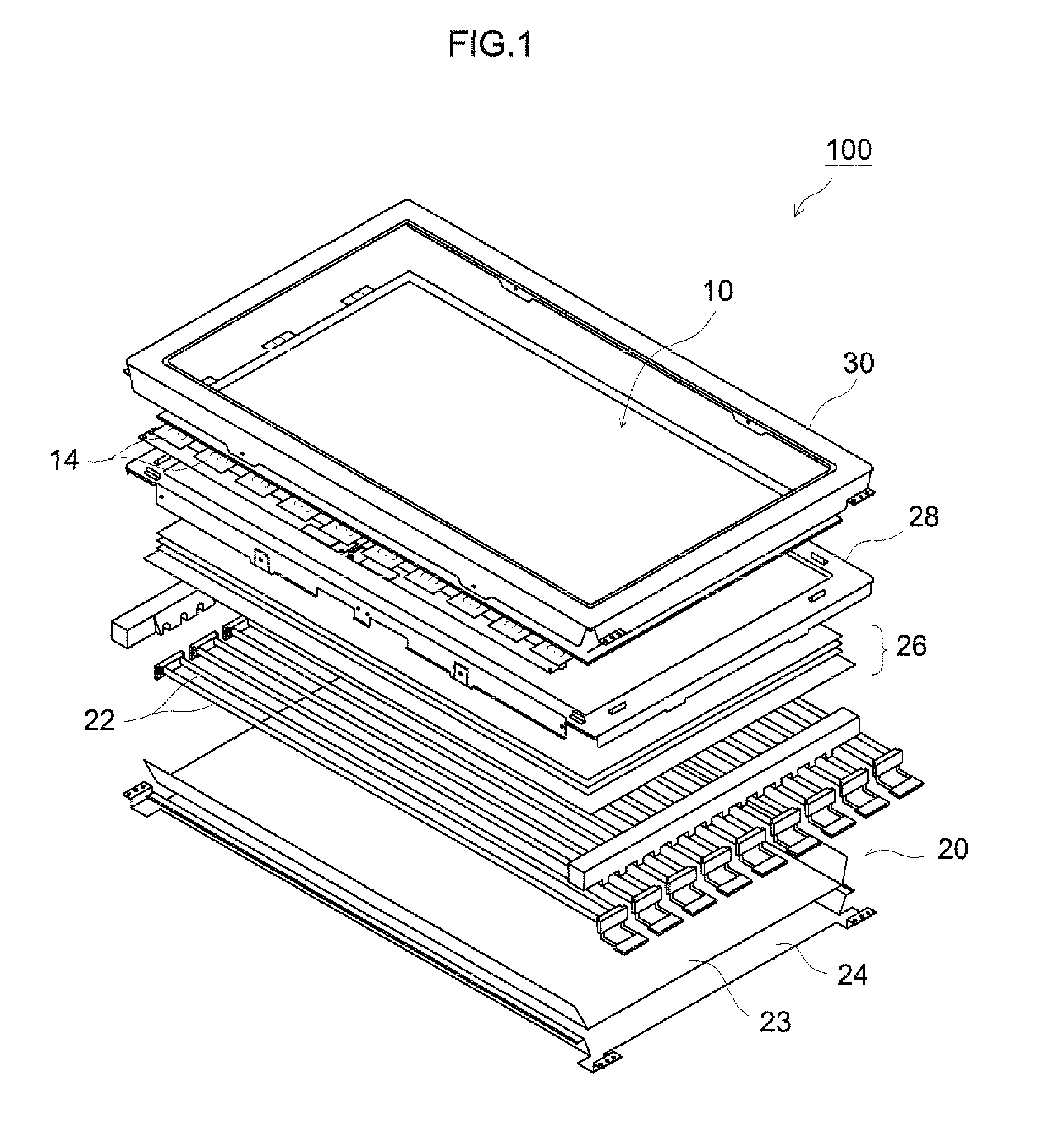

Display module and display unit

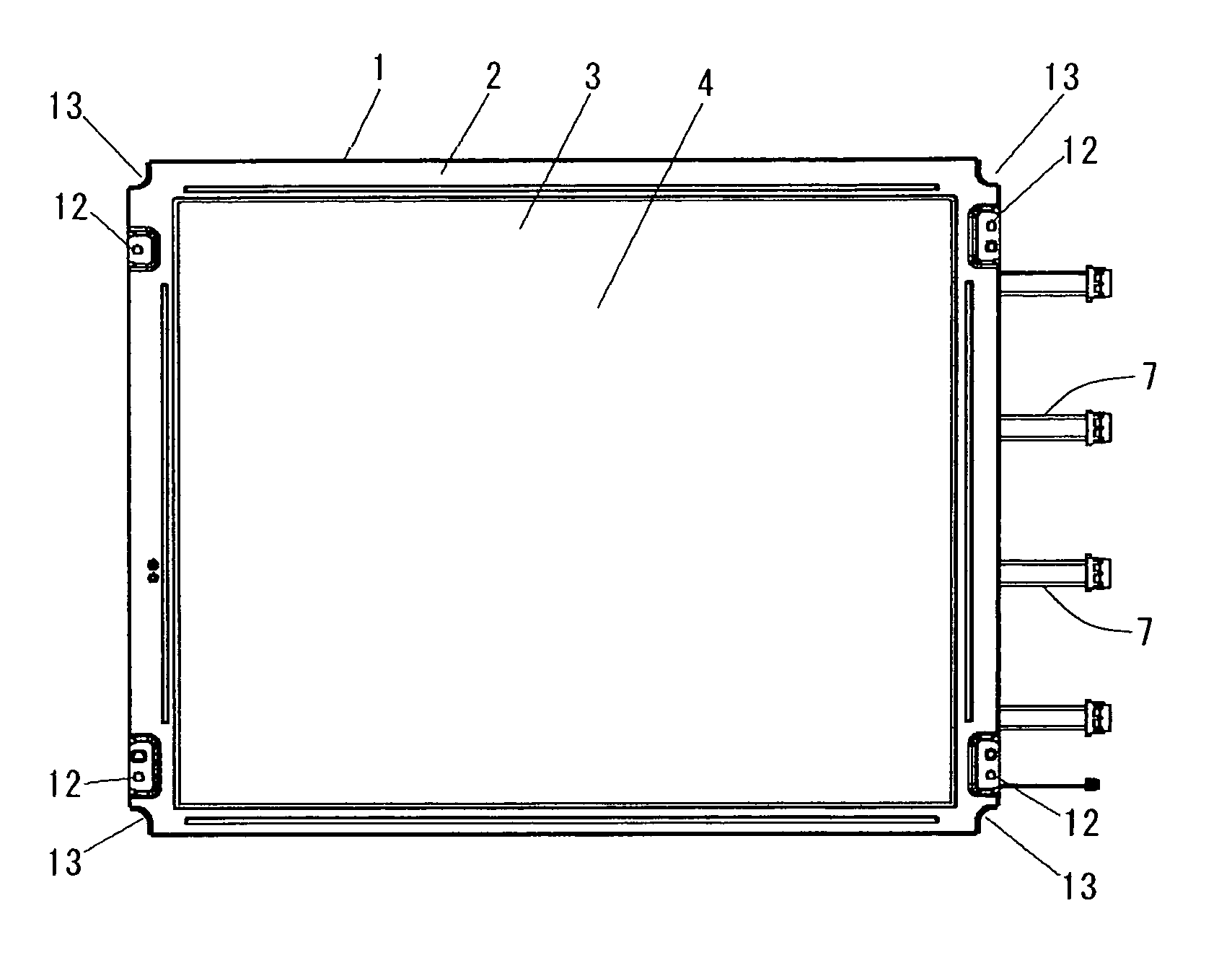

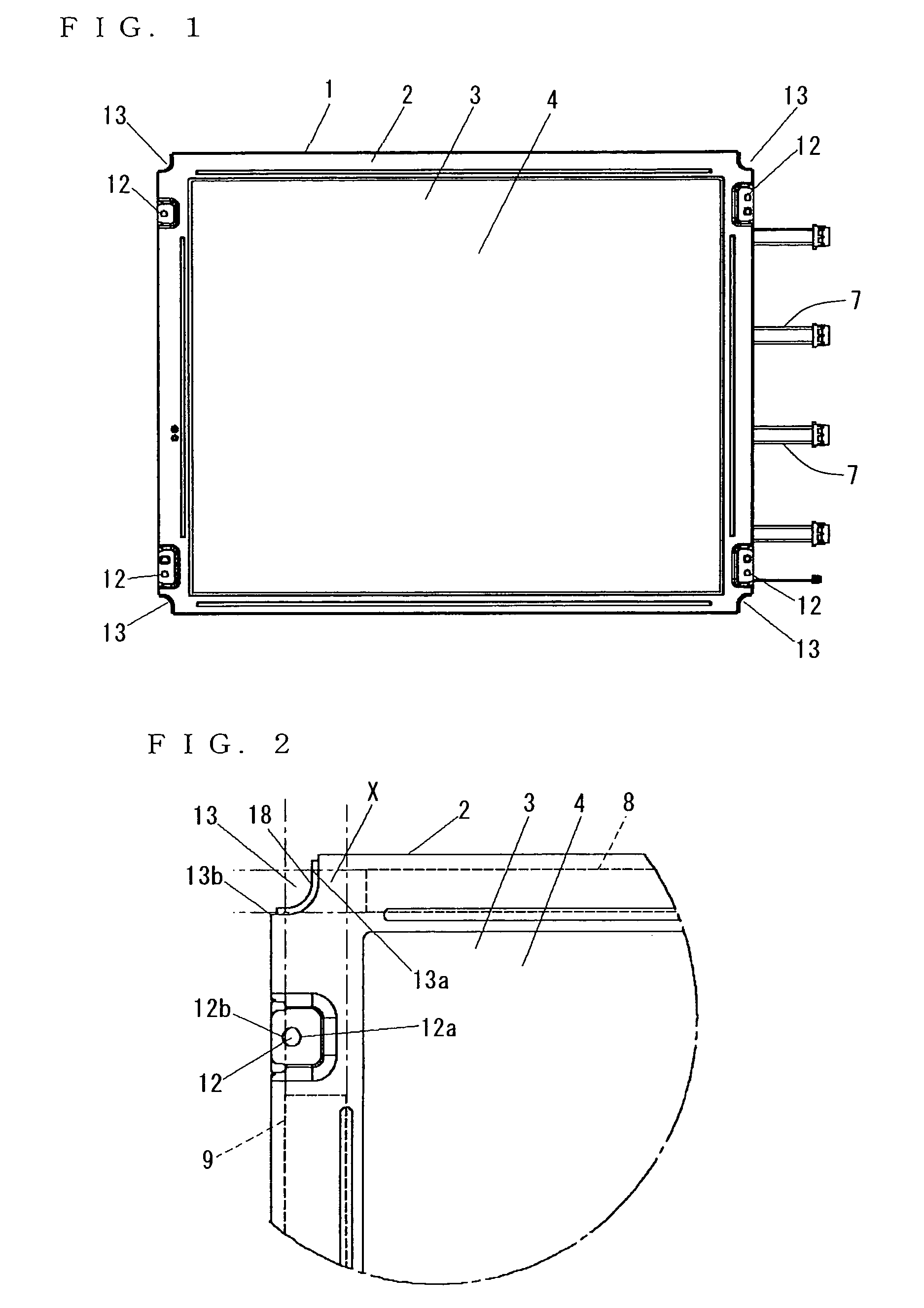

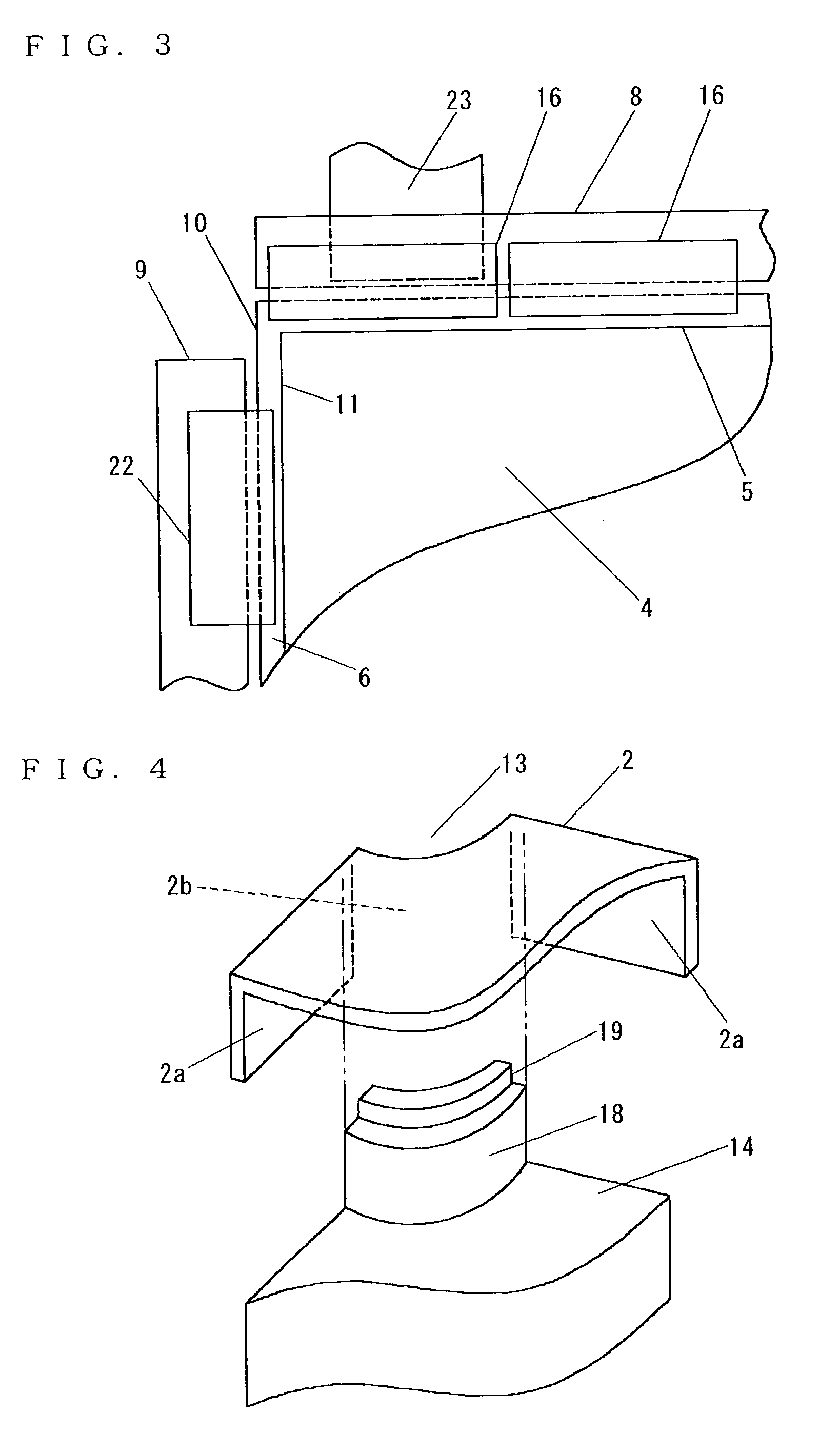

InactiveUS7206037B2Easy to disassembleSpace minimizationElectric discharge tubesMagnetic/electric field screeningComputer moduleMental detachment

In a display module having a picture-frame-shaped front frame, notches are formed at both ends of one side edge thereof so as to penetrate from the front surface to the rear surface thereof. This helps realize a compact display unit. Moreover, a metal film or the like is formed on a flexible printed circuit used in the display module, and the flexible printed circuit is fixed to a metal rear casing with a detachable protective plate. This helps realize a display module that permits easy attachment and detachment of a flexible printed circuit and in which sufficient shielding against EMI (the metal film is grounded via the rear casing) is achieved.

Owner:JAPAN DISPLAY WEST

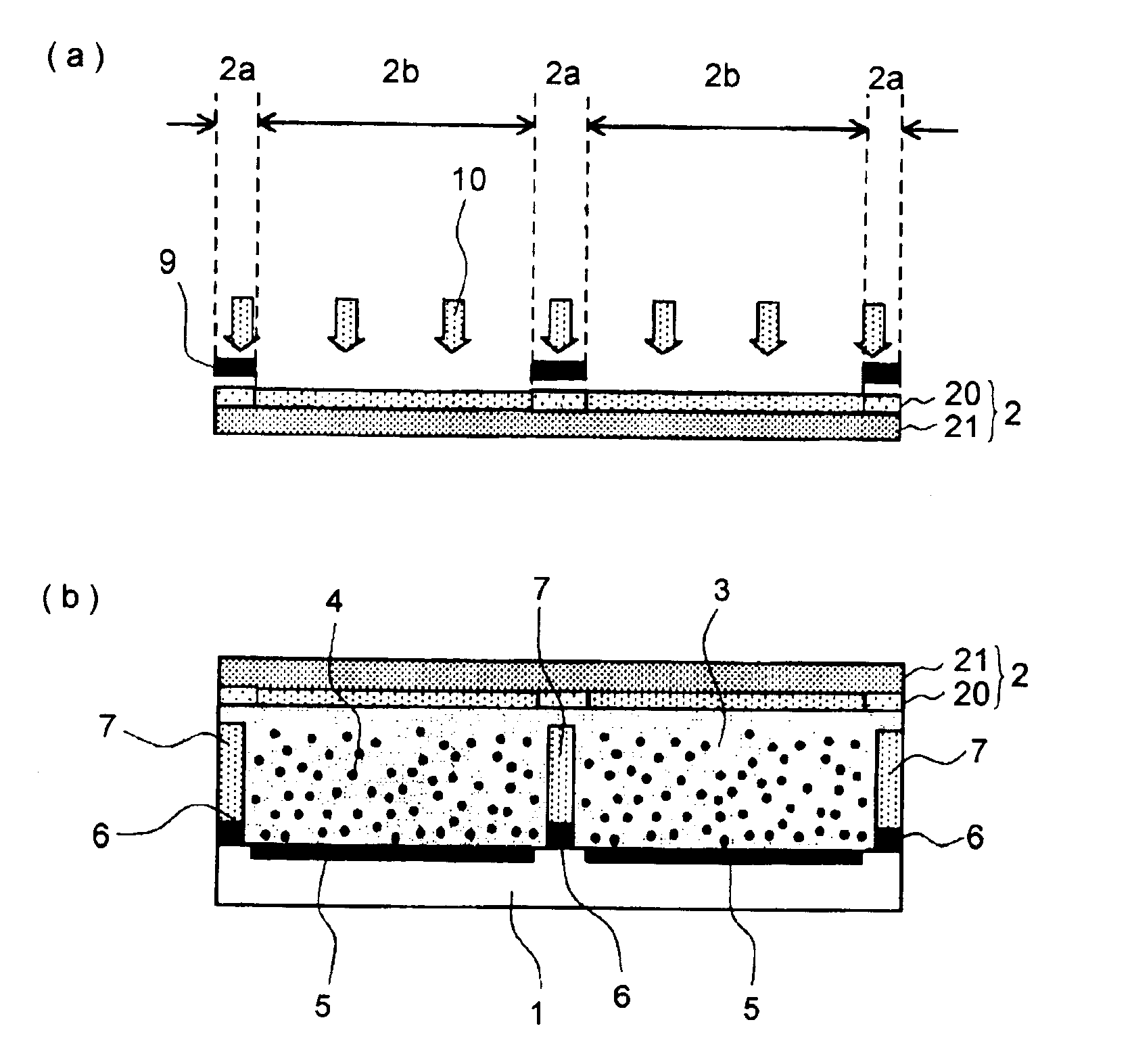

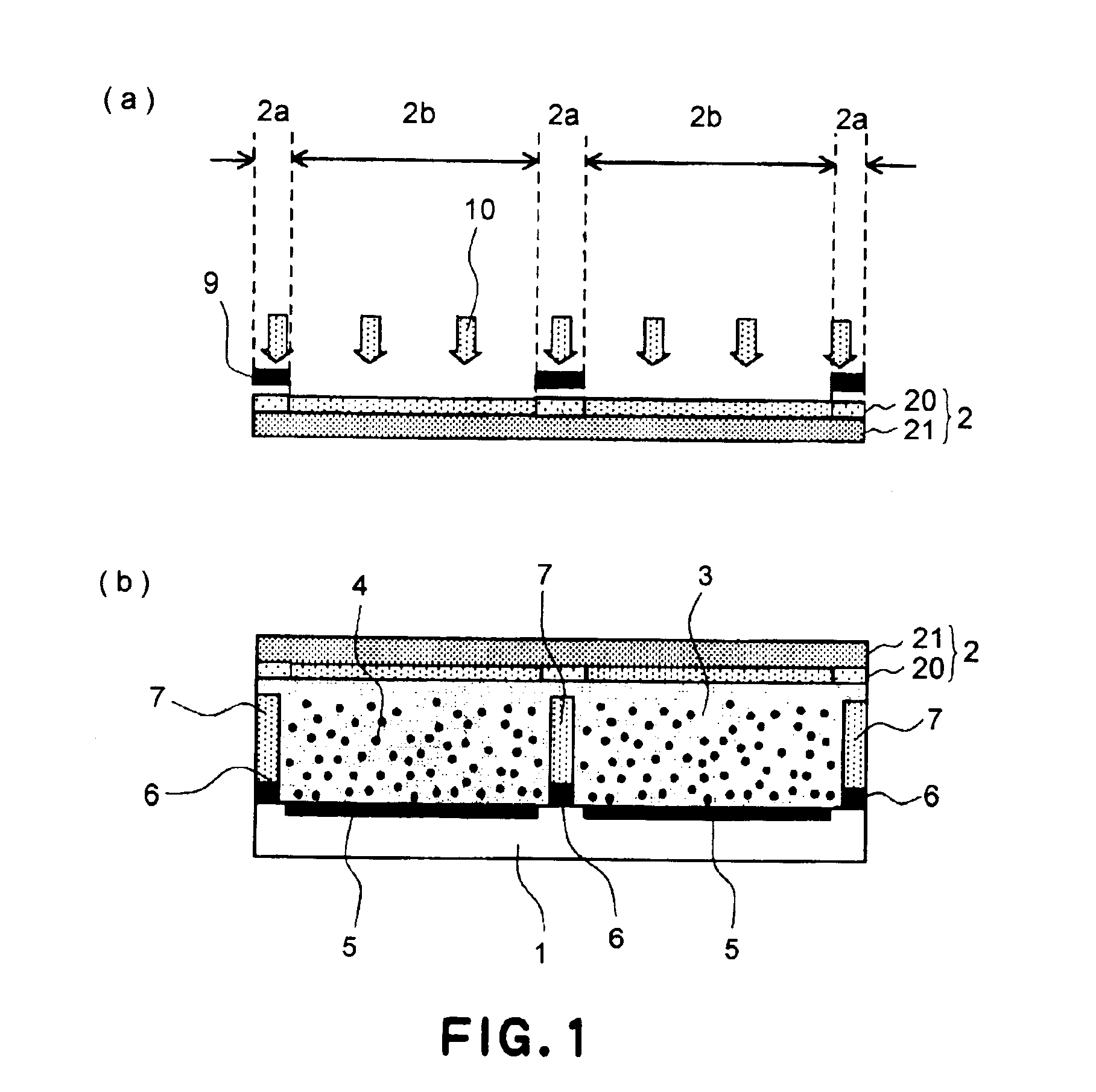

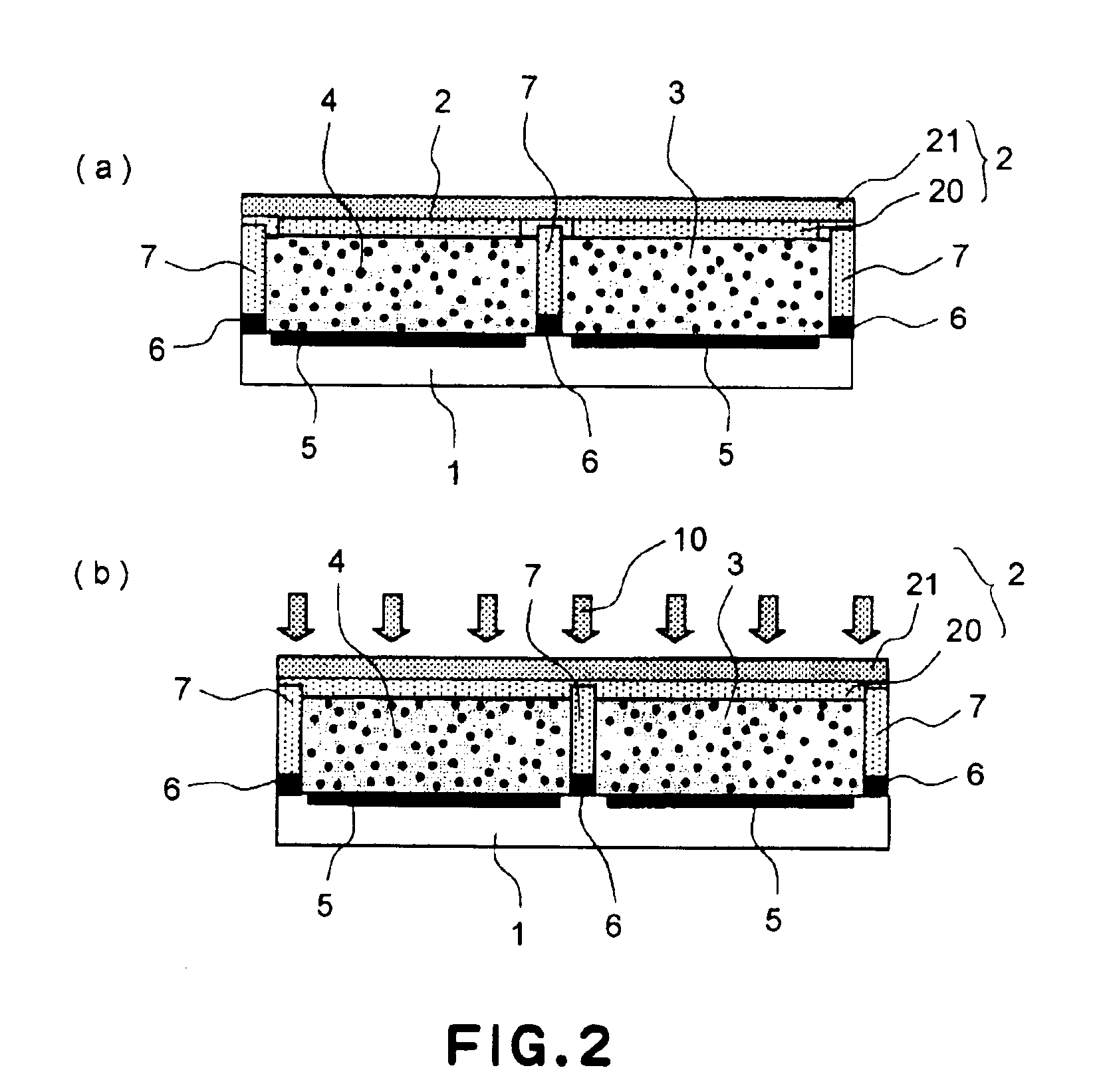

Process for producing electrophoretic display device

InactiveUS6950226B2Prevent display quality degradationSuppresses degradation of display qualityElectrographic process apparatusElectrographic processes using charge patternElectrophoresesDisplay device

An electrophoretic display device including first and second substrates disposed with a predetermined spacing, a partition member disposed between the first and second substrates, a plurality of electrophoretic particles and an insulating liquid which are sealed up by the substrates and the partition member, and first and second electrodes disposed close to the insulating liquid, is produced through a production process comprising the following steps (A), (B), (C) and (D): (A) a step of filling the insulating liquid and the electrophoretic particles in a recess defined by the first substrate and the partition member, (B) a step of placing a first area of the second substrate to be in contact with the partition member in an uncured state and a second area of the second substrate to be in contact with the insulating liquid in a cured state, (C) a step of causing the first area of the second substrate to contact the partition member and the second area of the second substrate to contact the insulating liquid, and (D) a step of curing the first area of the second substrate contacting the partition member.

Owner:CANON KK

Electro-optical device and electronic apparatus

InactiveUS20140160413A1Long product lifeSimple manufacturing processNon-linear opticsImpurityElectron

An electro-optical device includes a first substrate, a second substrate and a liquid crystal, and has a display region and a peripheral region. The peripheral region of the first substrate has a peripheral electrode and a first orientation film covering the peripheral electrode. Then, since the density of first orientation film in the display region is different from the density of the first orientation film in the peripheral region, it is possible to efficiently capture ionic impurities present in the liquid crystal.

Owner:SEIKO EPSON CORP

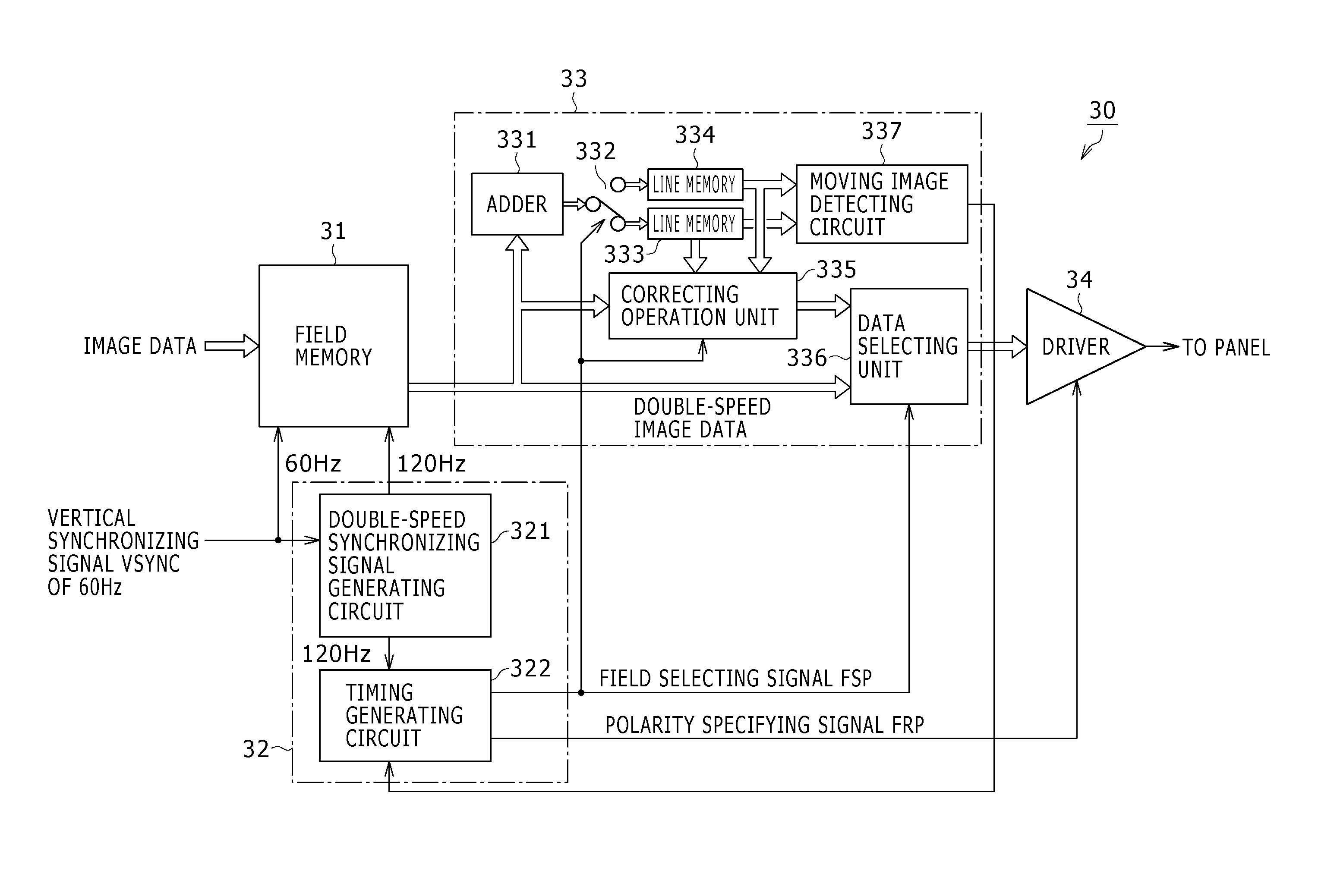

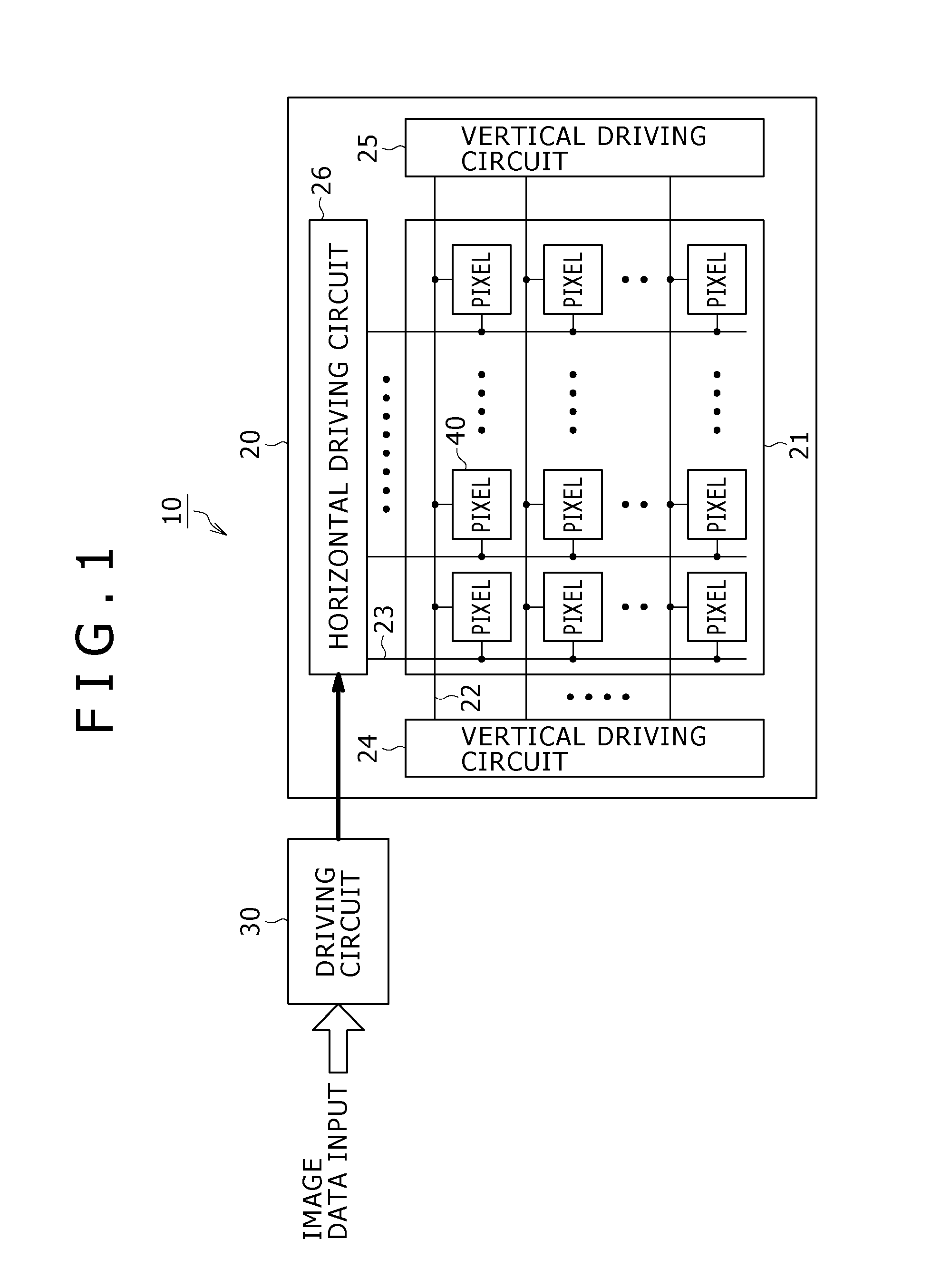

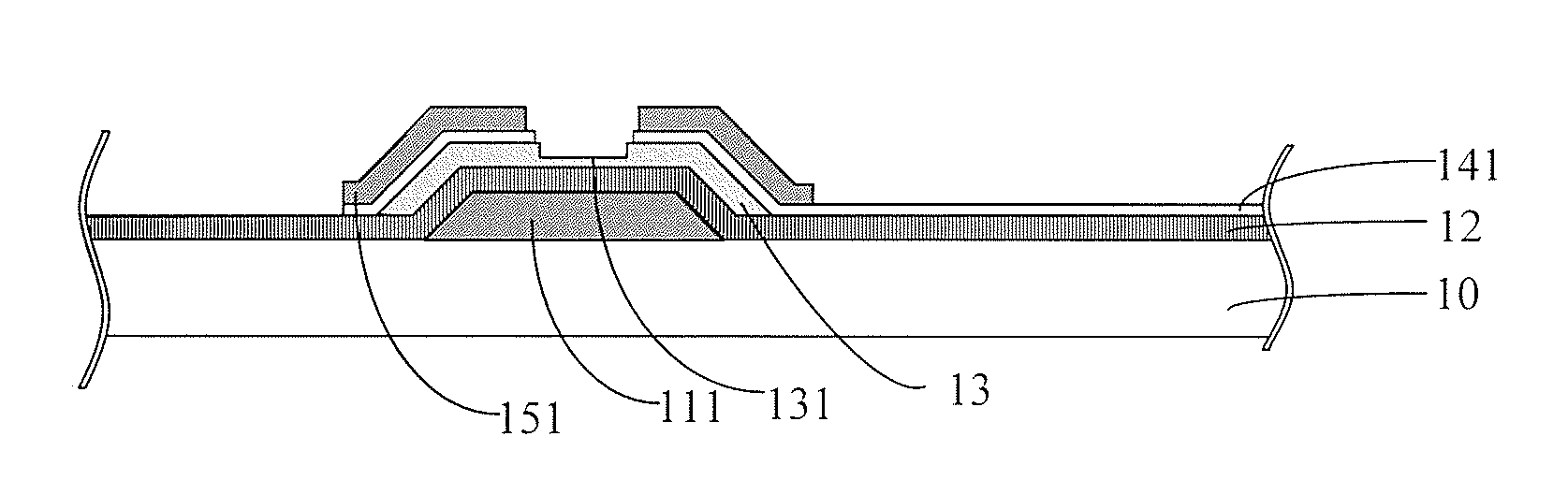

Display device and driving method of display device

ActiveUS20070146281A1Prevent display quality degradationReliable calibrationCathode-ray tube indicatorsNon-linear opticsDisplay deviceElectrical polarity

Disclosed herein is a display device using a field inversion driving system, the display device being formed by arranging pixels each including an electrooptic element in a form of a matrix and inverting polarity of a display signal to be written to each of the pixels in field periods, the display device including: double-speed converting means for converting an input display signal into a double-speed display signal having a field frequency twice a field frequency of said display signal; and crosstalk correcting means for correcting crosstalk in a second field of two fields as a unit of said double-speed display signal generated by said double-speed converting means, using information of the first field.

Owner:SONY CORP

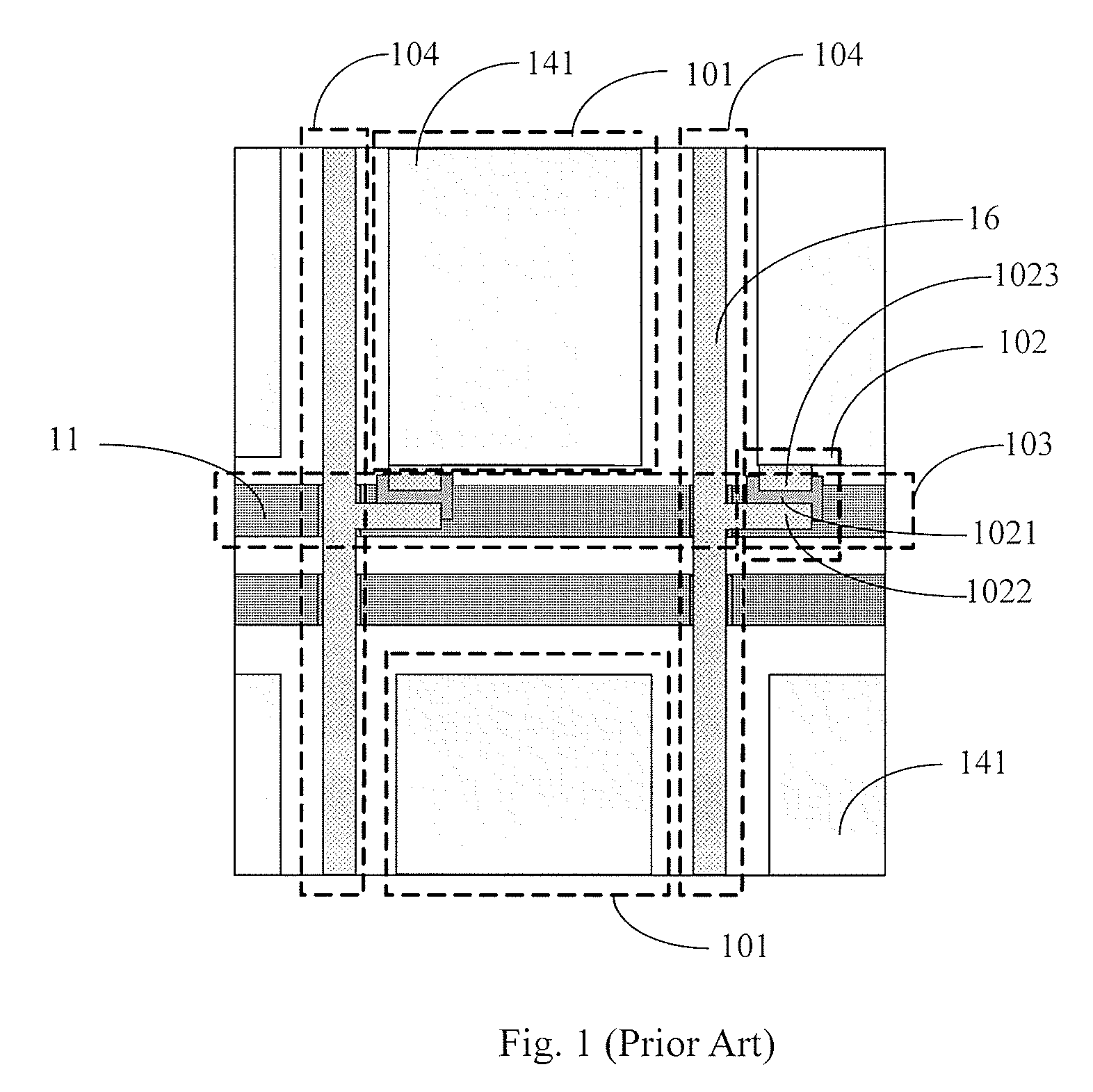

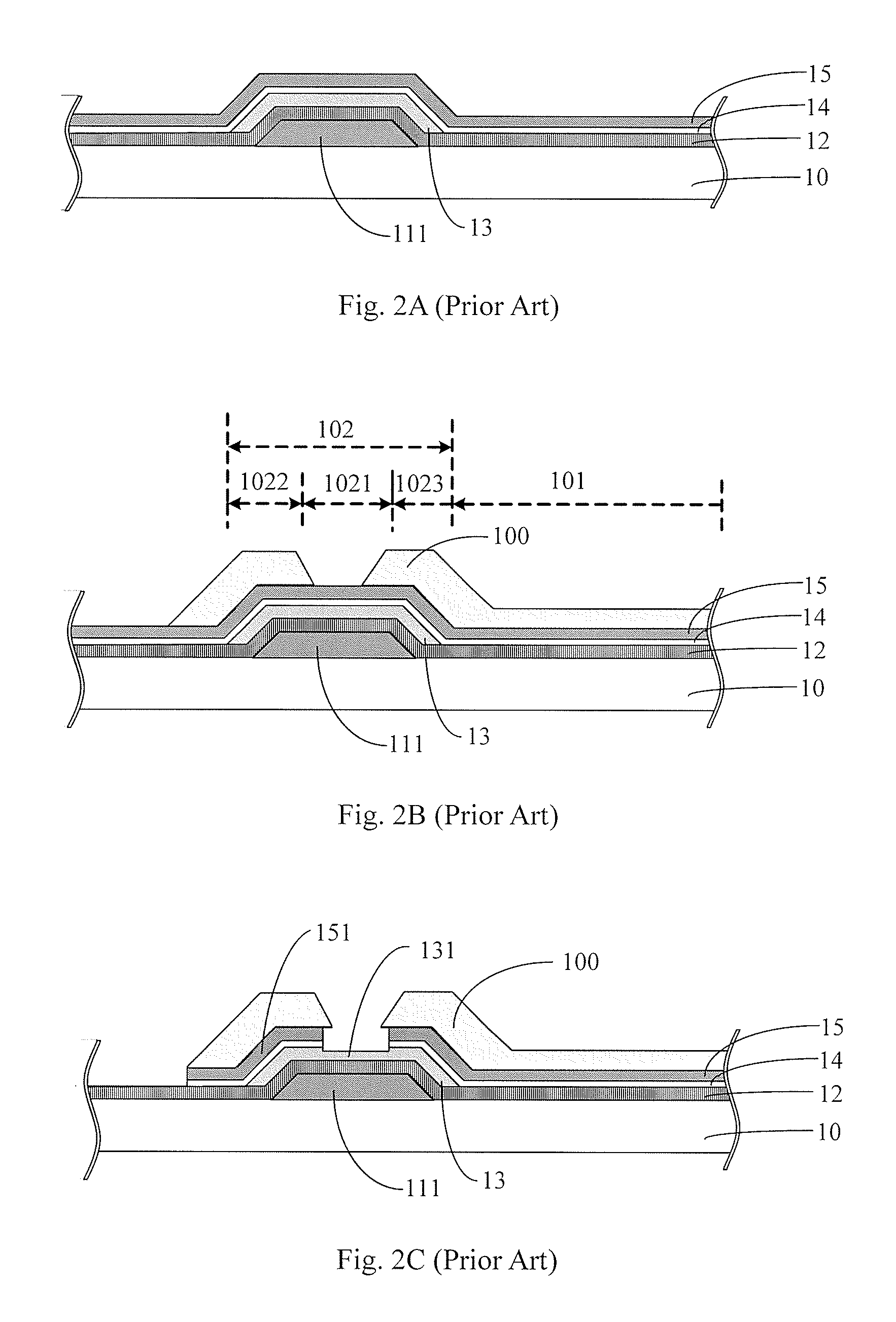

Method for manufacturing array substrate of liquid crystal display

ActiveUS20100075450A1Guaranteed display qualityOver-etching on the TFT channel can be reducedSolid-state devicesSemiconductor/solid-state device manufacturingLiquid-crystal displayActive layer

A method for manufacturing an array substrate of liquid crystal display comprising the following steps: providing a substrate having gate lines, a gate insulating layer and an active layer pattern formed thereon in this order; depositing a first transparent conductive layer and a source / drain metal layer in this order on the substrate; forming a photoresist pattern layer on the source / drain metal layer through a triple-tone mask; performing a wet-etching process on the source / drain metal layer and the first transparent conductive layer exposed from the photoresist pattern layer; performing a first ashing process on the photoresist pattern layer and performing a dry-etching process on the source / drain metal layer, the first transparent conductive layer and the active layer pattern exposed by the first ashing process; performing a second ashing process on the photoresist pattern layer and performing a wet-etching process on the source / drain metal layer exposed by the second ashing process; and removing the remaining photoresist pattern layer. According to the invention, the over-etching on the TFT channel region can be reduced and the display quality of the liquid crystal display can be ensured.

Owner:BEIJING BOE OPTOELECTRONCIS TECH CO LTD +1

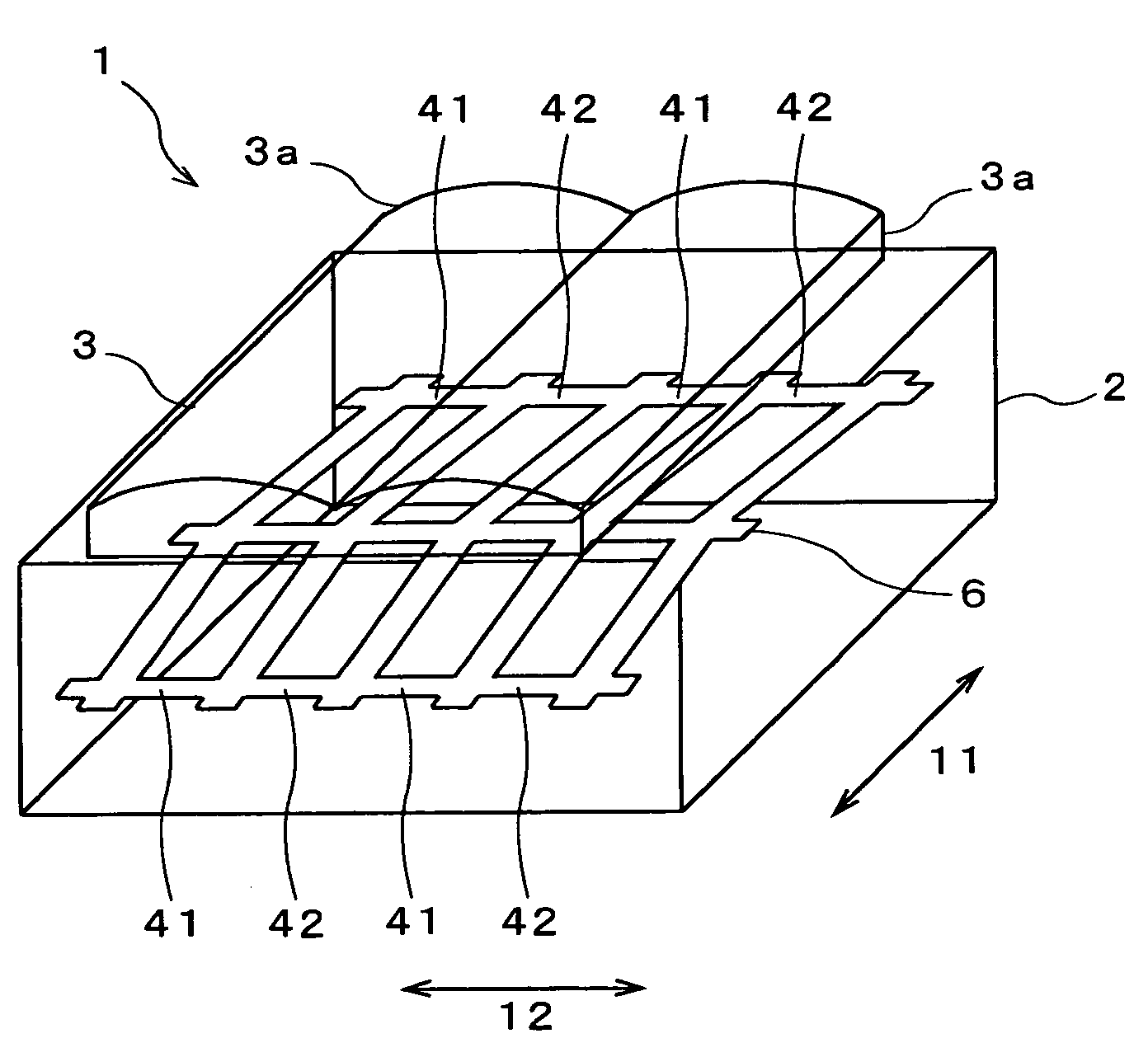

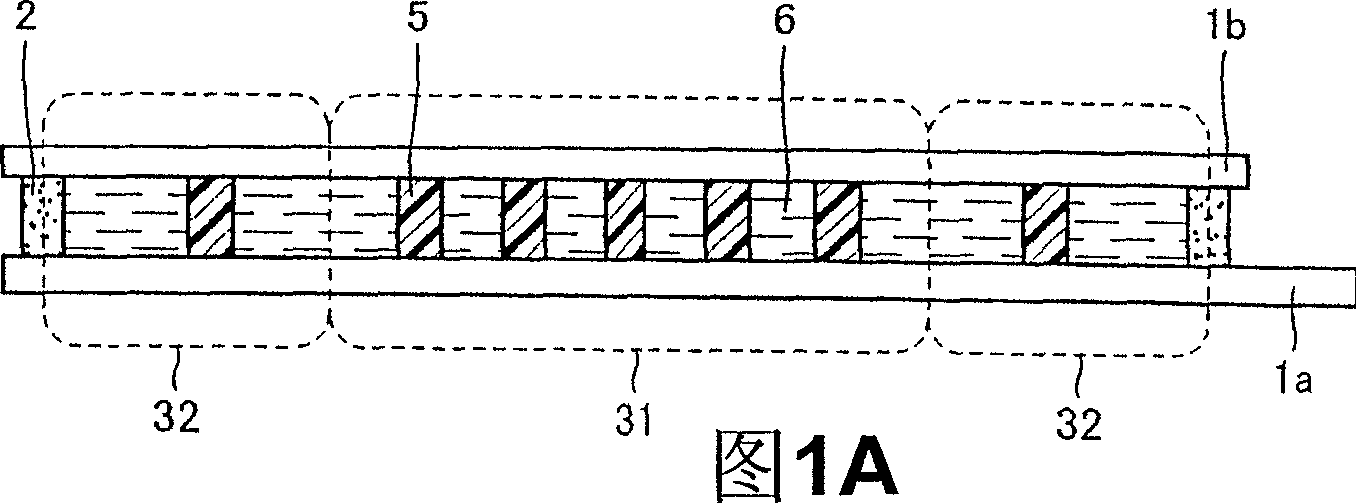

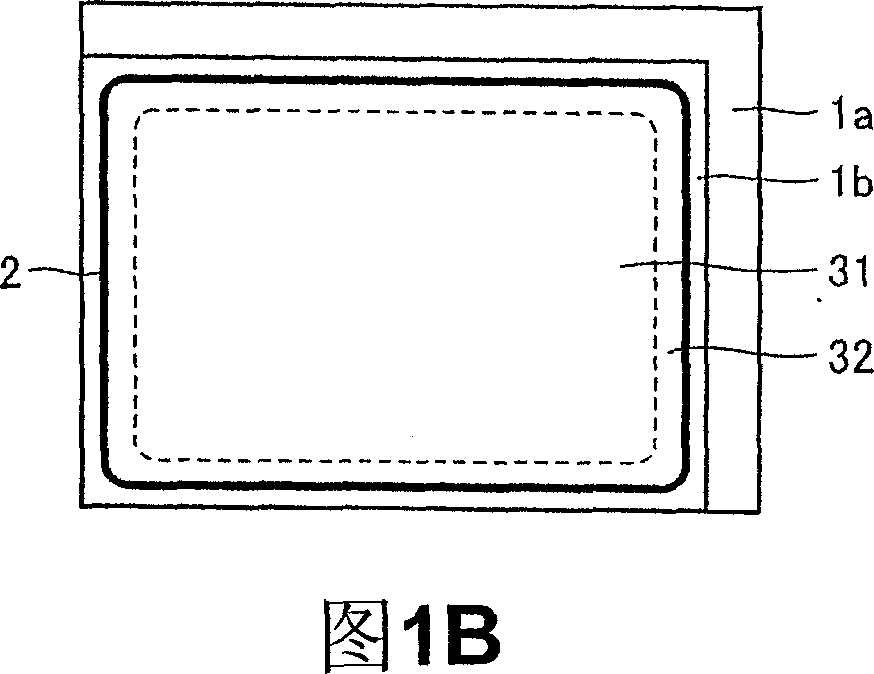

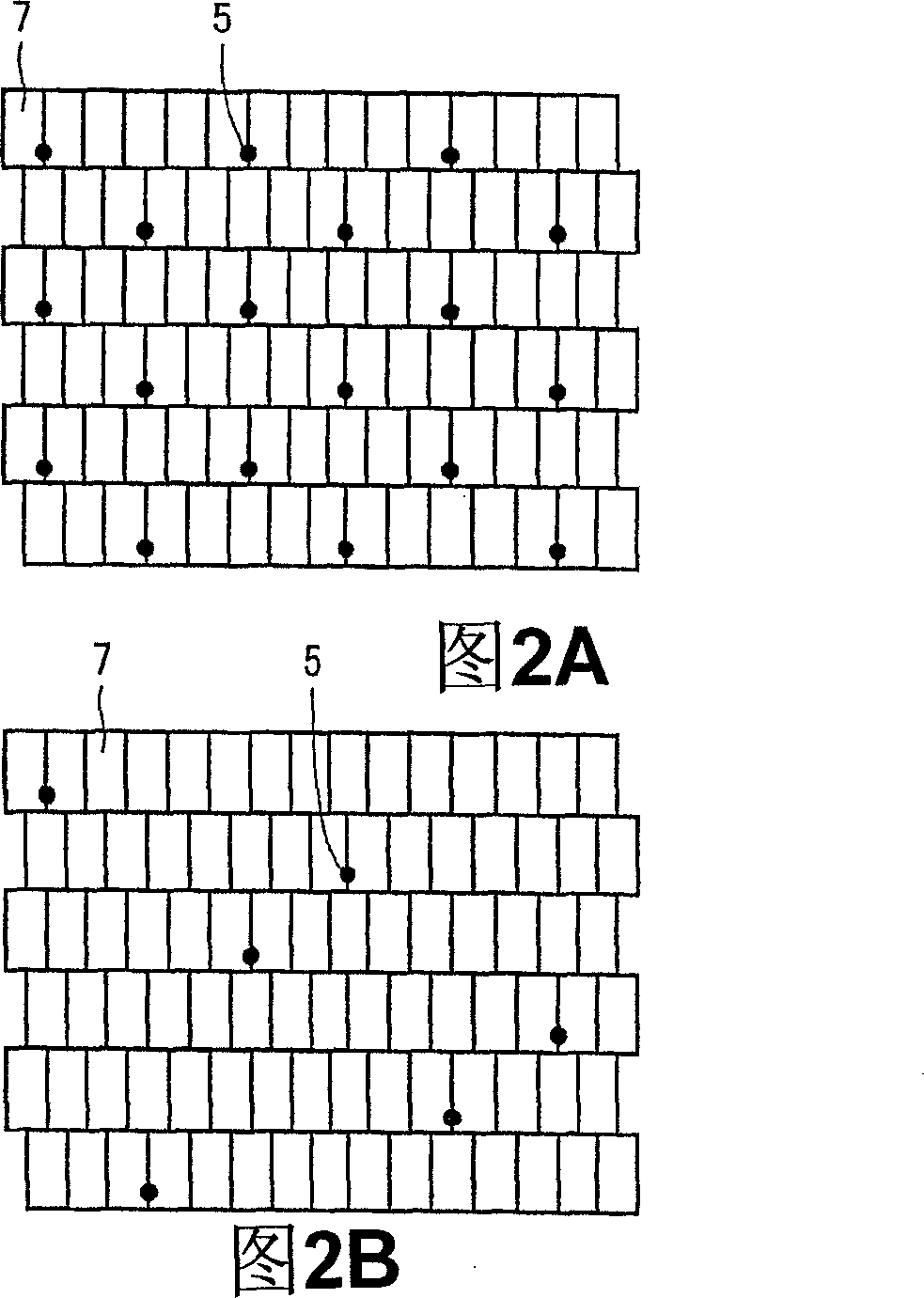

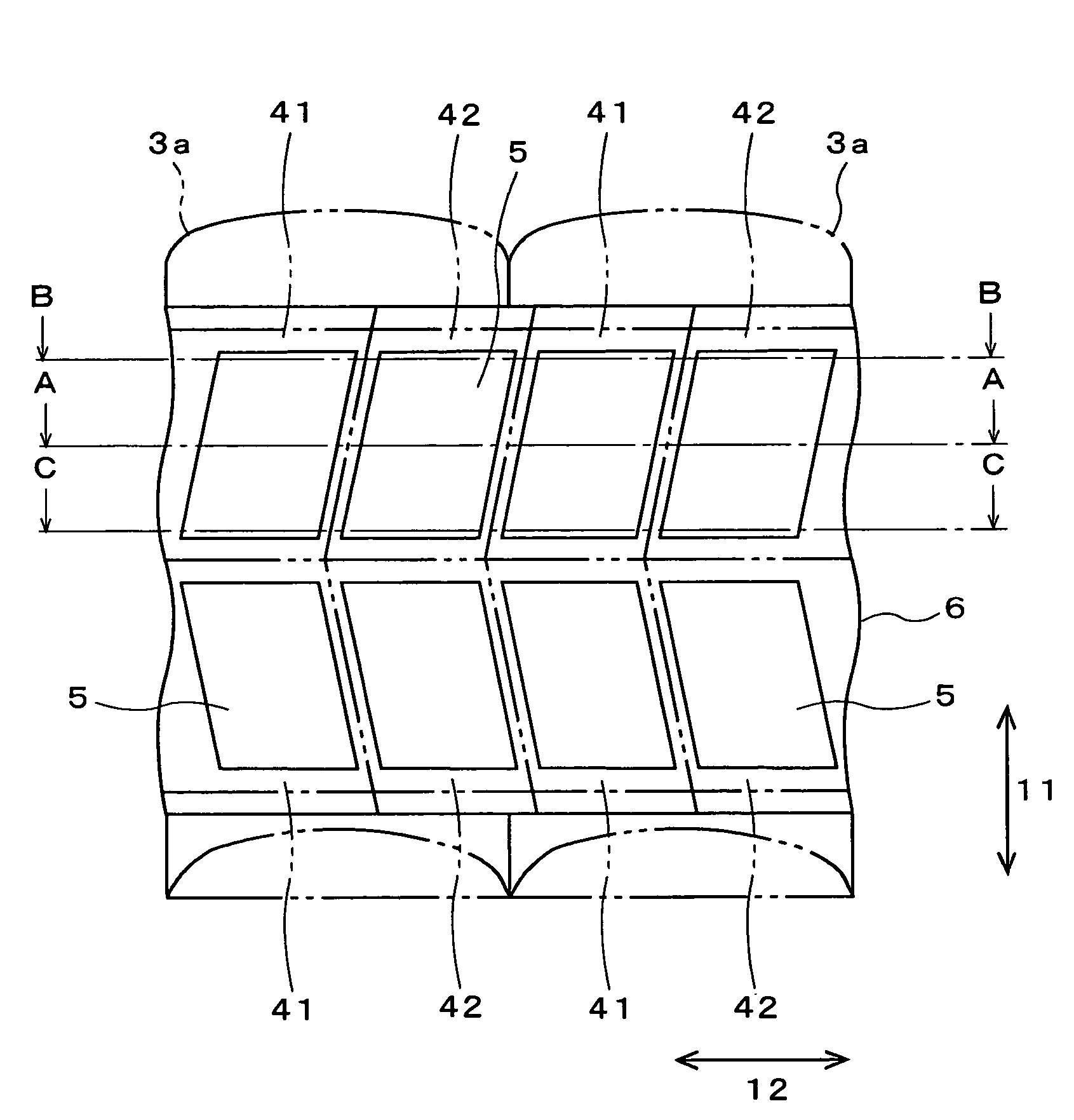

Substrate with spacer, panel, liquid crystal panel, method for producing panel, and method for producing liquid crystal panel

InactiveCN1930517APrevent display quality degradationAvoid damageNon-linear opticsHigh densityLiquid-crystal display

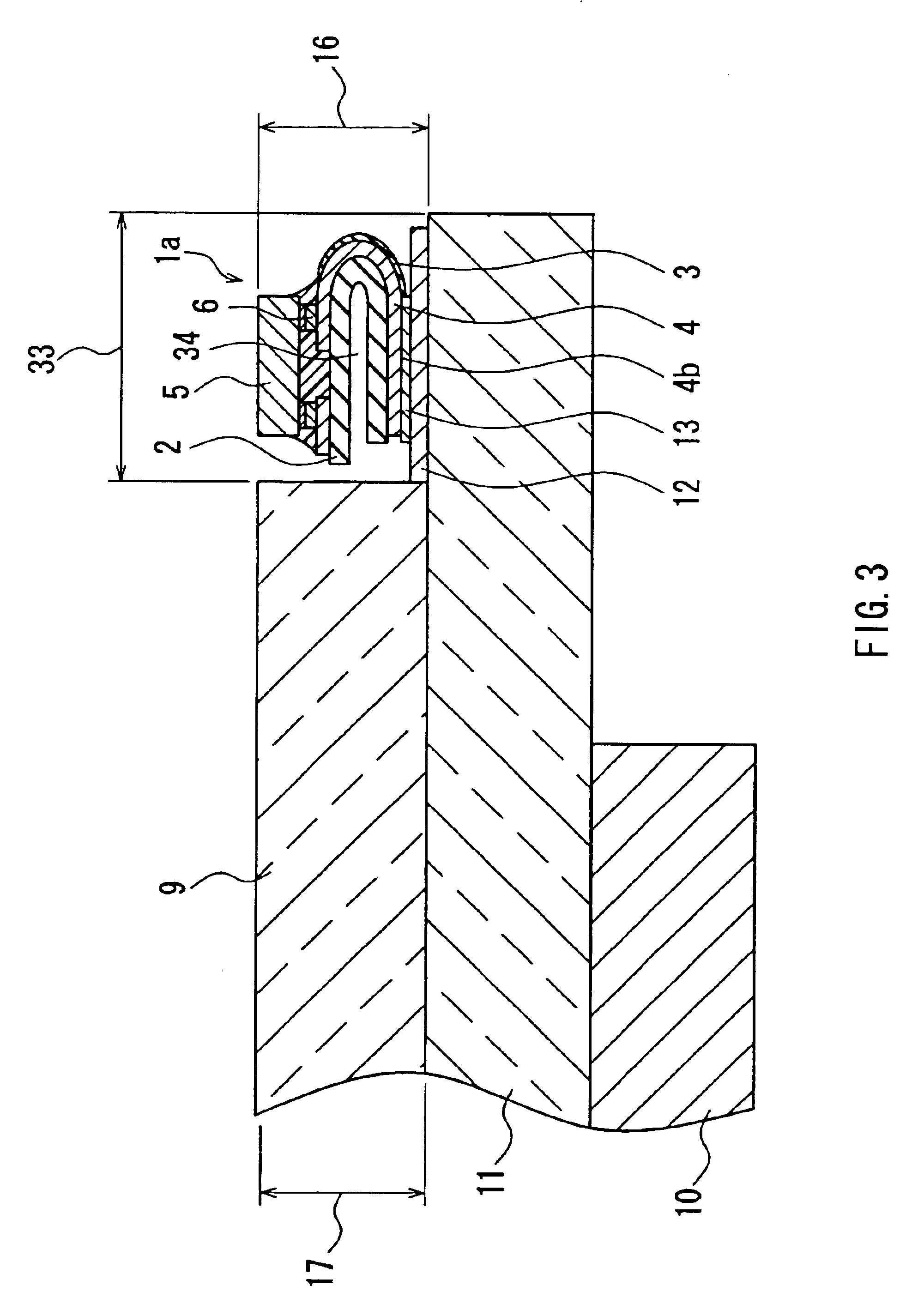

A liquid crystal display panel includes two substrates (1a and 1b) fixed together by a seal member (2) with their main surfaces opposed to each other, liquid crystal (6) sealingly stored in a region surrounded by the two substrates (1a and 1b) and the seal member (2), and a plurality of columnar spacers (5) arranged in a region surrounded by the two substrates (1a and 1b) and the seal member (2). A number density of the columnar spacers (2) in a low-density region (32) near the inner side of the seal member (2) is smaller than that in a high-density region (31) inside the low-density region (32). The substrate with the spacer has the substrate and the spacer formed on the substrate. The spacer has at least a first spacer portion, and a second spacer portion formed above the first spacer portion. An upper portion of the first spacer has a larger diameter than a bottom of the second spacer portion.

Owner:SHARP KK

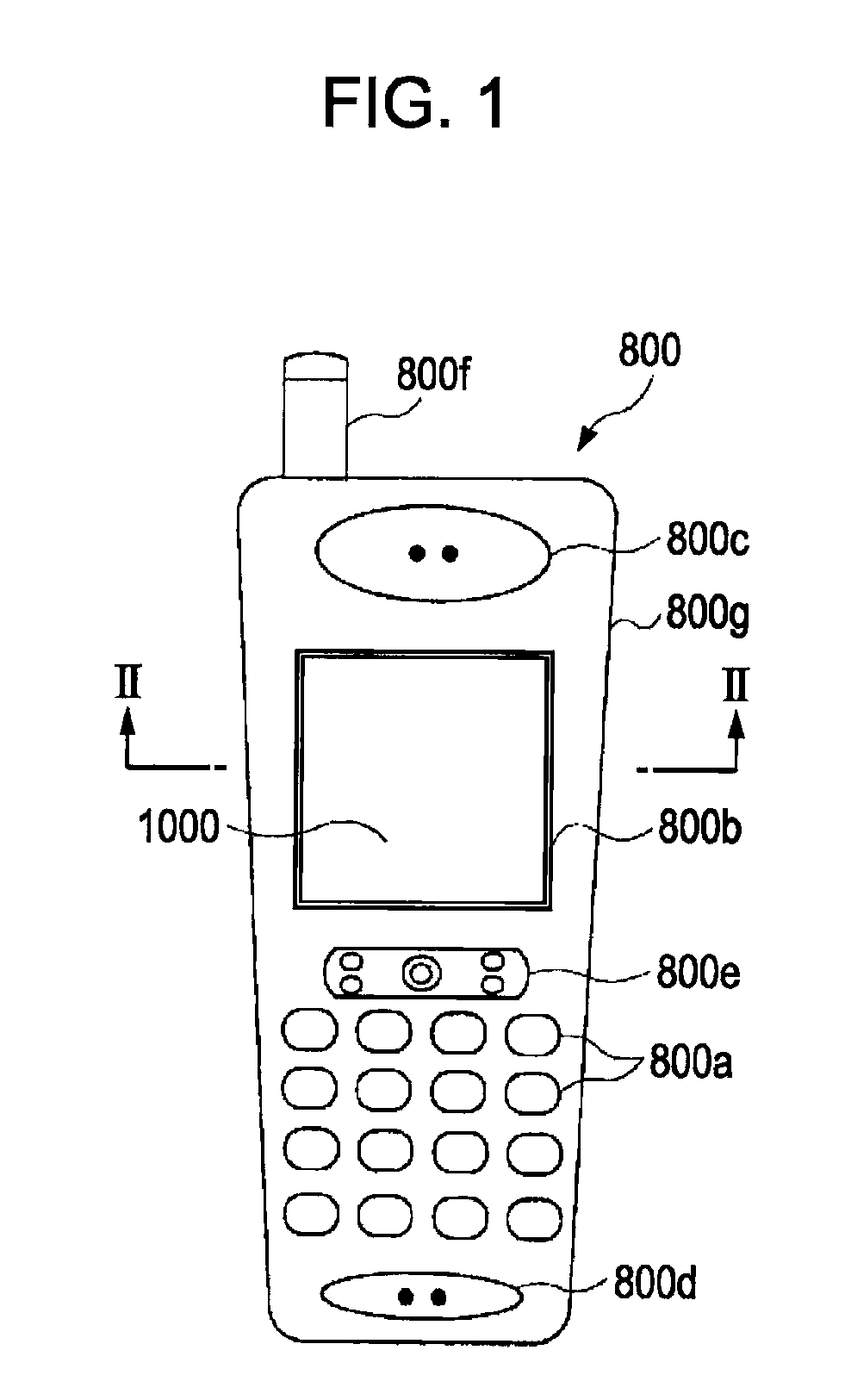

Image display device, portable terminal, display panel, and lens

ActiveUS7965365B2Prevent display quality degradationSteroscopic systemsNon-linear opticsCamera lensDisplay device

In an image display device where a lenticular lens, a display panel, and a light source are provided in order from a viewer side, when cylindrical lenses of the lenticular lens are arrayed in a horizontal direction, in first-viewpoint pixels and second-viewpoint pixels of the display panel, openings whose sides which intersect with straight lines in the horizontal direction are not parallel to a vertical direction are formed. And, a shape of the openings of a pair of pixels mutually adjacent in the vertical direction is made line-symmetric with respect to edges of the pixels extending in the horizontal direction as an axis.

Owner:NEC LCD TECH CORP

Electro-optical device, input device, and electronic apparatus

ActiveUS7969539B2Prevent display quality degradationImprove design qualityOptical light guidesNon-linear opticsEngineeringAdhesive materials

An electro-optical device includes: an electro-optical panel; a light-transmissive member that overlaps the electro-optical panel and has a protruding part that protrudes so as to be positioned outside an edge of the electro-optical panel, the light-transmissive member having a first area and a second area that is located outside the first area; a coloration layer that is formed on a surface of the light-transmissive member at the second area; an adhesive material that is provided between a part of the coloration layer and a corresponding part of the electro-optical panel as well as between the part of the light-transmissive member and a corresponding part of the electro-optical panel; and a first light-shielding layer formed over one surface of the light-transmissive member, and the first light-shielding layer being formed at an area where the coloration layer does not overlap the adhesive material in a plan view.

Owner:JAPAN DISPLAY WEST

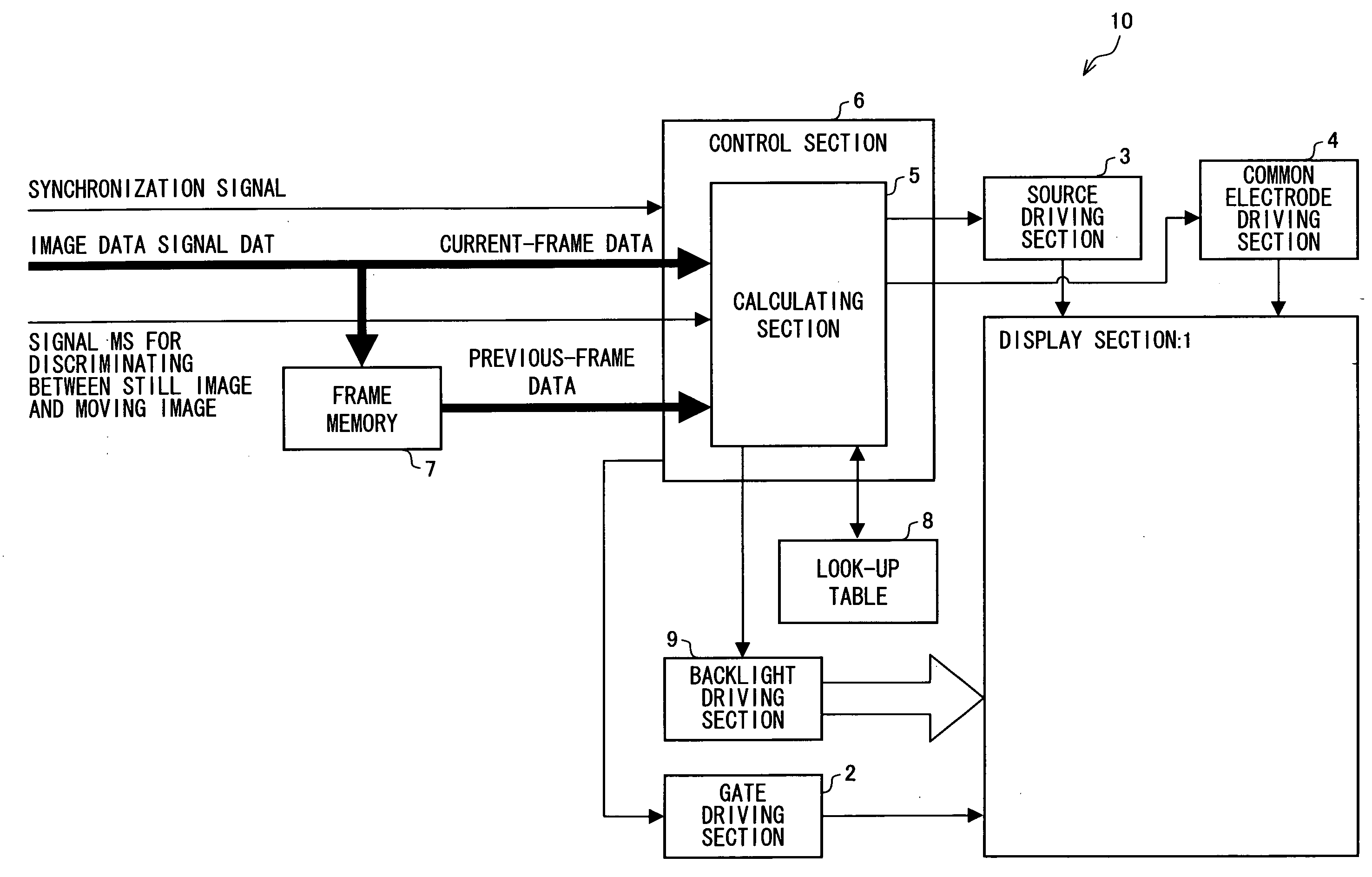

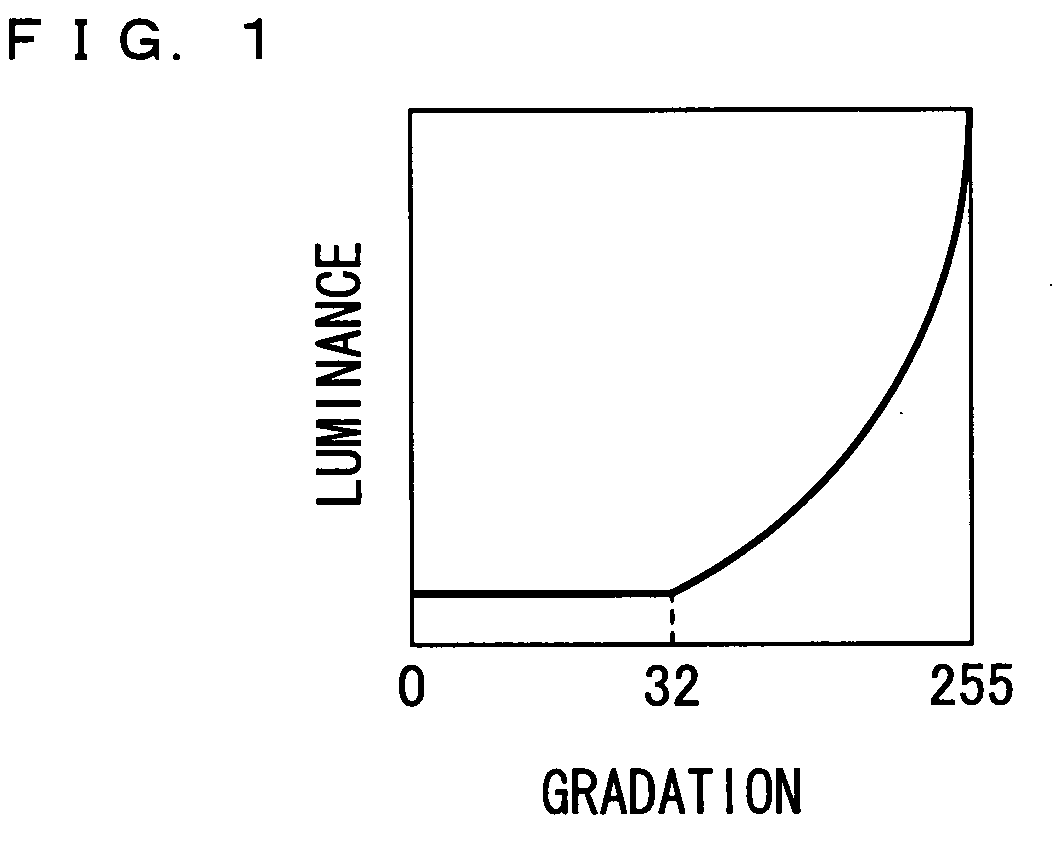

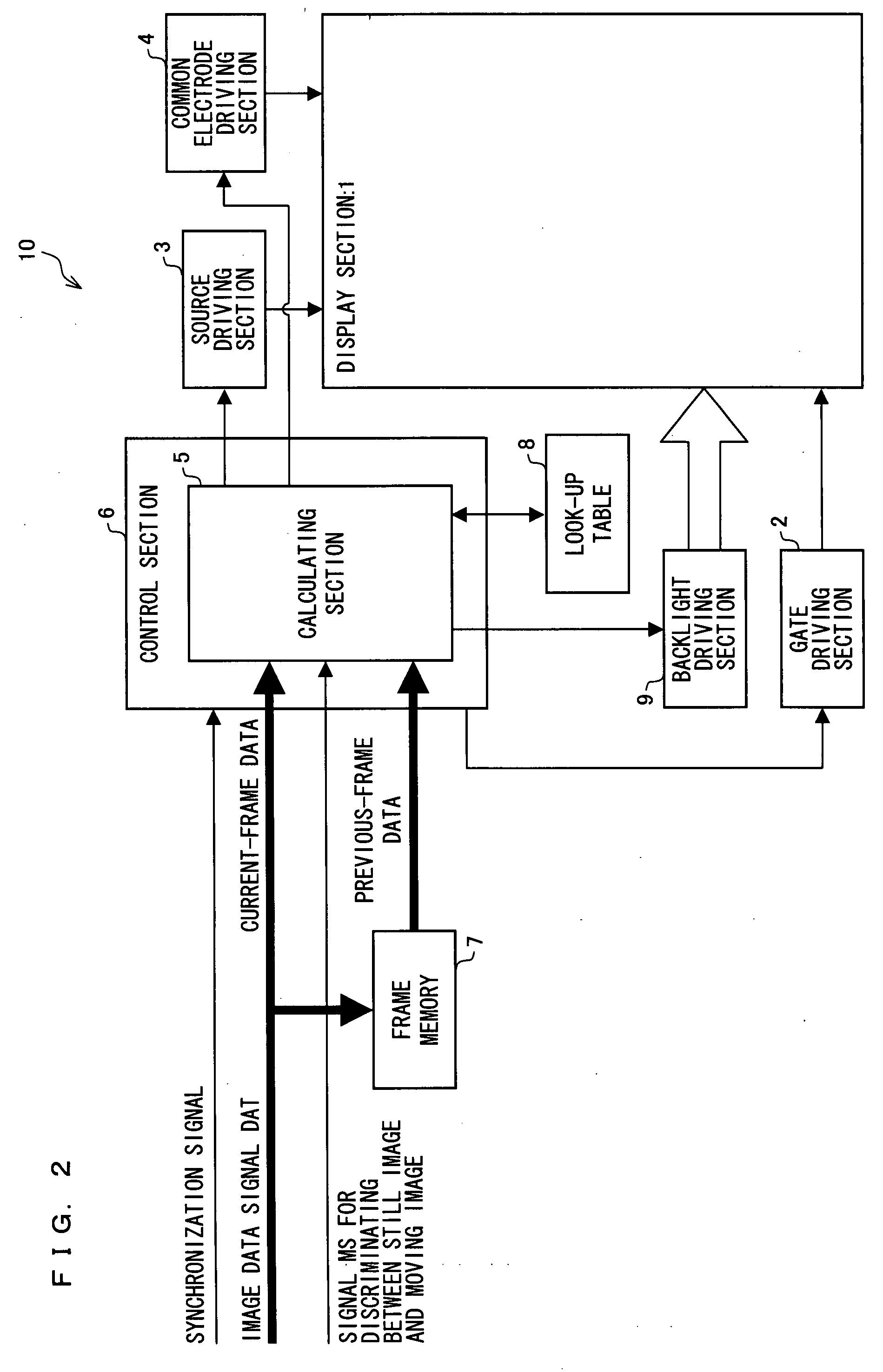

Method for driving liquid crystal display apparatus

InactiveUS20090079682A1Easily discriminatedImprove response speedCathode-ray tube indicatorsInput/output processes for data processingLiquid-crystal displayEngineering

In one embodiment of the present invention, when a still image is displayed, applied voltages respectively corresponding to a total of n (n being an integer of not less than 4) types of gradation 0 to (n−1) are outputted to pixels. On the other hand, when a moving image is displayed, an applied voltage corresponding to a predetermined gradation m (1≦m≦(n−2)) is applied to the pixels instead of applied voltages respectively corresponding to gradations of less than the predetermined gradation m.

Owner:SHARP KK

Liquid crystal display device and backlight

ActiveUS7570321B2Reduce in quantityReduce brightnessPlanar/plate-like light guidesPrinted circuitsLiquid-crystal displayLight guide

Owner:PANASONIC INTELLECTUAL PROPERTY CORP OF AMERICA +1

Display apparatus and display method

InactiveUS7295178B2Improve qualityImprove display qualityCathode-ray tube indicatorsTelephone set constructionsImage displayComputer science

Owner:SHARP KK

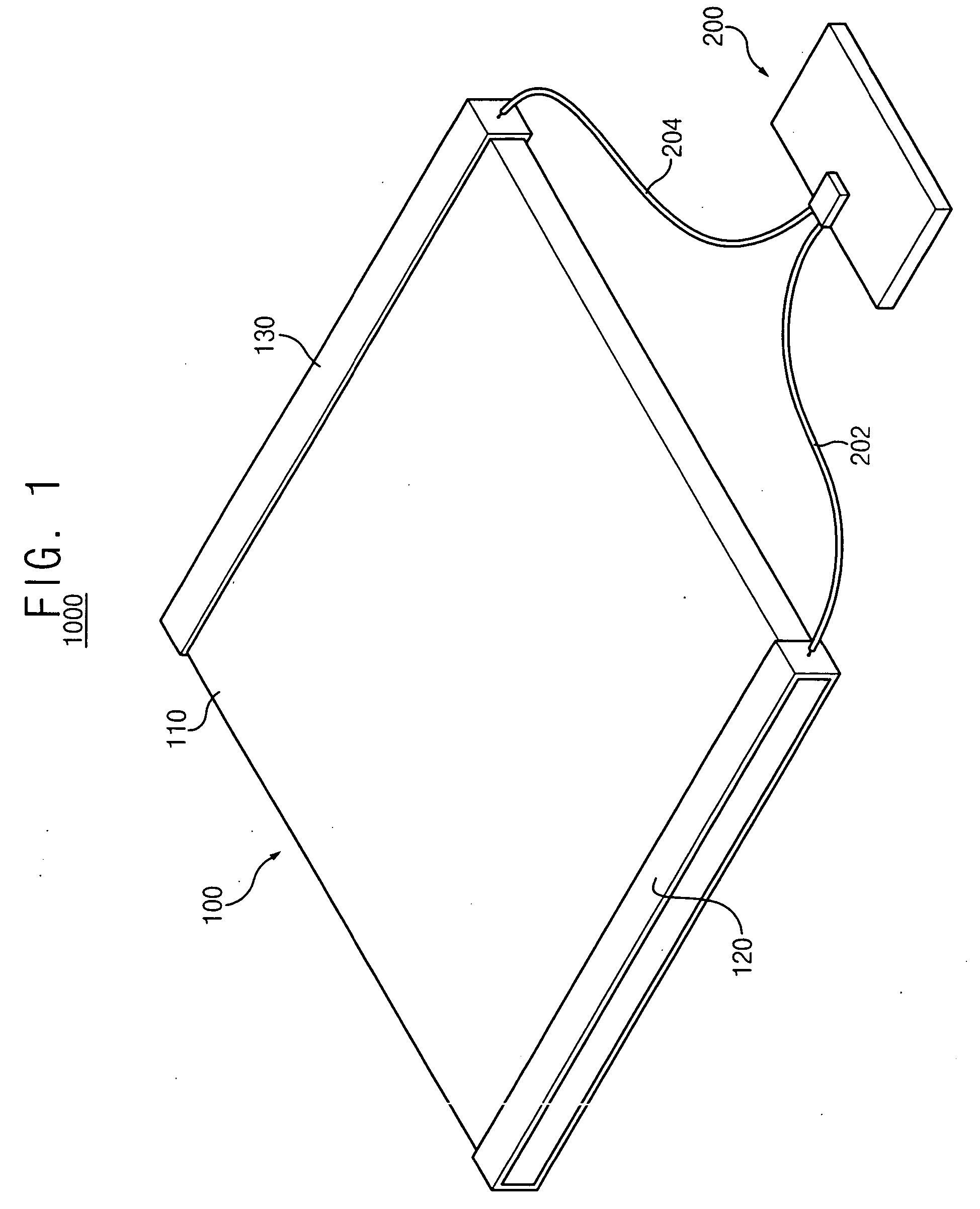

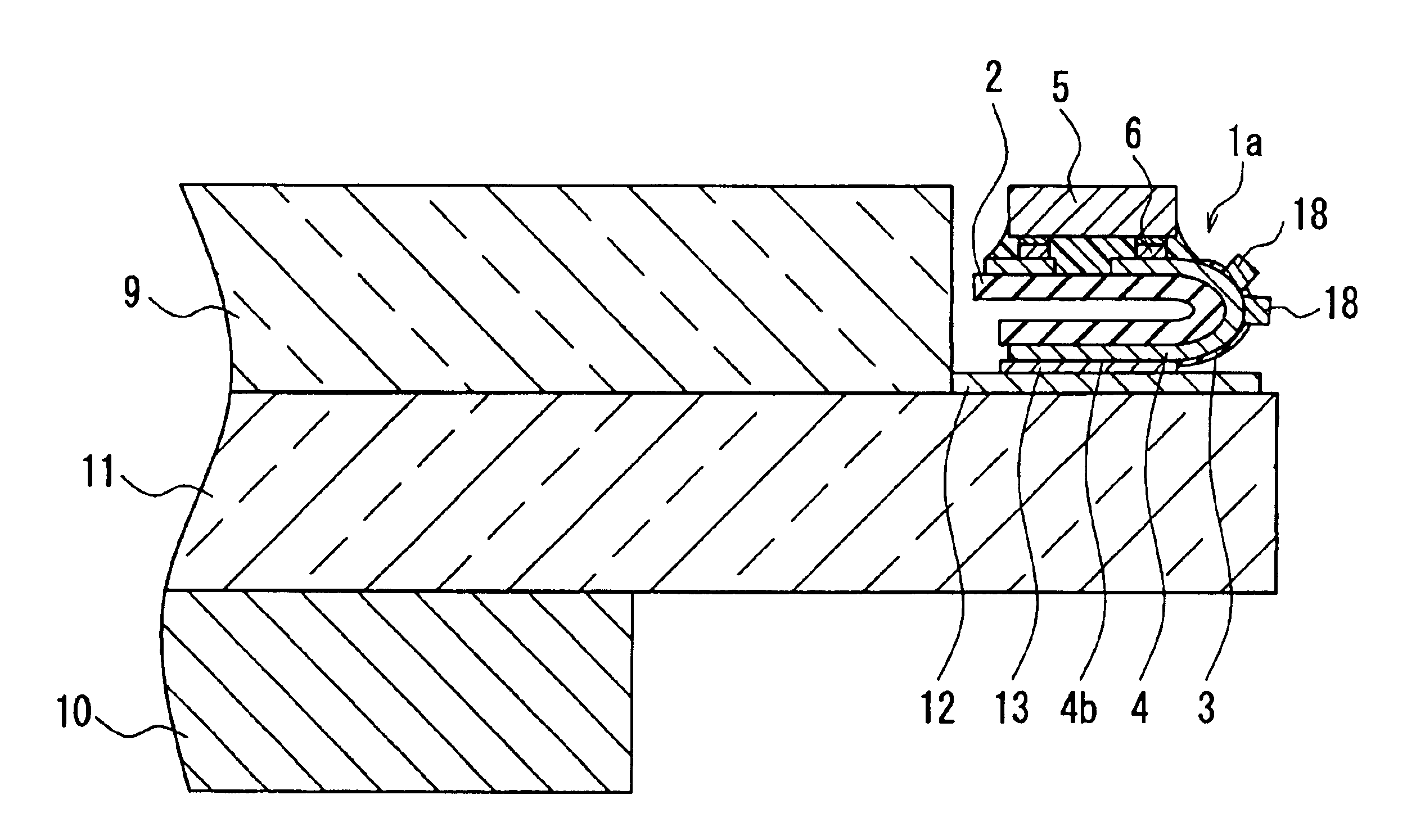

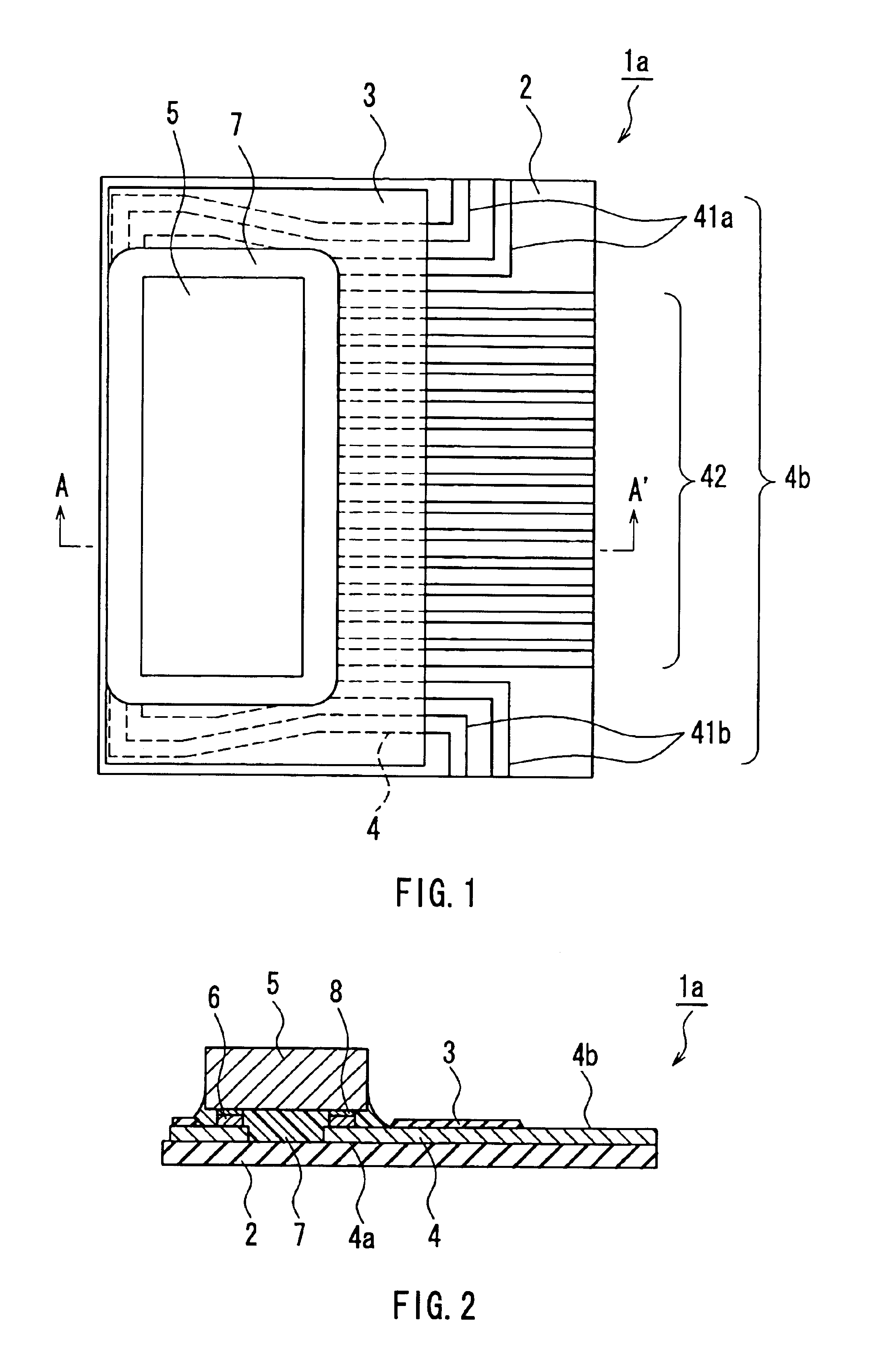

Semiconductor device with folded film substrate and display device using the same

ActiveUS6956288B2Low costReduce influence of its heat generationSemiconductor/solid-state device detailsSolid-state devicesDevice materialDisplay device

A semiconductor device to be mounted on an external electronic device includes a film substrate on which wiring electrodes are formed, the wiring electrodes being partially covered with a covering member; and a semiconductor chip mounted on the film substrate. In this semiconductor device, the film substrate is folded so that at least one edge of the film substrate is on a side opposite to a side on which the semiconductor chip is mounted, and portions of the wiring electrodes exposed from the covering member on a surface of the film substrate on which the semiconductor chip is mounted are to be connected to electrodes of an external electronic device.

Owner:TESSERA ADVANCED TECH

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com