Time-to-digital converter for measuring decimal phase error of all-digital phase-locked loop

An all-digital phase-locked loop, phase error technology, applied in the direction of automatic power control, electrical components, etc., can solve problems such as deteriorating the resolution and linearity of time-to-digital converters, increasing power consumption and module area, and process evolution violations. , to achieve the effect of saving power consumption, saving chip area and wide measurement range

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

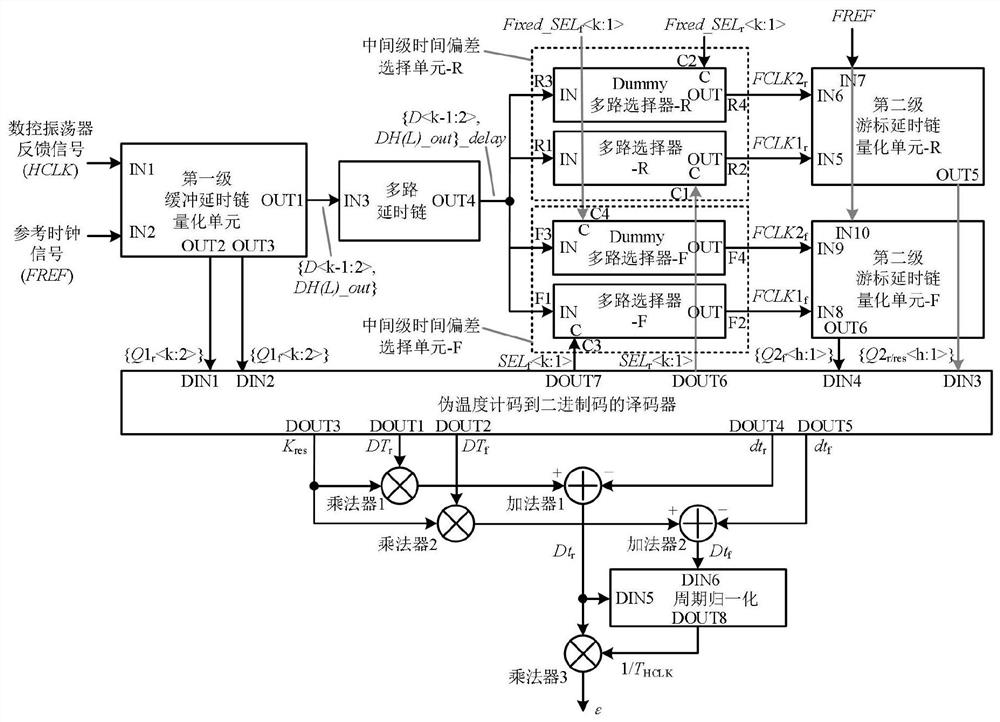

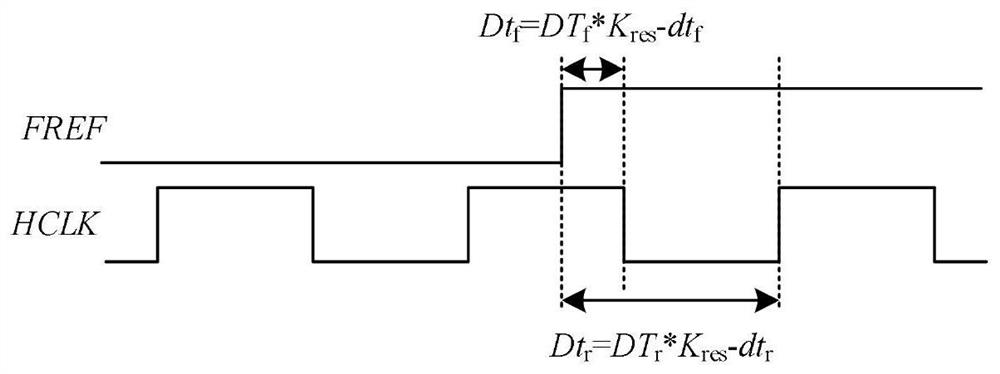

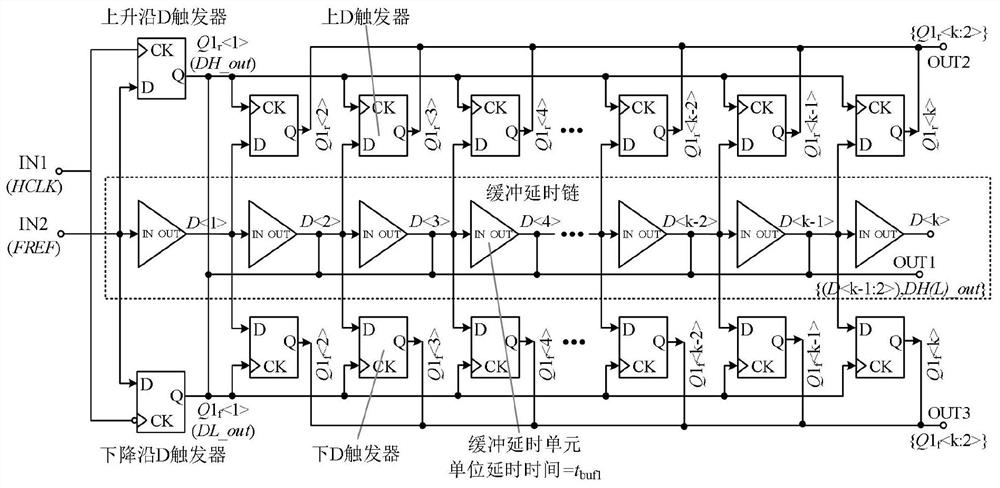

[0033] see figure 1 , the present invention is based on the cascade structure of the buffer delay chain and the vernier delay chain, including a core quantization unit and a decoding unit, and the core quantization unit includes a first-level buffer delay chain quantization unit, a multi-way delay chain, and an intermediate stage time The deviation selection unit and the second-stage vernier delay chain quantization unit; the decoding unit includes a decoder from pseudo-thermometer code to binary code, a logic operation unit and a cycle normalization unit. The input terminals IN1 and IN2 of the quantization unit of the first-stage buffer delay chain are respectively connected to the numerically controlled oscillator feedback signal HCLK and the reference clock signal FREF, and the output terminal OUT1 is for each stage of the buffer delay unit from the second stage to the k-1th stage output signal D (i=2,3,...,k-1) and the extracted HCLK rising edge / falling edge signal DH(...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More