Patents

Literature

81results about How to "Increased cost of testing" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

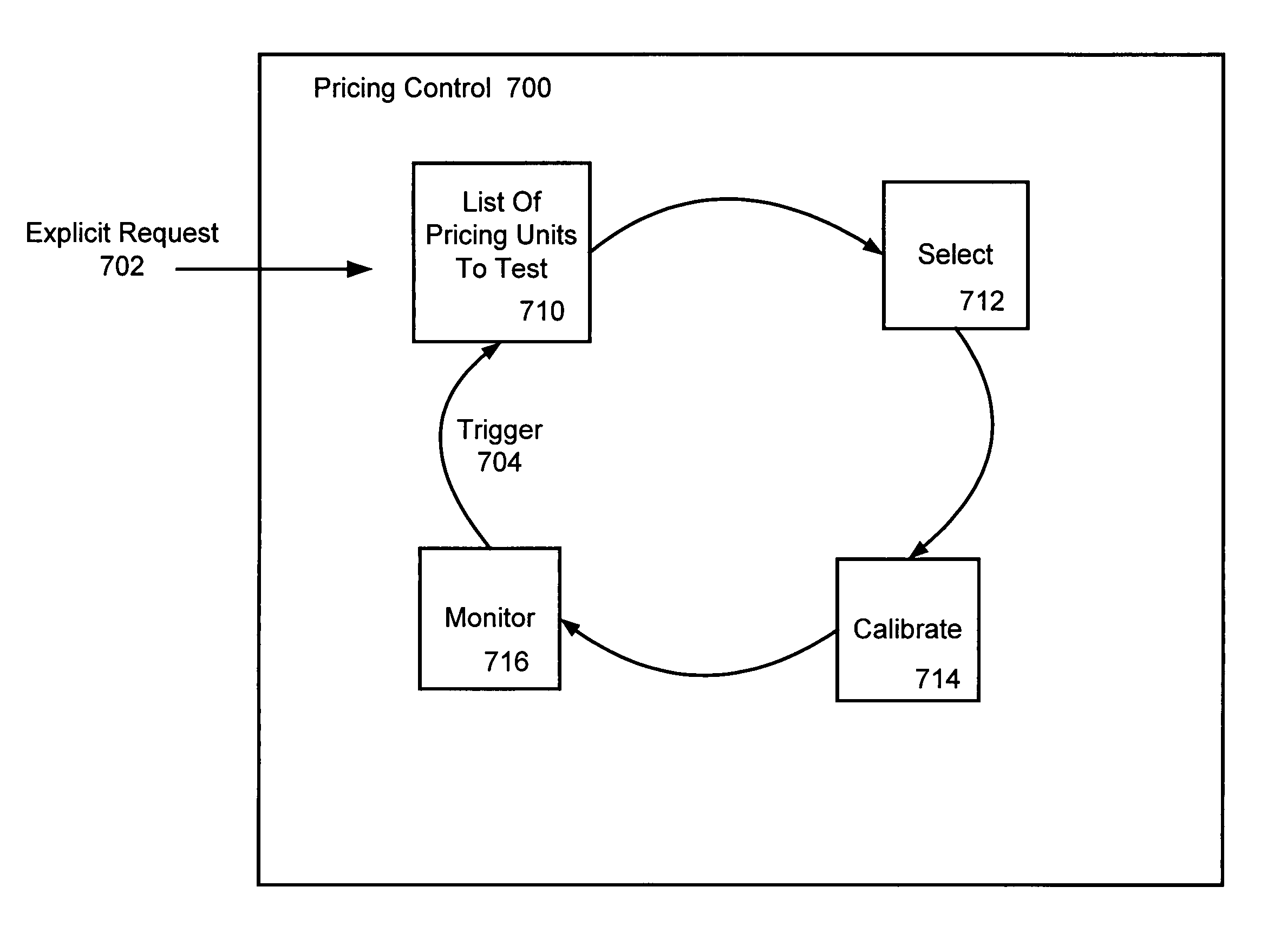

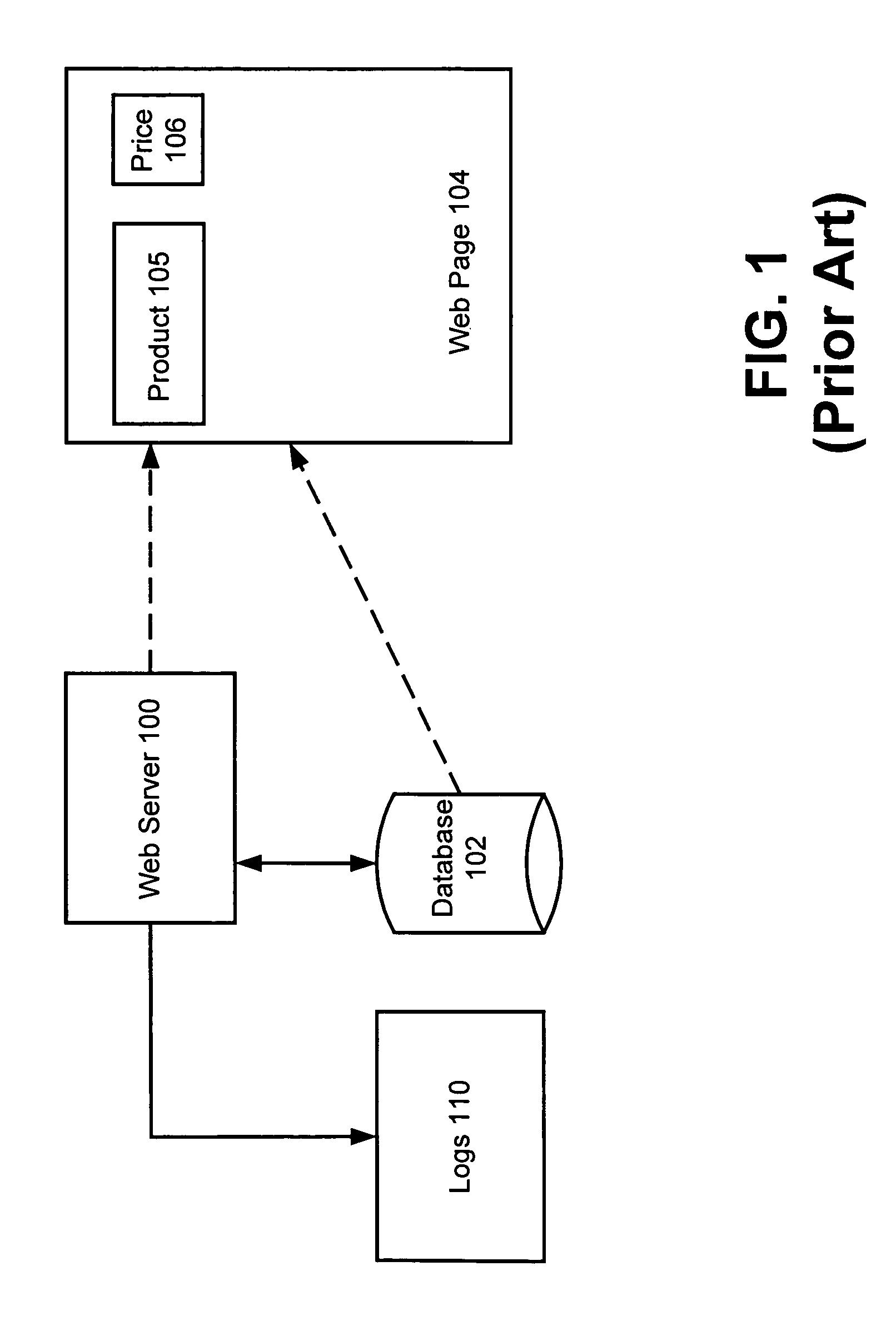

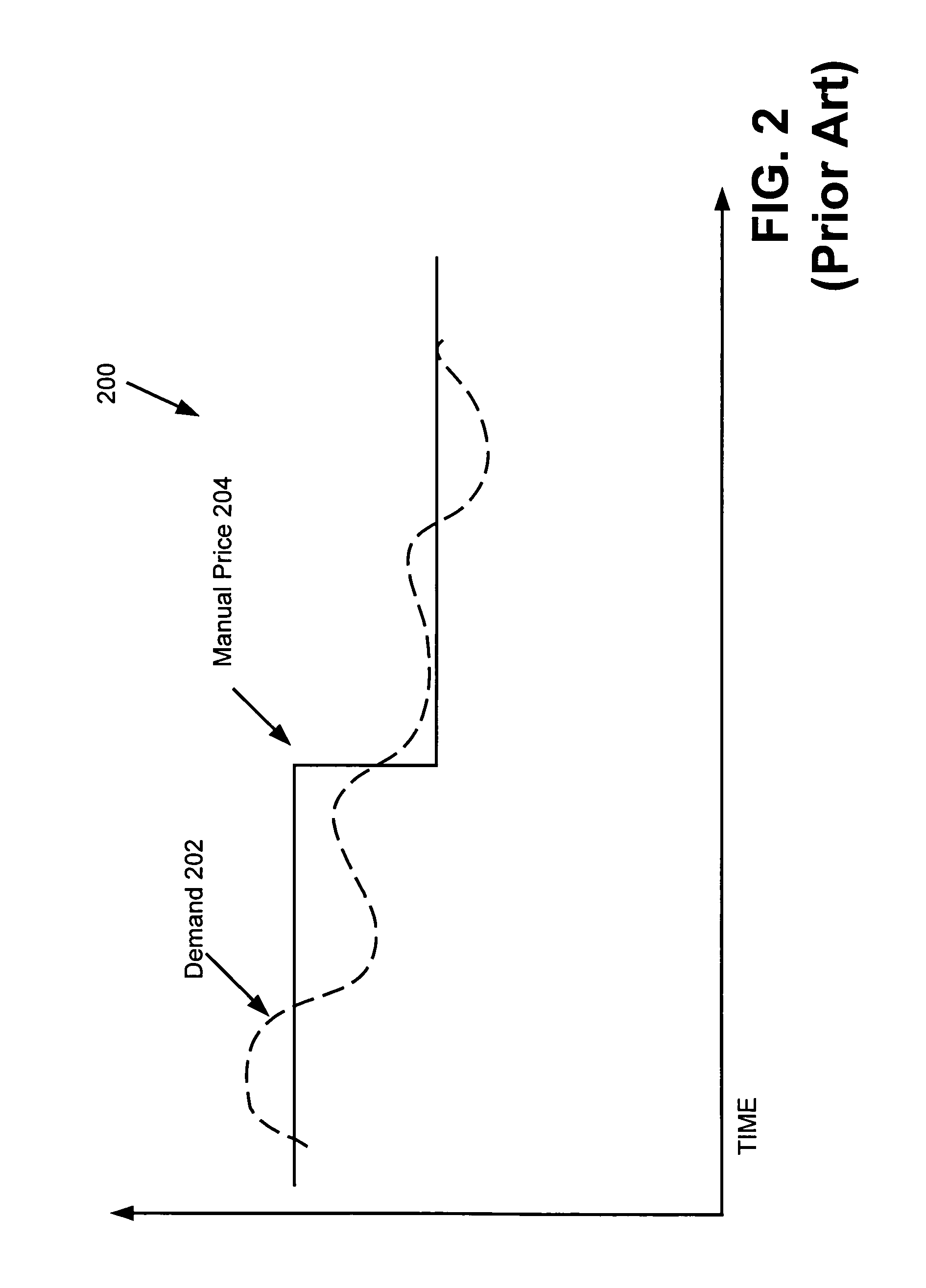

Method and apparatus for automatic pricing in electronic commerce

InactiveUS7970713B1Increased cost of testingReduce testing costsMarket predictionsBuying/selling/leasing transactionsE-commerceMajorization minimization

Owner:OIP TECH

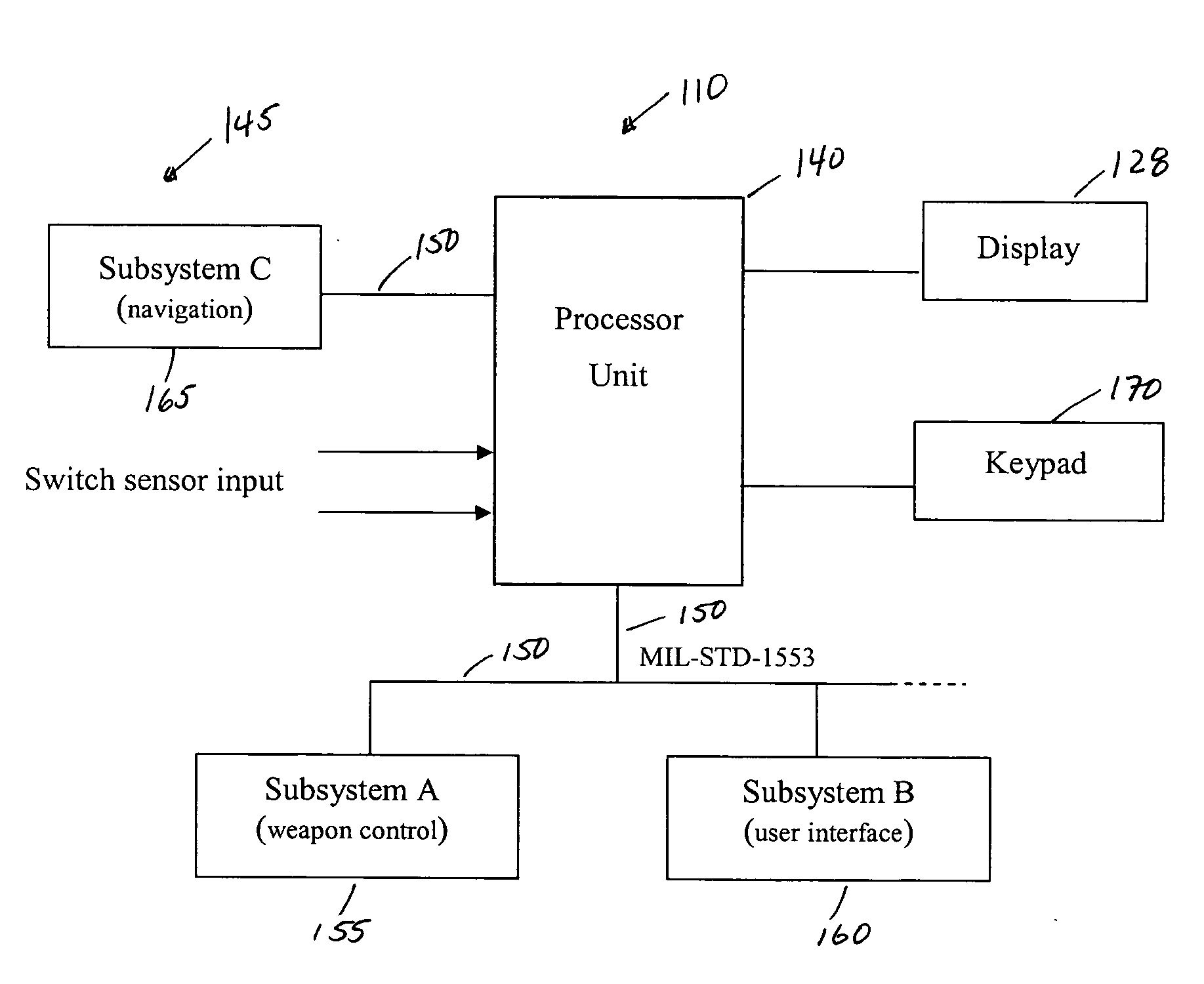

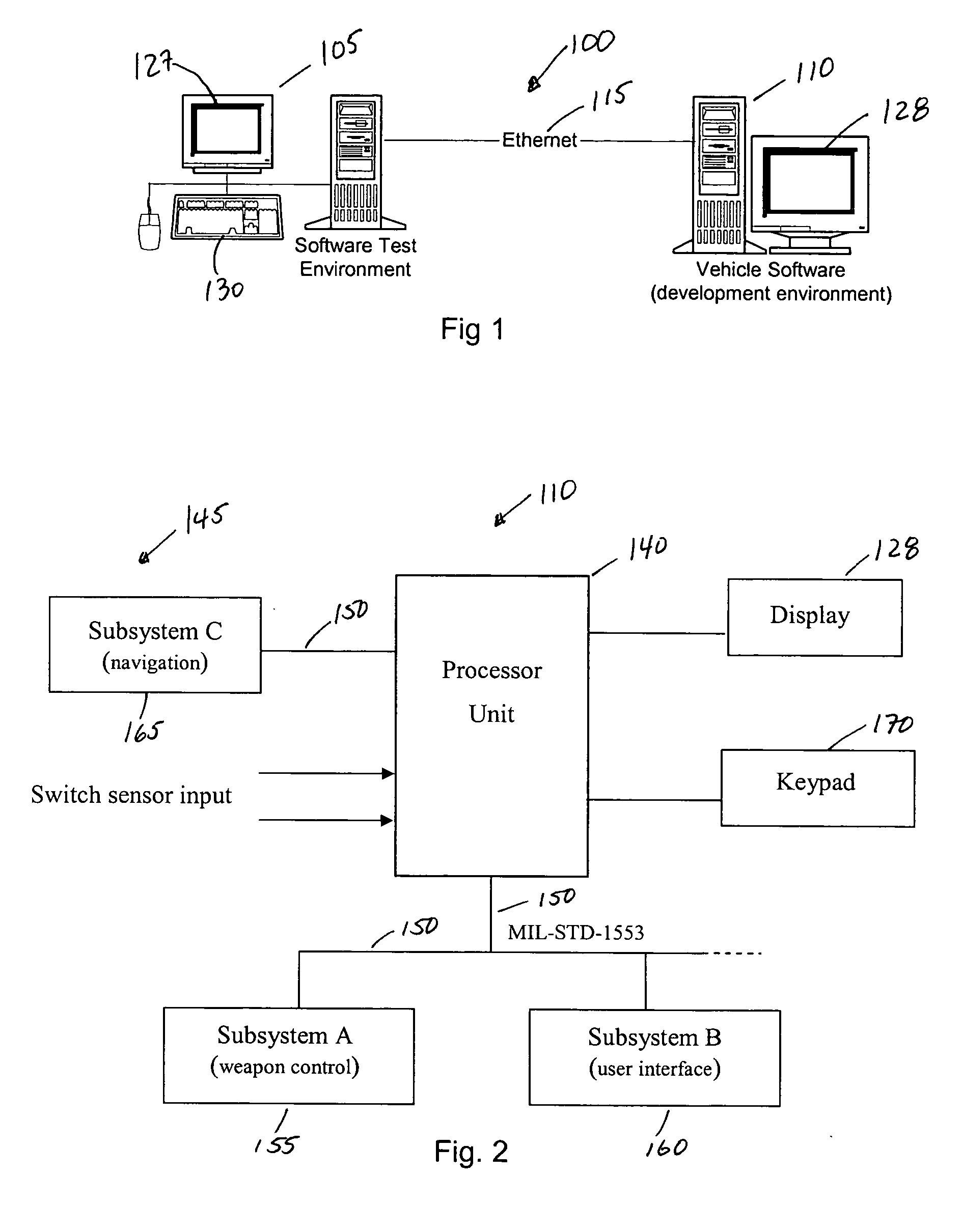

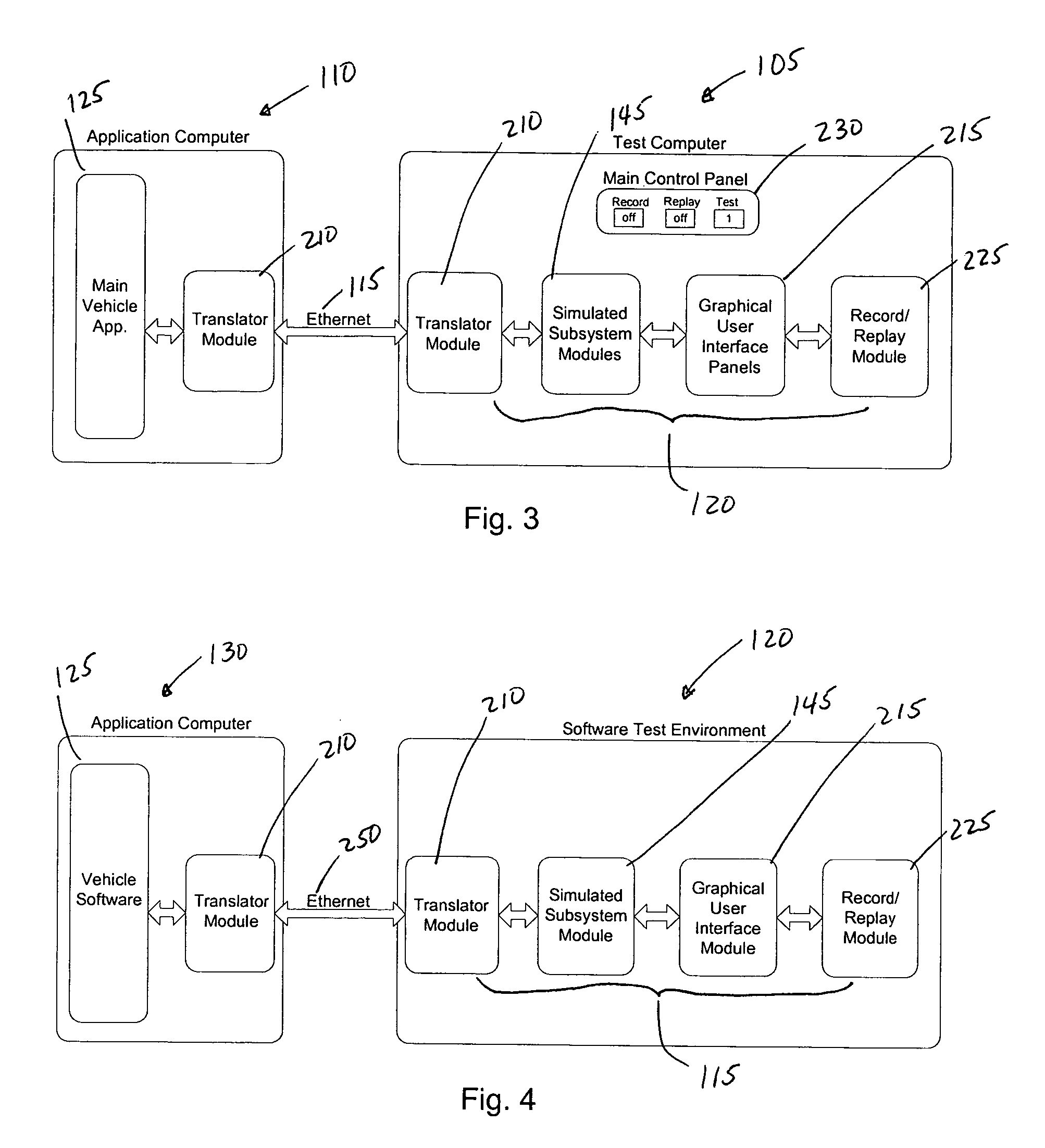

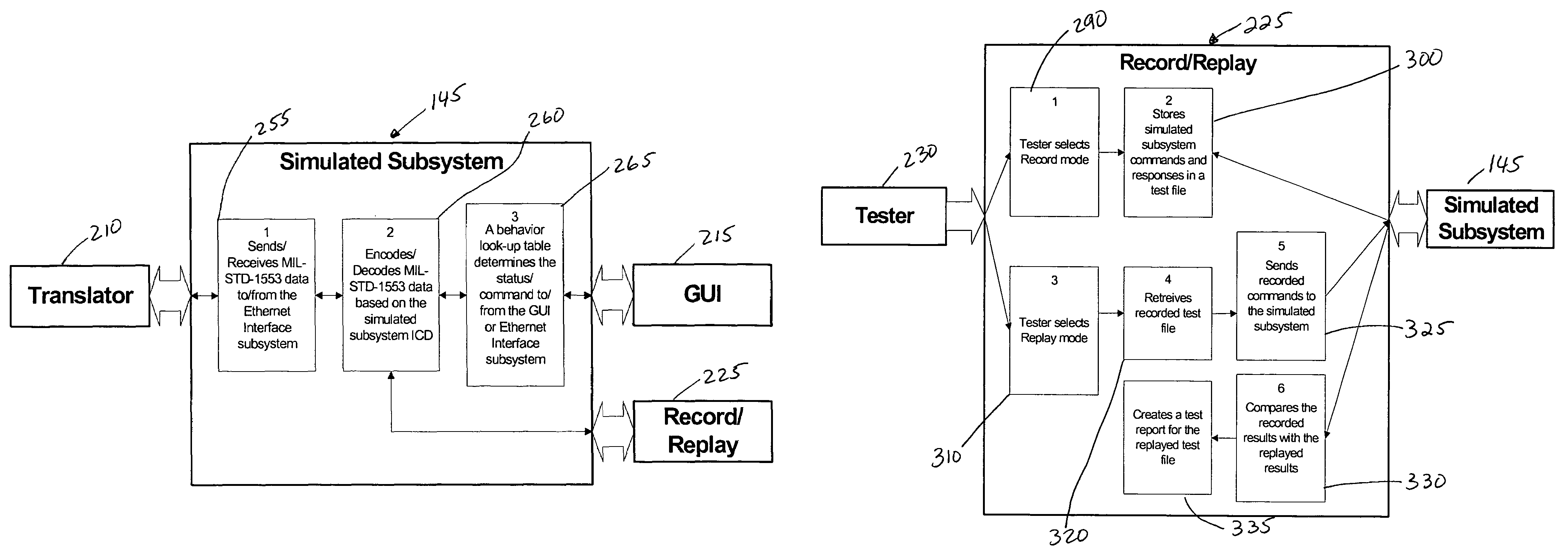

Software test environment for regression testing ground combat vehicle software

InactiveUS20060212540A1Increase software test coverageEffective supportError detection/correctionMultiple digital computer combinationsInteractive testingRegression testing

A STE for automated testing of ground combat vehicle software application to validate vehicle software logic provides a system and method to conduct interactive (manual) testing of the vehicle software while under development, record information related to the interactive testing activities, including but not limited to tester inputs and expected outcomes, and perform automated testing of the combat vehicle software application using the recorded information. Preferably, reconfiguration of the STE to support changes that arise due to the evolution of the combat vehicle software application system and the subsystems under control of the evolving software system is provided.

Owner:BAE SYSTEMS LAND & ARMAMENTS LP

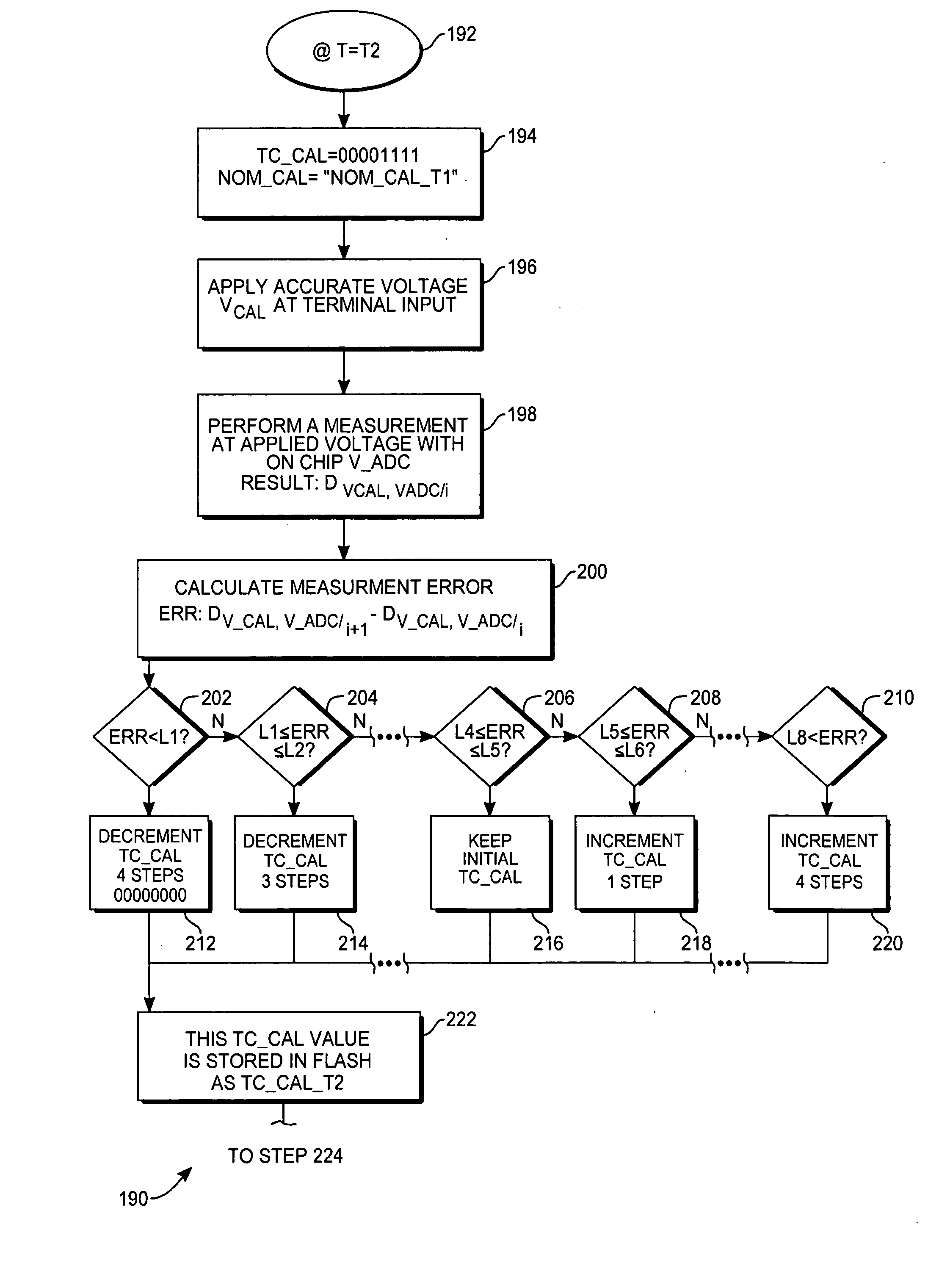

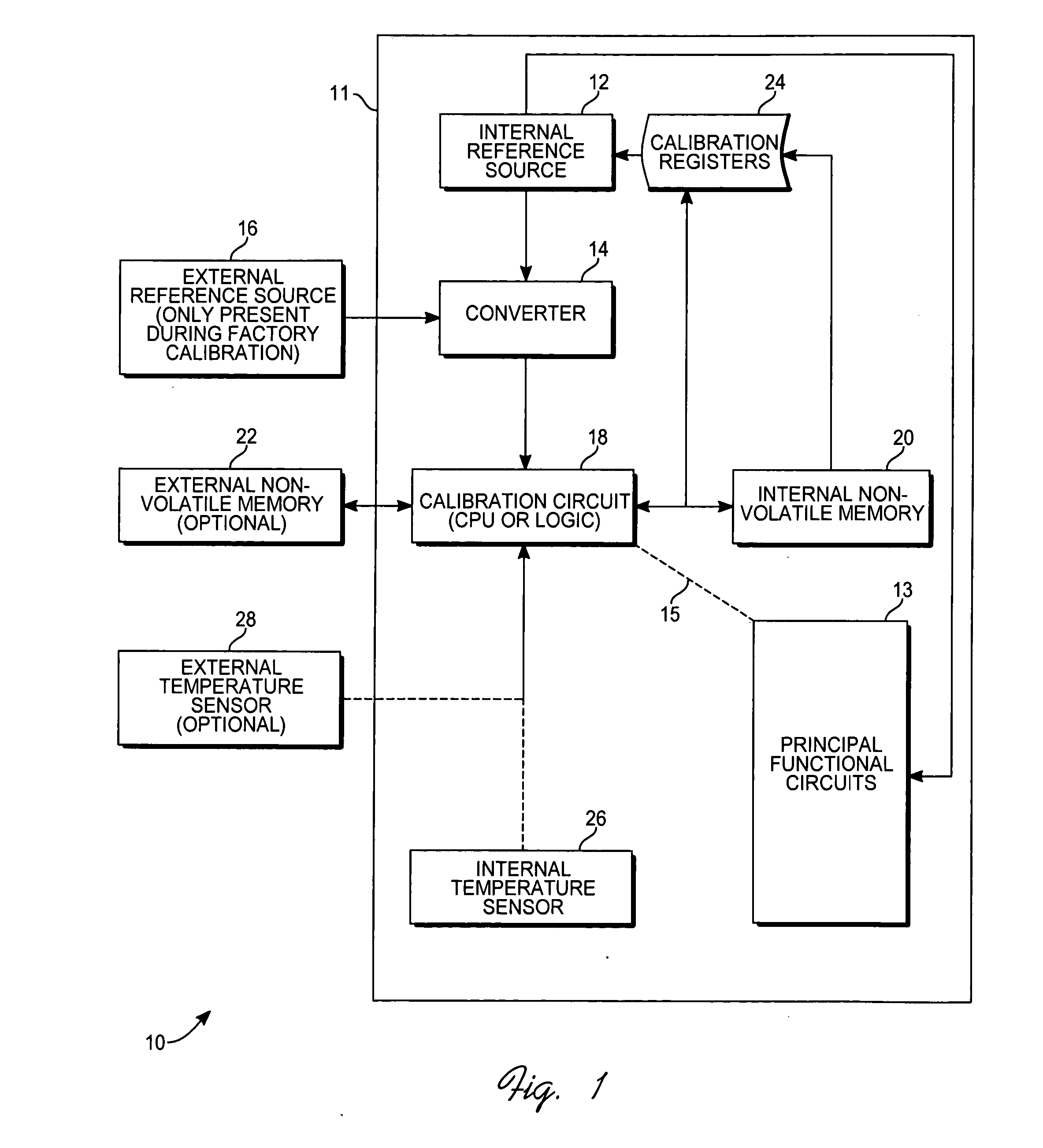

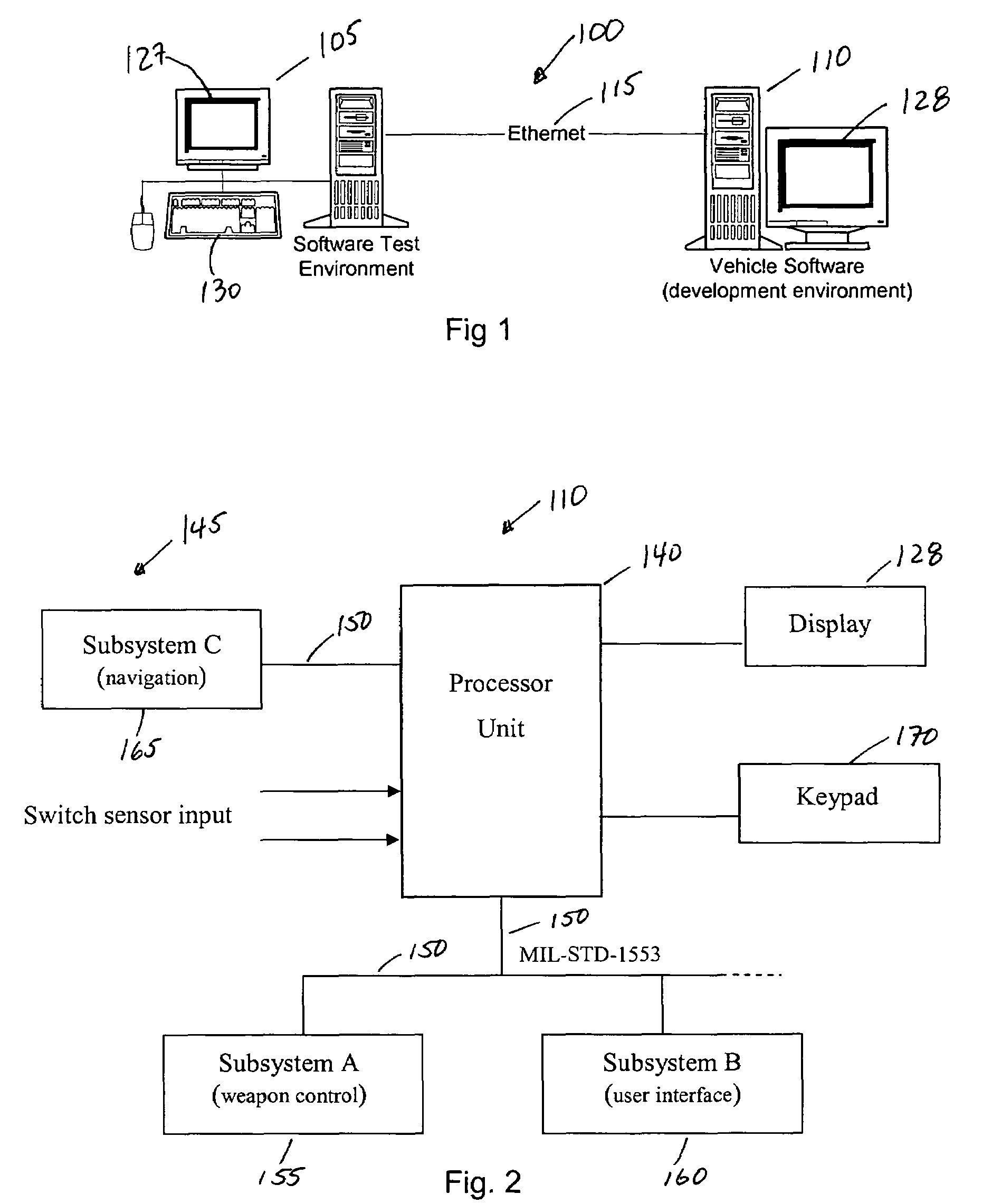

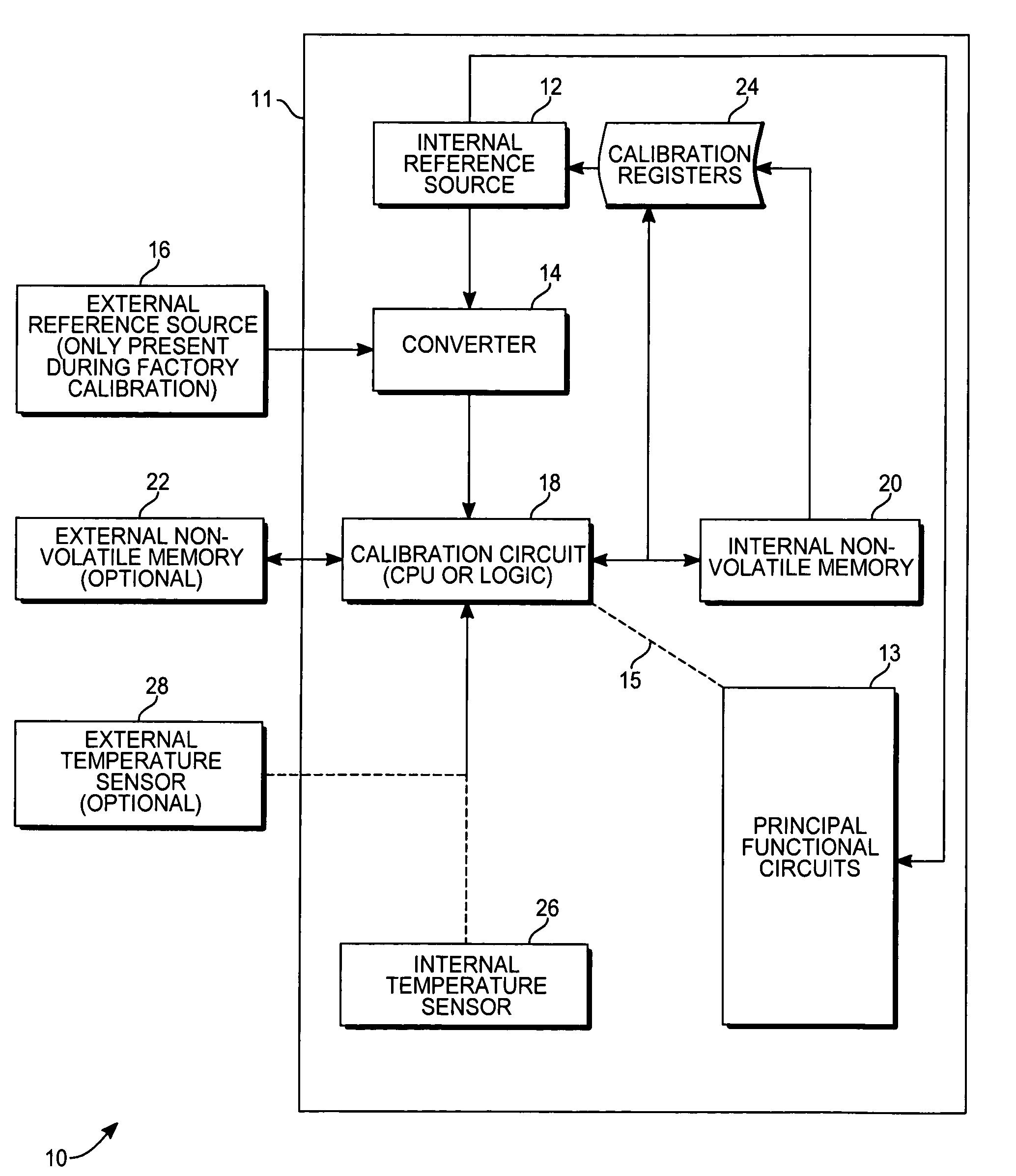

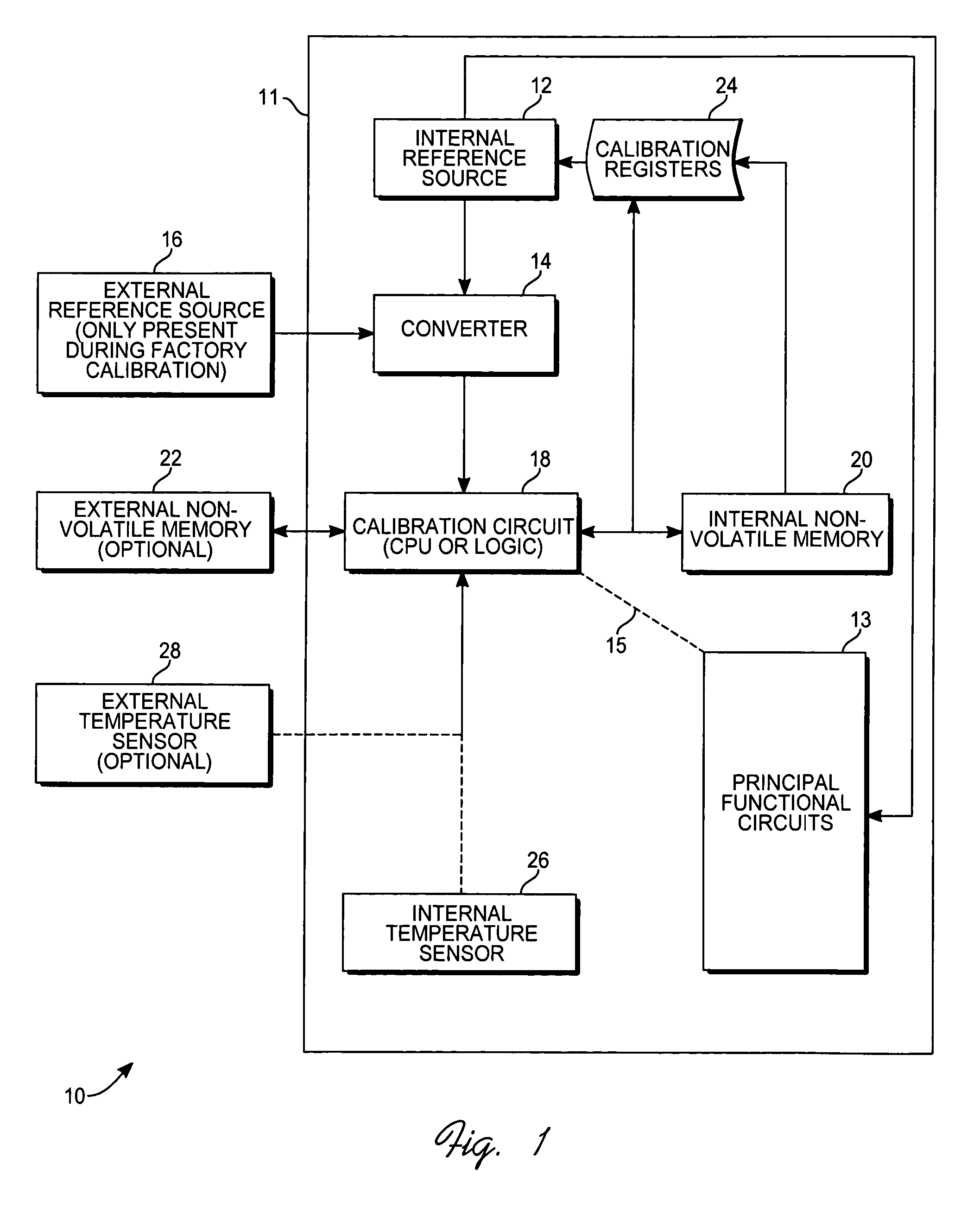

Method and apparatus of temperature compensation for integrated circuit chip using on-chip sensor and computation means

ActiveUS20050197795A1Shorten test timeMinimize temperature driftThermometer detailsThermometers using material expansion/contactionReference circuitIntegrated circuit

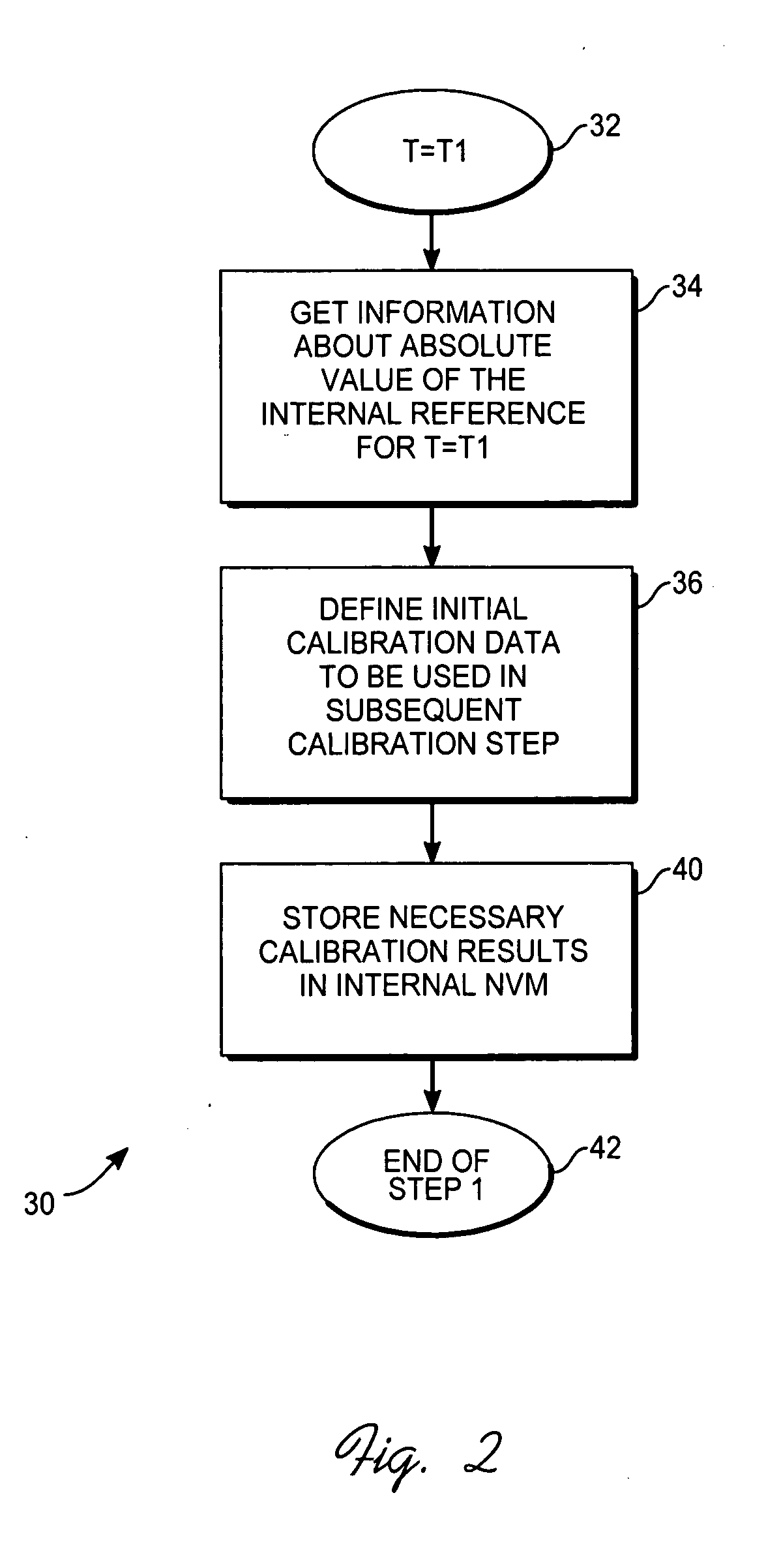

A method and apparatus of temperature compensation for an integrated circuit using on-chip circuits, sensors, and an algorithm. The chip includes an on-chip reference circuit, an on-chip sensor measuring a parameter relative to the reference, and an on-chip computation means for processing an algorithm. A supplemental off-chip reference circuit is also used. The algorithm carries out the following steps: (A) performing a first calibration of an internal reference residing in an integrated circuit system on-chip at a first (higher) temperature at a first testing site, and (B) utilizing calibration data obtained at the step (A) to perform a second calibration of the internal reference source residing on the integrated system on-chip at a second (lower) temperature at a second testing site.

Owner:ATMEL CORP

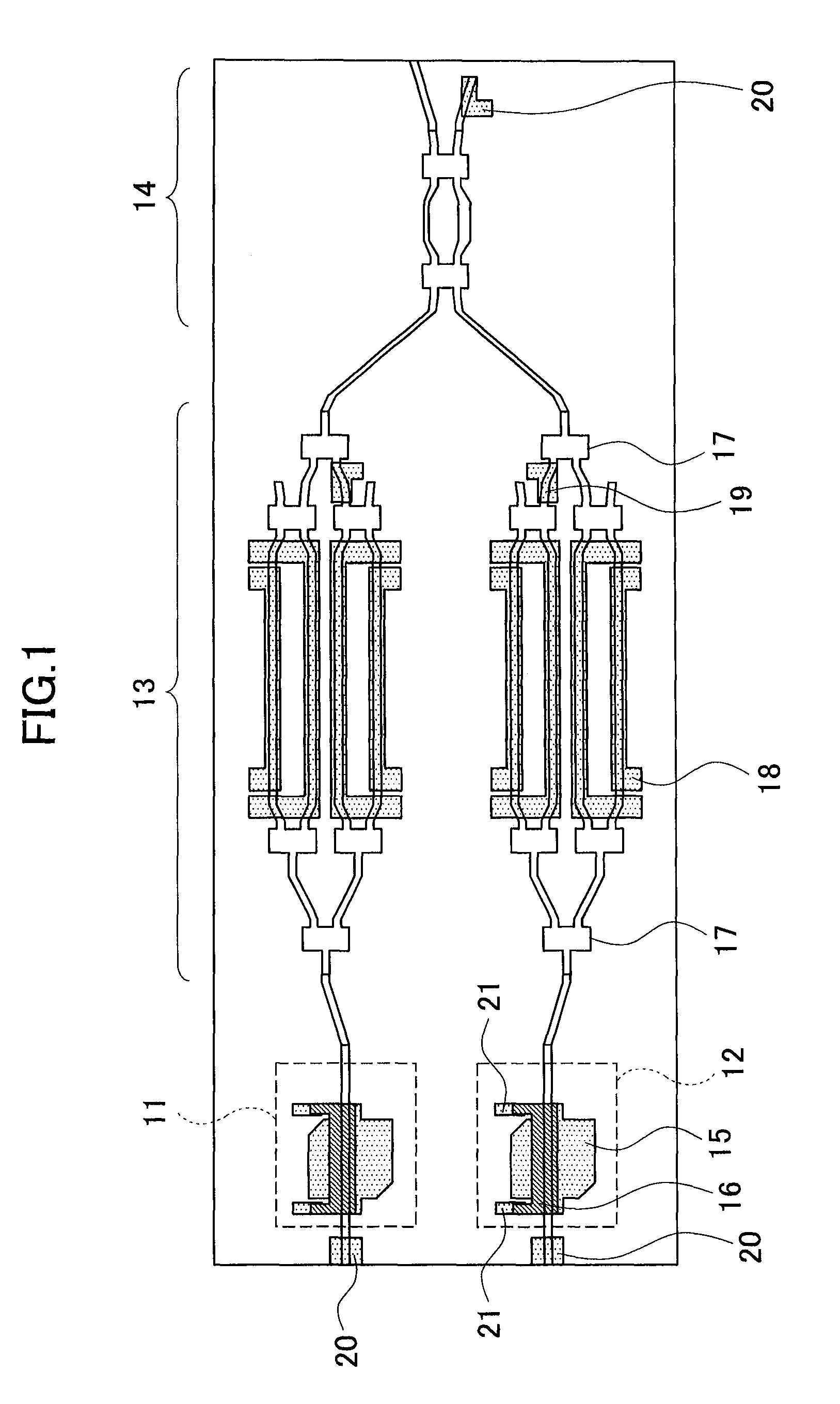

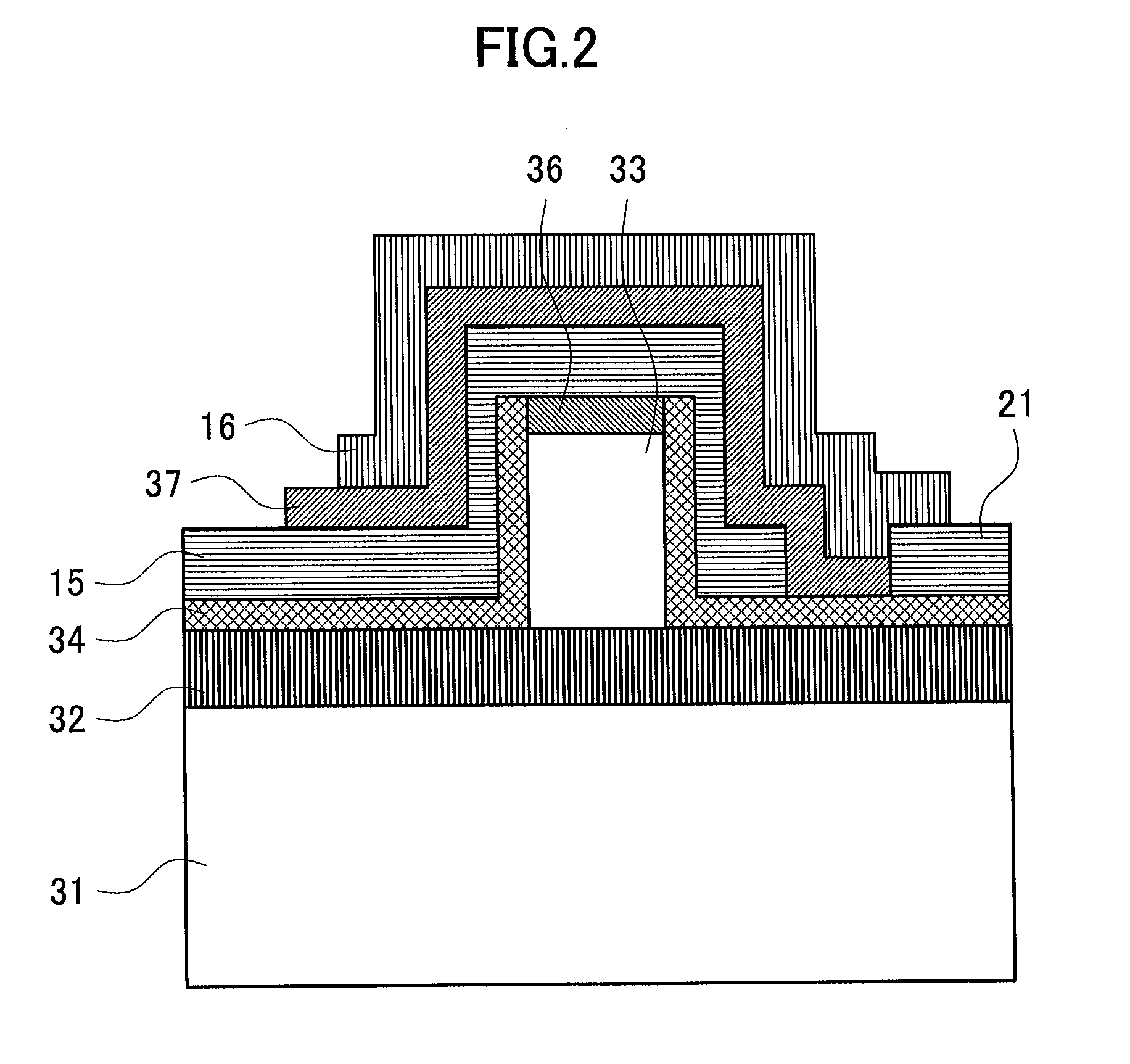

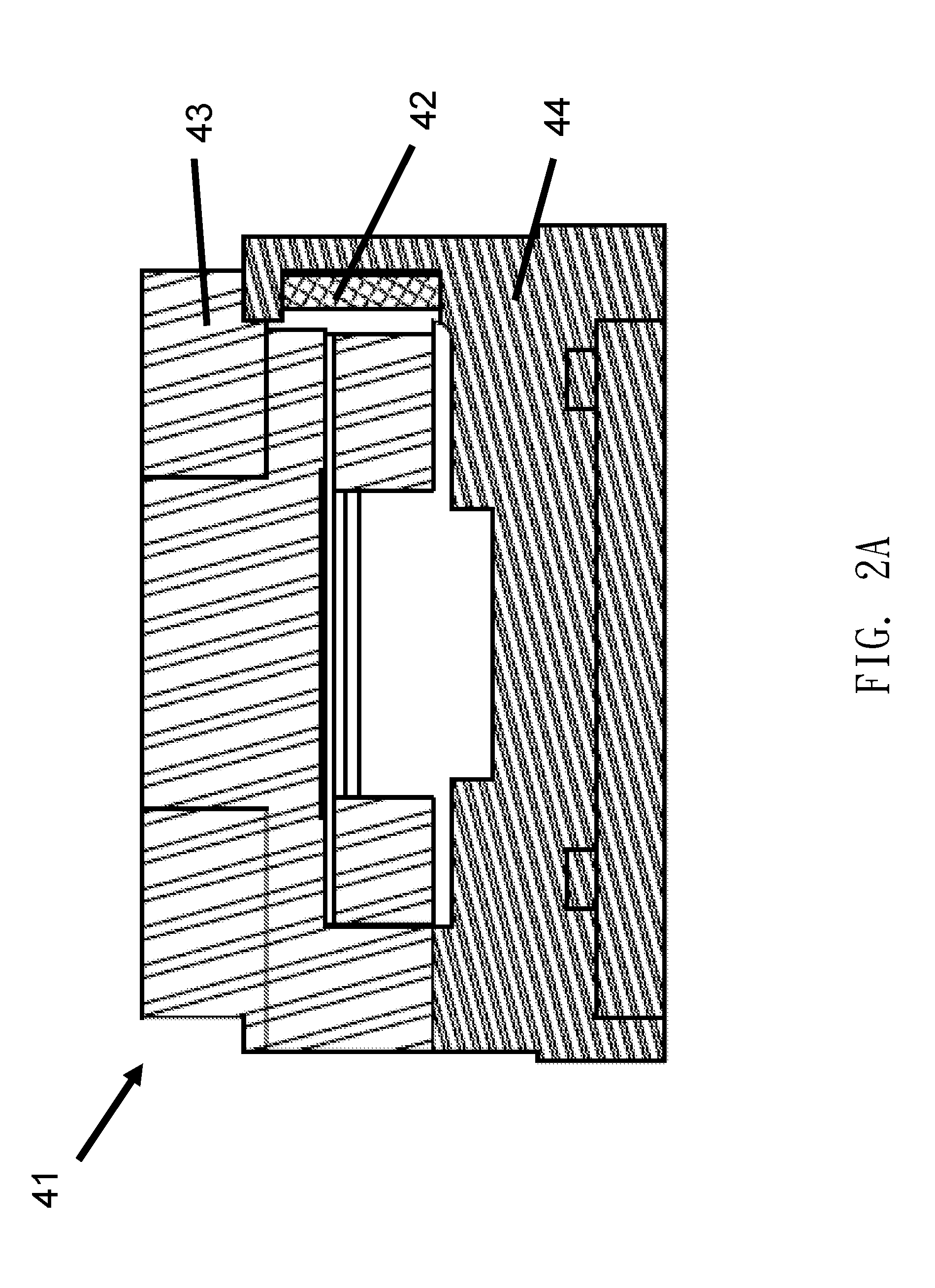

Optical semiconductor modulator device and optical module

ActiveUS20130209021A1Improve featuresHigh Polarization Extinction RatioOptical light guidesNon-linear opticsOptical ModuleMultiplexer

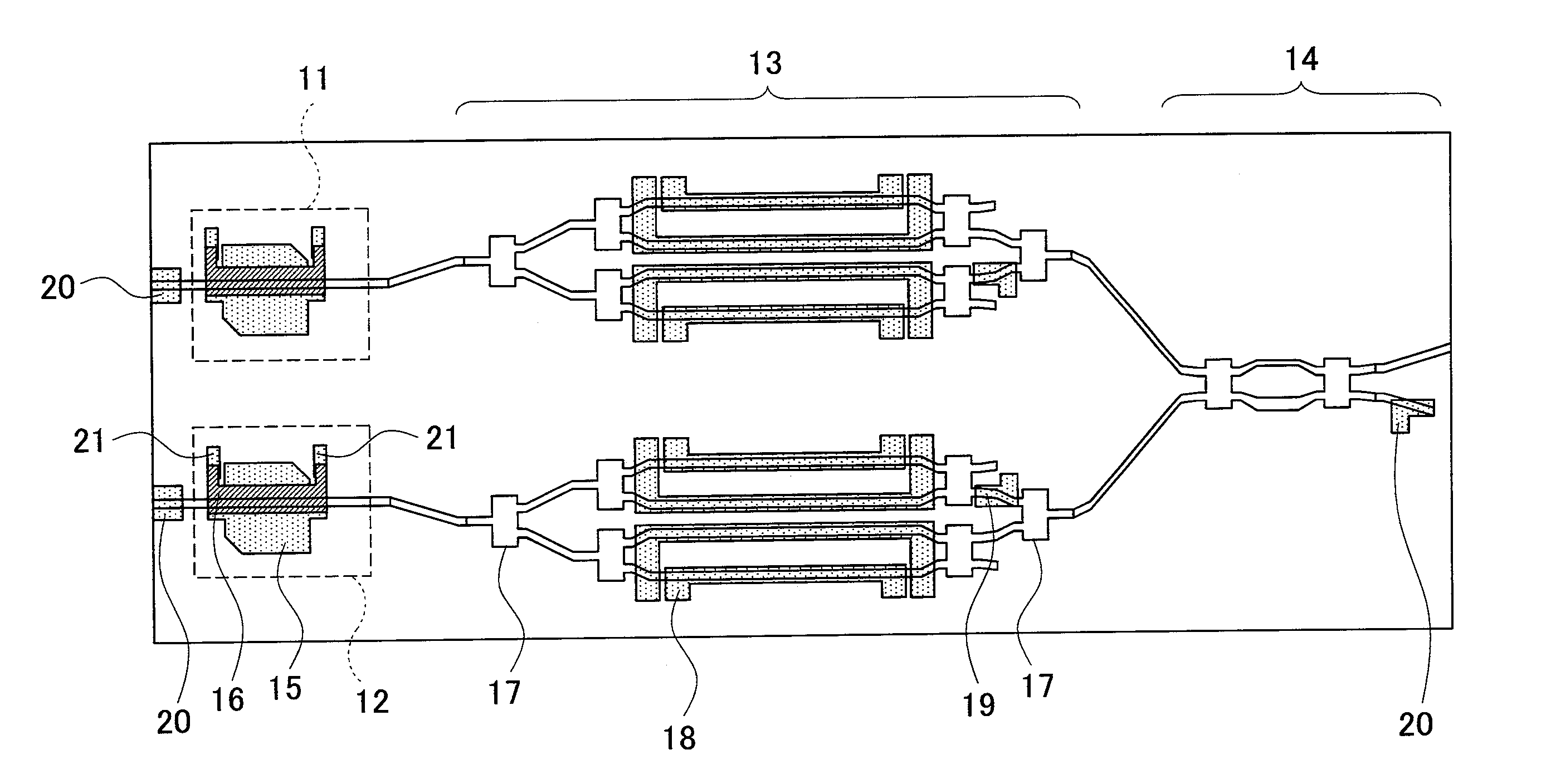

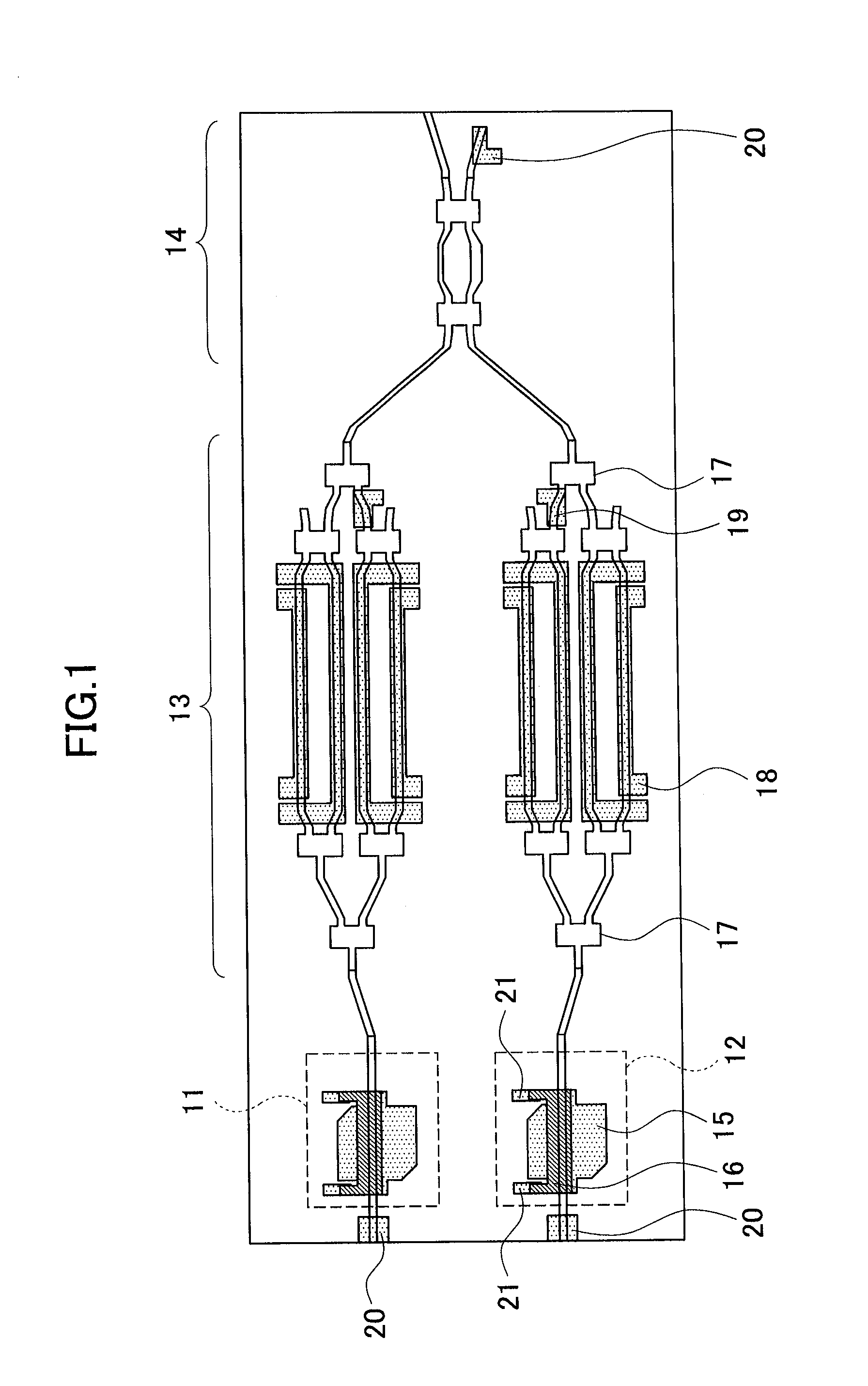

In an optical semiconductor device related to the present invention, a first light source outputting light having a first polarization, a second light source outputting light having a second polarization, a first optical modulator being optically connected to an output side of the first light source and modulating the light that is output from the first light source to output a light signal, a second optical modulator being optically connected to an output side of the second light source and modulating the light that is output from the second light source to output a light signal, and an optical multiplexer coupling the light signal that is output from the first optical modulator with the light signal that is output from the second optical modulator to output a coupled light signal, are integrated on a semiconductor substrate together.

Owner:LUMENTUM JAPAN INC

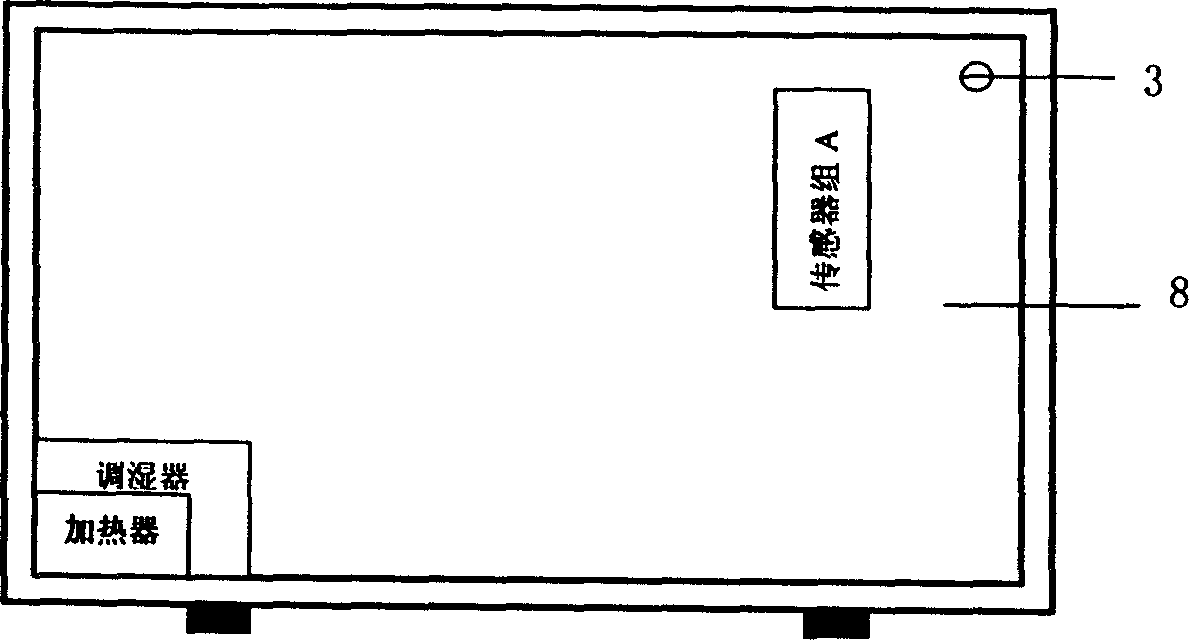

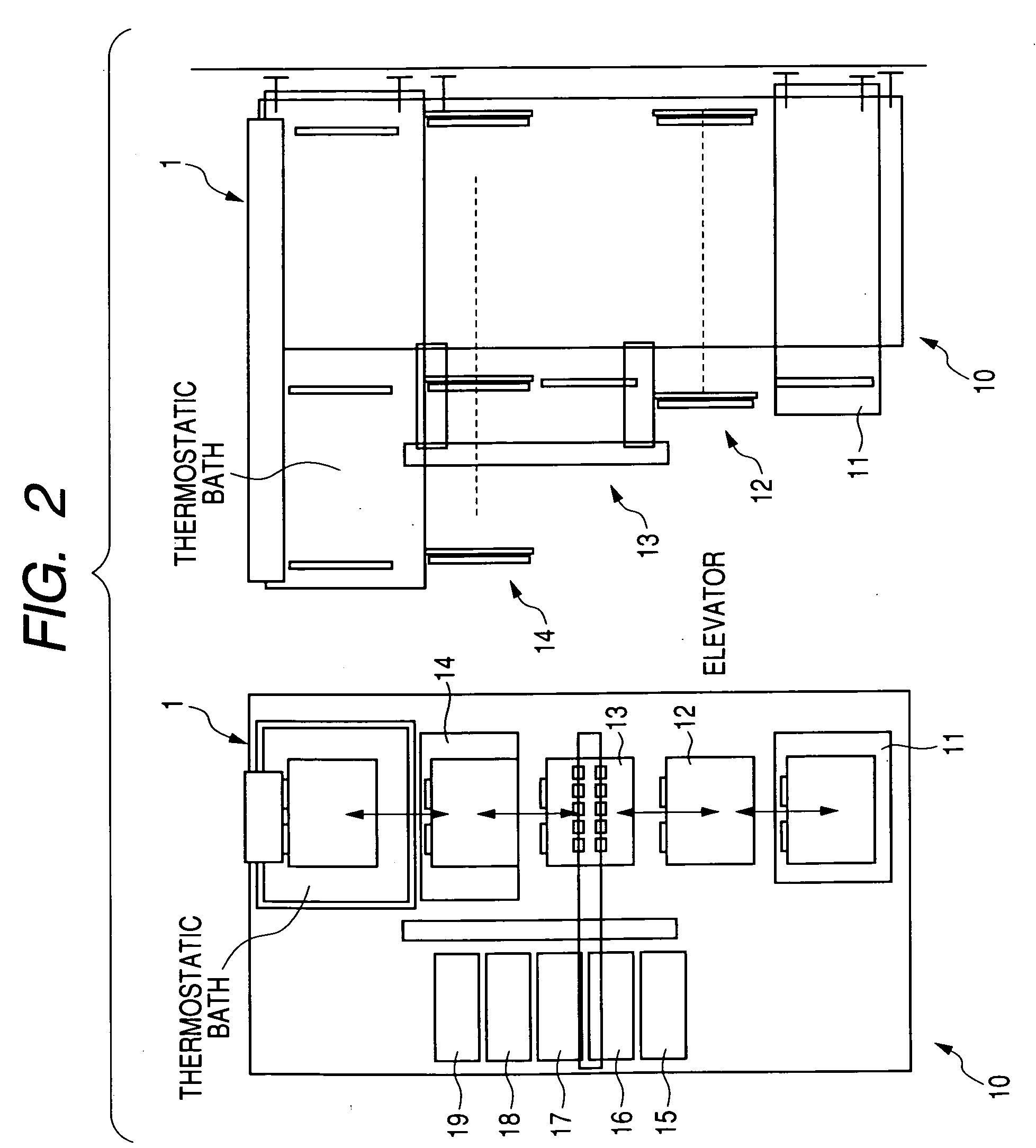

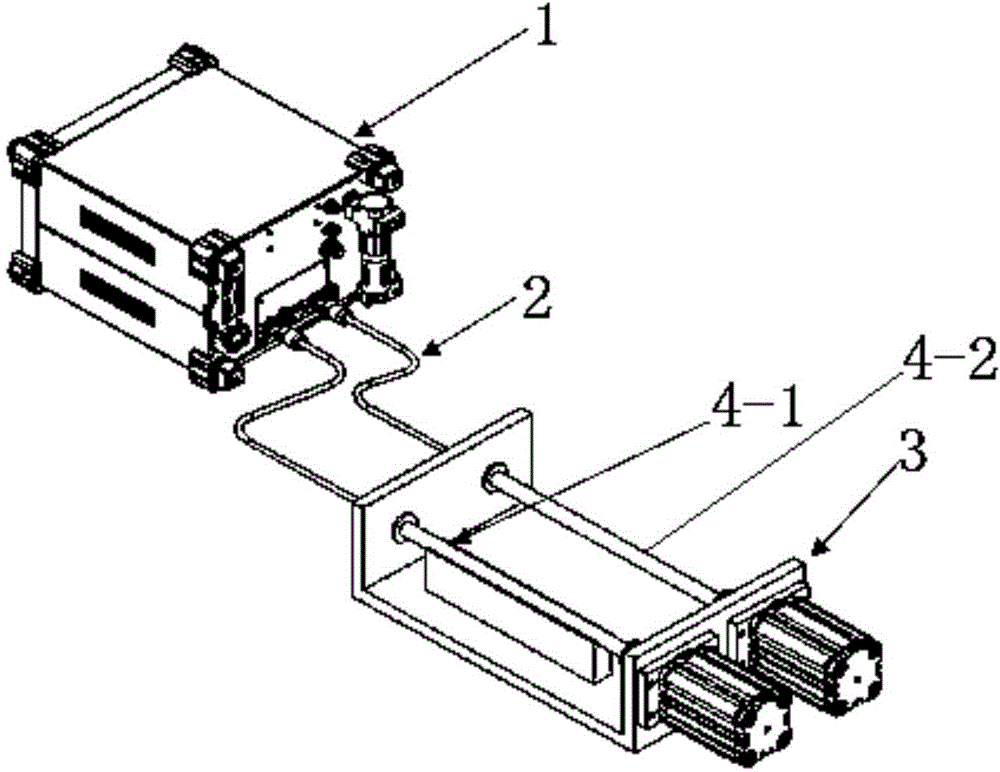

Apparatus for testing cement-based material deformation under multiple environmental conditions

InactiveCN1804624AReduce in quantityImprove efficiencyMaterial testing goodsMechanical solid deformation measurementsEngineeringCopper

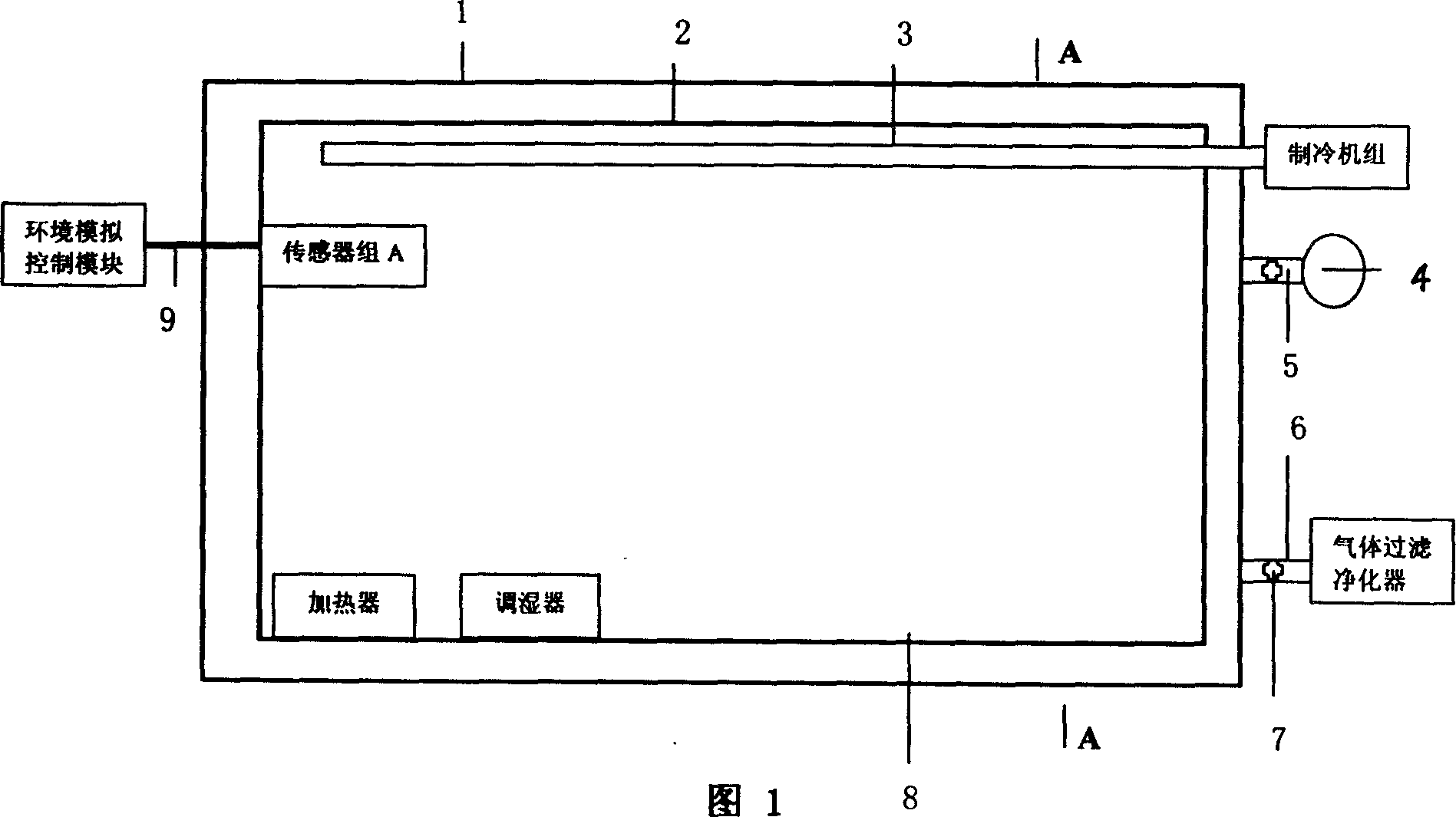

The invention relates to a gelatin backing material deformation measuring apparatus on the condition of multi-environment. It comprises an environment analog case (10), a table seat (14), a displacement sensor, a temperature sensor, a computer and a copper measuring head (34), which is characterized in that the displacement apparatus is positioned on the environment analog case (10); two displacement sensor measuring heads (25) are separately fixed on the brace (24) of the moving device whose left height can be adjusted and the brace (42) whose right height can be adjusted; the moving device comprises a motor (18), a guide screw (21), a bearing (24), a first bearing seat (17), a second bearing seat (23), a num (22), a right steel plate (15), a left steel plate (41), a brace (24) whose right height can be adjusted and a brace (42) whose right height can be adjusted.

Owner:WUHAN UNIV OF TECH

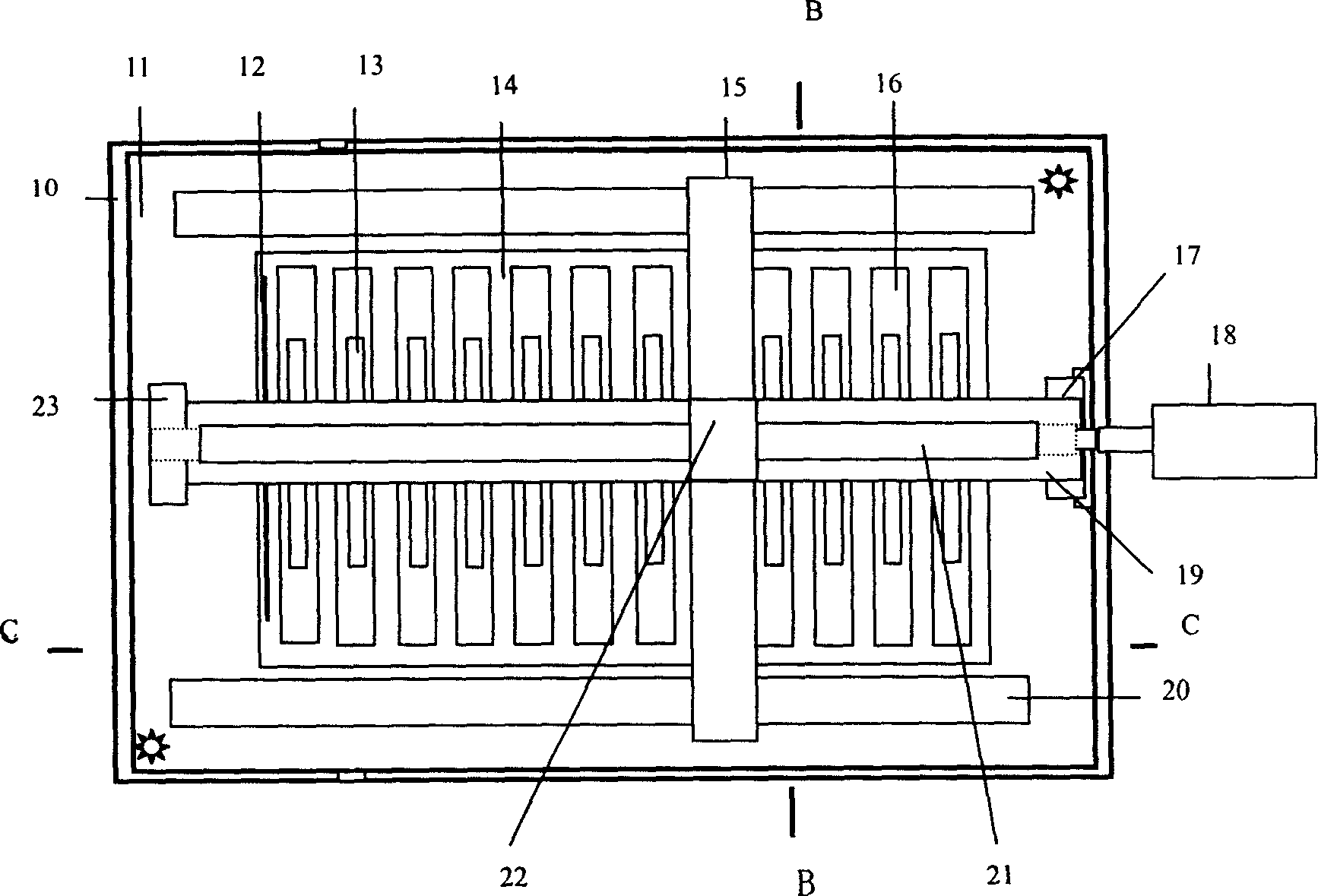

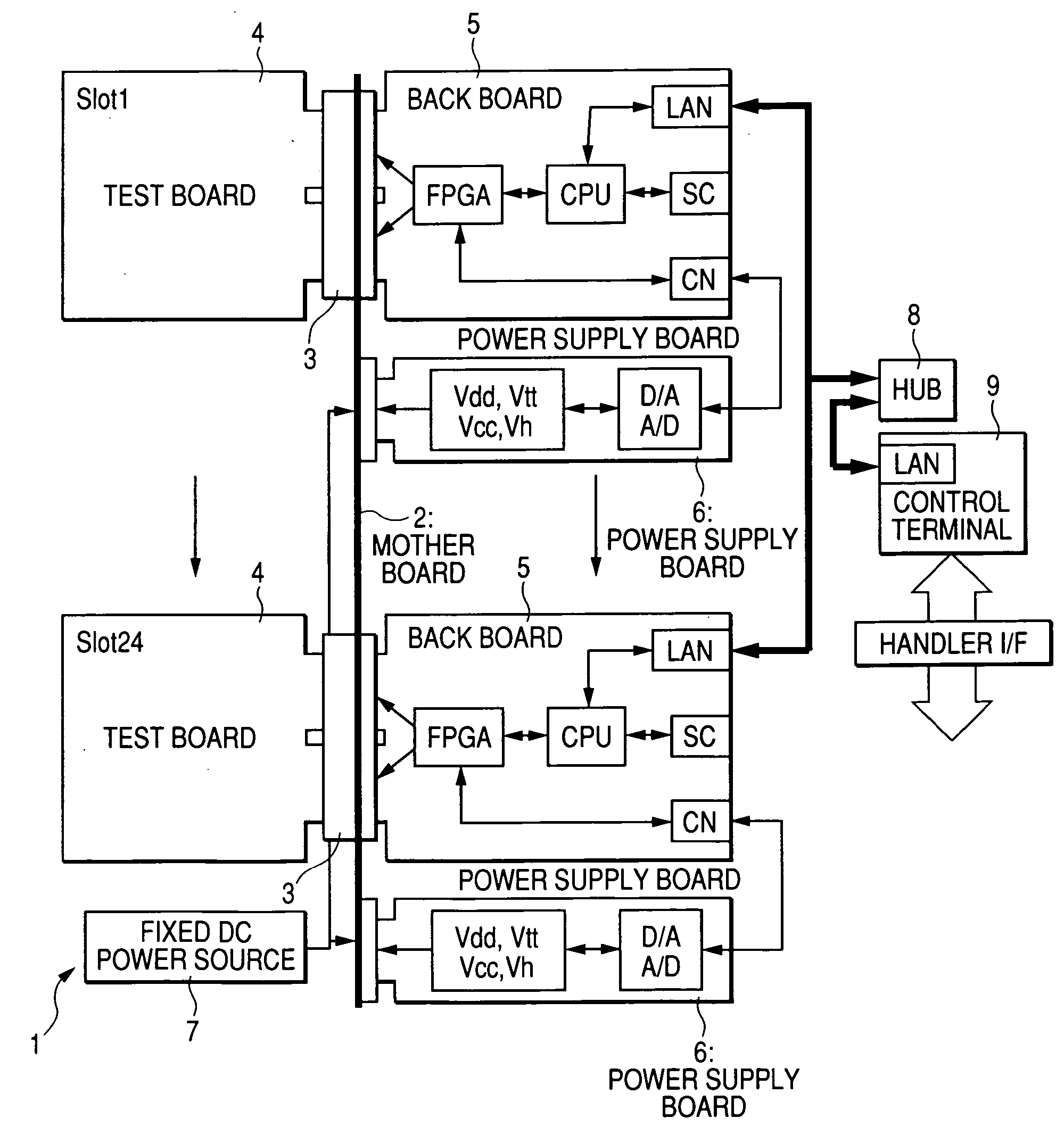

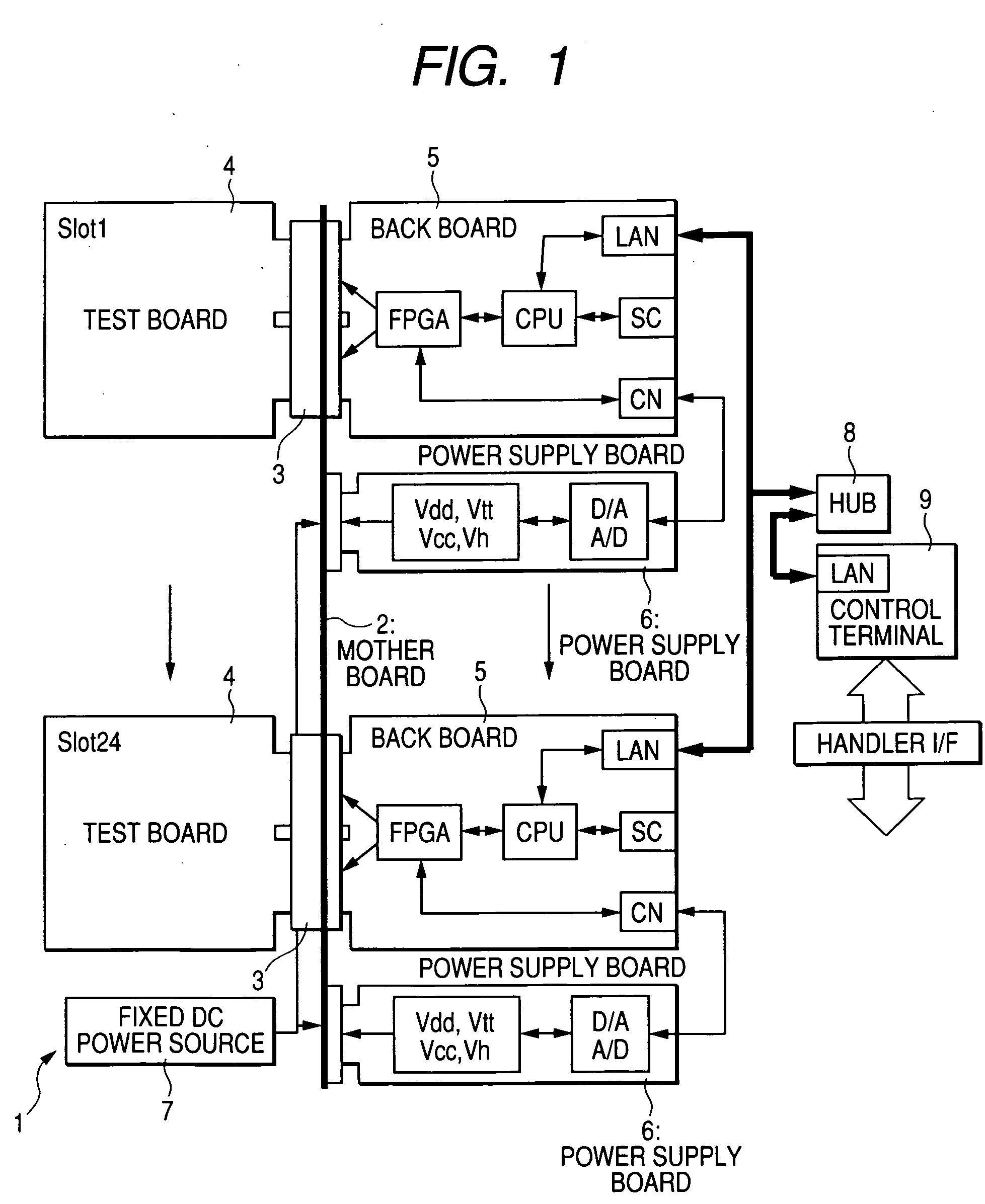

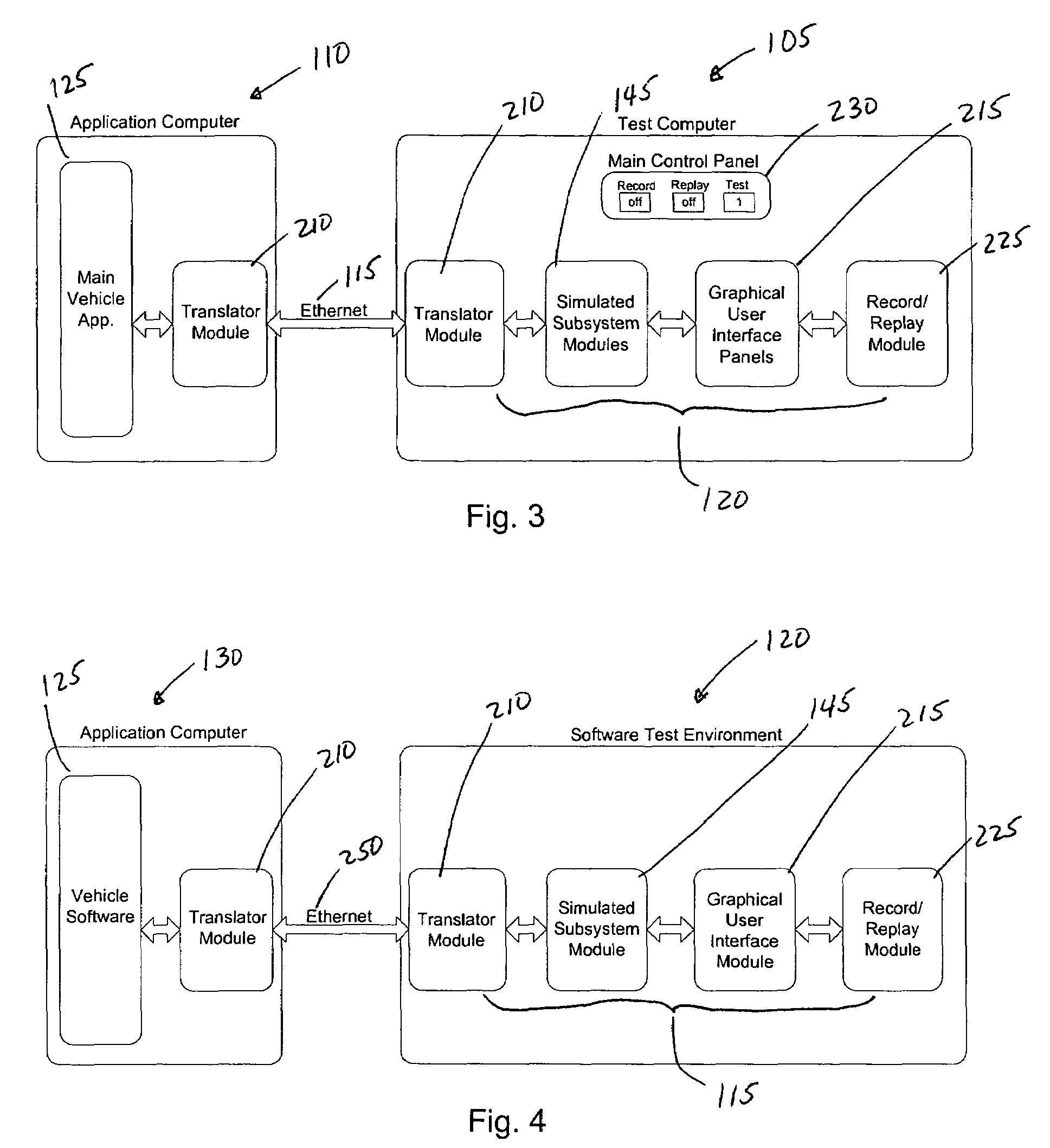

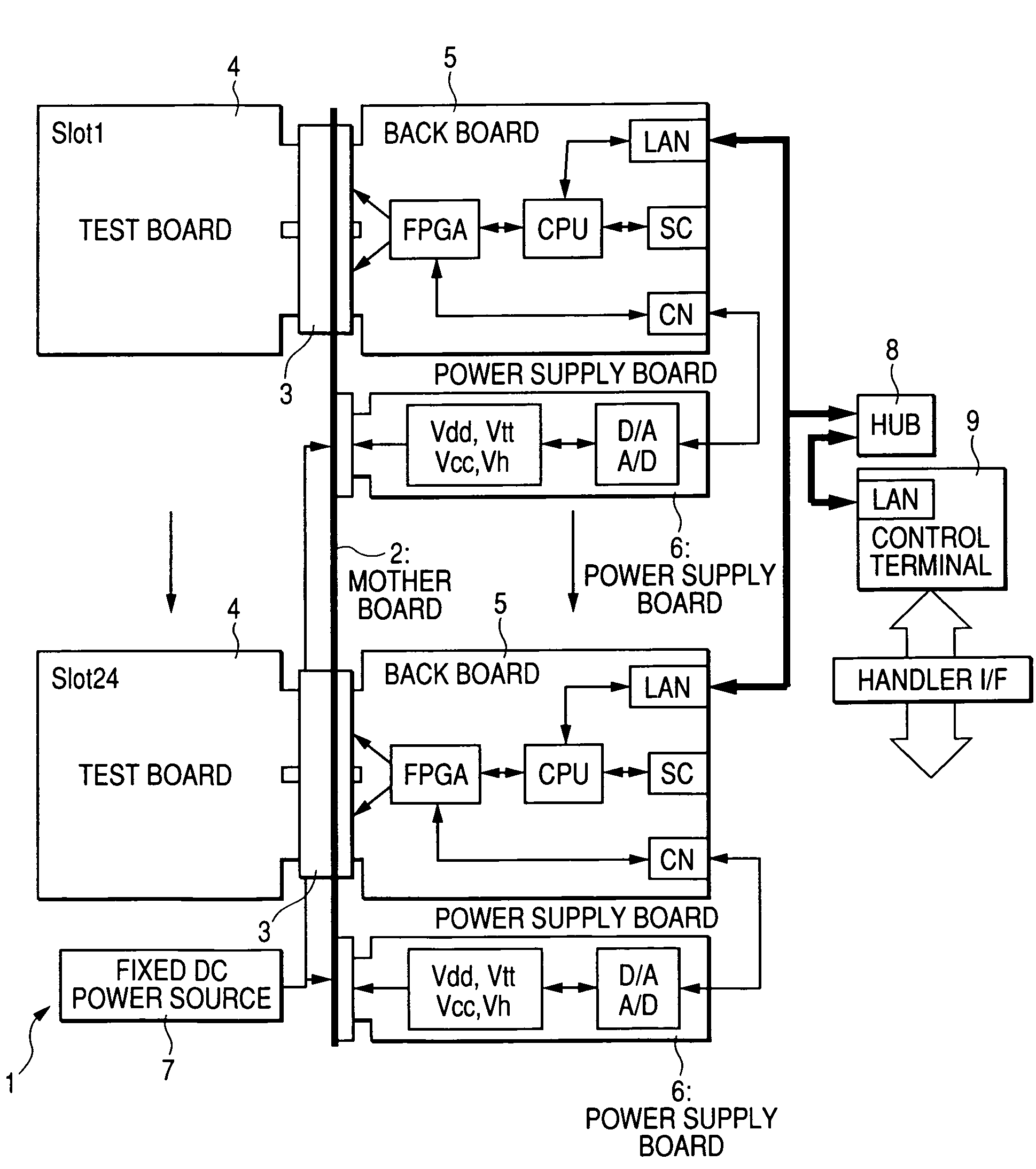

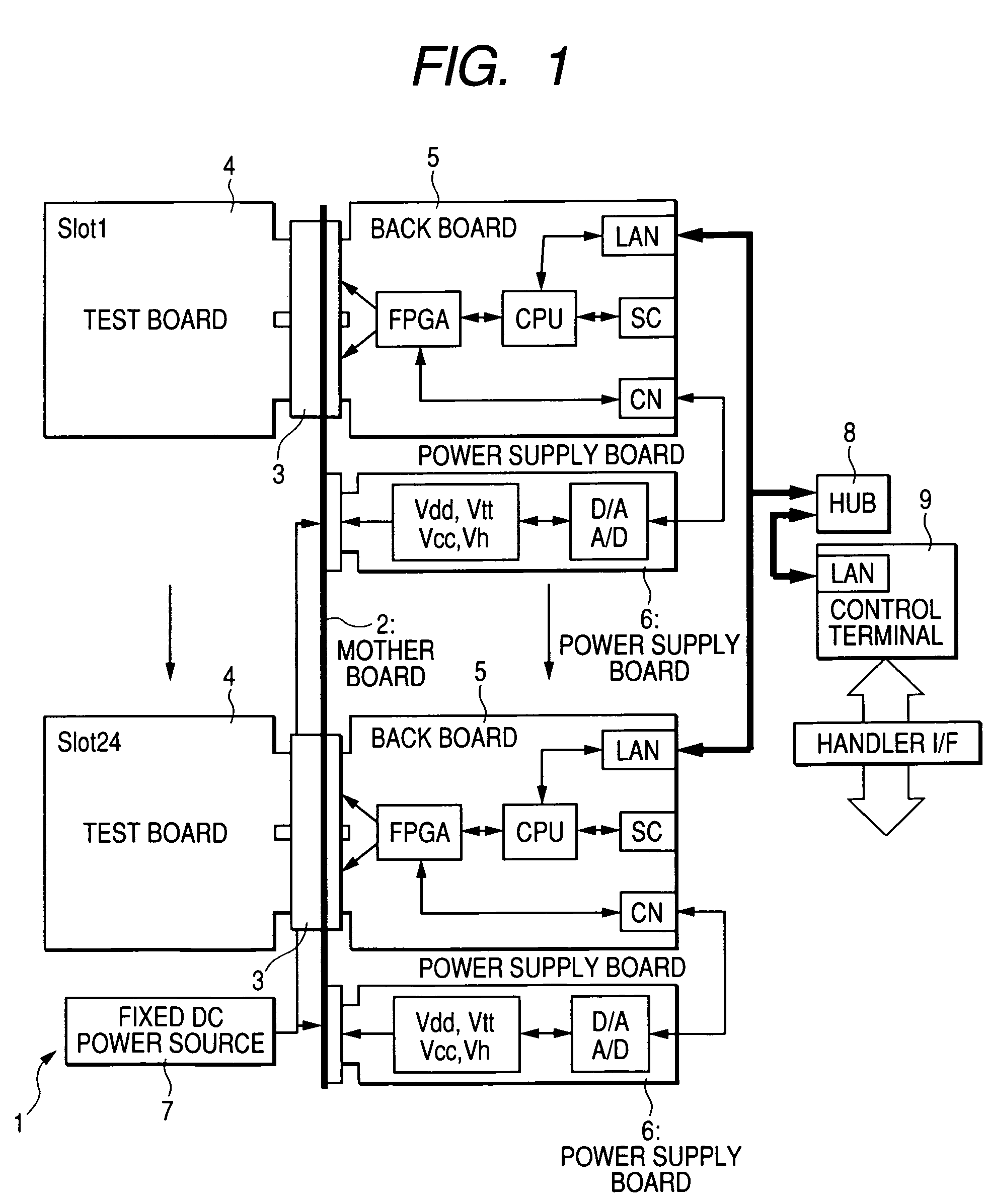

Fabrication method of semiconductor integrated circuit device

InactiveUS20050153465A1Shorten the timeLow costSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsEngineeringMonoboard

A memory test is carried out on semiconductor integrated circuit devices including a semiconductor memory at low cost with efficiency. In a test burn-in system, twenty-four test boards are processed in sequence with time differences, and the test boards are circulated one by one. In this case, the memory test is conducted with the sequence of single board processing: the test is started with a test board in which semiconductor integrated circuit devices have been embedded, and semiconductor integrated circuit devices are discharged, beginning with a test board that has undergone the test.

Owner:RENESAS ELECTRONICS CORP

Software test environment for regression testing ground combat vehicle software

InactiveUS7441236B2Effective supportImprove test coverageError detection/correctionMultiple digital computer combinationsRegression testingSoftware system

A STE for automated testing of ground combat vehicle software application to validate vehicle software logic provides a system and method to conduct interactive (manual) testing of the vehicle software while under development, record information related to the interactive testing activities, including but not limited to tester inputs and expected outcomes, and perform automated testing of the combat vehicle software application using the recorded information. Preferably, reconfiguration of the STE to support changes that arise due to the evolution of the combat vehicle software application system and the subsystems under control of the evolving software system is provided.

Owner:BAE SYSTEMS LAND & ARMAMENTS LP

Method and apparatus of temperature compensation for integrated circuit chip using on-chip sensor and computation means

ActiveUS7340366B2Increased cost of testingLow temperature driftThermometer detailsThermometers using material expansion/contactionReference circuitIntegrated circuit

A method and apparatus of temperature compensation for an integrated circuit using on-chip circuits, sensors, and an algorithm. The chip includes an on-chip reference circuit, an on-chip sensor measuring a parameter relative to the reference, and an on-chip computation means for processing an algorithm. A supplemental off-chip reference circuit is also used. The algorithm carries out the following steps: (A) performing a first calibration of an internal reference residing in an integrated circuit system on-chip at a first (higher) temperature at a first testing site, and (B) utilizing calibration data obtained at the step (A) to perform a second calibration of the internal reference source residing on the integrated system on-chip at a second (lower) temperature at a second testing site.

Owner:ATMEL CORP

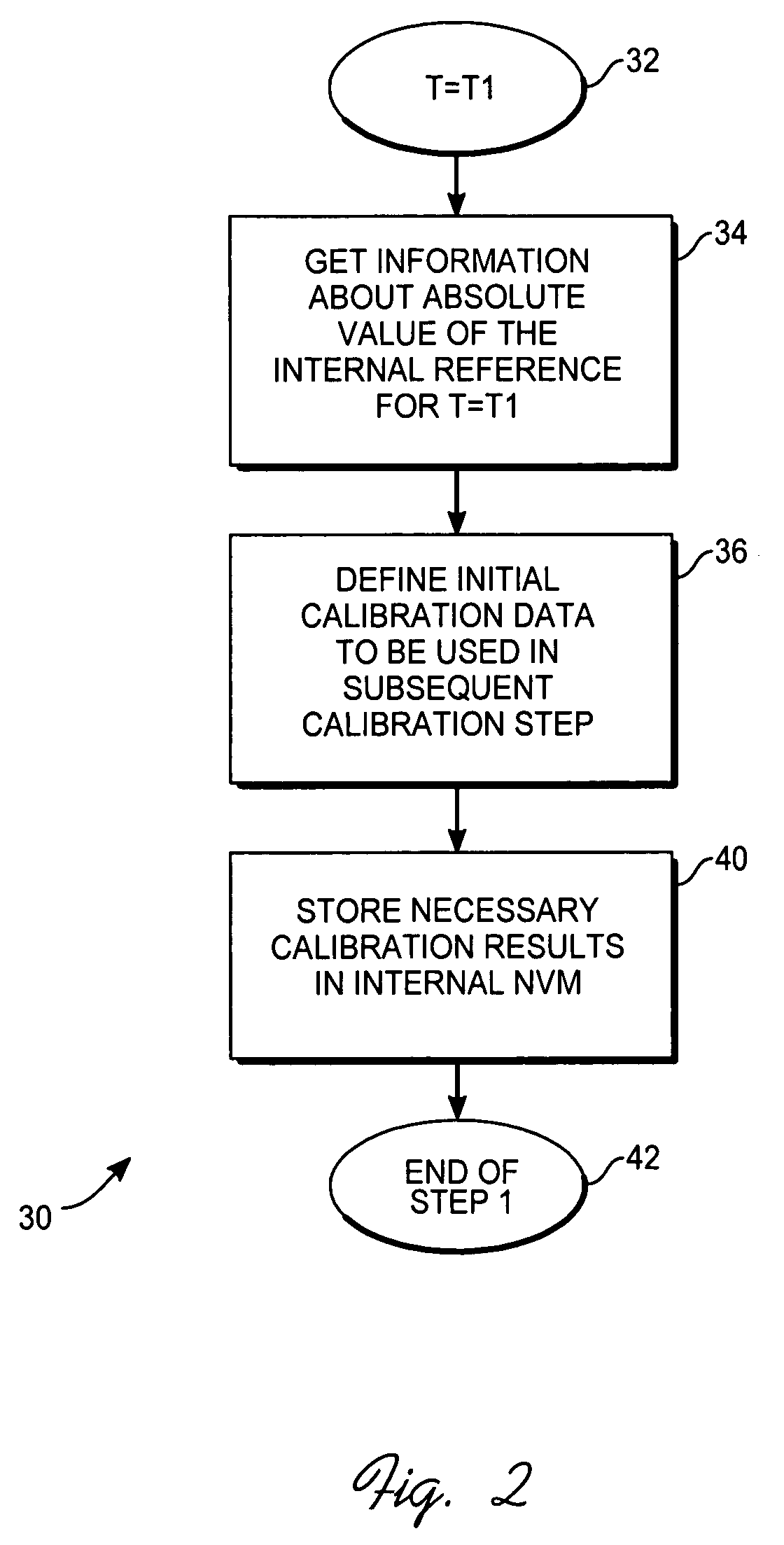

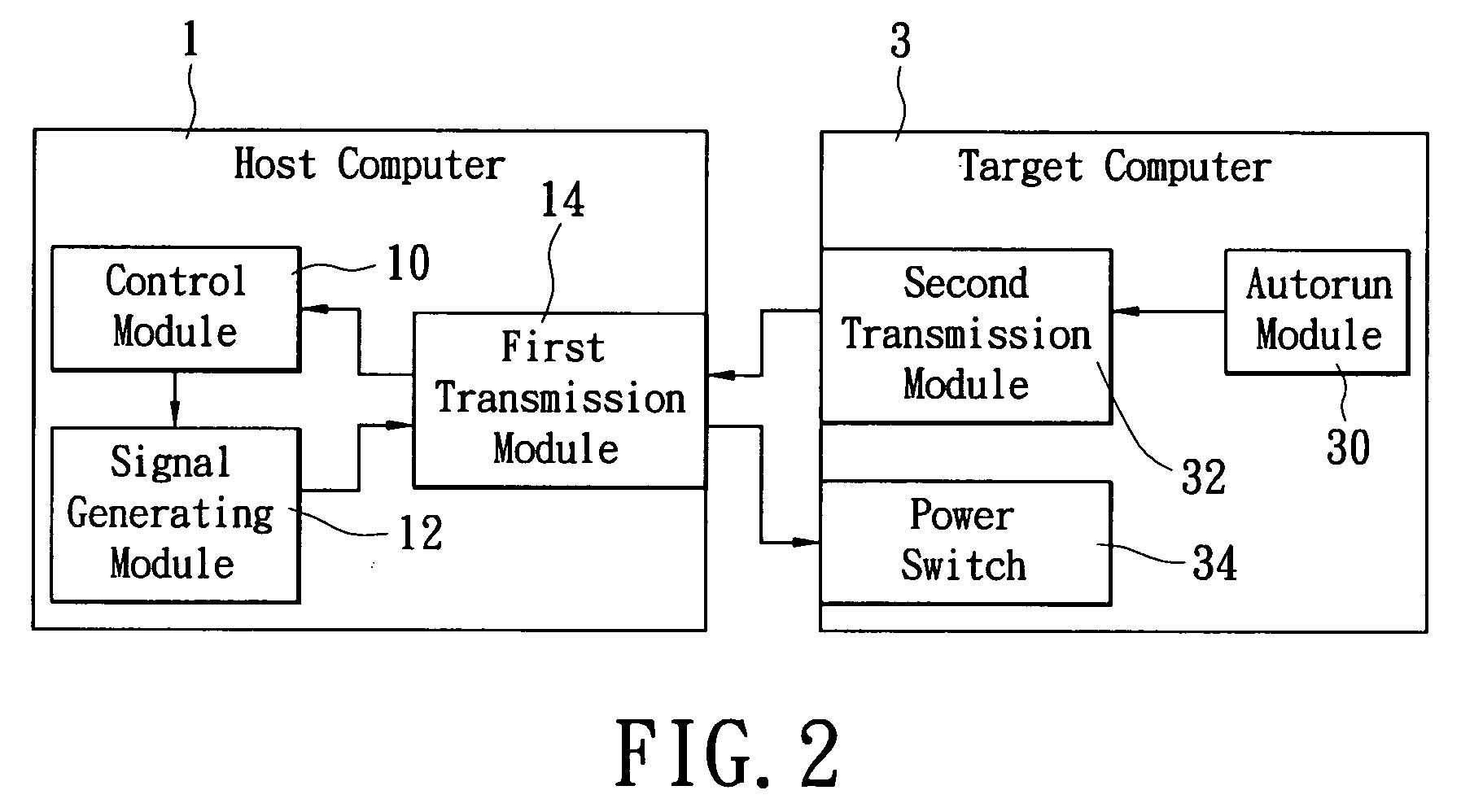

Boot test system and method thereof

ActiveUS20090292911A1Increased cost of testingLow costDetecting faulty hardware by power-on testDigital computer detailsEngineeringBootstrap test

A boot test system applied to test a cold boot in a target computer is provided. The boot test system includes a host computer and an autorun module. The host computer is used to test the target computer to turn power on / off and output a power-on signal and a power-off signal to the target computer based on a feedback signal. The autorun module installed in the target computer is used to output the feedback signal to the host computer during the boot of the target computer. Whereby, the present invention retains a fail result of the boot of the target computer for debugging by a worker.

Owner:UNIVERSAL SCIENTIFIC INDUSTRIAL (SHANGHAI) CO LTD +1

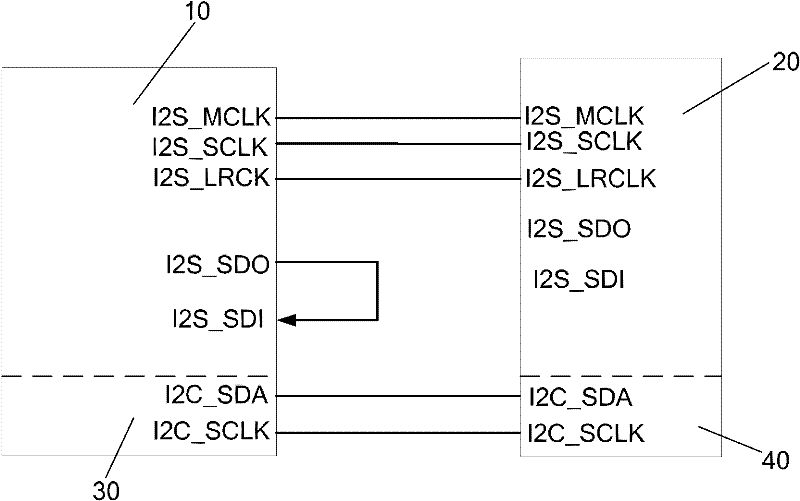

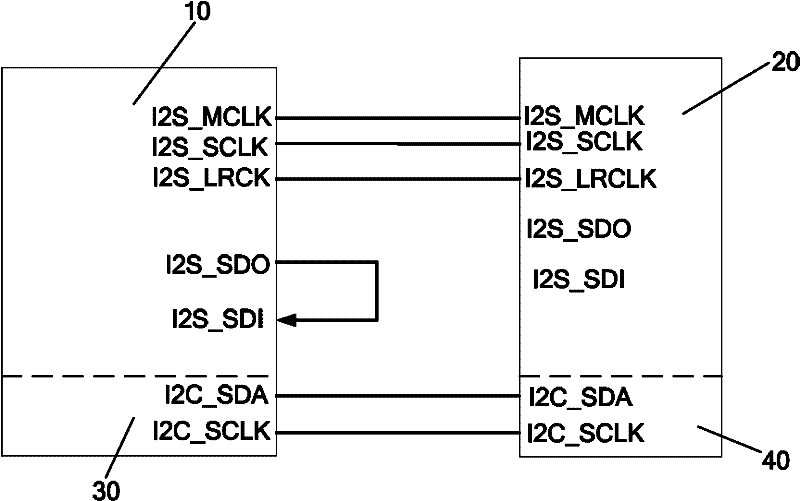

Functional test method of I2S (Inter-IC Sound Bus) interface

ActiveCN102346234AThe testing process is simpleImprove accuracyElectronic circuit testingFunctional testingStart up

The invention provides a functional test method of an I2S (Inter-IC Sound Bus) interface, which comprises the following steps that: the I2S interface of an SOC (system on chip) to be tested is correspondingly connected with three pins of external CODEC (coder / decoder) equipment, then the SOC to be tested and the external CODEC equipment are correspondingly connected by pins on respective I2C (Inter-IC bus) interfaces, and finally, I2S_SDO (serial data output) and I2S_SDI (serial data input) pins on the I2S interfaces are directly short-circuited; the I2S interface of the SOC to be tested is set into a slave mode, the external CODEC equipment is set into a master mode by the I2C interface of the external CODEC equipment, and the corresponding working frequency and sampling rate are set; the related initialization is carried out: test data are prepared, and the I2S interface of the SOC to be tested is started up to send the data; and the I2S interface of the SOC to be tested receives the data: the corresponding data of a receiving buffer are read to the corresponding memory, and the final test result is obtained by comparing the received data with the sent data. In the invention, the functional test and validation are conducted by stimulating the practical application of the I2S interface, so that the test range is wider.

Owner:FUZHOU ROCKCHIP SEMICON

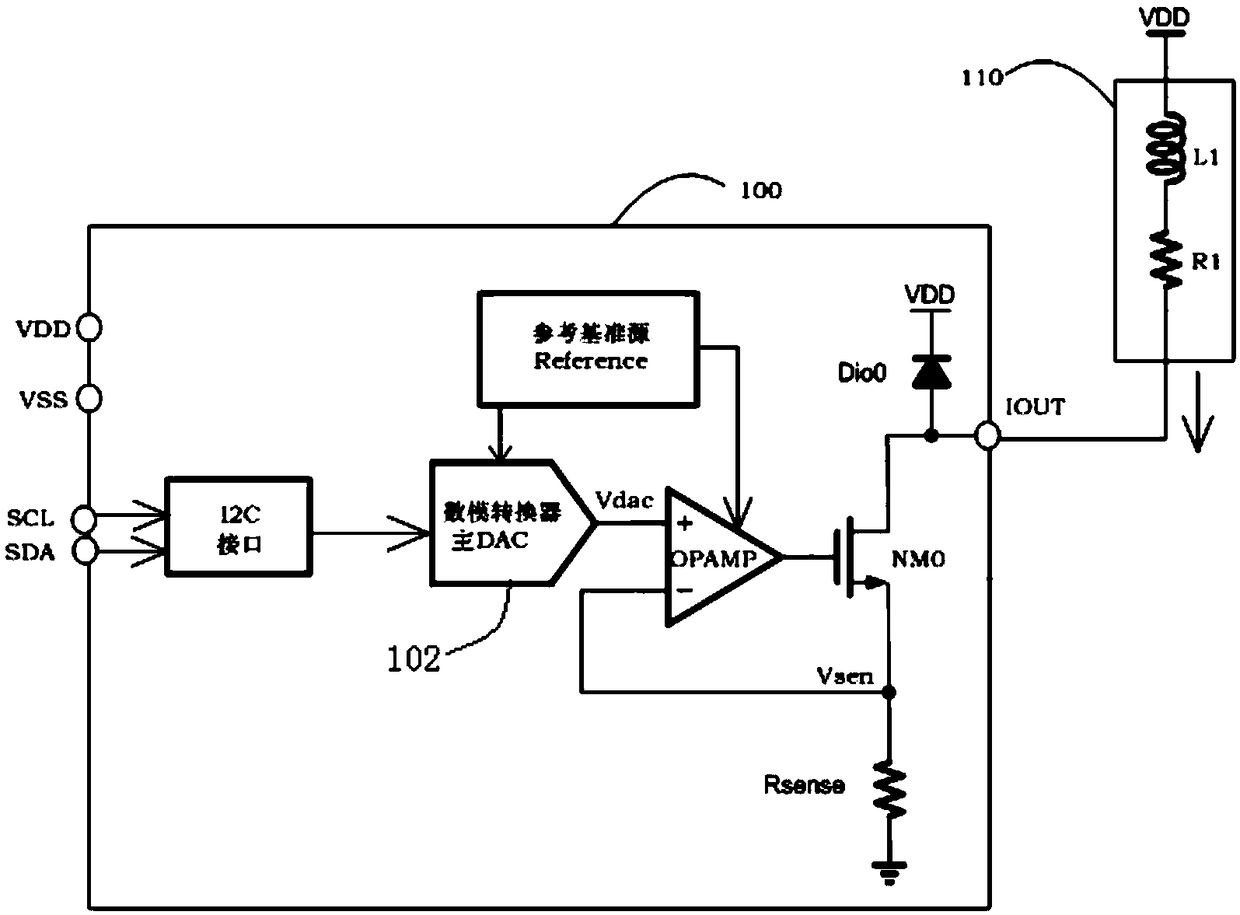

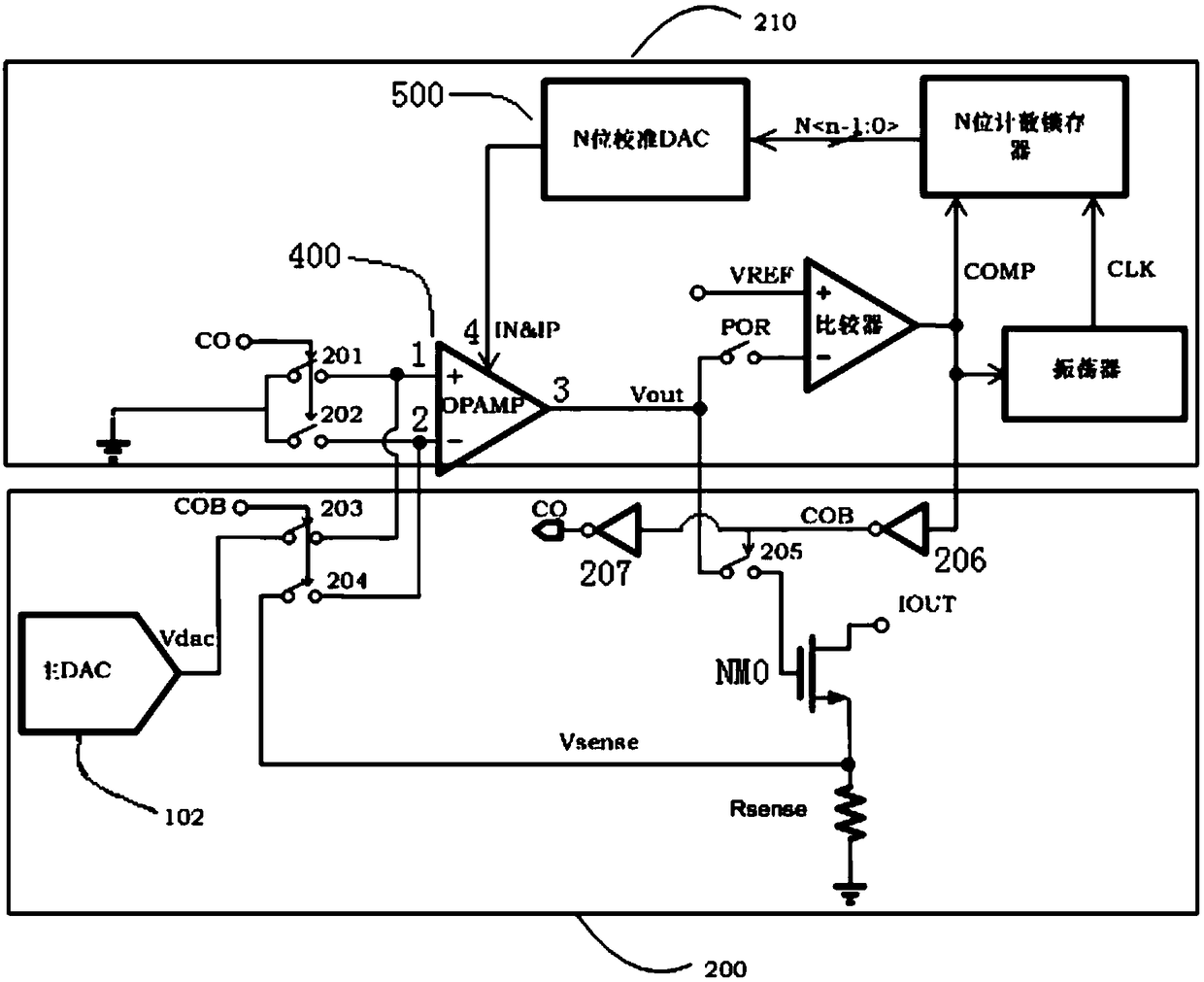

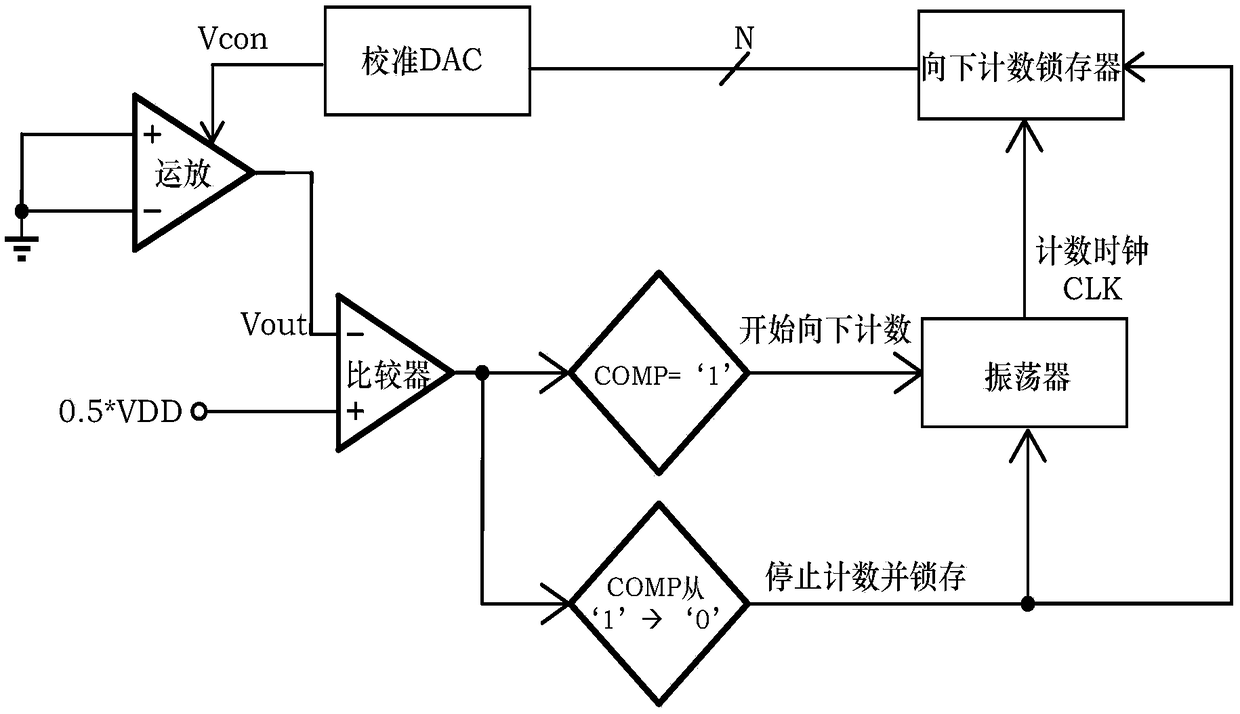

Operational amplifier offset self-calibration circuit applied to voice coil motor driver chip

ActiveCN108718196AIncrease development costsIncreased cost of testingPower saving provisionsElectric signal transmission systemsDigital analog converterOffset calibration

The invention discloses an operational amplifier offset self-calibration circuit applied to a voice coil motor driver chip. The operational amplifier offset self-calibration circuit comprises an operational amplifier (OPAMP), a counting latch, a comparator, an oscillator and a digital analog converter for calibration (DAC), wherein the output end of the OPAMP is connected with the negative pole input end of the comparator; the output end of the comparator is connected with the input end of the oscillator and one input end of the counting latch; the output end of the oscillator is connected with another input end of the counting latch; the output end of the counting latch is connected with the input end of the DAC for calibration; the output end of the DAC for calibration is connected witha signal feedback end of the OPAMP; and the input end and the output end of the OPAMP are further respectively connected with the voice coil motor driver chip. The offset of the OPAMP can be eliminated or greatly decreased, the accuracy of output current of the motor driver chip is improved, the service time of the system battery is prolonged, and the condition that the chip development and test cost is increased due to offset calibration by using a fuse wire is avoided.

Owner:武汉韦尔半导体有限公司

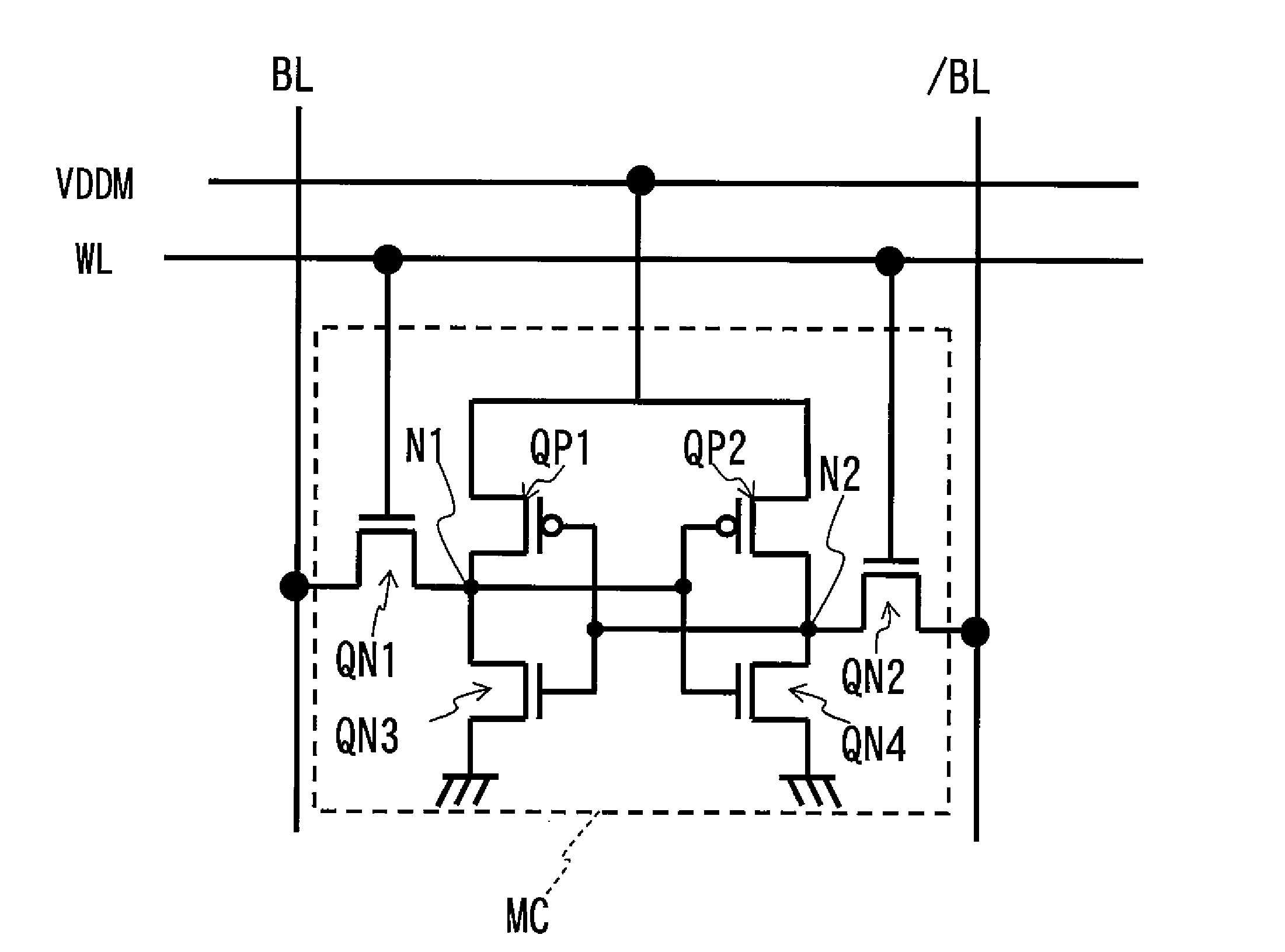

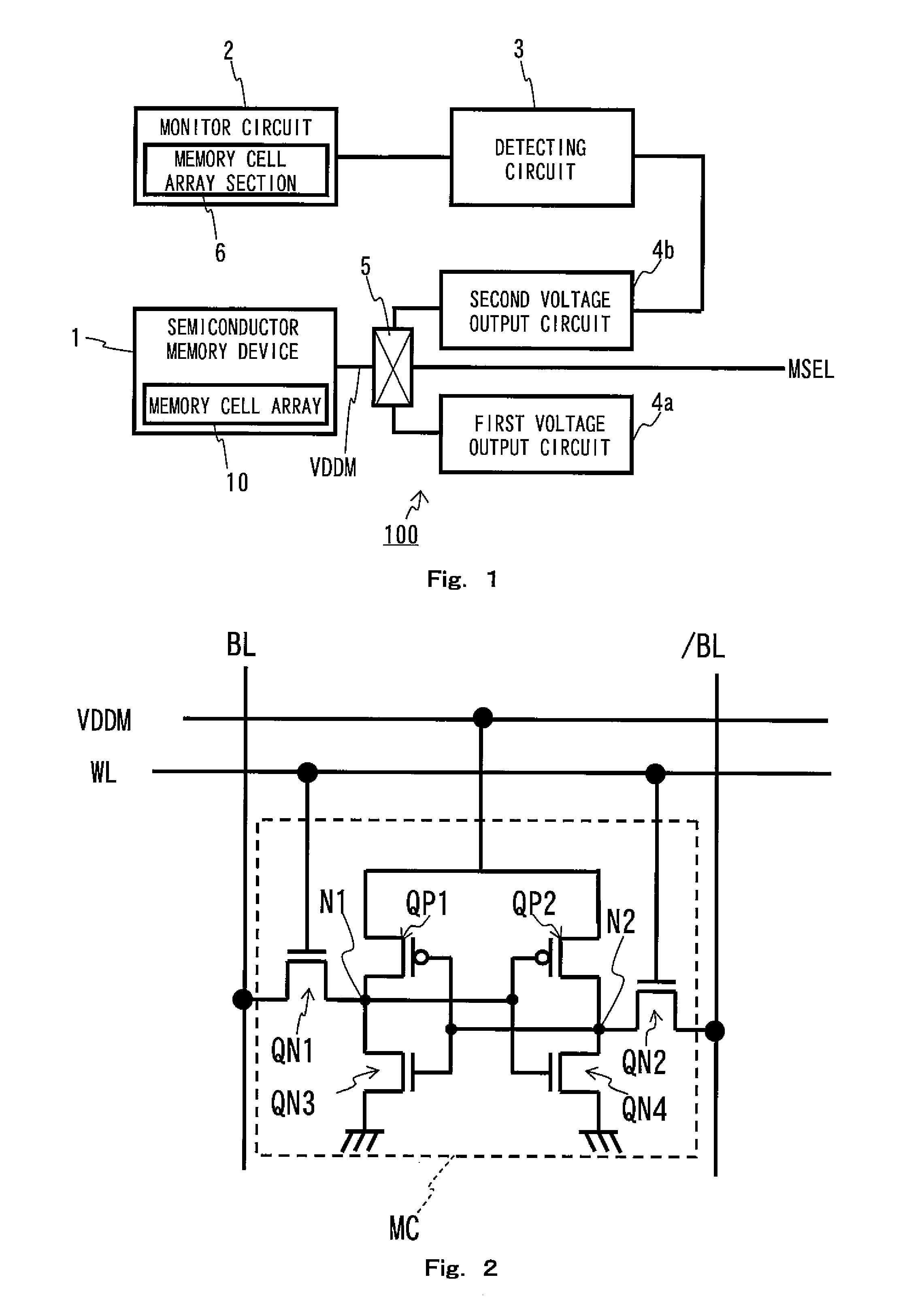

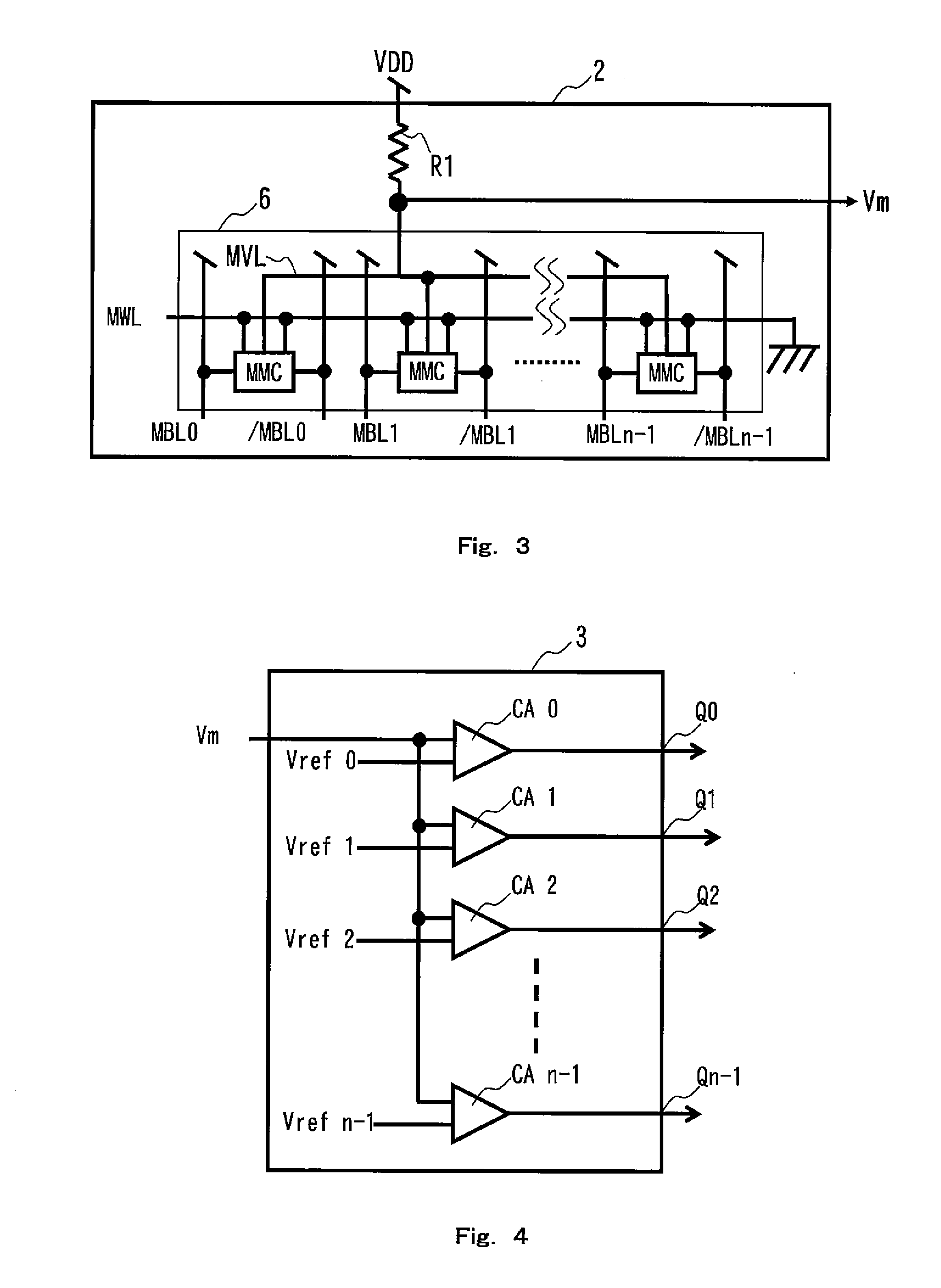

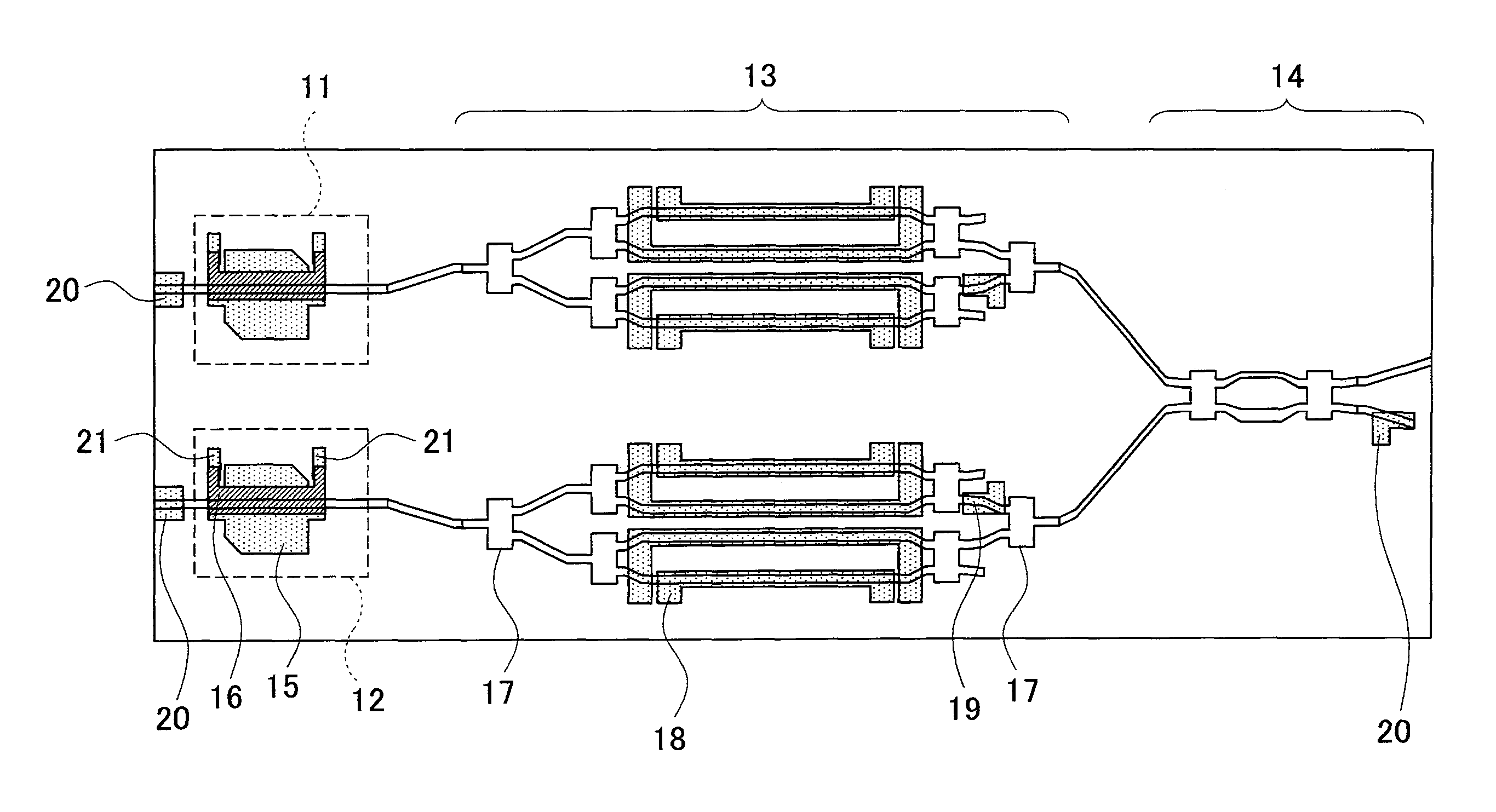

Semiconductor integrated circuit system and electronic equipment

InactiveUS20110141825A1Ensure voltage requiredEasy to readDigital storageElectric pulse generatorEngineeringElectric equipment

A semiconductor integrated circuit system comprises a semiconductor memory device including a memory cell array having a plurality of memory cells; a monitor circuit for monitoring characteristics of the memory cells; and a voltage output circuit connected to the semiconductor memory device to supply a power supply voltage to the semiconductor memory device; the voltage output circuit being configured to change an output voltage according to an output of the monitor circuit.

Owner:PANASONIC CORP

Optical semiconductor modulator device and optical module

ActiveUS9164349B2High Polarization Extinction RatioReduce component countOptical waveguide light guideNon-linear opticsOptical ModuleMultiplexer

Owner:LUMENTUM JAPAN INC

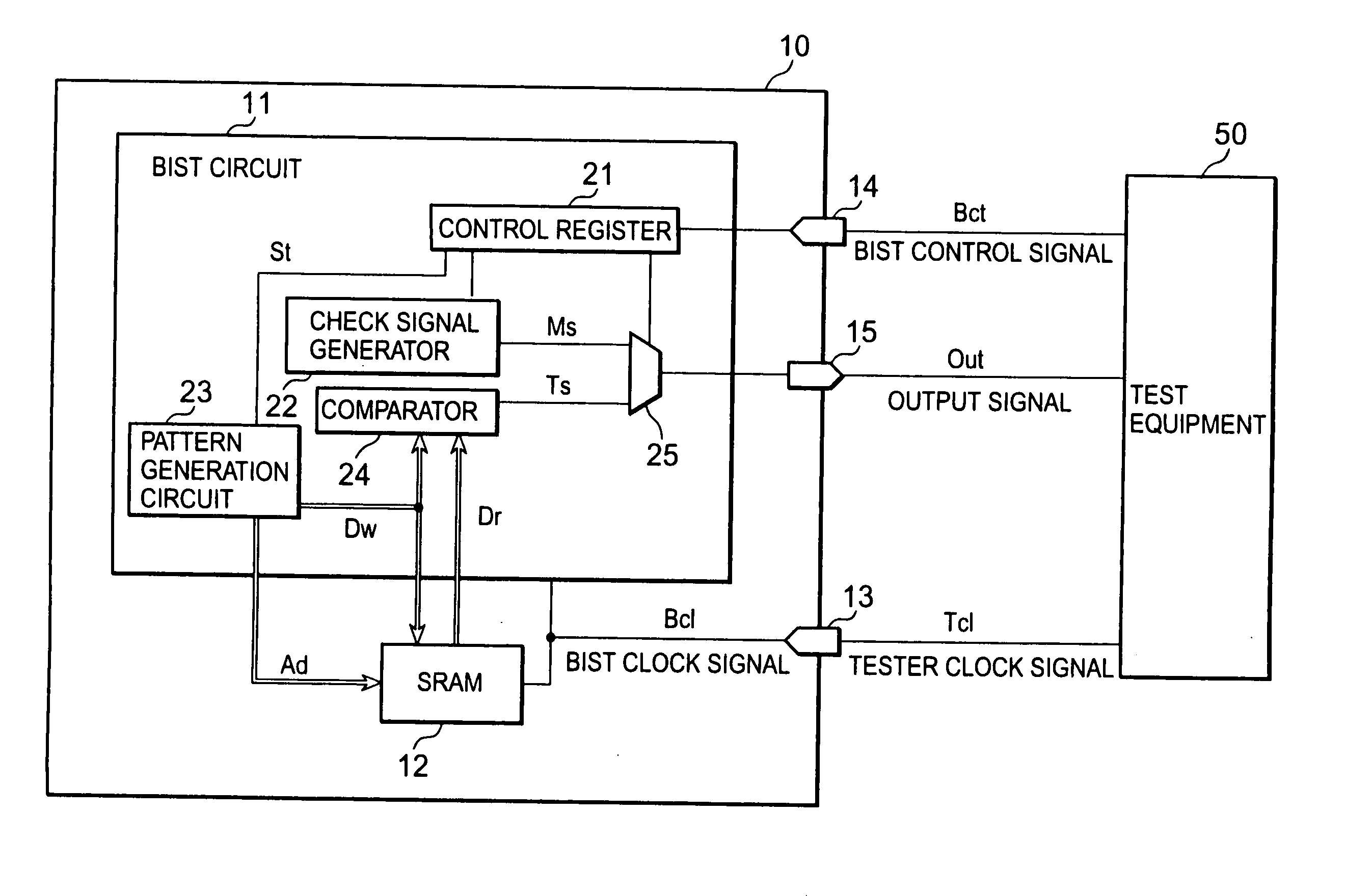

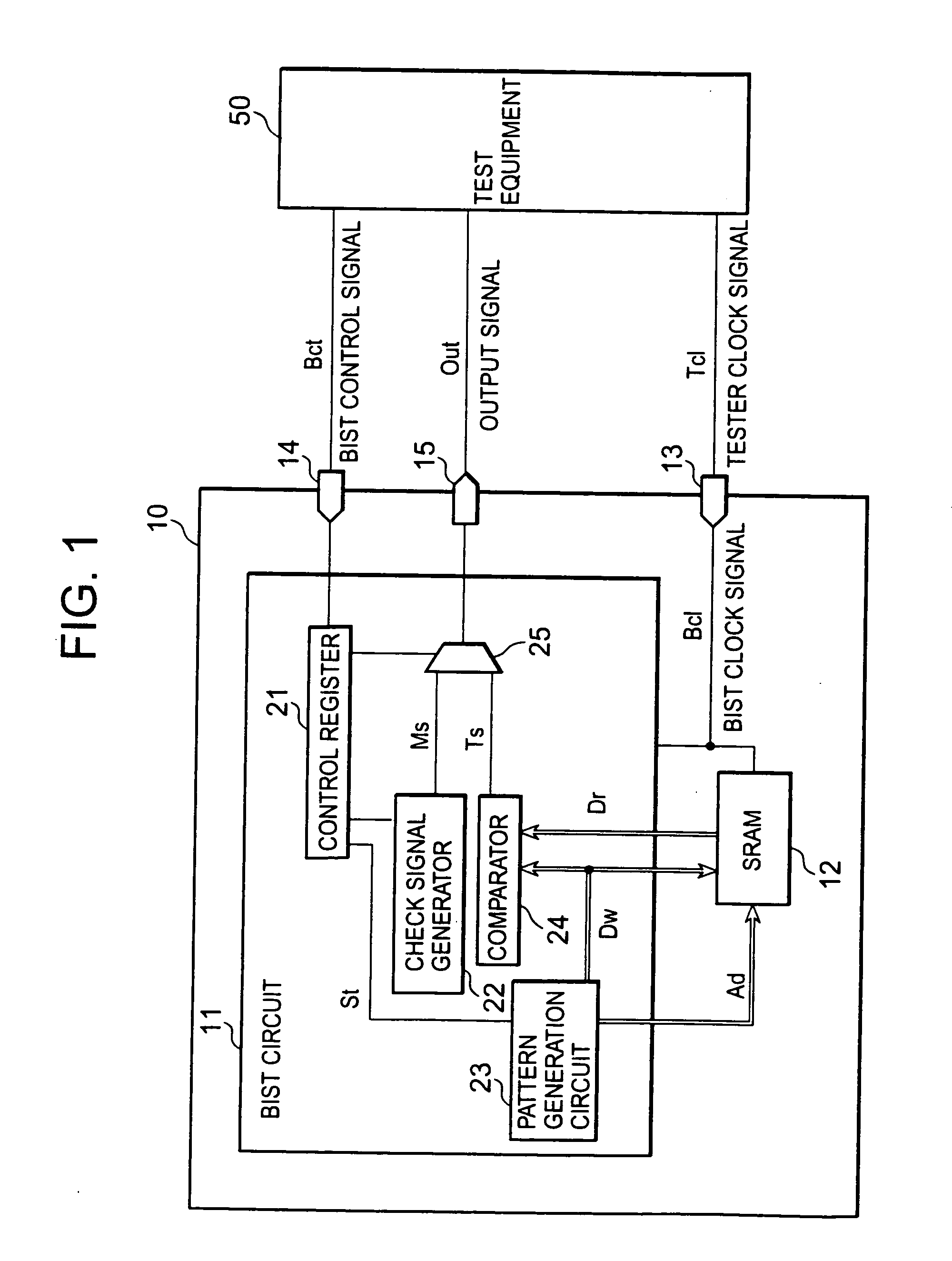

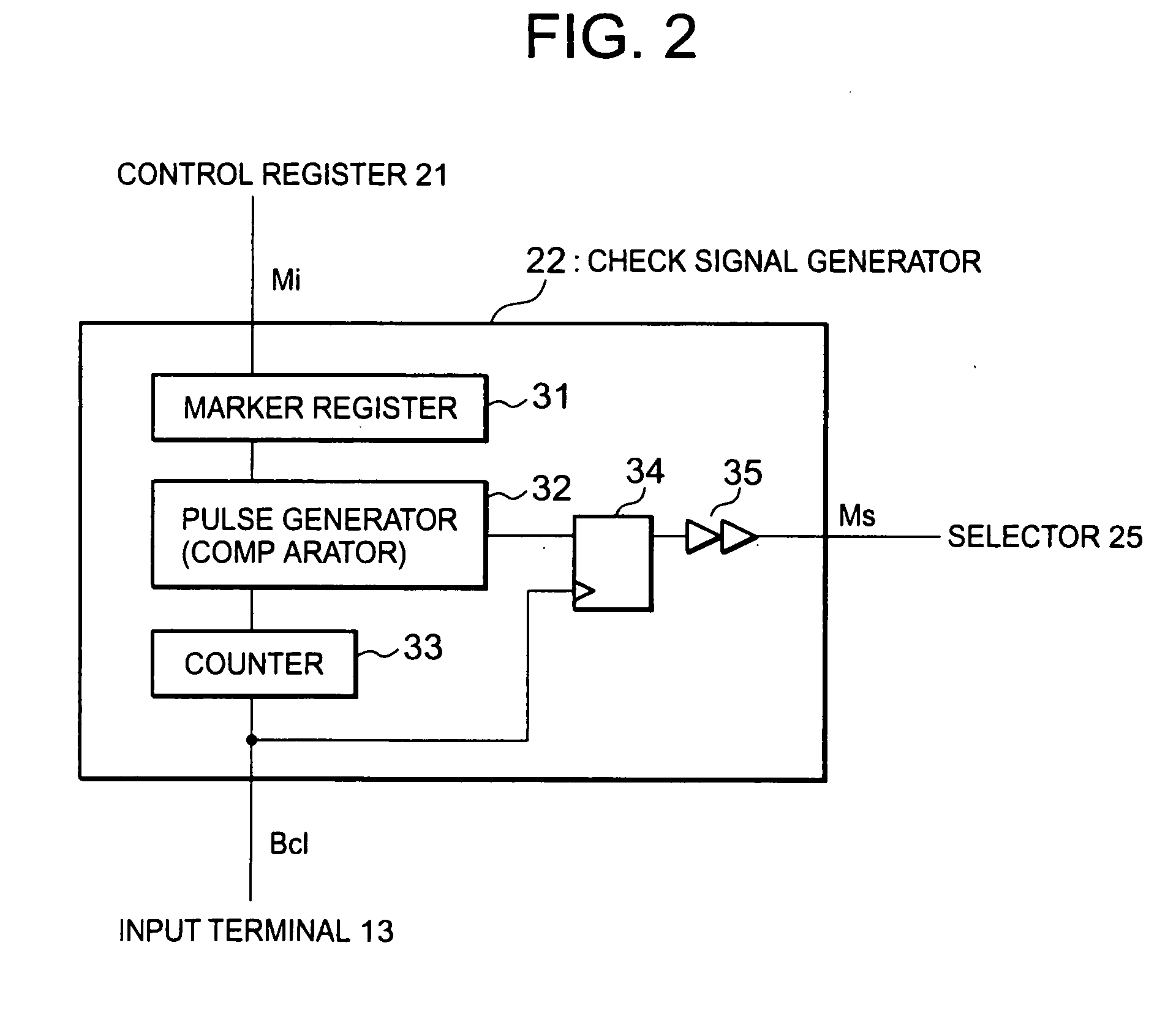

Semiconductor device having built-in self-test circuit and method of testing the same

InactiveUS20100107026A1Shorten the timeReduce testing costsElectronic circuit testingError detection/correctionBuilt-in self-testSemiconductor

A semiconductor device includes circuits to be tested, an input terminal for receiving a tester clock signal from outside, a built-in self-test (BIST) circuit for logically testing the circuit at every cycle of a tester clock signal, and an output terminal for outputting a test result signal representing a result of testing performed in the BIST circuit. Before generating a test result signal, the BIST circuit generates a marker signal, whose phase is identical to the phase of the test result signal, instead of the test result signal.

Owner:RENESAS ELECTRONICS CORP

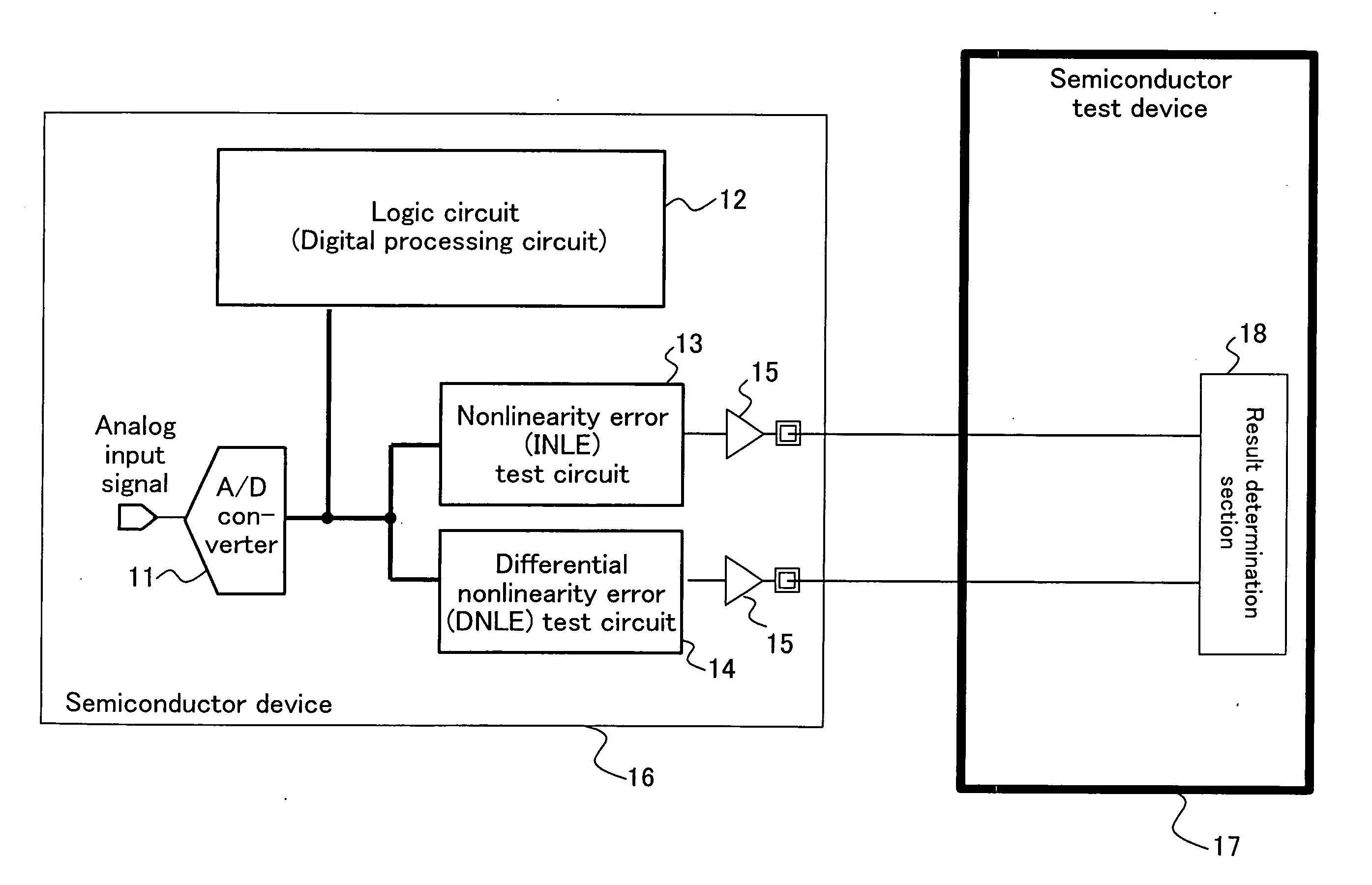

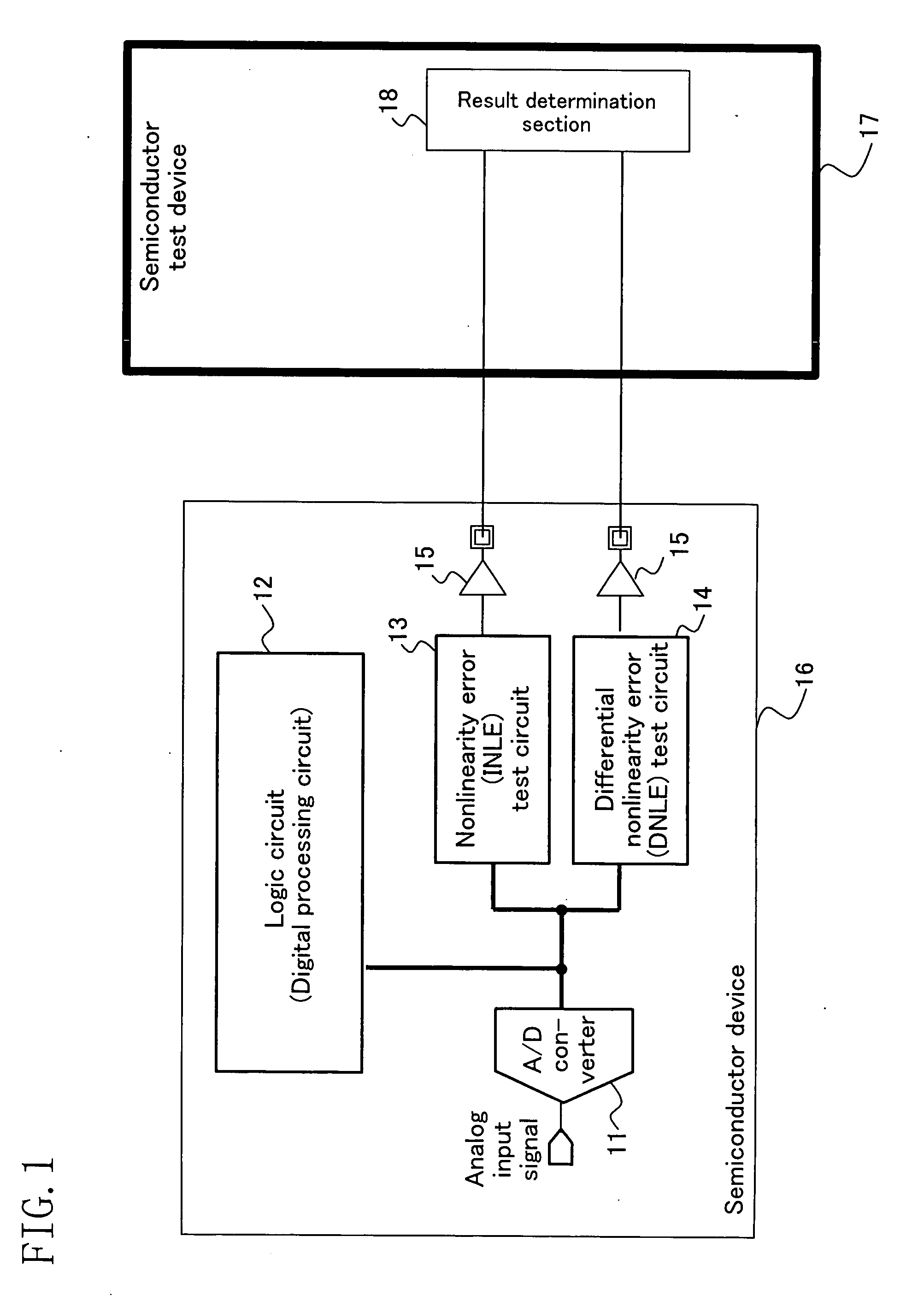

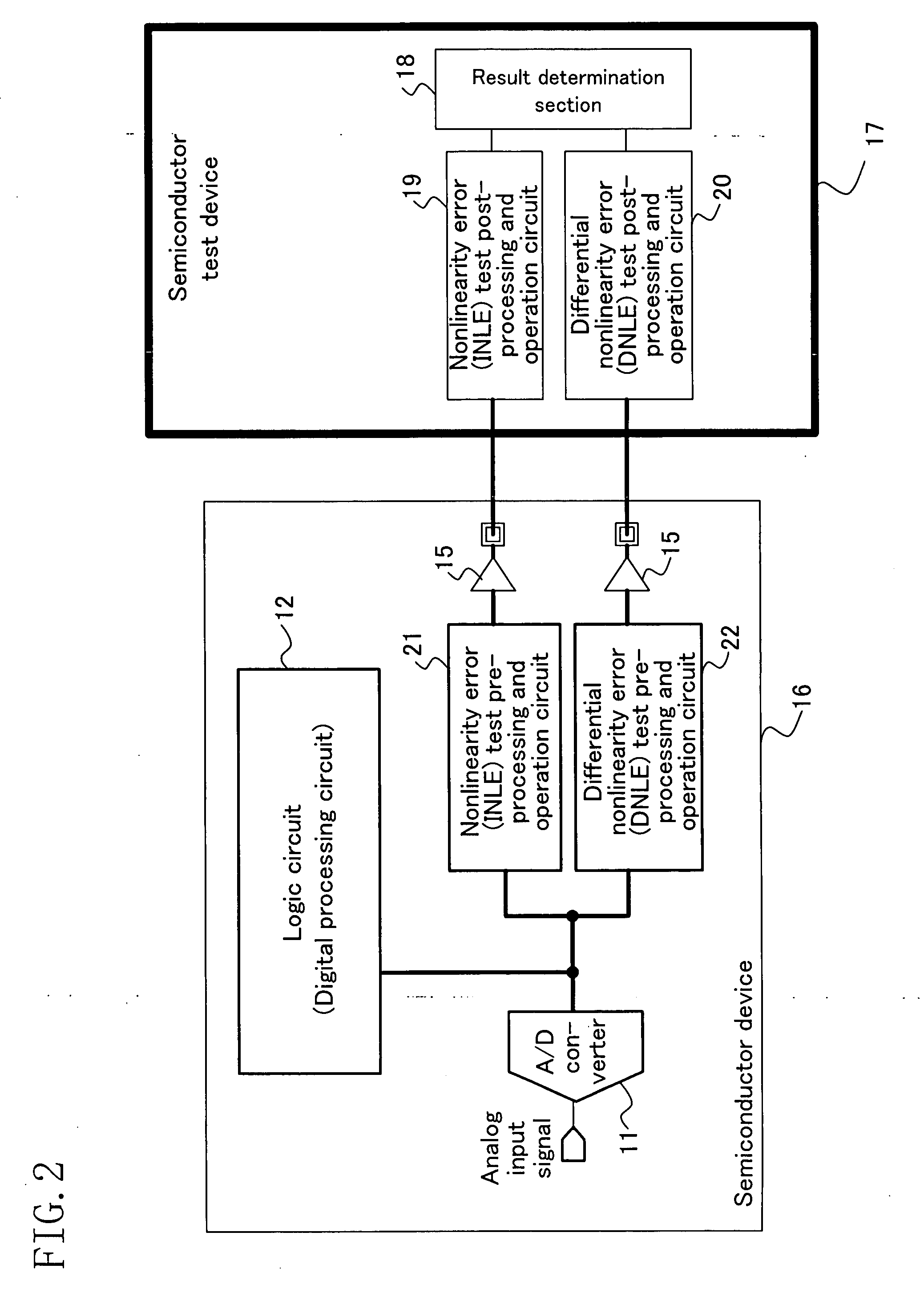

Semiconductor device including A/D converter

InactiveUS20080007439A1Easy to implementLower the volumeElectric signal transmission systemsAnalogue/digital conversion calibration/testingDifferential nonlinearityBuck converter

A semiconductor device includes: an A / D converter; a digital processing circuit for performing processing based on conversion results from the A / D converter; a first test circuit for performing operation processing for checking a nonlinearity error (INLE) of the conversion results from the A / D converter; and a second test circuit for performing operation processing for checking a differential nonlinearity error (DNLE) of the conversion results from the A / D converter. The first test circuit performs only part of the operation processing for checking the nonlinearity error (INLE) of the conversion results from the A / D converter. The second test circuit performs only part of the operation processing for checking the differential nonlinearity error (DNLE) of the conversion results from the A / D converter. An operation processing section for performing the rest of the operation processing for checking the nonlinearity error (INLE) and the rest of the operation processing for checking the differential nonlinearity error (DNLE) is in a semiconductor test device.

Owner:SOCIONEXT INC

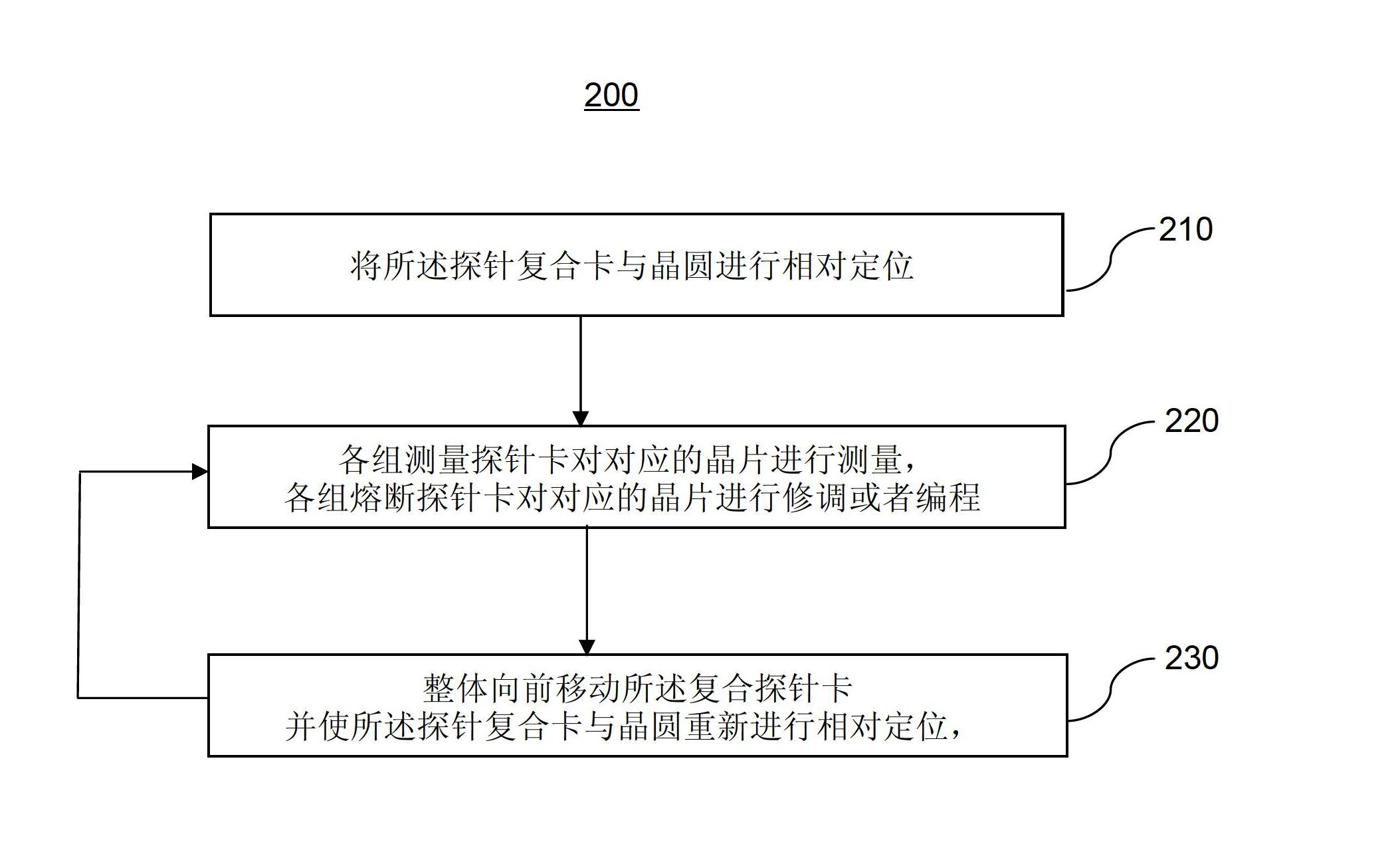

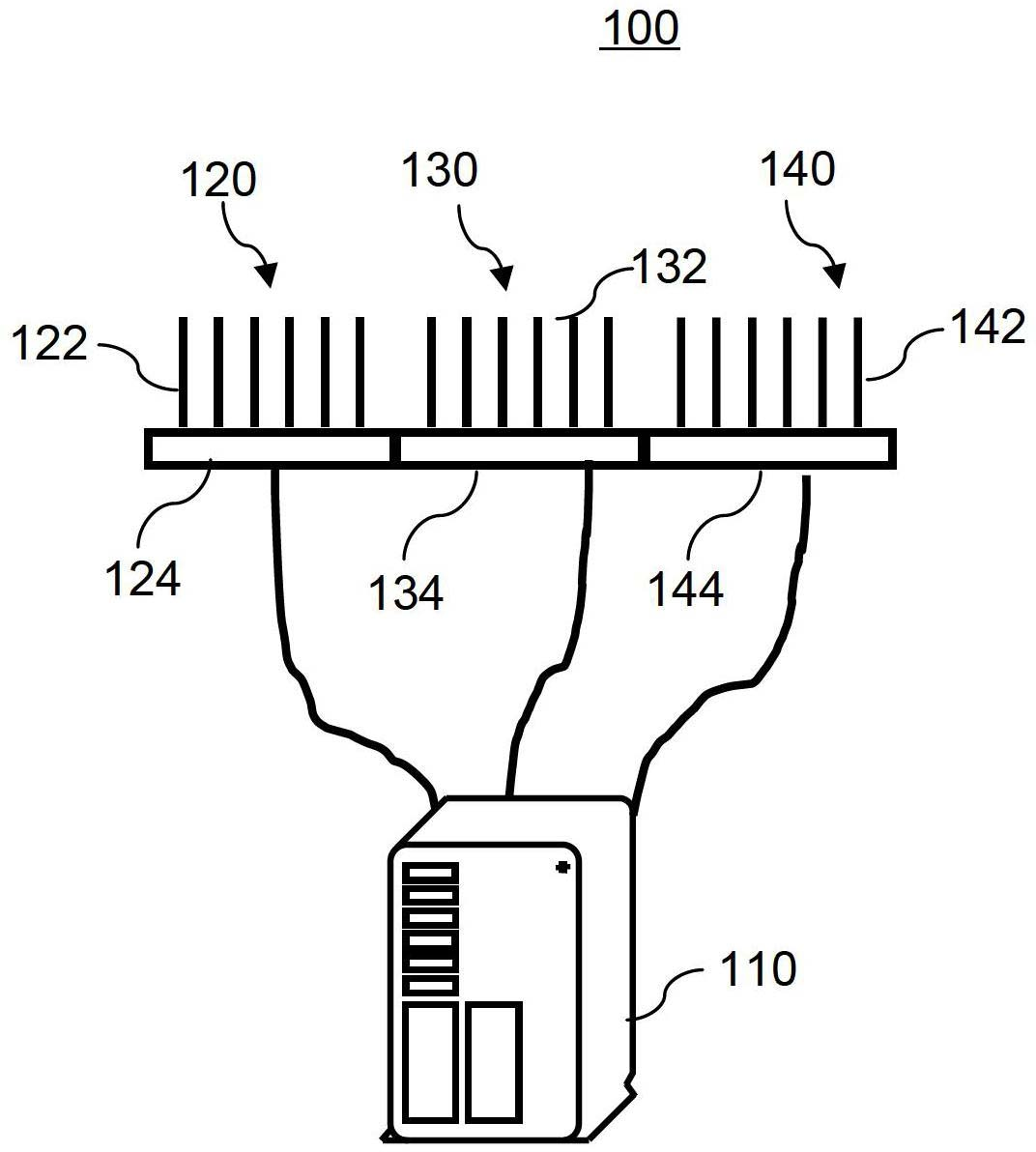

Device and method for testing wafer

ActiveCN102662092ADo not extend the occupancy time too muchHigh measurement accuracyElectrical measurement instrument detailsElectrical testingPhysicsAccuracy and precision

The invention discloses a device and a method for testing wafers. The wafer testing device comprises a set of composite probe cards, wherein the composite probe cards comprise at least one group of measurement probe cards, and the measurement probe cards comprise measurement probes used for measuring electrical signals of corresponding wafers and at least one group of fusing probe cards; the fusing probe cards comprise fusing probes used for trimming or programming corresponding wafers; when the composite probe cards are placed at the same position, various groups of probe cards respectively correspond to different wafers, so that during wafer testing, a measurement process and a fusing process of the same wafer are separately carried out, and the measurement precision is improved; moreover, because the measurement processes and the fusing processes of different wafers can be simultaneously carried out, occupied time of a testing machine is never prolonged excessively, and testing cost is proportional to testing time; and according to the device and the method, the measurement precision is improved, but the testing cost is never increased excessively.

Owner:WUXI ZGMICRO ELECTRONICS CO LTD

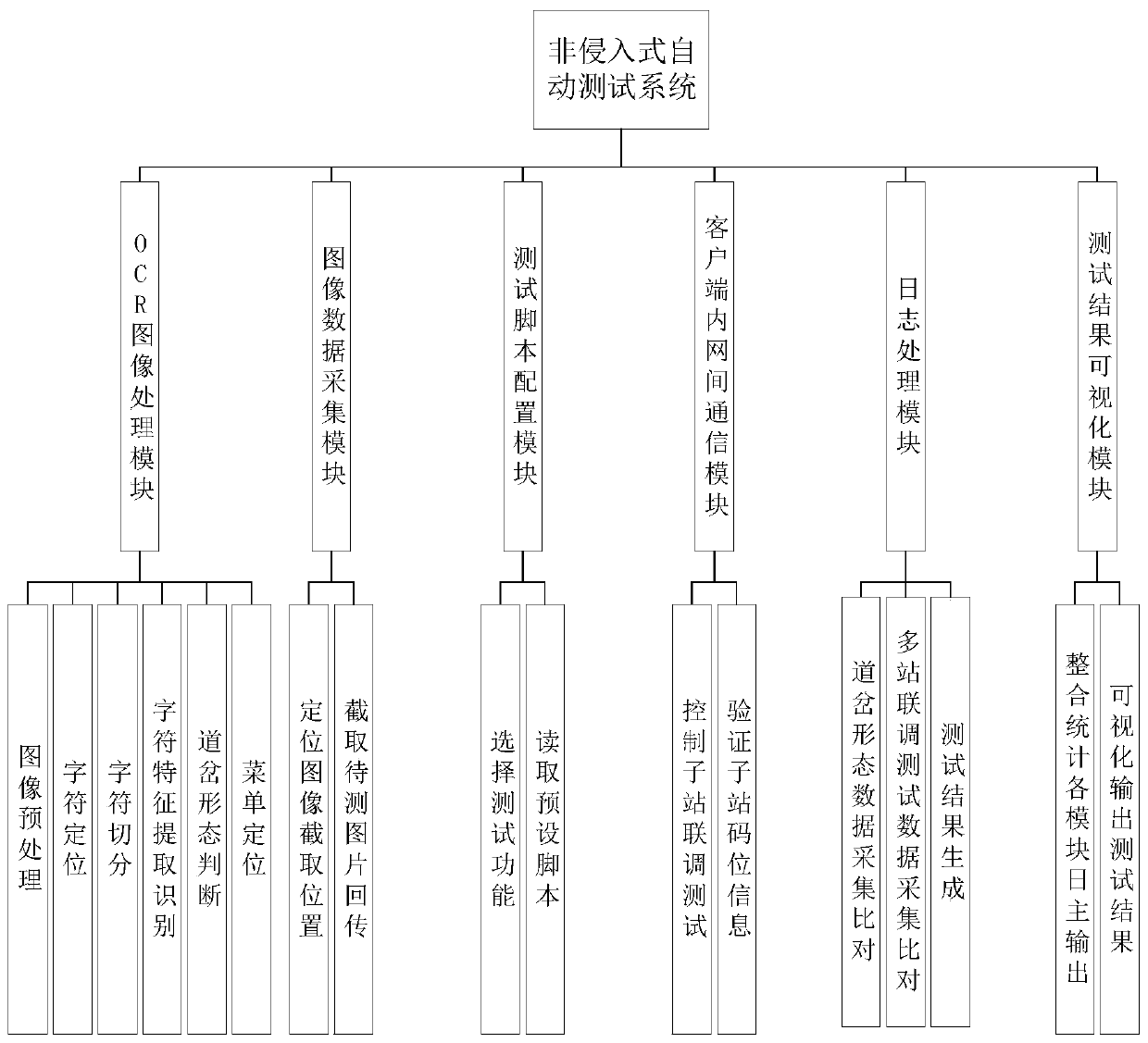

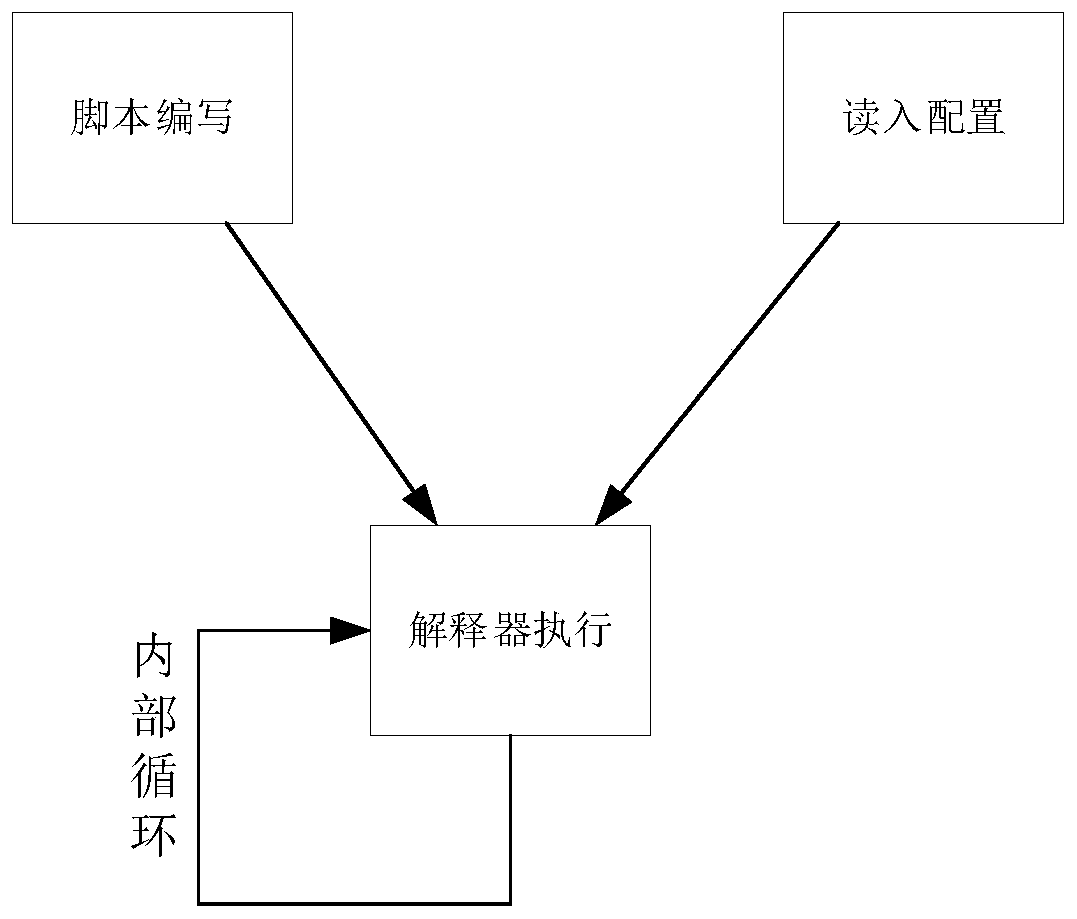

Non-invasive automatic test system for subway signal system test software

ActiveCN111290955AReduce in quantityThe testing process is simpleSoftware testing/debuggingCharacter recognitionTestwareTest script

The invention relates to a non-invasive automatic test system for subway signal system test software, and the system comprises an OCR image processing module which is used for recognizing and processing the information in a subway signal system test software interface; an image data acquisition module which is used for monitoring and acquiring a to-be-processed picture with test interested information in the graphical interface of the subway signal system test software in real time; a test script configuration module which is used for setting a test process; a client intranet inter-network communication module which is used for meeting the multi-machine linkage test requirement; a log processing module which is used for performing test logic comparison; and a test result visualization module which is used for visualizing the output result of the test logic. Compared with the prior art, the method has the advantages that the problems that subway signal system testing software depends too heavily on testing personnel and does not support automatic testing are solved, improvement of full automation of subway signal system testing is facilitated, promotion of the automation process ofa subway is facilitated, and the development and testing cost is reduced.

Owner:CASCO SIGNAL

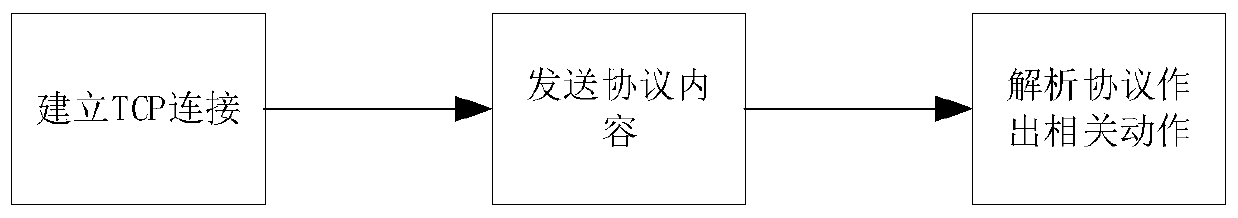

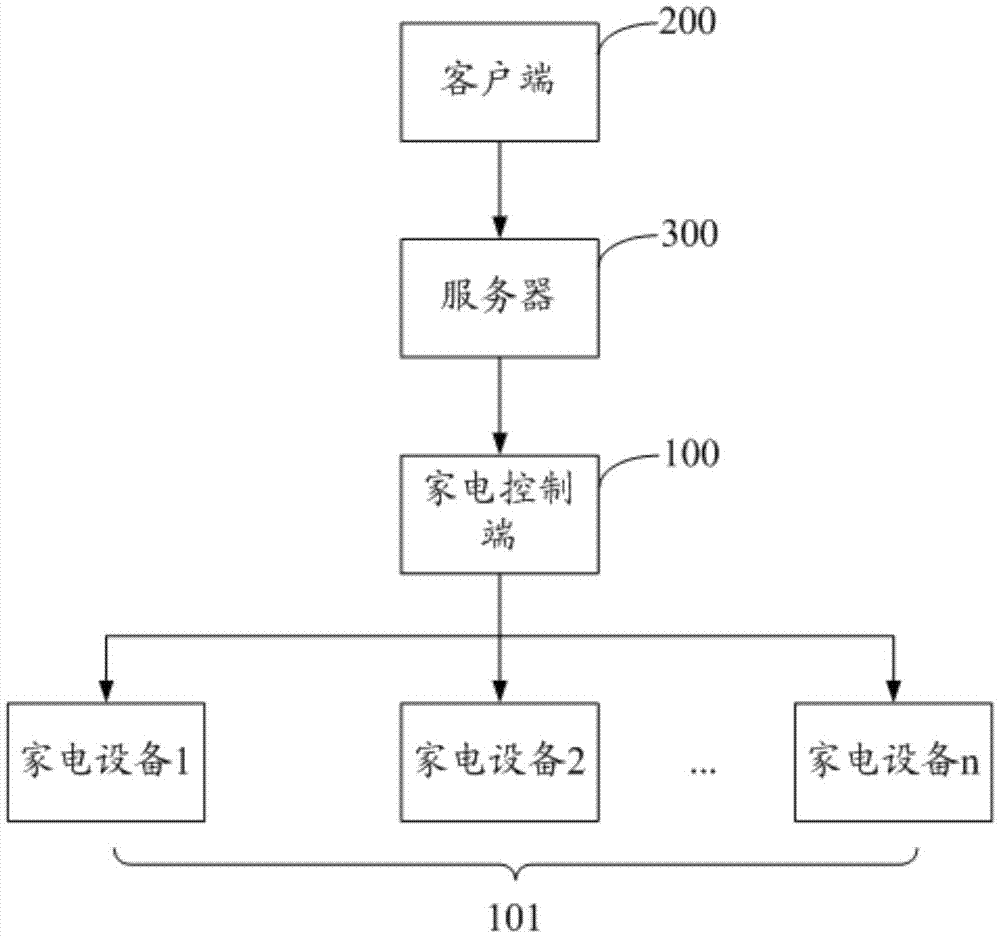

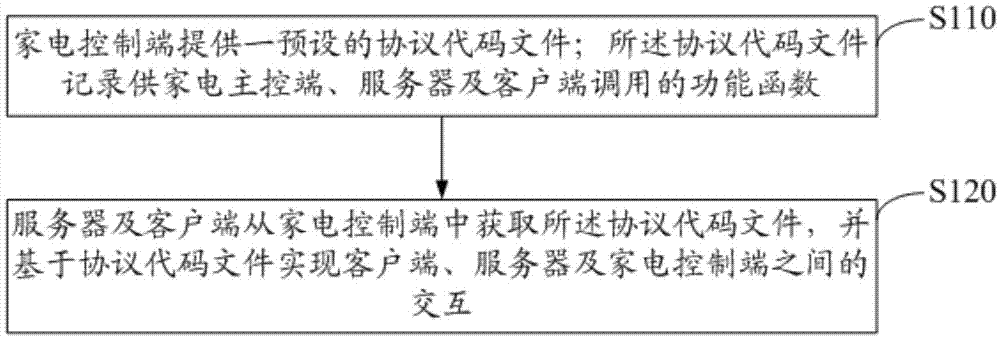

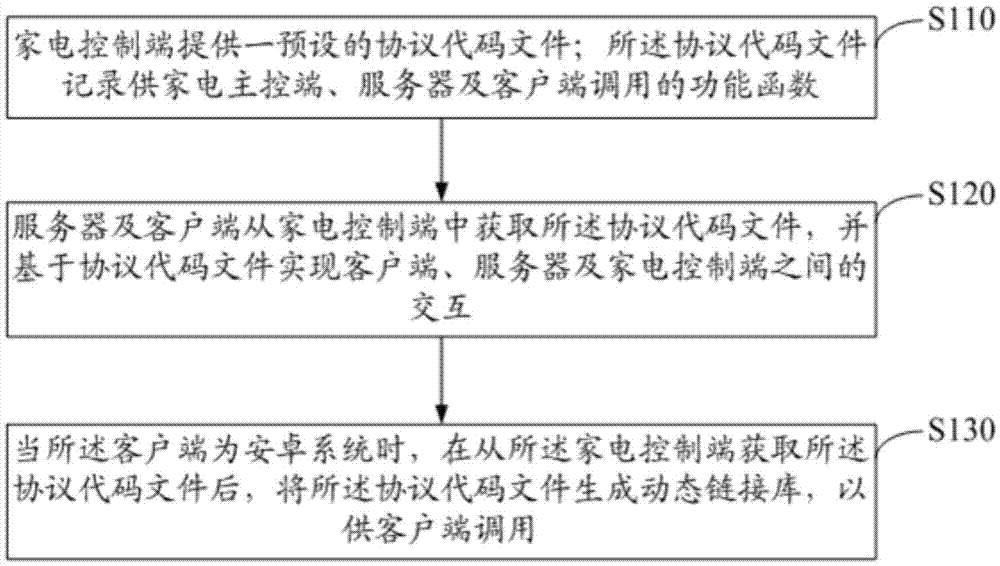

Control method and system of Internet-of-Things household electric appliances

ActiveCN105446154AIncrease development costsIncreased cost of testingComputer controlProgramme total factory controlControl systemComputer terminal

The invention discloses a control system of Internet-of-Things household electric appliances. The control system includes a household electric appliance control end, a server and a client; the household electric appliance control end is provided with a protocol code file; the protocol code file records functional functions which can be called by the household electric appliance control end, the server and the client; and the server and the client obtains the protocol code file from the household electric appliance control end and realizes interaction between the client, the server and the household electric appliance control end based on the protocol code file. The invention also discloses a control method of Internet-of-Things household electric appliances. With the control method and system of the invention adopted, development cost and test cost increase caused by a situation that each terminal maintains respective codes can be avoided.

Owner:GD MIDEA AIR-CONDITIONING EQUIP CO LTD +1

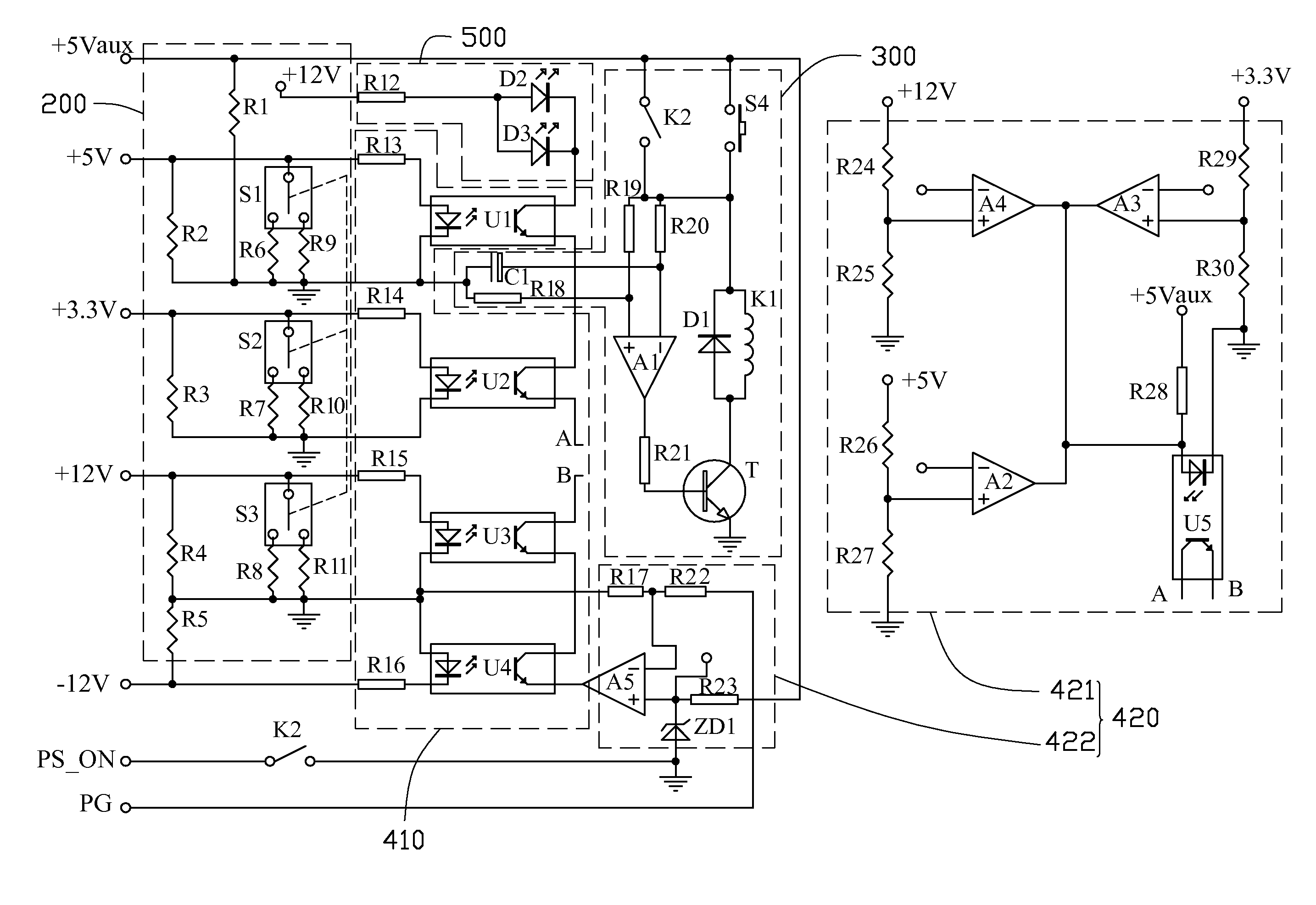

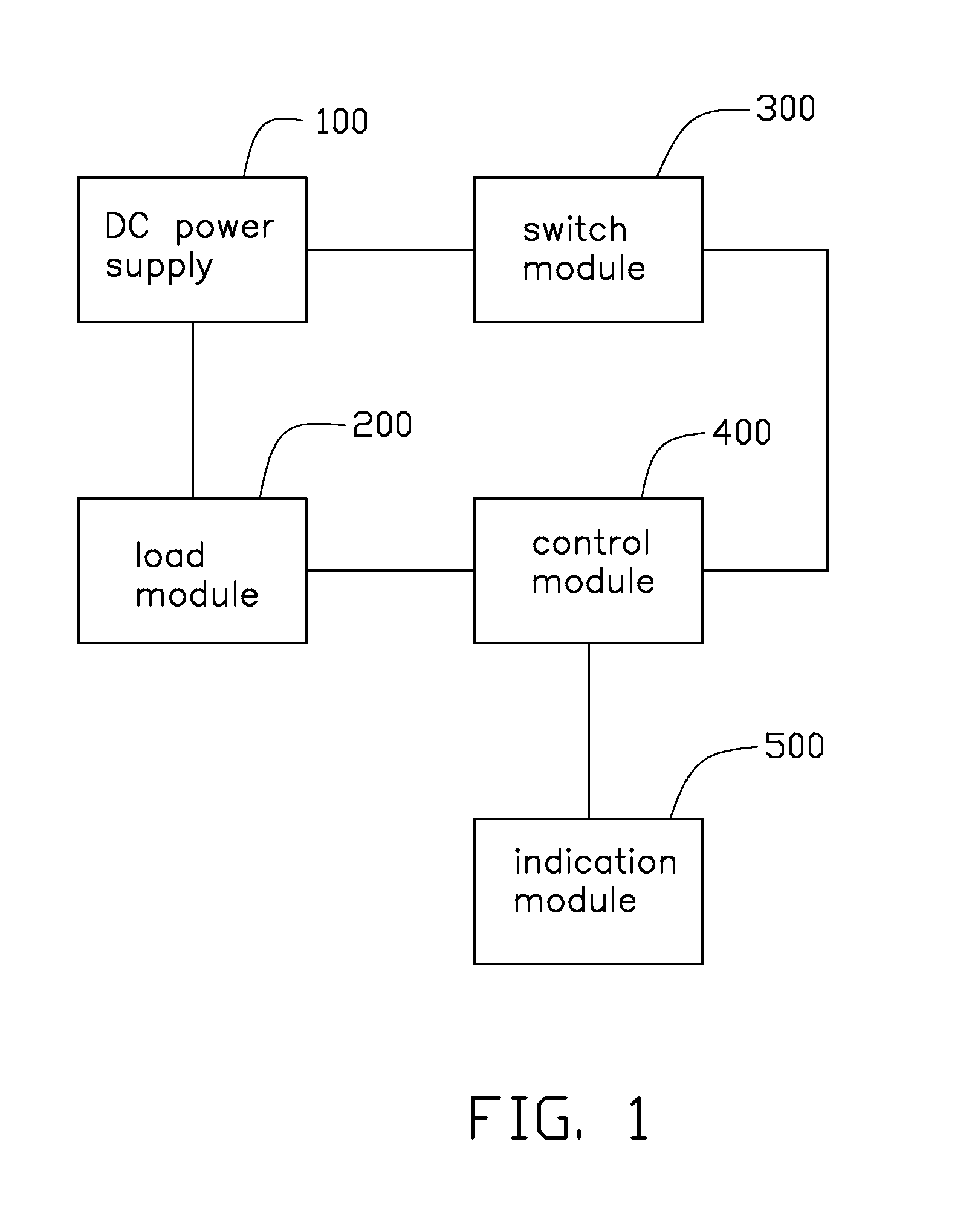

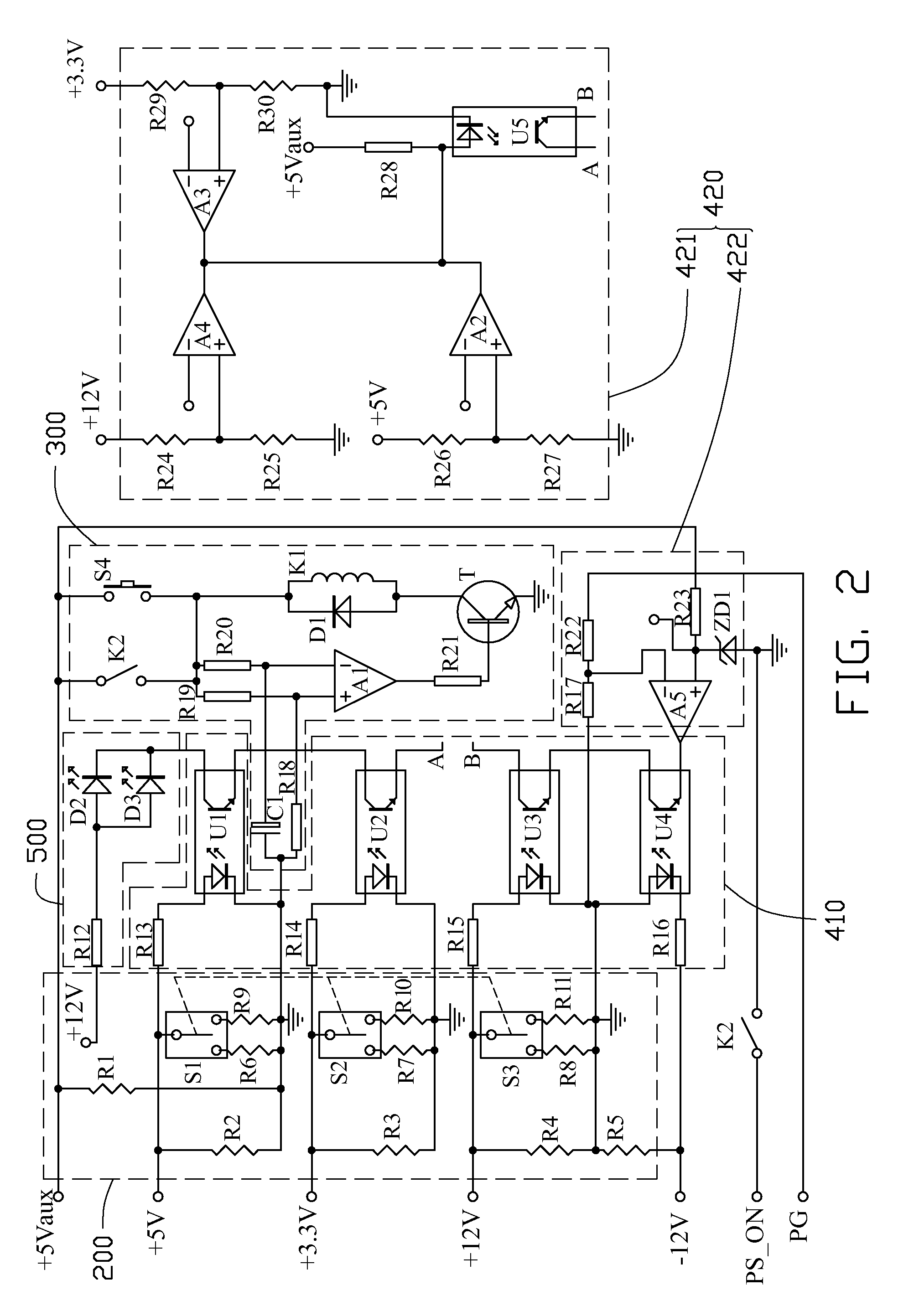

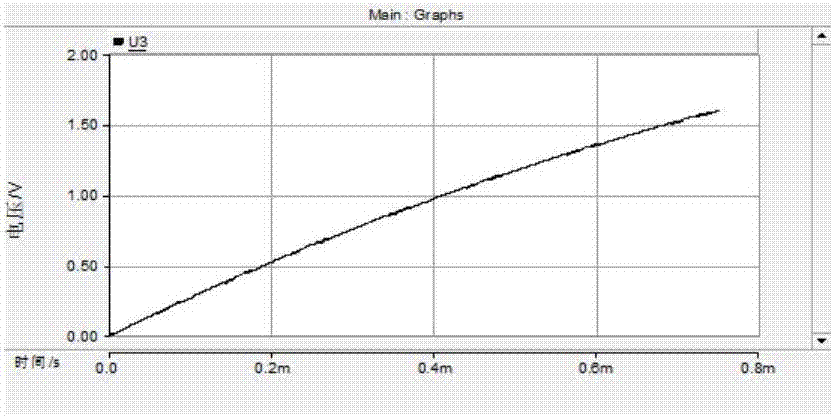

System for testing power supply performance

A system for testing a DC power supply performance includes a load module electrically coupled to the DC power supply, a switch module electrically coupled to the DC power supply, a control module electrically coupled to the load module and the switch module respectively, and an indication module electrically coupled to the control module. The control module includes a judge module and a comparison module. The judge module is configured for receiving DC voltage signals from the DC power supply; wherein the judge module is capable of turning on when the DC power supply is normal. The comparison module is configured for comparing the DC voltage signals with a reference voltage; wherein the comparison module is capable of outputting a control signal when the DC voltage signals are greater than the reference voltage. The indication module is configured for receiving the control signal and indicating status of the DC power supply.

Owner:HONG FU JIN PRECISION IND (SHENZHEN) CO LTD +1

Voice coil motor

ActiveUS20120051194A1Increased cost of testingLong initialization timeDC motor speed/torque controlAC motor controlAudio power amplifierElectric machine

A voice coil motor (VCM) includes a lens carrier physically connected to a magnetic device, an electromagnetic driving apparatus, constructed by a coil, a magnetic sensing element, a storage media and a controller. The magnetic sensing element detects a location of the lens carrier and outputs the location value relating to the location of the lens carrier via an amplifier. The storage media stores a gain value and an offset compensation value relating to the amplifier. The controller can make the lens carrier move between a top position and a bottom position in which the lens carrier can be moved within the voice coil motor. The lens carrier is moved using the coil interaction with a magnetic field of the magnetic device when current is applied to the coil.

Owner:VASSTEK INT

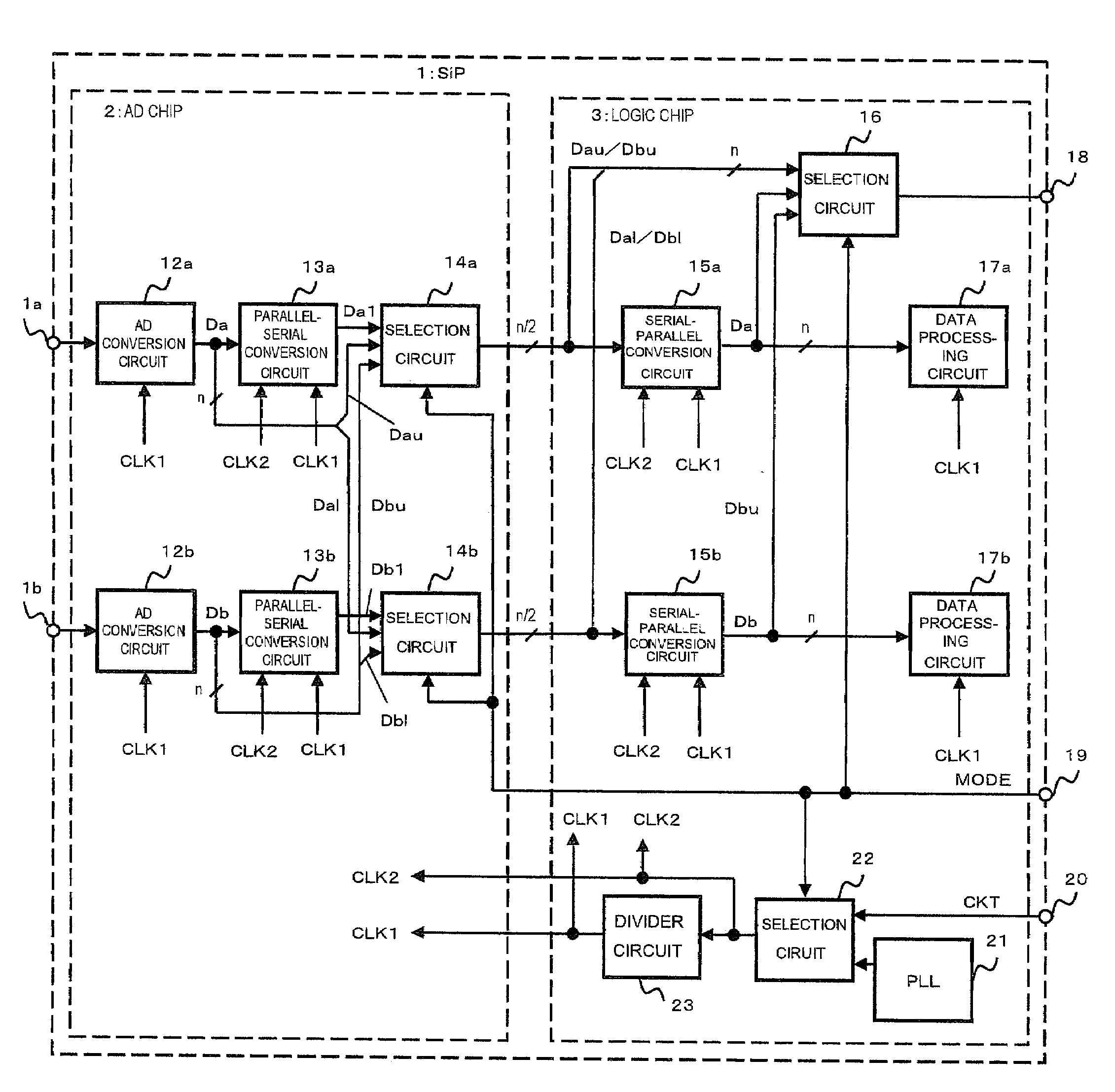

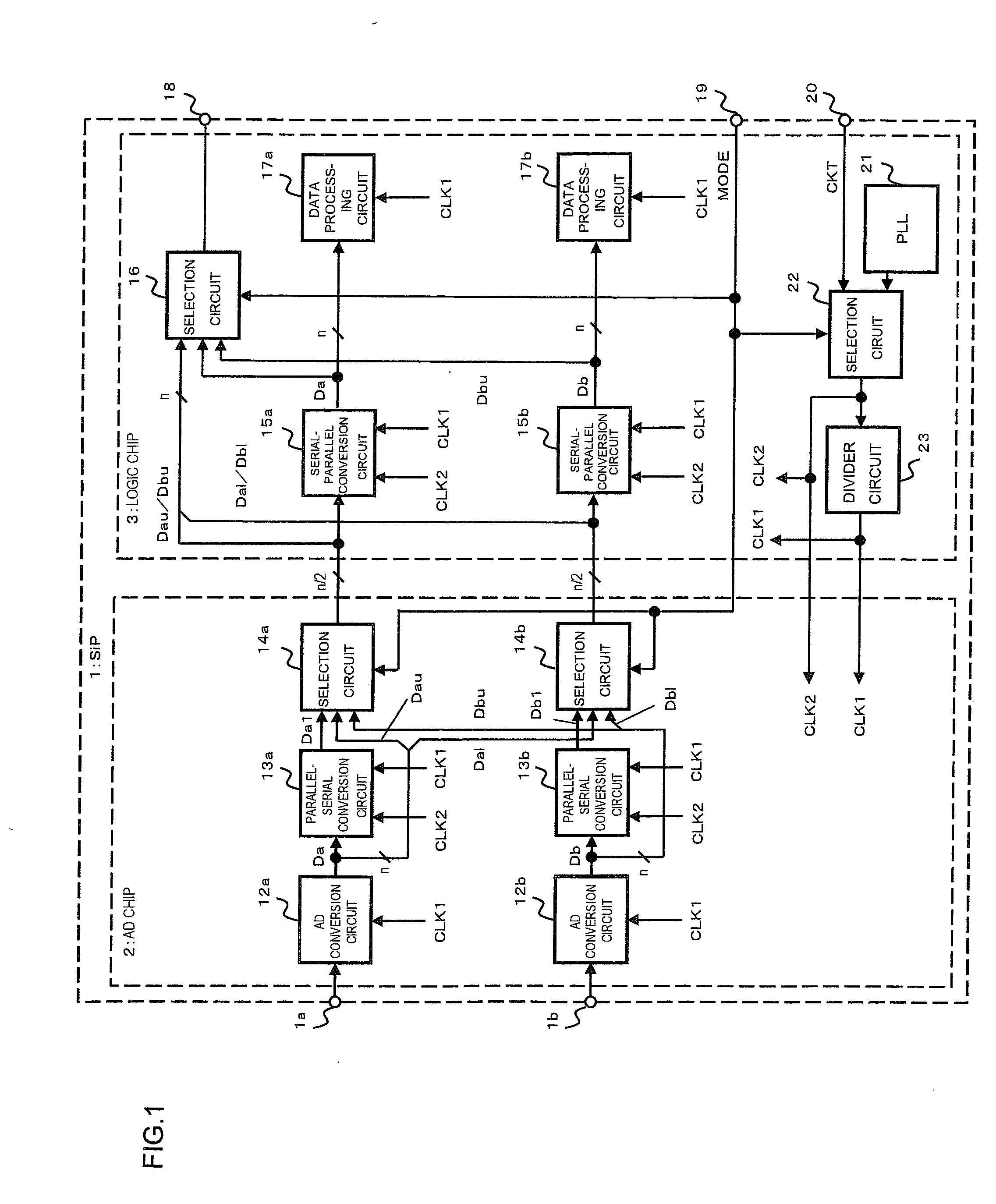

Semiconductor device

InactiveUS20090271140A1Reduce in quantityEfficient testingElectronic circuit testingResistance/reactance/impedenceData sortingComputer science

Cost of testing is reduced. An SiP (1) comprises an AD chip (2) and a logic chip (3) that perform transmission and reception of data. The AD chip (2) comprises AD conversion circuits (12a and 12b) that generate parallel data, parallel-serial conversion circuits (13a and 13b) that divide parallel data generated by the AD conversion circuits (12a and 12b) and perform time-based sorting, and selection circuits (14a and 14b) that select any of: output data of the parallel-serial conversion circuits (13a and 13b), or divided data obtained by dividing the parallel data so as to enable transmission of each thereof by said plural paths, and output to the logic chip (3). The logic chip (3) comprises serial-parallel conversion circuits (15a and 15b) that recover original parallel data from data sorted in a time-based manner, and a selection circuit (16) that selects: original parallel data obtained by combining the divided data, or original parallel data recovered by the serial-parallel conversion circuits (15a and 15b), and outputs to a terminal (18).

Owner:RENESAS ELECTRONICS CORP

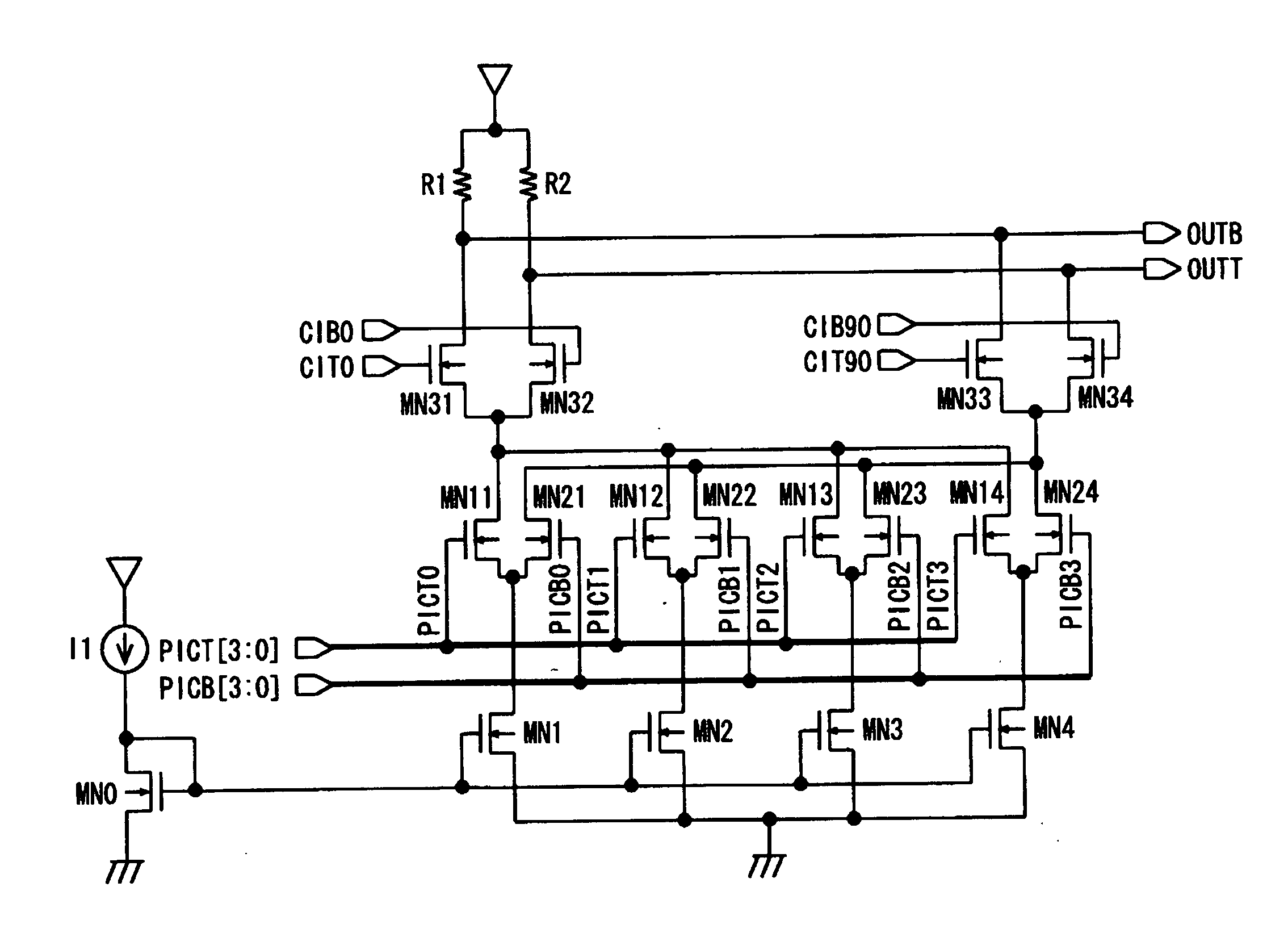

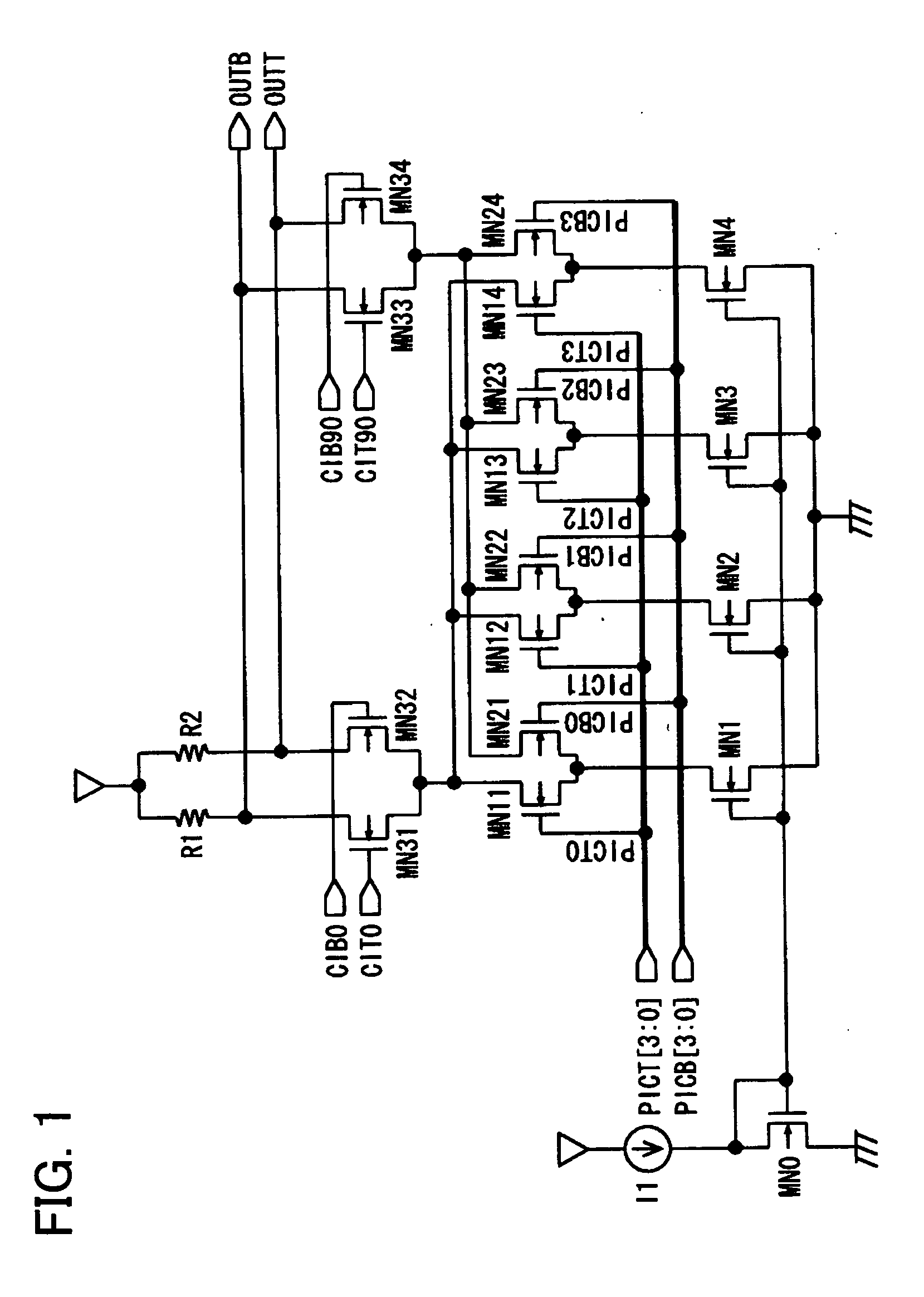

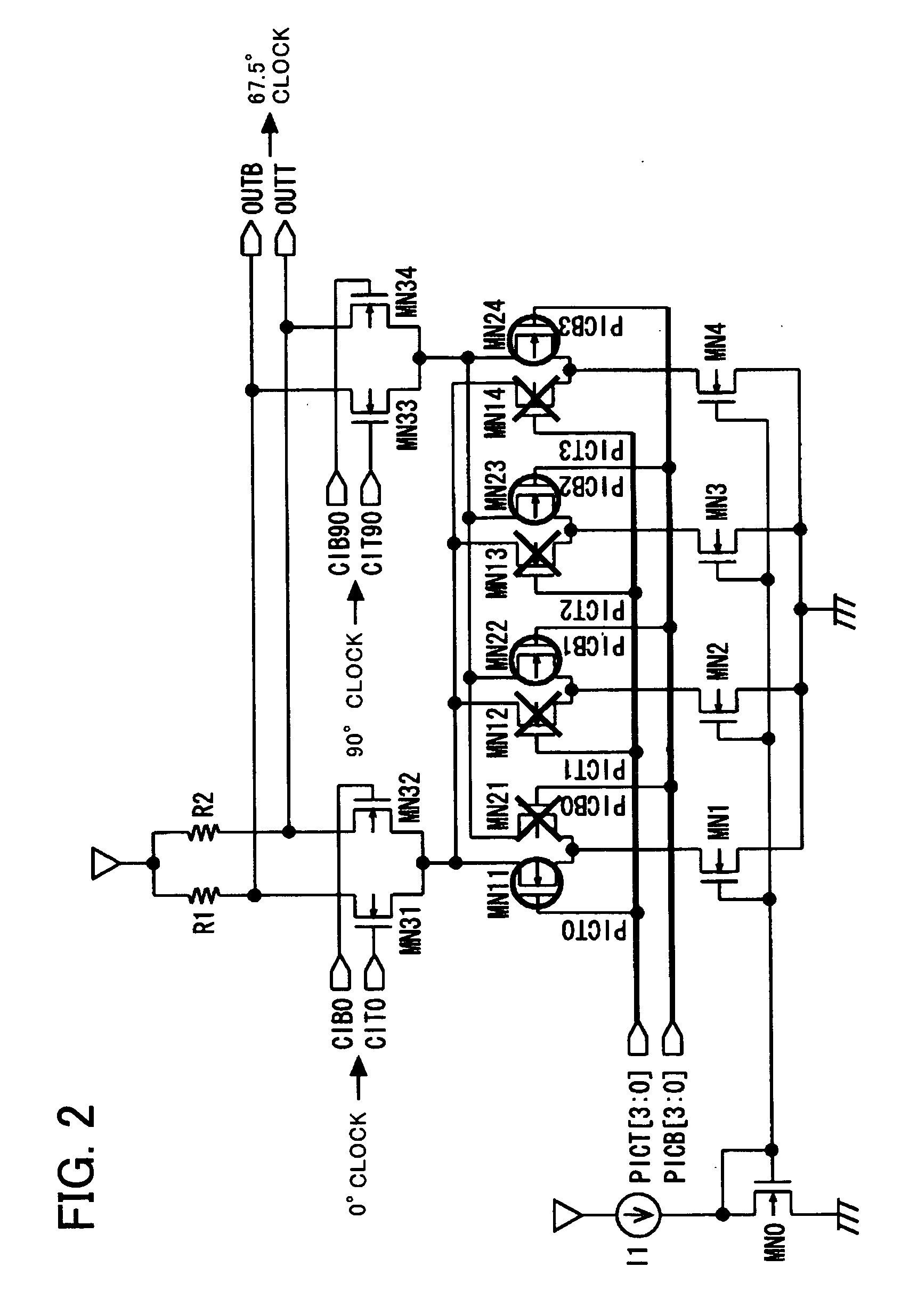

Semiconductor device and a method of testing the same

InactiveUS20070091701A1Improve testIncreased circuit areaSemiconductor/solid-state device testing/measurementElectronic circuit testingLoad circuitControl signal

The present invention comprises first and second differential pairs (MN31, MN32), (MN33, MN34) to which first and second differential input signals (CIB0, CIT0), (CIB90, CIT90) are input, output pairs of said first and second differential pairs being commonly connected to each other, further connected to load circuits (MN1 to MN4) and connected to differential output terminals (OUTT, OUTB); first to fourth current sources (MN1 to MN4); and first to fourth switch pairs (MN11, MN21), (MN12, MN22), (MN13, MN23), (MN14, MN24). Switches on one side of said first to N-th switch pairs are connected at one end thereof to said first to fourth current sources and are commonly connected at the other end thereof to said second differential pair. Control signals PICT [3:0], PICB [4:0] are connected to control terminals of said first to N-th switch pairs, so that a pattern is applied to the control signal. The operation of the current sources can be confirmed by a functional test in which output signals are compared with expected values.

Owner:RENESAS ELECTRONICS CORP

Leakage detection method for central air conditioner copper tube

InactiveCN103604572AEasy to check for tightnessIntuitive leak detectionMeasurement of fluid loss/gain rateVisibilityDifferential pressure

The invention discloses a leakage detection method for a central air conditioner copper tube. A differential pressure airtight leakage detection instrument is employed, with a detection mode of double end symmetrical counteraction, one end of a detected copper tube is connected to a detected end of the airtight leakage detection instrument, one end of a low leakage qualified copper tube is connected to the standard end of the airtight leakage detection instrument, high-pressure nitrogen or compressed air is introduced into the air inlet of the differential pressure airtight leakage detection instrument, the other end of each of the detected copper tube and the standard copper tube is sealed through a plugging head, and the detection of gas filling, pressure releasing, balancing, testing and gas discharging processes of the detected copper tube and the standard copper tube is carried out through the airtight leakage detection instrument at the same time. The method gas the advantages of simplicity, rapidness, accurate and reliable data, visibility, and good stability, a test field is clean and easy to maintain, and the disadvantages of the waste of water, high test cost and an easily dirty test field environment in the traditional water detection process can be effectively reduced.

Owner:ANHUI WAYEE SCI & TECH CO LTD

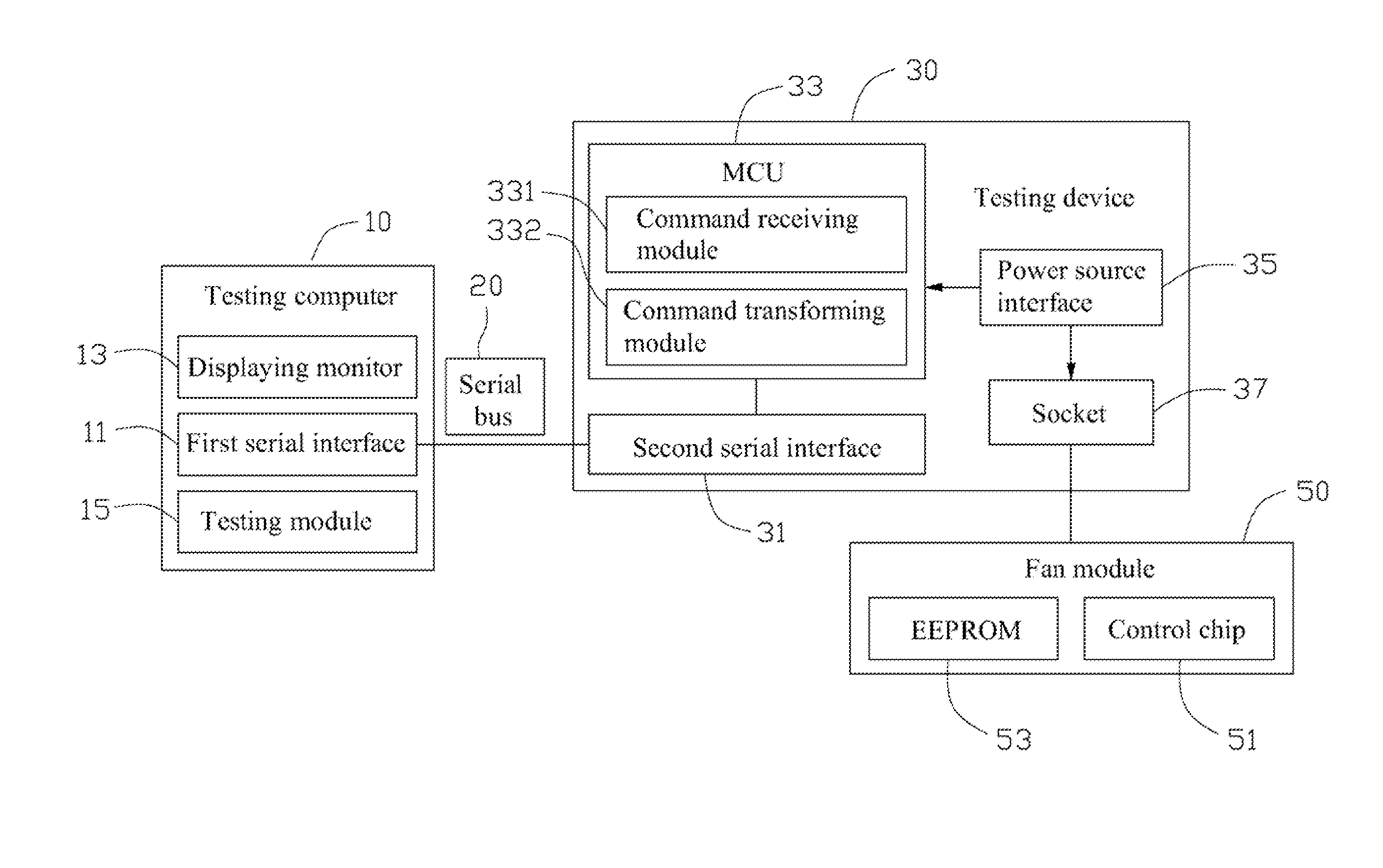

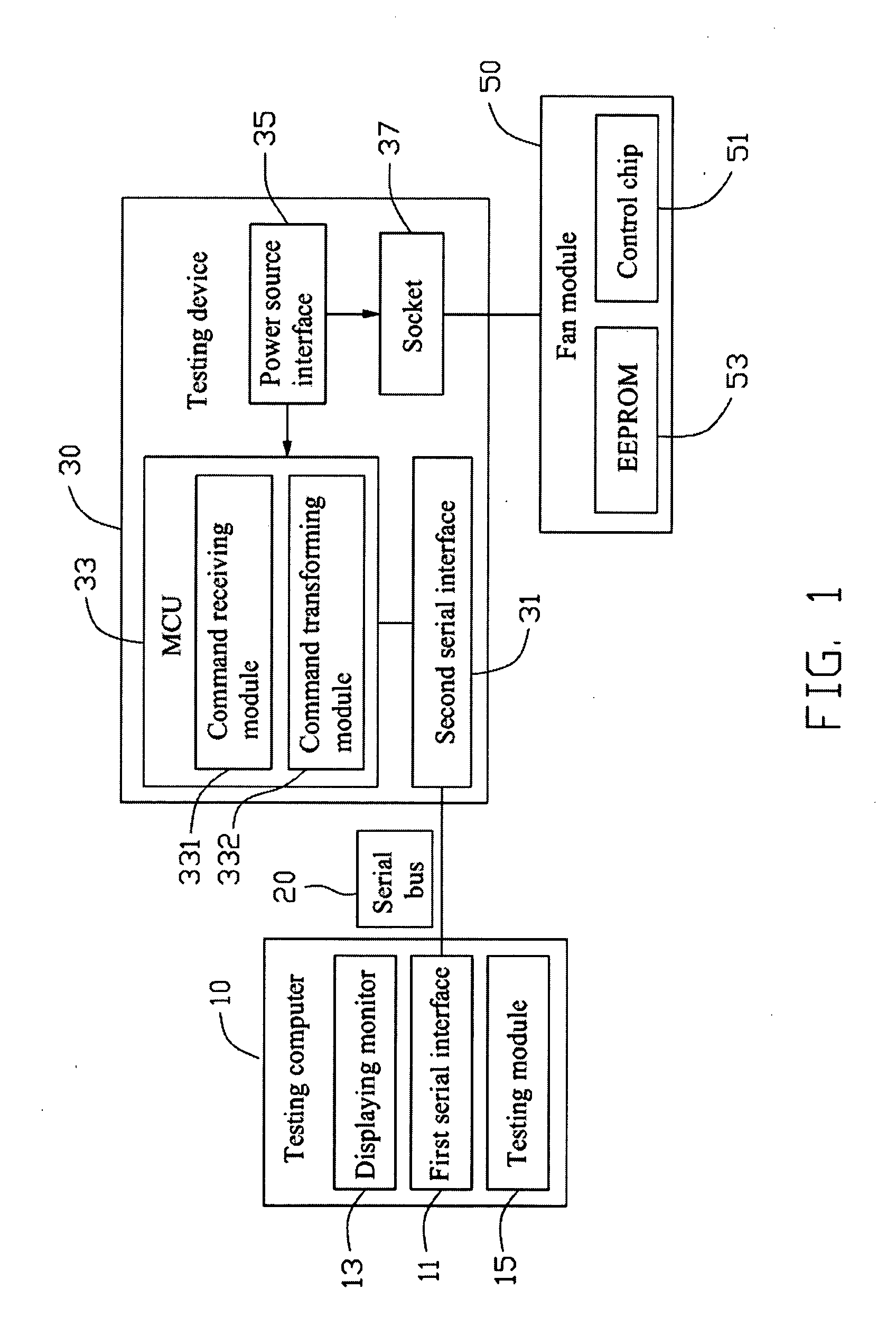

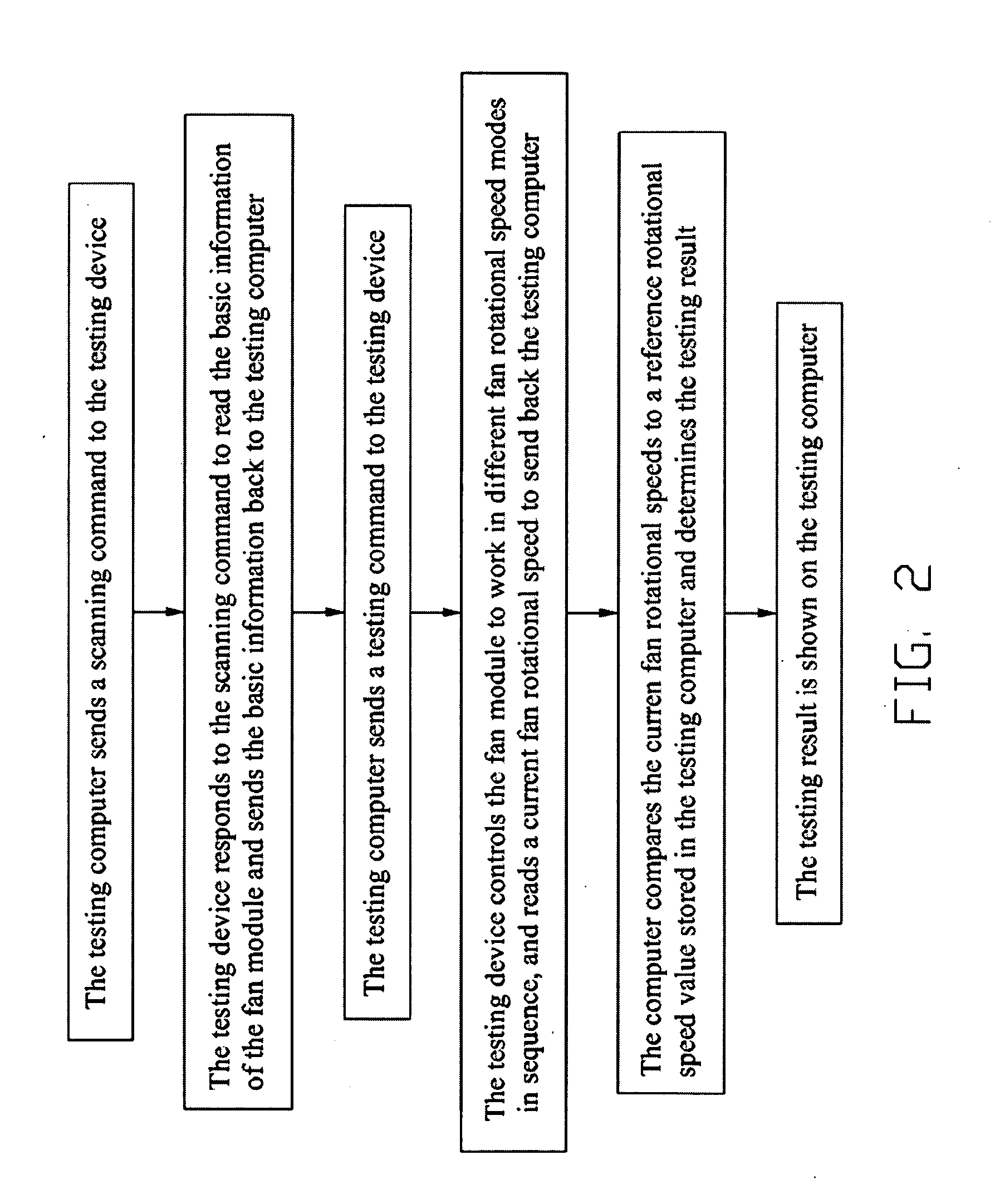

Testing system and method for fan module

InactiveUS20100268506A1Increased cost of testingVehicle testingDigital data processing detailsTest fixtureEngineering

A testing method for a fan module is provided. When the fan module is tested, a testing computer sends a testing command to a testing device first. Then, the testing device respond to the testing command and controls the fan module to work in a plurality of rotational speed modes in sequence. The testing device reads an actual rotational speed when the fan module works in one of the rotational speed modes and sends the actual rotational speed back to the testing computer. The testing computer compares the actual rotational speed with a corresponding reference rotational speed value stored in the testing computer, and determines the testing result. Finally, the testing result is shown.

Owner:HONG FU JIN PRECISION IND (SHENZHEN) CO LTD +1

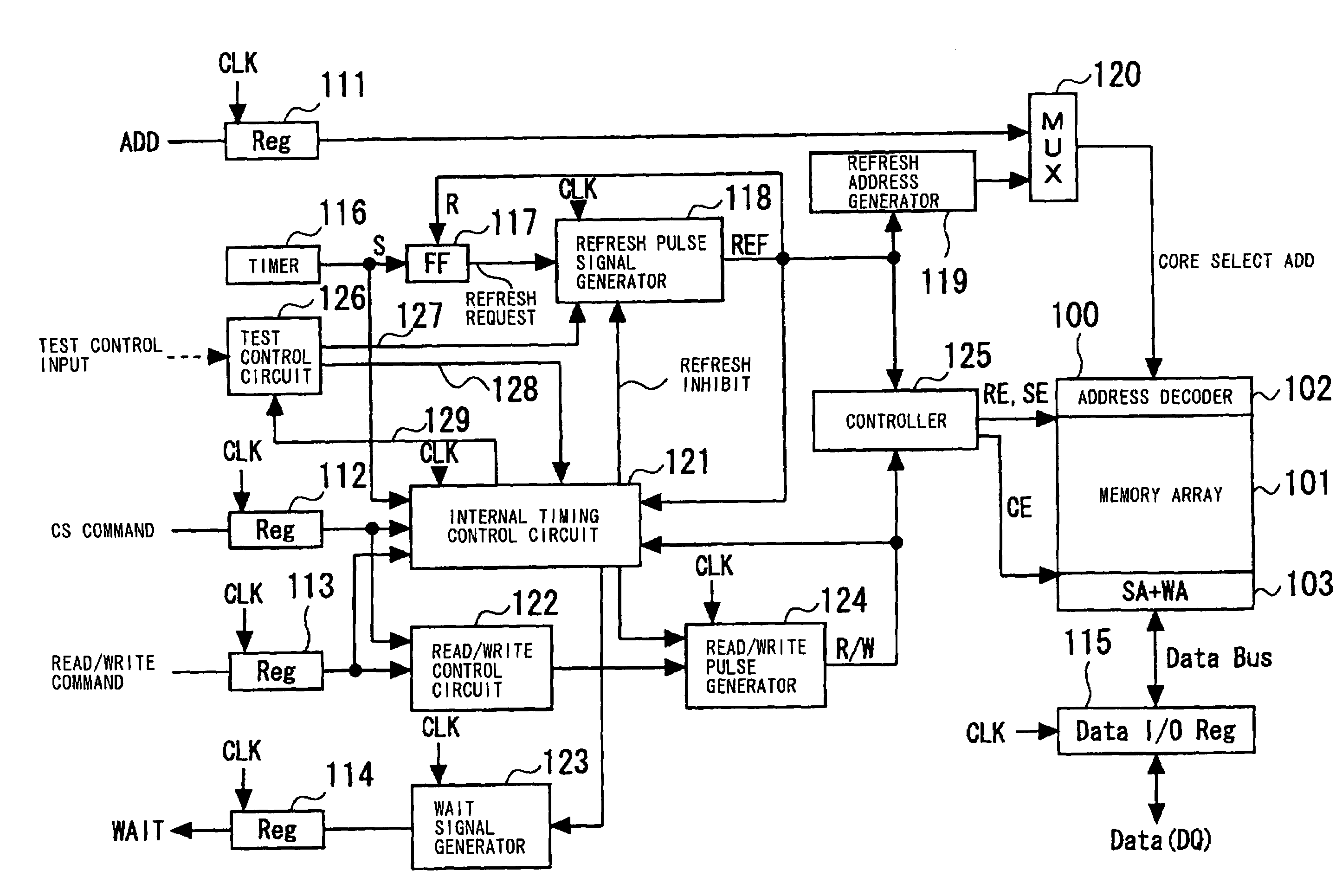

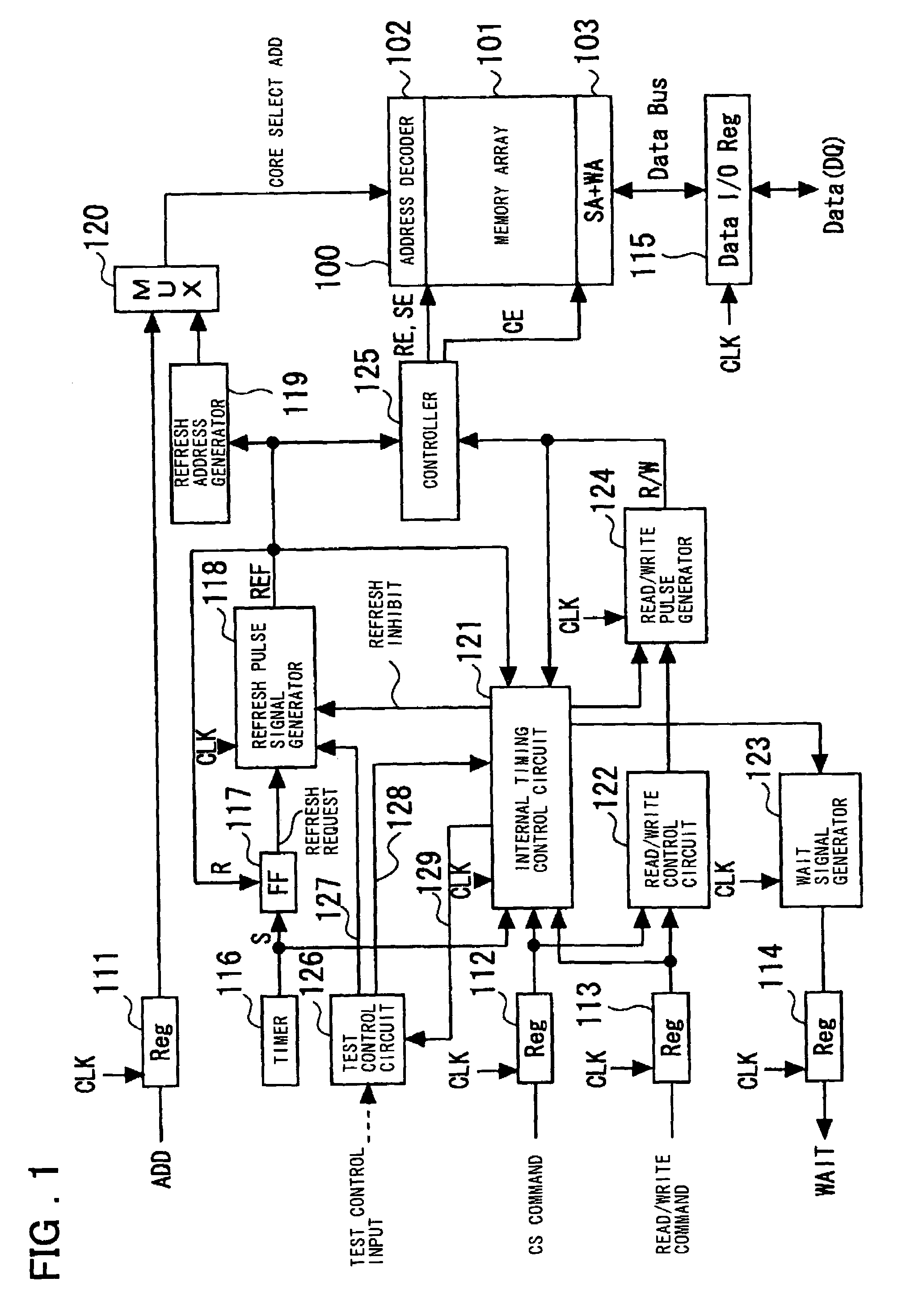

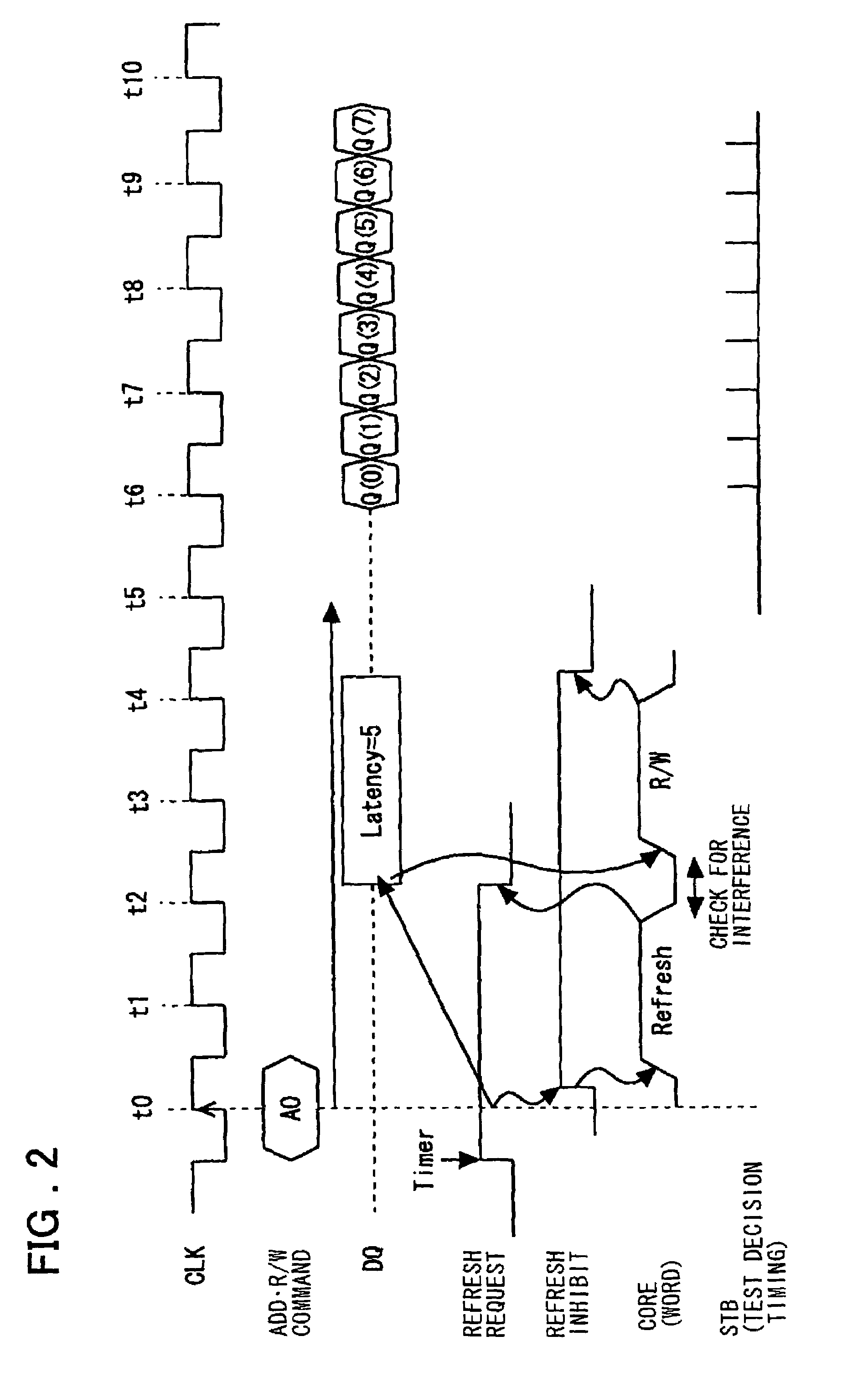

Semiconductor memory device, test circuit and test method

ActiveUS7652943B2Increased cost of testingImprove equipment qualityDigital storageControl circuitComputer science

Disclosed is a semiconductor memory device having memory cells that are in need of refresh for data retention, includes control circuits for necessarily generating the refresh immediately before the read / write operation, and for setting the latency to a first fixed value at all times, for the first mode during the testing, and for necessarily generating the refresh immediately after the read / write operation, and for setting the latency to a second fixed value at all times, for the second mode during the testing.

Owner:RENESAS ELECTRONICS CORP

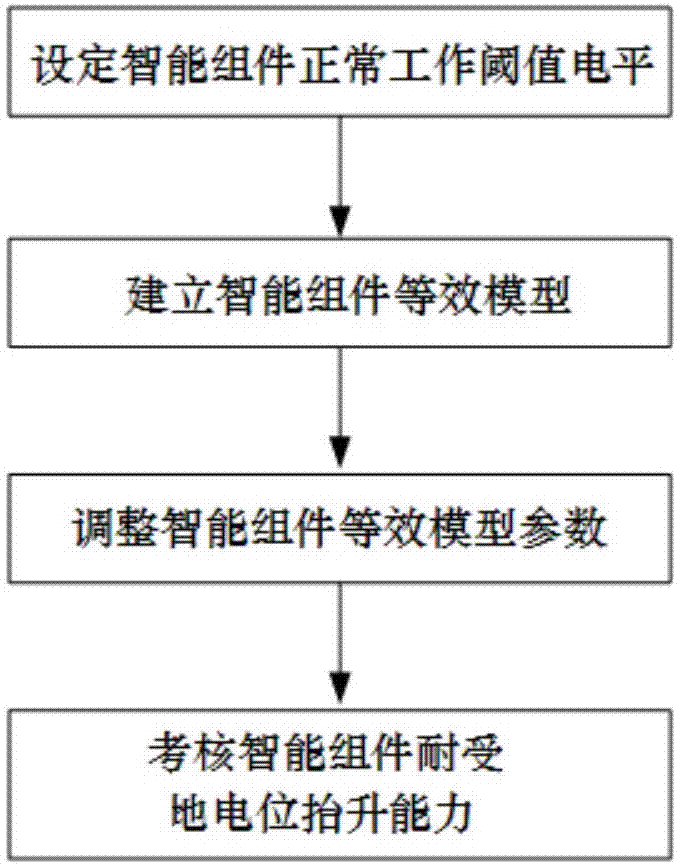

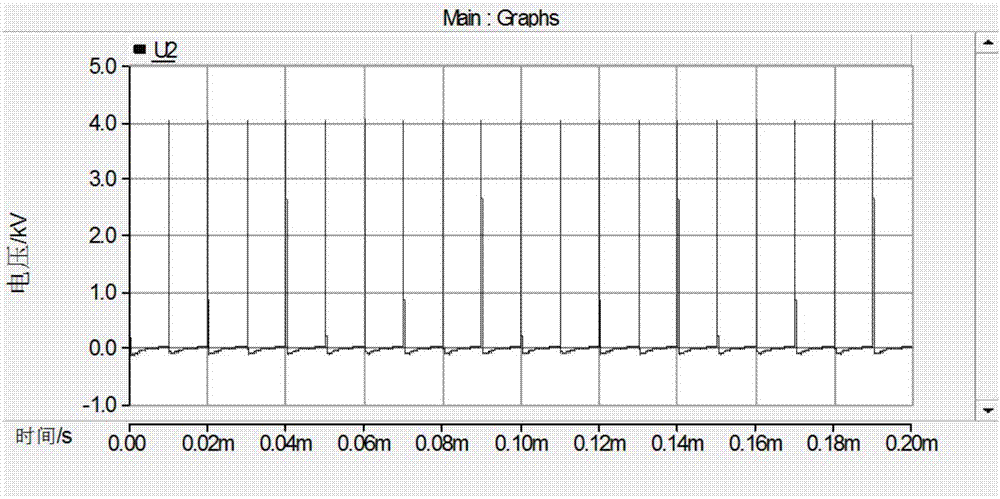

Method for evaluating ground potential rise tolerance capability of intelligent assembly

ActiveCN107449980AIncreased cost of testingQuickly grasp interference signal levelsTesting dielectric strengthDesign optimisation/simulationCharge currentPower flow

The invention discloses a method for evaluating ground potential rise tolerance capability of an intelligent assembly. The method comprises the following steps: 1) setting a normal working threshold level of the intelligent assembly; 2) establishing an equivalent model of the intelligent assembly; 3) adjusting parameters of the equivalent model of the intelligent assembly; and 4) evaluating ground potential rise tolerance capability of the intelligent assembly. For different voltage grades and GIS in different structures, difference of ground potential signals on a housing is larger under the condition of bus charging current switching, so that test cost is high when various ground potential signals are applied to the intelligent assembly one by one; and by applying the equivalent model of the intelligent assembly to simulation analysis, interference signal levels obtained after different actually-measured ground potential signals are applied to the intelligent assembly can be known quickly.

Owner:BEIHANG UNIV +2

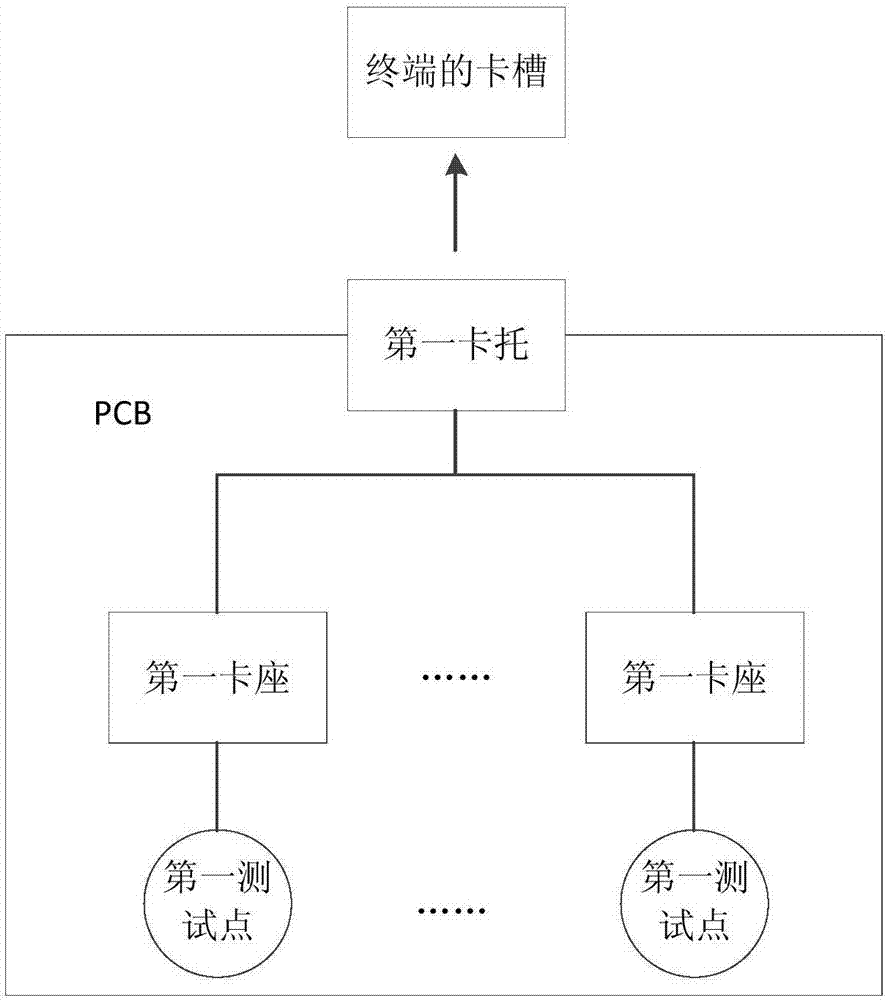

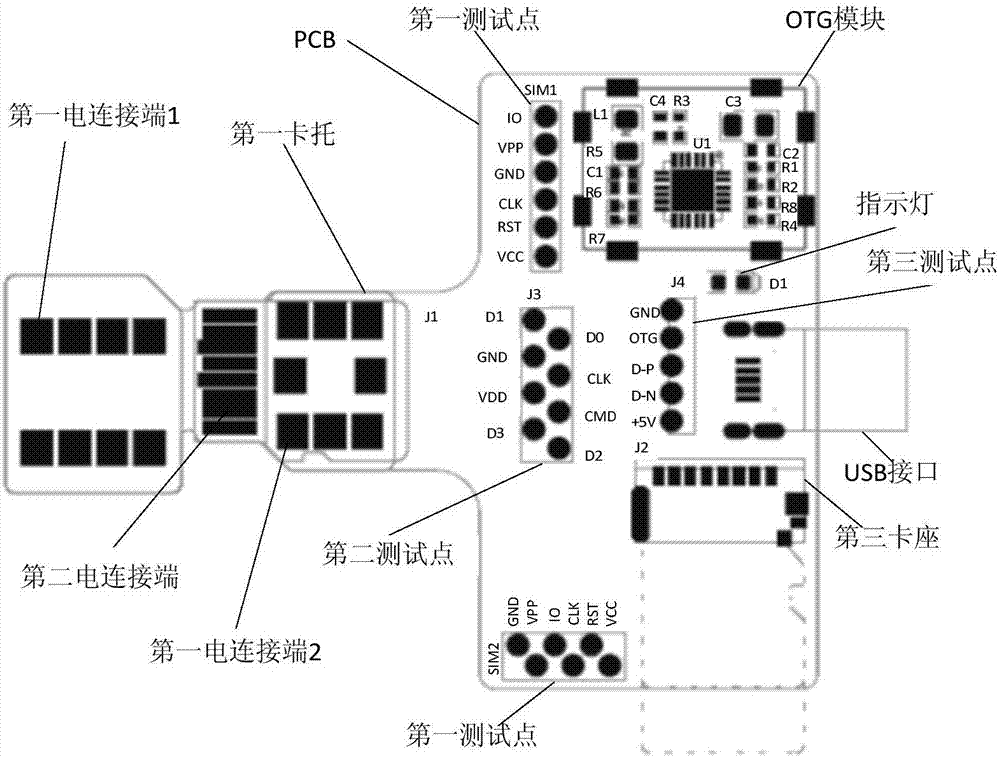

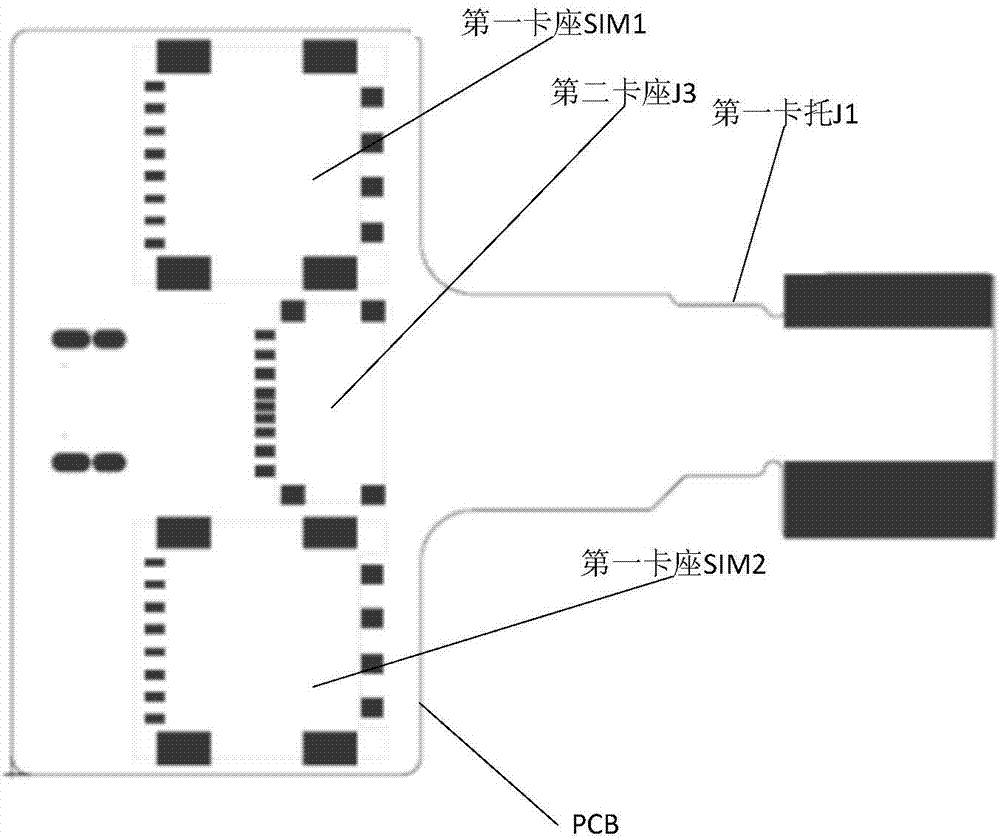

Terminal testing device

InactiveCN107231462AImprove test efficiencyIncreased cost of testingSubstation equipmentTest efficiencyEngineering

The invention provides a terminal testing device. The terminal testing device comprises a printed circuit board PCB, a first card support arranged on the PCB, and at least one first card seat used for installing a subscriber identity module SIM card, wherein the first card support is electrically connected with the at least one first card seat, at least one first electric connecting terminal is arranged on the first card support, and when the first card support is inserted in a card slot of the terminal, the terminal reads the SIM card installed on each first card seat through the at least one first electric connecting terminal. The terminal testing device provided by the invention can improve the test efficiency of the functions of the SIM card of the terminal, then the test time can be shortened, and the test cost is reduced.

Owner:BEIJING XIAOMI MOBILE SOFTWARE CO LTD

Fabrication method of semiconductor integrated circuit device

InactiveUS7306957B2Shorten the timeIncrease demandSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsMonoboardTime difference

A memory test is carried out on semiconductor integrated circuit devices including a semiconductor memory at low cost with efficiency. In a test burn-in system, twenty-four test boards are processed in sequence with time differences, and the test boards are circulated one by one. In this case, the memory test is conducted with the sequence of single board processing: the test is started with a test board in which semiconductor integrated circuit devices have been embedded, and semiconductor integrated circuit devices are discharged, beginning with a test board that has undergone the test.

Owner:RENESAS ELECTRONICS CORP

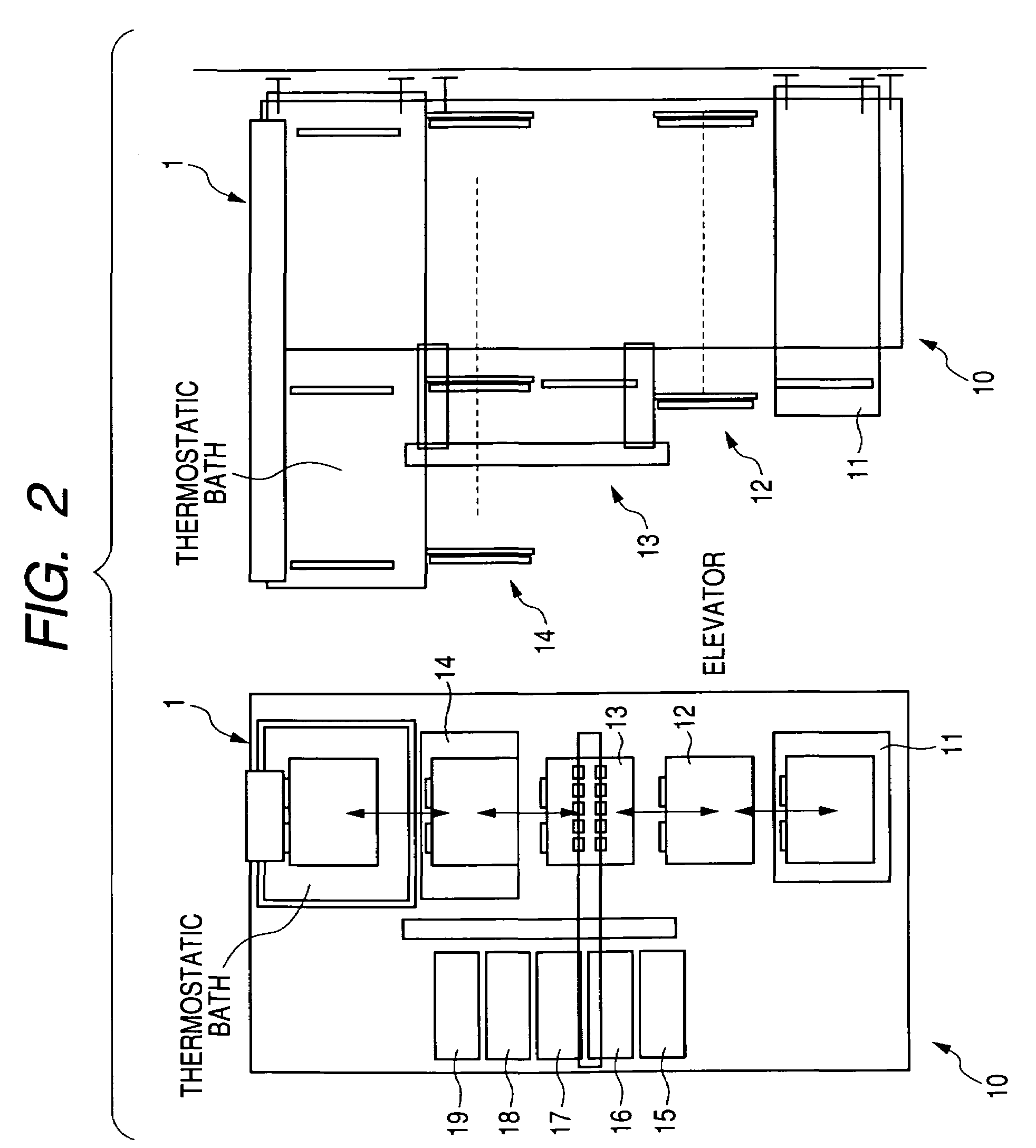

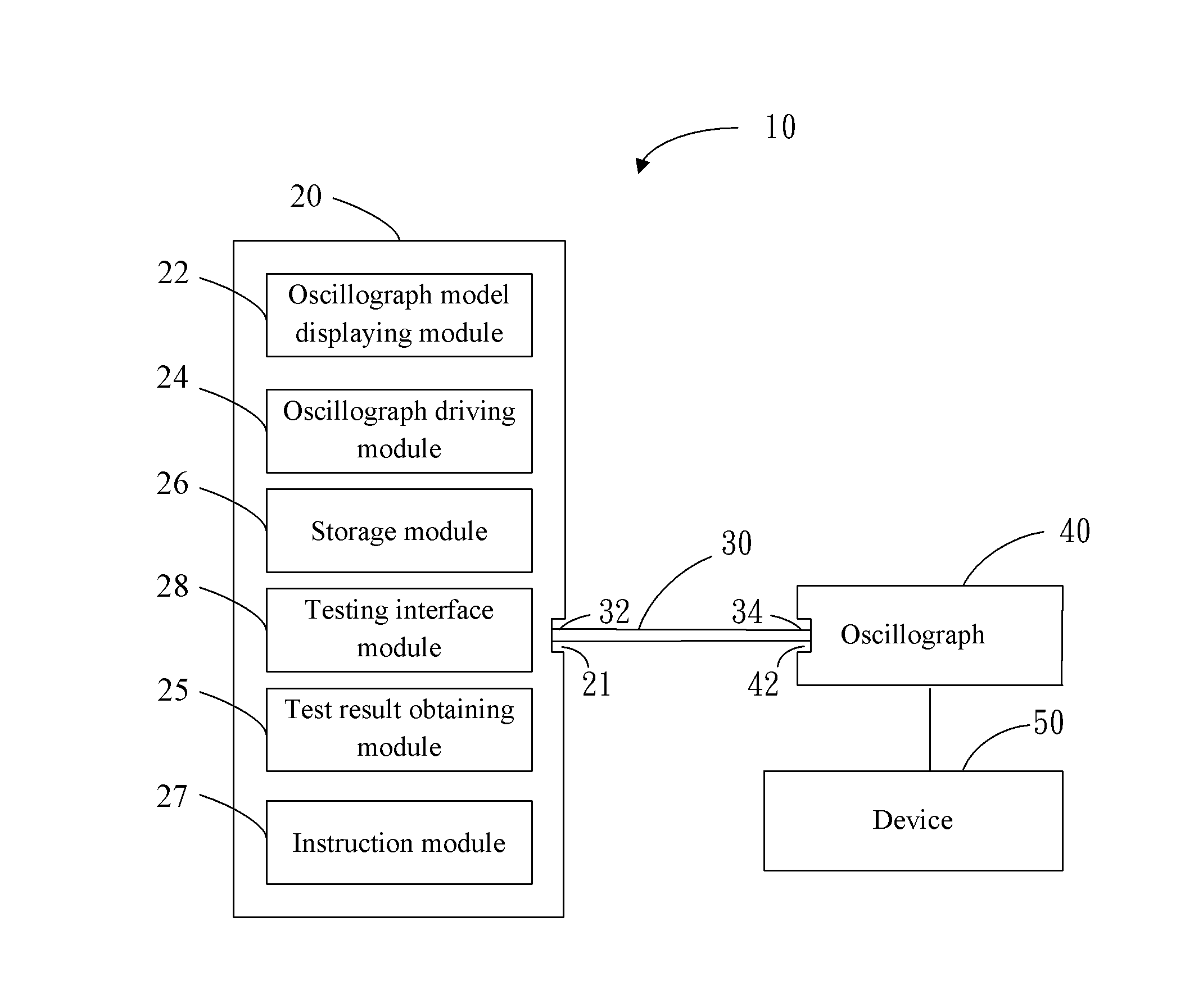

Testing system

InactiveUS20130311122A1Increased cost of testingDigital variable displayCurrent/voltage measurementComputer moduleEngineering

A testing system includes a computer, a connection cord, and a number of oscillographs. The each oscillograph has a GPIB port. The computer has a USB port. The connection cord has a USB connector for connection with the USB port and a GPIB connector for selectively connecting to a GPIB port of one of the oscillographs. The computer includes an oscillograph model displaying module, an oscillograph driving module, a storage module, and a testing interface module. The oscillograph model displaying module displays a number of oscillograph models for a user to select. The oscillograph driving module loads an oscillograph driver corresponding to the selected oscillograph model. The storage module stores a plurality of codes associated with a number of testing functions for different oscillographs. The testing interface module transmits the codes to the oscillograph, thereby driving the oscillograph to perform the associated testing functions to test a device.

Owner:HONG FU JIN PRECISION IND (SHENZHEN) CO LTD +1

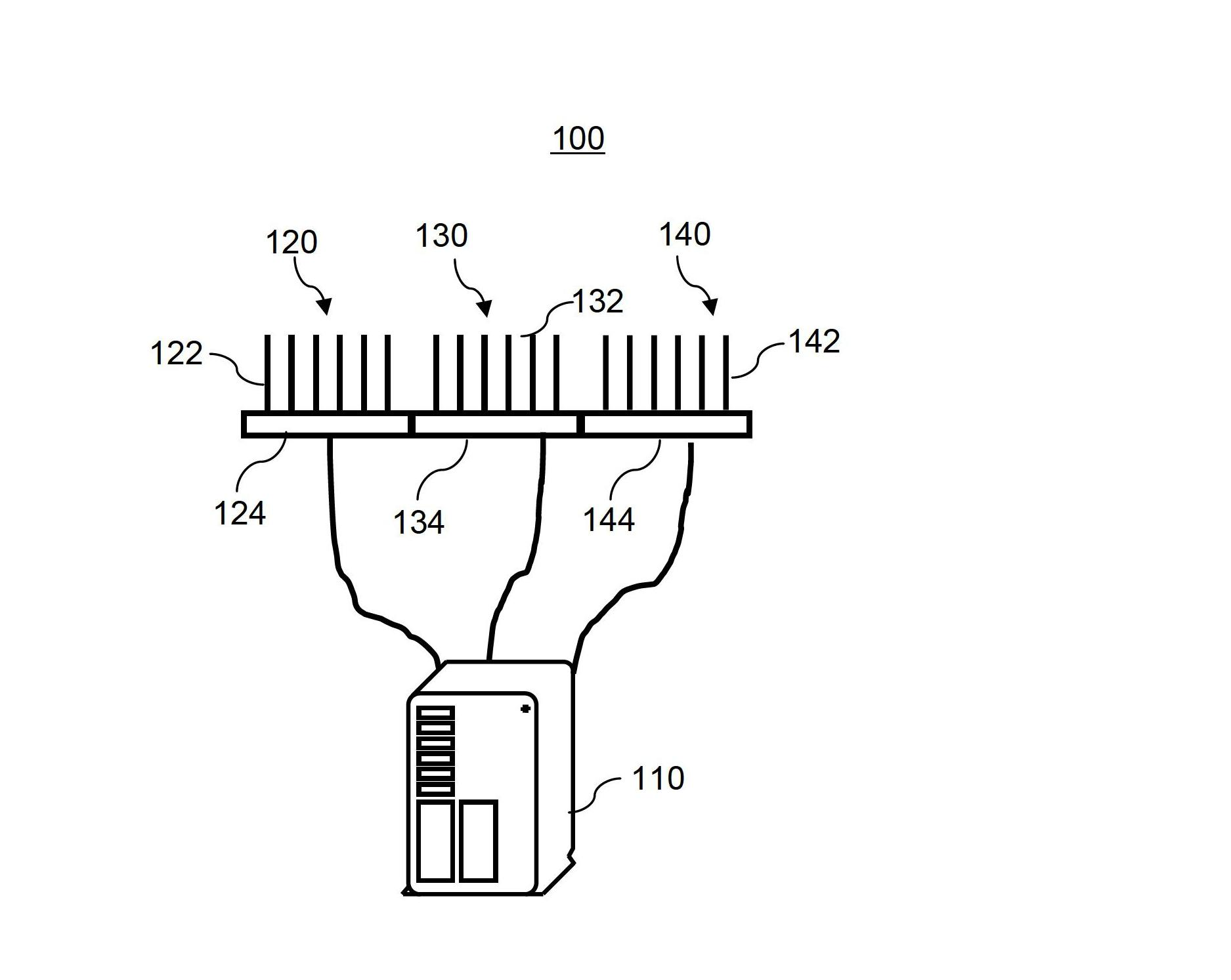

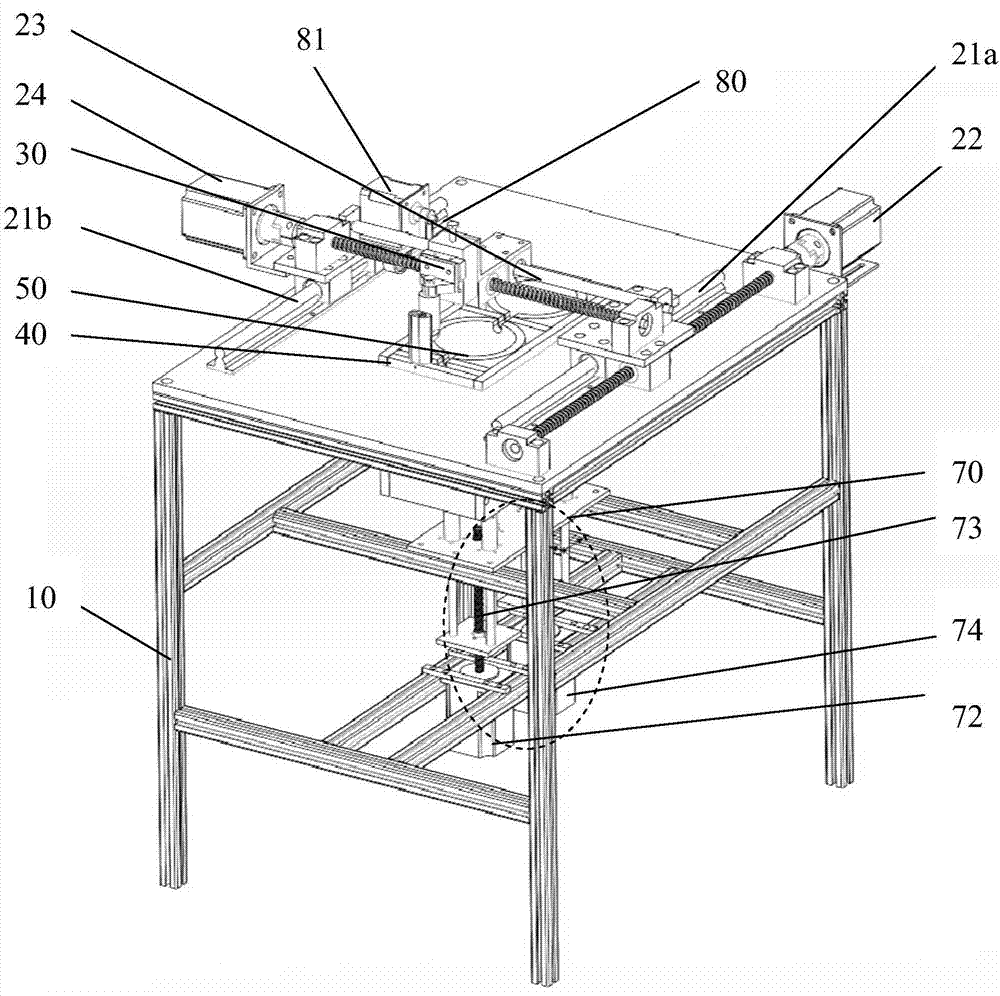

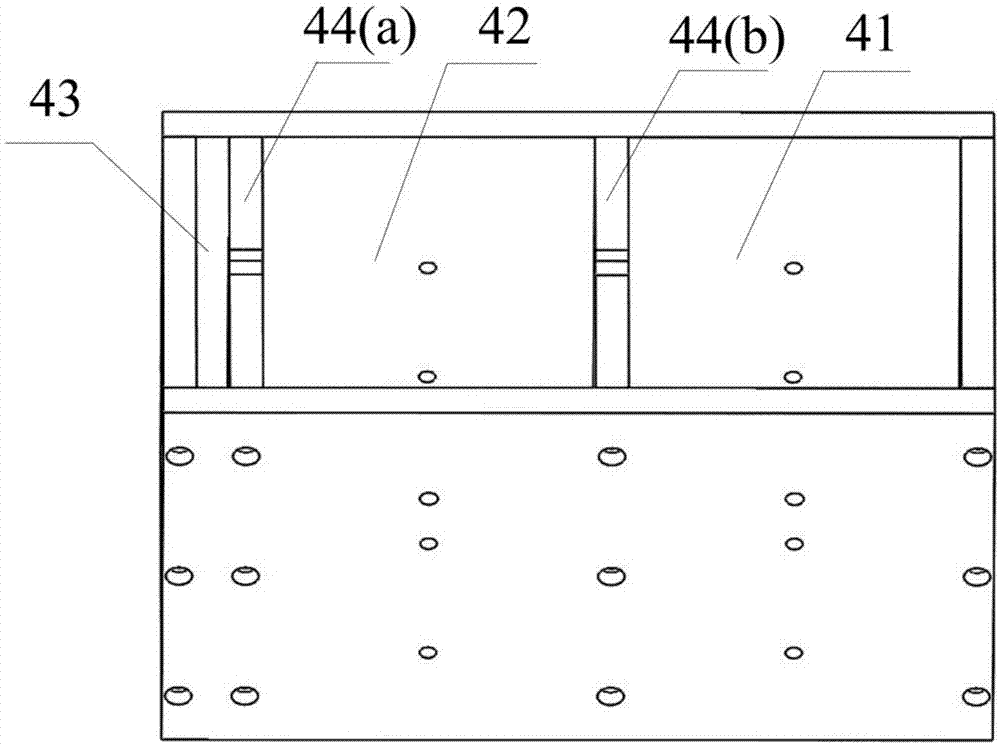

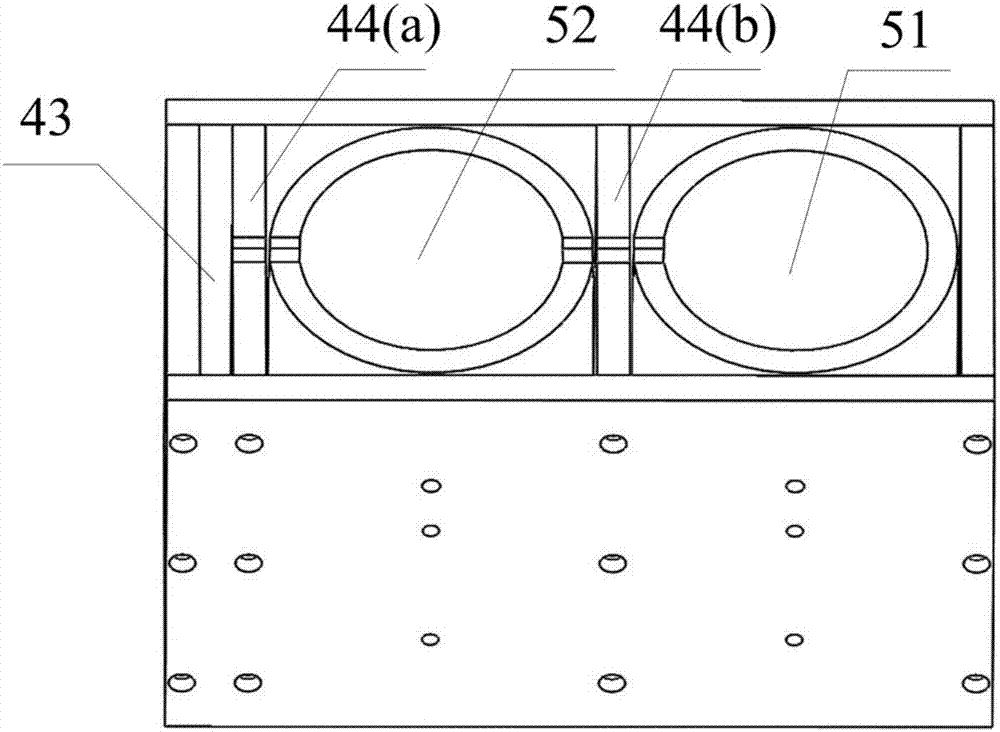

High-precision double-forming-mode 3D printer and forming method thereof

ActiveCN107984755ASwitch back and forth quicklyImprove experience3D object support structuresApplying layer meansEngineeringPrinting ink

The invention discloses a high-precision double-forming-mode 3D printer and a forming method thereof. The high-precision double-forming-mode 3D printer comprises a frame support structure, a plane mechanical motion structure, a piezoelectric micro nozzle structure and a powder forming bin which is inlaid in the upper surface of the frame support structure. A detachable gluing forming bin is arranged in the powder forming bin. A powder forming platform, a gluing forming platform and a vertical mechanical motion structure are arranged on the lower portion correspondingly, and the vertical mechanical motion structure drives the platforms to move. The plane mechanical motion structure, the piezoelectric micro nozzle structure and the vertical mechanical motion structure are connected to mastercontrol circuit control unit. According to the high-precision double-forming-mode 3D printer and the forming method thereof, the gluing forming bin is selectively installed in the powder forming bin,so that forming printing of different types of forming materials can be achieved; and through the piezoelectric glass combined micro nozzle structure, controllability of printing ink quantity can beimproved significantly, and the high-precision double-forming-mode 3D printer is particularly suitable for powder bonding of single-nozzle large ink quantity or gluing reflecting 3D printing forming.

Owner:NANJING NORMAL UNIVERSITY

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com