Semiconductor memory device, test circuit and test method

a memory device and semiconductor technology, applied in the field of semiconductor memory devices, can solve the problems of increasing test costs, unable to ensure the correctness of device quality, and unable to ensure so as to reduce the time and cost of testing and improve the quality of the devi

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

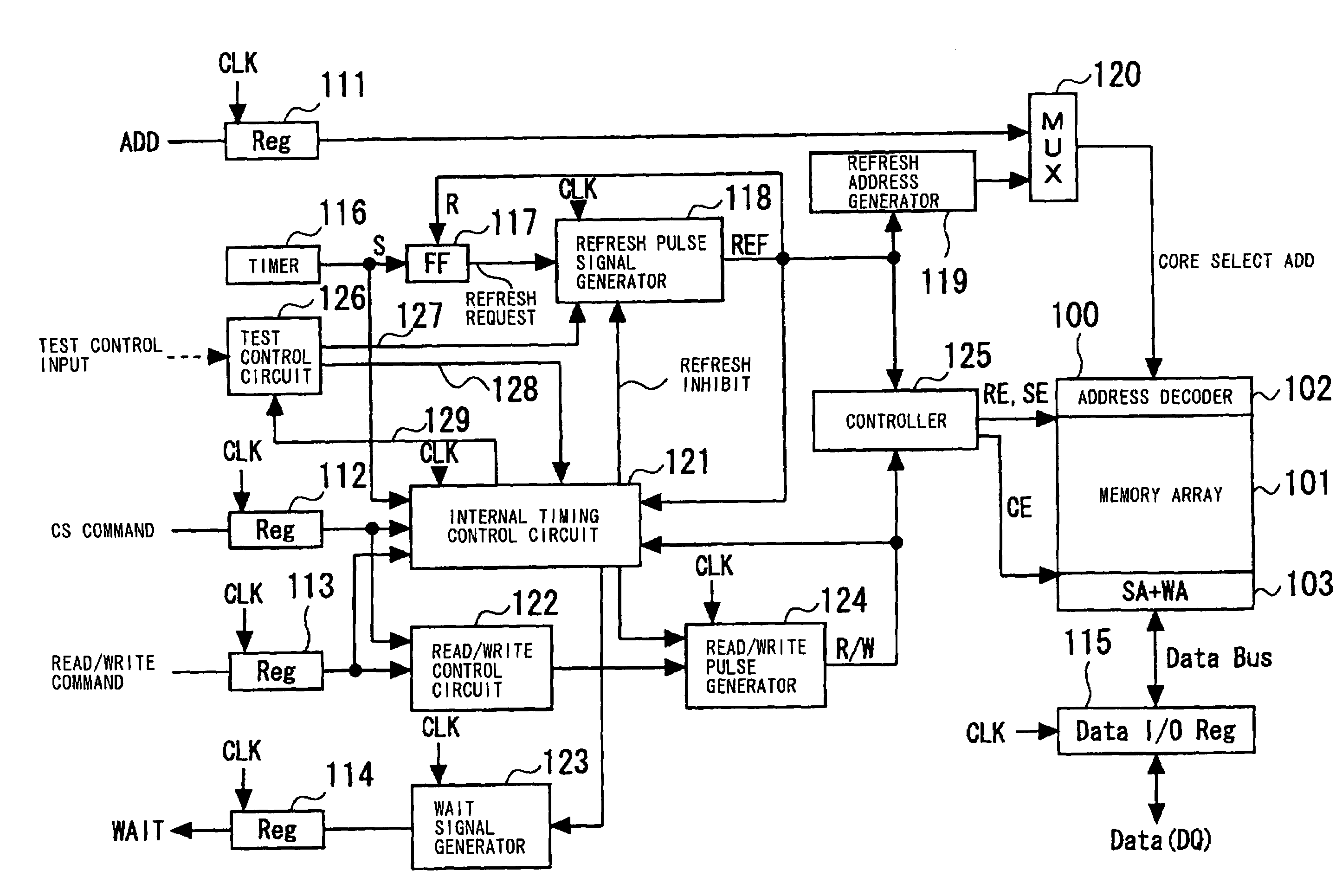

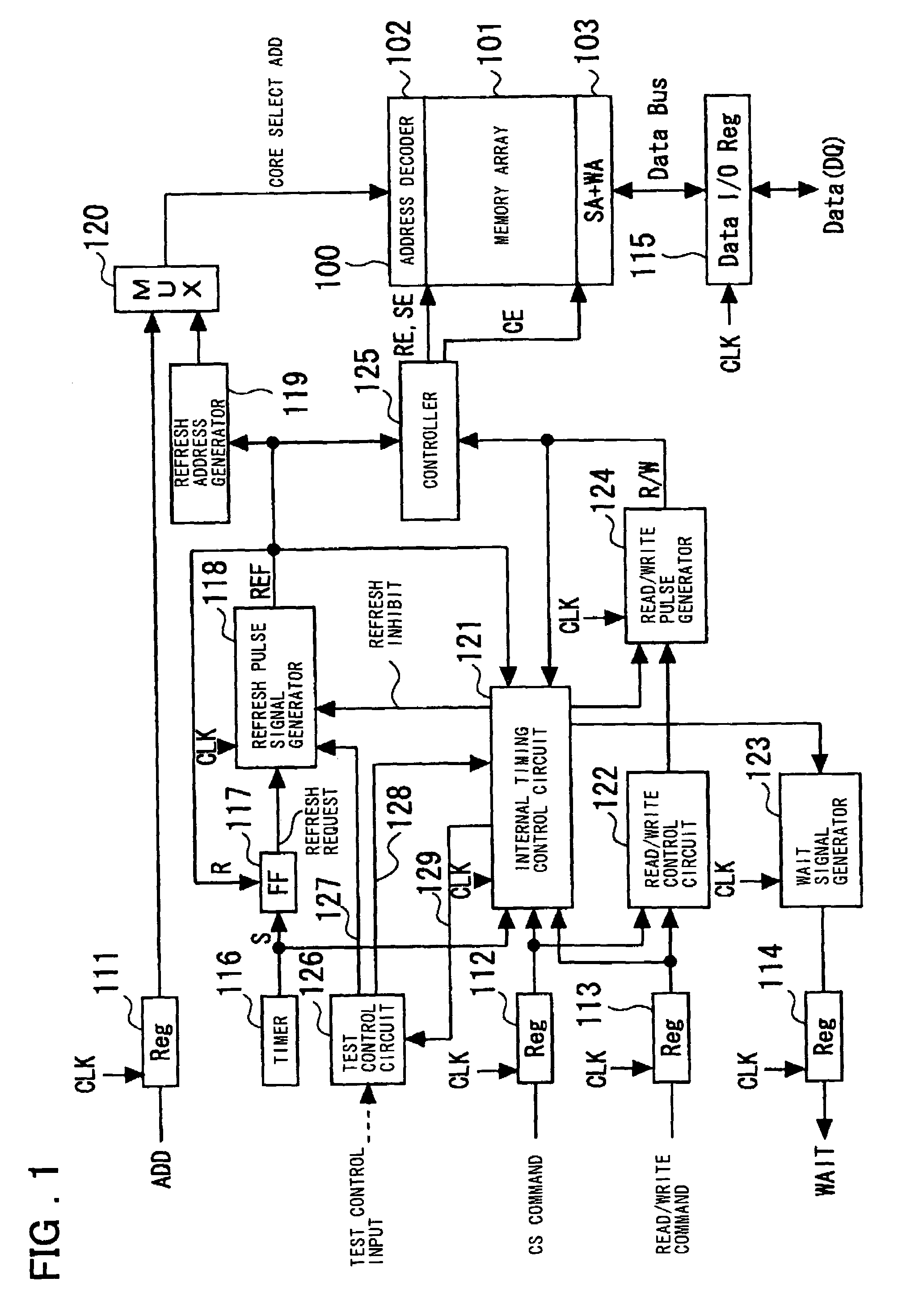

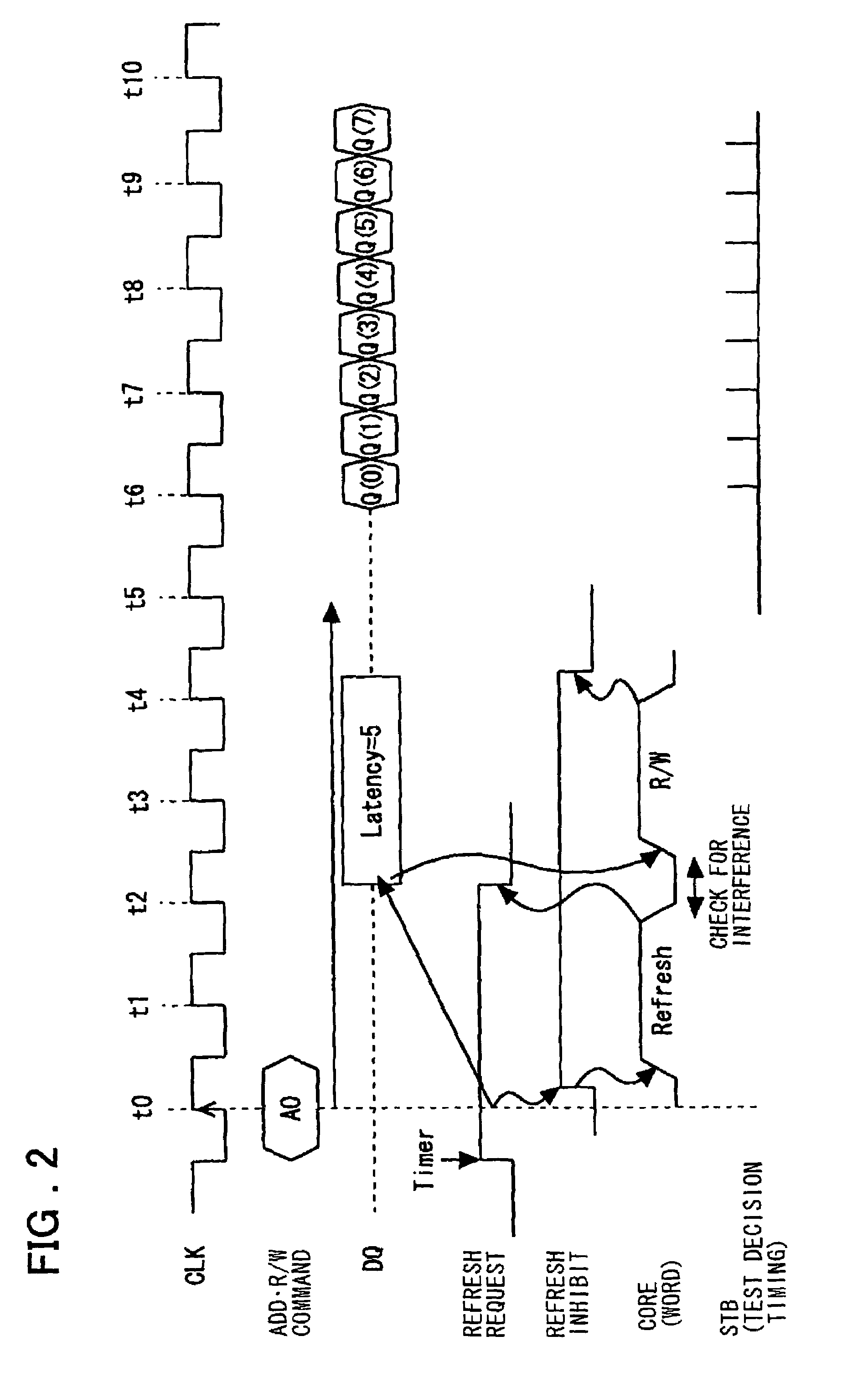

[0048]For elucidating the present invention in further detail, reference is made to the accompanying drawings. In an embodiment of the present invention, the relationship between the temporally forward state and the temporally backward state of the read / write and the refresh is prepared at the time of testing, in connection with the temporally preceding or succeeding states of the read / write and the refresh, such that the state of closest proximity of refresh→read / write (mode 1) and the state of closest proximity of read / write→refresh (mode 2) can be generated intentionally.

[0049]That is, in the mode 1, refresh is necessarily generated immediately before the read / write operation, and the latency is fixed at all times at a constant value, such as at 5. In the mode 2, refresh is necessarily generated immediately after the read / write operation, and the latency is fixed at all times at a constant value, such as at 3. In the mode 1, the read / write is fixedly generated immediately after t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More