Patents

Literature

97 results about "Track and hold" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

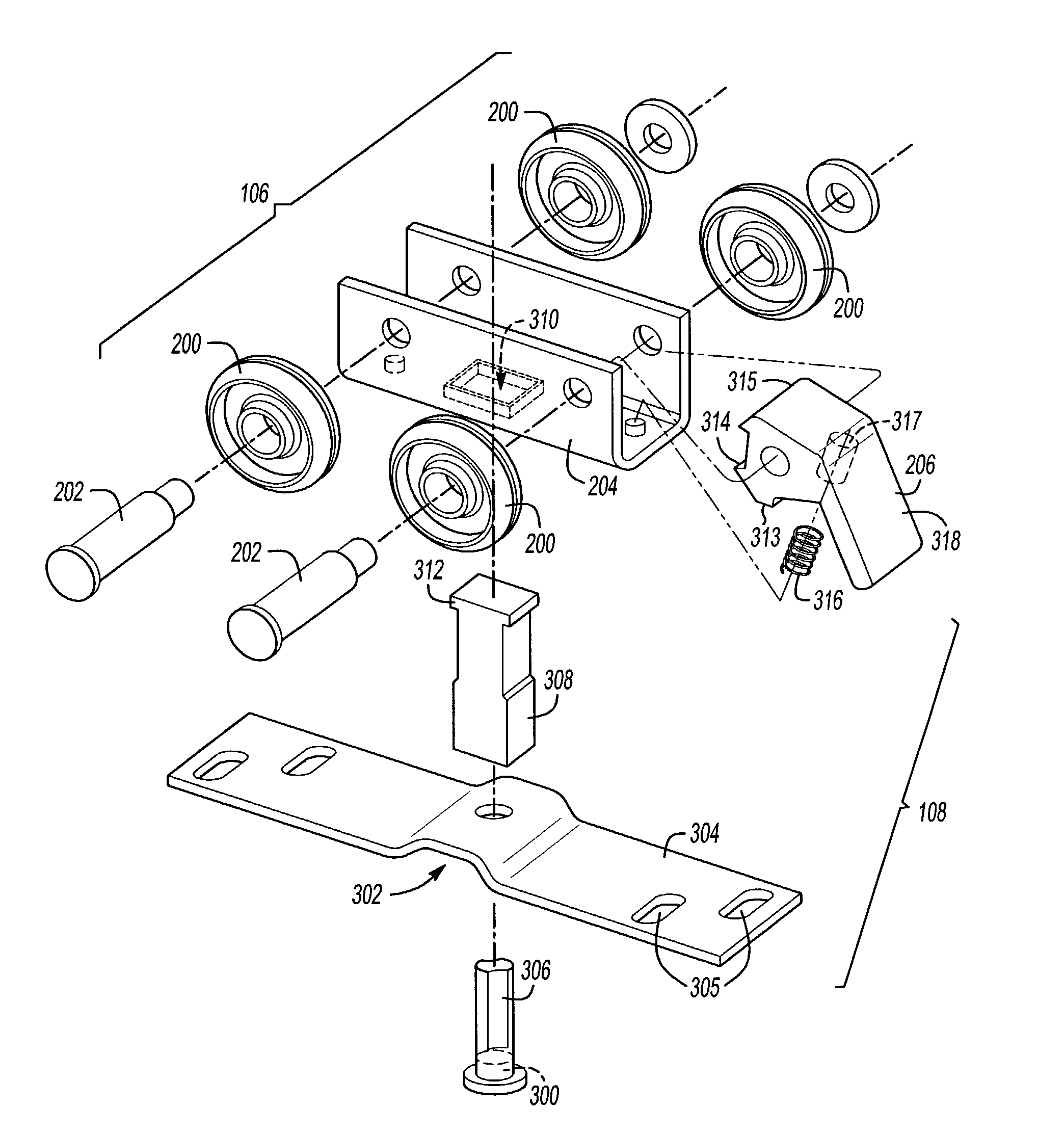

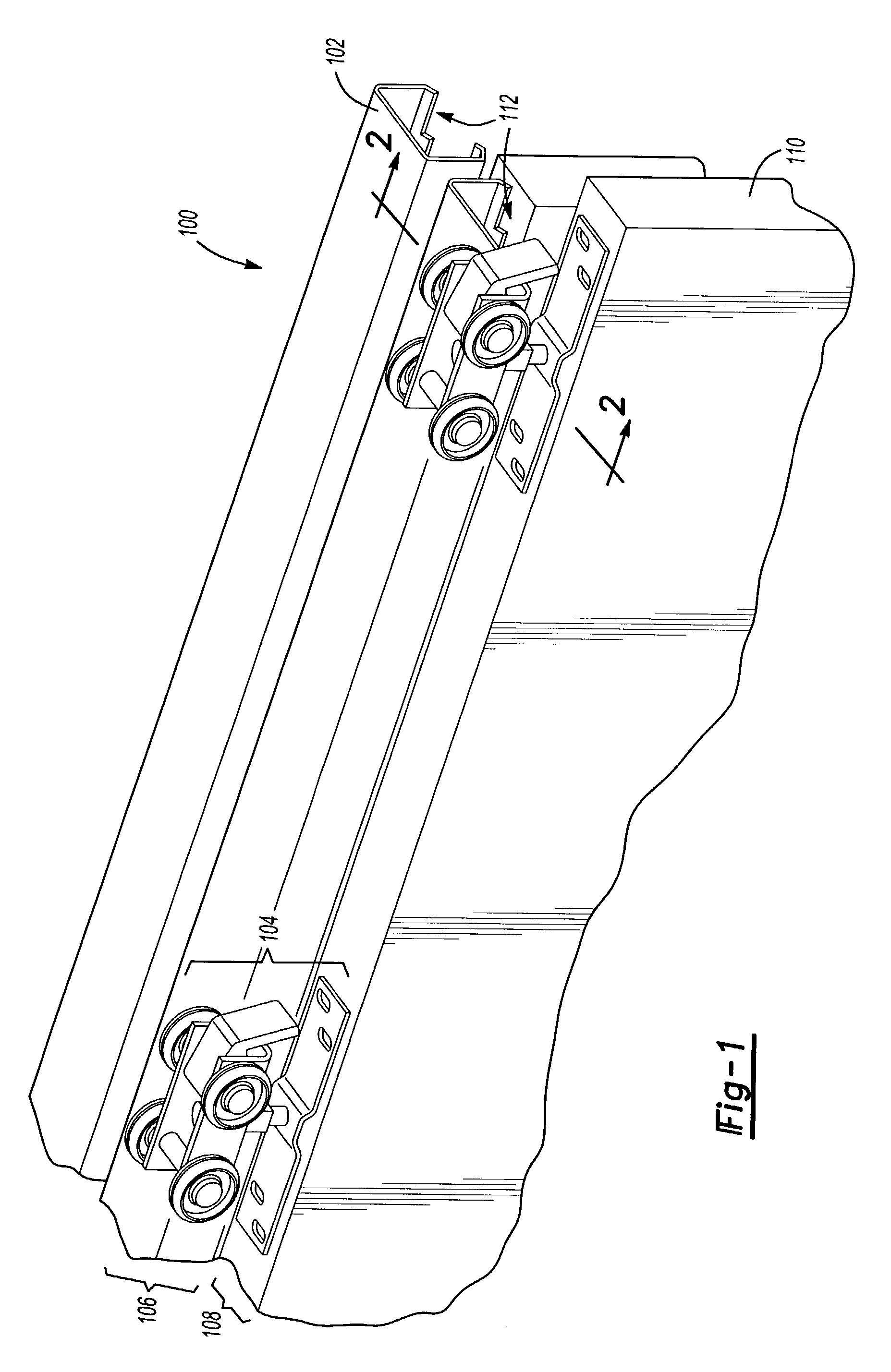

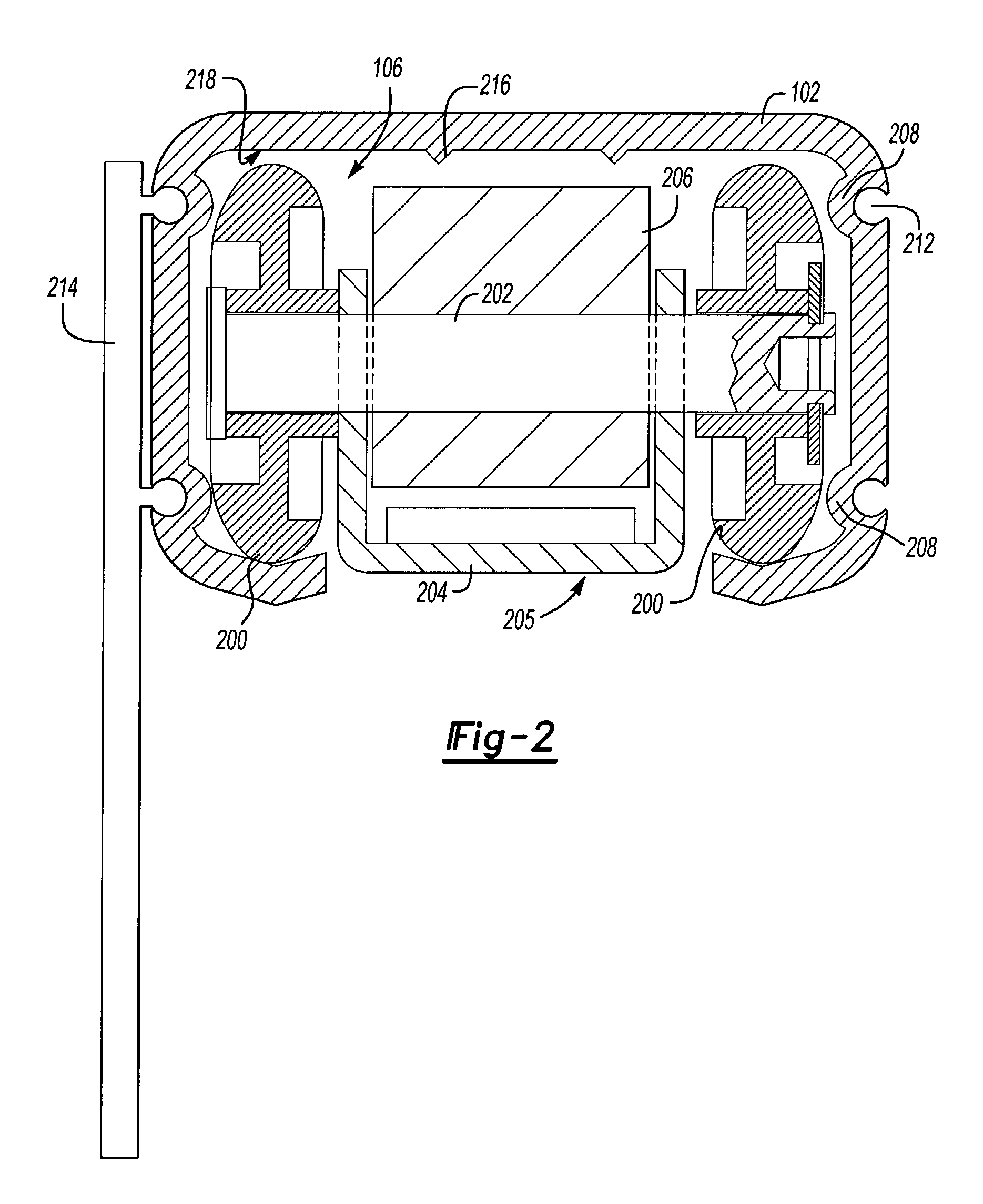

Movable door mounting assembly with trolley locking structure

ActiveUS6983512B2Firmly connectedSimple locking structureCurtain accessoriesBuilding braking devicesEngineeringCam

A movable door mounting assembly includes a stud assembly and a trolley assembly having a spring-biased cam piece that pivots between a normal position, which allows the trolley assembly to move freely on the track, and a locked position, which causes a locking surface on the cam piece to frictionally engage with a top surface of the track and hold the trolley assembly in place while the door is being hung. A catch in the stud assembly engages with the cam piece when the mounting assembly is fully assembled. Inserting the stud assembly into the trolley assembly, releases the cam piece from its locked position and, at the same time, positions the catch so that it engages with the cam piece when the door is hung.

Owner:LIBERTY HARDWARE MFG

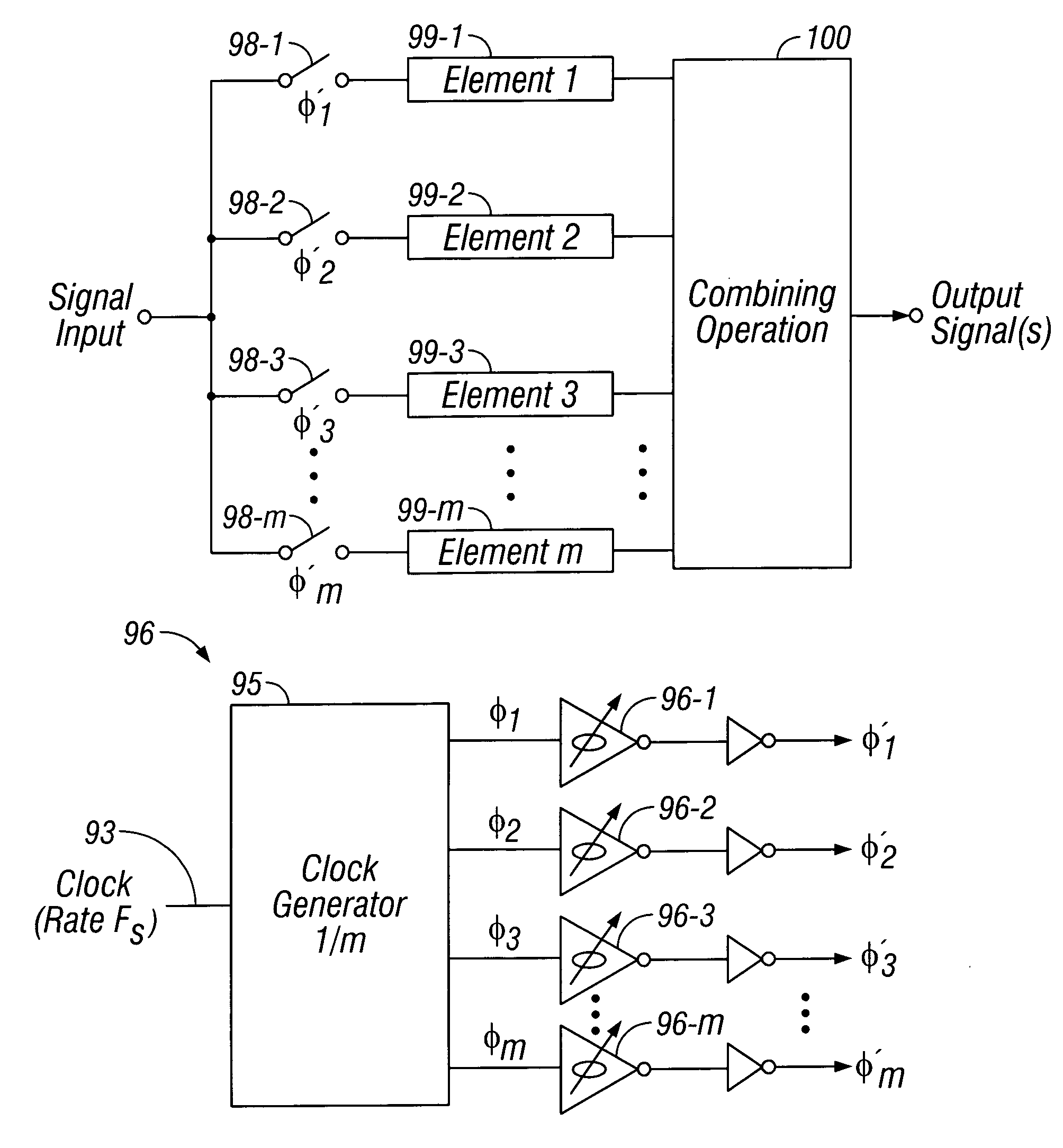

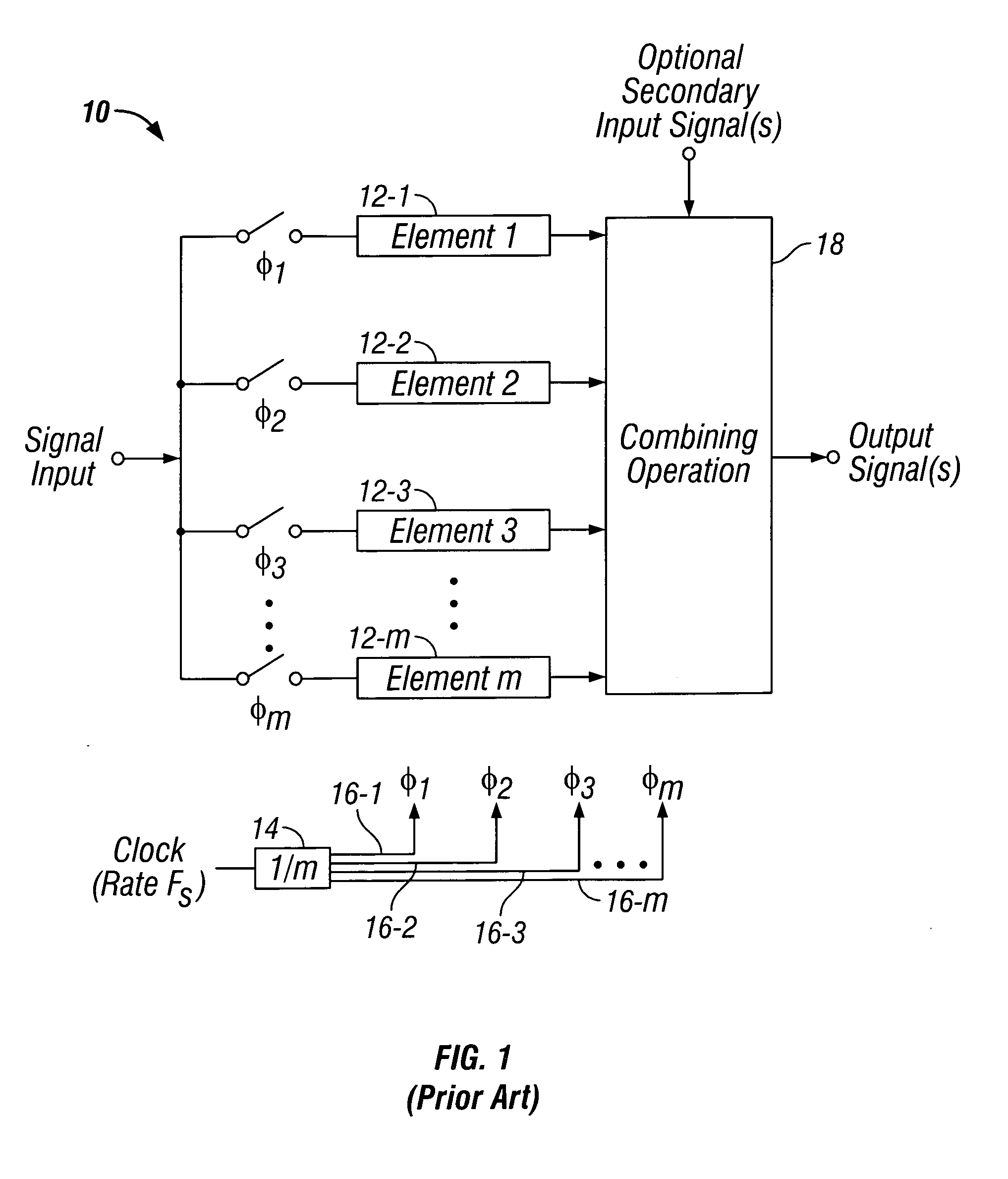

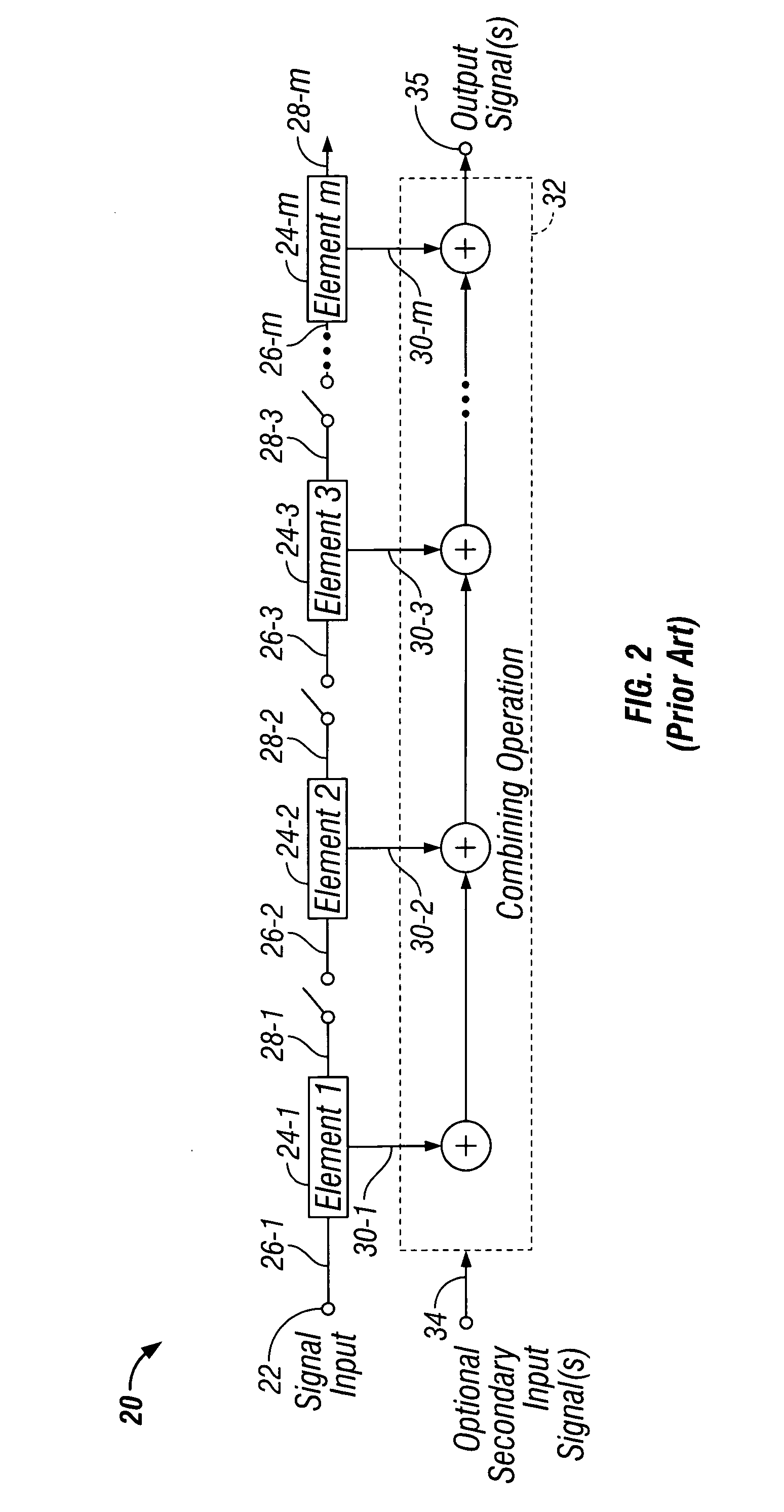

Use of analog-valued floating-gate transistors to match the electrical characteristics of interleaved and pipelined circuits

ActiveUS7049872B2Electric signal transmission systemsMultiple input and output pulse circuitsHemt circuitsEngineering

Methods of and apparatuses for matching the signal delay, clock timing, frequency response, gain, offset, and / or transfer function of signal pathways in electrical circuits such as, for example, time-interleaved and pipelined circuits using analog-valued floating-gate MOSFETs are disclosed. The methods and apparatuses disclosed are applicable to a variety of circuits, including but not limited to, sample-and-hold or track-and-hold circuits, quadrature mixers, analog-to-digital converters (ADCs), digital-to-analog converters (DACs), analog or digital filters, and amplifiers.

Owner:SYNOPSYS INC

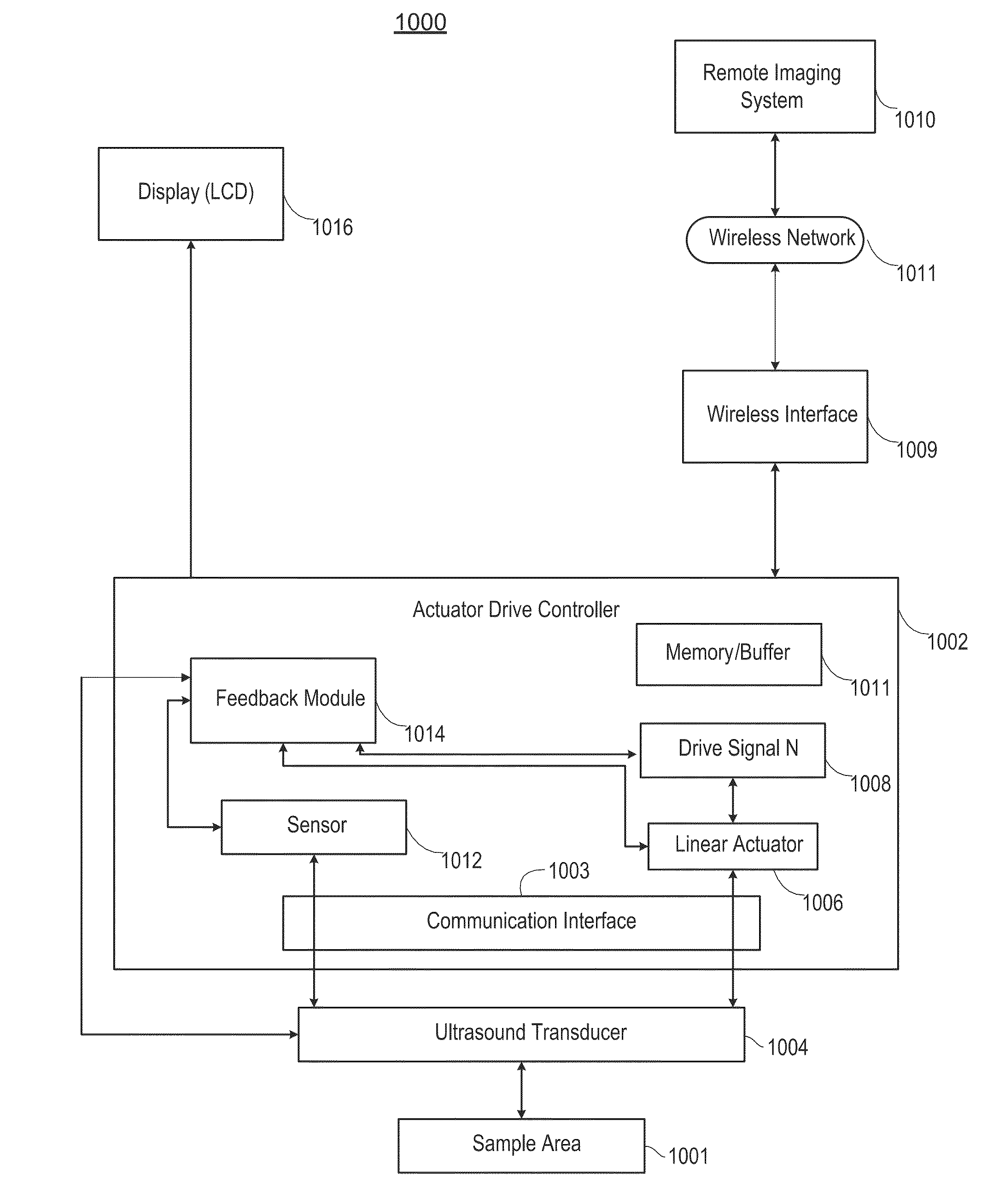

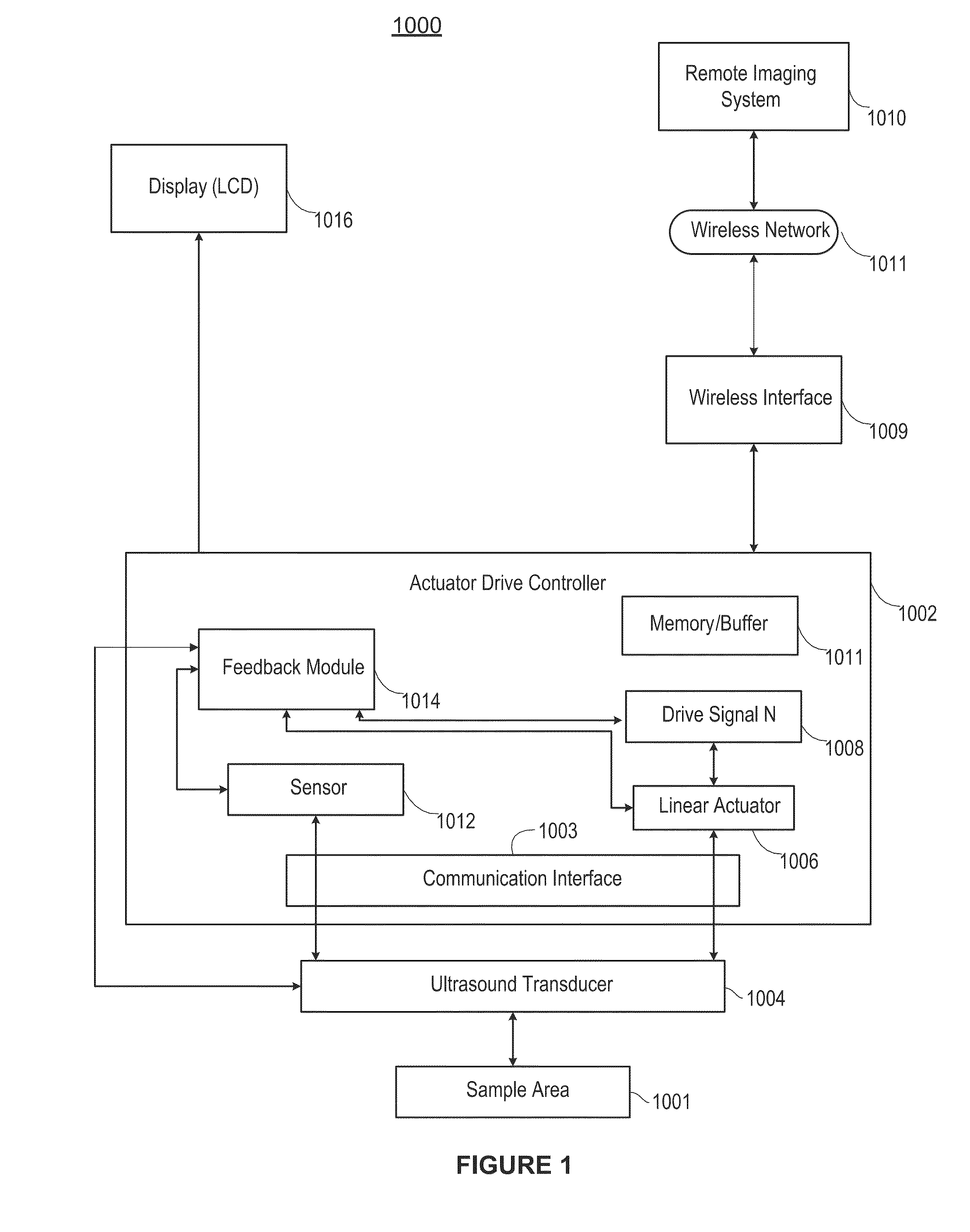

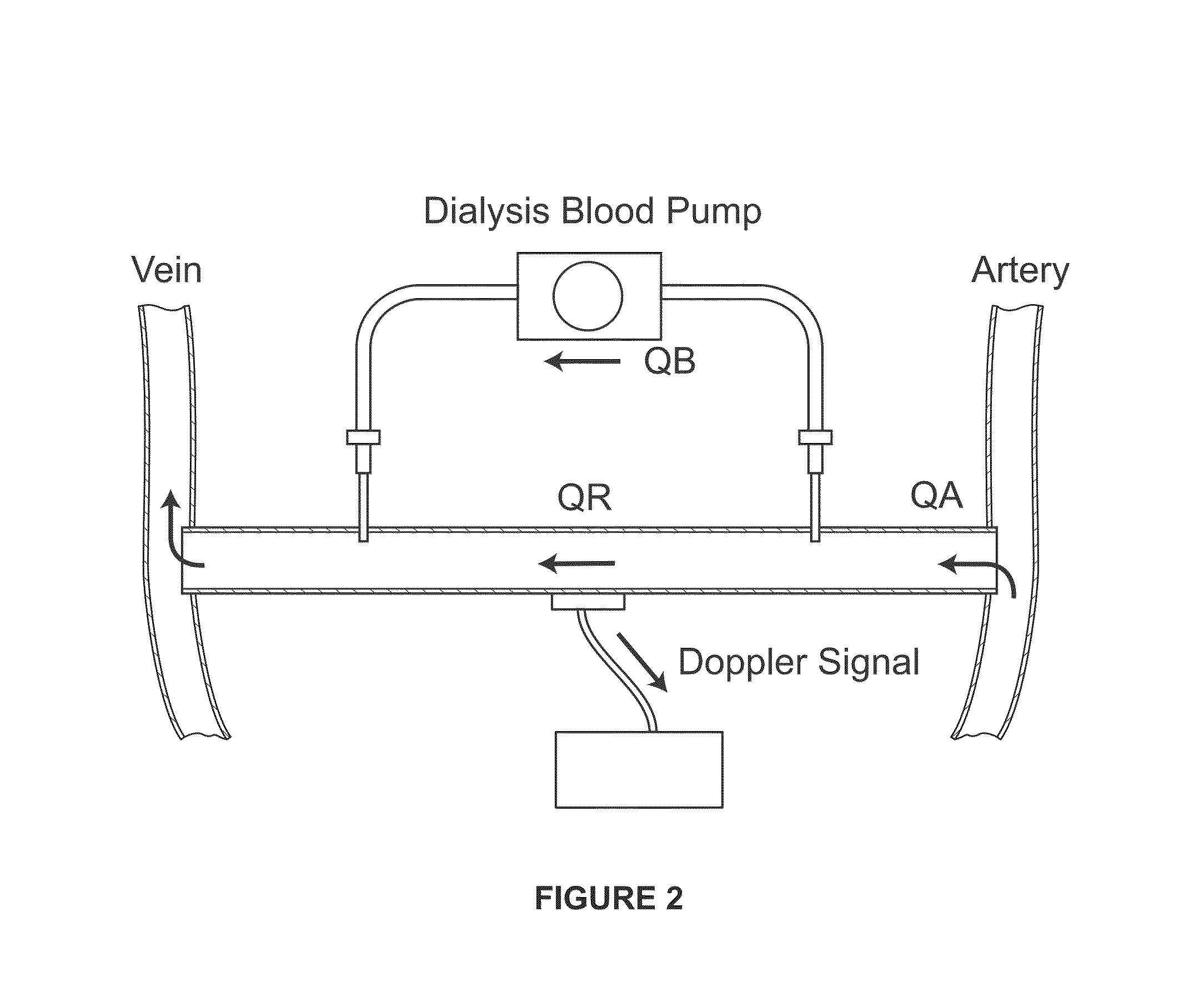

Linear magnetic drive transducer for ultrasound imaging

ActiveUS20130345566A1Improve performanceReduce manufacturing costMaterial analysis using sonic/ultrasonic/infrasonic wavesOrgan movement/changes detectionUltrasound imagingSonification

An ultrasound imaging system uses a magnetic linear motor driven ultrasound scanner, with accurate track and hold operation and / or other motion feedback, to scan a two dimensional or three dimensional area of a sample. The scanner is implemented in a low-power and low-bandwidth handheld device and is connected with a remote image processing system that receives raw data and performs full ultrasound image analysis and creation, allowing the handheld to be used for scanning, pre-processing, and display.

Owner:RGT UNIV OF MICHIGAN

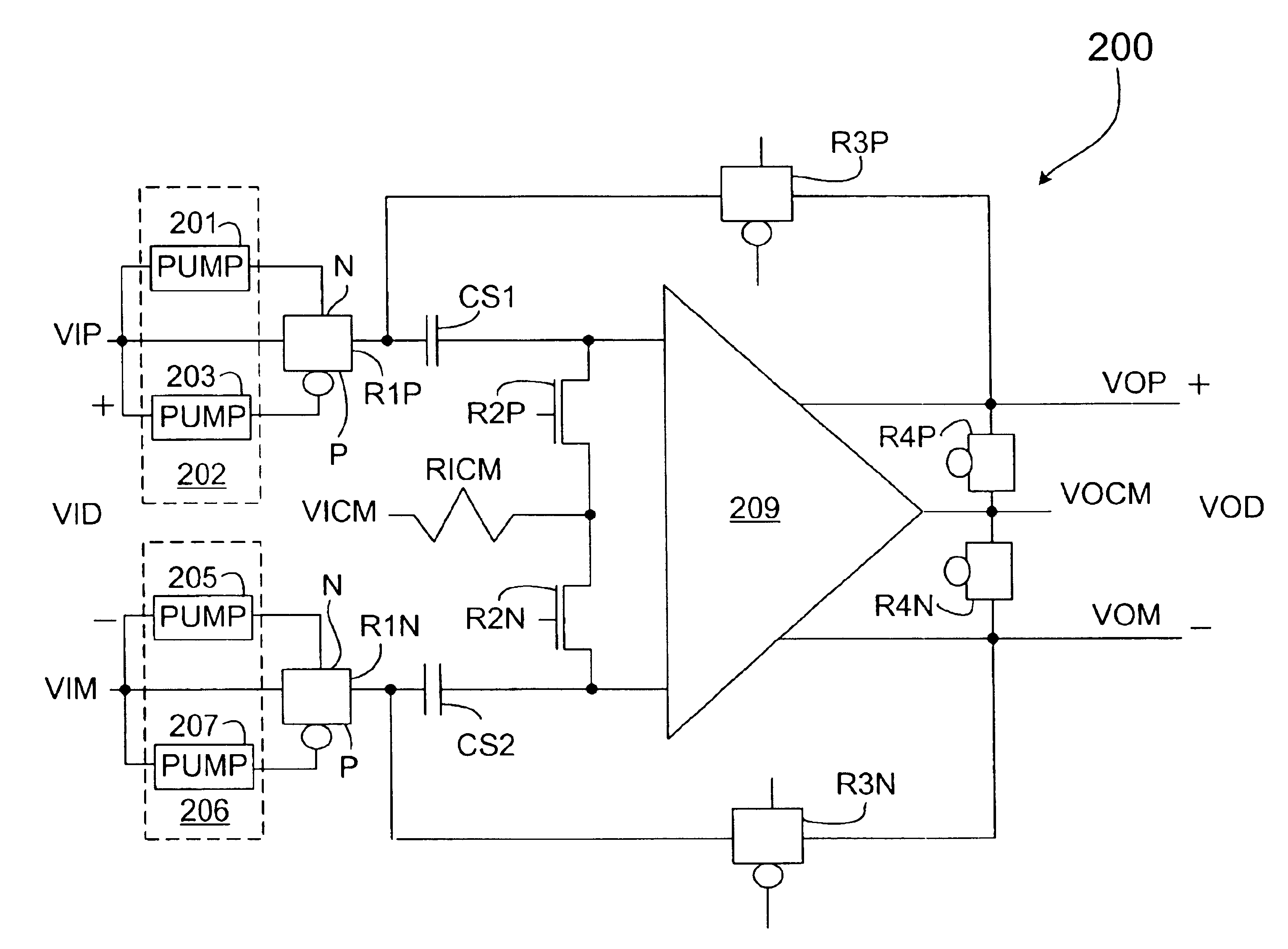

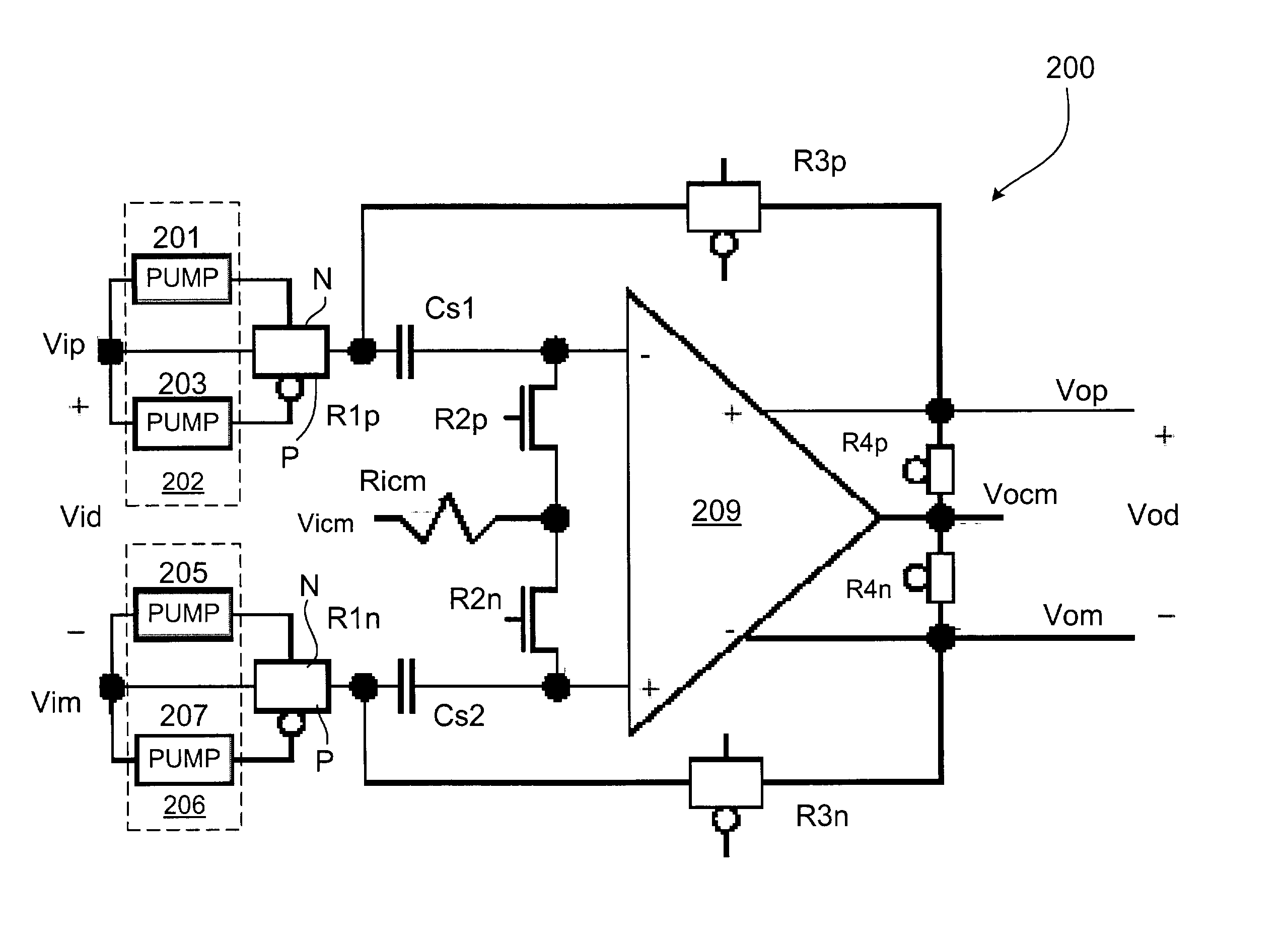

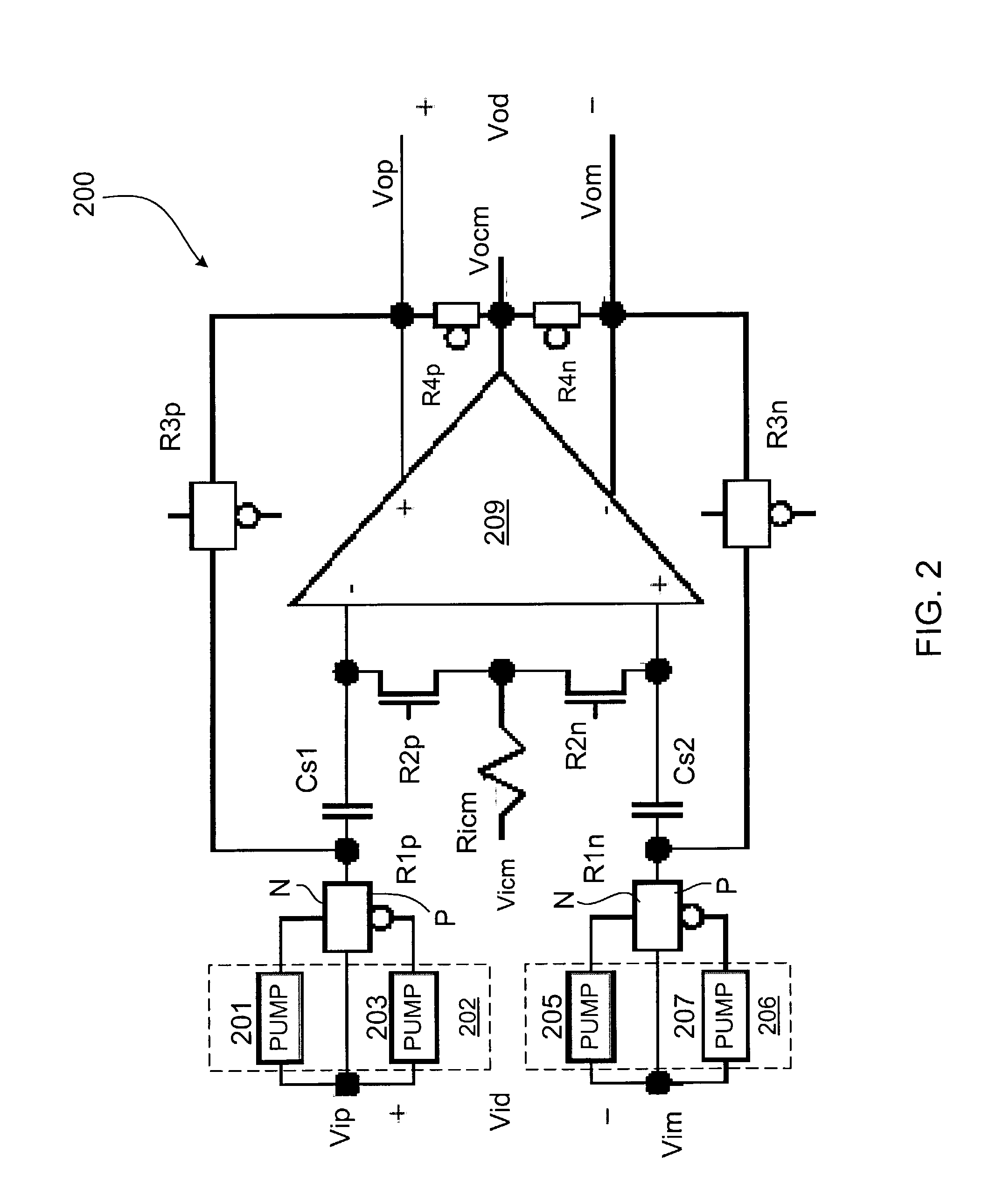

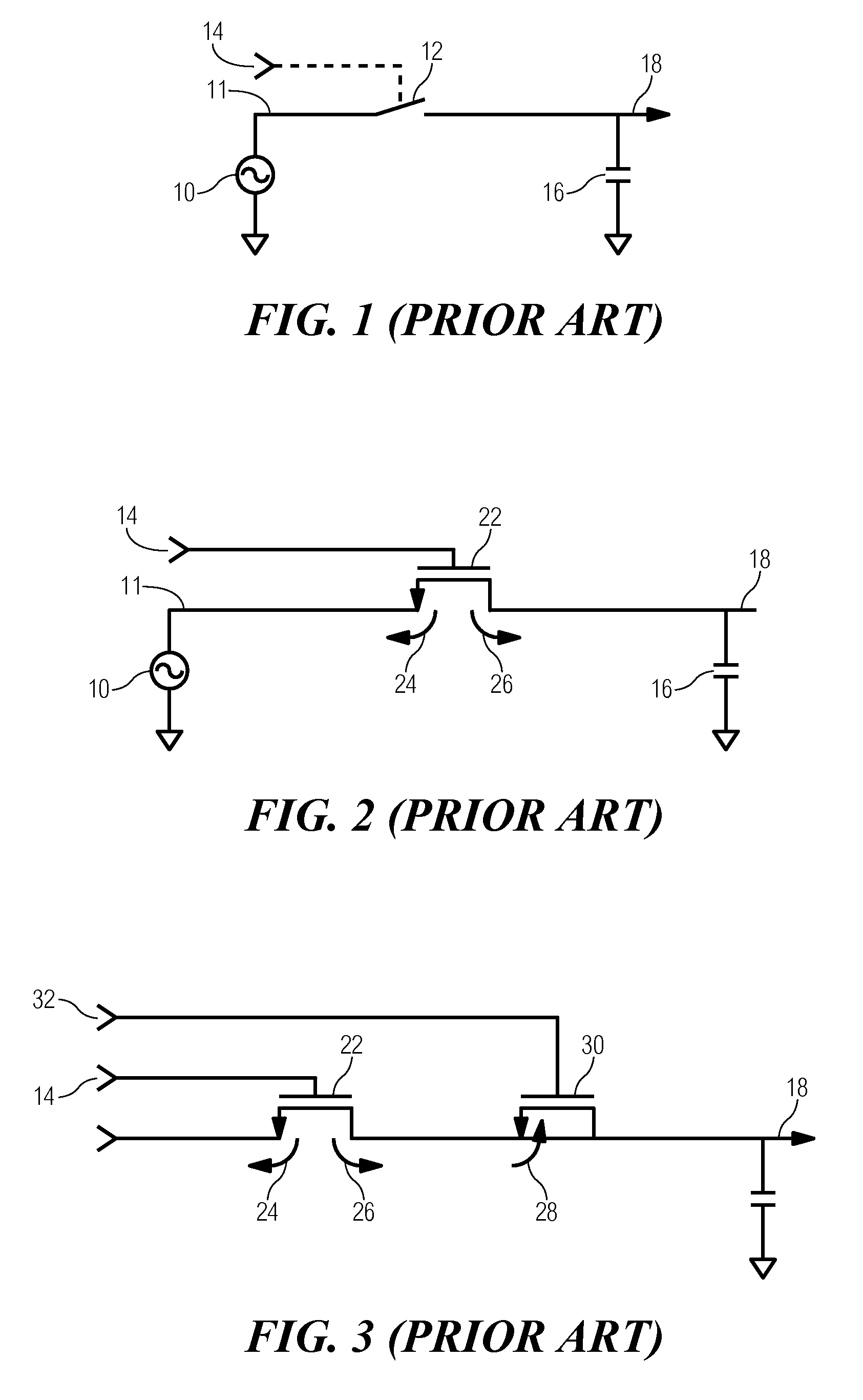

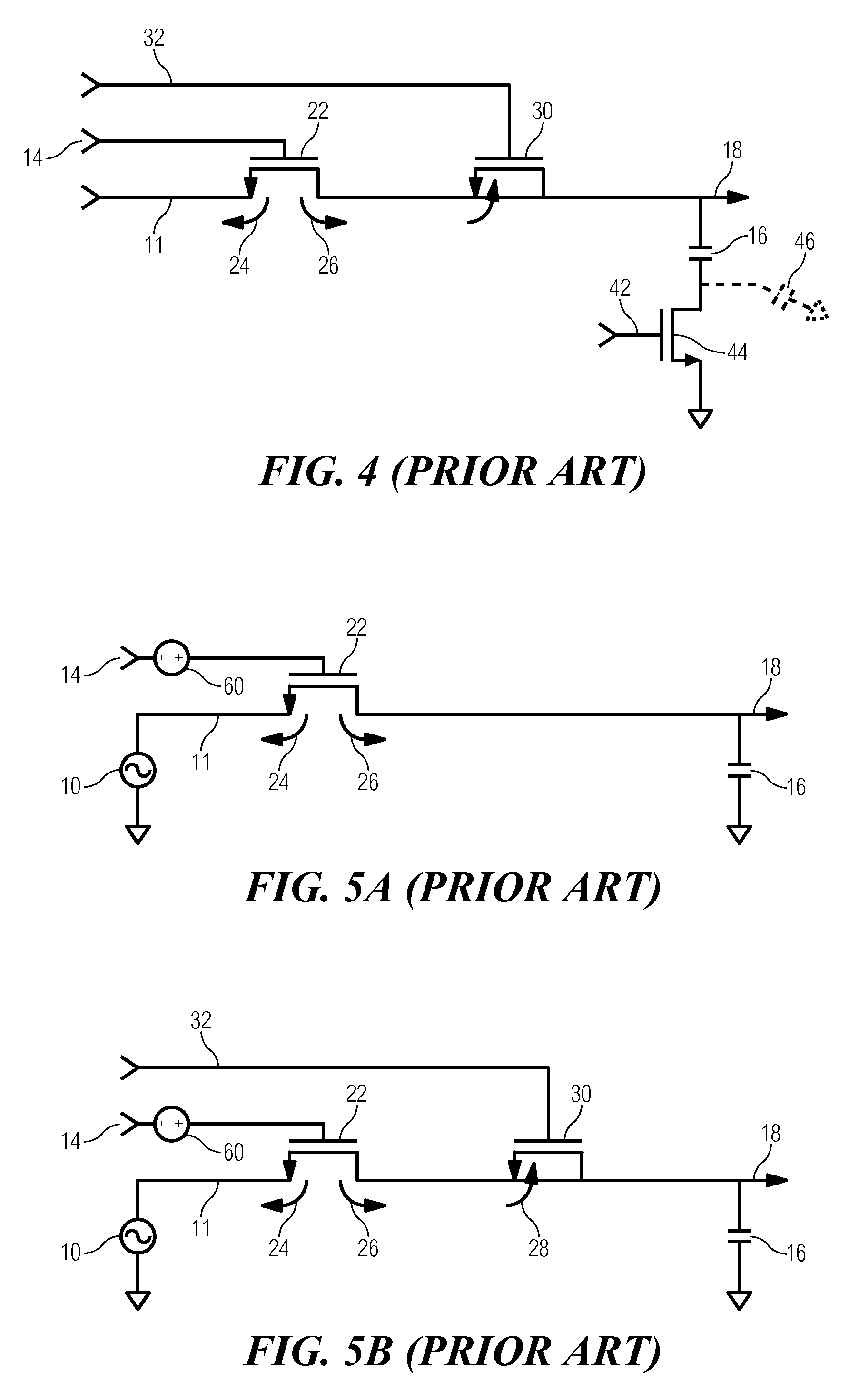

Track and hold with dual pump circuit

InactiveUS6731155B2Electric signal transmission systemsElectric analogue storesTransmission gateEngineering

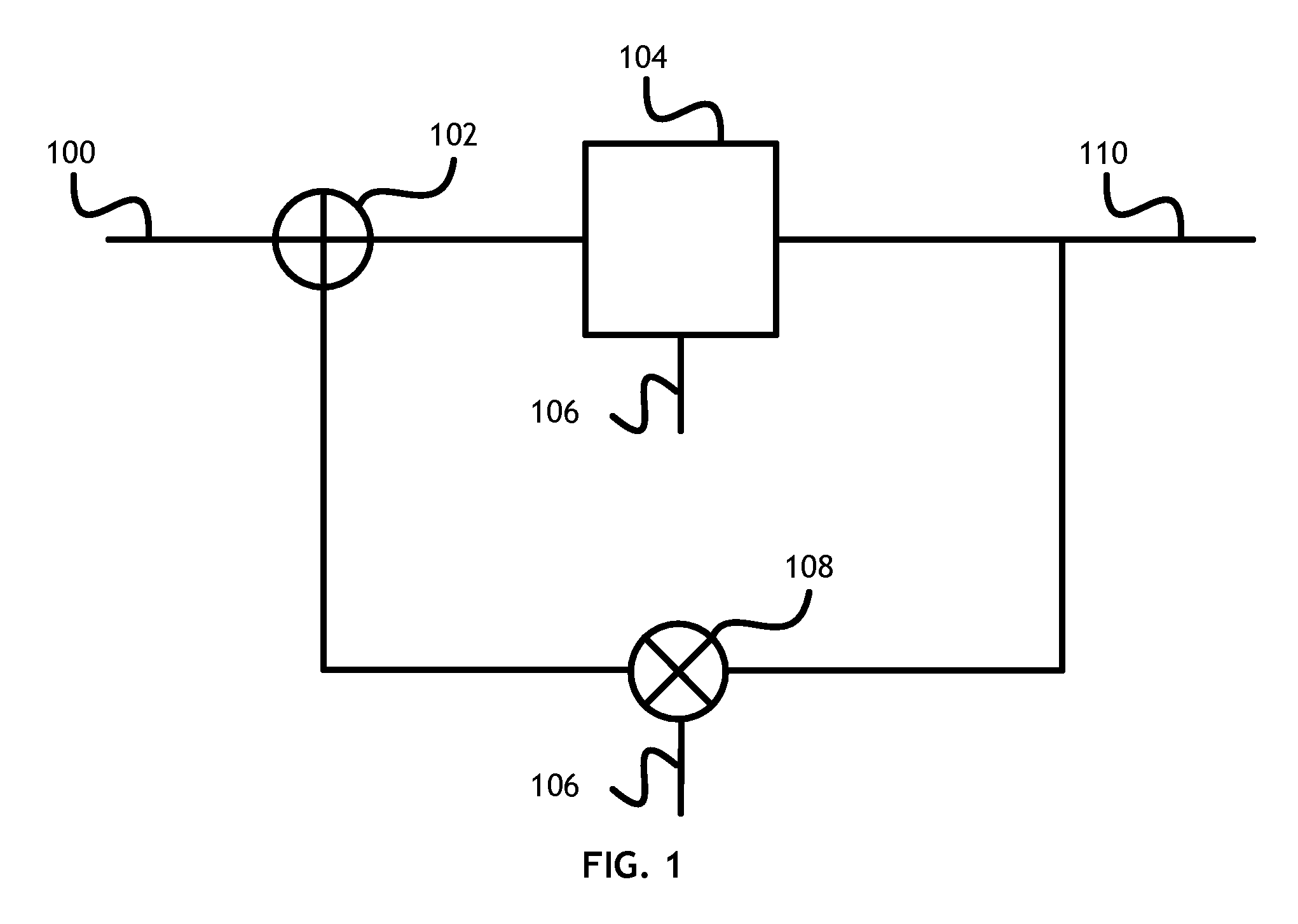

A dual pump circuit including a transmission gate and a dual charge pump. The transmission gate includes a p-channel transistor and an n-channel transistor, each having a control terminal and a pair of current terminals coupled between a dual pump input and a dual pump output. The dual charge pump includes first and second pump circuits, where each pump circuit is coupled to the dual pump input and to a control terminal of a corresponding one of the transmission gate transistors. Each pump circuit is operative to linearize operation of its corresponding transmission gate transistor by maintaining VGS-VT constant. The dual pump circuit is used in a track and hold circuit including at least one dual pump sampling circuit, at least one sampling capacitor, and a control circuit for controlling input signal sampling timing. Each dual pump sampling circuit includes the transmission gate and a dual charge pump.

Owner:INTERSIL INC

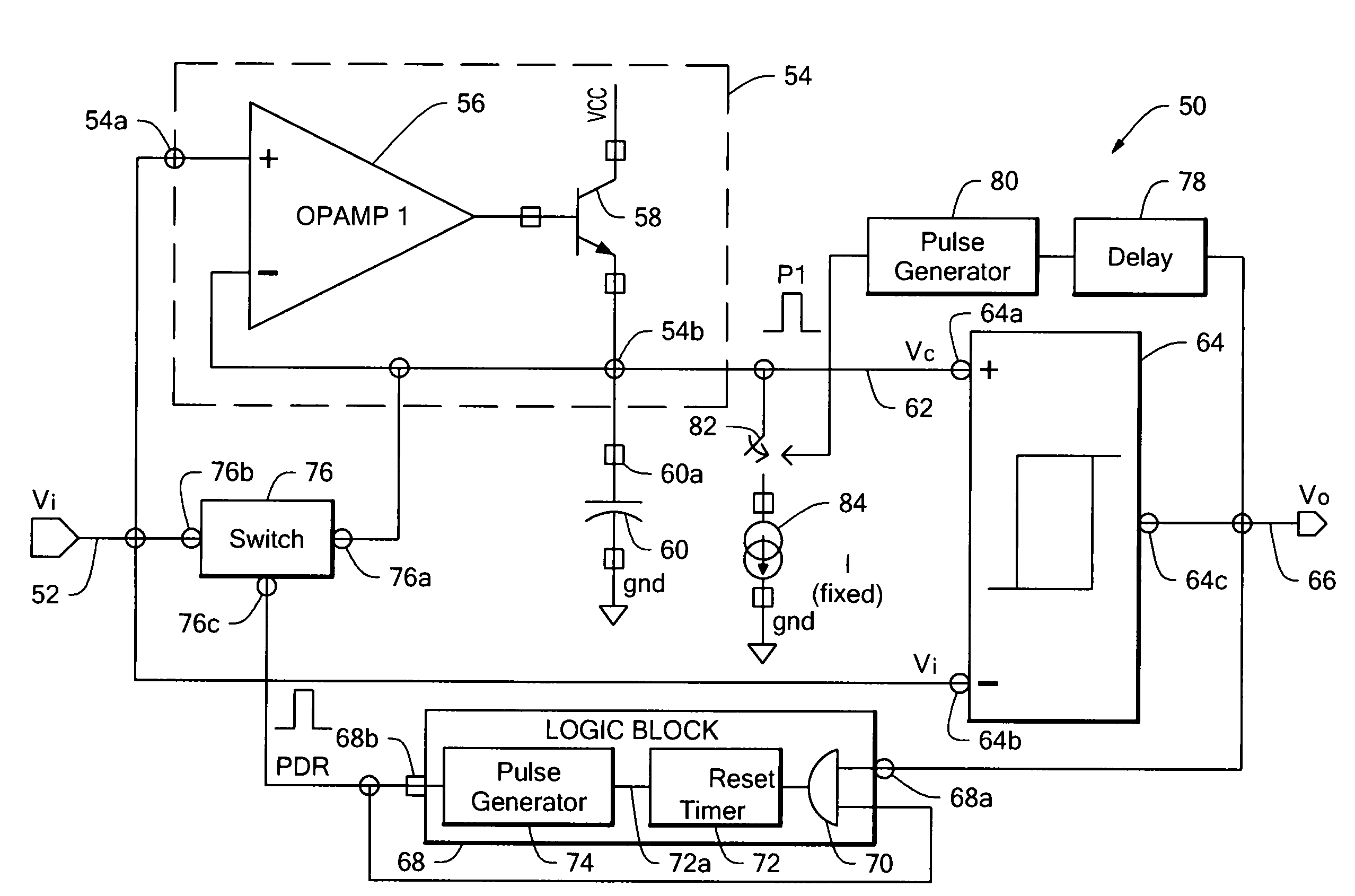

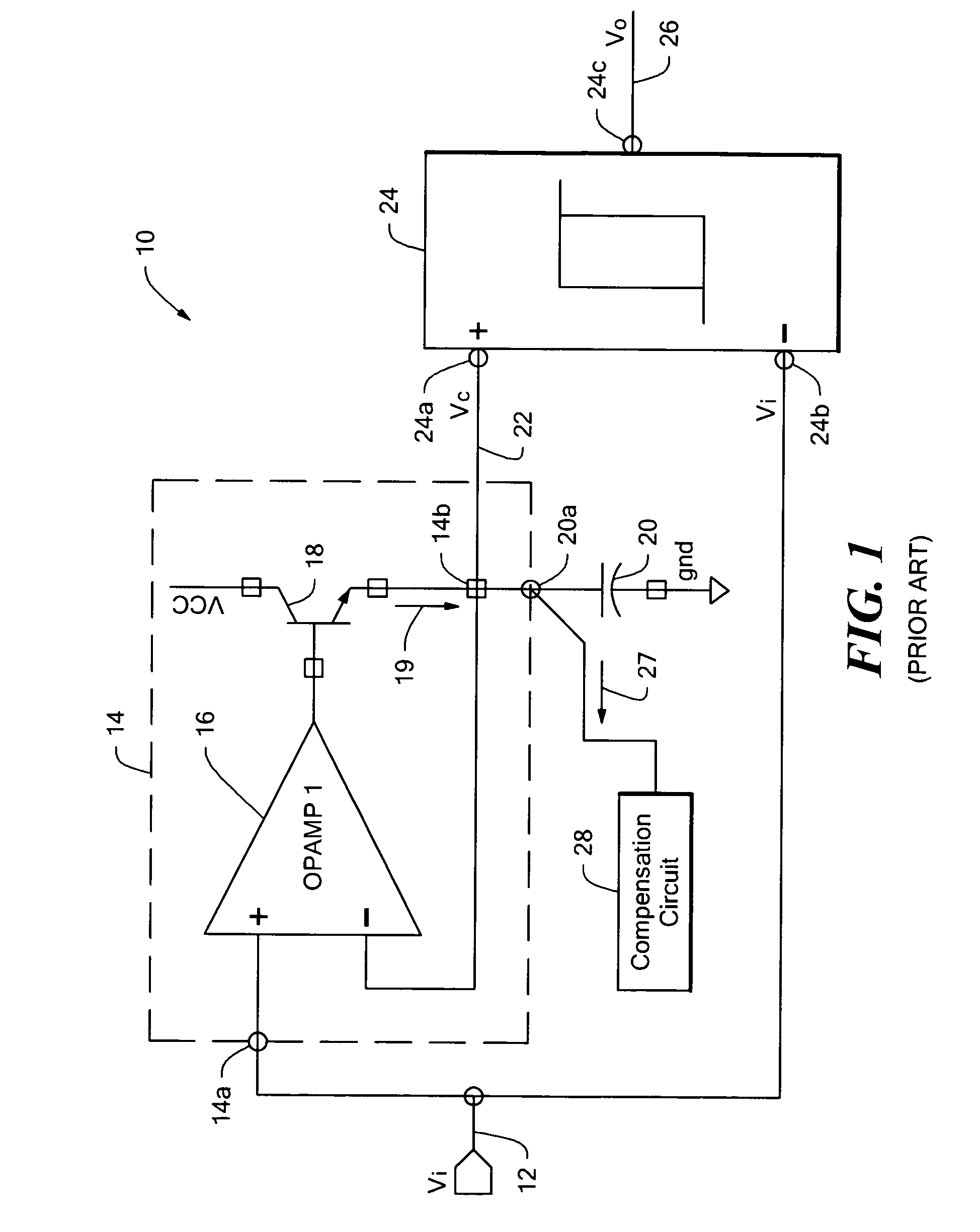

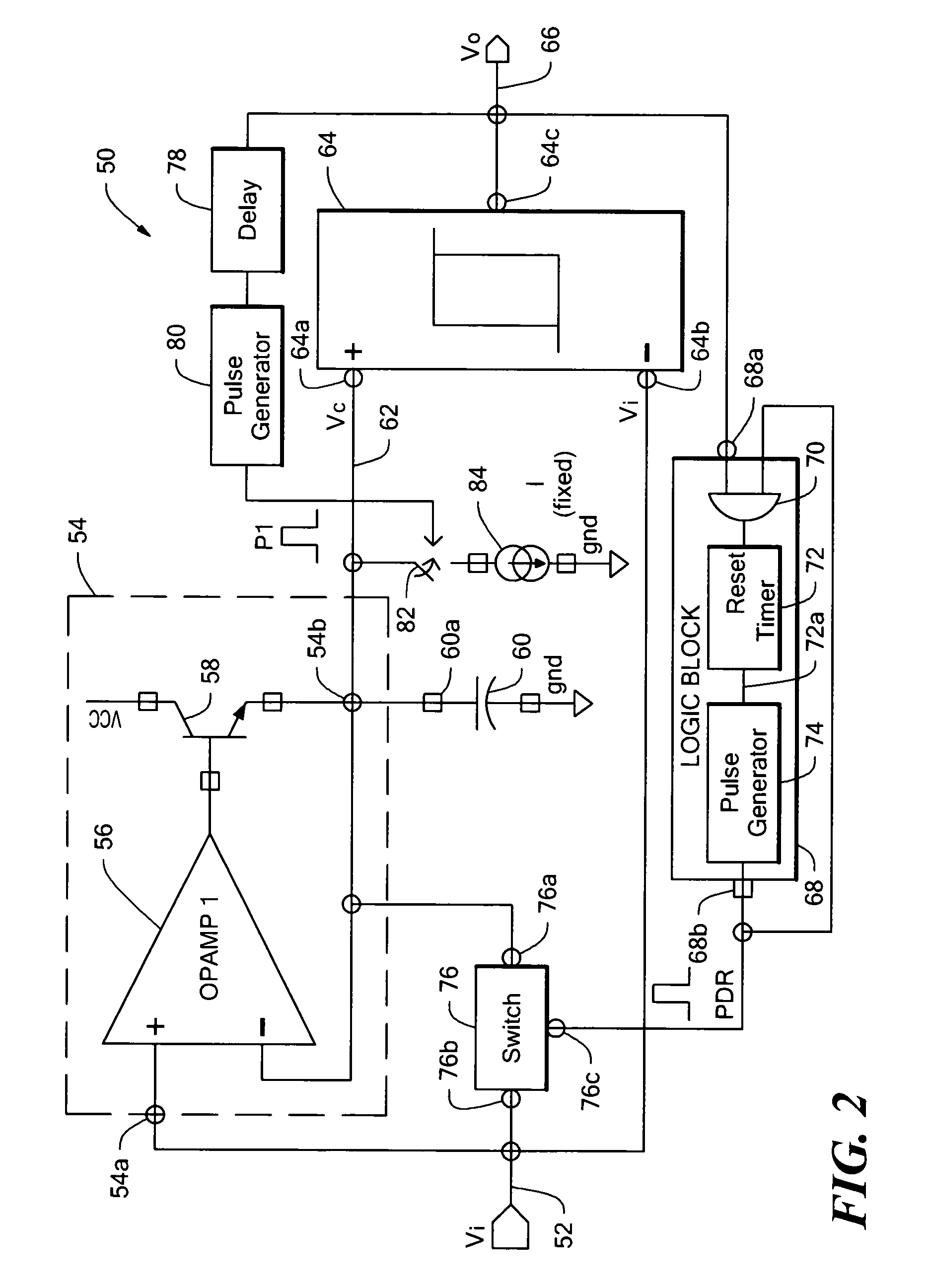

Track-and-hold peak detector circuit

ActiveUS7053674B1Small in value and size and costReduce operating frequencyCurrent/voltage measurementInstant pulse delivery arrangementsDetector circuitsHemt circuits

A track-and-hold peak detector circuit, which can operate at low input signal frequencies, includes a capacitor to hold a peak voltage of the input signal and logic circuitry that reduces an effect of leakage current into or out of the capacitor, and therefore, provides protection against self-switching of an output signal of the peak detector circuit.

Owner:ALLEGRO MICROSYSTEMS INC

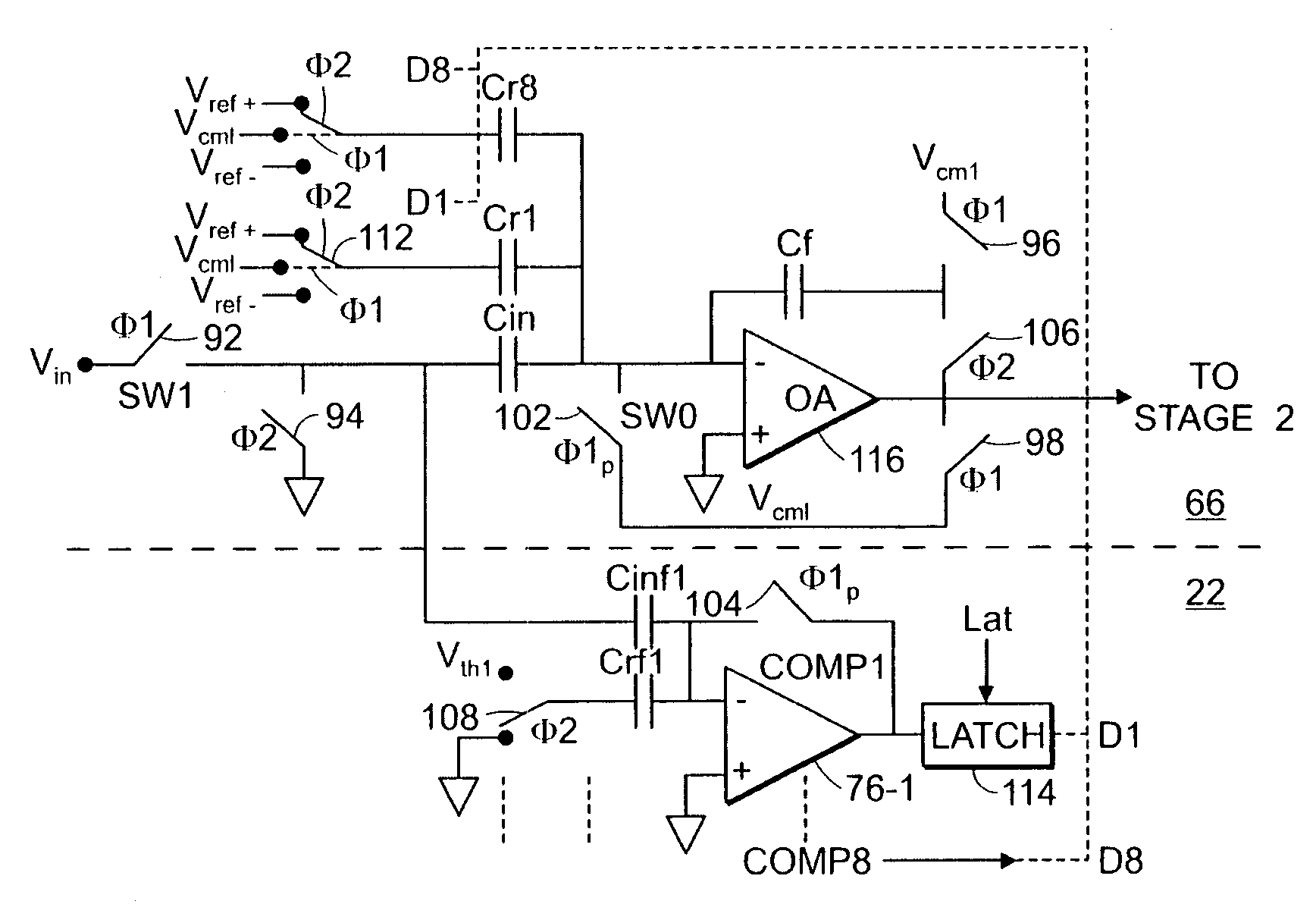

Analog-to-digital converter without track-and-hold

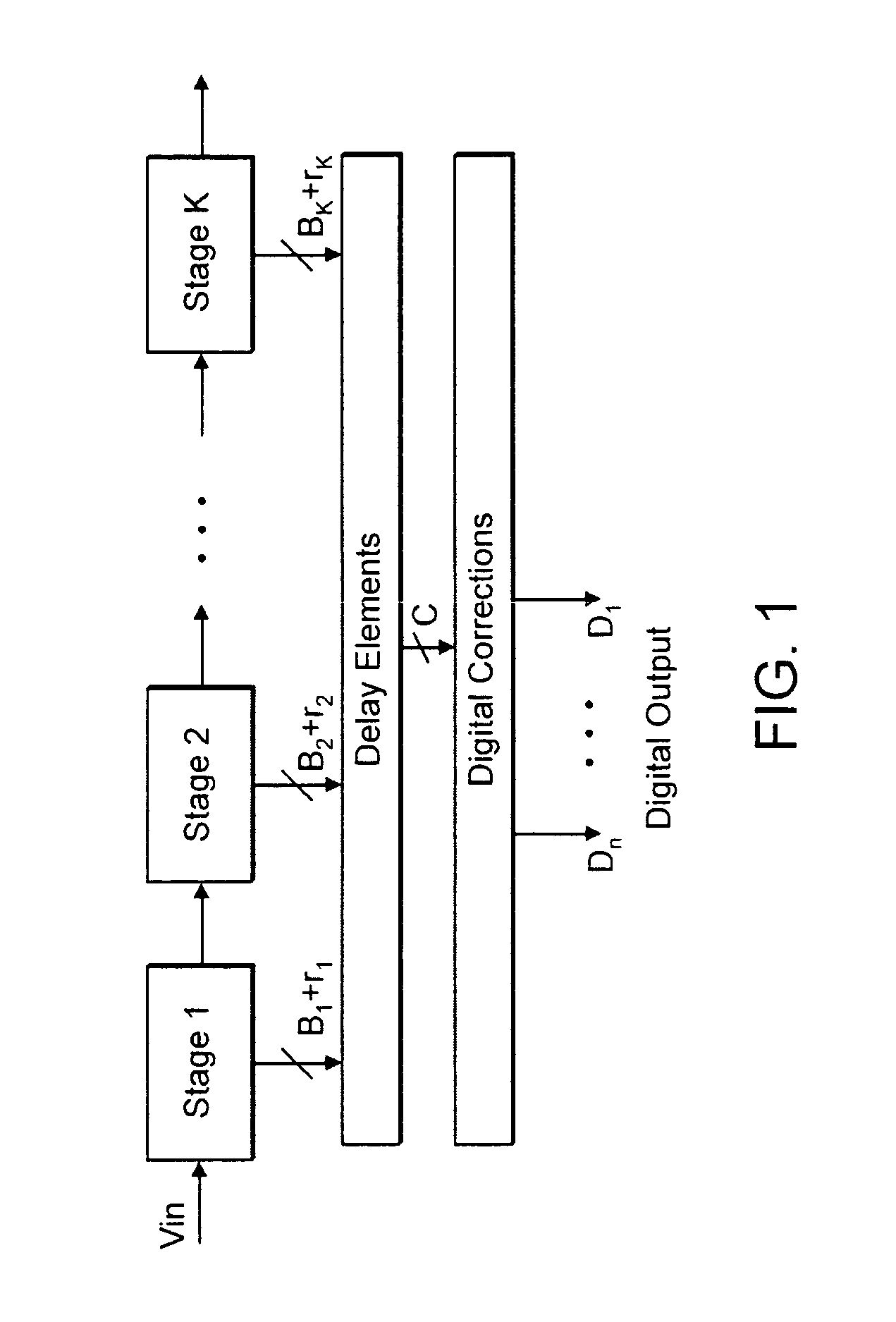

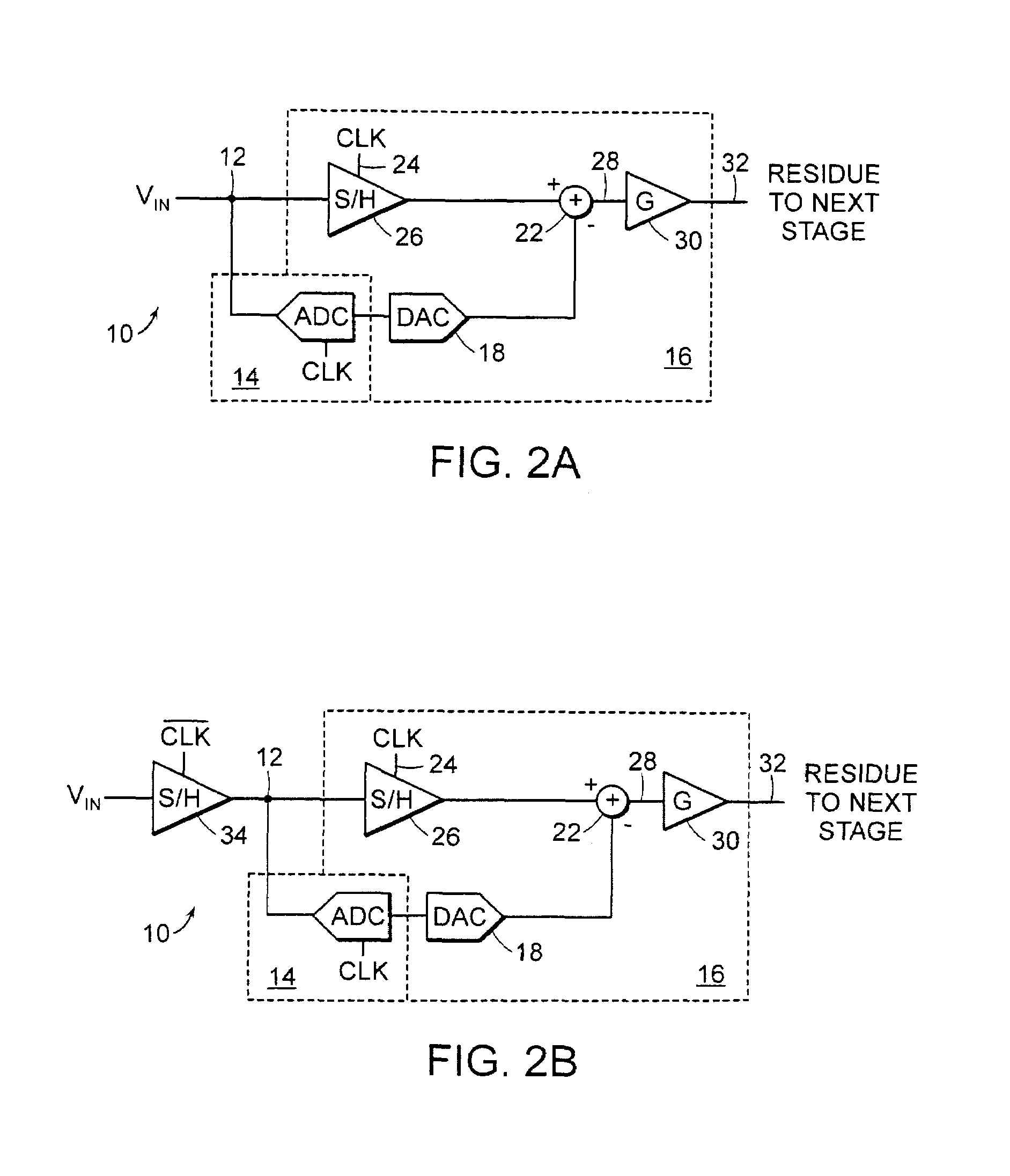

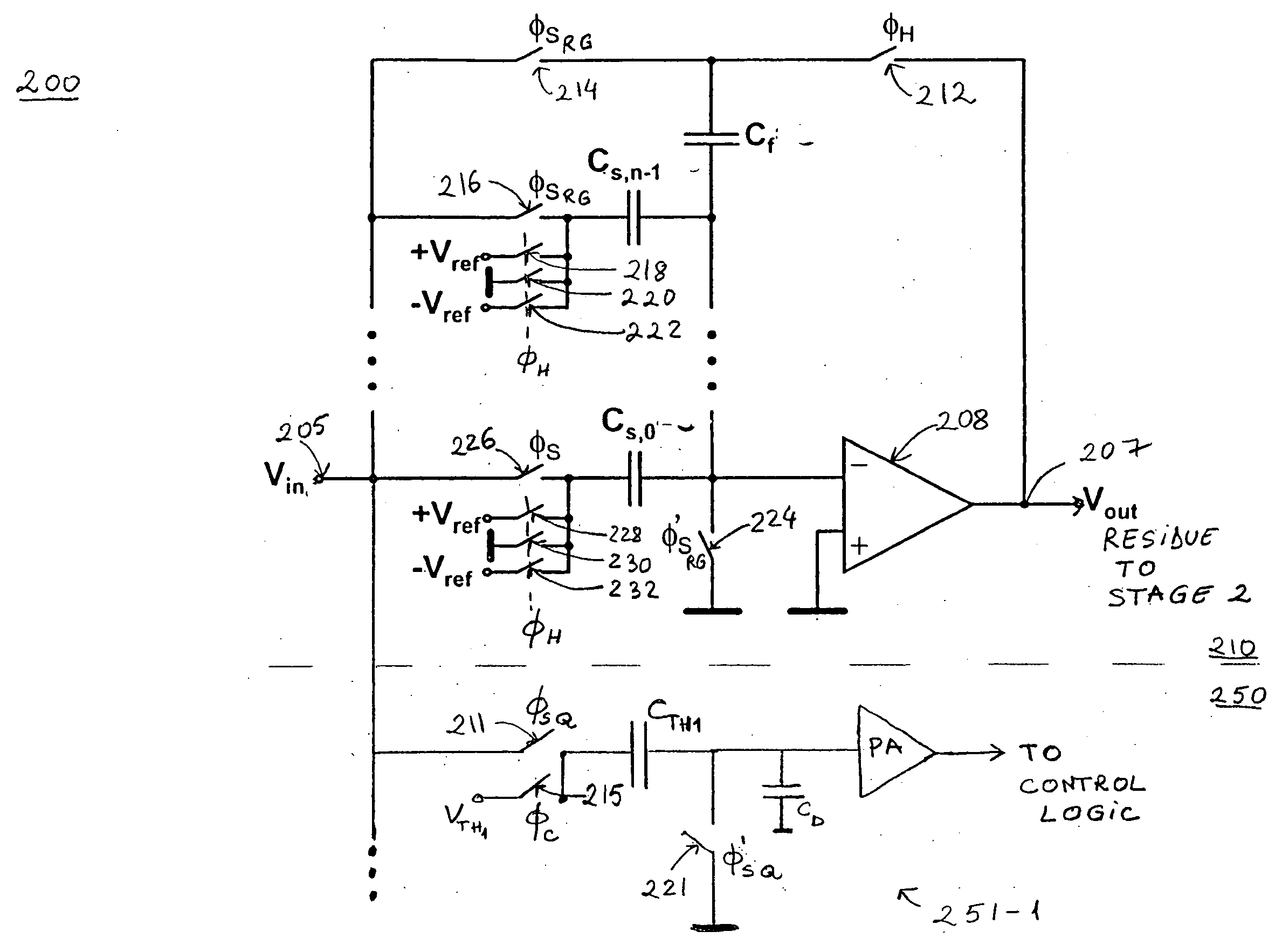

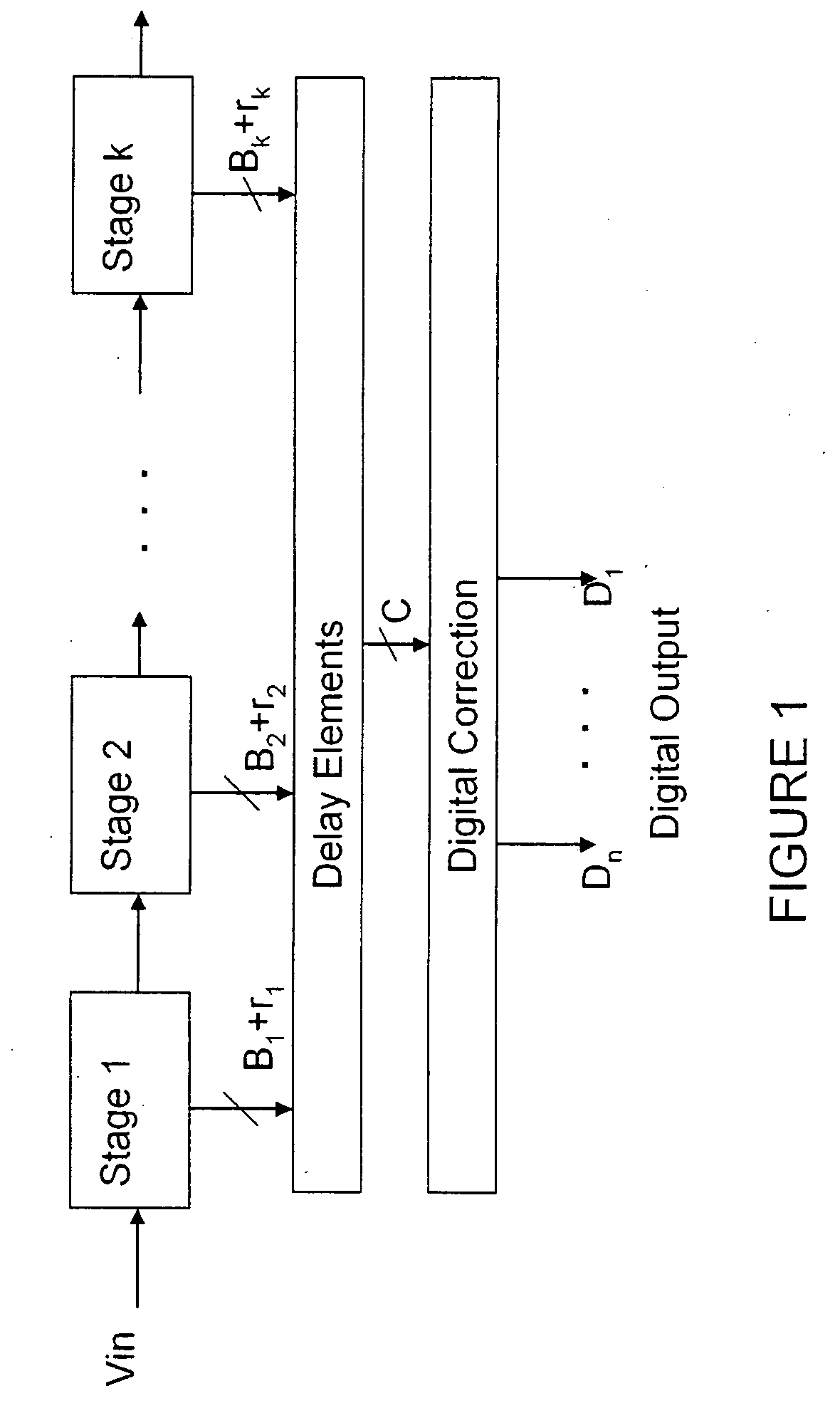

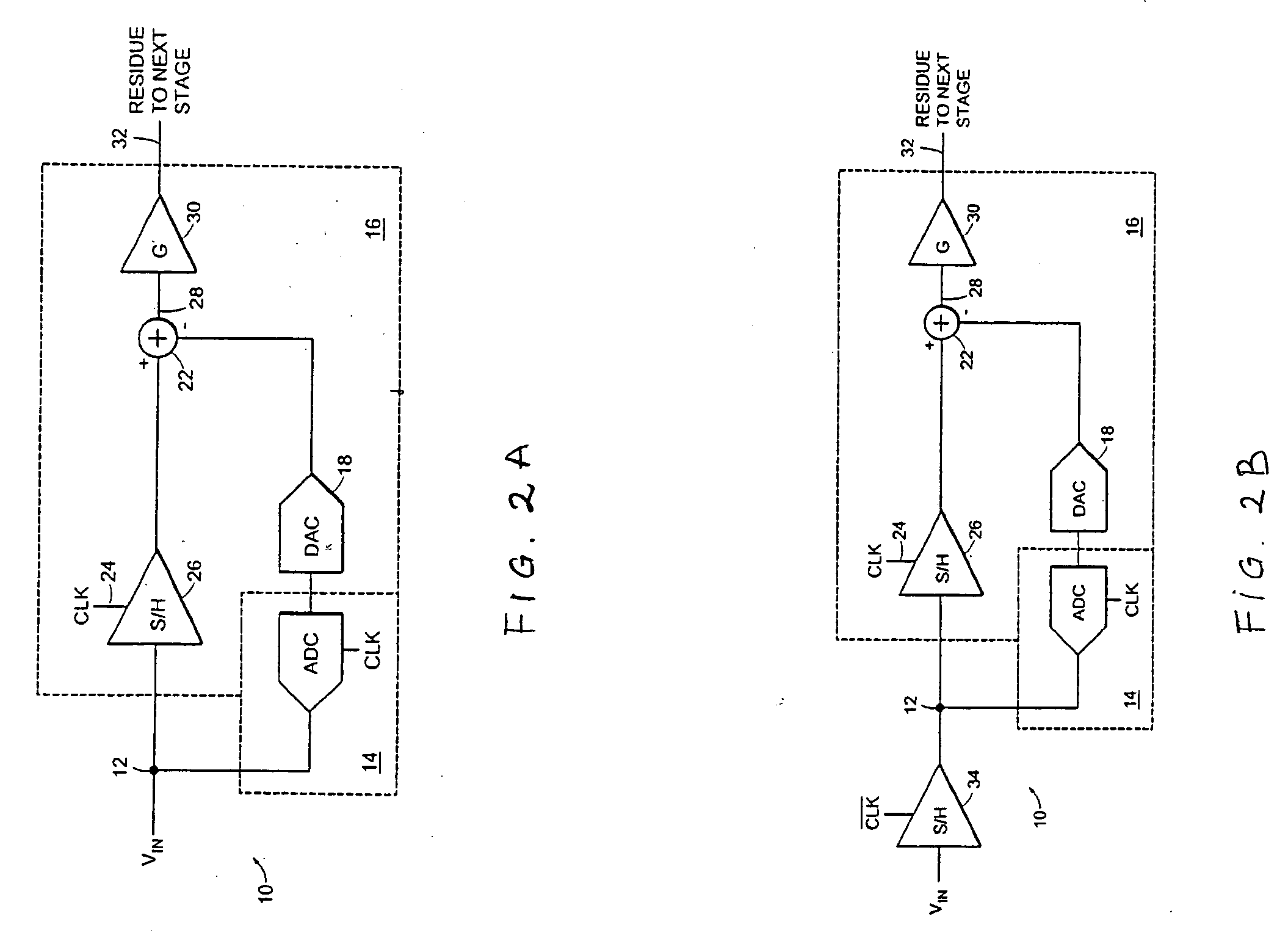

ActiveUS7339512B2Electric signal transmission systemsAnalogue-digital convertersDigital down converterEnd stages

A system and method for converting an analog signal to a digital signal is provided. The analog to digital conversion is achieved without a dedicated sample-and-hold circuit. An ADC stage, preferably the front-end stage in the case of a pipeline ADC, samples the input voltage within a quantizer and within a residue generator. The sampling is performed with associated clocking signals and with switch capacitors also fulfilling the comparison with threshold voltages, within the quantizer and the generation of a residue signal within the residue generator.

Owner:EDGEWATER WIRELESS SYST

Analog-to-digital converter without track-and-hold

ActiveUS20070035432A1Electric signal transmission systemsAnalogue-digital convertersEnd stagesA d converter

A system and method for converting an analog signal to a digital signal is provided. The analog to digital conversion is achieved without a dedicated sample-and-hold circuit. An ADC stage, preferably the front-end stage in the case of a pipeline ADC, samples the input voltage within a quantizer and within a residue generator. The sampling is performed with associated clocking signals and with switch capacitors also fulfilling the comparison with threshold voltages, within the quantizer and the generation of a residue signal within the residue generator.

Owner:EDGEWATER WIRELESS SYST

Track and hold with dual pump circuit

InactiveUS20030151430A1Electric signal transmission systemsElectric analogue storesTransmission gateEngineering

A dual pump circuit including a transmission gate and a dual charge pump. The transmission gate includes a p-channel transistor and an n-channel transistor, each having a control terminal and a pair of current terminals coupled between a dual pump input and a dual pump output. The dual charge pump includes first and second pump circuits, where each pump circuit is coupled to the dual pump input and to a control terminal of a corresponding one of the transmission gate transistors. Each pump circuit is operative to linearize operation of its corresponding transmission gate transistor by maintaining VGS-VT constant. The dual pump circuit is used in a track and hold circuit including at least one dual pump sampling circuit, at least one sampling capacitor, and a control circuit for controlling input signal sampling timing. Each dual pump sampling circuit includes the transmission gate and a dual charge pump.

Owner:INTERSIL INC

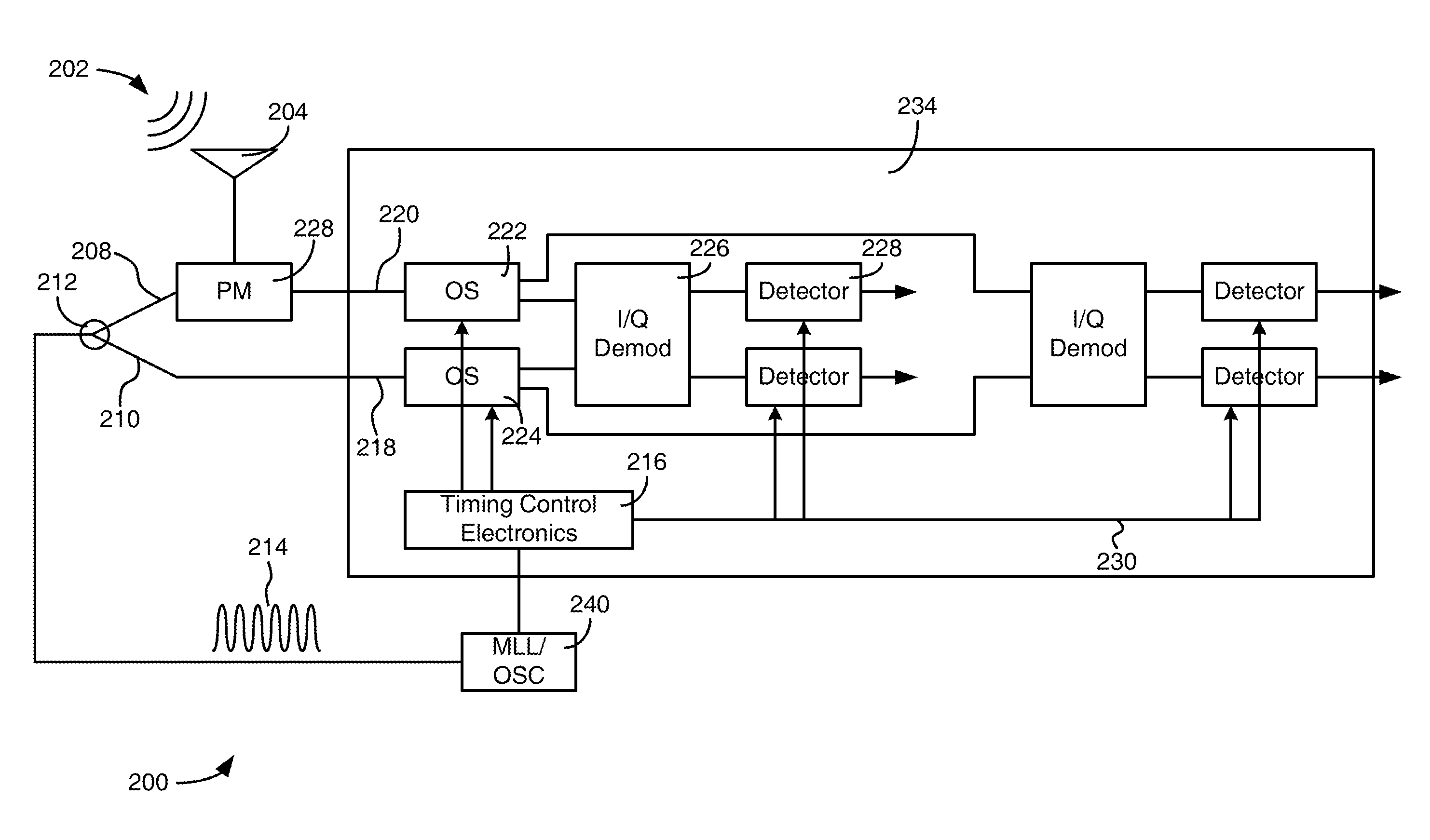

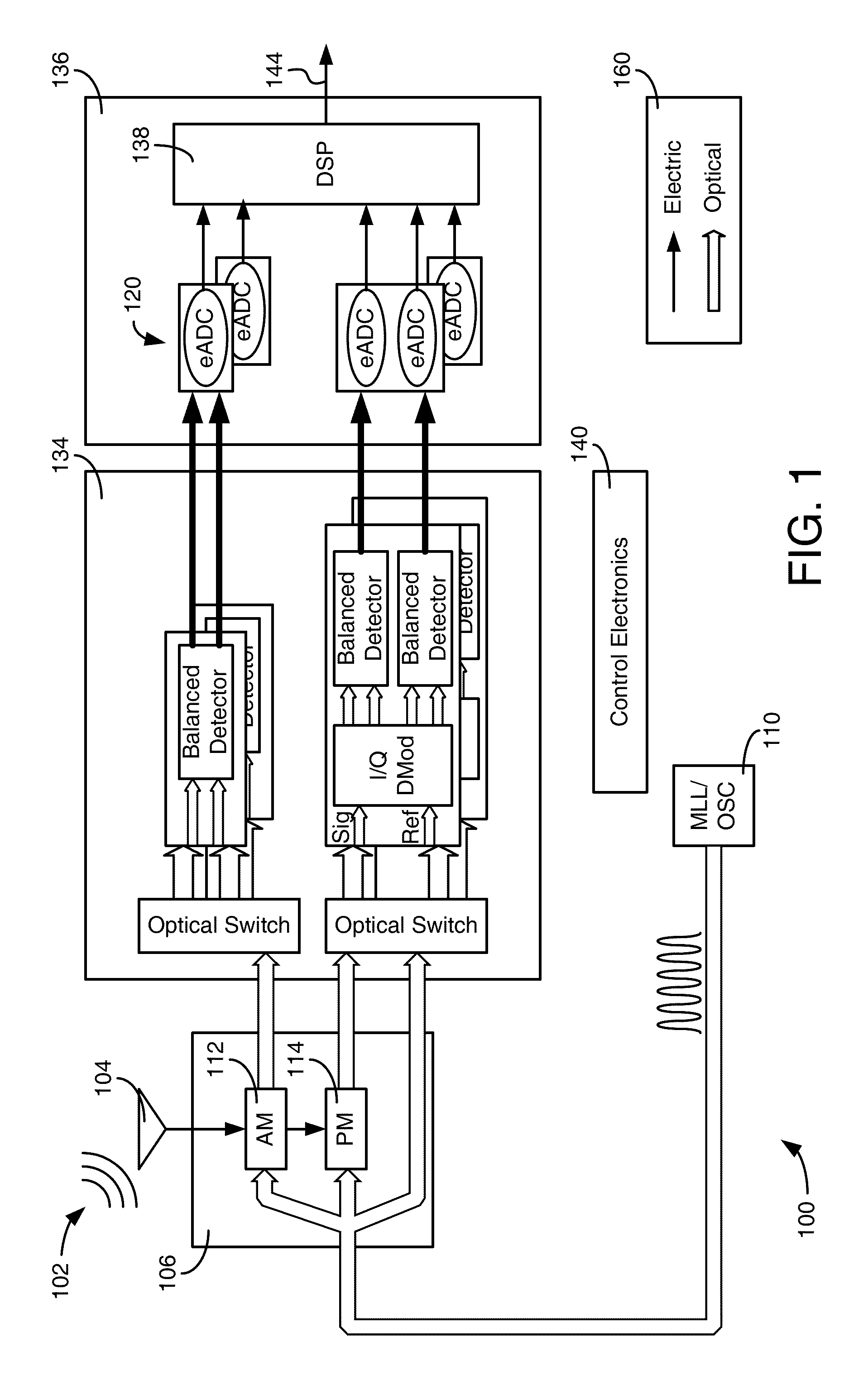

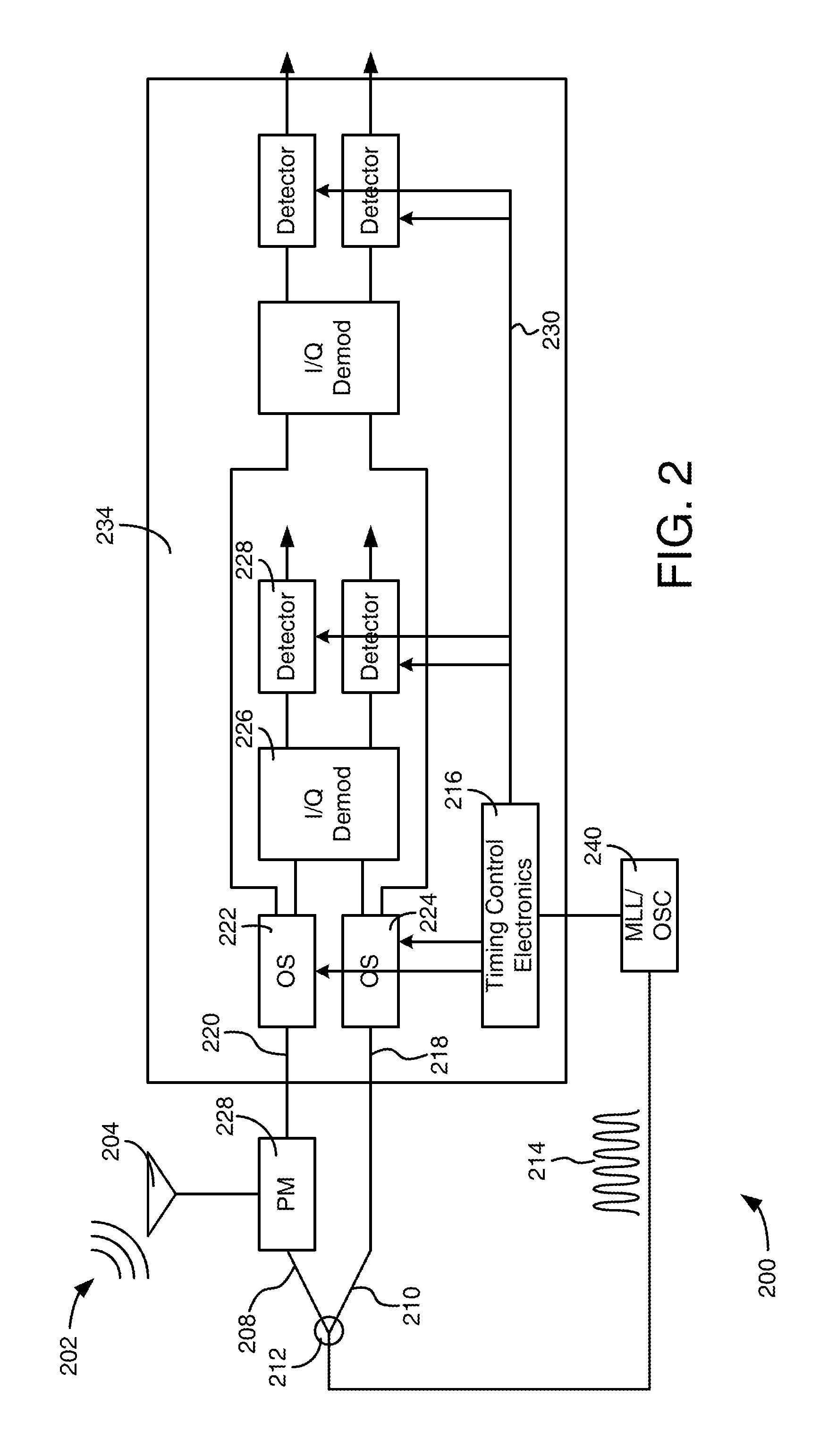

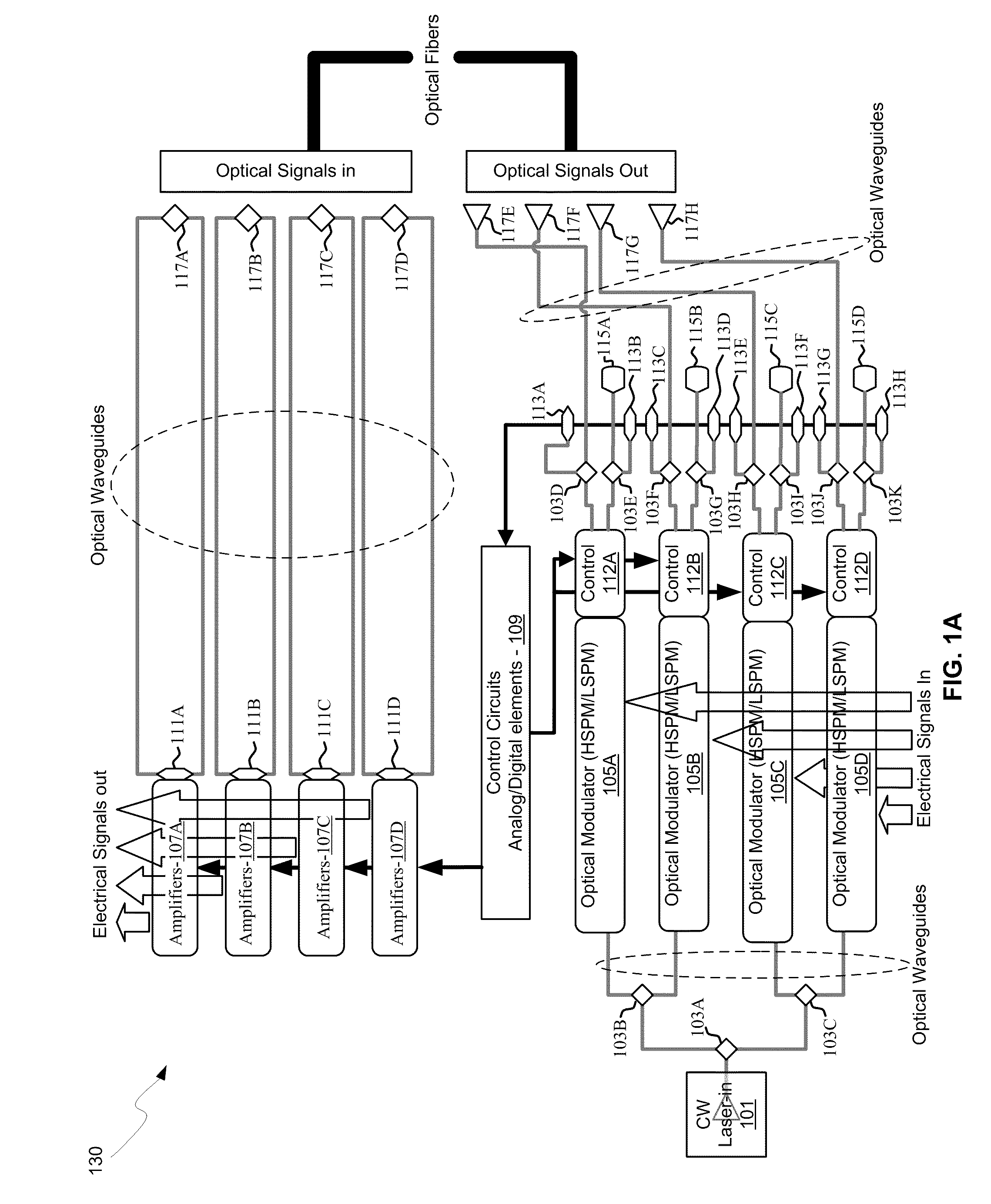

Optically interleaved photonic analog to digital converters

ActiveUS9197471B1Electromagnetic transmission non-optical aspectsOptical transmission for RF signal generation/processingAudio power amplifierPhotonics

A method of and system of processing a phase-modulated optical signal includes performing, by demodulators, demodulation of the phase-modulated optical signal and outputting optical demodulated signals. The processing further includes performing, by pairs of gated photo detectors respectively connected to the I / Q demodulators, photo detection of the demodulated signals. The processing further tracks and holds electronicversions of the demodulated signals with a track and hold amplifier.

Owner:ROCKWELL COLLINS INC

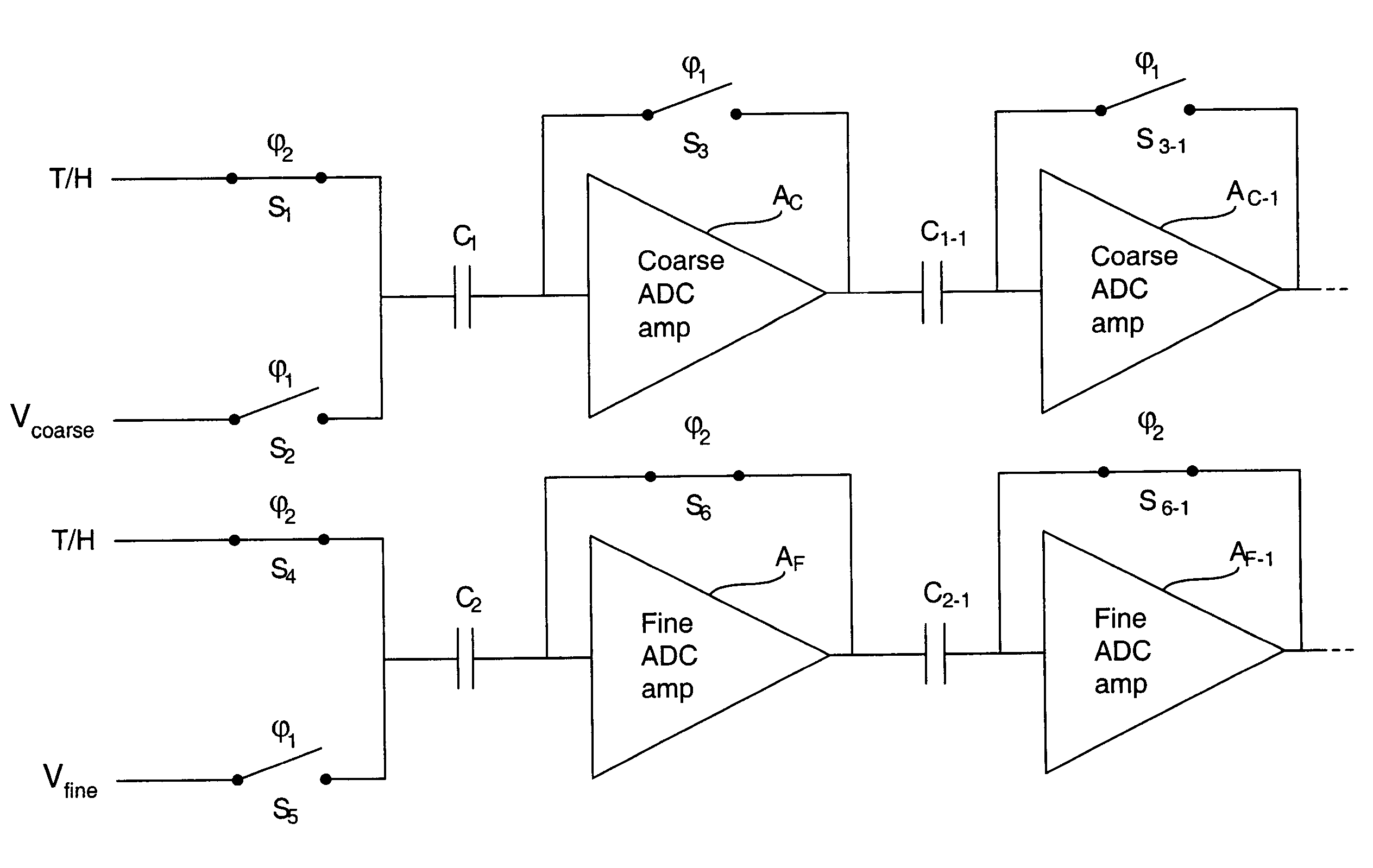

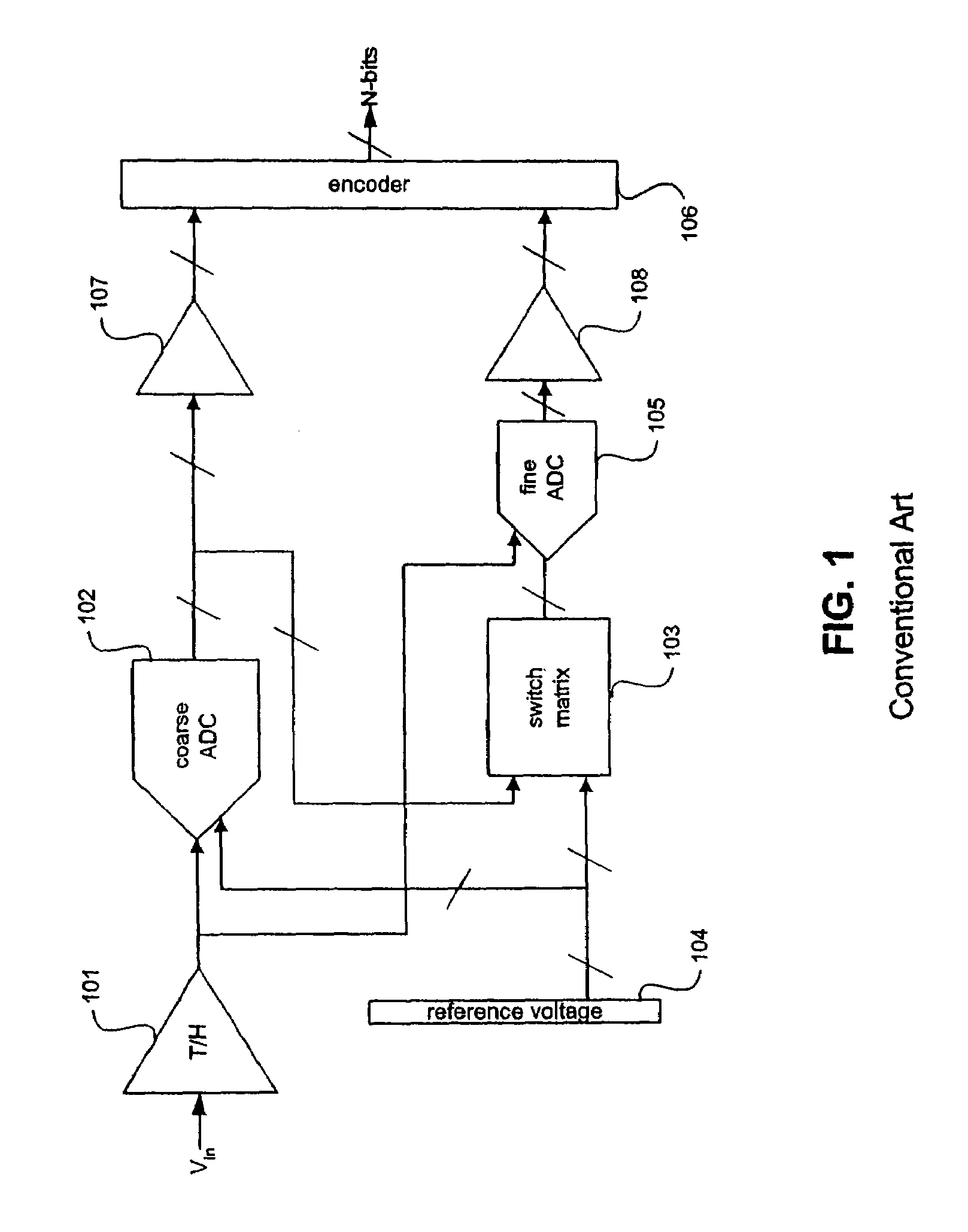

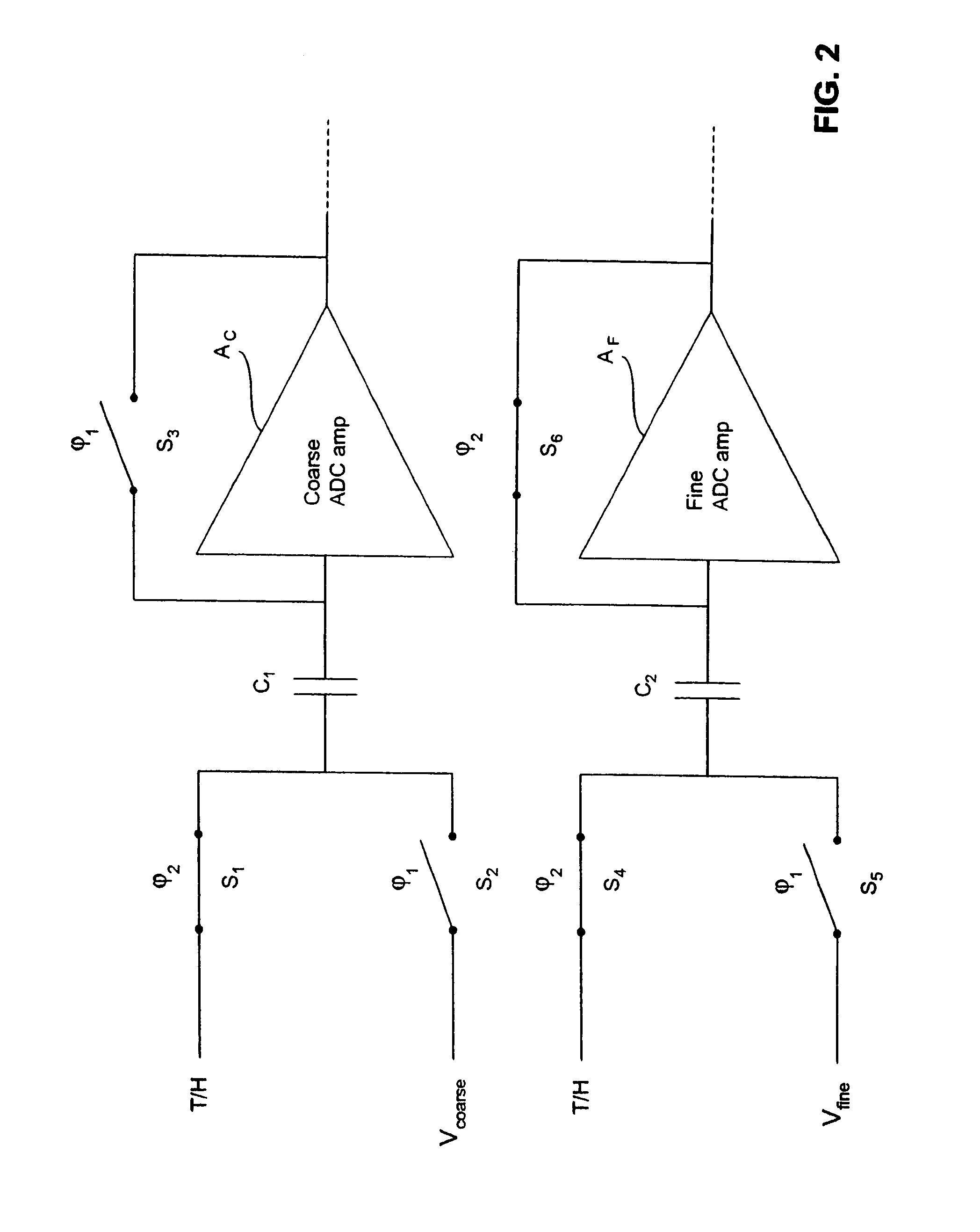

Subranging analog to digital converter with multi-phase clock timing

An N-bit analog to digital converter includes a reference ladder, a track-and-hold amplifier connected to an input voltage, a coarse ADC amplifier connected to a coarse capacitor at its input and having a coarse ADC reset switch controlled by a first clock phase of a two-phase clock, a fine ADC amplifier connected to a fine capacitor at its input and having a fine ADC reset switch controlled by a second clock phase of the two-phase clock, a switch matrix that selects a voltage subrange from the reference ladder for use by the fine ADC amplifier based on an output of the coarse ADC amplifier, and wherein the coarse capacitor is charged to a coarse reference ladder voltage during the first clock phase and connected to the T / H output during the second clock phase, wherein the fine capacitor is connected to a voltage subrange during the first clock phase and to the T / H output during the second clock phase, and an encoder that converts outputs of the coarse and fine ADC amplifiers to an N-bit output.

Owner:AVAGO TECH INT SALES PTE LTD

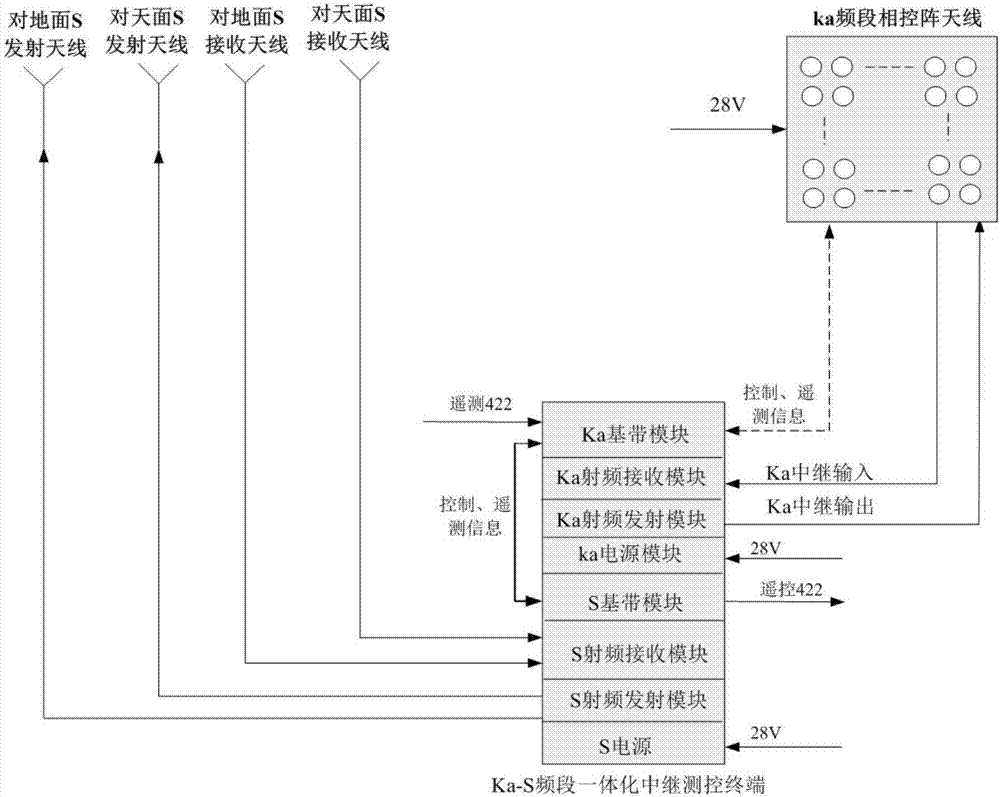

Measurement and control method based on Ka-S-band relay integrated measurement and control system

ActiveCN107332605AImprove efficiencyImprove reliabilitySpatial transmit diversityTelecommunications linkSky

The invention provides a measurement and control method based on a Ka-S-band relay integrated measurement and control system. The method comprises two communication links: S-band relay measurement and control and Ka-band relay measurement and control. An integrated association design technology is employed in the two kinds of band relay. Wide beam antennas are employed in the S-band relay measurement and control communication link and to-sky and to-ground array transmitting / receiving is realized, thereby realizing wide beam coverage. Phased array antennas are employed in the Ka-band relay measurement and control communication link, the Ka relay link can be rapidly tracked and held under the condition that platform postures are continuously changed, and to-sky and to-ground array transmitting / receiving is realized, thereby realizing wide beam coverage. According to the method, the problem that the communication rate is relatively low when the S-band relay measurement and control is employed independently, a real-time coverage range is small when the Ka-band relay measurement and control is employed independently, and the efficiency is relatively low when the two forms of relay measurement and control is not related, in aircraft relay measurement and control is solved.

Owner:SHANDONG INST OF AEROSPACE ELECTRONICS TECH

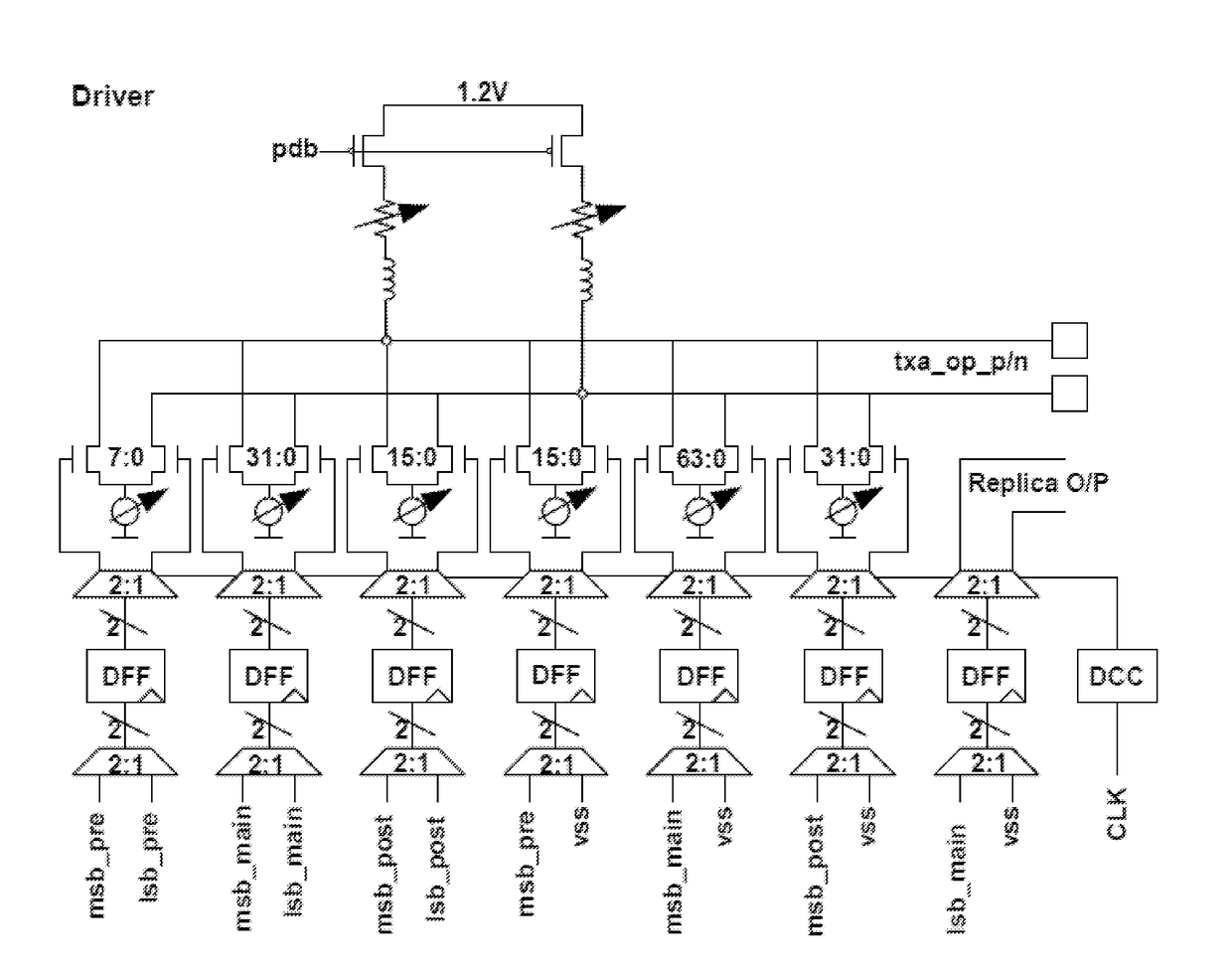

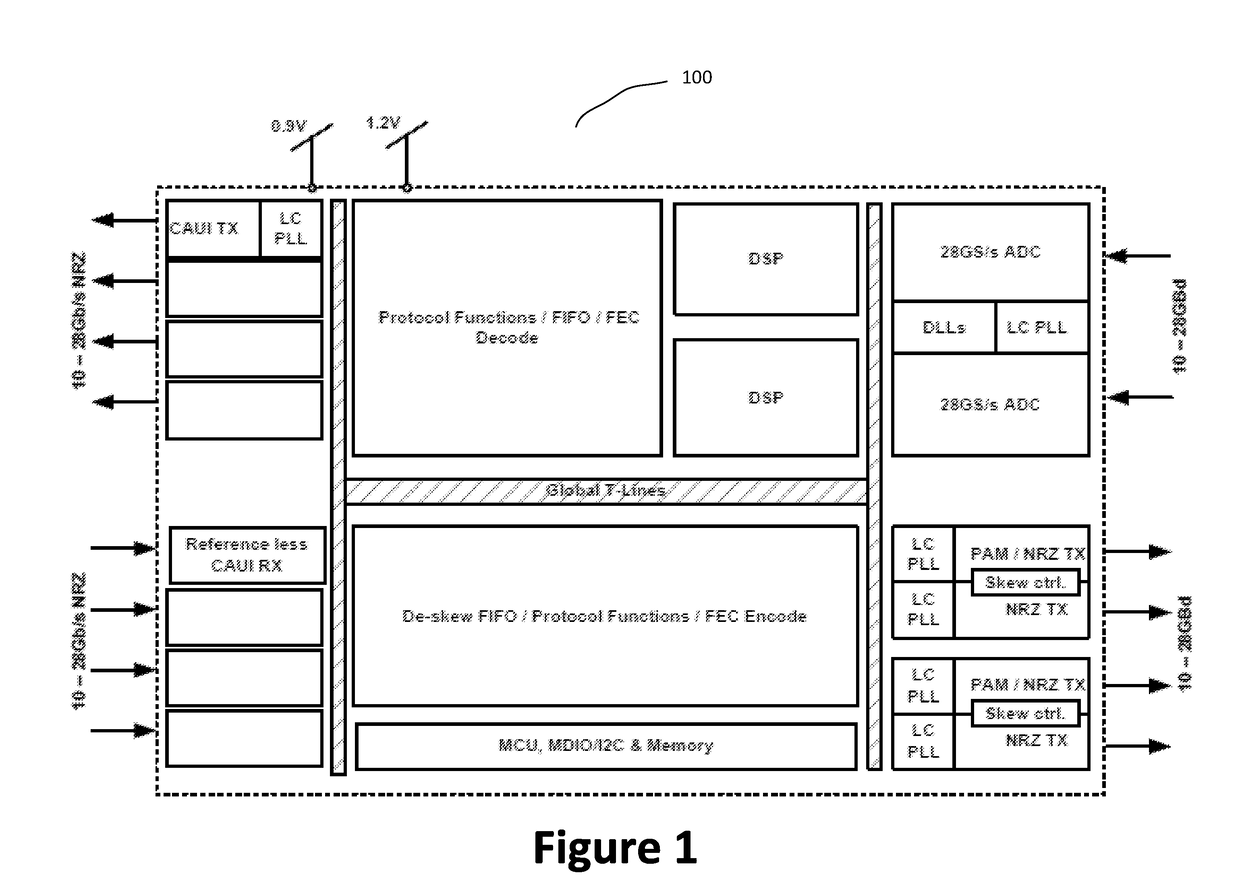

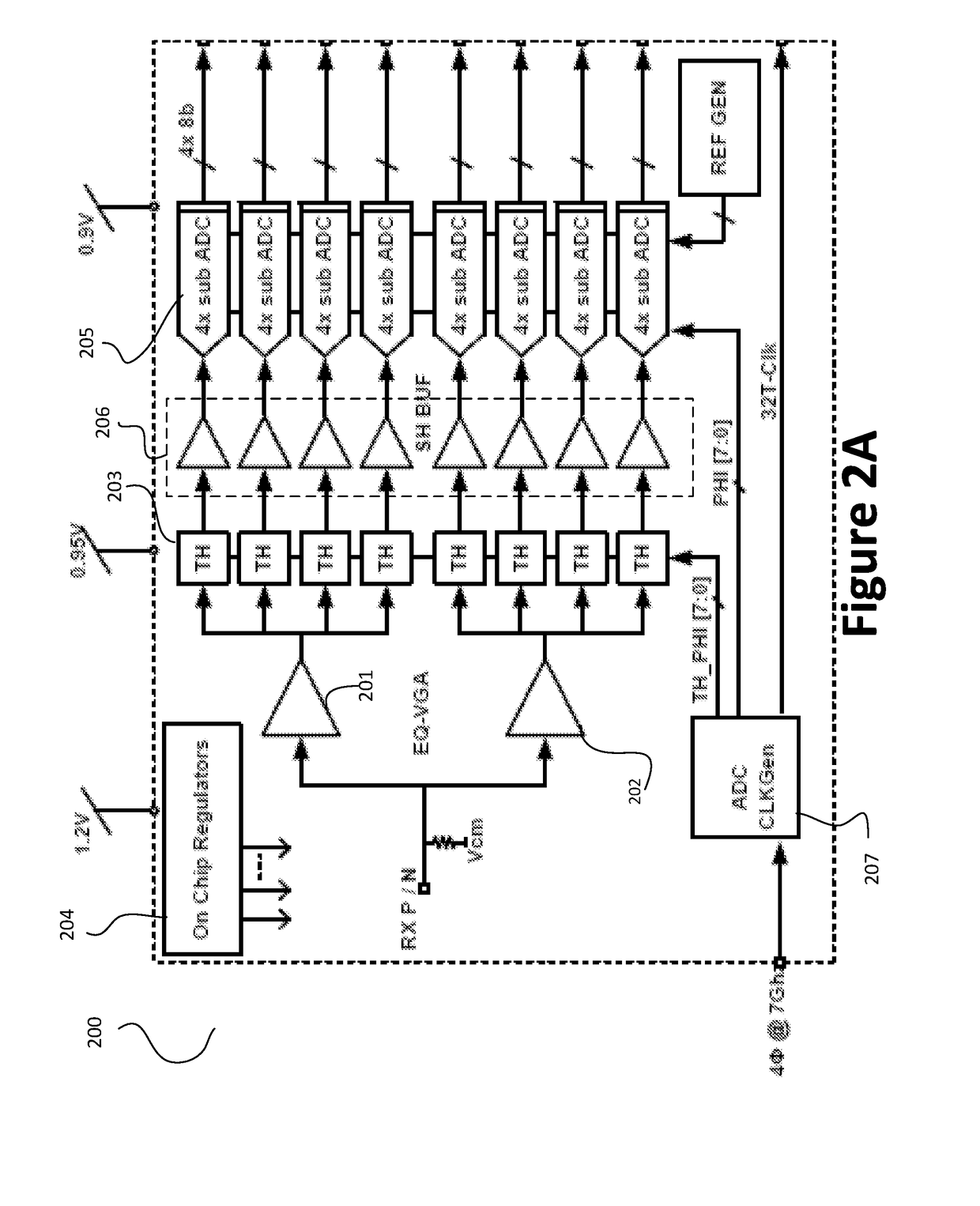

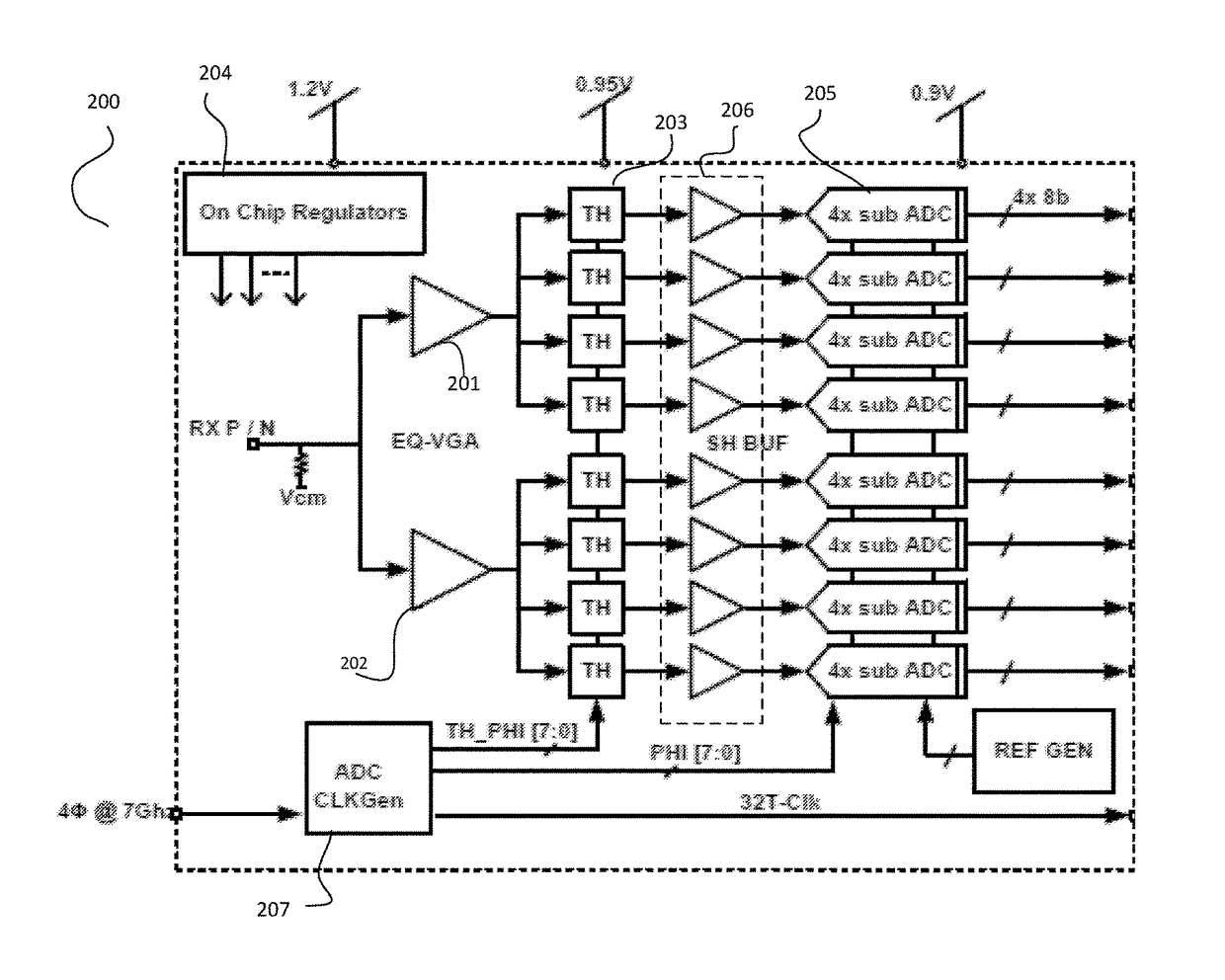

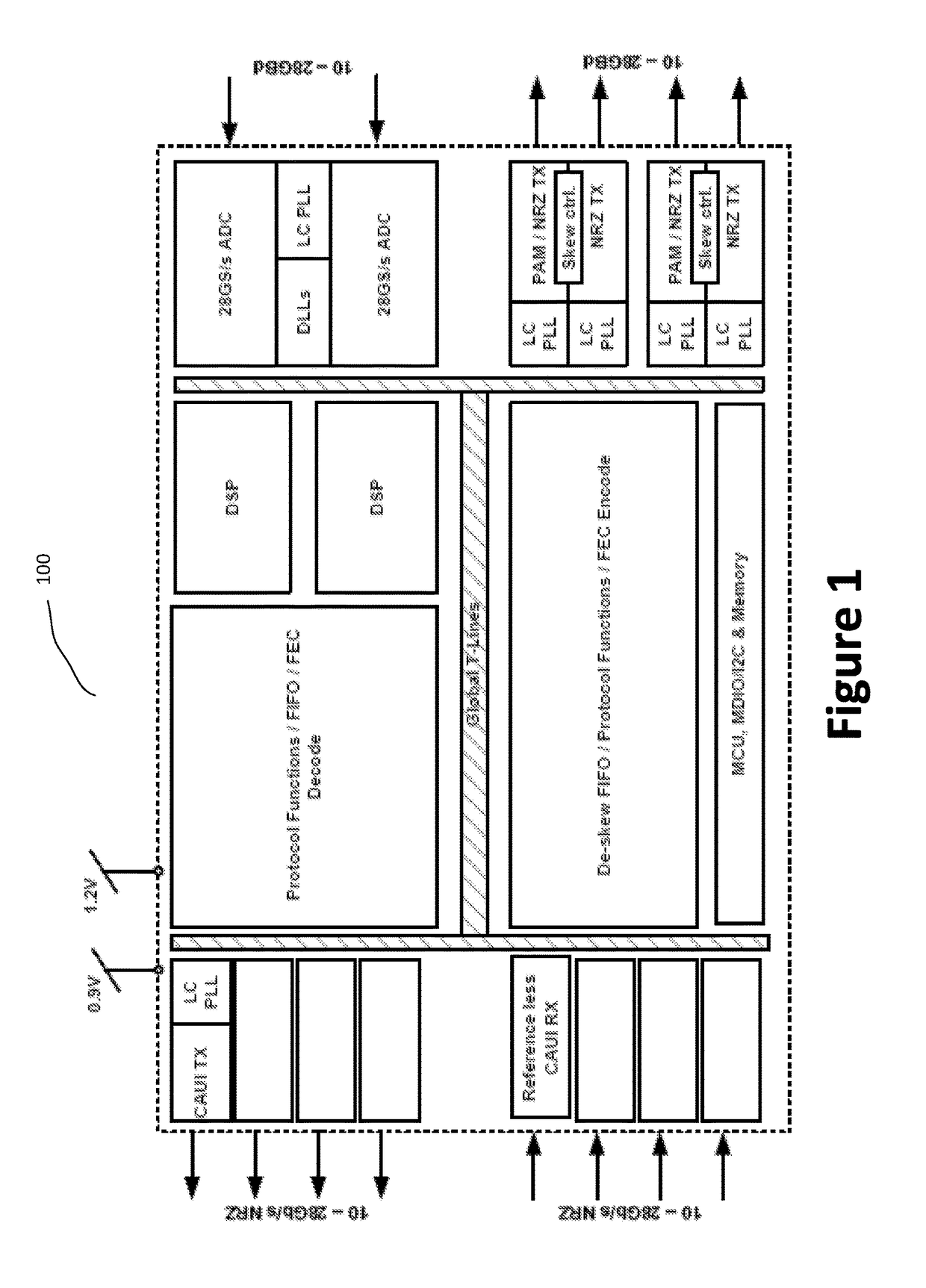

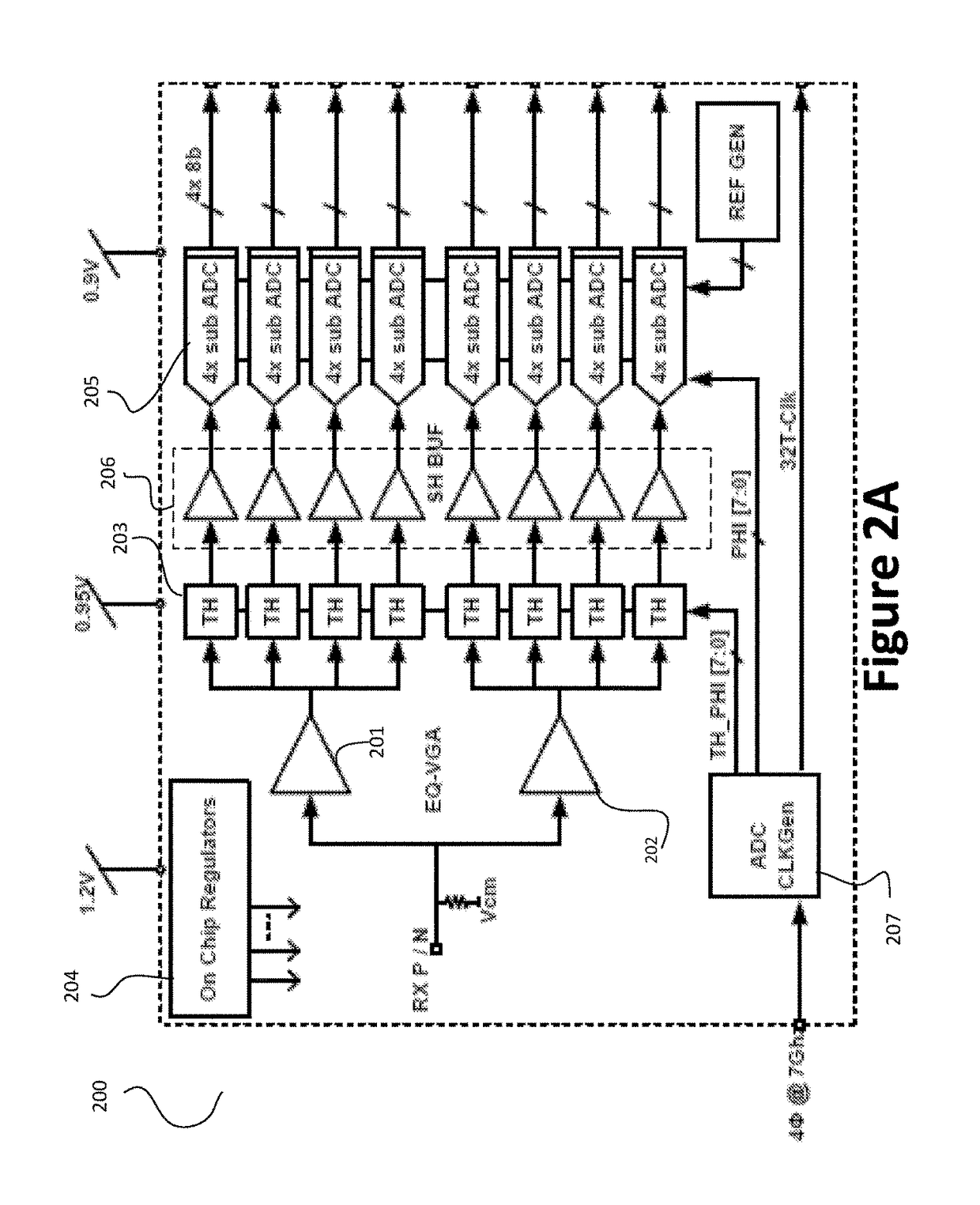

Pam4 transceivers for high-speed communication

ActiveUS20170257168A1Reduce power consumptionReduce noisePulse automatic controlSynchronisation receiversAudio power amplifierTransceiver

The present invention is directed to data communication. More specifically, embodiments of the present invention provide a transceiver that processes an incoming data stream and generates a recovered clock signal based on the incoming data stream. The transceiver includes a voltage gain amplifier that also performs equalization and provides a driving signal to track and hold circuits that hold the incoming data stream, which is stored by shift and holder buffer circuits. Analog to digital conversion is then performed on the buffer data by a plurality of ADC circuits. Various DSP functions are then performed over the converted data. The converted data are then encoded and transmitted in a PAM format. There are other embodiments as well.

Owner:MARVELL ASIA PTE LTD

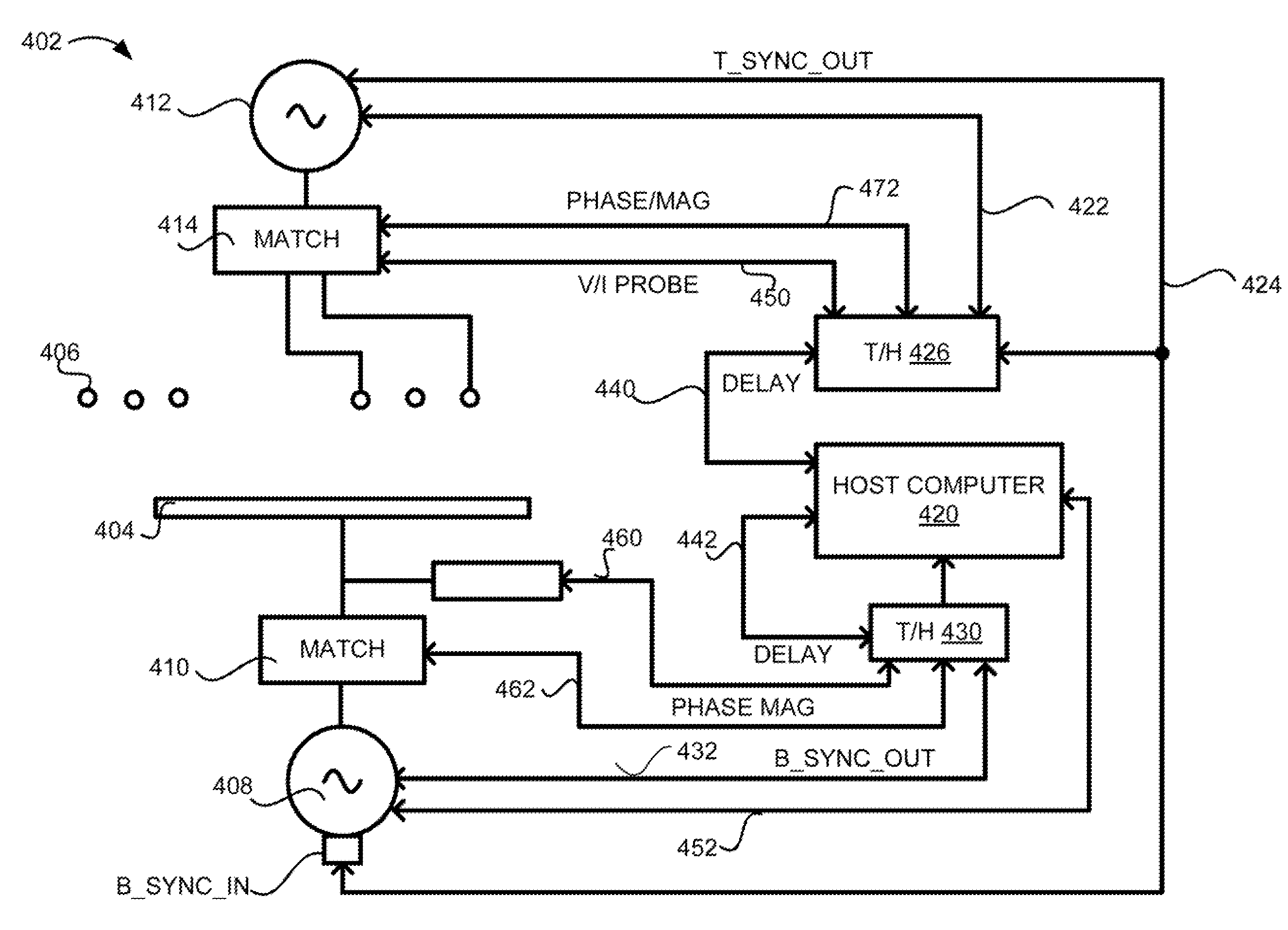

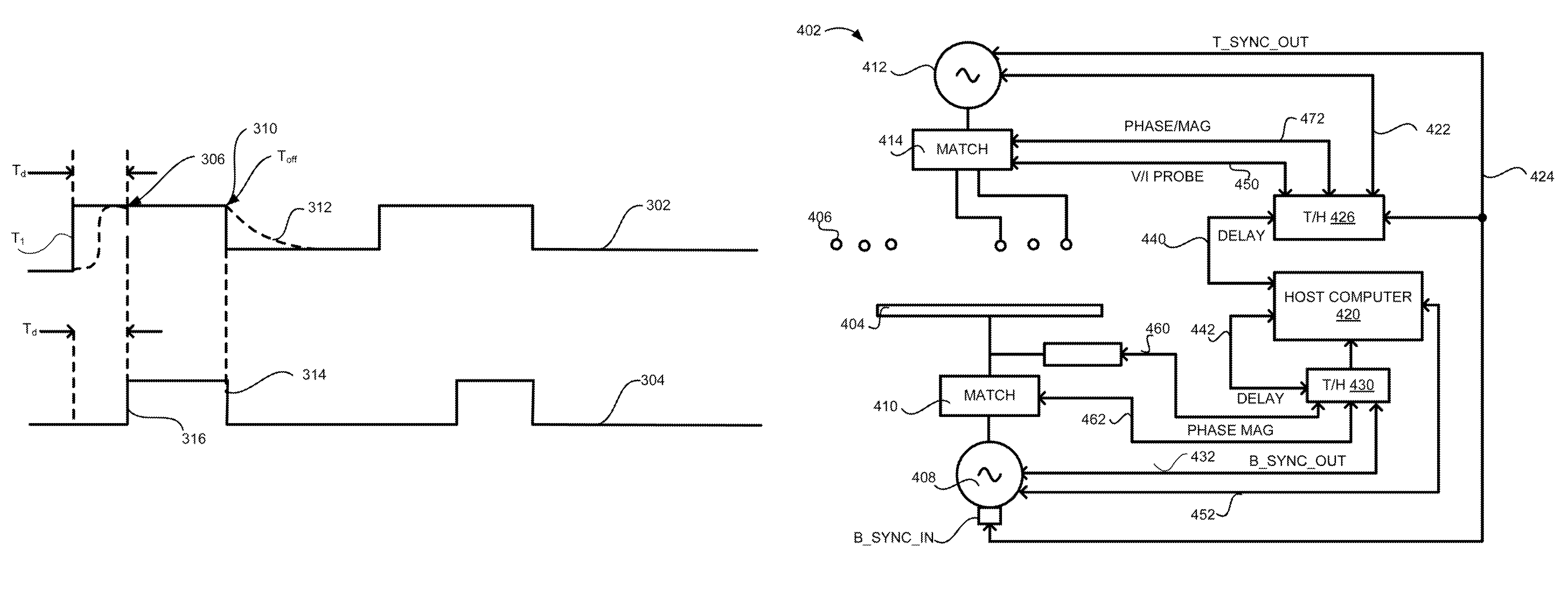

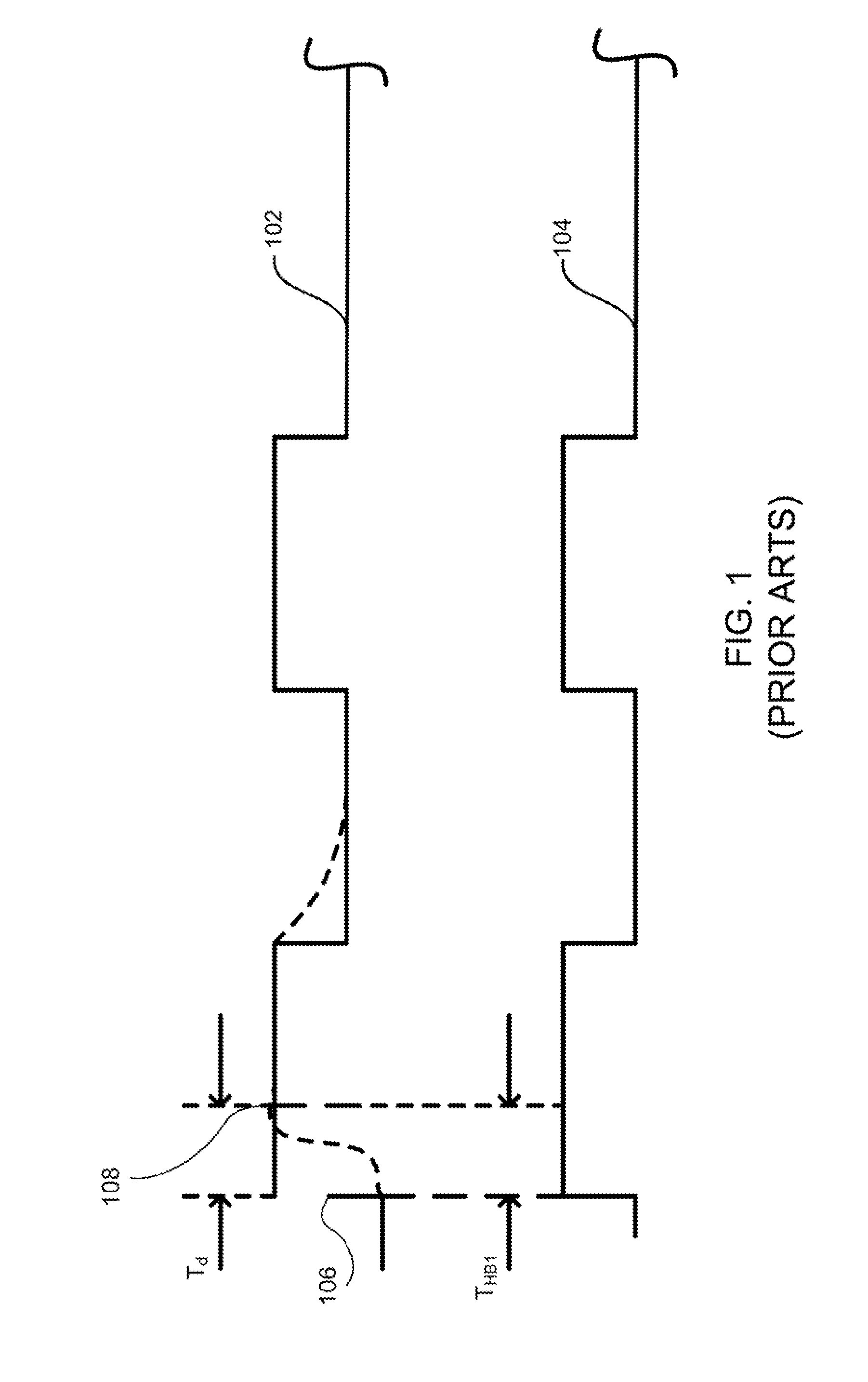

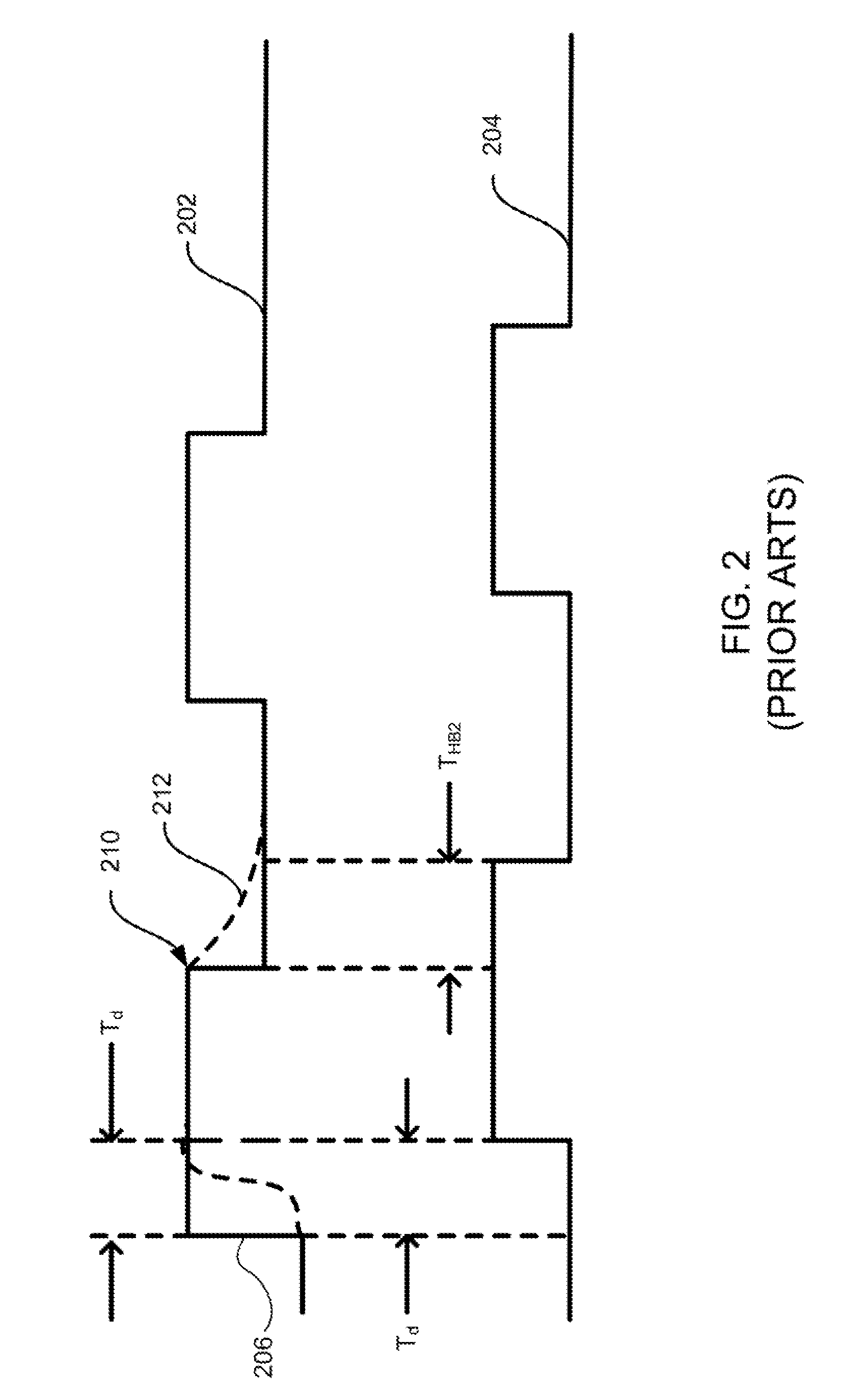

Synchronized and shortened master-slave RF pulsing in a plasma processing chamber

Plasma processing apparatuses and techniques for processing substrates, which include the use of synchronized RF pulsing of a first RF signal and a delayed-and-shortened second RF signal. The first RF signal may be the primary plasma-generating RF signal and the second RF signal may be the RF bias signal or vice versa. Alternatively or additionally, the first RF signal may be the high frequency RF signal and the second RF signal may be the lower frequency RF signal. Either the first RF signal or the second RF signal may act as the master, with the other acting as the slave signal. Alternatively, an external circuit may be employed as a master to control both the first RF signal and the second RF signal as slave signals. Track-and-hold techniques and circuits are provided to ensure accurate measurement for process control and other purposes.

Owner:LAM RES CORP

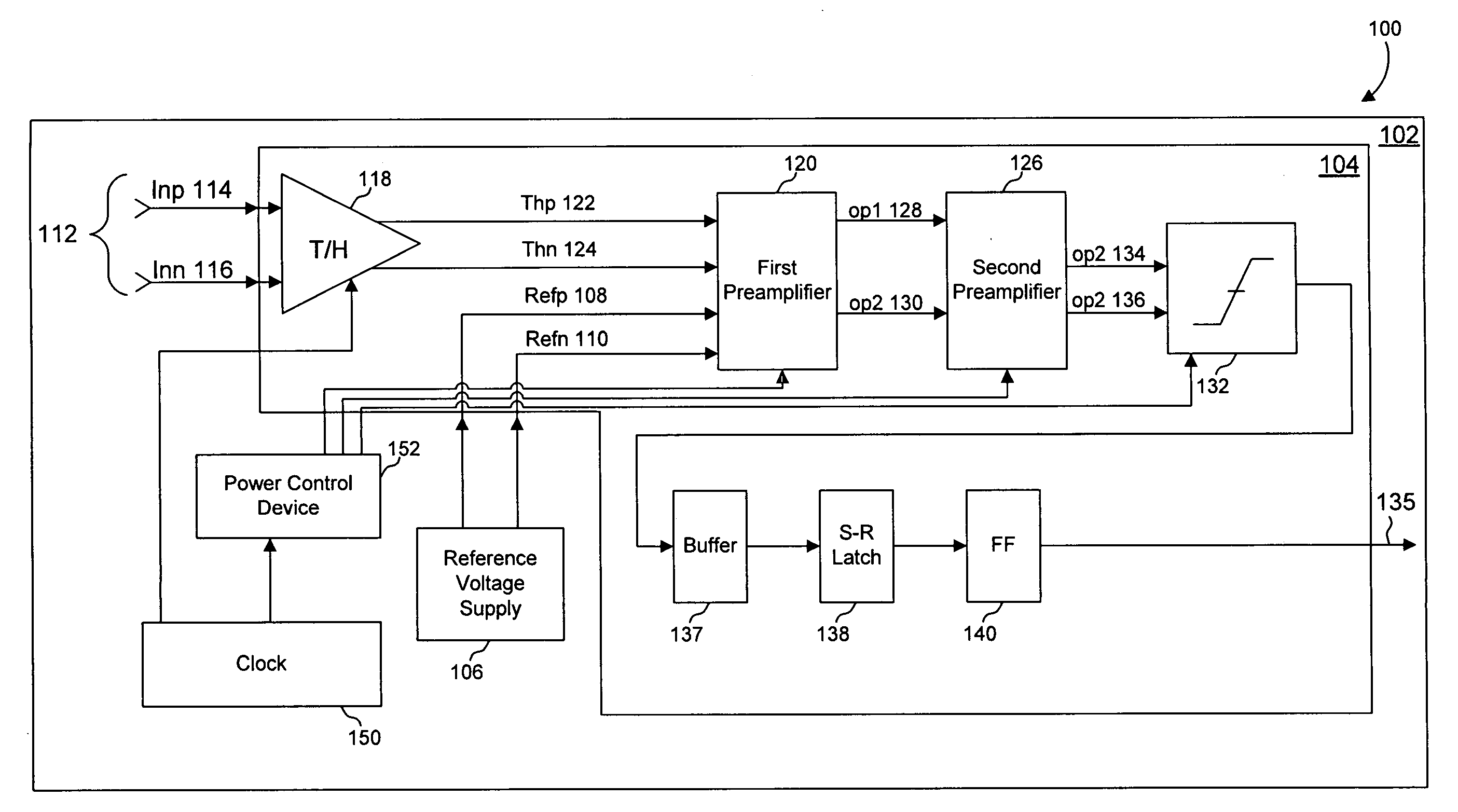

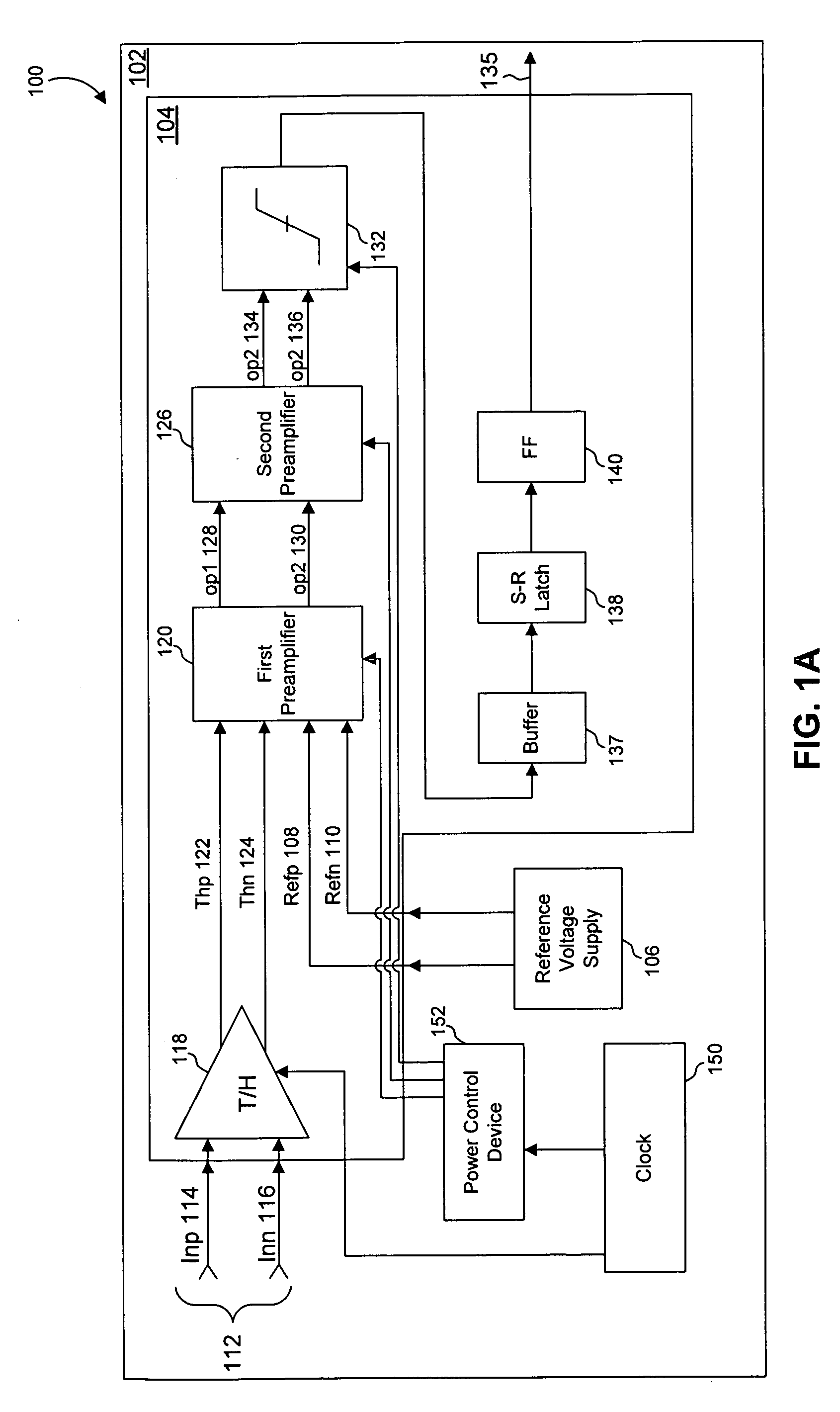

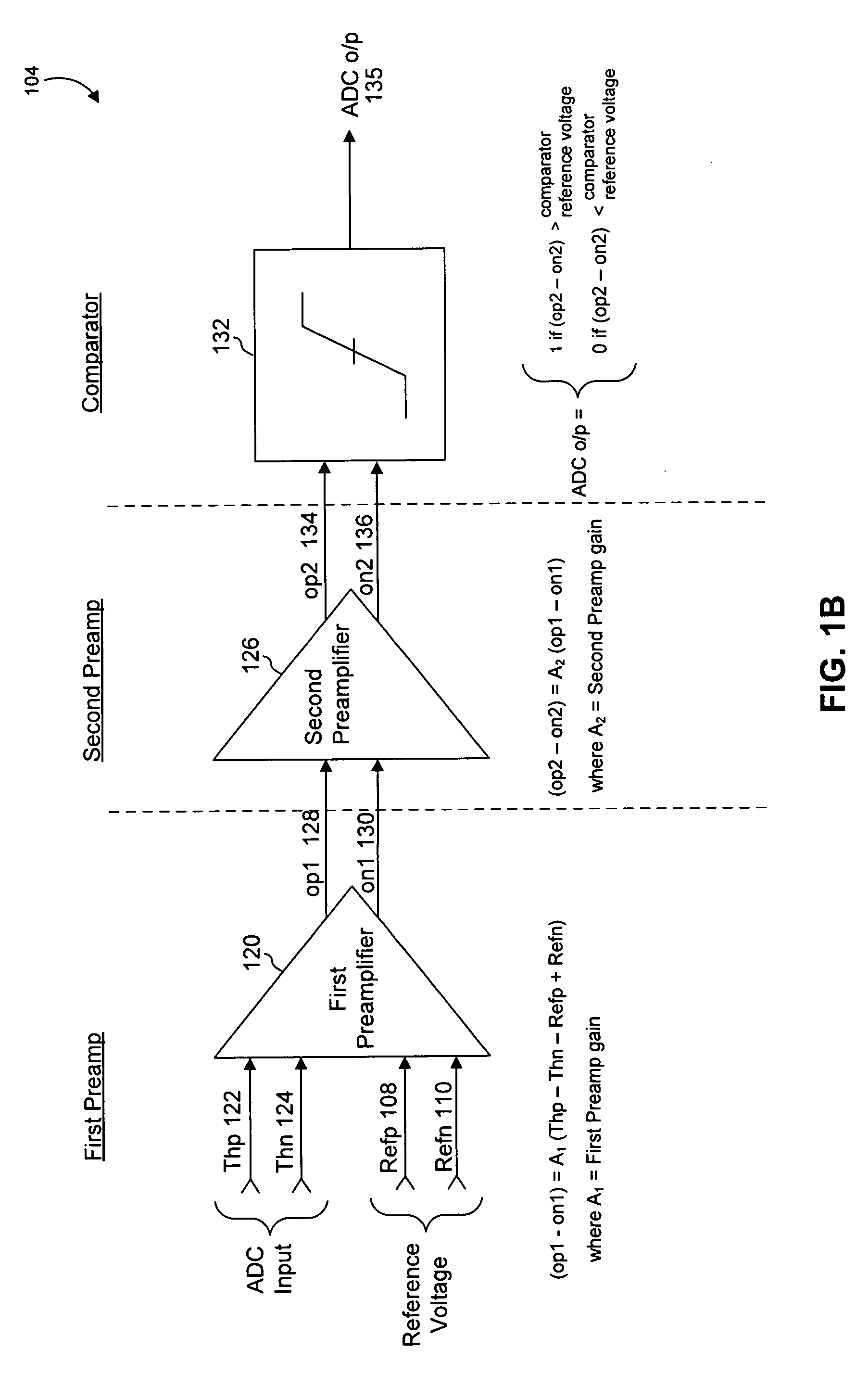

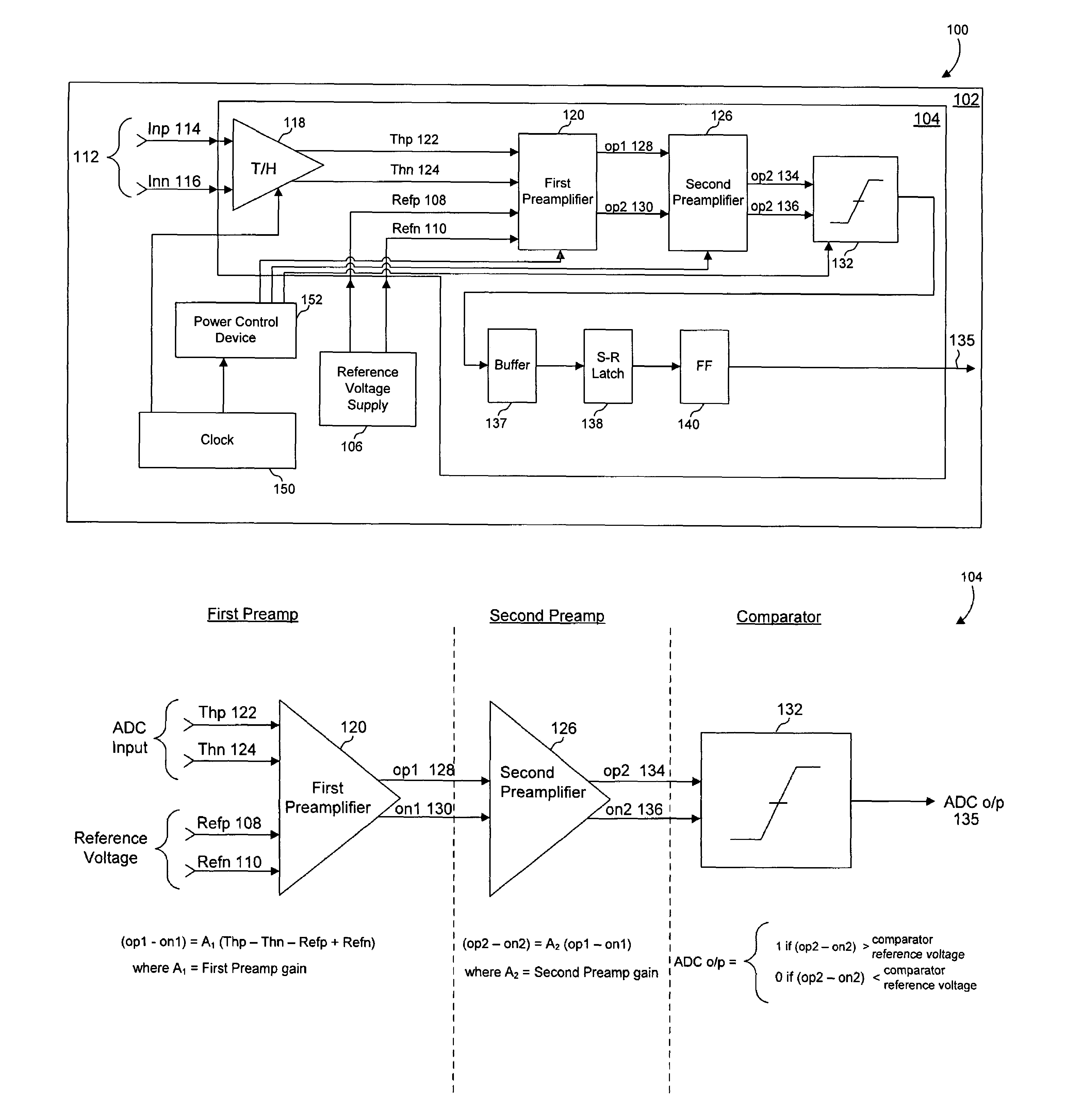

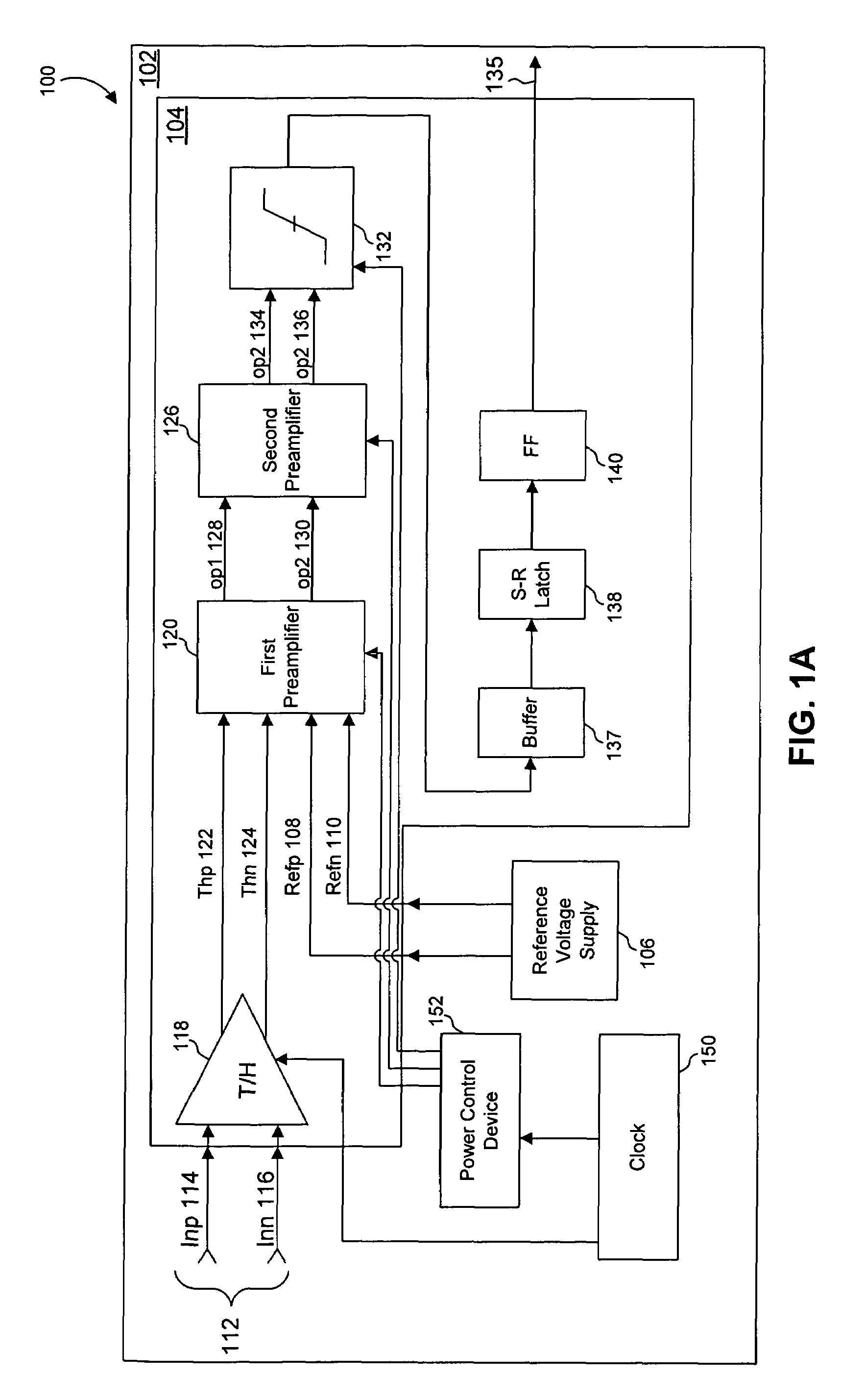

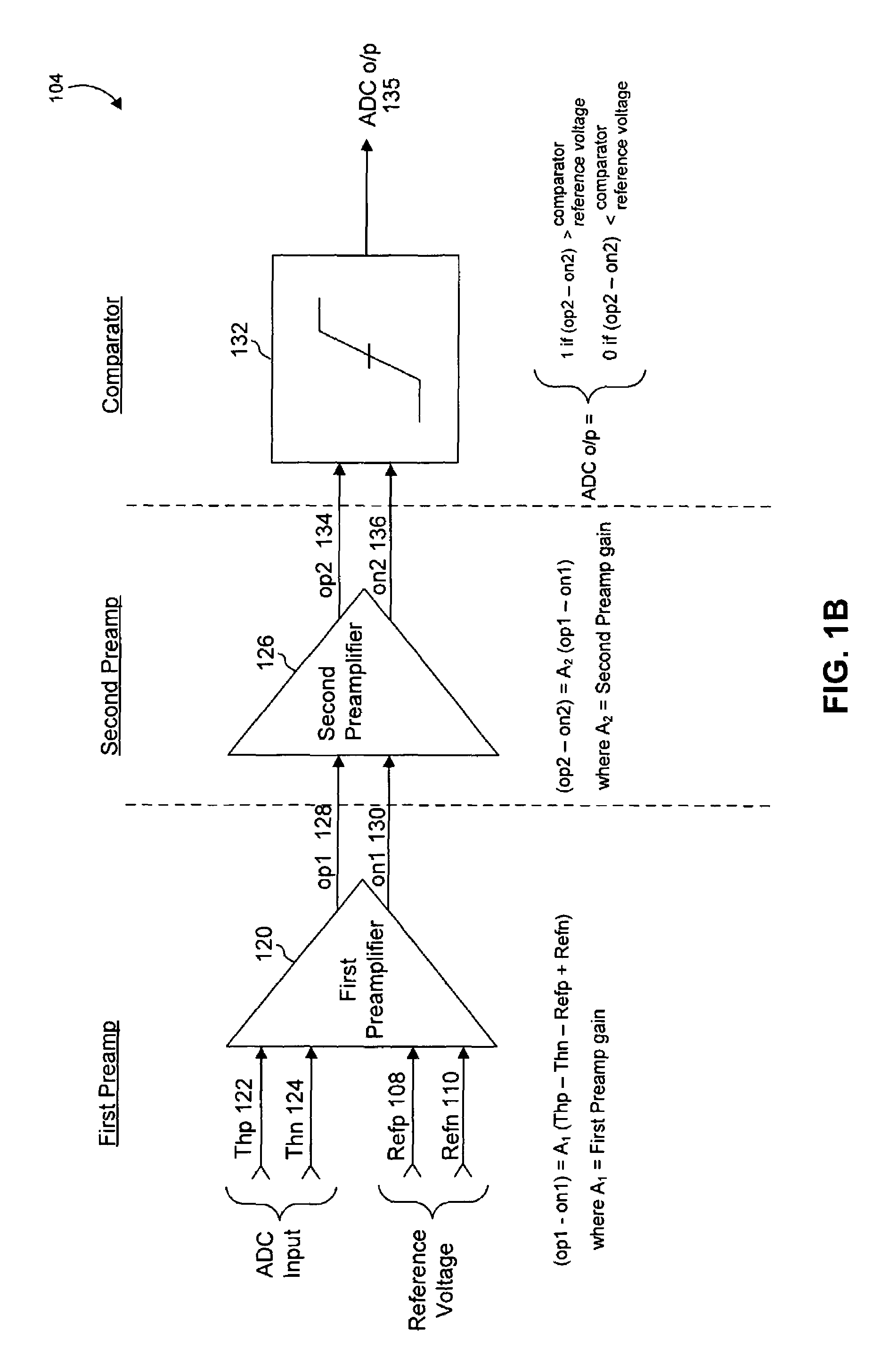

Analog to digital converter with dynamic power configuration

ActiveUS20070132628A1Reduce ADC power consumptionReduce power consumptionPower saving provisionsElectric signal transmission systemsAudio power amplifierA d converter

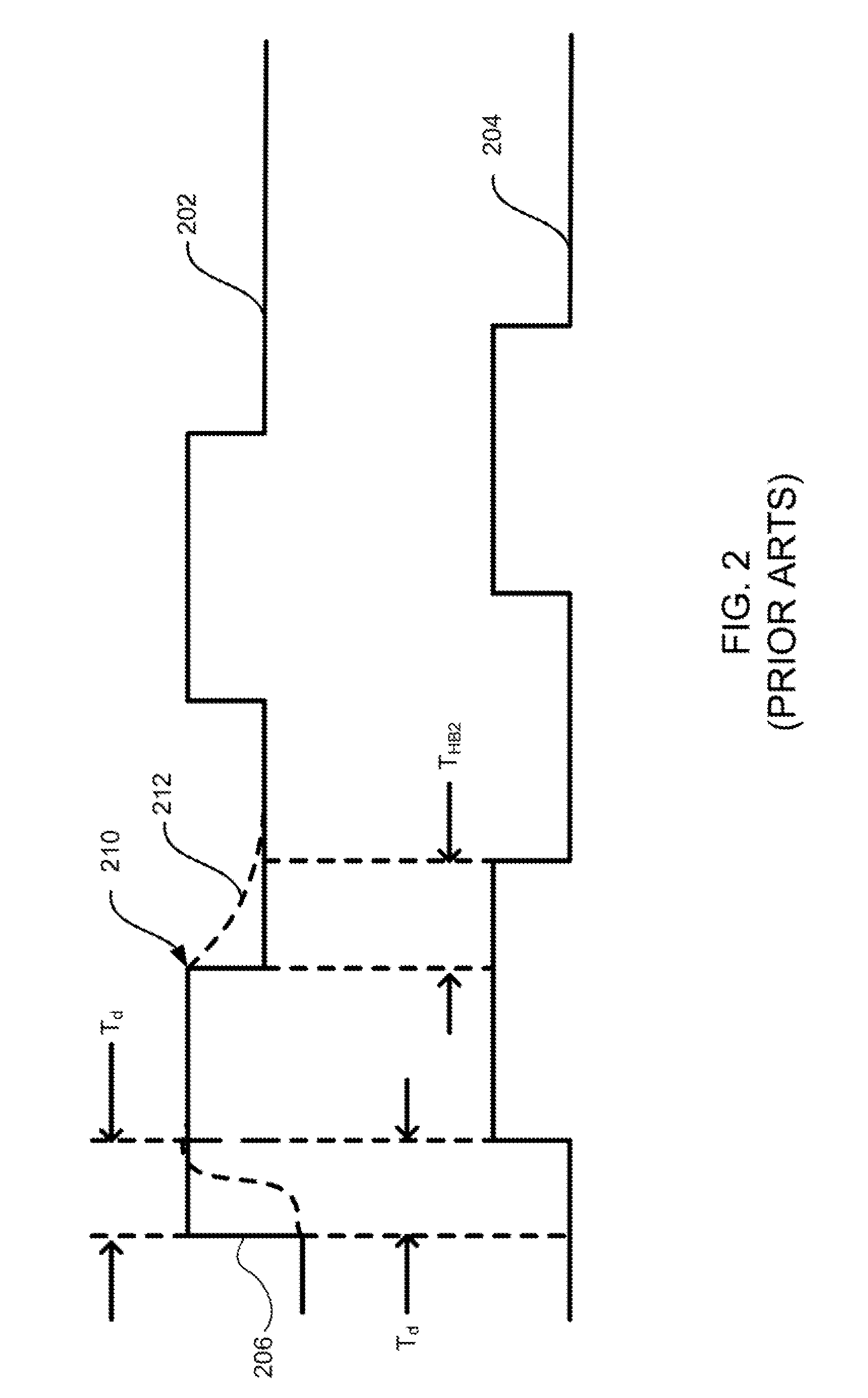

In an embodiment, an analog to digital converter (ADC) has a dynamic power circuit. The ADC has a track-and-hold circuit with an output and a track mode. The ADC also has a comparator with an input. A preamplifier is coupled between the track-and-hold output and the comparator input. At least one of a preamplifier current and a comparator current are limited during the track mode to reduce ADC power consumption.

Owner:AVAGO TECH INT SALES PTE LTD

Analog to digital converter with dynamic power configuration

ActiveUS7456764B2Reduce power consumptionPower saving provisionsElectric signal transmission systemsAudio power amplifierEngineering

In an embodiment, an analog to digital converter (ADC) has a dynamic power circuit. The ADC has a track-and-hold circuit with an output and a track mode. The ADC also has a comparator with an input. A preamplifier is coupled between the track-and-hold output and the comparator input. At least one of a preamplifier current and a comparator current are limited during the track mode to reduce ADC power consumption.

Owner:AVAGO TECH INT SALES PTE LTD

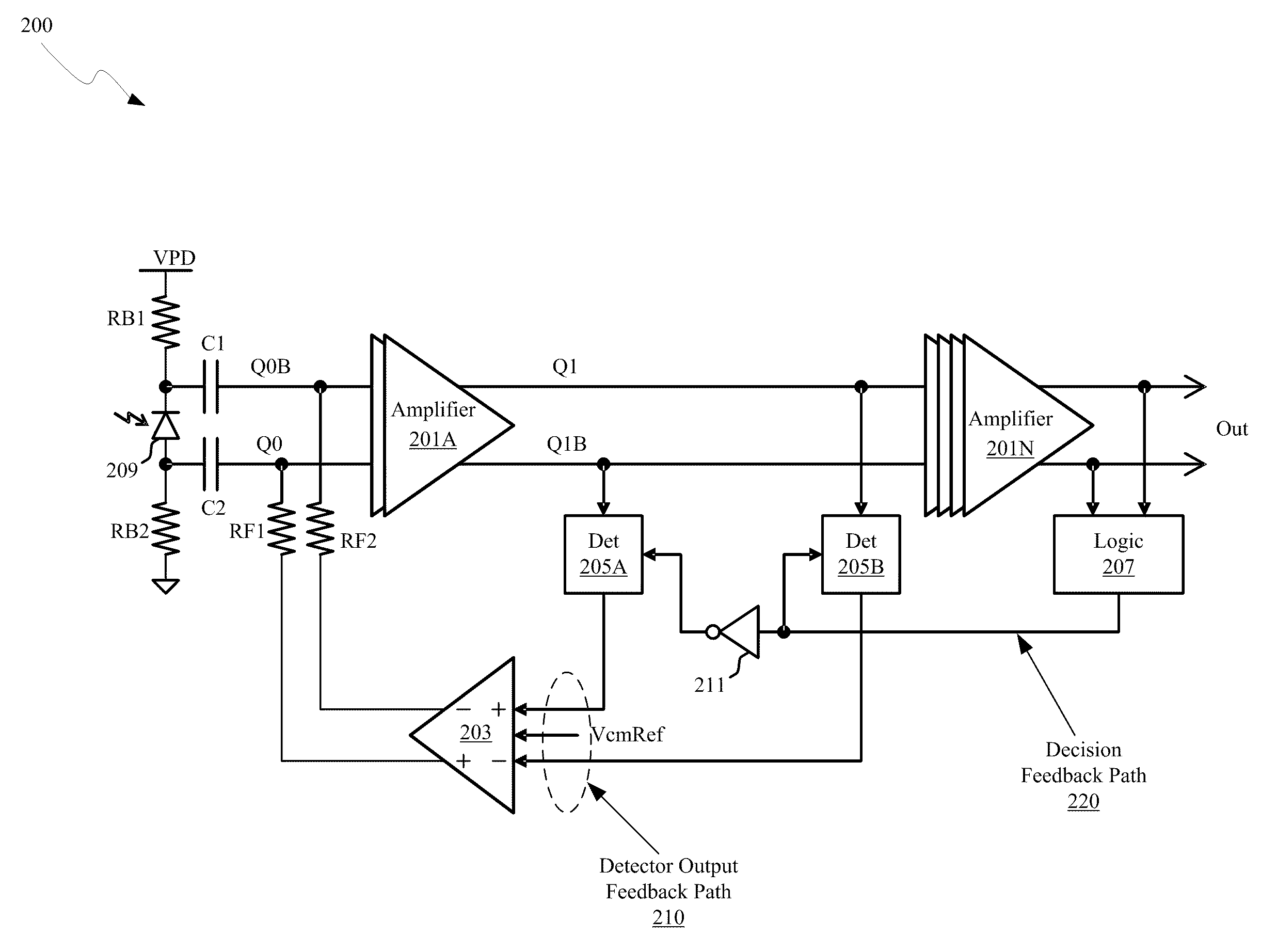

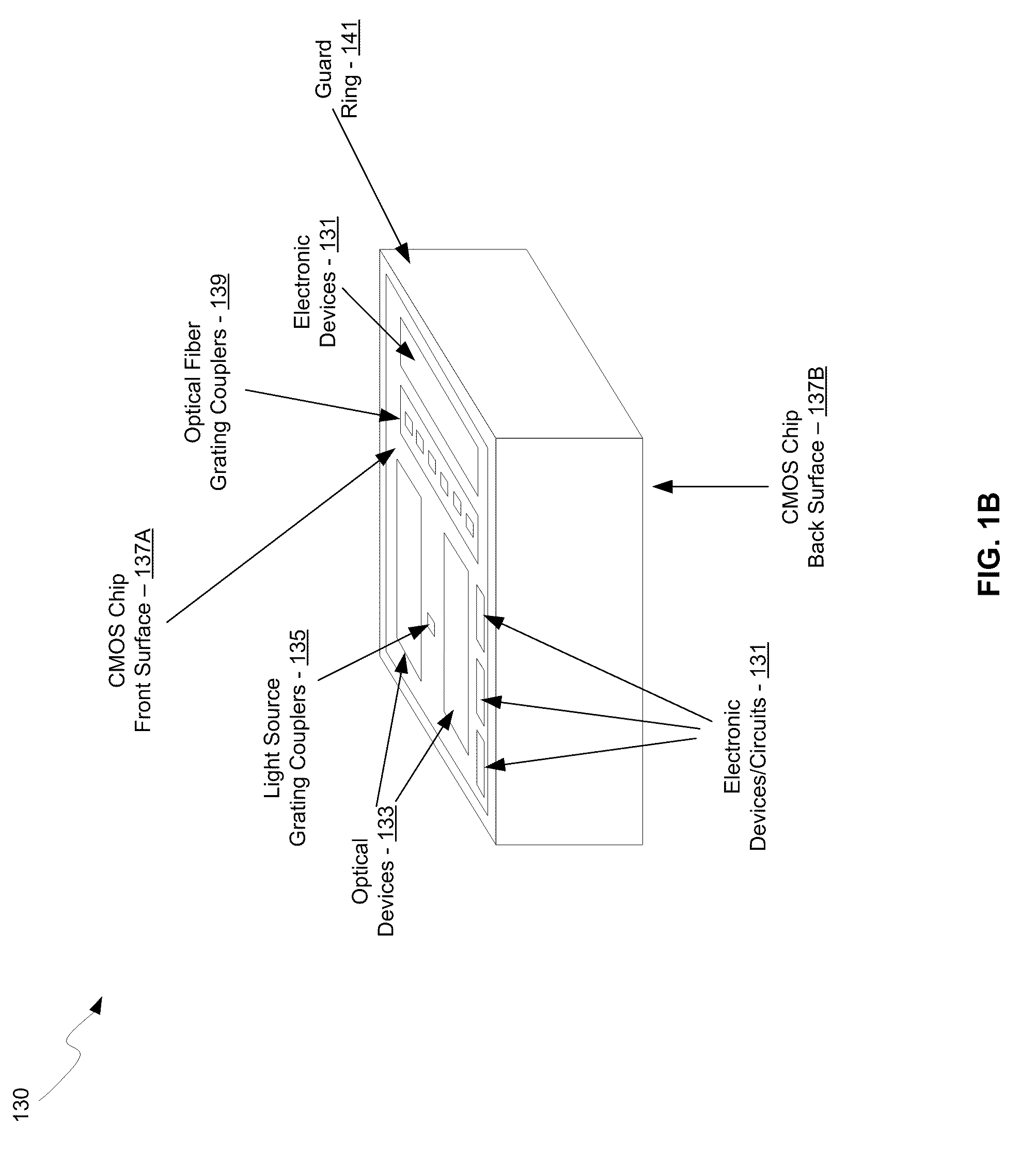

Method and system for optoelectronic receivers for uncoded data

A method and system for optoelectronic receivers for uncoded data are disclosed and may include amplifying received electrical signals in a signal amplifier comprising differential gain stages with signal detectors coupled to the outputs. First and second output voltages may be tracked and held utilizing the signal detectors. A difference between the tracked and held value may be amplified in a feedback path of the gain stage, which enables the dynamic configuration of a decision level. The received electrical signals may be generated from an optical signal by a PIN detector, an avalanche photodiode, or a phototransistor. The electrical signal may be received from a read channel. The feedback path may comprise digital circuitry, including an A / D converter, a state machine, and a D / A converter. The detectors may comprise envelope detectors utilized to detect maximum or minimum voltages. The signal amplifier may be integrated in a photonically-enabled CMOS chip.

Owner:CISCO TECH INC

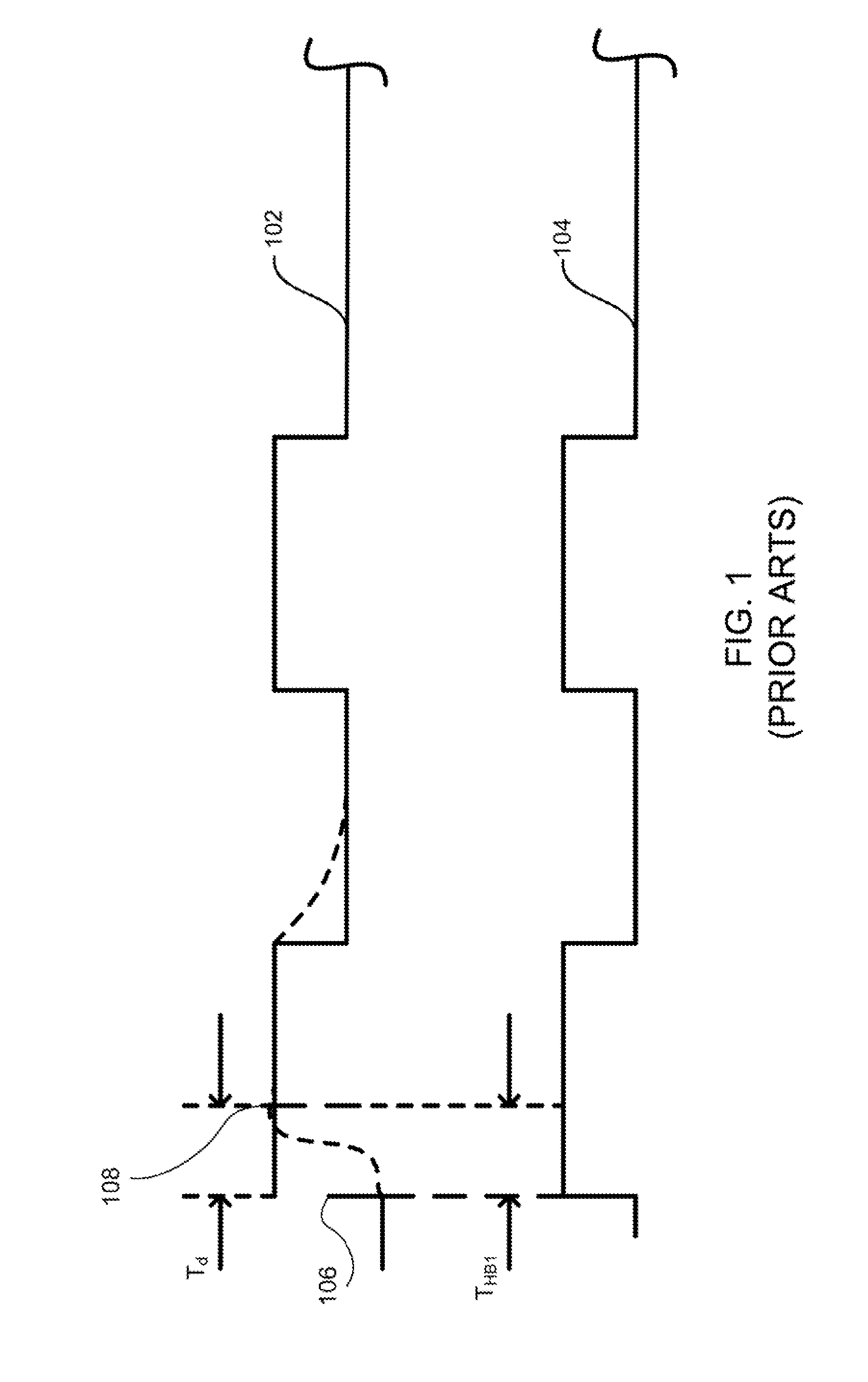

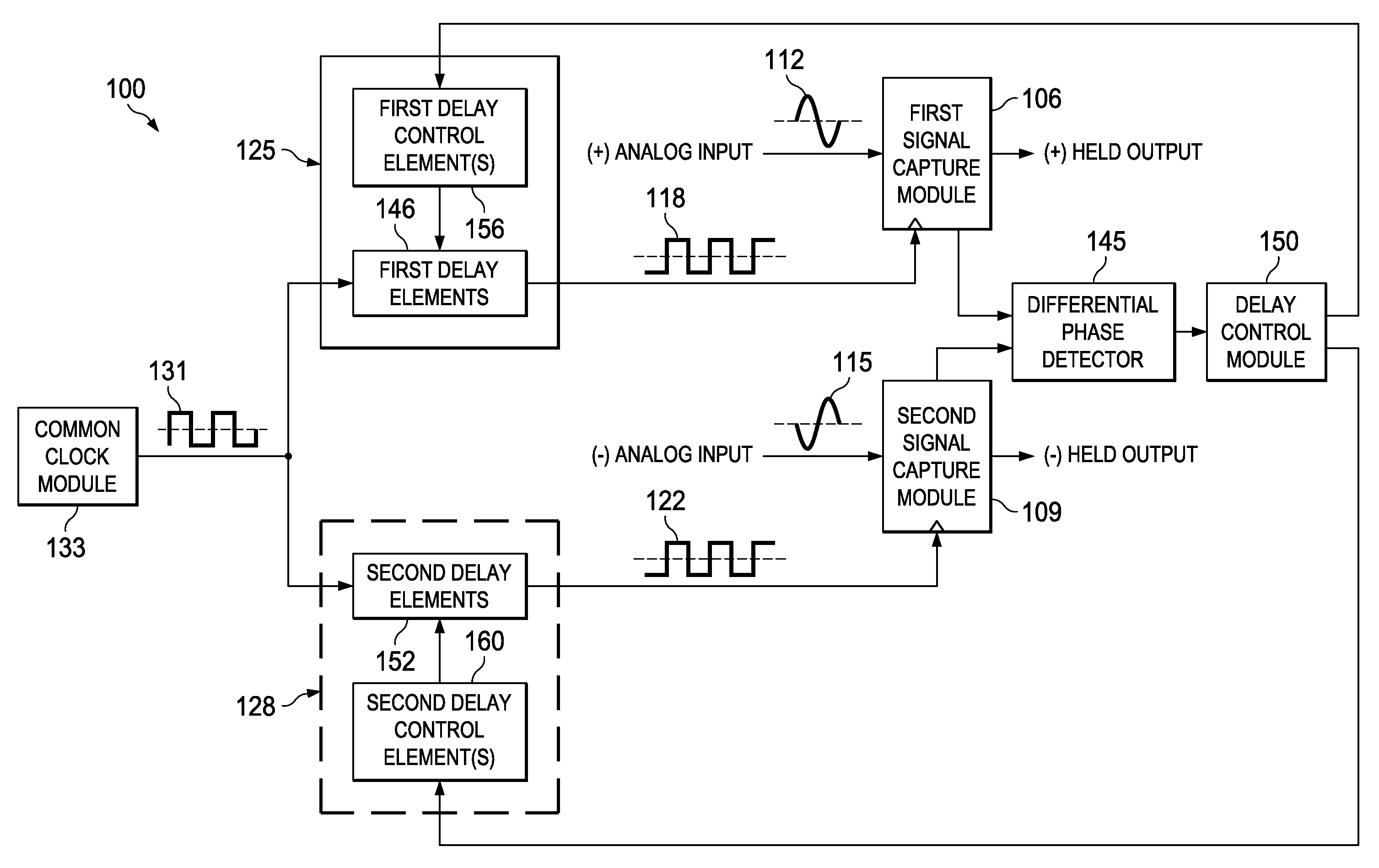

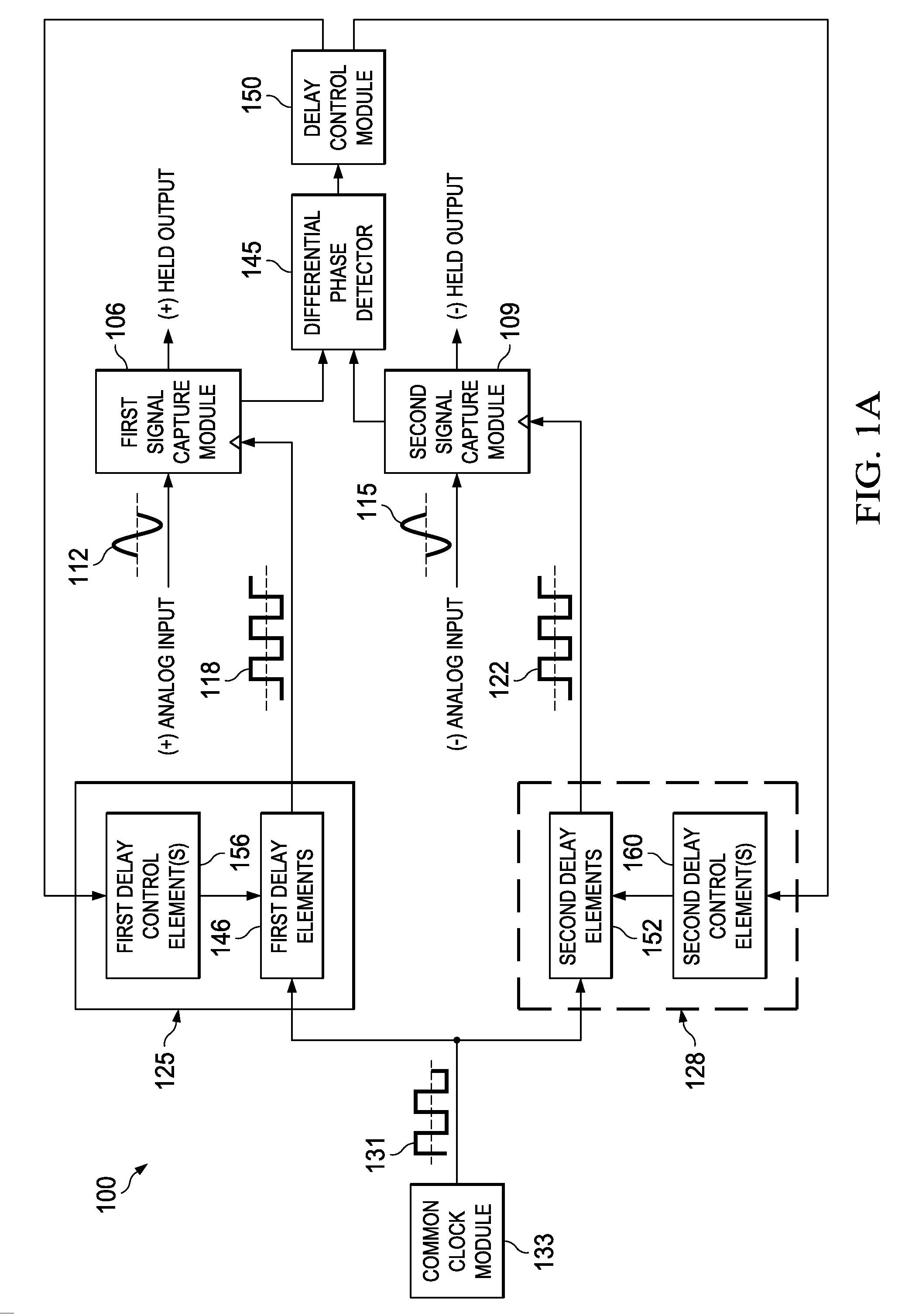

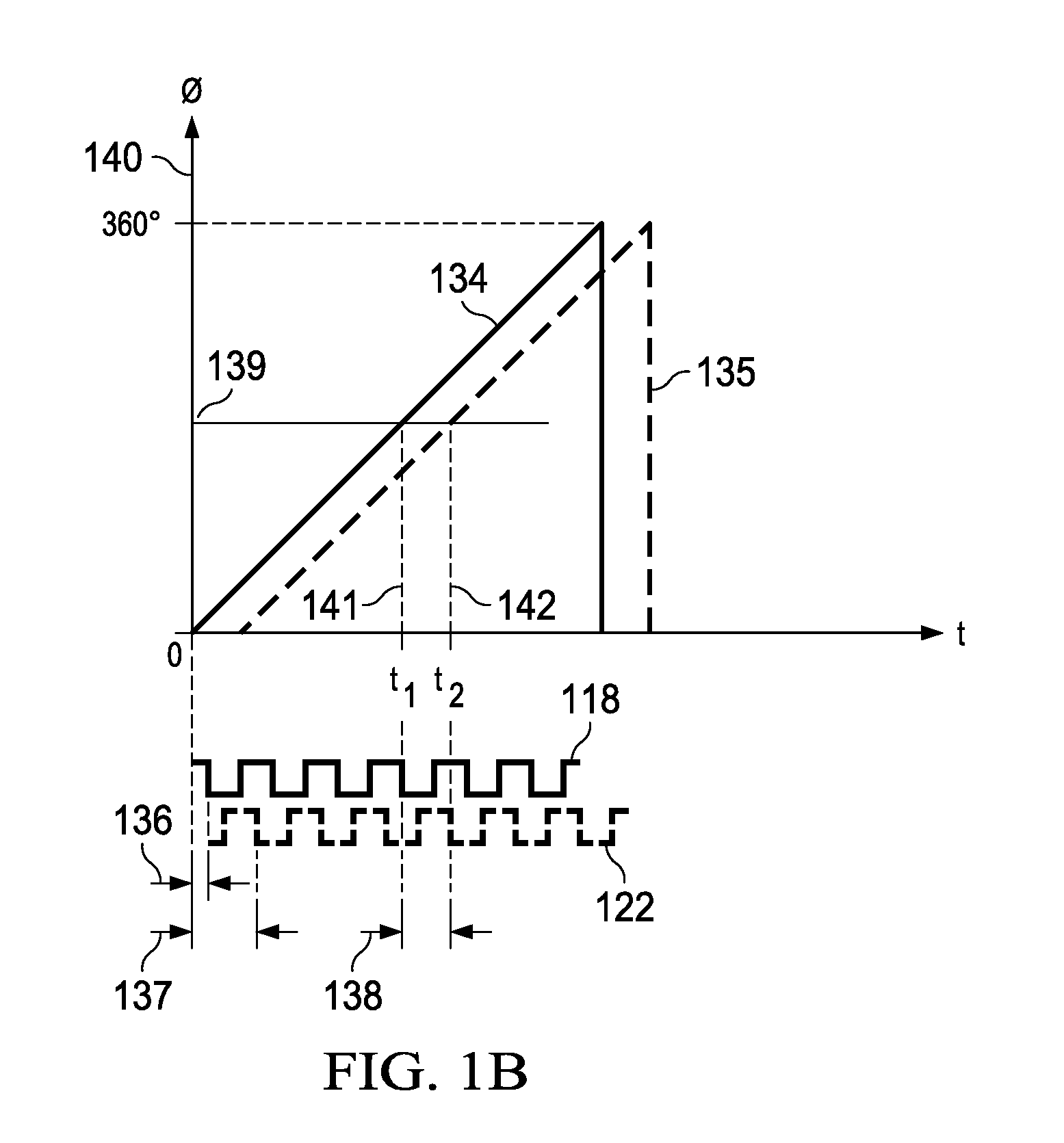

Timing skew error correction apparatus and methods

ActiveUS20120126869A1Efficient samplingAnalogue/digital conversionElectric signal transmission systemsElectricityDifferential phase

Apparatus and methods disclosed herein operate to compensate for skew between inverse phases (e.g., differential phases) of an analog signal appearing at the inputs of an analog signal capture circuit such as a track-and-hold or sample-and-hold circuit associated with an ADC or similar device. Each of two capture clocks is used to capture one of the inverse phases. One or more delay circuits are configured to create a differential delay between clock transitions associated with the two capture clocks. The differential delay is proportional to the input skew between the inverse phases. The phases are consequently sampled at substantially identical points on a phase domain axis. Embodiments operate to create phase sampling synchronicity and to thereby decrease the amplitude of a common-mode signal component that results from the skew. Increased linearity and decreased distortion may result.

Owner:TEXAS INSTR INC

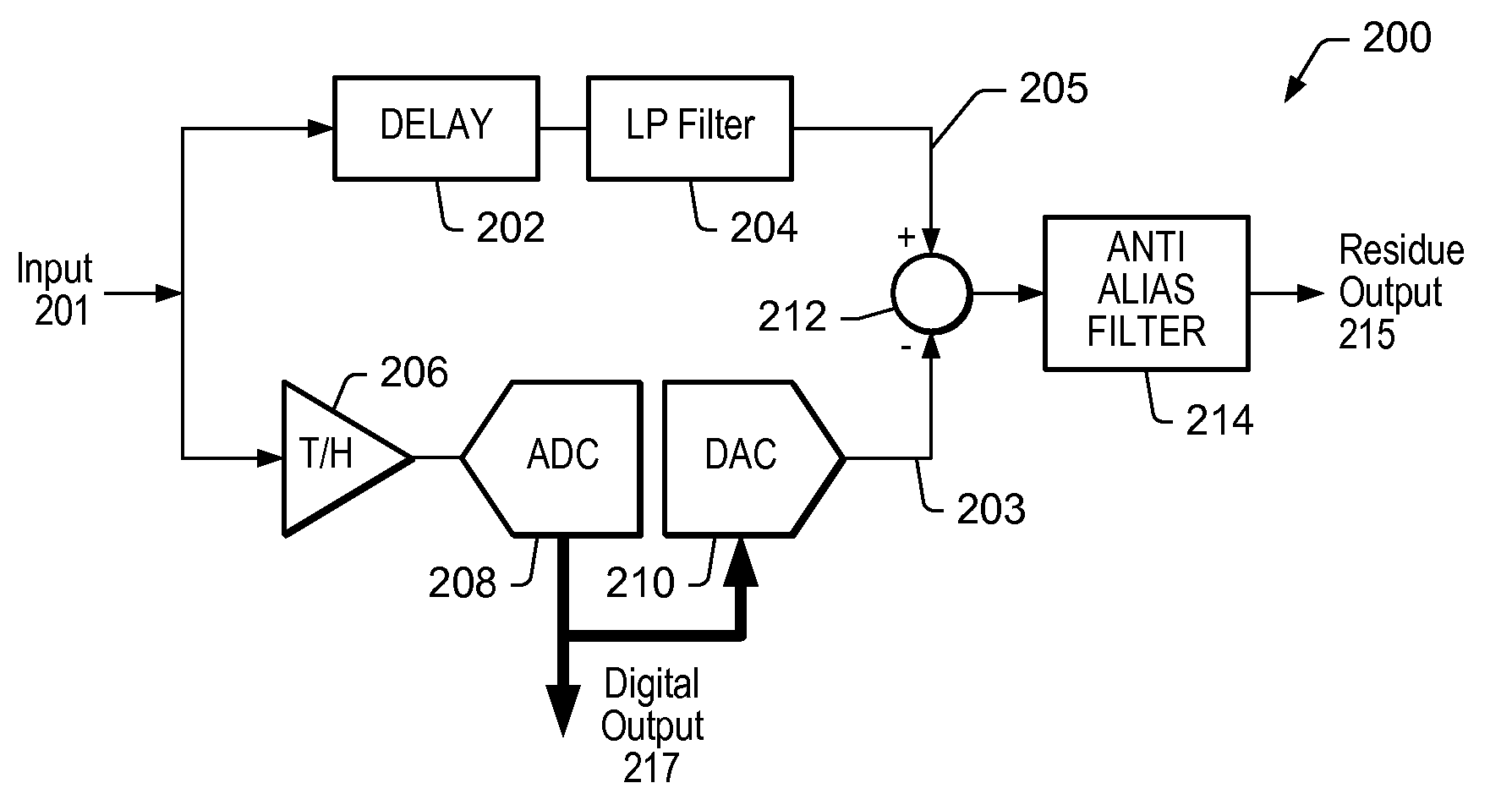

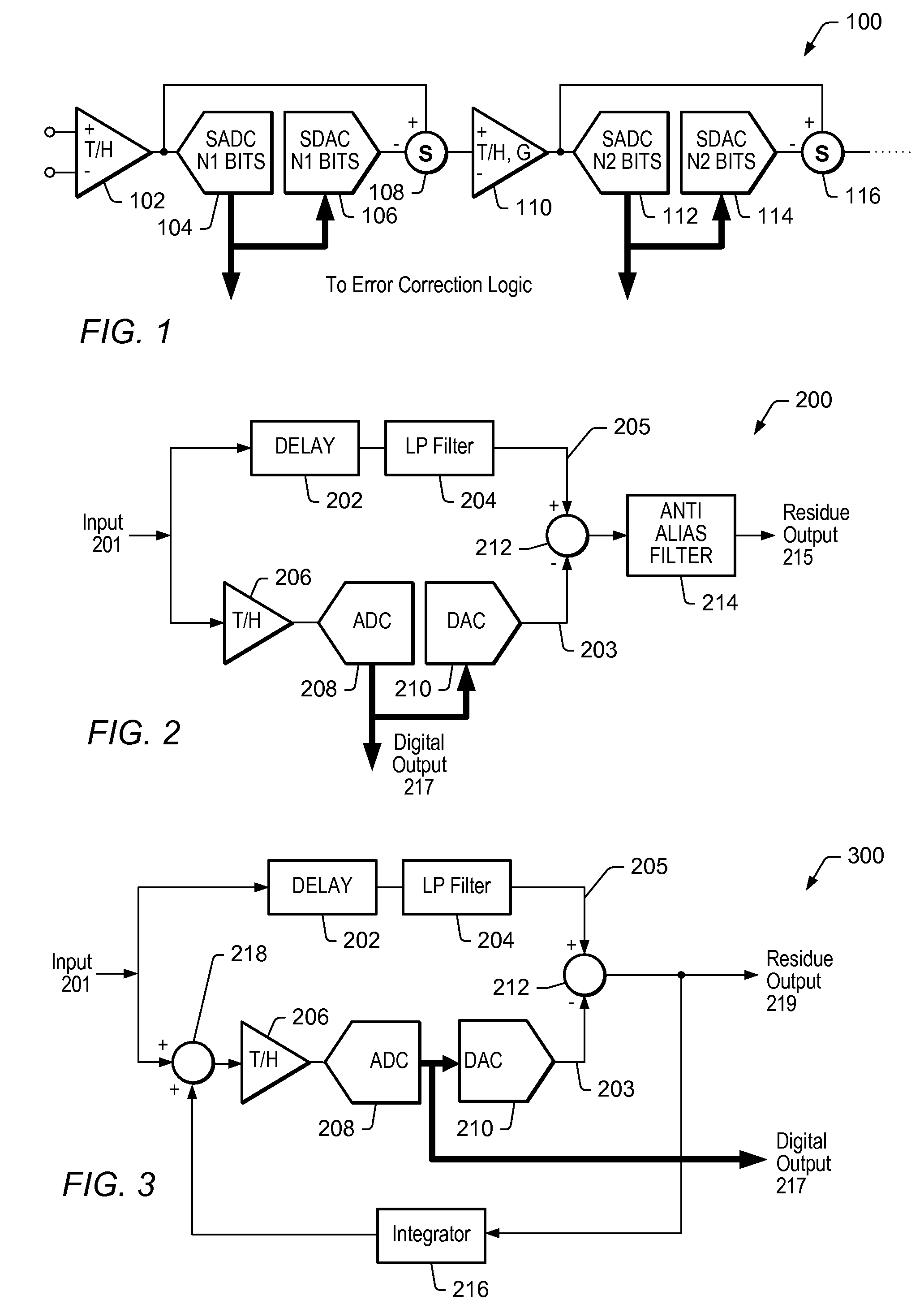

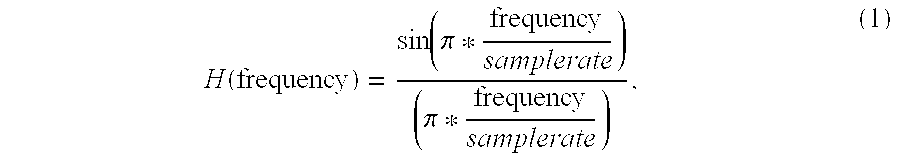

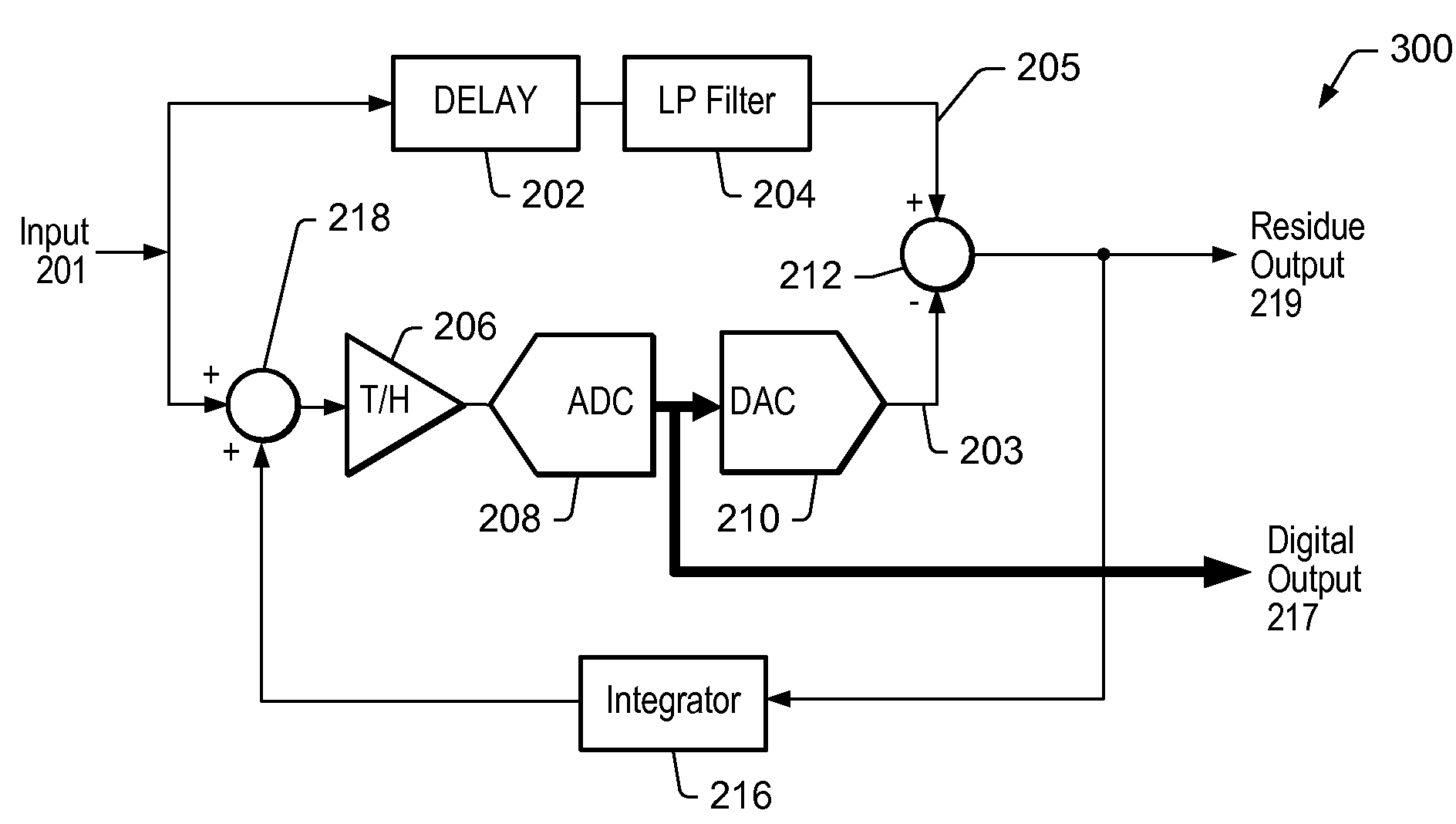

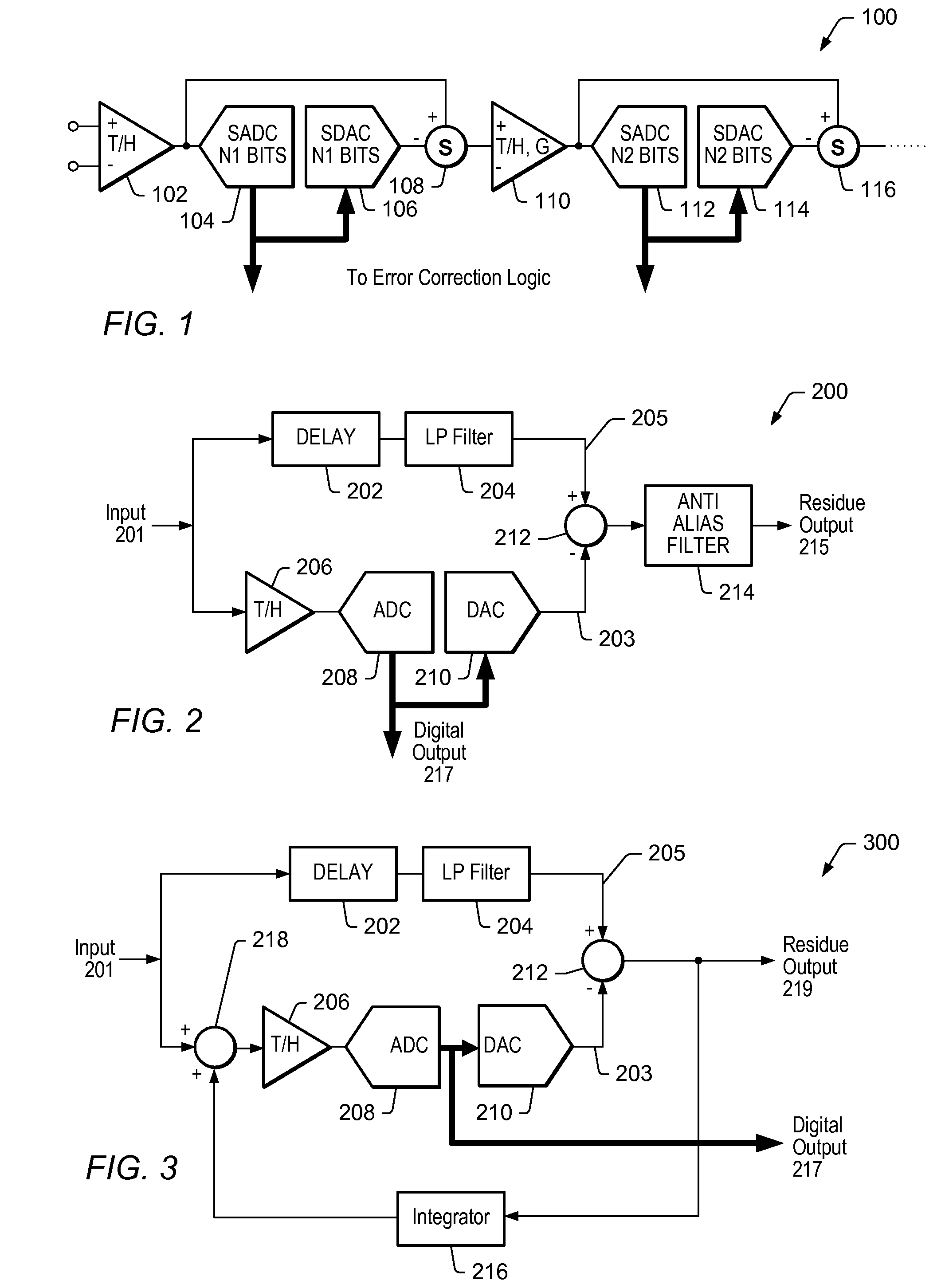

Time continuous pipeline analog-to-digital converter

ActiveUS20080238754A1Reduction of high-frequency broadband noiseEffectively be minimizedElectric signal transmission systemsAnalogue-digital convertersDigital down converterAnalog-to-digital converter

A Sampled Pipeline Subranging Converter (SPSC) may include at least one stage—e.g. at least the input stage—operating in a time-continuous fashion. In the time continuous input stage, the analog input may be processed in two parallel paths. A lower path may comprise a track-and-hold (T / H) element, an Analog-to-Digital-Converter (ADC) and a Digital-to-Analog-Converter (DAC). The T / H element may be optional and may be present if required by the ADC. The signal entering the lower path may be sampled at the desired conversion rate. The time continuous stage(s) may additionally be configured with an upper path that includes a delay element configured to receive the analog input, a Low-Pass (LP) filter coupled to the delay element, and an anti alias filter. The output generated by the DAC may be subtracted from the output of the LP filter, and the resulting difference signal may be provided to the anti alias filter, which in turn may generate the residue (or error) output. The digital output of the time continuous converter may be calculated by combining the digital outputs of the various sections.

Owner:NATIONAL INSTRUMENTS

Synchronized and shortened master-slave RF pulsing in a plasma processing chamber

ActiveUS8692467B2Alternating current plasma display panelsElectric arc lampsEngineeringExternal circuit

Plasma processing apparatuses and techniques for processing substrates, which include the use of synchronized RF pulsing of a first RF signal and a delayed-and-shortened second RF signal. The first RF signal may be the primary plasma-generating RF signal and the second RF signal may be the RF bias signal or vice versa. Alternatively or additionally, the first RF signal may be the high frequency RF signal and the second RF signal may be the lower frequency RF signal. Either the first RF signal or the second RF signal may act as the master, with the other acting as the slave signal. Alternatively, an external circuit may be employed as a master to control both the first RF signal and the second RF signal as slave signals. Track-and-hold techniques and circuits are provided to ensure accurate measurement for process control and other purposes.

Owner:LAM RES CORP

PAM4 transceivers for high-speed communication

ActiveUS9847839B2Reduce errorsReduce power consumptionPulse automatic controlSynchronisation receiversData streamTransceiver

Owner:MARVELL ASIA PTE LTD

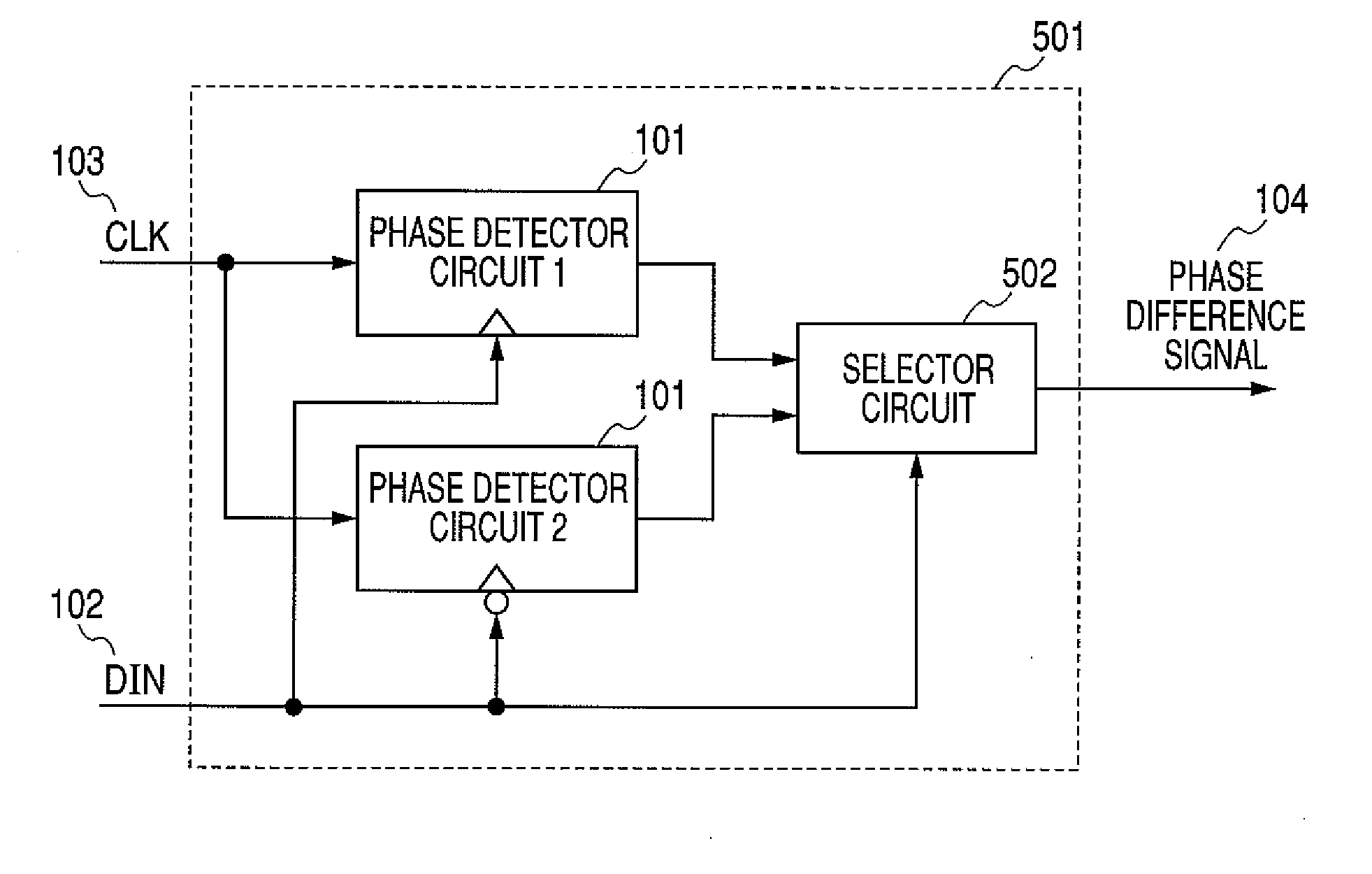

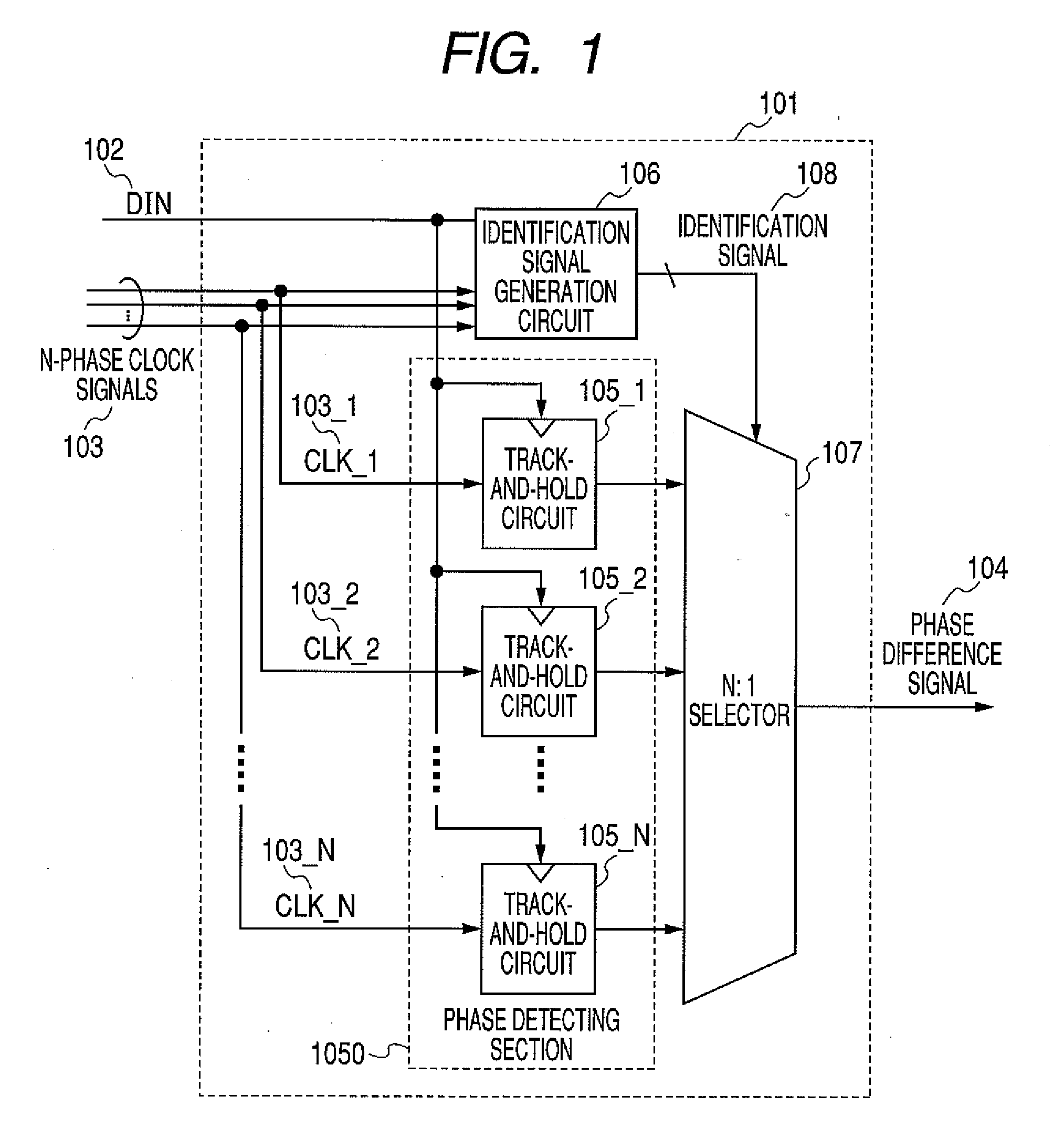

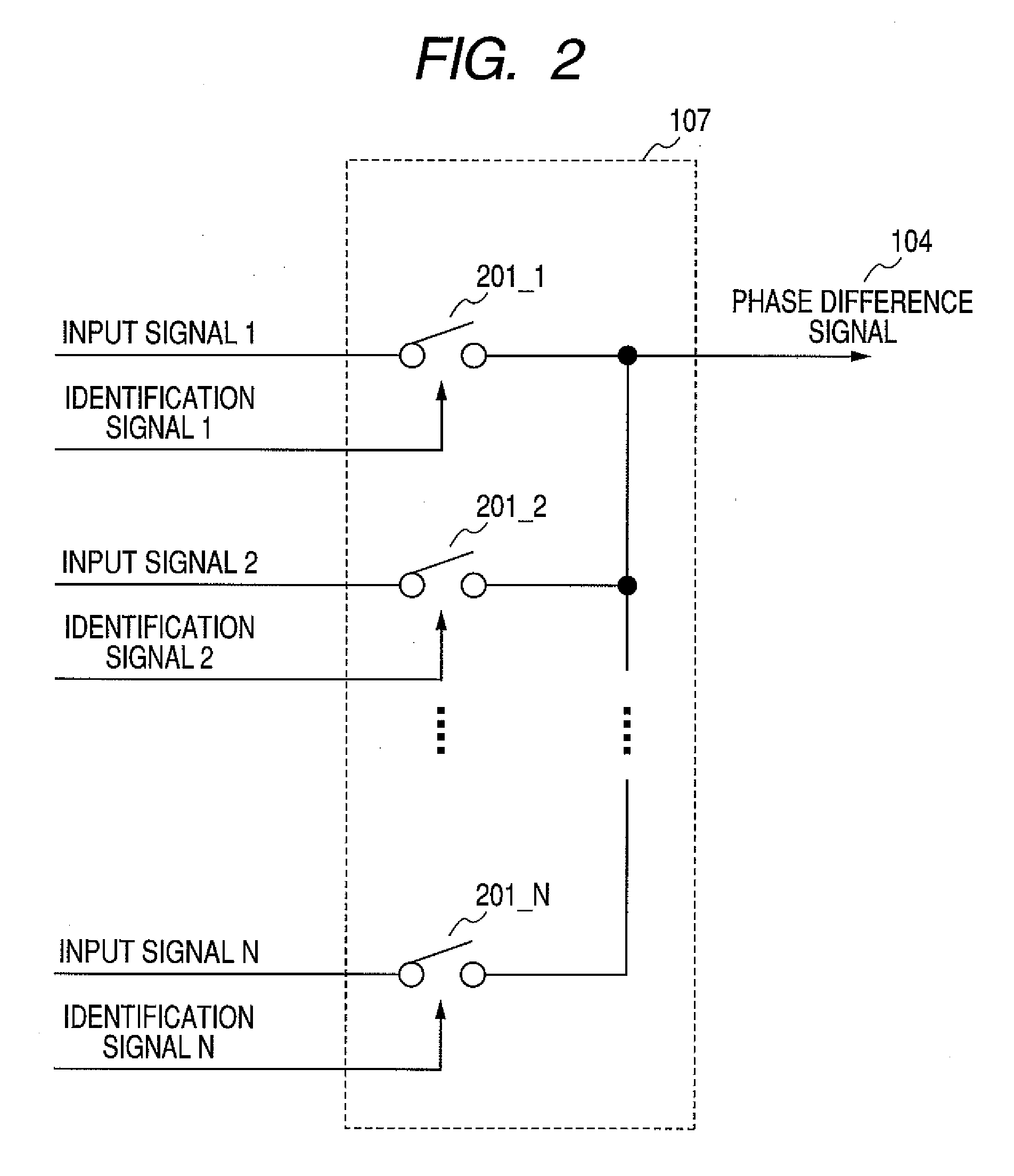

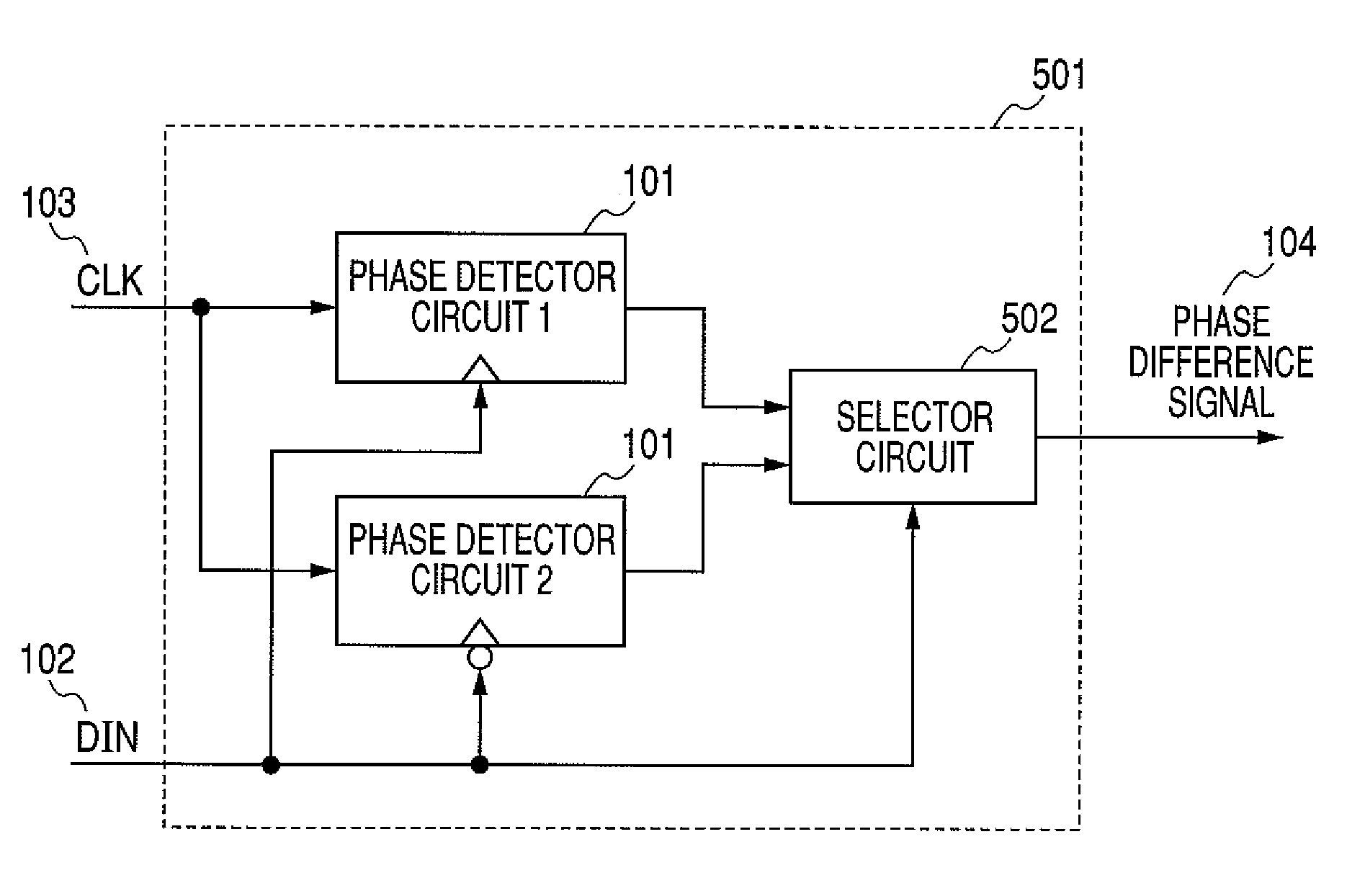

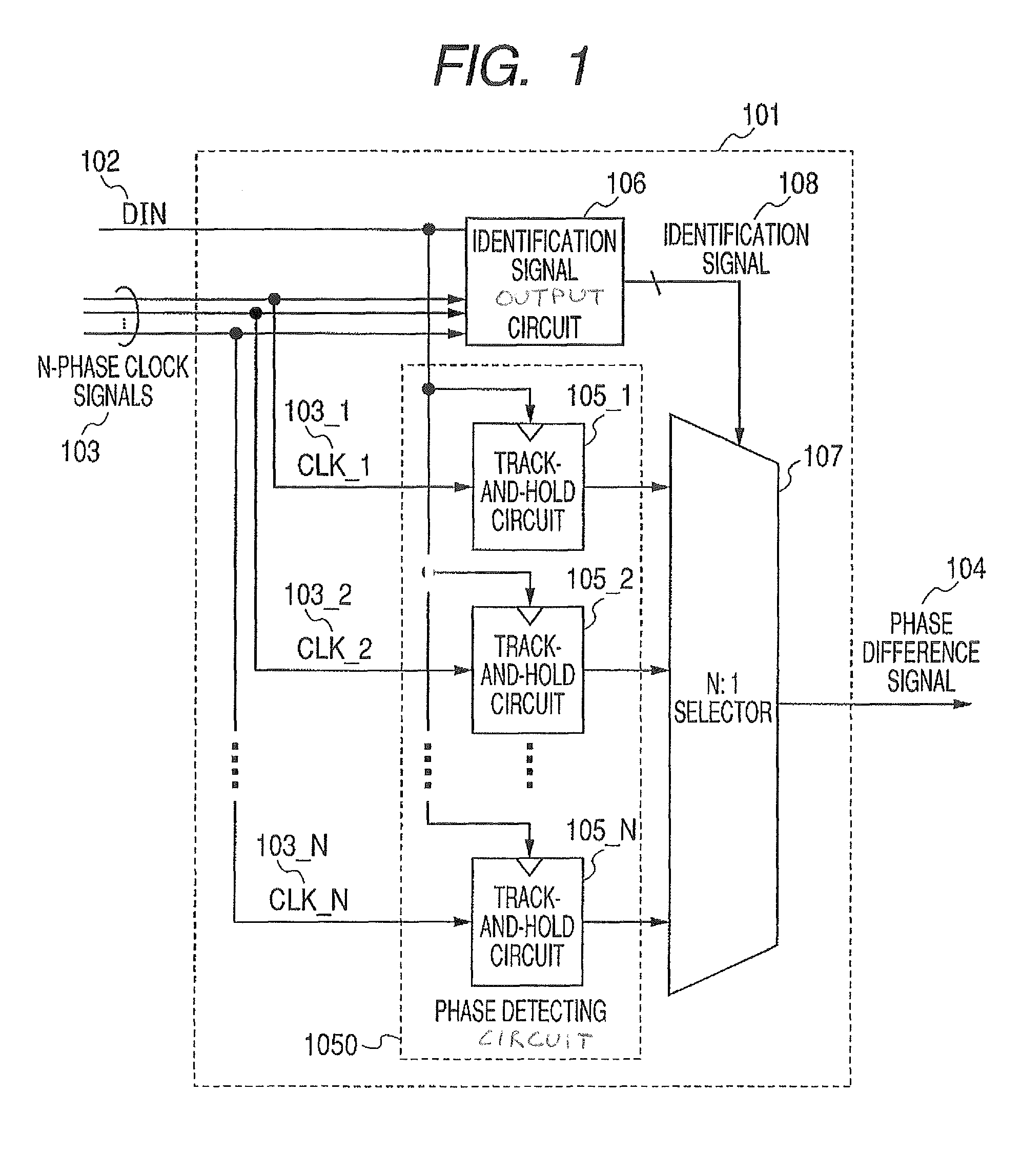

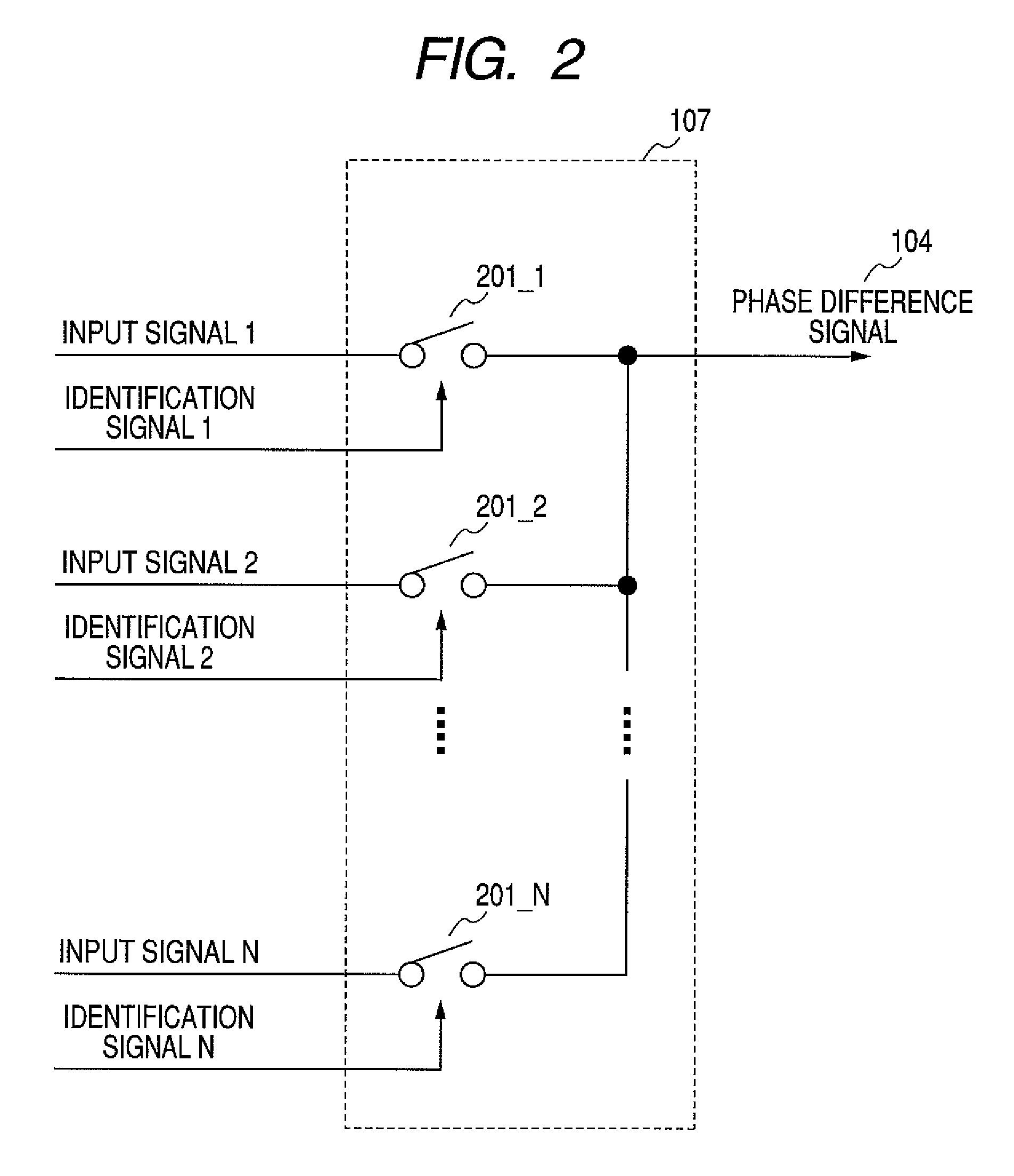

Phase Detector Circuit for Clock and Data Recovery Circuit and Optical Communication Device Having the Same

InactiveUS20100054760A1Low costMultiple input and output pulse circuitsPulse automatic controlPhase detectorDetector circuits

A high-accuracy phase detector circuit compatible with a 1 / N rate architecture is provided. The phase detector circuit has as many as N track-and-hold circuits for tracking and holding N-phase clock signals CLK—1 to CLK_N in synchronization with a rising edge of input data signal DIN. Out of the N-phase clock signals CLK—1 to CLK_N outputted from as many track-and-hold circuits, only the one whose rising edge is most synchronized with a rising edge of the input data signal DIN is selected and outputted as a phase difference signal.

Owner:HITACHI LTD

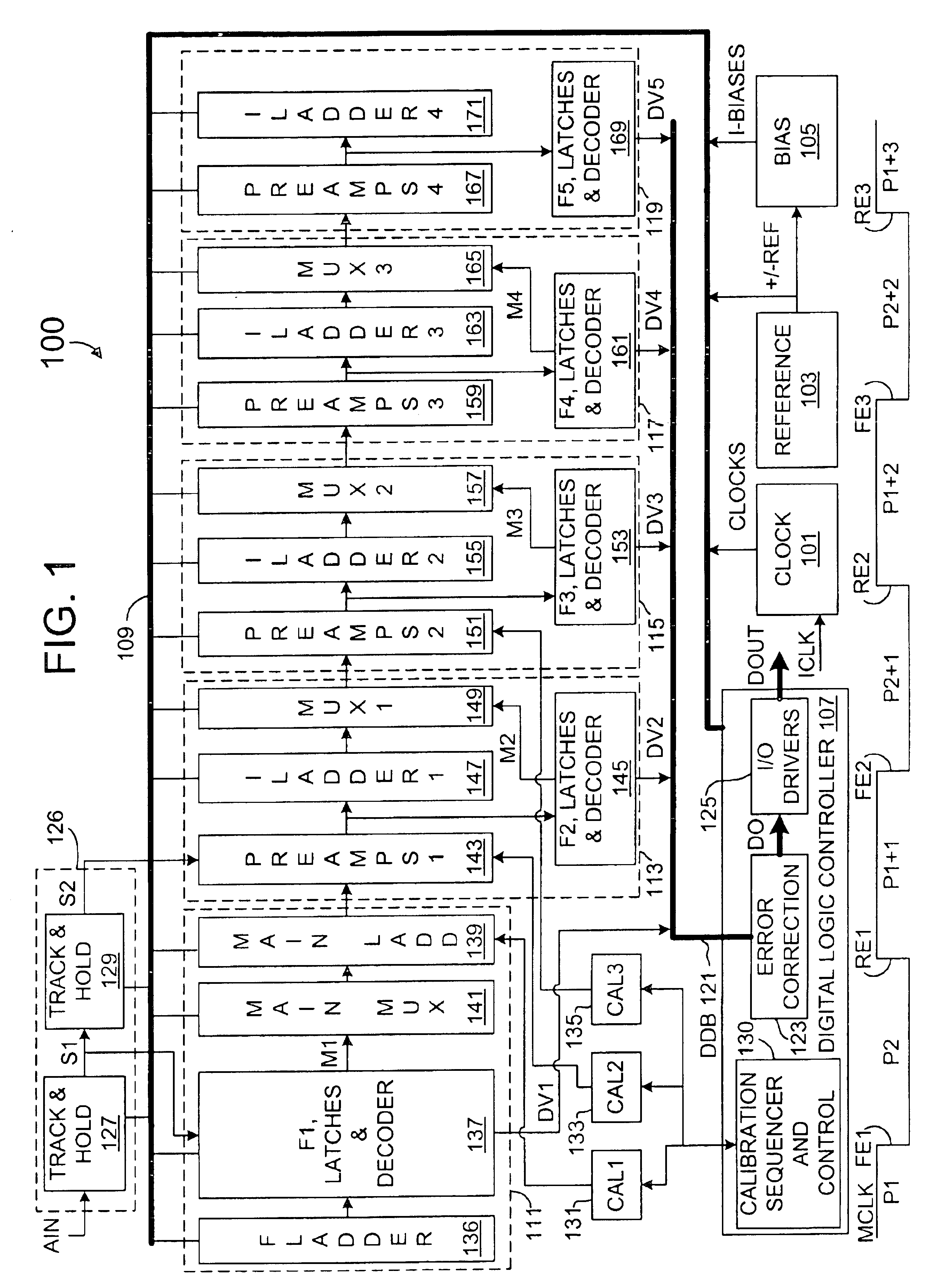

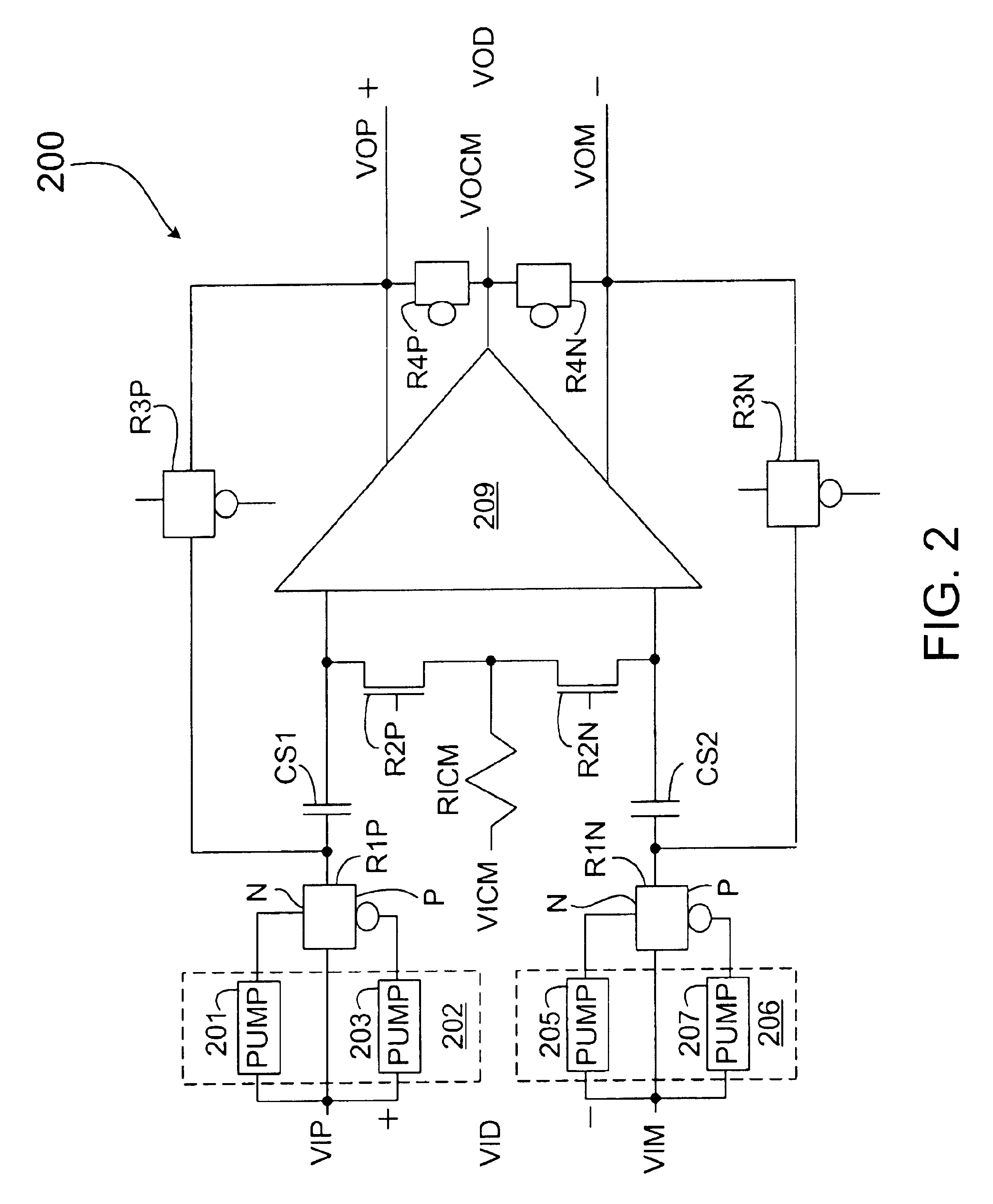

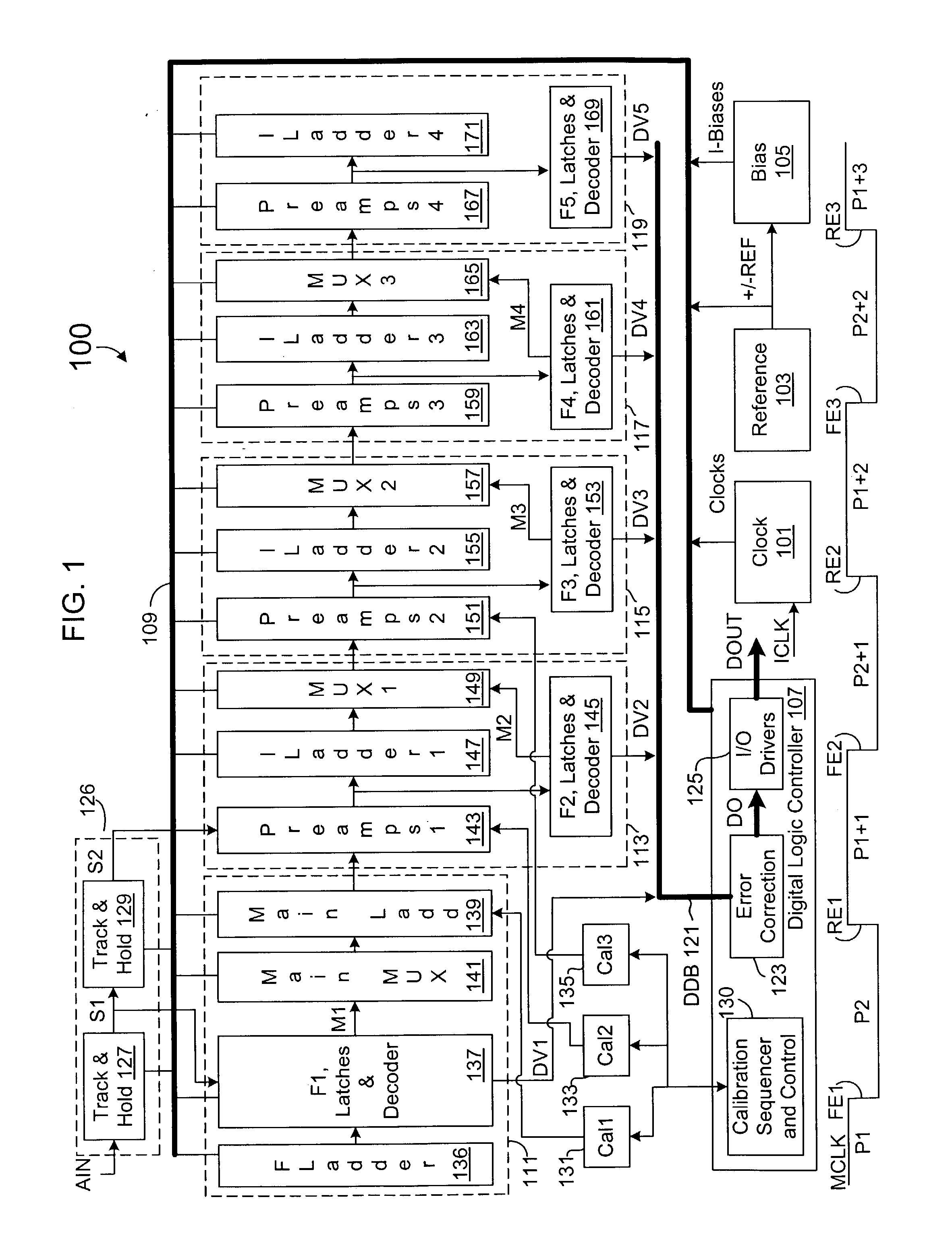

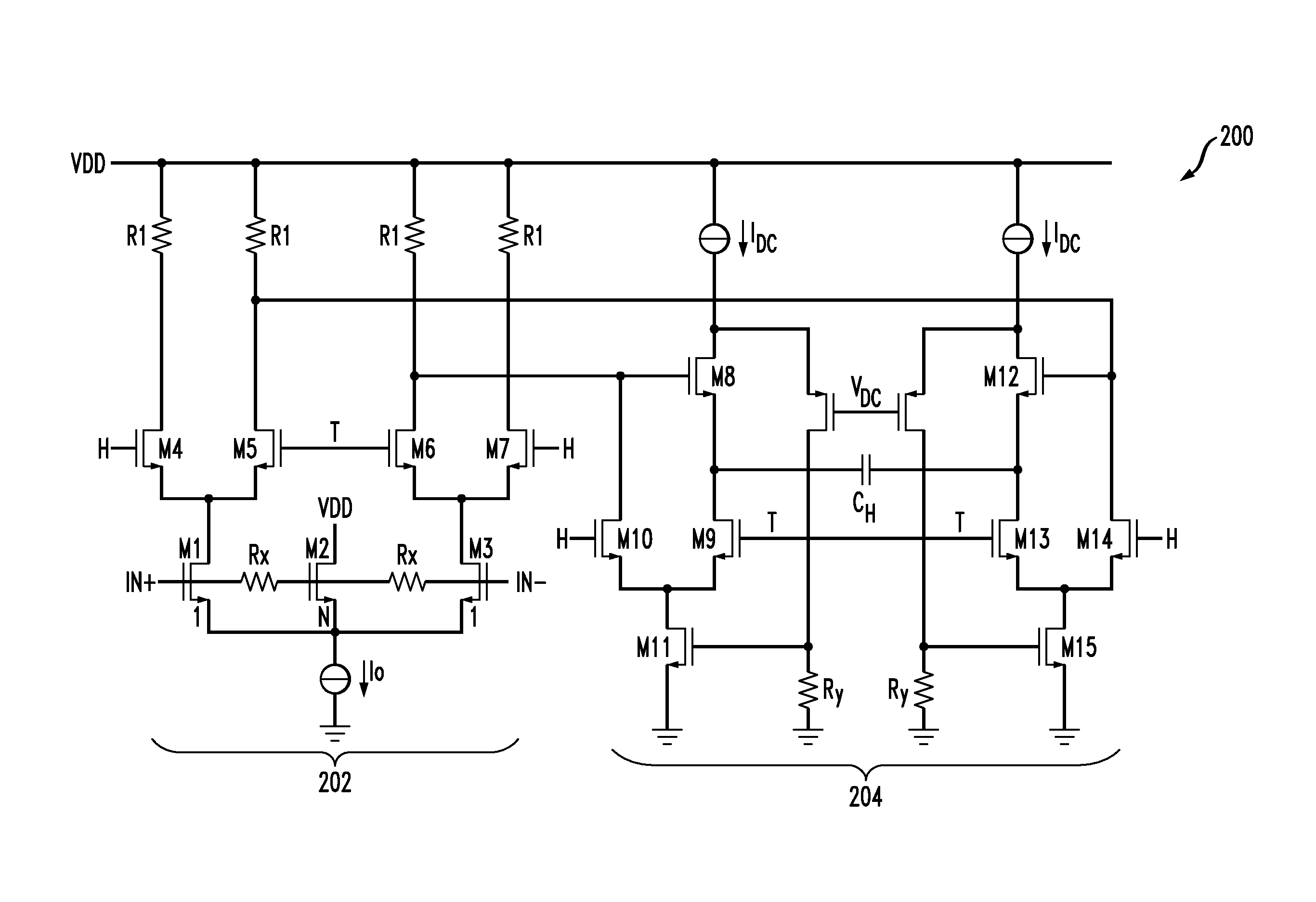

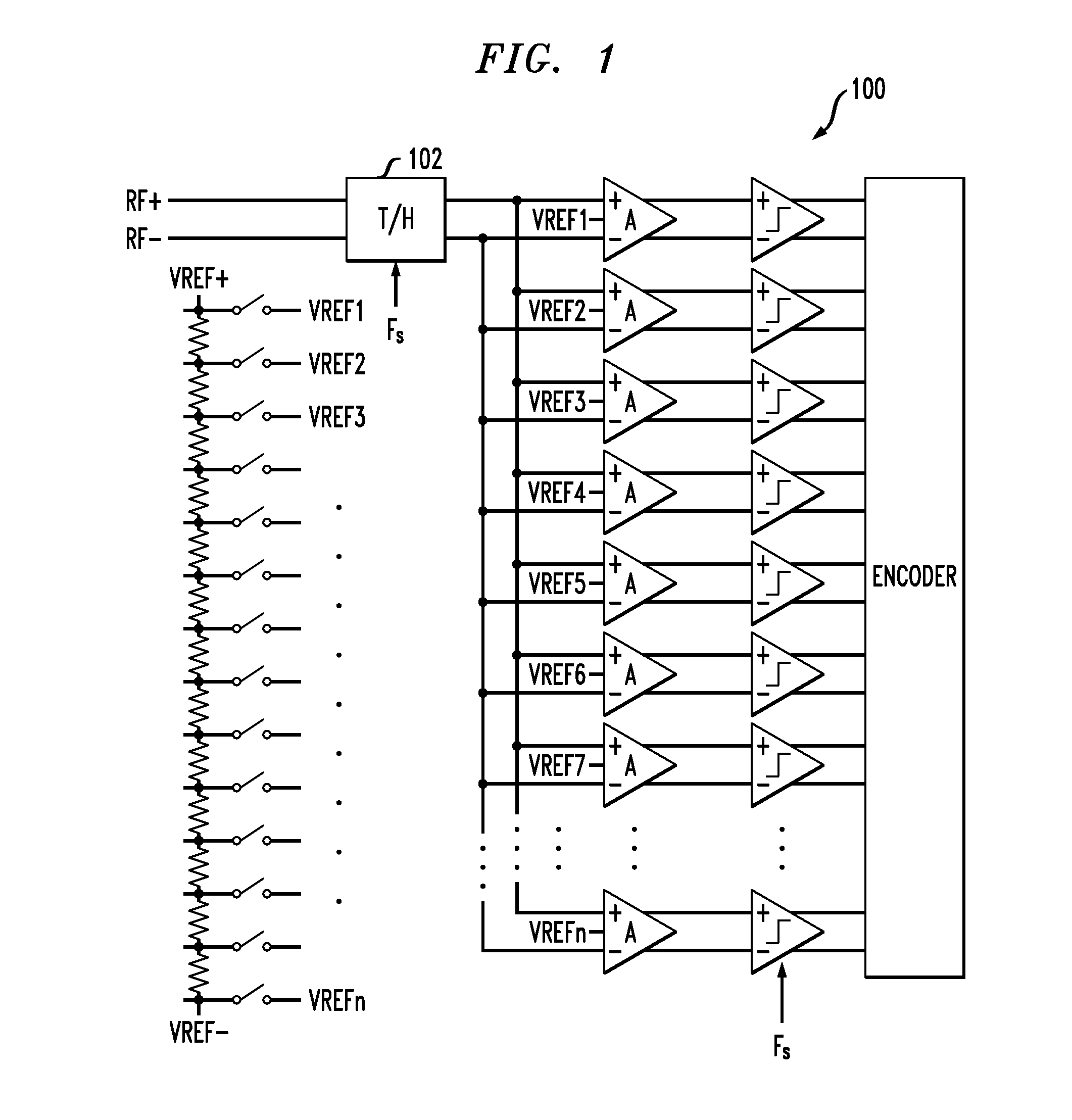

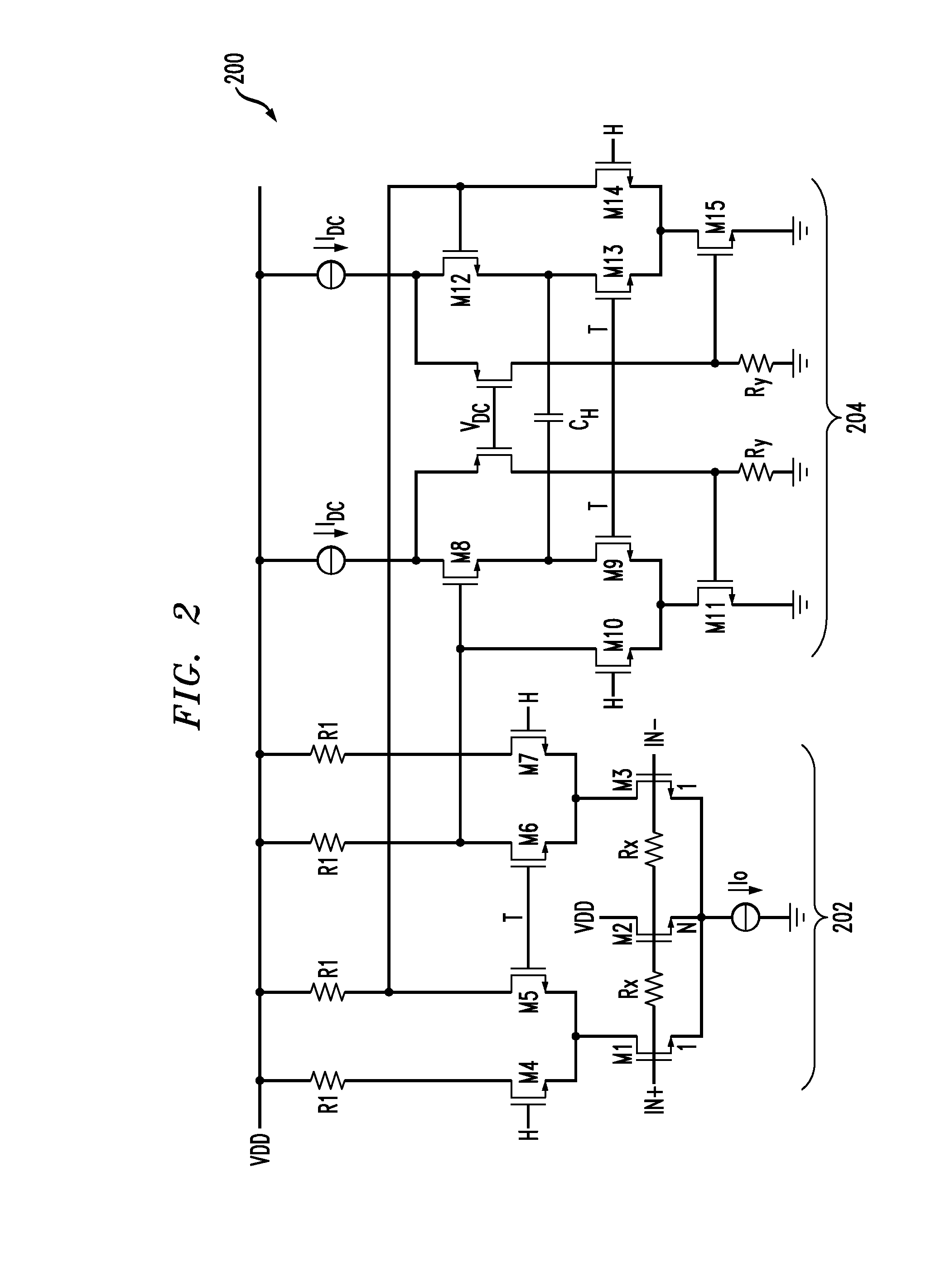

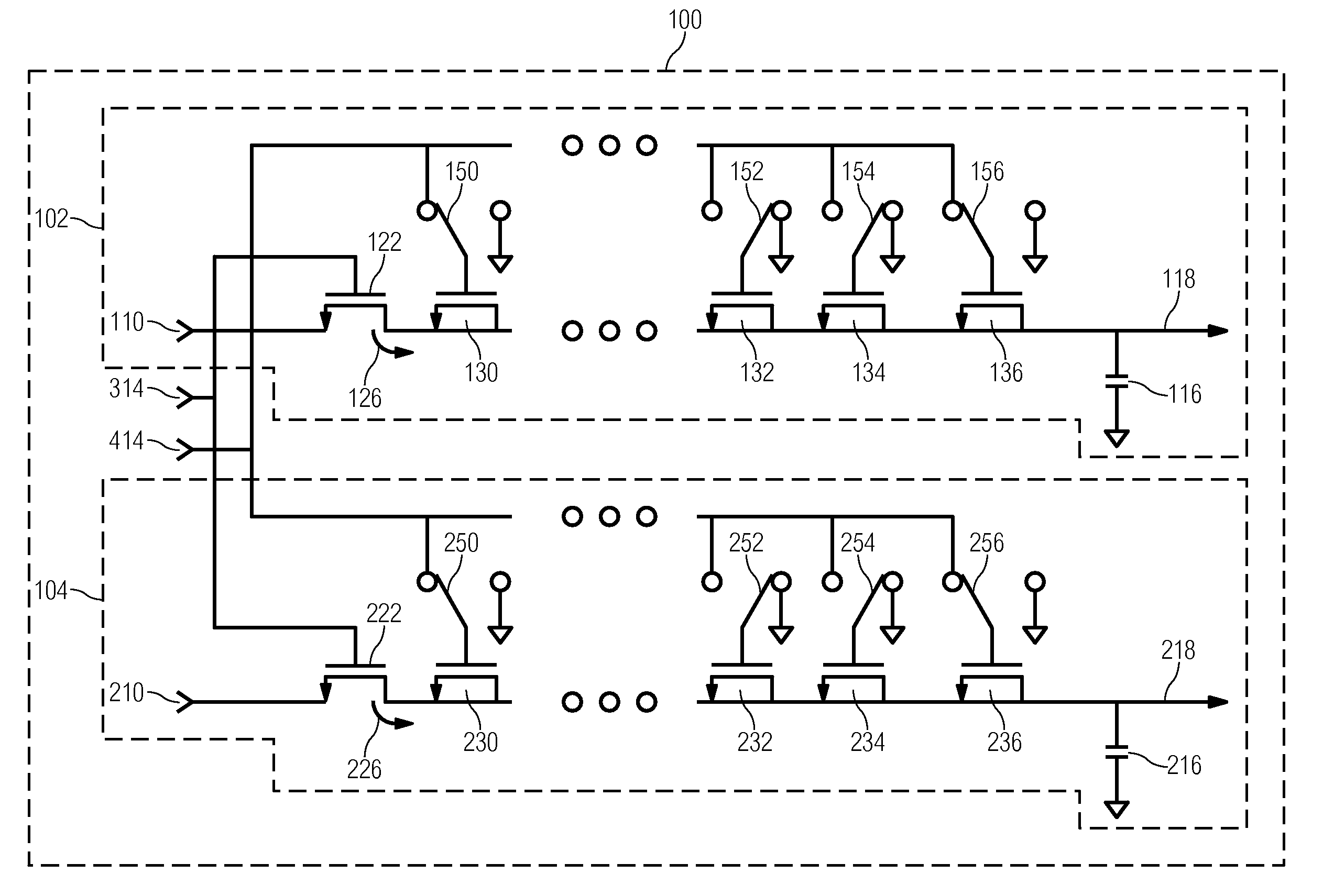

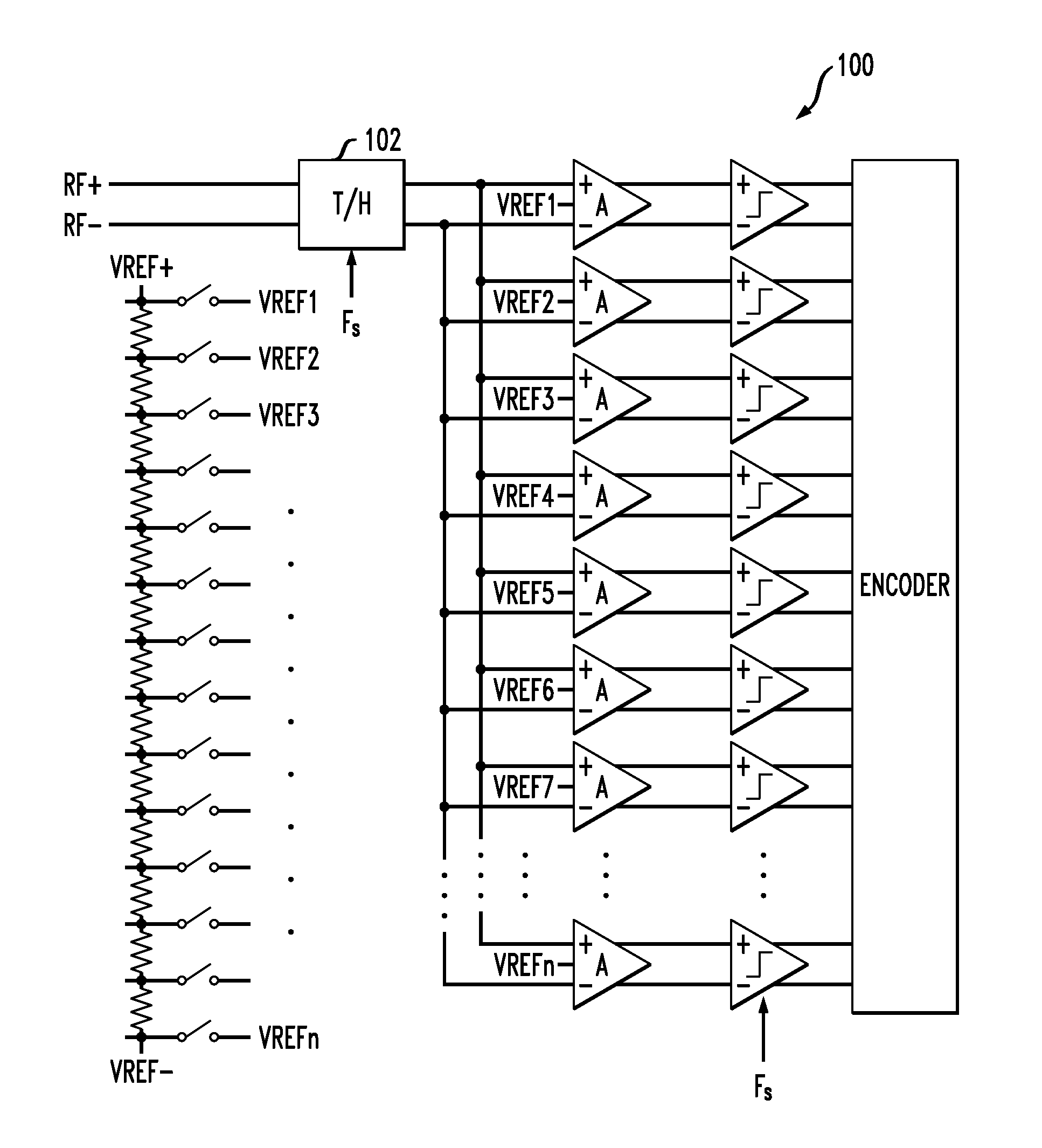

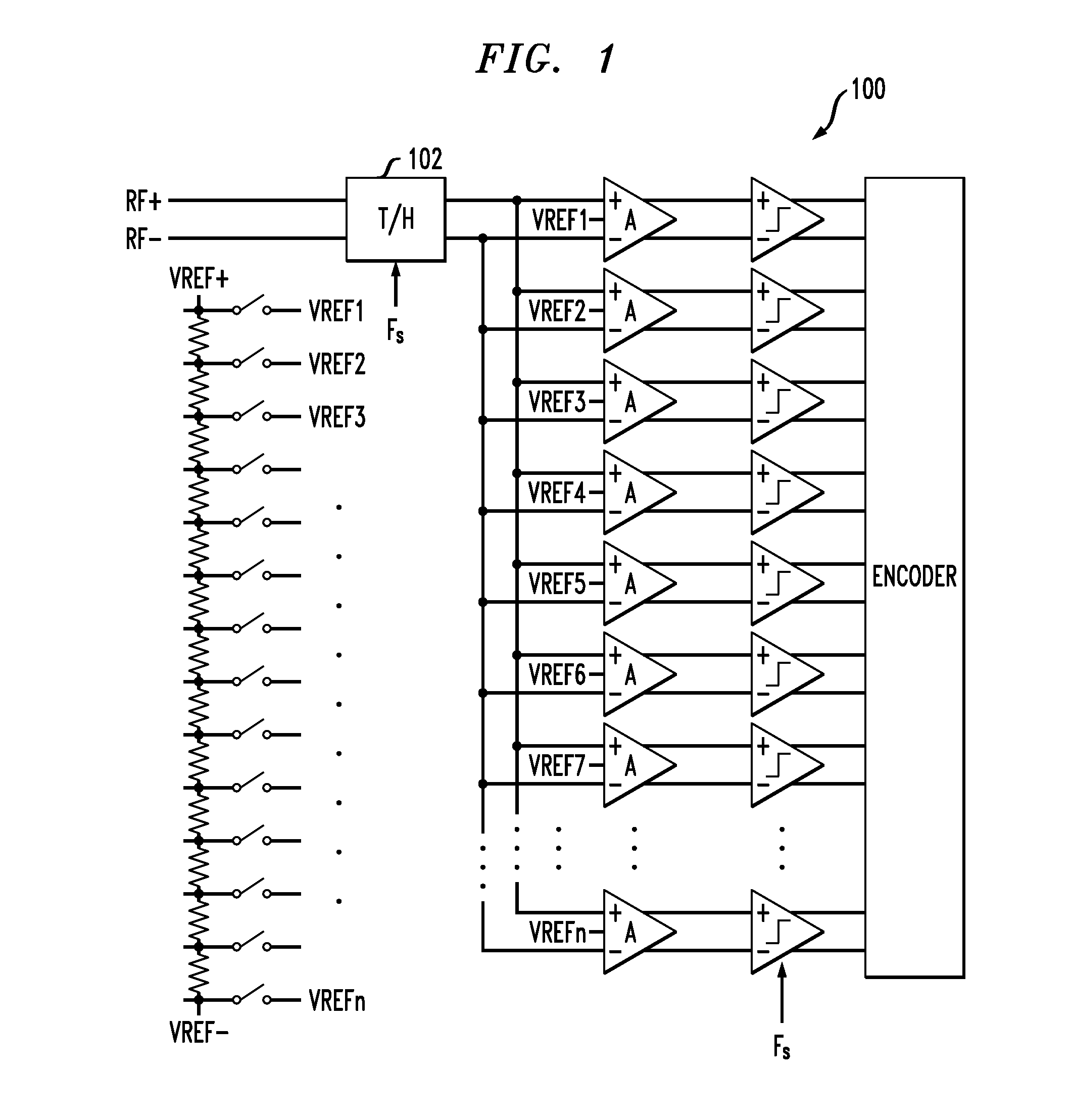

Track and hold amplifiers and digital calibration for analog-to-digital converters

ActiveUS8350738B2Electric signal transmission systemsElectric analogue storesDigital down converterAnalog-to-digital converter

Owner:GLOBALFOUNDRIES U S INC

Time continuous pipeline analog-to-digital converter

ActiveUS7443332B2Effectively be minimizedMinimizing amplitudeElectric signal transmission systemsAnalogue-digital convertersDigital down converterAnalog-to-digital converter

A Sampled Pipeline Subranging Converter (SPSC) may include at least one stage—e.g. at least the input stage—operating in a time-continuous fashion. In the time continuous input stage, the analog input may be processed in two parallel paths. A lower path may comprise a track-and-hold (T / H) element, an Analog-to-Digital-Converter (ADC) and a Digital-to-Analog-Converter (DAC). The T / H element may be optional and may be present if required by the ADC. The signal entering the lower path may be sampled at the desired conversion rate. The time continuous stage(s) may additionally be configured with an upper path that includes a delay element configured to receive the analog input, a Low-Pass (LP) filter coupled to the delay element, and an anti alias filter. The output generated by the DAC may be subtracted from the output of the LP filter, and the resulting difference signal may be provided to the anti alias filter, which in turn may generate the residue (or error) output. The digital output of the time continuous converter may be calculated by combining the digital outputs of the various sections.

Owner:NATIONAL INSTRUMENTS

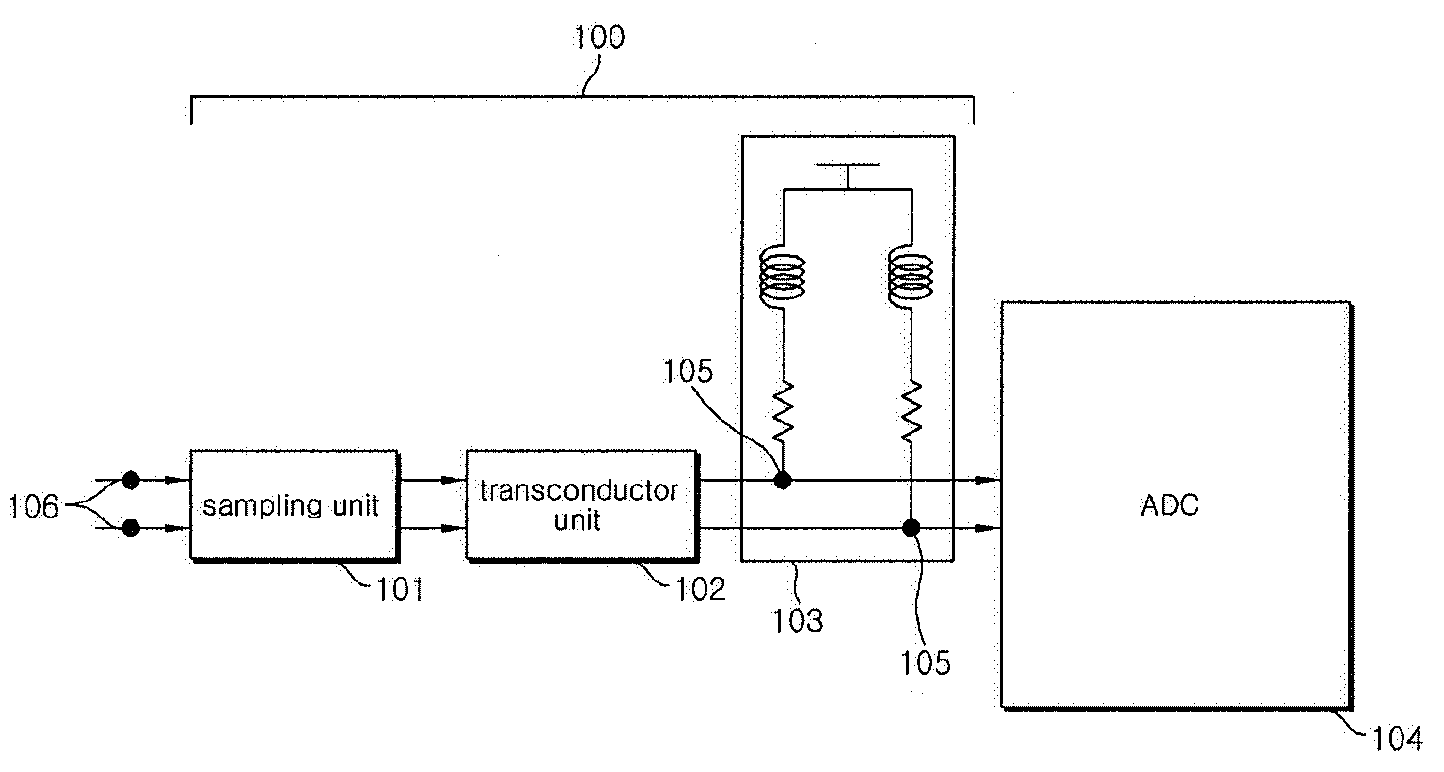

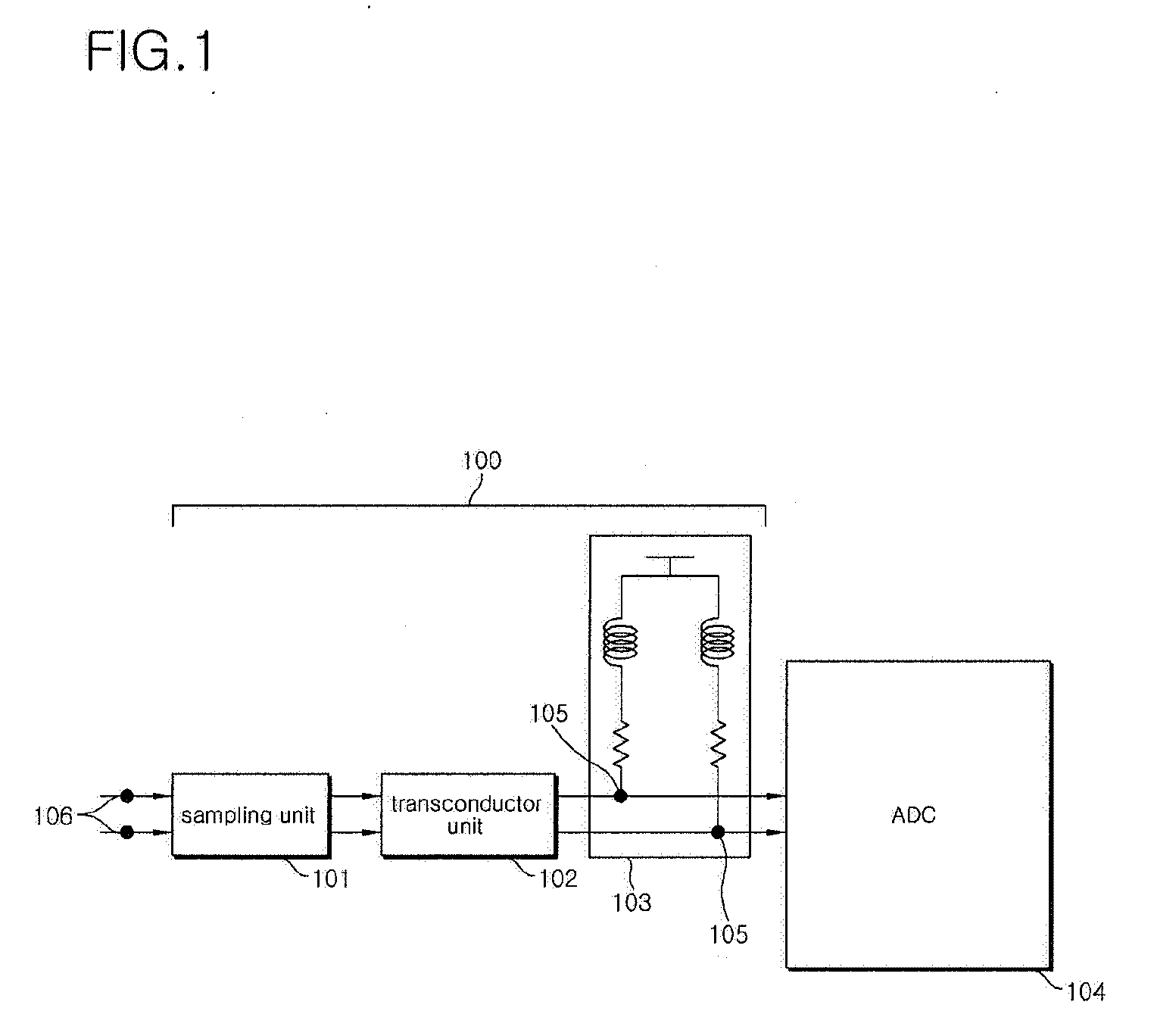

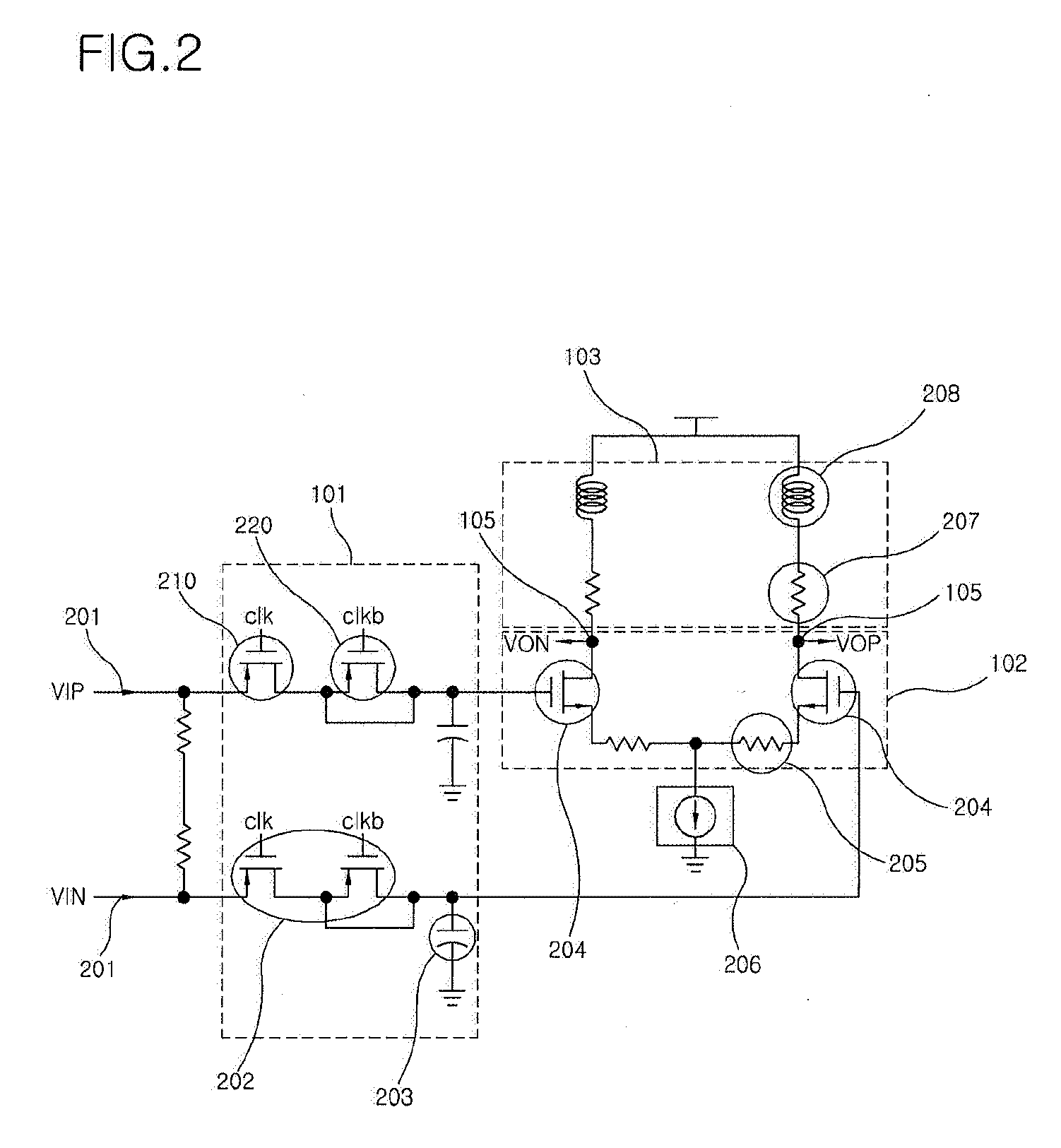

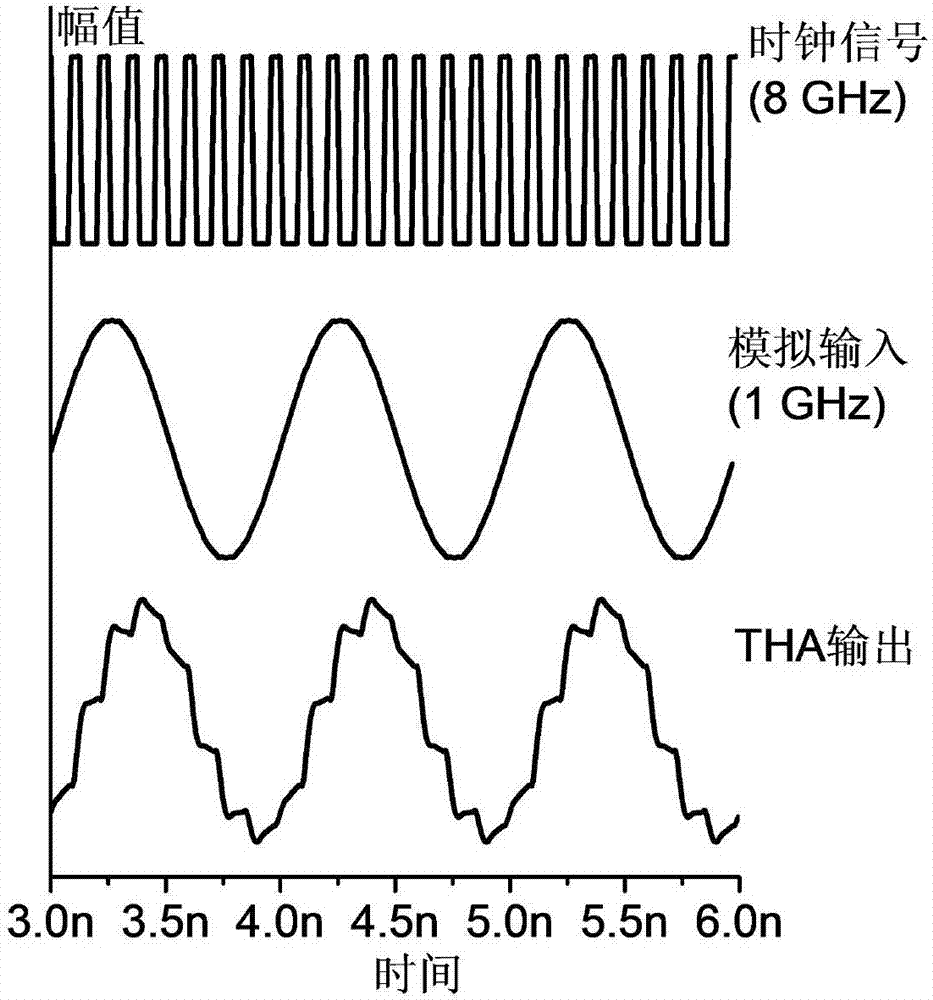

Wideband track-and-hold amplifier

InactiveUS20090072868A1Satisfactory linearityHigh speed machiningElectric analogue storesElectronic switchingCapacitanceAudio power amplifier

A wideband track-and-hold amplifier is provided. The wideband track-and-hold amplifier is provided in front of an analog-to-digital converter, receives and samples an analog signal, and transfers the sampled signal to the analog-to-digital converter, wherein an output load unit having an inductance component is connected to an input terminal of the analog-to-digital converter. Therefore, it is possible to compensate for a high capacitance component of an analog-to-digital converter, to increase the bandwidth of an output signal, and to improve system linearity.

Owner:SAMSUNG ELECTRONICS CO LTD

Pipelined decision feedback equalization in an interleaved serializer/deserializer receiver

An interleaved track-and-hold front-end with multiphase clocks computes and propagates unrolled decision feedback equalization results along a pipeline with the final outputs selected from one of the interleaved previous output bits with a multiplexer operating over multiple unit intervals instead of one unit interval. An n-way interleaved serializer / deserializer utilizes an n unit interval multiplexer or n one unit interval multiplexers. Pipelined decision feedback equalization allows multiple, slower multiplexers.

Owner:AVAGO TECH INT SALES PTE LTD

Track-And-Hold Circuit With Adjustable Charge Compensation

ActiveUS20090102517A1Analogue/digital conversionElectric signal transmission systemsControl channelCharge compensation

A circuit design incorporates charge compensation devices within a Track-and-Hold (T / H) circuit to control channel charge generated by a tracking switch. Calibrating a T / H circuit requires selecting charge compensation devices from an array of similar devices to function within the T / H circuit to absorb charge ejected from the tracking switch. The charge compensation devices can also be pseudorandomly selected to operate within the T / H circuit. Charge compensation devices are used to enhance the performance of bottom-plate sampling systems as well as bootstrapped T / H circuits.

Owner:KEYSIGHT TECH

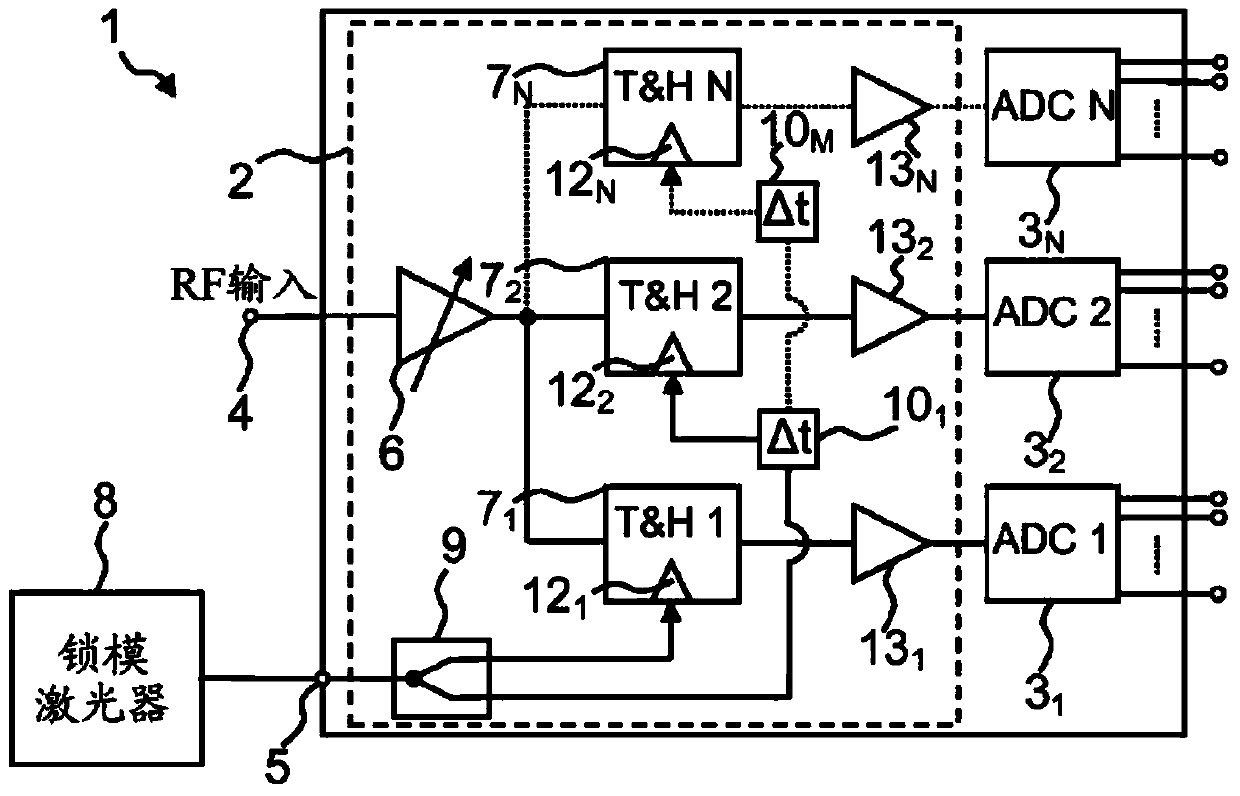

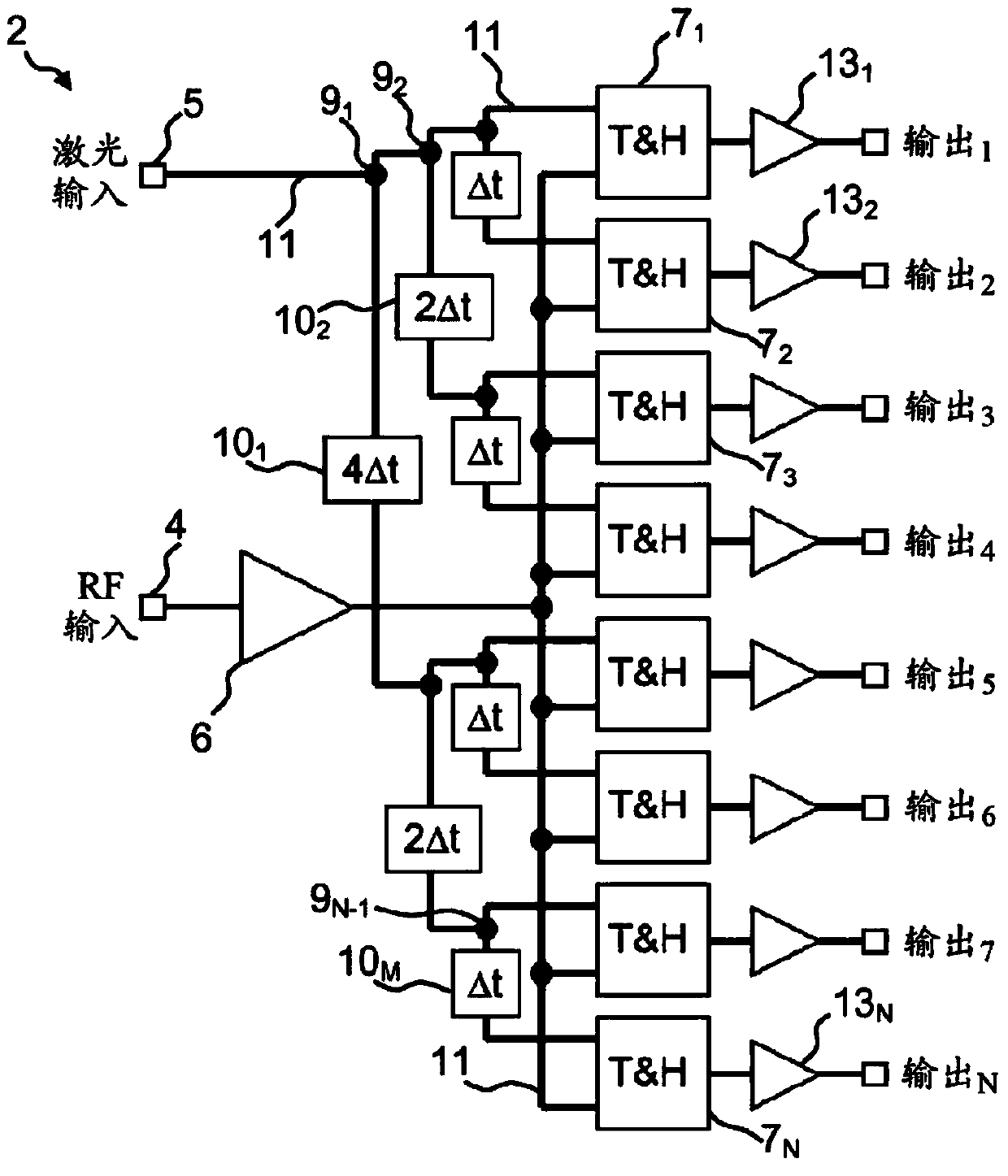

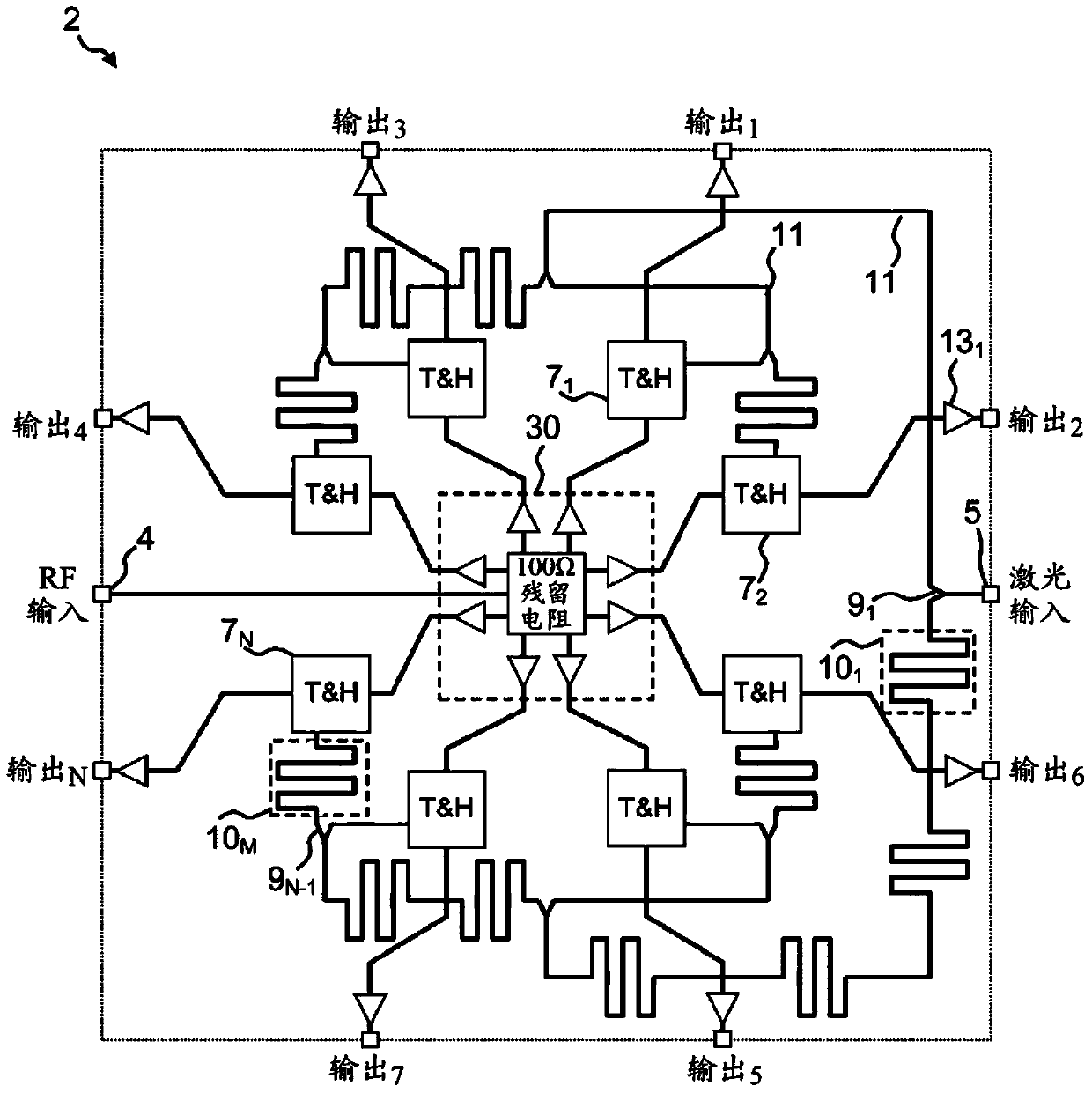

Sampling device with time-interleaved optical clocking

ActiveCN104272395ASure catchHigh sampling frequencyElectric analogue storesDigital storageOptical clockEngineering

A sampling device (2) comprising a first input port (4) and a second input port (5), wherein an input-signal is fed to the first input port (4) and wherein an optical clock signal is fed to the second input port (5). The sampling device (2) comprises a plurality of track and hold units (7 1 , 7 2 , 7 N ), wherein each of the plurality of track and hold units (7 1 , 7 2 , 7 N ) is connected to the first input port (4). The plurality of the track and hold units (7 1 , 7 2 , 7 N ) is further connected to the second input port (5) through an optical waveguide (11) in such a manner that the plurality of tack and hold units (7 1 , 7 2 , 7 N ) operate in a time-interleaved mode.

Owner:ROHDE & SCHWARZ GMBH & CO KG

Phase detector circuit for clock and data recovery circuit and optical communication device having the same

InactiveUS8483579B2Low costMultiple input and output pulse circuitsPulse automatic controlPhase detectorDetector circuits

A high-accuracy phase detector circuit compatible with a 1 / N rate architecture is provided. The phase detector circuit has as many as N track-and-hold circuits for tracking and holding N-phase clock signals CLK—1 to CLK_N in synchronization with a rising edge of input data signal DIN. Out of the N-phase clock signals CLK—1 to CLK_N outputted from as many track-and-hold circuits, only the one whose rising edge is most synchronized with a rising edge of the input data signal DIN is selected and outputted as a phase difference signal.

Owner:HITACHI LTD

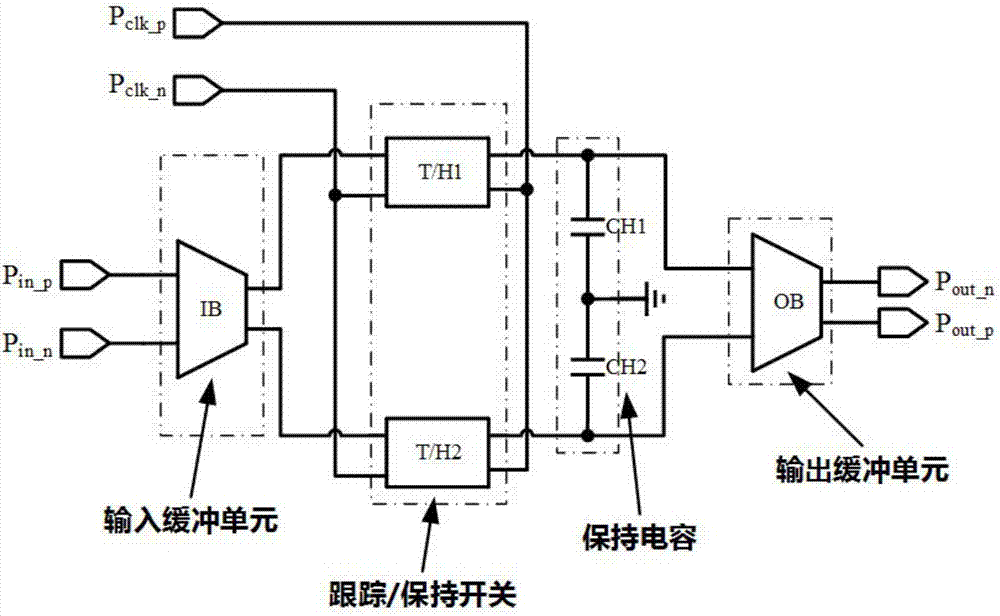

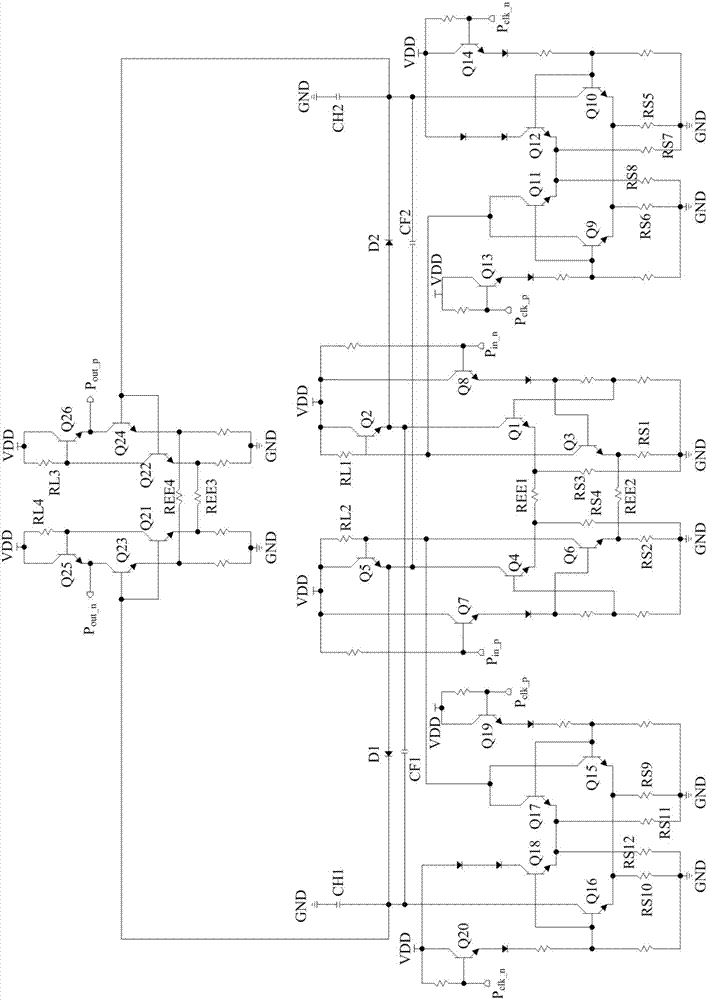

High-sampling-rate broadband track and hold circuit

ActiveCN107196637AAvoid disturbanceGood common mode noise rejectionLogic circuit coupling arrangementsCapacitanceLinearity

The invention discloses a high-sampling-rate broadband track and hold circuit and relates to the technical field of electrons. The track and hold circuit comprises an input buffer unit IB, a track / hold switch T / H, a holding capacitor CH and an output buffer unit OB. A full-differential circuit structure is introduced to realize good common-mode noise suppression ability; through the input and output buffers having emitter degeneration resistors, linearity of the track and hold circuit is improved; an improved switch emitter follower having a Schottky diode is adopted as a track and hold switch, so that circuit stability is improved; and the track and hold circuit is designed by utilizing a GaAs HBT device having high cut-off frequency and good base-emitter match, thereby solving the defects of low sampling rate and narrow bandwidth of an existing sampling and hold circuit.

Owner:XIDIAN UNIV

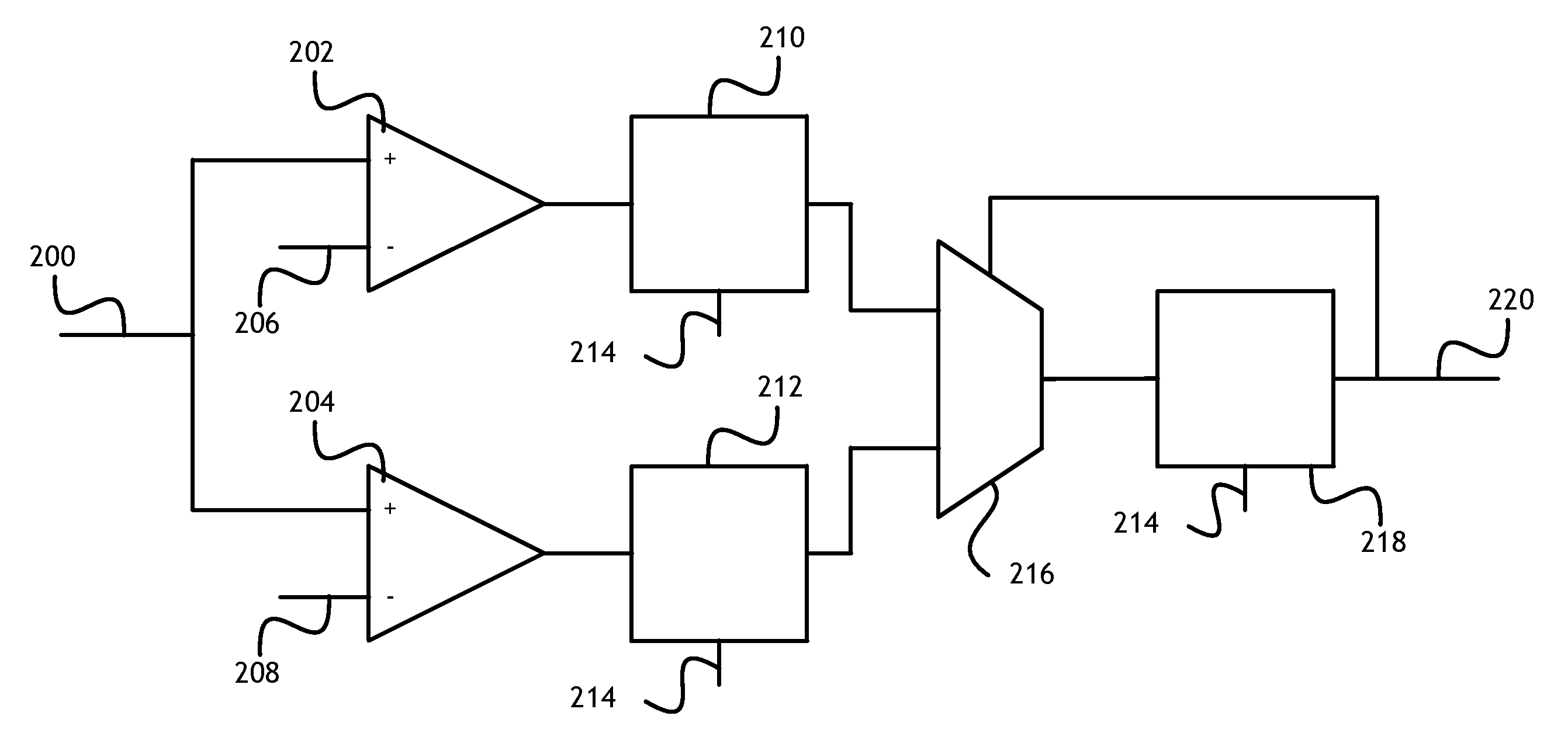

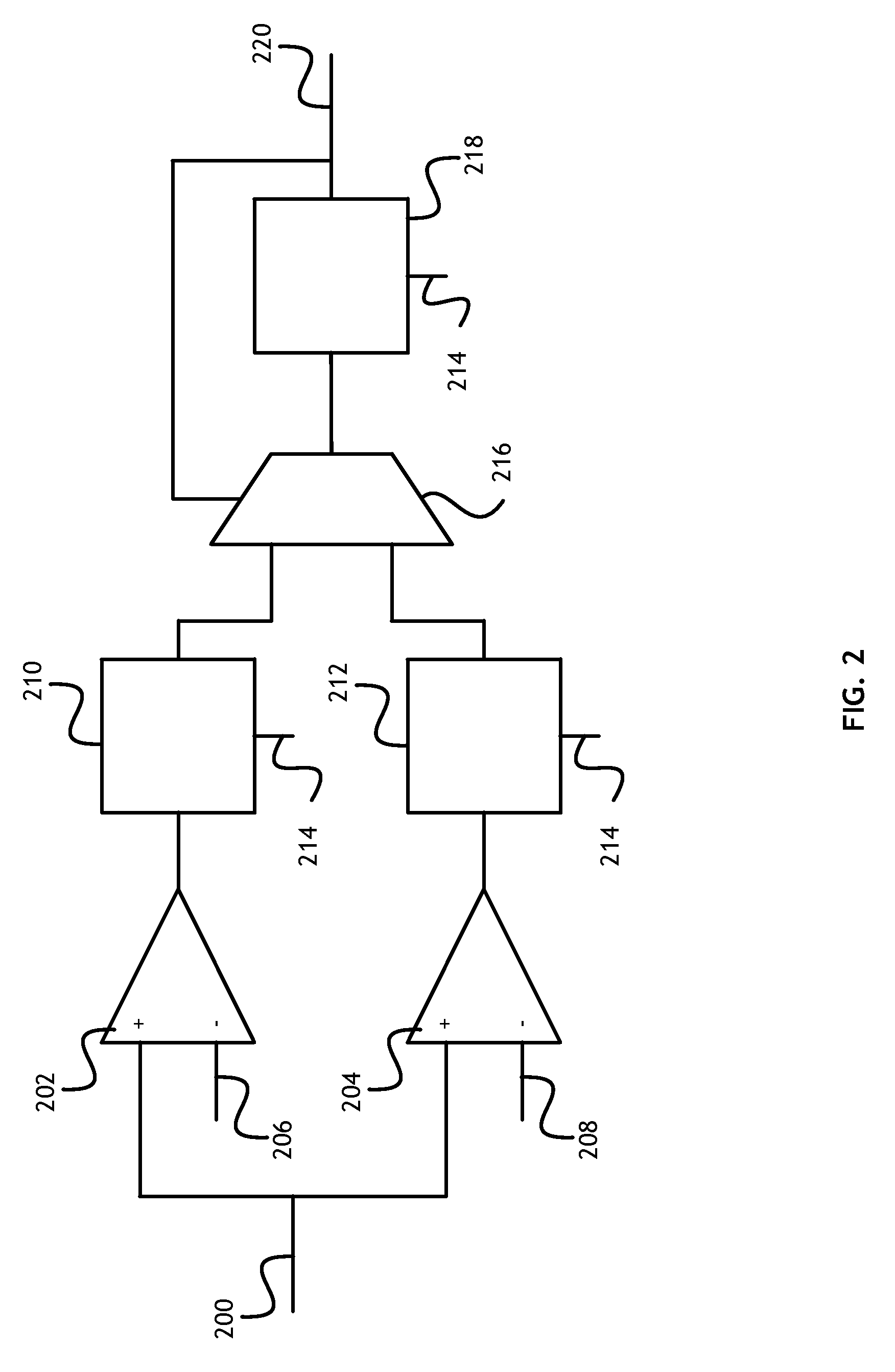

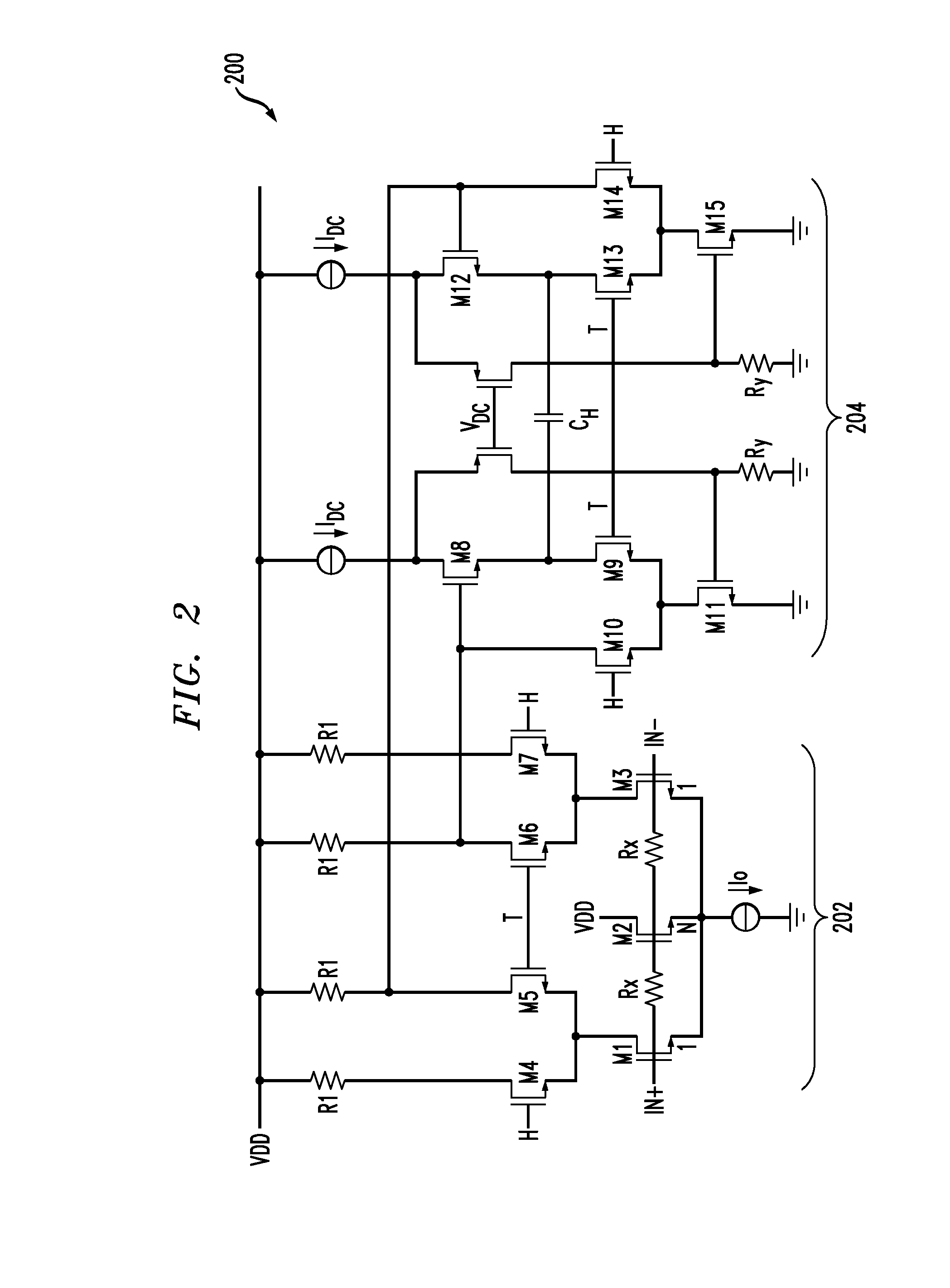

Track and Hold Amplifiers and Digital Calibration for Analog-to-Digital Converters

ActiveUS20120188109A1Electric signal transmission systemsElectric analogue storesAnalog-to-digital converterLinearity

An exemplary differential track and hold amplifier includes a track stage including first and second linearized pairs connected in series at their respective inputs and in parallel at their respective outputs. The differential track and hold amplifier also includes a hold stage selectively coupled to the outputs of the first and second linearized pairs. The hold stage includes a unity gain buffer with feedback having a hold capacitor interconnected across its outputs. The differential track and hold amplifier also includes an output buffer coupled to the outputs of the hold stage. An exemplary analog-to-digital converter includes a differential track-and-hold amplifier, a voltage ladder, and a plurality of slices. Each of the slices in turn includes a differential preamplifier coupled to the track-and-hold amplifier and to a corresponding location on the voltage ladder; a current mode logic latch comparator coupled to the differential preamplifier; a large-swing latch coupled to the current mode logic latch comparator; a complementary metal oxide semiconductor latch having a dummy load; a calibration digital to analog converter connected across outputs of the differential preamplifier to inject calibration currents; and a register coupled to the calibration digital to analog converter and storing calibration values for use thereby. The analog-to-digital converter also includes a multiplexer which multiplexes outputs of the complementary metal oxide semiconductor latches down to a predetermined number of outputs.

Owner:GLOBALFOUNDRIES US INC