Patents

Literature

482 results about "Time interleaved" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

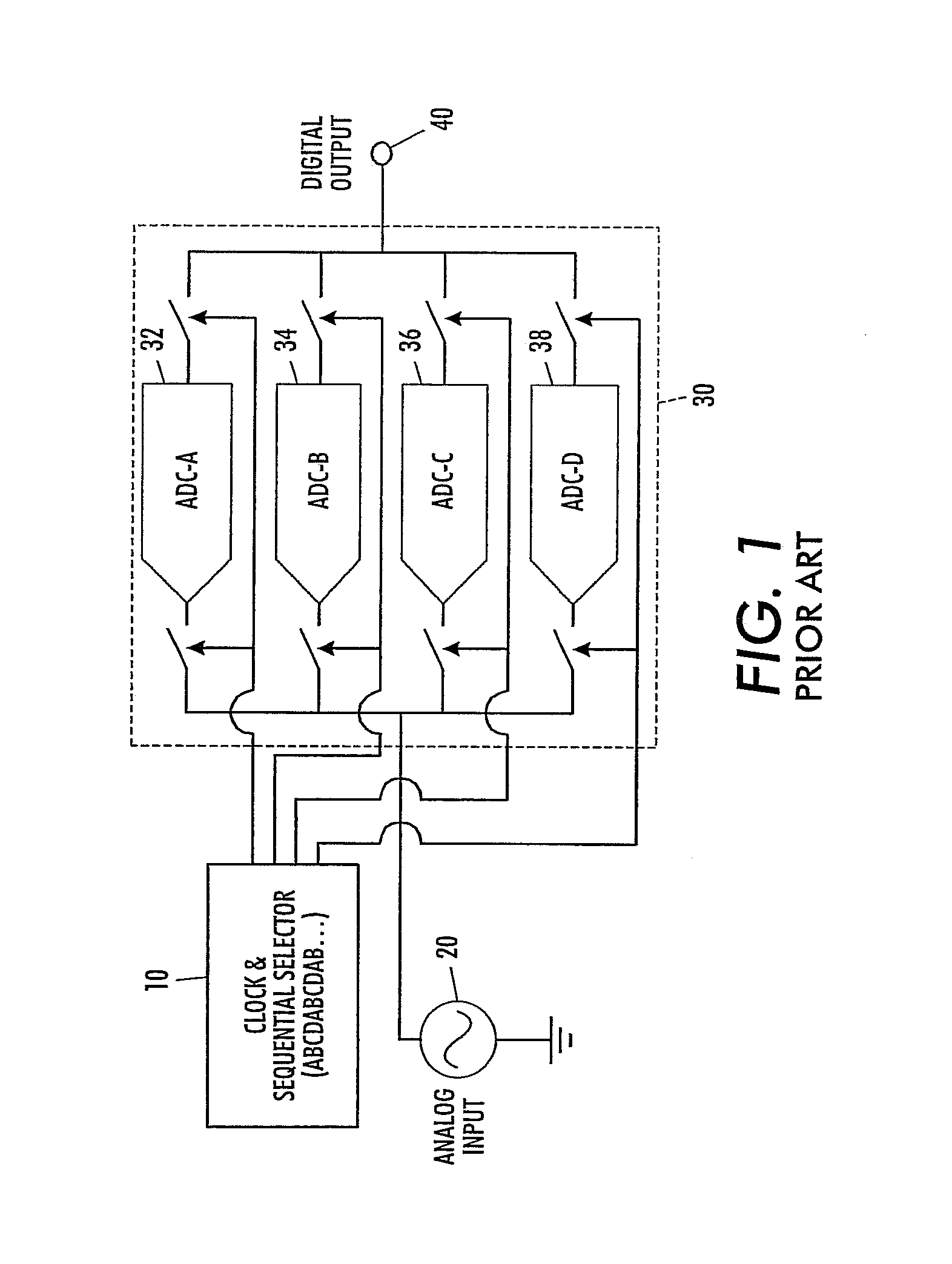

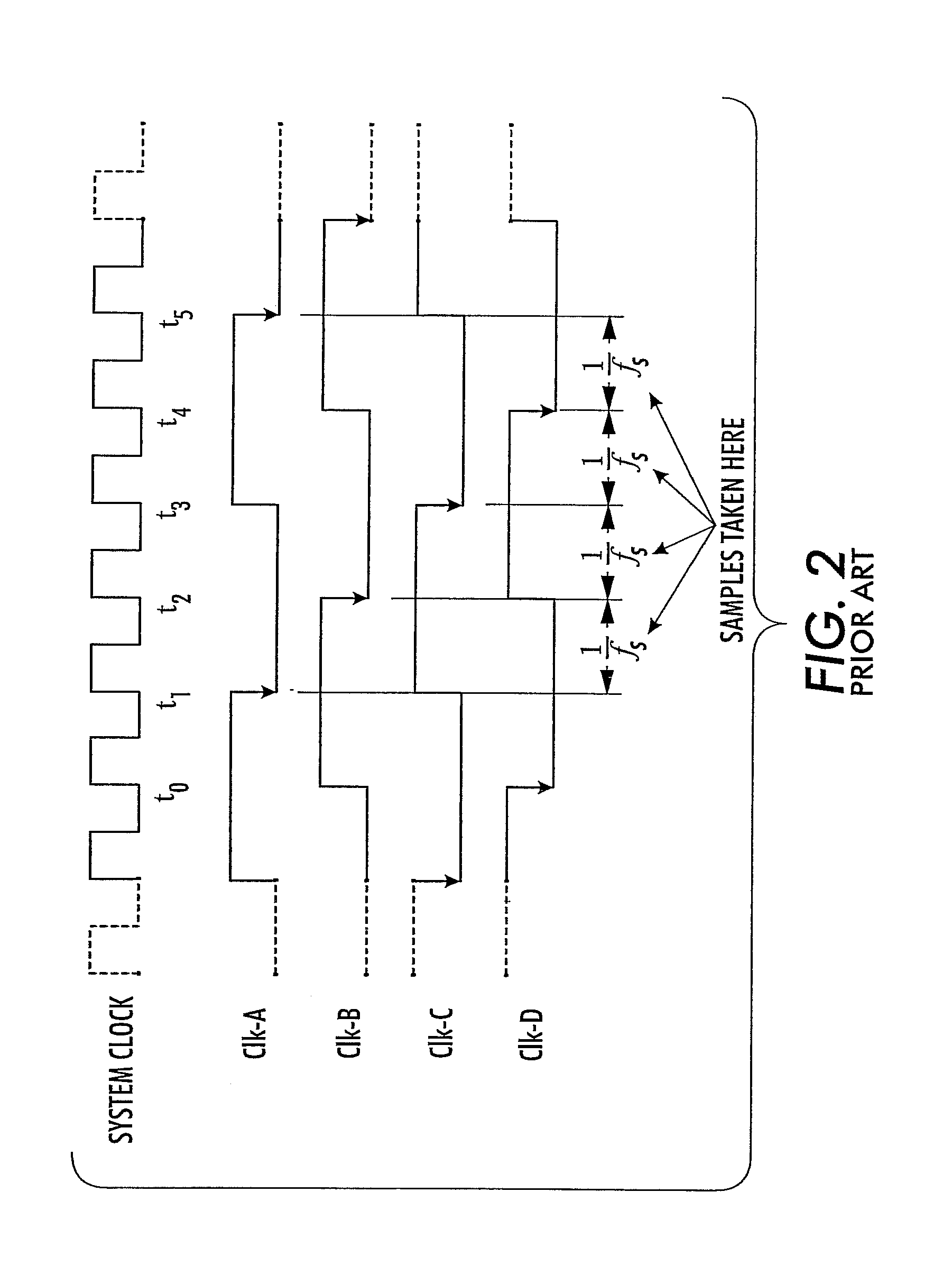

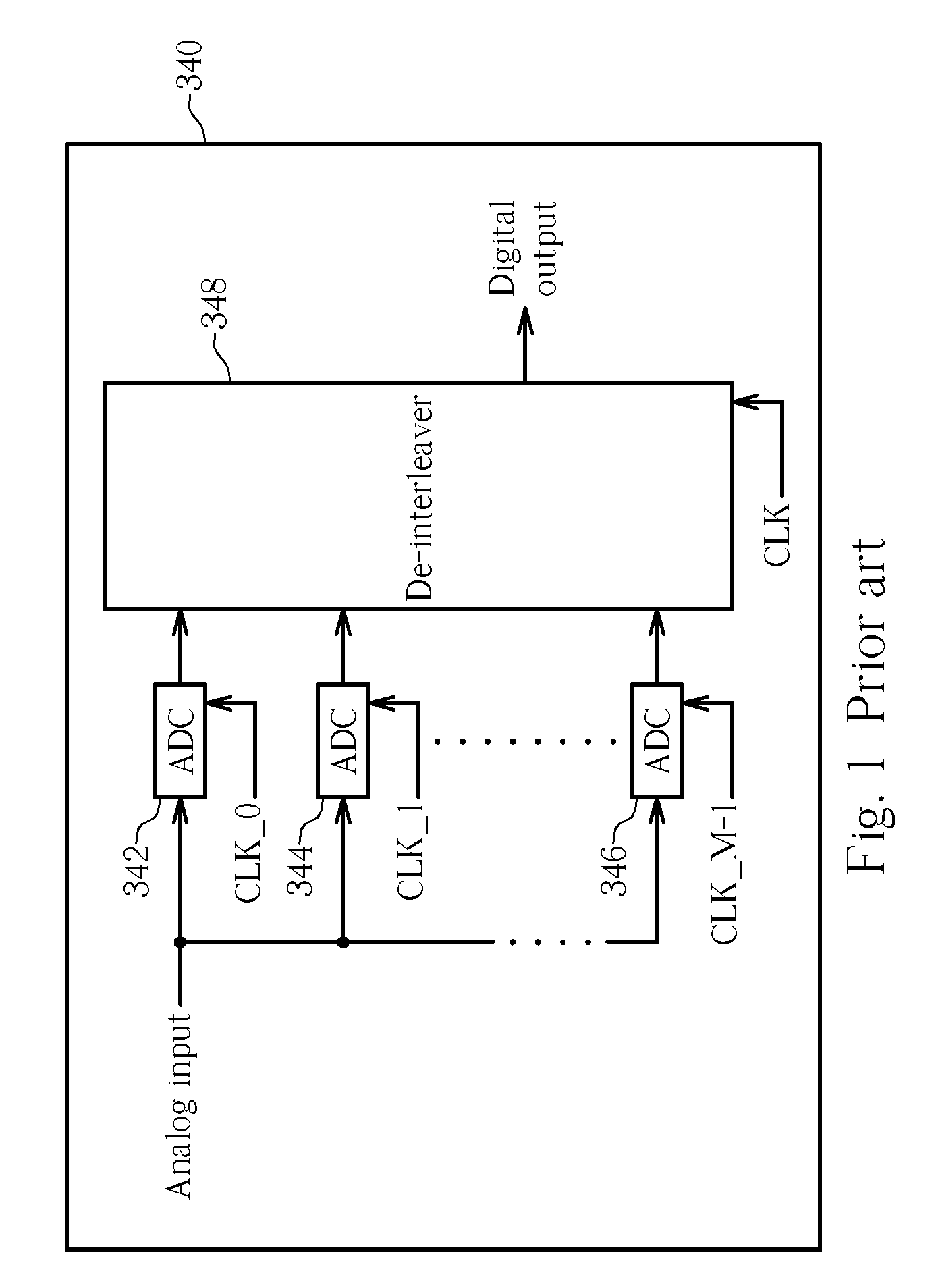

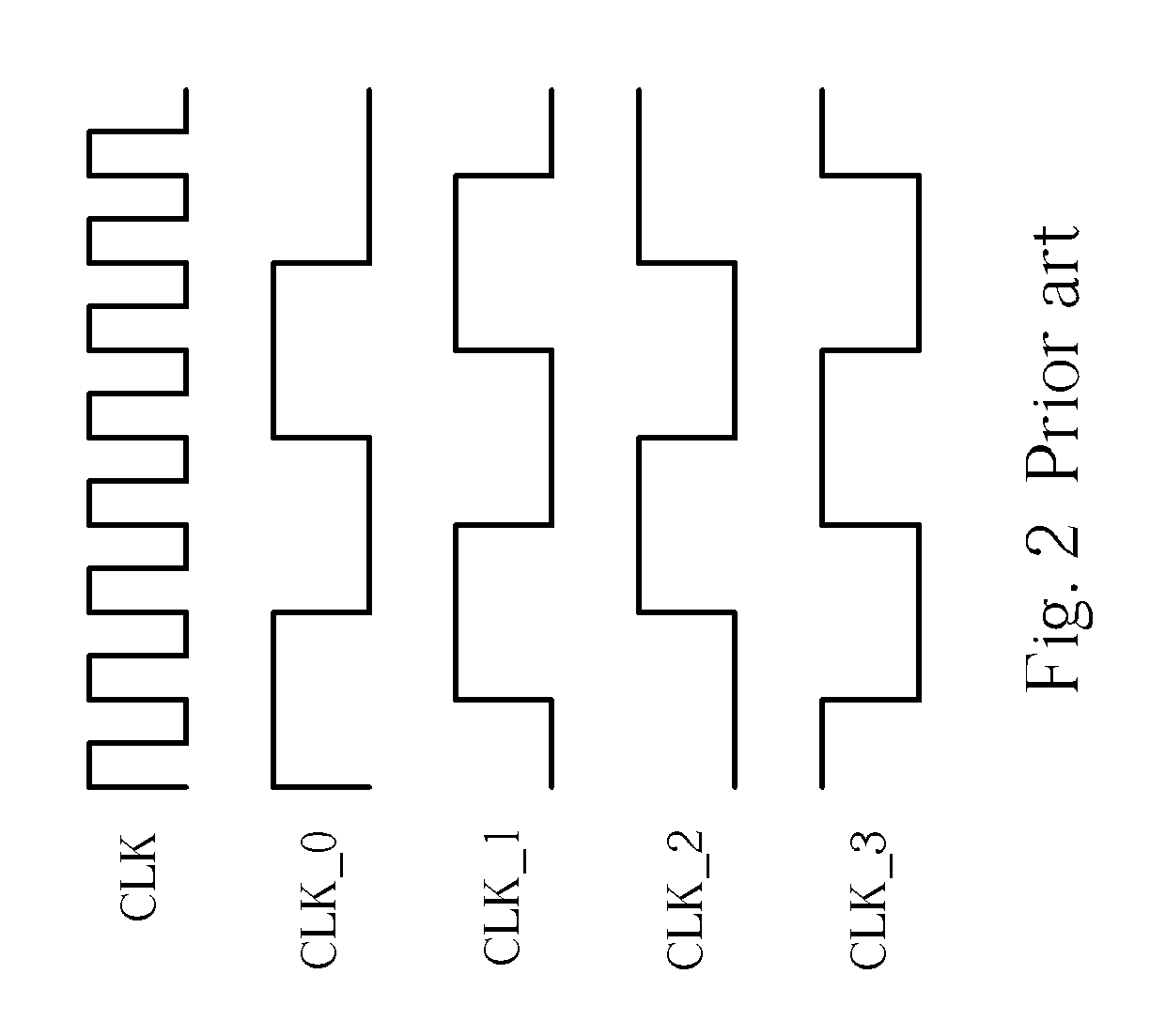

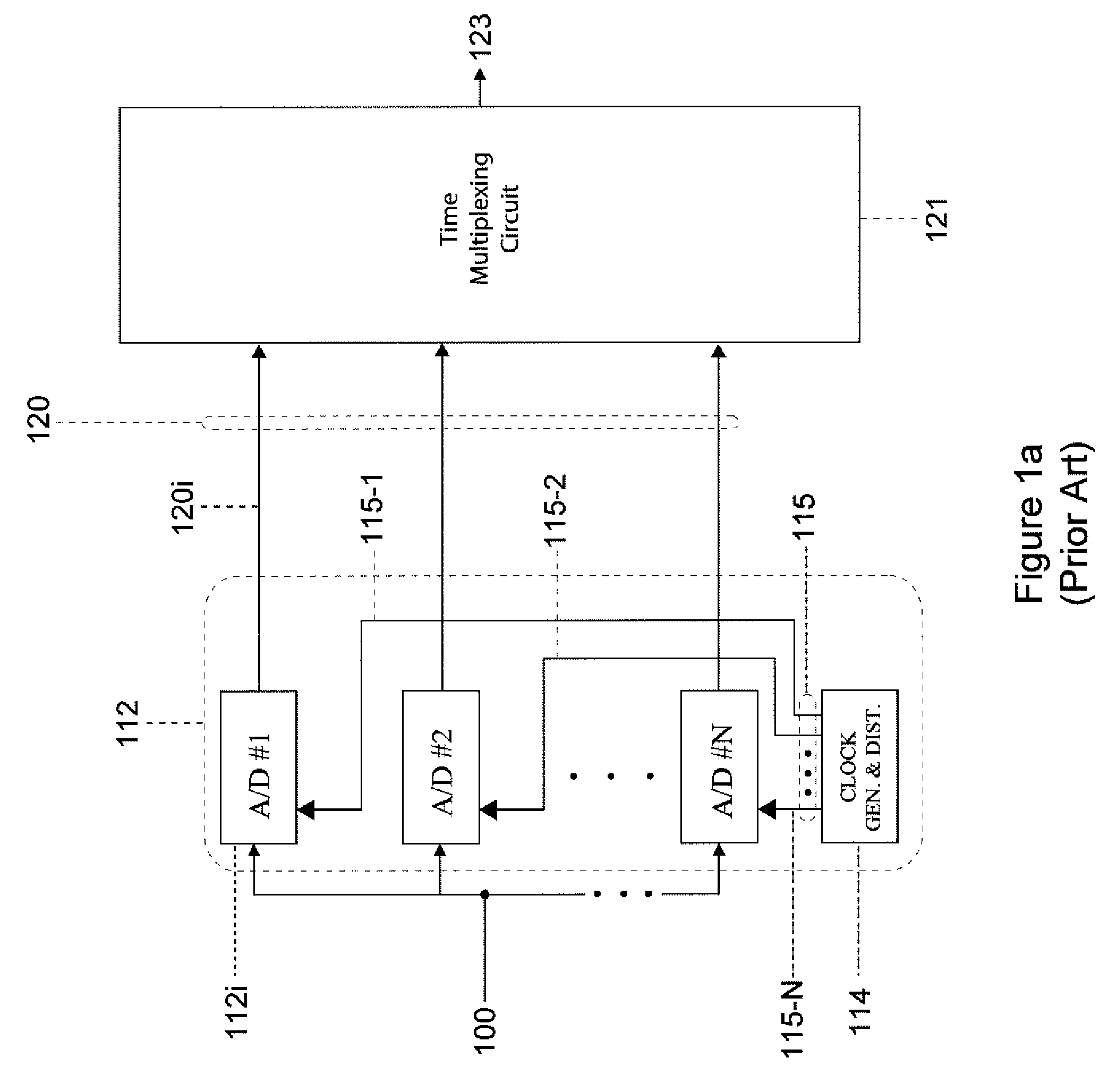

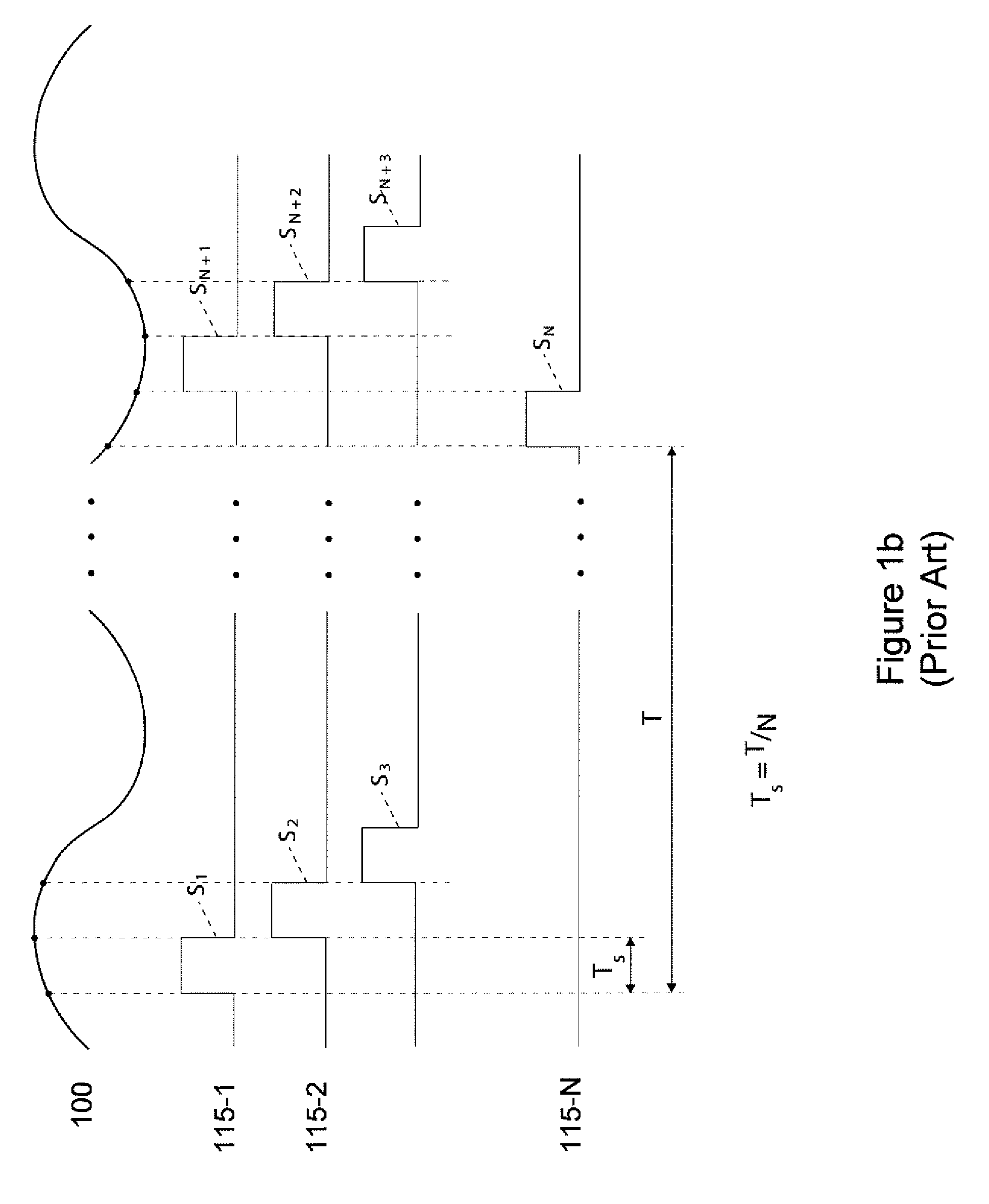

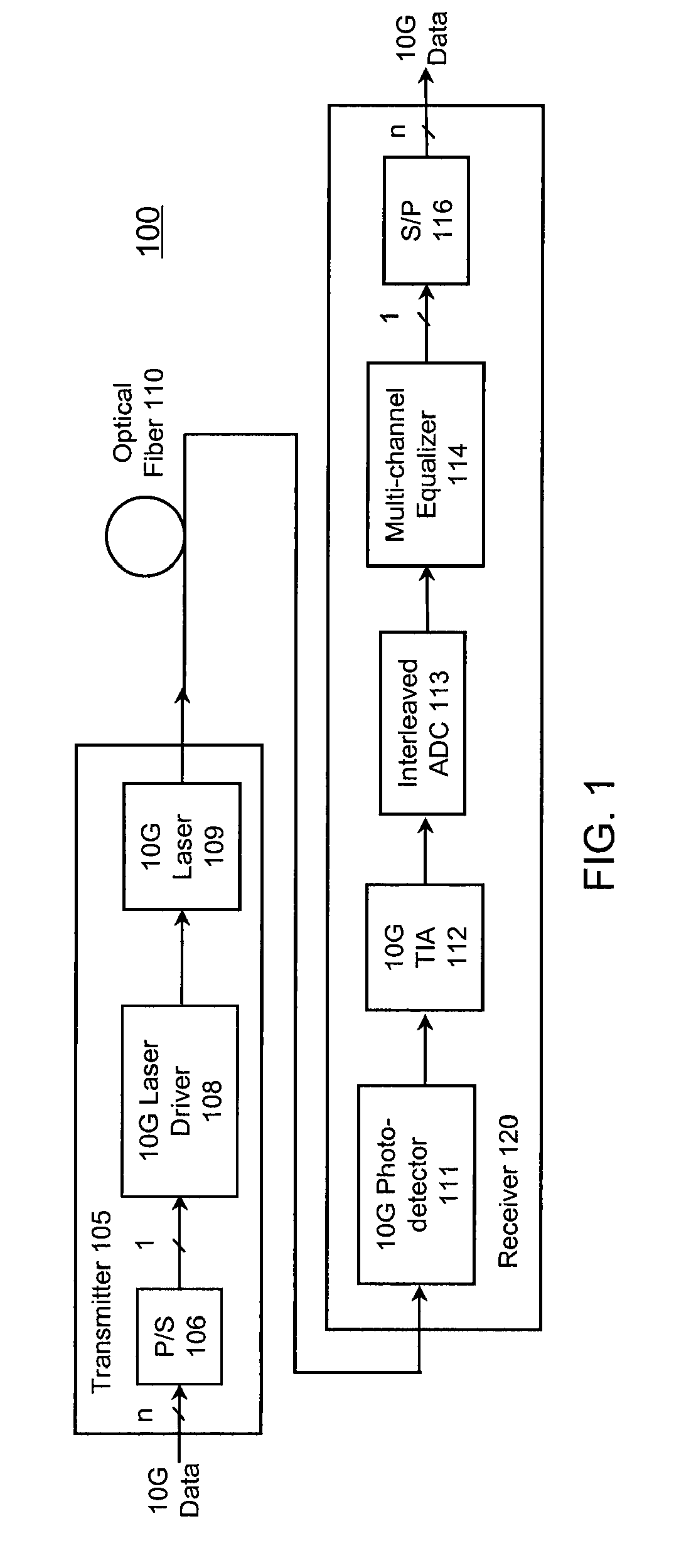

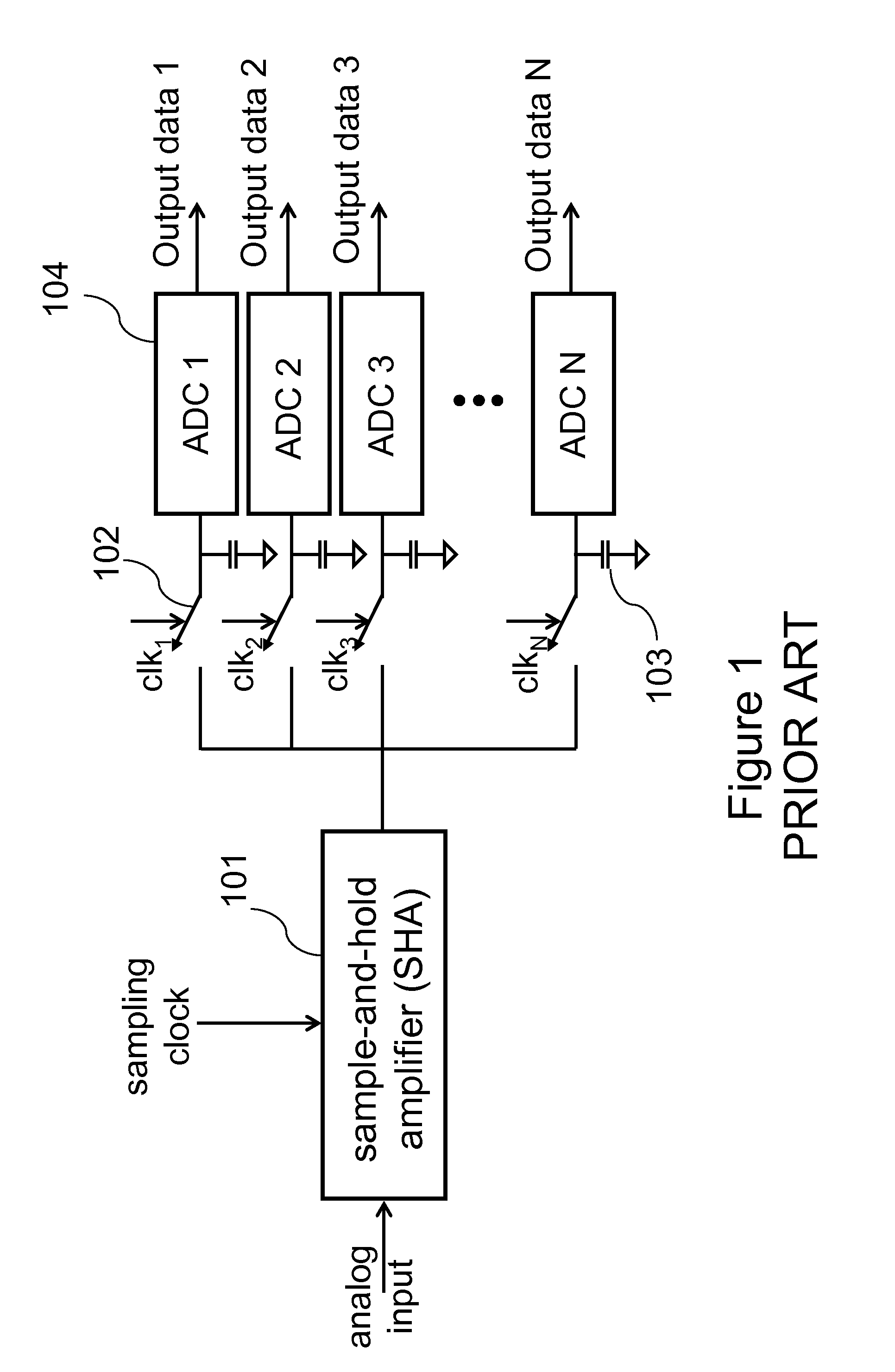

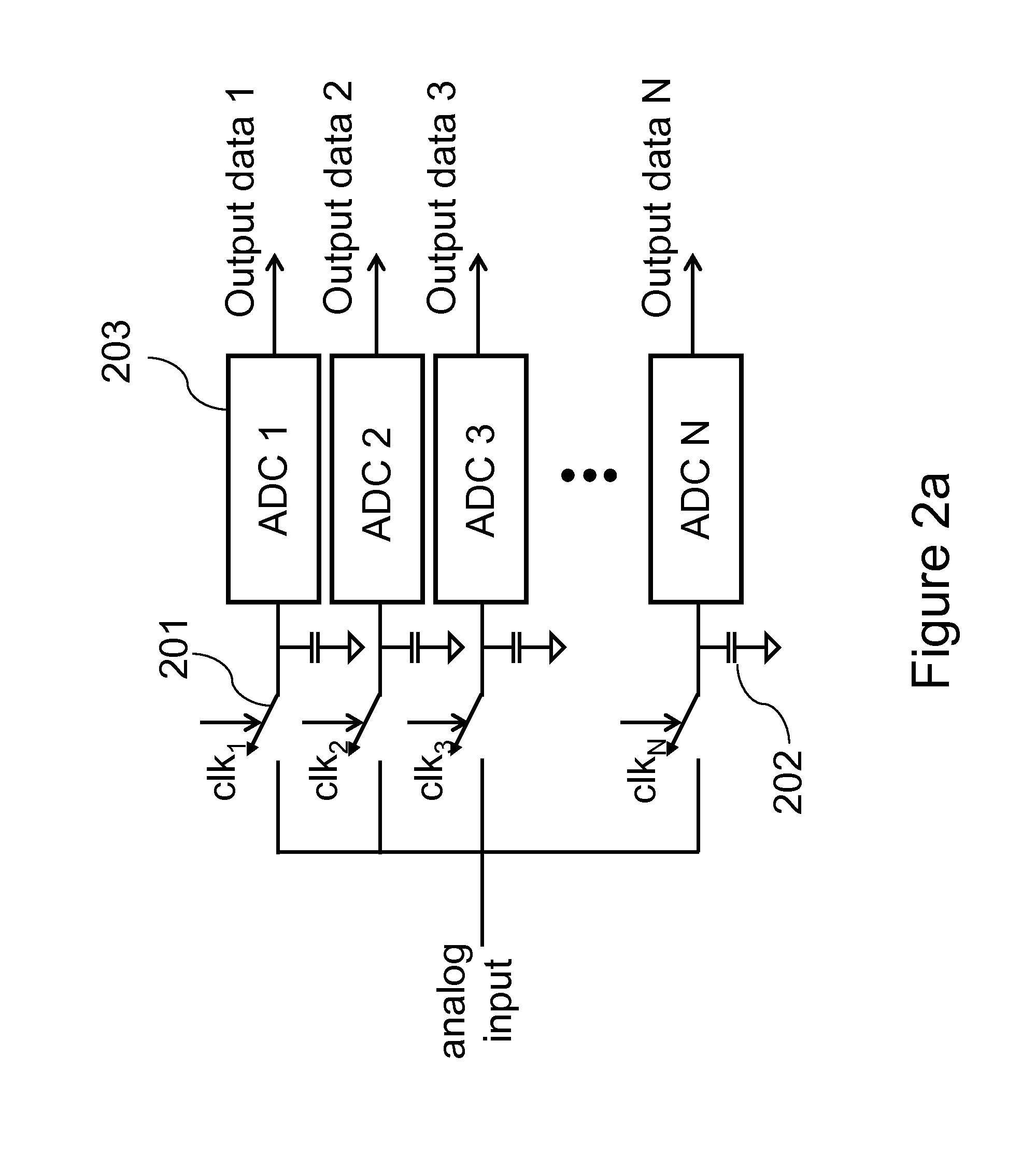

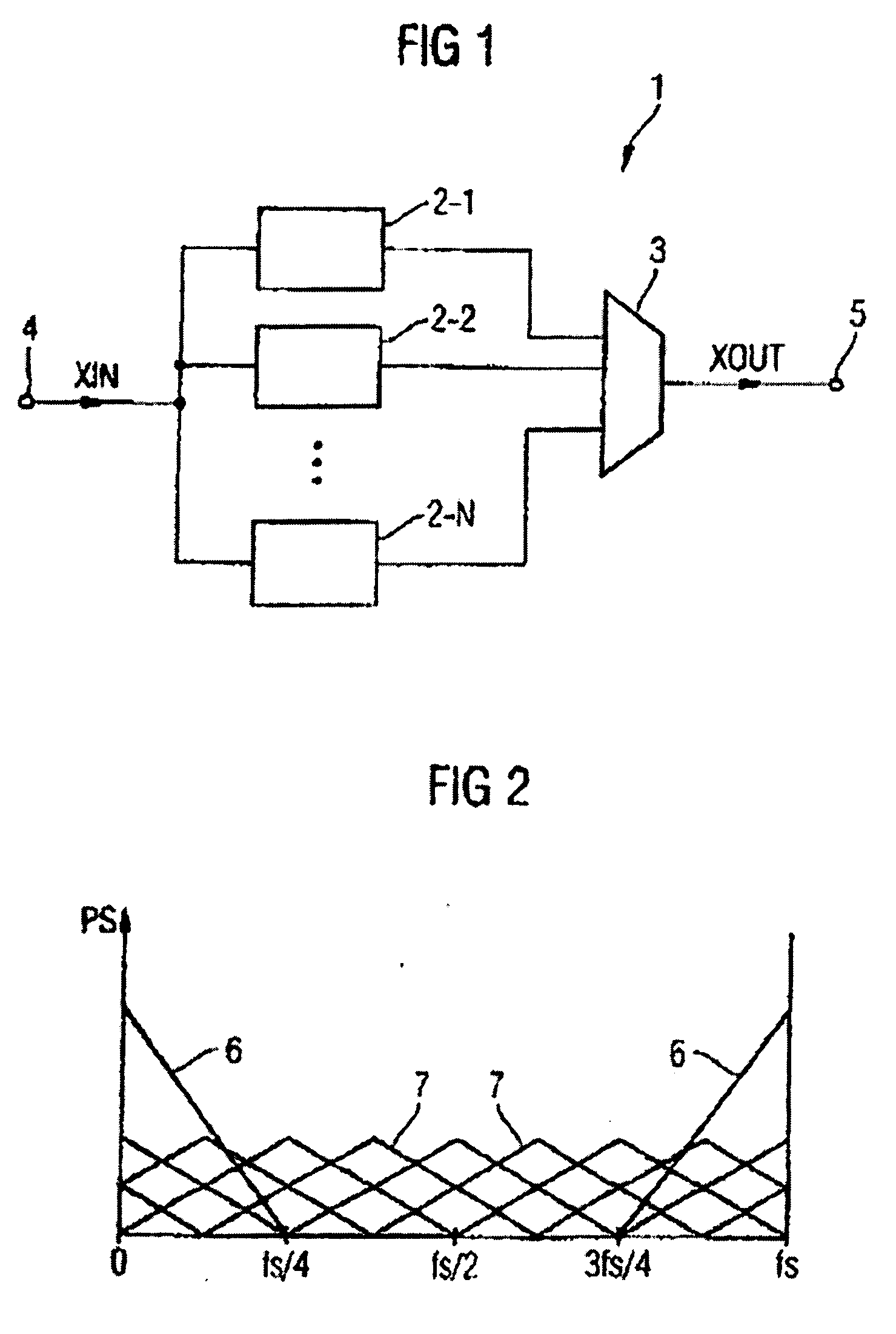

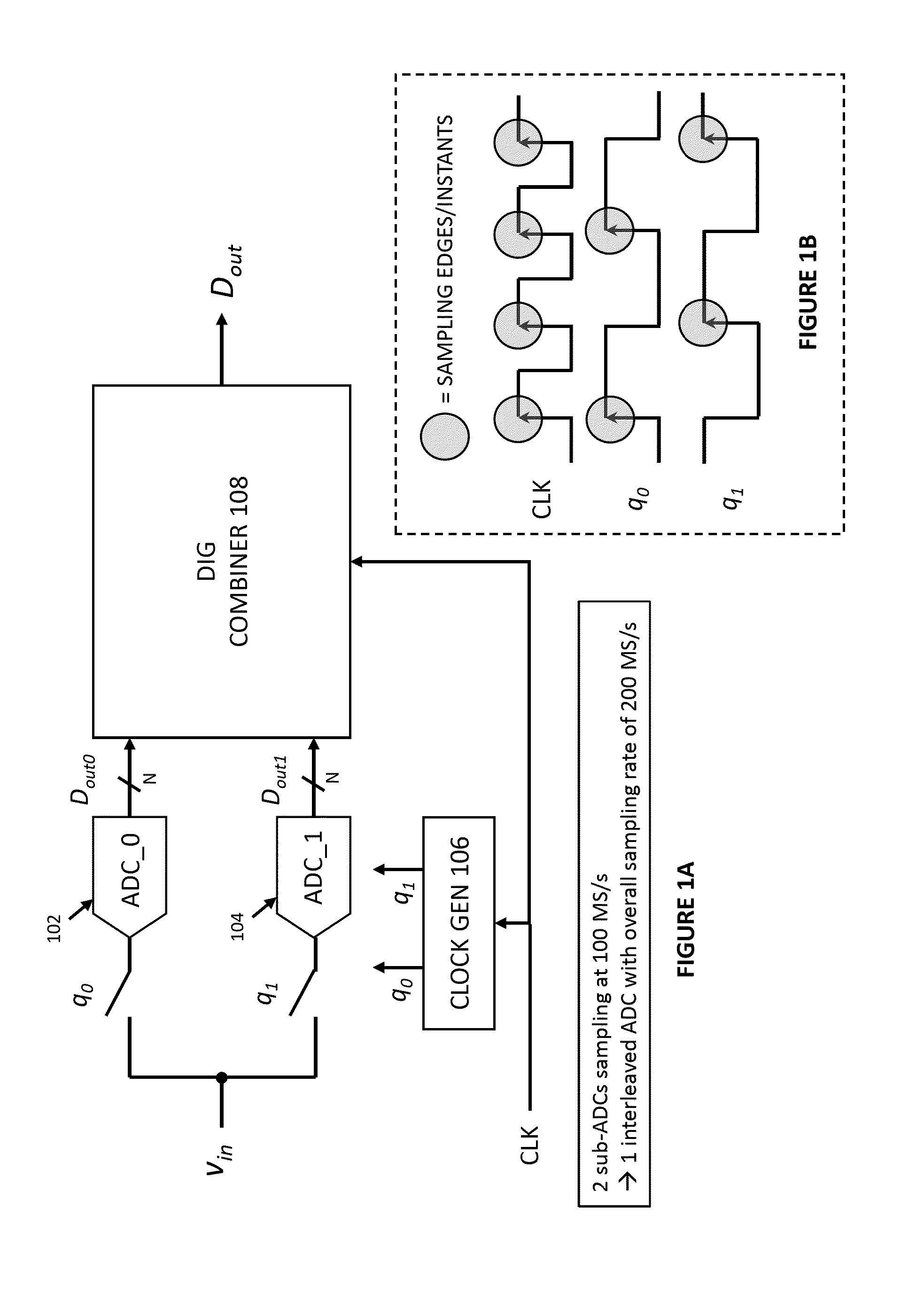

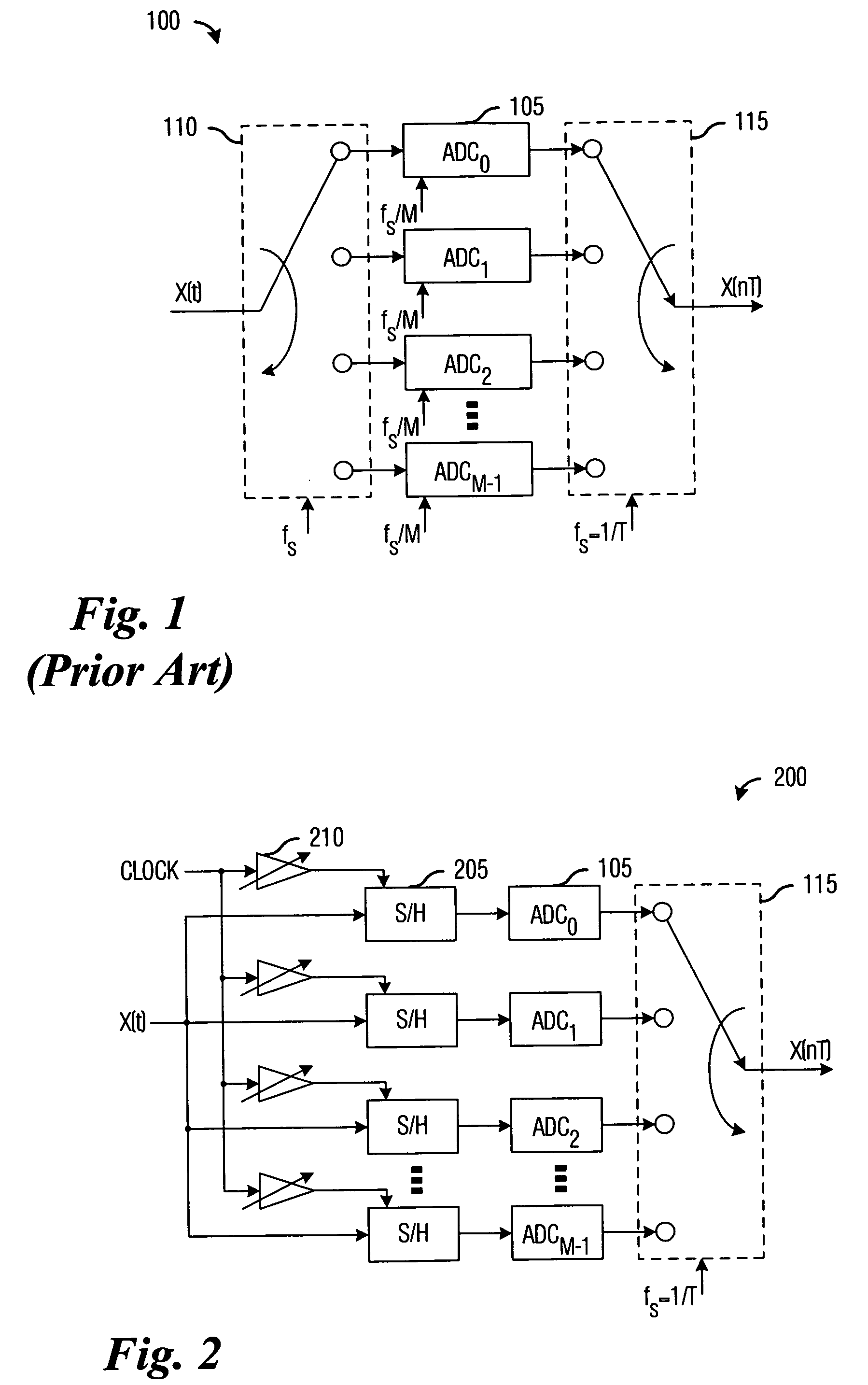

Time interleaving is a technique that allows the use of multiple identical analog-to-digital converters [1] (ADCs) to process regular sample data series at a faster rate than the operating sample rate of each individual data converter.

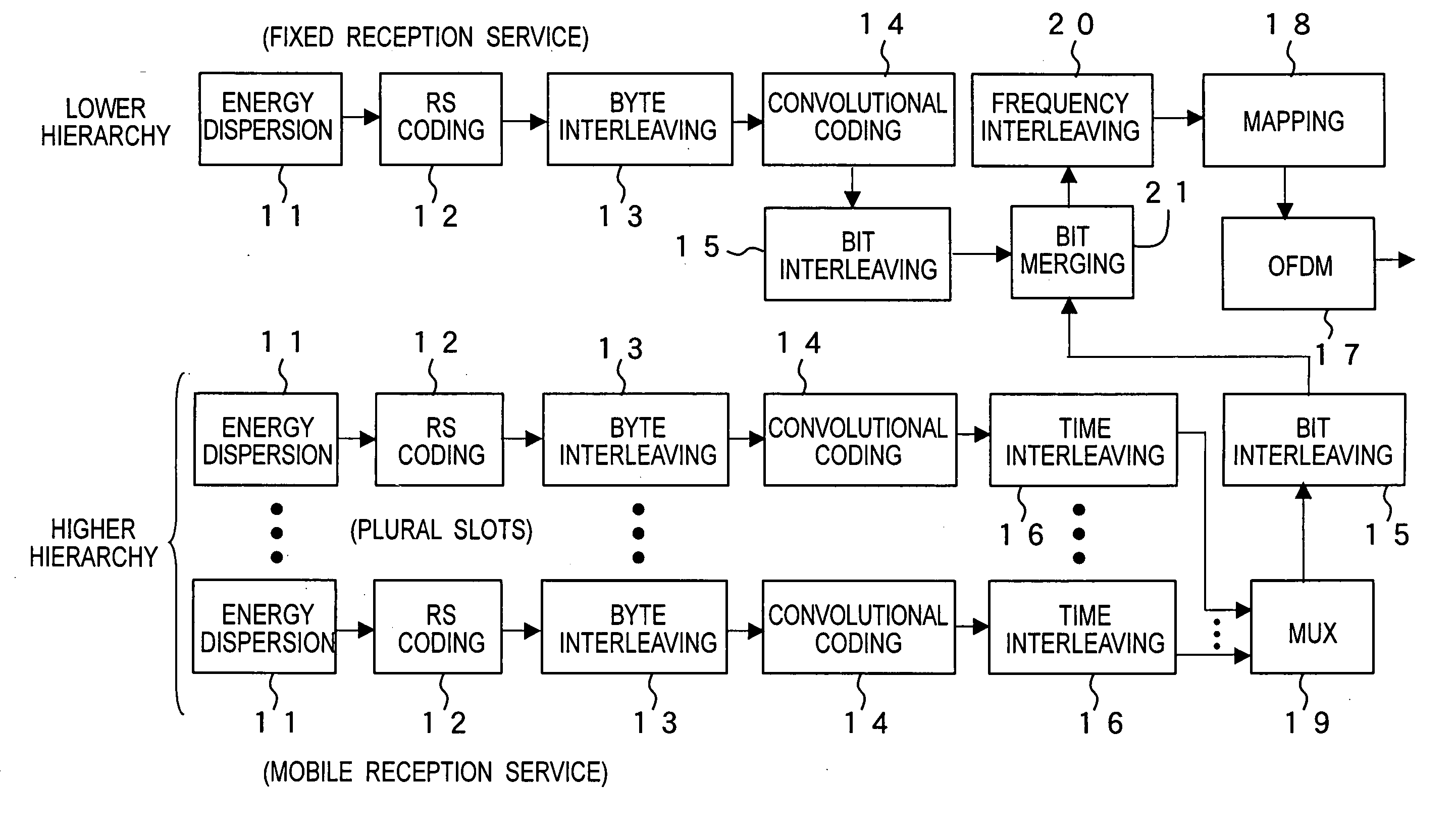

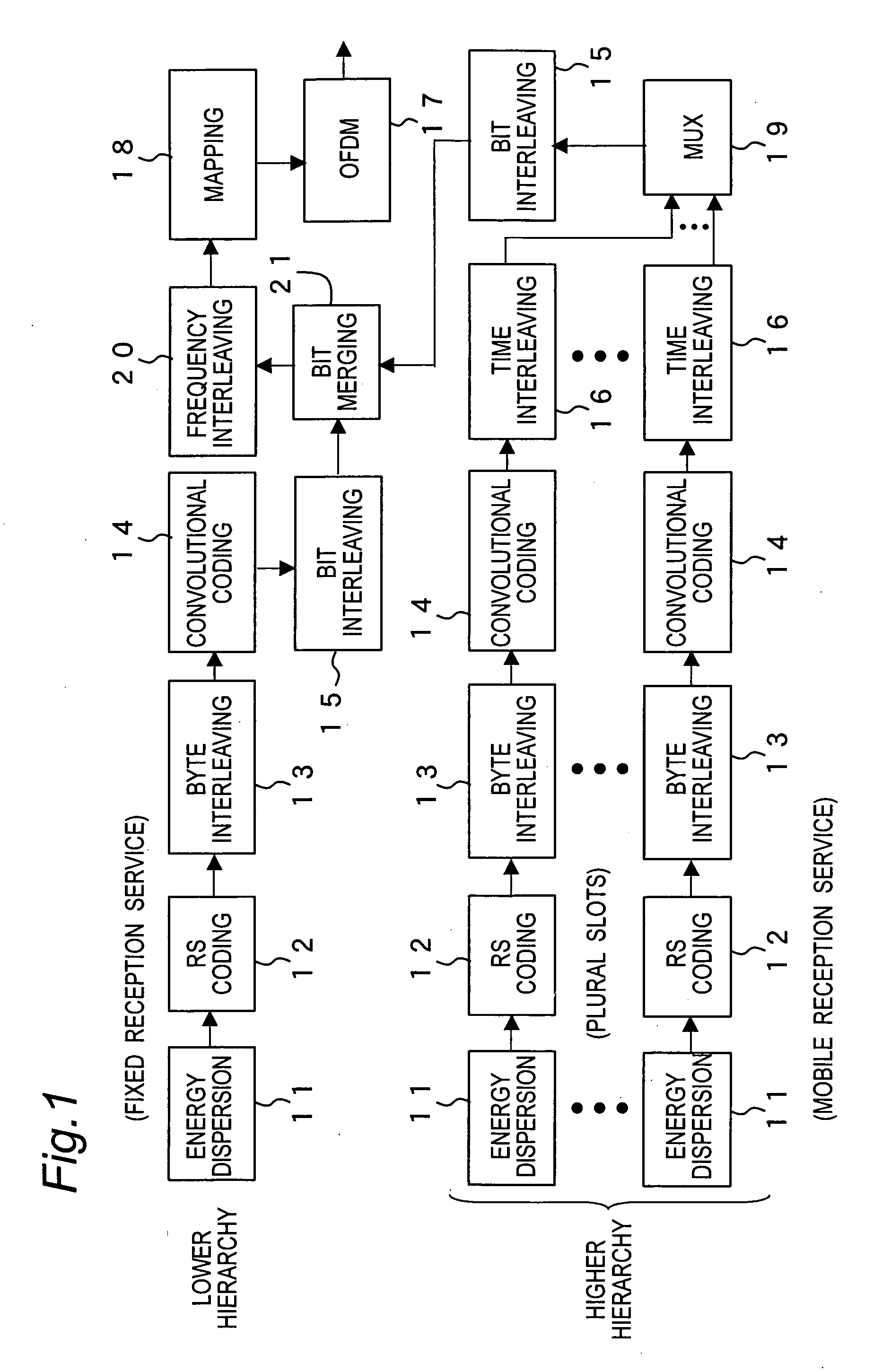

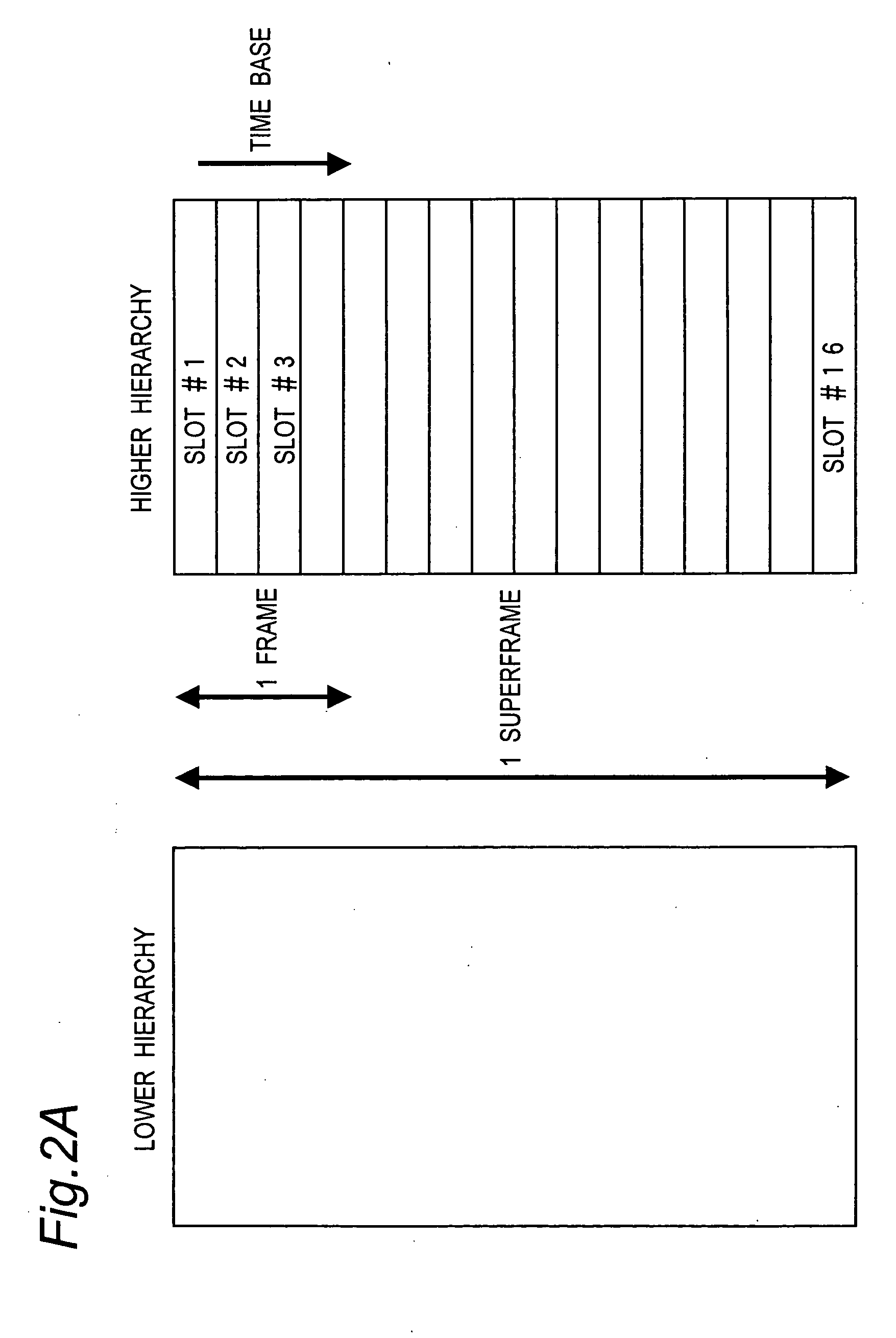

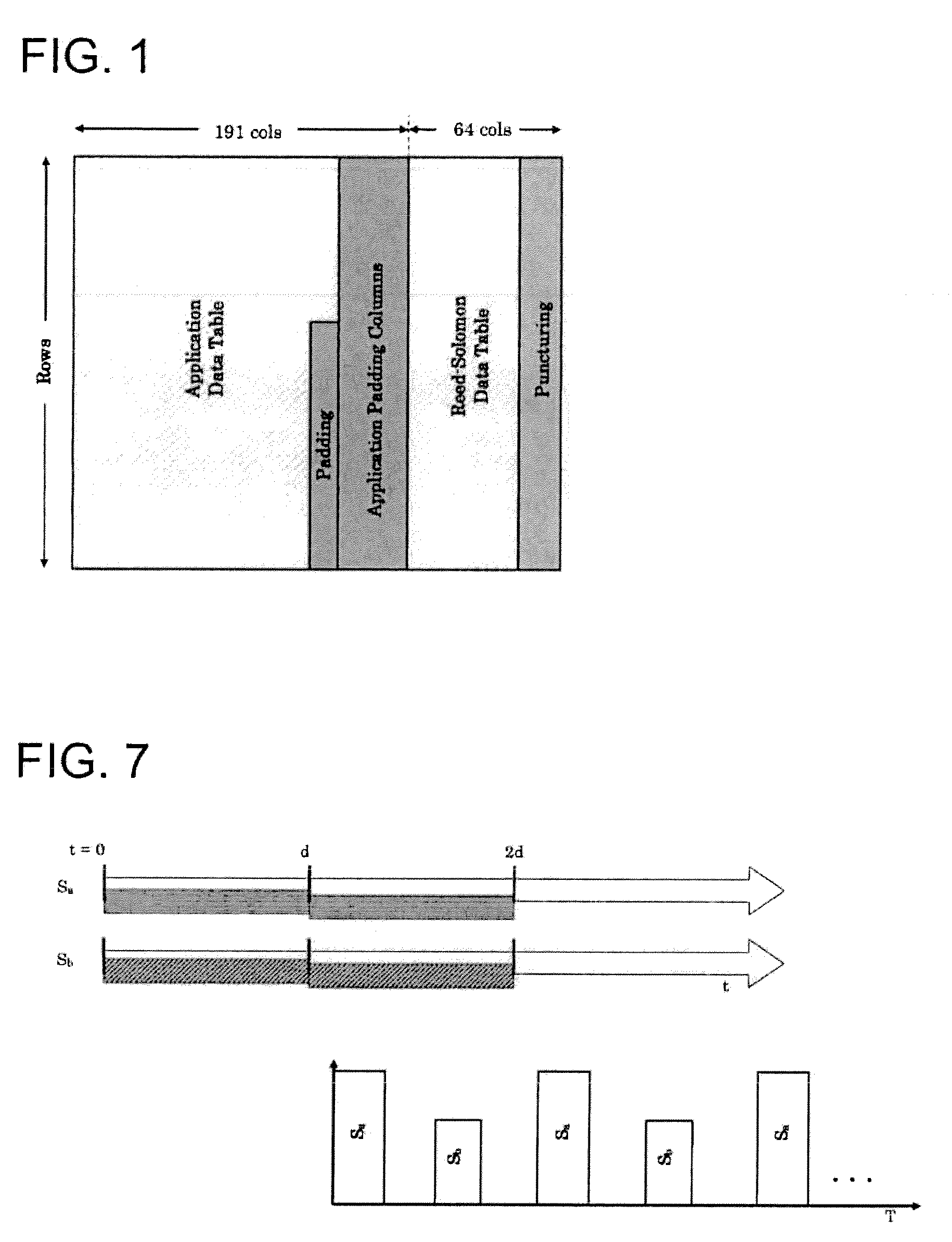

Ofdm signal transmission method, transmission apparatus, and reception apparatus

ActiveUS20070064588A1Maintain compatibilityReduce power consumptionTelevision system detailsColor television detailsDVB-TEnergy dispersion

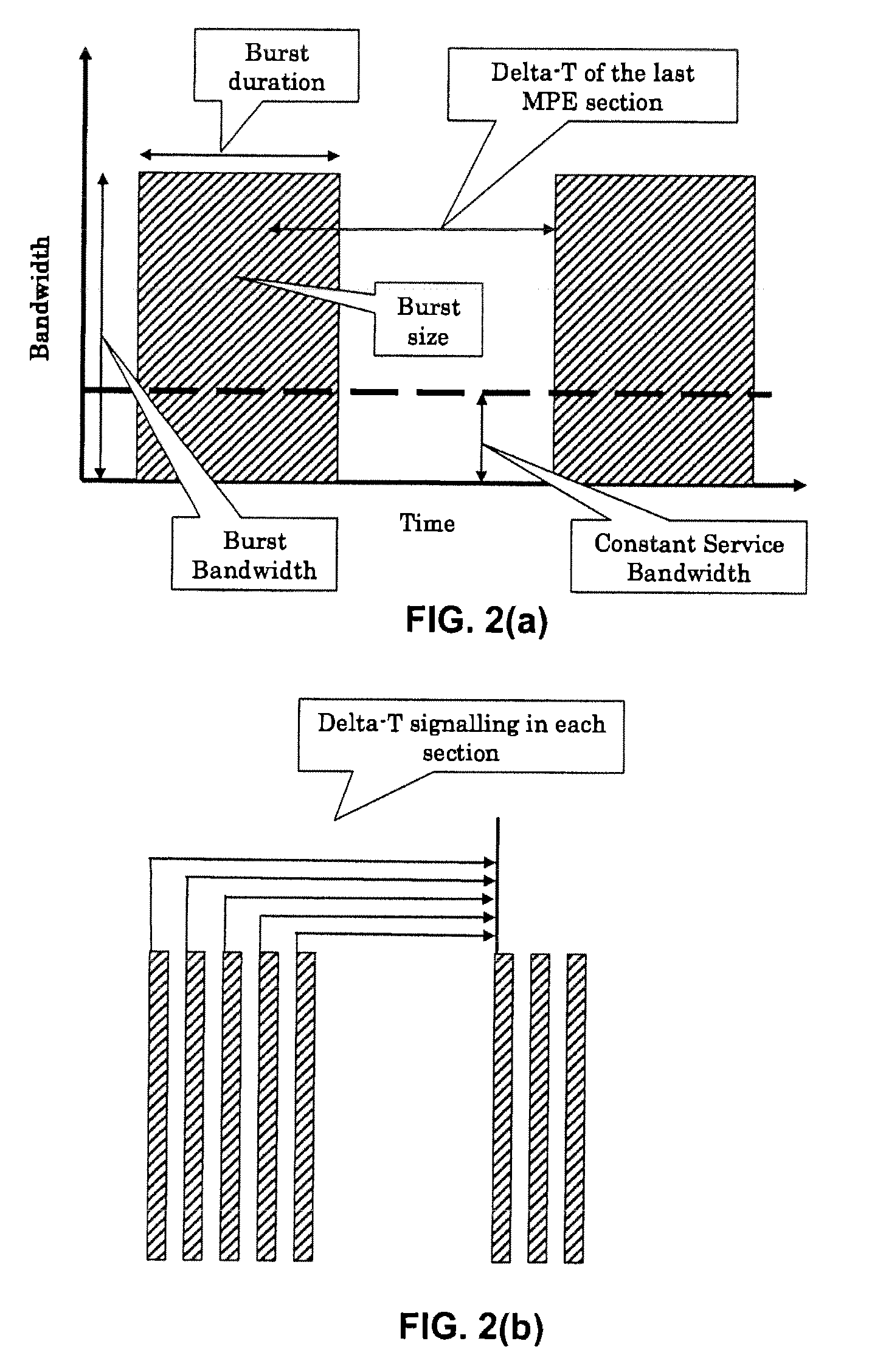

A transmission method of a digital broadcast which is compatible with the DVB-T terrestrial digital broadcast system in Europe and saves a battery in a mobile terminal is provided. Superframes in DVB-T are divided into units each including plural symbols so that an integer number of TS packets can be carried in each slot. At least one slot is used to transmit one service. Energy dispersion, Reed-Solomon coding, byte interleaving, convolutional coding, and time interleaving are applied to each service. When services for mobile terminal reception and services for fixed terminals are transmitted as the provided services, null packets may be transmitted before and after the slot carrying the mobile receiver service so that the fixed reception service and the mobile reception services are not mixed. If the fixed terminal handles TS packets of the mobile reception service as error packets, it could have no problem in reception.

Owner:PANASONIC CORP

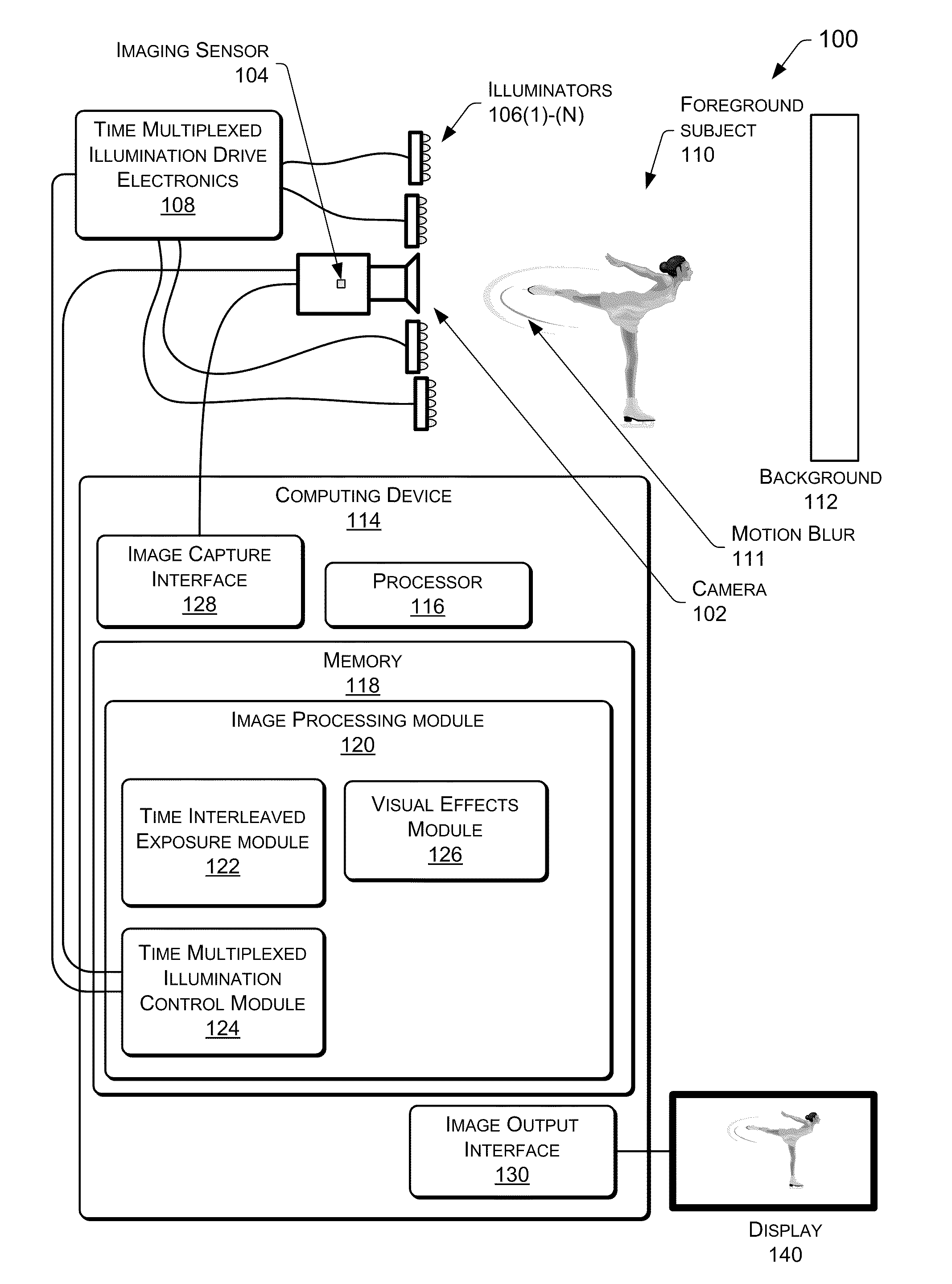

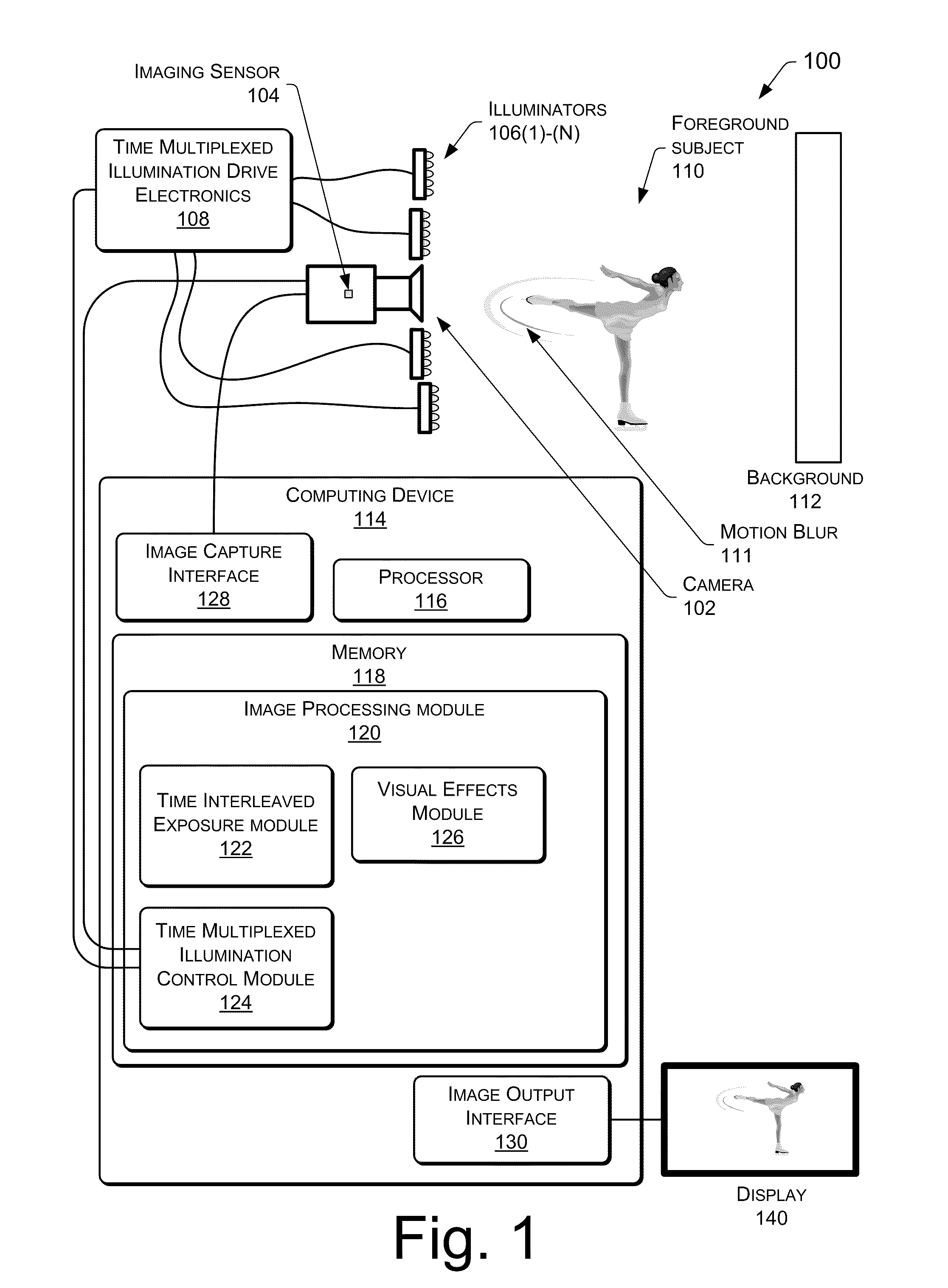

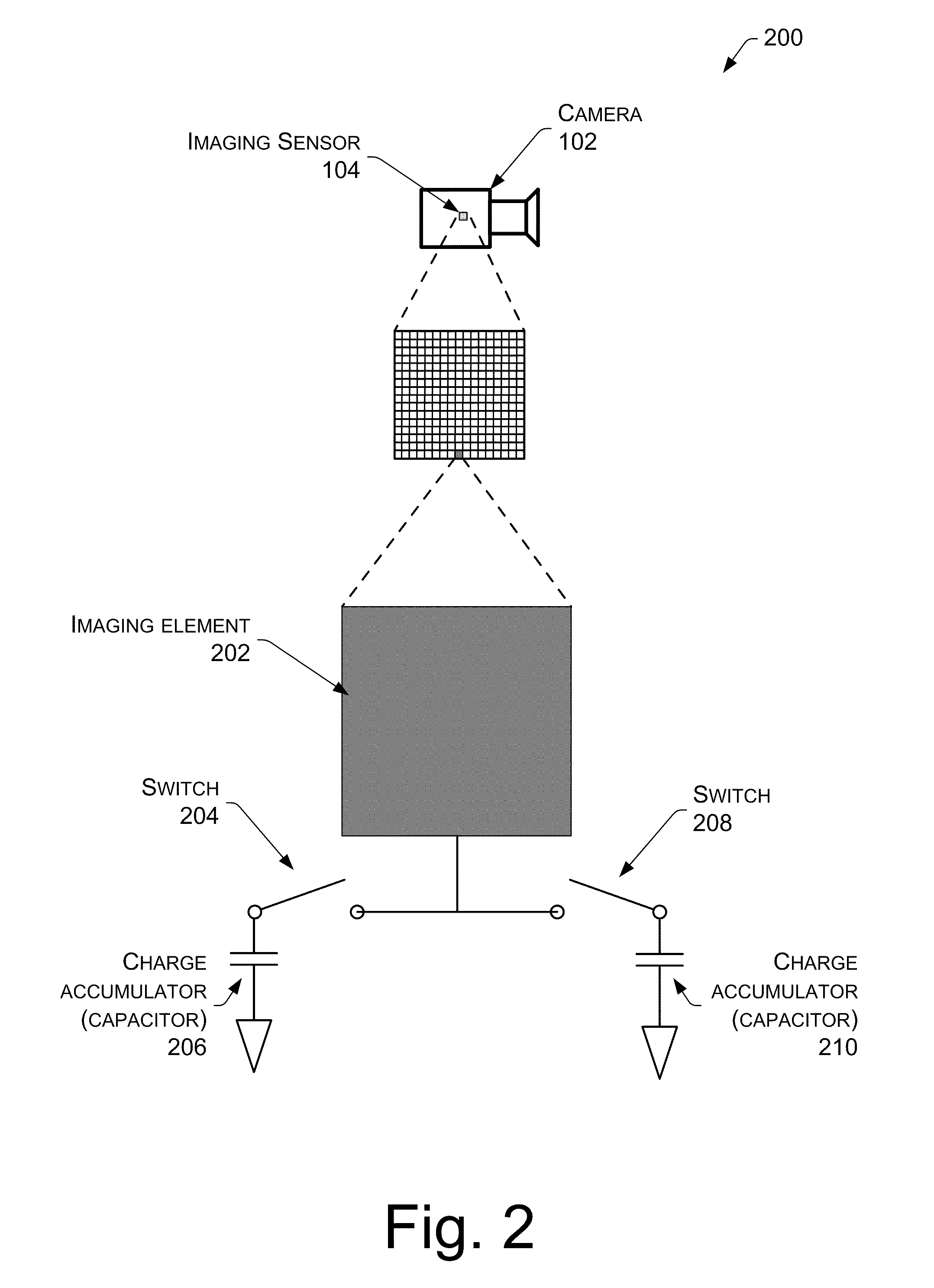

Time Interleaved Exposures And Multiplexed Illumination

InactiveUS20110242334A1Data rate outputImprove performanceTelevision system detailsColor signal processing circuitsTriangulationTime interleaved

Samples of a scene are acquired in synchronization with finely interleaved varying conditions such as lighting, aperture, focal length, and so forth. A time-varying sample at each pixel for each condition is reconstructed. Time multiplexed interleaving allows for real-time, live applications, while handling motion blur naturally. Effects such as real-time video relighting of a scene is possible. Time interleaved exposures also allow segmentation of a scene, and allows for constrained special effects such as triangulation matting using a multi-color interleaved chroma key.

Owner:MICROSOFT TECH LICENSING LLC

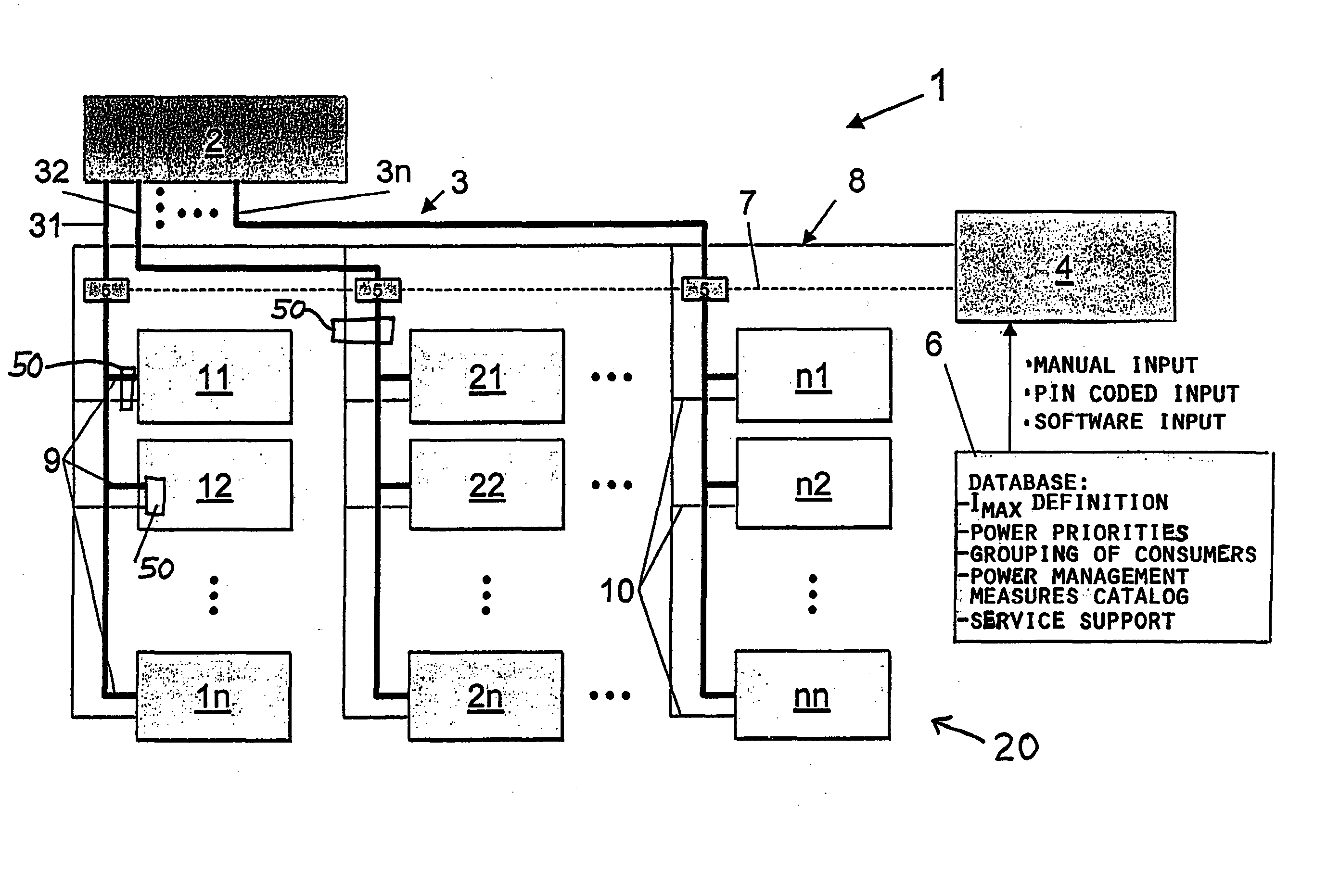

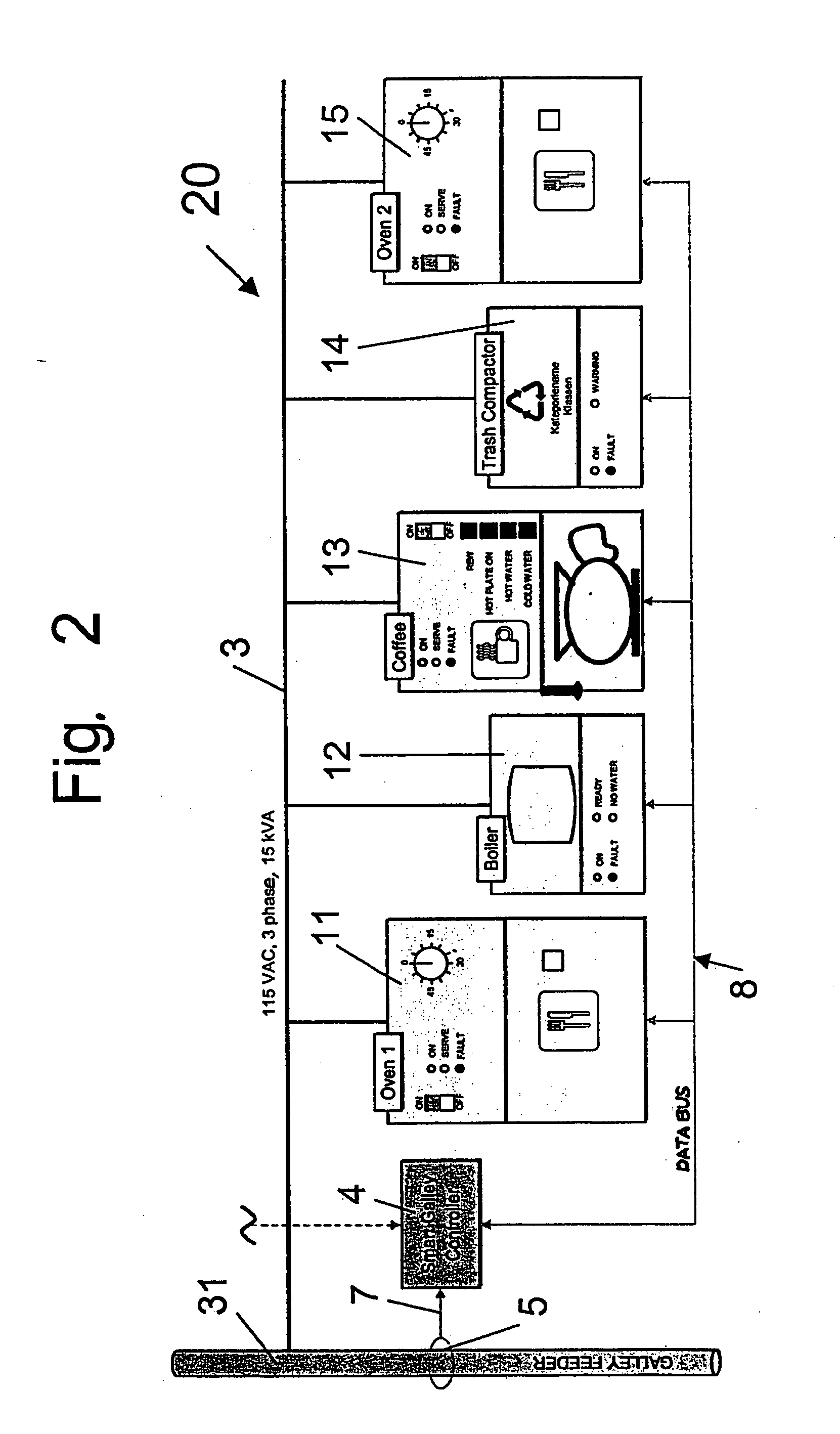

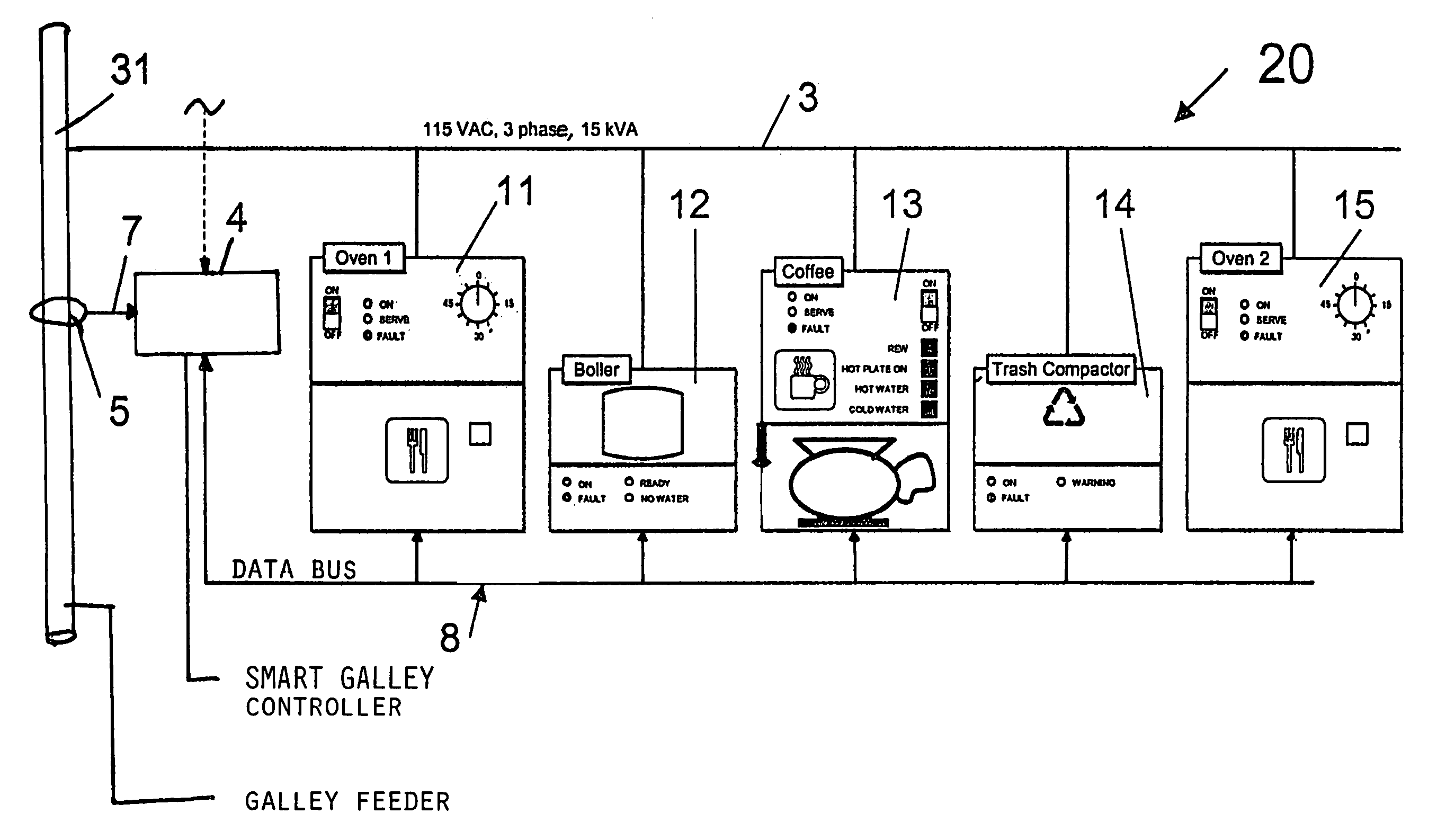

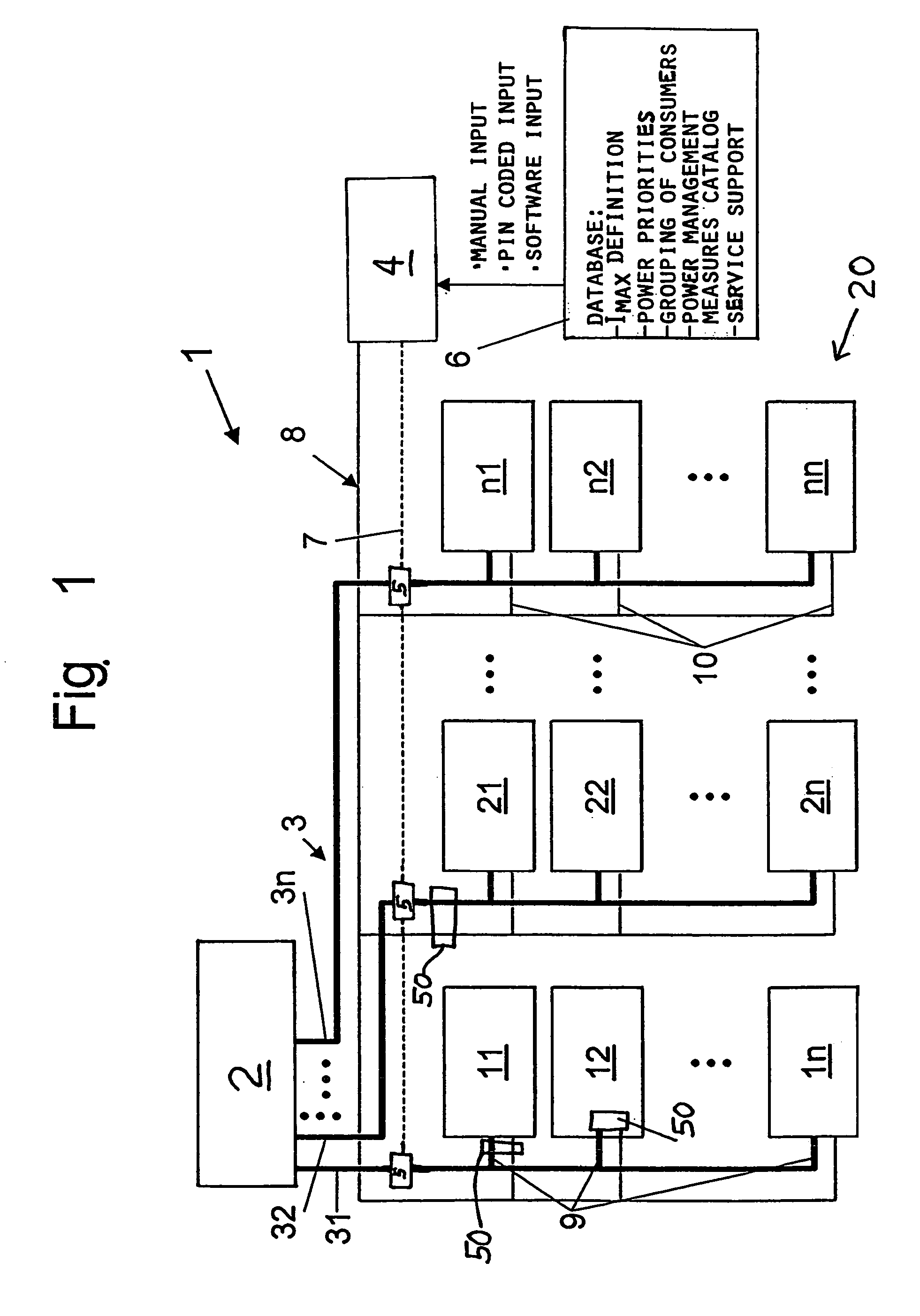

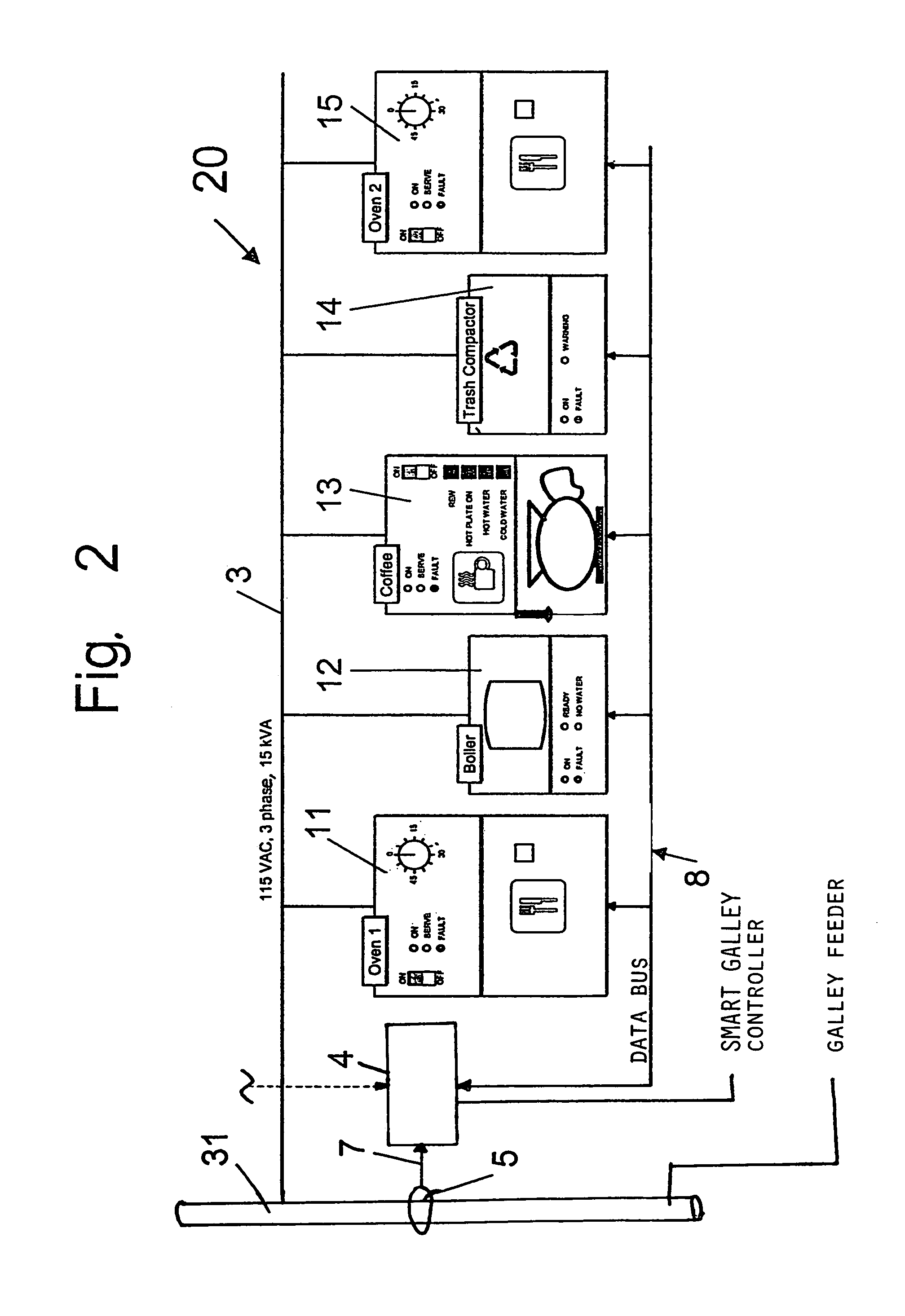

Intelligent power distribution management for an on-board galley of a transport vehicle such as an aircraft

ActiveUS20040057177A1Avoiding and reducing unnecessary over-consumptionReduce loadDc network circuit arrangementsPower network operation systems integrationControl signalOn board

In an aircraft galley, a power network distributes power from a source to electrical consuming devices (oven, water boiler, coffee machine, trash compactor, etc.). A control unit is connected to and can individually address each of the devices via a databus. The control unit compares the actual existing power consumption to a prescribed maximum value. If the actual consumption reaches the maximum value, the control unit calls up a power reduction procedure from a catalog in a database, and provides corresponding control signals to one or more of the devices to reduce the power consumption below the maximum value. The individual devices receive power in a time-sharing, power-sharing, or time-staggered manner. An intelligent distribution of available power resources avoids power overloads, and allows optimal utilization of all galley devices without limiting the normal catering process.

Owner:AIRBUS OPERATIONS GMBH

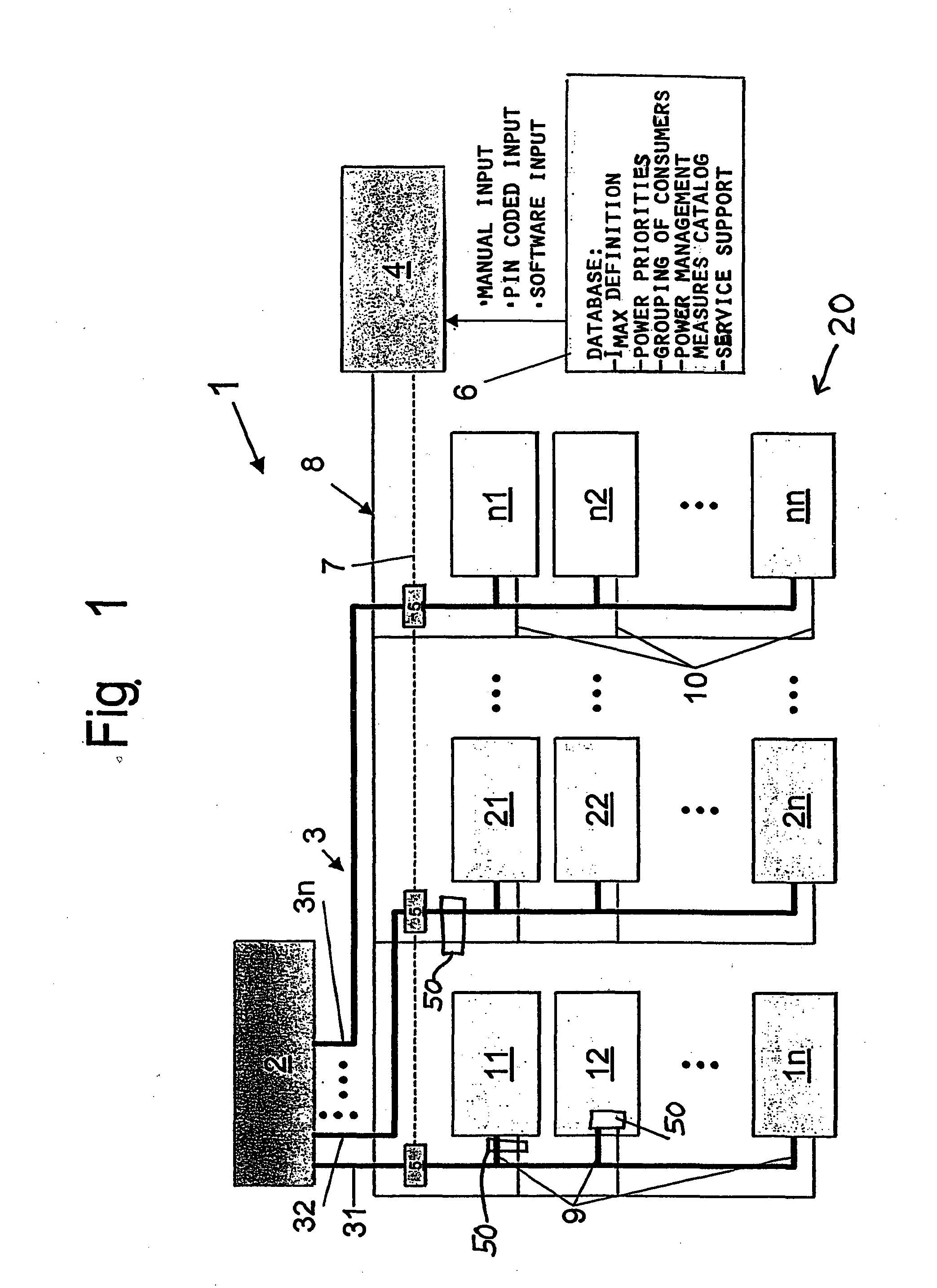

Intelligent power distribution management for an on-board galley of a transport vehicle such as an aircraft

ActiveUS7098555B2Preventing of supplyImprove user friendliness and full operabilityDc network circuit arrangementsPower network operation systems integrationOn boardControl signal

In an aircraft galley, a power network distributes power from a source to electrical consuming devices (oven, water boiler, coffee machine, trash compactor, etc.). A control unit is connected to and can individually address each of the devices via a databus. The control unit compares the actual existing power consumption to a prescribed maximum value. If the actual consumption reaches the maximum value, the control unit calls up a power reduction procedure from a catalog in a database, and provides corresponding control signals to one or more of the devices to reduce the power consumption below the maximum value. The individual devices receive power in a time-sharing, power-sharing, or time-staggered manner. An intelligent distribution of available power resources avoids power overloads, and allows optimal utilization of all galley devices without limiting the normal catering process.

Owner:AIRBUS OPERATIONS GMBH

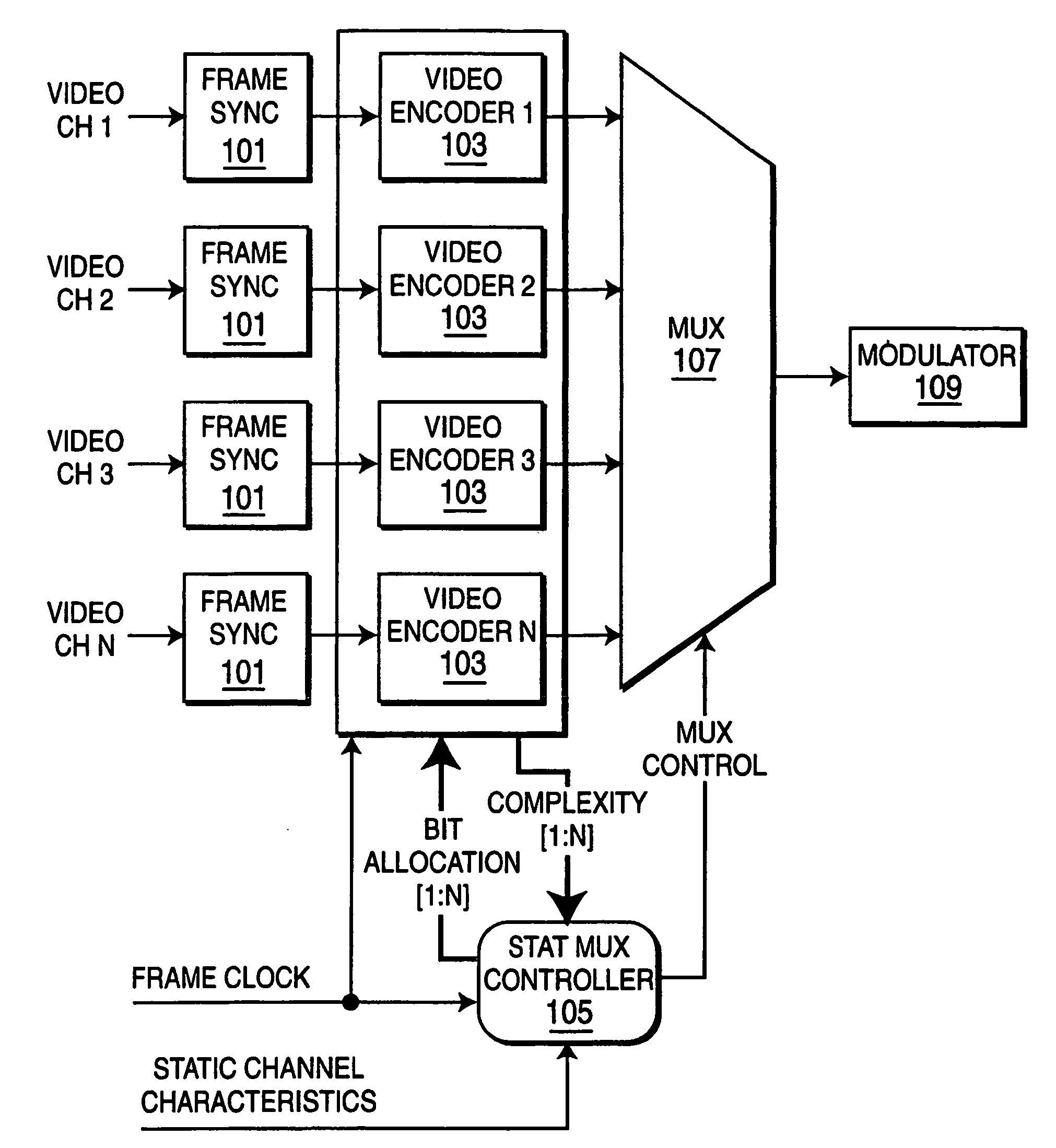

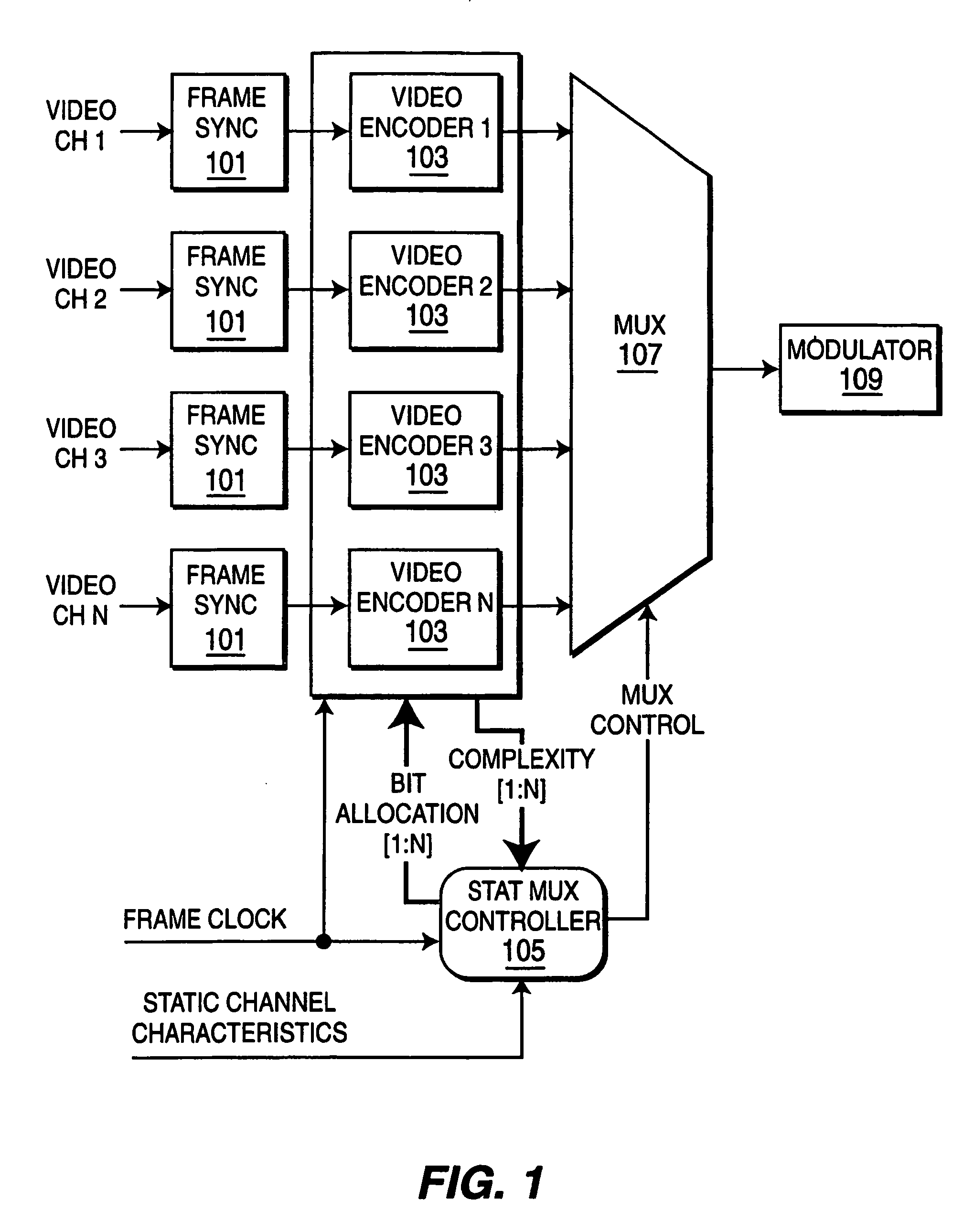

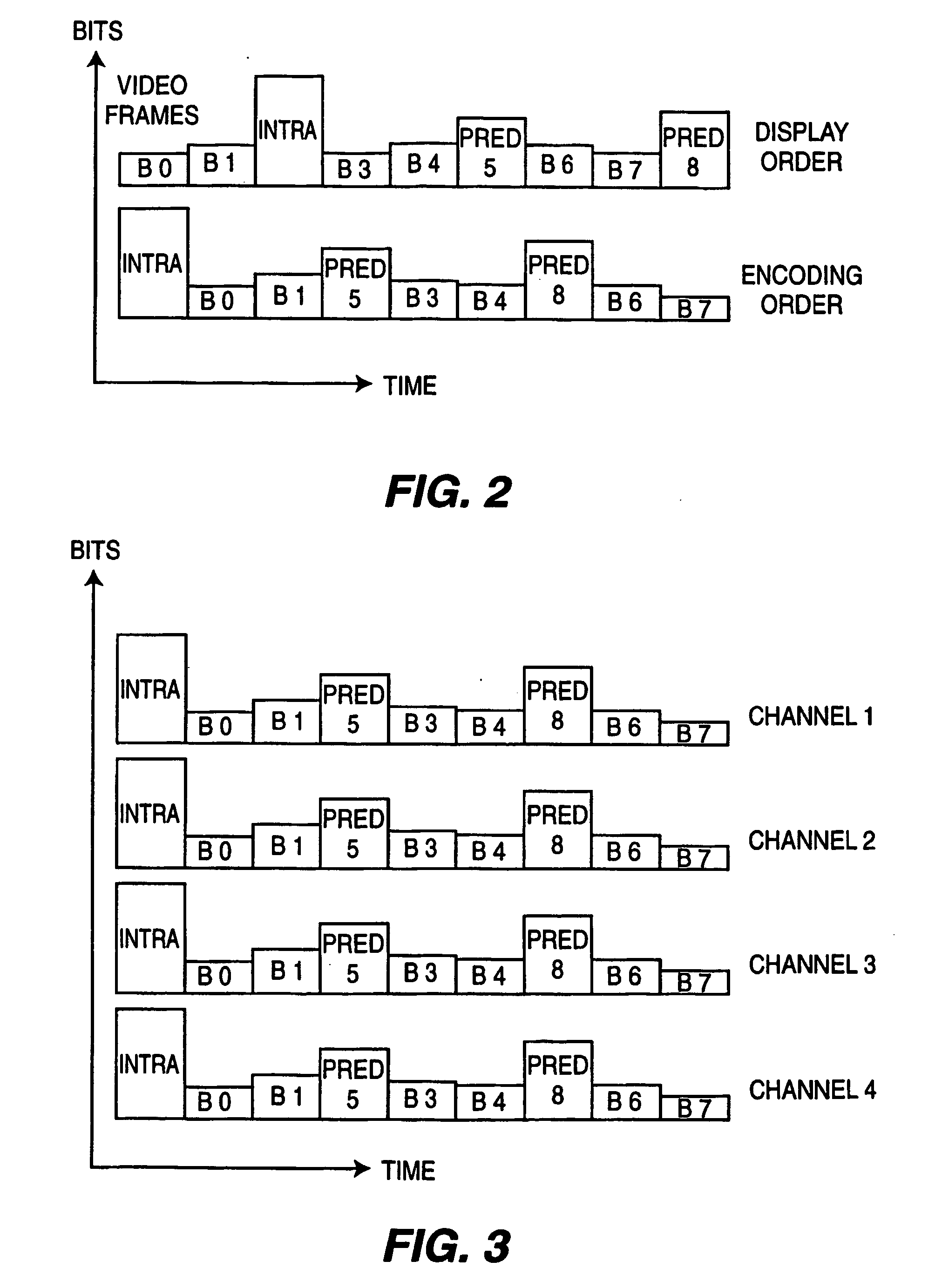

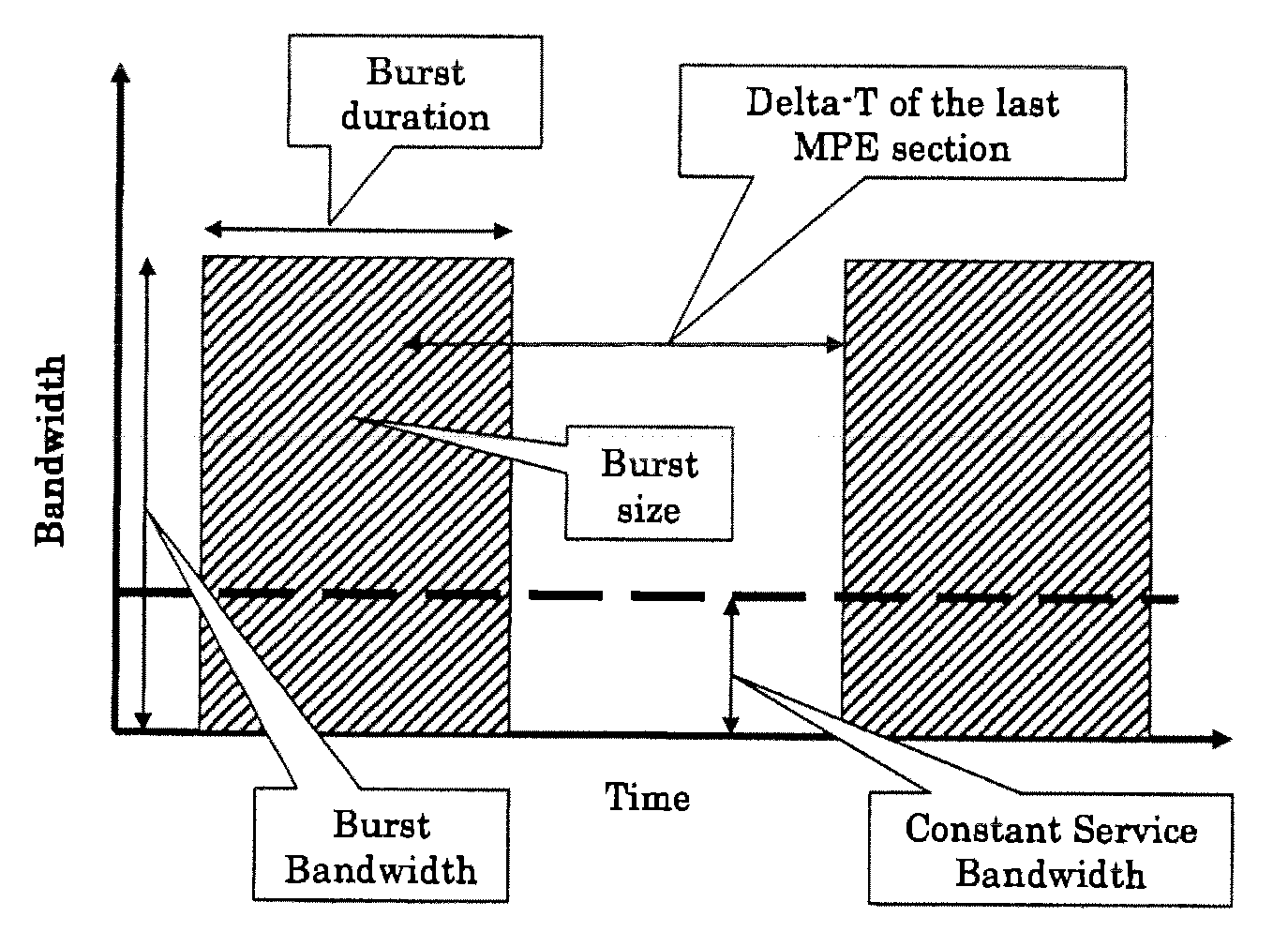

Method and system for staggered statistical multiplexing

ActiveUS20060018379A1Equally distributedPulse modulation television signal transmissionPicture reproducers using cathode ray tubesMultiplexingVideo transmission

In a multi-channel video transmission system in which channel video segments are operated on by corresponding channel video encoders to encode the video segments into frames organized into groups of defined frame types, an apparatus and method to cause a temporal staggering for the processing of a specific frame type among the various channels. In one preferred embodiment, the apparatus includes a frame counter to synchronize reset signals associated with the corresponding channel video encoders and a means for providing a timing offset to channel video encoders corresponding to a selected frame stagger for a particular corresponding channel.

Owner:INTERDIGITAL CE PATENT HLDG

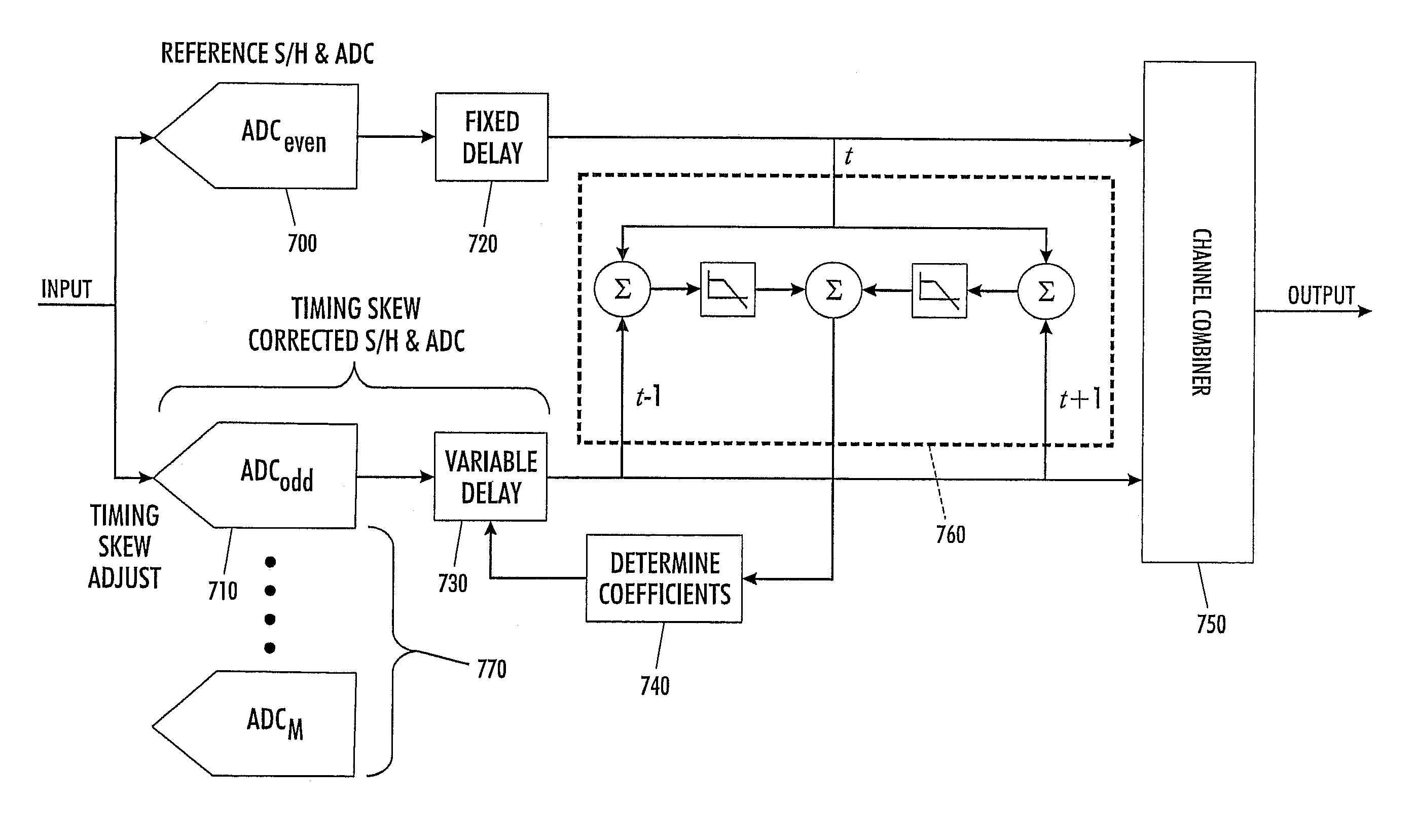

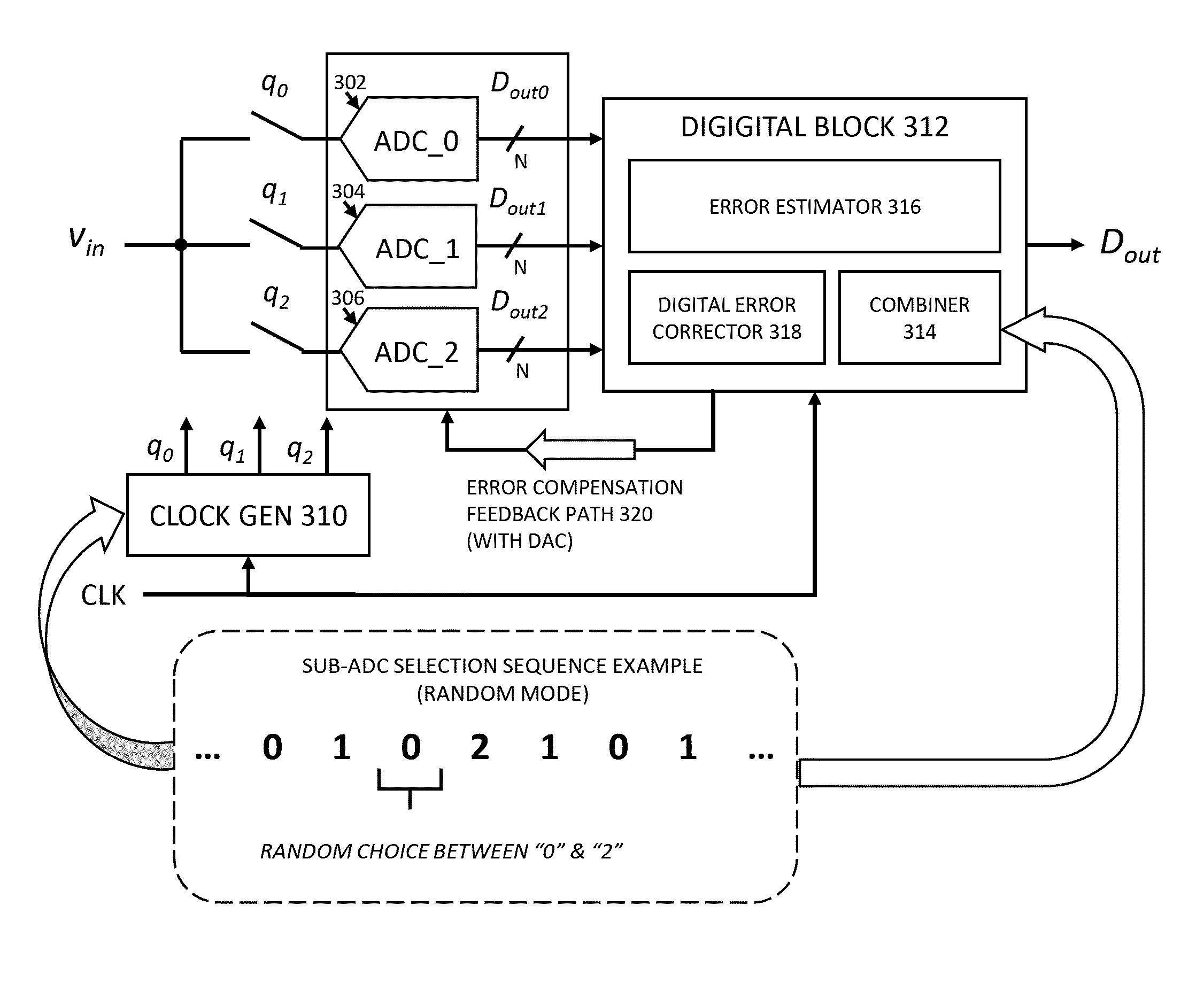

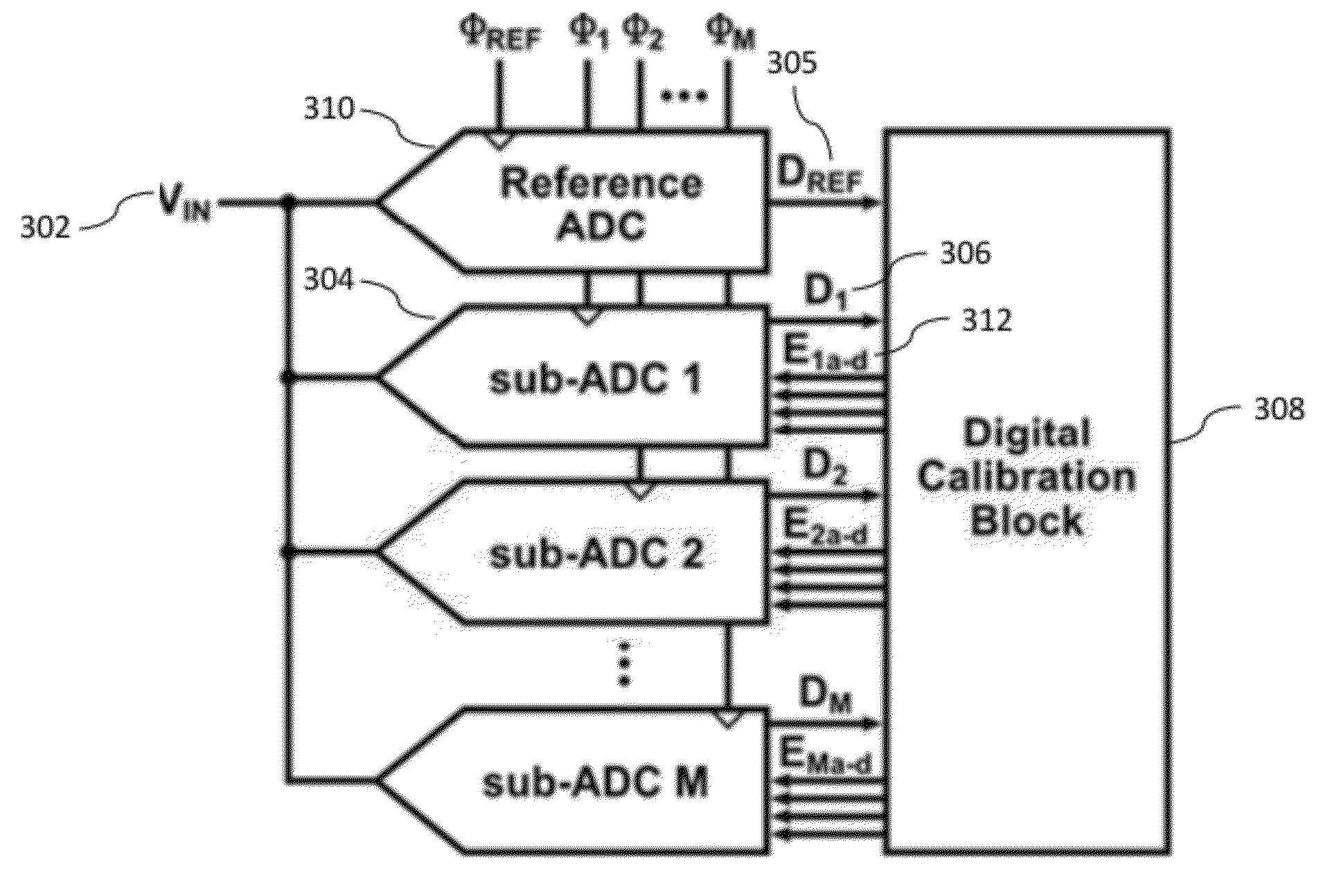

System and method for using timing skew estimation with a non-sequential time-interleaved analog-to-digital converter

ActiveUS7250885B1Electric signal transmission systemsAnalogue-digital convertersDigital down converterTime interleaved

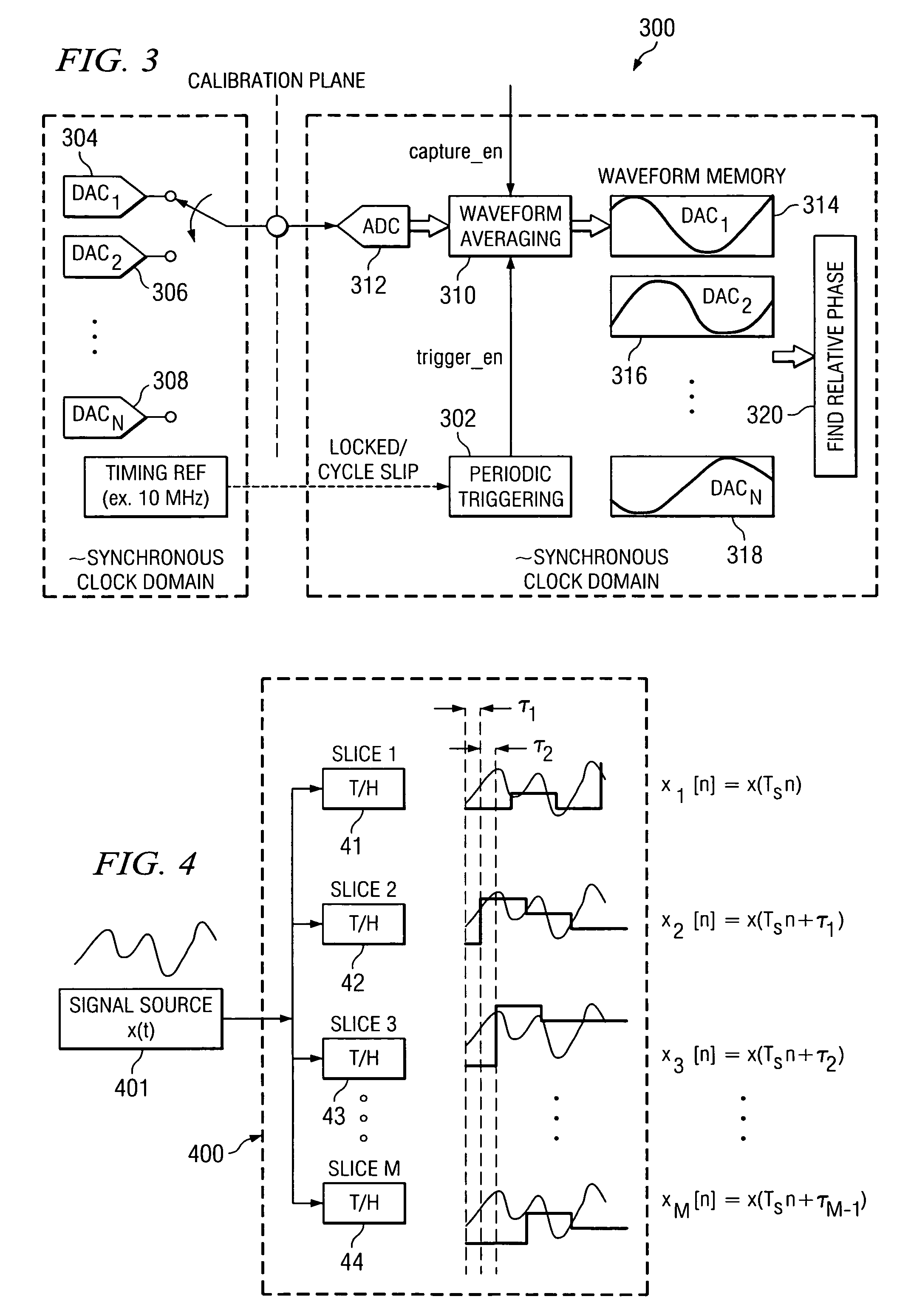

A multi-channel analog-to-digital converter system includes an array of sub-analog-to-digital converters wherein within the array of sub-analog-to-digital converters, there is at least one designated reference analog-to-digital converter. The analog-to-digital converter system also includes a non-sequential channel select circuit to control a selection of the analog-to-digital converters and the reference analog-to-digital converter to non-sequentially interleave the outputs of said analog-to-digital converters and said reference analog-to-digital converter. Each channel of the plurality of sub-analog-to-digital converters includes a timing skew estimation circuit. Each timing skew estimation circuit receives an output signal from the reference analog-to-digital converter and receives the output signal from the associated analog-to-digital converter. Each timing skew estimation circuit generates a timing signal to be used in shifting or adjusting the actual or apparent sample times for the appropriate analog-to-digital converter.

Owner:ANALOG DEVICES INC

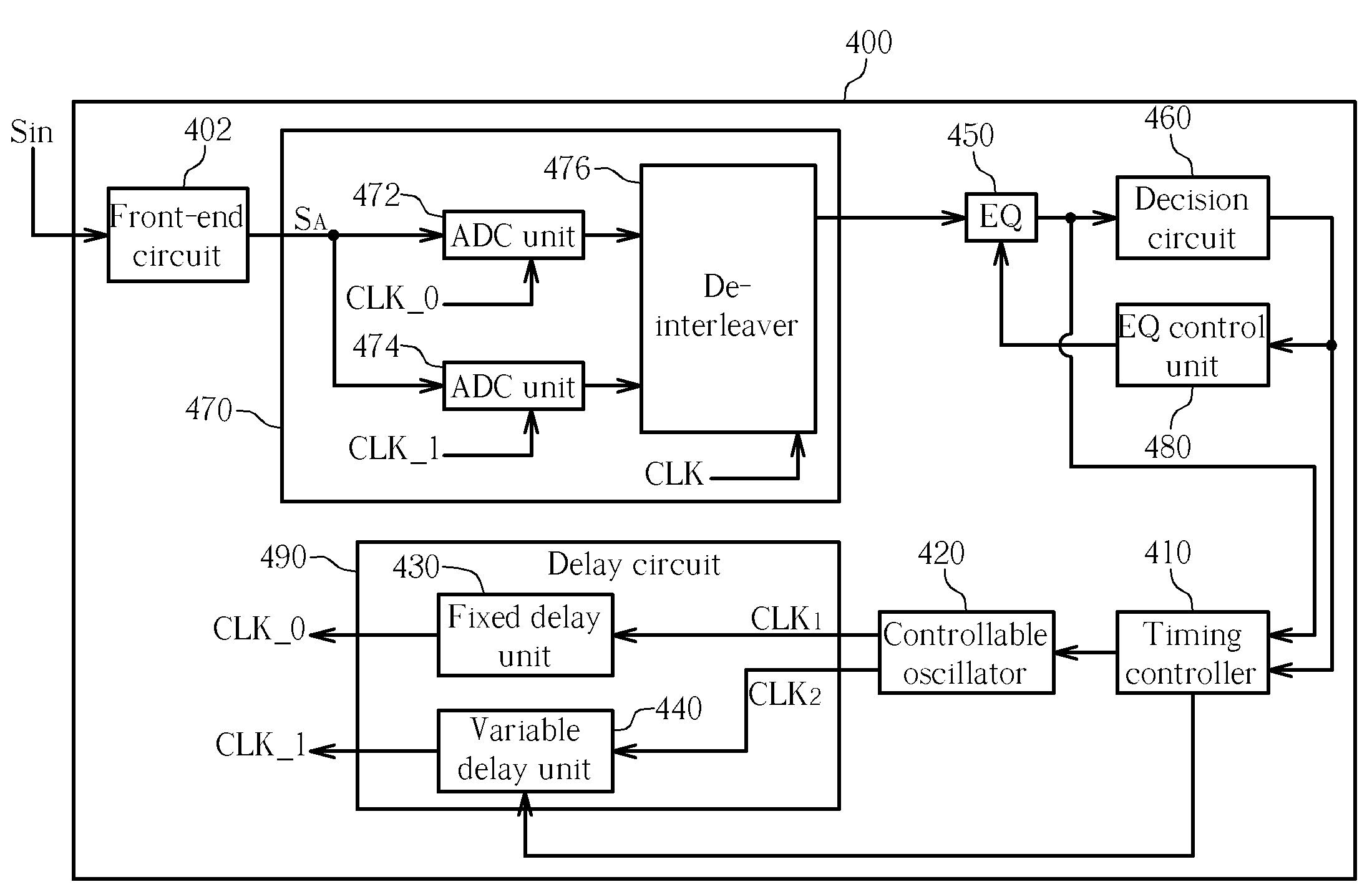

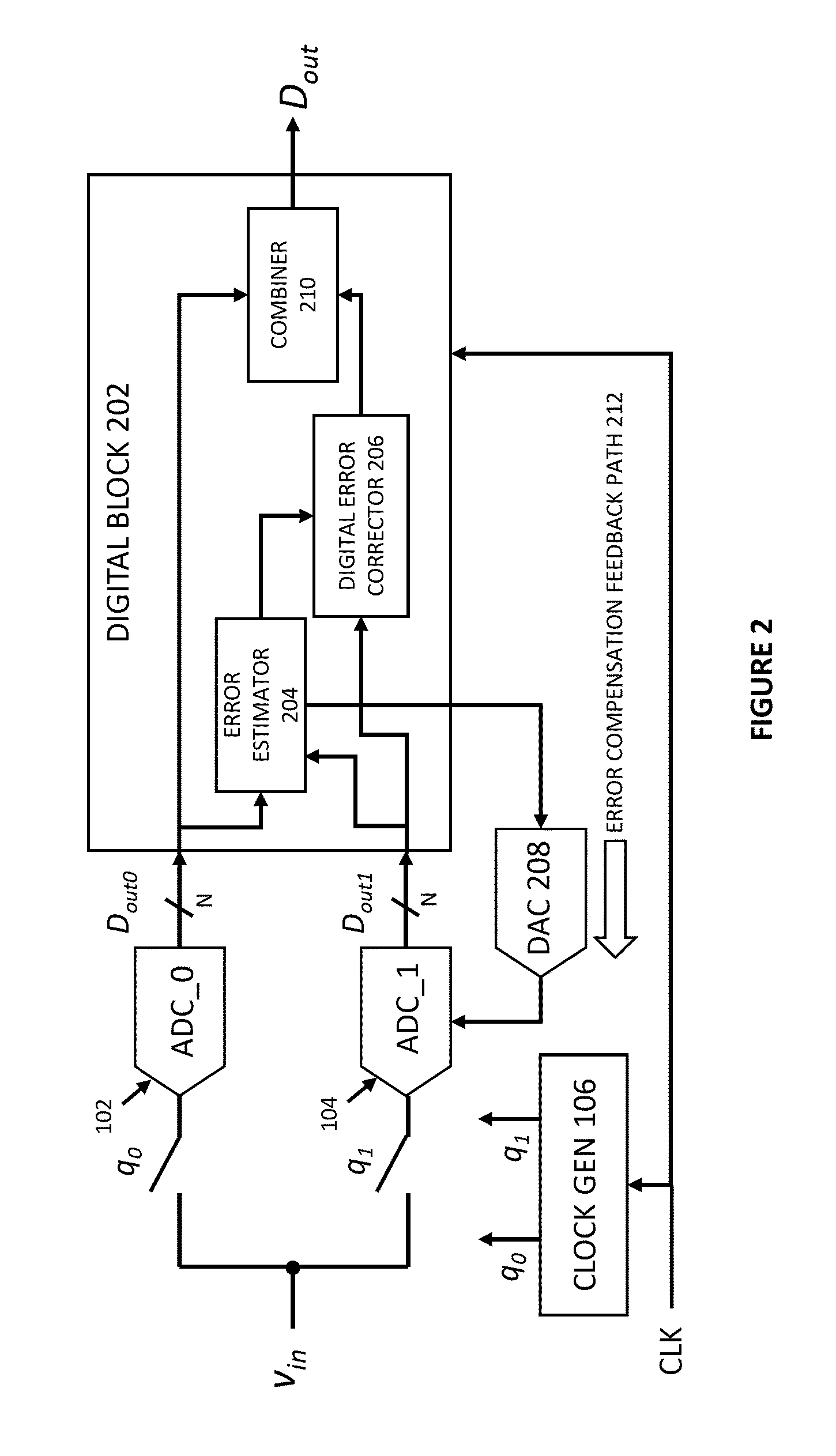

Receiver capable of correcting mismatch of time-interleaved parallel ADC and method thereof

ActiveUS7233270B2Electric signal transmission systemsPhysical parameters compensation/preventionTime interleavedAnalog-to-digital converter

A compensation method for a receiver is disclosed, the method includes: receiving and processing an incoming signal to generate an analog input signal; utilizing a time-interleaved parallel analog-to-digital converter (ADC) for converting the analog input signal to a digital input signal according to a plurality of clock signals of different phases; equalizing the digital input signal to generate a plurality of soft decision values; generating a plurality of hard decision values according to the soft decision values; calculating a plurality of error values according to the hard decision values and the soft decision values; and compensating the receiver according to at least part of the error values.

Owner:REALTEK SEMICON CORP

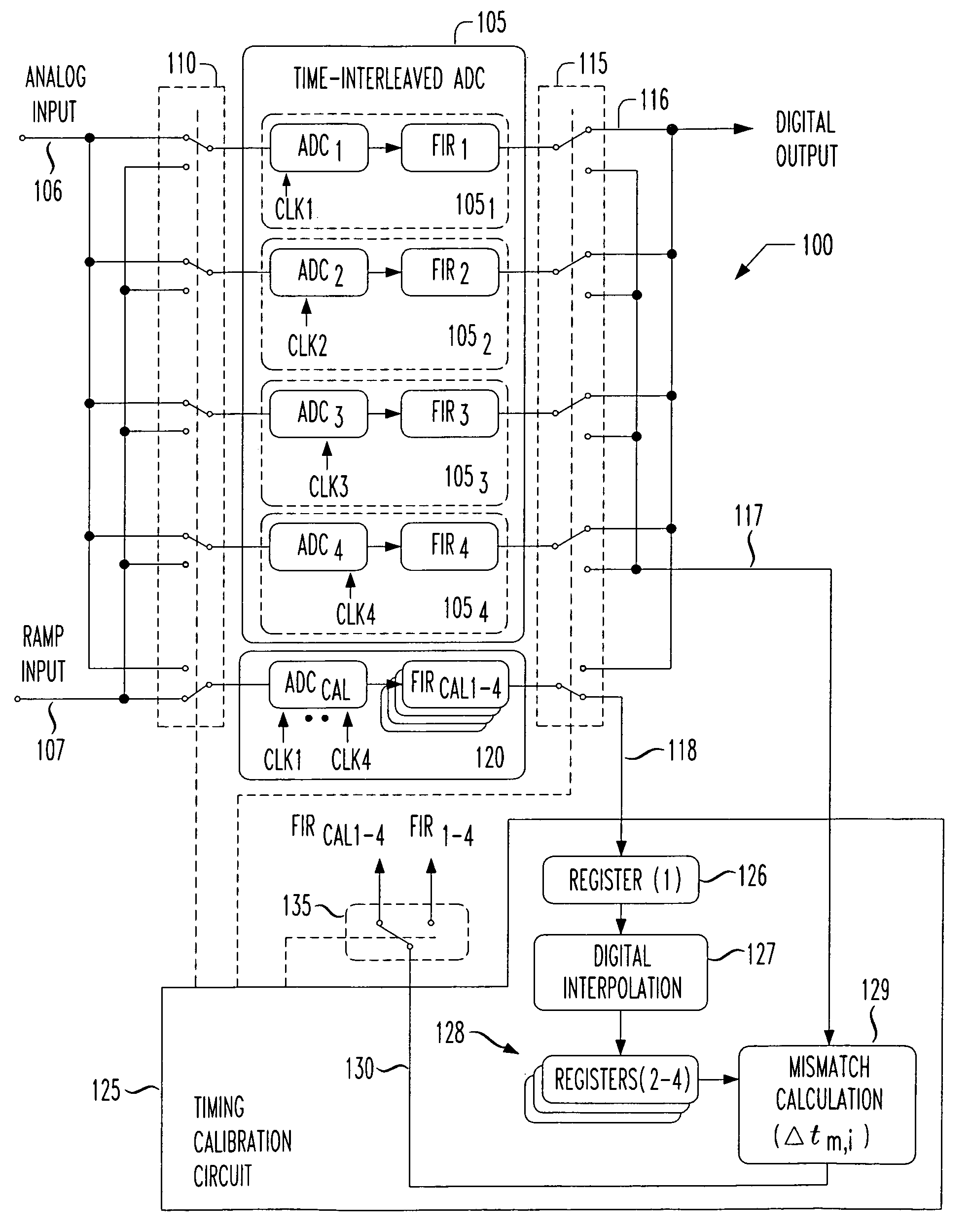

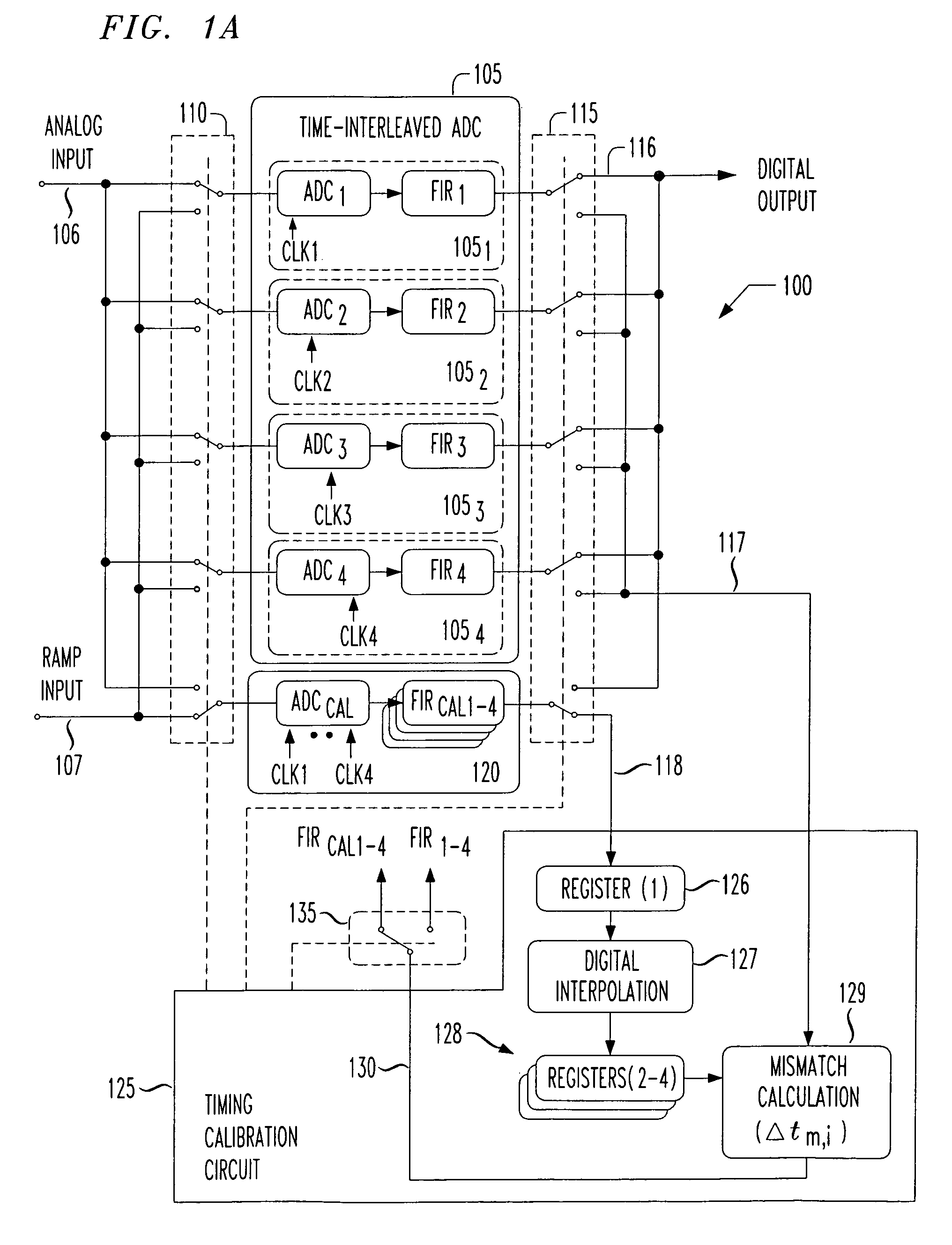

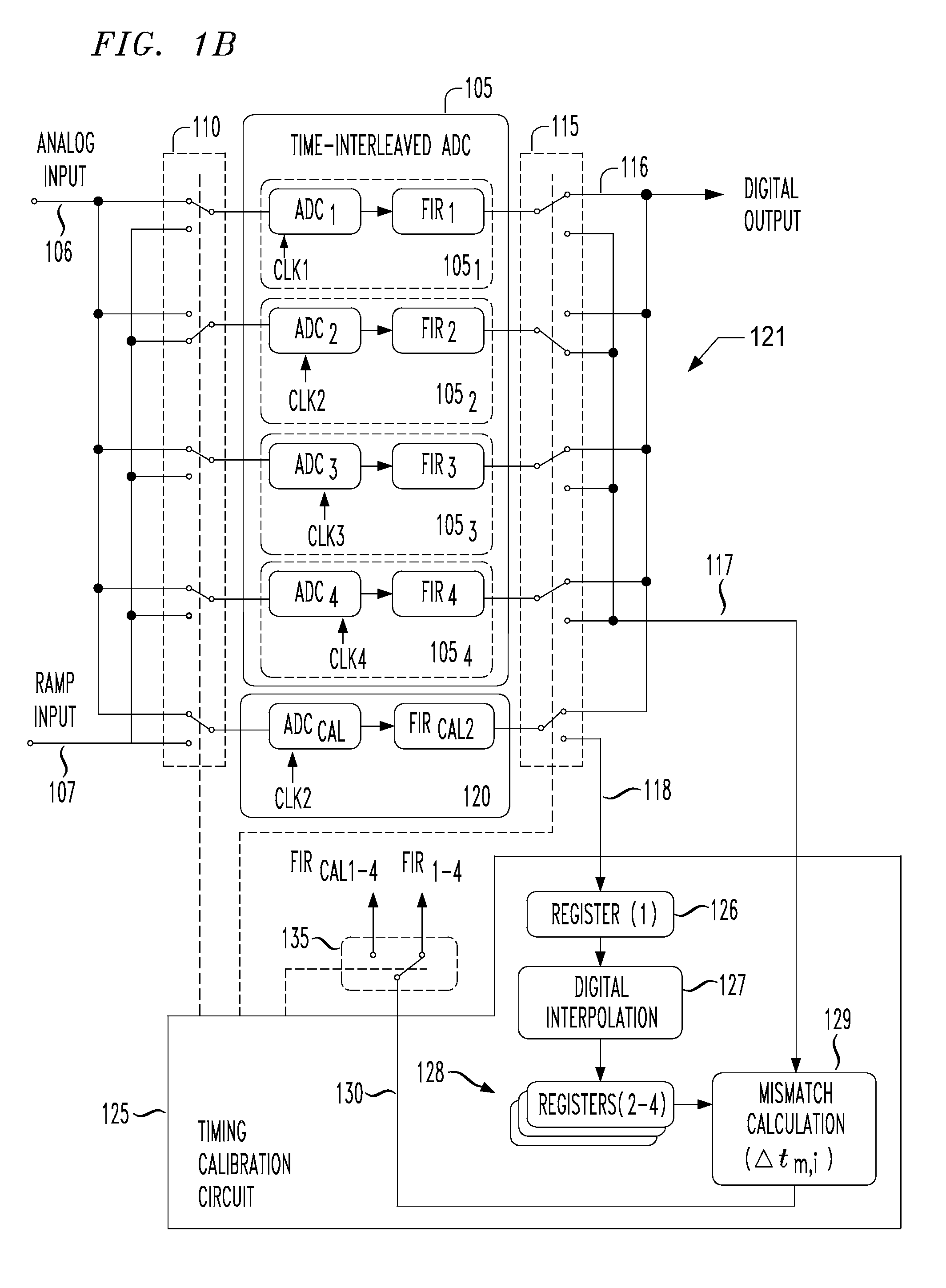

Digital background calibration for time-interlaced analog-to-digital converters

ActiveUS7227479B1Shorten the timeElectric signal transmission systemsAnalogue-digital convertersTime interleavedDigital converter

The present invention provides for background calibration of a time-interleaved analog-to-digital converter (TIADC). In one embodiment, a background calibrator includes a TIADC having a parallel array of time-interleaved main signal processors, each main signal processor including an ADC connected to a corresponding output FIR filter. The background calibrator also includes an auxiliary signal processor having an ADC connected to at least one corresponding output FIR filter. Additionally, the background calibrator further includes a timing calibration circuit, wherein the timing calibration circuit is configured to select one of the main signal processors, exchange the auxiliary signal processor with the selected main signal processor in the TIADC and connect the selected main signal processor to the timing calibration circuit. In an alternative embodiment, the timing calibration circuit is further configured to reduce a timing mismatch of the selected main signal processor.

Owner:LUCENT TECH INC

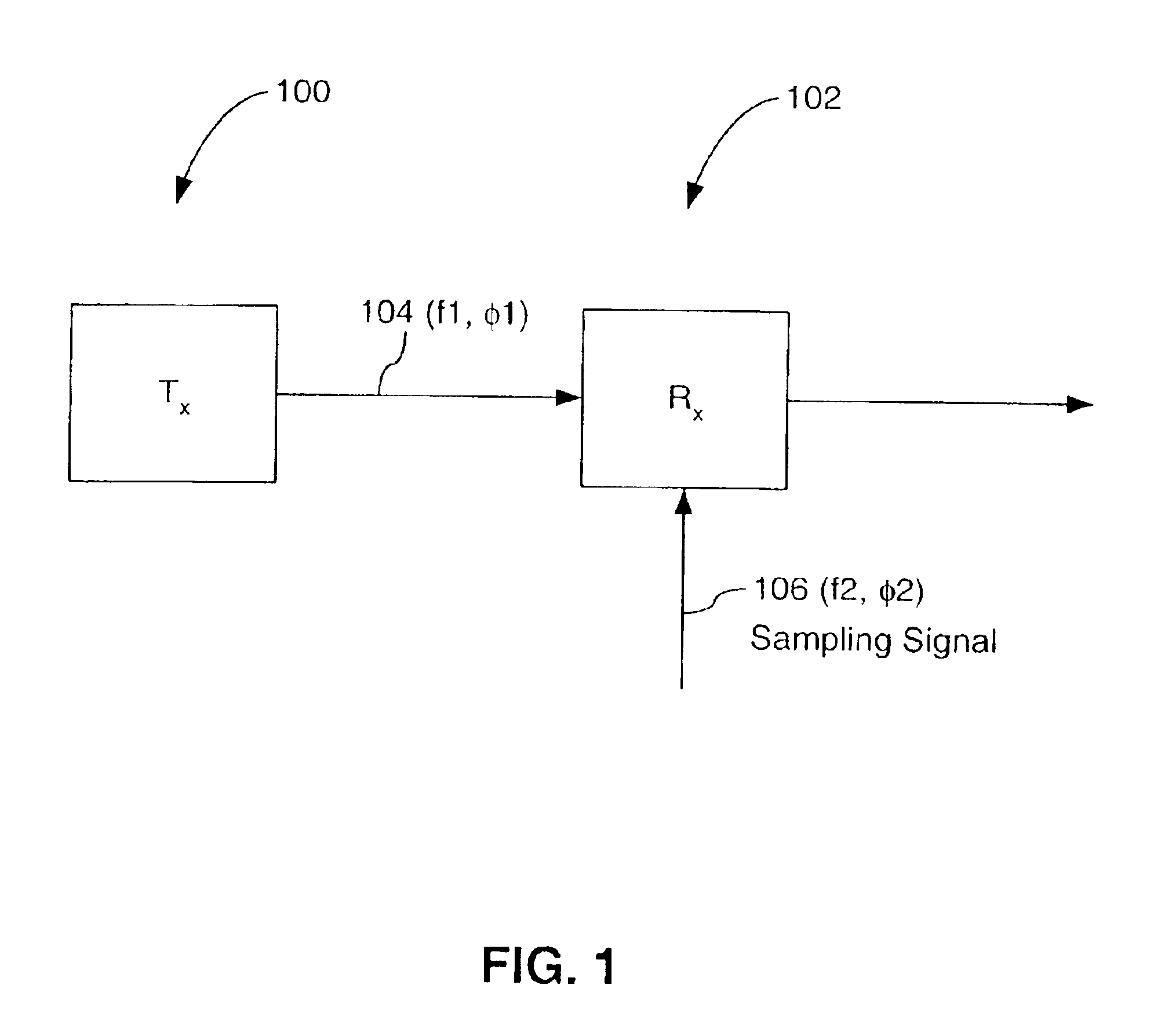

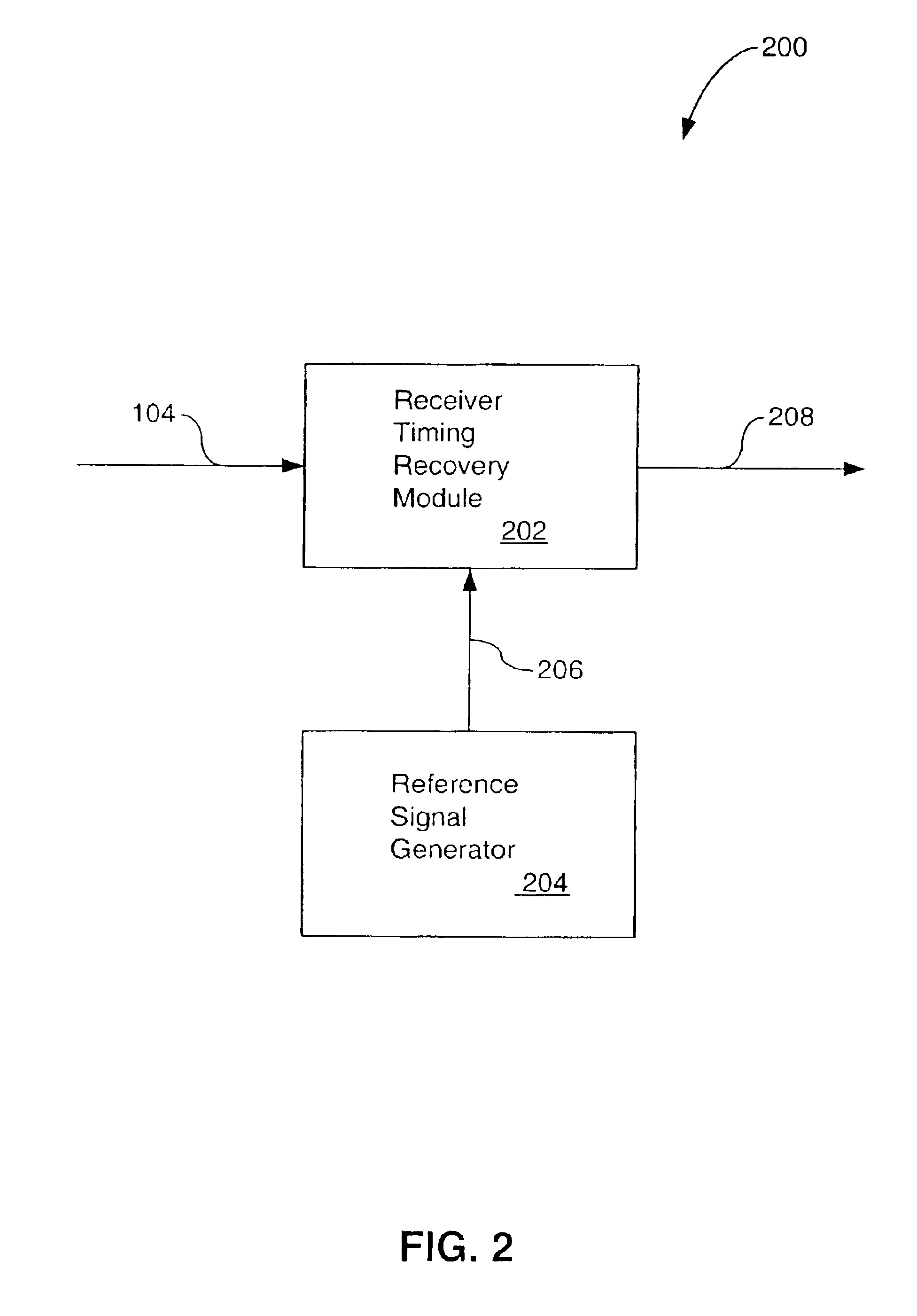

Phase interpolator device and method

InactiveUS6791388B2Reduce frequency offsetComputations using contact-making devicesPulse automatic controlTransceiverGigabit

A high-speed serial data transceiver includes multiple receivers and transmitters for receiving and transmitting multiple analog, serial data signals at multi-gigabit-per-second data rates. Each receiver includes a timing recovery system for tracking a phase and a frequency of the serial data signal associated with the receiver. The timing recovery system includes a phase interpolator responsive to phase control signals and a set of reference signals having different predetermined phases. The phase interpolator derives a sampling signal, having an interpolated phase, to sample the serial data signal. The timing recovery system in each receiver independently phase-aligns and frequency synchronizes the sampling signal to the serial data signal associated with the receiver. A receiver can include multiple paths for sampling a received, serial data signal in accordance with multiple time-staggered sampling signals, each having an interpolated phase.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

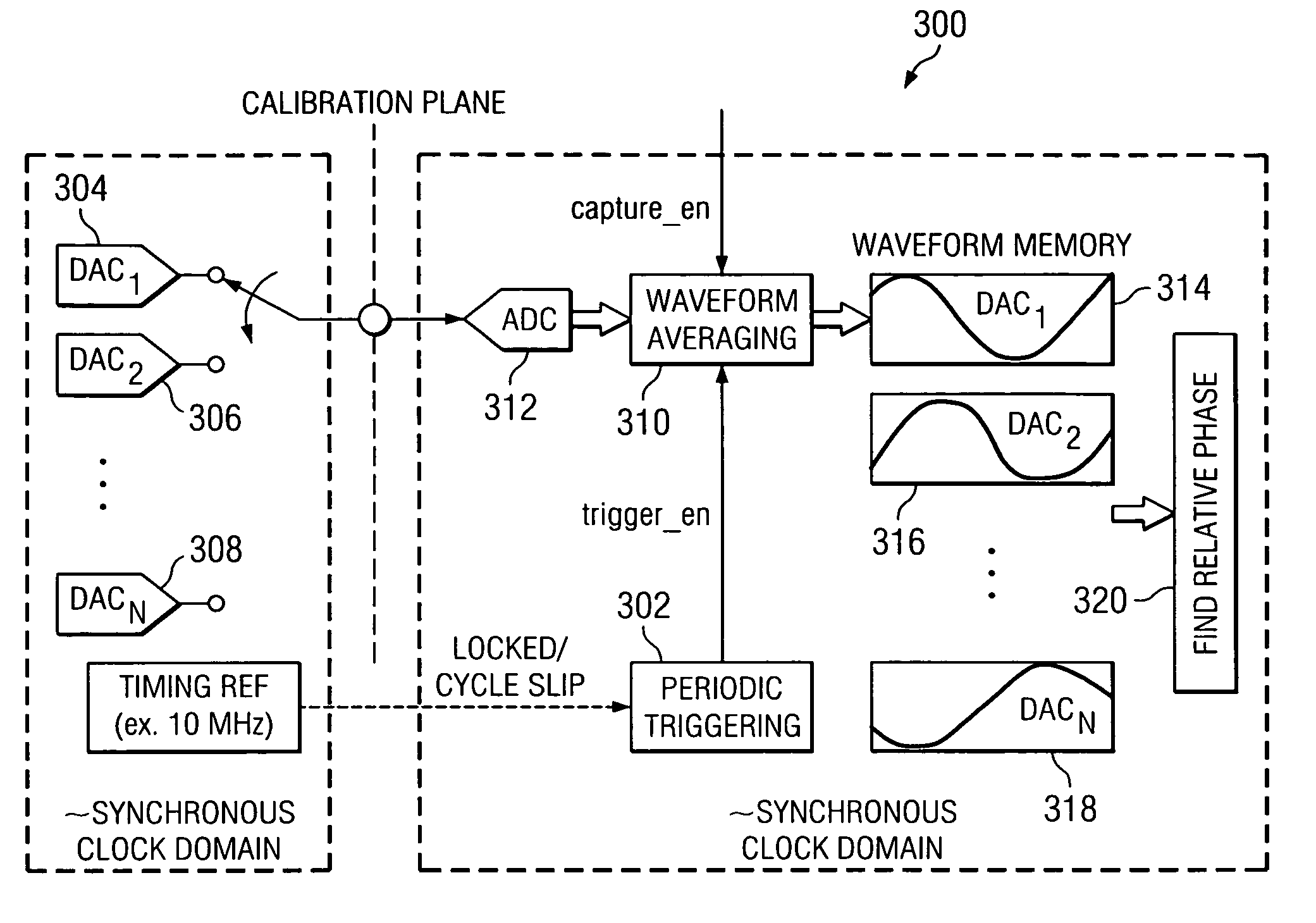

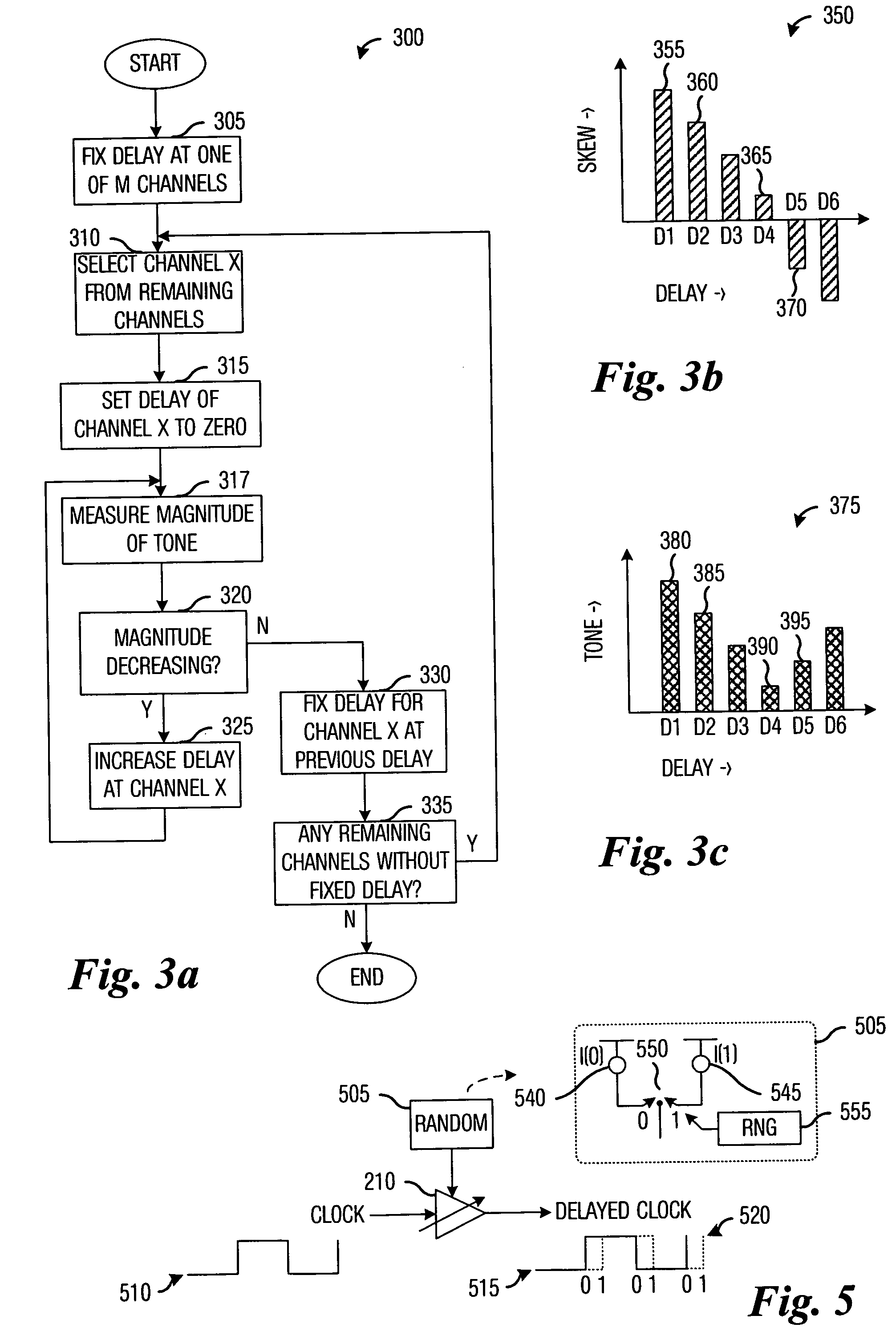

System and method for timing calibration of time-interleaved data converters

ActiveUS7148828B2Reduce supportShorten test timeElectric signal transmission systemsAnalogue/digital conversion calibration/testingFrequency spectrumTime interleaved

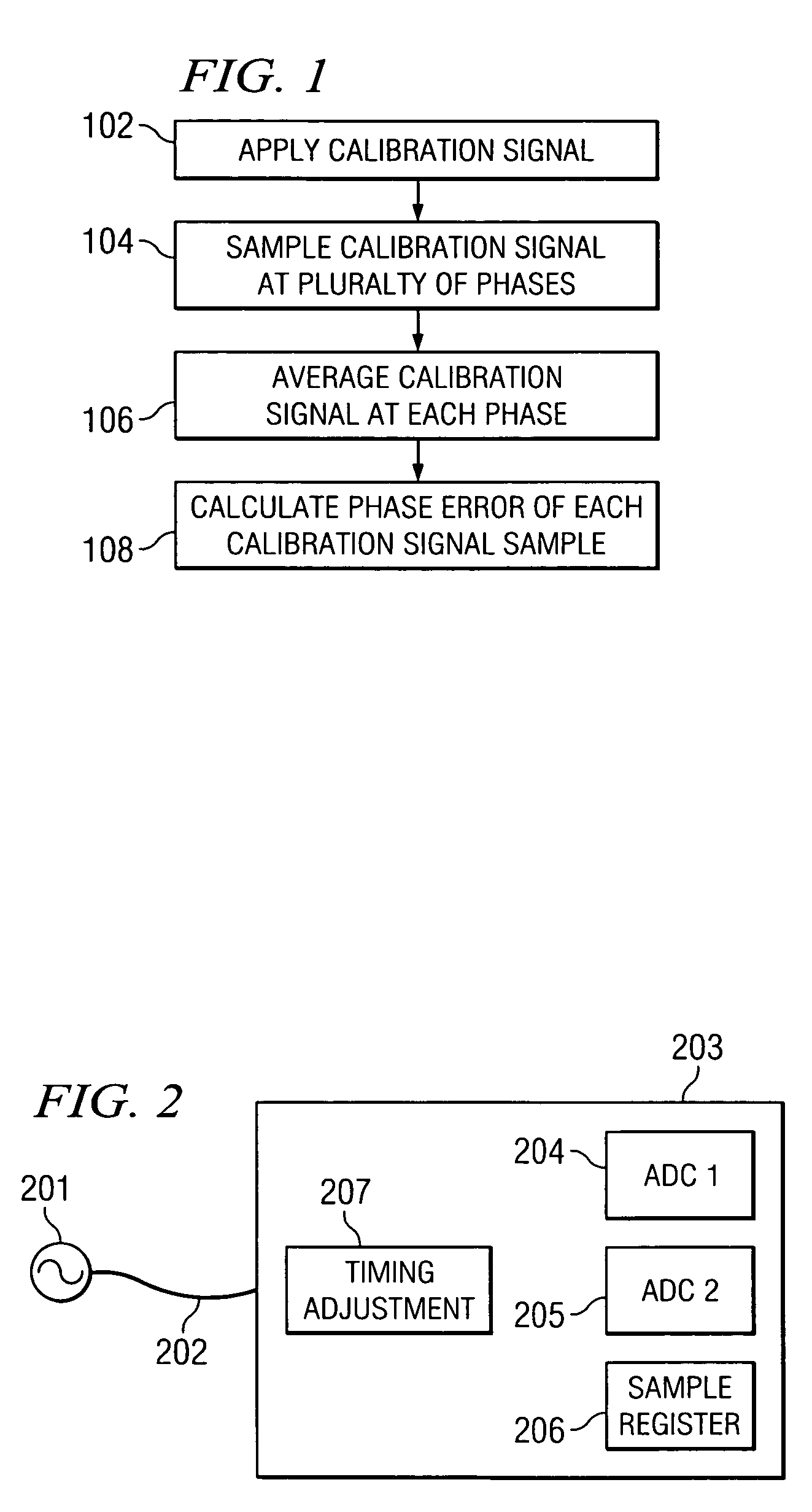

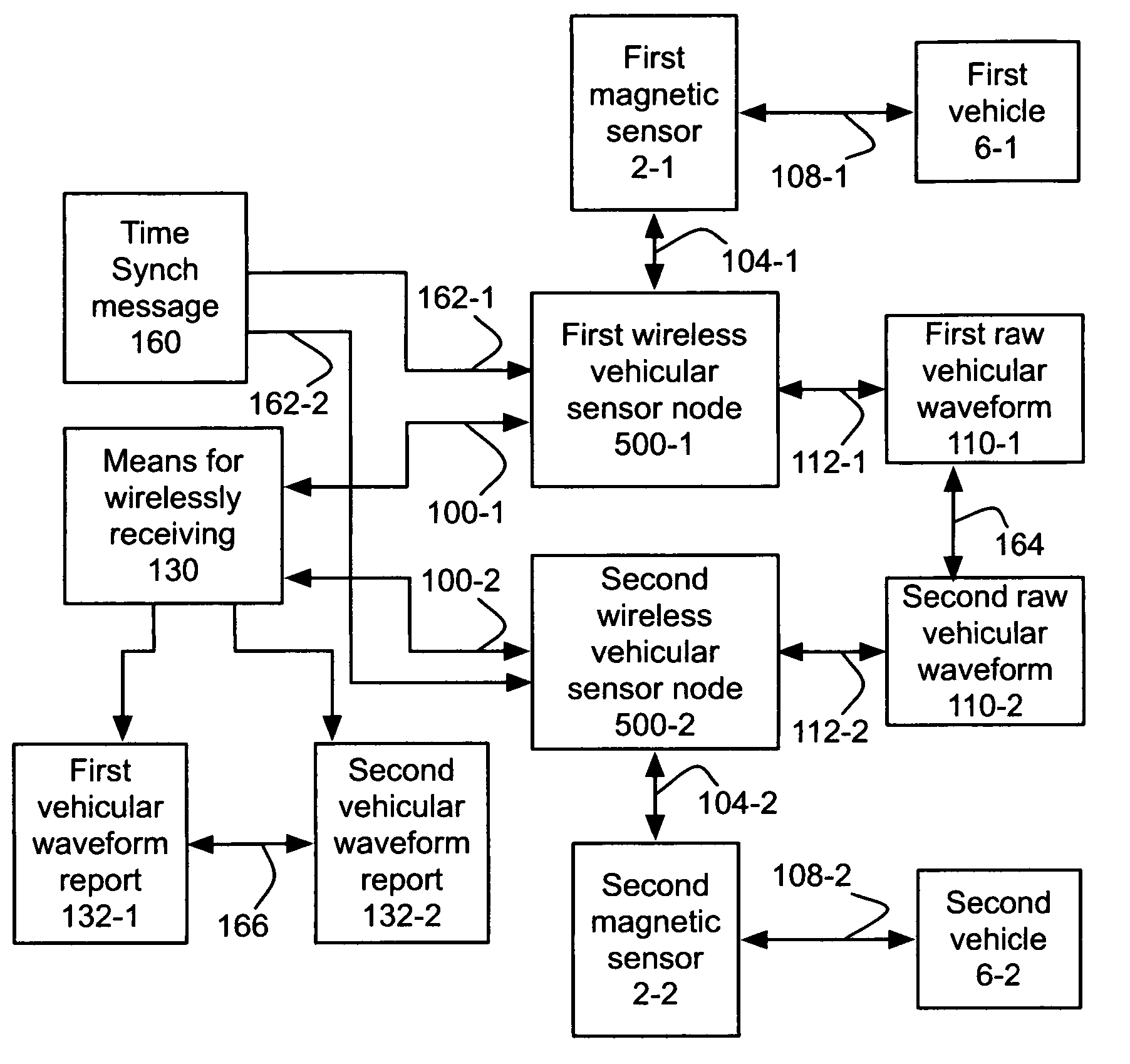

A method for calibrating time interleaved samplers comprising applying a calibration signal to a time-interleaved sampling device, wherein the signal is coherent with at least one sample clock on the device and is periodic and has a predetermined spectral content and frequency, sampling, by said time-interleaved sampling device, the calibration signal at a plurality of phases to form samples, averaging the formed samples, and calculating the phase error of each sample based on the average calibration signal sample.

Owner:KEYSIGHT TECH

Method and apparatus reporting a vehicular sensor waveform in a wireless vehicular sensor network

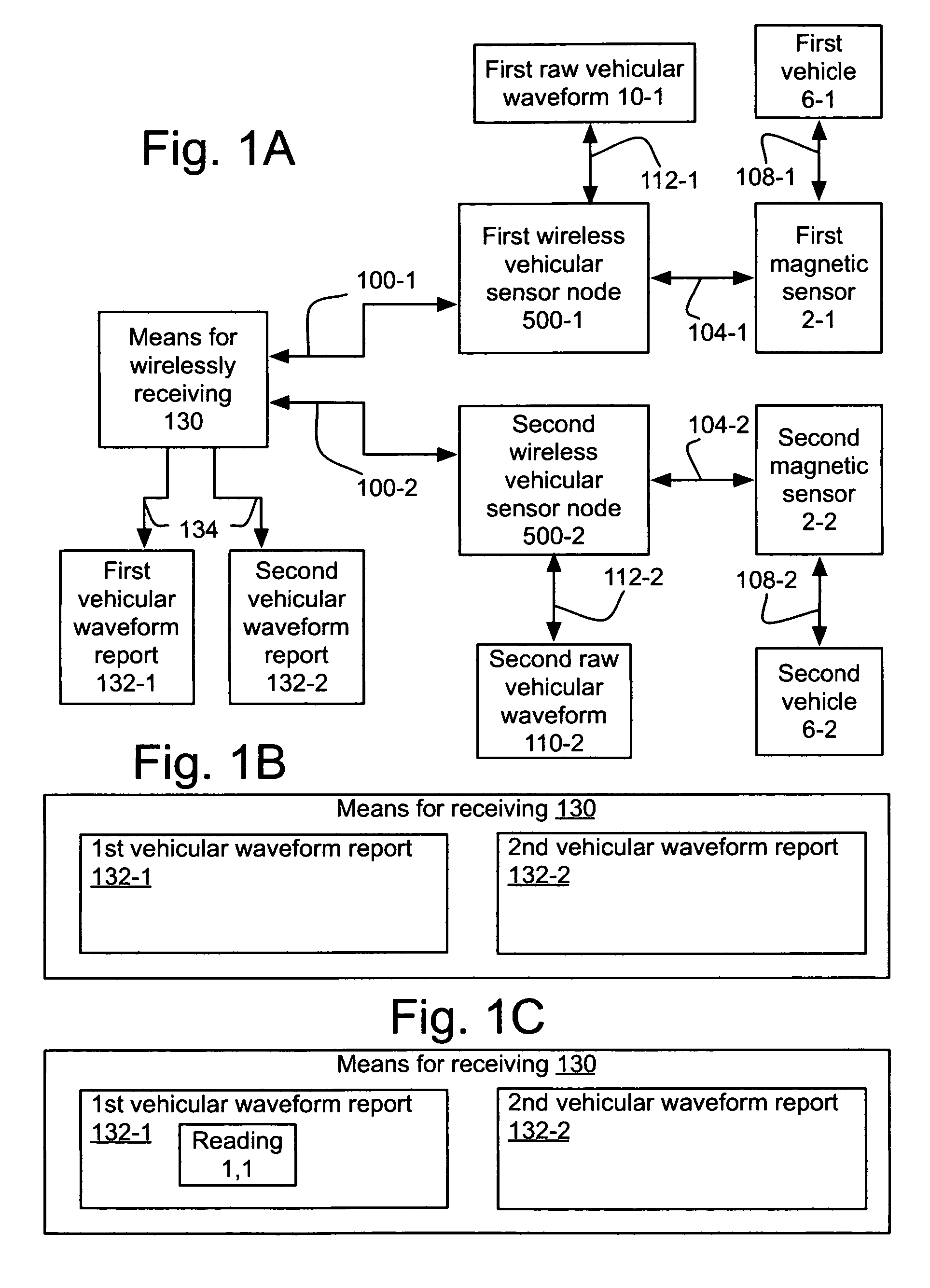

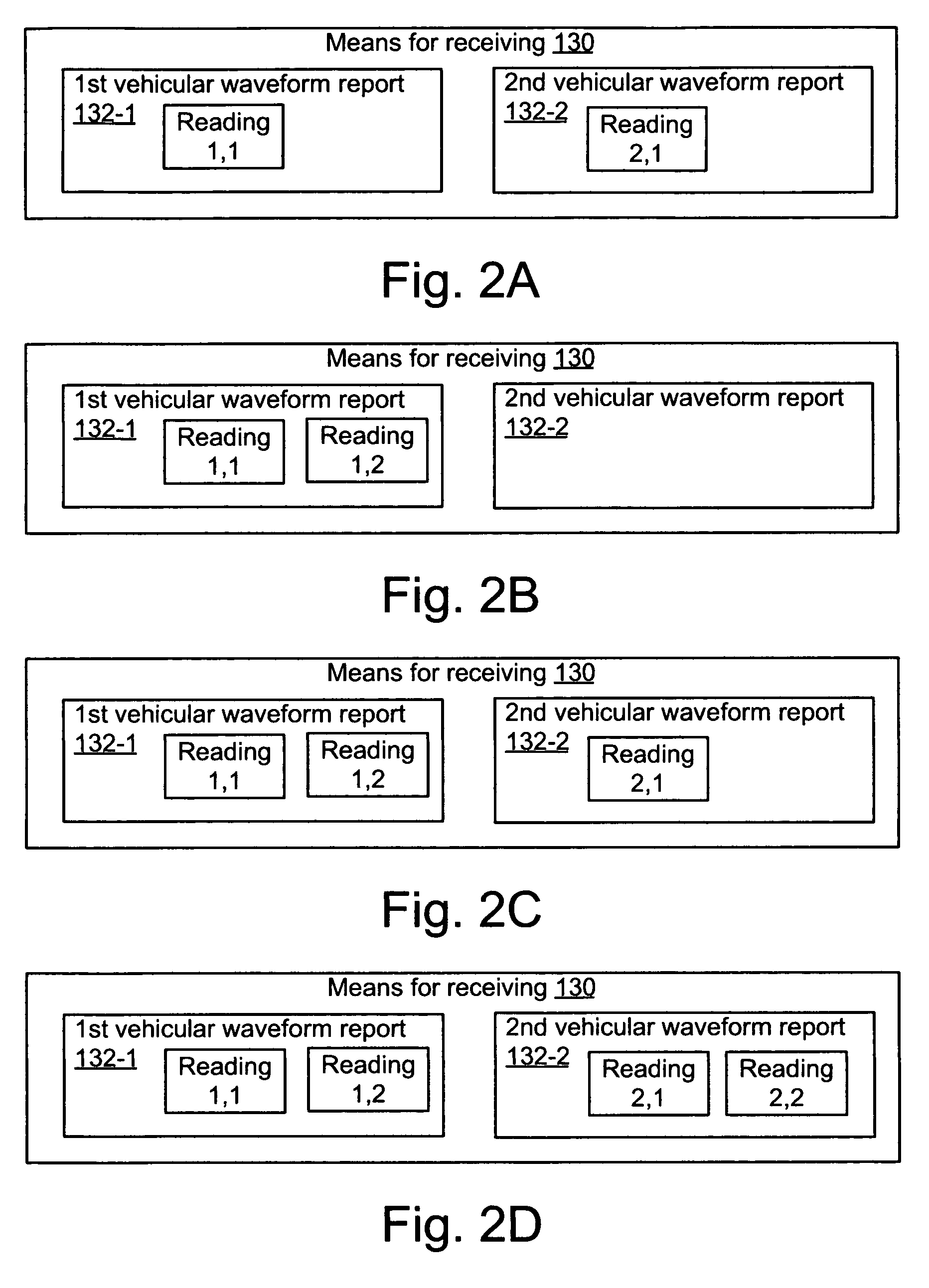

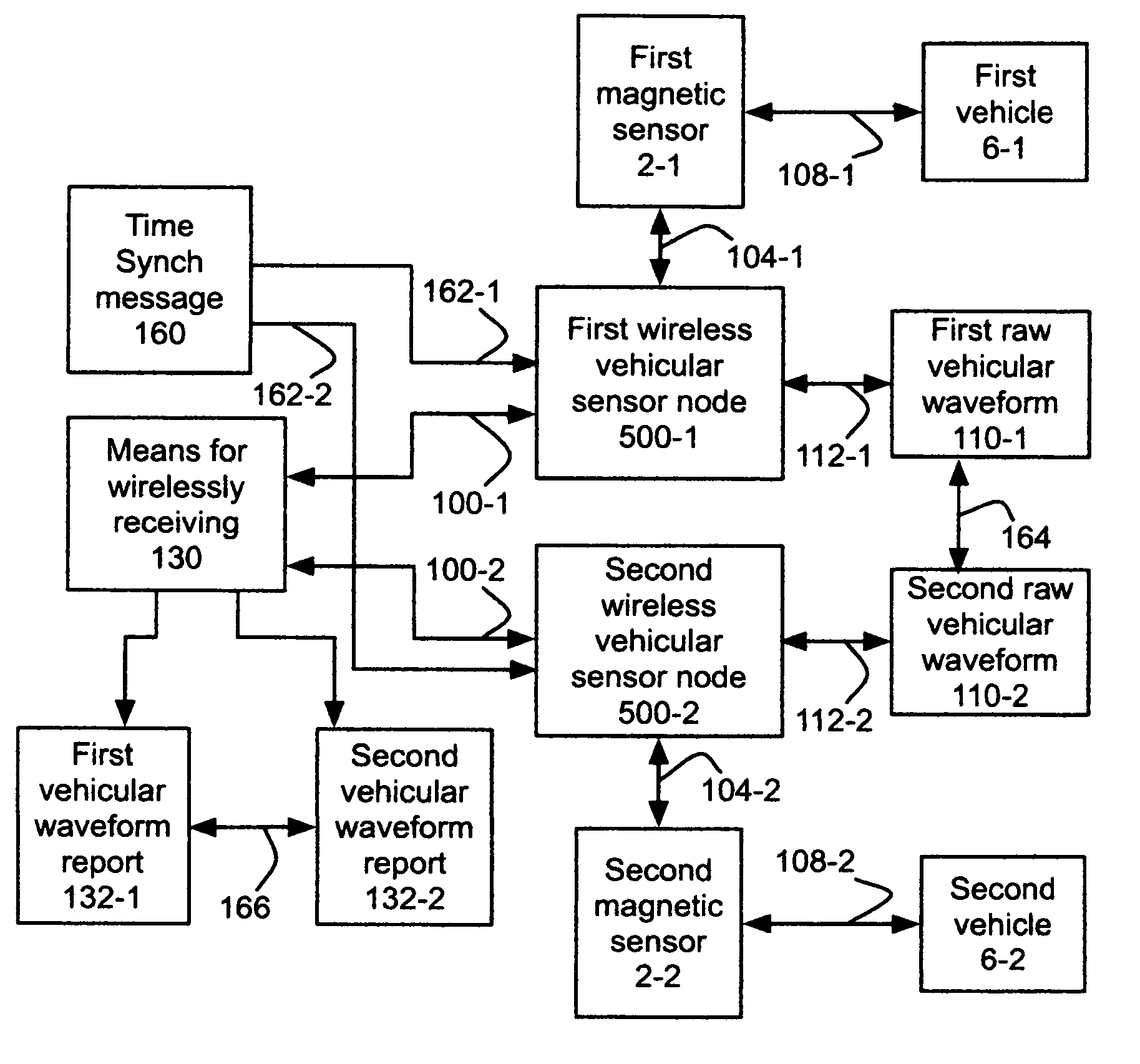

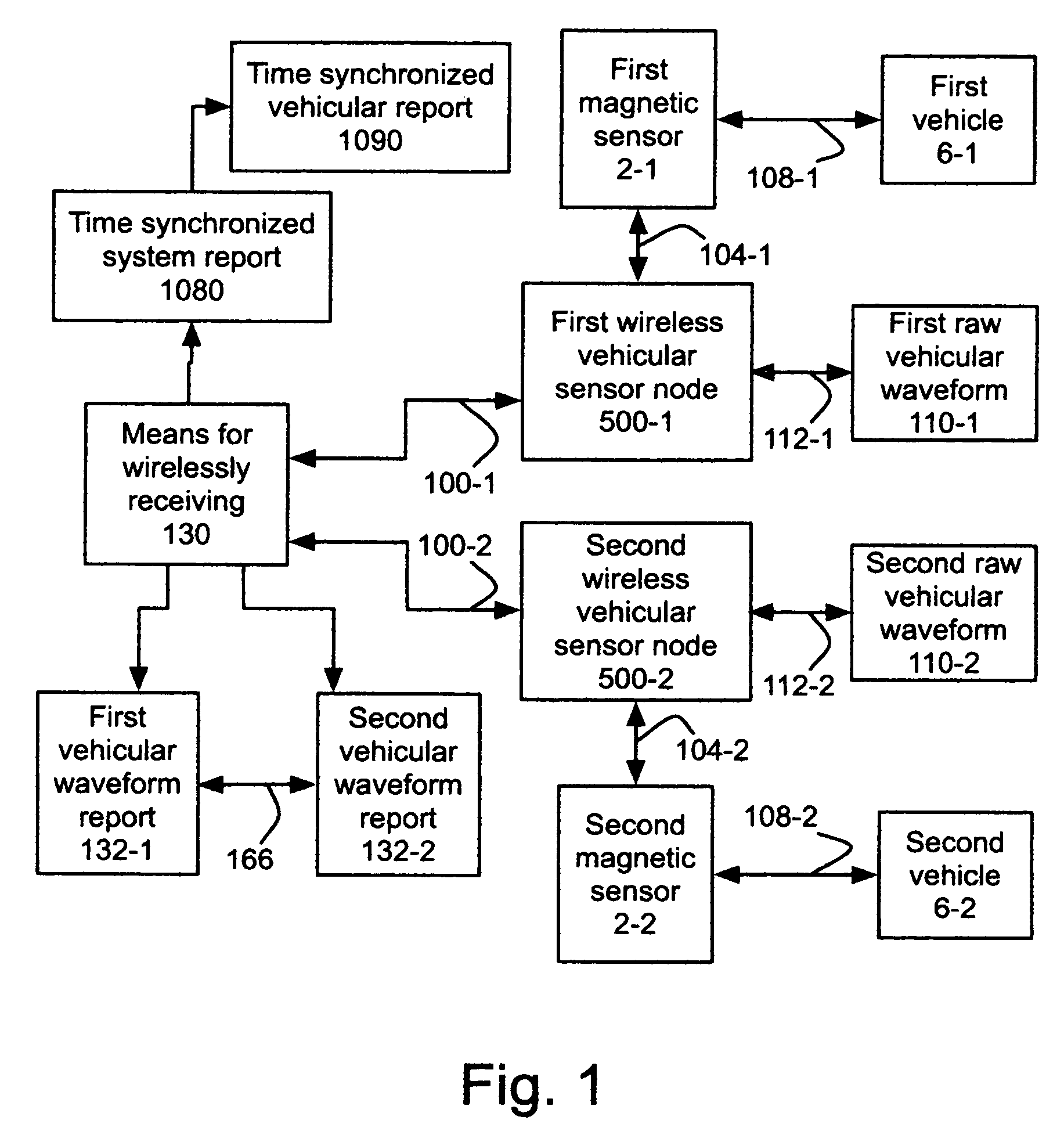

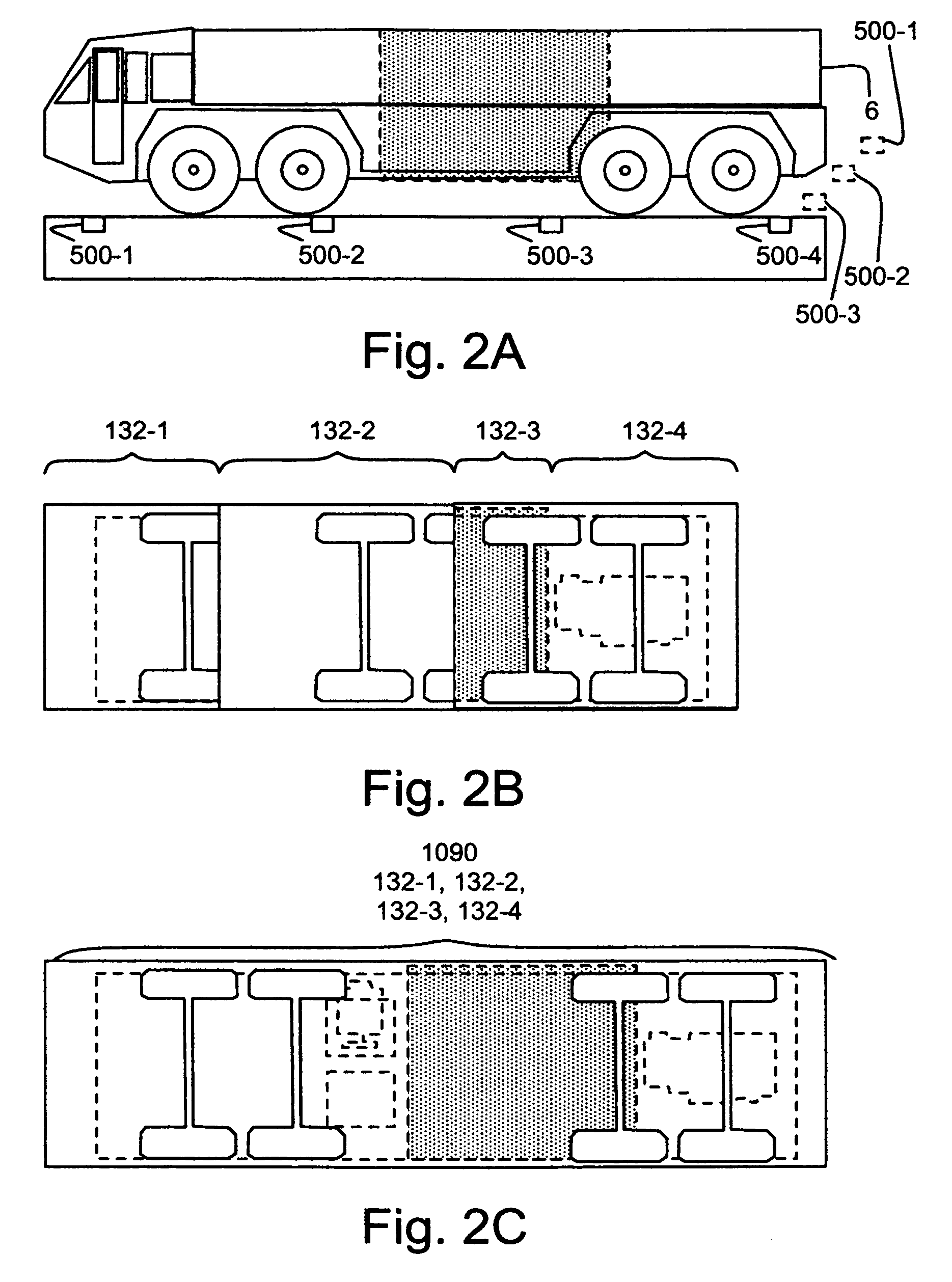

The invention includes using multiple wireless vehicular sensor nodes to wirelessly receive multiple, time-interleaved vehicular waveform reports from the nodes. Each vehicular waveform report approximates a raw vehicular sensor waveform observed by a magnetic sensor at the node based upon the presence of a vehicle. The vehicular waveform reports are products of this wirelessly receiving process. The invention includes apparatus supporting the above outlined process. The vehicular waveform reports may be time synchronized.

Owner:SENSYS NETWORKS

Timing enhancement methods and networks for time-interleaved analog-to-digital systems

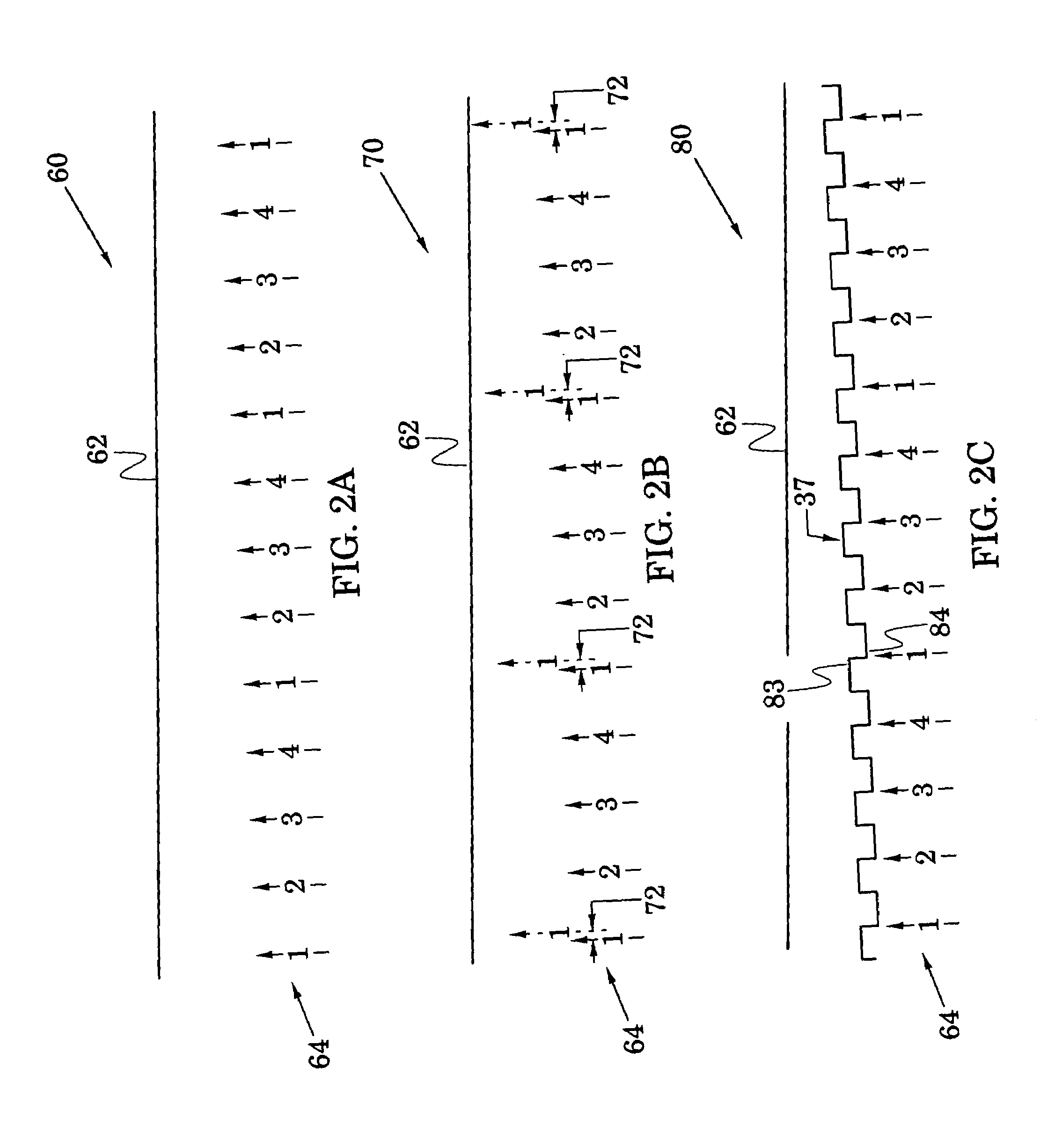

ActiveUS6982664B1Electric signal transmission systemsAnalogue-digital convertersPath lengthAnalog signal

Timing enhancements of embodiments of the invention are realized in time-interleaved converter systems with minimal network additions that facilitate the insertion of a timing signal into the system's input analog signal. The timing signal travels with the input analog signal so that it continues to accurately define predetermined sample times in the analog signal even as they travel over different path lengths to individual converters. Each converter has a feedback path which adjusts the timing of that converter's samples with a correction signal whose value is determined by contributions of first and second different amplitudes of the timing signal to that converter's output signals.

Owner:ANALOG DEVICES INC

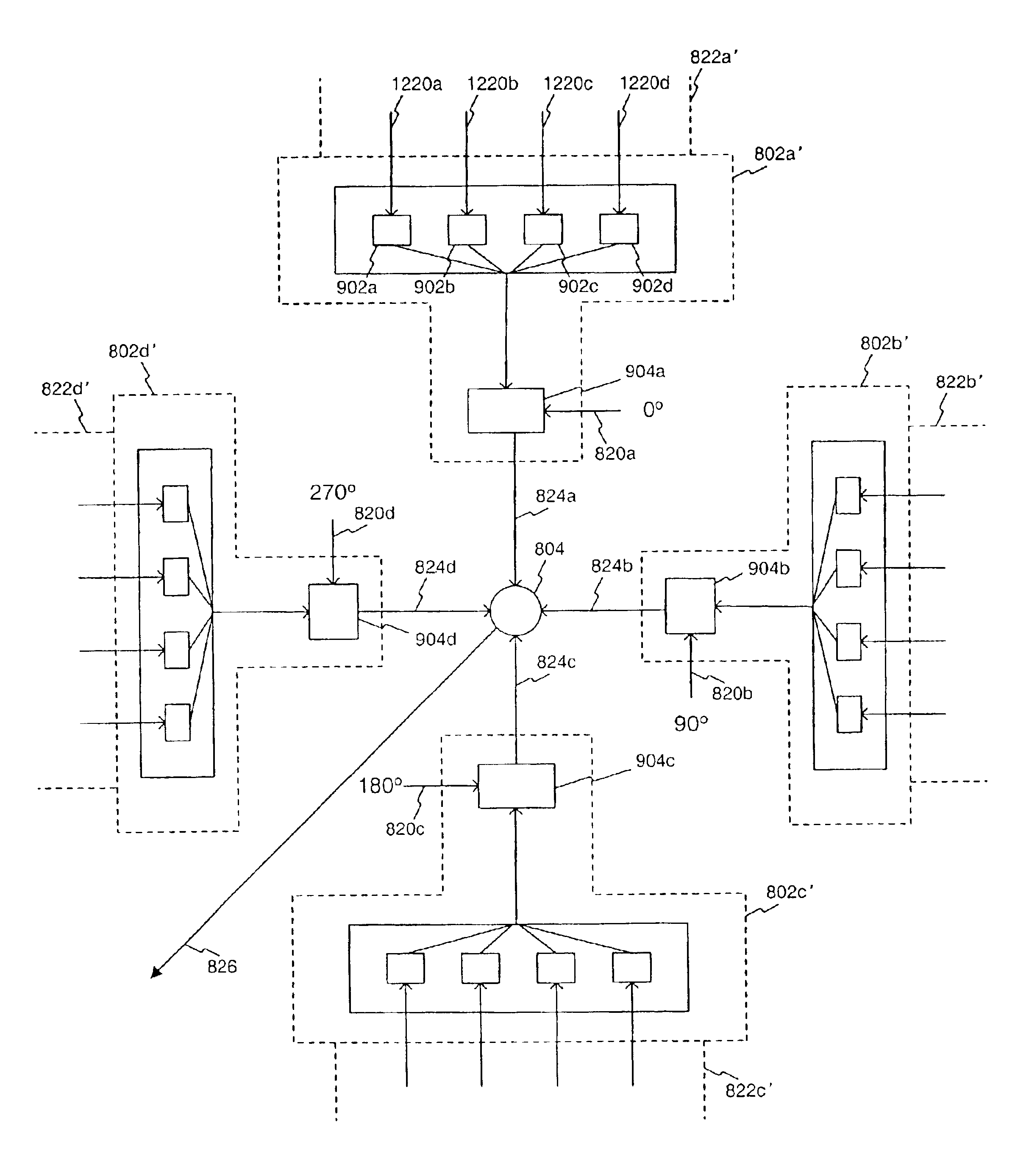

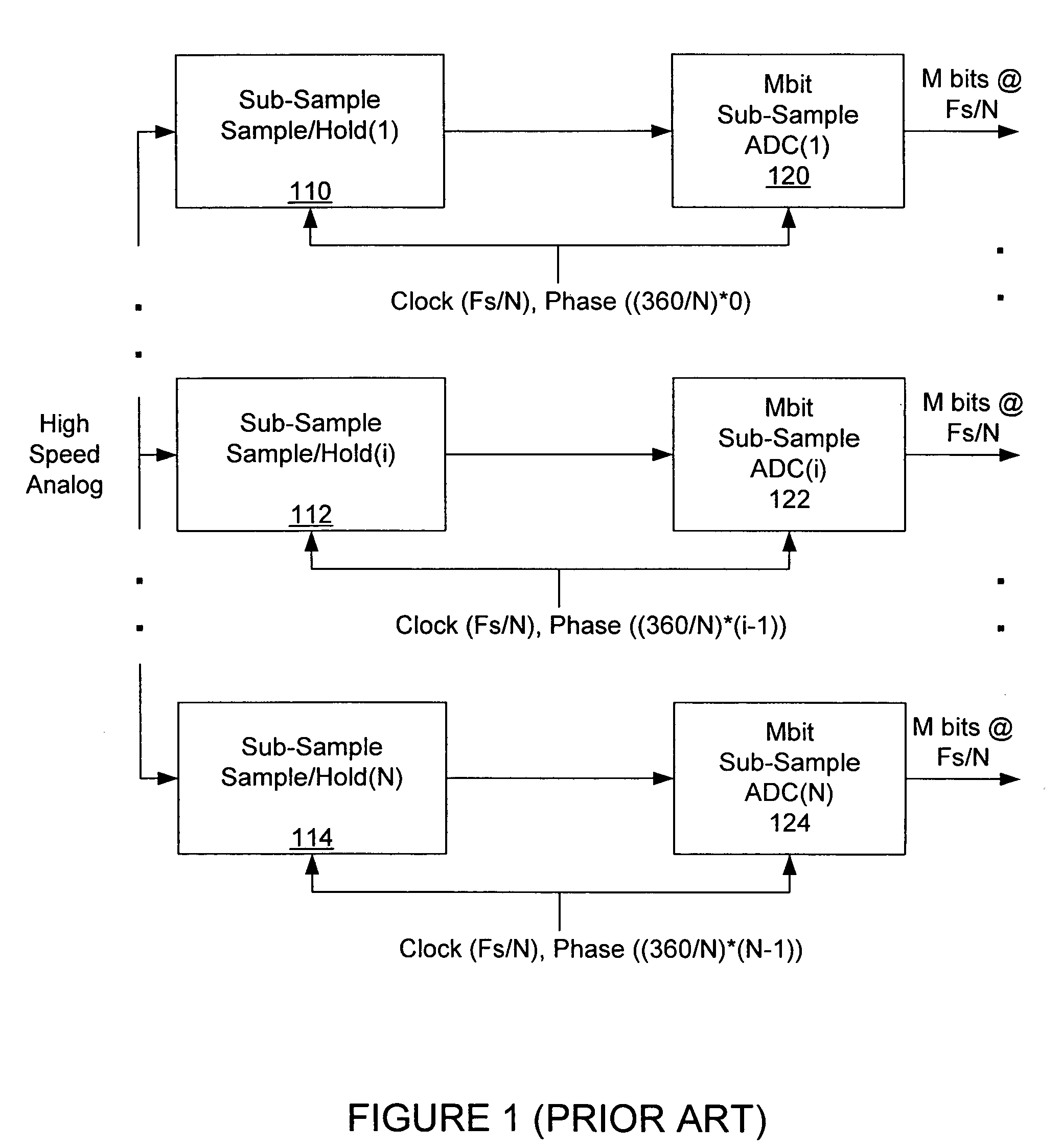

High-speed sampling architectures

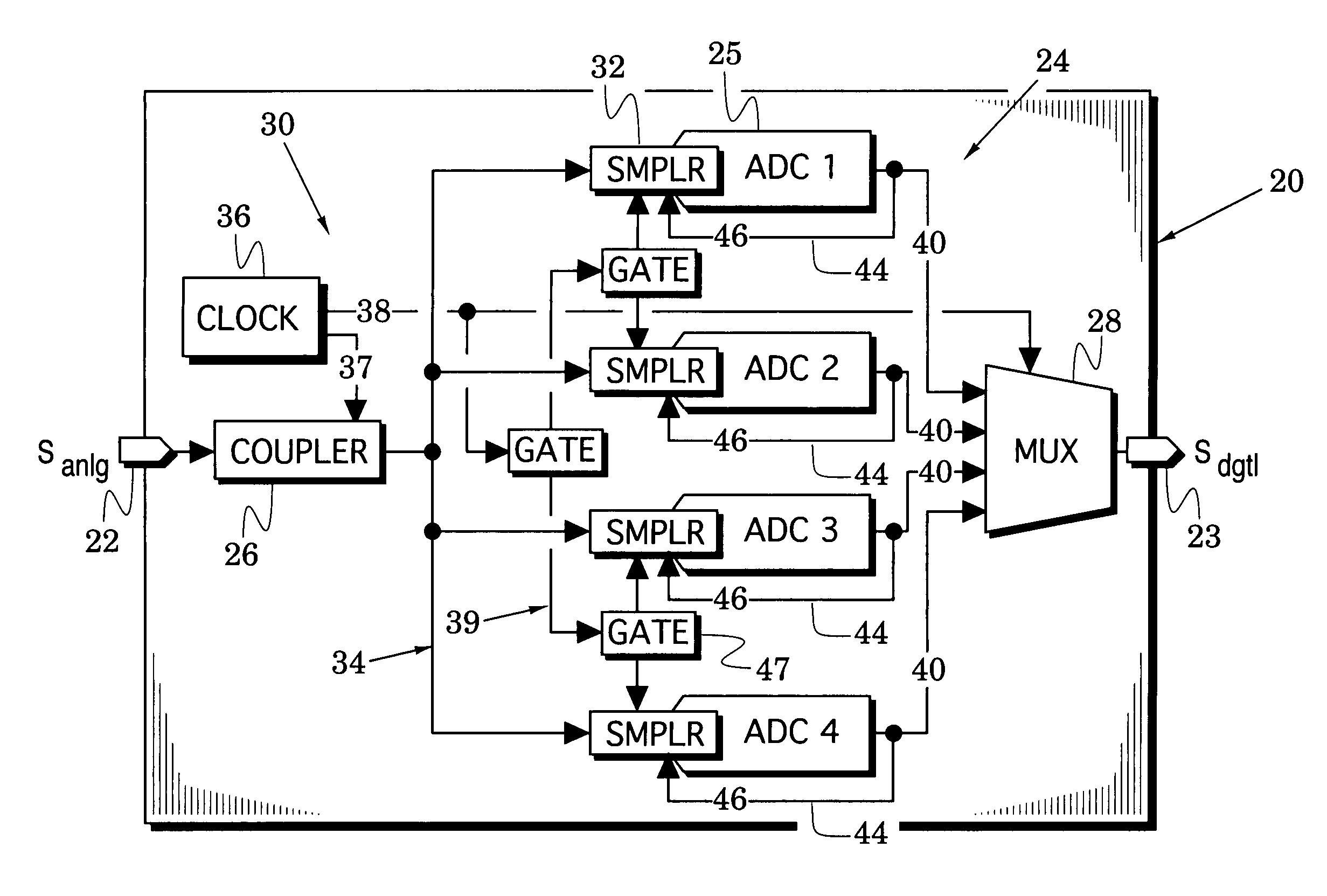

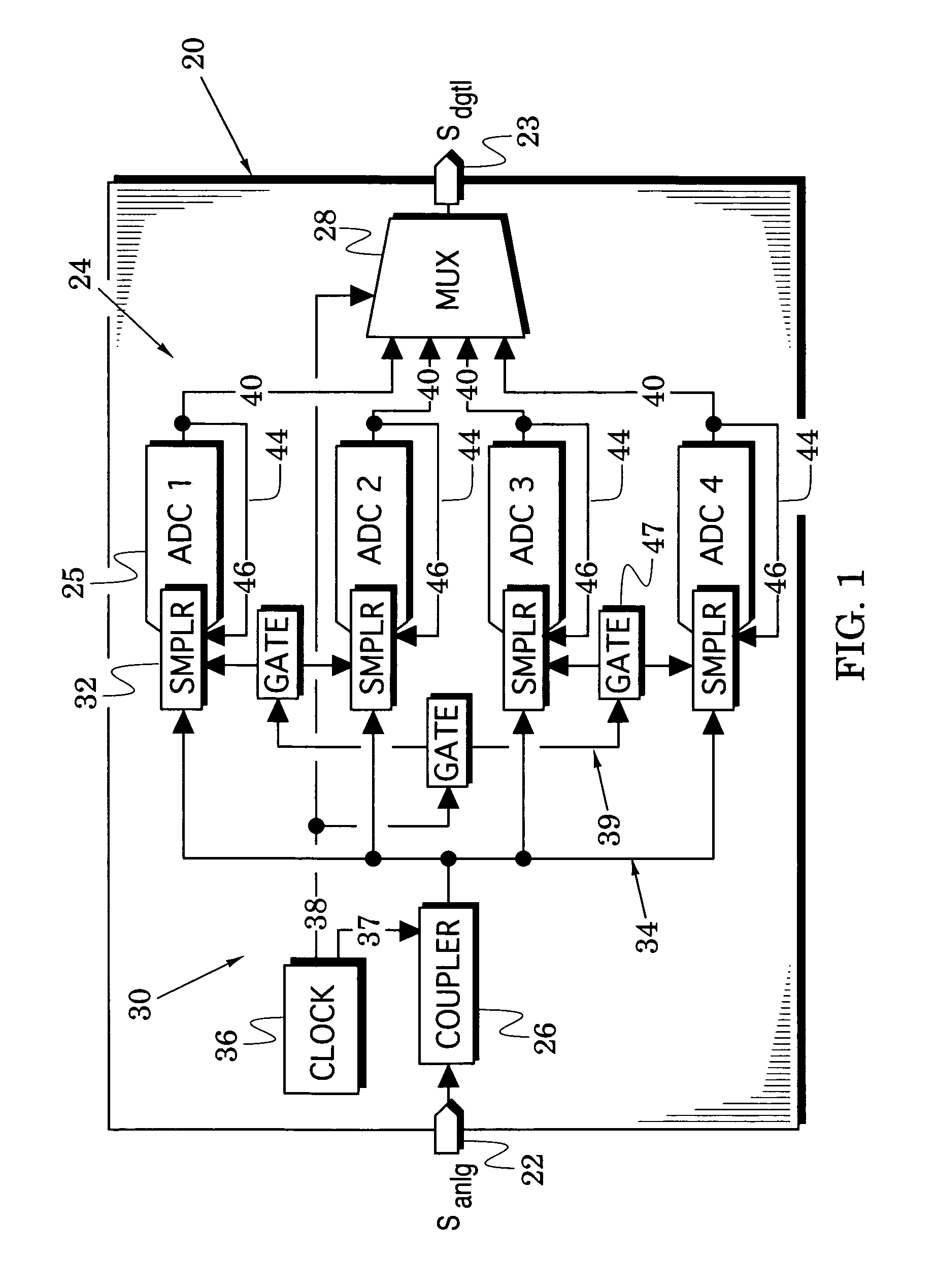

ActiveUS7015842B1Analogue/digital conversionElectric signal transmission systemsRelative phaseEngineering

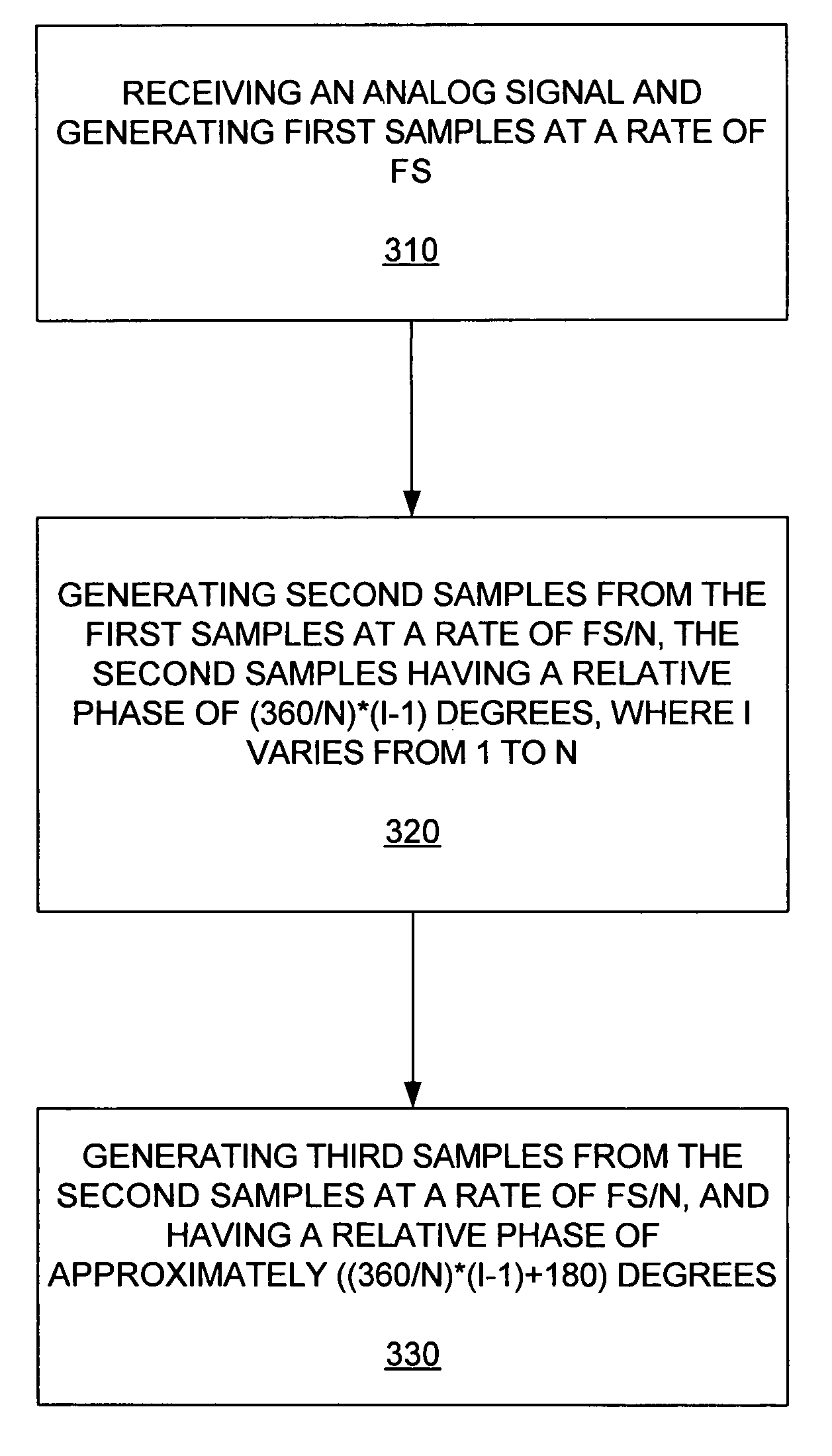

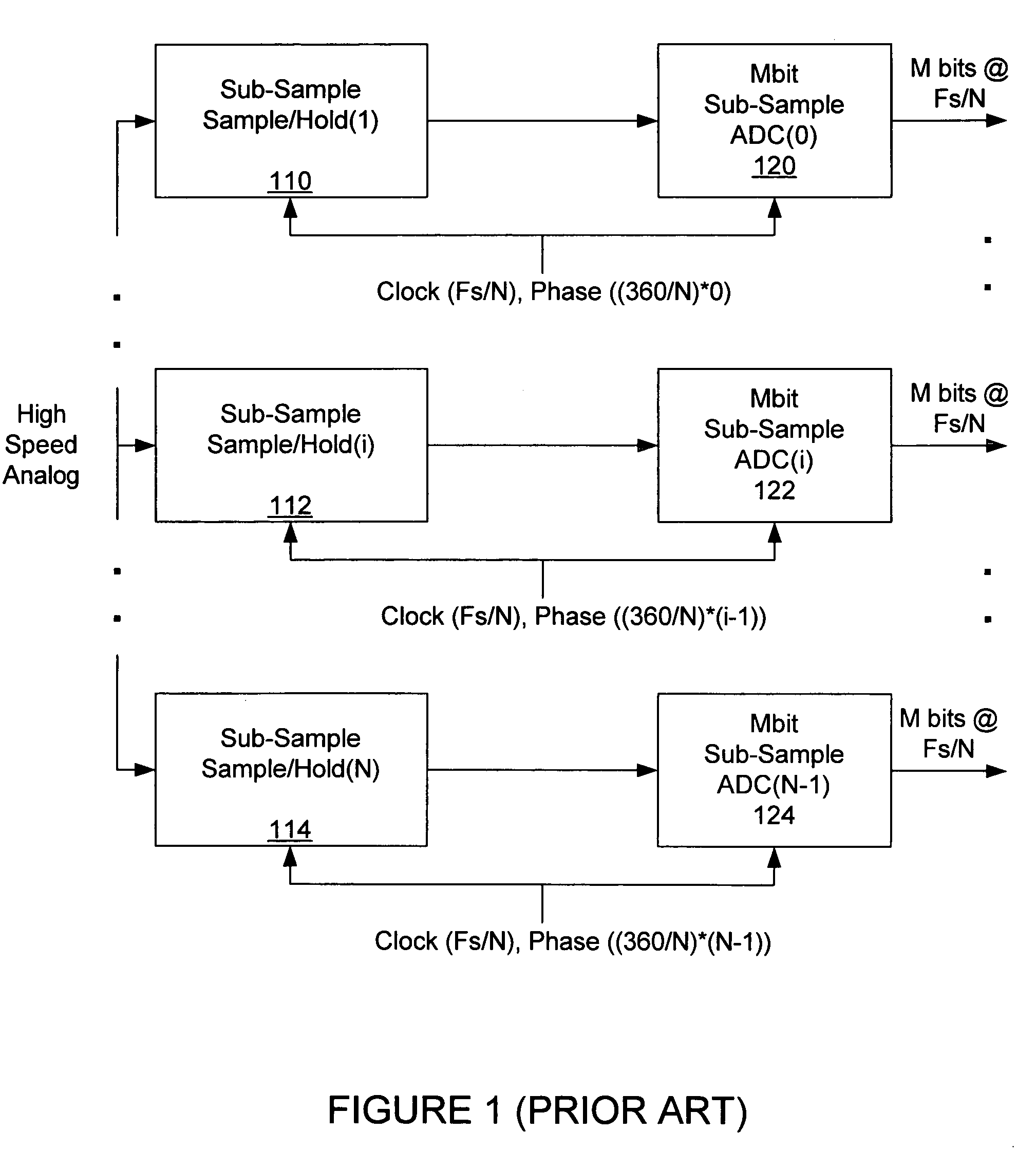

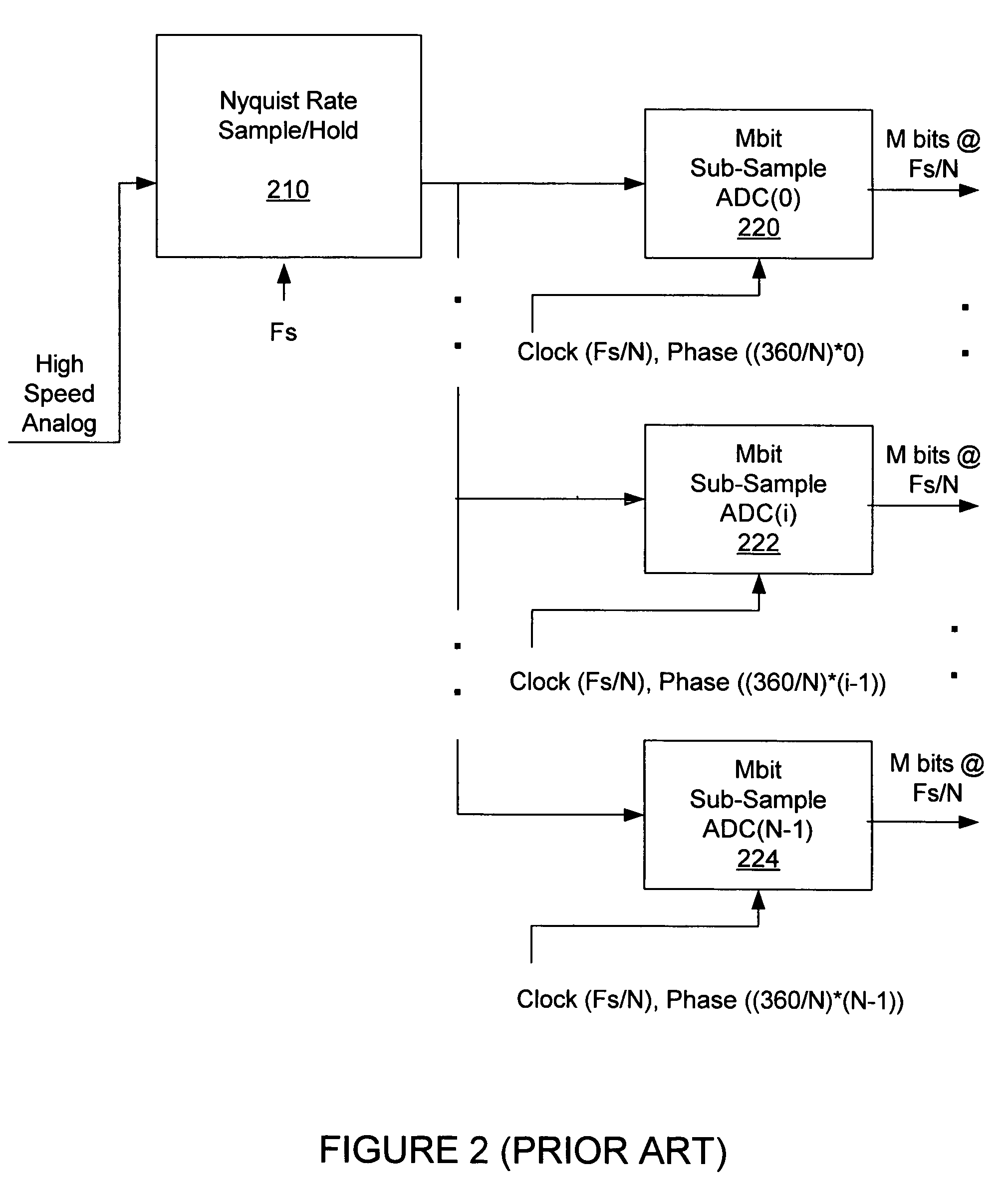

A high-speed sampling system and an analog to digital converter are disclosed. One embodiment of a method of sampling a signal includes receiving an analog signal and generating first samples at a rate of Fs, and generating second sub-samples from the first samples at a rate of Fs / N and having a relative phase of approximately (360 / N)*(i−1) degrees, where i varies from 1 to N. In a first embodiment, at most two second sub-samplers are tracking the output of the first sampler at any point in time. In a second embodiment, only one of the N second sub-samplers are tracking the output of the first sampler at any point in time. A third embodiment further includes generating third samples from the second samples at a rate of Fs / N, and having a relative phase of approximately ((360 / N)*(i−1)+180) degrees. A method of interleaved analog to digital converting includes corresponding time interleaved ADCs receiving the third samples.

Owner:AVAGO TECH INT SALES PTE LTD

Enhanced Time-Interleaved A/D Conversion Using Compression

InactiveUS20080018502A1Increase the compression ratioDegrade signal qualityAnalogue/digital conversionBinary multiplierAnalog signal

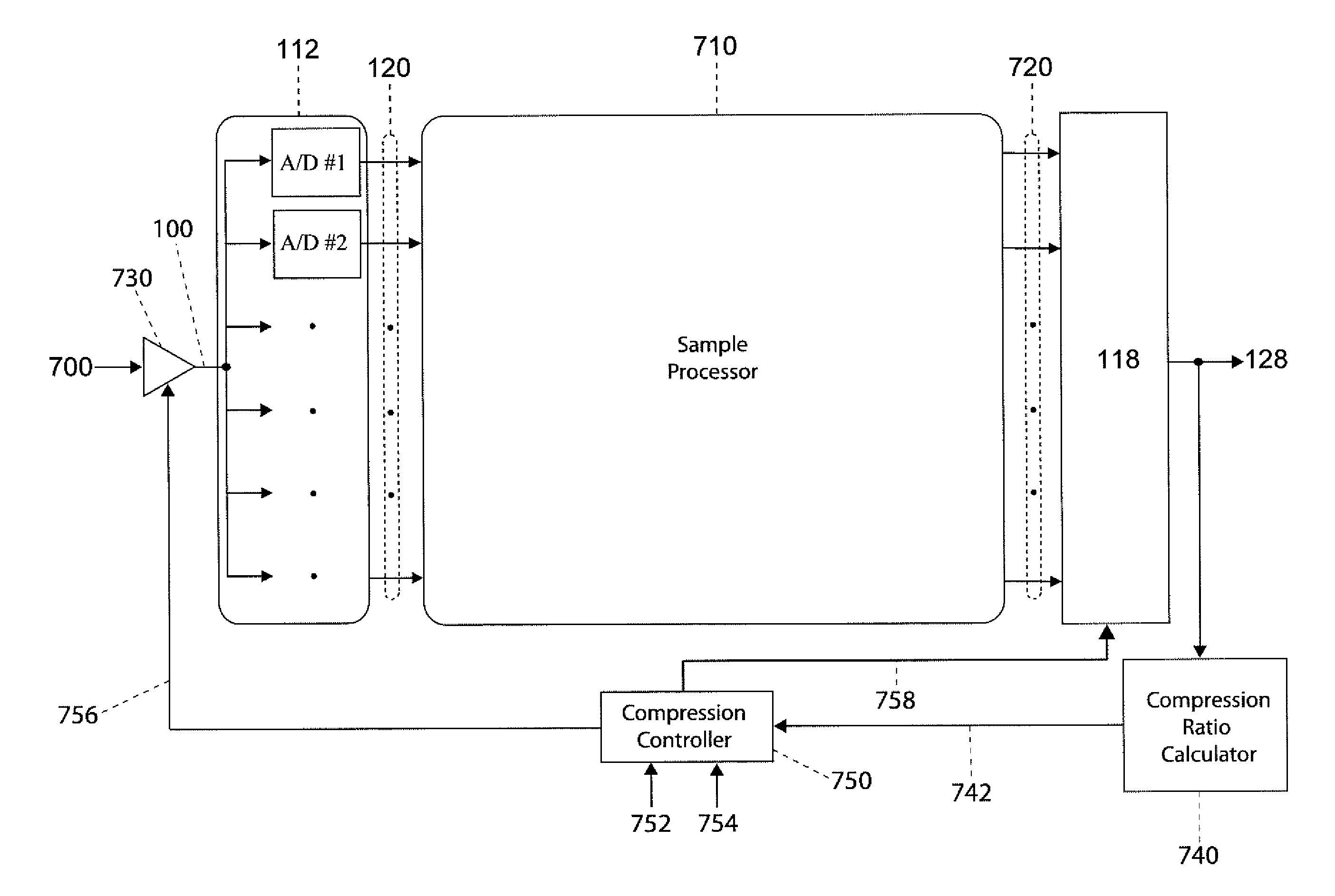

Compression of signal samples output from a parallel, time-interleaved analog to digital converter (TIADC) for a baseband signal, includes calculating first or higher order differences of consecutive signal samples followed by lossless or lossy encoding of the difference samples to produce compressed samples. Compression of a TIADC output signal with a nonzero center frequency, includes calculating sums or differences of pairs of signal samples separated by an appropriate number of sampling intervals followed by lossless or lossy encoding. The sums or differences of the signal samples have lower magnitudes than the original samples, allowing more efficient compression. Lossy compression alternatives produce compressed data with a fixed bit rate or with a fixed quality in the decompressed samples. Alternatives for lossy compression include attenuating the analog signal before sampling by the TIADC, applying bit shifters or multipliers after sampling to reduce the magnitudes of the signal samples, and lossy encoding.

Owner:ALTERA CORP

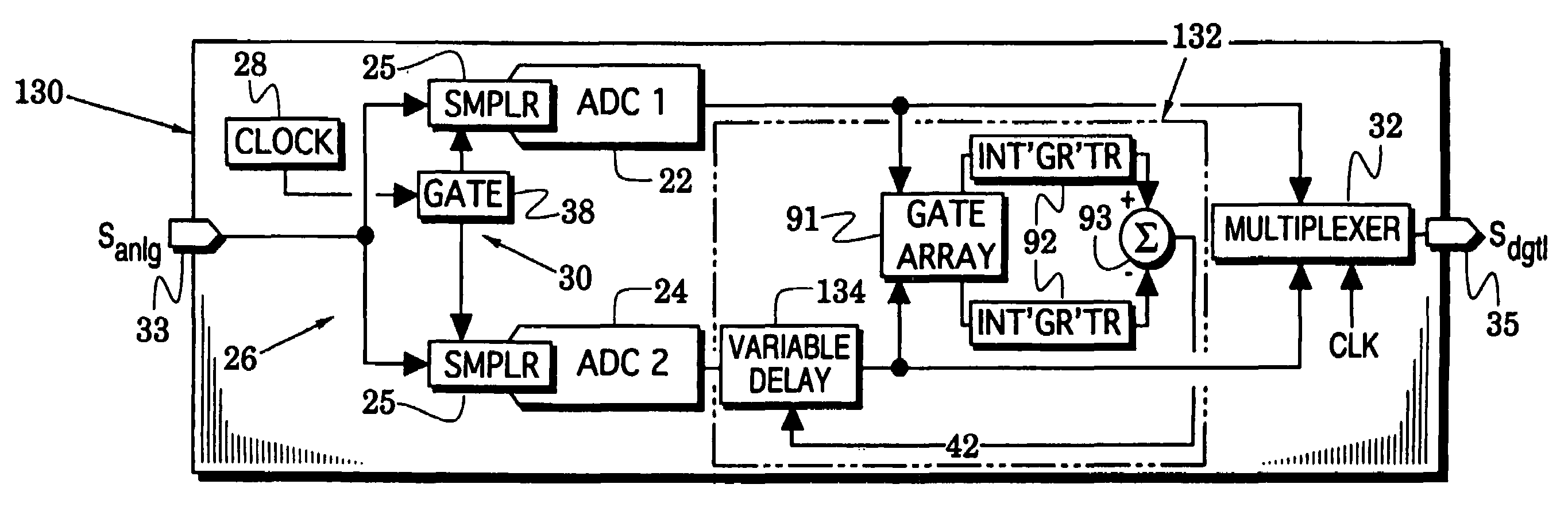

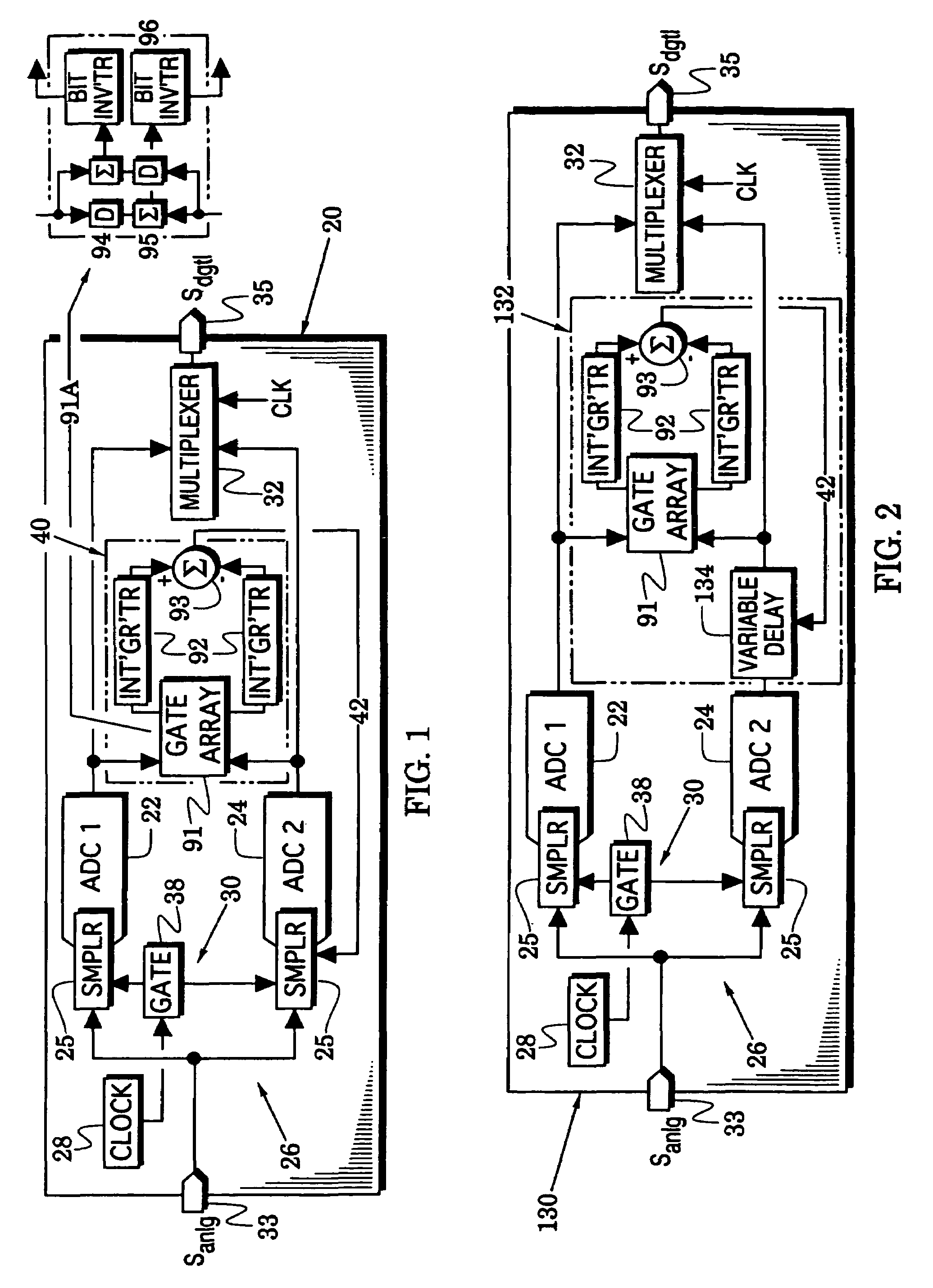

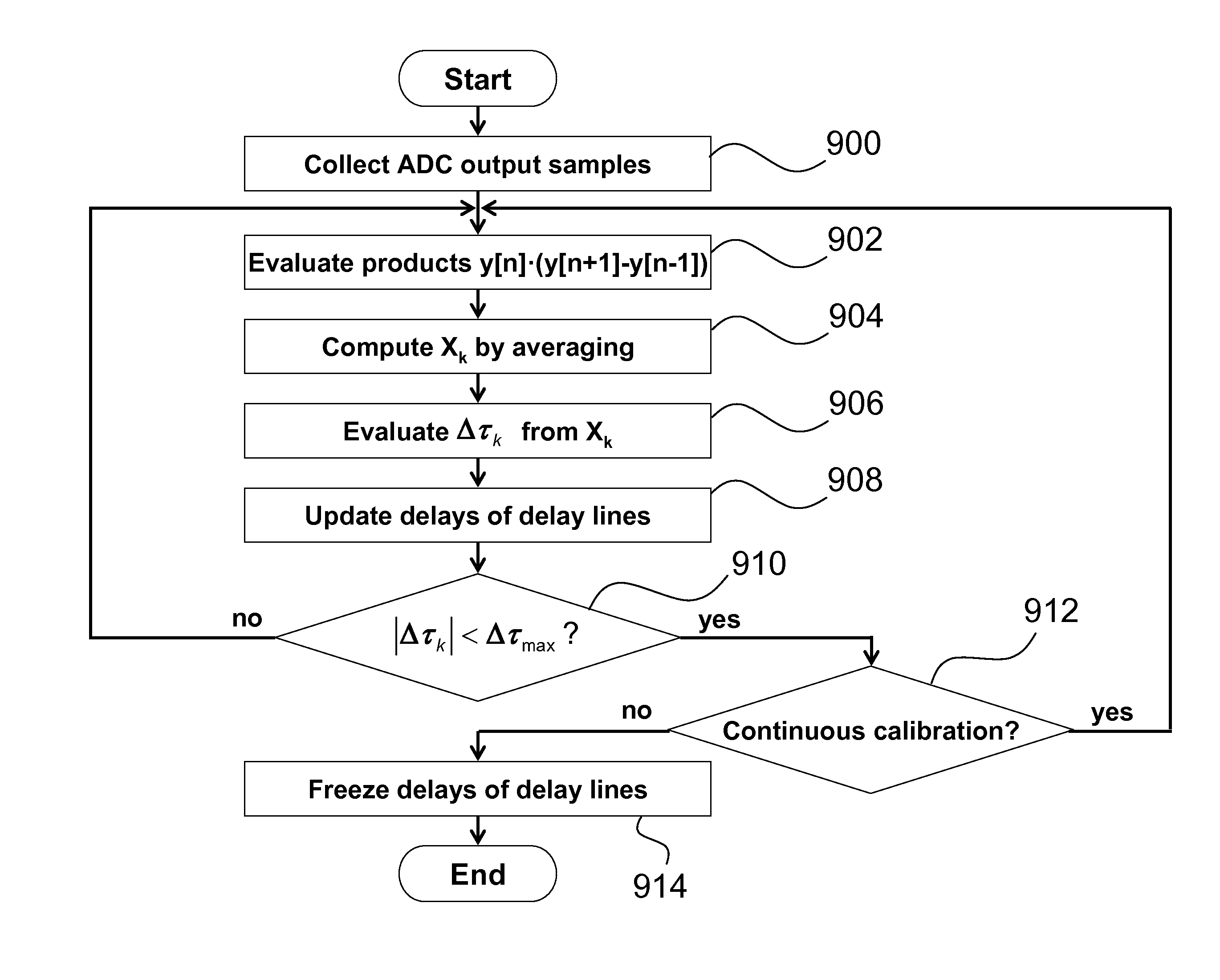

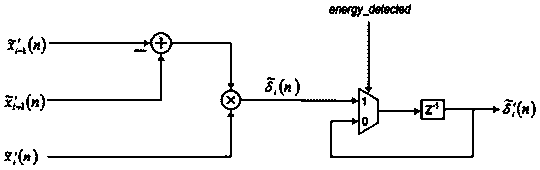

Phase-error reduction methods and controllers for time-interleaved analog-to-digital systems

ActiveUS7053804B1Electric signal transmission systemsPhysical parameters compensation/preventionTime interleavedReduction methods

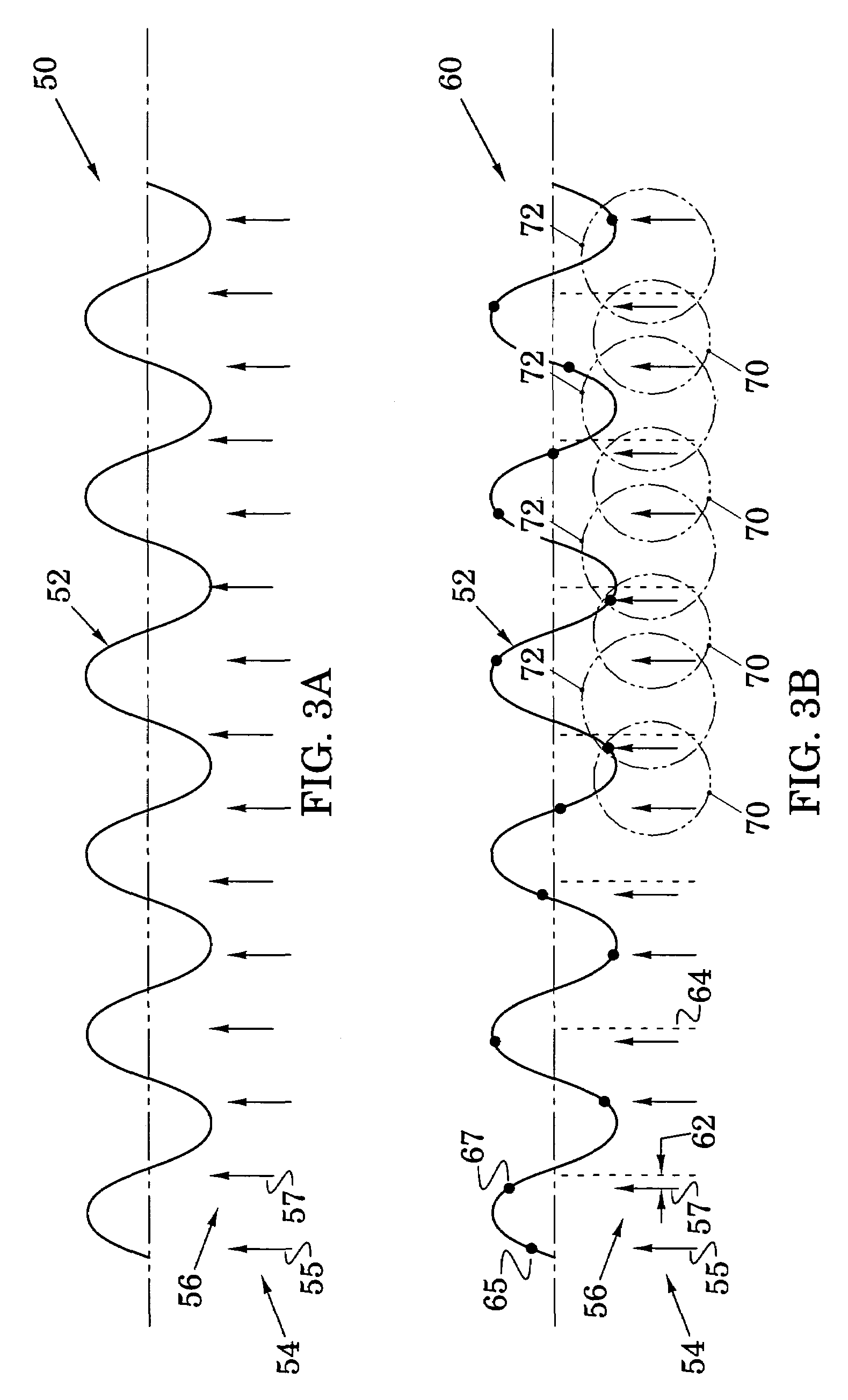

Methods and controllers are provided to estimate and reduce phase errors between converters of time-interleaved analog-to-digital systems by generating corresponding error signals in the form of difference signals. The difference signals concern differences between magnitudes of first adjacent samples and interleaved second adjacent samples of the converters. The difference signals can be applied (e.g., to a converter's input sampler or to a variable delay element inserted after the converter) to substantially reduce the phase errors. The methods and controllers may be economically implemented because they can be realized with simple operations (e.g., addition and subtraction). Although some embodiments are facilitated with knowledge of parameters of the analog input signal, others do not require this knowledge so long as the signal is restricted to lie within a single Nyquist zone.

Owner:ANALOG DEVICES INC

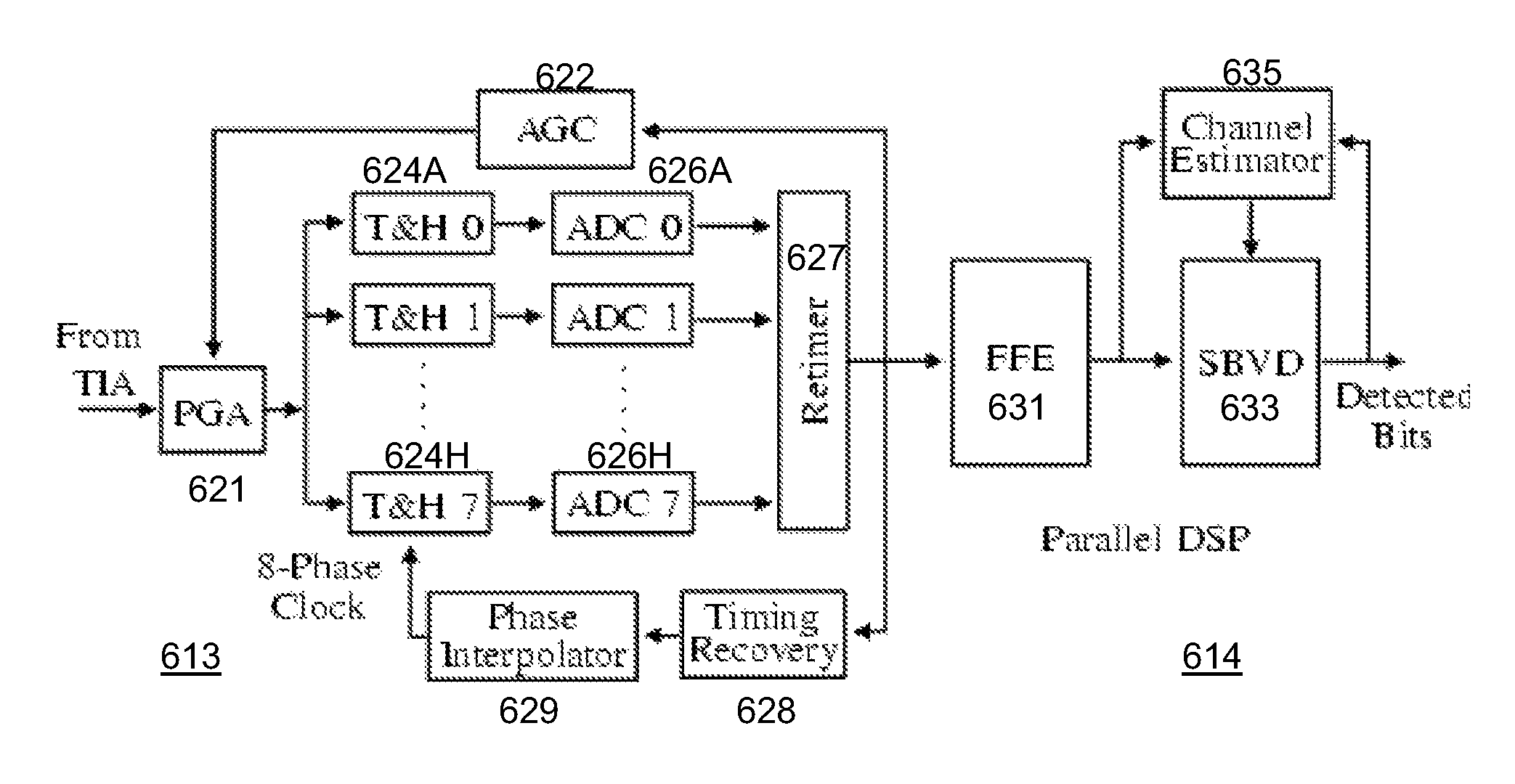

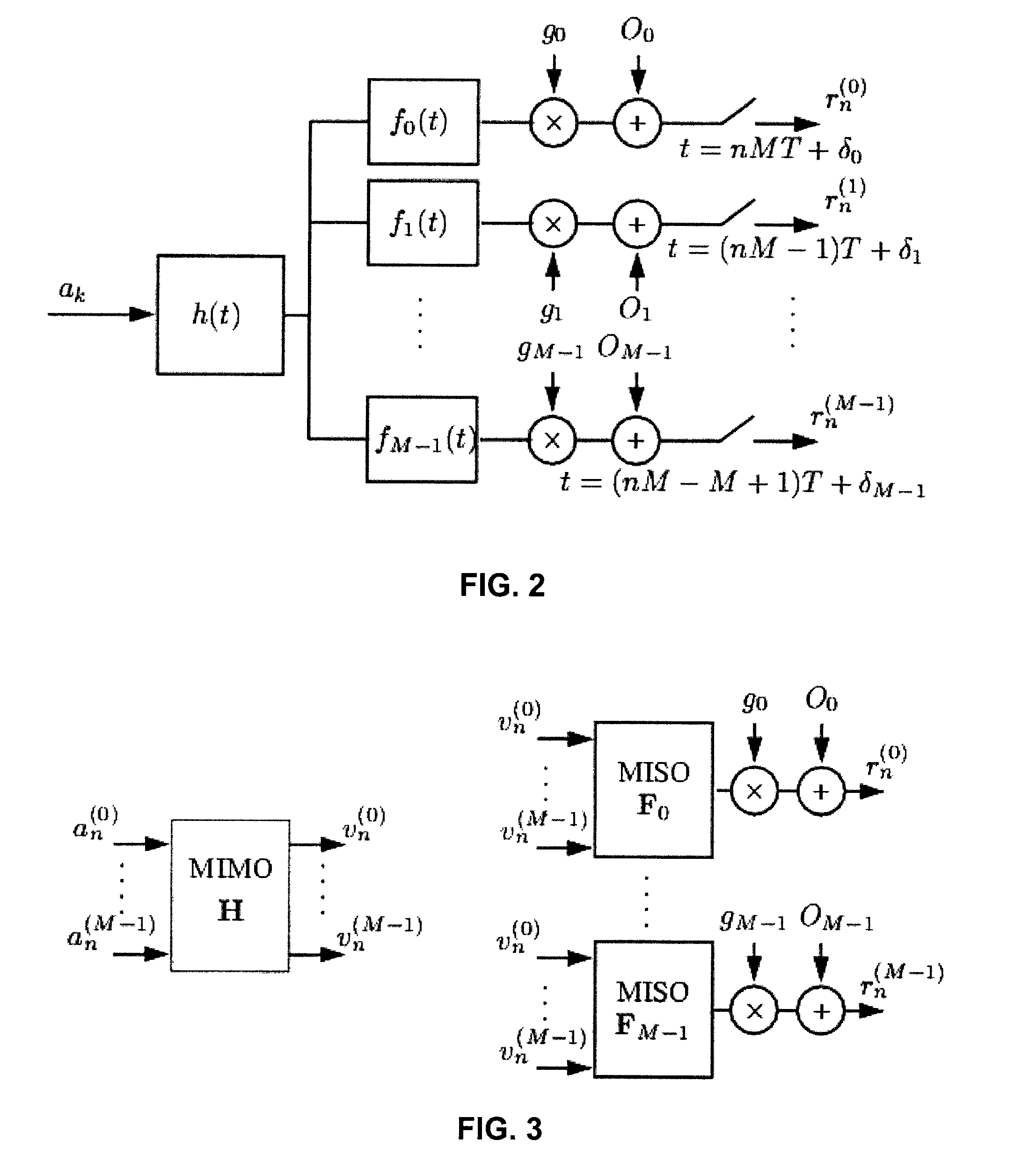

Multi-channel equalization to compensate for impairments introduced by interleaved devices

ActiveUS7778320B2Overcome limitationsAnalogue/digital conversionMultiple-port networksEngineeringTime interleaved

A system includes a time-interleaved device. An equalizer effectively can apply different equalization to different interleaved channels. For convenience, these equalizers will be referred to as multi-channel equalizers. In one aspect, an apparatus includes an interleaved device having M interleaved channels, and a multi-channel equalizer coupled to the interleaved device. The multi-channel equalizer is capable of applying a different equalization to different interleaved channels, thus compensating for channel-dependent impairments.

Owner:MARVELL ASIA PTE LTD

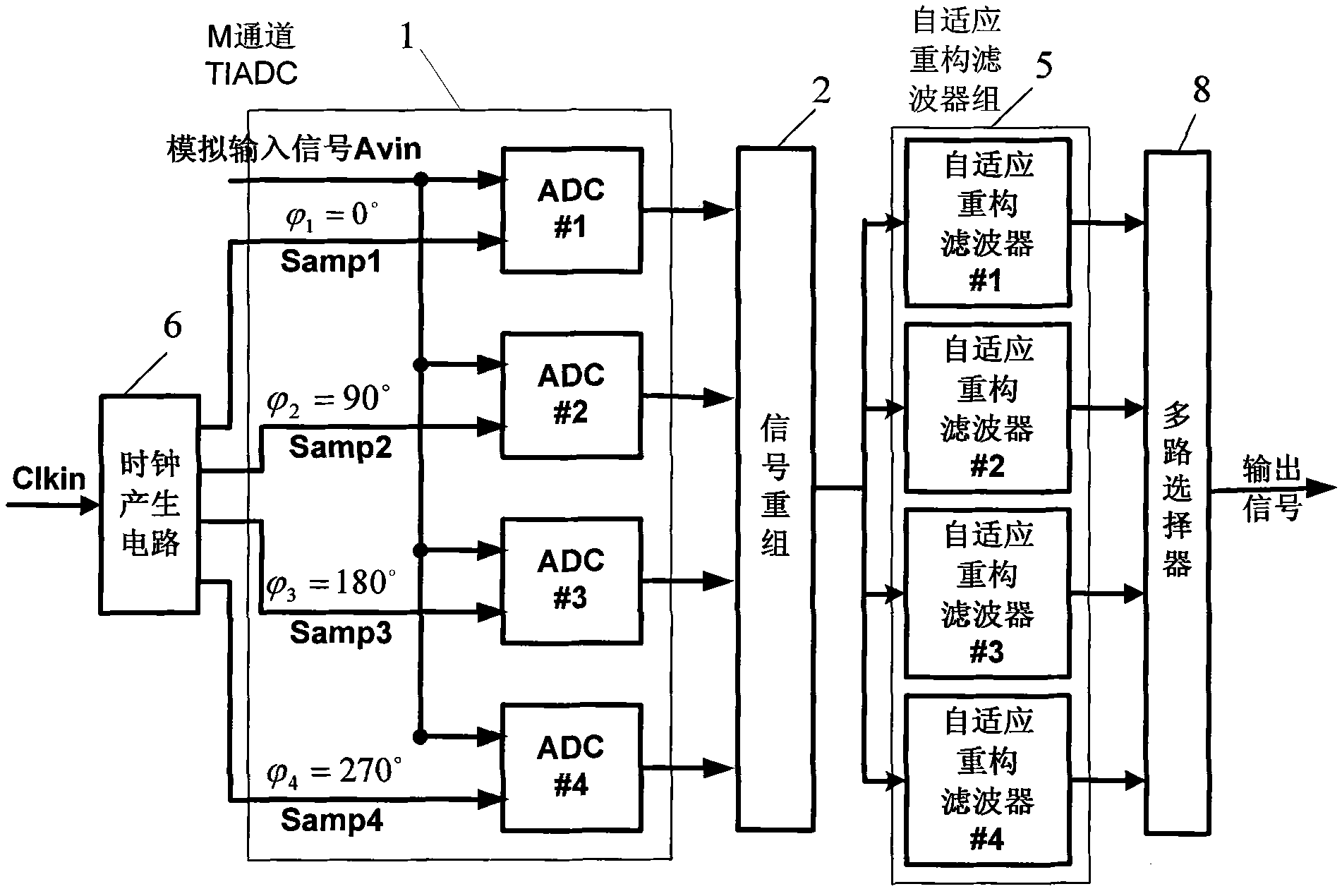

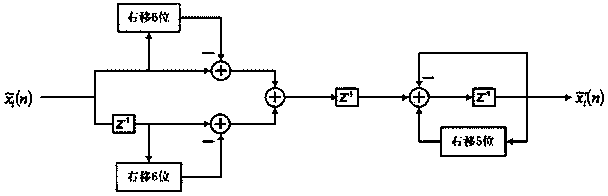

Self-adoptive correcting device of mismatch error of time-interleaved analog-digital converter

InactiveCN101888247AAvoid problems that are difficult to convert to hardware circuitsThere is no problem of implementation deviationAnalogue-digital convertersAnalogue/digital conversion calibration/testingTime errorDigital down converter

The invention discloses a self-adoptive correcting device of mismatch error of time-interleaved analog-digital converter, comprising an M channel TIADC, a signal recombination, a digital reference signal memorizer, a simulated reference signal generator, a self-adaptive reconstruction filter bank, a clock generation circuit and a subtraction device. Signals after passages are reconstructed are used to correct each passage instead of single correction on each passage, thereby solving the problem that when an input signal bandwidth is larger than the Nyquist frequency of each passage ADC, the time error can not be corrected due to aliasing. Each self-adoptive reconstruction filter is divided into a plurality of sub-filters for concurrent working, thereby not improving the requirement of thetreatment speed for a self-adoptive correcting filter while realizing the effect of signal recombination and ensuring the practicability of the hardware of the structure of the invention. A digital reference signal is internally installed in the device and is taken as a target to carry out the self-adoptive correction, pre-measuring or calculating a passage mismatch error is not needed, and the source of the error is not needed to be discriminated so that various mismatch errors can be corrected.

Owner:BEIJING UNIV OF TECH

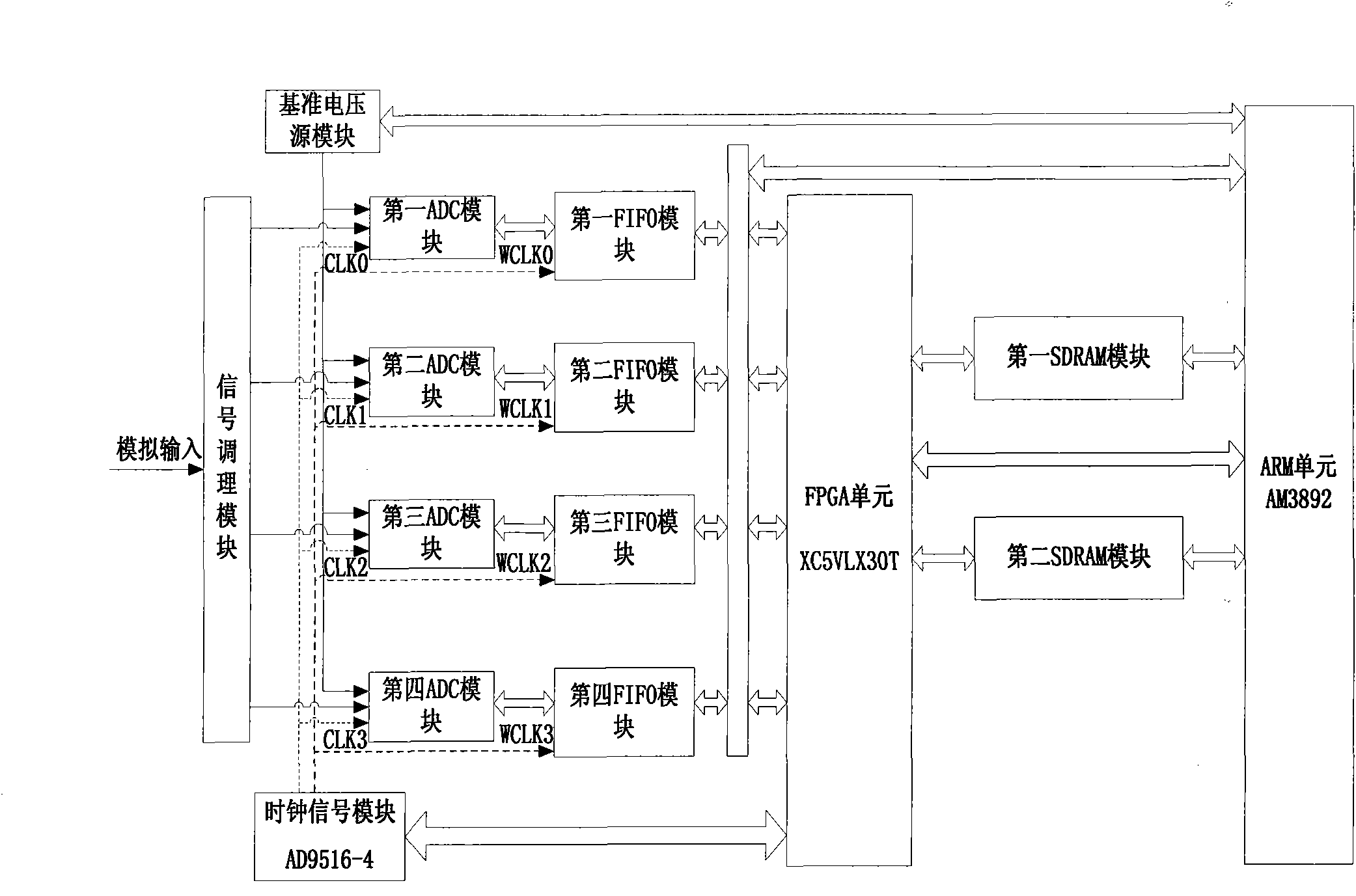

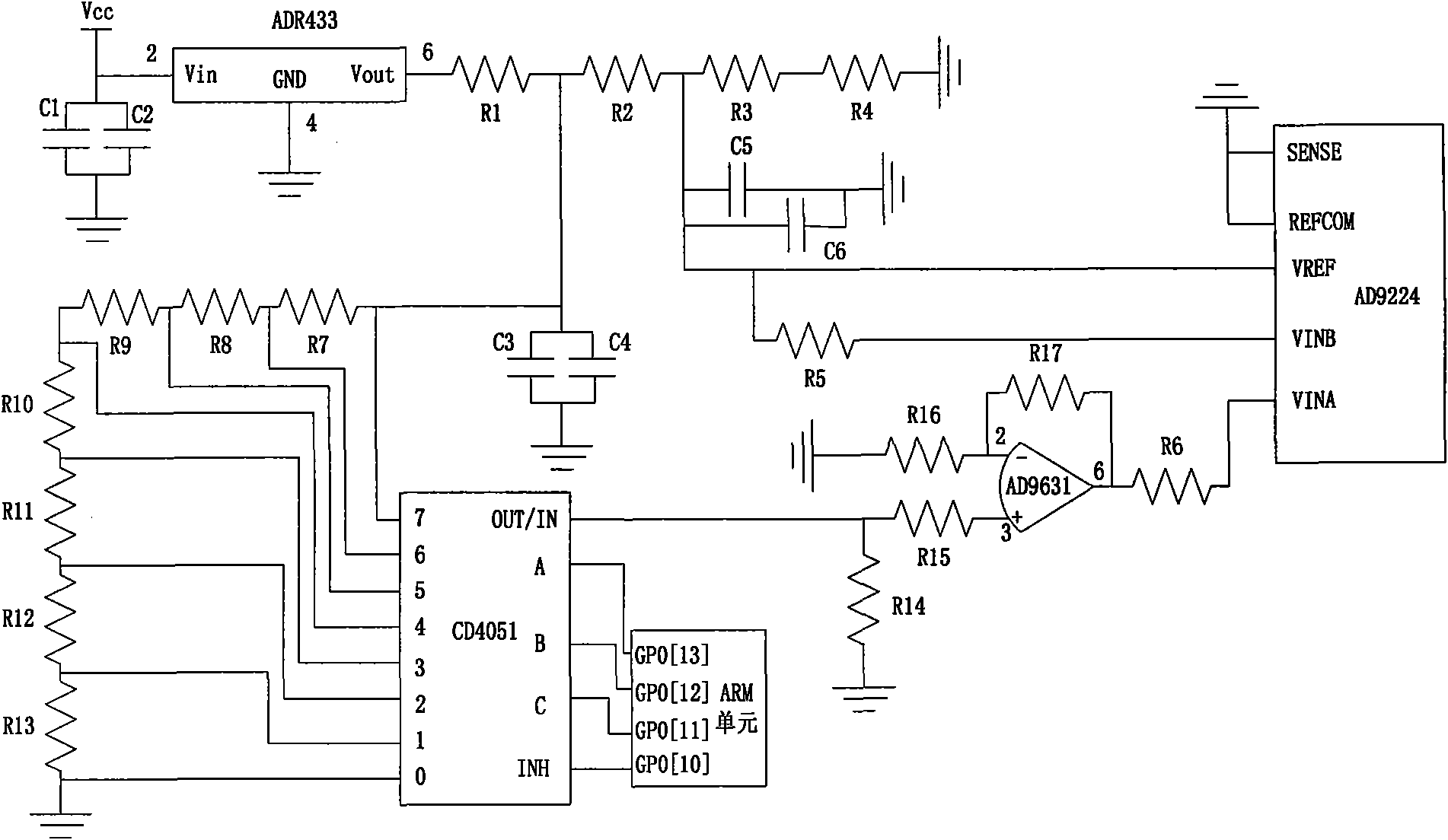

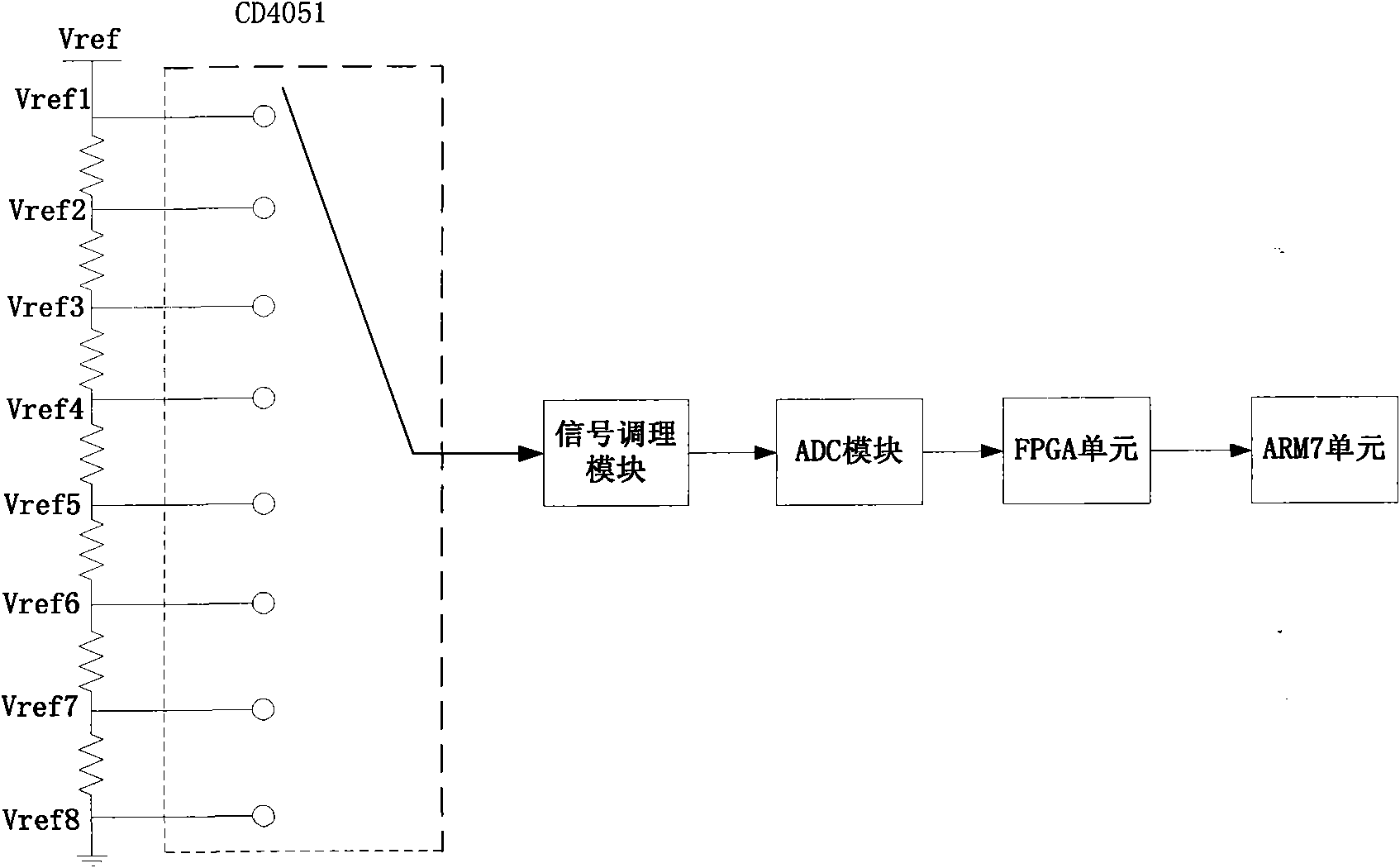

High-speed high-accuracy recorder and sampling data automatic-correction and high-order matching method thereof

InactiveCN102136841AHigh precisionReduce mismatchAnalogue/digital conversionElectric signal transmission systemsTimestampVoltage source

The invention discloses a high-speed high-accuracy recorder and a designing method thereof. The high-speed high-accuracy recorder comprises a signal conditioning module, four analogue-to-digital converter (ADC) modules, four first in first out (FIFO) modules, two synchronous dynamic random access memory (SDRAM) modules, a client-server architecture control module, a synchronous coherent clock module, a high-accuracy reference voltage source module and the like, wherein the client-server architecture control module consists of an advanced RISC machine (ARM) unit and a field programmable gate array (FPGA) unit; and the synchronous coherent clock module takes a clock chip as a core. The recorder finishes the operations of 'time-interleaved' sampling, encapsulation, caching, transmission, decapsulation combination, correction, storage, uploading and the like concurrently under the control of a concurrent time sequence logic, corrects sampling data based on an inter-ADC channel mismatchingautomatic-correction polynomial to reduce gain mismatching and offset / zero mismatching among ADC channels, reduces time mismatching among the ADC channels by using a synchronous coherent clock and a serpentine curve wire-length fine-adjustment technology, and solves the problems of associated global errors produced by data loss in the high-speed 'time-interleaved' sampling by using a high-order matching technology in which the encapsulation is performed by additional timestamp sequence numbers.

Owner:ZHEJIANG UNIV +1

System and method for interleaved analog-to-digital conversion having scalable self-calibration of timing

ActiveUS9000962B1Optimize timingComputationally efficientElectric signal transmission systemsAnalogue-digital convertersTime delaysAnalog signal

A system and method are provided for adaptive self-calibration to remove sample timing error in time-interleaved ADC of an analog signal. A plurality of ADC channels recursively sample the analog signal within a series of sample segments according to a predetermined sampling clock to generate a time-interleaved series of output samples. A timing skew detection unit is coupled to the ADC channels, which generates for each sample segment a timing skew factor indicative of sampling clock misalignment within the sample segment. Each timing skew factor is generated based adaptively on the output samples for a selective combination of segments including at least one preceding and at least one succeeding sample segment. A plurality of timing control units respectively coupled to the ADC channels adjust time delays for the sampling clock within respective sample segments responsive to the timing skew factors, thereby substantially aligning the sample segments with the sampling clock.

Owner:CADENCE DESIGN SYST INC

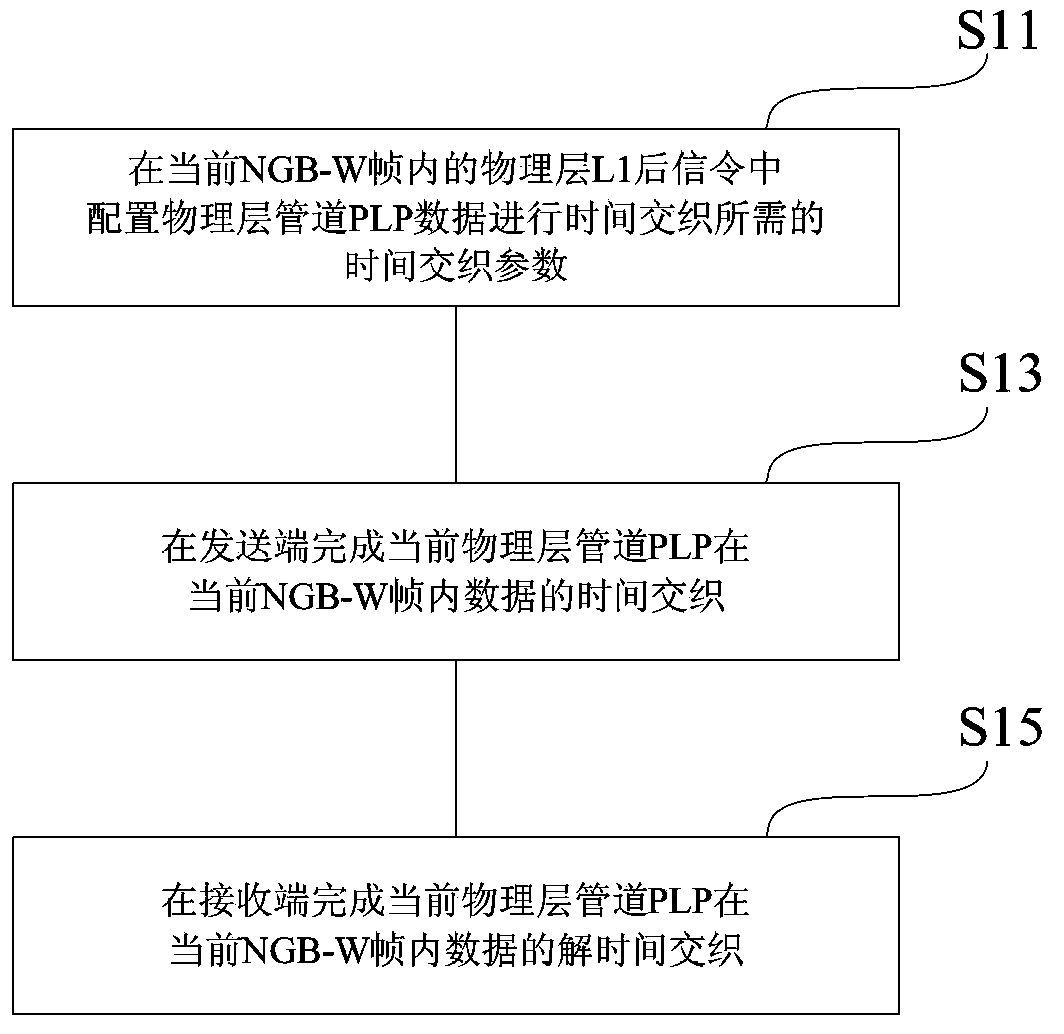

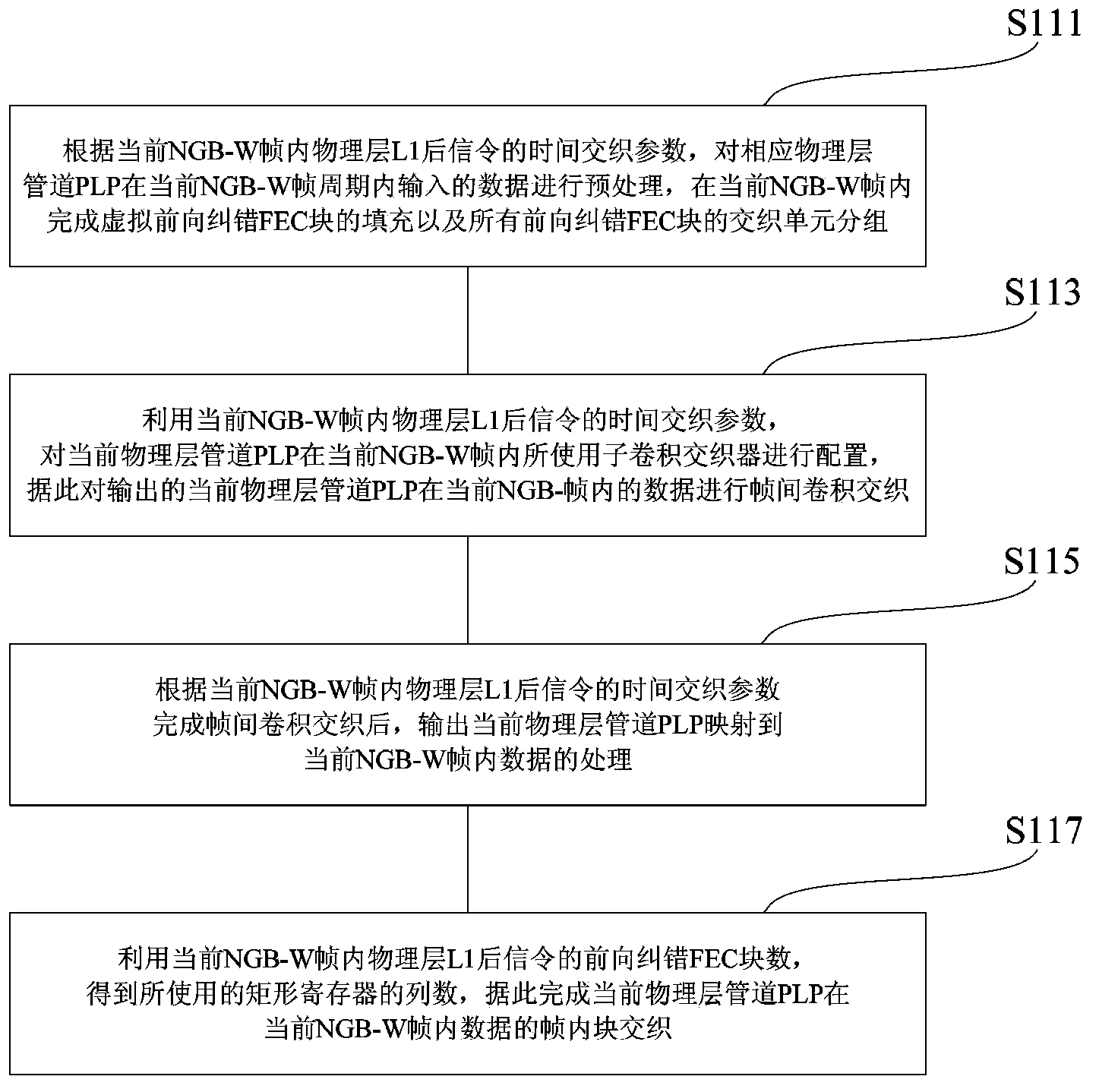

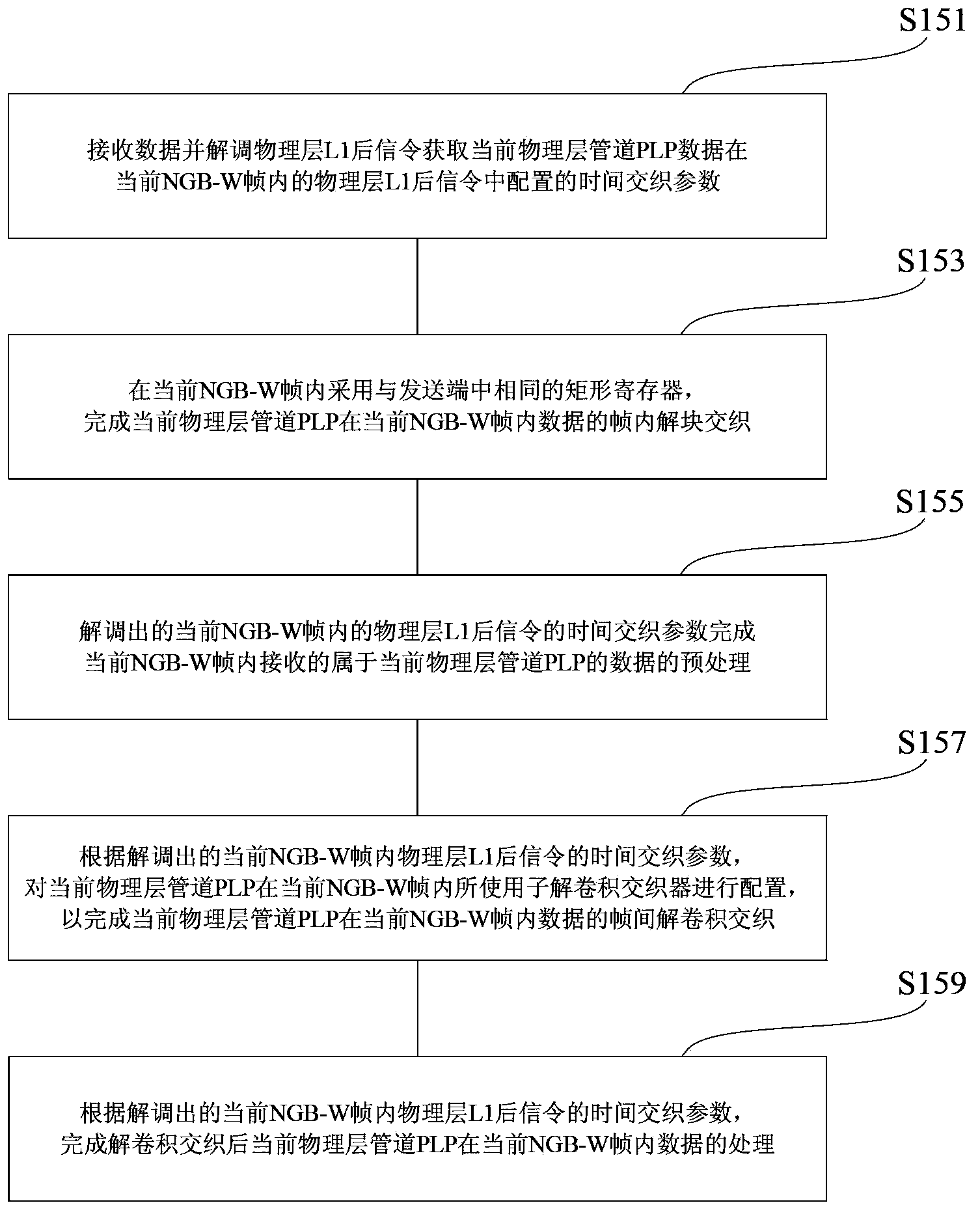

Method for achieving time-interleaving and time-deinterleaving in NGB-W communication system

The invention provides a method for achieving time-interleaving and time-deinterleaving in an NGB-W communication system. The method mainly comprises the following steps: time-interleaving parameters required for achieving time-interleaving and eliminating time-interleaving in the NGB-W communication system are added into a physical layer L1 post-signaling region, a transmitting end completes time-interleaving of data of a physical layer pipe (PLP) within each NGB-W frame according to the time-interleaving parameters, a receiving end acquires time-interleaving parameters of the physical layer pipe (PLP) within each NGB-W frame by demodulating an L1 post-signaling to complete time-deinterleaving of data of the corresponding physical layer pipe (PLP) within each NGB-W frame. Compared with the prior art, through the adoption of the method, the effect of uniform or non-uniform time-interleaving inter-frame convolution-interleaving and intra-frame interleaving cascade of unchangeable or changeable input rate data can be achieved, the achieving of a cascade-type time-interleaving plan by the NGB-W communication system is guaranteed, and meanwhile, the flexibility of achieving time-interleaving of the NGB-W communication system is improved.

Owner:SHANGHAI ADVANCED RES INST CHINESE ACADEMY OF SCI

Analog-to-digital converter operable with staggered timing

InactiveUS20060097901A1Reduce incorrect adaptationReduce complexityElectric signal transmission systemsAnalogue-digital convertersFrequency spectrumControl signal

An arrangement for a time interleaved analog-to-digital converter that converts an signal to a digital signal and has a converter array with a plurality of analog-to-digital converters arranged in a fixed sequence in parallel with one another and can be operated with staggered timing with respect to one another is disclosed. The arrangement has a connection network which, for the purposes of actuation with staggered timing, generates in each case one control signal for an individual analog-to-digital converter in each case, with the connection network predefining the time sequence with which the control signals actuate the individual analog-to-digital converters in such a way that owing to this sequence of the control signals and thus the sequence of the actuated individual analog-to-digital converters there is at least a reduction in an interference spectrum in the spectrum of the input and / or output signal. A sorting method for operating this analog-to-digital converter is also disclosed.

Owner:INFINEON TECH AG

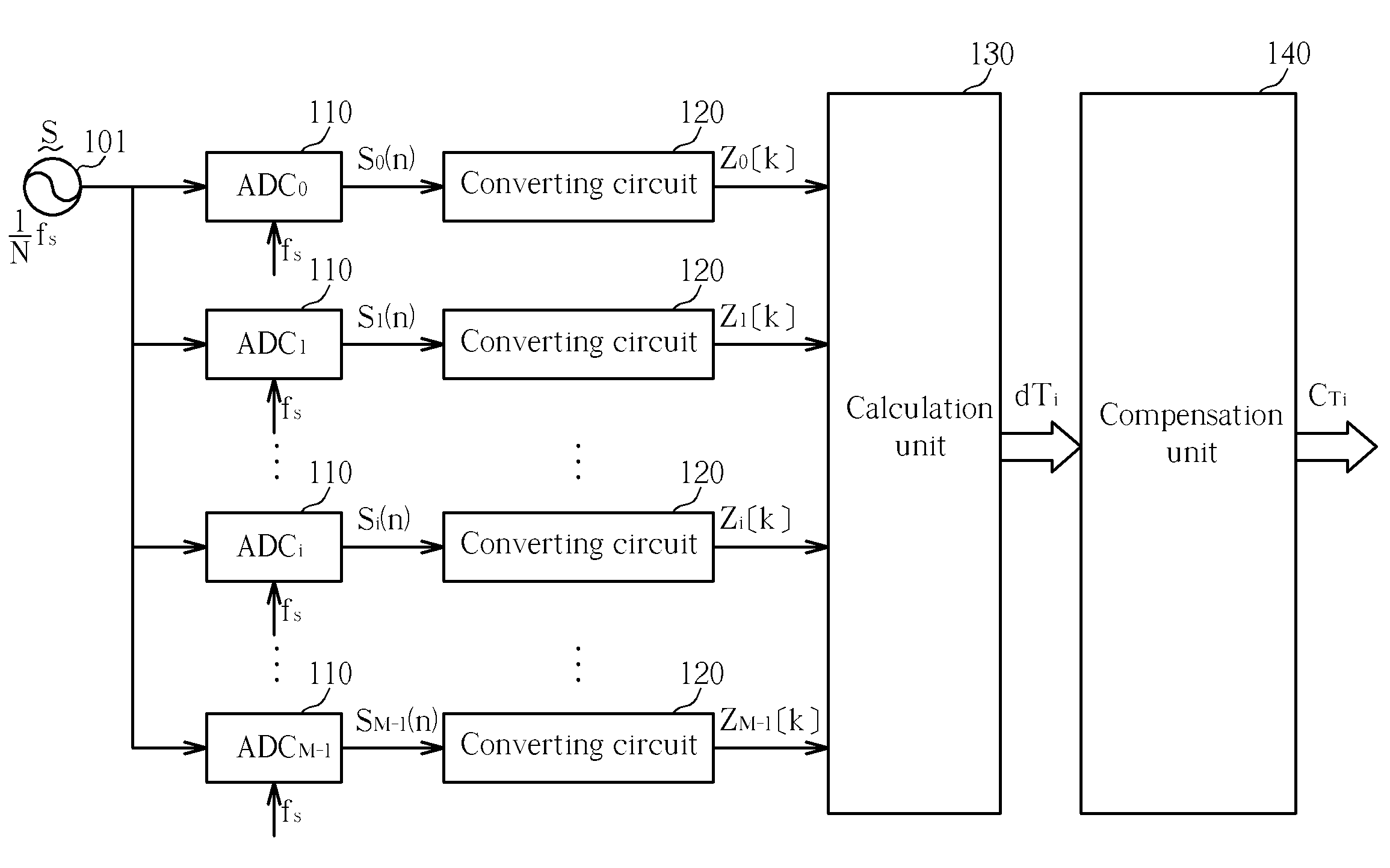

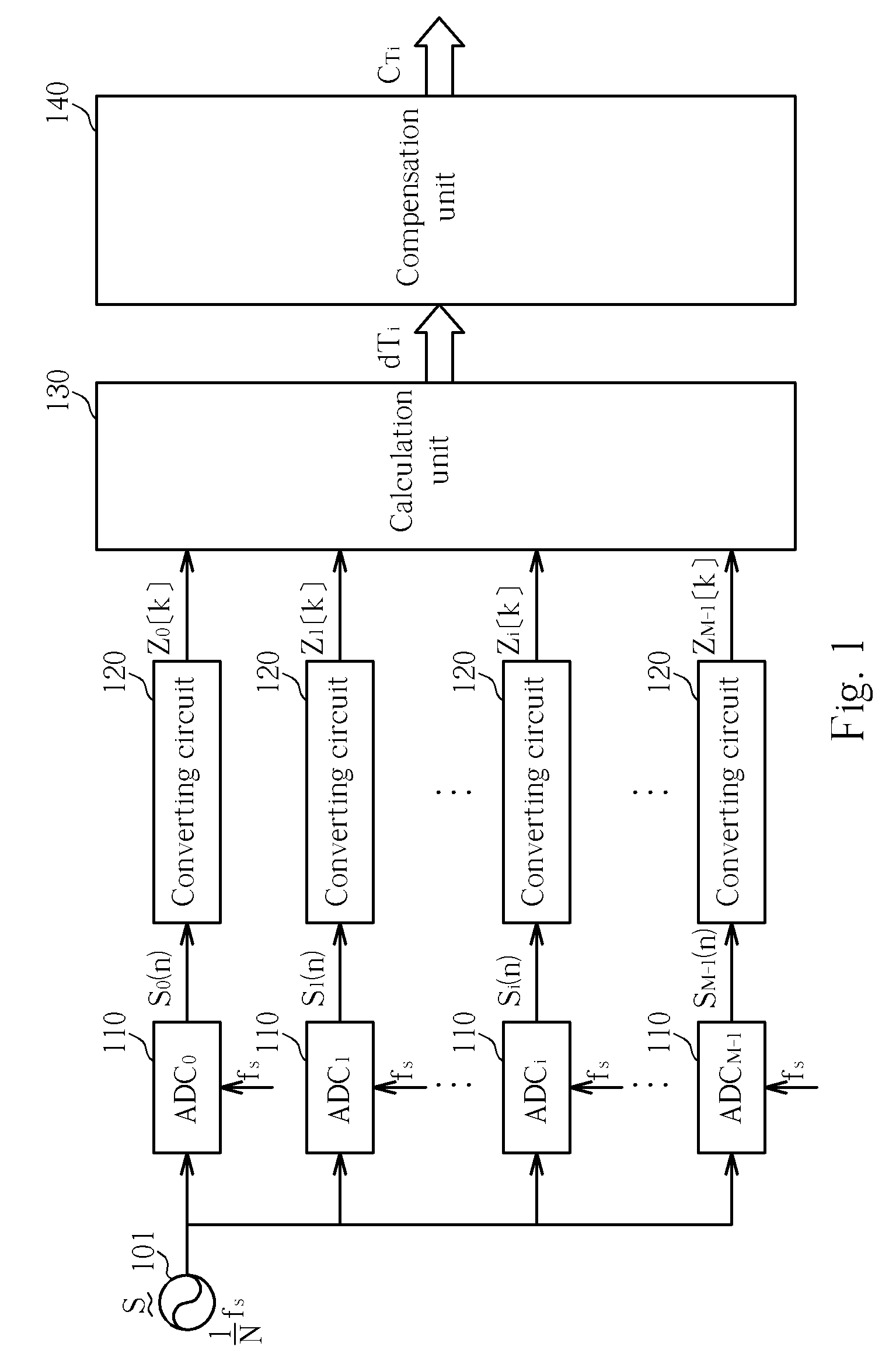

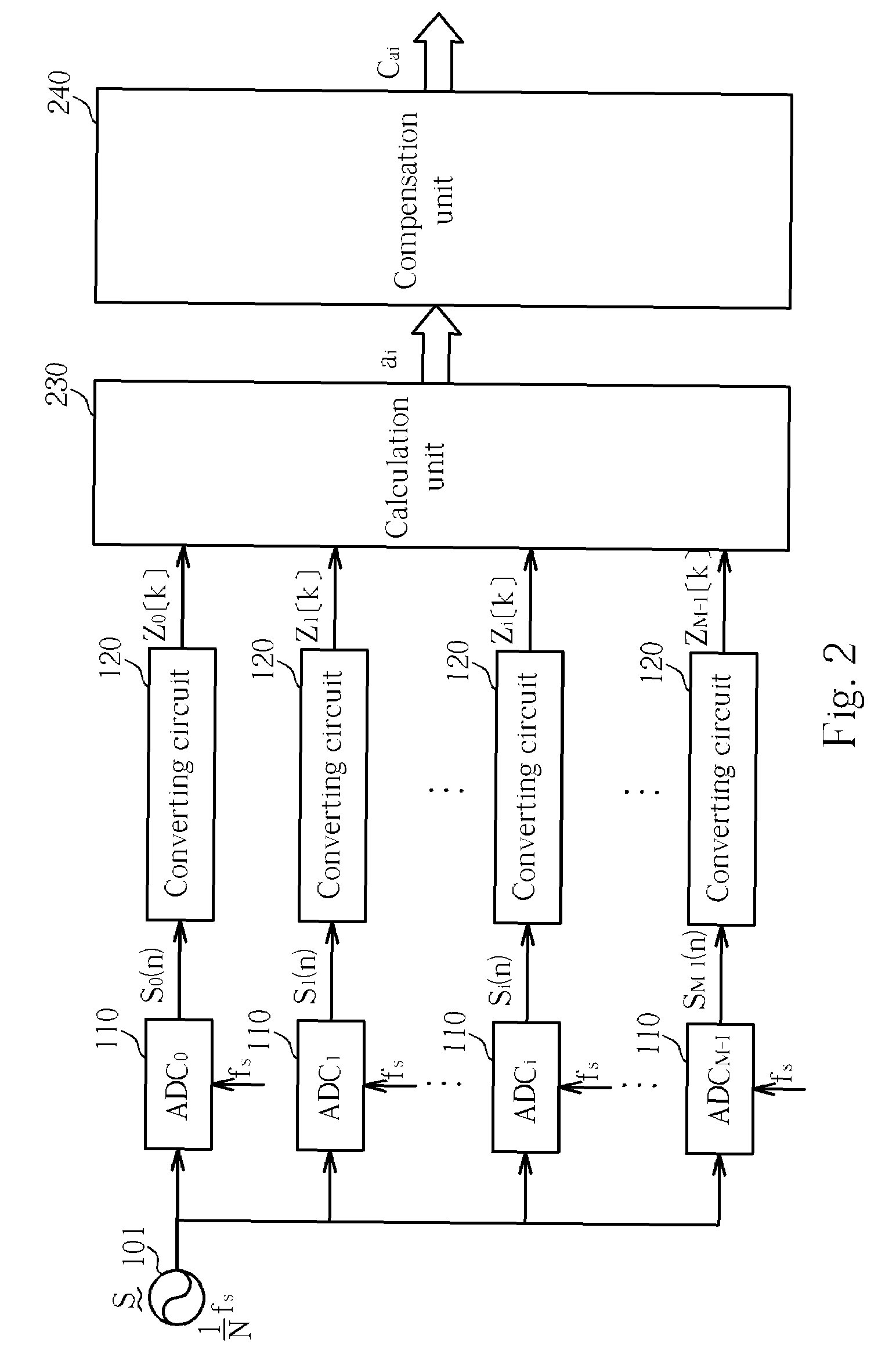

Multi-channel time-interleaved analog-digital converter

ActiveCN104038226AControl workflowAccurately Calculate Timing Mismatch ErrorAnalogue/digital conversion calibration/testingDigital down converterTransverter

The invention provides a multi-channel time-interleaved analog-digital converter. The multi-channel time-interleaved analog-digital converter is characterized in that a clock generation circuit generates a work clock for the converter; an ADC channel set including M ADC channels is configured into a time-interleaved structure; the ADC channels operate in turns in a time division multiplexing under control of the clock generation circuit, a high-speed analog input signal is converted into M low-speed digital output signals, and M is an integer not smaller than 2; a channel mismatch detection circuit detects timing sequence mismatch errors of signals output by the M ADC channel, in real time, so that a timing sequence mismatch parameter of each ADC channel relative to a reference ADC channel is acquired; a signal compensation and reconstruction circuit compensates and reconstructs the digital output signals output by the ADC channel set according to the timing sequence mismatch errors that the channel mismatch detection circuit detects; a signal combiner circuit combines the M low-speed output signals subjected to channel compensation and generated by the signal compensation and reconstruction circuit, and finally a high-speed digital output signal is obtained.

Owner:HUAWEI TECH CO LTD

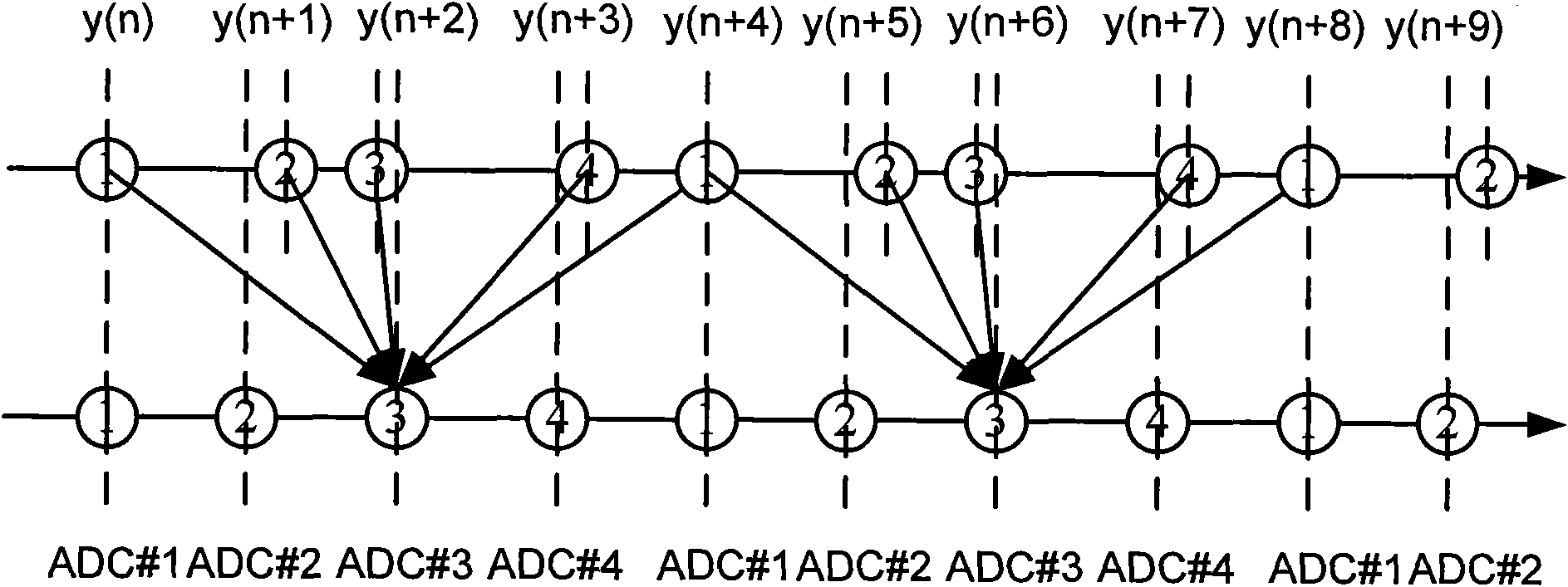

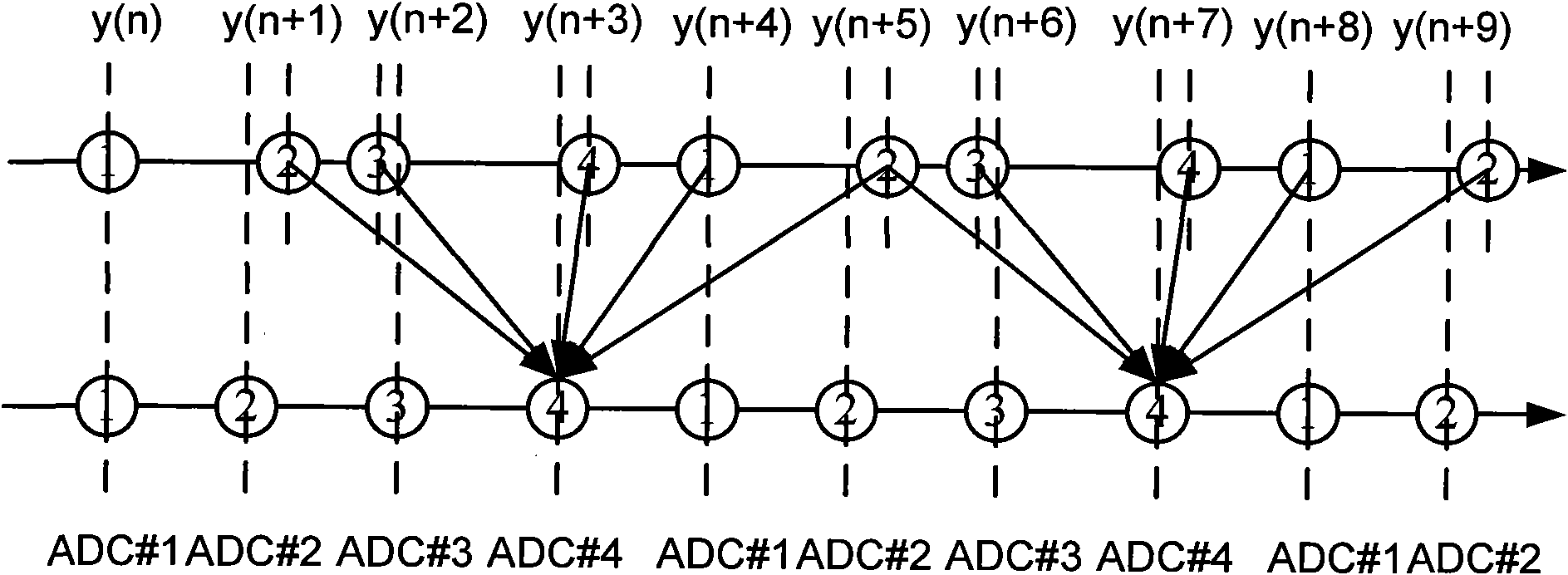

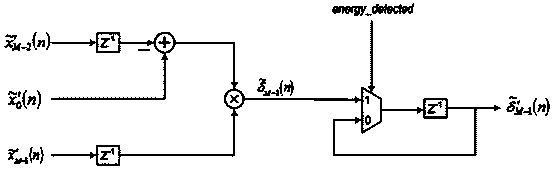

Methods and systems for reducing order-dependent mismatch errors in time-interleaved analog-to-digital converters

ActiveUS9294112B1High dynamic range performanceFast sampling speedElectric signal transmission systemsAnalogue-digital convertersDigital down converterCoupling

A time-interleaved analog-to-digital converter (ADC) uses M sub-analog-to-digital converters (sub-ADCs) to, according to a sequence, sample an analog input signal to produce digital outputs. When the M sub-ADCs are interleaved, the digital outputs exhibit mismatch errors between the M sub-ADCs due to mismatches between the sub-ADCs. A more second order subtle effect is that the mismatch error for a particular digital output from a particular ADC, due to internal coupling or other such interaction and effects between the M sub-ADCs, can vary depending on which sub-ADC(s) were used before and / or after the particular sub-ADC. If M sub-ADCs are time-interleaved randomly, the mismatches between the M sub-ADCs become a function of the sub-ADC selection pattern in the sequence. The present disclosure describes mechanisms for measuring and reducing these order-dependent mismatches to achieve high dynamic range performance in the time-interleaved ADC.

Owner:ANALOG DEVICES INC

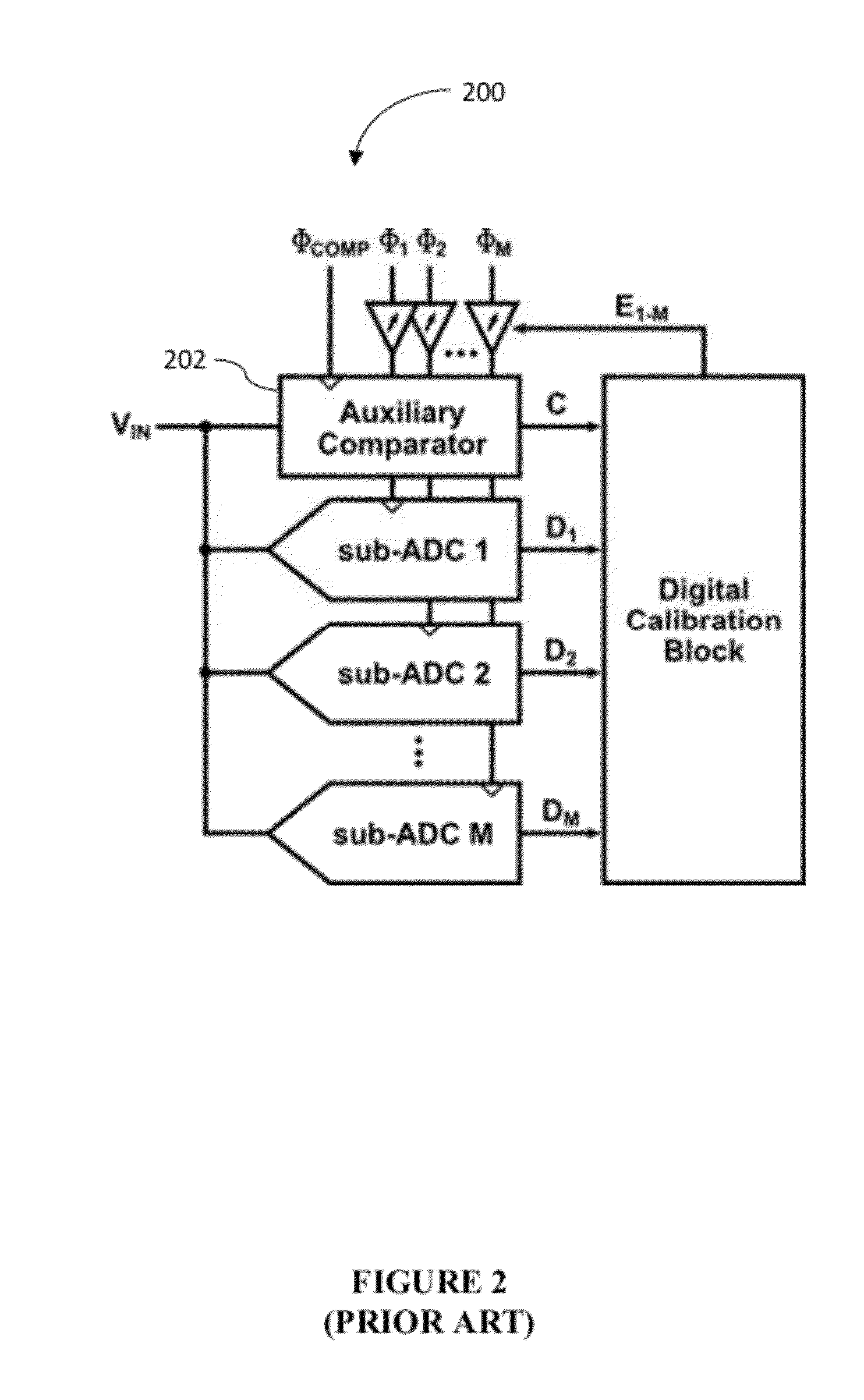

System and Method for Background Calibration of Time Interleaved Analog to Digital Converters

ActiveUS20120262318A1Reduce errorsElectric signal transmission systemsAnalogue/digital conversion calibration/testingTime interleavedAnalog-to-digital converter

Various embodiments allow for background calibration of channel-to-channel mismatch errors.In certain embodiments calibration is accomplished by comparing the output of I-ADCs against the output of a reference ADC and correlating the difference to a known function to obtain a correction signal that can be used to correct channel-to-channel mismatch errors.

Owner:MAXIM INTEGRATED PROD INC

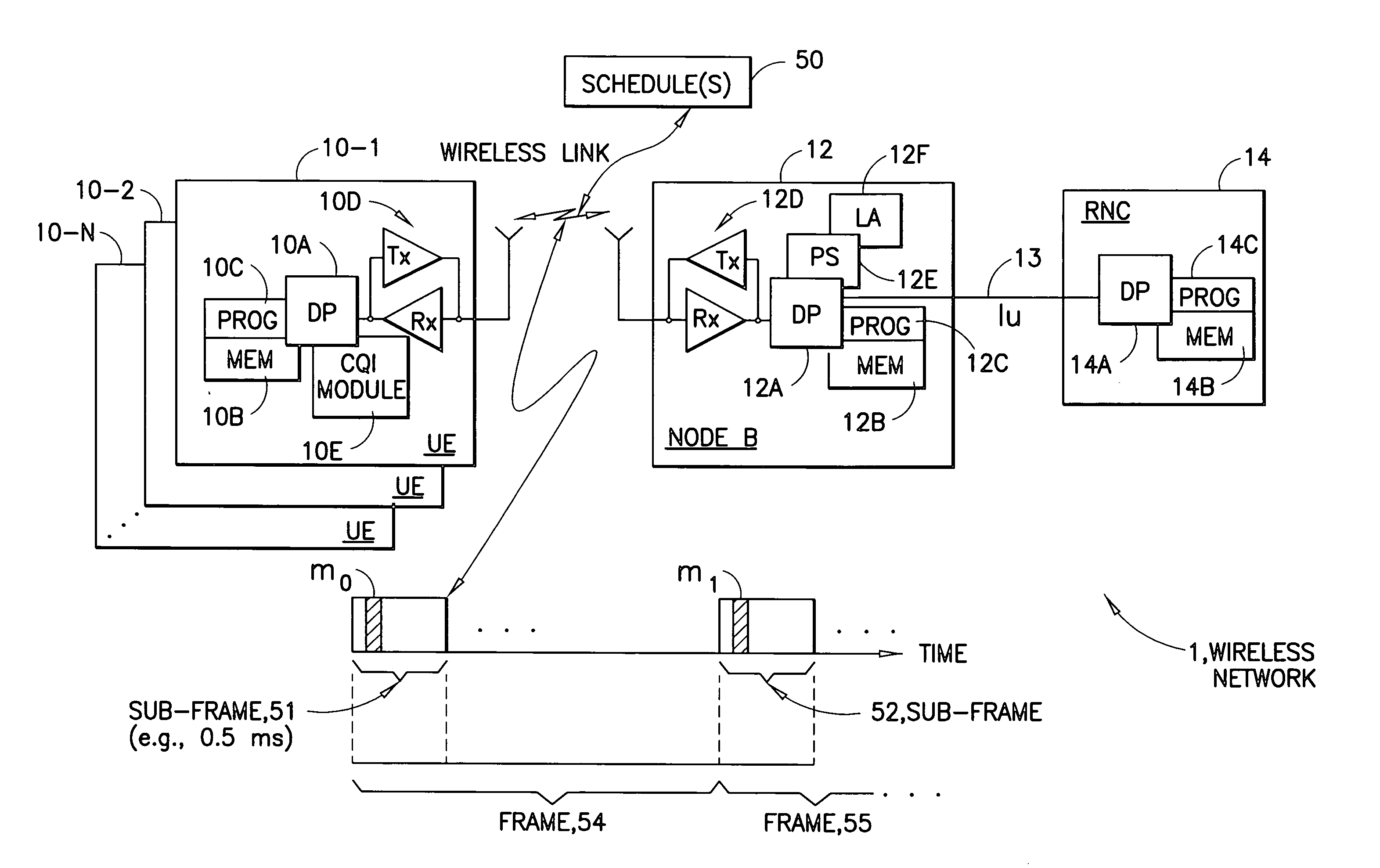

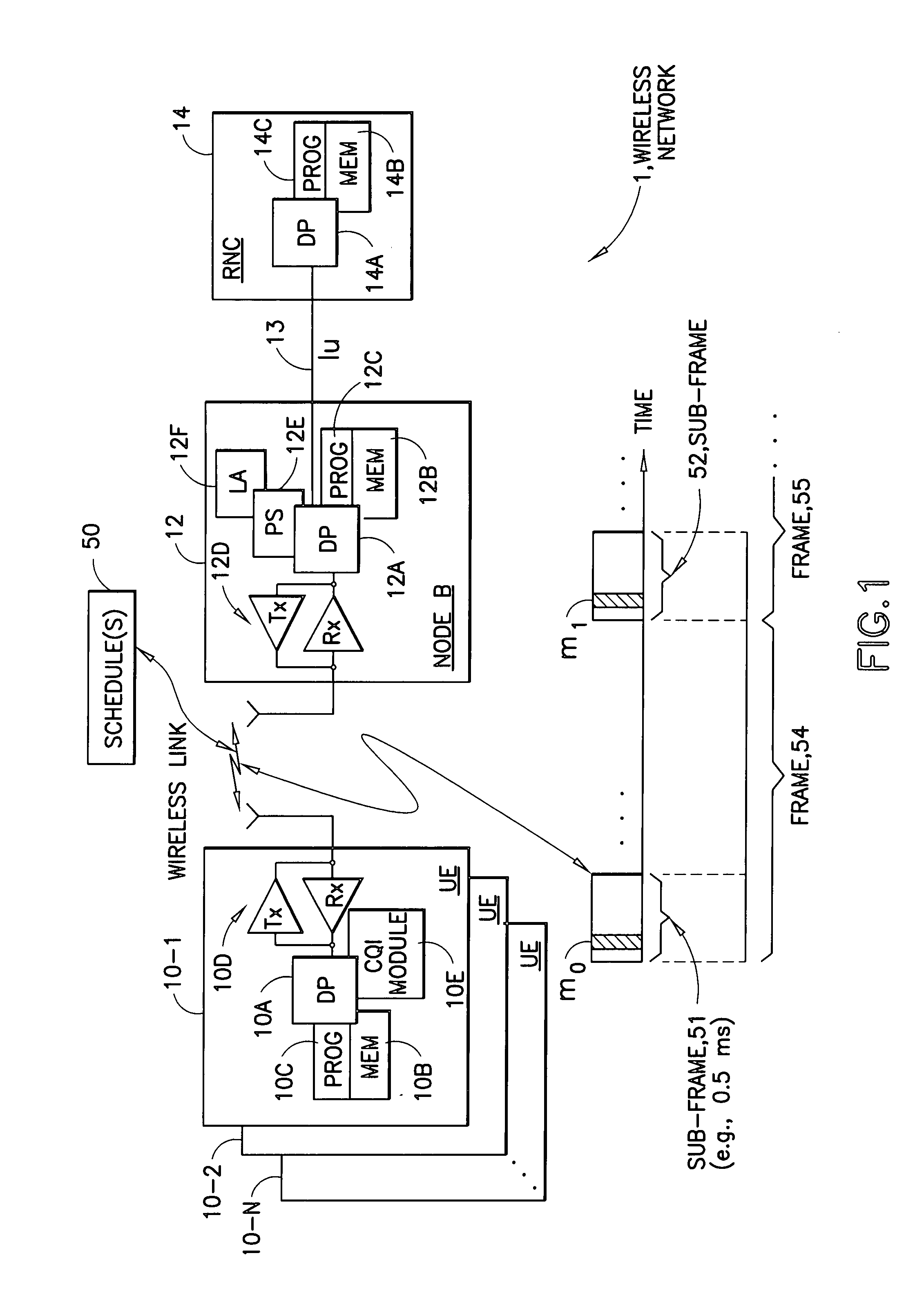

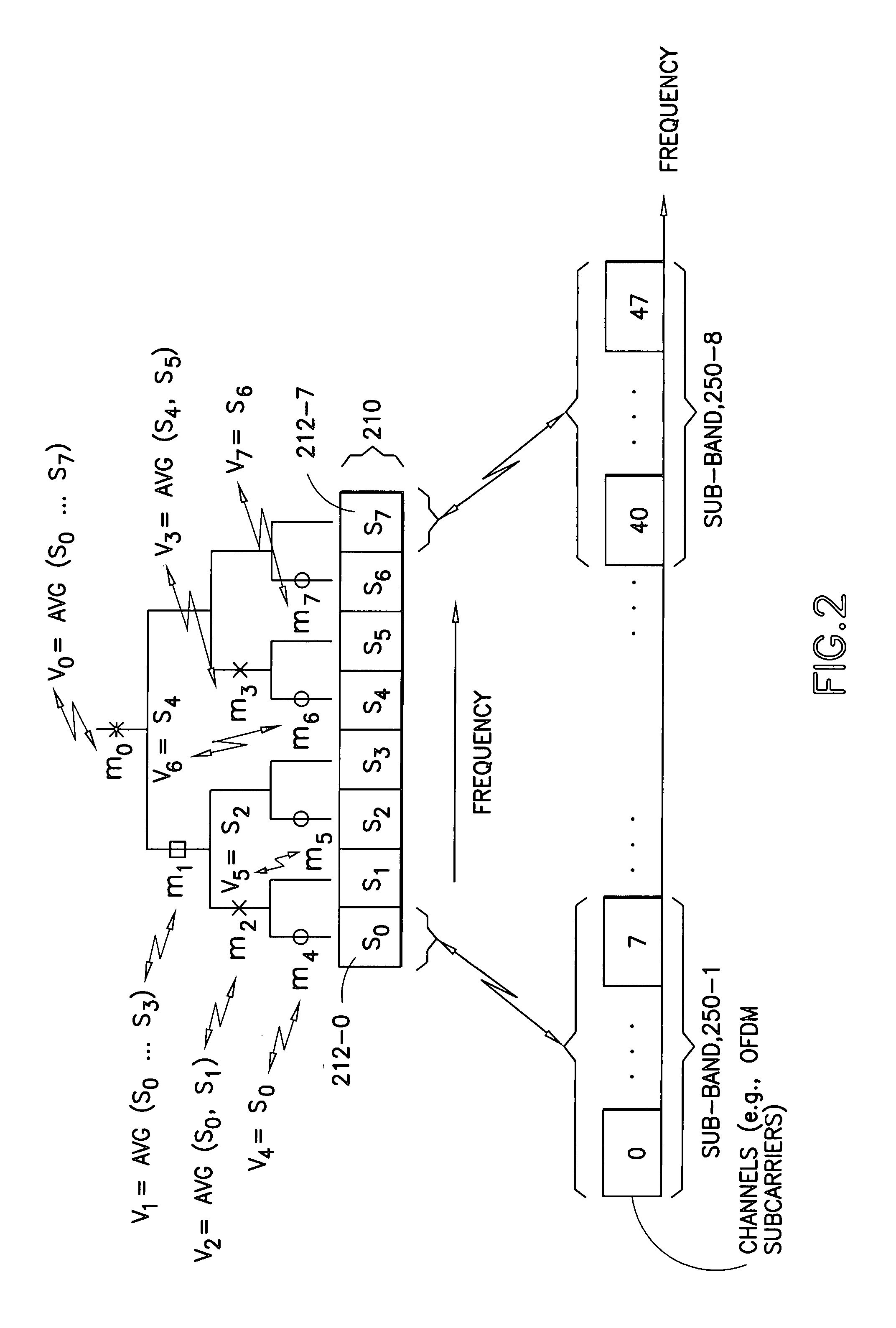

Apparatus, methods and computer program products providing signaling of time staggered measurement reports and scheduling in response thereto

InactiveUS20070224995A1Error detection/prevention using signal quality detectorRadio/inductive link selection arrangementsAdditional valuesTime interleaved

Owner:NOKIA CORP

Estimation circuit for time-interleaved ADC and method thereof

ActiveUS7253762B2Electric signal transmission systemsAnalogue-digital convertersEngineeringTime interleaved

Owner:REALTEK SEMICON CORP

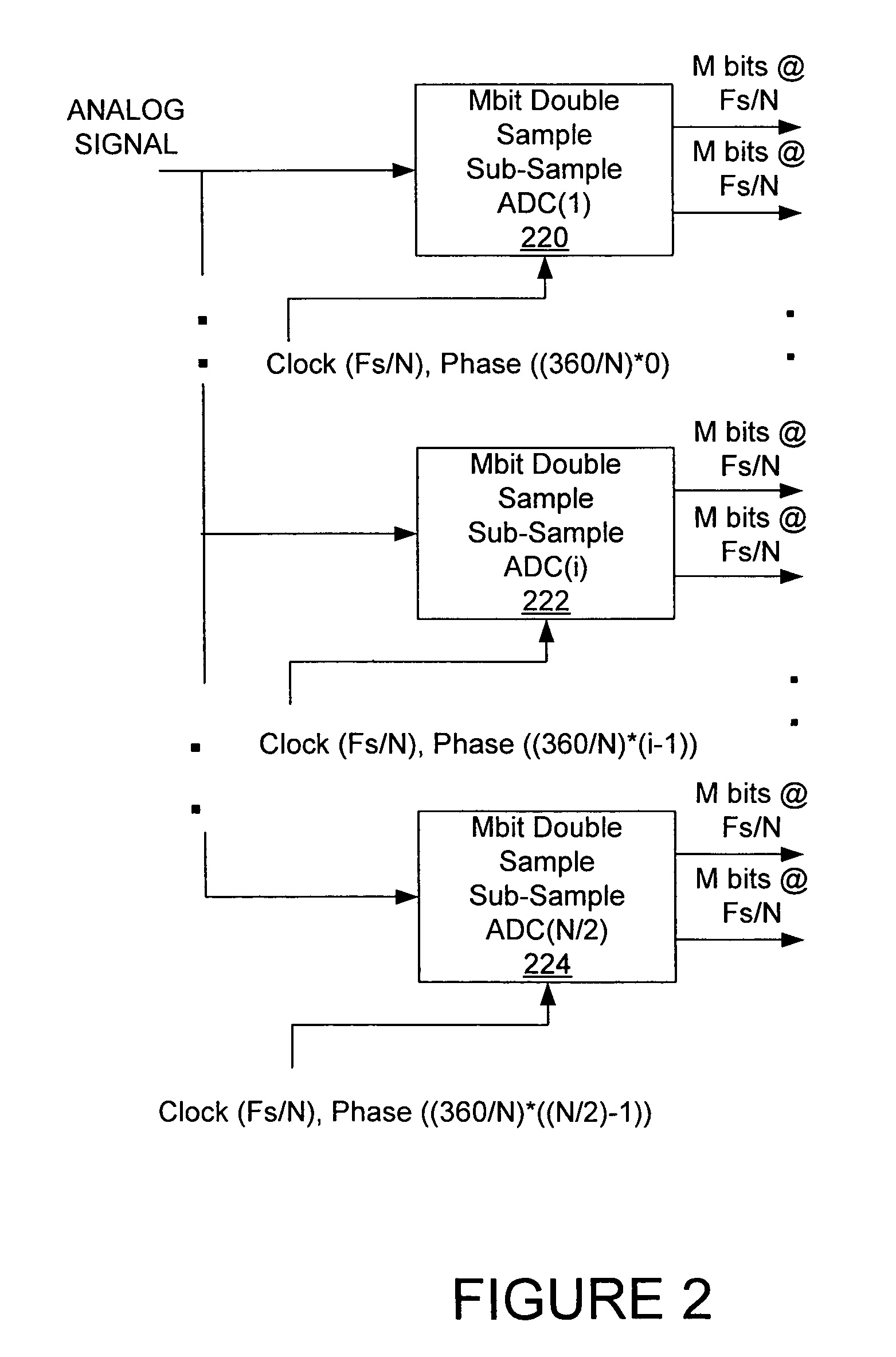

Double-sampled, time-interleaved analog to digital converter

ActiveUS7075471B1Electric signal transmission systemsAnalogue-digital convertersA d converterAnalog signal

An apparatus and method for high-speed analog to digital conversion are disclosed. An ADC system includes a plurality of N / 2 sub-ADCs, each sub-ADC receiving an analog signal and a clock signal and generating two digital samples at a rate of Fs / N. The two digital samples are generated with approximately 180 degree phase relationship relative to a frequency of Fs / N. The plurality of N / 2 sub-ADCs of the time-interleaved ADC system, generate combined output samples at a rate of Fs. An ADC method includes a plurality of N / 2 sub-ADCs receiving the analog signal, clocking each sub-ADC at a rate of FS / N. Each sub-ADC generates two digital samples at a rate of FS / (2N), the two digital samples being generated with approximately 180 degree phase relationship relative to a frequency of Fs / N. Outputs of the sub-ADCs are combined to generate digital samples at a rate of Fs.

Owner:AVAGO TECH INT SALES PTE LTD

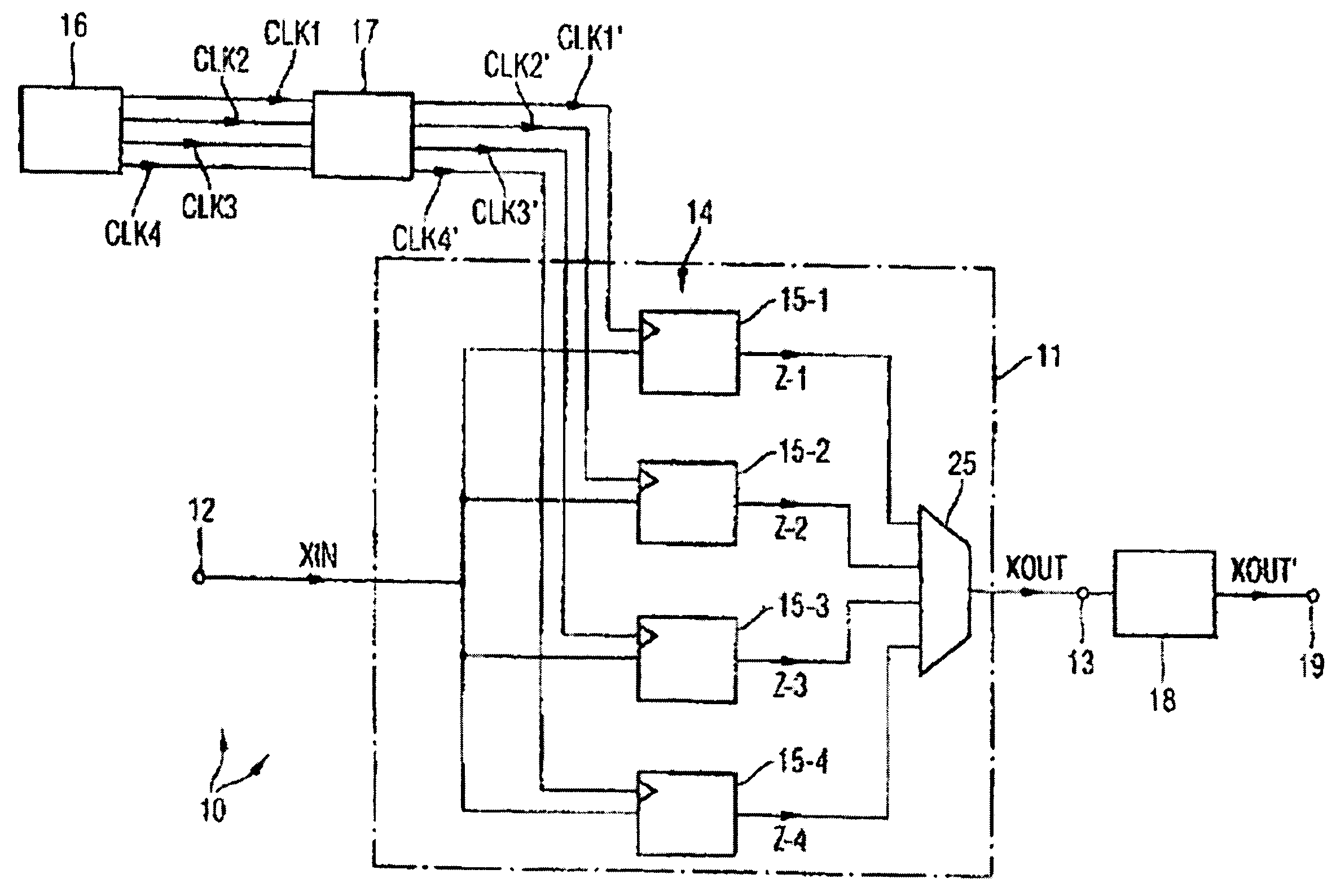

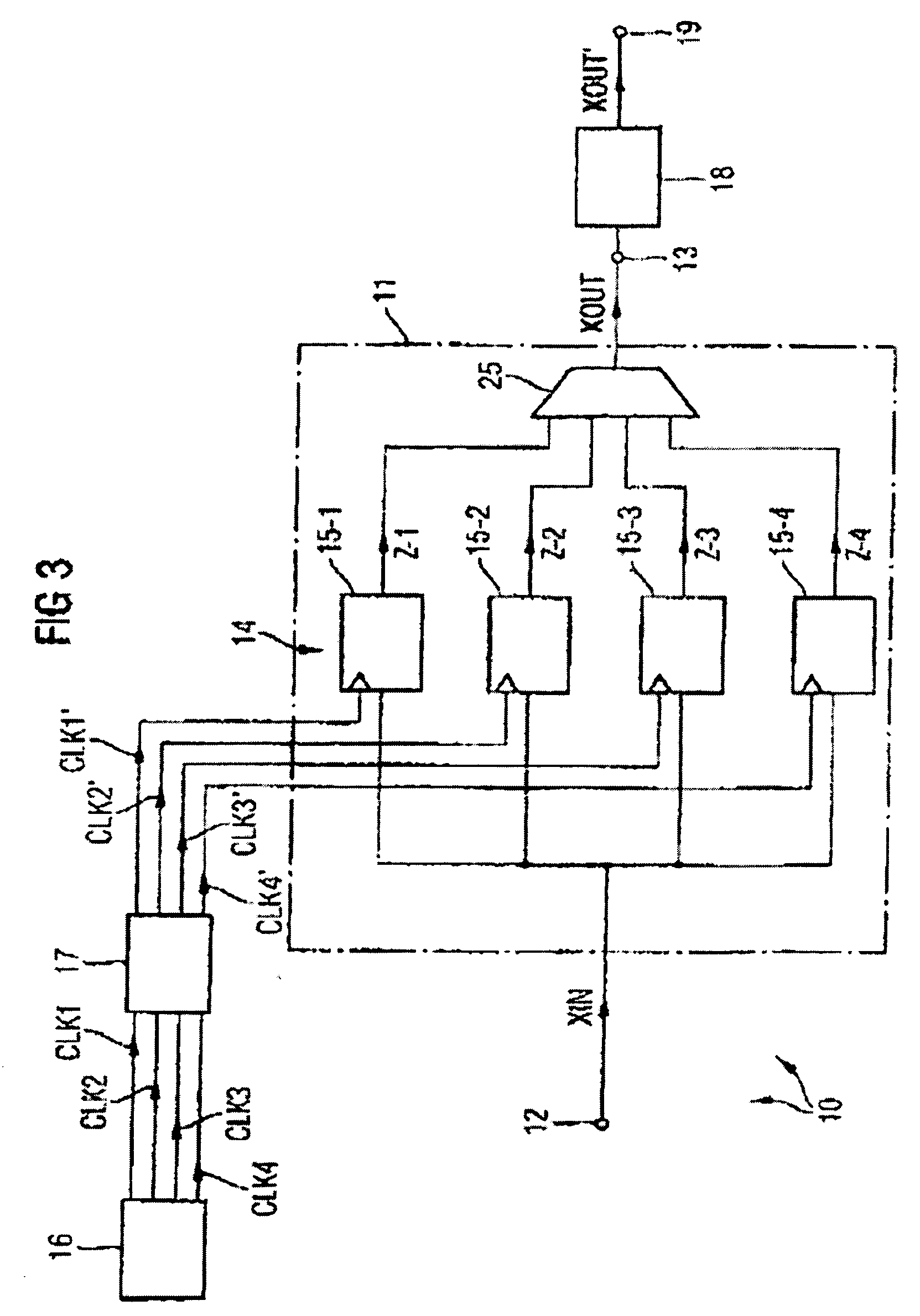

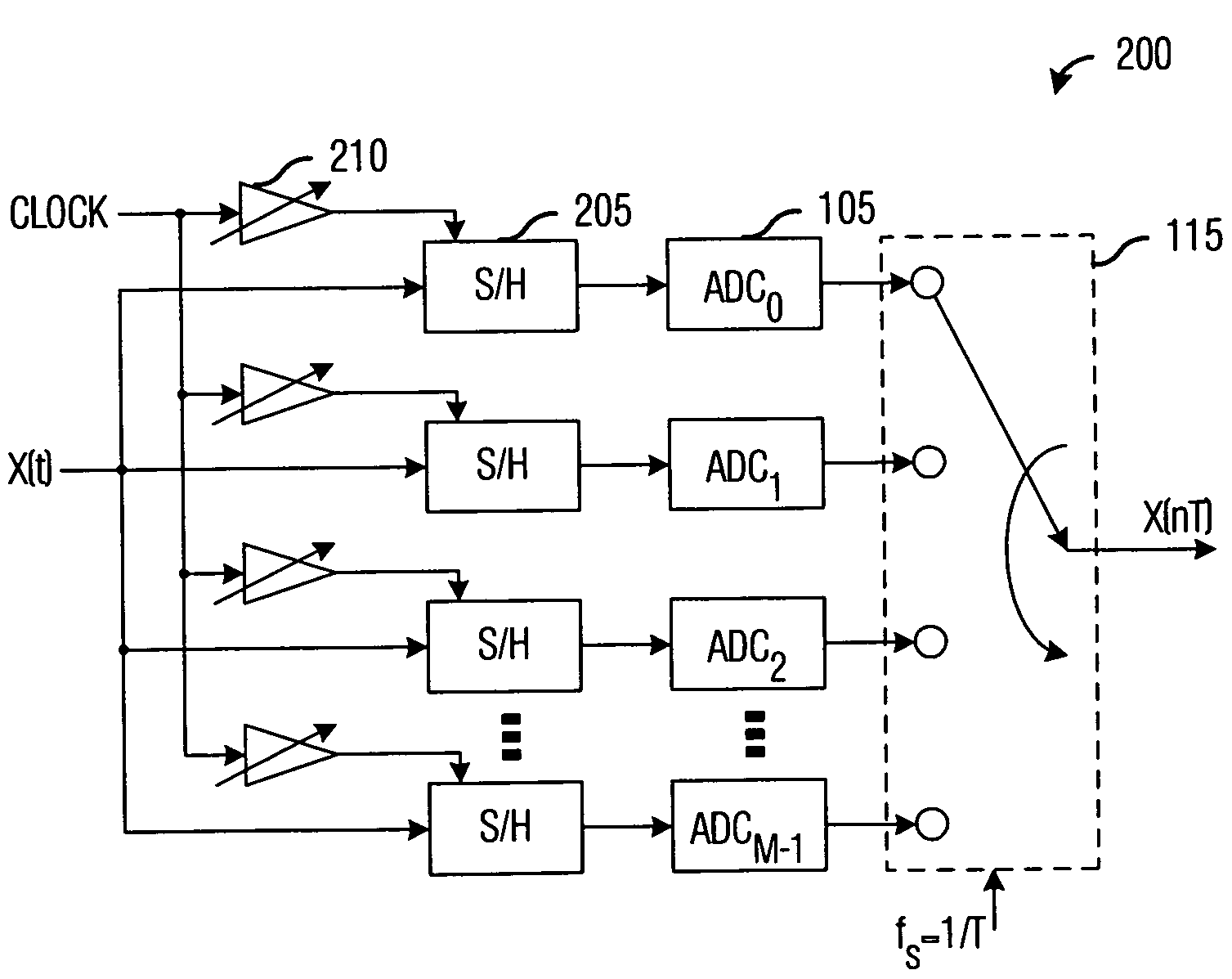

System and method for improved time-interleaved analog-to-digital converter arrays

ActiveUS7292170B2Reduce distortion problemsReducing non-uniform sample mismatchElectric signal transmission systemsAnalogue conversionEngineeringTime interleaved

System and method for improved time-interleaved analog-to-digital converter arrays which reduces sampling mismatch distortion found in prior art arrays. There may be two causes of non-uniform sampling mismatch in a TI-ADC array, a mismatch due to skew and a mismatch due to clock jitter. To minimize non-uniform sampling mismatch, the mismatch due to skew can be addressed. A preferred embodiment comprises adjusting a delay imparted on the sampling clock by an adjustable delay in each channel of a plurality of channels in the TI-ADC array to minimize skew and randomly switching between two delays that span a zero-skew delay to reduce residual skew in each channel and thus eliminate (or reduce) frequency domain tones caused by non-uniform sampling mismatch.

Owner:TEXAS INSTR INC

Time-interleaved simulcast for tune-in reduction

InactiveUS20080301742A1Error resiliencyColor television with pulse code modulationColor television with bandwidth reductionSource materialBroadcast transmission

A system and method for providing faster tuning into a chosen program in a time-sliced multicast and / or broadcast transmission environment. Multimedia data of the same source material but of different transmission and presentation characteristics are coded and compressed. According to various embodiments, simulcast streams of a program are time-sliced, placed maximally apart from each other in terms of transmission time, and sent over the channel.

Owner:NOKIA CORP