Patents

Literature

175 results about "Fixed sequence" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A fixed-sequence robot is a robot that performs a single, preprogrammed task or set of tasks, making exactly the same movements each time. There is no exception or variation to the routine. Fixed-sequence robots are ideally suited to assembly-line work.

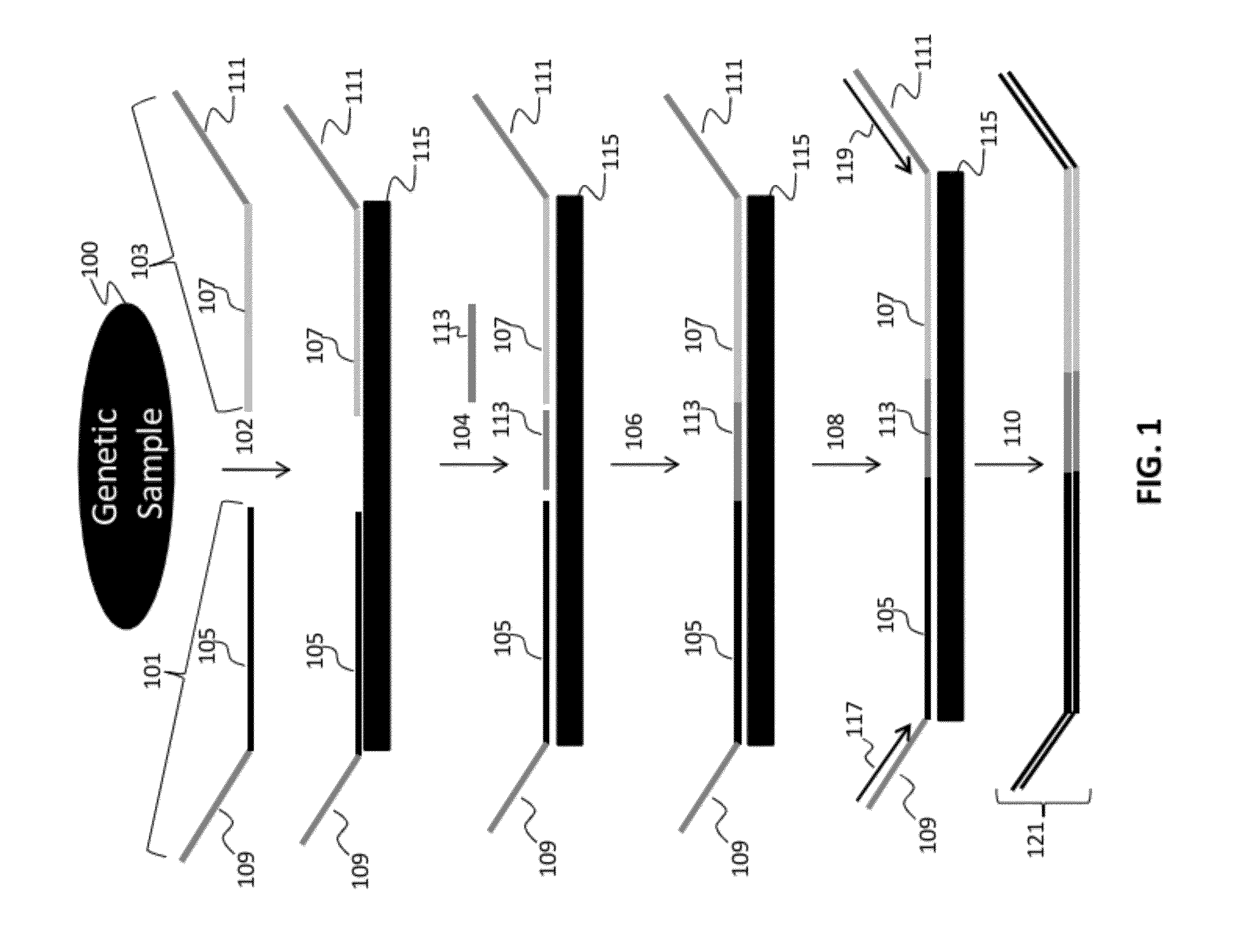

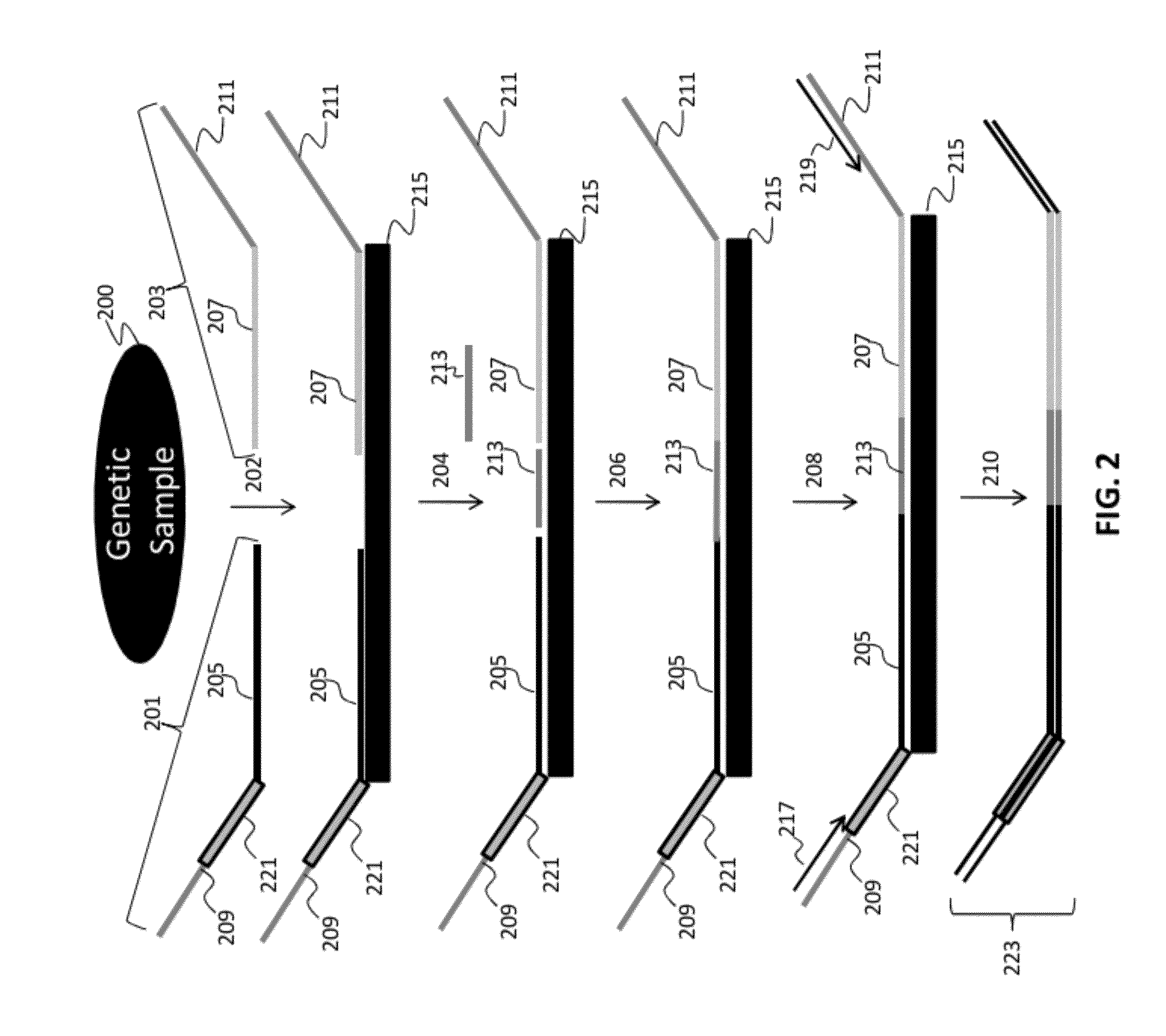

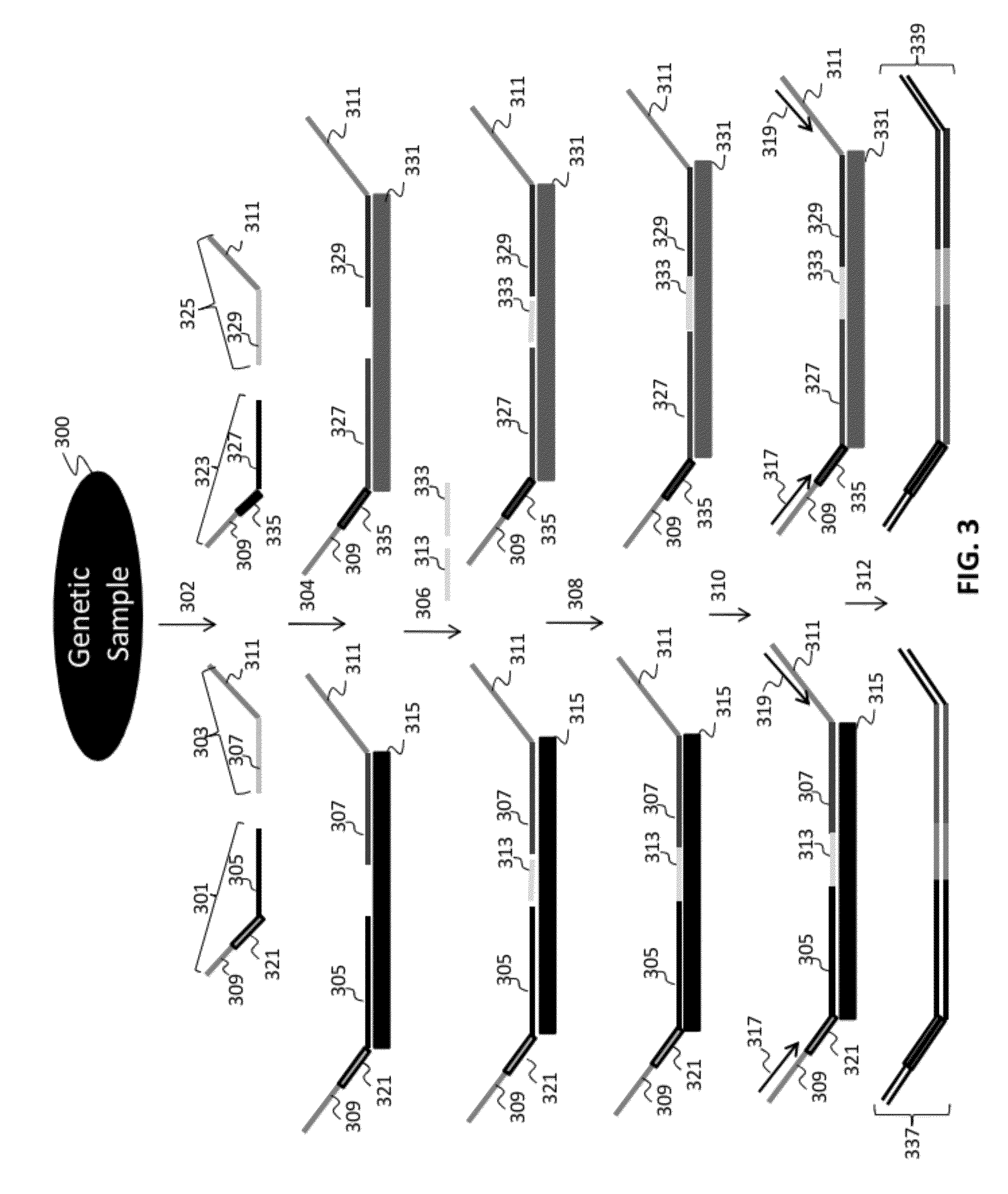

Ligation-based detection of genetic variants

InactiveUS20120034603A1Eliminate needElimination contentMicrobiological testing/measurementGeneticsOligonucleotide

The present invention provides assays systems and methods for detection of genetic variants in a sample, including copy number variation and single nucleotide polymorphisms. The invention preferably employs the technique of tandem ligation, i.e. the ligation of two or more fixed sequence oligonucleotides and one or more bridging oligonucleotides complementary to a region between the fixed sequence oligonucleotides.

Owner:TANDEM DIAGNOSTICS

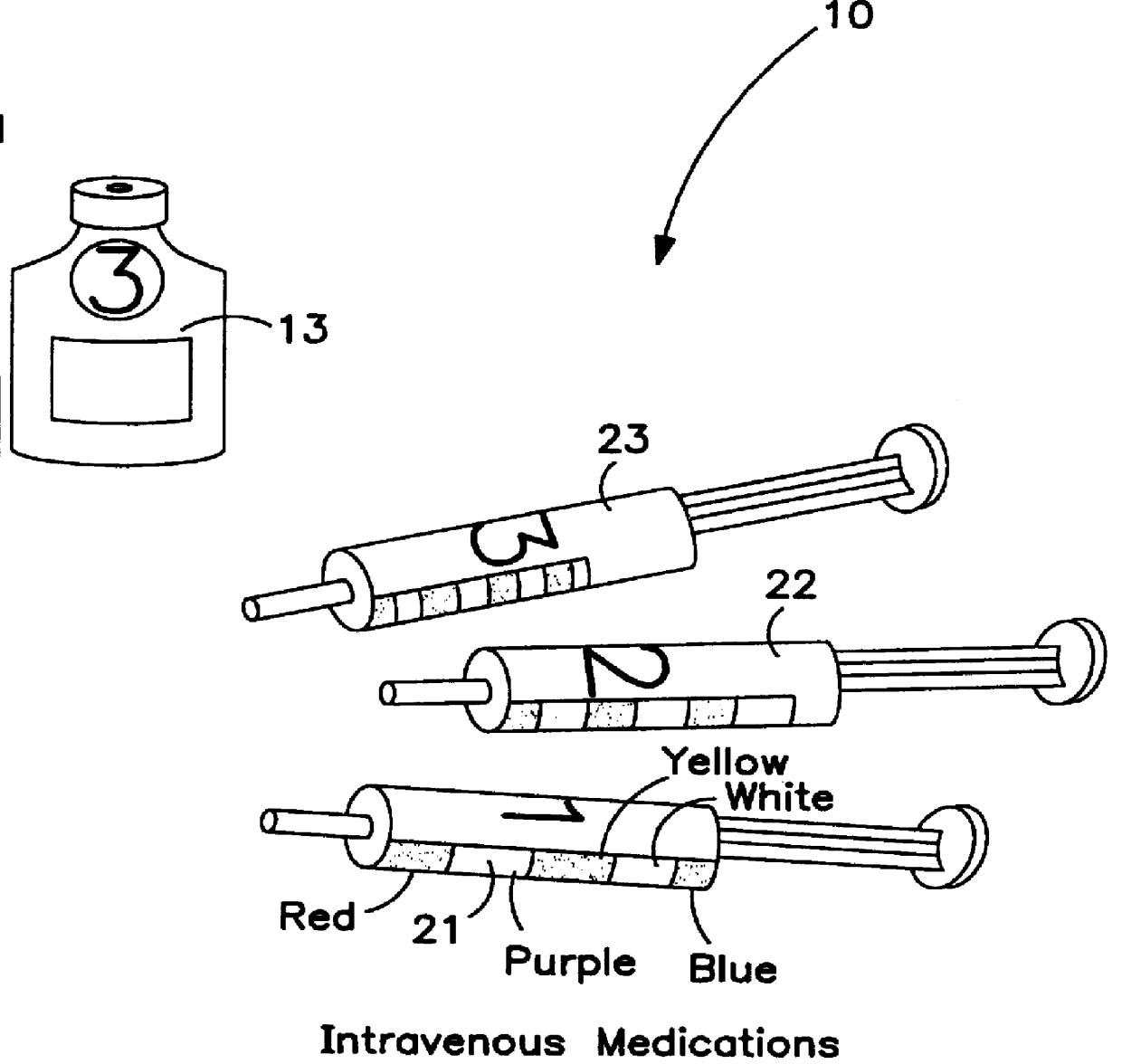

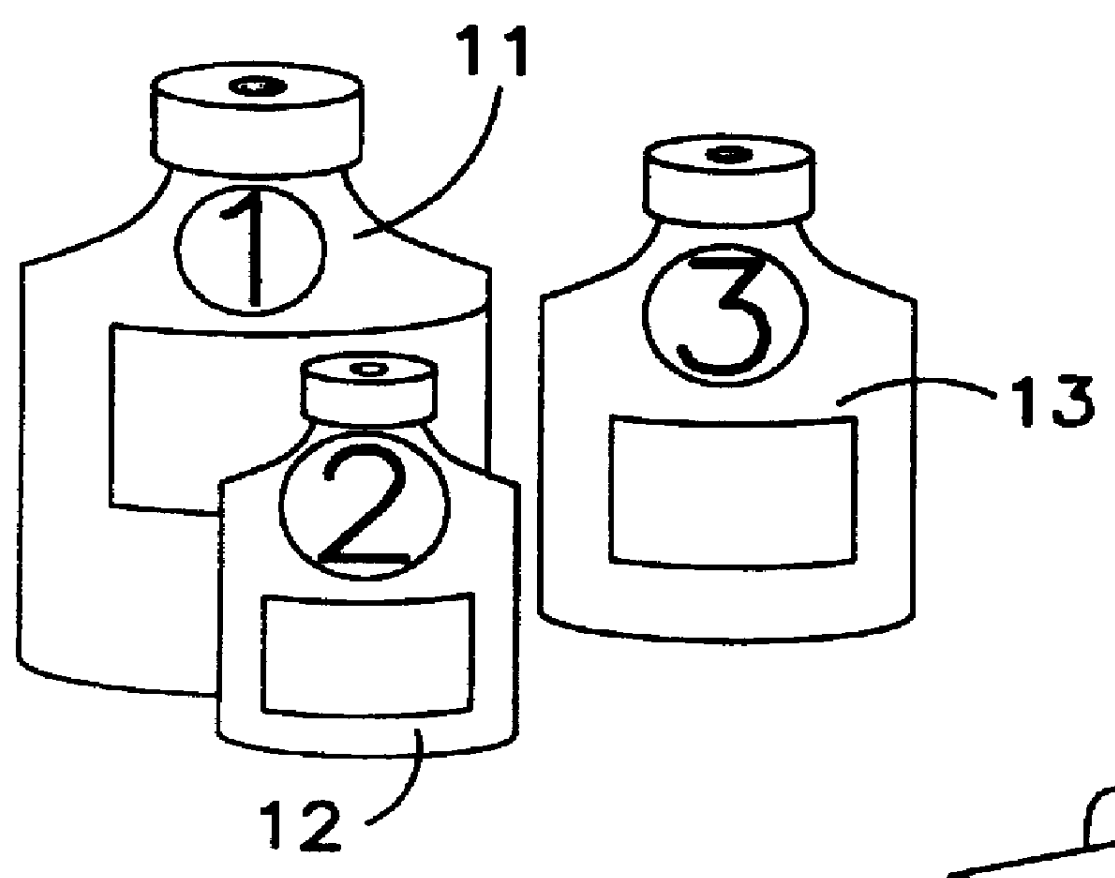

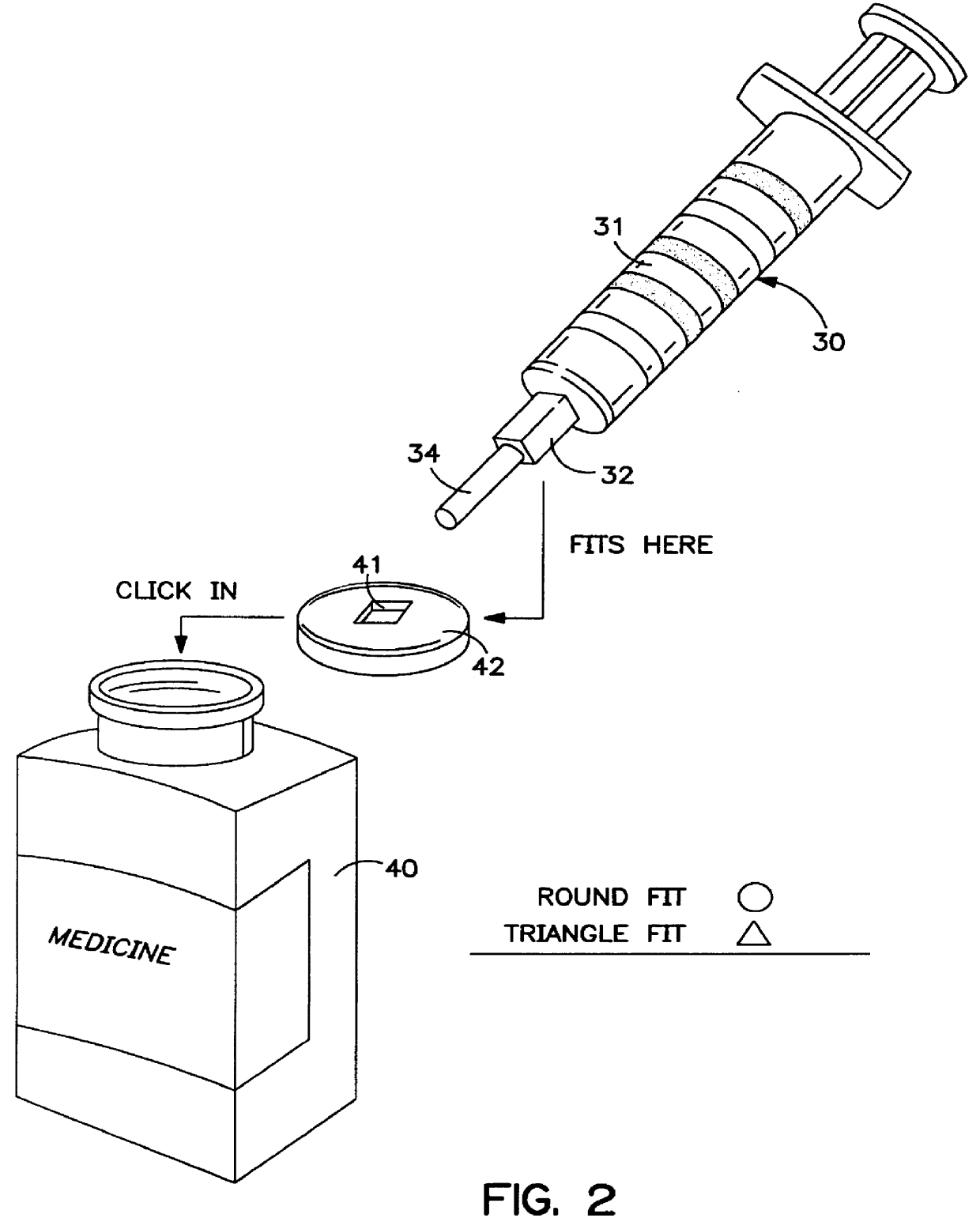

Universal medication dosing system

InactiveUS6132416AReduce the possibilityDosing becomes easy and reliableDiagnosticsSurgeryMedication doseWeight range

A method of determining the proper medication dosage for a patient, including the steps of correlating a plurality of dosages of a plurality of medications to respective weight-related values indicative of the proper dosage of each of the medications for a given patient weight range, assigning a color to each of the respective weight-related values within a predetermined, fixed sequence of colors collectively representing a dosage range for each of the medications, wherein each of the colors represents a proper dosage for each medication for a patient having a weight within the weight range to which the color is assigned, and providing a dosing system which correlates each of the dosages of the medications with the assigned color within the fixed sequence of colors without regard to the potency of said medication.

Owner:CERTA DOSE INC

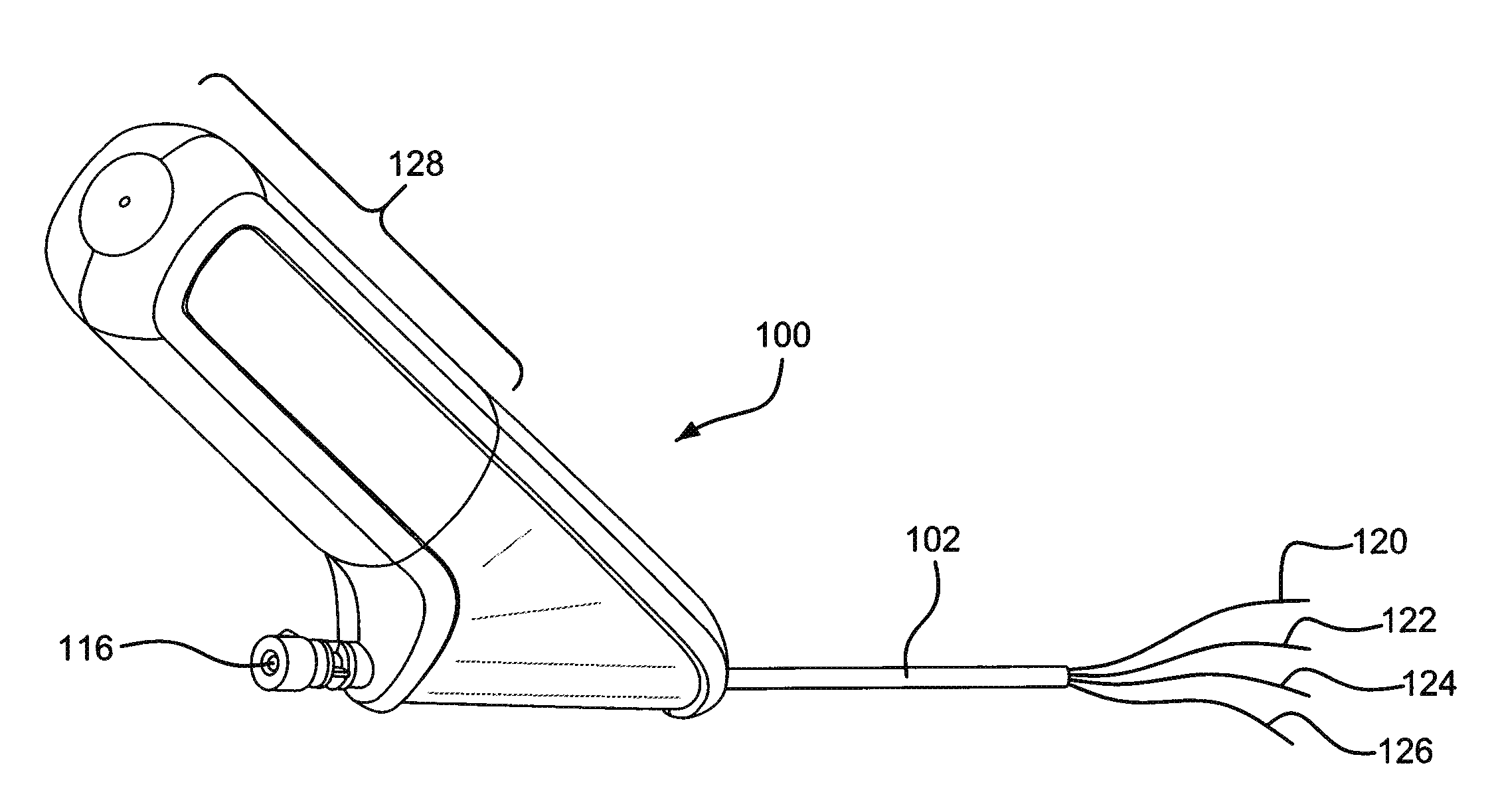

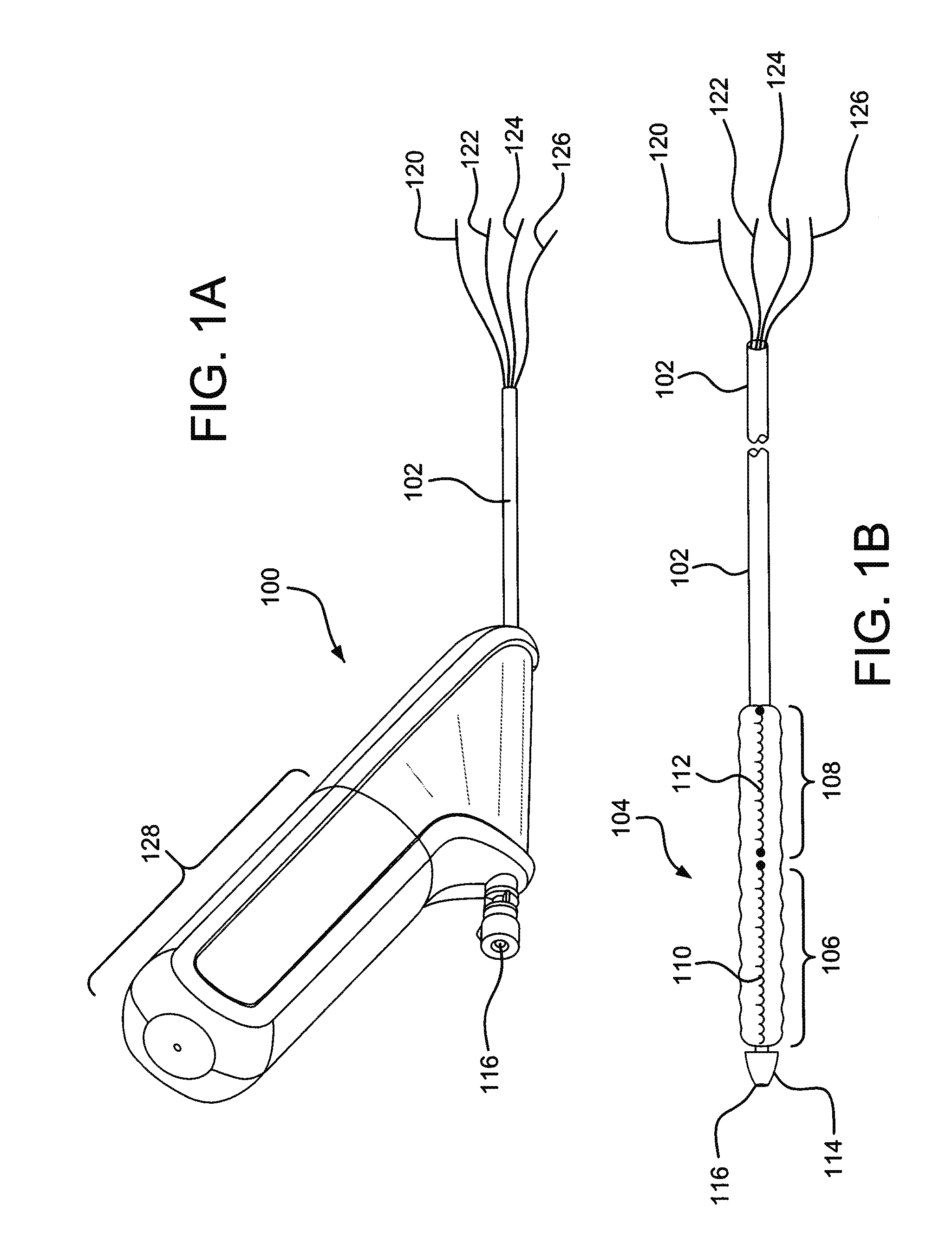

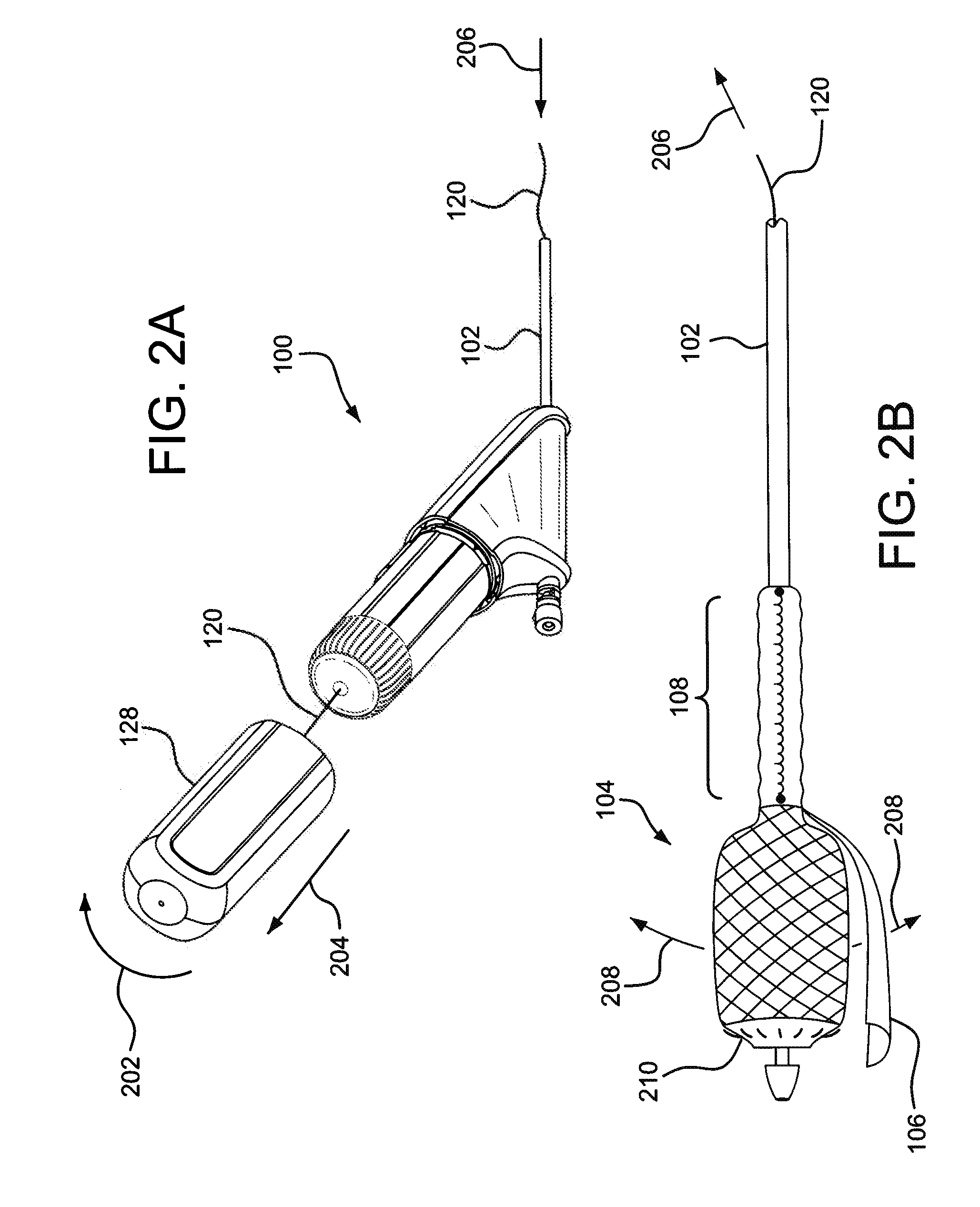

Forced deployment sequence

ActiveUS20100211052A1Suitable for useStentsRopes and cables for vehicles/pulleyBiological activationMedical device

A fixed sequence activation handle is described that forces a predetermined activation sequence. Such handles are suitable for use in the delivery of medical devices or for other application that require a fixed sequence of activations.

Owner:WL GORE & ASSOC INC

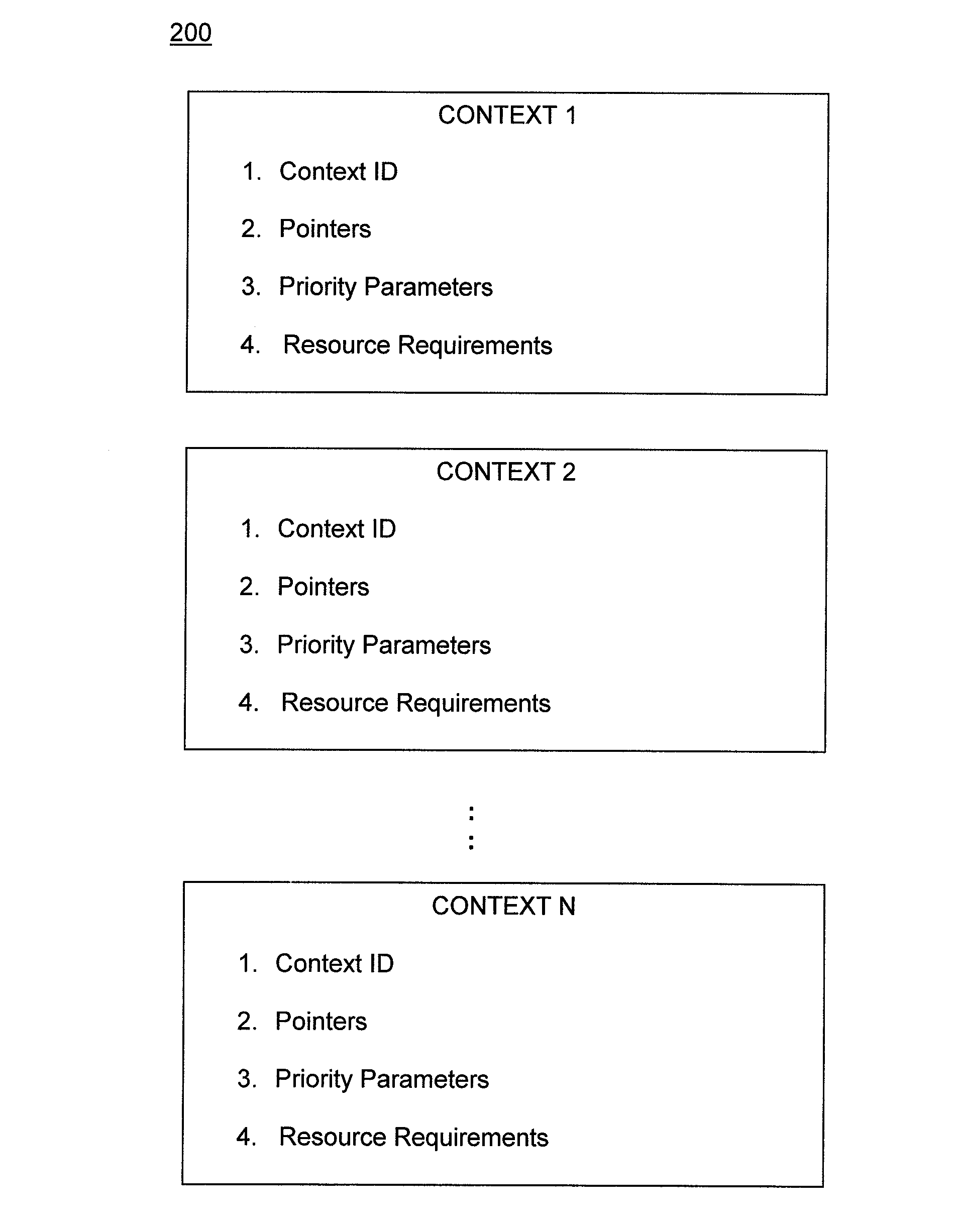

Autonomous Context Scheduler For Graphics Processing Units

InactiveUS20090160867A1Processor architectures/configuration3D-image renderingMultiple contextGraphics

Embodiments directed to an autonomous graphics processing unit (GPU) scheduler for a graphics processing system are described. Embodiments include an execution structure for a host CPU and GPU in a computing system that allows the GPU to execute command threads in multiple contexts in a dynamic rather than fixed order based on decisions made by the GPU. This eliminates a significant amount of CPU processing overhead required to schedule GPU command execution order, and allows the GPU to execute commands in an order that is optimized for particular operating conditions. The context list includes parameters that specify task priority and resource requirements for each context. The GPU includes a scheduler component that determines the availability of system resources and directs execution of commands to the appropriate system resources, and in accordance with the priority defined by the context list.

Owner:ADVANCED MICRO DEVICES INC

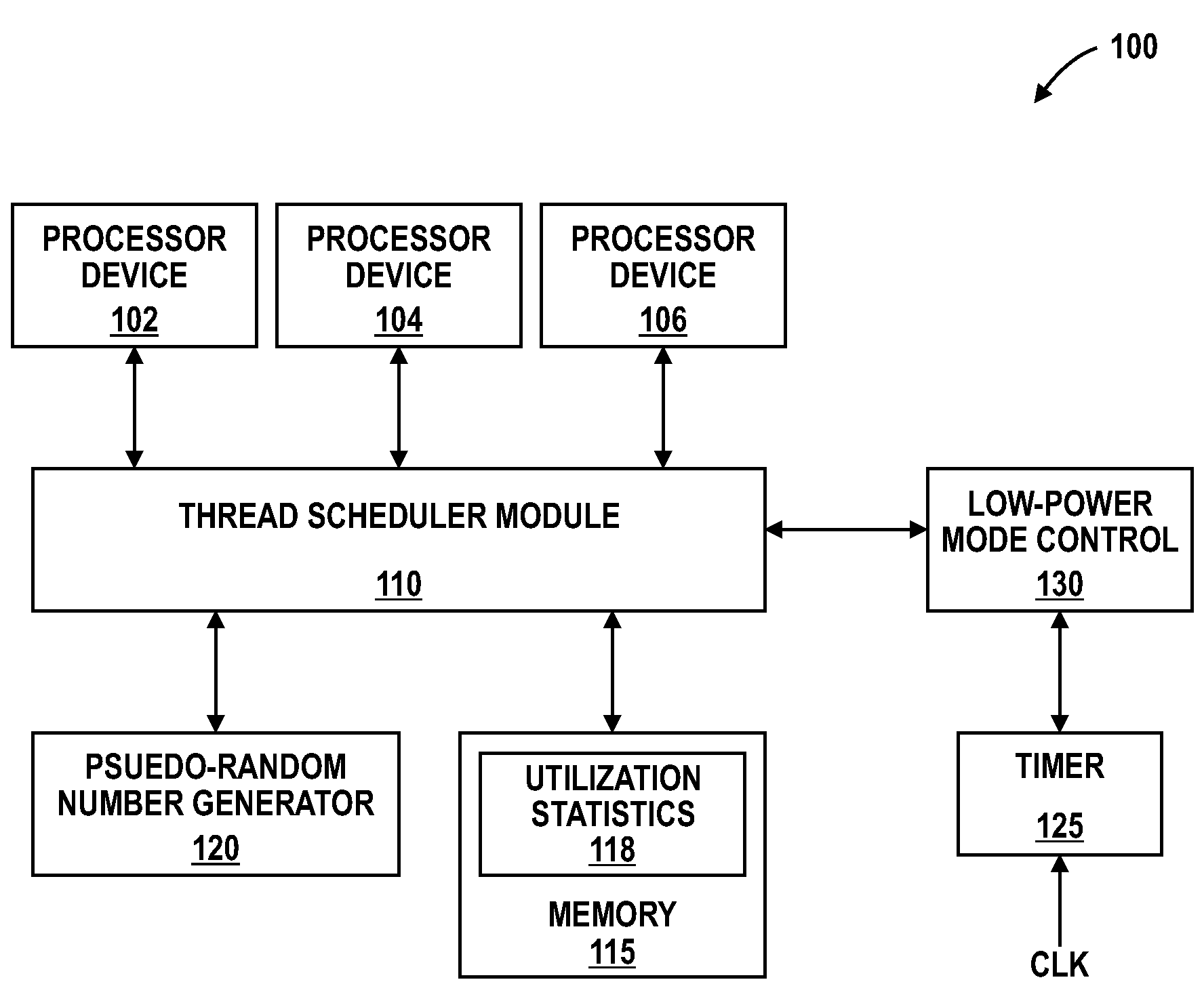

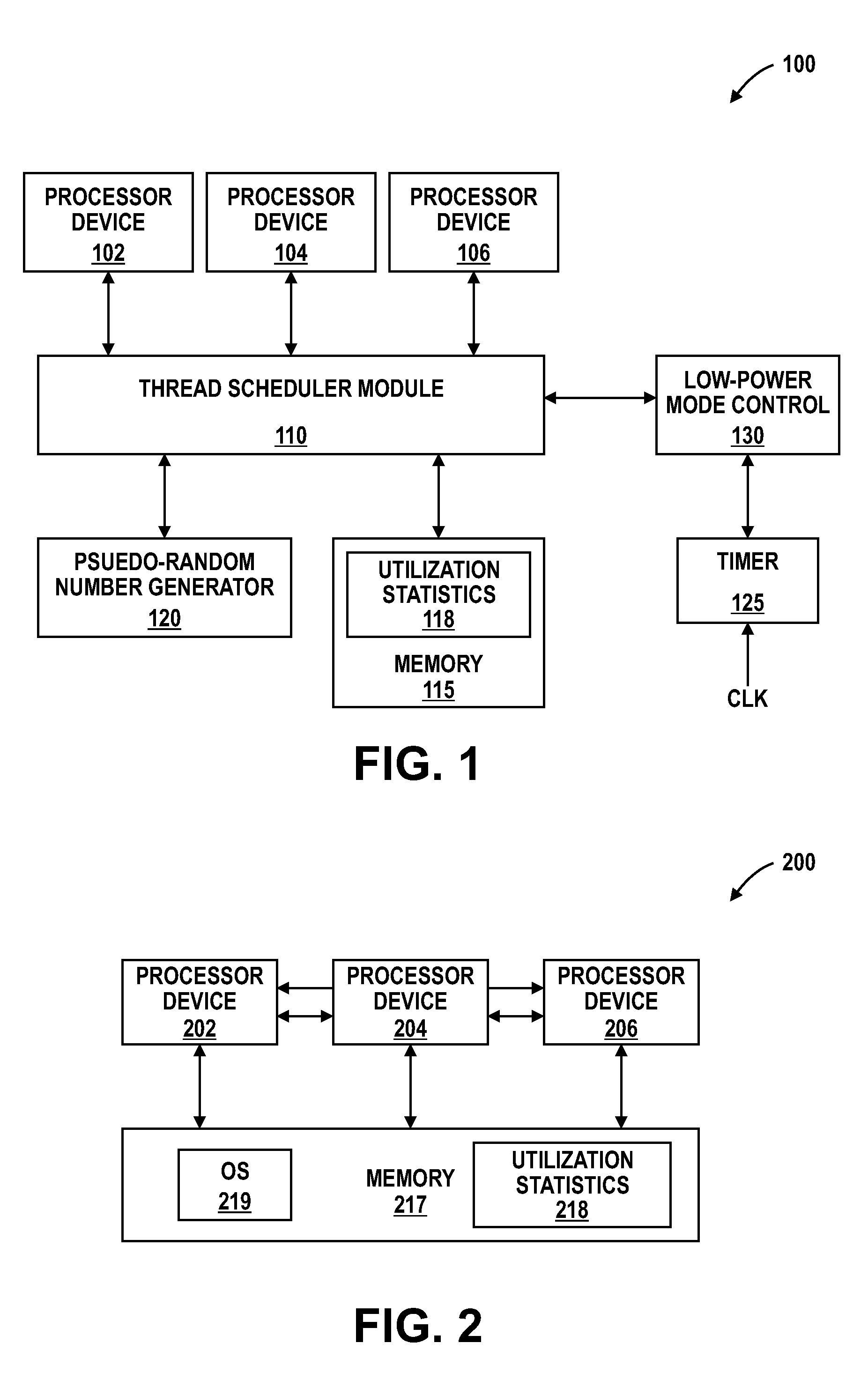

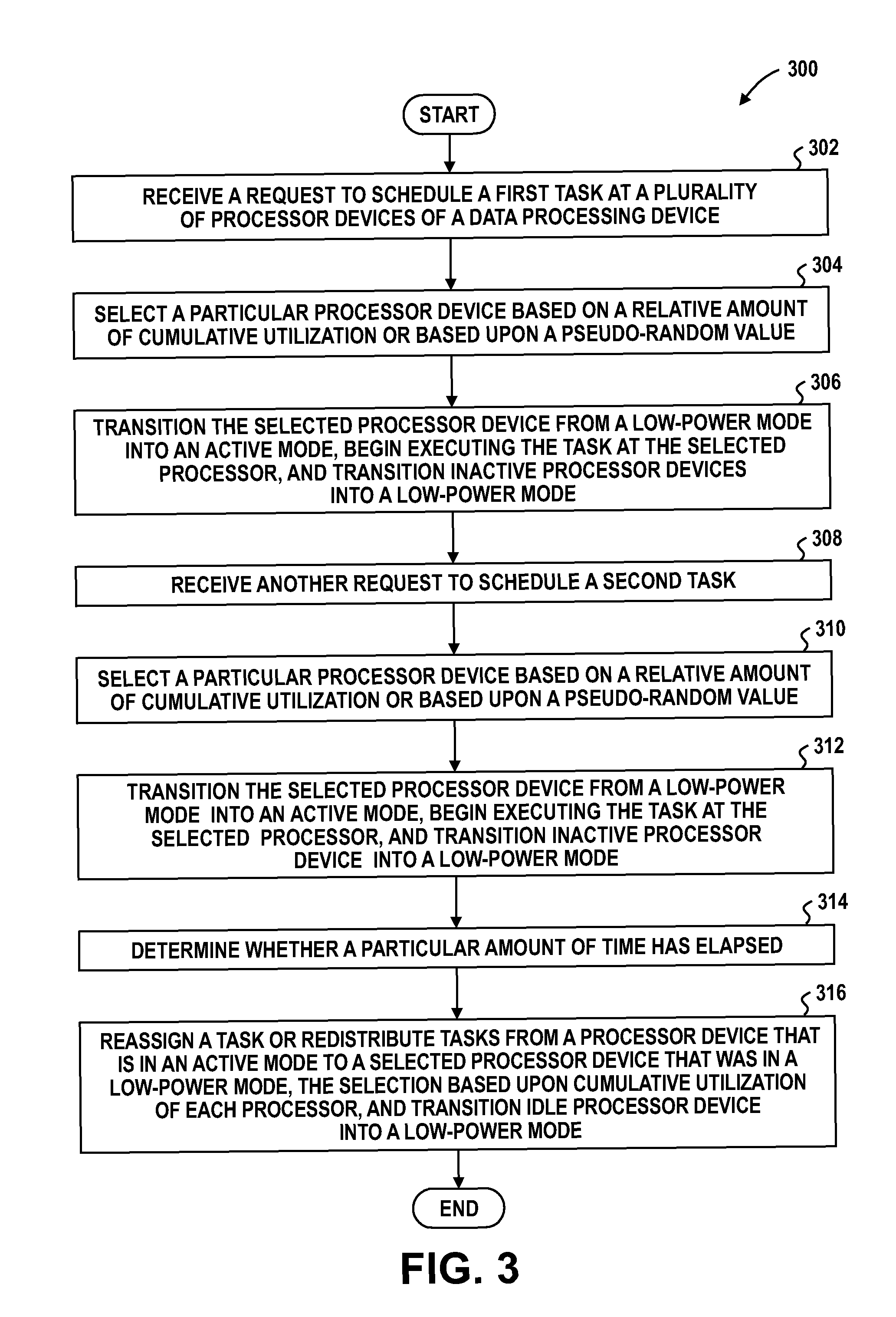

Scheduler for processor cores and methods thereof

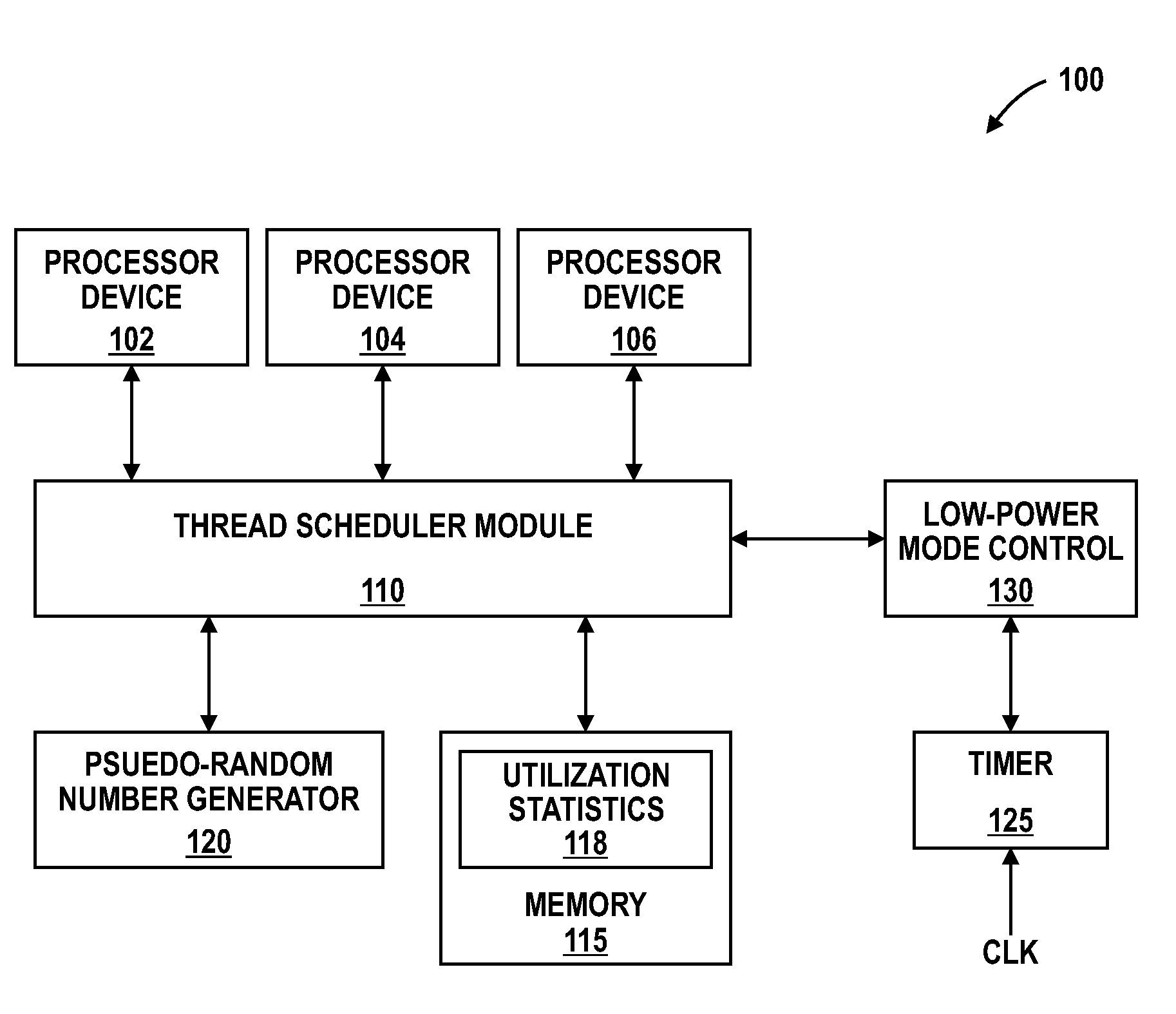

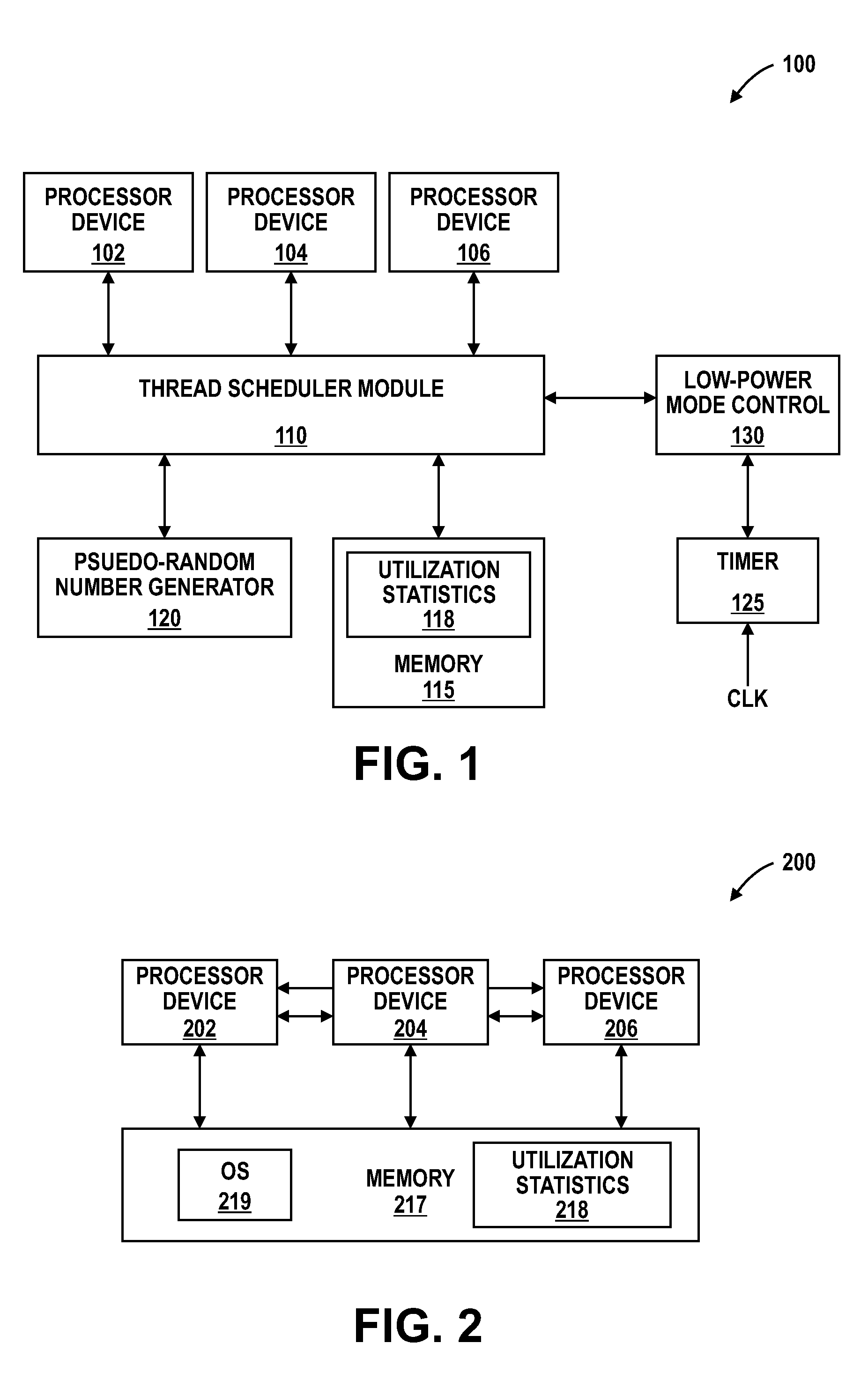

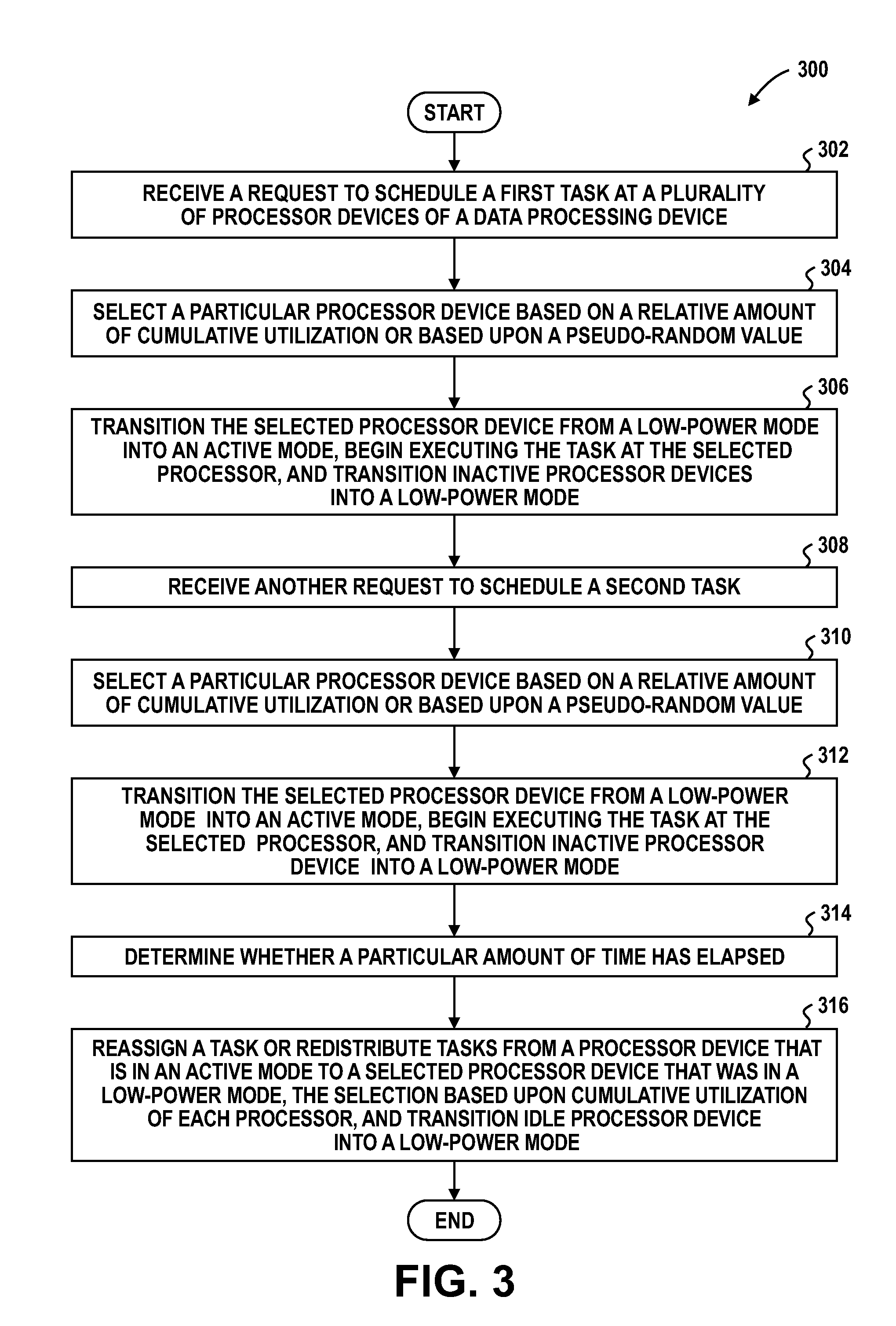

ActiveUS20100107166A1Digital computer detailsMultiprogramming arrangementsParallel computingFixed sequence

A data processing device assigns tasks to processor cores in a more distributed fashion. In one embodiment, the data processing device can schedule tasks for execution amongst the processor cores in a pseudo-random fashion. In another embodiment, the processor core can schedule tasks for execution amongst the processor cores based on the relative amount of historical utilization of each processor core. In either case, the effects of bias temperature instability (BTI) resulting from task execution are distributed among the processor cores in a more equal fashion than if tasks are scheduled according to a fixed order. Accordingly, the useful lifetime of the processor unit can be extended.

Owner:MEDIATEK INC

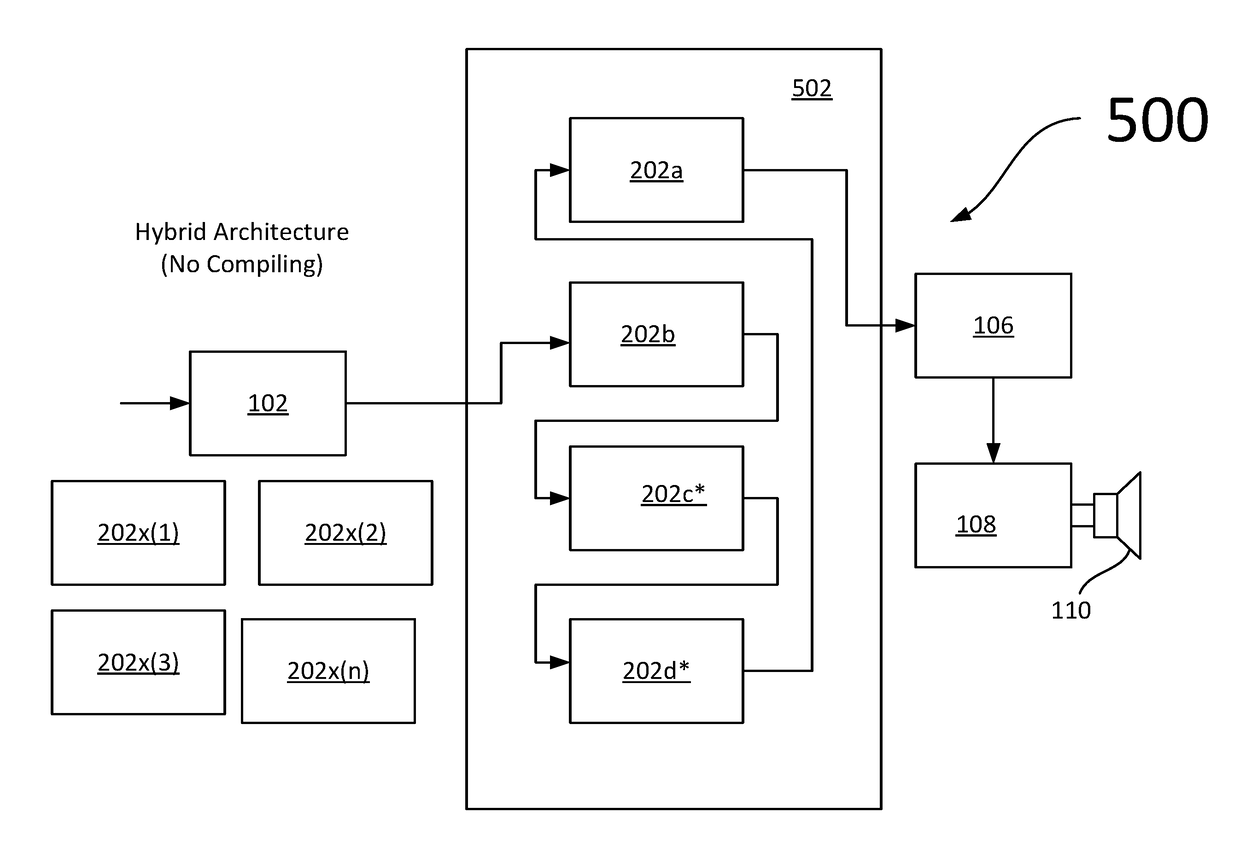

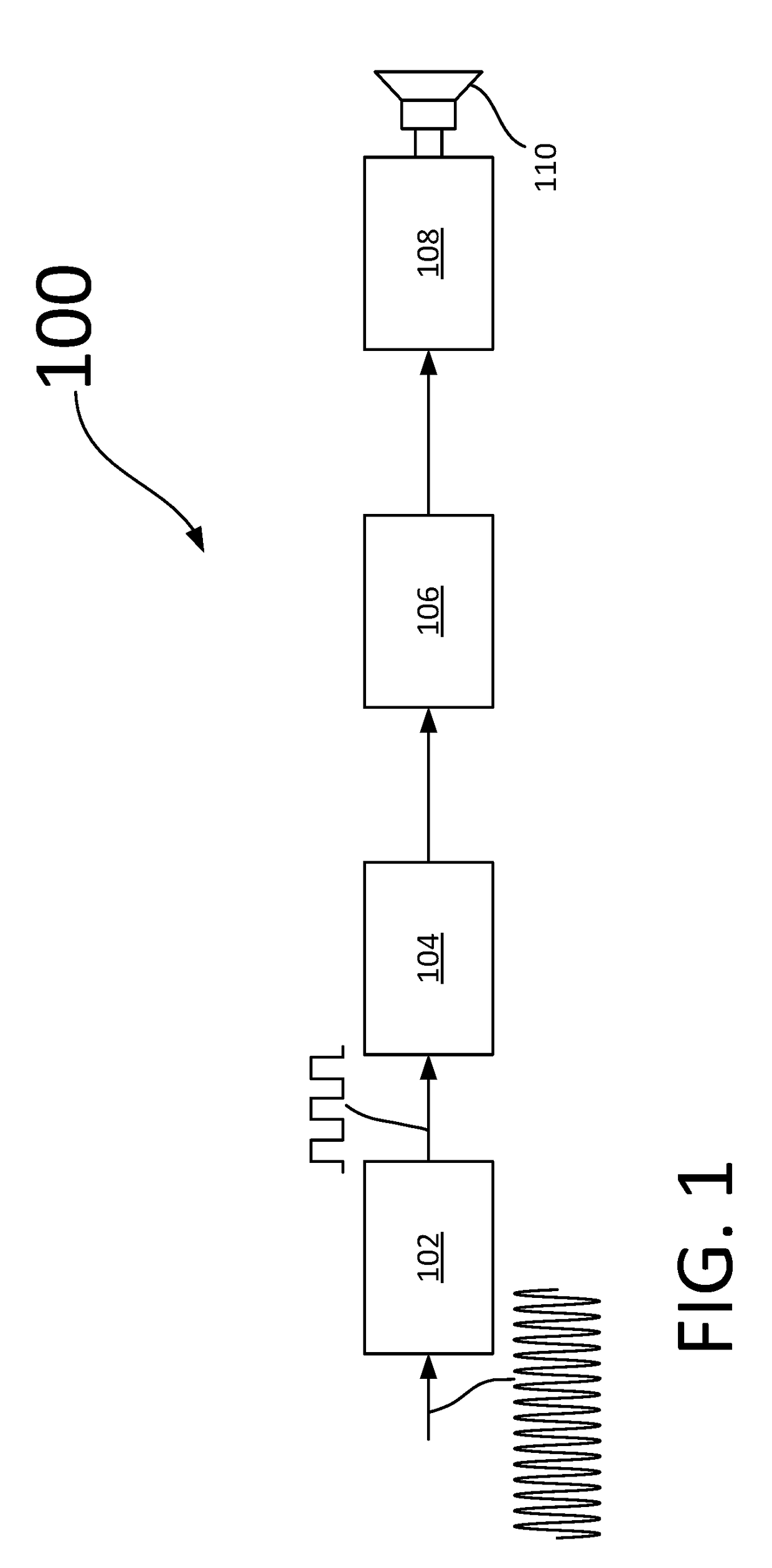

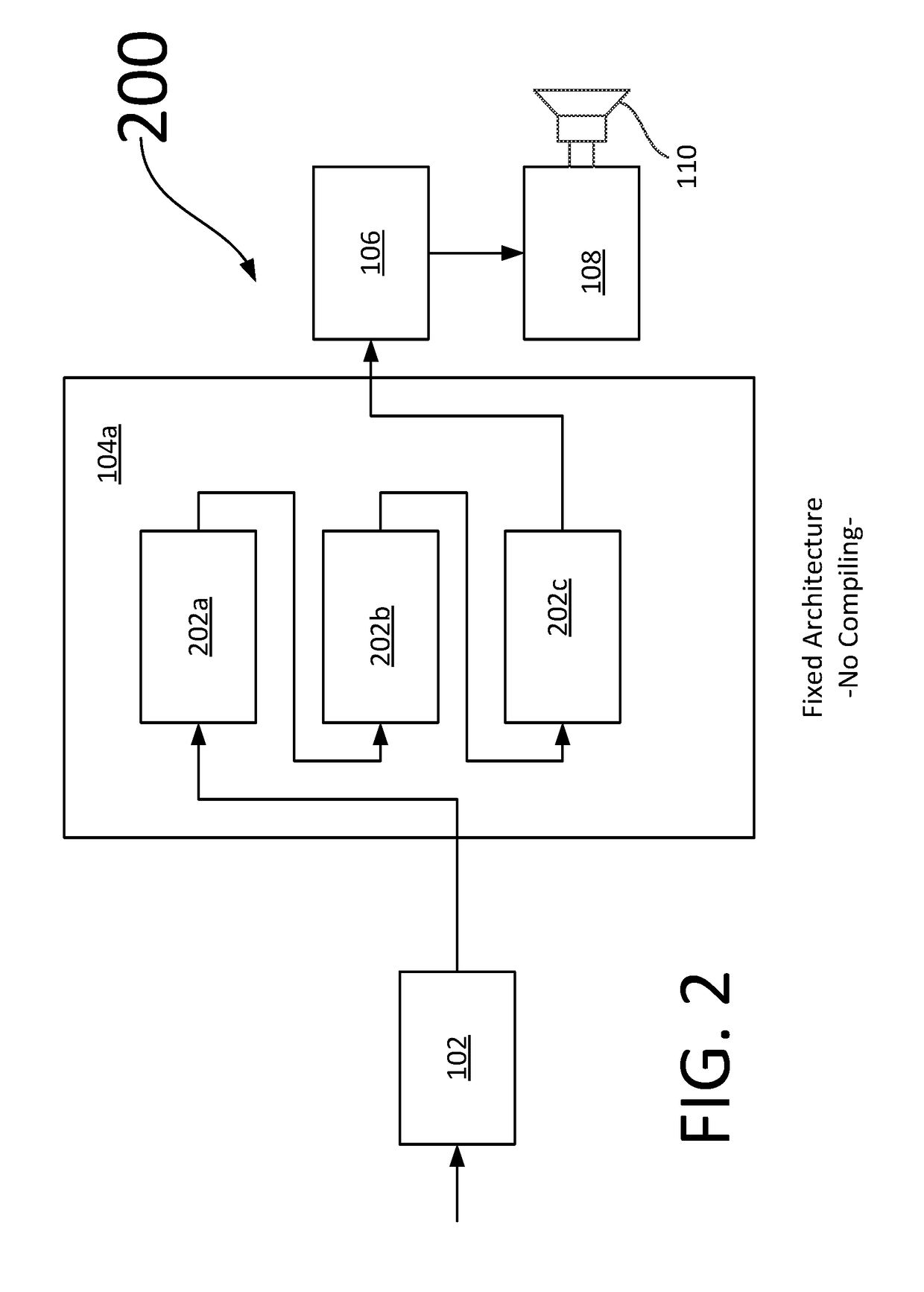

Audio digital signal processor utilizing a hybrid network architecture

ActiveUS20170352357A1Hybrid switching systemsSpeech analysisNetwork architectureDigital audio signals

A system and method executed by audio processing software on one or more electronic devices in a computer system to process digital audio signals. The system comprises a digitizer for digitizing a received audio signal; and processor for performing a plurality of audio processing functions on the digitized audio signals, each of the audio processing functions having at least one programmable parameter, and wherein each of the audio processing functions are categorized and grouped as audio objects, and organized into a channel strip, the channel strip processing digitized audio signals for a particular received audio signal, and wherein, the audio objects are fixed in order, so that the digitized received audio signals are processed by a predefined number of N audio objects, and wherein the N audio objects occur in a fixed sequence, and further wherein, the N audio objects comprise a first subset of non-exchangeable audio objects and a second subset of exchangeable audio objects, such that any one or more of the second subset of audio objects can be exchanged by a replacement audio object, and further wherein when the audio processing functions are programmed, they can be saved without compiling the audio processing software.

Owner:CRESTRON ELECTRONICS

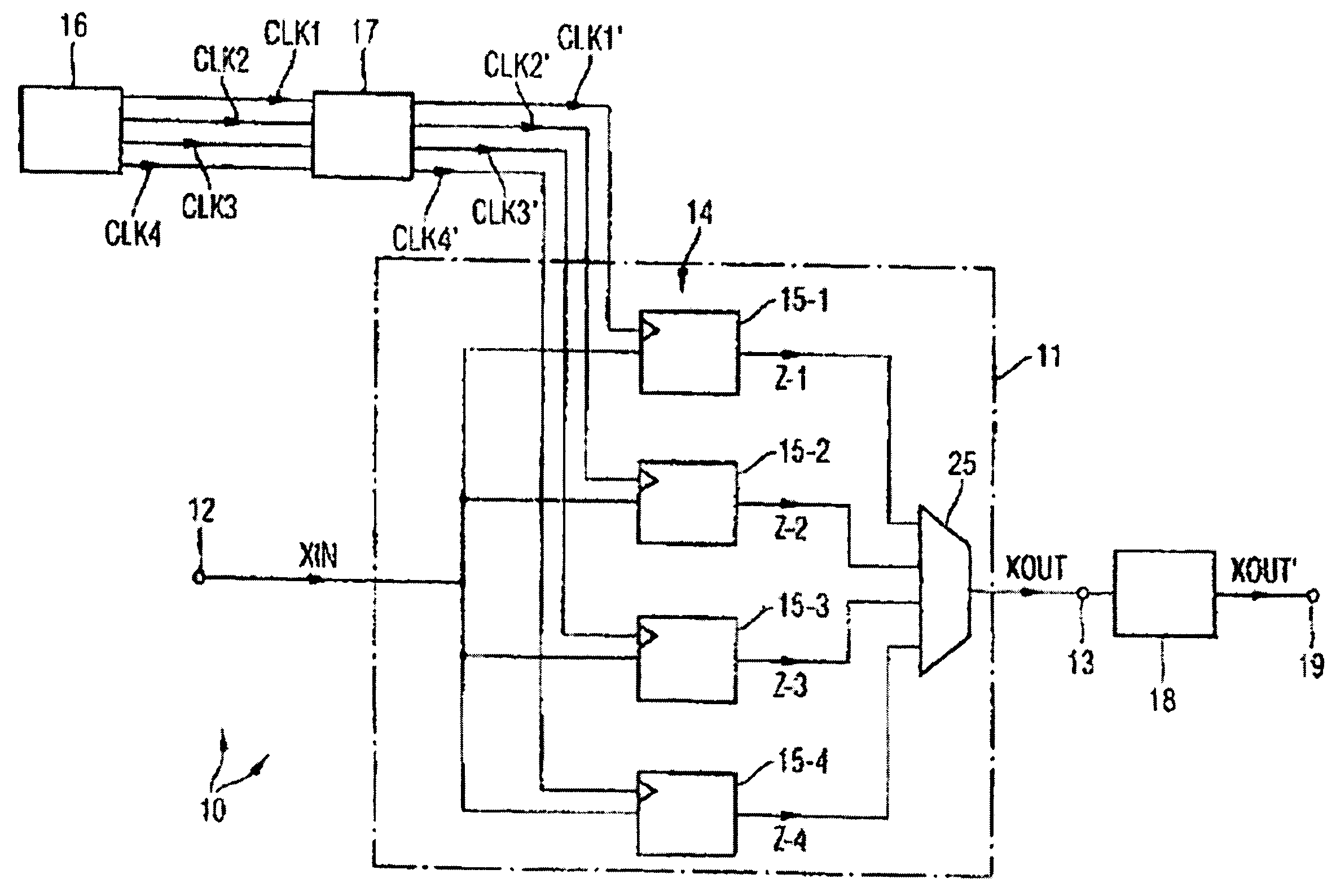

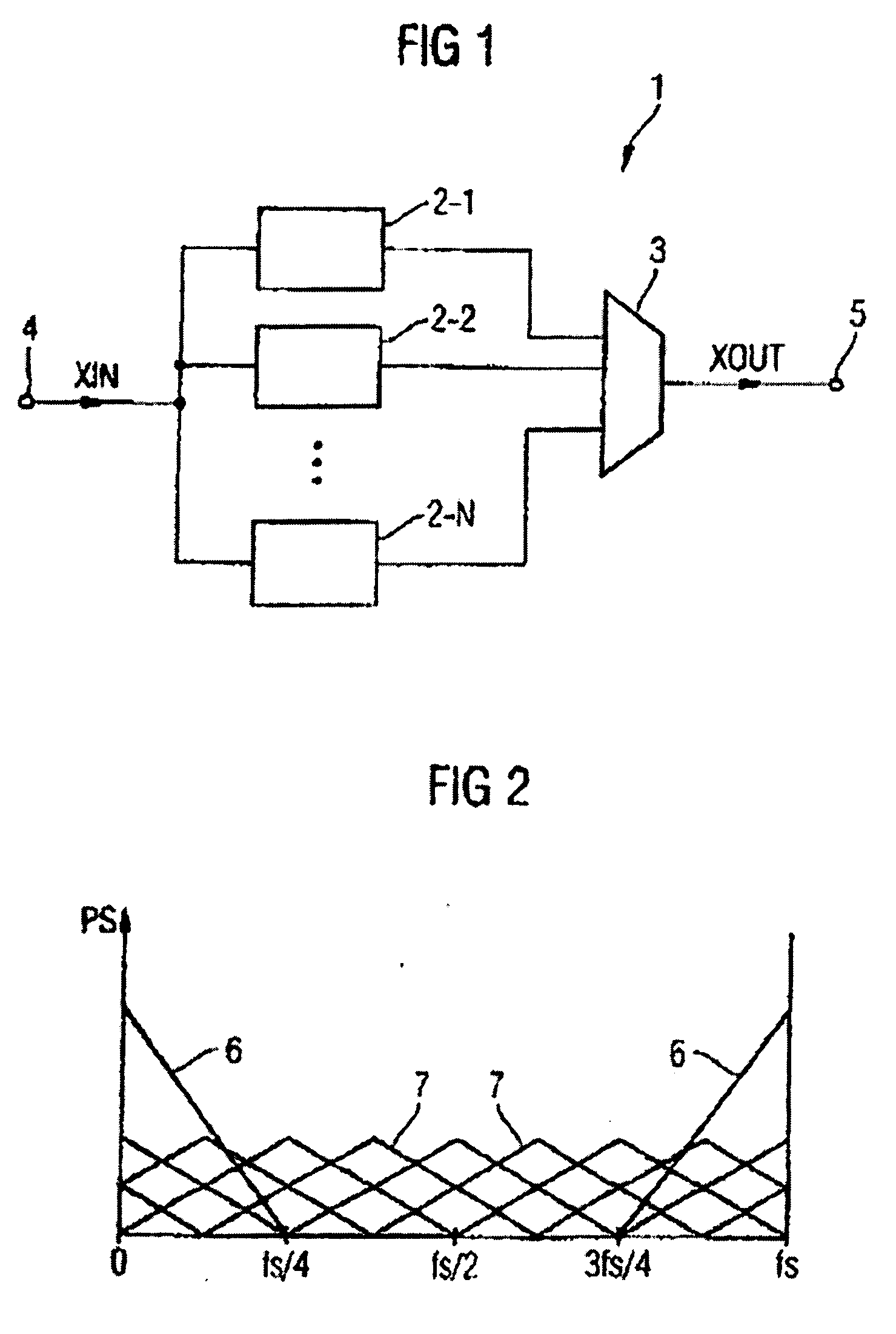

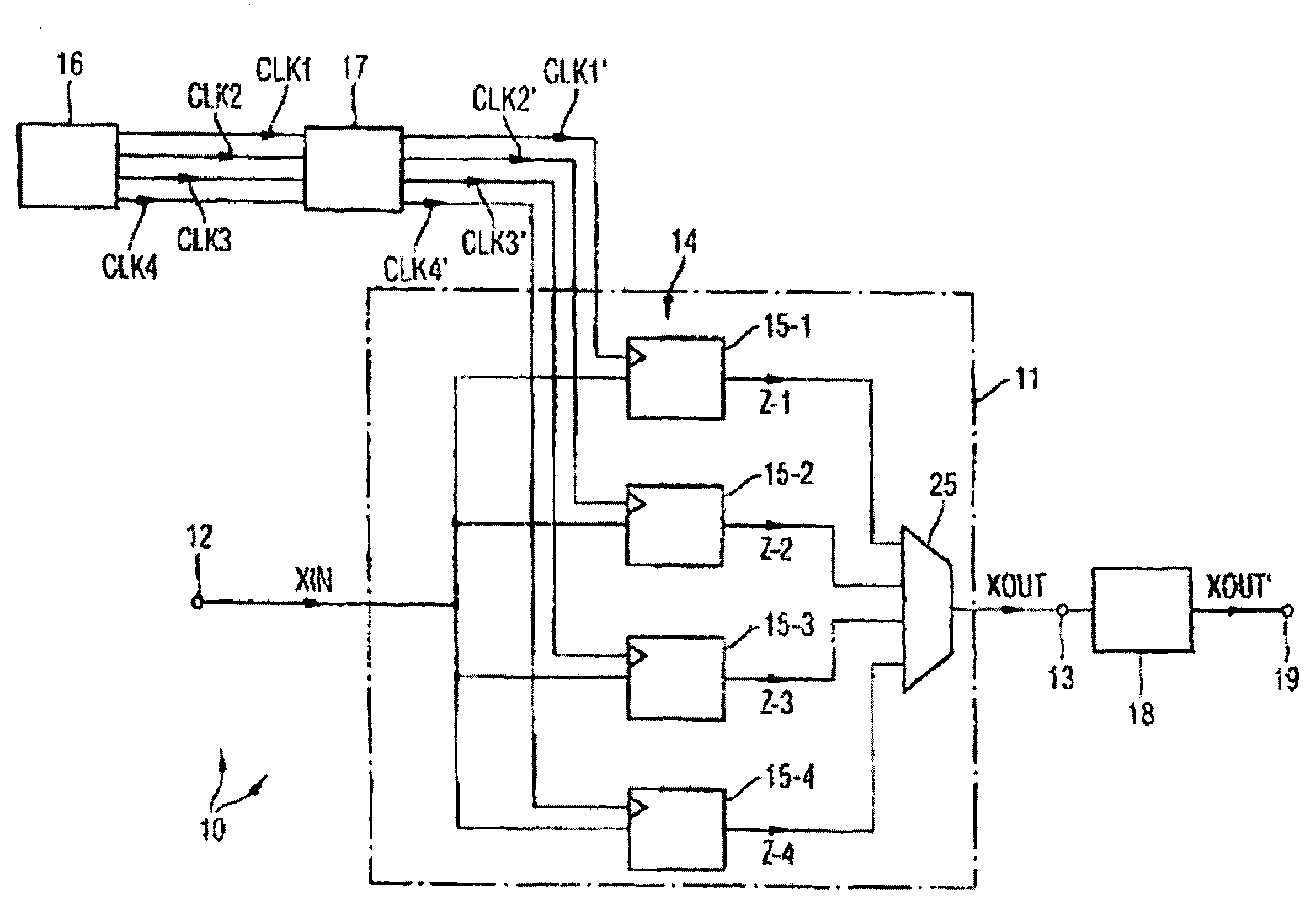

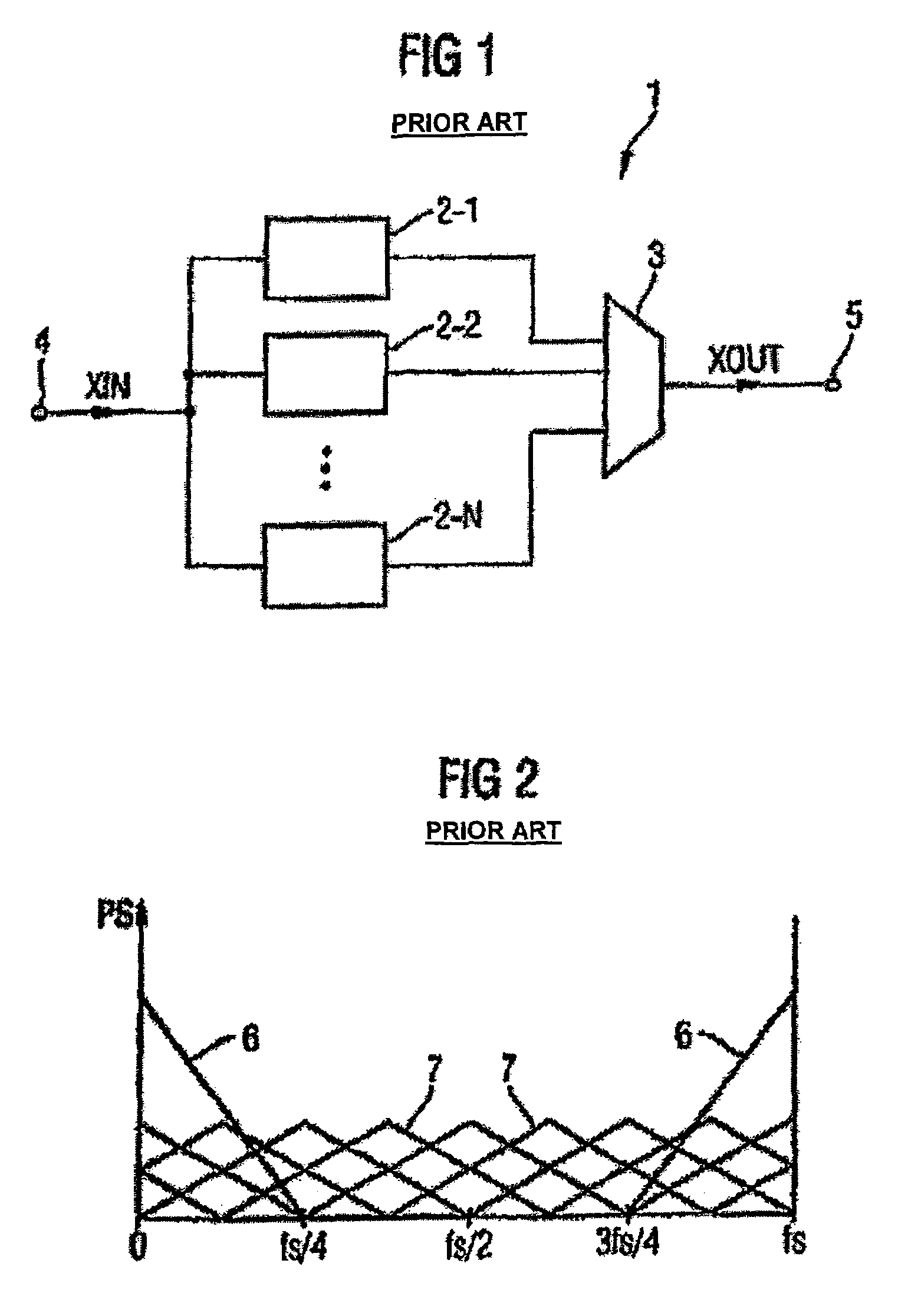

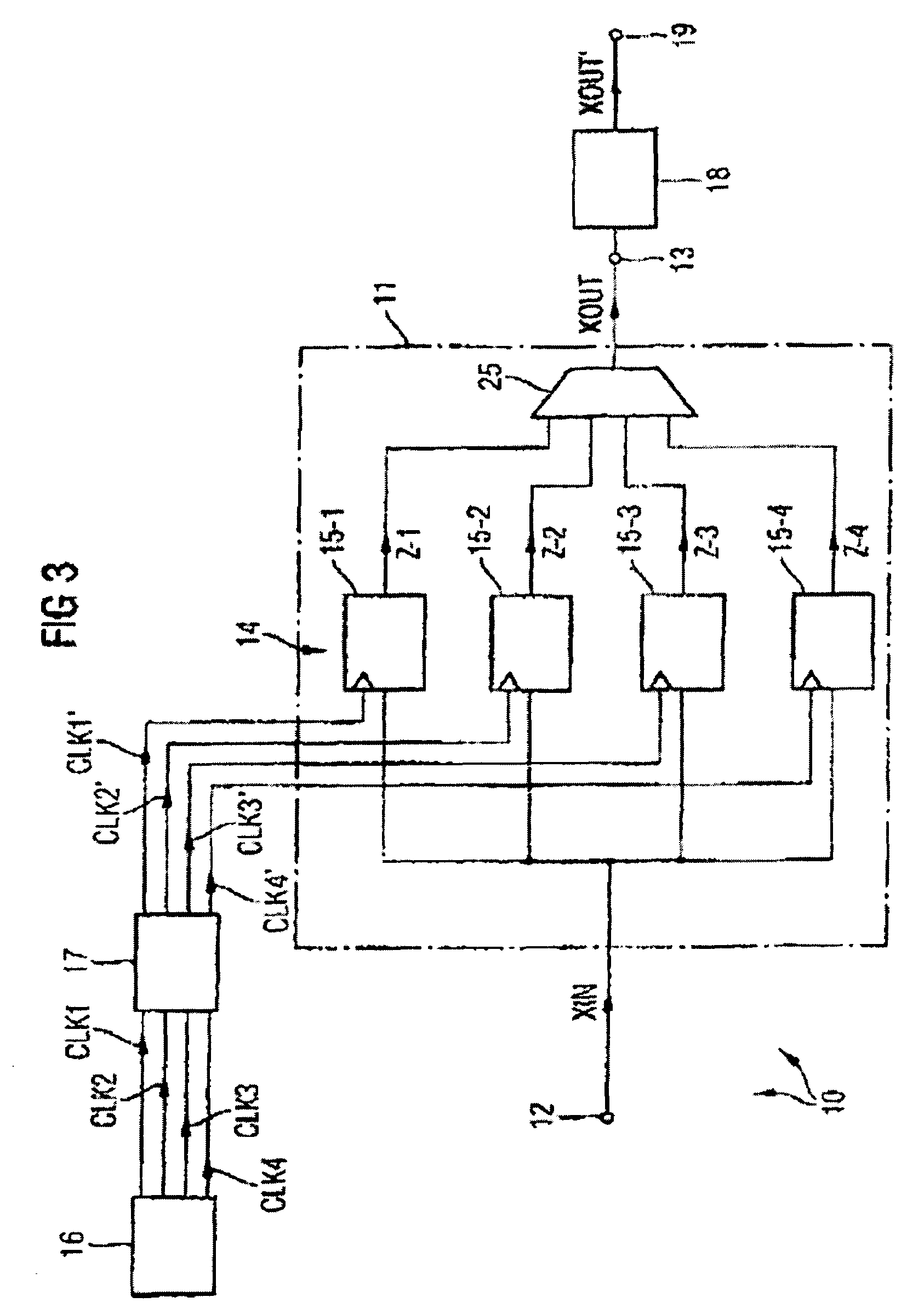

Analog-to-digital converter operable with staggered timing

InactiveUS20060097901A1Reduce incorrect adaptationReduce complexityElectric signal transmission systemsAnalogue-digital convertersFrequency spectrumControl signal

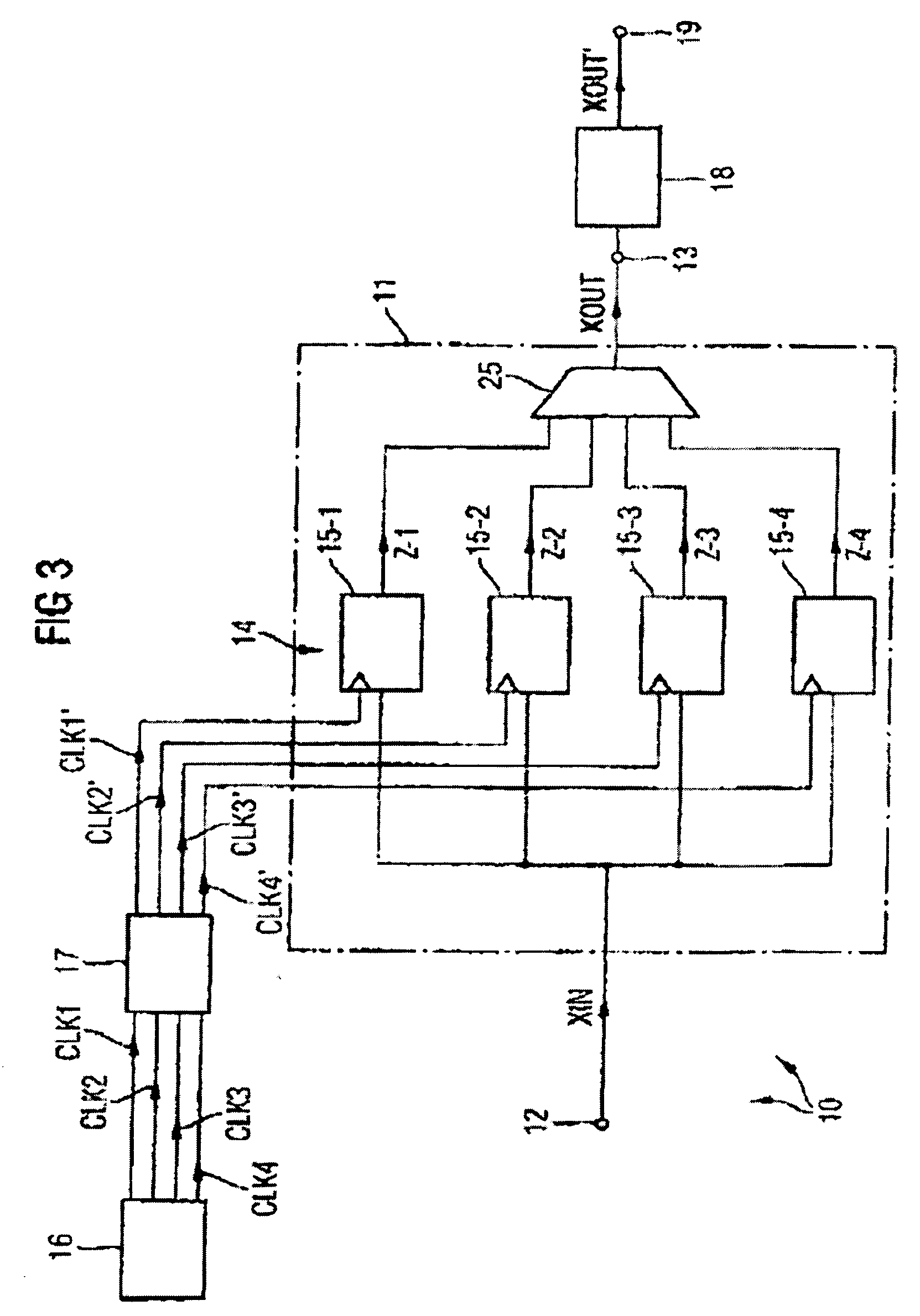

An arrangement for a time interleaved analog-to-digital converter that converts an signal to a digital signal and has a converter array with a plurality of analog-to-digital converters arranged in a fixed sequence in parallel with one another and can be operated with staggered timing with respect to one another is disclosed. The arrangement has a connection network which, for the purposes of actuation with staggered timing, generates in each case one control signal for an individual analog-to-digital converter in each case, with the connection network predefining the time sequence with which the control signals actuate the individual analog-to-digital converters in such a way that owing to this sequence of the control signals and thus the sequence of the actuated individual analog-to-digital converters there is at least a reduction in an interference spectrum in the spectrum of the input and / or output signal. A sorting method for operating this analog-to-digital converter is also disclosed.

Owner:INFINEON TECH AG

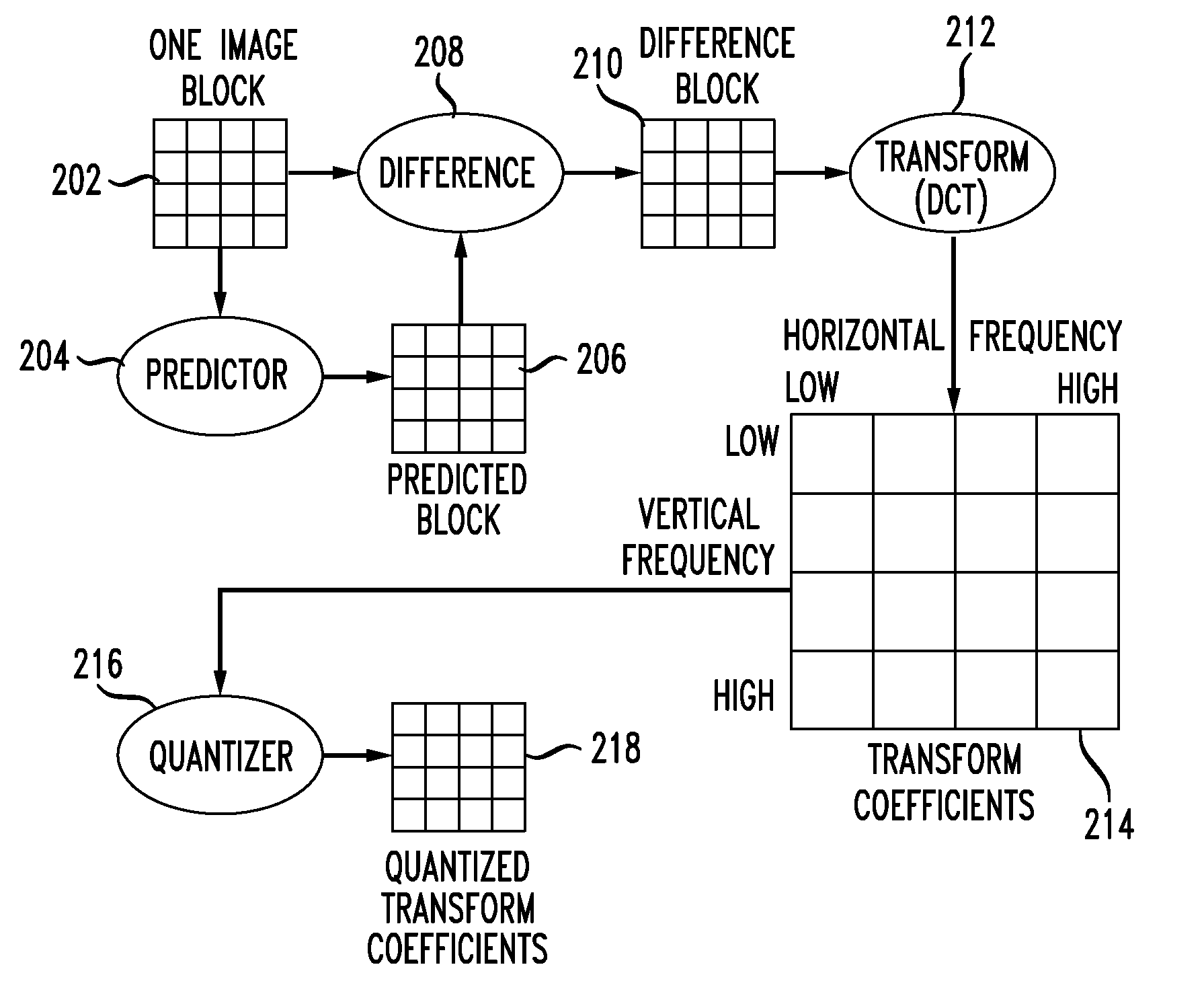

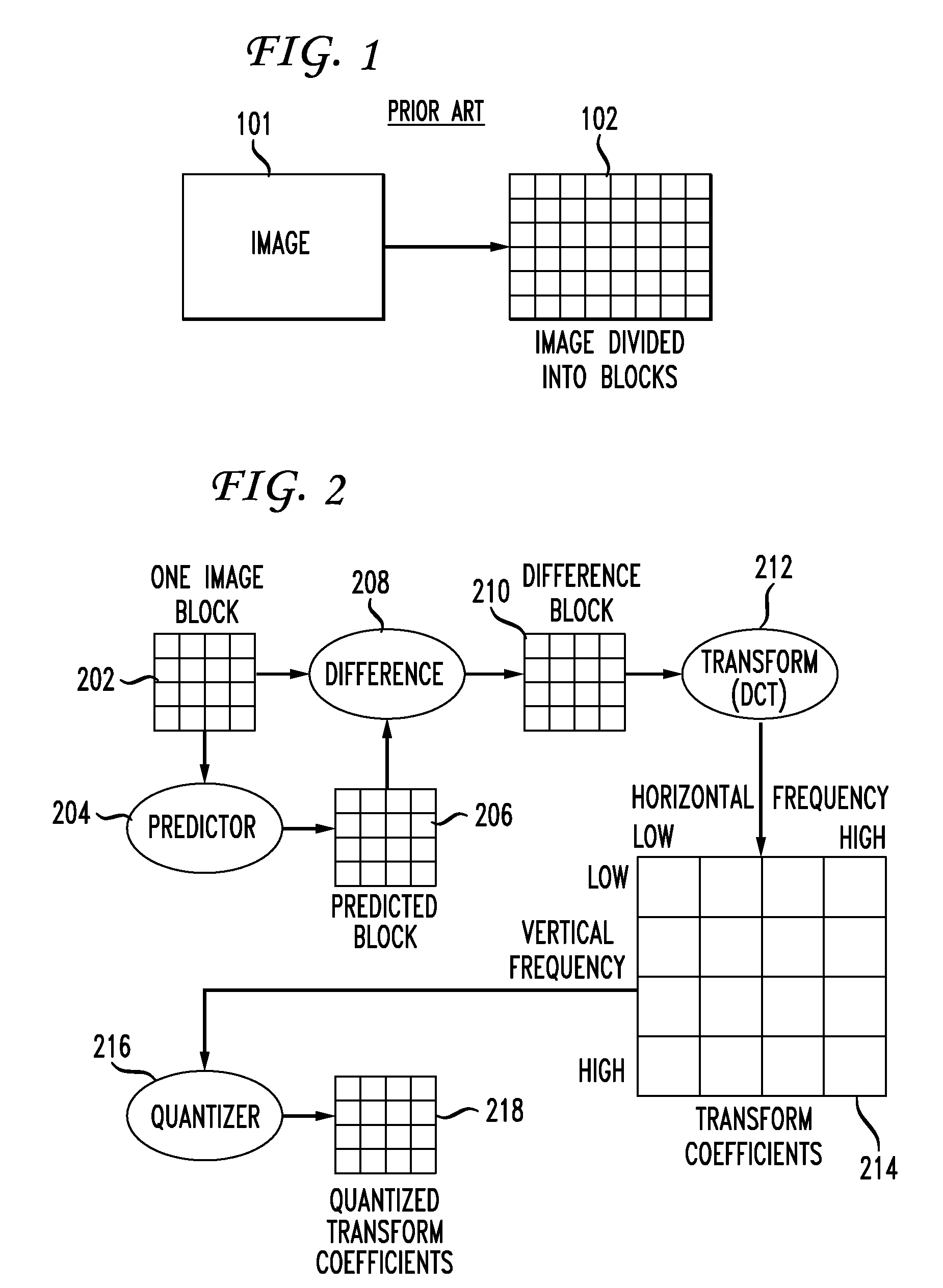

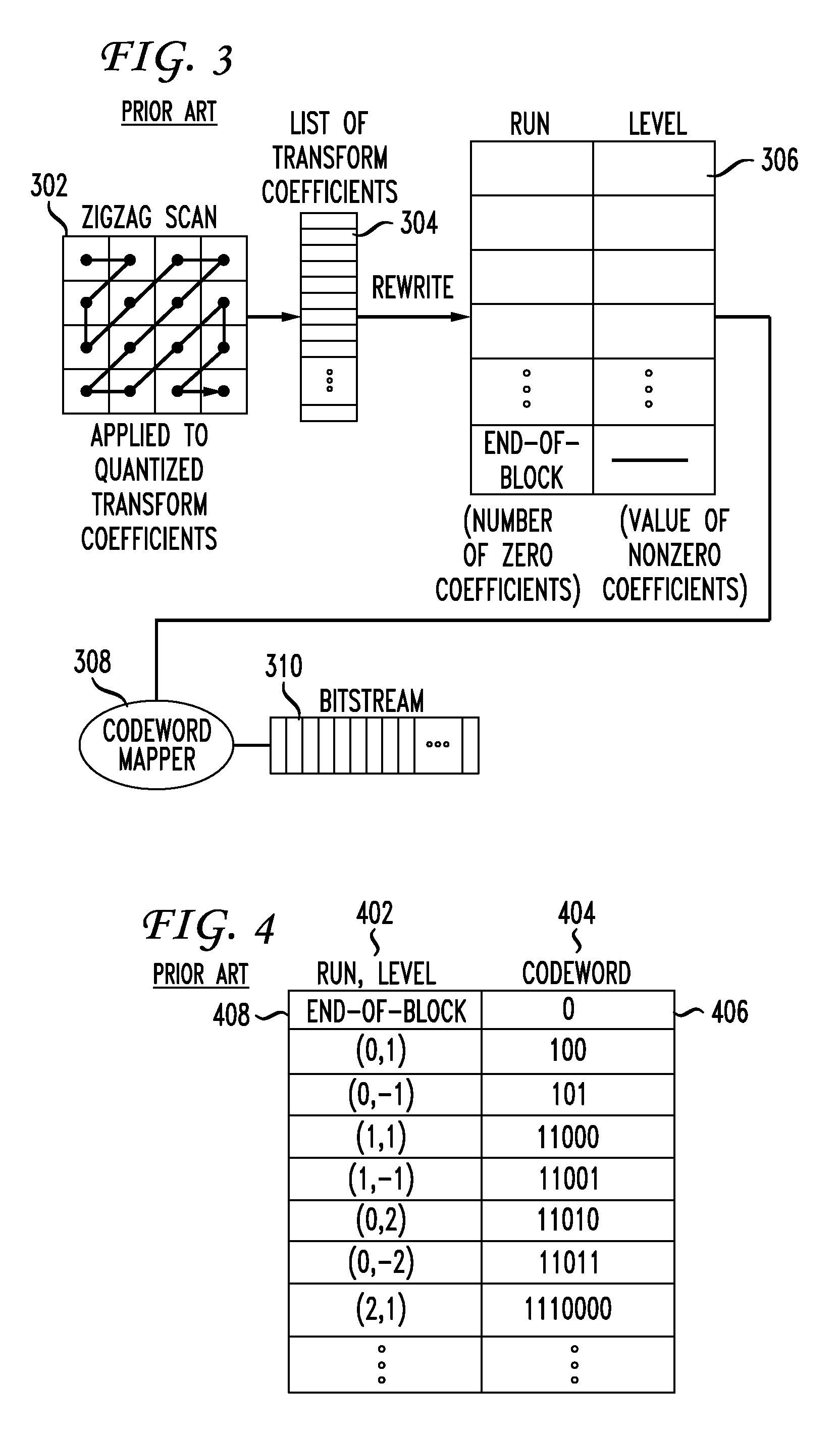

System and method for using pattern vectors for video and image coding and decoding

InactiveUS7206448B2Poor imageImprove codec efficiencyPicture reproducers using cathode ray tubesCode conversionComputer graphics (images)Self adaptive

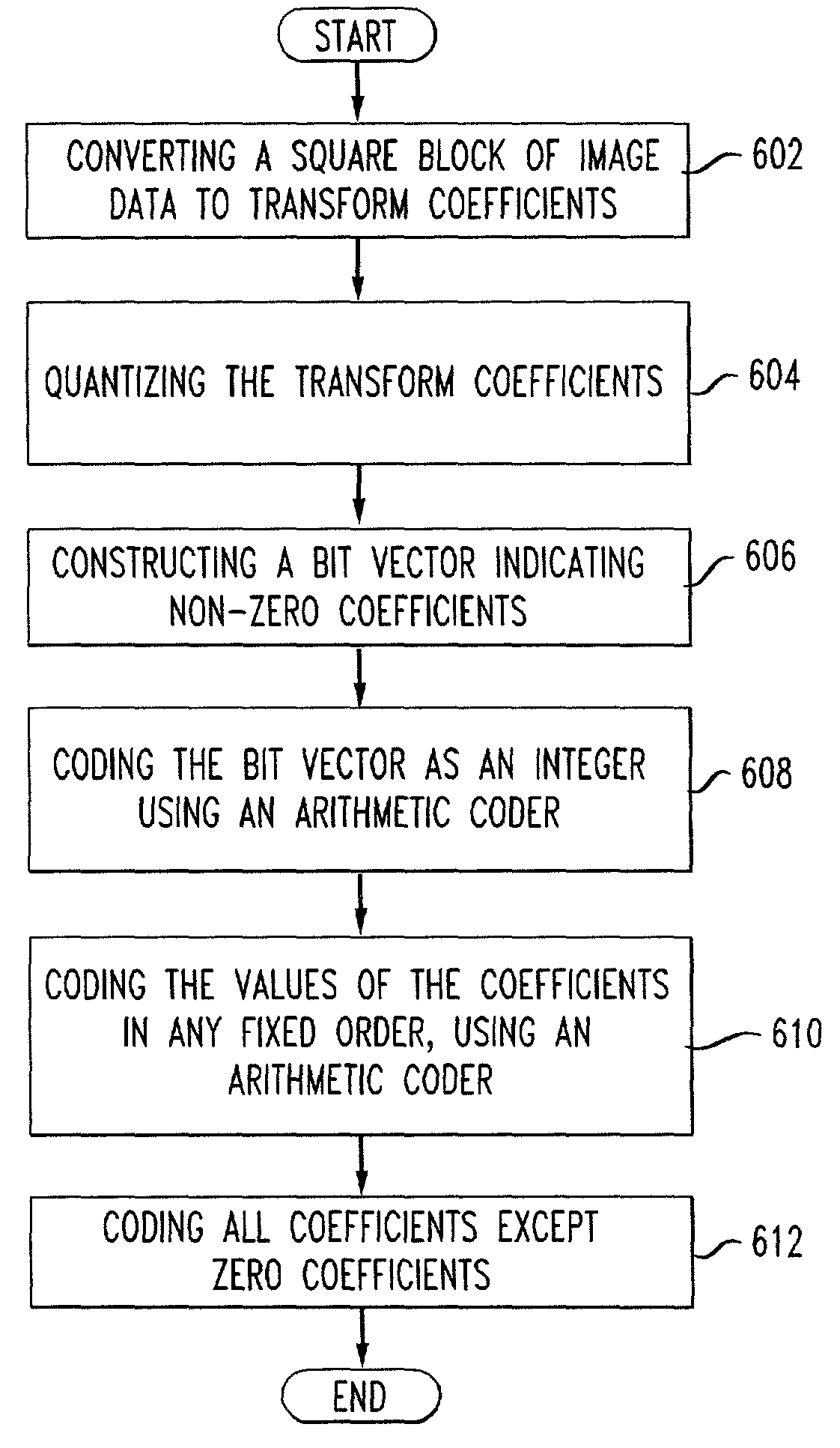

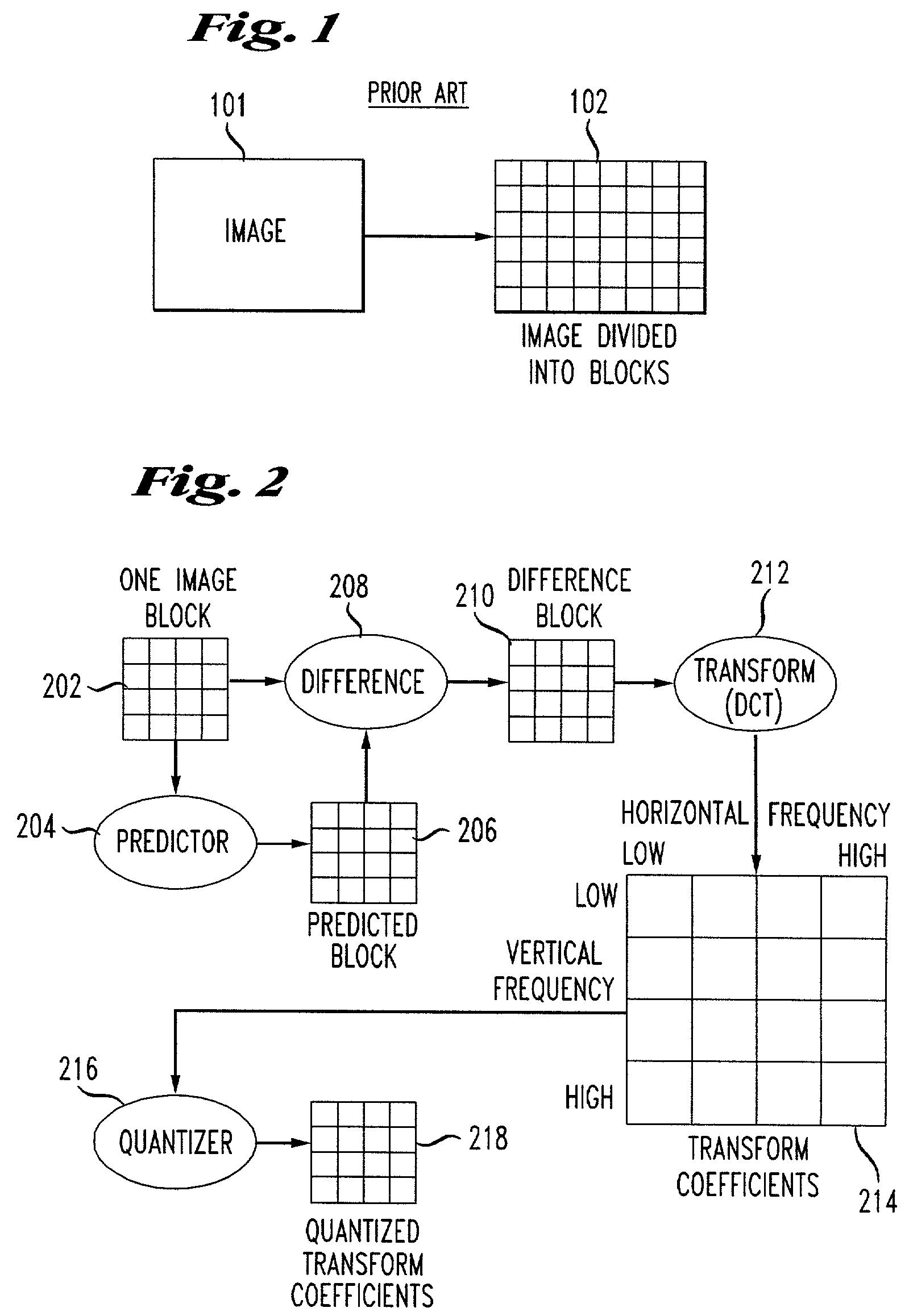

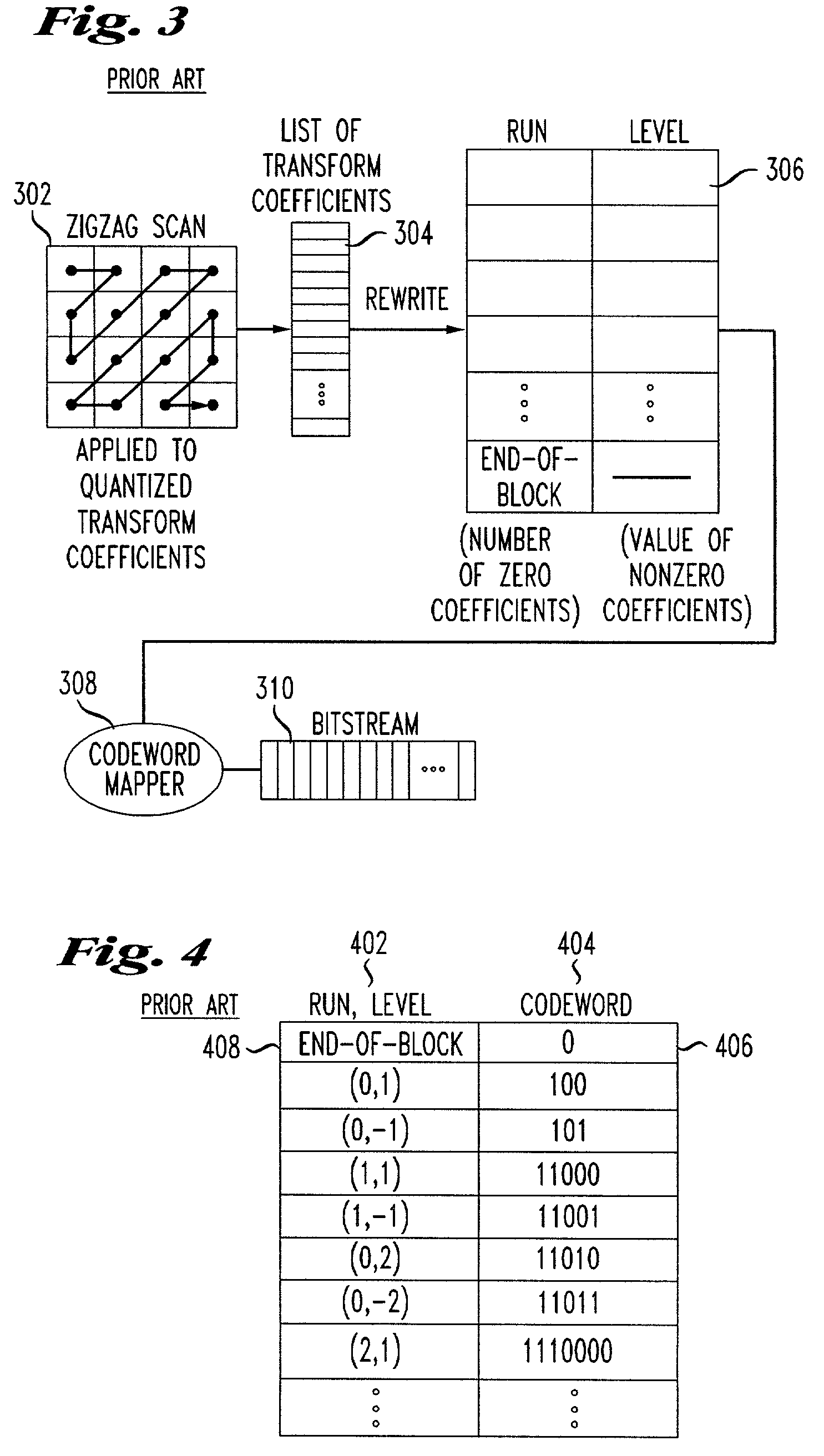

An exemplary embodiment of the invention relates to a method of using pattern vectors for image coding and decoding. The method comprises converting a block of image data into a set of transform coefficients, quantizing the transform coefficients such that a number of the coefficients become zero, constructing a single entity or bit vector indicating which coefficients are non-zero, coding the single entity or bit vector as an integer using an adaptive, semi-adaptive or non-adaptive arithmetic coder, coding the values of the coefficients in any fixed order, using an adaptive, semi-adaptive or non-adaptive arithmetic coder, or some other coder, and coding all coefficients except the zero coefficients. The system and method of decoding data relate to the corresponding hardware and process steps performed by the decoder when decoding a bitstream coded as described herein.

Owner:AT&T INTPROP II L P

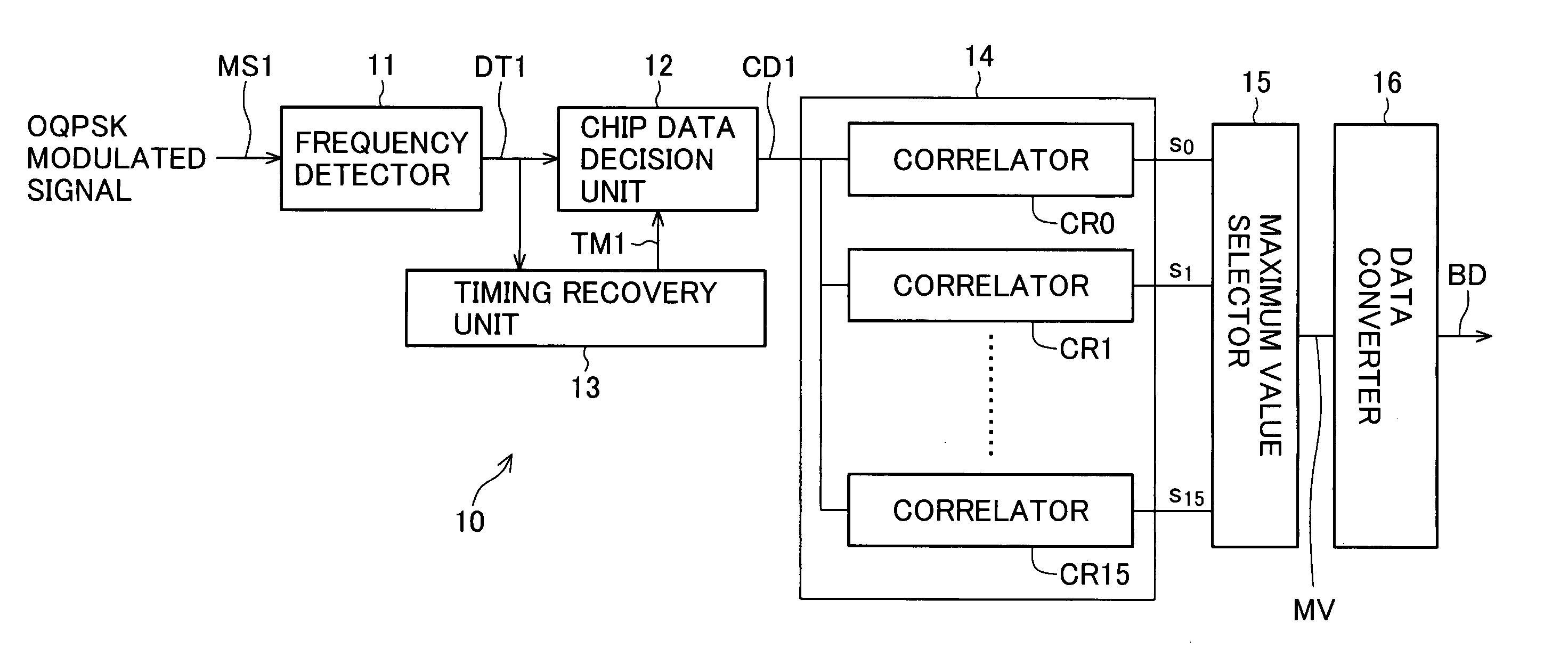

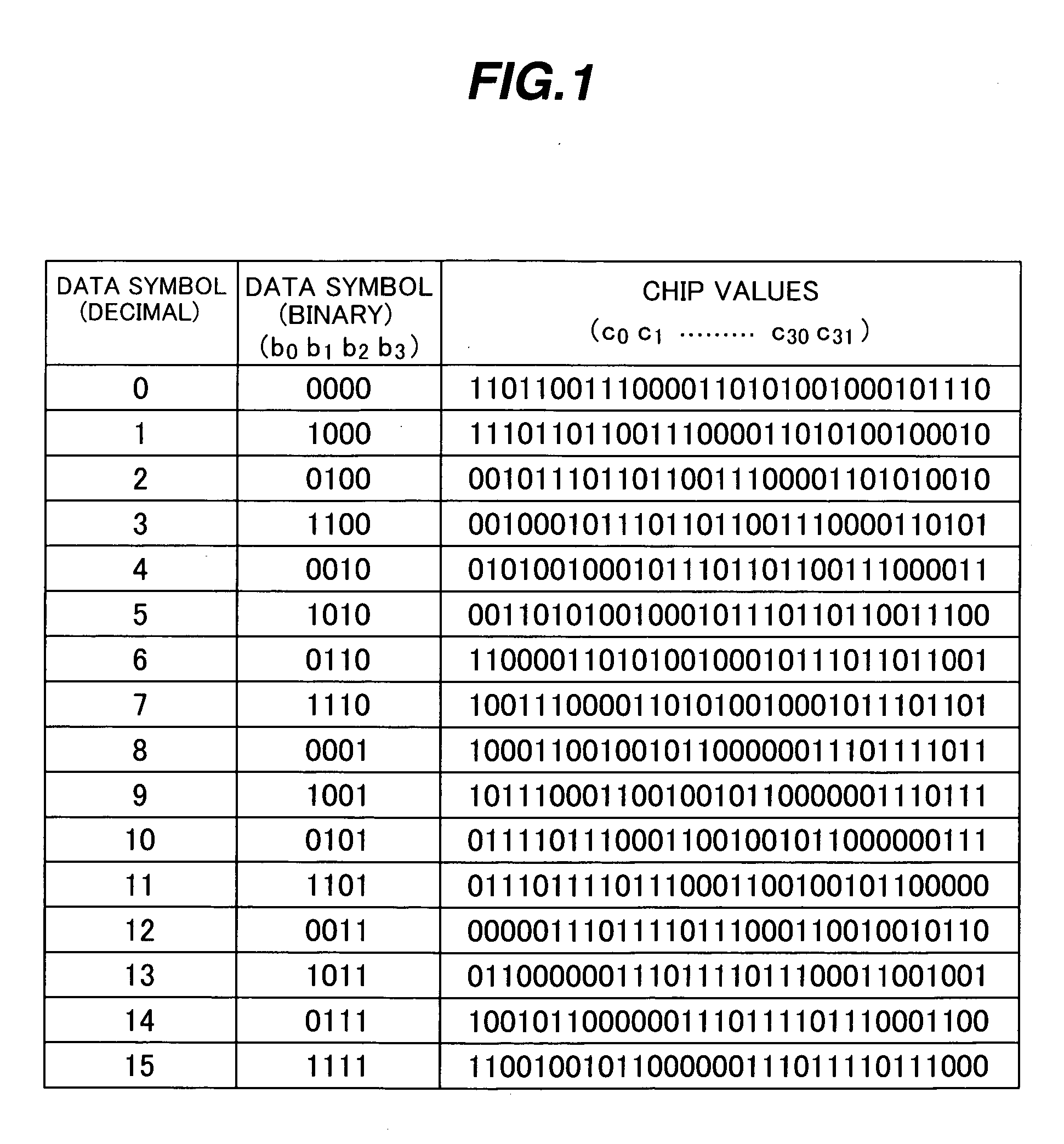

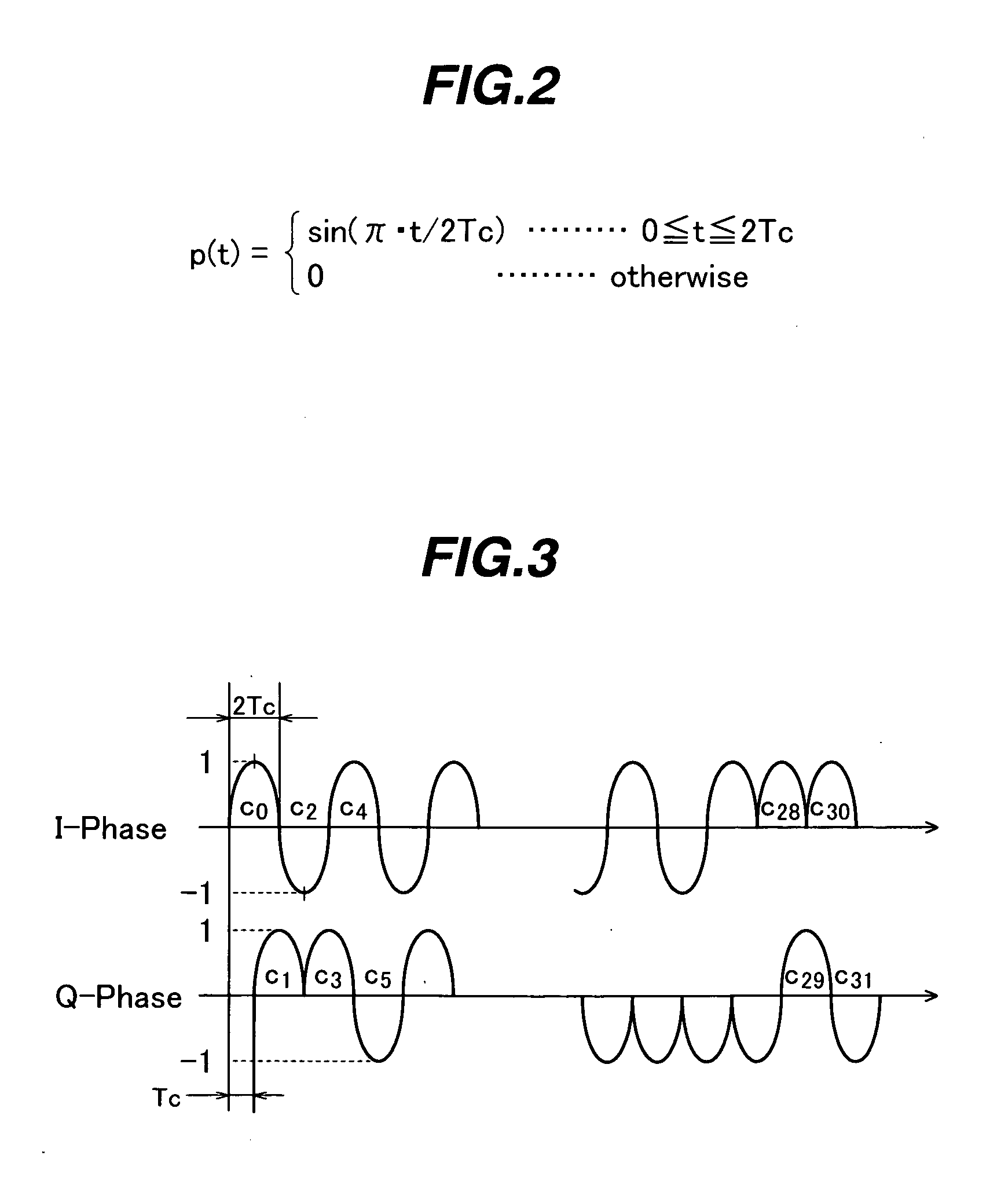

Spread spectrum demodulator employing frequency detection

ActiveUS20050157777A1Error preventionLine-faulsts/interference reductionCorrelation coefficientDecision circuit

A simplified spread spectrum demodulator uses a frequency detector to demodulate a modulated spread spectrum signal to obtain successive chip values. A correlation unit correlates the successive chip values with fixed sequences of correlation coefficients to generate correlation values. A decision circuit selects one of the correlation values to decide what symbol the spread spectrum signal represents. The correlation coefficients are obtained by applying the same modulation method as used to modulate the spread spectrum signal, and then the same demodulation method as used by the frequency detector, to the sequences of chips representing different symbols. Since synchronous detection is not employed, no carrier recovery circuit is needed.

Owner:LAPIS SEMICON CO LTD

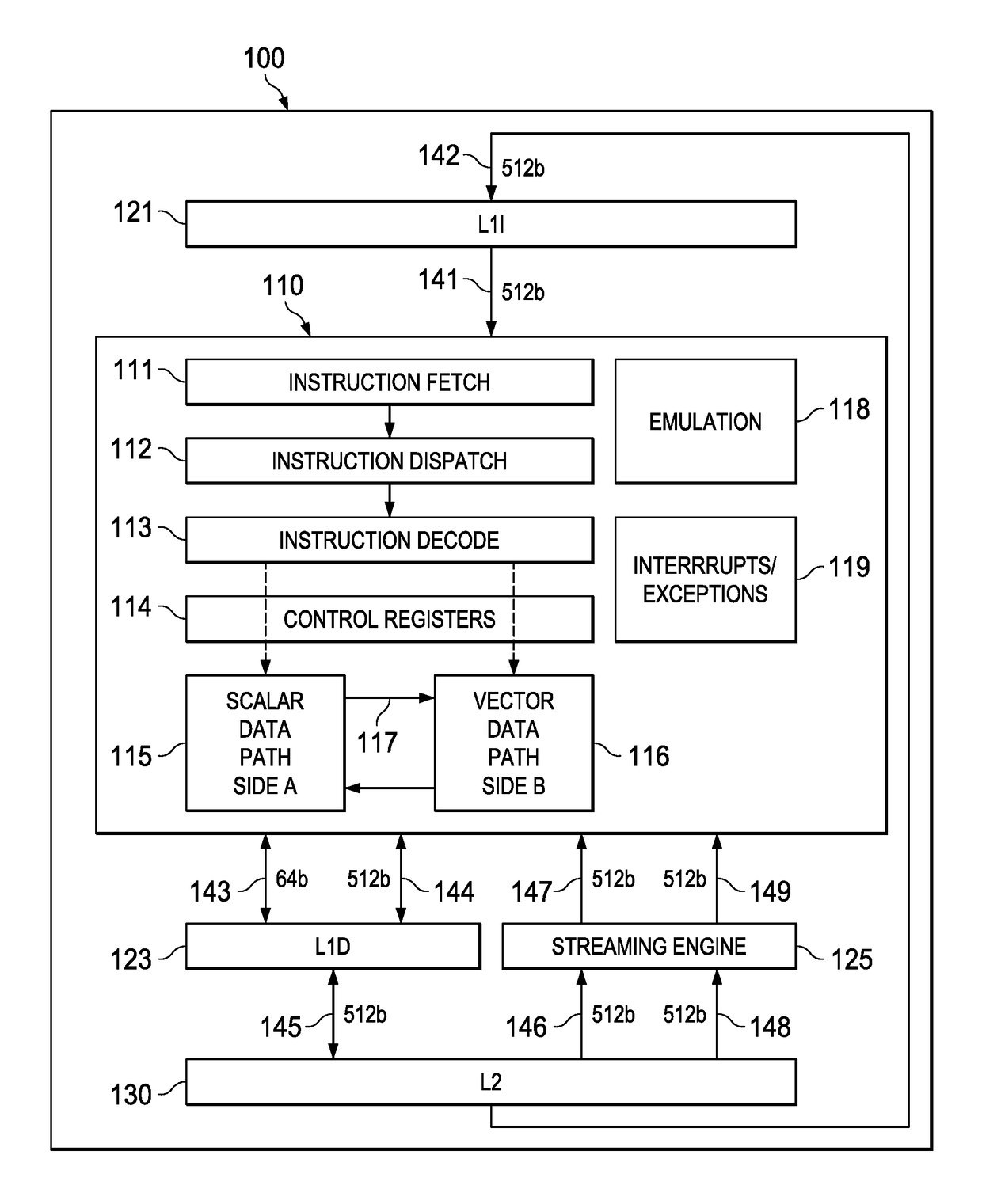

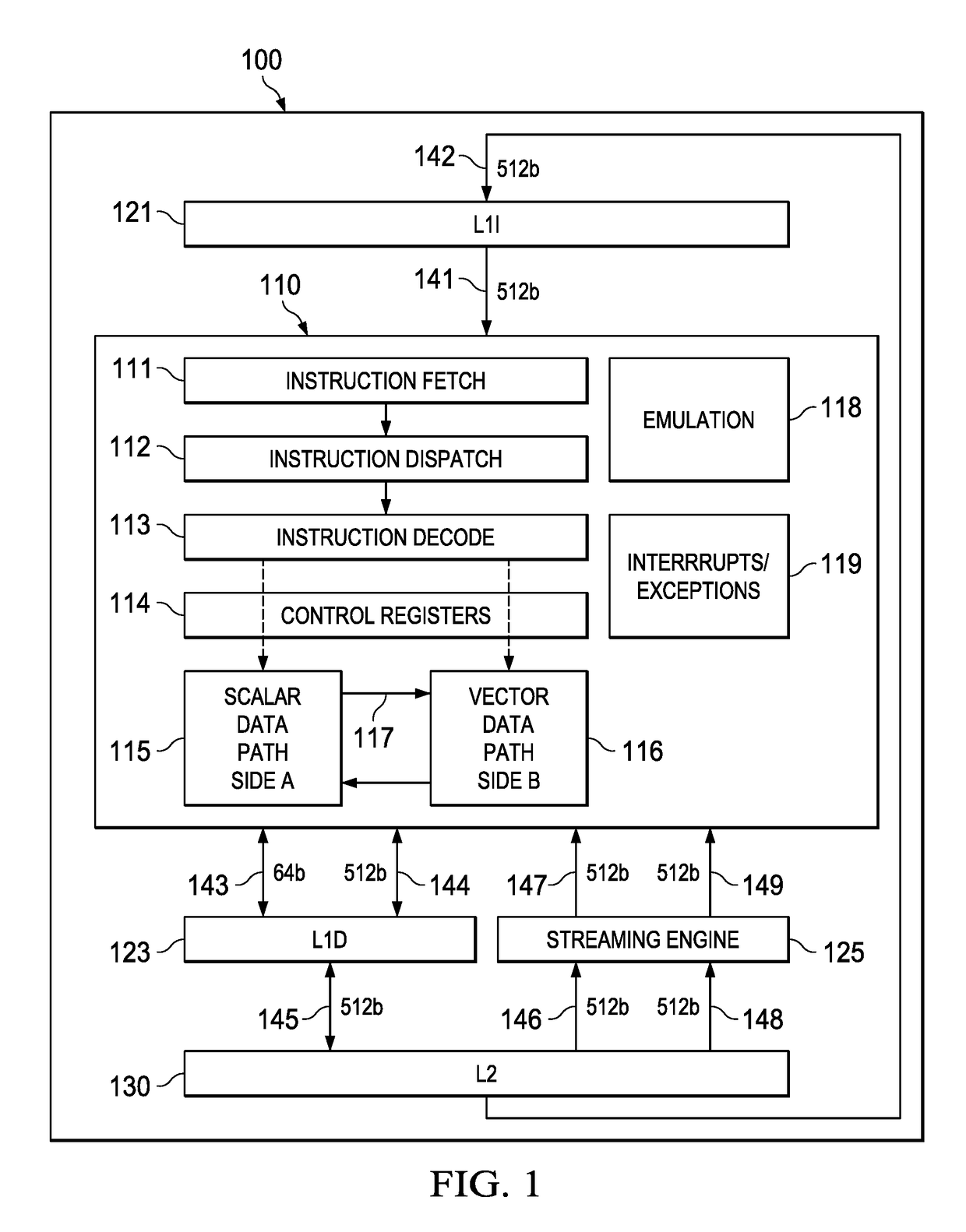

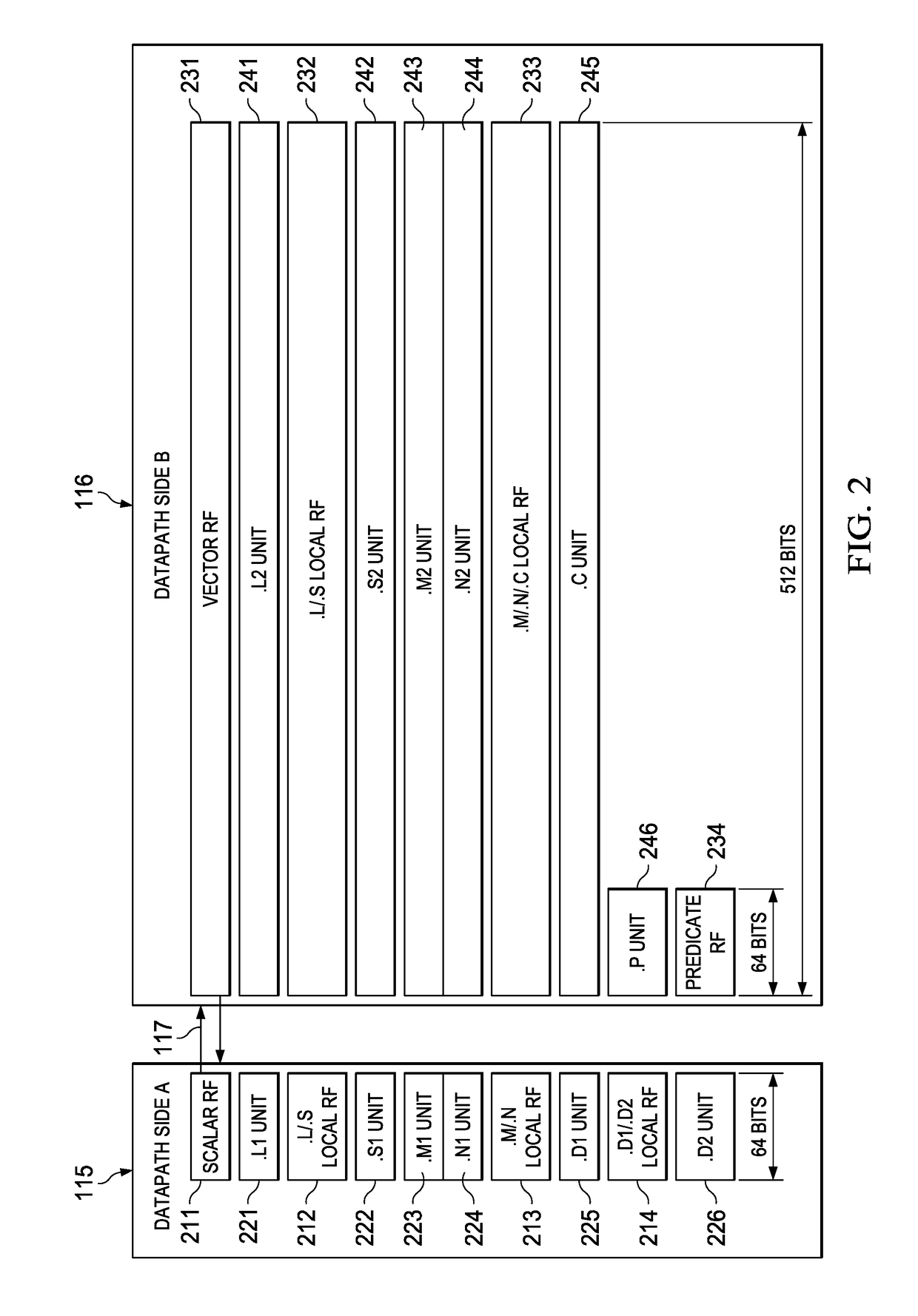

Data processing apparatus having streaming engine with read and read/advance operand coding

A streaming engine employed in a digital signal processor specified a fixed data stream. Once started the data stream is read only and cannot be written. Once fetched the data stream is stored in a first-in-first-out buffer for presentation to functional units in the fixed order. Data use by the functional unit is controlled using the input operand fields of the corresponding instruction. A read only operand coding supplies the data an input of the functional unit. A read / advance operand coding supplies the data and also advances the stream to the next sequential data elements. The read only operand coding permits reuse of data without requiring a register of the register file for temporary storage.

Owner:TEXAS INSTR INC

System and method for using pattern vectors for video and image coding and decoding

InactiveUS20070154090A1Improve codec efficiencyPicture reproducers using cathode ray tubesCode conversionComputer graphics (images)Self adaptive

An exemplary embodiment of the invention relates to a method of using pattern vectors for image coding and decoding. The method comprises converting a block of image data into a set of transform coefficients, quantizing the transform coefficients such that a number of the coefficients become zero, constructing a single entity or bit vector indicating which coefficients are non-zero, coding the single entity or bit vector as an integer using an adaptive, semi-adaptive or non-adaptive arithmetic coder, coding the values of the coefficients in any fixed order, using an adaptive, semi-adaptive or non-adaptive arithmetic coder, or some other coder, and coding all coefficients except the zero coefficients. The system and method of decoding data relate to the corresponding hardware and process steps performed by the decoder when decoding a bitstream coded as described herein.

Owner:AT&T INTPROP II L P

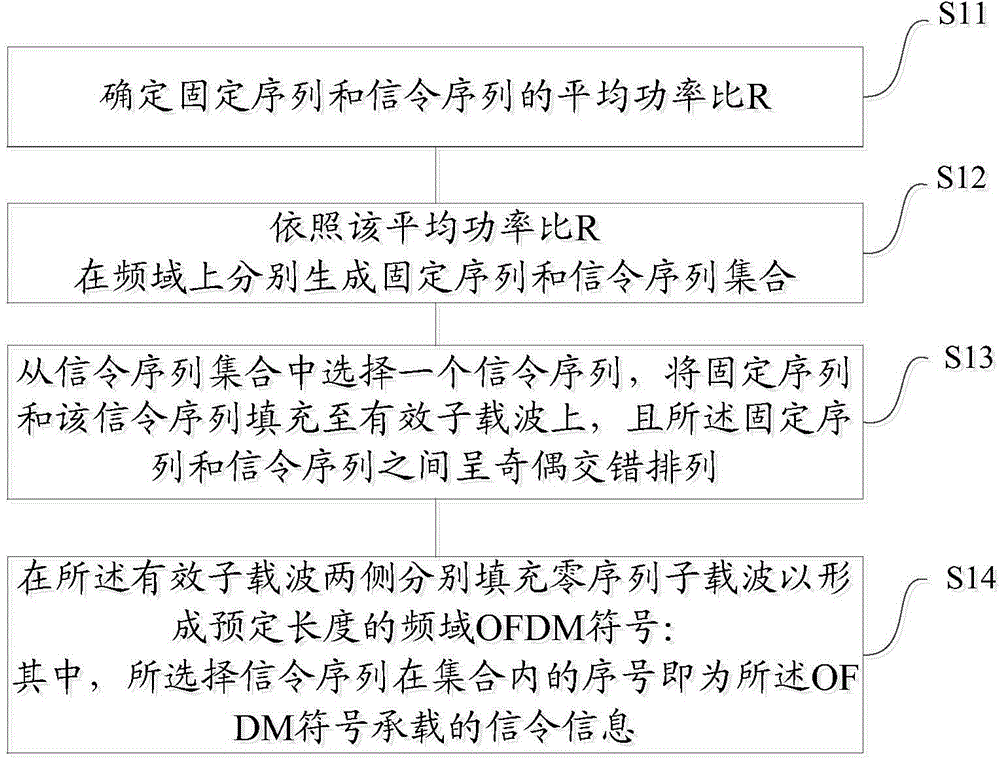

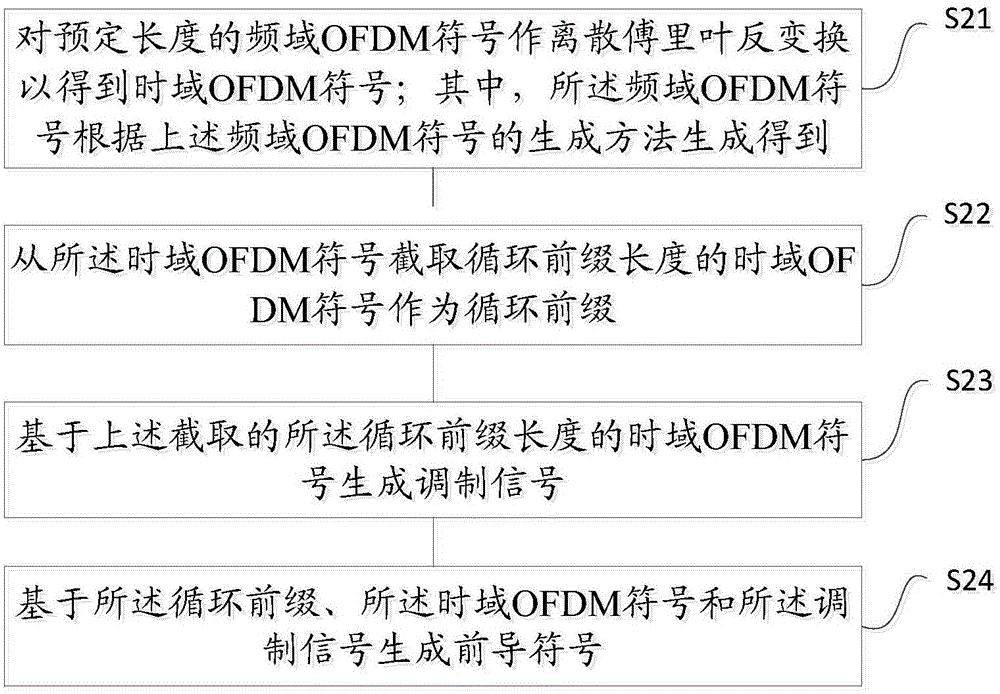

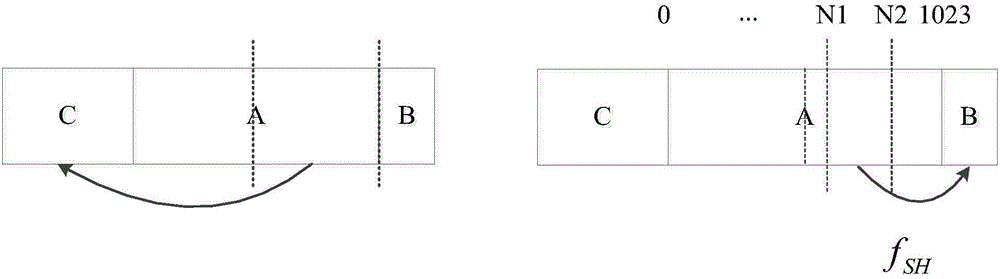

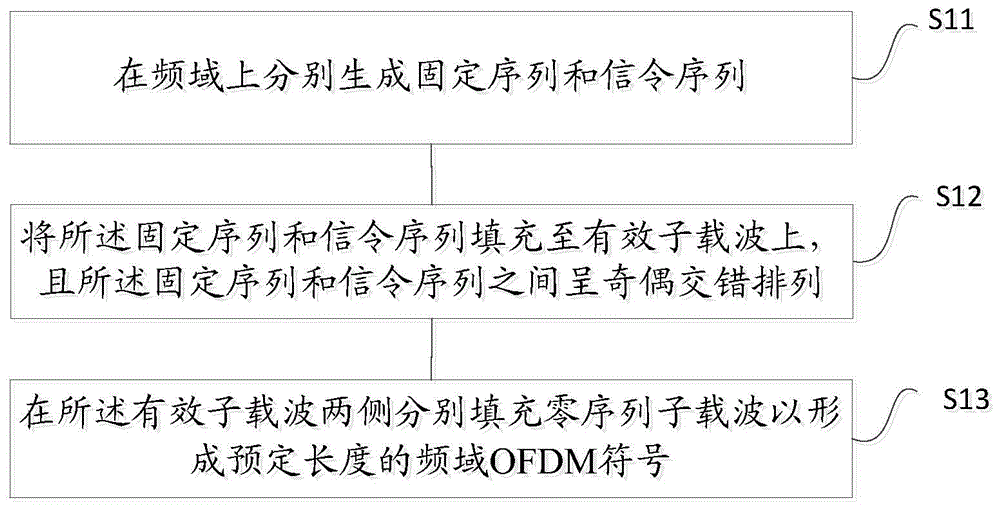

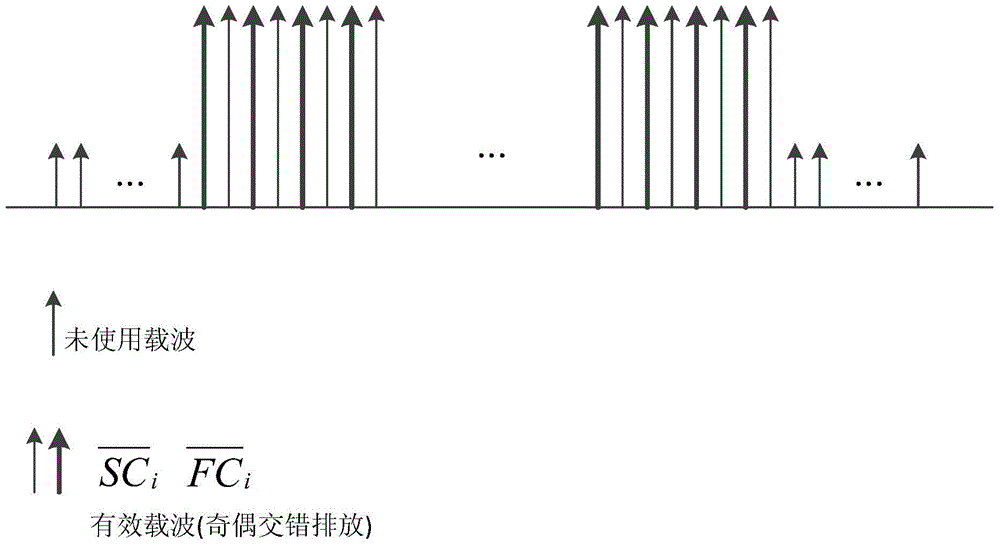

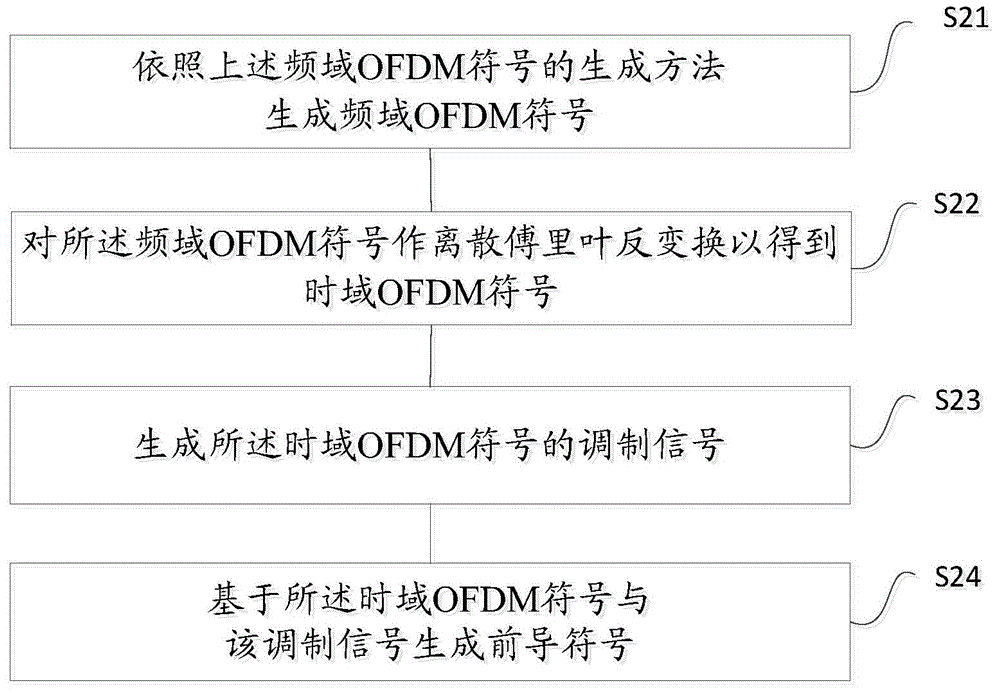

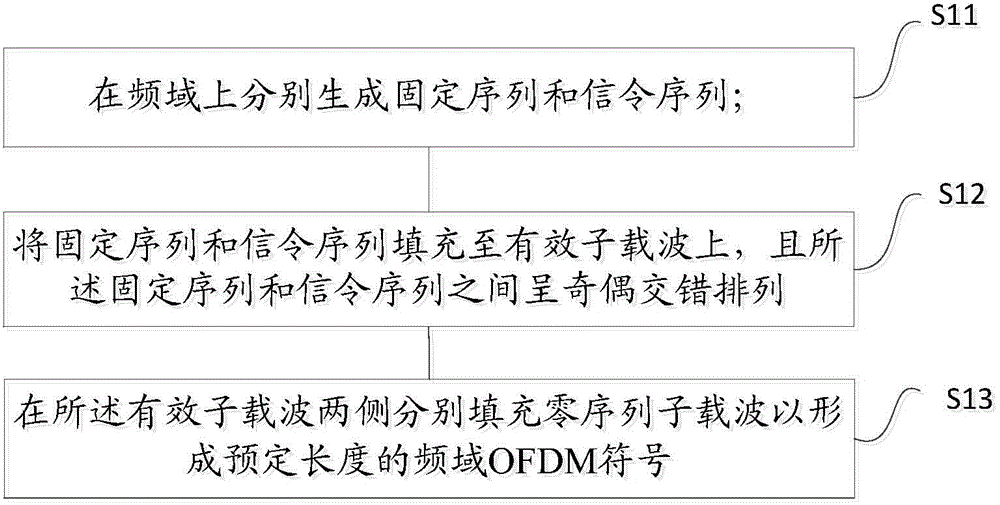

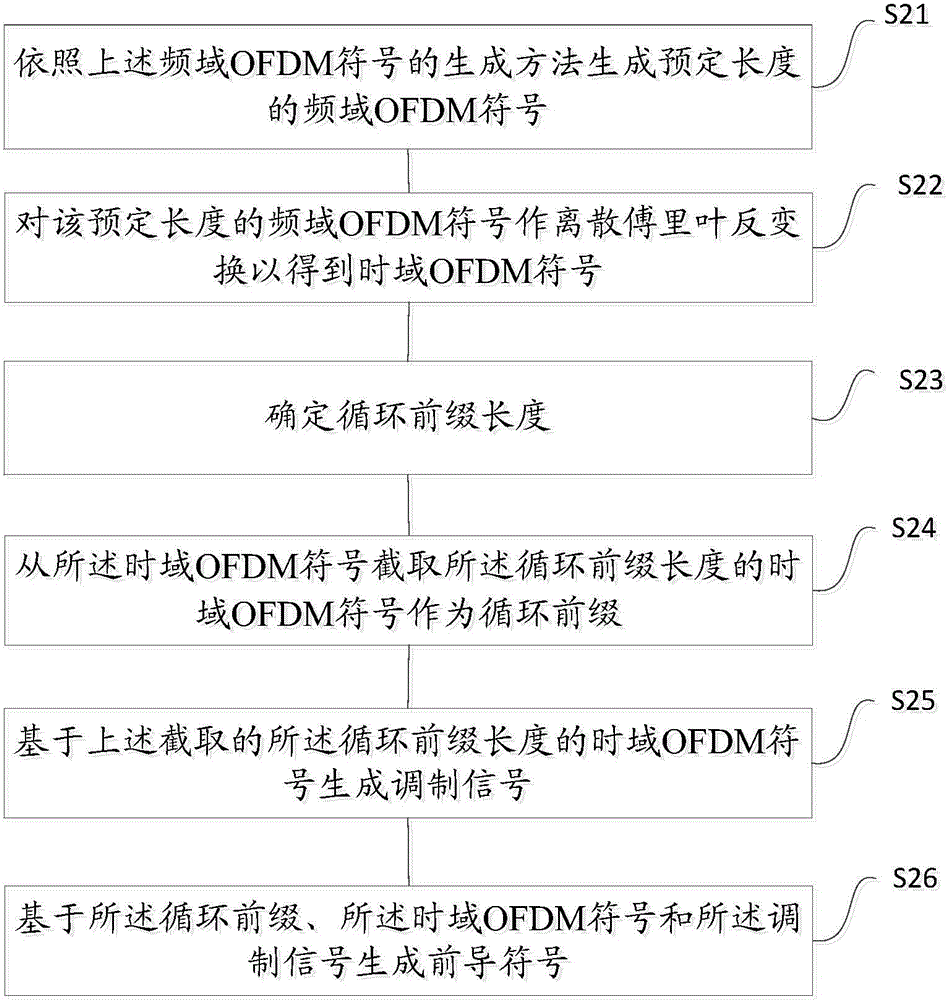

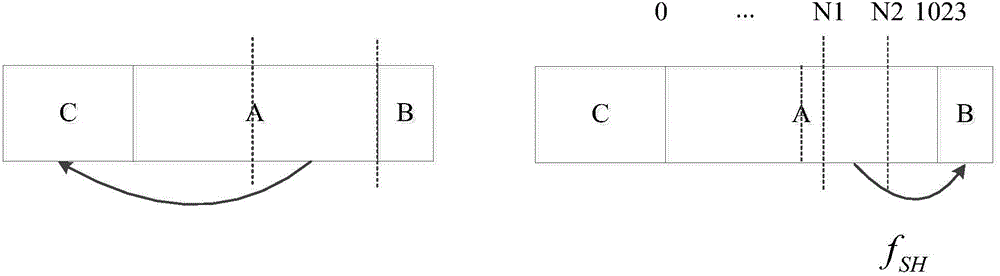

Generation method of preamble symbols and generation method of frequency-domain OFDM symbols

ActiveCN105282076AEasy to decode and demodulateReduce peak-to-average power ratioMulti-frequency code systemsCarrier signalEngineering

The invention discloses a generation method of frequency-domain OFDM symbols and a generation method of preamble symbols in physical frames. The generation method of the frequency-domain OFDM symbols includes the following steps that: the average power ratio of a fixed sequence and a signaling sequence is determined; fixed sequences and a signaling sequence set are respectively generated in the frequency domain according to the average power ratio R; one signaling sequence is selected from the signaling sequence set, and the fixed sequences and the signaling sequences fill effective sub carriers, odd-even staggered arrangement exists between the fixed sequences and the signaling sequences; two sides of the effective sub carriers are filled with zero-sequence sub carriers respectively to form a frequency domain OFDM symbol with a preset length; and the serial number of the selected signaling sequence in the set is the signaling information carried by OFDM symbols. With the generation methods provided by the technical scheme of the invention adopted, the problem of failure probability in low-complexity receiving algorithm detection on preamble symbols in a frequency selective fading channel in the current DVB_T2 standard and other standards can be solved.

Owner:SHANGHAI NAT ENG RES CENT OF DIGITAL TELEVISION

Method for generating preamble symbol and method for generating frequency domain OFDM symbol

ActiveCN105007145AEasy to decode and demodulateReduce peak-to-average power ratioMulti-frequency code systemsTransmission path multiple useCarrier signalComputer science

The invention discloses a method for generating a preamble symbol and a method for generating a frequency domain OFDM symbol. The method for generating the frequency domain OFDM symbol comprises the following steps: respectively generating a fixed sequence and a signaling sequence on a frequency domain; filling an effective subcarrier with the fixed sequence and the signaling sequence, wherein the fixed sequence and the signaling sequence are in odd-even staggered arrangement; and respectively filling the two sides of the effective subcarrier with a zero sequence subcarrier so as to form the frequency domain OFDM symbol with a predetermined length. According to the technical scheme provided by the invention, the problem of failure probability of the preamble symbol in low-complexity receiving algorithm detection in case of a frequency selective fading channel in a conventional DVB_T2 standard or other standards is solved.

Owner:SHANGHAI NAT ENG RES CENT OF DIGITAL TELEVISION

Frequency domain OFDM symbol generation method and preamble symbol generation method

InactiveCN105024963AEasy to decode and demodulateFix Estimation Performance DropMultiplex code generationMulti-frequency code systemsTime domainPhase shifted

The invention discloses a frequency domain OFDM symbol generation method and a preamble symbol generation method. The frequency domain OFDM symbol generation method comprises the steps of: generating fixed sequences and signaling sequences in a frequency domain respectively; filling the fixed sequences and the signaling sequences which are arranged in an odd even interleaving manner to an effective subcarrier; and filling zero-sequence subcarriers on both sides of the effective subcarrier to form a frequency domain OFDM symbol with a preset length. According to the technical scheme provided by the invention, the frequency domain OFDM symbol generation method and preamble symbol generation method prevent the generated signaling sequences from having a property of circular shift or circular shift plus phase shift in a time domain, solves the degradation problem of channel estimation performance of the frequency domain, and further ensures that a receiving end can process and receive signals when carrier frequency deviation ranges from -500kHz to 500kHz.

Owner:SHANGHAI NAT ENG RES CENT OF DIGITAL TELEVISION

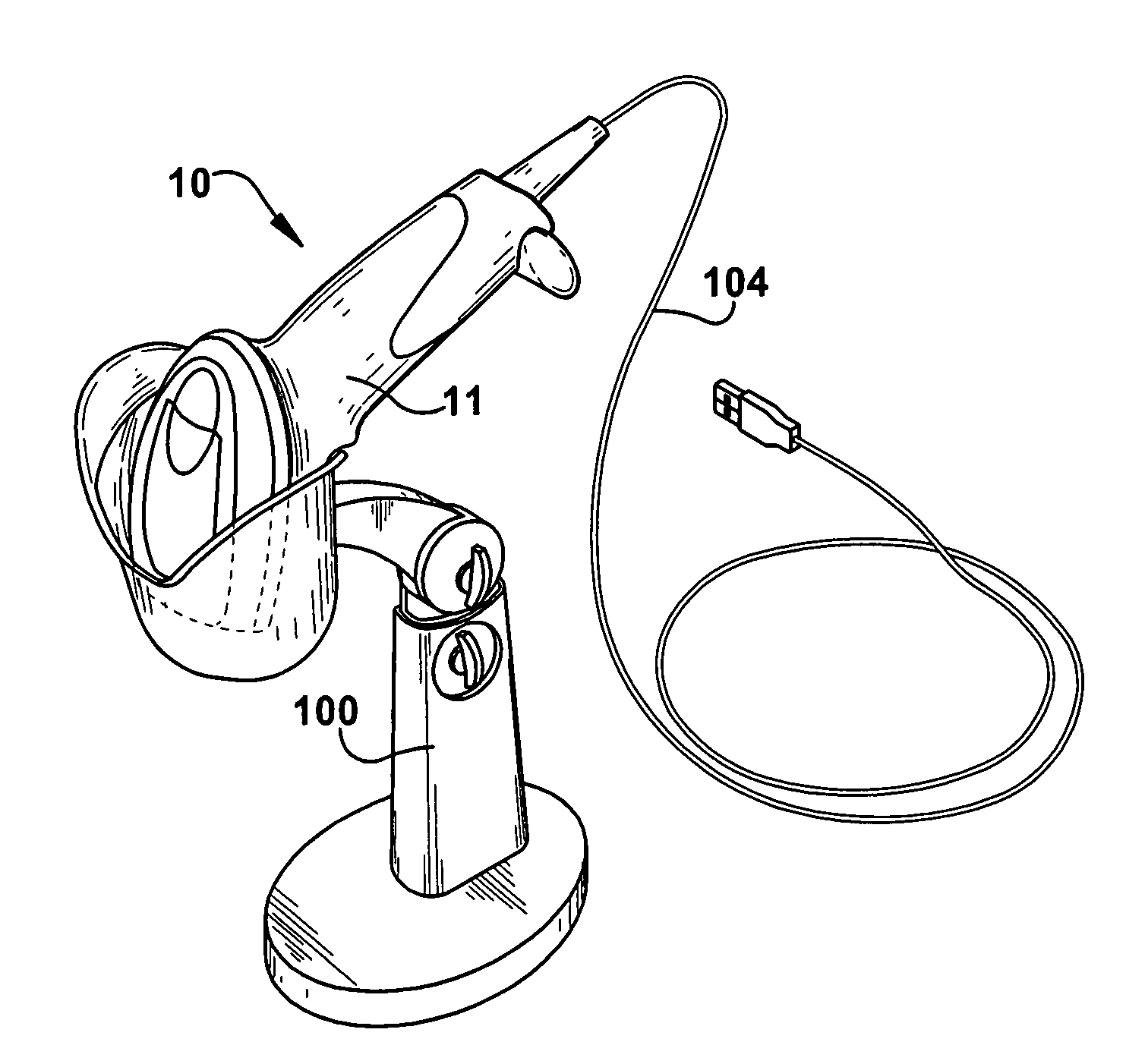

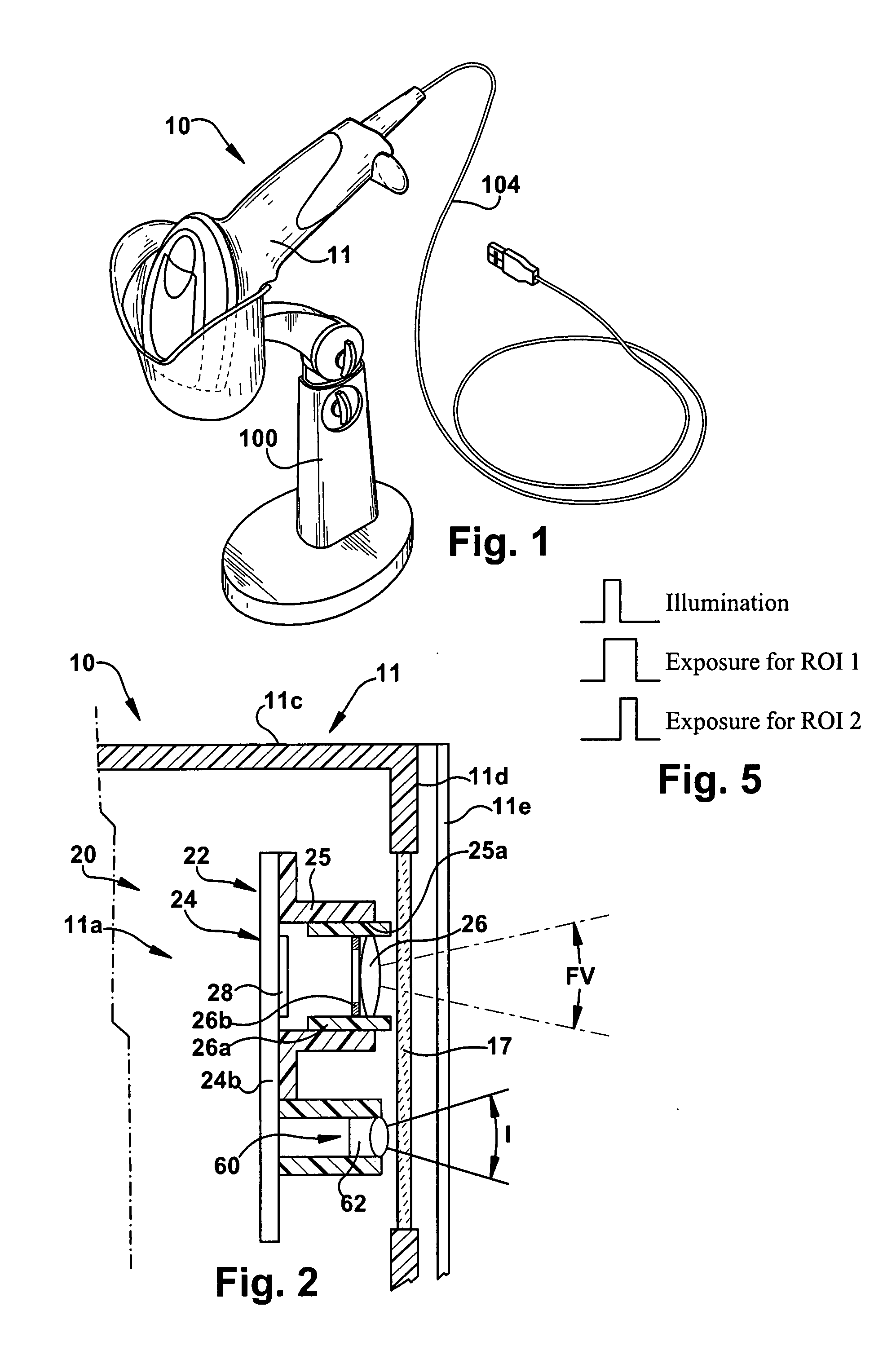

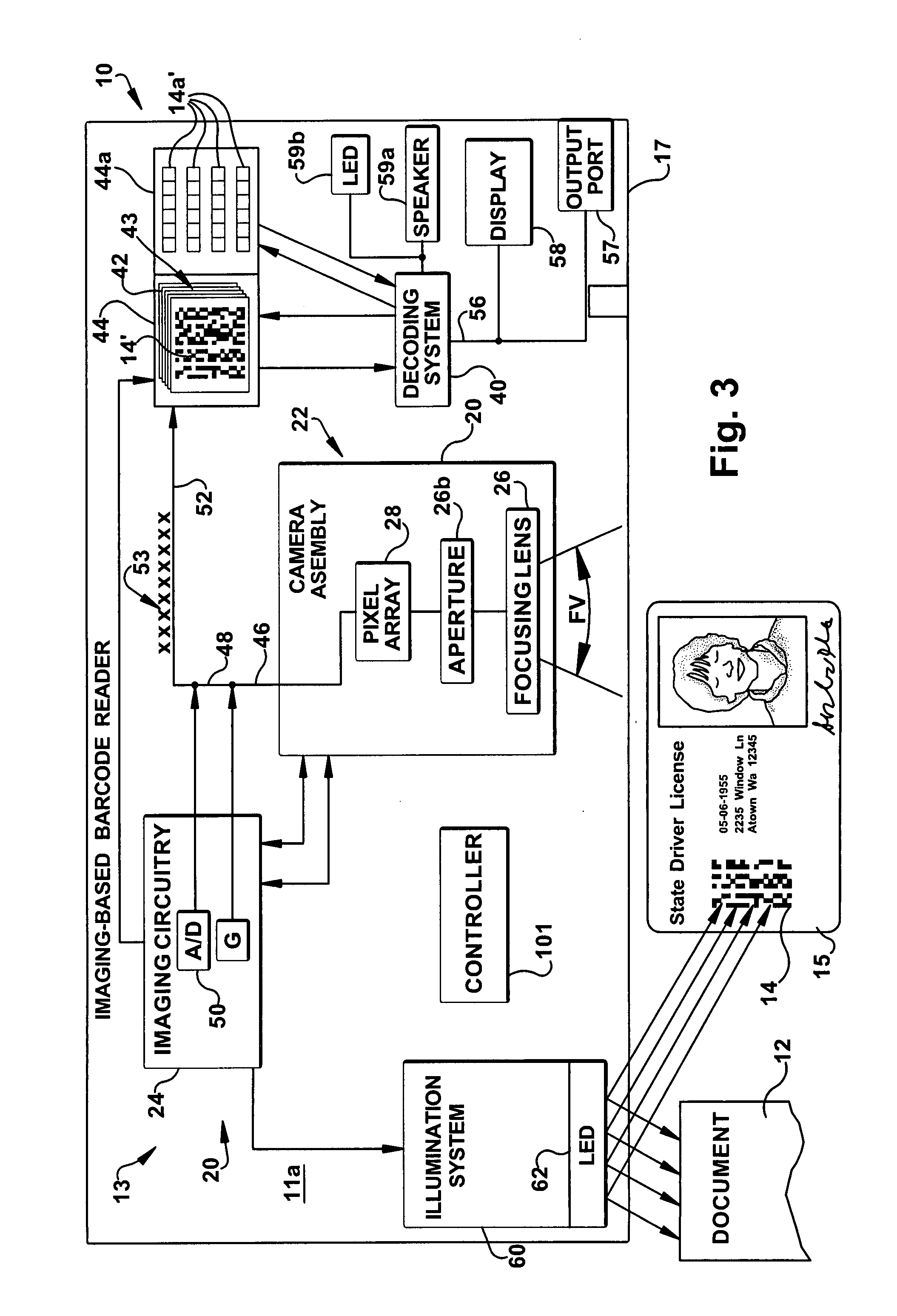

Multiple Configuration Image Scanner

InactiveUS20090078773A1Exposure controlSpecial data processing applicationsSensor arrayProcessor register

An imaging-based bar code reader that includes an imaging and decoding system. Focusing optics and a sensor array define a field of view. An exemplary system has an image sensor includes multiple configuration registers. With multiple configuration registers a video mode can be implemented where the video consists of a continuous sequence of frames with a fixed sequence a number of configurations. The configurations can vary the frame size, exposure time, gain, etc. Compared to a sensor with only one set of configuration registers, successive frames can be captured with different configurations without synchronization issues or frame lag.

Owner:SYMBOL TECH INC

Work balancing scheduler for processor cores and methods thereof

A data processing device assigns tasks to processor cores in a more distributed fashion. In one embodiment, the data processing device can schedule tasks for execution amongst the processor cores in a pseudo-random fashion. In another embodiment, the processor core can schedule tasks for execution amongst the processor cores based on the relative amount of historical utilization of each processor core. In either case, the effects of bias temperature instability (BTI) resulting from task execution are distributed among the processor cores in a more equal fashion than if tasks are scheduled according to a fixed order. Accordingly, the useful lifetime of the processor unit can be extended.

Owner:MEDIATEK INC

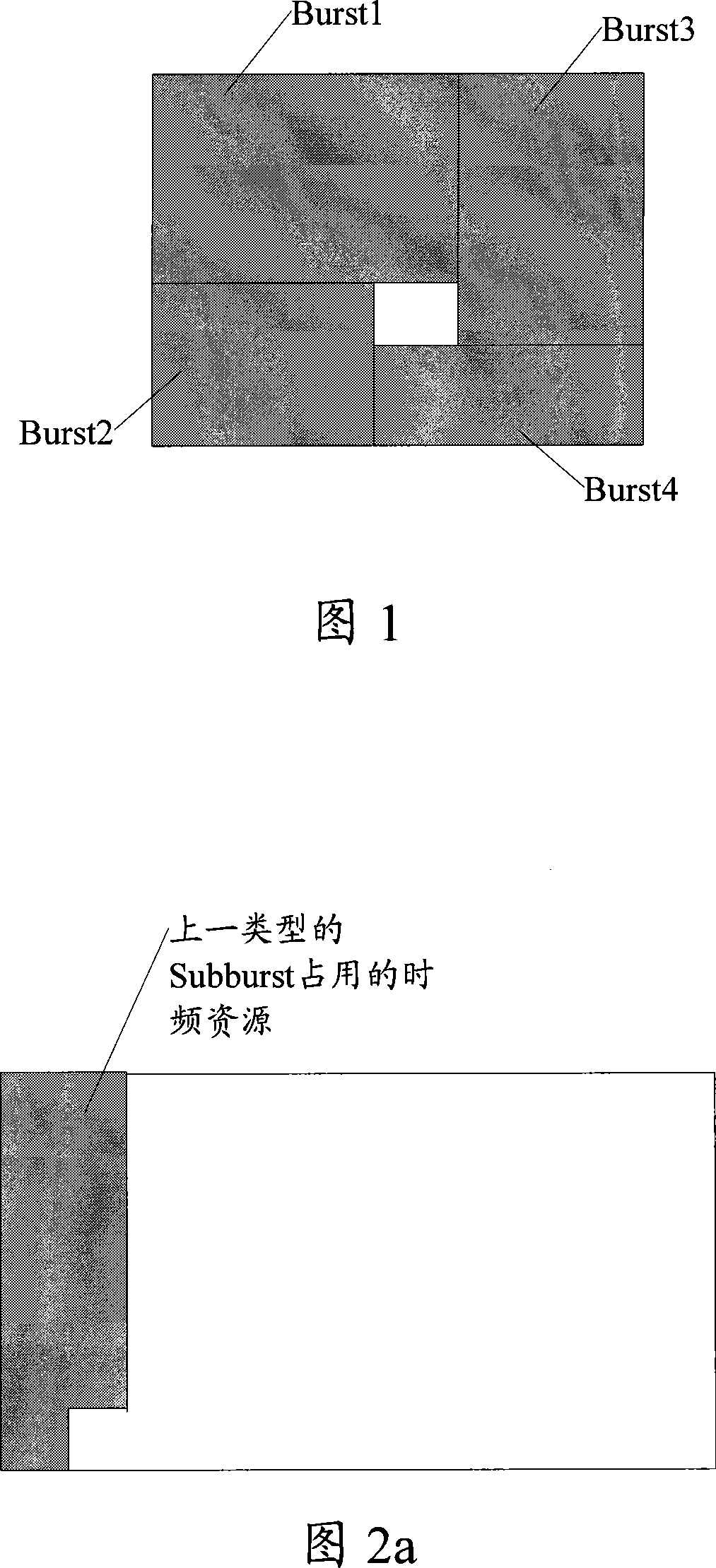

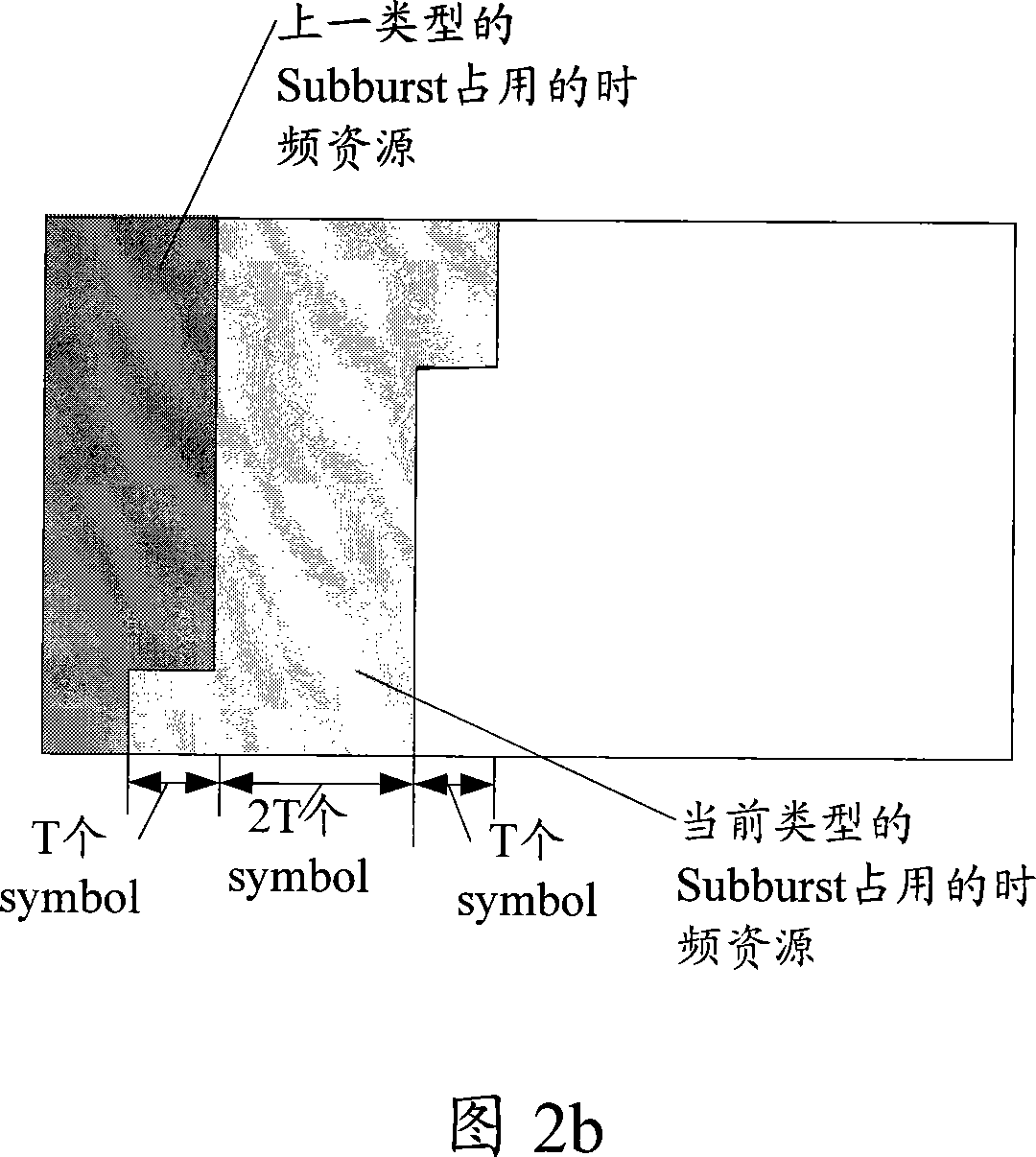

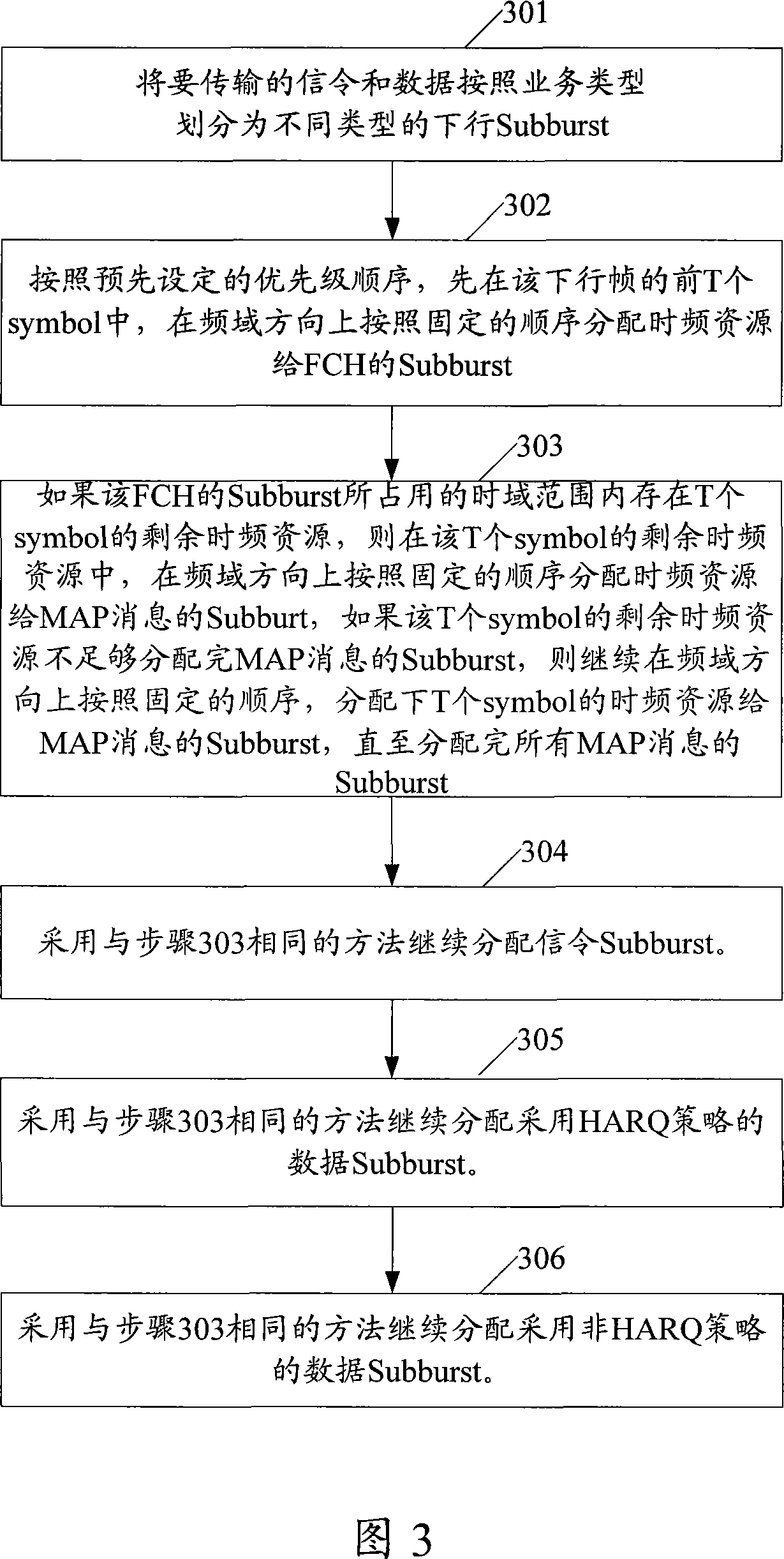

A resource allocation method and device

ActiveCN101170743AAvoid wastingAvoid wasteful situationsError prevention/detection by using return channelData switching by path configurationTime domainData transmission time

The present invention provides a method and device for resource allocation. The method is: if there are T remaining time-frequency resources of data transmission time (symbol) in the time domain range occupied by the previous type of downlink sub-transmission block, then Among the remaining time-frequency resources of T symbols, allocate time-frequency resources to the current type of downlink sub-transport blocks in a fixed order in the frequency domain direction; if the remaining time-frequency resources of the T symbols are not enough to allocate the current type of downlink The sub-transport block continues to allocate the time-frequency resources of the next T symbols to the current type of downlink sub-transport block in a fixed order in the frequency domain direction; the downlink sub-transport block uses T symbols as the smallest unit in the time domain, In the frequency domain, F subcarriers are used as the minimum unit, the number of symbols in the downlink frame is an integer multiple of T, and the number of subcarriers in the entire bandwidth is an integer multiple of F, thereby avoiding waste of time-frequency resources and simple implementation.

Owner:XFUSION DIGITAL TECH CO LTD

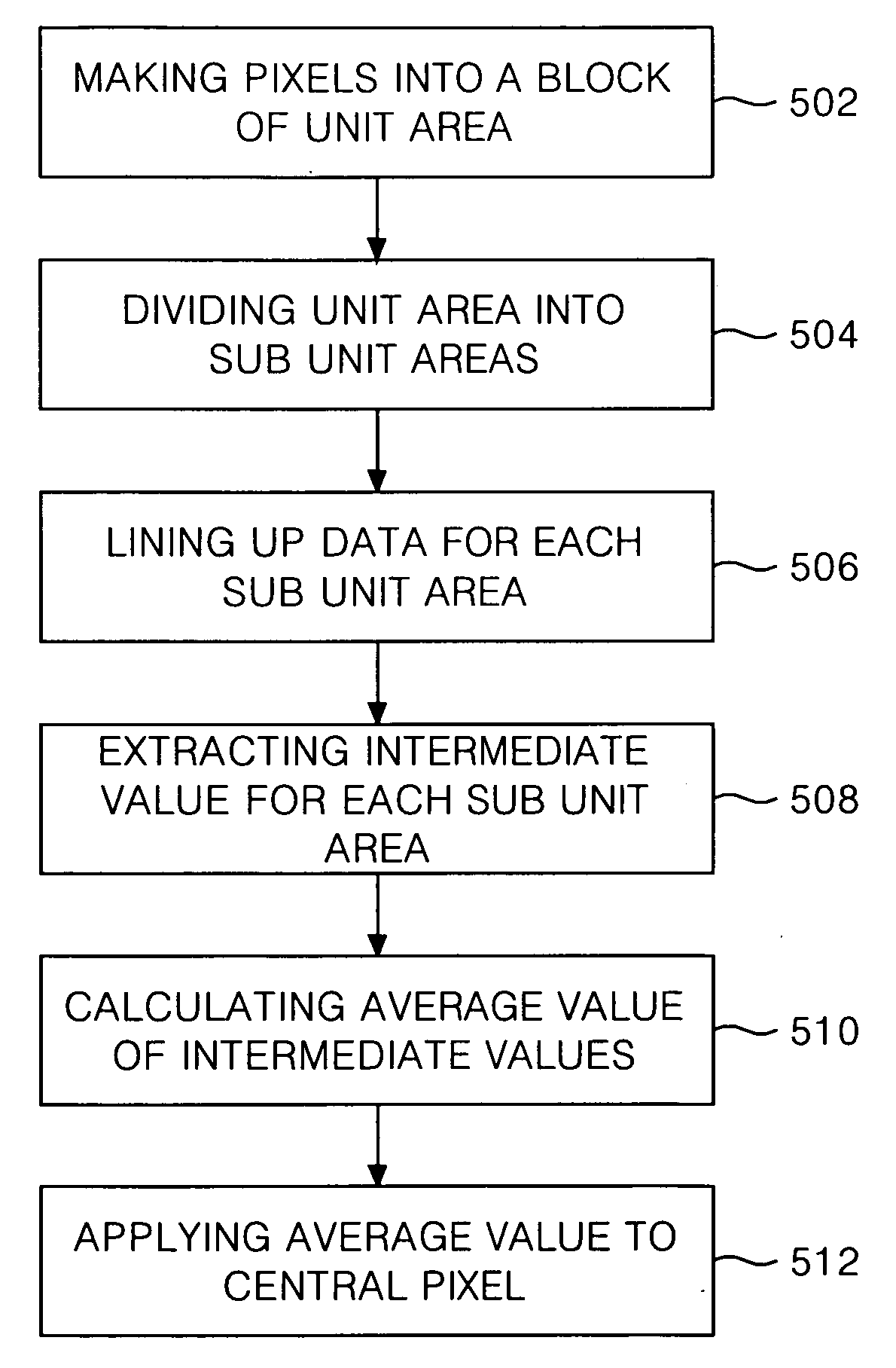

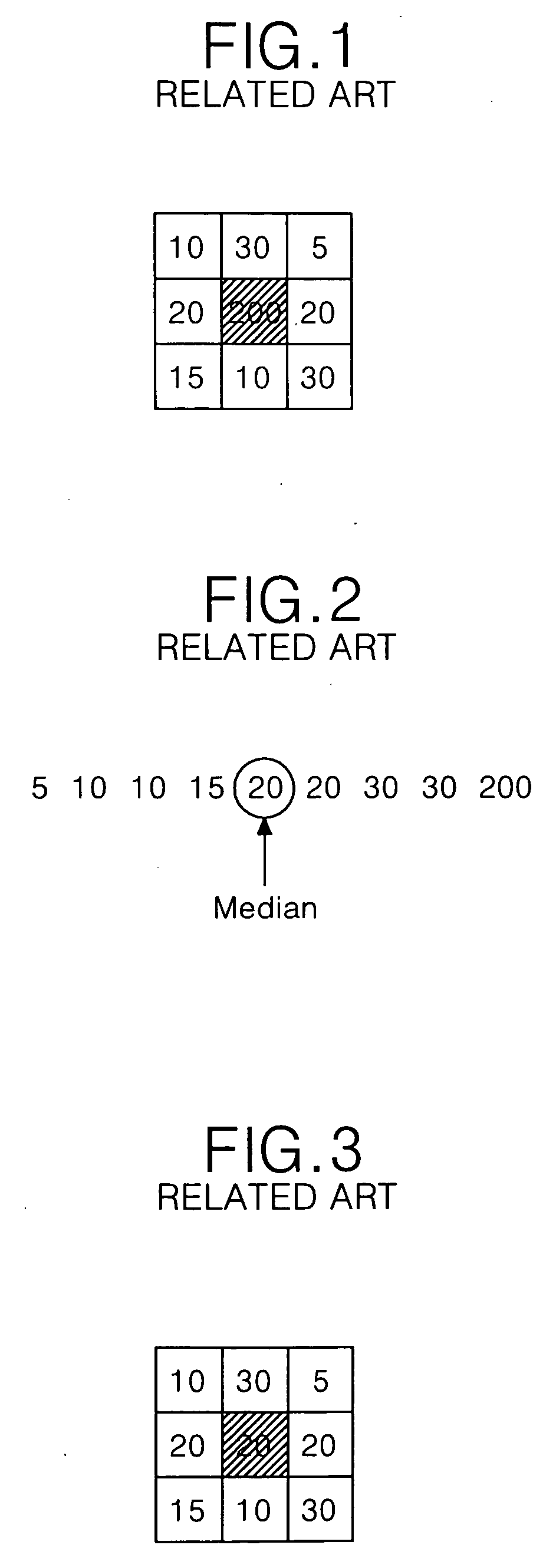

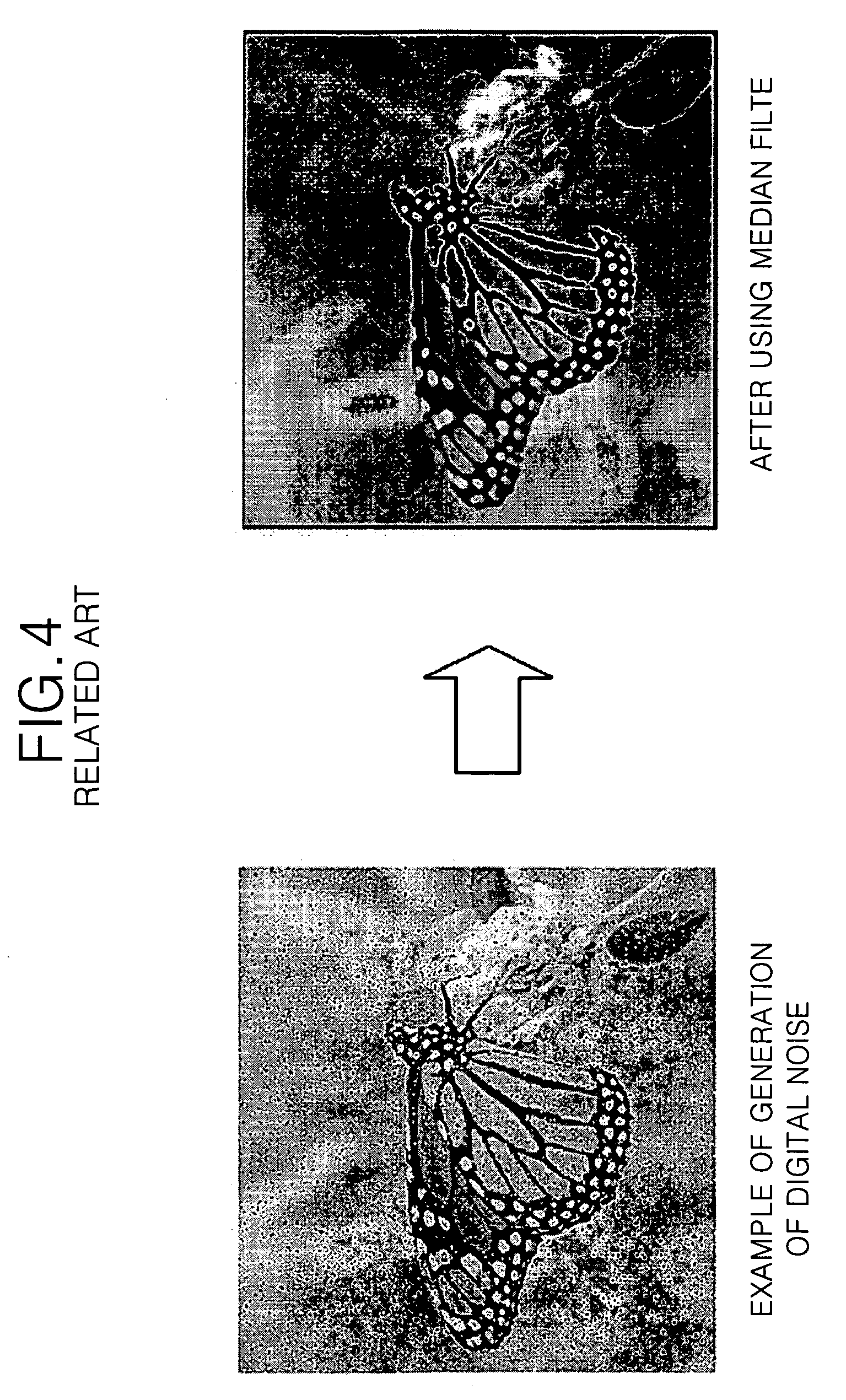

Method of median filtering

A median filtering method makes a plurality of pixel data into a block of fixed unit area which includes a central pixel and a plurality of ambient pixels adjacent to the central pixel. Pixel data within the unit area is divided into sub unit areas which are smaller than the unit area. The data value of the divided pixel data is arranged in a fixed order for each of the sub unit areas. An intermediate value is determined from the arranged pixel data in each of the sub unit areas. An average value of the intermediate values which are extracted from each of the sub unit areas, and the central pixel data is determined corresponding to the central pixel of the unit area with the average value.

Owner:LG DISPLAY CO LTD

Cache coherency in a shared-memory multiprocessor system

ActiveUS20060259705A1Reduce disadvantagesEnergy efficient ICTEnergy efficient computingExternal storageTerm memory

A method of making cache memories of a plurality of processors coherent with a shared memory includes one of the processors determining whether an external memory operation is needed for data that is to be maintained coherent. If so, the processor transmits a cache coherency request to a traffic-monitoring device. The traffic-monitoring device transmits memory operation information to the plurality of processors, which includes an address of the data. Each of the processors determines whether the data is in its cache memory and whether a memory operation is needed to make the data coherent. Each processor also transmits to the traffic-monitoring device a message that indicates a state of the data and the memory operation that it will perform on the data. The processors then perform the memory operations on the data. The traffic-monitoring device performs the transmitted memory operations in a fixed order that is based on the states of the data in the processors' cache memories.

Owner:SK HYNIX INC

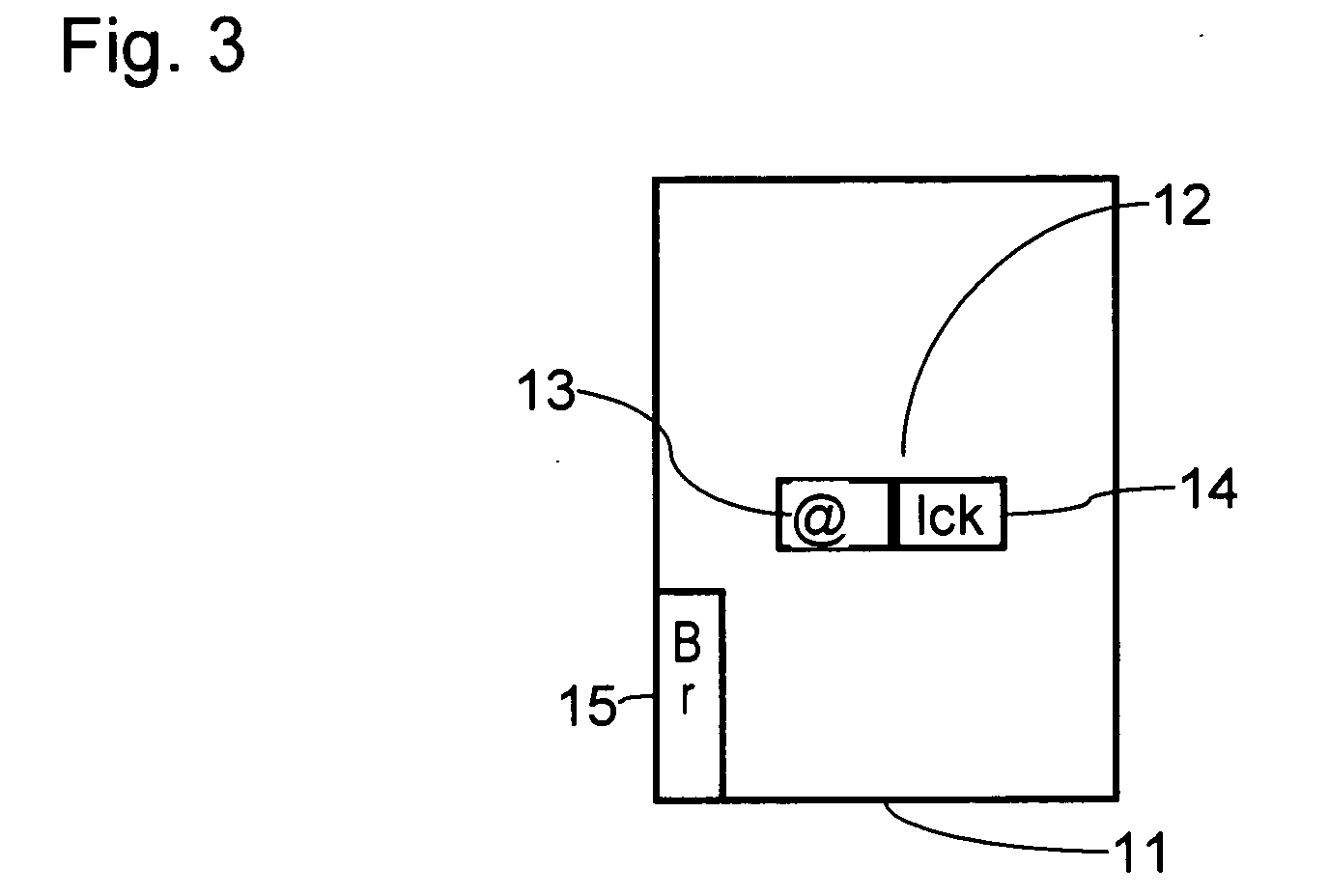

Alarm clock system based on robot and using method of alarm clock system

The invention provides an alarm clock system based on a robot and a using method of the alarm clock system. The alarm clock system comprises a voice recognition and test conversion module, a memory module, an alarm clock detecting system, a walking control module and a sensor password unlocking module, and the walking control module comprises a walking module, an automatic obstacle avoidance module and an alarm clock alerting module. After the alarm clock system based on the robot is started, the robot can walk to other places in a room to wait for unlocking of a user to be alerted, the user to be alerted needs to find the robot and touches each part of the robot according to a fixed sequence in the process, and a purpose of rapidly regaining consciousness of the user to be alerted can be achieved in an execution process.

Owner:陈璟东

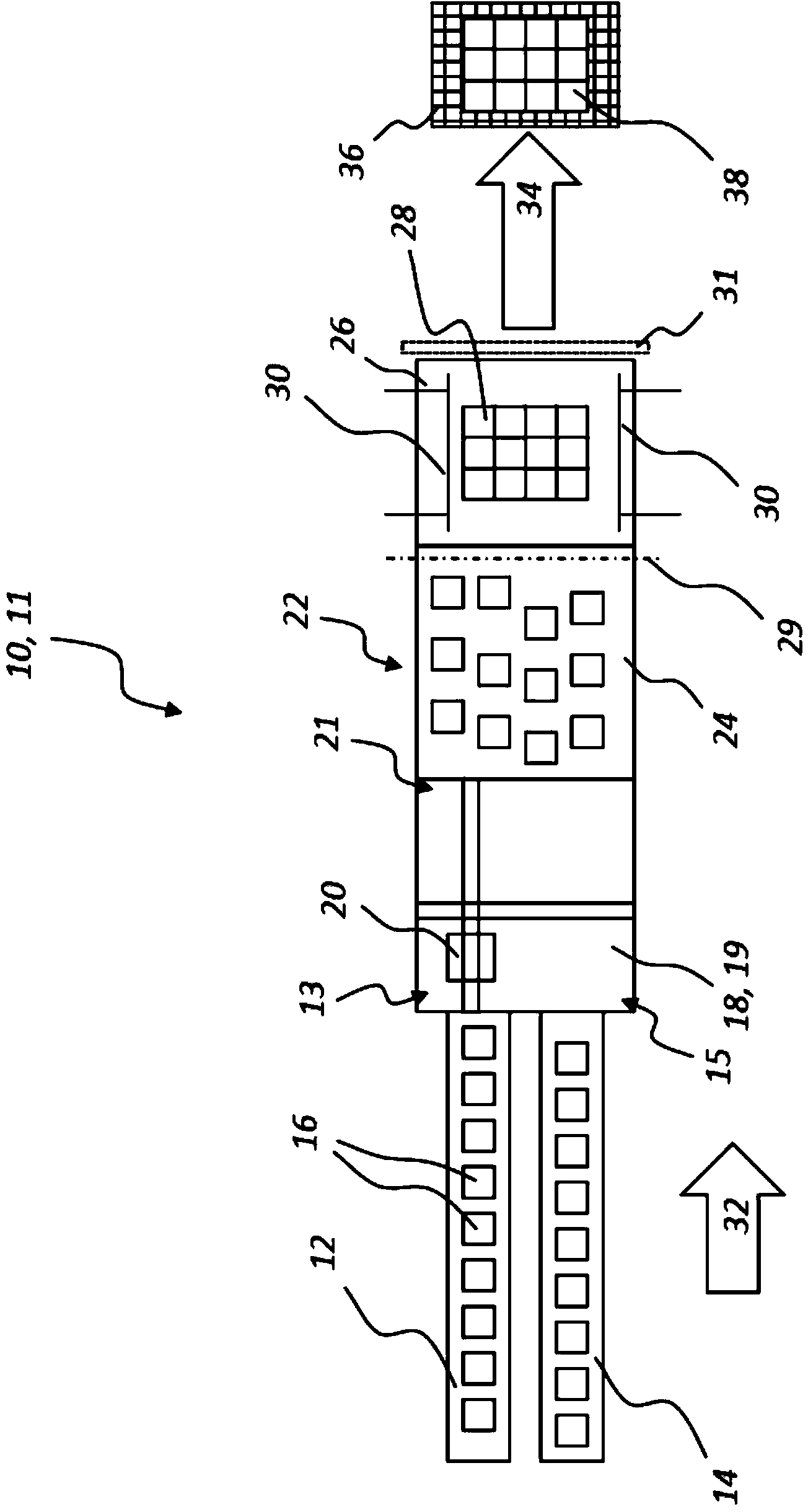

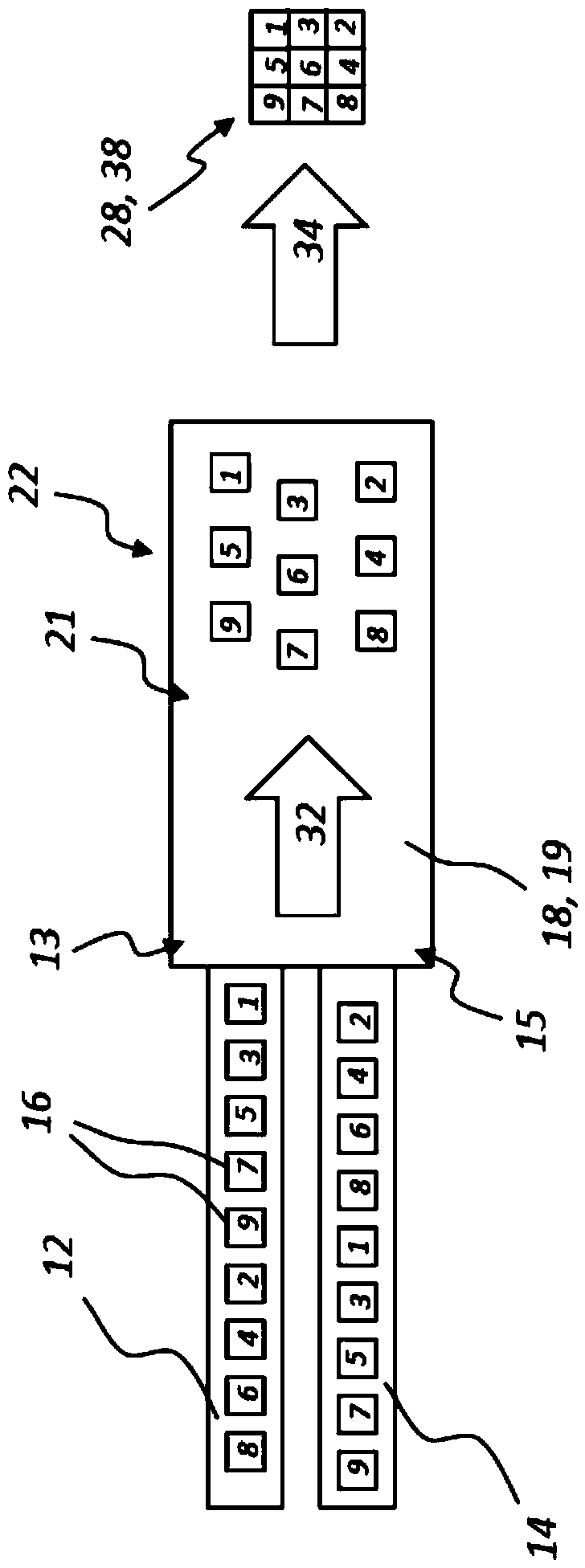

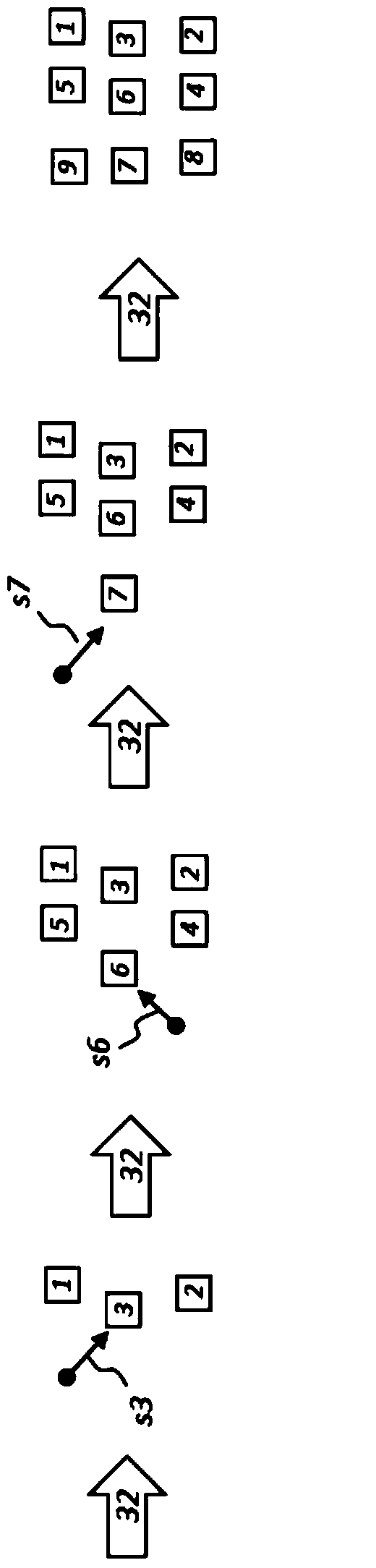

Method and apparatus for forming layers of articles or multipacks

The invention relates to a method for forming palletizable layers (22, 28) of adjacent articles (16), multipacks (17) or the like at a layer-forming location using at least one program-controlled manipulator (20) for picking up one or more articles (16) or multipacks (17) at, and / or transferring them to, at least two spatially remote and / or spatially offset feeding stations and for positioning the articles (16) or multipacks (17), by rotation and / or displacement in predeterminable release positions at the layer-forming location, wherein, in dependence on a current supply situation of the articles (16) or multipacks (17) at the at least two feeding stations, the at least one manipulator (20) picks up the articles (16) or multipacks (17) selectively and without any fixed sequence, at the feeding stations and transfers them, with flexible adaptation of the respective transfer path, to the release position. The invention also relates to a corresponding apparatus for forming planar layers (22, 28) of articles (16) using a layer-forming location and at least one manipulator (20). The feeding stations are assigned sensor devices (52) which are intended for detecting the degree to which the feeding stations are occupied by conveyed articles (16) and which are coupled to a control device (54) for activating the at least one manipulator (20).

Owner:KRONES AG

Analog-to-digital converter operable with staggered timing

InactiveUS7501967B2Reduce incorrect adaptationReduce complexityElectric signal transmission systemsAnalogue-digital convertersFrequency spectrumControl signal

An arrangement for a time interleaved analog-to-digital converter that converts an signal to a digital signal and has a converter array with a plurality of analog-to-digital converters arranged in a fixed sequence in parallel with one another and can be operated with staggered timing with respect to one another is disclosed. The arrangement has a connection network which, for the purposes of actuation with staggered timing, generates in each case one control signal for an individual analog-to-digital converter in each case, with the connection network predefining the time sequence with which the control signals actuate the individual analog-to-digital converters in such a way that owing to this sequence of the control signals and thus the sequence of the actuated individual analog-to-digital converters there is at least a reduction in an interference spectrum in the spectrum of the input and / or output signal. A sorting method for operating this analog-to-digital converter is also disclosed.

Owner:INFINEON TECH AG

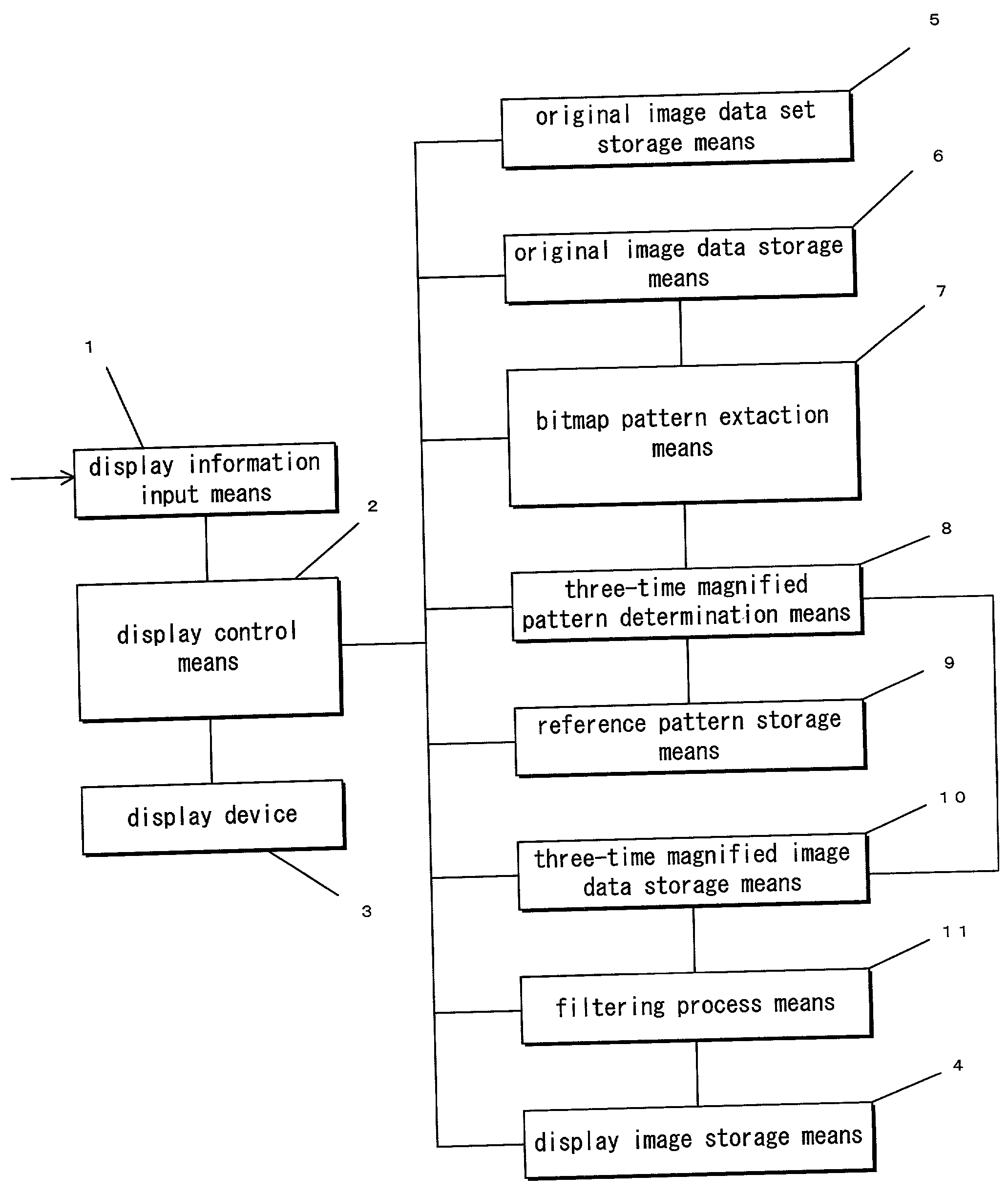

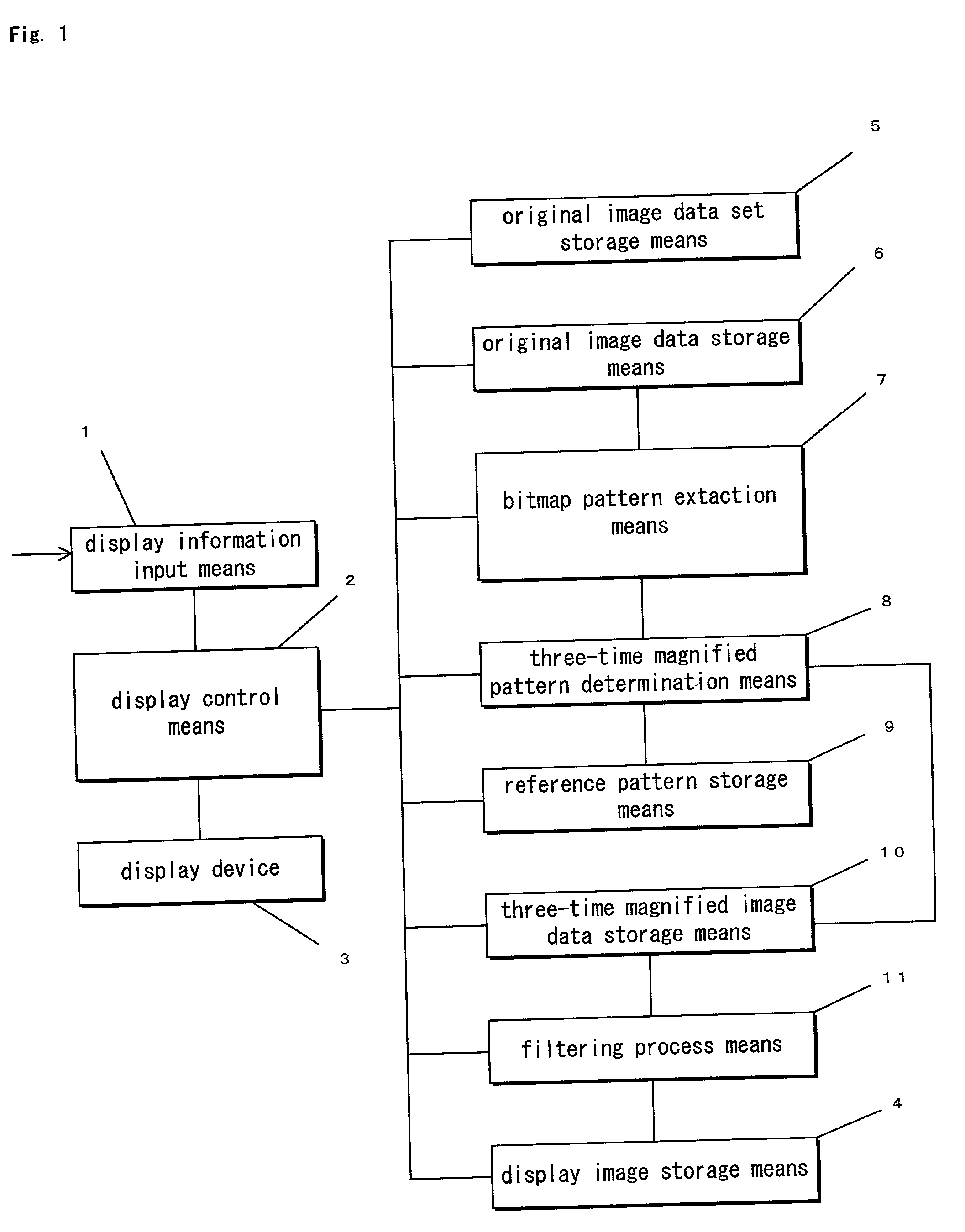

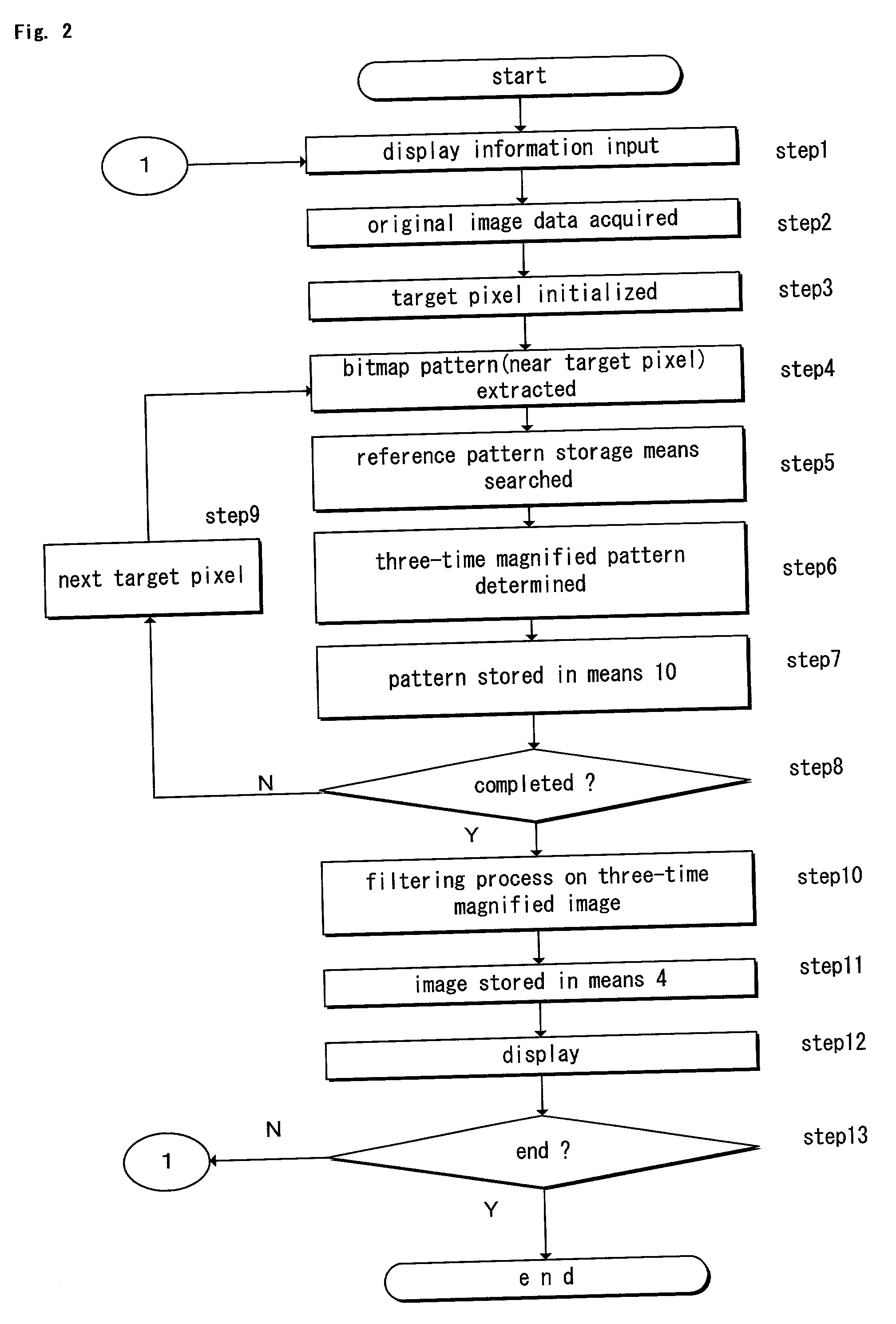

Display equipment, display method, and storage medium storing a display control program using sub-pixels

InactiveUS20020008713A1Improve uniformityEasy to operateTelevision system detailsCharacter and pattern recognitionGratingComputer graphics (images)

In a display device, three light-emitting elements, which respectively emit light of the three primary colors of R, G, and B, are aligned in a fixed order in a first direction to form one pixel. A plurality of such pixels are aligned in a the direction to form one line. A plurality of such lines are aligned in a second direction, which is orthogonal to the first direction, to form a display screen. With this display device, a three-times magnified pattern, with which a target pixel in a raster image to be displayed currently is magnified by three in the first direction, is determined dynamically in accordance with a rectangular reference pattern of 3.times.3 pixels consisting of the target pixel and pixels surrounding the target pixel. Display is performed upon allocating this three-times magnified pattern to the three light-emitting elements that comprise one pixel. Character interval adjustment and color display of sub-pixel precision precision are enabled.

Owner:PANASONIC CORP

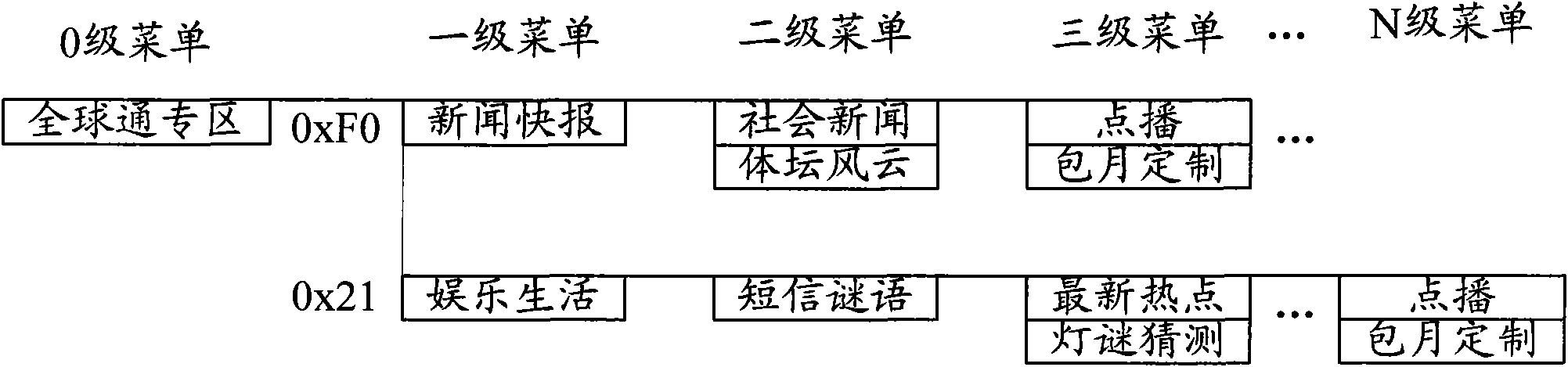

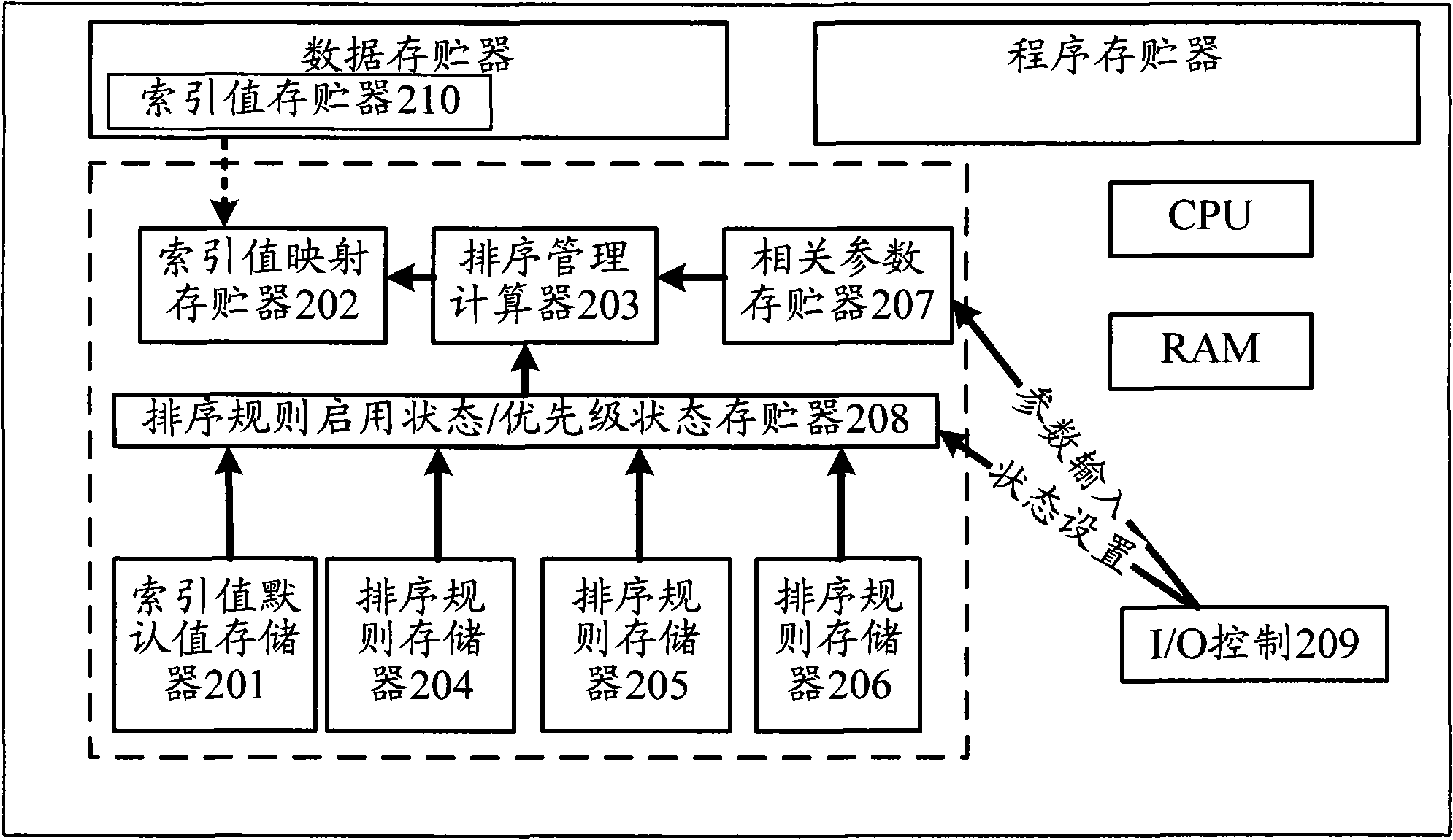

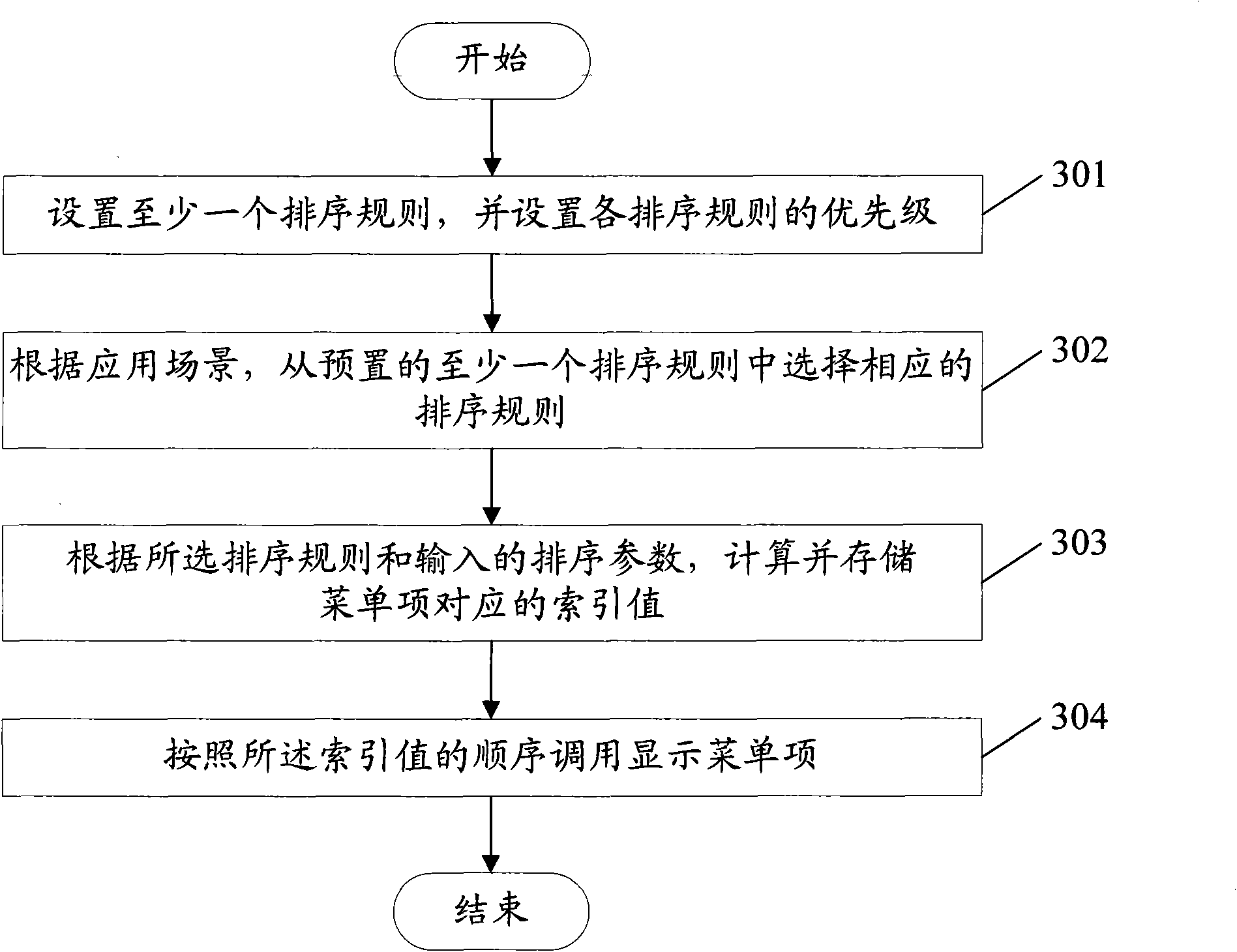

Menu display method and communication intelligent card

ActiveCN101778147AEasy to useTelephone sets with user guidance/featuresInput/output processes for data processingSmart cardHuman–computer interaction

Owner:DATANG MICROELECTRONICS TECH CO LTD

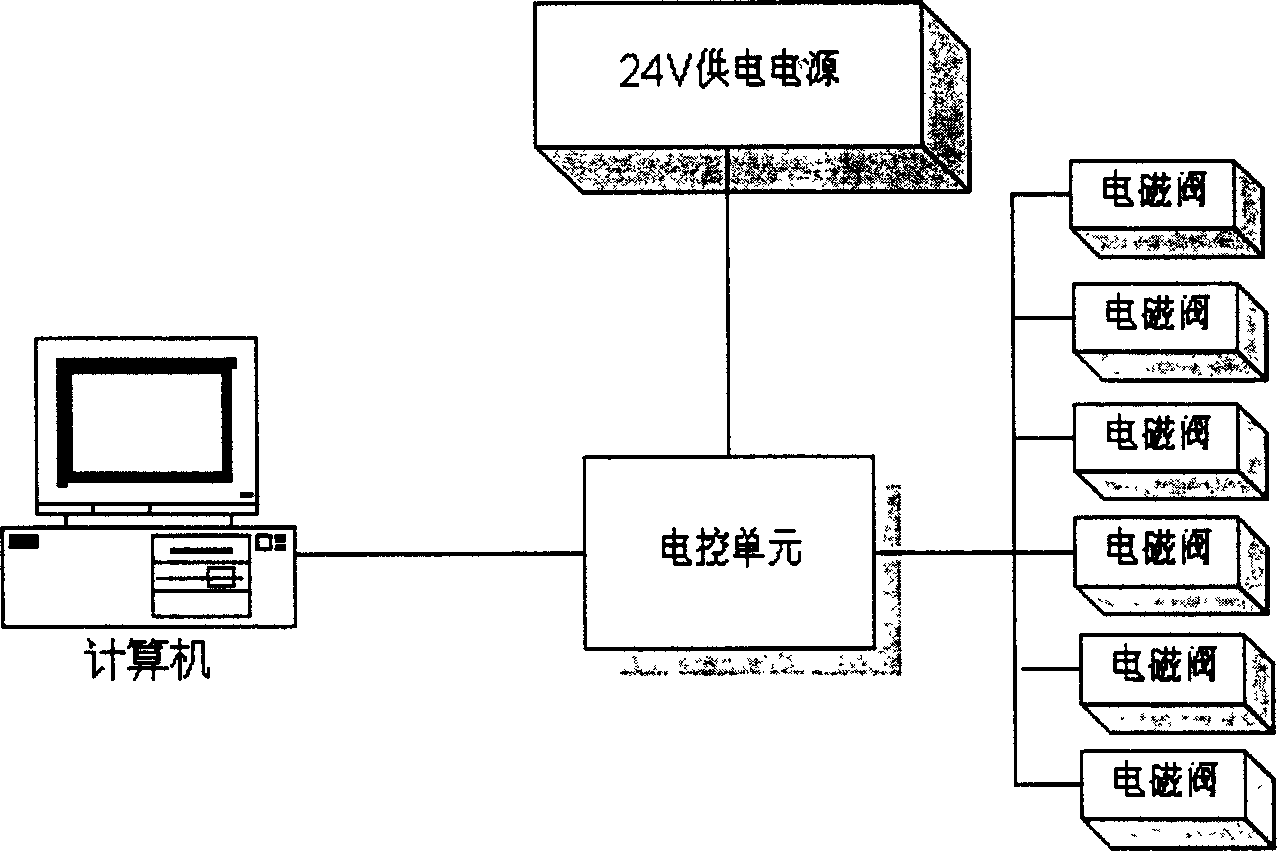

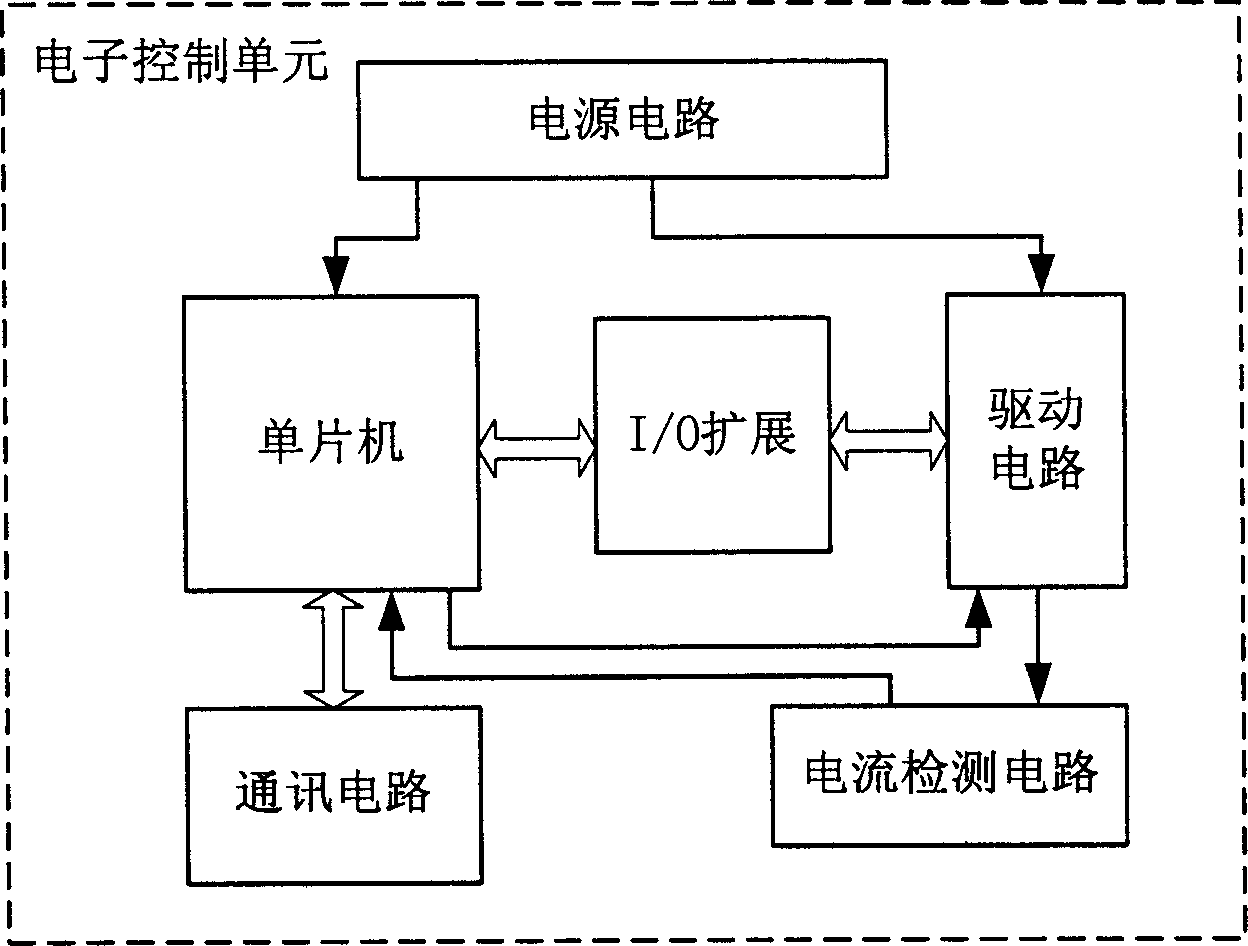

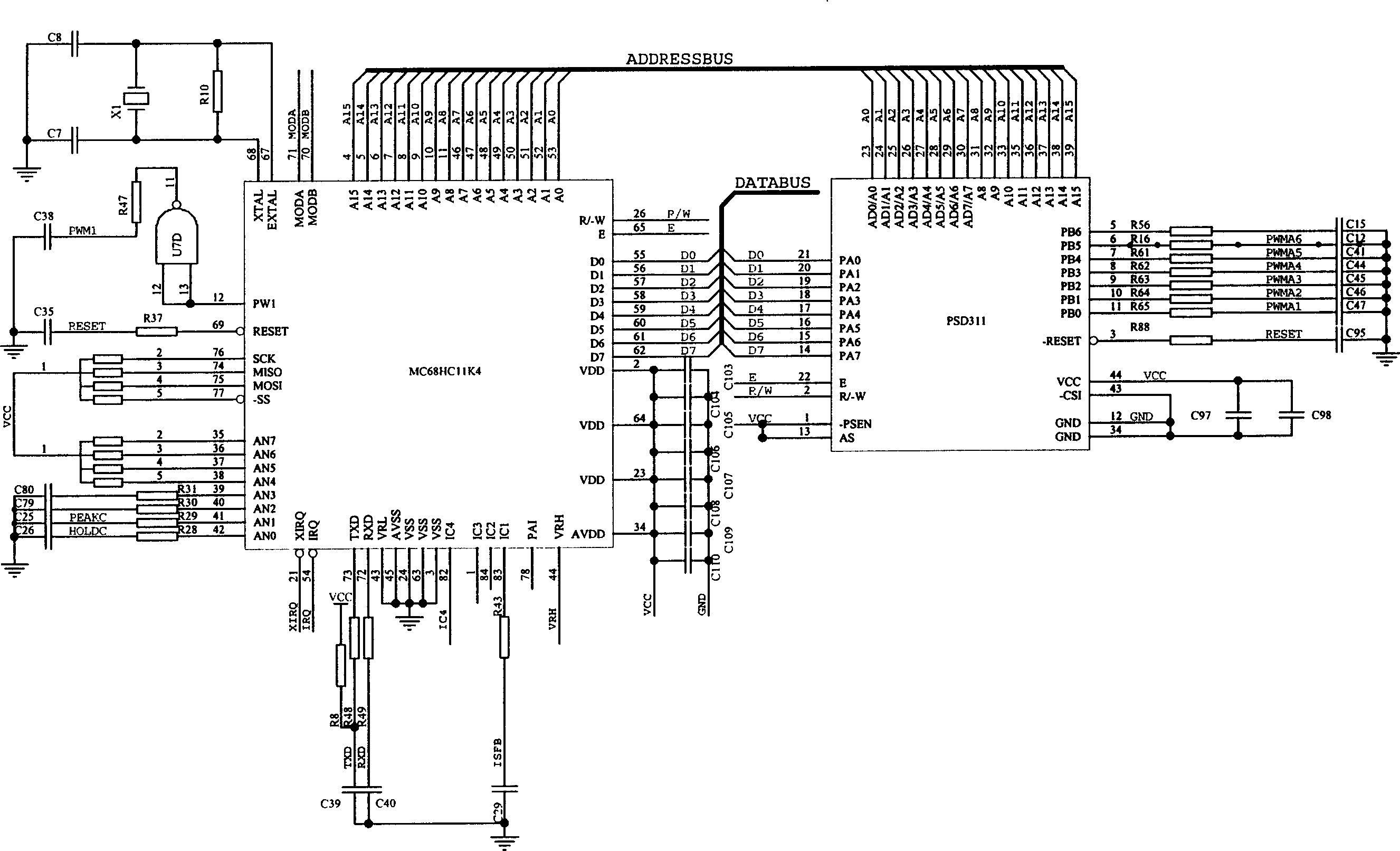

Method and device for diagnosing and testing switch electromagnetic valve running-in for electric controlled diesel engine

InactiveCN1450452AAdjust mechanical propertiesHigh working reliabilityOperating means/releasing devices for valvesSpecific program execution arrangementsMicrocontrollerElectric control

The invention is run-in tester and the method for switching electrical-magnetism valve in electrical controlled diesel engine; it refers to the run-in and malfunction testing of high-speed punchy electrical-magnetism valve in electrical controlled fuel ejecting system of diesel machine. The invention includes monitoring computer, electrical controlling unit and the power. The electrical controlling unit receives the order of monitor procedure from the computer, and drives the valve according to the fixed sequence. The hardware circuit tests the current valve of the coil in valve, the valve istransmitted to the singlechip. The control procedure calculates the switch time and the particular current valve of the valve and judges the valve is abnormal or not, and transmits the result to the computer to display. The device is convenient.

Owner:TSINGHUA UNIV

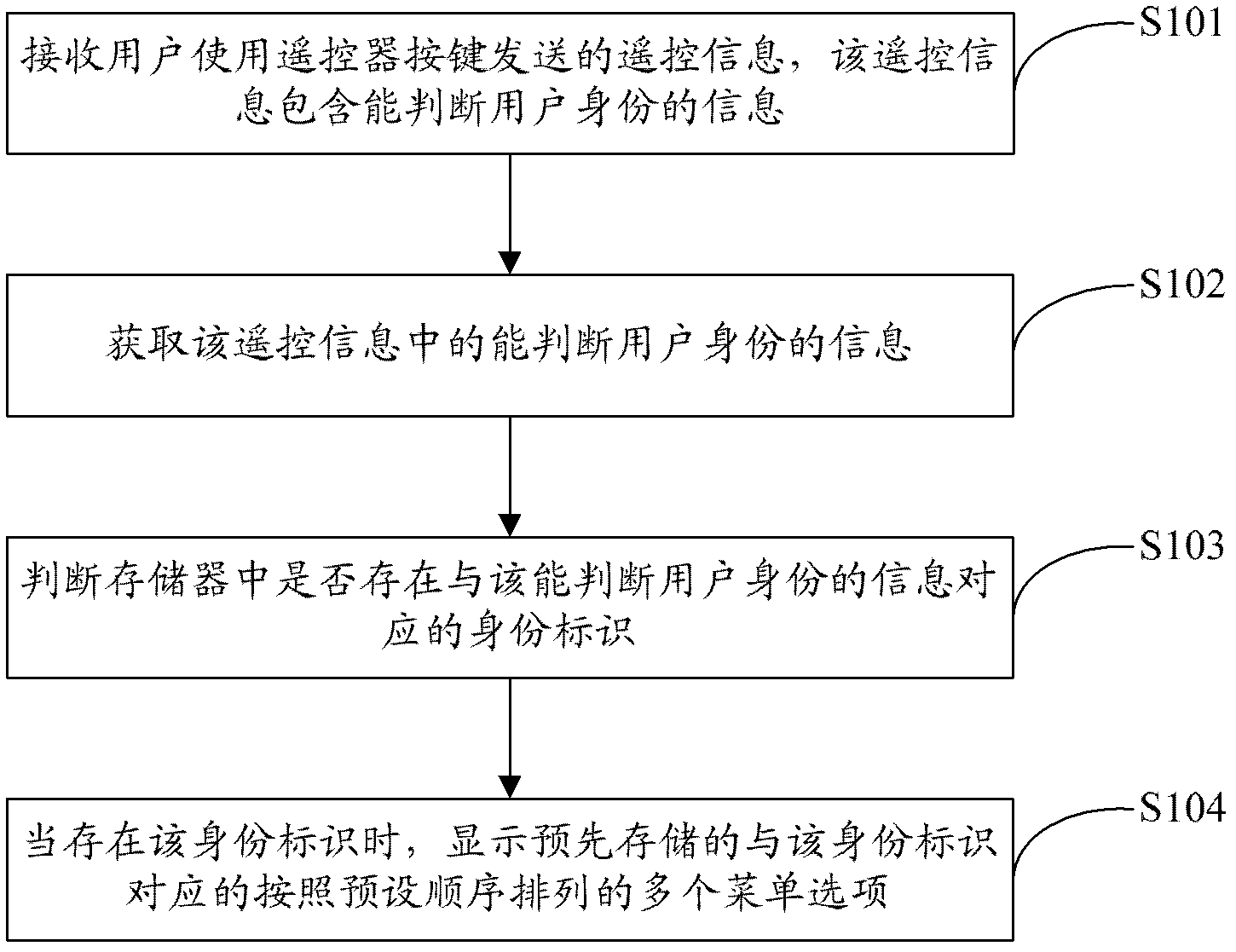

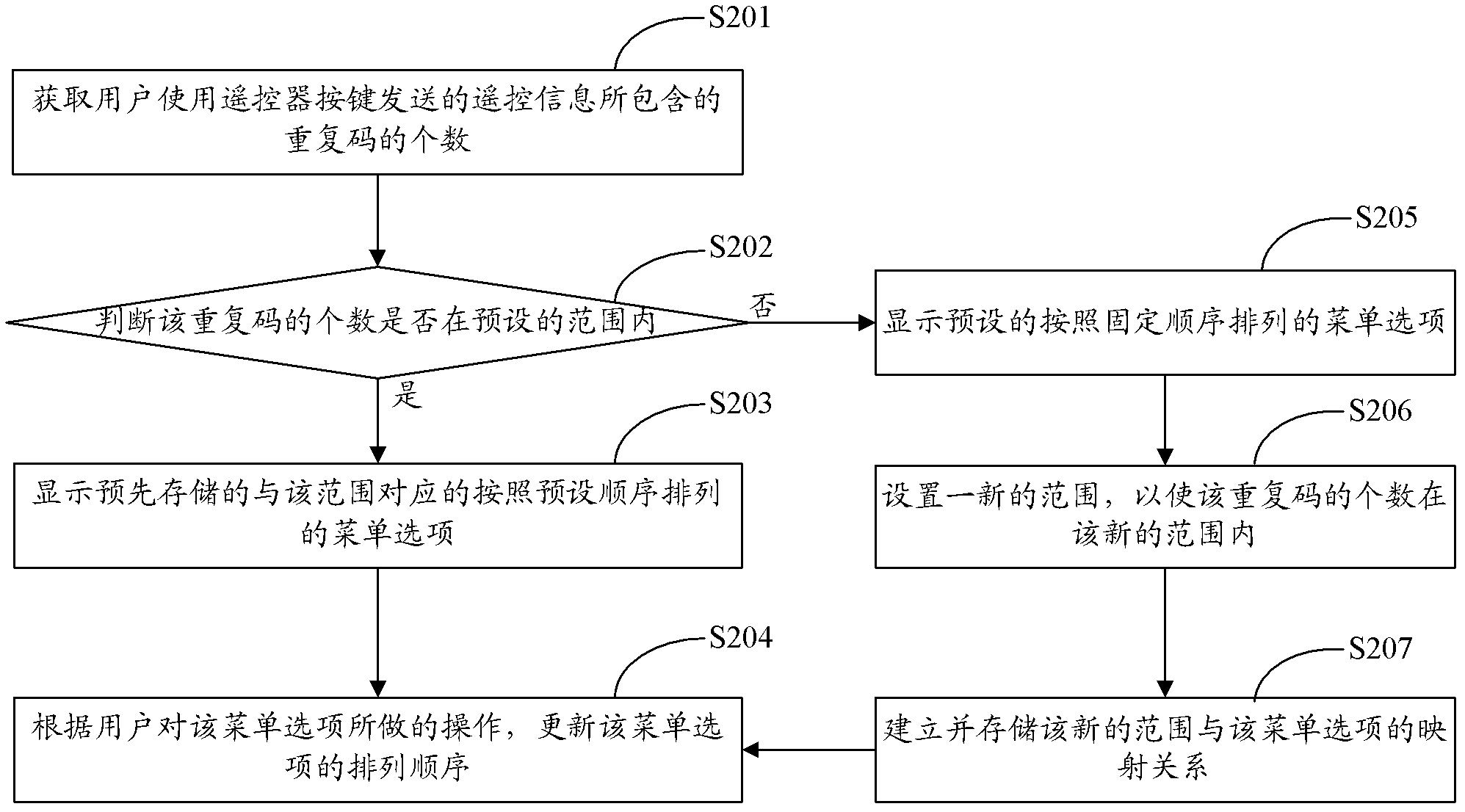

Menu option displaying method, apparatus thereof and television set

ActiveCN102316381ASolve operational problemsSolve the experienceSelective content distributionRemote controlInternet privacy

The invention is suitable for the household electrical appliance field, and provides a menu option displaying method, an apparatus thereof and a television set. The method comprises the following steps: receiving remote control information transmitted by a user by using a remote controller button, wherein the remote control information comprises information which can determine user identity, obtaining the information which can determine user identity in the remote control information, determining whether exists an identity identification corresponding to the information can determine user identity in a memory, and if exists, displaying a plurality of menu options which are stored in advance, corresponding to the identity identification and arranged in a preset order. According to the invention, problems that since menu options of a present television set are arranged according to a fixed order, user operation is inconvenient, and experience feeling of a user is poor are solved, operation convenience of the user selecting common menu options is improved, and experience feeling of the user is improved.

Owner:SHENZHEN SKYWORTH RGB ELECTRONICS CO LTD

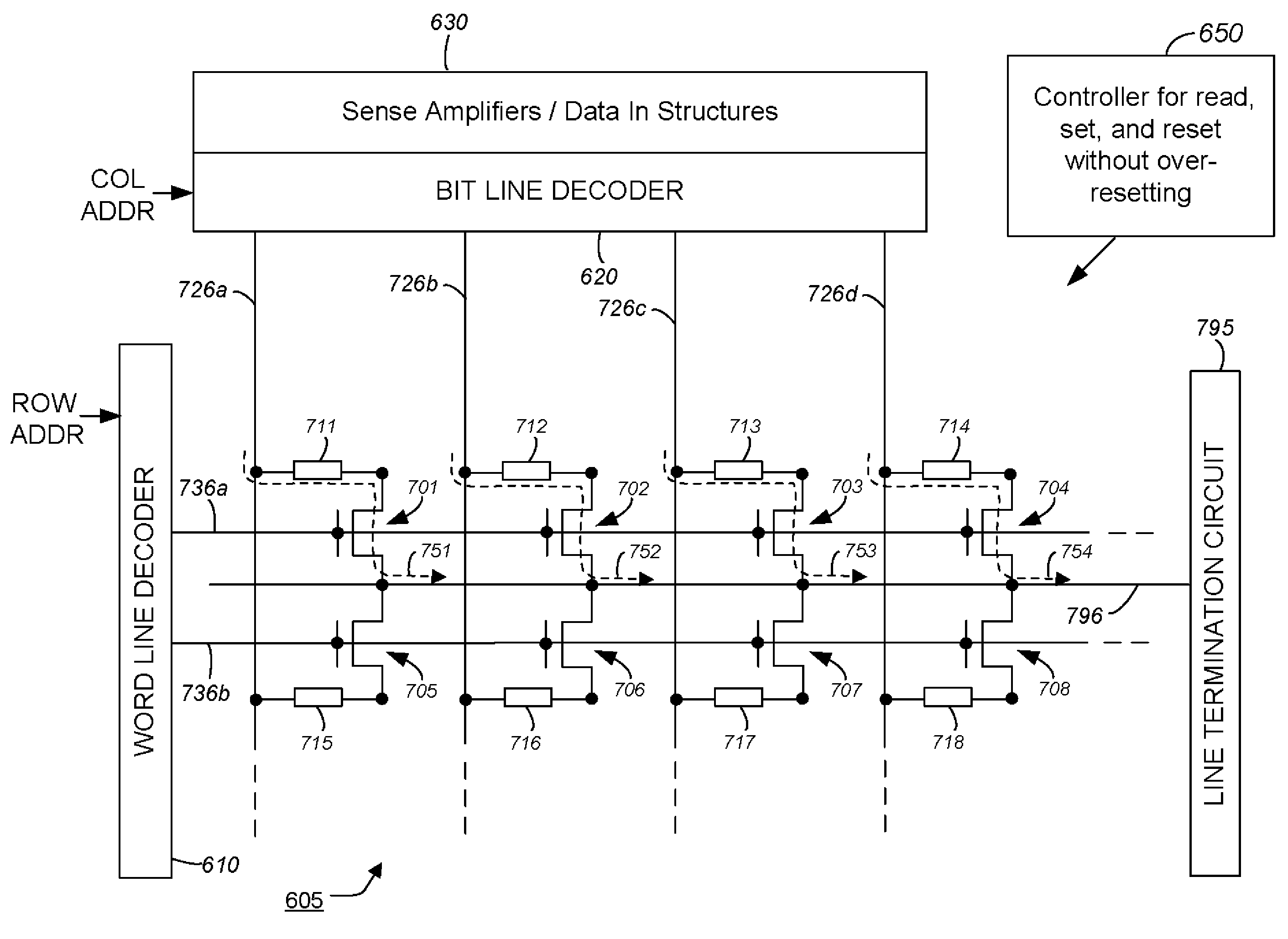

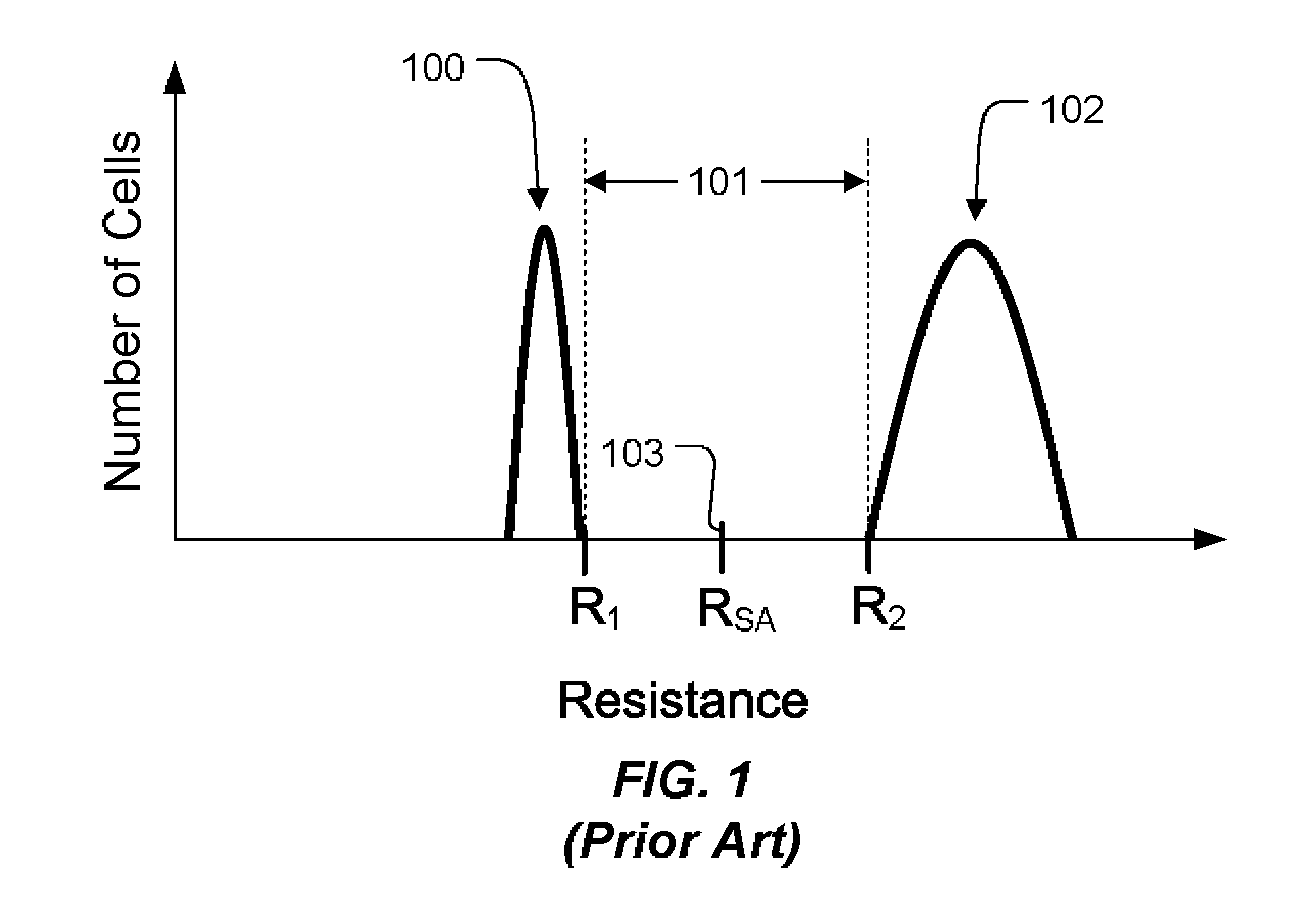

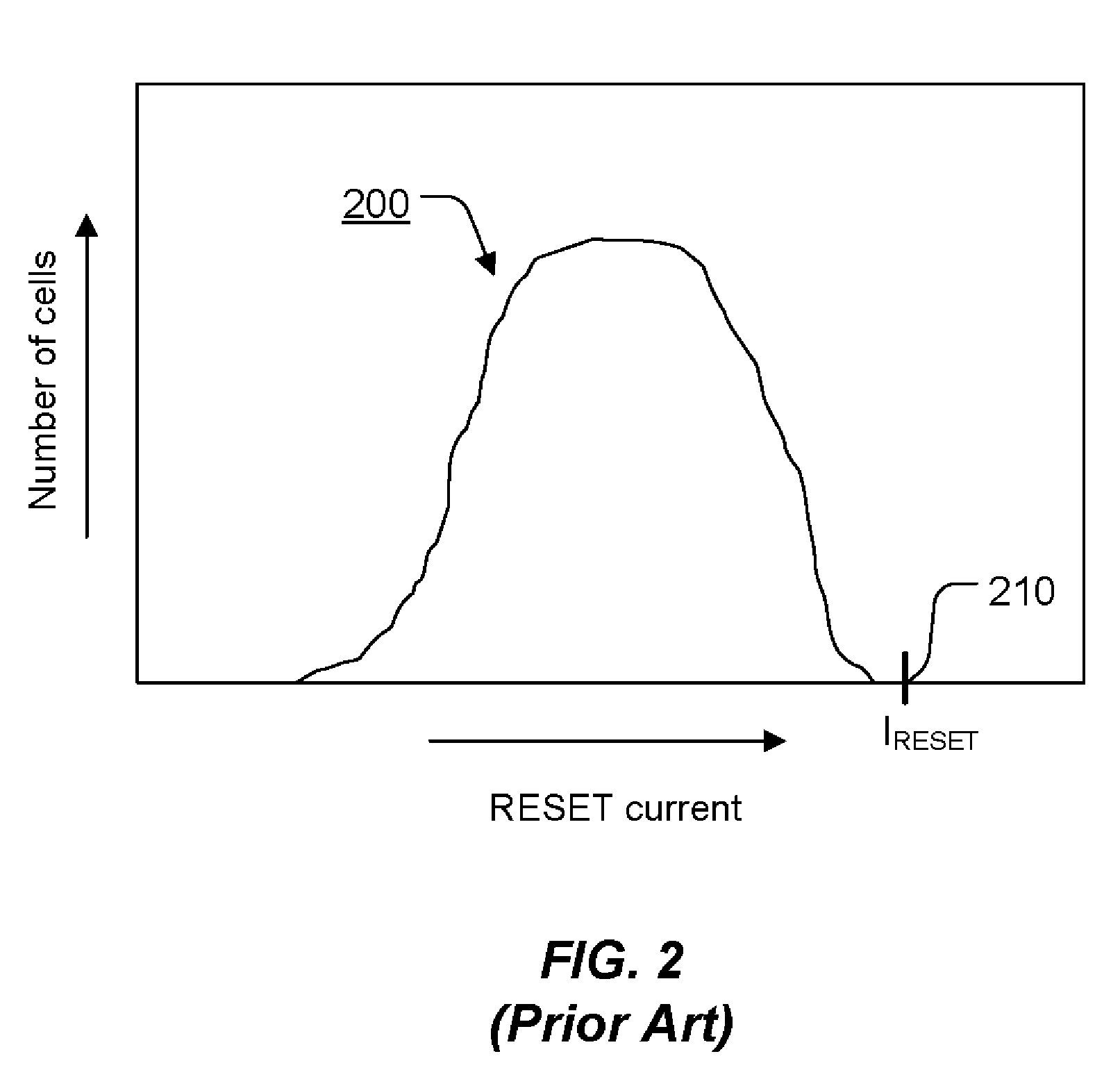

Phase change memory program method without over-reset

ActiveUS20100110778A1Reduce usageAvoid over-resetDigital storageHigh resistanceElectrical resistance and conductance

Memory devices and methods for operating such devices are described herein. A method as described herein includes applying a fixed sequence of voltage pulses across the memory cell of increasing pulse height to change the resistance state from the lower resistance state to the higher resistance state. The fixed sequence of voltage pulses cause increasing current through the phase change memory element until change to the higher resistance state occurs, and after the change the voltage pulses in the fixed sequence causing a voltage across the phase change memory element less than the threshold voltage.

Owner:MACRONIX INT CO LTD +1

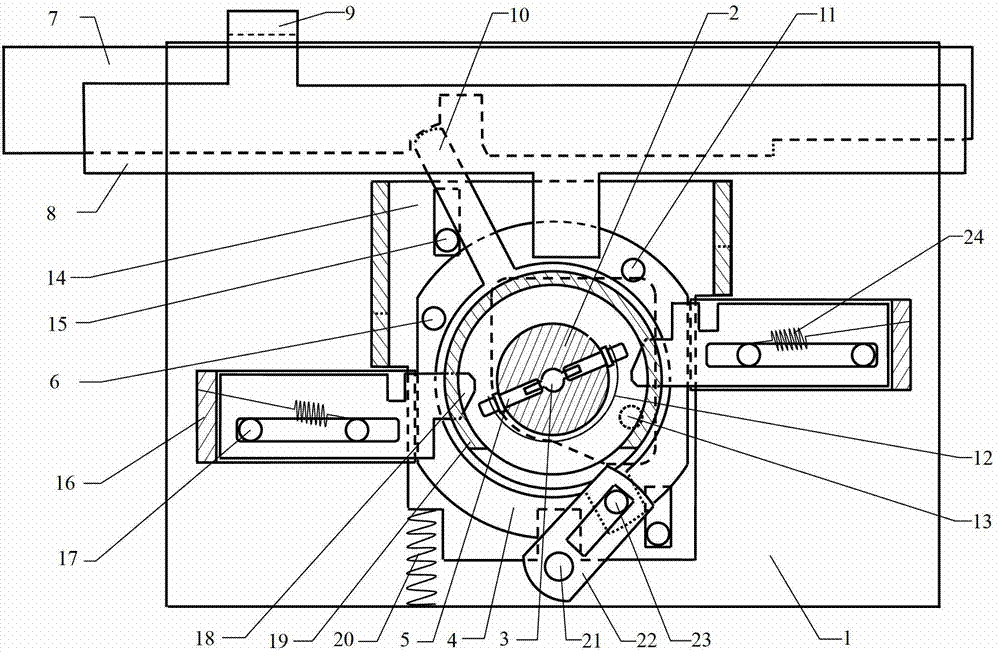

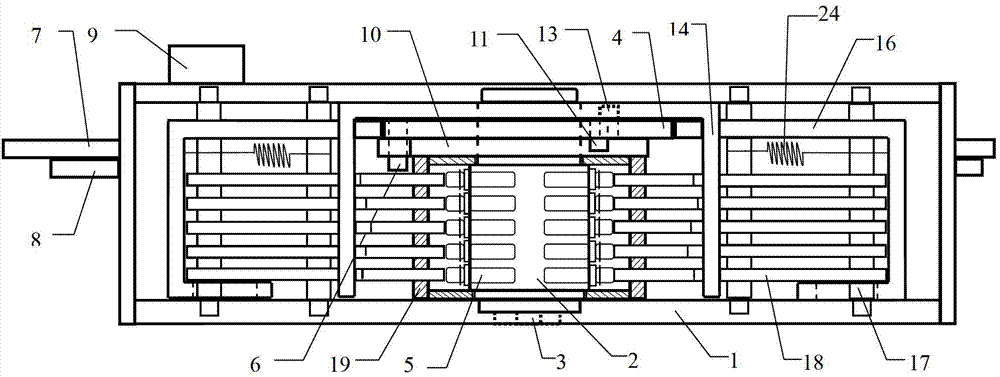

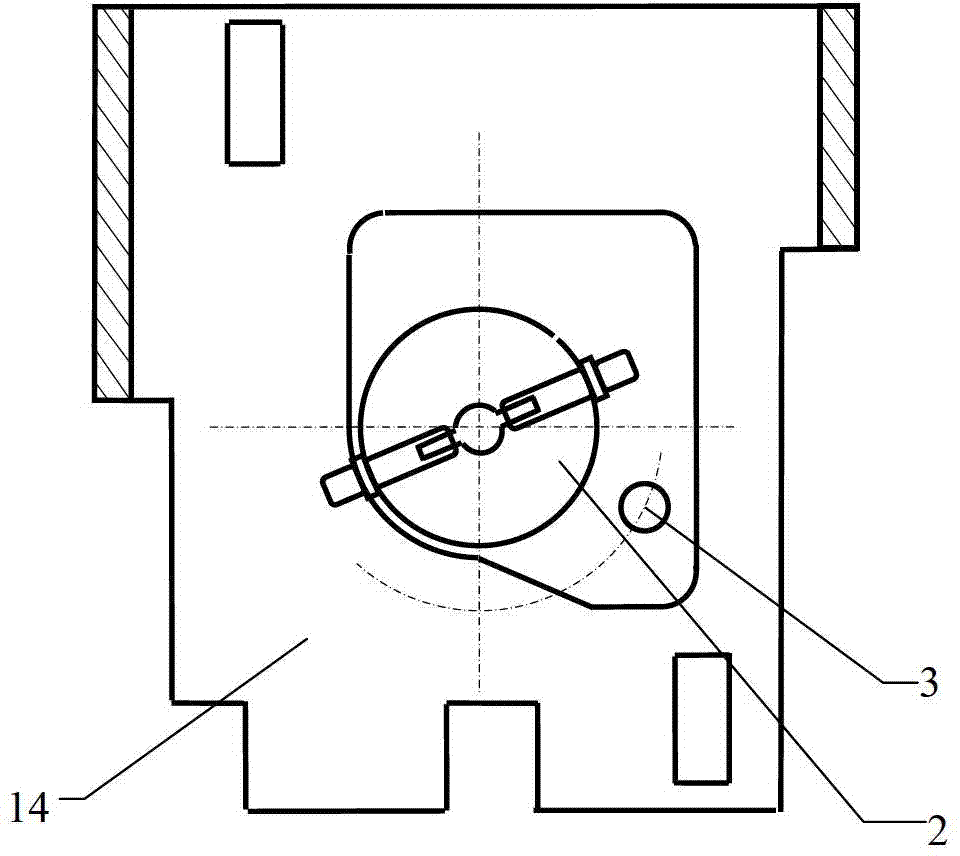

Clamping type mechanical antitheft lock

The invention relates to a clamping type mechanical antitheft lock, which comprises a lock body, a lock cylinder, a transmission mechanism, a spring bolt, a lock bolt and a matched key, wherein a protection ring is arranged between the lock body and the lock cylinder; one end of each of a plurality of sliding sheets is inserted into the protection ring; openings are formed in the upper edges of the sliding sheets; before the lock is unlocked, a ball of the lock cylinder is in no contact with the sliding sheets; when the lock cylinder rotates preliminarily, the ball of the lock cylinder is in contact with the sliding sheets and pushes the sliding sheets to the openings in the upper edges to form a straight line; during rotation of the lock cylinder, the ball in the lock cylinder is separated from the sliding sheets, and then a shifting pin A on a cam fixed at one end of the lock cylinder drives a stopping plate to downwards move and be clamped in the openings of the sliding sheets, so that the lock cylinder can continuously rotate and sequentially drive a swing rod, the lock bolt and the spring bolt to move; and therefore, unlocking operation can be finished.

Owner:如东县岔河污水处理有限公司

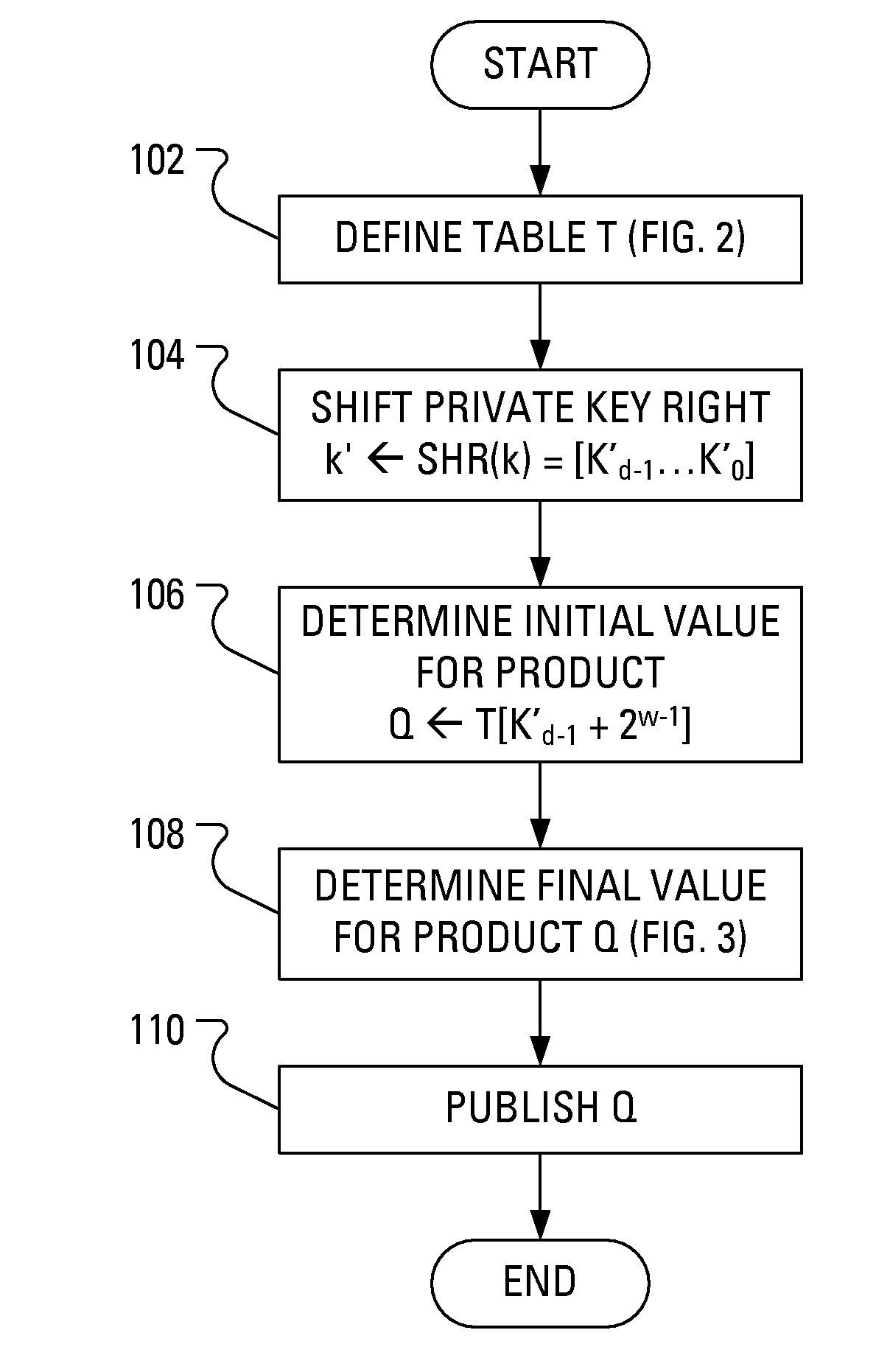

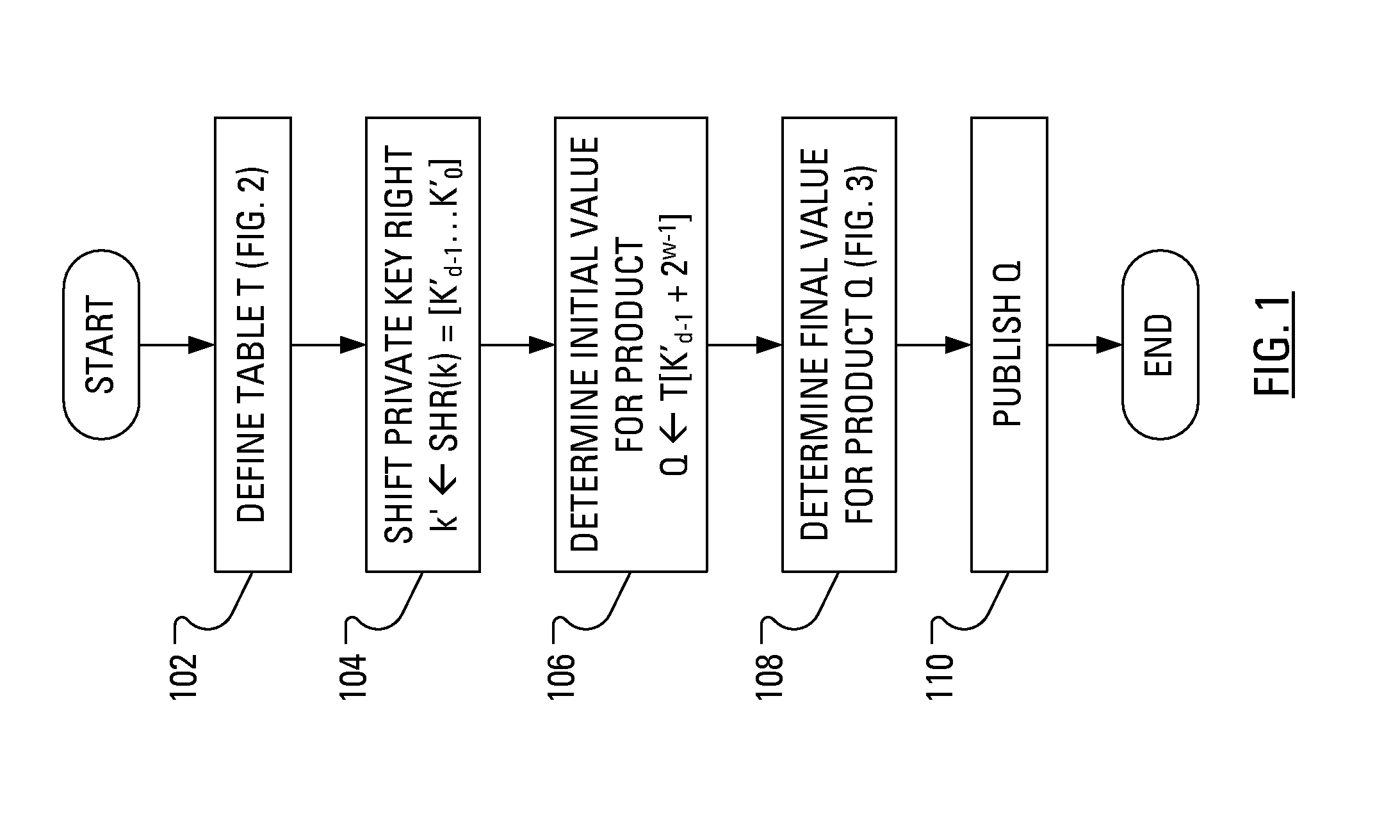

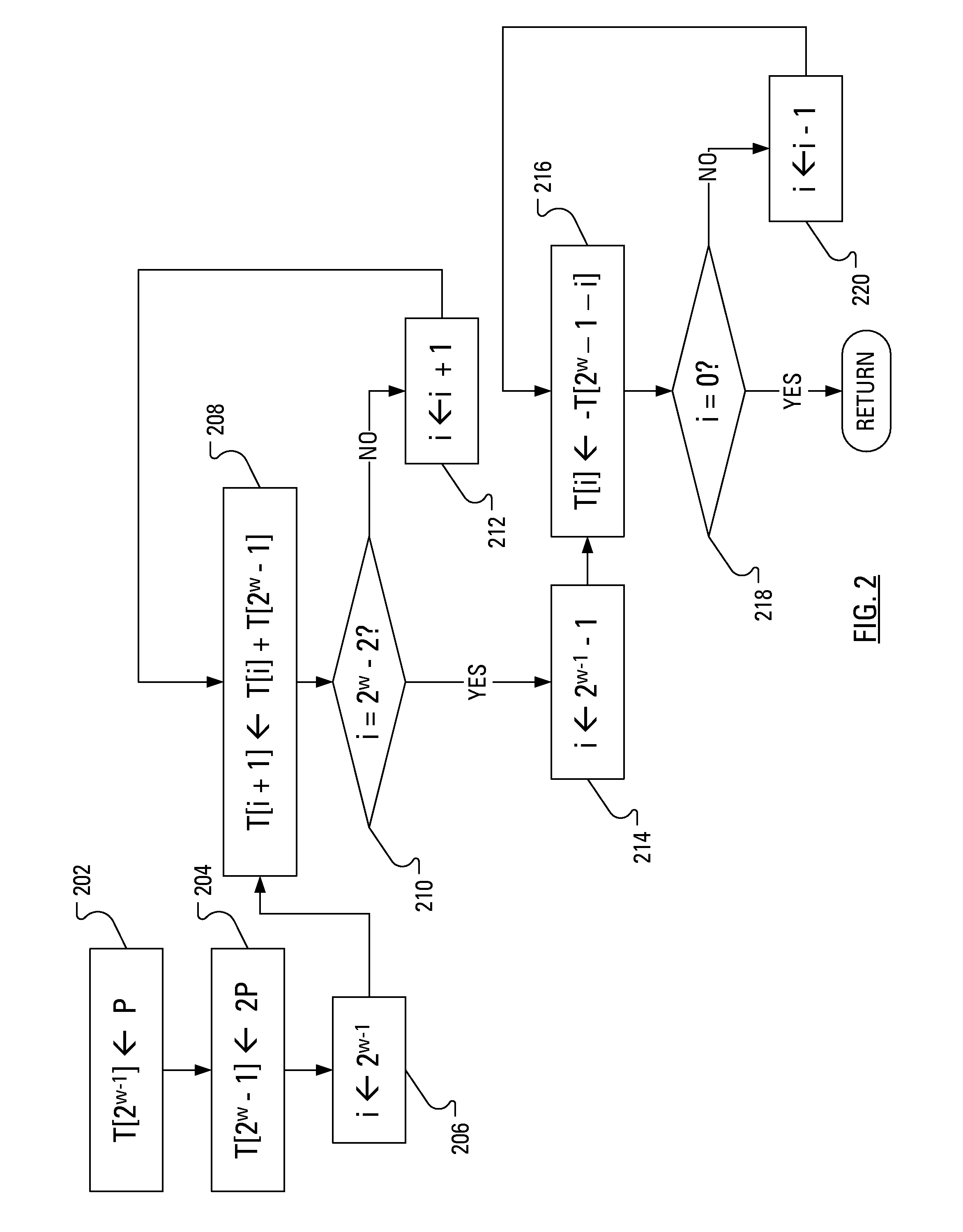

Method and Apparatus for Generating a Public Key in a Manner That Counters Power Analysis Attacks

ActiveUS20080219438A1Key distribution for secure communicationPublic key for secure communicationPower analysisCountermeasure

A public key for an Elliptic Curve Cryptosystem is generated in a manner that acts as a countermeasure to power analysis attacks. In particular, a known scalar multiplication method is enhanced by, in one aspect, performing a right shift on the private key. The fixed-sequence window method includes creation and handling of a translated private key. Conveniently, as a result of the right shift, the handling of the translated private key is made easier and more efficient.

Owner:MALIKIE INNOVATIONS LTD

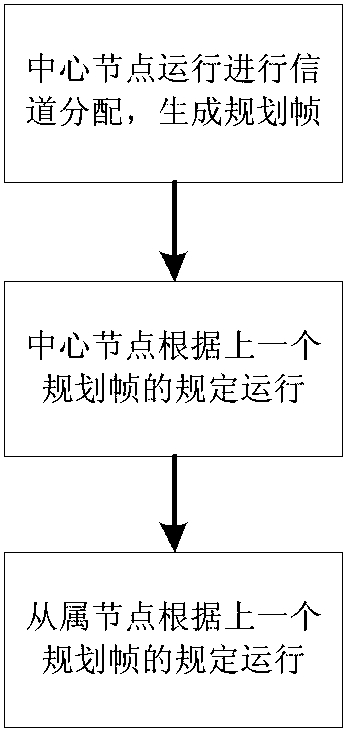

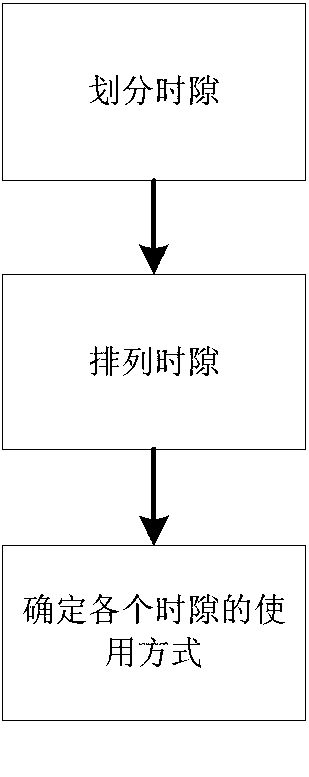

Fixed-length time slot based dynamic channel allocation method for time division duplex/time division multiple access

ActiveCN103023822AImprove channel utilization efficiencyMeet granularityData switching networksDynamic channelCode division multiple access

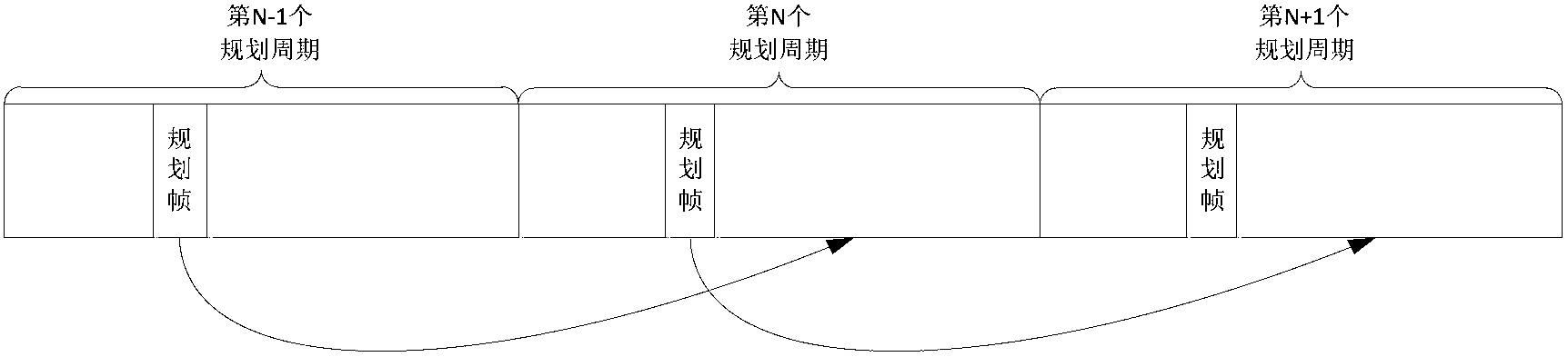

The invention discloses a fixed-length time slot based dynamic channel allocation method for time division duplex / time division multiple access. The method mainly solves the problems of insufficient channel utilization rate or complexity of a scheduling algorithm and a planning frame, too high requirement on equipment and the like of an existing channel allocation method. The method includes the implementation steps: performing channel allocation once every a plurality of planning cycles by a central node, namely dividing the planning cycles into various fixed-length time slots; arranging the time slots according to the fixed sequence; dynamically determining a utilization method of each time slot, and presenting the utilization methods into a planning frame; enabling slave nodes to use various time slots according to stipulations of a previous planning frame; and enabling the central node to use various time slots according to stipulation of the previous planning frame. The fixed-length time slot based dynamic channel allocation method for time division duplex / time division multiple access is high in channel utilization rate, simple in scheduling algorithm and planning frame and low in requirement on equipment, and can be applied to the field of various local area networks and access networks adopting time division duplex / time division multiple access communication.

Owner:XIDIAN UNIV +3