Patents

Literature

99 results about "Track and hold circuit" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

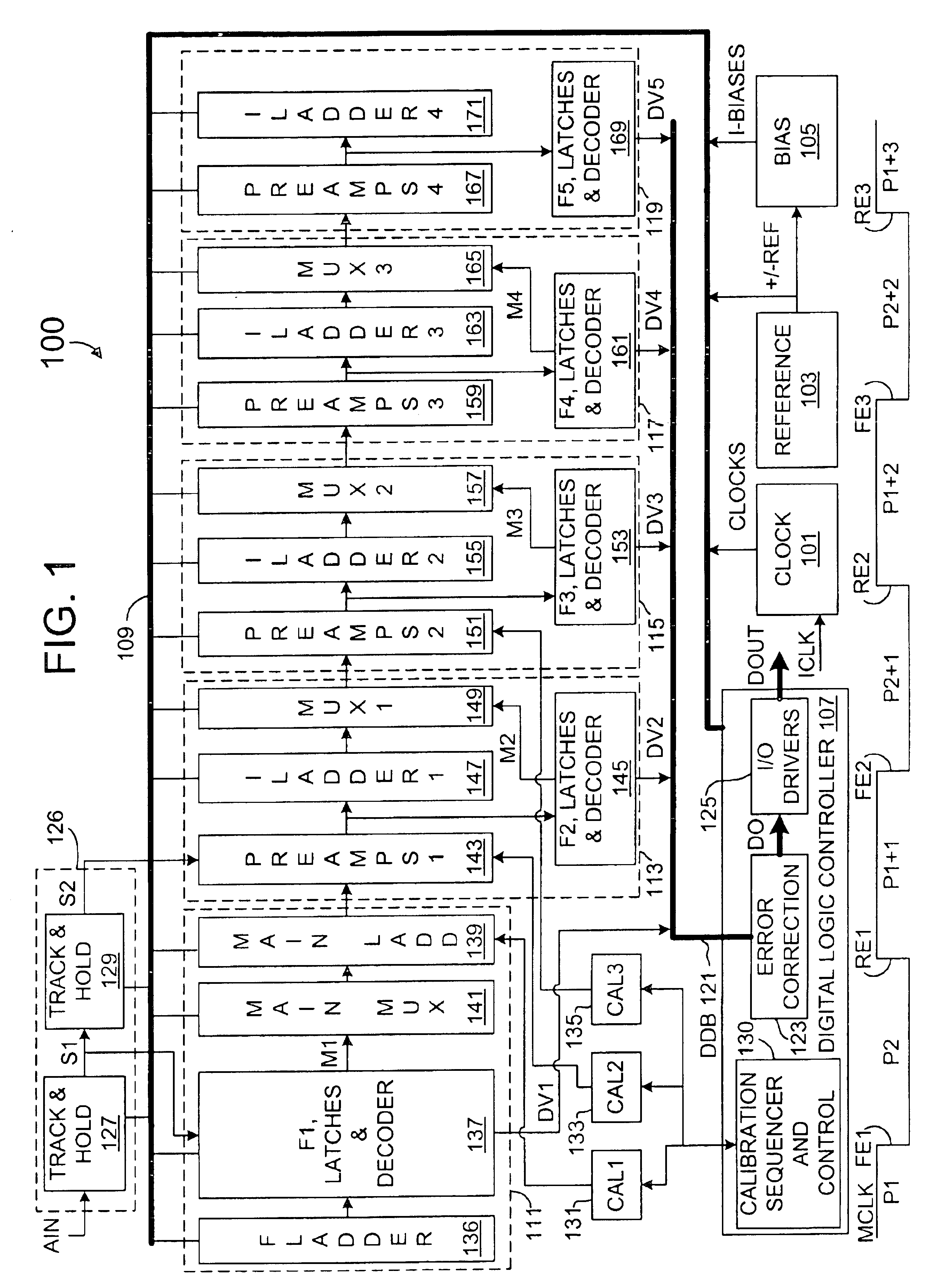

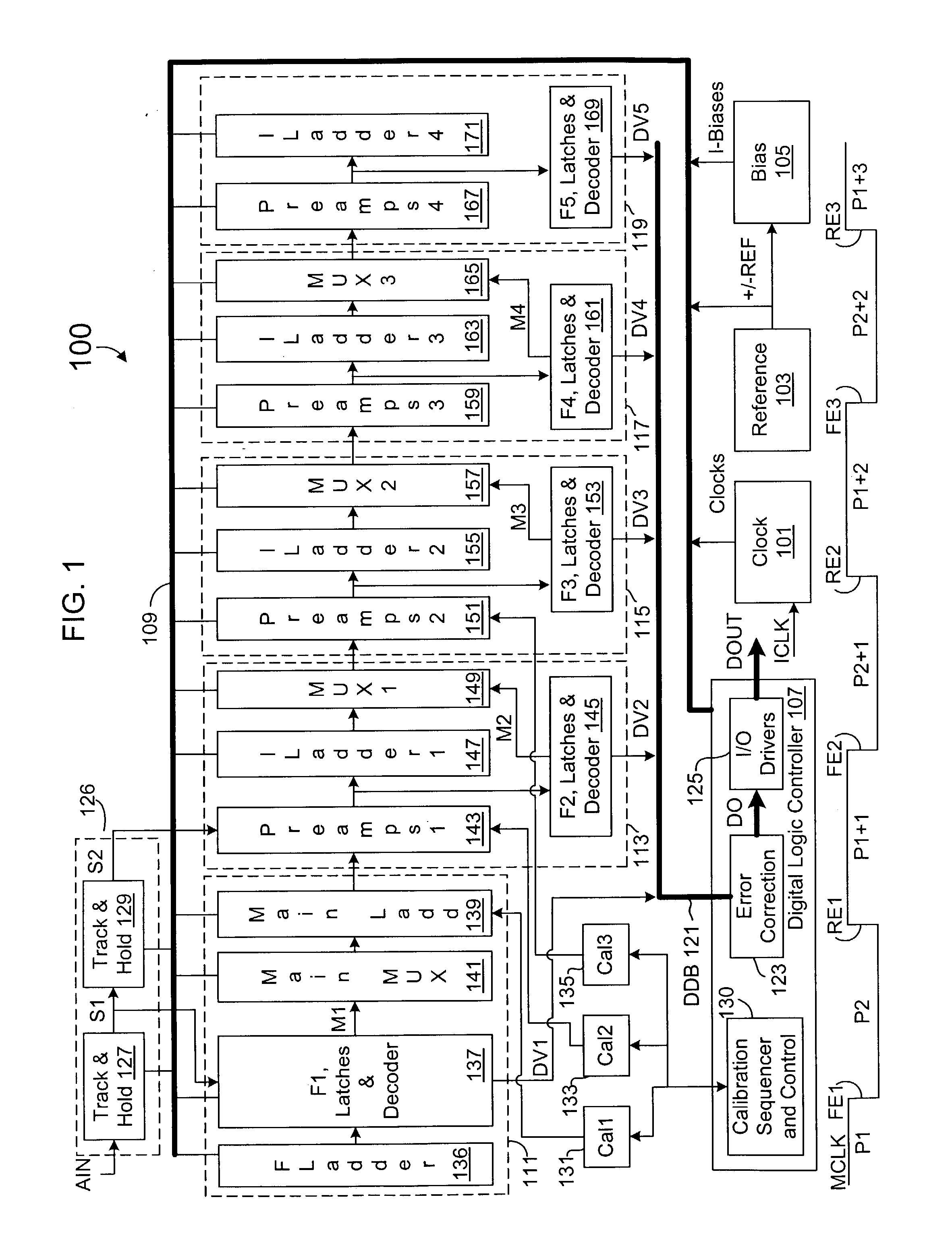

Pipelined analog-to-digital converter (ADC) systems, methods, and computer program products

InactiveUS6169502B1Electric signal transmission systemsAnalogue-digital convertersCapacitanceAudio power amplifier

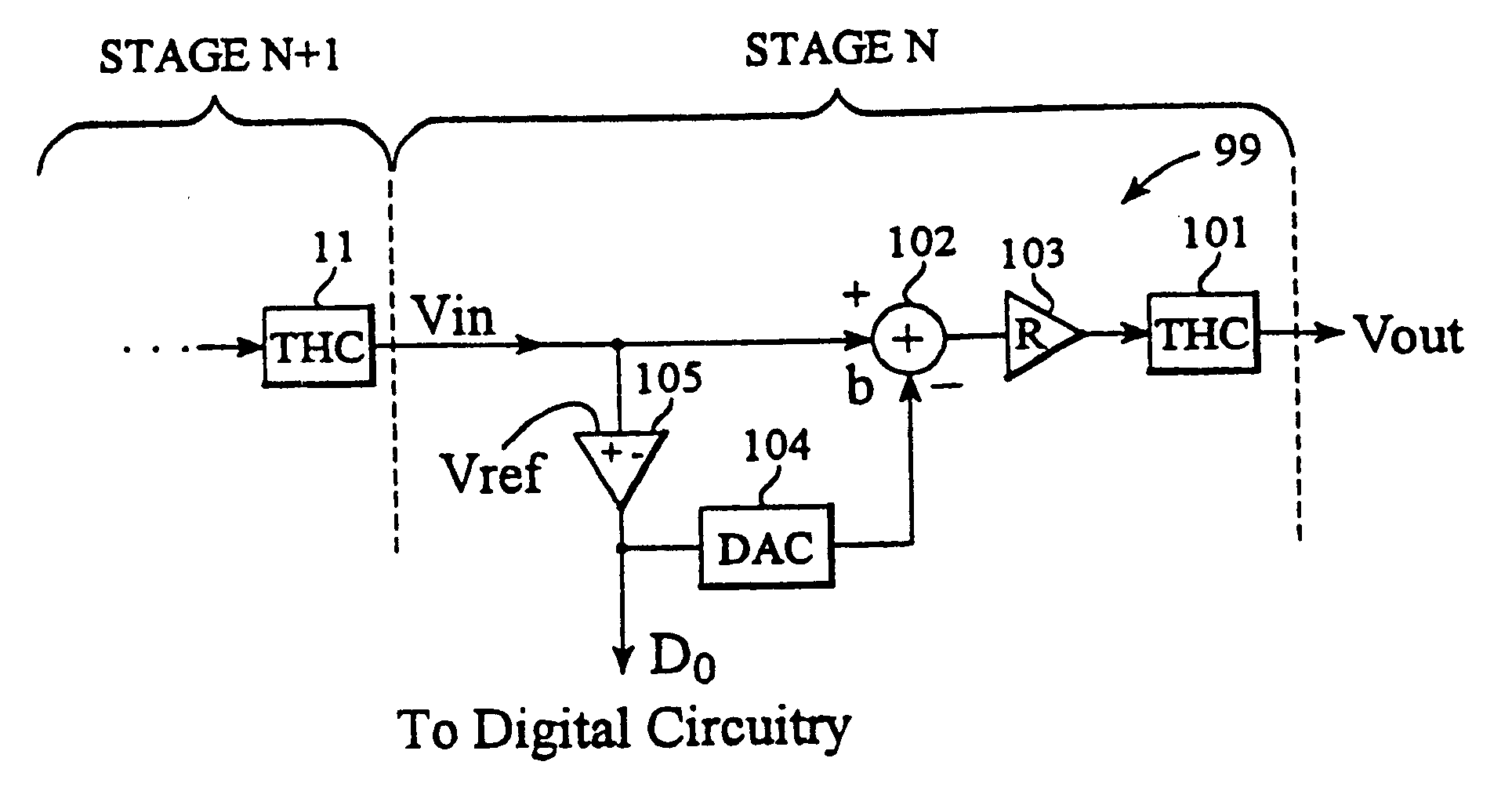

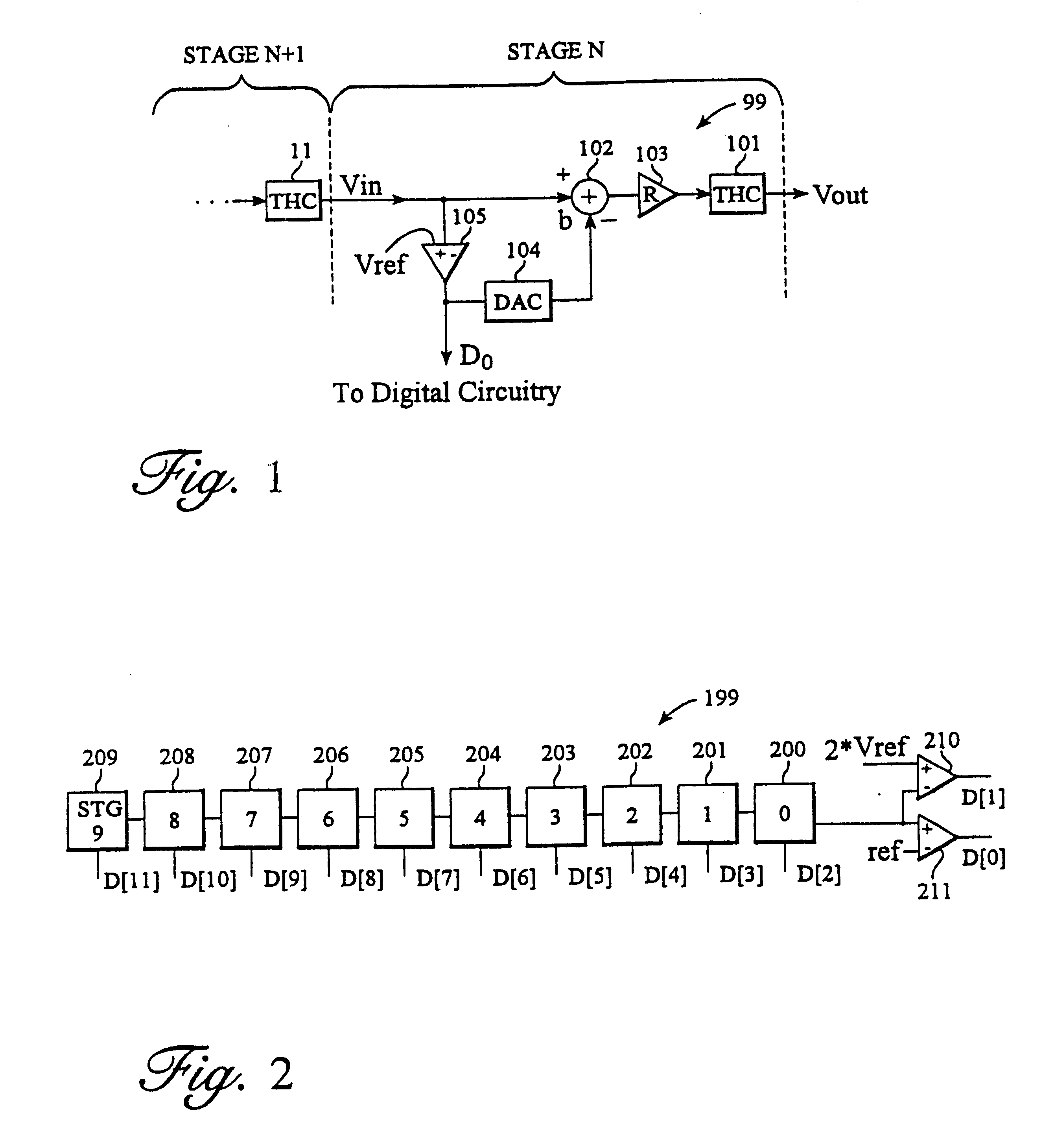

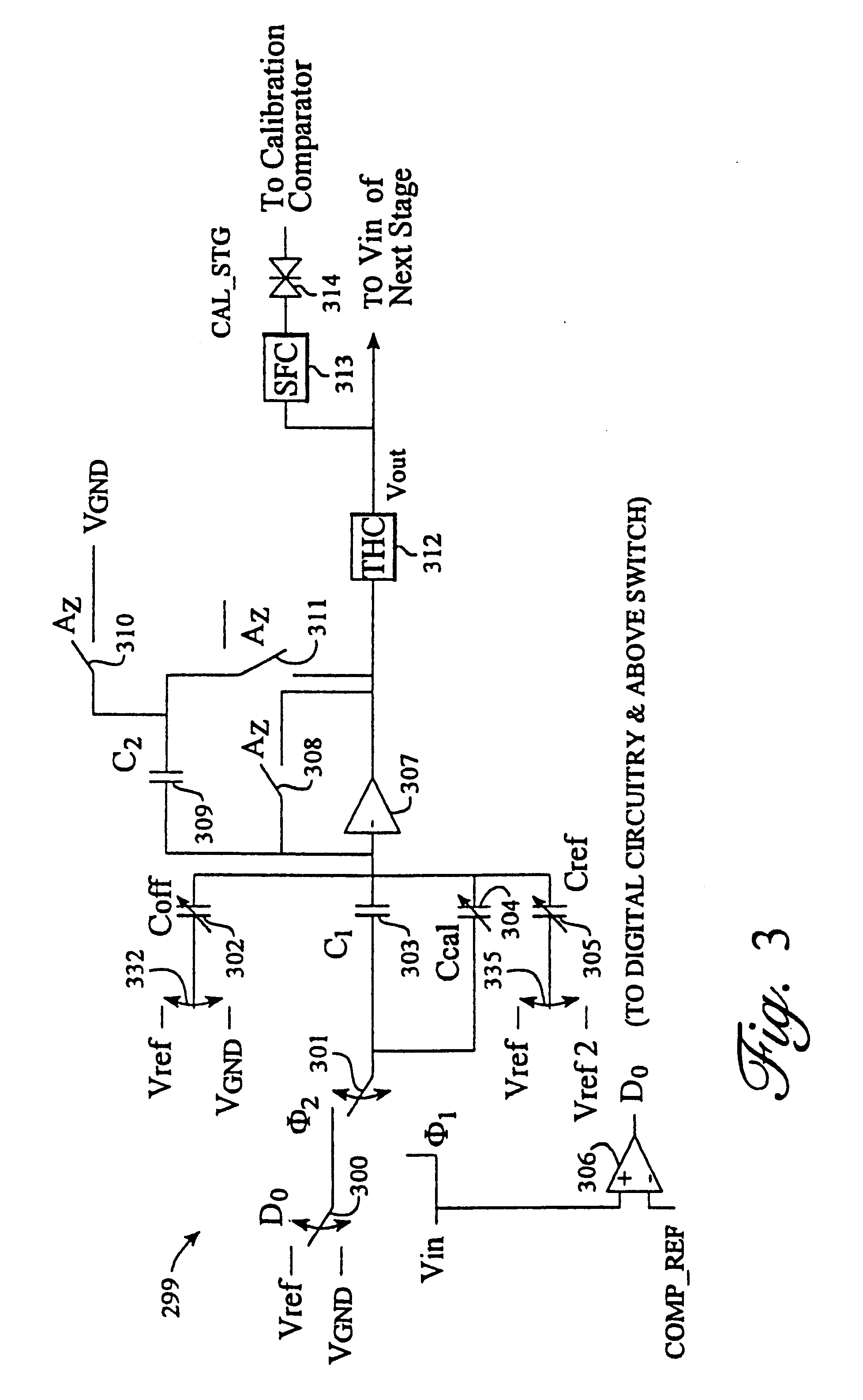

A pipelined analog-to-digital converter (ADC) is calibrated to enable production of an n-bit digital output representing an n-2 bit binary word, where "n" is a selected large positive integer, for example without limitation on the order of ten (10). In an analog-to-digital converter (ADC) having a plurality stages, each stage includes a stage input connection, a stage output connection, and a capacitor circuit including first and second predetermined capacitors (C1 and C2) and a variable capacitance calibration capacitor (Ccal). The first and second capacitors and the variable capacitance calibration capacitor are connected to each other at a capacitor common node. An amplifier input connection is connected to a capacitor common node. A comparator input connection (CIC) is connected to a stage input connection. A track and hold circuit (THC) is coupled to an amplifier output connection, and a source follower circuit (SF) is connected to a stage output connection.

Owner:CIRRUS LOGIC INC

Use of analog-valued floating-gate transistors to match the electrical characteristics of interleaved and pipelined circuits

ActiveUS7049872B2Electric signal transmission systemsMultiple input and output pulse circuitsHemt circuitsEngineering

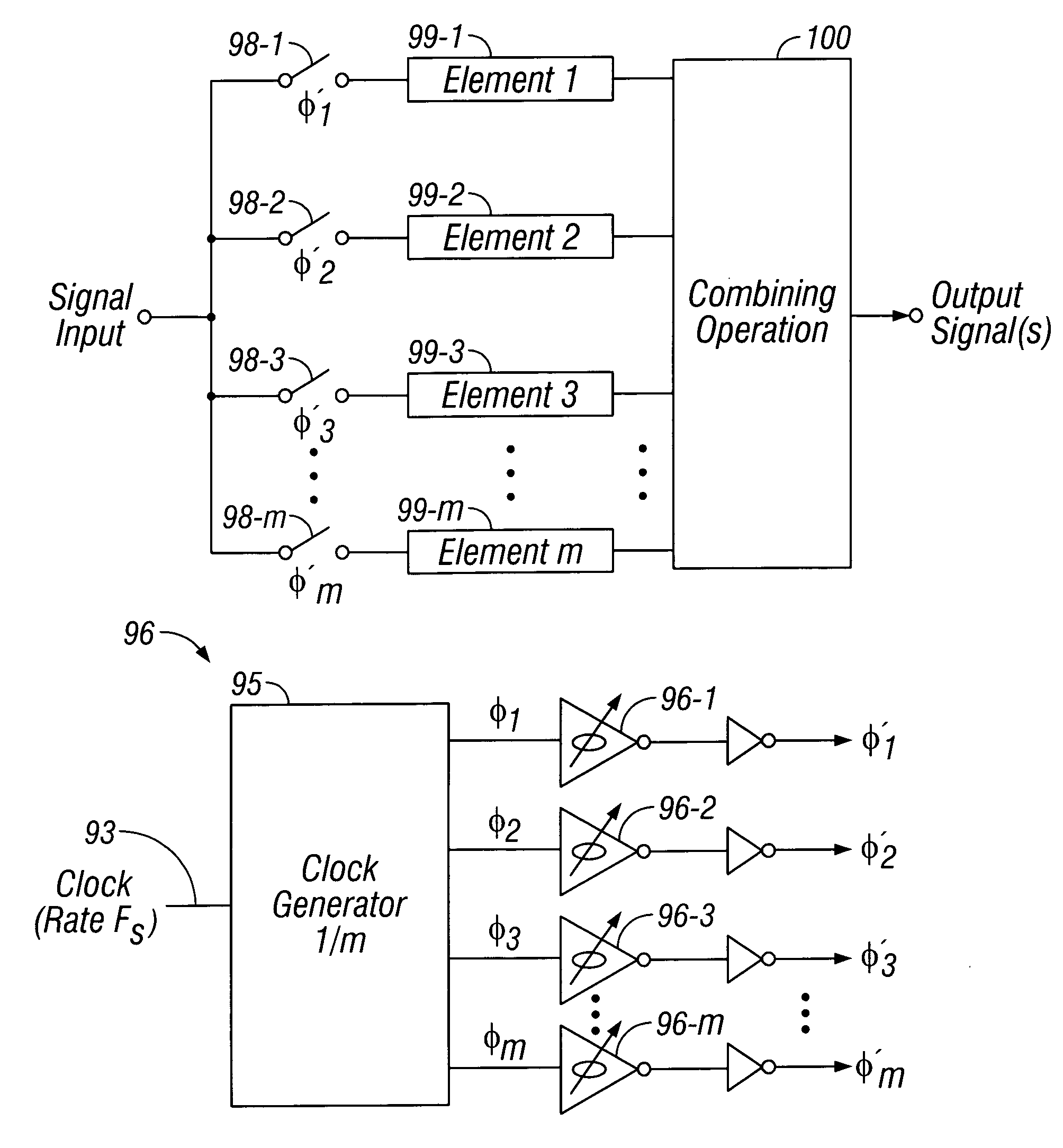

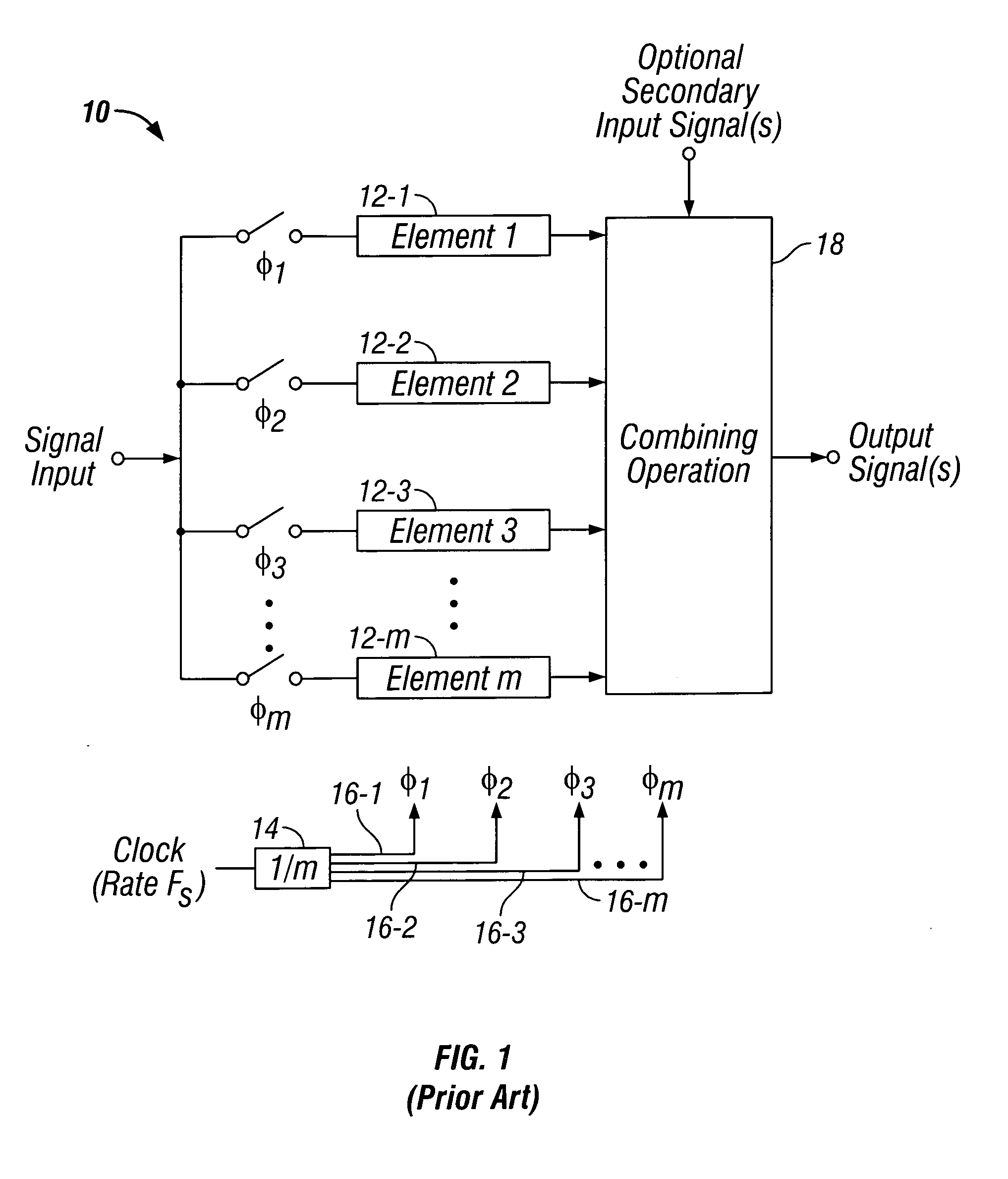

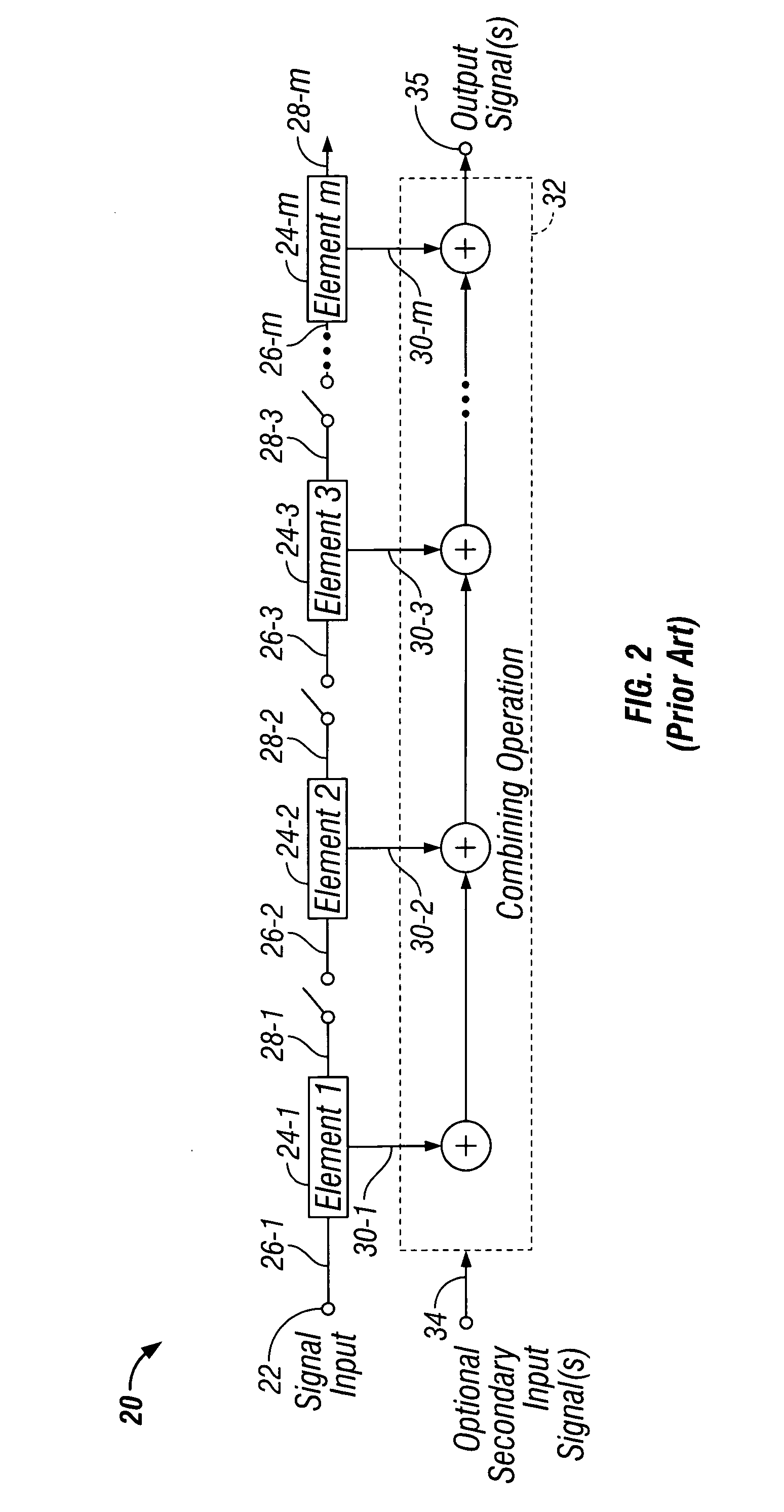

Methods of and apparatuses for matching the signal delay, clock timing, frequency response, gain, offset, and / or transfer function of signal pathways in electrical circuits such as, for example, time-interleaved and pipelined circuits using analog-valued floating-gate MOSFETs are disclosed. The methods and apparatuses disclosed are applicable to a variety of circuits, including but not limited to, sample-and-hold or track-and-hold circuits, quadrature mixers, analog-to-digital converters (ADCs), digital-to-analog converters (DACs), analog or digital filters, and amplifiers.

Owner:SYNOPSYS INC

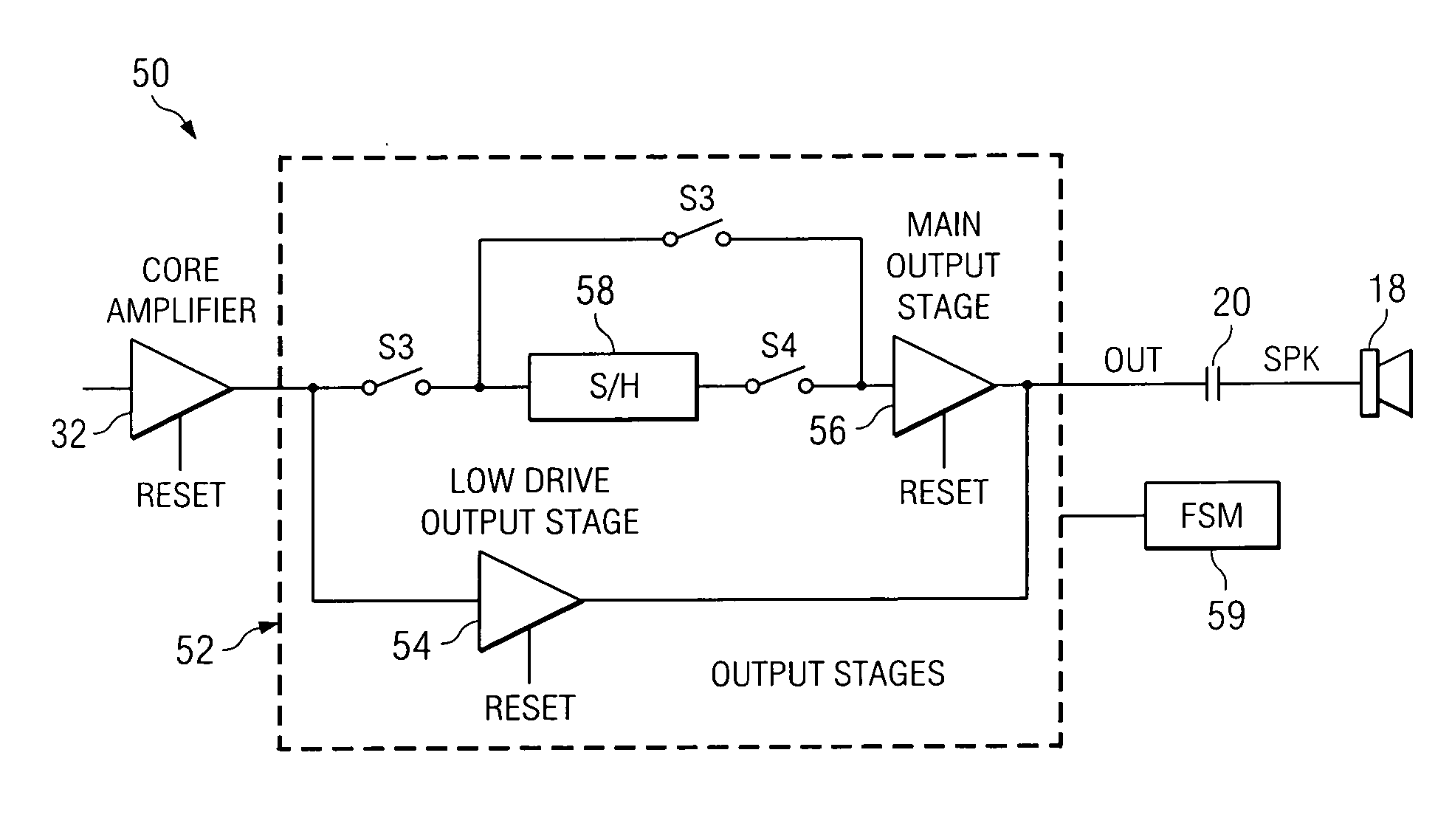

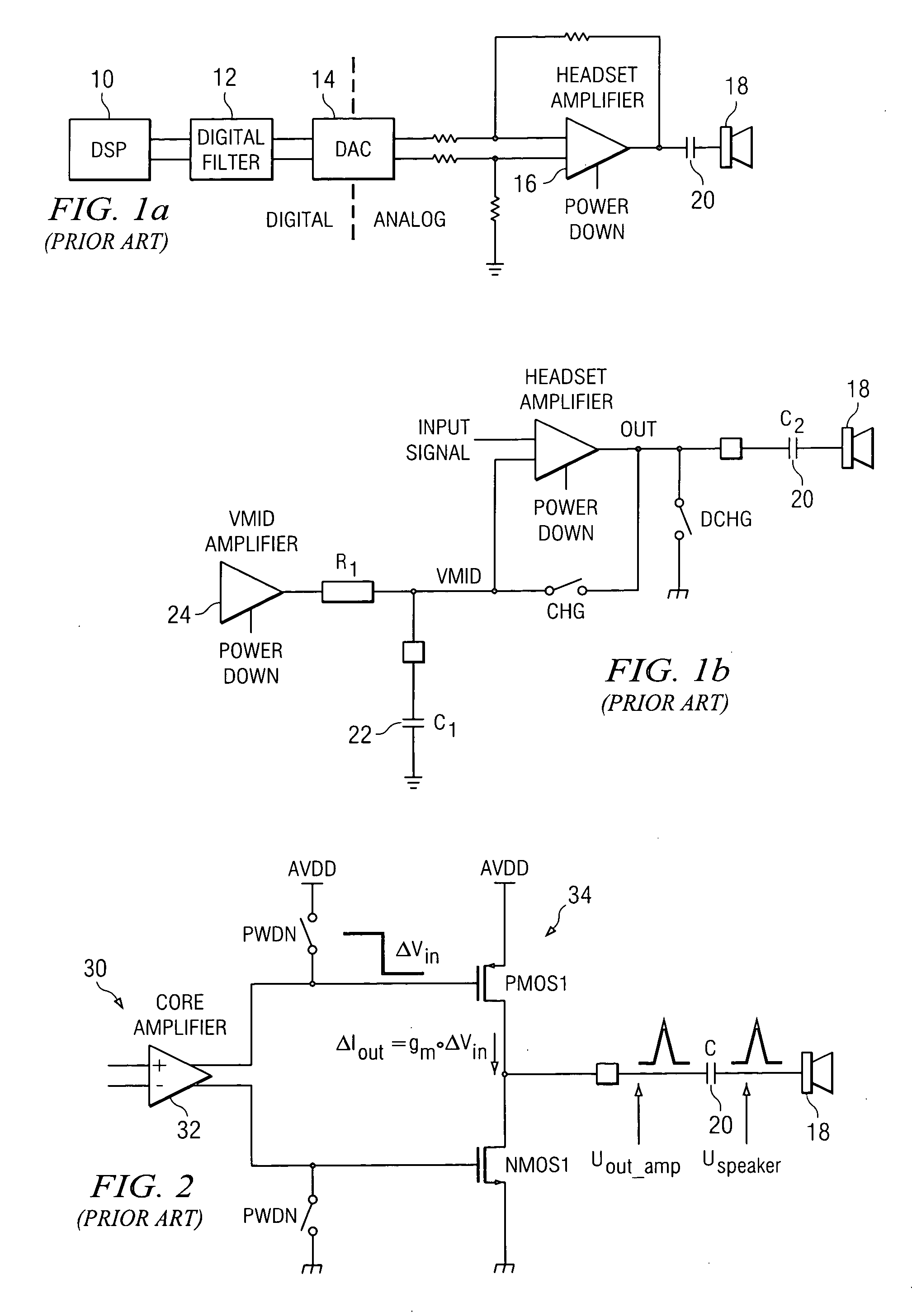

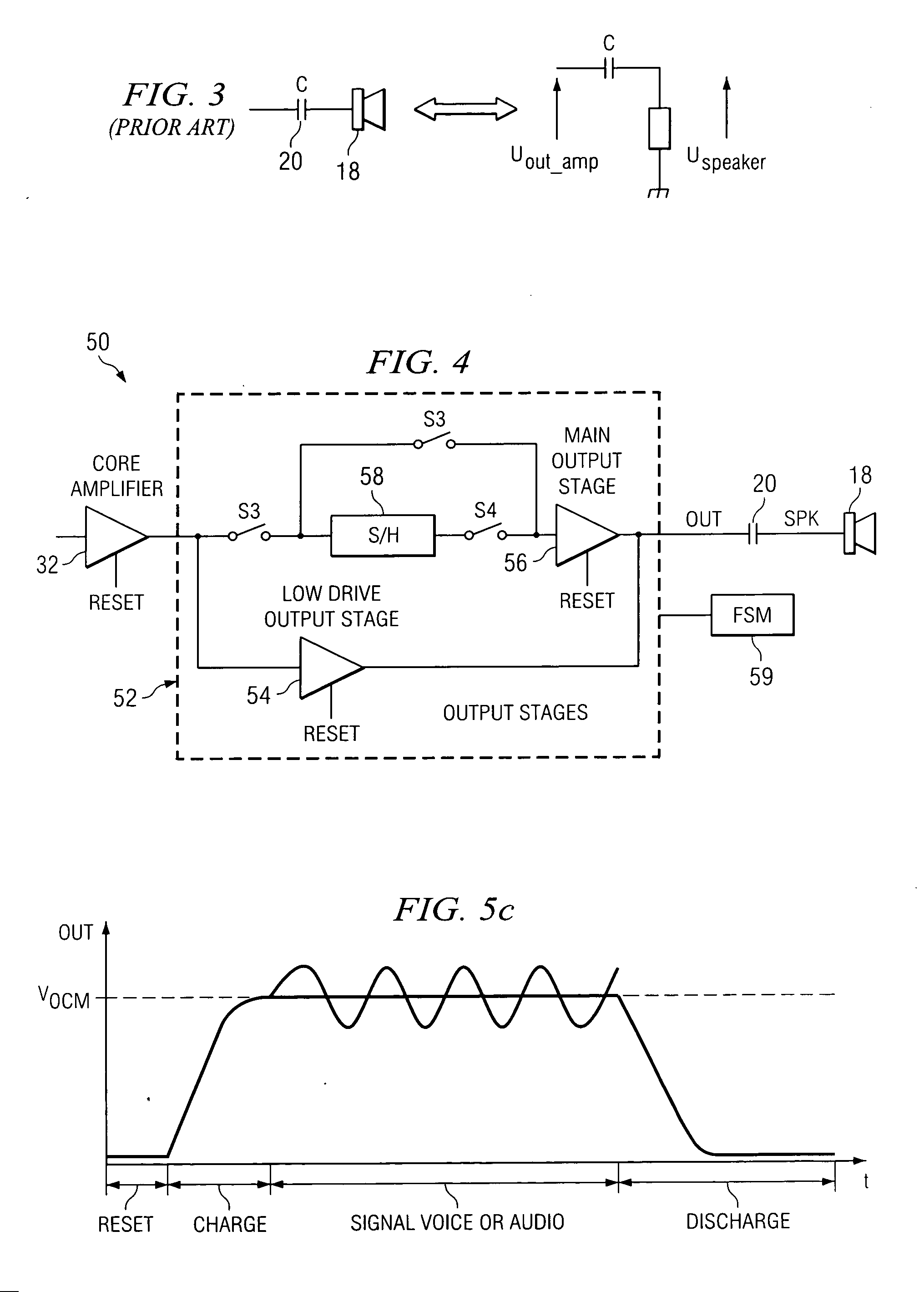

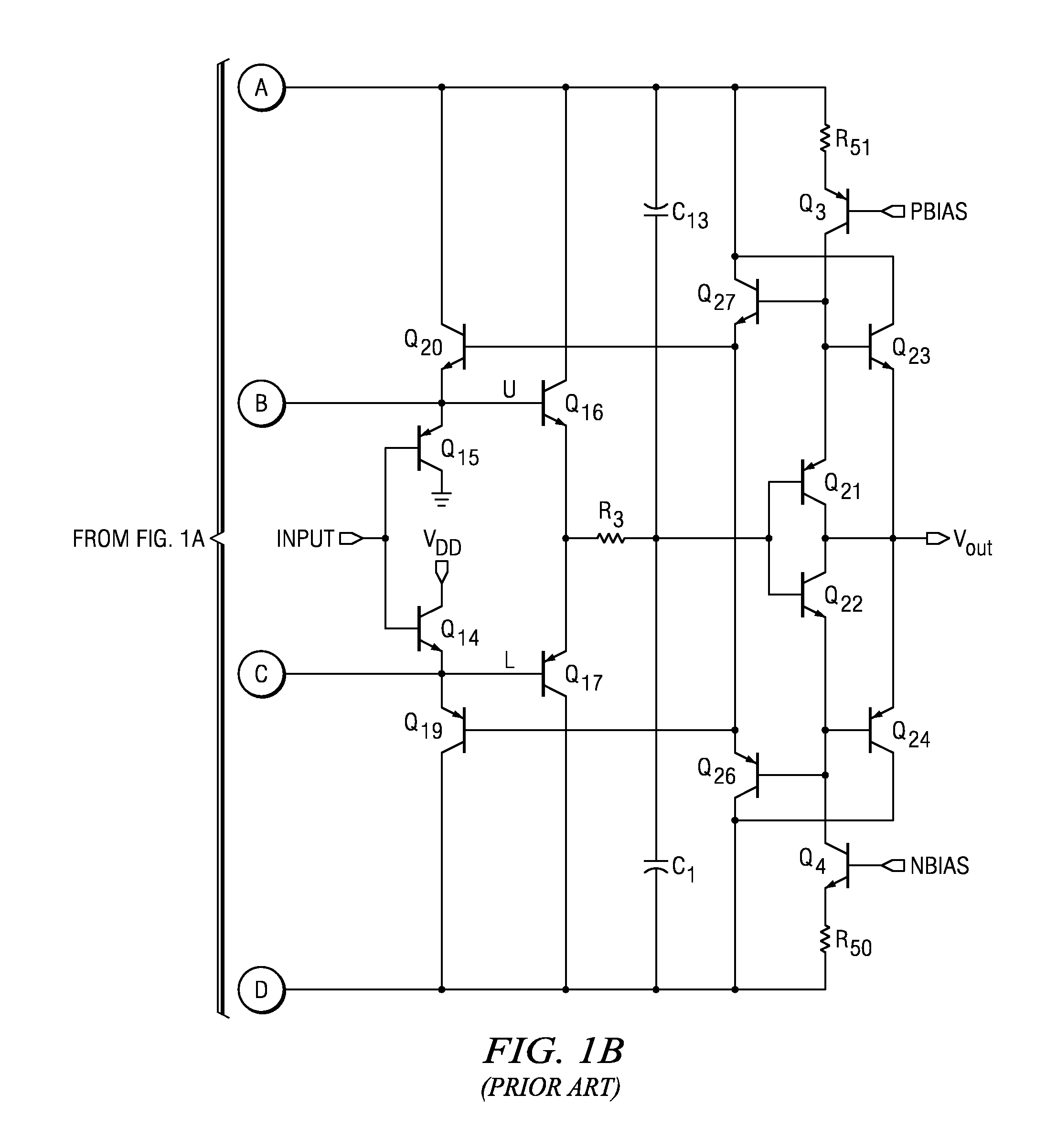

Track and hold circuit to reduce pop noise

ActiveUS20060182266A1Prevents popping noiseAvoid noiseInterconnection arrangementsSubstation equipmentCapacitanceAudio power amplifier

An amplifier (50) for voice or audio signals, and particularly for headset applications, uses a low gm amplifier (54) for initially charging an output node (OUT) at the beginning of a power-on phase. After charging the output node, a main amplifier (56) is enabled to amplify the voice or audio signal. At power-down, a sample-and-hold circuit (58) drives an output transistor to discharge an AC coupling capacitor (20). Thus, spikes at the output node are eliminated and an external filtering capacitor is not needed.

Owner:TEXAS INSTR INC

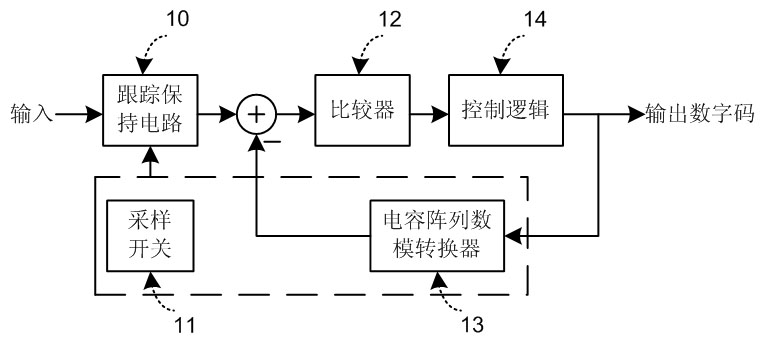

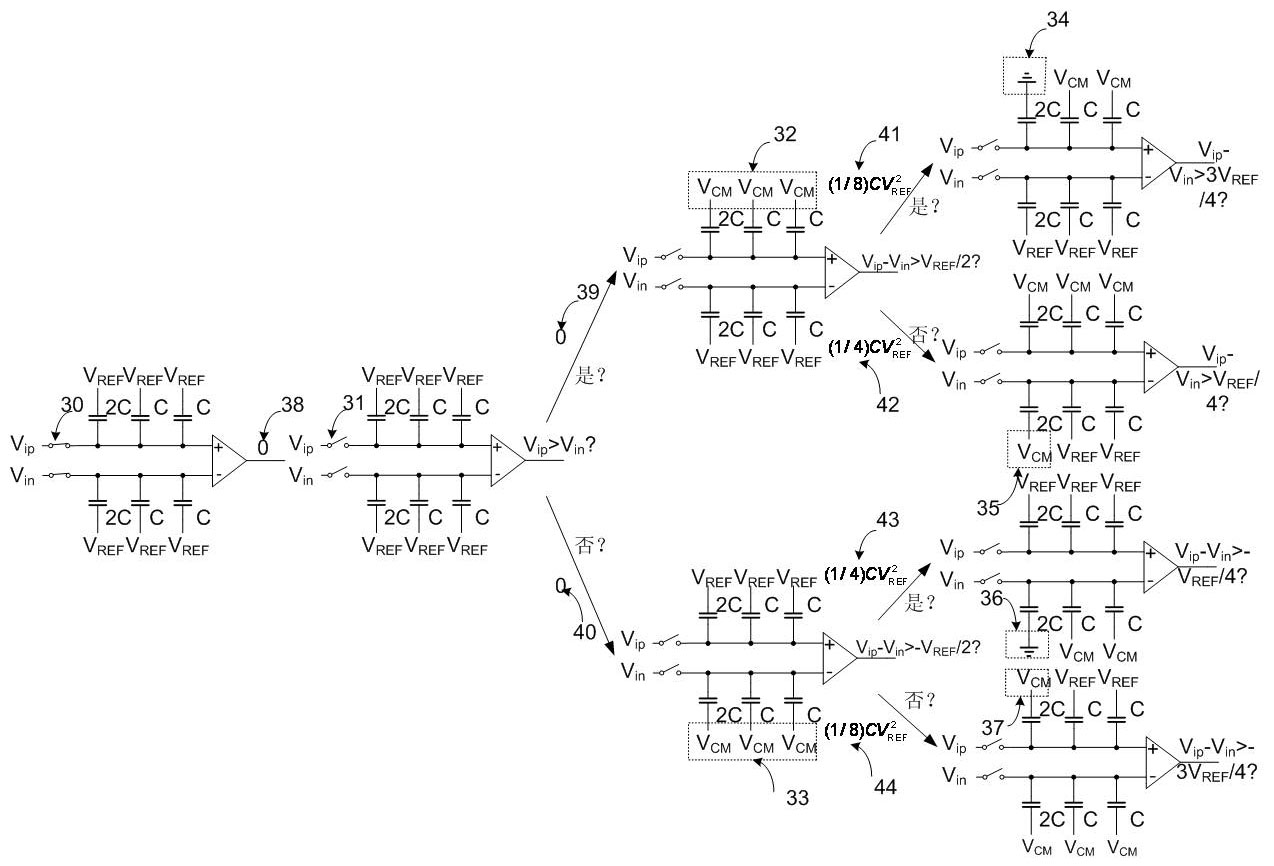

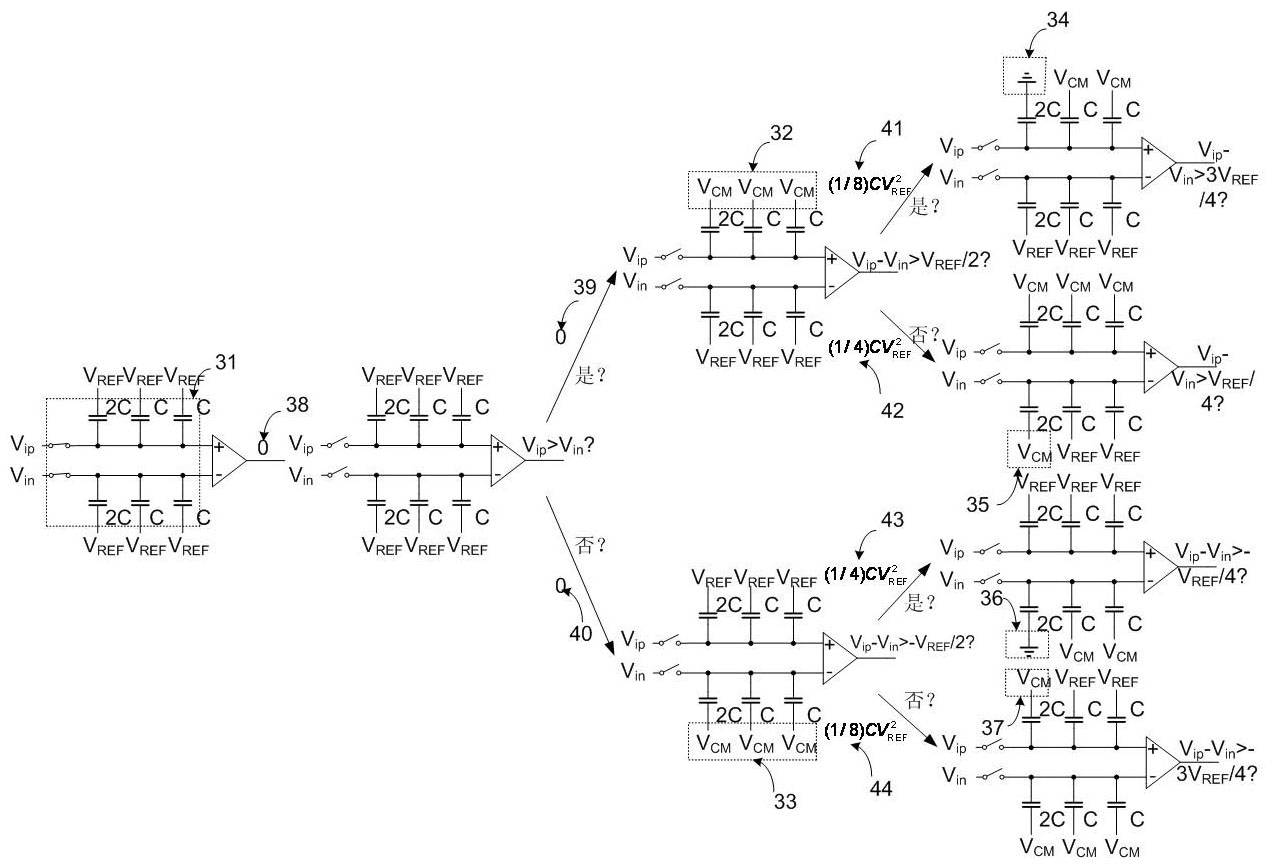

Successive approximation type analog-to-digital converter of energy-saving capacitor array

ActiveCN102006075AAnalogue/digital conversionElectric signal transmission systemsCapacitanceDigital analog converter

The invention belongs to the technical field of integrated circuits, in particular to a successive approximation type analog-to-digital converter of an energy-saving capacitor array. The analog-to-digital converter comprises a sampling switch, a track and hold circuit, a comparator, control logic and a capacitor array digital-to-analog converter, wherein the capacitor array digital-to-analog converter adopts a switch mode of the novel capacitor array digital-to-analog converter provided by the invention. By using the mode, the average switch consumption of the capacitor can be reduced.

Owner:FUDAN UNIV

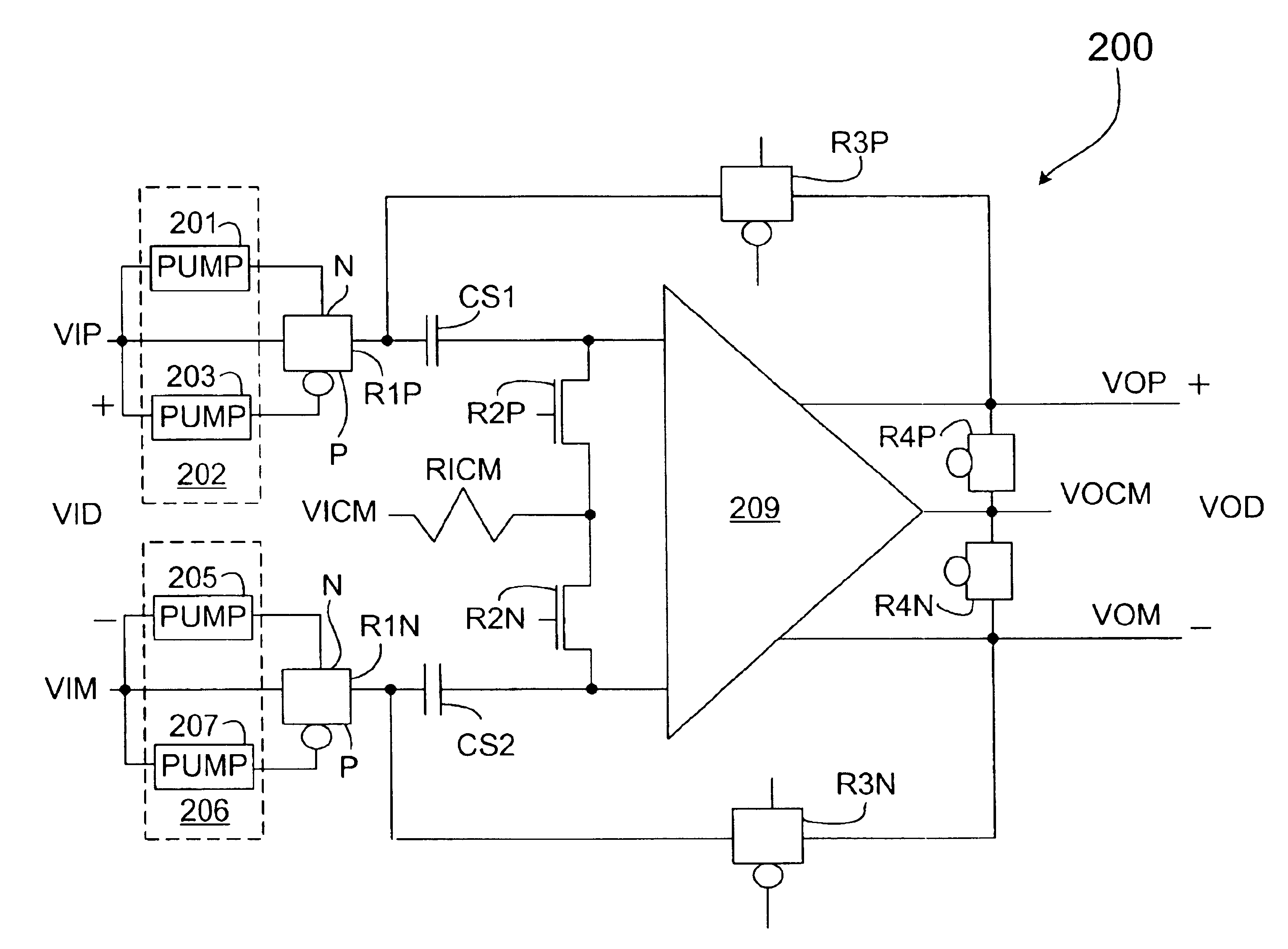

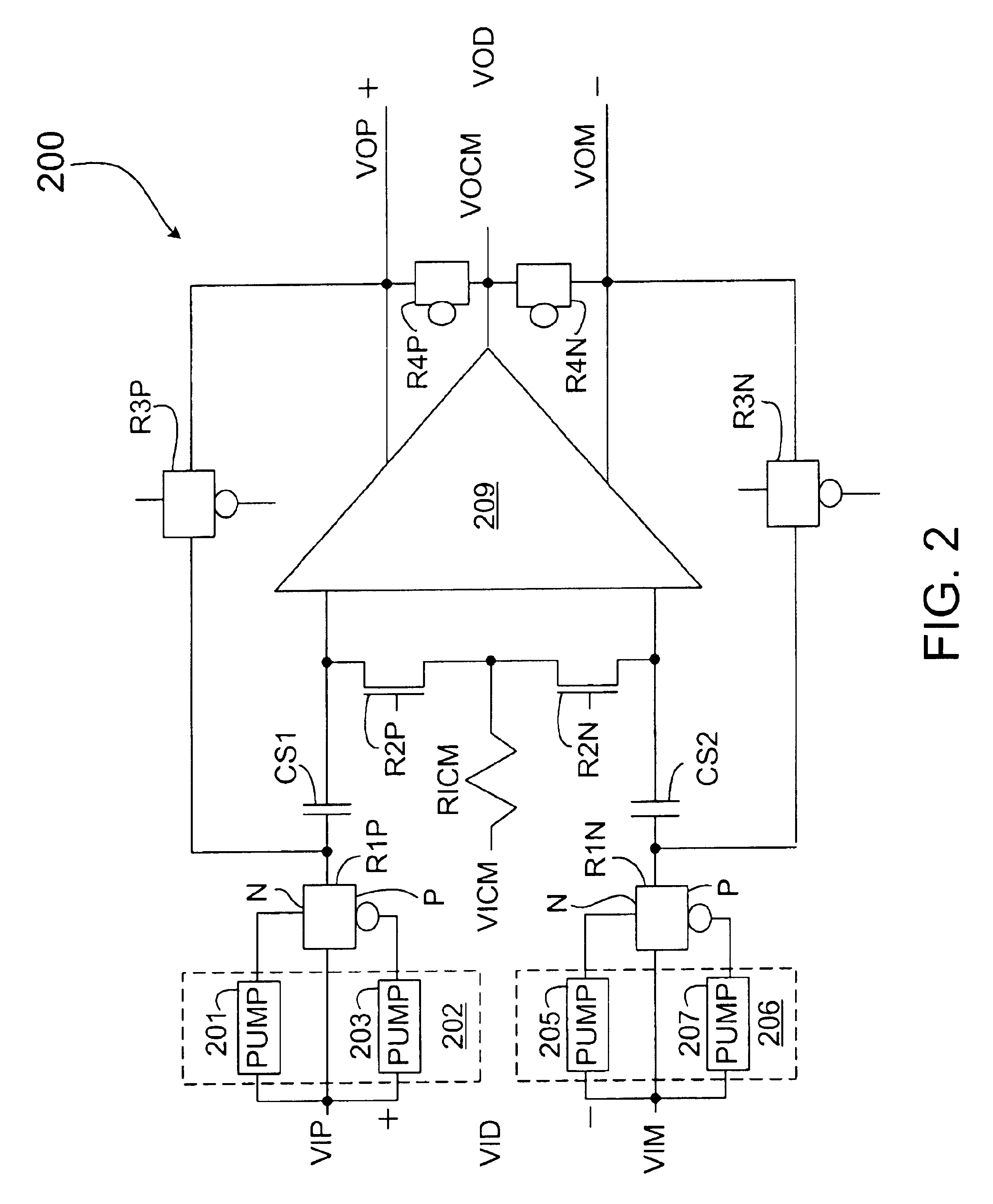

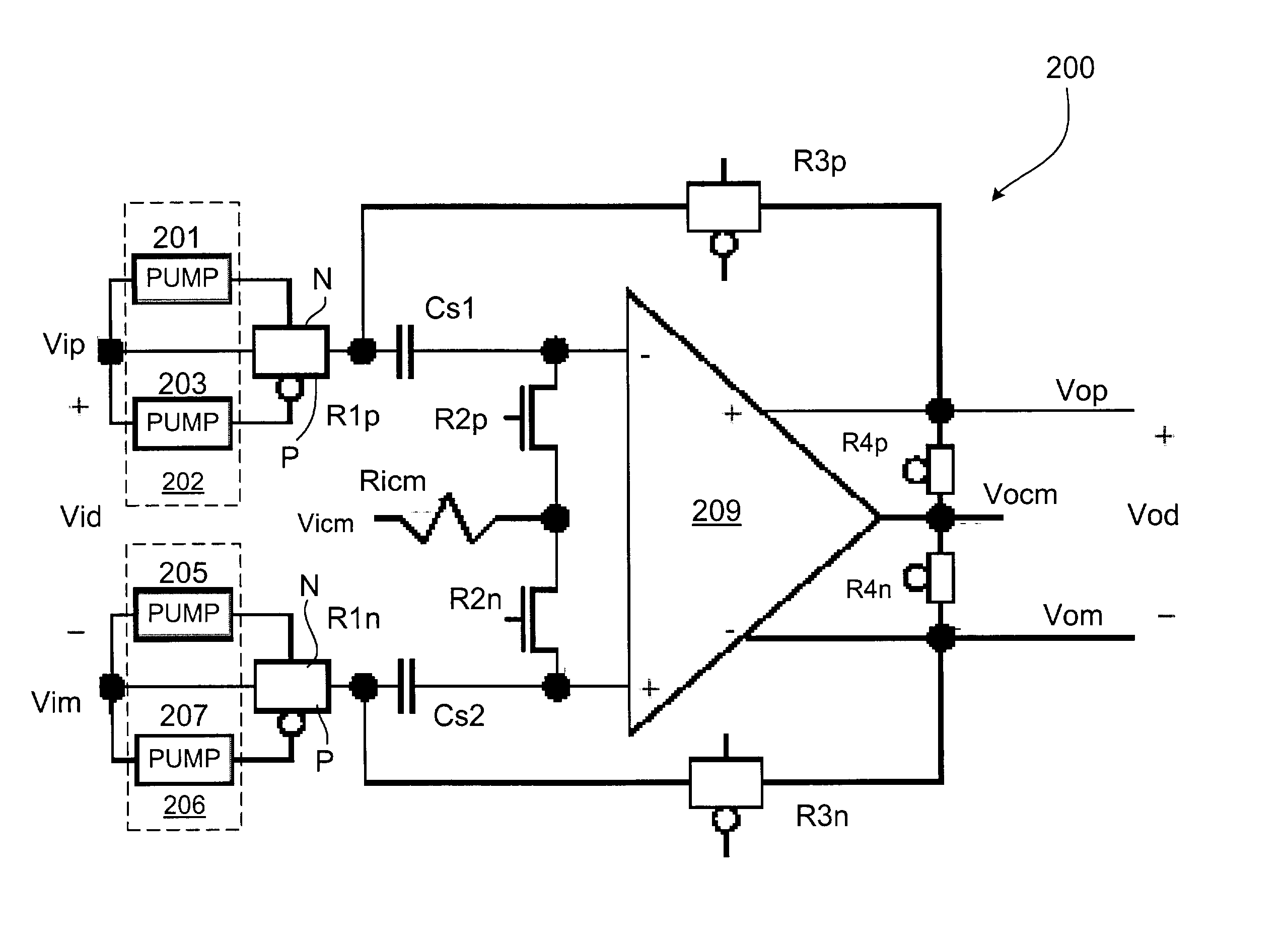

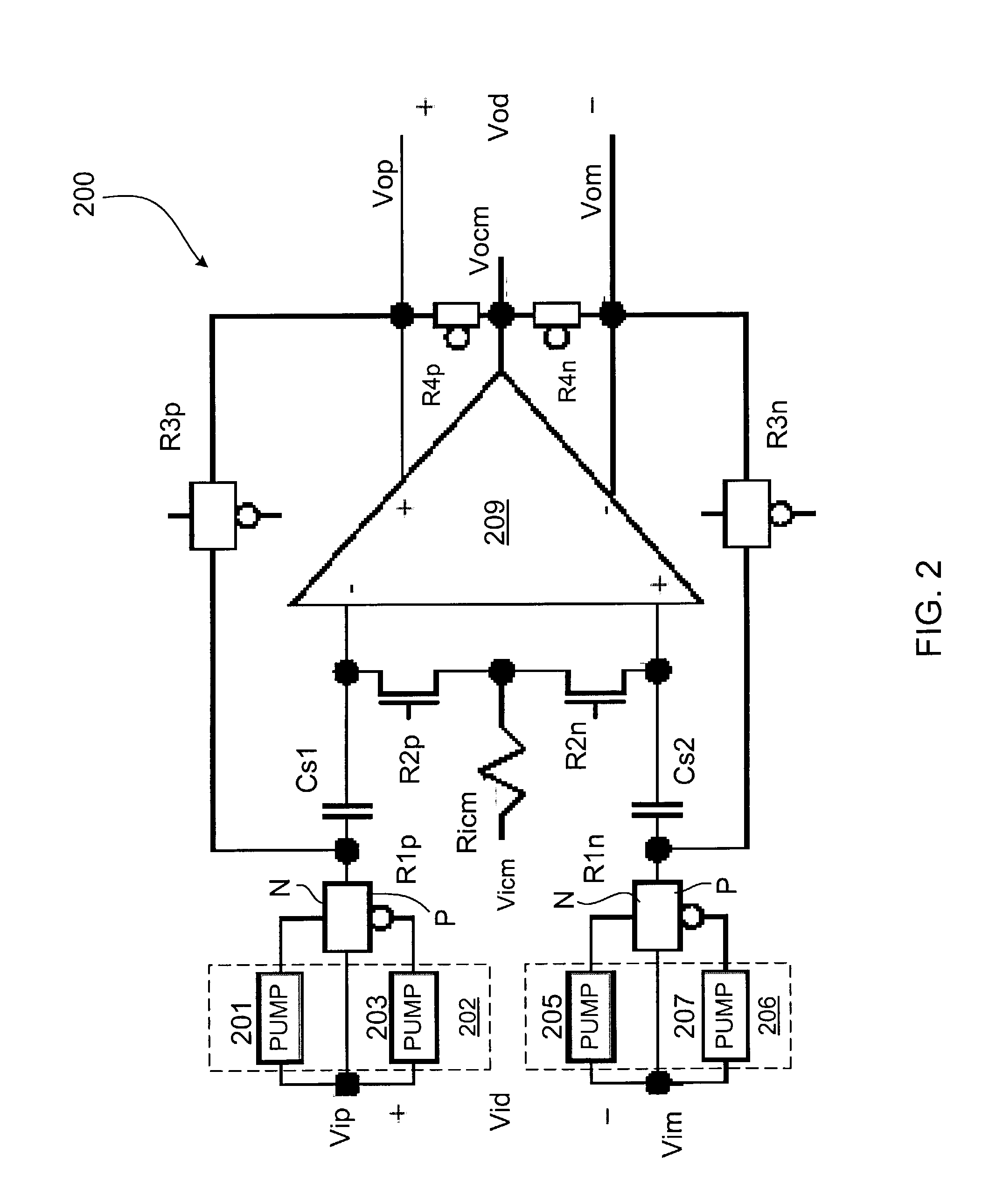

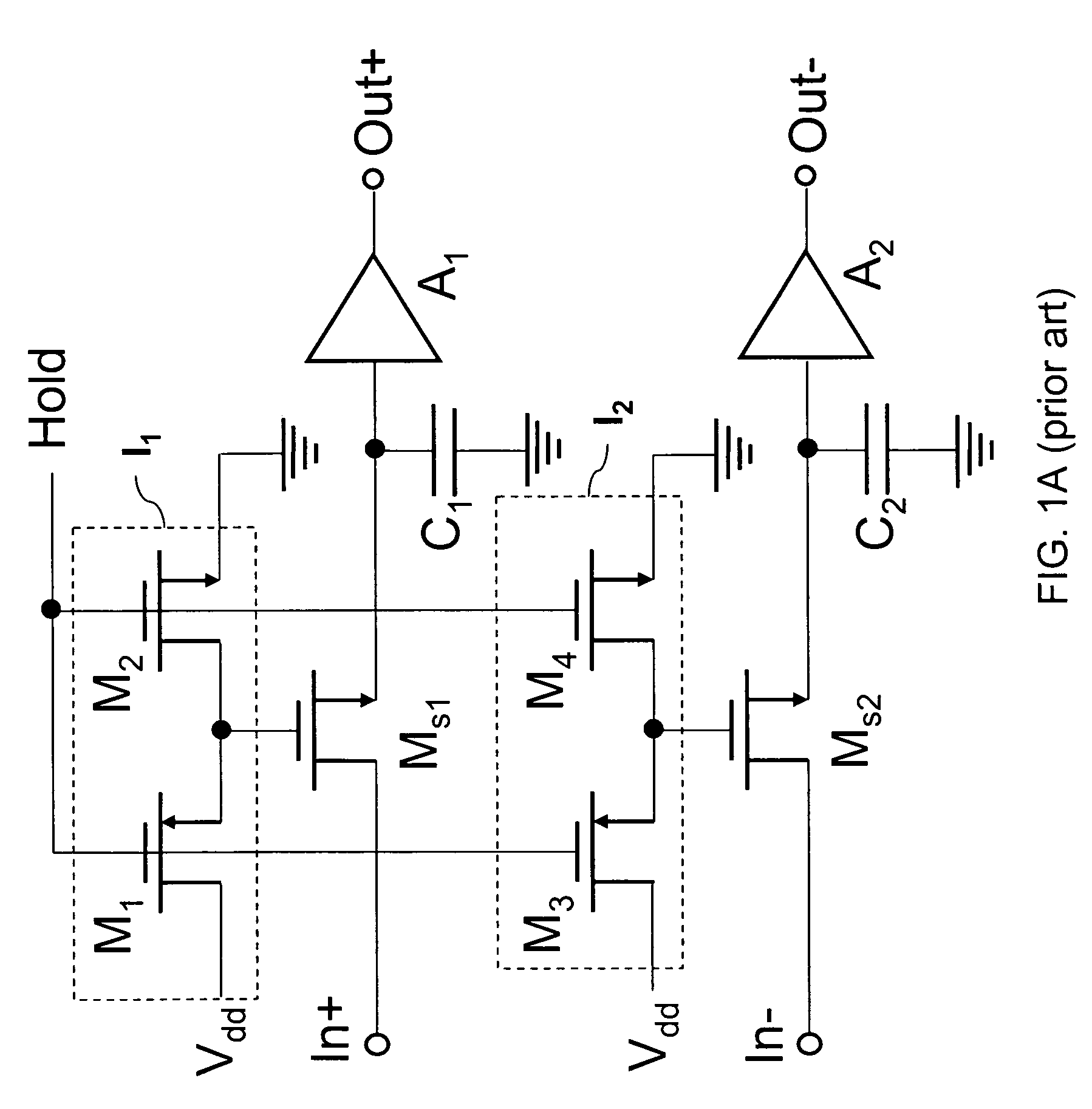

Track and hold with dual pump circuit

InactiveUS6731155B2Electric signal transmission systemsElectric analogue storesTransmission gateEngineering

A dual pump circuit including a transmission gate and a dual charge pump. The transmission gate includes a p-channel transistor and an n-channel transistor, each having a control terminal and a pair of current terminals coupled between a dual pump input and a dual pump output. The dual charge pump includes first and second pump circuits, where each pump circuit is coupled to the dual pump input and to a control terminal of a corresponding one of the transmission gate transistors. Each pump circuit is operative to linearize operation of its corresponding transmission gate transistor by maintaining VGS-VT constant. The dual pump circuit is used in a track and hold circuit including at least one dual pump sampling circuit, at least one sampling capacitor, and a control circuit for controlling input signal sampling timing. Each dual pump sampling circuit includes the transmission gate and a dual charge pump.

Owner:INTERSIL INC

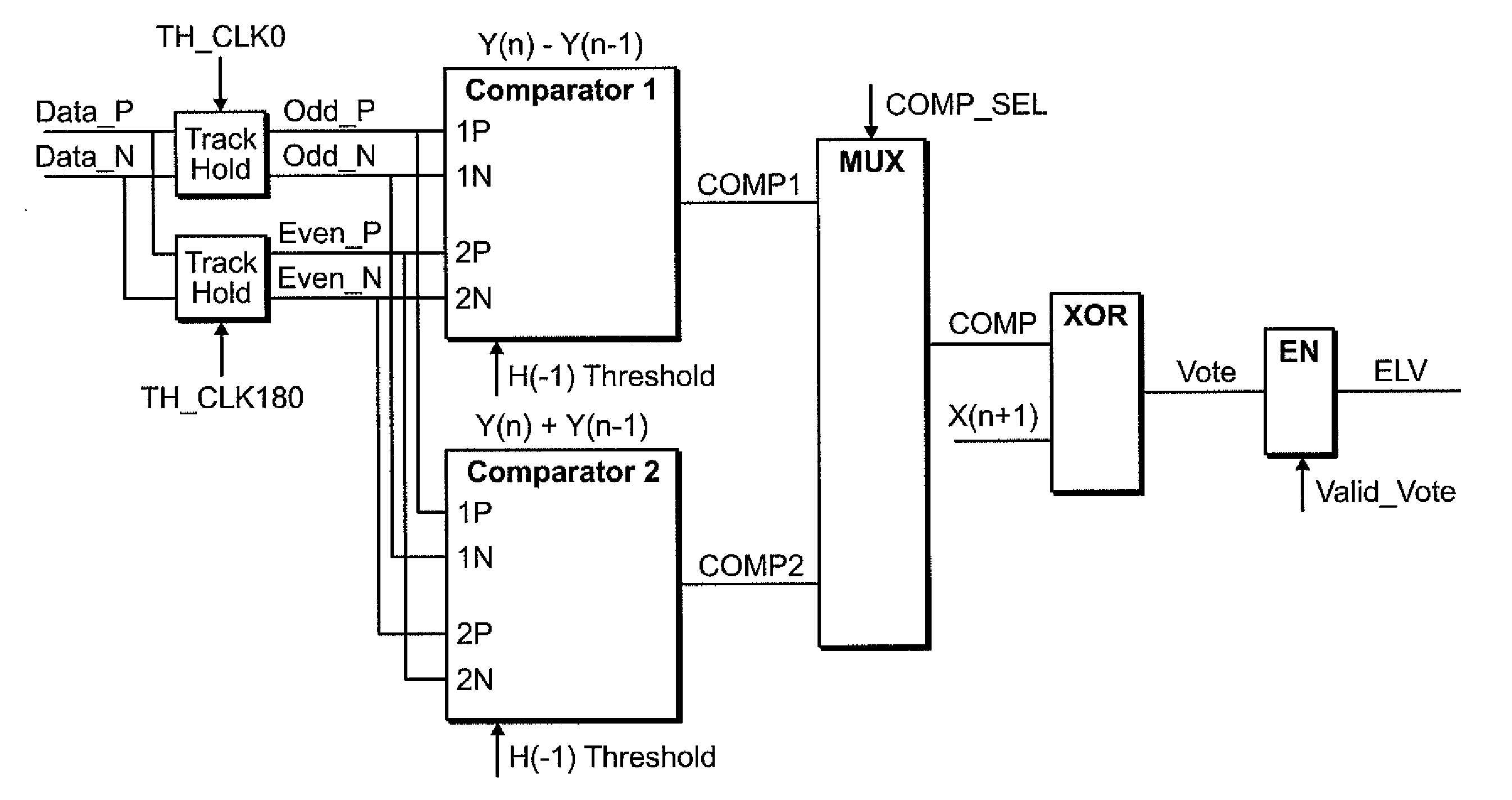

Analog baud rate clock and data recovery

ActiveUS20090224806A1Multiple input and output pulse circuitsInstant pulse delivery arrangementsComparators circuitsEngineering

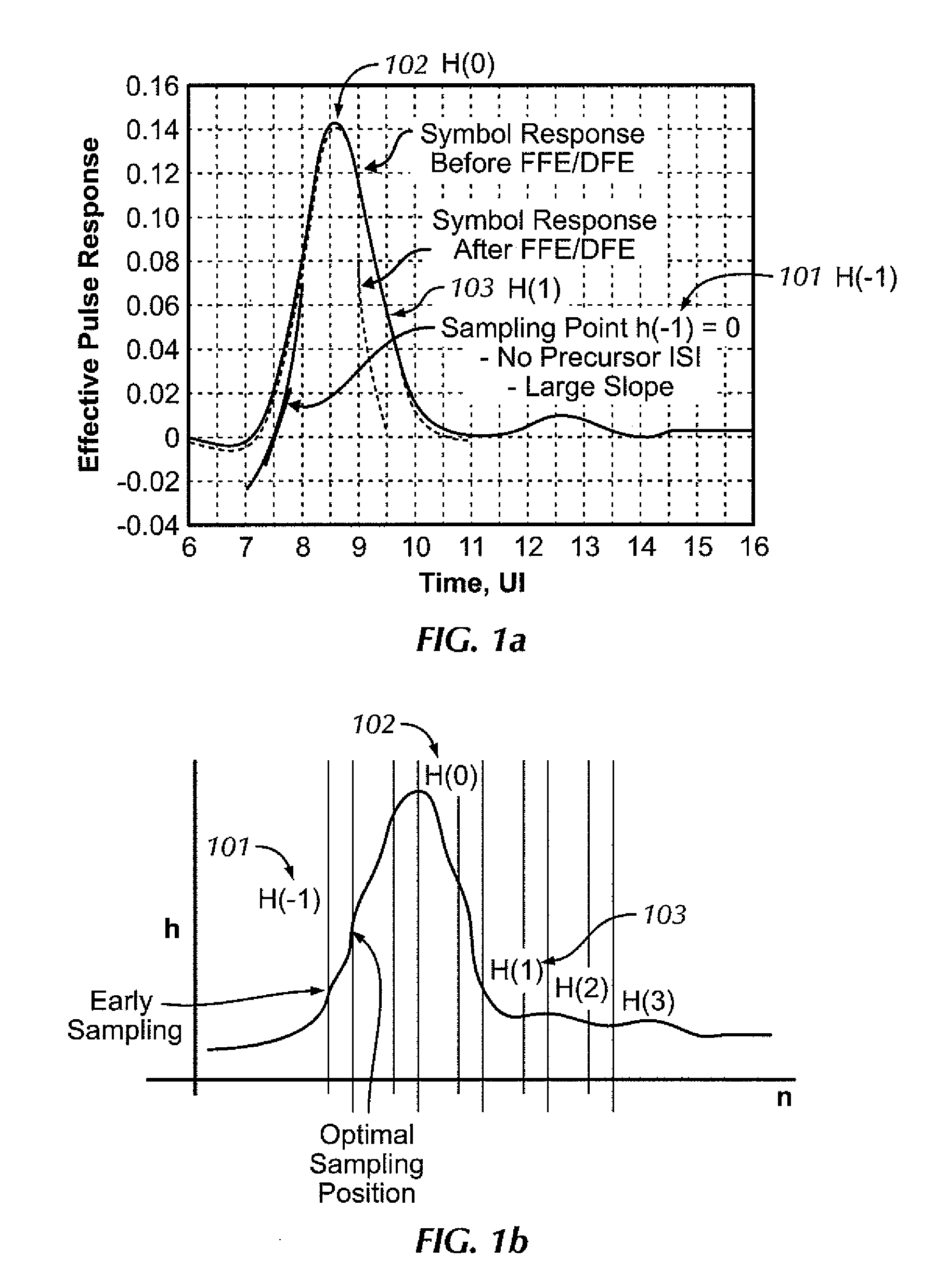

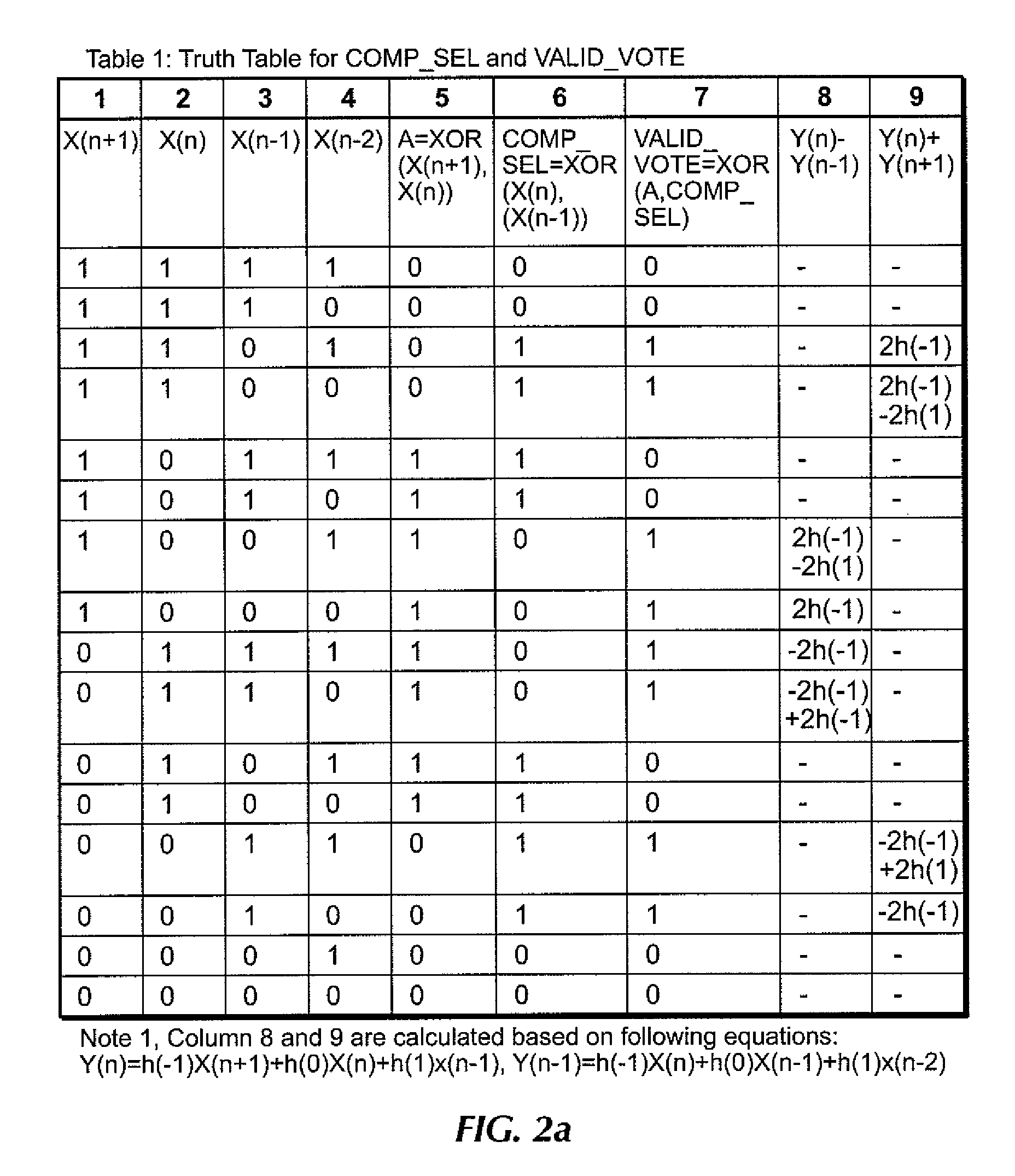

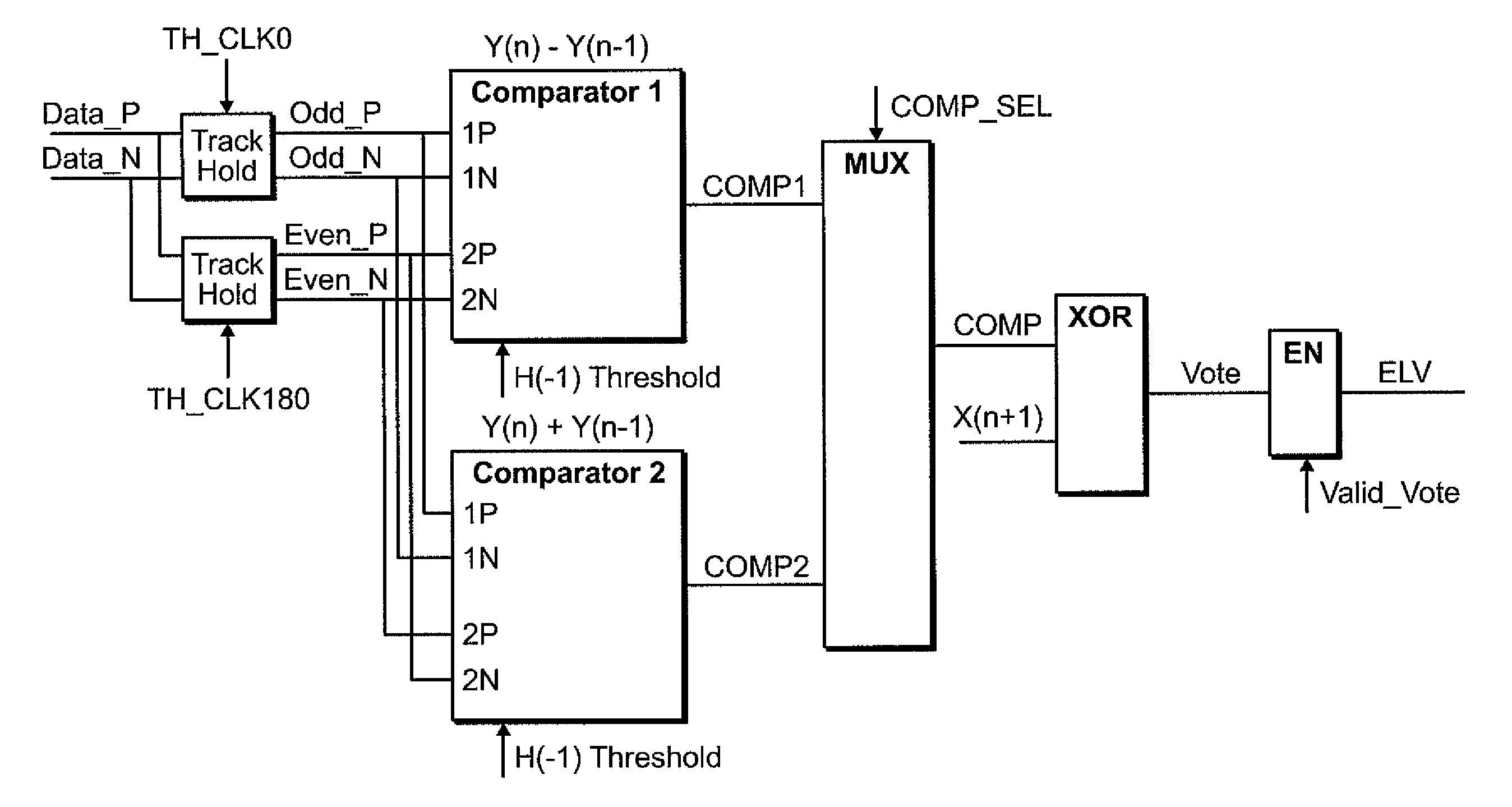

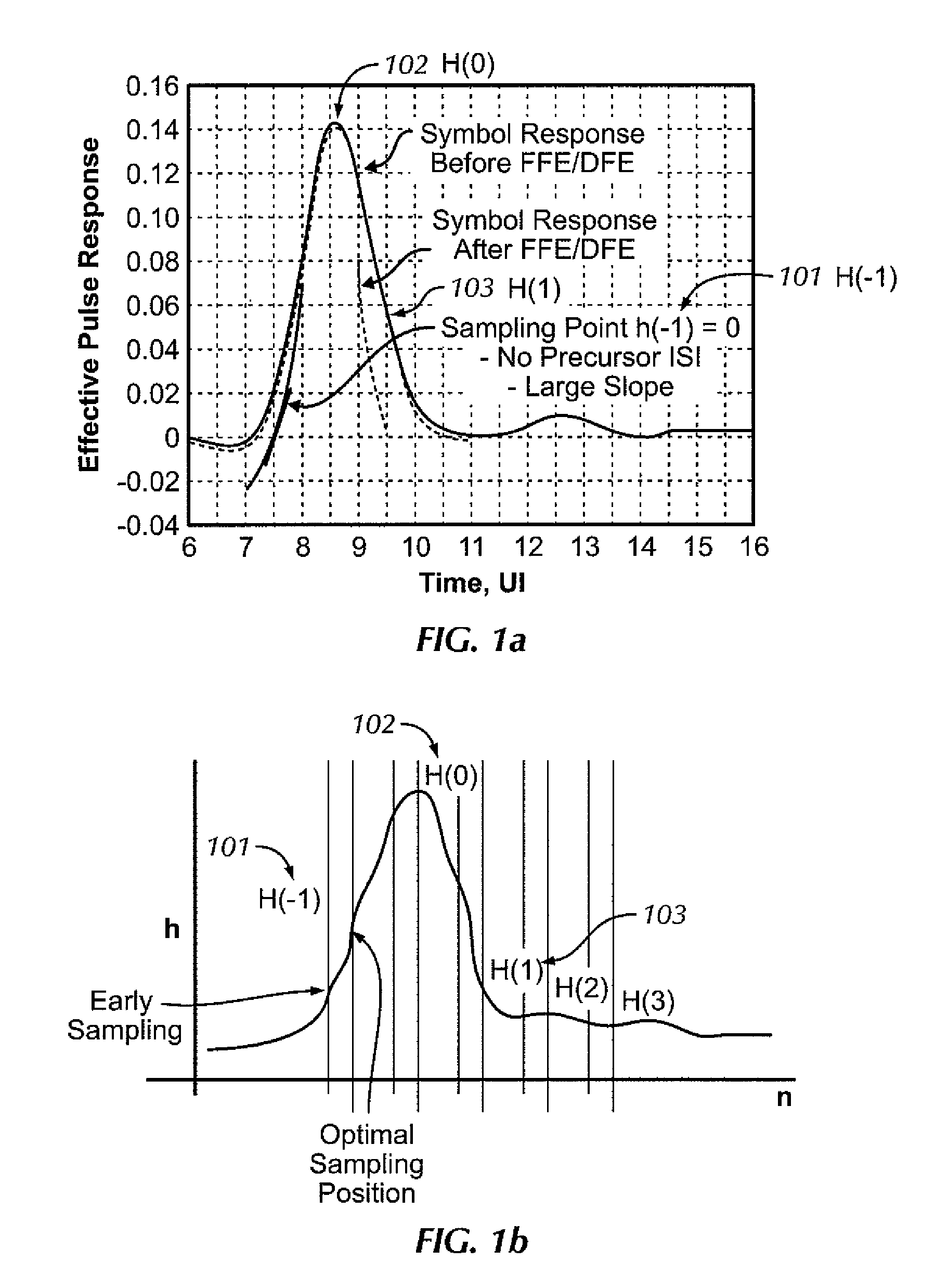

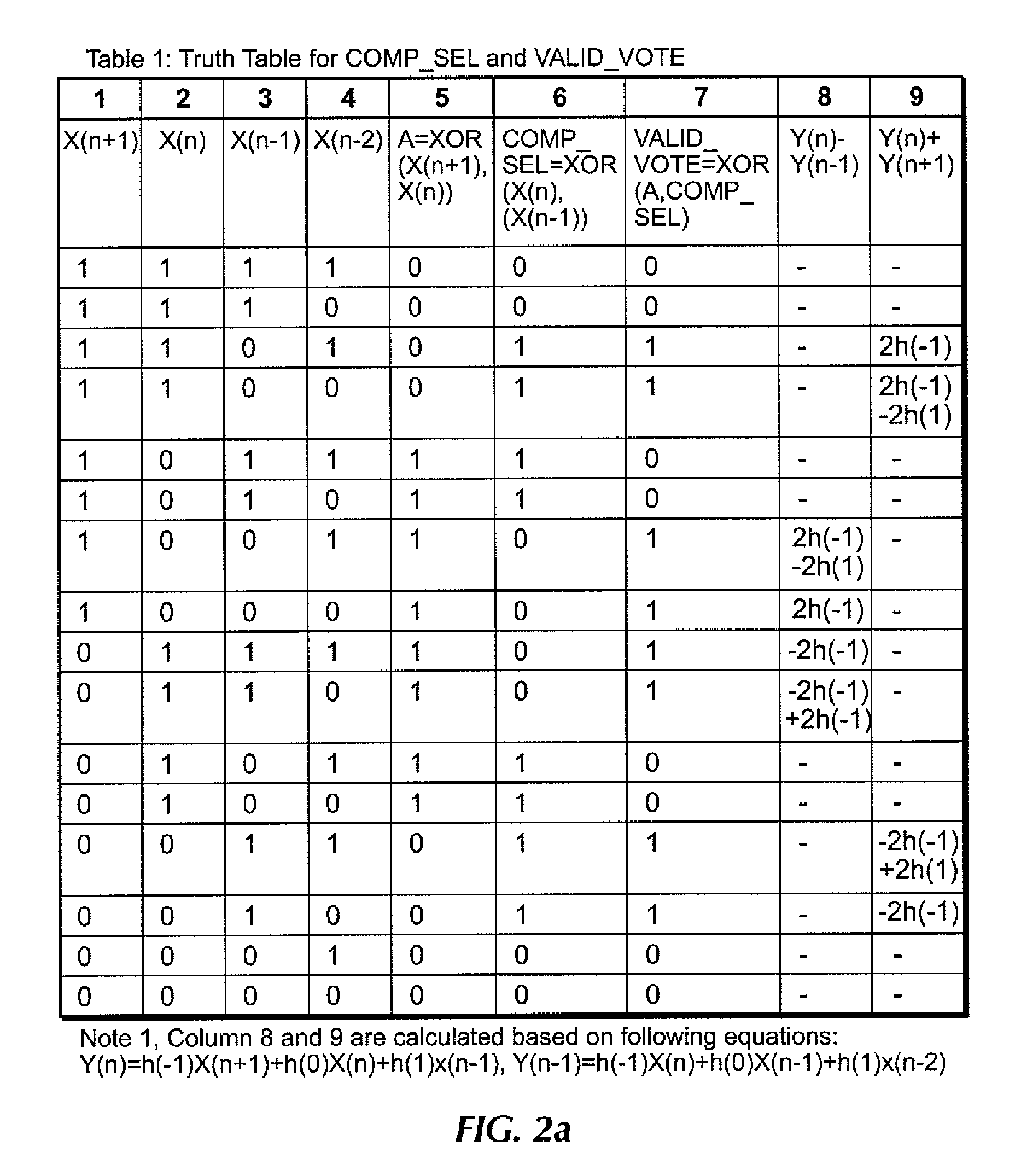

An analog baud rate clock and data recovery apparatus includes a first track and hold circuit that delays a received signal by one unit interval to create an odd signal; a second track and hold circuit that delays the received signal by one unit interval to create an even signal; a first comparator circuit; and a second comparator circuit. The first track and hold circuit outputs the odd signal to the first comparator circuit and the second comparator circuit. The second track and hold circuit outputs the even signal to the first comparator circuit and the second comparator circuit. The first comparator adds the odd signal to the even signal and outputs a first potential timing error. The second comparator subtracts the odd signal and the even signal and outputs a second potential timing error signal. A desired timing error signal is derived from the first and second potential timing error signals. The desired timing error signal is used to determine whether signal sampling is early or late.

Owner:ORACLE INT CORP

ADC

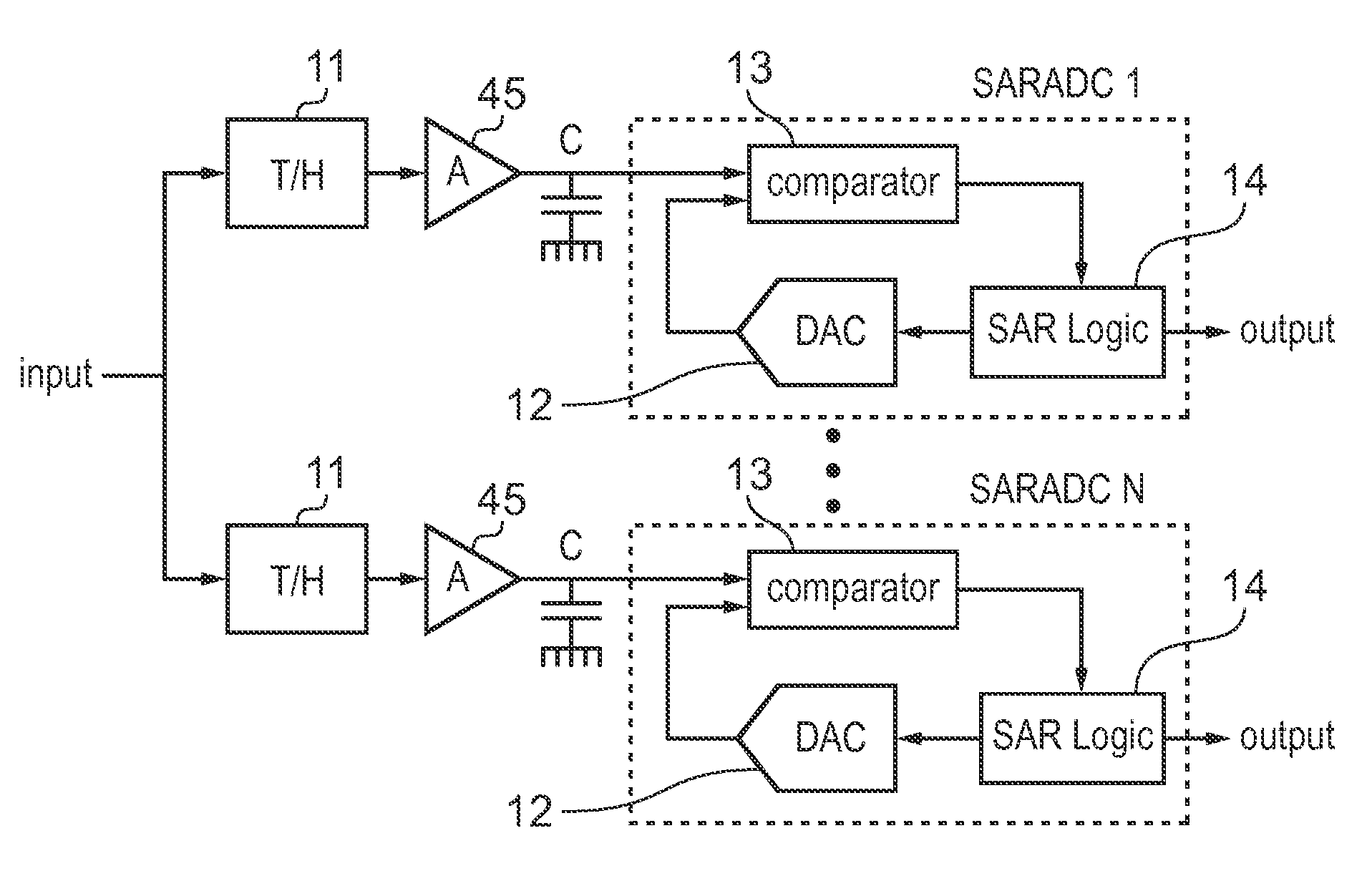

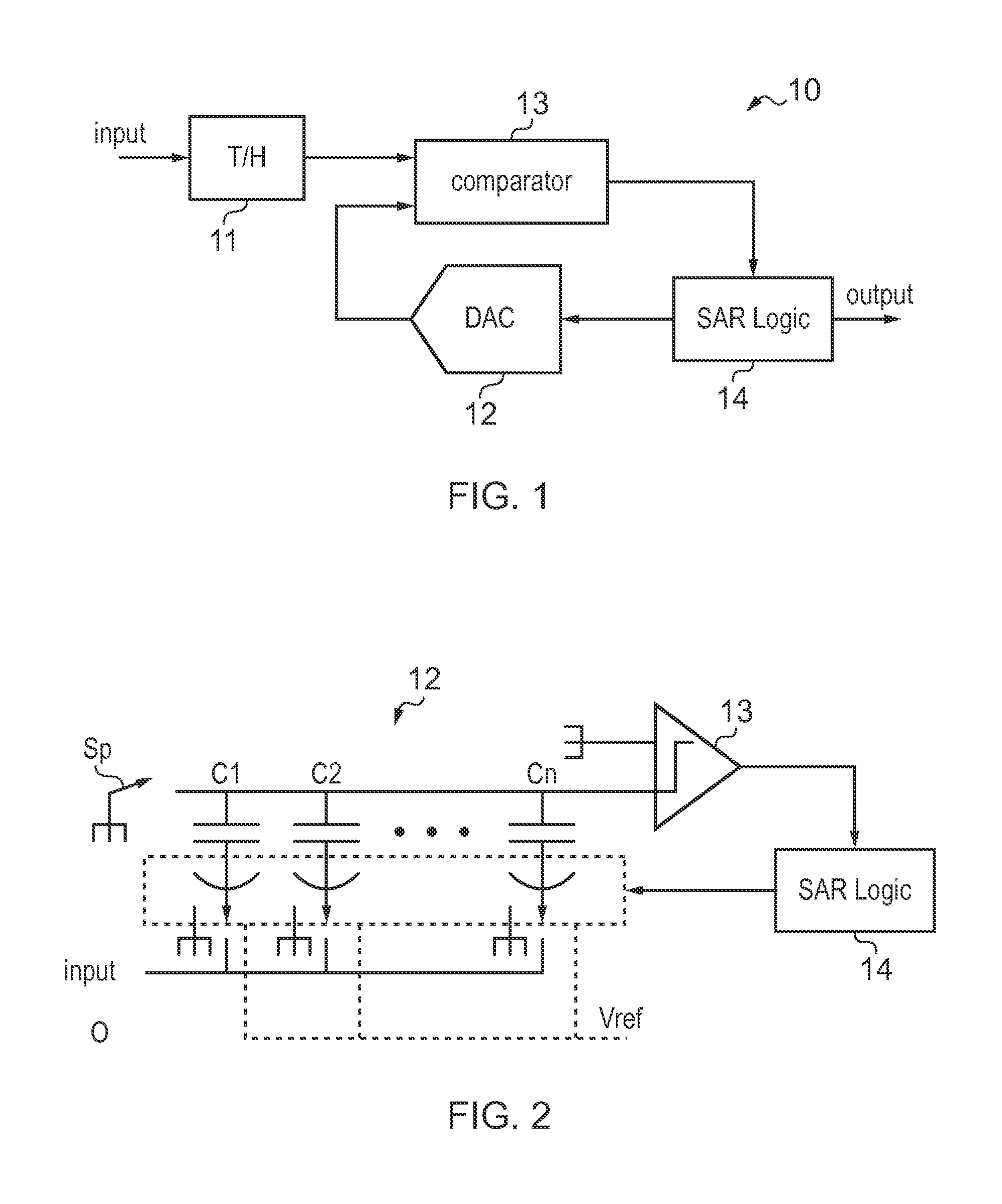

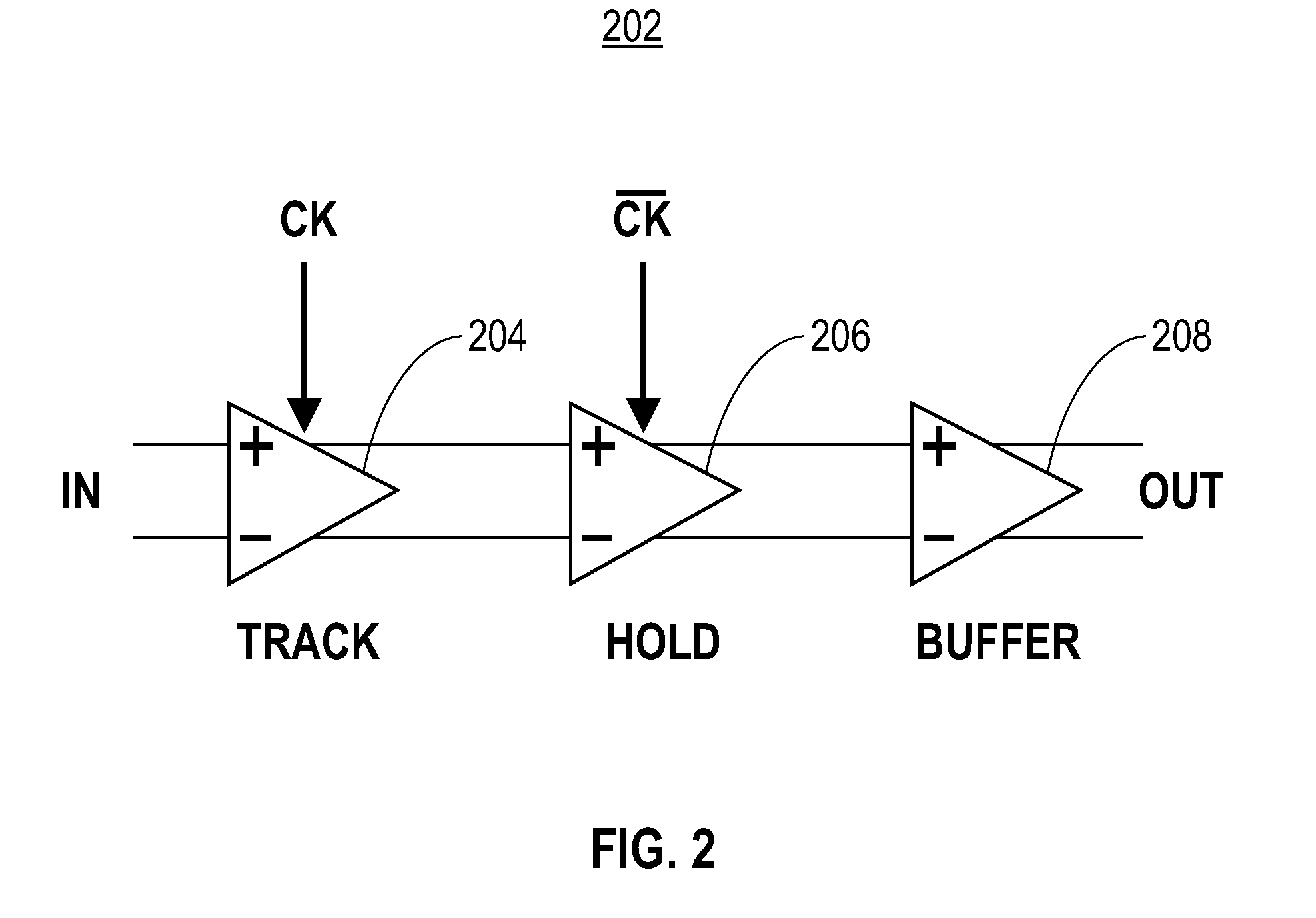

ActiveUS20110241912A1Run fastMore degree of design freedomElectric signal transmission systemsAnalogue-digital convertersCapacitanceAlternating current

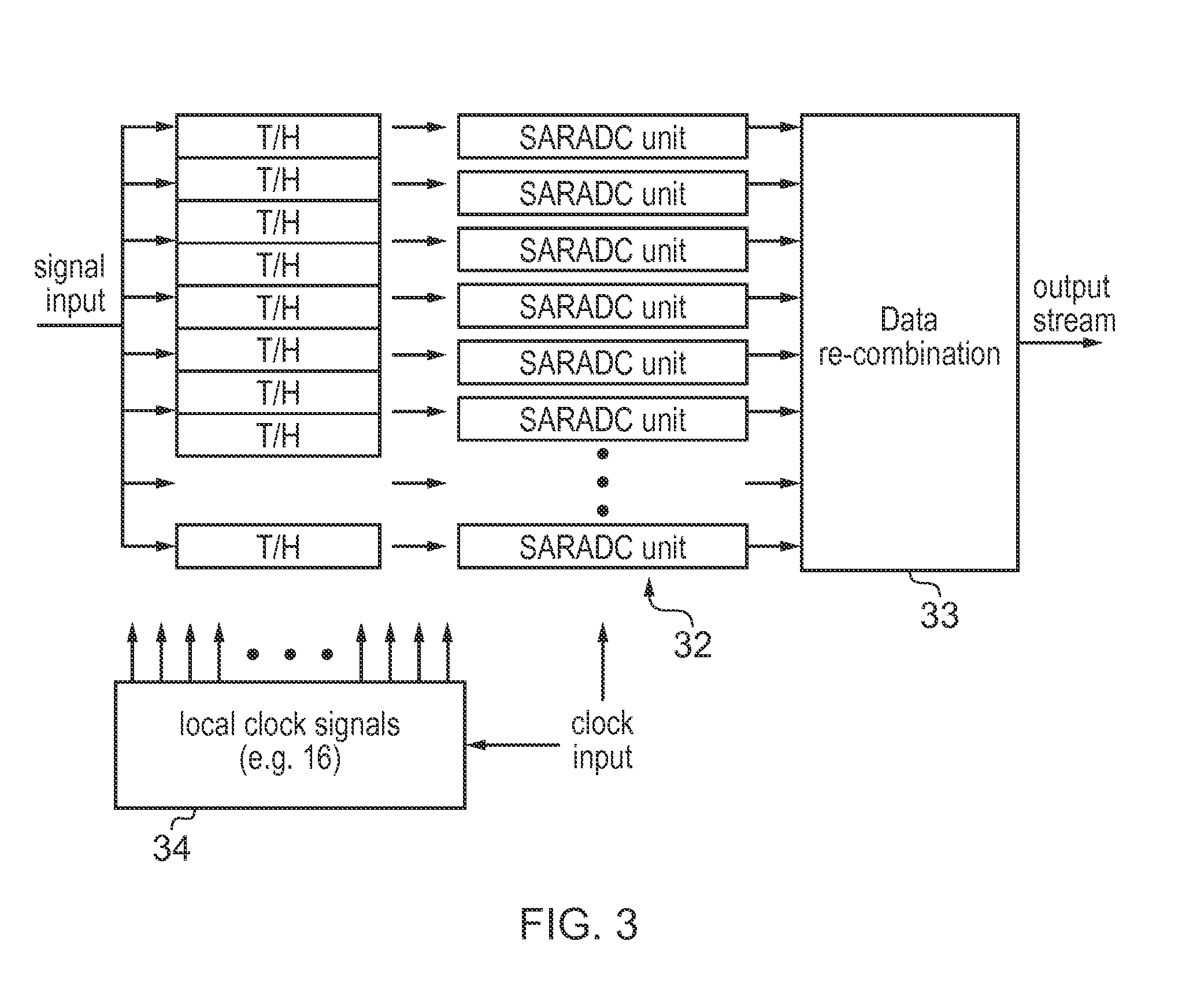

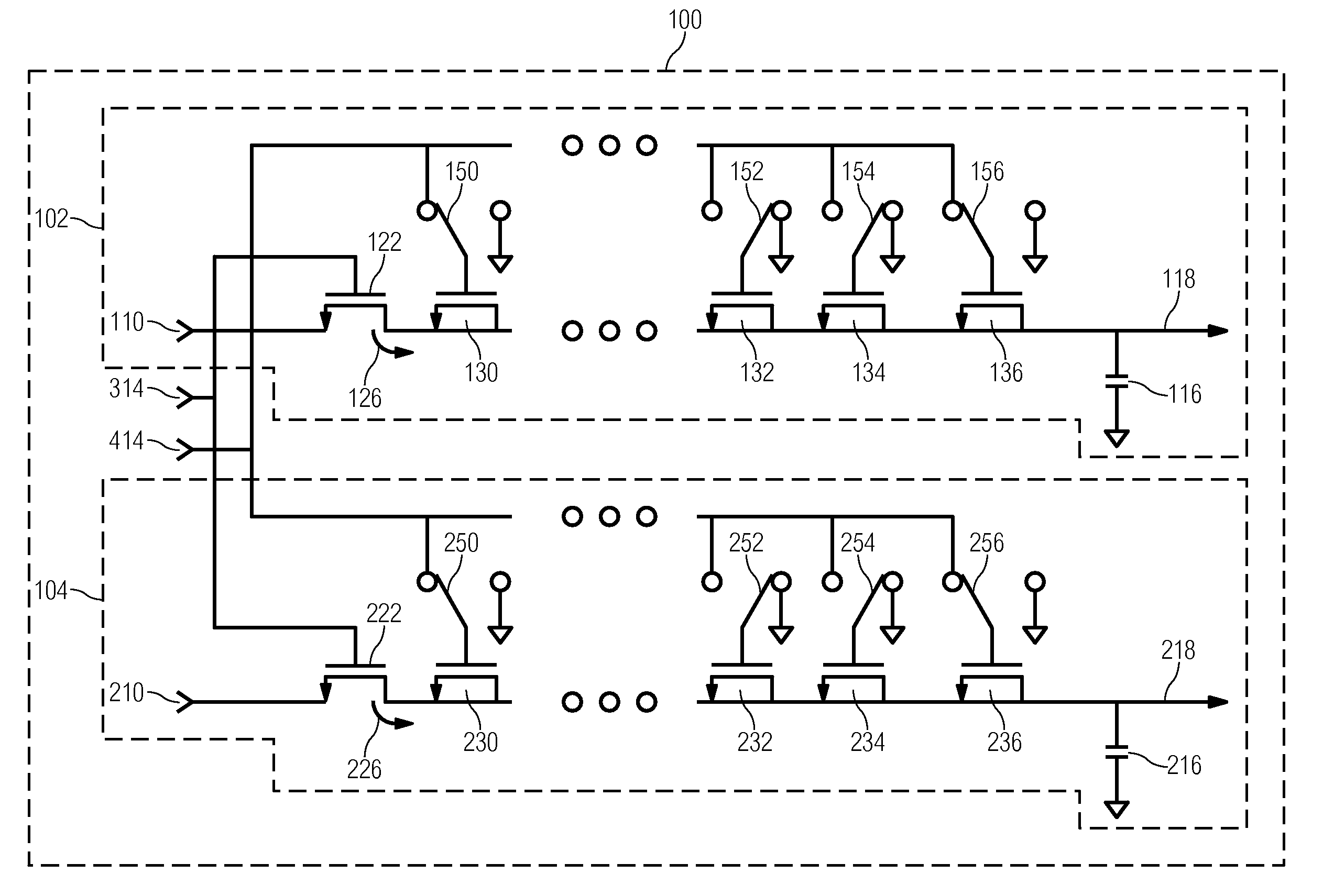

This invention relates to Analog to Digital Converters (ADC) and, inter alia, to Time Interleaved ADCs and Successive Approximation Register (SAR) ADC's. In a conventional Time Interleaved ADC employing SAR ADC units, the input signal is processed through a track-and-hold circuit (T / H), and then through a buffer circuit, before the SAR ADC unit. There, by means of a comparator, the signal is compared with a Digital-to-Analog Converter (DAC) signal from the SAR logic. The buffer reduces the influence of capacitive loading and physical layout design on the SAR ADC input, but typically has a non-linear response and thus introduces distortion to the input signal. This can limit the ADC linearity, particularly for high-speed ADCs operating with low-supply voltages. An objective of the invention is to reduce or eliminate the effect of the buffer non-linearity. This is done in some embodiments by routing both the signals to the comparator through the same buffer circuit. In another embodiment the DAC signal is routed through a separate second buffer circuit. By use of a single buffer circuit, or where there is ideal matching of the buffer circuits in the latter embodiment, the distortion effects are completely eliminated; however, for practical imperfectly matched buffer circuits according to the latter embodiment, the gain and off-set mismatches can be accommodated through calibration of the buffers or, in suitable applications, through the DAC calibration.

Owner:NXP BV

Analog baud rate clock and data recovery

ActiveUS8243866B2Multiple input and output pulse circuitsInstant pulse delivery arrangementsComparators circuitsSignal delay

An analog baud rate clock and data recovery apparatus includes a first track and hold circuit that delays a received signal by one unit interval to create an odd signal; a second track and hold circuit that delays the received signal by one unit interval to create an even signal; a first comparator circuit; and a second comparator circuit. The first track and hold circuit outputs the odd signal to the first comparator circuit and the second comparator circuit. The second track and hold circuit outputs the even signal to the first comparator circuit and the second comparator circuit. The first comparator adds the odd signal to the even signal and outputs a first potential timing error. The second comparator subtracts the odd signal and the even signal and outputs a second potential timing error signal. A desired timing error signal is derived from the first and second potential timing error signals. The desired timing error signal is used to determine whether signal sampling is early or late.

Owner:ORACLE INT CORP

Track and hold with dual pump circuit

InactiveUS20030151430A1Electric signal transmission systemsElectric analogue storesTransmission gateEngineering

A dual pump circuit including a transmission gate and a dual charge pump. The transmission gate includes a p-channel transistor and an n-channel transistor, each having a control terminal and a pair of current terminals coupled between a dual pump input and a dual pump output. The dual charge pump includes first and second pump circuits, where each pump circuit is coupled to the dual pump input and to a control terminal of a corresponding one of the transmission gate transistors. Each pump circuit is operative to linearize operation of its corresponding transmission gate transistor by maintaining VGS-VT constant. The dual pump circuit is used in a track and hold circuit including at least one dual pump sampling circuit, at least one sampling capacitor, and a control circuit for controlling input signal sampling timing. Each dual pump sampling circuit includes the transmission gate and a dual charge pump.

Owner:INTERSIL INC

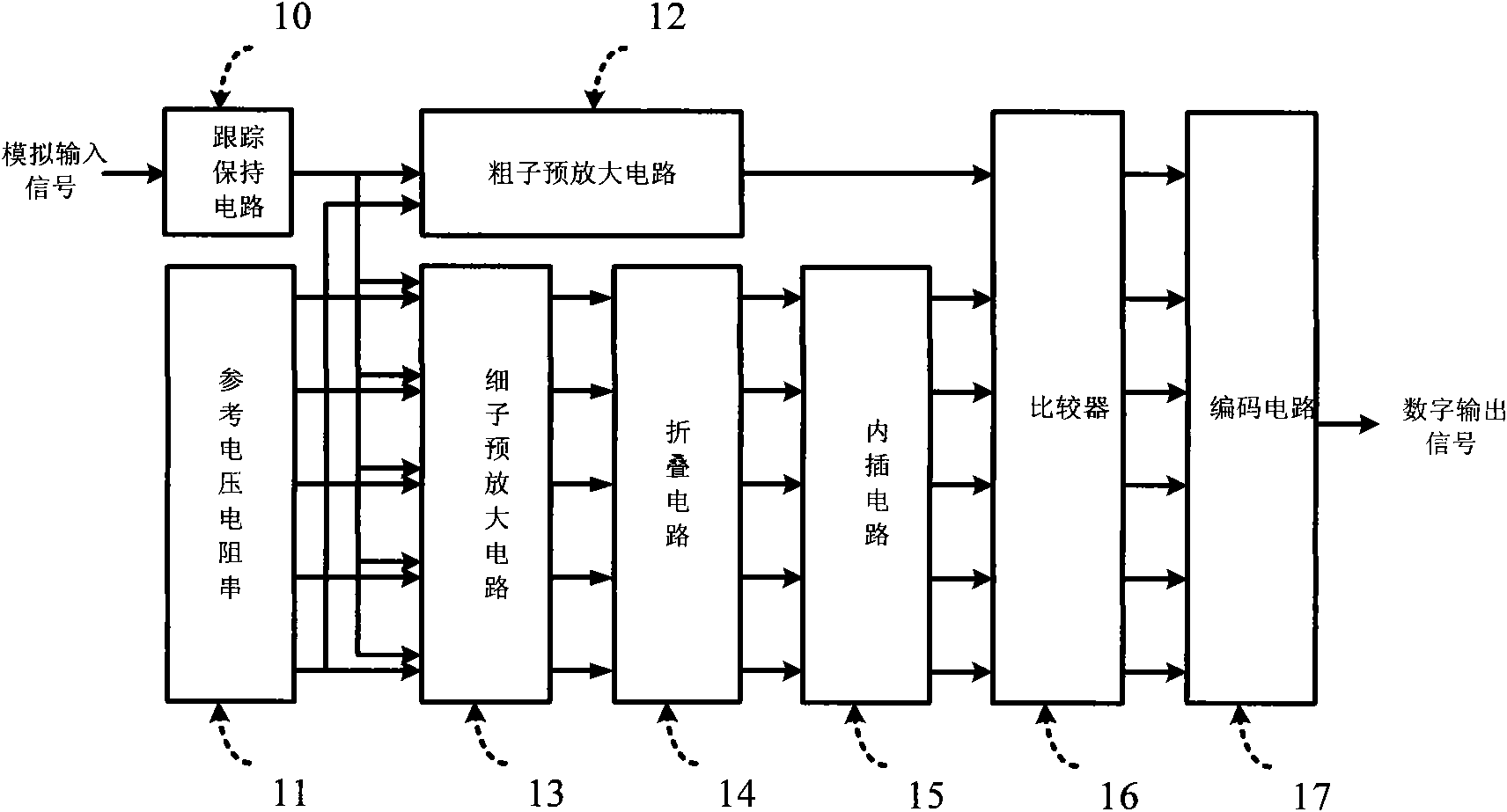

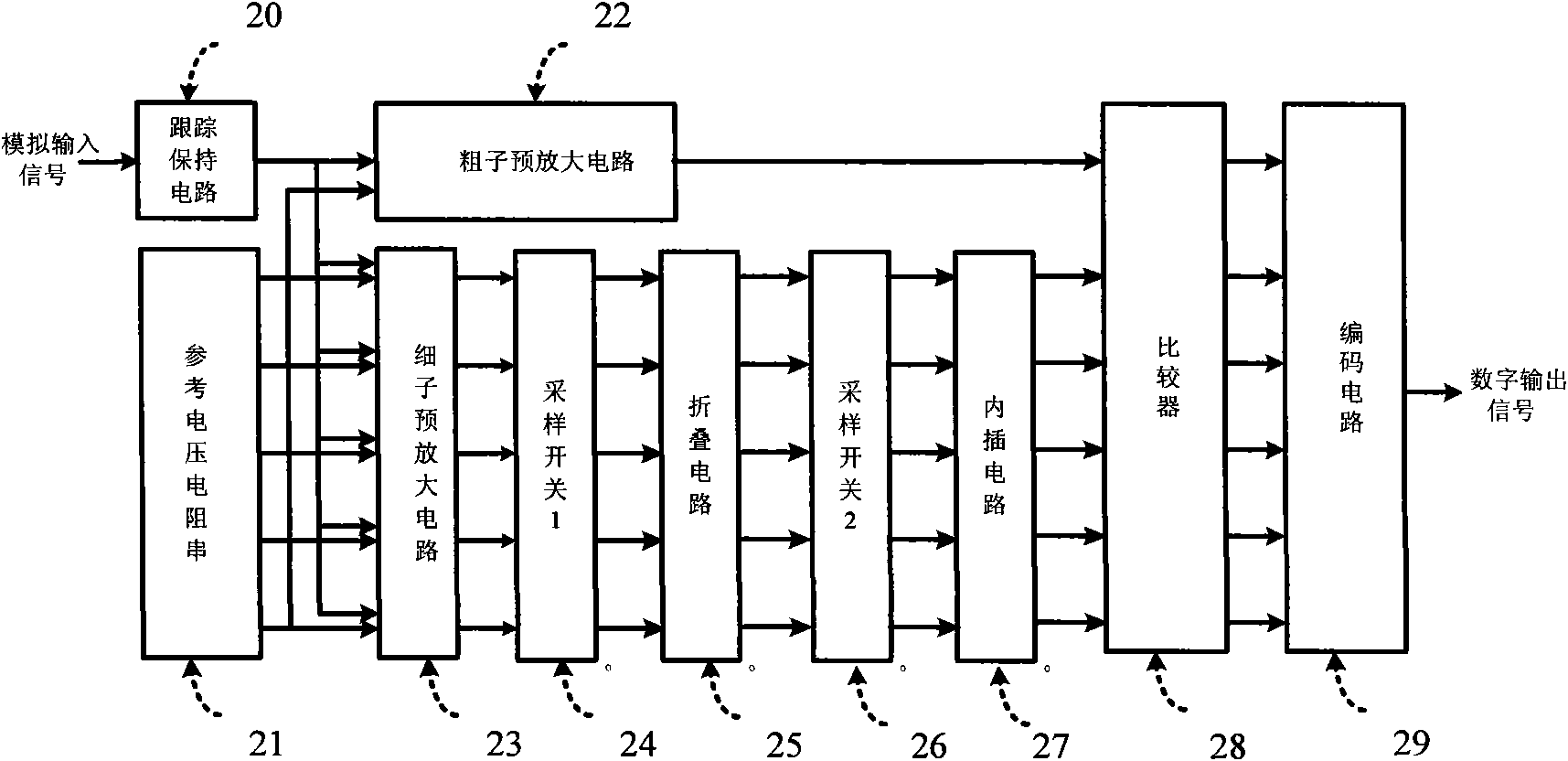

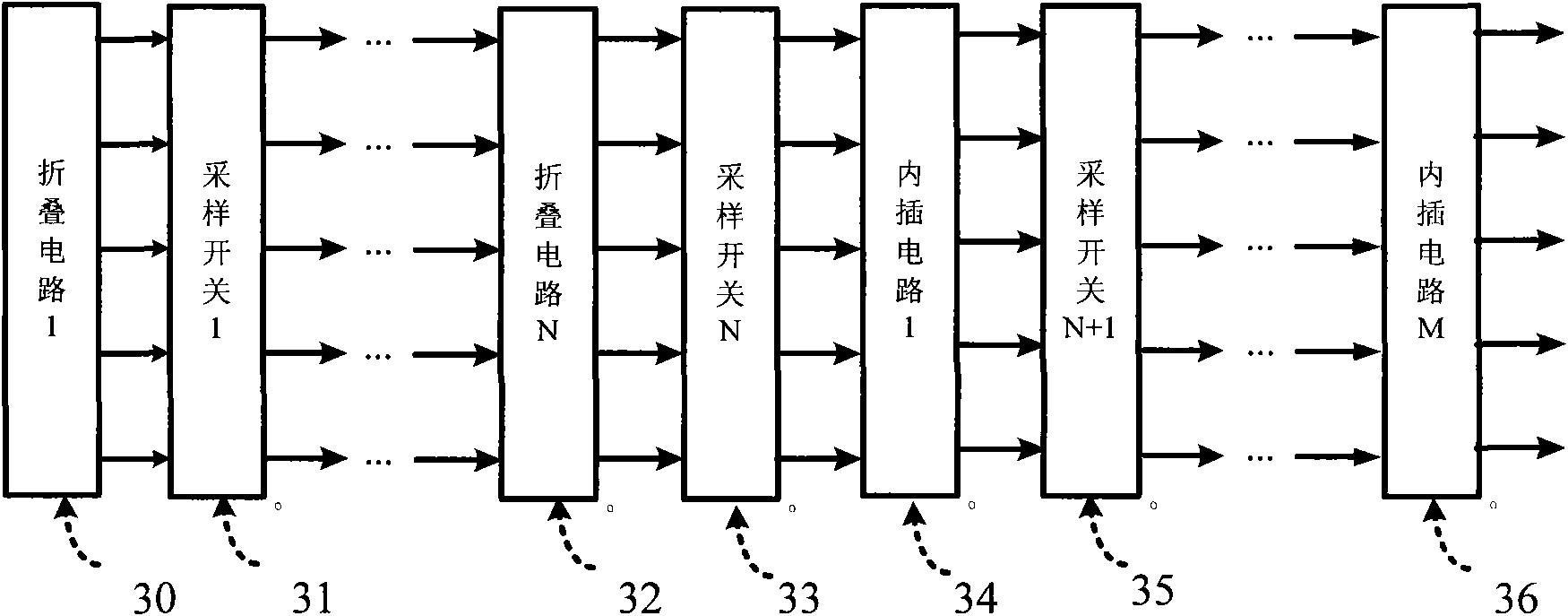

Low supply voltage pipelined folded interpolating analog-to-digital converter

InactiveCN101645710AReduce time delayIncrease conversion rateAnalogue/digital conversionElectric signal transmission systemsVoltage referenceAnalog-to-digital converter

The invention belongs to the technical field of integrated circuit, in particular to a low supply voltage pipelined folded interpolating analog-to-digital converter. The invention comprises a track and hold circuit, a reference voltage resistance string, a coarse pre-amplifier circuit, a fine pre-amplifier circuit, a first sampling switch, a folded circuit, a second sampling circuit, an interpolating circuit, a comparator and a coding circuit, wherein, the sampling circuit adopts grid voltage bootstrapped switch. The structure of the invention is able to decrease the time delay of analog-to-digital converter key route, effectively raising the conversion rate of the low supply voltage pipelined folded interpolating analog-to-digital converter.

Owner:FUDAN UNIV

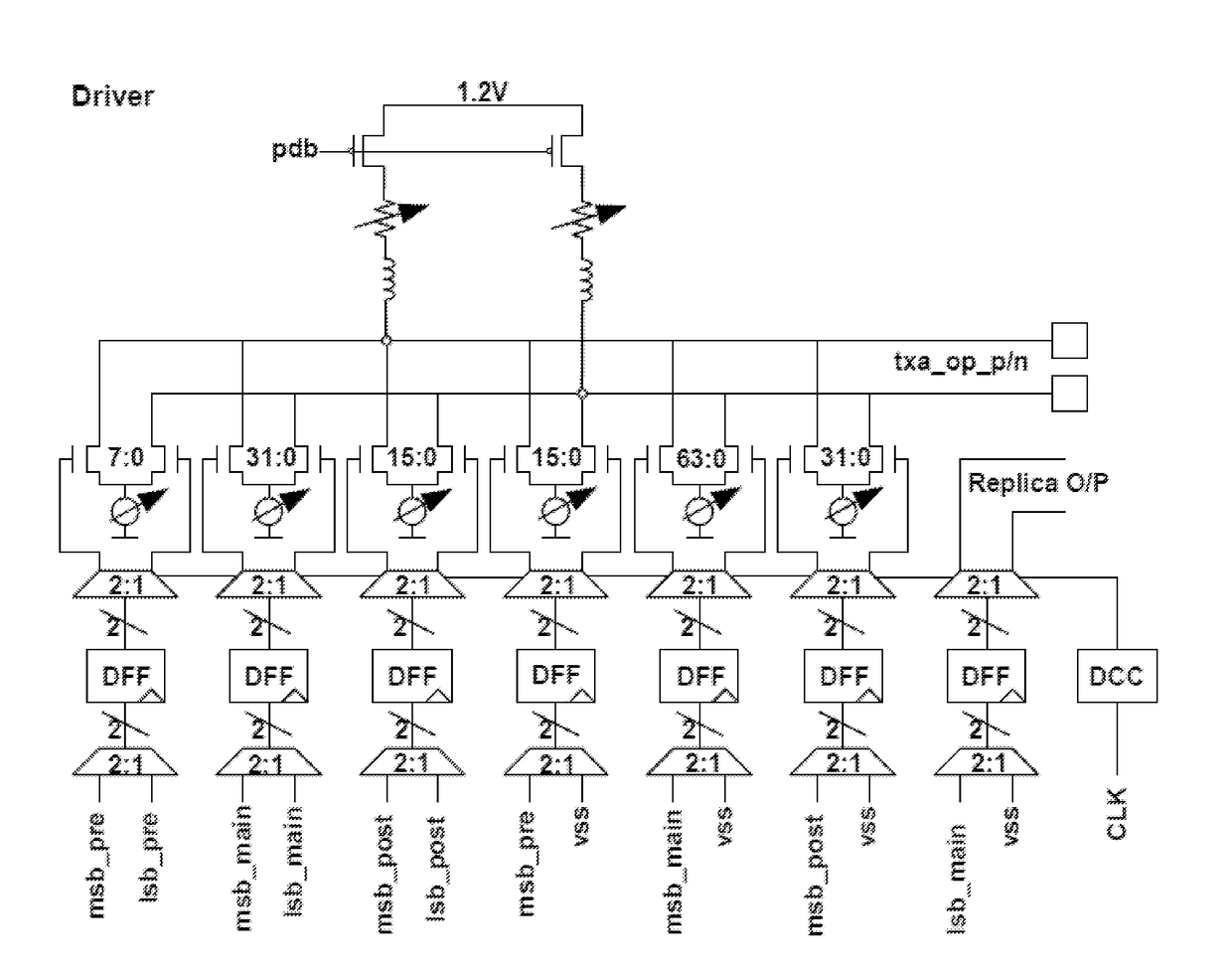

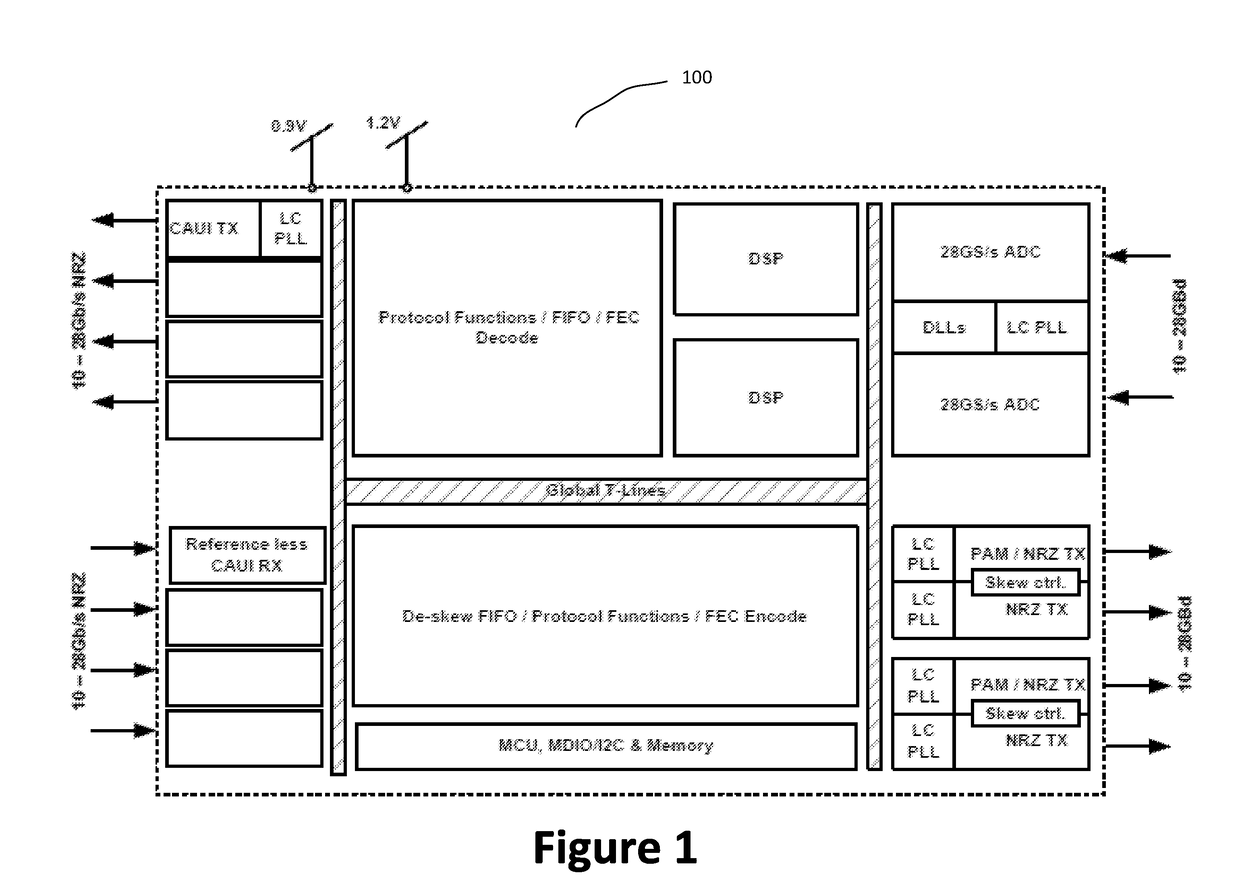

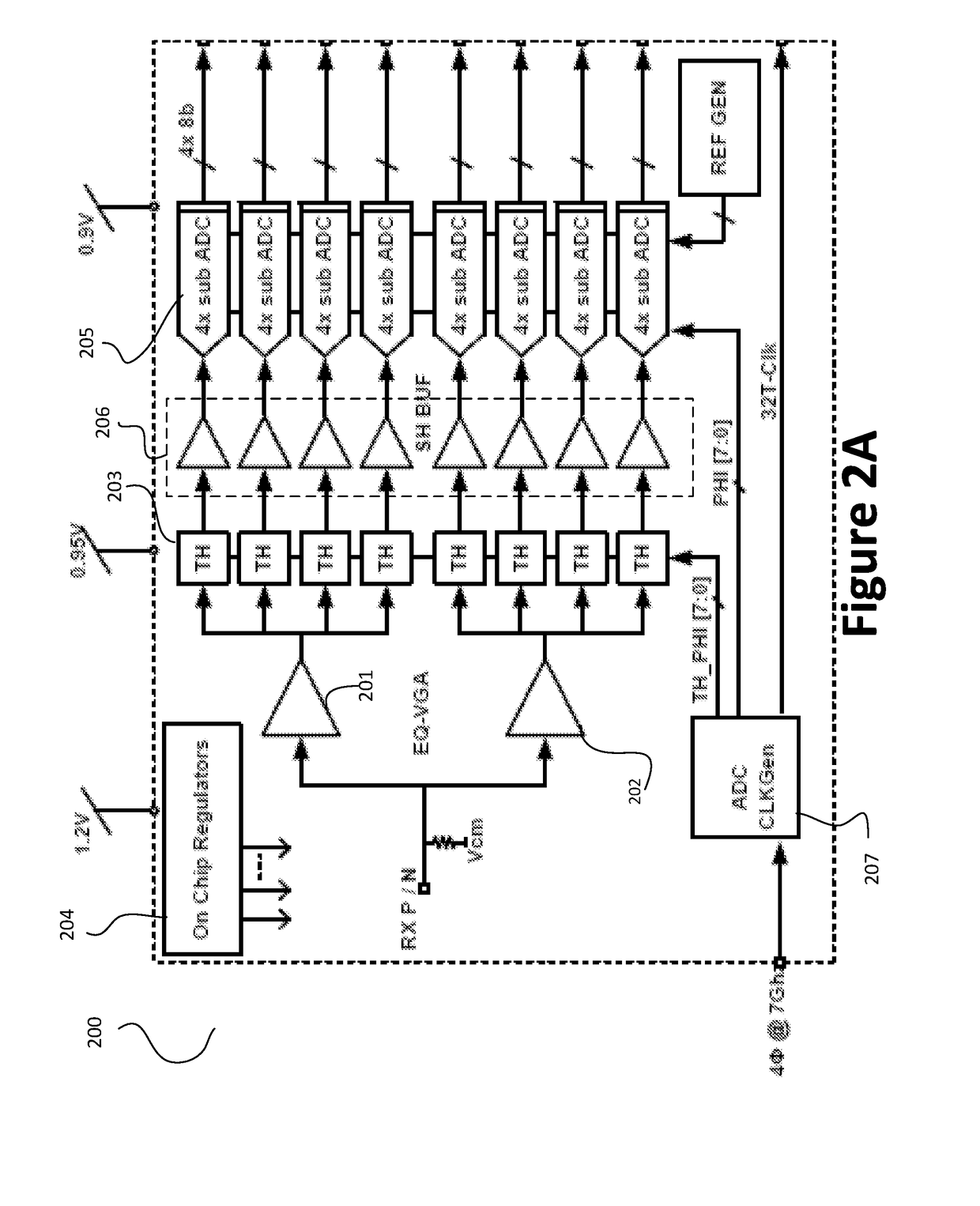

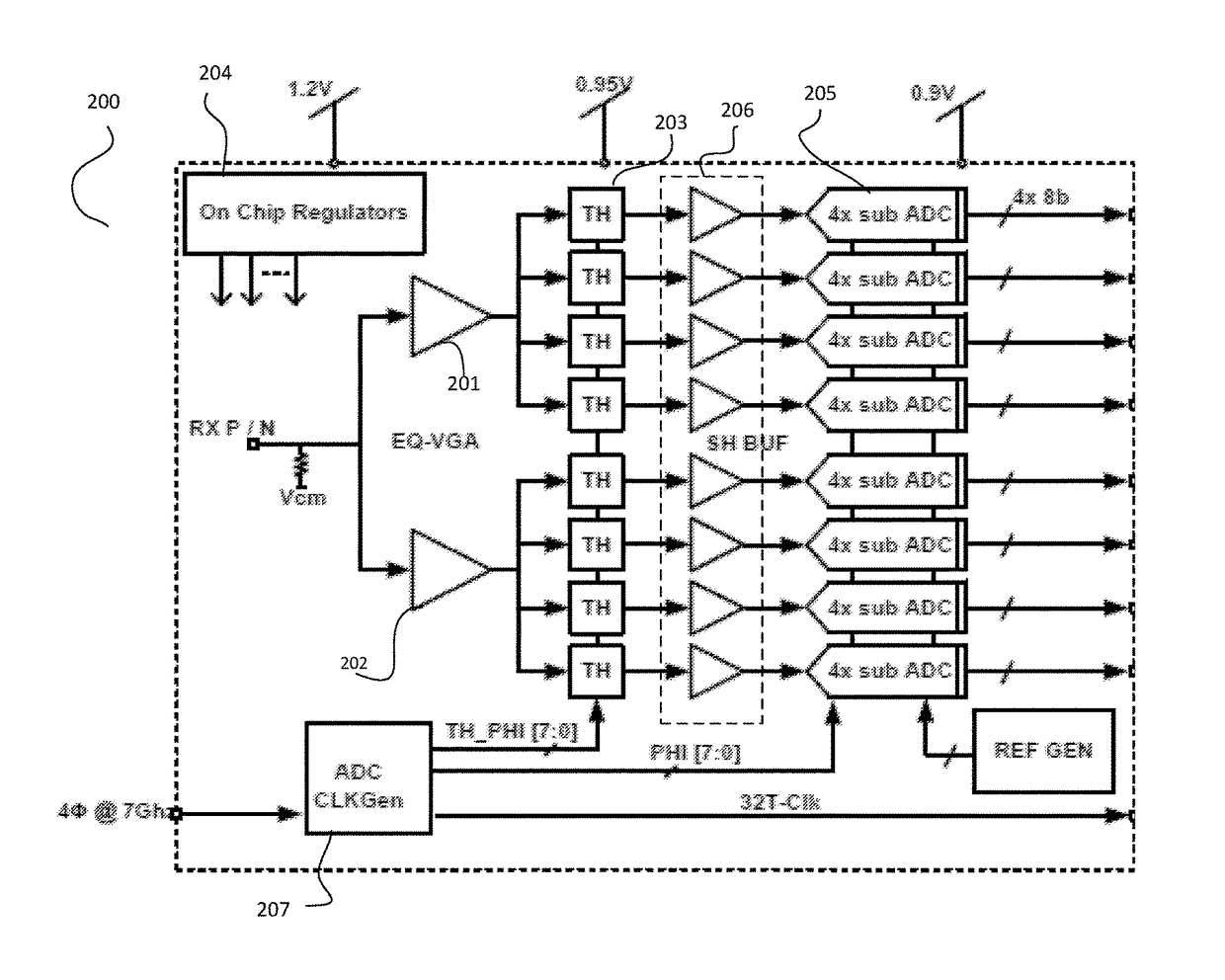

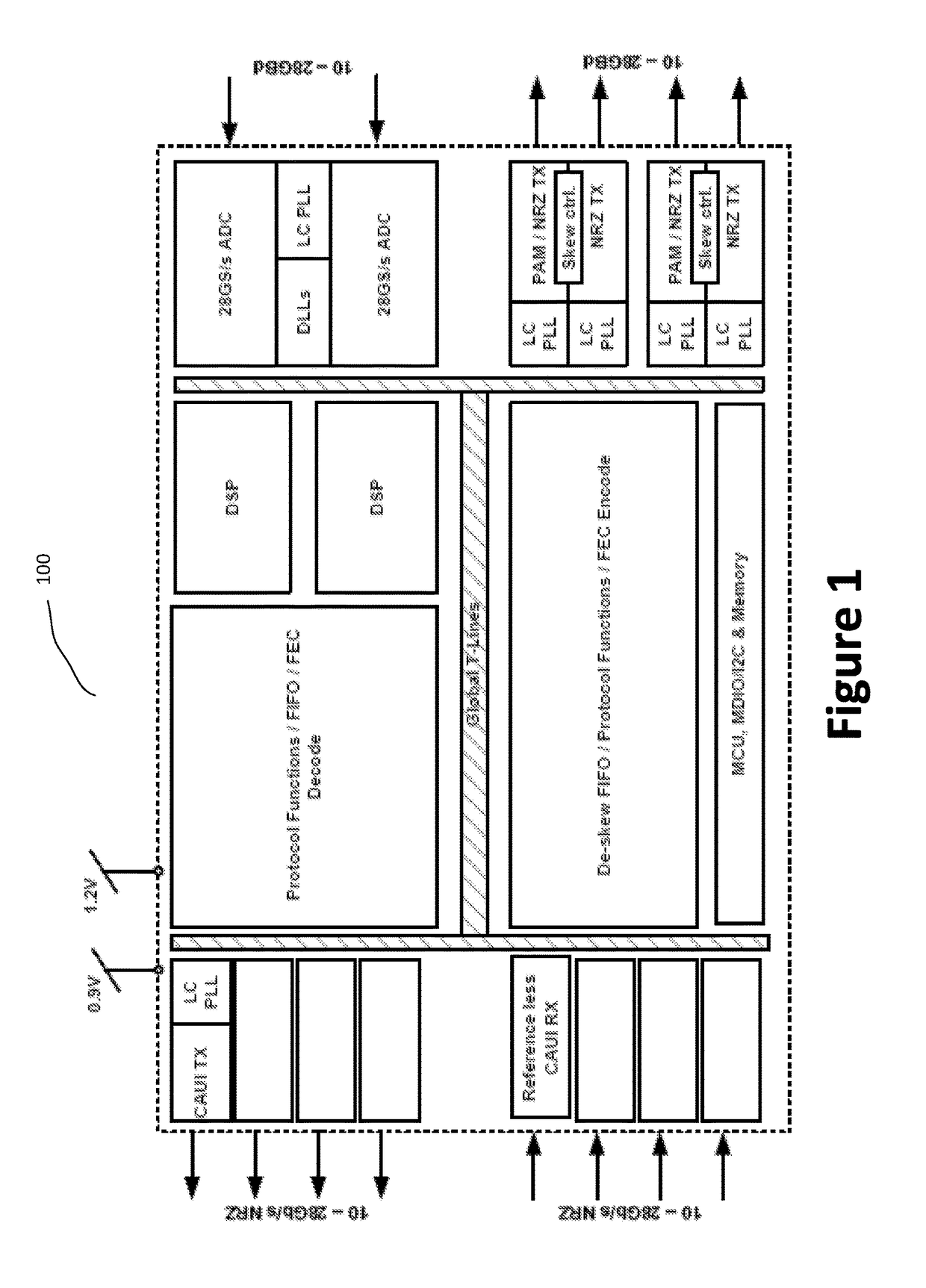

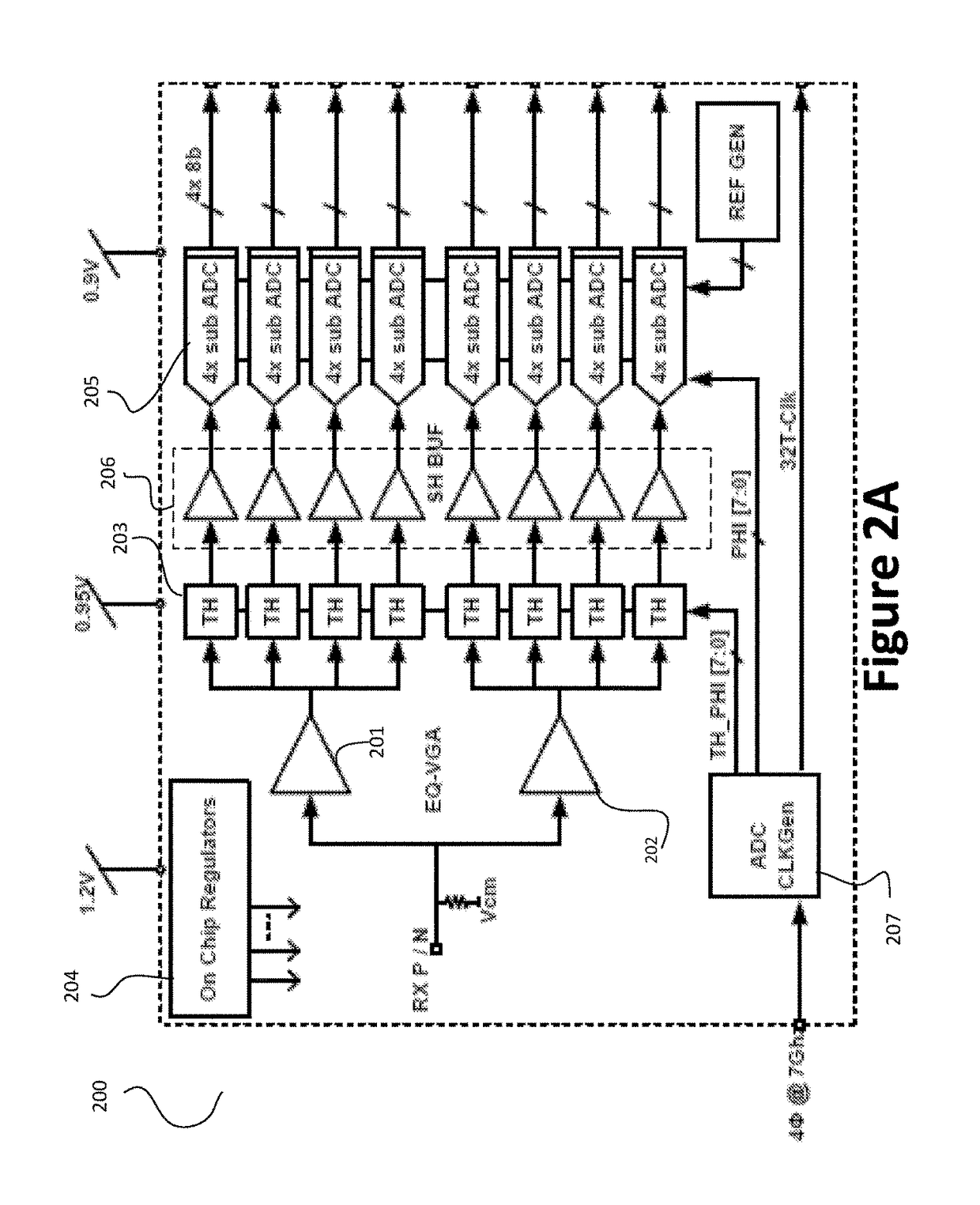

Pam4 transceivers for high-speed communication

ActiveUS20170257168A1Reduce power consumptionReduce noisePulse automatic controlSynchronisation receiversAudio power amplifierTransceiver

The present invention is directed to data communication. More specifically, embodiments of the present invention provide a transceiver that processes an incoming data stream and generates a recovered clock signal based on the incoming data stream. The transceiver includes a voltage gain amplifier that also performs equalization and provides a driving signal to track and hold circuits that hold the incoming data stream, which is stored by shift and holder buffer circuits. Analog to digital conversion is then performed on the buffer data by a plurality of ADC circuits. Various DSP functions are then performed over the converted data. The converted data are then encoded and transmitted in a PAM format. There are other embodiments as well.

Owner:MARVELL ASIA PTE LTD

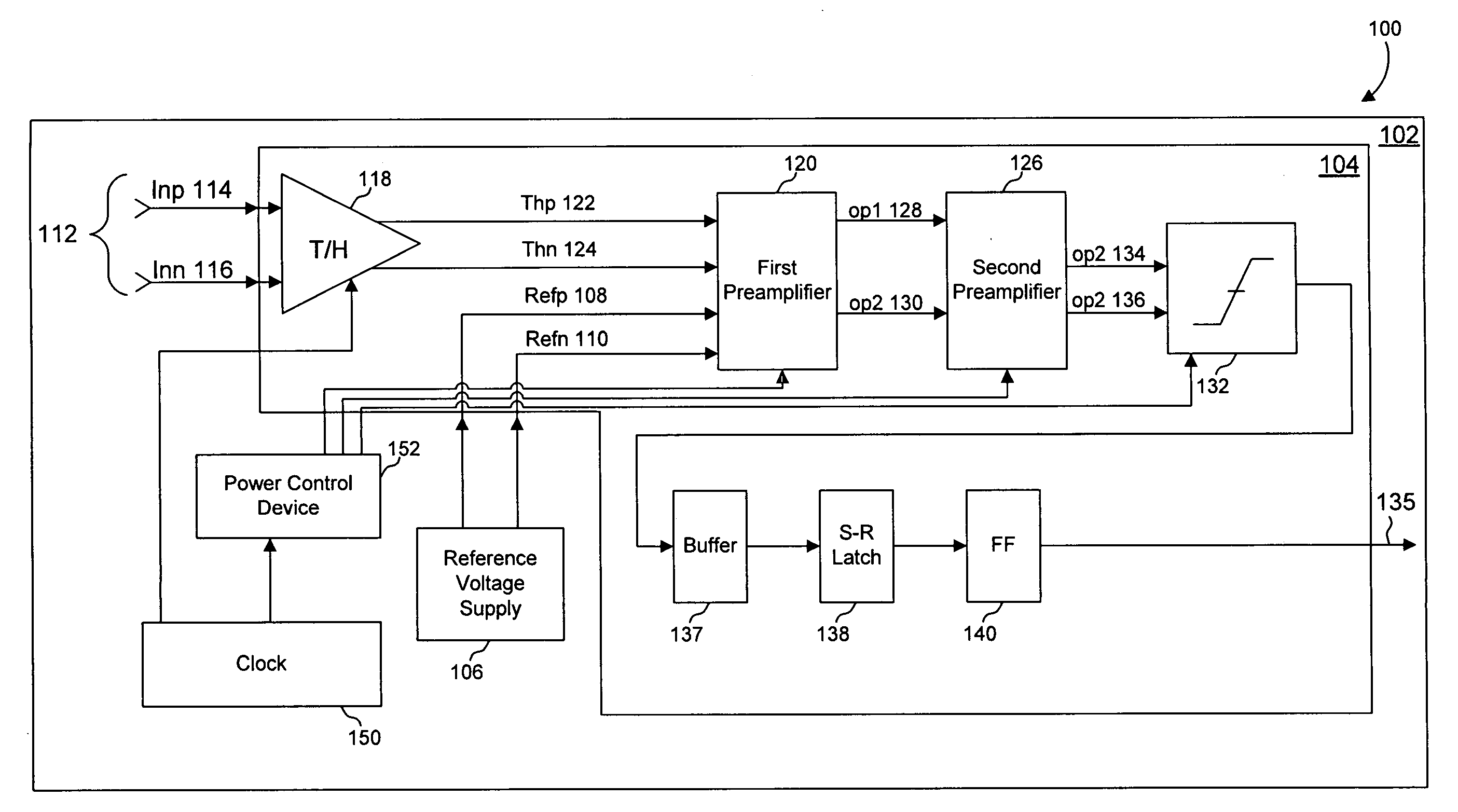

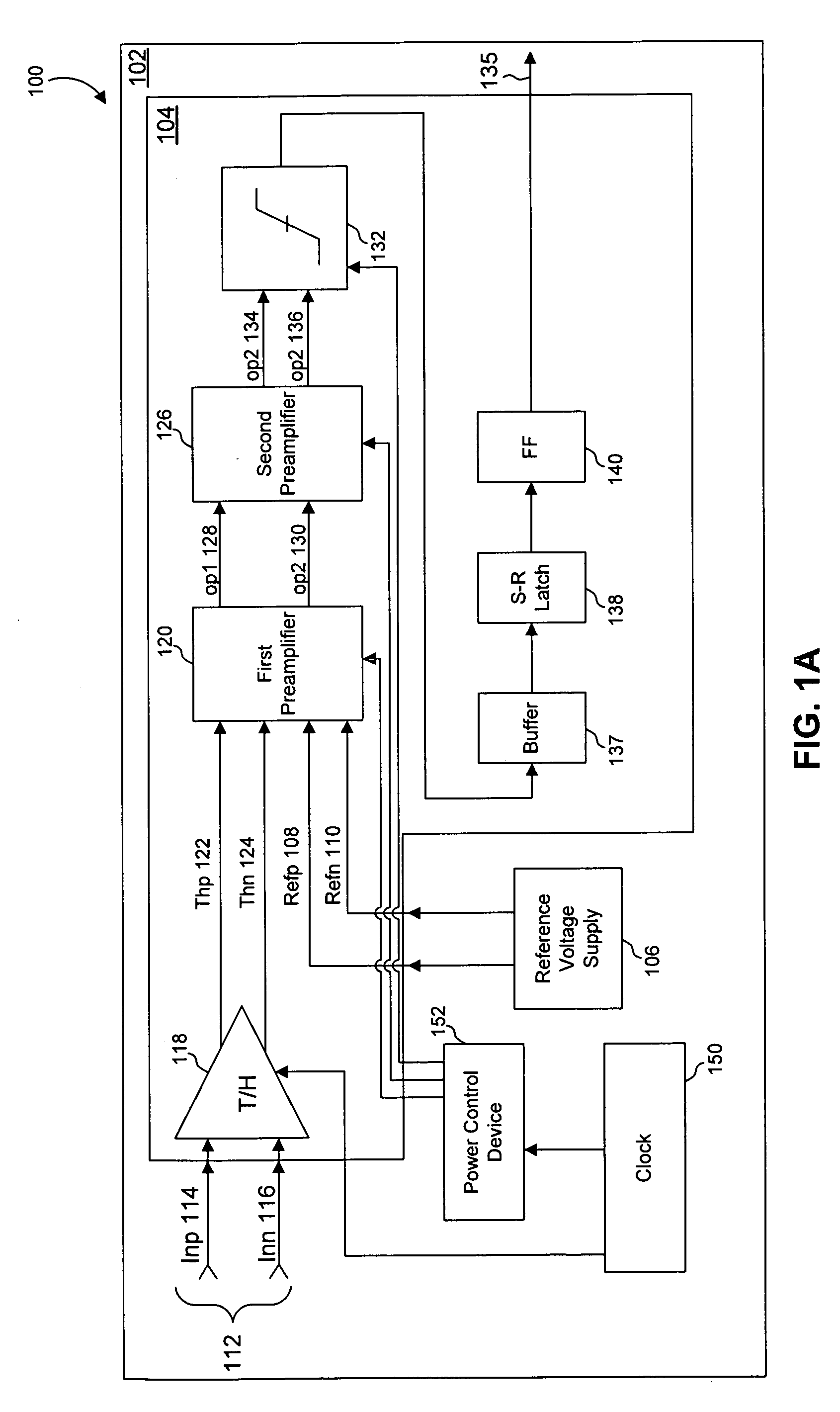

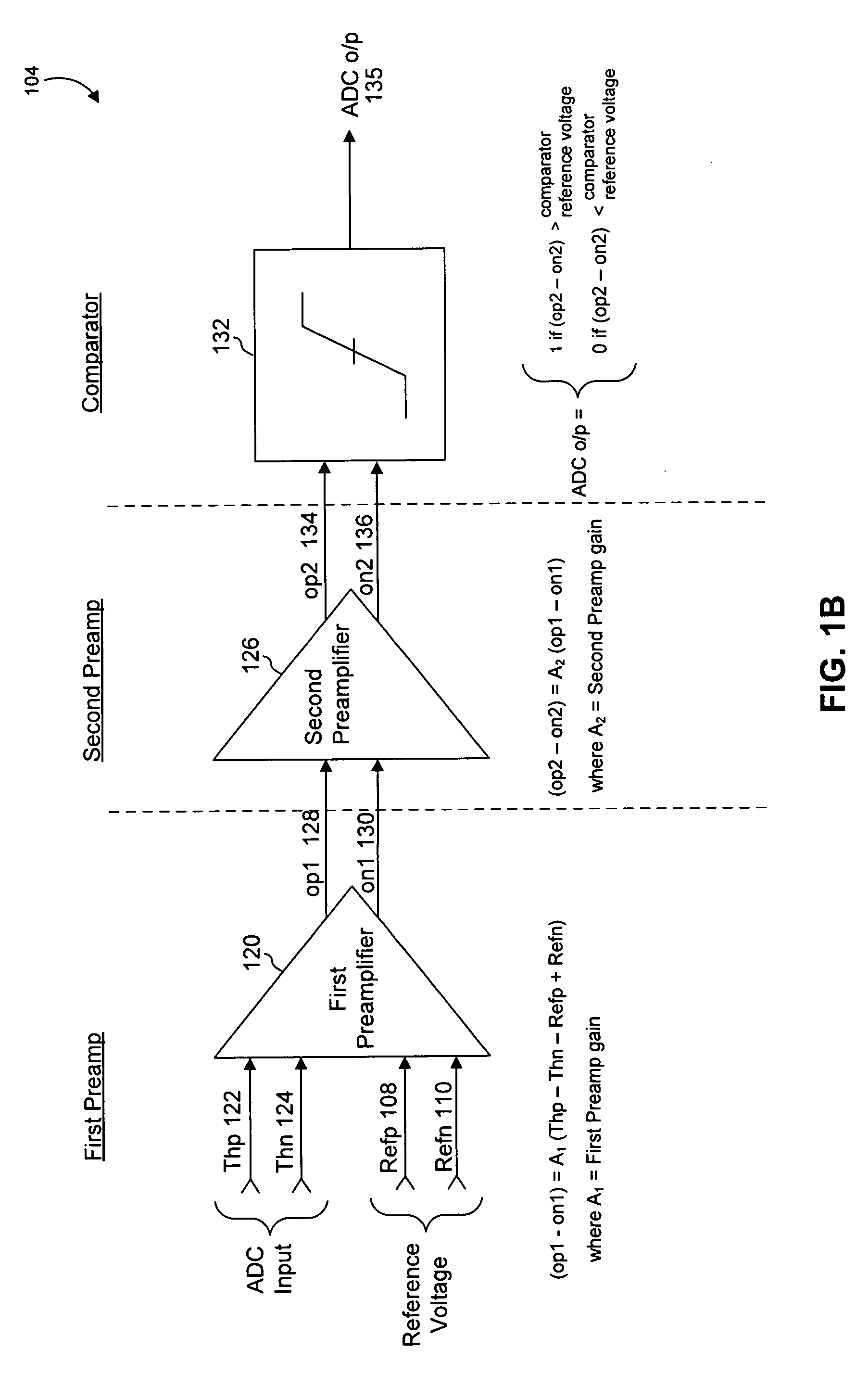

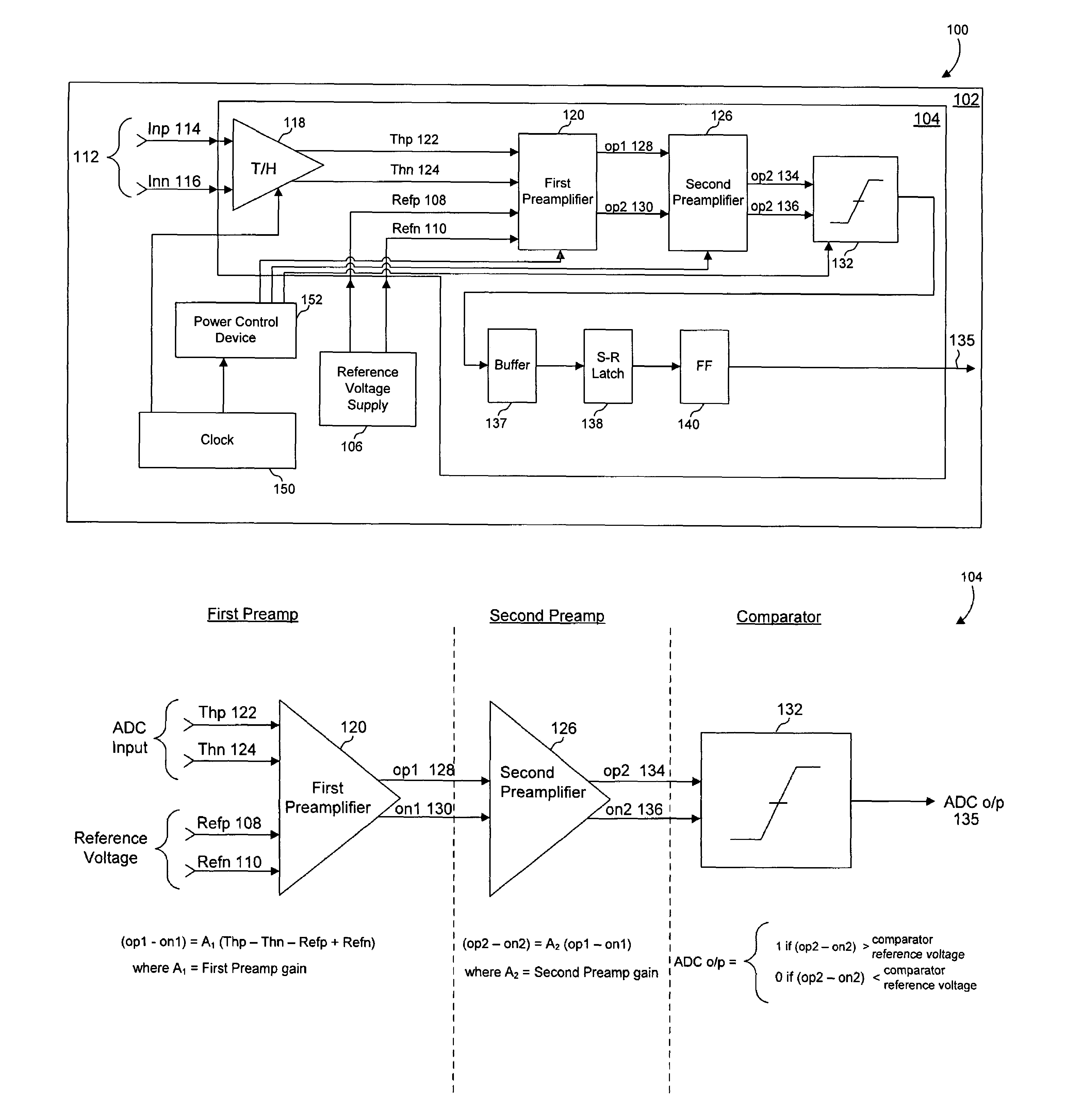

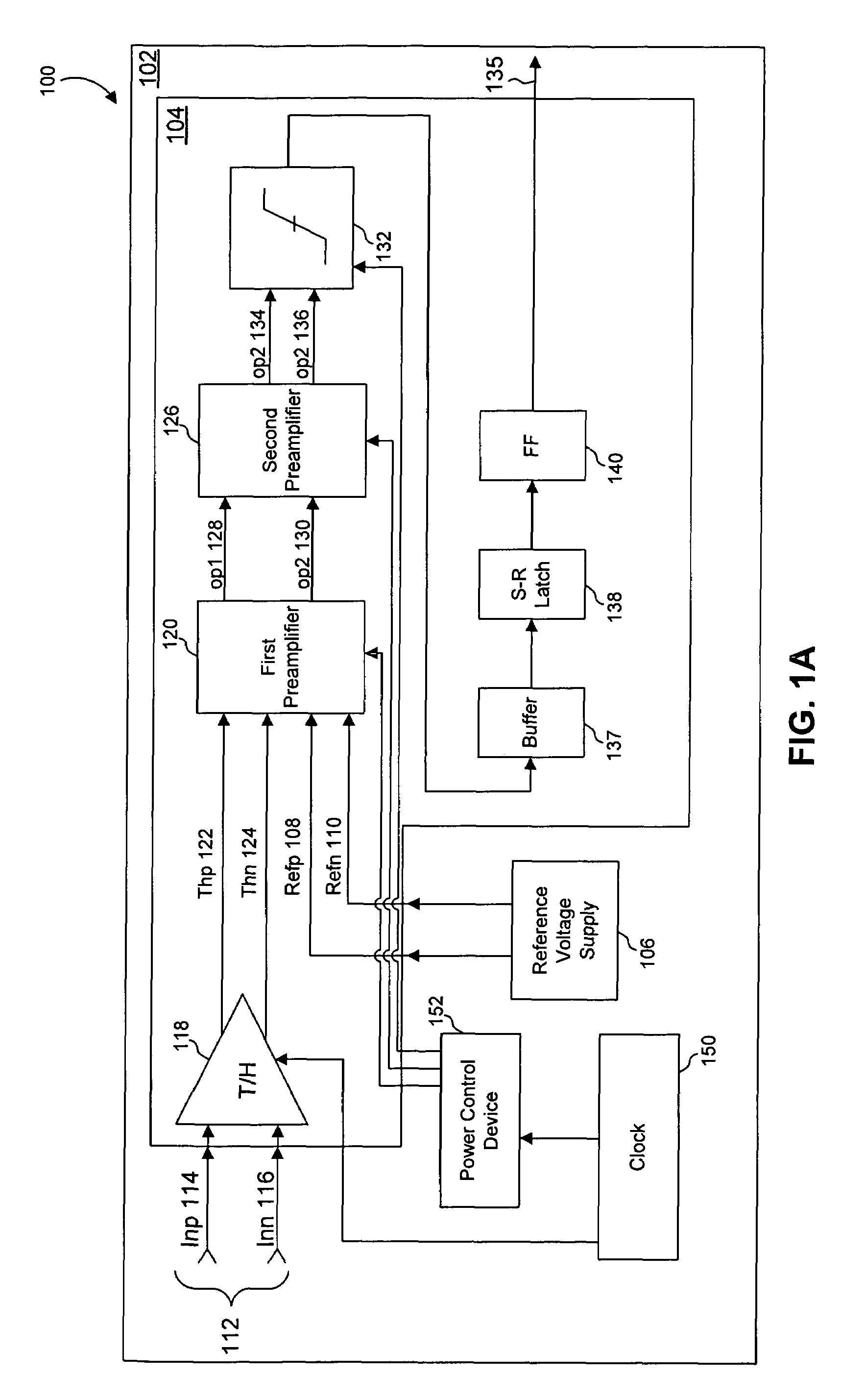

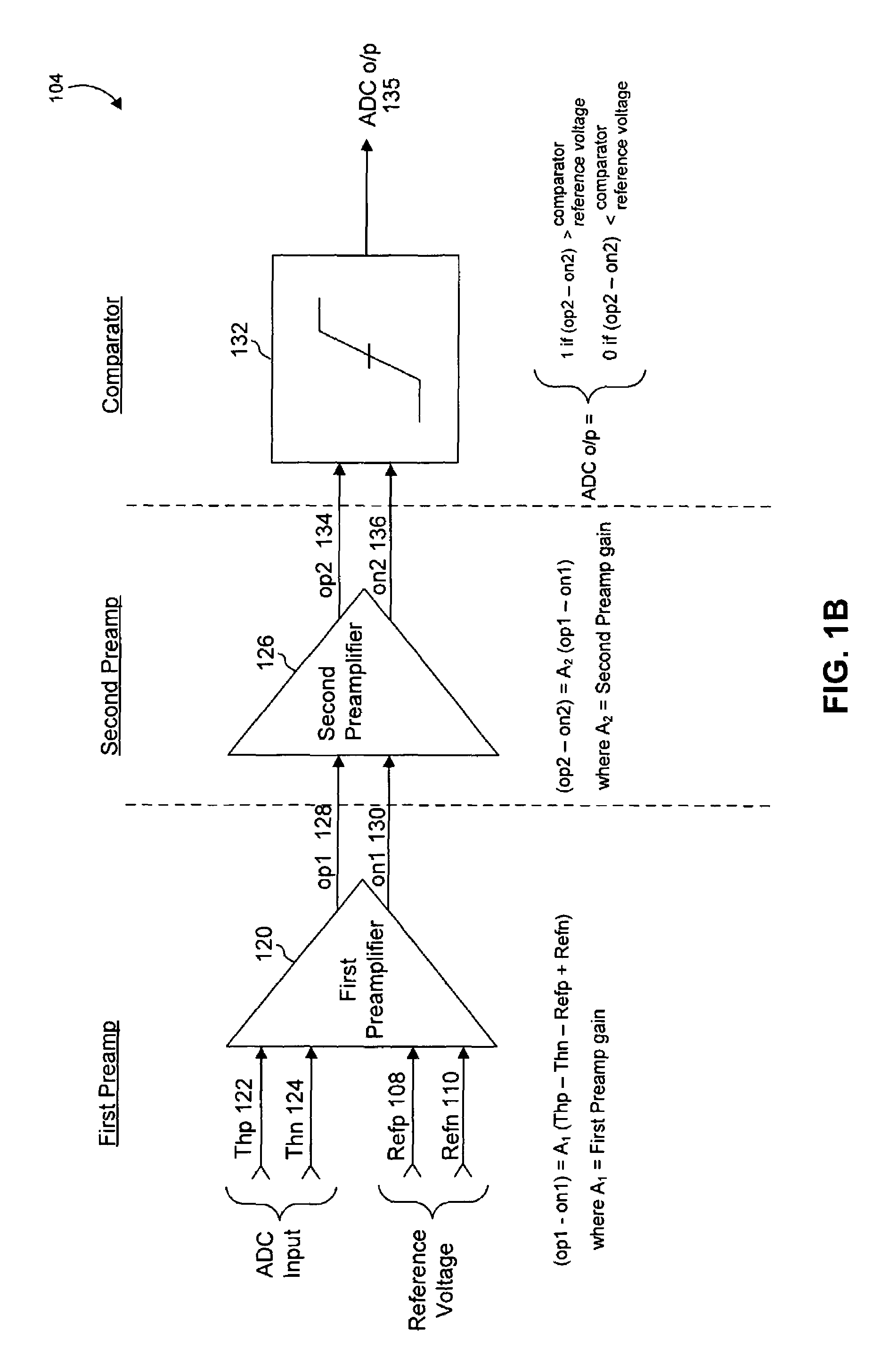

Analog to digital converter with dynamic power configuration

ActiveUS20070132628A1Reduce ADC power consumptionReduce power consumptionPower saving provisionsElectric signal transmission systemsAudio power amplifierA d converter

In an embodiment, an analog to digital converter (ADC) has a dynamic power circuit. The ADC has a track-and-hold circuit with an output and a track mode. The ADC also has a comparator with an input. A preamplifier is coupled between the track-and-hold output and the comparator input. At least one of a preamplifier current and a comparator current are limited during the track mode to reduce ADC power consumption.

Owner:AVAGO TECH INT SALES PTE LTD

Analog to digital converter with dynamic power configuration

ActiveUS7456764B2Reduce power consumptionPower saving provisionsElectric signal transmission systemsAudio power amplifierEngineering

In an embodiment, an analog to digital converter (ADC) has a dynamic power circuit. The ADC has a track-and-hold circuit with an output and a track mode. The ADC also has a comparator with an input. A preamplifier is coupled between the track-and-hold output and the comparator input. At least one of a preamplifier current and a comparator current are limited during the track mode to reduce ADC power consumption.

Owner:AVAGO TECH INT SALES PTE LTD

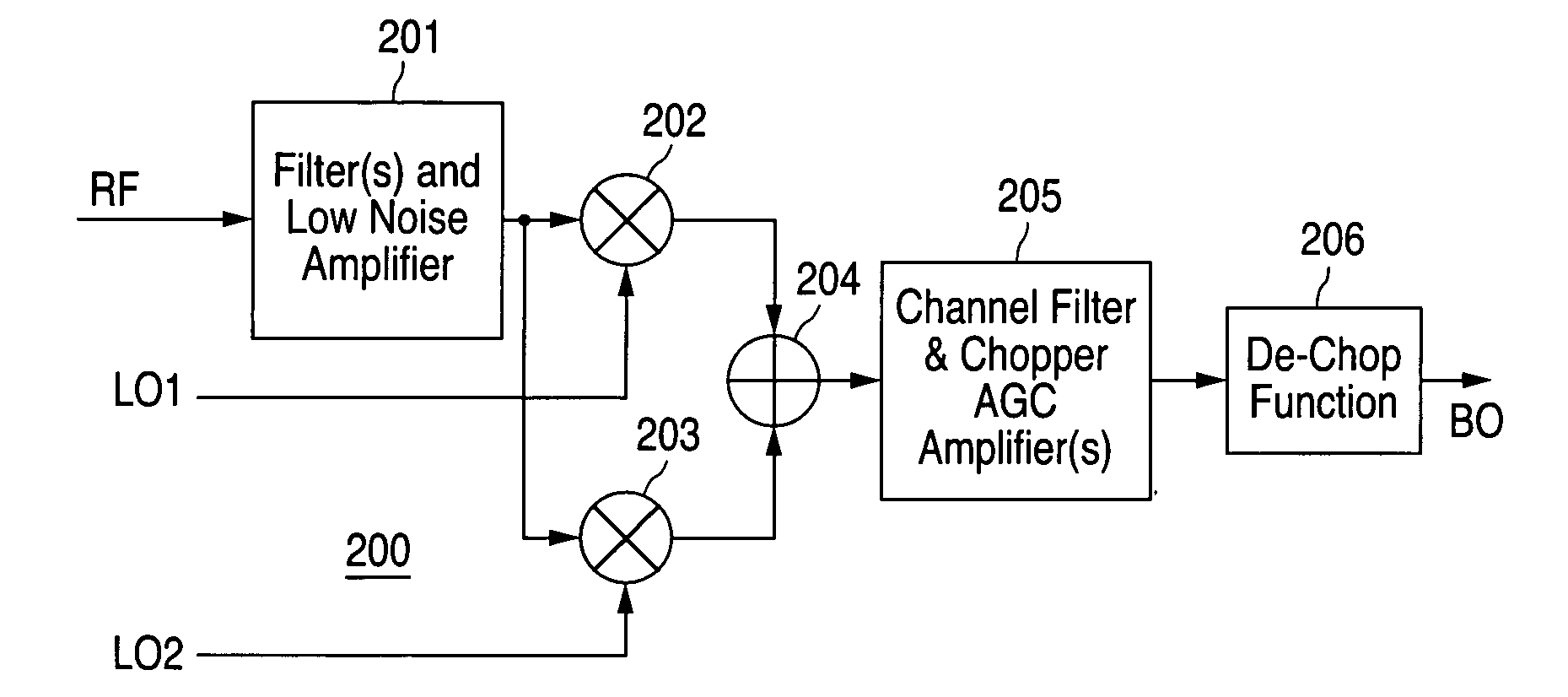

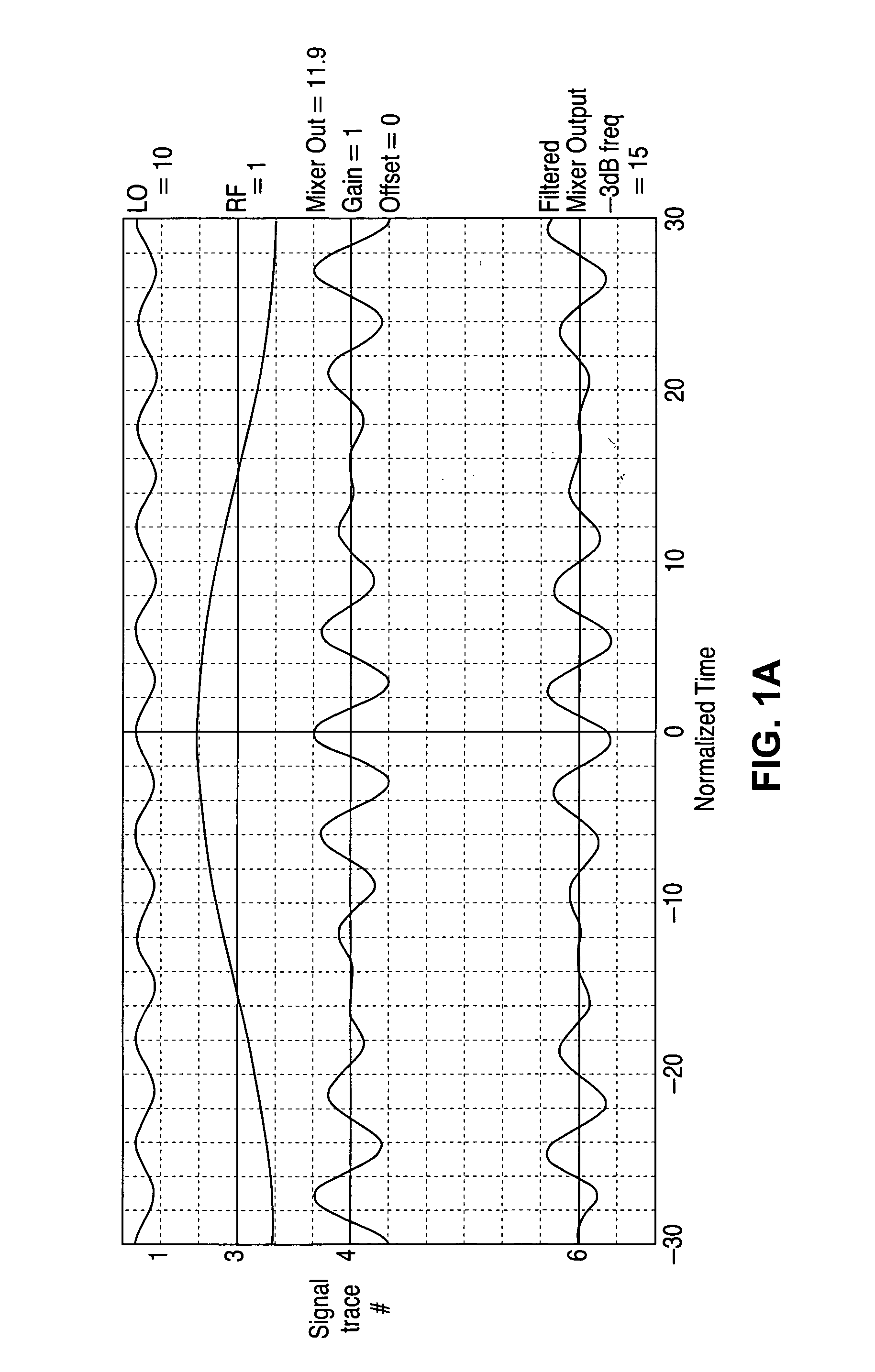

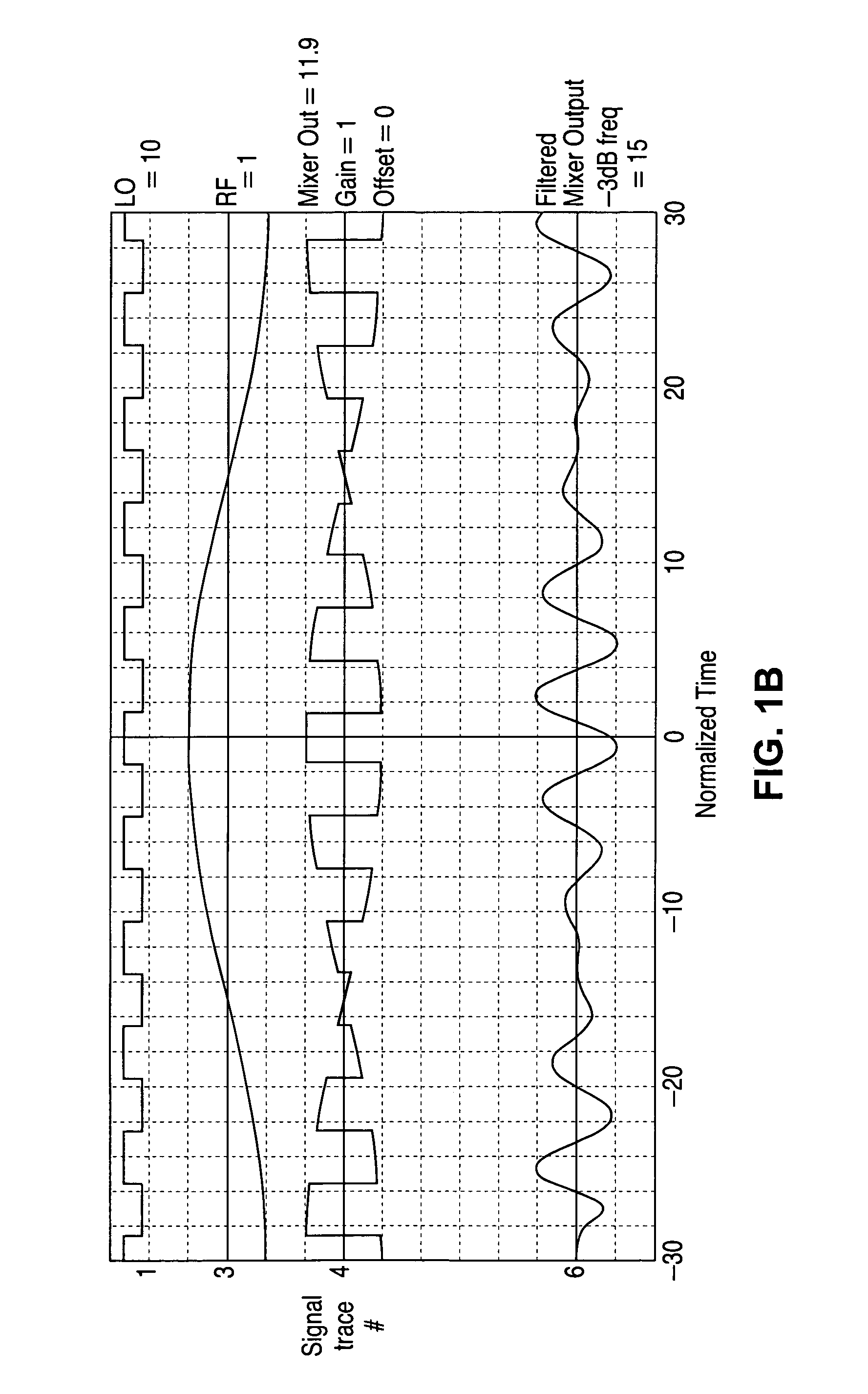

Chopper-direct-conversion (CDC) radio architecture

ActiveUS7177609B1Solve the real problemAmplitude demodulation by homodyne/synchrodyne circuitsModulation with suppressed carrierLocal oscillator signalRadio reception

A chopper-direct-conversion (CDC) radio receiver includes a phase-alternating mixer receiving an antenna input signal and at least one local oscillator signal and generating a double sideband signal in a single mixing step. The phase-alternating mixer may be implemented by two parallel mixers each mixing the input signal with one of two local oscillator signals and an adder receiving and summing outputs from the two parallel mixers, by a track-and-hold circuit sampling the input signal based upon the local oscillator signal, or by a window averaging circuit averaging the input signal across a period of the local oscillator signal. The CDC architecture is suitable for fabrication on a single chip and offers solutions to virtually all problems found in conventional direct-conversion receivers.

Owner:NAT SEMICON CORP

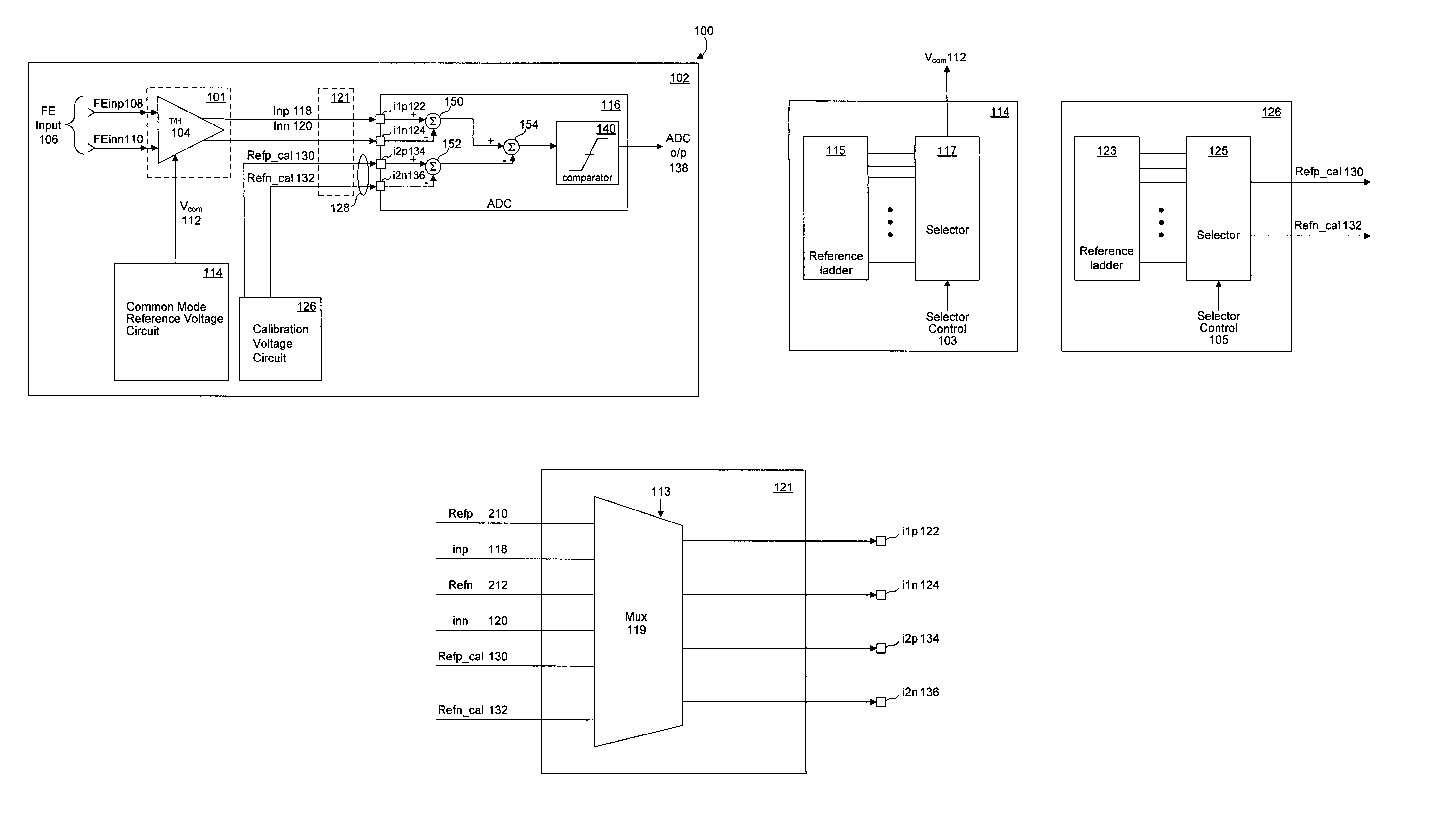

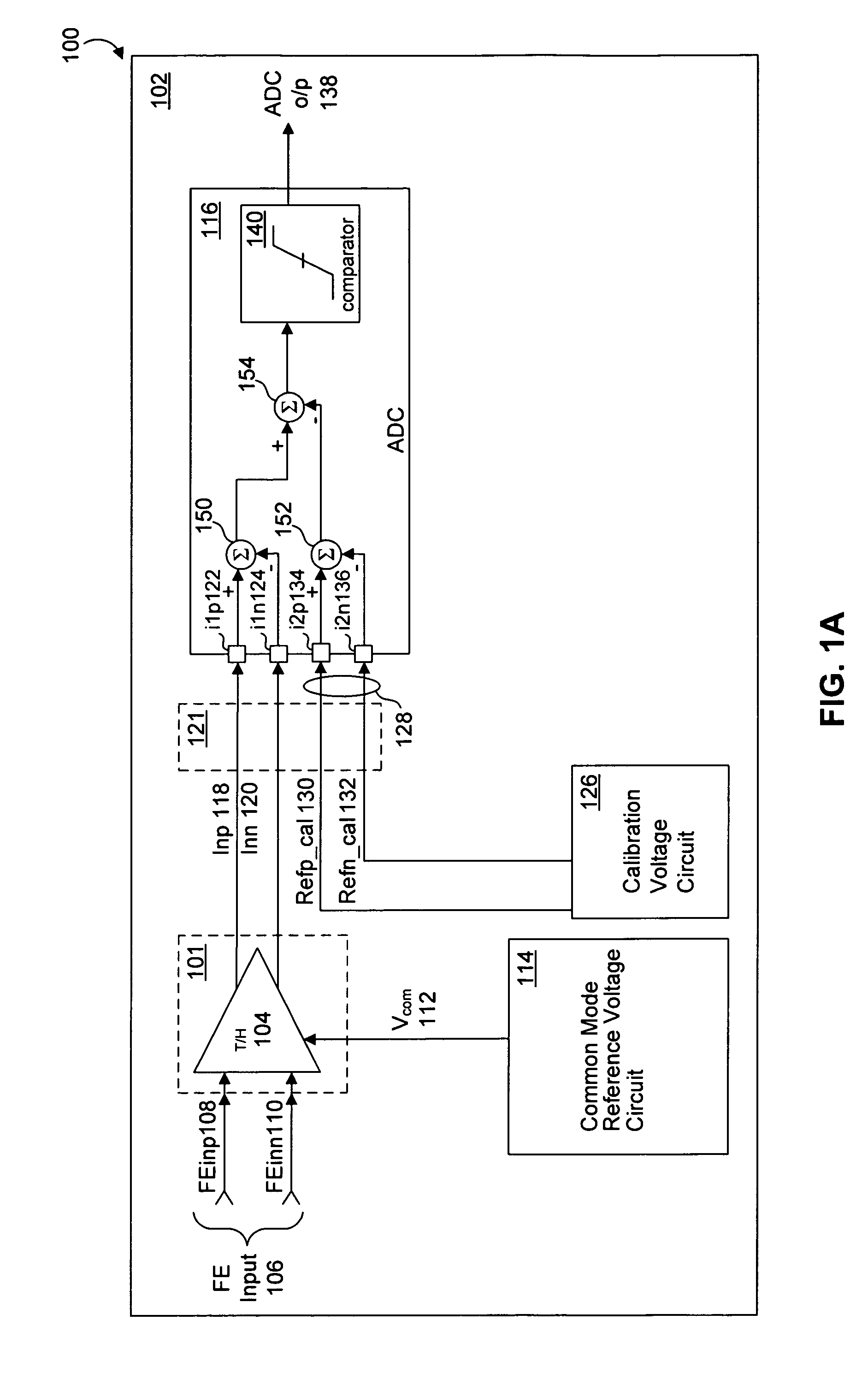

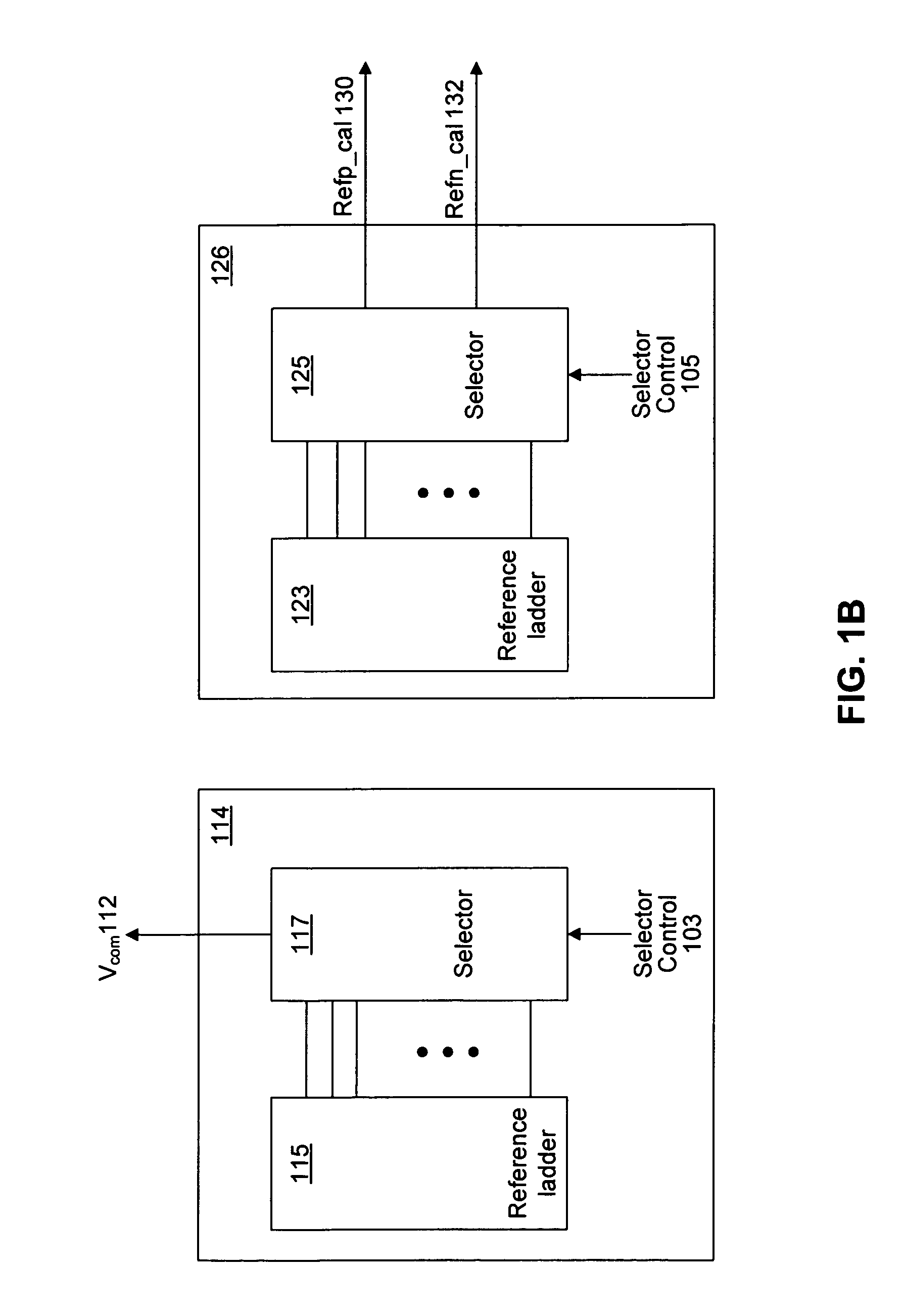

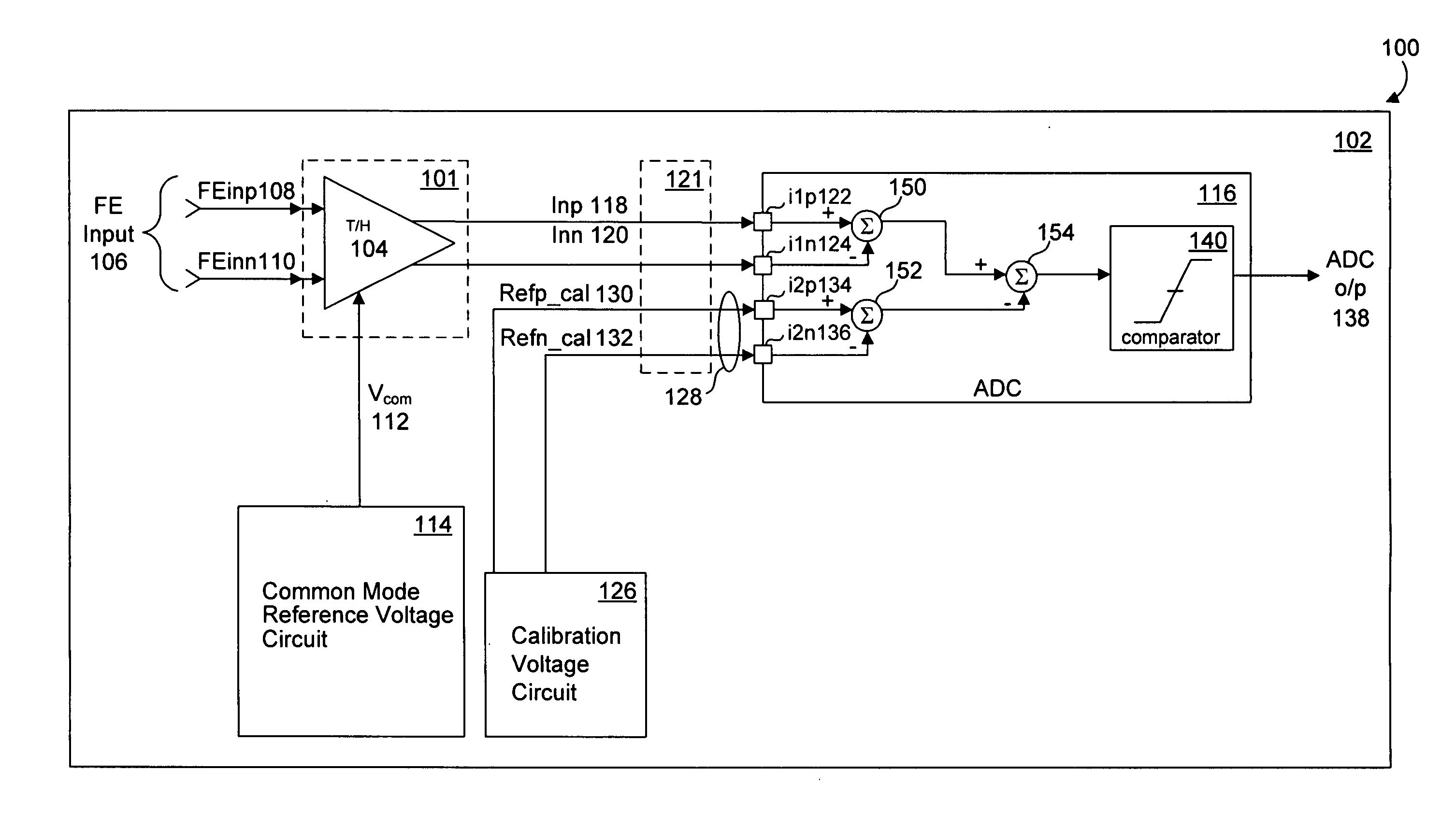

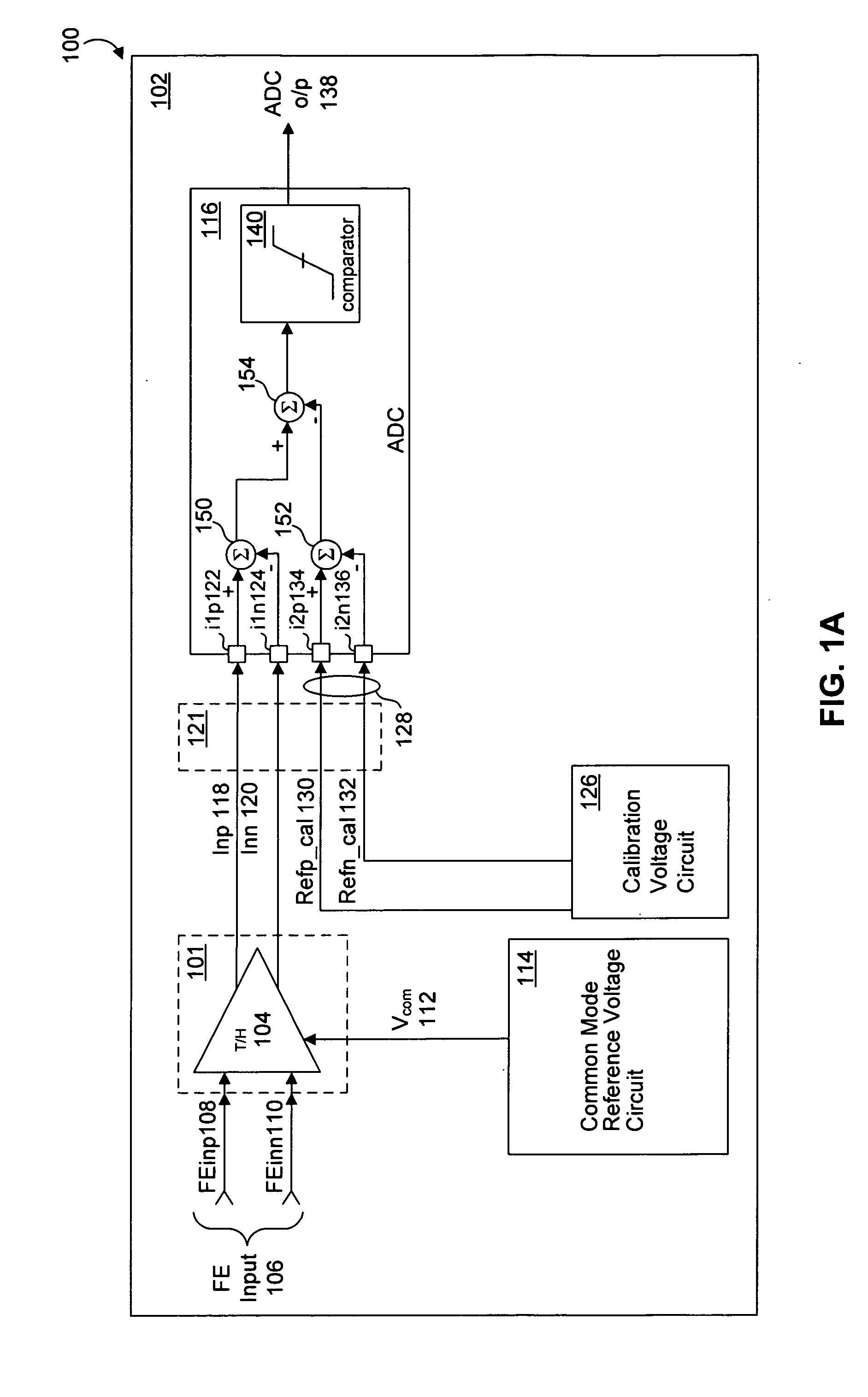

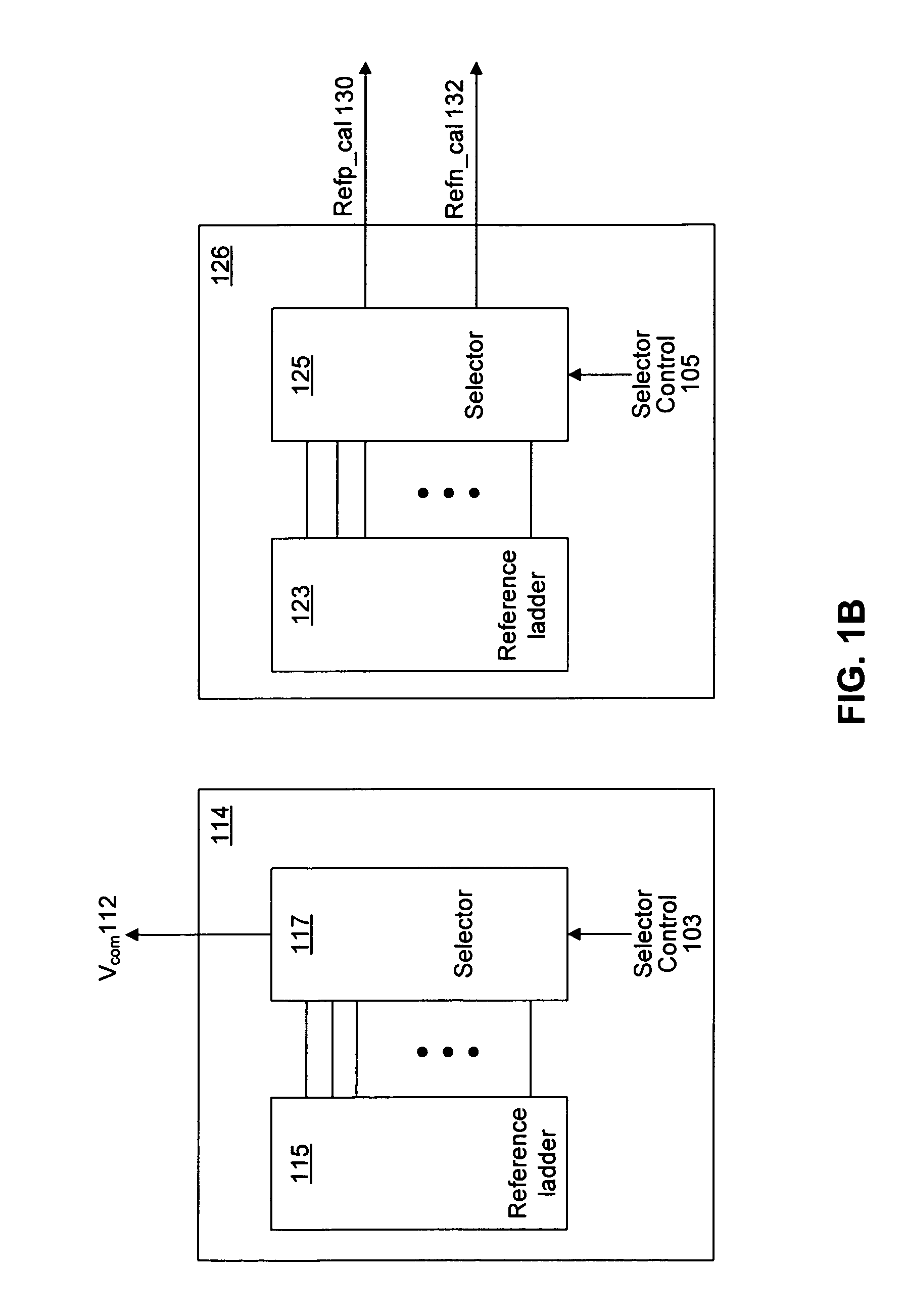

System and method for common mode calibration in an analog to digital converter

ActiveUS7466249B2Increased gainMinimize offsetElectric signal transmission systemsAnalogue-digital convertersFeedback controllerAnalog-to-digital converter

A conversion circuit increases a gain of an analog-to-digital converter (ADC) preamplifier by minimizing a common mode offset voltage between an input signal and a reference signal. The feedback controller circuit calibrates an input common mode voltage to mitigate a common mode offset voltage. Reduction of the common mode offset voltage increases the gain of the ADC preamplifier. In an example, the method is executed during a hold phase of a track-and-hold circuit that transmits the input signal to the ADC.

Owner:AVAGO TECH INT SALES PTE LTD

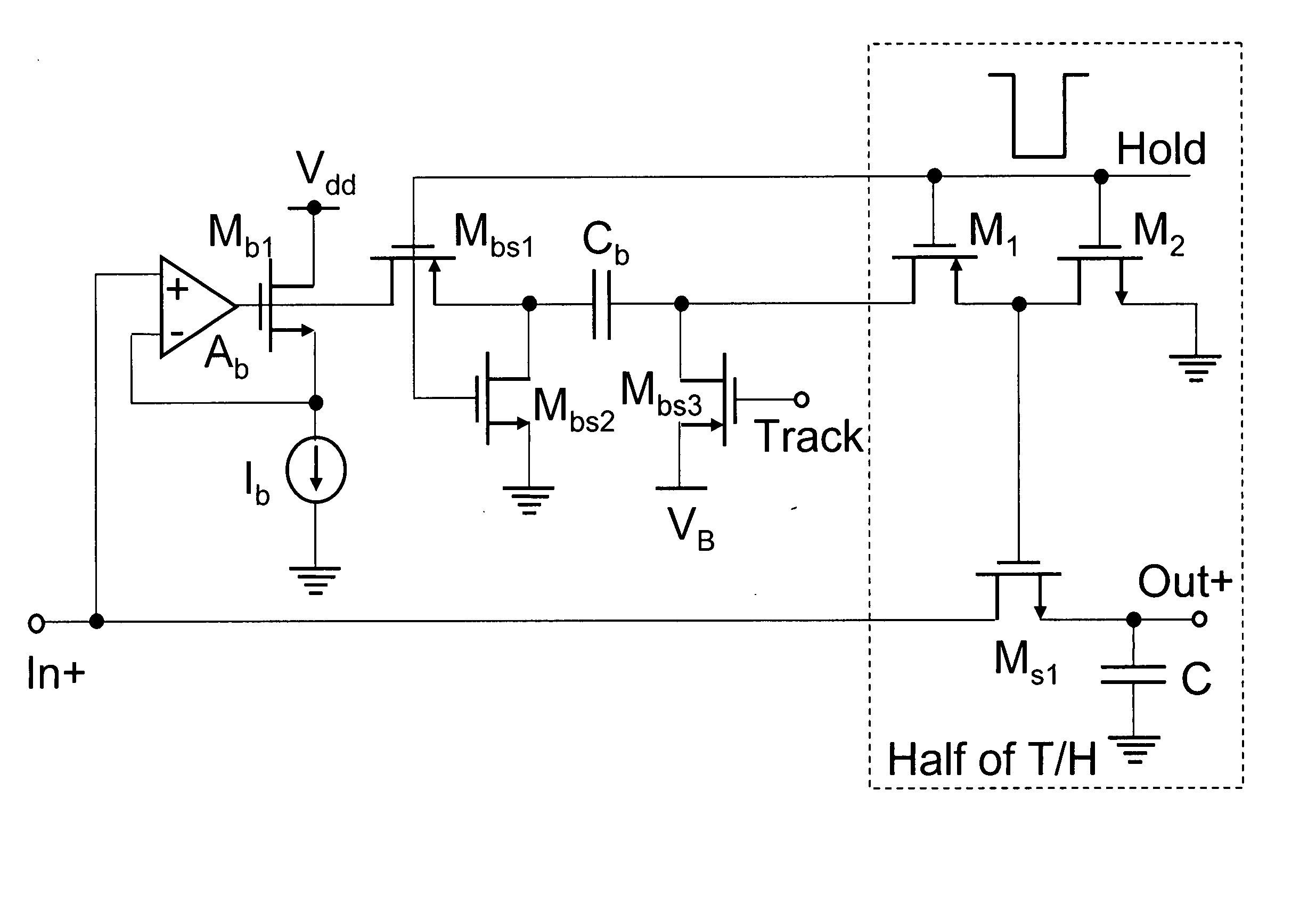

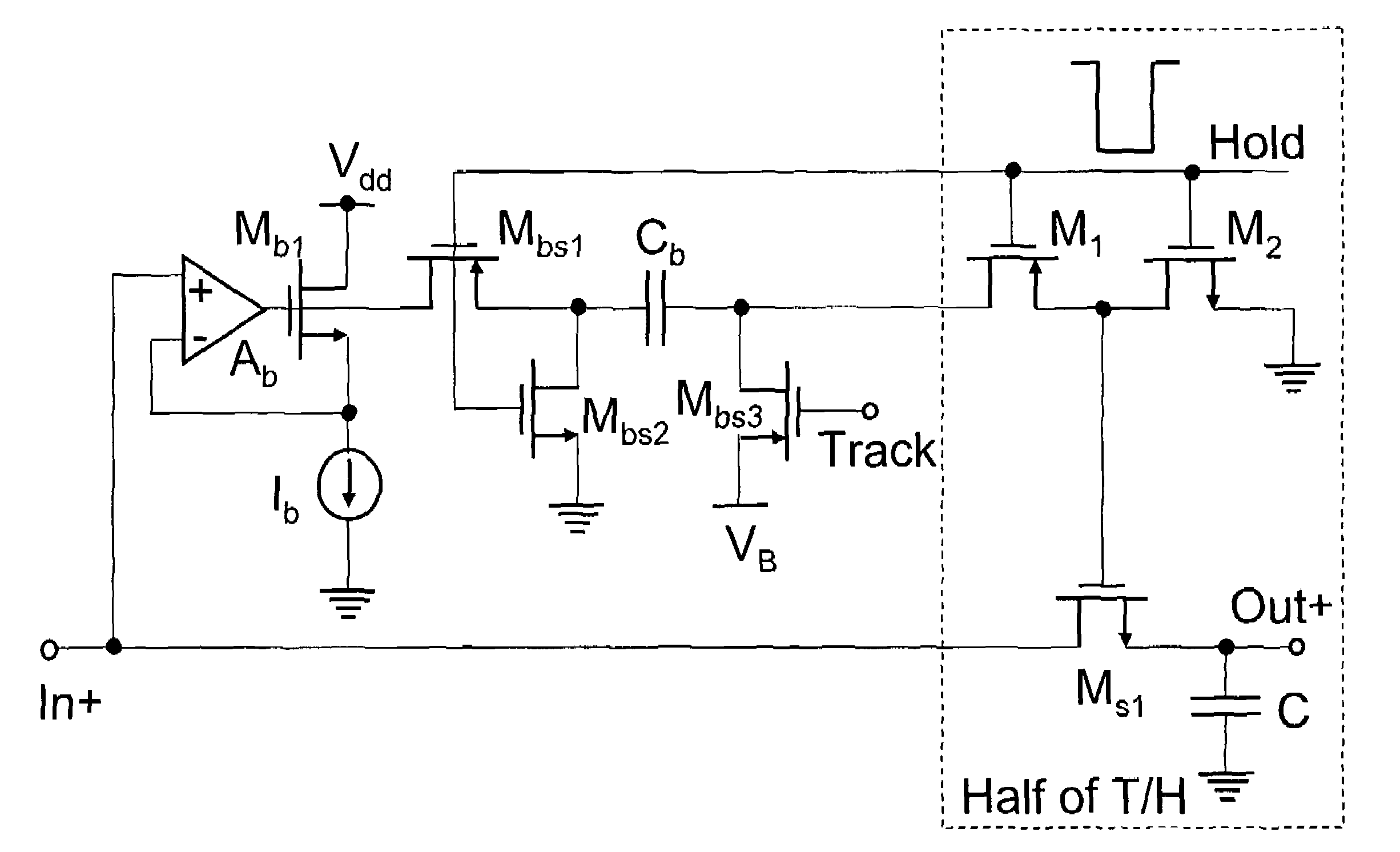

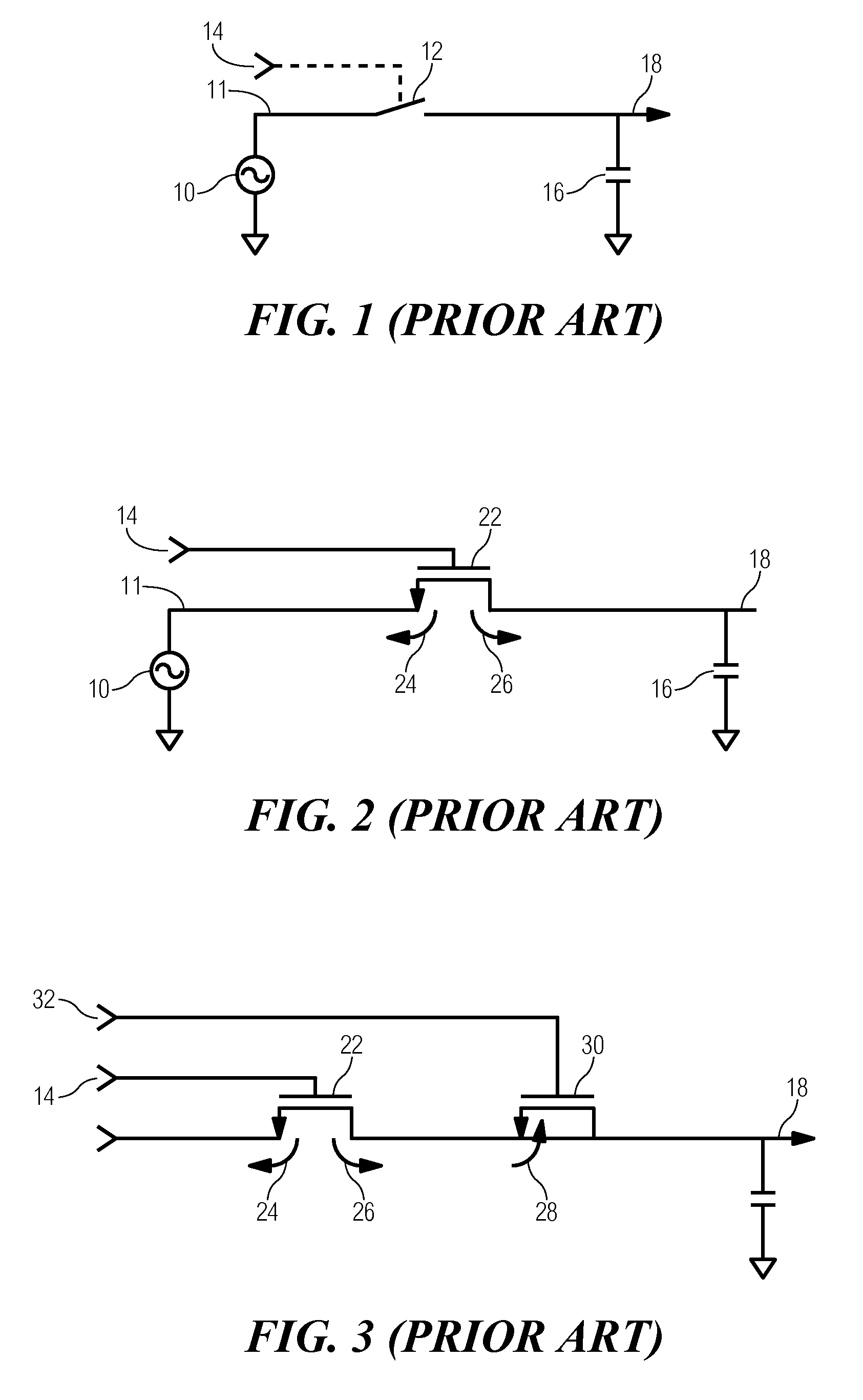

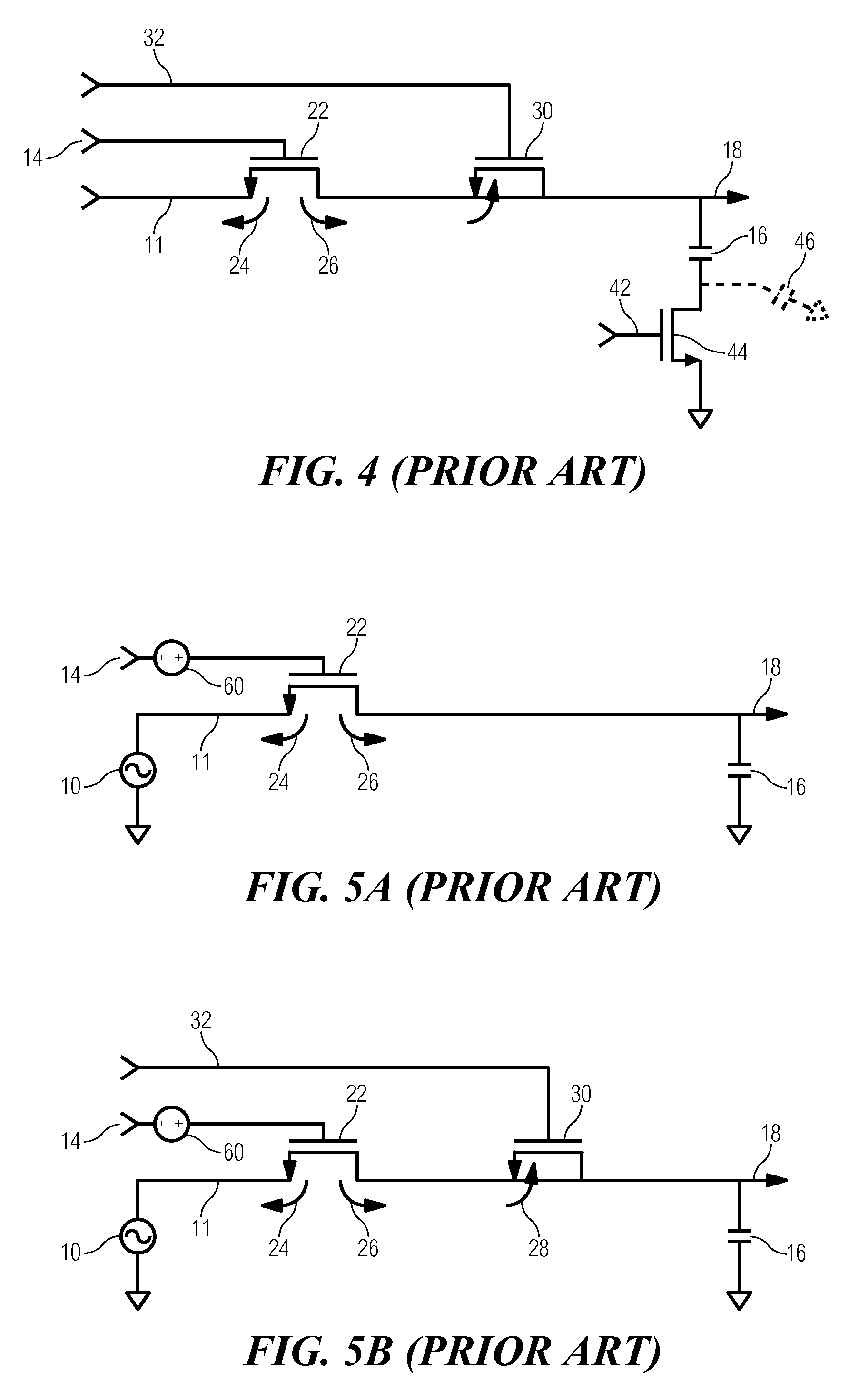

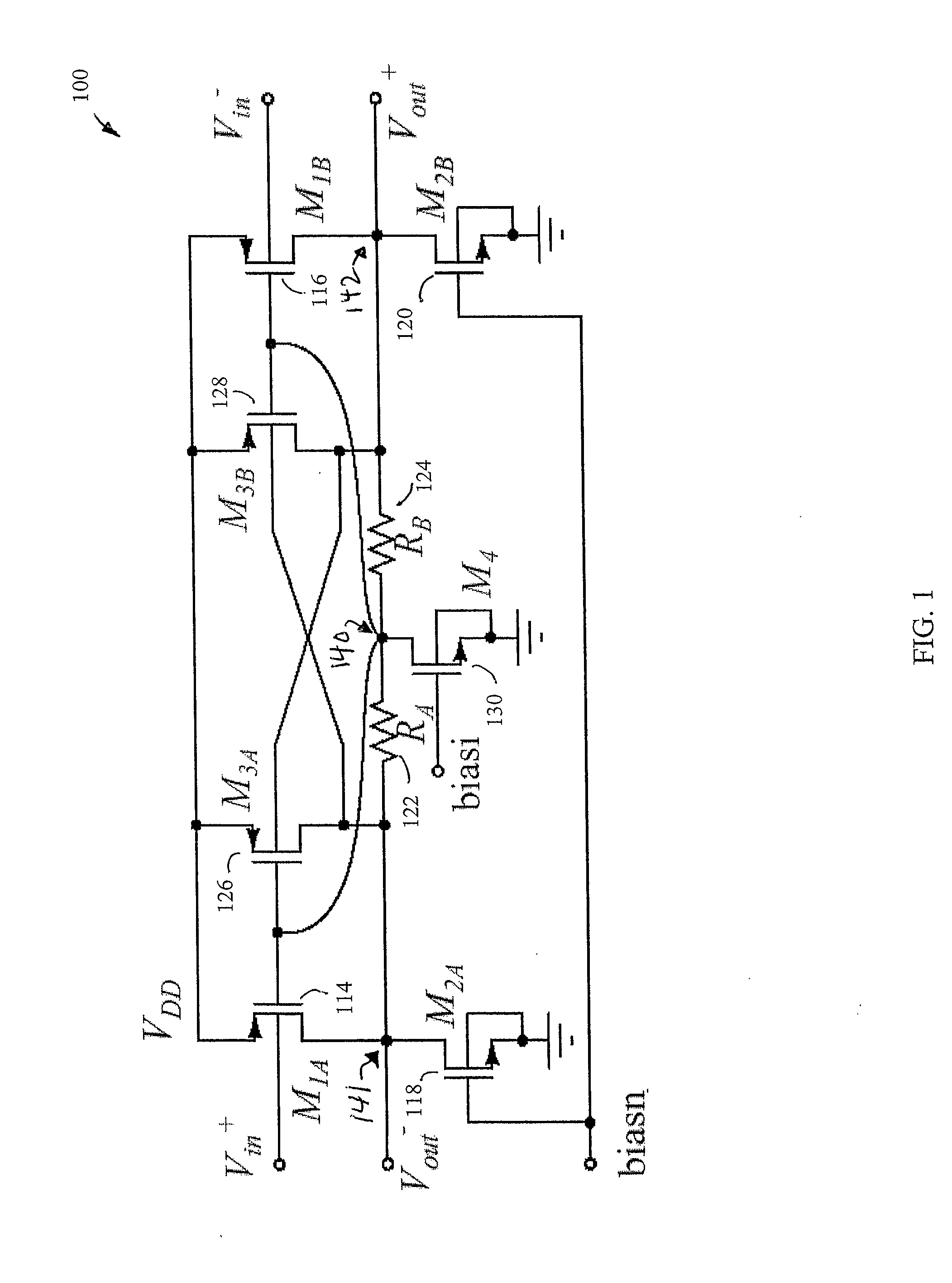

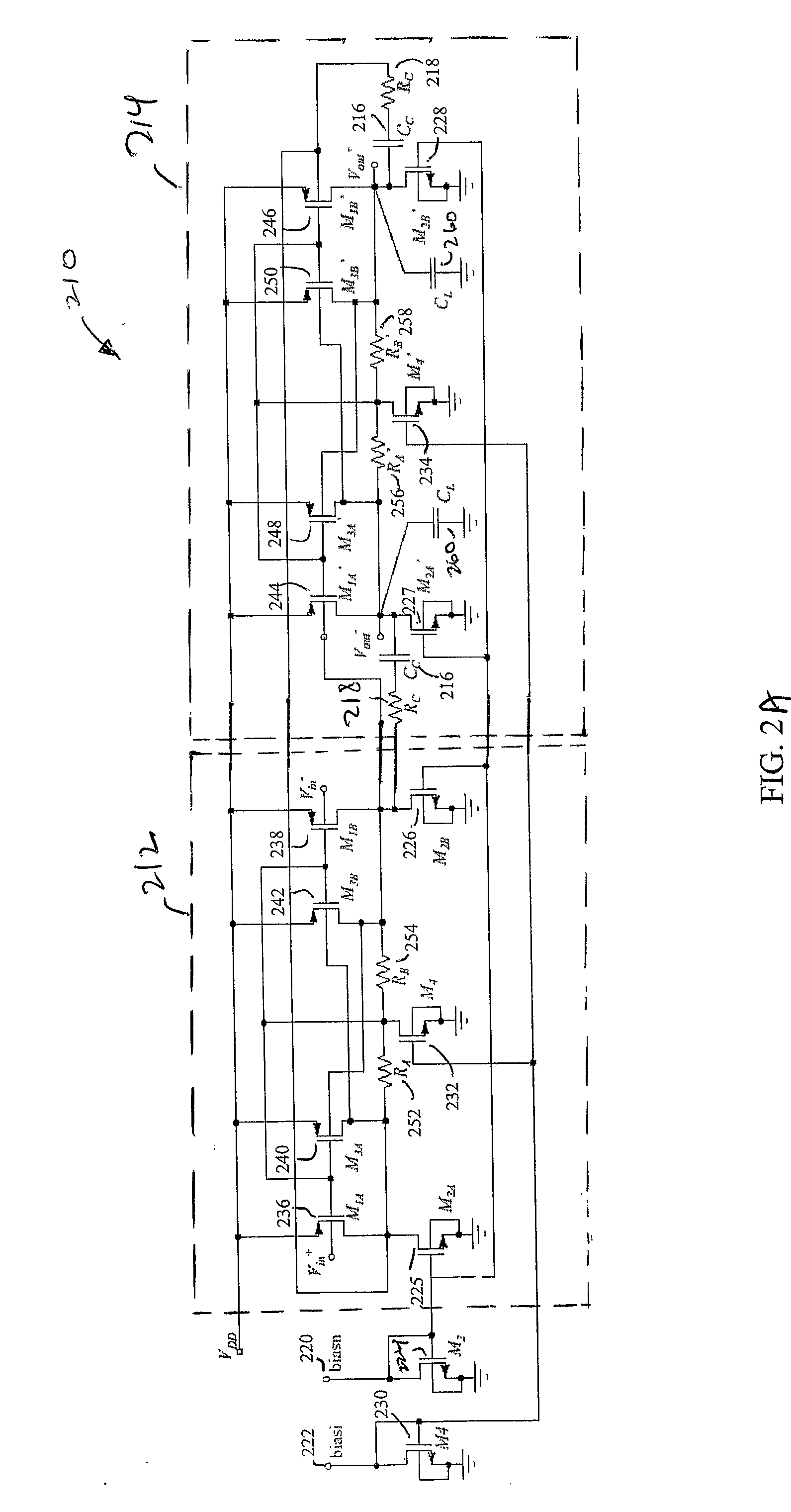

Switch linearized track and hold circuit for switch linearization

Circuits that provide a gate boost to address non-linear threshold voltage variation in a CMOS T / H circuit. In embodiments of the invention, a boost capacitor and a feedback amplifier add a signal-dependent threshold voltage to the switch gate over-drive voltage of a switch that controls track and hold circuit sampling. In a modified embodiment, capacitive boost is omitted and the feedback amplifier provides the signal-dependent threshold voltage boost. In another embodiment, a boost capacitor and a diode connected transistor provide the signal-dependent threshold voltage boost. In a modified embodiment, capacitive boost is omitted and the diode connected transistor provides the signal-dependent threshold voltage.

Owner:RGT UNIV OF CALIFORNIA

System and method for common mode calibration in an analog to digital converter

ActiveUS20070132625A1Increased gainMinimize offsetElectric signal transmission systemsAnalogue-digital convertersAudio power amplifierFeedback controller

A conversion circuit increases a gain of an analog-to-digital converter (ADC) preamplifier by minimizing a common mode offset voltage between an input signal and a reference signal. The feedback controller circuit calibrates an input common mode voltage to mitigate a common mode offset voltage. Reduction of the common mode offset voltage increases the gain of the ADC preamplifier. In an example, the method is executed during a hold phase of a track-and-hold circuit that transmits the input signal to the ADC.

Owner:AVAGO TECH INT SALES PTE LTD

PAM4 transceivers for high-speed communication

ActiveUS9847839B2Reduce errorsReduce power consumptionPulse automatic controlSynchronisation receiversData streamTransceiver

Owner:MARVELL ASIA PTE LTD

Switch linearized track and hold circuit for switch linearization

Circuits that provide a gate boost to address non-linear threshold voltage variation in a CMOS T / H circuit. In embodiments of the invention, a boost capacitor and a feedback amplifier add a signal-dependent threshold voltage to the switch gate over-drive voltage of a switch that controls track and hold circuit sampling. In a modified embodiment, capacitive boost is omitted and the feedback amplifier provides the signal-dependent threshold voltage boost. In another embodiment, a boost capacitor and a diode connected transistor provide the signal-dependent threshold voltage boost. In a modified embodiment, capacitive boost is omitted and the diode connected transistor provides the signal-dependent threshold voltage.

Owner:RGT UNIV OF CALIFORNIA

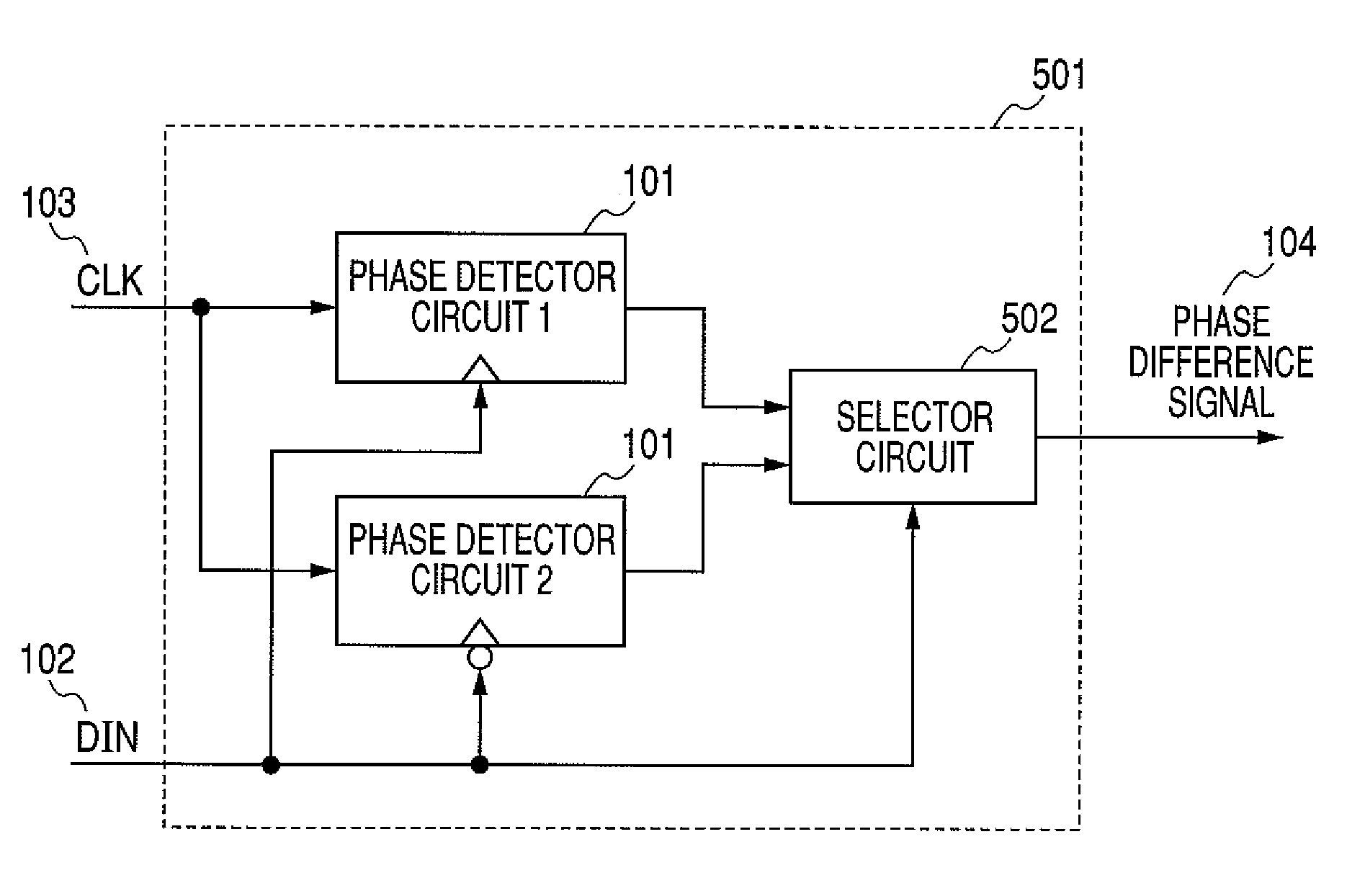

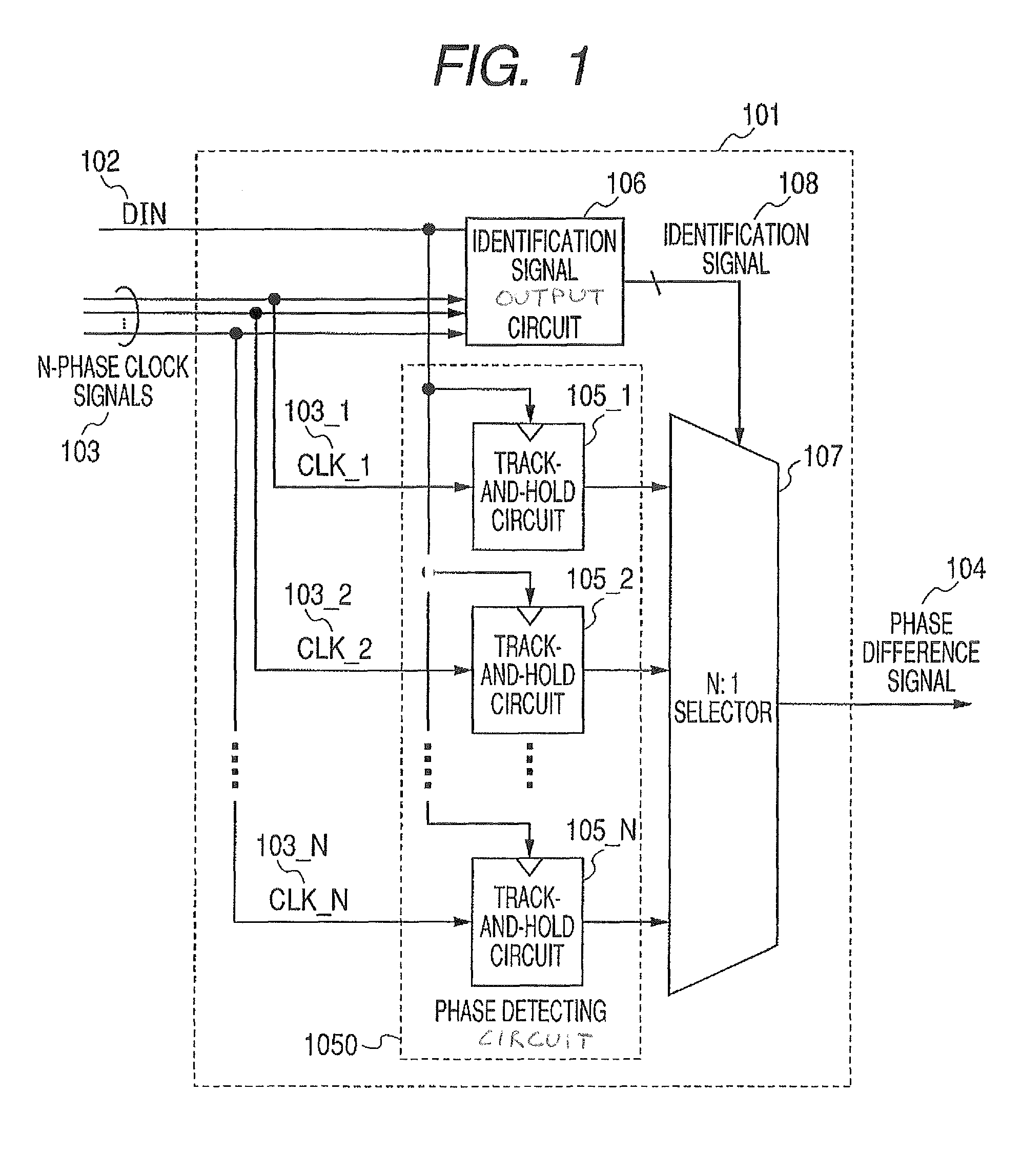

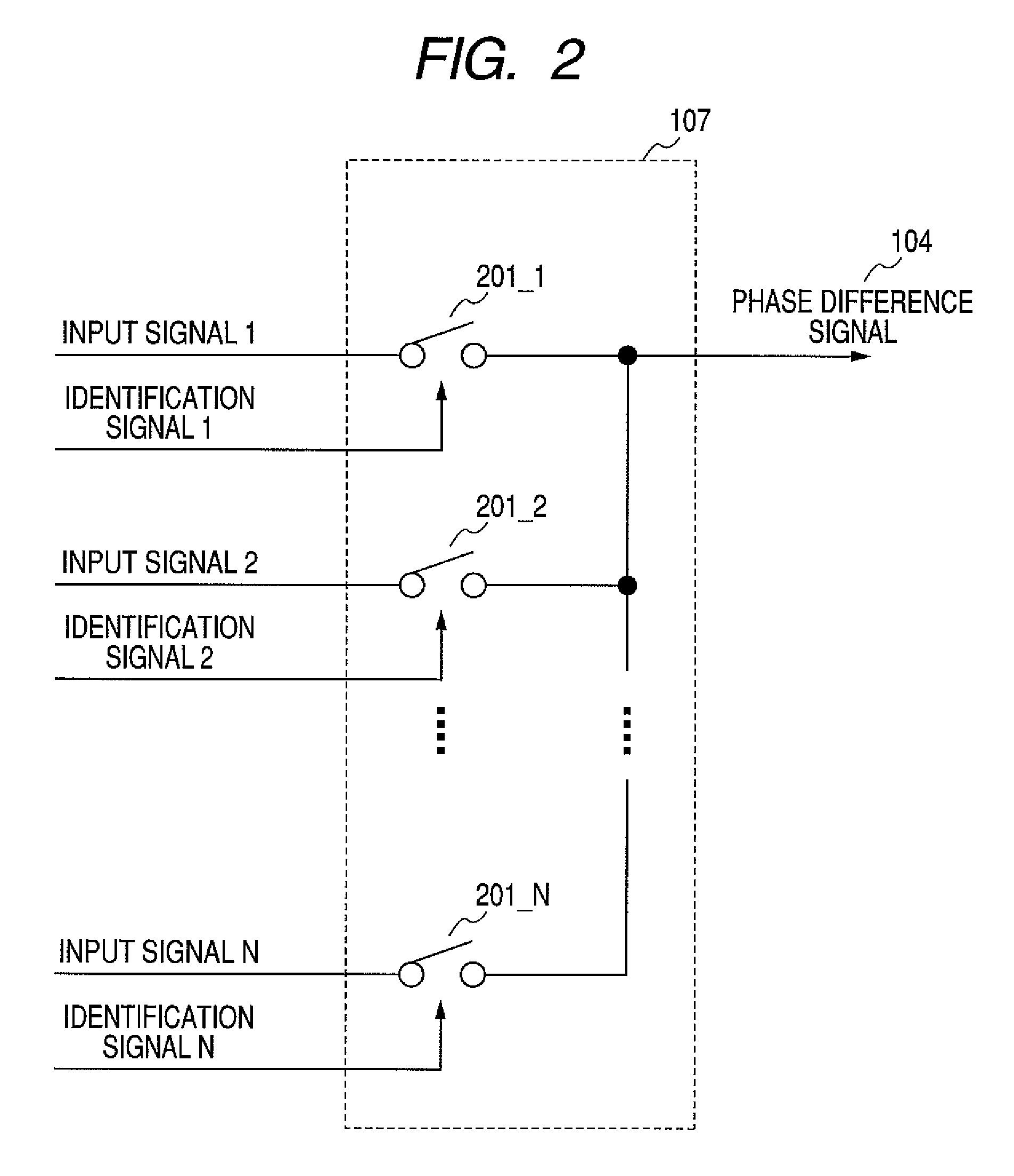

Phase Detector Circuit for Clock and Data Recovery Circuit and Optical Communication Device Having the Same

InactiveUS20100054760A1Low costMultiple input and output pulse circuitsPulse automatic controlPhase detectorDetector circuits

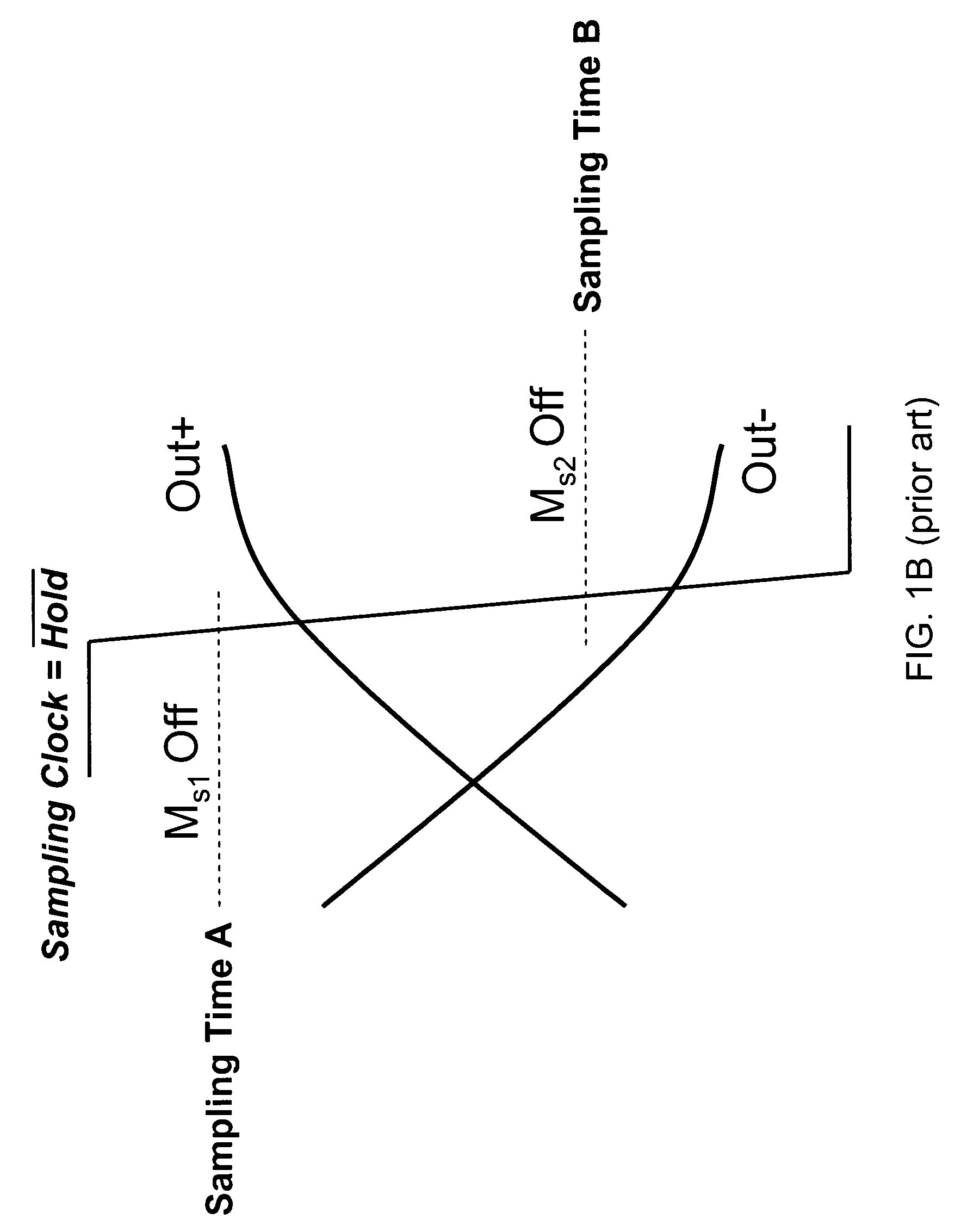

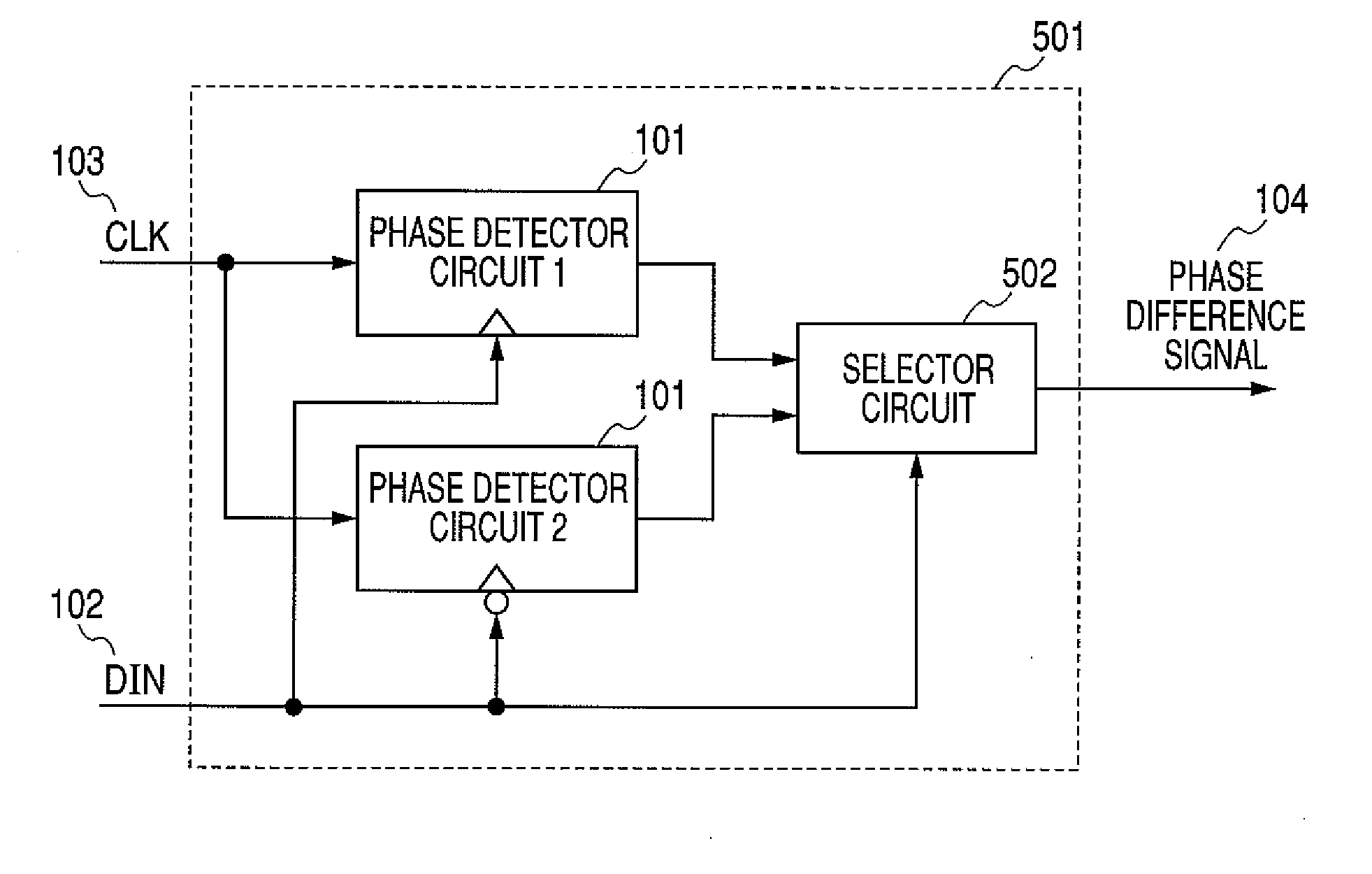

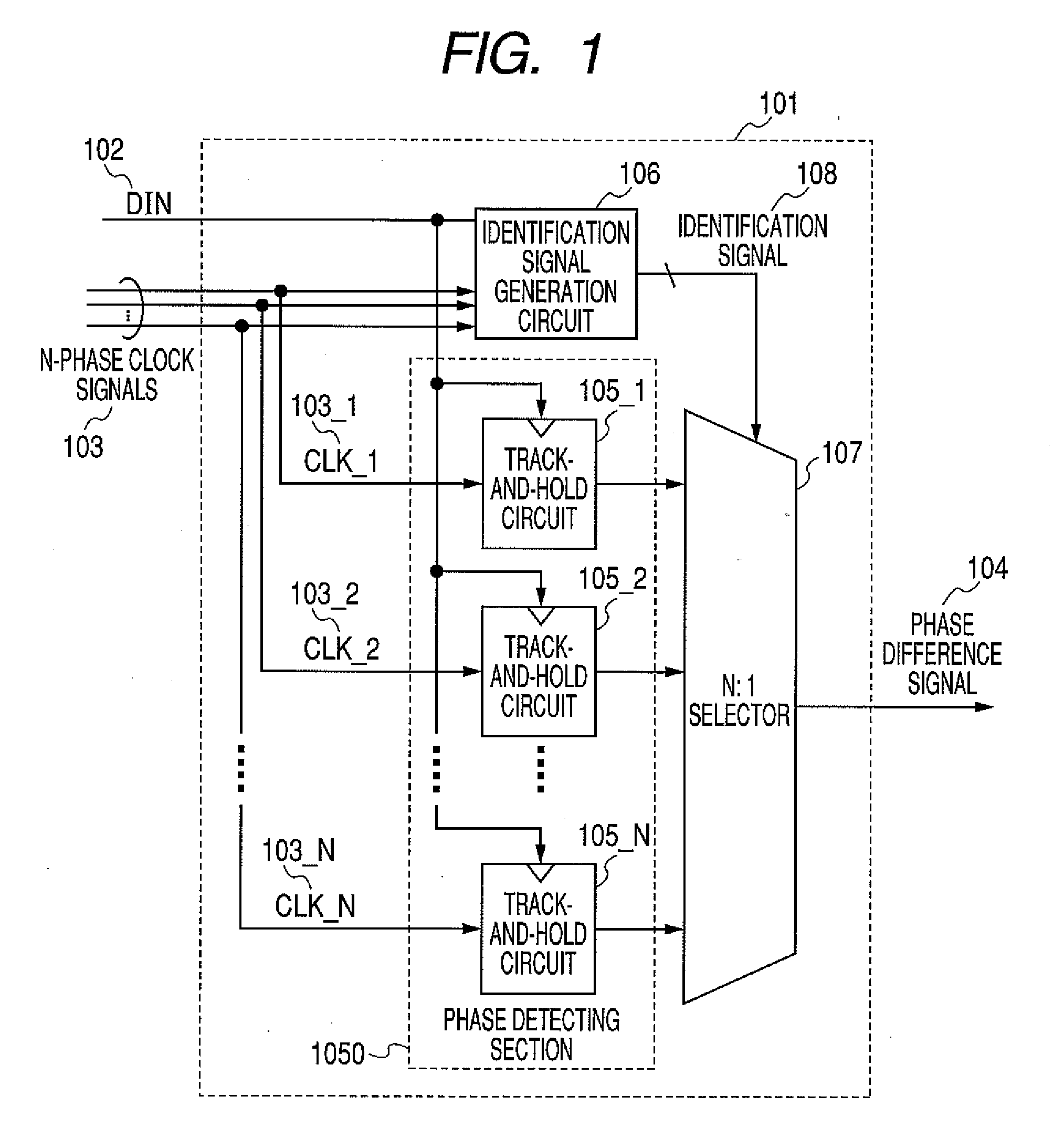

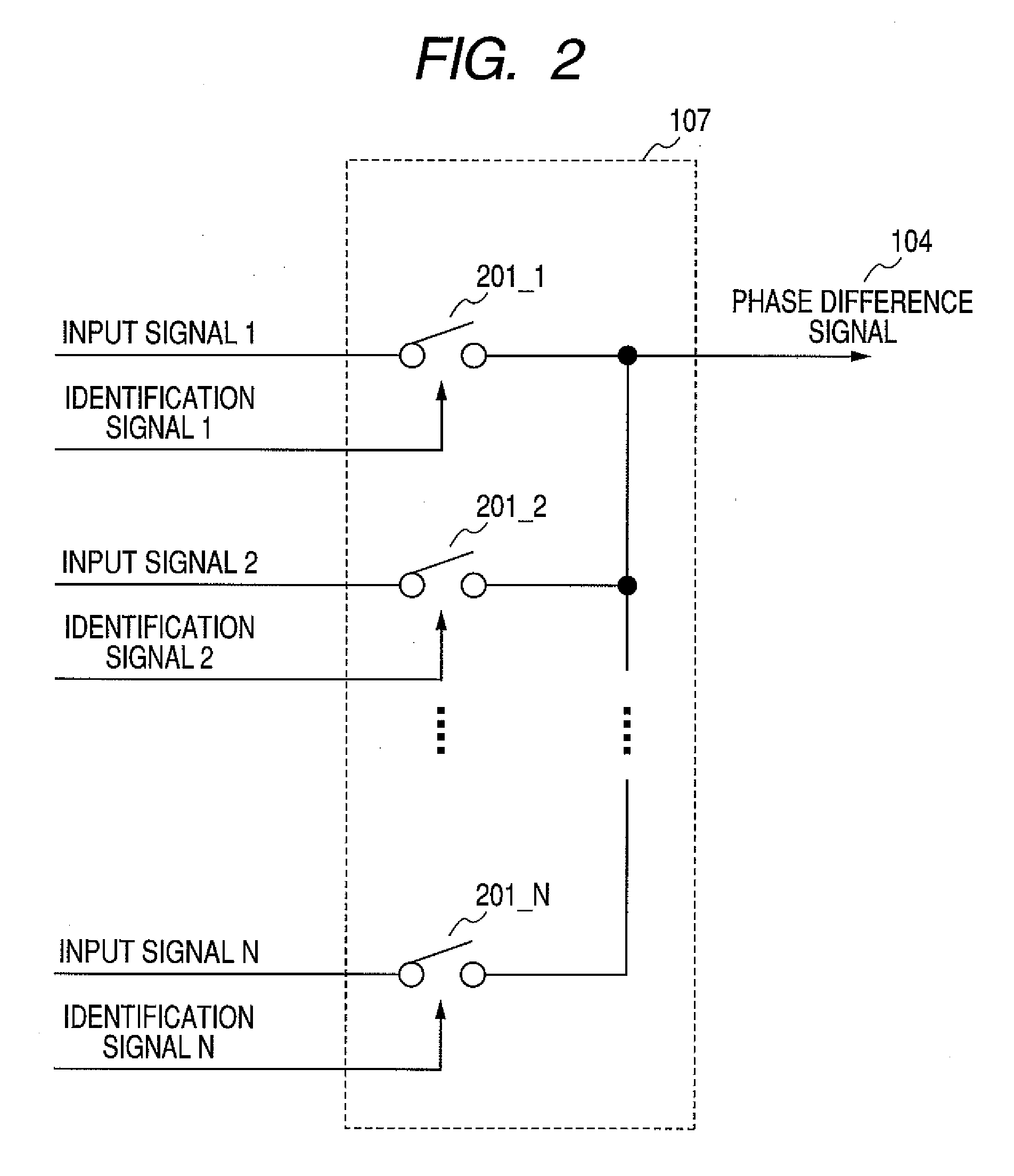

A high-accuracy phase detector circuit compatible with a 1 / N rate architecture is provided. The phase detector circuit has as many as N track-and-hold circuits for tracking and holding N-phase clock signals CLK—1 to CLK_N in synchronization with a rising edge of input data signal DIN. Out of the N-phase clock signals CLK—1 to CLK_N outputted from as many track-and-hold circuits, only the one whose rising edge is most synchronized with a rising edge of the input data signal DIN is selected and outputted as a phase difference signal.

Owner:HITACHI LTD

Track-And-Hold Circuit With Adjustable Charge Compensation

ActiveUS20090102517A1Analogue/digital conversionElectric signal transmission systemsControl channelCharge compensation

A circuit design incorporates charge compensation devices within a Track-and-Hold (T / H) circuit to control channel charge generated by a tracking switch. Calibrating a T / H circuit requires selecting charge compensation devices from an array of similar devices to function within the T / H circuit to absorb charge ejected from the tracking switch. The charge compensation devices can also be pseudorandomly selected to operate within the T / H circuit. Charge compensation devices are used to enhance the performance of bottom-plate sampling systems as well as bootstrapped T / H circuits.

Owner:KEYSIGHT TECH

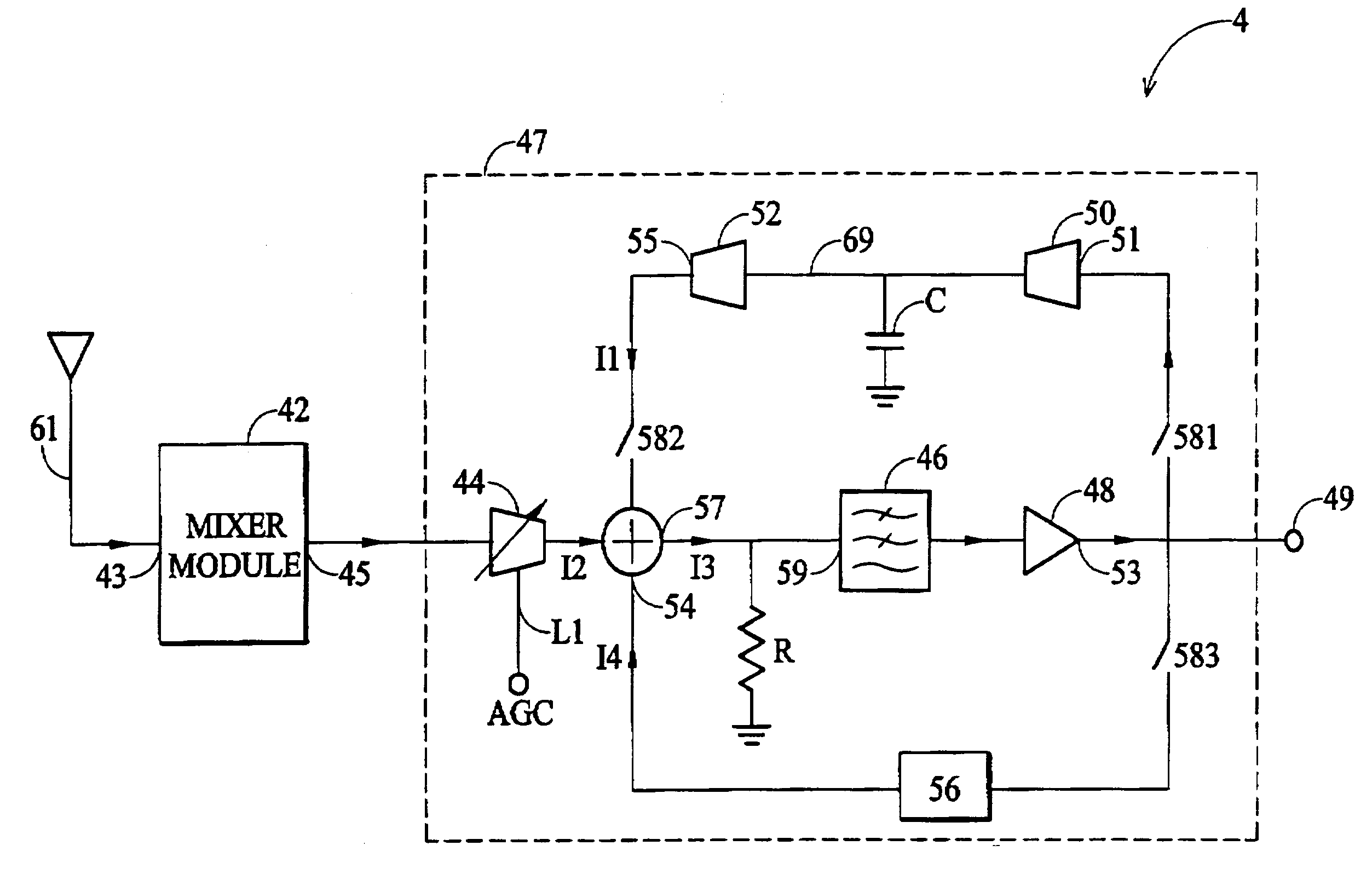

Direct conversion receiver with DC offset compensation and method thereof

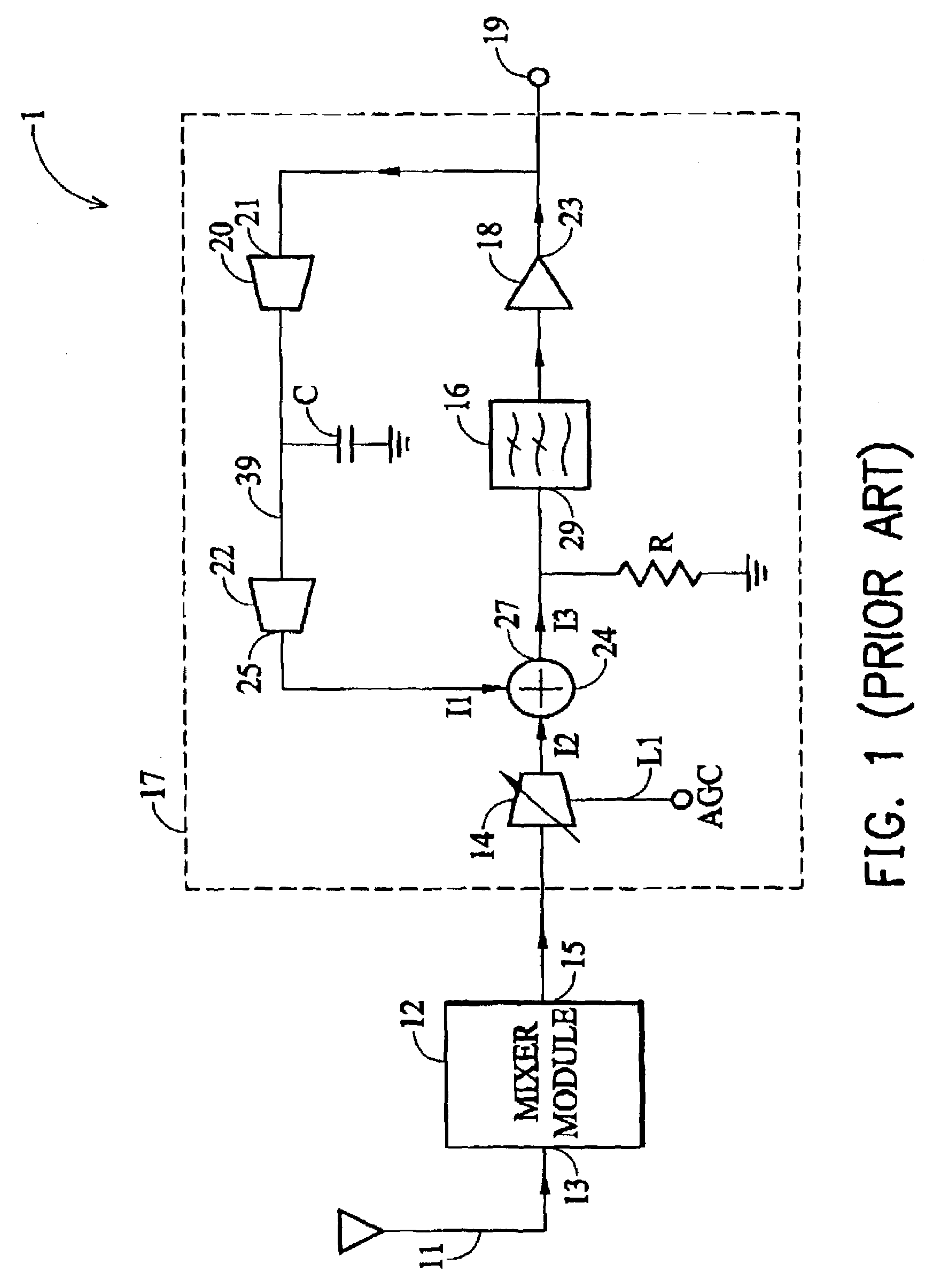

ActiveUS7146141B2Fast and accurate offset compensationFast and accurate DC offset compensationGain controlAmplitude-modulated carrier systemsAudio power amplifierOffset cancellation

A direct conversion receiver with DC offset compensation. The receiver includes an antenna receiving a RF signal, a mixture module converting the RF signal to a baseband signal, a gain amplifier amplifying the baseband signal, an adder subtracting a DC offset current from the baseband signal, a DC offset cancellation circuit obtaining and converting a DC offset value to the DC offset current, a track-and-hold circuit receiving the baseband signal, holding and transferring a DC offset voltage to the DC offset current, and a switching circuit alternatively coupling and decoupling the DC offset cancellation and track-and-hold circuit to receive the baseband signal.

Owner:VIA TECH INC

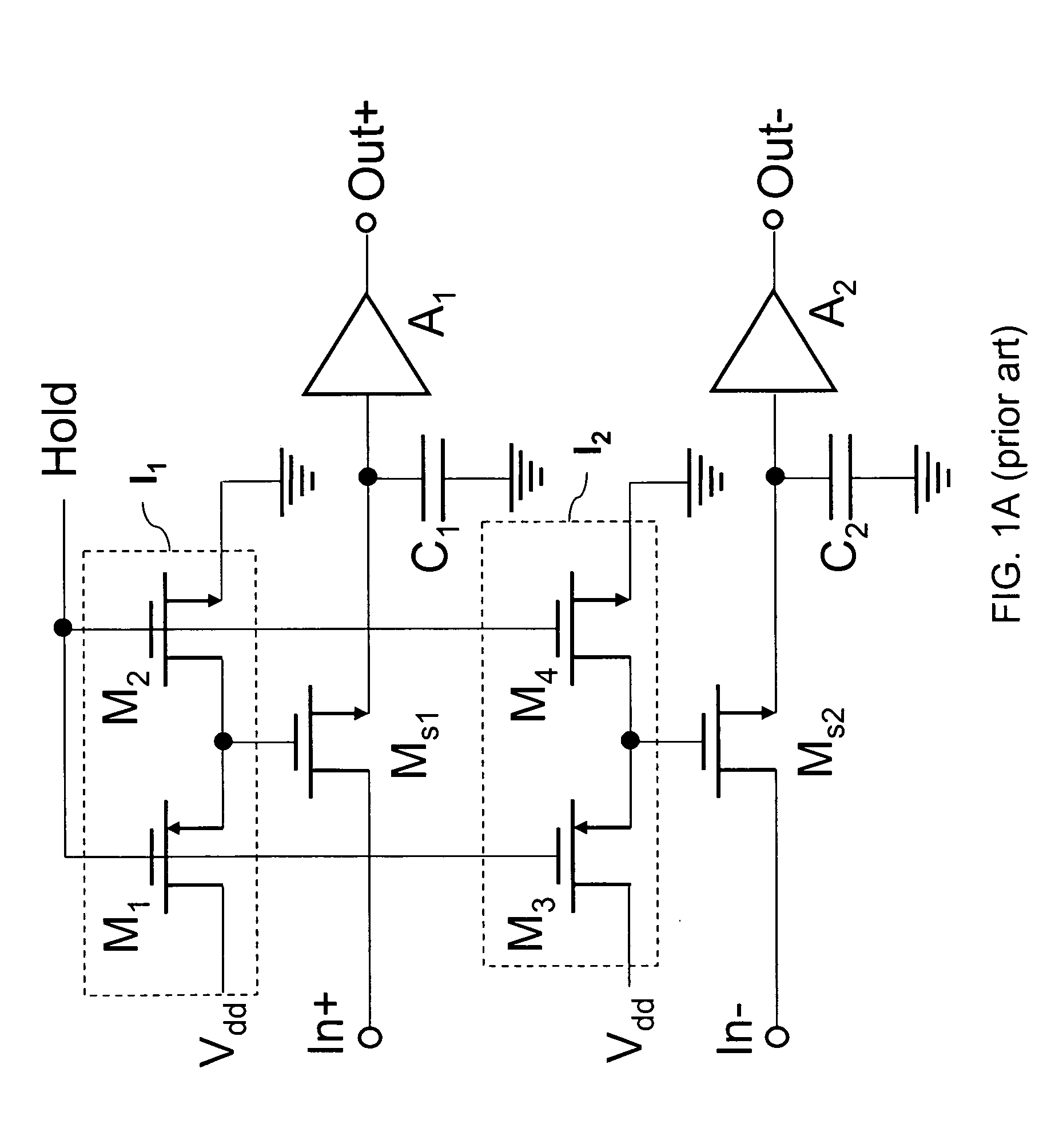

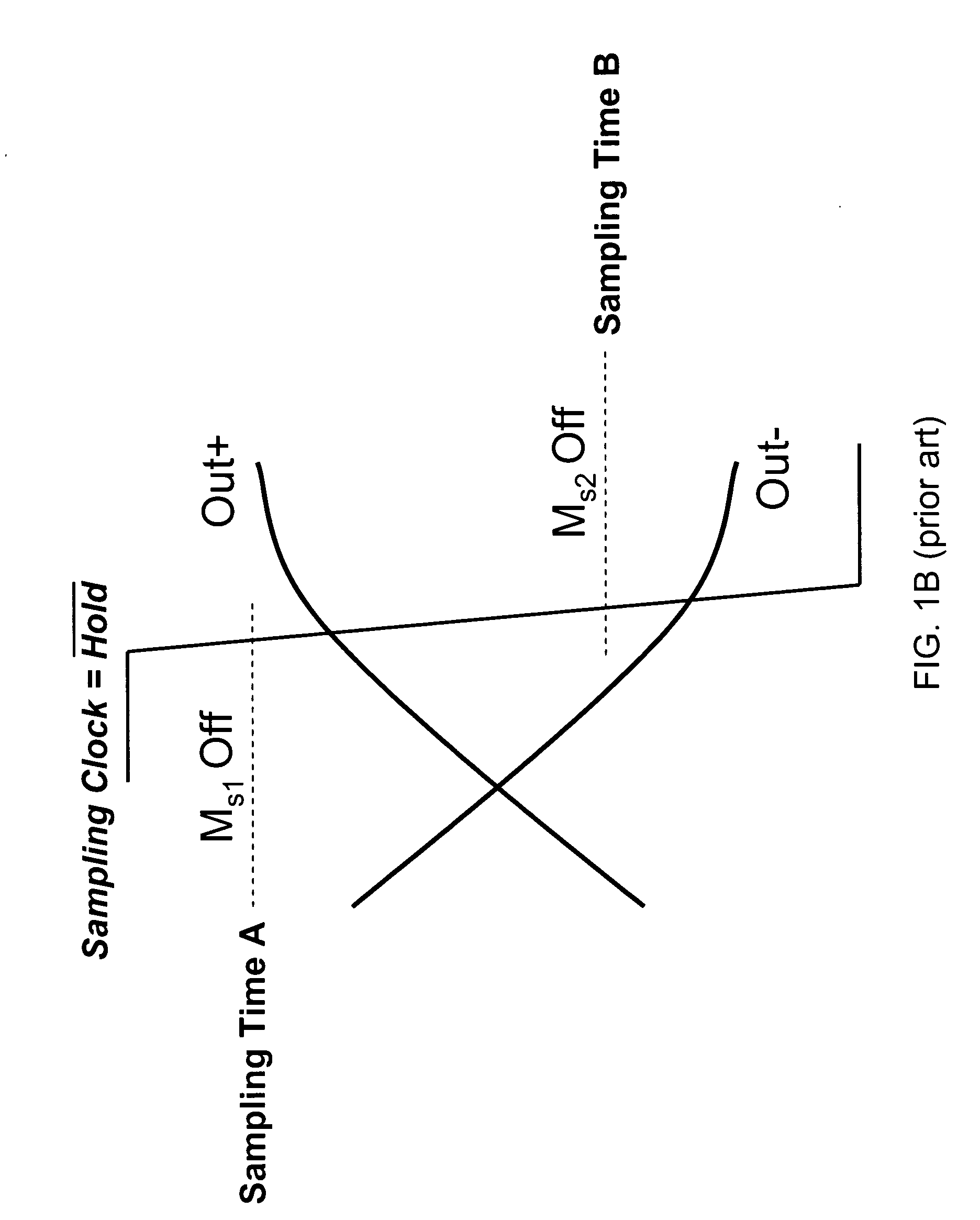

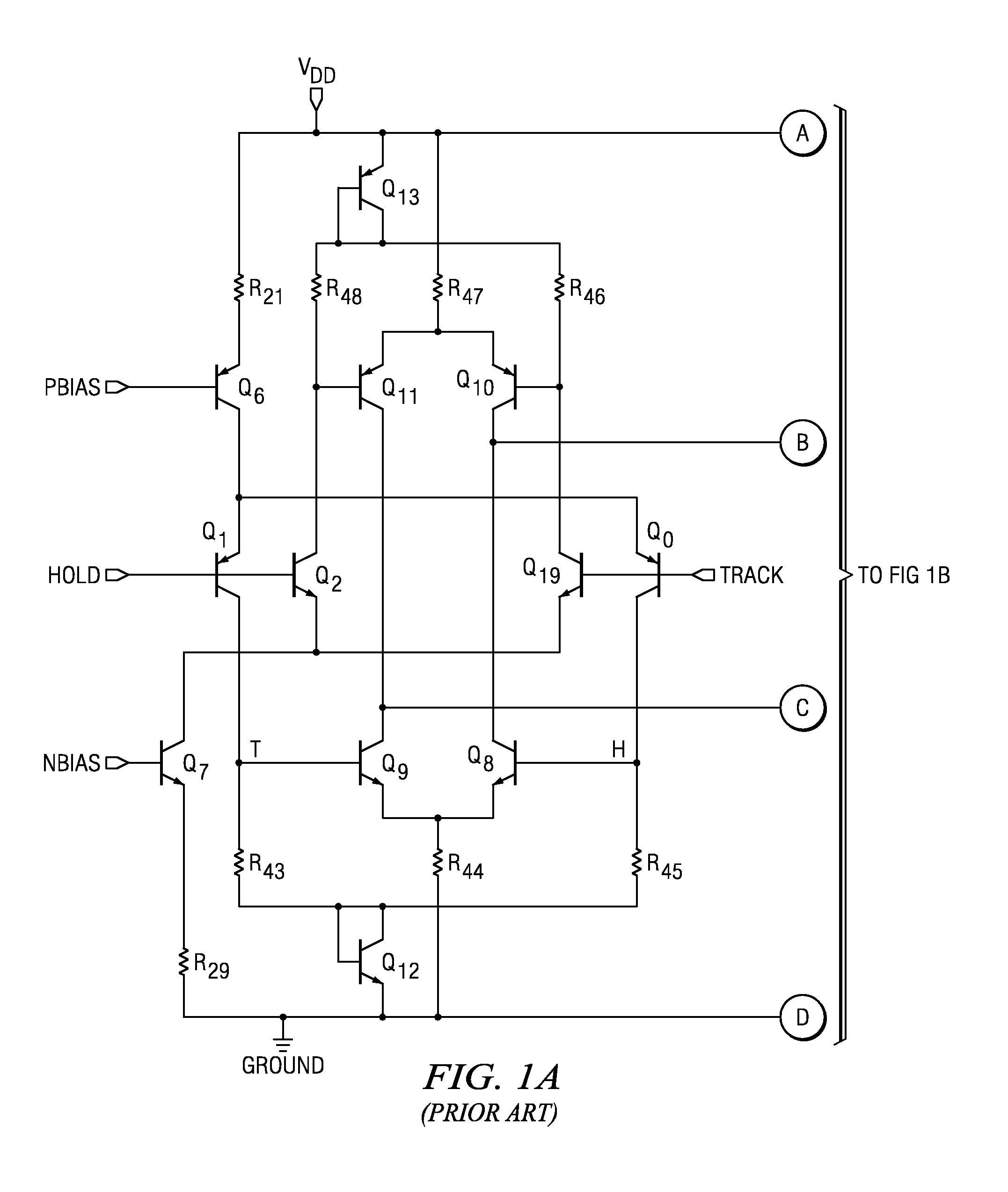

Track-and-hold circuit with low distortion

ActiveUS7782096B2Reduce Harmonic DistortionAnalogue/digital conversionElectric analogue storesSampling instantLow distortion

A track-and-hold circuit capable of tracking an analog input signal and holding a sampled voltage of the analog input signal at a sampling instant for processing by other circuitry, in response to a track signal that alternates with a hold signal. A first capacitor is provided, having a first terminal connected to a power supply terminal. Tracking circuitry operates when in an on state to apply through a resistor a tracking voltage to a second terminal of the first capacitor that corresponds to the voltage of the analog input signal, by applying the tracking voltage to a first terminal of the resistor, the second terminal of the resistor being connected to the second terminal of the first capacitor. A switch, responsive to the track signal and the hold signal, operates to switch the tracking circuitry to an on state in response to the track signal and to an off state in response to the hold signal, the time of change from the track signal to the hold signal comprising the sampling instant. A second capacitor is provided, having a first terminal connected to the first terminal of the resistor and having a second terminal connected to a power supply terminal. The second capacitor substantially reduces frequency-dependent harmonic distortion.

Owner:TEXAS INSTR INC

Phase detector circuit for clock and data recovery circuit and optical communication device having the same

InactiveUS8483579B2Low costMultiple input and output pulse circuitsPulse automatic controlPhase detectorDetector circuits

A high-accuracy phase detector circuit compatible with a 1 / N rate architecture is provided. The phase detector circuit has as many as N track-and-hold circuits for tracking and holding N-phase clock signals CLK—1 to CLK_N in synchronization with a rising edge of input data signal DIN. Out of the N-phase clock signals CLK—1 to CLK_N outputted from as many track-and-hold circuits, only the one whose rising edge is most synchronized with a rising edge of the input data signal DIN is selected and outputted as a phase difference signal.

Owner:HITACHI LTD

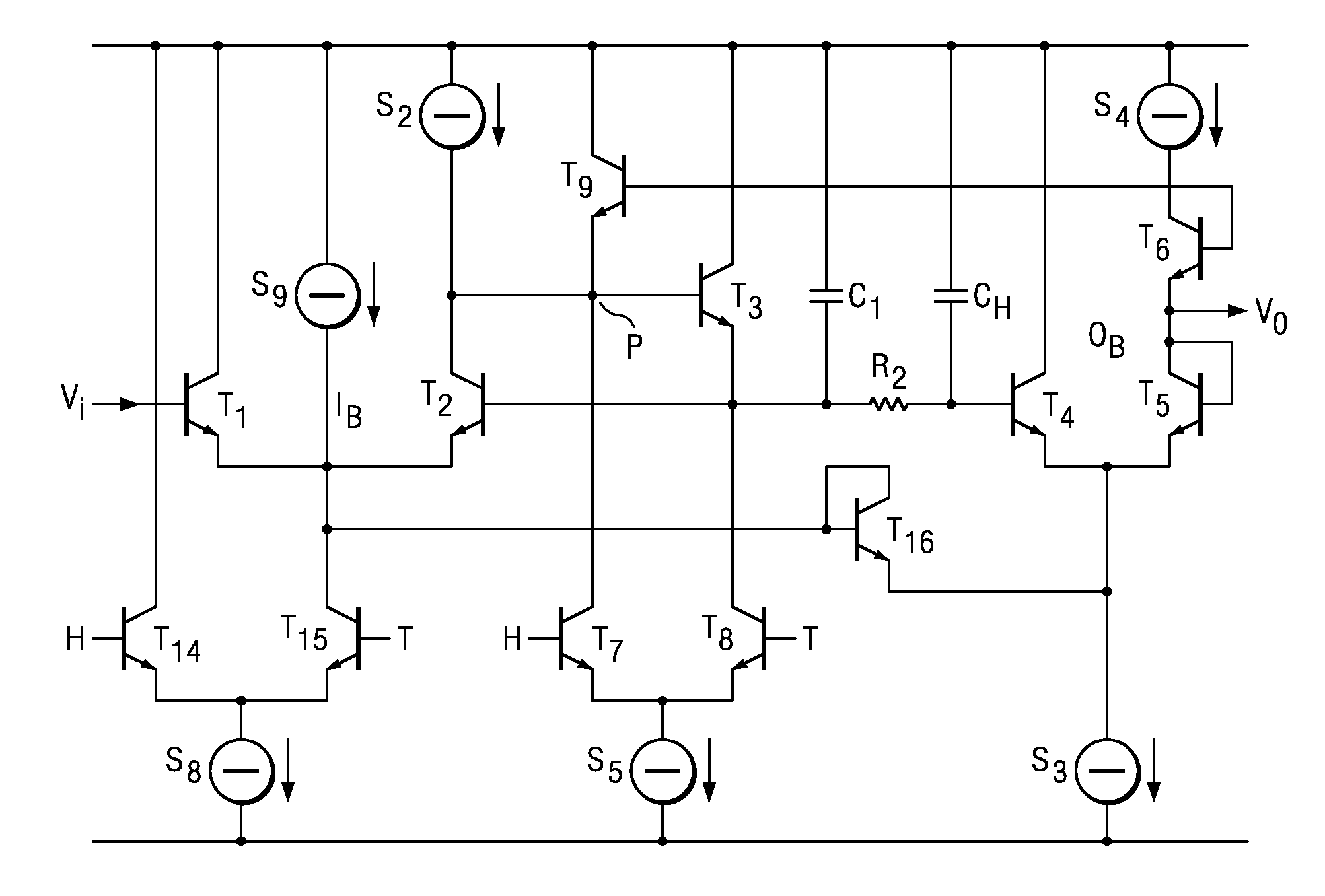

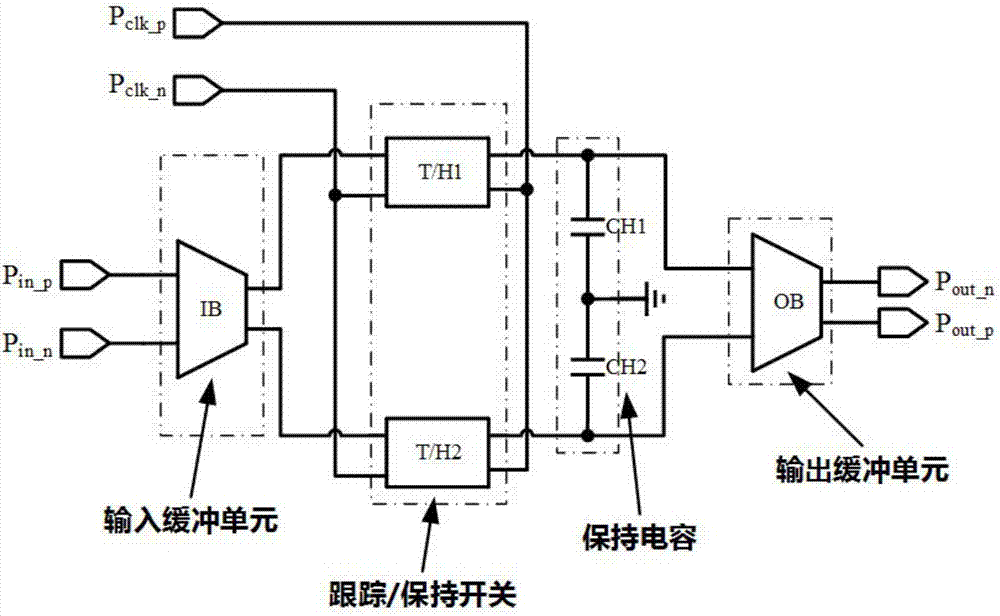

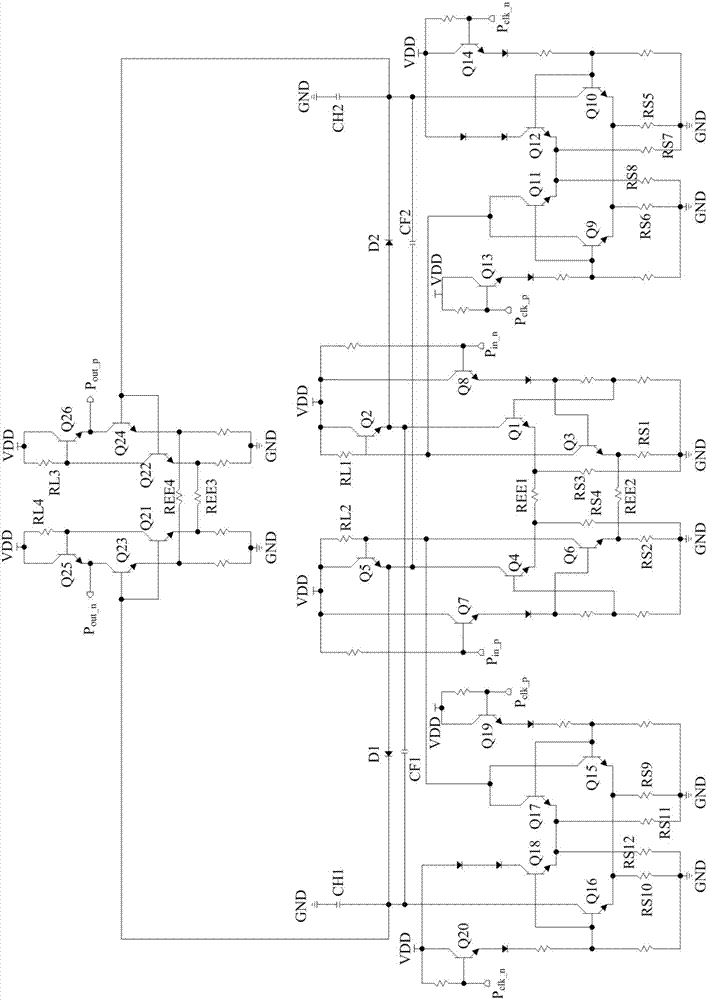

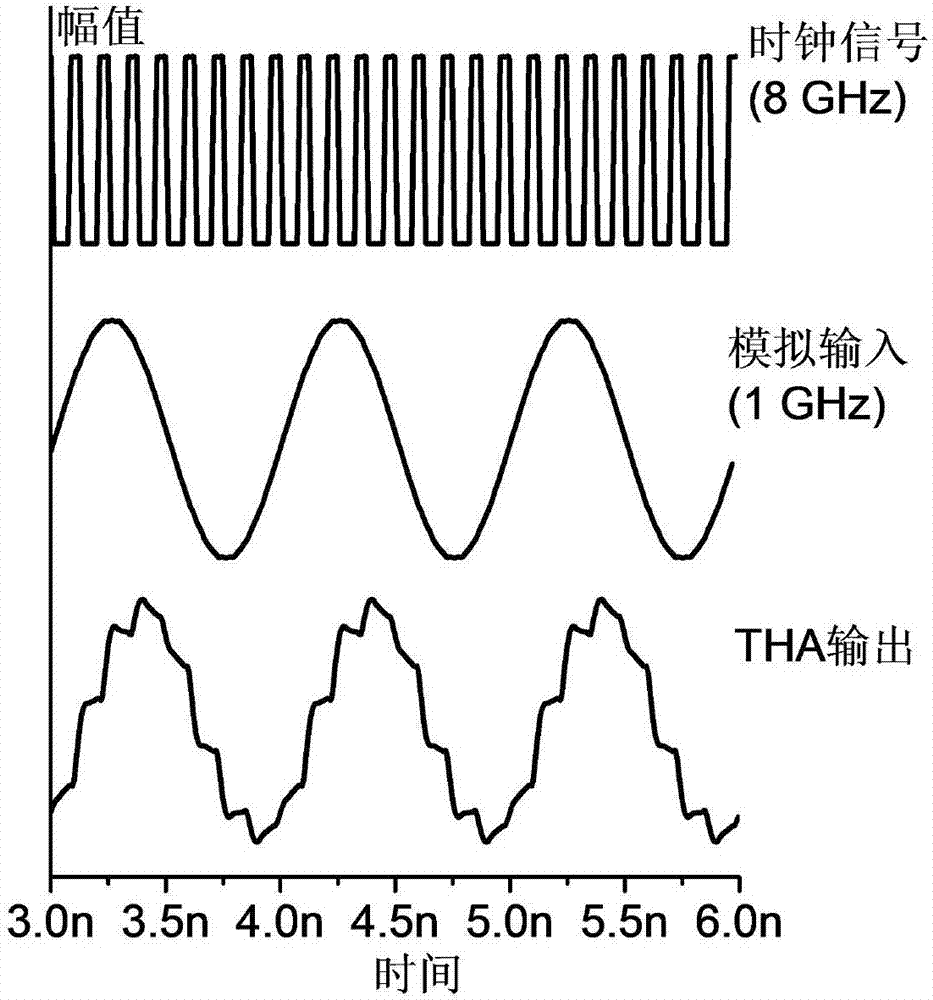

High-sampling-rate broadband track and hold circuit

ActiveCN107196637AAvoid disturbanceGood common mode noise rejectionLogic circuit coupling arrangementsCapacitanceLinearity

The invention discloses a high-sampling-rate broadband track and hold circuit and relates to the technical field of electrons. The track and hold circuit comprises an input buffer unit IB, a track / hold switch T / H, a holding capacitor CH and an output buffer unit OB. A full-differential circuit structure is introduced to realize good common-mode noise suppression ability; through the input and output buffers having emitter degeneration resistors, linearity of the track and hold circuit is improved; an improved switch emitter follower having a Schottky diode is adopted as a track and hold switch, so that circuit stability is improved; and the track and hold circuit is designed by utilizing a GaAs HBT device having high cut-off frequency and good base-emitter match, thereby solving the defects of low sampling rate and narrow bandwidth of an existing sampling and hold circuit.

Owner:XIDIAN UNIV

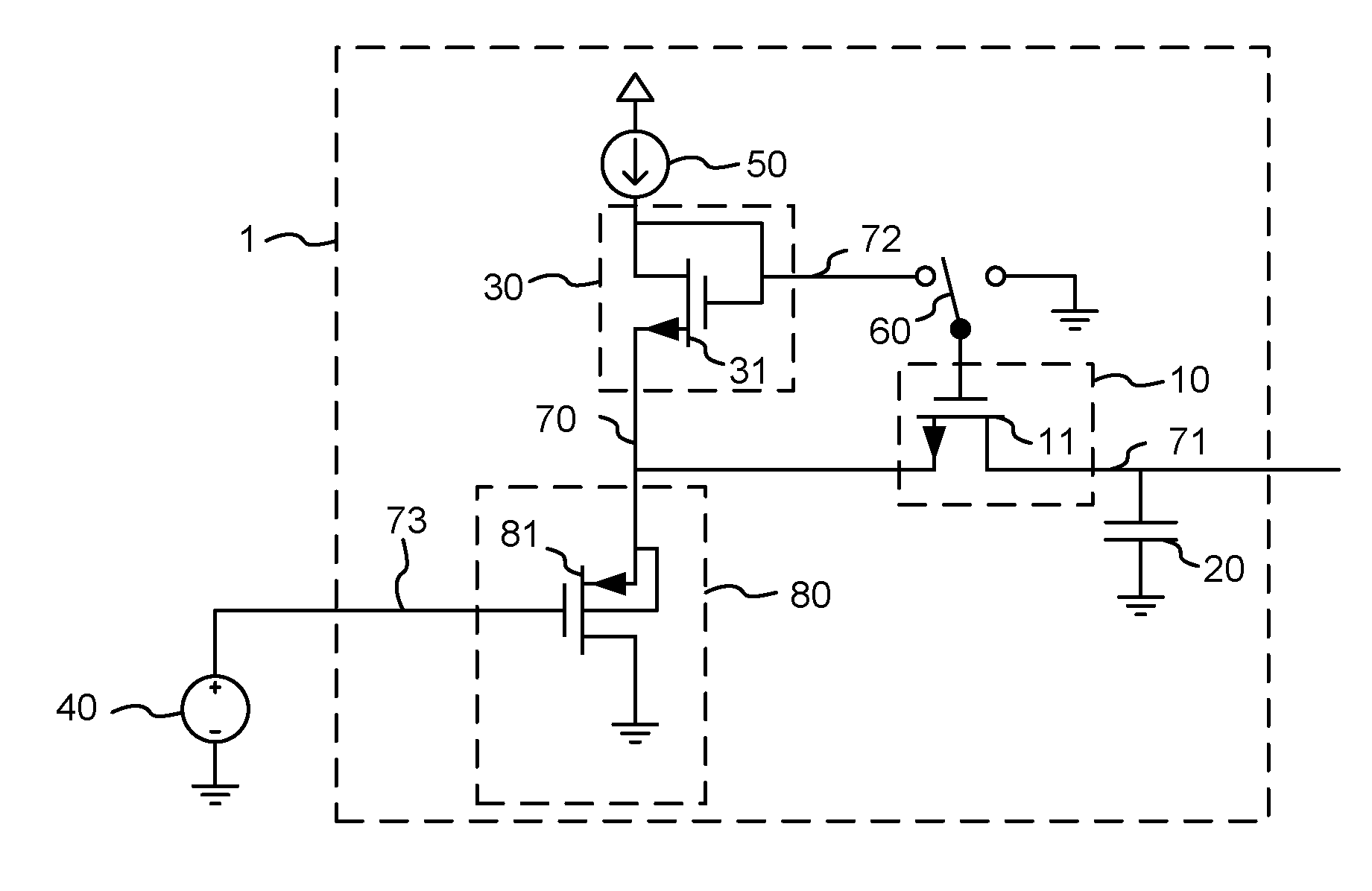

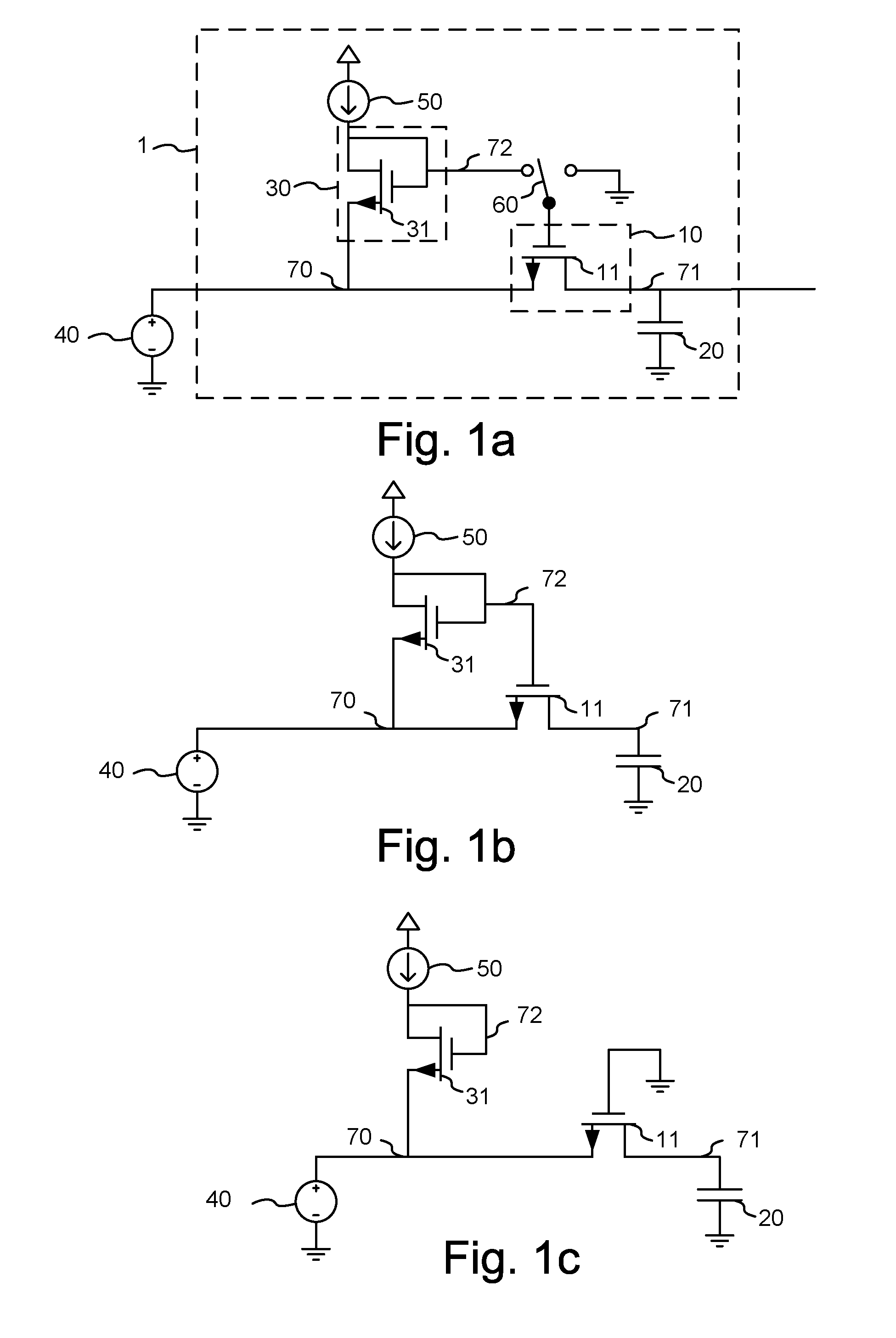

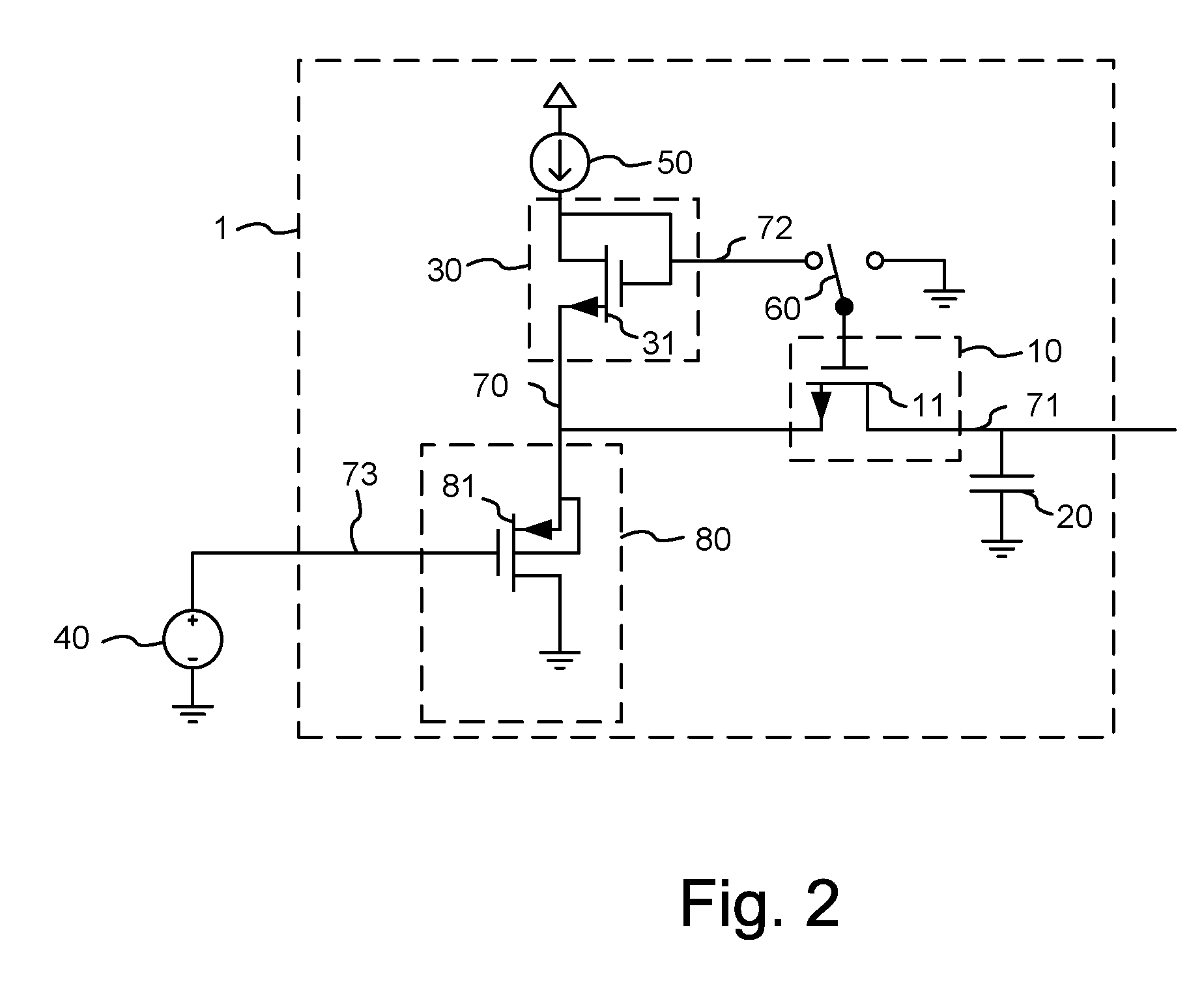

Track and hold circuit

ActiveUS20090206885A1Increased signal noiseImproved signal-to-noise-and-distortion-ratioElectric analogue storesAmplifier with semiconductor-devices/discharge-tubesCapacitanceSignal on

A track and hold circuit (1) comprising a switch device (10) and a capacitive hold device (20). The track and hold circuit (1) comprises a track-voltage generating device (30) adapted to generate a control voltage based on a signal on an input terminal of the switch device (10) and supply the control voltage to the switch device (10) during track phases of the track and hold circuit (1). The control voltage provides a channel charge, which is the same for each track phase, in the switch device (10).

Owner:CSR TECH INC

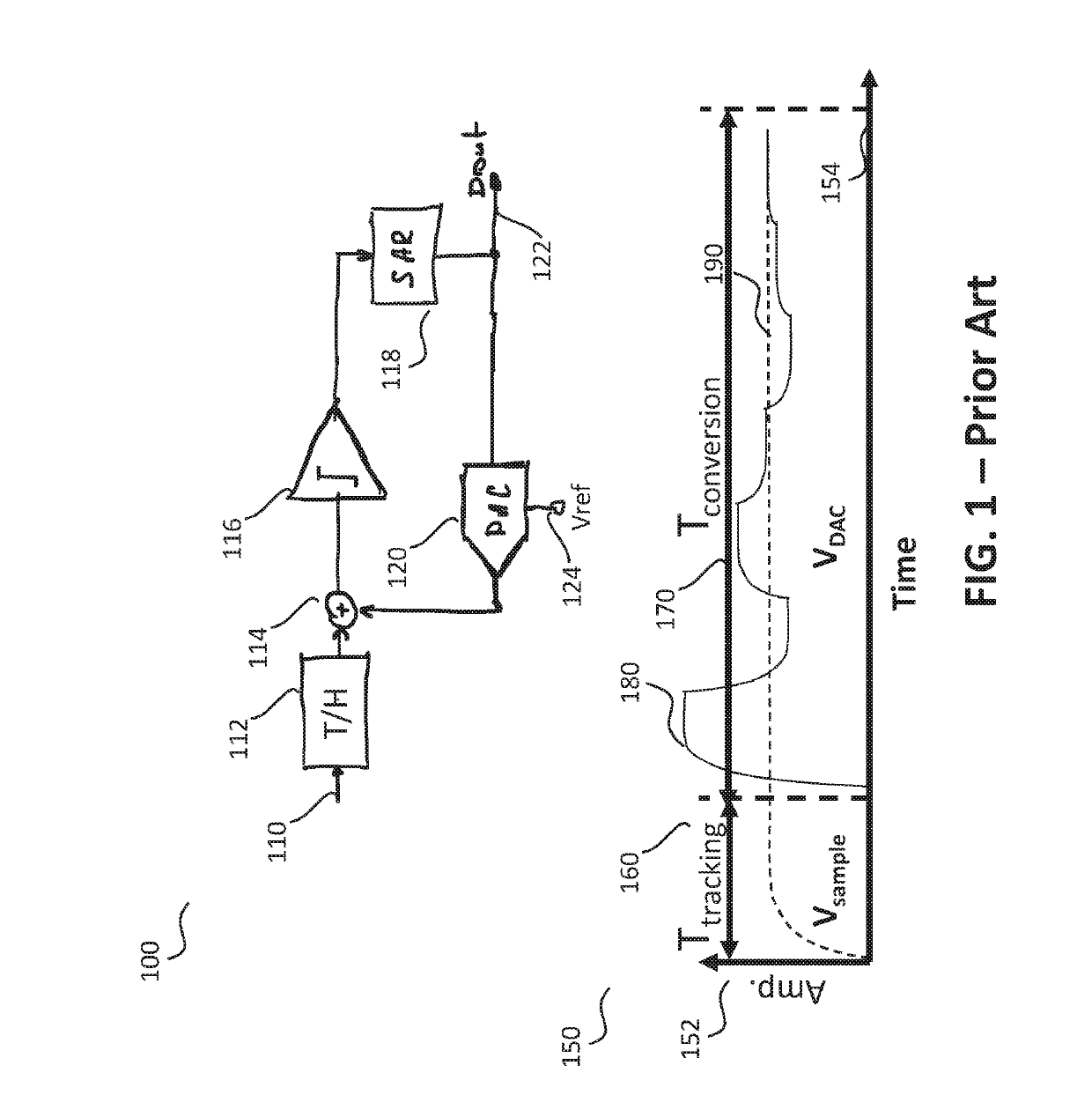

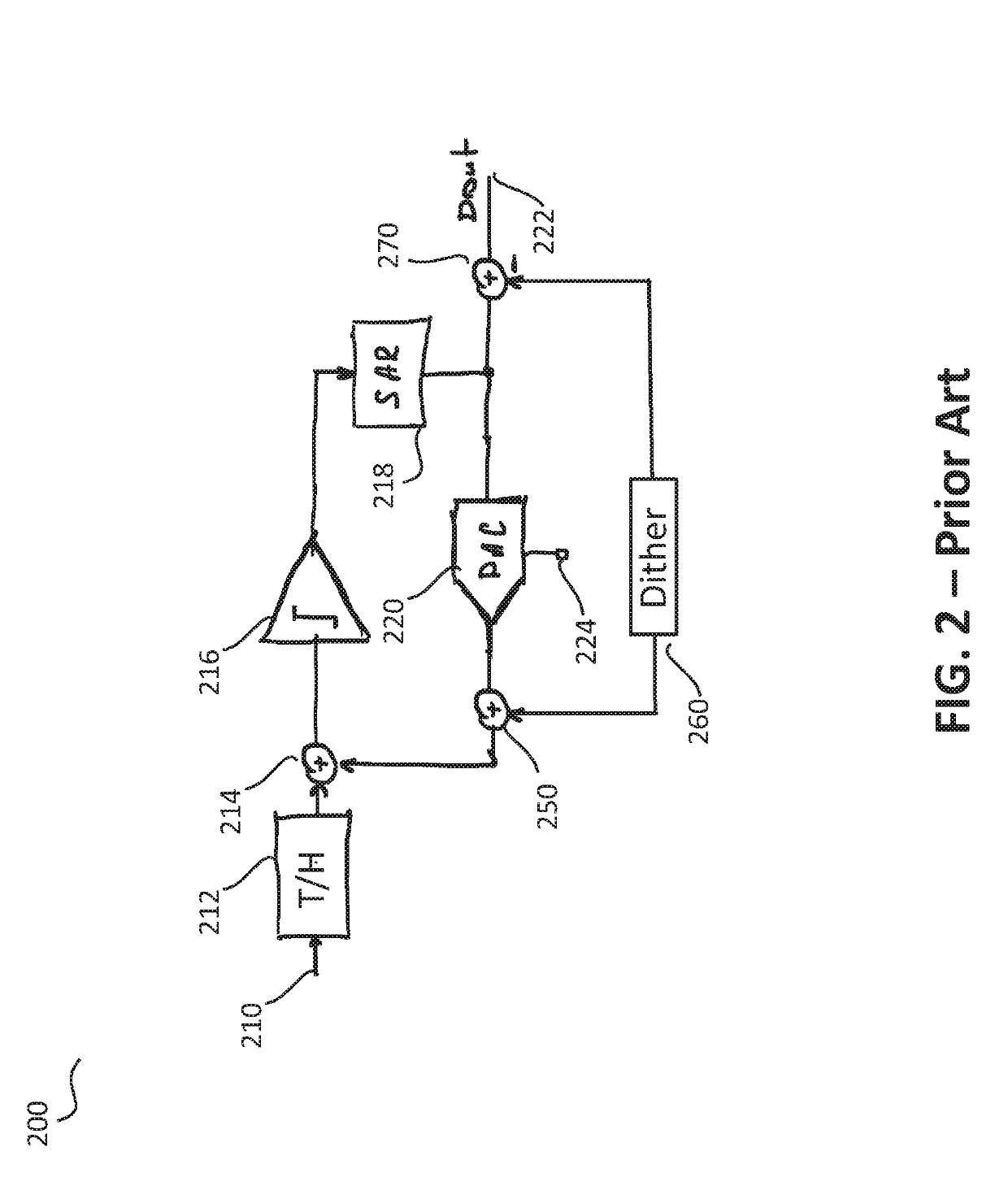

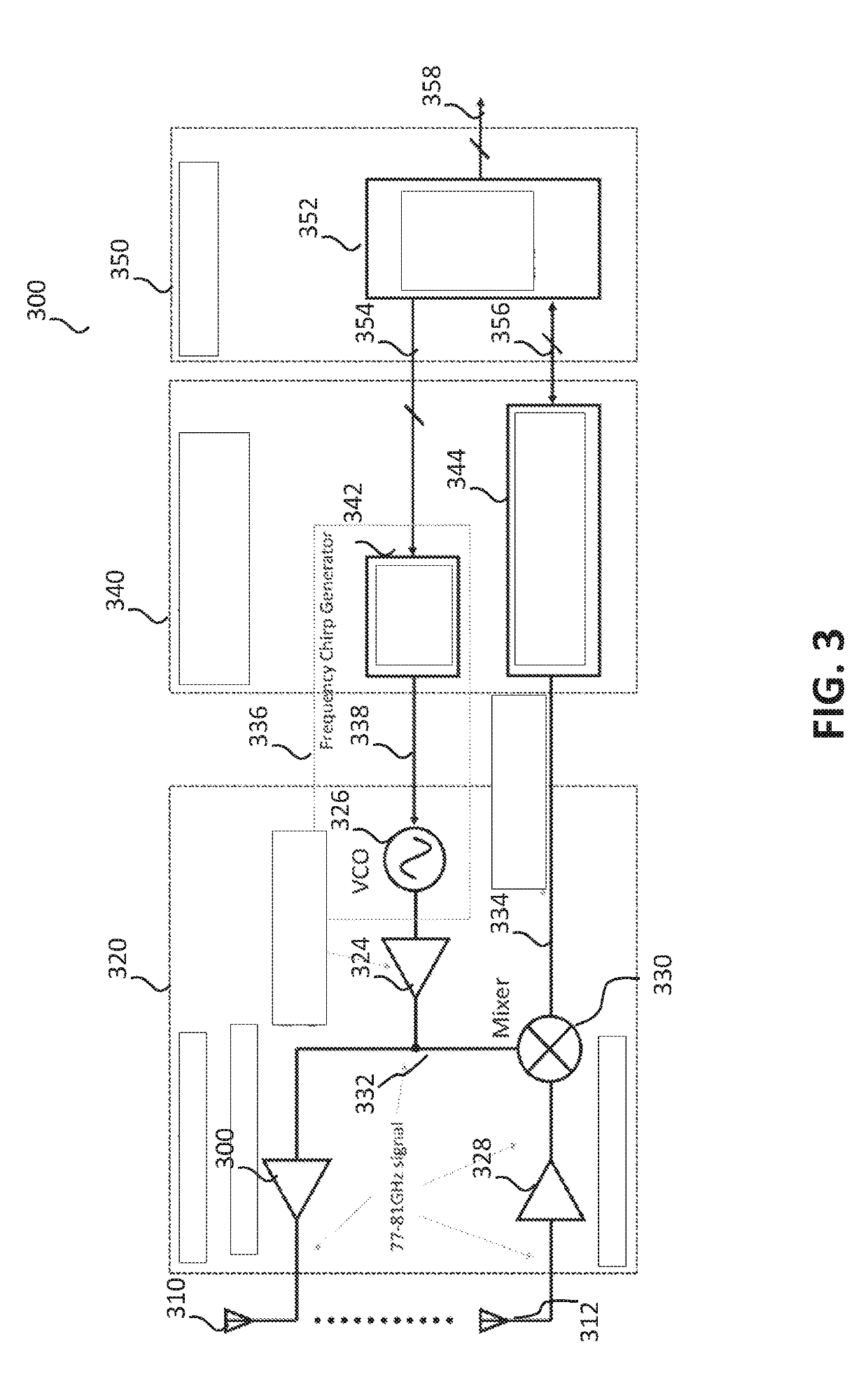

Successive approximation register (SAR) analog-to-digital converter (ADC), radar unit and method for improving harmonic distortion performance

ActiveUS20190173479A1Improve linearityWave based measurement systemsPhysical parameters compensation/preventionDigital down converterHarmonic

A successive approximation register, SAR, analog-to-digital converter, ADC, (400) is described. The SAR ADC (400) includes: a track and hold circuit (414) configured to sample an analog input signal (410); a comparator (416) coupled to the track and hold circuit and configured to compare the sampled analog input signal (410) with a DAC (444) output voltage; and a feedback path (422) that comprises a digital-to-analog converter, DAC, (444) configured to generate the reference voltage that approximates the input analog signal (410). The SAR ADC (400) further includes a dither circuit (468) coupled to or located in the feedback path (422) and arranged to add a dither signal at an input of the DAC (444) in a first time period and subtract the dither signal from the output digital signal routed via the feedback path (422) and input of the DAC (444) in a second time period during a conversion phase of the SAR ADC (400).

Owner:NXP BV

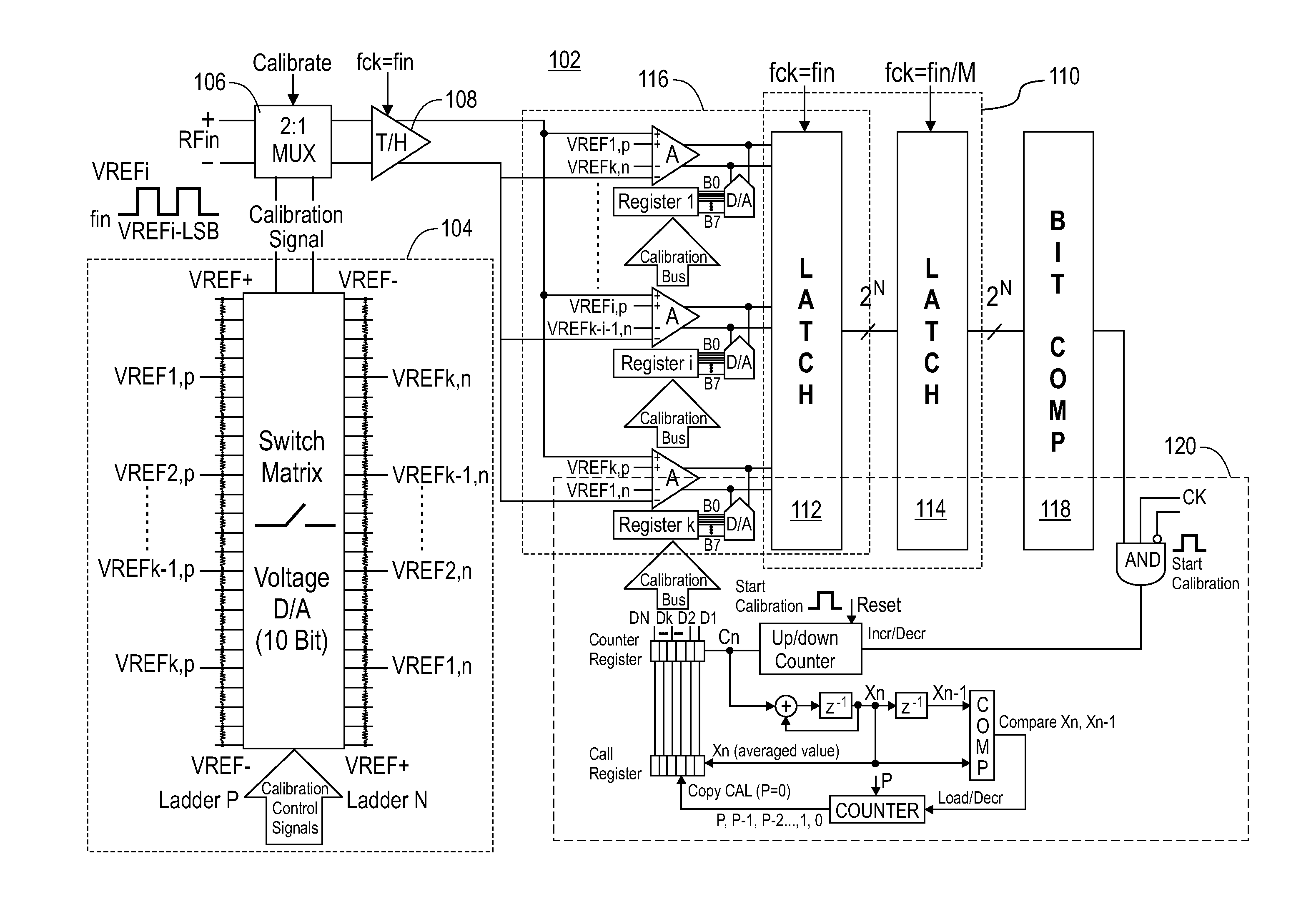

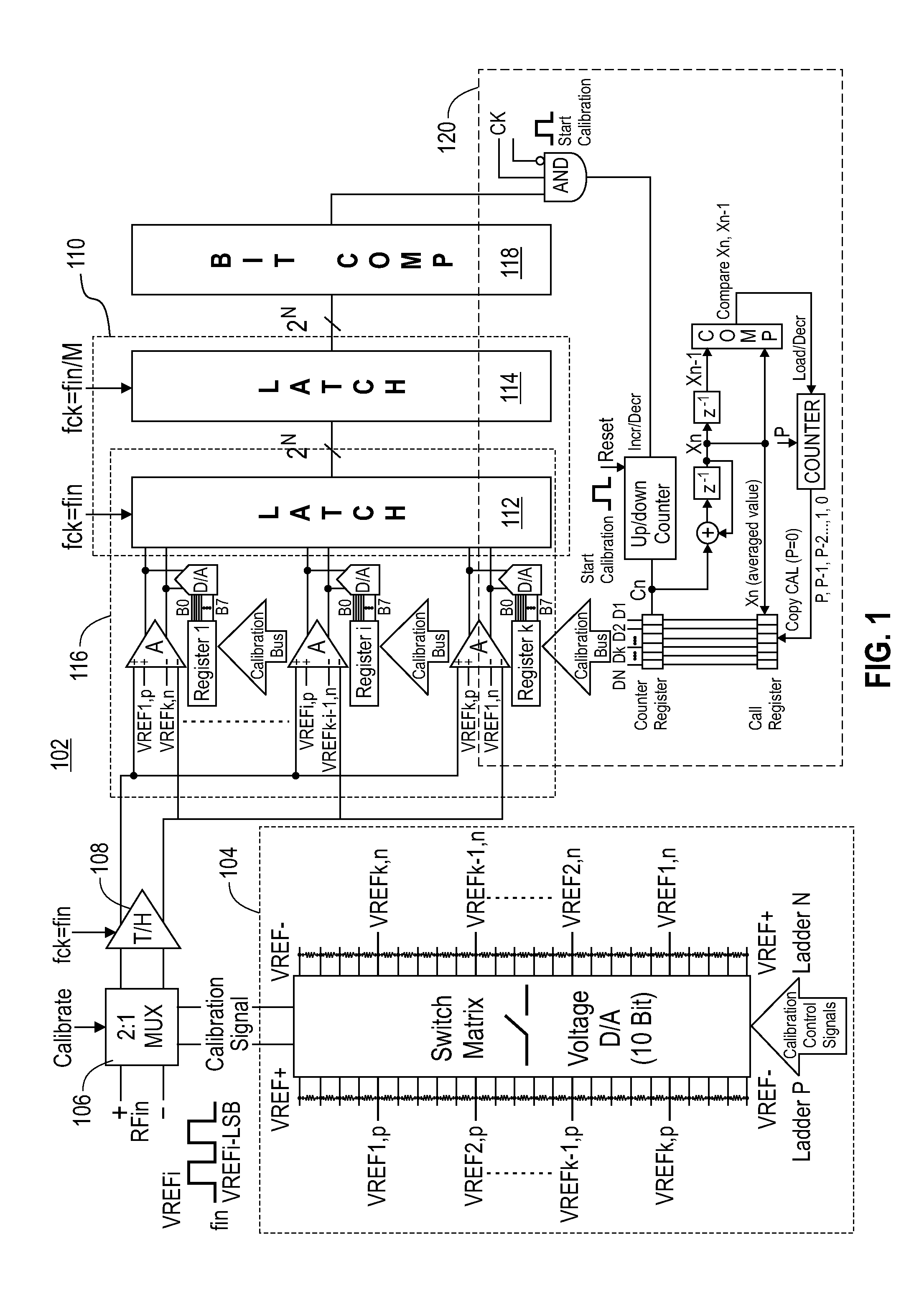

Flash analog to digital converter with method and system for dynamic calibration

ActiveUS8350737B2Electric signal transmission systemsAnalogue conversionDigital down converterEngineering

A flash analog to digital converter and a method and system for dynamically calibrating the flash analog to digital converter. The analog to digital converter may include a track and hold circuit and a plurality of comparators. The analog to digital converter may also include an under-sampling circuit configured to convert a digitized reference signal into an under-sampled digitized reference signal with a frequency of the calibration frequency divided by a positive number M. The under-sampling circuit may be further configured to calibrate a subsequent signal based on the under-sampled digitized reference signal.

Owner:GLOBALFOUNDRIES U S INC

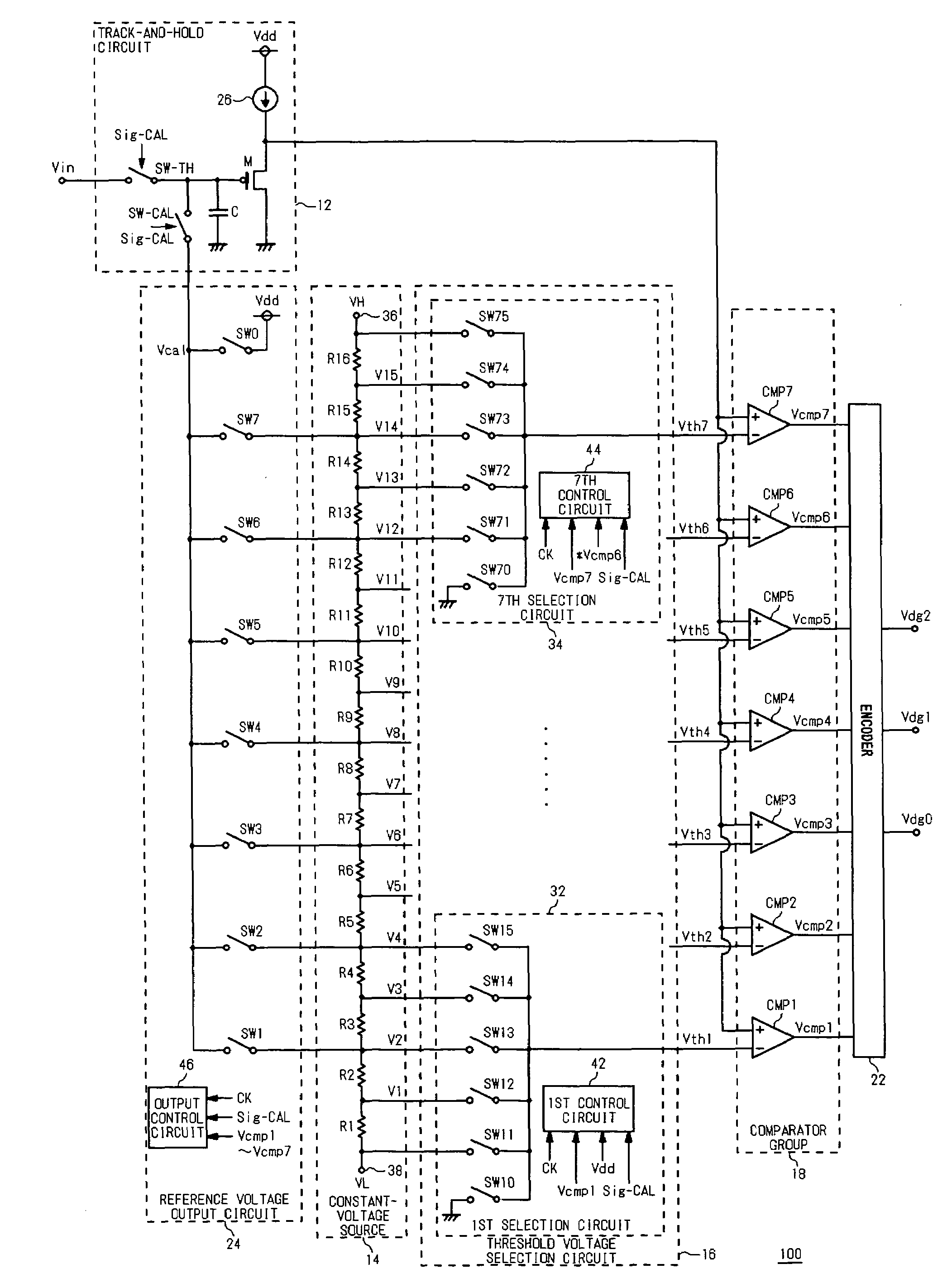

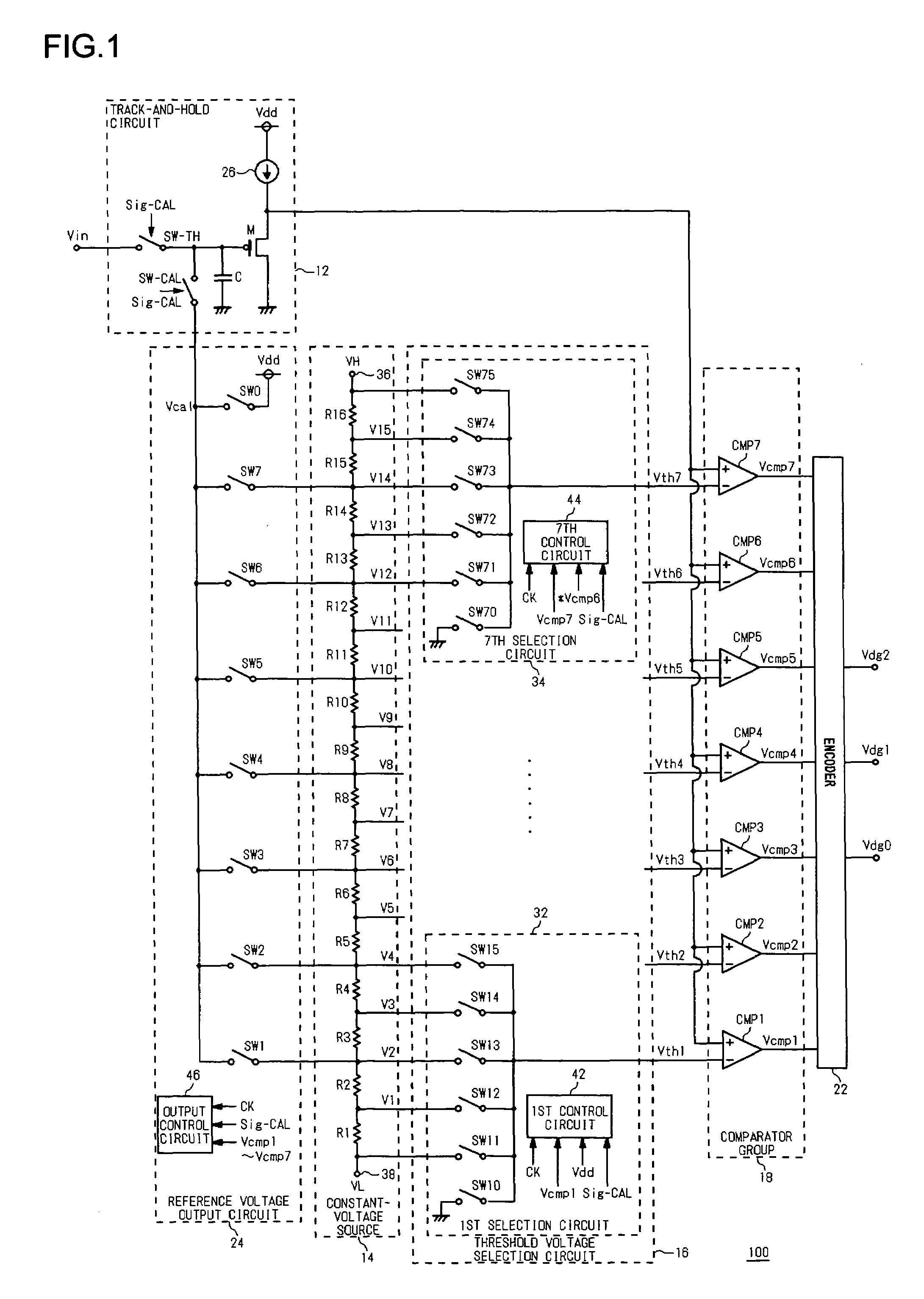

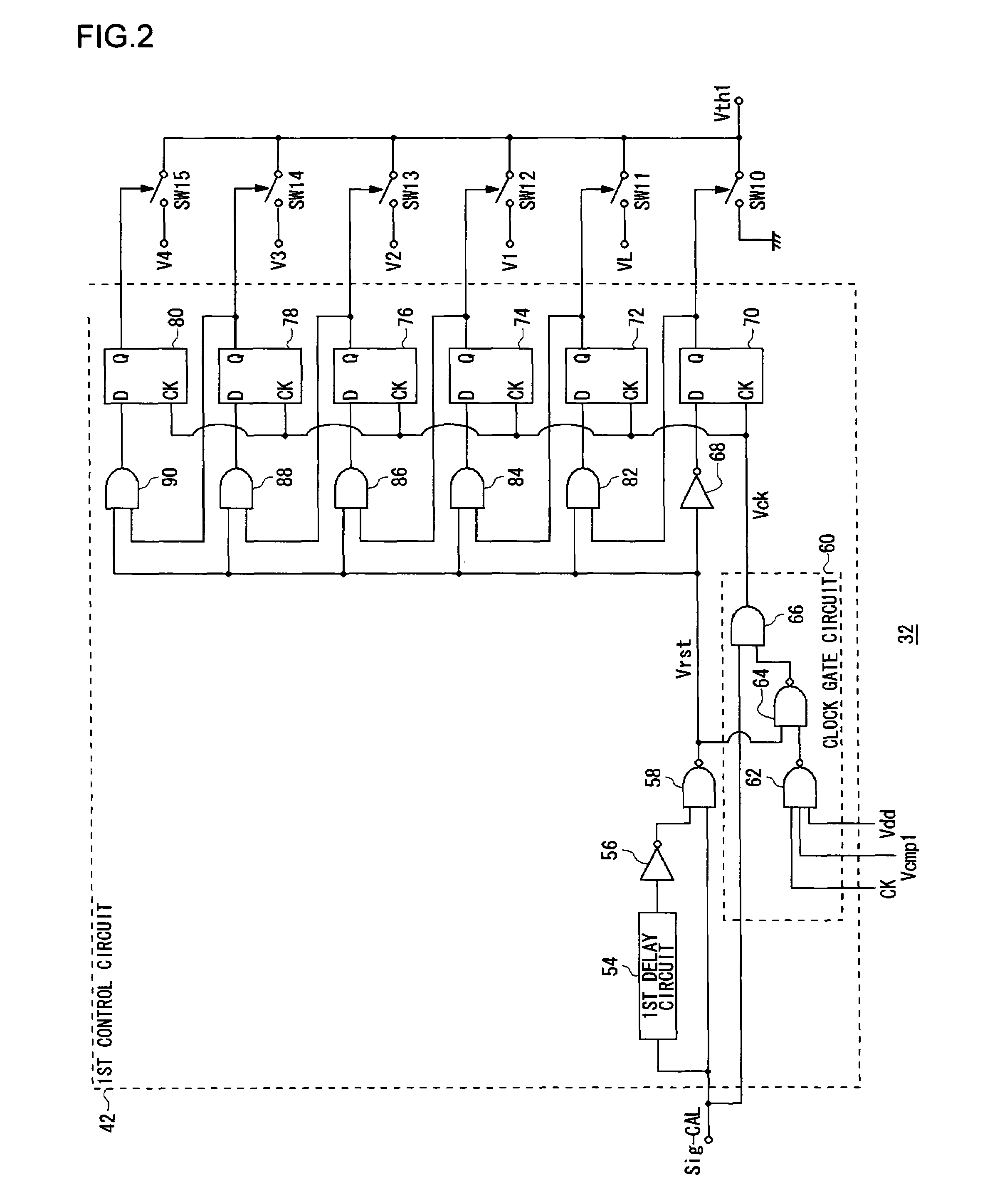

Analog-to-digital converter and threshold-value correcting method

ActiveUS7420499B2Improve frequency characteristicsReduce distortionElectric signal transmission systemsAnalogue-digital convertersVoltage referenceEngineering

An analog-to-digital converter includes a track-and-hold circuit, a constant-voltage source, a threshold voltage selection circuit, a first comparator to a seventh comparator, an encoder, and a reference voltage output circuit. In a correction mode where the offsets of the first to seventh comparators are to be corrected, a track-and-hold circuit shuts off the input of an analog voltage to the first to seventh comparators by turning off the track-hold switch.

Owner:SEMICON COMPONENTS IND LLC

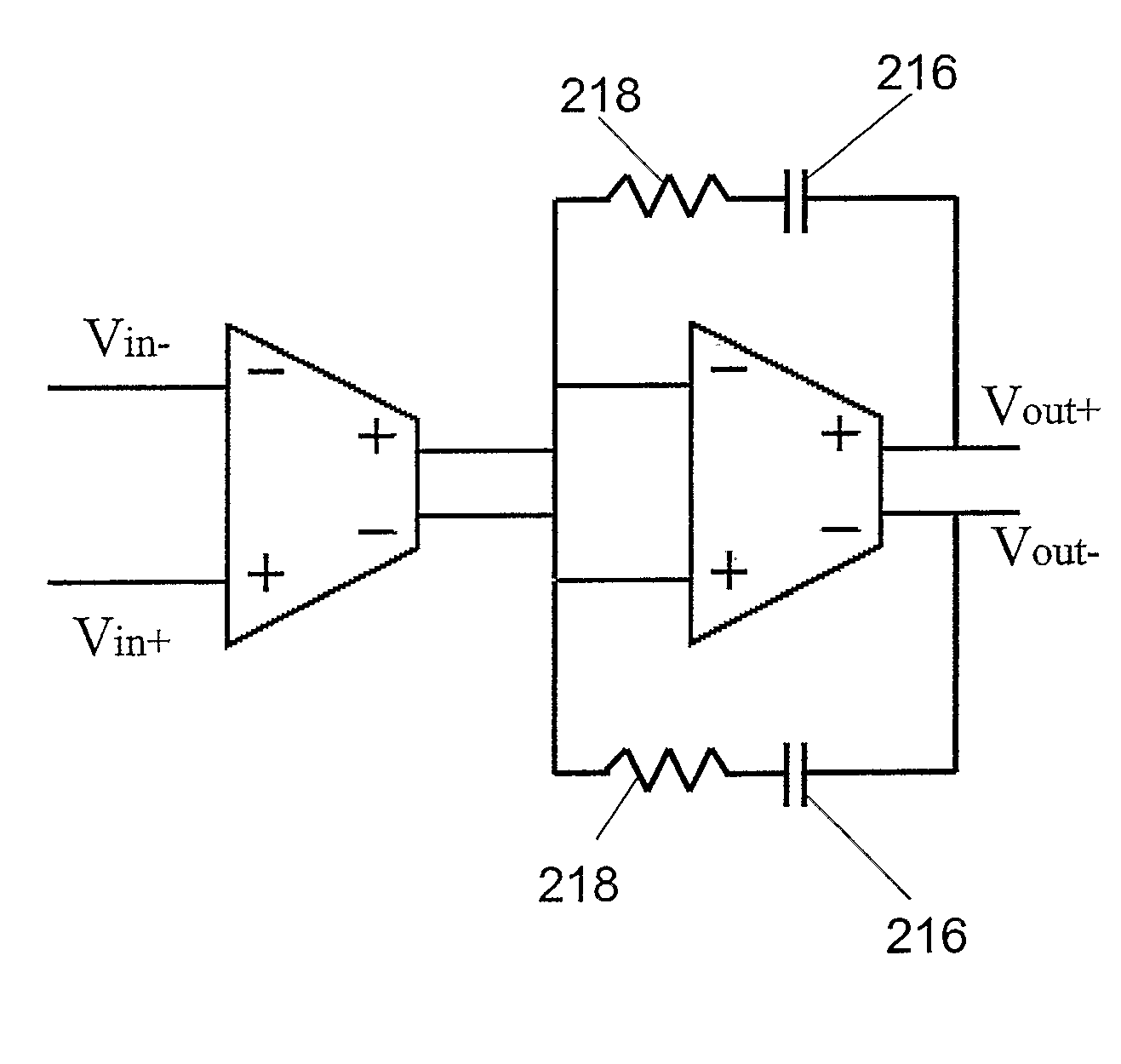

Low Voltage Operational Transconductance Amplifier Circuits

ActiveUS20080191802A1Multiple input and output pulse circuitsDifferential amplifiersIntegratorLow voltage

Circuits that operate with power supplies of less than 1 volt are presented. More particularly, circuits that operate with supply voltages (VDD) near or lower than the threshold voltage of the transistors (310, 312, etc.) in those circuits are presented. Various circuits and embodiments such as operational transconductance amplifiers (346), biasing circuits, integrators, continuous-time sigma delta modulators, track-and-hold circuits, and others are presented. The techniques and circuits can be used in a wide range of applications and various transistors from metal-oxide-semiconductor to bipolar junction transistors may implement the techniques presented herein.

Owner:THE TRUSTEES OF COLUMBIA UNIV IN THE CITY OF NEW YORK