Successive approximation register analog-digital converter

A successive approximation, analog-to-digital converter technology, applied in analog-to-digital conversion, instrument, code conversion, etc., can solve the problem of low working speed and achieve the effect of improving working speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

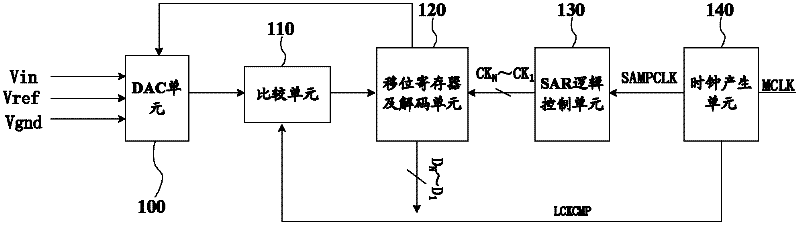

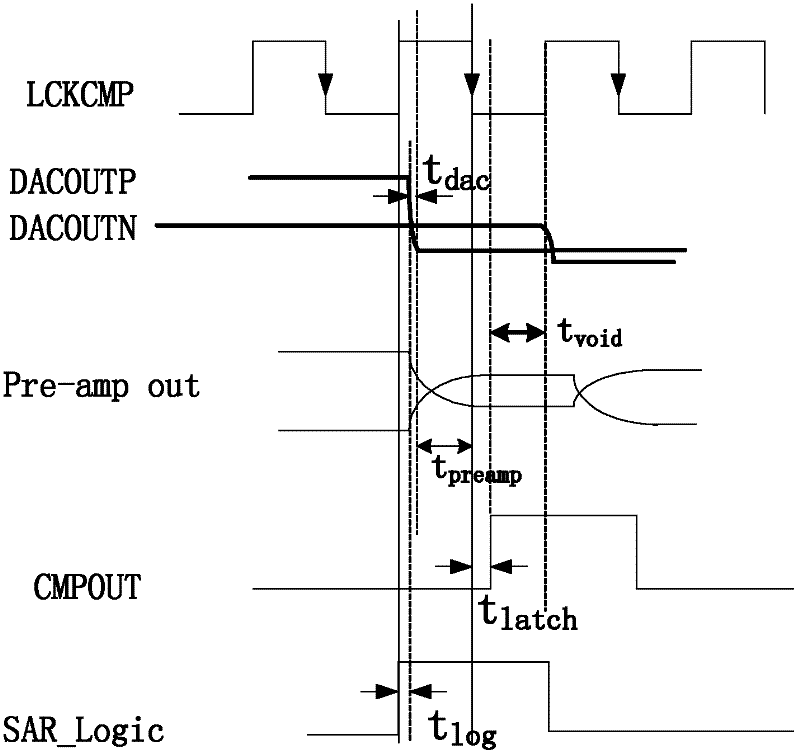

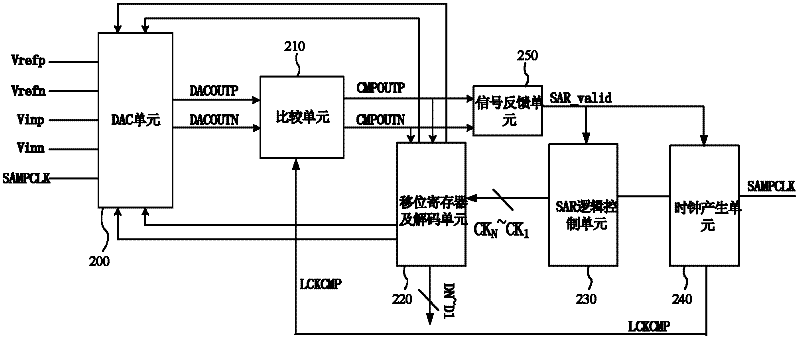

[0021] The inventor of the present invention finds that in the existing SAR ADC structure, every time an analog-to-digital conversion is completed, there is an unavoidable idle time in the whole working unit, which makes it difficult for the working speed of the SAR ADC to be higher than 5Msps (5 million samples per second) Second-rate). The reason is that, in the existing SAR ADC structure, the conversion time for completing an analog voltage to digital conversion consists of a sampling time P and a shift time T. Specifically, such as figure 1 and figure 2 As shown, the clock generation unit 140 receives an external main clock, and then generates sub-clocks such as synchronous latch clock LCKCMP and SAR logic control clock through frequency division. In the first two cycles of the main clock, the sample / hold circuit in the DAC unit 100 samples / holds the differential input signal Vin, and outputs the differential signal to the comparison unit 110 for amplification, comparis...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More