Successive approximation analog-to-digital converter and correction method

An analog-to-digital converter, successive approximation technology, applied in the direction of analog-to-digital converter, analog/digital conversion, analog/digital conversion calibration/test, etc. Avoid switch switching and increase the effect of conversion accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

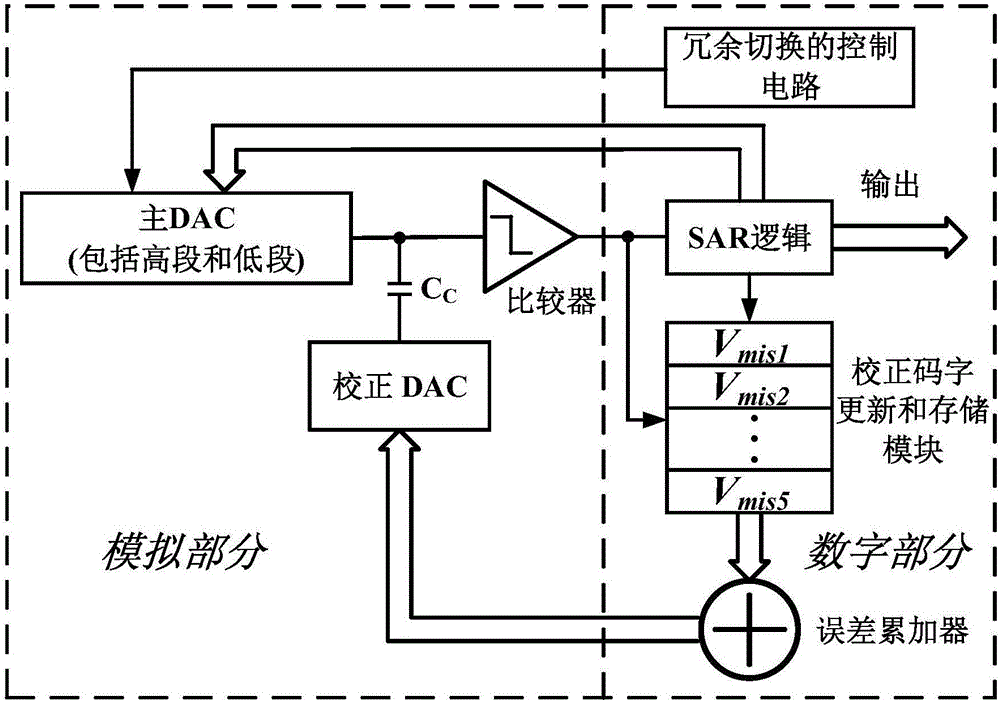

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0041] Below in conjunction with accompanying drawing, provide the concrete implementation case of the present invention. It should be noted that the parameters in the implementation examples do not affect the generality of the present invention.

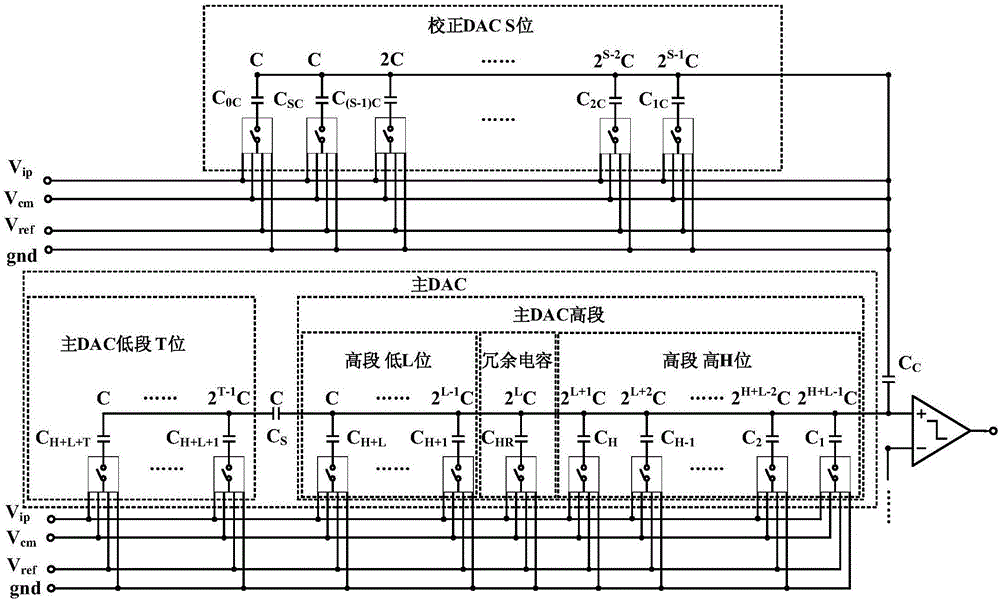

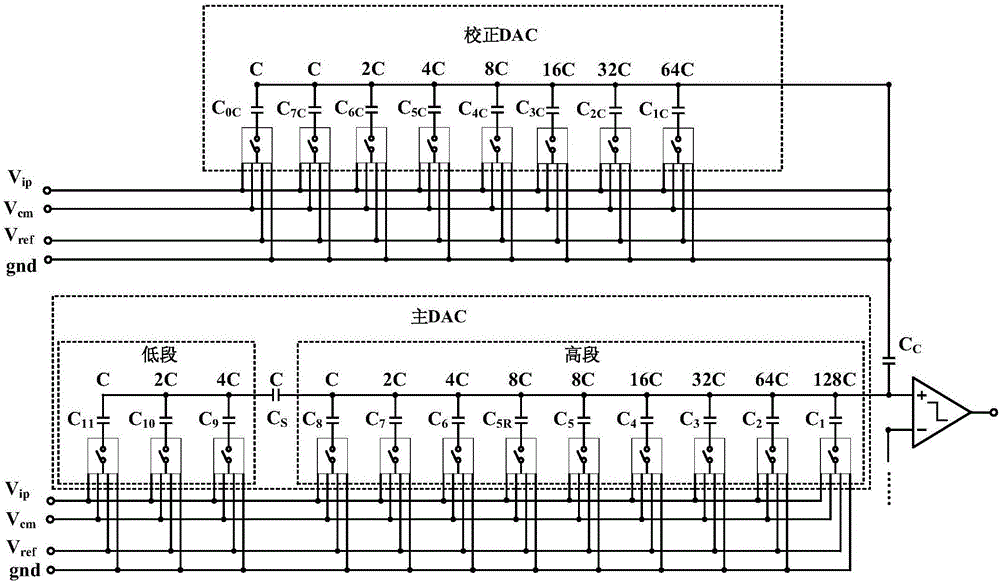

[0042] The DAC array consists of a main DAC and a correction DAC (eg image 3 shown). Among them, the main DAC is a binary segment capacitor structure, the high segment has 8 binary capacitors and a redundant capacitor, and the low segment has 3 binary capacitors; the correction DAC has a 7-bit binary capacitor structure. Main DAC high-level redundancy capacitor C 5R The position is between the high 5 bits and the low 3 bits of the high section of the main DAC, and its capacitance is the same as the minimum capacitance C among the high 5-bit capacitors. 5 The capacitance values are equal, and its role is to replace the low 3-bit capacitors of the main DAC high stage and all capacitors in the low stage during redundant switching...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More