Patents

Literature

433results about "Frequency to pulse train conversion" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

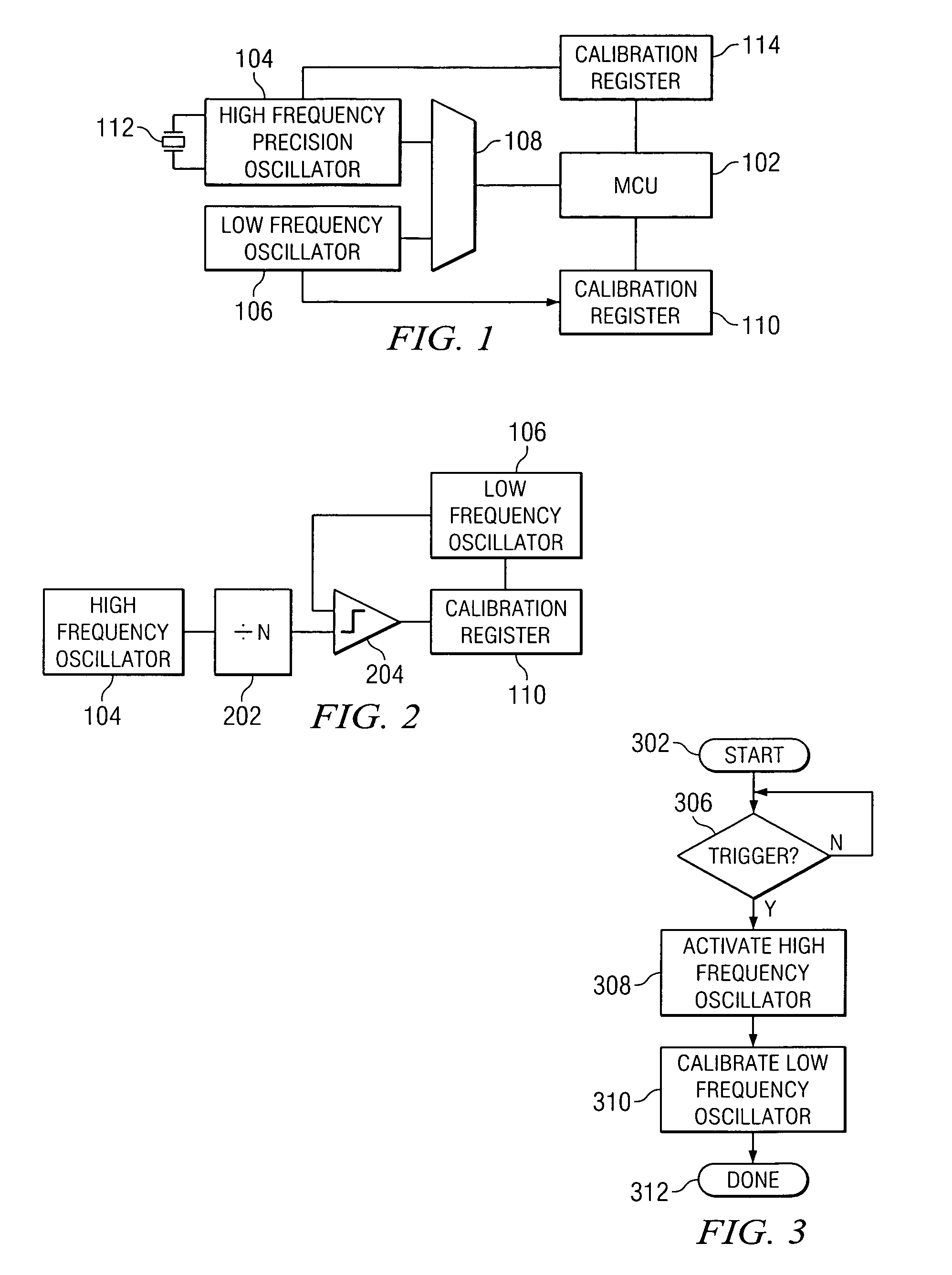

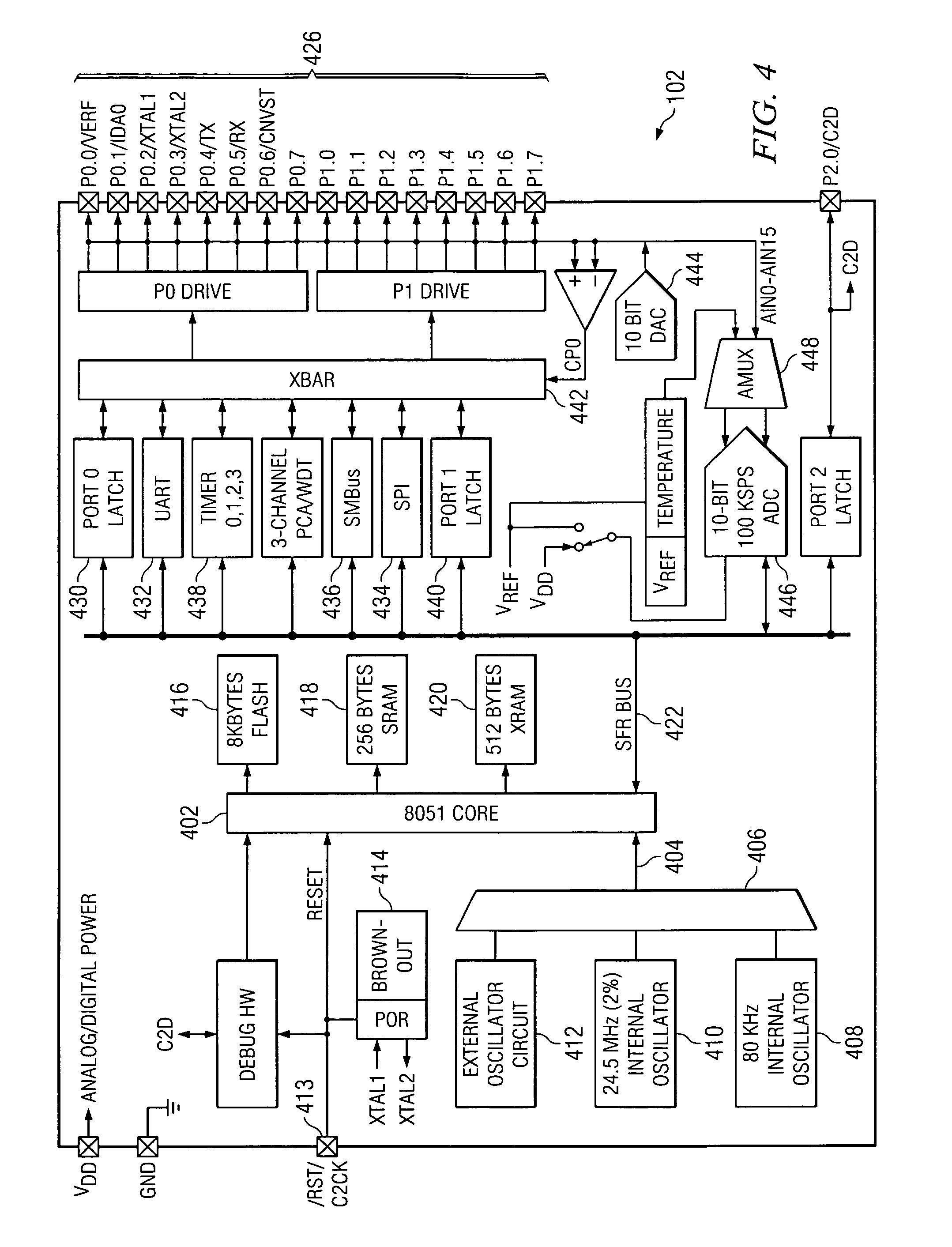

Method and apparatus for calibration of a low frequency oscillator in a processor based system

Owner:SILICON LAB INC

AC. frequency monitoring method

ActiveCN1815248APrecise positioningEliminate harmonicsFrequency to pulse train conversionAlternating currentSmall data

The method includes steps: sampling AC current to be monitored; based on sampled values, looking up crossover points of the sampled waveform; calculating period T of AC current to be monitored based on crossover points; calculating frequency of AC current monitored. Crossover points are searched through software directly so as to reduce hardware spending. Averaging results of multiple times of calculation obtains final outcome in high precision. Anti-interference ability is high since questionable data including too large and too small data are thrown off. Advantages are: simple and reasonable, accurate and reliable data, and high practicability.

Owner:VERTIV CORP

Frequency measurement method based on FPGA

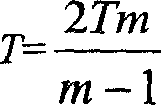

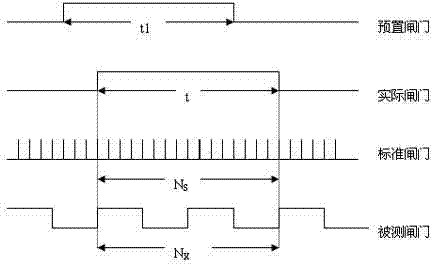

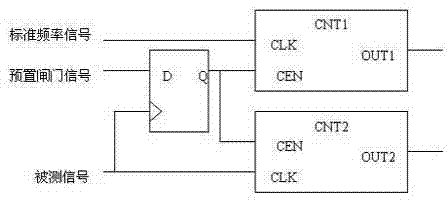

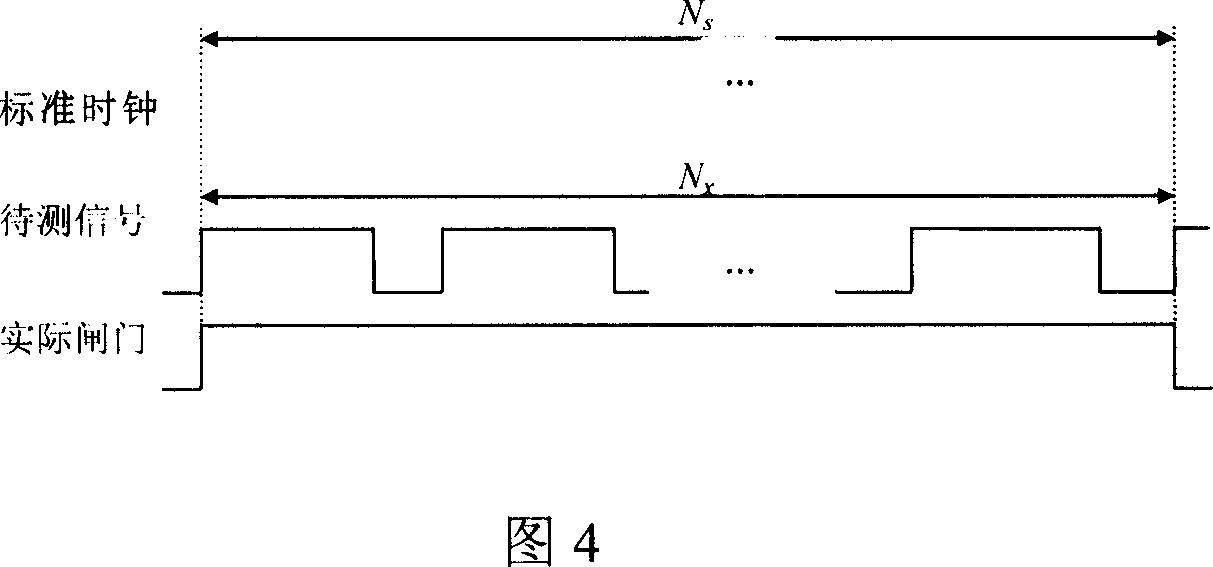

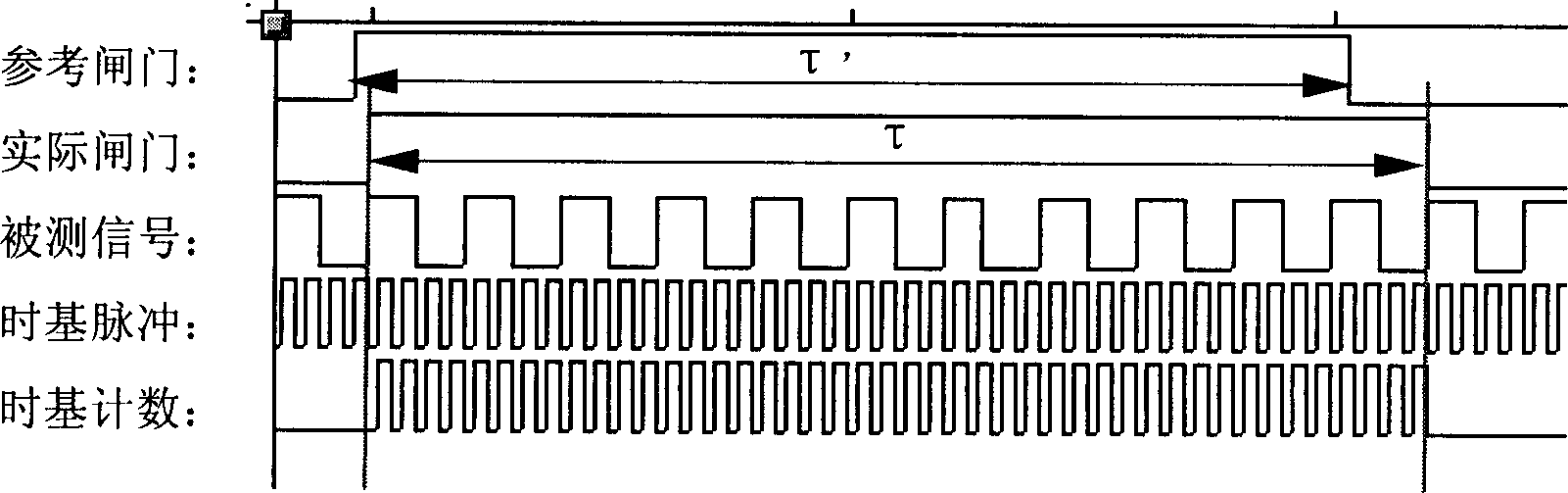

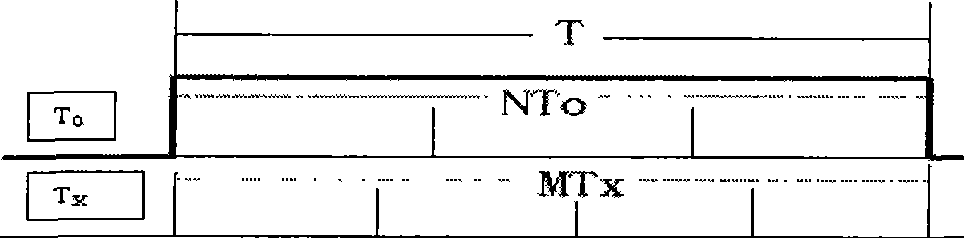

InactiveCN103499739ASolve inaccurateImprove accuracyFrequency to pulse train conversionFrequency measurementsLow frequency band

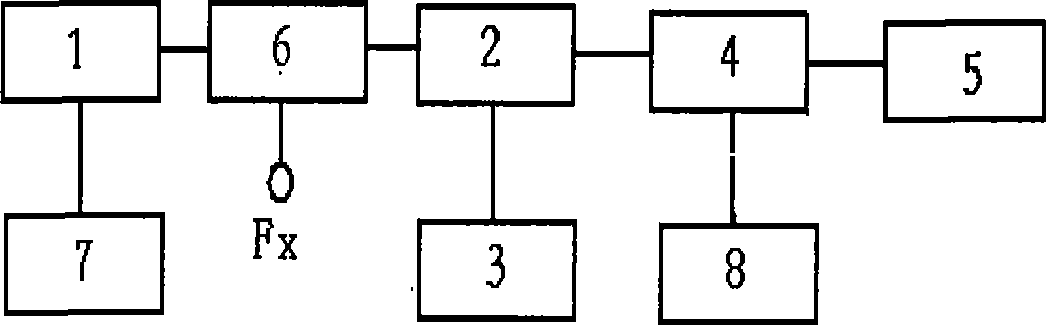

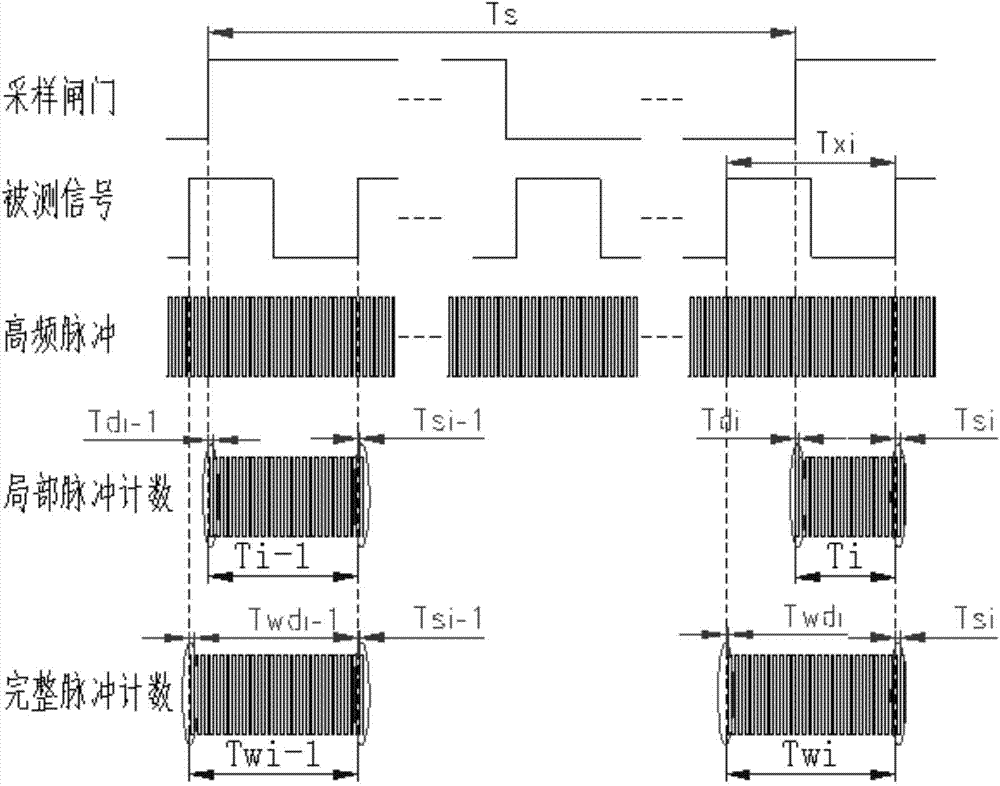

The invention provides a frequency measurement method based on an FPGA. A standard reference clock is adopted to count the number of pulses of a measured signal in a unit time (1s) and the number of the pulses of the measured signal in the unit time (1s) is the frequency of the signal. Due to the fact that the starting moment of a gate and the finishing moment of the gate are random for the signal, a pulse period quantization error can be produced, and measurement accuracy needs to be analyzed further: the pulse period of a signal to be measured is set to be Tx, the frequency is set to be Fx, and when the measuring time T equals to 1s, the measurement accuracy & meets the equation that &=Tx / T=1 / Fx. The fact that measurement accuracy in a direct frequency measurement method is relevant to the frequency of the signal is known, the higher the frequency of the signal to be measured is, the higher the measurement accuracy is, and otherwise, the lower the frequency of the signal to be measured is, the lower the measurement accuracy is. The direct frequency measurement method is only suitable for measurement of the signal at the higher frequency and can not meet the demand that the measurement accuracy remains unchanged in the whole measurement frequency band. In order to overcome the defect of inaccuracy in low-frequency-band measurement, gating signals and the measured signal are used for carrying out dual control on enable signals of the counter, and therefore accuracy is improved.

Owner:LANGCHAO ELECTRONIC INFORMATION IND CO LTD

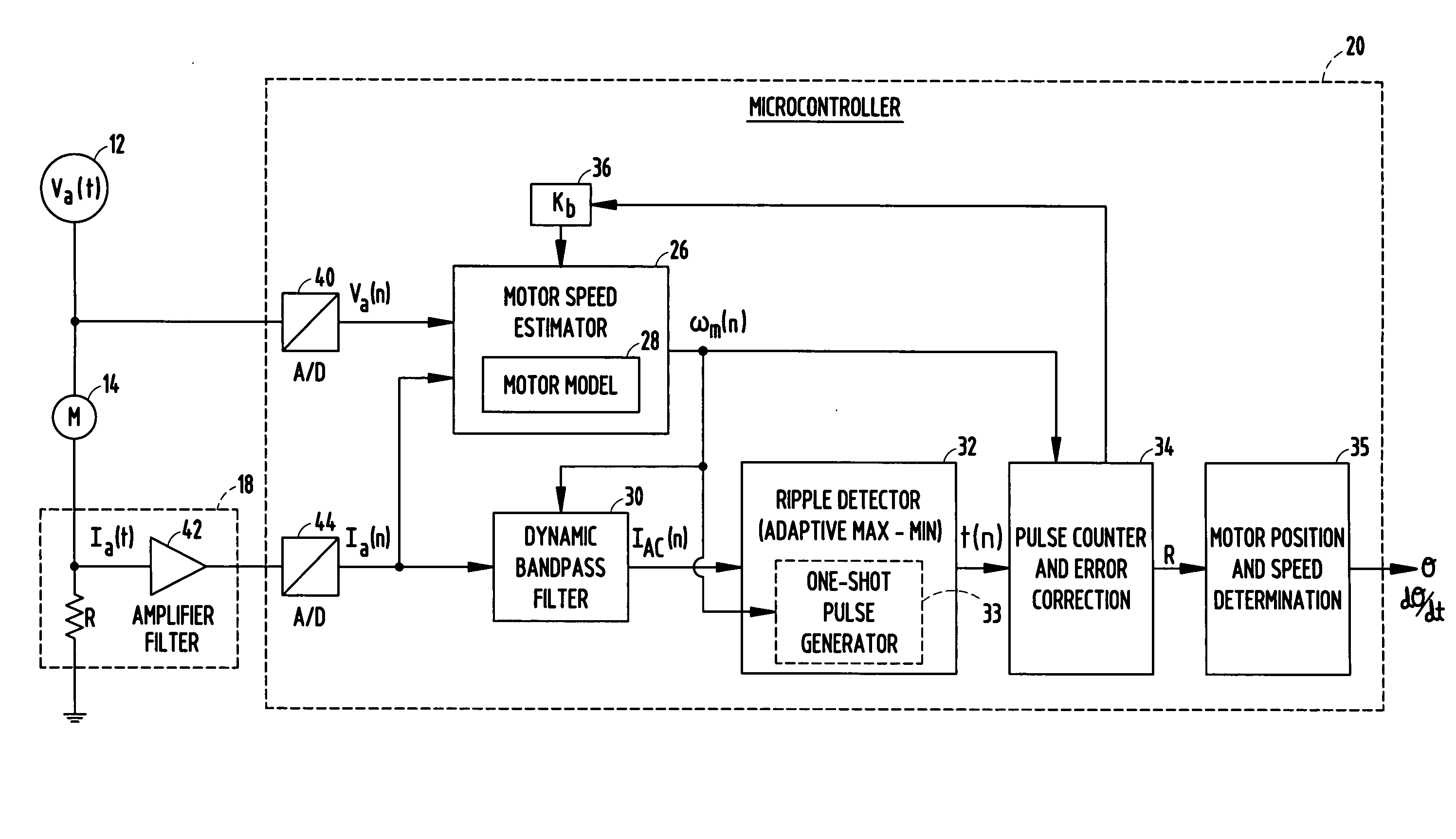

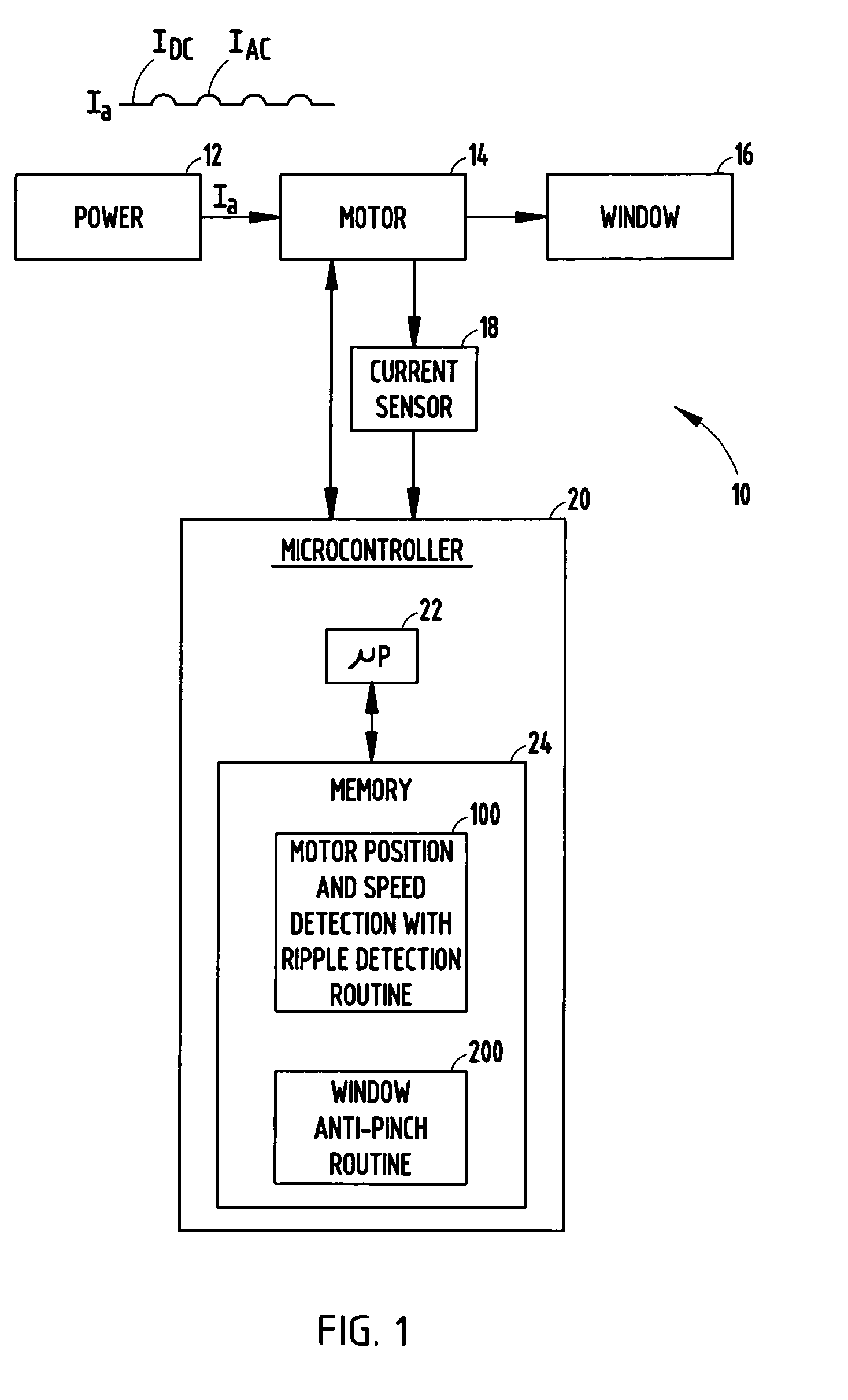

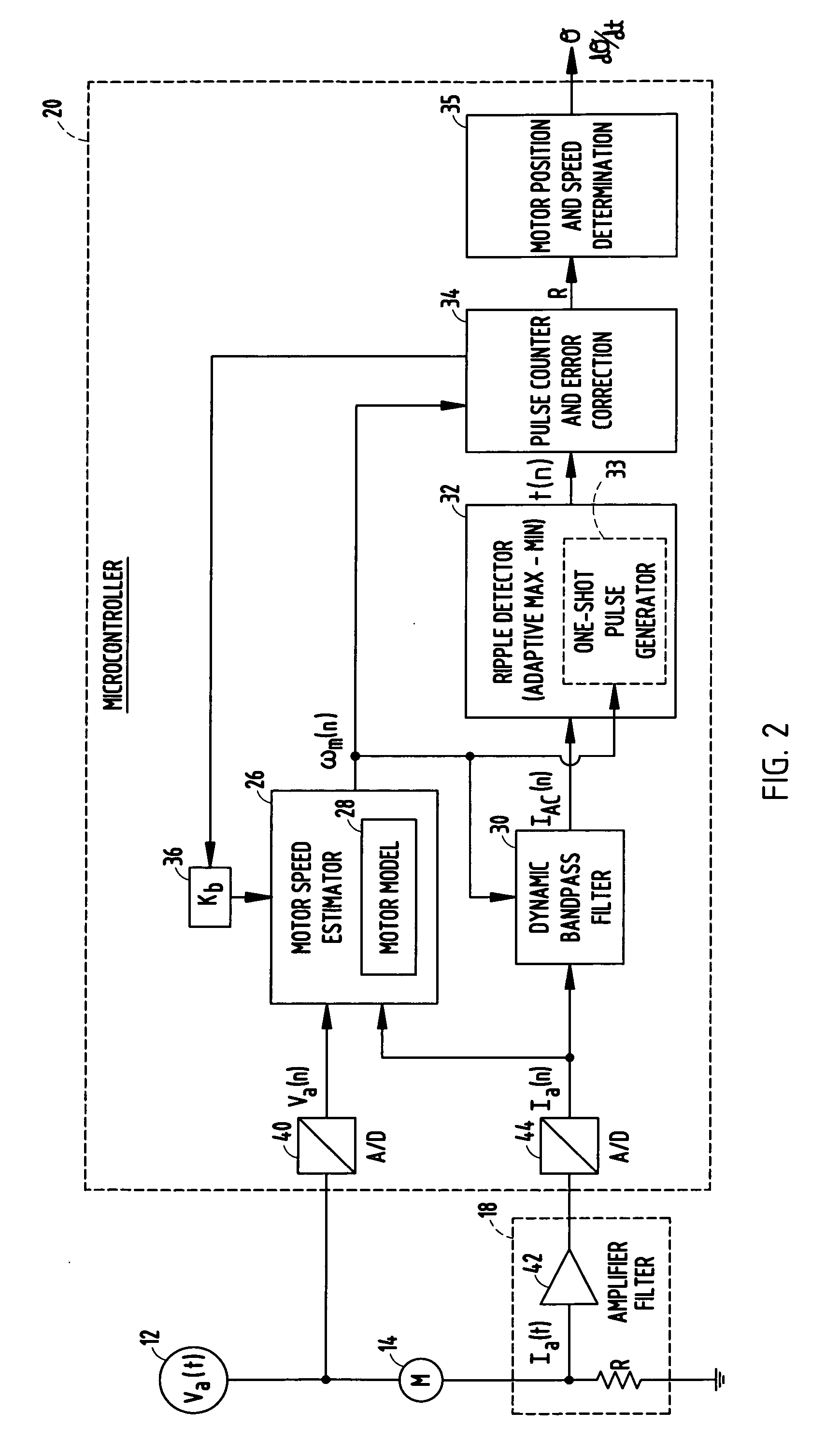

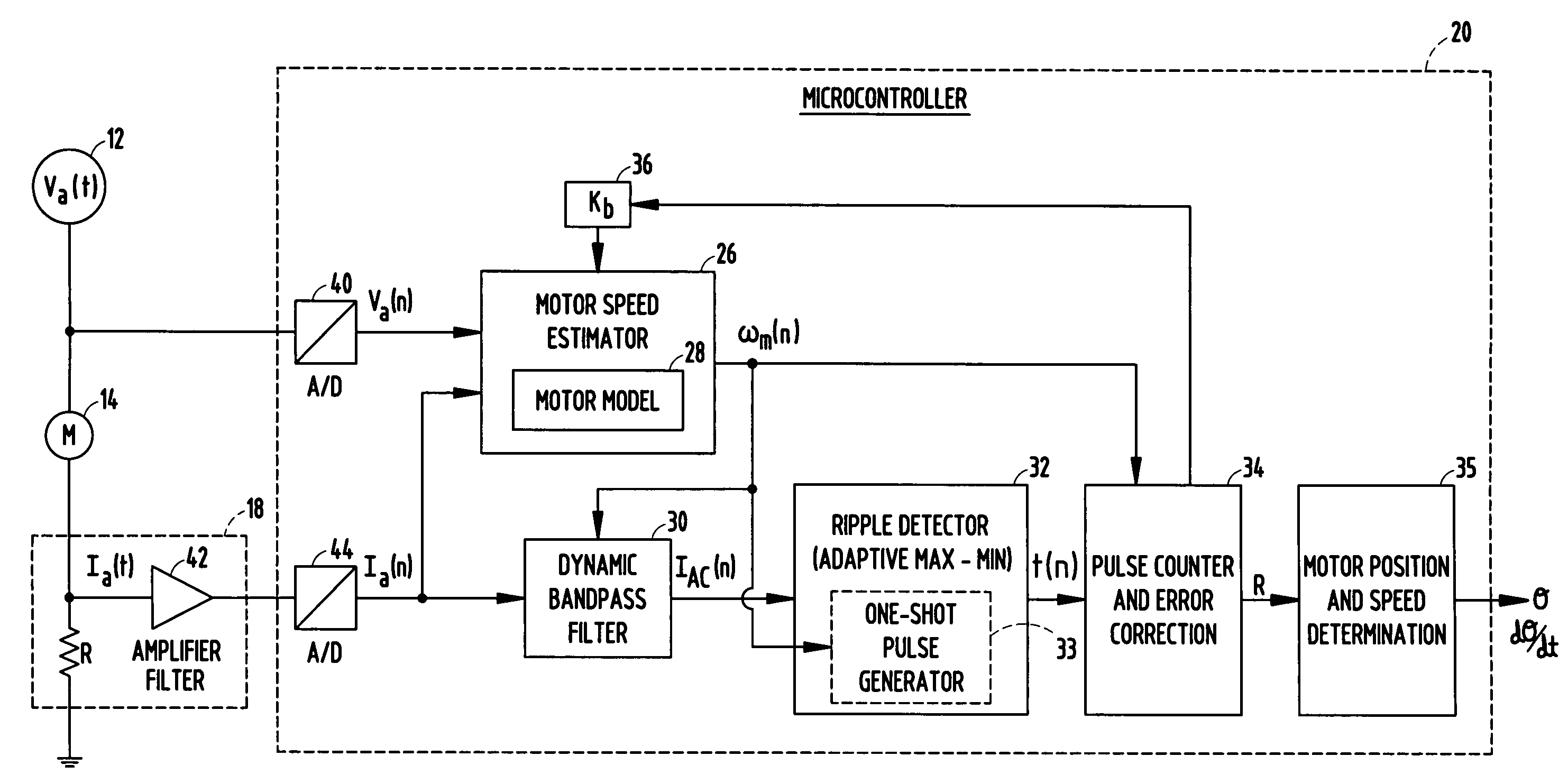

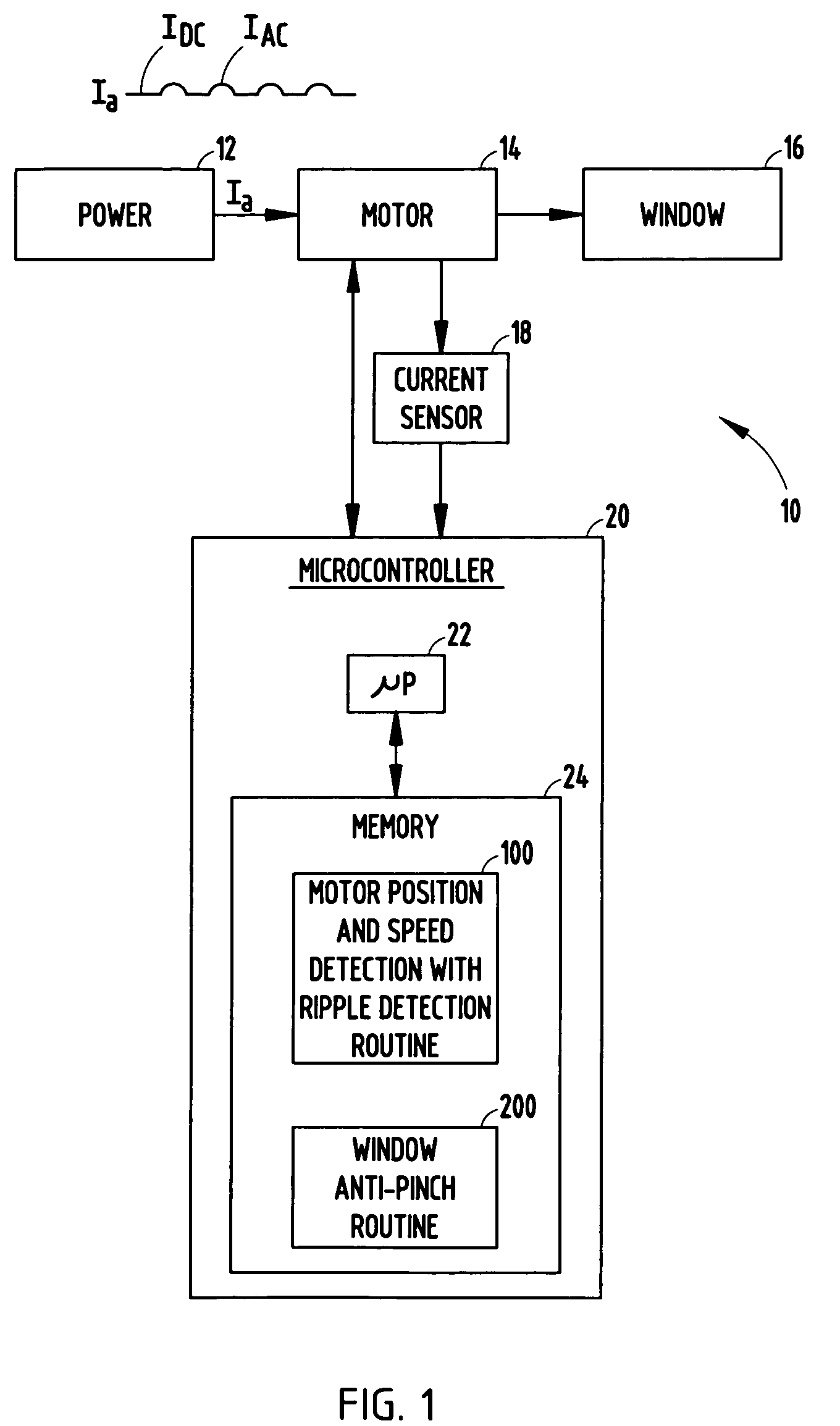

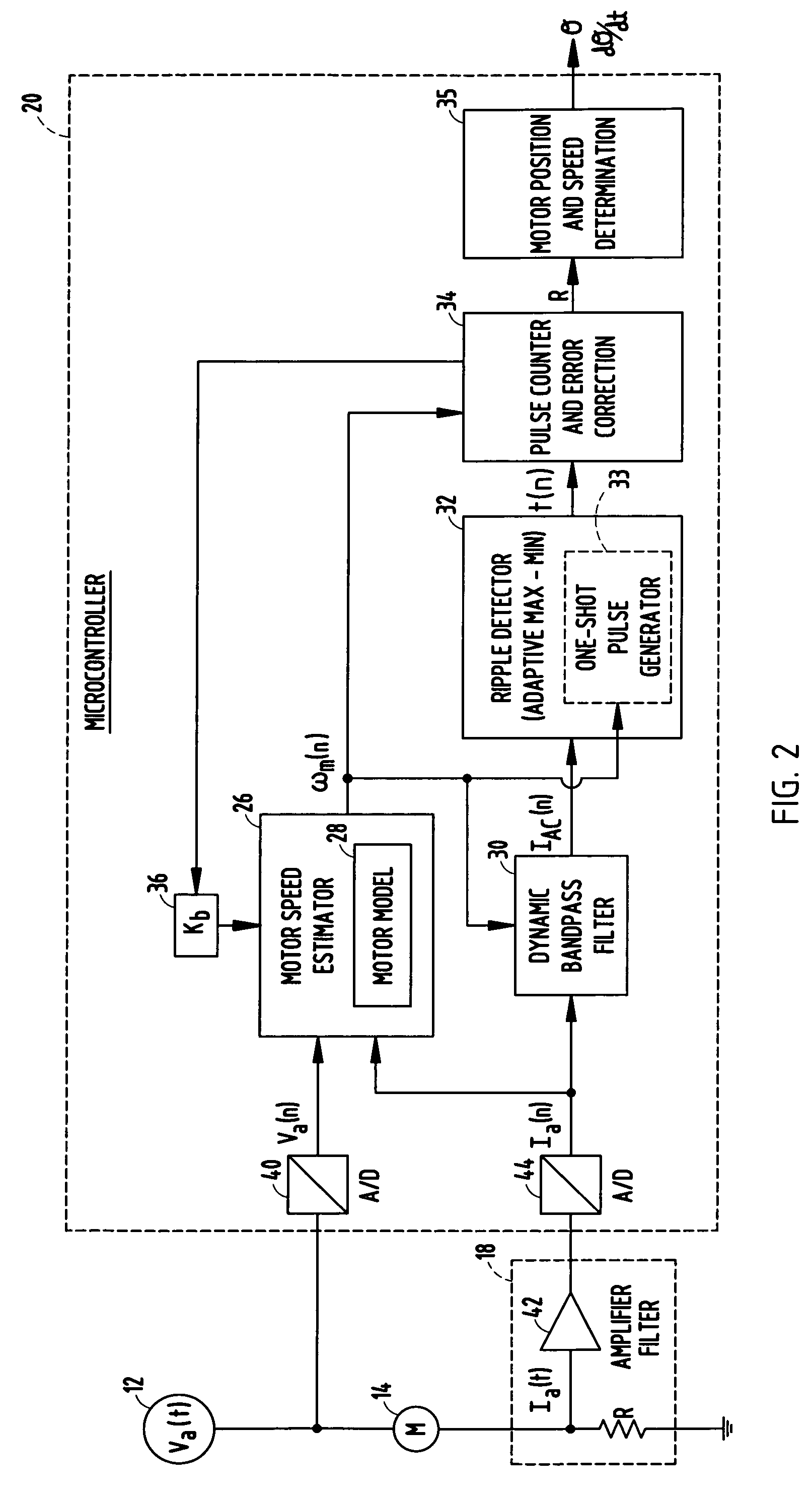

System and method for determining position or speed of a commutated DC motor with error correction

ActiveUS20090254300A1Torque ripple controlEmergency protective circuit arrangementsMotor speedControl system

A motor control system and method are provided for detecting current ripple in a commutated DC motor and further determining position and speed of the motor based on the detected ripple current. Ripples in the motor current are detected and a ripple frequency is calculated based on the time between successive ripples. A ripple count between successive frequencies is determined and the ripple count is compared to a threshold value, and an estimated ripple frequency is determined from a motor model when the ripple count exceeds the threshold value. A corrected ripple count is calculated from a ratio of the calculated ripple frequency and the estimated ripple frequency, and motor position and motor speed are determined based on the corrected ripple count.

Owner:APTIV TECH LTD

High frequency measuring circuit

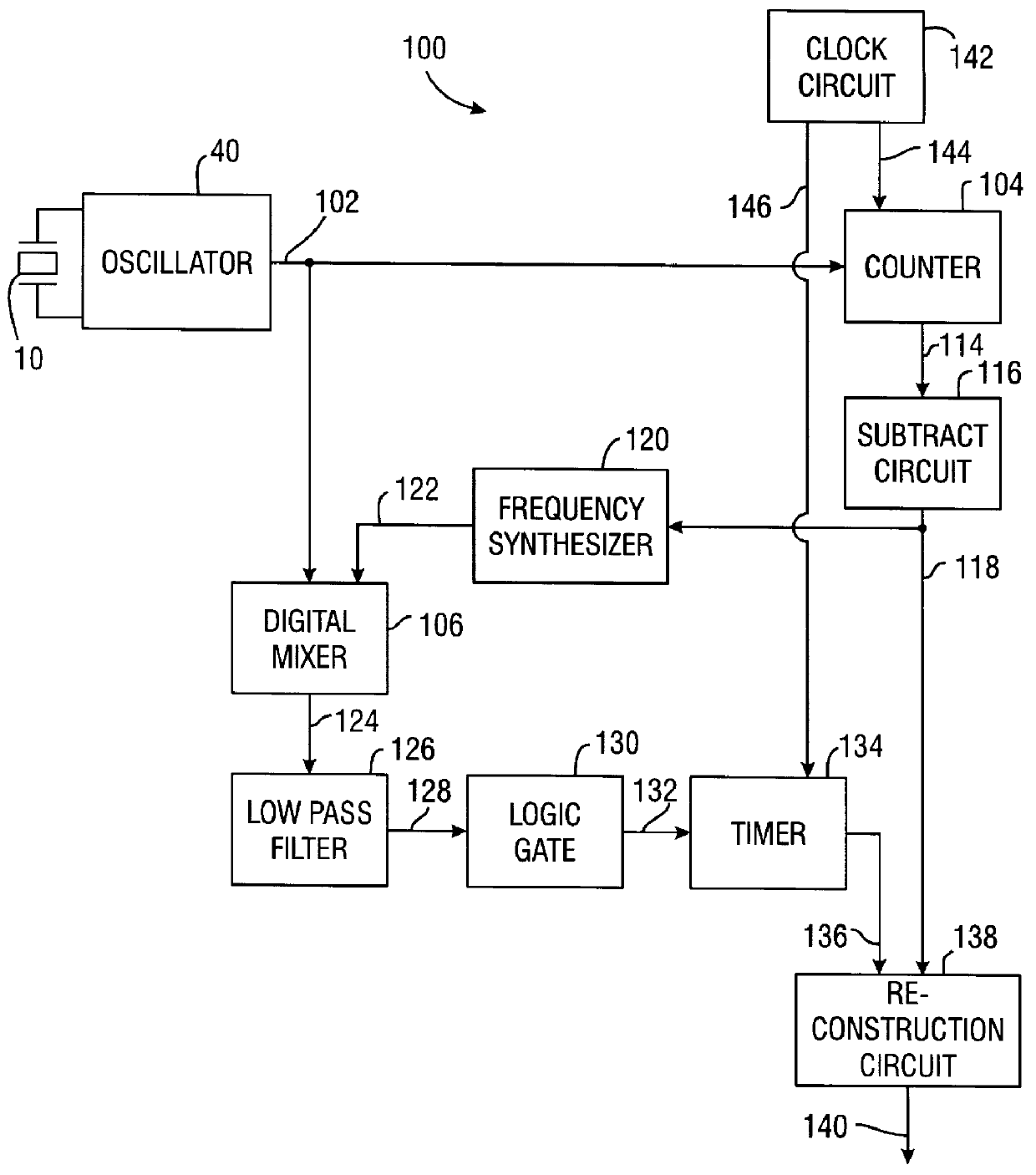

InactiveUS6161420ALow costReduce concentrationVibration measurement in solidsAnalysing fluids using sonic/ultrasonic/infrasonic wavesAcoustic waveOscillistor

An electrical circuit and method for measuring small variations in a high frequency signal is disclosed. The circuit generates a coarse measurement of the input signal frequency and a reference signal having the same frequency as the frequency represented by the coarse measurement. The circuit measures the difference in frequency between the input signal and the reference signal, and adds the coarse measurement and the difference measurement to determine the frequency of the input signal. The circuit may be used in conjunction with a piezoelectric acoustic wave device and oscillator to provide an apparatus for accurately measuring low concentrations of a gas.

Owner:FISHER CONTROLS INT LLC

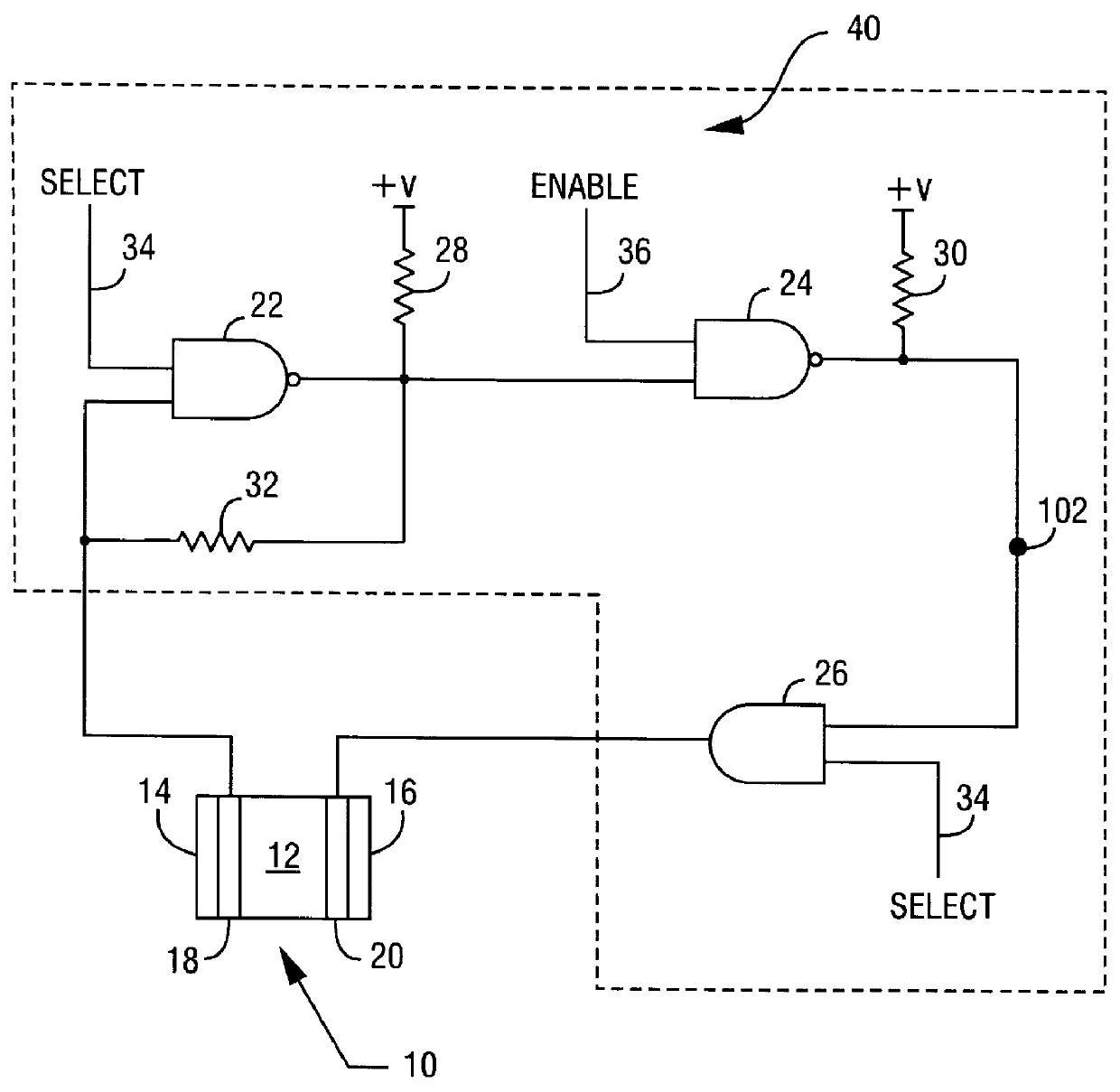

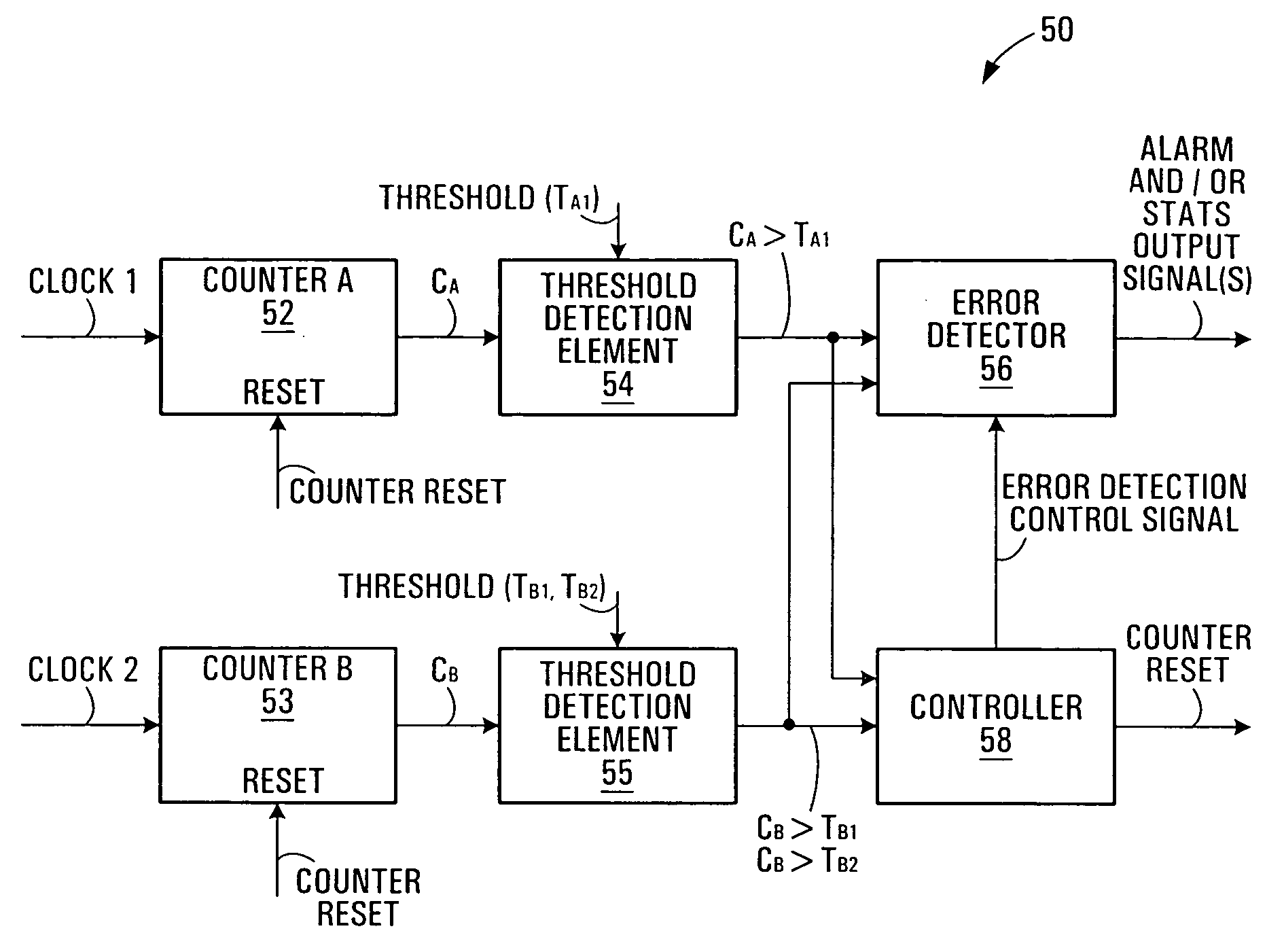

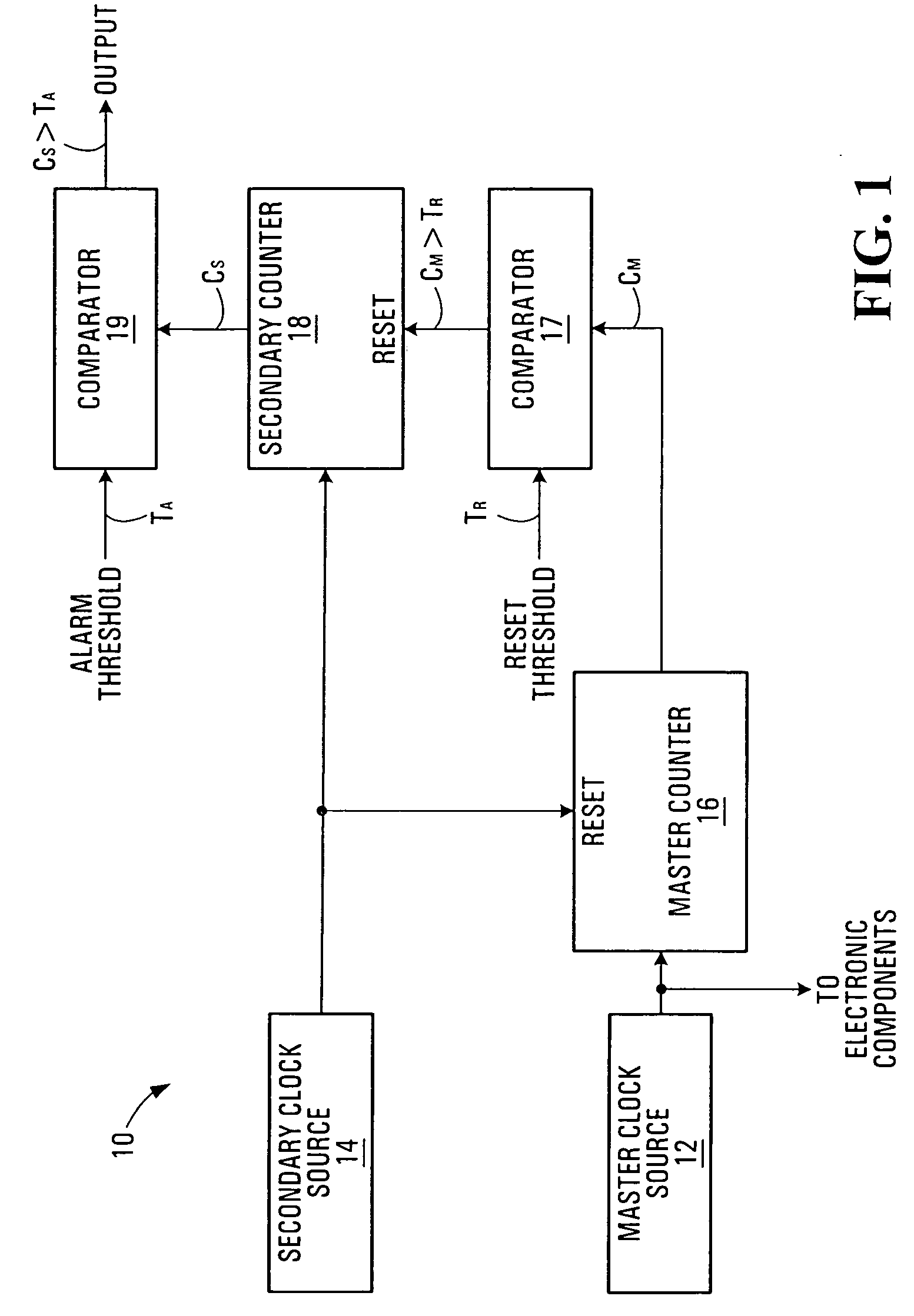

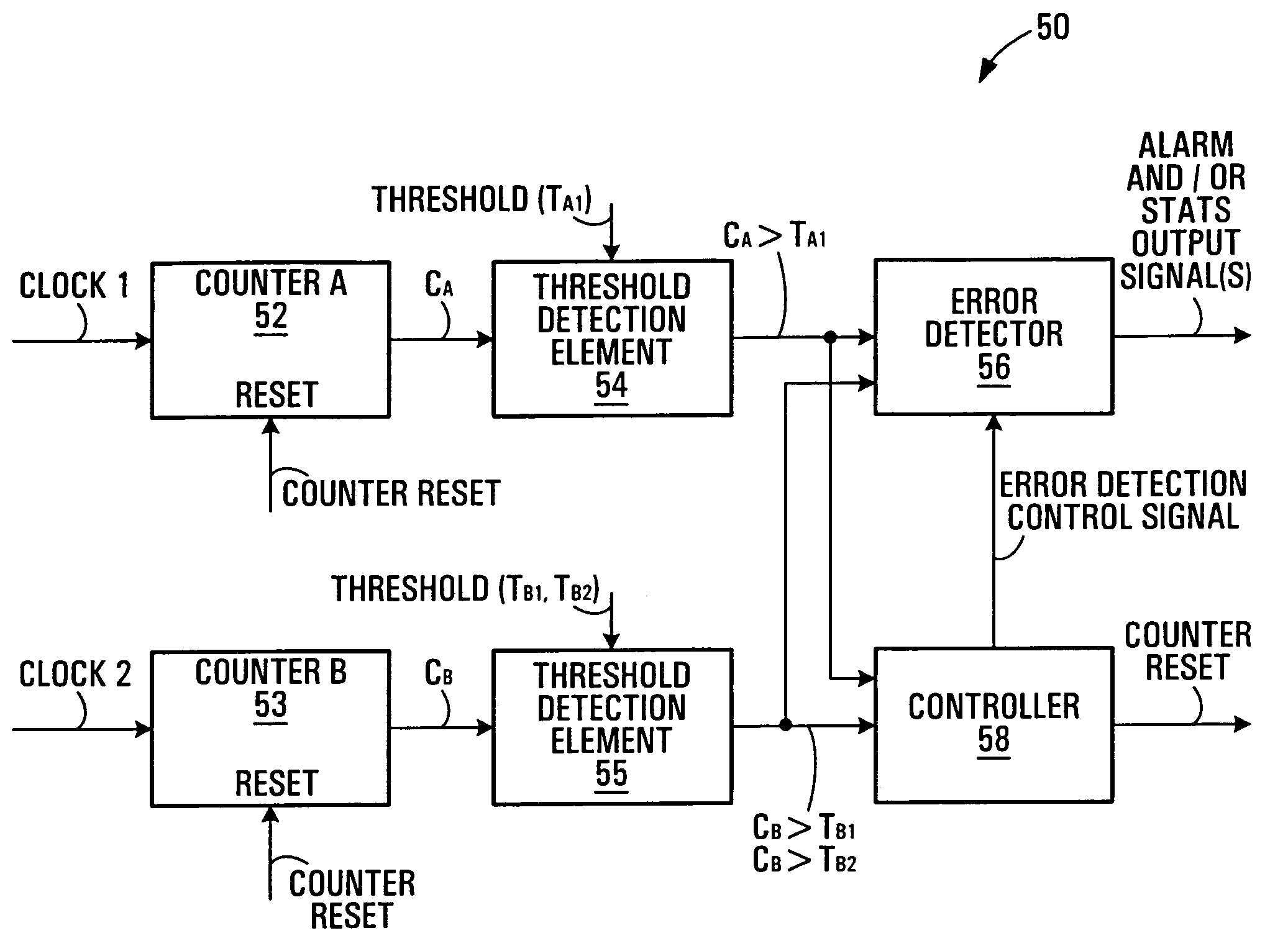

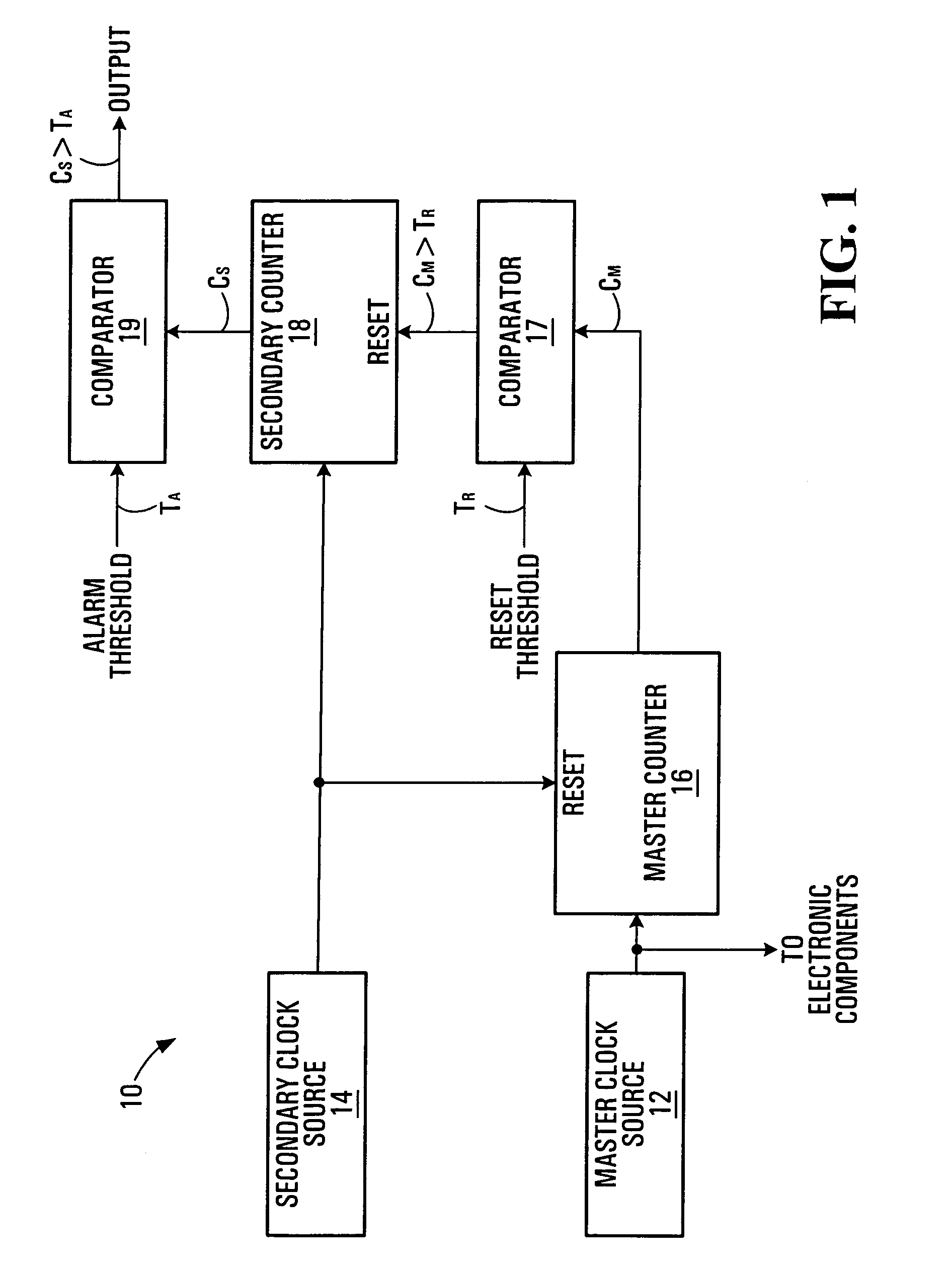

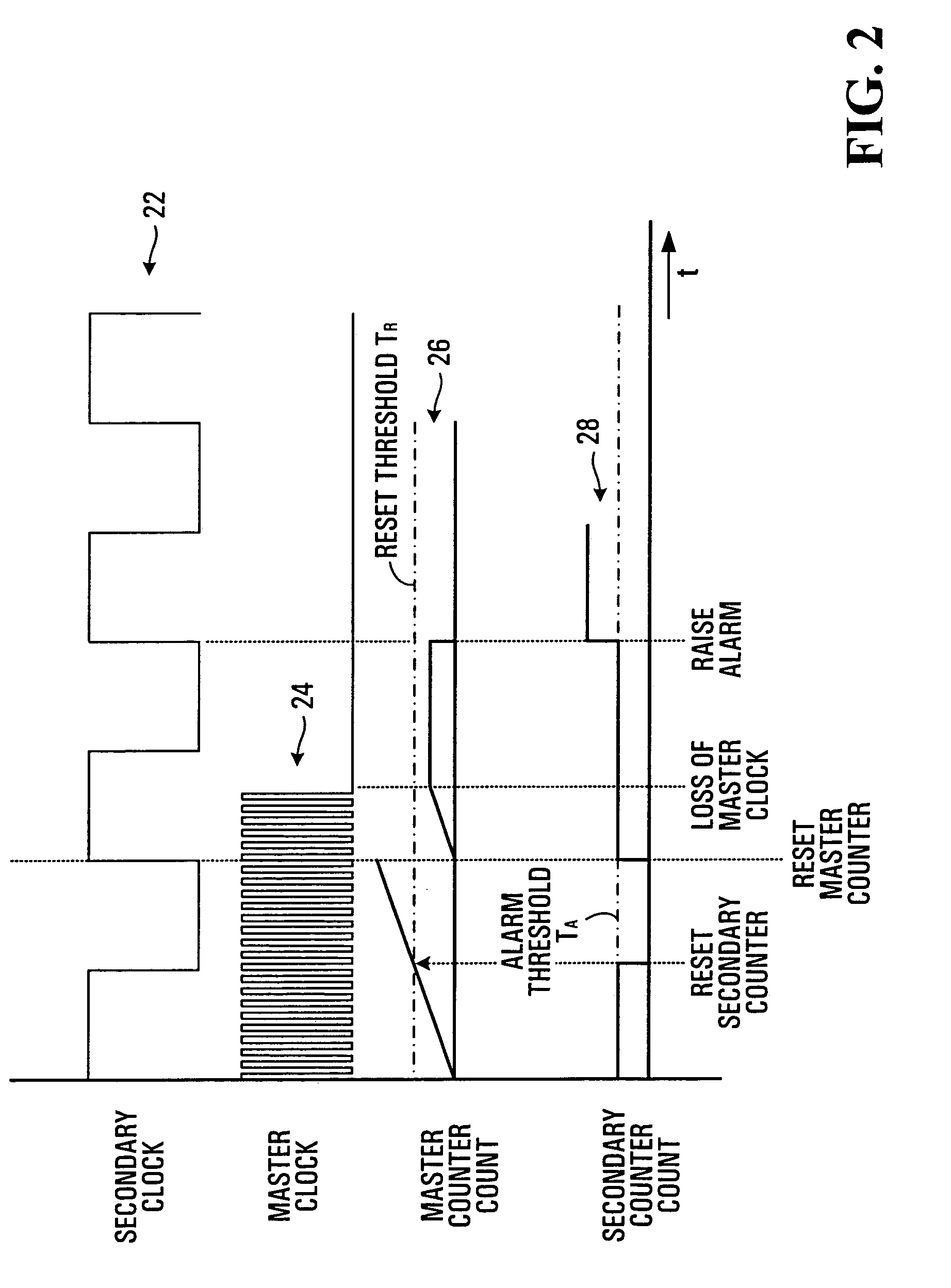

Periodic electrical signal frequency monitoring systems and methods

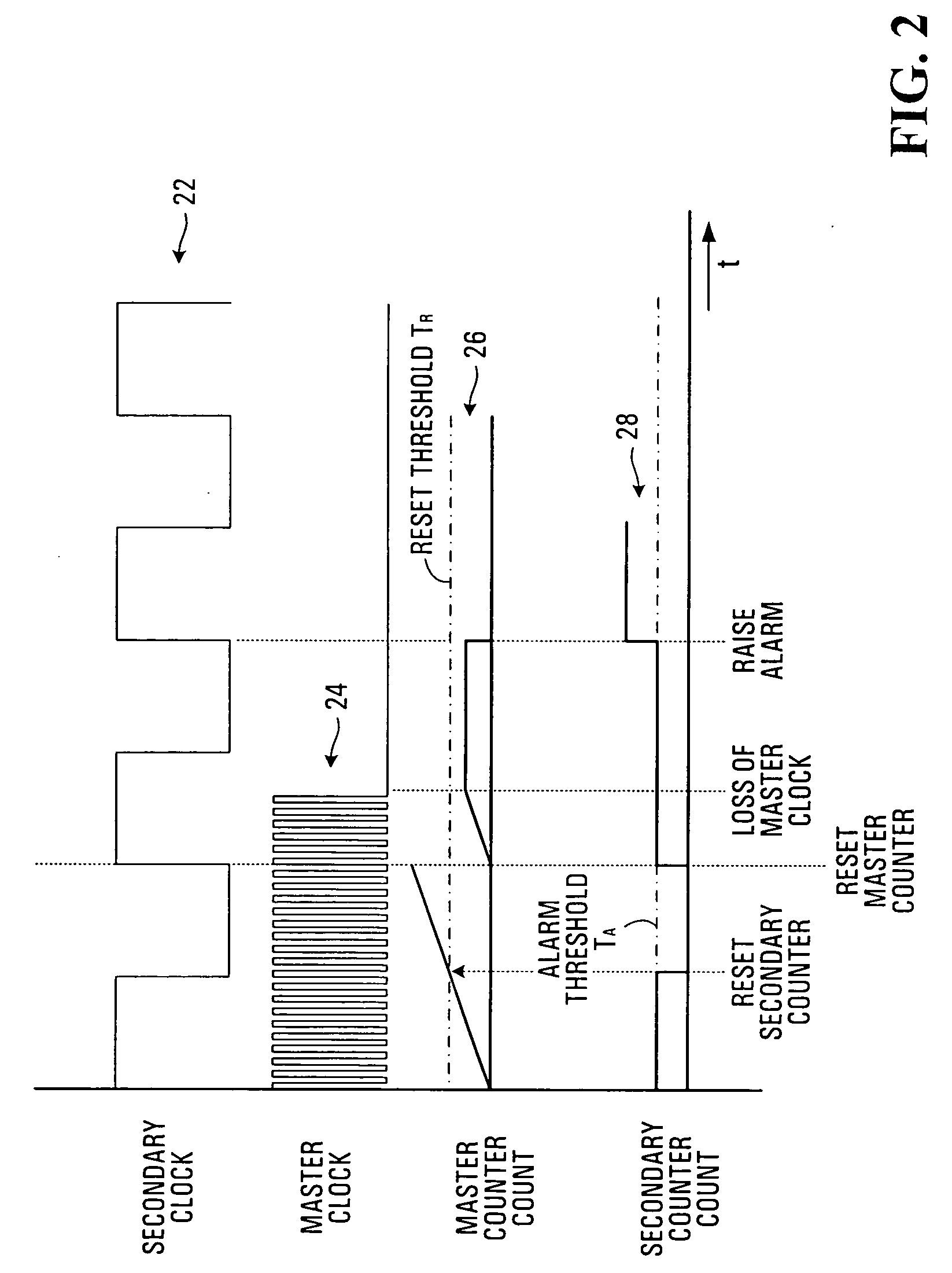

ActiveUS20060132190A1Frequency/rate-modulated pulse demodulationFrequency to pulse train conversionElectricityEngineering

Systems and methods for monitoring frequencies of periodic electrical signals are disclosed. According to one technique, a first and second counters are respectively clocked by a first periodic electrical signal to be monitored and a second periodic electrical, and a threshold detector resets one of the counters when a count of the other counter crosses a reset threshold and determines whether a frequency error has occurred based on whether a count of the one of the counters crosses an alarm threshold. Another technique according to an embodiment of the invention also involves clocking counters with respective periodic electrical signals, although error detection is based on whether the counts of the counters cross respective associated thresholds in other than a particular sequence with respect to each other.

Owner:ALCATEL LUCENT SAS

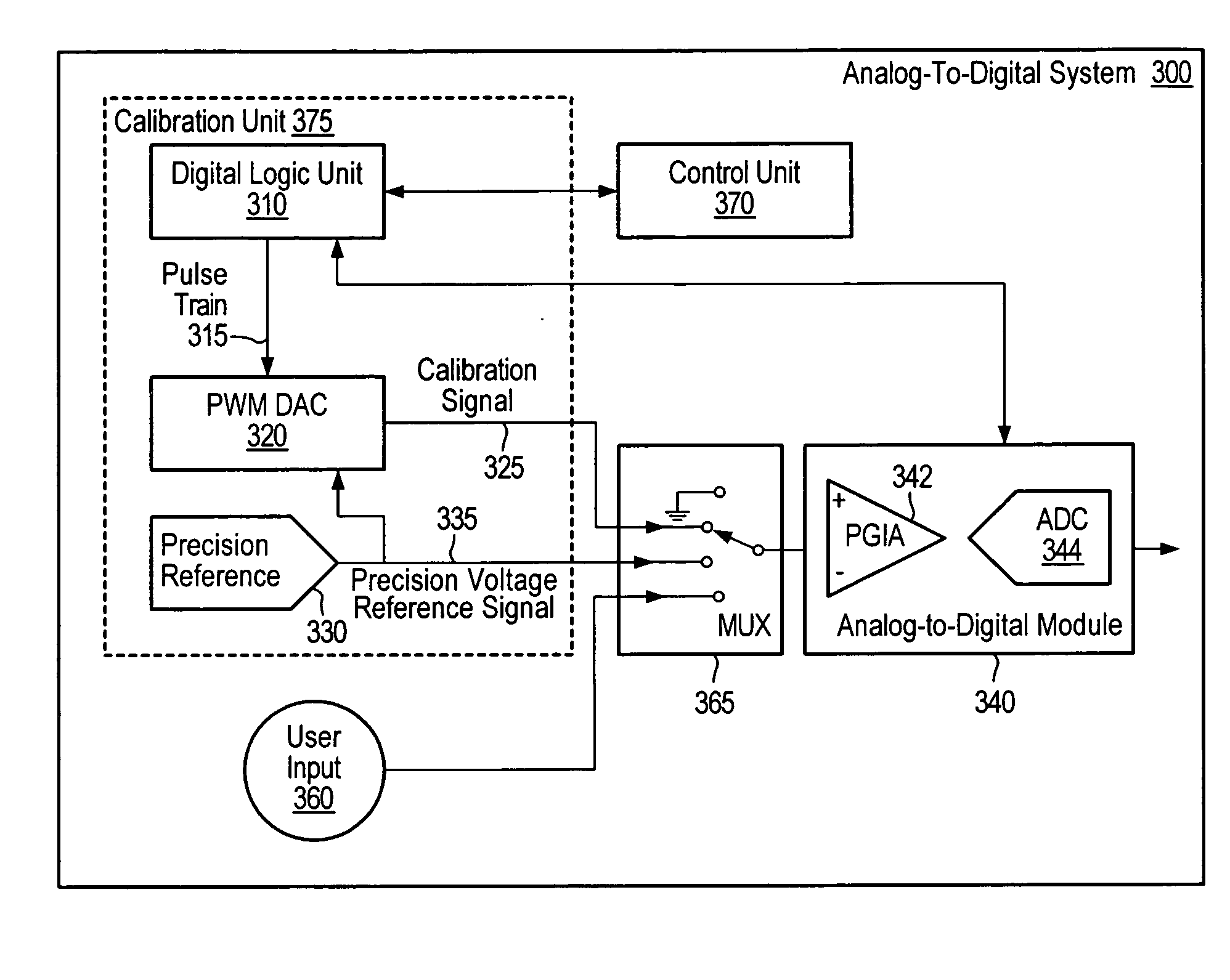

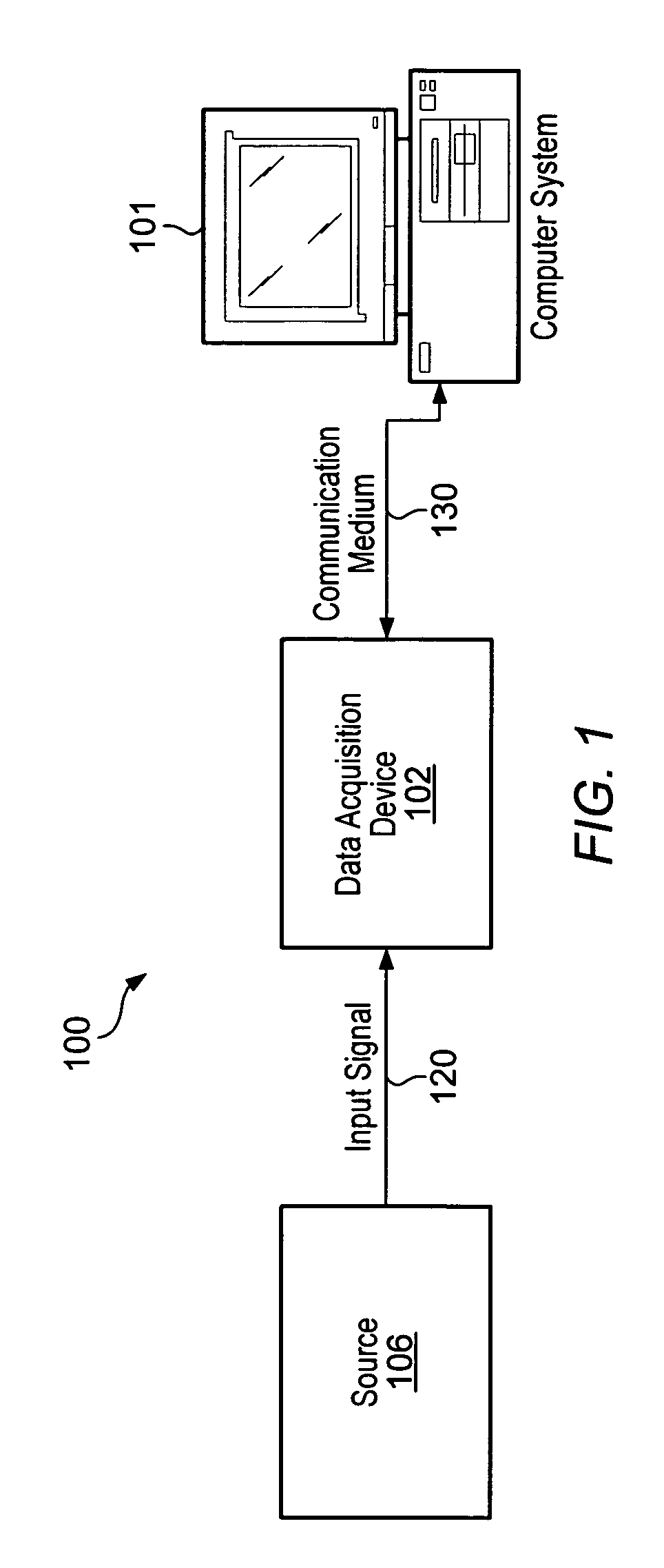

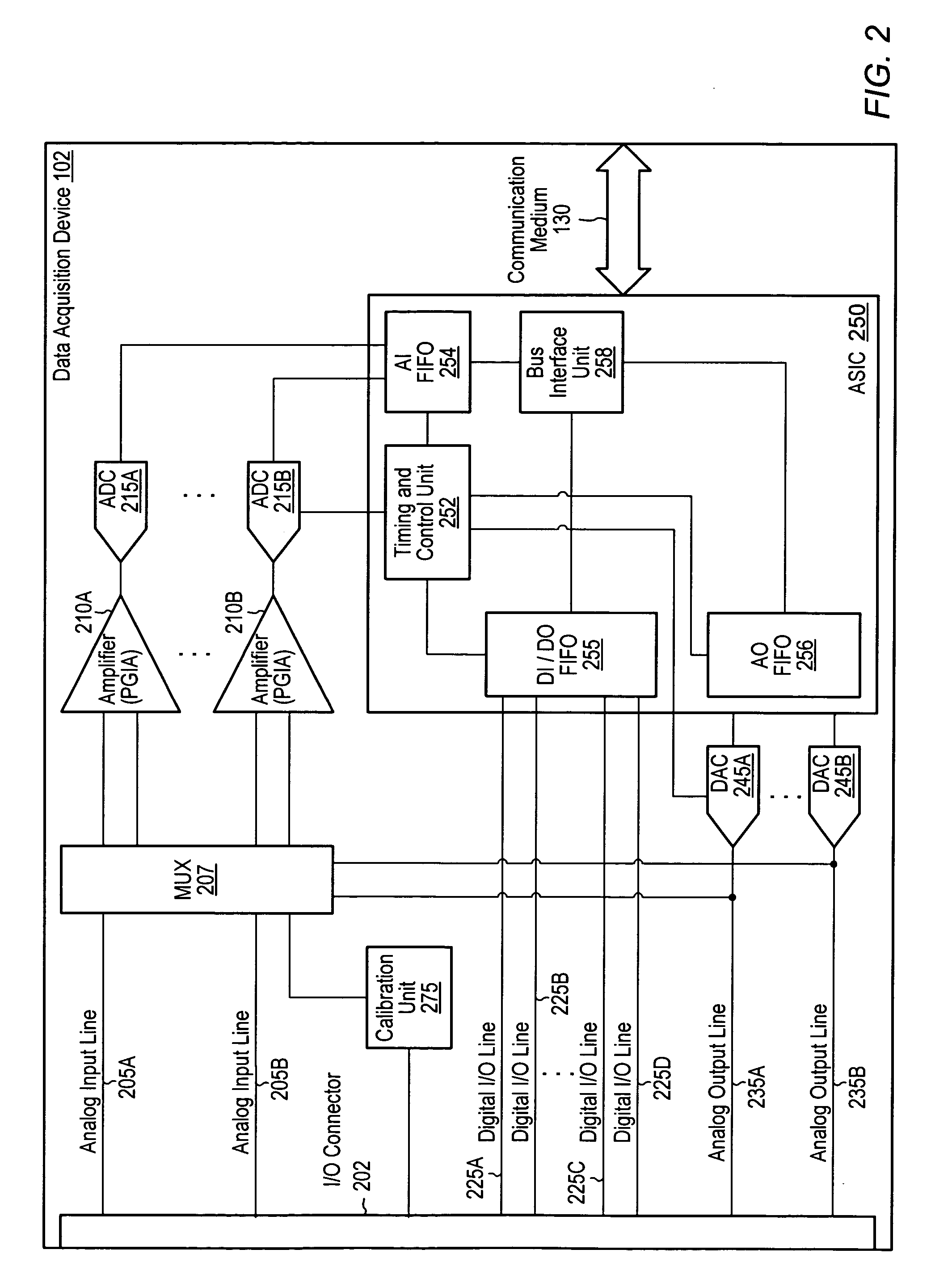

Calibrating analog-to-digital systems using a precision reference and a pulse-width modulation circuit to reduce local and large signal nonlinearities

ActiveUS20050197796A1Reduce measurementReduce large signal nonlinearitiesElectric signal transmission systemsVoltage-current phase angleElectrical resistance and conductanceData acquisition

A calibration unit and technique for calibrating A / D systems (e.g., data acquisition devices) using a pulse-width modulation (PWM) circuit to reduce nonlinearity. The calibration unit may be coupled to an analog-to-digital module (ADM) of the A / D system. The PWM circuit may generate a calibration signal with intentional ripple, which may exercise a region of a transfer curve of the ADM to reduce local nonlinearities in measurements associated with the calibration of the system. Pulse trains of varying frequency and duty cycle may be generated to sweep the PWM circuit through an ADM range and to calculate an ADM linearity correction function, which may be used to perform gain and offset correction with respect to a best-fit line through an ADM transfer curve to reduce large signal nonlinearities. The PWM circuit may include a resistor divider circuit including a plurality of taps to improve the ability to calibrate small input ranges.

Owner:NATIONAL INSTRUMENTS

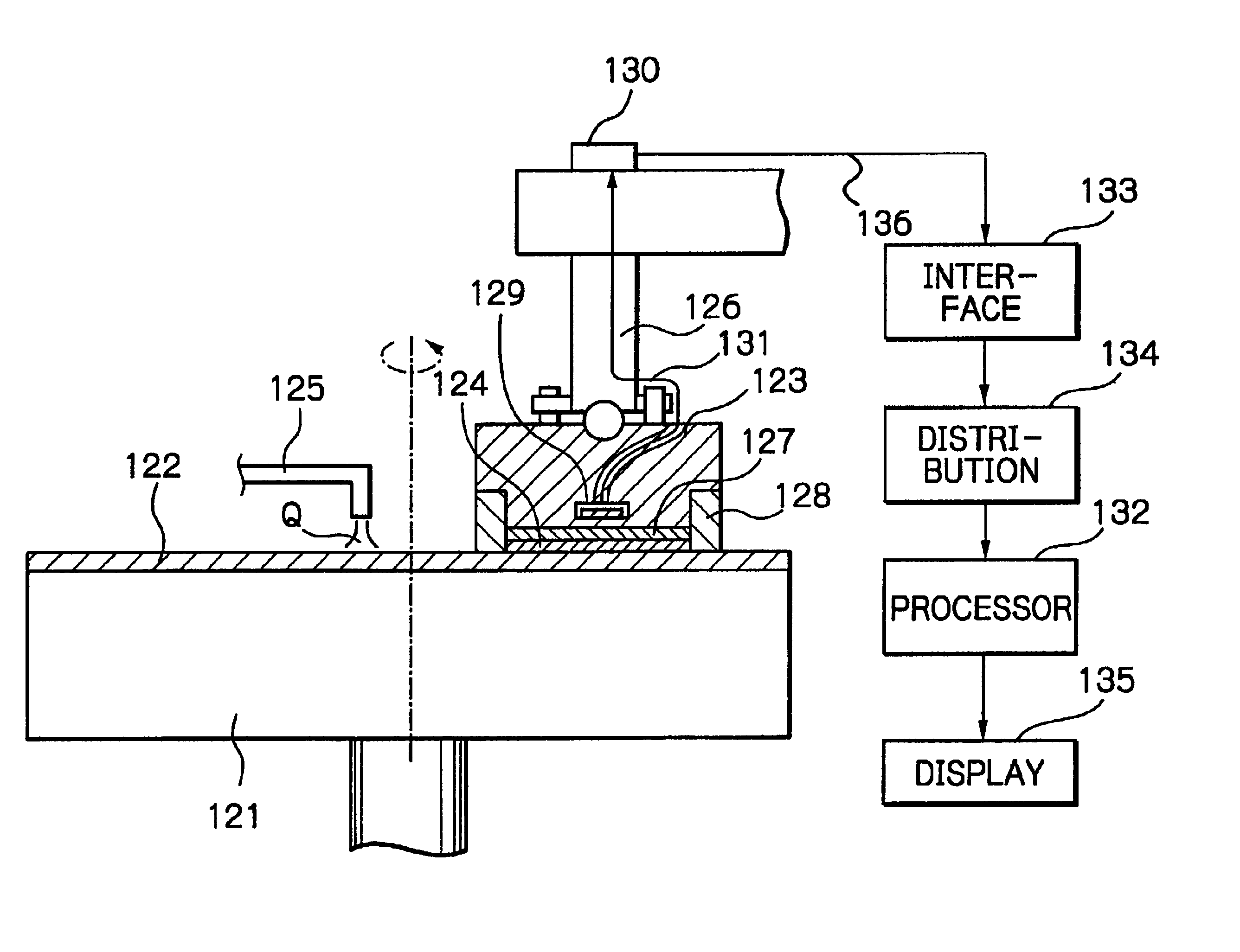

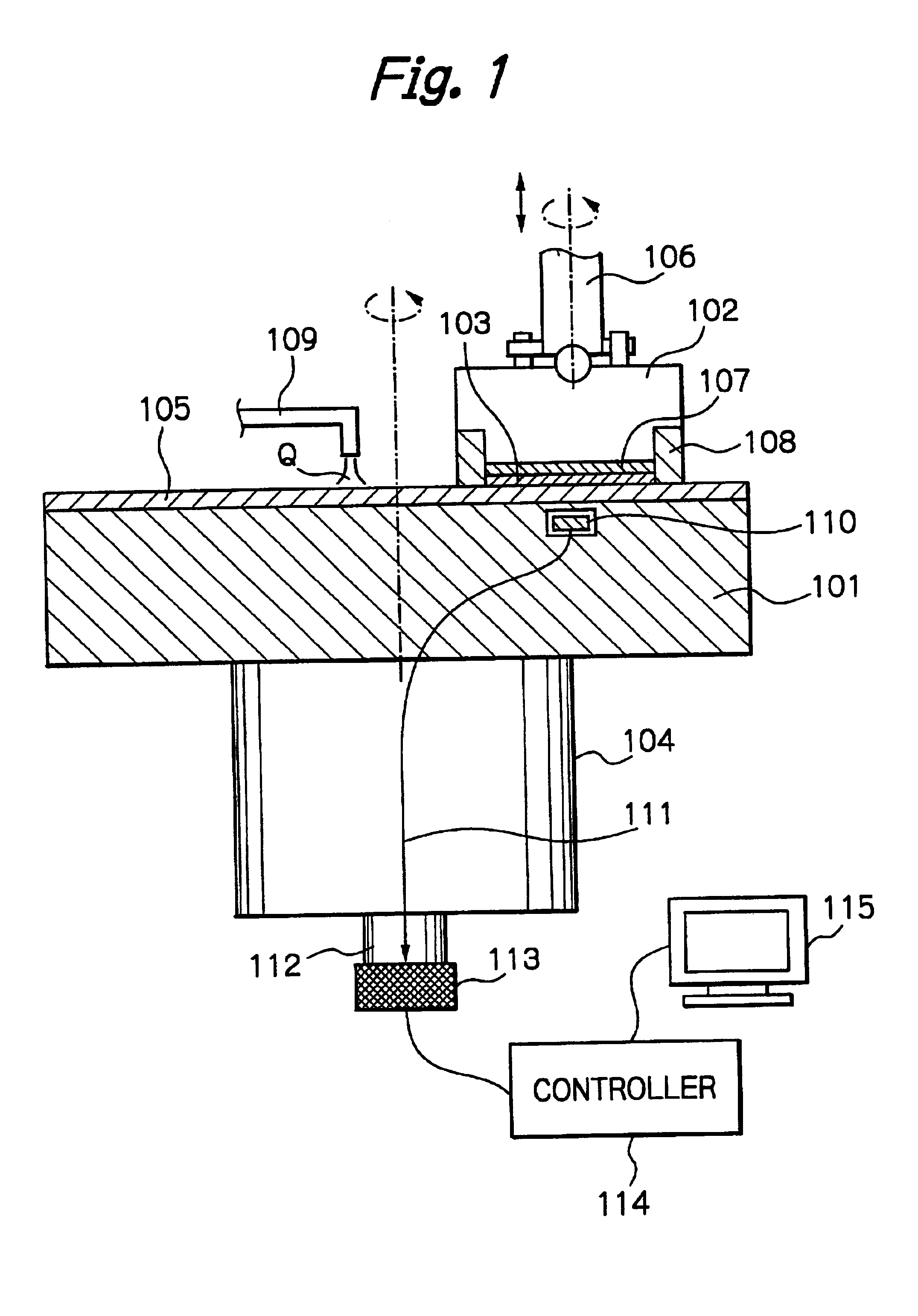

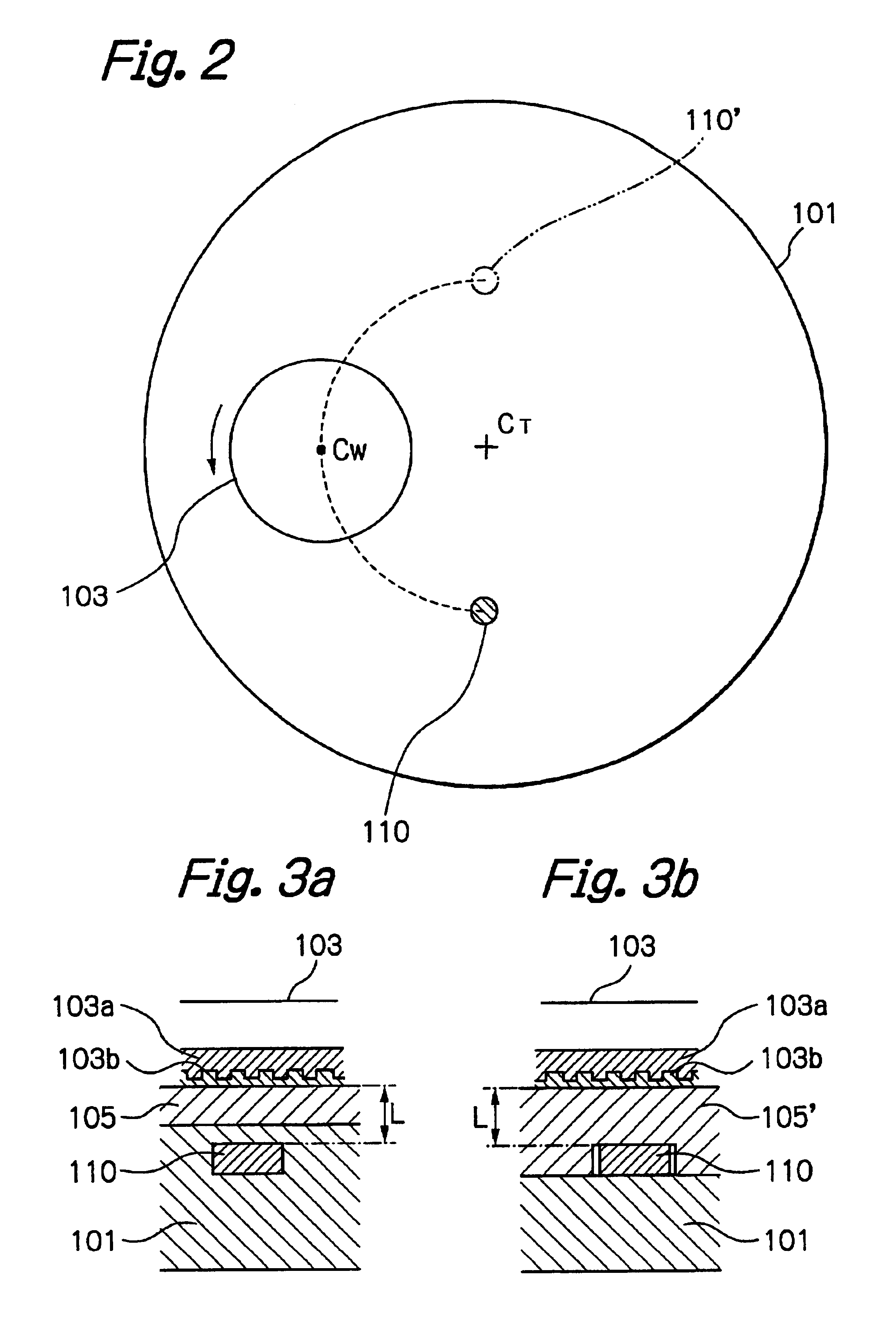

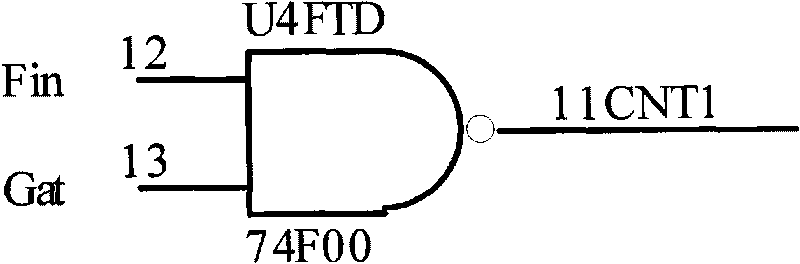

Frequency measuring device, polishing device using the same and eddy current sensor

InactiveUS7046001B2Improve accuracyShort time intervalSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingFrequency measurementsCurrent sensor

A frequency measuring device capable of accurately detecting an end point of polishing a semiconductor wafer by obtaining a frequency measurement result highly accurately in a short period of time. A device FC, which measures the frequency of a measured signal comprises a counting section including a plurality of n-nary counters, a time reference circuit which outputs a time reference signal for every predetermined time interval, and a plurality of gate circuits whose outputs are connected to the inputs of the n-nary counters. The gate circuits receive the measured signal at a first input and receive the time reference signal at the predetermined time intervals at a second input. With this structure, the counting section supplies the frequency measured result of the measured signal every predetermined time interval.

Owner:SCI MED LIFE SYST +1

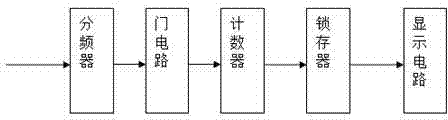

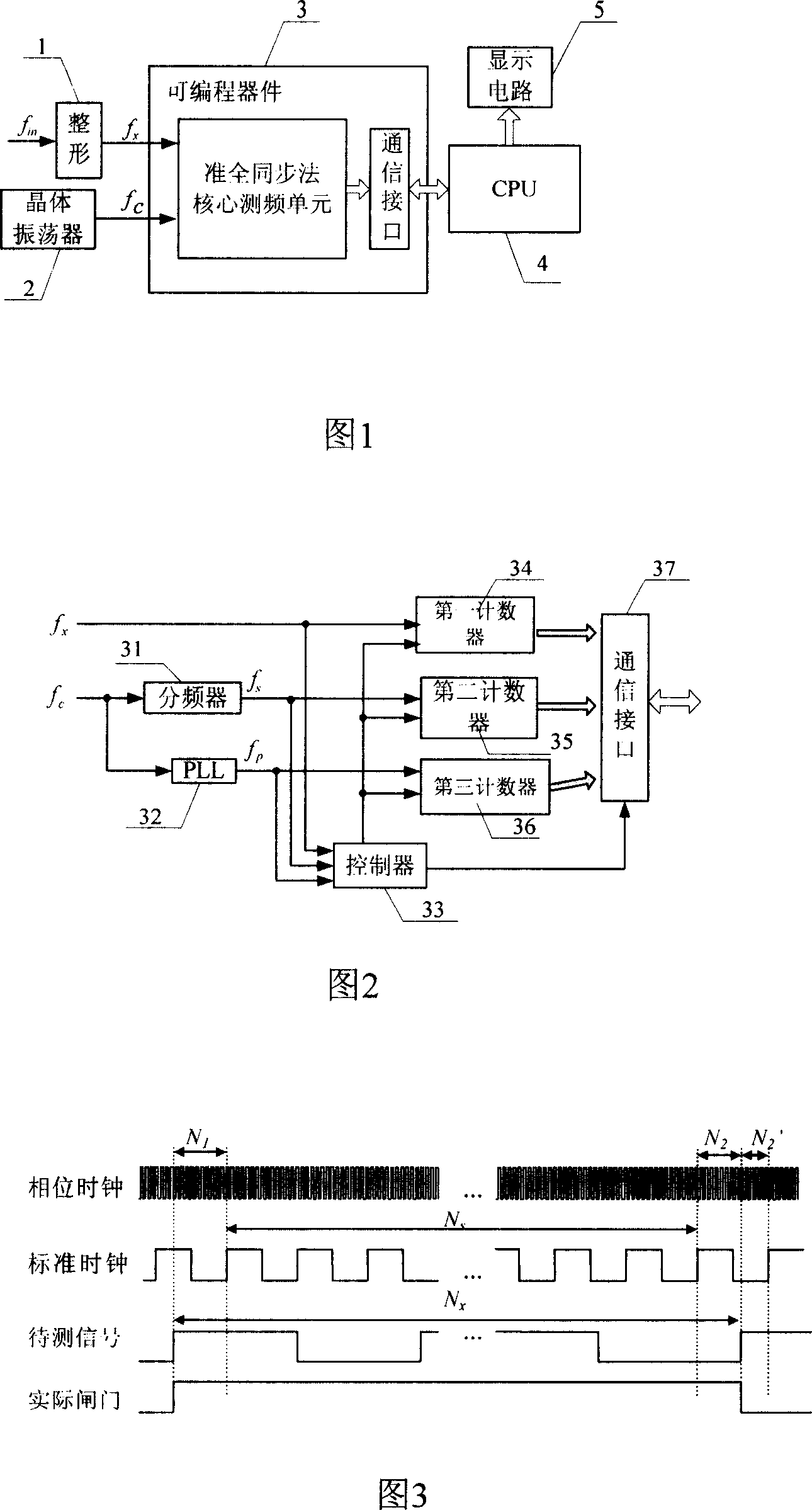

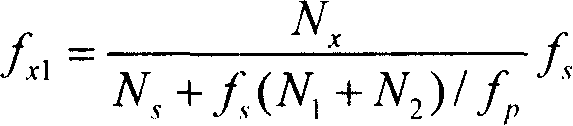

Quasi full-synchronous high-precision rapid frequency measuring device and method

InactiveCN101026781ASolving Complex DefectsReduce occupancyFrequency to pulse train conversionSelection arrangementsPhase differenceFpga implementations

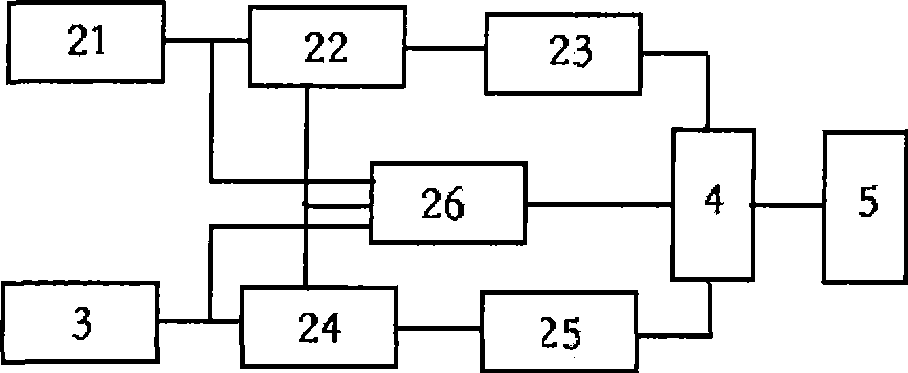

The measuring device includes waveform shaping circuit, crystal oscillator, programmable device, CPU and display unit. The input end of the waveform shaping circuit is connected to the input end of the programmable device. Connecting the programmable device, the crystal oscillator provides clock source for the programmable device. The programmable device is connected to CPU. CPU is in use for calculating frequency value. The output end of CPU is connected to the input end of the display circuit. The display circuit displays calculated result. Measuring phase difference between signal to be measured and standard clock raises measuring accuracy. Advantages are: quick measuring frequency with high precision, simple structure of circuit hardware, using dedicated chip to measure frequency to reduce cost, and using FPGA to implement the device.

Owner:NINGBO UNIV

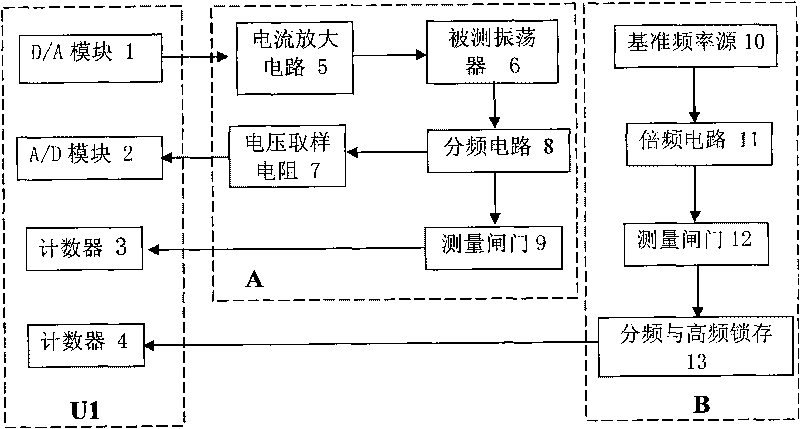

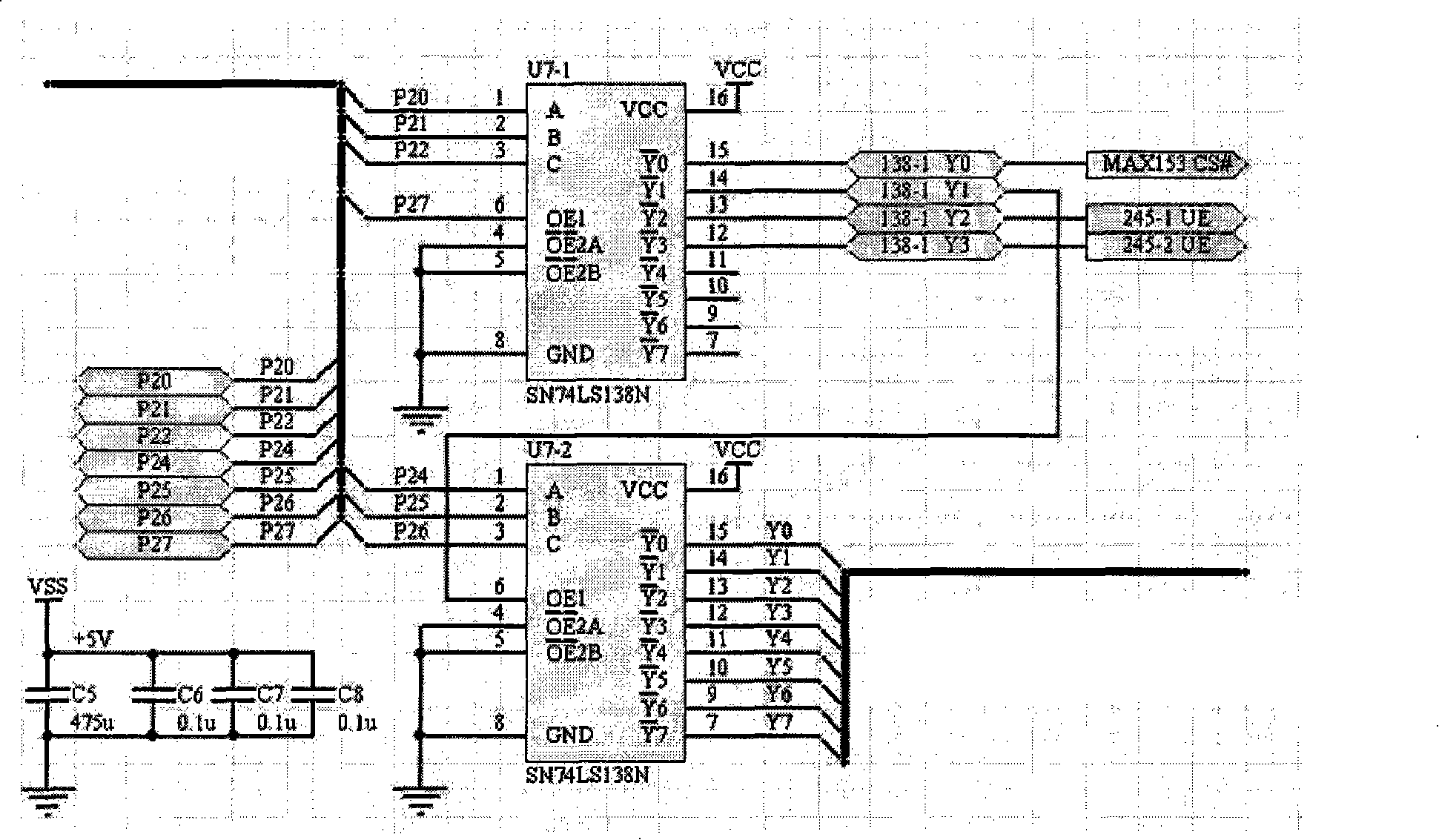

System for automatically testing parameters of quartz crystal oscillator

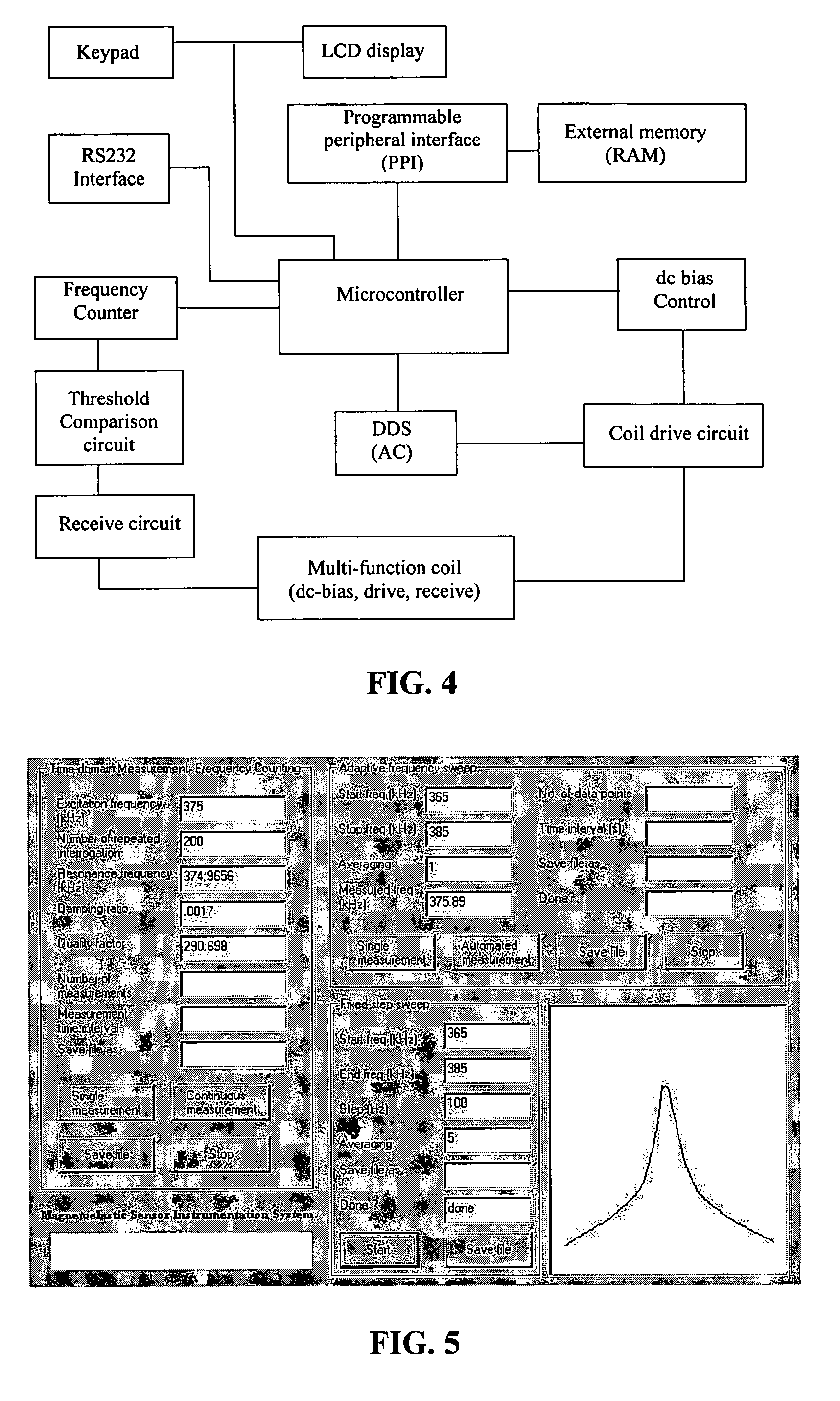

InactiveCN101713811AElectronic circuit testingFrequency to pulse train conversionMicrocontrollerFrequency counter

The invention discloses a system for automatically testing the parameters of a quartz crystal oscillator, which comprises a master computer and a parameter test card connected with the main board of the master computer, wherein the parameter test card comprises a singlechip and a test circuit and a reference circuit which are connected with the singlechip respectively. The singlechip has a D / A module, an A / D module, a first counter, a second counter and a timer. The test circuit comprises a current amplification circuit, a voltage sampling resistor, a frequency dividing circuit, a first measurement gate control circuit and the crystal oscillator to be measured. The reference circuit comprises a reference frequency source, a frequency multiplication circuit, a second measurement gate control circuit and a frequency dividing and high-frequency signal latch circuit. In the invention, the test card integrates the functions of all apparatuses such as a frequency counter, a digital voltmeter and a digital oscillometer and can be directly inserted in the main board of the computer, and the fully automatic test of various parameters, such as working frequency, working current and start up time, of the quartz crystal oscillator can be realized by a control program.

Owner:天津必利优科技发展有限公司

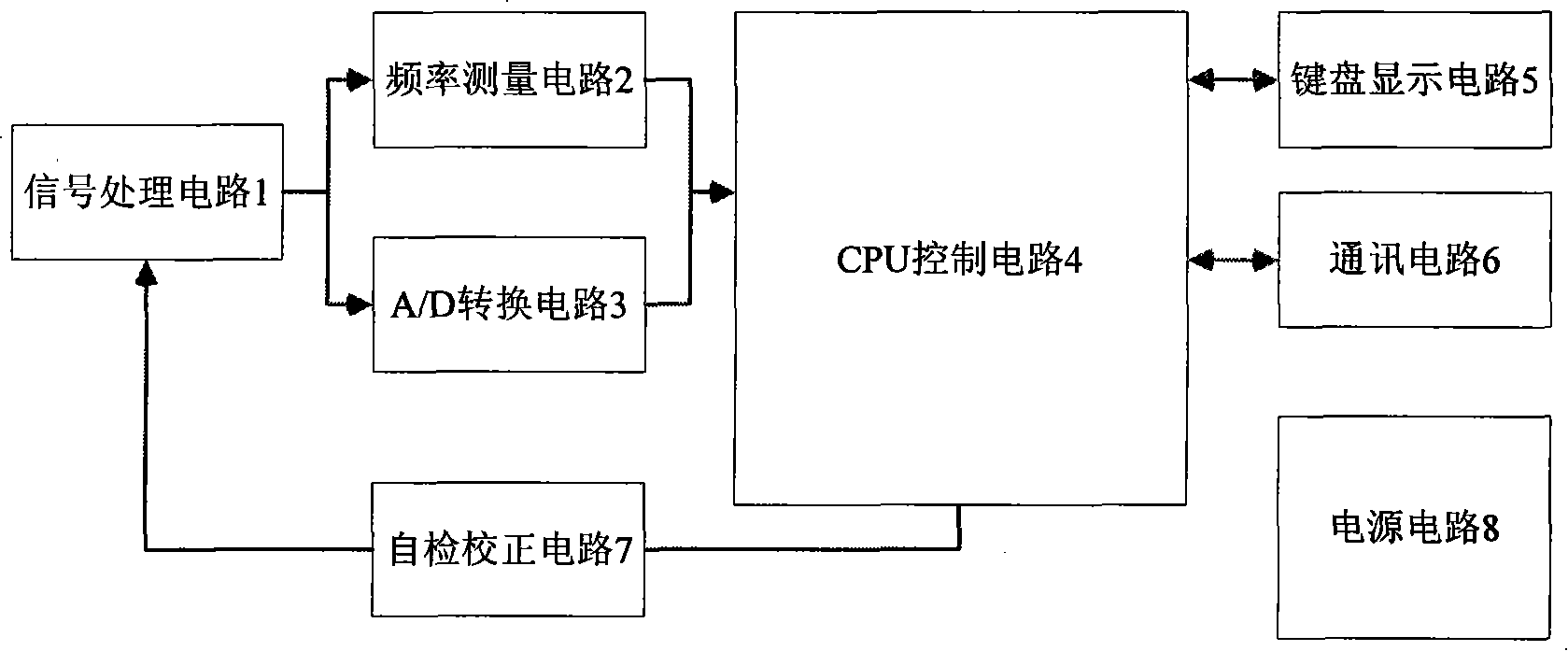

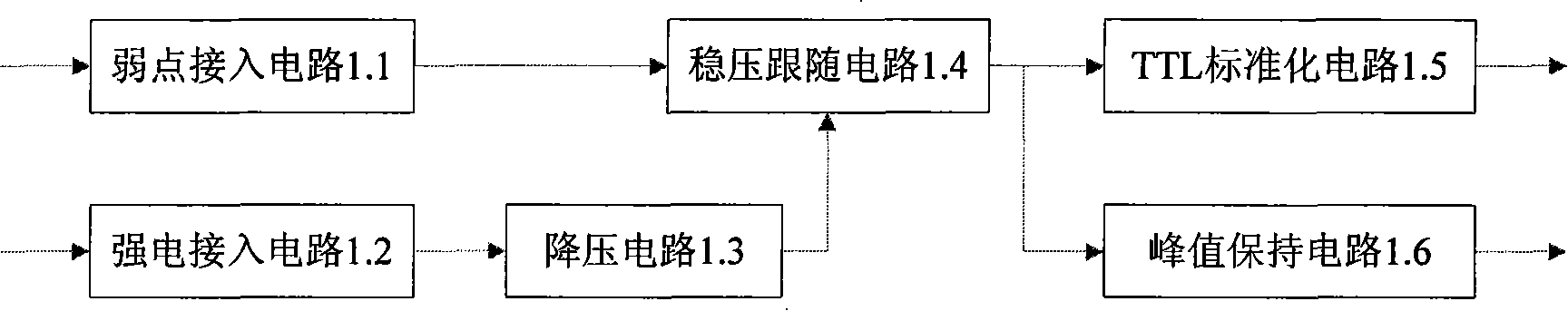

System and method for measuring and analyzing voltage frequency

InactiveCN101201365AHigh measurement accuracyWith visual analysis functionDigital variable displayFrequency to pulse train conversionFrequency conversionData acquisition

The invention provides a measurement and analysis system of the voltage and frequency and its analysis method. The invention can be applied in the fields of the detection, data acquisition and analysis, and the frequency conversion technology. The device can measure the voltage signal and the frequency signal, and the precision can reach as high as 10<-6>. The invention provides a calculation and analysis method of the linearity of the voltage-frequency curve Alpha out, the ratio of the voltage and frequency Kout and the base point of the voltage and frequency V50Hz, coordinates with the drawing and analysis method of the voltage-time, the frequency-time and the voltage-frequency curve, to provide the effective auxiliary analysis method for the operation condition of the variable frequency equipment, thereby realizing the function of low cost, high precise, wide-range measurement on the voltage and frequency and intelligent analysis function of the measurement results.

Owner:BEIJING UNIV OF TECH

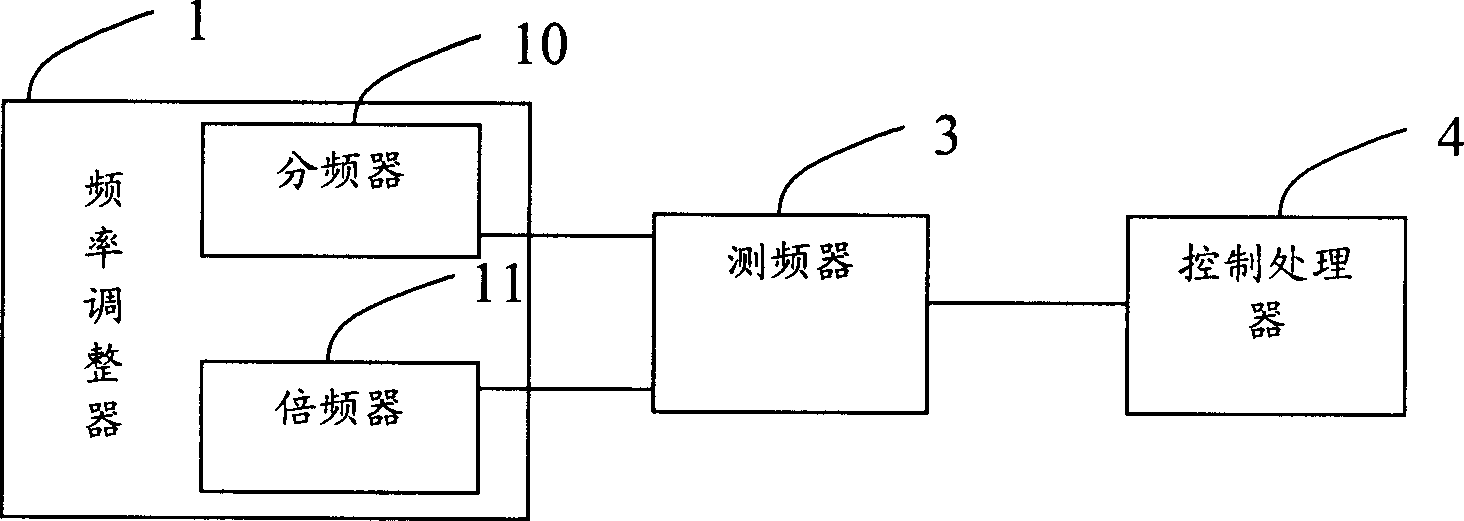

Fast frequency measuring system and method

InactiveCN1862263AQuick measurementHigh precisionFrequency to pulse train conversionFrequency measurementsPhysics

The present invention relates to a quick frequency measurement system and its method, belonging to the field of communication technology. Said system includes frequency regulator, frequency measurer and control processor. Said invention utilizes the frequency regulator to regulate tested signal and reference signal, prolong testing time length of tested signal, raise frequency of reference signal so as to obtain high-frequency count pulse, then the frequency measurer can utilize the above-mentioned high-frequency count pulse to measure regulated tested signal.

Owner:HUAWEI TECH CO LTD

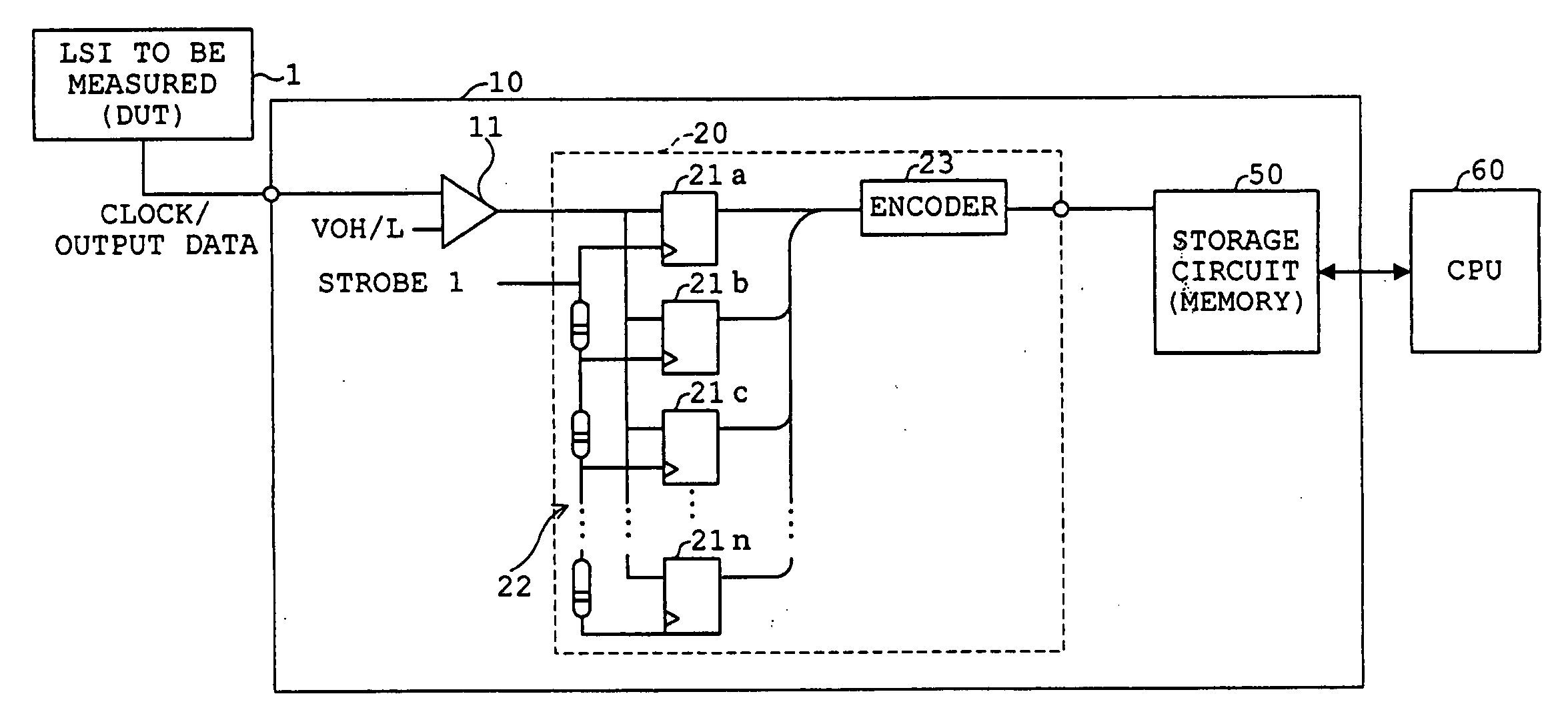

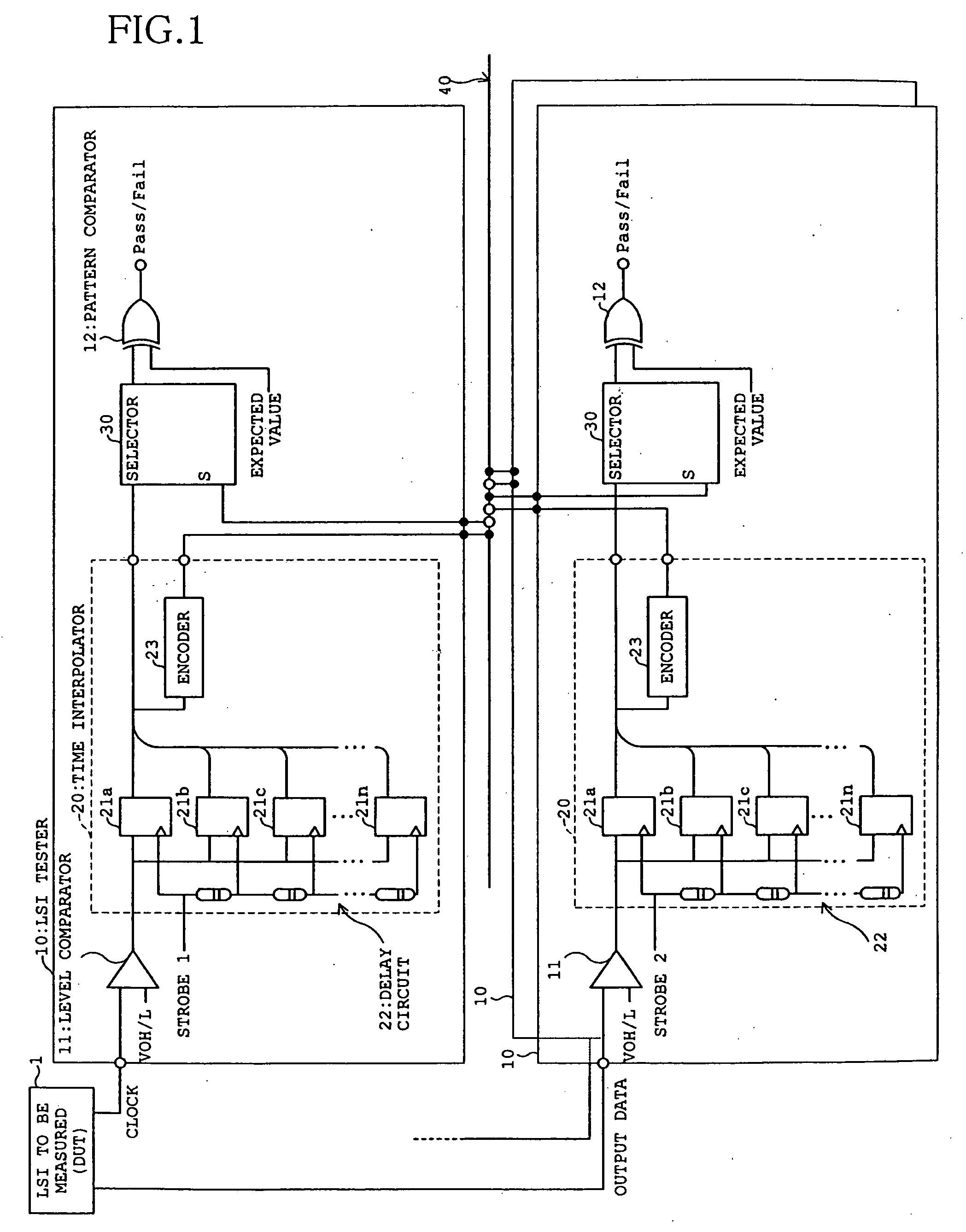

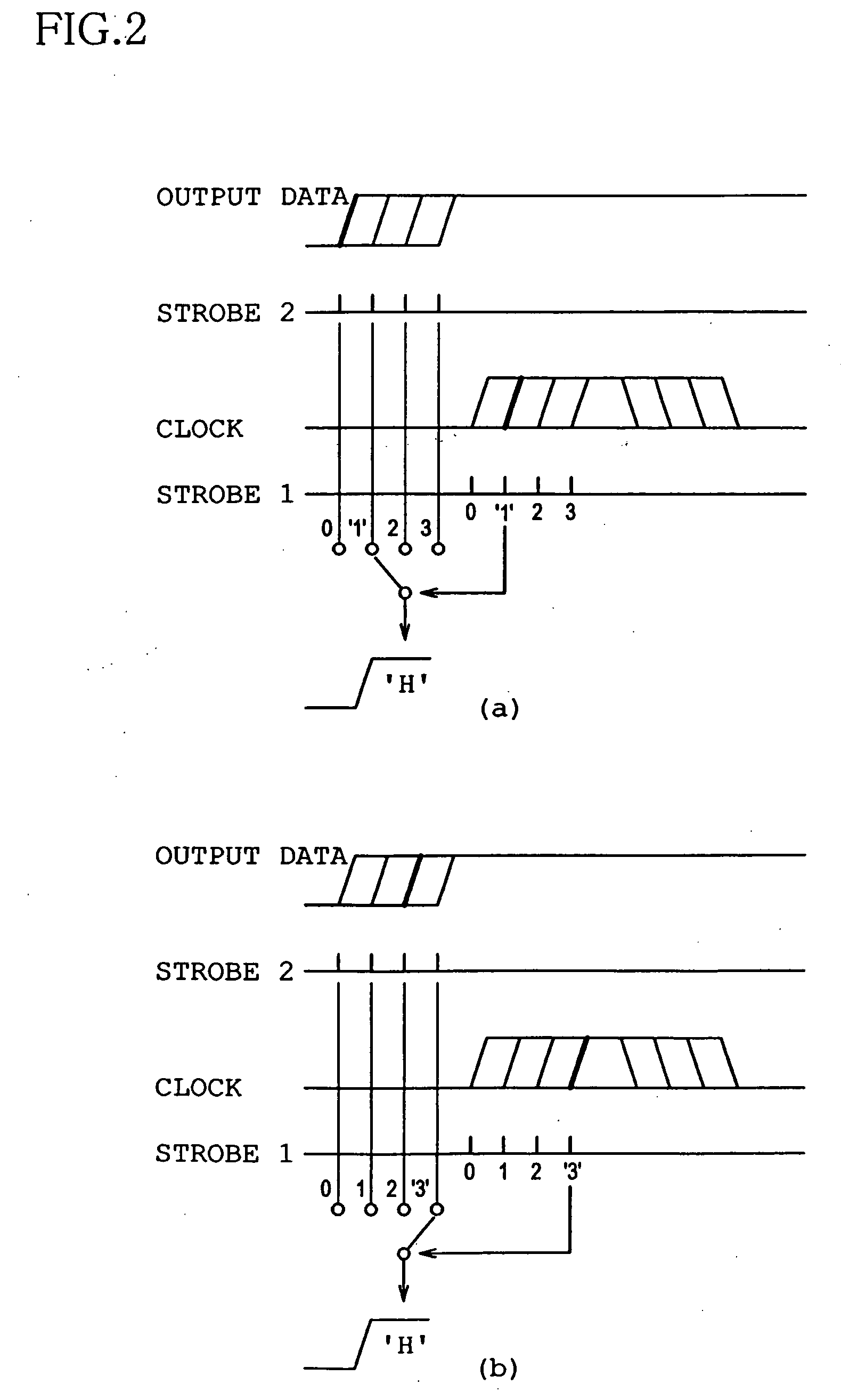

Device for testing lsi to be measured, jitter analyzer, and phase difference detector

InactiveUS20050080580A1High versatility and convenienceDigital circuit testingError detection/prevention using signal quality detectorData synchronizationPhase difference

An LSI test equipment can acquire output data of an LSI as a device under test by a clock signal output from the LSI to be measured and acquire measurement data synchronously with the output data having jitter. The LSI test equipment (10) includes a clock side time interpolator (20) for acquiring the clock output from the LSI (1) to be measured by a plurality of strobes having a predetermined timing interval and outputting it as encoded level data of time series, a data side time interpolator (20) for acquiring the output data output from the LSI (1) to be measured by a plurality of strobes having a predetermined timing interval and outputting it as level data of time series, and a selector (30) for receiving the level data from both of the time interpolators, selecting output data at the clock edge timing, and outputting it as data to be measured.

Owner:ADVANTEST CORP

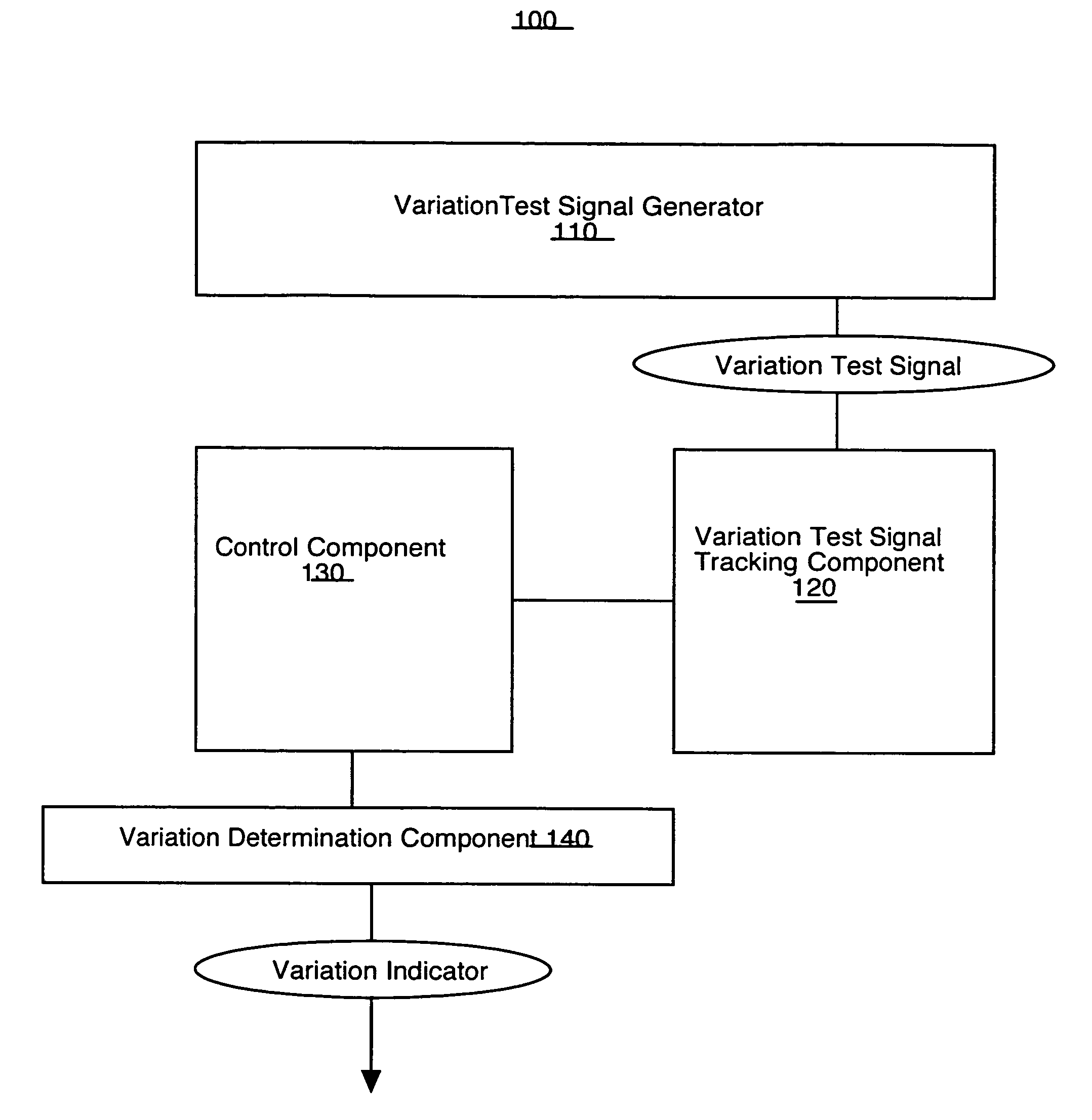

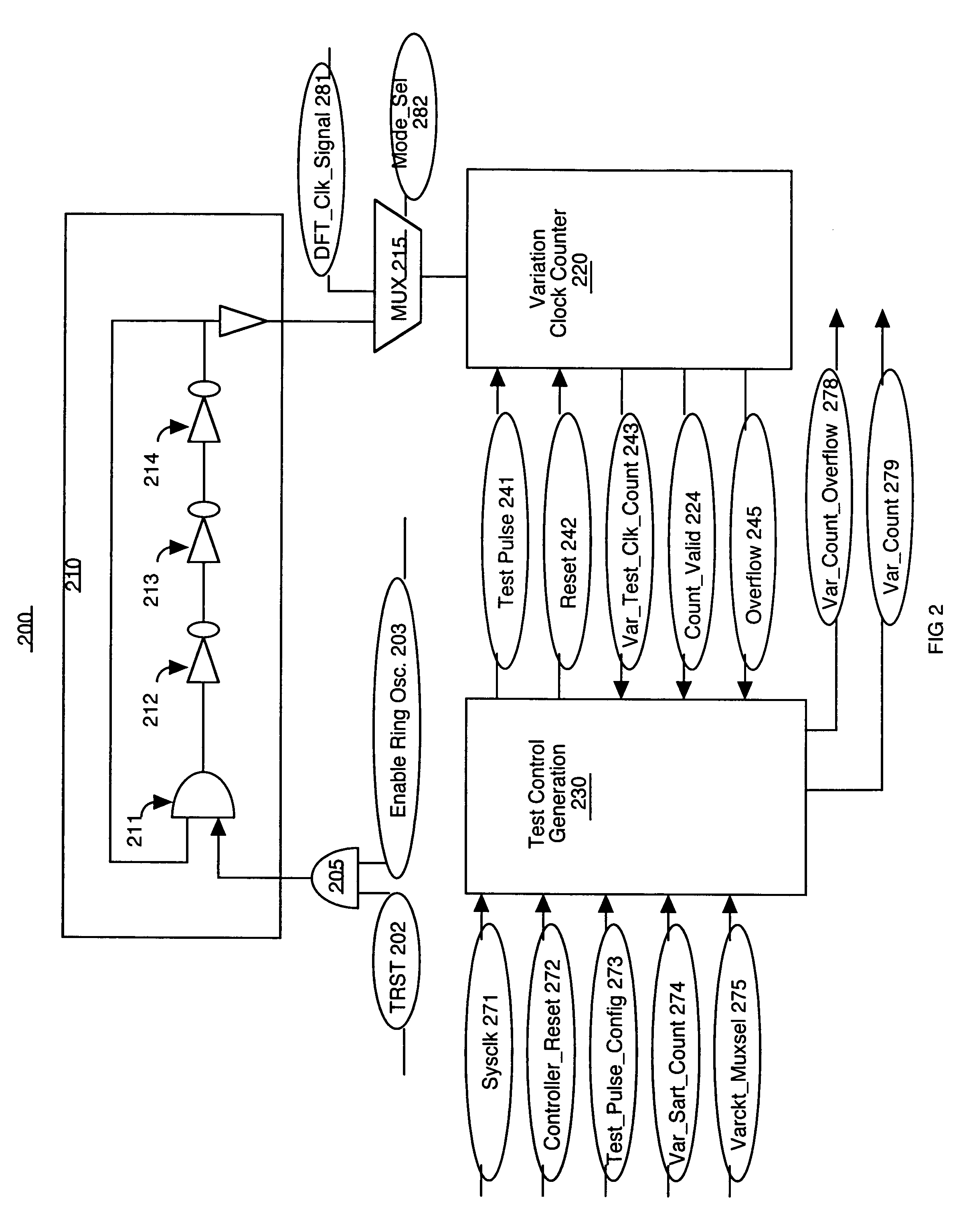

Timing variation measurement system and method

InactiveUS7184936B1Easy to measureAccurate modelingTesting/calibration apparatusNoise figure or signal-to-noise ratio measurementSemiconductor chipSignal tracking

The present invention is a system and method that facilitates measurement of timing variations (e.g., timing delays) in a semiconductor chip. The timing variations are measured and presented as digital values without extensive off chip measurement and analysis equipment. The timing variation measurements provides insight into timing variations (e.g., delays) inside a semiconductor chip and across different chips, including timing impacts experienced in end use after manufacturing. A timing variation measurement system includes a variation test signal generator for passing a signal through a portion of a circuit and generating a variation test signal. A variation test signal tracking component digitally counts cycles in a variation test signal and a control component controls the counting (e.g., the length of time the cycles are counted). Timing variation information, including a digital value associated with the variation test signal cycle count, can be communicated via pins and / or a processor interface.

Owner:CISCO TECH INC

System and method for determining position or speed of a commutated DC motor with error correction

ActiveUS7668690B2Torque ripple controlEmergency protective circuit arrangementsMotor speedControl system

Owner:APTIV TECH LTD

Frequency Detector and Phase Locked Loop Having the Same

InactiveUS20090310730A1Spectral/fourier analysisModulated-carrier systemsFrequency detectionComputer science

A frequency detector includes an error measurement unit measuring a time interval between zero-crossing points of an input signal that is modulated. An error conversion unit quantizes the measured time interval using one of modulation time intervals. An error calculation unit calculates a frequency error based upon a difference between the measured time interval and the quantized time interval. An error generation control unit controls whether to output the frequency error based upon the quantized time interval, the calculated frequency error, and a predetermined critical value.

Owner:SAMSUNG ELECTRONICS CO LTD

Time base frequency real time calibration frequency measuring method and apparatus

InactiveCN101441232AImprove accuracyRealize high-precision frequency measurementFrequency to pulse train conversionFrequency measurementsBase frequency

The invention discloses a real-time calibration and frequency measurement method for time base frequency and a device thereof, wherein the method comprises the following steps: 1) calibration step: a frequency measurement device acquires an external high-accuracy standard-frequency signal with Fs of given frequency as a calibration signal; the actual frequency value measured by the frequency measurement device is Fs'; a calibration factor K which is equal to Fs / Fs' is calculated and stored, and the calibration factor K can not be updated until the next calibration step is finished; 2) measurement step: the frequency of the unknown signal measured by the frequency measurement device is Fx', and the calculated and revised frequency value of the unknown signal Fx is equal to K * Fx'; 3) the process returns to step 1). The method and the device can ensure that, the time base frequency can be as accurate as 5E-10 and the second gate time frequency measurement can be as accurate as 1E-9 when measuring frequency and the accuracy of the measured frequency can be determined, thereby solving the problems of undetermined frequency timing base frequency accuracy, low precision, and the like of the prior art.

Owner:CENT SOUTH UNIV

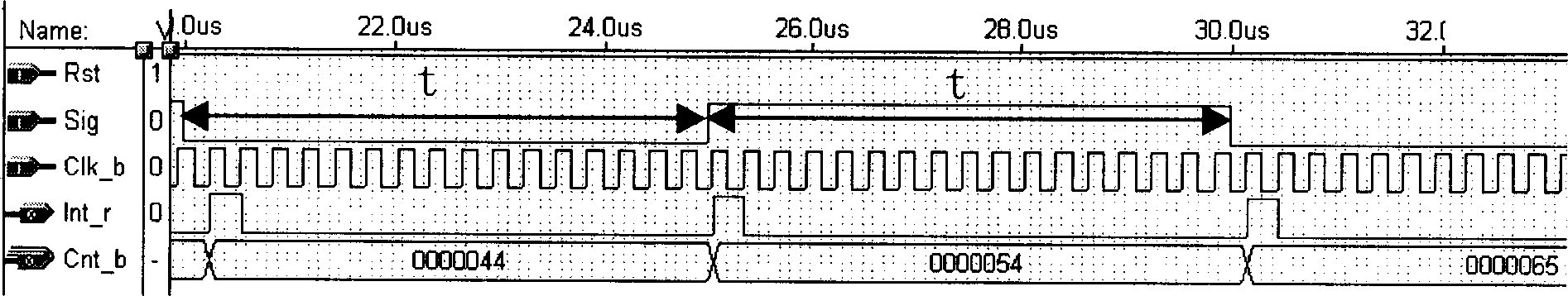

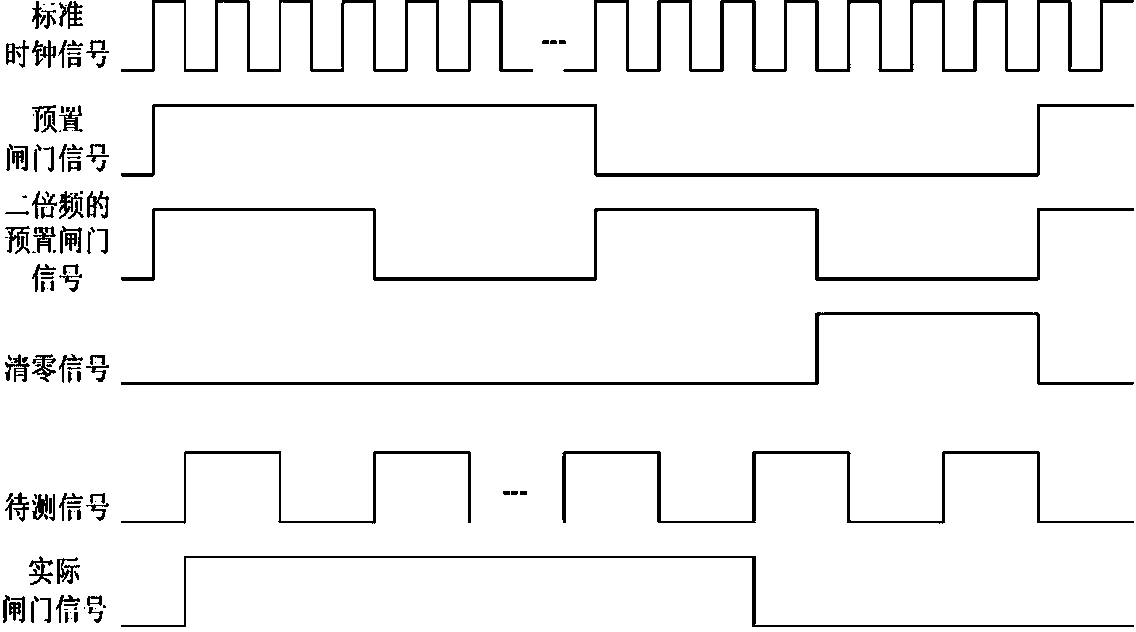

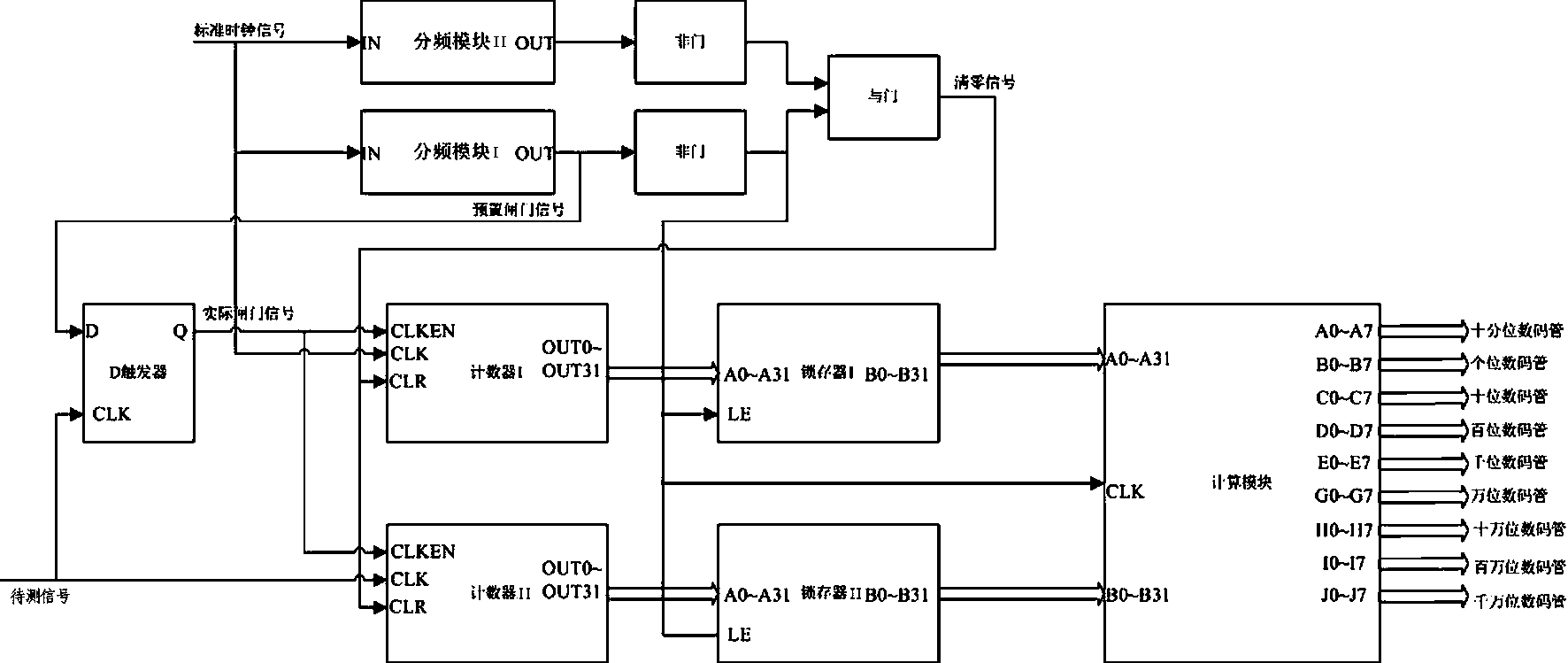

Equal-precision frequency testing system based on FPGA and design method thereof

InactiveCN103837741AHigh measurement accuracyMeasurement accuracy unchangedFrequency to pulse train conversionEngineeringMeasurement precision

The invention discloses an equal-precision frequency testing system and method based on an FPGA. According to the system, frequency demultiplication is carried out on outer standard clock signals, a preset gate signal is obtained, and then an actual gate signal is obtained. The rising edge of an outer signal to be tested and the rising edge of the standard clock signal are counted so that the periodicity of the outer signal to be tested and the standard clock signal in the actual gate signal can be obtained. The frequency of the signal to be tested is obtained according to the obtained periodicity and the frequency of the standard clock signal, and finally the frequency of the signal to be tested is sent to a nixie tube to be displayed. Through the method, high frequency measurement precision can be obtained, and the measurement precision of the frequency is almost equal.

Owner:HENAN UNIV OF SCI & TECH

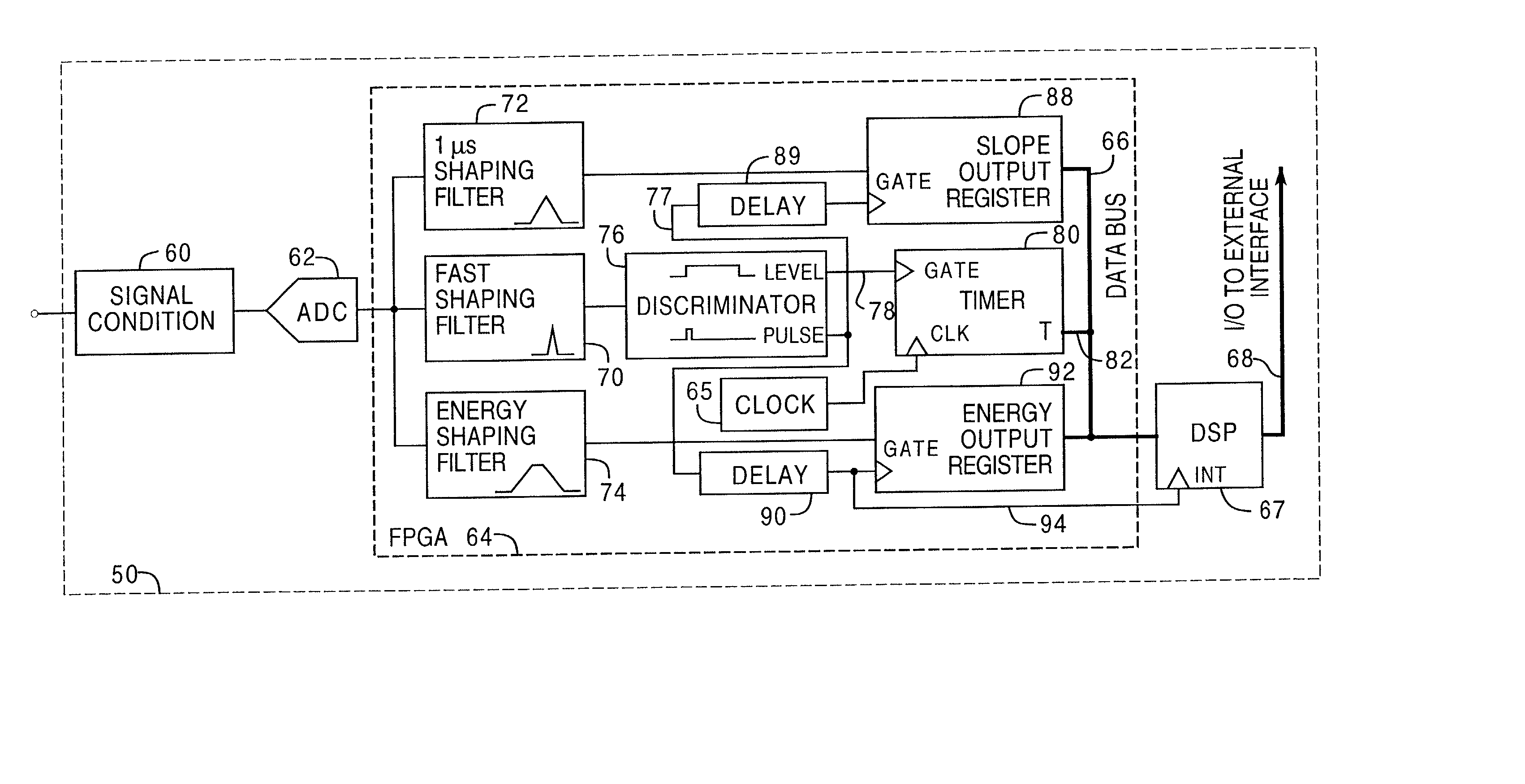

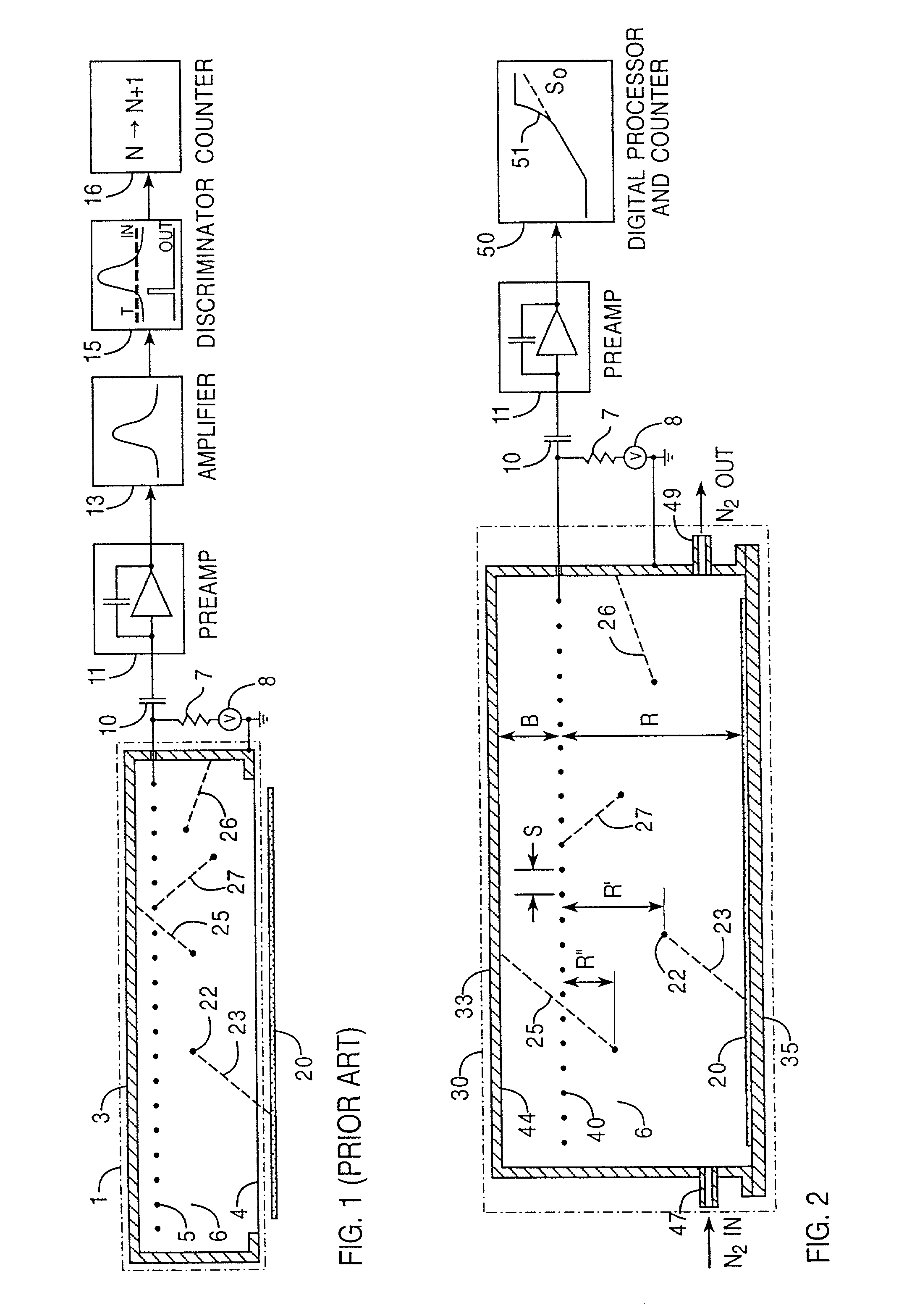

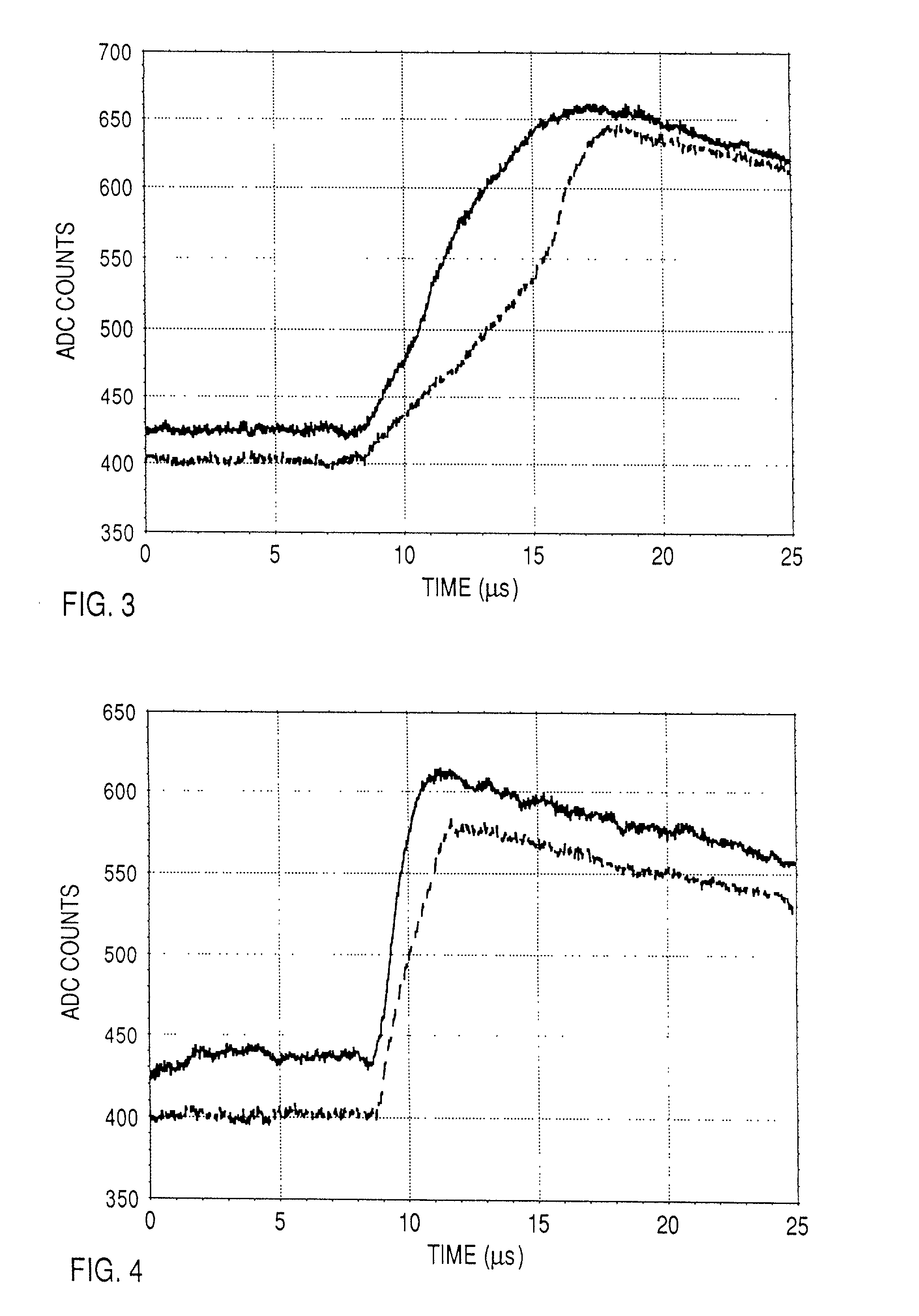

Ultra-low background gas-filled alpha counter

InactiveUS20030040877A1Reduce rateLow count rateSolid-state devicesAmplifiers controlled by lightParallel plateLarge sample

A method and counter for reducing the background counting rate in gas-filled alpha particle counters wherein the counter is constructed in such a manner as to exaggerate the differences in the features in preamplifier pulses generated by collecting the charges in ionization tracks produced by alpha particles emanating from different regions within the counter and then using pulse feature analysis to recognize these differences and so discriminate between different regions of emanation. Thus alpha particles emitted from the sample can then be counted while those emitted from the counter components can be rejected, resulting in very low background counting rates even from large samples. In one embodiment, a multi-wire ionization chamber, different electric fields are created in different regions of the counter and the resultant difference in electron velocities during charge collection allow alpha particles from the sample and counter backwall to be distinguished. In a second embodiment, a parallel-plate ionization chamber, the counter dimensions are adjusted so that charge collection times are much longer for ionization tracks caused by sample source alpha particles than for those caused by anode source alpha particles. In both embodiments a guard electrode can be placed about the anode's perimeter and secondary pulse feature analysis performed on signal pulses output from a preamplifier attached to this guard electrode to further identify and reject alpha particles emanating from the counter's sidewalls in order to further lower the counter's background.

Owner:WARBURTON WILLIAM K

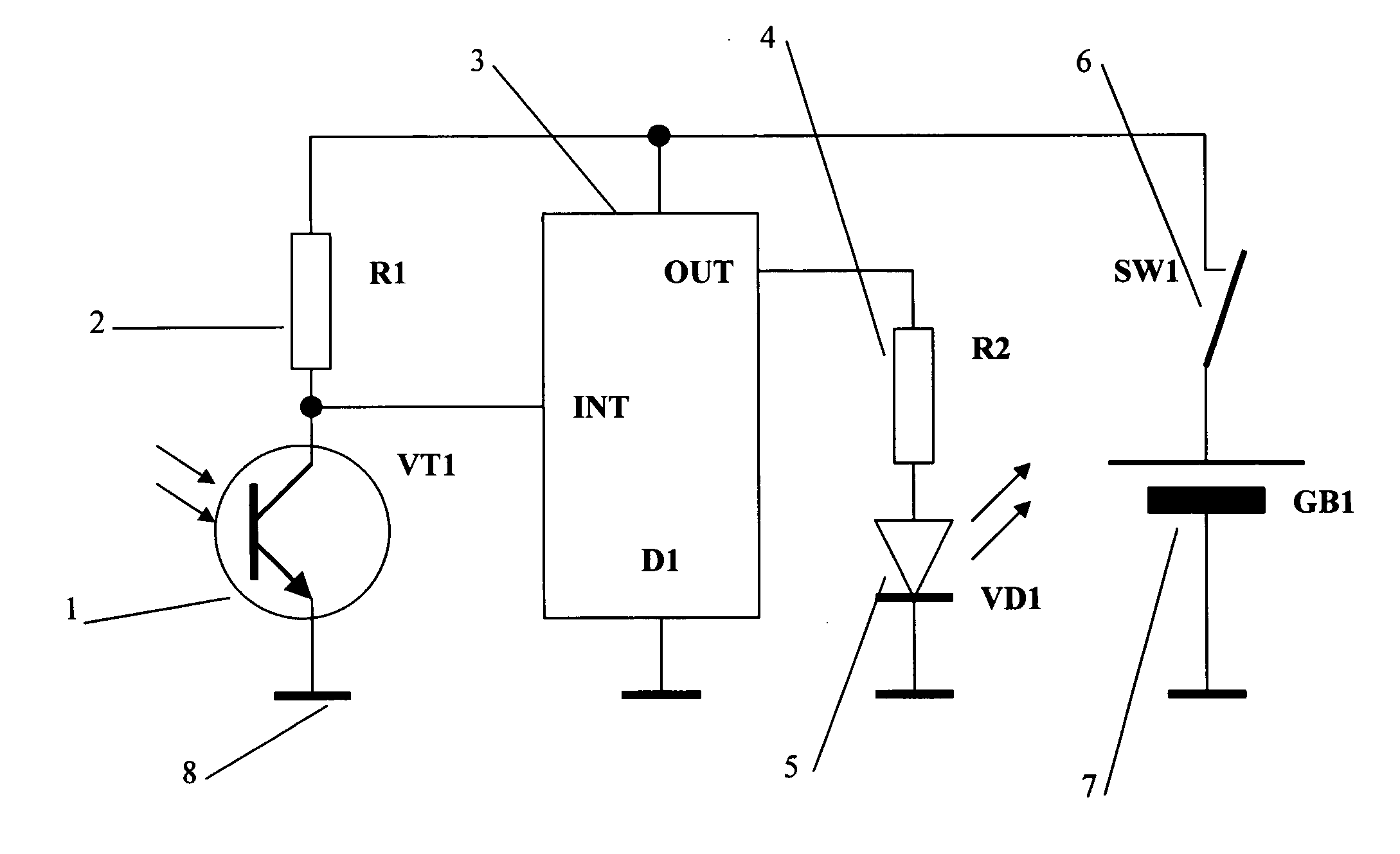

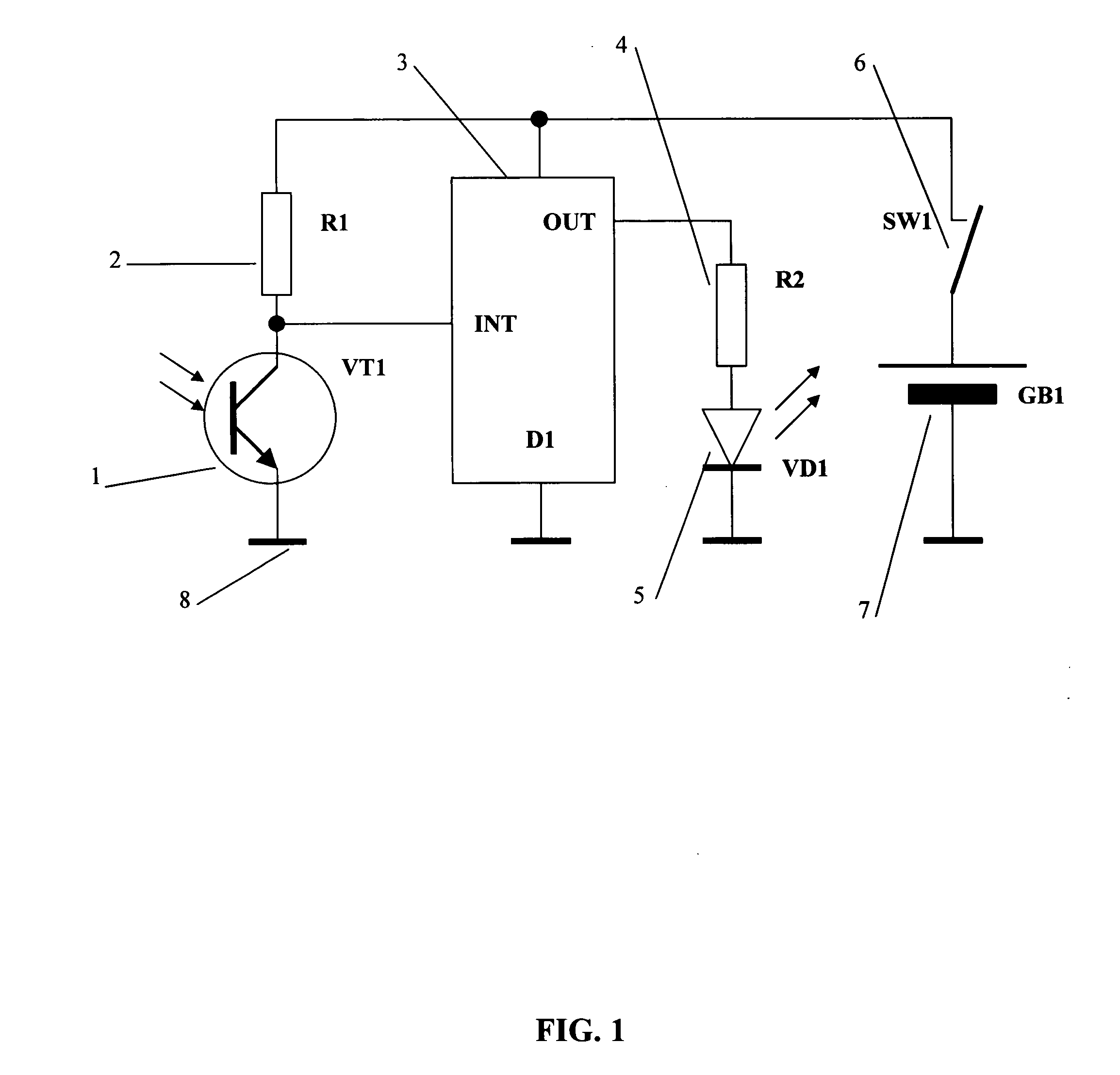

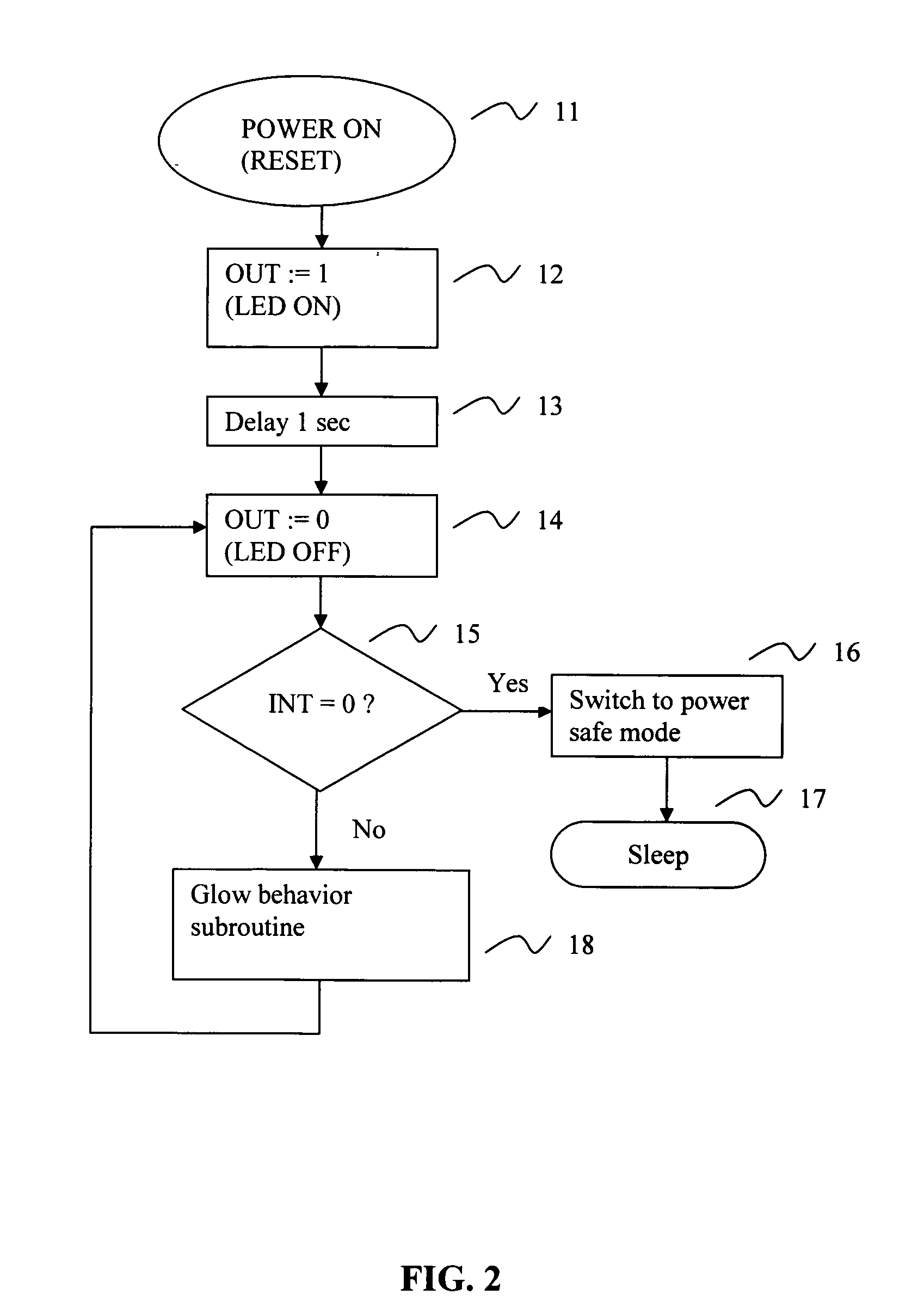

Periodic lighting device

InactiveUS20110109236A1Prevent penetrationSimplify disassemblyAnimal huntingBaitBiological bodyRadiation pulse

There is presented a detailed electronic method for simulation of a firefly, other insects, or organisms producing bioluminescence and with light radiation functions similar to a real firefly, other insects, or organisms producing bioluminescence. An illuminated artificial firefly, other insects, or organisms producing bioluminescence can be placed on trees and shrubs in landscape, or at home to produce radiation, at night time, and blinking a gradually decaying light. More particularly it relates to a decorative type of device in the form of a firefly, other insects, or organisms producing bioluminescence and with light radiation functions similar to a real firefly, other insects, or organisms producing bioluminescence. The light is simulated by an electronics program that is a part of compact device with the form of a real firefly, other insects, or organisms producing bioluminescence. Short radiation pulses of microsecond-millisecond duration time in violet and ultraviolet range of radiation wavelengths can be utilized for scaring birds or other animals from undesirable or dangerous places of human activity, such as airports, contaminated ponds, wind turbines, electorized fences and antennas.

Owner:SCHAAL HERBERT RUDOLF +1

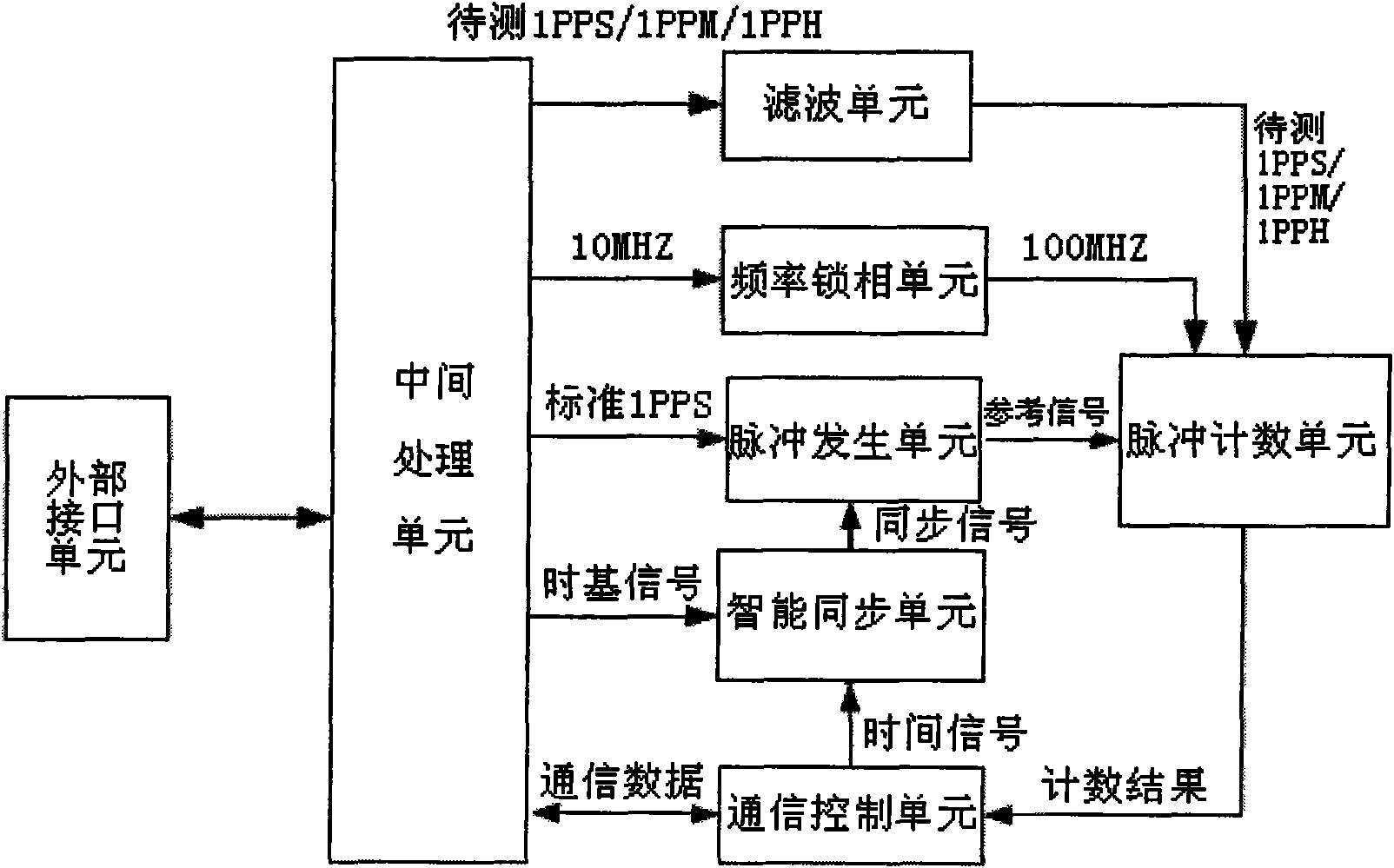

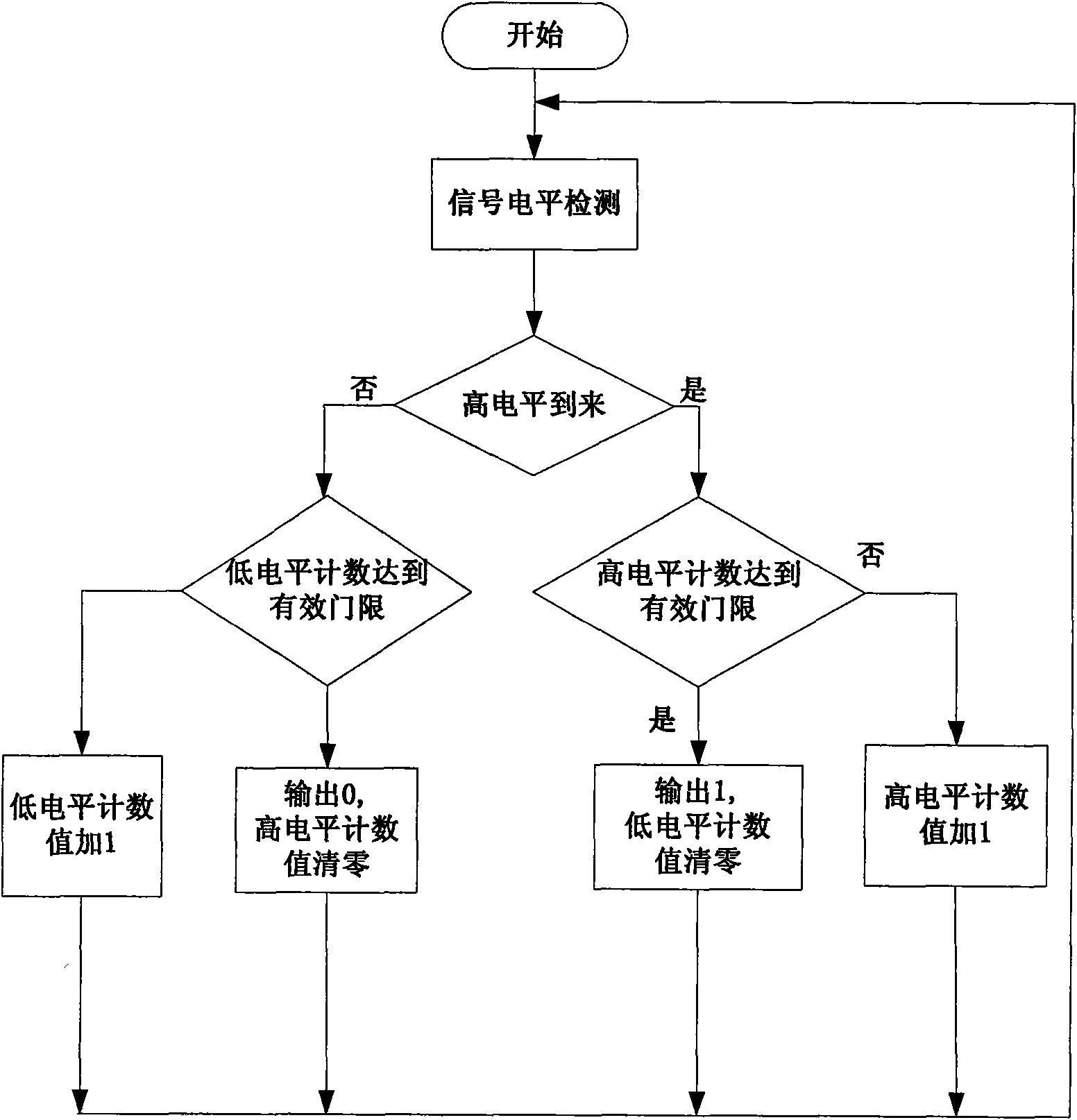

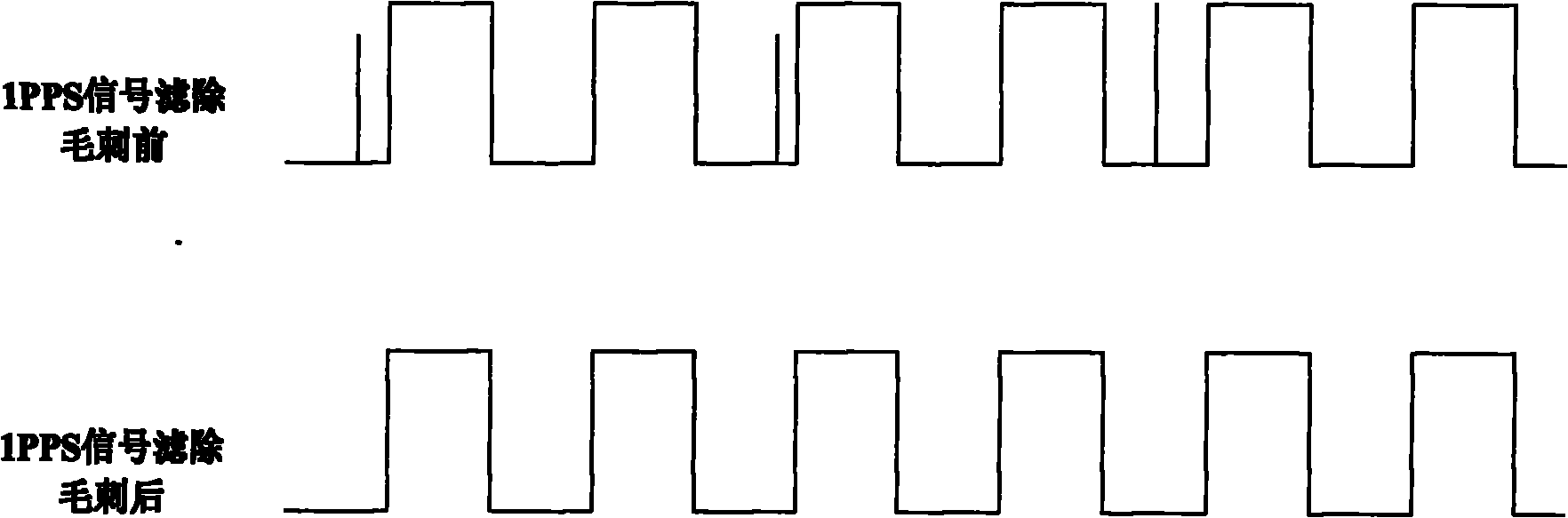

Reliable time scale pulse measurement method and measurement device thereof

ActiveCN101871968ASolve glitchesImprove performanceComputer controlPulse shapingTime markMeasurement device

The invention discloses a reliable time scale pulse measurement method, which comprises the following steps: 1) converting a 10MHz frequency signal of a precise clock source, a standard 1PPS signal and 1PPS, 1PPM and 1PPH signals to be measured to pulse signals; 2) carrying out frequency doubling on the 10MHz frequency signal of the precise clock source for obtaining a 100MHz frequency signal, and taking the 100MHz frequency signal as the working frequency of an FPGA; simultaneously carrying out frequency division on the standard 1PPS signal and respectively obtaining a 1PPM reference signal and a 1PPH reference signal; and 3) measuring the precision of the 1PPS, the 1PPM and the 1PPH signals to be measured according to the reference signals of 1PPS, 1PPM and 1PPH under the working frequency of 100MHz. The method can realize the high-speed and high-efficient counting operation by adopting a field programmable logic sequence, realize the multi-path and multi-group pulse fast detection, and send the detection result to a user and is characterized by stable performances and convenient maintenance.

Owner:郑州威科姆科技股份有限公司

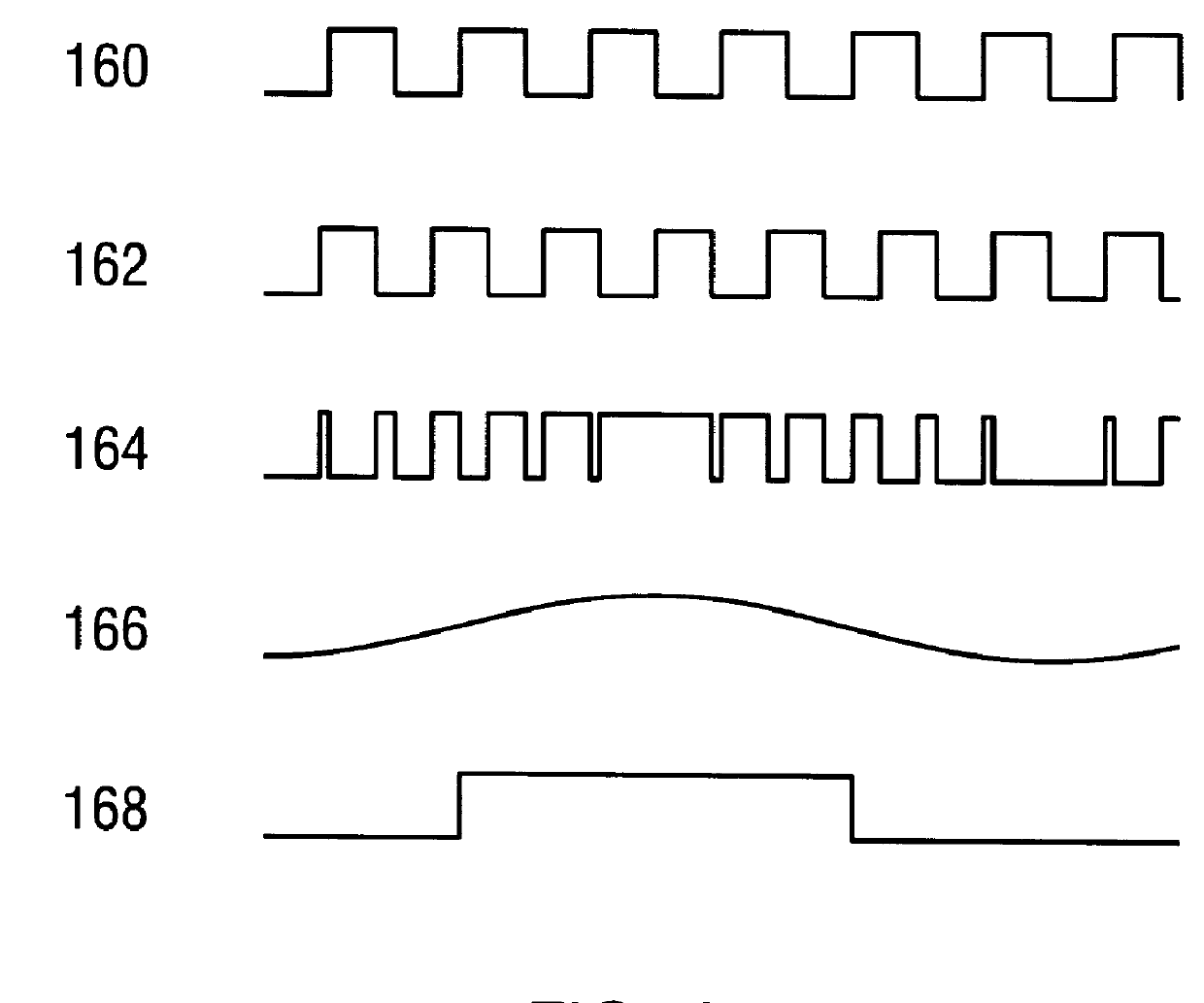

Frequency measurement device and measurement method

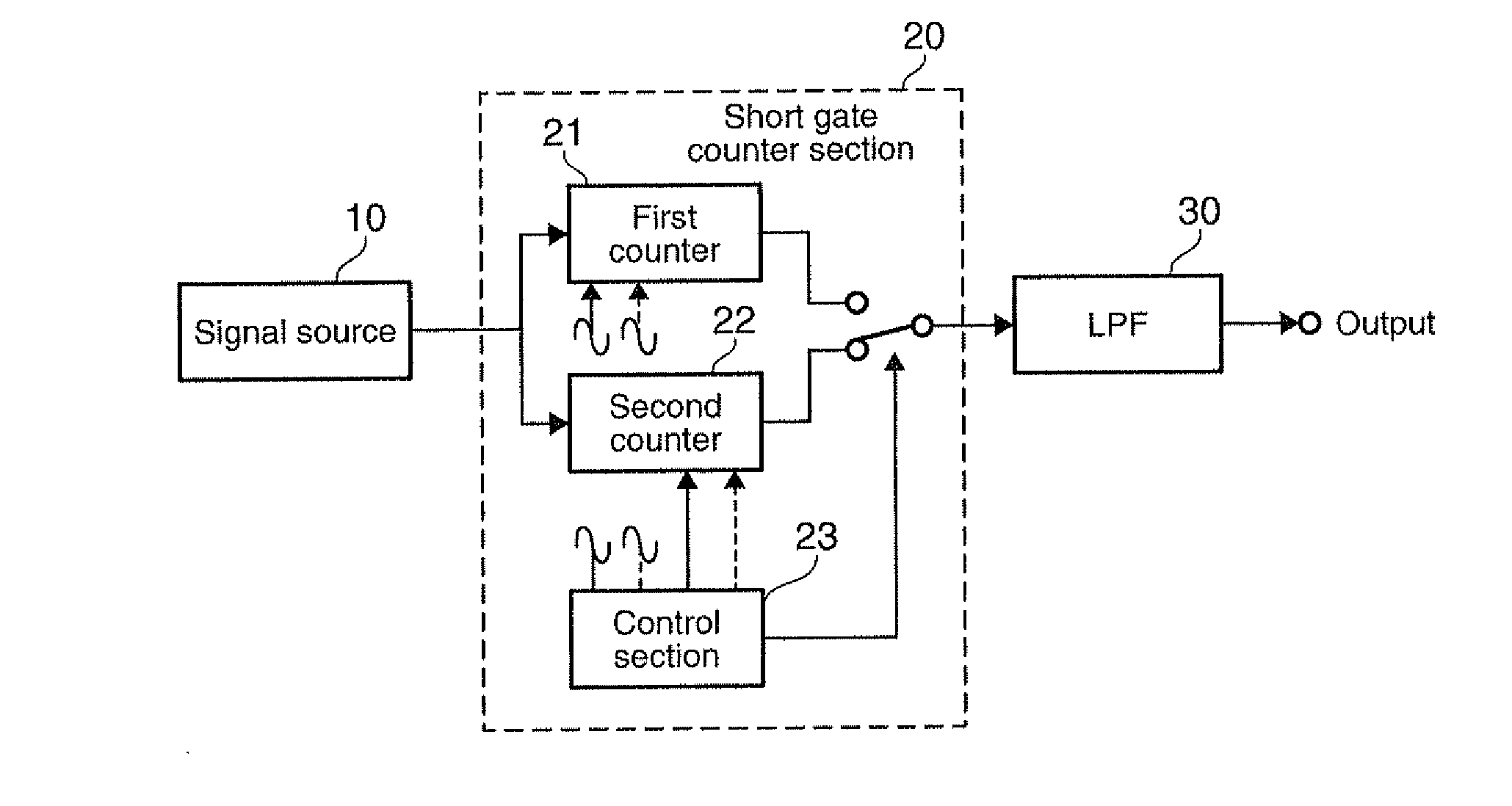

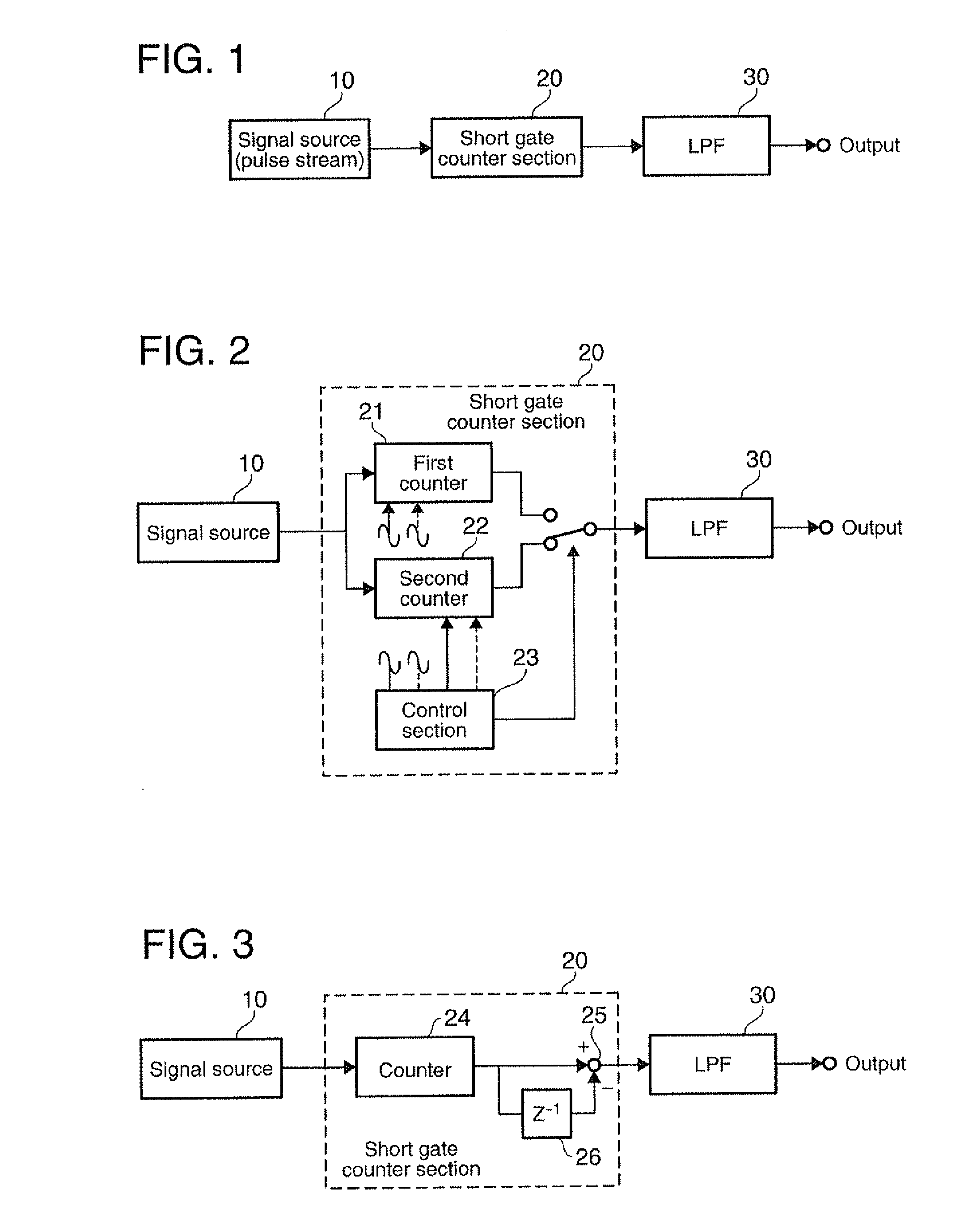

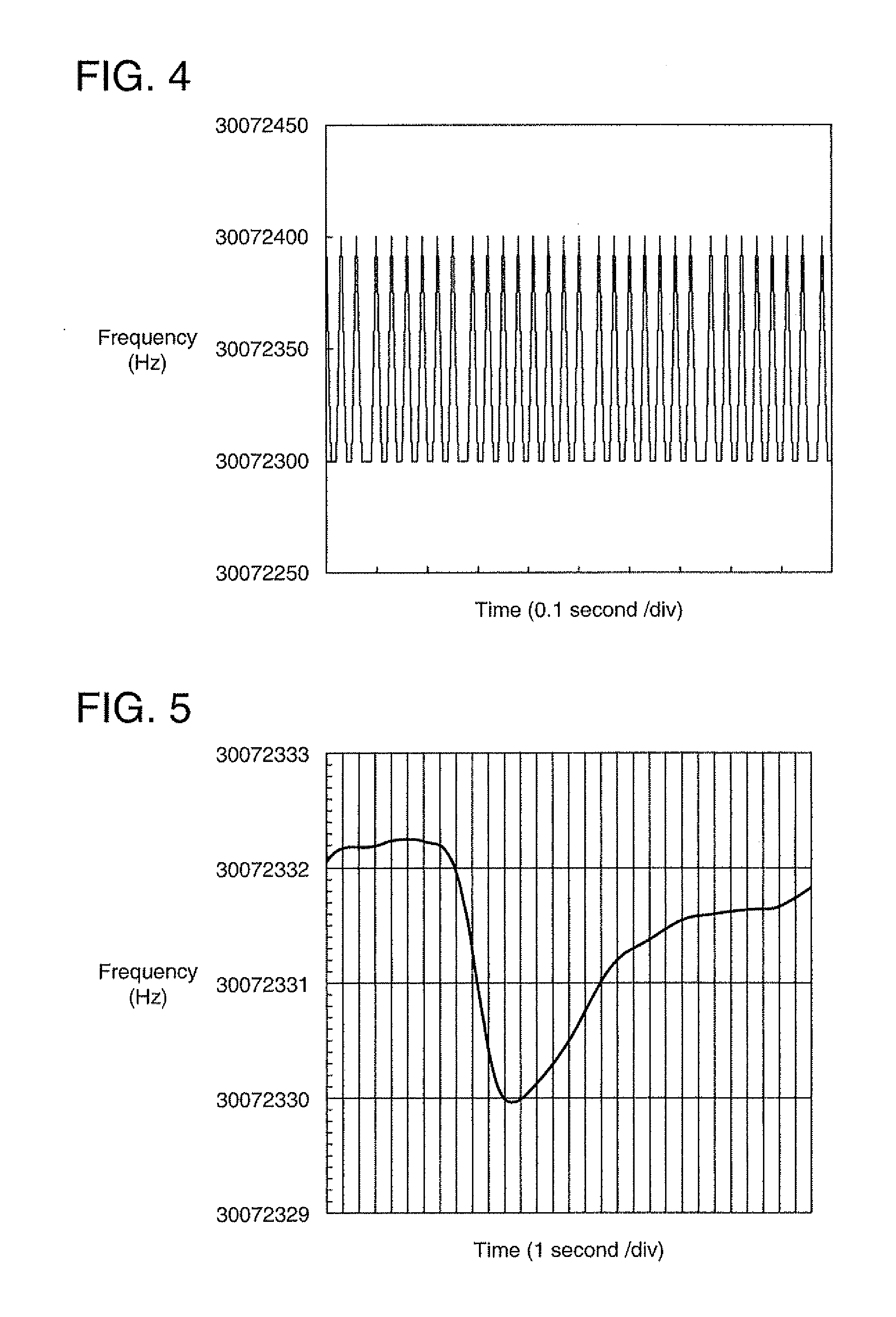

InactiveUS20090251129A1Improved frequency measurement resolving powerHigh resolutionVolume indication and recording devicesFrequency to pulse train conversionMeasurement deviceFrequency measurements

A frequency measurement device includes: a short gate time counter section that continuously measures a pulse stream signal supplied, and outputs a series of count values that behave like a pulse stream corresponding to a frequency of the pulse stream signal; and a low-pass filter that removes high frequency components from the series of count values to obtain a level signal corresponding to the frequency of the pulse stream signal supplied.

Owner:SEIKO EPSON CORP

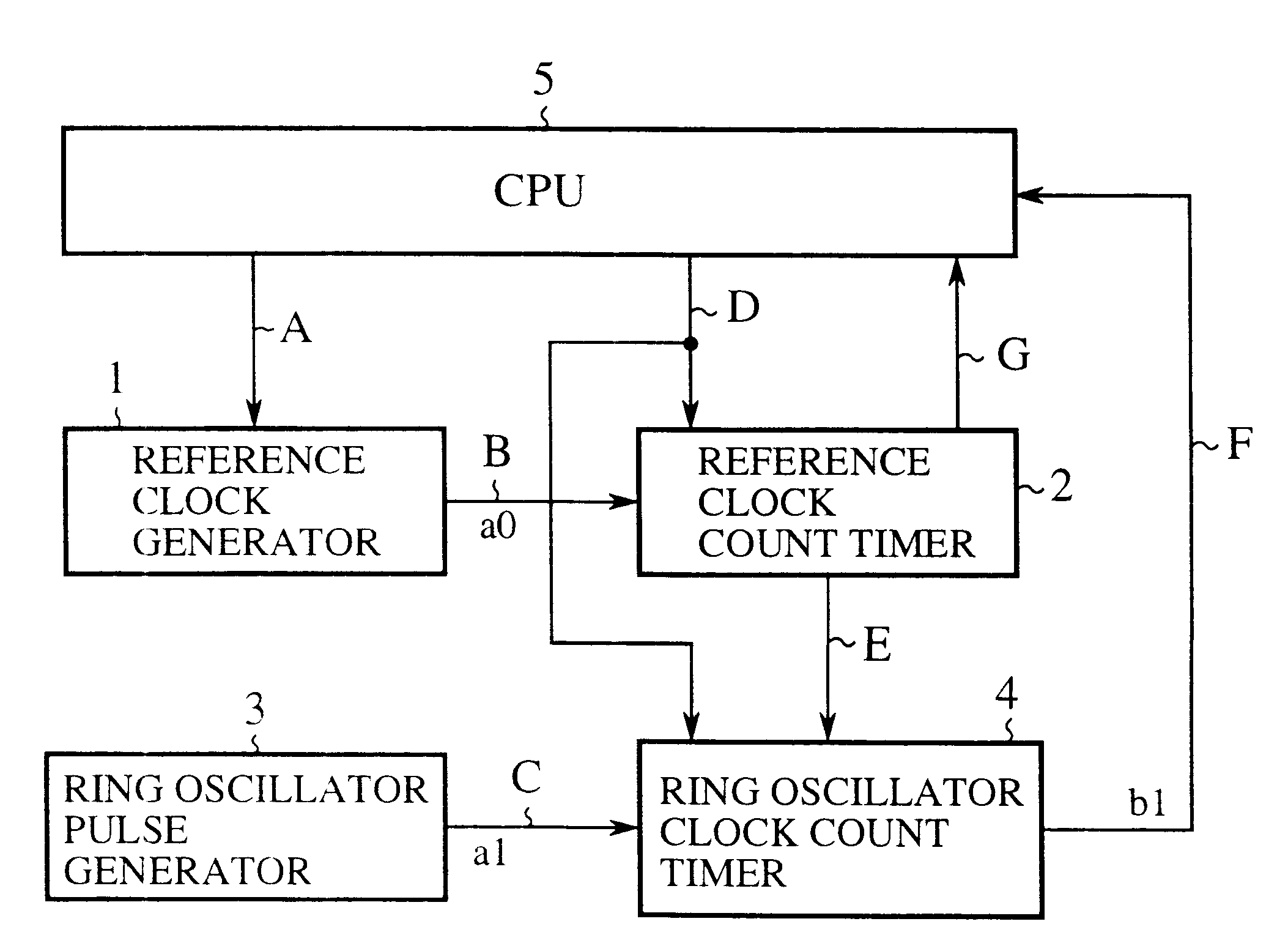

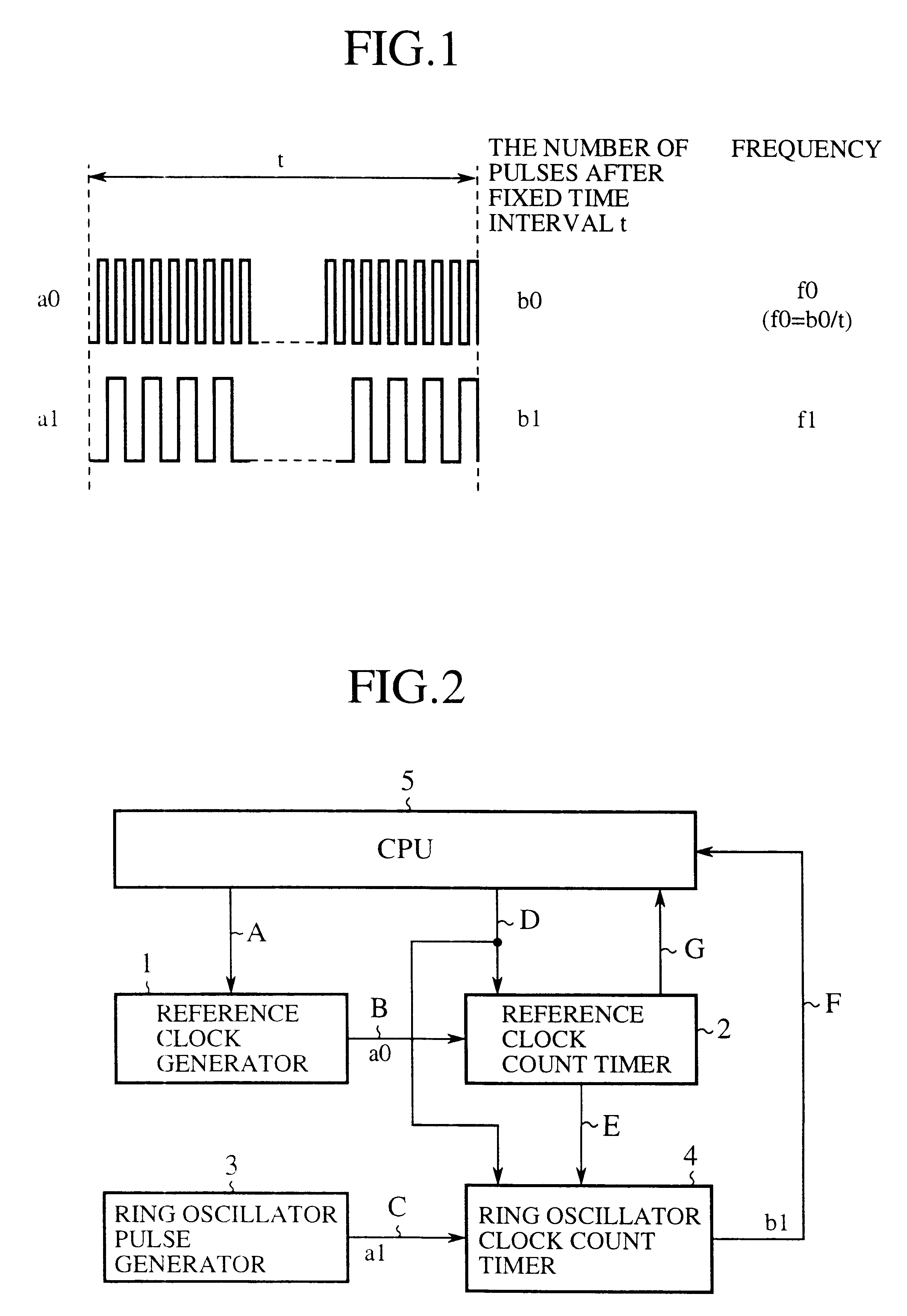

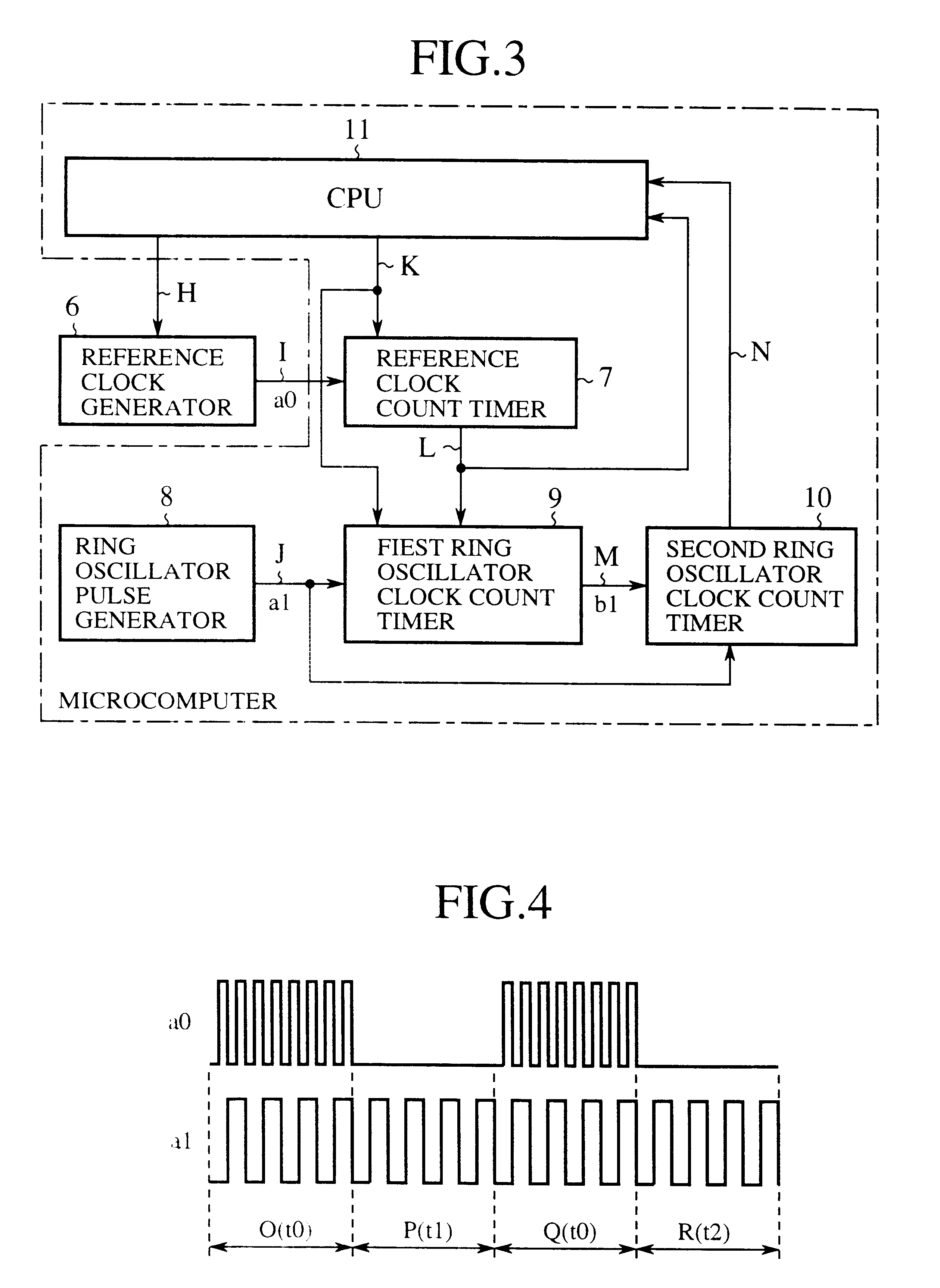

Ring oscillator clock frequency measuring method, ring oscillator clock frequency measuring circuit, and microcomputer

InactiveUS6442704B1Improve accuracyHigh precision measurementPulse train pattern monitoringPulse generation by logic circuitsMicrocomputerFrequency measurements

A ring oscillator clock frequency measuring circuit includes a reference clock count timer and a ring oscillator clock count timer. The reference clock count timer starts its counting of a reference clock signal in response to a start instruction fed from a CPU, and outputs an overflow signal when its counting reaches a preset value. The ring oscillator clock count timer starts its counting of pulses of a ring oscillator clock signal in response to the start instruction fed from the CPU, and continues its counting until the reference clock count timer generates the overflow signal. The frequency of the ring oscillator clock signal is obtained from the count value of the ring oscillator clock count timer. This makes it possible to measure the frequency of the ring oscillator clock signal at high accuracy, and to reduce the current consumption by operating the CPU based on the ring oscillator clock signal after the measurement.

Owner:MITSUBISHI ELECTRIC SYST LSI DESIGN +1

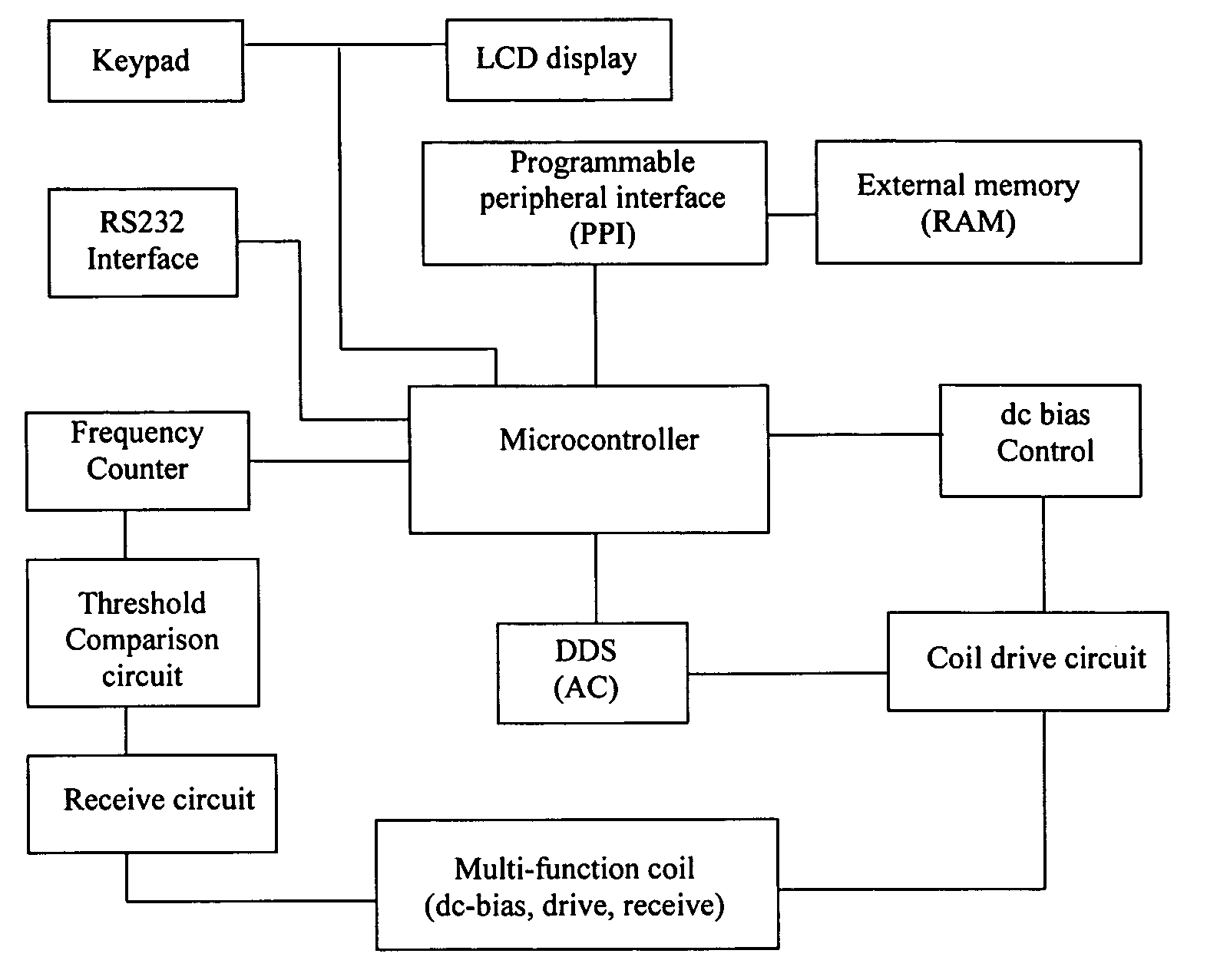

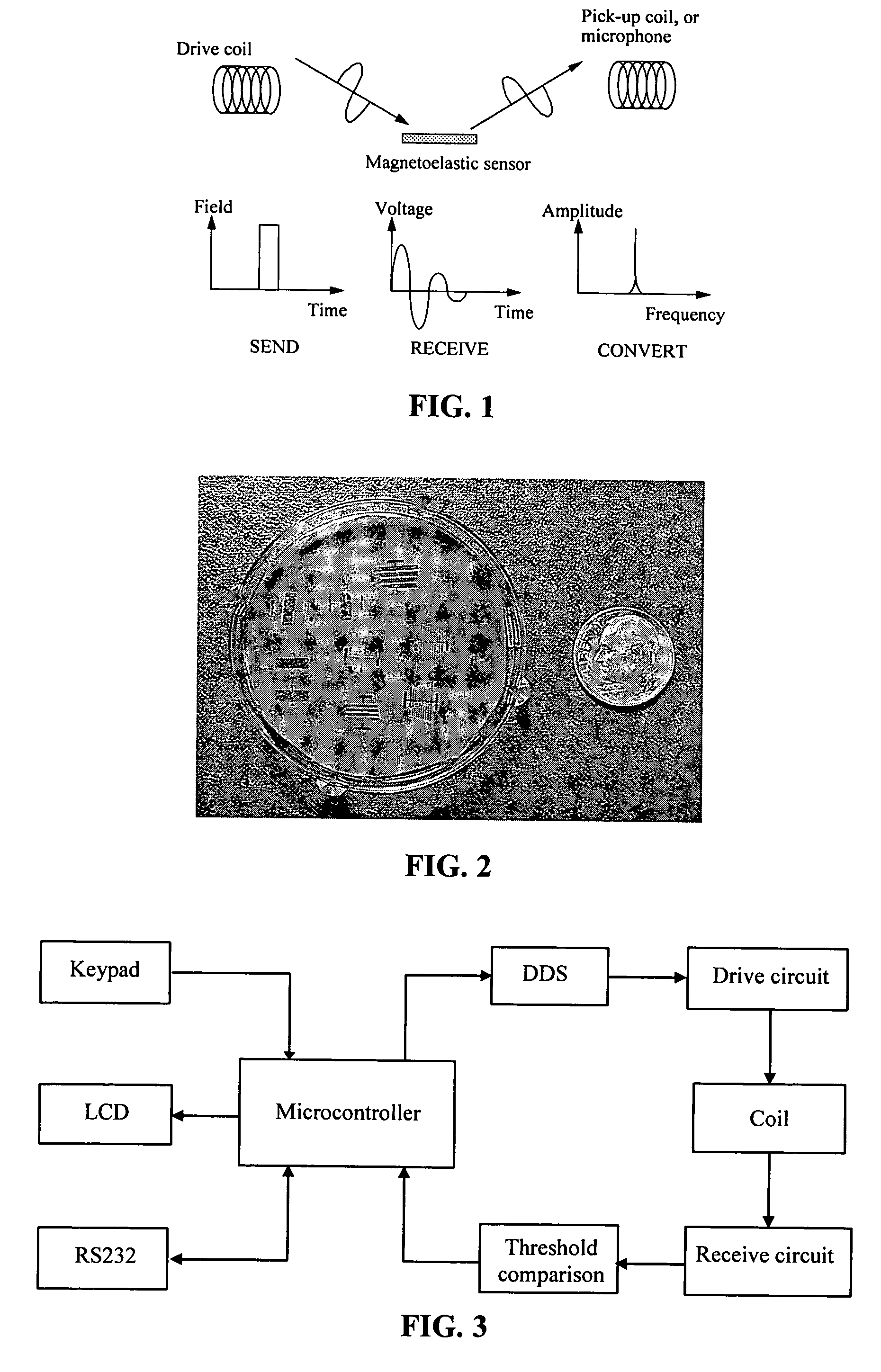

Technique and electronic circuitry for quantifying a transient signal using threshold-crossing counting to track signal amplitude

InactiveUS7113876B2Analysing solids using sonic/ultrasonic/infrasonic wavesNoise figure or signal-to-noise ratio measurementDamping factorEngineering

Circuitry adapted for carrying out associated techniques for: (a) calculating a damping factor, e.g., a damping ratio represented by ζ, or a quality factor Q, where ζ≈1 / 2Q, for a transient signal received, having been emitted from a resonator-type sensor element; (b) determining amplitude, A, of the transient signal; or (c) generating a frequency response dataset of interrelated points for the transient signal. A threshold comparison circuit is included for converting the transient signal received into a first and second digital waveform; the first digital waveform represents cycle crossings of the transient signal associated with a first threshold value, and the second digital waveform represents cycle crossings of the transient signal associated with a second threshold value. The transient signal may be converted, likewise, into third, and so on, digital waveforms, whereby the third digital waveform represents cycle crossings of the transient signal associated with a third threshold value. Respective digital counters are included, each of which is adapted for determining a total number of cycles of the first, second, third, and so on, digital waveform. A processing unit of suitable speed and capacity is employed for the calculating of the damping factor, determining an amplitude, and / or generating a frequency response dataset.

Owner:SEN TECH BIOMED CORP A BUSINESS ENTITY ORGANIZED UNDER LAWS OF COMMONWEALTH OF PENNSYLVANIA

Semiconductor integrated circuit and information processing system

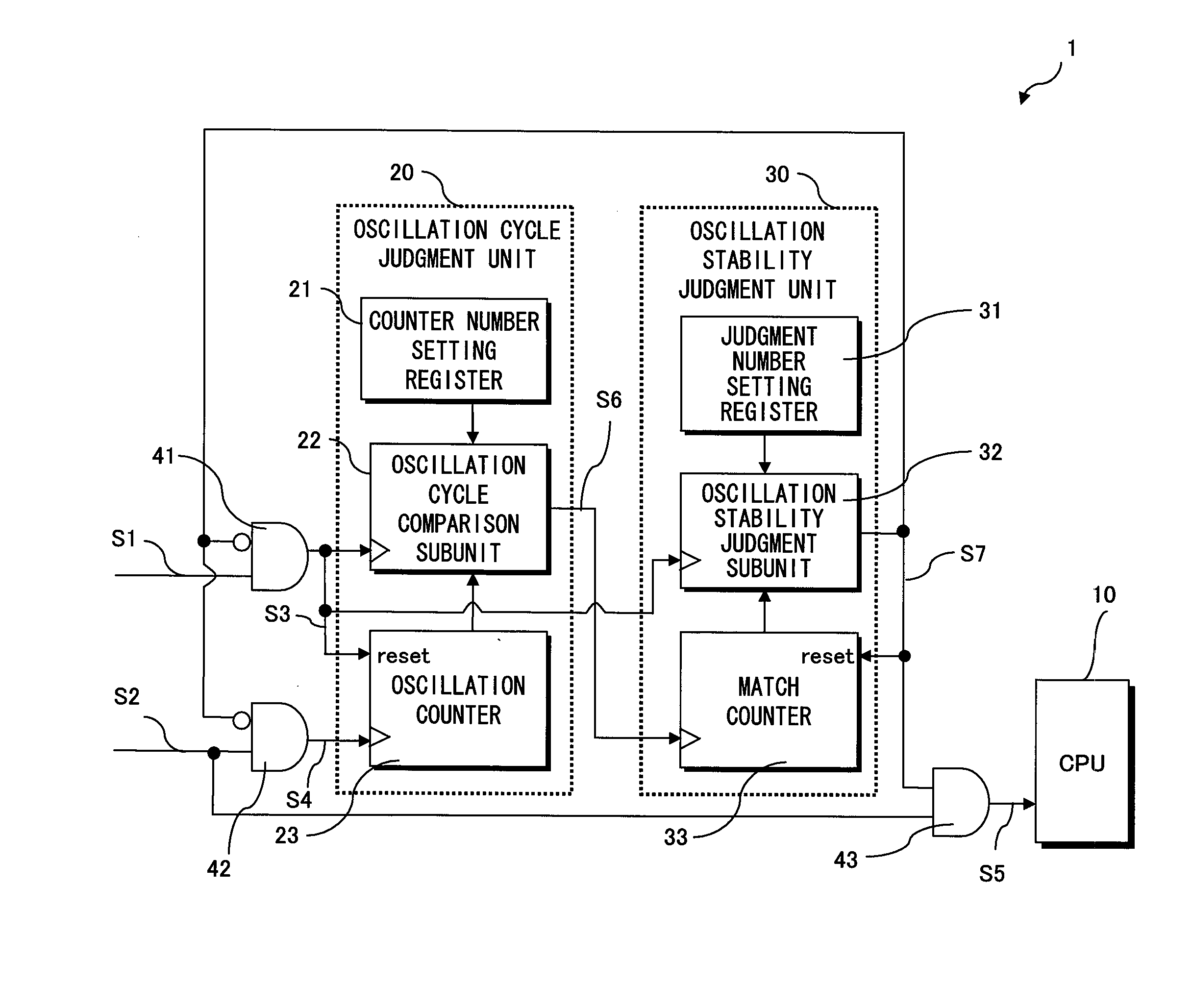

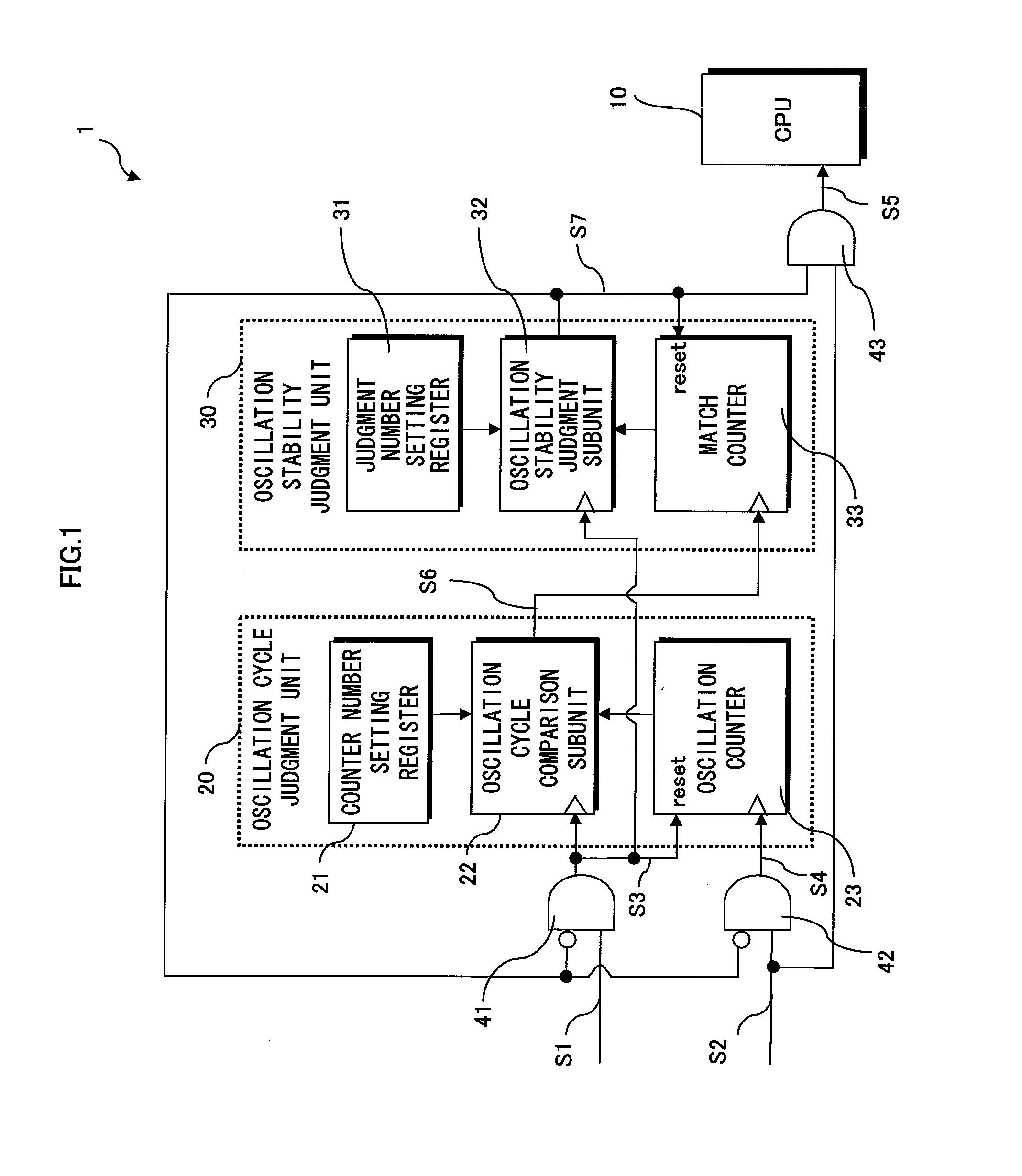

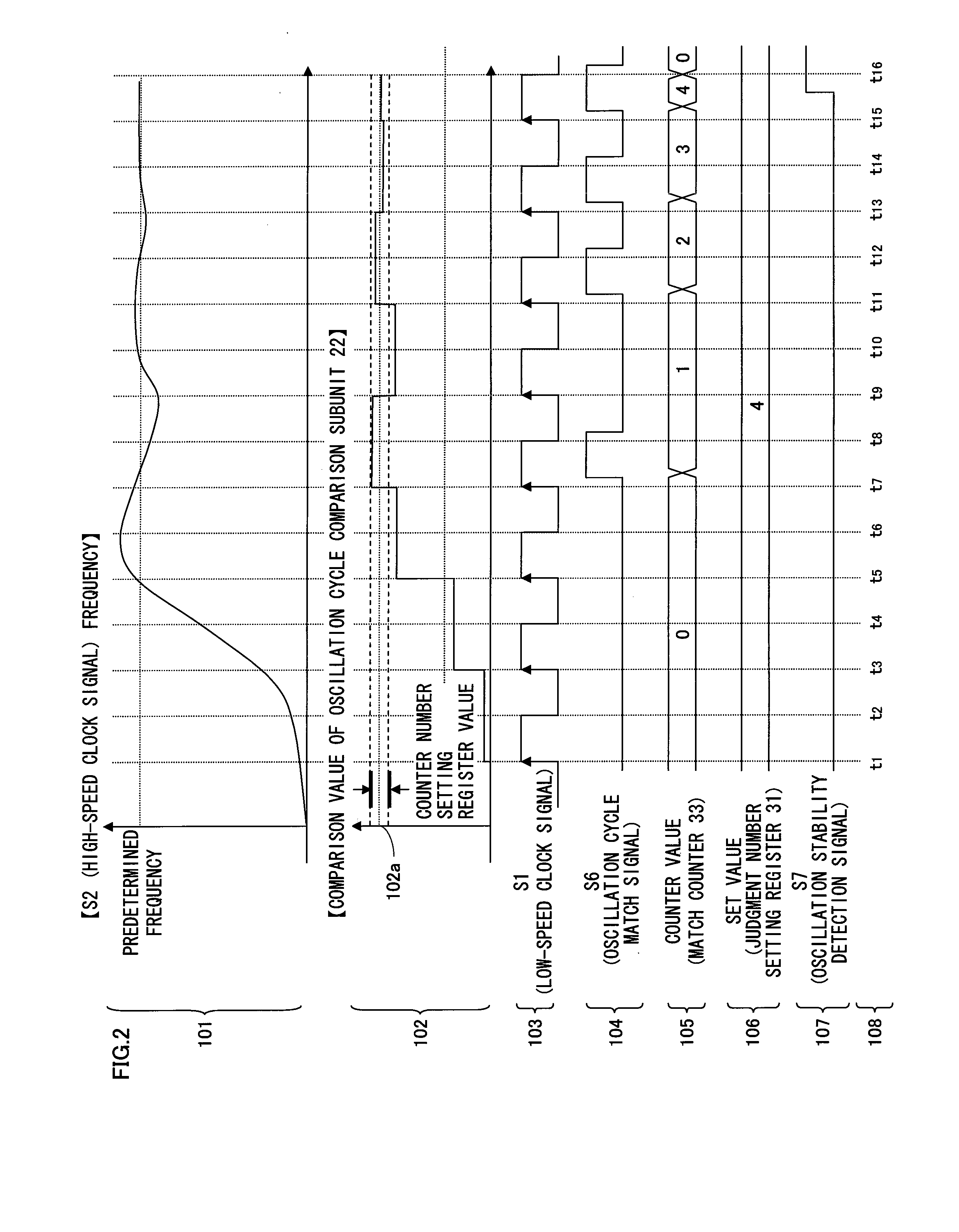

InactiveUS20080297202A1Improve reliabilityHighly reliable detectionPulse automatic controlPulse train pattern monitoringInformation processingLow speed

In a semiconductor integrated circuit, a counter counts the number of high-speed clock signals that have been generated in a predetermined number of clock cycles of a low-speed clock signal. In synchronization with the low-speed clock signal, the semiconductor integrated circuit compares the counter value and a predetermined value, and judges whether the frequency of the high-speed clock signal has reaches a predetermined frequency. Since variations in the frequency become smaller as the oscillation of a high-speed oscillator stabilizes, the semiconductor integrated circuit detects that the oscillation is stable when the semiconductor integrated circuit has judged affirmatively a plurality of times.

Owner:PANASONIC CORP

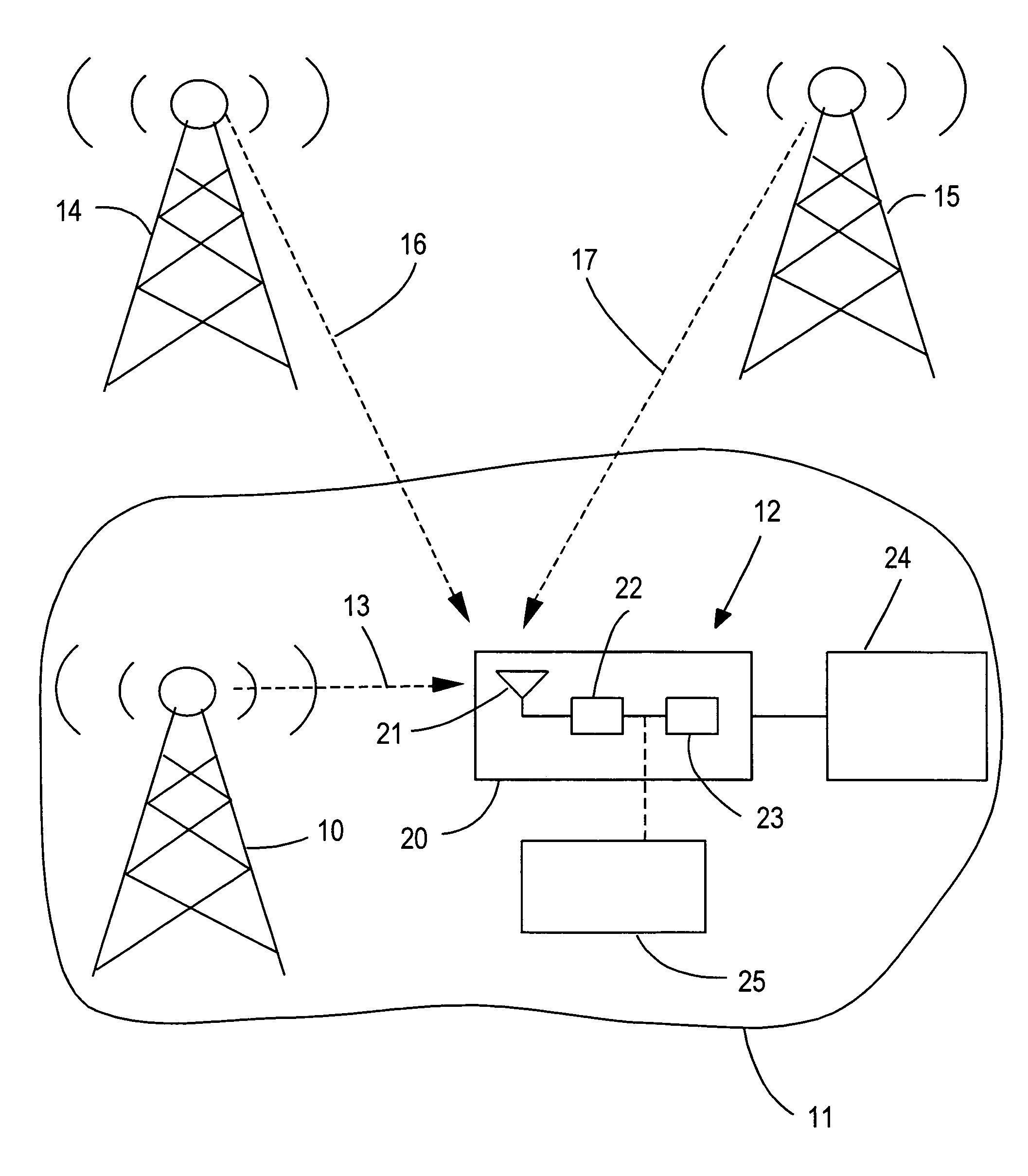

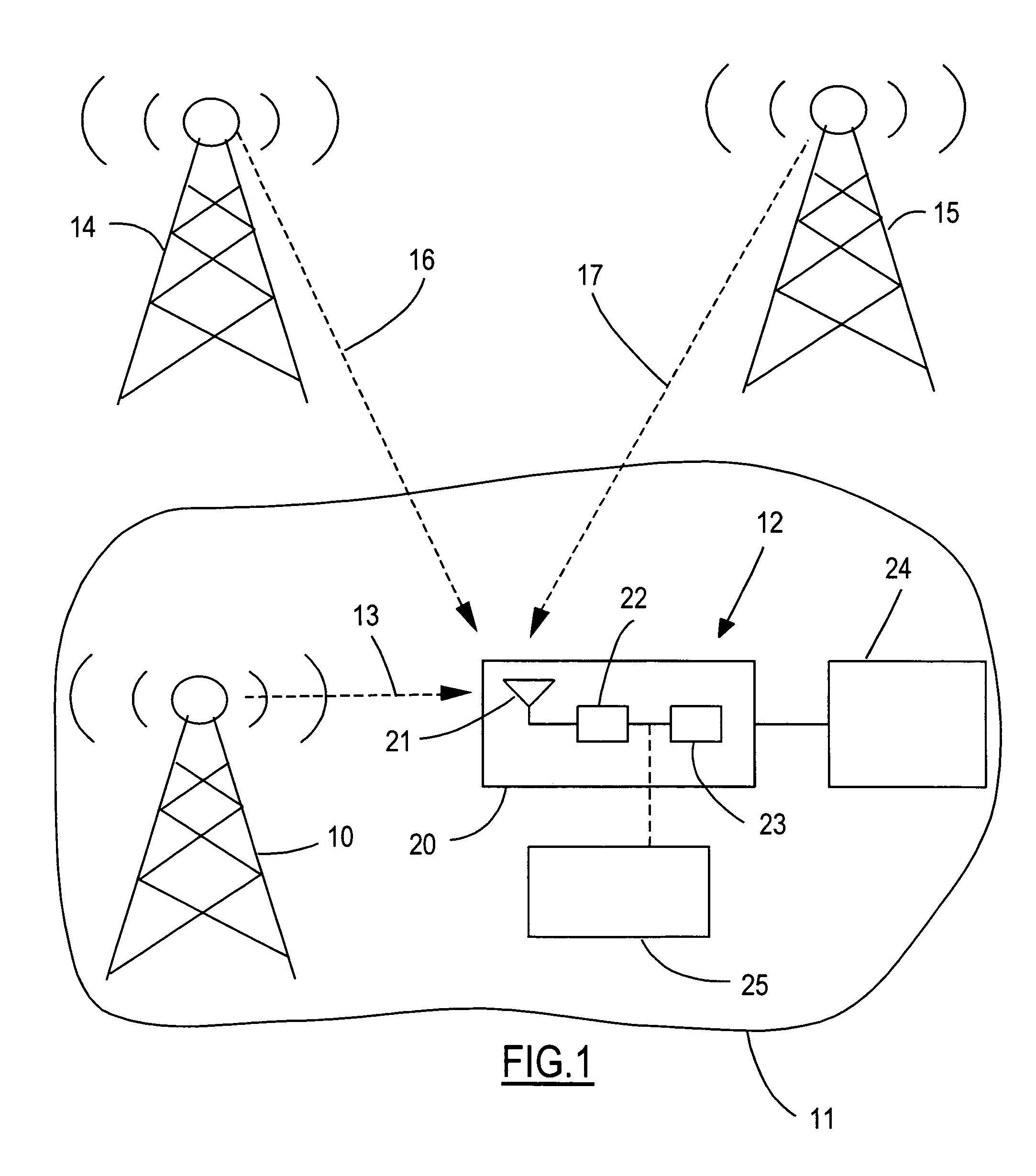

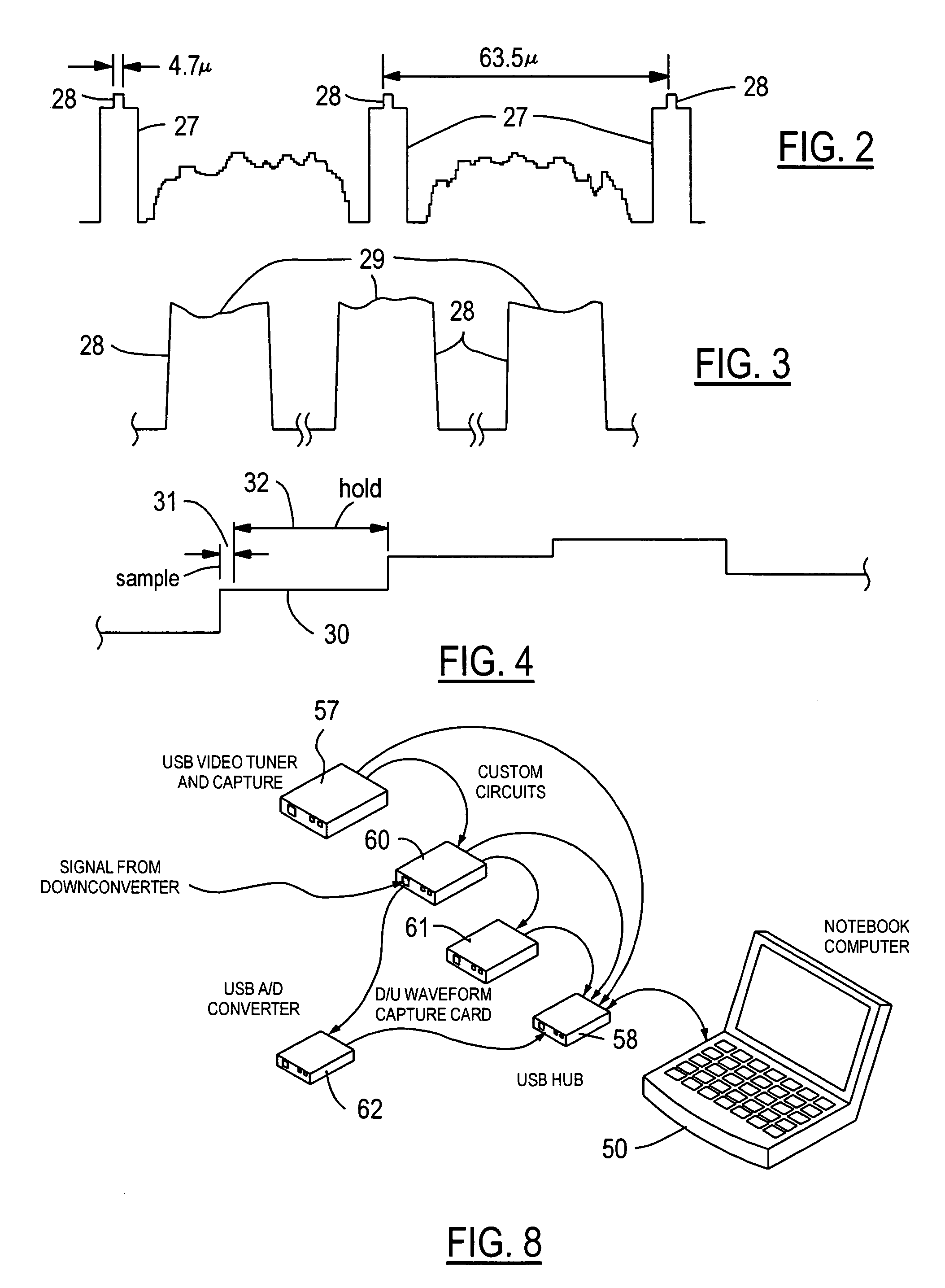

Measurement system for determining desired/undesired ratio of wireless video signals

ActiveUS7751996B1Accurate and convenient and methodAccurate and convenient systemTelevision system detailsReceivers monitoringFrequency spectrumWireless video

A D / U ratio is measured for desired and undesired signals in a wireless video transmission system at a shared channel frequency based on a received signal at a geographic location in proximity to regions within respective service areas for the desired and undesired signals. A video tuner demodulates the received signal to generate a baseband video signal. A leveling circuit normalizes the baseband signal. A video processor identifies horizontal sync pulses within the baseband signal, generates a sampled signal comprising the horizontal sync pulses, and removes components of the desired signal from the sampled signal to generate an undesired signal component. A D / U analyzer determines a Fourier transform having a plurality of bins in response to the undesired signal component, identifies at least one of the bins having a spectral peak corresponding to an undesired signal, and calculates the D / U ratio in response to a magnitude of the identified peak.

Owner:T MOBILE INNOVATIONS LLC

Periodic electrical signal frequency monitoring systems and methods

ActiveUS7154305B2Frequency/rate-modulated pulse demodulationFrequency to pulse train conversionElectricityFrequency of occurrence

Systems and methods for monitoring frequencies of periodic electrical signals are disclosed. According to one technique, a first and second counters are respectively clocked by a first periodic electrical signal to be monitored and a second periodic electrical, and a threshold detector resets one of the counters when a count of the other counter crosses a reset threshold and determines whether a frequency error has occurred based on whether a count of the one of the counters crosses an alarm threshold. Another technique according to an embodiment of the invention also involves clocking counters with respective periodic electrical signals, although error detection is based on whether the counts of the counters cross respective associated thresholds in other than a particular sequence with respect to each other.

Owner:ALCATEL LUCENT SAS

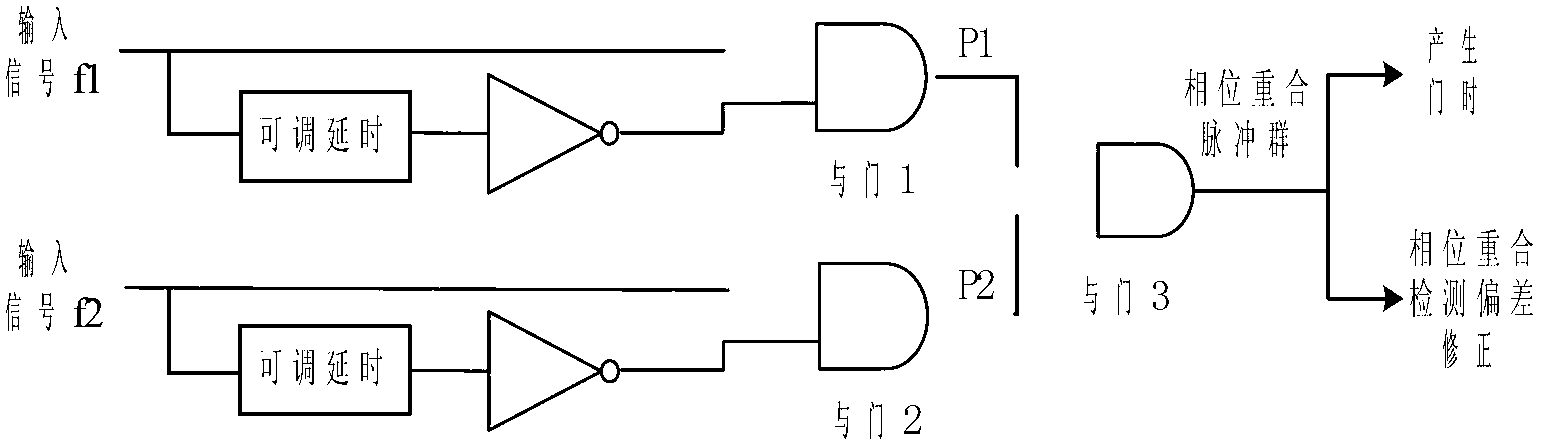

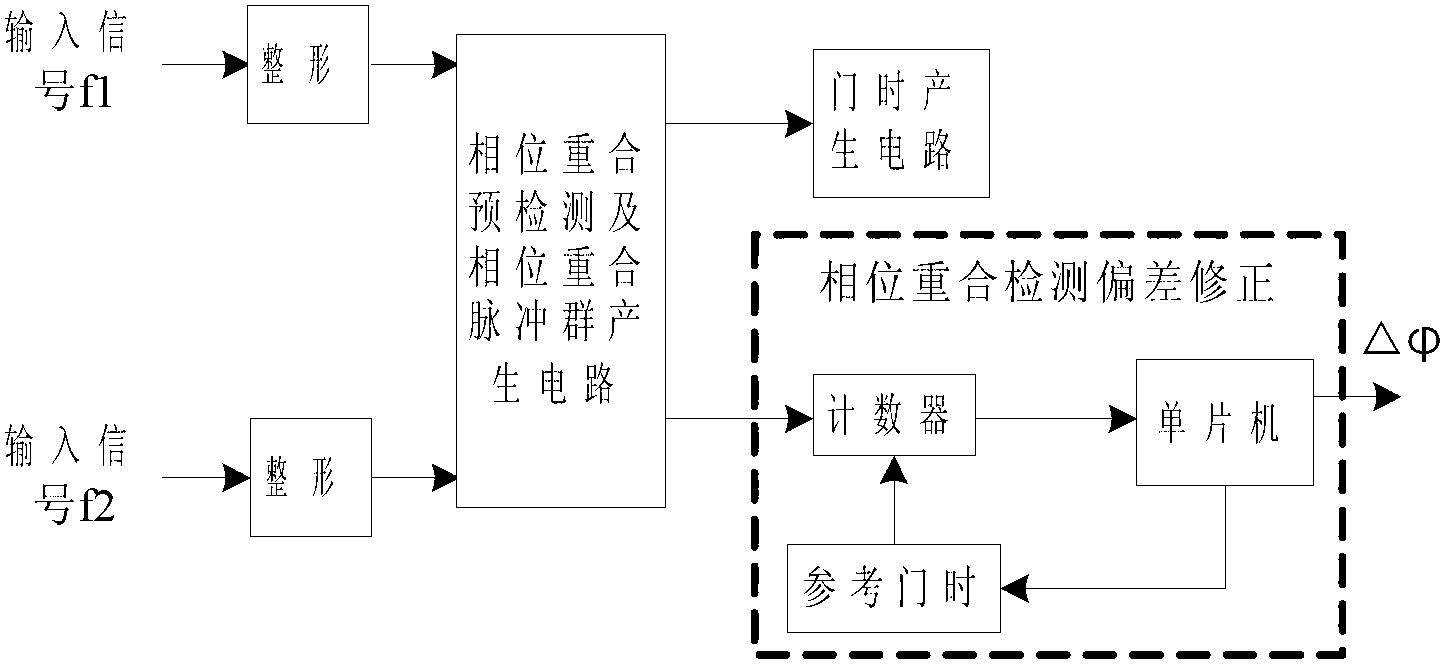

Method and system for pilot frequency bi-phase coincidence detection based on coincidence pulse counting

InactiveCN103176045ASimple structureHigh-resolutionVoltage-current phase angleFrequency to pulse train conversionPhase noisePhase difference

The invention discloses a system and a method for pilot frequency bi-phase coincidence detection based on coincidence pulse counting. The system comprises a pilot frequency signal phase coincidence pre-detection and phase coincidence pulse group generation circuit, a bi-phase coincidence detection phase deviation correction circuit and a gate delay generation circuit. By utilizing a group phase coincidence principle among pilot frequency signals and by combining the phase coincidence pre-detection and phase coincidence pulse group generation circuit and coincidence pulse counting, gate information needed by measurement comparison is given, and a phase coincidence detection deviation value can be resolved by the aid of a coincidence pulse count value so as to correct a final measurement result. By the method, influences of phase noise and trigger error on phase coincidence detection are eliminated, and the realized phase difference coincidence detection can reach measurement resolution superior to picosecond. Besides, the method is capable of improving precision of phase coincidence detection and measurement resolution, and a circuit is simple in structure and easy for integration and productization.

Owner:XIDIAN UNIV

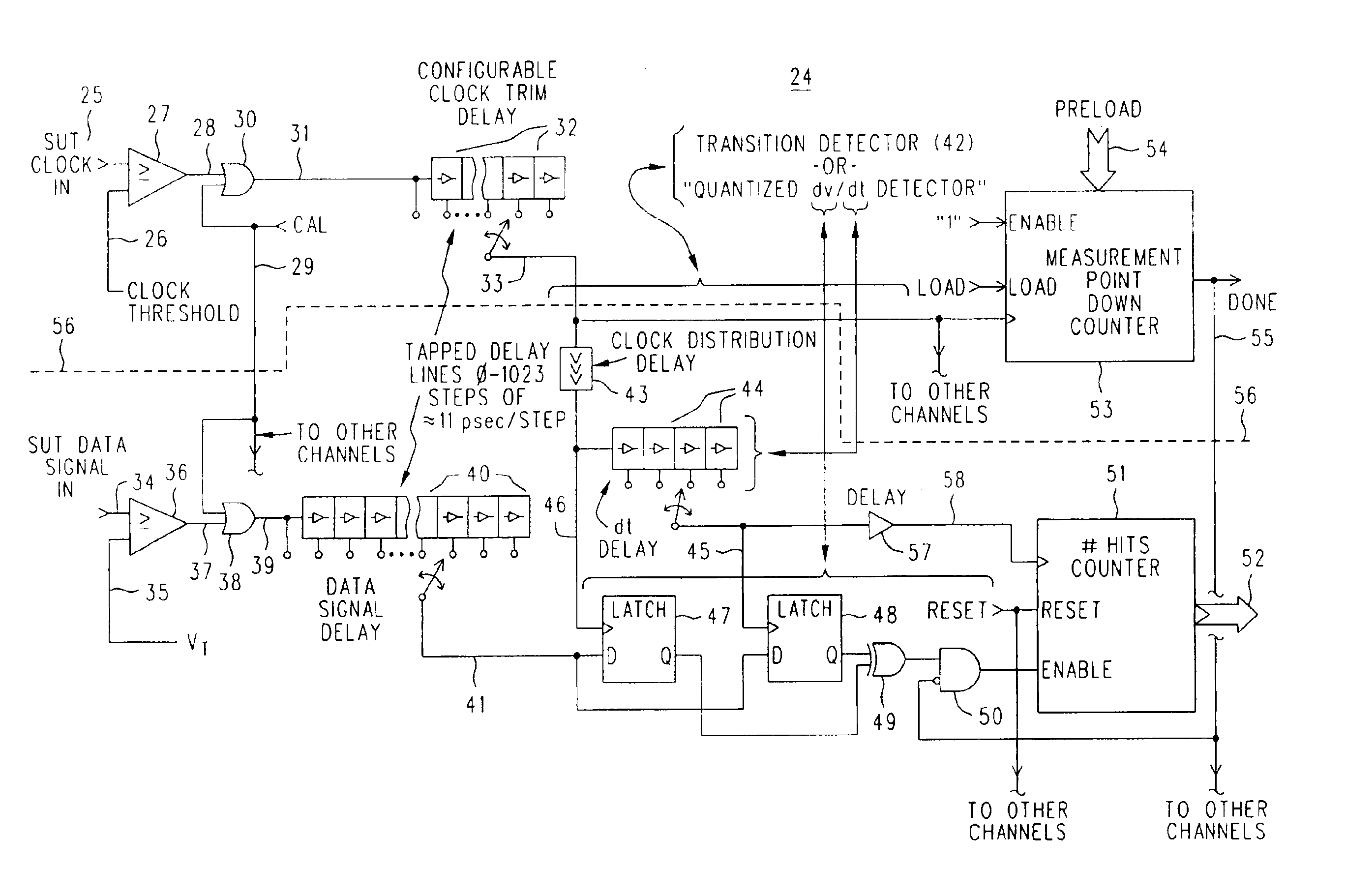

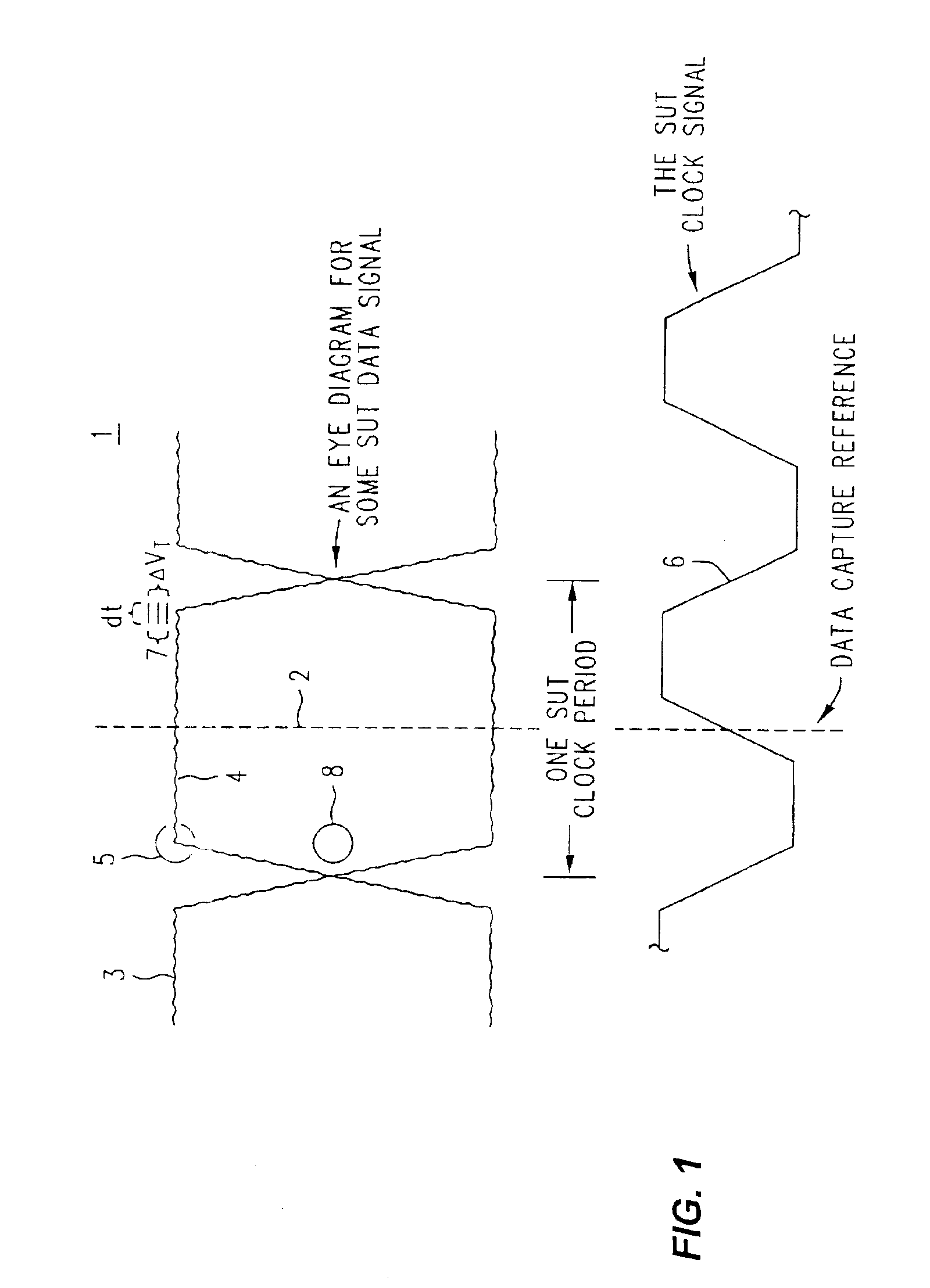

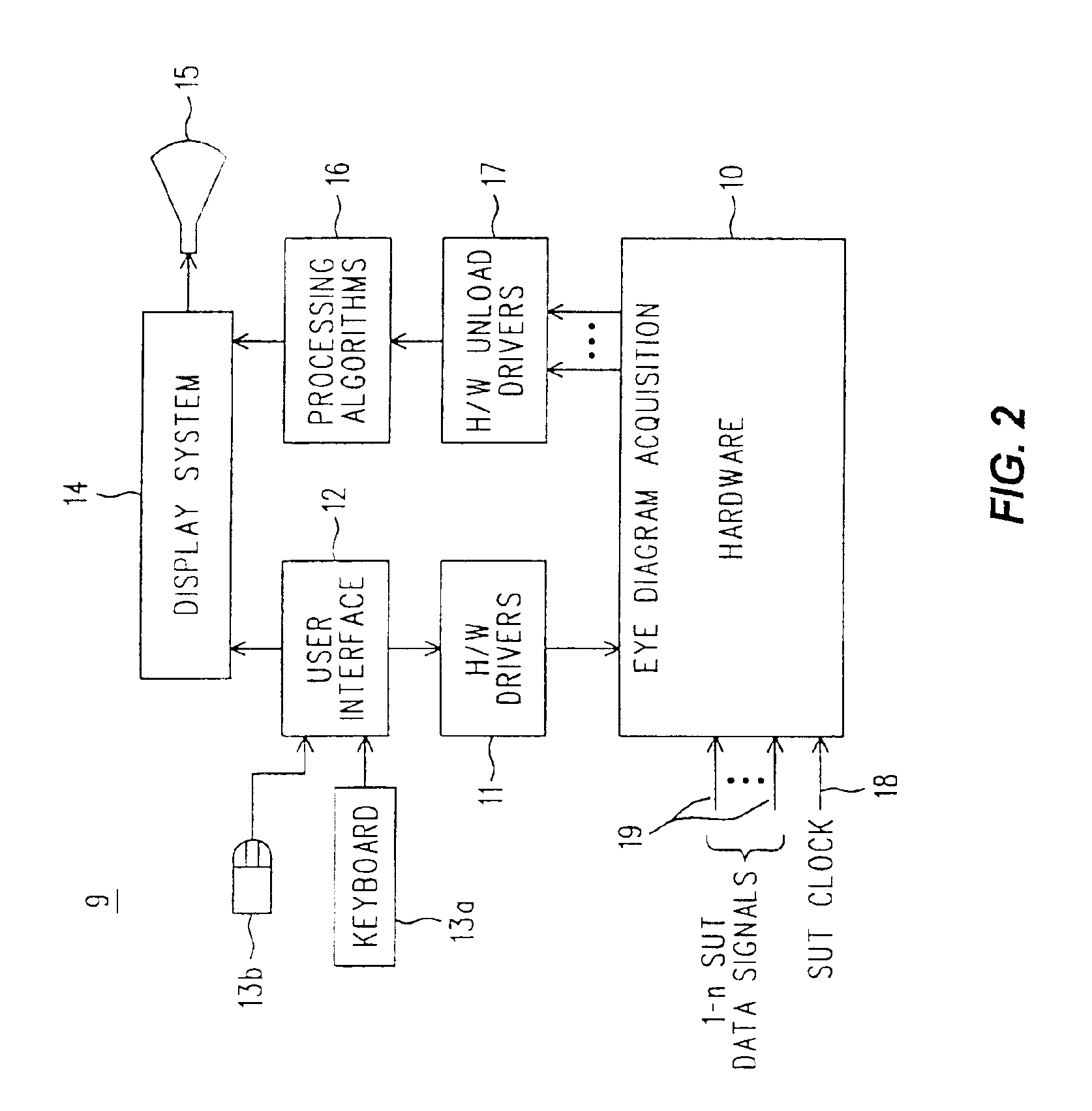

Method and apparatus for performing eye diagram measurements

An eye diagram analyzer equips each SUT data and clock signal input channel with individually variable delays in their respective paths. For a range of signal delay of n-many SUT clock cycles, the SUT clock signal delay might be set at about n / 2. For each data channel there is specified a point in time relative to an instance of the delayed clock signal (data signal delay) and a voltage threshold. The specified combination (data signal delay, threshold and which channel) is a location on an eye diagram, although the trace may or may not ever go through that location. A counter counts the number of SUT clock cycles used as instances of the reference for the eye diagram, and another counter counts the number of times the specified combination of conditions was met (“hits”). After watching a specified combination for the requisite length of time or number of events, the number of SUT clock cycles involved and the associated number of hits are stored in memory using a data structure indexed by the components of the specified combination (data signal delay, threshold). Next, a new combination of data signal delay and threshold is specified and a measurement taken and recorded in the data structure. The process is repeated until all possible combinations within a stated range of data signal delay and threshold voltage (using specified resolution / step sizes for delay and voltage) have been investigated. As this process proceeds under the control of firmware within the logic analyzer, other firmware can be examining the data structure and generating a partial eye diagram visible on a display, and that will be complete soon after the measurement itself is finished.” has been changed to “An eye diagram analyzer equips each SUT data and clock signal input channel with individually variable delays in their respective paths. For a range of signal delay of n-many SUT clock cycles, the SUT clock signal delay might be set at about n / 2. For each data channel there is specified a point in time relative to an instance of the delayed clock signal (data signal delay) and a voltage threshold. The specified combination (data signal delay, threshold and which channel) is a location on an eye diagram, although the trace may or may not ever go through that location.

Owner:AGILENT TECH INC

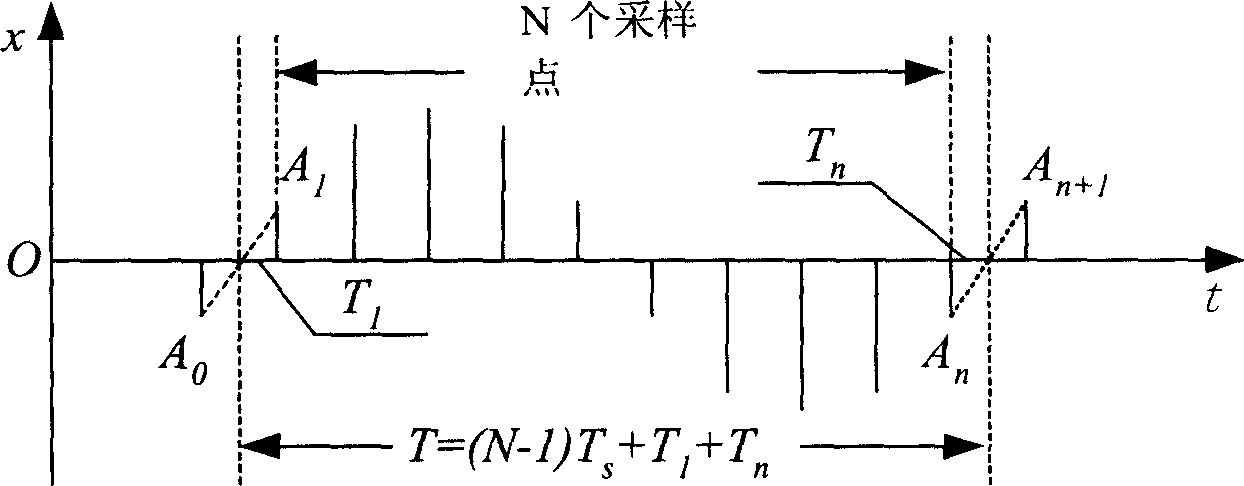

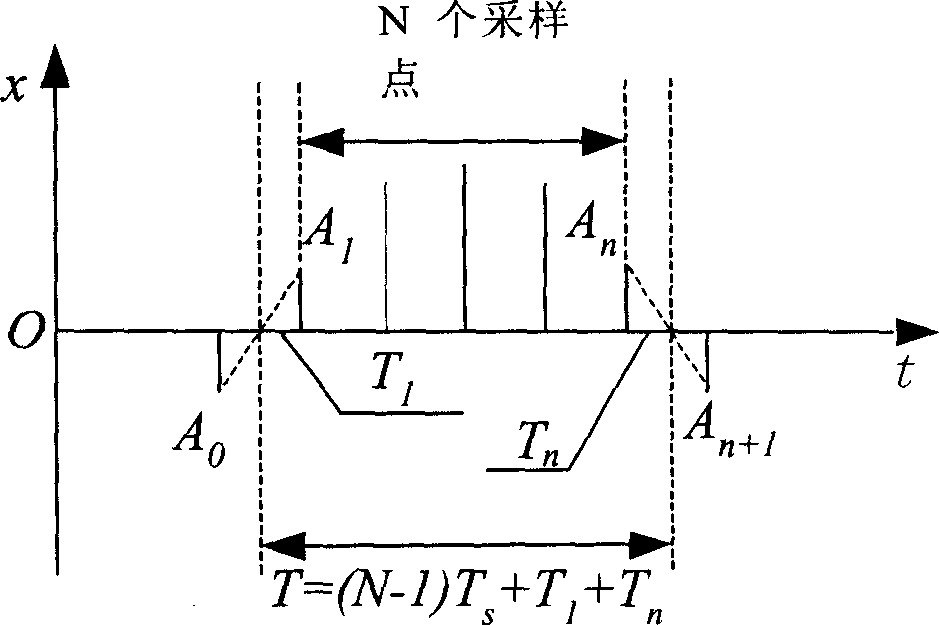

Large dynamic high-precision synchronization continuous frequency measurement method

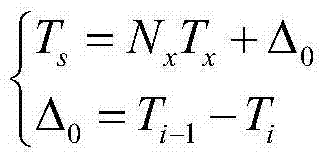

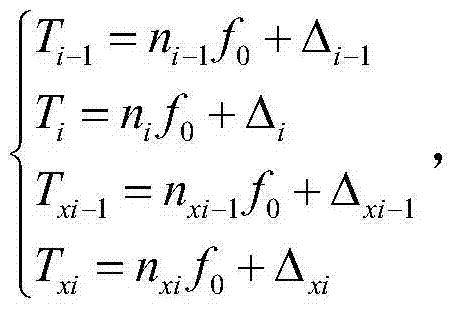

ActiveCN103698602ASynchronized continuous frequency measurement implementationReduce counter requirementsFrequency to pulse train conversionFrequency measurementsSynchronizing

The invention belongs to the technical field of frequency measurement and particularly relates to a large dynamic high-precision synchronization continuous frequency measurement method. The method disclosed by the invention comprises the following steps: S1, counting synchronized sampling time gate signals by adopting a measured signal; S2, counting by adopting a high-frequency impulse; S3, counting by adopting delay cell interpolation; S4, performing error correction to determine the frequency of the measured signal. According to the method disclosed by the invention, quantization errors which cannot be recognized by a high-frequency clock in a multi-period synchronizing method are subdivided, and therefore, the resolution ratio of the errors is improved, and large dynamic multichannel signal short time synchronization continuous high-precision measurement is realized.

Owner:BEIJING AUTOMATION CONTROL EQUIP INST