Time to digital converter with error protection

a time to digital converter and error protection technology, applied in the field of time to digital converters, can solve problems such as the difficulty of improving the estimation resolution of conventional tdcs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0019]The following description shows the embodiments of carrying out the invention. This description is made for the purpose of illustrating the general principles of the invention and should not be taken in a limiting sense. The scope of the invention is best determined by reference to the appended claims.

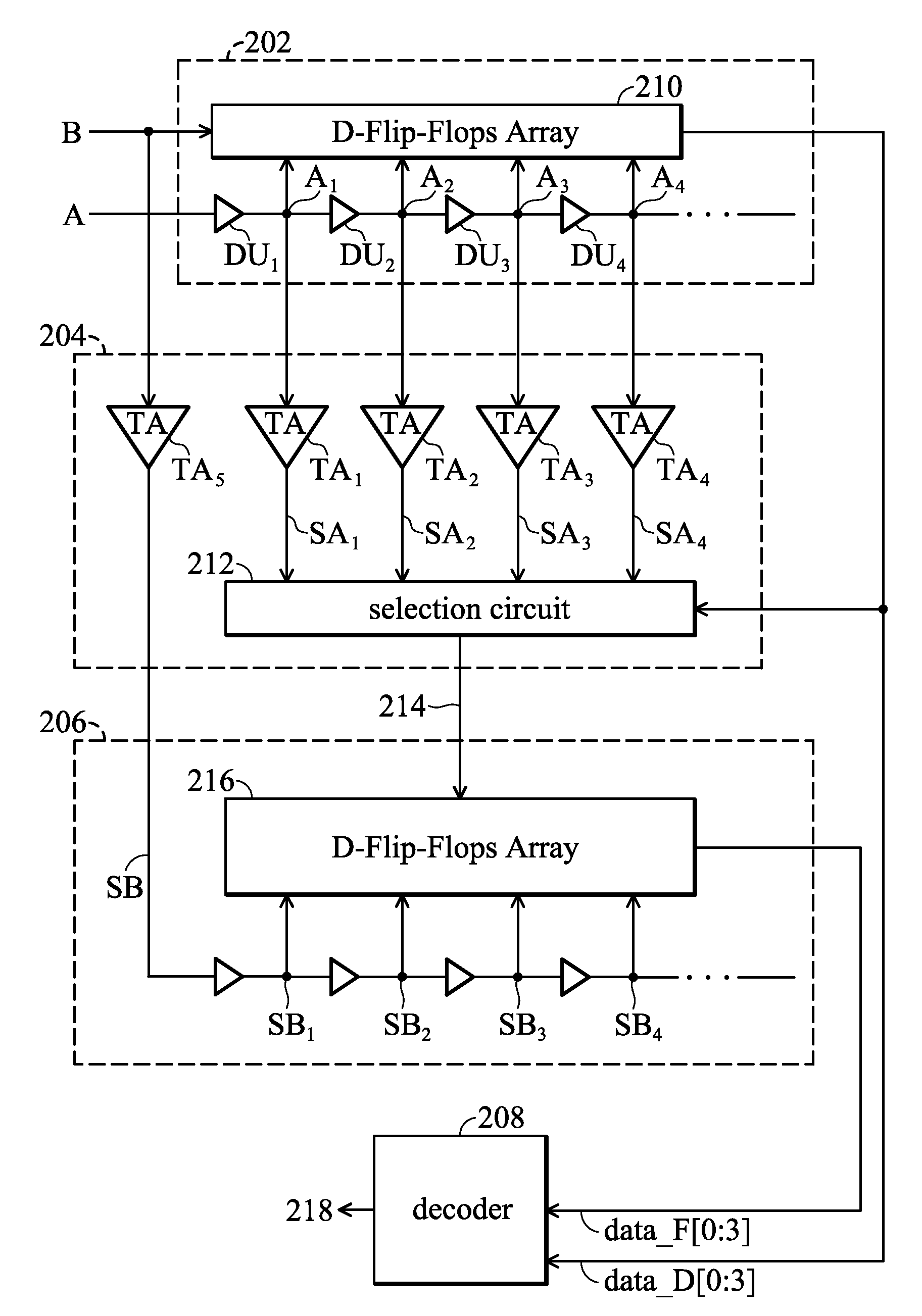

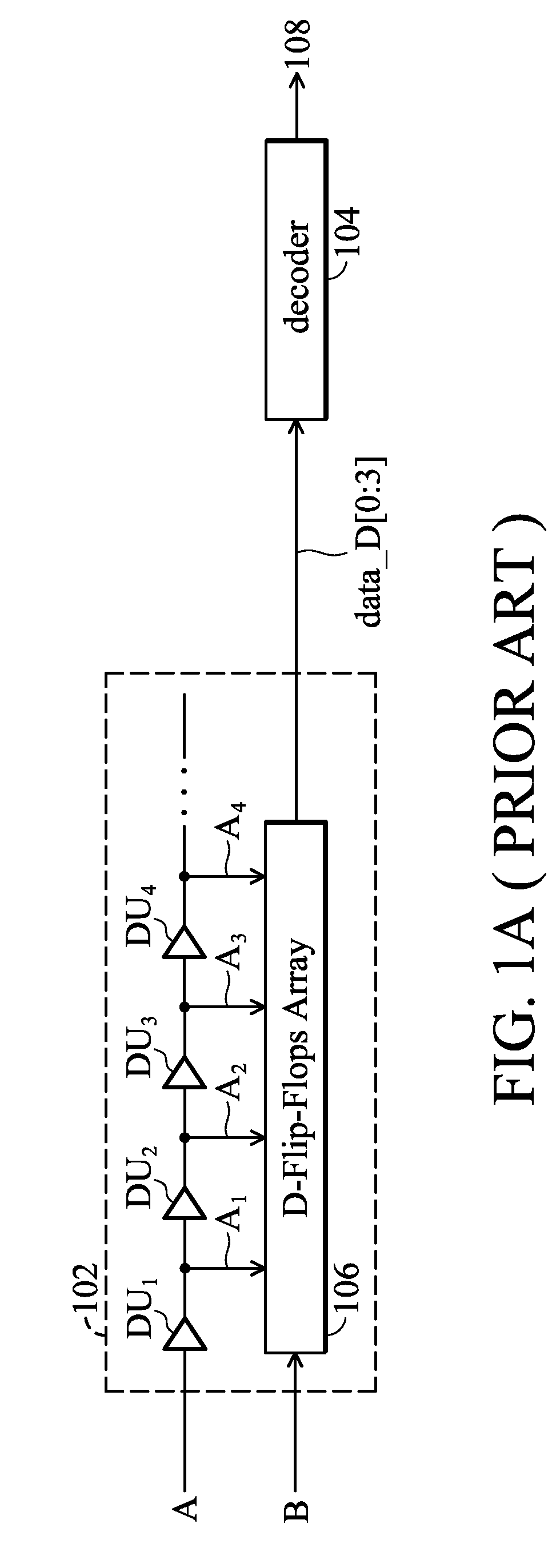

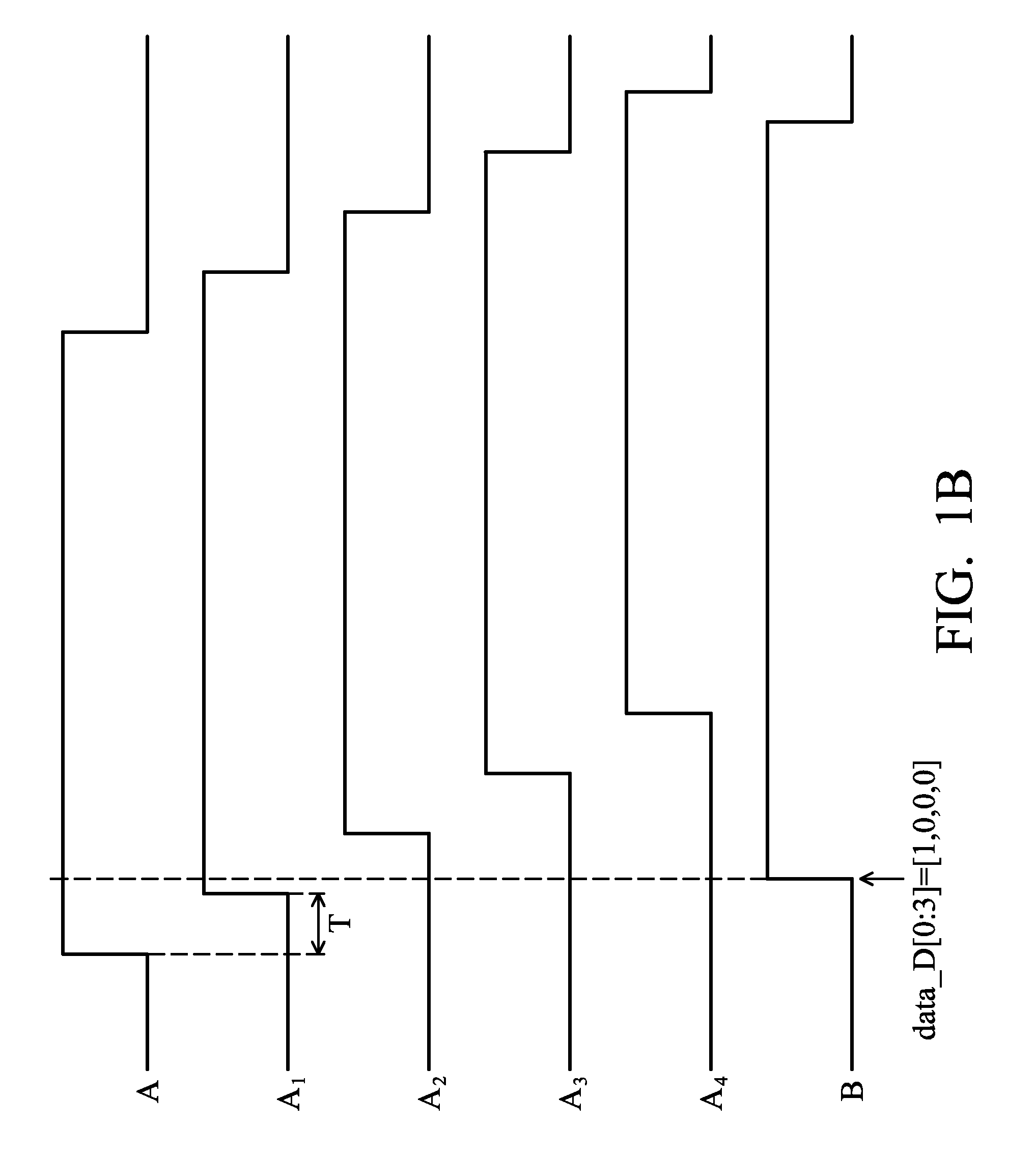

[0020]FIG. 2A illustrates an embodiment of the time to digital converter of the invention, which estimates a time difference between a first signal A and a second signal B. The time to digital converter comprises a first time to digital converting module 202, a selection and time-amplifying module 204, a second time to digital converting module 206 and a decoder 208. In this embodiment, the first time to digital converting module 202 comprises a plurality of delay units DU1˜DU4 and a D-Flip-Flops array 210. The delay units DU1˜DU4 are coupled in series to delay the first signal A to generate a plurality of delayed first signals A1˜A4. The D-Flip-Flops array 210 is triggered by th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More