Patents

Literature

938 results about "Control delay" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

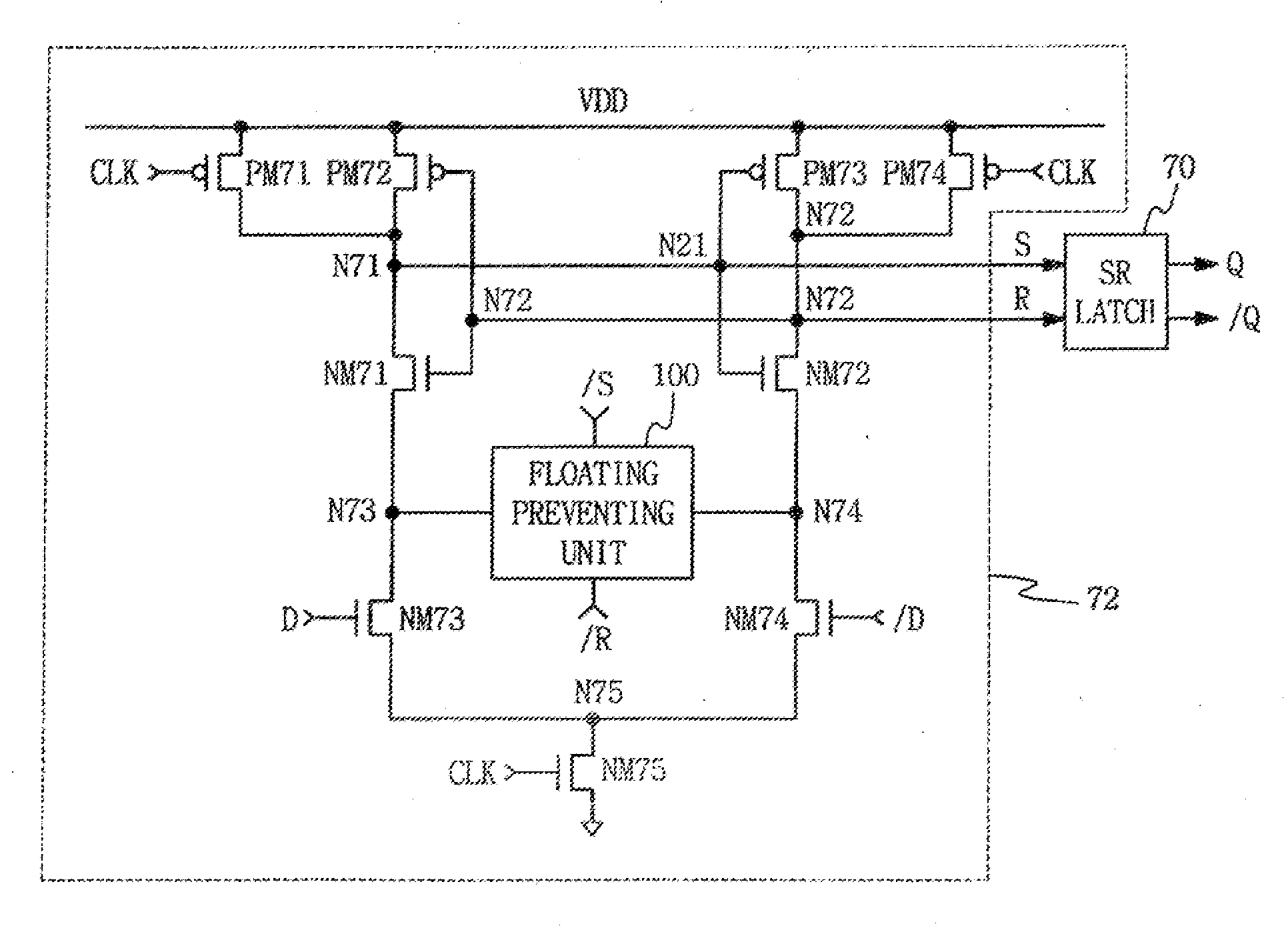

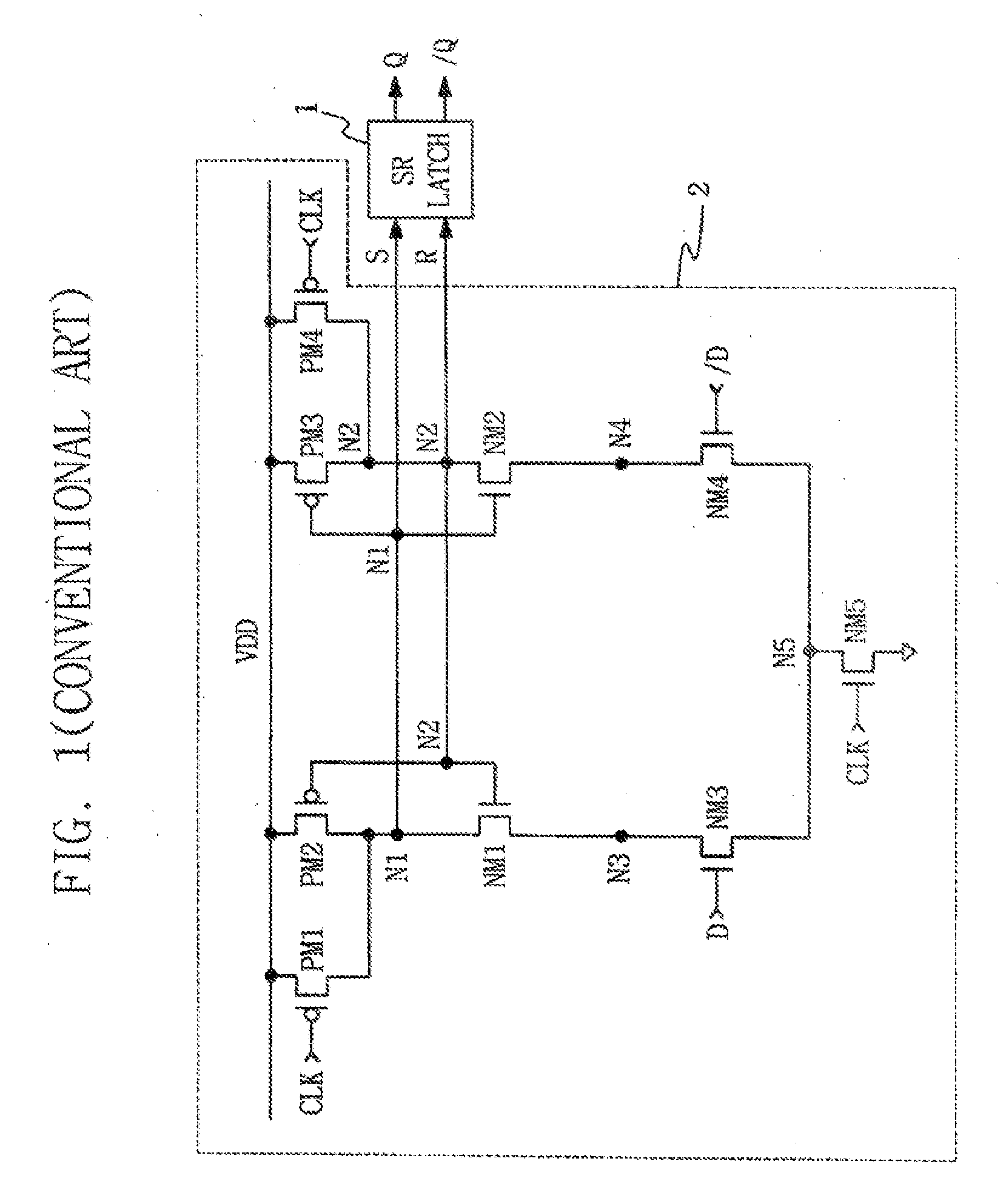

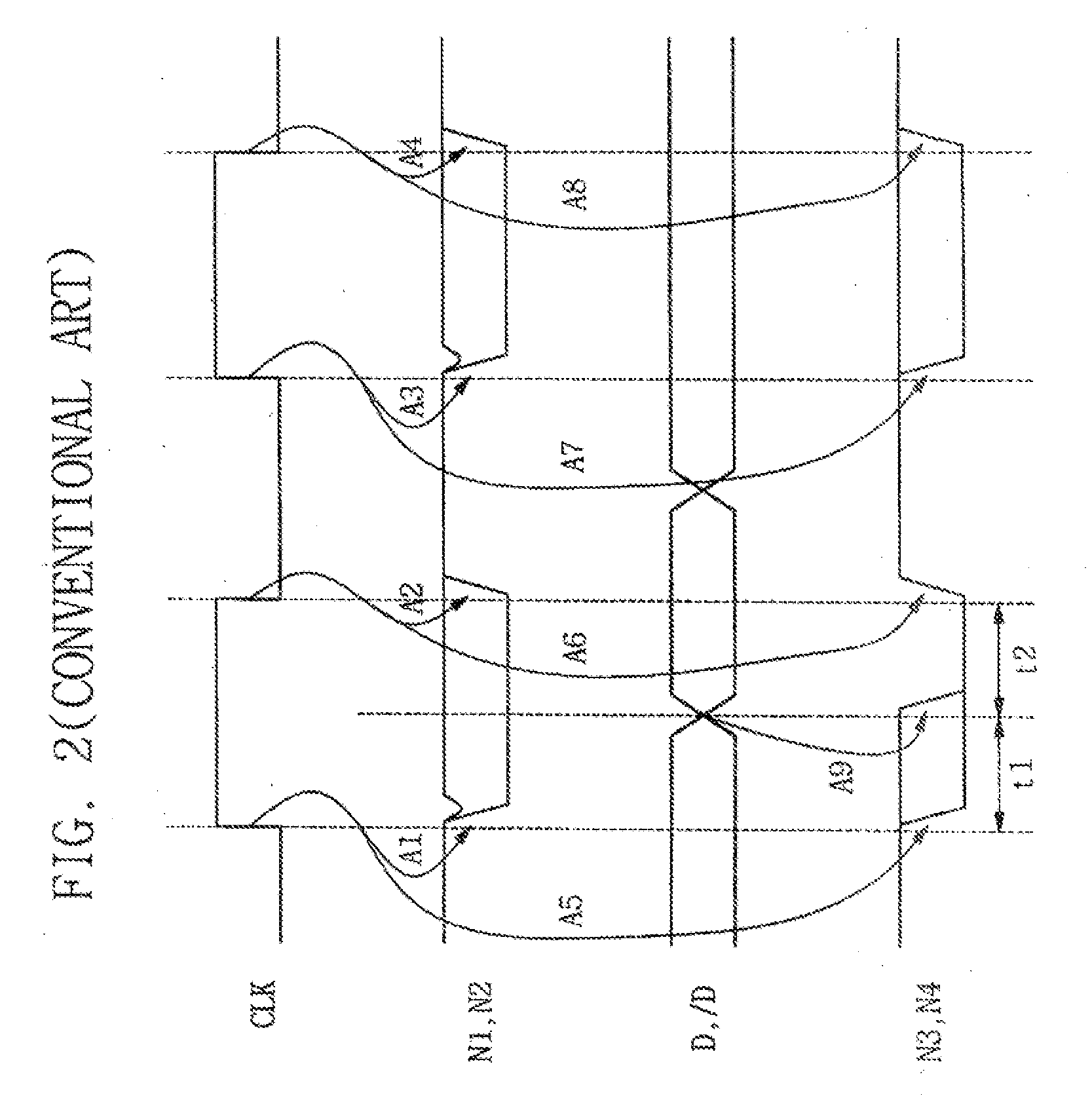

Sense amplifier circuit and sense amplifier-based flip-flop having the same

ActiveUS20070285131A1Reducing signal delay timePrevent degradation of outputCurrent/voltage measurementDigital storageAudio power amplifierControl delay

A sense amplifier-based flip-flop includes a first latch, a second latch, a floating reduction unit, an input signal applying unit, a ground switch and a delay reduction unit. The first latch outputs a signal to a first output terminal pair, and outputs an evaluation signal pair corresponding to an input single pair to the first output terminal pair. The second latch latches the evaluation signal pair and outputs the evaluation signal pair to a second output terminal pair. The floating reduction unit is controlled by signals of the first output terminal pair and is operationally connected between current passing nodes of the first latch to prevent the first output terminal pair from floating. The input signal applying unit is disposed between the current passing nodes and a ground terminal, and receives the input signal pair. The ground switch is disposed between the input signal applying unit and the ground terminal, and is controlled by the clock signal. The delay reduction unit is disposed between the input signal applying unit and the ground switch, and reduces a signal delay from when the clock signal to when the evaluation signal pair is output from the second output terminal pair.

Owner:SAMSUNG ELECTRONICS CO LTD

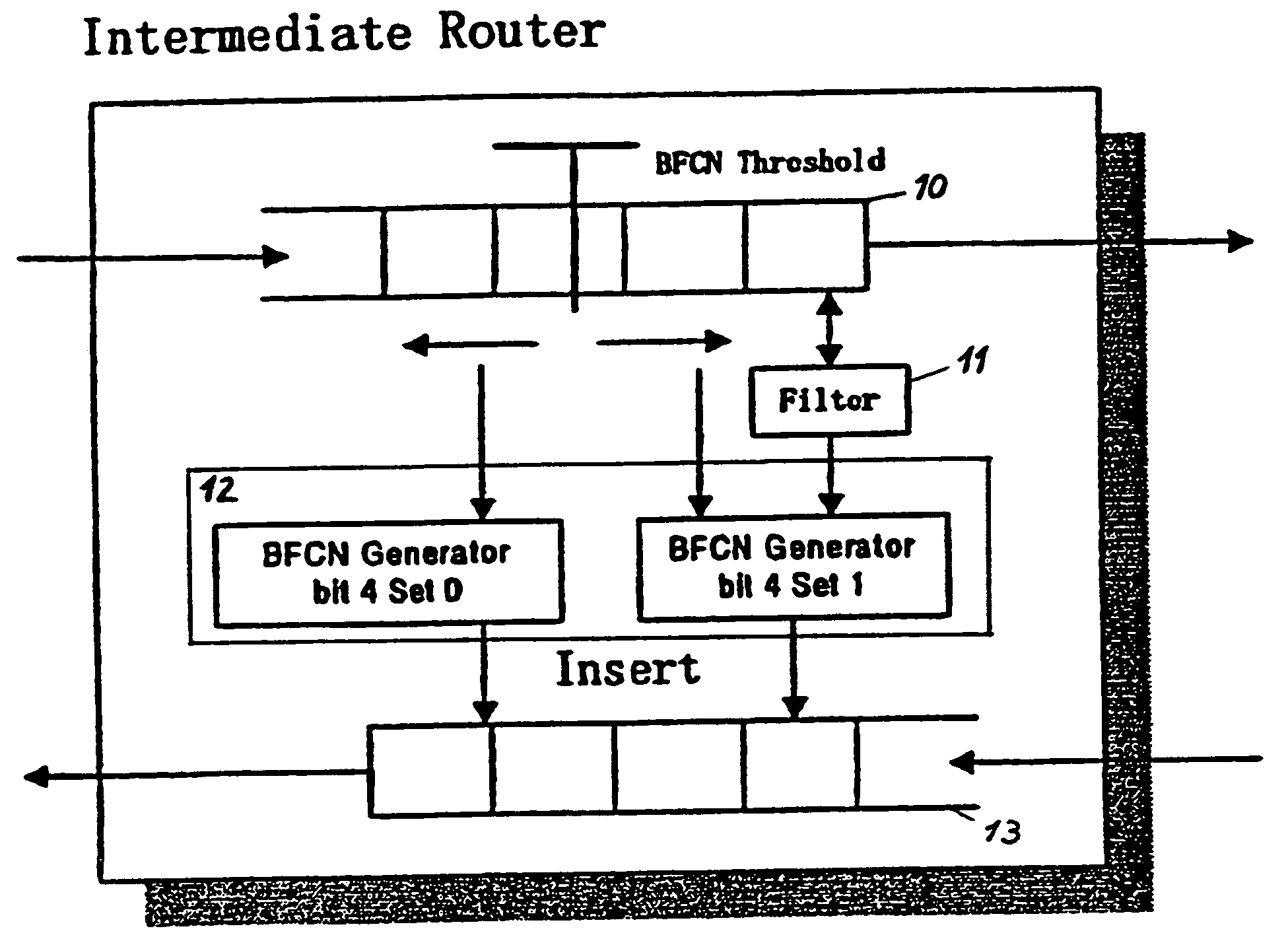

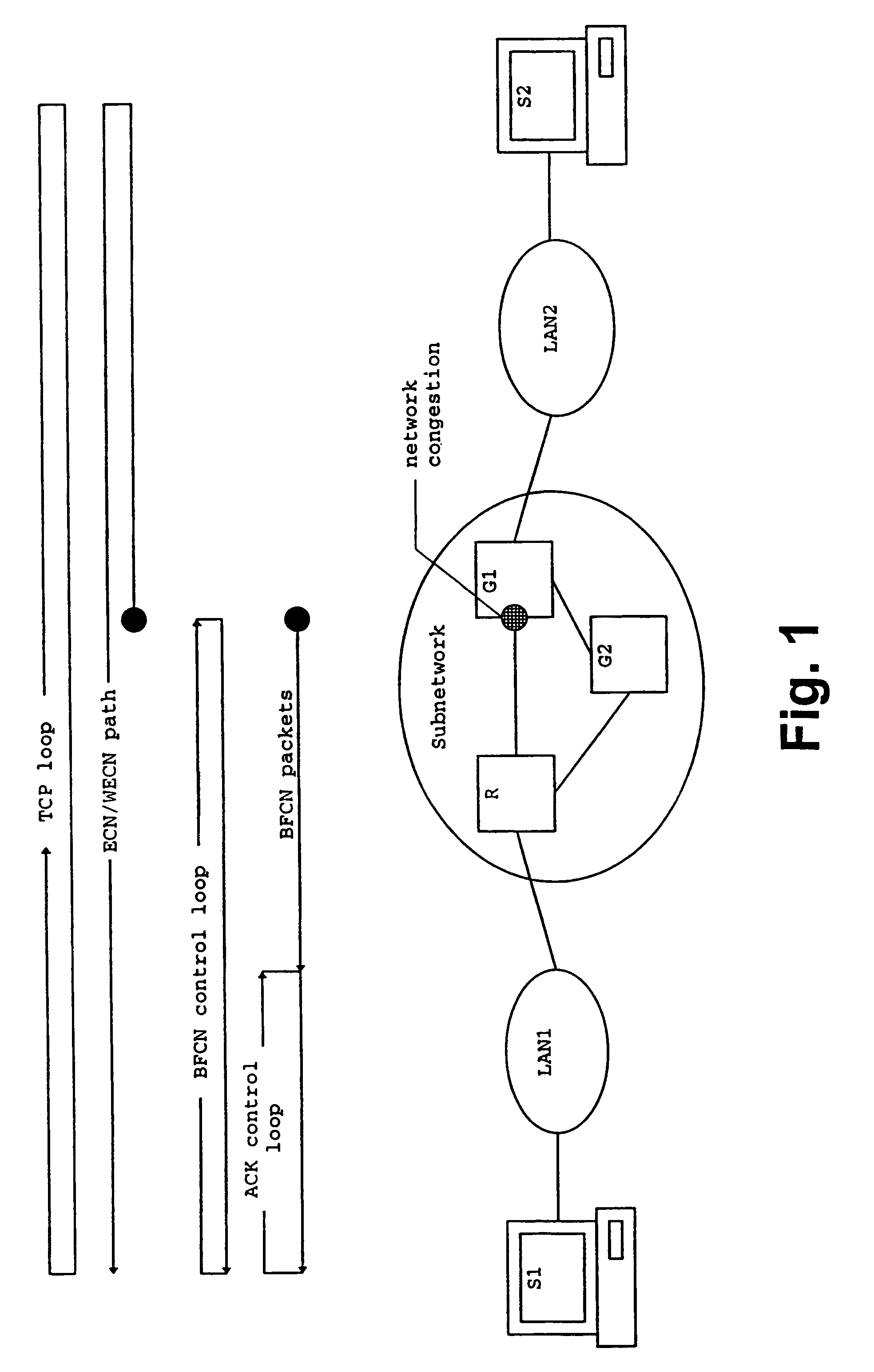

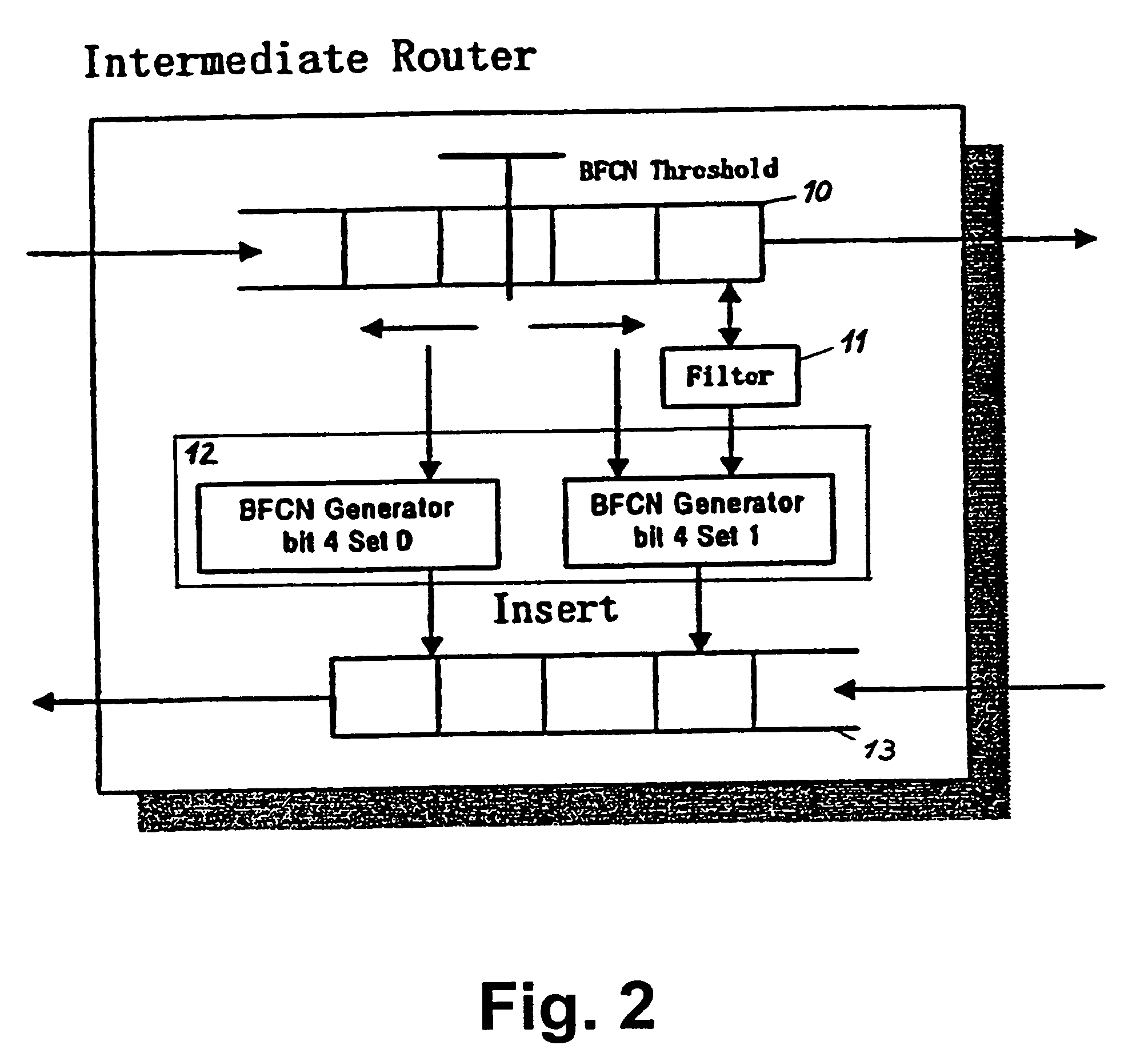

Congestion control method for a packet-switched network

InactiveUS7369498B1Increase profitError preventionFrequency-division multiplex detailsTraffic capacityPacket loss

The present invention relates to a method and network for controlling congestion in a packet-switched network, comprising traffic sources, traffic destinations and network nodes, wherein a packet queue length in a network node is determined and a congestion notification is transmitted back towards the source address of an incoming data packet received at the network node, if the detected packet queue length exceeds a predetermined threshold. Then, congestion control is performed at a predetermined intermediate network node in response to the receipt of the congestion notification. Thereby, burts of source traffic can be constrained and unnecessary packet losses can be avoided already at an intermediate access node and within the network. The congestion notification message generated due to an incipient congestion is immediately routed back according to its source address. As a result, control delay time is shortened, such that buffer size requirements and number of congestion notification messages are reduced.

Owner:NOKIA CORP

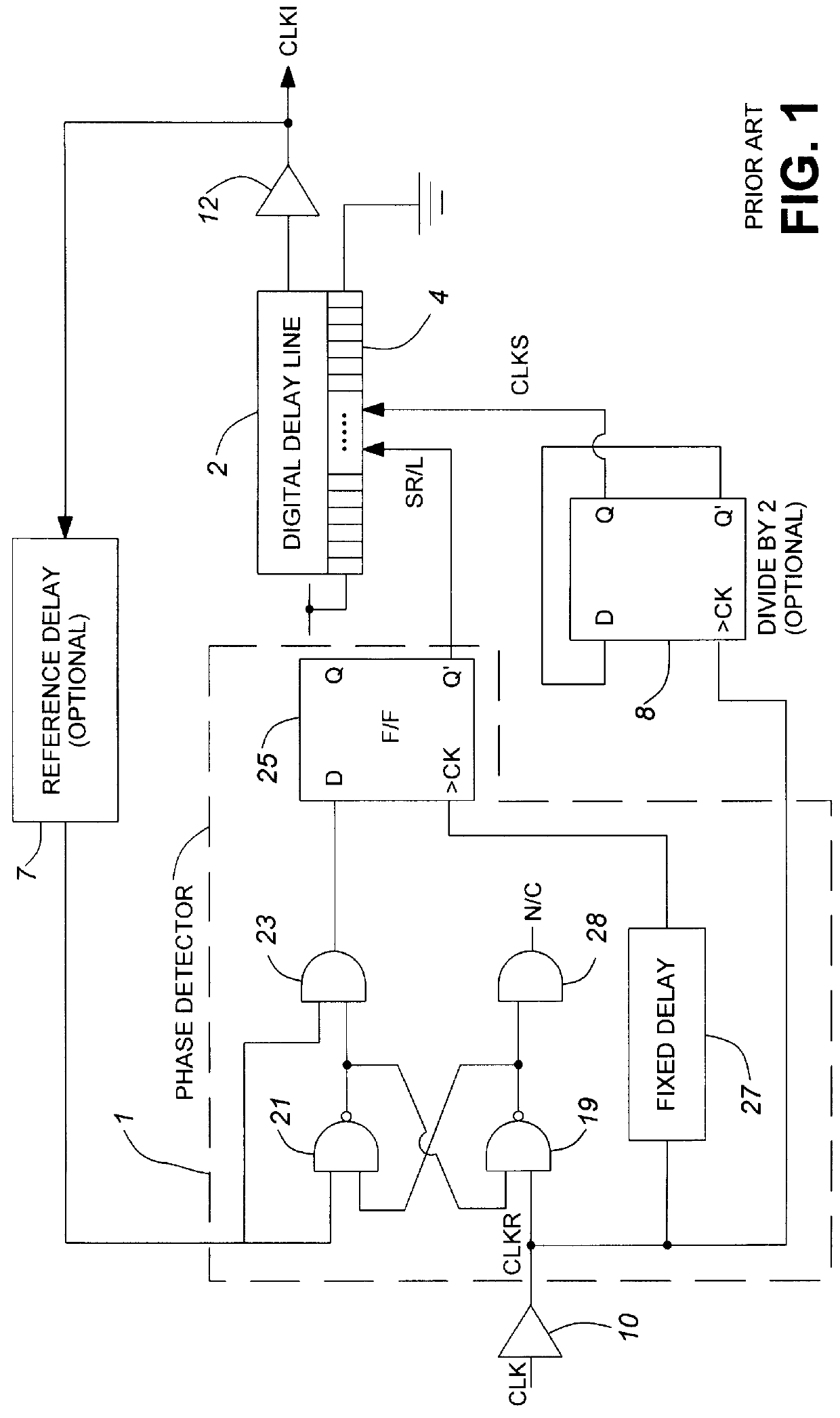

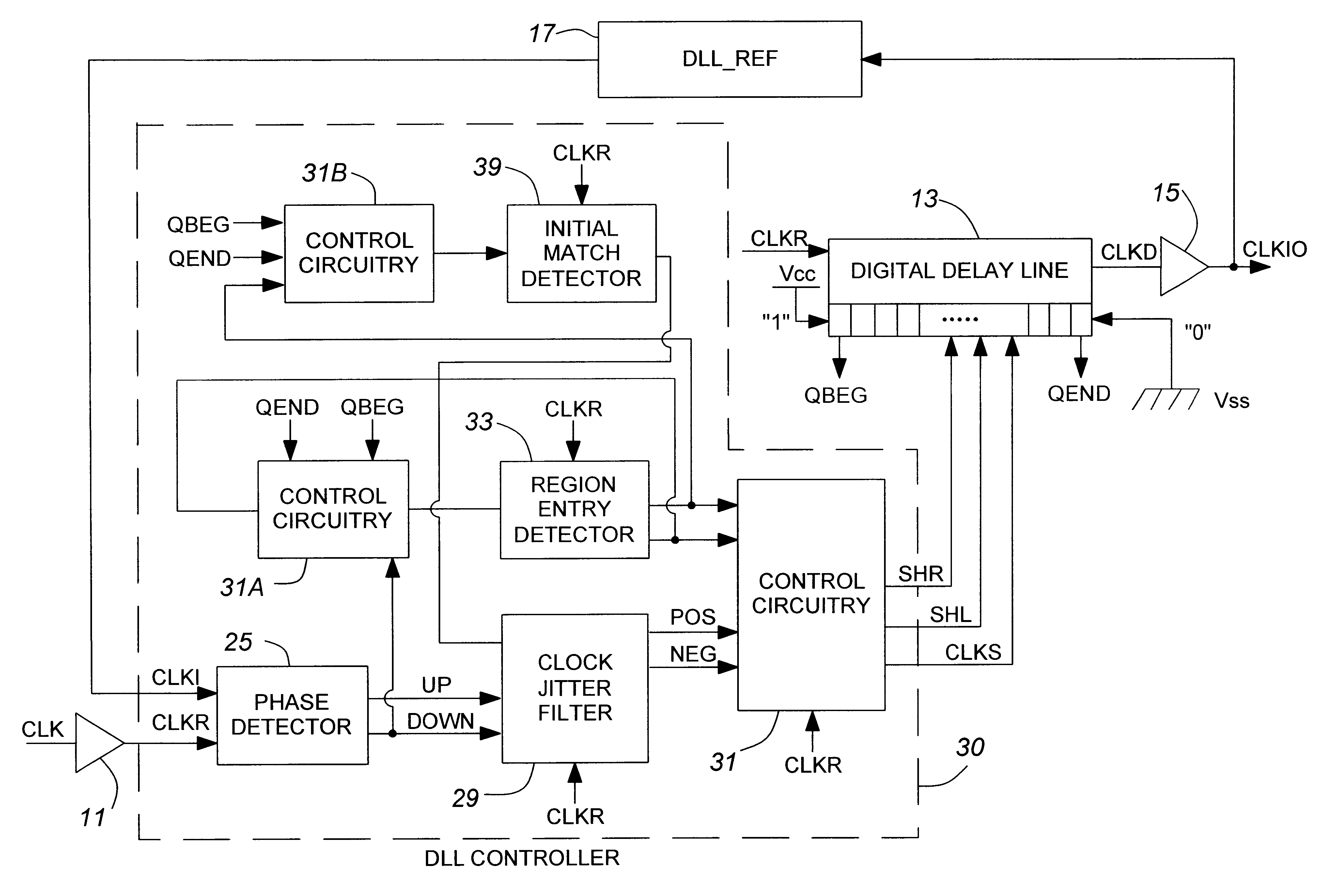

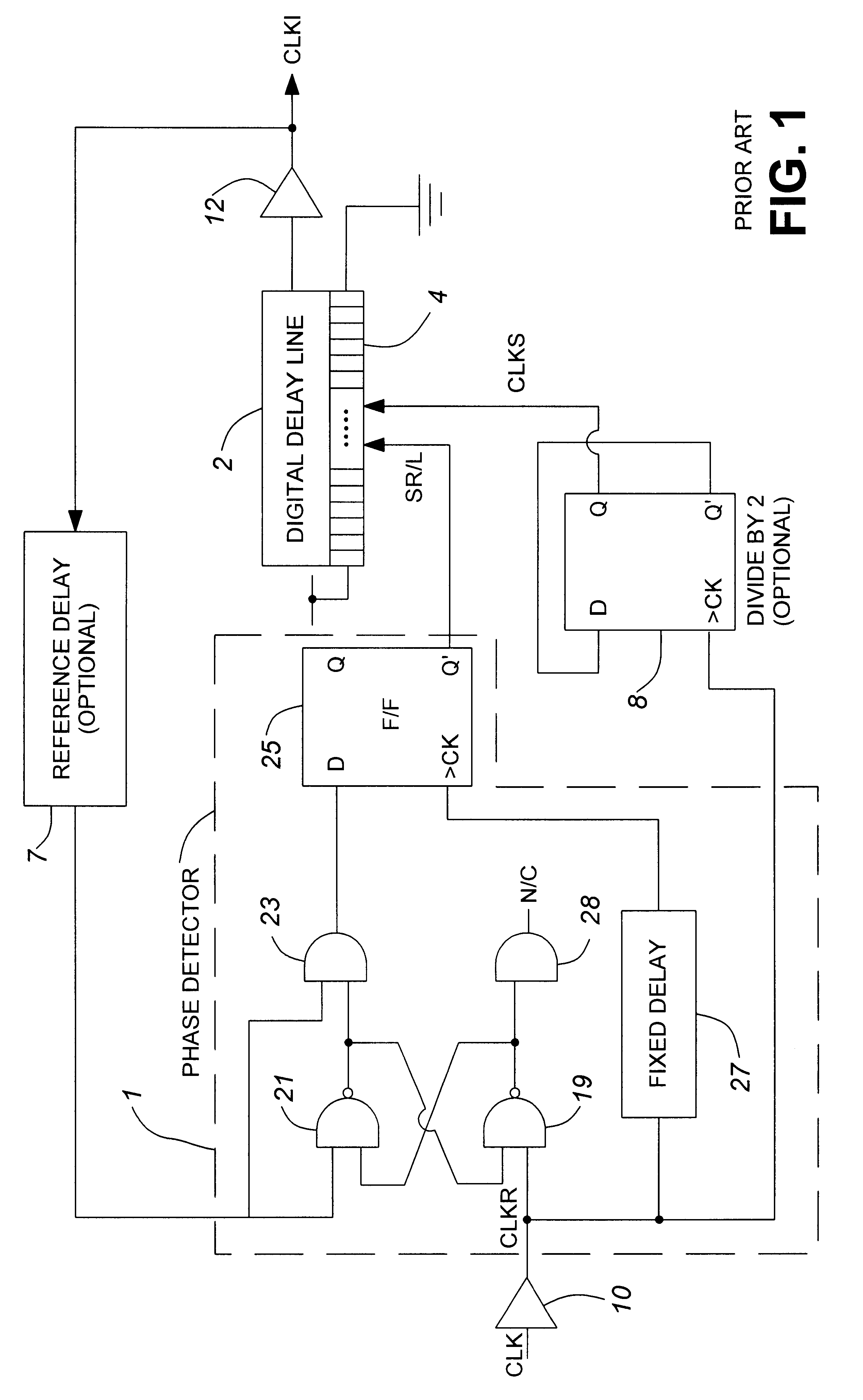

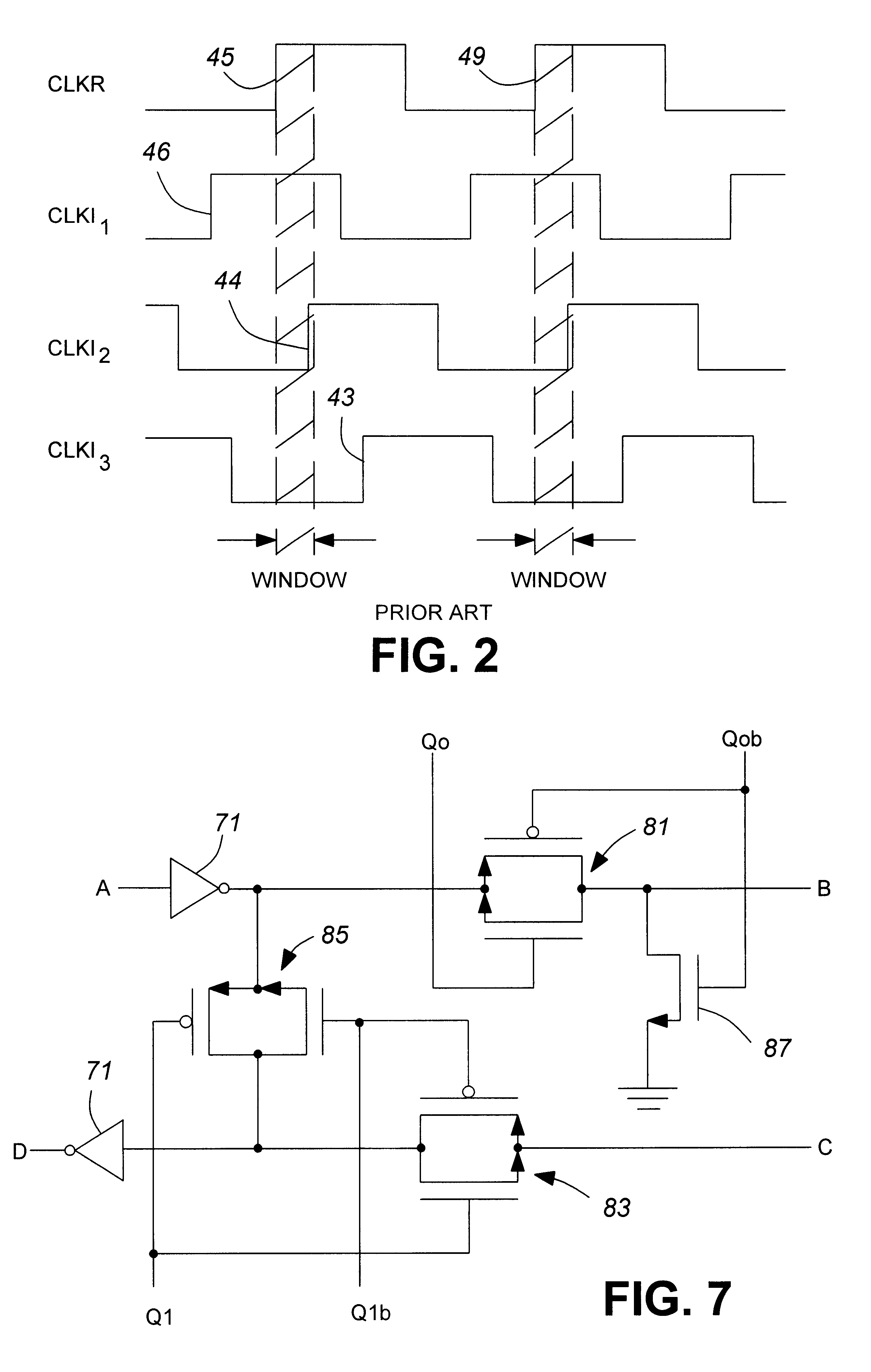

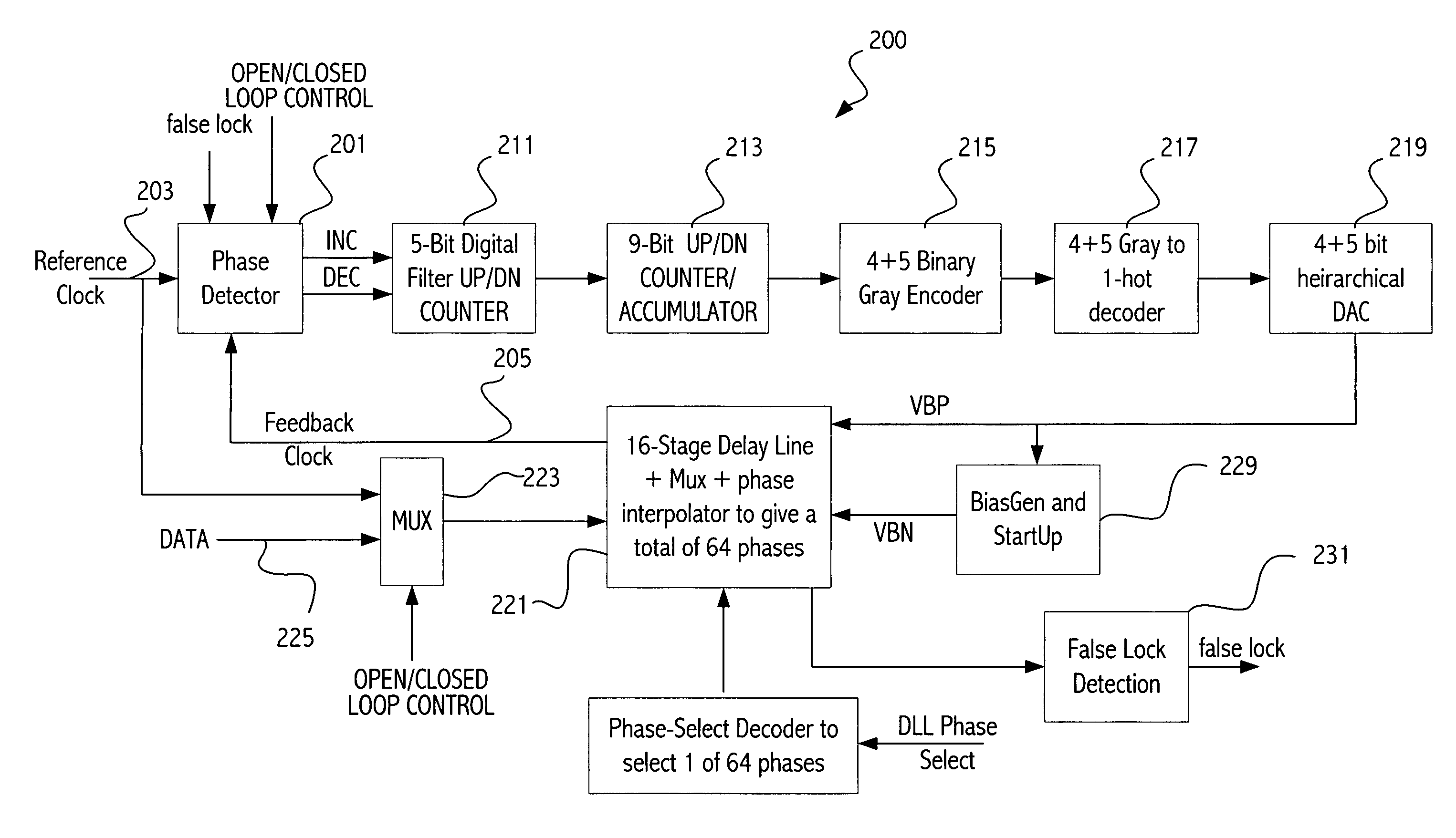

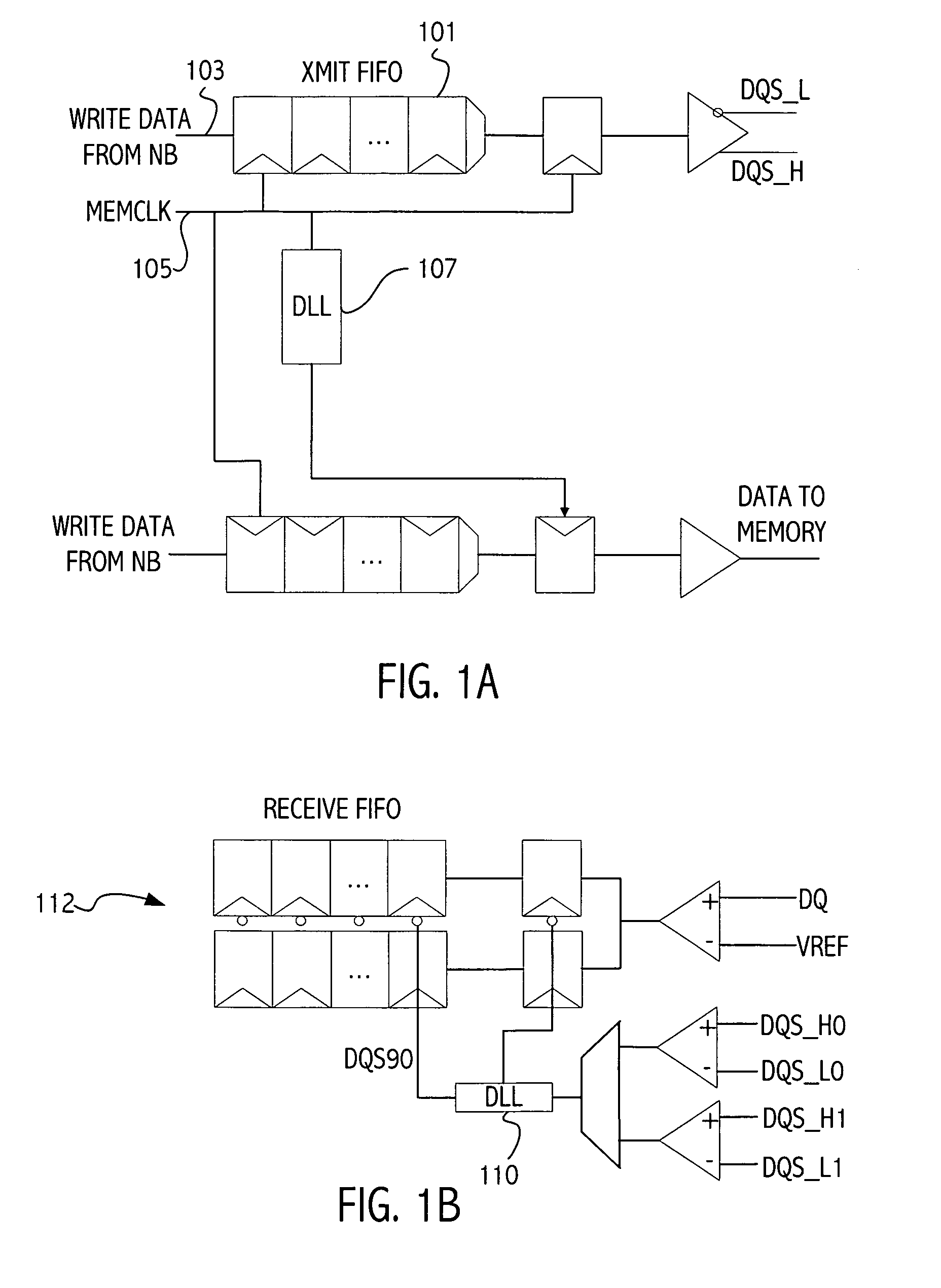

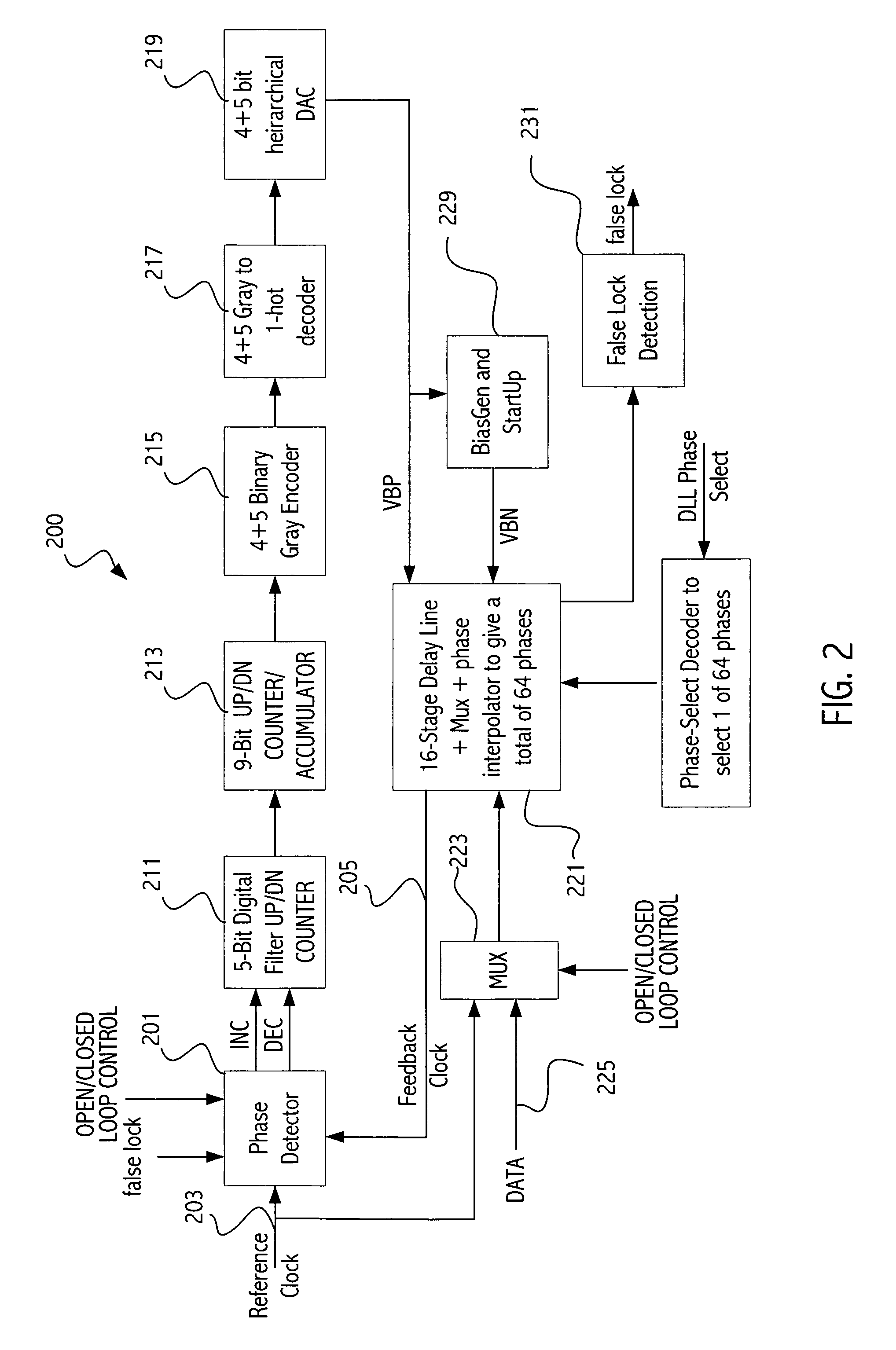

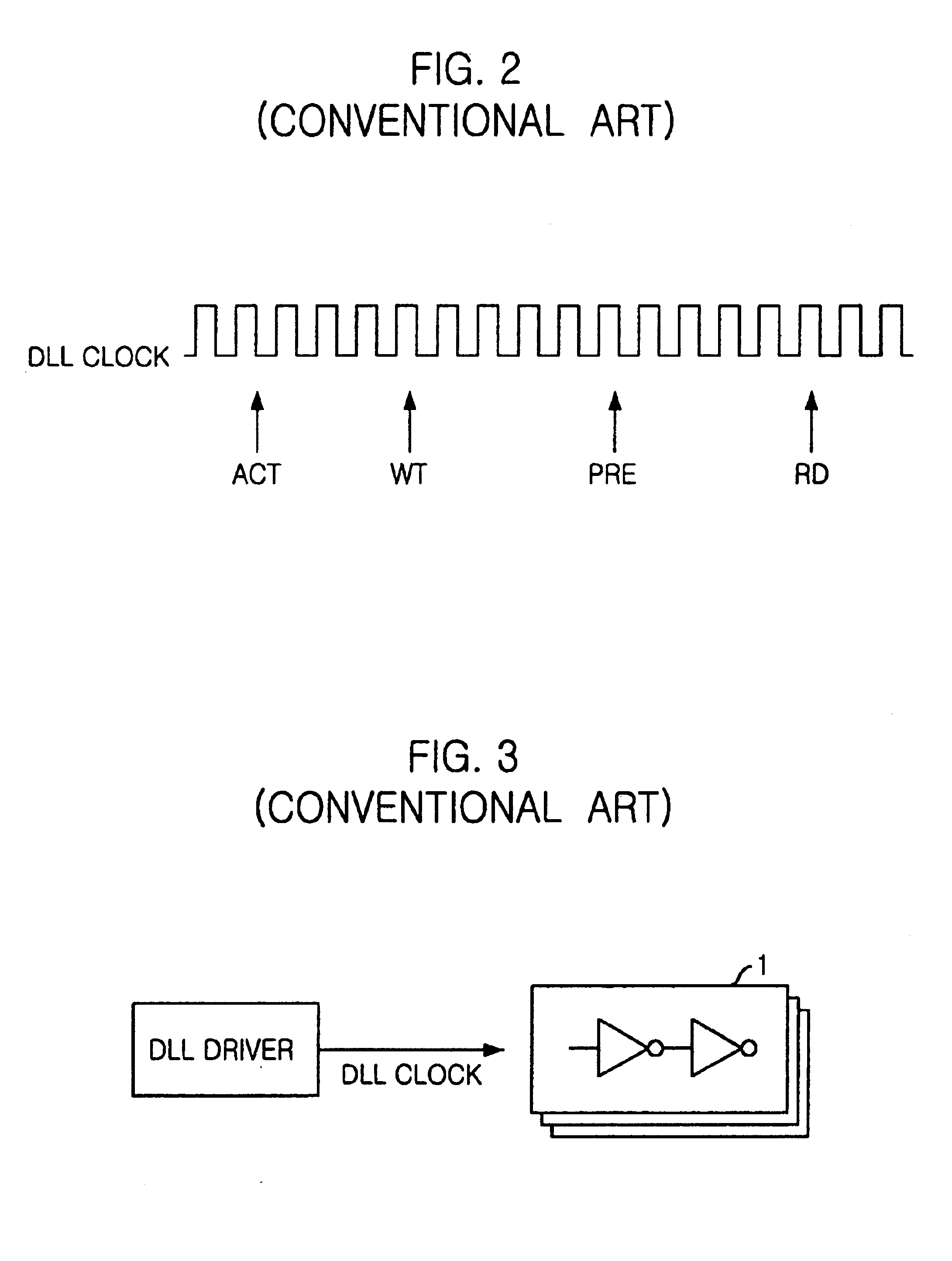

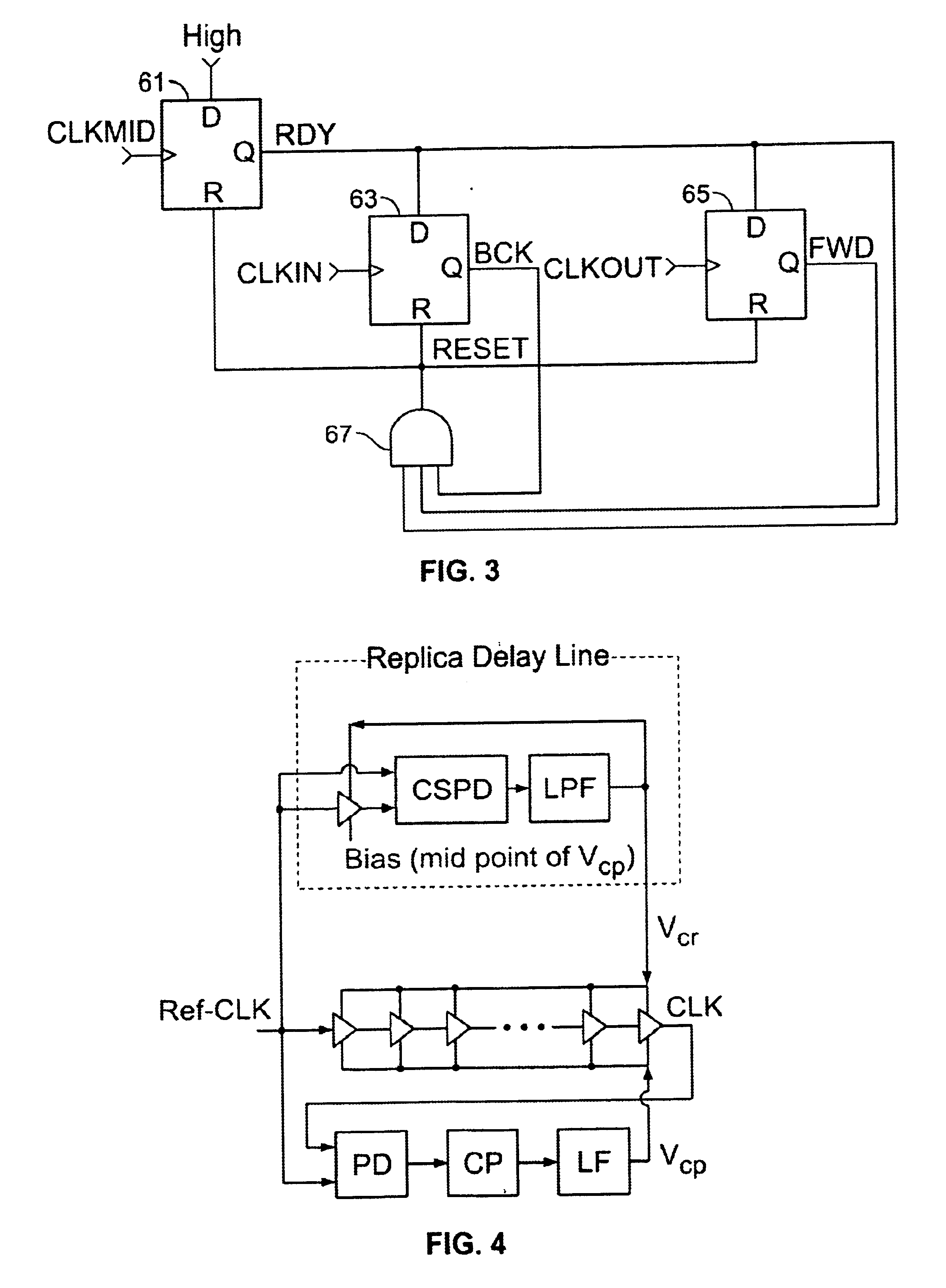

Digital delay locked loop

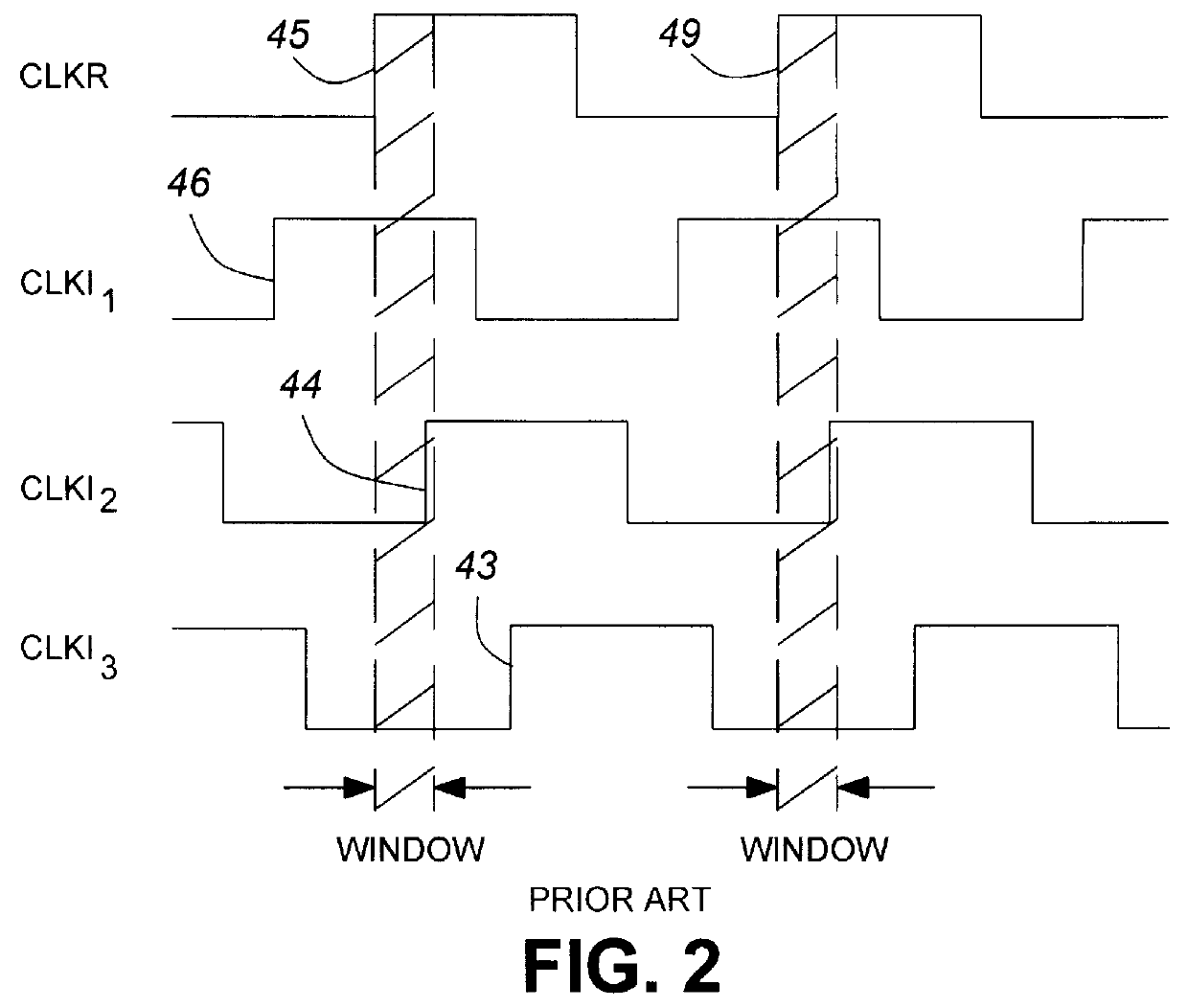

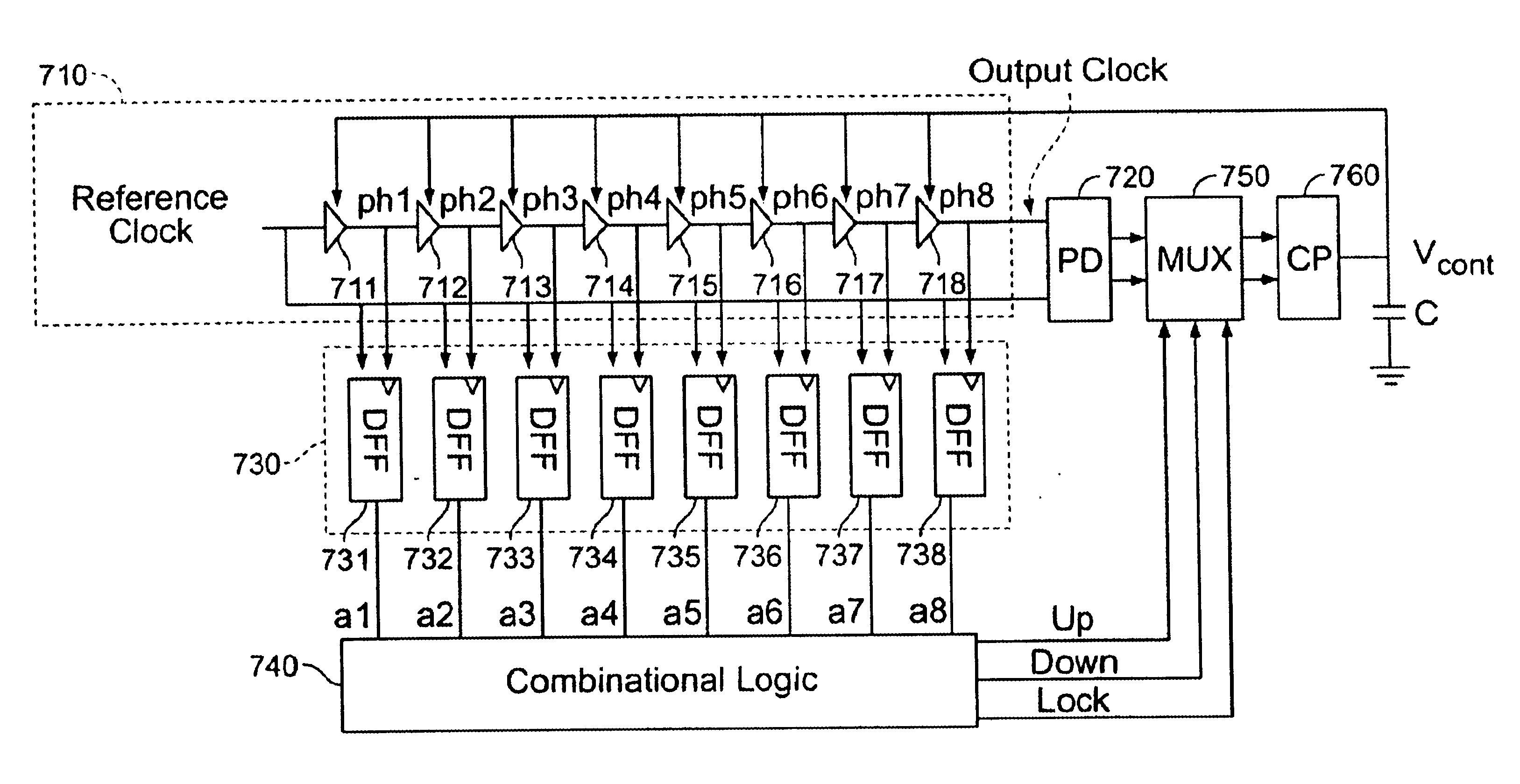

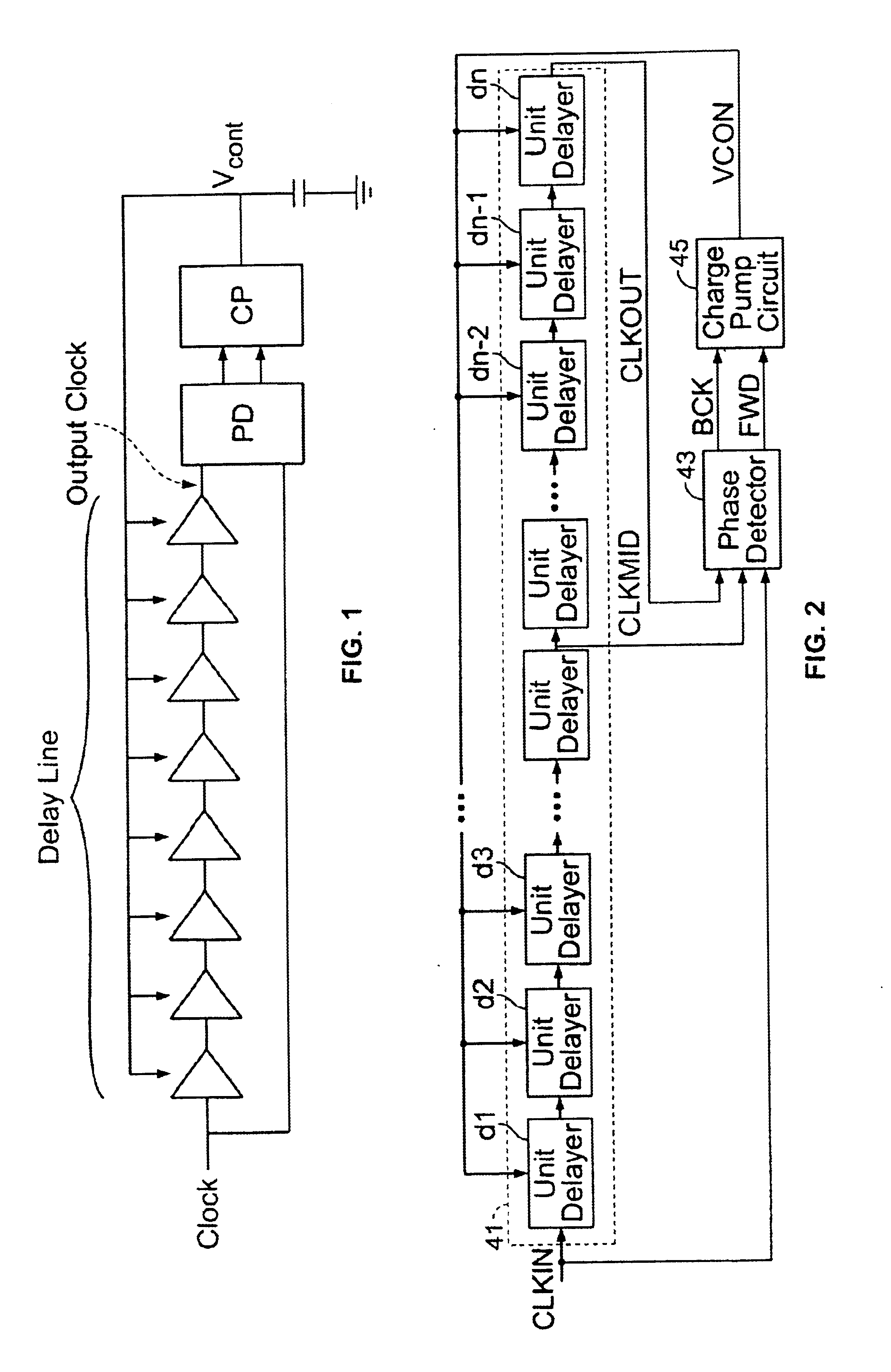

An improved edge-triggered fully digital delay locked loop (DLL), which maintains reliable synchronization from startup and in spite of system clock jitter is described. An internal clock signal is synchronized with a reference clock signal by propagating the reference clock signal through a variable digital delay path. A wide phase detection region surrounds a selected rising edge of the internal clock signal. The DLL loop is open as long as the internal clock signal and a target edge of the reference clock signal are not simultaneously within the phase detection region. To achieve a DLL locked condition, the variable delay is increased from a minimum setting until the edge of the phase detection region is shifted in time just past the target edge of the reference clock. Once the DLL loop has been closed, a clock jitter filter is enabled to reject reference clock jitter effects on the DLL locked condition. A digital phase detector controls the delay line propagation delay to establish synchronization between the internal clock and the reference clock. Unused delay elements within the variable delay path are deactivated to save power.

Owner:CONVERSANT INTPROP MANAGEMENT INC

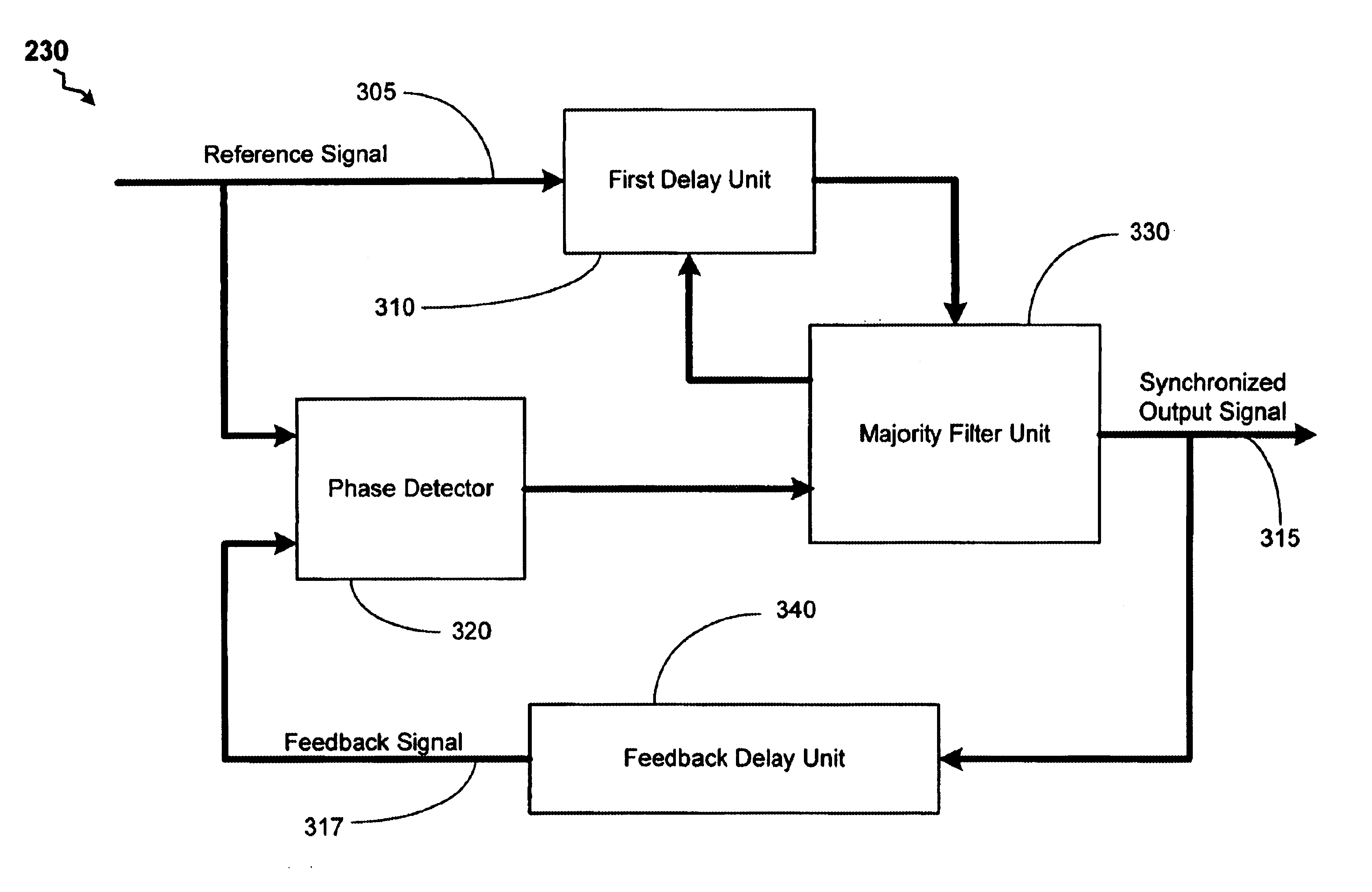

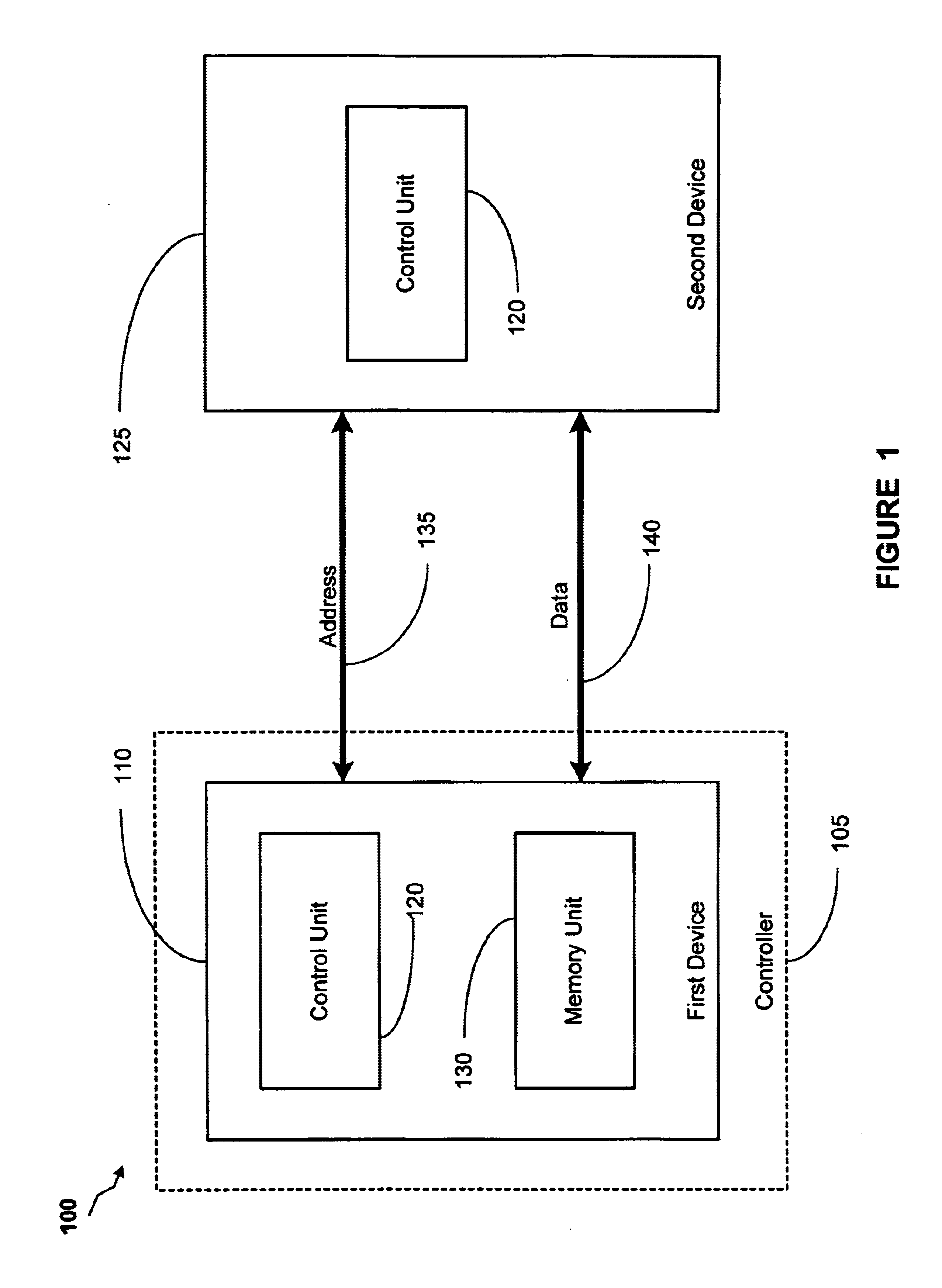

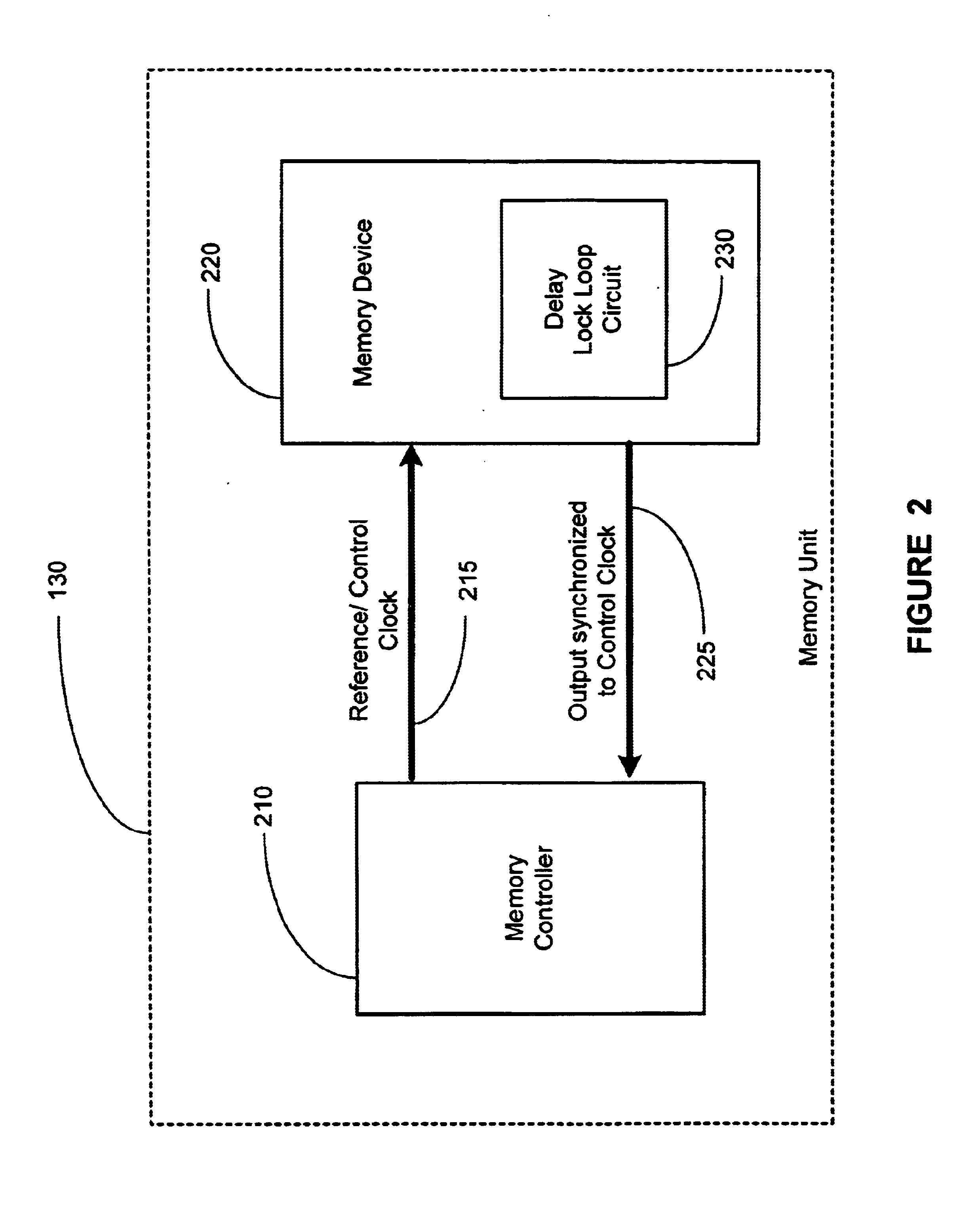

Controlling a delay lock loop circuit

A method and apparatus is provided for performing a filter control of a delay lock loop circuit. A coarse delay and / or a fine delay are implemented upon a reference signal based upon a phase shift between the reference signal and a feedback signal. A synchronized output signal is generated based upon the coarse delay and the fine delay. The apparatus of the present invention includes a delay lock loop to provide an output signal based upon a phase difference between a reference signal and a feedback signal. The delay lock loop comprises a filter to provide a filter response to the phase difference. The filter response is capable of providing a coarse delay and / or a fine delay.

Owner:MICRON TECH INC

Digital delay locked loop

Owner:CONVERSANT INTPROP MANAGEMENT INC

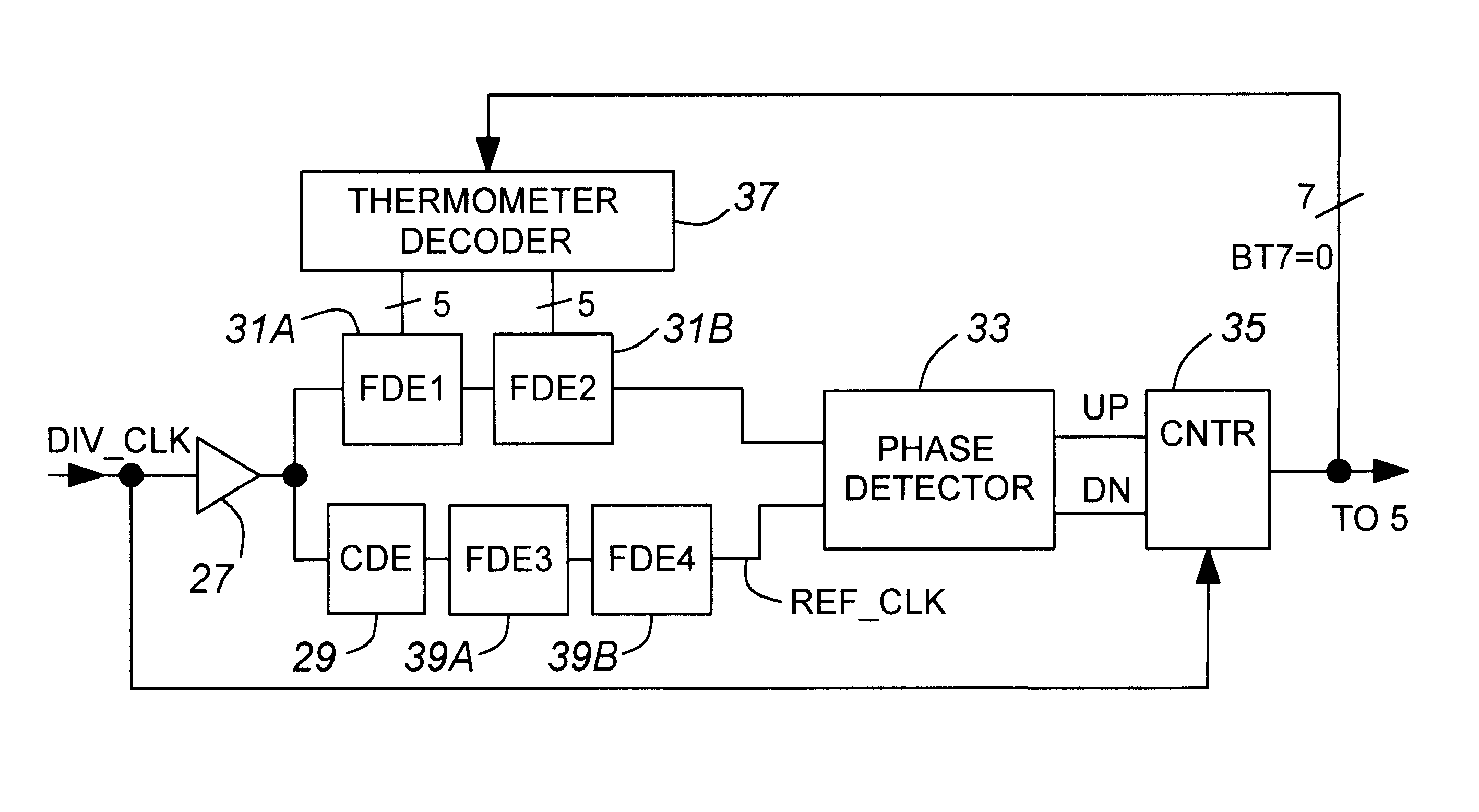

Process, voltage, temperature independent switched delay compensation scheme

InactiveUS6327318B1Pulse automatic controlAngle demodulation by phase difference detectionDelay-locked loopEngineering

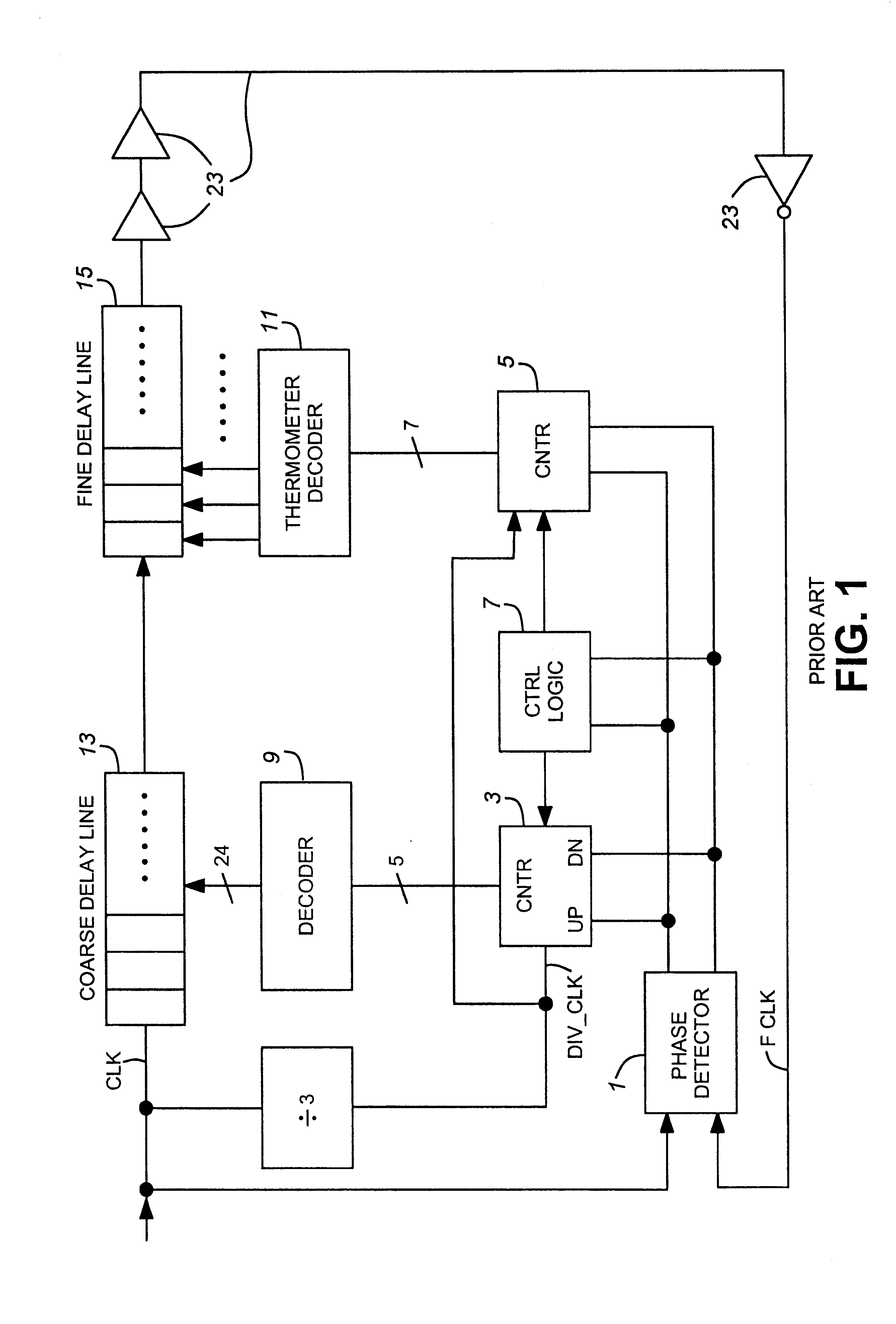

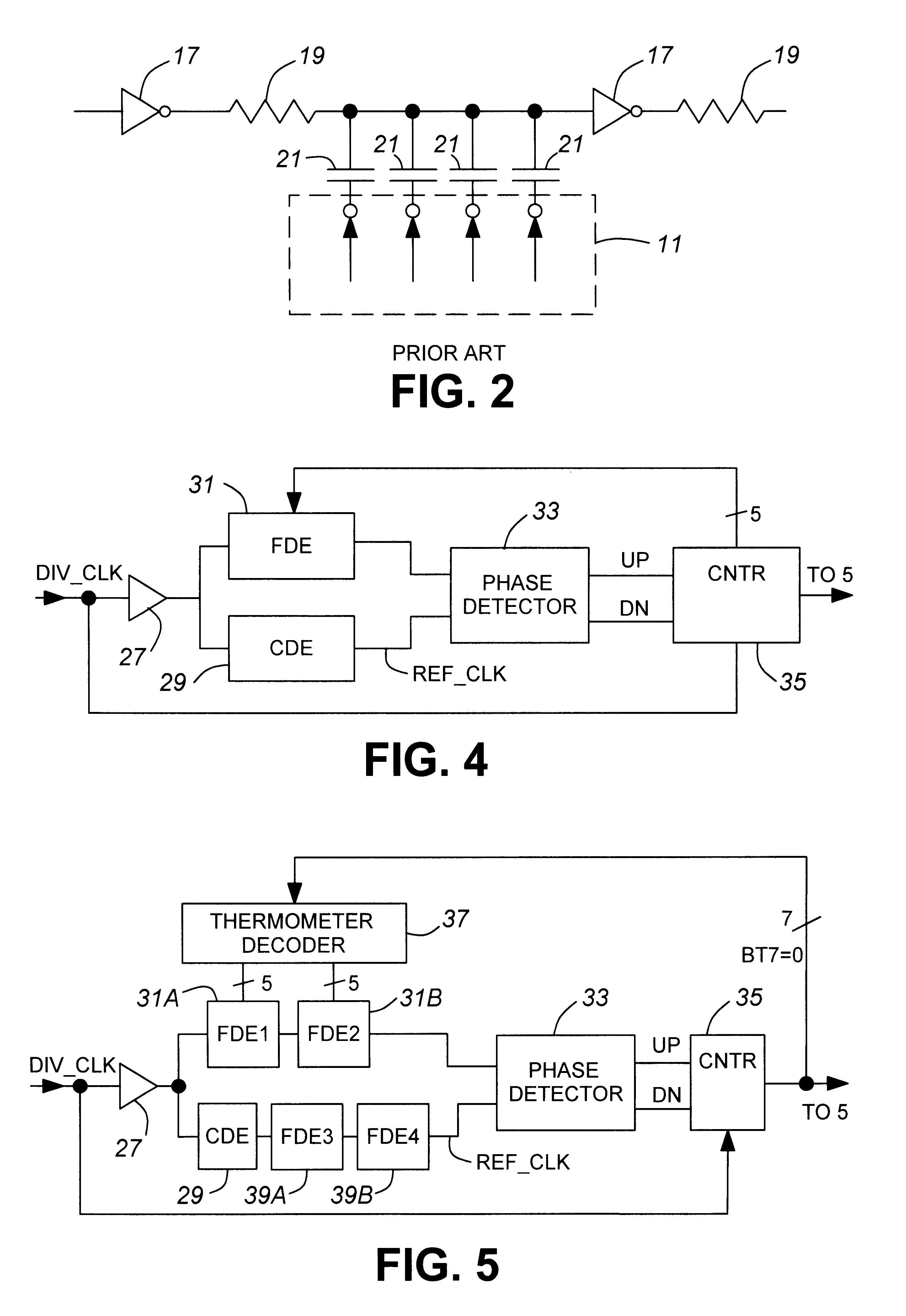

A delay compensation circuit for a delay locked loop which includes a main delay line having a fine delay line comprising fine delay elements and a coarse delay line comprising coarse delay elements, the main delay line being controlled by a controller, the delay compensation circuit comprising: an adjustable fine delay for modeling a coarse delay element, a counter for controlling the adjustable fine delay to a value which is substantially the same as that of a coarse delay element, a circuit for applying a representation of the system clock to the delay compensation circuit, and a circuit for applying the fine delay count from the counter to the controller for adjusting the fine delay line of the main delay line to a value which is substantially the same as that of a coarse delay element of the main delay line.

Owner:CONVERSANT INTPROP MANAGEMENT INC

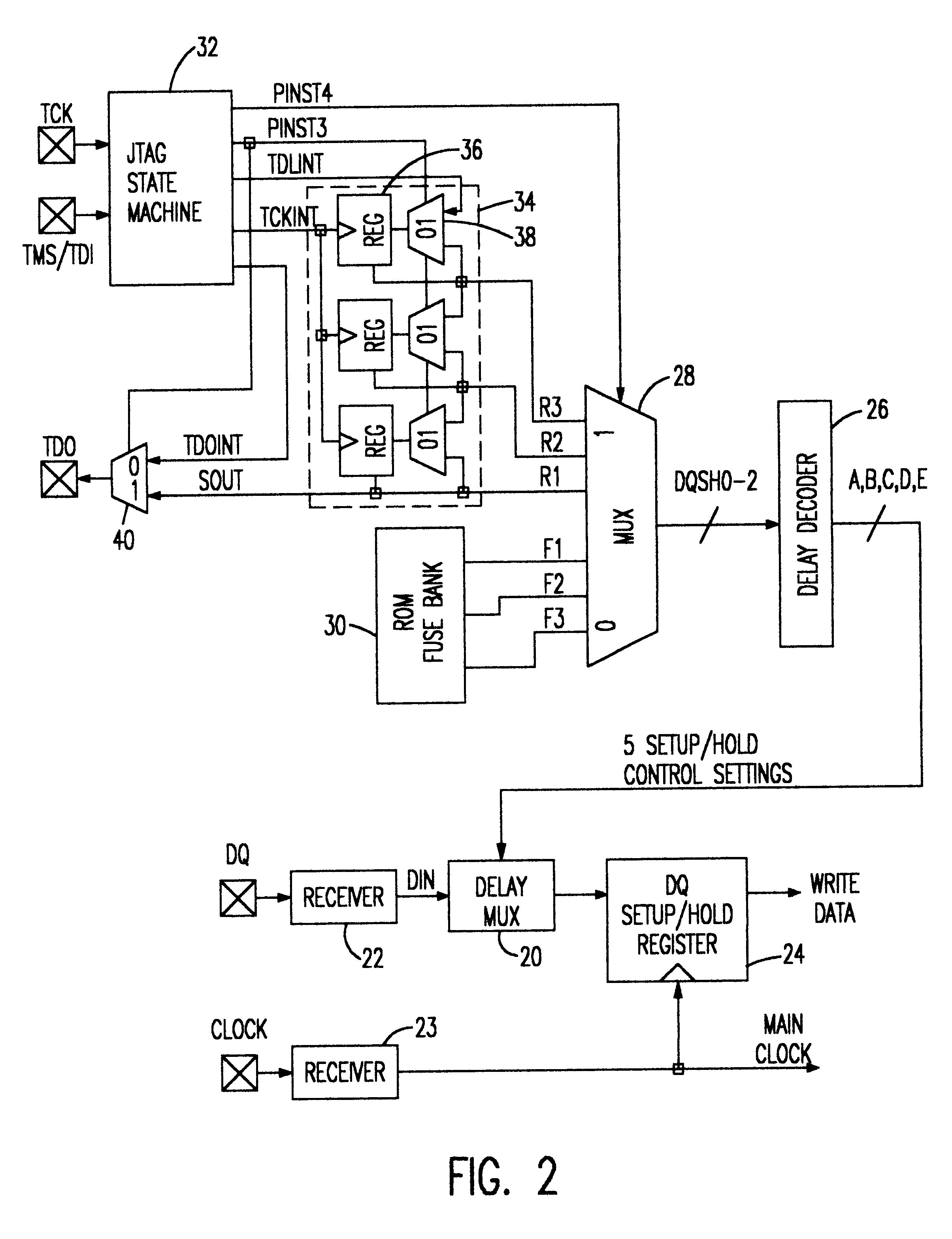

Memory having user programmable AC timings

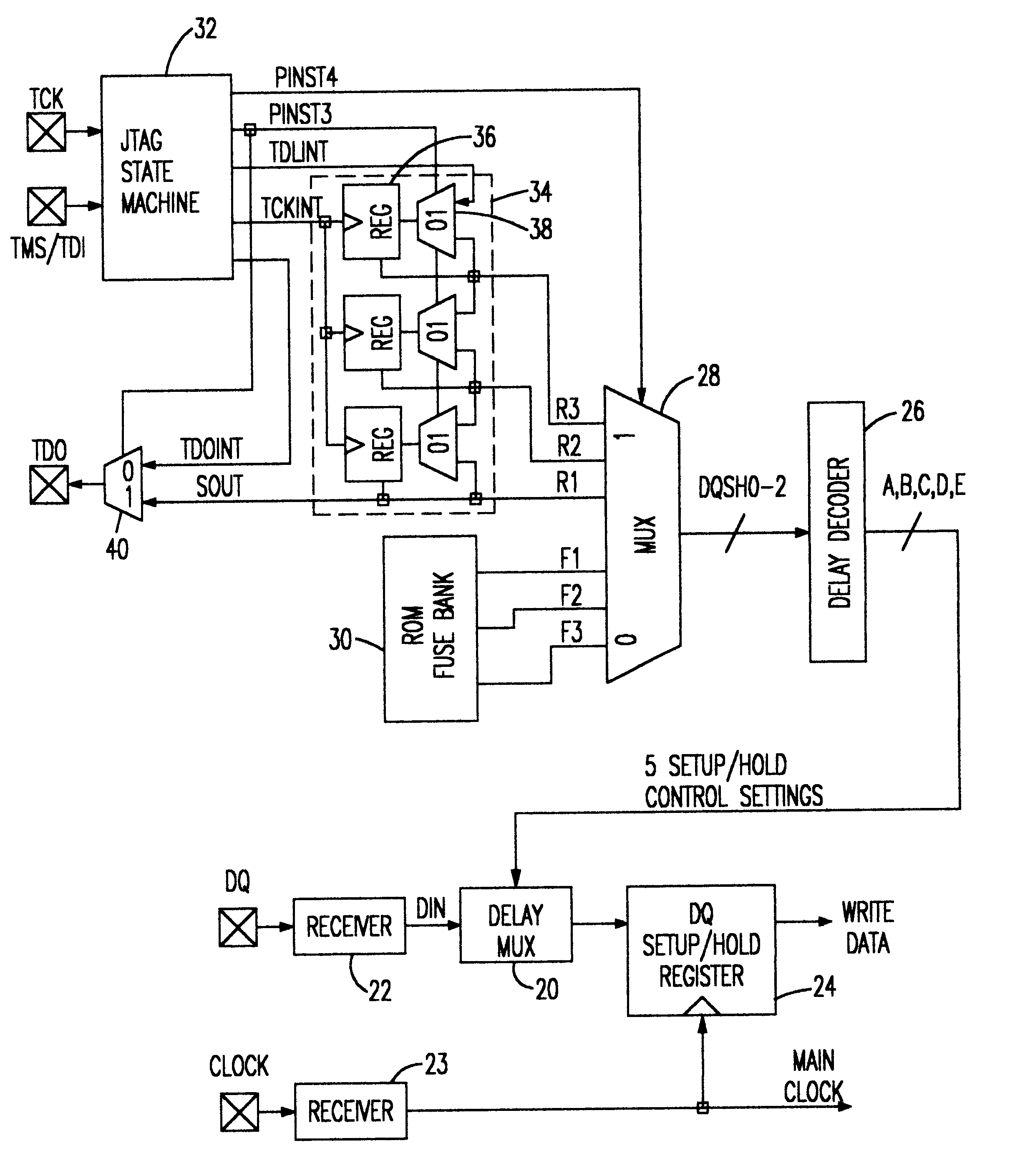

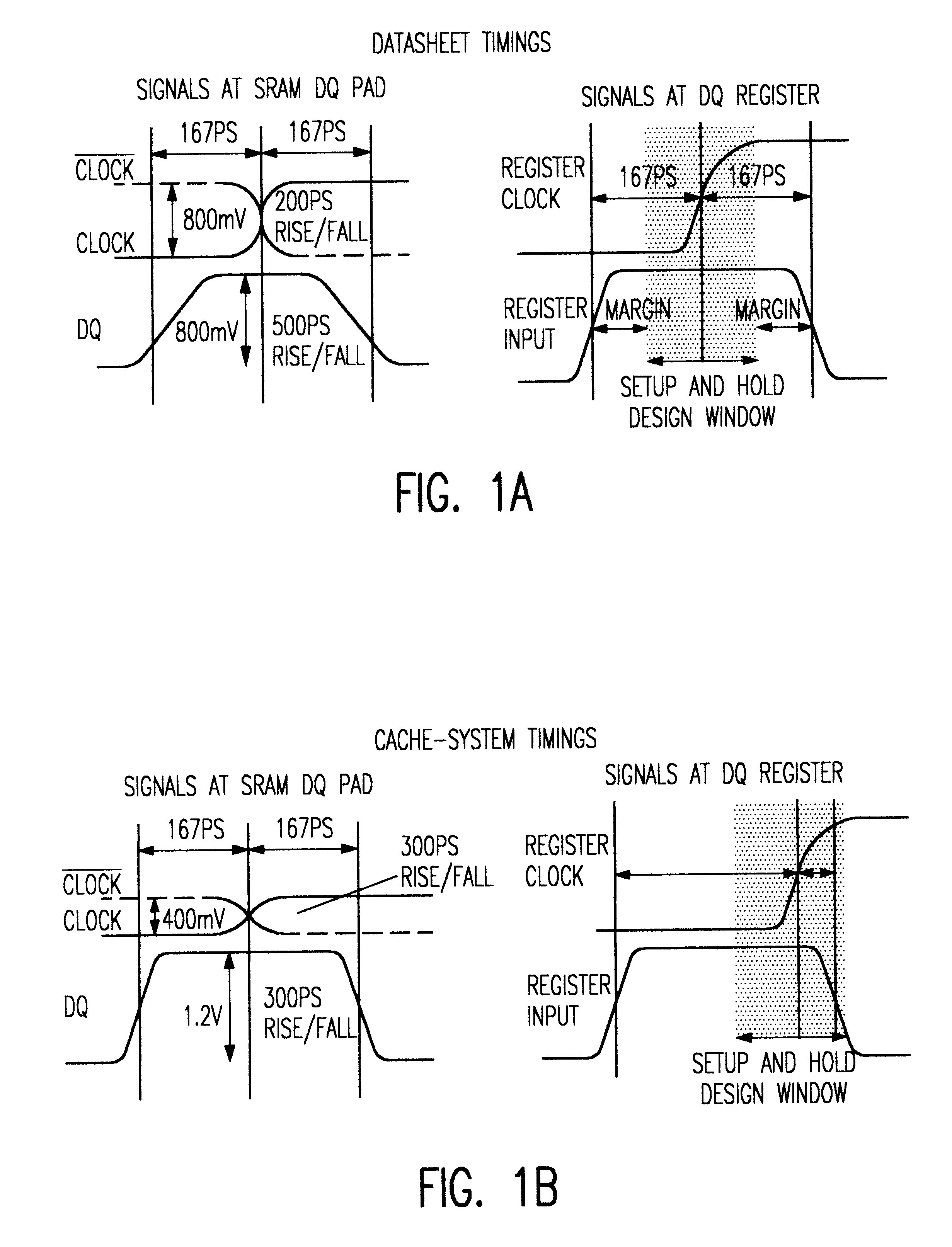

A SRAM module provides programmability of AC timings such that an end user can adjust or "tweak" the AC timings to maximize system performance. A variable delay circuit is placed in the path between a signal (e.g., data signal or address signal)and the SRAM set-up and hold register which allows the user to shift the setup-and-hold window by selected increments. The delay circuit can either advance or retard the AC timings. A delay program controlling the delay circuit is selected in one of two ways; either by a default AC timing program stored in a ROM device and preset by the manufacturer, or by a private JTAG instruction and AC programming data input by the user through the JTAG state machine provided on the SRAM chip. Once the optimum delay (or advance) is selected to optimize the SRAM to the cache system this user program may be permanently burned into the default ROM such that the optimum timings are used thereafter as the default.

Owner:IBM CORP

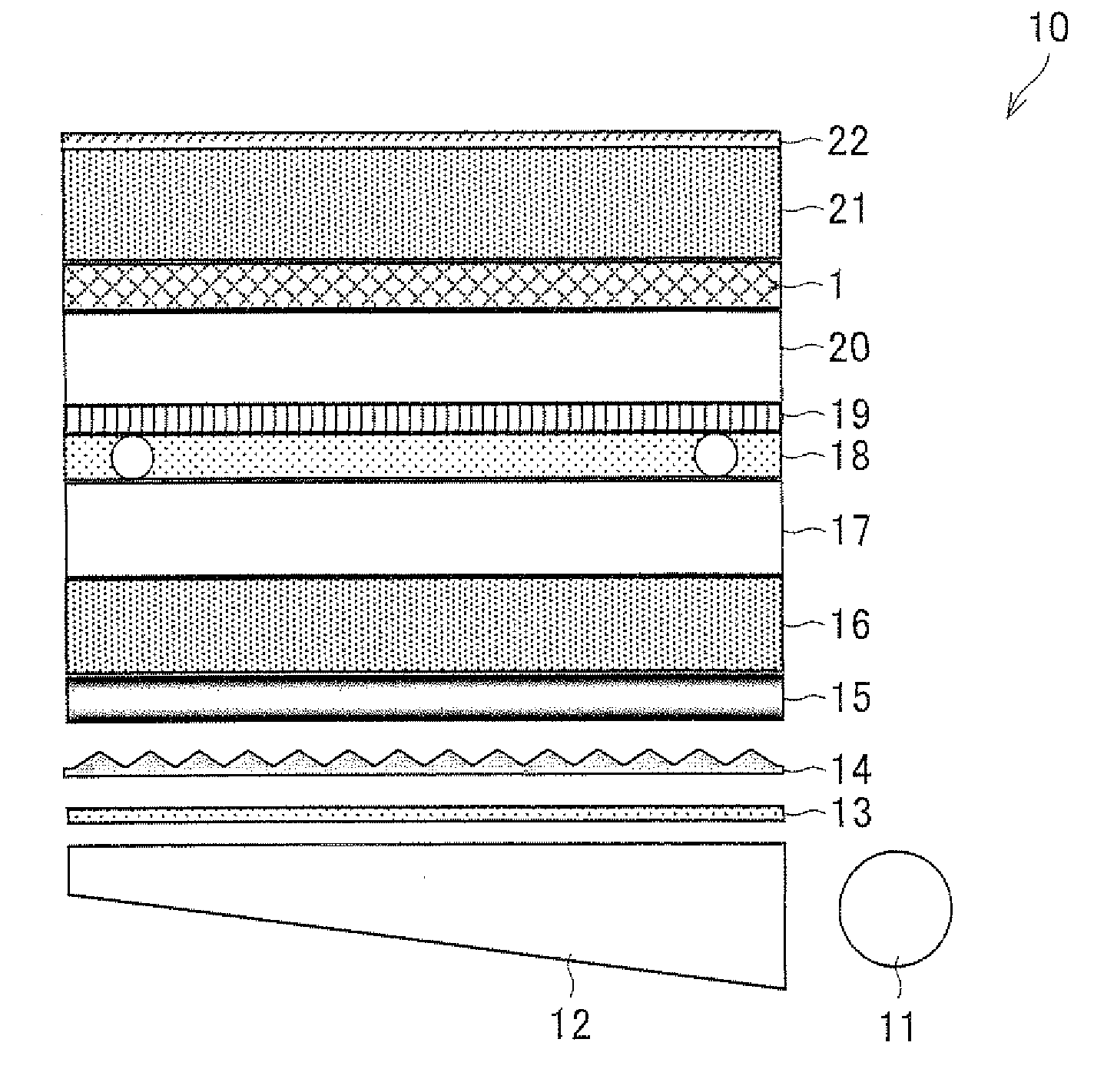

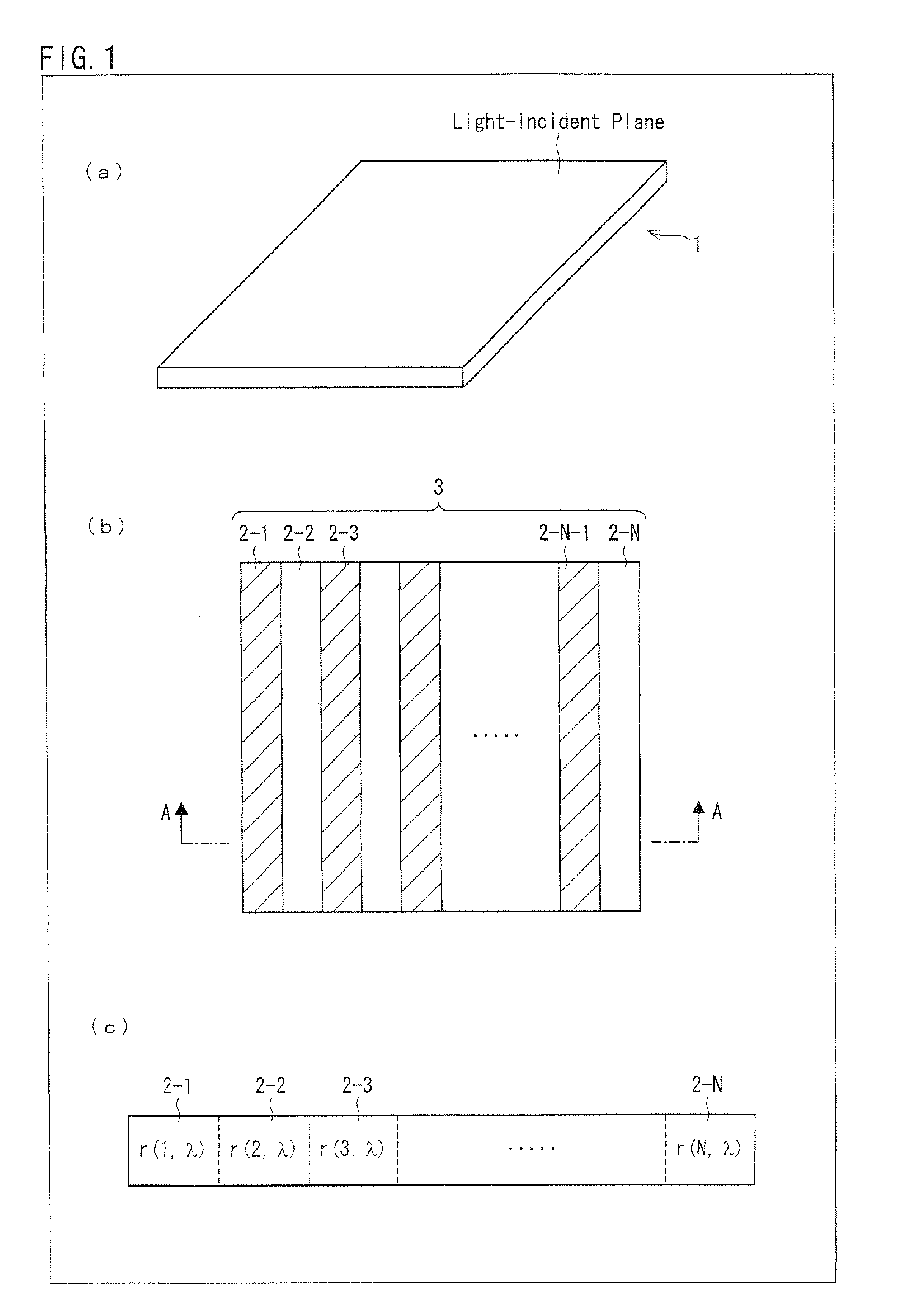

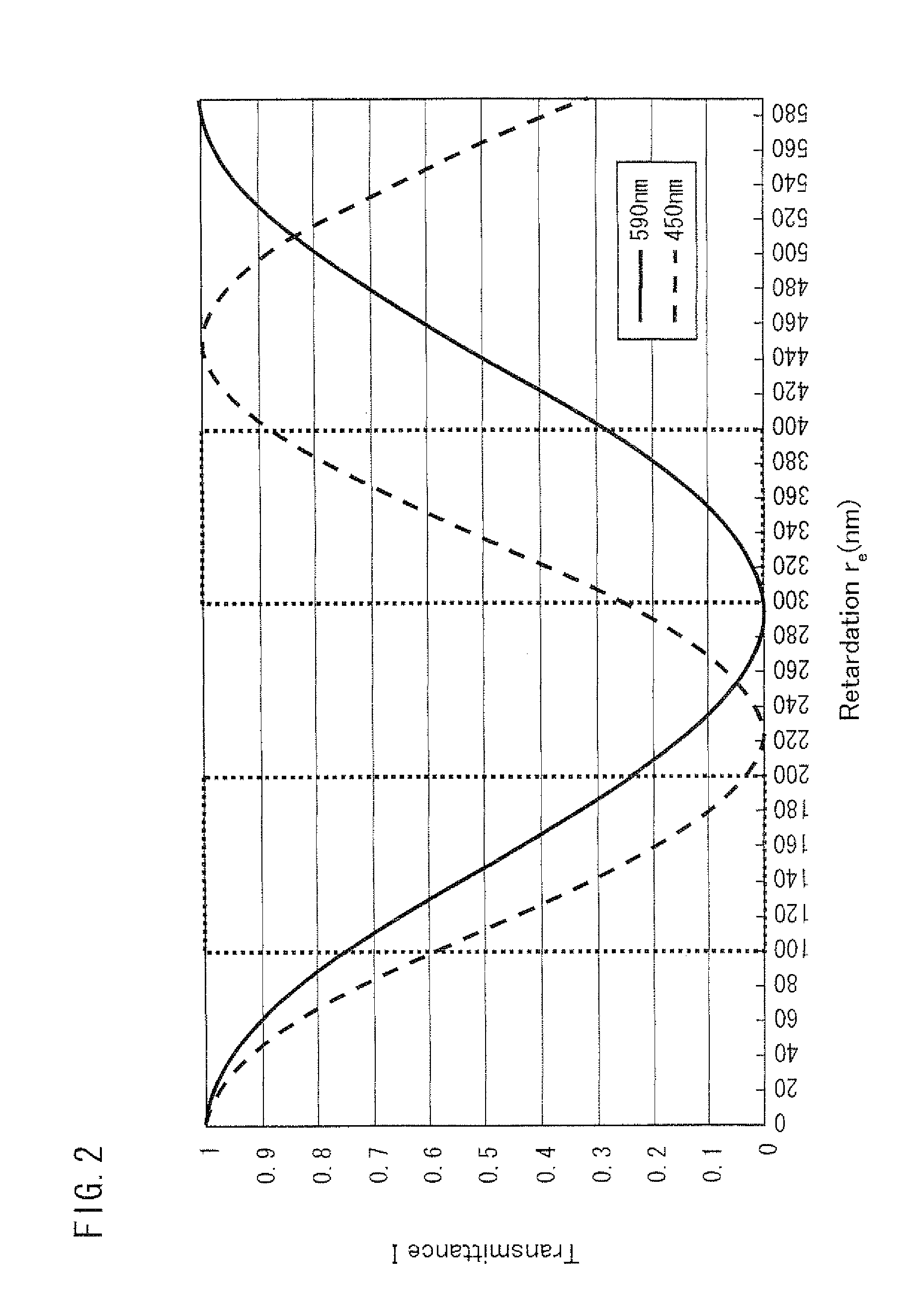

Optical element, display device, and optical device

InactiveUS20100165275A1Easy to controlSolid-state devicesPolarising elementsDisplay deviceControl delay

A retardation film includes a plurality of unit areas in a direction parallel to a light-incident plane of the optical element, and the unit areas includes a plurality of unit areas 2 whose retardation with respect to light of a certain wavelength is different by 10 nm or more from retardation of adjacent unit areas with respect to light of the certain wavelength. The retardation film utilizes a difference in wavelength dependence between retardation r(n, λ) of each of the unit areas and synthetic retardation R(λ) of a whole area including all of the unit areas. This realizes an optical element capable of easily controlling wavelength dispersion of retardation, without being constrained by a material.

Owner:KANEKA CORP

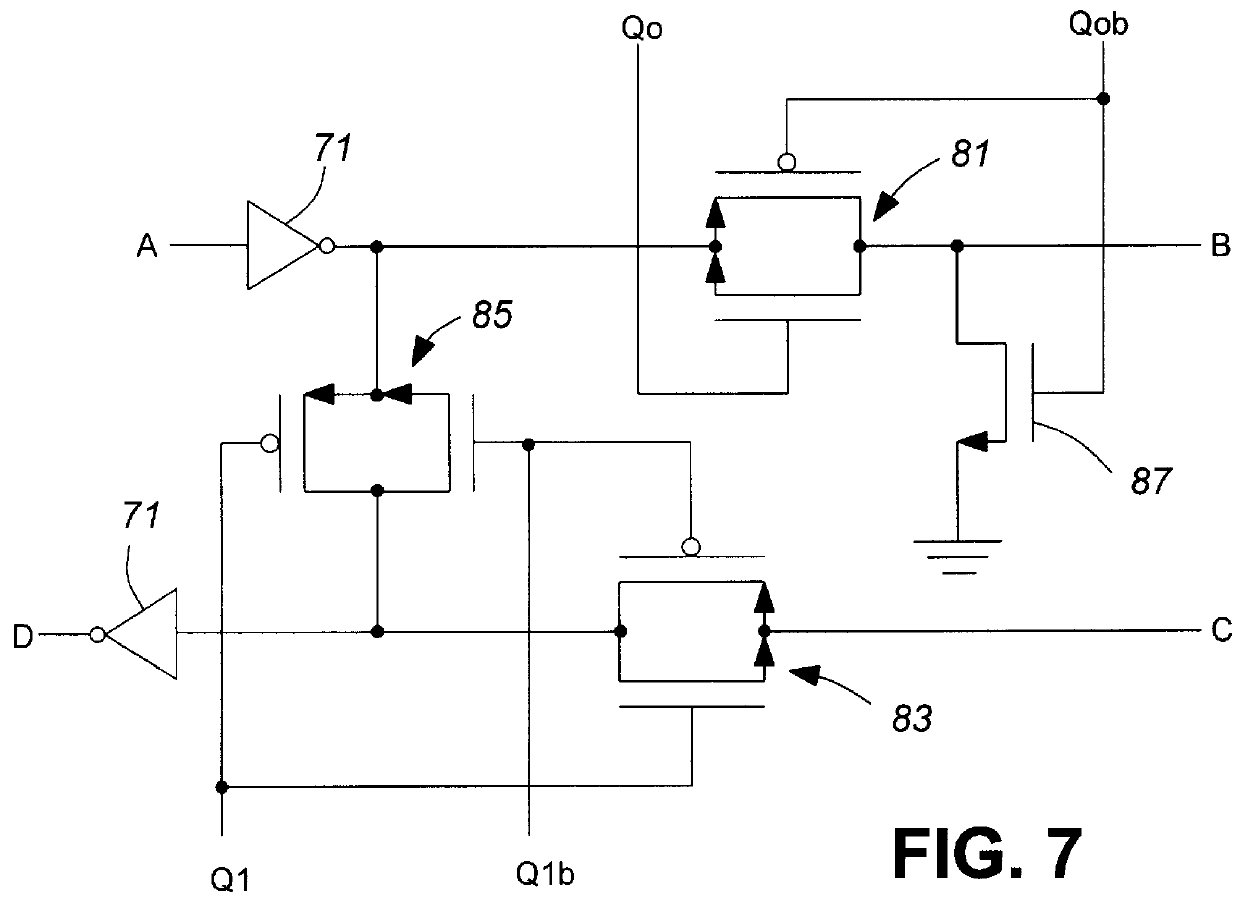

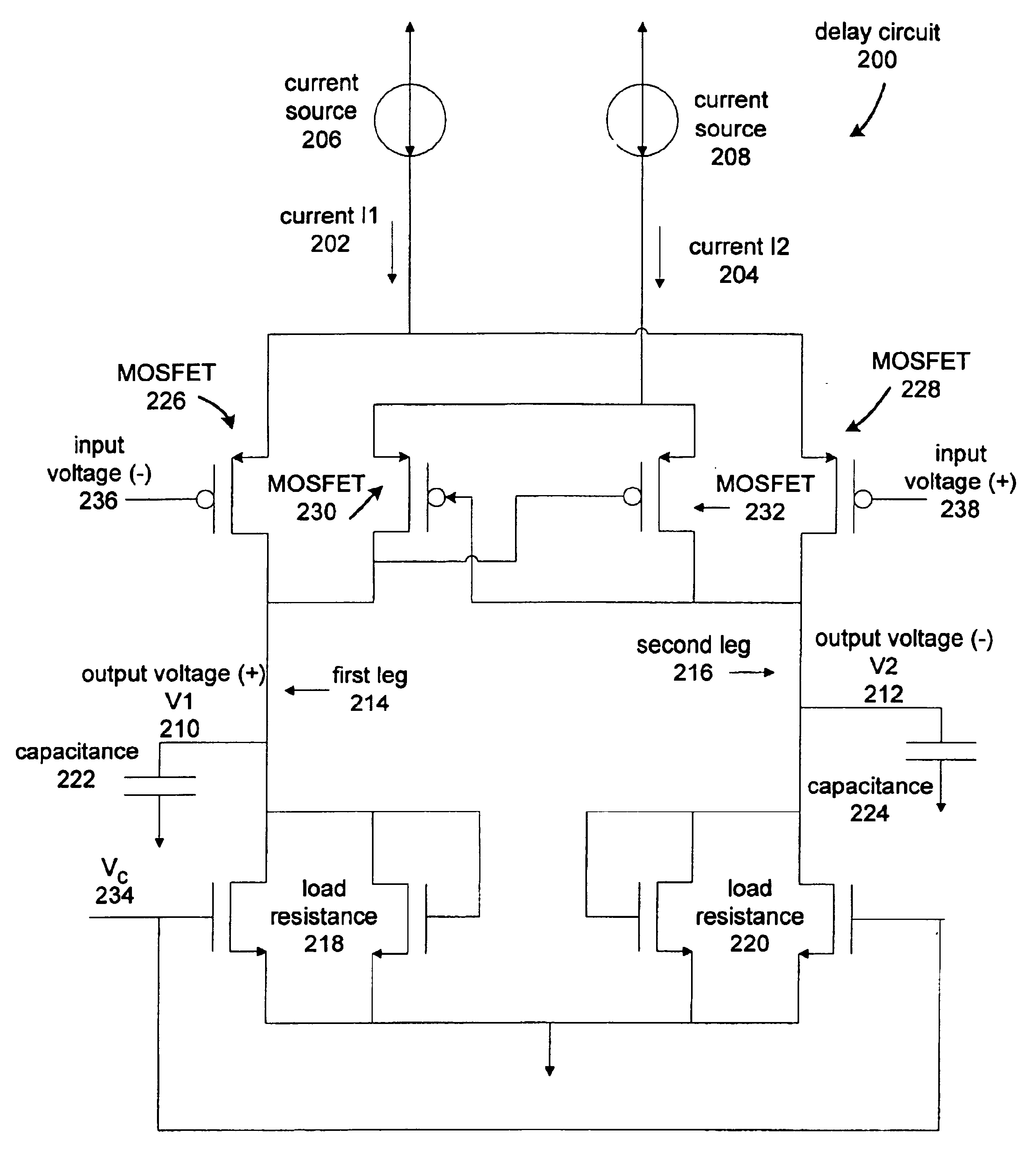

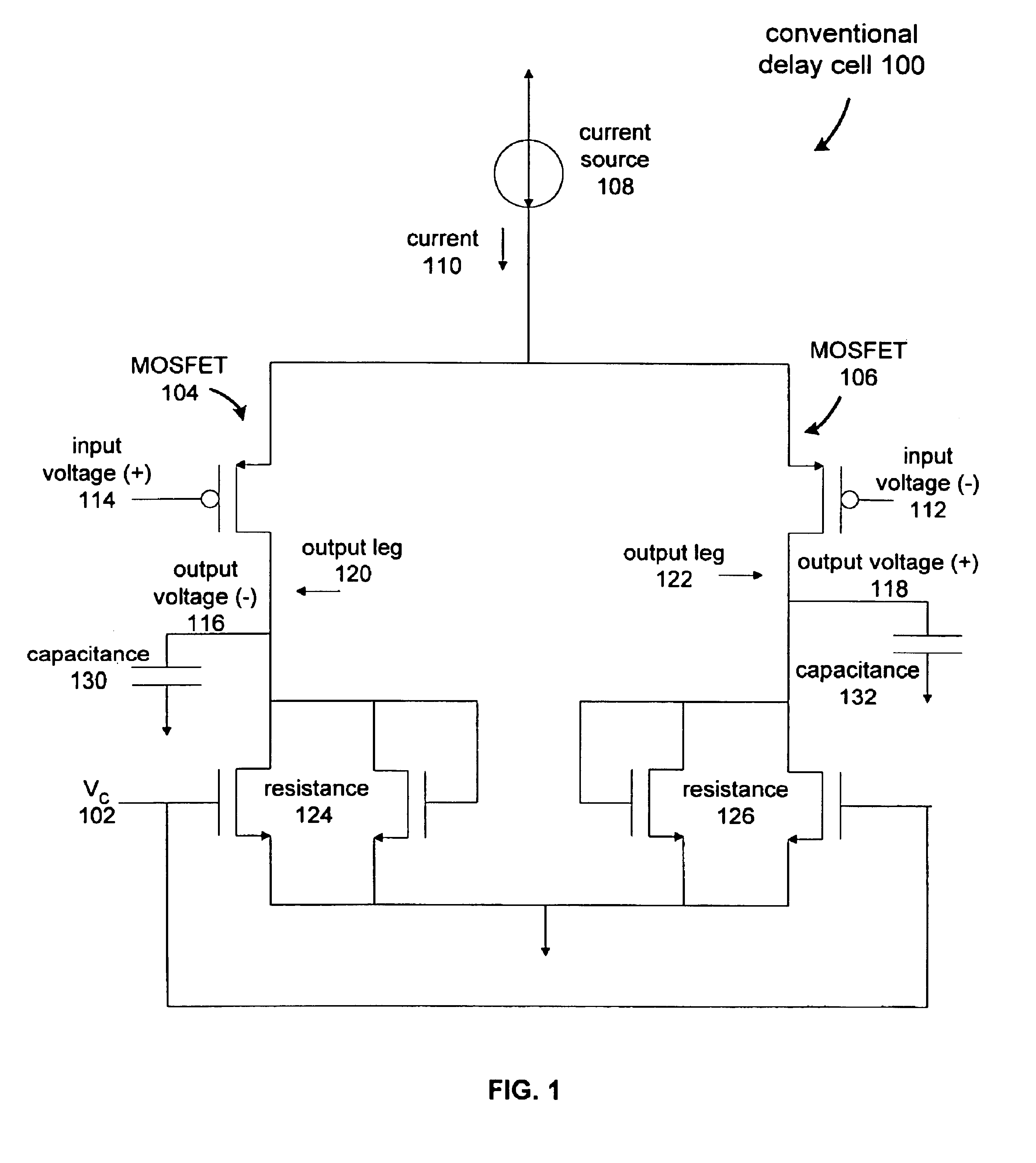

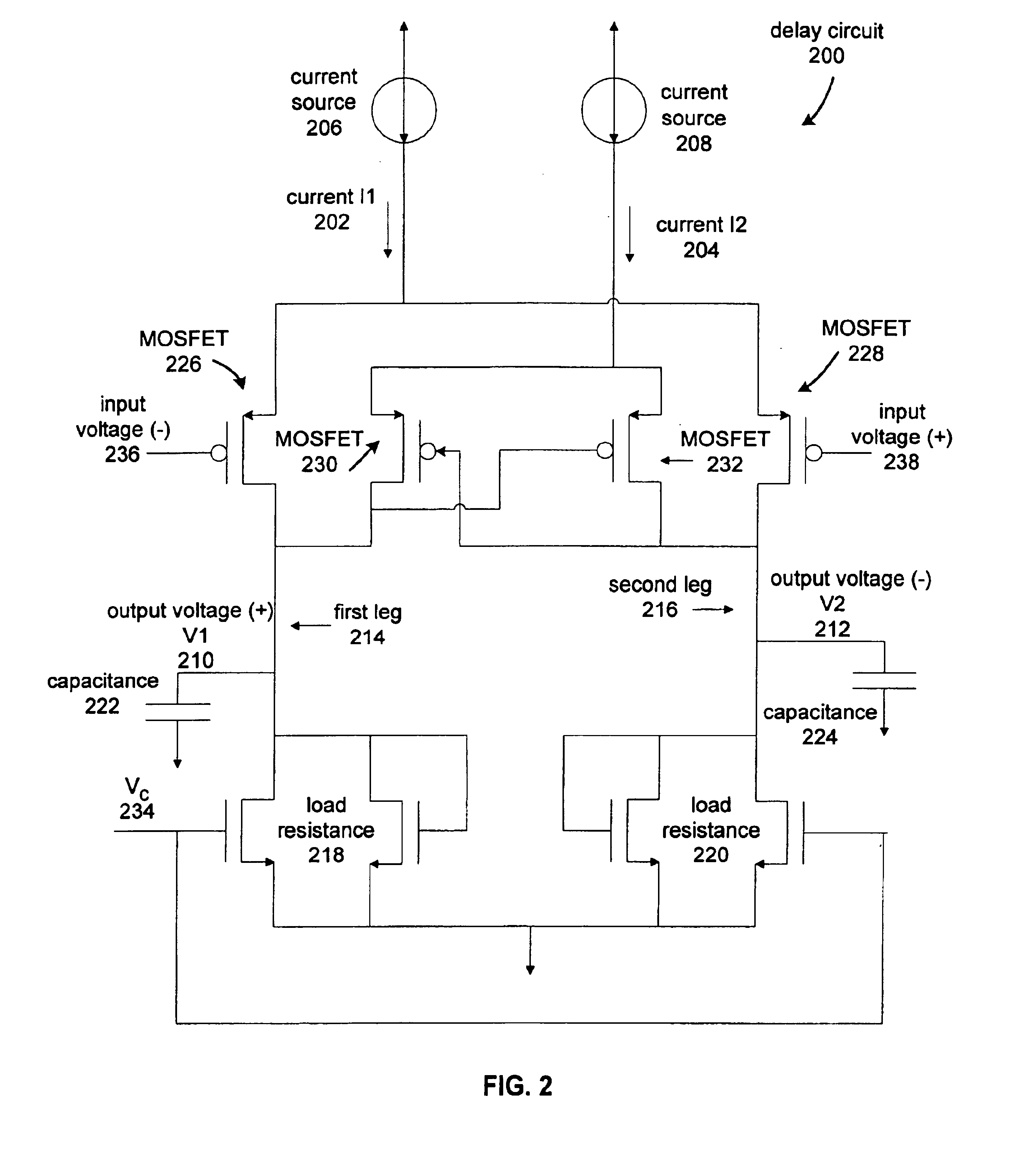

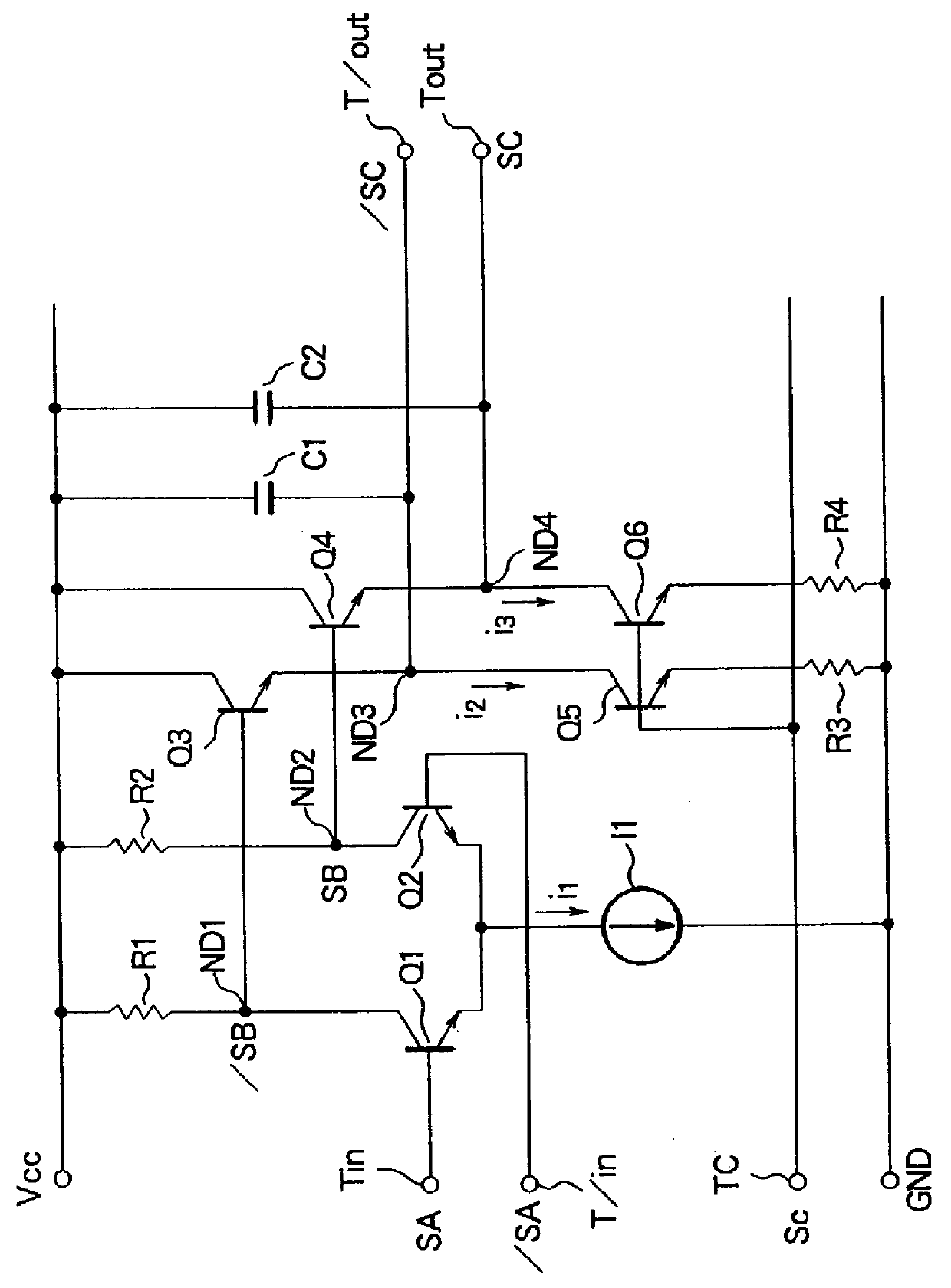

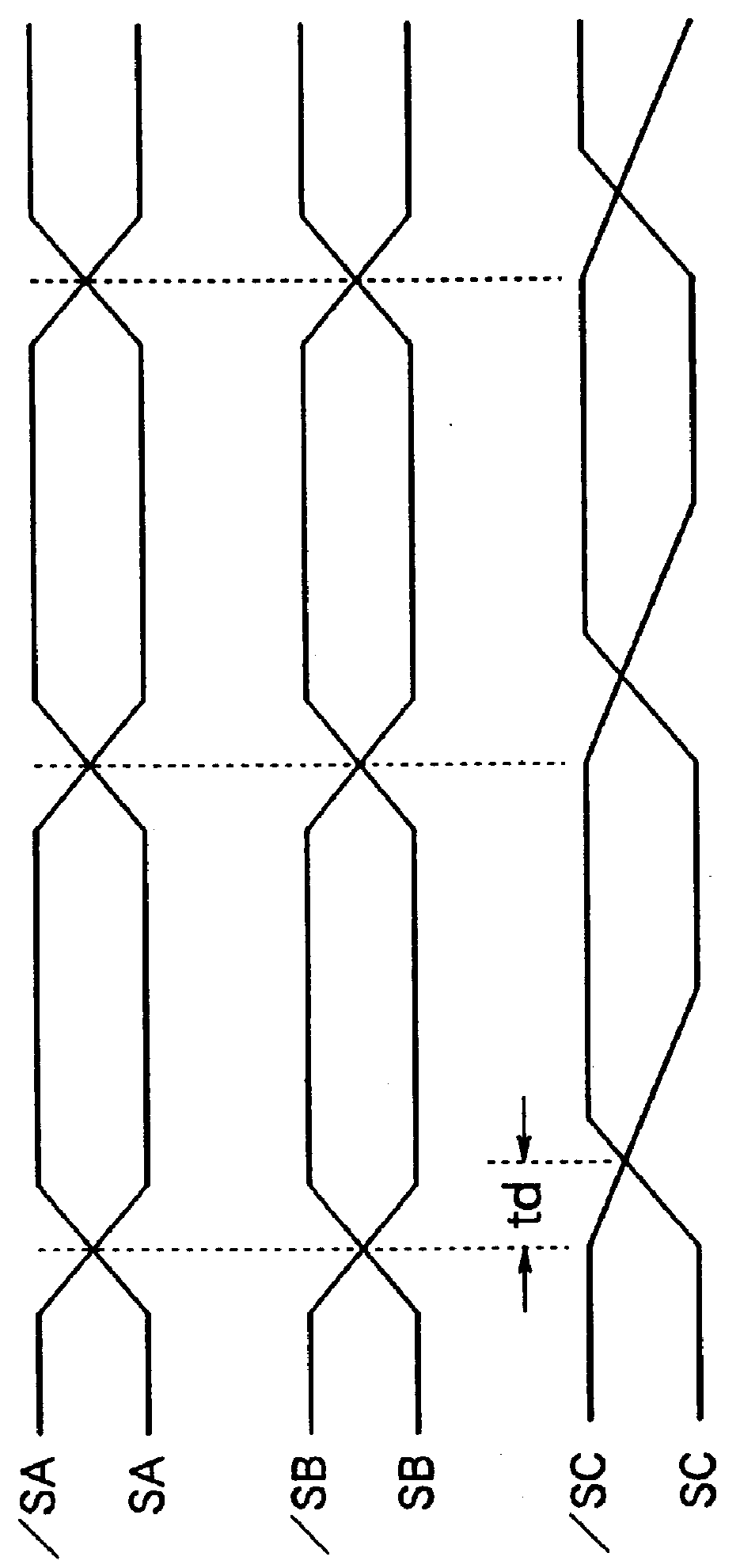

Current controlled delay circuit

A current controlled delay circuit is disclosed. Two currents of constant sum are generated to control the delay of the circuit. The circuit includes a differential pair to switch one of the two currents from one leg of the circuit to another leg of the circuit. The circuit includes a cross-coupled pair to switch the other of the two currents from one leg of the circuit to another leg of the circuit. The circuit may include a fixed or variable load.

Owner:CYPRESS SEMICON CORP

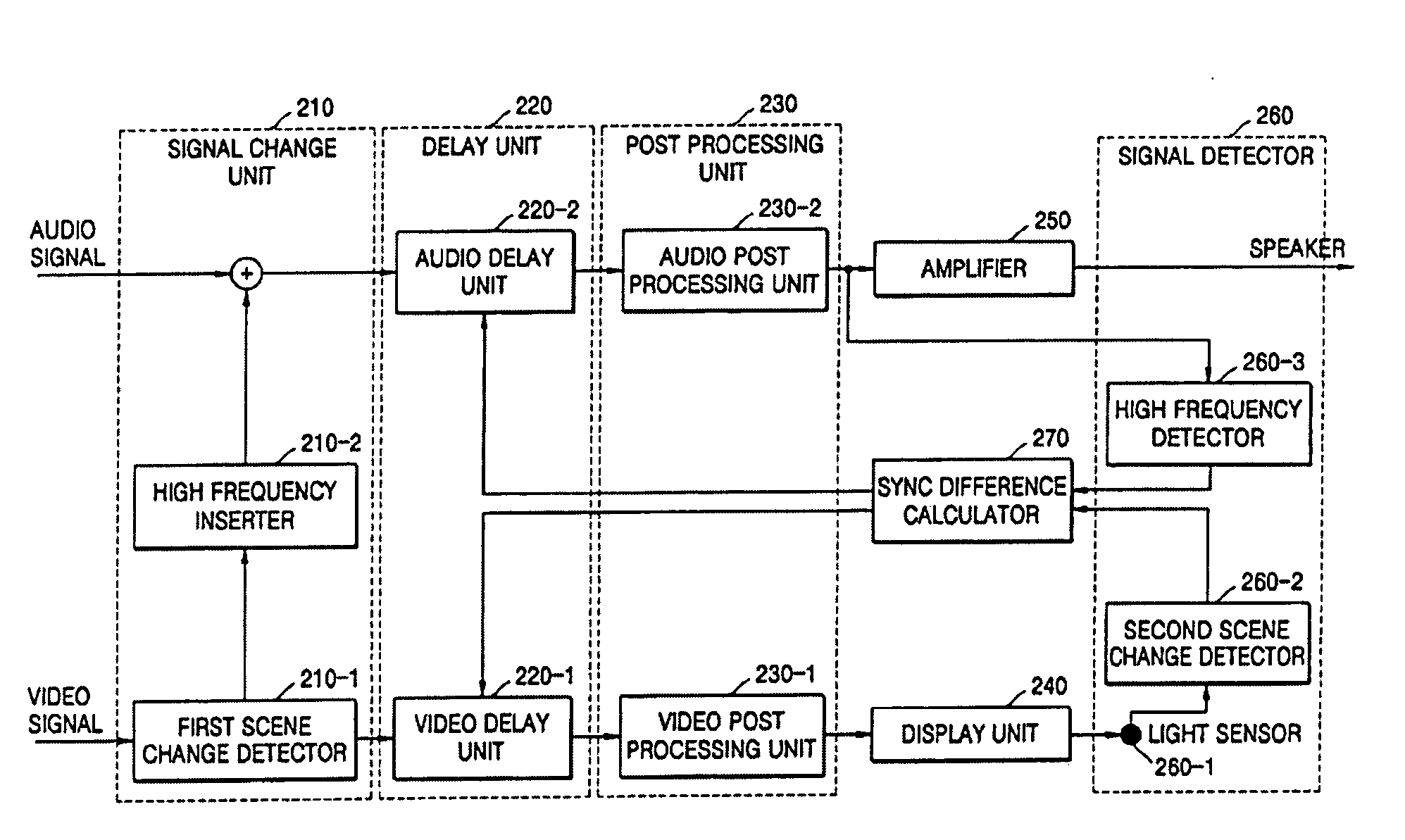

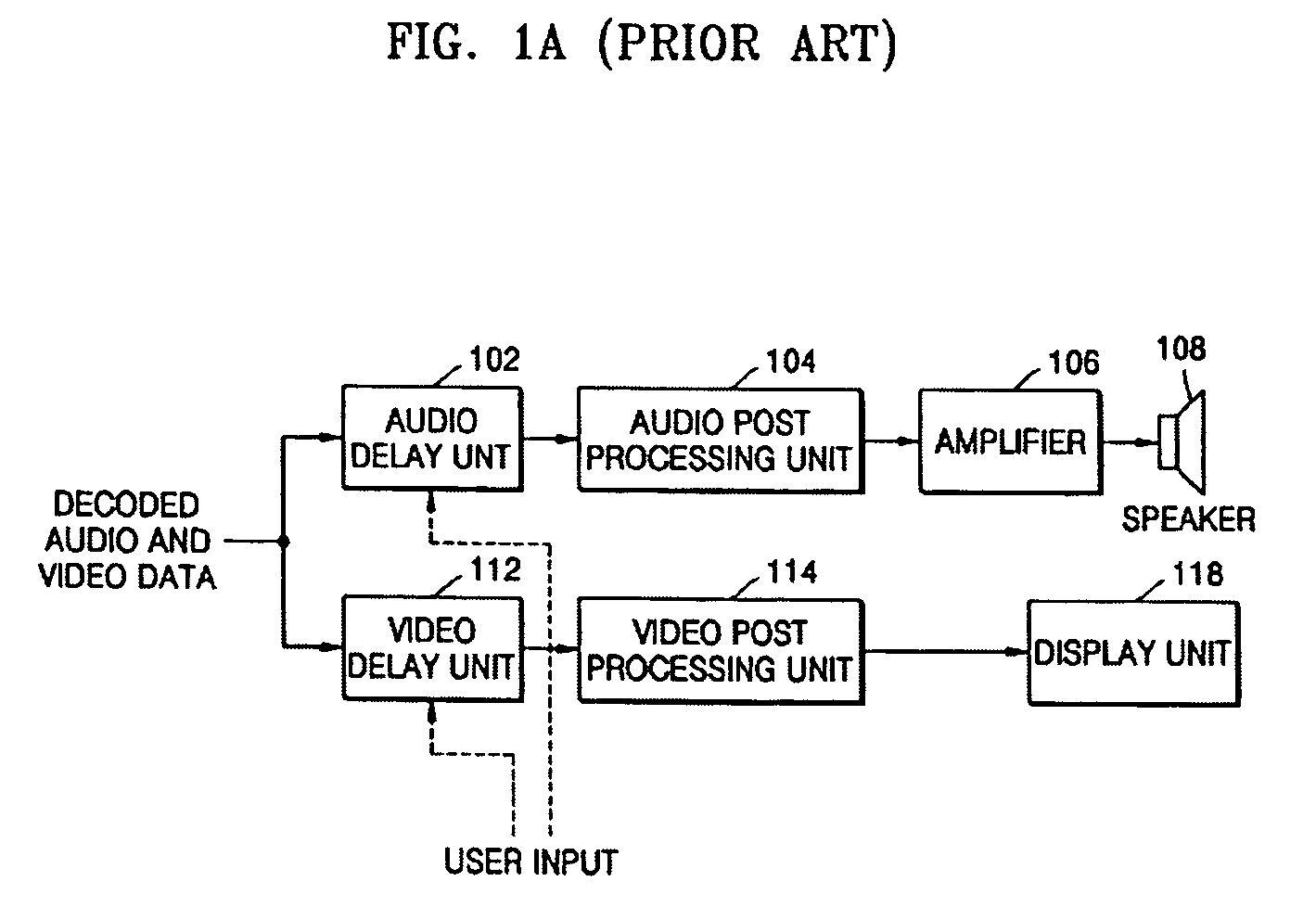

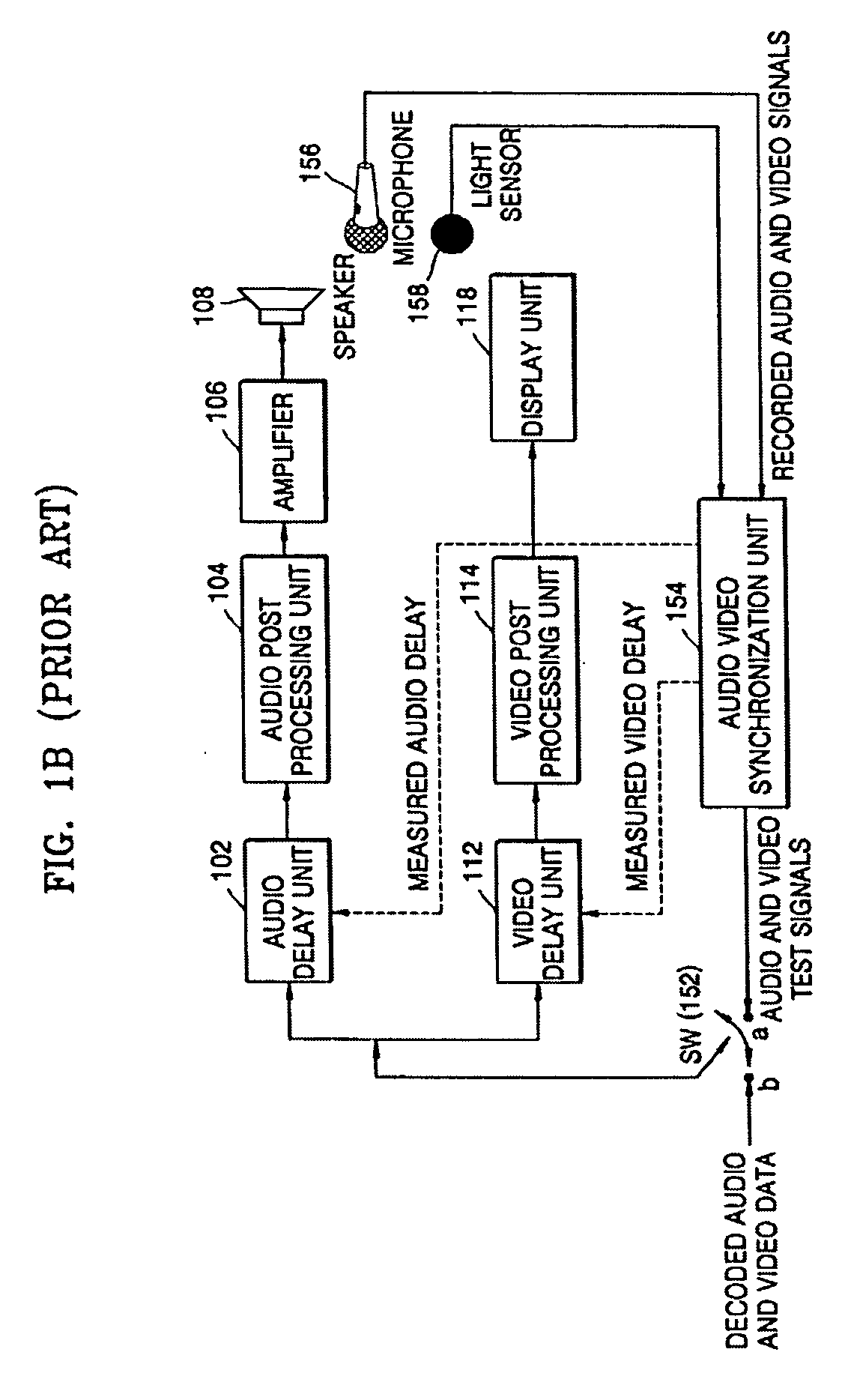

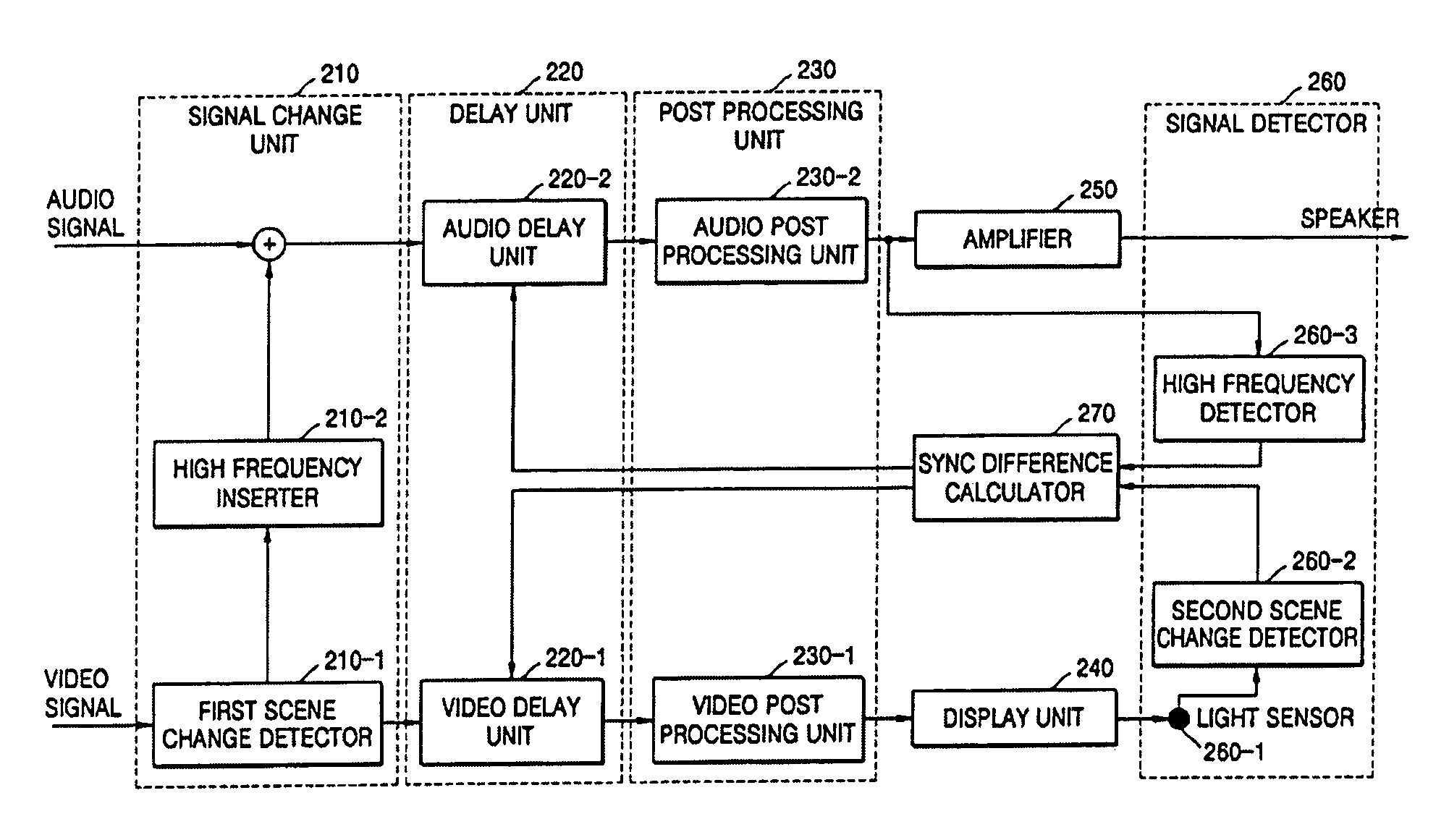

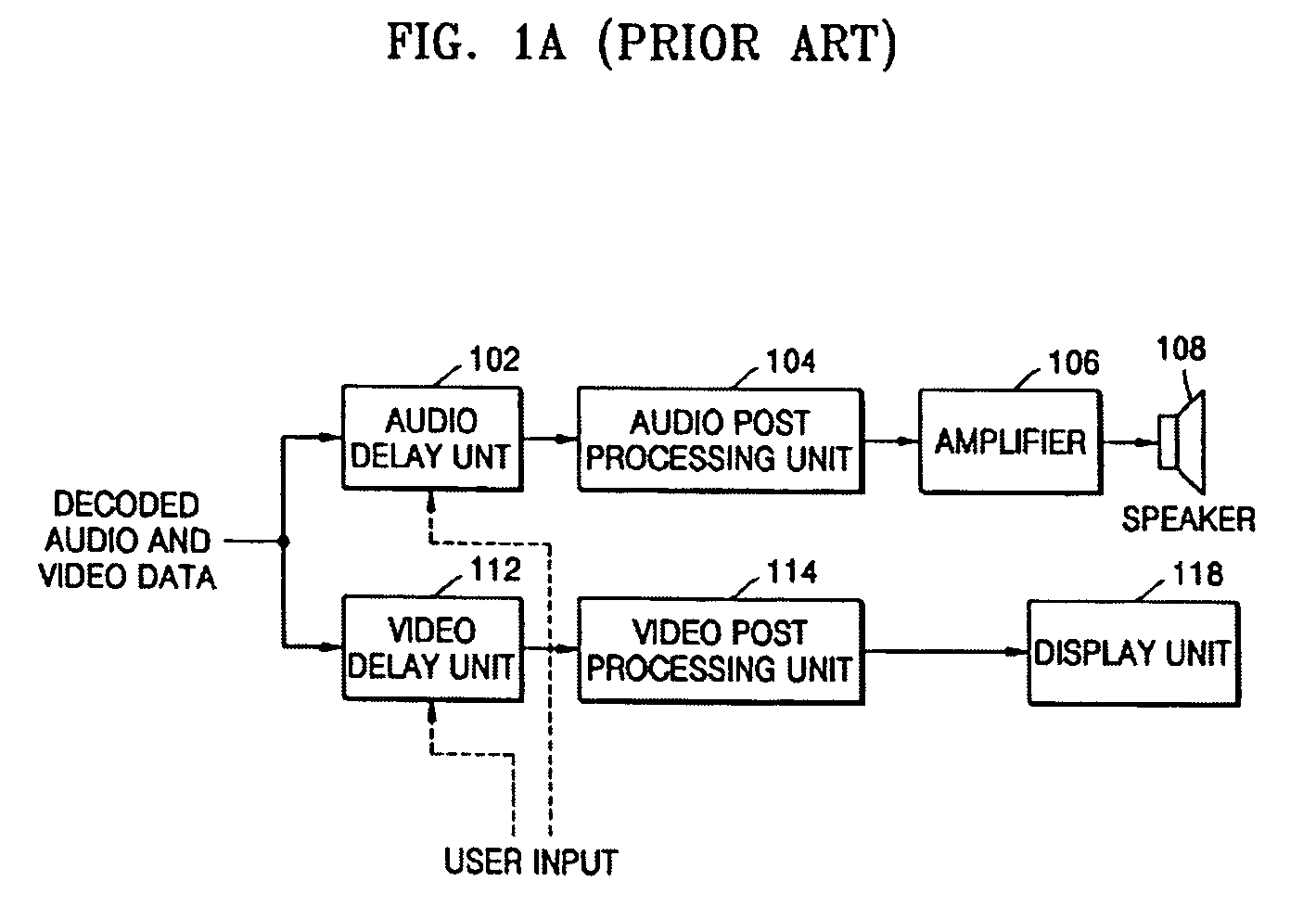

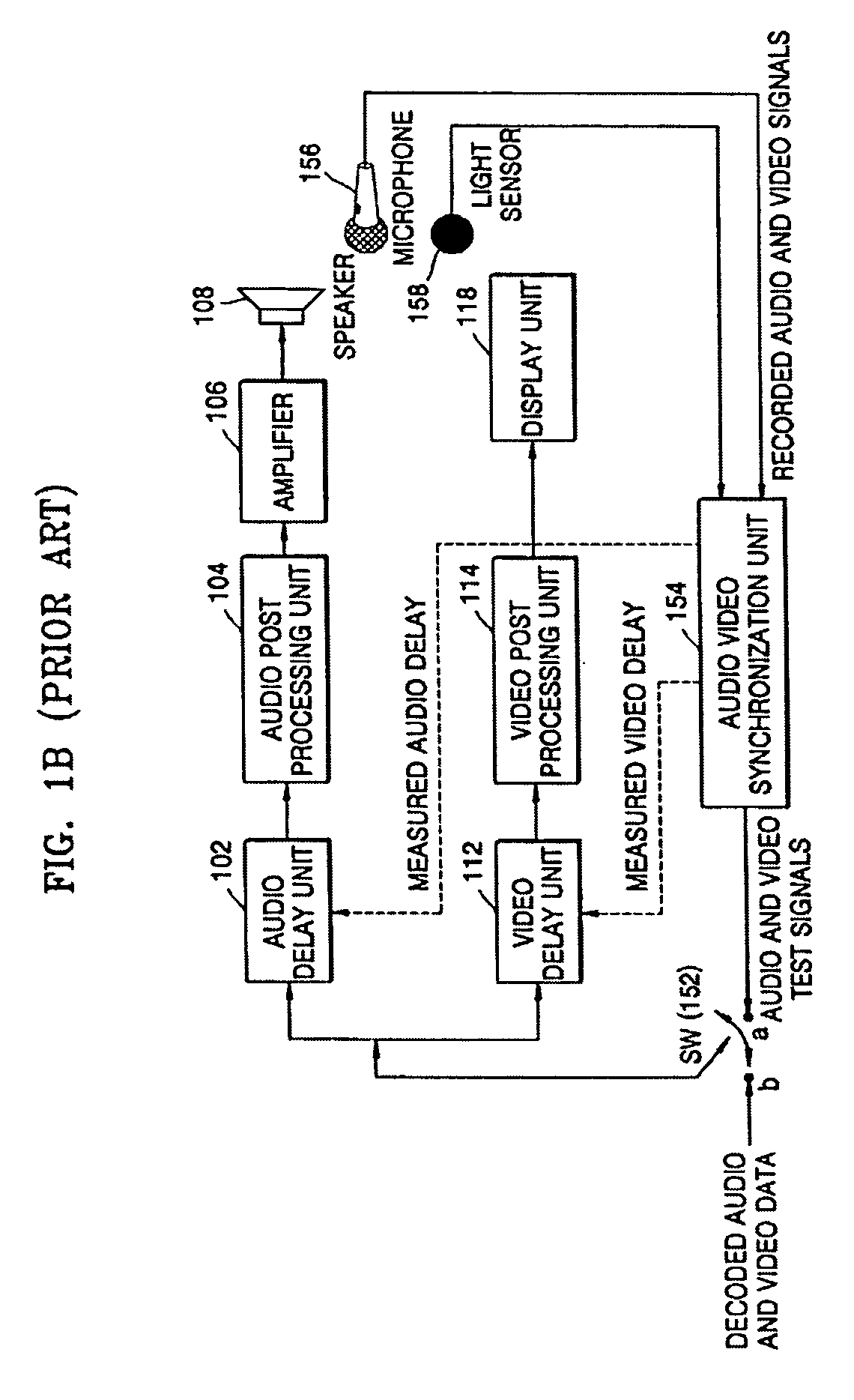

Method and apparatus to synchronize audio and video

InactiveUS20060078305A1Television system detailsColor television signals processingControl delayTime difference

A method and an apparatus to synchronize an audio signal and a video signal. The method includes: displaying video on a screen that corresponds to an audio signal including a high frequency component having a predetermined pattern inserted therein to indicate when a scene change occurs in a video signal, detecting a scene change in the displayed video and detecting the high frequency component having the predetermined pattern in the audio signal, calculating a time difference between a time when the scene change is detected in the displayed video and a time when the high frequency component having the predetermined pattern is detected in the audio signal, and controlling delay times of the audio signal and the video signal according to the calculated time difference. Accordingly, the audio signal and the video signal can be automatically synchronized without performing a separate measuring operation.

Owner:SAMSUNG ELECTRONICS CO LTD

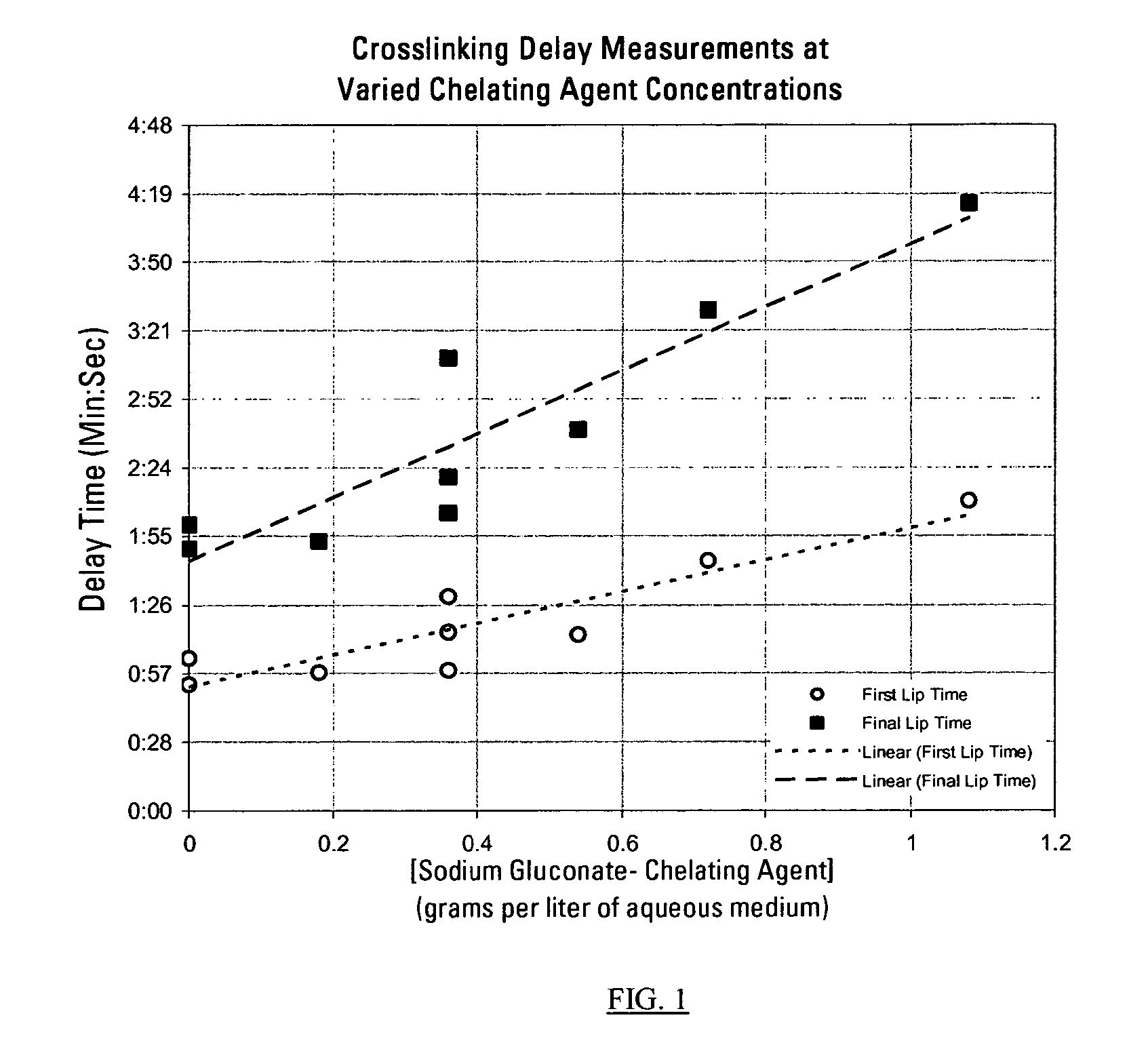

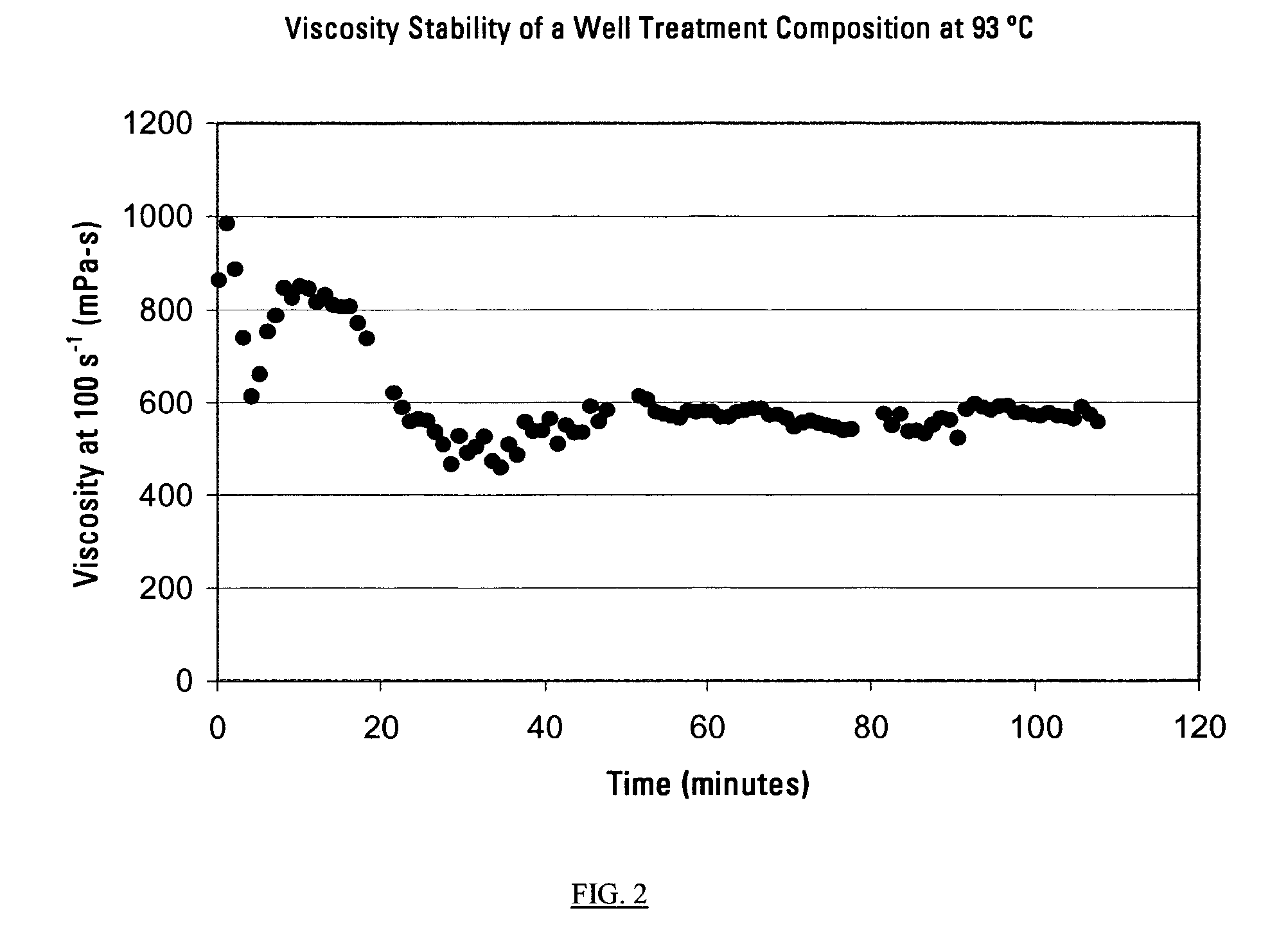

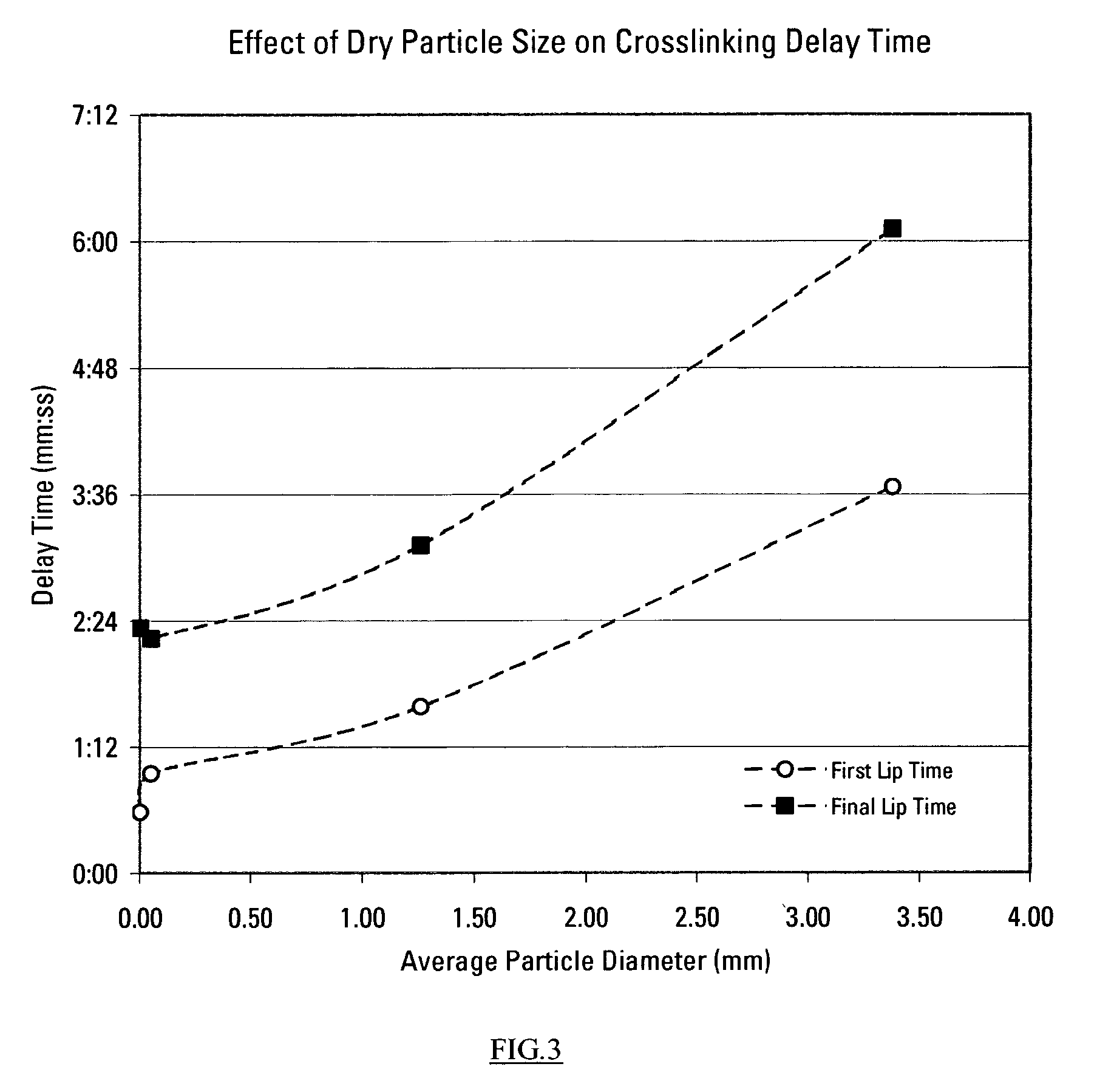

Well treatment composition crosslinkers and uses thereof

This invention relates to compositions used in treating subterranean formations, which include a hydrated polymer, and a dry blended multi-functional component. The hydrated polymer and dry blended multi-functional component are mixed at the ground surface of a wellsite, and subsequently injected into the formation providing controlled delay in crosslinking to achieve targeted fluid viscosity properties. The hydrated polymer may be a guar, hydroxypropyl guar, carboxymethyl guar, carboxymethylhydroxypropyl guar, synthetic polymers, and guar-containing compounds. The dry blended multi-functional component may include a crosslinker and a chelating agent, and the well treatment fluid may further include an activator mixed with the hydratable polymer. The chelating agent may be a polyols, gluconate, sorbitol, mannitol, carbonate, or any mixtures thereof. The crosslinker may be any source of boron, alkaline earth metal borates, alkali metal borates, zirconium compounds, titanium compounds, or any combination thereof, while the activator may be a caustic soda or magnesium oxide compound. The invention further provides methods for producing a well treatment composition including providing a hydrated polymer, and providing a dry blended multi-functional component. Also, methods of hydraulically fracturing a subterranean formation, as well as cleanup operations and gravel packing a wellbore are provided as well.

Owner:SCHLUMBERGER TECH CORP

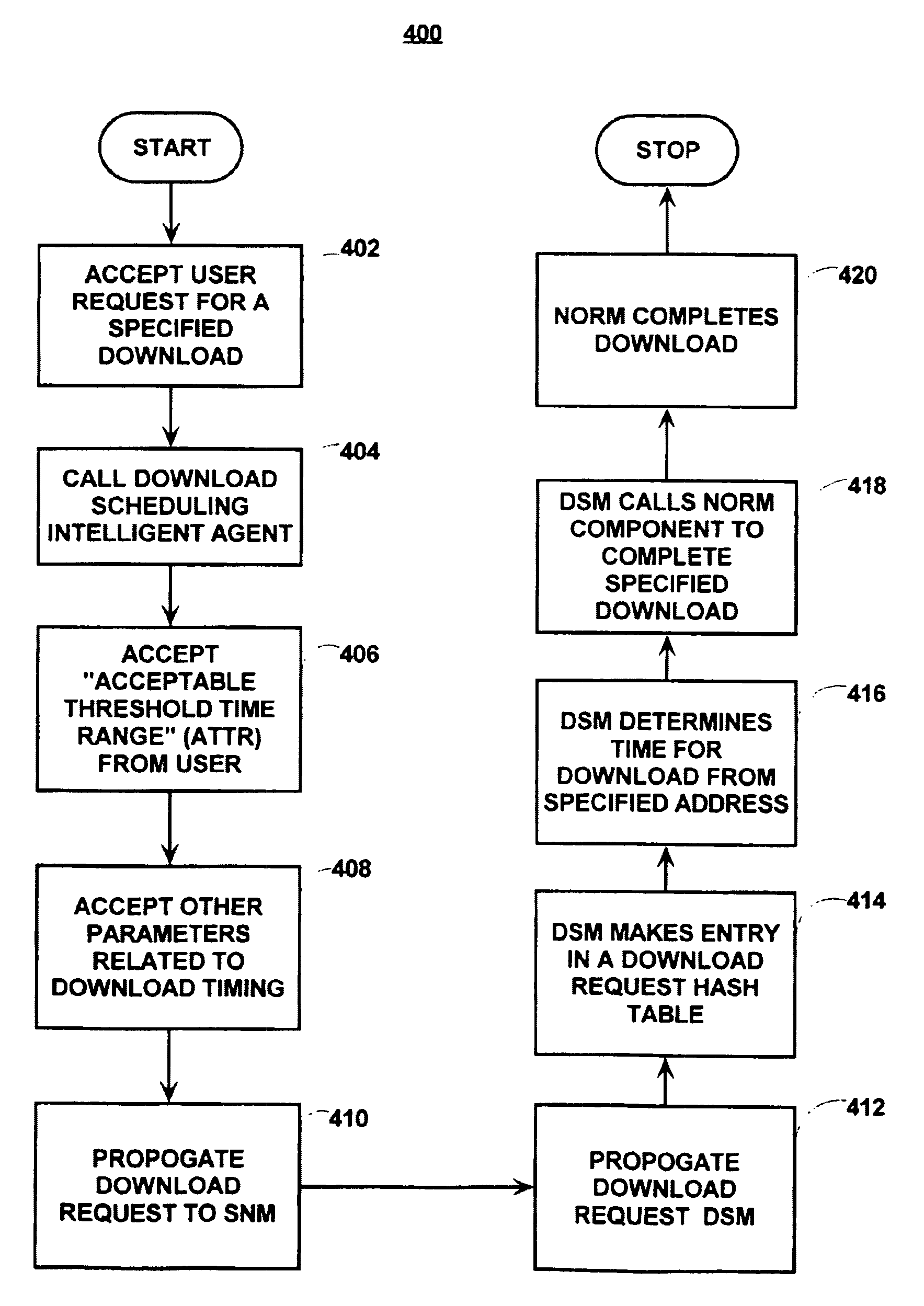

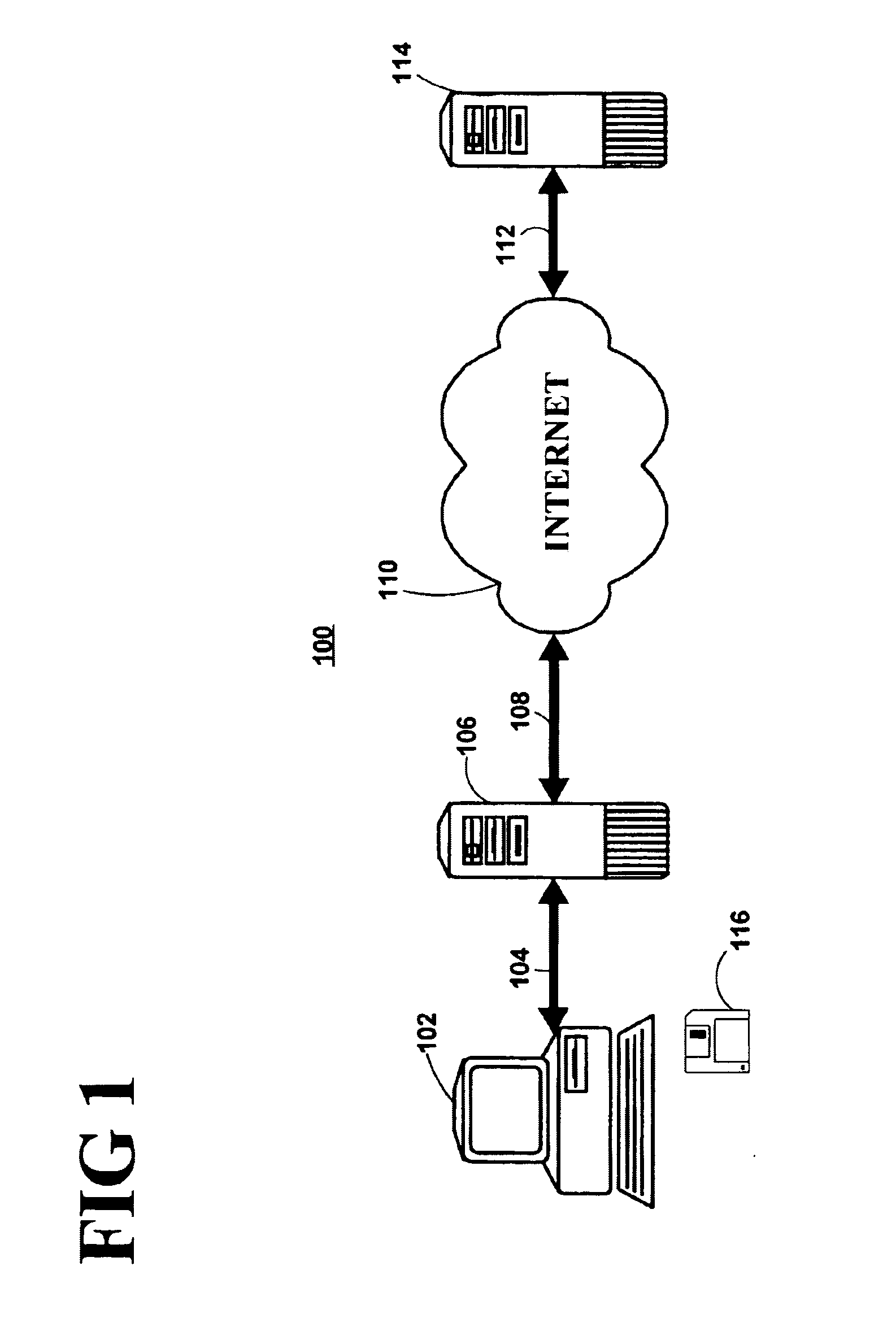

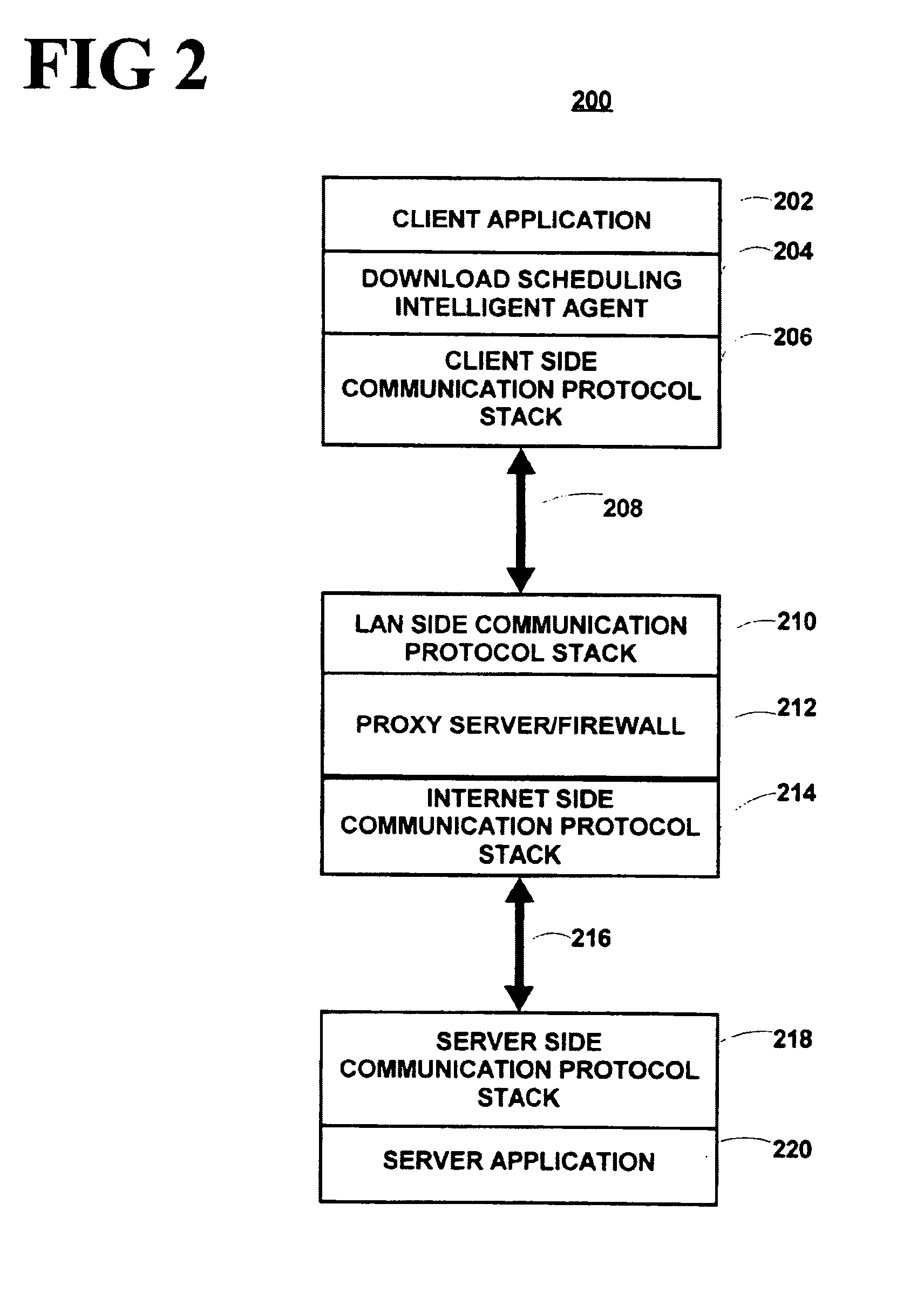

Software and method for controlling the timing of delayed downloads

InactiveUS6934735B1Multiple digital computer combinationsTransmissionControl delayDistributed computing

A system for accepting a specification of a time interval during which a download is to be performed on a delayed basis is described. The system can also select a time within the specified period. The selection can be randomized with the aim of distributing the load placed on computer and communication resources, or the selection may be based on testing a number of measures of computer and communication resource availability, and selecting a time of low utilization. A fuzzy measure of resource availability can be obtained, e.g., as a weighted sum of multiple measures, or each measure can be tested against a limit separately. According to another aspect of the invention a system and computer readable medium is disclosed for carrying out the above method.

Owner:IBM CORP

Delay-locked loop having a plurality of lock modes

A delay-locked loop (DLL) has a counter that is incremented or decremented by the loop in the process of achieving lock. The counter value is converted using an digital to analog converter (DAC) to an analog voltage that controls the delay through the delay line. During faster lock modes, the loop increments / decrements intermediate bits of the counter (with the bits less significant being held at a constant value, e.g., 0) to provide a coarse lock, rather than incrementing / decrementing the least significant bit of the counter. After coarse lock is achieved, a better lock is then achieved by incrementing / decrementing the counter using a smaller increment, i.e., a less significant bit is updated, until finally, the LSB is utilized to achieve fine lock. Utilizing the coarse lock first, and then one or more finer locks, allows the lock to be achieved more quickly.

Owner:MEDIATEK INC

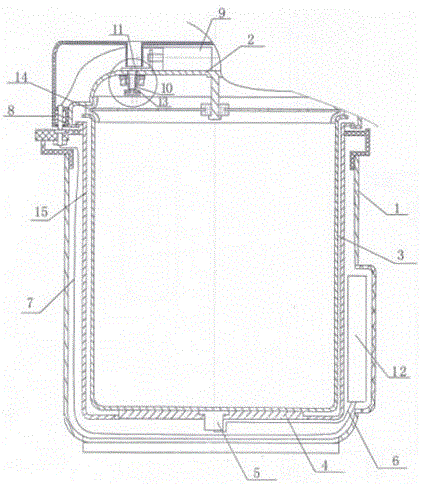

Electromagnetic control delay booster electric pressure cooker

InactiveCN106691171ASolve the problem of poor cooking effectEasy to solvePressure-cookersAtmospheric airControl delay

Disclosed is an electromagnetic control delay booster electric pressure cooker. A floater limited block is connected with an electromagnet, and the electromagnet drives the floater limited block to the position of the limiting floater or the releasing floater. At the position of the limited floater, the floater limited block blocks the floater, and limits the rising of the float, keeping expelling the steam in the cooker to the atmosphere through the vent hole of the floater; At the position of the releasing floater, the floater rises and falls freely; the line control institutions are provided with a delay control unit to control the electromagnet, and start the delay unit to control the work of the electromagnet in the specified delay time when the temperature of the temperature detector rises to the set delay startup time. The cooker has the advantages that: when the electric pressure cooker is cooking rice, the cooker releases partial steam insides after the rice boiling, and grain of rice in the cooker continues boiling in the condition of half a high-pressure, forcing the grain of rice absorb moisture quickly; close the outlet after reaching the set time, making the pressure in the cooker rises; shut off the power and keep heat to cook the rice. In this way, the rice grain is through core, chewiness and smooth when entering the mouth.

Owner:陆一铭

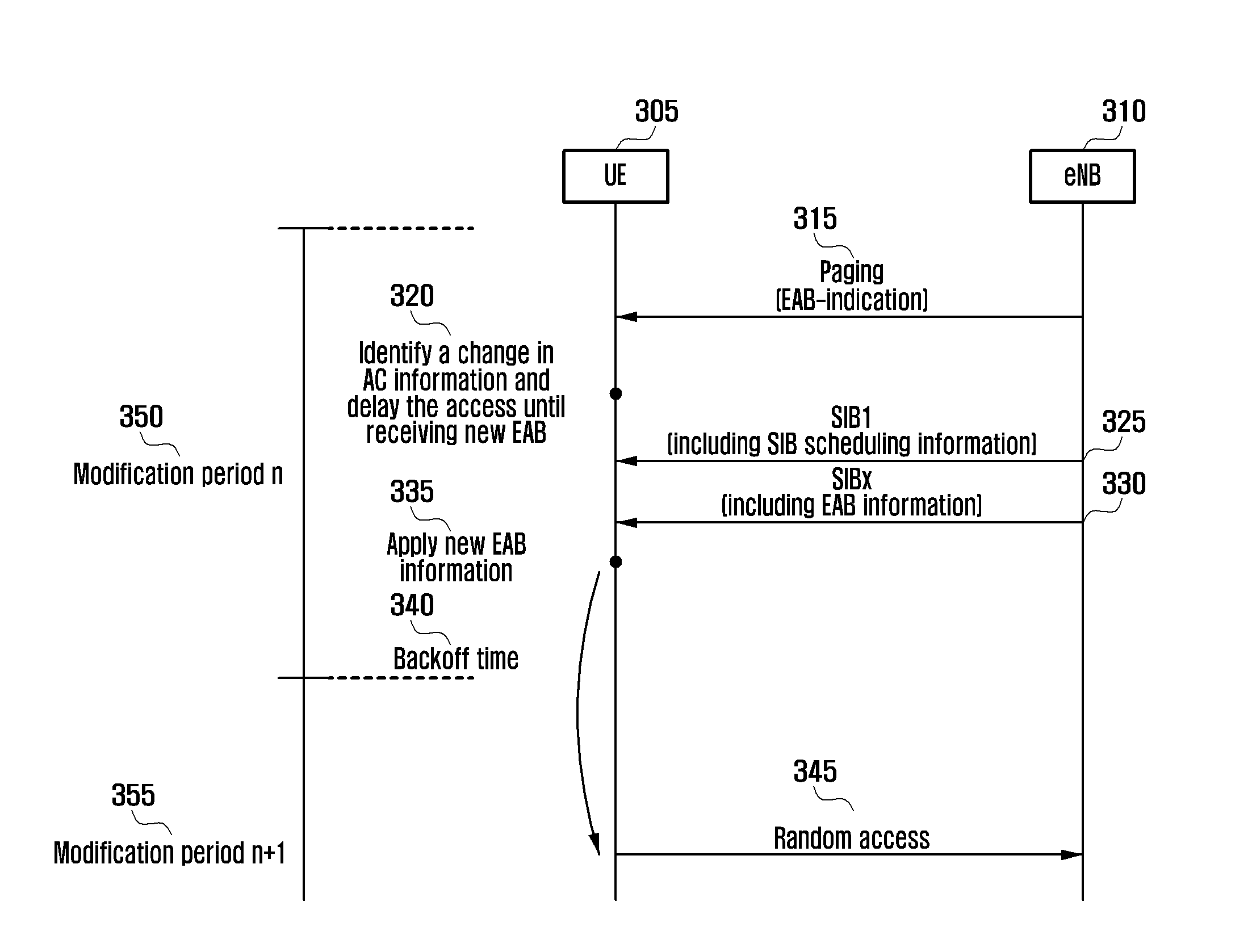

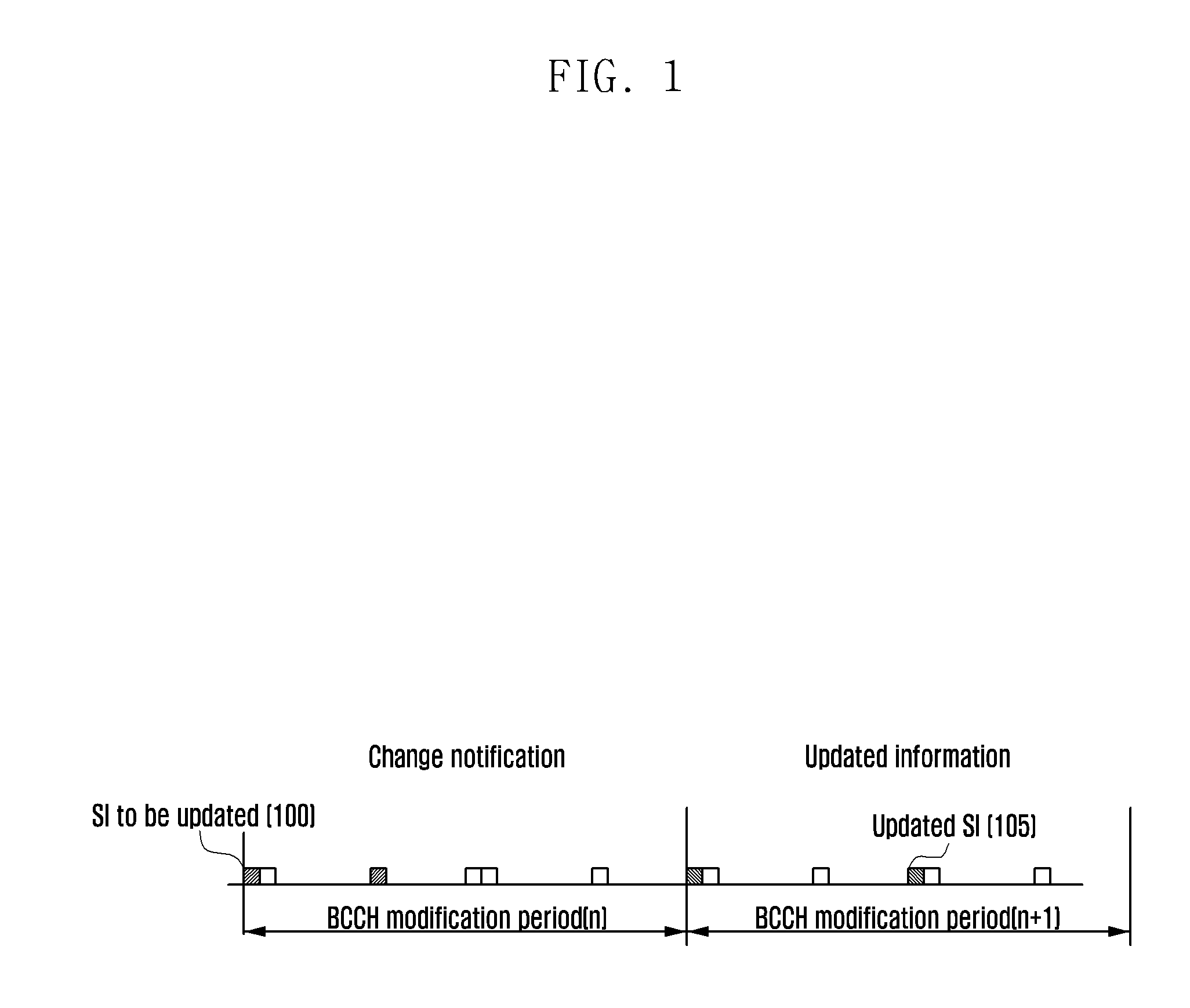

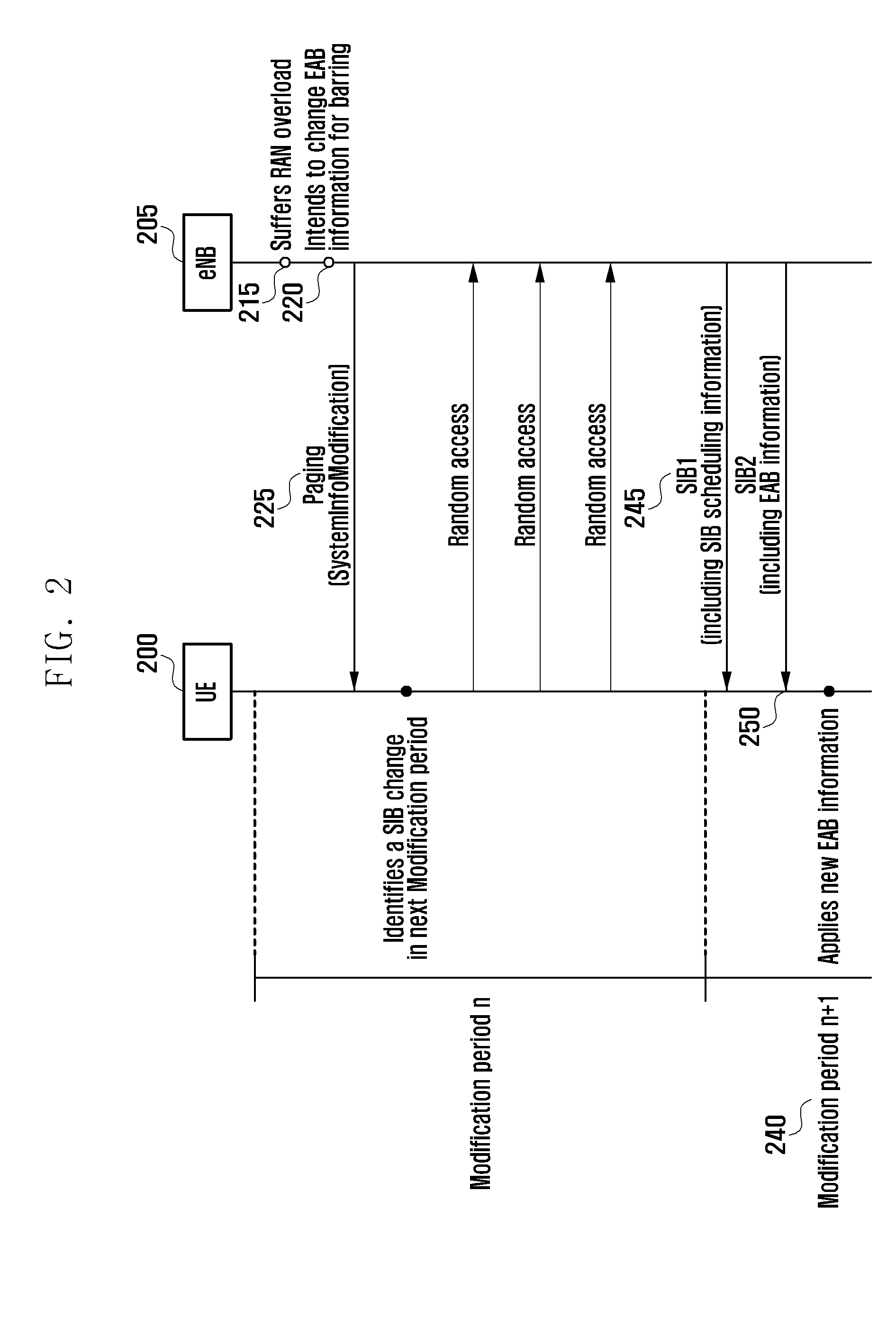

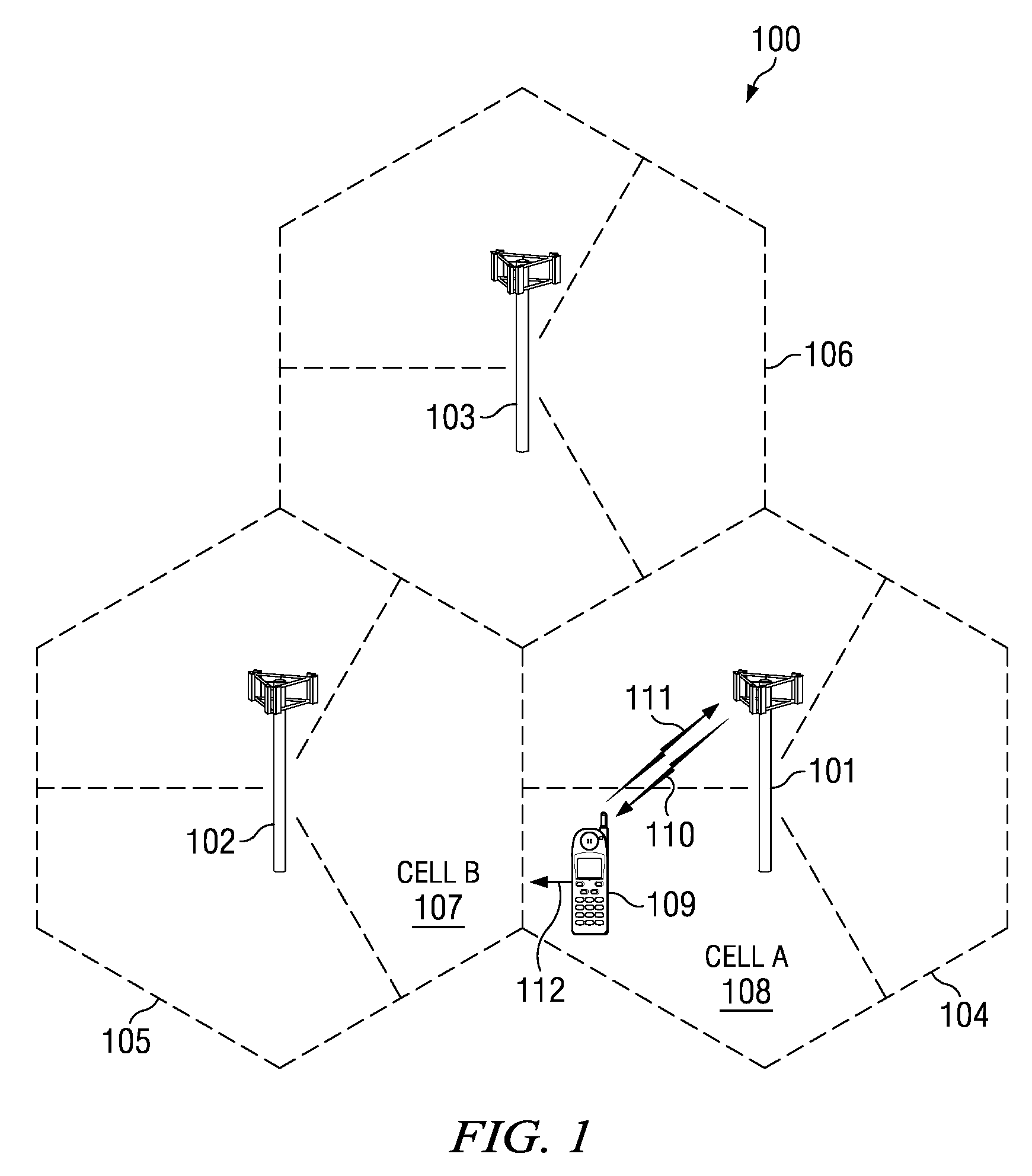

Access control method and apparatus of ue

ActiveUS20120282965A1Efficiently reducing loadAssess restrictionNetwork topologiesControl delayCommunication device

A method for controlling delay tolerant access of a Machine-Type Communication (MTC) device based on a backoff mechanism is provided. The method includes receiving, at a terminal, a paging message including an access barring information update indicator from a base station, and receiving a System Information Block (SIB) including updated access barring information, the SIB being received regardless of modification periods. The terminal receives the SIB including the updated access barring information immediately without waiting for the arrival of next modification period, resulting in improvement of access barring efficiency.

Owner:SAMSUNG ELECTRONICS CO LTD

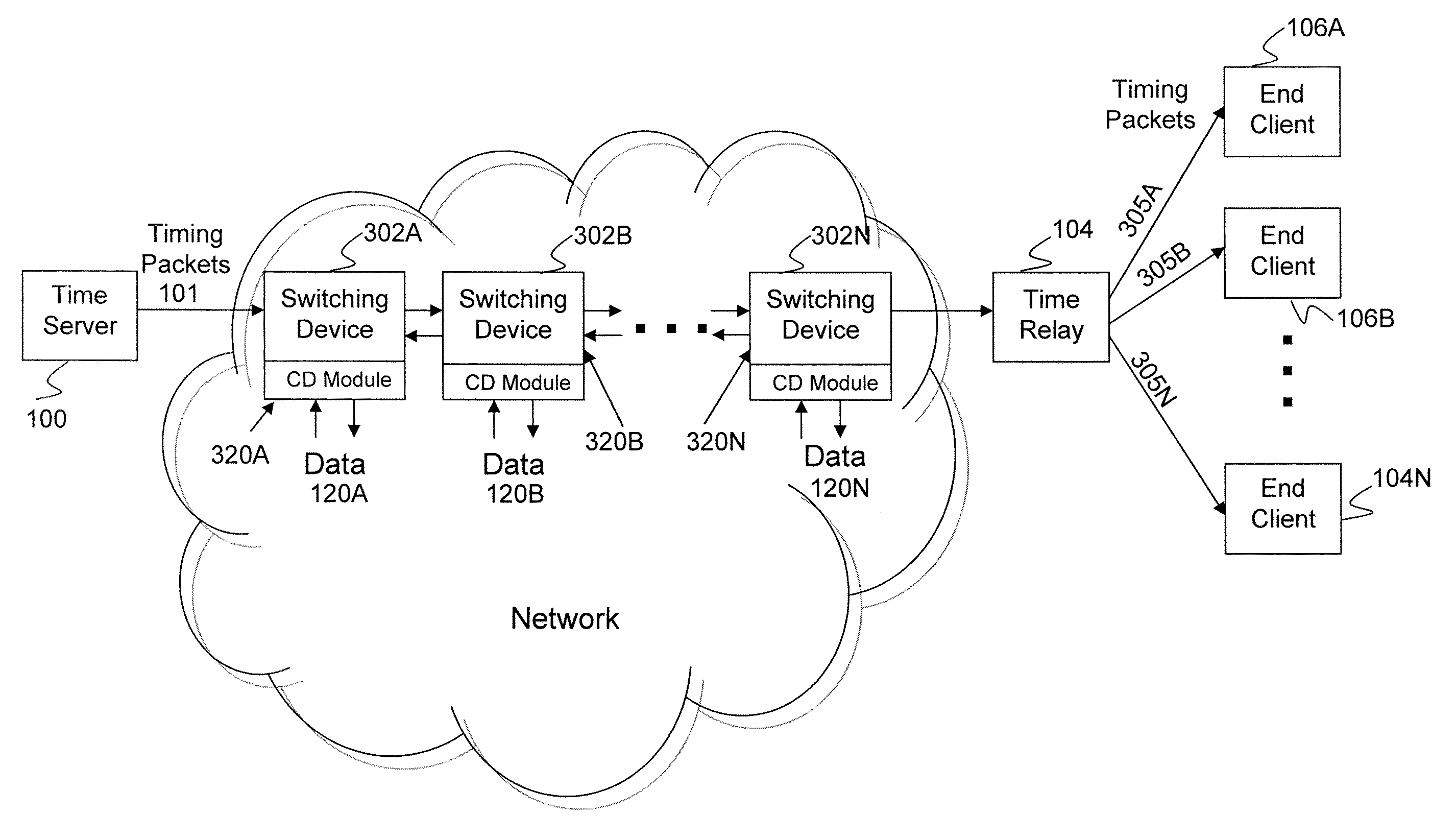

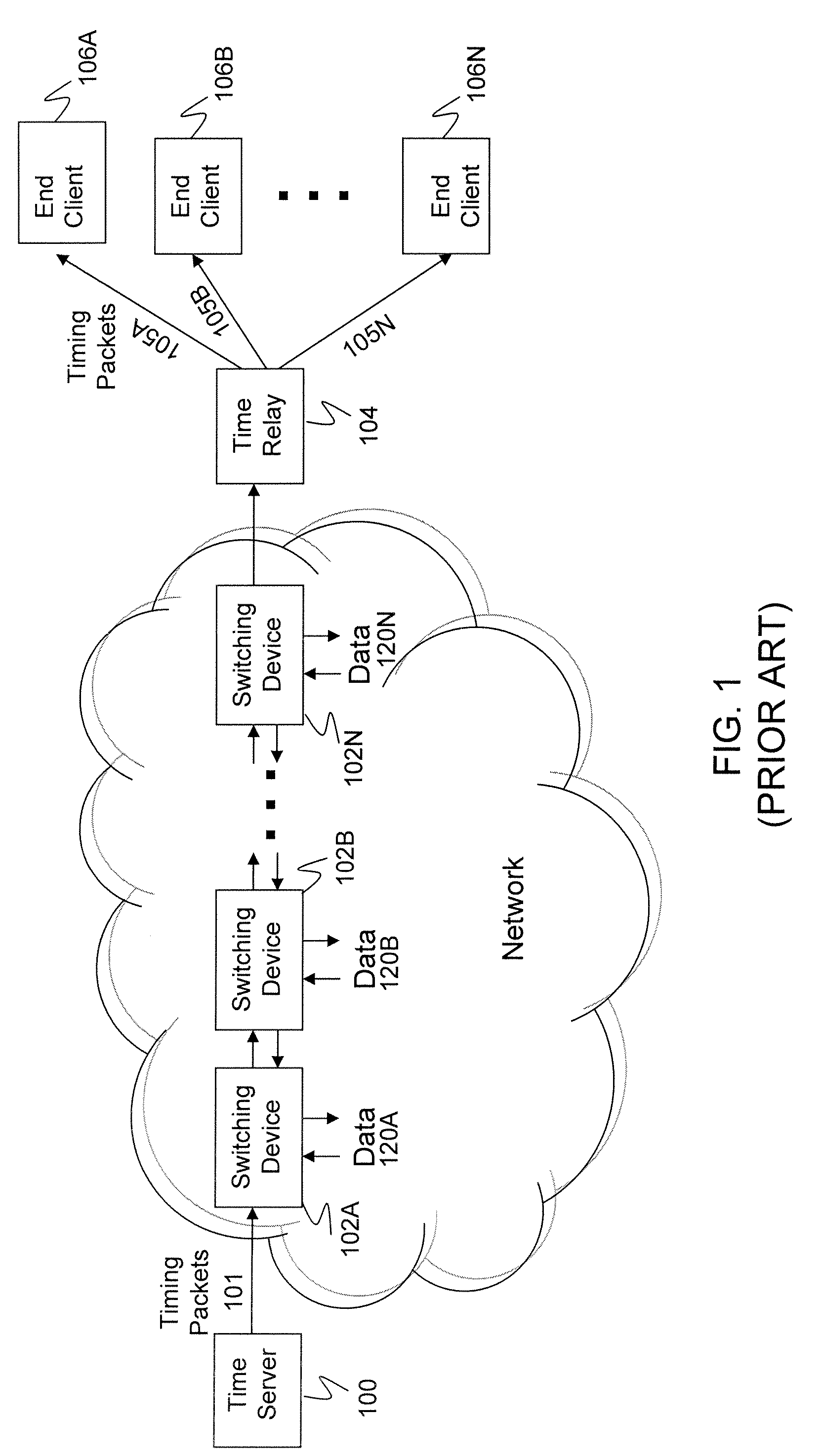

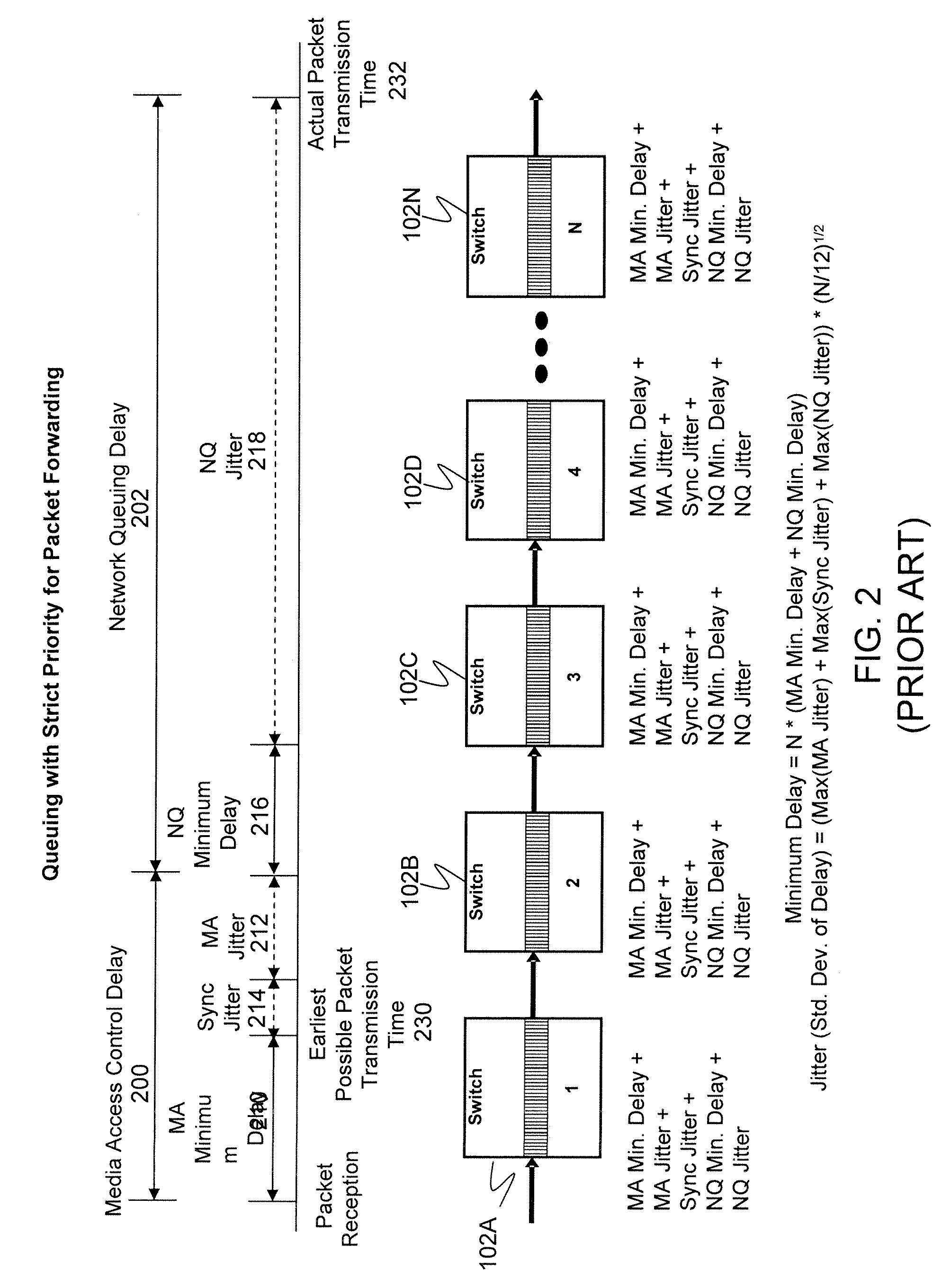

Apparatus and method of controlled delay packet forwarding

An apparatus and method are described for forwarding of packets with controlled delay. In one embodiment, the invention includes controlled delay queuing logic to hold a packet in a first class for a queuing time of at least a controlled delay value, and scheduling logic to determine whether to delay transmission of a packet in a second class to allow the transmission of the packet in the first class when the queuing time reaches the controlled delay value.

Owner:JUMIPER NETWORKS INC

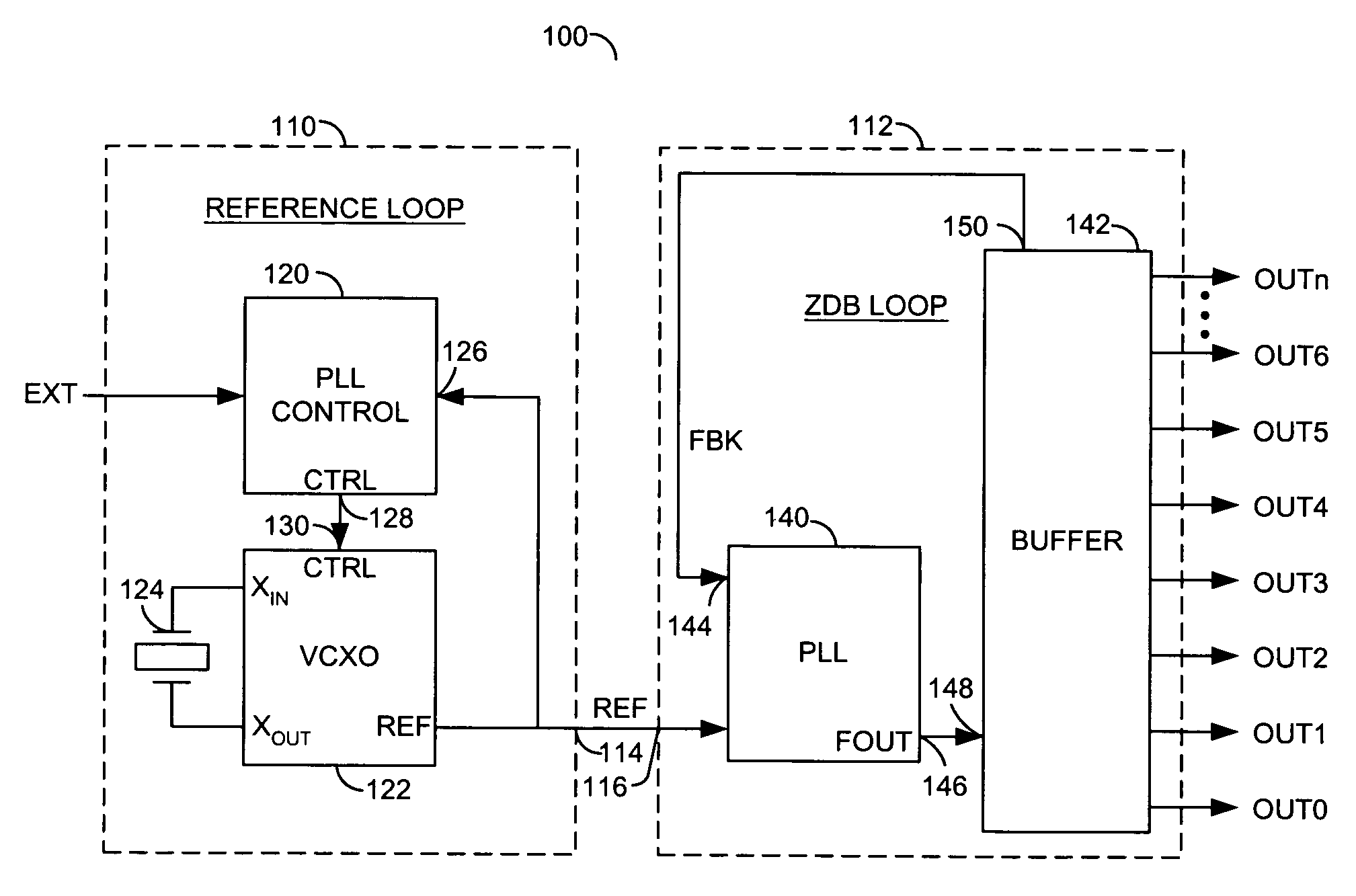

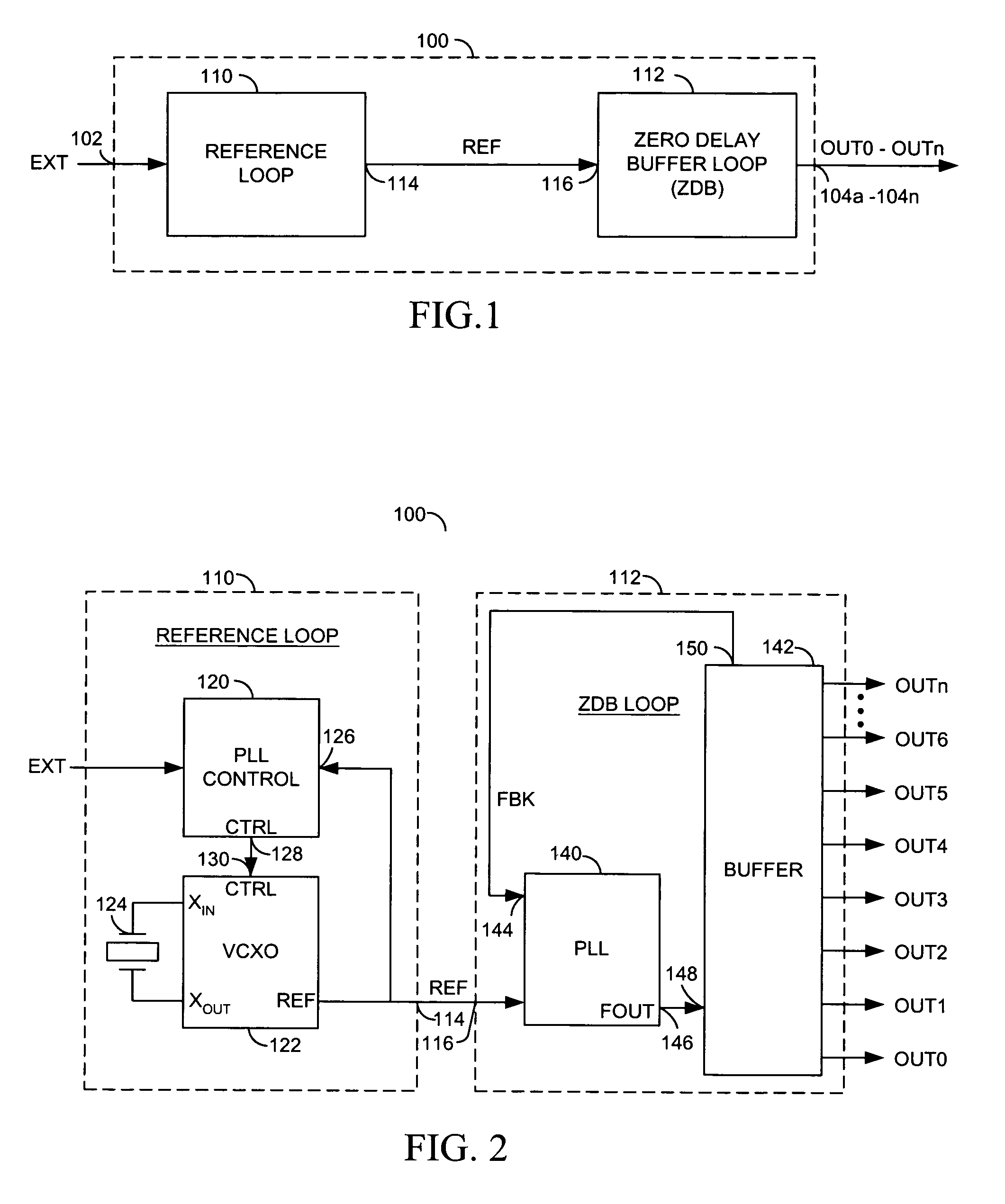

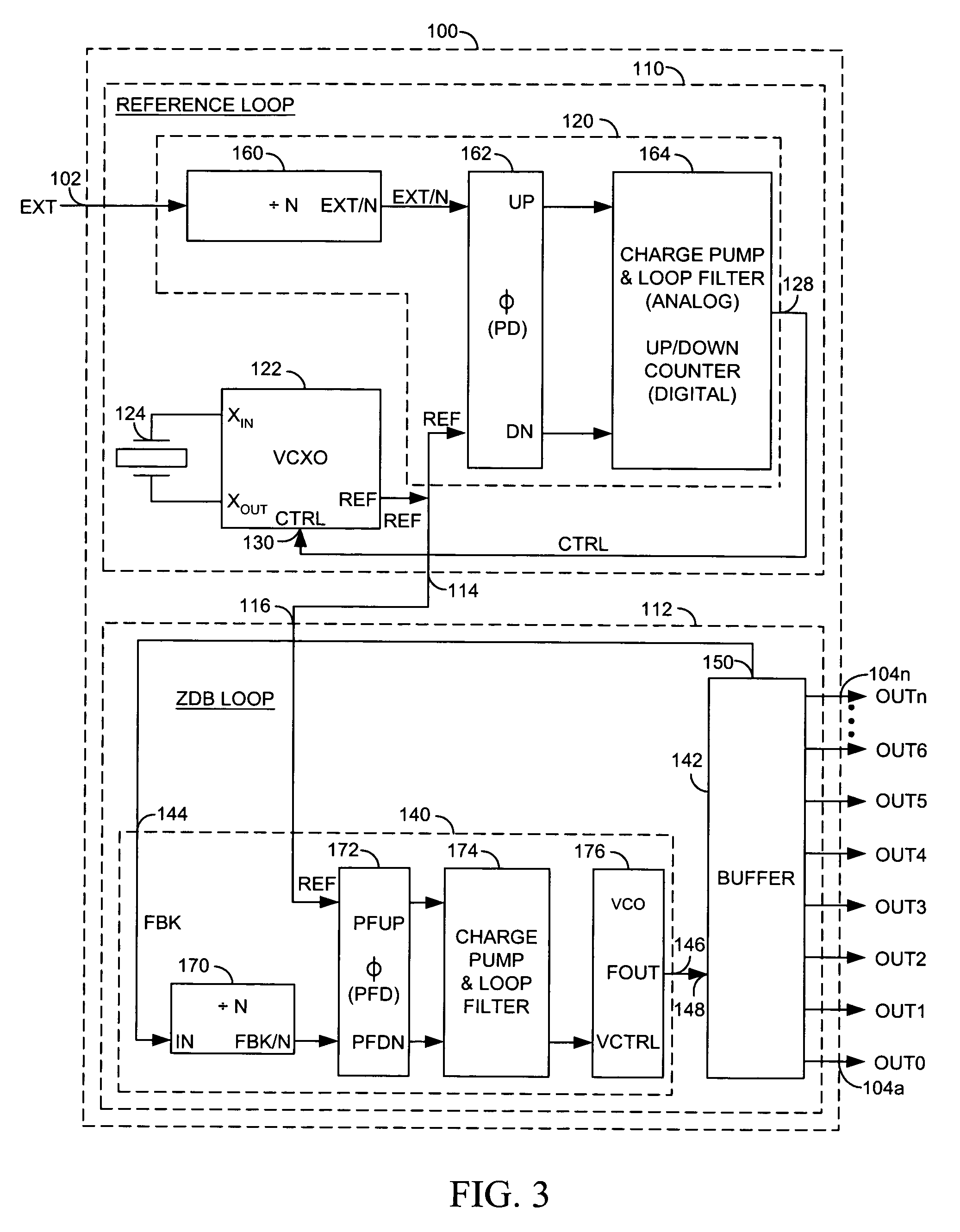

Fail-safe zero delay buffer with automatic internal reference

InactiveUS6956419B1Simple designReduce and eliminate complicated decision making/control logicPulse automatic controlControl signalControl delay

An apparatus comprising a first circuit and a second circuit. The first circuit may comprise a control circuit and an oscillator. The control circuit may be configured to generate a control signal in response to a first reference signal and a second reference signal. The oscillator may be configured to generate the second reference signal in response to the control signal and a timing signal. The control signal is generally held when the first reference signal is lost. The second circuit may be configured to generate one or more output signals in response to the second reference signal and one of the one or more output signals. The one or more output signals may have a controlled delay with respect to the first reference signal.

Owner:MONTEREY RES LLC

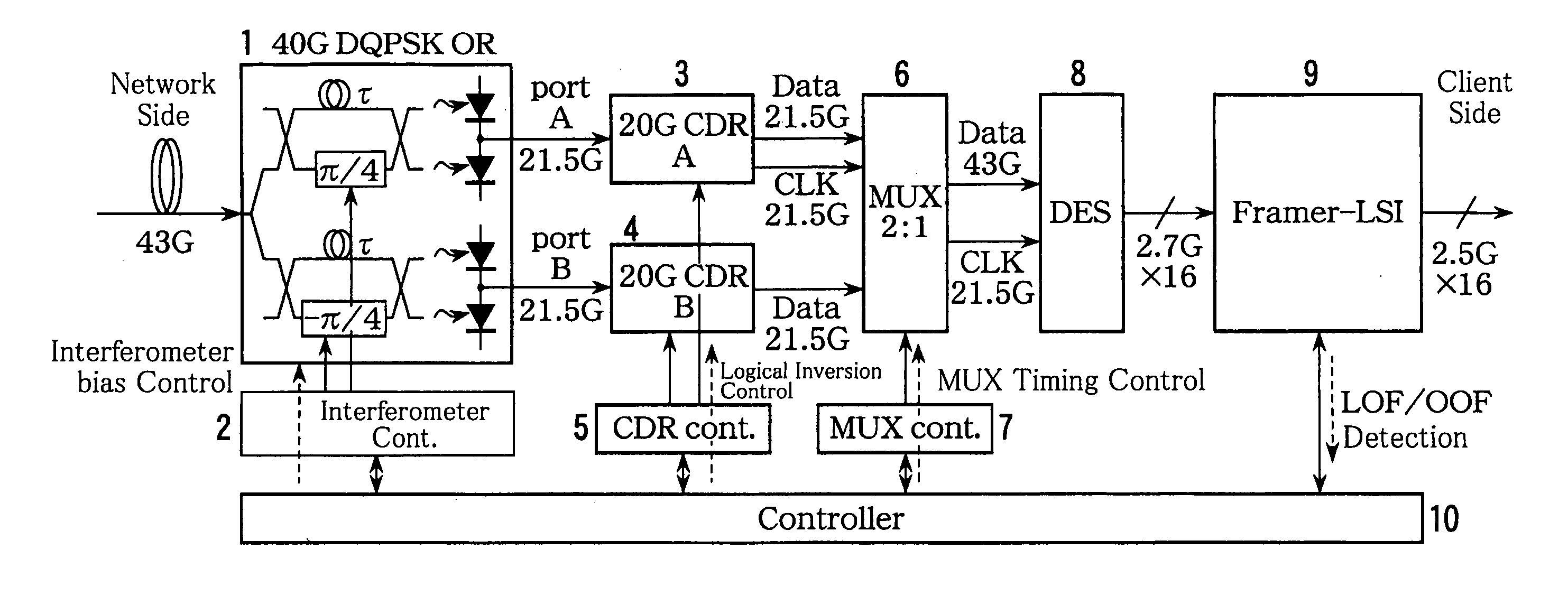

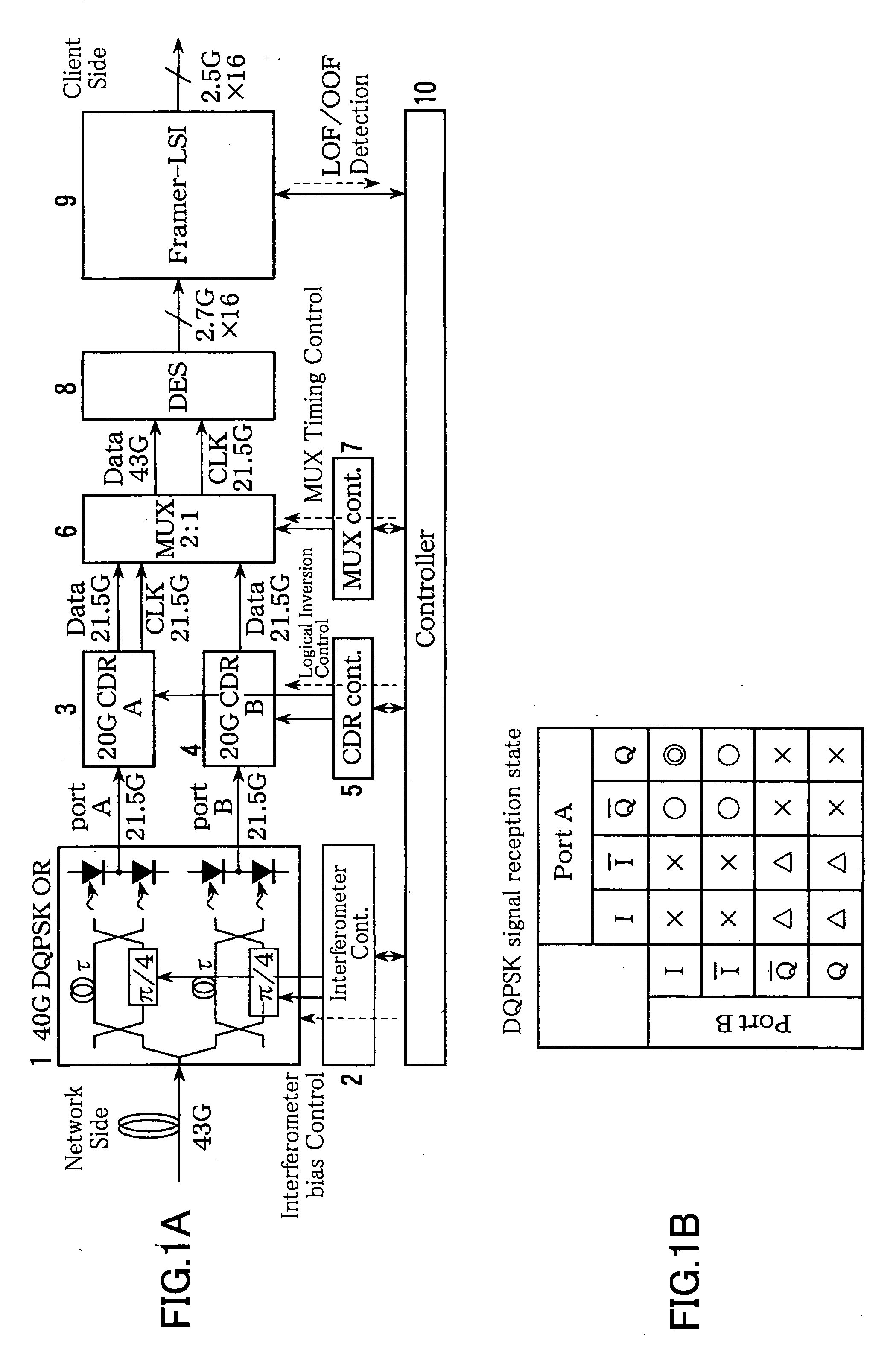

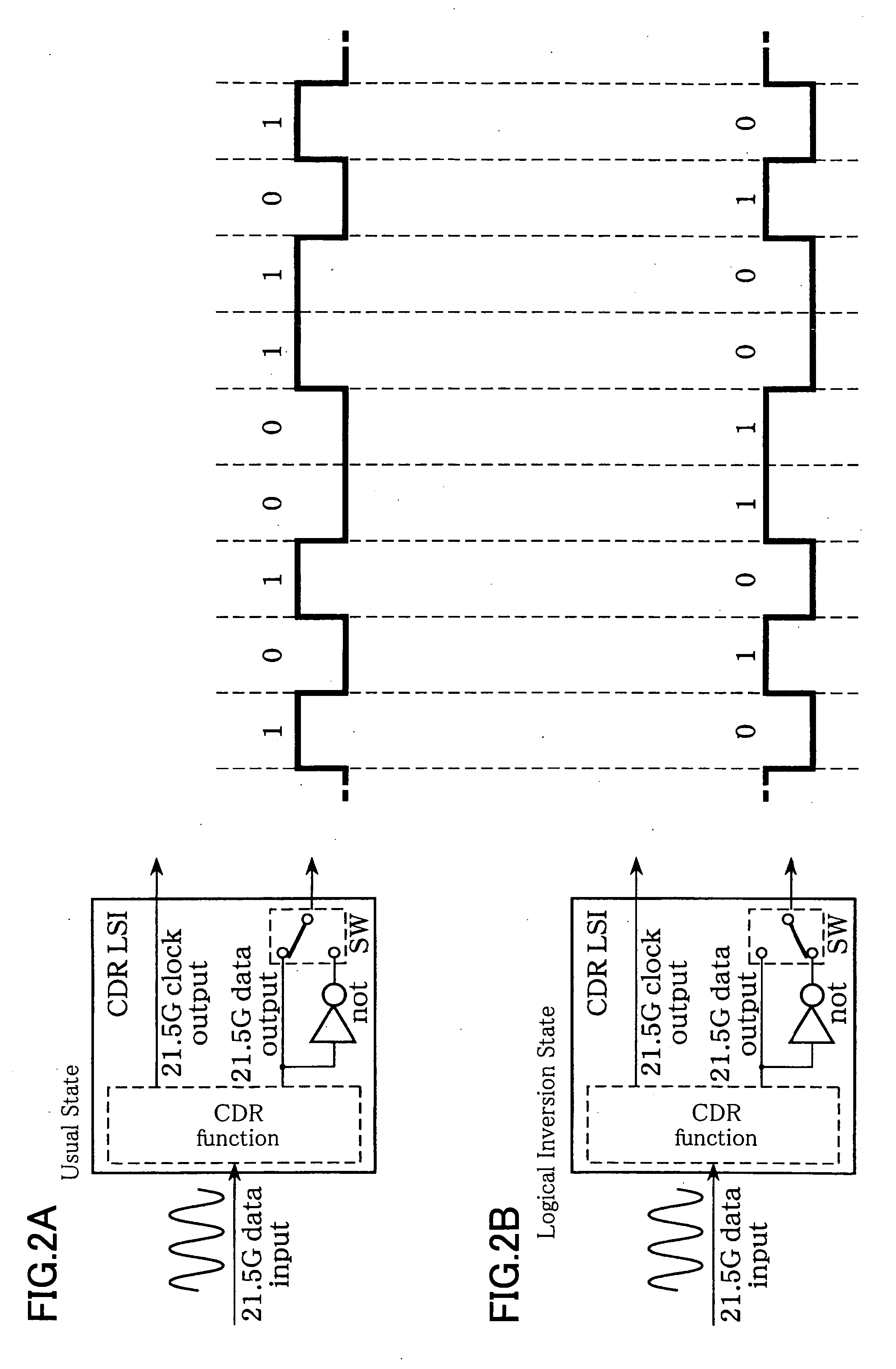

Optical signal reception device and method of controlling optical signal reception

ActiveUS20070065157A1Quickly identify the signal reception statePerform the frame synchronization pull-in operations quicklyModulated-carrier systemsElectromagnetic transmittersMultiplexingMultiplexer

An optical signal reception device is disclosed that receives and demodulates an optical signal modulated by DQPSK and performs logical inversion and other controls to transit to the object reception state. The signal reception device includes a front end including a delay interferometer and an opto-electric conversion element that receive the DQPSK optical signal and convert it into an in-phase signal and a quadrature-phase signal, a clock regenerator that regenerates a clock signal based on the in-phase signal and the quadrature-phase signal, a multiplexer that multiplexes the in-phase signal and the quadrature-phase signal, a reception frame processing unit that detects frame synchronization based on the signal multiplexed by the multiplexer and de-maps the received frames, and a controller that, based on out-of-frame-synchronization information (LOF / OOF) from the reception frame processing unit, performs logical inversion control in the clock regenerator, multiplexing timing control in the multiplexer, and controls the delay interferometer in the front end so as to transit to the object reception state.

Owner:FUJITSU LTD

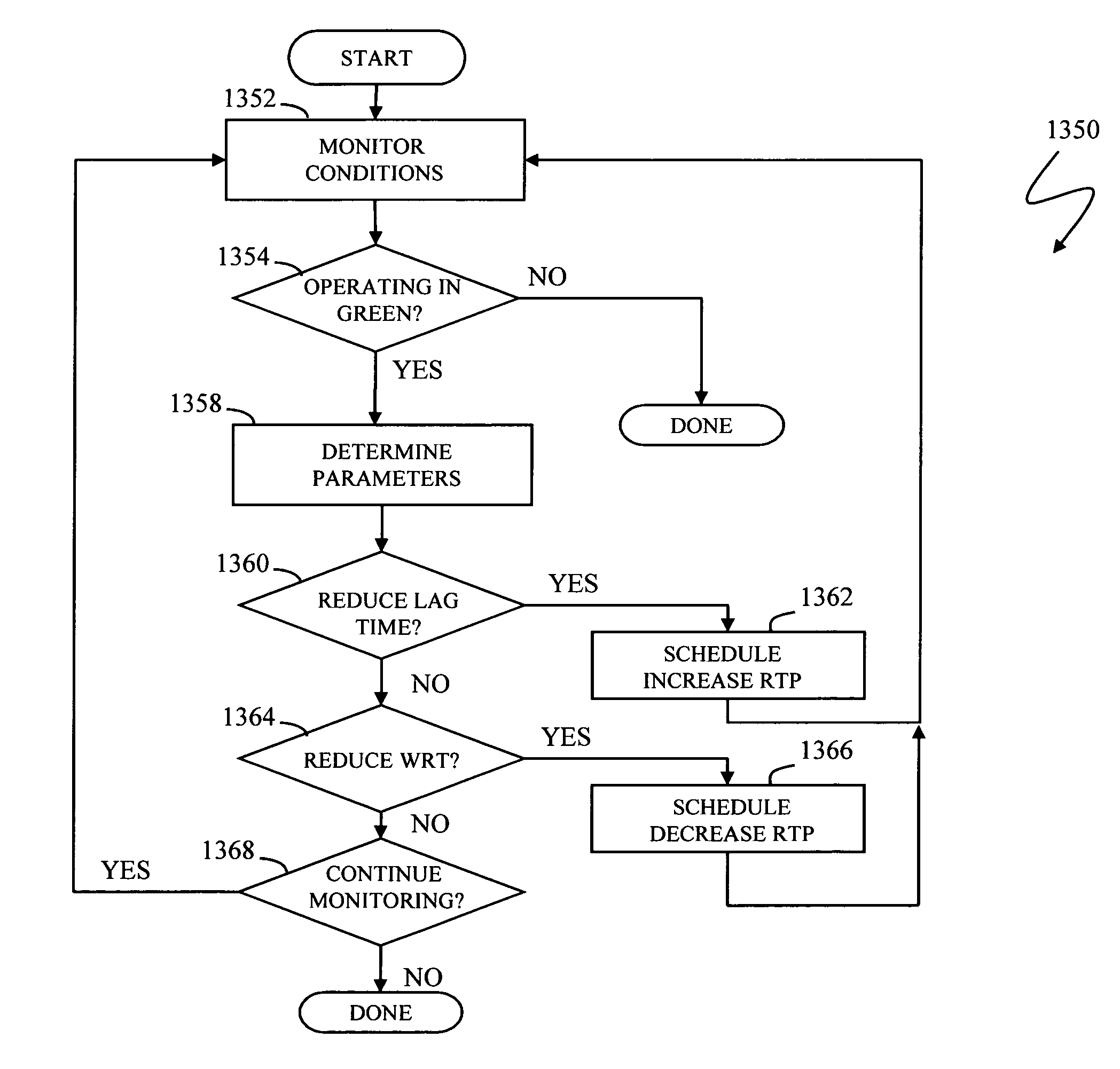

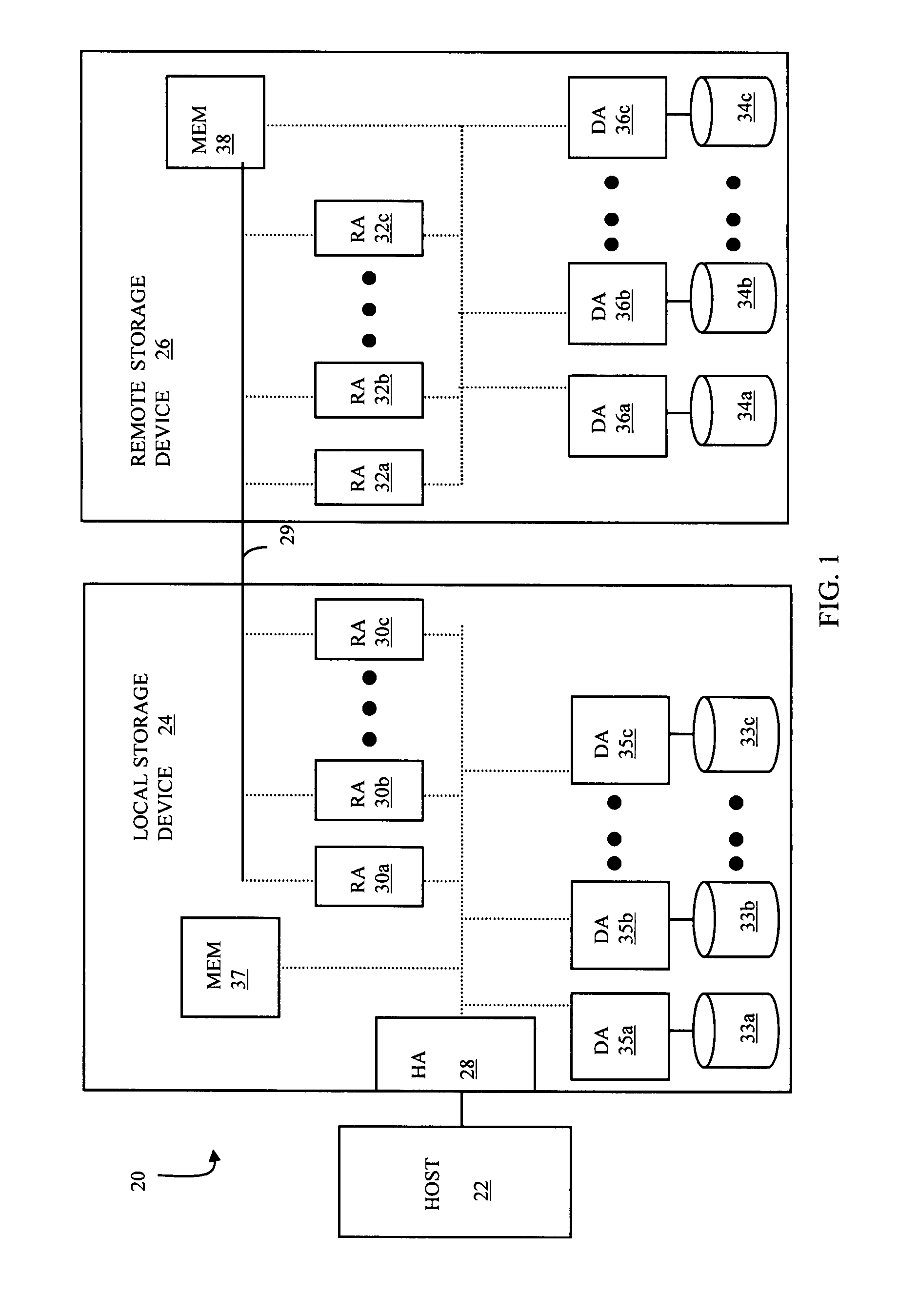

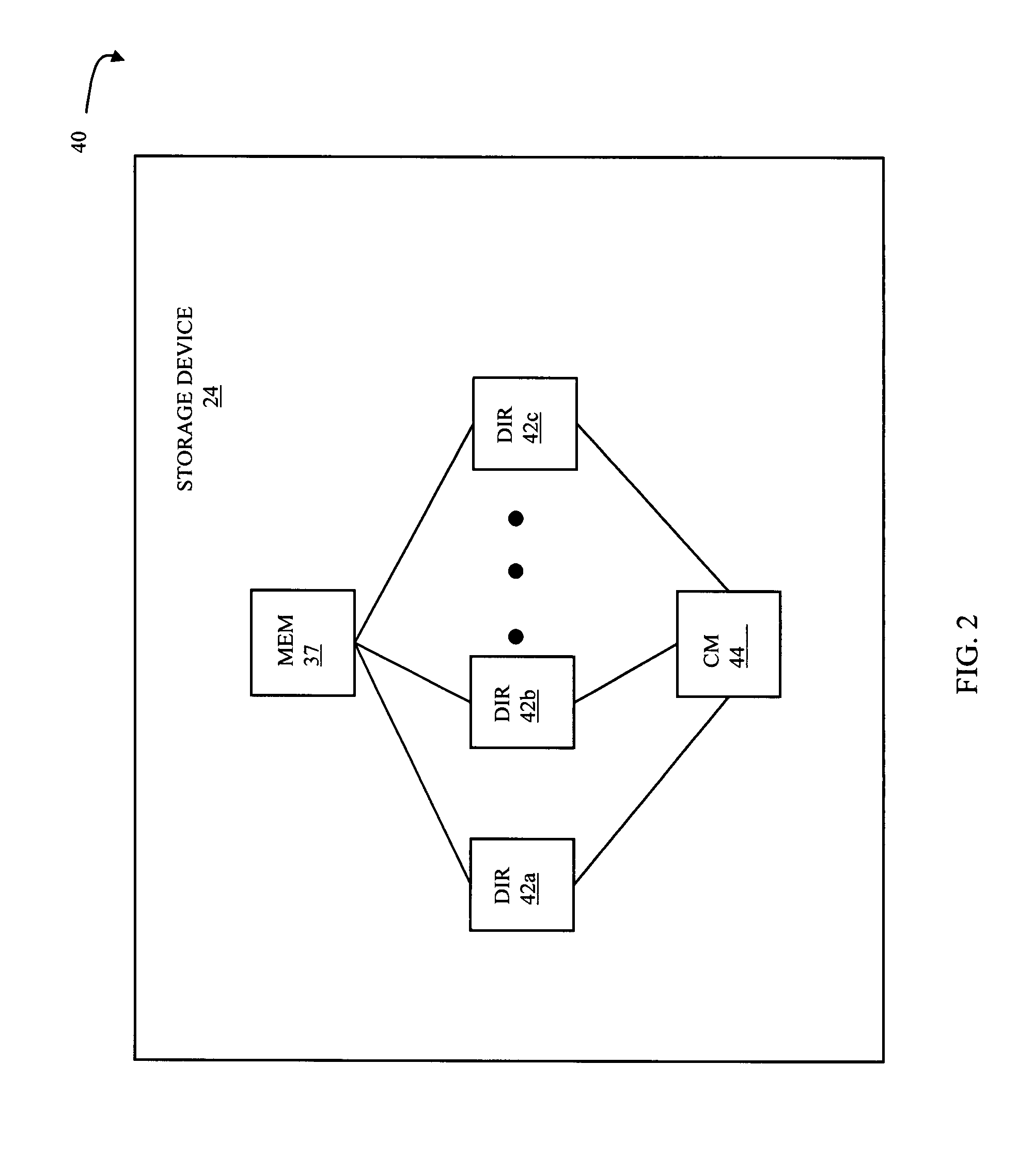

Write pacing

A system for controlling the pacing of host data writes in response to changing system conditions allows for the use of variably controlled delays that facilitate asynchronous replication with bounded lag and smooth steady-state performance. Adding delay to the writes slows down the host and dampens activity spikes. A first storage device receives a write request, transmits data to a second storage device, and acknowledges the write request. An amount of additional write response time is controlled between when the write request is received and when the write request is acknowledged by the first storage device, where the amount of additional write response time is controlled according to system parameters including an amount of lag time between when the write request is received and when the write request is committed at the second storage device.

Owner:EMC IP HLDG CO LLC

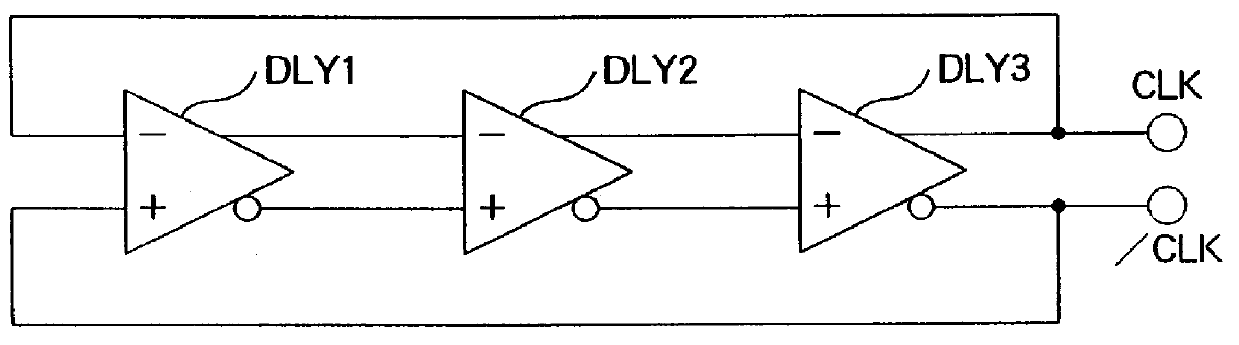

Ring oscillators having inverting and delay elements

InactiveUS6028490APulse generation by logic circuitsOscillations generatorsCharge currentDelayed time

An oscillator circuit constituted by connecting in a ring an odd number of stages of inverting delay circuits comprising inverting elements, for example, inverters INV1, INV2, and INV3, and delay elements D1, D2, and D3 connected to the output terminals of the inverting elements. In each delay element, the capacitor is charged and discharged in accordance with the output signal level from the inverter, the voltage of the capacitor and the reference voltage are compared by a comparison circuit, and a signal in accordance with the result of comparison is input to the inverting delay circuit of the next stage, therefore the delay time can be controlled by controlling the charging current of the delay element and the oscillation frequency can be controlled in accordance with this. Accordingly, the control property thereof is good, the range of variation can be broadened, and a reduction of jitter can be realized.

Owner:SONY CORP

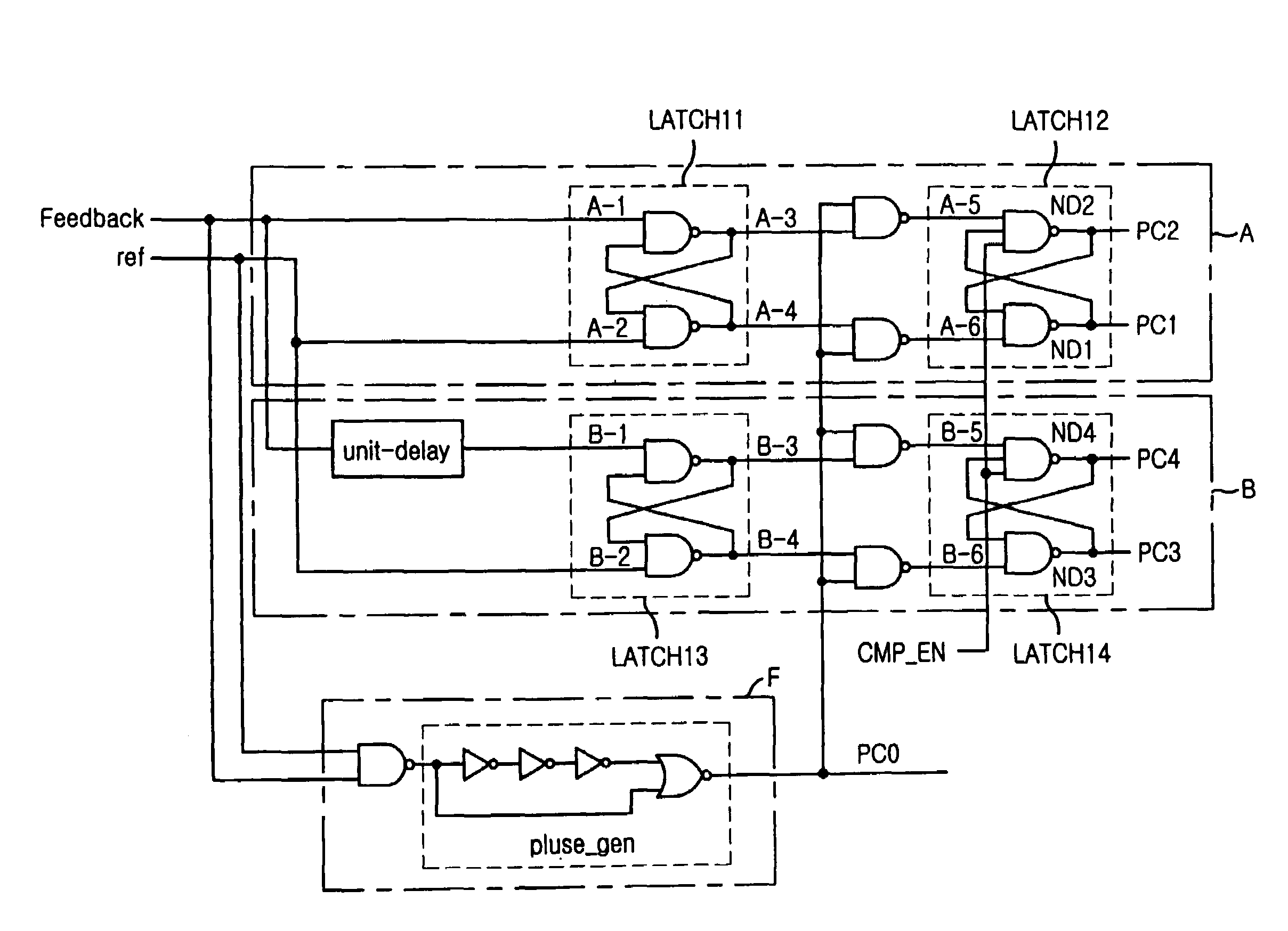

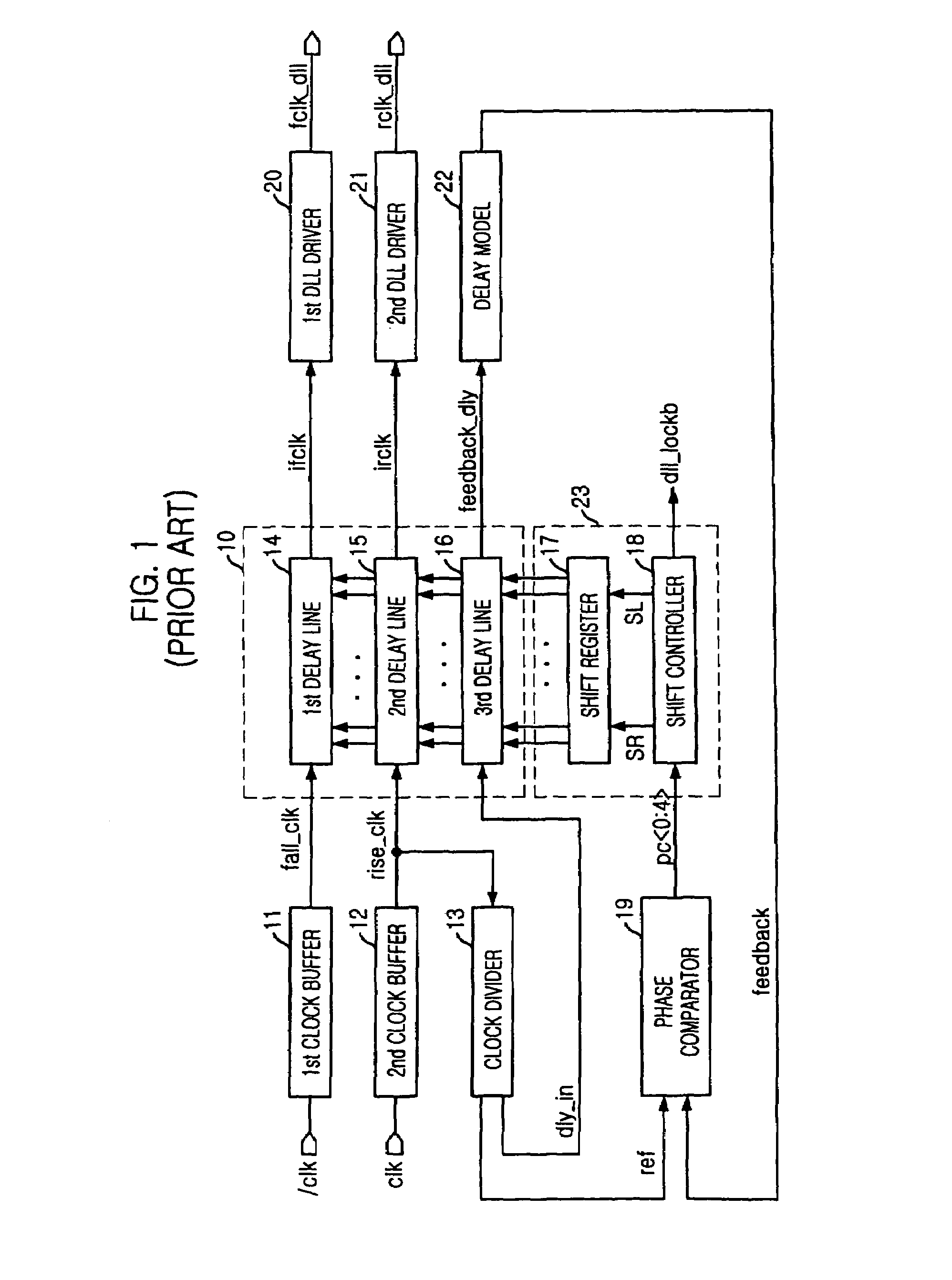

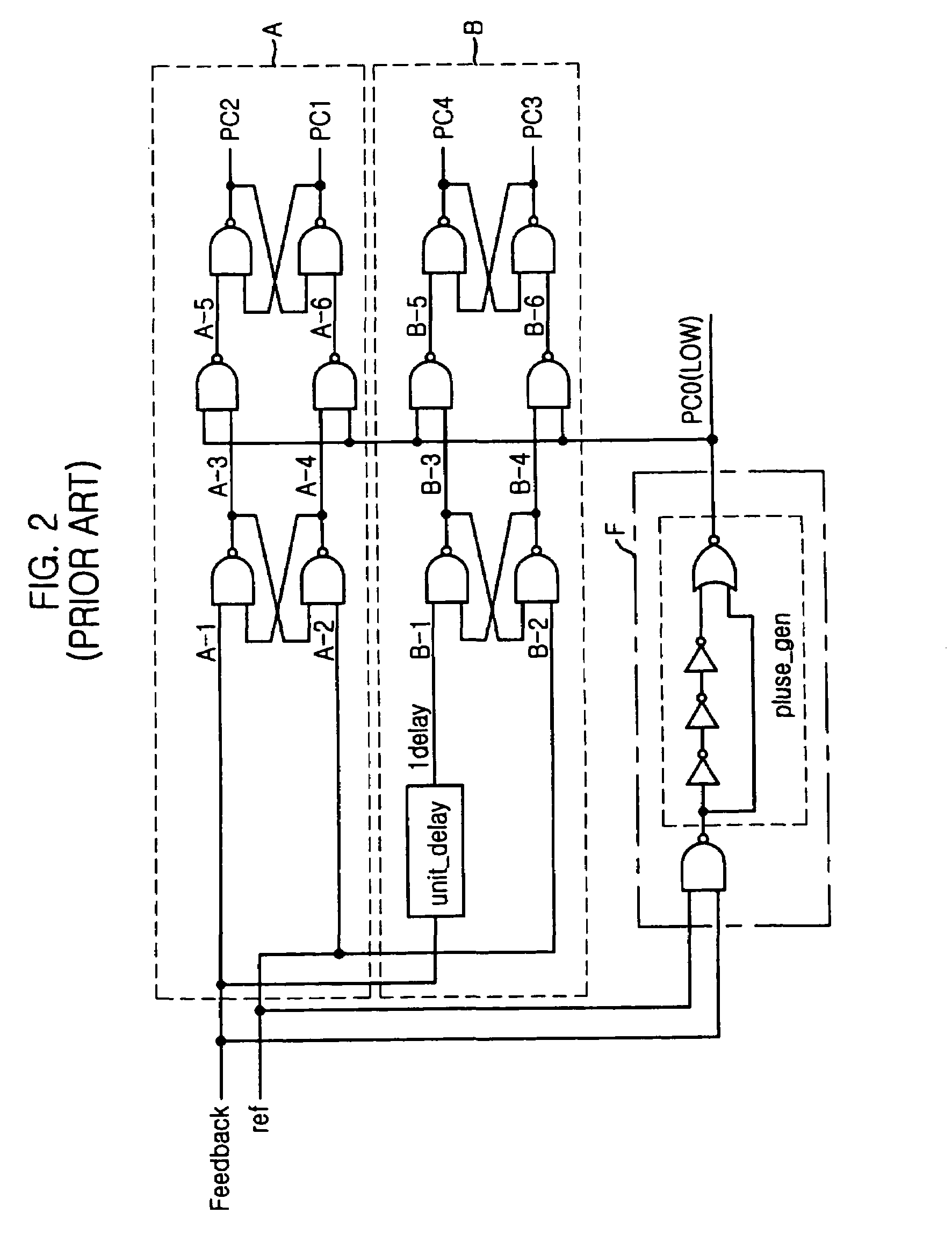

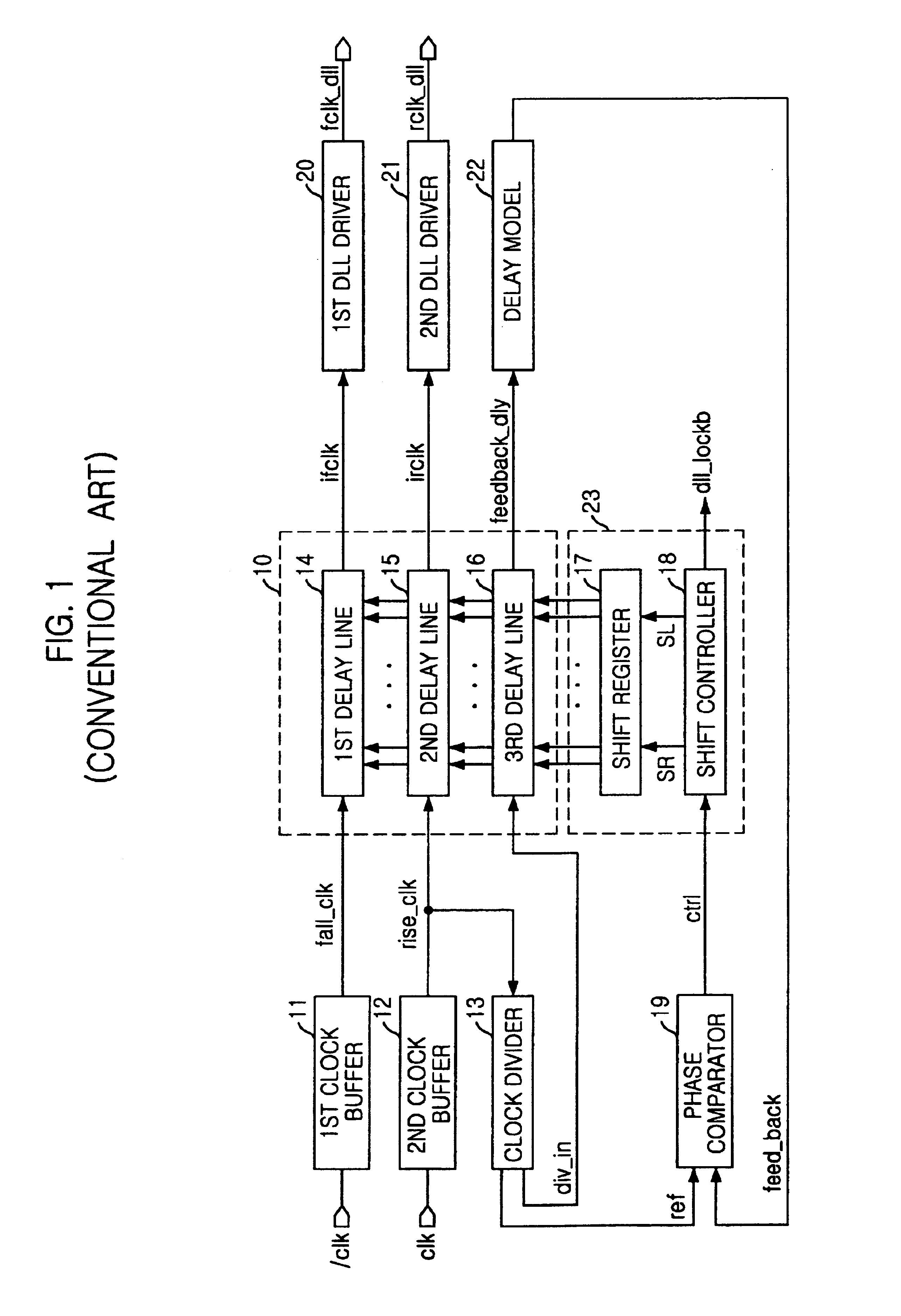

Register controlled delay locked loop circuit

A register controlled delay locked loop (DLL) includes a clock divider, a shift controller, a delay unit and a delay model to synchronize an external clock signal with an internal clock. The register controlled DLL further includes a reset signal generator to generate a reset signal used to initialize the delay locked loop (DLL), a phase comparator to initialize a phase comparison signal in which the phase of a feedback clock signal delayed by a reference clock signal and the delay model is compared and outputted into a predetermined signal by using a comparison enable signal having an inverse phase to that of the reset signal, and a shift register to block an electric current running on a first latch of a plurality of latches with the reset signal during the initialization.

Owner:SK HYNIX INC

Communication device and communication method

InactiveUS20080008276A1Preferable communicationModulated-carrier systemsPolarisation/directional diversityTime correlationEngineering

There is provided a radio communication device having a high quality and accuracy regardless of fluctuation degree of the transmission path characteristic. The radio communication device estimates the fluctuation speed of the transmission path characteristic from the time correlation of the reception signal, judges the diversity technique used between the communication devices from the estimated value, and feeds back the judgment information so as to switch the diversity between the communication devices, thereby increasing the diversity gain. The feedback information is minimized by defining a correspondence table. Moreover, diversity switching is performed at a timing considering a control delay and a propagation path delay so as to prevent an instantaneous disconnection of the communication.

Owner:FUJITSU LTD

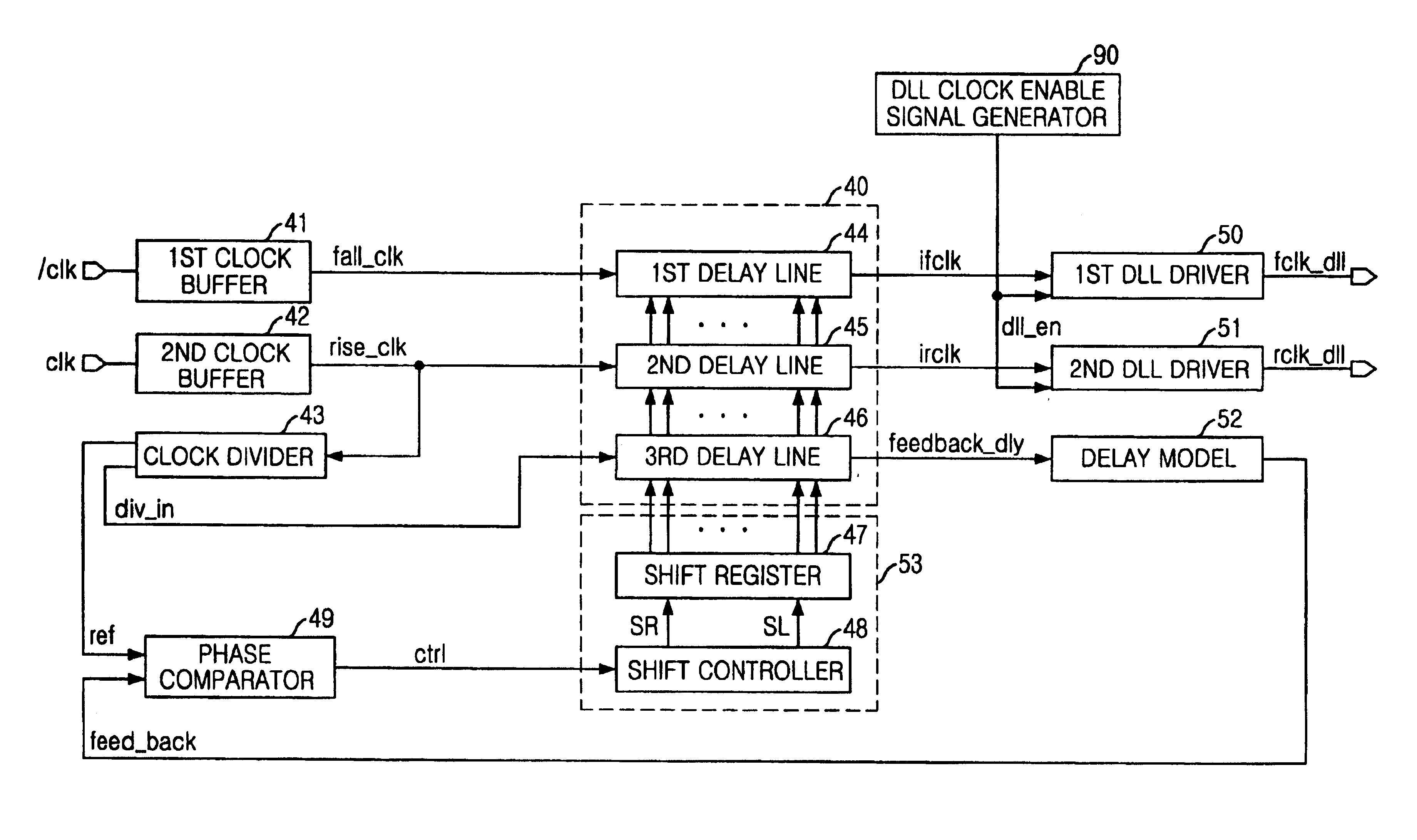

Register controlled DLL for reducing current consumption

InactiveUS6914798B2Reduce current consumptionTotal current dropPulse automatic controlSingle output arrangementsDelay-locked loopEngineering

A register controlled delay locked loop (DLL) usable in a semiconductor device is provided. The register controlled delay locked loop includes an internal clock generating unit generating a delayed clock signal and a reference clock signal, a first delay unit compensating for an amount of delay caused by a signal transmission path of the delayed clock signal, a phase comparator detecting a difference between the reference clock signal and the delayed clock signal and thereby generating a detection signal, a controller having a plurality of second delay units for controlling an amount of delay of the delayed clock signal in response to the detection signal, a driver driving a DLL clock signal, and an enable signal generator enabling the driver in response to an activation or non-activation signal of the semiconductor device.

Owner:SK HYNIX INC

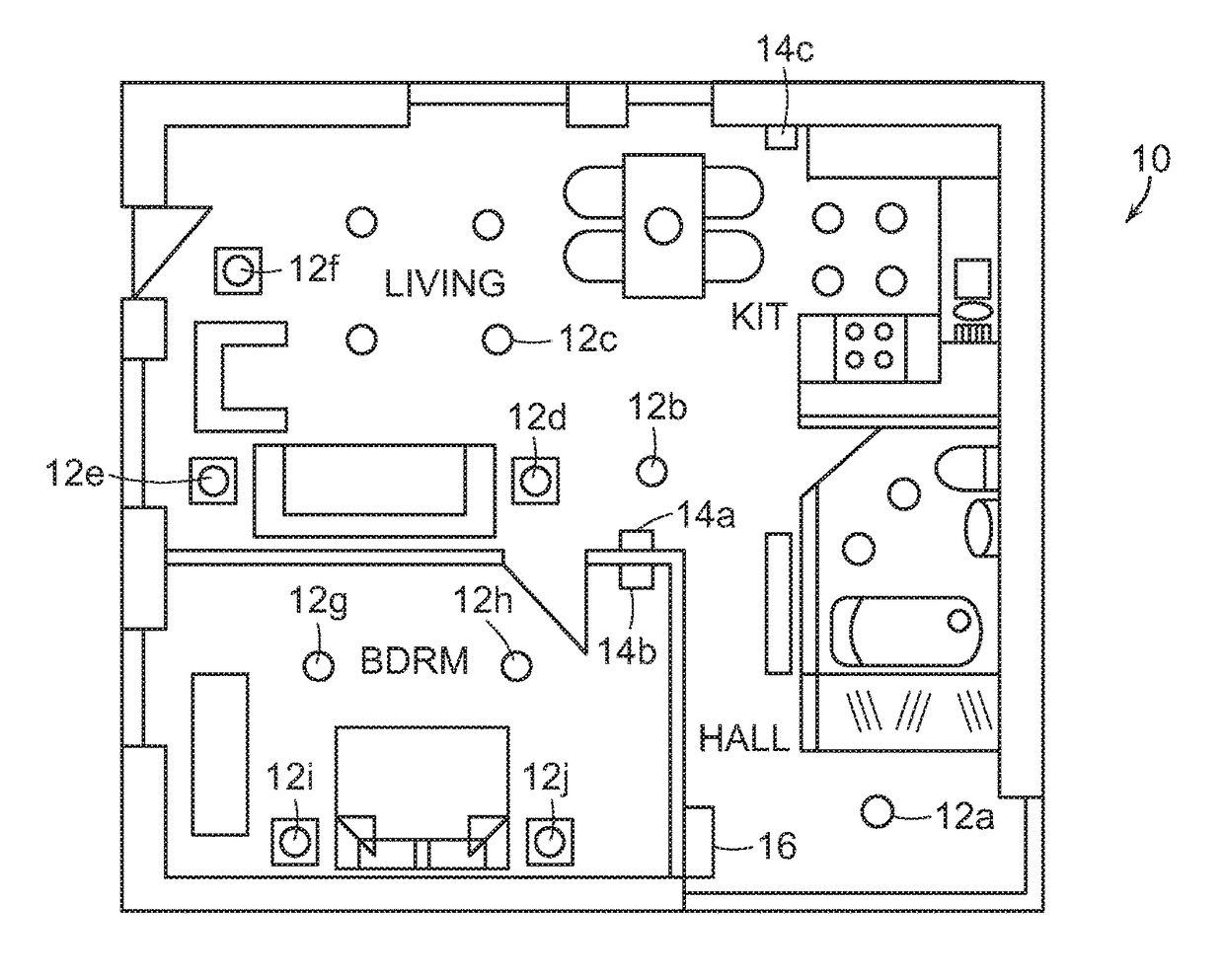

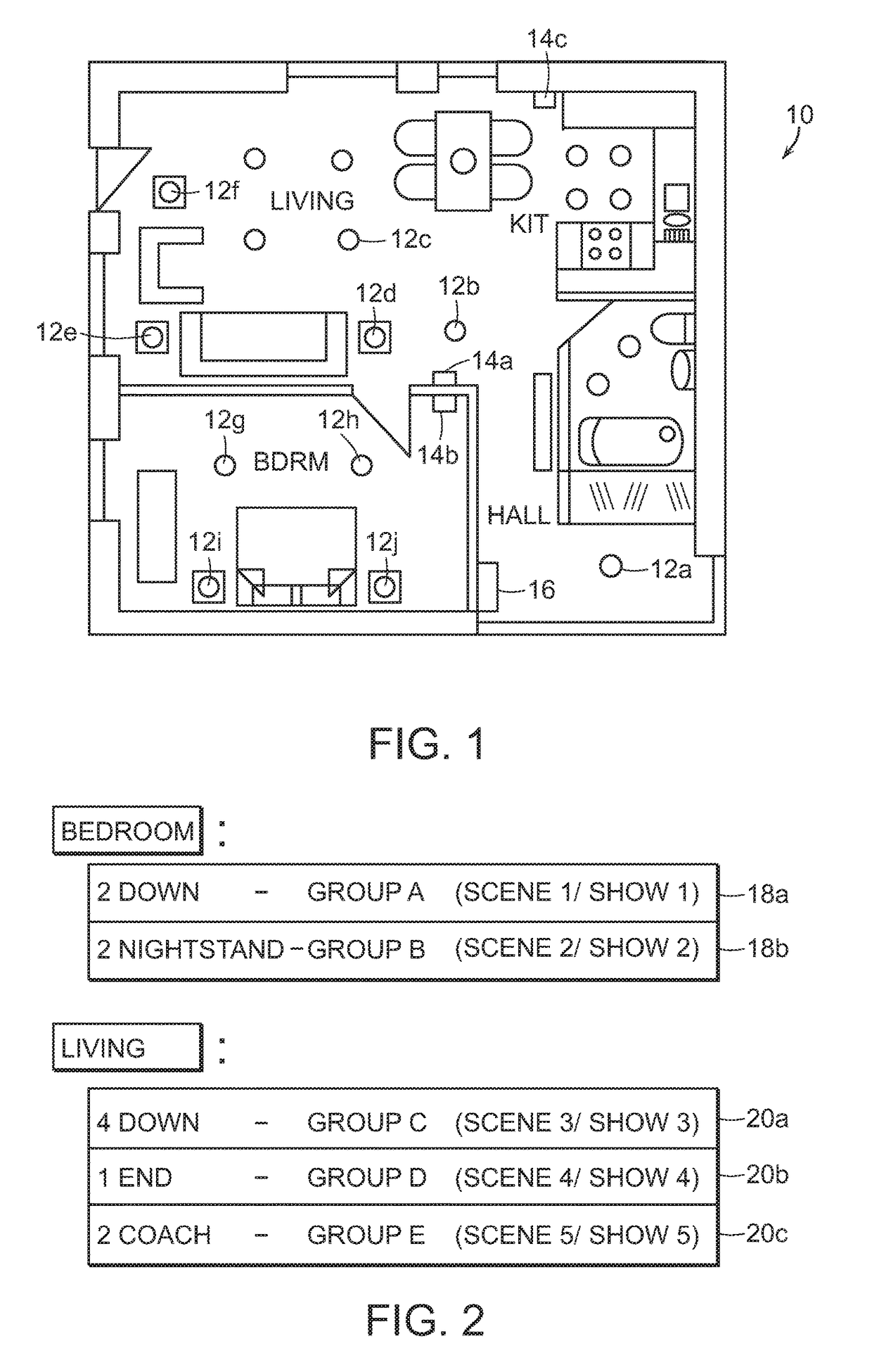

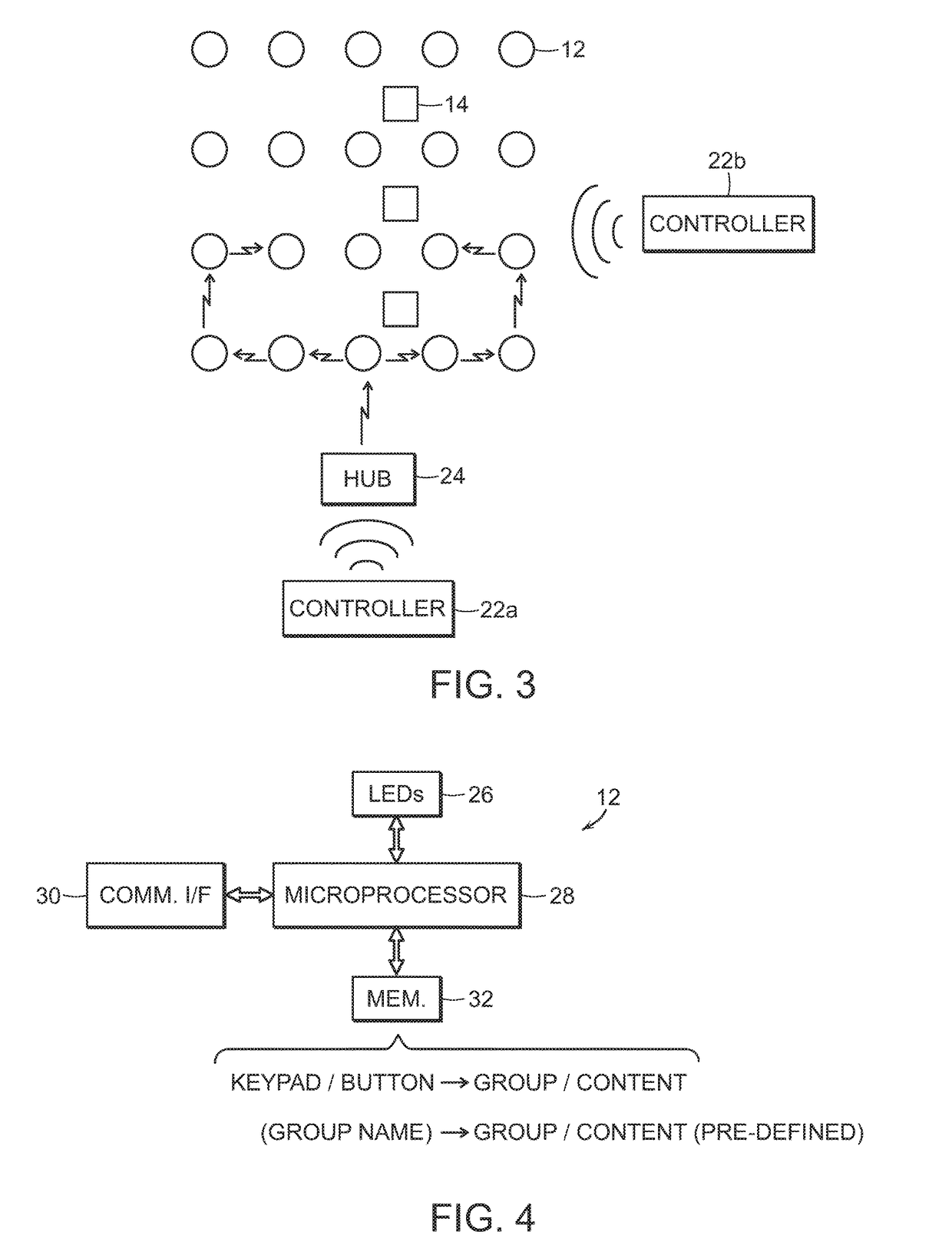

System and method for ensuring minimal control delay to grouped illumination devices configured within a wireless network

ActiveUS9655215B1Hamper bandwidthGood delayElectroluminescent light sourcesElectric light circuit arrangementControl delayEmbedded system

A lighting control system and method is disclosed for not only controlling visual content loaded within a group set of illumination devices configured within a wireless network, but also for ensuring minimal control delay to those grouped devices. The lighting control system can include a lighting controller device that controls a plurality of lamps within a mesh network, not only to group those lamps but also to assign content to lamps within that group. The combination of a guaranteed groupcast to each of the group of lamps and an acknowledge back from those lamps that is aggregated over a single path achieves the improved lighting control system disclosed herein.

Owner:LUTRON TECH CO LLC

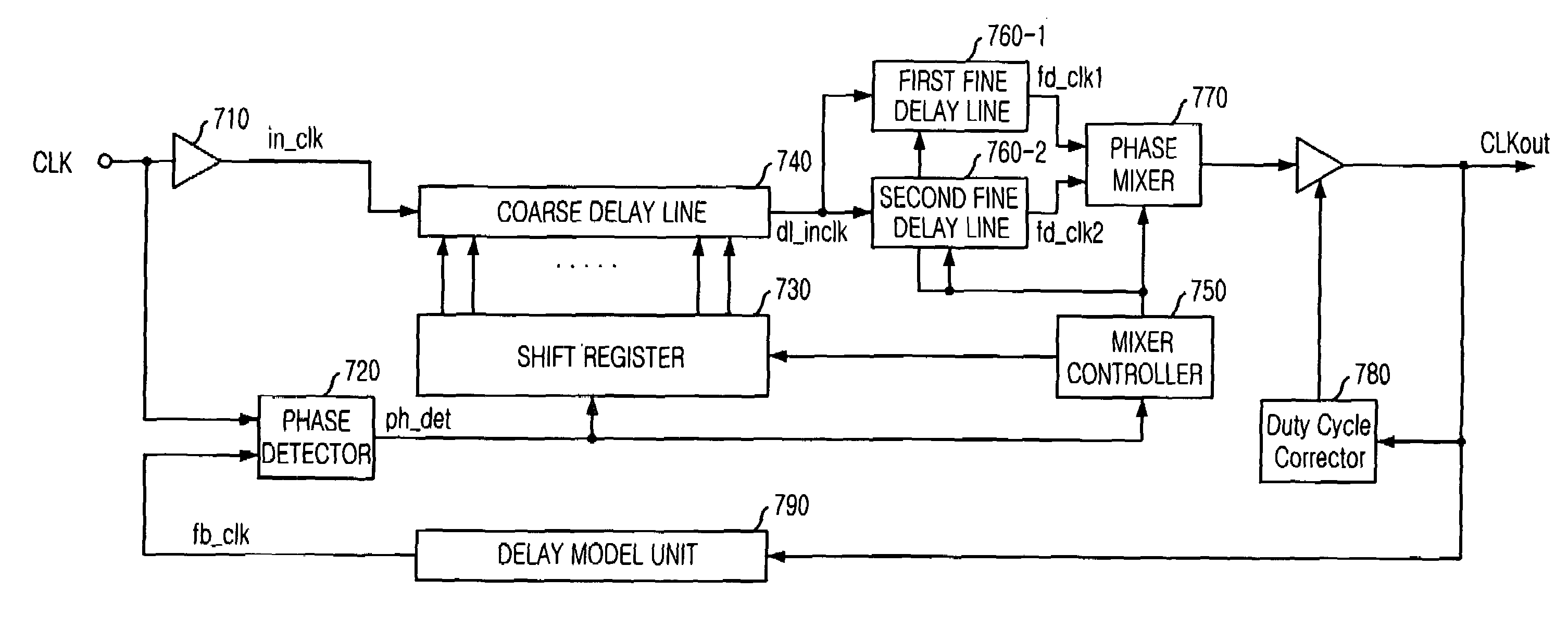

Register controlled delay locked loop and its control method

A register controlled delay locked loop (DLL), including: a coarse delay line for generating a delayed input clock signal by delaying an external clock signal; a fine delay line unit for receiving the delayed input clock signal in order to generate a first fine delayed clock signal and a second fine delayed clock signal; a phase detector for comparing phases of the external clock signal and a feed-backed clock signal in order to generate a phase detection signal based on the comparison result; a phase mixer for generating a mixed clock signal by mixing phases of the first fine delayed clock signal and the second fine delayed clock signal based on a weight value; and a mixer controller for generating the weight value based on the phase detection signal.

Owner:SK HYNIX INC

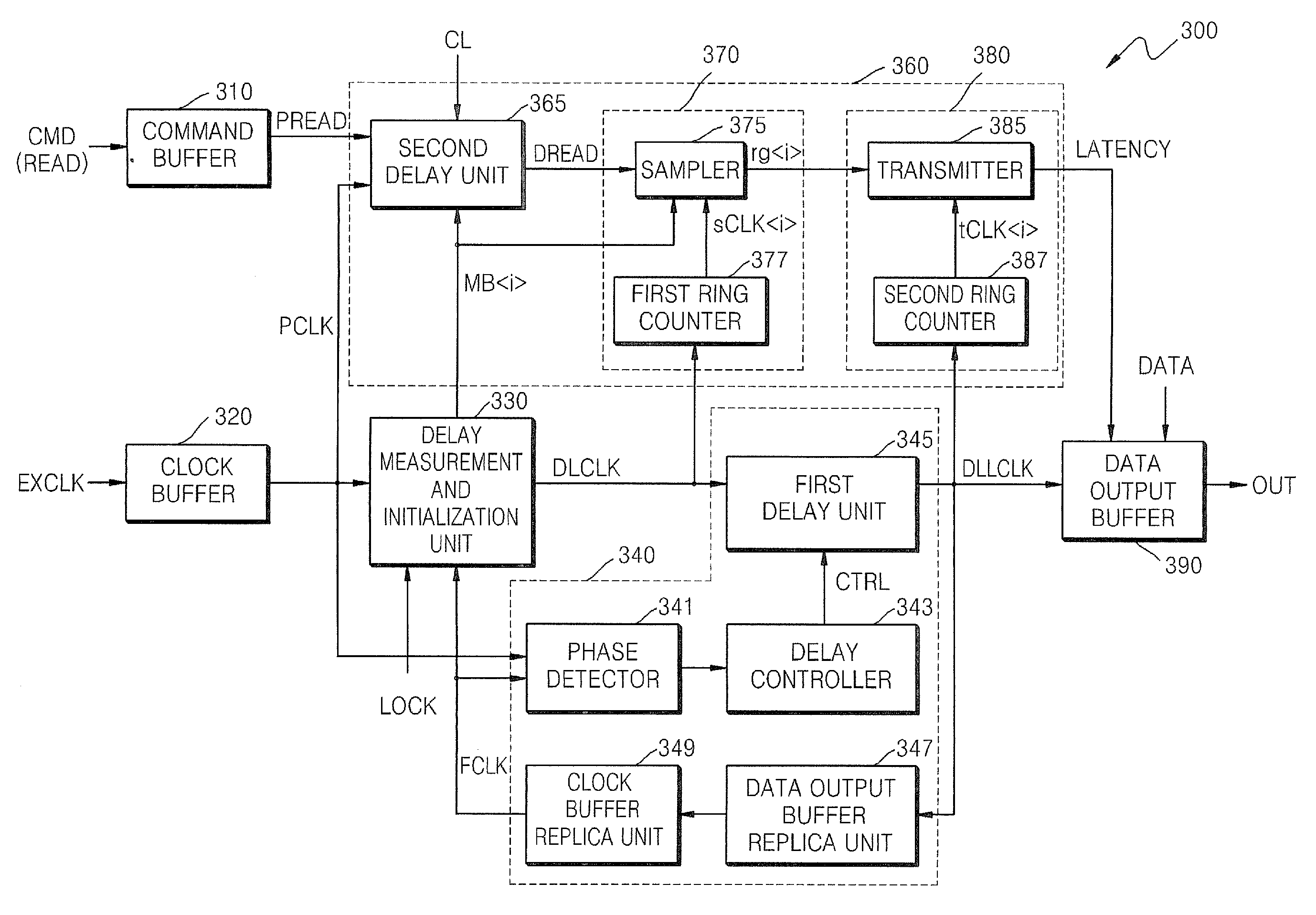

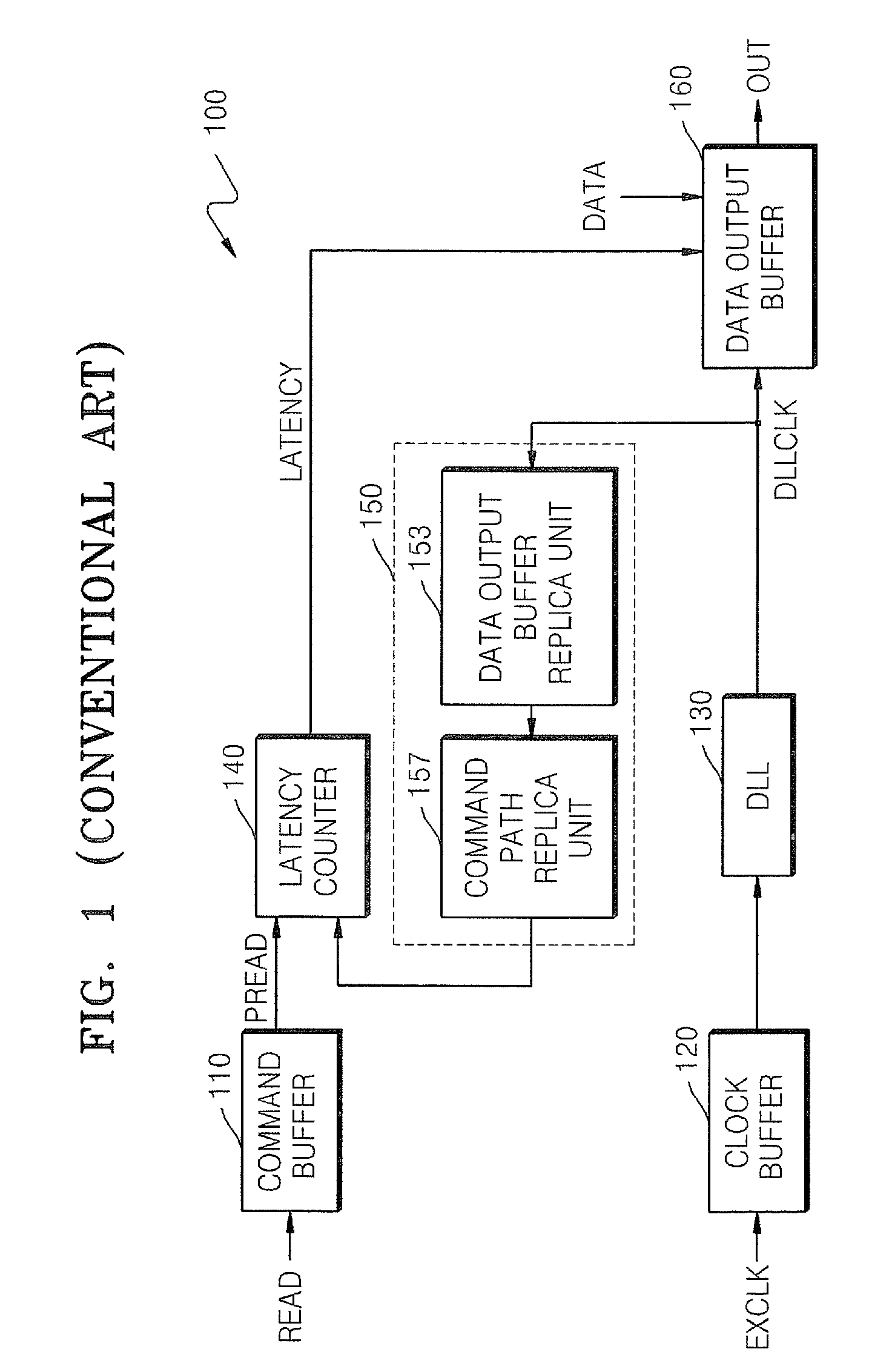

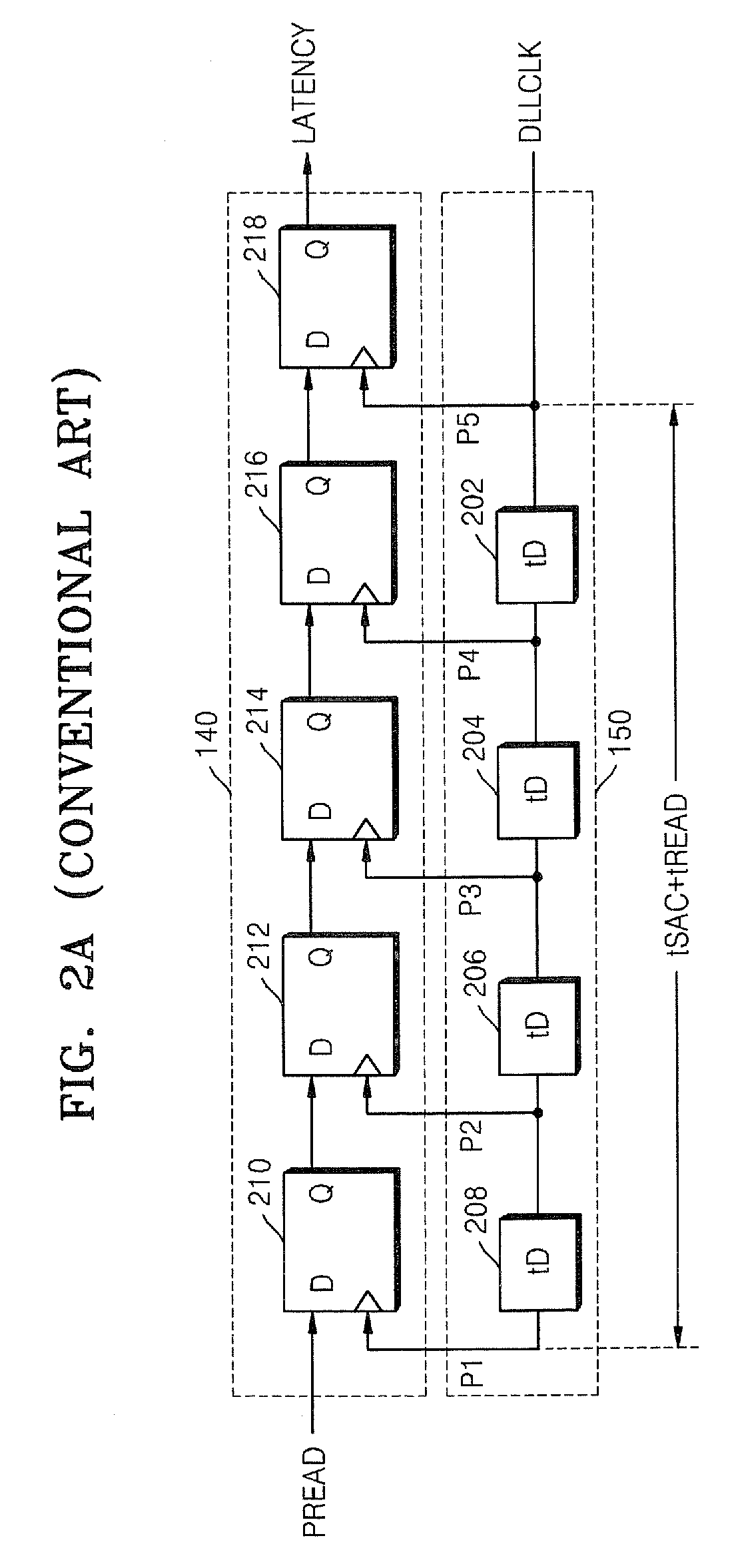

Semiconductor memory devices for controlling latency

A semiconductor memory device includes a command buffer that receives an external command and outputs a first command signal, a clock buffer that receives an external clock signal and outputs a first internal clock signal, a delay measurement and initialization unit that receives the first internal clock signal and a fourth internal clock signal and responsively outputs a second internal clock signal and a plurality of delayed signals corresponding to a delay time between when the external clock signal is input and data is output, a delay locked loop that receives the second internal clock signal and outputs a third internal clock signal and the fourth internal clock signal, a latency signal generation unit that delays the first command signal by a delay time between when the second internal clock signal is input to the delay locked loop and when the third internal clock signal is output from the delay locked loop, and then outputs the delayed first command signal as a latency signal, in response to the second and third internal clock signals and the delayed signals, and a data output buffer that outputs the data in response to the latency signal and the third internal clock signal.

Owner:SAMSUNG ELECTRONICS CO LTD

DLL with false lock protector

A system and method are disclosed for providing a DLL with false lock protector to avoid false lock and ensure accurate lock. The false lock protector operates when the initial delay time between signals from an input reference clock and an output clock exceeds the lock range during operation of the DLL. The DLL with false lock protector includes a reference clock, a delay line composed of several delay cells connected in series, a phase detector, comparator for comparing phases of signals from the reference and output clocks, a determinator and a controller for controlling the delay of the delay line.

Owner:QUALCOMM INC

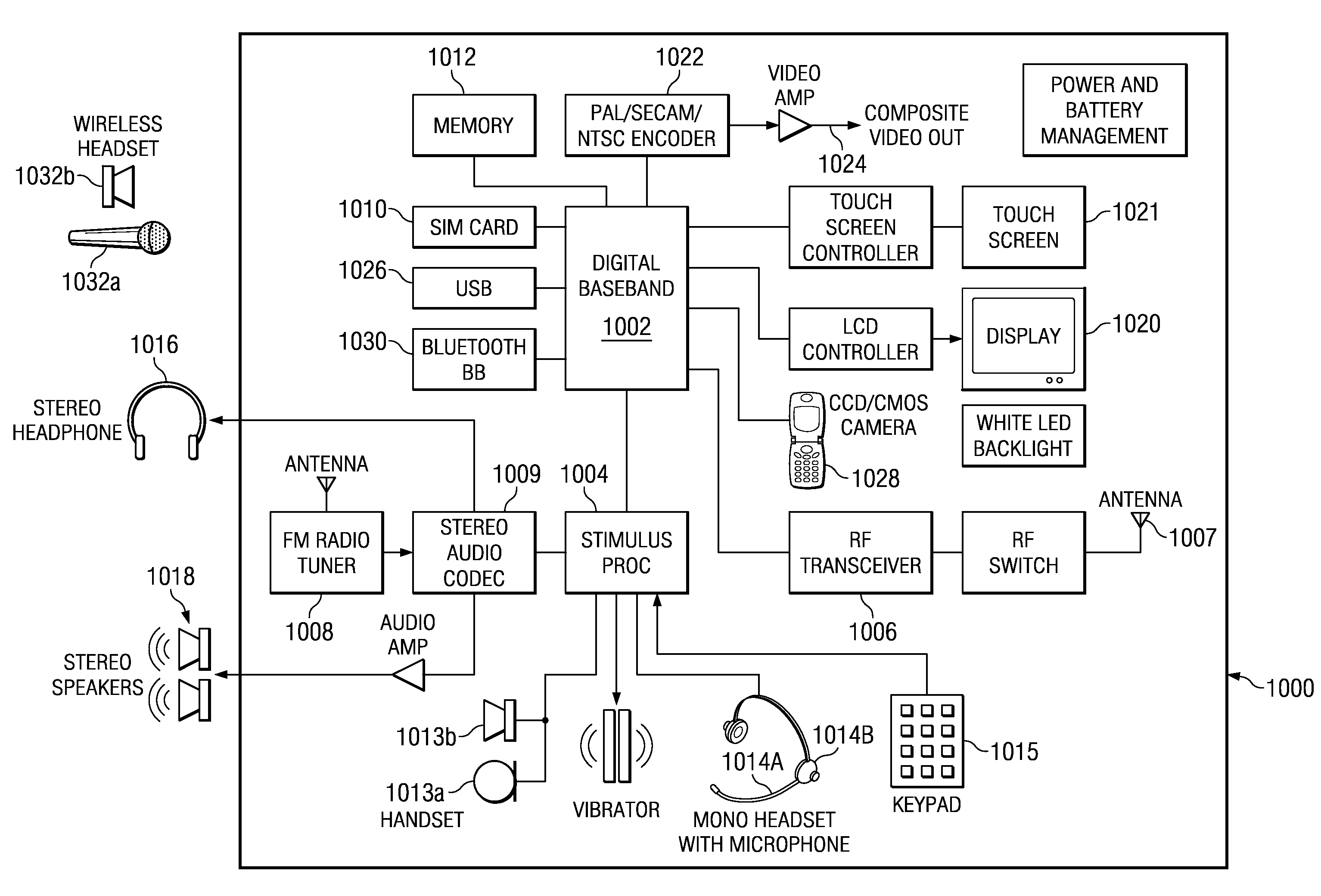

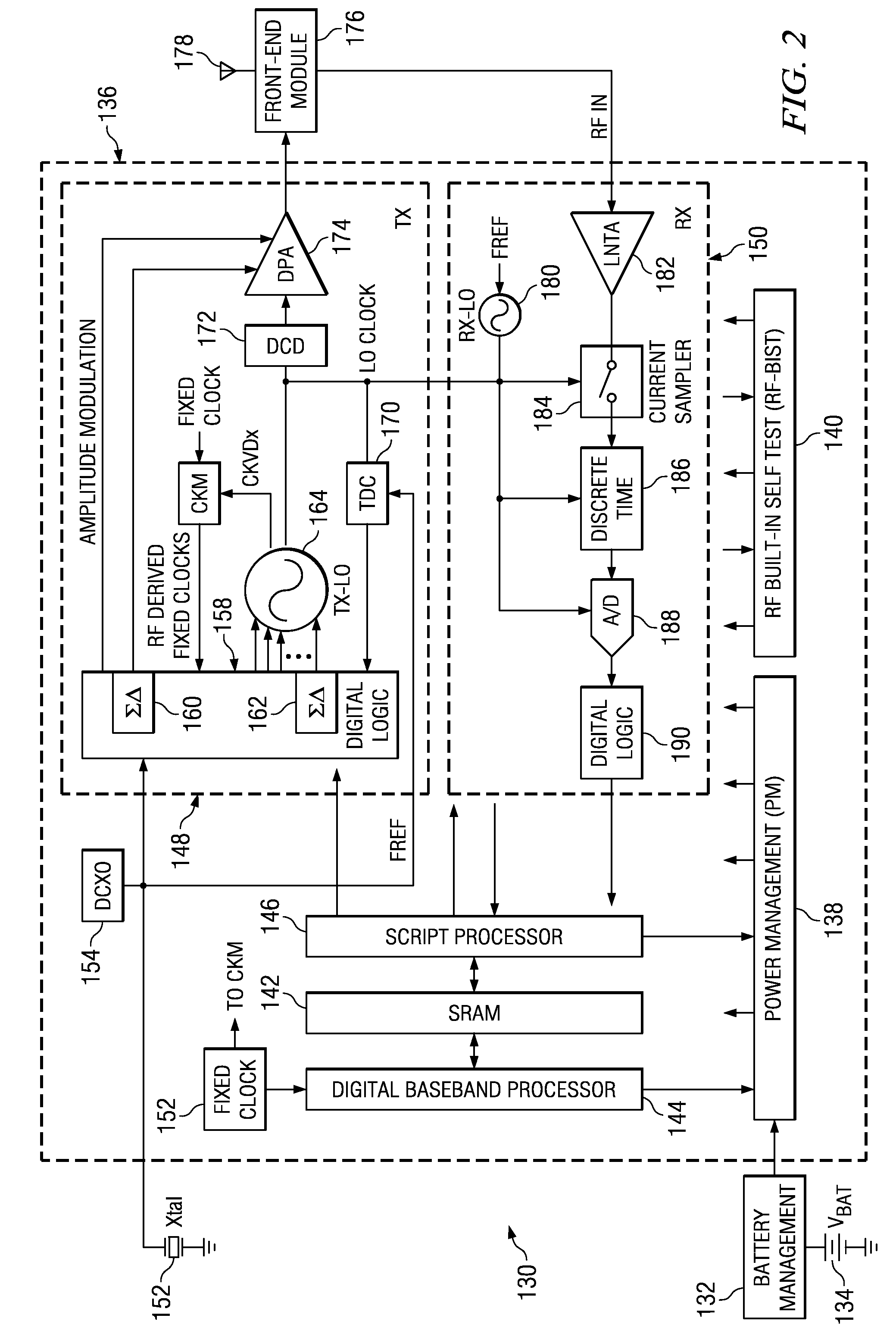

Mitigation of RF Oscillator Pulling through Adjustable Phase Shifting

InactiveUS20100283665A1Wave based measurement systemsSubstation equipmentVibration amplitudeSelf interference

A digitally controlled mechanism for the minimization of the self-interference caused by an amplitude modulated signal generated within a polar transmitter to the oscillator circuit, where the carrier of that transmitter is created. A digitally controlled delay between the circuit where the signal is generated and the circuit where it is amplitude-modulated allows adjustment of the delay or phase-shift between the aggressing and victim signals. The optimal delay that is to be introduced in the path is determined, and a corresponding control word is generated to arrive at the selected delay / phase-shift.

Owner:TEXAS INSTR INC

Method and apparatus to synchronize audio and video

InactiveUS7692724B2Television system detailsColor television signals processingControl delayComputer science

A method and an apparatus to synchronize an audio signal and a video signal. The method includes: displaying video on a screen that corresponds to an audio signal including a high frequency component having a predetermined pattern inserted therein to indicate when a scene change occurs in a video signal, detecting a scene change in the displayed video and detecting the high frequency component having the predetermined pattern in the audio signal, calculating a time difference between a time when the scene change is detected in the displayed video and a time when the high frequency component having the predetermined pattern is detected in the audio signal, and controlling delay times of the audio signal and the video signal according to the calculated time difference. Accordingly, the audio signal and the video signal can be automatically synchronized without performing a separate measuring operation.

Owner:SAMSUNG ELECTRONICS CO LTD

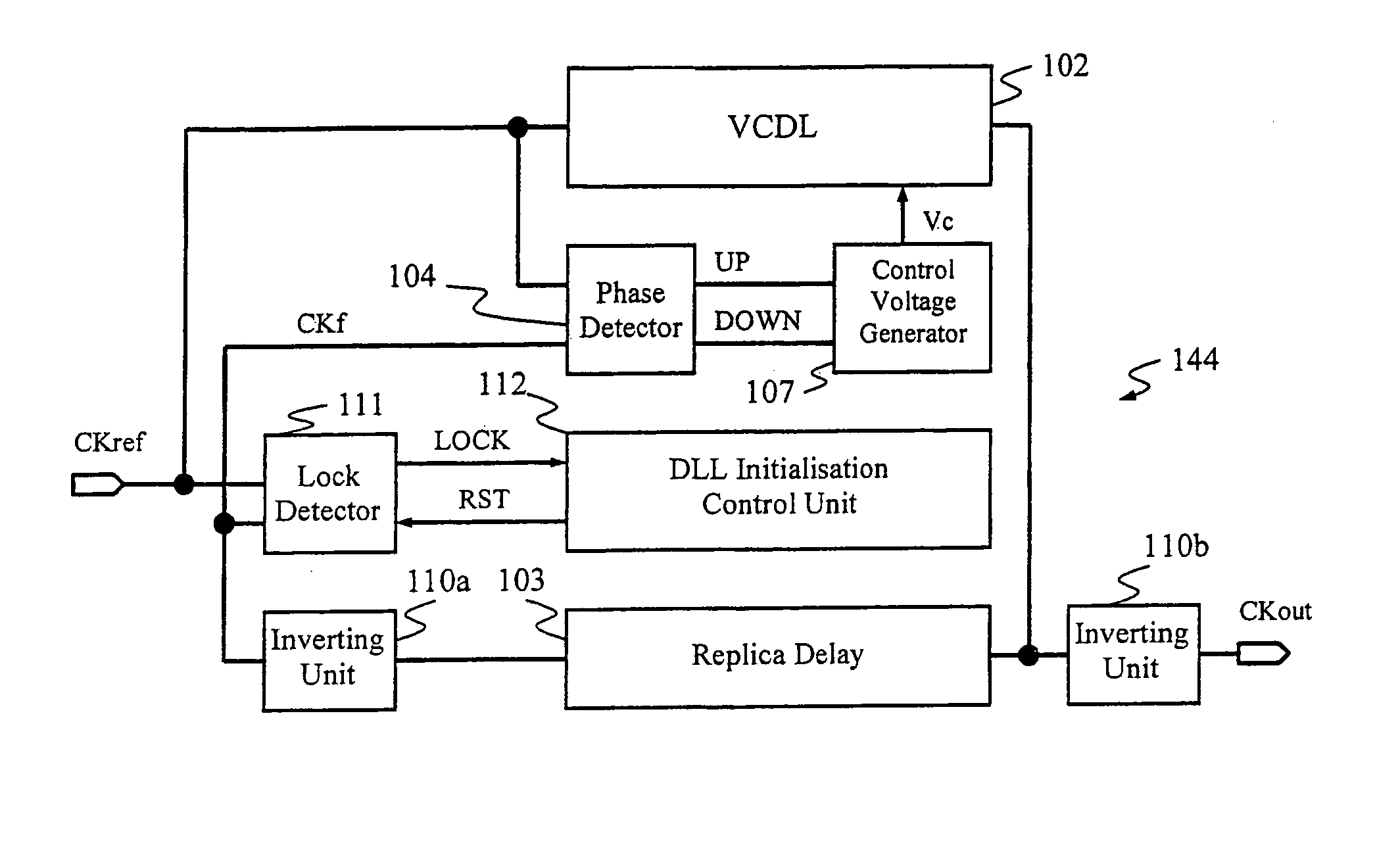

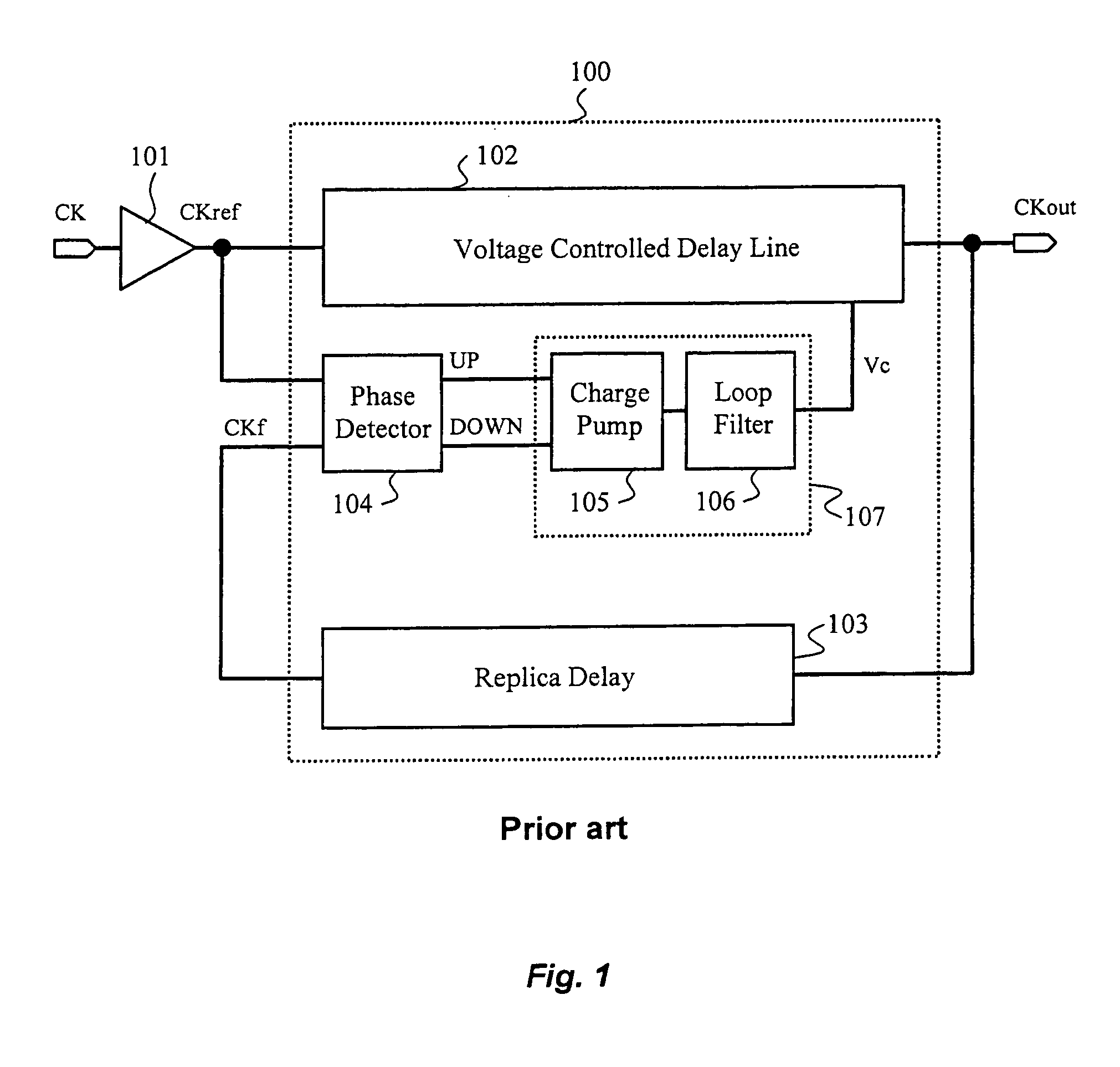

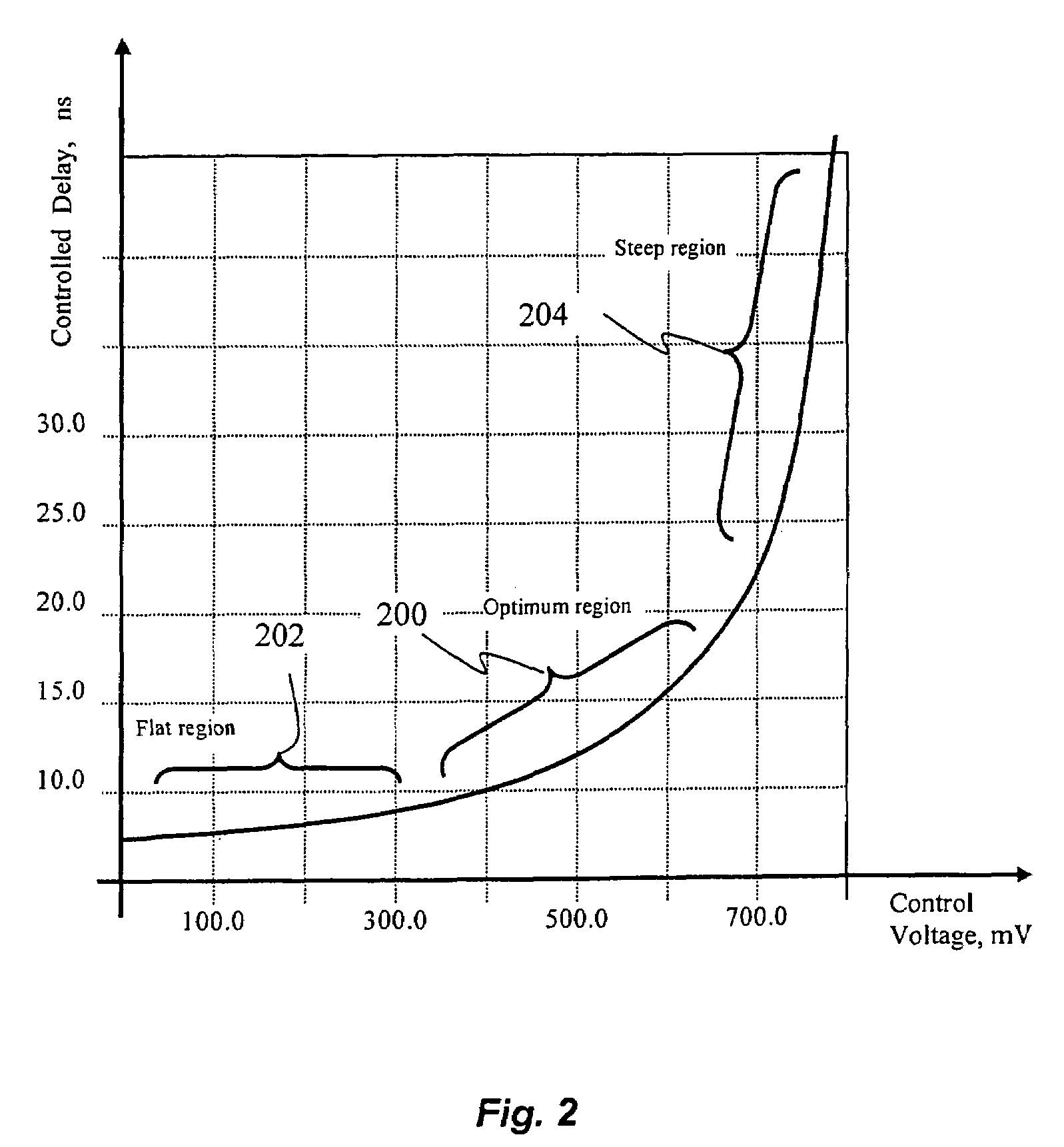

Method and apparatus for initializing a delay locked loop

ActiveUS7190201B2Improve performanceMinimize the numberPulse automatic controlOperating pointDelay-locked loop

A delay locked loop includes initialization circuitry that ensures that a DLL is initialized to an operating point that is not to close to either end of a delay vs. control voltage characteristic. The initialization circuitry forces the DLL to initially search for a lock point starting from an initial delay, the delay is varied in one direction, forcing the DLL to skip the first lock point. The initialization circuitry only allows the DLL to vary the delay of the voltage controlled delay loop in the one direction from the initial delay until the operating point is reached.

Owner:MOSAID TECH