Patents

Literature

52 results about "Digital delay locked loop" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

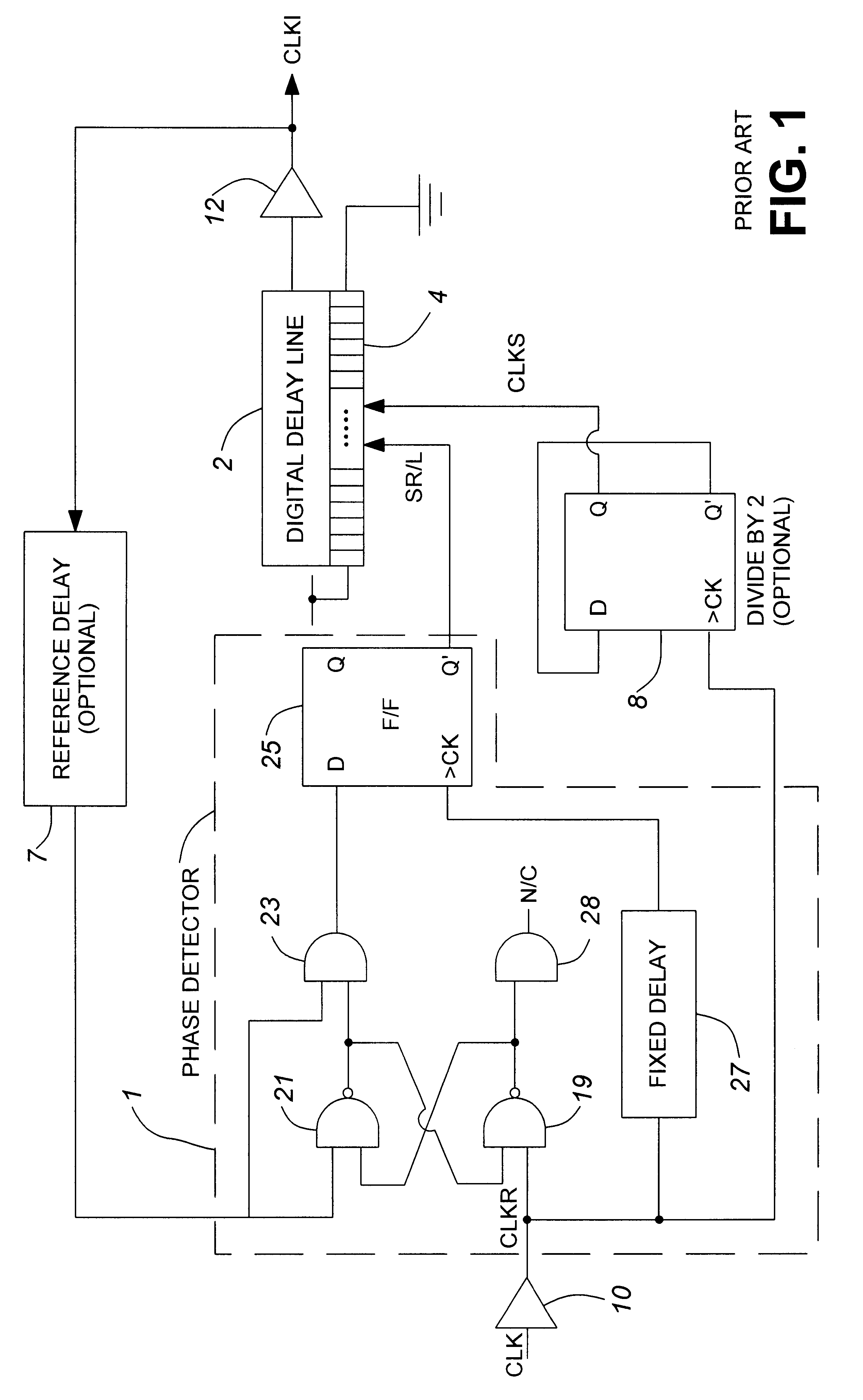

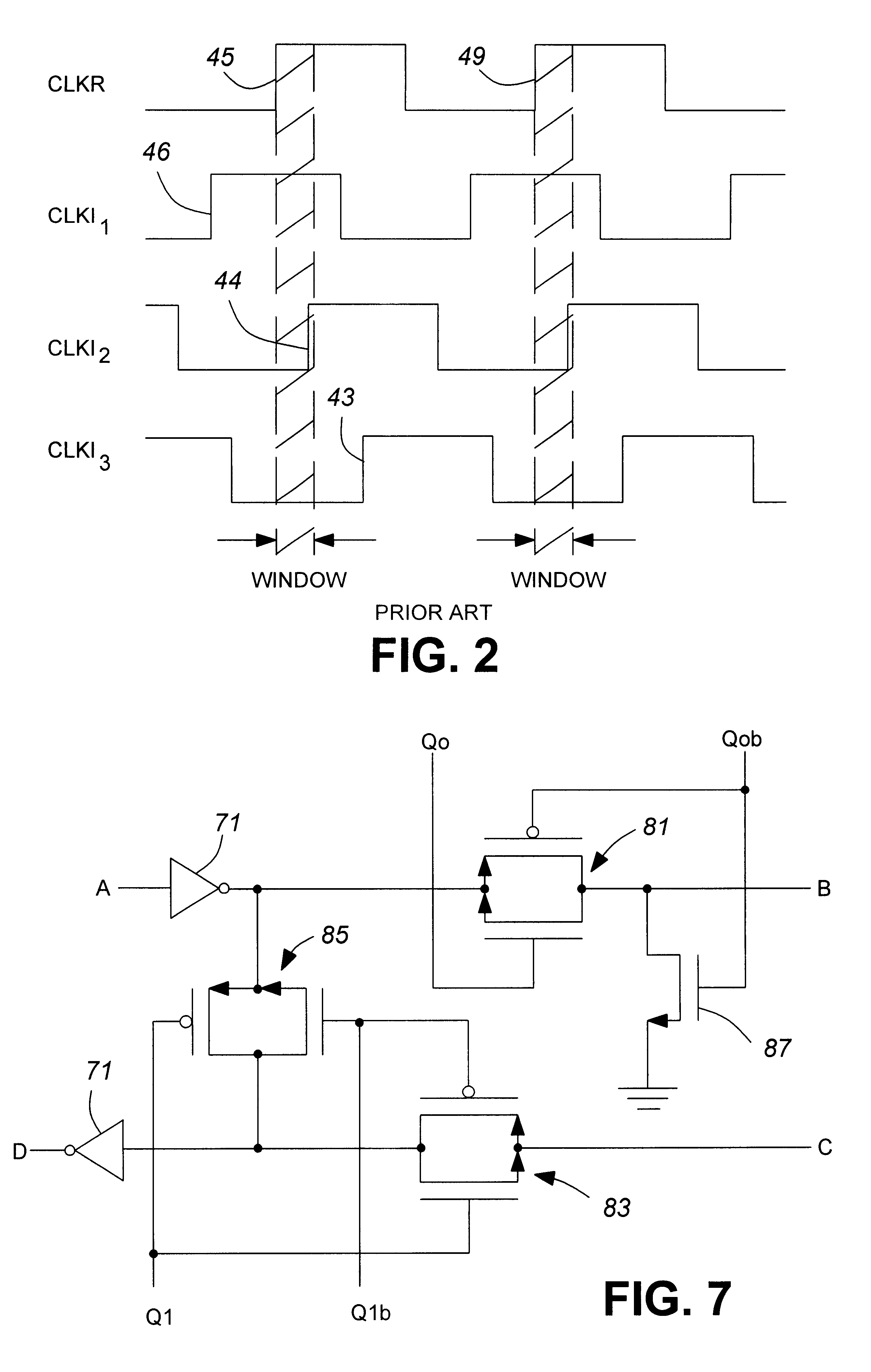

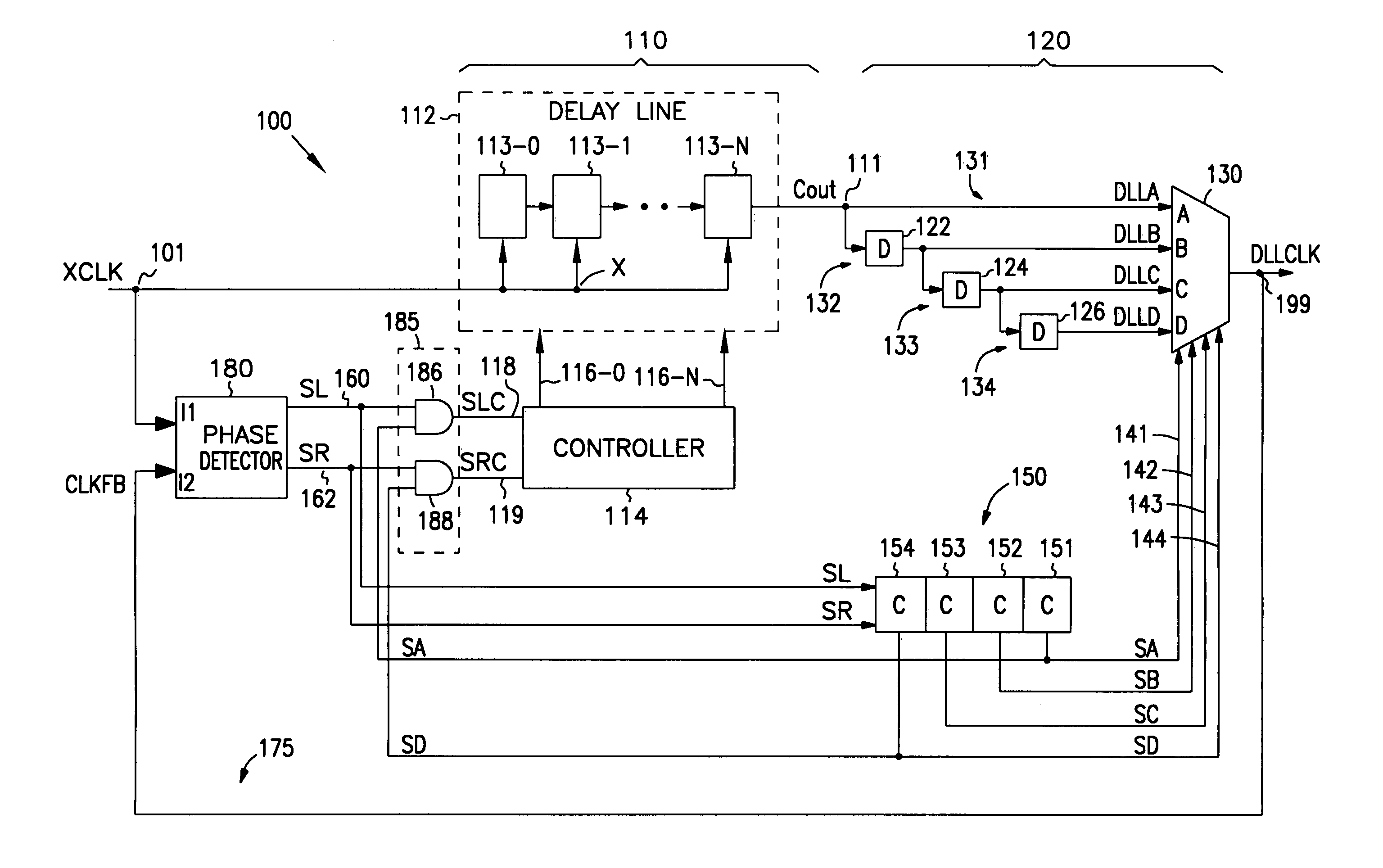

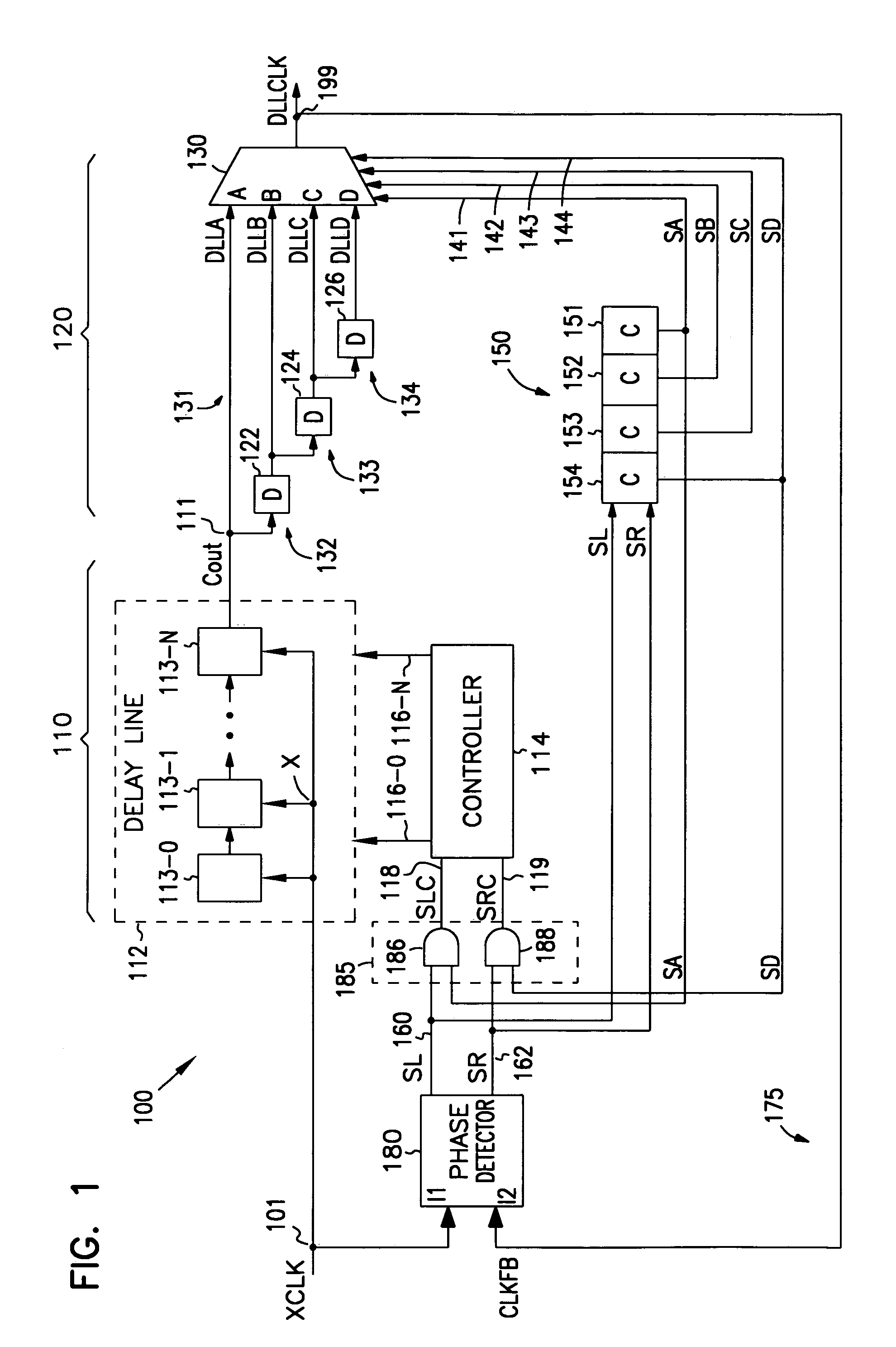

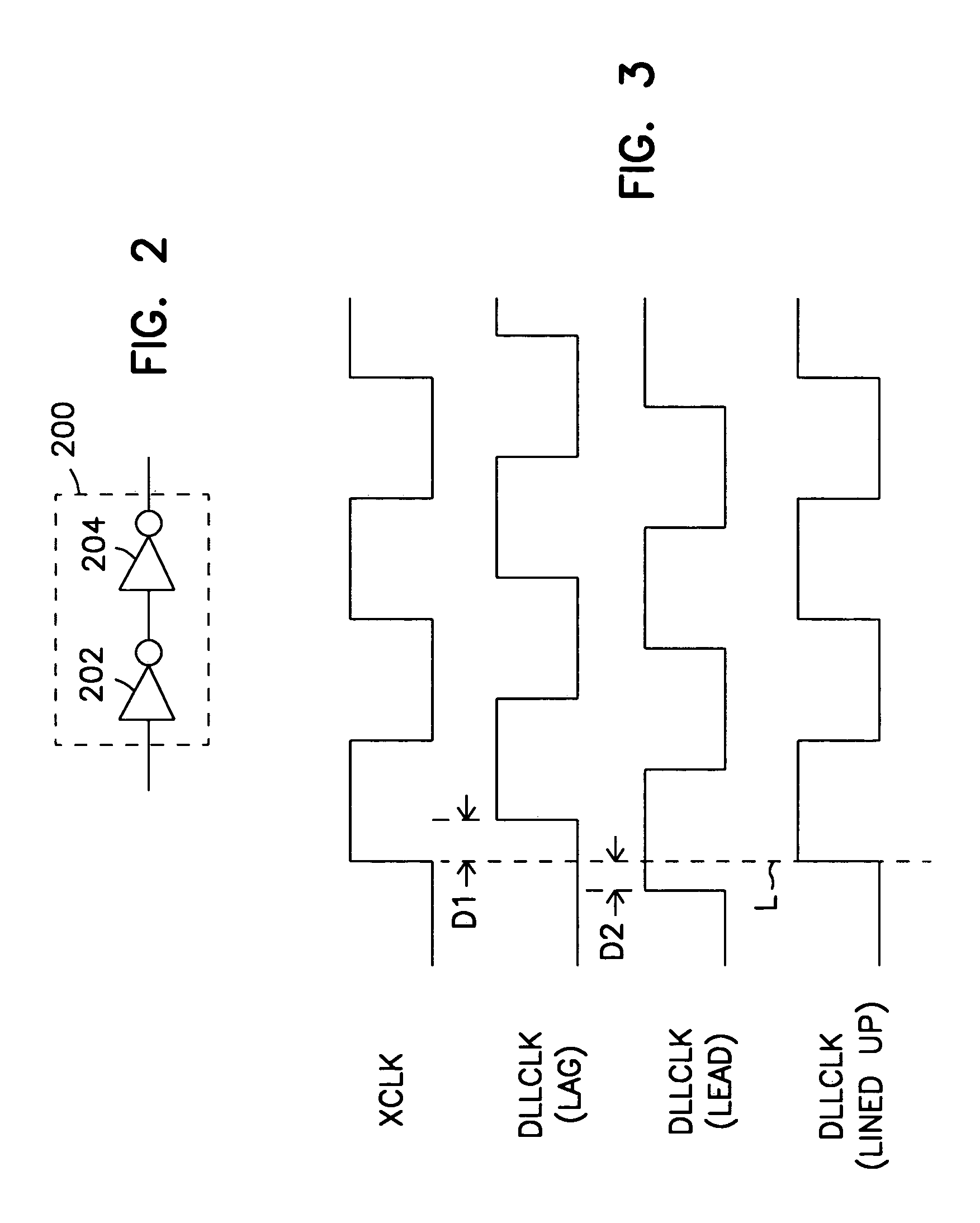

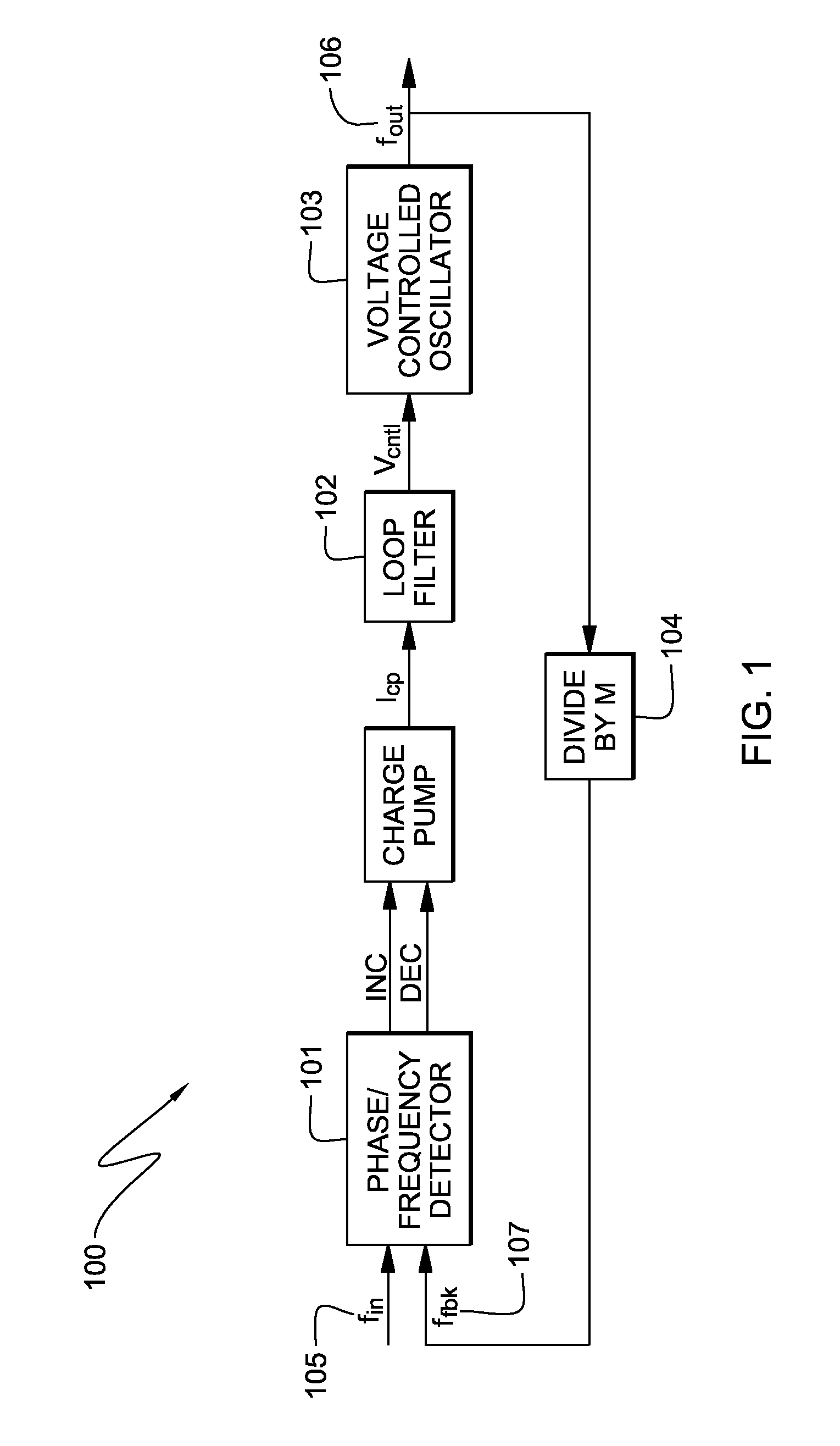

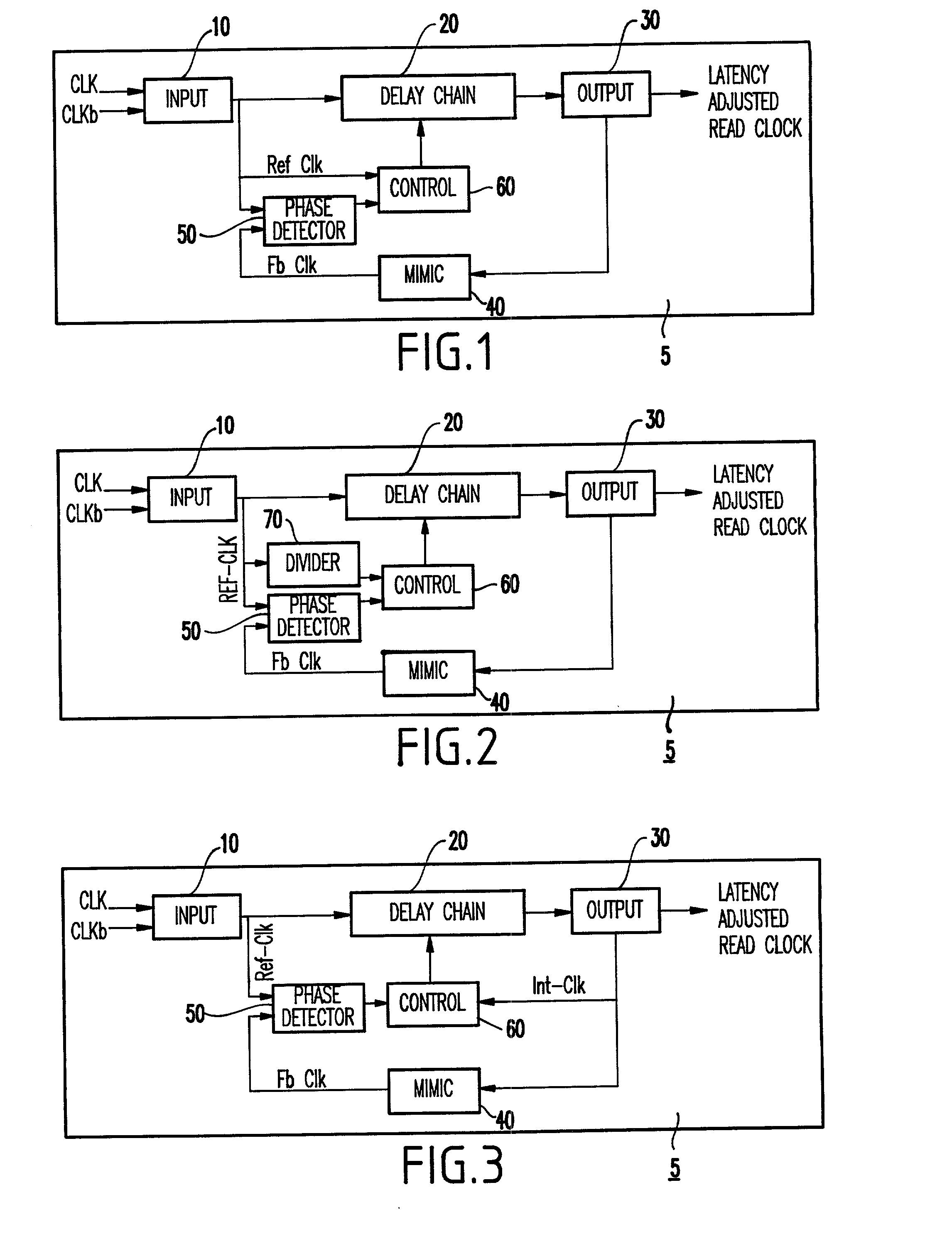

Digital delay locked loop

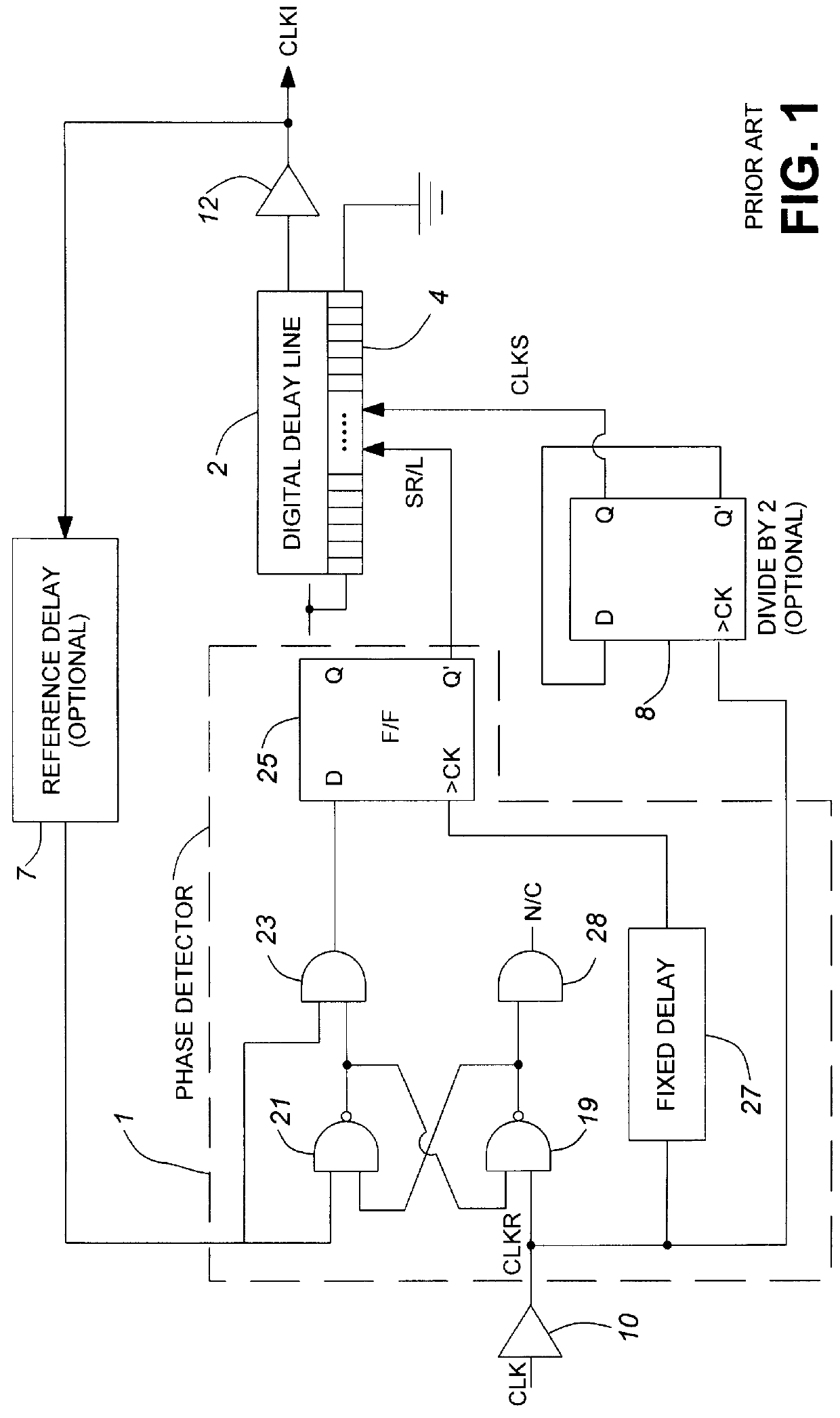

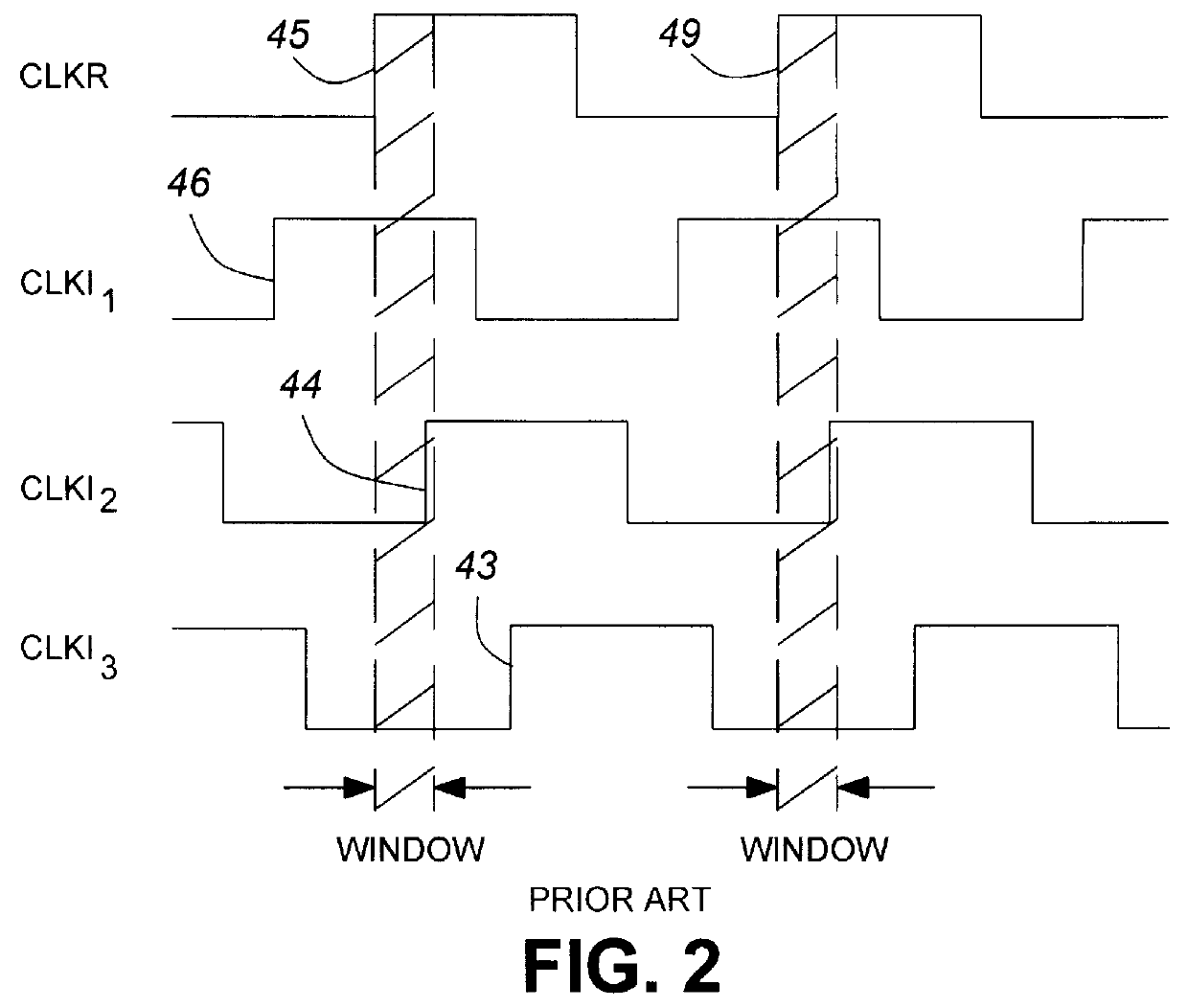

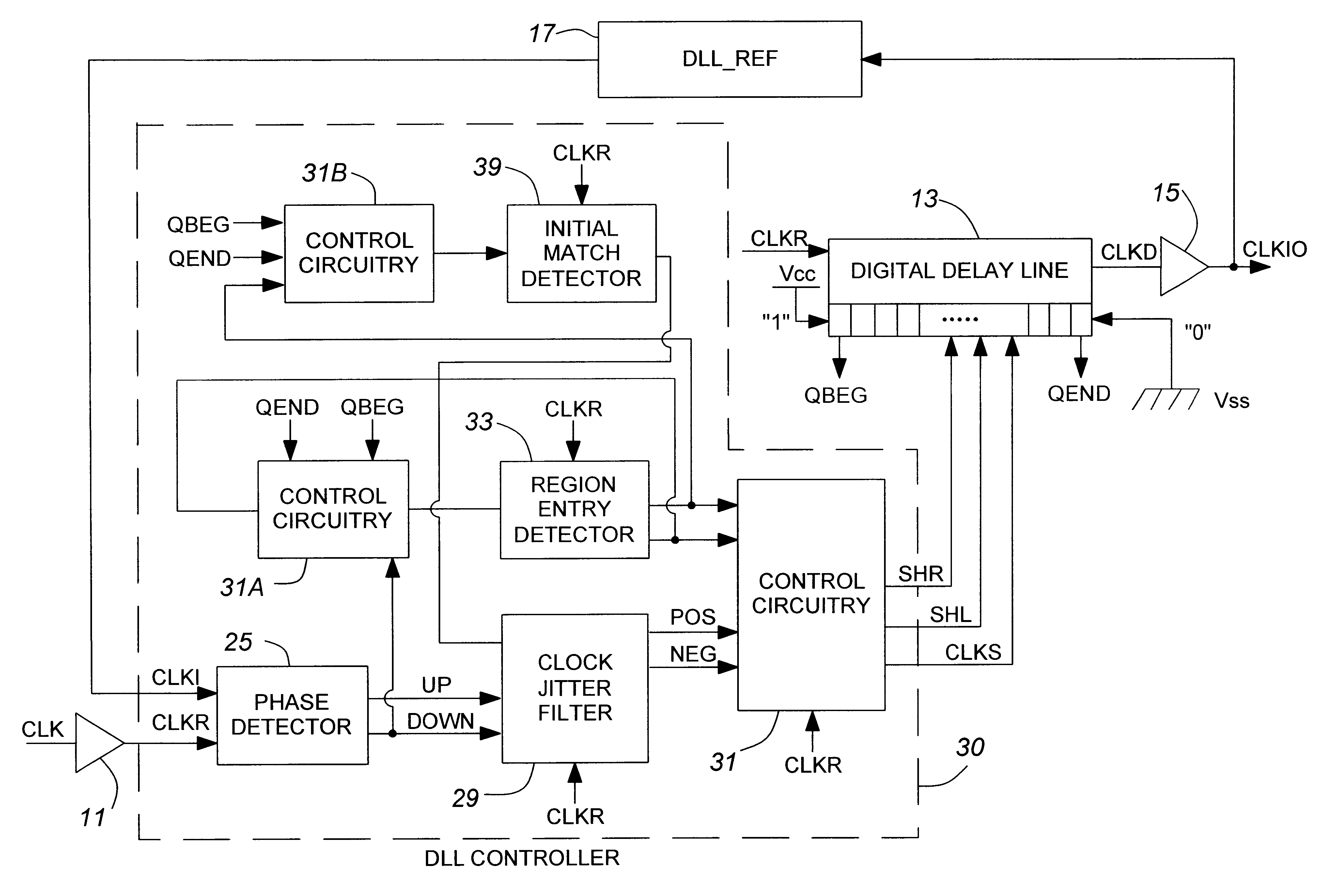

An improved edge-triggered fully digital delay locked loop (DLL), which maintains reliable synchronization from startup and in spite of system clock jitter is described. An internal clock signal is synchronized with a reference clock signal by propagating the reference clock signal through a variable digital delay path. A wide phase detection region surrounds a selected rising edge of the internal clock signal. The DLL loop is open as long as the internal clock signal and a target edge of the reference clock signal are not simultaneously within the phase detection region. To achieve a DLL locked condition, the variable delay is increased from a minimum setting until the edge of the phase detection region is shifted in time just past the target edge of the reference clock. Once the DLL loop has been closed, a clock jitter filter is enabled to reject reference clock jitter effects on the DLL locked condition. A digital phase detector controls the delay line propagation delay to establish synchronization between the internal clock and the reference clock. Unused delay elements within the variable delay path are deactivated to save power.

Owner:CONVERSANT INTPROP MANAGEMENT INC

Digital delay locked loop

Owner:CONVERSANT INTPROP MANAGEMENT INC

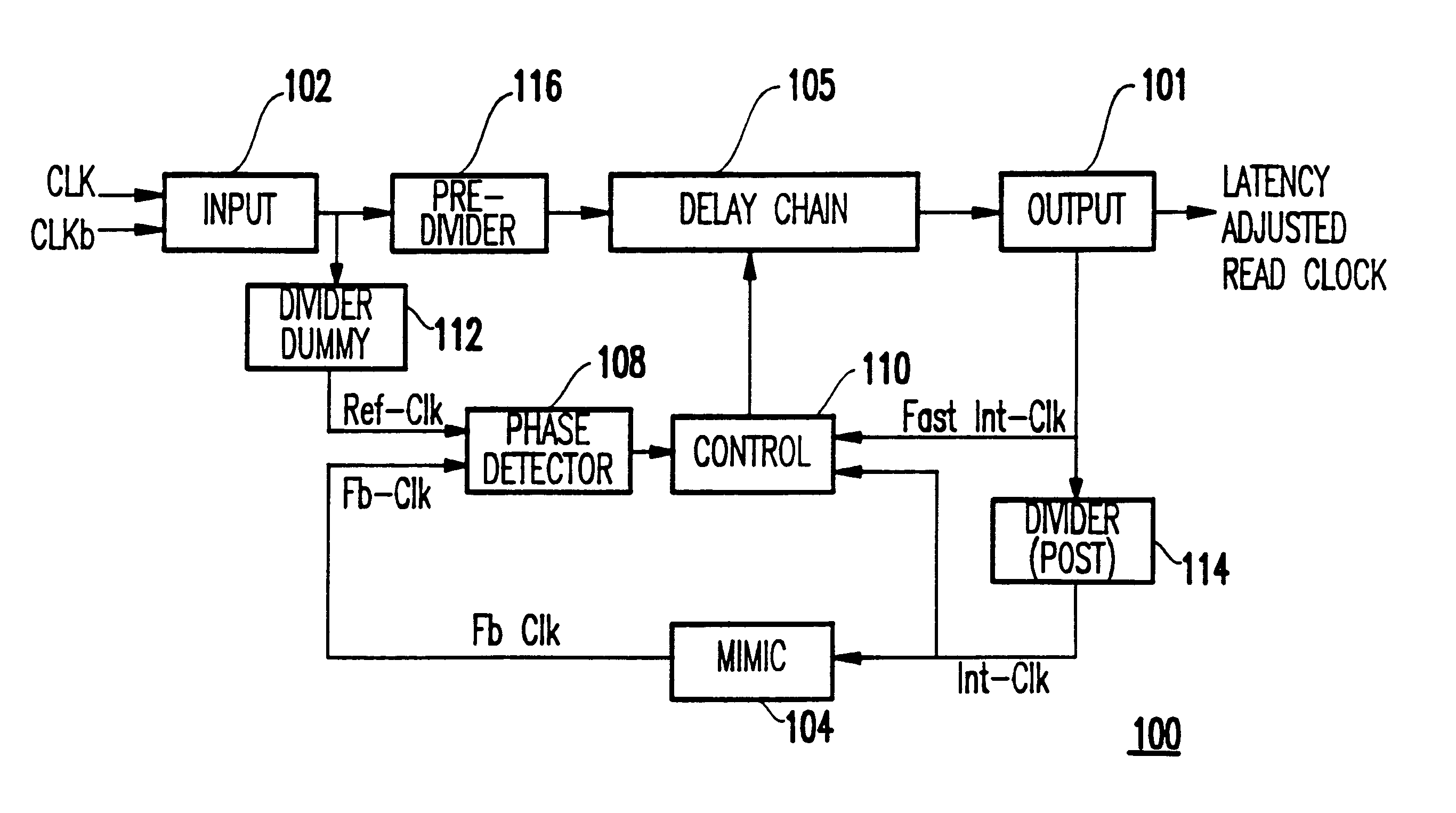

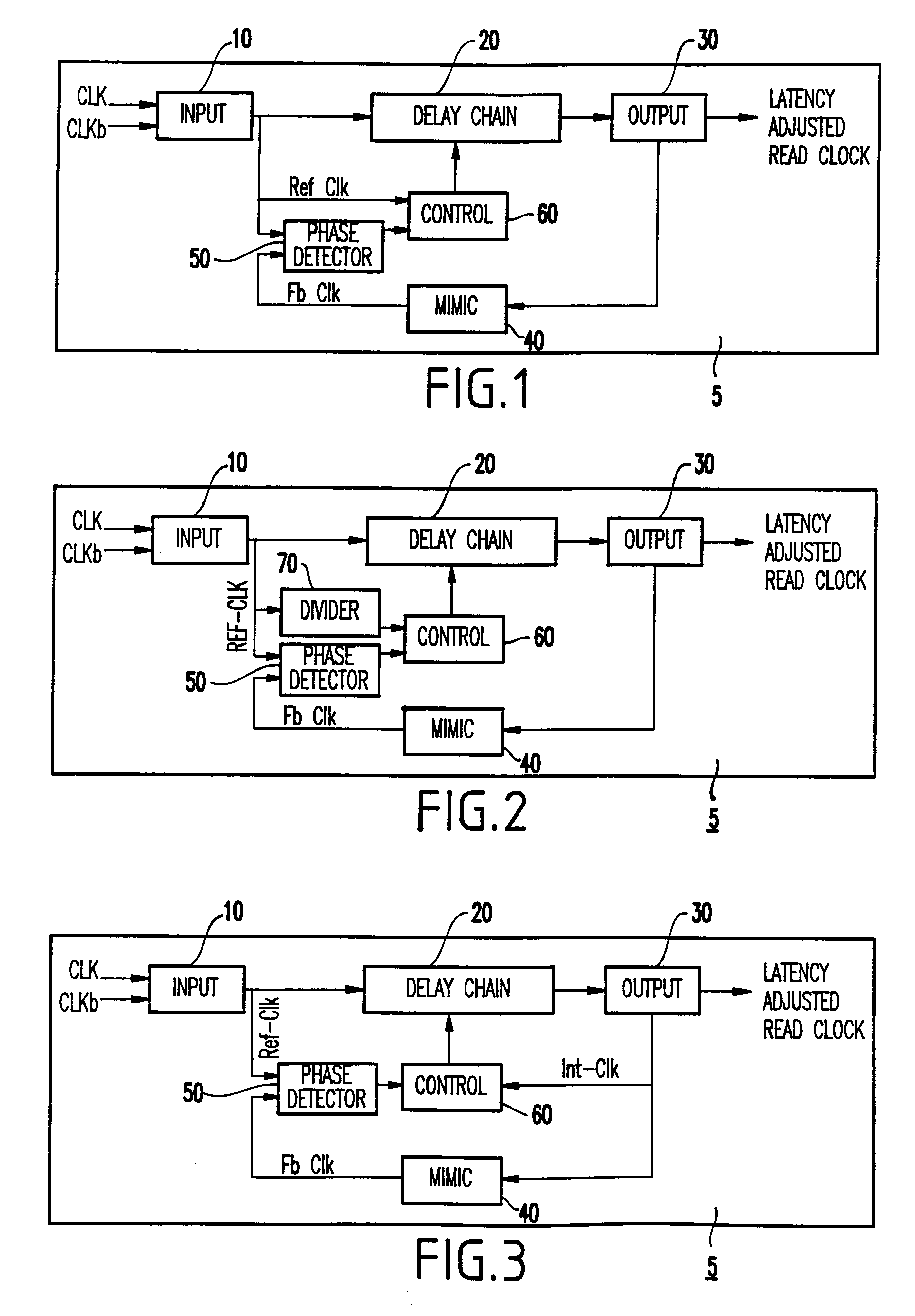

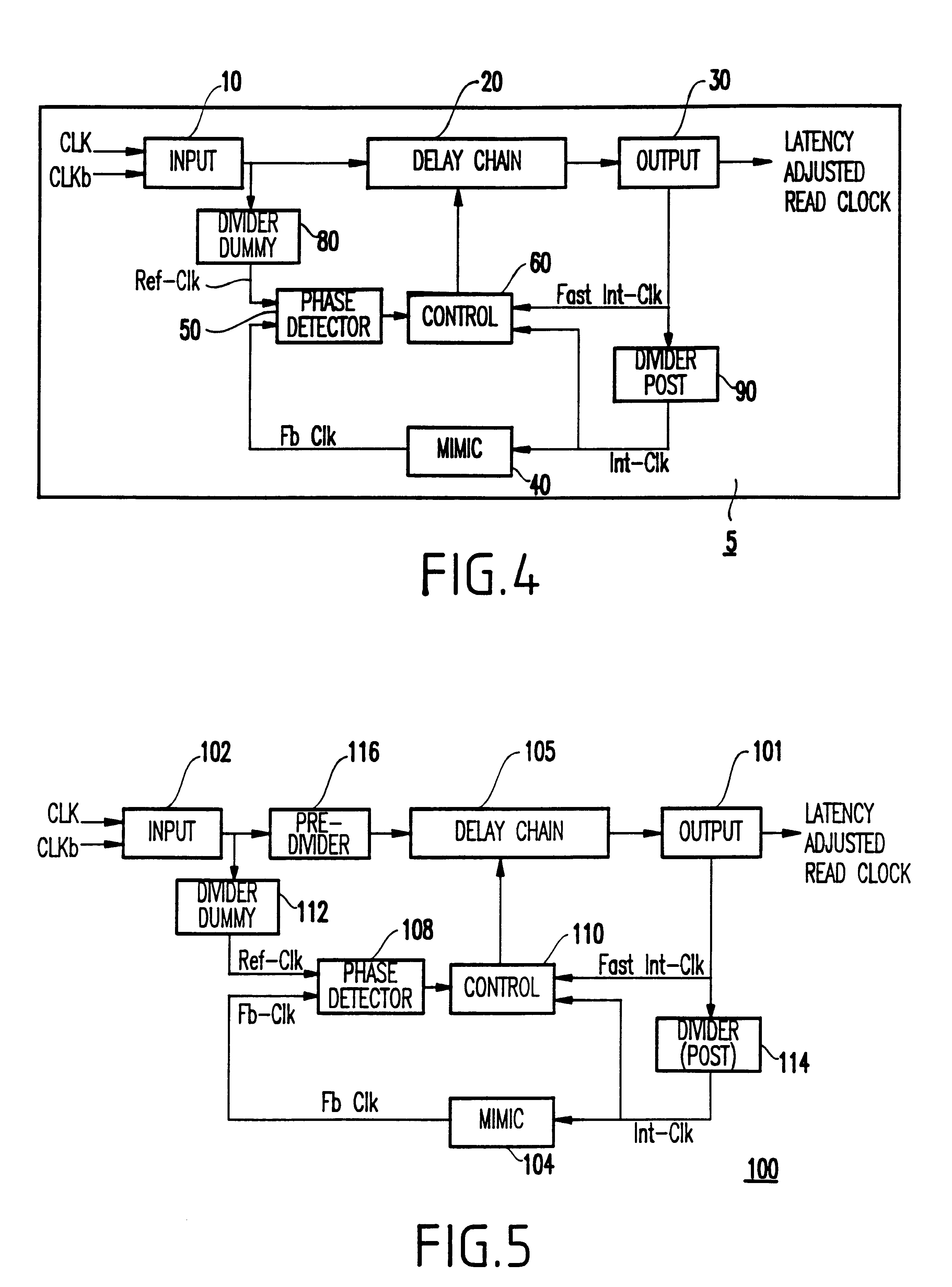

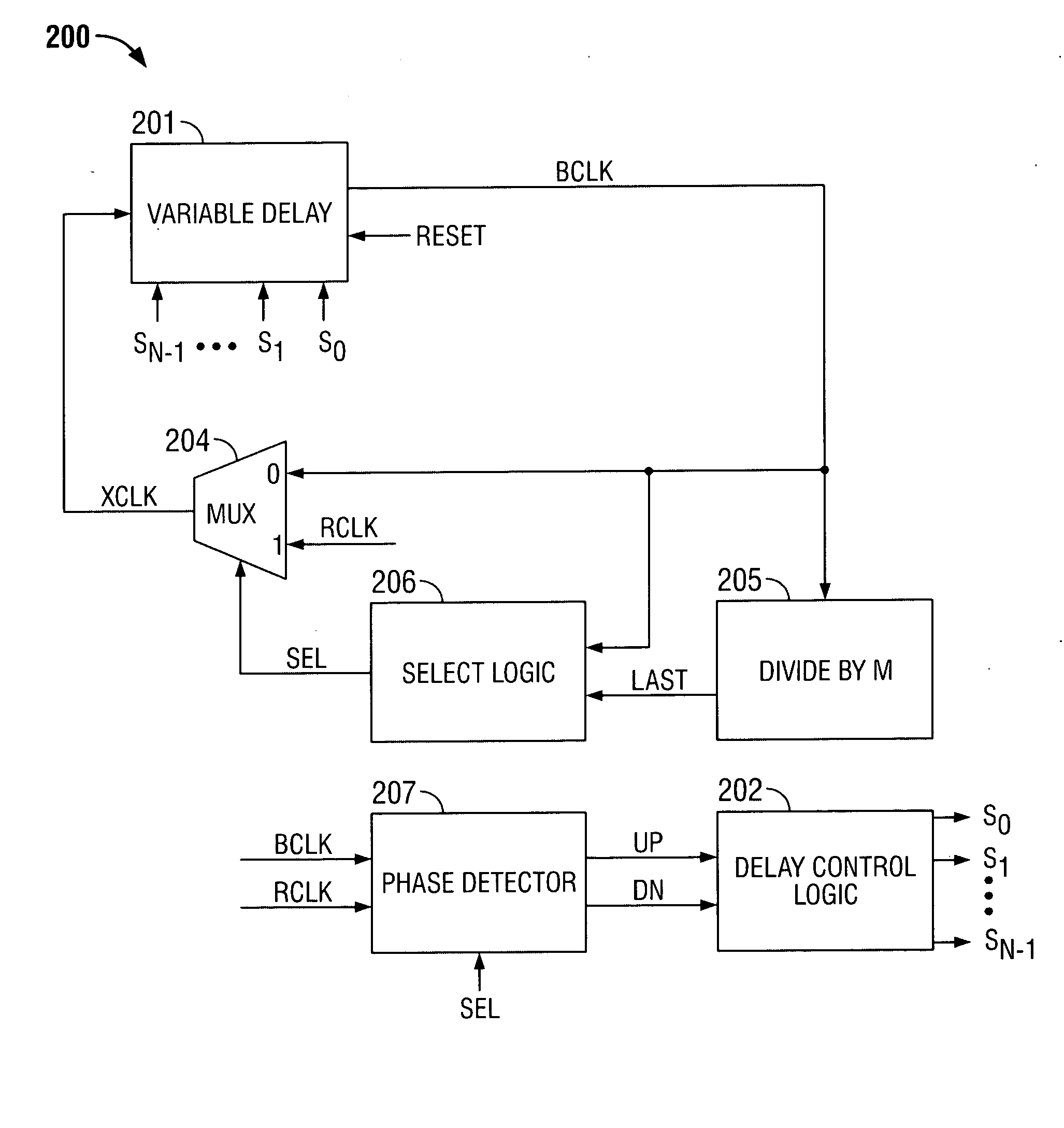

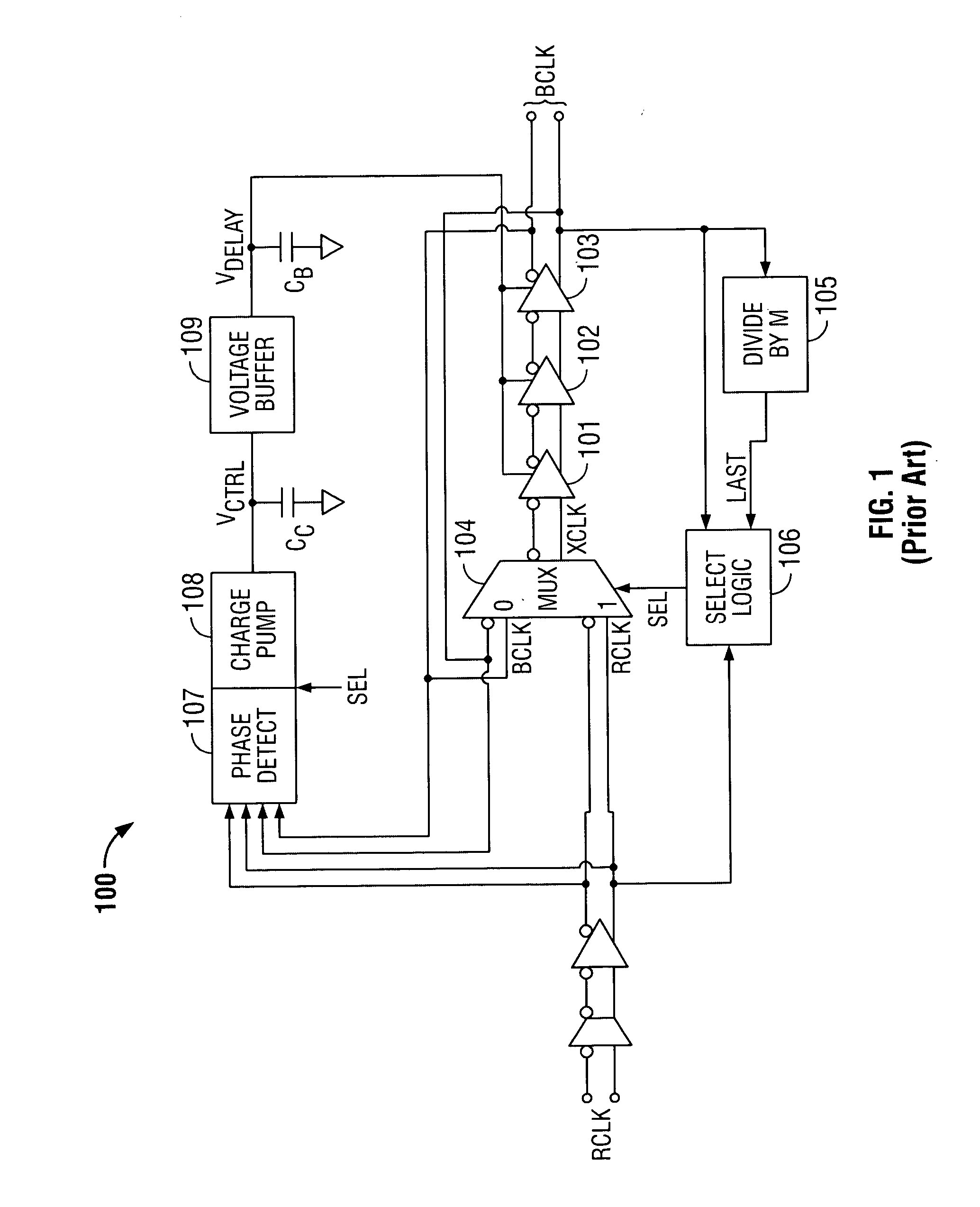

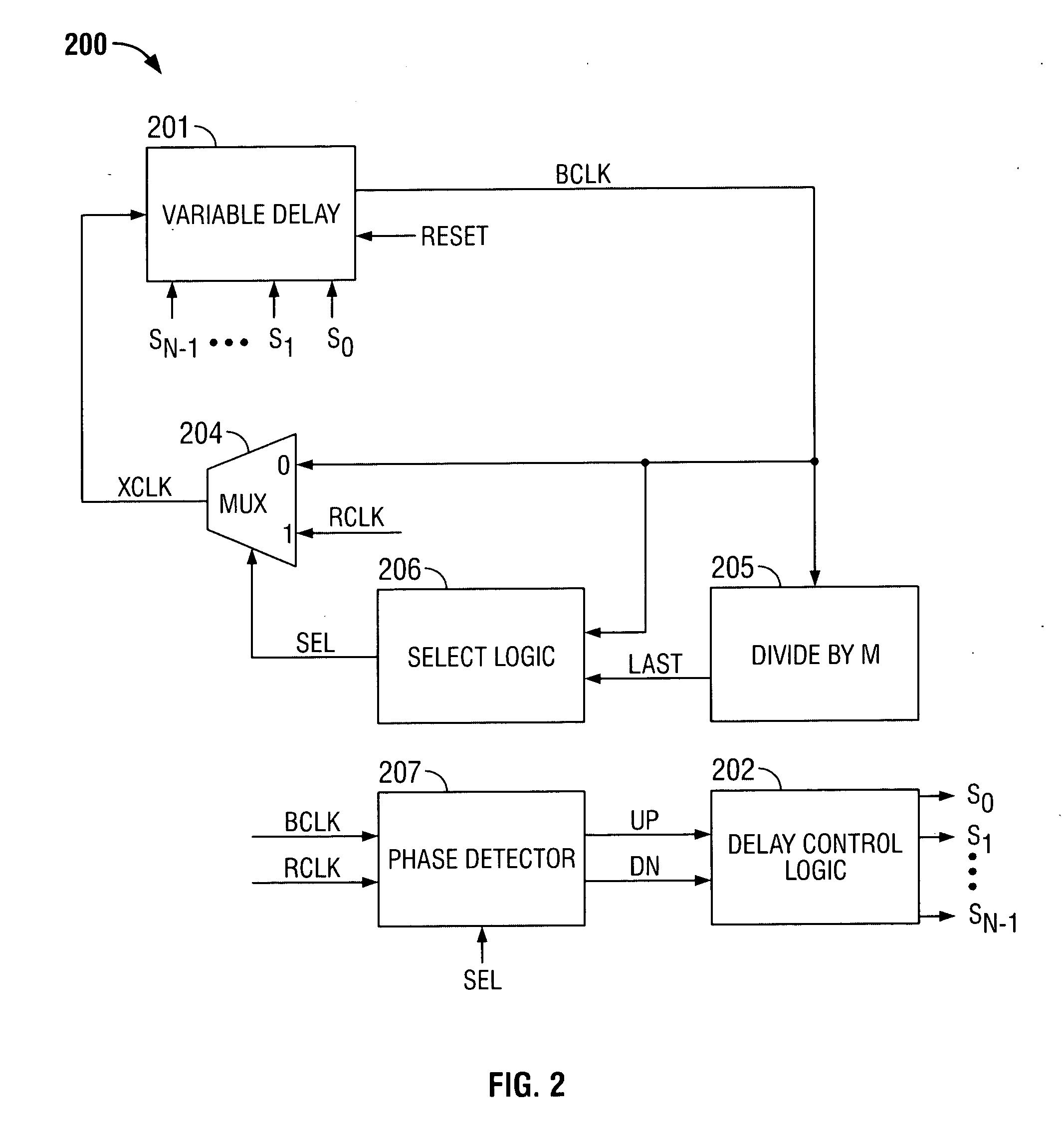

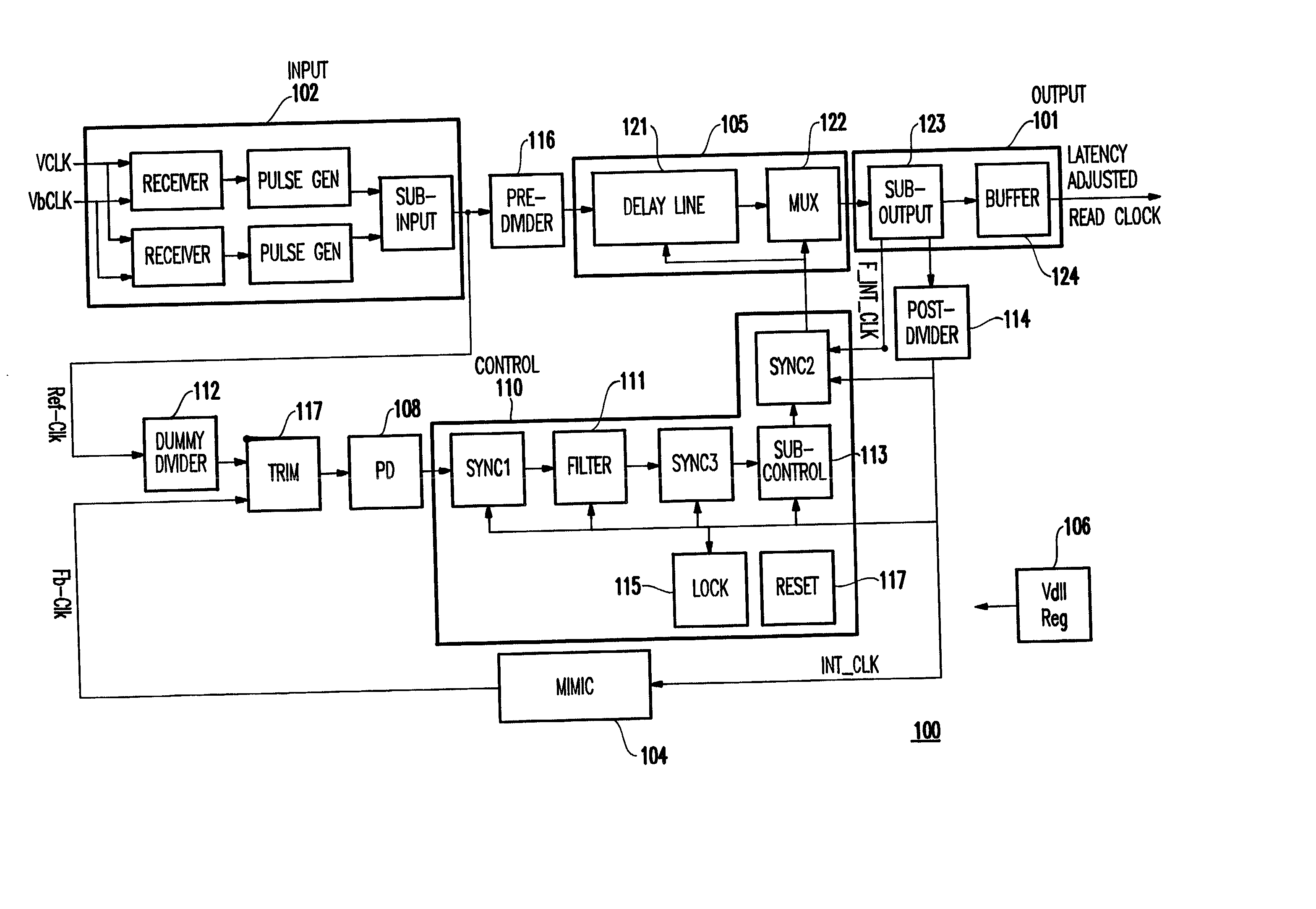

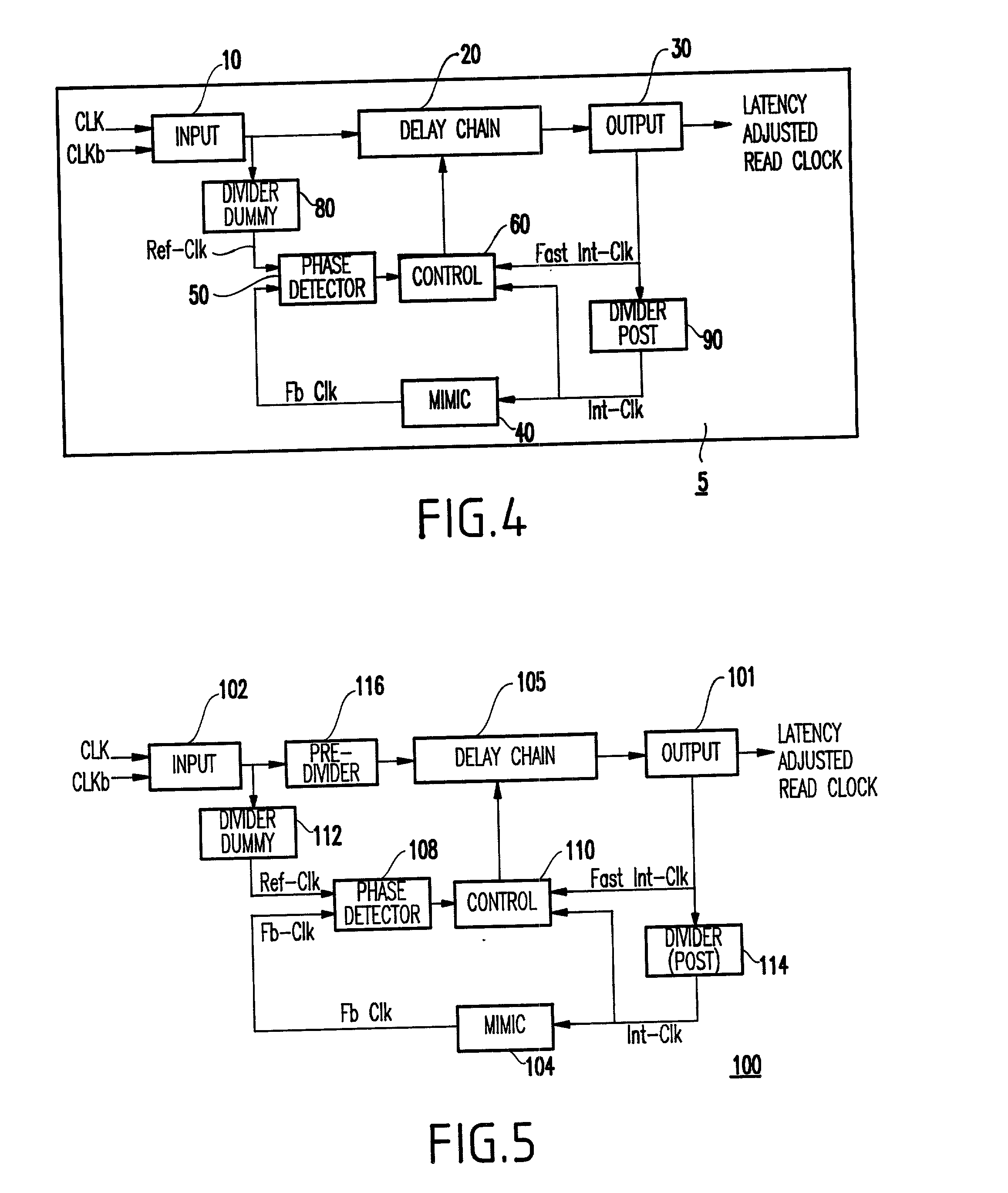

Pre-divider architecture for low power in a digital delay locked loop

InactiveUS6492852B2Pulse automatic controlDigital storageSemiconductor chipDigital delay locked loop

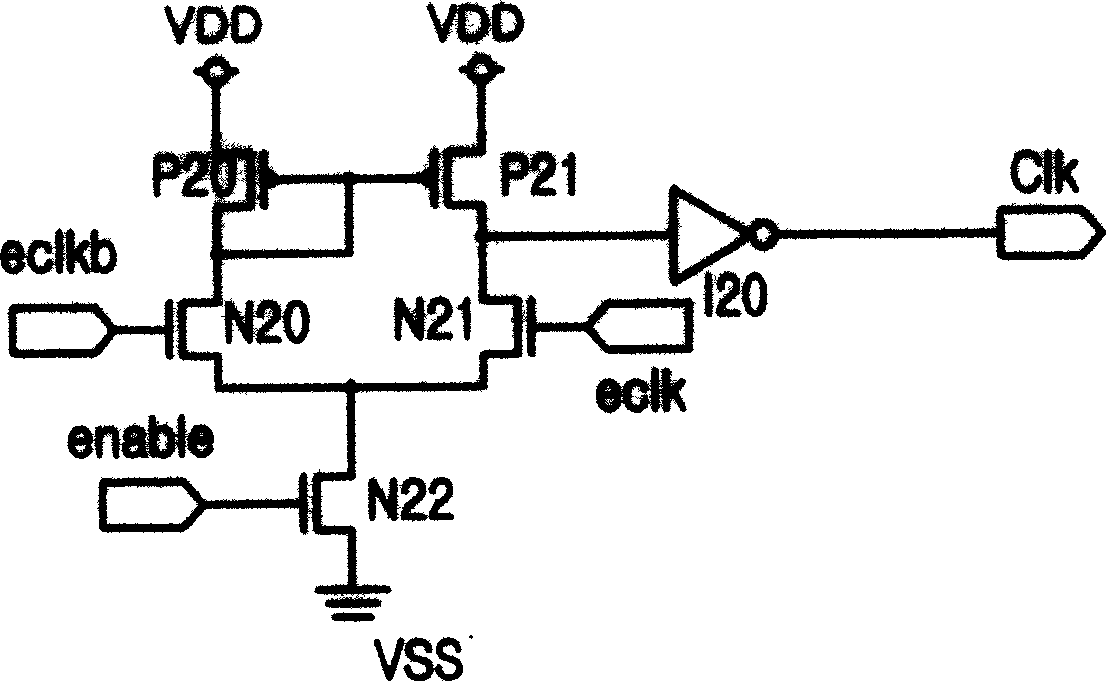

A delay locked loop circuit for conserving power on a semiconductor chip is provided. The circuit includes a delay chain circuit responsive to a clock input signal for generating an output clock signal having a selectively adjustable delay at an output circuit; a feedback loop circuit connects to and controls said delay chain circuit; and a pre-divider circuit connected to said delay chain circuit, wherein said pre-divider circuit is configured to disable the delay chain circuit when the output clock signal is inactive and the memory device is in an idle state (i.e., all banks closed).

Owner:INT BUSINESS MASCH CORP

Delay locked loop fine tune

InactiveUS7072433B2Reduce chanceImprove accuracyPulse automatic controlSingle output arrangementsEngineeringDigital delay locked loop

A digital delay locked loop (DLL) includes a coarse delay segment and fine delay segment. The coarse delay segment includes a coarse delay range. The fine delay segment includes a fine delay range. The coarse delay segment and the fine delay segment apply a coarse delay and a fine delay to an external clock signal to generate an internal clock signal. To keep the external and internal clock signals synchronized, the DLL adjusts the fine delay or coarse delay by increasing or decreasing the fine delay or the coarse delay. The coarse delay is adjusted only when the fine delay is at a minimum or maximum delay of the fine delay range and an increase or decrease in delay is needed respectively.

Owner:ROUND ROCK RES LLC

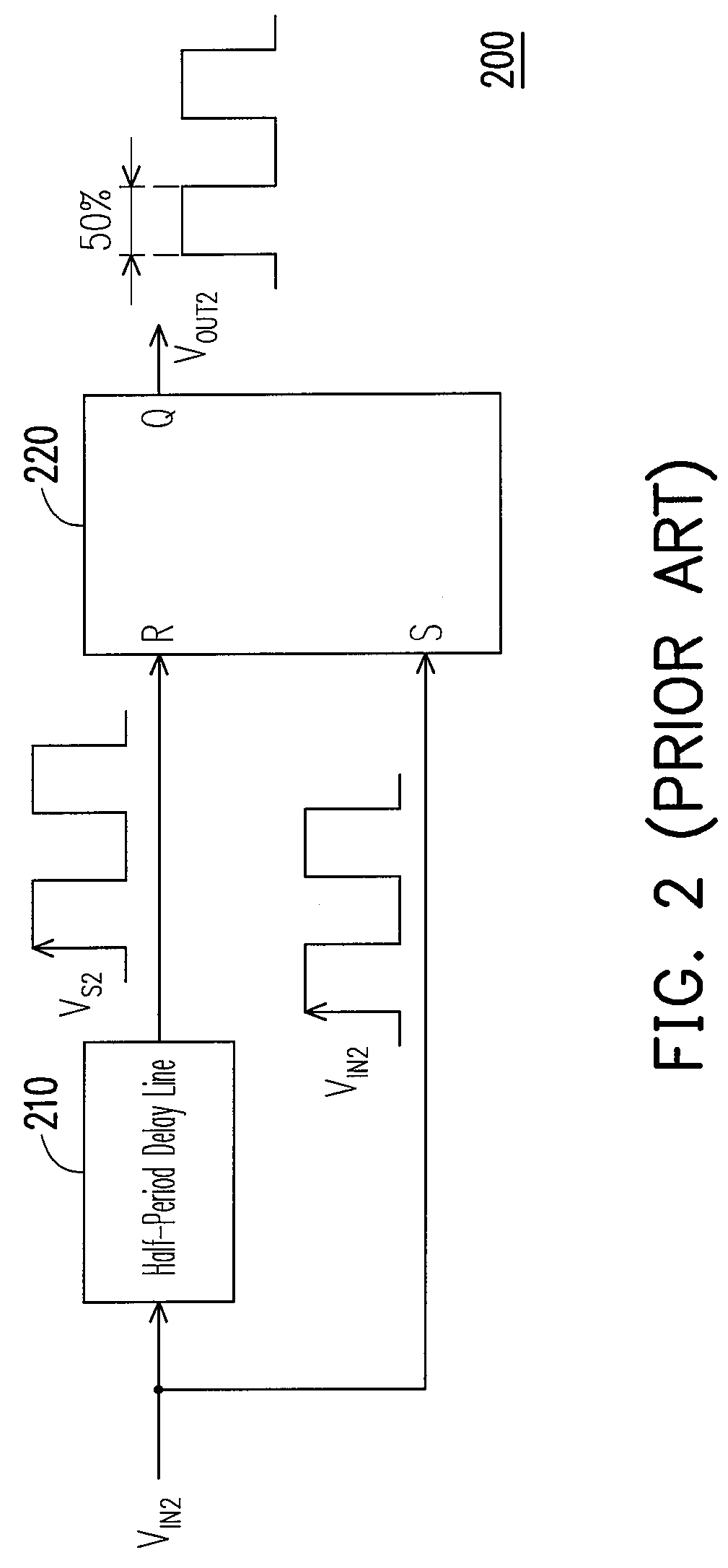

Digital delay locked loop capable of correcting duty cycle and its method

ActiveUS7161397B2Reduce latencyShorten the timePulse automatic controlDigital storageMultiplexingEngineering

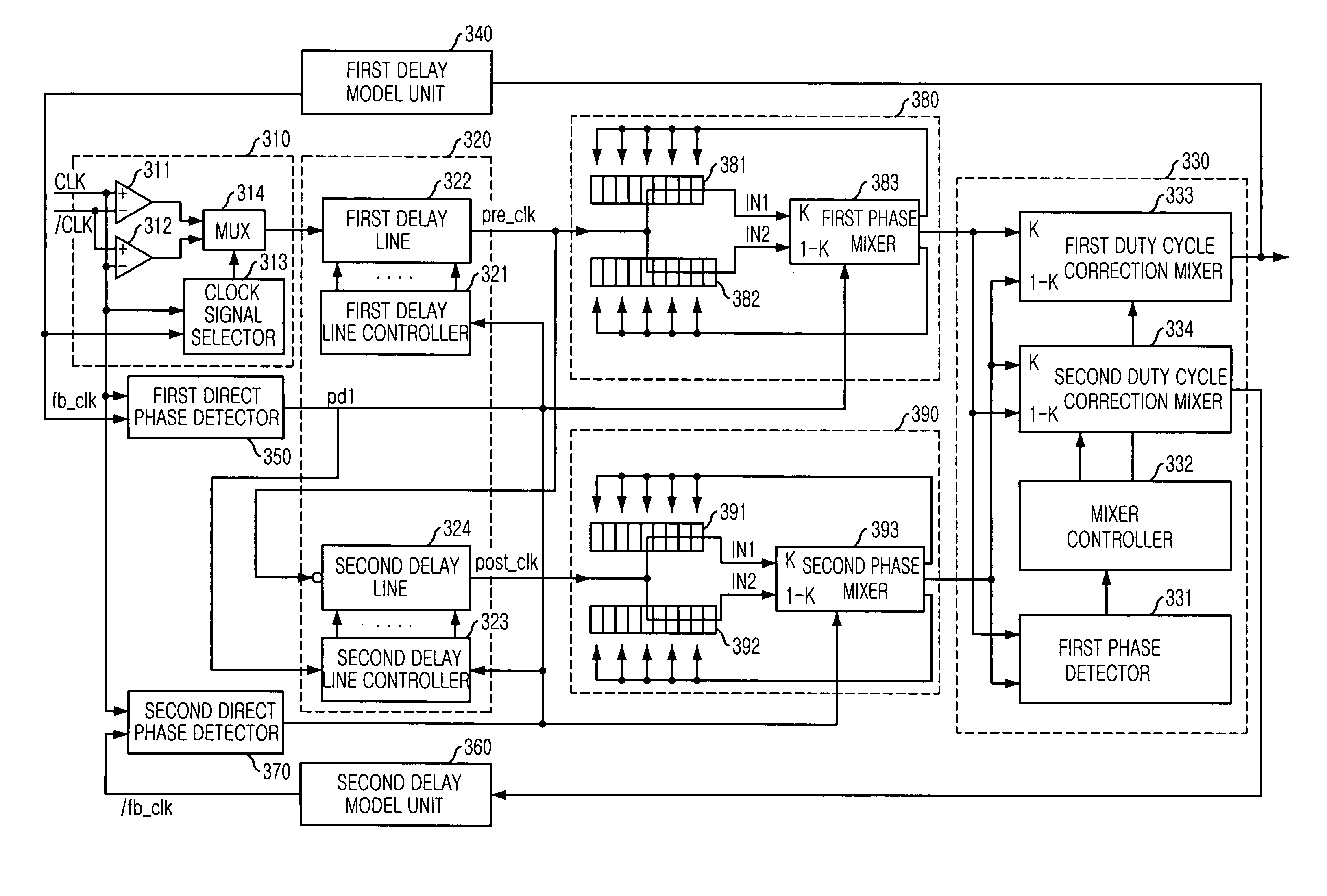

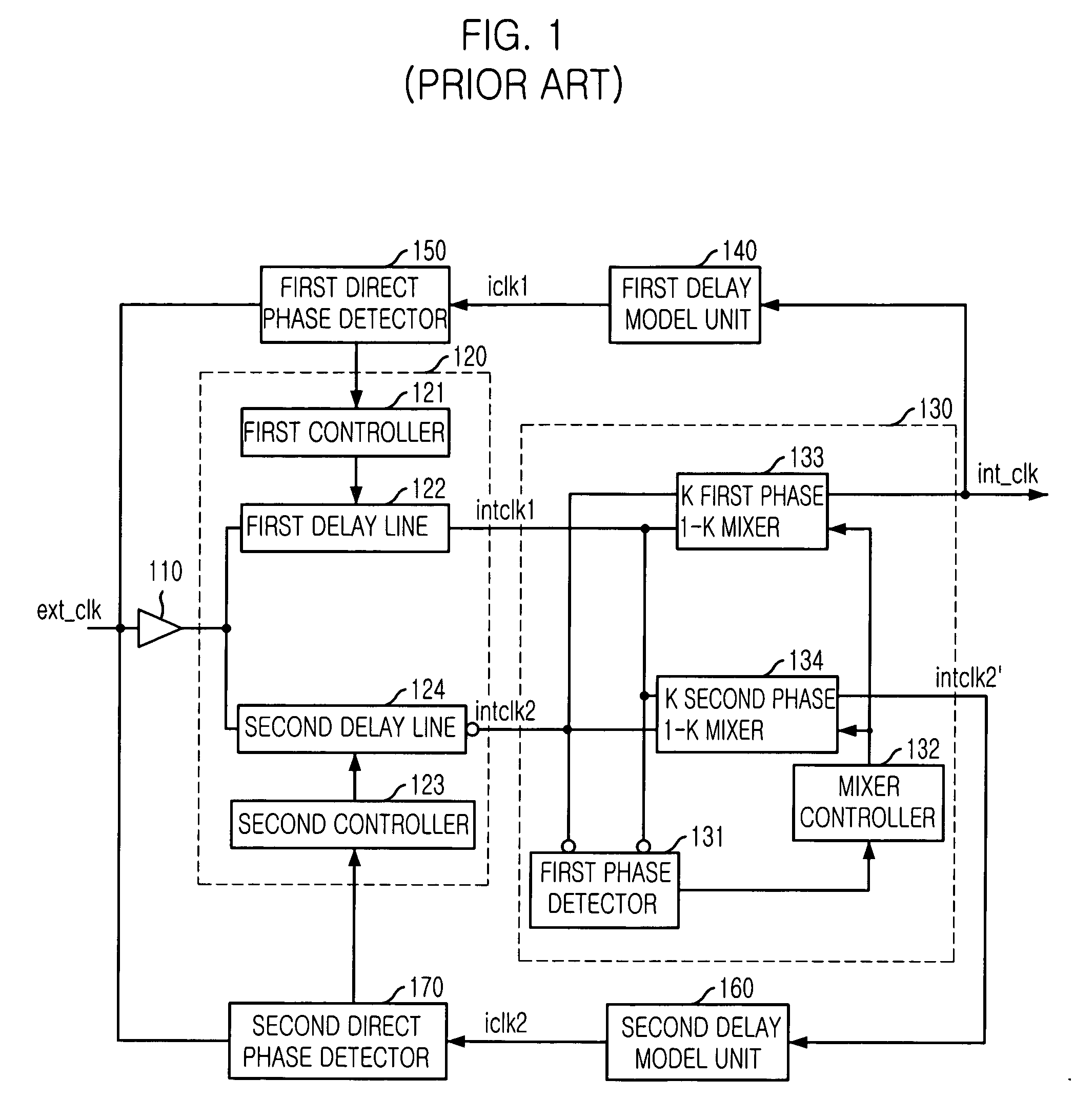

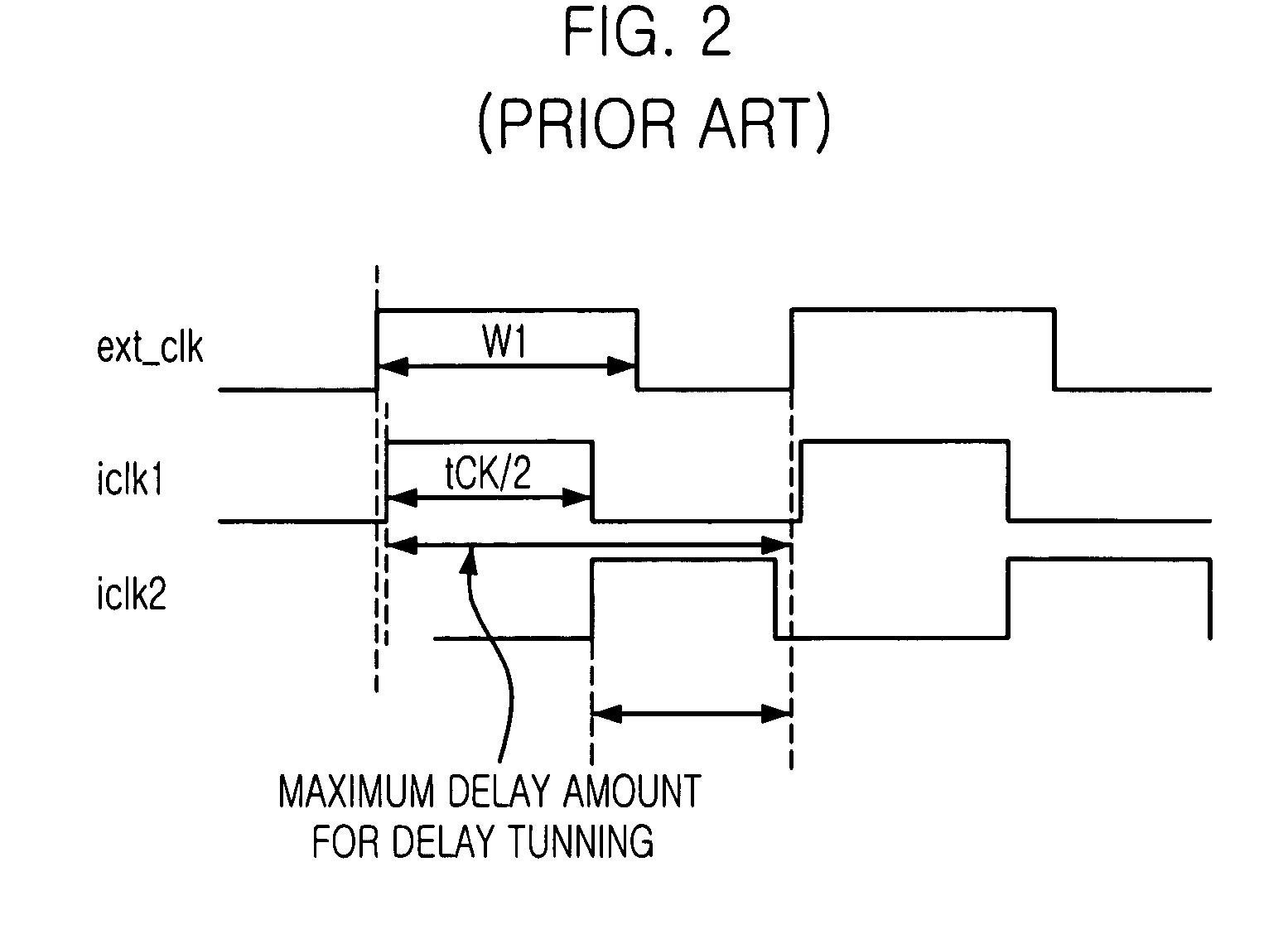

An apparatus for adjusting a clock signal, including: a clock multiplexing unit for receiving an external clock signal, an external clock bar signal and a feed-backed clock signal in order to select one of the external clock signal and the external clock bar signal as an output signal of the clock multiplexing unit based on a result of comparing a phase of the external clock signal with a phase of the feed-backed clock signal; and a delay locked loop (DLL) for generating a duty corrected clock signal and the feed-backed clock signal in response to the output signal of the clock multiplexing unit.

Owner:SK HYNIX INC

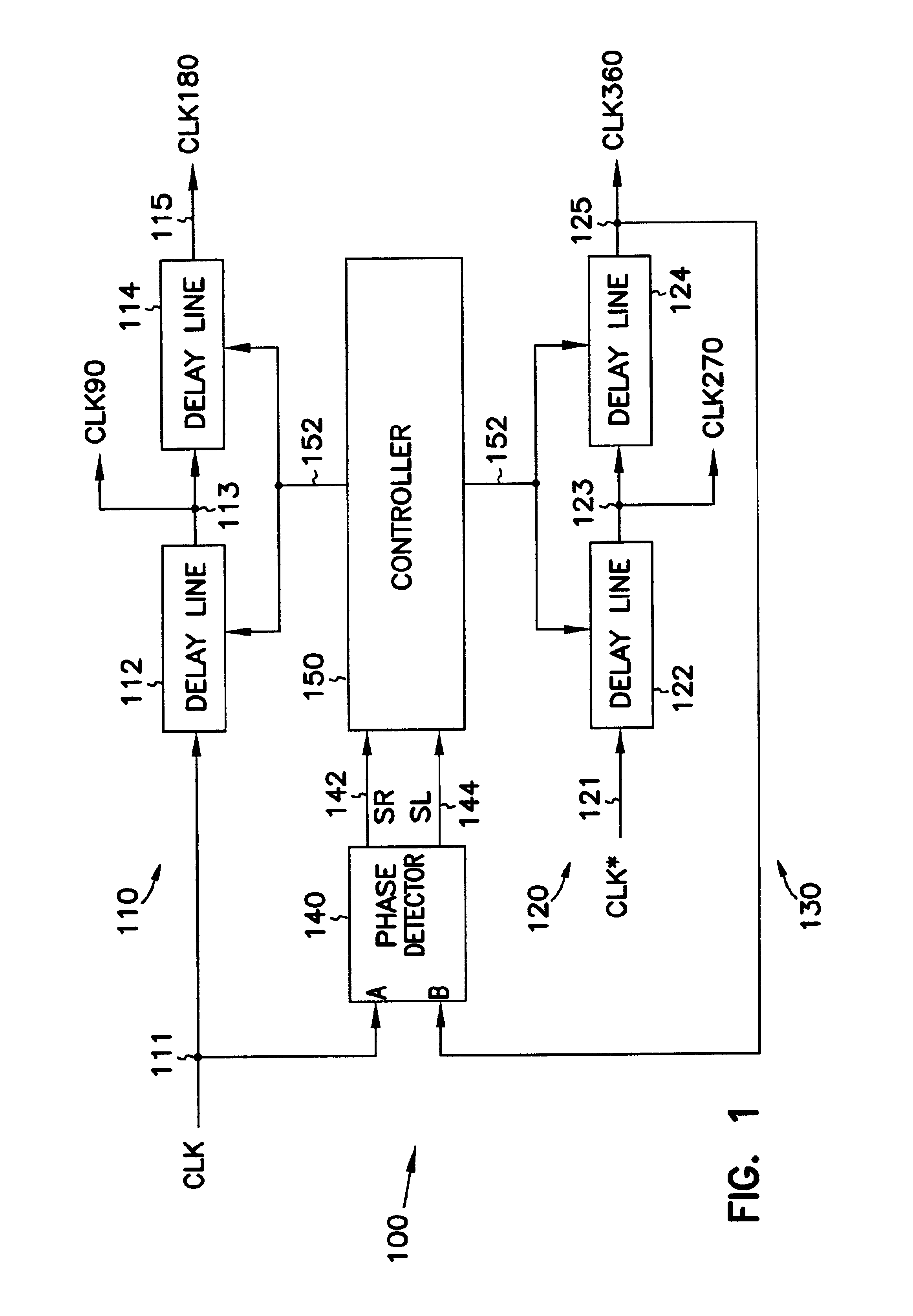

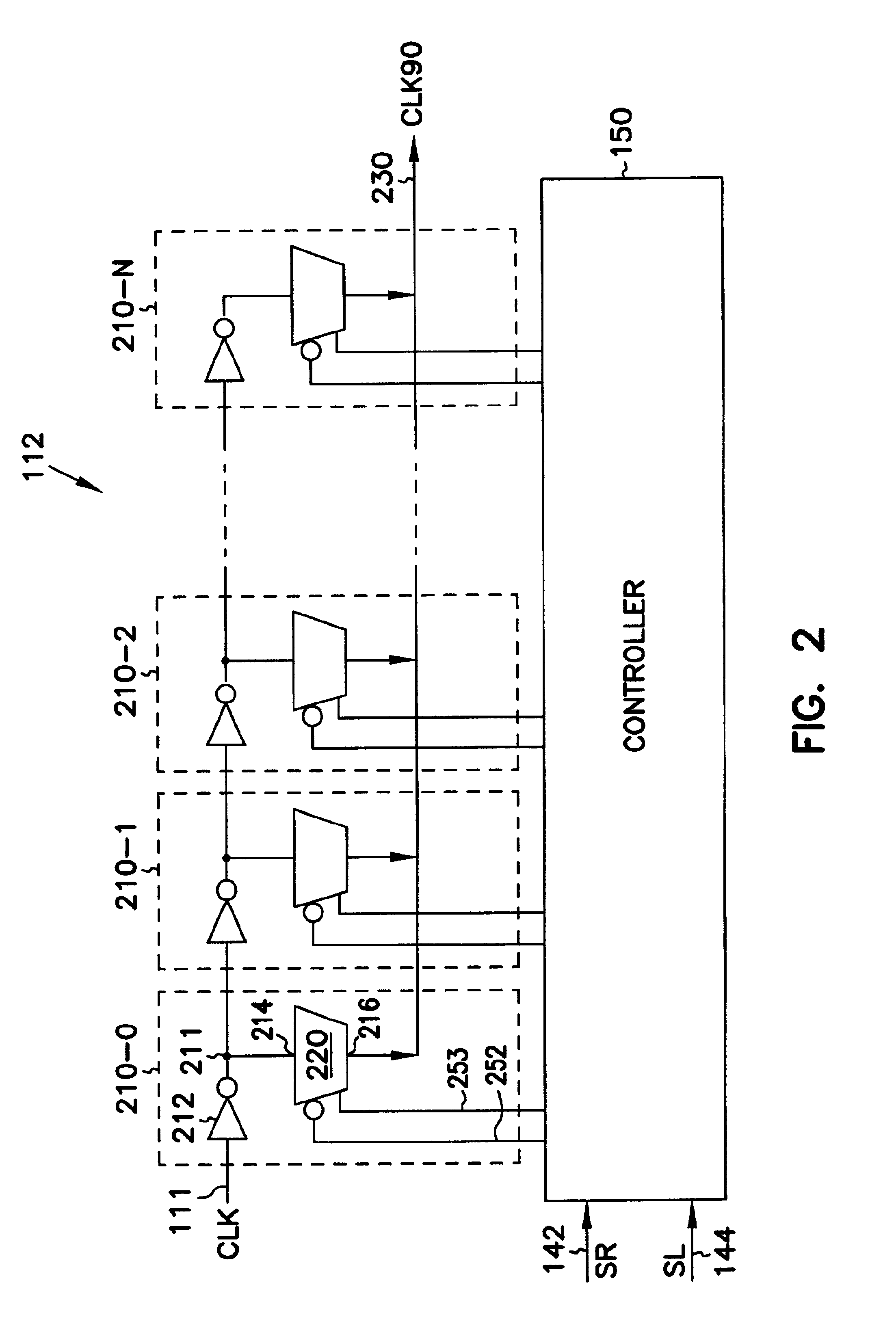

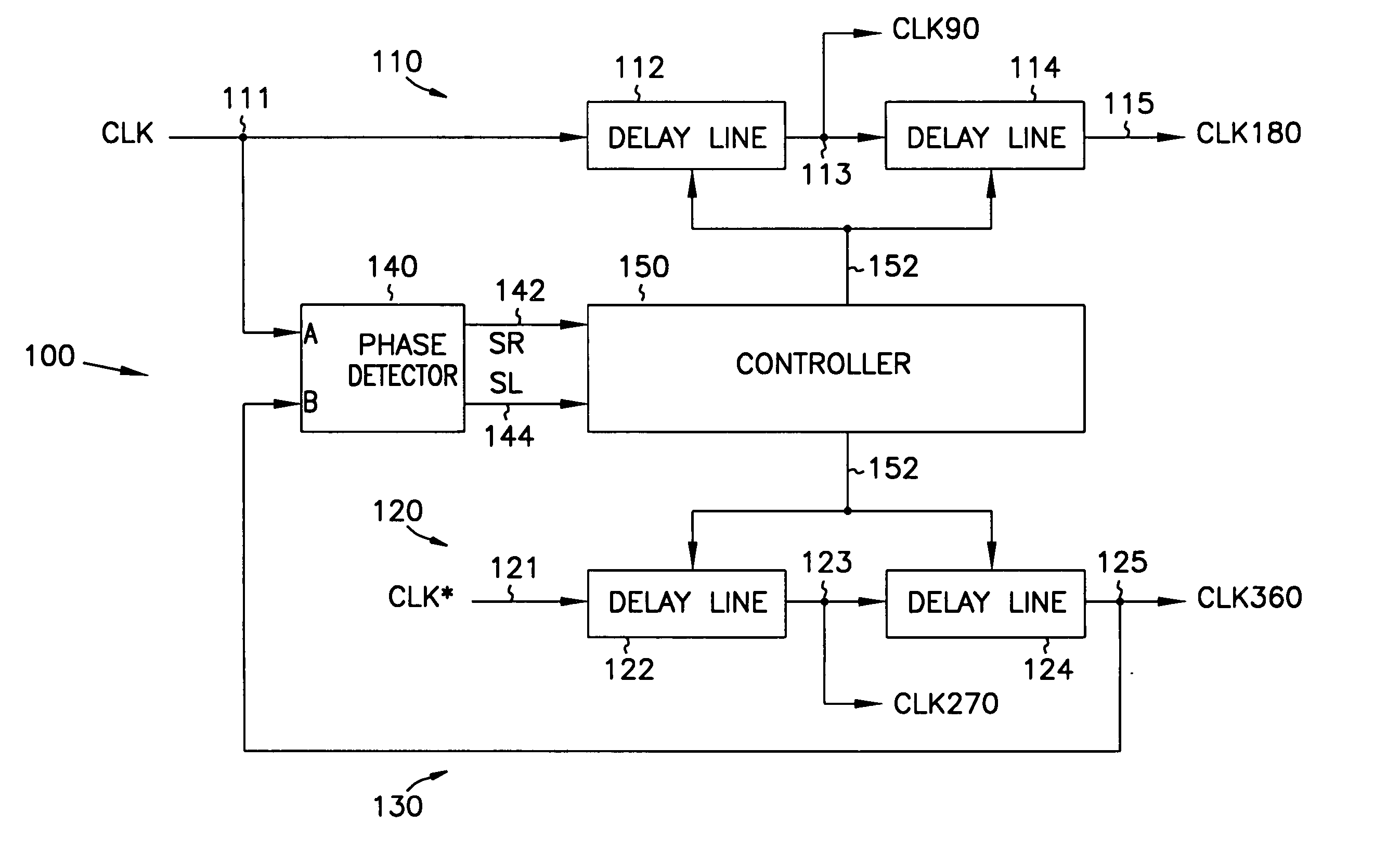

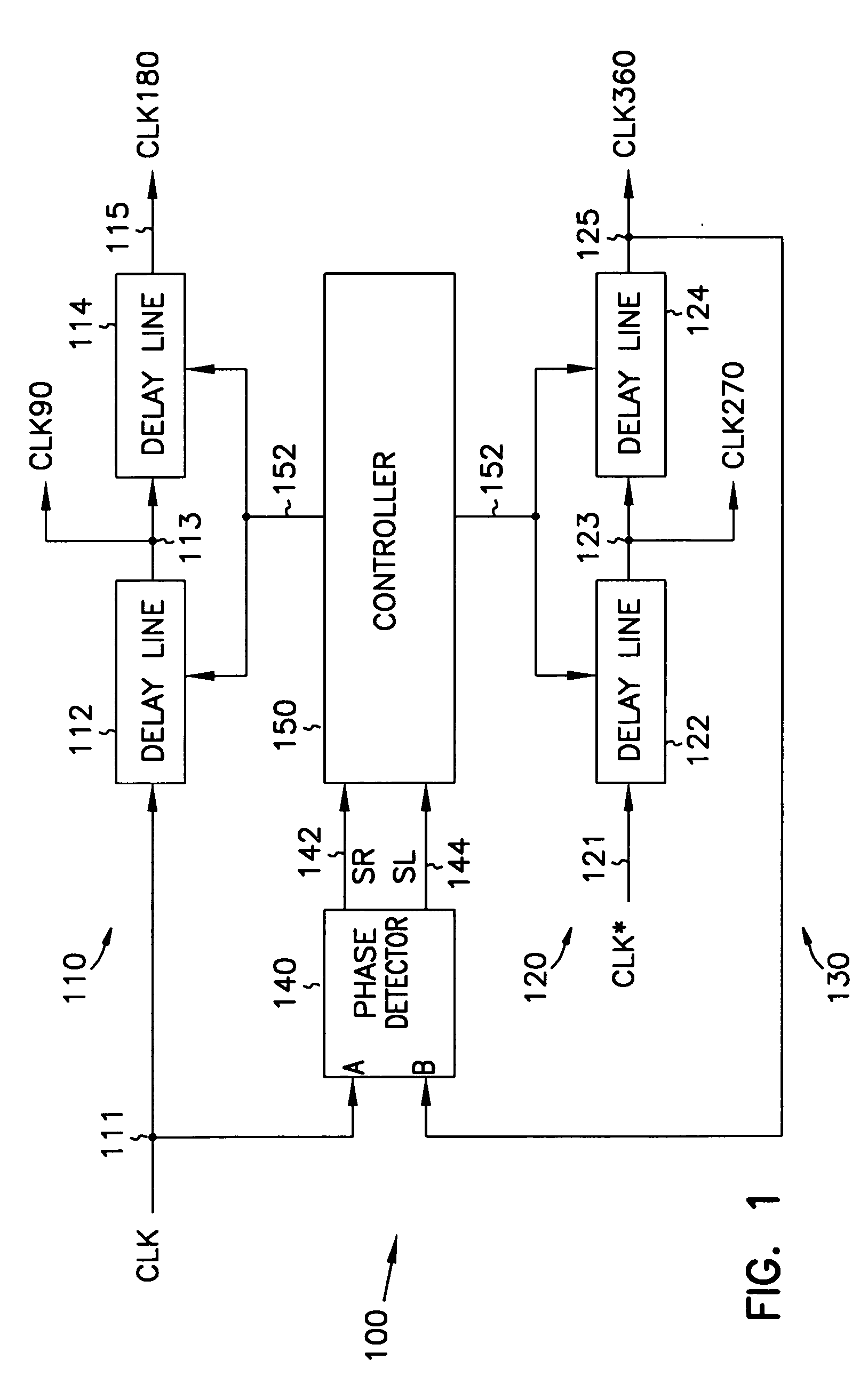

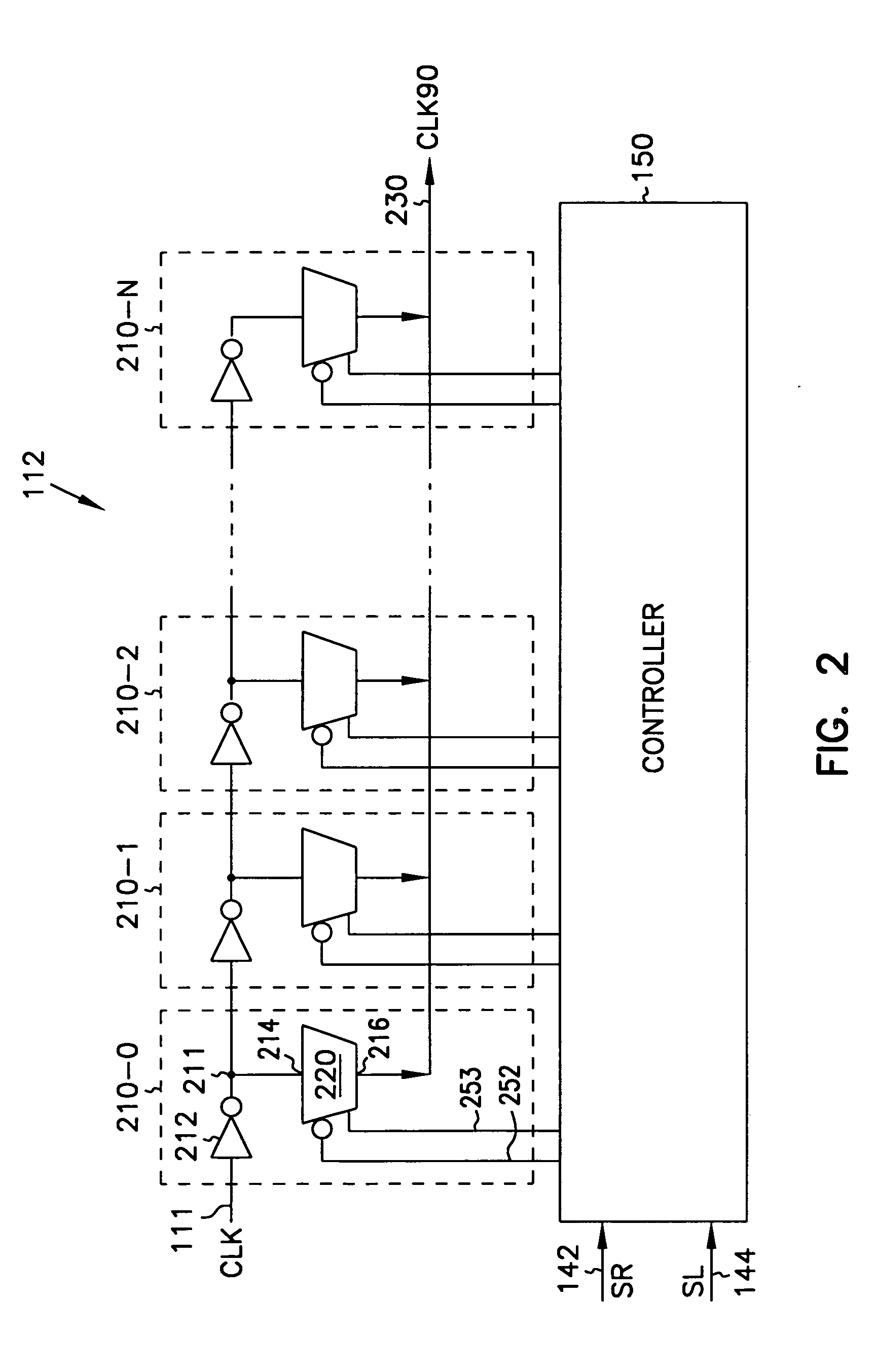

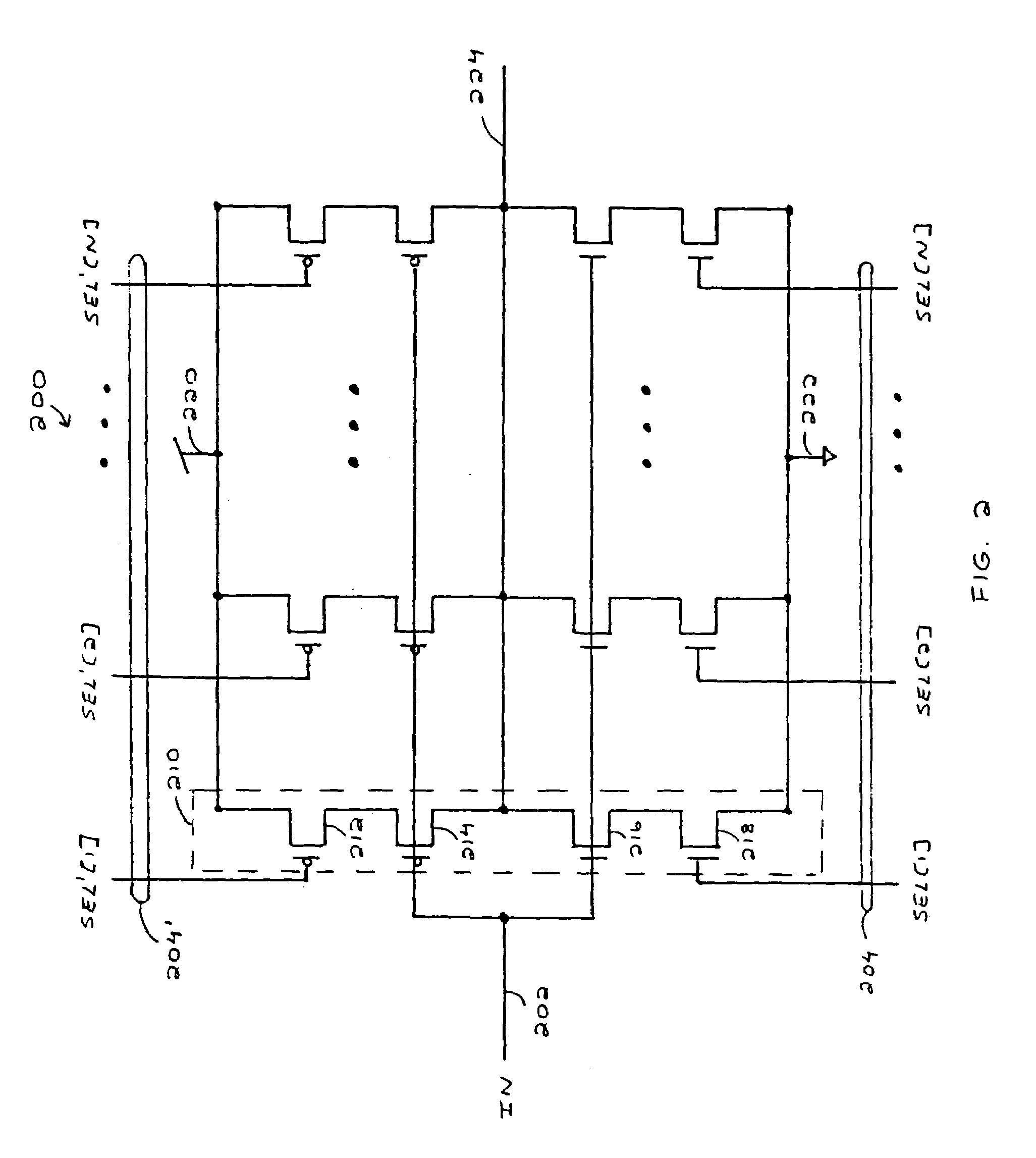

Phase splitter using digital delay locked loops

InactiveUS6950487B2Pulse automatic controlAngle demodulation by phase difference detectionPhase shiftedPhase splitter

A phase splitter using digital delay locked loop (DLL) to receive complementary input clock signals to generate a plurality of output signals having different phase shifts. When the DLL is locked, the delay resolution of the phase splitter is equal to two delay stages of the DLL.

Owner:ROUND ROCK RES LLC

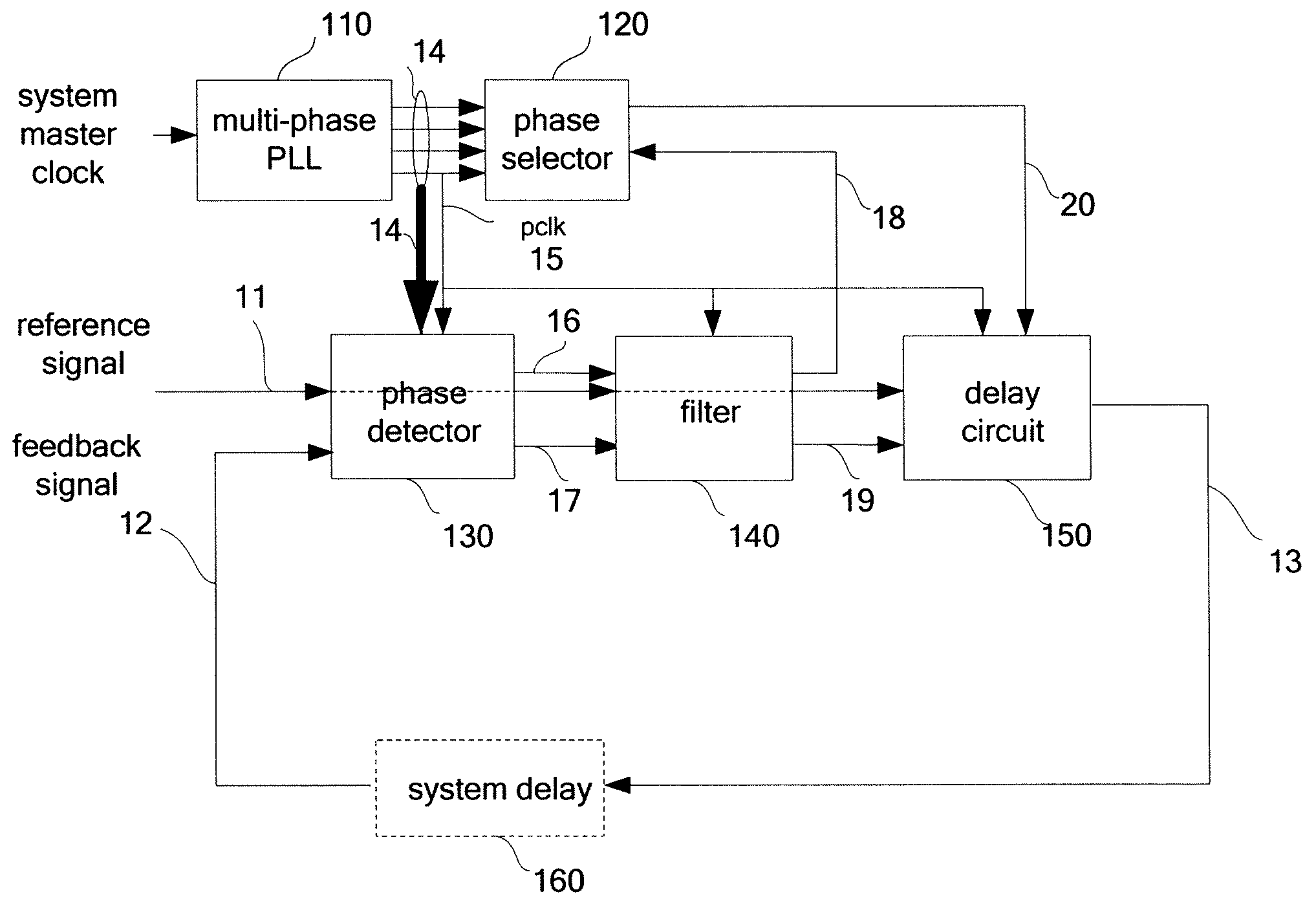

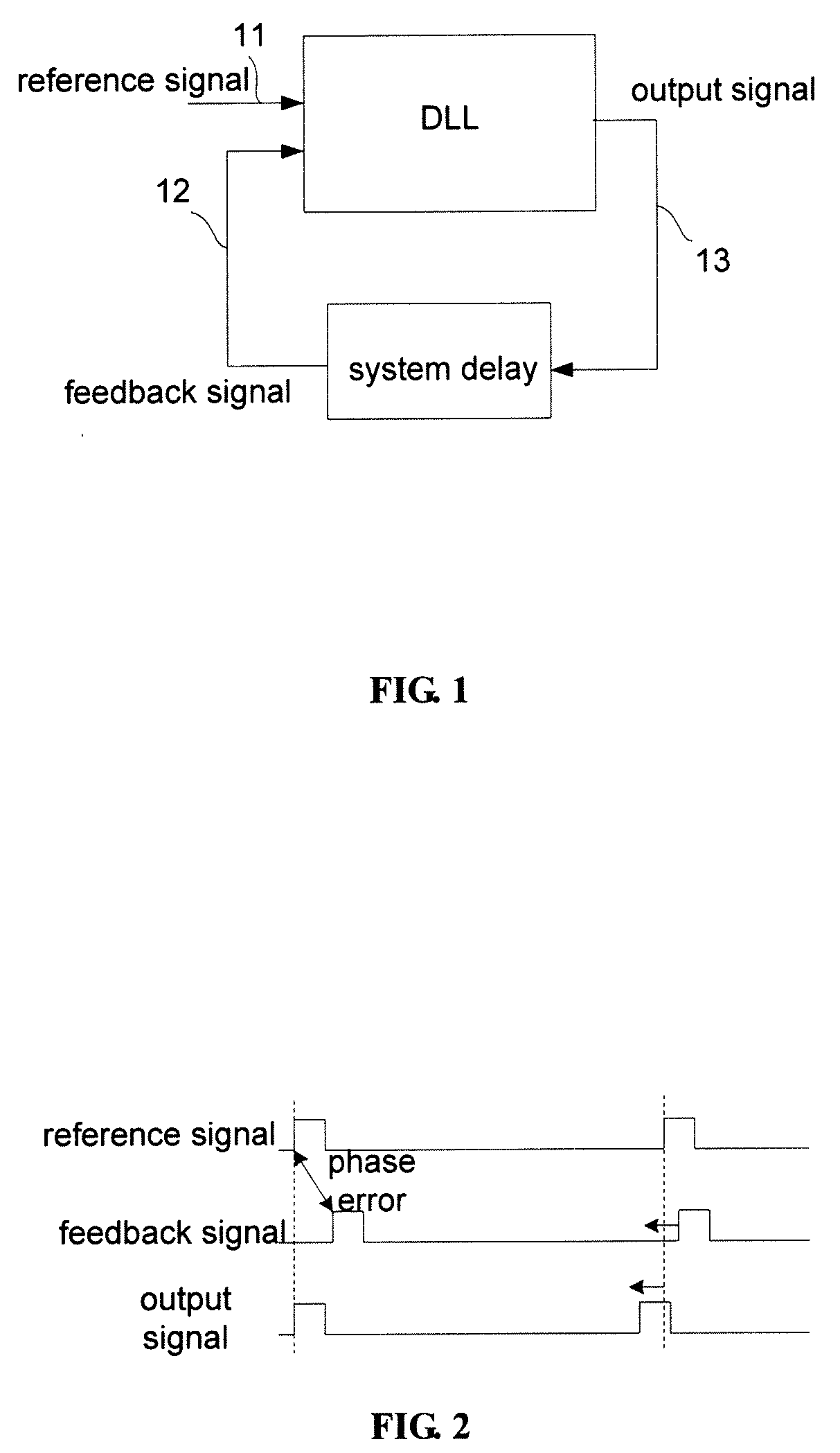

Semi-Digital Delay Locked Loop Circuit and Method

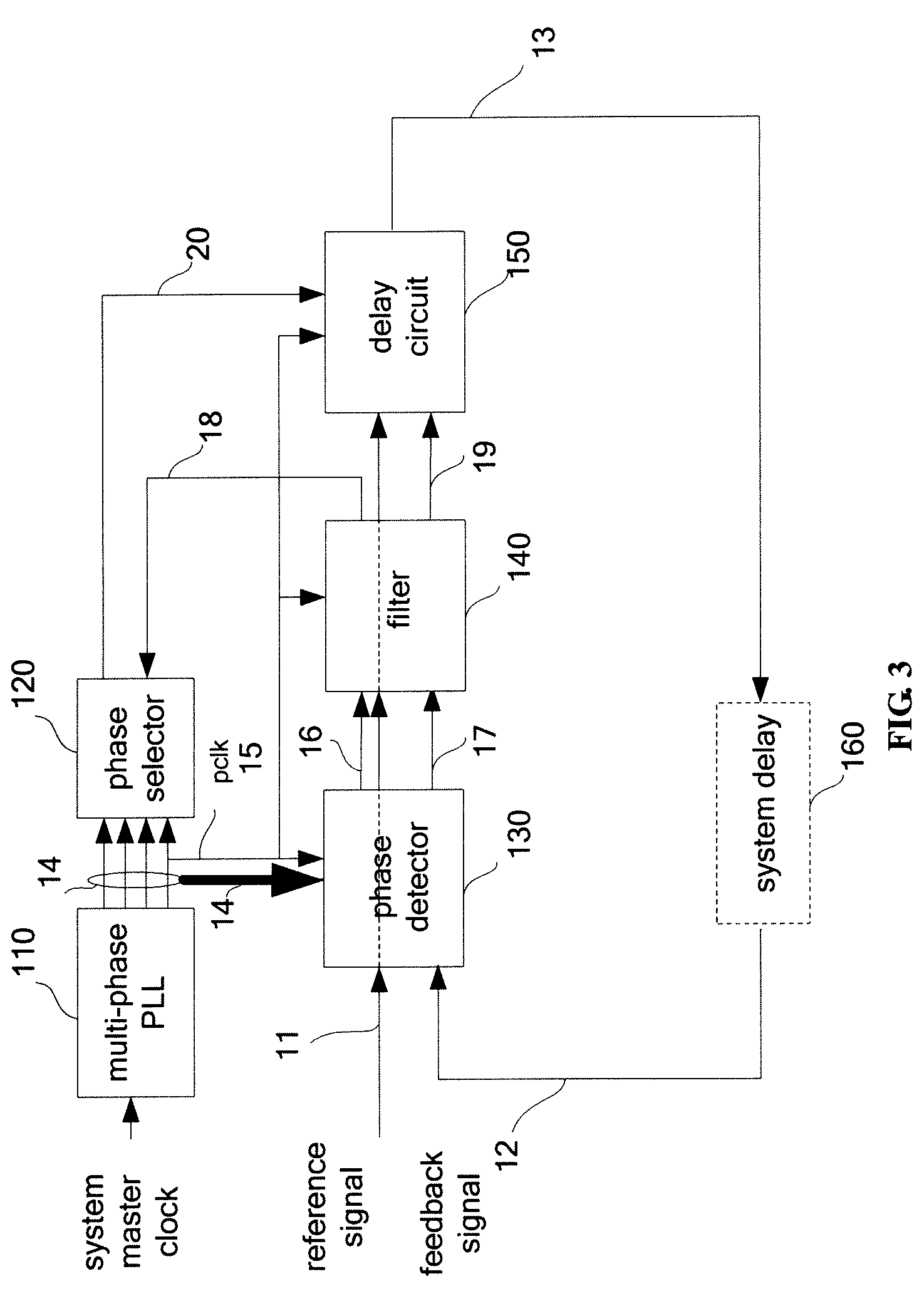

ActiveUS20090243679A1High resolutionSmall DLL jitterTelevision system detailsPulse automatic controlPhase detectorPhase locked loop circuit

A scalable DLL (delay locked loop) circuit that has a calibration mechanism to auto tune locking precision. The delay locked loop circuit includes a multi-phase phase locked loop circuit for generating a plurality of phase signals according to a system clock, wherein one of the phase signals is a pixel clock; a phase detector for detecting an integral phase error and a fractional phase error between a reference signal and a feedback signal according to the pixel clock; a phase selector for selecting one of the phase signals according to the fractional phase error; and a delay circuit for shifting the phase of the reference signal according to the integral phase error and the selected phase signal to generate an output signal.

Owner:XUESHAN TECH INC

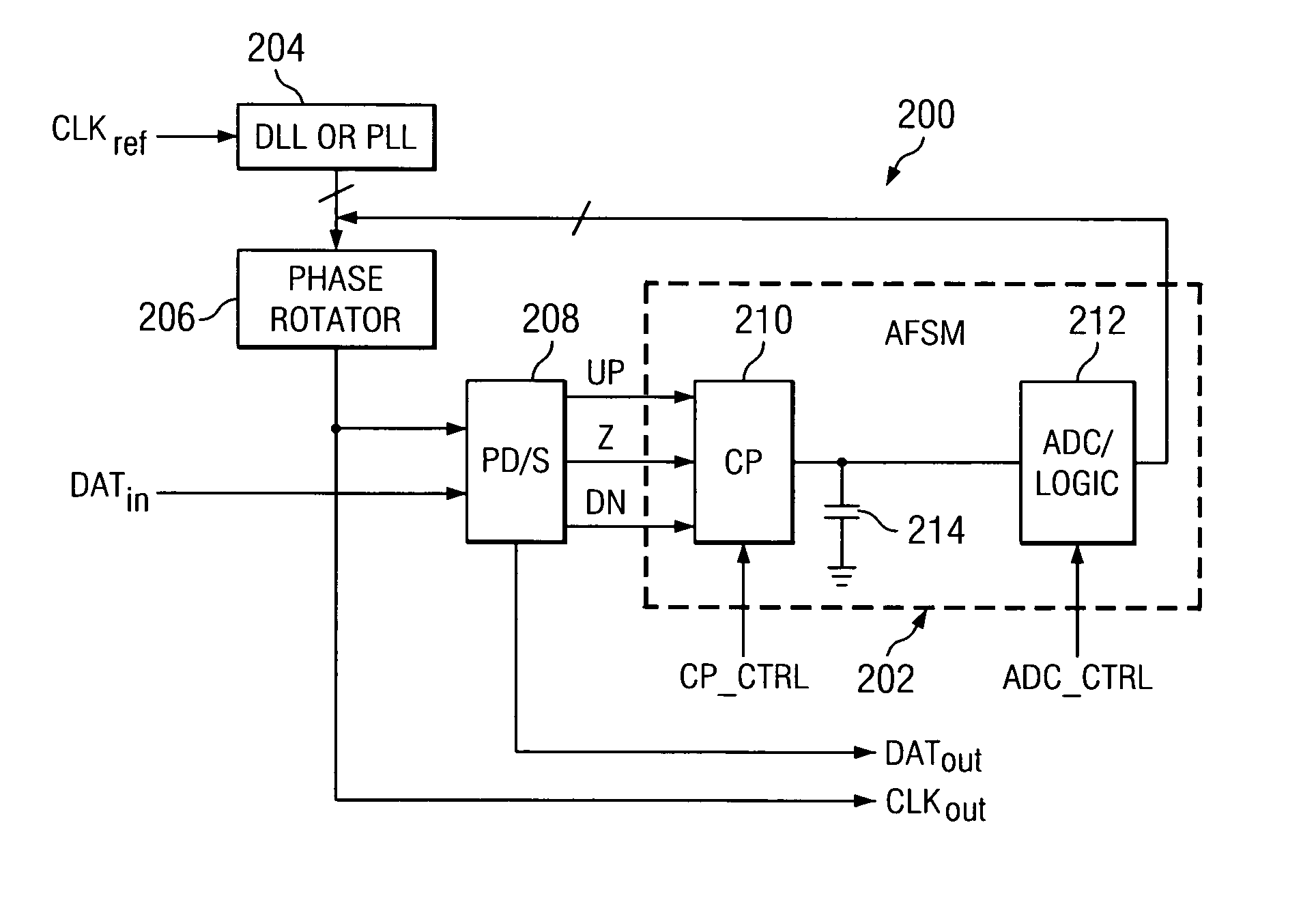

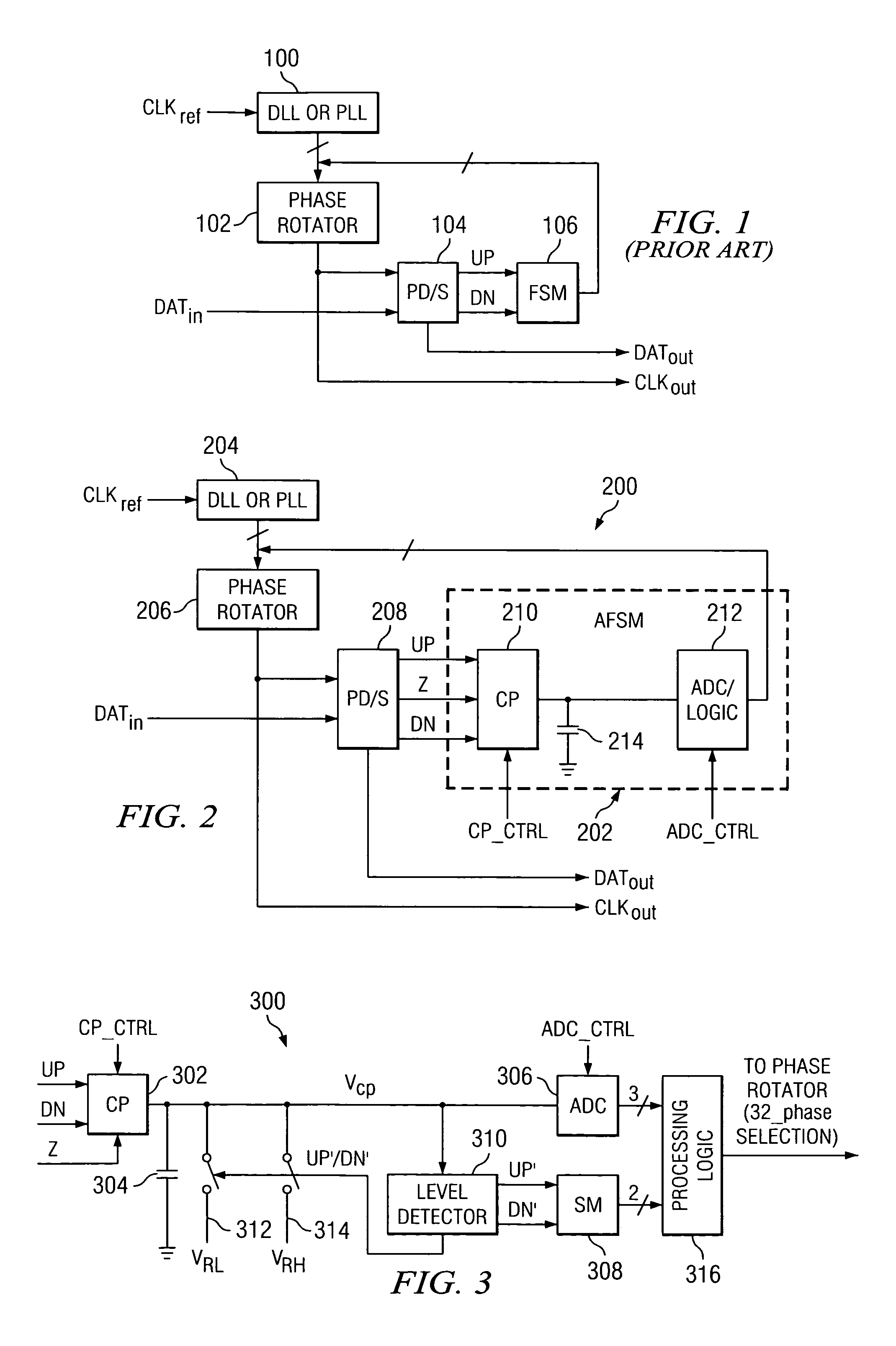

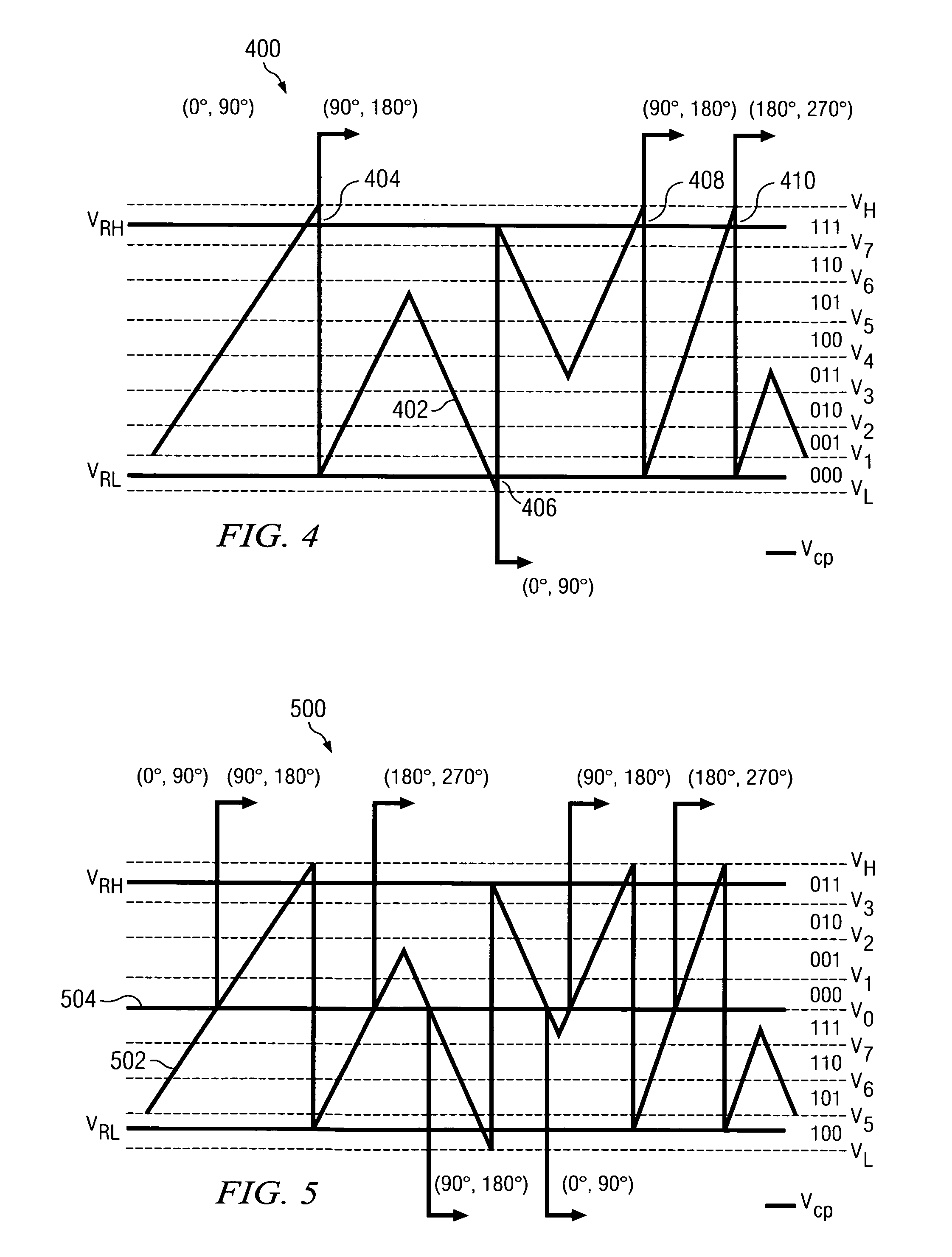

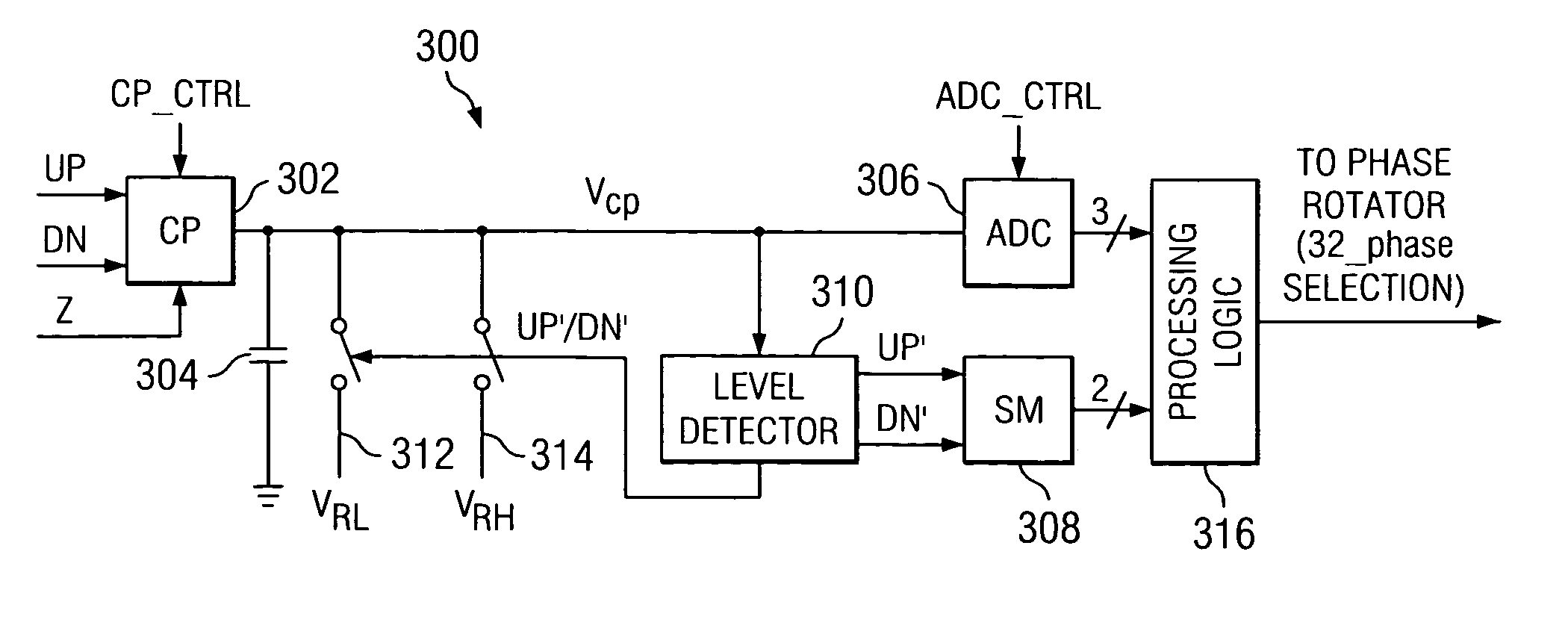

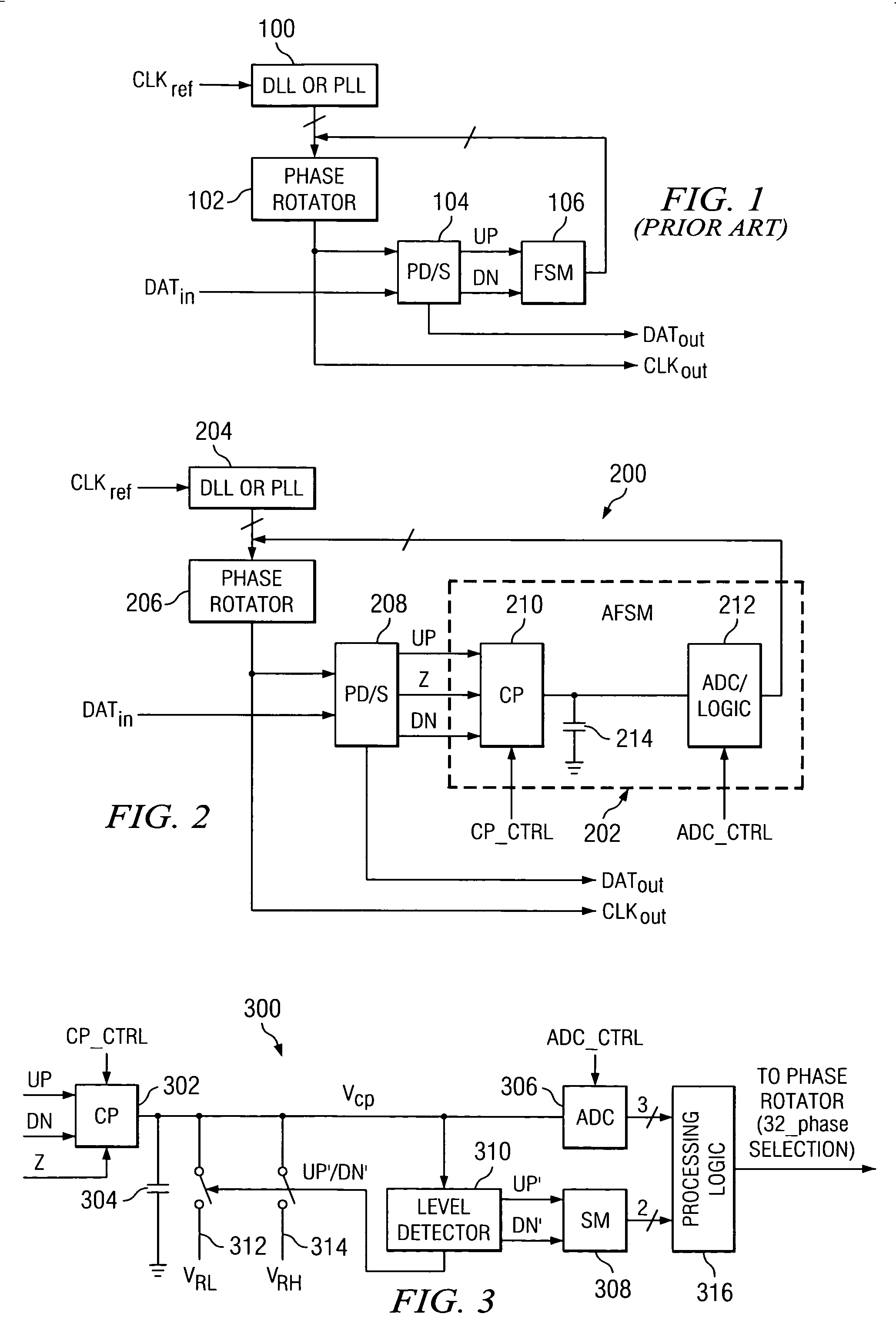

Semidigital delay-locked loop using an analog-based finite state machine

InactiveUS6927611B2Increase powerComplexity of hardwarePulse automatic controlSynchronising arrangementDigital signal processingEngineering

A low-power full-rate semidigital DLL architecture using an analog-based FSM (AFSM). The AFSM is a mixed-mode FSM in which analog integration is substituted for digital filtering, thus enabling a lower power implementation of the clock and data recovery function. An integrated voltage is converted to a digital code by an analog-to-digital converter (ADC), and the digital code is used either directly or after (low frequency) digital signal processing to control a controllable delay element, such as, a phase rotator, for data edge tracking.

Owner:GLOBALFOUNDRIES US INC

Circuit and method for on-chip jitter measurement

ActiveUS20080012549A1Noise figure or signal-to-noise ratio measurementPulse automatic controlImage resolutionEngineering

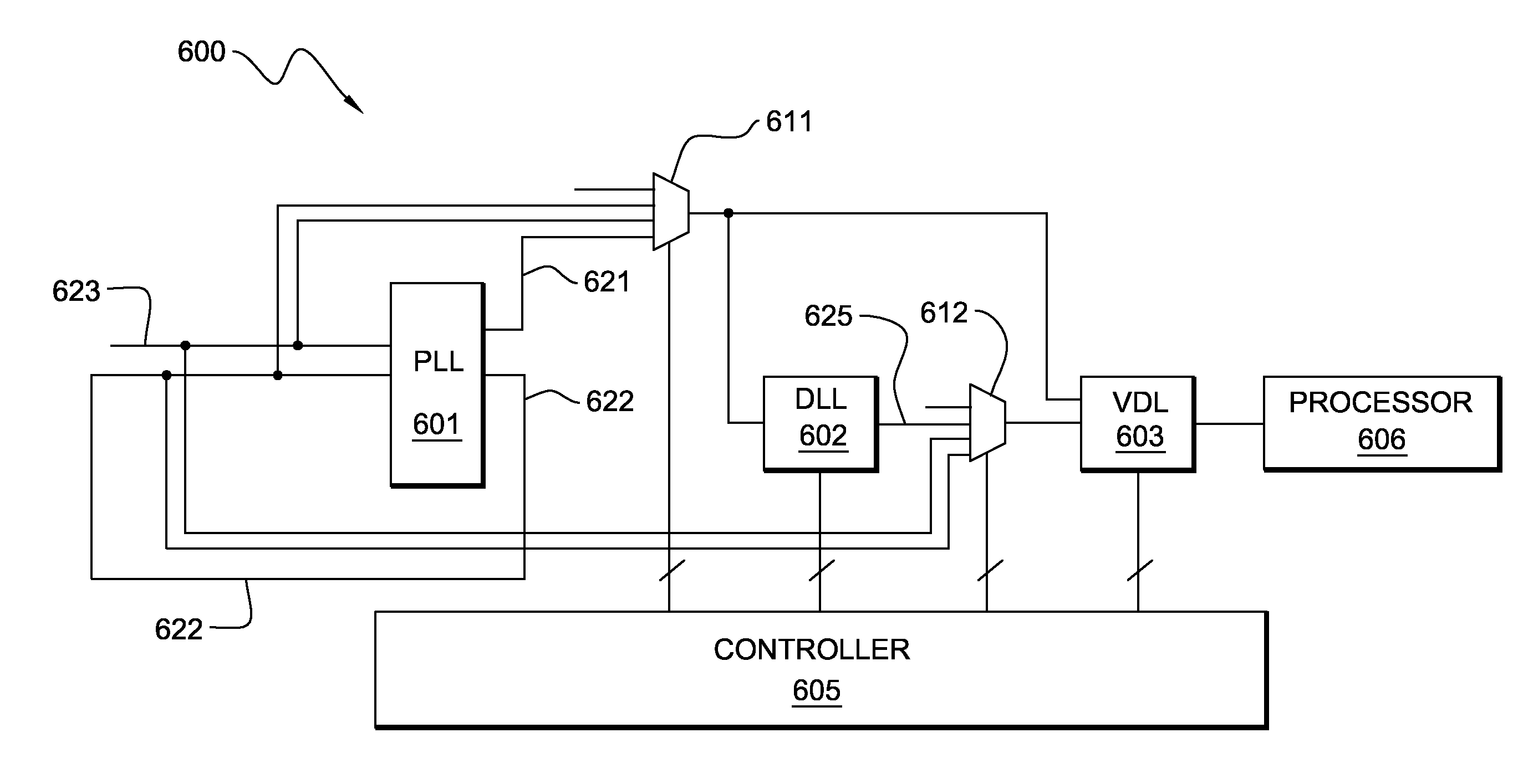

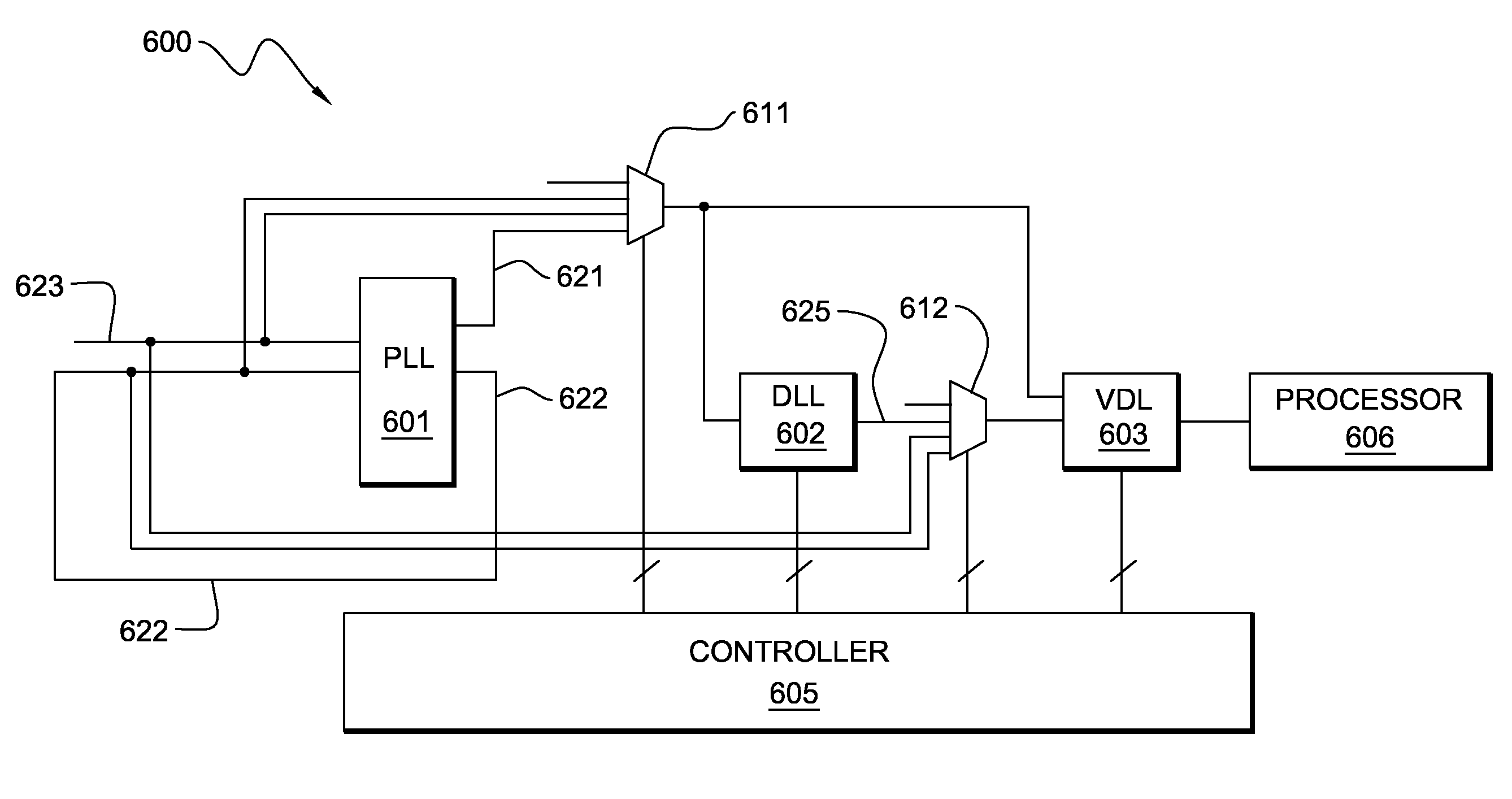

Disclosed herein are embodiments of an improved built-in self-test (BIST) circuit and an associated method for measuring phase and / or cycle-to-cycle jitter of a clock signal. The embodiments of the BIST circuit implement a Variable Vernier Digital Delay Locked Line method. Specifically, the embodiments of the BIST circuit incorporate both a digital delay locked loop and a Vernier delay line, for respectively coarse tuning and fine tuning portions of the circuit. Additionally, the BIST circuit is variable, as the resolution of the circuit changes from chip to chip, and digital, as it is implemented with standard digital logic elements.

Owner:META PLATFORMS INC

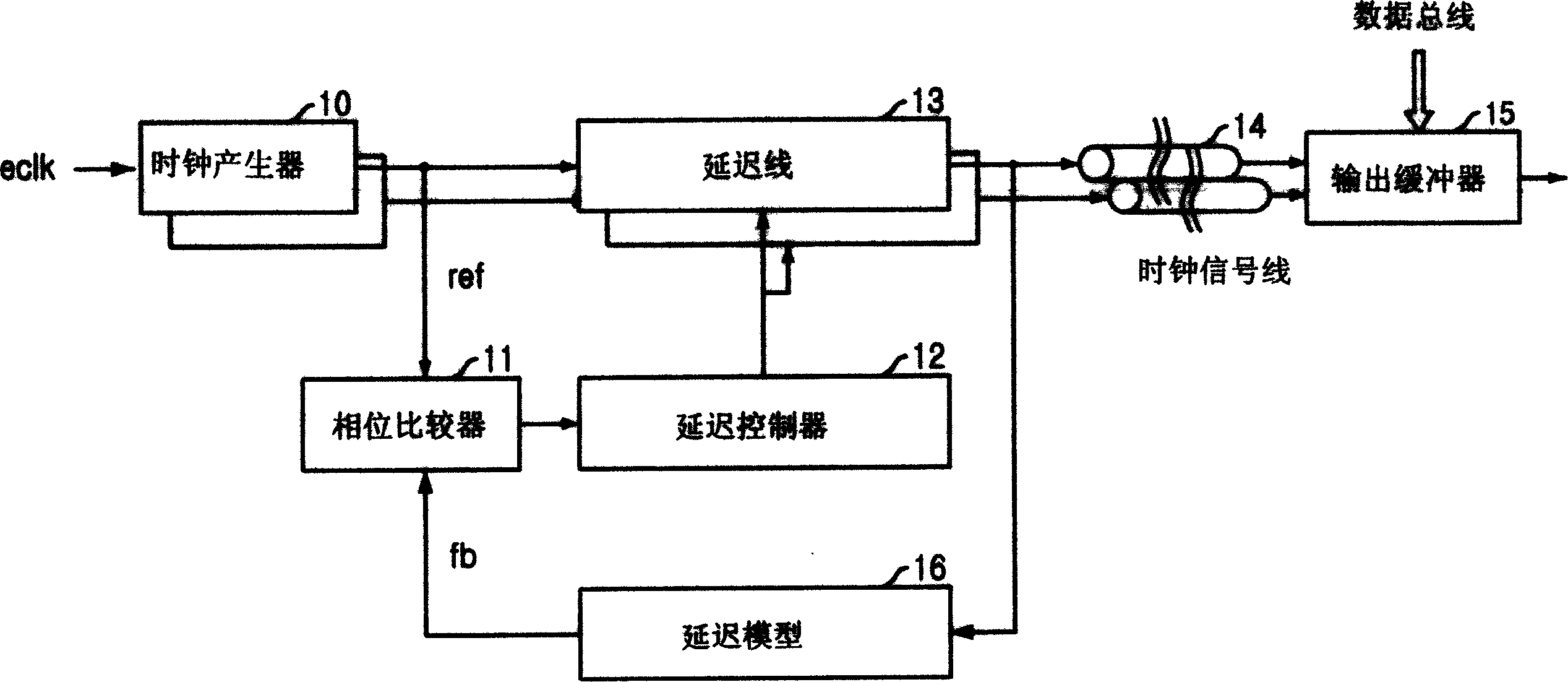

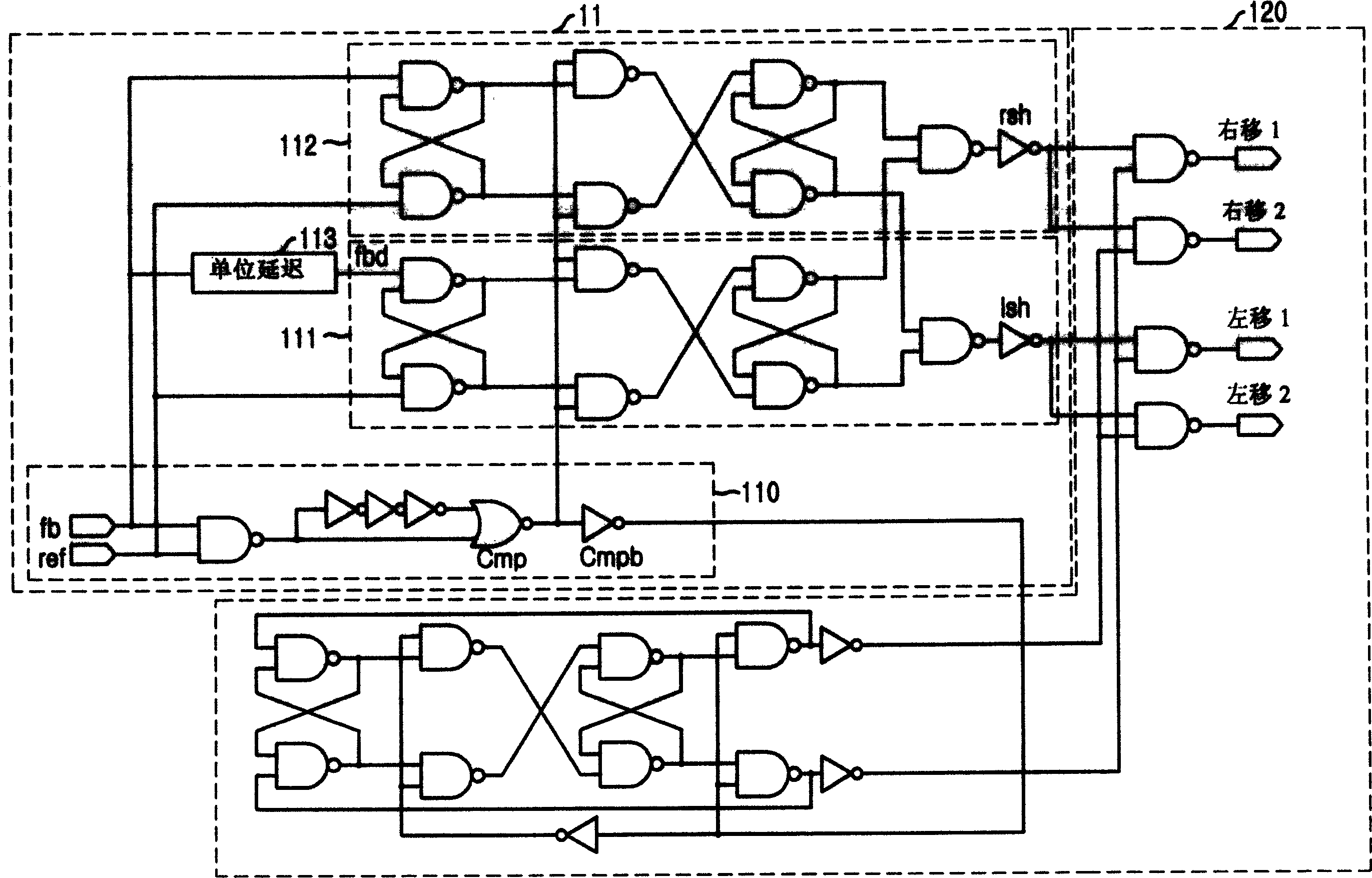

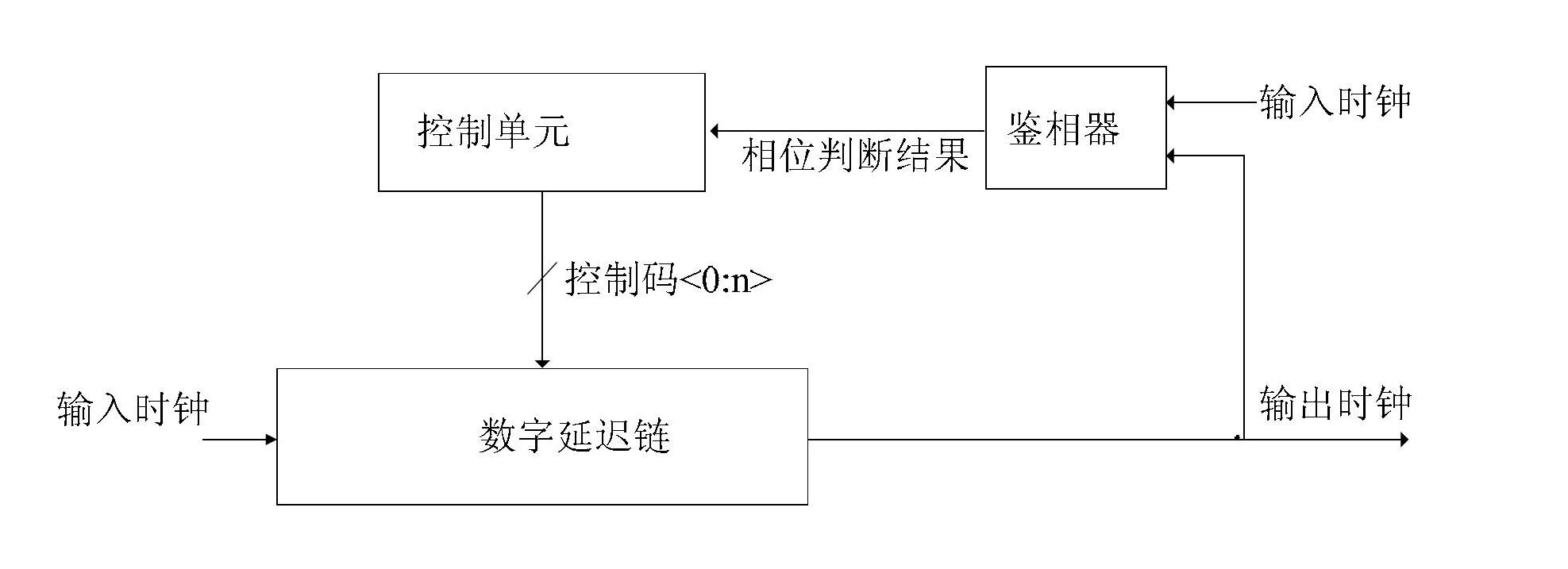

Digital delay locked loop and control method thereof

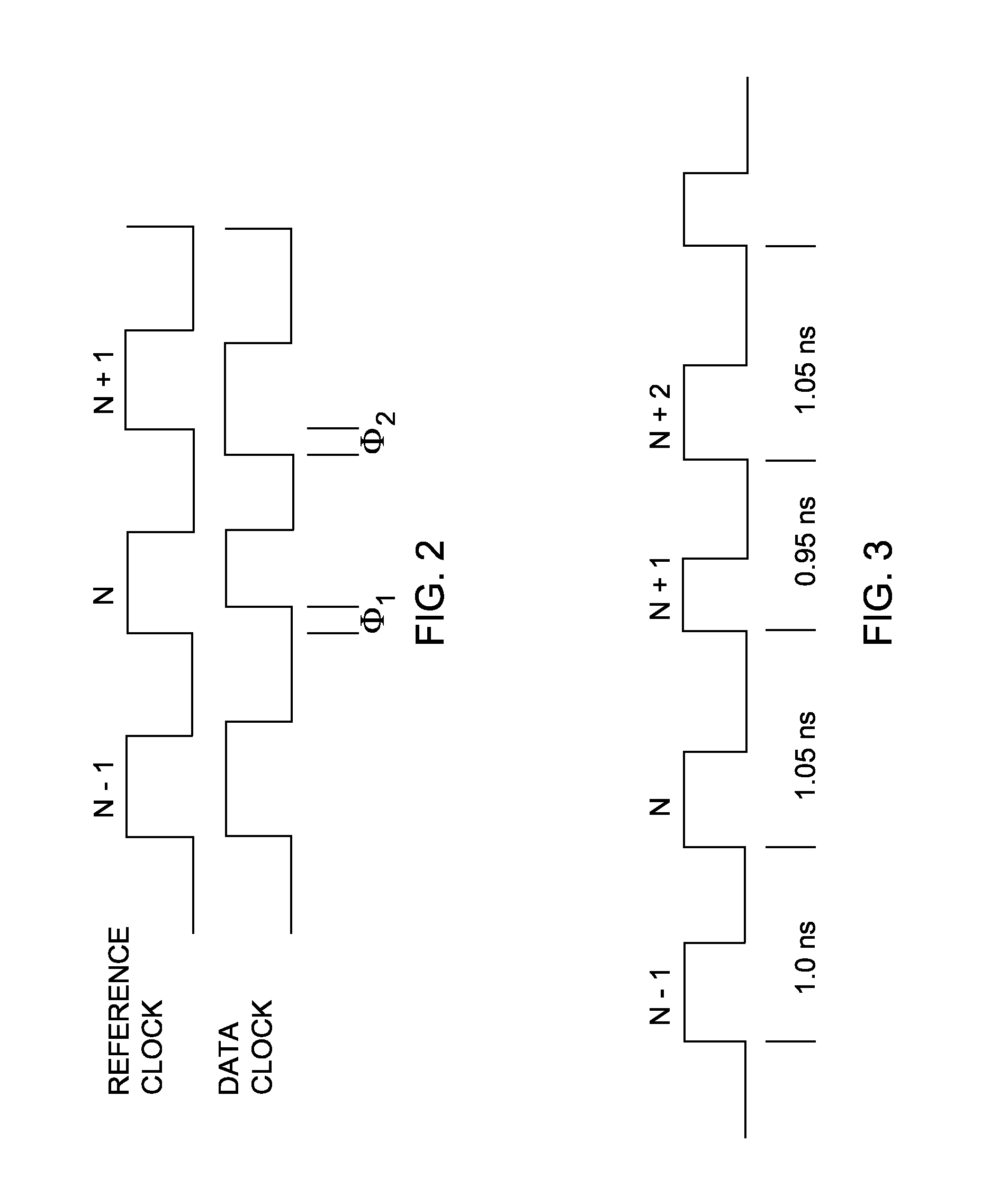

A digital delay locked loop(DLL) and a method for controlling the same are provided to improve the reliability of the DLL circuit by minimizing jitter. A digital delay locked loop(DLL) includes a clock generation unit, a delay line, a delay model, a phase comparison unit, a jitter detection unit and a delay control unit. The clock generation unit generates a source clock and a reference clock. The delay line is provided with a plurality of unit delays to delay the source clock by a predetermined time. The delay model reflects the delay time of the practical inner circuit on the output of the delay line. The phase comparison unit compares the reference clock with the phase of the feedback clock outputted from the delay model. The jitter detection unit detects the maximum jitter time in response to the phase comparison signal outputted from the phase comparison unit to output the multi-delay enable signal. And, the delay control unit controls the delay amount of the delay line to the unit delay or the multi-delay unit in response to the phase comparison signal and the multi-delay enable signal.

Owner:SK HYNIX INC

Circuit and method for on-chip jitter measurement

ActiveUS7339364B2Noise figure or signal-to-noise ratio measurementPulse automatic controlImage resolutionEngineering

An improved built-in self-test (BIST) circuit and an associated method for measuring phase and / or cycle-to-cycle jitter of a clock signal, the BIST circuit implement a Variable Vernier Digital Delay Locked Line method. Specifically, the embodiments of the BIST circuit incorporate both a digital delay locked loop and a Vernier delay line, for respectively coarse tuning and fine tuning portions of the circuit. Additionally, the BIST circuit is variable, as the resolution of the circuit changes from chip to chip, and digital, as it is implemented with standard digital logic elements.

Owner:META PLATFORMS INC

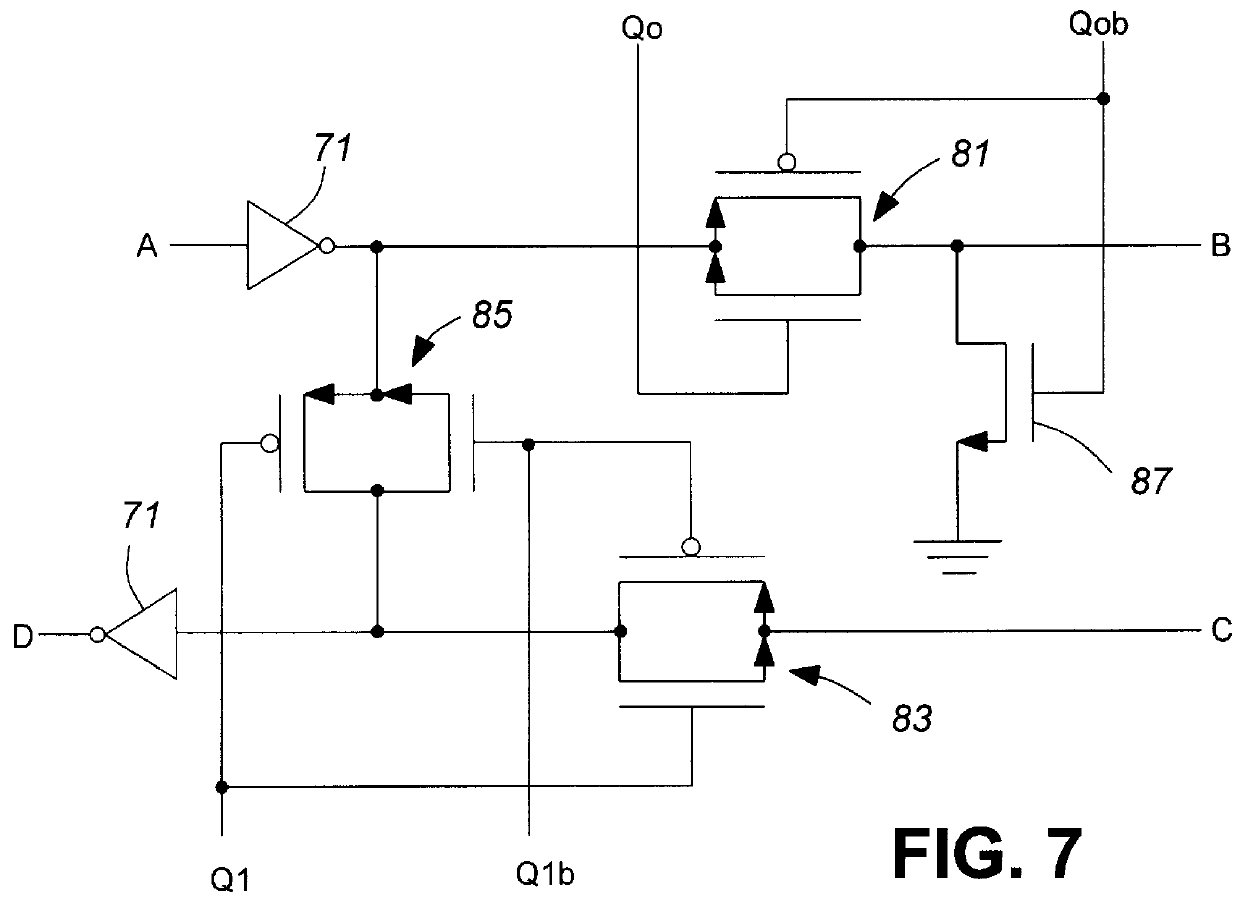

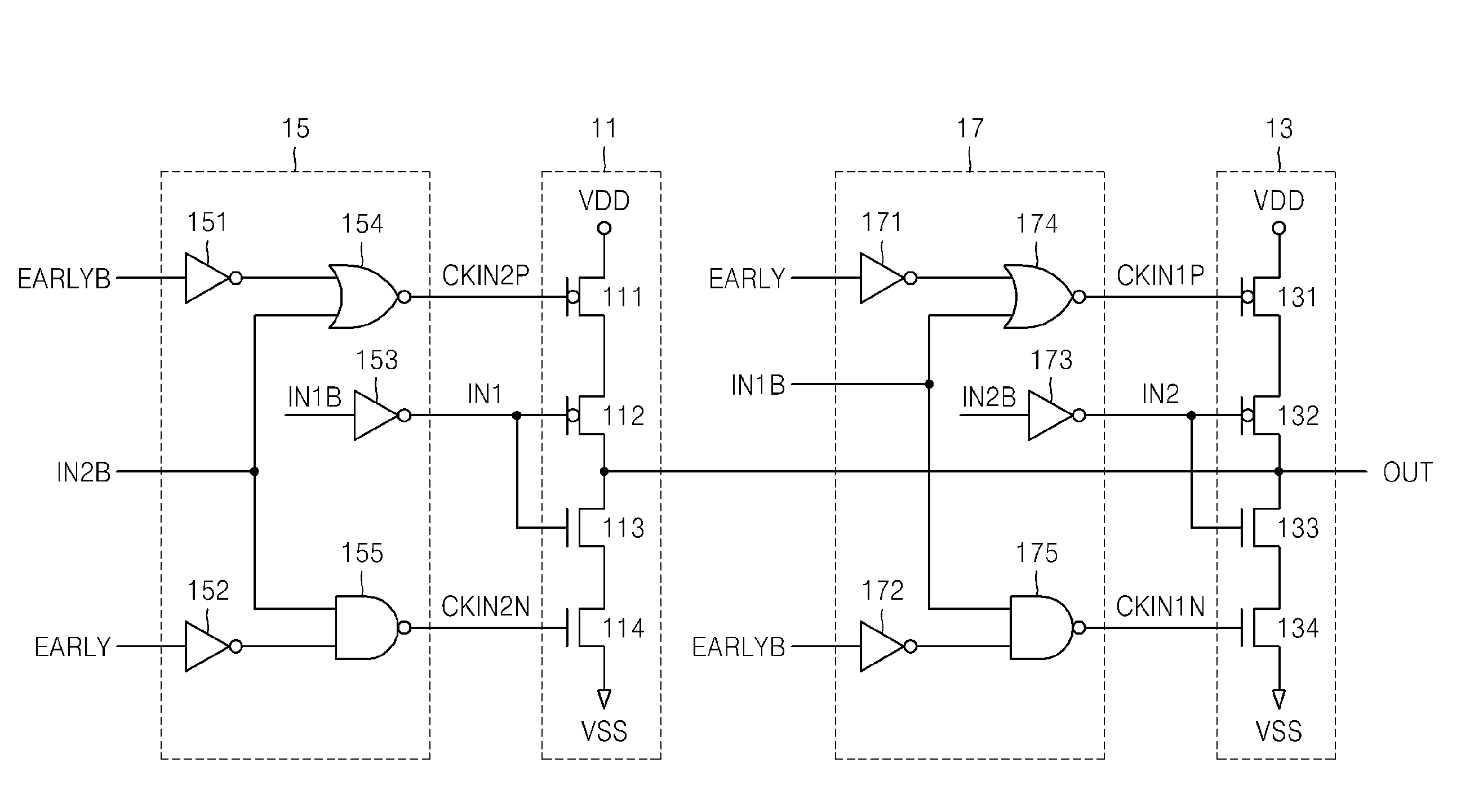

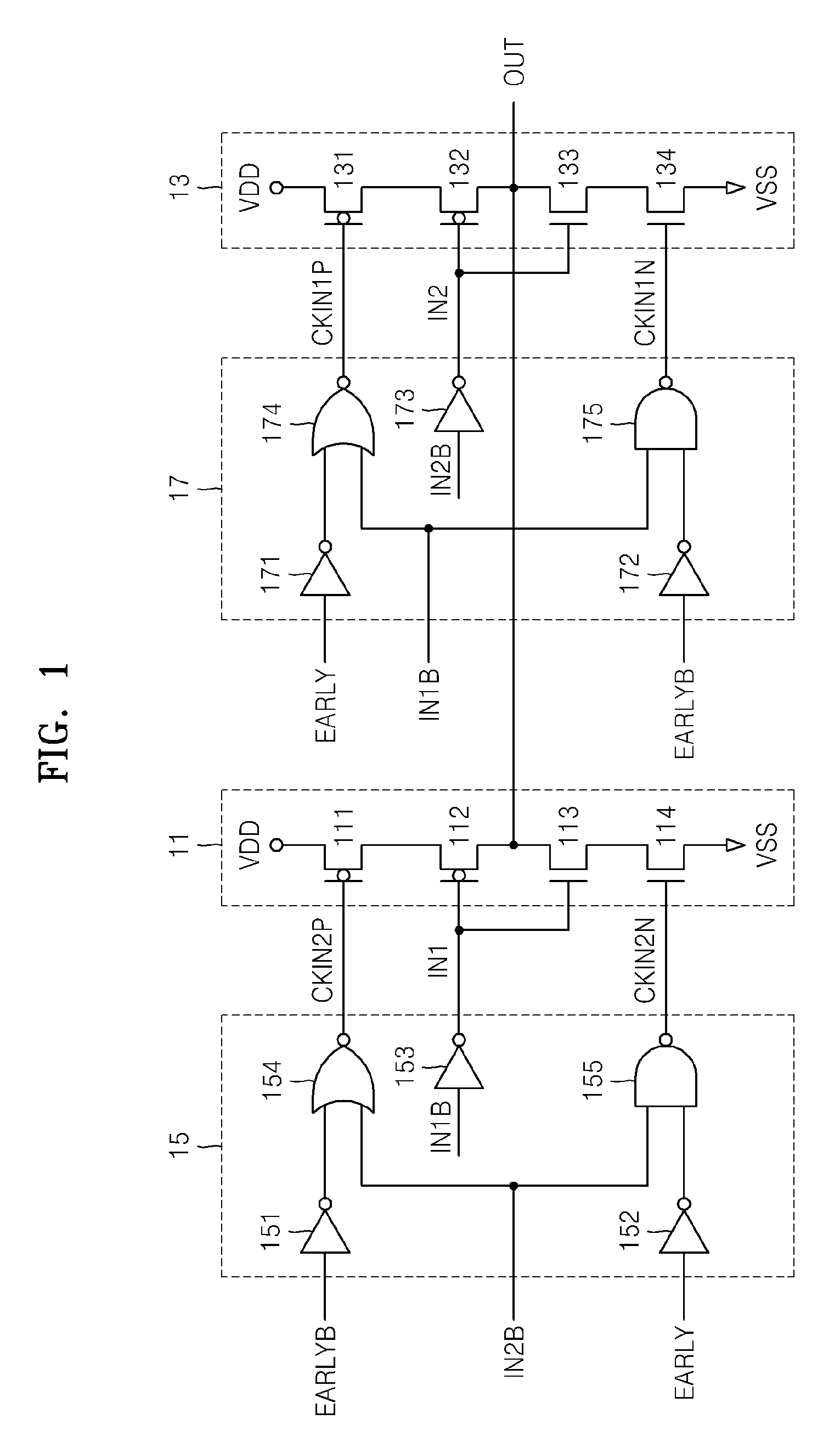

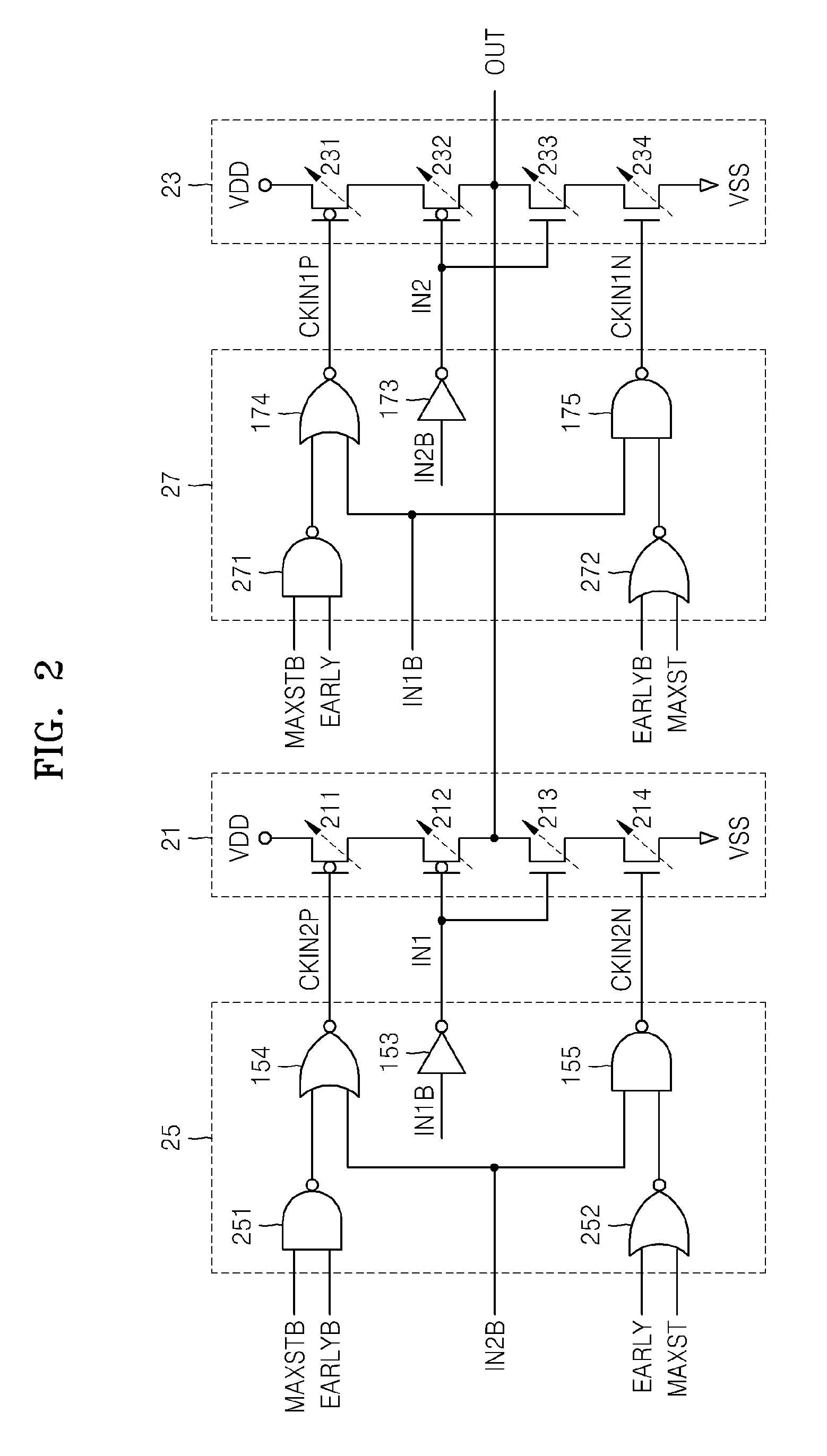

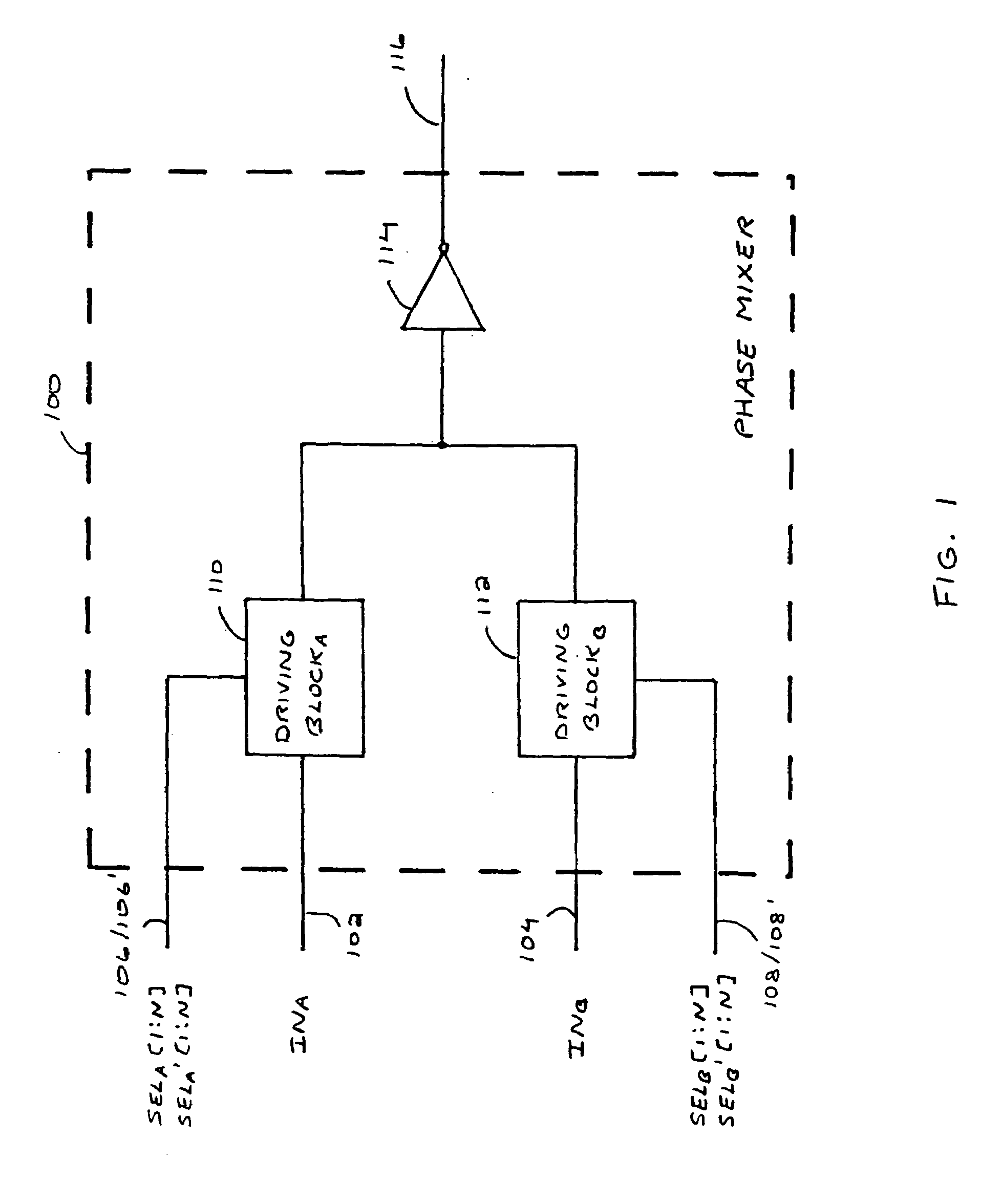

Linear digital phase interpolator and semi-digital delay locked loop (DLL)

Provided are a digital phase interpolator, which performs linear phase interpolation irrelevantly to input order of two input signals, and a semi-digital delay locked loop (DLL), which includes and controls the same. The phase interpolator includes: a first clocked inverter controlled by a phase indicating signal and providing a first output signal to a common output terminal by inverting a first input signal, and a second clocked inverter controlled by the phase indicating signal and providing a second output signal to the common output terminal by inverting the second input signal. The second clocked inverter is clocked by the first input signal when the phase indicating signal is in a first logic state, and the first clocked inverter is clocked by the second input signal when the phase indicating signal is in a second logic state. The phase indicating signal indicates a lead / lag phase relationship between the first and second input signals and is generated in a controller of a circuit of the semi-digital DLL.

Owner:SAMSUNG ELECTRONICS CO LTD

Phase splitter using digital delay locked loops

InactiveUS20050286672A1Pulse automatic controlAngle demodulation by phase difference detectionPhase shiftedPhase splitter

A phase splitter using digital delay locked loop (DLL) to receive complementary input clock signals to generate a plurality of output signals having different phase shifts. When the DLL is locked, the delay resolution of the phase splitter is equal to two delay stages of the DLL.

Owner:ROUND ROCK RES LLC

Digital delay locked loop capable of correcting duty cycle and its method

ActiveUS20060001463A1Reduce latencyReducing delay locking timePulse automatic controlDigital storageMultiplexingSignal delay

An apparatus for adjusting a clock signal, including: a clock multiplexing unit for receiving an external clock signal, an external clock bar signal and a feed-backed clock signal in order to select one of the external clock signal and the external clock bar signal as an output signal of the clock multiplexing unit based on a result of comparing a phase of the external clock signal with a phase of the feed-backed clock signal; and a delay locked loop (DLL) for generating a duty corrected clock signal and the feed-backed clock signal in response to the output signal of the clock multiplexing unit.

Owner:SK HYNIX INC

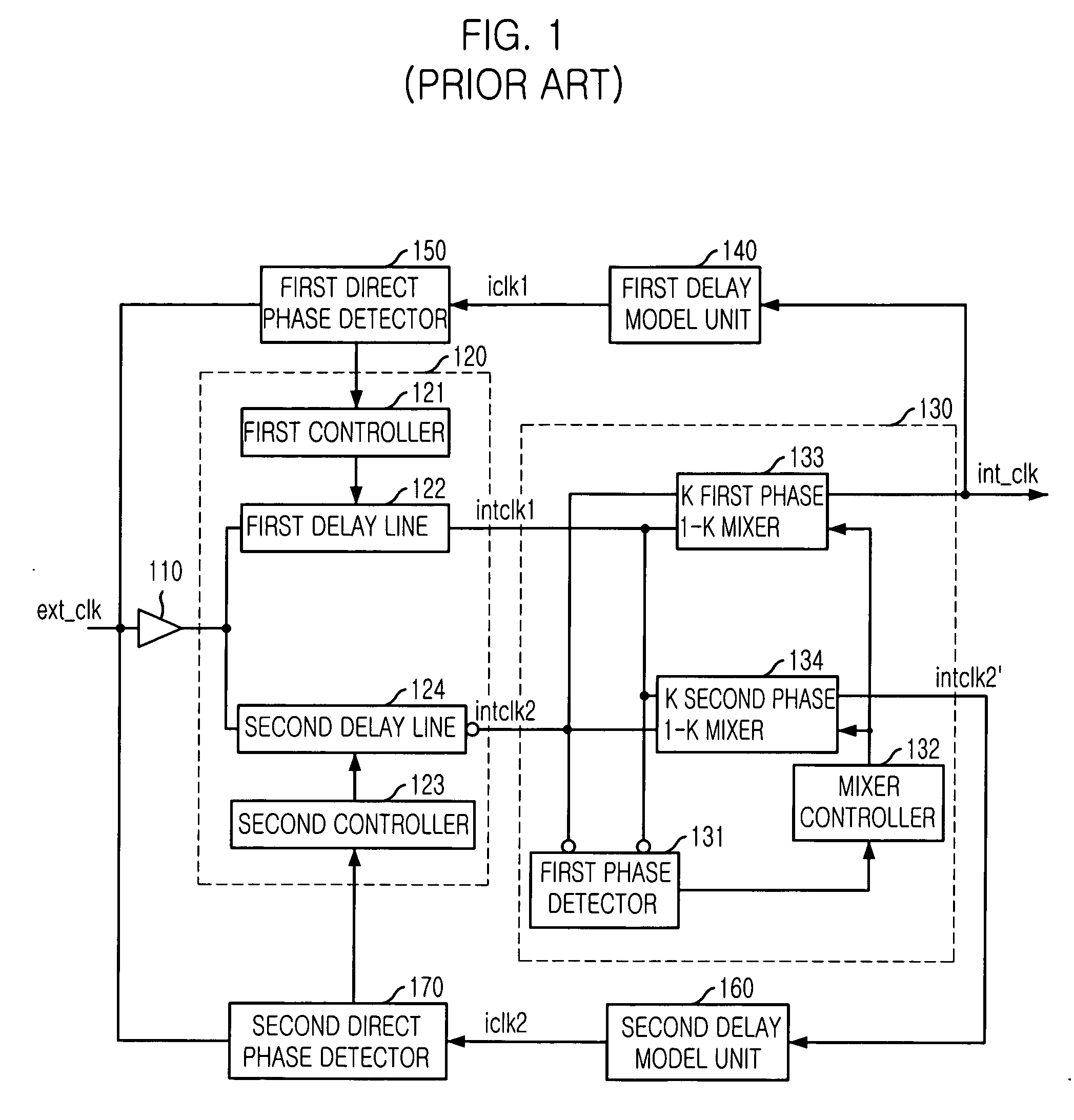

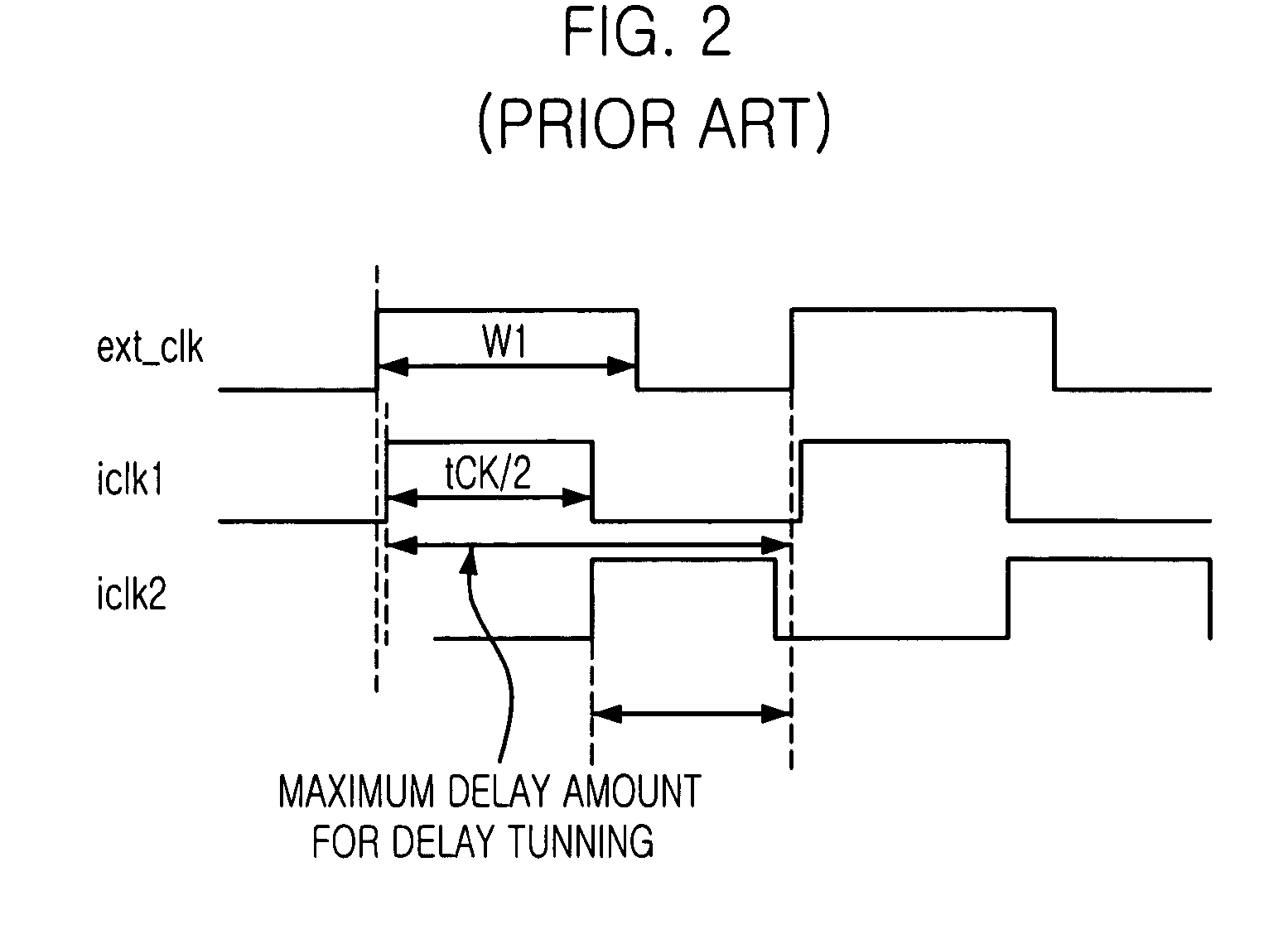

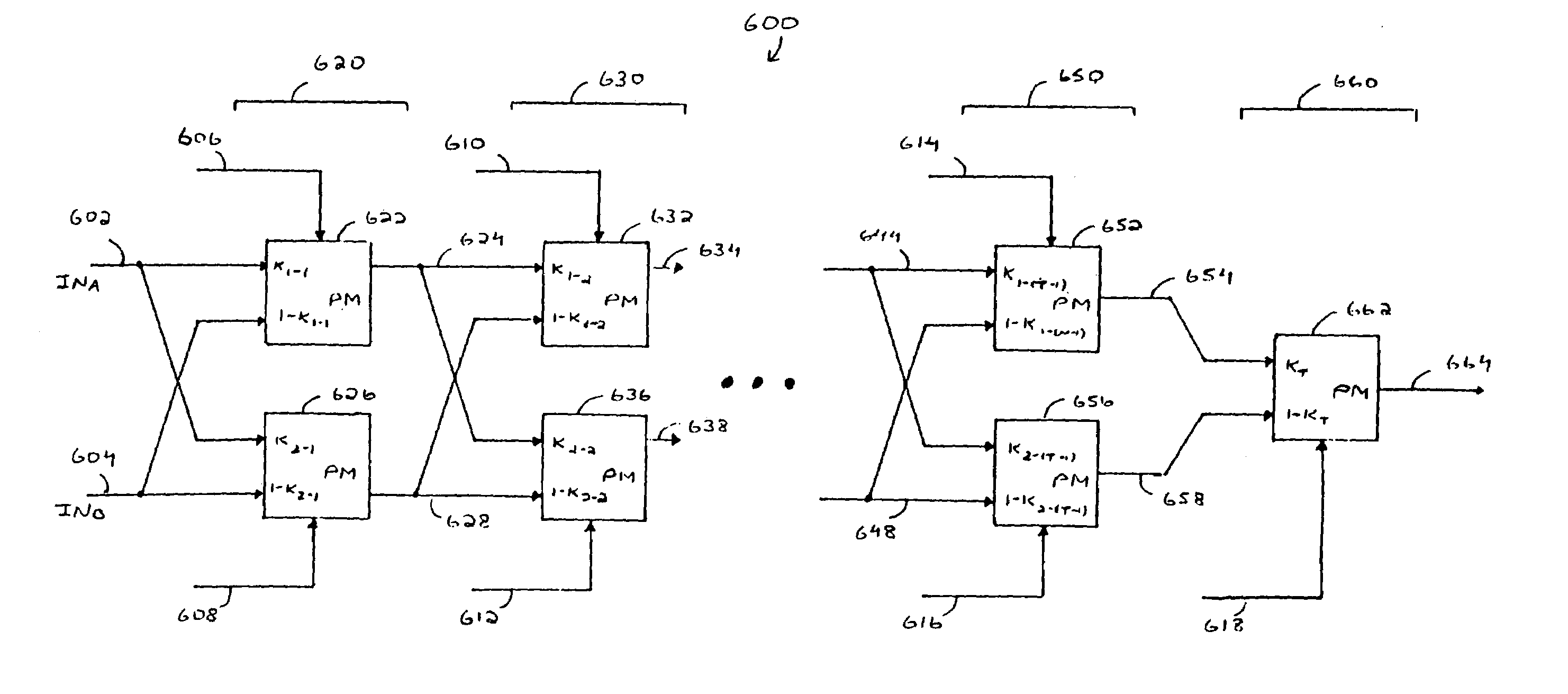

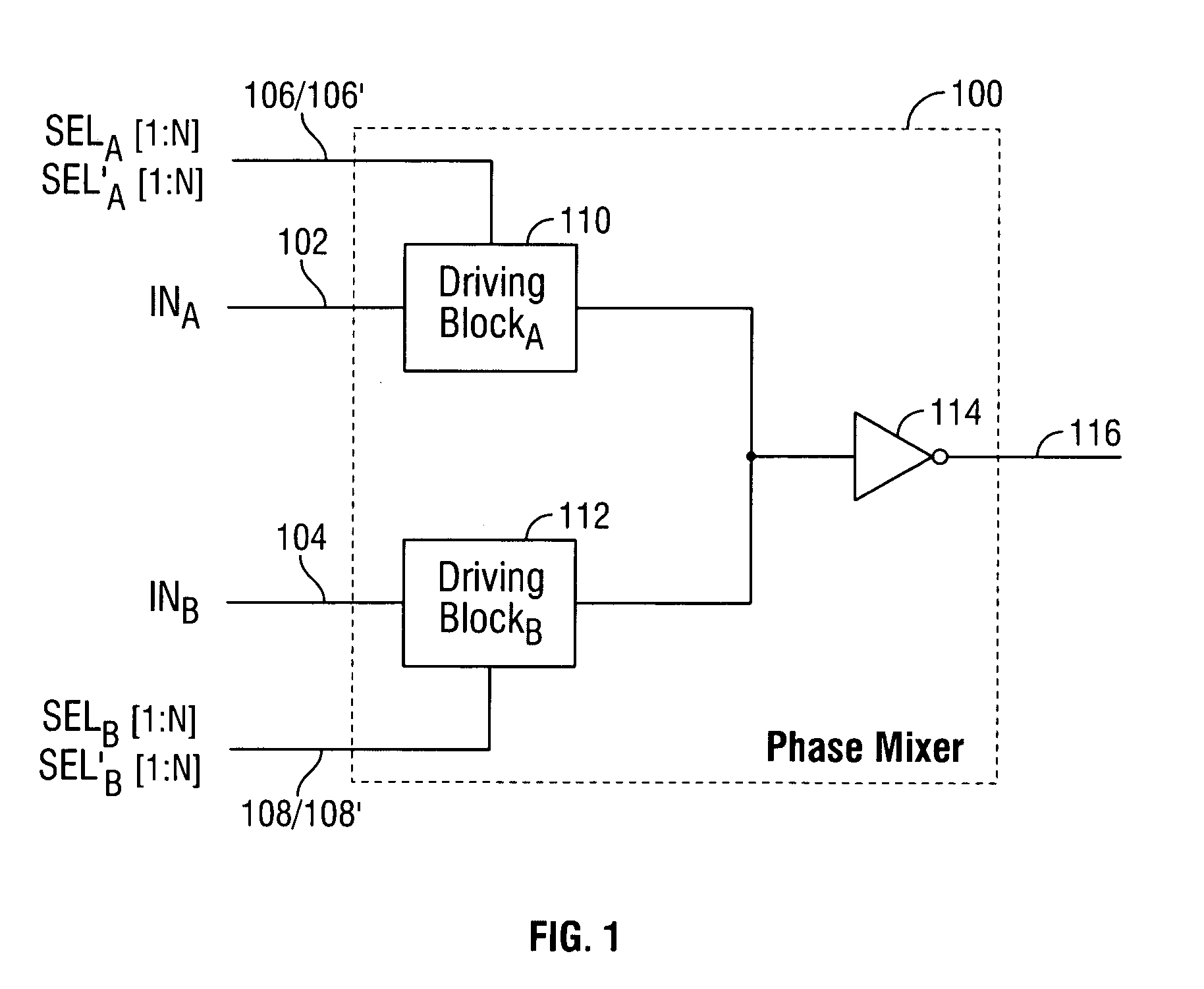

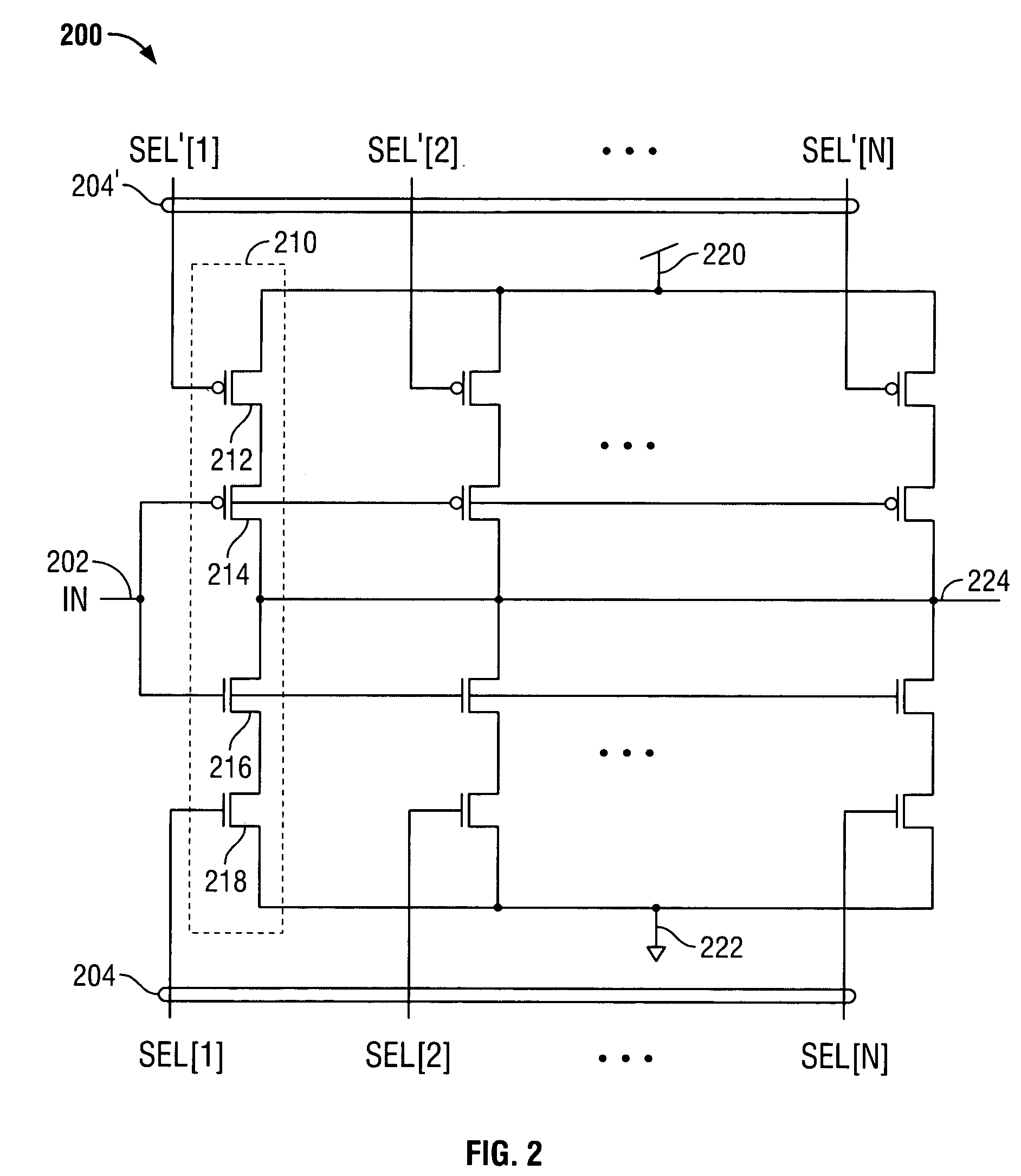

Digital delay-locked loop circuits with hierarchical delay adjustment

InactiveUS6982578B2Computations using contact-making devicesPulse automatic controlPhase differenceDigital delay locked loop

Fine tuned signal phase adjustments are provided by multiple cascaded phase mixers. Each phase mixer outputs a signal having a phase between the phases of its two input signals. With each subsequent stage of phase mixers, the signals generated by the phase mixers have a smaller phase difference, thereby providing finer delay adjustments. Multiple stages of phase mixers can be provided in digital delay-locked loop circuitry to provide additional hierarchical delay adjustment.

Owner:ROUND ROCK RES LLC

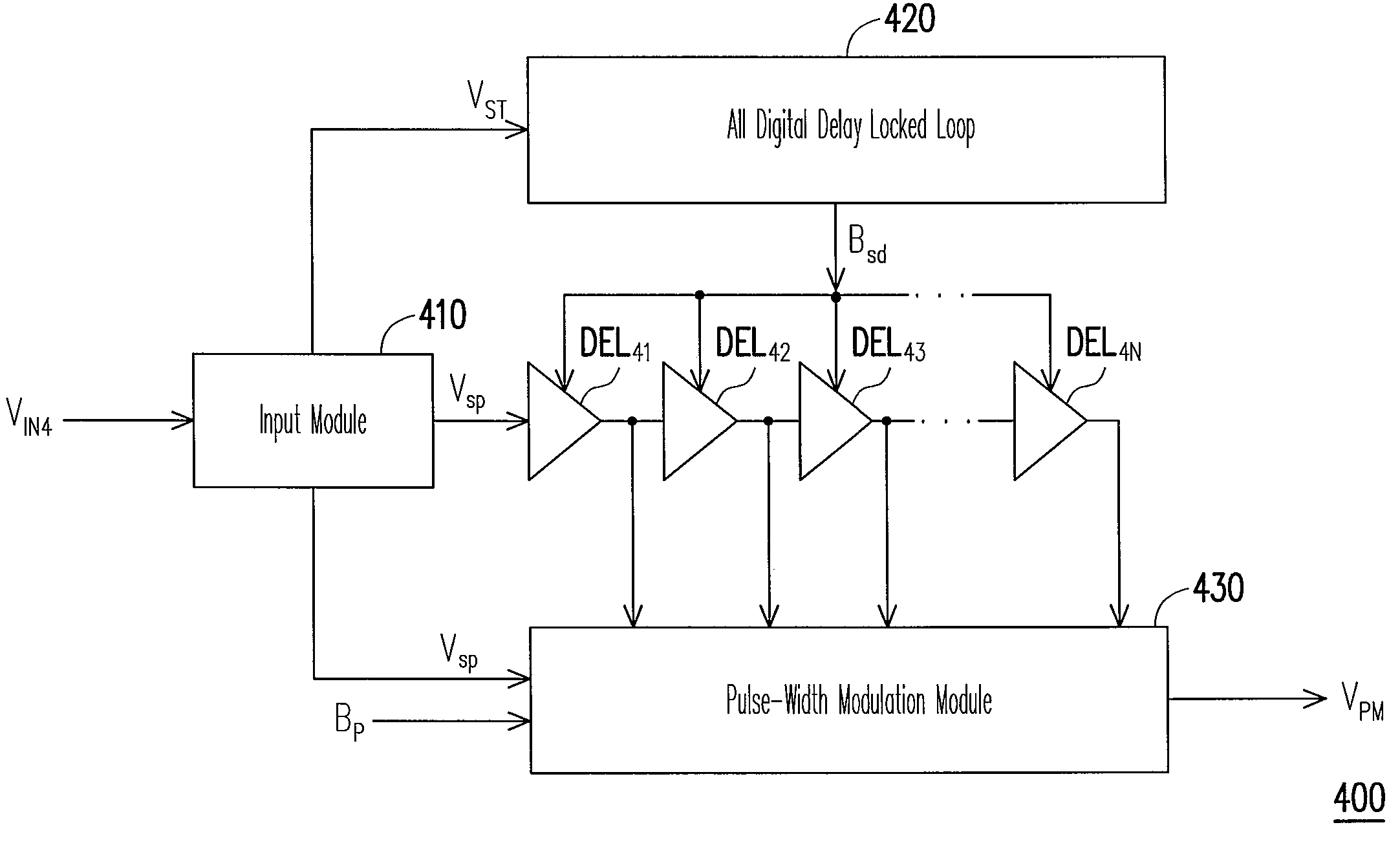

Digital pulse-width control apparatus

InactiveUS7528640B2Reduce restrictionsReduce in quantityPulse automatic controlElectric pulse generatorEngineeringControl equipment

A digital pulse-width control apparatus including an input module, a digital delay locked loop, a plurality of programmable delay circuits connected in series, and a pulse-width modulation module is provided. The present invention uses the input module to vary a clock signal to reduce the limitation of a duty cycle of the clock signal to the digital pulse-width control apparatus.

Owner:IND TECH RES INST

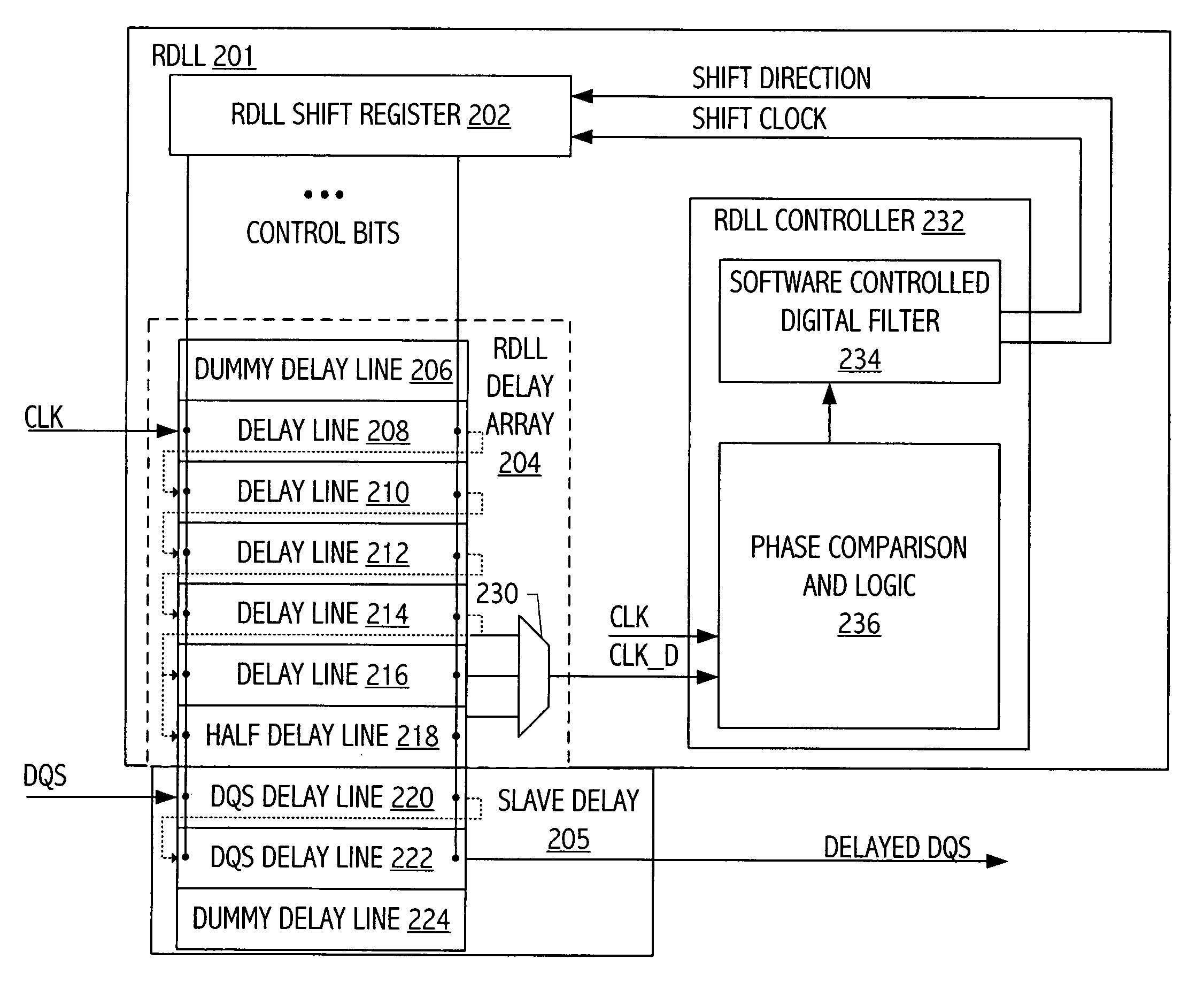

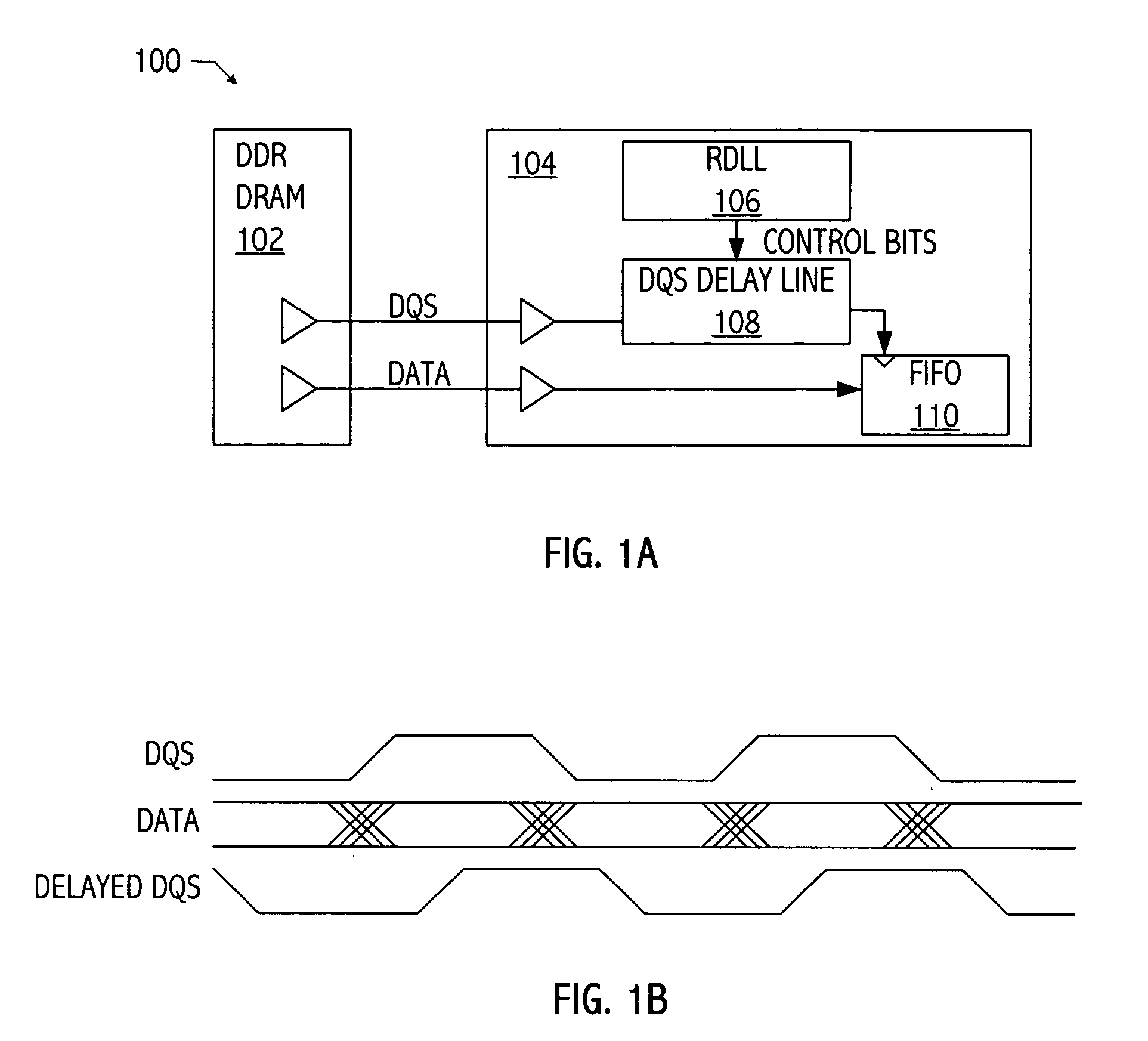

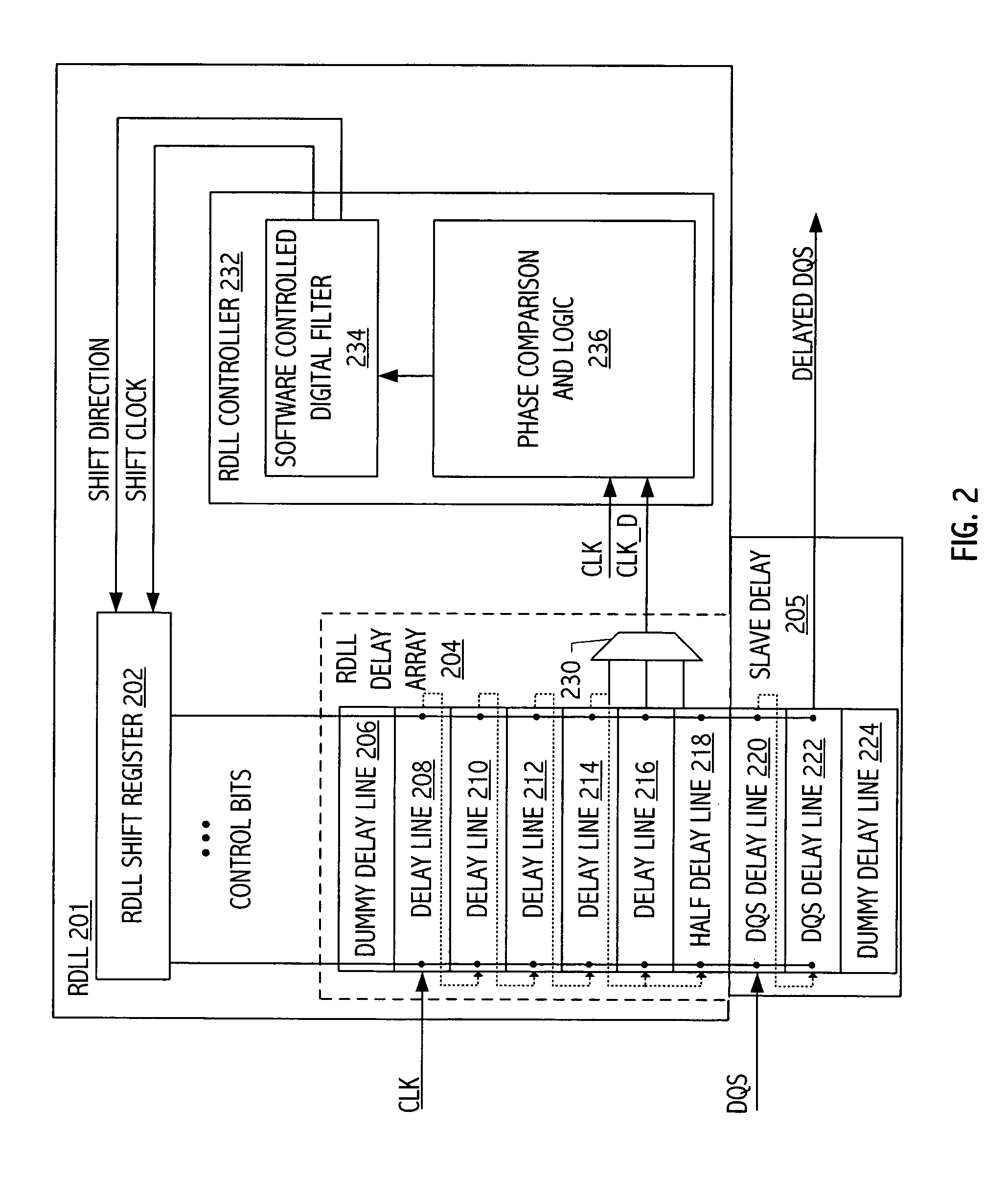

Register controlled delay locked loop with low power consumption

InactiveUS6995591B2Reduce power consumptionReduce loadPulse automatic controlSingle output arrangementsDouble data rateControl delay

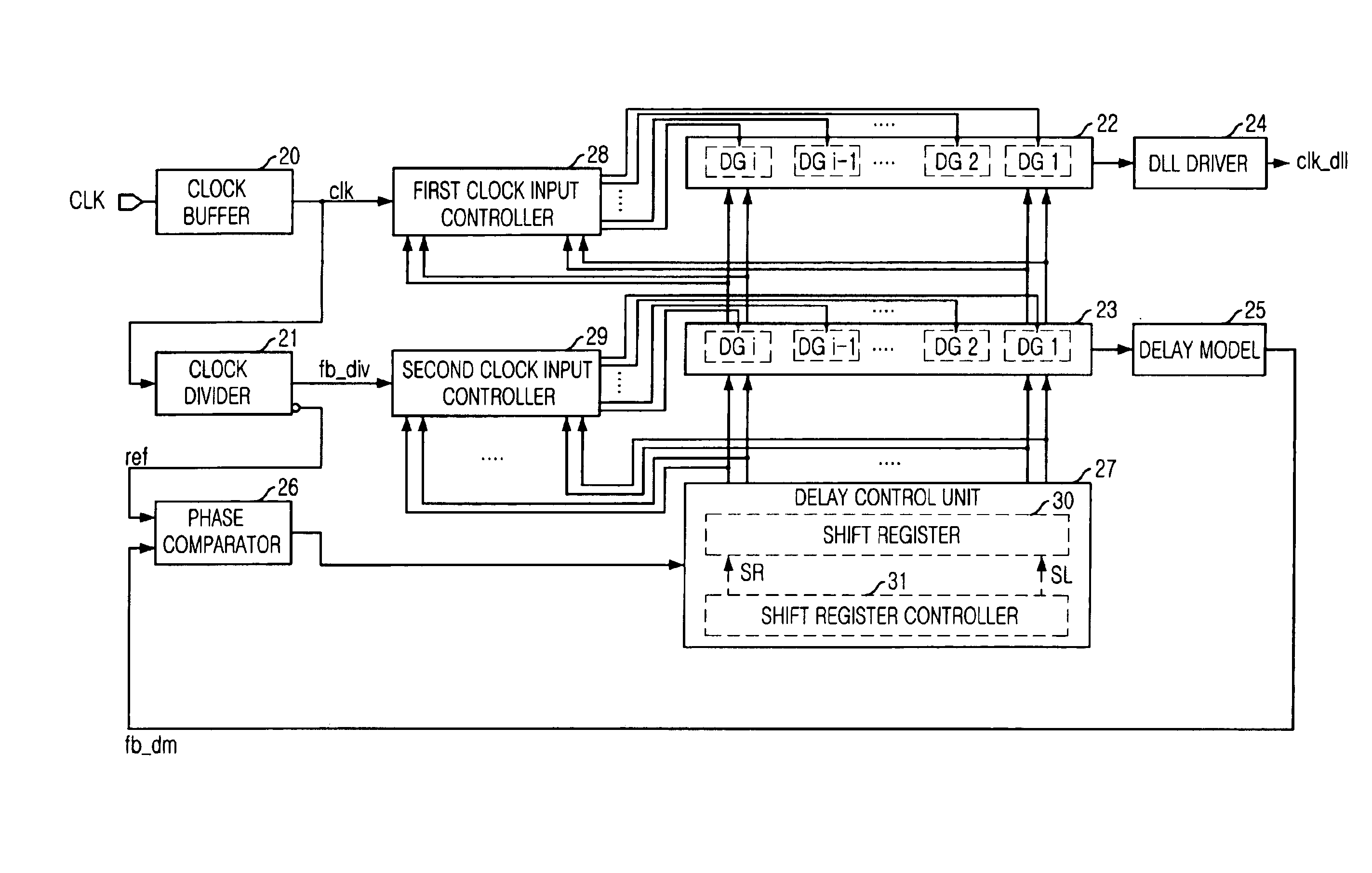

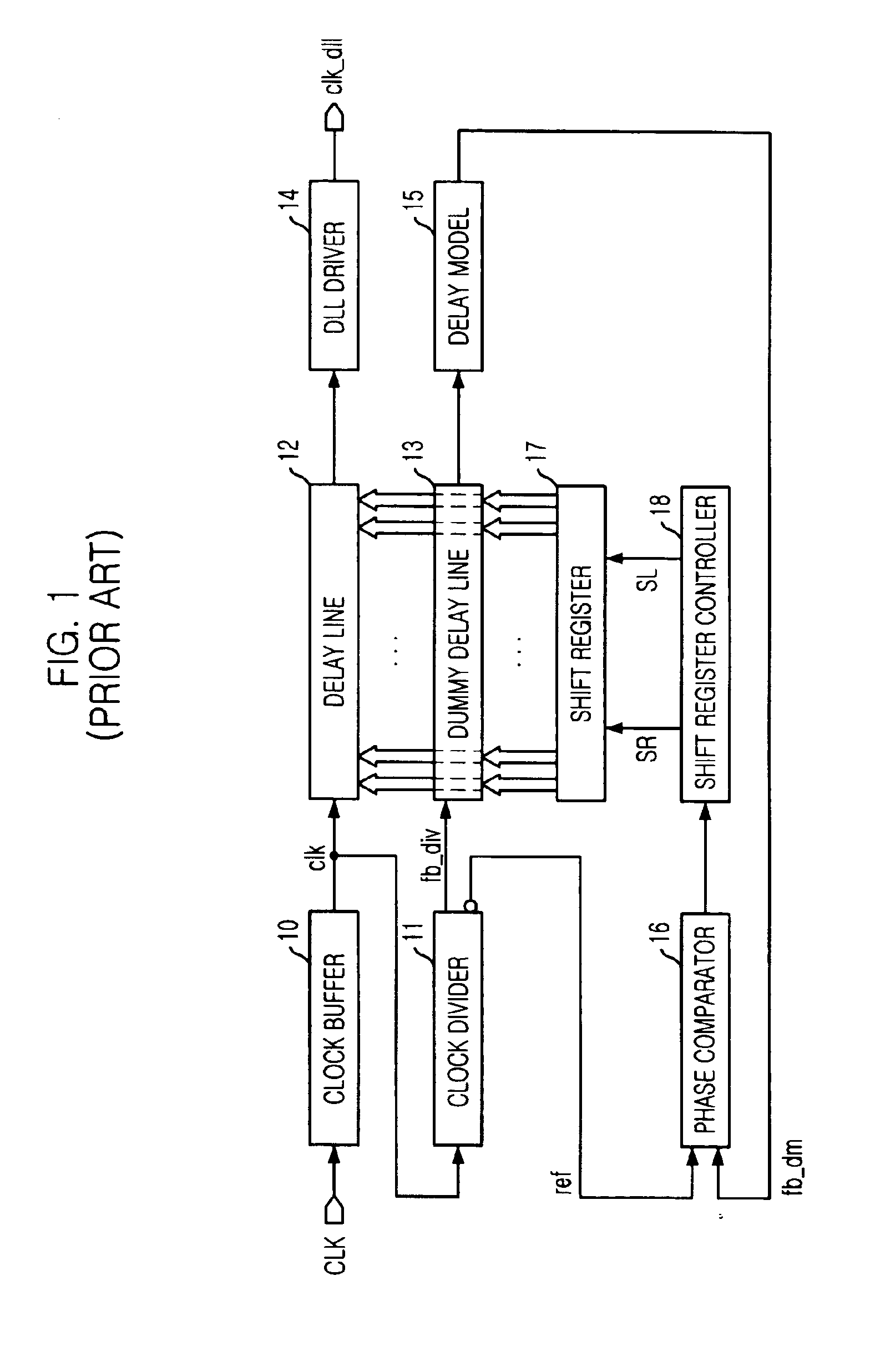

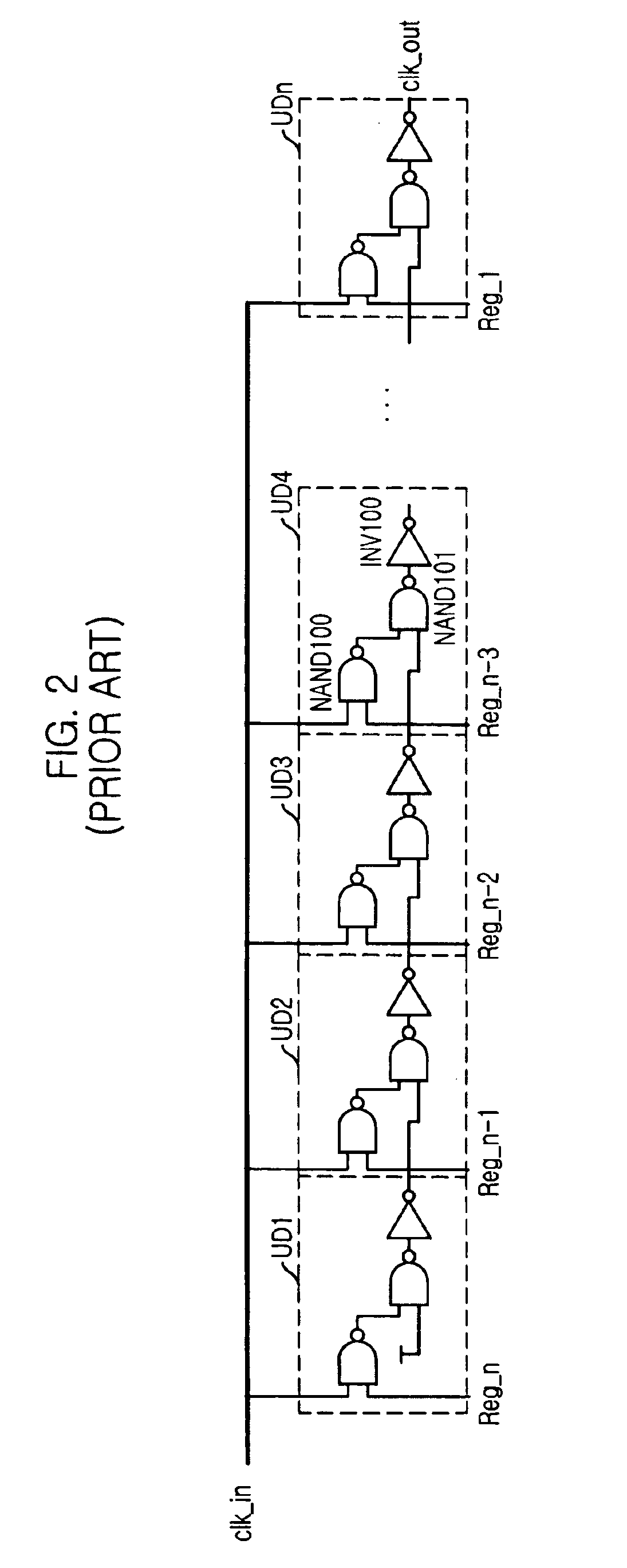

The present invention relates to a digital delay locked loop (DLL) in DDR SDRAM (Double Data Rate Synchronous DRAM). The digital delay locked loop according to the present invention includes: first and second delay lines, each of which includes a plurality of delay groups, for delaying a source clock signal and a delay monitoring signal, wherein each of the delay groups include a plurality of programmable unit delayers; a delay model receiving an output signal of the second delay line for modeling a delay component of a clock signal path; a comparator for comparing a feedback clock signal from the delay model with a reference clock signal; a delay controller for controlling an amount of delay time of the first and second delay lines in response to a comparison result of the comparator; and first and second clock input controllers, which selectively provides the source clock signal and the delay monitoring clock signal to one of delay groups in the first and second delay lines, respectively, in response to output signals of the delay controller.

Owner:SK HYNIX INC

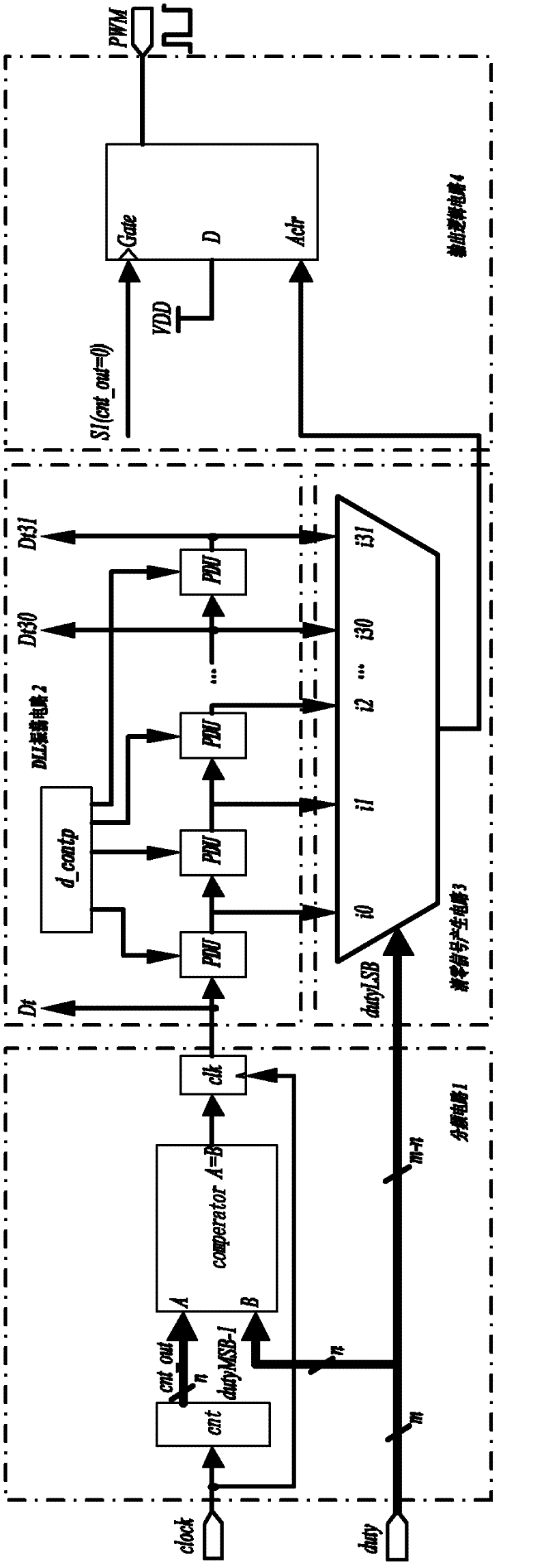

Digital pulse width modulator based on digital delayed-locked loop (DLL)

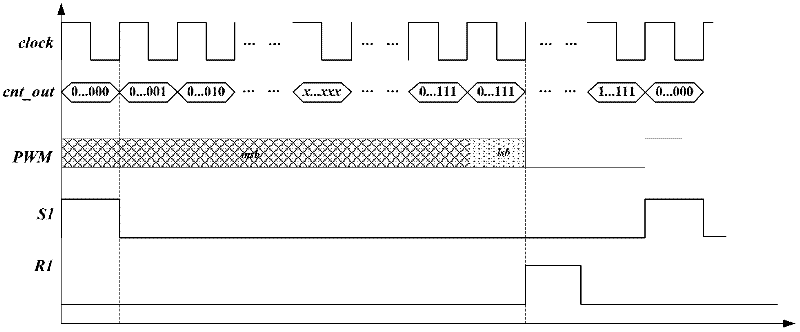

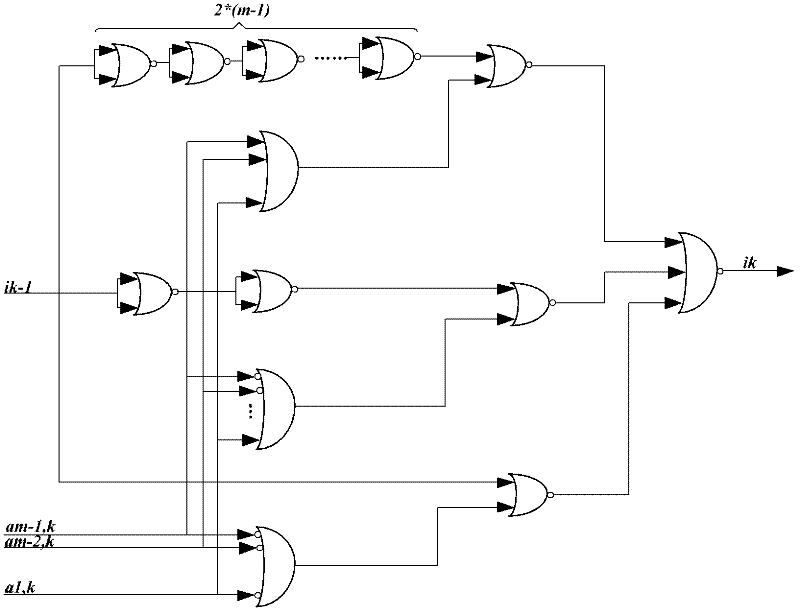

The invention discloses a digital pulse width modulator based on a digital delayed-locked loop (DLL). The digital pulse width modulator comprises: a frequency division circuit, a DLL oscillation loop circuit, a reset signal generation circuit and a PWM output logic circuit. By using inputting a high frequency clock signal fs, the DLL oscillation loop triggers a oscillation loop to perform concussion outputting a 2 channel signal and then the signal is sent to the reset signal generation circuit. The reset signal generation circuit combines the input fs and a duty ratio command signal of mbits so as to generate a pulse signal PWM_clr. Under an effect of post-stage PWM output logic circuit, the PWM signal is generated so as to be taken as the output of the system. The DLL oscillation loop circuit uses a programmable delay unit (PDU) to real-timely track the input signal so that the effect of outputting a good pulse width modulation wave under different process corners and differentworking environments can be achieved. By using the digital pulse width modulator of the invention, areas needed by a chip can be minimized to a larger degree and costs of chip development can be saved.

Owner:SOUTHEAST UNIV

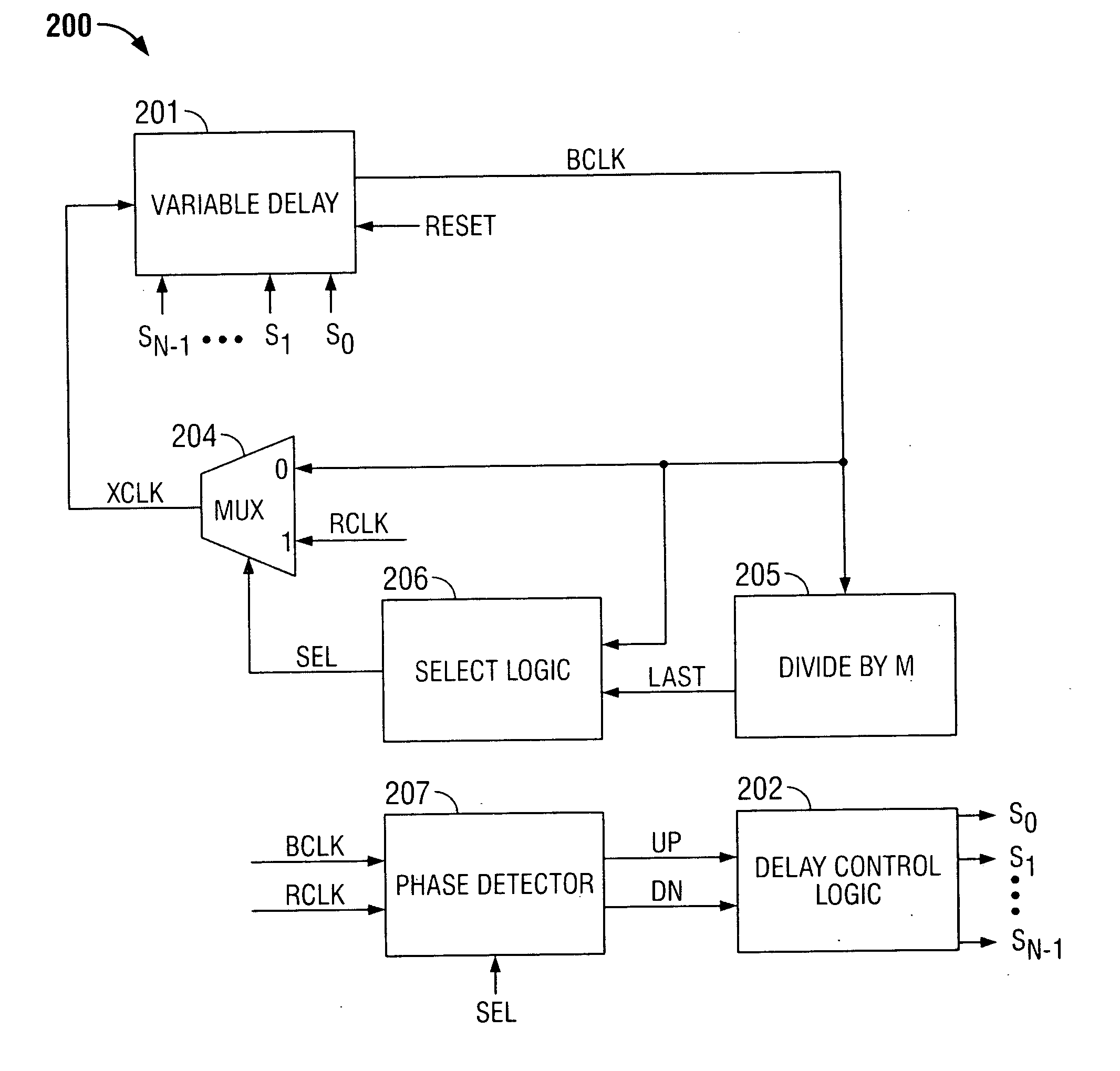

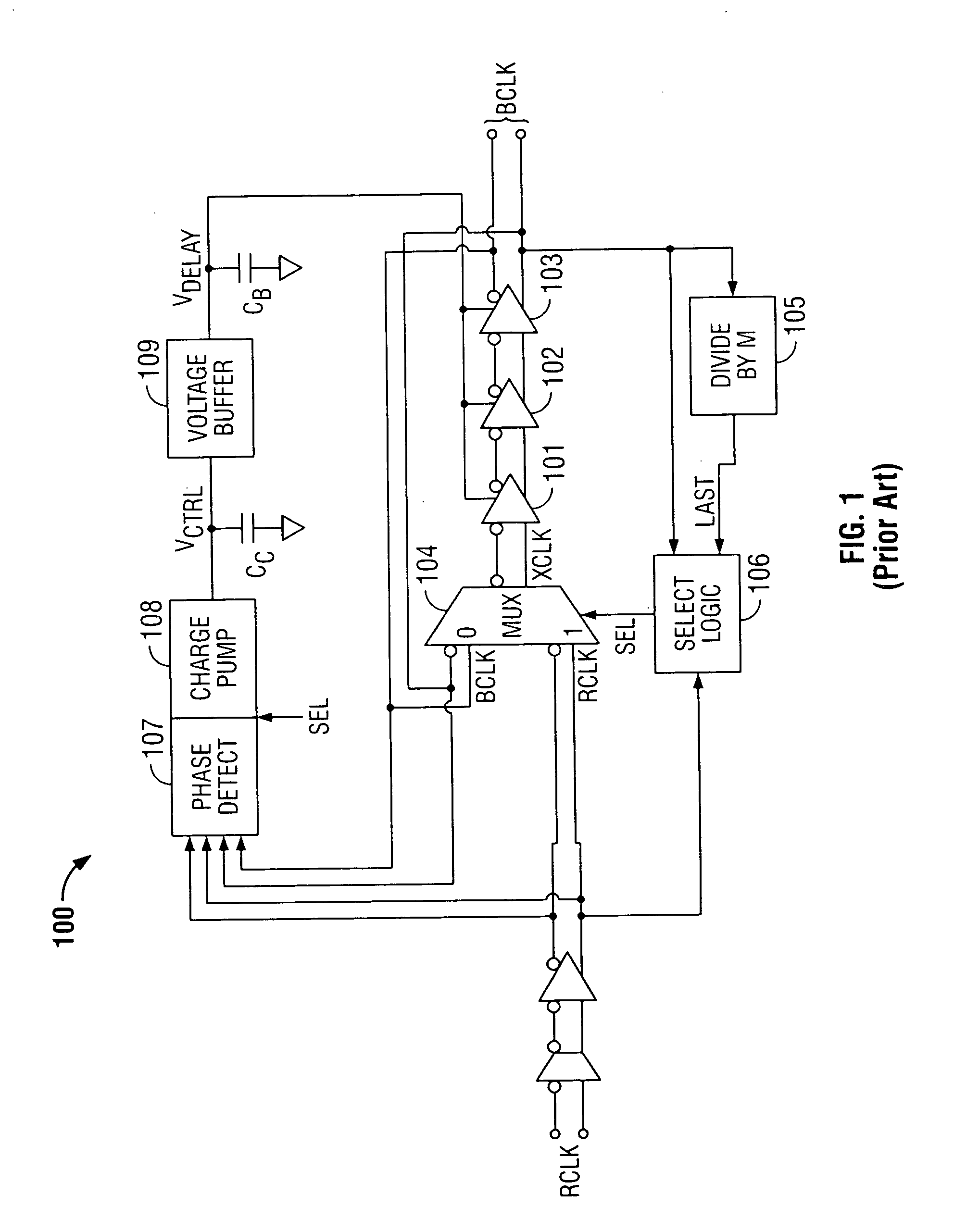

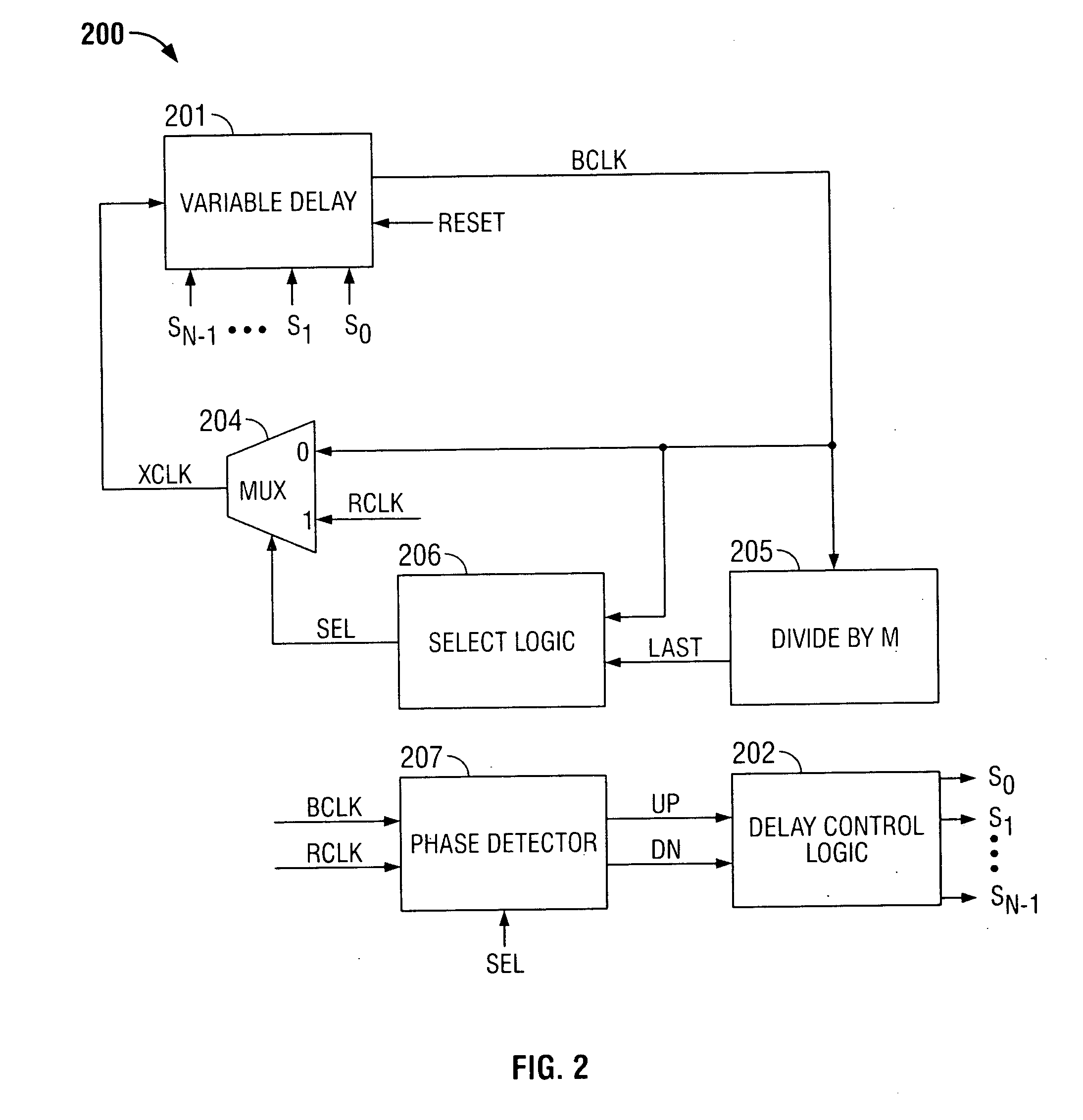

Digital frequency-multiplying DLLs

InactiveUS20050127964A1Reduce resolutionVary numberPulse automatic controlCounting chain pulse countersPhase mixingDelayed time

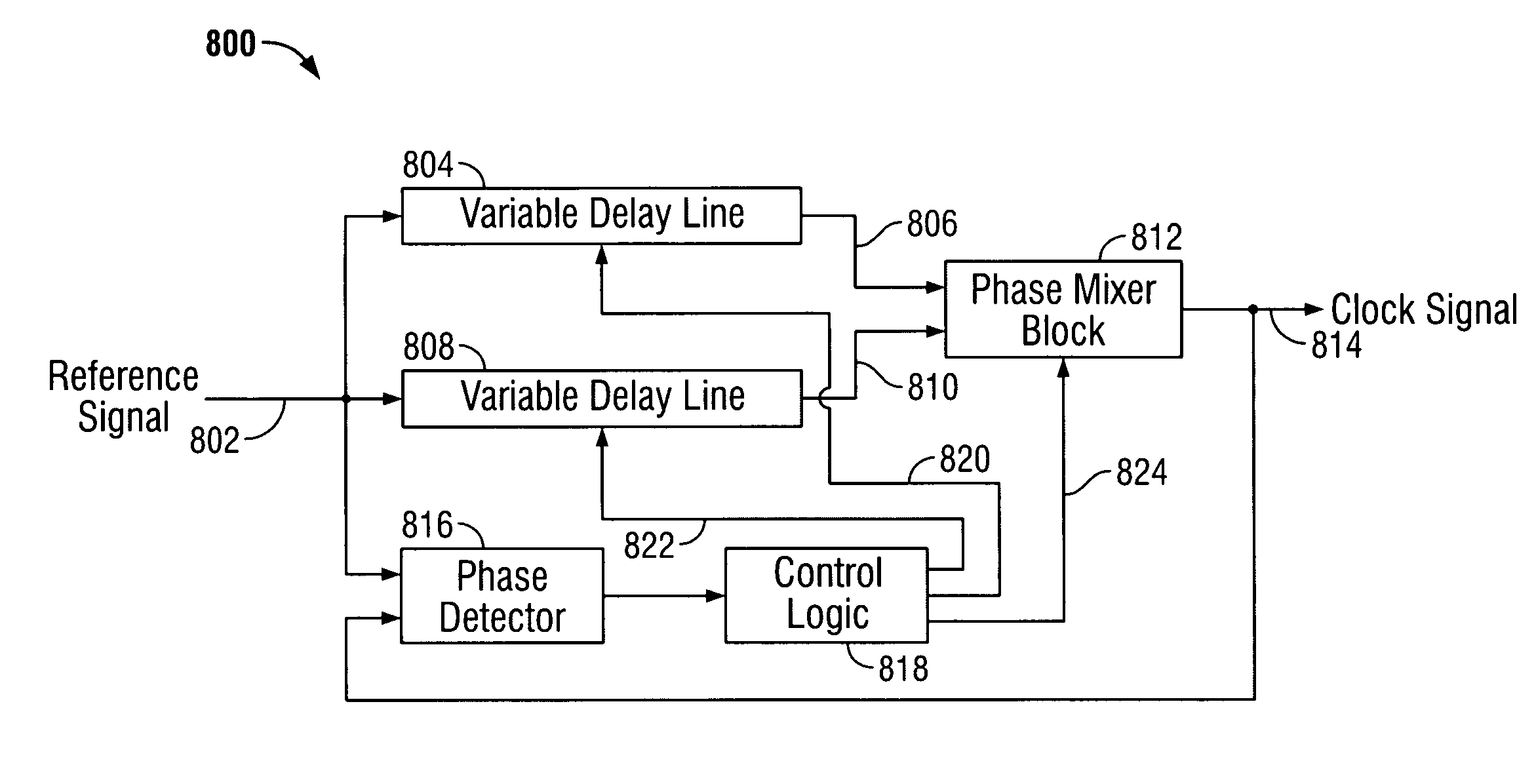

Digital delay-locked loops (DLLs) and methods are provided for signal frequency multiplication. Analog delay elements of typical frequency-multiplying DLLs are replaced with digital and digitally-controlled elements including a variable delay line. The number of unit delay elements in the delay line can be selected to produce a desired output signal delay. Phase-mixing of multiple variable delay line outputs achieves finer delay-time adjustments.

Owner:MICRON TECH INC

Generating different delay ratios for a strobe delay

ActiveUS7109767B1Reduce areaReduce ratePulse automatic controlDigital delay locked loopControl delay

A digital delay-locked loop has been discovered having a reduced area as compared to typical register-controlled delay-locked loops (RDLLs) used to control strobe delay lines that provide delay to strobe signals driving asynchronous FIFOs. This result is achieved by reducing ratio computation (i.e. gear logic) circuitry of the RDLL. A master delay line receives a control code to delay a reference clock by one clock period. A slave delay line receives the control code to delay a strobe signal by a predetermined fraction of the clock period. The master delay line may include individual sections responsive to the control code which effectively delay a signal by a portion of the clock period, the delay having a fixed relationship to a delay associated with individual sections of the slave delay line.

Owner:ORACLE INT CORP

Digital delay-locked loop circuits with hierarchical delay adjustment

InactiveUS20050110539A1Computations using contact-making devicesPulse automatic controlPhase differenceDigital delay locked loop

Fine tuned signal phase adjustments are provided by multiple cascaded phase mixers. Each phase mixer outputs a signal having a phase between the phases of its two input signals. With each subsequent stage of phase mixers, the signals generated by the phase mixers have a smaller phase difference, thereby providing finer delay adjustments. Multiple stages of phase mixers can be provided in digital delay-locked loop circuitry to provide additional hierarchical delay adjustment.

Owner:ROUND ROCK RES LLC

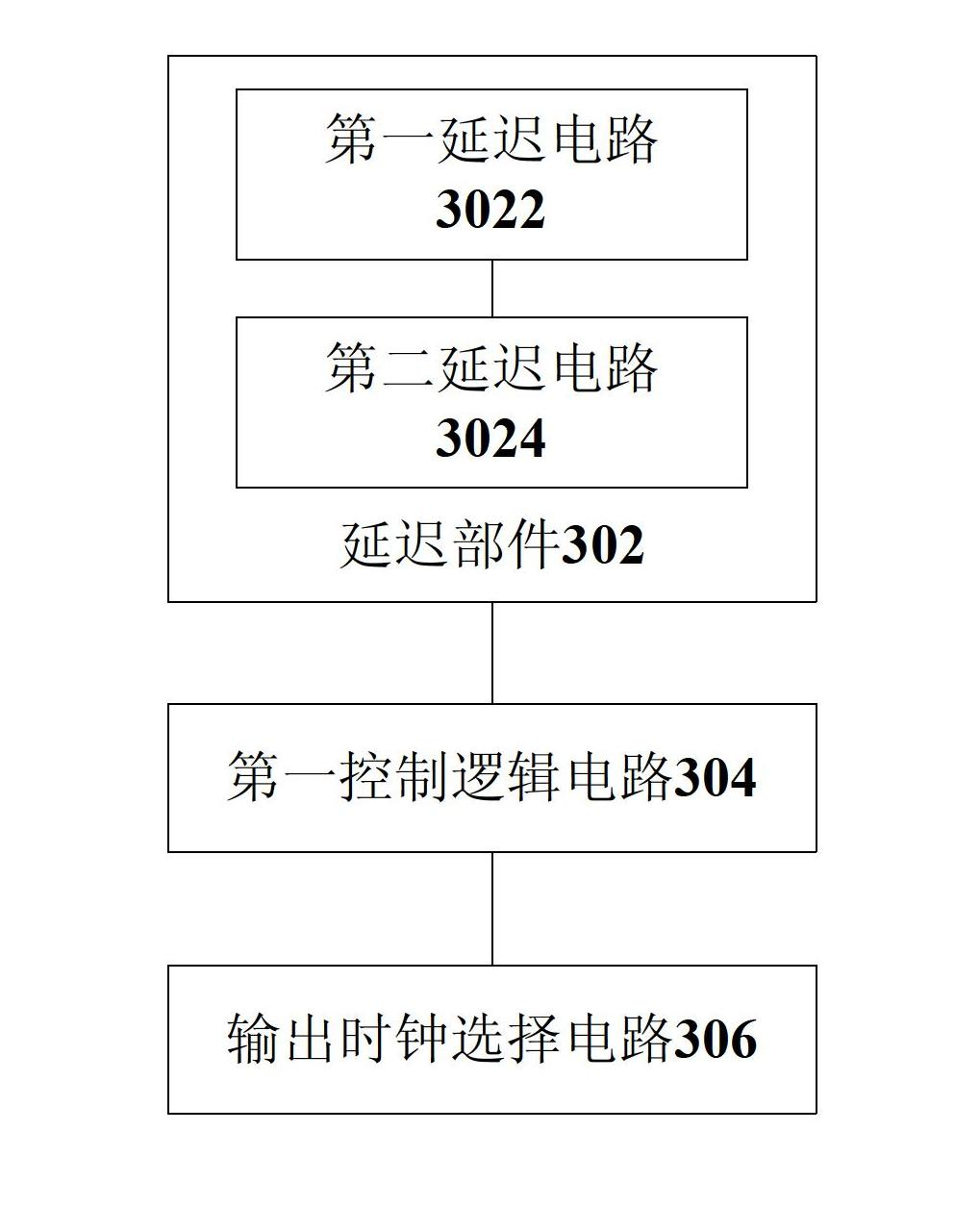

Digital delay device

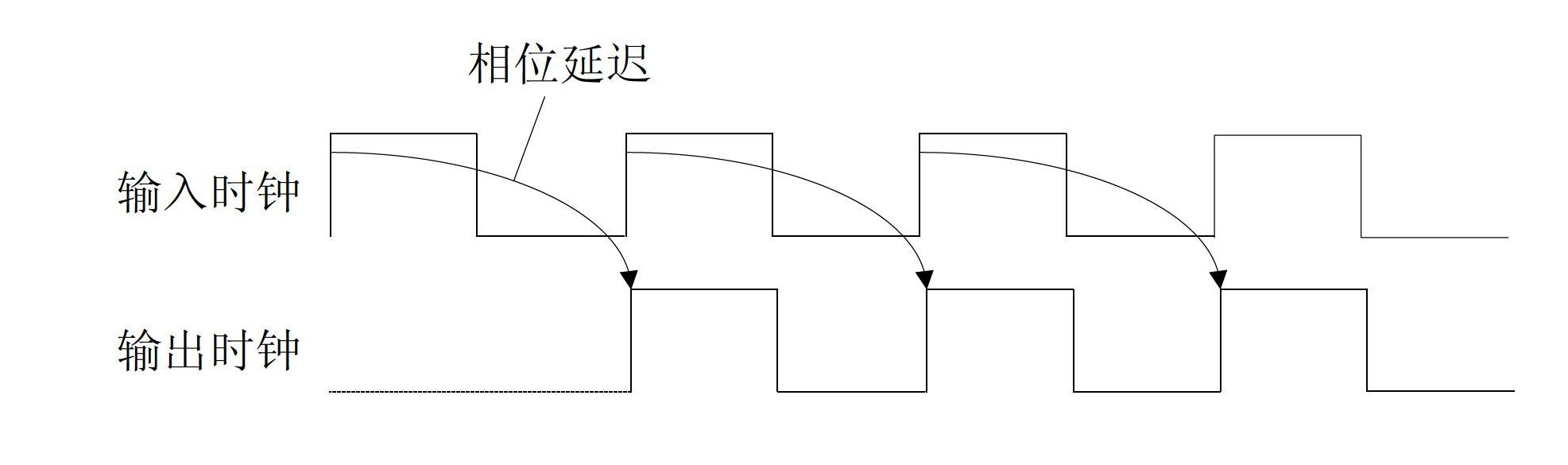

ActiveCN102664623AReduce in quantityReduce dithering noisePulse automatic controlDifferential signalingJitter noise

The invention discloses a digital delay device, which comprises a delay part, a first control logic circuit and an output clock selection circuit, wherein the delay part comprises a first delay circuit and a second delay circuit, which are used for processing digital signals respectively, and the digital signals are differential signals of each other; the first control logic circuit is used for controlling the first and second delay circuits to output a first clock signal and a second clock signal respectively; and the output clock selection circuit is used for outputting a third clock signal according to the first clock signal and / or the second clock signal. The problem that a great number of delay units of a delay chain are required to cause loud clock jitter noise when a digital delay locked loop is required to have maximum delay time in related technologies is solved, and the effect of lowering the clock jitter noise is achieved.

Owner:LOONGSON TECH CORP

Pre-divider architecture for low power in a digital delay locked loop

A delay locked loop circuit for conserving power on a semiconductor chip is provided. The circuit includes a delay chain circuit responsive to a clock input signal for generating an output clock signal having a selectively adjustable delay at an output circuit; a feedback loop circuit connects to and controls said delay chain circuit; and a pre-divider circuit connected to said delay chain circuit, wherein said pre-divider circuit is configured to disable the delay chain circuit when the output clock signal is inactive and the memory device is in an idle state (i.e., all banks closed).

Owner:IBM CORP

Digital frequency-multiplying DLLs

InactiveUS20050285643A1Vary numberReduce resolutionPulse automatic controlCounting chain pulse countersPhase mixingDelayed time

Digital delay-locked loops (DLLs) and methods are provided for signal frequency multiplication. Analog delay elements of typical frequency-multiplying DLLs are replaced with digital and digitally-controlled elements including a variable delay line. The number of unit delay elements in the delay line can be selected to produce a desired output signal delay. Phase-mixing of multiple variable delay line outputs achieves finer delay-time adjustments.

Owner:MICRON TECH INC

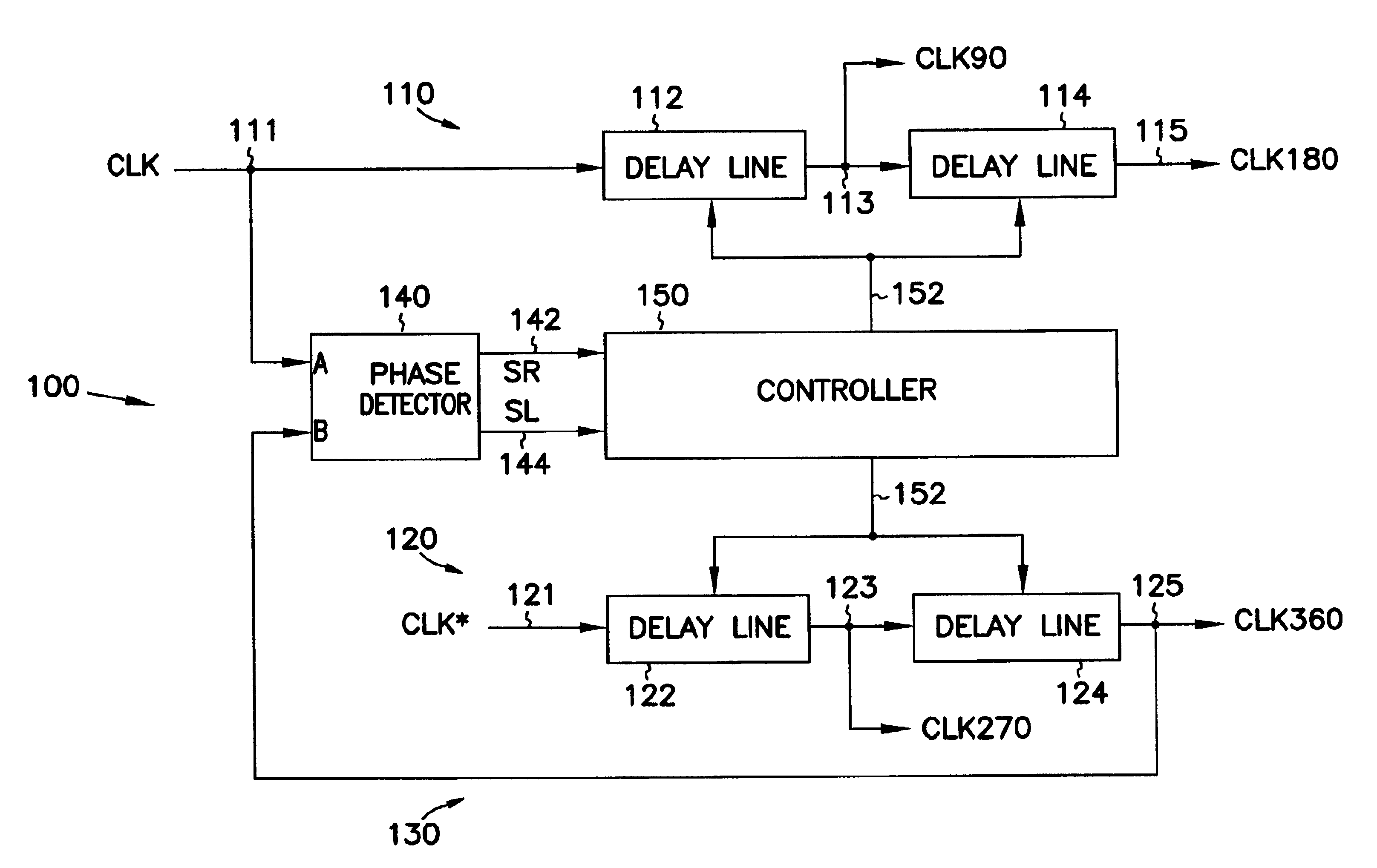

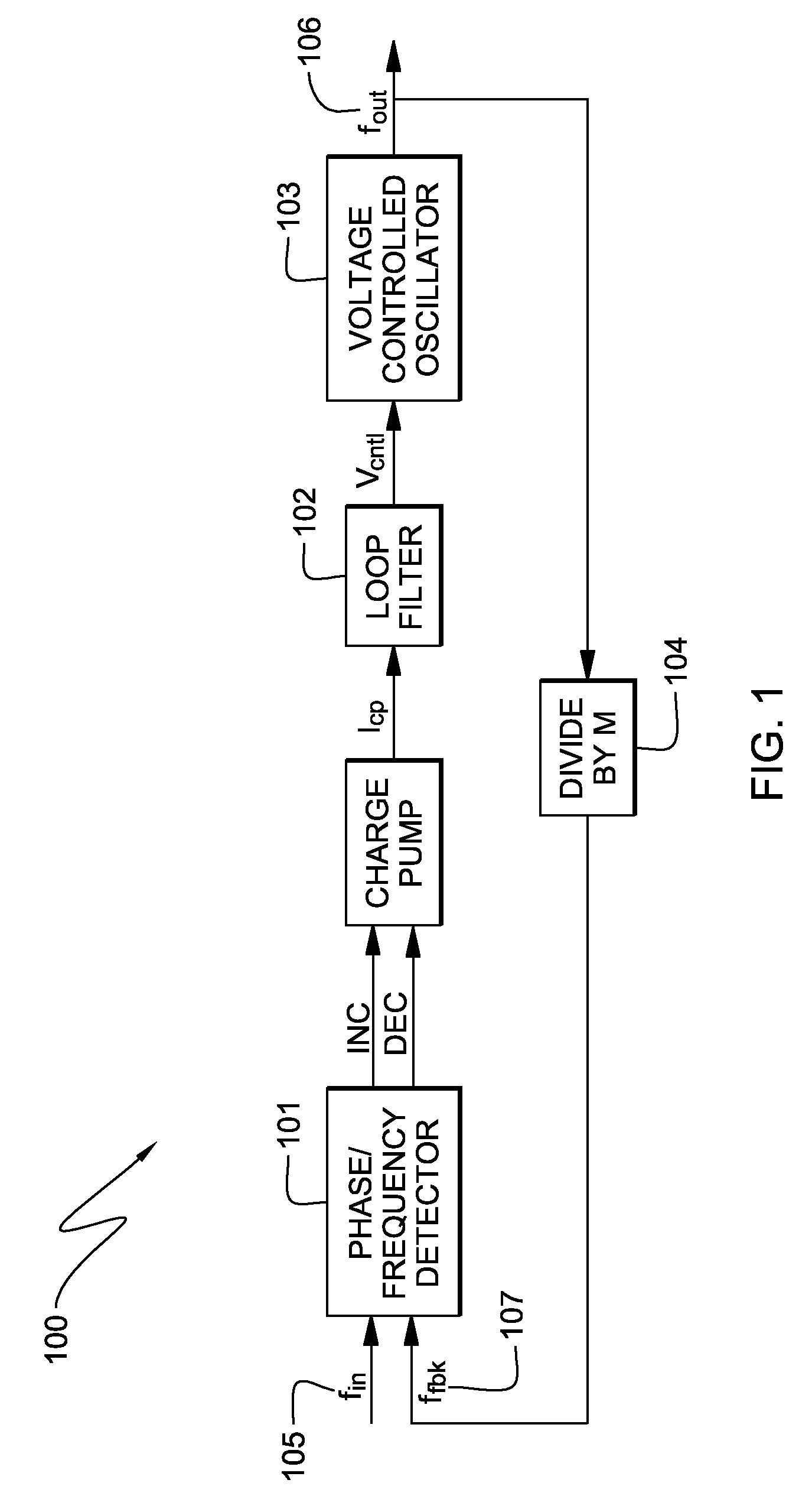

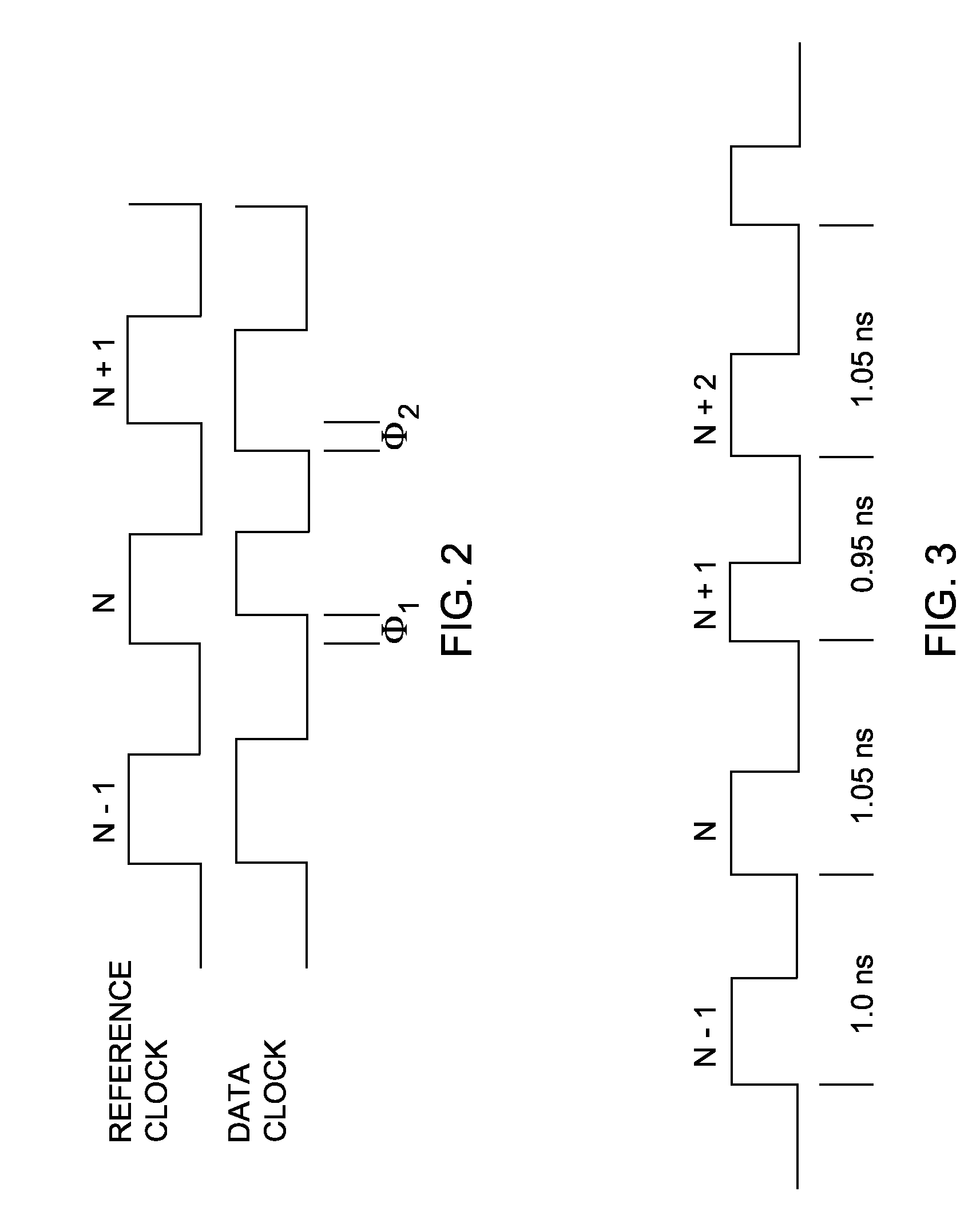

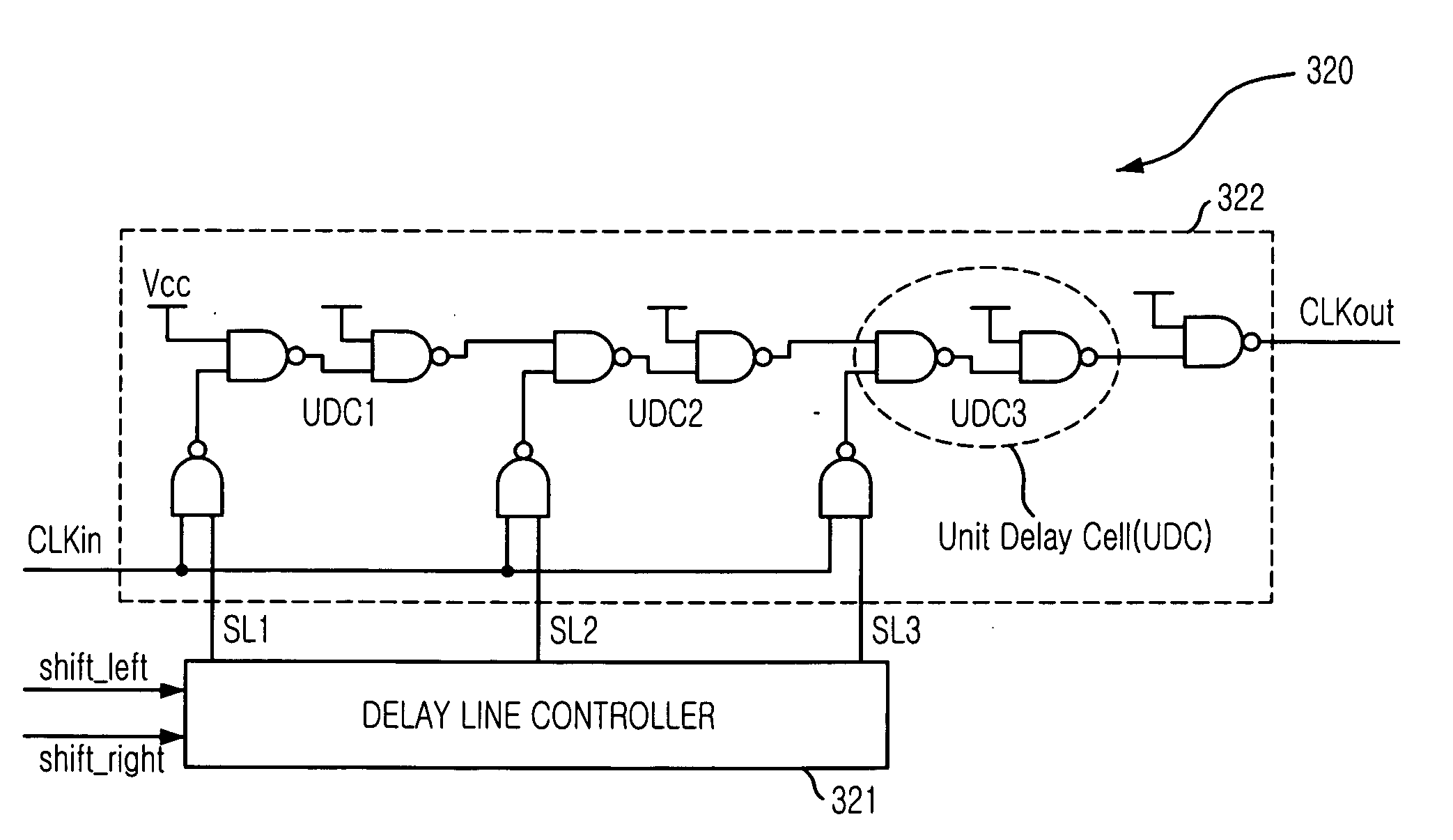

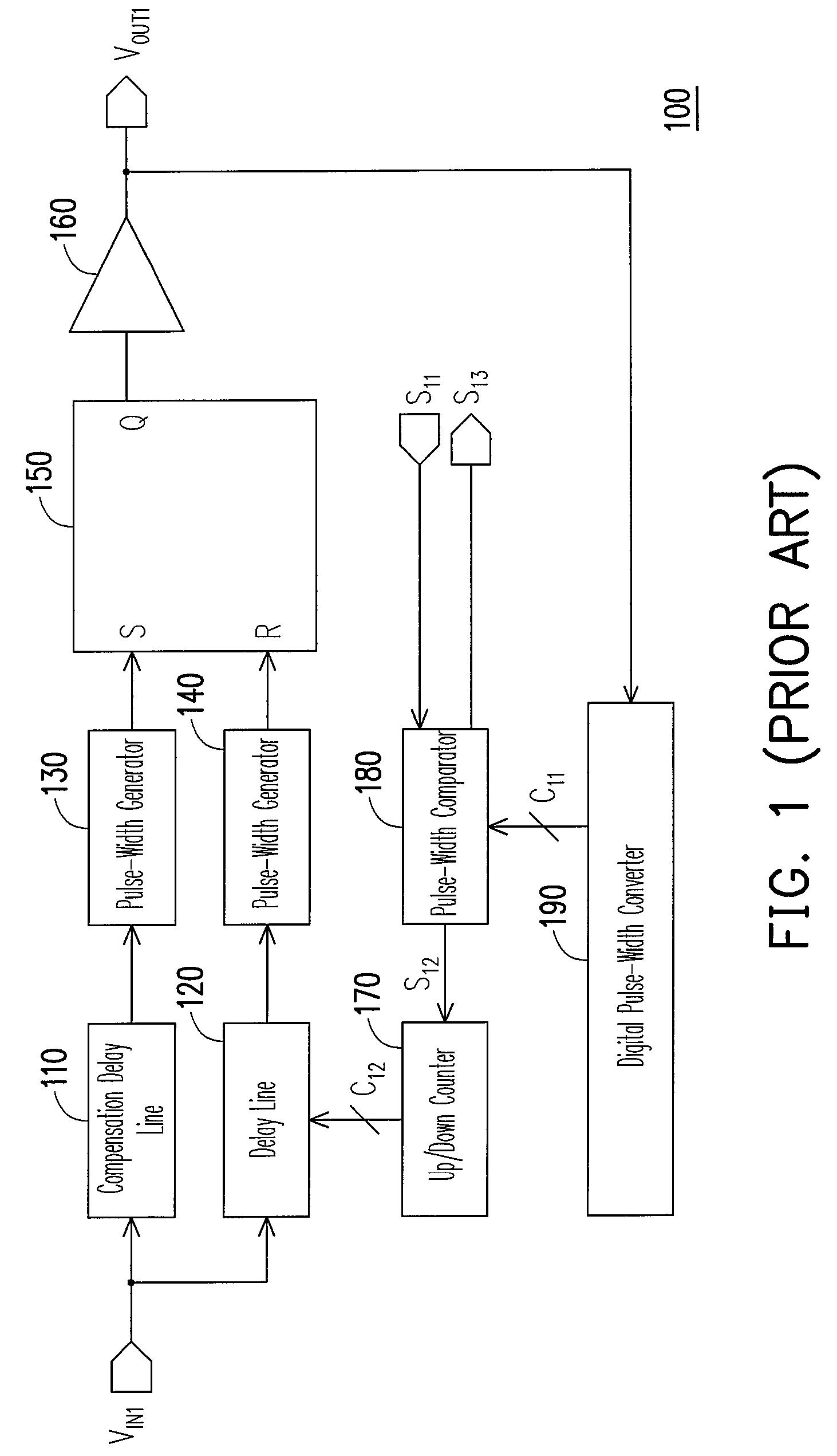

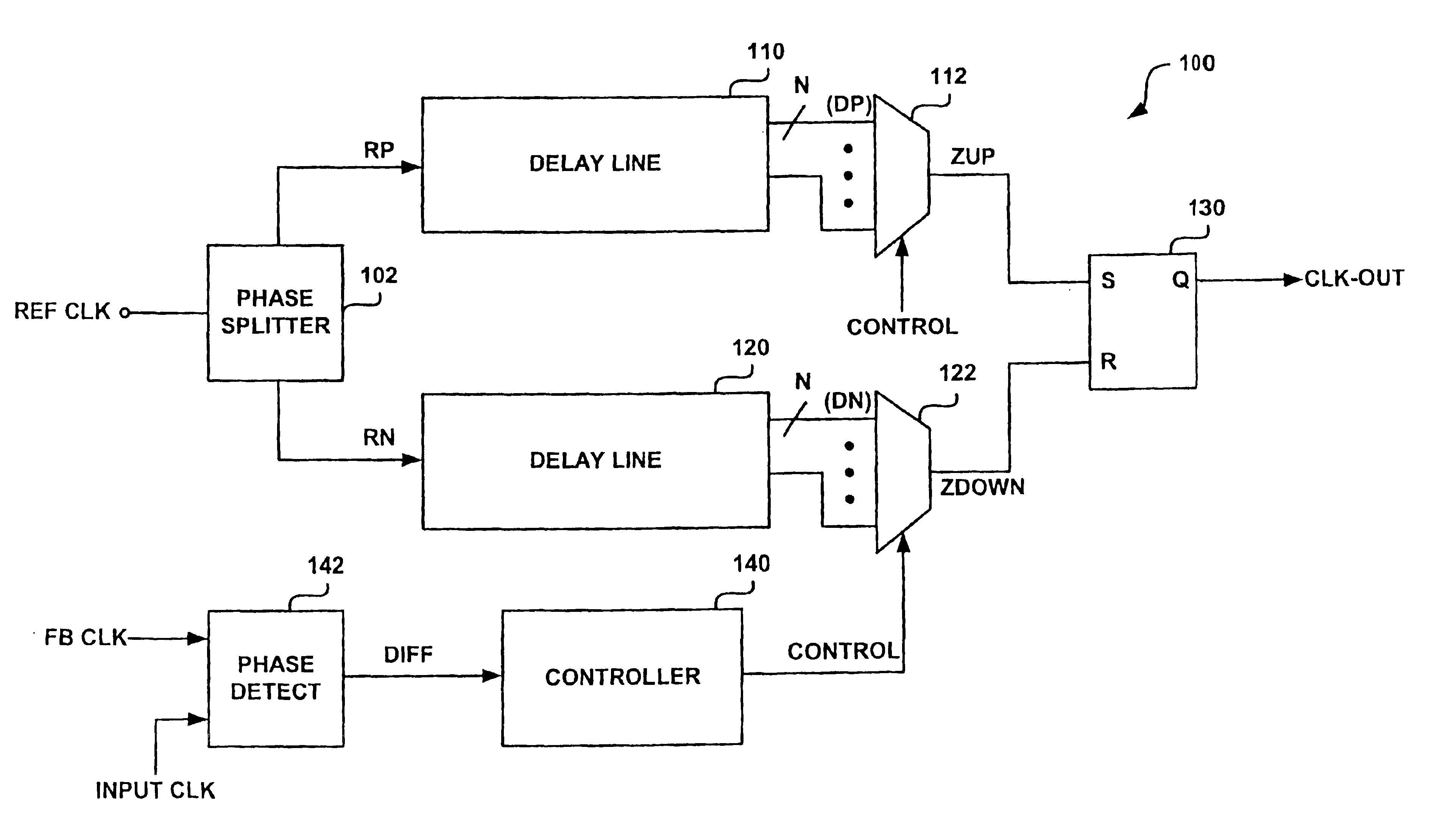

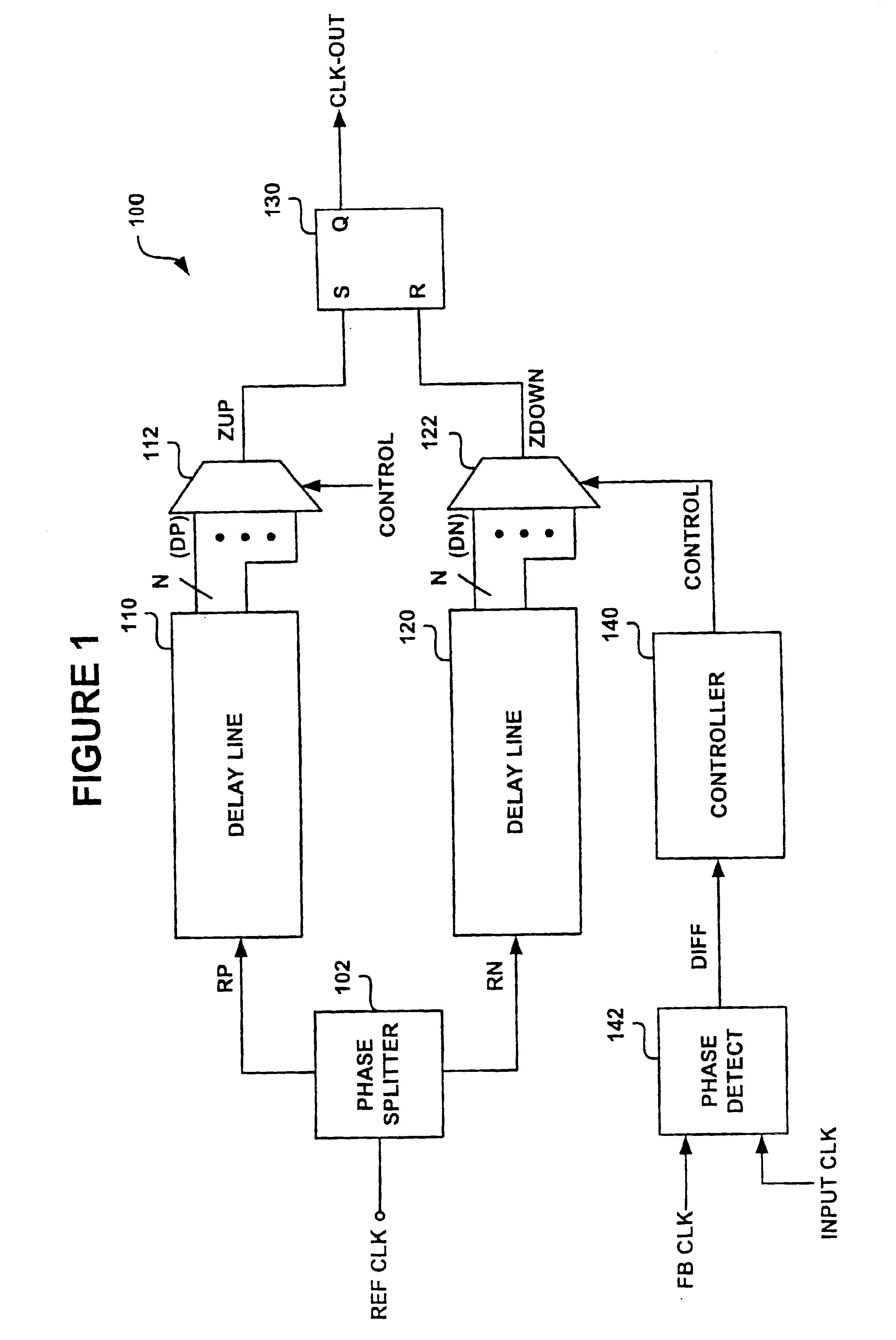

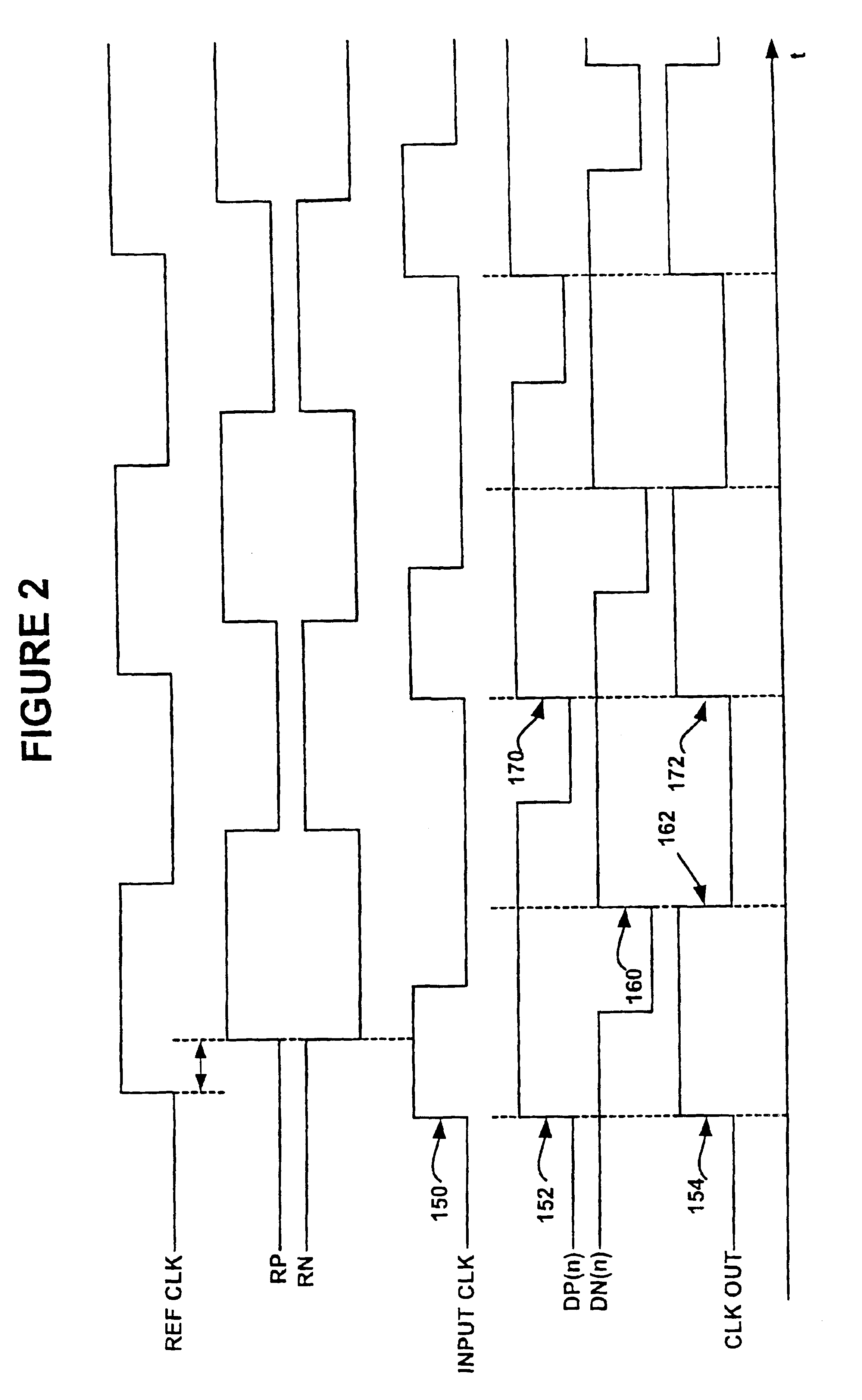

Apparatus and method for a digital delay locked loop

A circuit and method is shown for digital control of delay lines in a delay locked loop (DLL) system. A pair of multiplexors (MUXes) is used to select output taps from a pair of complementary delay lines that delay a reference clock signal in order to lock onto a received clock signal. An output tap from one delay line is used to produce a rising edge in an output clock signal while a corresponding tap in the complementary delay line is used to produce a falling edge in the output signal in order to correct for distortion. The MUXes are controlled based on a phase difference detected between the received clock signal and a feedback clock corresponding to the output clock signal. Another aspect of the present invention provides for generation of a quadrature clock by interpolating between the rising and falling edges selected for the output clock signal. Still another aspect of the present invention provides for selectively disabling unused elements of the delay lines to reduce power consumption.

Owner:RAMBUS INC

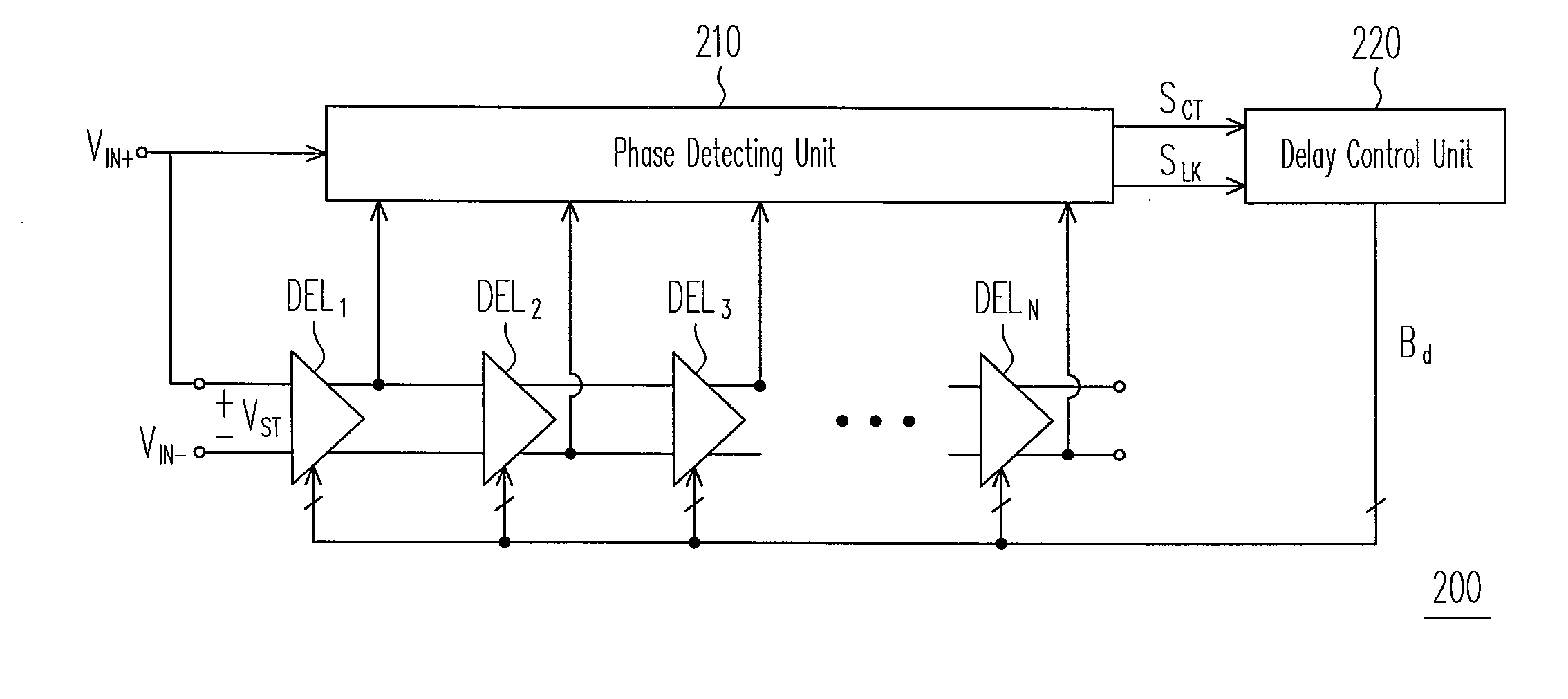

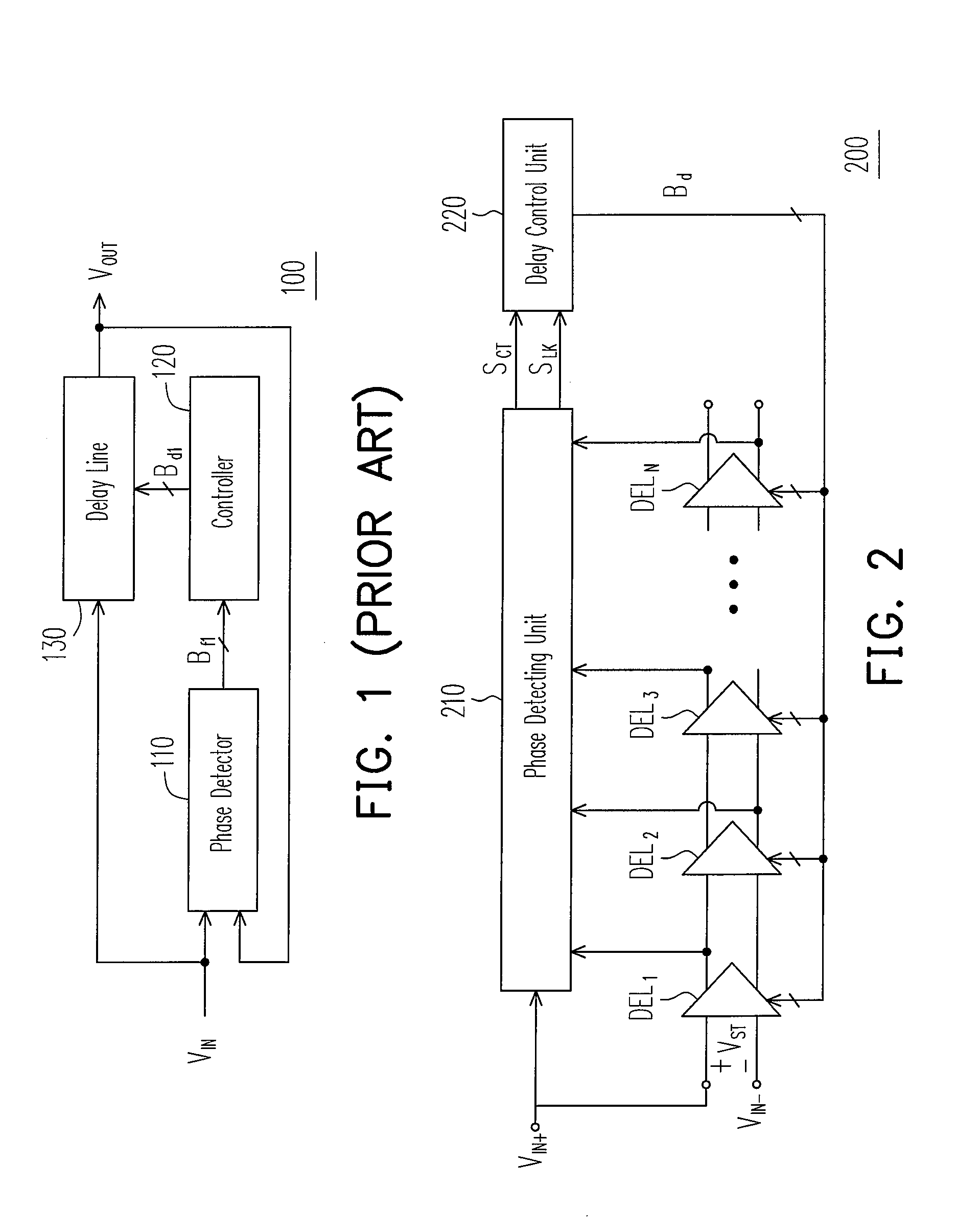

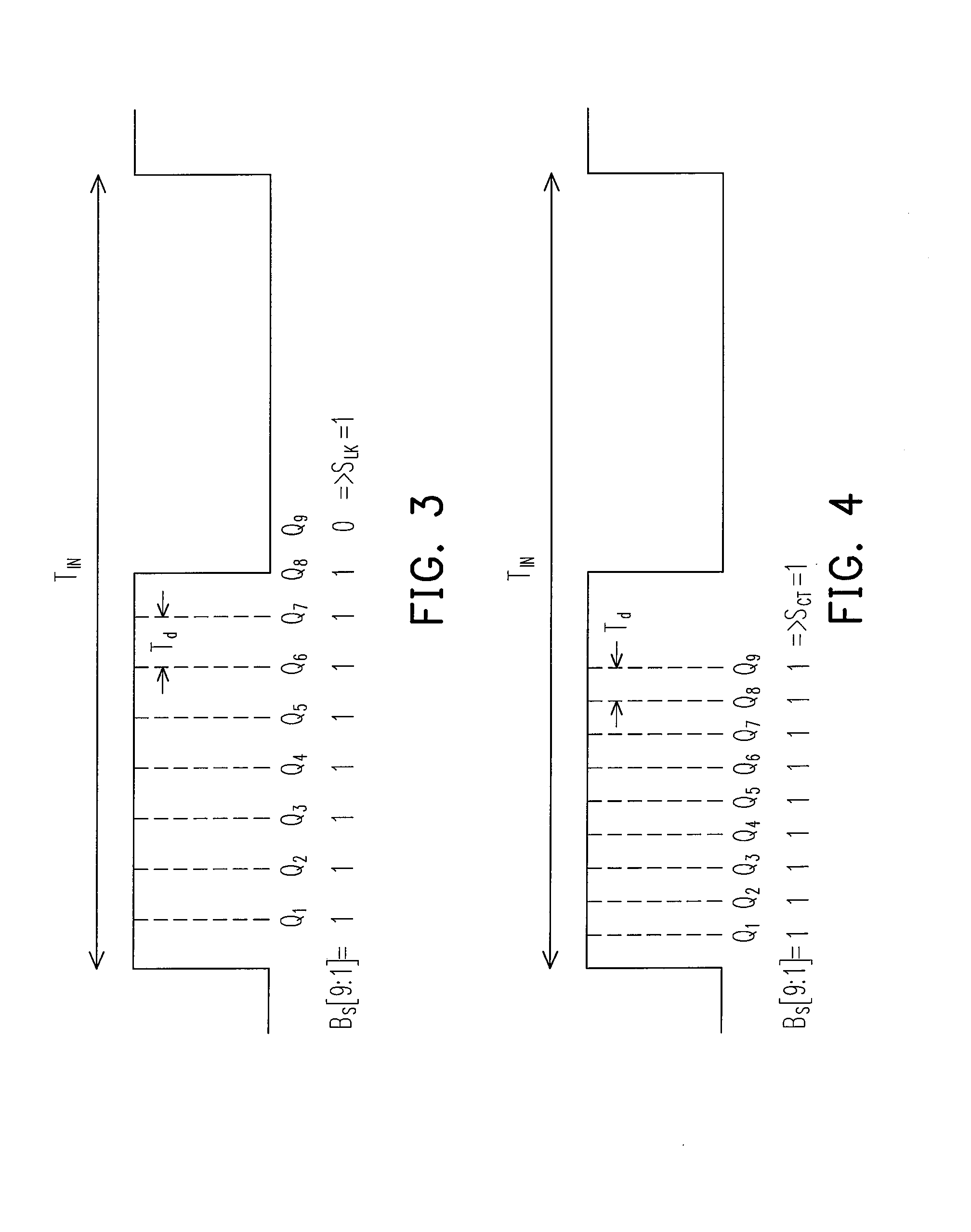

Digital delay locked loop

InactiveUS20080143403A1Reduce the overall heightPulse automatic controlPulse manipulationEngineeringTransition point

A digital delay locked loop including a plurality of controllable delay circuits connected in series, a phase detecting unit, and a delay control unit is disclosed. As an output end of each of the controllable delay circuits is coupled to the phase detecting unit, the phase detecting unit samples a positive received signal at the transition points of a specific period signal transmitted by each of the controllable delay circuits.

Owner:IND TECH RES INST

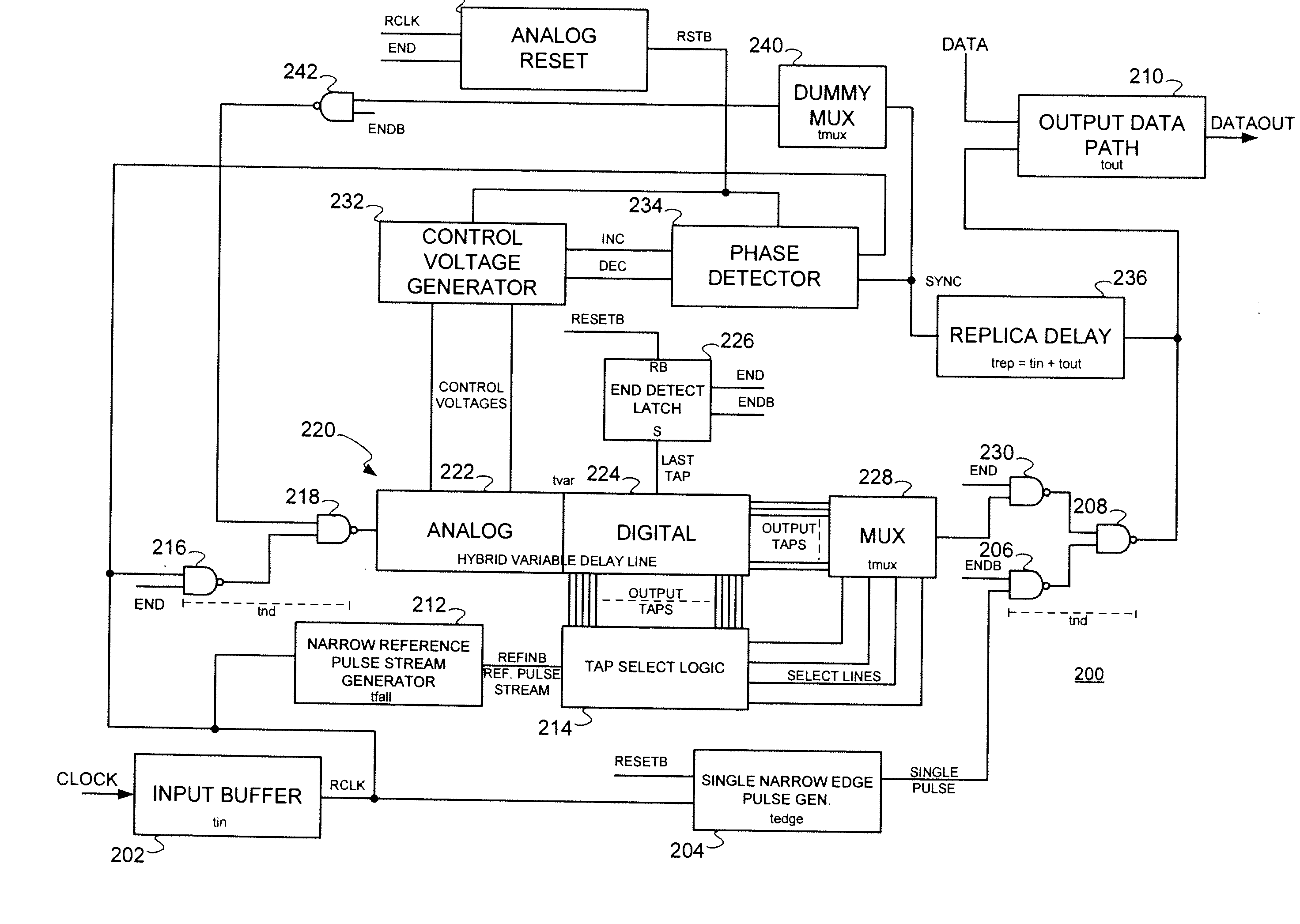

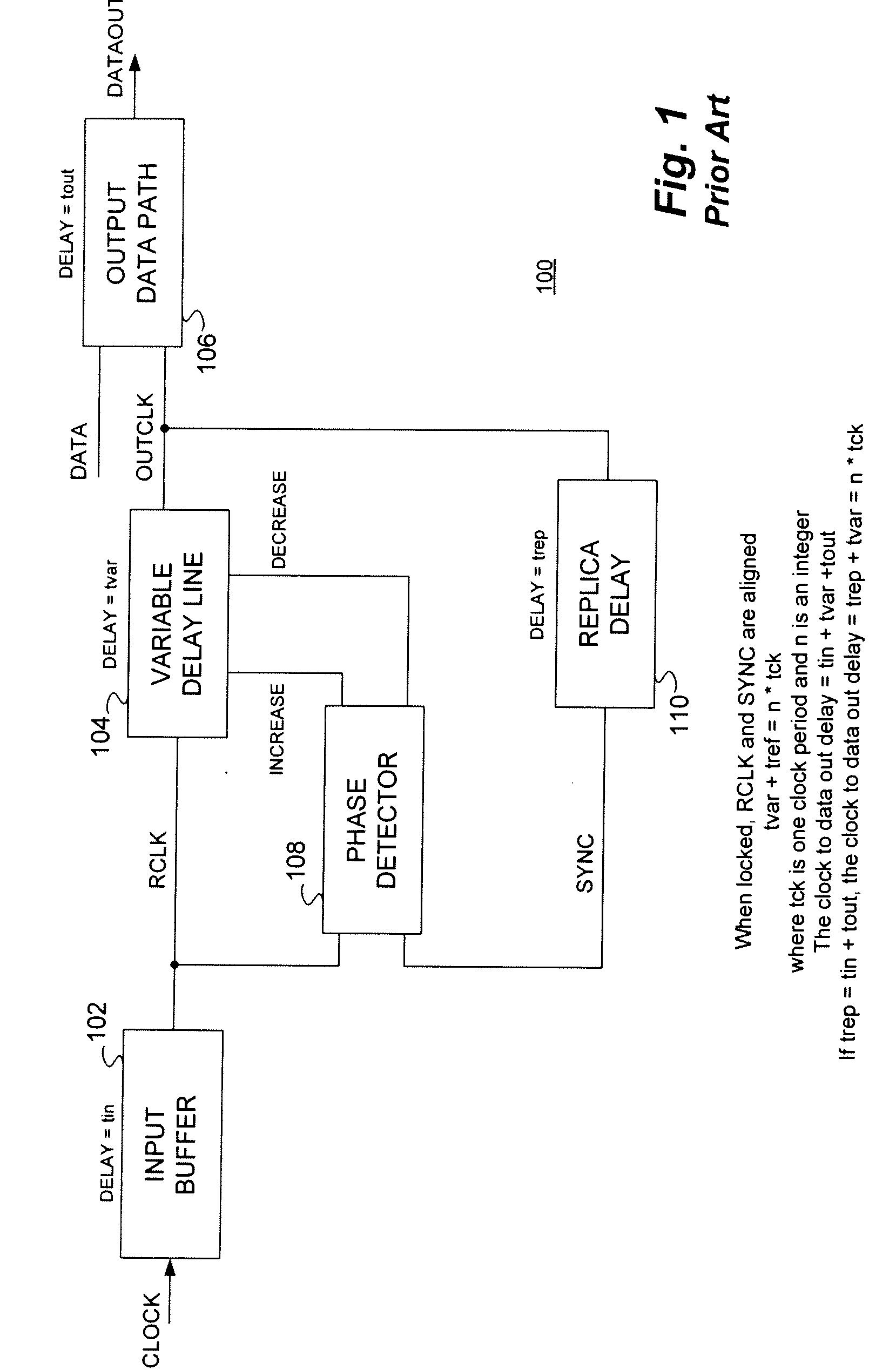

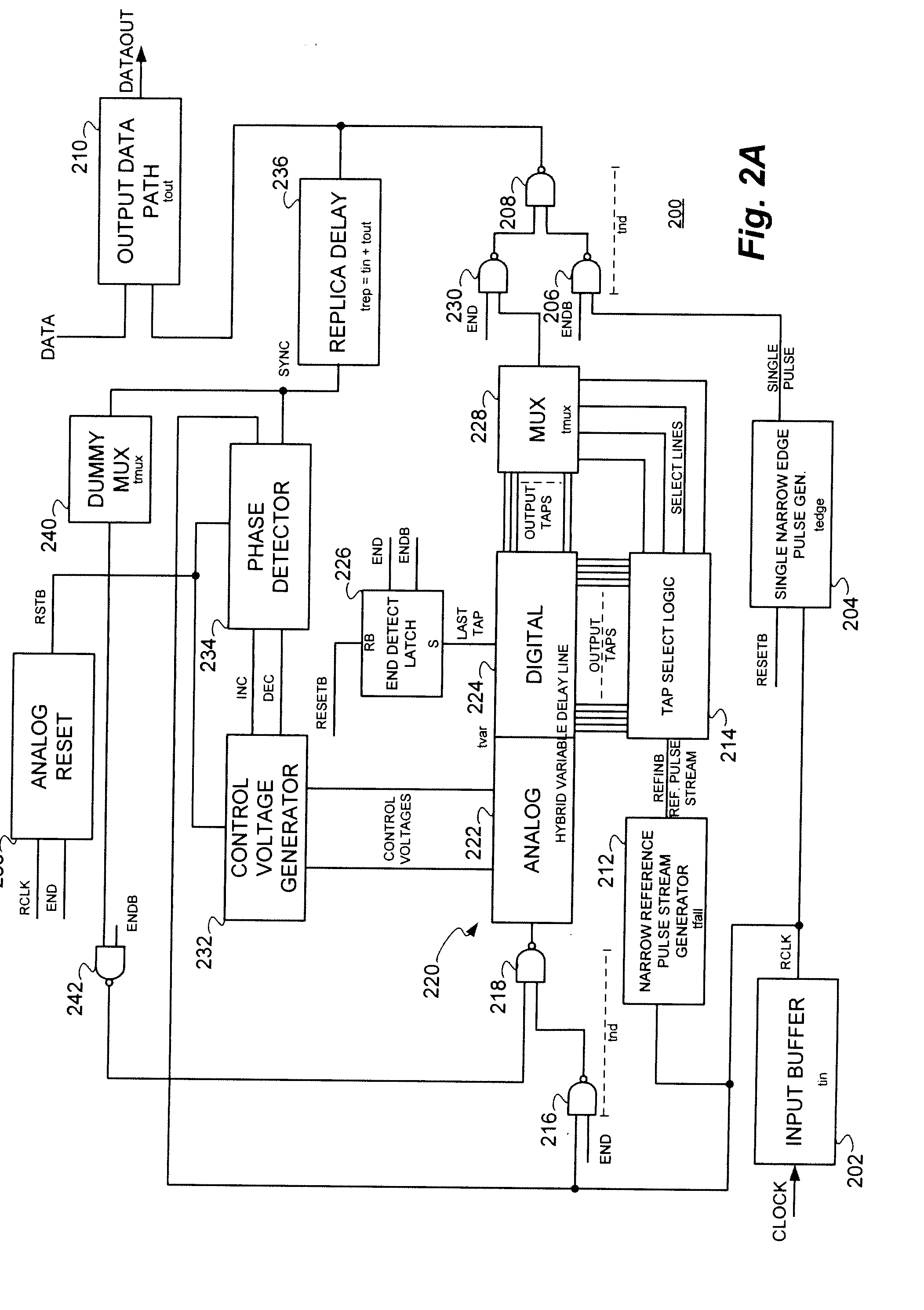

Configurable architecture hybrid analog/digital delay locked loop (DLL) and technique with fast open loop digital locking for integrated circuit devices

A configurable architecture, hybrid analog / digital delay locked loop and technique with fast open loop digital locking for integrated circuit dynamic random access memory (DRAM) devices and devices incorporating embedded DRAM. The DLL design and technique disclosed employs a hybrid analog / digital delay line, but does not use conventional closed loop architecture during the digital phase of the locking process.

Owner:PROMOS TECH INC

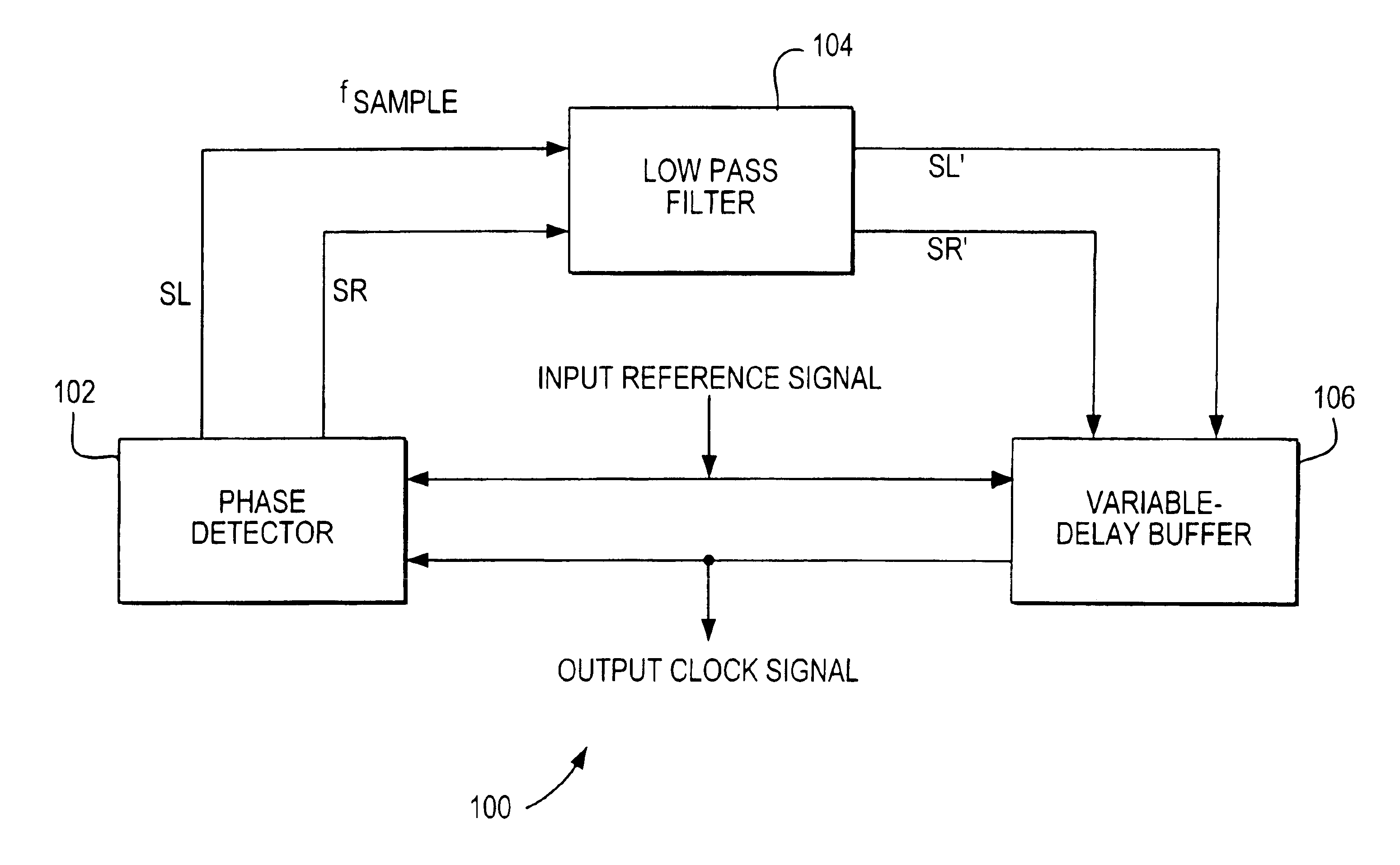

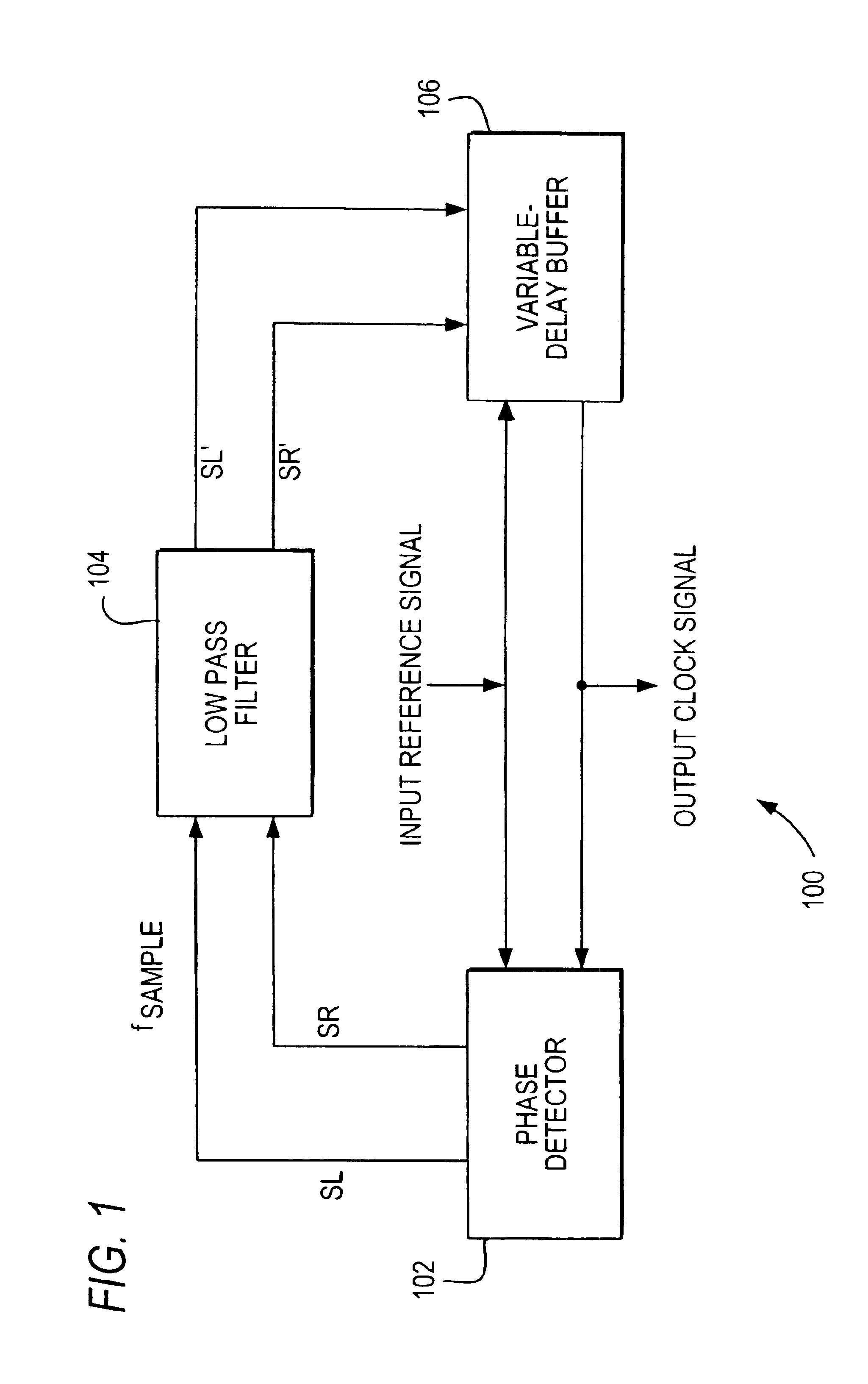

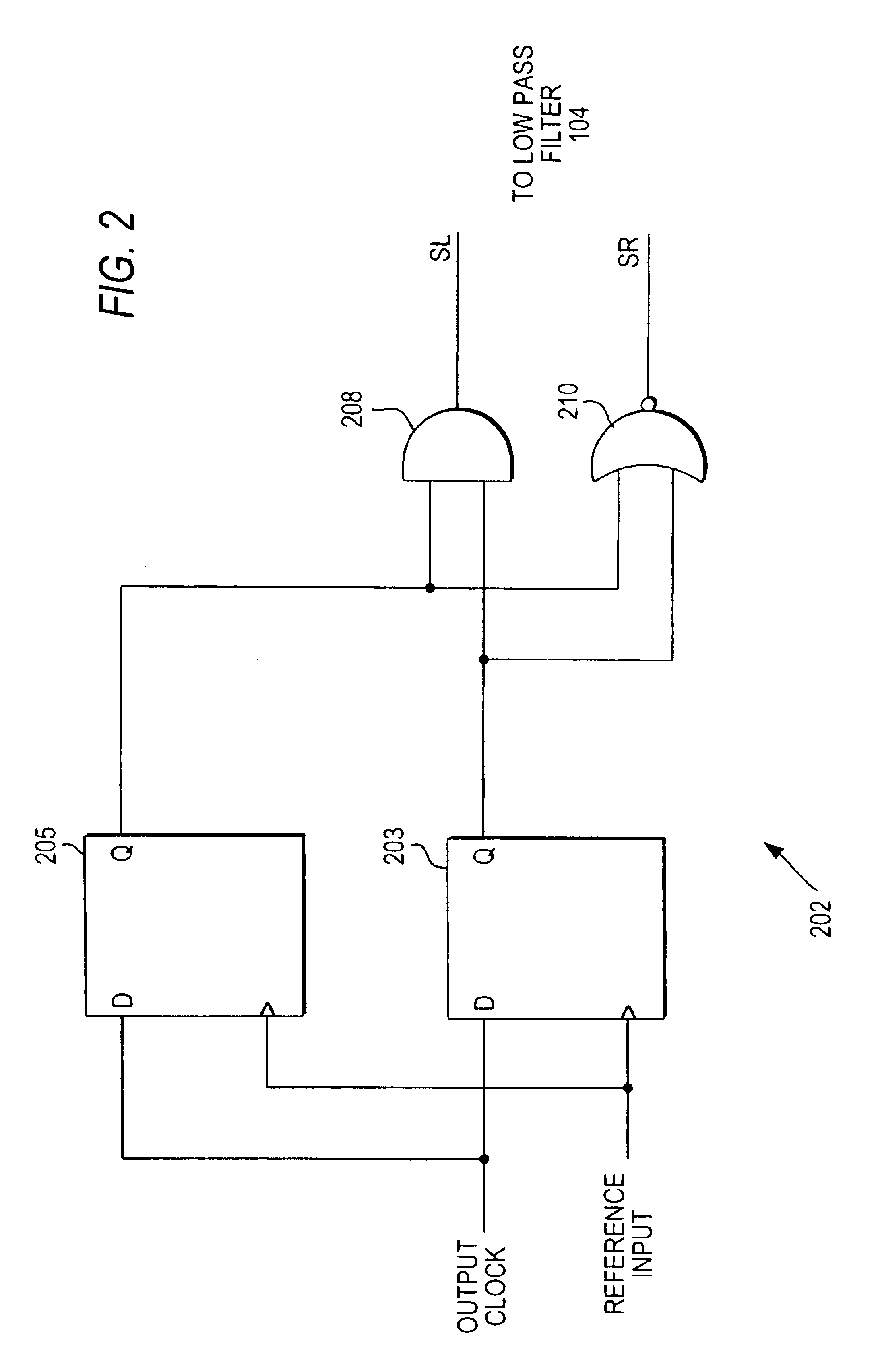

Low pass filters in DLL circuits

InactiveUS6917230B2Prevents and adverse effect of inputPulse automatic controlSingle output arrangementsPhase detectorLow-pass filter

Circuits and methods are provided that reduce, if not prevent, the adverse effects of transient noise on phase adjustments made by digital delay lock loop (DLL) circuits, which typically generate a periodic output signal having a particular phase relationship with a periodic input signal. A digital low pass filter of a DLL circuit includes circuitry, such as, for example, a thermometer register, coupled to receive the outputs of a DLL phase detector. The low pass filter prevents the DLL circuit from making frequent changes to the phase of the DLL output signal.

Owner:ROUND ROCK RES LLC

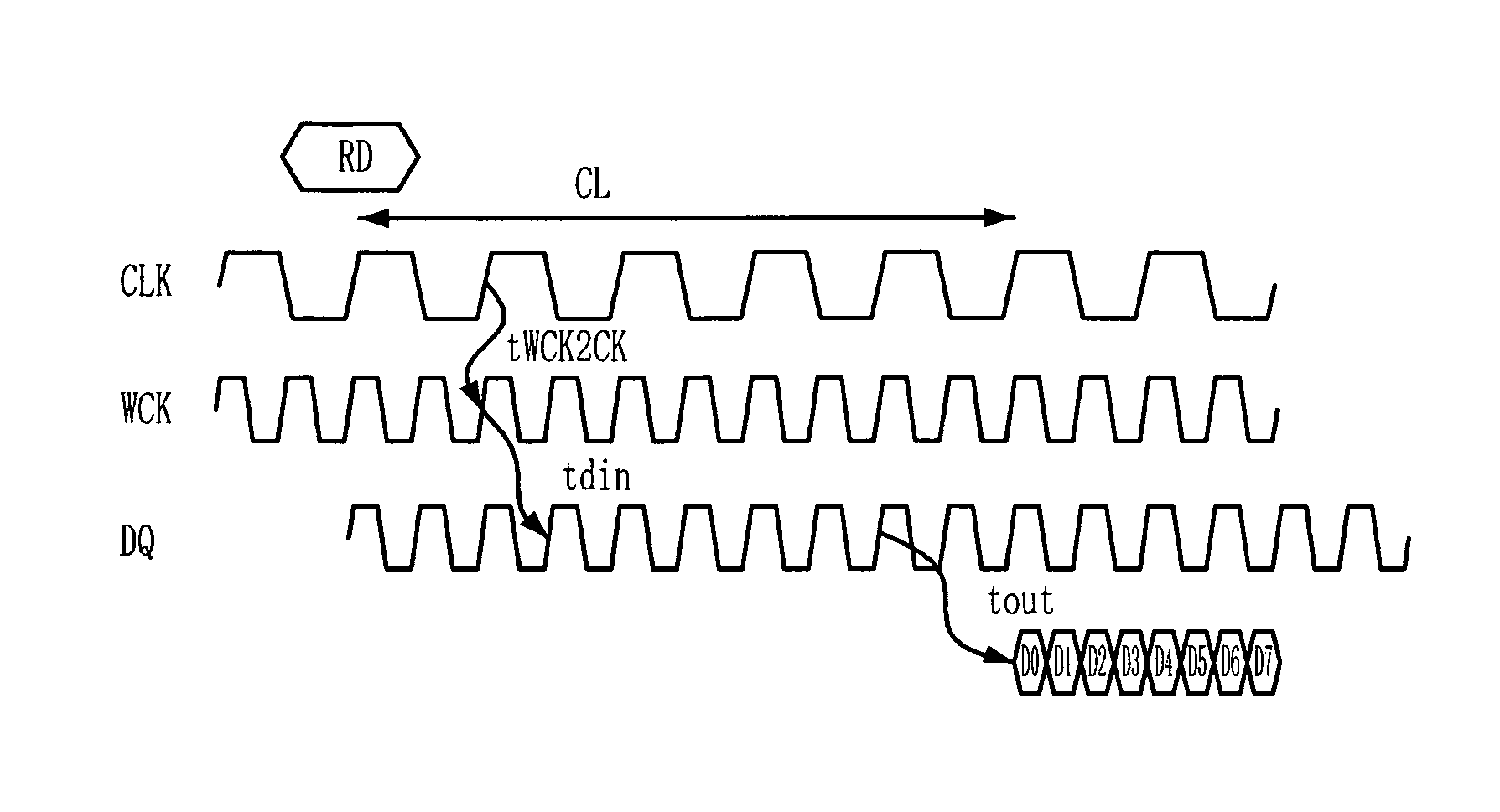

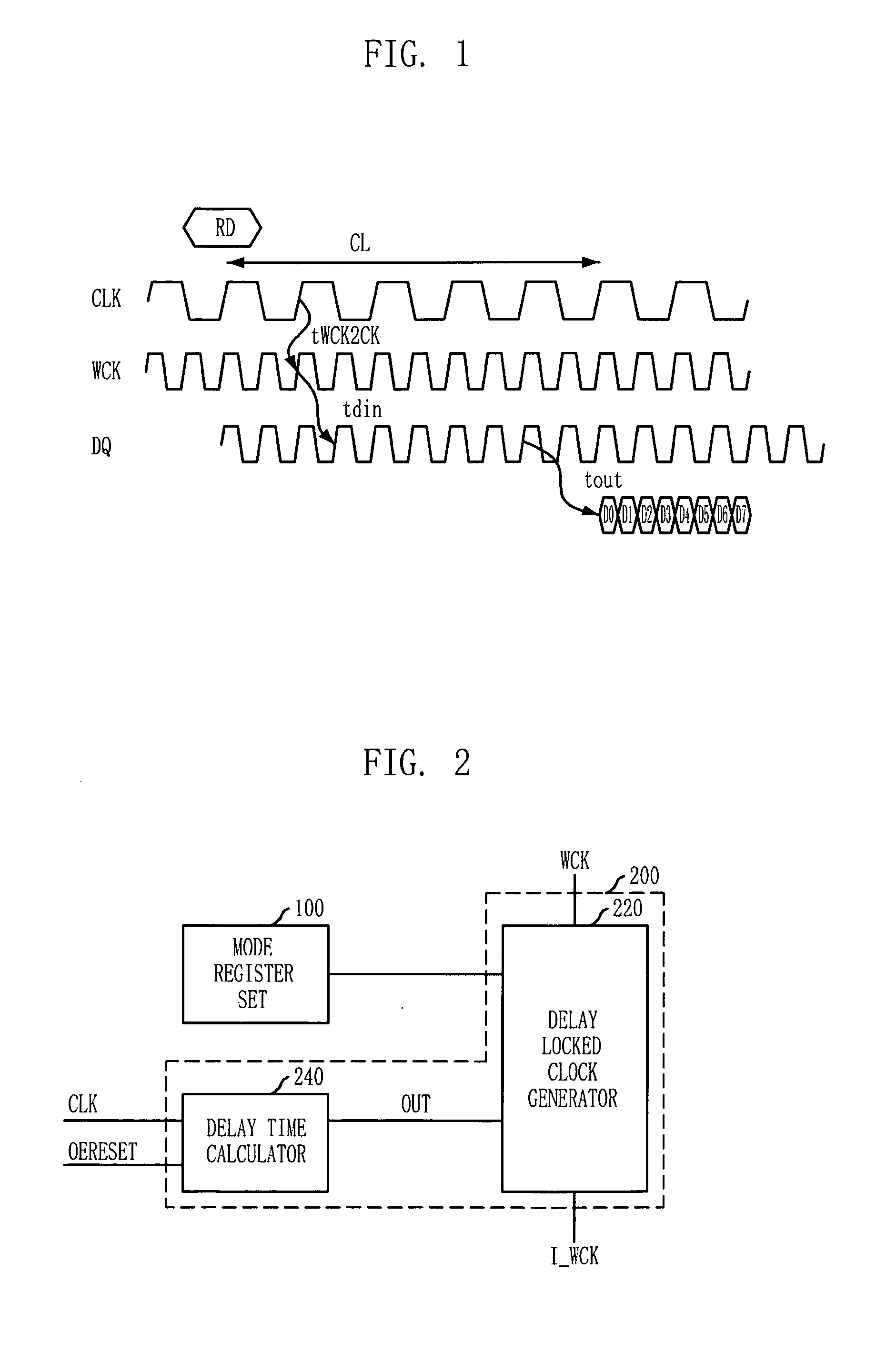

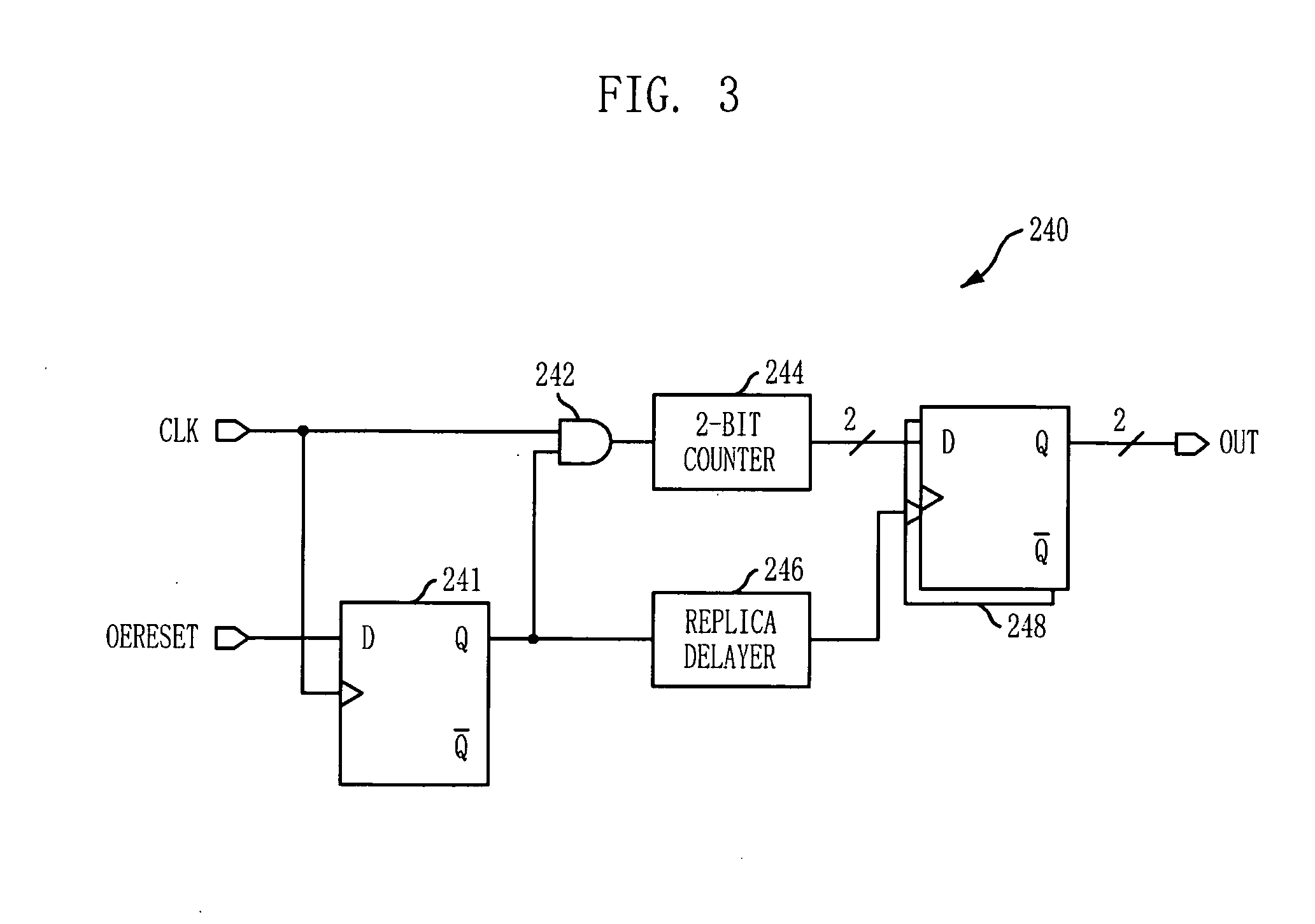

Digital delay locked loop circuit using mode register set

ActiveUS20090119533A1Easy to controlReduce errorsFault responseCode conversionClock generatorComputer science

A semiconductor memory device includes a mode register set for establishing information on a delay time, a delay time calculator for calculating an I / O path delay time of a data clock on a basis of a unit period of a system clock, and a delay locked clock generator for reflecting in the data clock a value of subtracting an output of the delay time calculator from the information established in the mode register set.

Owner:SK HYNIX INC

Semidigital delay-locked loop using an analog-based finite state machine

ActiveUS20050093591A1Doubles hardware complexityIncrease powerPulse automatic controlSynchronising arrangementDigital signal processingEngineering

A low-power full-rate semidigital DLL architecture using an analog-based FSM (AFSM). The AFSM is a mixed-mode FSM in which analog integration is substituted for digital filtering, thus enabling a lower power implementation of the clock and data recovery function. An integrated voltage is converted to a digital code by an analog-to-digital converter (ADC), and the digital code is used either directly or after (low frequency) digital signal processing to control a a controllable delay element, such as, a phase rotator, for data edge tracking.

Owner:GLOBALFOUNDRIES US INC