Digital delay device

A delay device, digital technology, applied in the direction of electrical components, automatic power control, etc., can solve problems such as large clock jitter noise, and achieve the effect of reducing jitter noise

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

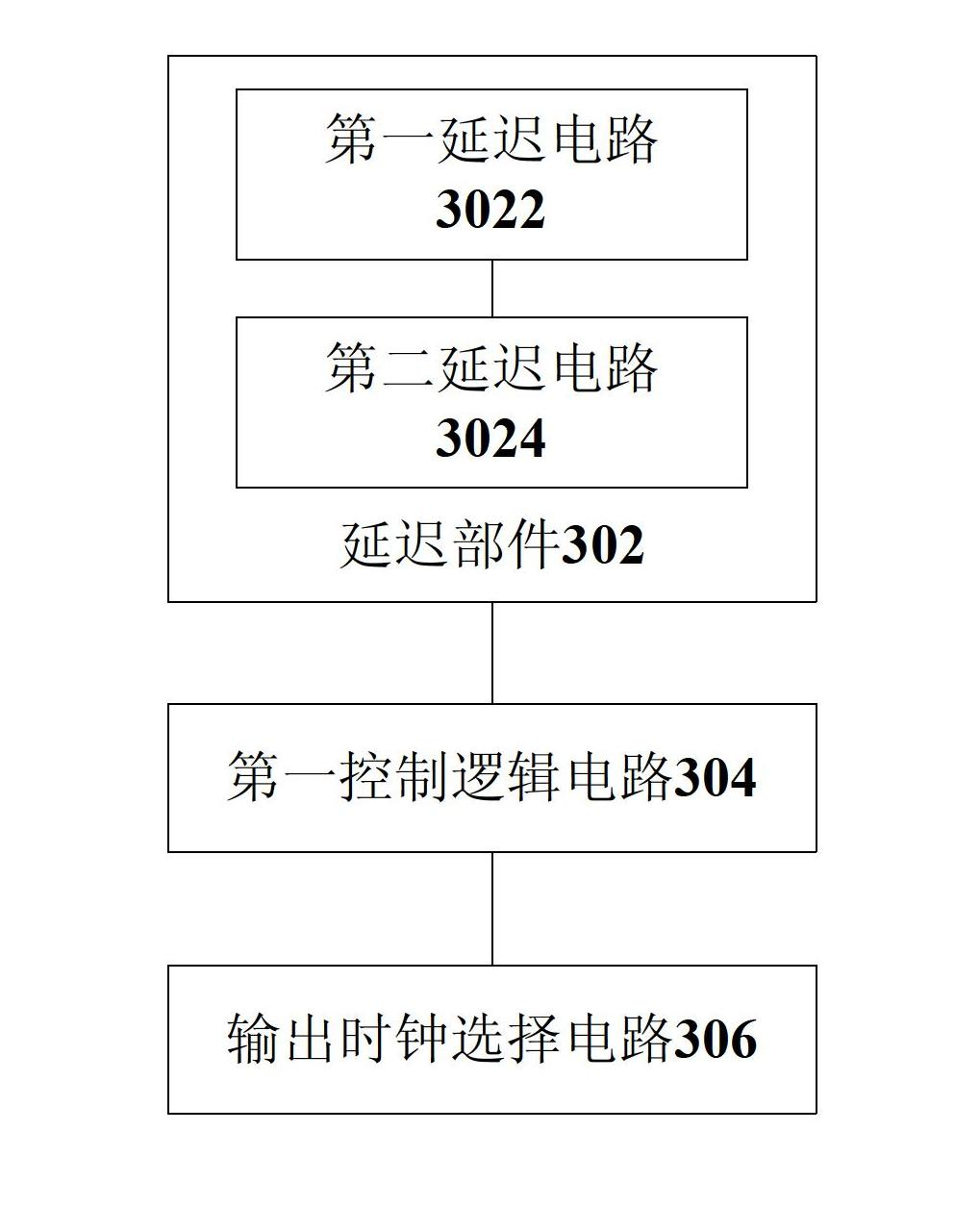

[0038] The present invention provides a digital delay device, specifically, such as image 3As shown, the device includes: a delay unit 302, and the delay unit 302 includes a first delay circuit 3022 and a second delay circuit 3024, wherein the first delay circuit 3022 and the second delay circuit 3024 are used to respectively process digital signals that are differential signals signal, the input signal of the first delay circuit 3022 and the input signal of the second delay circuit 3024 are mutually differential signals, the output signal of the first delay circuit 3022 and the output signal of the second delay circuit 3024 are mutually differential signals, and the first delay circuit 3022 and the second delay circuit 3024 are all formed by cascading delay units; the first control logic circuit 304 is used to control the first delay circuit 3022 and the second delay circuit 3024 to output the first clock signal and the second clock signal respectively; the output clock The ...

Embodiment 2

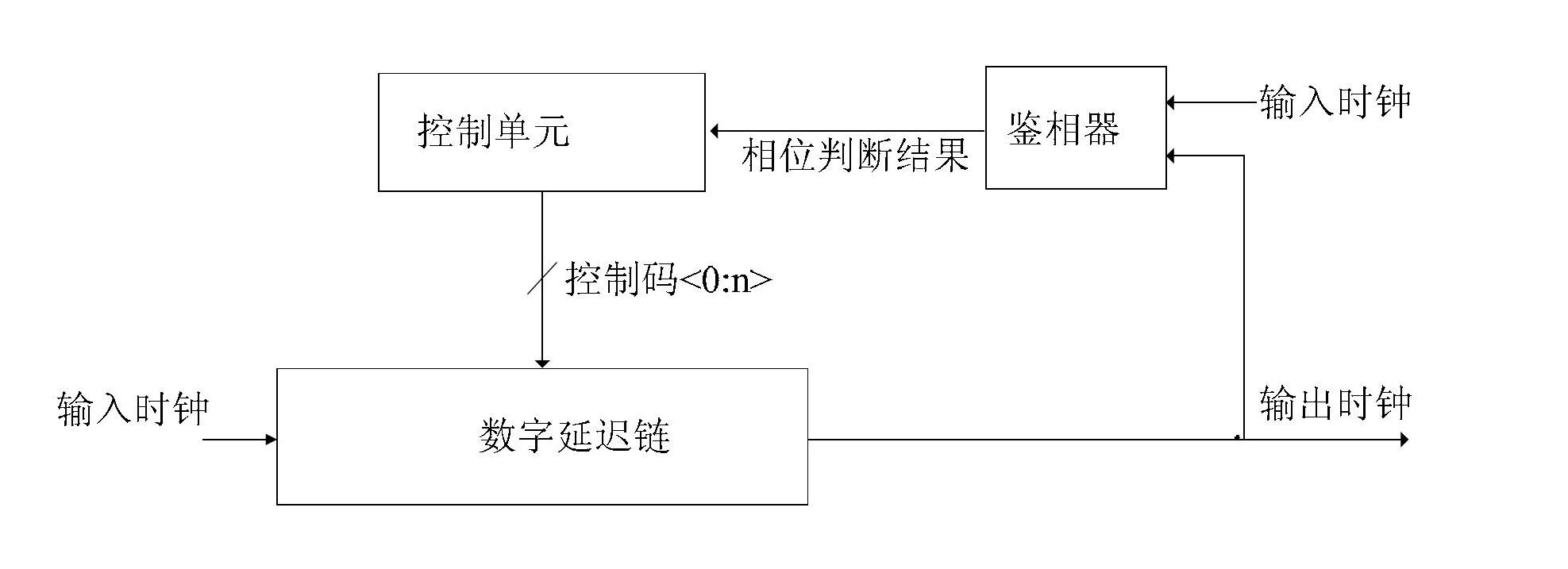

[0046] Figure 10 A schematic diagram showing a preferred structure of the digital delay device of the present invention, the components of the delay chain include a differential chain, a control logic circuit, a coupling unit, and an output clock selection circuit, wherein the differential chain includes two chains, respectively called positive The chain (the first delay circuit) and the anti-chain (the second delay circuit) are composed of cascaded differential delay units in a ladder structure. The input clock is a pair of differential clock signals, and the output clock is a clock signal delayed by a differential chain delay unit and a selection circuit. The working principle of each component is as follows:

[0047] Delay unit: built with N-level non-logic gates for delay time, including two working states: the first working state and the second working state, the working principle of which has been described in Embodiment 1, and will not be repeated here.

[0048] The ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More