Testability circuit for digital/analog mixed signal chip

A signal and circuit technology, applied in the field of testable circuits, to achieve the effect of enhancing ESD capability and reducing test pins

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

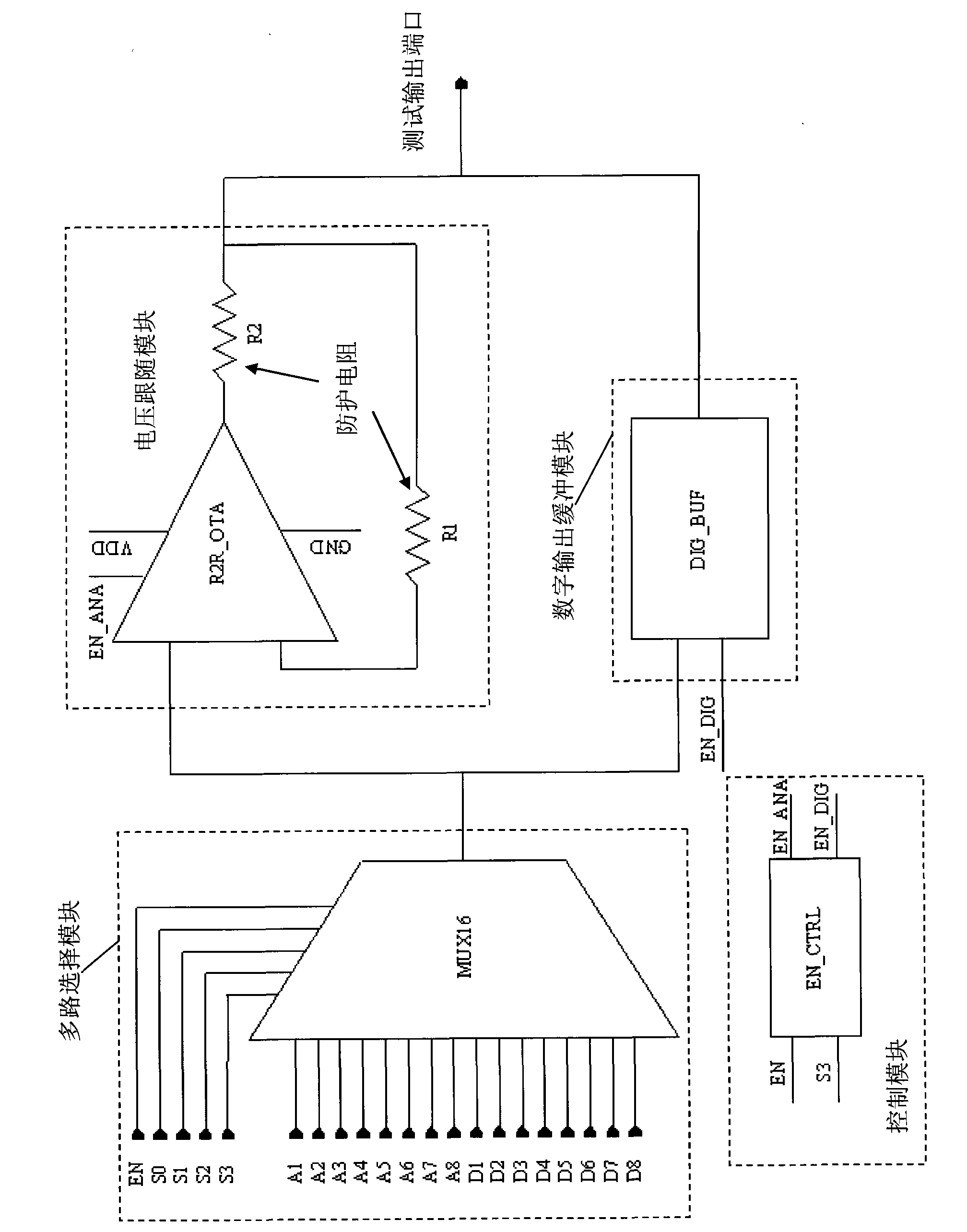

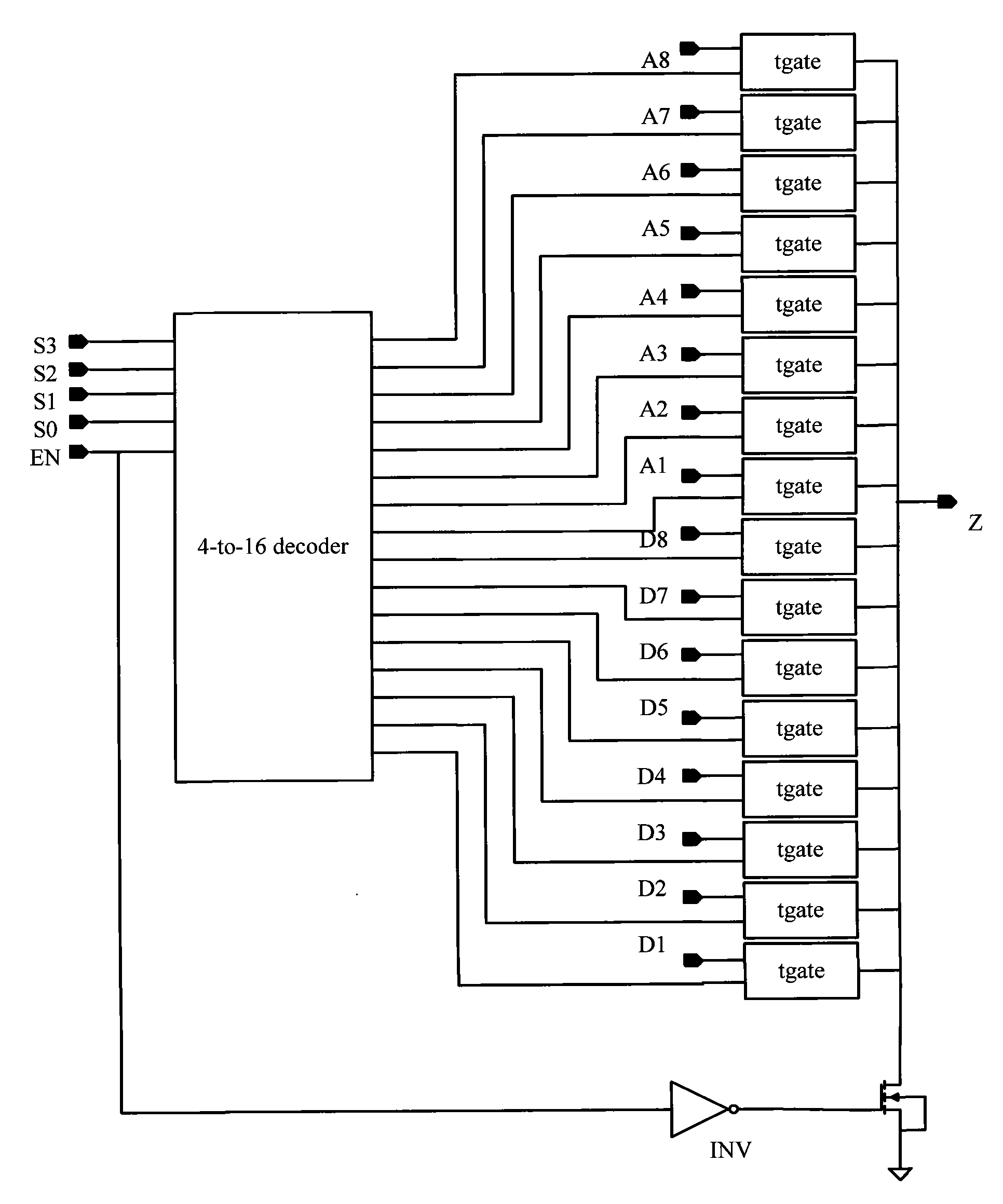

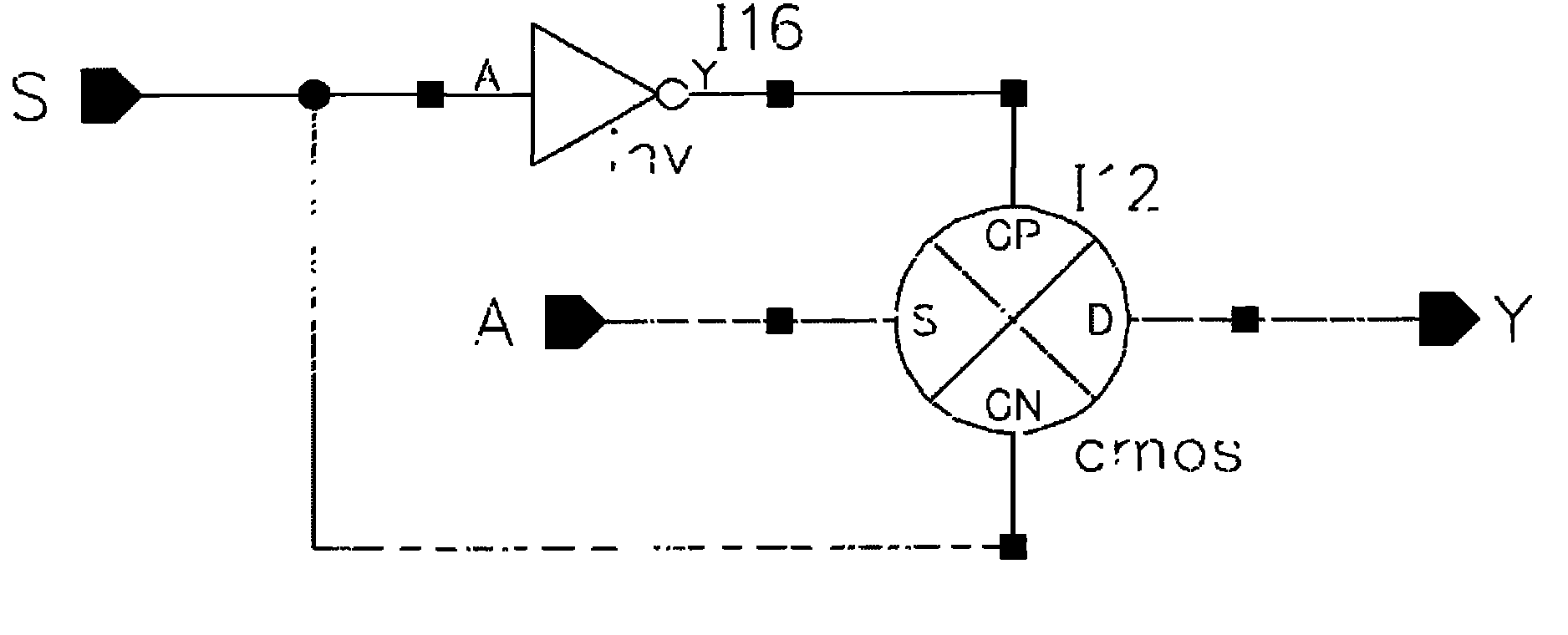

[0023] The testability circuit for the digital-analog mixed-signal chip of the present invention (see figure 1 ), including: a multiplexer module, a control module, a voltage follower module, and a digital output buffer module; the multiplexer module is used to select the signal to be observed according to the enable signal and the selection signal, and send it to the voltage Follower module or digital output buffer module, if it is a digital signal, it will be sent to the digital output buffer module, if it is an analog signal, it will be sent to the voltage follower module; the control module is used to generate control signals according to the enable signal and selection signal , to control whether to turn on the voltage follower module or the digital output buffer module, if it is an analog signal, turn on the voltage follower module, and if it is a digital signal, turn on the digital output buffer module. The control module is a combined logic circuit, which can be formed...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More