Patents

Literature

31results about How to "Improve ESD capability" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

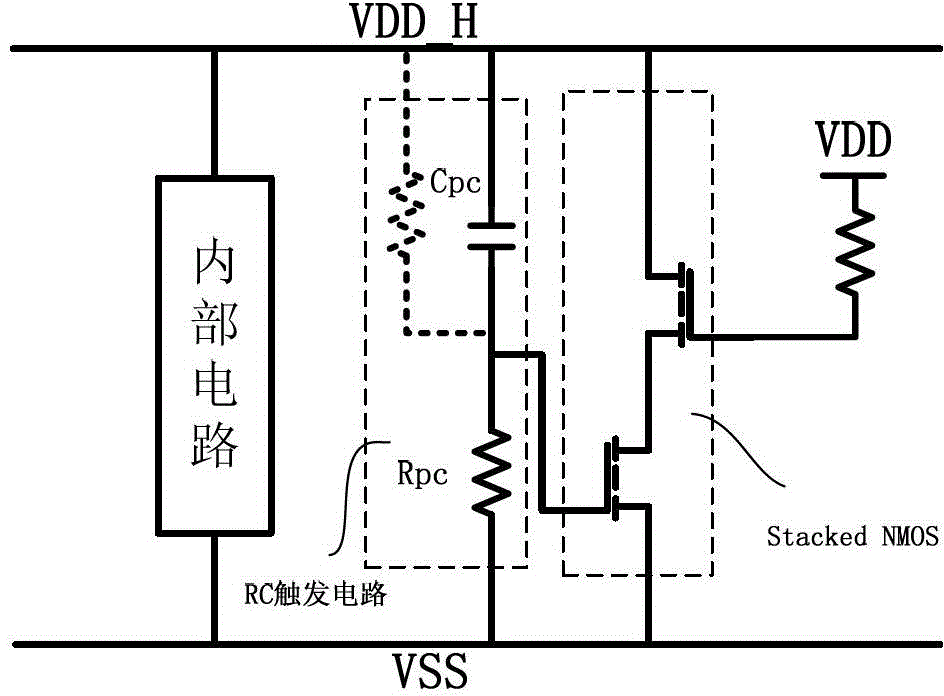

Trigger circuit structure with integrated circuit power supply rail antistatic protection

InactiveCN103151350ALower the trigger voltageImprove ESD capabilitySolid-state devicesSemiconductor devicesOxide semiconductorIntegrated circuit

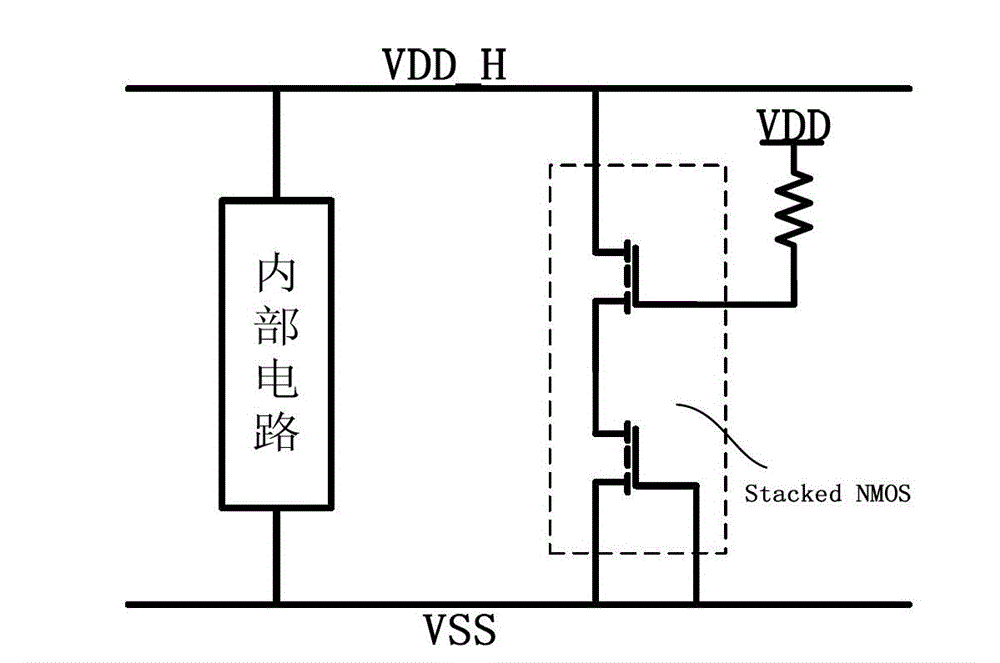

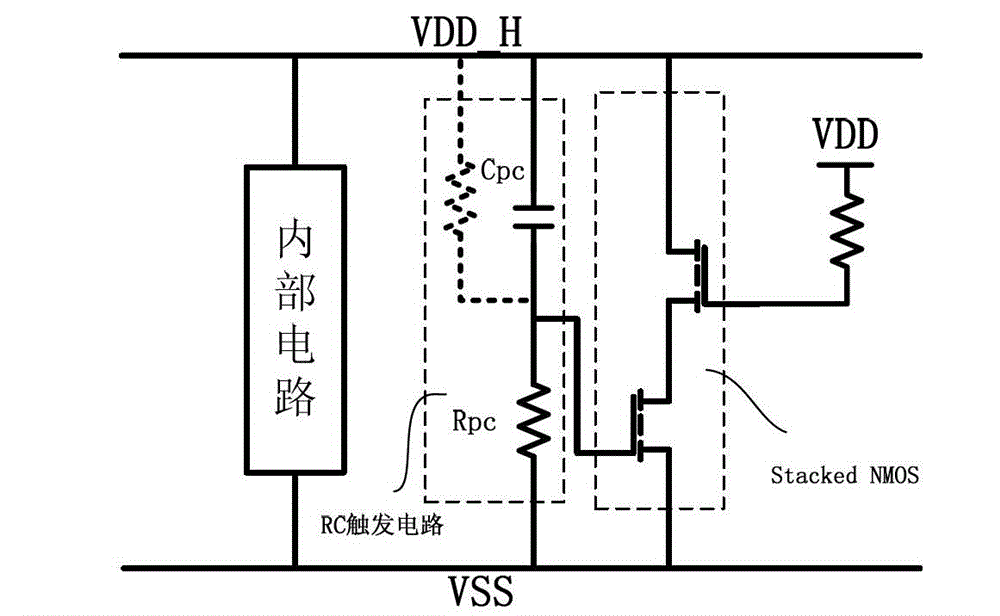

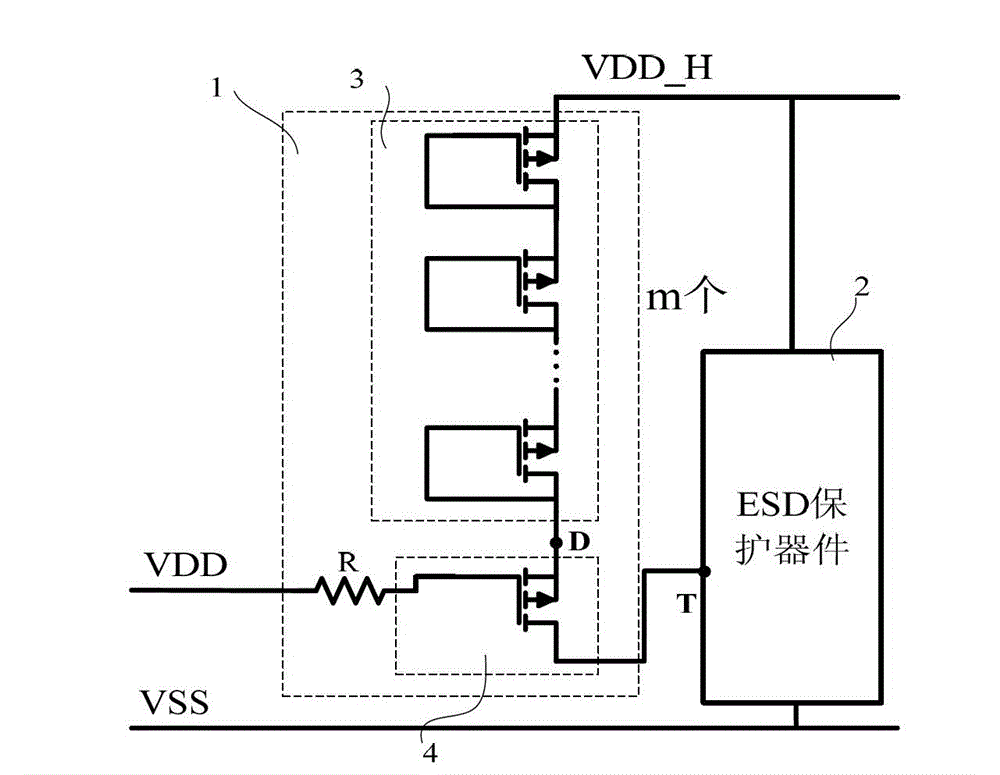

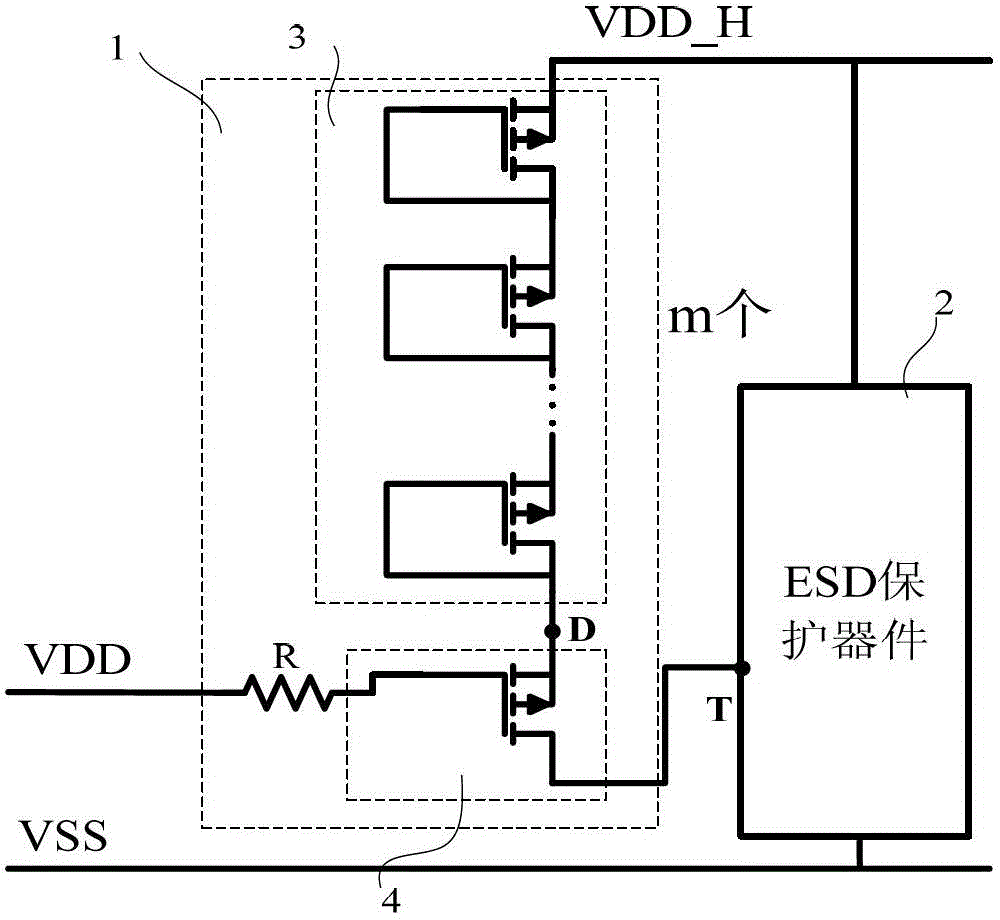

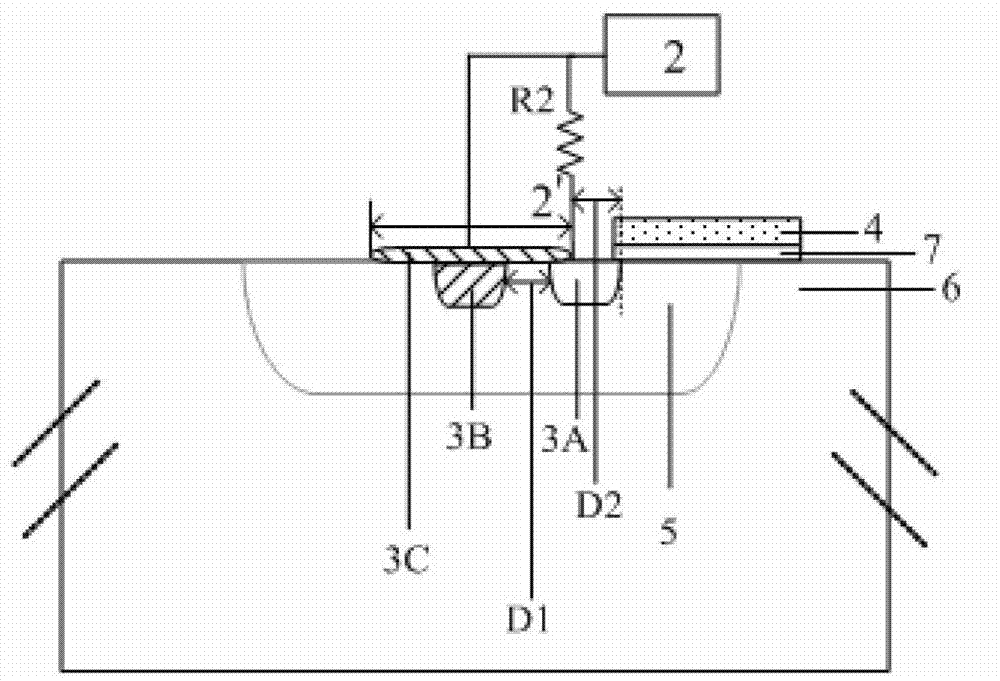

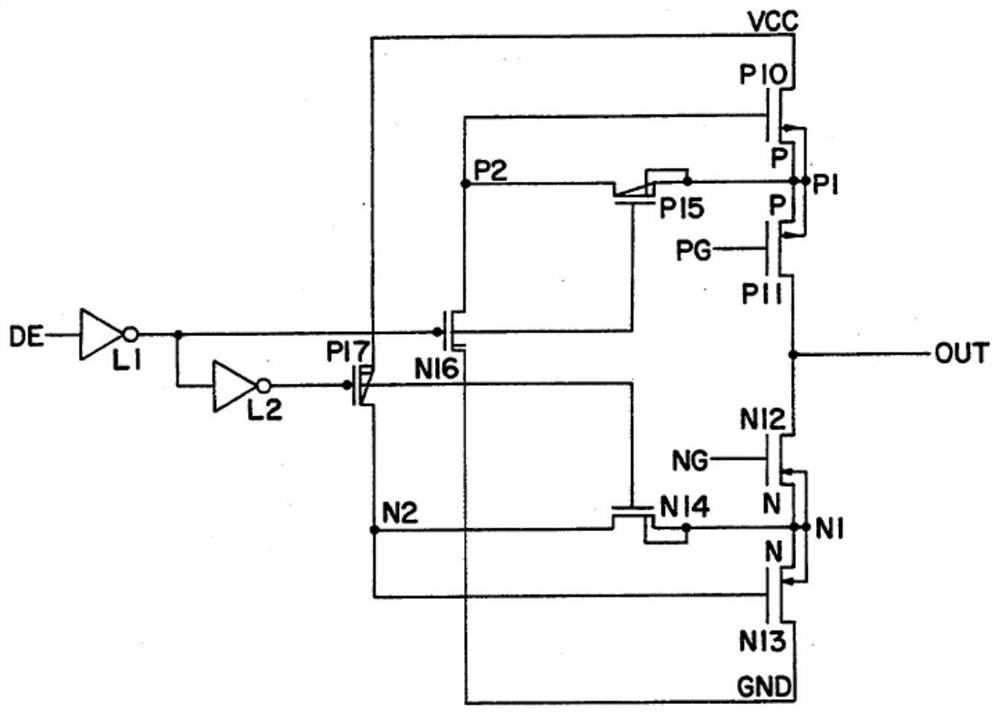

The invention provides a trigger circuit structure with circuit power supply rail antistatic protection, belonging to the technical field of electronics. The structure is used for triggering an integrated circuit high voltage power supply rail antistatic protective device with mixed working voltage, and comprises a series circuit, a second PMOS (positive channel metal oxide semiconductor) tube and a resistor R, wherein the series circuit consists of m (a positive integer) first PMOS tubes and is formed by connection of diodes; the source electrode of the most top first PMOS tube in the series circuit is connected with VDD_H (voltage drain drain_high); the drain electrode of the second PMOS tube is connected with a triggering end T of an ESD (electro-static discharge) protective device; the grid electrode of the second PMOS tube is connected with VDD (voltage drain drain) through the resistor R. The trigger circuit structure consists of a low voltage device, however, the trigger circuit structure can tolerate VDD_H voltage of a high voltage power supply rail, reduce the trigger voltage of the device, promote uniform conduction of the device, and improve ESD capability, and meanwhile, no capacitor device exists in the circuit, thus, the leakage current of the protected integrated circuit under normal working is smaller.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA

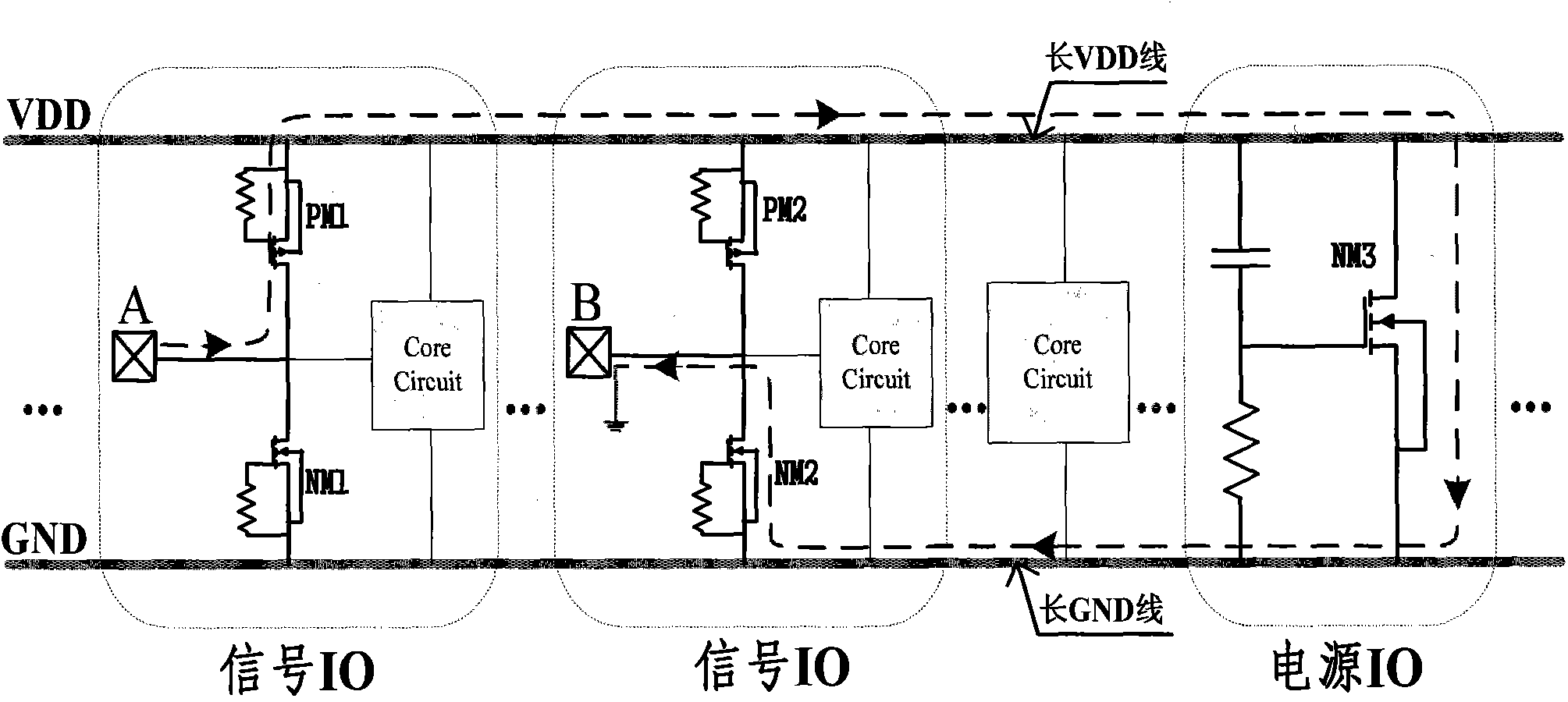

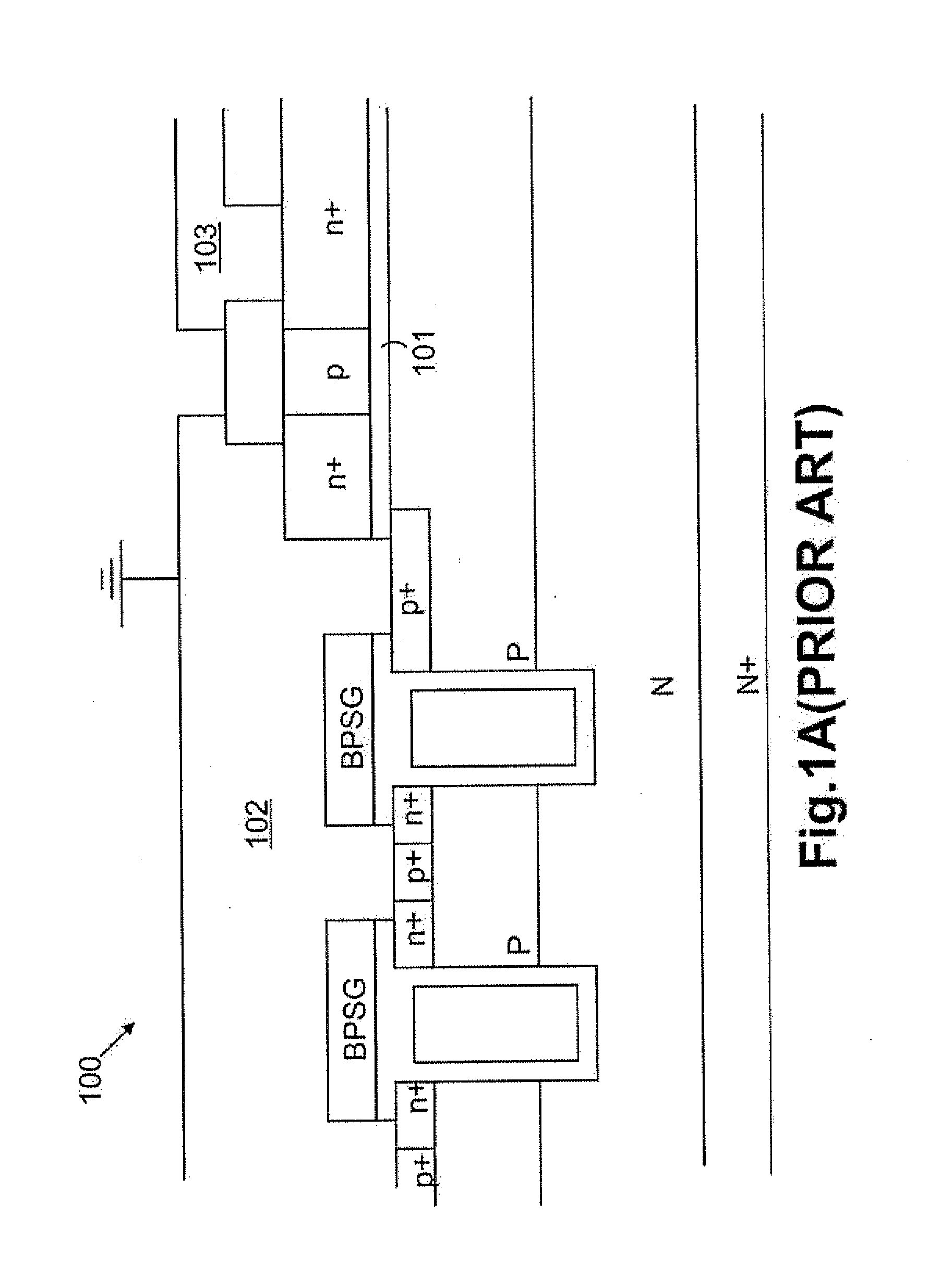

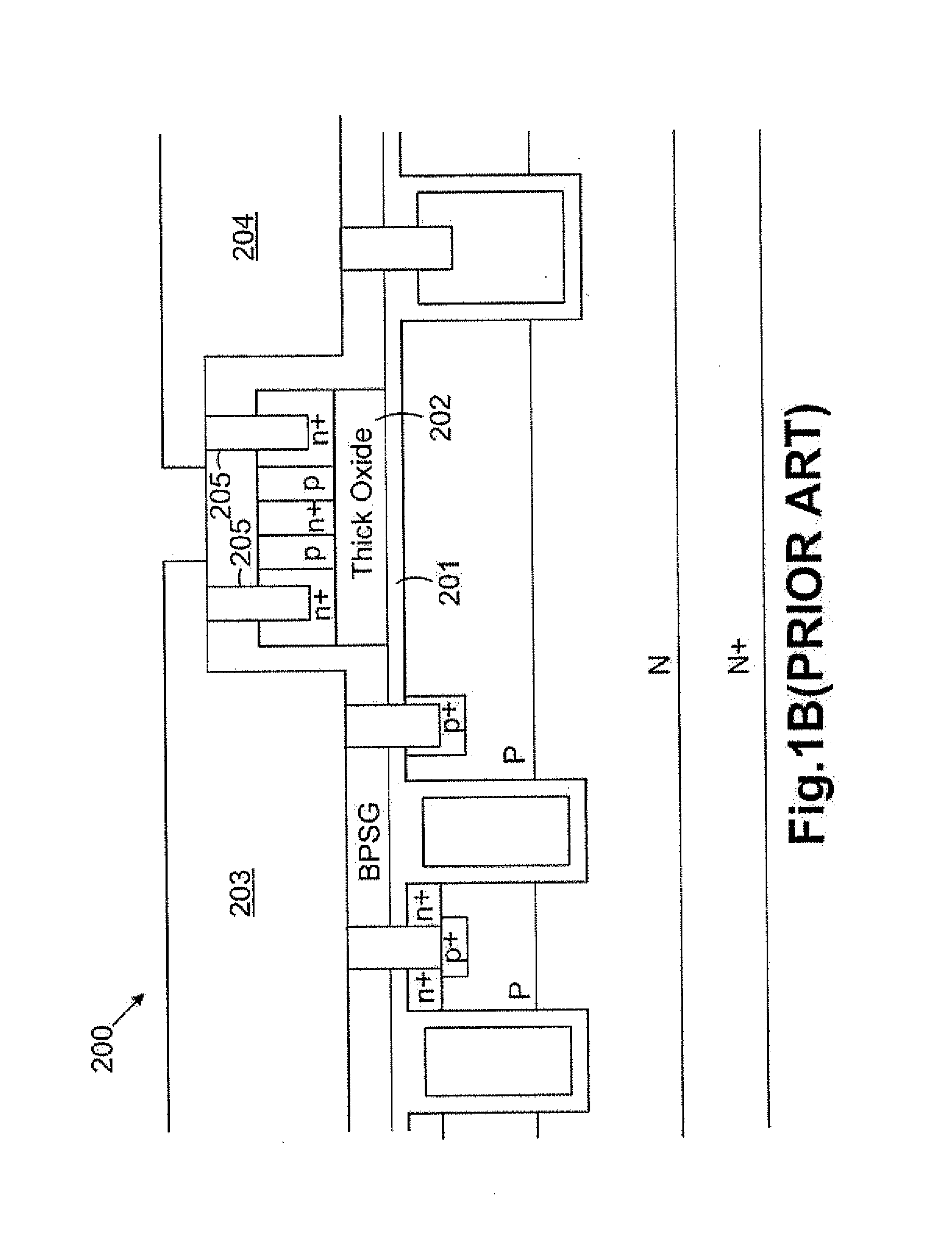

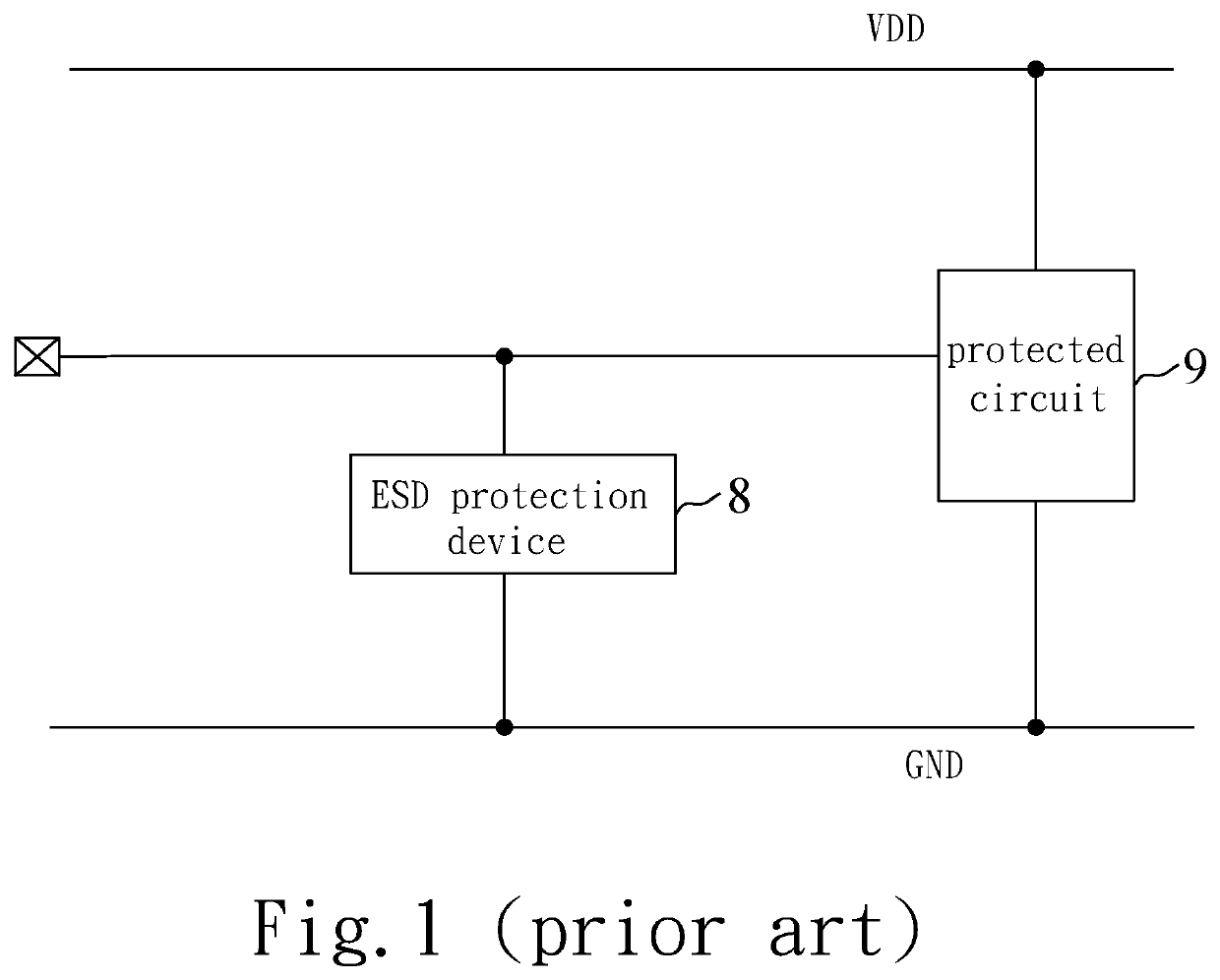

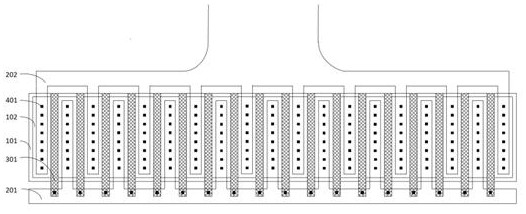

Integrated circuit full-chip electro static discharge protection method and circuit

InactiveCN103647265AReduce areaReduce voltage dropEmergency protective arrangements for limiting excess voltage/currentDischarge efficiencyEngineering

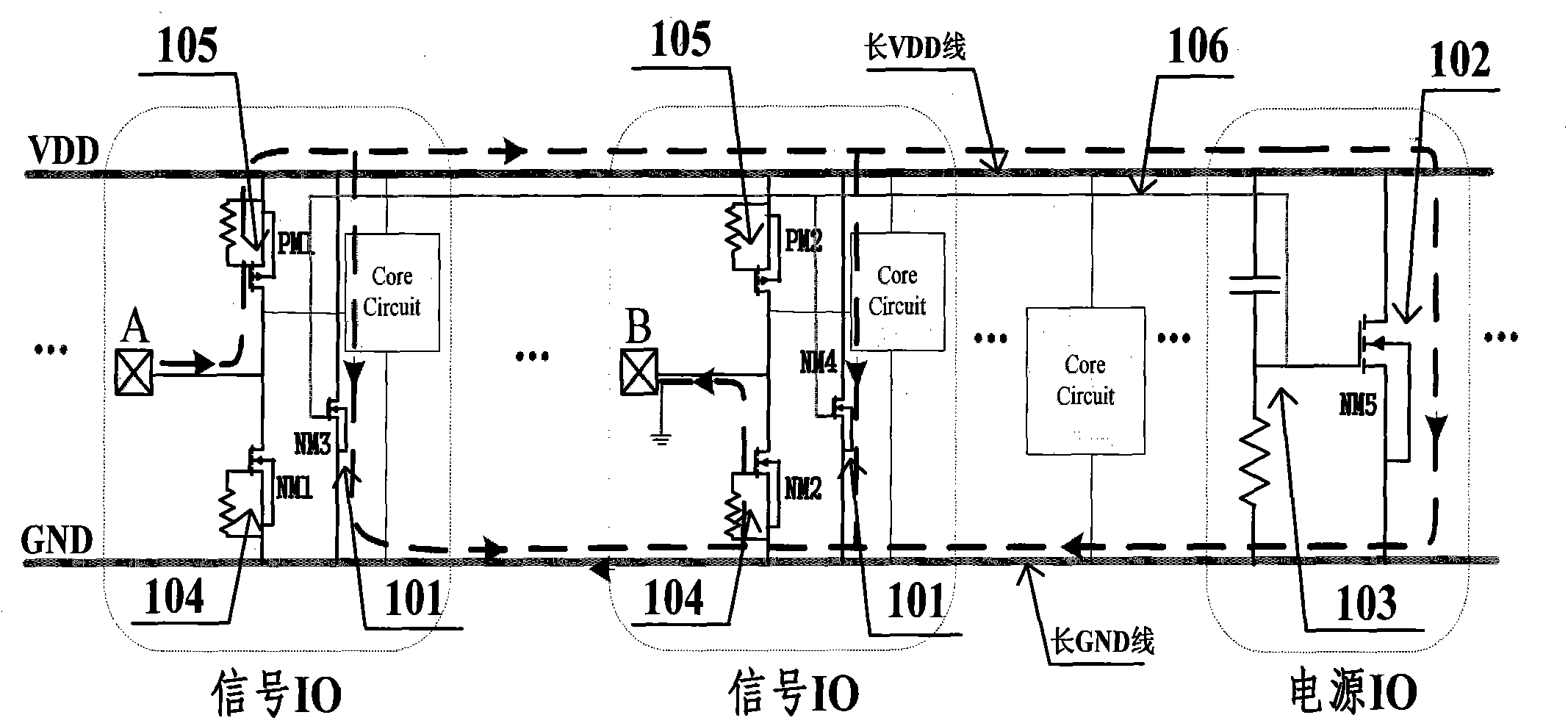

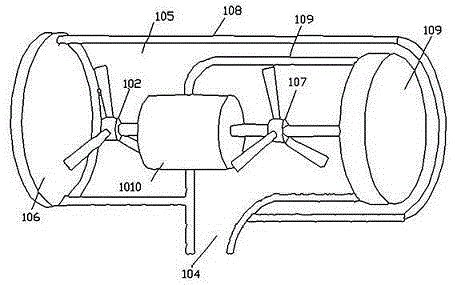

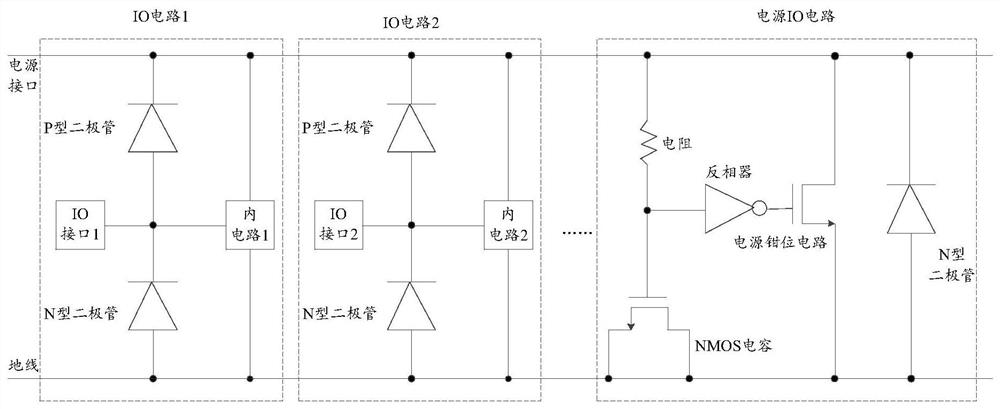

The invention is an integrated circuit full-chip electro static discharge (ESD, Electro Static Discharge) protection method. According to an integrated circuit full-chip ESD structure of the method, one power-ground ESD discharge path is added in each signal IO unit, namely, a full chip not only contains an electro static discharge path 102 in a power IO unit, but also contains the electro static discharge path 101 in each signal IO unit. Therefore, the number of the electro static discharge paths in the full chip is increased, the electro static discharge path between IO is shortened, the discharge resistance between IO is reduced, the full-chip electro static discharge efficiency is improved, and the full-chip ESD level is upgraded.

Owner:BEIJING CEC HUADA ELECTRONIC DESIGN CO LTD

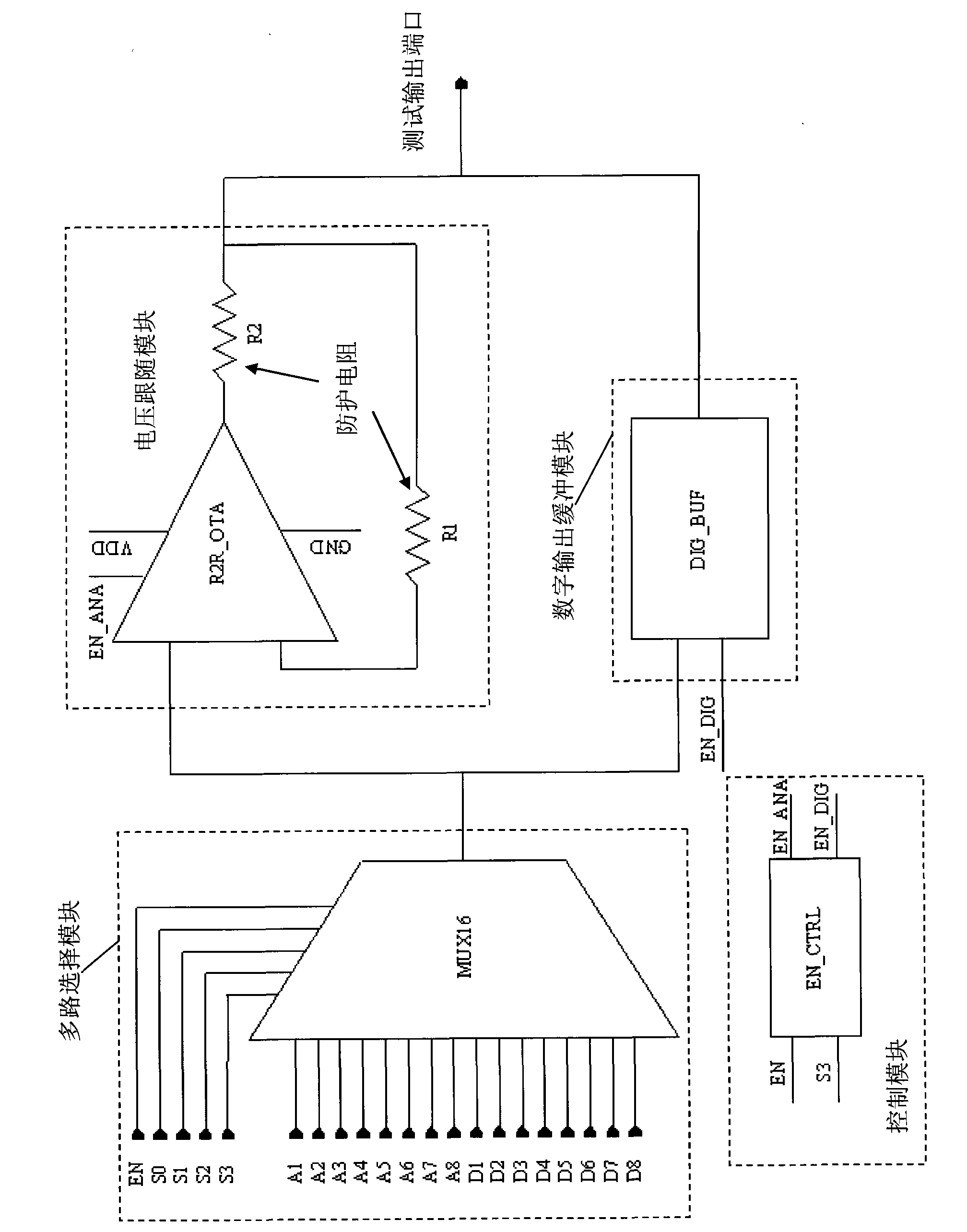

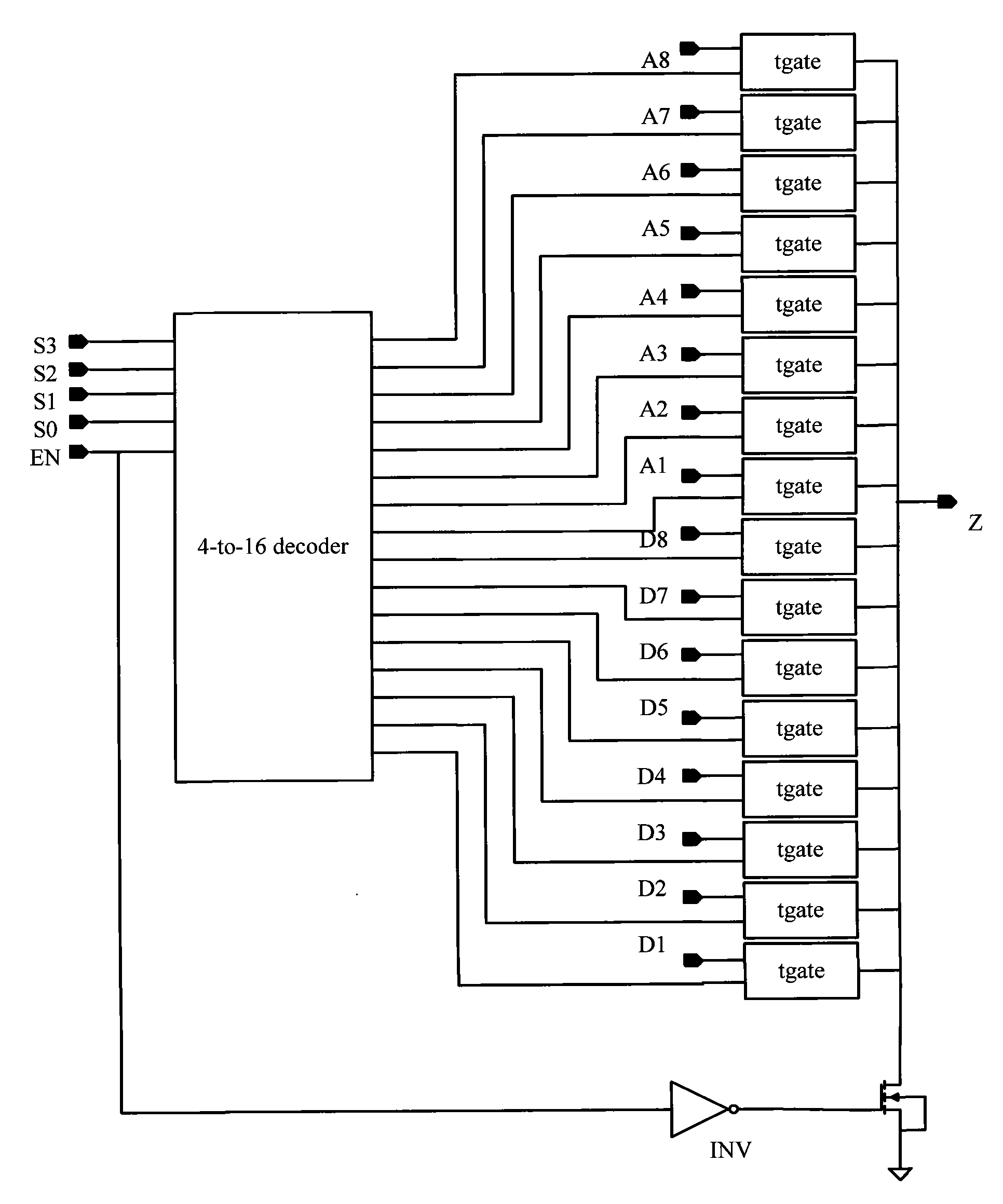

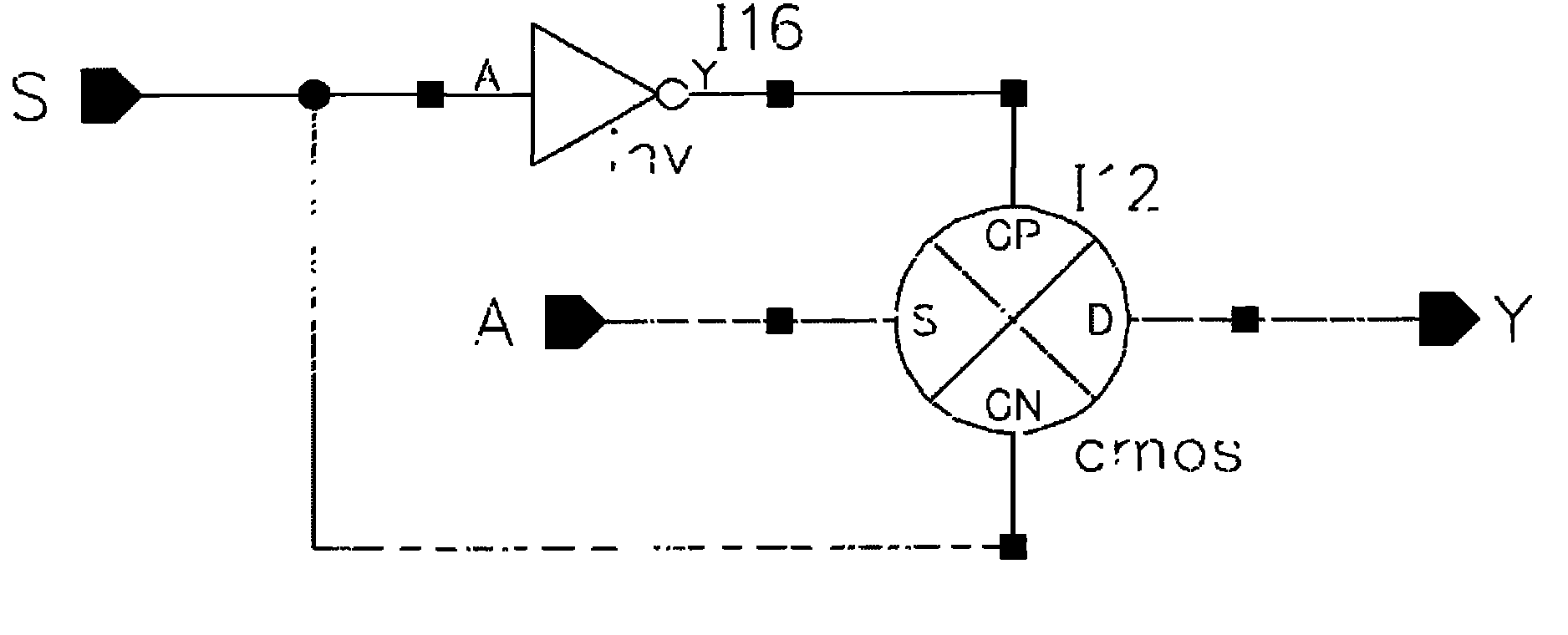

Testability circuit for digital/analog mixed signal chip

InactiveCN102117343AImprove ESD capabilitySpecial data processing applicationsFull customControl signal

The invention discloses a testability circuit for a digital / analog mixed signal chip. The testability circuit comprises a multi-path selection module, a control module, a voltage follower module and a digital output buffer module, wherein the multi-path selection module is used for selecting the signal to be observed and transmitting the signal to the voltage follower module or the digital output buffer module; the control module is used for generating a control signal to selectively open the voltage follower module or the digital output buffer module; and the selected signal is transmitted to the voltage follower module if the selected signal is an analog signal, or the selected signal is transmitted to the digital output buffer module if the selected signal is a digital signal. The testability circuit can observe the important digital signal and the analog signal in the chip through an output pin of the chip, which facilitates the chip fault analysis and debugging. The testability circuit is suitable for the digital / analog mixed signal chip and full-custom chip.

Owner:SHANGHAI HUAHONG INTEGRATED CIRCUIT

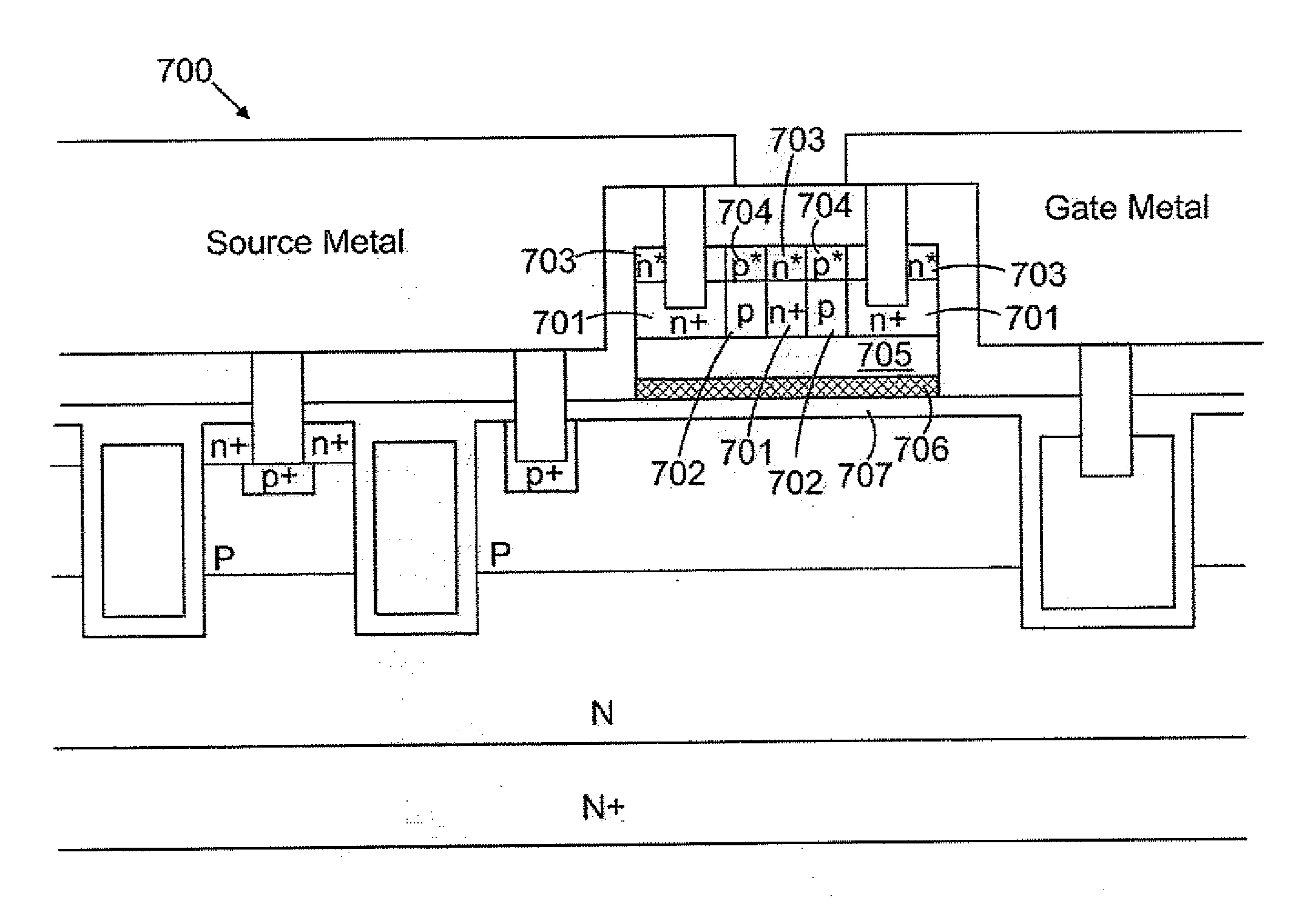

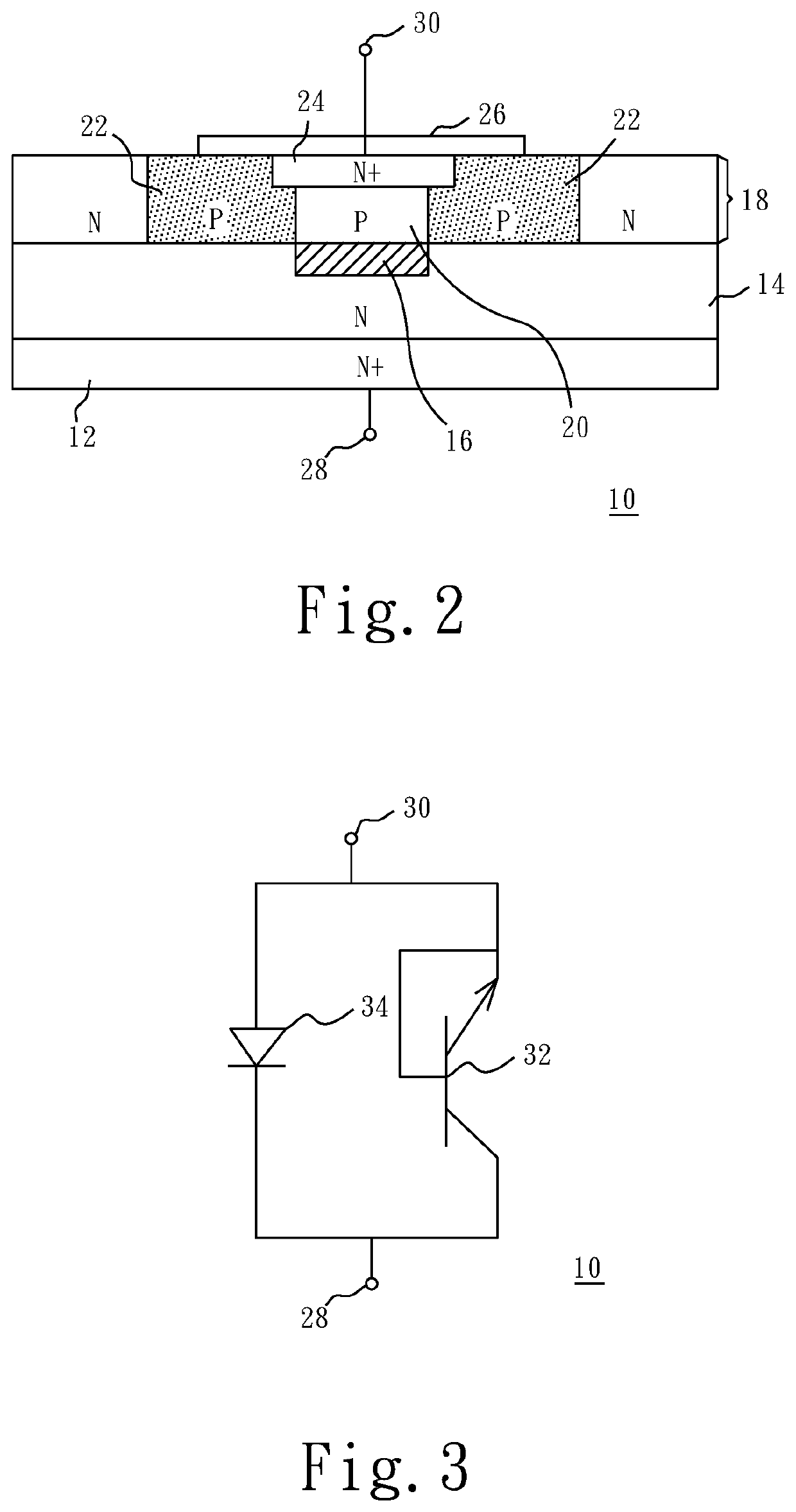

Semiconductor power device integrated with clamp diodes having dopant out-diffusion suppression layers

InactiveUS20130234237A1Reduce power consumptionDegrading ESD capabilityTransistorSolid-state devicesDopantEngineering

A semiconductor power device integrated with clamp diodes is disclosed by offering dopant out-diffusion suppression layers to enhance the ESD protection between gate and source, and avalanche capability between drain and source.

Owner:FORCE MOS TECH CO LTD

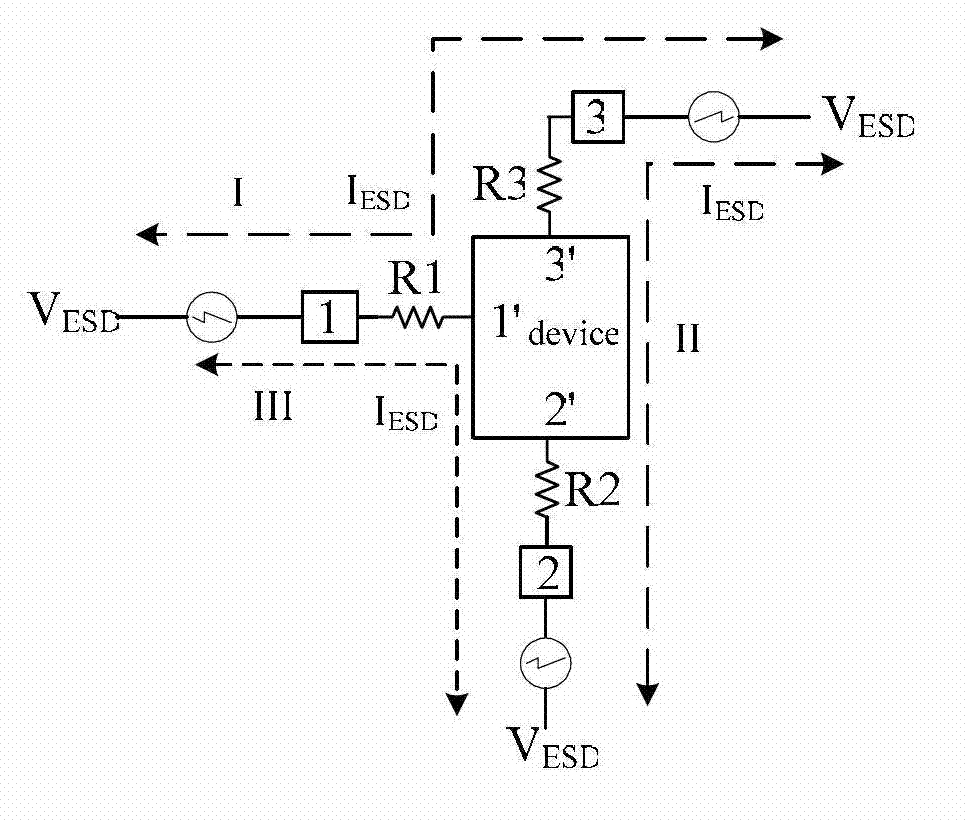

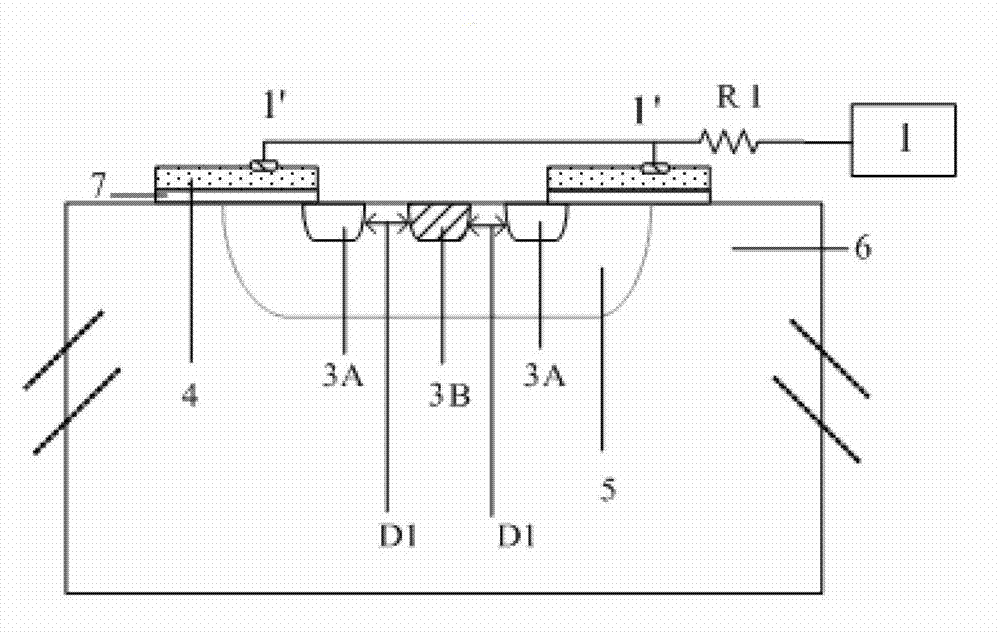

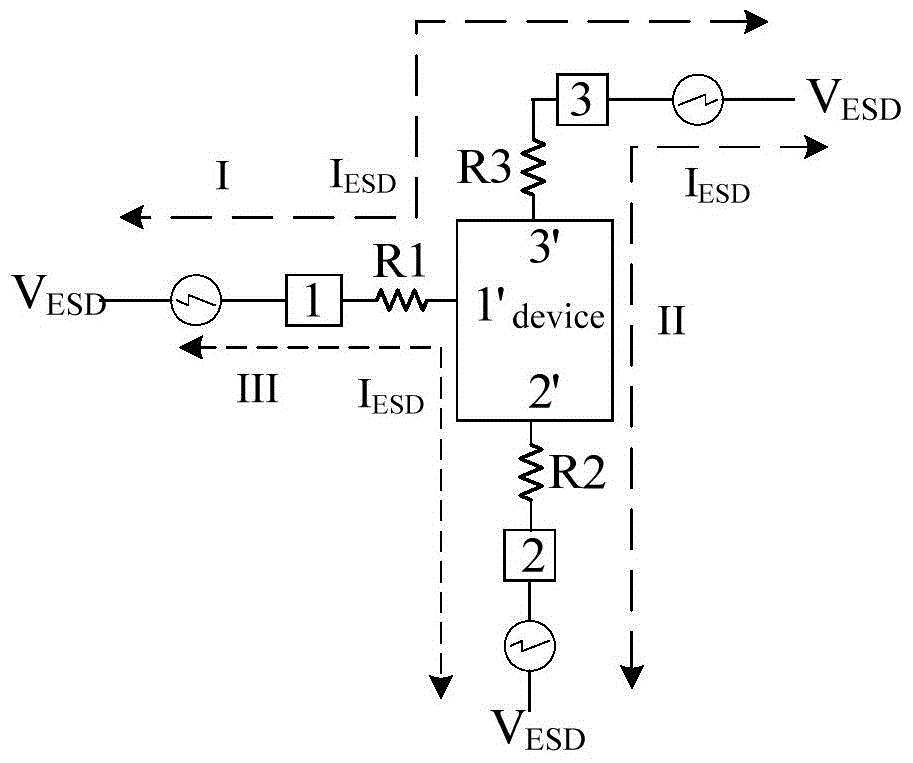

Power semiconductor device with antistatic discharge capacity and manufacturing method

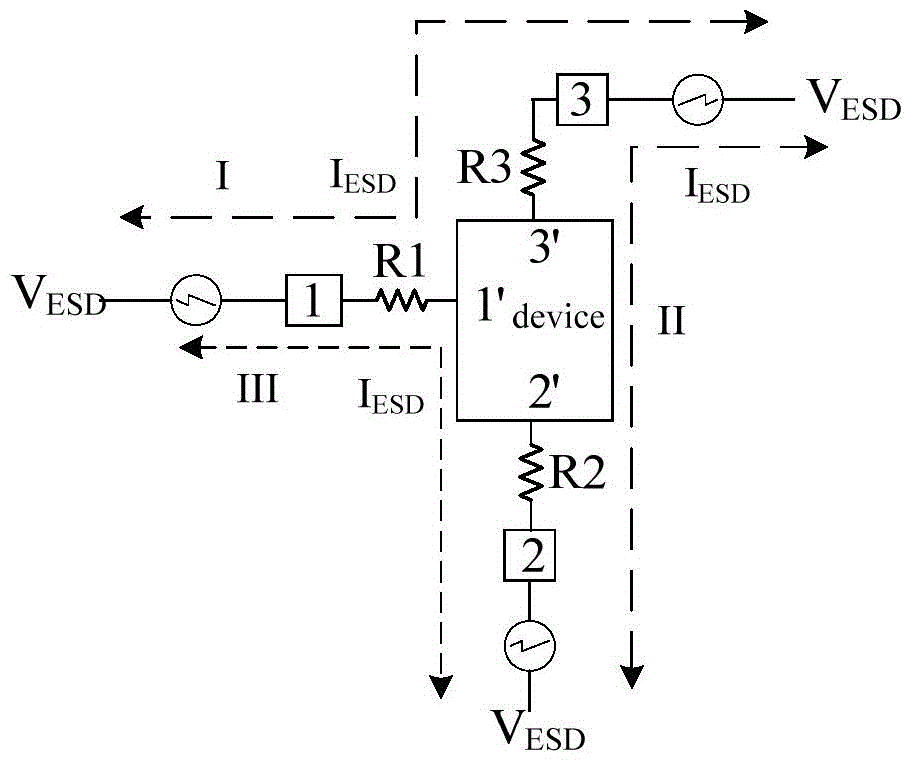

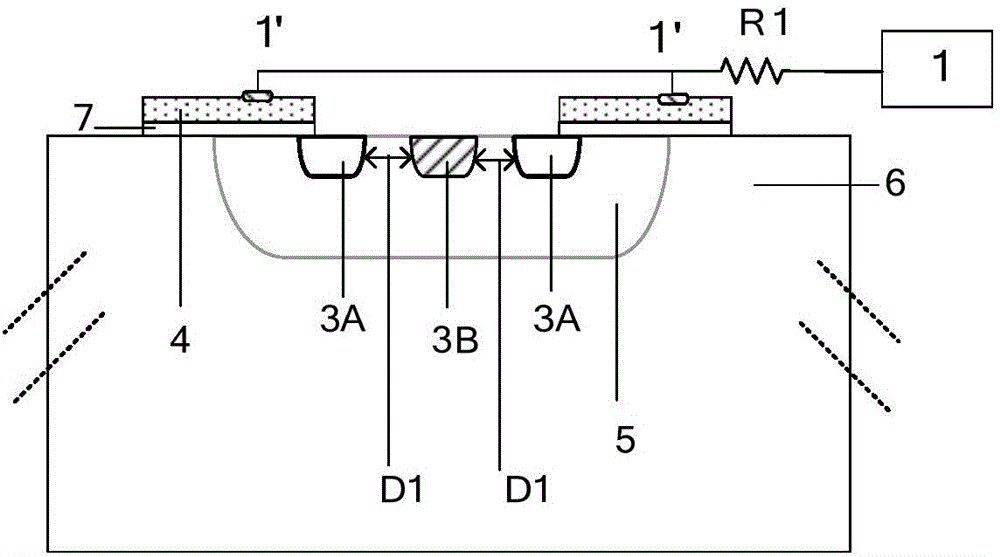

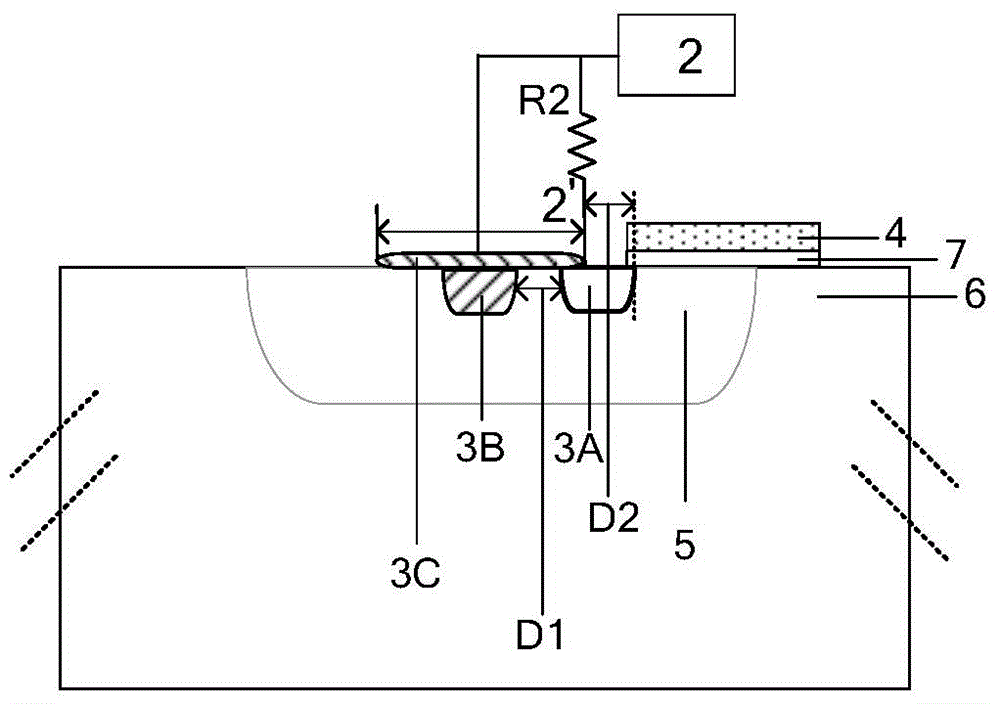

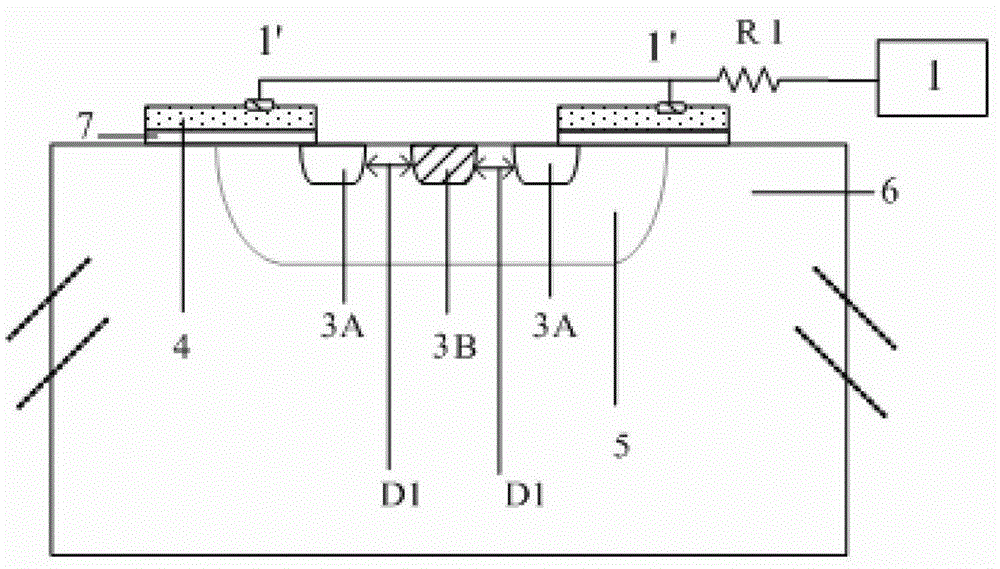

InactiveCN103050442AImprove ESD capabilityLow costSolid-state devicesSemiconductor/solid-state device manufacturingPower semiconductor deviceElectrical resistance and conductance

The invention provides a manufacturing method for a power semiconductor device with antistatic discharge capacity. The manufacturing method comprises the following steps of: providing the power semiconductor device with a first port, a second port and a third port, wherein the power semiconductor device is formed by arranging cell arrays; and respectively connecting any one port or more than one port of the three ports to a resistor to form the power semiconductor device with the antistatic discharge capacity. The invention also provides the power semiconductor device with the antistatic discharge capacity. By the power semiconductor device with the antistatic discharge capacity and the manufacturing method, a series resistor of any one port or more than one port of three ports of the power semiconductor device serves as an electrostatic discharge (ESD) protective component to improve the ESD capacity; the series resistor can meet the requirements on a plurality of grades of ESD by slightly adjusting a protected device layout structure; and the design flexibility is high.

Owner:HANGZHOU SILAN MICROELECTRONICS

The Trigger Circuit Structure of IC Power Rail Antistatic Protection

InactiveCN103151350BReduce leakage currentUniform conductionSolid-state devicesSemiconductor devicesLow voltageEngineering

The invention provides a trigger circuit structure with circuit power supply rail antistatic protection, belonging to the technical field of electronics. The structure is used for triggering an integrated circuit high voltage power supply rail antistatic protective device with mixed working voltage, and comprises a series circuit, a second PMOS (positive channel metal oxide semiconductor) tube and a resistor R, wherein the series circuit consists of m (a positive integer) first PMOS tubes and is formed by connection of diodes; the source electrode of the most top first PMOS tube in the series circuit is connected with VDD_H (voltage drain drain_high); the drain electrode of the second PMOS tube is connected with a triggering end T of an ESD (electro-static discharge) protective device; the grid electrode of the second PMOS tube is connected with VDD (voltage drain drain) through the resistor R. The trigger circuit structure consists of a low voltage device, however, the trigger circuit structure can tolerate VDD_H voltage of a high voltage power supply rail, reduce the trigger voltage of the device, promote uniform conduction of the device, and improve ESD capability, and meanwhile, no capacitor device exists in the circuit, thus, the leakage current of the protected integrated circuit under normal working is smaller.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

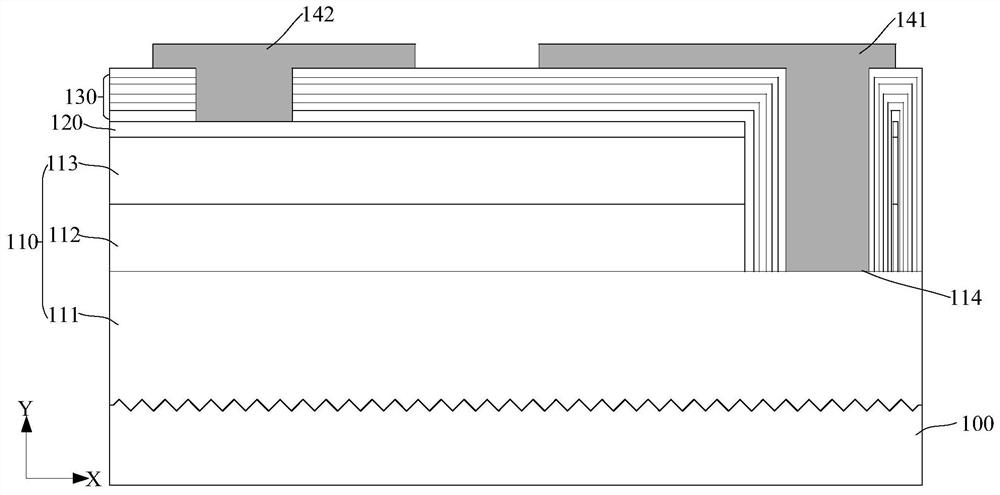

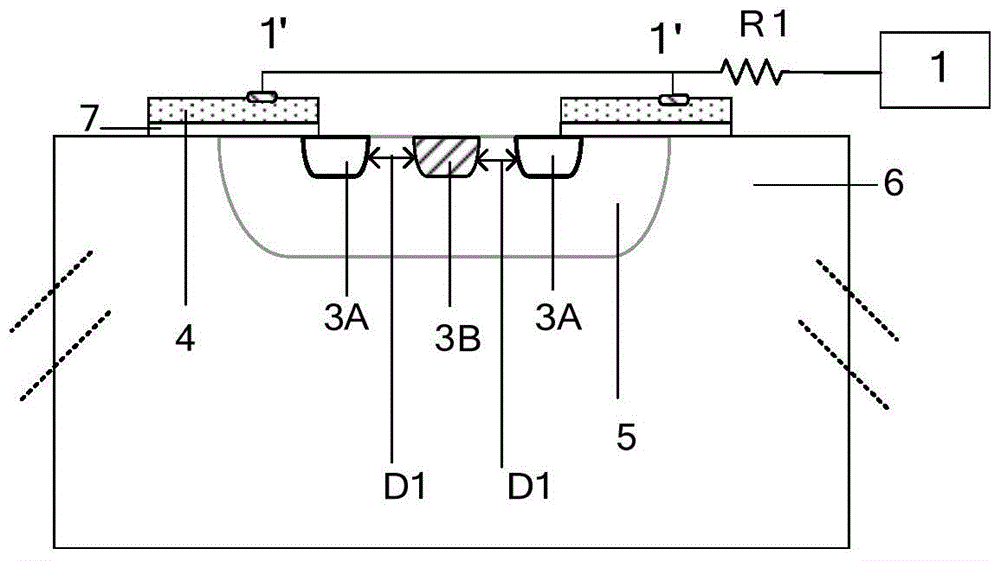

Semiconductor device

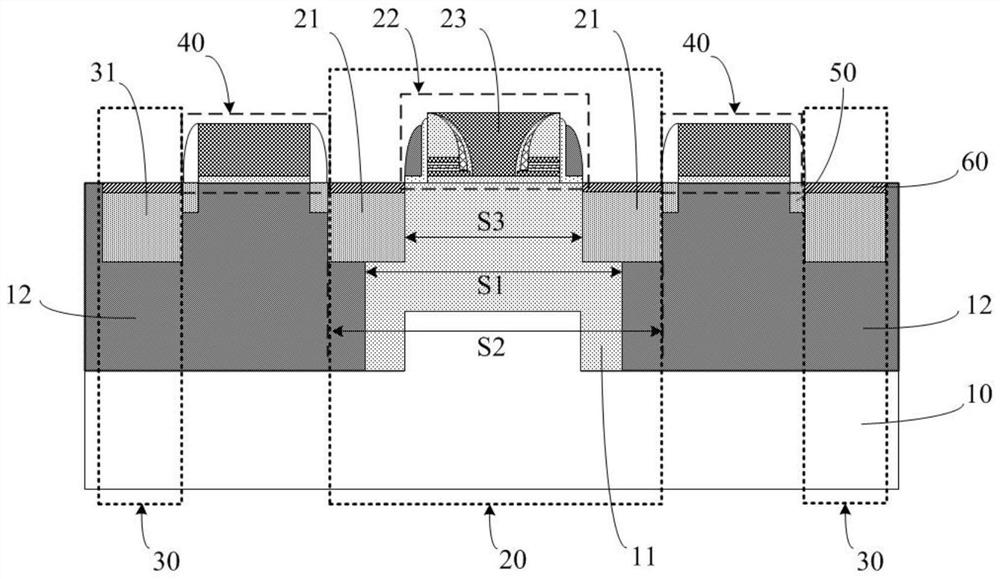

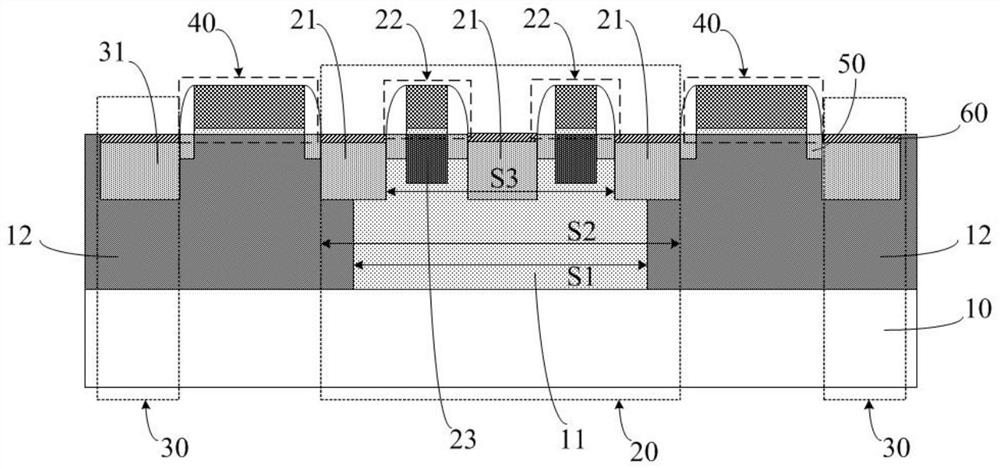

PendingCN113192948APrevent electrical breakdownImprove ESD capabilitySolid-state devicesSemiconductor devicesManufacturing technologyDevice material

The invention provides a semiconductor device comprising a substrate having a first region and second regions, the first region being located between two adjacent second regions; two sub drain regions located in the first region of the substrate; a dummy structure positioned on the substrate between the two adjacent sub drain regions; a source region located in the second region of the substrate; a gate structure positioned on the substrate between the first region and the second regions. The ESD capacity of the device is improved through the dummy structure, an SAB photomask in the prior art is not needed, a new technological process does not need to be introduced, and the dummy structure can be directly and synchronously formed in the manufacturing process, so that the manufacturing cost of the device is reduced.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

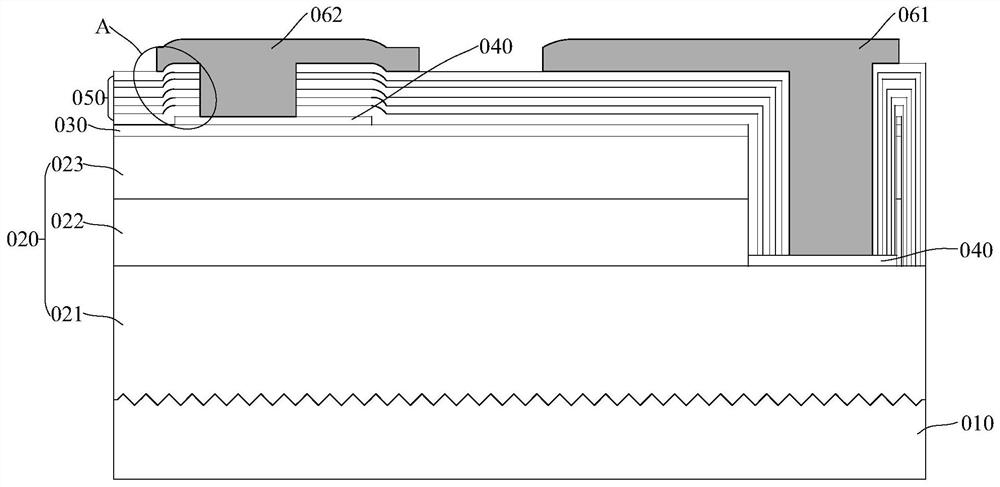

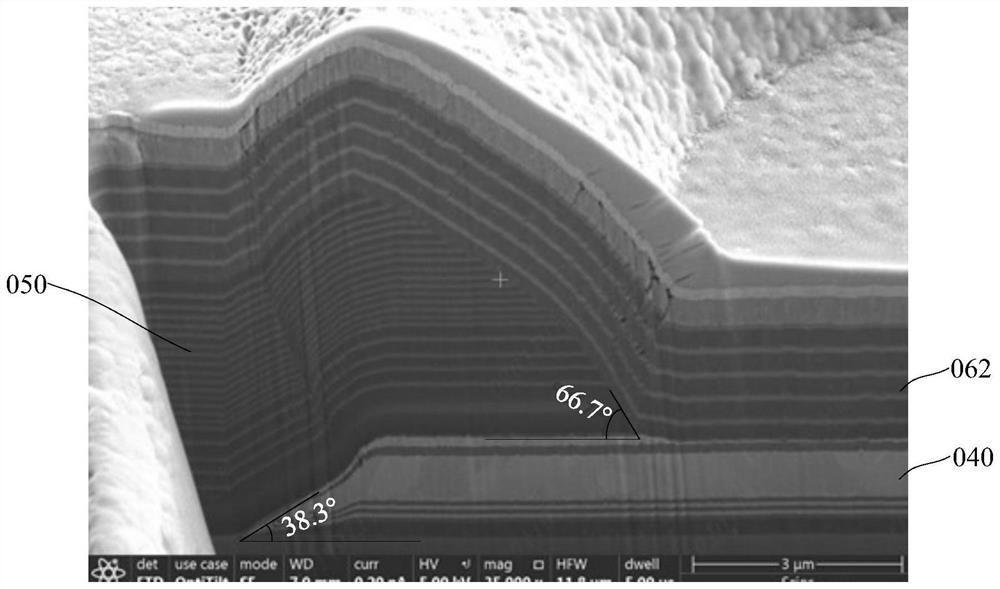

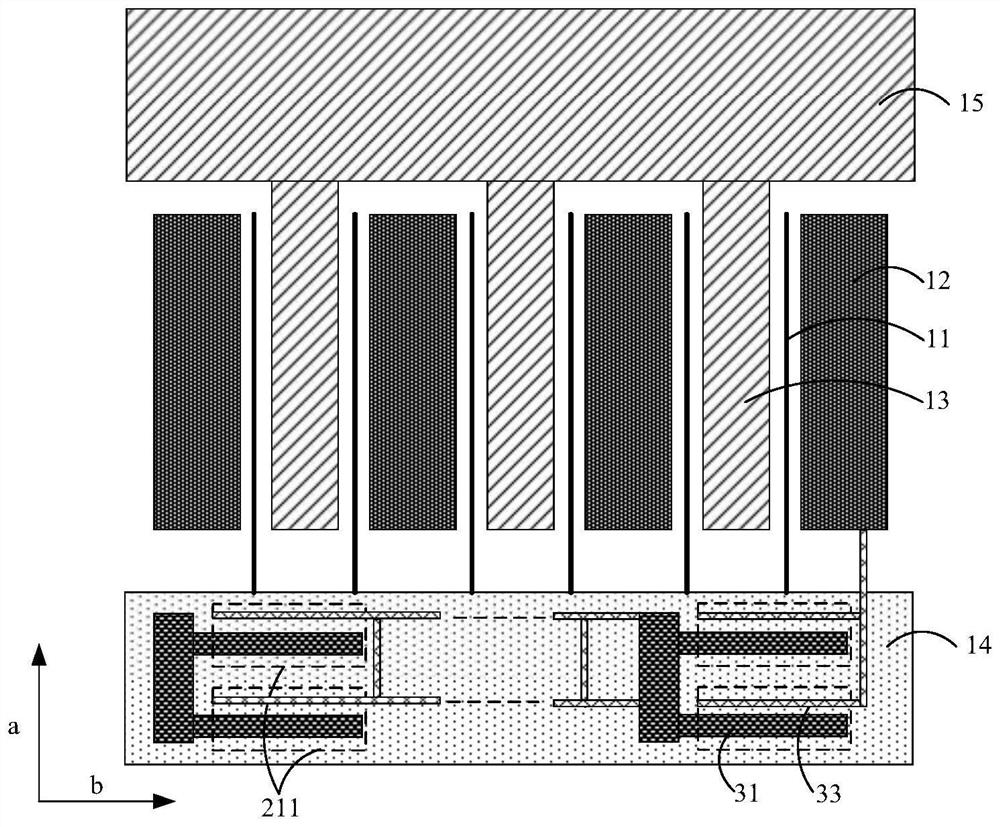

Flip semiconductor light-emitting element, semiconductor light-emitting device and display device

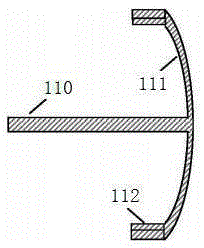

ActiveCN113659051AImprove flatnessGuaranteed flatnessSolid-state devicesSemiconductor devicesDisplay deviceSemiconductor

The invention provides a flip semiconductor light-emitting element, a semiconductor light-emitting device and a display device. The semiconductor light-emitting element comprises a substrate and a light-emitting epitaxial layer formed on the substrate. When an electrode structure is formed above the light-emitting epitaxial layer, a first electrode layer partially covering the light-emitting epitaxial layer above the light-emitting epitaxial layer is omitted, so that the surface of the light-emitting epitaxial layer is relatively high in flatness. When an insulating reflection layer and an insulating protection layer are formed subsequently, the flatness of the insulating reflection layer and the insulating protection layer can be ensured. Moreover, the overall thickness of the insulating reflection layer and the insulating protection layer is not greater than 3 microns, so that abnormal protrusions cannot occur when the electrode through holes are formed in the insulating reflection layer and the insulating protection layer, the electrode through holes have good morphology, the adhesion of a subsequently formed electrode bonding pad in the electrode through hole and the adhesion of the subsequently formed electrode bonding pad above the insulating protection layer are enhanced, and the electrode bonding pad does not have defects such as cracks or fractures, so that the stability and reliability of the device are enhanced.

Owner:XIAMEN SANAN OPTOELECTRONICS CO LTD

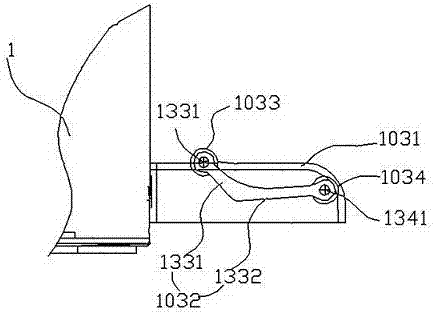

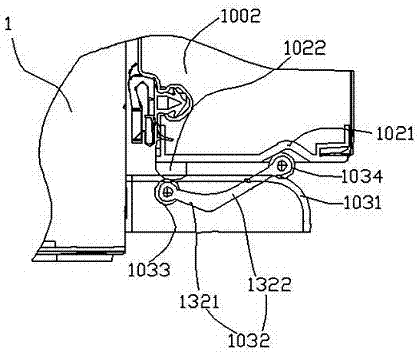

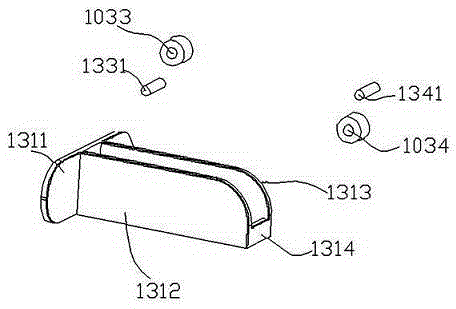

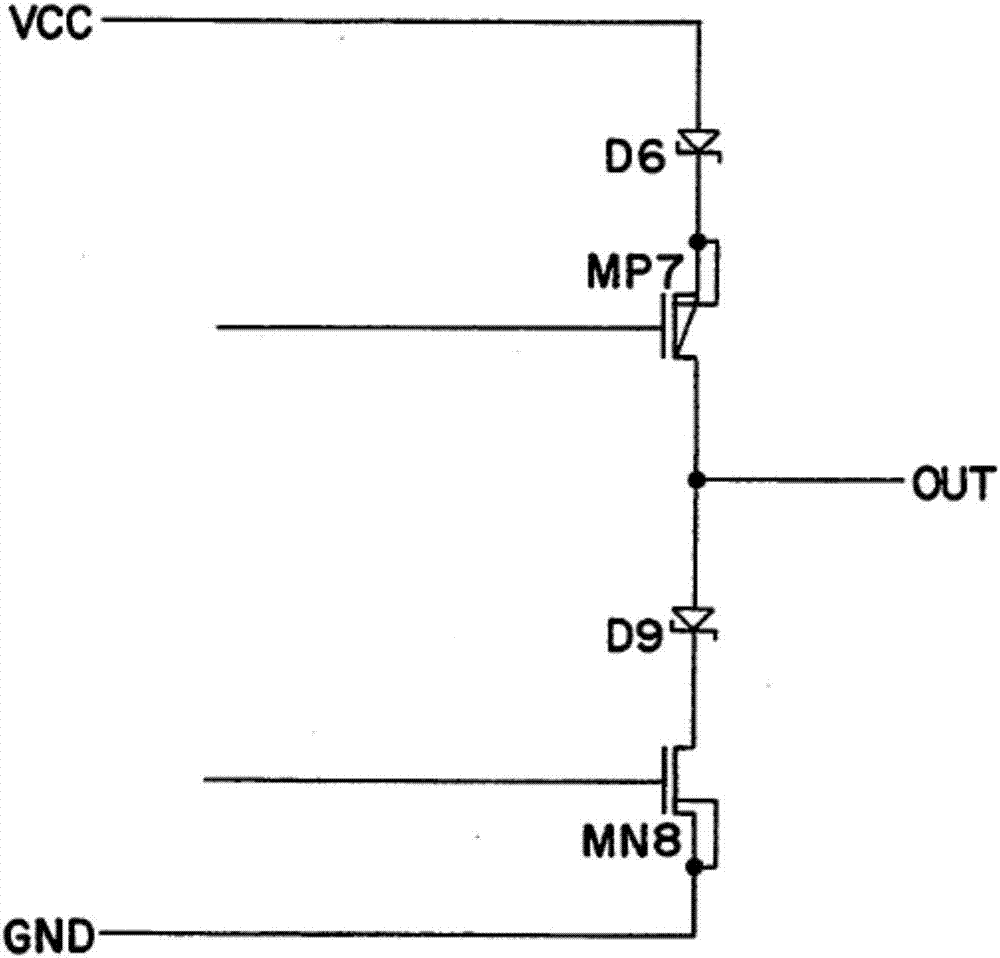

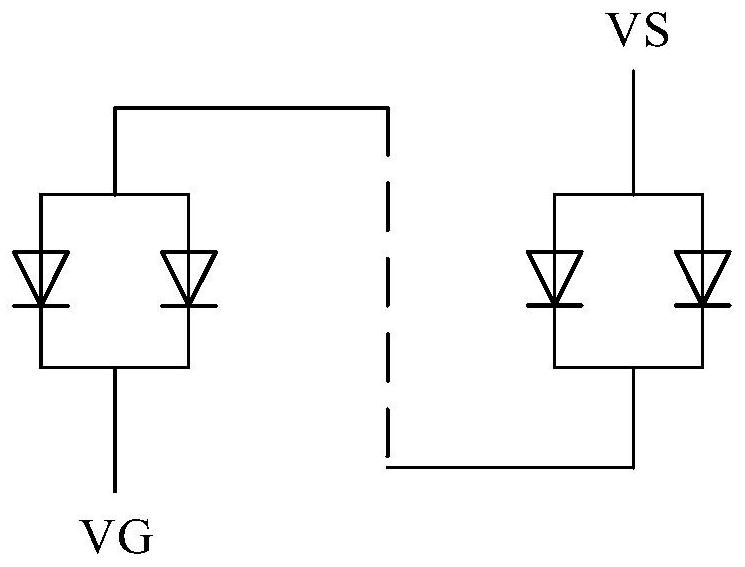

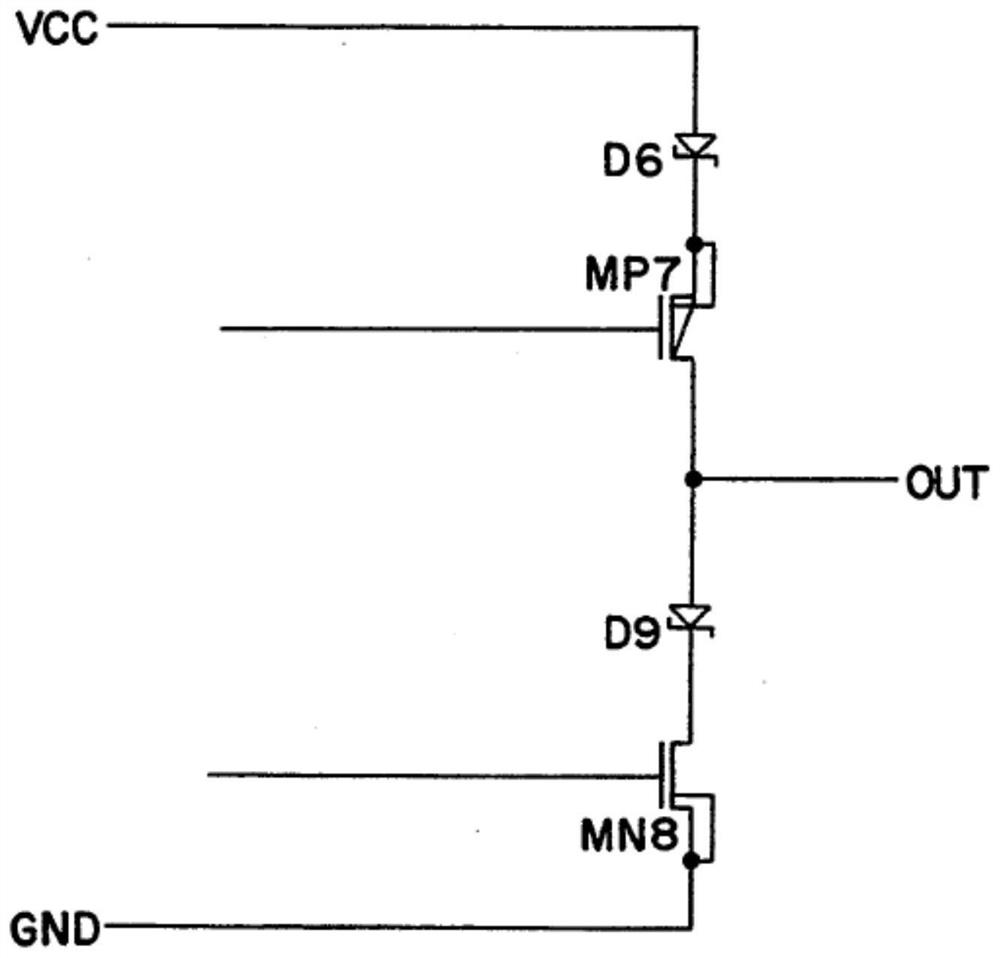

Logic conversion circuit device

ActiveCN105163565APrevent crookedImprove ESD capabilityCasings/cabinets/drawers detailsCooling/ventilation/heating modificationsDouble loopOxide semiconductor

The invention discloses a logic conversion circuit device, which comprises a logic conversion circuit, wherein double-loop protection is adopted by a circuit port structure of the logic conversion circuit; an ESD input layer is added to an N-channel metal oxide semiconductor (NMOS) tube part of the circuit; a radiating pipe is coiled in a cabinet body; the logic conversion circuit is arranged in the cabinet body; a refrigerant outlet and a refrigerant outlet, which are communicated with the radiating pipe are formed in the cabinet body; in addition, the cabinet body comprises a front cover board and front cover board accessories; and the front cover board can be pivoted on the cabinet body between the direction in which the cabinet body is uncovered and the direction in which the cabinet body is covered. According to the structure, the ESD capacity of a circuit port is improved; a protective diode is added between a power supply circuit and the ground; the ESD capacity of the circuit is also improved; and the defect that the front cover board frequently warps in the device of covering the front cover board in the prior art is avoided.

Owner:江苏万邦微电子有限公司

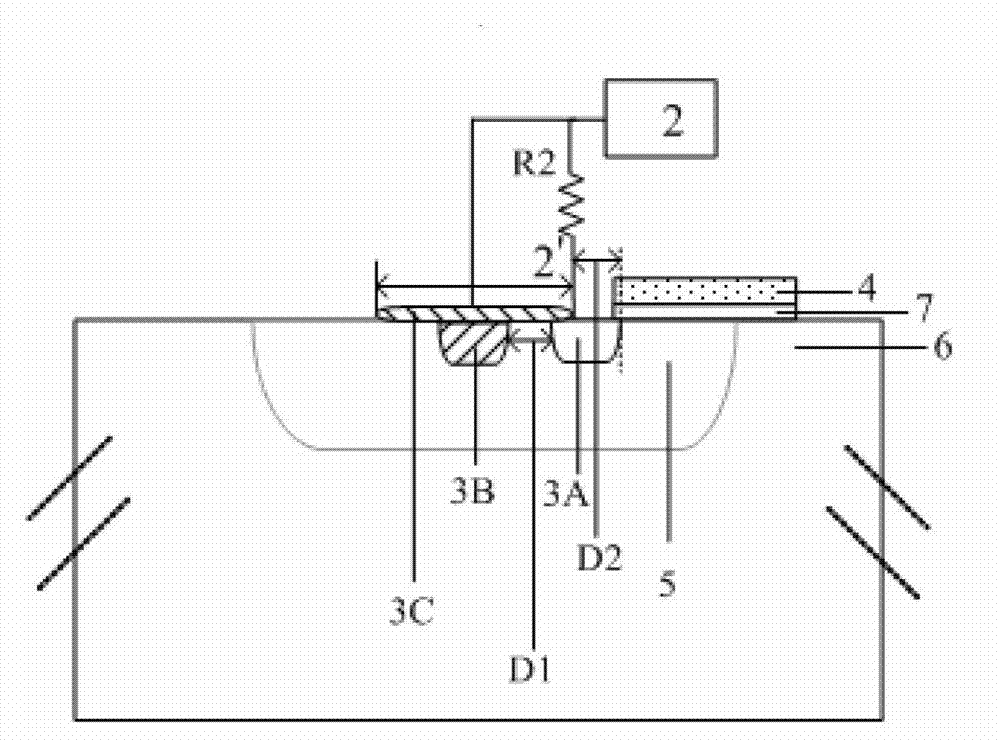

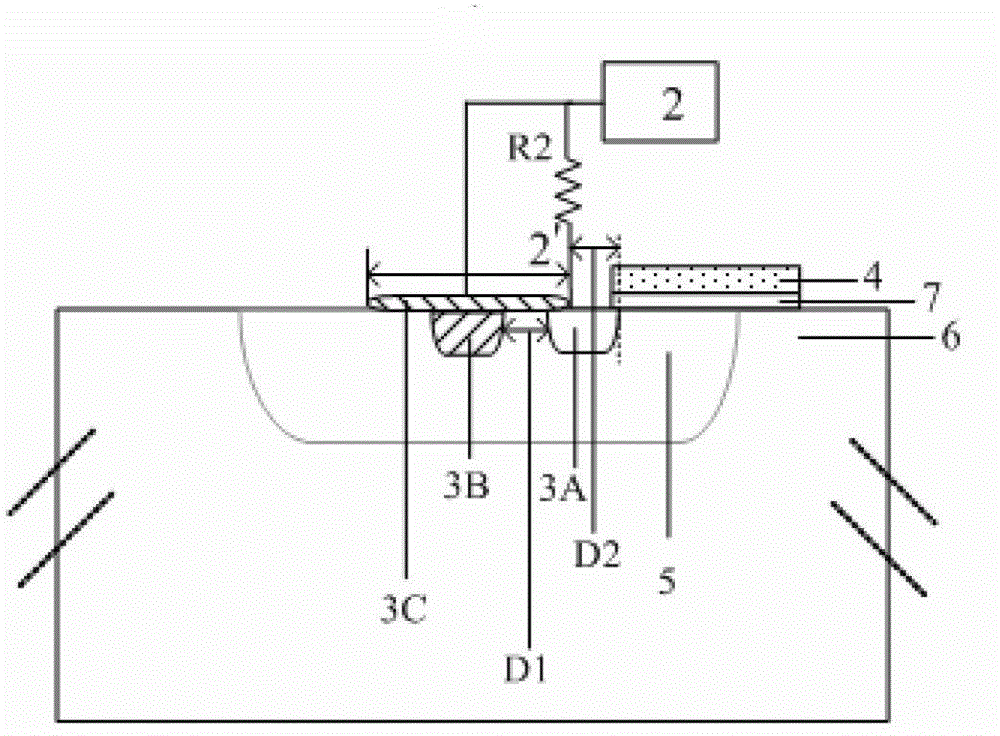

Low-clamping protection device structure and manufacturing method thereof

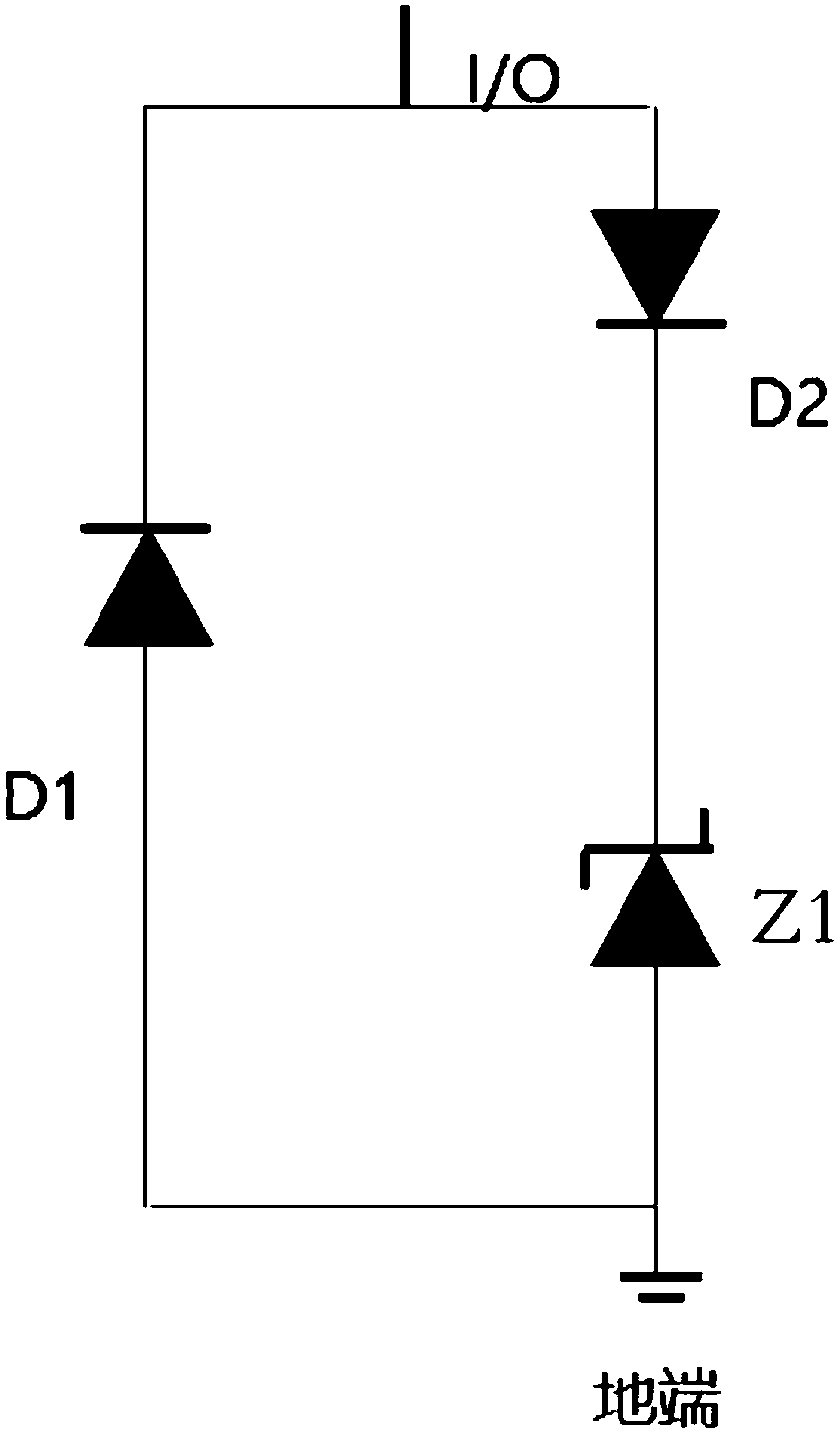

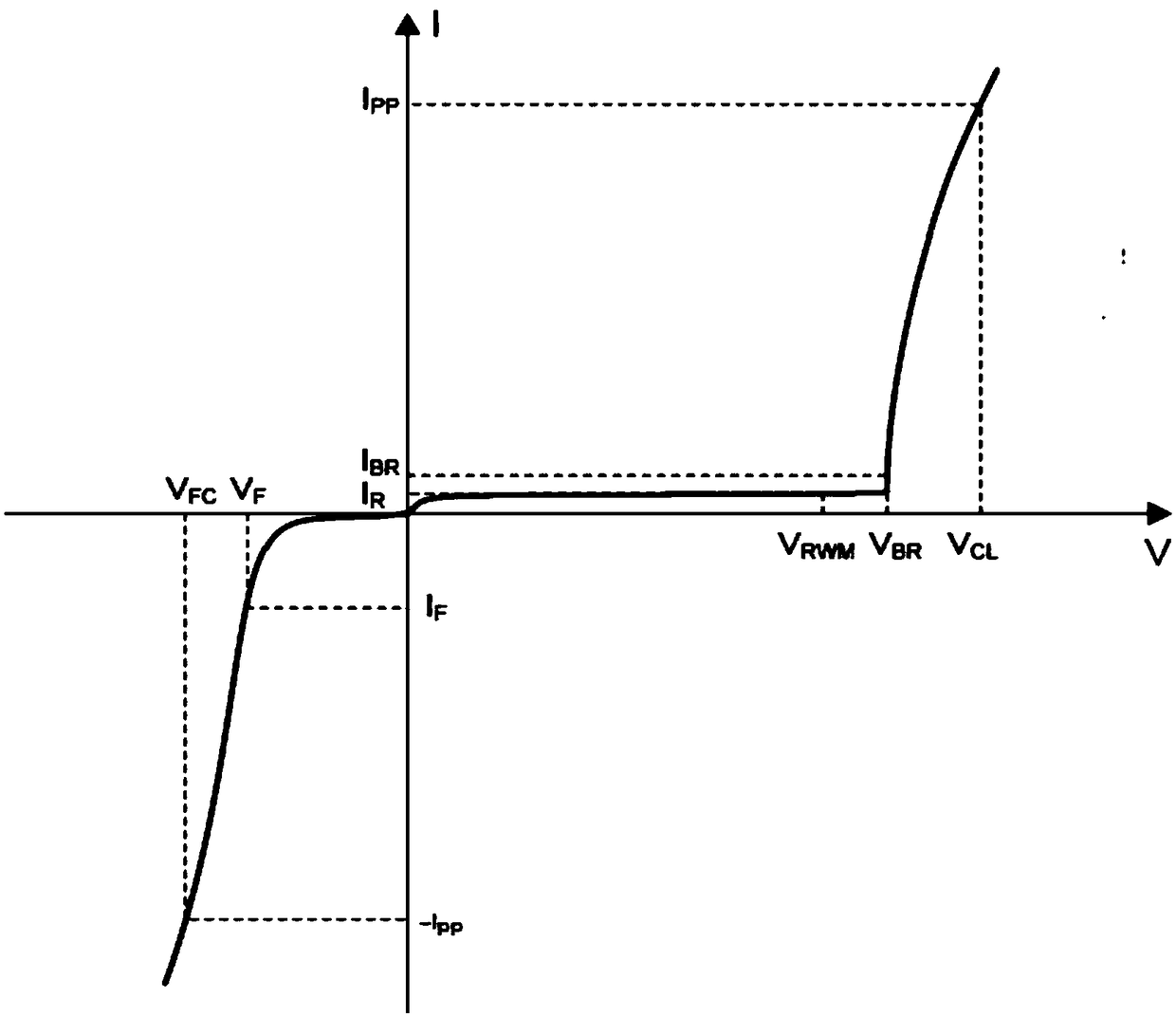

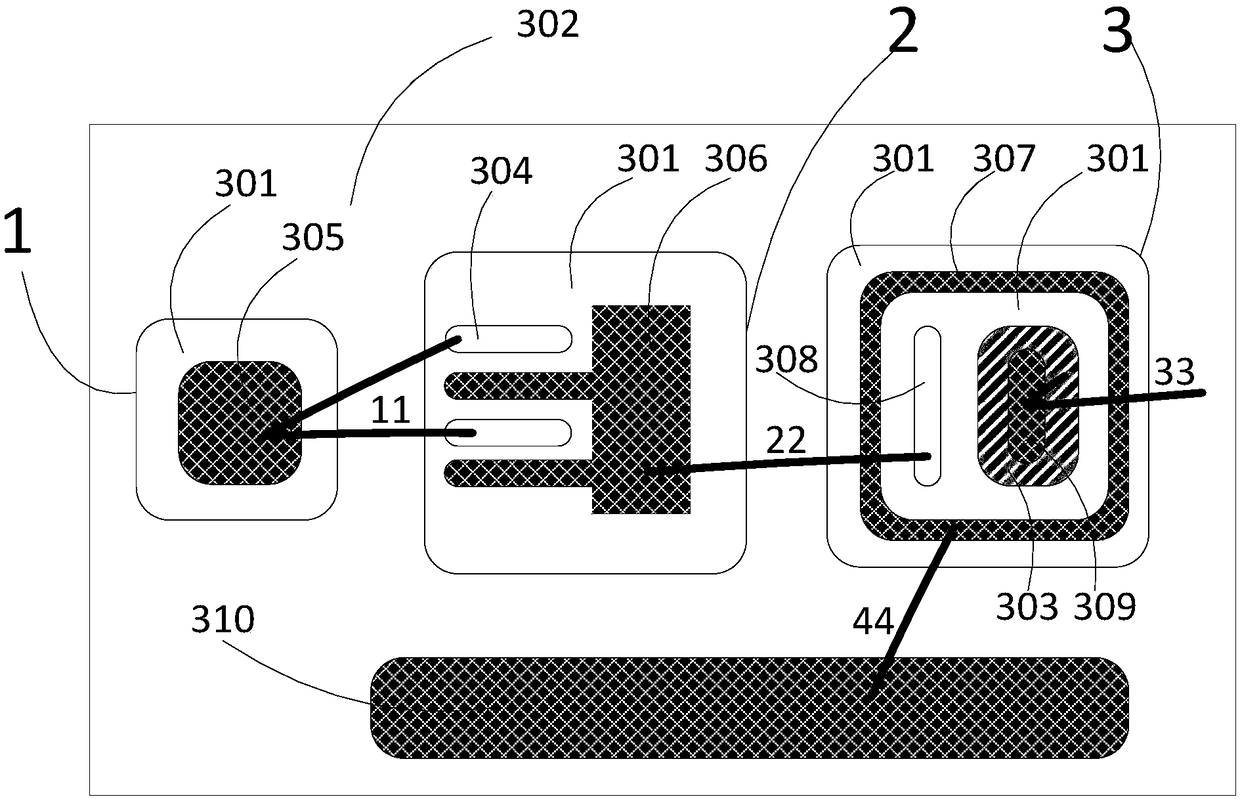

PendingCN109346465ALower clamping voltageAvoid burnsSolid-state devicesSemiconductor/solid-state device manufacturingCapacitanceData integrity

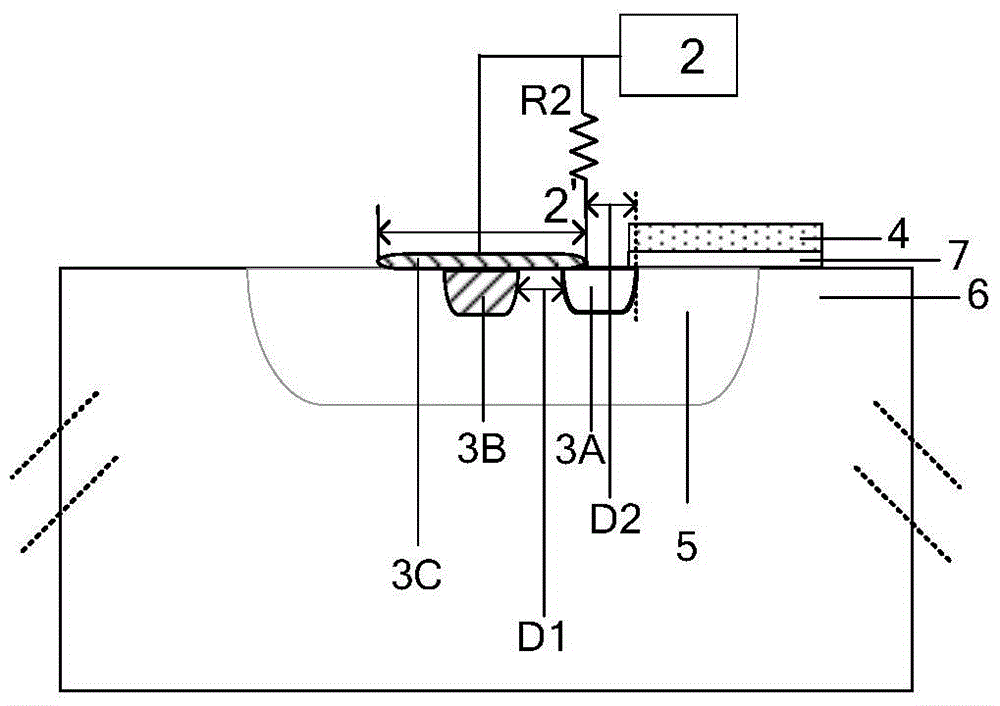

The invention belongs to the technical field of semiconductor protection devices, and relates to a low-clamping protection device structure and a manufacturing method thereof. A first conduction typeisolation structure which divides a device into three regions is arranged in a second conduction type epitaxial layer; a low-capacitance diode D1 is formed in the first region; a low-capacitance diodeD2 is formed in the second region; a discharge tube TSS is formed in the third region; a TVS voltage-stabilizing diode Z1 is formed in the first conduction type isolation structure; the TVS voltage-stabilizing diode Z1 is connected in parallel with the discharge tube TSS, and is connected with the diode D2 in series; the positive electrode of the diode D2 is connected with the negative electrodeof the TVS voltage-stabilizing diode Z1, and is connected with an I / O port; and the positive electrode of the diode Z1 is connected with the positive electrode of the diode D1 are grounded. By addingthe discharge tube TSS structure, on the basis of not enlarging the device area and increasing the process cost, a clamping voltage is reduced, and the current capacity is improved, so that the ESD capacity of a high-speed data transmission channel port is improved, the data integrity is guaranteed, and meanwhile burnout caused by excessively high dissipation power is prevented.

Owner:无锡欣昱微电子有限公司

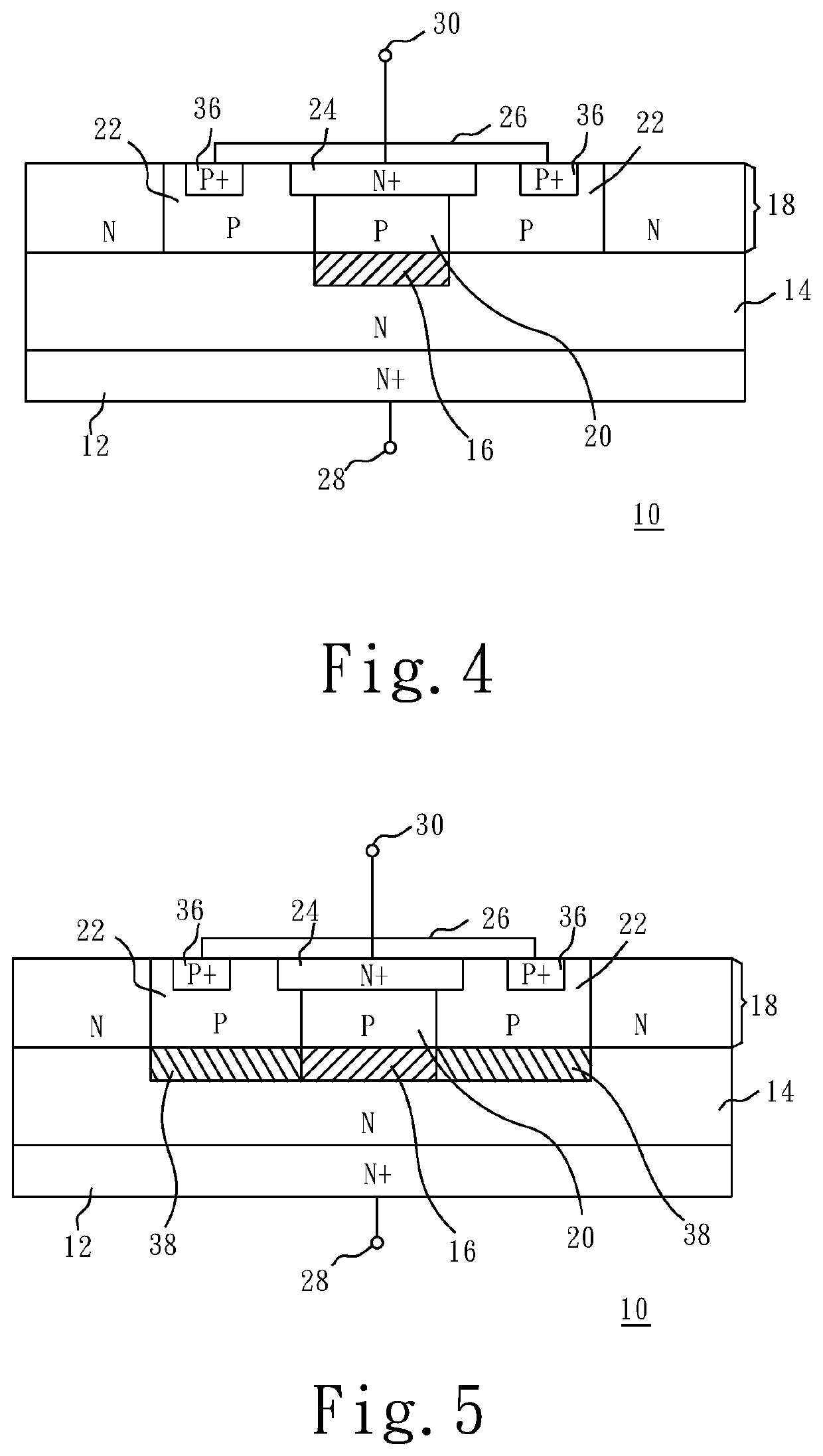

Vertical electrostatic discharge protection device

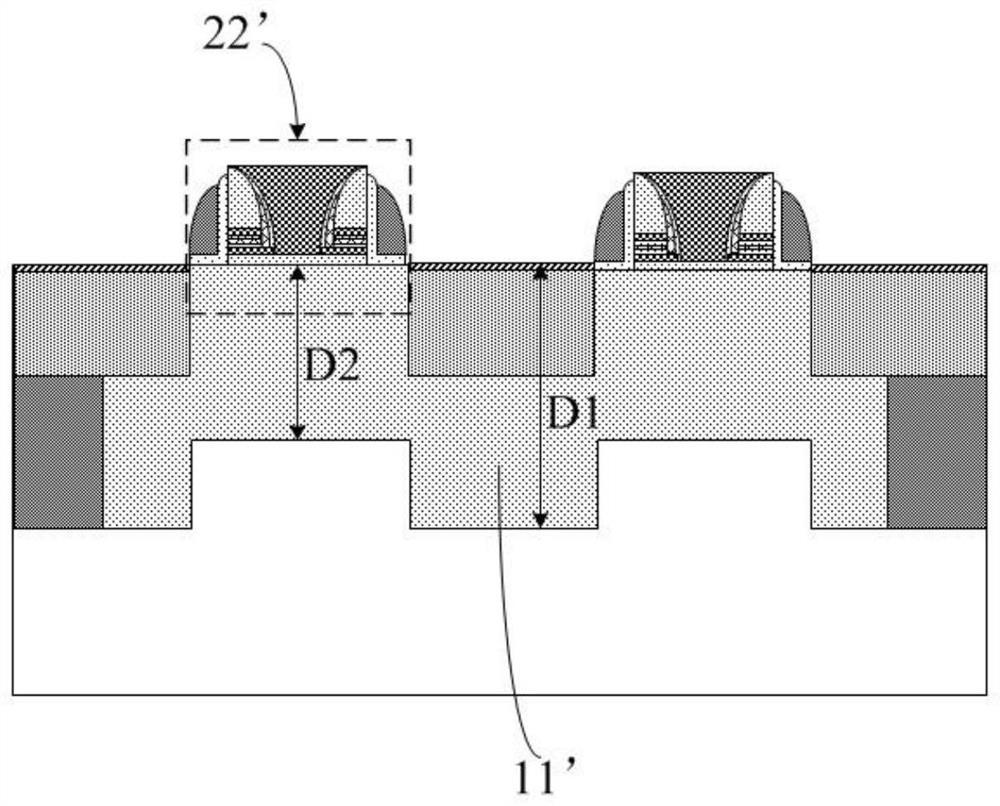

PendingUS20220052035A1Improve ESD capabilityLower forward voltageTransistorSolid-state devicesPhysicsElectrostatic discharge protection

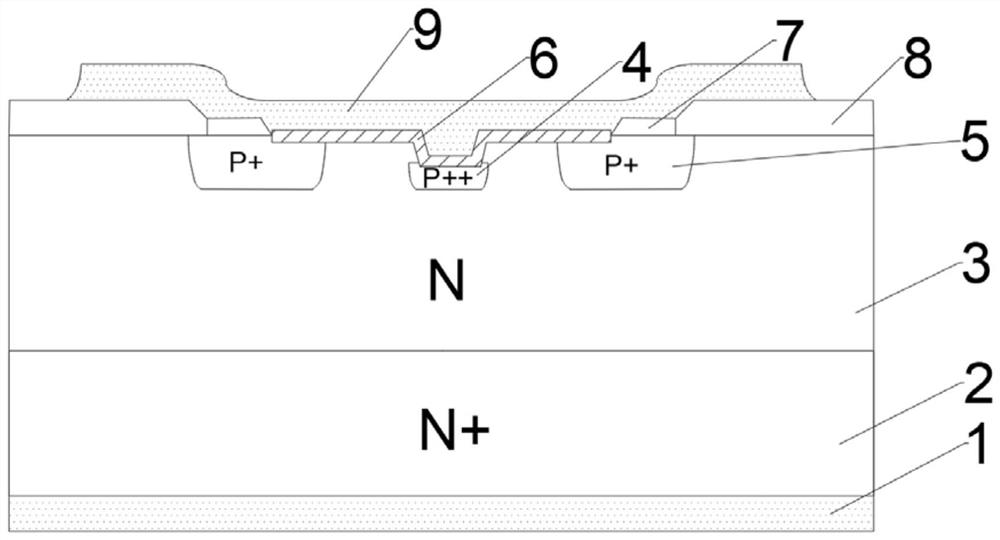

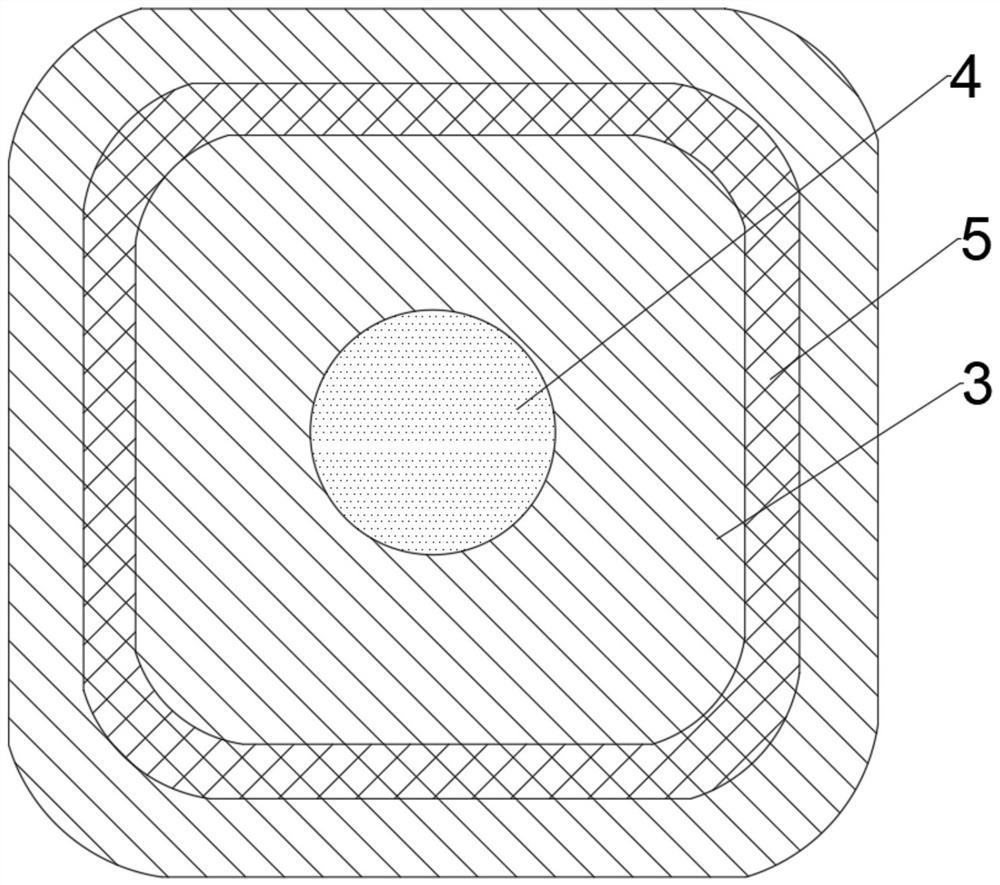

A vertical electrostatic discharge protection device includes a heavily-doped semiconductor substrate, a first semiconductor epitaxial layer, a first doped buried layer, a second semiconductor epitaxial layer, a first doped well, at least one second doped well, and a first heavily-doped area. The epitaxial layers are stacked on the substrate. The first doped buried layer is formed in the first semiconductor epitaxial layer. The first doped well is formed in the second semiconductor epitaxial layer. The first doped well is formed on the first doped buried layer, and the doping concentration of the first doped well is lower than that of the first doped buried layer. The second doped well is formed in the second semiconductor epitaxial layer. The second doped well is adjacent to the first doped well.

Owner:AMAZING MICROELECTRONICS

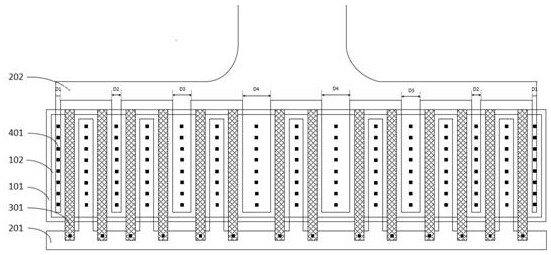

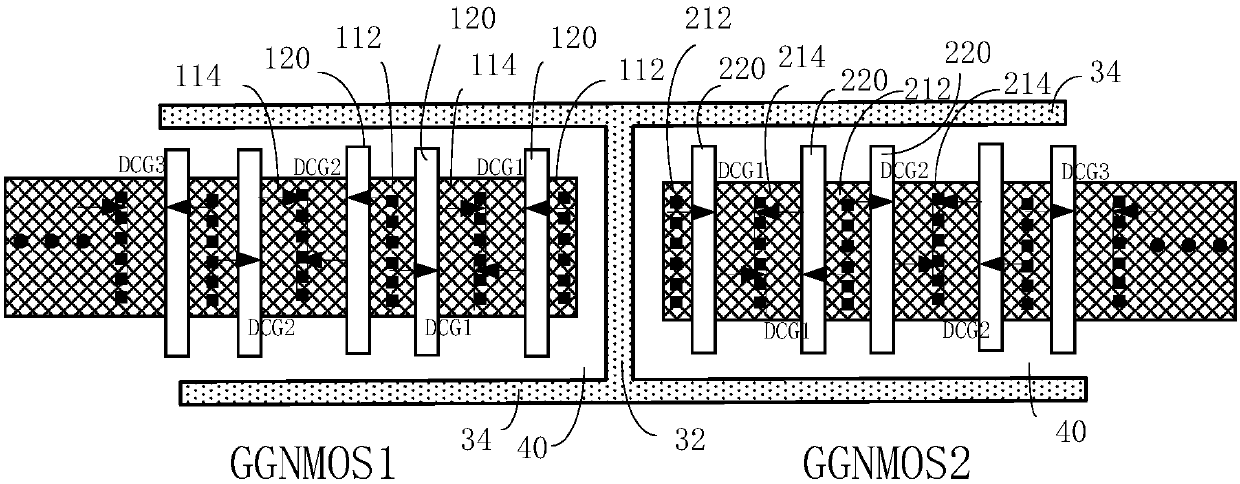

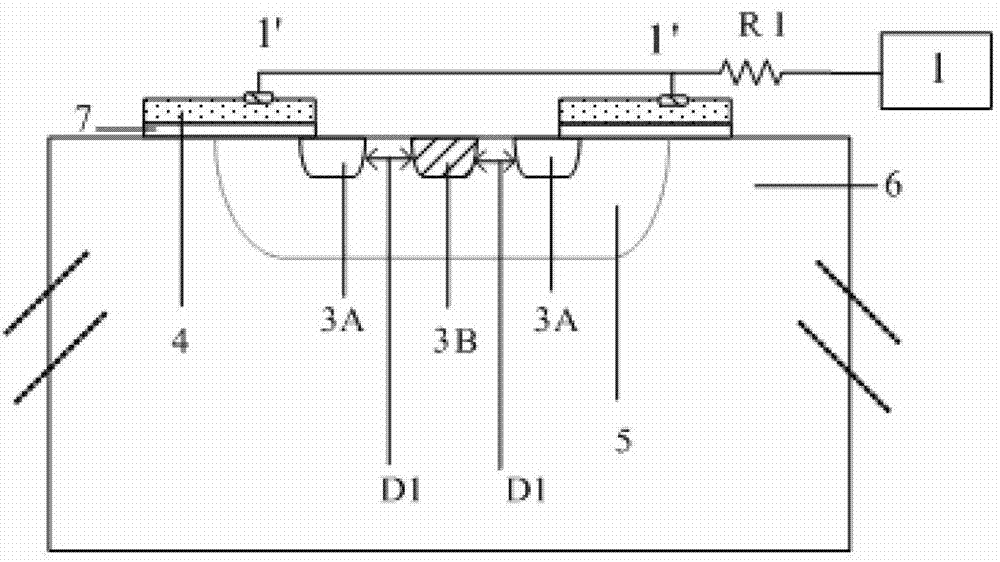

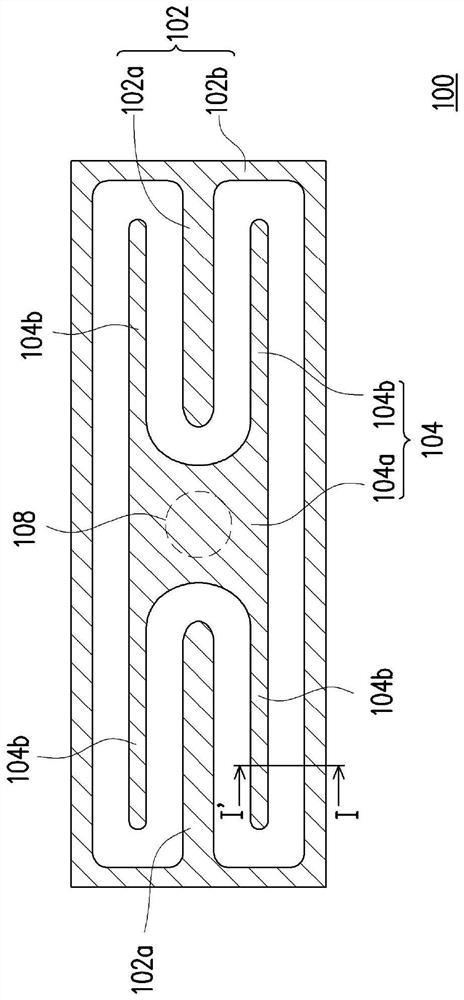

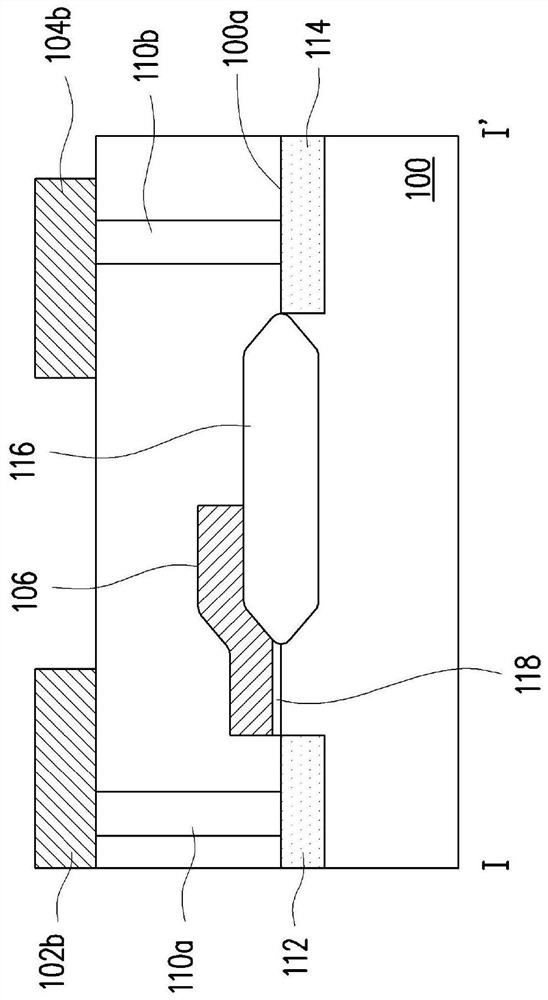

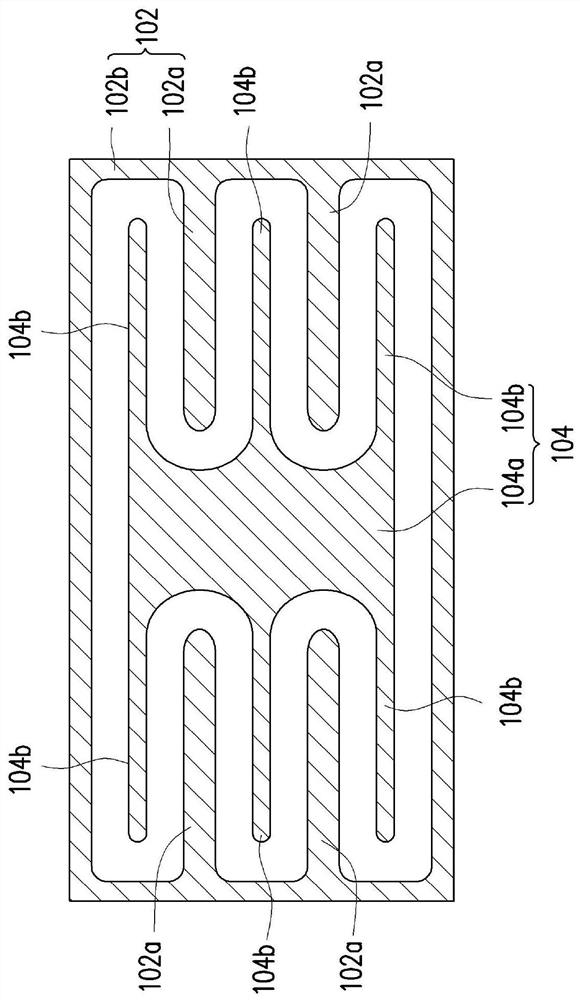

Layout design method for improving ESD (Electro-Static Discharge) protection capability of interdigital structure type device

PendingCN114492285AImprove ESD capabilityReduce areaComputer aided designSpecial data processing applicationsElectrostatic dischargeSource structure

A layout design method for improving the ESD protection capability of an interdigital structure type device is characterized in that on the basis of a traditional interdigital type ESD protection device, the length of a drain region interdigital is increased at the center of an interdigital structure, and according to the fact that the total length of a gate structure and a source structure is not changed, the farther the distance from the center of the interdigital structure is, the farther the distance from the center of the interdigital structure is; and designing the interdigital length of the drain region according to the principle that the interdigital length of the drain region is smaller. Finally, under the condition that the total length of the gate and source structures is not changed and the area is the same, the ESD capability is higher; when the ESD capacity is the same, the area is smaller; the influence of current heterogeneity during ESD protection of the interdigital structure type device is relieved, compared with a traditional interdigital structure device, the MOS device using the method is better in ESD protection capacity, higher in current discharge capacity and higher in reliability, layout modification only needs to be conducted on a chip, and the manufacturing cost is reduced. The performance of the interdigital structure can be improved without influencing the basic parameters of the device, and the ESD protection capability, the reliability and the electrostatic discharge capability of the interdigital structure type device are improved.

Owner:NORTHWEST UNIV

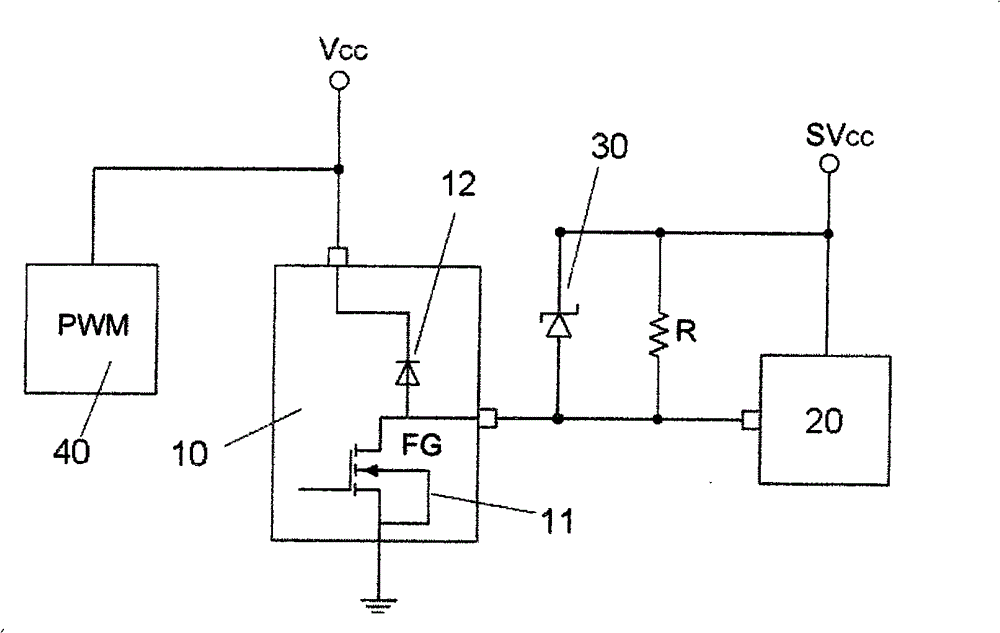

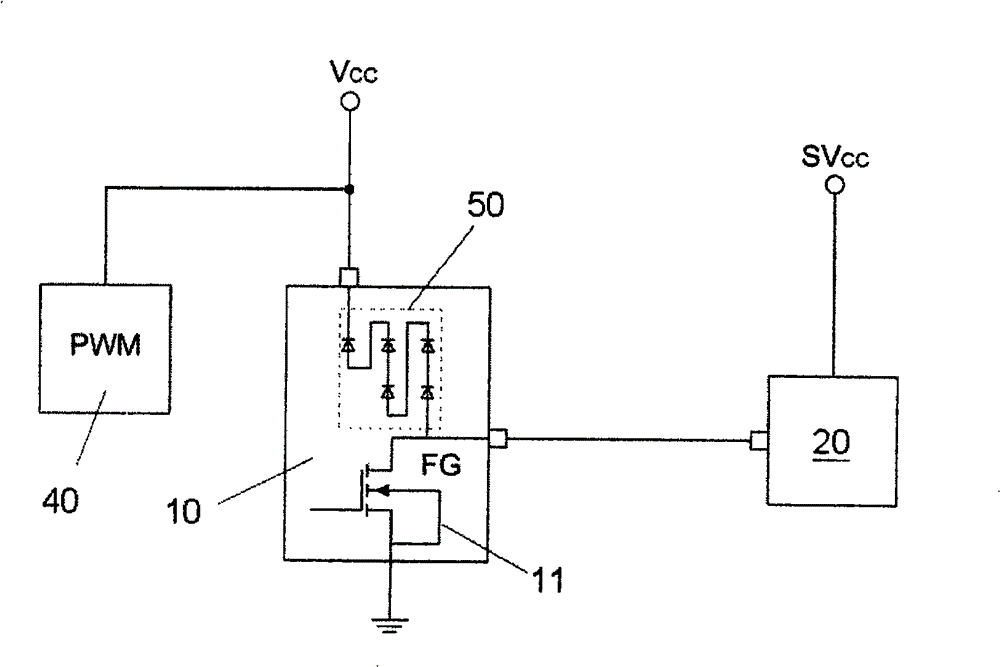

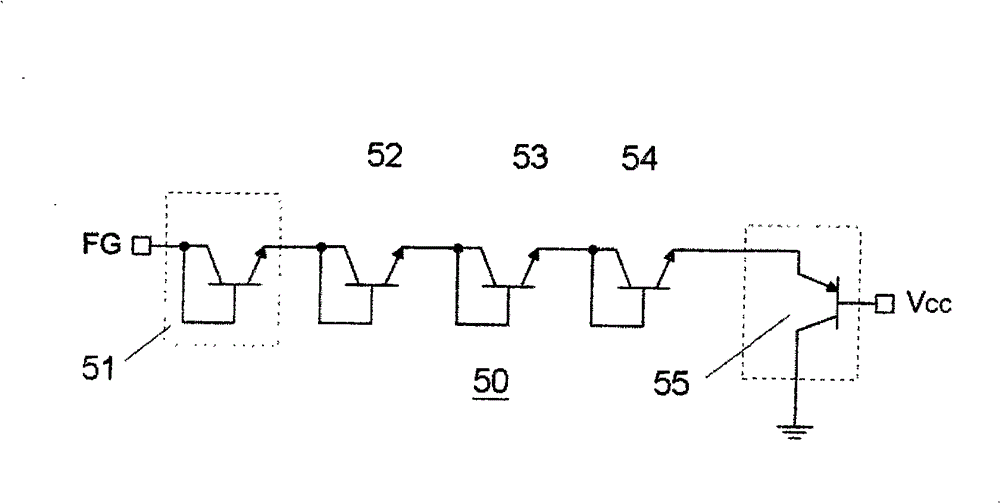

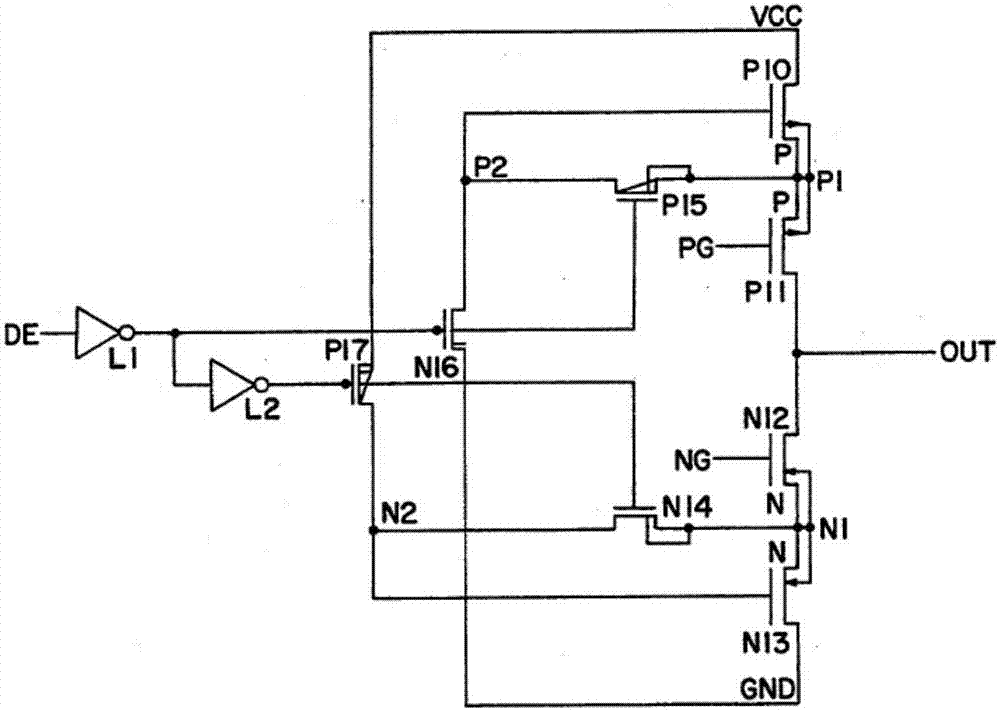

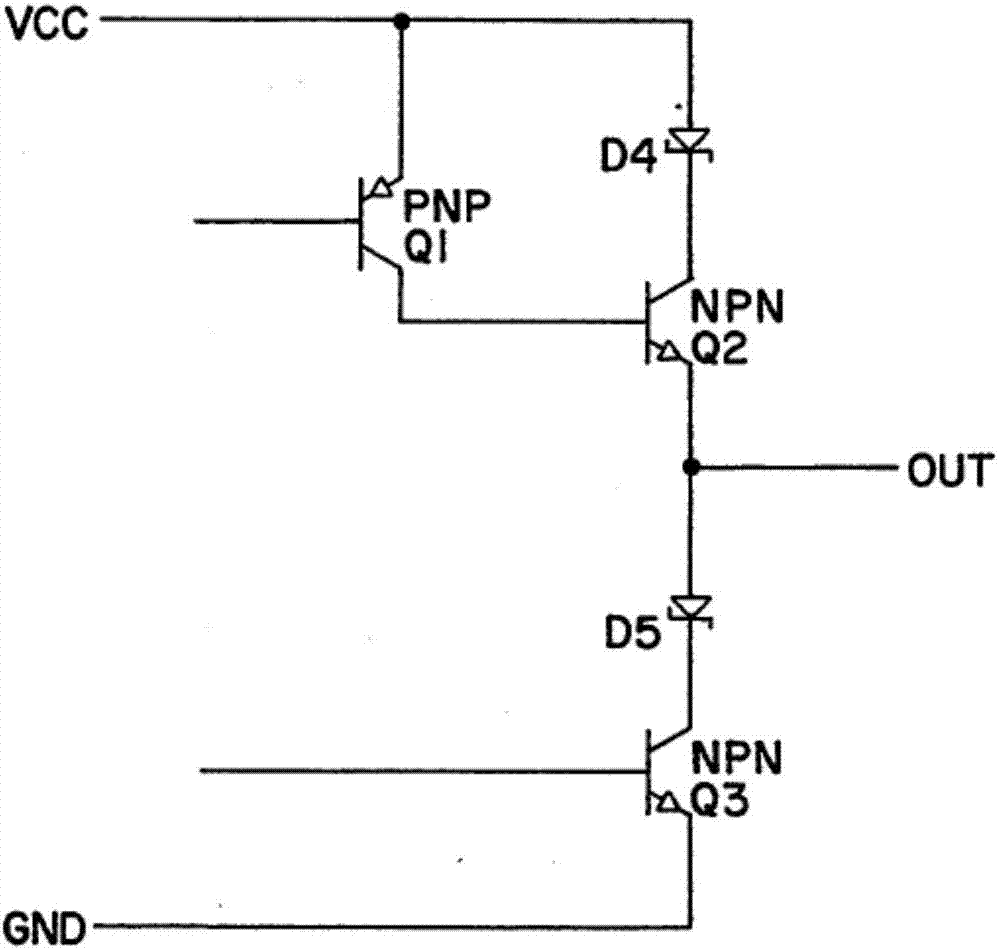

Motor-driven control chip provided with ESD circuit

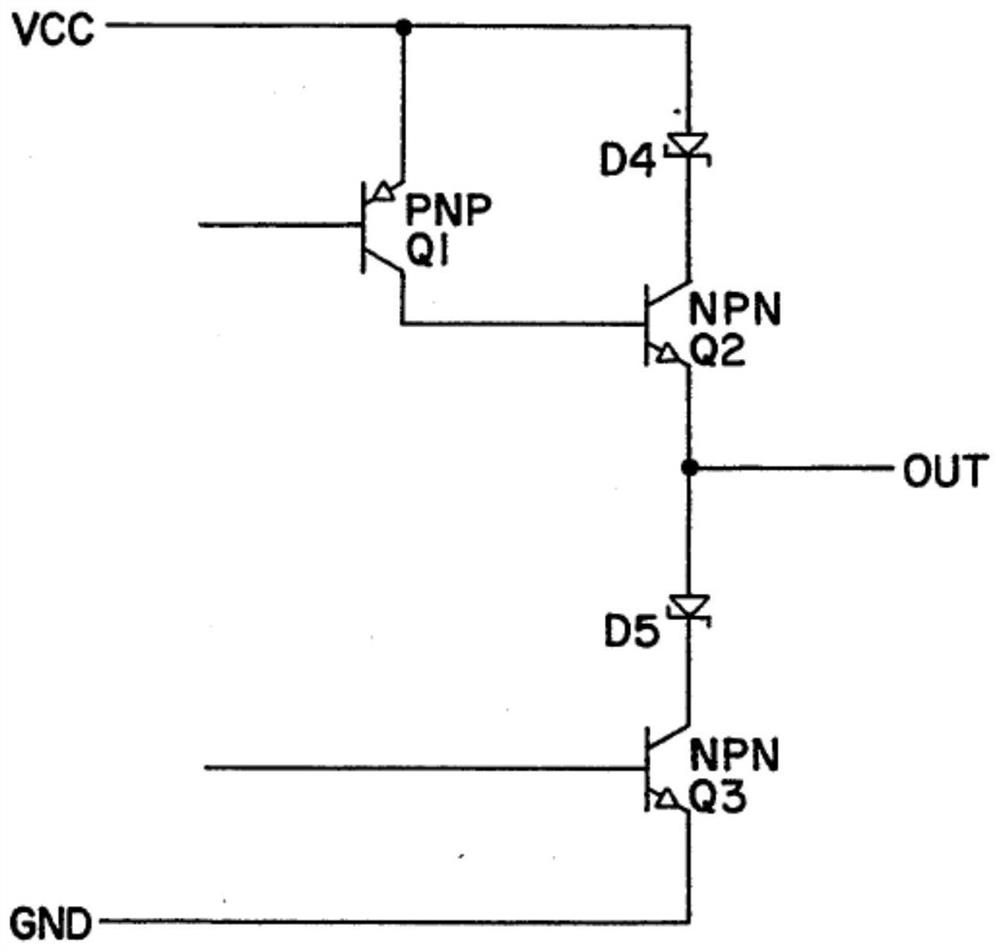

ActiveCN101888085BImprove protectionVoltage will not be clampedEmergency protective arrangements for limiting excess voltage/currentMotor speedMotor drive

The invention relates to a motor-driven control chip, comprising a voltage terminal and a motor rotating speed output terminal as well as an ESD circuit arranged between the voltage terminal and the motor rotating speed output terminal; wherein the ESD circuit is composed of at least one PNP semiconductor element and a plurality of NPN semiconductor elements, and the size of one NPN semiconductorelement in a plurality of NPN semiconductor elements is larger than the sizes of other NPN semiconductor elements.

Owner:AMTEK SEMICON

A logic conversion circuit device

ActiveCN105163565BPrevent crookedImprove ESD capabilityCasings/cabinets/drawers detailsCooling/ventilation/heating modificationsRefrigerantHeat pipe

A logic conversion circuit device, including a logic conversion circuit, the circuit port structure of the logic conversion circuit adopts double ring protection, and an ESD input layer is added to the NMOS tube part of the circuit at the same time; there is a cooling pipe inside the cabinet, and the logic conversion circuit is just It is arranged in the cabinet body, and the inlet and outlet of the refrigerant communicated with the heat dissipation pipe are opened on the cabinet body. In addition, the cabinet body includes a front cover and front cover accessories, and the front cover is in the The location where the cabinet is opened and the location where the cabinet is covered can be pivotally connected to the cabinet. This structure improves the ESD capability of the circuit port; and increases the protection diode between the circuit power supply and ground, which also improves The ESD capability of the circuit is improved, and the defect that the front cover is often crooked in the device for closing the front cover of the prior art is avoided.

Owner:江苏万邦微电子有限公司

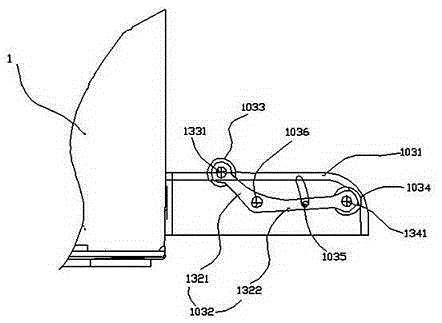

Logic conversion circuit device with cooling effect

ActiveCN105307454APrevent crookedImprove ESD capabilityCasings/cabinets/drawers detailsCooling/ventilation/heating modificationsCooling effectDouble ring

The invention discloses a logic conversion circuit device with a cooling effect. A circuit port structure of a logic conversion circuit employs double-ring protection, and an NMOS tube part of the circuit is additionally provided with an ESM input layer. A bulged tail end forms a profile from the head to the tail from the low to the high, wherein the profile has slope. A left vertical-type sheet body is provided with a left hole which is disposed in the lateral direction of the left vertical-type sheet body and passes through the left vertical-type sheet body. A right vertical-type sheet body is provided with a right hole which is disposed in the lateral direction of the right vertical-type sheet body and passes through the right vertical-type sheet body. The above structure improves the ESD capability of a circuit port. Moreover, a protection diode is additionally disposed between the circuit and a power supply, thereby also improving the ESD capability of the circuit, and ironing out the defects in the prior art that a front cover plate is inclined when the front cover plate of the device is closed and the flexibility is poor.

Owner:江苏万邦微电子有限公司

RS485 driver of low bit error rate, low working power supply voltage and high ESD

ActiveCN107491403AReduce transmission error rateImprove ESD capabilityElectric digital data processingEngineeringConstant current source

The invention discloses an RS485 driver of a low bit error rate, a low working power supply voltage and high ESD, and relates to integrated-circuit technology. The driver includes two power tube circuits. Each power tube circuit includes a front-stage driving unit, a power tube unit and a feedback detection unit. The driver is characterized in that power tube substrates in the power tube unit are floating, and the front-stage driving unit adopts constant-current source front-stage driving. The driver has the advantages that the working power supply voltage is low, costs are low, the bit error rate is low, ESD performance is high, the bit error rate of RS485 transmission can be effectively decreased, and ESD capability of power tubes can be improved.

Owner:CHENGDU SINO MICROELECTRONICS TECH CO LTD

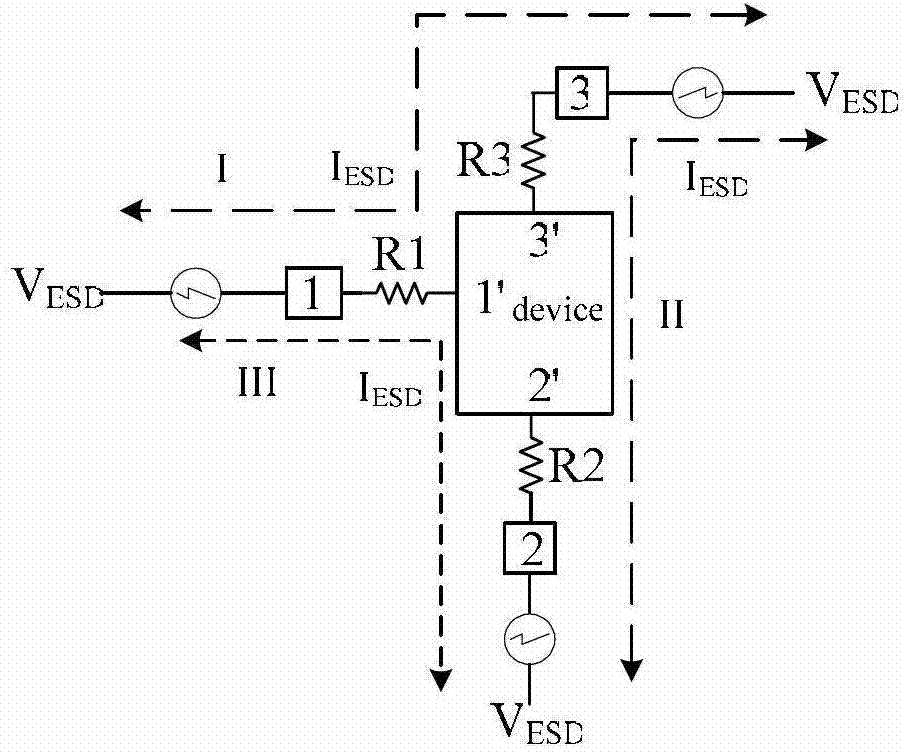

Power semiconductor device with electro-static discharging capability and manufacturing method

InactiveCN104157645AImprove ESD capabilityLow costSolid-state devicesSemiconductor/solid-state device manufacturingElectrostatic dischargePower semiconductor device

The application of the invention is divisional application of 201210559280.0 and discloses a manufacturing method for a power semiconductor device with electro-static discharging capability. The manufacturing method comprises the following steps: the power semiconductor with a first end, a second end and a third end is provided; the power semiconductor device is formed by arranging a cellular array; one port or multiple port of the three ports is connected with a resistor respectively to form the power semiconductor device with the electro-static discharging capability; the invention further provides the power semiconductor device with the electro-static discharging capability. According to the power semiconductor device, as the resistors connected in series with one port or multiple port of the three ports serve as ESD(Electro-Static discharge)protective components to improve the ESD capability, the capacity of the resistors connected with one port or multiple port of the three ports in series can meet the demands of the ESD in various grades through slightly adjusting a protected device layout structure and the flexibility of the design is high.

Owner:HANGZHOU SILAN MICROELECTRONICS

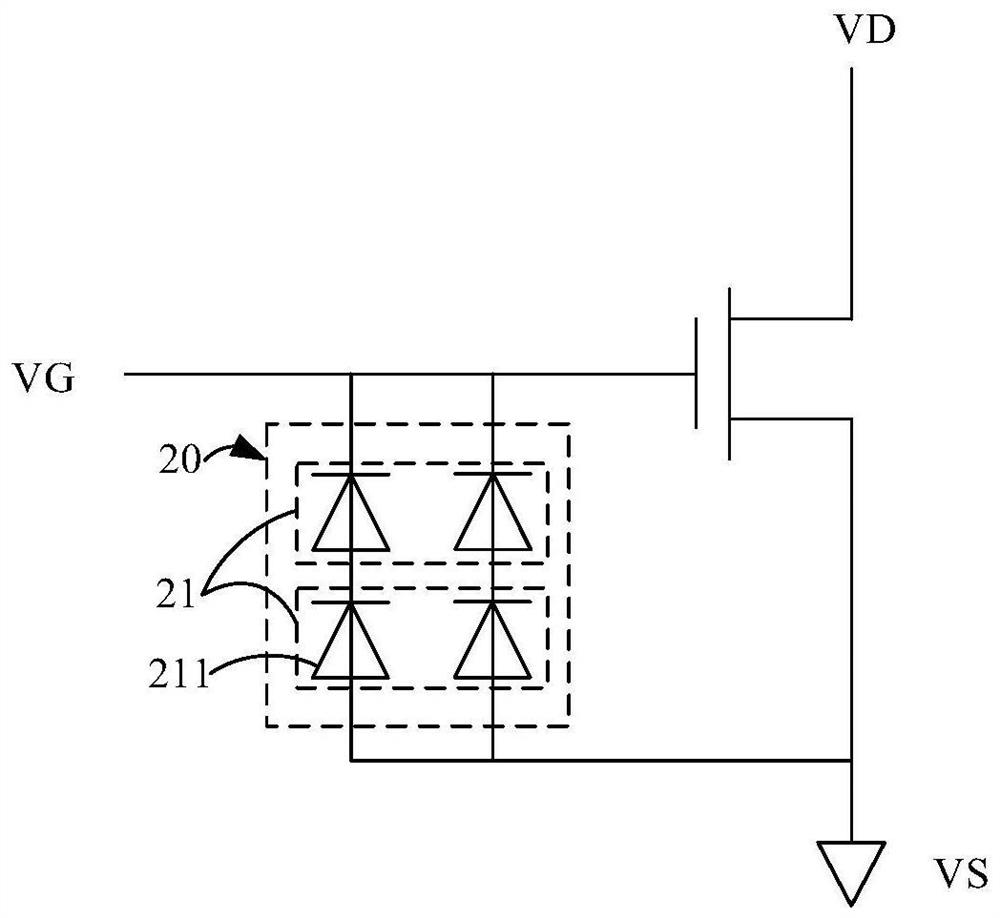

Semiconductor device and preparation method thereof

PendingCN114551410AImprove ESD capabilityIncrease the areaSemiconductor/solid-state device detailsSolid-state devicesDevice materialEngineering

A semiconductor device and a preparation method thereof relate to the technical field of semiconductors. The device comprises a depletion type HEMT device body and an ESD protection structure, the ESD protection structure comprises a diode group connected between a grid electrode of the depletion type HEMT device body and a source electrode of the depletion type HEMT device body, and the diode group comprises a Schottky diode which is conducted from the source electrode of the depletion type HEMT device body to the grid electrode direction of the depletion type HEMT device body; the ESD protection structure is located below a grid electrode bonding pad of the depletion mode HEMT device body; and / or, the ESD protection structure is located below the source electrode thickening metal of the depletion mode HEMT device body, and the orthographic projection of the ESD protection structure on the substrate of the depletion mode HEMT device body and the orthographic projection of the active region of the depletion mode HEMT device body on the substrate are not overlapped. According to the device, the ESD protection level can be improved on the premise that the effective chip area of the device is not occupied.

Owner:深圳市时代速信科技有限公司

Power semiconductor device with anti-static discharge capability and manufacturing method

InactiveCN104157645BImprove ESD capabilityLow costSolid-state devicesSemiconductor/solid-state device manufacturingPower semiconductor deviceElectrical resistance and conductance

The application of the invention is divisional application of 201210559280.0 and discloses a manufacturing method for a power semiconductor device with electro-static discharging capability. The manufacturing method comprises the following steps: the power semiconductor with a first end, a second end and a third end is provided; the power semiconductor device is formed by arranging a cellular array; one port or multiple port of the three ports is connected with a resistor respectively to form the power semiconductor device with the electro-static discharging capability; the invention further provides the power semiconductor device with the electro-static discharging capability. According to the power semiconductor device, as the resistors connected in series with one port or multiple port of the three ports serve as ESD(Electro-Static discharge)protective components to improve the ESD capability, the capacity of the resistors connected with one port or multiple port of the three ports in series can meet the demands of the ESD in various grades through slightly adjusting a protected device layout structure and the flexibility of the design is high.

Owner:HANGZHOU SILAN MICROELECTRONICS

Semiconductor device

PendingCN113192949APrevent electrical breakdownImprove ESD capabilitySolid-state devicesSemiconductor devicesManufacturing technologyDevice material

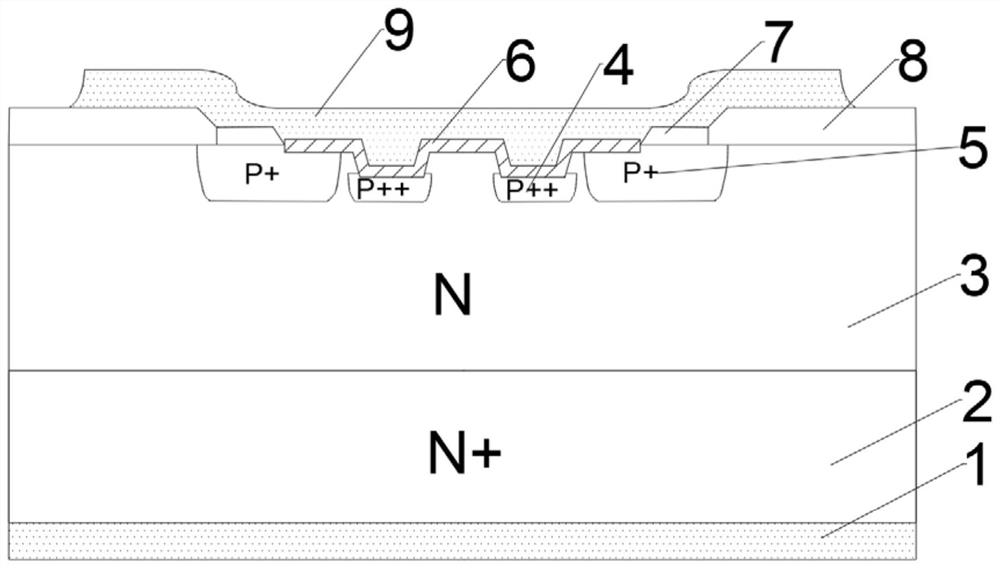

The invention provides a semiconductor device comprising a substrate having a first region and second regions, the first region being located between two adjacent second regions; three sub drain regions located in the first region of the substrate; two dummy structures respectively positioned on the substrate between the two adjacent sub drain regions; a source region located in the second regions of the substrate; a gate structure positioned on the substrate between the first region and the second regions. The ESD capacity of the device is improved through the dummy structure, an SAB photomask in the prior art is not needed, a new technological process does not need to be introduced, and the dummy structure can be directly and synchronously formed in the manufacturing process, so that the manufacturing cost of the device is reduced.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

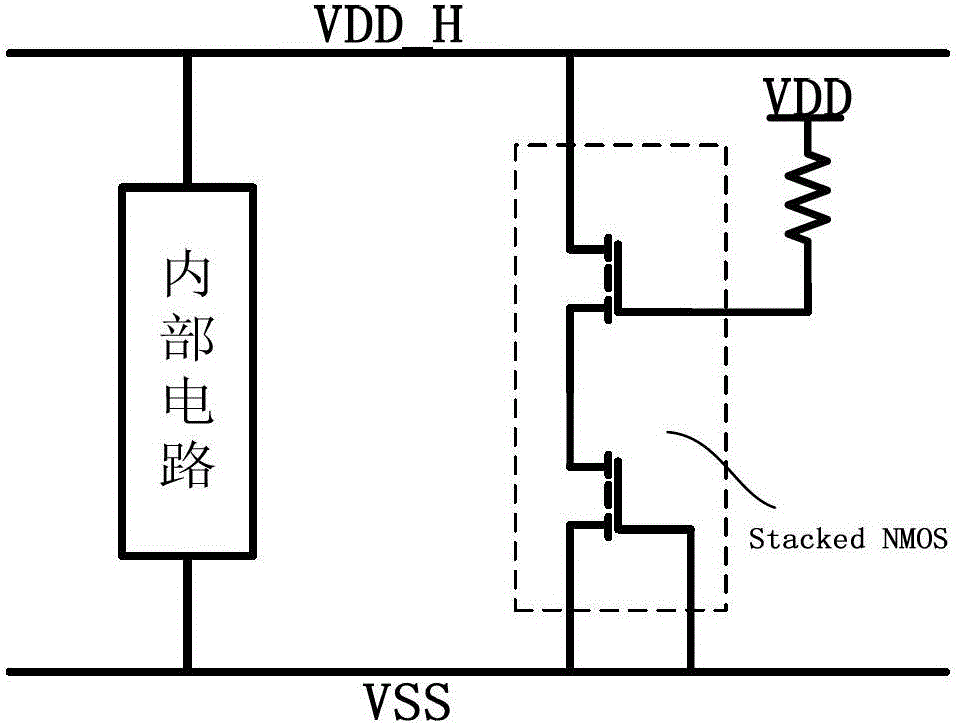

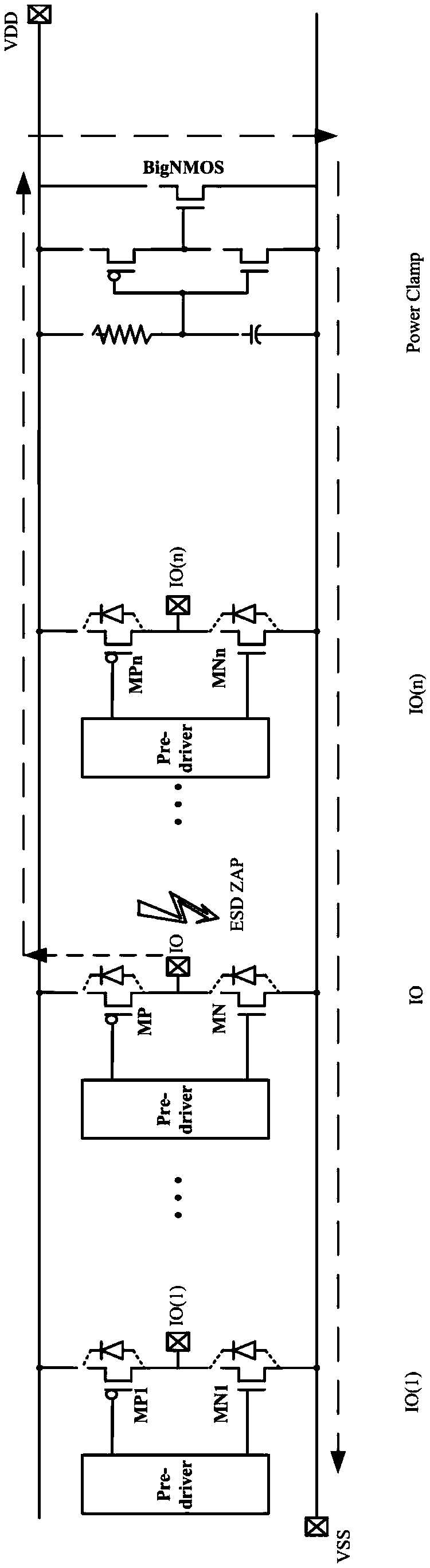

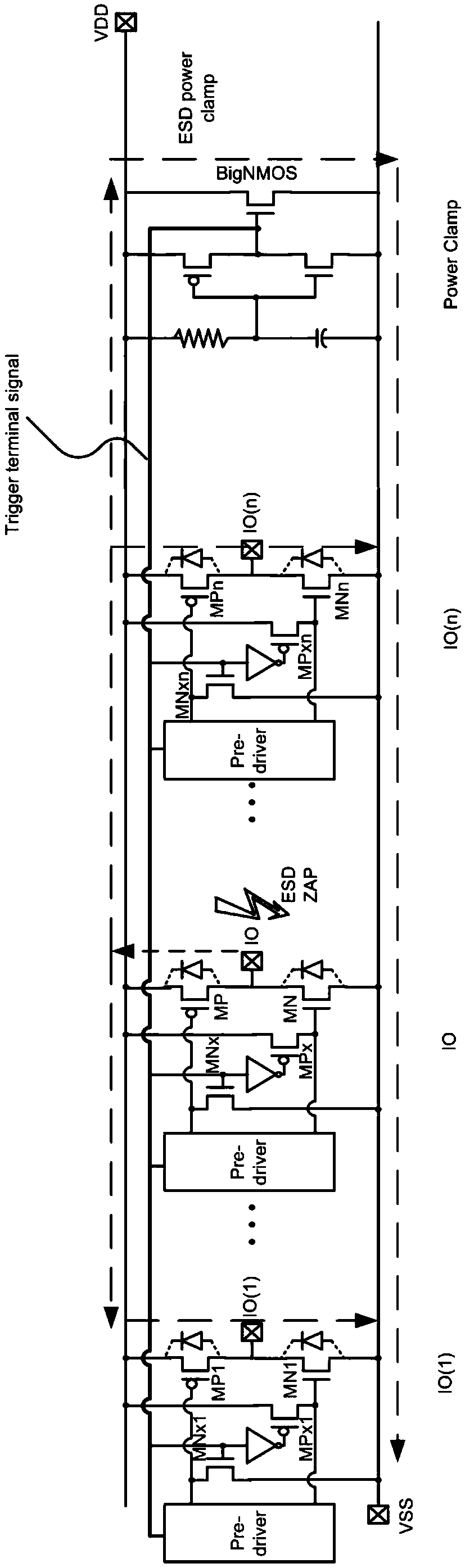

Full-chip electrostatic discharge network

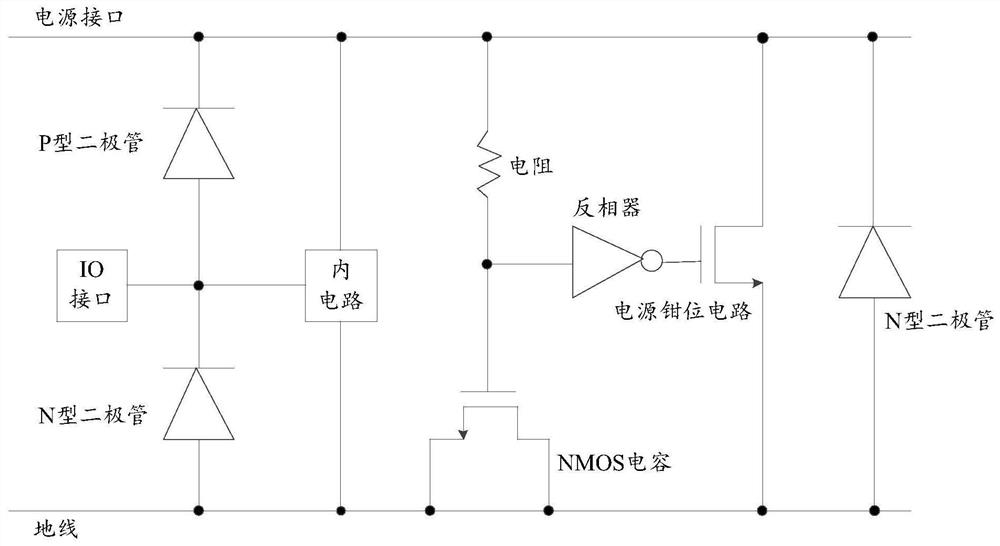

InactiveCN109148439AImprove ESD capabilitySolid-state devicesSemiconductor devicesControl signalControl circuit

The invention discloses a full-chip electrostatic discharge network, which comprises a power clamp circuit and a plurality of IO units. The power clamp circuit is connected between the power supply and the ground. The power clamp circuit also comprises an ESD detection circuit, which is used for detecting the ESD signal and generating a trigger signal after detecting the ESD signal. The pluralityof IO units are a plurality of IO units connected in parallel and connected between the power supply and the ground as well as the power clamp circuit. Each unit of the IO units has an IO port, and the IO port is an IO port which will be affected by the electrostatic discharge. The IO unit comprises a precursor circuit, a control circuit and a back drive circuit, wherein the control circuit and the back drive circuit are connected with a power supply and a ground; All the precursor circuits of the IO unit are connected to the ESD trigger signal terminal of the ESD detection circuit to receivethe ESD trigger signal, and then the output terminal of the precursor circuit generates a corresponding control signal to be provided to the control circuit.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

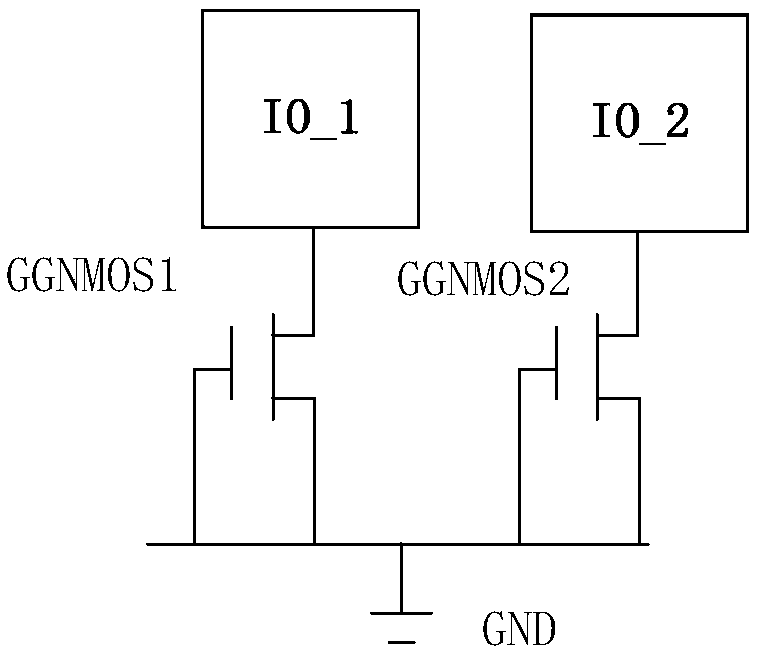

Electrostatic discharge protection device

ActiveCN111276477AImprove ESD capabilityGood ESD abilityTransistorSolid-state devicesManufacturing cost reductionGgNMOS

Owner:CSMC TECH FAB2 CO LTD

Cell structure and manufacturing method thereof

ActiveCN103050491BImprove ESD capabilityLow costSolid-state devicesSemiconductor/solid-state device manufacturingPower semiconductor deviceElectrical resistance and conductance

The invention provides a cell structure. A plurality of cells are arranged to form a cell array structure so as to form a power semiconductor device with three ports, any one or more of the three ports are respectively connected with a resistor, each cell comprises an epitaxial layer; a second type light doped region is formed in the epitaxial layer; a first type heavy doped region and a second type heavy doped region are respectively formed in the second light doped region; heavy doped region short circuit holes are formed in the first heavy doped region and the second heavy doped region; gate medium dielectric layers are formed on the surfaces of the epitaxial layer, the second light doped region closely adjacent to the epitaxial layer and a part of the first heavy doped region closely adjacent to the second light doped region; first polycrystalline silicon strips are formed on the gate medium dielectric layers; and regions surrounded by the first heavy doped regions and the heavy doped region short circuit holes of the all cells in the second light doped region are resistors which are connected with a second port, wherein the serial resistors can improve the ESD (electronic static discharge) capability and the cell structure is slightly adjusted so as to be capable of meeting requirements of ESD with various grades.

Owner:HANGZHOU SILAN MICROELECTRONICS

Power semiconductor device with antistatic discharge capacity and manufacturing method

InactiveCN103050442BImprove ESD capabilityLow costSolid-state devicesSemiconductor/solid-state device manufacturingPower semiconductor deviceElectrical resistance and conductance

Owner:HANGZHOU SILAN MICROELECTRONICS

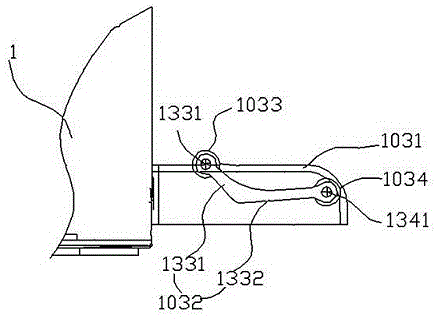

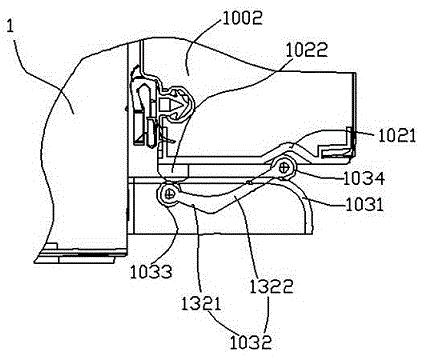

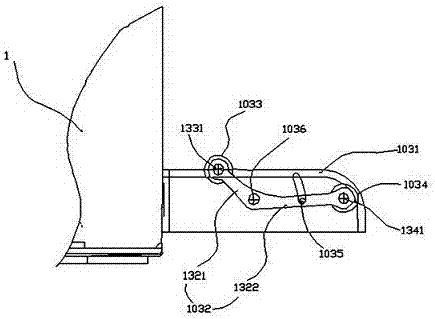

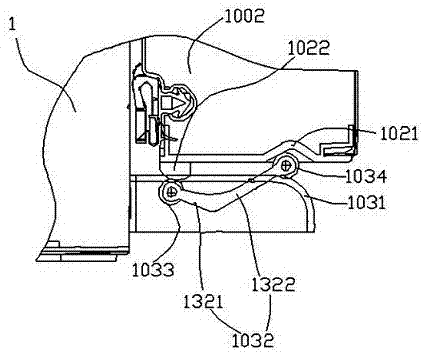

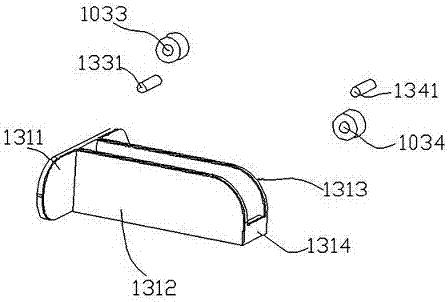

Ultrahigh voltage element

PendingCN114068714ADoes not affect performanceReduce areas of high curvatureSemiconductor/solid-state device manufacturingSemiconductor devicesUltra high voltageEngineering

The invention provides an ultrahigh voltage element. The ultrahigh voltage element comprises a substrate, an interdigital source electrode, an interdigital drain electrode and a grid electrode, and the interdigital source electrode is arranged on the surface of the substrate. The interdigital source electrode comprises a plurality of first interdigital parts and a peripheral part surrounding the first interdigital parts. The interdigital drain electrode is arranged on the surface of the substrate, and the interdigital drain electrode is a pattern which is in mirror symmetry and complementary with the interdigital source electrode. The grid electrode is arranged on the substrate between the interdigital source electrode and the interdigital drain electrode. The layout of the interdigital source electrode and the interdigital drain electrode enables the electric field distribution to be uniform and prevents the occurrence of a corner current crowding effect.

Owner:NUVOTON

rs485 driver with low bit error rate, low power supply voltage and high esd

ActiveCN107491403BReduce transmission error rateImprove ESD capabilityElectric digital data processingHemt circuitsEngineering

The invention discloses an RS485 driver of a low bit error rate, a low working power supply voltage and high ESD, and relates to integrated-circuit technology. The driver includes two power tube circuits. Each power tube circuit includes a front-stage driving unit, a power tube unit and a feedback detection unit. The driver is characterized in that power tube substrates in the power tube unit are floating, and the front-stage driving unit adopts constant-current source front-stage driving. The driver has the advantages that the working power supply voltage is low, costs are low, the bit error rate is low, ESD performance is high, the bit error rate of RS485 transmission can be effectively decreased, and ESD capability of power tubes can be improved.

Owner:CHENGDU SINO MICROELECTRONICS TECH CO LTD

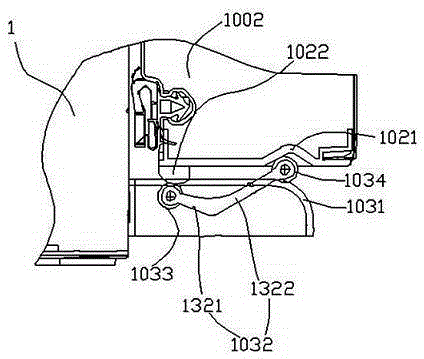

Enhanced logic conversion circuit device

InactiveCN105262473AImprove ESD capabilityImprove protectionLogic circuit coupling/interface arrangementsReverse osmosisImpurity

The invention relates to an enhanced logic conversion circuit device. A circuit port structure of a logic conversion circuit is in double-loop protection; simultaneously, an ESD (Electronic Static Discharge) input layer is additionally arranged at an NMOS (N-channel Metal Oxide Semiconductor) tube part of the circuit; a particle impurity channel is formed between a first hollow cover body and a second hollow cover body; a clean airflow channel is formed between a reverse osmosis membrane of the first hollow cover body and an air outlet; and the head face of the reverse osmosis membrane is an arched surface or a reduced surface capable of separating particle impurities from the reverse osmosis membrane under driving of external force. By means of such a structure, the disadvantages that bad effects are brought about to performances of the logic conversion circuit due to the fact that impurity particles are often attached in the logic conversion circuit, and the removing difficulty of the current impurity particle removing device is often high while removing the impurity particles in the prior art can be avoided; the ESD capability of the circuit port is also increased; and the ESD capability of the circuit is also increased by additionally arranging a protective diode between the circuit and a power ground.

Owner:江苏万邦微电子有限公司

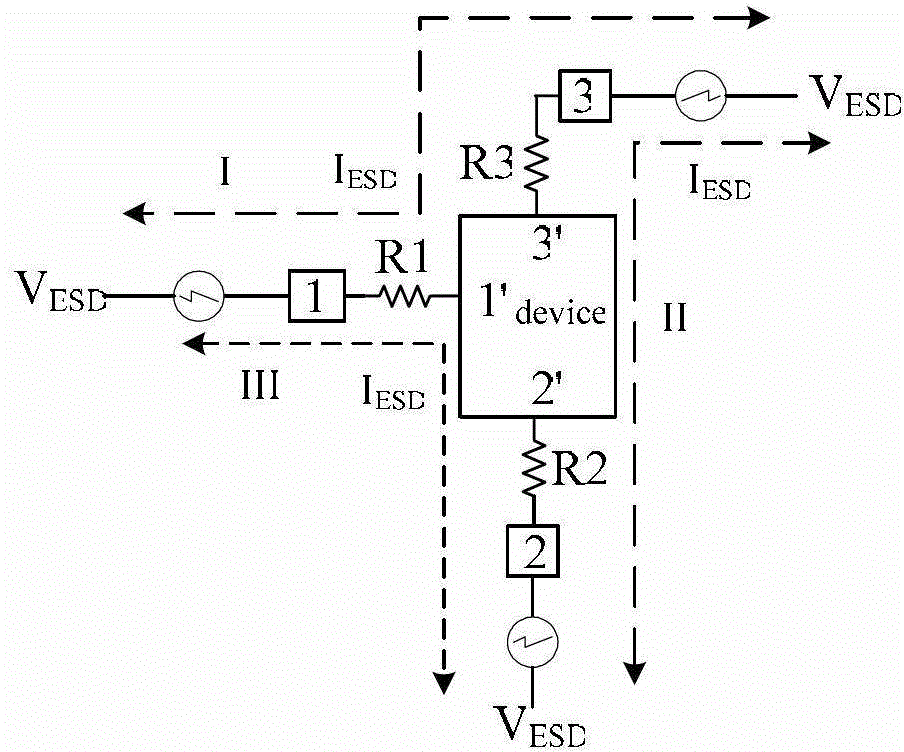

An electrostatic discharge protection circuit and protection method

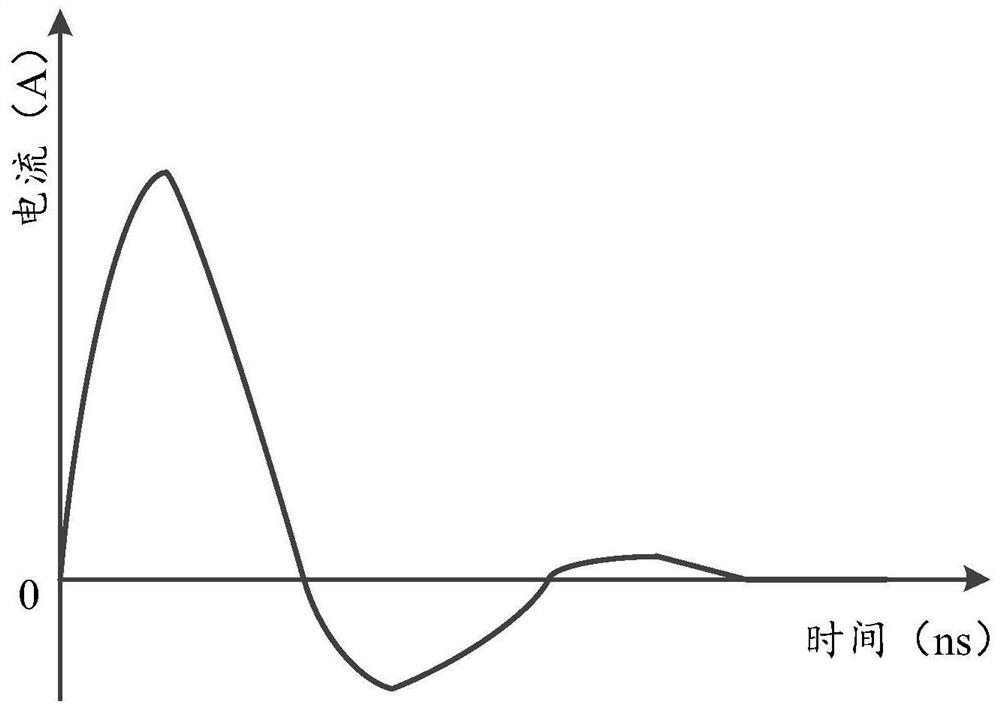

ActiveCN112930014BExtended release timeIncrease capacitanceEmergency protective arrangements for limiting excess voltage/currentElectrostatic chargesCapacitanceResistance capacitance

The present invention provides an electrostatic discharge protection circuit and a protection method, the circuit comprising: a main structure connected to a power interface and a ground wire respectively, including a first resistor-capacitor circuit and a first positive current release circuit; at least one slave structure, Each slave structure is connected to a power interface, a ground wire, and an IO interface corresponding to the slave structure, and the IO interface is connected to the power interface, including a second resistor-capacitor circuit, a second positive current release circuit, a first negative current release circuit and a second Two negative current release circuits; the capacitive elements of the first resistor-capacitor circuit and the second resistor-capacitor circuit are connected in parallel, and share the resistor elements of the first resistor-capacitor circuit. The present invention disperses the capacitance in the main circuit and the slave circuit through the master-slave distributed structure, makes full use of the chip area, realizes larger capacitance, and improves the ESD discharge time; adds a positive current release circuit in each slave circuit to improve the discharge time The efficiency of the discharge current improves the overall ESD capability.

Owner:青岛信芯微电子科技股份有限公司

A High Power High Voltage Schottky Barrier Diode

ActiveCN112289867BReduced impact of SSG capabilitiesImprove reliabilitySemiconductor/solid-state device manufacturingSemiconductor devicesSchottky barrierMetal silicide

Owner:YANGZHOU GUOYU ELECTRONICS