Layout design method for improving ESD (Electro-Static Discharge) protection capability of interdigital structure type device

An interdigital structure and layout design technology, which is applied in the field of layout design to improve the ESD protection ability of interdigital structure devices, can solve the problems affecting the on-chip ESD protection ability of high-voltage circuits, and it is difficult to trigger uniformly, so as to alleviate the current non-uniformity , Improve performance, increase the effect of withstand voltage and current discharge capacity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

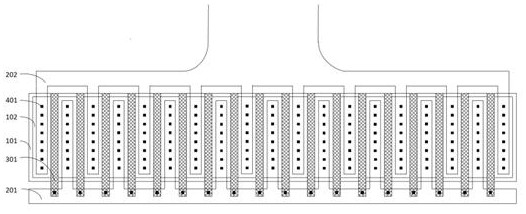

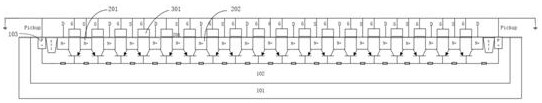

[0036] In order to solve the problems existing in the prior art, the present invention proposes a layout design method for improving the ESD protection capability of interdigitated structure devices. The method of the present invention will be further described below in conjunction with the embodiments, wherein, image 3 It is a schematic diagram of the layout structure of GGNMOS in the interdigitated ESD device; Figure 4 It is a schematic cross-sectional view of GGNMOS in the interdigitated ESD device described in the present invention;

[0037] The schematic diagram of the conventional GGNMOS structure in the ESD protection device is as follows figure 2 As shown, the length of each finger in the source and drain regions is equal, and its structure is an interdigital structure, which has non-uniform current, and may cause permanent damage to the device due to excessive voltage during electrostatic discharge.

[0038] Therefore, a kind of interdigitated GGNMOS device struct...

Embodiment 2

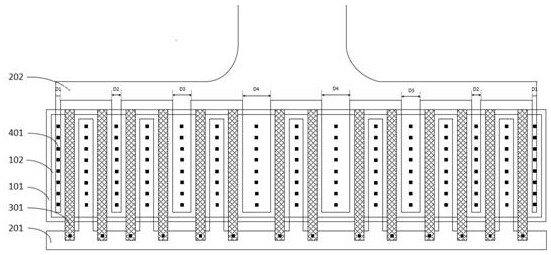

[0048] refer to Image 6 , Image 6 The general multi-finger source-liner connection NMOS device is designed for the layout design method for improving the ESD protection capability of the interdigitated device according to the present invention. Its structure is basically the same as the standard source-lined connection NMOS structure, but the interdigit length D4 of the drain region at the center of the interdigit structure is greater than the interdigit length of the drain region gradually away from the interdigit center, that is, D4>D3>D2>D1. The gate connection method can be any one of routePolydir (top, bottom, both). For the sake of simplicity in the schematic diagram, the gate connection method is not shown.

[0049] In view of the poor reliability of GGNMOS and the shortcomings of general current discharge capability, the present invention can increase the reliability of GGNMOS without affecting the basic parameters of the device itself by only changing the drawing m...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More