An electrostatic discharge protection circuit and protection method

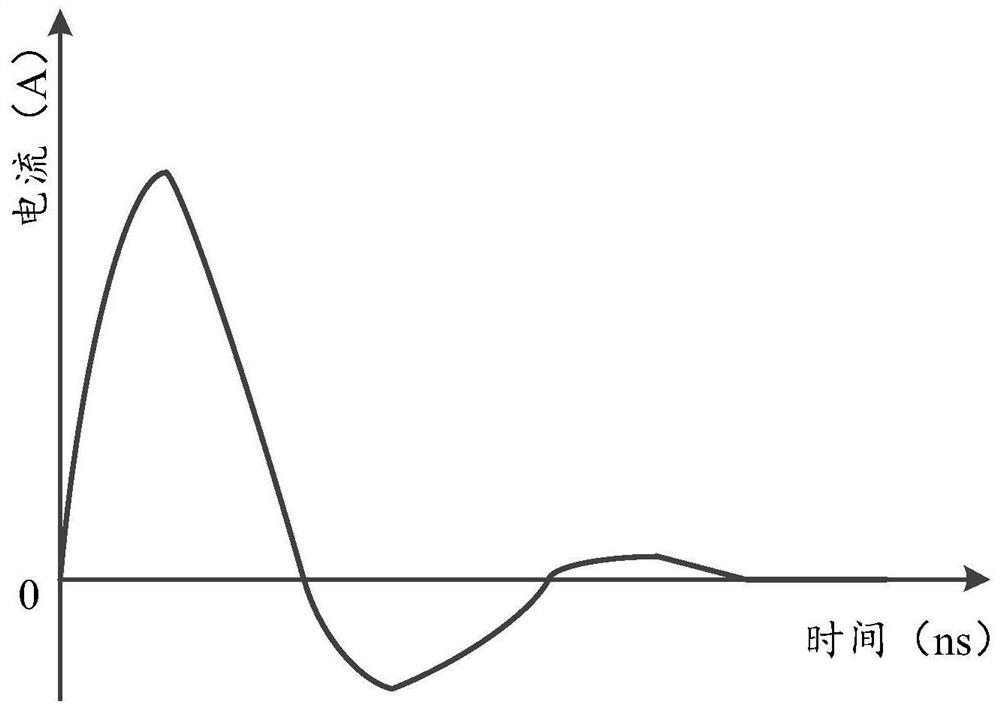

A release circuit, electrostatic discharge technology, applied to emergency protection circuit devices, static electricity, emergency protection circuit devices for limiting overcurrent/overvoltage, etc., can solve the problem that it is difficult to achieve the required ESD capability and cannot fully discharge the ESD current , ESD discharge time is small, etc., to improve the overall ESD capability, improve ESD discharge time, and improve efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

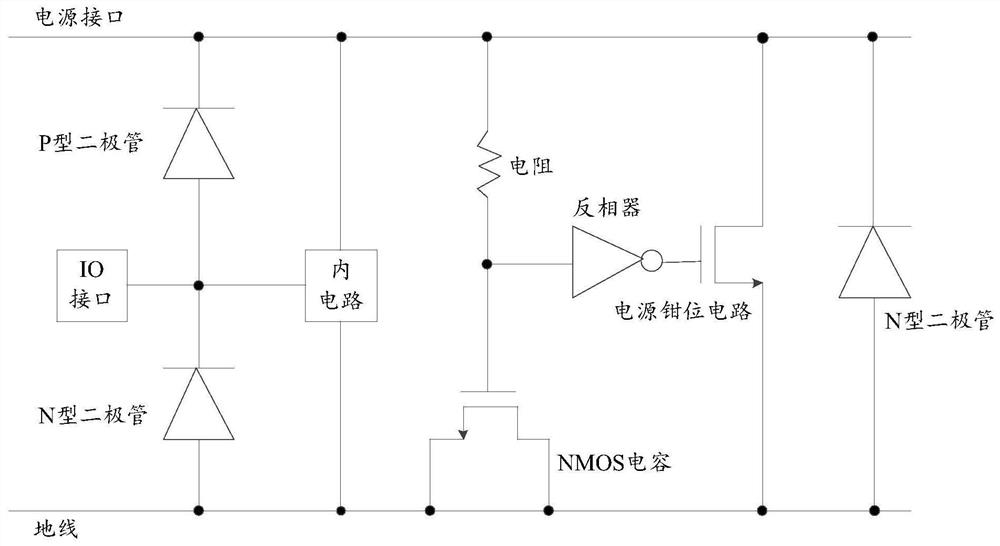

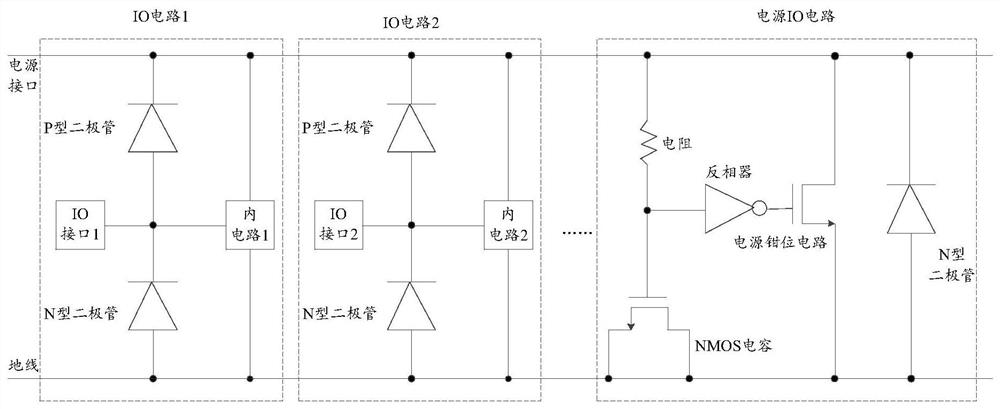

[0062] An embodiment of the present invention provides a schematic diagram of an electrostatic discharge protection circuit, such as Figure 4 shown, including:

[0063] The main structure 401 is respectively connected to the power interface 403 and the ground wire 404, including a first resistor-capacitor circuit 401-1 and a first positive current release circuit 401-2;

[0064] At least one slave structure 402, each slave structure is respectively connected to the power interface, the ground wire and the IO interface 405 corresponding to the slave structure, and the IO interface is connected to the A power interface, including a second resistor-capacitor circuit 402-2, a second positive current release circuit 402-3, a first negative current release circuit 402-4, and a second negative current release circuit 402-5;

[0065] the above Figure 4 Inside the dotted line box on the left side, that is, 401 is the main circuit structure, and inside the dotted line box on the rig...

Embodiment 2

[0145] An embodiment of the present invention provides a flowchart of an electrostatic discharge protection method, such as Figure 8 shown, including:

[0146] Step S801, when the power interface and / or the IO interface generates a positive electrostatic current, release the positive electrostatic current to the ground through the first positive current releasing circuit in the master structure and the second positive current releasing circuit in each slave structure Wire;

Embodiment approach 1

[0148] Implementation mode 1: When a +ESD event occurs on the IO interface, the specific current release process is:

[0149] When a +ESD event occurs on the IO interface, the +ESD current is released. The above +ESD current is conducted to the power interface VDD through P1, and then passes through the shared resistance R in the distributed structure and each capacitive element. Figure 5 The NMOS1 and NMOS2 in the circuit form an RC circuit to control the RC time. During an RC time, the potential on the capacitor NMOS2 is low, and after passing through the inverter F2, the Gate terminal of Q2 is at a high potential. At this time, Q2 is turned on, and the above-mentioned +ESD current is discharged to the ground through the above-mentioned Q2.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More