Integrated circuit full-chip electro static discharge protection method and circuit

An electrostatic discharge protection and electrostatic discharge technology, applied in the field of ESD protection design and integrated circuit ESD protection design, can solve problems such as the decline of ESD capability, and achieve the effect of improving ESD capability and reducing voltage drop.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

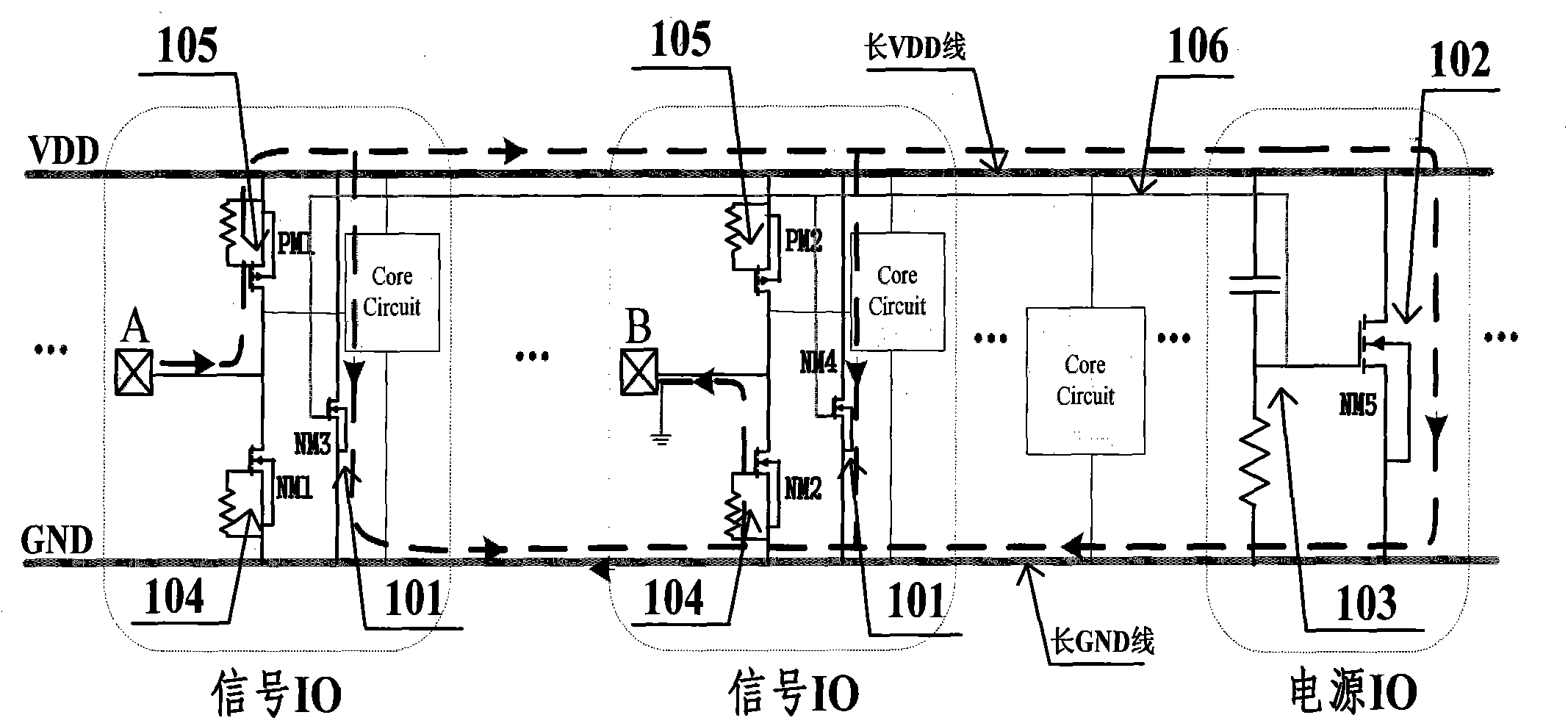

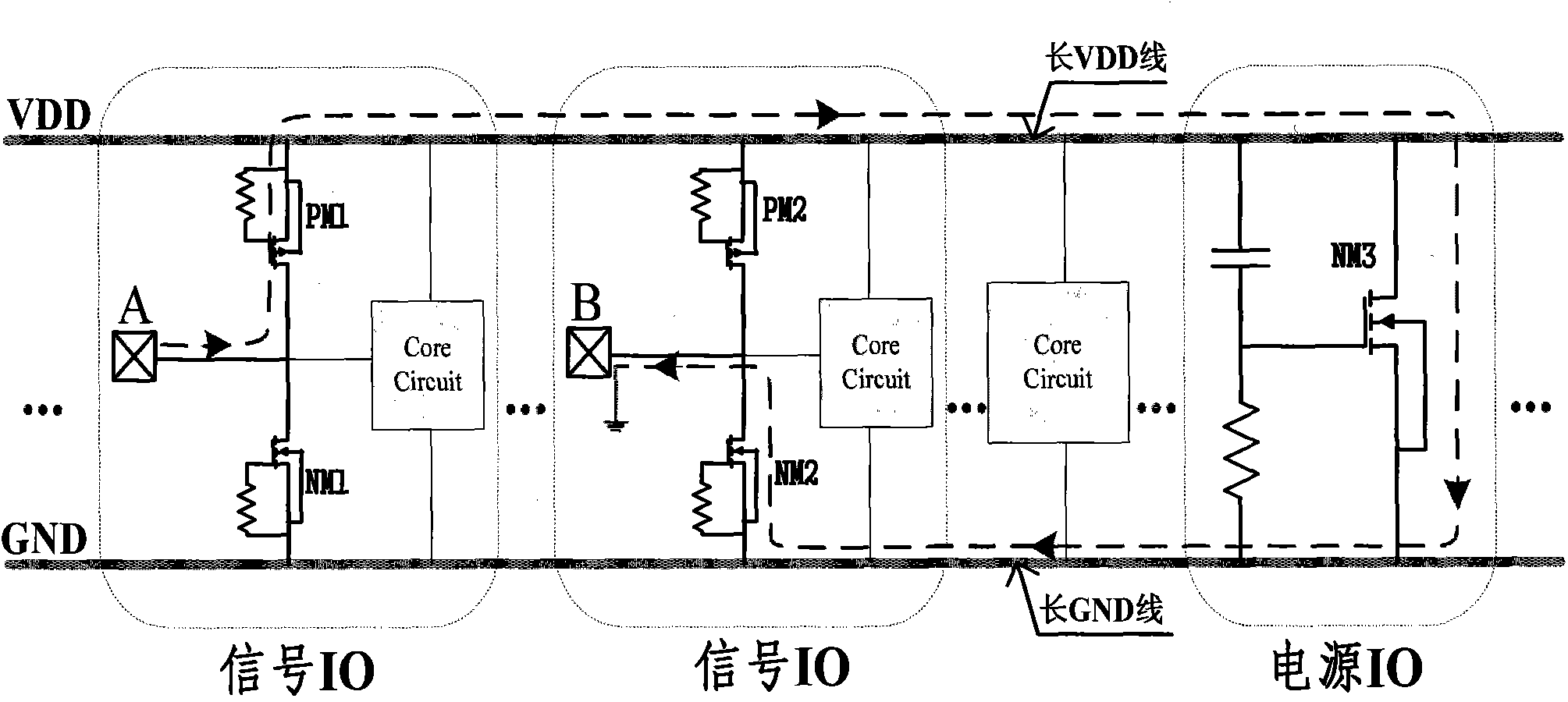

[0013] Generally, there are global power lines and ground lines in the integrated circuit, and all signal IOs and power / ground IOs are connected between the power / ground lines. The ESD test includes IO-VDD, IO-GND, IO-IO, and VDD-GND. Taking the IO-IO test as an example, when the +ESD test is performed on IO A and IO B is grounded, the electrostatic discharge current is as follows: figure 1 , 2 The discharge path shown by the arrow in the middle curve, in the traditional ESD design, the current flows through A->PM1->long VDD line->NM3->long GND line->NM2->B (ground). In large-scale integrated circuits, VDD lines and GND lines are generally long, and their parasitic resistance can reach more than 4 ohms. The on-resistance of an ESD device is about 5 ohms. For HBM2000V testing, its discharge current is about 1.33A. In traditional ESD design , the voltage drop of the discharge loop of this circuit can reach more than 30V, that is, the A node voltage in the IO unit exceeds 30V, w...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More