Patents

Literature

73results about How to "Lower clamping voltage" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

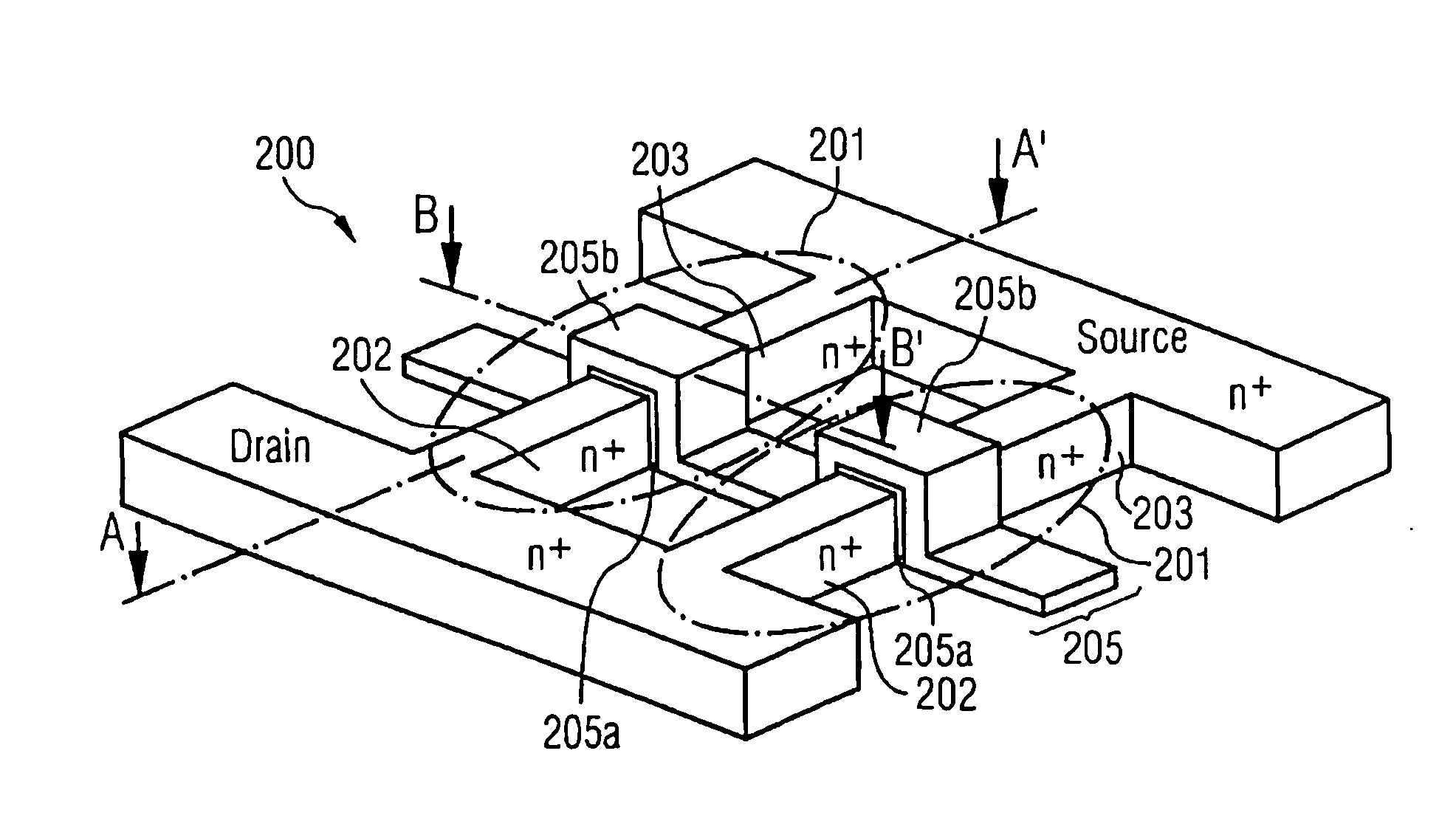

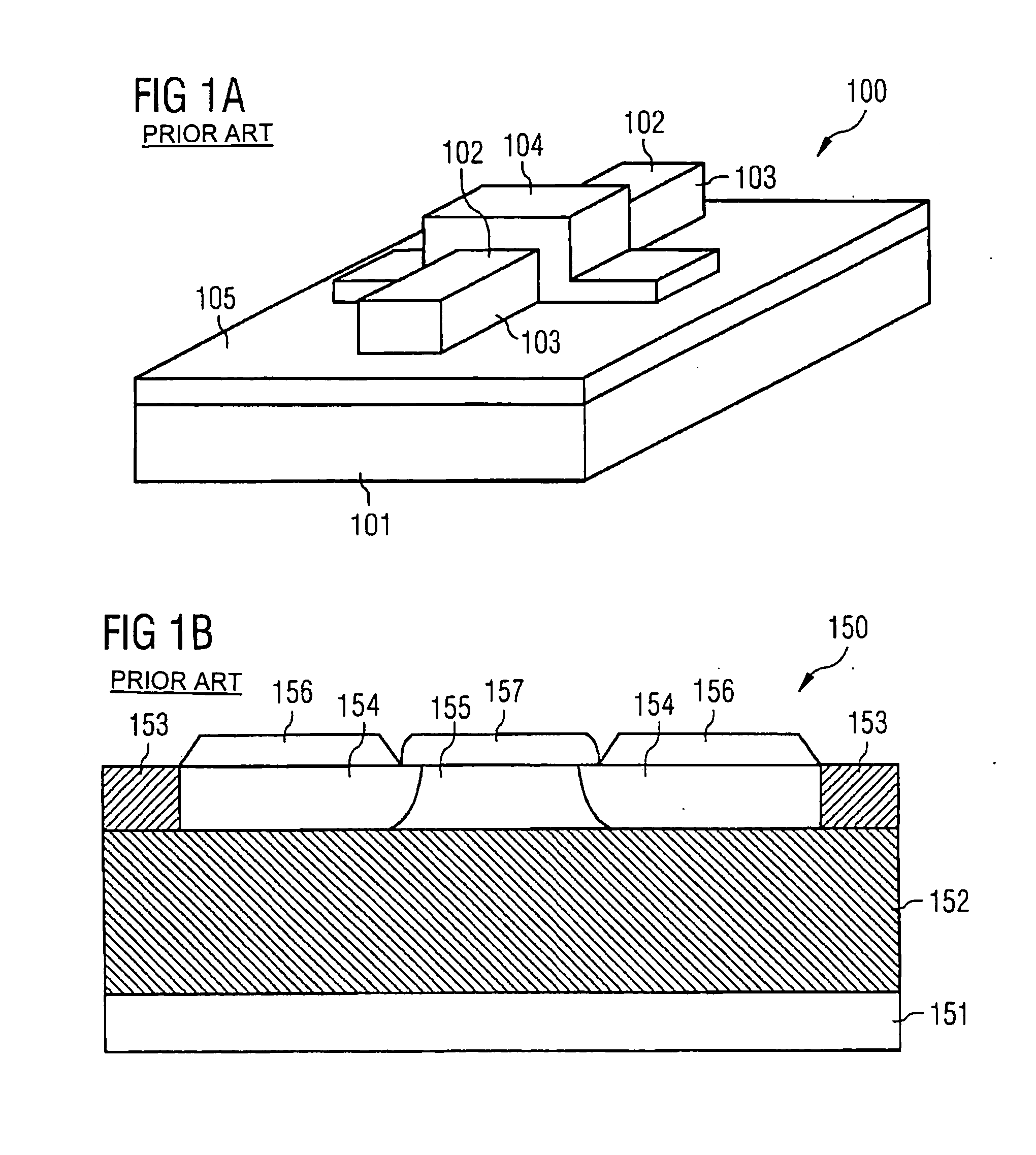

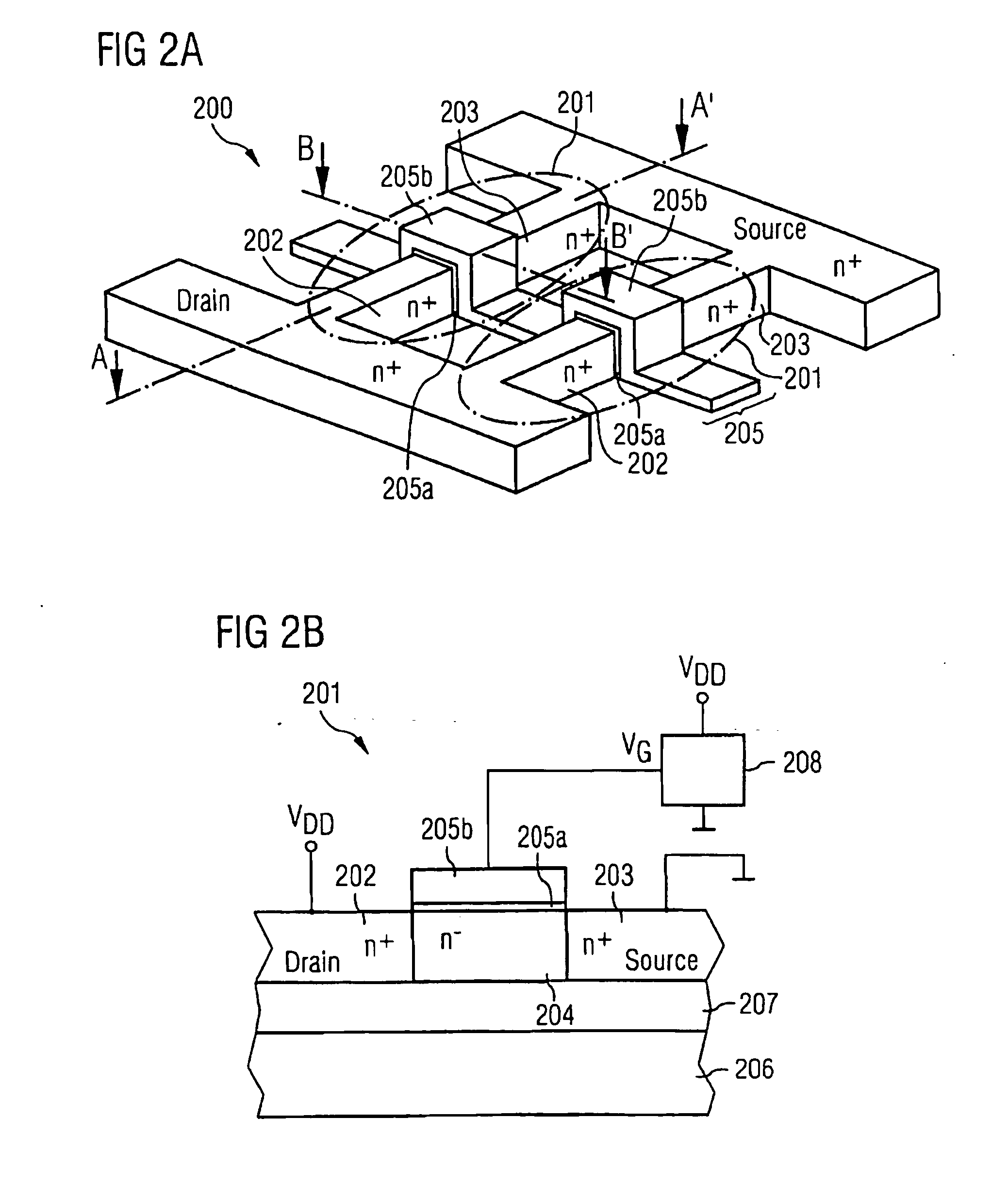

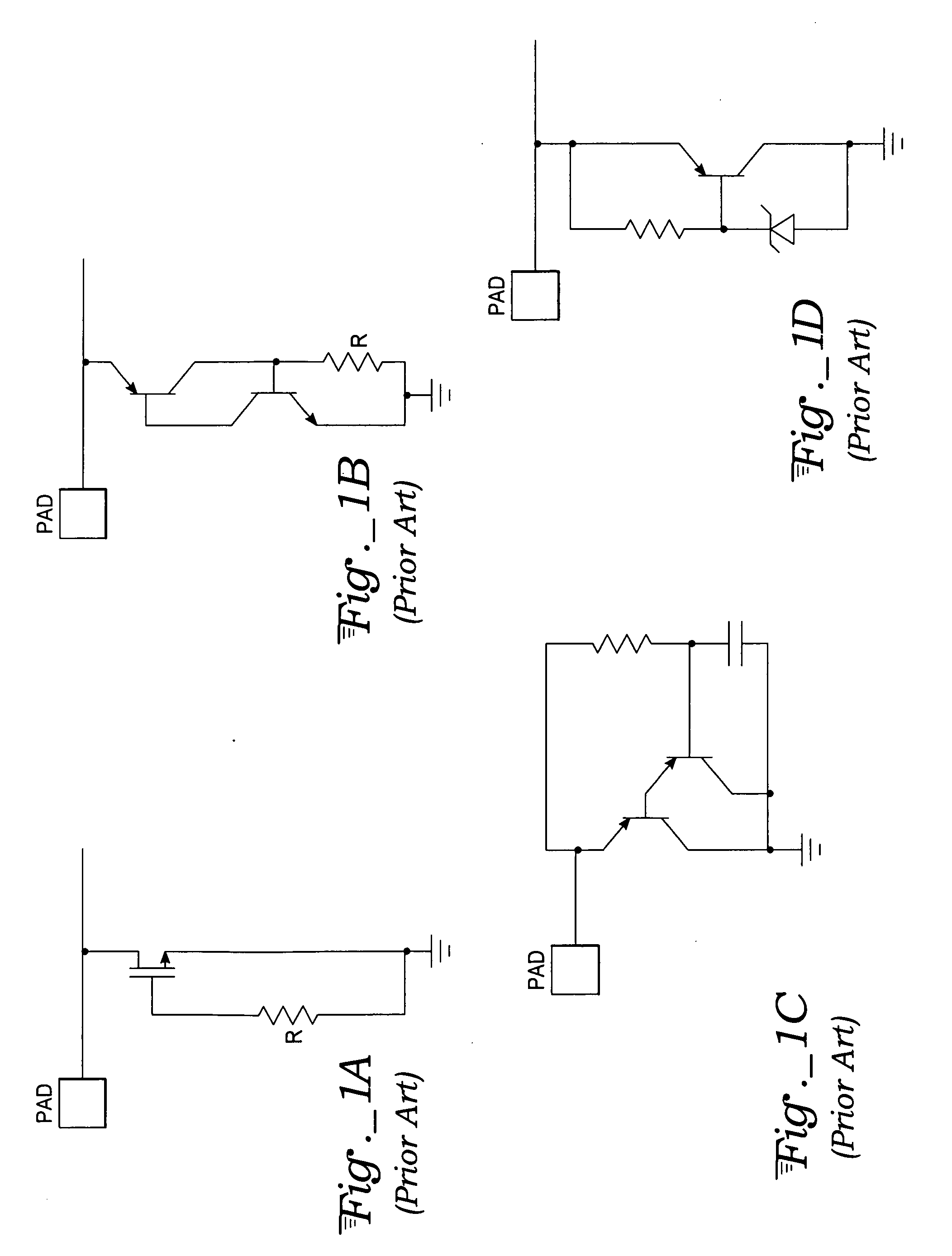

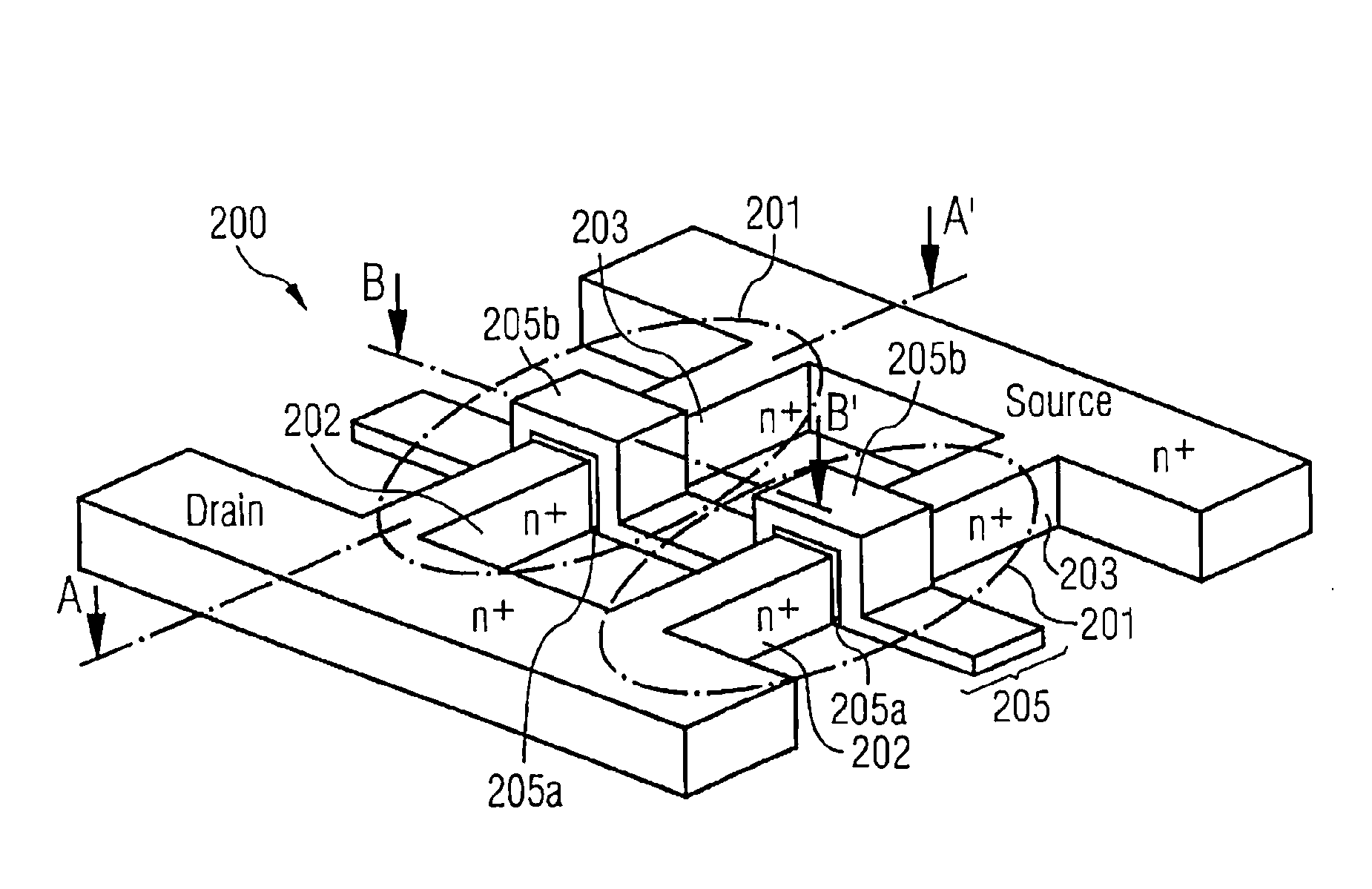

Electrostatic discharge protection element

ActiveUS20070040221A1Increase resistanceEnhanced ESD robustnessSemiconductor/solid-state device detailsSolid-state devicesElectrical resistance and conductanceEngineering

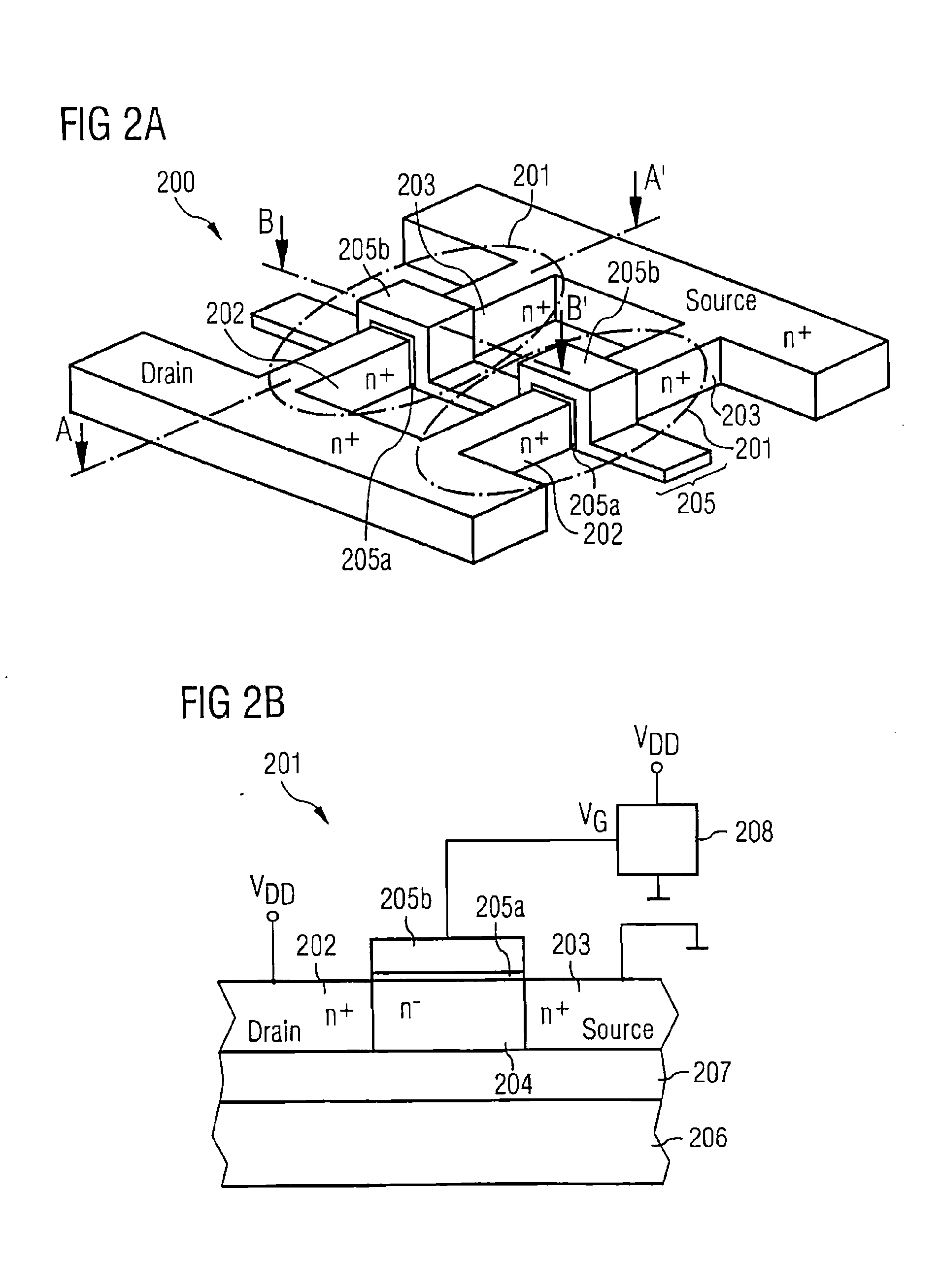

A gate controlled fin resistance element for use as an electrostatic discharge (ESD) protection element in an electrical circuit has a fin structure having a first connection region, a second connection region and a channel region formed between the first and second connection regions. Furthermore, the fin resistance element has a gate region formed at least over a part of the surface of the channel region. The gate region is electrically coupled to a gate control device, which gate control device controls an electrical potential applied to the gate region in such a way that the gate controlled fin resistance element has a high electrical resistance during a first operating state of the electrical circuit and a lower electrical resistance during a second operating state, which is characterized by the occurrence of an ESD event.

Owner:INFINEON TECH AG

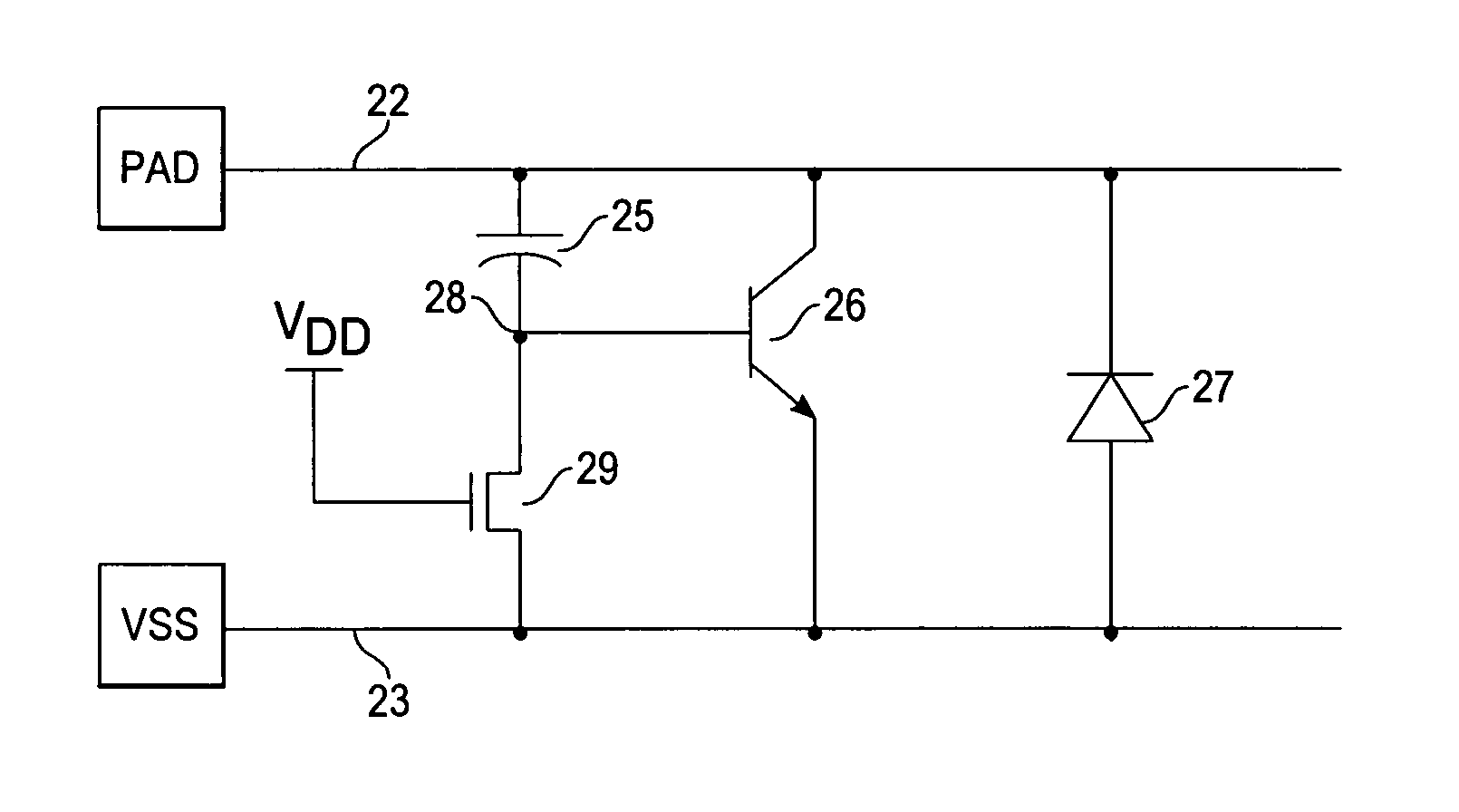

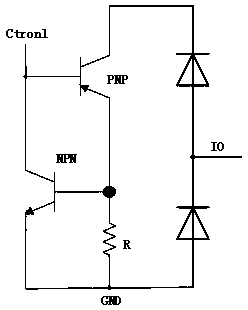

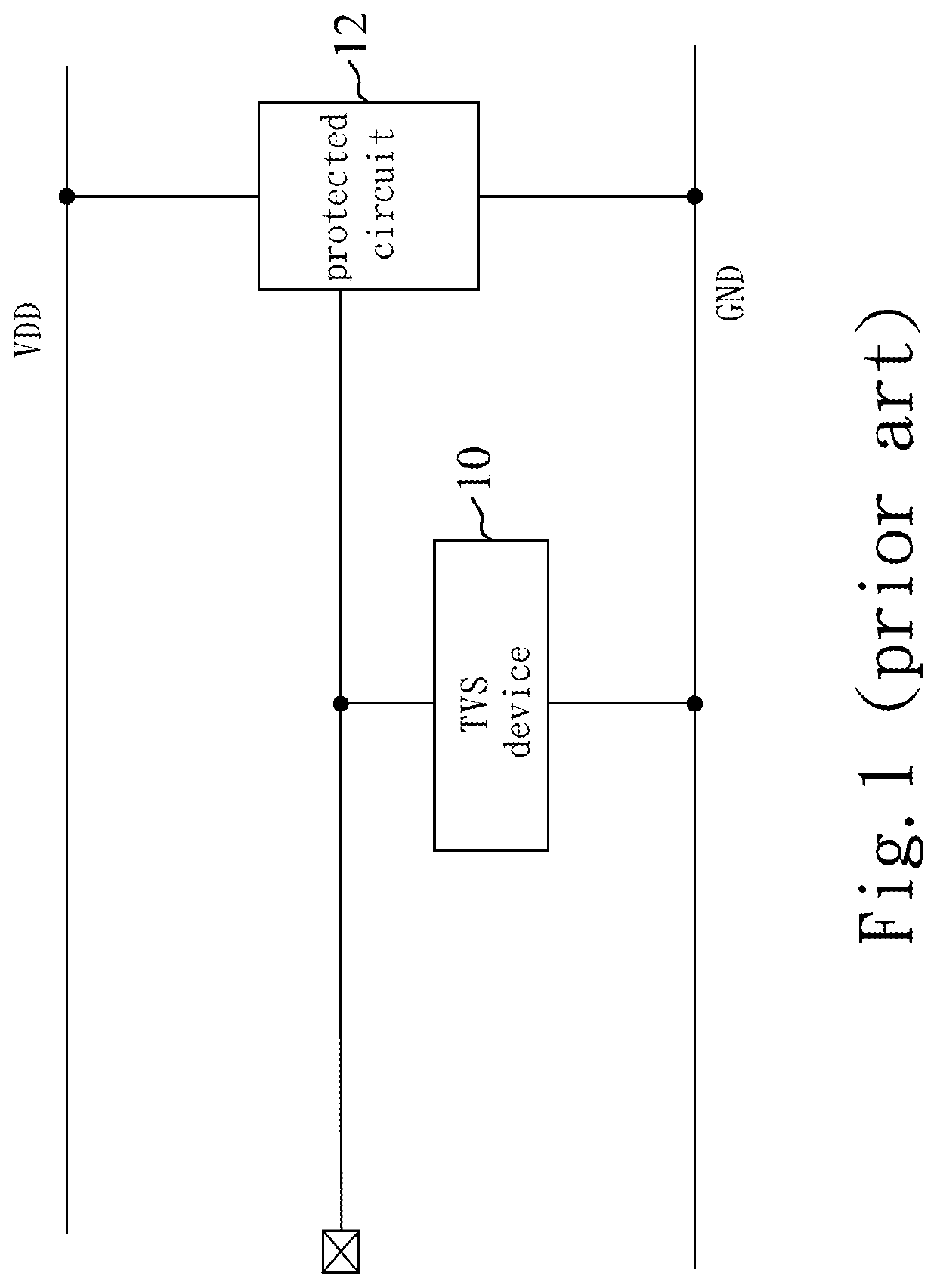

Transient pulse, substrate-triggered biCMOS rail clamp for ESD abatement

InactiveUS20060250732A1High currentLower clamping voltageTransistorEmergency protective arrangements for limiting excess voltage/currentVoltage pulseEngineering

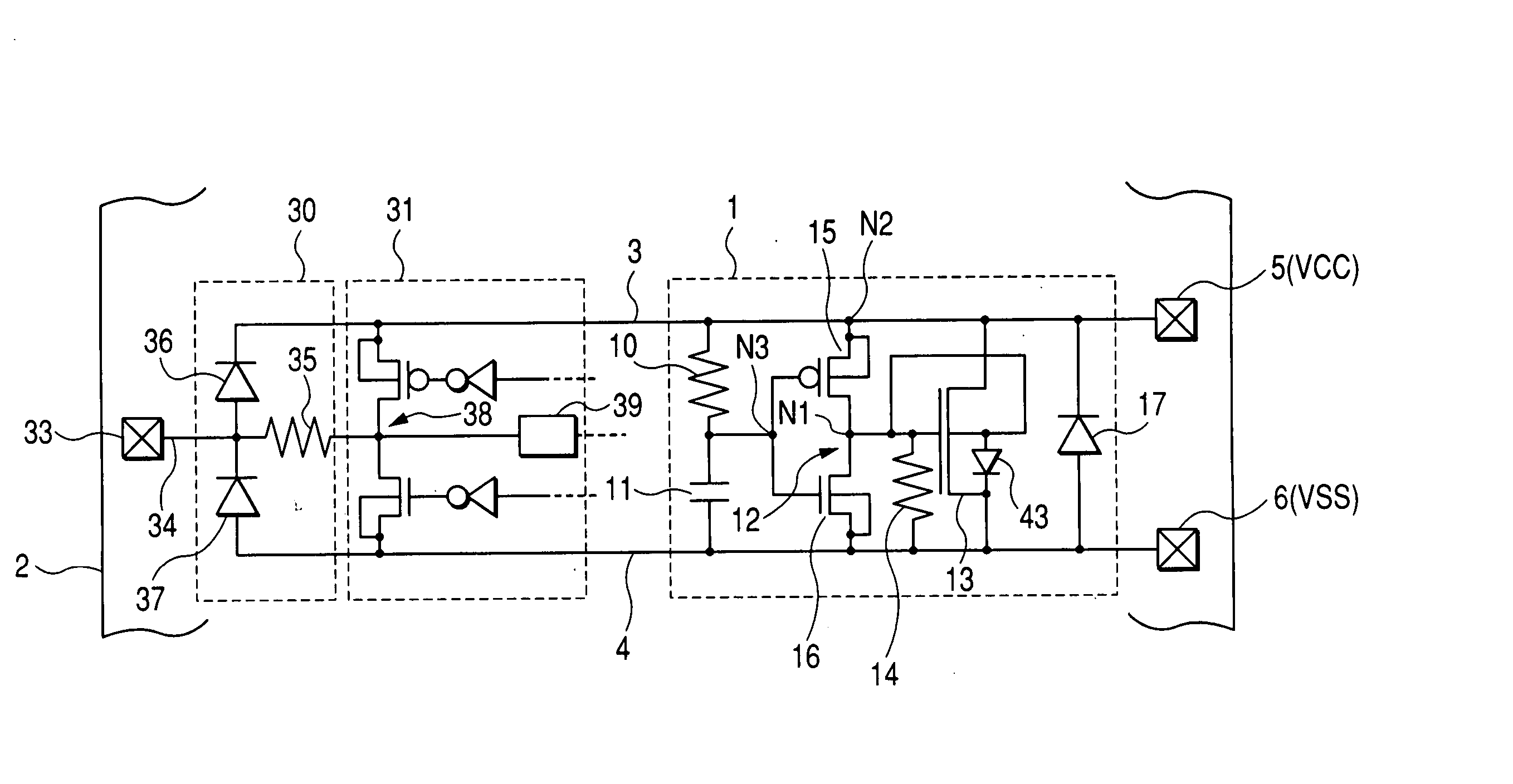

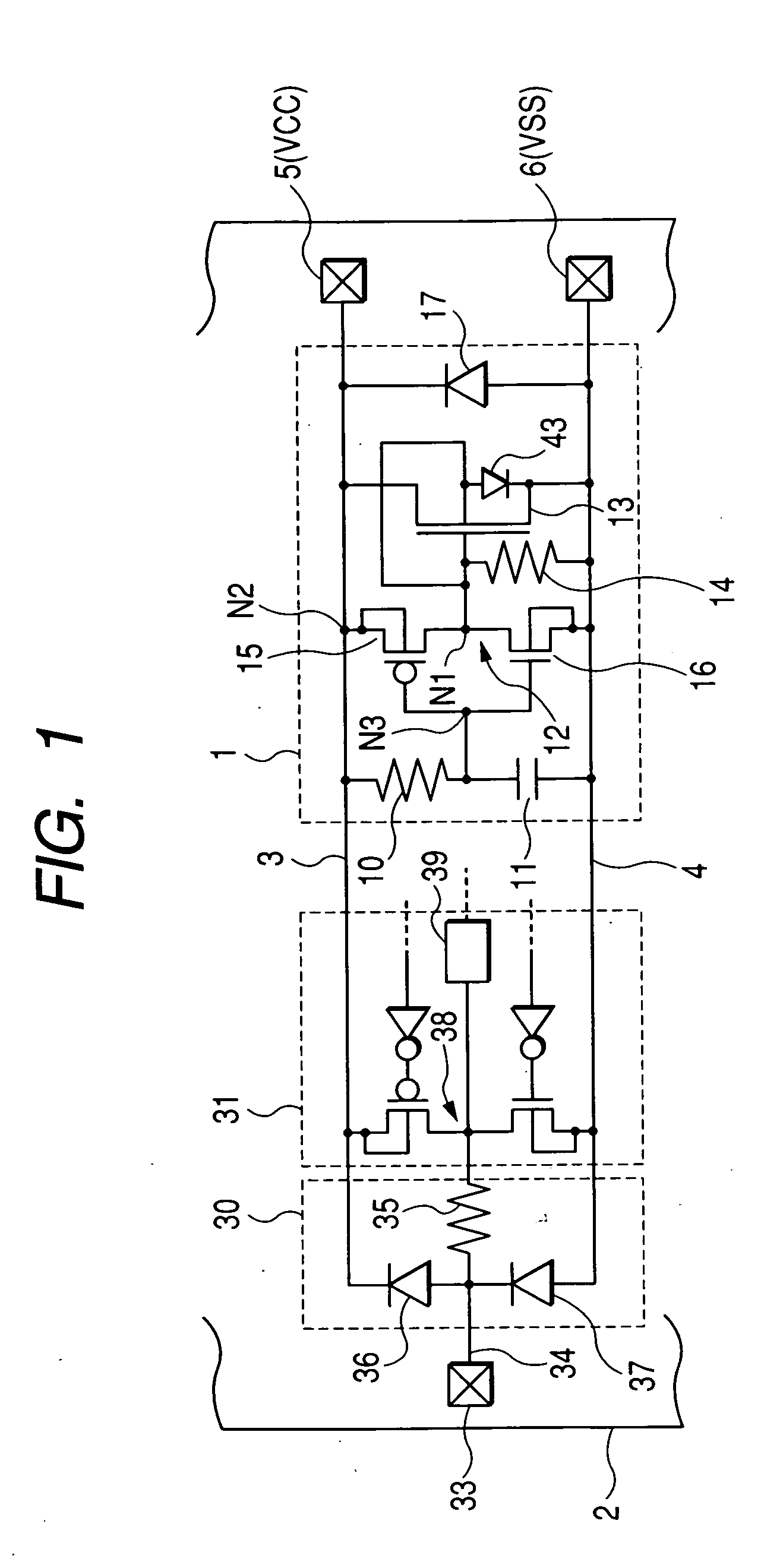

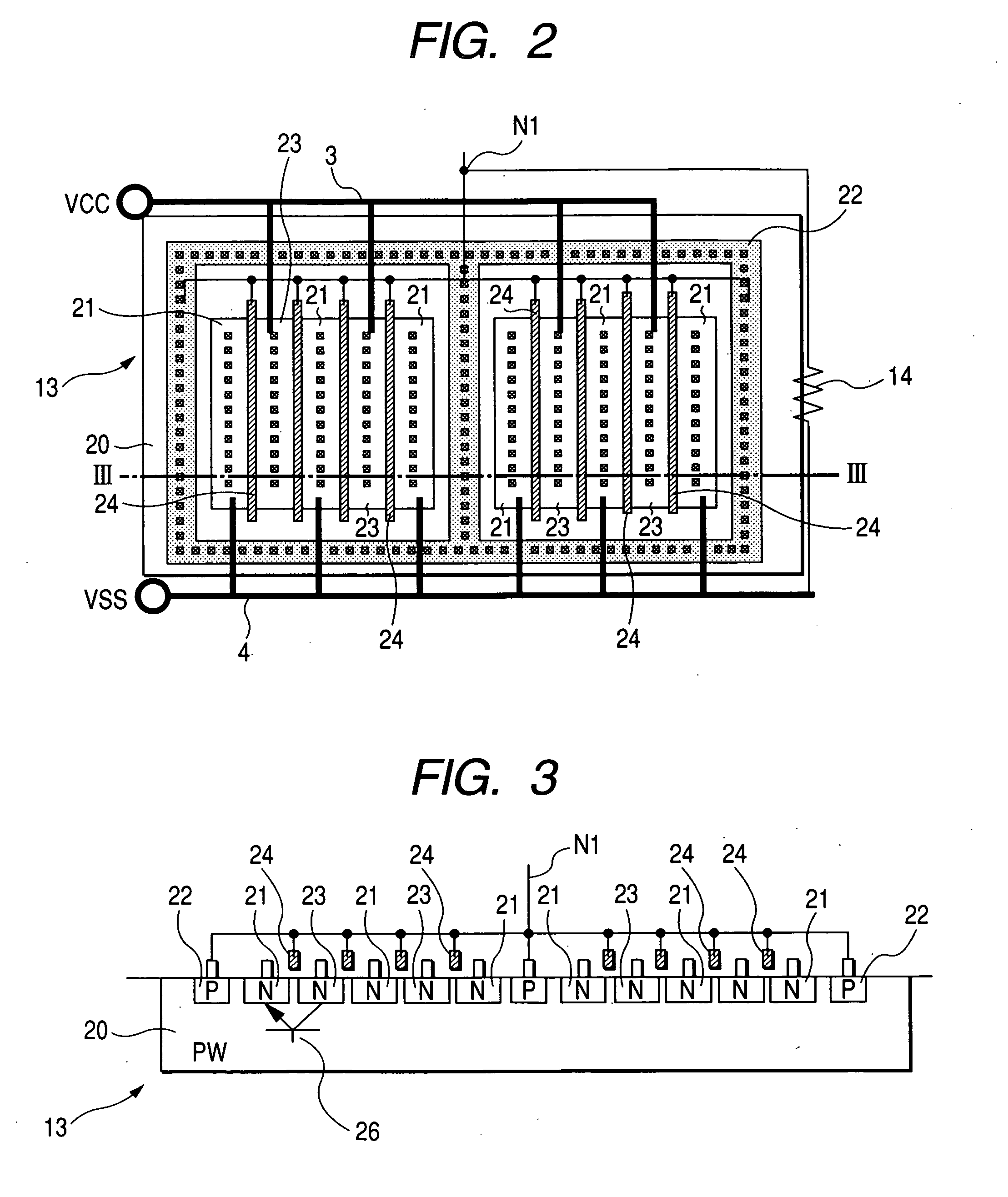

A circuit for protecting a circuit device against electrostatic discharge (ESD), power line, and voltage supply line surges. A transistor, diode, resistor, and capacitor are configured to clamp voltage pulses between the power and ground lines. The circuit is constructed using a single bipolar npn transistor formed using an isolated p-well.

Owner:ATMEL CORP

Electrostatic discharge protection element

ActiveUS20080277729A1Improve featuresImprove robustnessSemiconductor/solid-state device detailsSolid-state devicesElectrical resistance and conductanceEngineering

A gate controlled fin resistance element for use as an electrostatic discharge (ESD) protection element in an electrical circuit has a fin structure having a first connection region, a second connection region and a channel region formed between the first and second connection regions. Furthermore, the fin resistance element has a gate region formed at least over a part of the surface of the channel region. The gate region is electrically coupled to a gate control device, which gate control device controls an electrical potential applied to the gate region in such a way that the gate controlled fin resistance element has a high electrical resistance during a first operating state of the electrical circuit and a lower electrical resistance during a second operating state, which is characterized by the occurrence of an ESD event.

Owner:INFINEON TECH AG

Semiconductor integrated circuit

ActiveUS20060087781A1Increase resistanceReduce stepsSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringHigh voltage

The present invention is provided to suppress occurrence of an erroneous operation in a protection circuit due to a relatively small power source fluctuation such as a power source noise. The protection circuit has a first resistor and a capacitor connected in series between a power source line and a ground line, an inverter whose input is connected between the first resistor and the capacitor, and a MOS transistor whose gate electrode receives an output of the inverter and whose drain electrode and source electrode are connected to the power source line and the ground line. When a high voltage fluctuation occurs in the power source line, a level change at a connection point between the first resistor and the capacitor is delayed according to a time constant. By the delay, the MOS transistor that receives an output of the inverter is temporarily turned on and discharges a high voltage to the ground line. Since an output of the inverter is pulled down to the ground line via a second resistor, even if an output of the inverter fluctuates undesirably, fluctuations in a gate input of the MOS transistor are suppressed.

Owner:RENESAS ELECTRONICS CORP

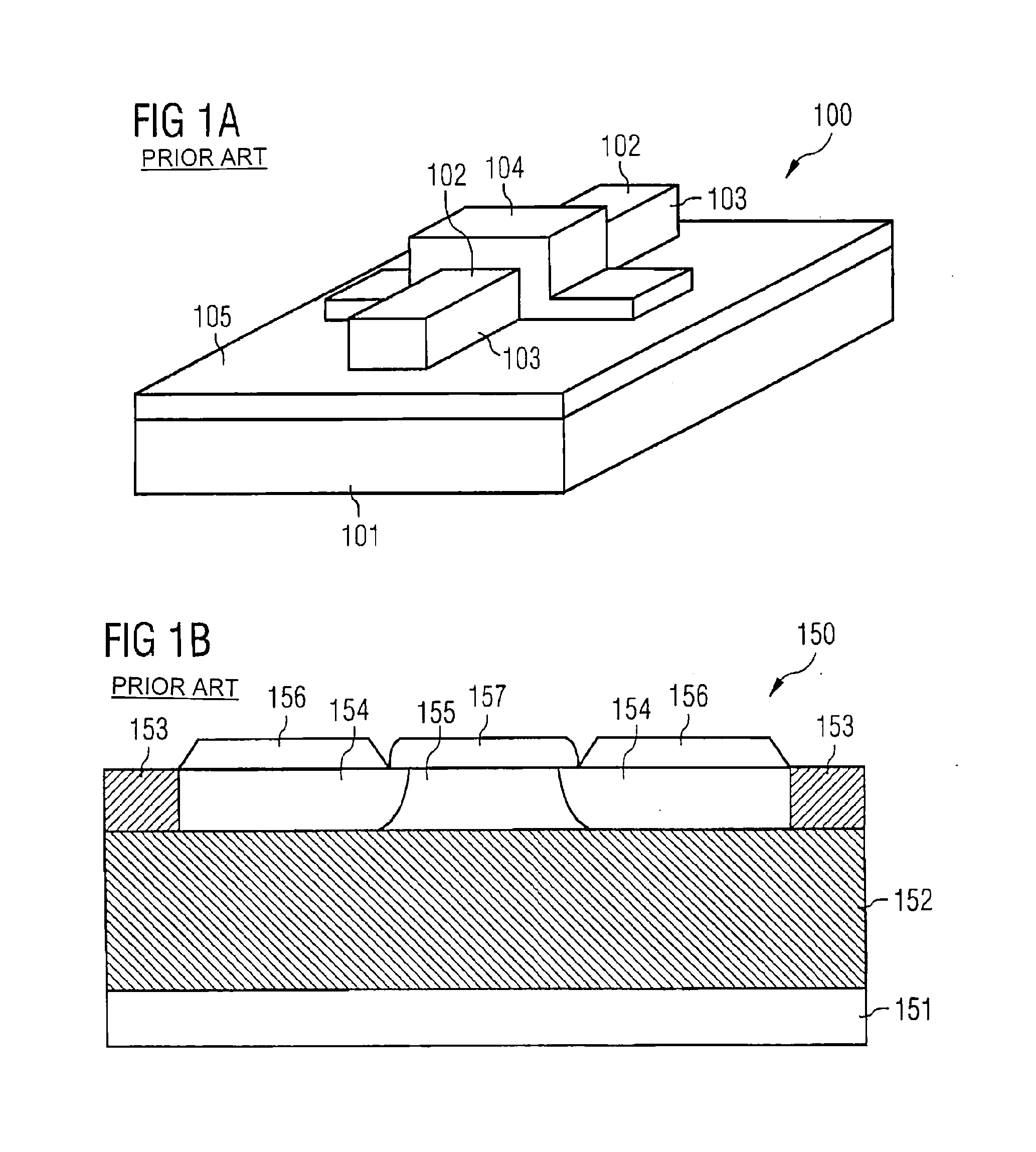

Protective structure

ActiveUS20080290462A1Shorten the lengthReduced structureSolid-state devicesSemiconductor/solid-state device manufacturingSemiconductorOptoelectronics

A protective structure is produced by providing a semiconductor substrate with a doping of a first conductivity type. A semiconductor layer with a doping of a second conductivity type is applied at a surface of the semiconductor substrate. A buried layer with doping of a second conductivity type is formed in a first region of the semiconductor layer, wherein the buried layer is produced at the junction between the semiconductor layer and semiconductor substrate. A first dopant zone with a doping of a first conductivity type is formed in the first region of the semiconductor layer above the buried layer. A second dopant zone with a doping of a second conductivity type is formed in a second region of the semiconductor layer. An electrical insulation is formed between the first region and the second region of the semiconductor layer. A common connection device is formed for the first dopant zone and the second dopant zone.

Owner:INFINEON TECH AG

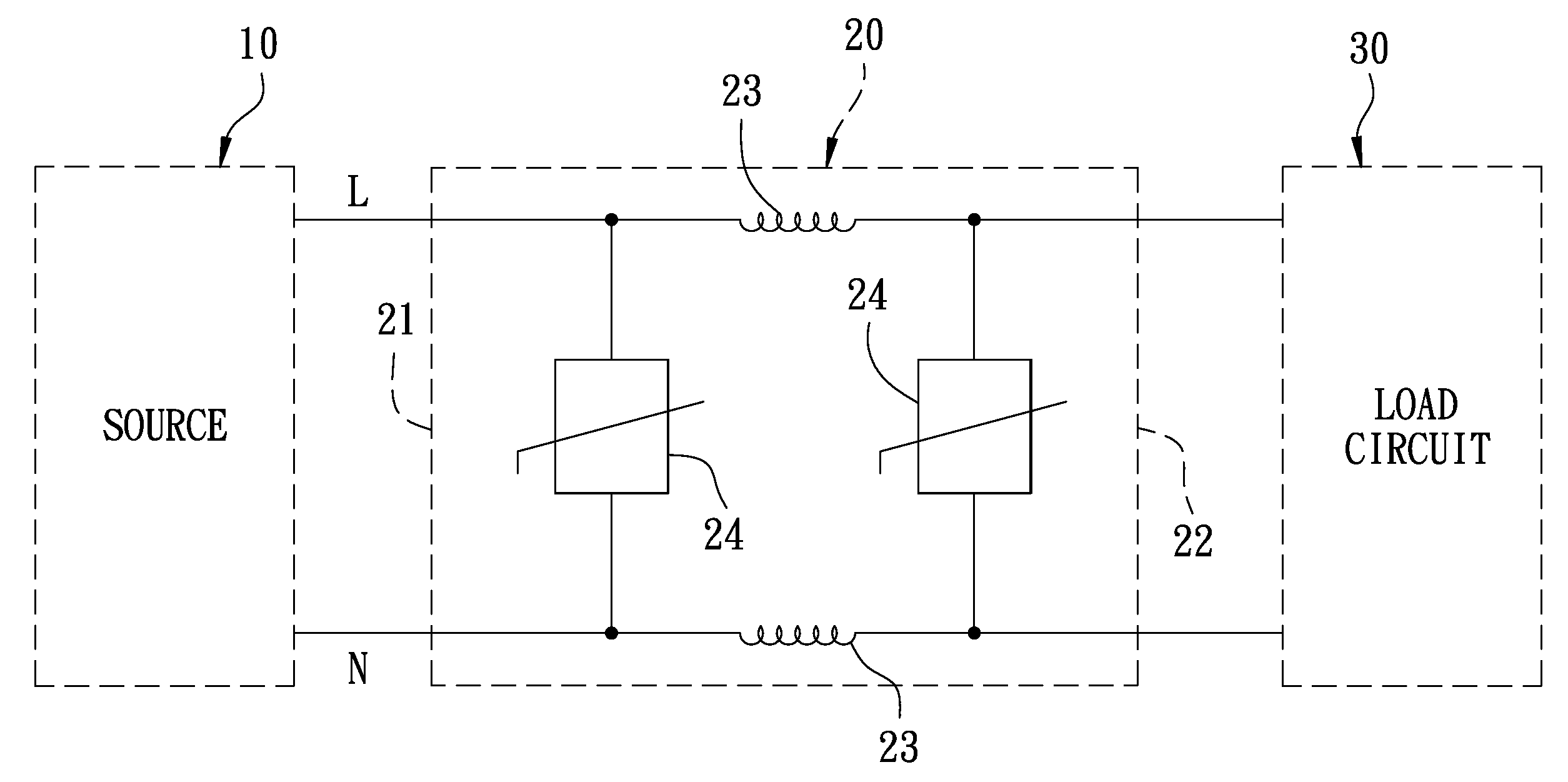

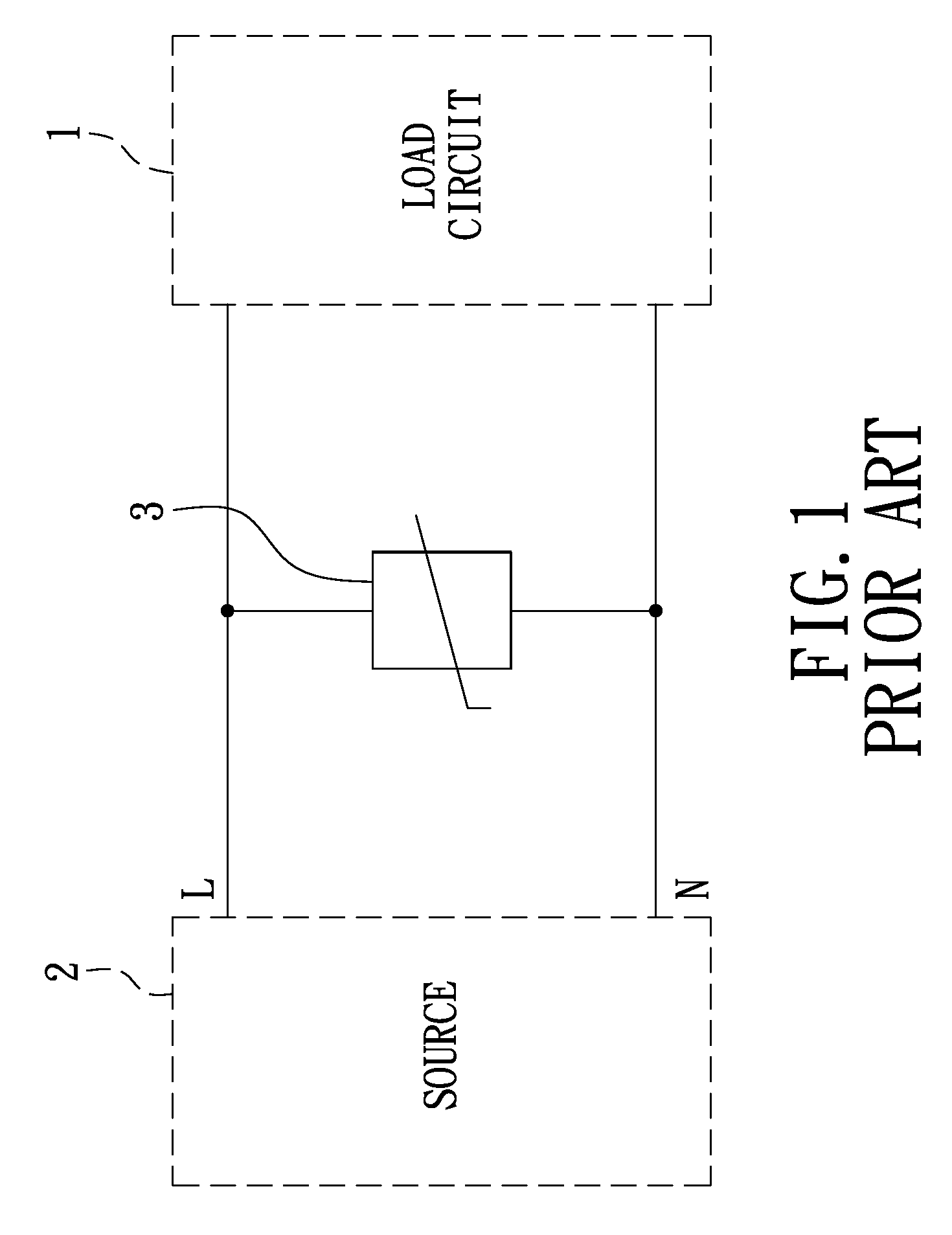

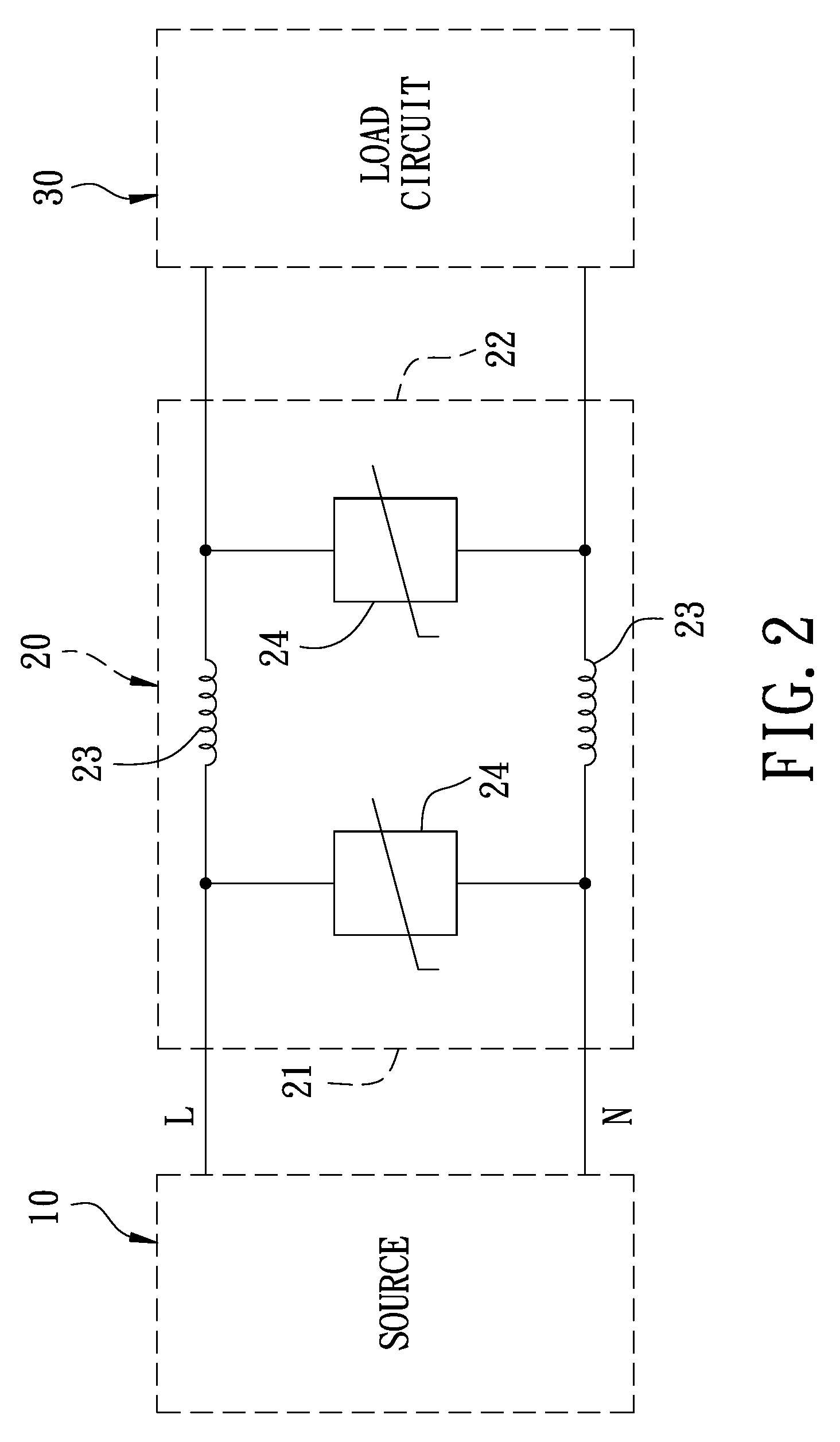

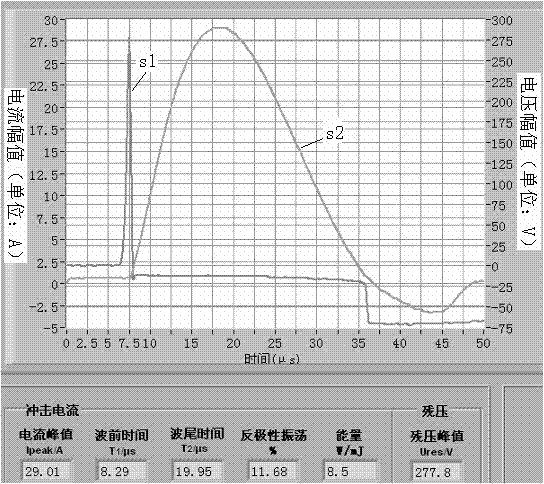

Surge absorbing circuit capable of reducing a clamping voltage with a great extent

InactiveUS20090073618A1Clamping voltageSurge can be consumed more quicklyEmergency protective arrangements for limiting excess voltage/currentLoad circuitCapacitance

A surge absorbing circuit capable of reducing a clamping voltage with a great extent includes an input, an output, at least two inductors respectively connected between the input and the output in series, and at least two capacitances respectively connected at two sides of the inductors in parallel. The input is employed to let an AC power source pass in. The output is to transmit the AC power source having been treated by the surge absorbing circuit to a load circuit. By means of the surge absorbing circuit, the clamping voltage of the varistors can be greatly lowered and the surge can be consumed more quickly.

Owner:CERAMATE TECH CO LTD

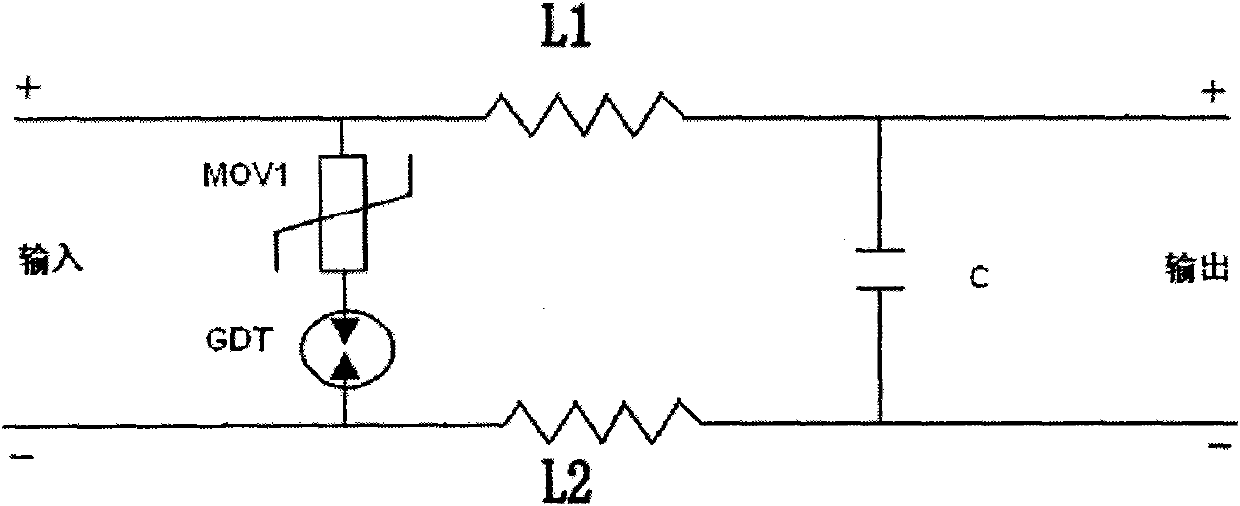

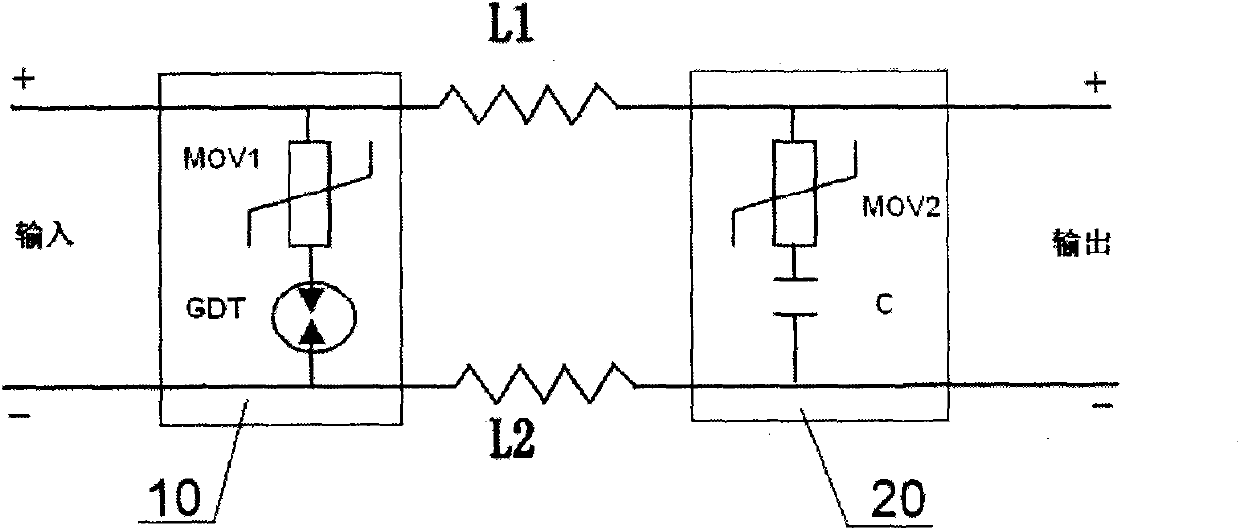

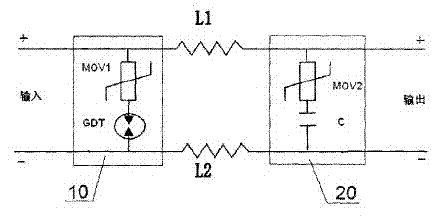

Anti-surge protection circuit

InactiveCN102025141AImprove surge protection efficiencyExtended service lifeEmergency protective arrangements for limiting excess voltage/currentCapacitancePower flow

The invention relates to an anti-surge protection circuit connected between a power supply and electronic equipment. The anti-surge protection circuit comprises a first-stage protection circuit, a second-stage protection circuit and an inductance element, wherein the first-stage protection circuit and the second-stage protection circuit are connected in parallel and instantaneously discharge the surge currents of a signal input end; the inductance element is connected in series between the first-stage protection circuit and the second-stage protection circuit and inhibits the surge currents of the first-stage protection circuit from flowing into the second-stage protection circuit; and the second-stage protection circuit comprises a second voltage dependent resistor and a capacitor. The anti-surge protection circuit not only enables most surges to be discharged on the first-stage protection circuit, but also effectively solves the problems of current following and current leakage of the first-stage protection circuit through the effective matching action of the first-stage protection circuit, the second-stage protection circuit and the inductance element; in addition, spike voltages and clamp voltages which are generated from the first-stage protection circuit are greatly reduced, therefore the surge protection efficiency of the integral protection circuit is enhanced, the service life of the protection circuit is prolonged, and the safety of the protection circuit is greatly enhanced.

Owner:SHENZHEN BENCENT ELECTRONICS CO LTD

ESD protection device and manufacturing method therefor

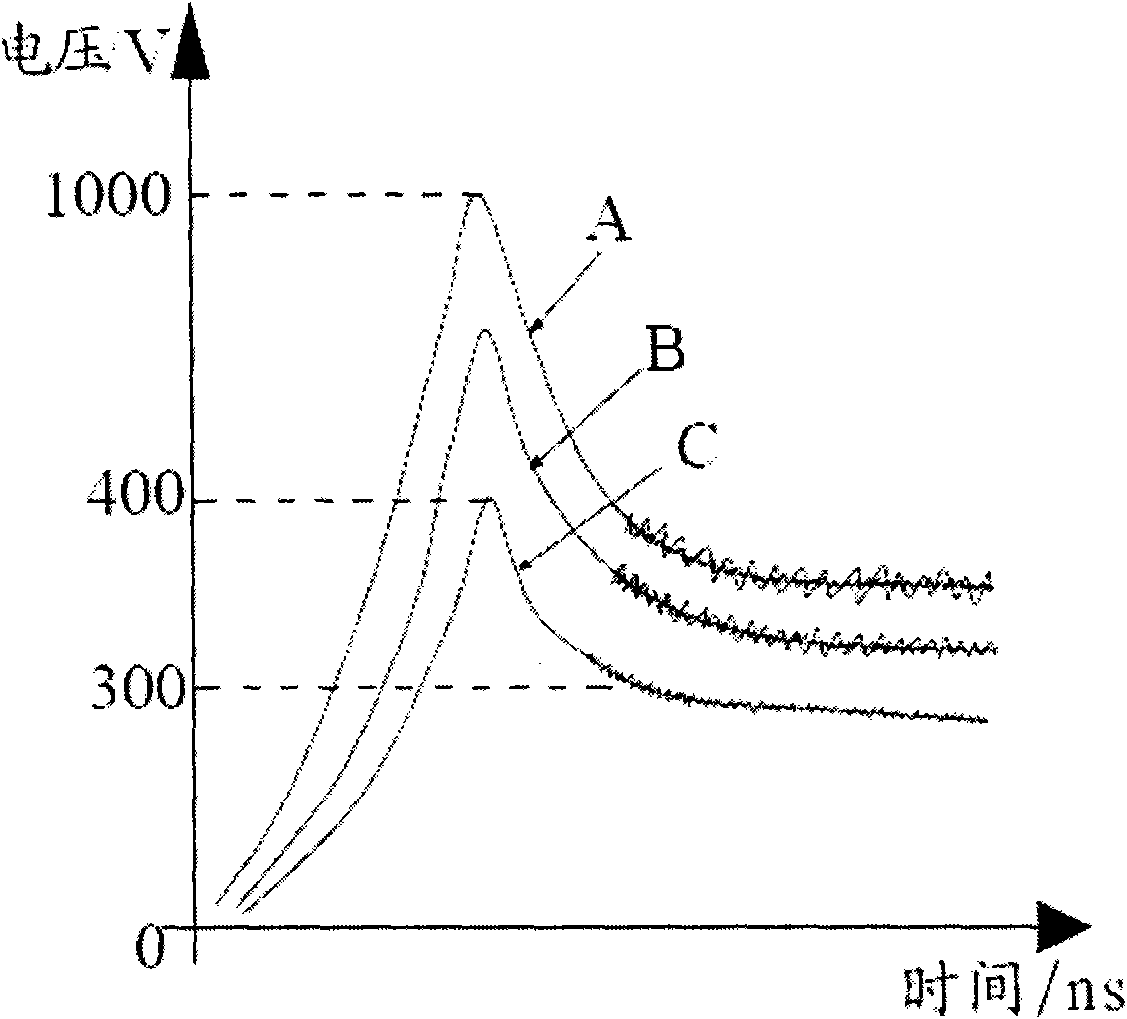

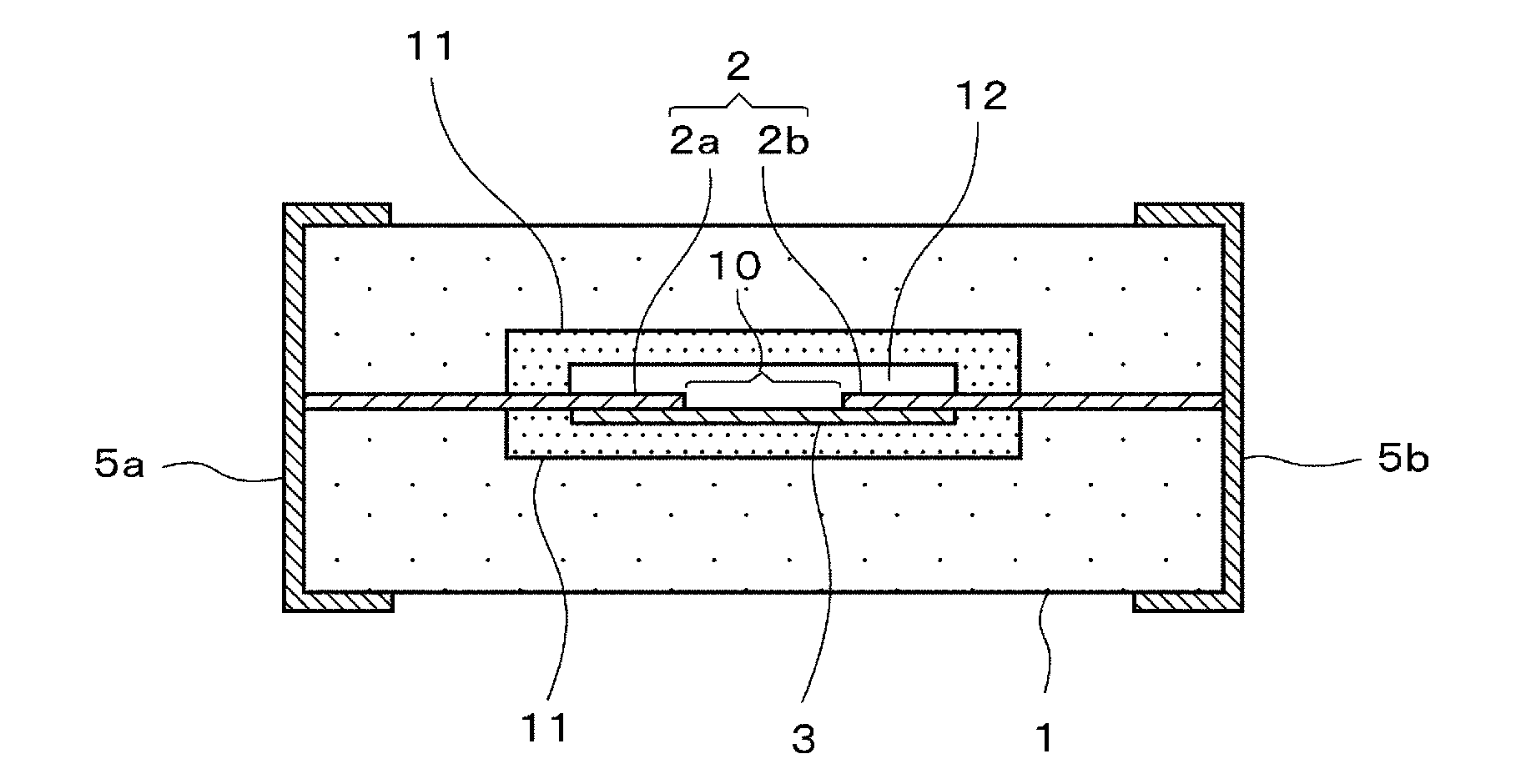

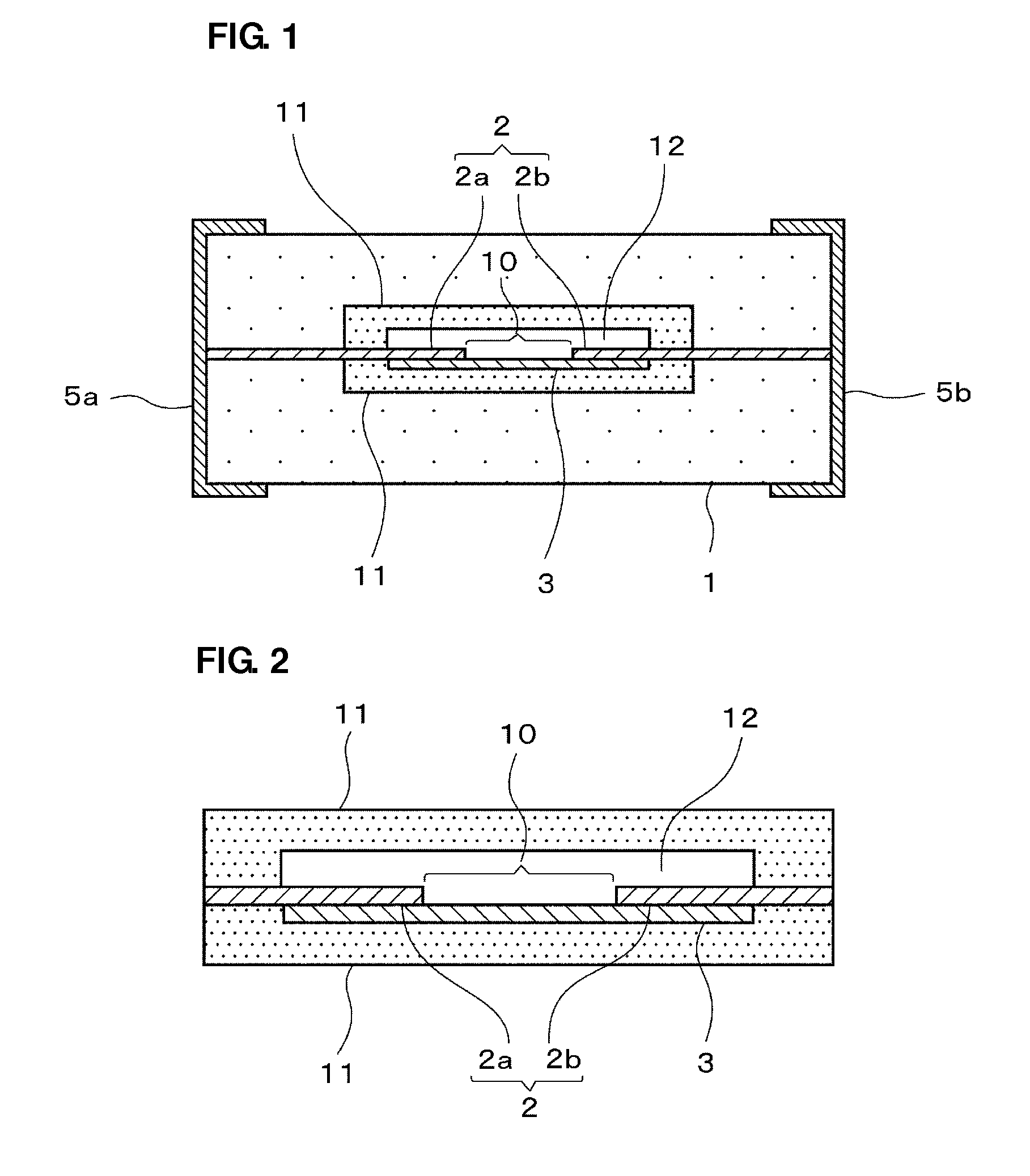

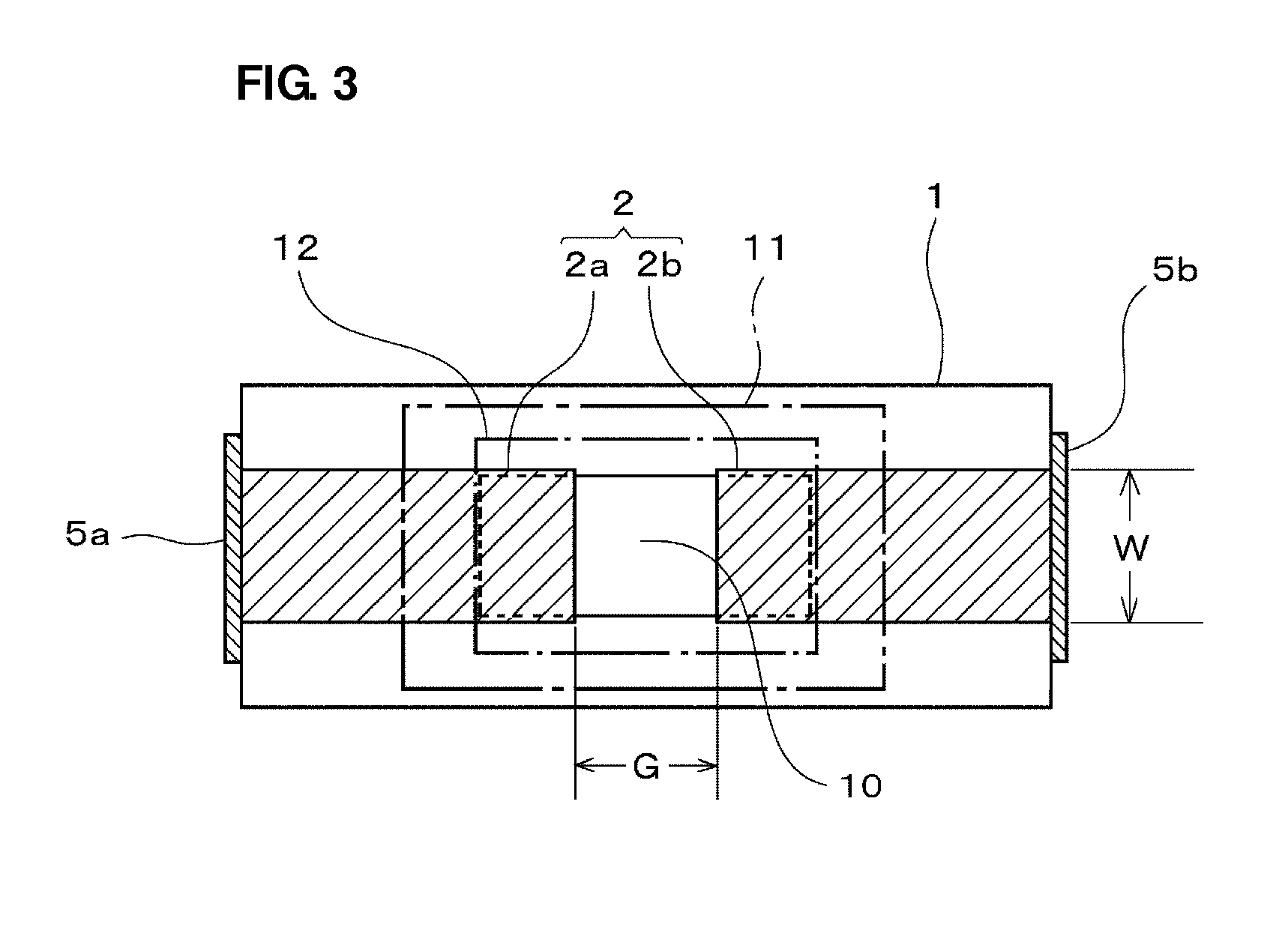

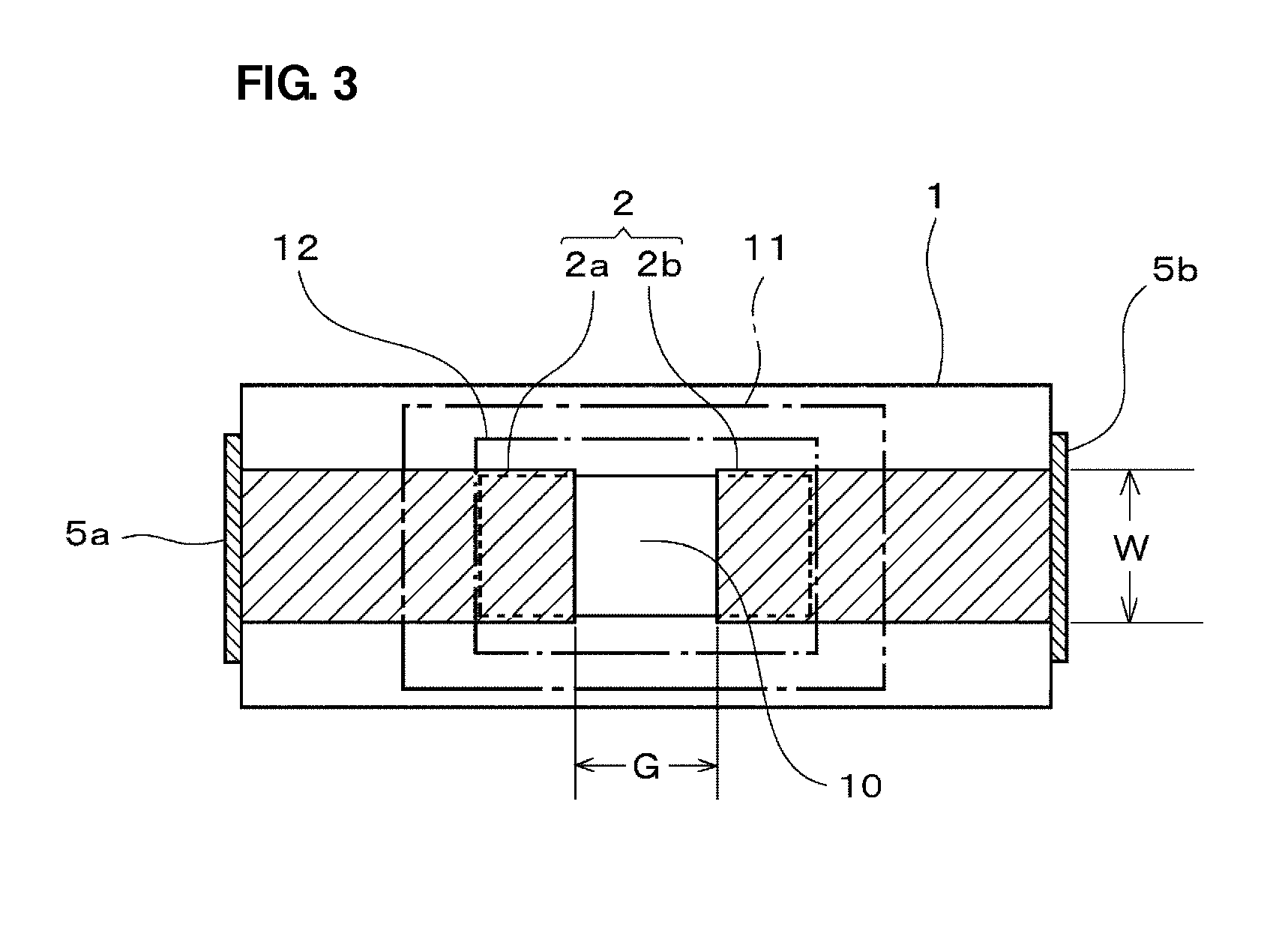

ActiveUS20120169452A1Efficiently manufactureReduce peak voltageSparking plugsSpark gap detailsAuxiliary electrodeMetallurgy

An ESD protection device includes opposed electrodes in a ceramic base material and a discharge auxiliary electrode in contact with each of the opposed electrodes which is arranged so as to provide a bridge from the opposed electrode on one side to the opposed electrode on the other side, the discharge auxiliary electrode includes metallic particles, semiconductor particles, and a vitreous material, and bonding is provided through the vitreous material between the metallic particles, between the semiconductor particles, and between the metallic particles and the semiconductor particles. The metallic particles have an average particle diameter X of about 1.0 μm or more, and the relationship between the thickness Y of the discharge auxiliary electrode and the average particle diameter X of the metallic particles satisfies about 0.5≦Y / X≦ about 3.

Owner:MURATA MFG CO LTD

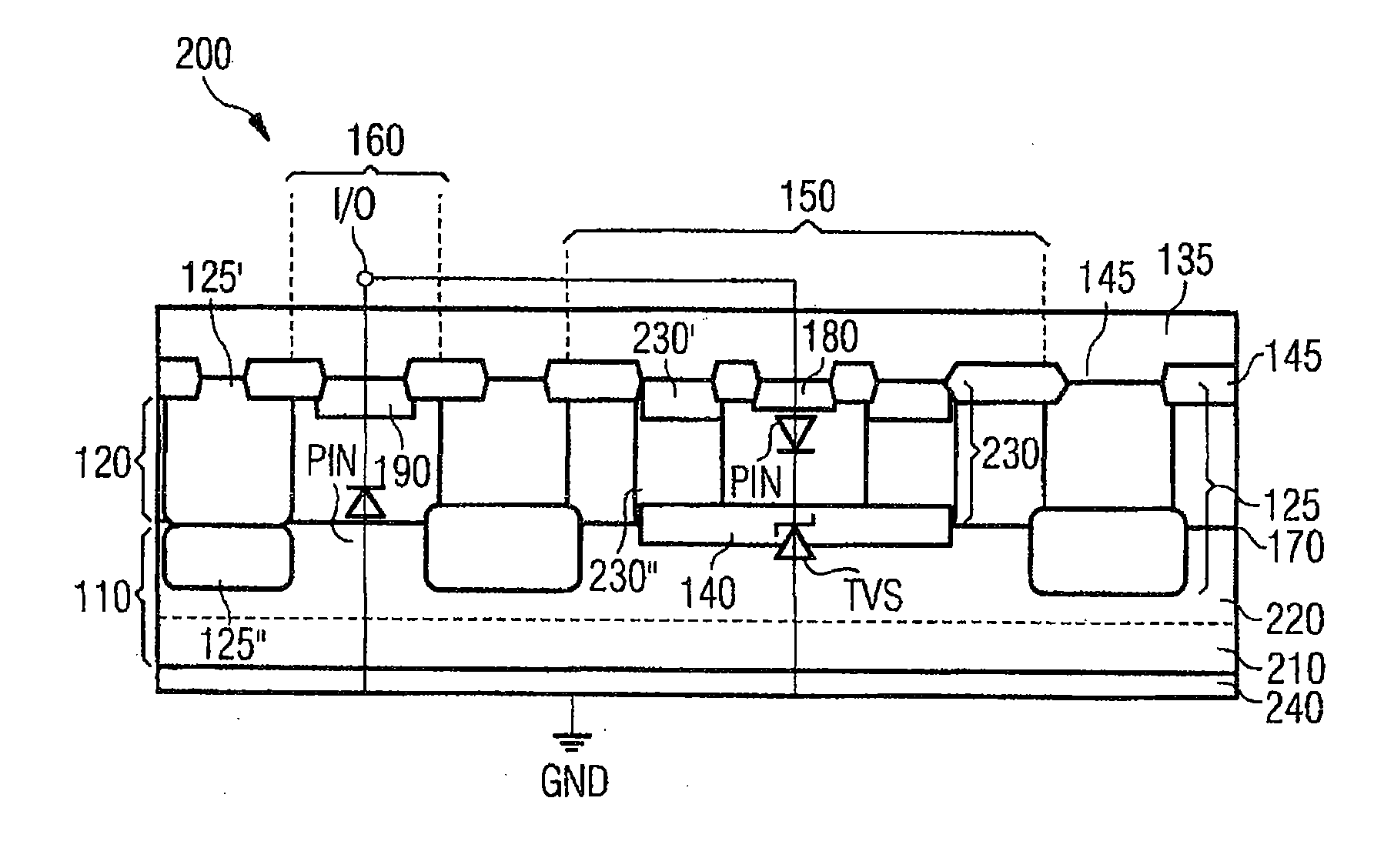

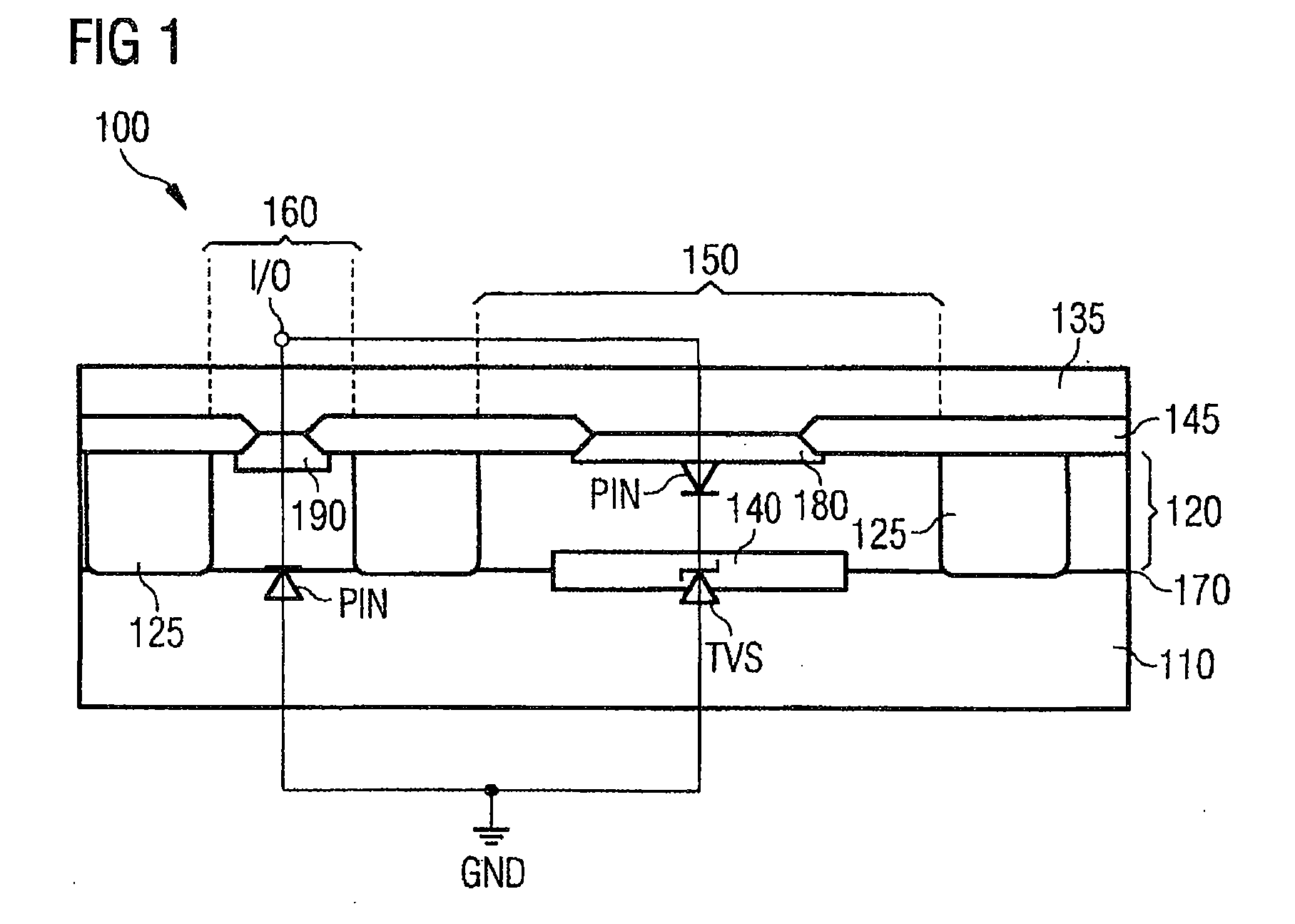

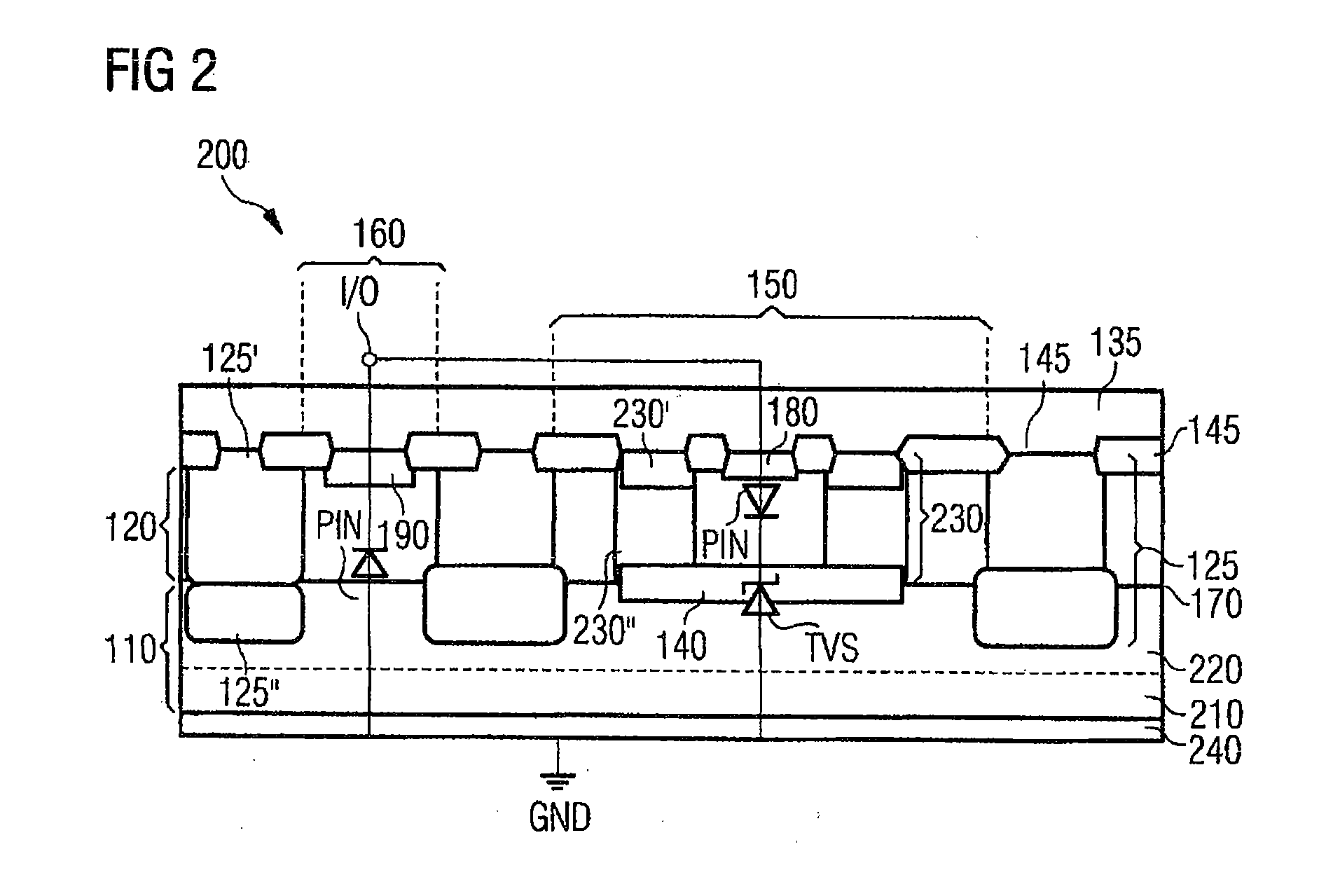

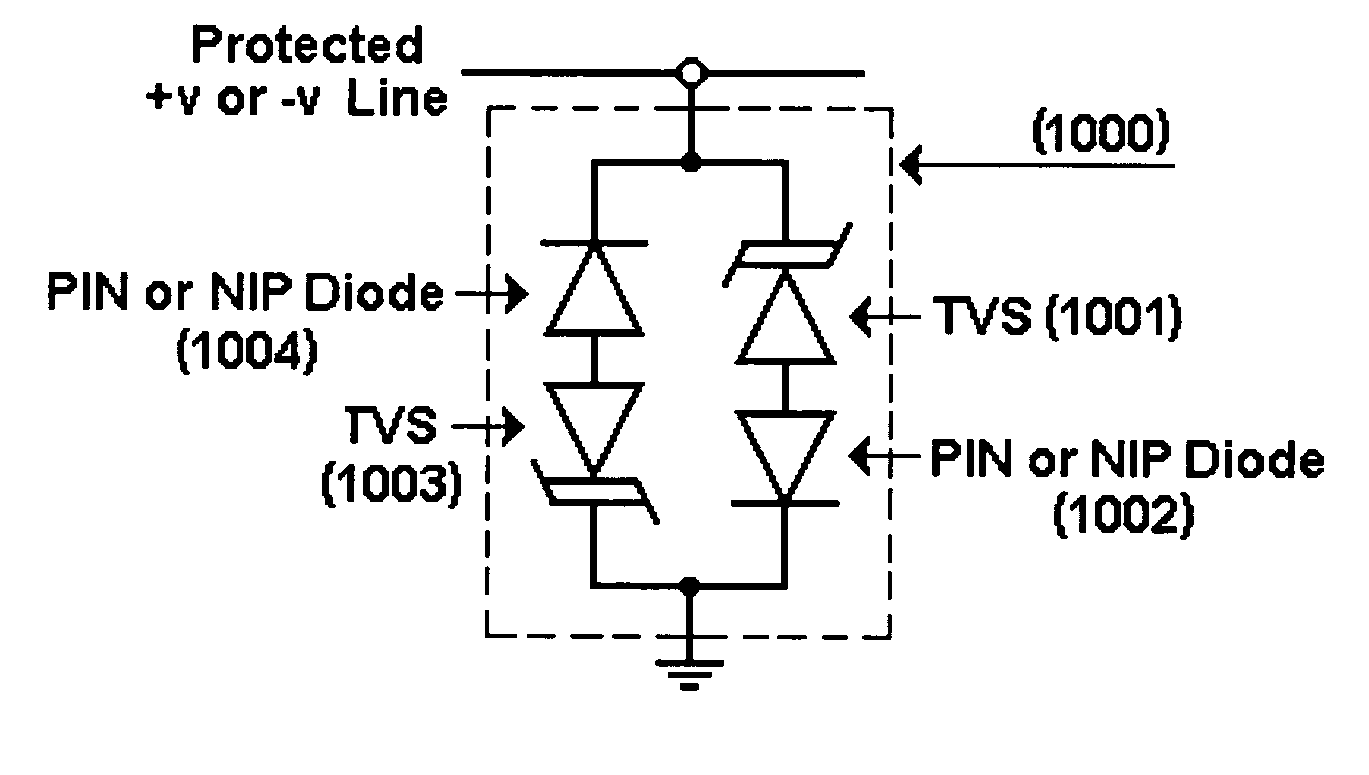

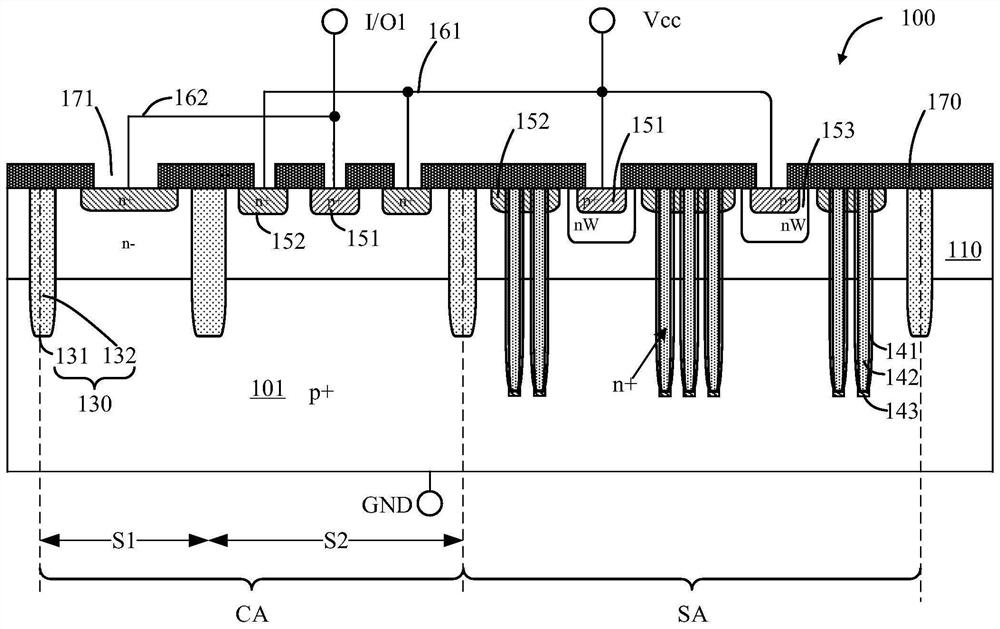

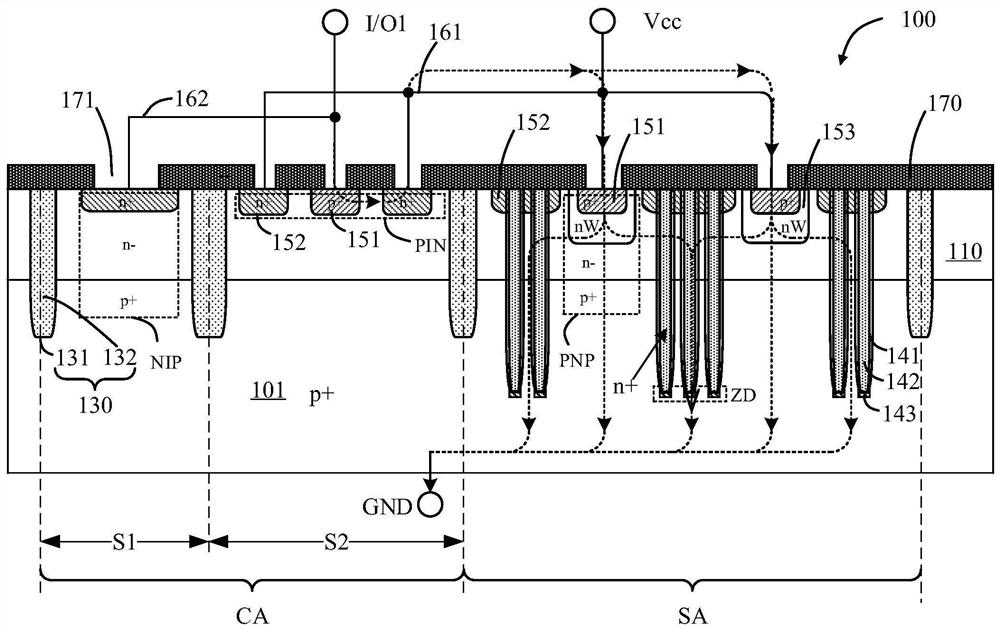

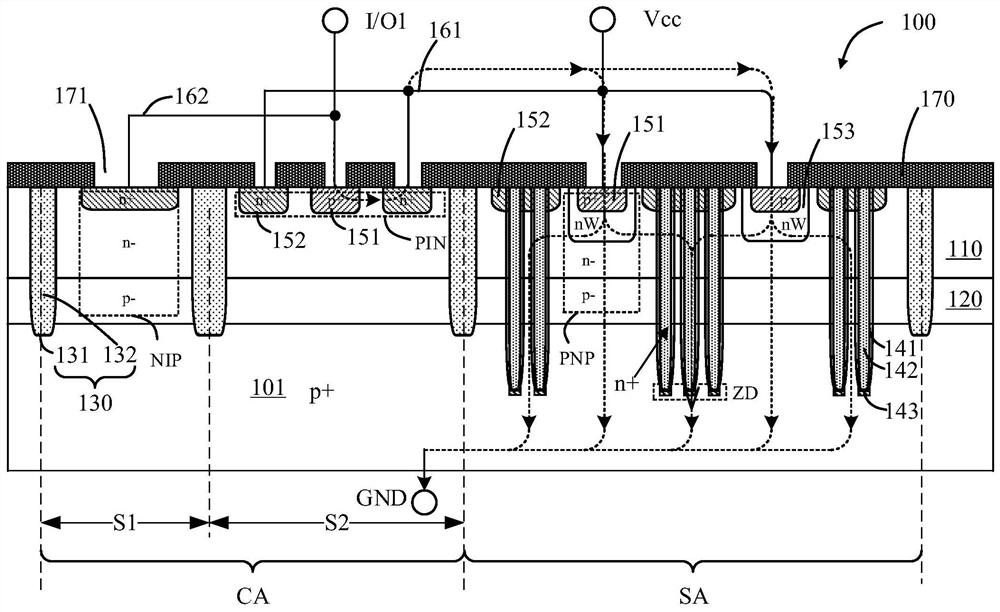

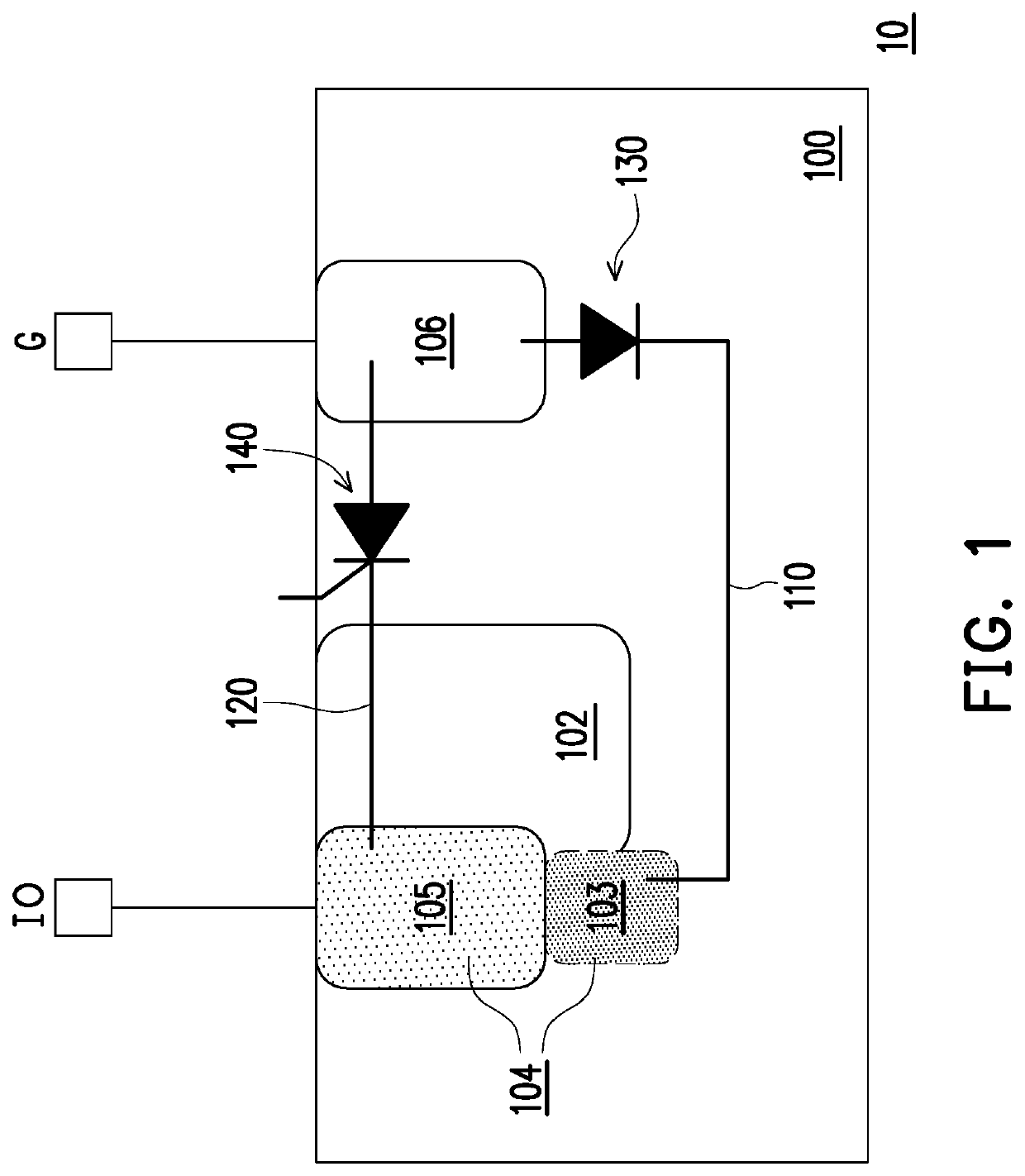

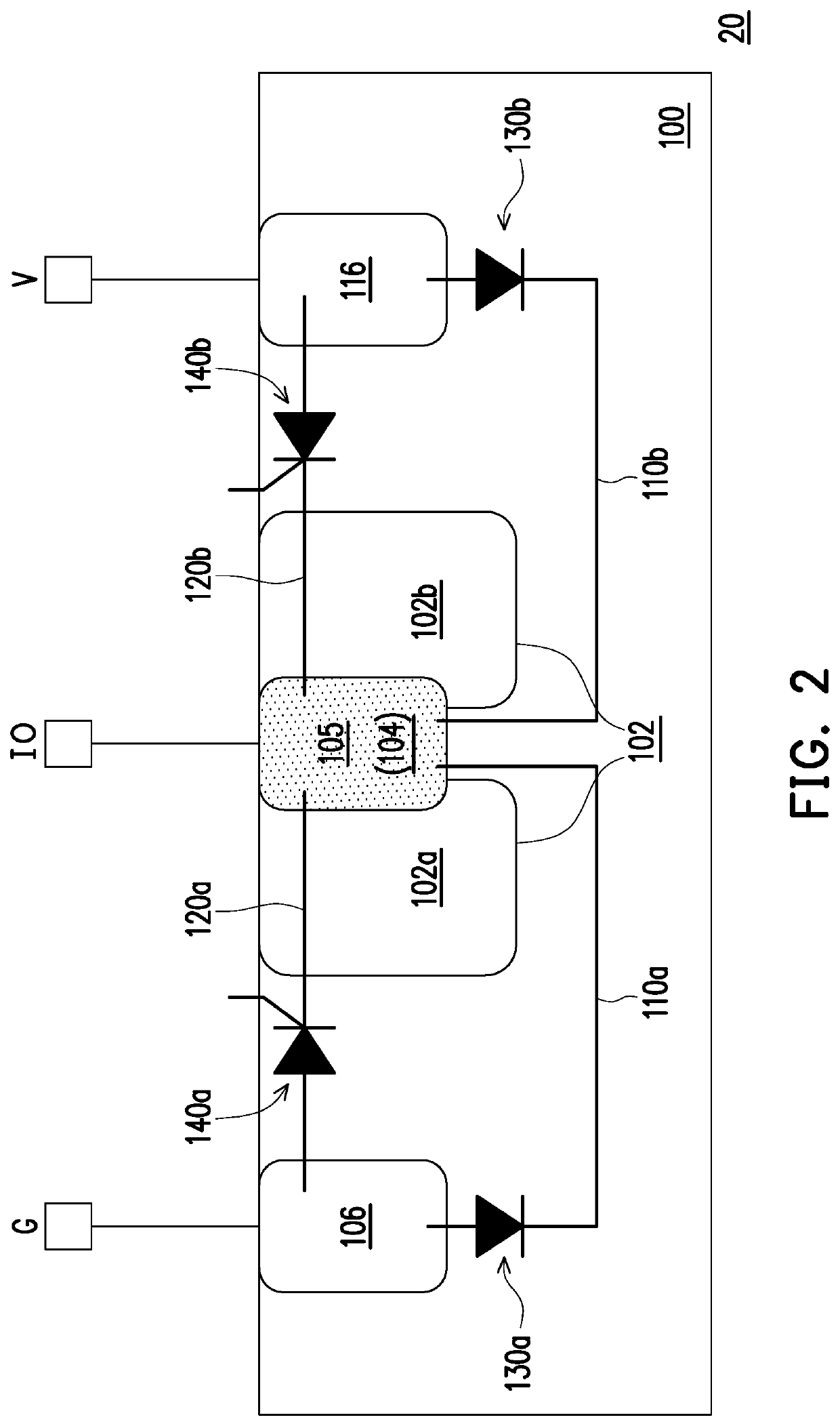

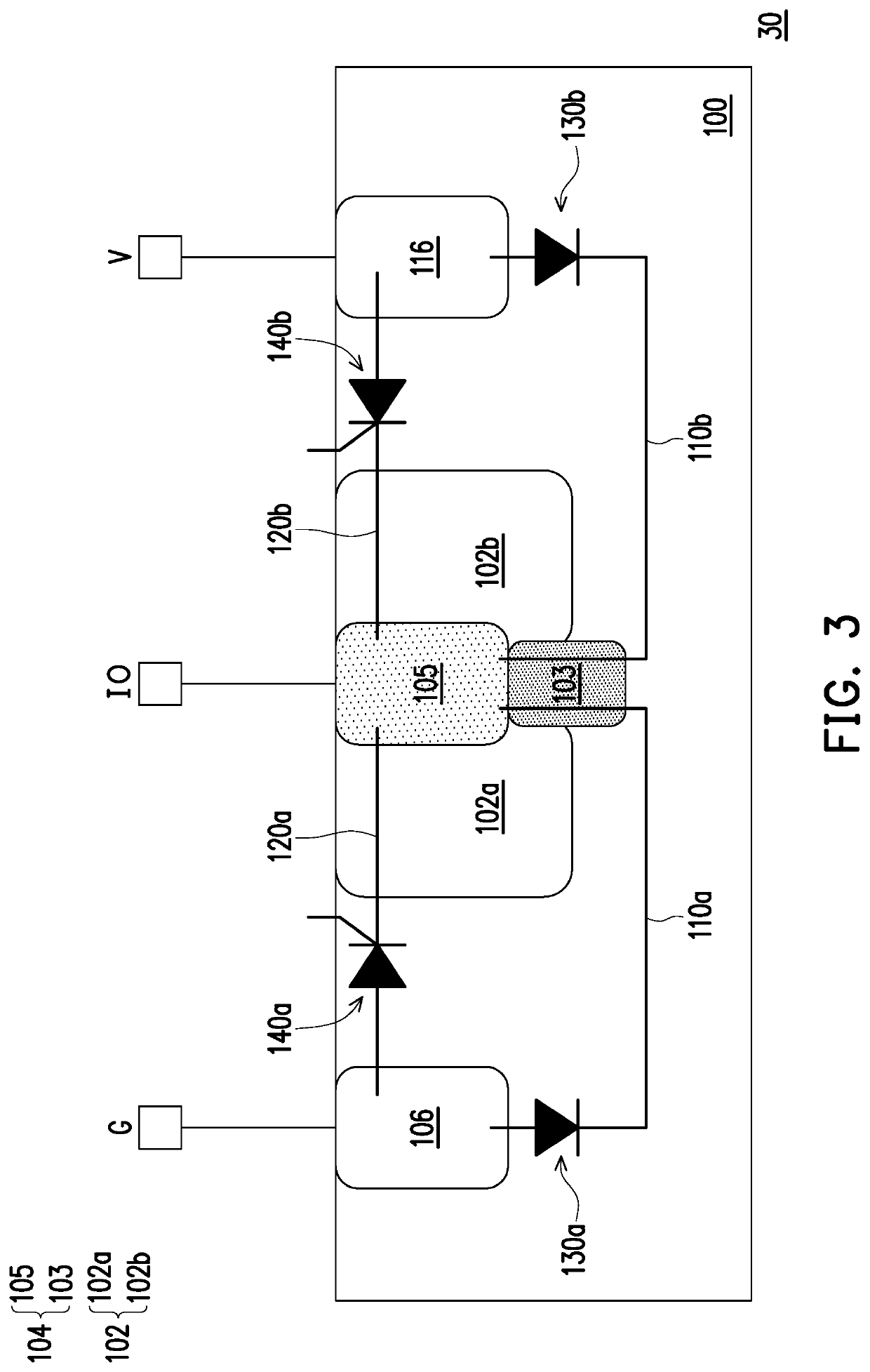

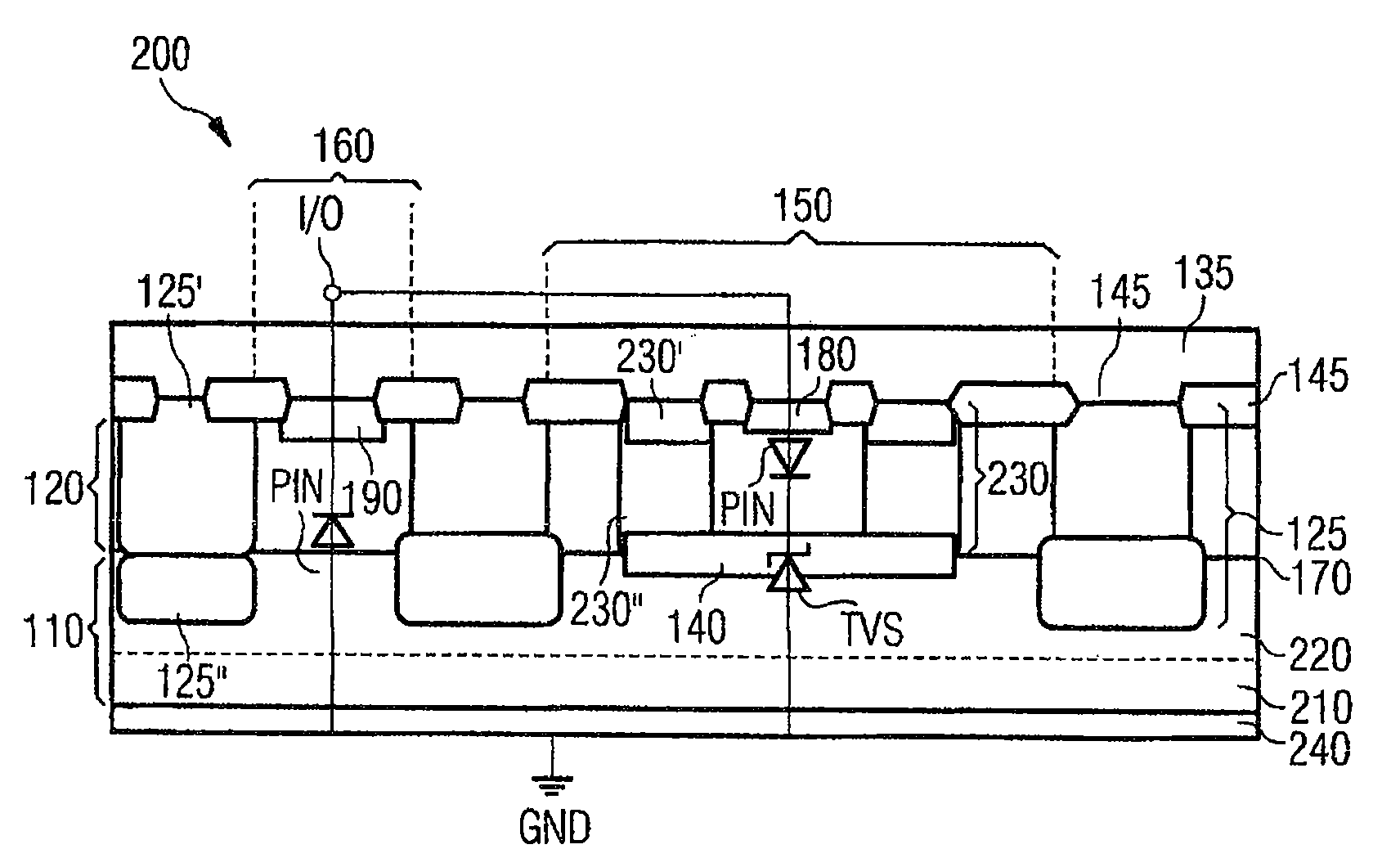

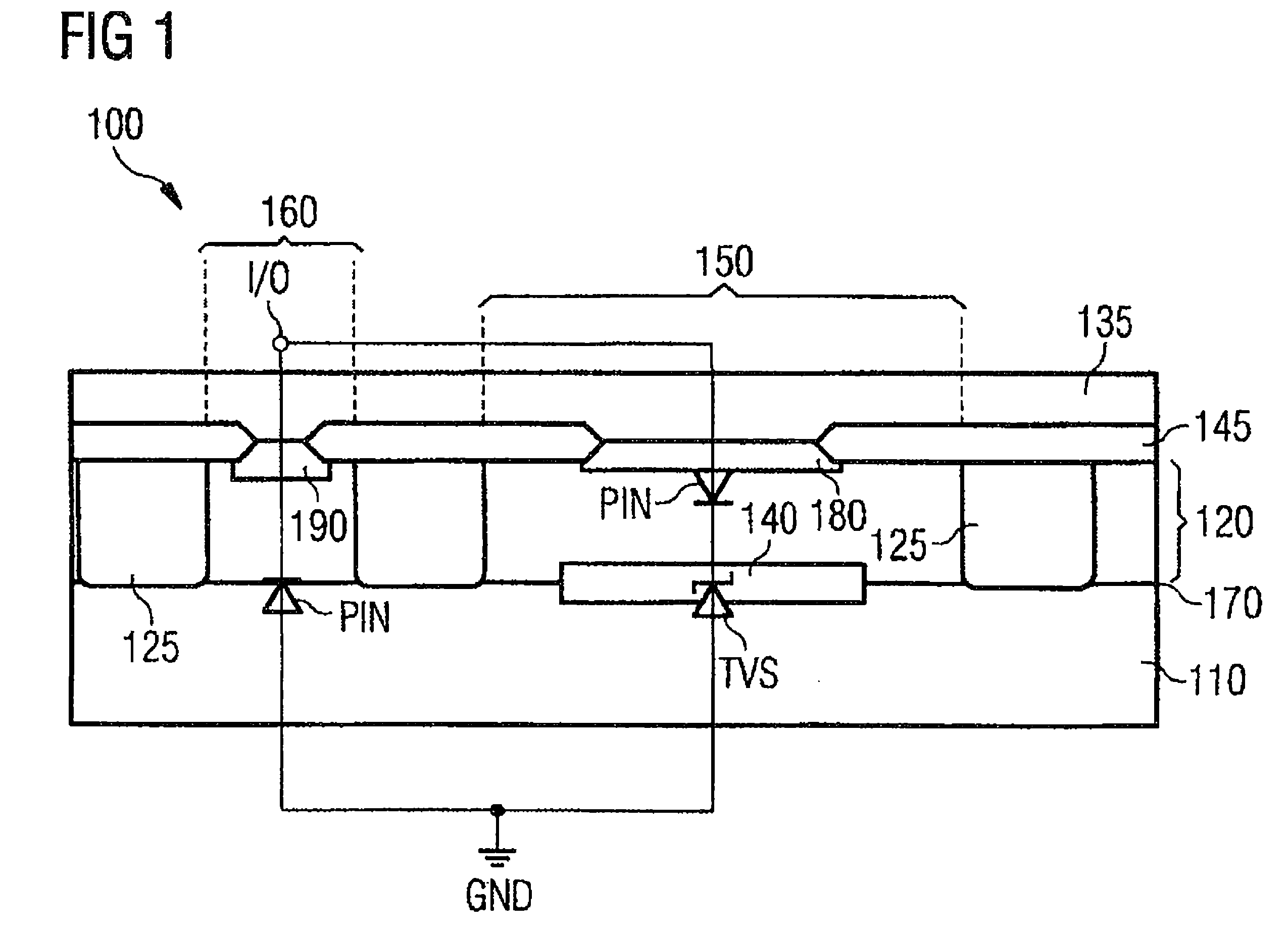

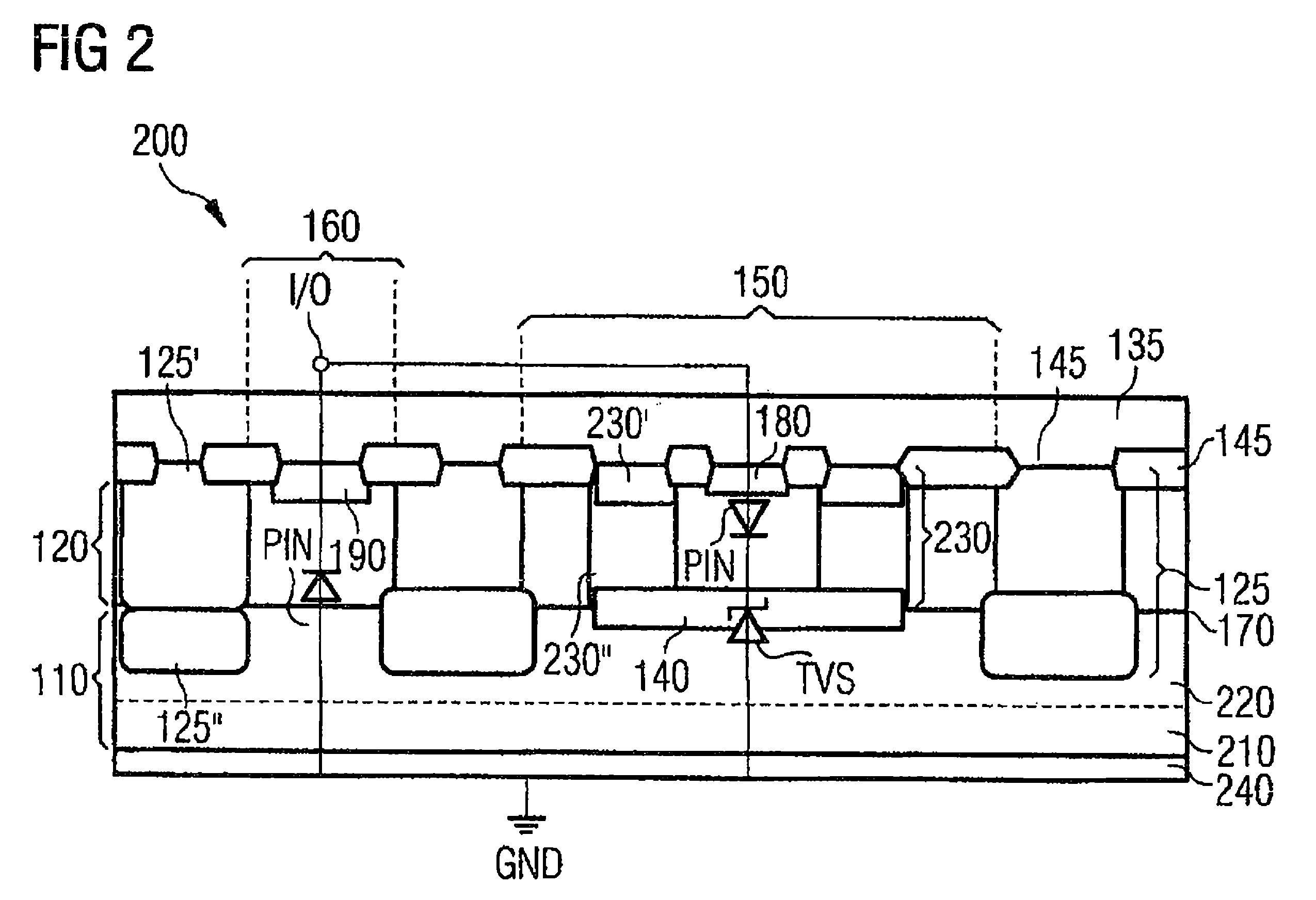

Device for protecting I/O lines using PIN or NIP conducting low capacitance transient voltage suppressors and steering diodes

ActiveUS20050190514A1Excellent capacitance performanceEasy to holdDc-dc conversionPhotovoltaic energy generationCapacitanceTransient voltage suppressor

A device for protecting I / O lines using low capacitance steering diodes (1200) and PIN or NIP diodes (1202), (1203) is disclosed. A low capacitance diode arrangement configured as steering diodes protect a signal line or input / output (I / O) port (1201) from high voltage transients by diverting or directing the transient to either the positive side of the power supply line (1204) or to ground (1205).

Owner:BANK OF AMERICA N A

ESD protection device and manufacturing method therefor

ActiveUS8421582B2Reduce peak voltageLower clamping voltageSparking plugsSpark gap detailsAuxiliary electrodeSemiconductor

Owner:MURATA MFG CO LTD

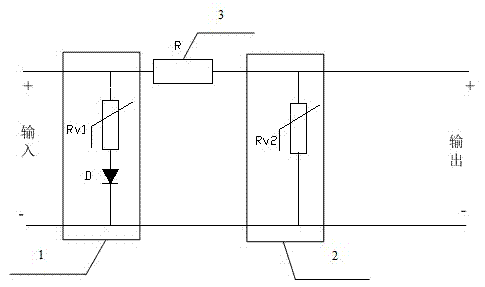

Surge protection circuit for signal circuit

ActiveCN103050959ASmall transmission impactLower clamping voltageEmergency protective arrangements for limiting excess voltage/currentCapacitanceMagnetic bead

The invention discloses a surge protection circuit for a signal circuit. The surge protection circuit for the signal circuit comprises a primary protection circuit, a secondary protection circuit and a resistor element. The primary protection circuit and the secondary protection circuit are connected in parallel with a protected circuit; the resistor element with low resistance is connected in series between the primary protection circuit and the secondary protection circuit. The primary protection circuit comprises a piezoresistor and a diode or a piezoresistor and a magnetic bead; the piezoresistor is connected in series with the diode or the magnetic bead; and the secondary protection circuit comprises a piezoresistor with low capacitance. Under a normal operation condition of a line, the primary protection circuit and the secondary protection circuit are in a high-impedance state, and thus, influence on signal transmission is small. When a surge peak is generated, a quick response is made by the primary protection circuit so as to discharge a surge in low-impedance state; surge current is further restrained by the resistor element so as to reduce the surge flowing into the secondary protection circuit; and a clamp voltage is further reduced by the piezoresistor in the secondary protection circuit, so that a protection level is improved.

Owner:SHENZHEN SUNLORD ELECTRONICS

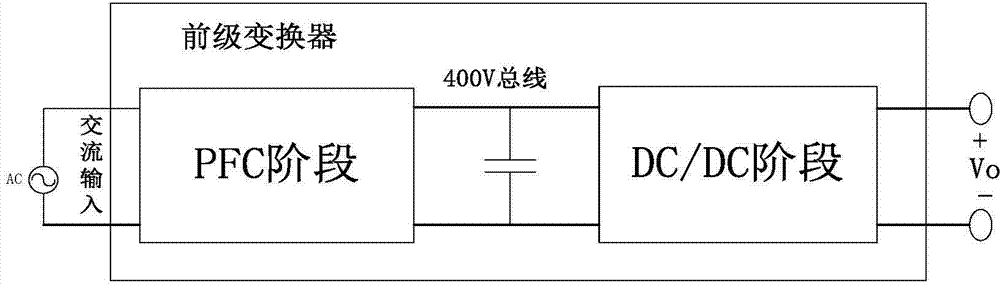

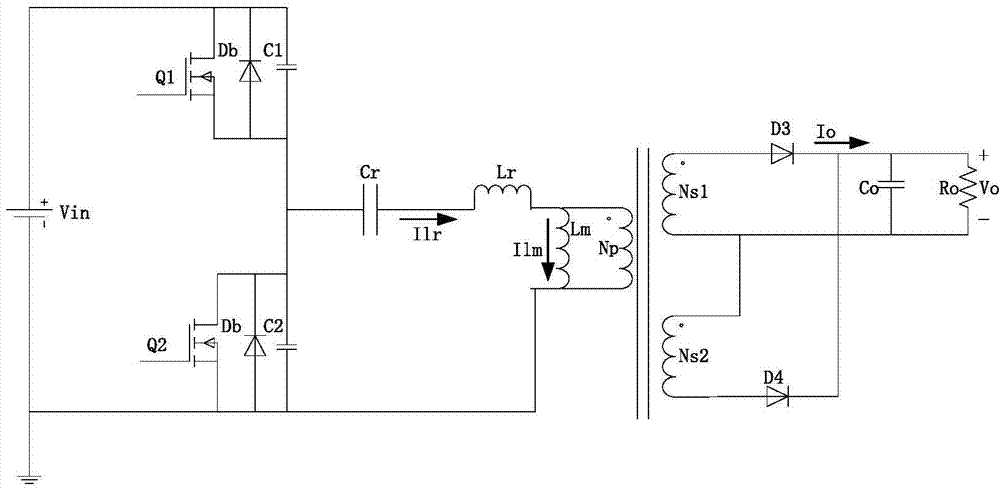

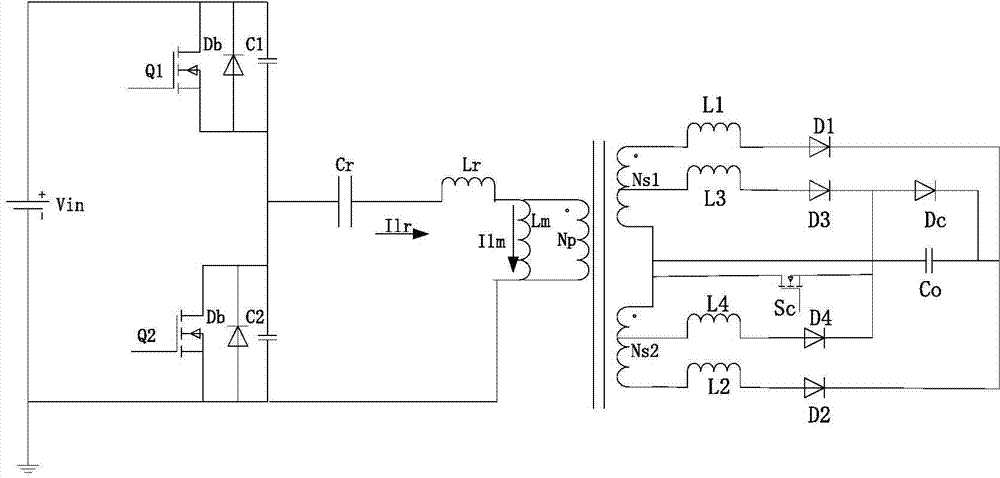

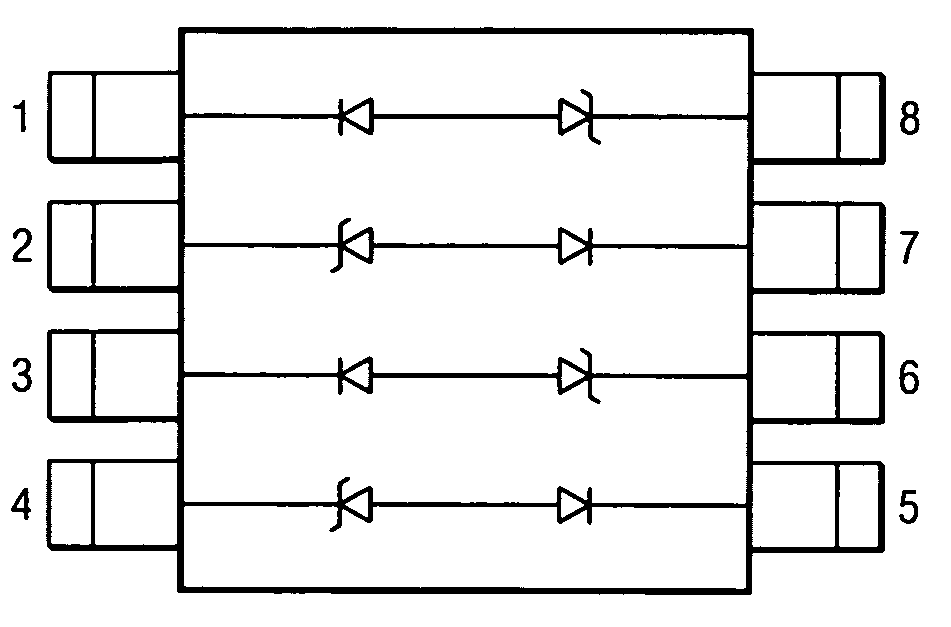

LLC resonance transducer applied to distributed power source

ActiveCN104779807ANormal conversion efficiencyLower clamping voltageDc-dc conversionElectric variable regulationConductor CoilAuxiliary circuit

The invention discloses an LLC resonance transducer applied to a distributed power source. The LLC resonance transducer comprises a direct-current power supply source (Vin), wherein an inverter circuit is connected to the direct-current power supply source (Vin), a resonance network is connected to the inverter circuit in parallel and is connected with a primary side winding of a transformer in series, and a secondary side winding of the transformer is connected with an output rectification filter circuit. According to the LLC resonance transducer, higher voltage gain can be obtained at the same frequency, and because the improved LLC resonance transducer has the function of promoting currents, under the circumstance that no voltage boosting link of changing an alternating current (AC) to a direct current (DC) exists, the operating frequency of an LLC resonant transducing link can be reduced. When the LLC resonance transducer, provided by the invention, with an auxiliary circuit normally works, the operating state can be improved, and power density and working efficiency are higher.

Owner:WUXI QUANYU ELECTRONICS TECH

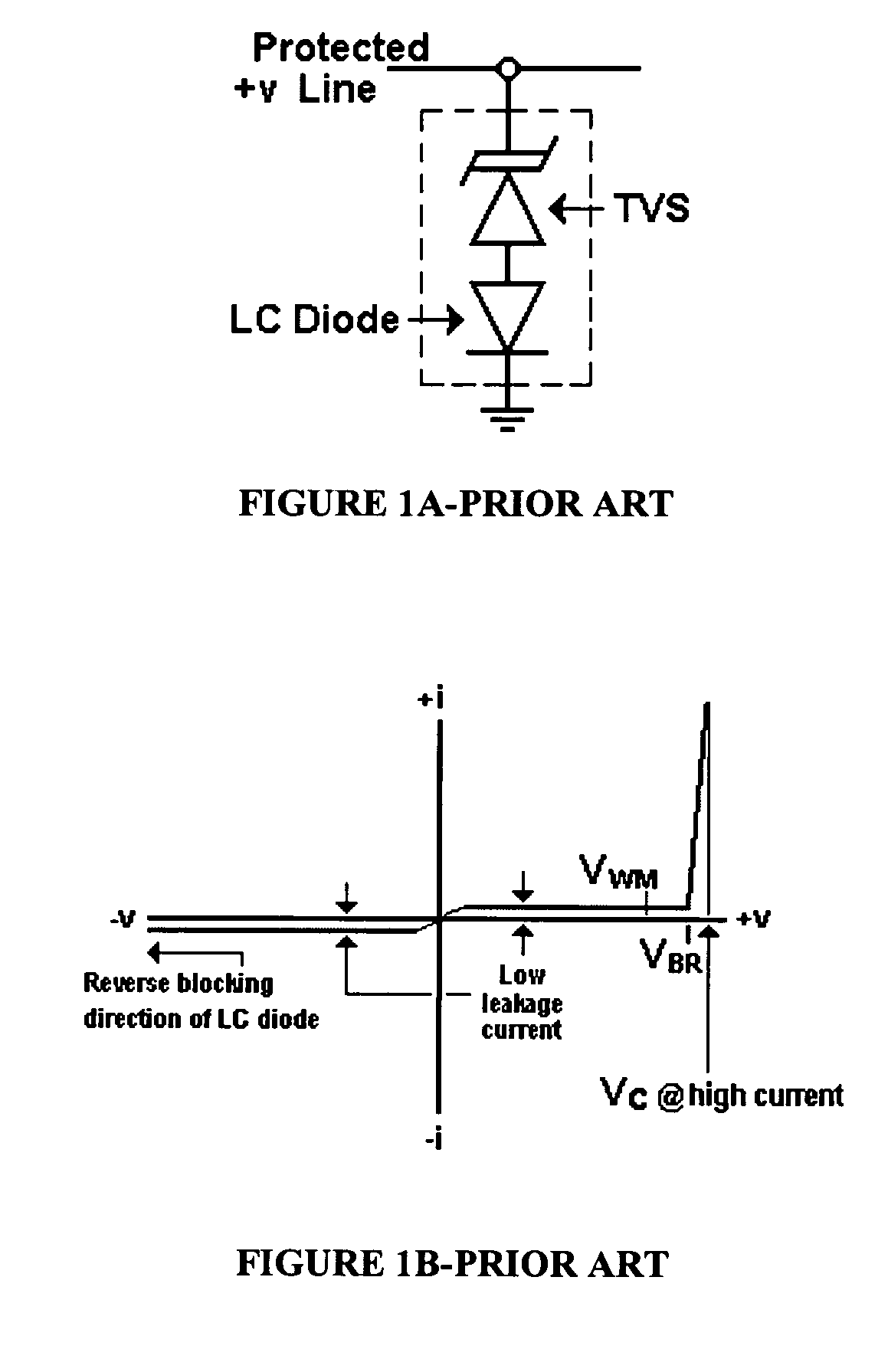

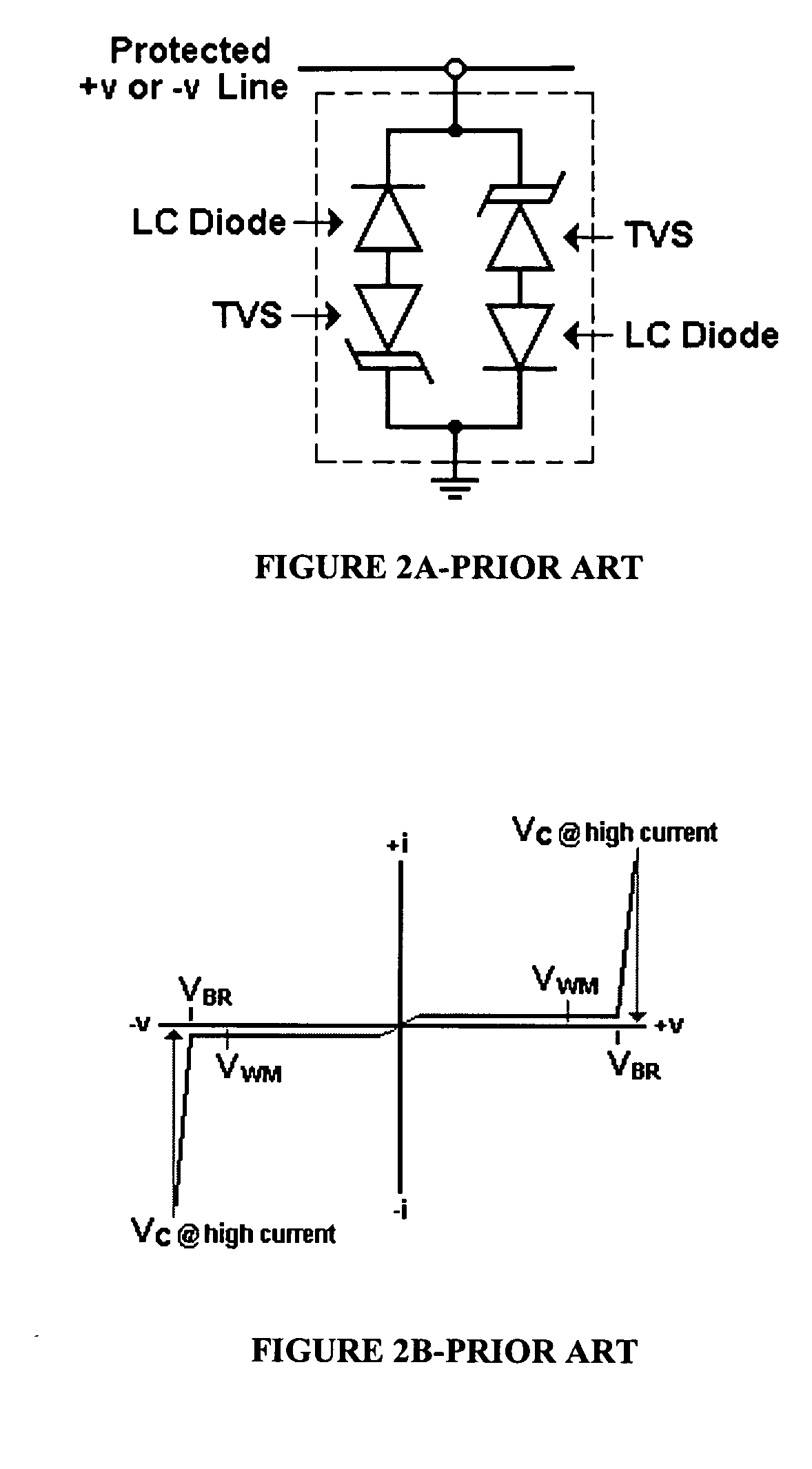

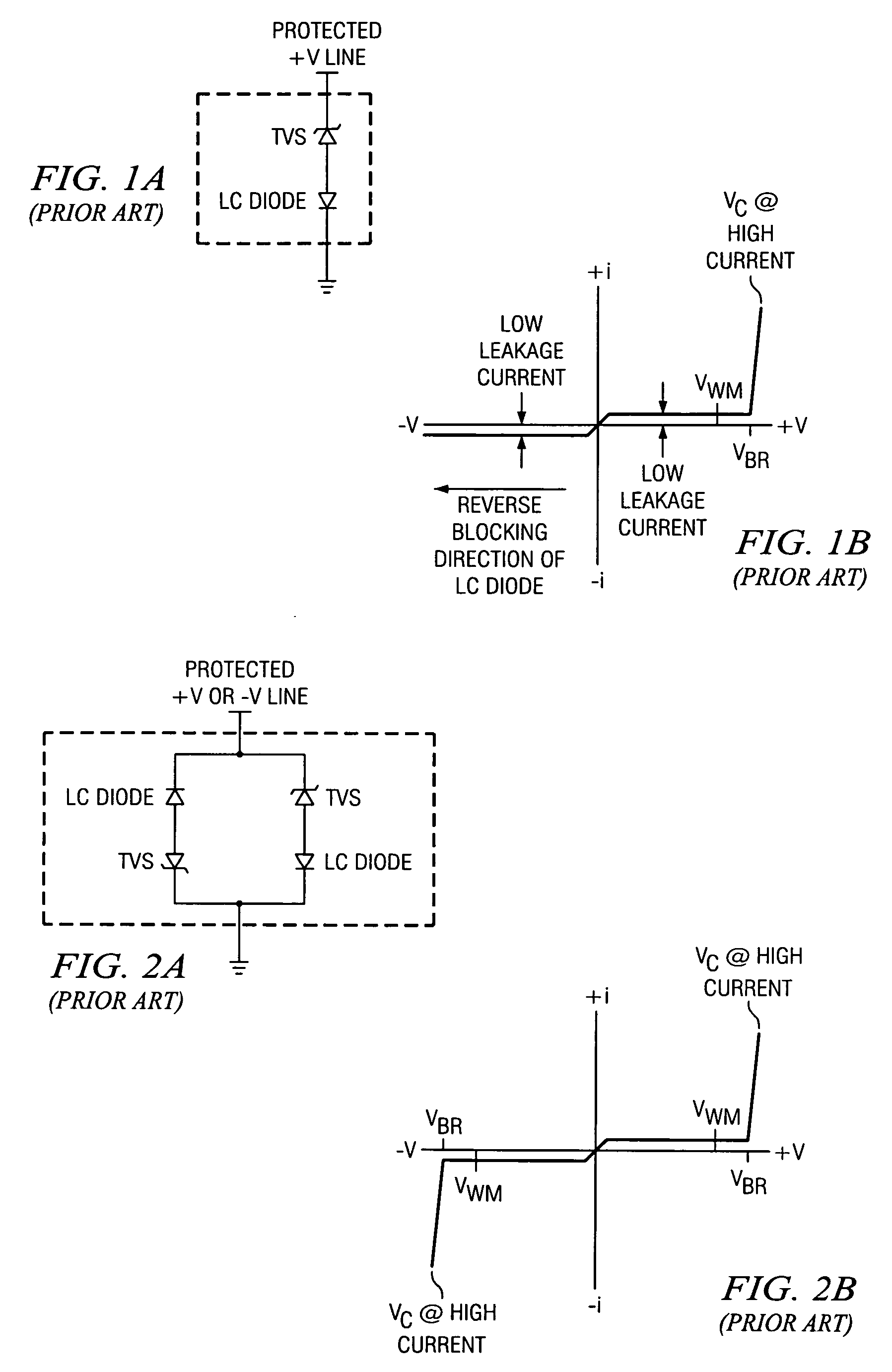

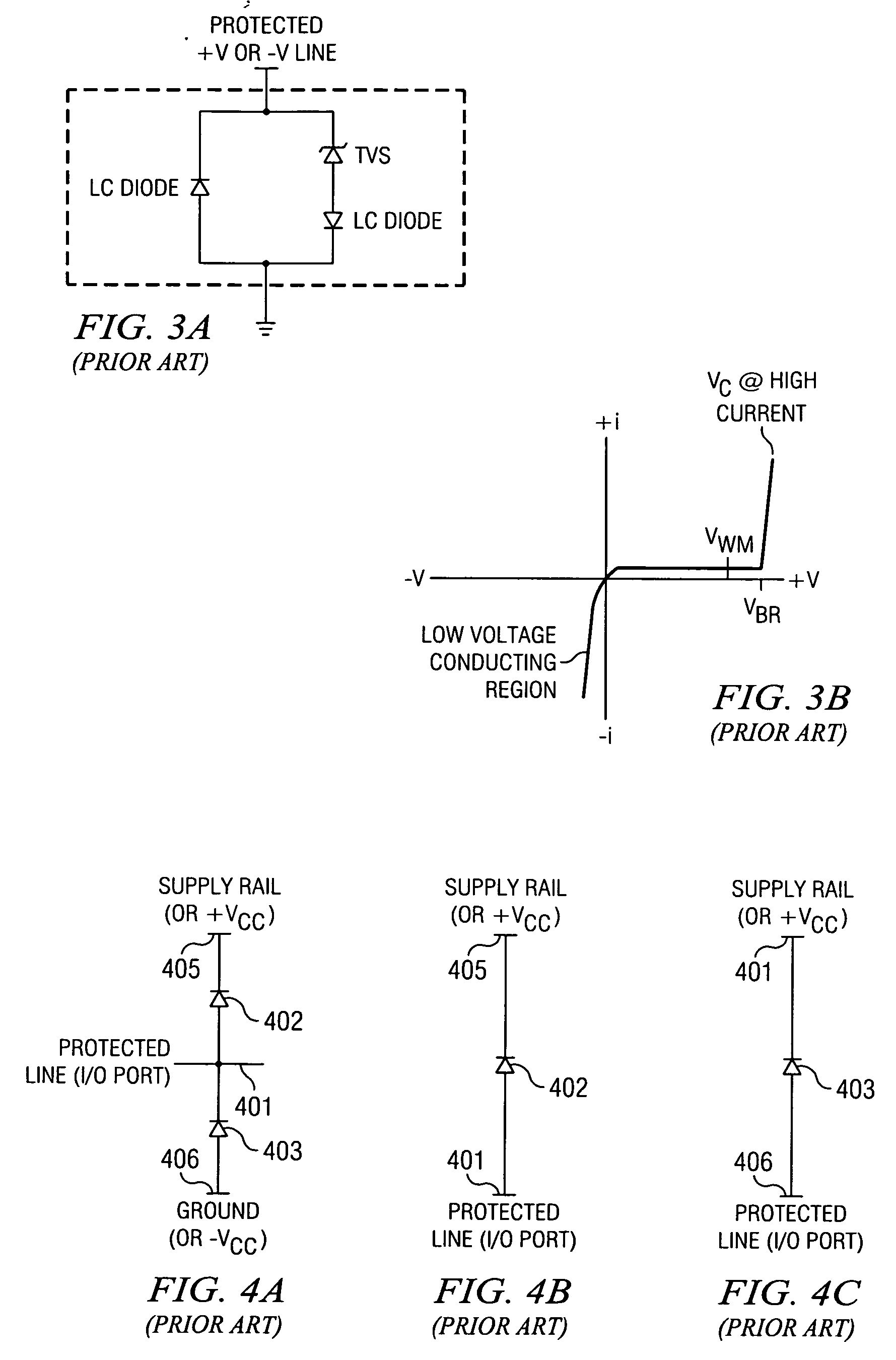

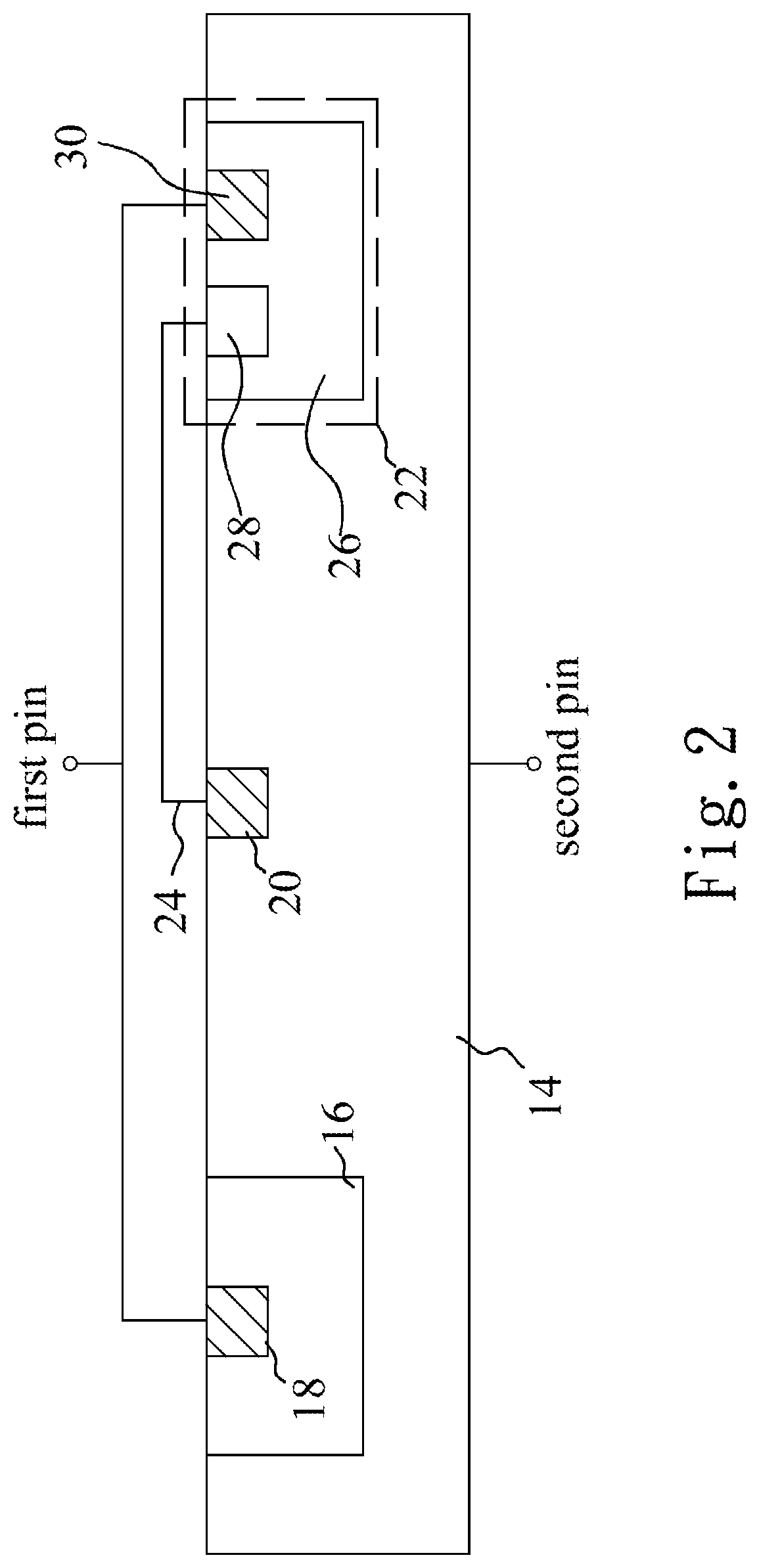

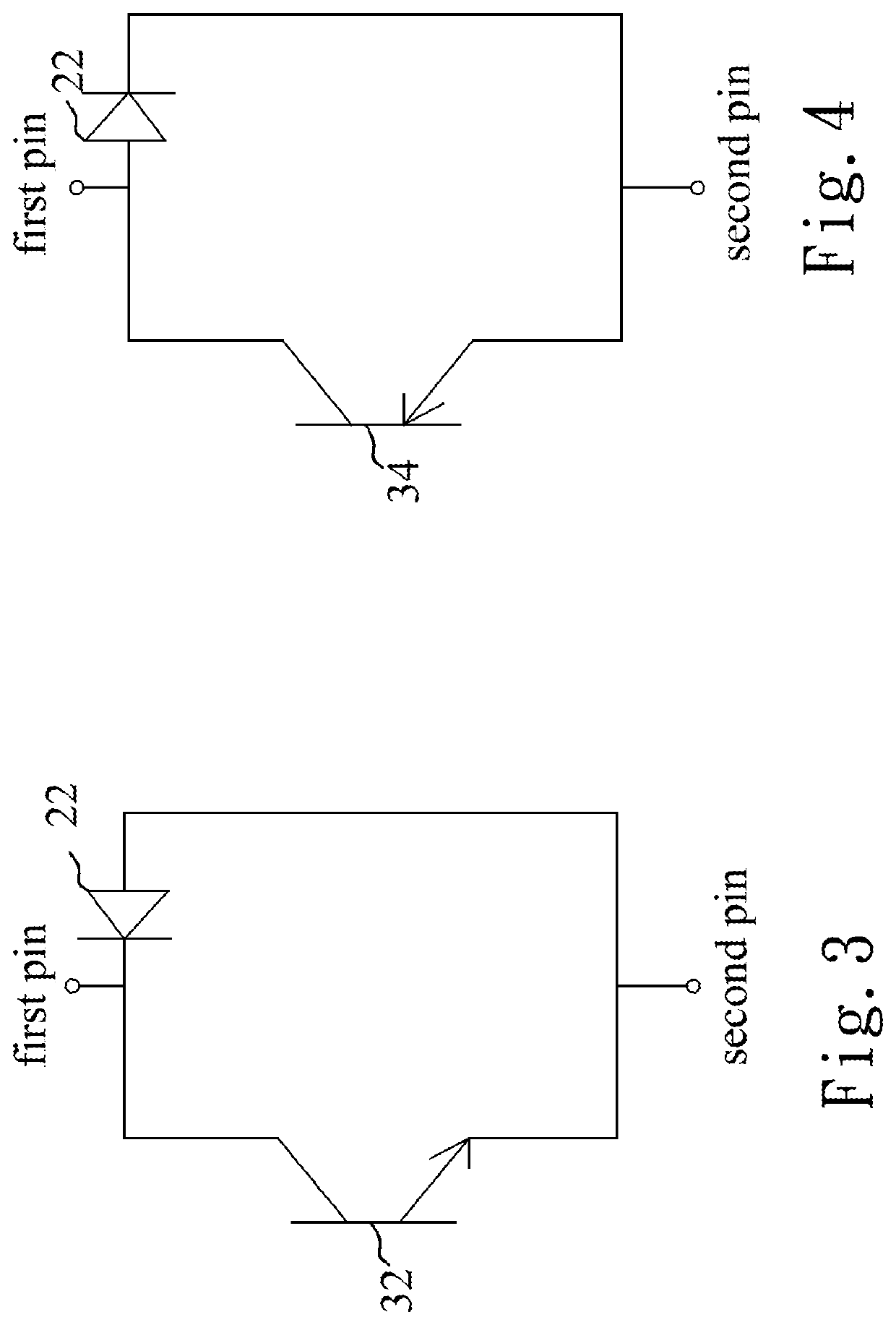

PIN or NIP low capacitance transient voltage suppressors and steering diodes

ActiveUS20050189619A1Excellent capacitance performanceEasy to holdDc-dc conversionEmergency protective arrangement detailsCapacitanceElectrical polarity

Unidirectional and bi-directional low capacitance transient voltage suppressors (“TVS”) and steering diodes are disclosed. In one embodiment, the TVS comprise TVS p-n junction diode element(s), (101) low-capacitance (“LC”) PIN or NIP diode element(s) (102), the TVS p-n junction diode element(s) (101) being placed in series with and in opposite polarity to the LC PIN or NIP diodes (102). In another embodiment, the steering diode comprise only LC PIN or NIP diode(s) (402, 403) arranged as steering diodes. This circuit arrangement is operable to clamp high-voltage transients of either polarity to a predetermined level, minimizes parasitic losses and signal-line distortion, and minimize capacitance variation. The present invention is also operable to reduce the complexity of impedance matching within a high frequency circuit.

Owner:MICROSEMI

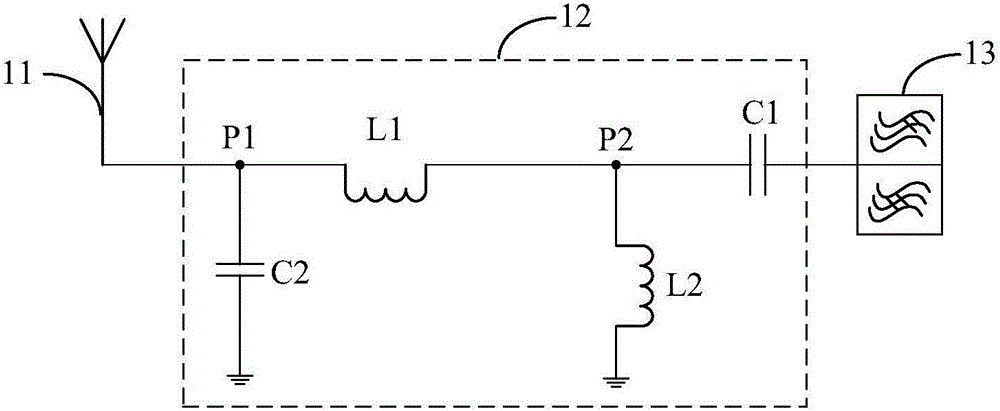

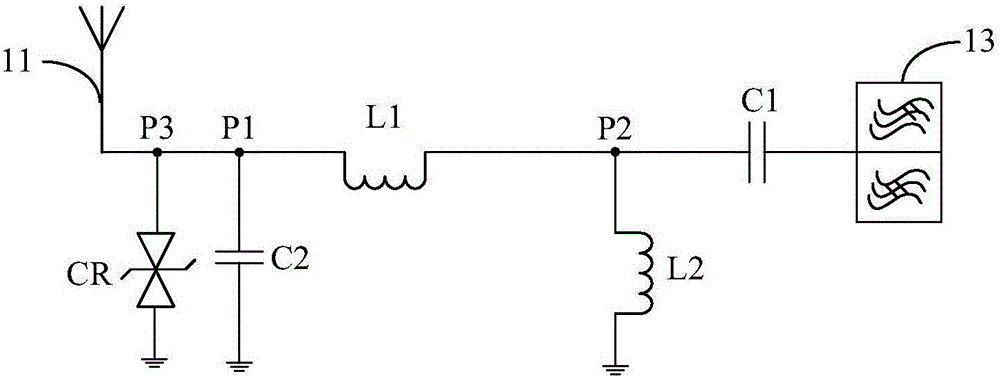

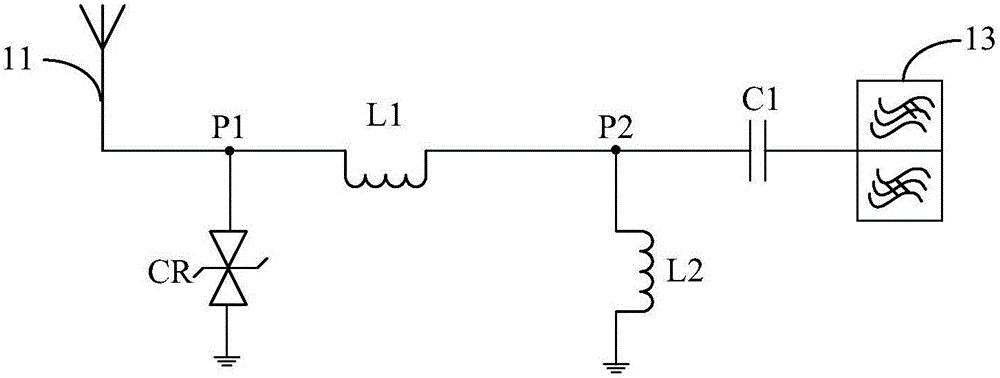

Classifying antenna and mobile terminal

InactiveCN106058433AImprove reliabilityReduce areaAntenna supports/mountingsAntennas earthing switches associationCapacitanceSuppressor

This invention provides a classifying antenna and a mobile terminal. The classifying antenna comprises a classifying antenna main body, a matching circuit, a filter and a static protection circuit, wherein the classifying antenna main body is used for receiving and sending electromagnetic waves; the matching circuit is matched with the classifying antenna main body to receive the electromagnetic waves and send the electromagnetic waves to the filter; the filter is used for filtering radio frequency signals of at least two frequency bands; the matching circuit at least comprises a first inductor (L1) and a first capacitor (C) connected between the classifying antenna main body and the filter in series; the static protection circuit is a static suppressor (CR) connected onto the feeder line of the classifying antenna main body; and, one end of the static suppressor (CR) is connected with the feeder line of the classifying antenna main body, and the other end is connected with the ground. By adoption of the classifying antenna, the static protection performance of the mobile terminal is effectively improved; and the reliability of the mobile terminal is improved.

Owner:BEIJING XIAOMI MOBILE SOFTWARE CO LTD

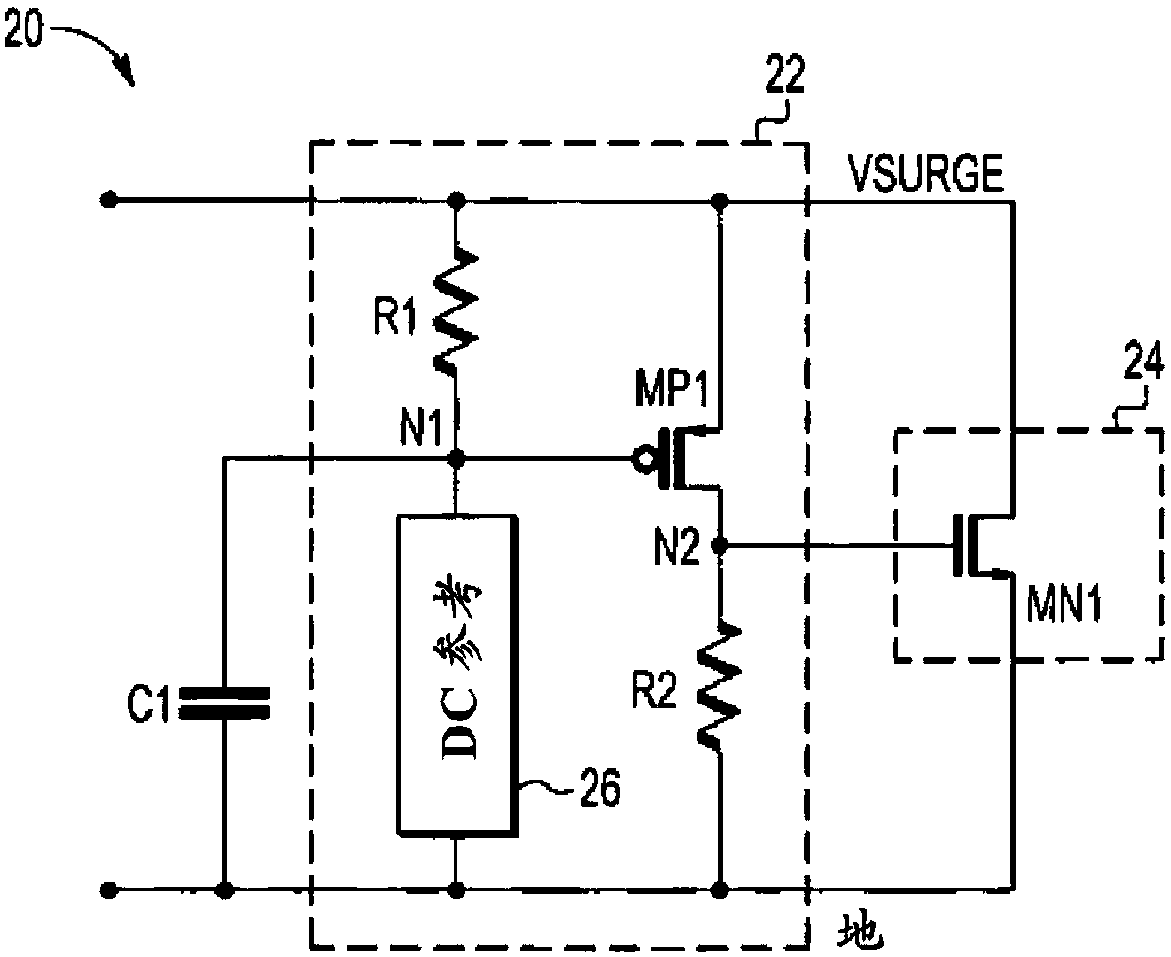

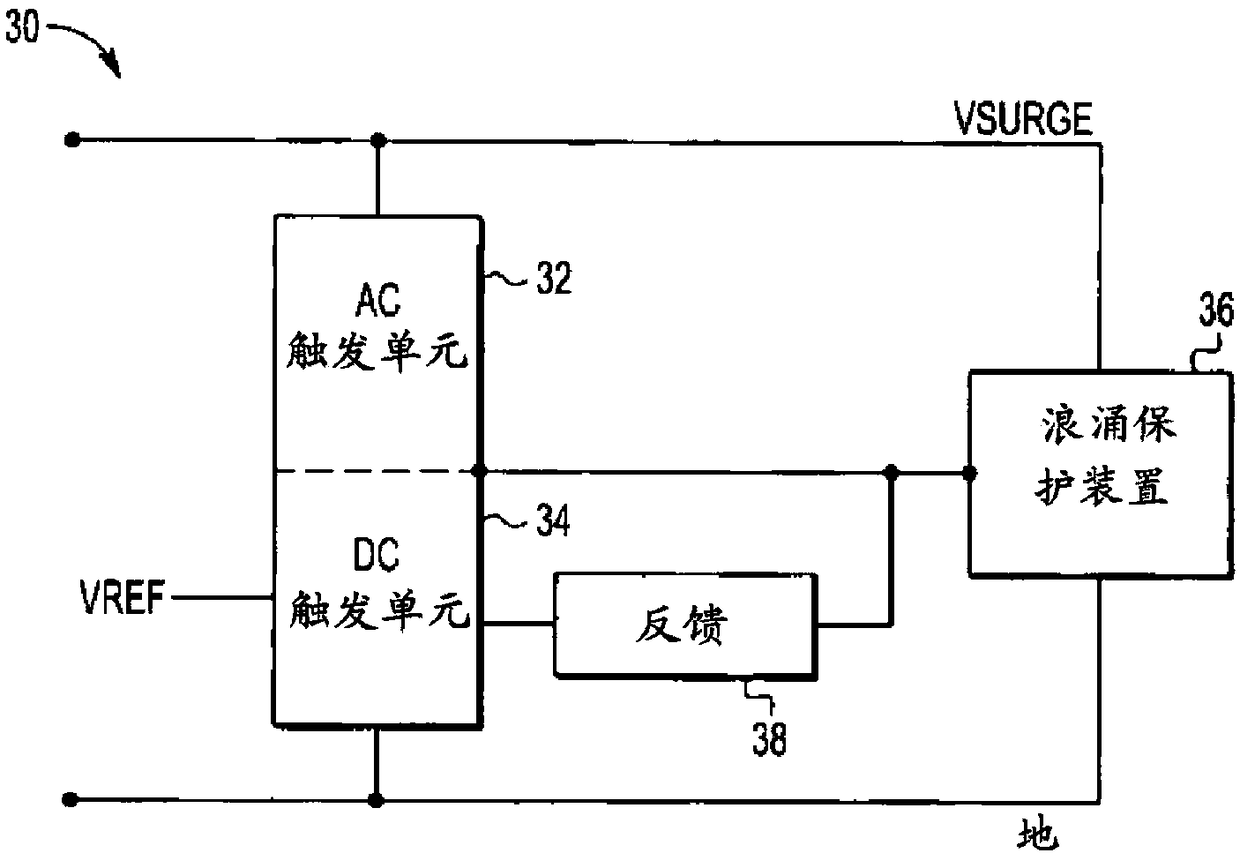

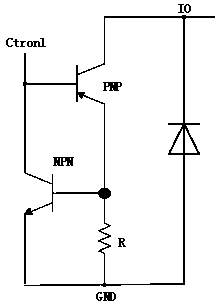

Surge protection circuit having feedback control function

ActiveCN108075460ALower clamping voltageEmergency protective arrangements for limiting excess voltage/currentFeedback circuitsFeedback control

The invention discloses a surge protection circuit having the feedback control function. The surge protection circuit comprises a DC trigger circuit and a surge protection device connected with the DCtrigger circuit, when surge pulse occurs, a trigger signal is generated by the DC trigger circuit, a clamping voltage taken as an output voltage of the surge protection circuit is generated by the surge protection device for responding to the trigger signal, the surge current is conducted to the ground, a feedback circuit is arranged between the surge protection device and the DC trigger circuit,and the clamping voltage is reduced through the feedback circuit so that the clamping voltage does not surpass a fault voltage of the surge protection device.

Owner:NXP BV

Voltage nonlinear resistive element and method for manufacturing the same

ActiveUS20150270036A1Lower volume resistivityReduce voltageCurrent responsive resistorsResistor manufactureOxide ceramicZinc

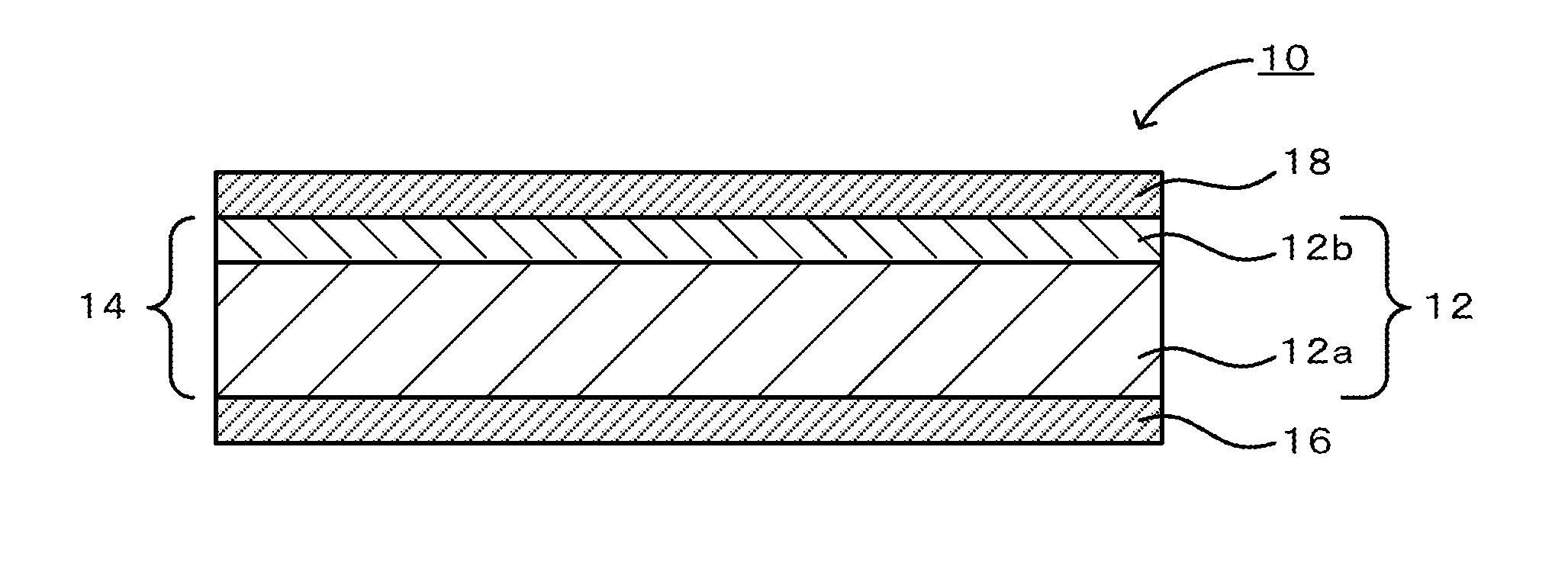

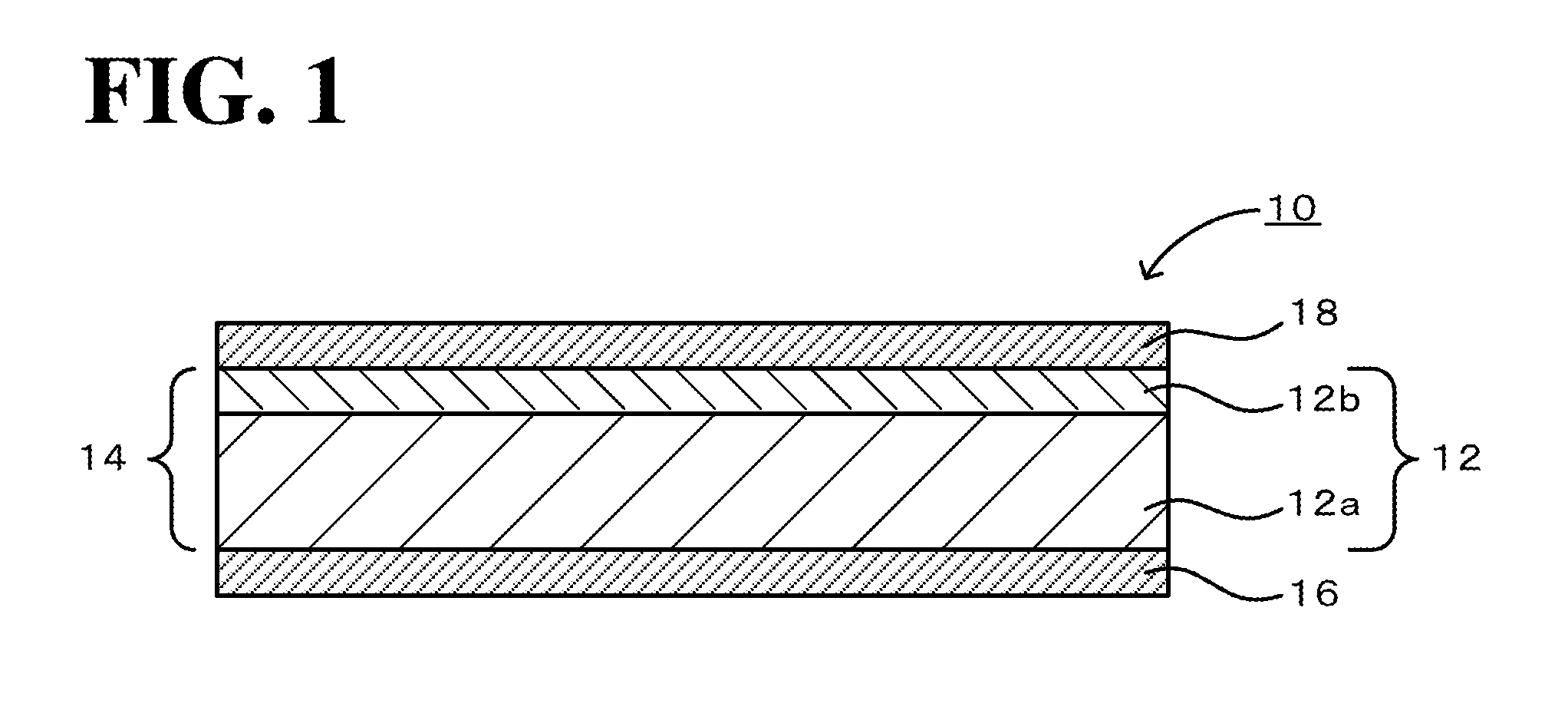

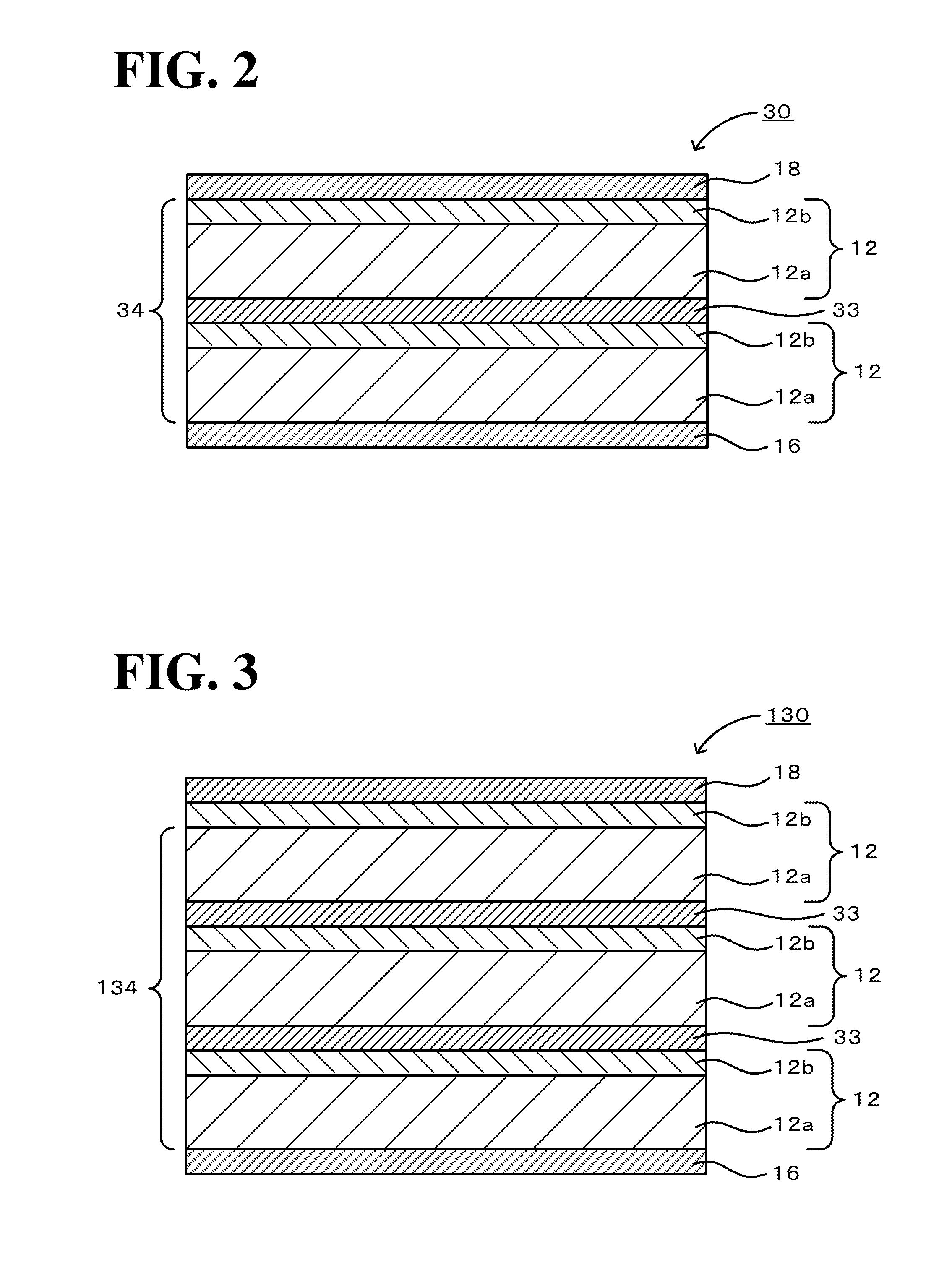

A voltage nonlinear resistive element 10 includes a resistor 14 containing a joined body 12 in which a zinc oxide ceramic layer 12a composed mainly of zinc oxide and having a volume resistivity of 1.0×10−1 Ωcm or less is joined to a bismuth oxide layer 12b composed mainly of bismuth oxide, and a pair of electrodes 16 and 18 disposed on the resistor 14 such that an electrically conductive path passes through a junction between the zinc oxide ceramic layer 12a and the bismuth oxide layer 12b. In this element 10, the zinc oxide ceramic layer 12a of the joined body 12 has a lower volume resistivity than before. This can result in a lower clamping voltage in a high-current region than before.

Owner:NGK INSULATORS LTD

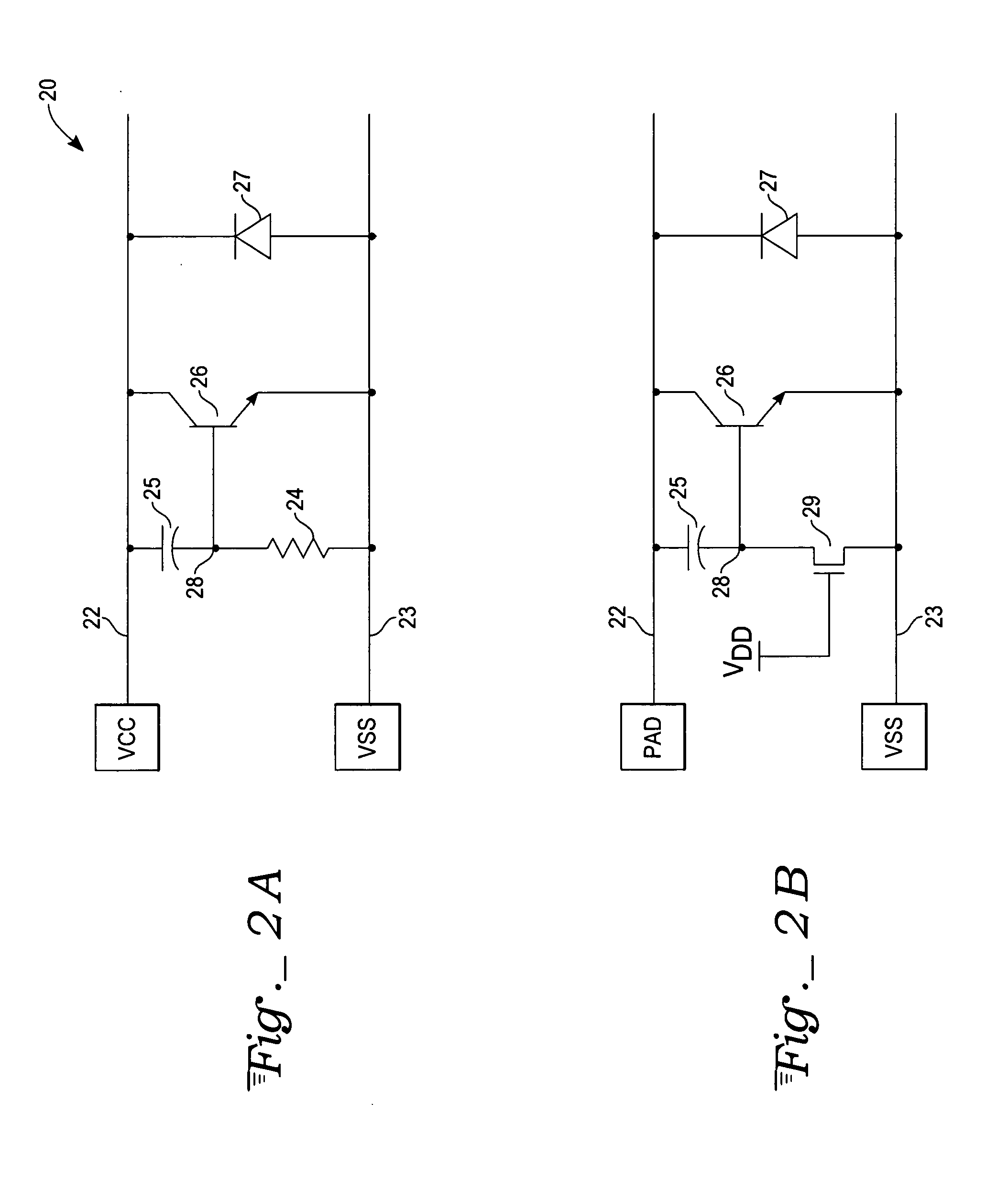

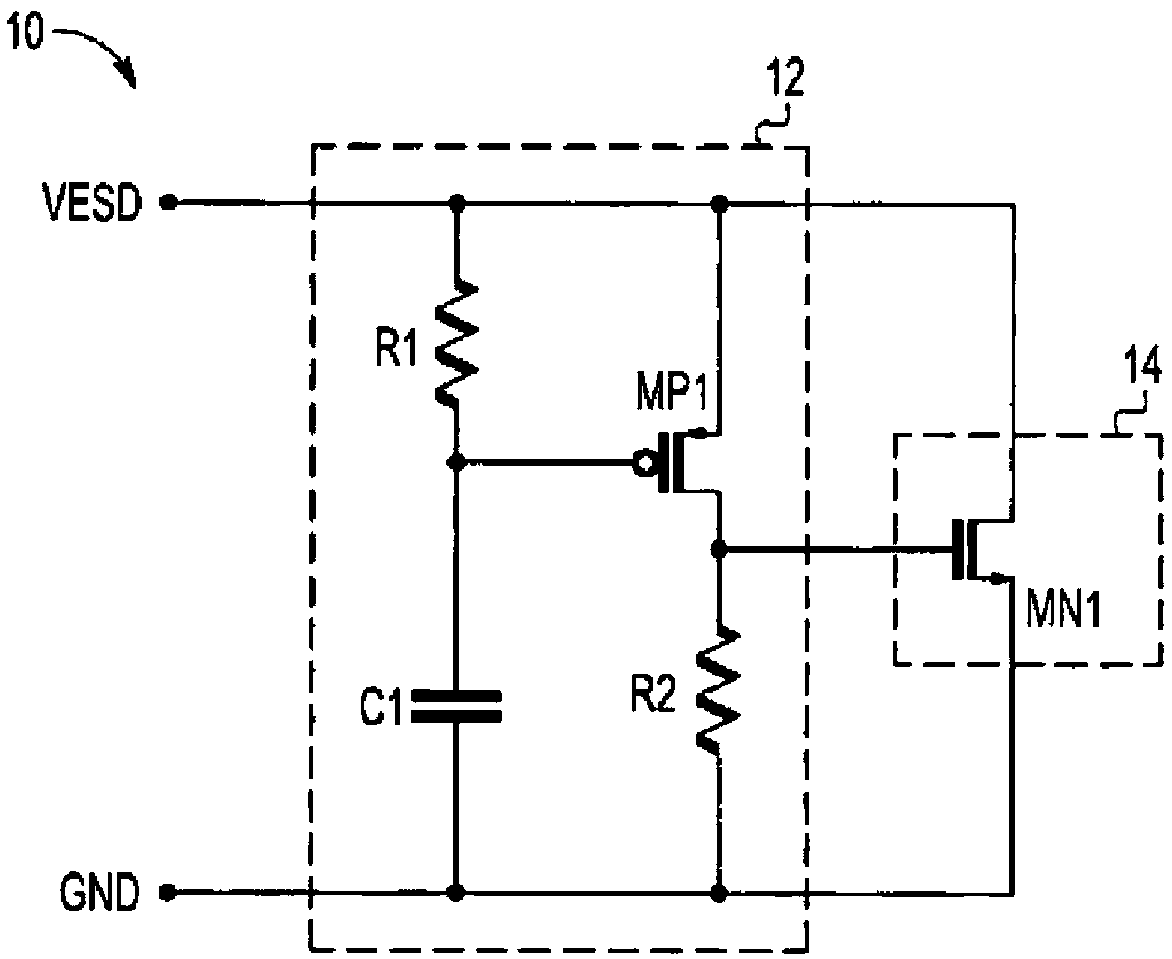

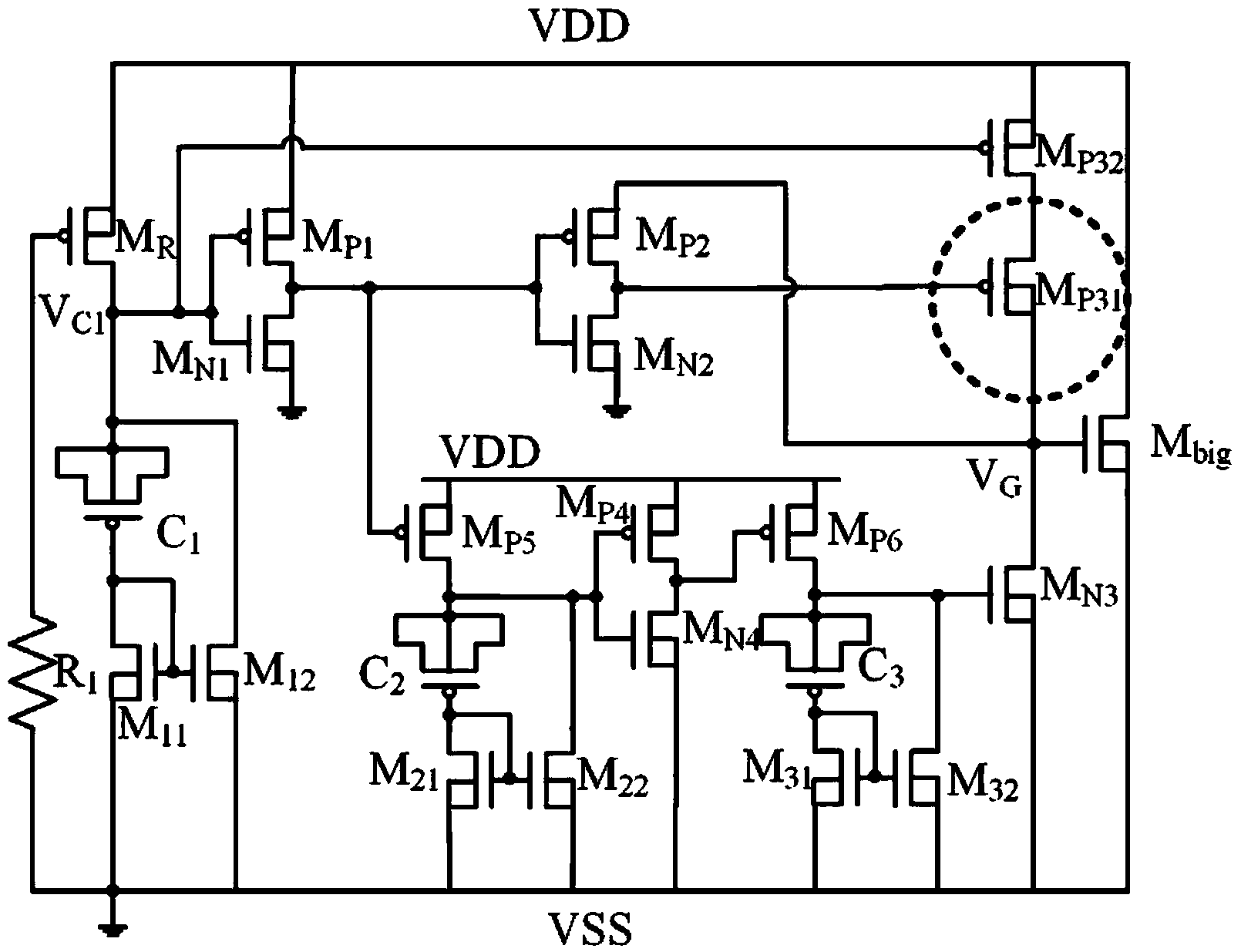

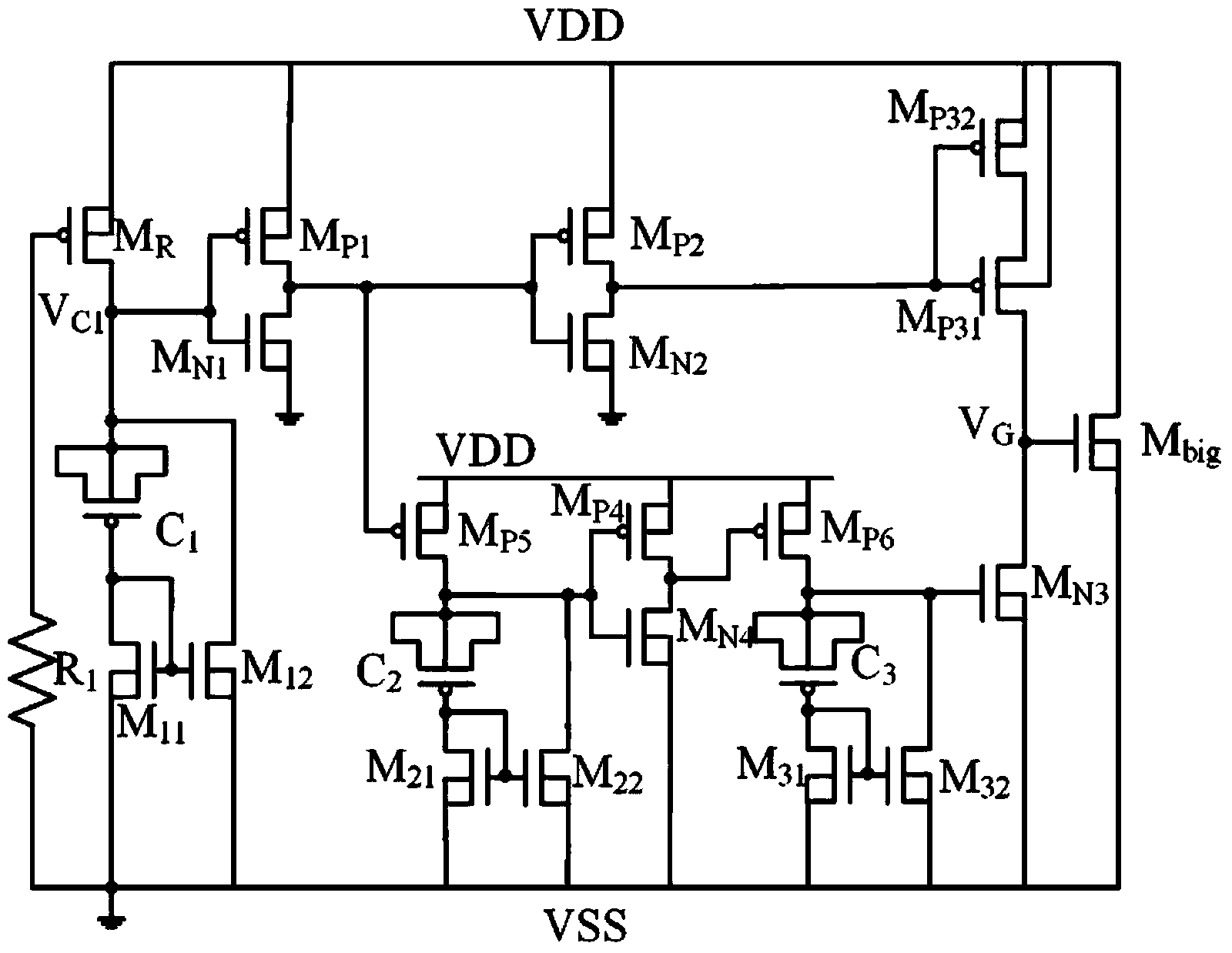

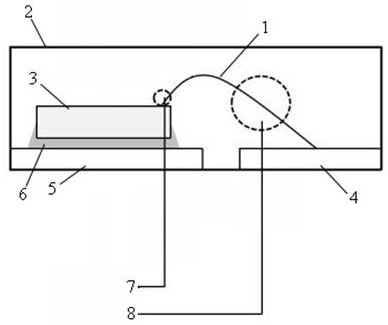

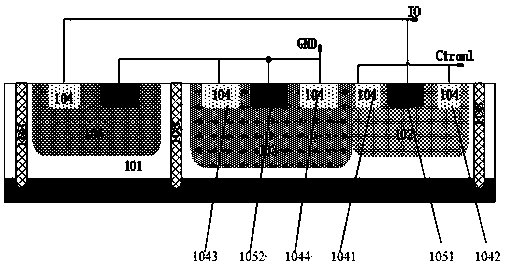

Power source clamping electrostatic discharge protective circuit

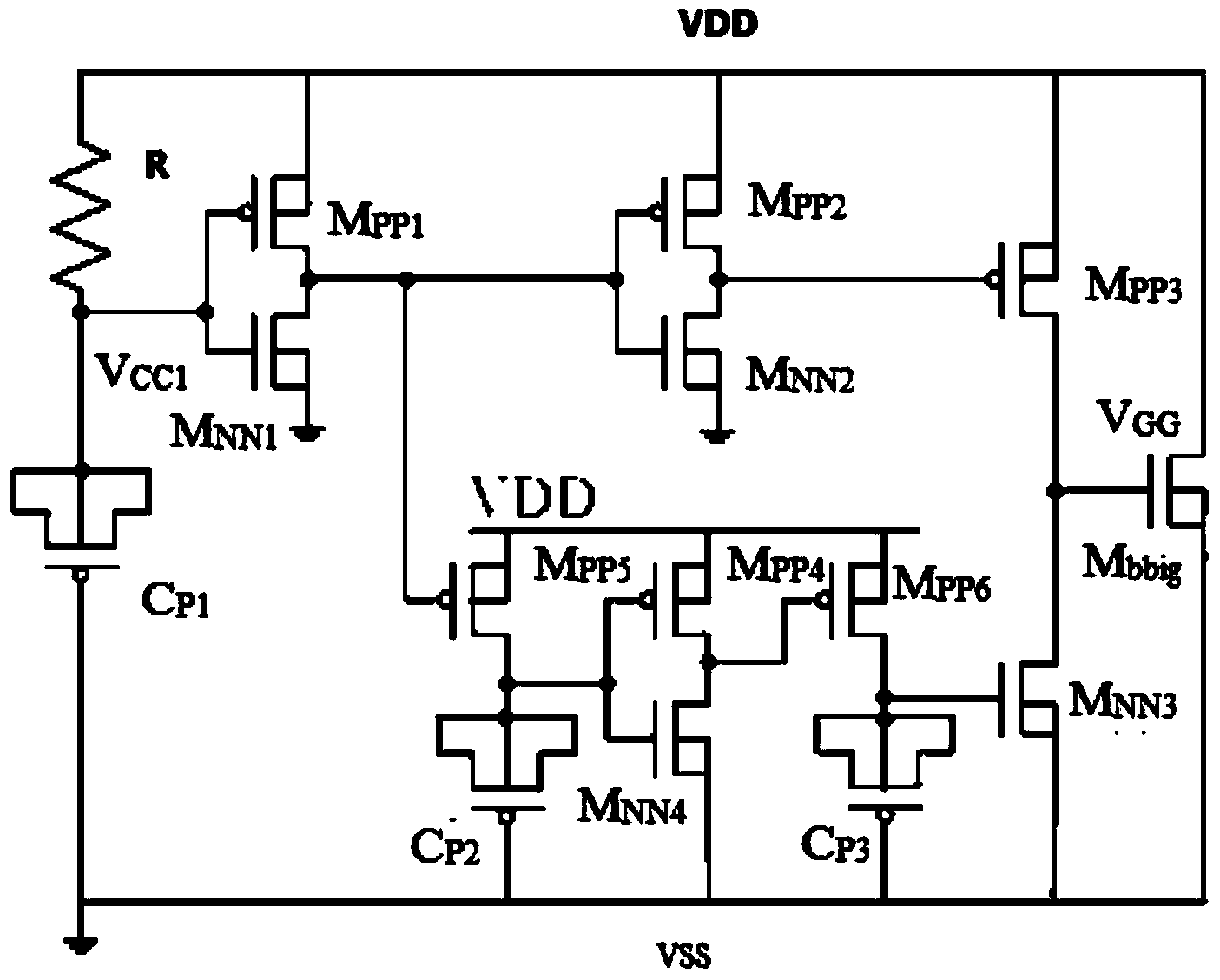

InactiveCN104377678AReduce areaLower clamping voltageEmergency protective arrangements for limiting excess voltage/currentVoltage pulseCharge discharge

The invention discloses a power source clamping electrostatic discharge protective circuit. The circuit comprises a transient trigger module, a clamping transistor switch-on module, a clamping transistor switch-off module and a clamping transistor. The instant trigger module is used for judging whether electrostatic discharge impact happens or not according to voltage pulse rising time of a power source pin VDD and issuing a response signal; the clamping transistor switch-on module is used for switching on a clamping transistor Mbig according to the response signal; the clamping transistor switch-off module is used for switching off the clamping transistor Mbig according to the response signal; and when switched on, the clamping transistor Mbig is used for discharging electrostatic charges caused by electrostatic discharge impact. According to the circuit, a current mirror and a PMOS transistor are introduced to do equivalent resistance; the area of the electrostatic discharge protective circuit is greatly reduced, and meanwhile the switching-on time of the transistor is longer; and the electrostatic charge discharging speed is higher and sufficient.

Owner:PEKING UNIV

Conductor lead for protection circuit and protection circuit comprising lead

ActiveCN113249613ASo as not to damageLower clamping voltageSemiconductor/solid-state device detailsSolid-state devicesElectrical conductorCerium

The invention discloses a conductor lead for a protection circuit. The lead is made of a copper alloy, and the copper alloy comprises the following raw materials in percentage by weight of 0.6%-0.9% of zinc powder, 2.5%-3.5% of nickel powder, 0.5%-0.8% of zirconium powder, 0.4%-0.5% of cerium powder, 0.6%-0.8% of silicon powder, 0.06%-0.08% of tin powder, 0.3%-0.8% of iron powder, 0.2%-0.4% of boron powder and the balance of copper powder, totaling 100%. The protection circuit open circuit product manufactured by adopting the lead is suitable for a DFN packaging series, has very low clamping voltage, quick response and relatively high surge bearing capability, and can quickly respond to switching off to ensure that the protection circuit is not damaged under the condition that the voltage and the current are higher than the designed rated voltage and the rated current.

Owner:江西萨瑞微电子技术有限公司

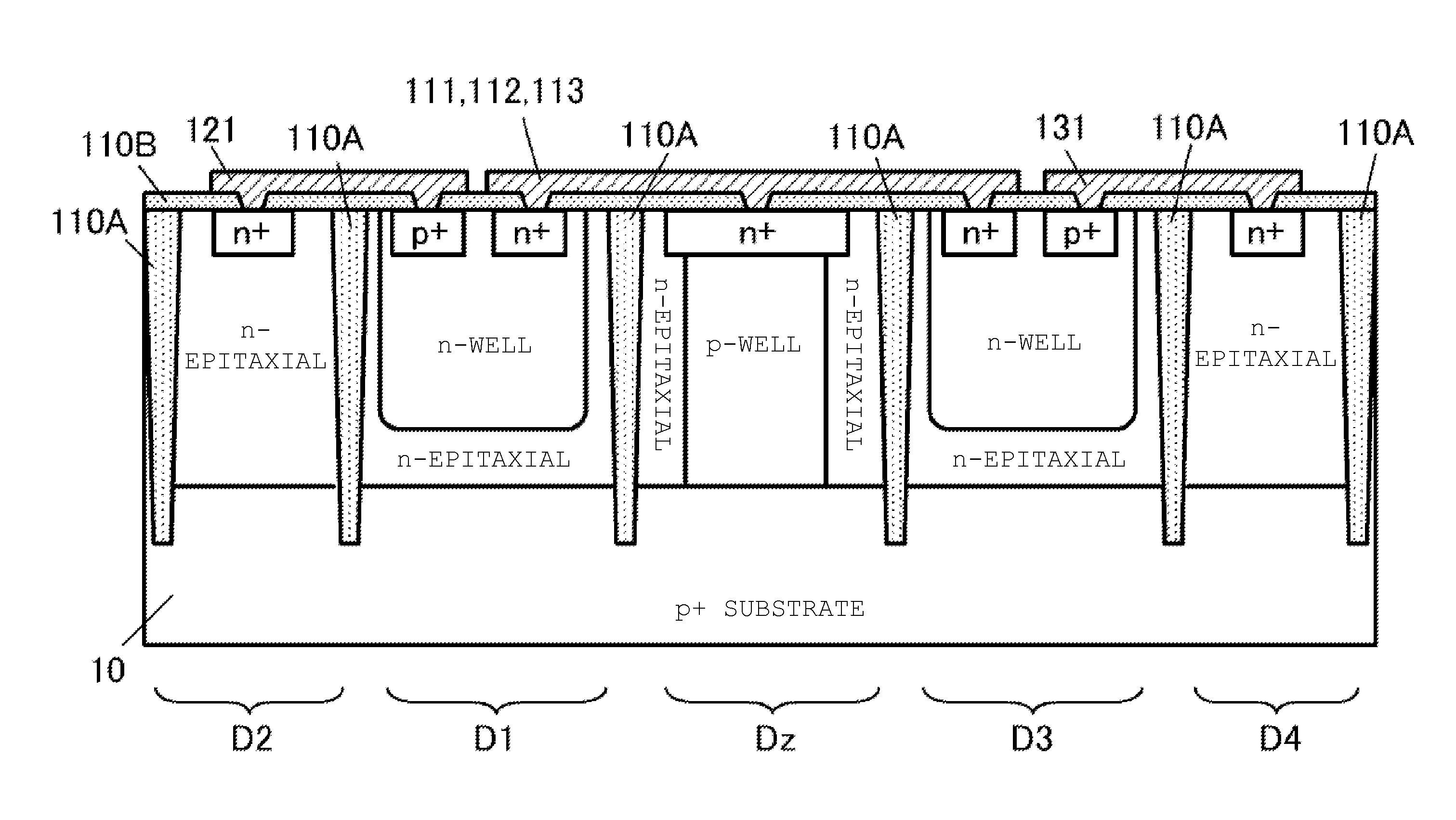

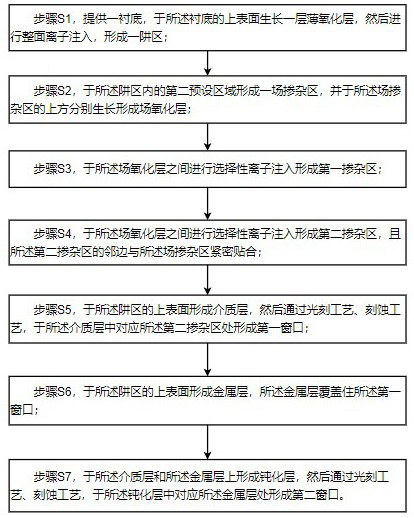

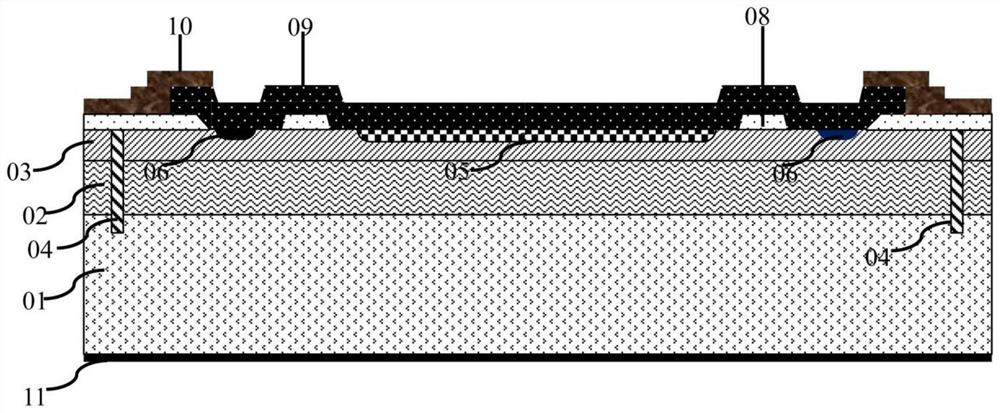

Novel silicon controlled rectifier device with low-clamping embedded capacitance-reducing diode

PendingCN111092117ALower clamping voltageSolve the problem of high clamping voltageTransistorThyristorSilicon-controlled rectifierCapacitance

A novel silicon controlled rectifier device with a low-clamping embedded capacitance-reducing diode comprises a silicon controlled rectifier module and a diode module, the silicon controlled rectifiermodule and the diode module are formed on a heteroepitaxial layer of a silicon substrate, and the silicon controlled rectifier module and the diode module are isolated through deep trench DTI. The problem of high clamping voltage of a silicon controlled rectifier device integrated with a diode is solved, and a device with lower clamping voltage under the conditions of the same area and the same capacitance is obtained.

Owner:SHANGHAI CHANGYUAN WAYON MICROELECTRONICS

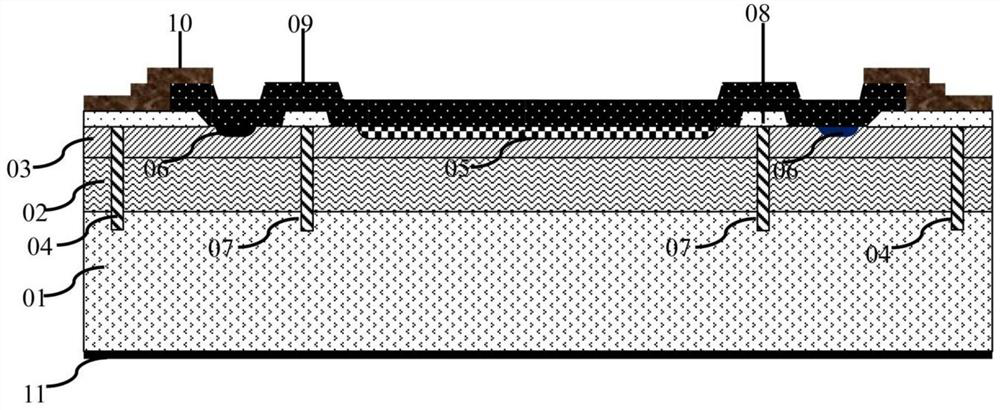

Transient voltage suppression device and manufacturing method thereof

ActiveCN113130477ASmall sizeIncrease peak-to-peak currentTransistorSolid-state devicesPeak currentTransient voltage suppressor

The invention discloses a transient voltage suppression device and a manufacturing method thereof. The transient voltage suppression device comprises a semiconductor substrate, a first epitaxial layer located on the semiconductor substrate, a plurality of isolation structures, a plurality of first groove structures, a first injection region and a second injection region; the isolation structures penetrate through the first epitaxial layer and extend into the semiconductor substrate, the plurality of isolation structures divide the transient voltage suppressor into a plurality of regions in the transverse direction, the plurality of regions comprise a voltage stabilization region and at least one group of guide diode regions, and each group of guide diode regions comprise a first region and a second region; the plurality of first groove structures are positioned in the voltage stabilization region and penetrate through the first epitaxial layer; the first injection region is located in the first epitaxial layer of the second region and the voltage stabilization region; and the second injection region is located in the first epitaxial layer of the first region and the second region. A clamping diode and a triode are formed in the voltage stabilization region, the clamping diode and the triode form a composite voltage stabilizing tube, the clamping diode and the triode share current at the same time, the peak-peak value current in the breakdown direction is improved, the clamping voltage during large current conduction is reduced, and the size of the device is reduced.

Owner:HANGZHOU SILAN INTEGRATED CIRCUIT

Vertical transient voltage suppression device

ActiveUS20200035664A1Reduce voltageLower clamping voltageTransistorSolid-state devicesEngineeringCondensed matter physics

A vertical transient voltage suppression device includes a semiconductor substrate having a first conductivity type, a first doped well having a second conductivity type, a first heavily-doped area having the first conductivity type, a second heavily-doped area having the first conductivity type, and a diode. The first doped well is arranged in the semiconductor substrate and spaced from the bottom of the semiconductor substrate, and the first doped well is floating. The first heavily-doped area is arranged in the first doped well. The second heavily-doped area is arranged in the semiconductor substrate. The diode is arranged in the semiconductor substrate and electrically connected to the second heavily-doped area through a conductive trace.

Owner:AMAZING MICROELECTRONICS

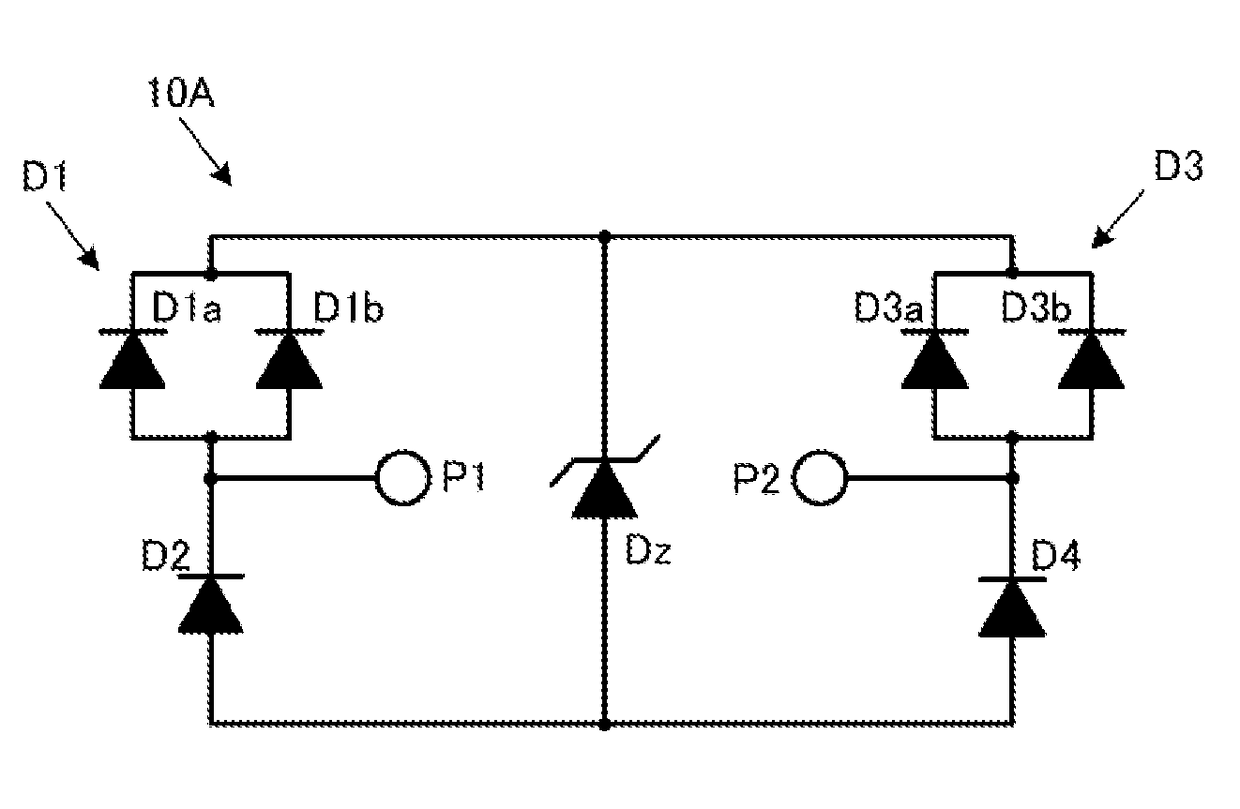

ESD protection device

ActiveUS20150364461A1Low ESLTotal current dropSemiconductor/solid-state device detailsSolid-state devicesZener diodeEngineering

An ESD protection device includes a zener diode, and a series circuit of diodes and a series circuit of diodes that are connected in parallel with the zener diode. At the connection point between the diodes, an Al electrode film is formed on the surface of a Si substrate, and at the connection point between diodes, an Al electrode film is formed on the surface of the Si substrate. The diodes are formed on the surface of the Si substrate, and the diodes are formed in the thickness direction of the Si substrate. The Si substrate has a longitudinal direction and a shorter direction orthogonal to the longitudinal direction in planar view, and the Al electrode films are formed respectively at both ends in the shorter direction of the Si substrate. Thus, provided is an ESD protection device which suppresses the ESL, and keeps the clamp voltage low.

Owner:MURATA MFG CO LTD

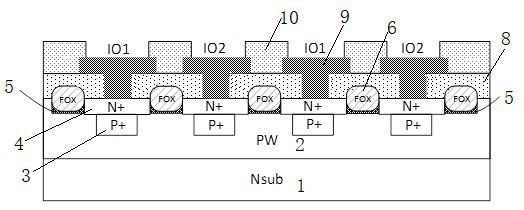

Bidirectional transient voltage suppression device and preparation method thereof

ActiveCN113380787ALower breakdown voltageLarge negative resistance characteristicsTransistorSolid-state devicesHemt circuitsEngineering

The invention discloses a bidirectional transient voltage suppression device and a preparation method thereof, which belong to the field of semiconductor protection devices. Thebidirectional transient voltage suppression device comprises a substrate and a well region. The well region comprises a first preset region and a second preset region, and the first preset region comprises first doped regions arranged at intervals; the second preset region comprises field doped regions which are arranged in the well region at intervals andsecond doped regions. The second doped regions are arranged between the field doped regions, the adjacent sides of the second doped regions are tightly attached to the field doped regions, and the second doped regions are located on the upper surfaces of the first doped regions respectively; the field oxide layer is formed in the field doped region and protrudes out of the field dopedregion. The technical scheme of the invention has the beneficial effects that the characteristics of low breakdown voltage and higher negative resistance characteristic are simultaneously realized, so that the characteristics of lower clamping voltage, ultralow trigger voltage and ultralow clamping voltage are realized, and the capability of protecting a post-stage circuit is higher.

Owner:SHANGHAI CHANGYUAN WAYON MICROELECTRONICS

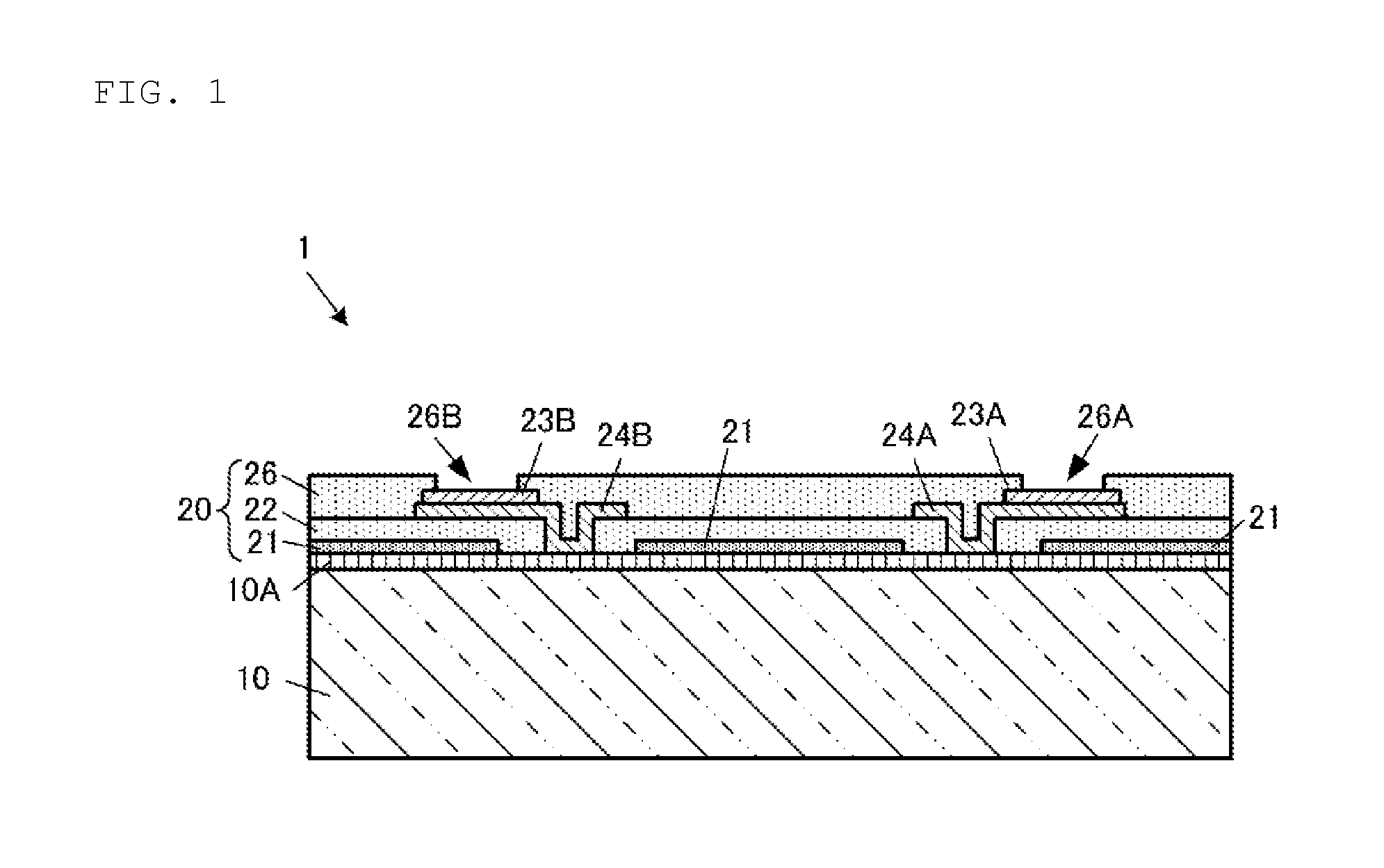

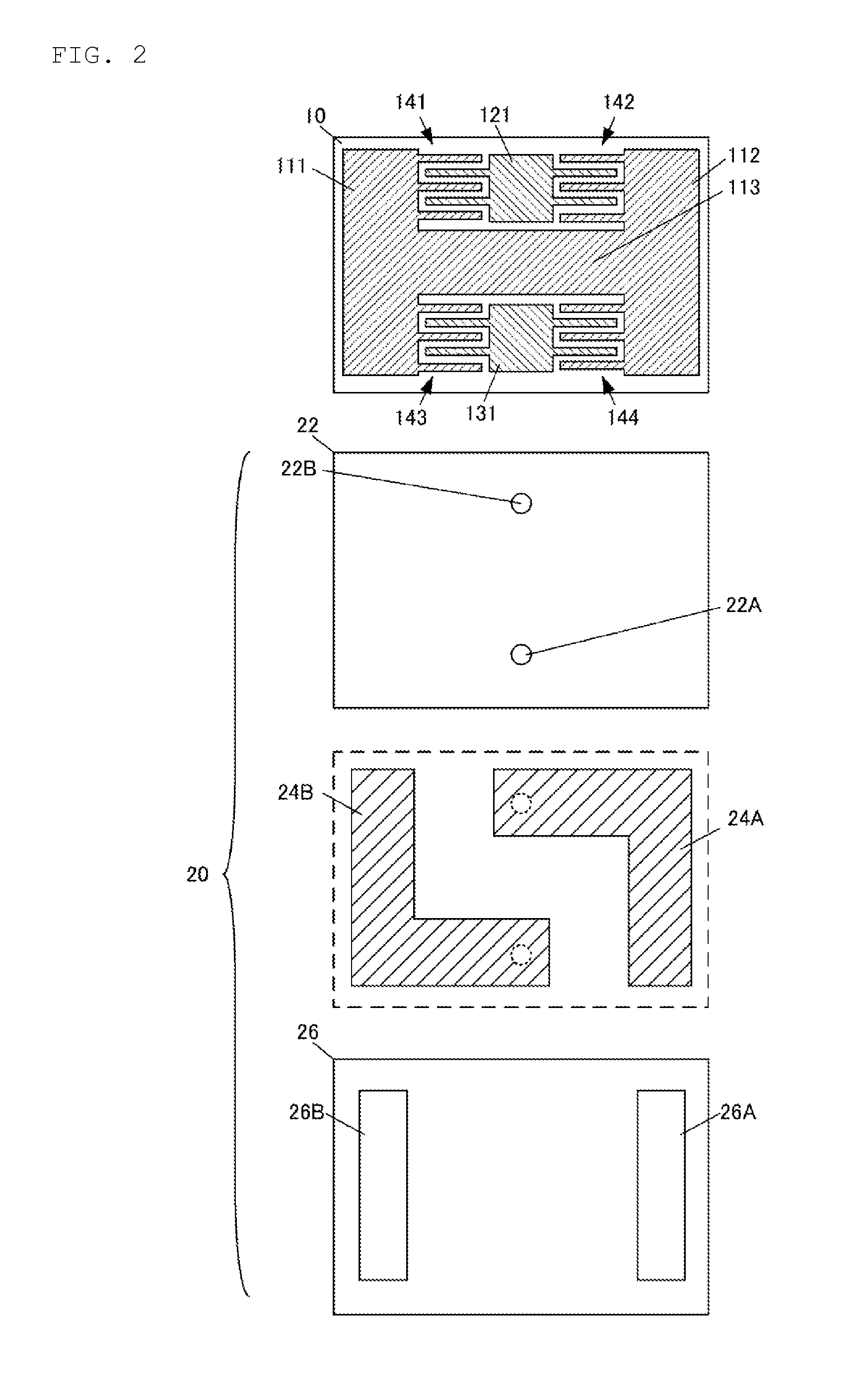

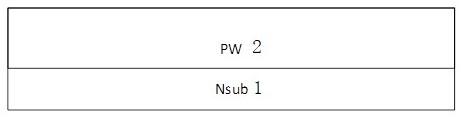

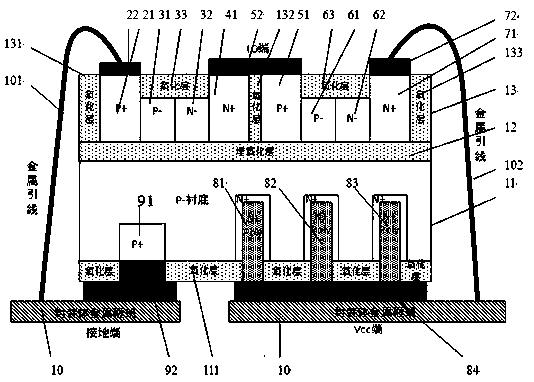

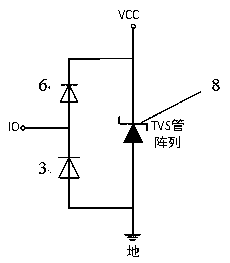

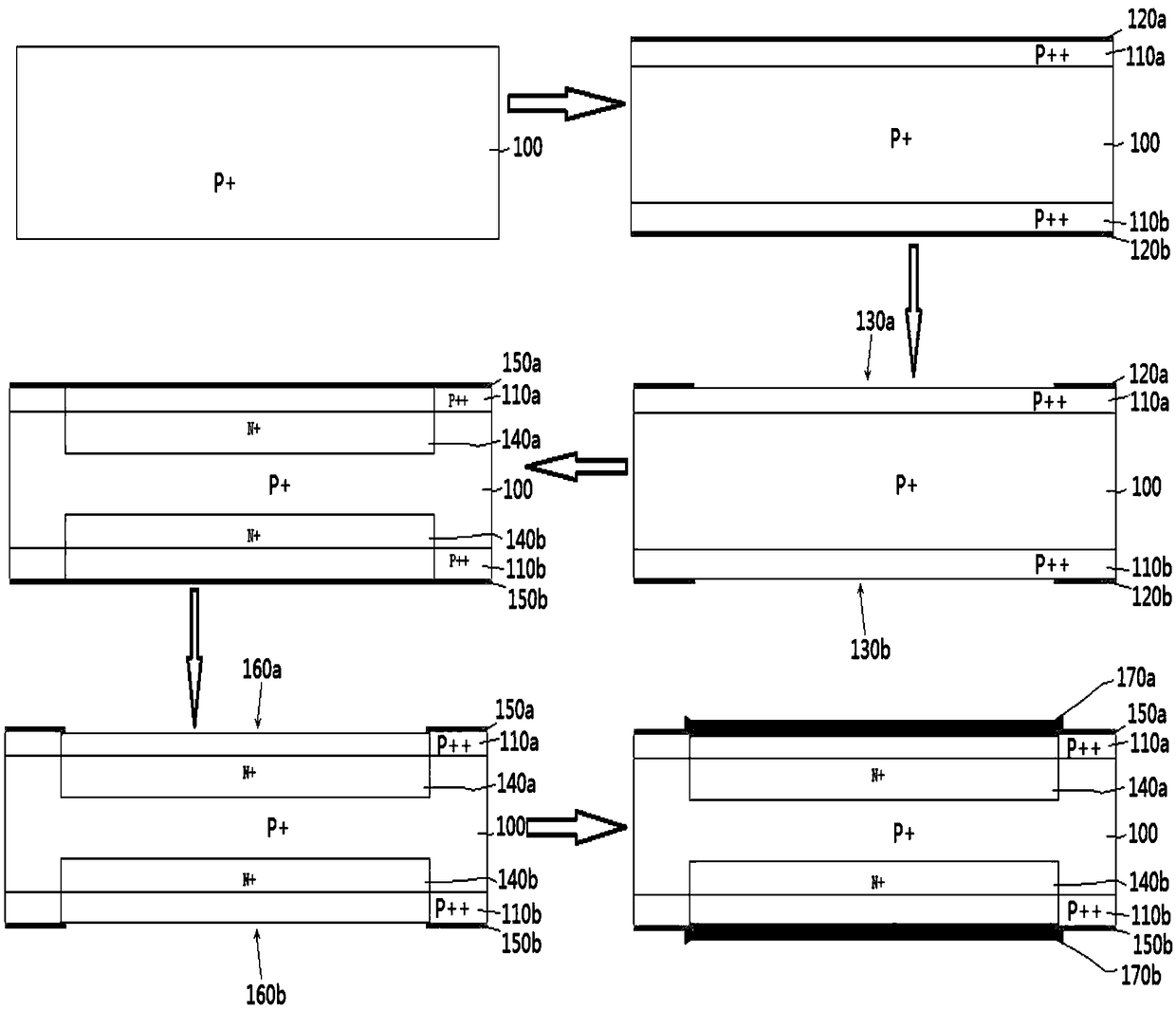

TVS protection device based on P-type SOI substrate, and manufacturing method thereof

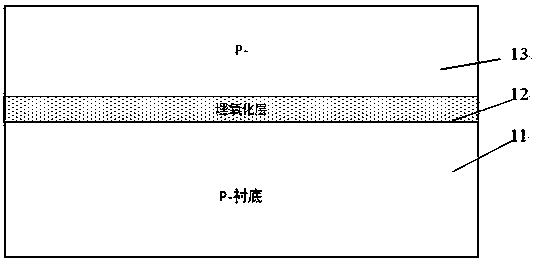

PendingCN111029399AEliminate parasitic capacitanceReduce layout areaSolid-state devicesSemiconductor devicesJunction formationParasitic capacitance

The invention discloses a TVS protection device based on a P-type SOI substrate. According to the device, a P-type SOI substrate silicon wafer is adopted, and is packaged by a metal frame; a P-type SOI substrate comprises a P-substrate, an oxide buried layer and a P-layer from bottom to top, has three ends of an IO end, a VCC end and a grounding end, and can protect the IO signal end and the powersupply VCC end in a circuit at the same time; a first capacitance reducing diode and a second capacitance reducing diode on the P-layer are formed by P- / N-junctions on the front surface; and a main TVS8 pipe is formed by three N+ / P-substrate arrays on the back surface. According to the invention, the device is manufactured on the front side and the back side at the same time, so that the layout area of the single device is small so as to easily improve the yield and reduce the cost; the two capacitance reducing diodes have low capacitance values, and completely eliminates the substrate parasitic capacitance, so that the device is suitable for being used in high-frequency interfaces such as HDMI2.0, USB3.0 and other high-speed ports; and large surge current can pass through the TVS pipe onthe back surface.

Owner:SHANGHAI CHANGYUAN WAYON MICROELECTRONICS

Semiconductor device with diode and silicon controlled rectifier (SCR)

ActiveUS20200365716A1Reduce capacitanceOpen quicklyTransistorThyristorSilicon-controlled rectifierDevice material

Provided is a semiconductor device with a diode and a silicon controlled rectifier (SCR) including a substrate having a first conductivity type, a well region having a second conductivity type, a first doped region having the first conductivity type, and a second doped region having the second conductivity type. The well region is disposed in the substrate. The first doped region is disposed in the substrate. The second doped region is disposed in the substrate. The well region and the first doped region form a first PN junction, the well region and the substrate form a second PN junction, and the substrate and the second doped region form a third junction. The first, second, and third PN junctions form the SCR, and the first doped region and the third PN junction form the diode.

Owner:UPI SEMICON CORP

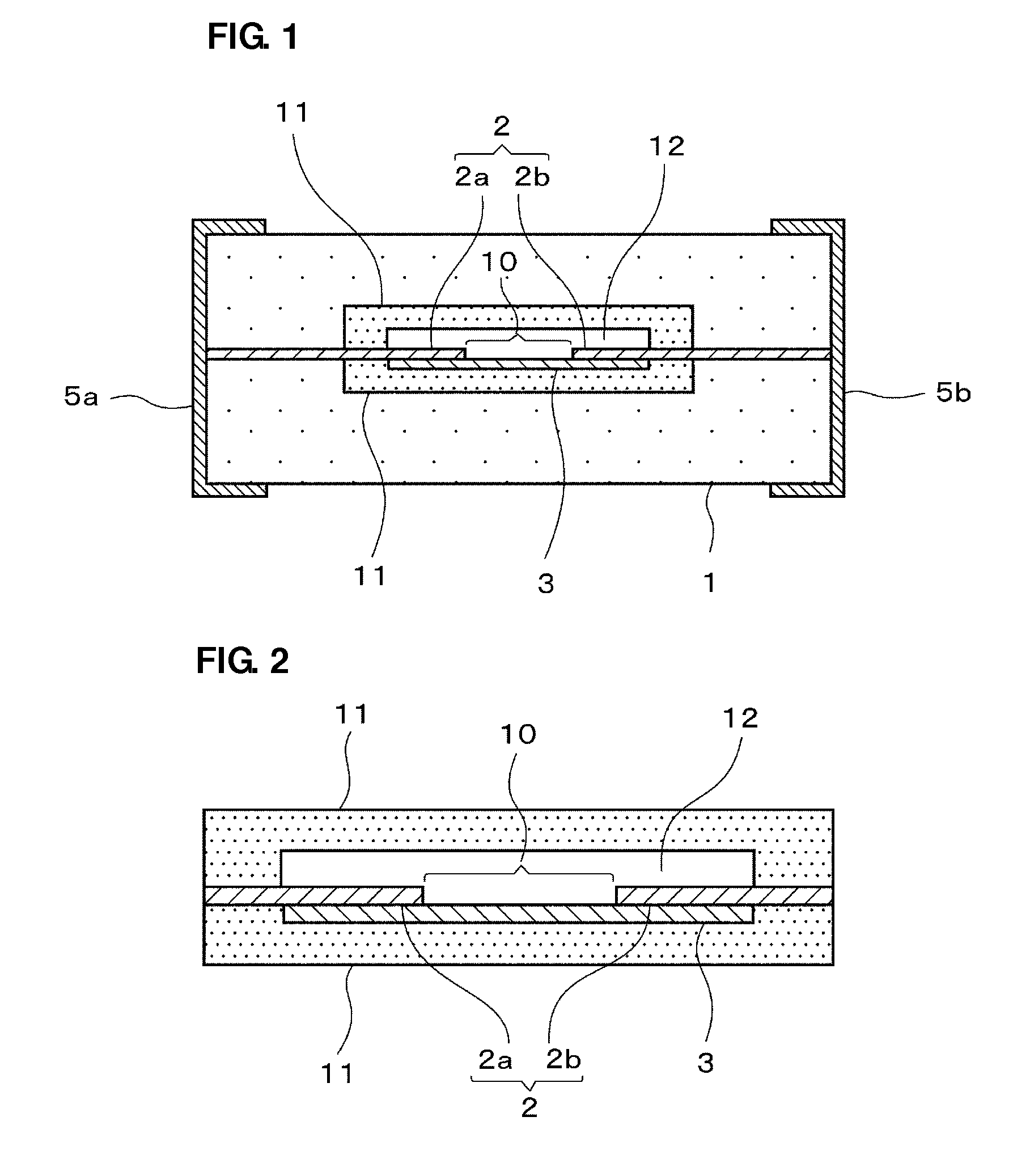

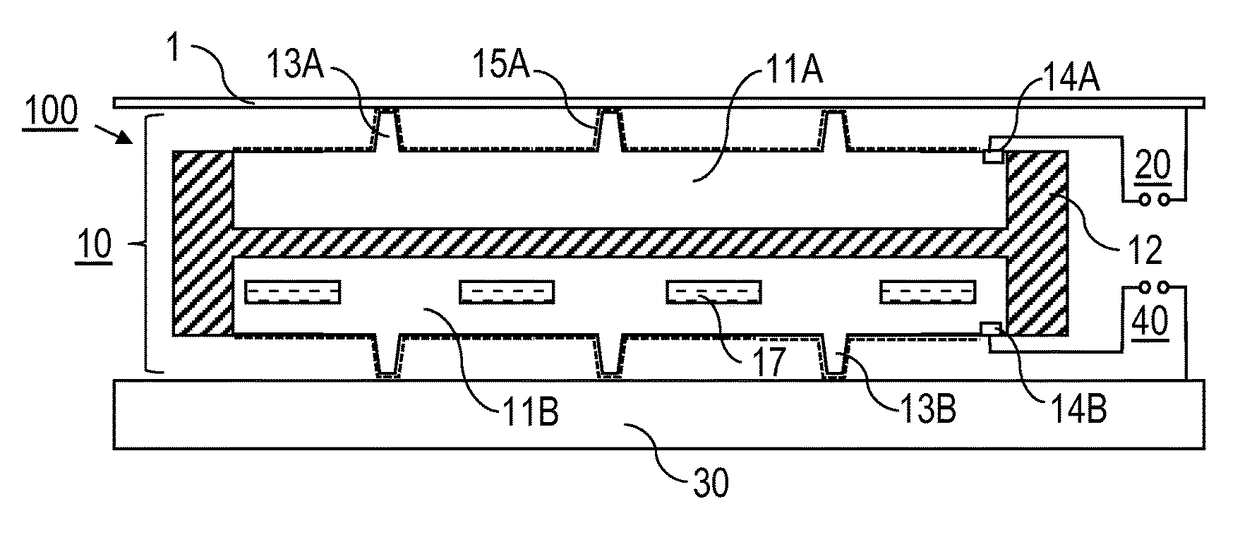

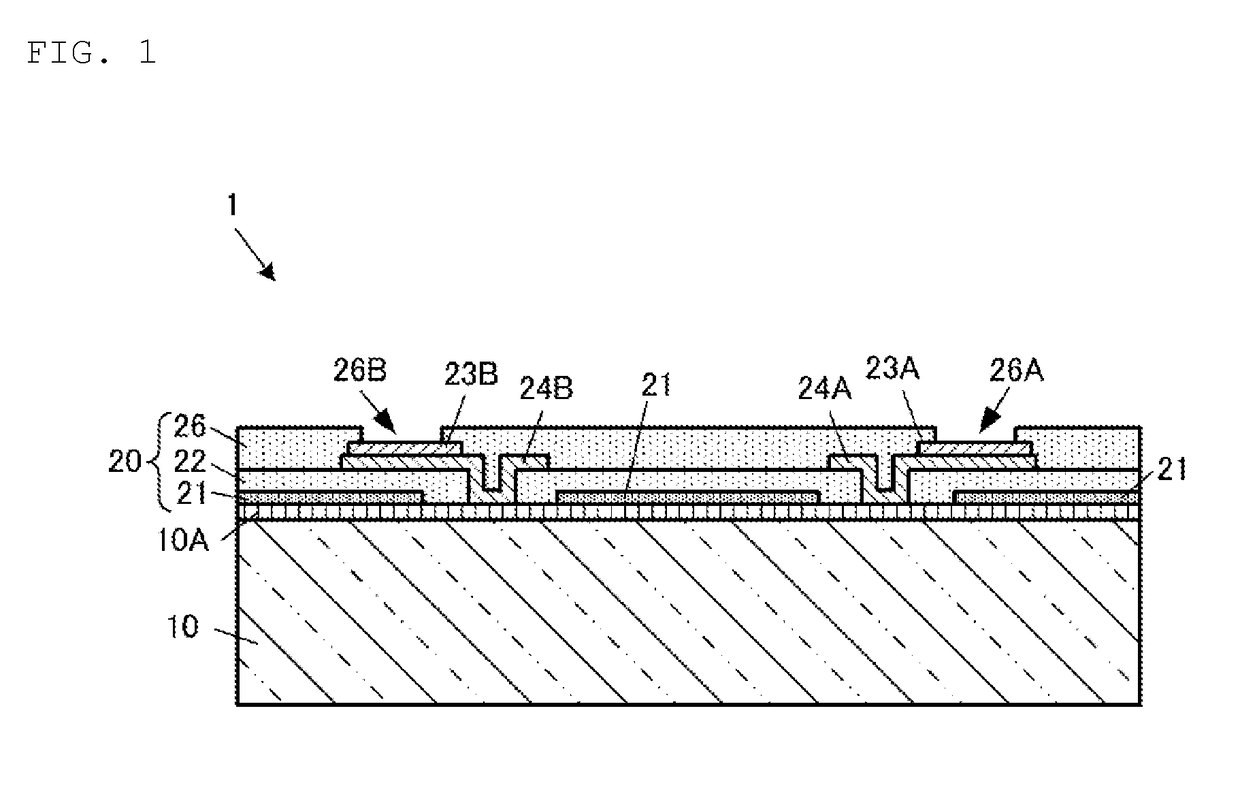

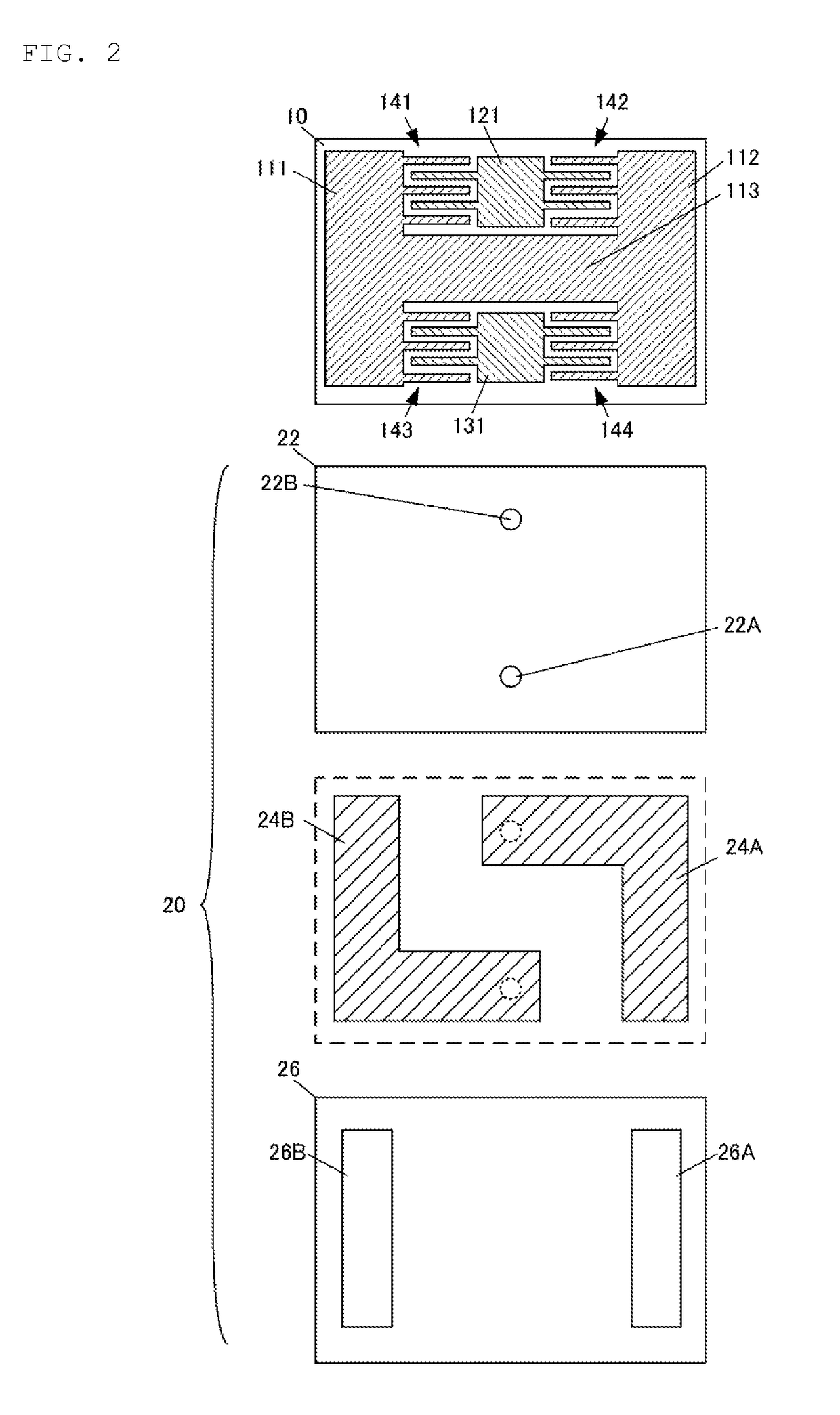

Clamp with ceramic electrode

ActiveUS9673737B2Avoid disadvantagesEasy to manufactureSemiconductor/solid-state device manufacturingOther manufacturing equipments/toolsBiomedical engineeringCeramic

A holding apparatus (100) for electrostatically holding a component (1), in particular a silicon wafer, includes at least one base body (10, 10A, 10B) which is composed of a first plate (11A) and a second plate (12), the first plate (11A) being arranged on an upper side (10A) of the base body (10, 10A, 10B) and the second plate are made of an electrically insulating material, a plurality of projecting, upper burls (13A) which are arranged on the upper side (10A) of the base body (10, 10A, 10B) and form a support surface for the component (1), and a first electrode which is arranged to receive a clamping voltage, wherein the first plate (11A) is made of an electrically conductive, silicon-including ceramic and forms the first electrode. A method for producing the holding apparatus (100) is also described.

Owner:ASML NETHERLANDS BV

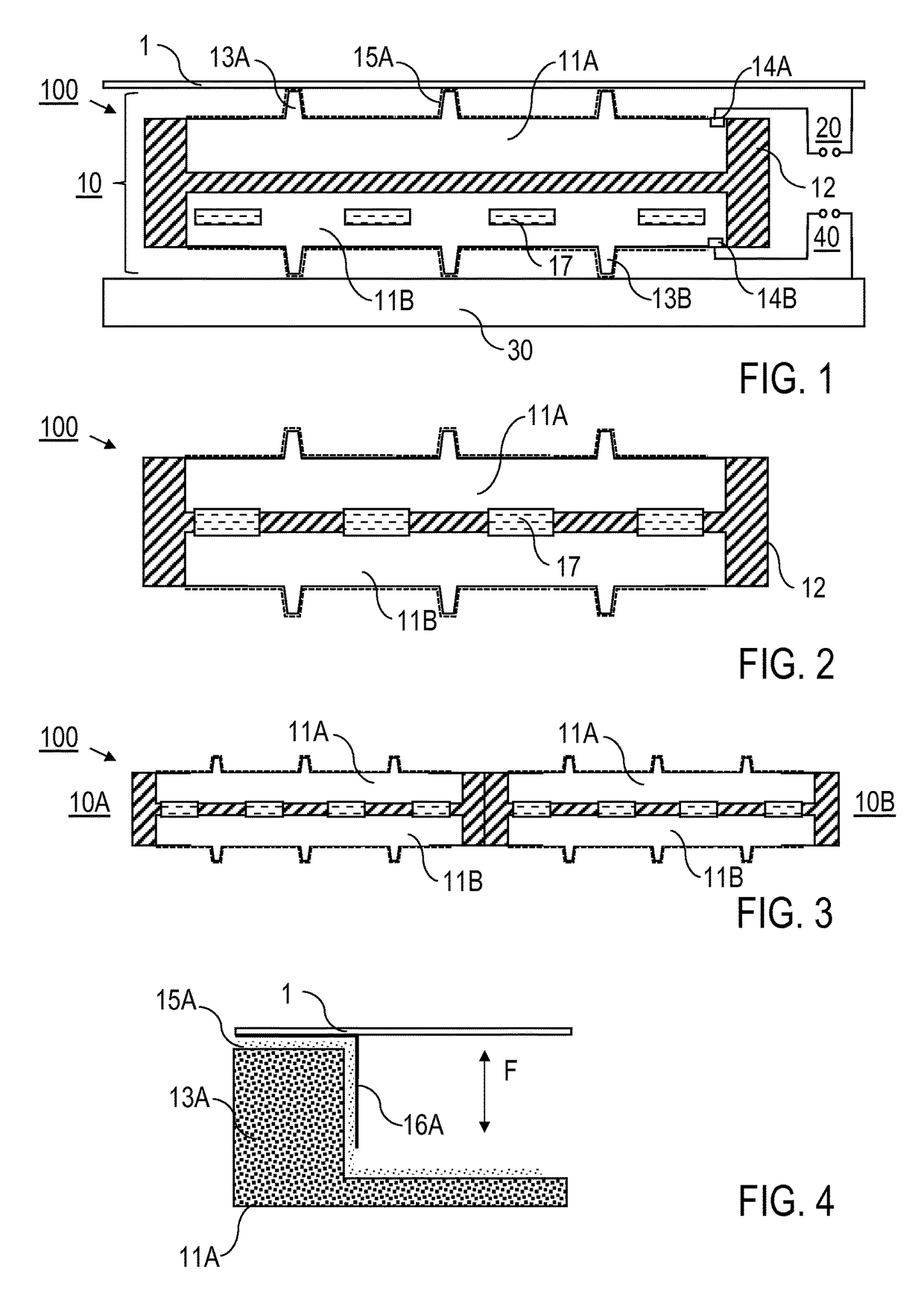

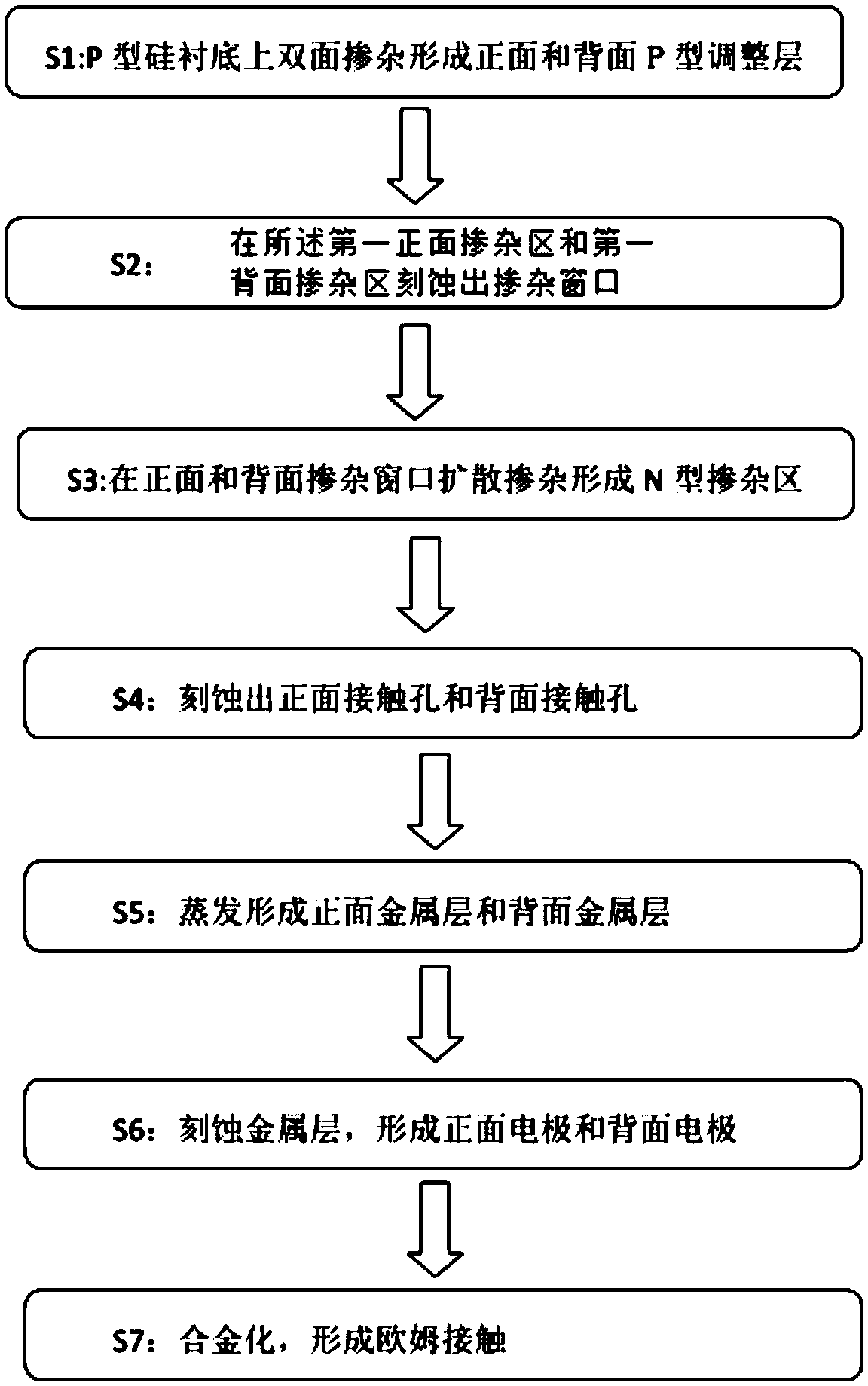

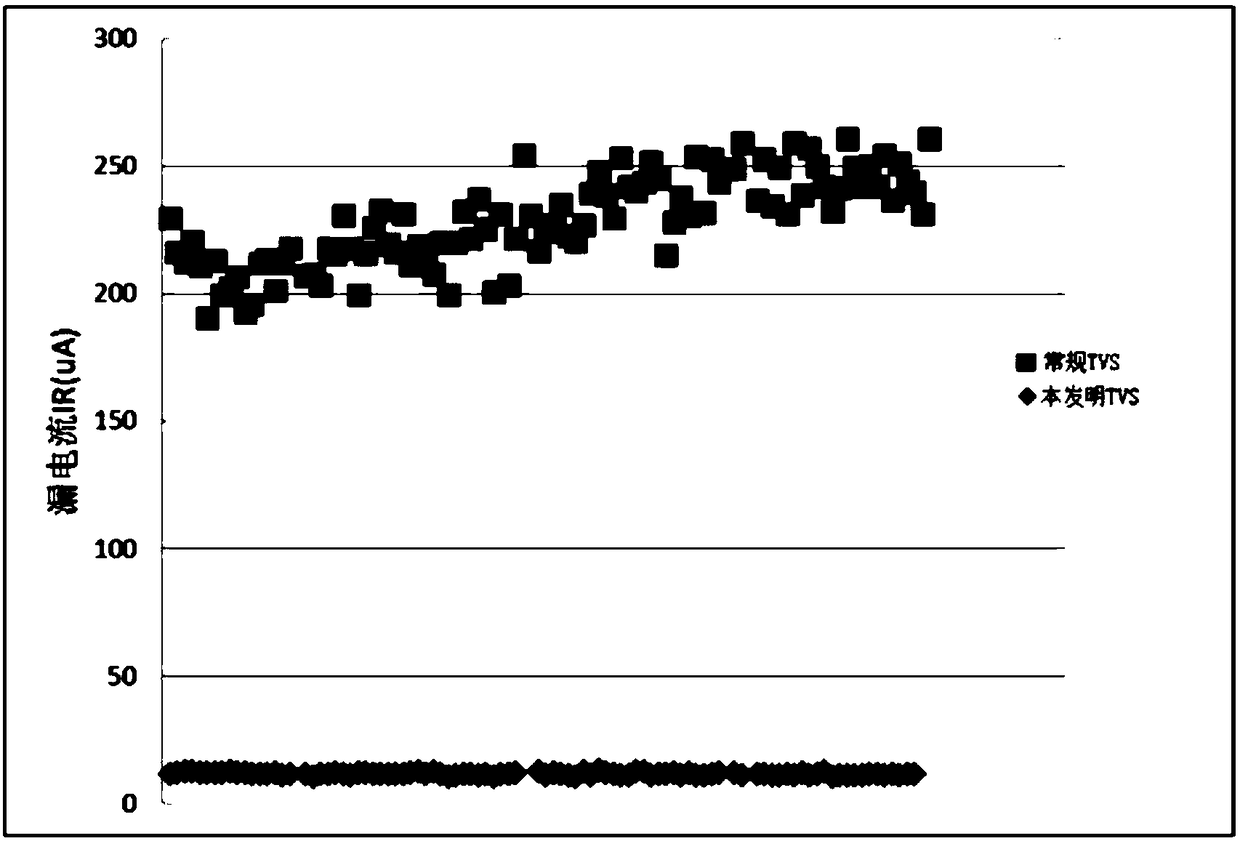

A bidirectional low-voltage planar transient voltage suppression diode and a manufacturing method thereof

ActiveCN108987458AIncreasing concentration gradientReduce leakage currentSemiconductor/solid-state device manufacturingSemiconductor devicesLow voltageConcentration gradient

The invention discloses a bidirectional low-voltage planar transient voltage suppression diode and a manufacturing method thereof, comprising a P-type heavily doped silicon substrate; A first front doping region and a first back doping region are respectively formed on the front and back sides of the substrate, A second front doping region and a second back doping region are respectively formed bydiffusion doping through a doping window on the front surface and the back surface of the substrate, a second front doped region oxide layer and a second back doped region oxide layer are formed on the second front doped region and the second back doped region, respectively, a front contact hole and a back contact hole are formed on the second front doped region oxide layer and the second back doped region oxide layer; A front metal electrode and a back metal electrode are formed on the front contact hole and the back contact hole, respectively. A front doping region and a back doping regionwith the same doping type as the silicon substrate are added so as to adjust the substrate concentration, thereby increasing the concentration gradient across the formed PN junction, reducing the movable ions and reducing the TVS leakage current.

Owner:西安卫光科技有限公司

Method for producing a protective structure

ActiveUS7888232B2Shorten the lengthReduced structureSolid-state devicesSemiconductor/solid-state device manufacturingSemiconductor

A protective structure is produced by providing a semiconductor substrate with a doping of a first conductivity type. A semiconductor layer with a doping of a second conductivity type is applied at a surface of the semiconductor substrate. A buried layer with doping of a second conductivity type is formed in a first region of the semiconductor layer, wherein the buried layer is produced at the junction between the semiconductor layer and semiconductor substrate. A first dopant zone with a doping of a first conductivity type is formed in the first region of the semiconductor layer above the buried layer. A second dopant zone with a doping of a second conductivity type is formed in a second region of the semiconductor layer. An electrical insulation is formed between the first region and the second region of the semiconductor layer. A common connection device is formed for the first dopant zone and the second dopant zone.

Owner:INFINEON TECH AG

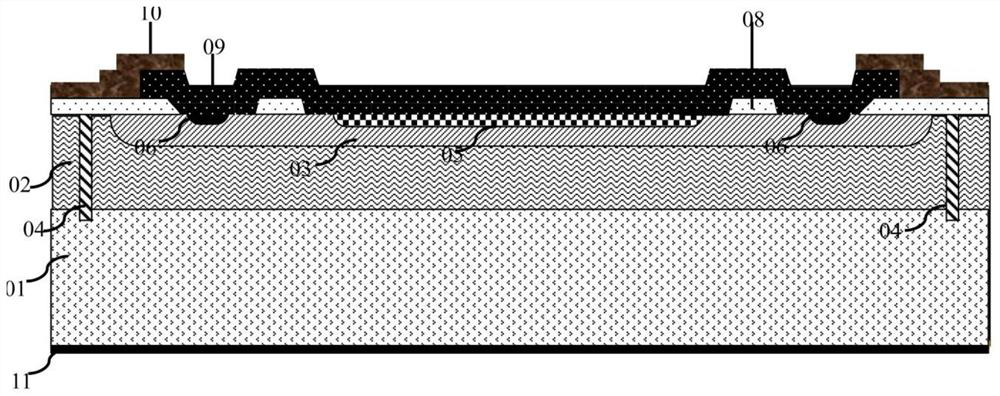

Unidirectional high-voltage transient voltage suppression protection device and preparation method thereof

PendingCN111668210ALower clamping voltageSmall dynamic impedanceTransistorSolid-state devicesPhysicsElectrically conductive

An unidirectional high-voltage transient voltage suppression protection device comprises a substrate of a first conductive type; a first epitaxial layer of a second conductivity type, the first epitaxial layer being formed over the top surface of the substrate; a semiconductor layer in a second conductivity type, the semiconductor layer being a well region formed in the top surface of the first epitaxial layer or a second epitaxial layer formed above the top surface of the first epitaxial layer; a group of first injection regions and second injection regions formed in the top surface of the semiconductor layer, the first injection region being formed on the periphery of the second injection region, and the first injection region and the second injection region being horizontally spaced bya preset distance; and a first isolation groove on the periphery of the first injection region, the first isolation groove being formed in the substrate, the first epitaxial layer and the semiconductor layer, and the first isolation groove being filled with an insulating material. The embodiment of the invention provides a unidirectional high-working-voltage transient voltage suppression protection device of a transient voltage suppression protection device.

Owner:WILL SEMICON (SHANGHAI) CO LTD

ESD protection device

ActiveUS9633989B2Lower clamping voltageHigh voltageSemiconductor/solid-state device detailsSolid-state devicesZener diodeVoltage

Owner:MURATA MFG CO LTD