A bidirectional low-voltage planar transient voltage suppression diode and a manufacturing method thereof

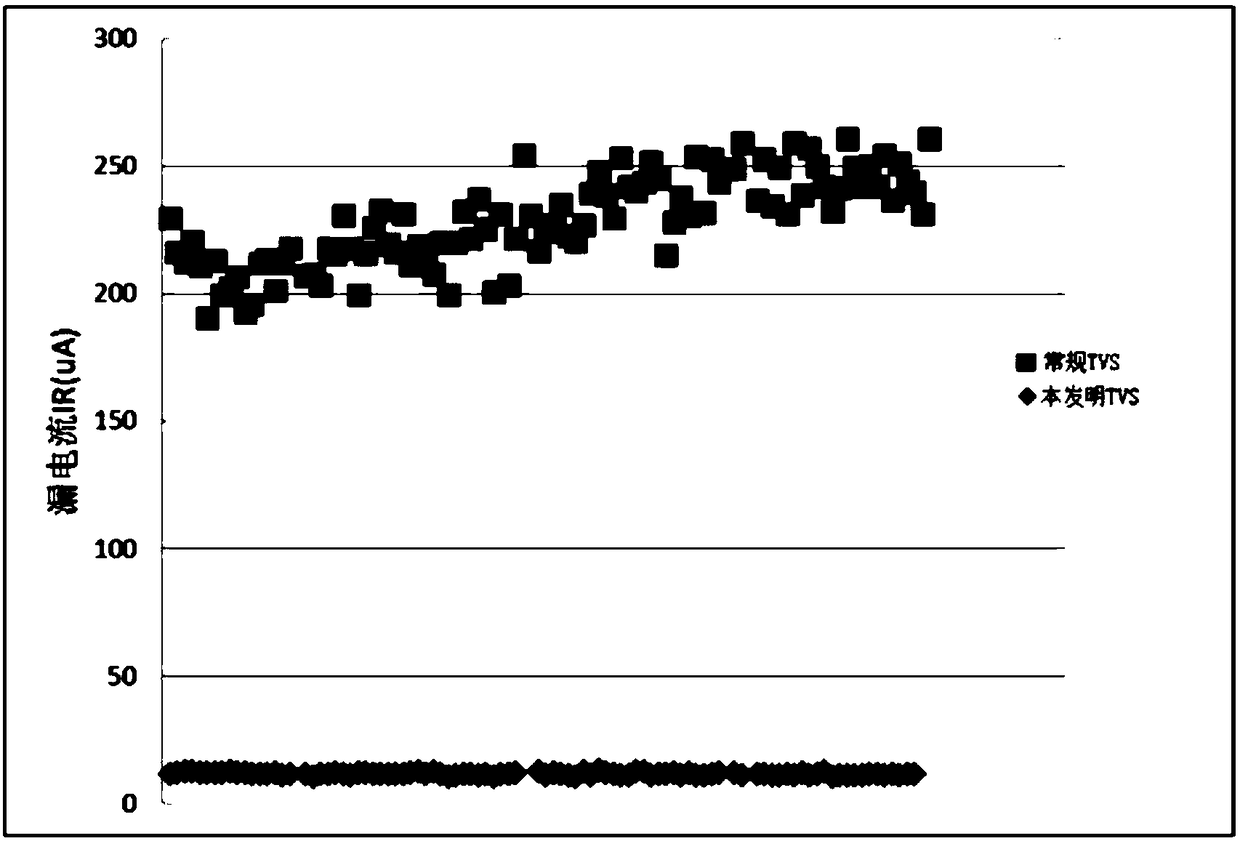

A technology of transient voltage suppression and manufacturing method, applied in semiconductor/solid-state device manufacturing, circuits, electrical components, etc., can solve the problem of large reverse leakage current of diodes, reduce leakage current, reduce losses, and reduce short-circuit risks Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

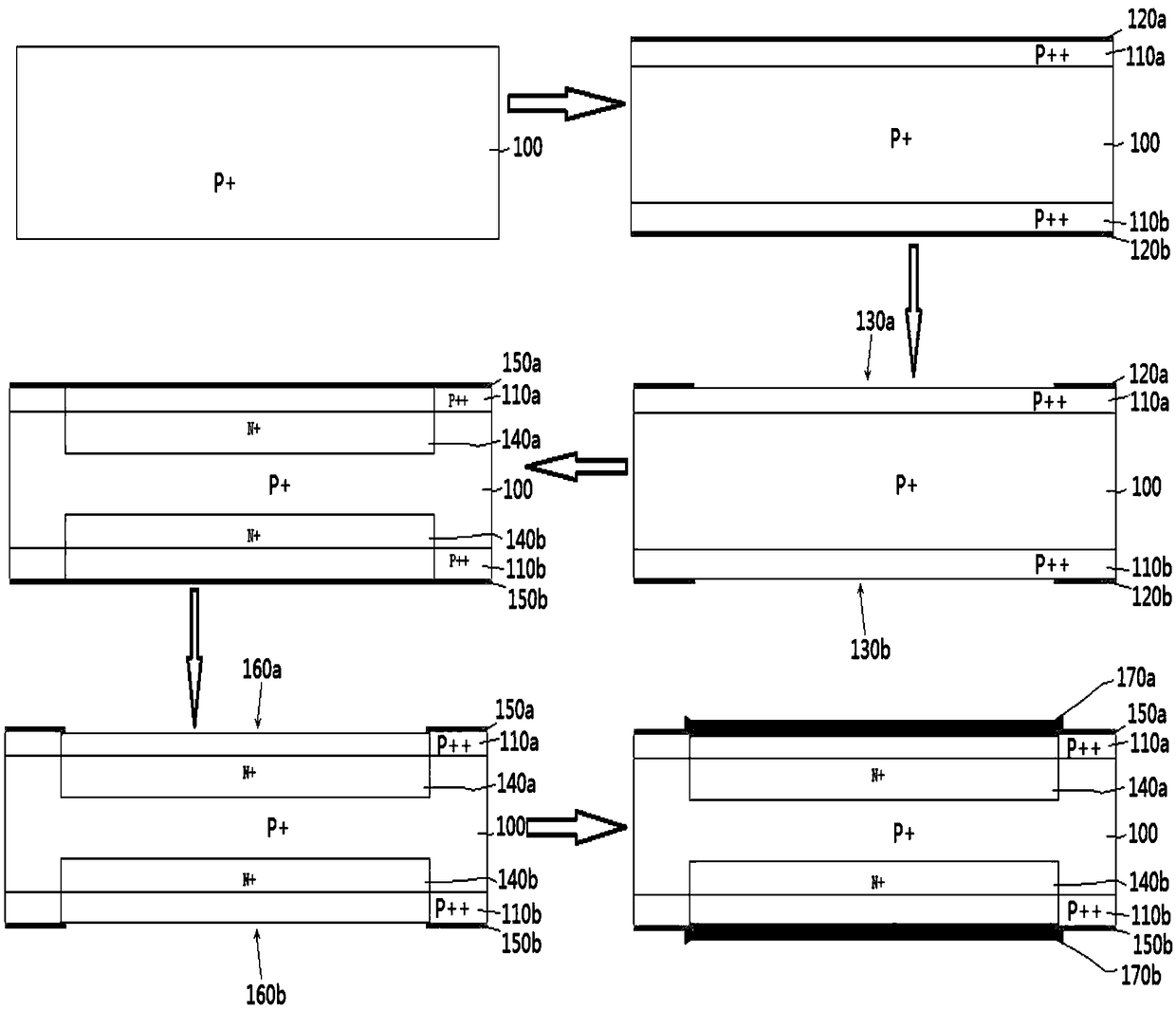

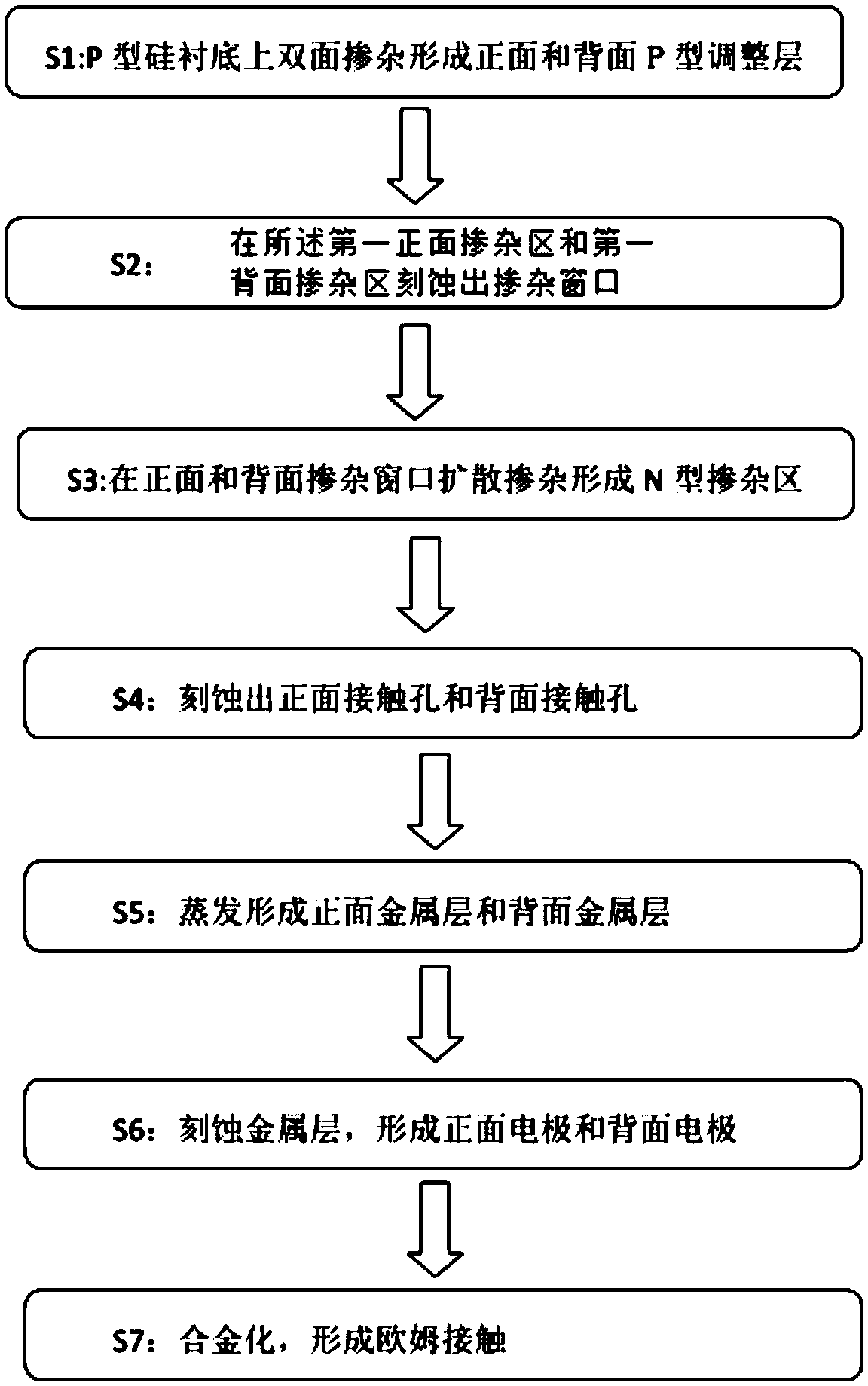

[0047] 1. A heavily doped silicon substrate 100 is provided.

[0048] In this embodiment, the silicon substrate is a P+ silicon substrate. The resistivity of the P+ silicon substrate is between 0.003 Ω·m, 111 crystal orientation, and the thickness is 180 μm.

[0049] 2. Simultaneously diffuse doping to the front and back of the silicon substrate 100 to form a doped region.

[0050] The front doped region of the silicon substrate 100 is called the first front doped region 110a, and the back doped region is called the first back doped region 110b, and the first front doped region 110a and the first back doped region The doping type of the region 110 b is the same as that of the silicon substrate 100 .

[0051] Preferably, diffusion doping adopts two-step diffusion:

[0052] In the first step, prediffusion is performed on the silicon substrate to form a limited B impurity source;

[0053] In the second step, chlorine is added to oxidize when re-diffusion pushes the junction d...

Embodiment 2

[0064] 1. A heavily doped silicon substrate 100 is provided. The P+ silicon substrate has a resistivity of 0.01Ω·m, a 111 crystal orientation, and a thickness of 200 μm.

[0065] 2. Simultaneously diffuse doping to the front and back of the silicon substrate 100 to form a first front doped region 110a and a first back doped region 110b, the first front doped region 110a and the first back doped region 110b The doping type is the same as that of the silicon substrate 100 .

[0066] A two-step diffusion doping is employed:

[0067] In the first step, prediffusion is performed on the silicon substrate to form a limited B impurity source;

[0068] In the second step, chlorine is added to oxidize when re-diffusion pushes the junction deep.

[0069] While doping to form the doped region, a first front oxide layer 120a is formed on the first front doped region 110a, and a first rear oxide layer 120b is formed on the first back doped region 110b. The first front doped region 110a ...

Embodiment 3

[0079] 1. A heavily doped silicon substrate 100 is provided. The resistivity of the P+ silicon substrate is between 0.02 Ω·m, 111 crystal orientation, and the thickness is 240 μm.

[0080] 2. Simultaneously diffuse doping to the front and back of the silicon substrate 100 to form a first front doped region 110a and a first back doped region 110b, the first front doped region 110a and the first back doped region 110b The doping type is the same as that of the silicon substrate 100 .

[0081] A two-step diffusion doping is employed:

[0082] In the first step, prediffusion is performed on the silicon substrate to form a limited B impurity source;

[0083] In the second step, chlorine is added to oxidize when re-diffusion pushes the junction deep.

[0084] While doping to form the doped region, a first front oxide layer 120a is formed on the first front doped region 110a, and a first rear oxide layer 120b is formed on the first back doped region 110b. The first front doped re...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Resistivity | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More