Novel silicon controlled rectifier device with low-clamping embedded capacitance-reducing diode

A diode and low-clamping technology, which is applied in the design of semiconductor components and new thyristor devices, can solve the problems of high clamping voltage and low clamping voltage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

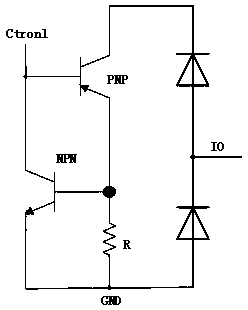

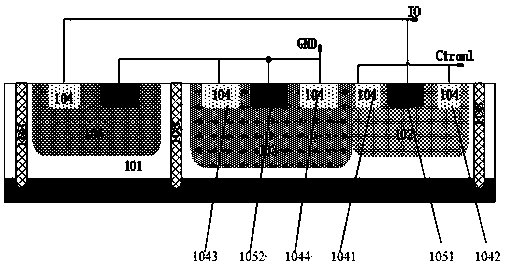

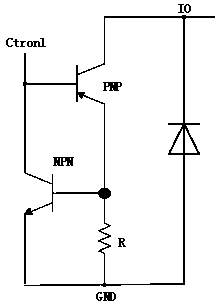

[0052] Such as figure 2 It is a structural schematic diagram of the novel thyristor device of this embodiment, image 3 It is the schematic diagram of the equivalent circuit of the novel thyristor device of the present embodiment and Figure 4 It is shown in the schematic diagram of the layout design of the novel thyristor device of this embodiment:

[0053] A new type of thyristor device with low clamping built-in decapitation diode, such as figure 2 As shown, it includes a thyristor module, which is composed of P-type heavily doped region SP, N-type well region Nwell102, P-type well region Pwell103, and N-type heavily doped region SN104, wherein SP-1051 / in Nwell102 Nwell102 / Pwell103 constitutes a parasitic PNP structure, and SN104 in Nwell102 / Pwell103 / Pwell103 constitutes a parasitic NPN structure. Since the base of the parasitic NPN transistor is connected to the collector of the parasitic PNP transistor, the base current of the former is equal to the collector of the ...

Embodiment 2

[0069] A new type of thyristor device with low clamping built-in decapitation diode, such as Figure 5 As shown, the others are the same as Embodiment 1, except that this embodiment adds a trigger junction 115 (GGNmos can also be added) to adjust the trigger voltage.

[0070] Such as Figure 5 As shown; trigger junction 115 injection is added in Nwell, which is located at the interface of Nwell102 and Pwell103, and is no longer connected to SN104 in Nwell102. When the trigger junction is implanted as an N-type heavily doped impurity region, the avalanche breakdown of the trigger junction 115 and Pwell 103 determines the trigger voltage of the thyristor; when the trigger junction 115 is implanted as a P-type heavily doped impurity region, the trigger junction 115 and Pwell 103 The avalanche breakdown of Nwell102 determines the trigger voltage of the SCR. Alternatively, GGNmos can be added to replace the region of the trigger junction 115, and the trigger voltage of the device...

Embodiment 3

[0072] A new type of thyristor device with low clamping built-in decapitation diode, such as Figure 6 As shown, the others are the same as Embodiment 1, except that this embodiment adopts SOI substrate material, and there is a buried oxide layer 116 on the substrate 100 to further reduce device capacitance.

[0073] Such as Figure 6 As shown; the difference from Embodiment 1 is that the substrate material of SOI is used, and the buried oxide layer 116 is dielectric silicon dioxide. Due to the existence of the oxide layer, the parasitic capacitance of the substrate is reduced, thereby reducing the capacitance of the thyristor. Such as Figure 6 Among them, the SOI substrate 100 can be an N-type or P-type substrate, and correspondingly, the epitaxial layer 101 is an N-type high-resistance epitaxy, or a P-type high-resistance epitaxy.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More