Trigger circuit structure with integrated circuit power supply rail antistatic protection

An integrated circuit and electrostatic protection technology, applied in the electronic field, can solve the problems of large leakage current and high chip power consumption, achieve the effects of small leakage current, reduce trigger voltage, and improve ESD capability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment approach 1

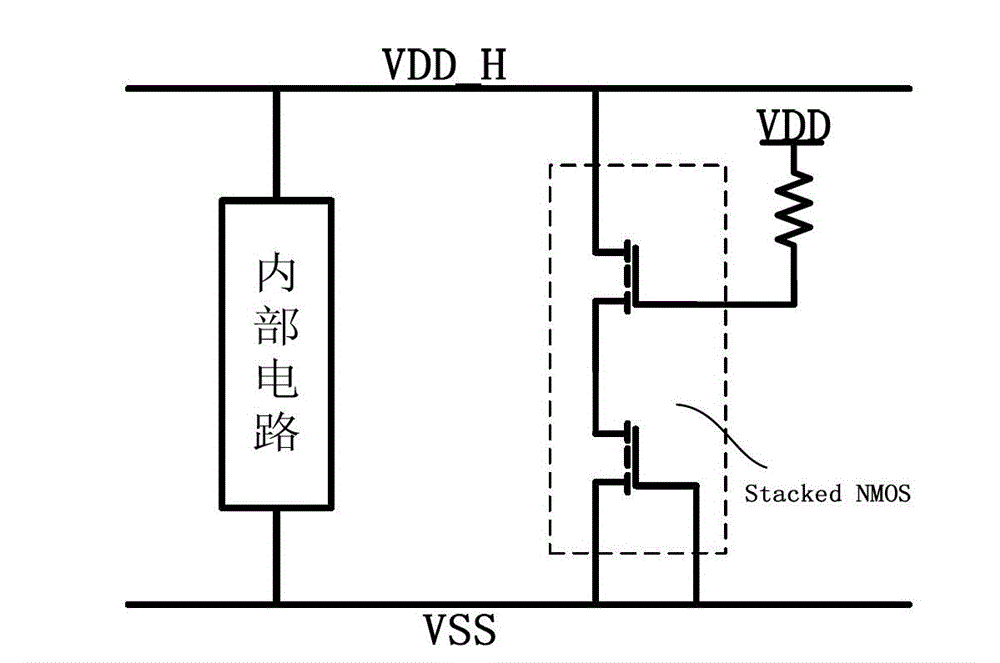

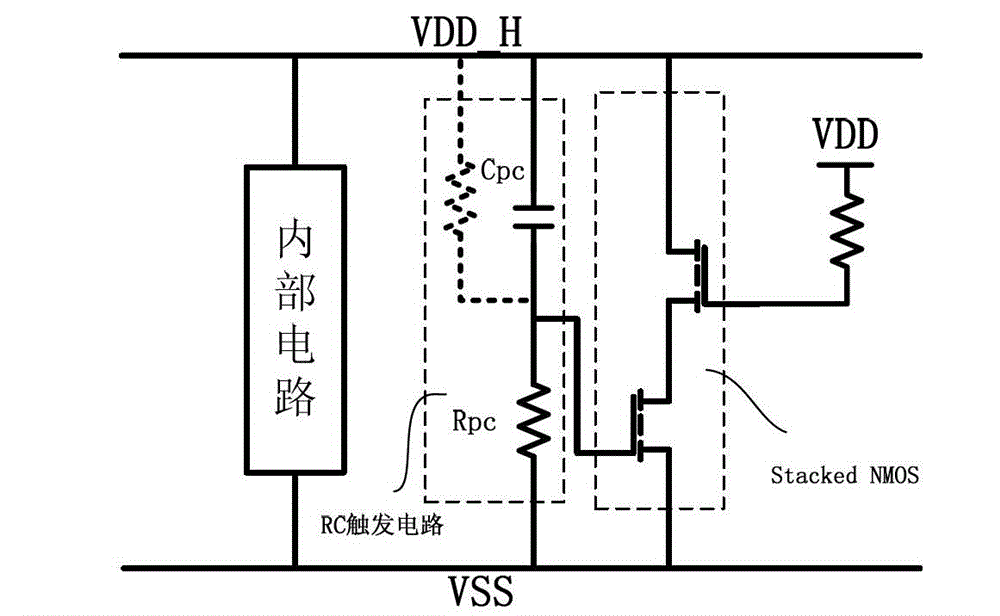

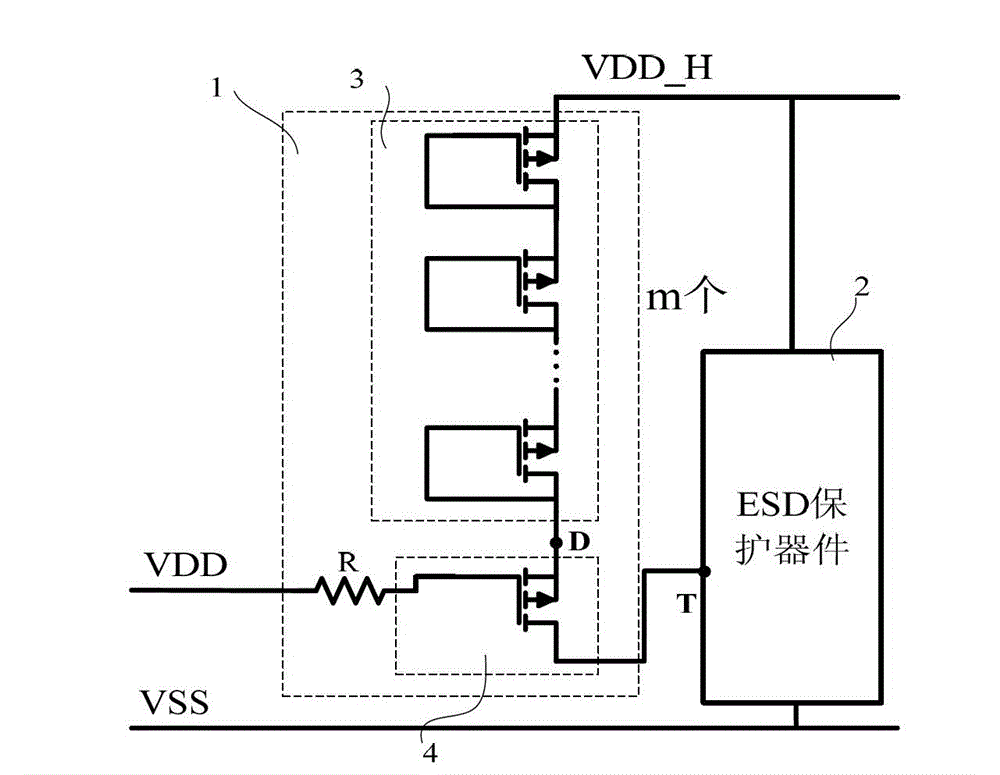

[0016] Trigger circuit structure 1 for integrated circuit power rail anti-static protection, used to trigger integrated circuit high-voltage power rail anti-static protection devices with mixed operating voltages, such as image 3 As shown, it includes a diode-connected series circuit 3 composed of m (m is a positive integer) first PMOS transistors, a second PMOS transistor 4 and a resistor R; the diode connection formed by the m first PMOS transistors In the series circuit 3 of the form, the gate of each first PMOS transistor is connected to the drain, the substrate is connected to the source, and the source of each first PMOS transistor is connected to the drain of a first PMOS transistor above it; The source of the two PMOS transistors 4 is short-circuited to the substrate, and then connected to the drain of the bottom first PMOS transistor in the series circuit 3 of the diode connection form formed by m first PMOS transistors; the gate of the second PMOS transistor 4 It is...

specific Embodiment approach 2

[0022] The structure of the second embodiment is that an NMOS transistor 5 is added on the basis of the first embodiment, such as Figure 5 As shown, an NMOS transistor 5 is connected under the PMOS transistor 4 . The source of the NMOS transistor 5 is short-circuited to the substrate and connected to the ground rail VSS, the drain of the NMOS transistor 5 is connected to the drain of the second PMOS transistor 4; the gates of the NMOS transistor 5 and the PMOS transistor 4 are connected to each other through a resistor R Low Voltage Supply Rail VDD.

[0023] The function of the NMOS transistor 5 in the above scheme is: when the protected integrated circuit works normally, since the gates of the second PMOS transistor 4 and the NMOS transistor 5 are connected to the low-voltage power supply rail VDD, the second PMOS transistor 4 is turned off at this time. The NMOS transistor 5 is turned on, and the voltage of the trigger terminal of the ESD protection device 2 is pulled to a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More