Manufacturing method for ESD gate grounding NMOS transistor

A manufacturing method and transistor technology, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problems of wasting the area occupied by devices, and achieve the effects of saving area, saving cost, and simplifying the process

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

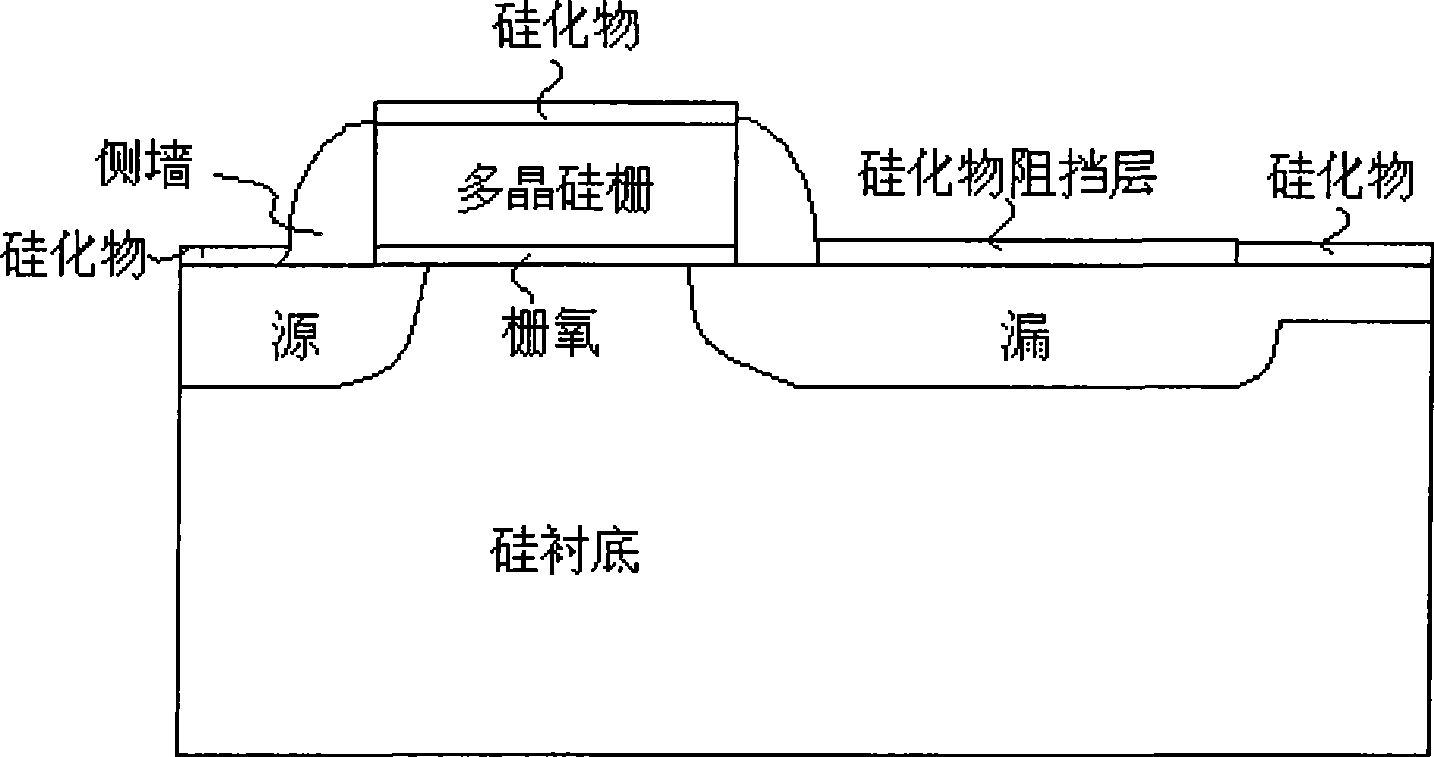

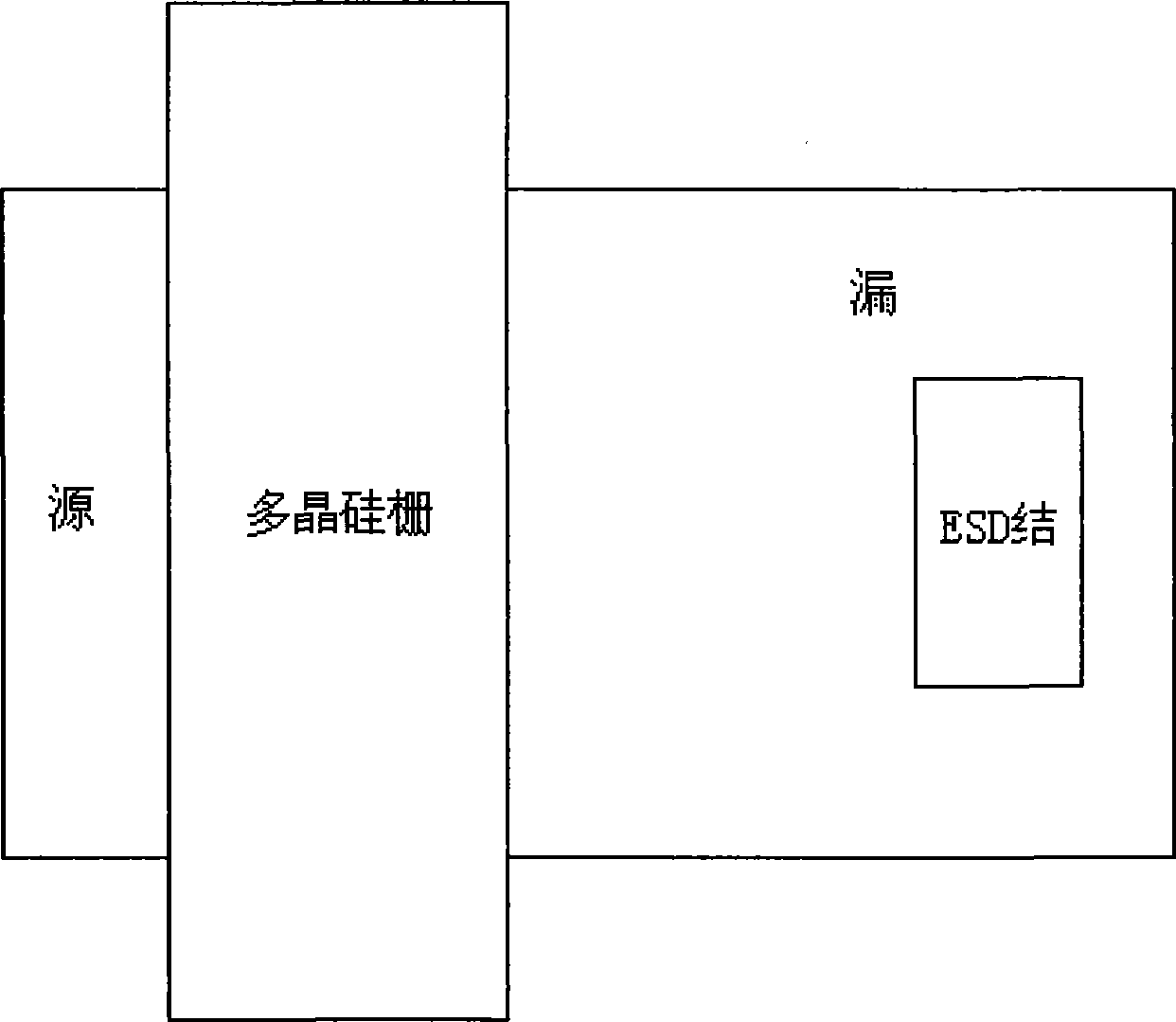

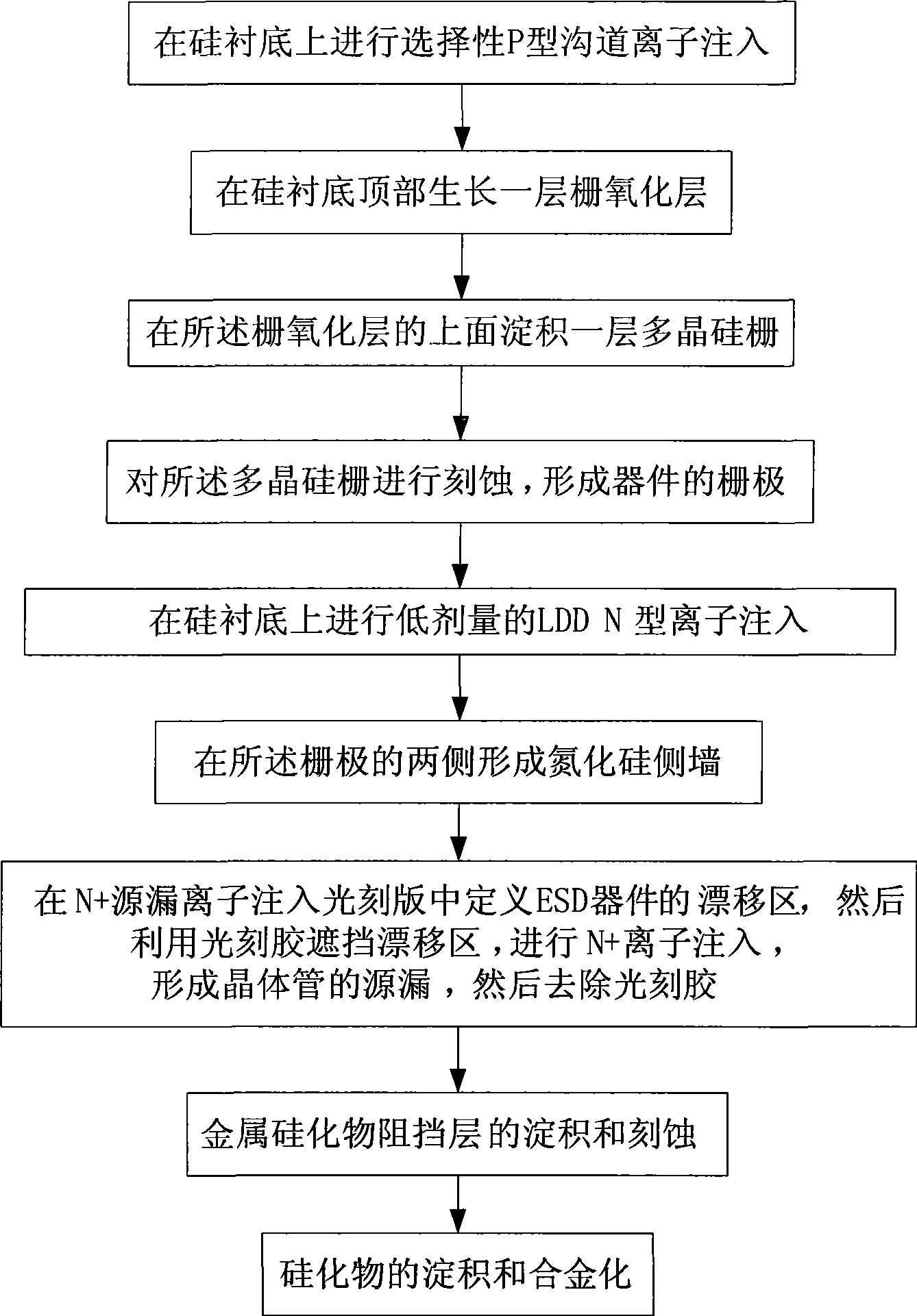

[0016] In one embodiment, such as image 3 As shown, the ESD gate grounding NMOS transistor manufacturing method of the present invention comprises the following steps:

[0017] In the first step, selective P-type channel ion implantation is performed on the silicon substrate.

[0018] In the second step, a gate oxide layer is grown on the top of the silicon substrate, and then a polysilicon gate is deposited on the gate oxide layer.

[0019] The third step is to use known photolithography technology to etch the polysilicon gate to form the gate of the device. The cross-sectional structure at this time is as follows Figure 4a shown.

[0020] The fourth step is to perform selective low-dose LDD (Lightly Doped Drain, lightly doped drain) N-type ion implantation on the silicon substrate to form a lightly doped LDD region, where the implanted ion dose ranges from E13 to E14cm -2 .

[0021] In the fifth step, silicon nitride sidewalls are formed on both sides of the gate.

...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More