Patents

Literature

34results about How to "Small conduction current" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Transferring method

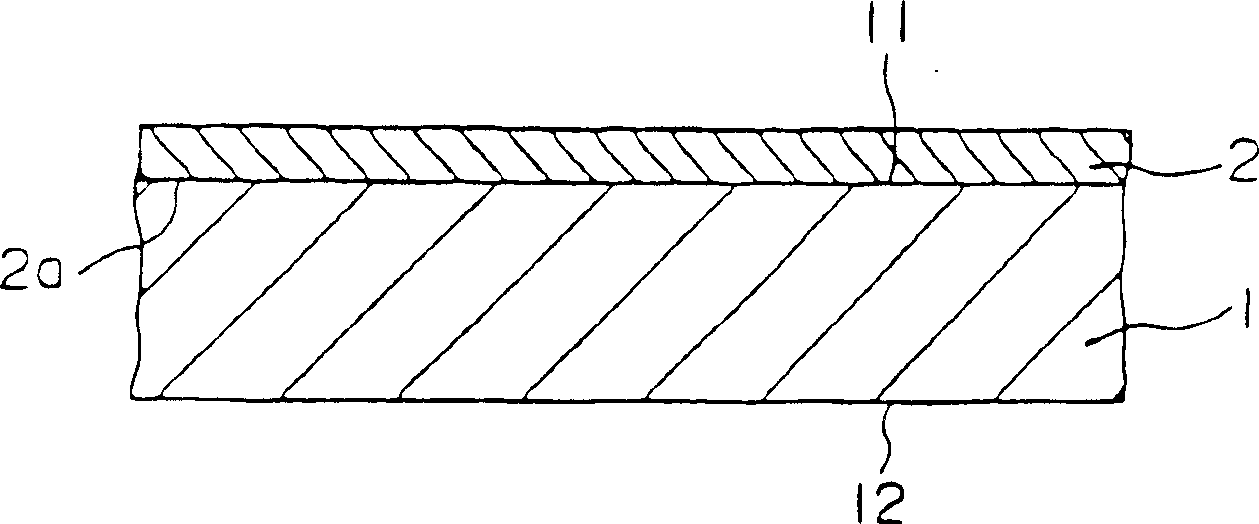

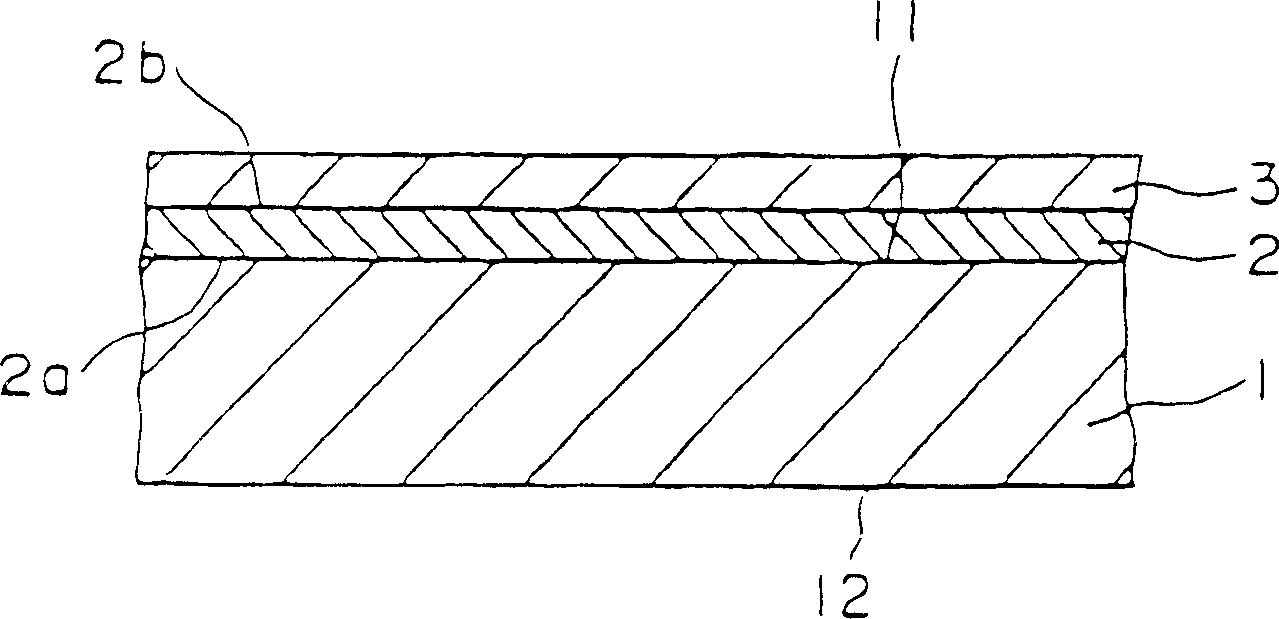

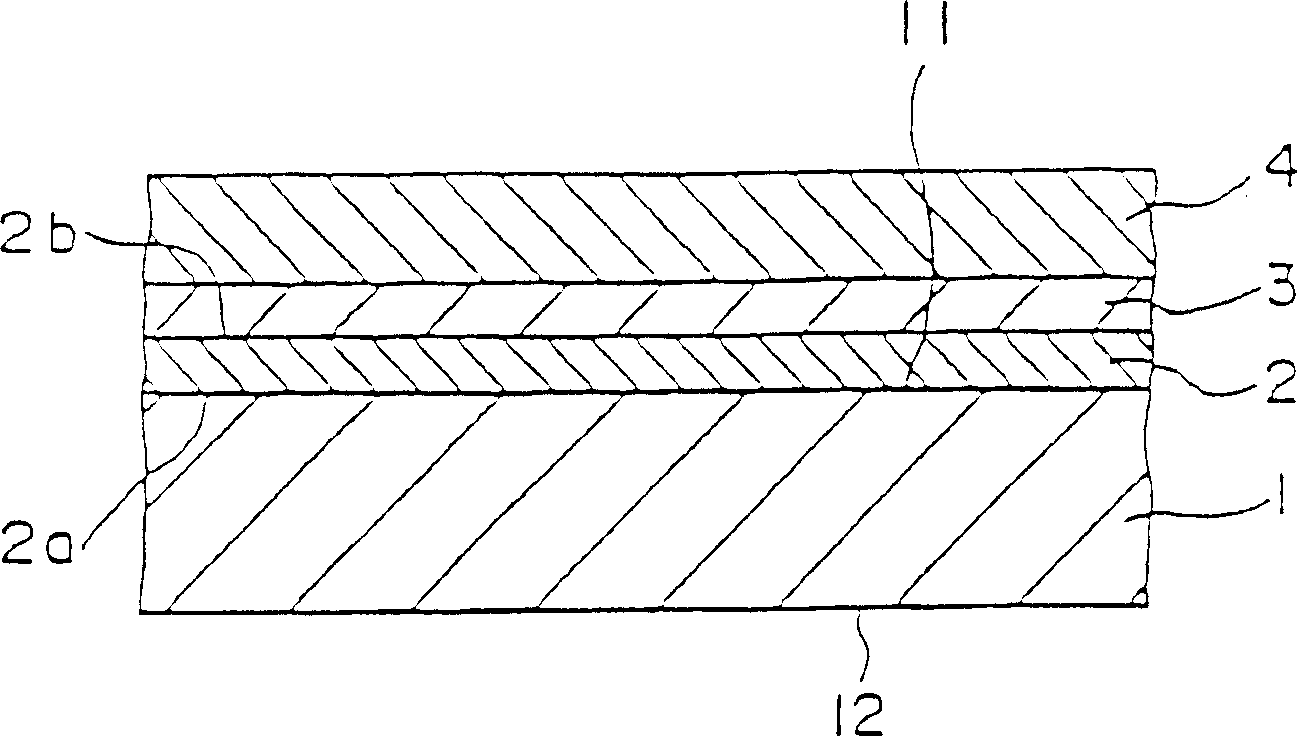

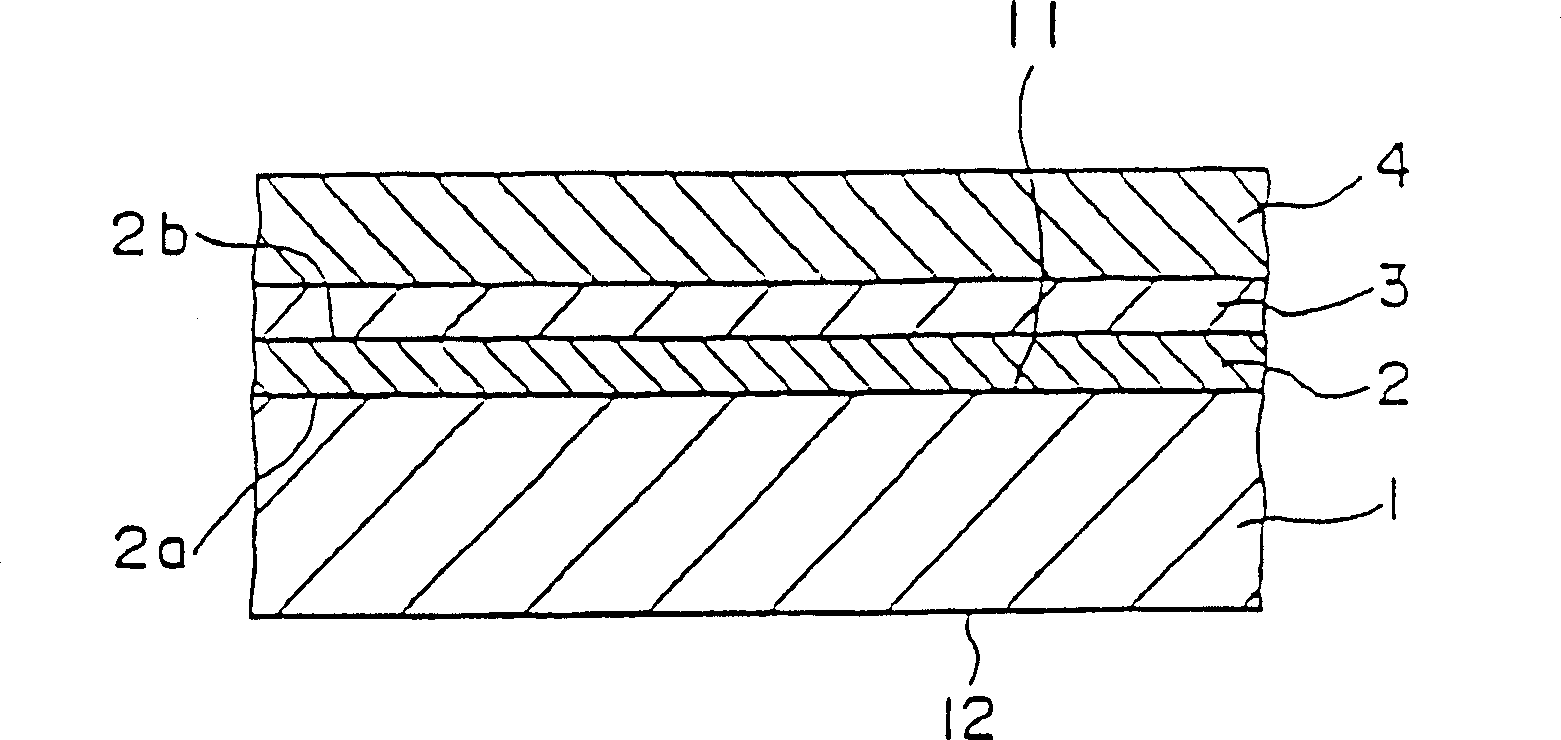

InactiveCN1897219AAvoid damageSmall conduction currentSemiconductor/solid-state device manufacturingNon-linear opticsContinuous beamIrradiation

Owner:SAMSUNG ELECTRONICS CO LTD

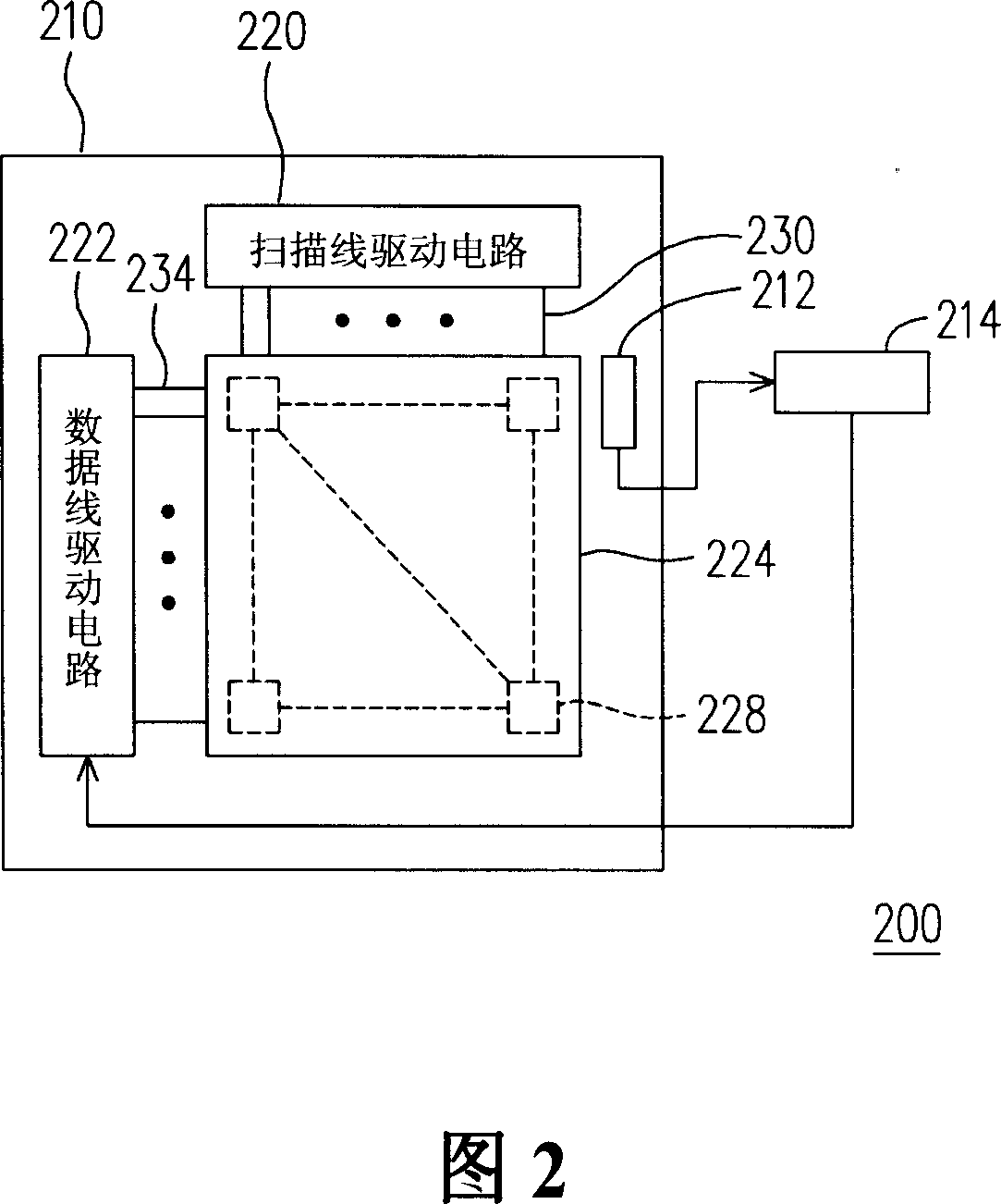

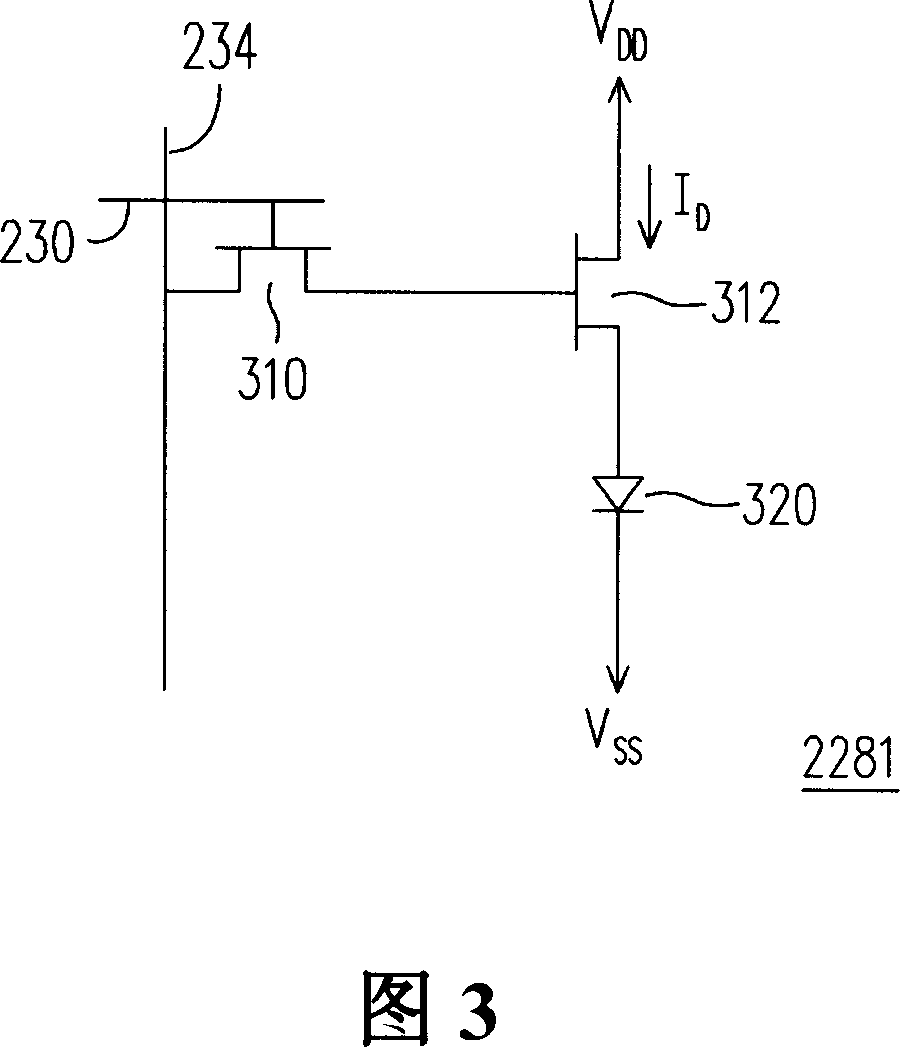

Active organic LED panel and control method thereof

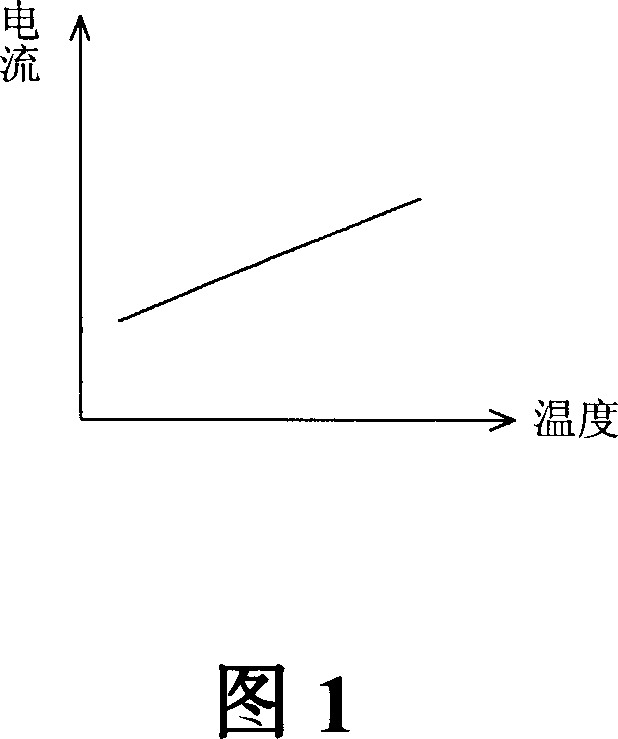

ActiveCN1949943AExtended service lifeSmall conduction currentStatic indicating devicesElectroluminescent light sourcesEngineeringFeedback control

The invention discloses an active organic LED panel and the control method thereof. And it comprises a pixel array, temperature sensor and feedback control circuit, where the temperature sensor detects its operating temperature; and the feedback control circuit regulates its operating current according to the sensed result of the temperature sensor. And its operating current amplitude is in inverse proportion to the sensed operating temperature amplitude, mainly avoiding it is on high temperature and heavy current conditions, and prolonging its service life.

Owner:AU OPTRONICS CORP

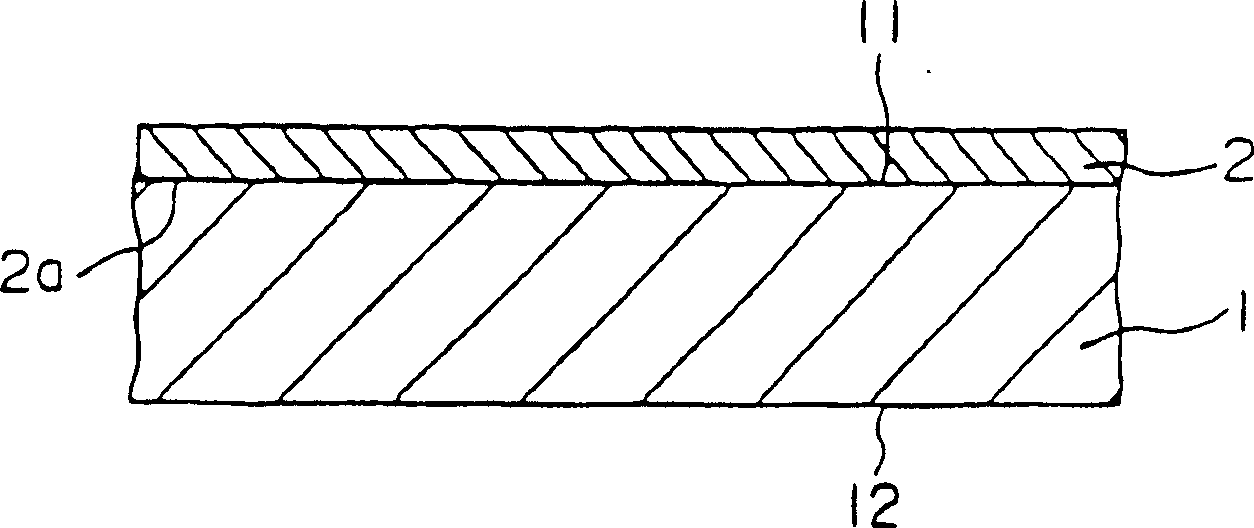

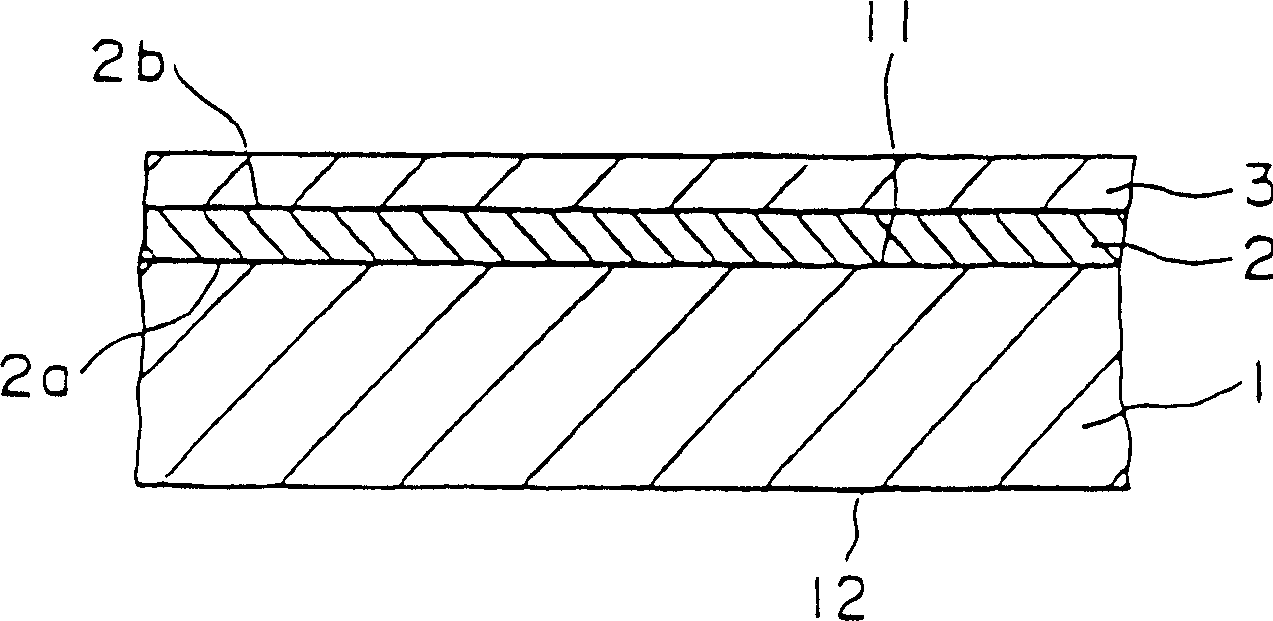

Transferring method of thin film device, production method of active matrix substrate

InactiveCN1734749AAvoid incidenceInhibit deteriorationSemiconductor/solid-state device manufacturingNon-linear opticsActive matrixEngineering

Owner:SAMSUNG ELECTRONICS CO LTD

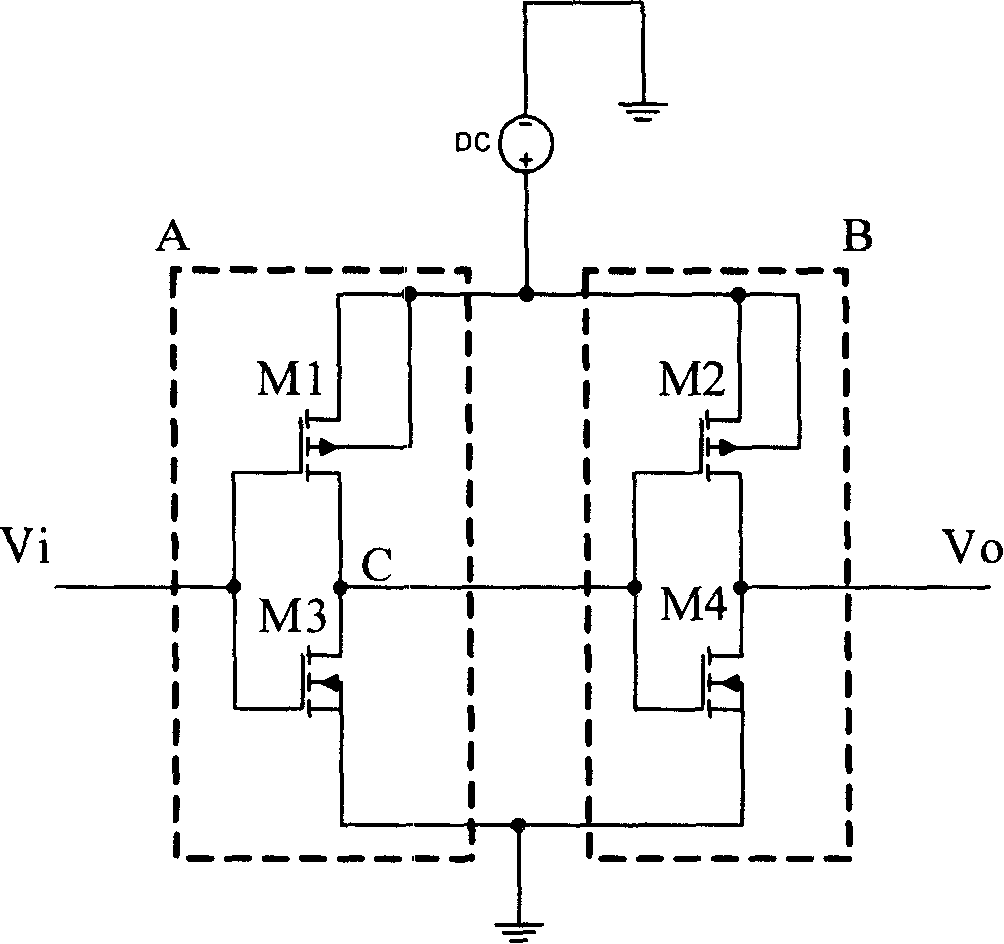

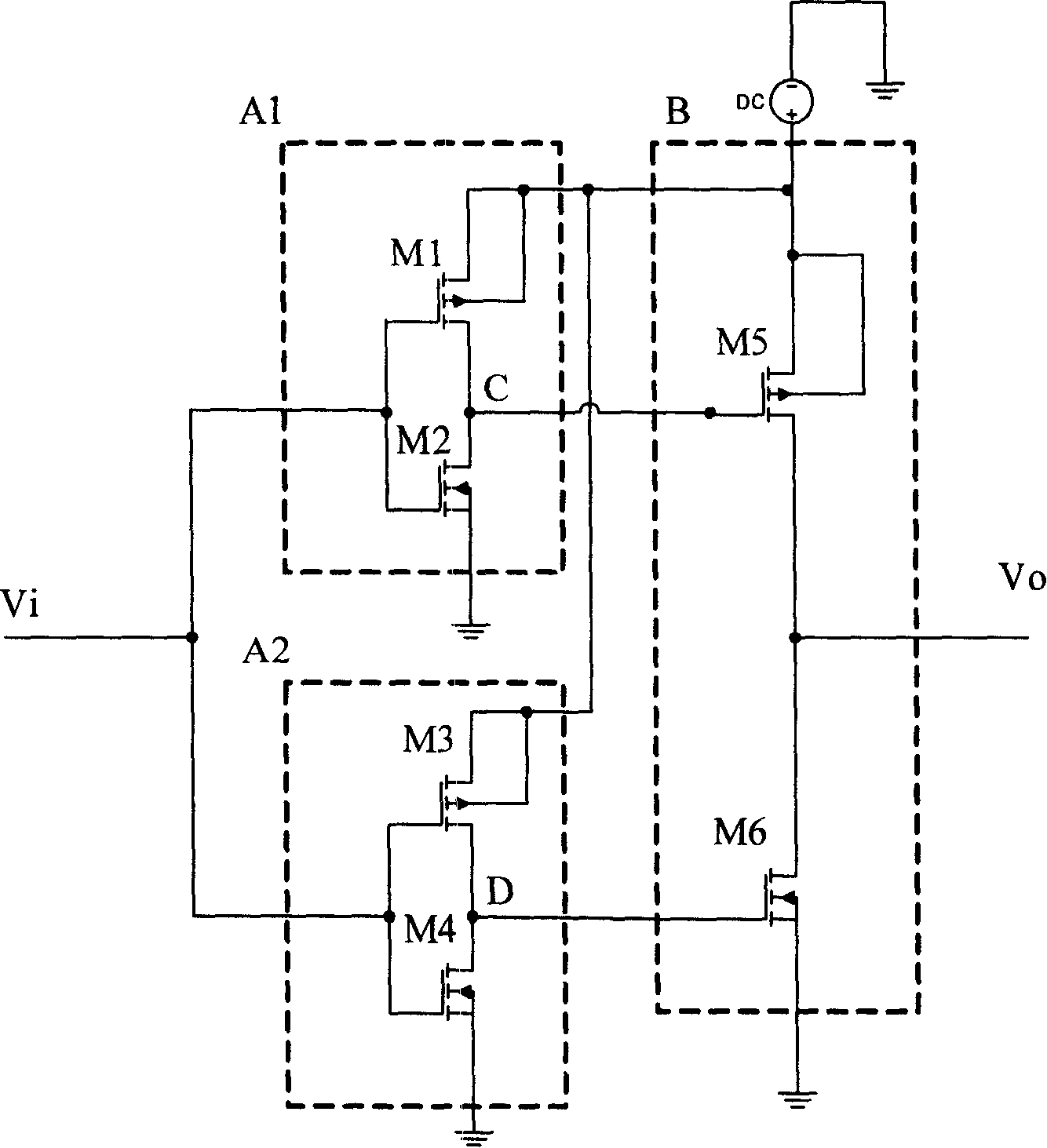

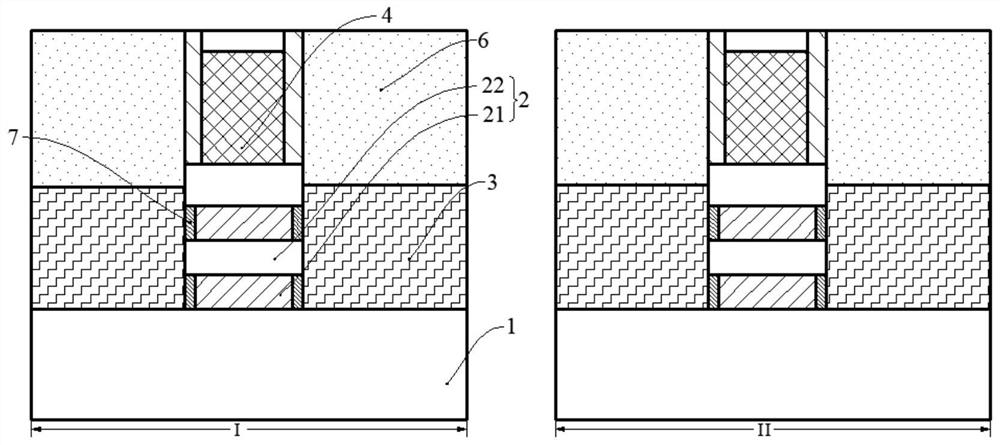

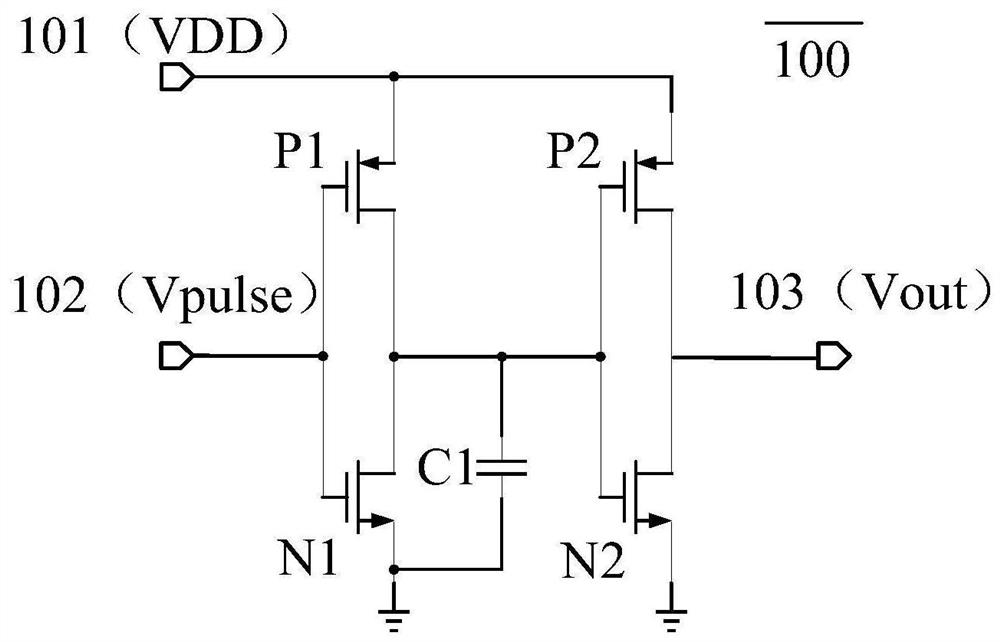

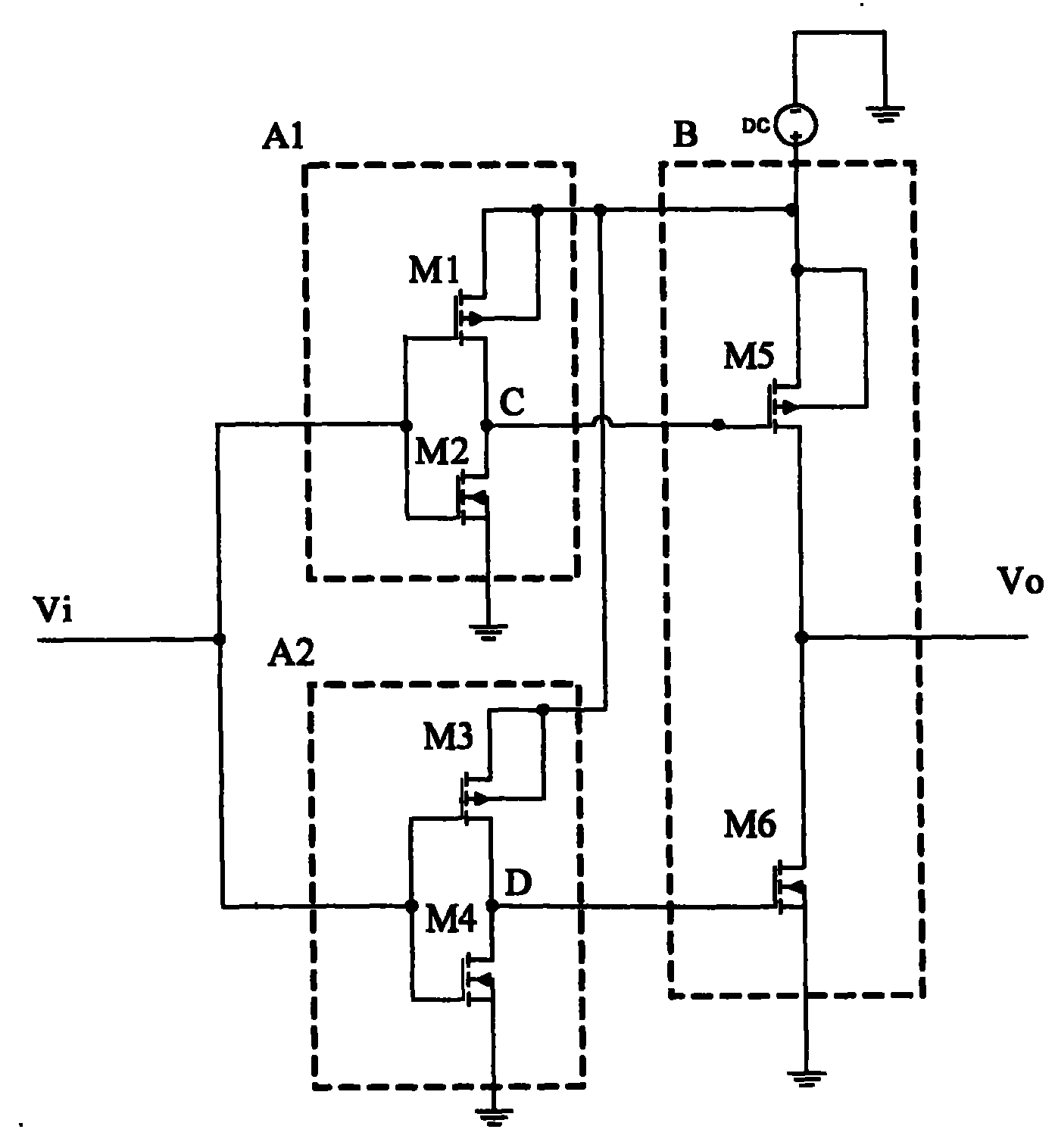

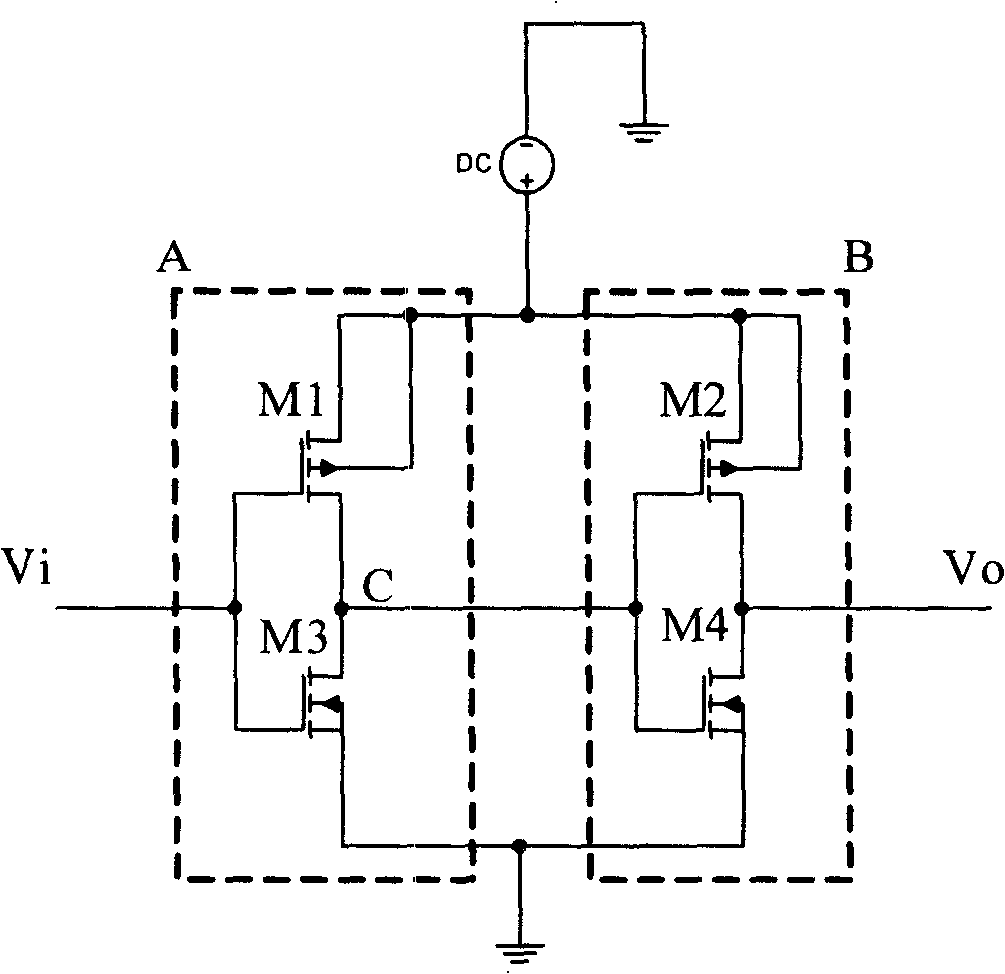

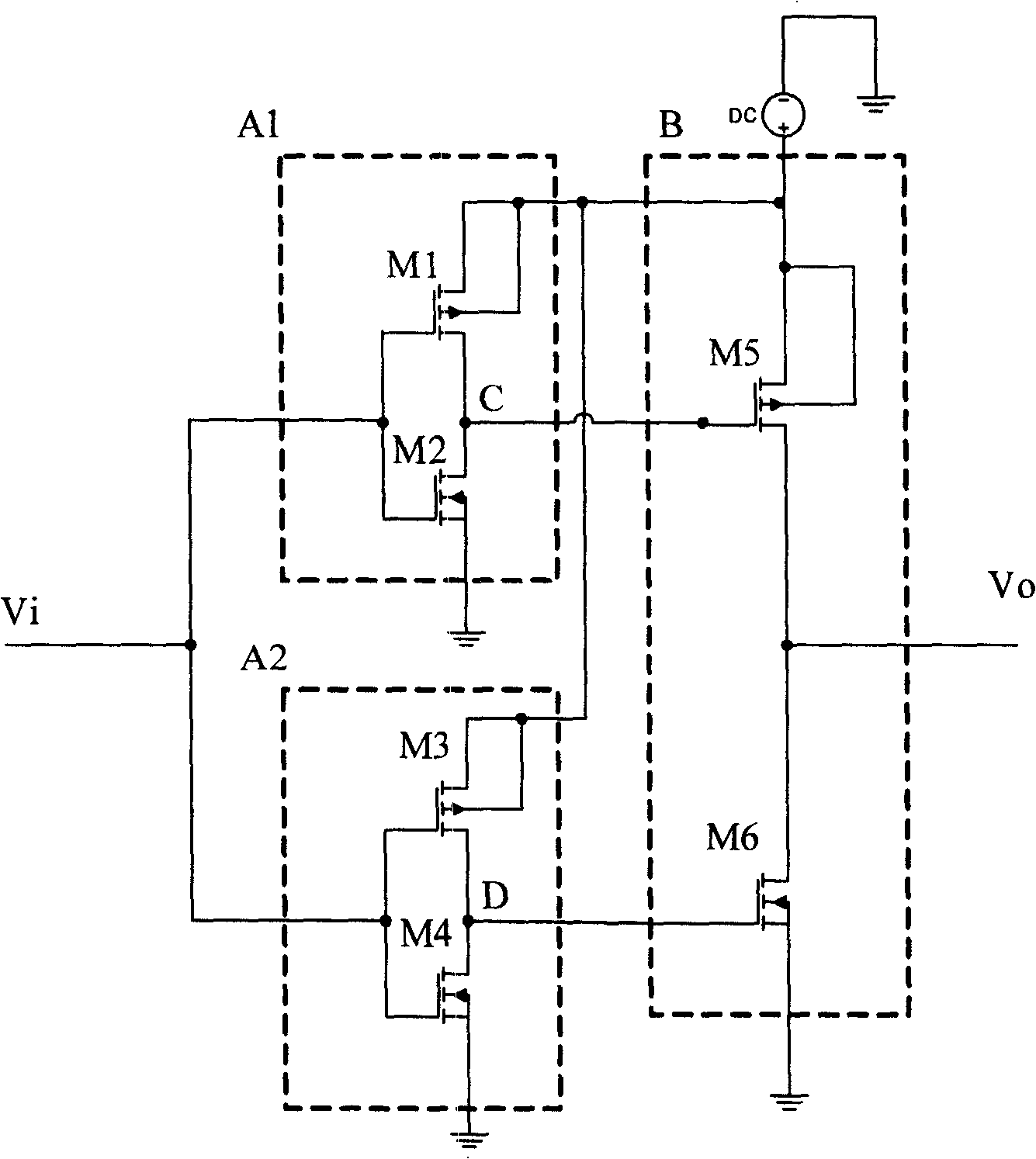

Buffer in ultra-low power consumption integrated circuit

ActiveCN101212221APrevent conduction currentAvoid simultaneous conductionReliability increasing modificationsLogic circuits coupling/interface using field-effect transistorsUltra low powerIntegrated circuit

The invention discloses a buffer in an integrated circuit with ultra low power consumption. The invention applies voltage generated by two first level inverters to drive a second level inverter to reach a target of the buffer; at the same time, the wide length ratios of a PMOS pipe and a NMOS pipe in the two first level inverters are different from each other, thus leading to a different on-stage time, so that time points of the generated voltage reaching the second level inverter are different, which can prevent the PMOS pipe and the NMOS pipe in the second level inverter from being on at the same time and thus generate on-state current. The invention can be used in the integrated circuit with ultra low power consumption.

Owner:SHANGHAI HUAHONG INTEGRATED CIRCUIT

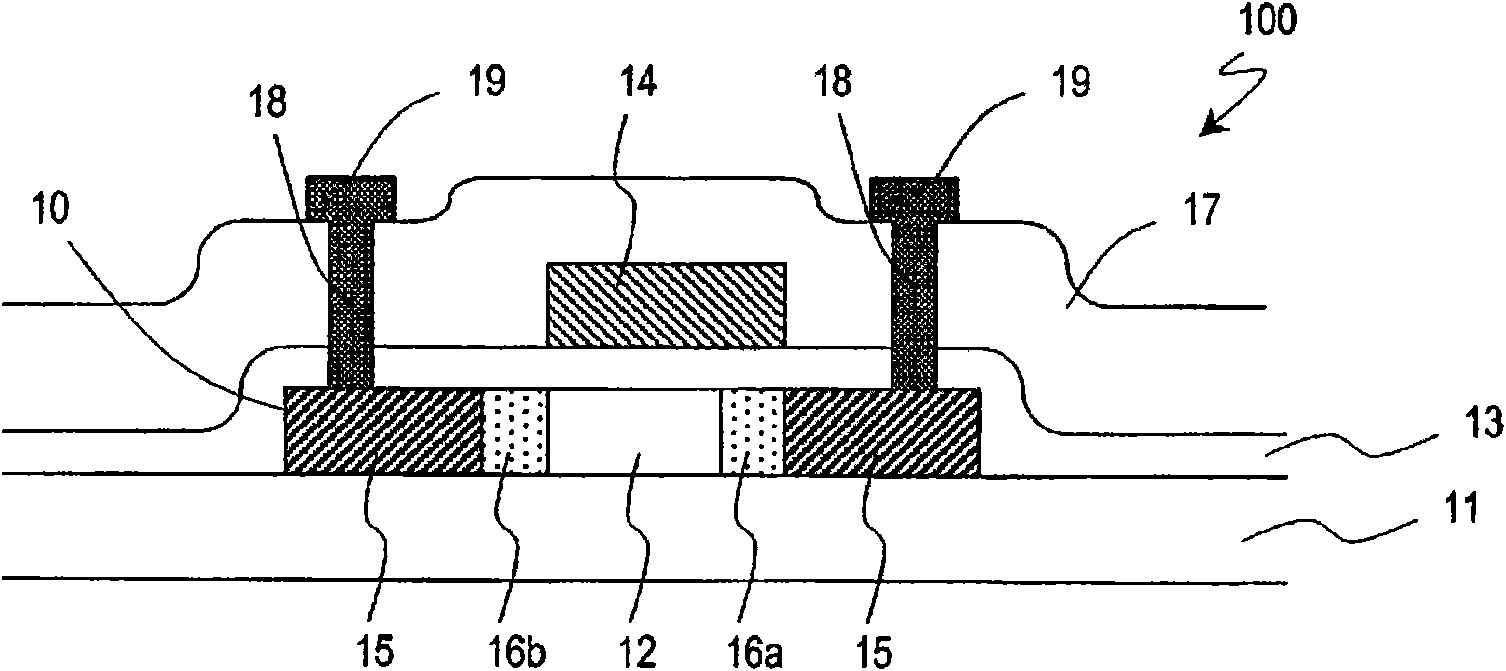

Semiconductor device and method for manufacturing the same

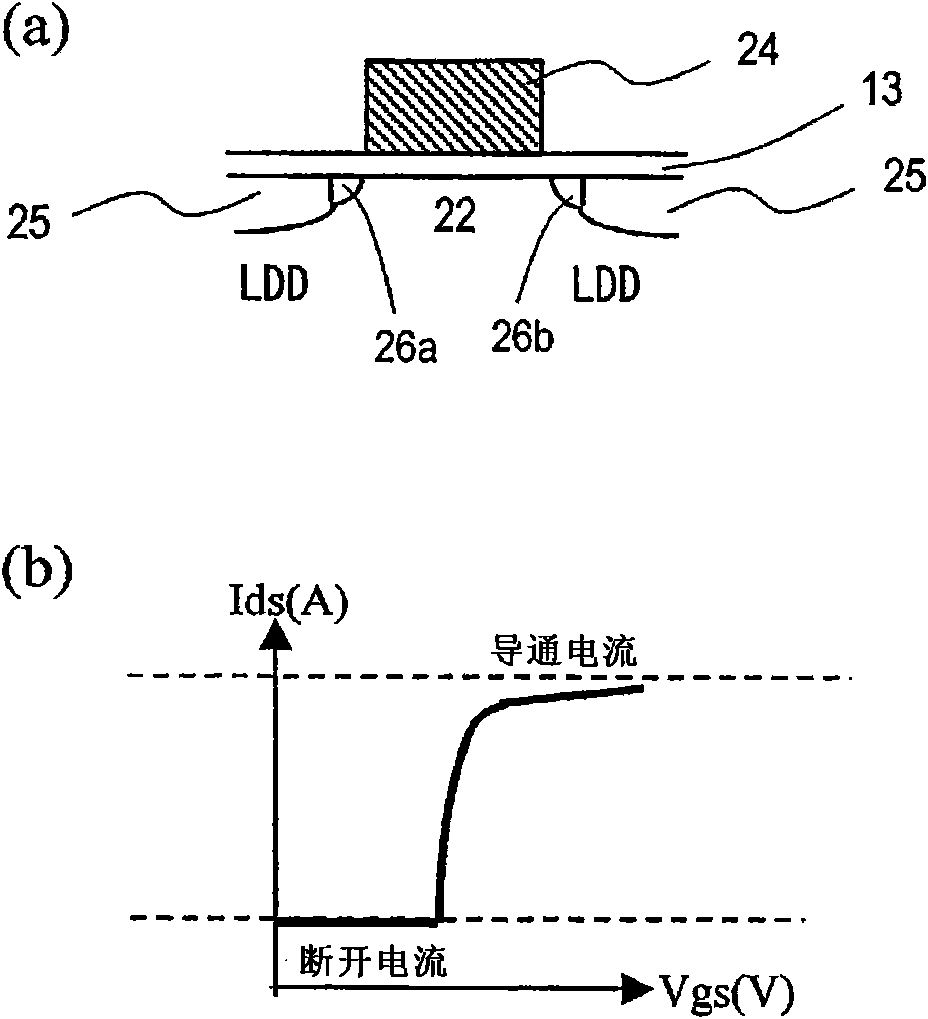

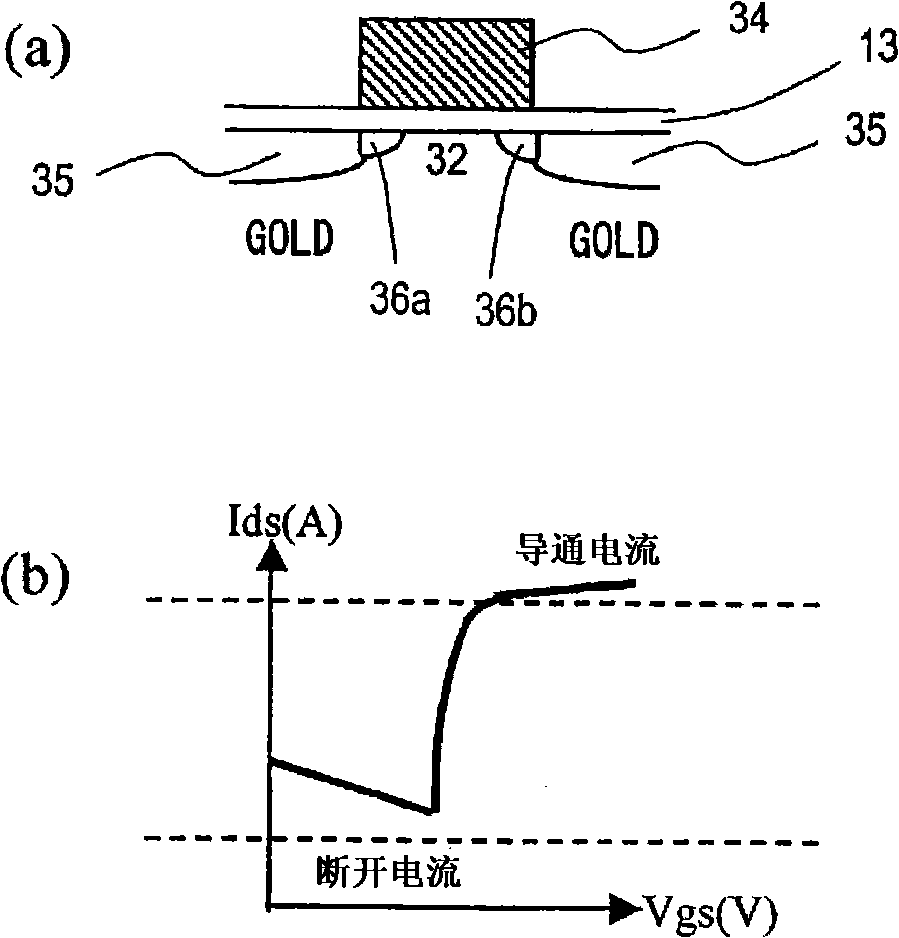

InactiveCN101925988AEnsure current driving forceReduce the number of manufacturing processesTransistorSemiconductor/solid-state device manufacturingImpuritySemiconductor

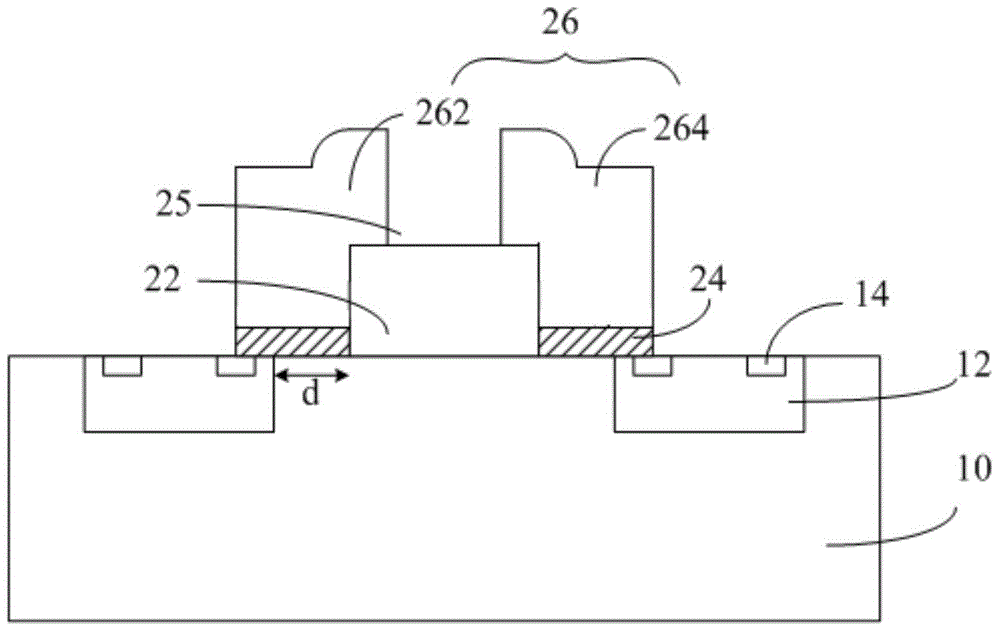

Provided is a semiconductor device wherein a gate electrode (14) of a thin film transistor (100) is formed of a single conductive film, and a semiconductor layer (10) is provided with a first low-concentration impurity region, which is arranged between the channel region (12) and the source region (15), and has an impurity concentration lower than the impurity concentrations of the source region and the drain region (15), and a second low-concentration impurity region, which is arranged between the channel region (12) and the drain region (15), and has an impurity concentration lower than the impurity concentrations of the source region and the drain region (15). A region (16a), which is one of the first and the second low-concentration impurity regions, entirely overlaps with the gate electrode (14), and a region (16b), which is the other one of the first and the second low-concentration impurity regions, does not overlap with the gate electrode (14).

Owner:SHARP KK

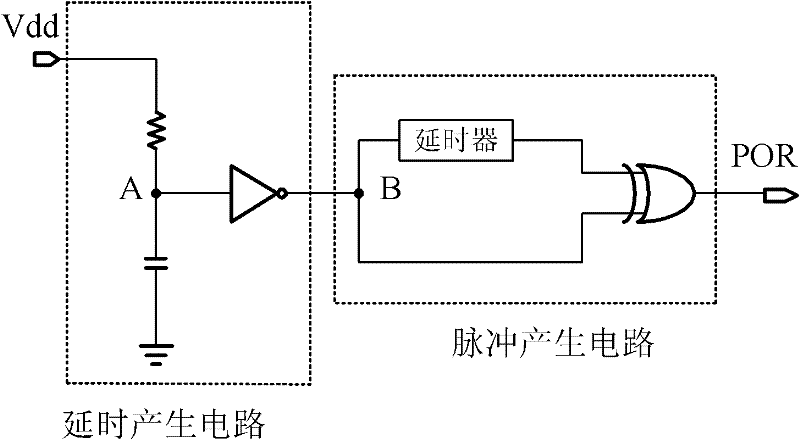

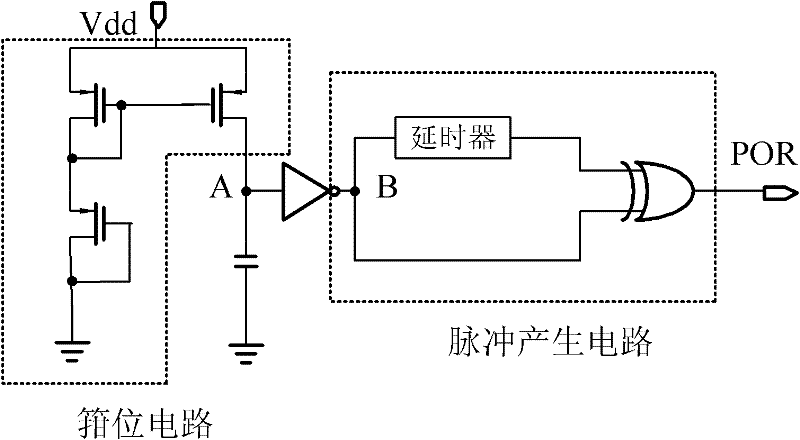

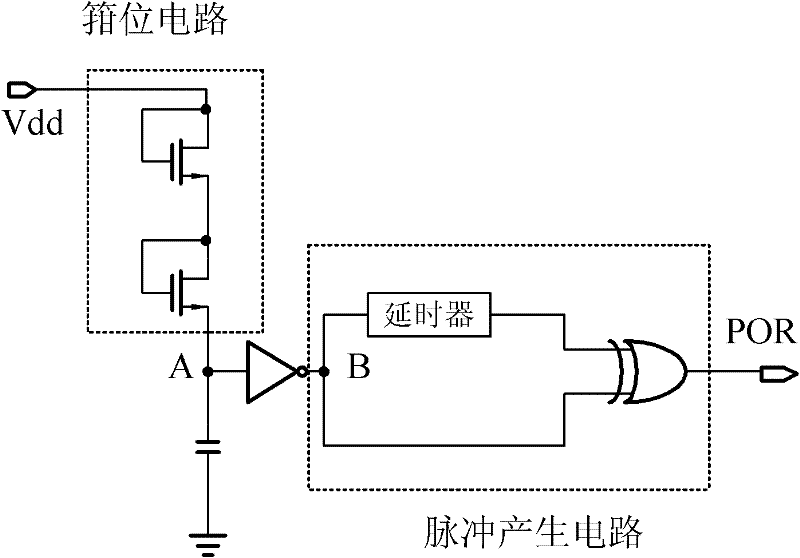

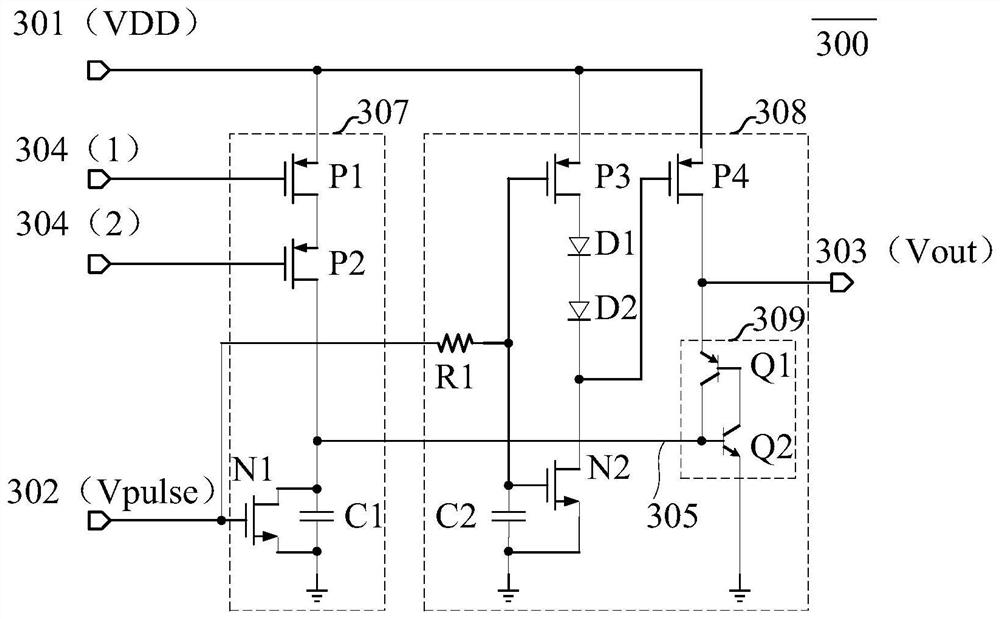

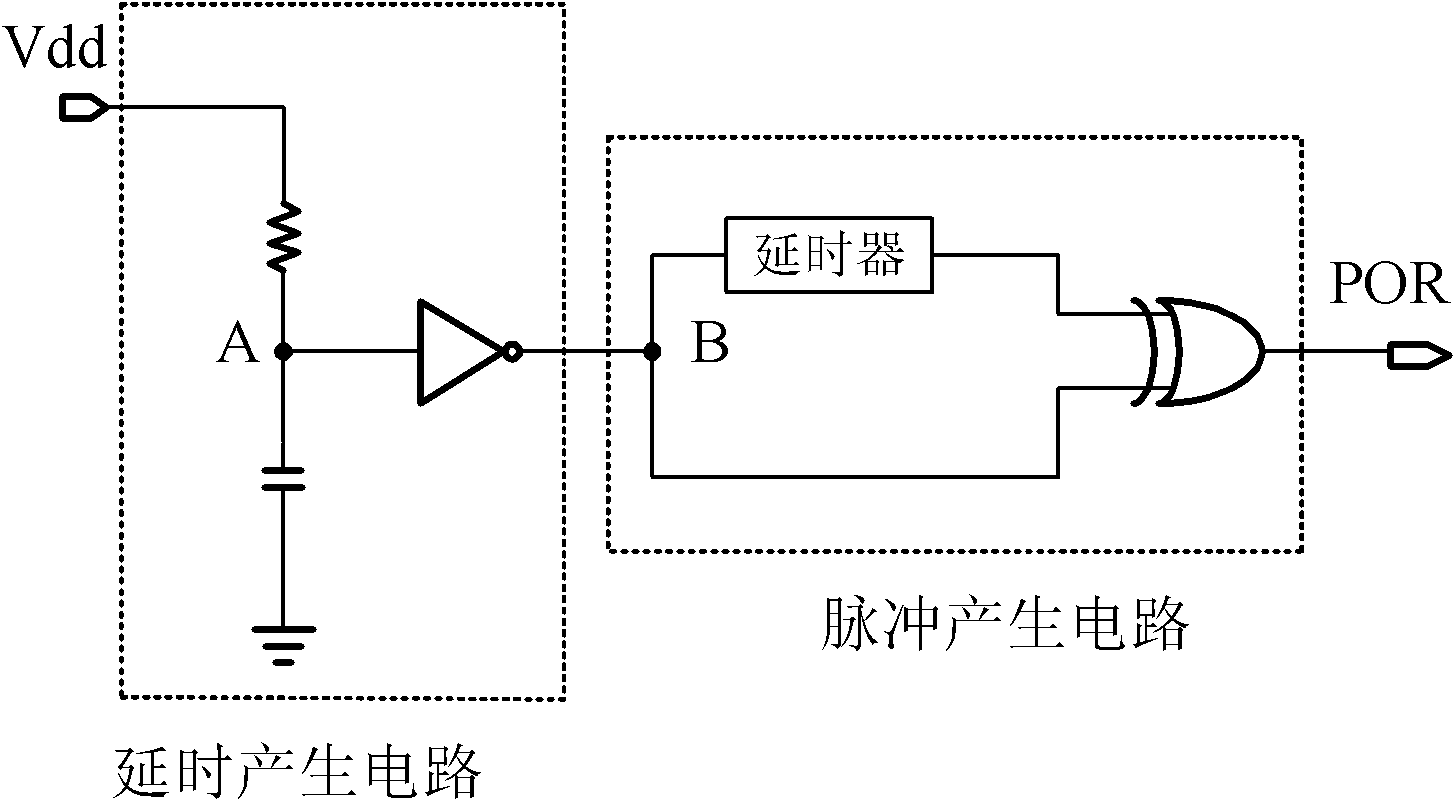

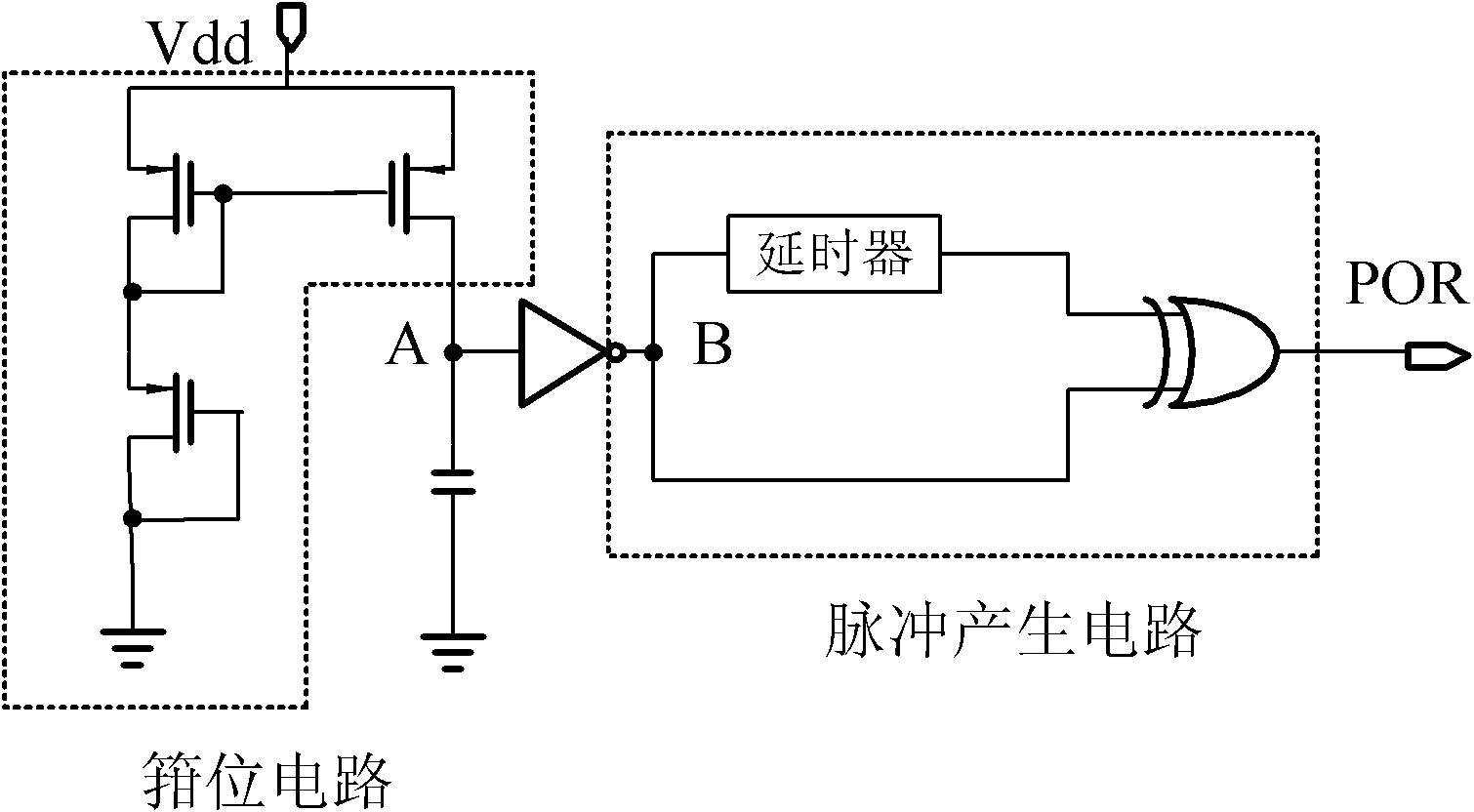

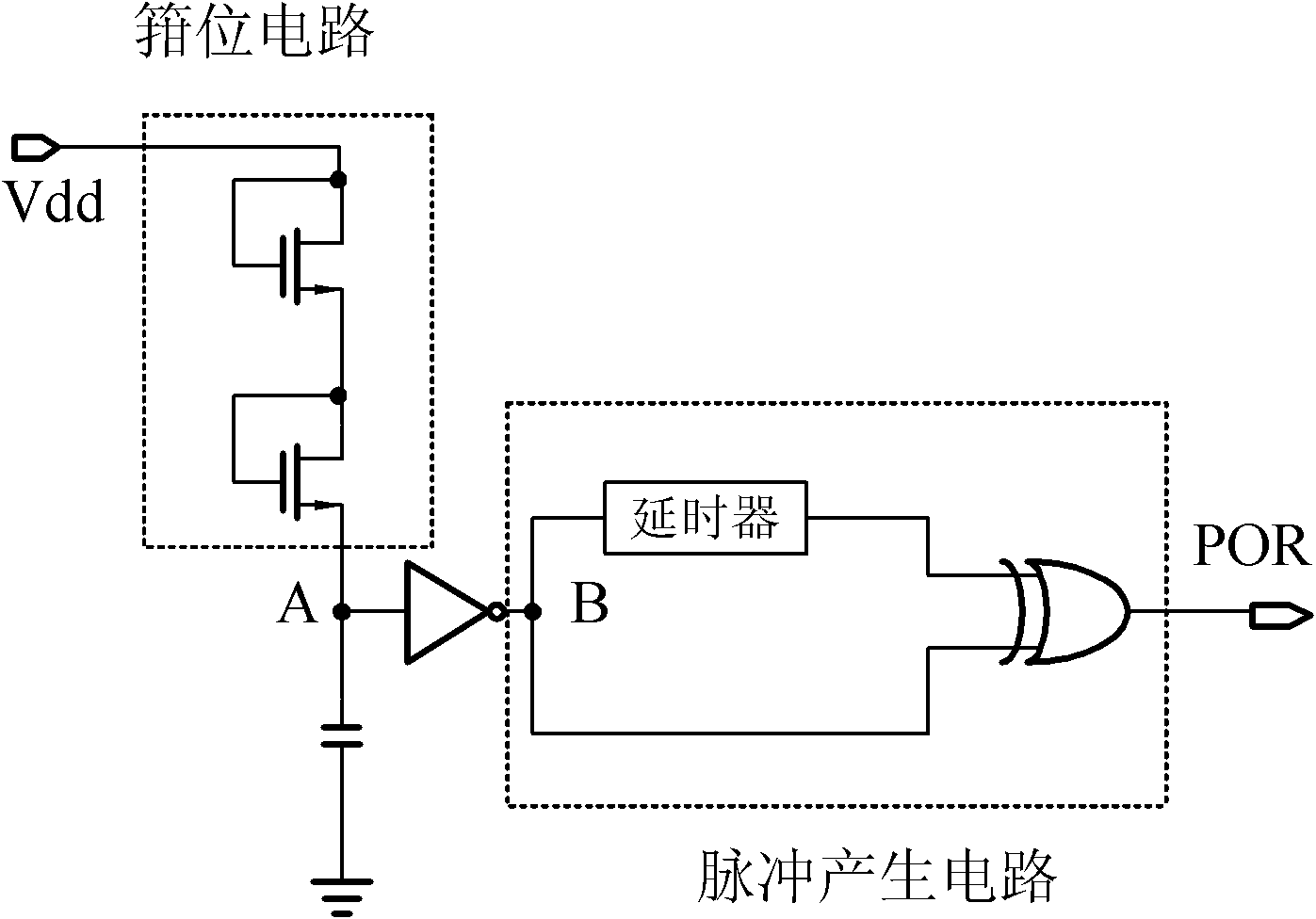

Power-on reset circuit of electronic label of RFID (radio frequency identification device) system

ActiveCN102456153ASmall conduction currentReduce power consumptionRecord carriers used with machinesPower-on resetEngineering

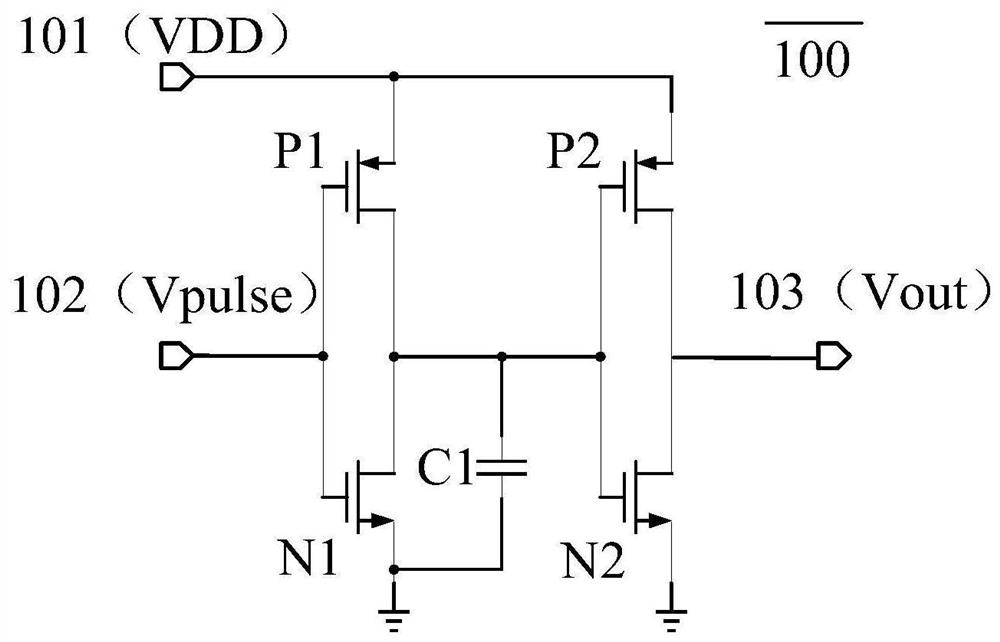

The invention discloses a power-on reset circuit of an electronic label of an RFID (radio frequency identification device) system, which comprises two input ends, one output end, nine MOS (metal oxide semiconductor) transistors, one resistor and two capacitors, wherein input signals (voltage drain drain (VDD)) of the first input end and the second input end are working voltage signals output by aregulator of a radio-frequency analog front end circuit of the electronic label of the RFID system; and output signals (power-on reset (POR)) of the output end are power-on reset signals provided by a digital baseband circuit of the electronic label of the RFID system. The power-on reset circuit has an extremely low breakover current, and achieves the purpose of low power consumption.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

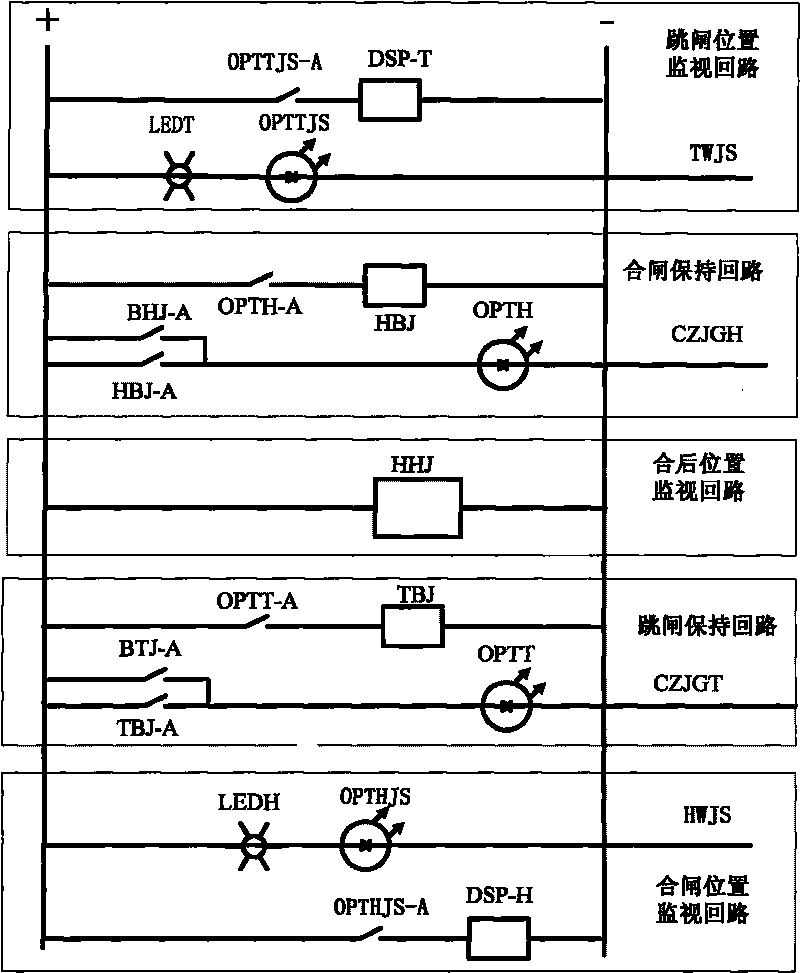

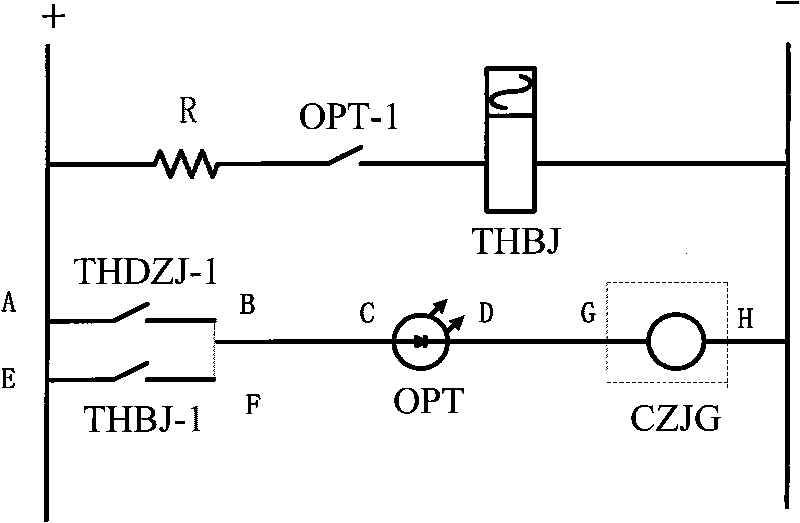

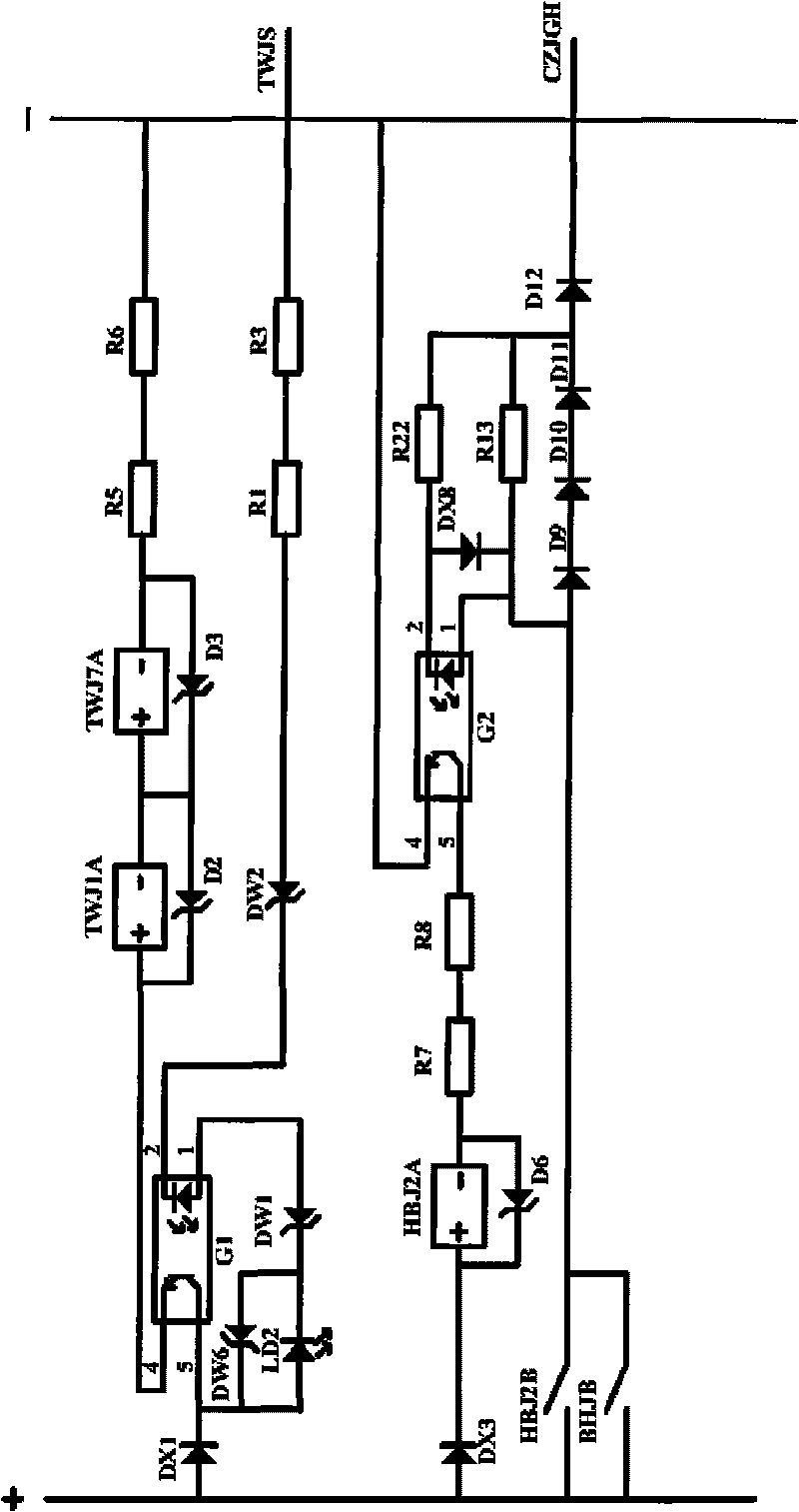

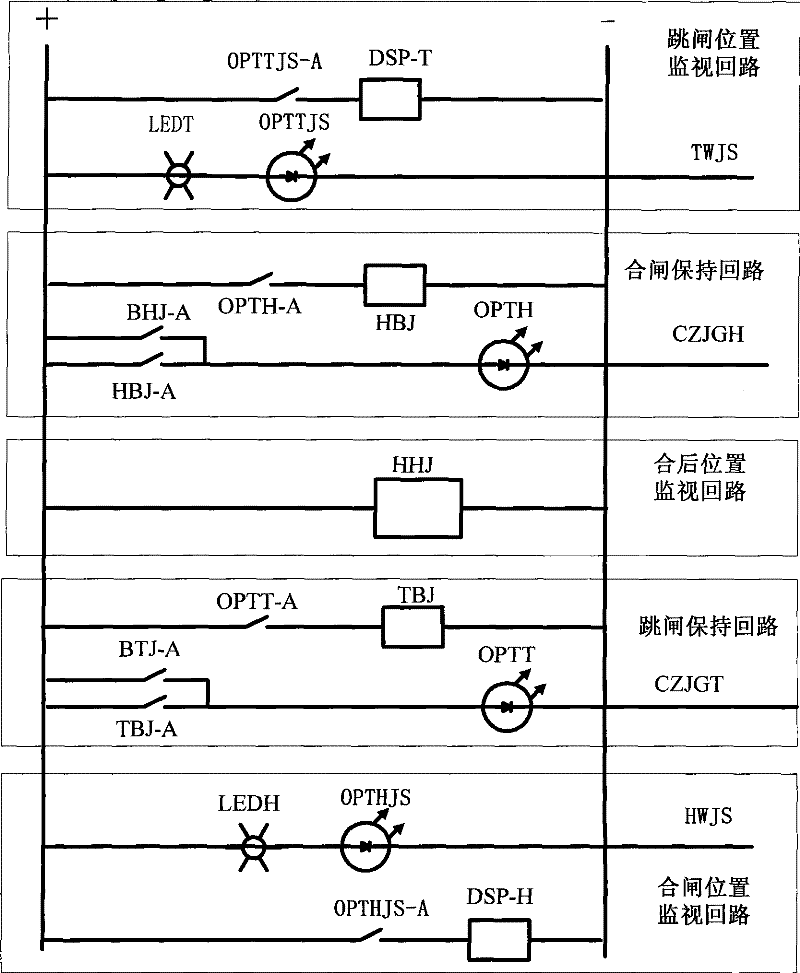

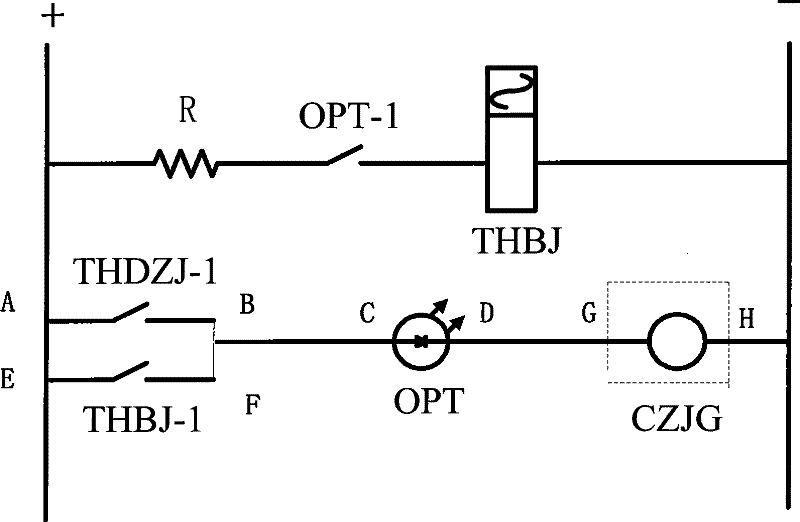

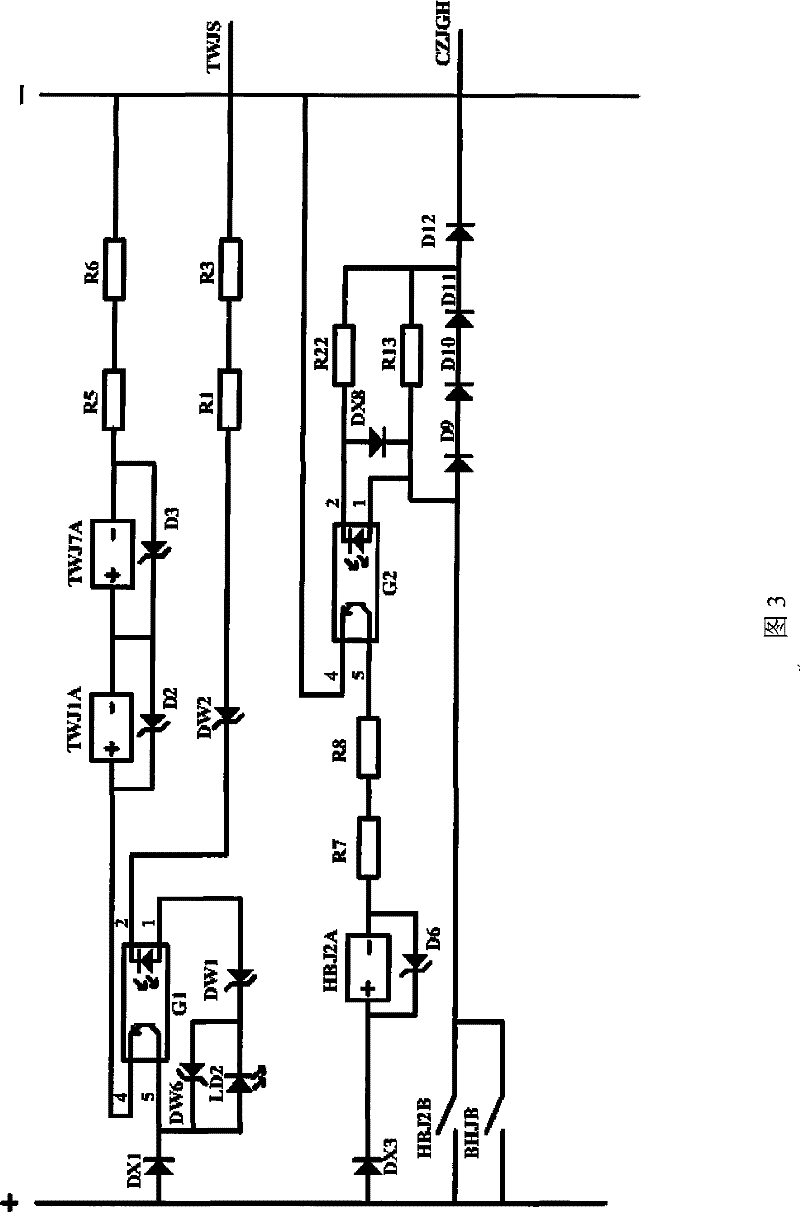

Full-adaptive high-voltage switch controller based on light-coupled control

ActiveCN101728773ASmall conduction currentImprove isolationBoards/switchyards circuit arrangementsCurrent rangeControl system

The invention discloses a full-adaptive high-voltage switch controller based on light-coupled control, belonging to control equipment of a high-voltage substation. The switch controller is connected with the operating mechanism of a high-voltage circuit breaker, and is composed of a tripping / switching retaining circuit and a position monitoring circuit. Optical couplers arranged in a switching retaining circuit, a tripping retaining circuit, a tripping position monitoring circuit and a switching position monitoring circuit. One end of each optical coupler luminous component is connected with the operating mechanism of the high-voltage circuit breaker, the other end is connected with the positive pole of a power supply by a position indicating lamp or the normally open contact of a relay, and the contact conductive parts of the optical couplers are connected on the input end of each circuit relay. The controller fully utilizes the characteristics of sensitivity and smaller conductive current of the optical couplers to realize the control of small current on high power devices and the control of various tripping / switching operating mechanisms of which the full adaptive tripping / switching retaining current ranges from 10mA to 15mA on the circuit breaker, thereby greatly improving the safety and reliability of substation protective relaying equipment and an intelligent operating box, relieving the potential safety hazard of the substation, and being applicable to railway and other control systems.

Owner:成都智达电力自动控制有限公司

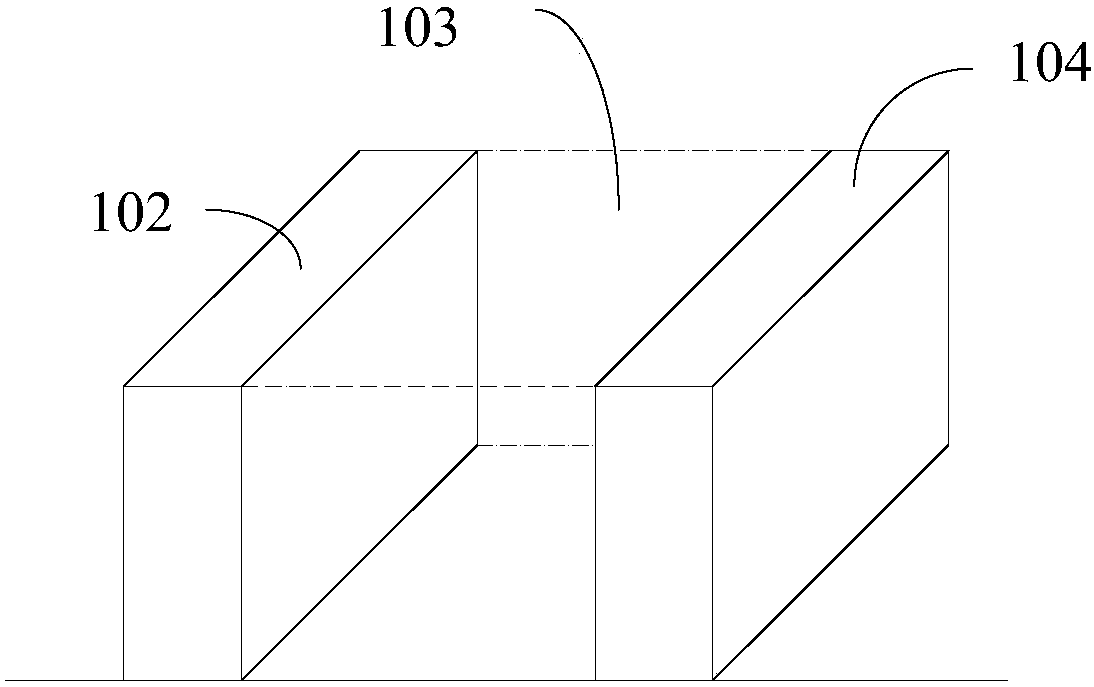

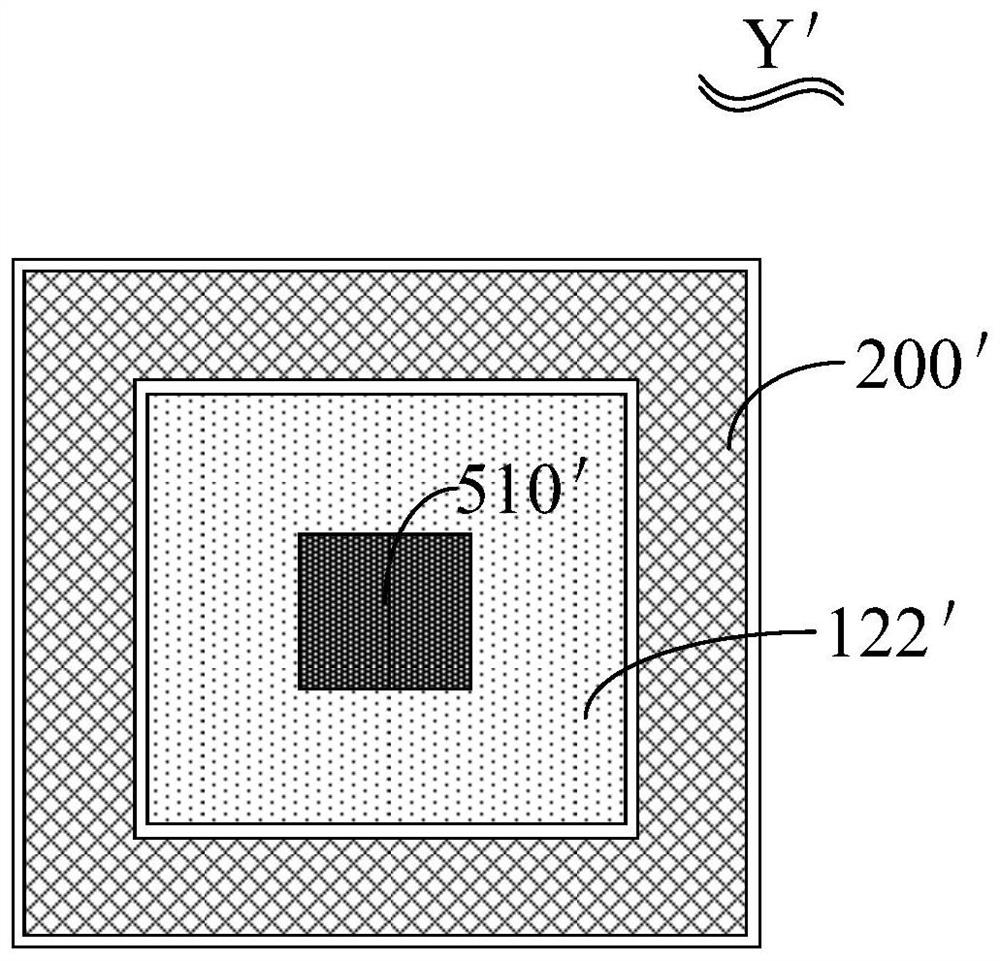

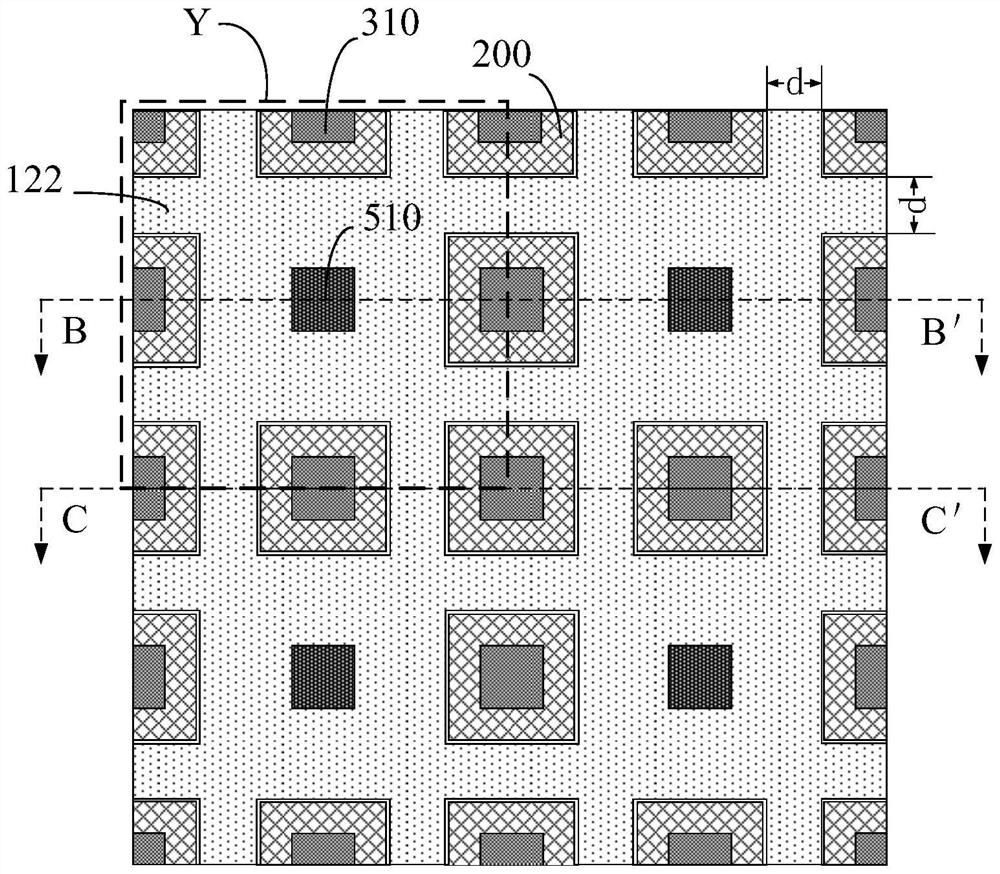

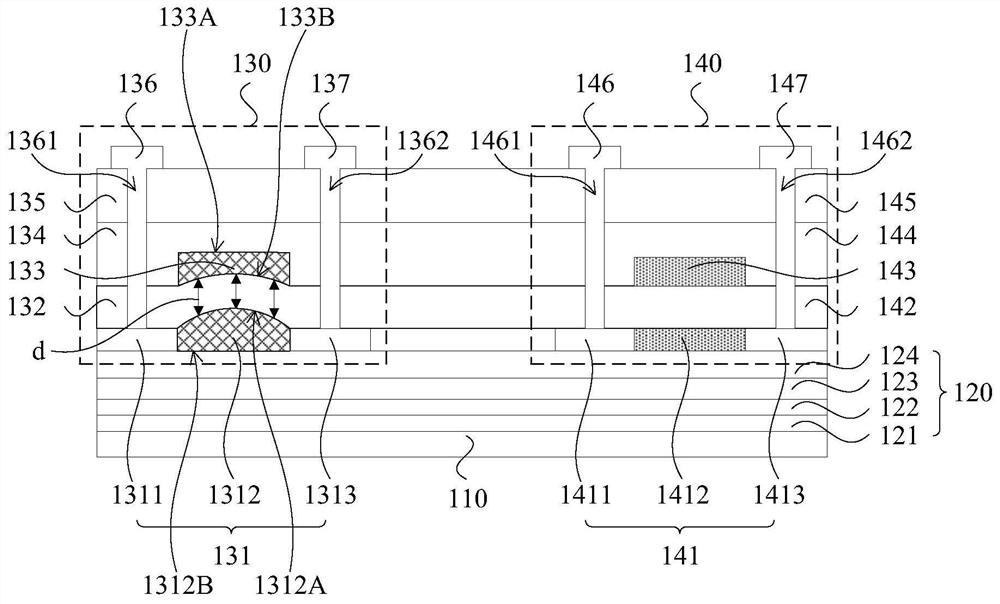

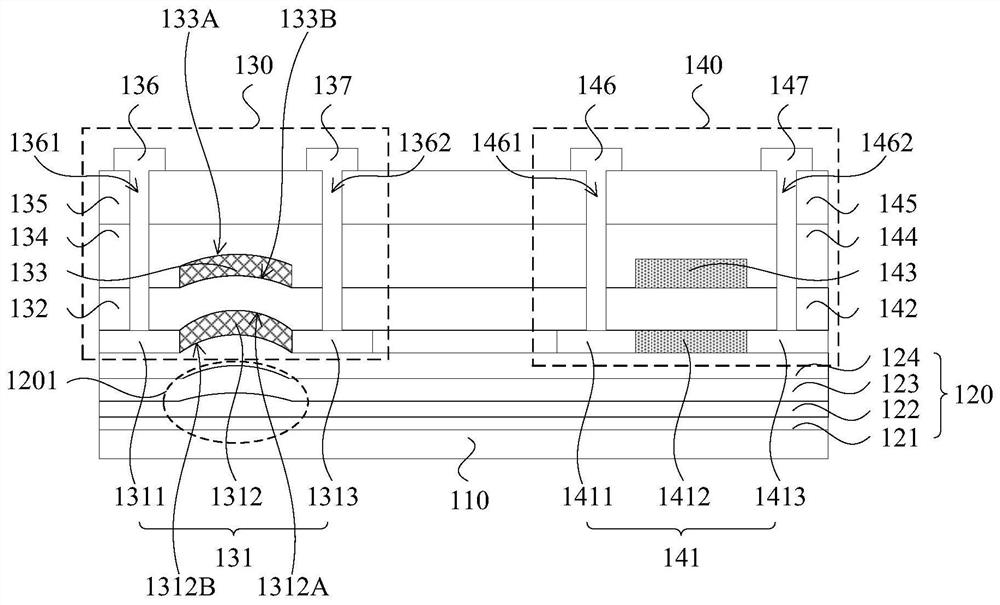

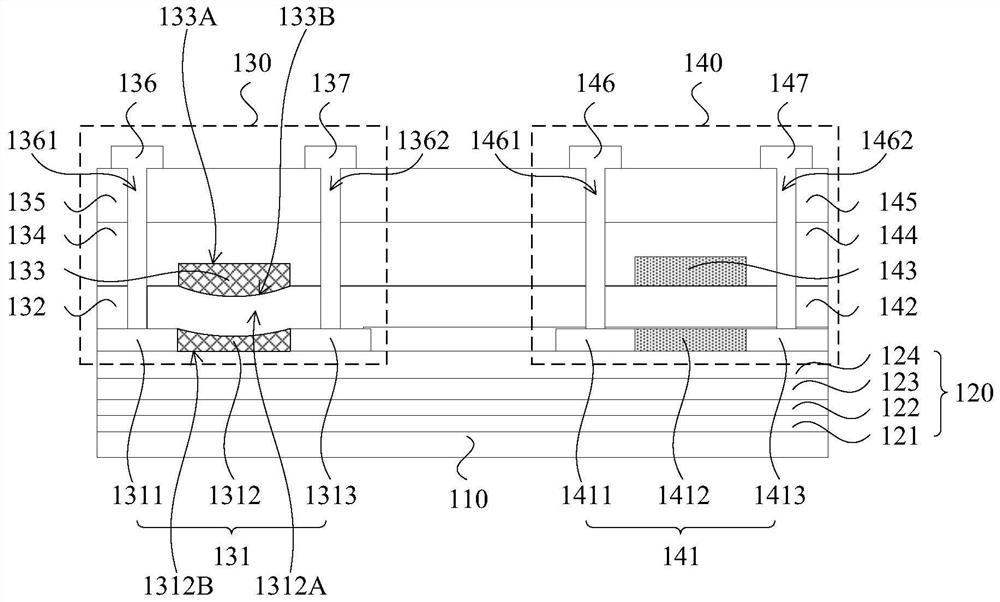

Array substrate and display panel

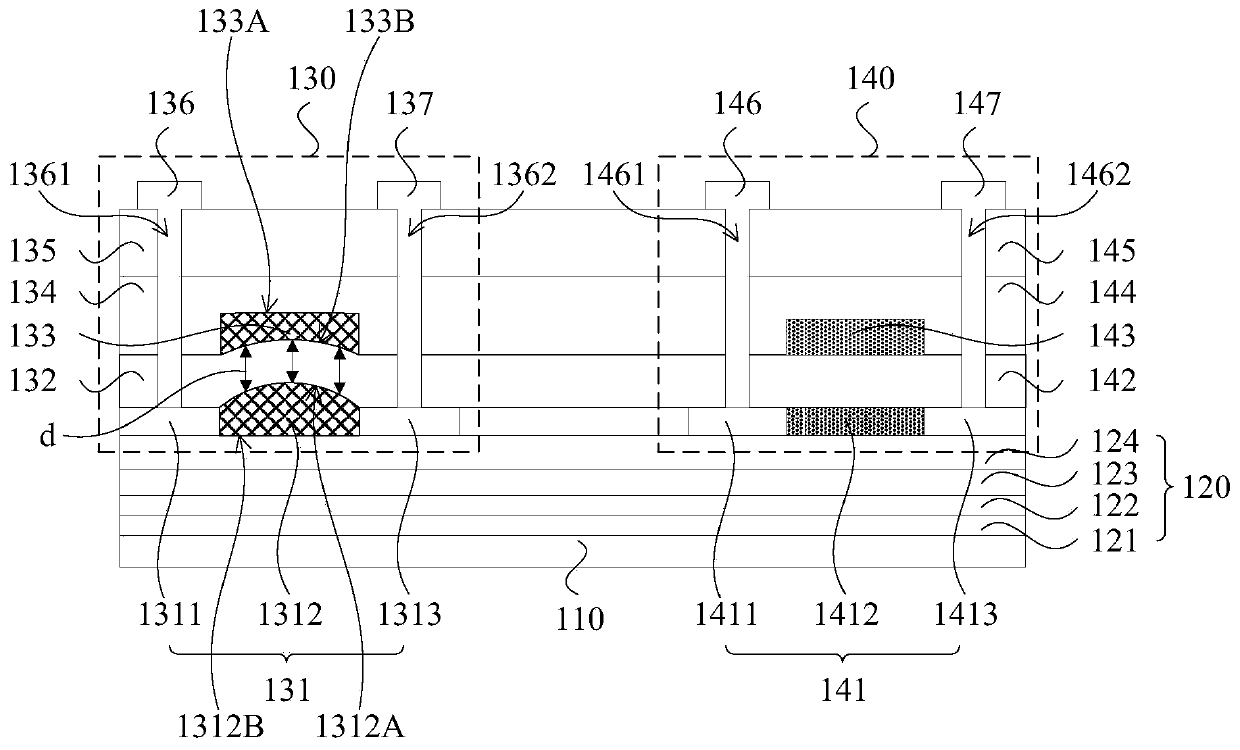

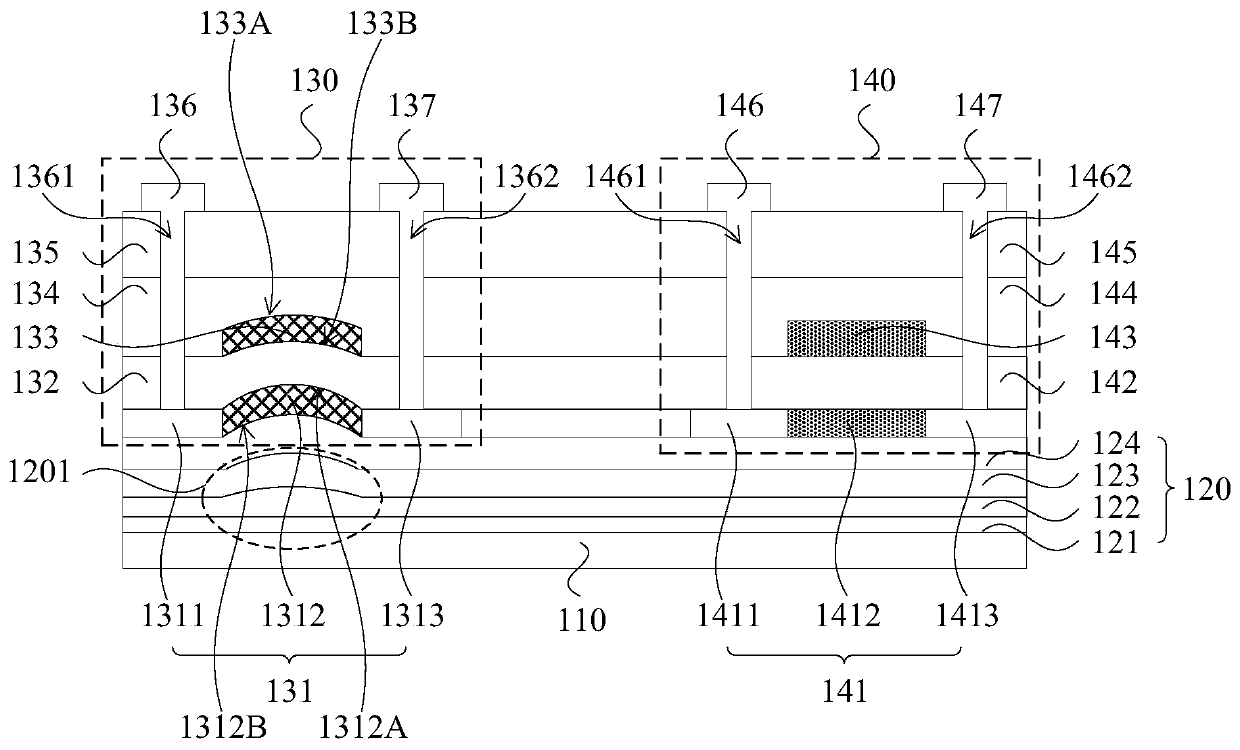

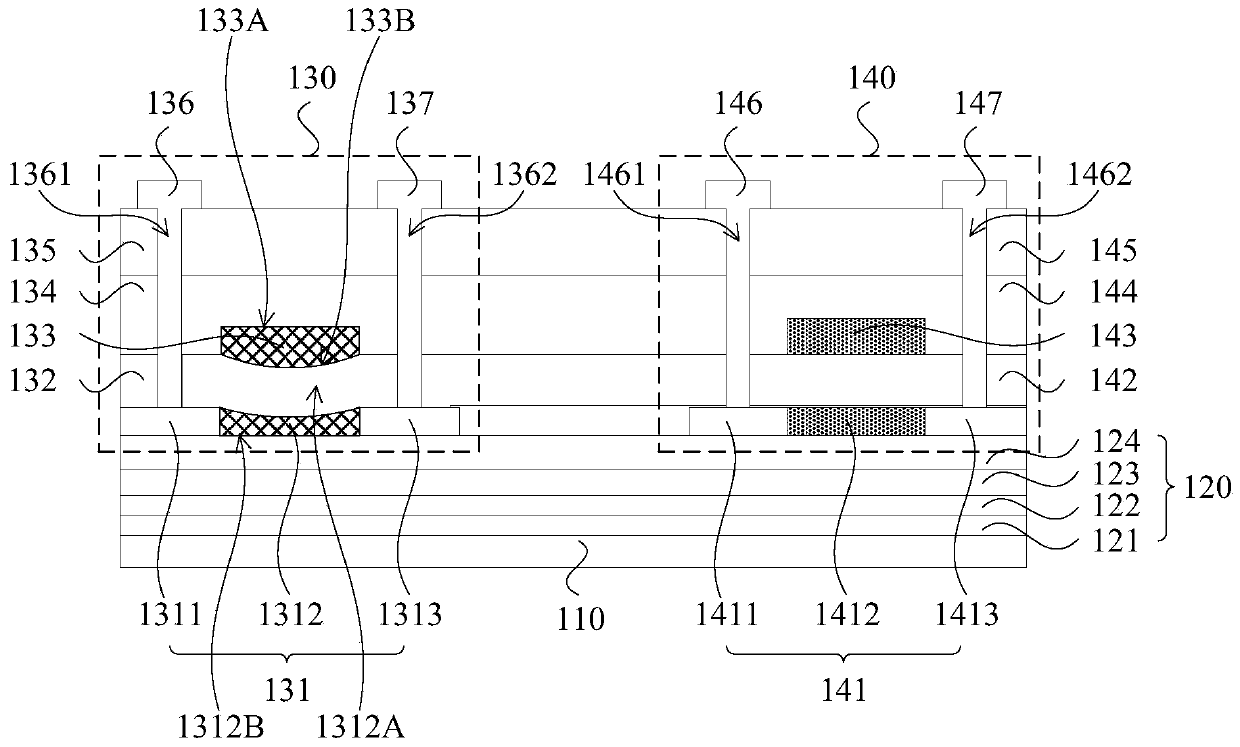

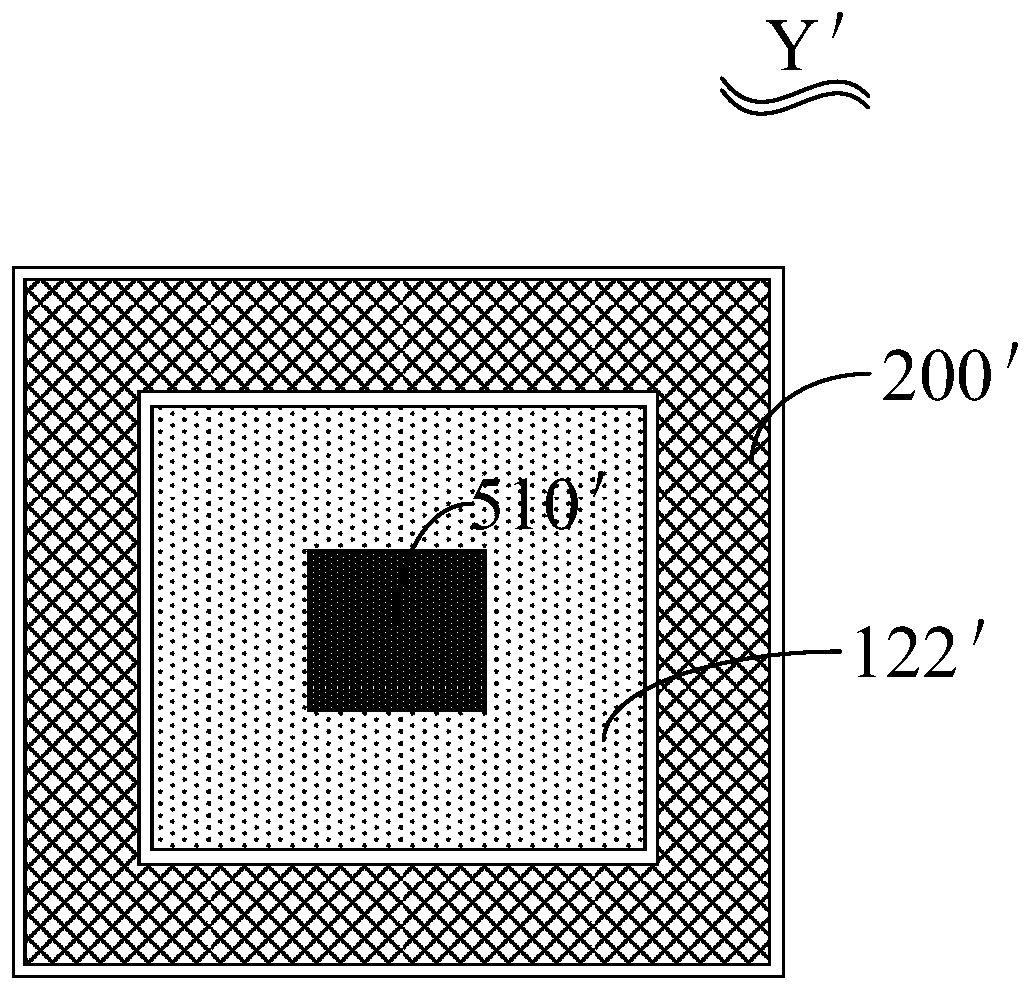

ActiveCN110931514AIncrease the areaIncrease capacitySolid-state devicesSemiconductor/solid-state device manufacturingVertical projectionInsulation layer

The embodiment of the invention discloses an array substrate and a display panel. The array substrate comprises a first thin film transistor arranged on the substrate, and the first thin film transistor comprises a first active layer, a first gate insulation layer and a first gate layer, wherein the surface area, close to the first gate layer, of a first channel region of the first active layer islarger than the area of the vertical projection of the first channel region on the substrate, the surface area of the first gate layer close to the first active layer is greater than the area of thevertical projection of the first gate layer on the substrate, and along the direction perpendicular to the substrate, the distances from all points on the surface, close to the first active layer, ofthe first gate layer to the surface, close to the first gate layer, of the first channel region are equal. Compared with the prior art, the characteristics of the switching thin film transistor are improved, and the driving characteristics of the array substrate and the display effect of the display panel are improved.

Owner:YUNGU GUAN TECH CO LTD

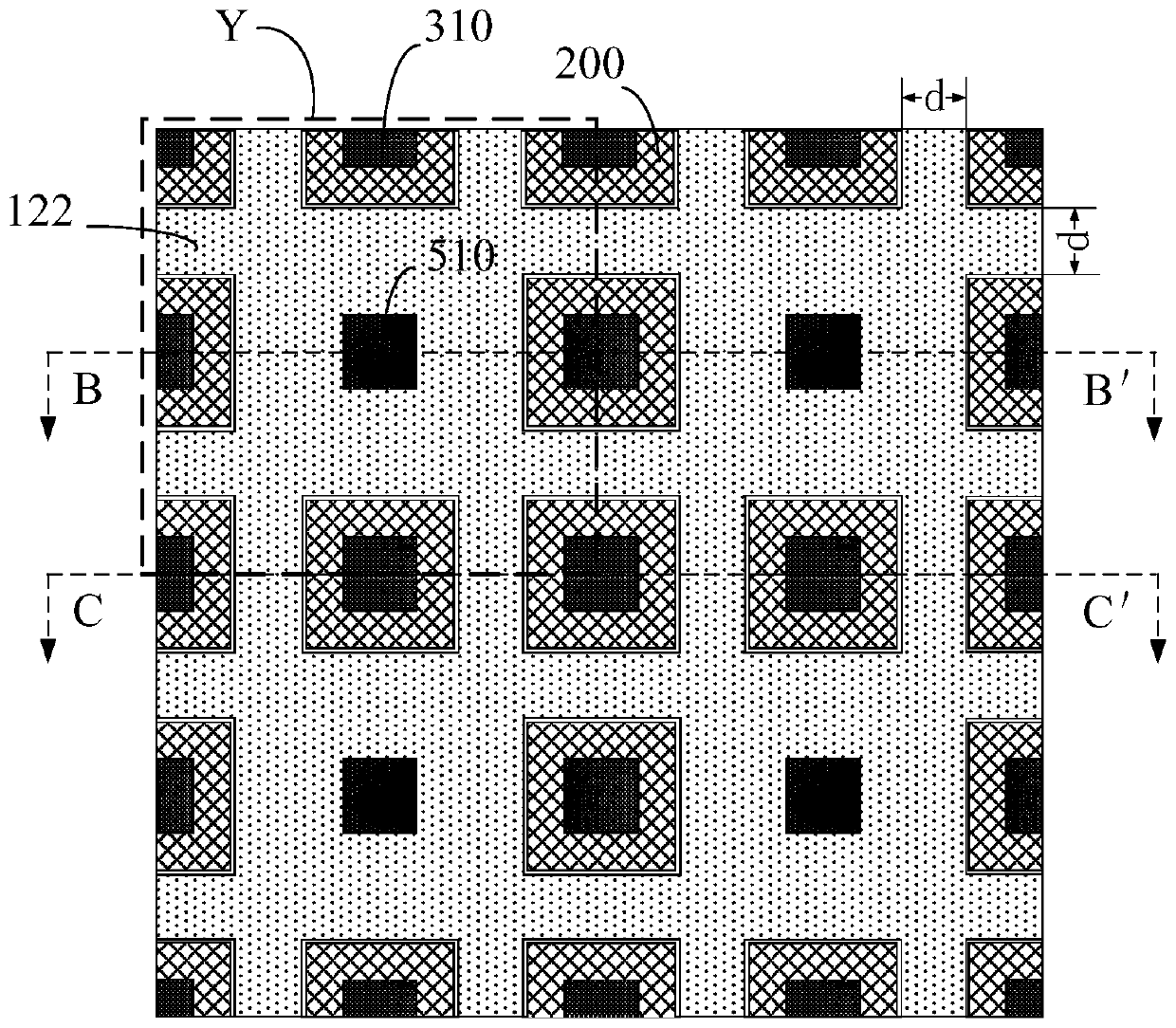

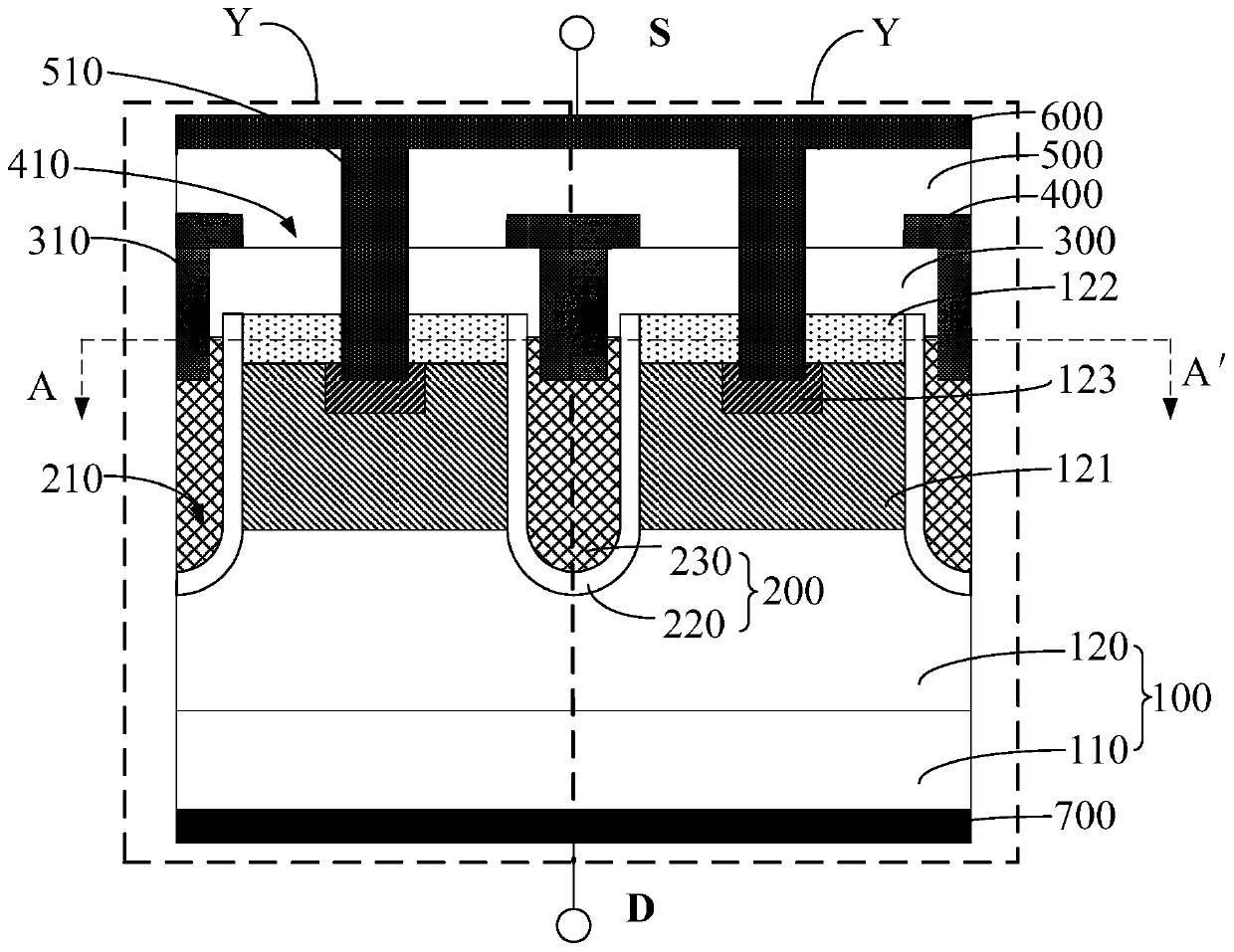

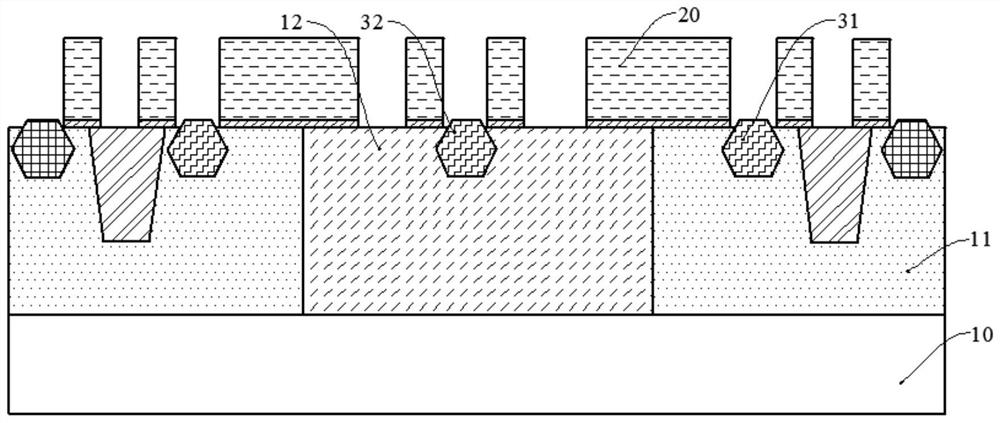

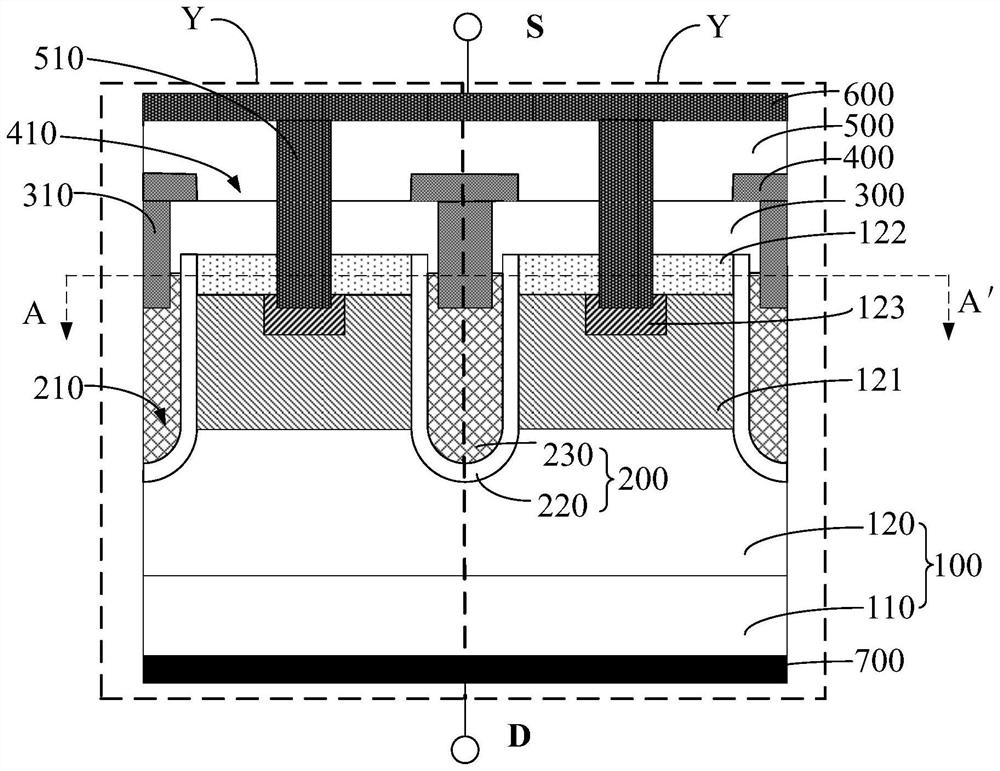

Trench type vertical double-diffusion metal oxide semiconductor field effect transistor

ActiveCN111370485AHighly integratedSmall footprintSolid-state devicesSemiconductor devicesGate dielectricEngineering

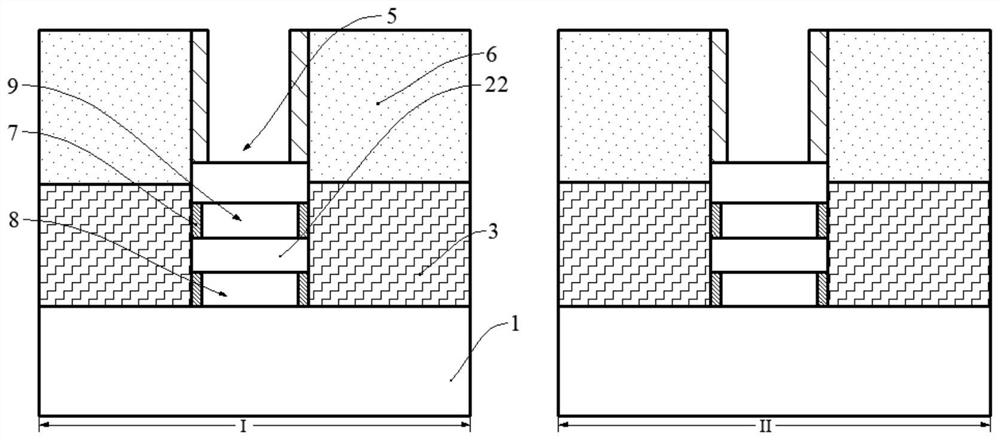

The invention relates to a VDMOS, which comprises a semiconductor substrate, a body region formed in the substrate and a source region formed in the body region, wherein a trench penetrates through the source region and the body region and extends to the substrate, each trench gate structure comprises a gate dielectric layer formed on the inner wall of the trench and a gate layer filled in the trench, a first interlayer dielectric layer, a first metal layer, a second interlayer dielectric layer and a second metal layer are sequentially stacked on the source region and each trench gate structure, one of the first metal layer and the second metal layer is a gate metal layer and is connected with each gate layer through a gate region contact hole, the other one is a source metal layer and isconnected with the body region through a source region contact hole, and the number N of the trench gate structures on the same side of the source region contact hole in each cell structure is greaterthan or equal to 2. According to the invention, the number N of the trench gate structures on the same side of the source region contact holes in the cell structure is larger than or equal to 2, so that large breakover current can be obtained under the condition that the occupied area of trench gates is small.

Owner:CSMC TECH FAB2 CO LTD

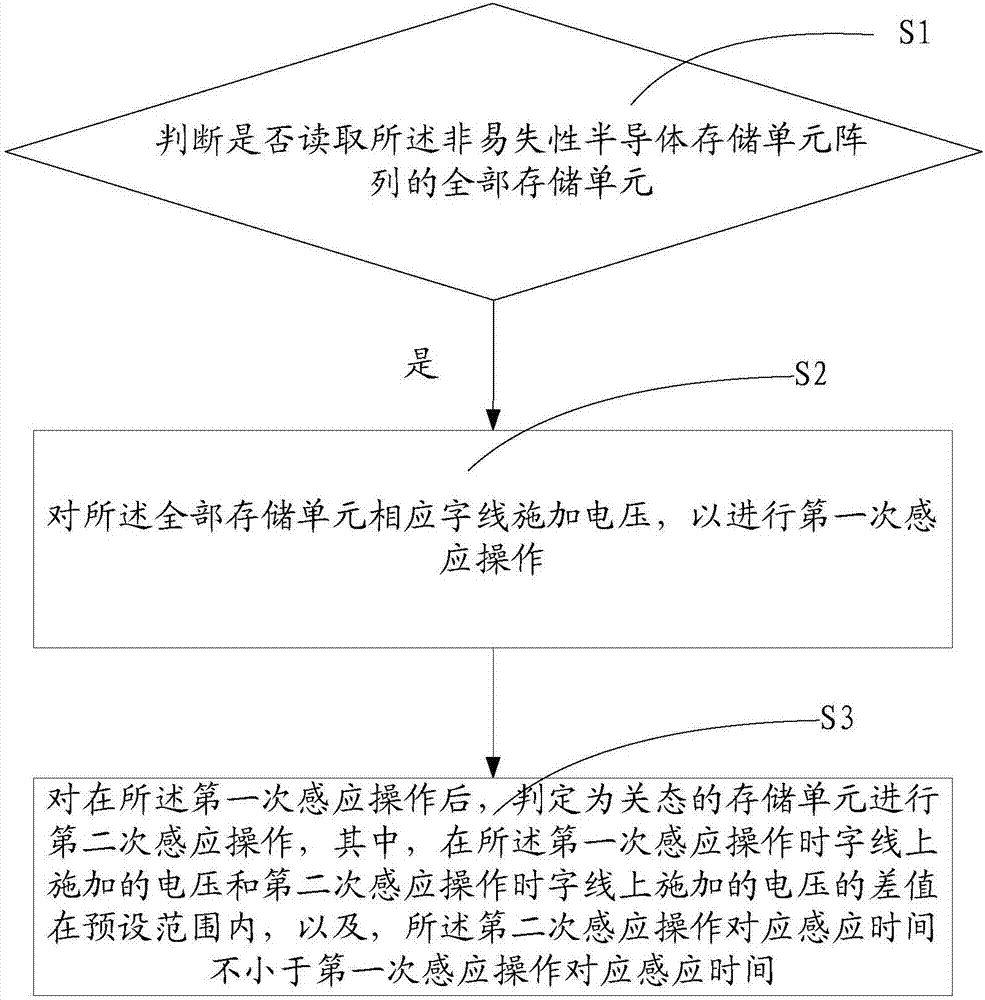

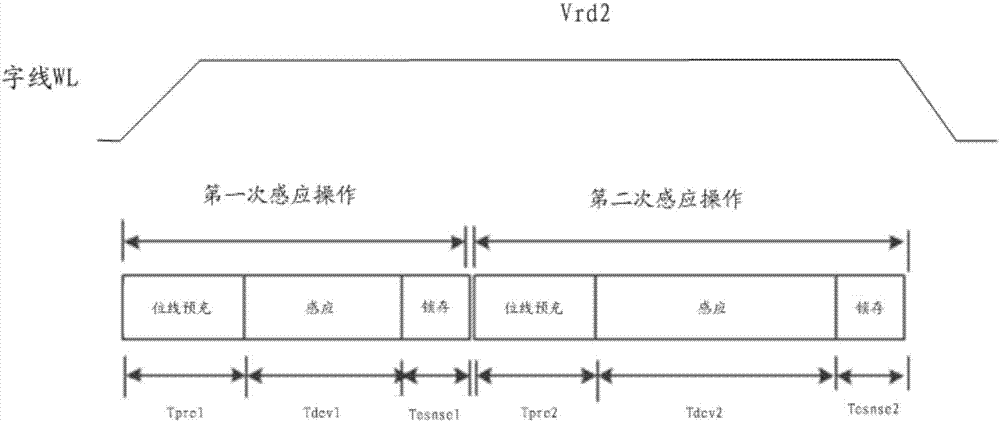

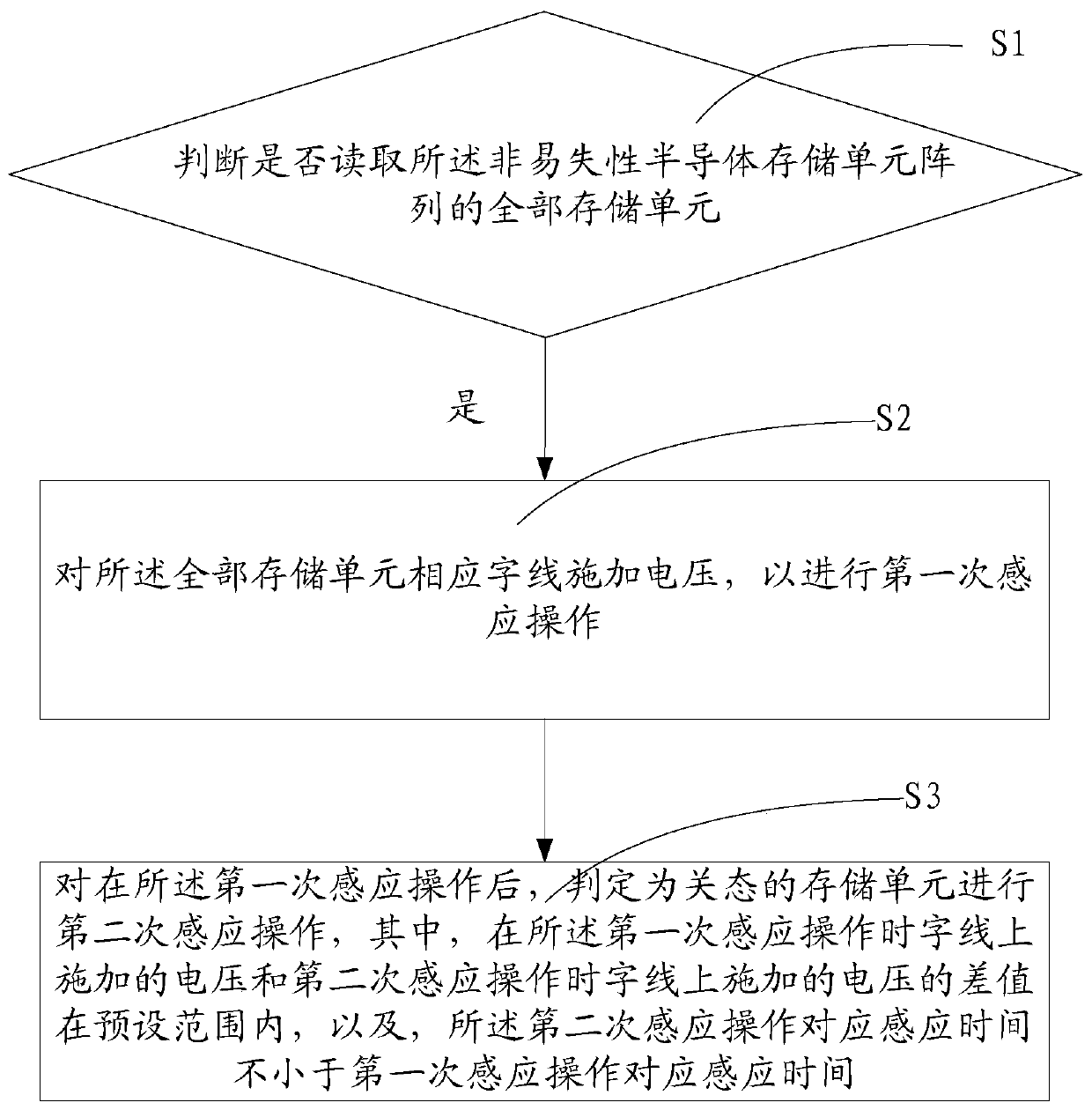

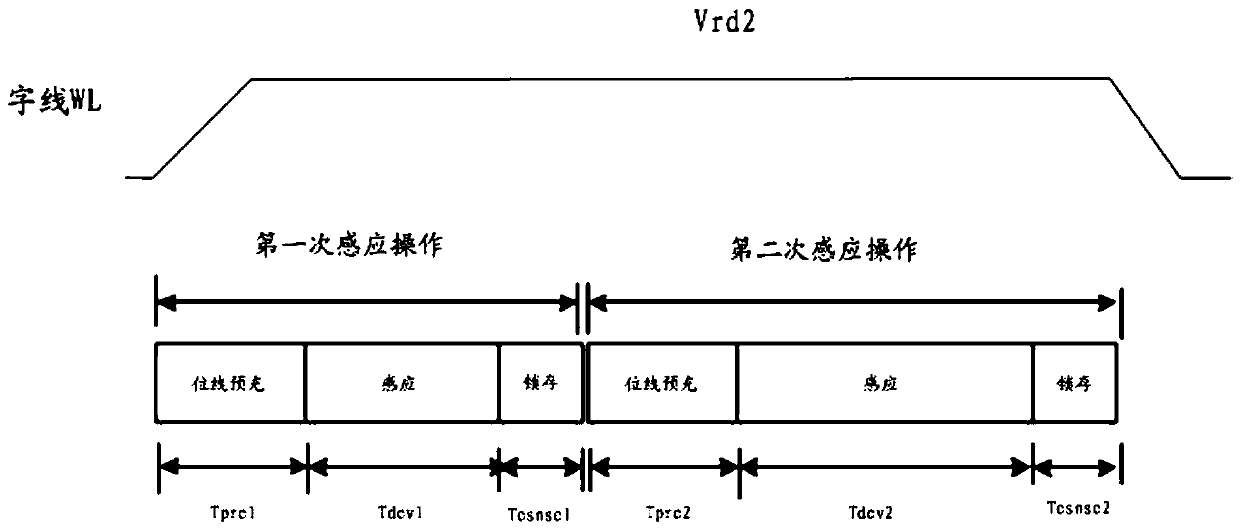

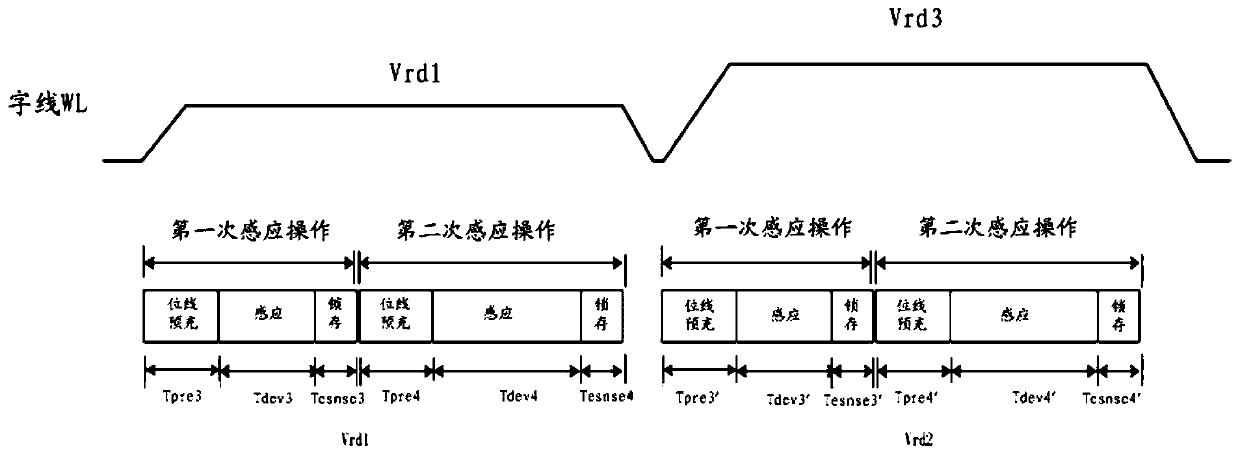

Reading method and flash memory device

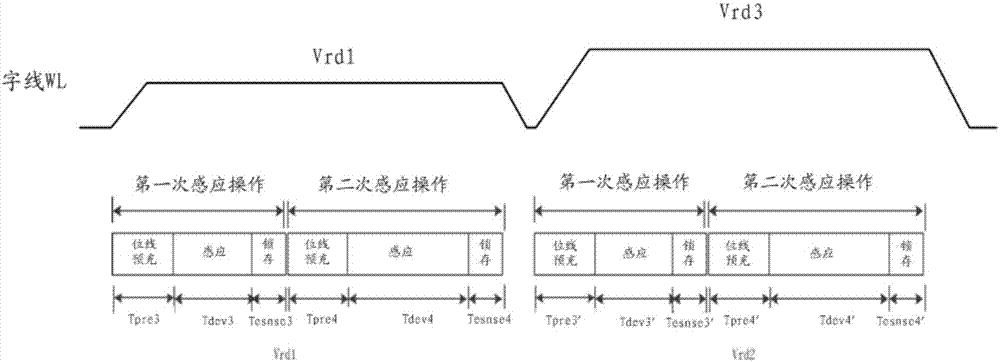

ActiveCN106960686AReduce noiseSmall conduction currentRead-only memoriesComputer scienceClosed state

The invention discloses a reading method and a flash memory device. The reading method is applied to the flash memory device comprising a nonvolatile semiconductor memory unit array. The method comprises the steps of judging whether to read all memory units of the nonvolatile semiconductor memory unit array, if yes, applying voltage to corresponding word lines of all memory units to perform a first sensing operation; and after the first sensing operation, performing a second sensing operation on the memory unit determined to be in a closed state, wherein a difference between the voltage applied to the word lines during the first sensing operation and the voltage applied to the work lines during the second sensing operation is within a preset range, and sensing time corresponding to the second sensing operation is not less than that corresponding to the first sensing operation. According to the technical scheme of the method and the device provided by the invention, the flash memory device can be read via the two sensing operations, and thus noise of a common source line is reduced, and accuracy of the reading operation is ensured.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

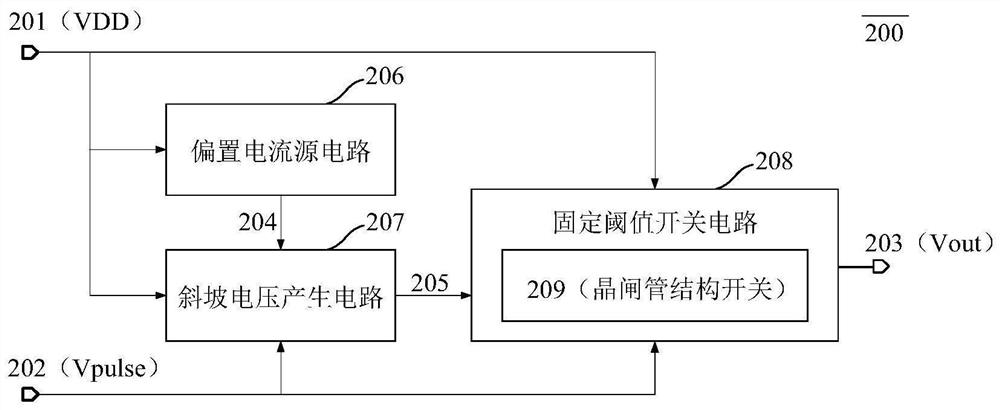

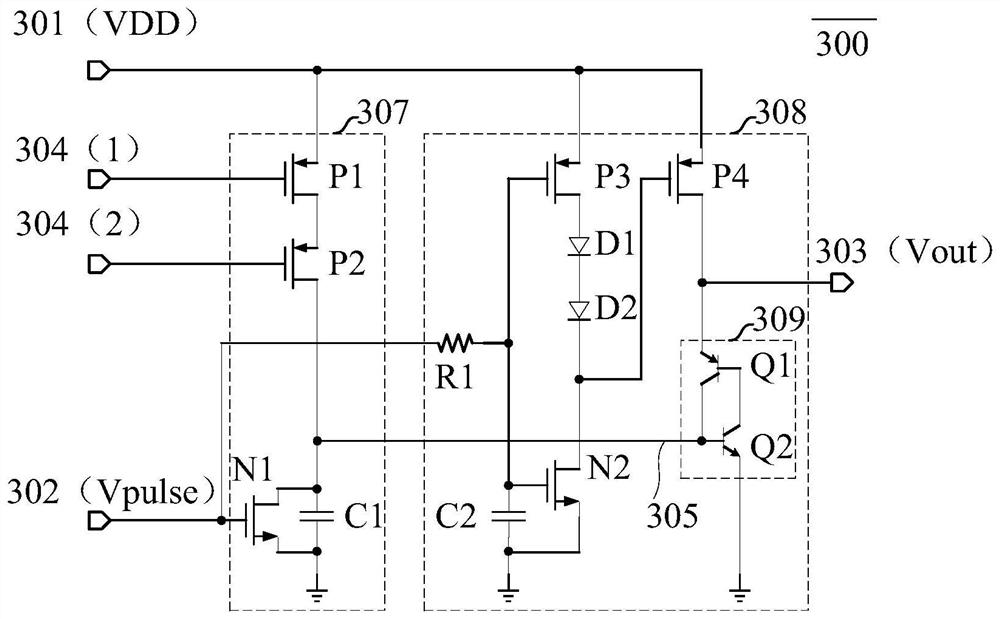

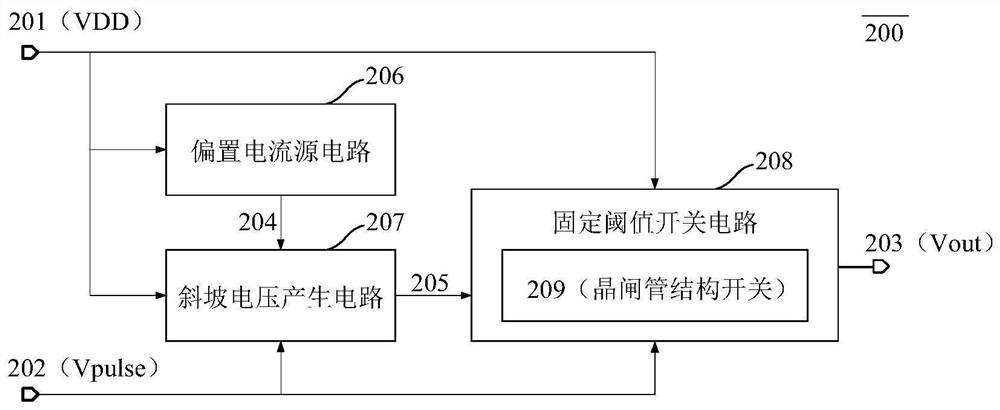

Low-temperature drift time-delay circuit

The invention discloses a low-temperature drift time-delay circuit. The circuit comprises a bias current source circuit, a slope voltage generation circuit and a fixed threshold switching circuit. Thebias current source circuit is used for generating negative temperature coefficient current bias, the input end of the bias current source circuit is connected with power voltage, and the output endof the bias current source circuit is connected with the ramp voltage generation circuit. The bias input end of the ramp voltage generating circuit is connected with the output end of the bias currentsource circuit, the digital signal input end of the ramp voltage generating circuit is connected with digital signal input, and the output end of the ramp voltage generating circuit is connected withthe fixed threshold switching circuit. The pull-down switch input end of the fixed threshold switch circuit is connected with the output end of the ramp voltage generation circuit, the pull-up switchinput end of the fixed threshold switch circuit is connected with digital signal input, and the output end of the fixed threshold switch circuit outputs delayed digital signals. According to the invention, delay processing can be carried out on a digital signal without being influenced by temperature and power supply voltage. The fixed threshold switch circuit adopts a thyristor structure as a pull-down switch, and has the advantages of stable threshold, high speed, simple structure and the like.

Owner:HUAZHONG UNIV OF SCI & TECH

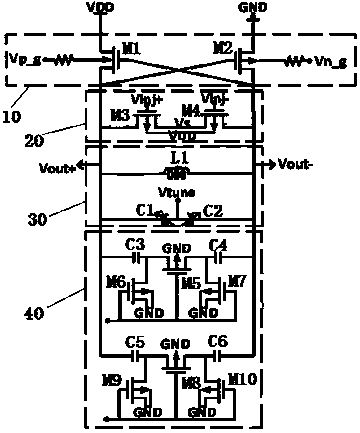

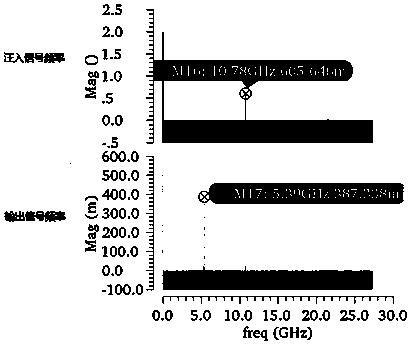

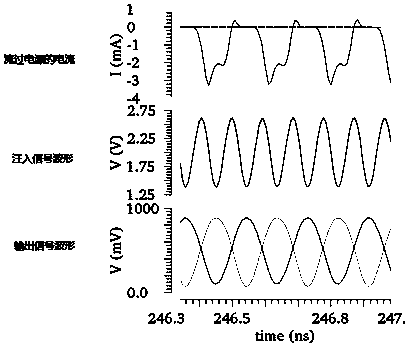

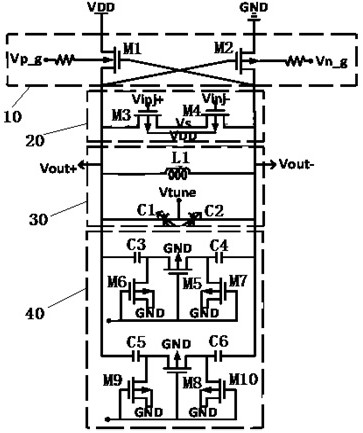

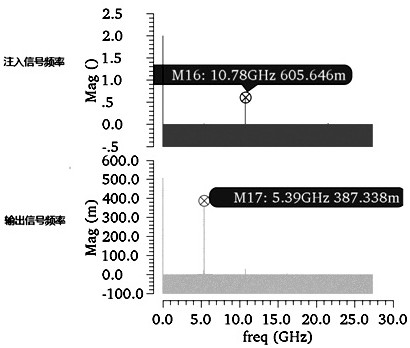

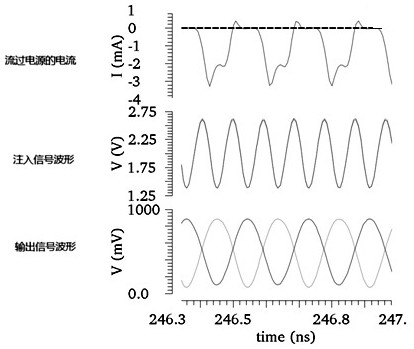

Dual-mode injection locking frequency divider with low power consumption and wide locking range

ActiveCN108599762AReduce power supply voltageSmall conduction currentPulse automatic controlConduction currentCapacitance

The invention discloses a dual-mode injection locking frequency divider with low power consumption and wide locking range, comprising a negative resistance unit, an injection unit, a resonance unit and a switched capacitor array unit, which are all connected in parallel with each other. The invention realizes the low power consumption performance by reducing the power supply voltage and reducing the half conduction current though setting the negative resistance unit adopting the current multiplexing structure and the substrate bias technology, and avoids compromises in circuit parameters due to the locking range versus power consumption and quality factor since the switching signal controls the capacitance of the capacitor array to achieve a wide range by designing the switched capacitor array unit, without significantly increasing power consumption. The dual-mode frequency division is achieved by setting the injection unit of the double-tube direct injection method, and the specific offset design of the injection tube reduces the influence of the injection power on the wide range, thereby achieving the advantages maintaining of the wide locking range at a lower injection power.

Owner:SHENZHEN UNIV

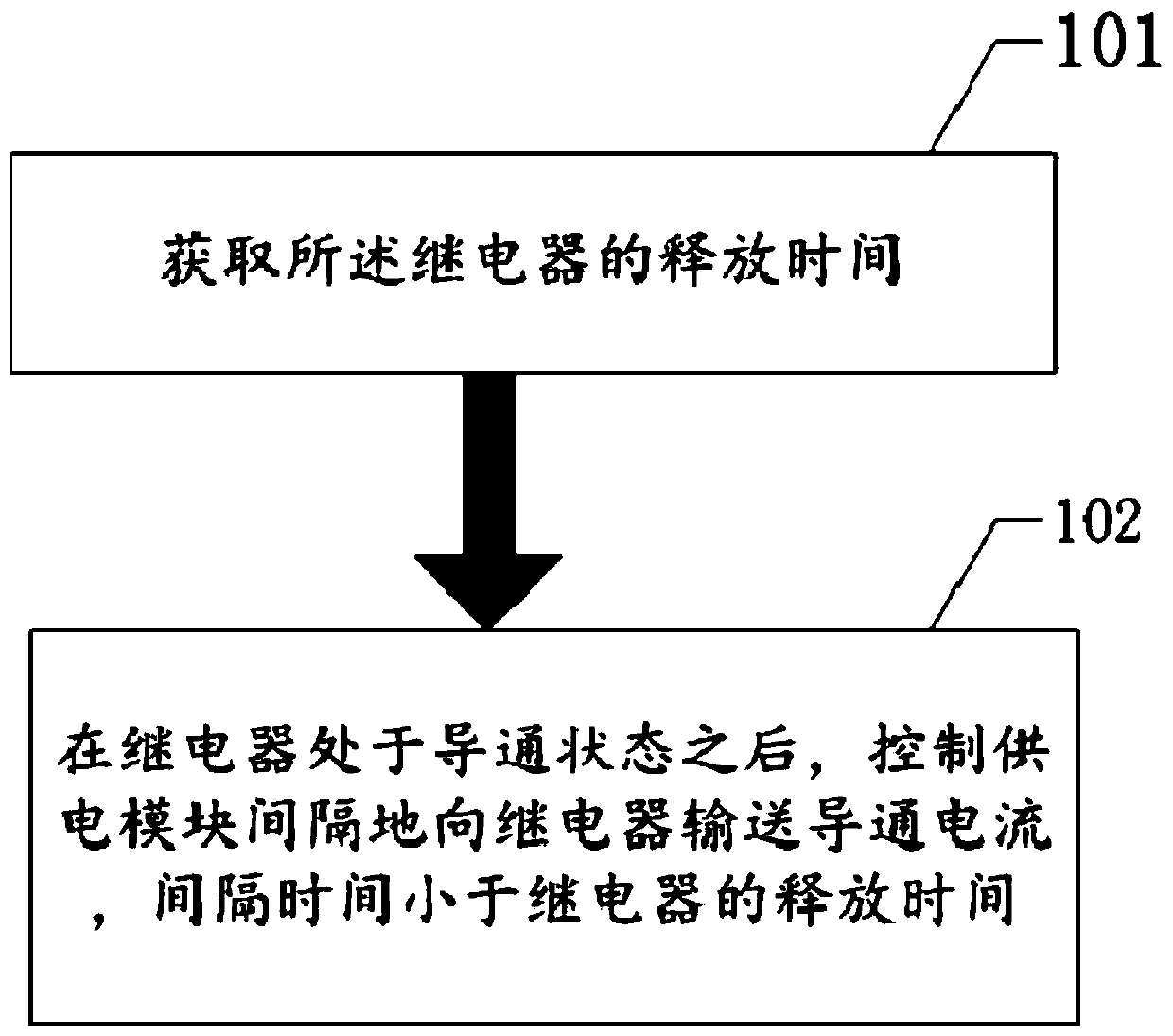

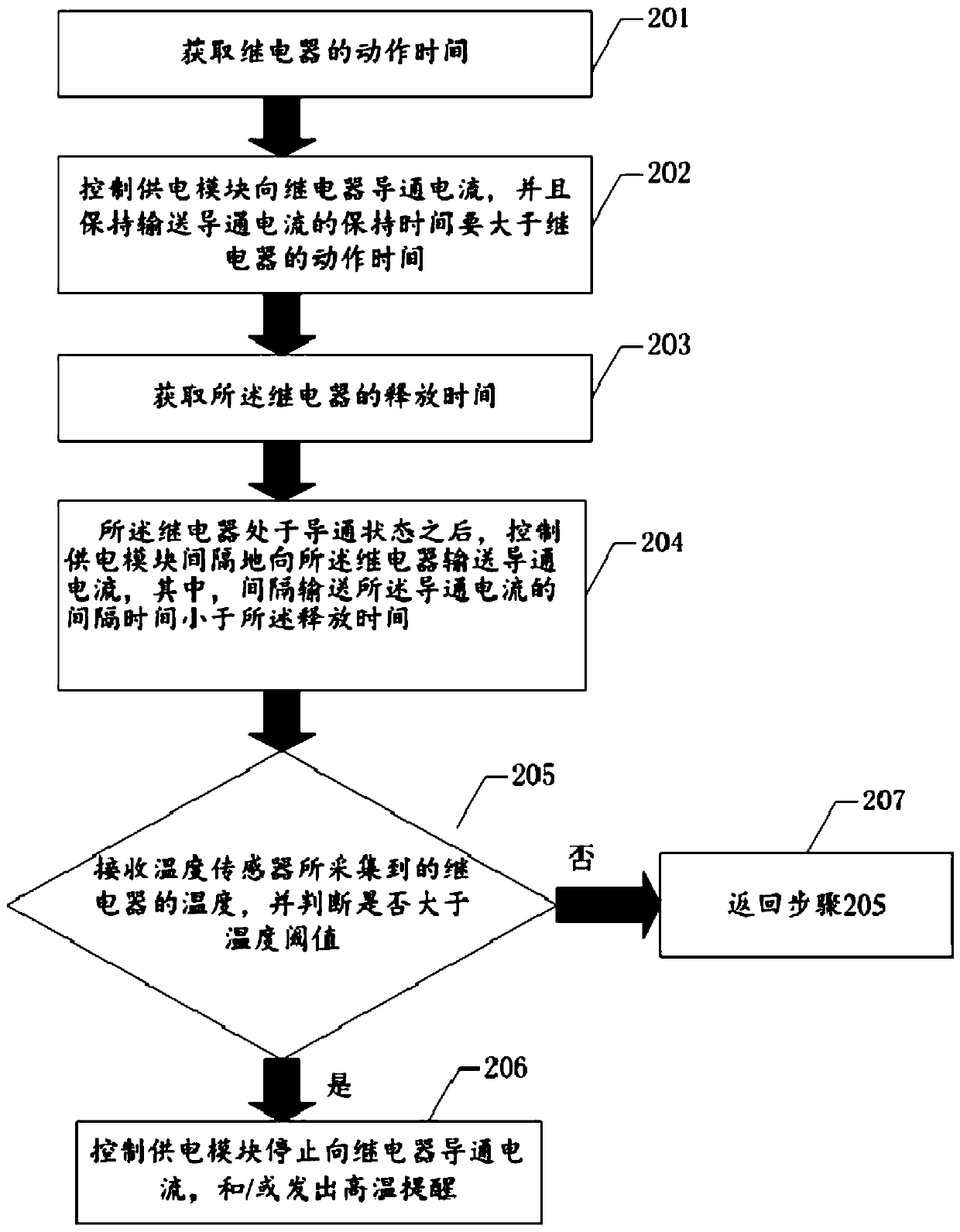

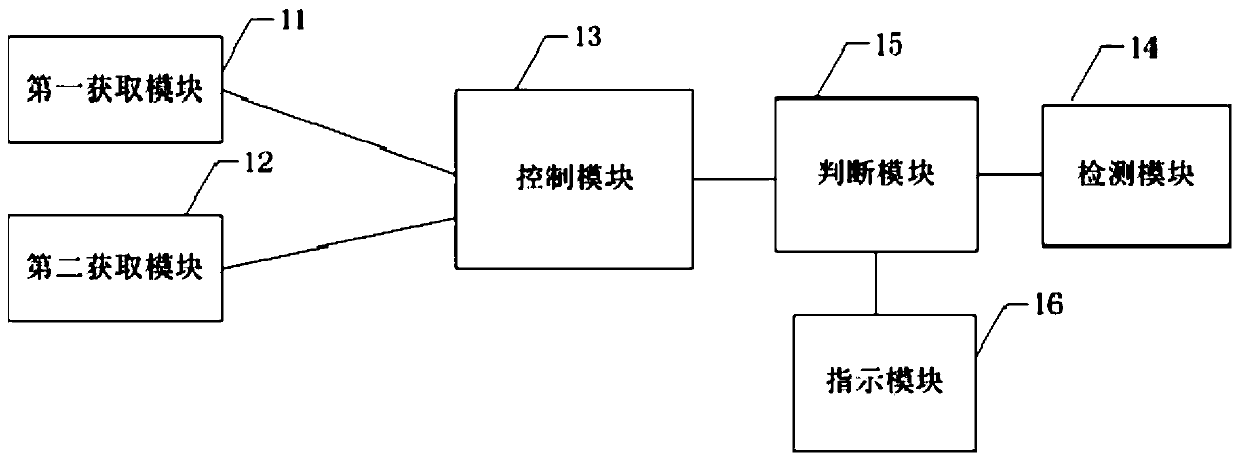

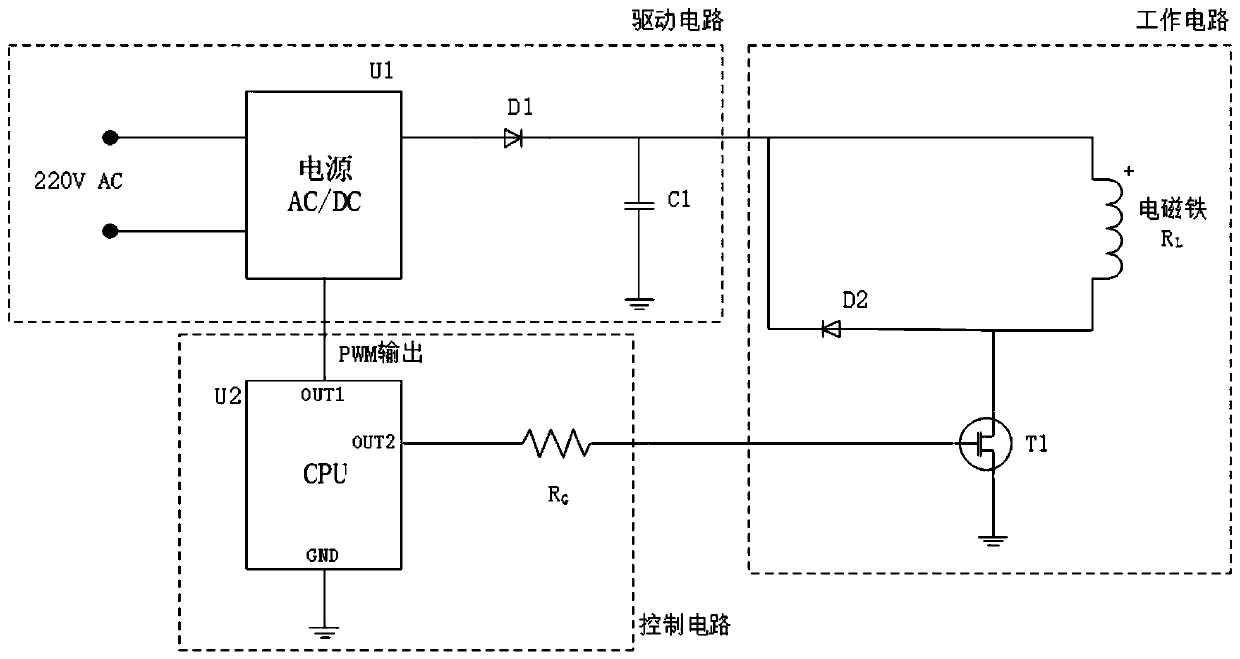

Method and device for controlling relay, and electronic device

The invention relates to the field of relay control, in particular to a method and a device for controlling a relay. The method for controlling a relay comprises the following steps: obtaining releasetime, wherein the release time of the relay refers to time starting from stopping supplying current to the relay to disconnecting a relay switch; obtaining action time, wherein the action time of therelay refers to the time from starting to supply current to the relay to disconnecting the relay switch; receiving the temperature of the relay collected by a temperature sensor and judging whether the temperature is greater than a preset temperature threshold; and when the temperature is higher than a preset temperature threshold, sending a high temperature reminder. In the above manner, it is possible to reduce the heat of the relay without disconnecting the relay switch.

Owner:SHENZHEN H&T INTELLIGENT CONTROL

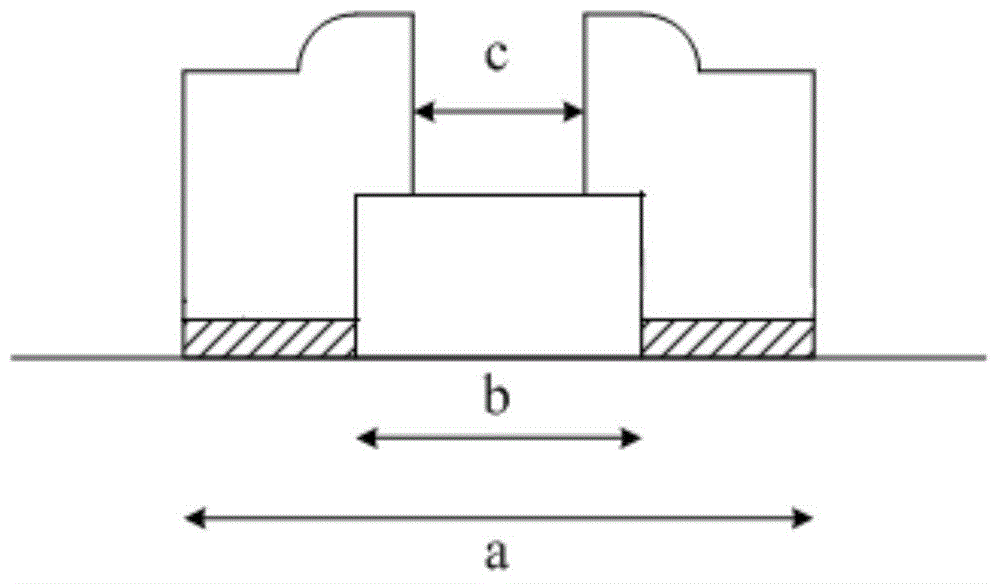

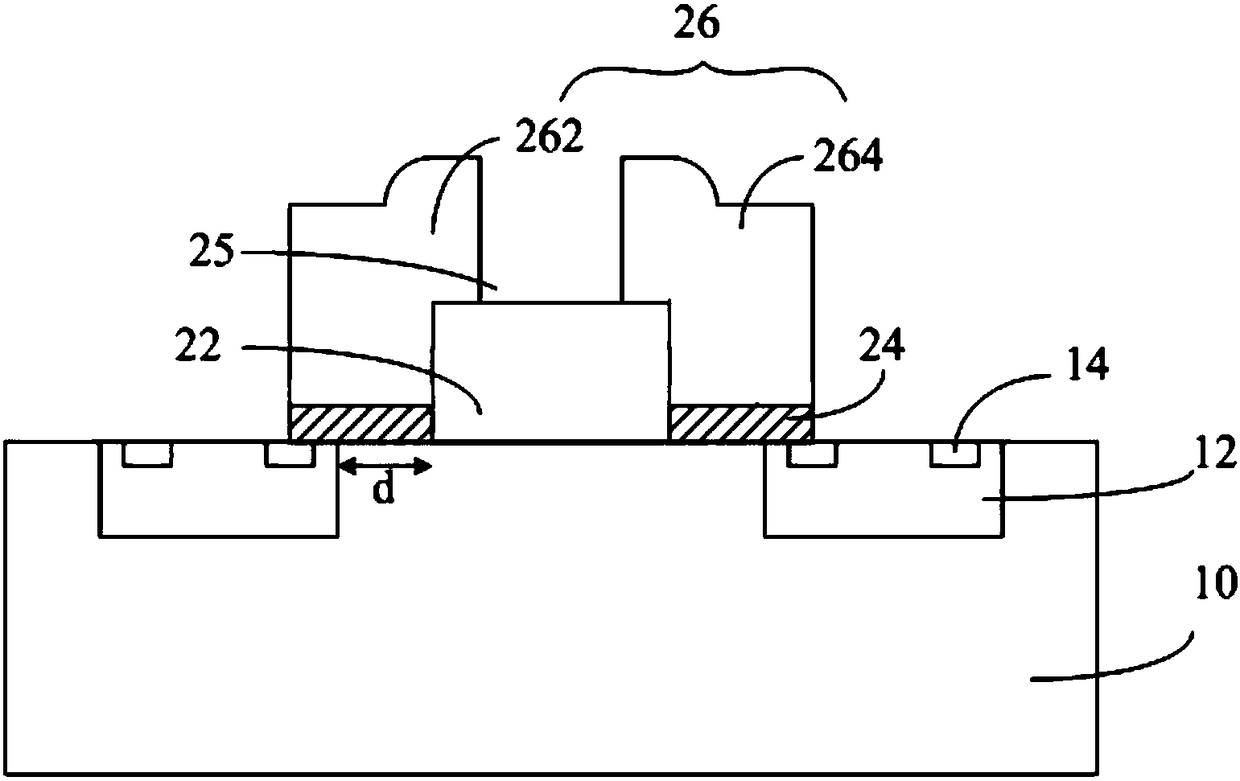

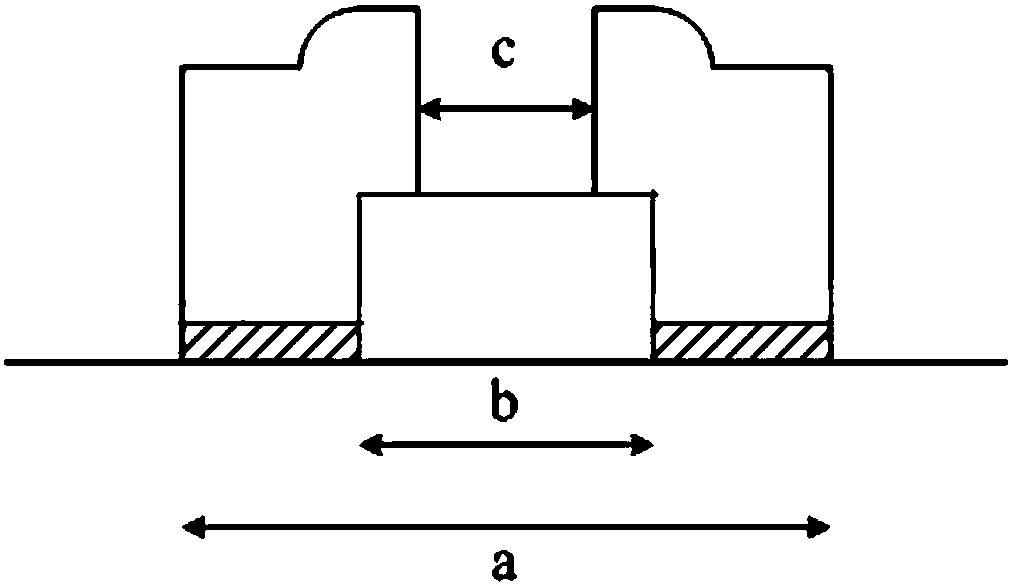

Gate structure of semiconductor device and fabrication method of gate structure

ActiveCN105140273ALower resistanceLarge grid widthSemiconductor devicesDouble diffusionField-effect transistor

The invention relates to a gate structure of a semiconductor device. The gate structure comprises a gate oxide layer, a field oxide structure and a poly-silicon split gate, wherein the gate oxide layer is arranged on a substrate, the field oxide structure is arranged on the gate oxide layer, the poly-silicon split gate is arranged on the gate oxide layer and the field oxide structure, the width of the field oxide structure is smaller than the distance of two surfaces, deviating from each other, between a first gate structure and a second gate structure, and greater than the distance between the first gate structure and the second gate structure, and the orthographic projection of an interval region between the first gate structure and the second gate structure on the field oxide structure is not beyond the edge of the field oxide structure. The invention also relates to a fabrication method for the gate structure of the semiconductor device. The fabrication method is compatible and consistent with the traditional fabrication methods of a power vertical double-diffusion metal oxide semiconductor field effect transistor (VDMOS) and an insulated gate bipolar transistor (IGBT) chip, the process difficulty and the photoetching frequency are not increased, the specific turn-on resistance, the gate charge Qg and the leakage current Idss are low, the reliability is high, the chip area is small, the production cost can be greatly reduced, and the fabrication method can be used for manufacturing the power VDMOS and the IGBT chip at a large scale, low cost and high reliability.

Owner:深圳深爱半导体股份有限公司

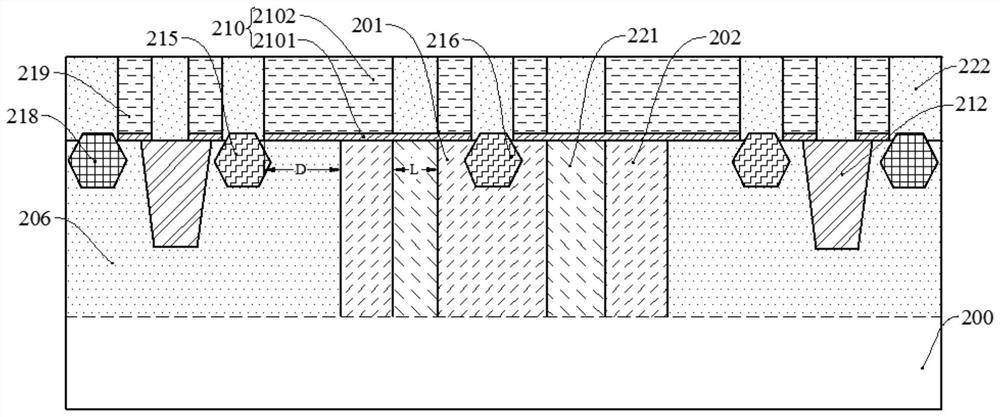

Semiconductor structure and forming method thereof

PendingCN114823841AImprove electrical performanceImprove breakdown voltageSemiconductor/solid-state device manufacturingSemiconductor devicesLDMOSSemiconductor structure

The invention discloses a semiconductor structure and a forming method thereof, and the semiconductor structure comprises a gate structure which is located on a substrate and is parallel to the surface of the substrate and is perpendicular to the extending direction of the gate structure as the transverse direction; the drain electrode is positioned on one side of the gate structure; the first drift region and the drain electrode are located on the same side of the gate structure, and the projection of the first drift region in the substrate covers the projection of the drain electrode in the substrate; the second drift region is located at the end, close to the drain electrode, of the gate structure, the first drift region and the second drift region are spaced in the transverse direction, and the ion doping concentration of the second drift region is higher than that of the first drift region. In the embodiment of the invention, the projection of the first drift region in the substrate covers the projection of the drain electrode in the substrate, so that the drain electrode voltage drop borne by the first drift region is relatively high, and the breakdown voltage of the LDMOS is relatively high; and the ion doping concentration of the second drift region is higher than that of the first drift region, so that the on-resistance of the first drift region is relatively small, and the on-current of the LDMOS is relatively large.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

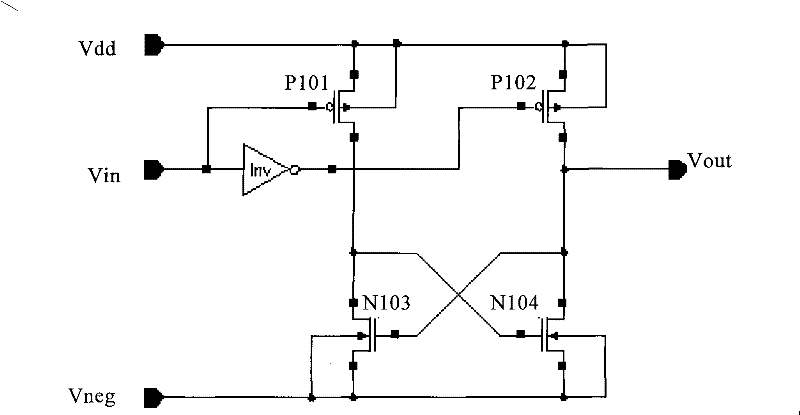

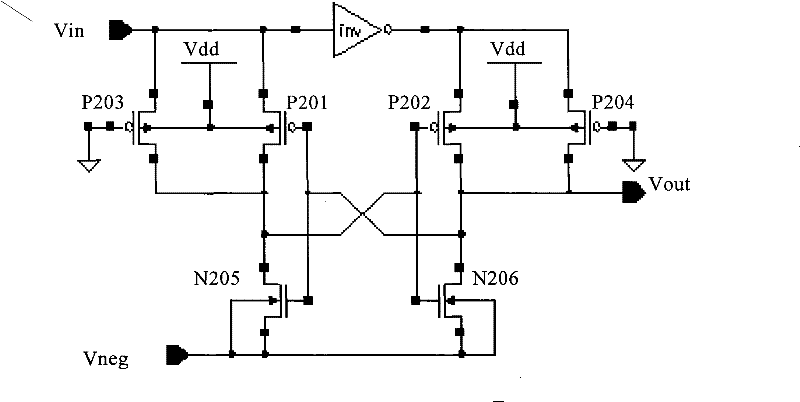

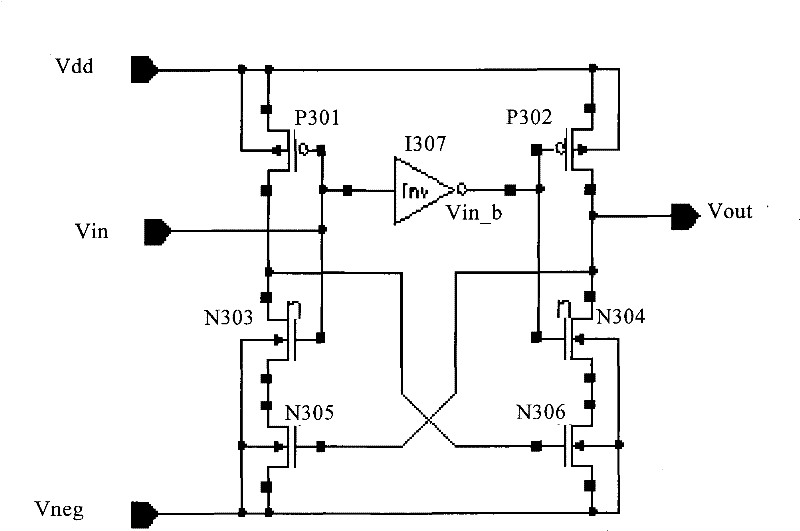

Negative voltage level switching circuit

ActiveCN101764605BSmall conduction currentSmall sizeLogic circuits coupling/interface using field-effect transistorsPositive feedbackSwitching power

A negative voltage level switching circuit, including: 2 inserted N tubes; 2 pull-up P tubes, the sources of which are connected to the forward voltage Vdd, and the drains are respectively connected to the drains of the inserted N tubes; 2 positive feedback The source of the N tube is connected to the negative voltage Vneg, and the drains are respectively connected to the sources of the two inserted N tubes; the node between the second inserted N tube and the second pull-up P tube is the output Vout, and the first inserted The gates of the N tube and the first pull-up P tube are connected to the input signal Vin, the gate of the first positive feedback N tube is connected to the output voltage Vout; the second insertion N tube and the second pull-up P tube gate are connected to The output end of the inverter and the input end of the inverter are connected to the input signal Vin; the gate of the second positive feedback N transistor is connected to the node between the first insertion N transistor and the drain of the first pull-up P transistor. The conduction current required by the P tube can be reduced under the same conduction condition, and the area of the P tube can be reduced; and the voltage switching speed can be accelerated and the switching power consumption can be reduced.

Owner:GIGADEVICE SEMICON (BEIJING) INC

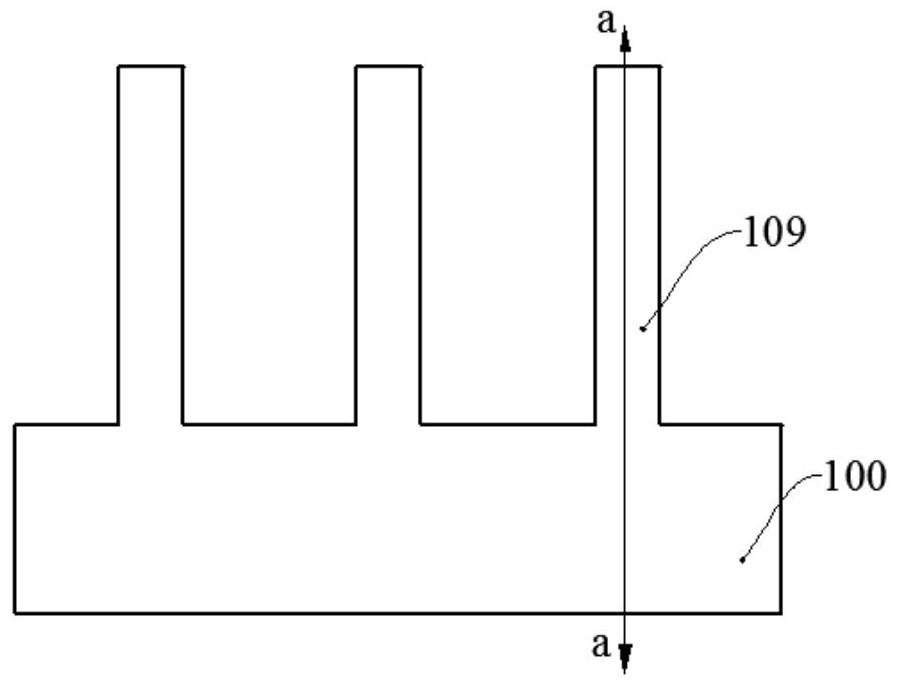

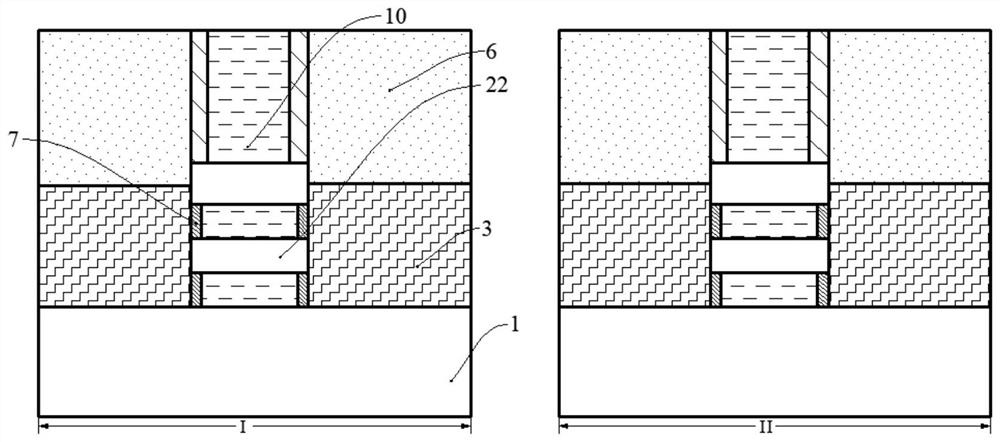

Semiconductor structure and forming method thereof, and SRAM device

PendingCN114551356AImprove electrical performanceStrong control abilityTransistorSolid-state devicesSemiconductor structureEngineering

A semiconductor structure and a forming method thereof, and an SRAM device, the forming method comprising: providing a substrate, the substrate comprising a substrate, a plurality of channel stacks discrete on the substrate, and a dummy gate structure crossing the plurality of channel stacks, the dummy gate structure covering a portion of the top wall and a portion of the side wall of the channel stacks, the channel stacks comprising sacrificial layers and channel layers located on the sacrificial layers; forming a side wall covering the pseudo gate structure and exposing an interlayer dielectric layer at the top of the pseudo gate structure; removing the pseudo gate structure, and forming a gate opening in the interlayer dielectric layer; removing one or more channel layers at the top of the channel stack; removing the sacrificial layer to form a channel; a gate structure is formed in the gate opening and the channel. According to the embodiment of the invention, one or more channel layers at the top of the channel lamination layer are removed, so that the number of the channel layers in the semiconductor structure is reduced, the overall conduction current of the channels of the semiconductor structure is reduced when the semiconductor structure works, and the semiconductor structure can meet the process requirement.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

A gate structure of a semiconductor device and its manufacturing method

ActiveCN105140273BLower resistanceLarge grid widthSemiconductor devicesDouble diffusionField-effect transistor

The invention relates to a gate structure of a semiconductor device. The gate structure comprises a gate oxide layer, a field oxide structure and a poly-silicon split gate, wherein the gate oxide layer is arranged on a substrate, the field oxide structure is arranged on the gate oxide layer, the poly-silicon split gate is arranged on the gate oxide layer and the field oxide structure, the width of the field oxide structure is smaller than the distance of two surfaces, deviating from each other, between a first gate structure and a second gate structure, and greater than the distance between the first gate structure and the second gate structure, and the orthographic projection of an interval region between the first gate structure and the second gate structure on the field oxide structure is not beyond the edge of the field oxide structure. The invention also relates to a fabrication method for the gate structure of the semiconductor device. The fabrication method is compatible and consistent with the traditional fabrication methods of a power vertical double-diffusion metal oxide semiconductor field effect transistor (VDMOS) and an insulated gate bipolar transistor (IGBT) chip, the process difficulty and the photoetching frequency are not increased, the specific turn-on resistance, the gate charge Qg and the leakage current Idss are low, the reliability is high, the chip area is small, the production cost can be greatly reduced, and the fabrication method can be used for manufacturing the power VDMOS and the IGBT chip at a large scale, low cost and high reliability.

Owner:深圳深爱半导体股份有限公司

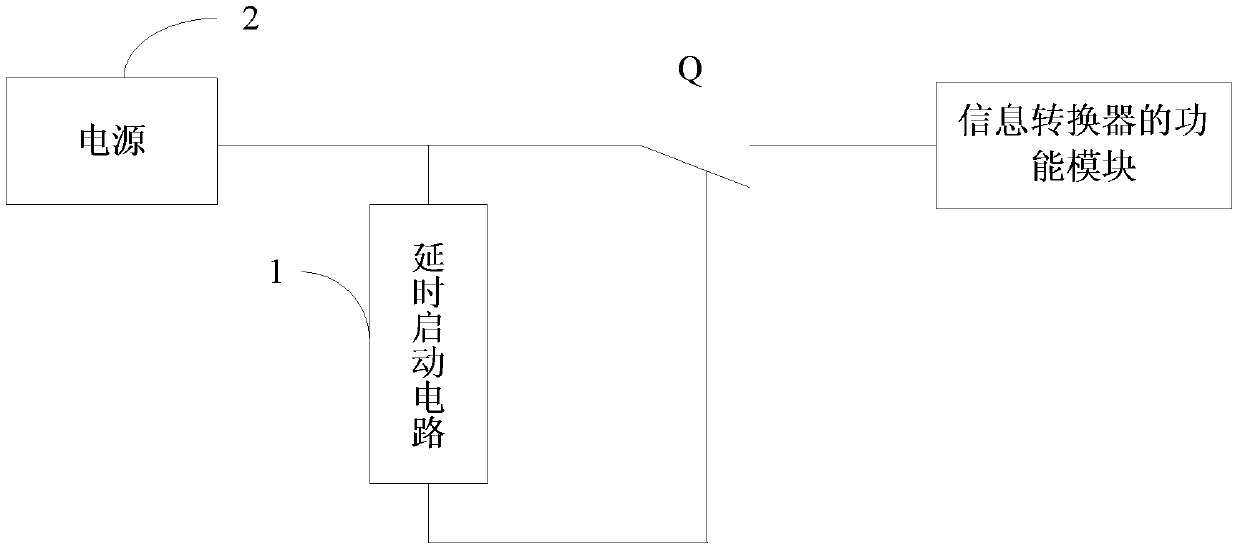

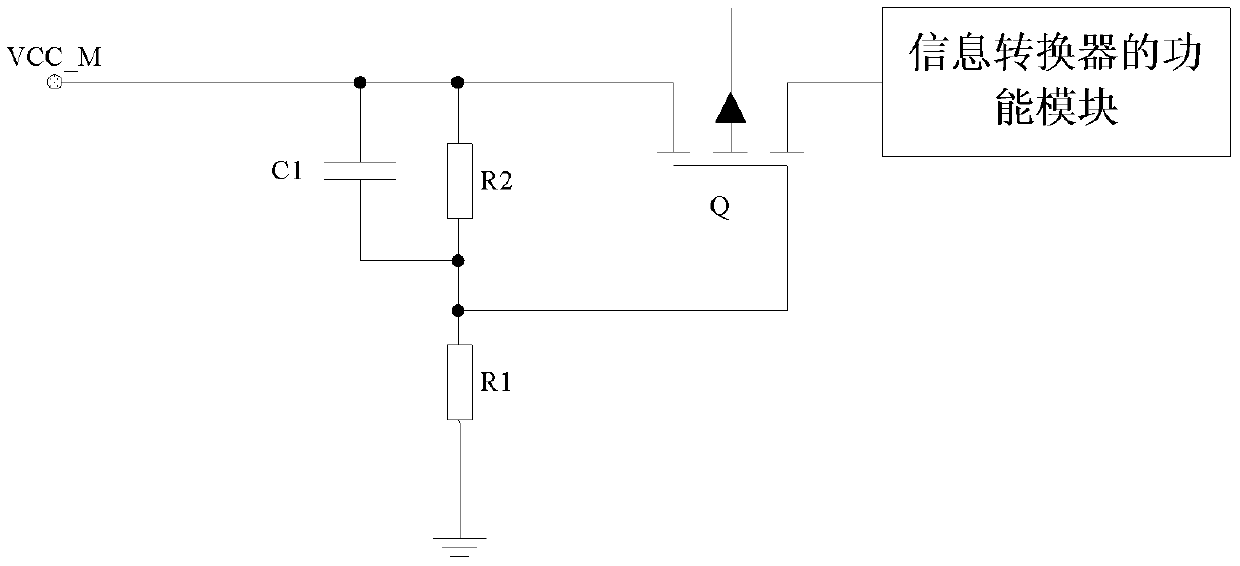

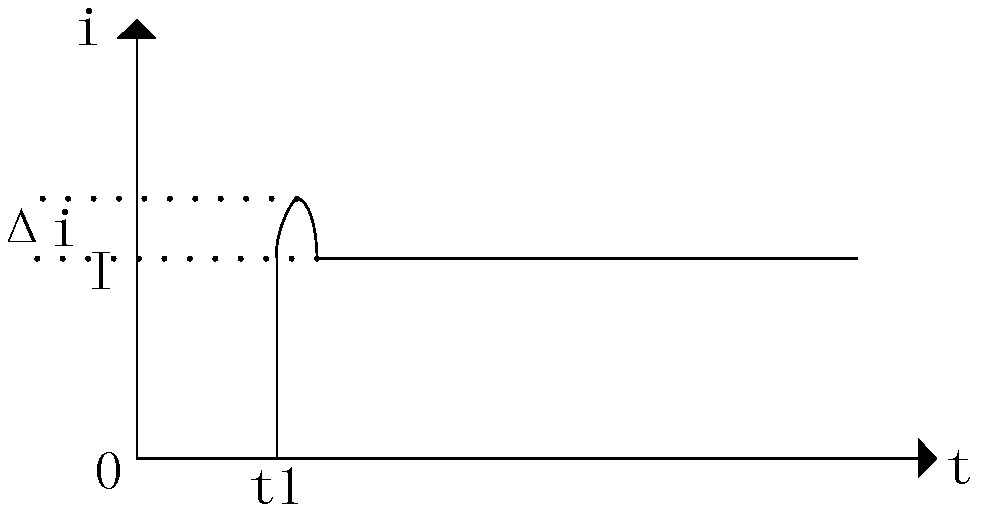

Power supply circuit, system and power supply method of information converter

ActiveCN105684313BAvoid overshoot currentImprove securityElectronic switchingPulse manipulationElectricityOvercurrent

An information converter power supply circuit, system, and power supply method, relating to the technical field of power supply circuits. The power supply circuit comprises a control circuit on-off switch transistor and a delay start-up circuit; when the power supply circuit is connected to a power source, the delay start-up circuit controls a slow voltage rise of the control end of the switch transistor, such that the switch transistor is slowly started up (conducts) from an off state, and then the output voltage of the output end of the switch transistor slowly rises, i.e. the power supply voltage of the information converter slowly rises. The overshoot current caused by the switch transistor starting up too fast is prevented, the overcurrent in the power supply circuit of the information converter is reduced, and the safety of the power supply circuit of the information converter is improved.

Owner:NEW SINGULARITY INT TECHN DEV

A low temperature drift delay circuit

The invention discloses a low-temperature drift delay circuit. The circuit includes: a bias current source circuit, a slope voltage generating circuit and a fixed threshold switch circuit; the bias current source circuit is used to generate a negative temperature coefficient current bias, Its input terminal is connected to the power supply voltage, and its output terminal is connected to the slope voltage generating circuit; the bias input terminal of the slope voltage generating circuit is connected to the output terminal of the bias current source circuit, and its digital signal input terminal is connected to the digital signal input , the output terminal of which is connected to the fixed threshold switch circuit; the input terminal of the pull-down switch of the fixed threshold switch circuit is connected to the output terminal of the slope voltage generating circuit, the input terminal of the pull-up switch is connected to the digital signal input, and the output terminal of the fixed threshold switch circuit is delayed subsequent digital signals. The invention can perform time-delay processing on digital signals without being affected by temperature and power supply voltage; the fixed threshold switch circuit adopts a thyristor structure as a pull-down switch, and has the advantages of stable threshold value, high speed, simple structure and the like.

Owner:HUAZHONG UNIV OF SCI & TECH

A dual-mode injection-locked frequency divider with low power consumption and wide locking range

ActiveCN108599762BAvoid Compromising DesignsSmall conduction currentPulse automatic controlCapacitanceInjection locked

Owner:SHENZHEN UNIV

Trench type vertical double diffused metal oxide semiconductor field effect transistor

ActiveCN111370485BHighly integratedSmall footprintSolid-state devicesSemiconductor devicesGate dielectricEngineering

Owner:CSMC TECH FAB2 CO LTD

Fully Adaptable High Voltage Switch Controller Based on Optocoupler Control

ActiveCN101728773BSmall conduction currentImprove isolationBoards/switchyards circuit arrangementsControl systemHigh pressure

The fully adaptive high-voltage switch controller based on optocoupler control belongs to the high-voltage substation control equipment. Connected with the operating mechanism of the high-voltage circuit breaker, it is composed of a tripping and closing holding circuit and a position monitoring circuit. Set the optocoupler in the closing hold, trip hold and trip position monitoring, closing position monitoring circuits. One end of each optocoupler light-emitting part is connected to the operating mechanism of the circuit high-voltage circuit breaker, and the other end is connected to the positive pole of the control power supply through the position indicator light or the normally open contact of the relay. The conductive part of the contact of the optocoupler is connected to the input end of each circuit relay. This controller makes full use of the characteristics of optocoupler sensitivity and small conduction current to realize the control of small currents on high-power devices, and is fully suitable for various tripping and closing operating mechanisms with currents ranging from 10mA to 5A. The control of the relay greatly improves the safety and reliability of the relay protection device and the intelligent operation box of the substation, eliminates the potential safety hazard of the substation, and can also be used in other control systems such as railways.

Owner:成都智达电力自动控制有限公司

Array substrate and display panel

ActiveCN110931514BThe second capacitor is smallReduced subthreshold swingSolid-state devicesSemiconductor/solid-state device manufacturingVertical projectionEngineering

The embodiment of the invention discloses an array substrate and a display panel. The array substrate includes: a first thin film transistor disposed on the substrate, the first thin film transistor includes a first active layer, a first gate insulating layer and a first gate layer; wherein, the first channel of the first active layer The surface area of the region close to the first gate layer is greater than the area of the vertical projection of the first channel region on the substrate; the surface area of the first gate layer close to the first active layer is greater than the vertical area of the first gate layer on the substrate Projected area; and along the direction perpendicular to the substrate, the distances from each point on the surface of the first gate layer close to the first active layer to the surface of the first channel region close to the first gate layer are all the same. Compared with the prior art, the embodiment of the present invention improves the characteristics of the switching thin film transistor, improves the driving characteristics of the array substrate and the display effect of the display panel.

Owner:YUNGU GUAN TECH CO LTD

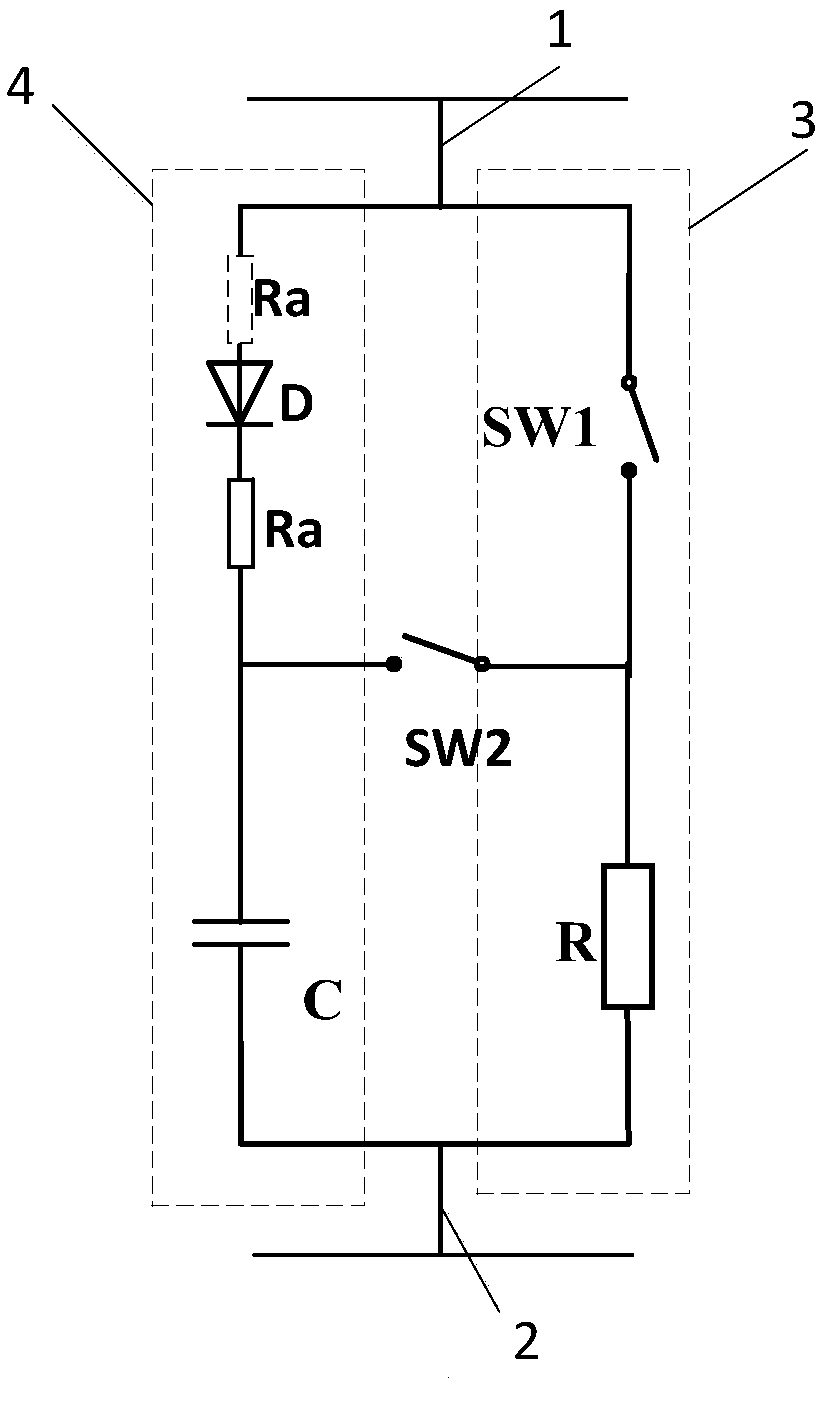

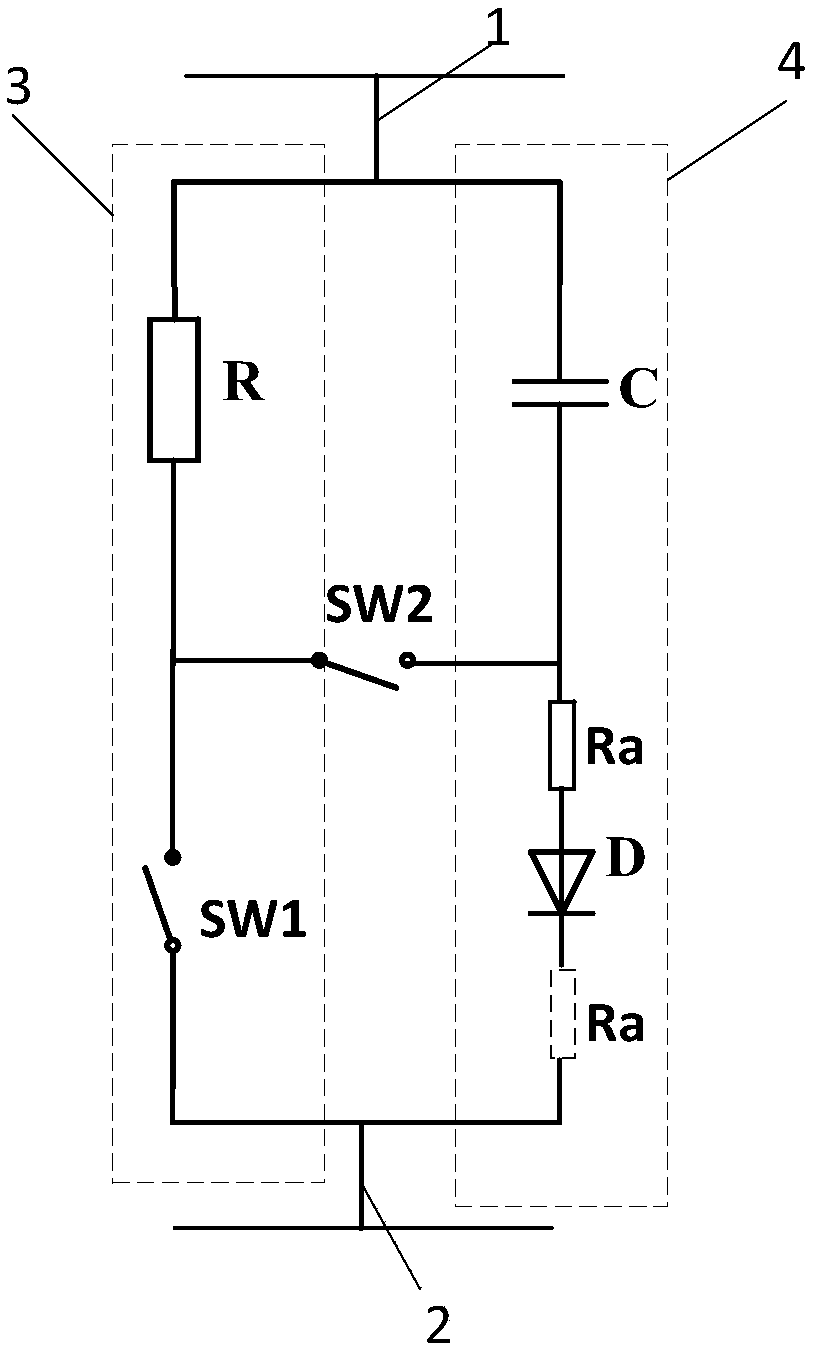

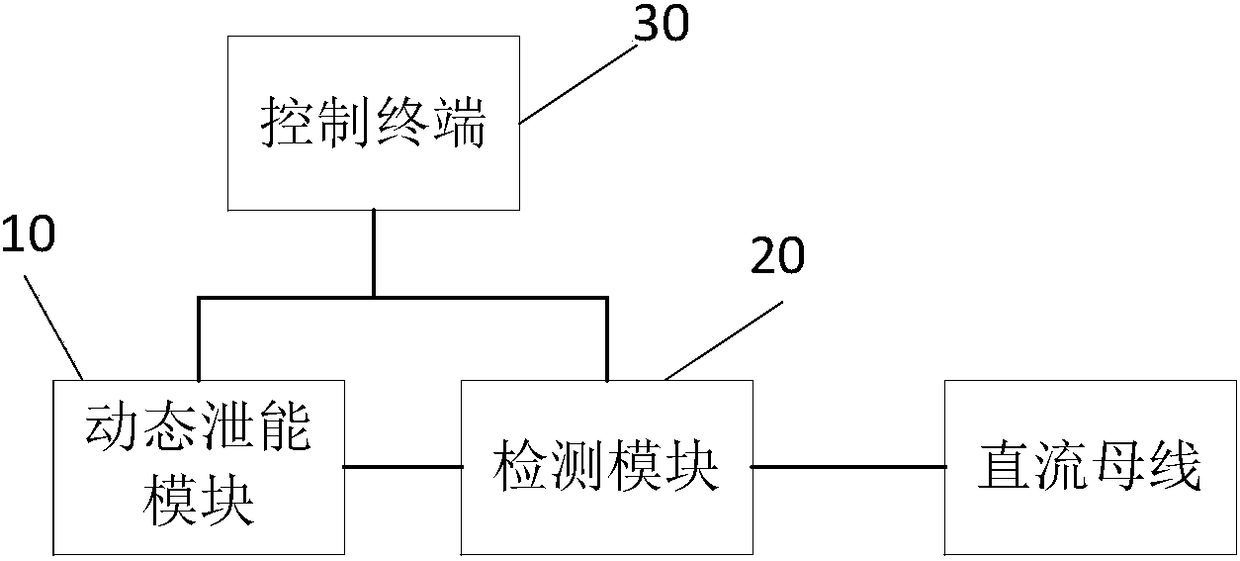

Dynamic energy release module, device and direct-current transmission system

PendingCN108376977AAvoid misleadingIncrease resistanceElectric power transfer ac networkEmergency protective arrangements for limiting excess voltage/currentCapacitanceElectrical resistance and conductance

The invention provides a dynamic energy release module, a dynamic energy release device and a direct-current transmission system. The dynamic energy release module comprises a first branch and a second branch which are connected in parallel between a positive pole connection end and a negative pole connection end; the first branch includes a first resistor and a first switch which are connected inseries; the second branch includes a diode and a capacitor which are connected in series; one end of a second switch is connected between the first resistor and the first switch; the other end of thesecond switch is connected between the diode and the capacitor; and one of two ends of the diode is connected in series with a second resistor. After the oscillation of the capacitor ends, the secondresistor is adopted in the energy release link of the first resistor after a receiving end current converter is locked, and therefore, the resistance of the diode branch is increased, current flowingthrough the second switch is greatly reduced, and the second switch can cut off the current through a conventional alternating current circuit breaker; and the resistors are properly set, so that thewrong turning on of the diode after the diode is turned off can be prevented.

Owner:STATE GRID CORP OF CHINA +2

Buffer in ultra-low power consumption integrated circuit

ActiveCN101212221BPrevent conduction currentSmall conduction currentReliability increasing modificationsLogic circuits coupling/interface using field-effect transistorsUltra low powerIntegrated circuit

The invention discloses a buffer in an integrated circuit with ultra low power consumption. The invention applies voltage generated by two first level inverters to drive a second level inverter to reach a target of the buffer; at the same time, the wide length ratios of a PMOS pipe and a NMOS pipe in the two first level inverters are different from each other, thus leading to a different on-stagetime, so that time points of the generated voltage reaching the second level inverter are different, which can prevent the PMOS pipe and the NMOS pipe in the second level inverter from being on at the same time and thus generate on-state current. The invention can be used in the integrated circuit with ultra low power consumption.

Owner:SHANGHAI HUAHONG INTEGRATED CIRCUIT

A reading method and flash memory device

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

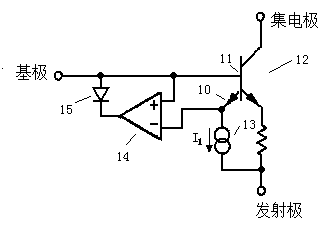

Overheating protection circuit for power transistor

InactiveCN103532364ASmall conduction currentPower conversion systemsDifferential amplifierTransistor

An overheating protection circuit for a power transistor comprises a sensing emitting electrode. One differential amplifier is driven from a base and the sensing emitting electrode of the transistor and is provided with an output end which is coupled to the power transistor. When the potential of the sensing emitting electrode exceeds that of the base electrode, the output of the amplifier can lower the voltage of the base electrode to limit a current of the power transistor. For a silicon transistor, a circuit can restrain the sensing emitting electrode to work at the maximum temperature of about 250 DEG C; and when a hot point doesn't exist, and the sensing emitting electrode is heated uniformly, the temperature of the transistor is limited to about 200 DEG C.

Owner:SUZHOU BATELAB MICROELECTRONICS

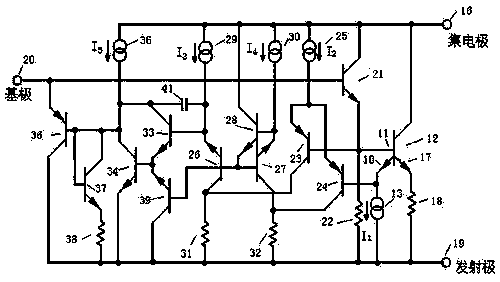

A control system of presser foot lifter electromagnet driven by multi-mode output

ActiveCN109322067BLinear adjustableQuick liftSewing-machine control devicesPressersCapacitanceHemt circuits

Owner:ZHEJIANG UNIV

Power-on reset circuit of electronic label of RFID (radio frequency identification device) system

ActiveCN102456153BSmall conduction currentReduce power consumptionRecord carriers used with machinesPower-on resetEngineering

The invention discloses a power-on reset circuit of an electronic label of an RFID (radio frequency identification device) system, which comprises two input ends, one output end, nine MOS (metal oxide semiconductor) transistors, one resistor and two capacitors, wherein input signals (voltage drain drain (VDD)) of the first input end and the second input end are working voltage signals output by a regulator of a radio-frequency analog front end circuit of the electronic label of the RFID system; and output signals (power-on reset (POR)) of the output end are power-on reset signals provided by a digital baseband circuit of the electronic label of the RFID system. The power-on reset circuit has an extremely low breakover current, and achieves the purpose of low power consumption.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP