Semiconductor structure and forming method thereof, and SRAM device

A technology of semiconductor and gate structure, which is applied in the direction of semiconductor devices, semiconductor/solid-state device manufacturing, electric solid-state devices, etc. The probability of channel leakage current, the effect of improving electrical performance and strong control ability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0015] It can be known from the background art that the devices formed at present still have the problem of poor performance. Now combined with a method of forming a semiconductor structure, the reasons for the poor performance of the device are analyzed.

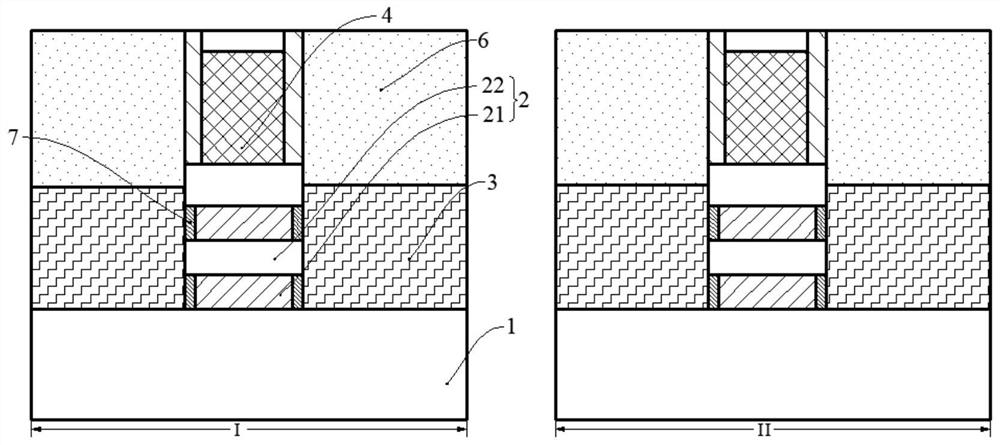

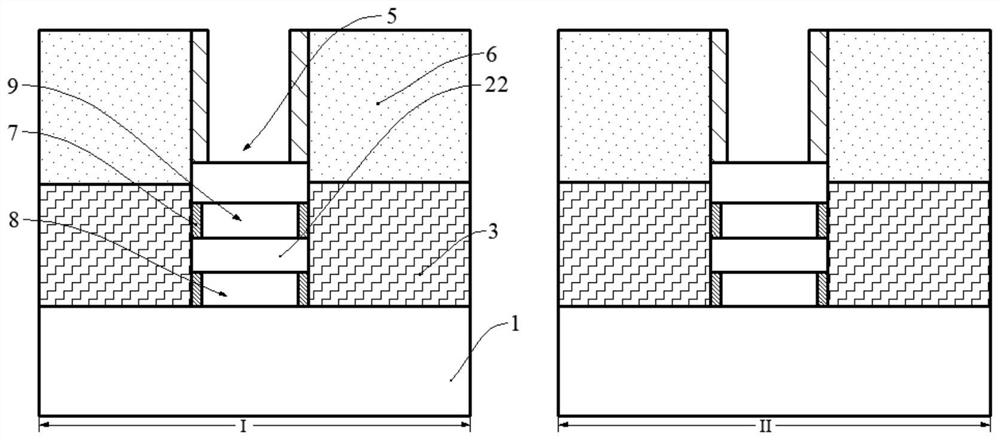

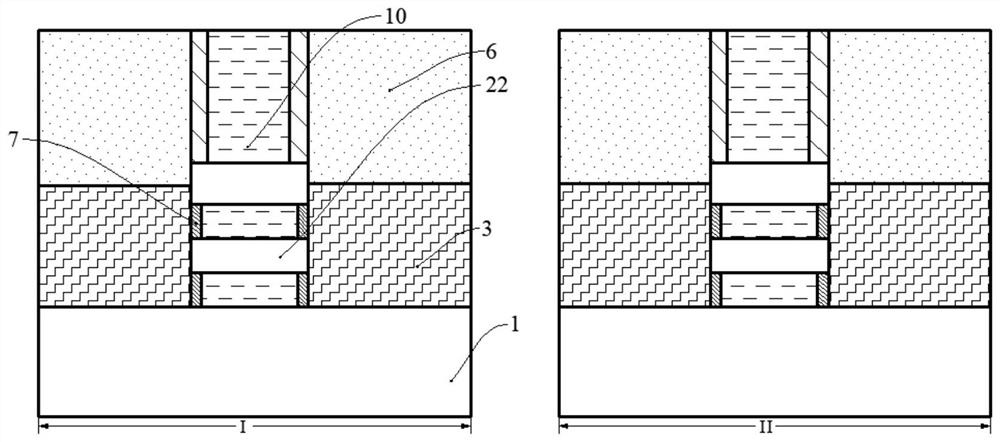

[0016] refer to Figure 1 to Figure 3 , showing a schematic structural diagram of key steps in a method for forming a semiconductor structure.

[0017] like figure 1 As shown, a substrate is provided, the substrate including a first device region I and a second device region II, the substrate including a substrate 1 and a channel stack 2 on the substrate 1, the channel stack 2 includes a sacrificial layer 21 and a channel layer 22 on the sacrificial layer 21 ; a dummy gate structure 4 spans the channel stack 2 , and the dummy gate structure 4 covers the channel stack 2 Part of the top wall and part of the sidewall are laterally parallel to the surface of the substrate 1 and perpendicular to the extension direction of the...

PUM

| Property | Measurement | Unit |

|---|---|---|

| relative permittivity | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More