Negative voltage level switching circuit

A level switching, negative voltage technology, applied in the direction of logic circuit connection/interface layout, logic circuit coupling/interface using field effect transistors, etc., can solve the problem of increased circuit layout area, increased switching power consumption, and reduced switching speed etc. to achieve the effects of speeding up voltage switching, reducing switching power consumption, and improving circuit performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

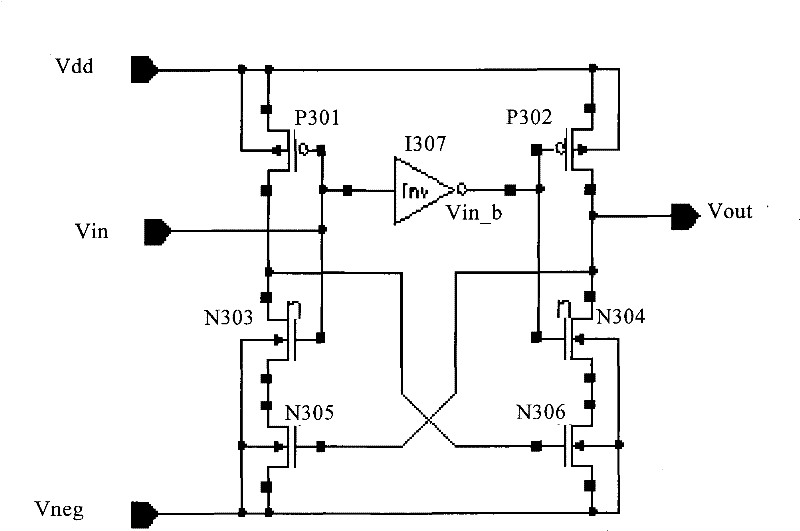

[0026] Negative voltage level switching circuit of the present invention such as image 3 shown. It includes an inverter I307, two P-channel metal oxide semiconductor field effect transistors (MOSFET) P301, P302; 4 N channel metal oxide semiconductor field effect transistors (MOSFET) N303, N304, N305, N306; for For the convenience of description, MOSFET will be referred to as transistor for short, P-channel metal oxide semiconductor field effect transistor (MOSFET) will be referred to as P channel transistor, and N channel metal oxide semiconductor field effect transistor (MOSFET) will be referred to as N channel transistor for short. .

[0027] see image 3 , wherein Vdd is a positive voltage, Vneg is a negative voltage, Vin is an input signal, the input signal of Vin is reversed after passing through the inverter I307, and the reverse input signal is Vin_b, and the output of the negative voltage level switching circuit is Vout. There are two sets of transistor circuits be...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More