Digital-analog converter of successive approximation type

A digital-to-analog converter, successive approximation technology, applied in analog-to-digital conversion, code conversion, instruments, etc., can solve the problems of high switching power consumption and large capacitor array area, and achieve reduced switching power consumption and capacitor array area. Reduced, highly linear effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

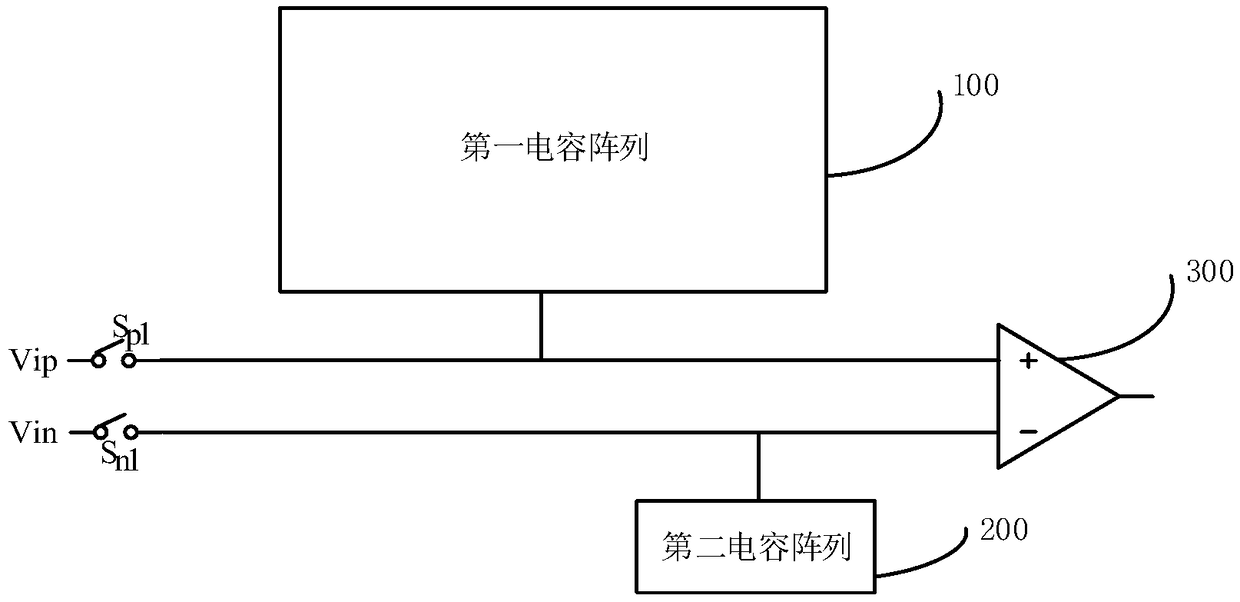

[0035] Such as figure 1 The successive approximation digital-to-analog converter shown includes: a first input terminal Vip, a second input terminal Vin, a first capacitor array 100; a second capacitor array 200, a first switch S p1 , the second switch S n1 and comparator 300, wherein the first input terminal Vip passes through the first switch S p1 It is electrically connected to the non-inverting input terminal of the comparator 300, and the first capacitor array 100 is electrically connected to the non-inverting input terminal of the comparator 300; the second input terminal Vin passes through the second switch S n1 It is electrically connected to the inverting input terminal of the comparator 300 , and the second capacitor array 200 is electrically connected to the inverting input terminal of the comparator 300 .

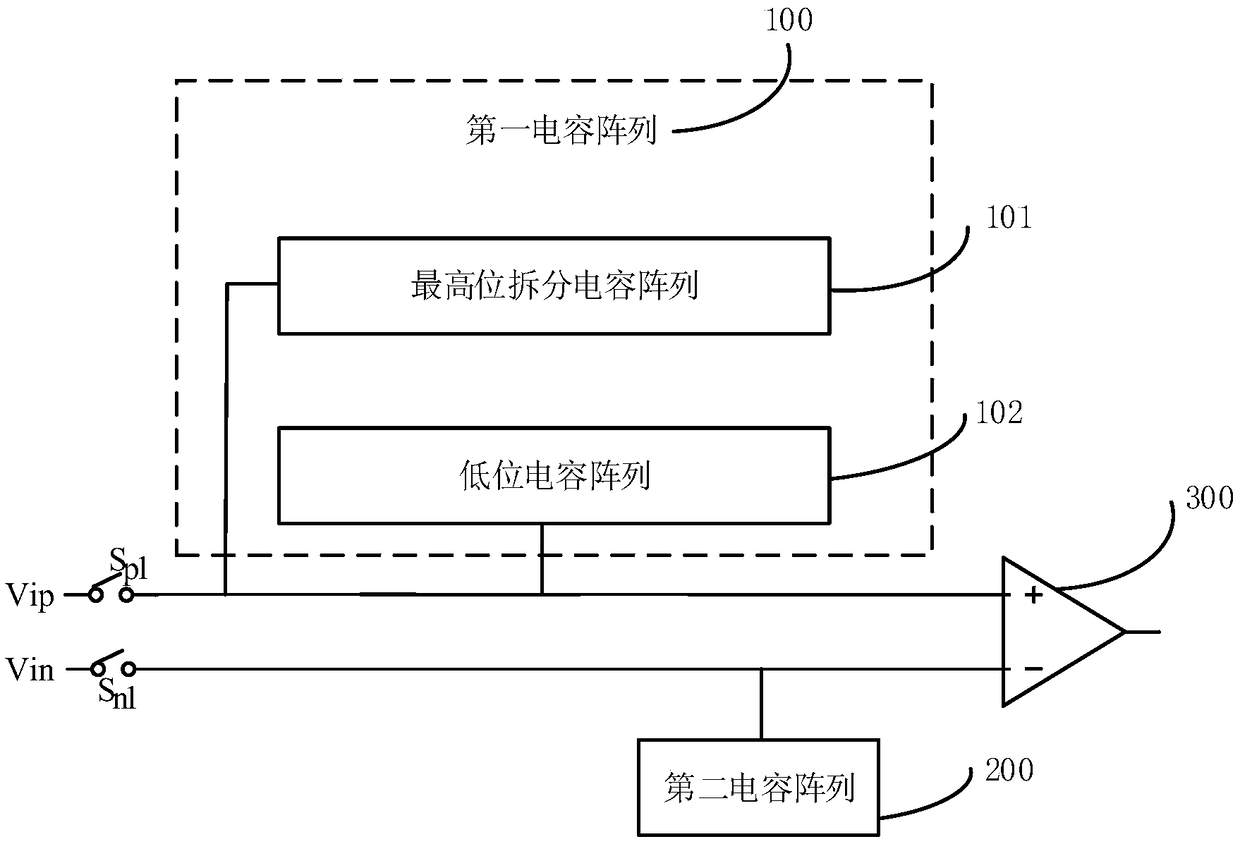

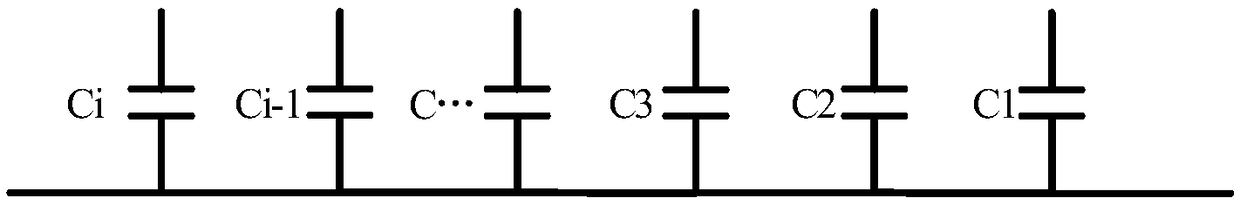

[0036] Such as figure 2 As shown, the first capacitor array 100 includes a highest-order split capacitor array 101 and a low-order capacitor array 102 , and...

Embodiment 2

[0061] Such as Figure 5 to Figure 10 As shown, in this embodiment, the switching sequence of 10 bits is taken as an example, and the 10 bits are compared ten times by successive approximation. The specific instructions are as follows:

[0062] In the sampling phase, the upper plate of the first capacitor array 100 and the upper plate of the second capacitor array 200 sample the input analog signal; after the sampling is completed, the 10th bit is compared, and after completion, the successive approximation control logic is based on the result of the initial comparator 300 Determine b(N), 1≤N≤10, if Vip10>Vin10, b10=1, then control the unit capacitance of the second capacitor array 200 to switch from the common mode voltage Vcm to the power supply potential Vref; if Vip<Vin, then the second The unit capacitance of the capacitor array 200 is switched from the common mode voltage Vcm to the ground Gnd, b10=0;

[0063] In the comparison of the 9th bit, if Vip9>Vin9, the voltage...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More