Patents

Literature

290results about How to "Improve breakdown resistance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Interlayer film for laminated glass, and laminated glass

ActiveCN103080037ALow breakdown resistanceImprove breakdown resistanceGlass/slag layered productsThin material handlingHigh water contentLaminated glass

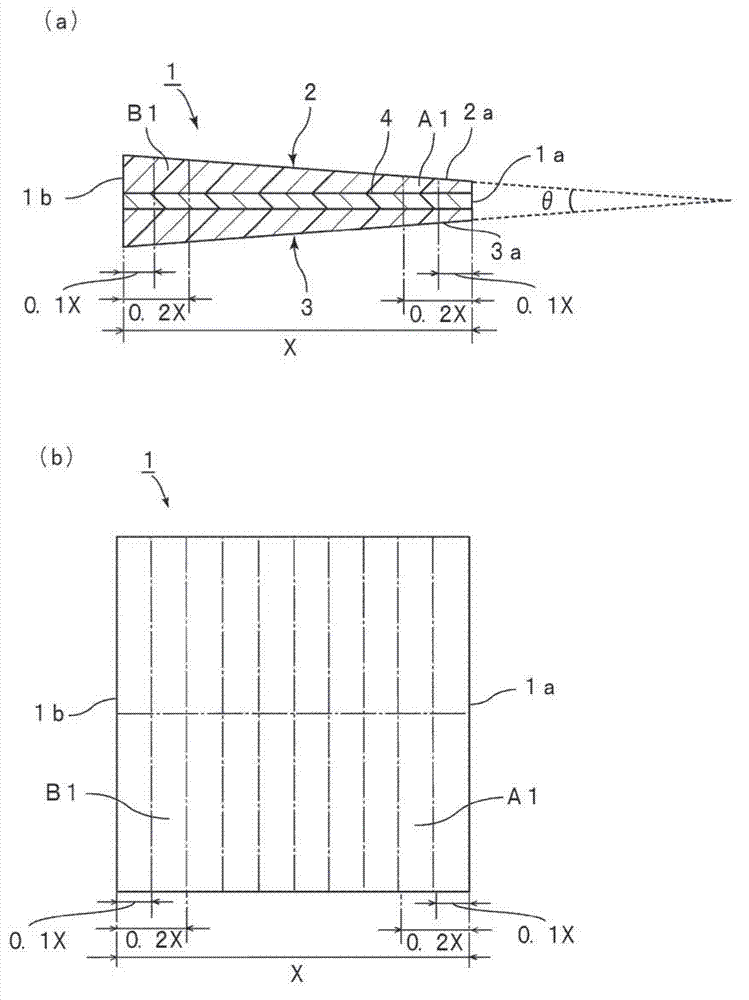

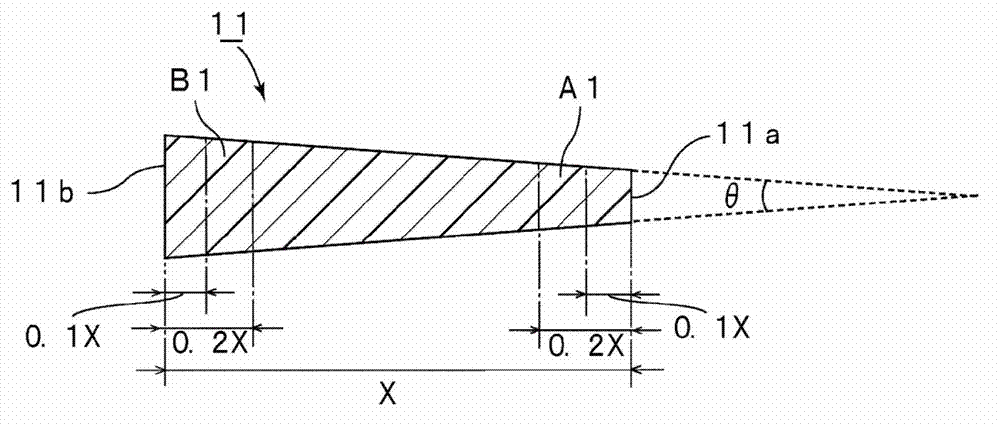

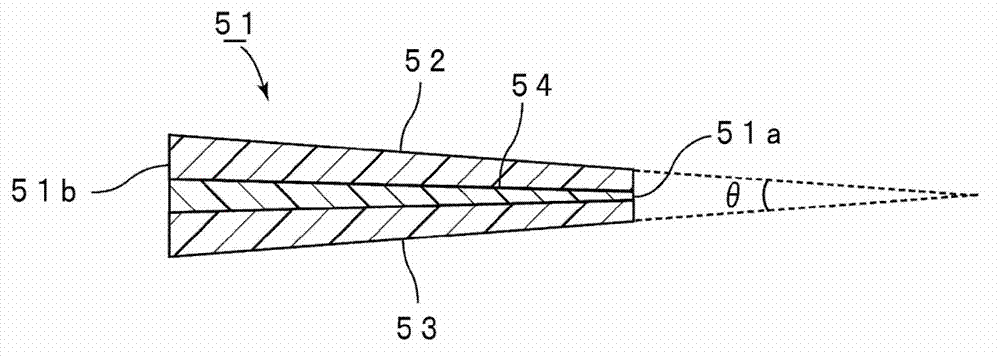

Provided are an interlayer film for laminated glass, configured so that the interlayer film increases the penetration resistance of the entire area of the laminated glass when used in the laminated glass, and laminated glass using the interlayer film for laminated glass. An interlayer film (1) for laminated glass has one end (1a) having a thickness less than that of the other end (1b). The thin region of the interlayer film (1) for laminated glass has higher water content than the thick region thereof. Laminated glass (21) comprises a first laminated glass-forming member (22), a second laminated glass-forming member (23), and the interlayer film (1) for laminated glass, sandwiched between the first and second laminated glass-forming members (22, 23).

Owner:SEKISUI CHEM CO LTD

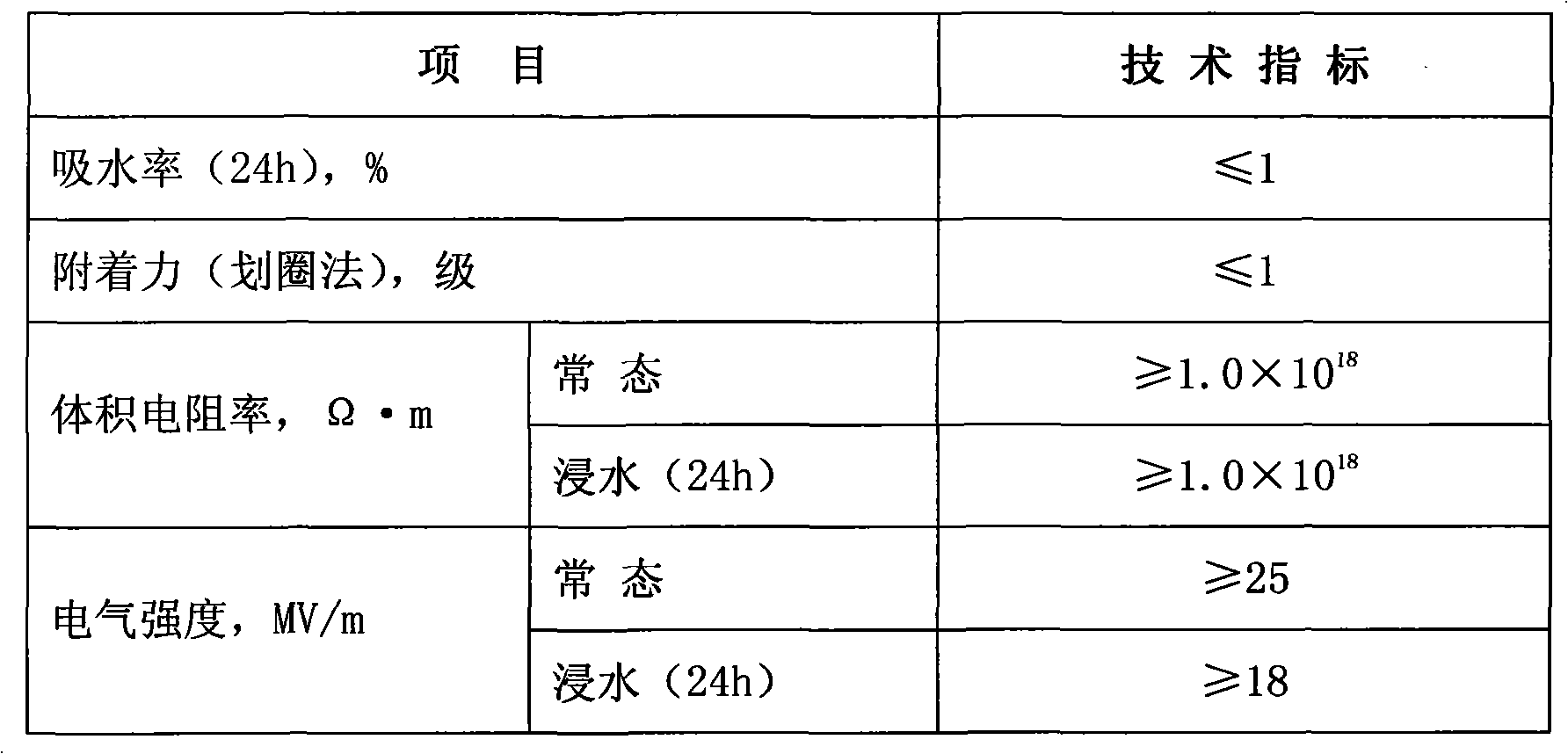

Electric steel insulating paint, and preparation method and coating method thereof

InactiveCN101659799AImprove insulation performanceConvenient coatingCoatingsElectrical resistance and conductanceElectrical steel

The invention relates to an electric steel insulating paint, and a preparation method and a coating method thereof. The electric steel insulating paint is prepared from the following components by mass percent: 25-65% of aluminium dihydrogen phosphate, 0.5-3% of silica sol, 1-5% of phosphoric acid, 1-5% of magnesium oxide, 0.1-1% of nitrate additive containing rare earth, 1-5% of silane coupling agent and the balance water as a solvent. The thickness of the electric steel insulating paint is 0.3-8 mu m. The electric steel insulating paint has the advantages of favorable insulating property, favorable coating performance, high interface resistance, high breakdown resistance, high corrosion resistance, high adhesion property and the like. The environmental-protection insulating paint does not contain chromium, and thereby being clean and having no pollution. In addition, the electric steel insulating paint also has the advantages of rich material sources, low cost, high performance priceratio, strong market competitiveness and wide application prospects.

Owner:艾宝魁

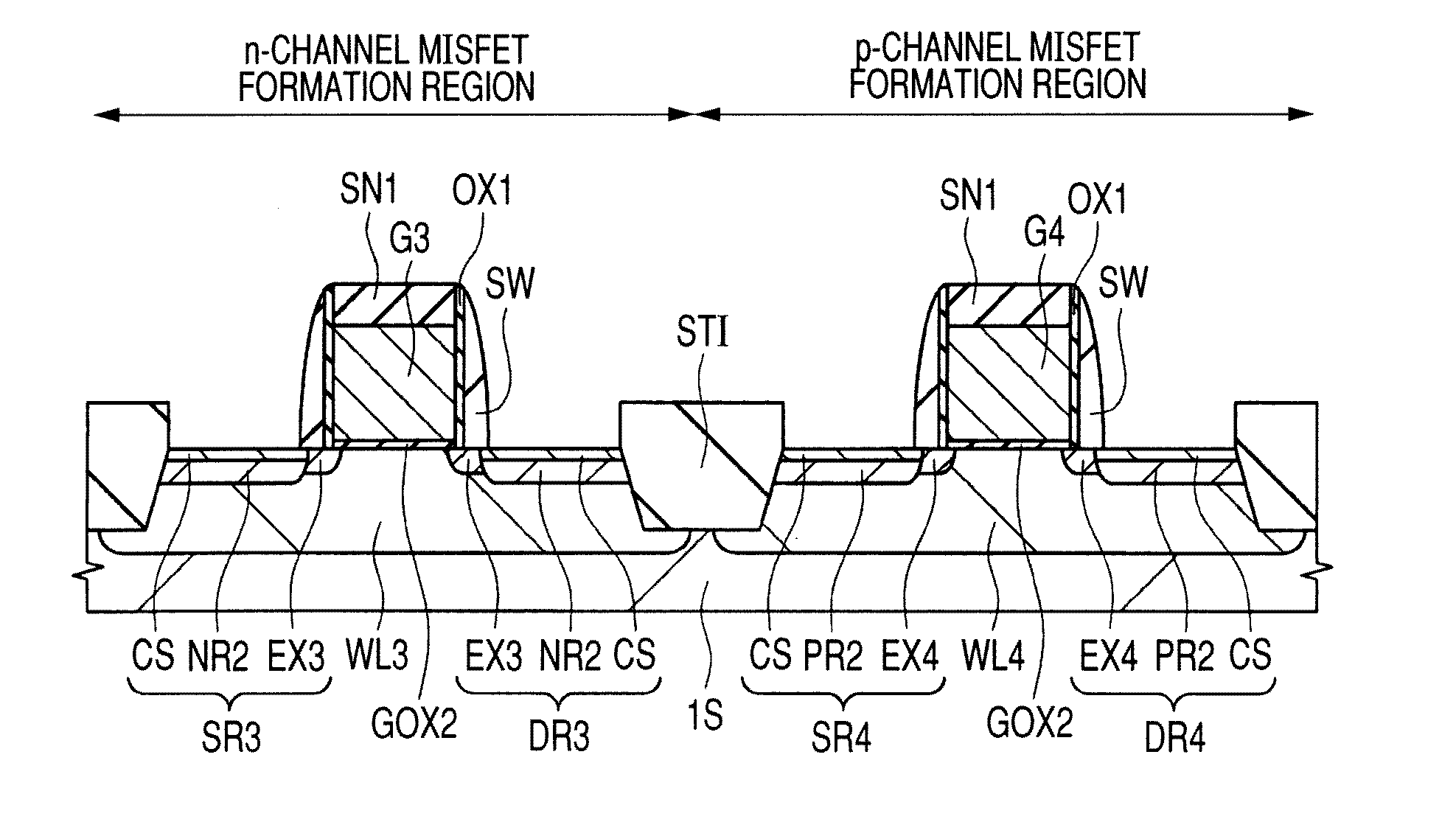

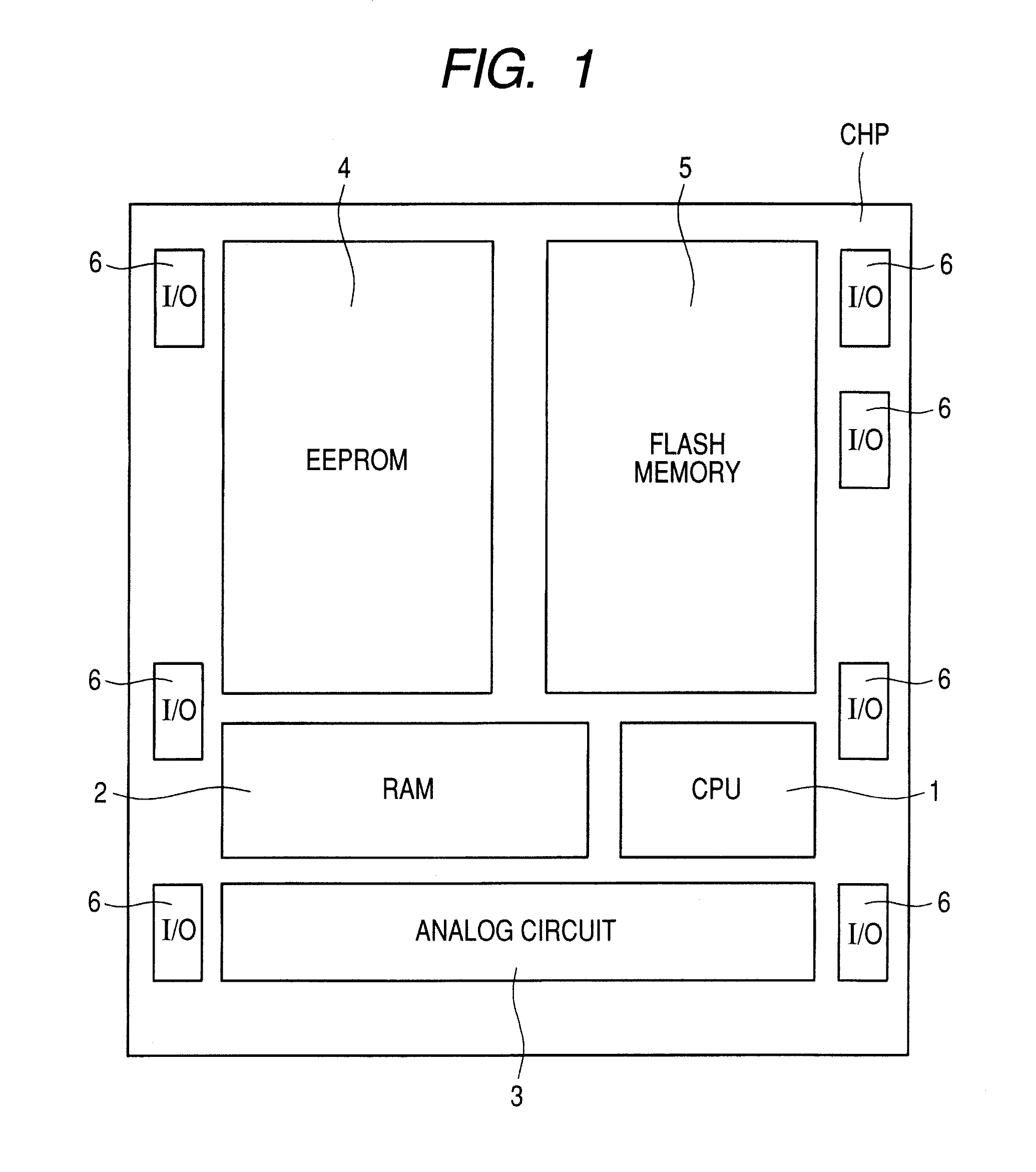

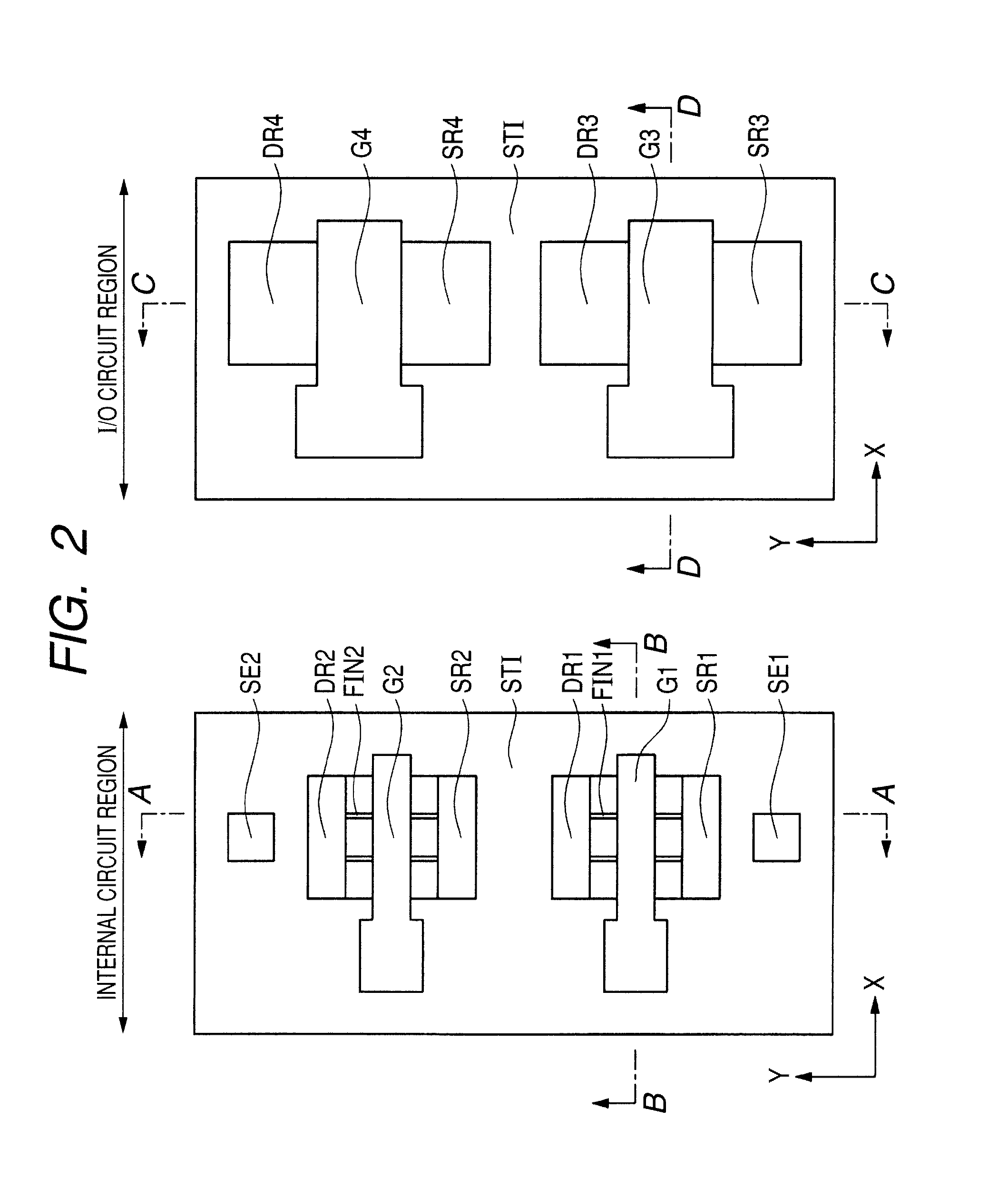

Semiconductor device and manufacturing method thereof

InactiveUS20110031552A1Improve breakdown resistanceEliminate the effects ofSolid-state devicesSemiconductor/solid-state device manufacturingDevice materialWork function

To provide, in FINFET whose threshold voltage is determined essentially by the work function of a gate electrode, a technology capable of adjusting the threshold voltage of FINFET without changing the material of the gate electrode. FINFET is formed over an SOI substrate comprised of a substrate layer, a buried insulating layer formed over the substrate layer, and a silicon layer formed over the buried insulating layer. The substrate layer has therein a first semiconductor region contiguous to the buried insulating layer. The silicon layer of the SOI substrate is processed into a fin. A ratio of the height of the fin to the width of the fin is adjusted to fall within a range of from 1 or greater but not greater than 2. In addition, a voltage can be applied to the first semiconductor region.

Owner:RENESAS ELECTRONICS CORP

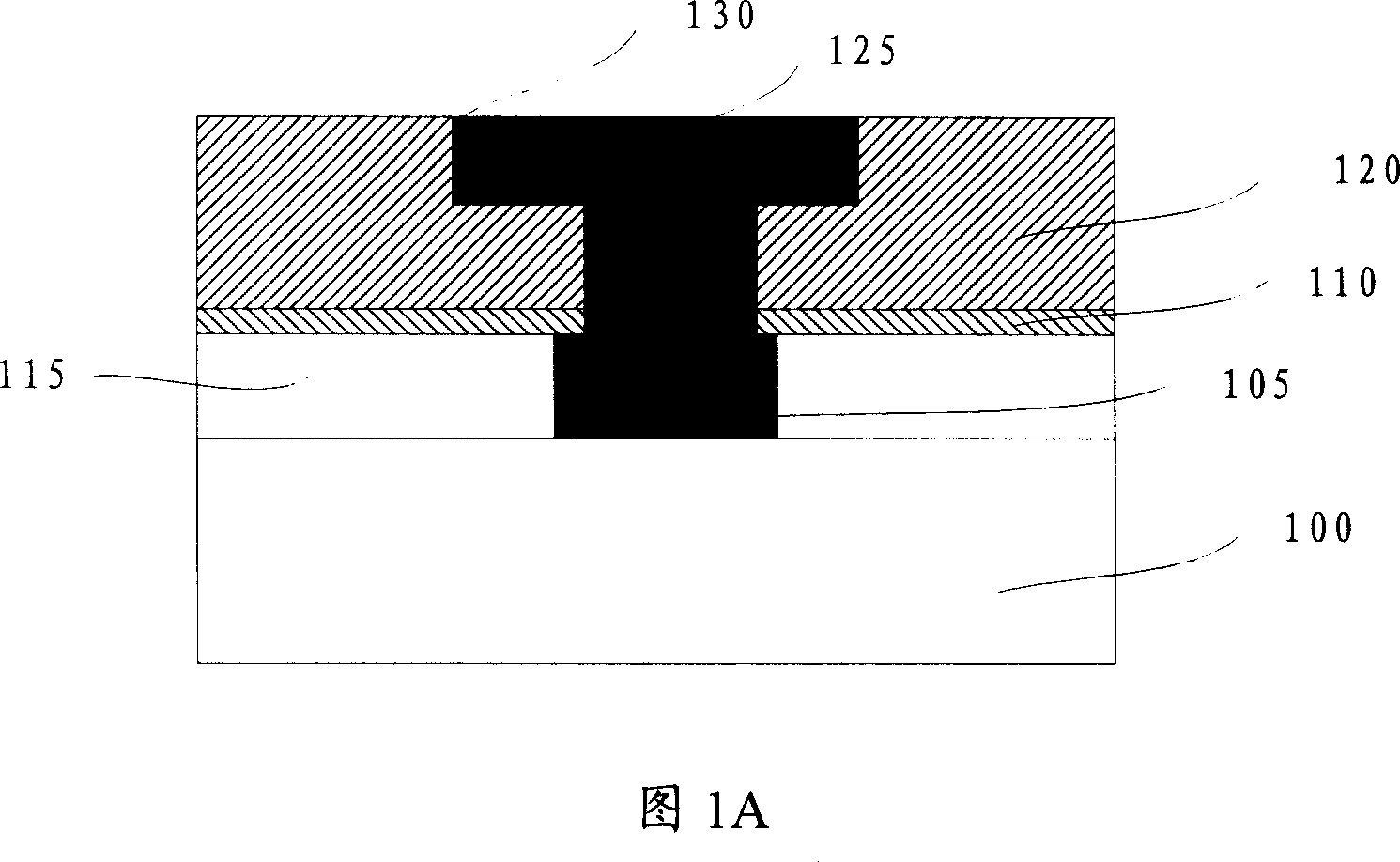

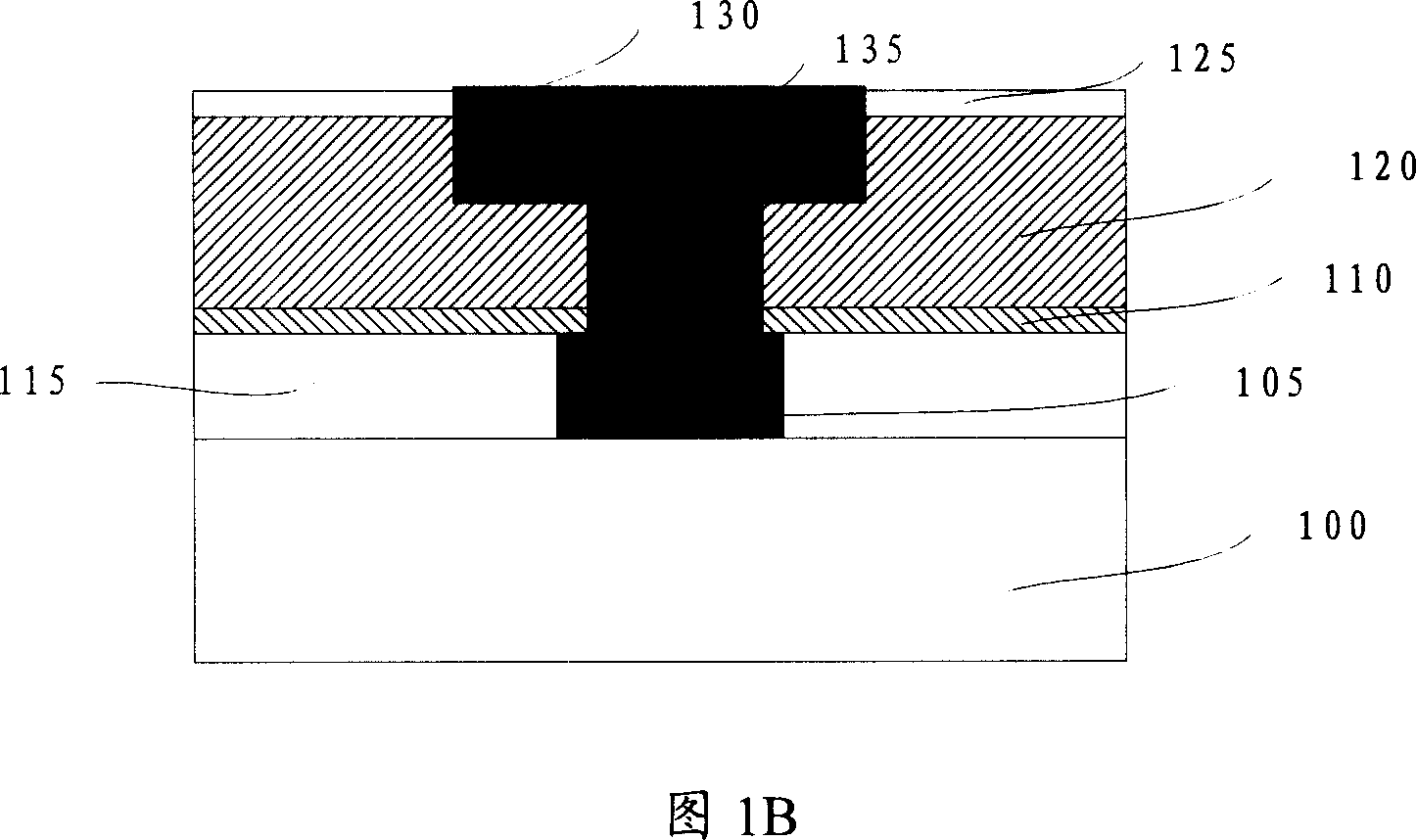

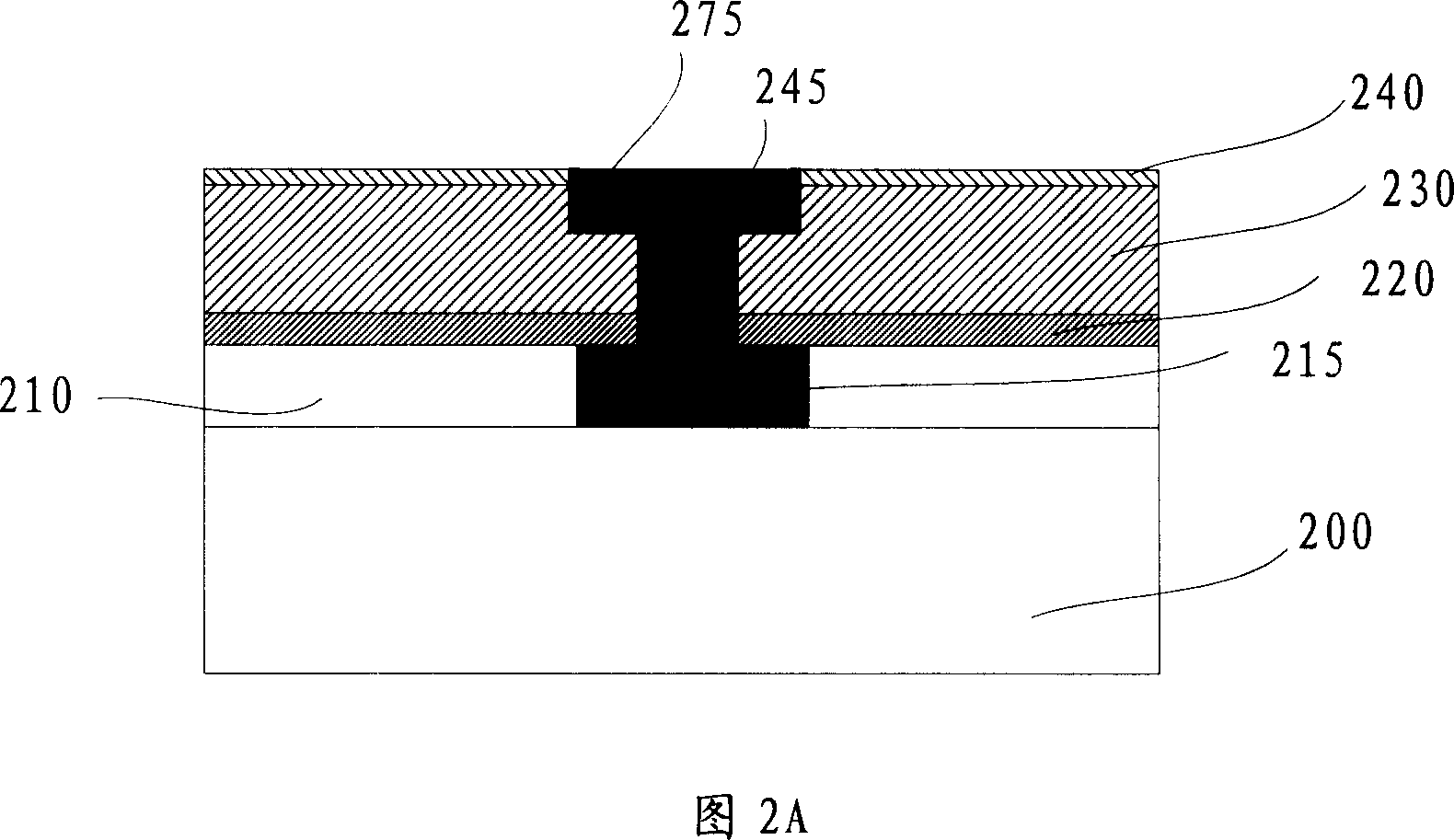

Double-inlay structure and its making method

InactiveCN101079408ASo as not to damageImprove reliabilitySemiconductor/solid-state device detailsSolid-state devicesDielectric layerSediment

The invention discloses a making method of double-mosaic structure, which comprises the following steps: making burying covering layer on the metal dielectric layer to form the metal dielectric layer and through-hole and groove in the burying covering layer; covering etching stopping layer on the substrate with metal pattern; covering the metal dielectric layer on the etching stopping layer; forming burying covering layer on the metal dielectric layer; etching the groove and through-hole to sediment metal through photoetching; making the meta dielectric layer surface protected by burying covering layer from damaging in the moving photoetching agent course of chemical mechanic grinding and plasma; improving the reliability of elements.

Owner:SEMICON MFG INT (SHANGHAI) CORP

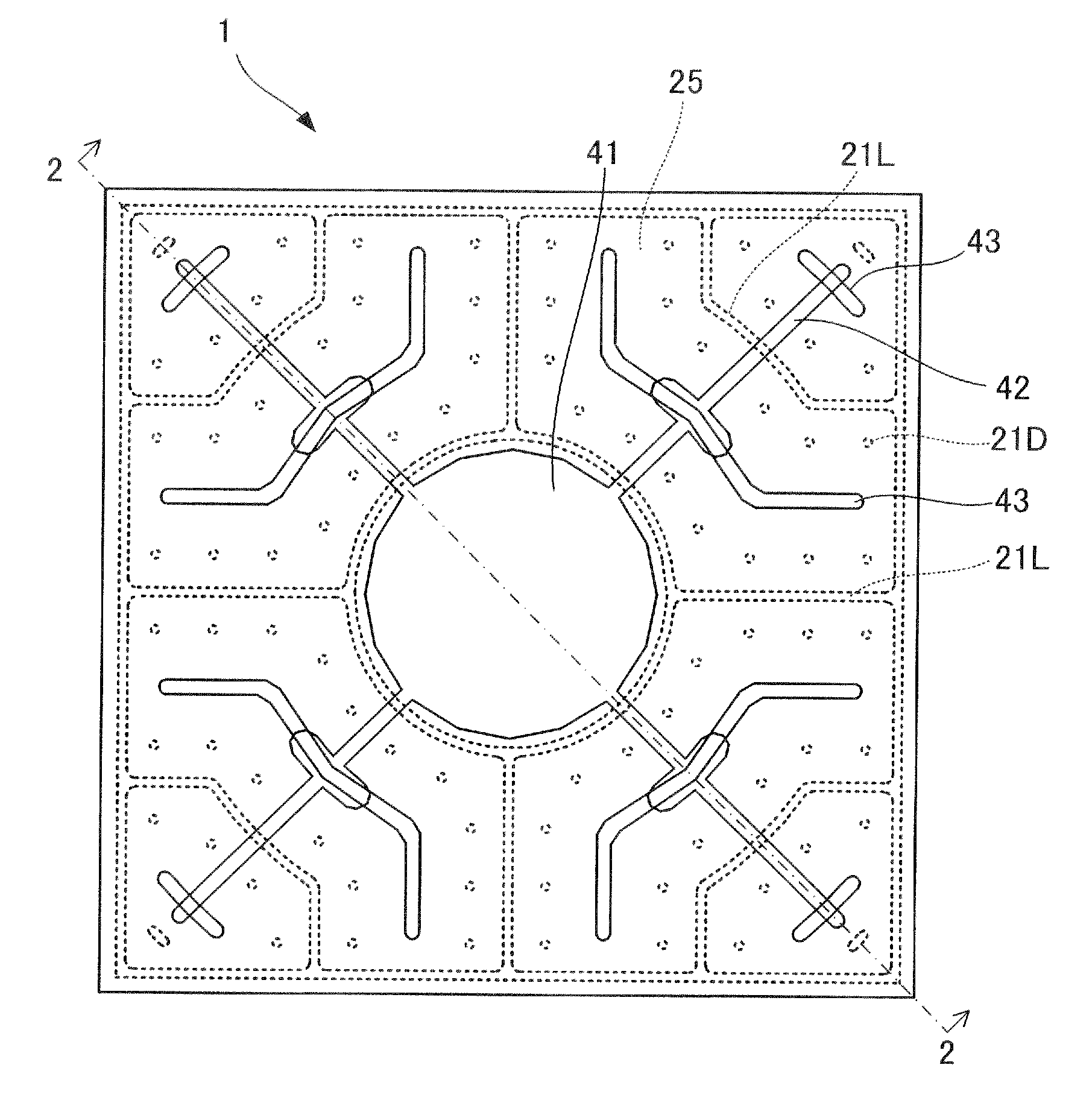

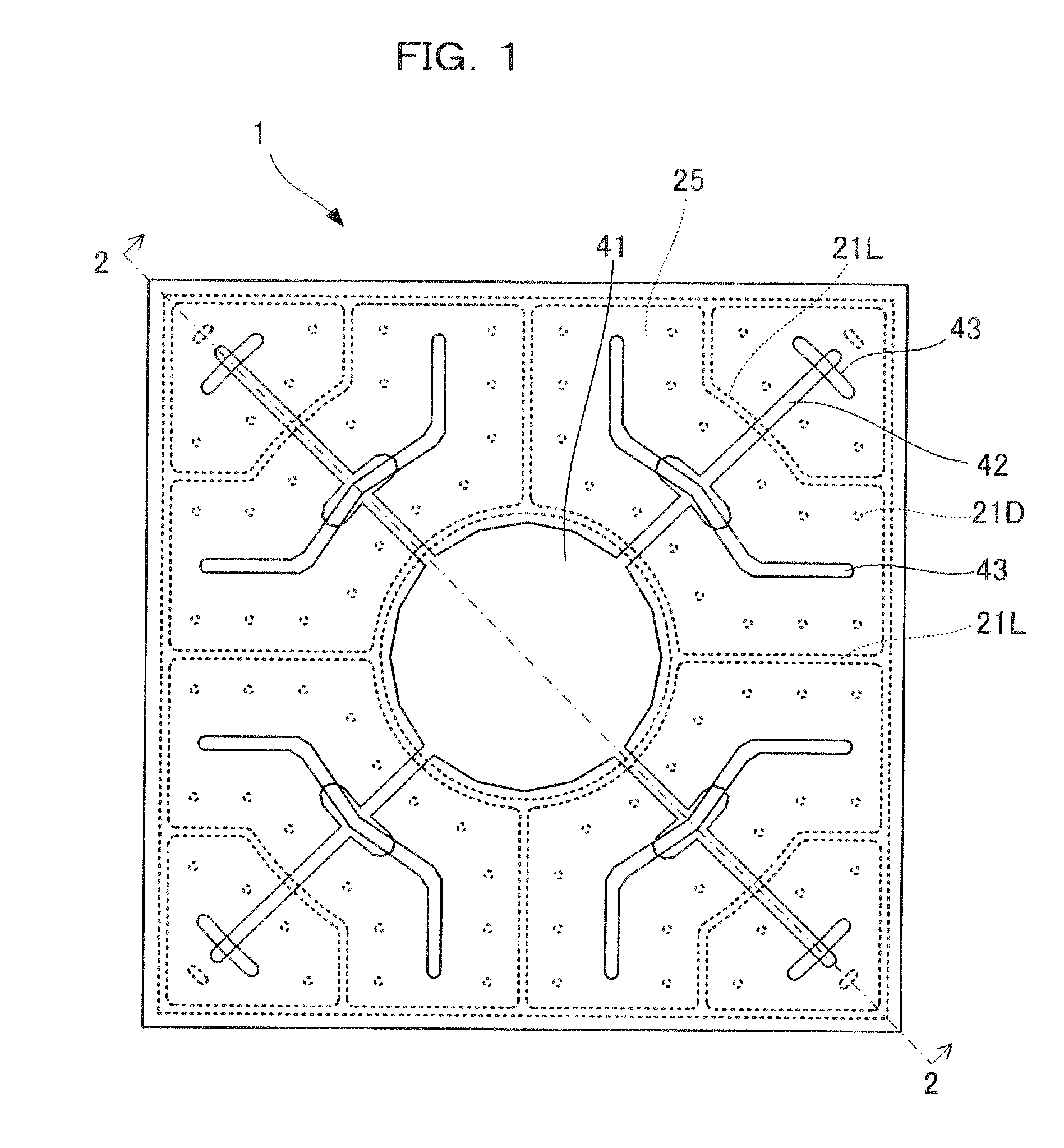

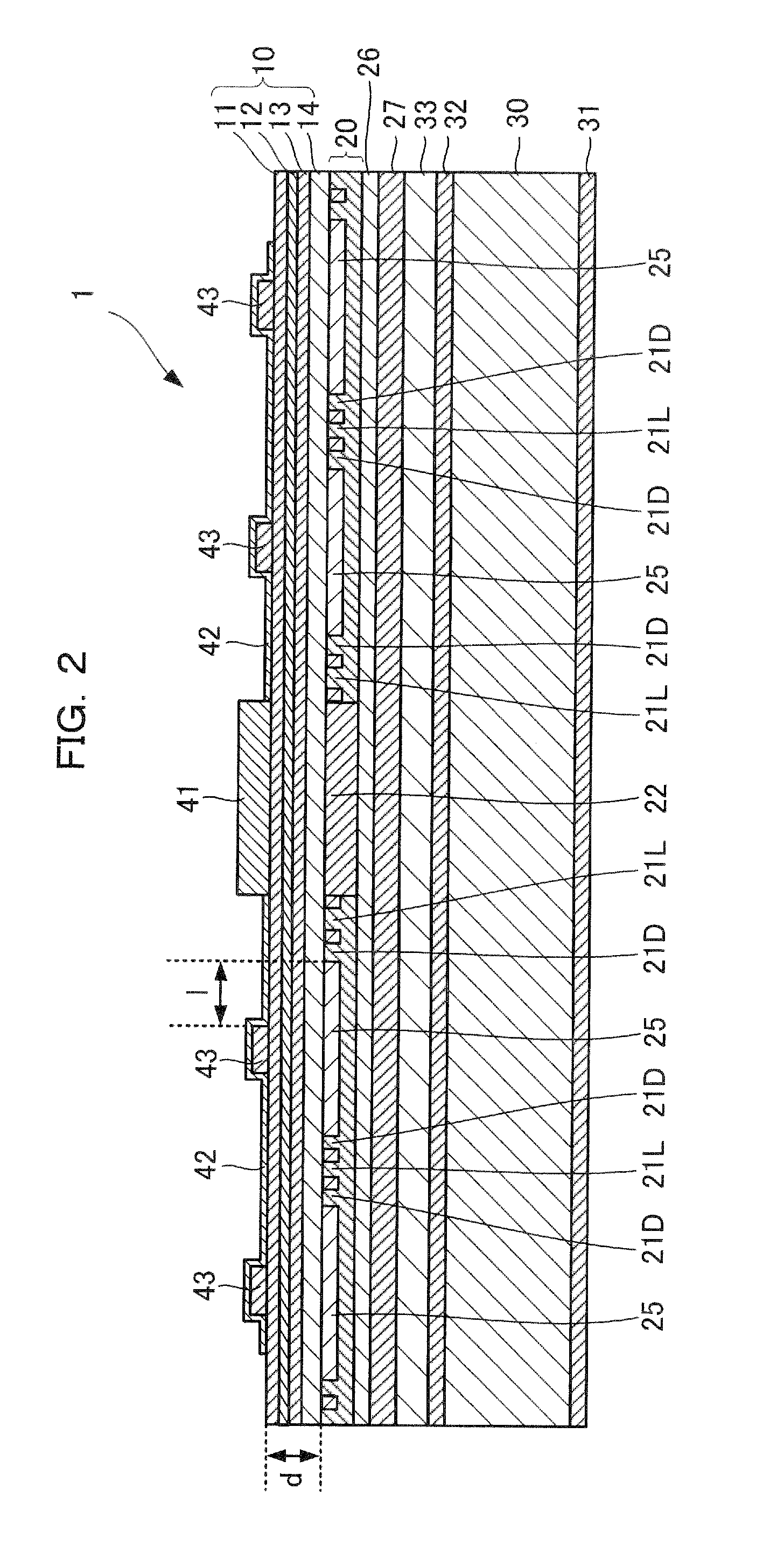

Semiconductor light emitting element

InactiveUS20130037839A1Improve breakdown resistanceDecreased light extractionSolid-state devicesSemiconductor/solid-state device manufacturingSurface electrodeOhmic contact

A semiconductor light emitting element of the present invention includes a support substrate, a semiconductor film including a light emitting layer, a surface electrode provided on the surface on a light-extraction-surface side of the semiconductor film, and a light reflecting layer. The surface electrode includes first electrode pieces that form ohmic contact with the semiconductor film and a second electrode piece electrically connected to the first electrode pieces. The light reflecting layer includes a reflecting electrode, and the reflecting electrode includes third electrode pieces that form ohmic contact with the semiconductor film and a fourth electrode piece electrically connected to the third electrode pieces and placed opposite to the second electrode piece. Both the second electrode piece and the fourth electrode piece form Schottky contact with the semiconductor film so as to form barriers to prevent forward current in the semiconductor film.

Owner:STANLEY ELECTRIC CO LTD

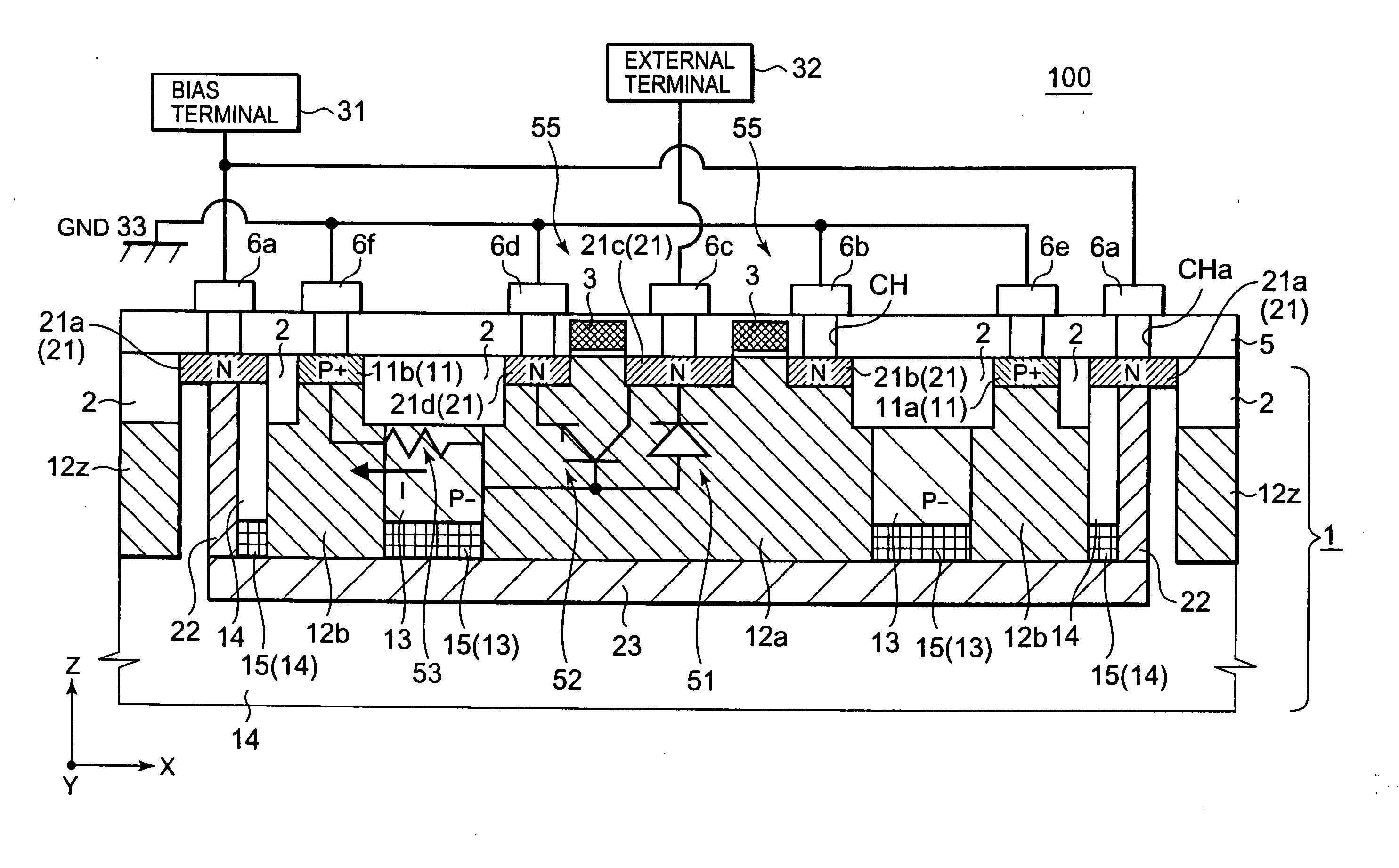

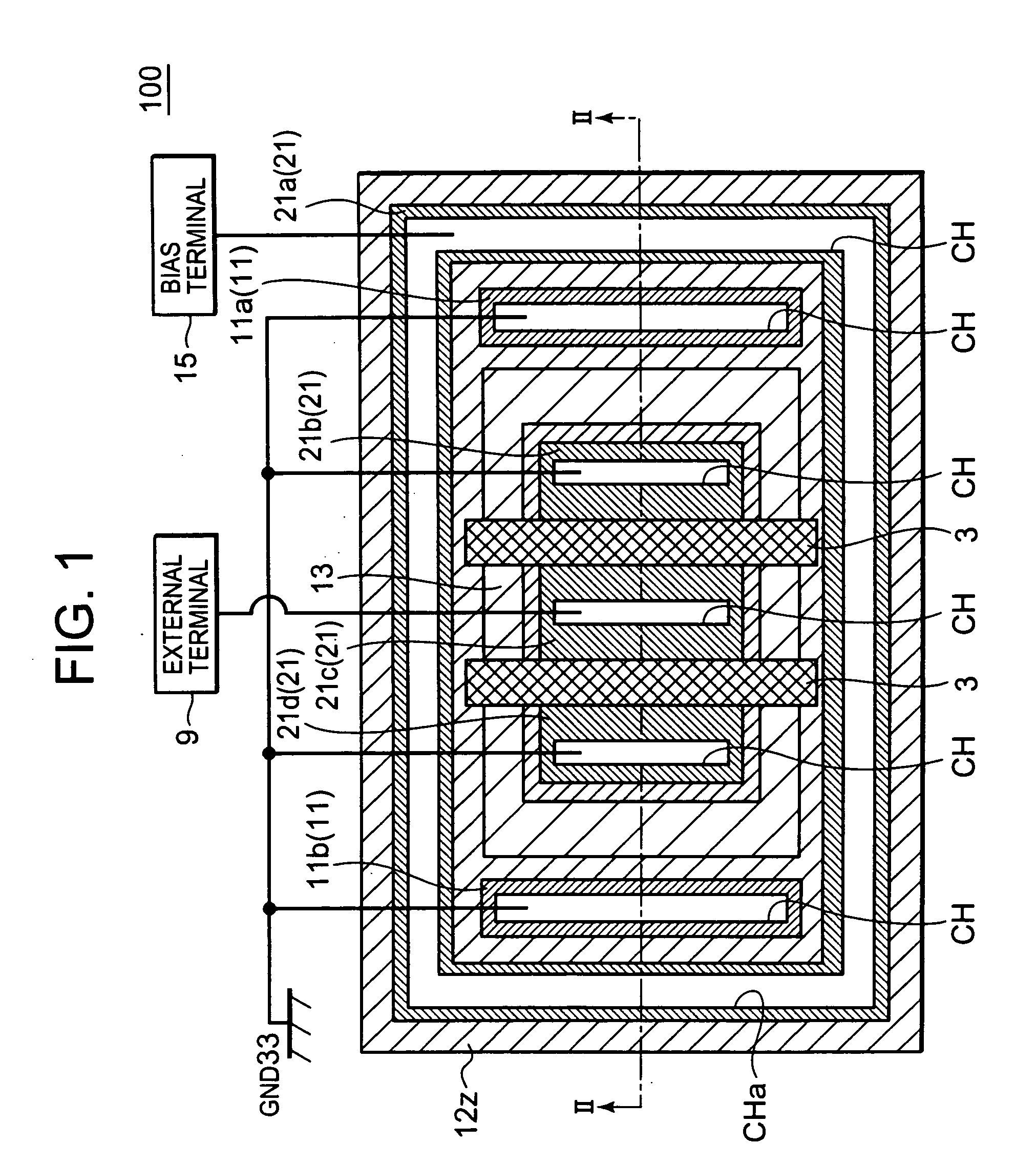

Semiconductor device having electro-static discharge protection element

InactiveUS20100193869A1Increase parasitic resistanceReduce in sizeTransistorSemiconductor/solid-state device detailsElectrostatic discharge protectionEngineering

A semiconductor device includes a semiconductor substrate of a first conductivity-type, a buried diffusion layer of a second conductivity-type formed in the semiconductor substrate, a first well of the second conductivity-type having a bottom portion in contact with a top portion of the buried diffusion layer, the first well having an annular shape in a planar view, and a second well of the first conductivity-type formed to be surrounded by the first well. The semiconductor device further includes a diffusion region formed between a first portion of the second well and a second portion of the second well, the diffusion region having an impurity concentration lower than that of the second well, so that a depletion layer formed in the diffusion region can be provided, a transistor formed on the second well to function as an ESD (electro-static discharge) protection element, and an external terminal connected to a drain of the transistor.

Owner:RENESAS ELECTRONICS CORP

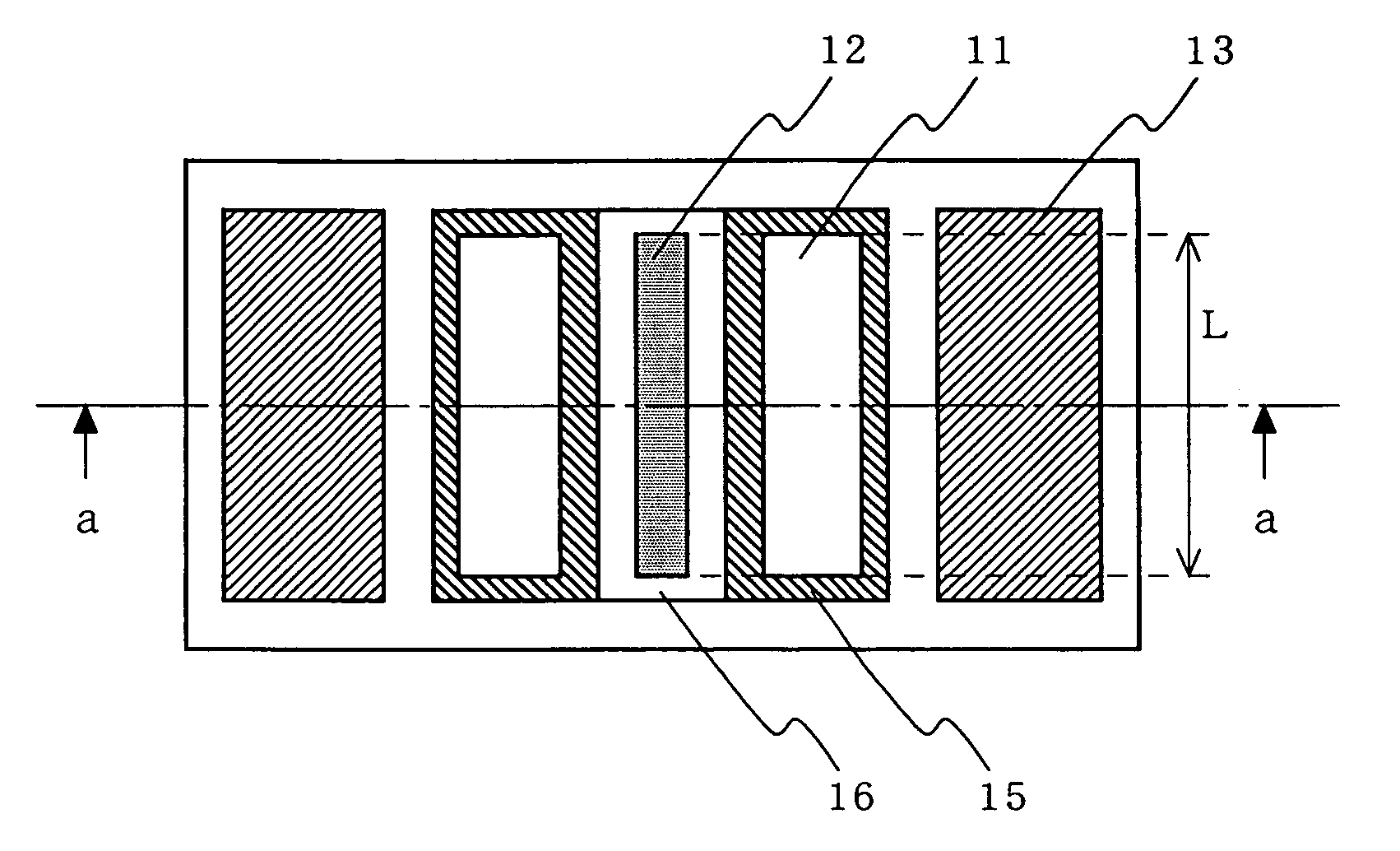

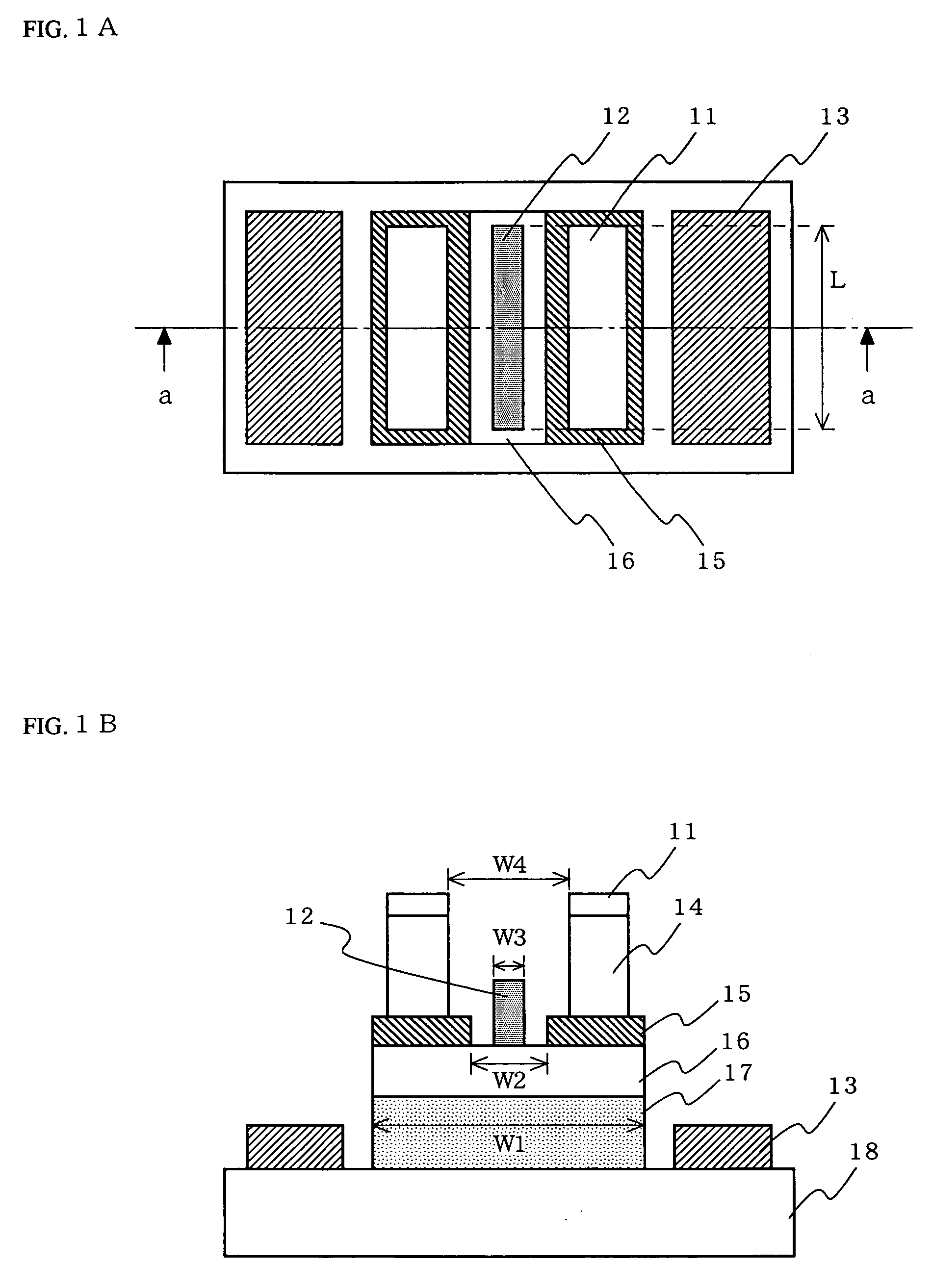

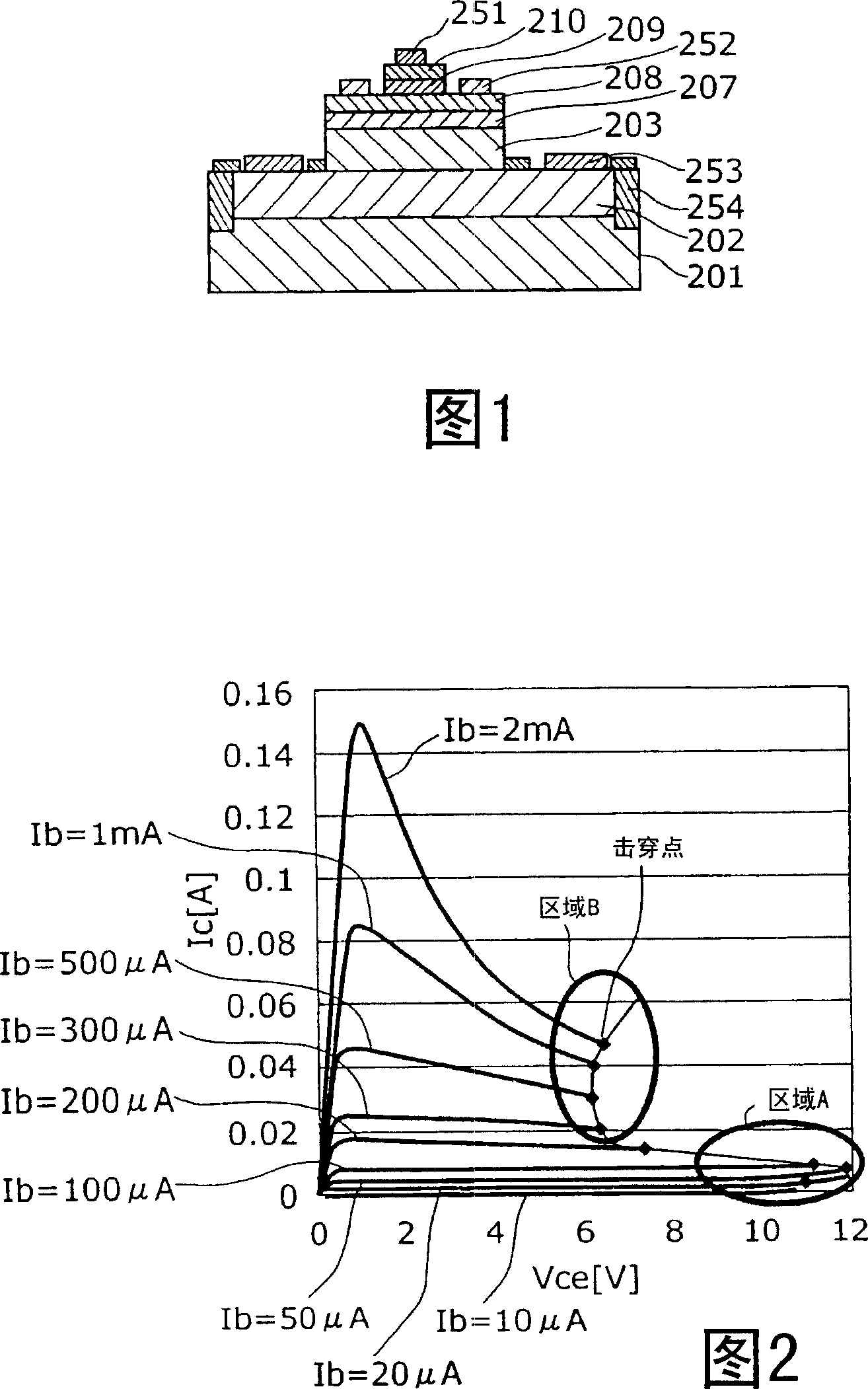

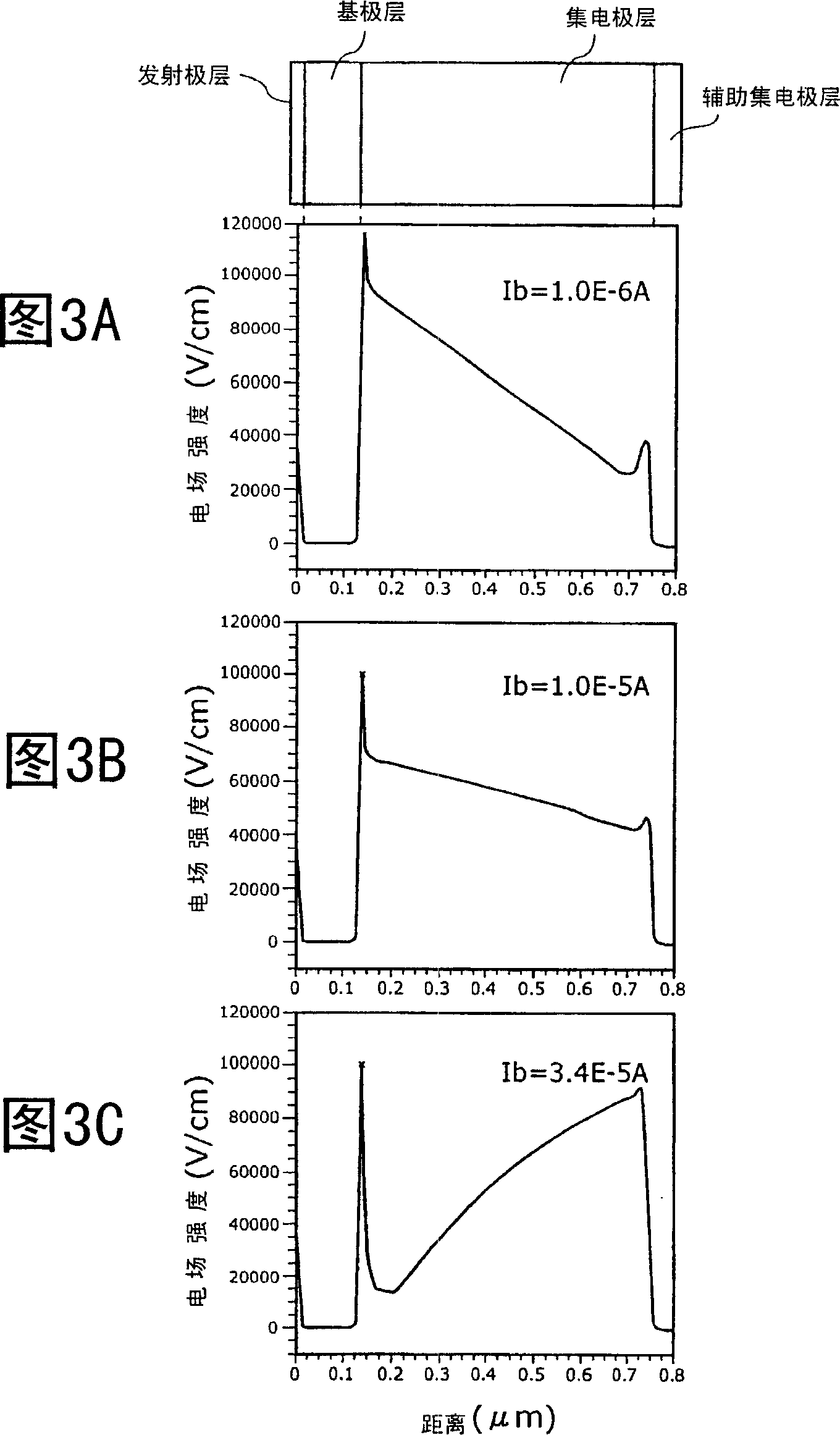

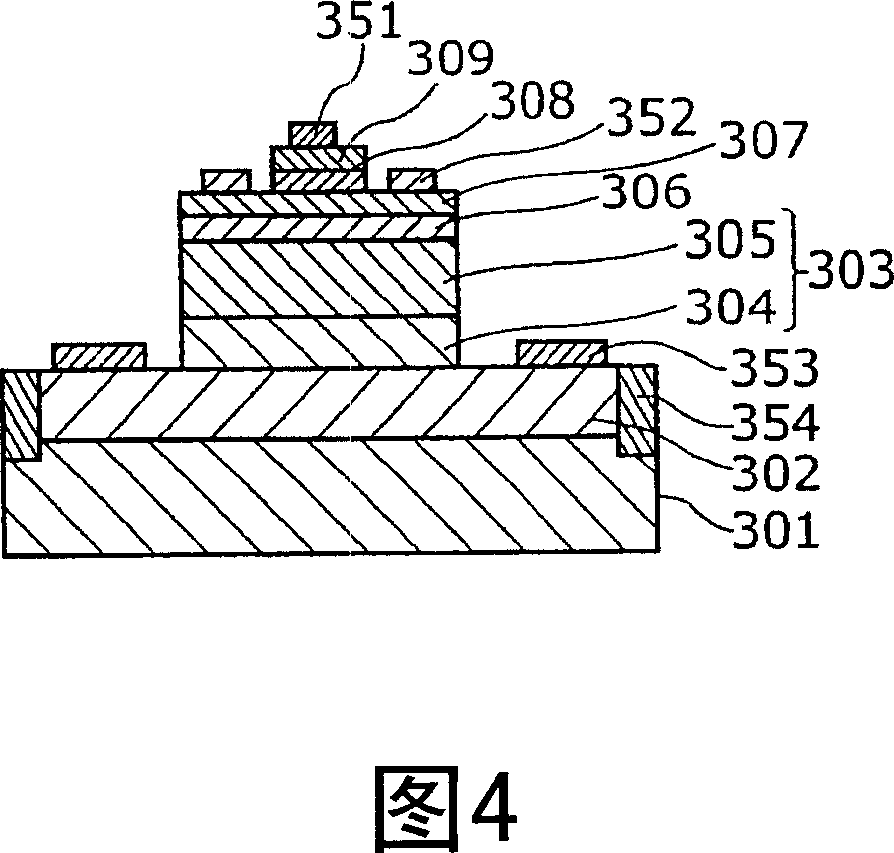

Bipolar transistor and power amplifier

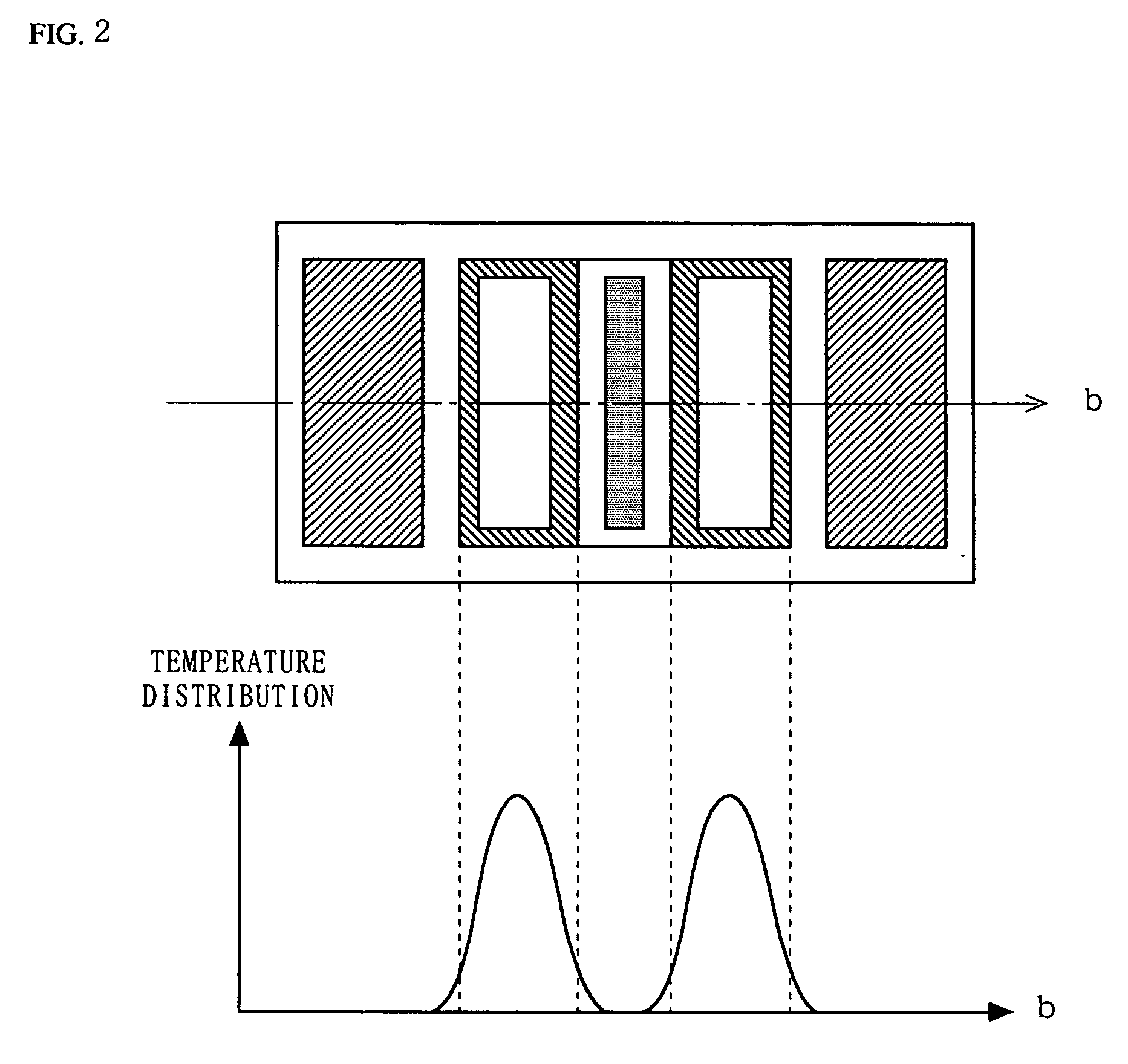

ActiveUS20070012949A1Evenly heatedImprove featuresSemiconductor/solid-state device manufacturingSemiconductor devicesAudio power amplifierEngineering

A base mesa finger (an emitter ledge layer 15, a base layer 16, and a collector layer 17) is interposed between two collector fingers (collector electrodes 13), and on the base mesa finger, a base finger (a base electrode 12) and two emitter fingers (an emitter layer 14 and an emitter electrode 11) on both sides of the base finger, are formed. The two emitter fingers are formed symmetric with respect to the base finger as a reference.

Owner:PANASONIC SEMICON SOLUTIONS CO LTD

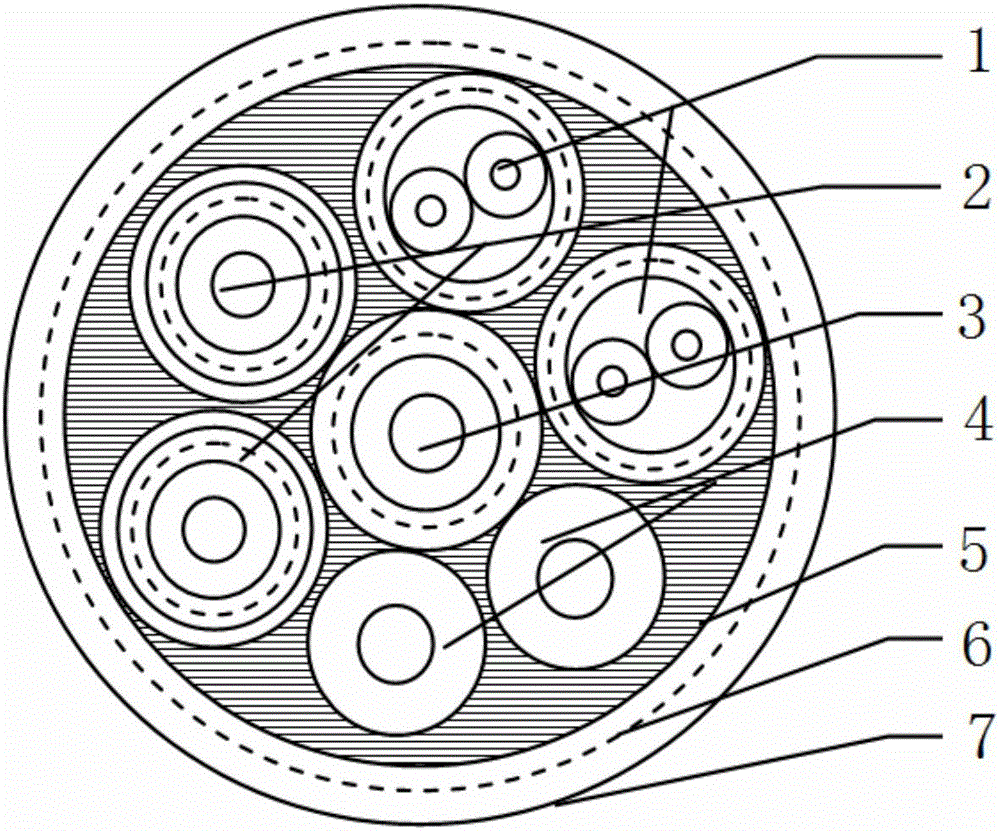

Anti-static, anti-corrosion, waterproof and stretching-resistant insulated cable

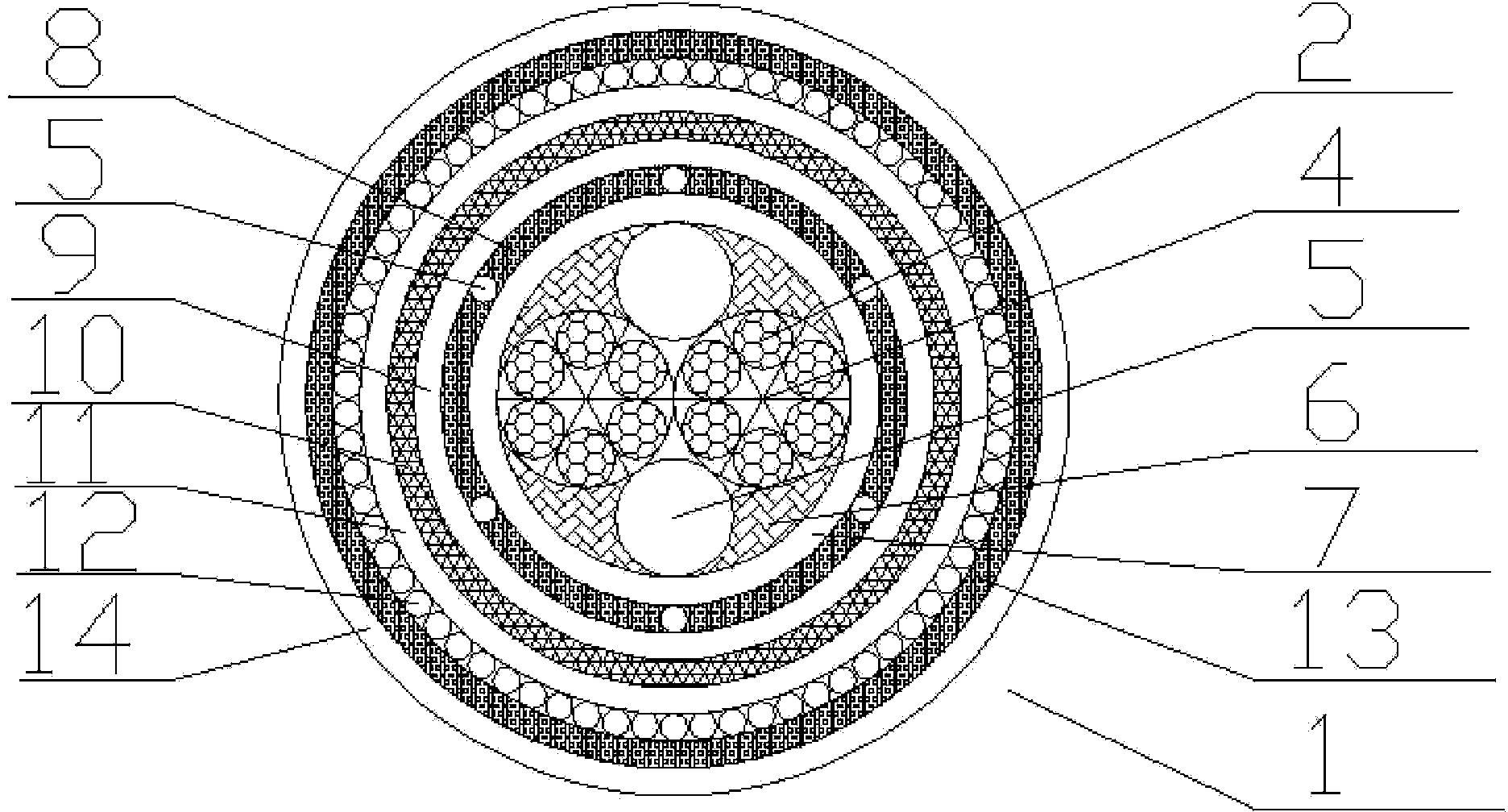

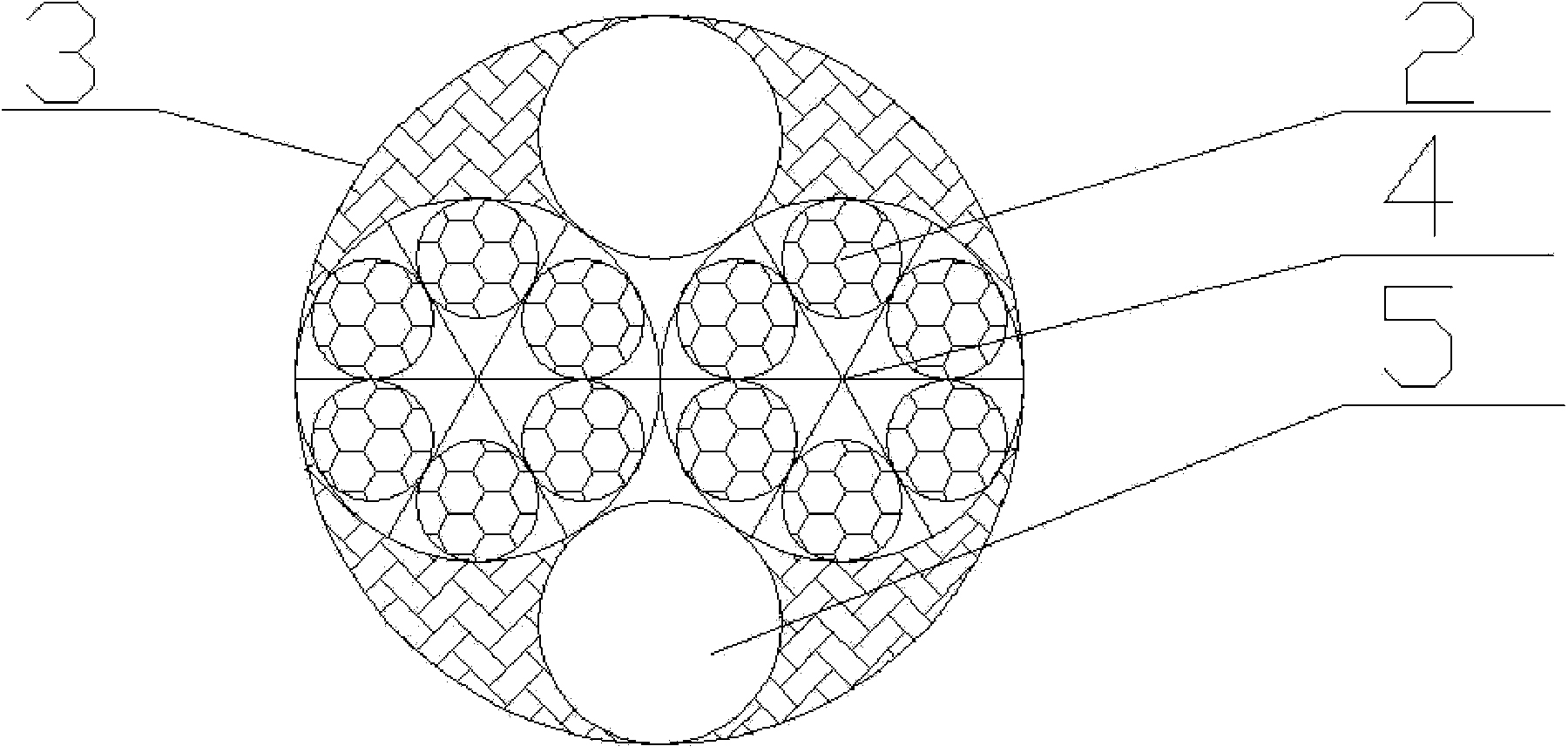

InactiveCN104318986AReasonable structural designImprove anti-static abilityInsulated cablesInsulated conductorsGraphiteStatics

The invention discloses an anti-static, anti-corrosion, waterproof and stretching-resistant insulated cable. The anti-static, anti-corrosion, waterproof and stretching-resistant insulated cable comprises a cable body. The cable body comprises cable cores, a cable core protective layer, an insulating layer, a shielding layer and an outer jacket. The cross section of the cable core protective layer is of a circular structure, and the multiple evenly-arranged cable cores are arranged in the cable core protective layer and separated through PVC plastic connecting rods; a plurality of current guide cores are arranged outside the cable core protective layer and are tangent with the cable core protective layer; the insulating layer is arranged outside the cable core protective layer; waterproof fillers are arranged in a gap between the insulating layer and the cable core protective layer; the shielding layer is tightly extruded on the insulating layer and internally provided with the multiple evenly-arranged current guide cores; a breakdown resistant layer, a steel core protective layer and a waterproof layer are sequentially extruded on the shielding layer from inside to outside; an armor layer is extruded outside the waterproof layer, the outer jacket is arranged outside the armor layer, and a graphite layer is arranged between the armor layer and the outer jacket. The anti-static, anti-corrosion, waterproof and stretching-resistant insulated cable has the advantages of being reasonable in structural design, high in anti-static capacity, good in anti-corrosion performance and the like.

Owner:珠海长盛电缆有限公司

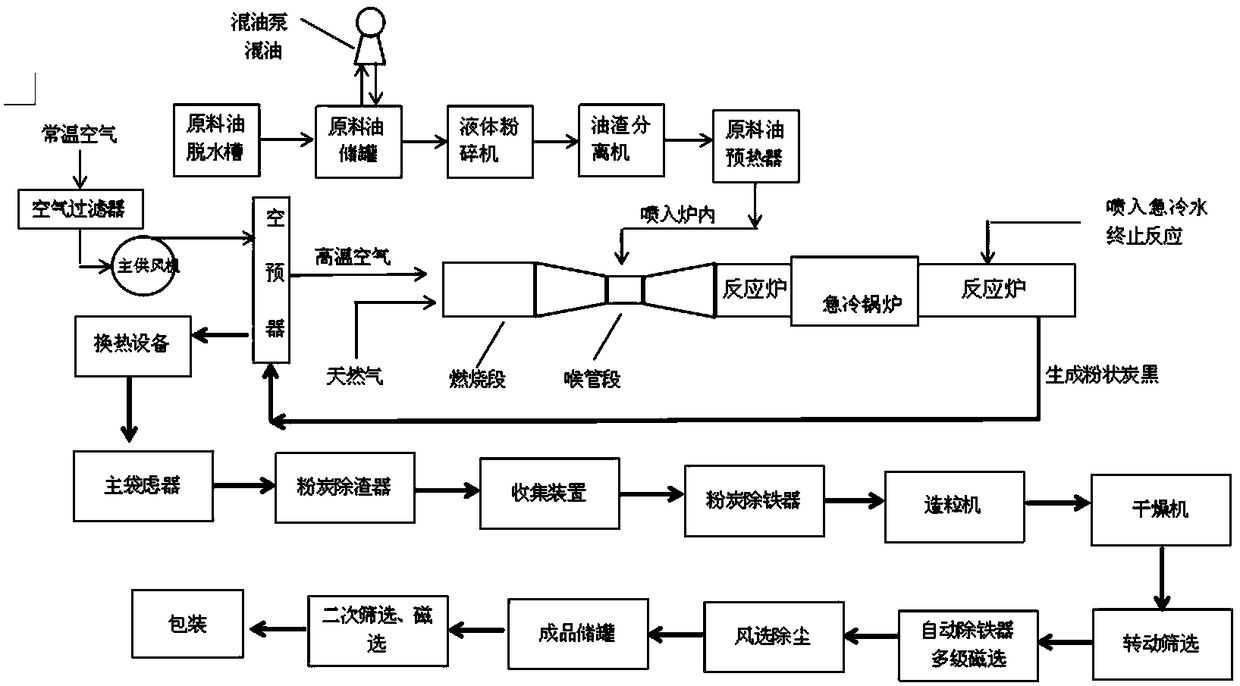

Production method for high-purity carbon black

ActiveCN109321005AImprove purityExtend your lifePigmenting treatmentCombustion chamberCrack resistance

The invention discloses a production method for a high-purity carbon black, which comprises the following steps: (Step 1) anthracene oil with a moisture content less than or equal to 0.2 percent and ethylene tar are sufficiently mixed according to the proportion of 8:2, and the mixed material is sequentially injected into a liquid pulverizer and an oil-residue separator and refined, so that refined material oil is obtained; (Step 2) natural gas and air are respectively filtered and then injected into the combustion chamber of a reaction furnace, wherein, after being filtered, the air is heatedto 900 DEG C, so that the temperature of the reaction furnace reaches 1800 DEG C to 2200 DEG C, wherein the refined material oil is heated to 250 DEG C to 300 DEG C, and the refined material oil andadditive are injected into a carbon black reactor of the reaction furnace to rapidly react for pyrolysis, so that the powdery carbon black is produced. The carbon black product produced by the invention has high purity and low ash, heavy metal, polycyclic aromatic hydrocarbon and sulfur contents, and can be highly dispersed to be completely combined with ingredients, the applicability, wear resistance, extrusion property, crack resistance, insulating property and conductivity of the product are increased, and the life of the product is greatly prolonged.

Owner:山东联科新材料有限公司

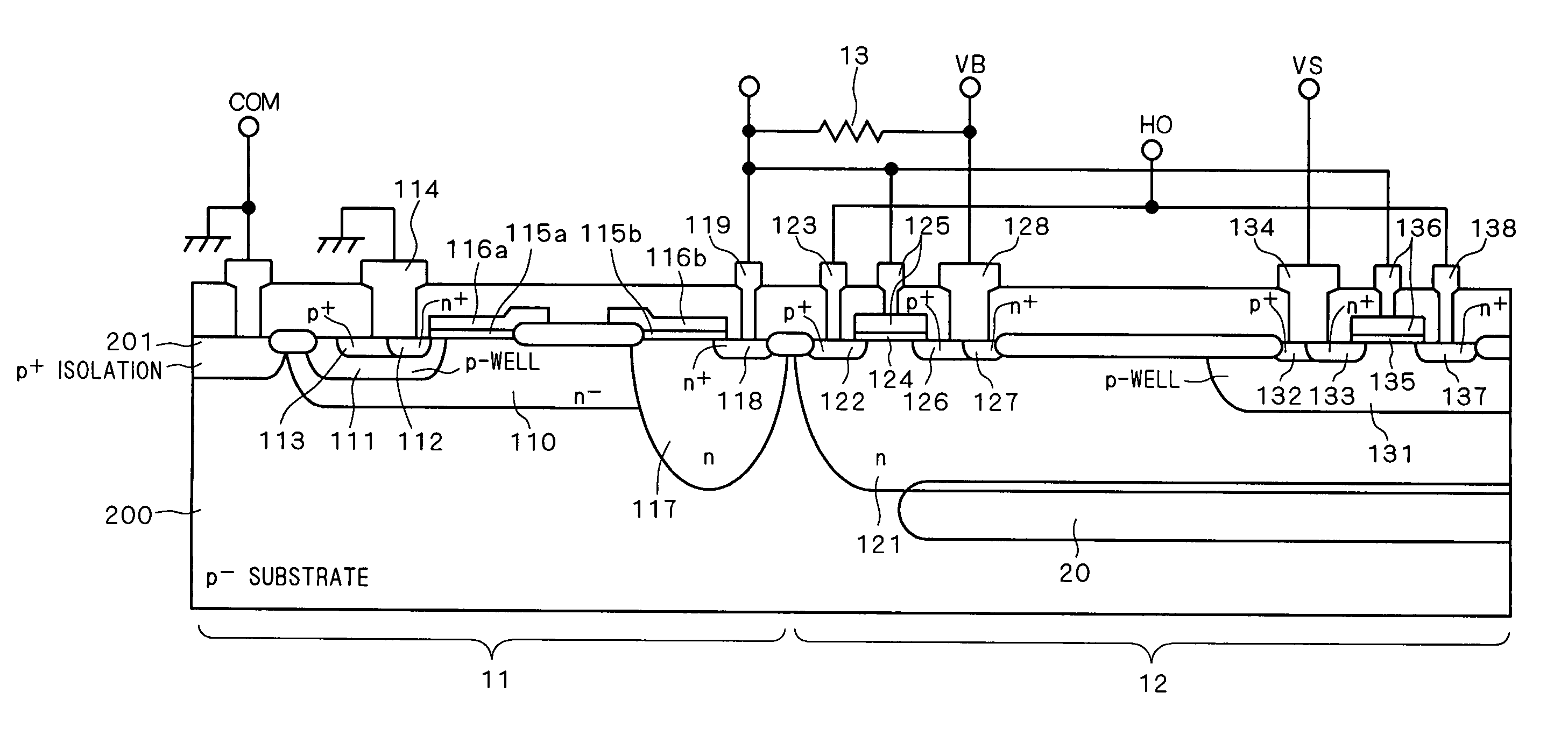

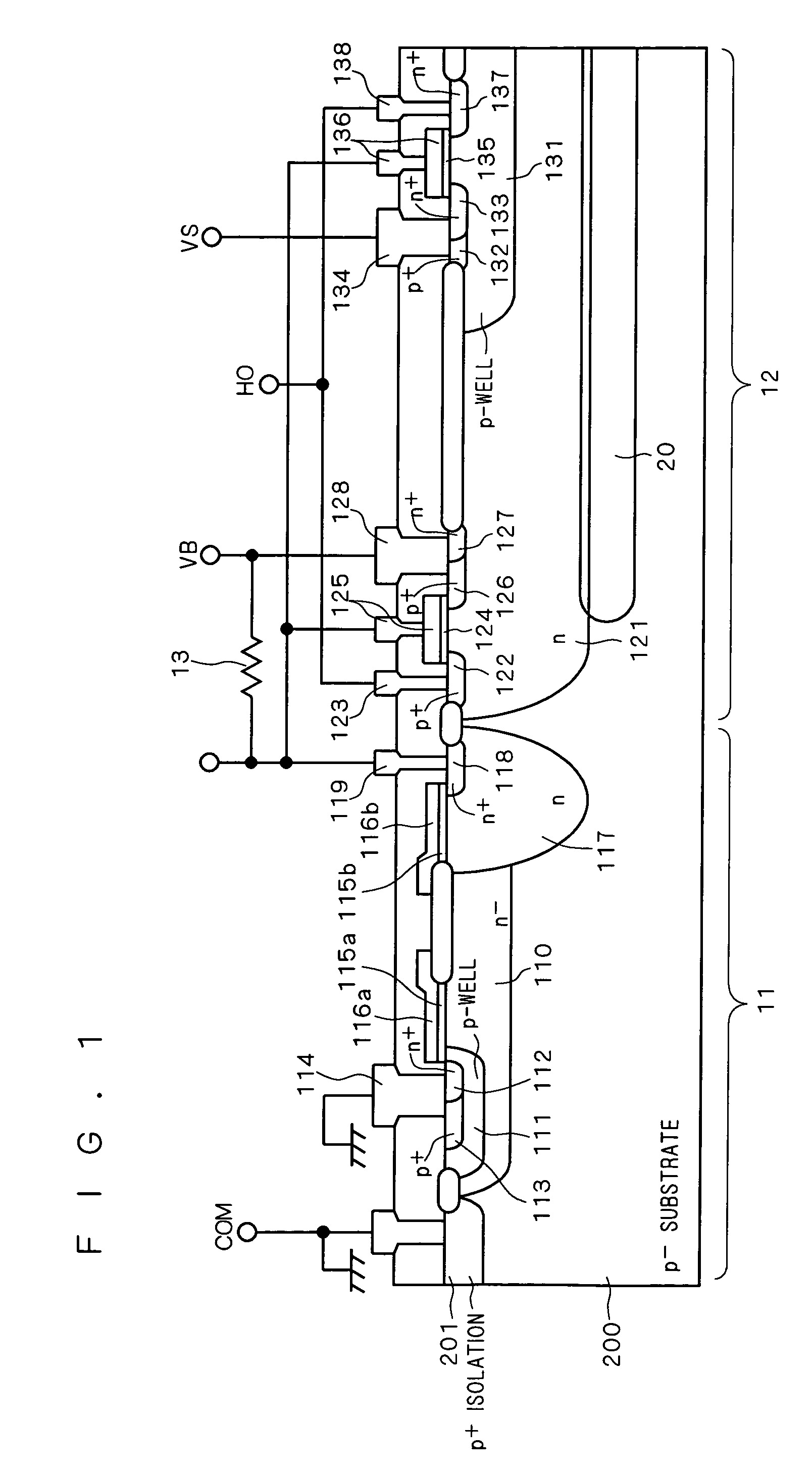

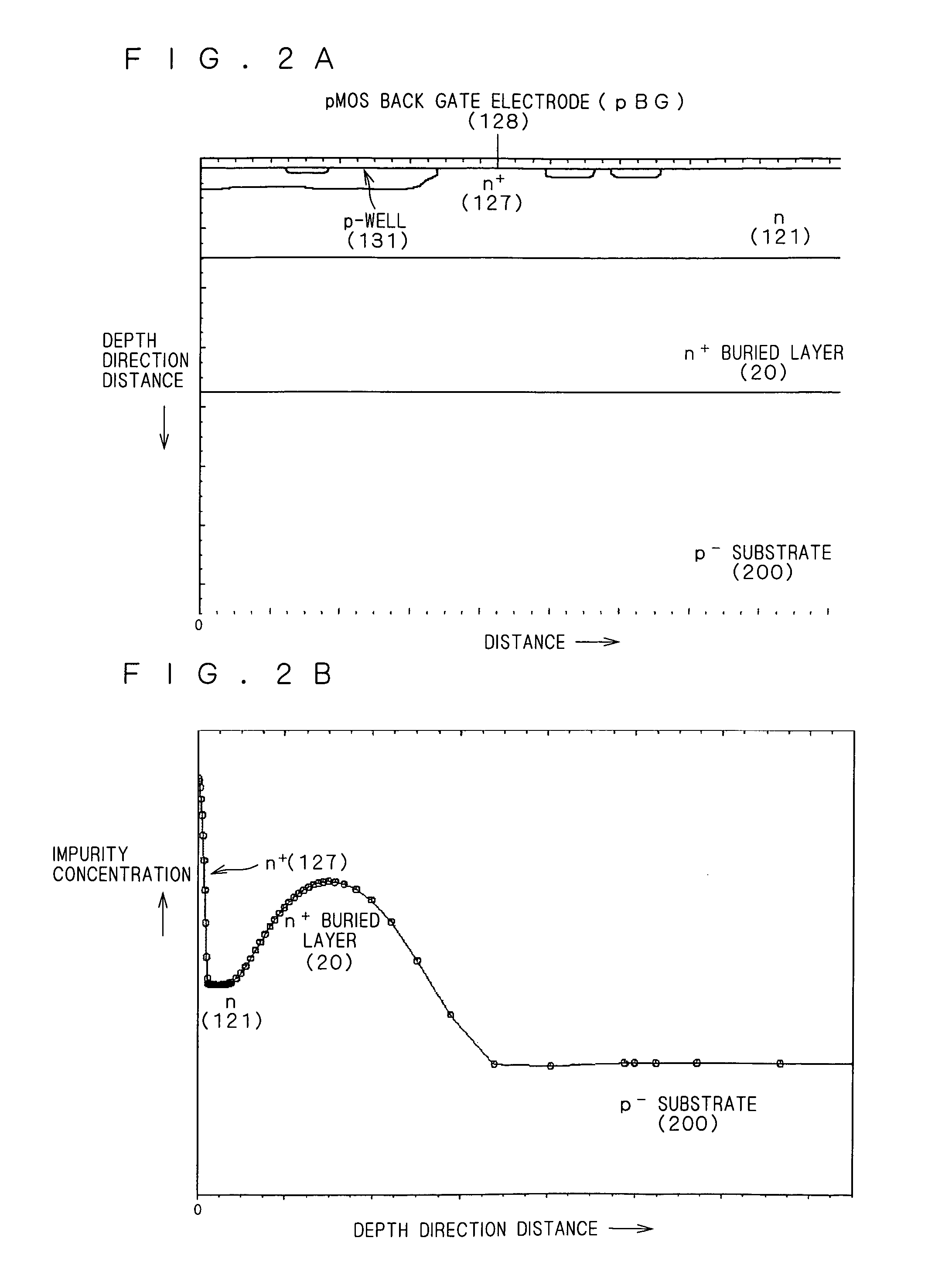

Semiconductor device

ActiveUS7812402B2Improve breakdown voltageImprove breakdown resistanceTransistorSemiconductor/solid-state device detailsImpuritySemiconductor

In the upper surface of a p− substrate, an n-type impurity region is formed. In the upper surface of the n-type impurity region, a p-well is formed. Also in the upper surface of the n-type impurity region, a p+-type source region and a p+-type drain region are formed. In the upper surface of the p-well, an n+-type drain region and an n+-type source region are formed. In the p− substrate, an n+ buried layer having an impurity concentration higher than that of the n-type impurity region is formed. The n+ buried layer is formed in contact with the bottom surface of the n-type impurity region at a greater depth than the n-type impurity region.

Owner:MITSUBISHI ELECTRIC CORP

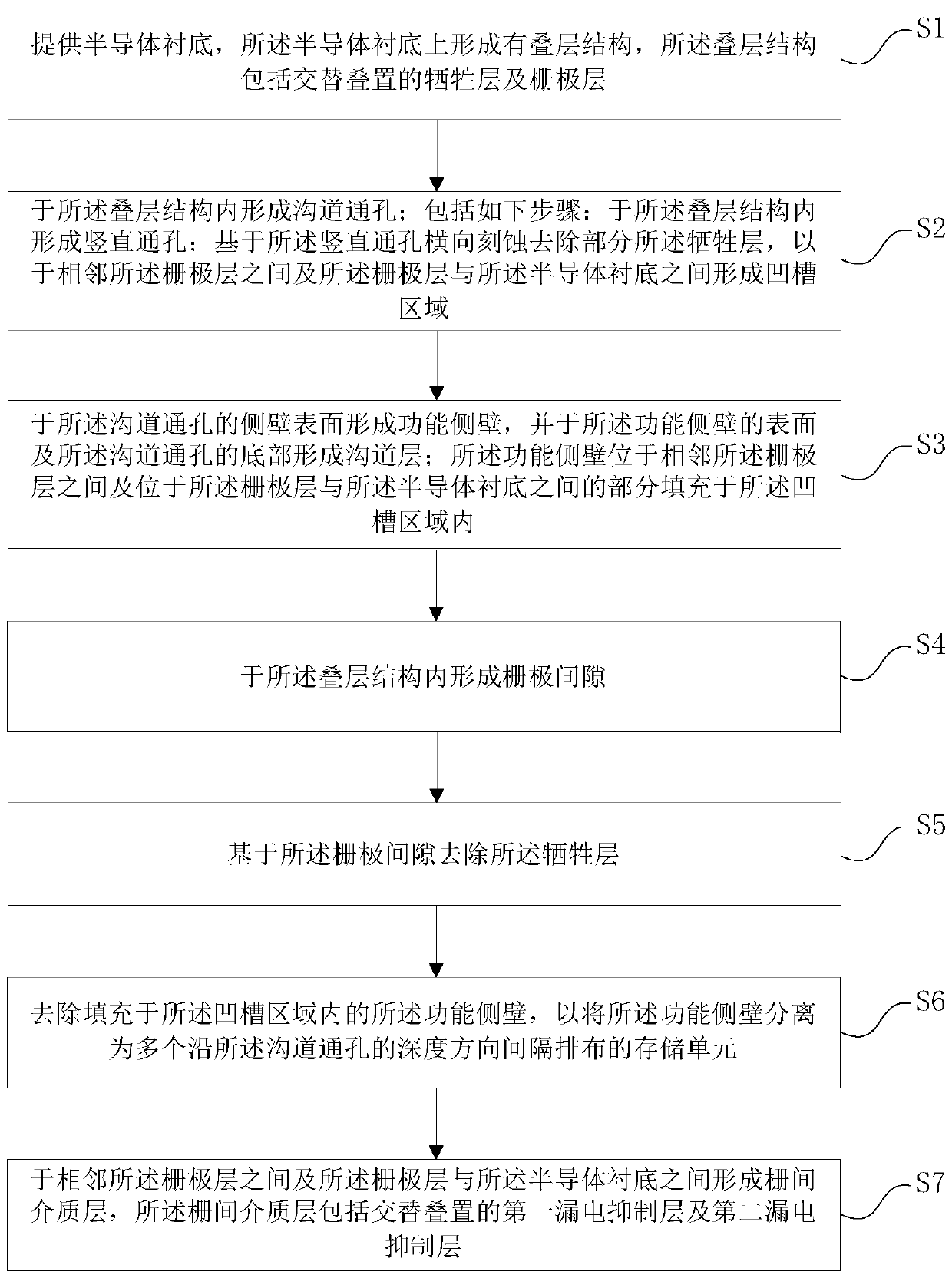

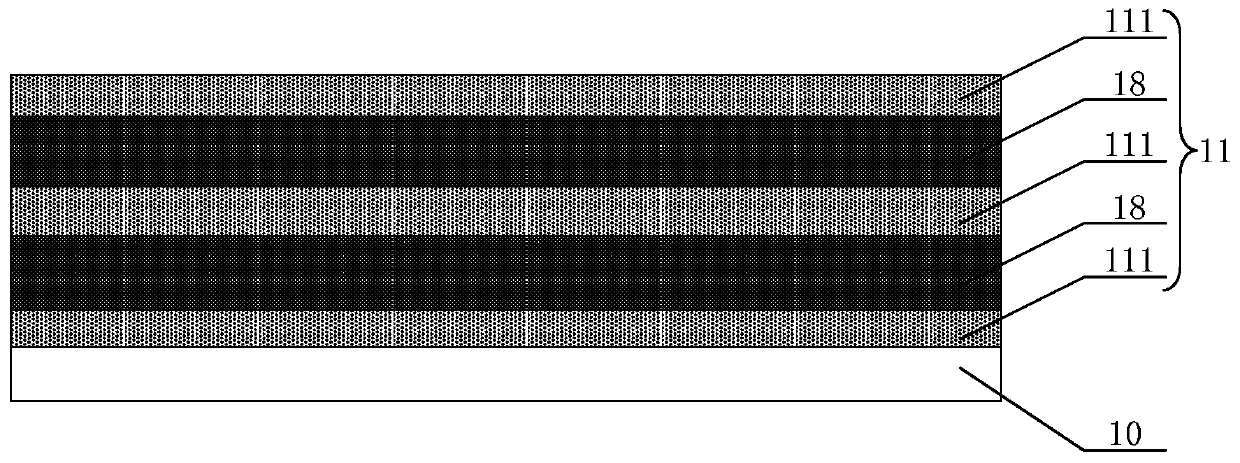

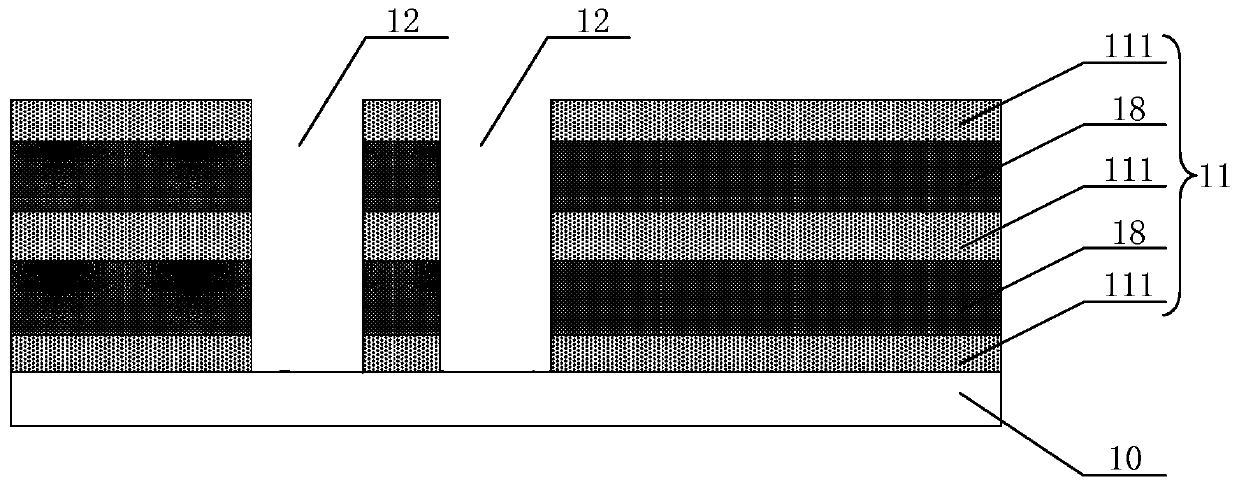

3D NAND flash memory and preparation method

ActiveCN110047839AReduce leakageImprove breakdown resistanceSolid-state devicesSemiconductor devicesEngineeringElectrical and Electronics engineering

The invention provides a 3D NAND flash memory and a preparation method. The 3D NAND flash memory comprises a semiconductor substrate, a laminated structure, a channel through hole, a functional side wall and a channel layer, wherein the laminated structure is positioned on the semiconductor substrate, the laminated structure comprises inter-gate dielectric layers and grid layers which are superposed alternately; each inter-gate dielectric layer comprises first leakage inhibition layers and second leakage inhibition layers which are superposed alternately; the channel through hole is positionedinside the laminated structure; the functional side wall is positioned on the side wall surface of the channel through, the functional side wall comprises a plurality of separated storage units arranged along the depth direction of the channel through hole at intervals, and the storage units and the grid layers are arranged in a one-to-one correspondence mode; the channel layer is positioned inside the channel through hole, and is positioned on the surface of the functional side wall and the bottom of the channel through hole. According to the 3D NAND flash memory and the preparation method,electric leakage between adjacent grid layers can be reduced effectively, the breakdown resistance of the inter-gate dielectric layers between the adjacent grid layers is improved, and the coupling effect between the adjacent grid layers is reduced.

Owner:YANGTZE MEMORY TECH CO LTD

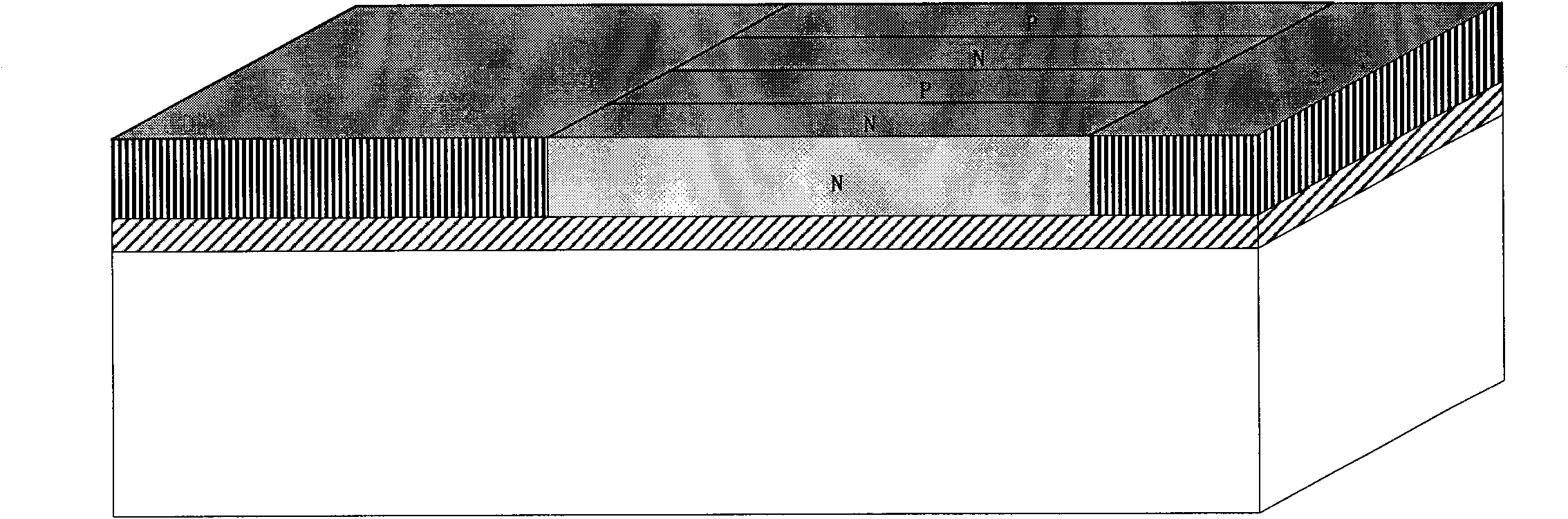

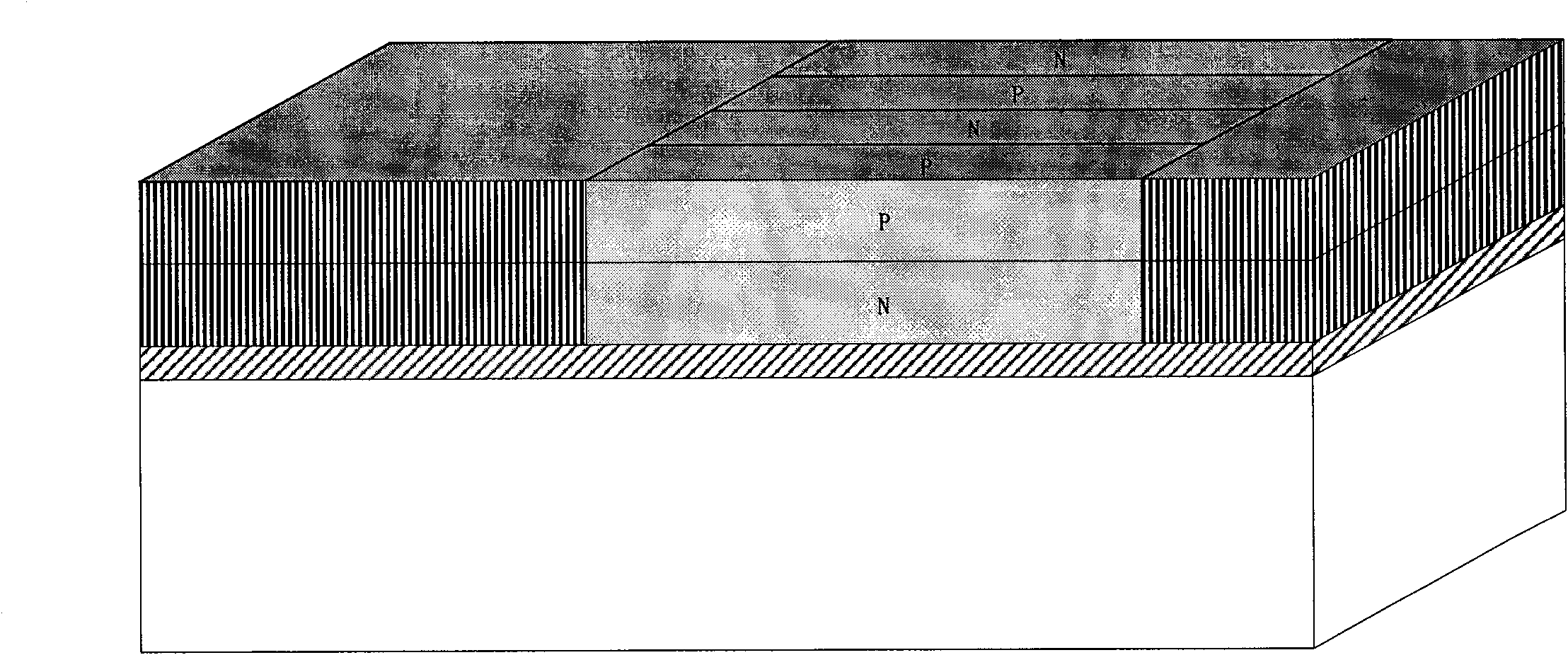

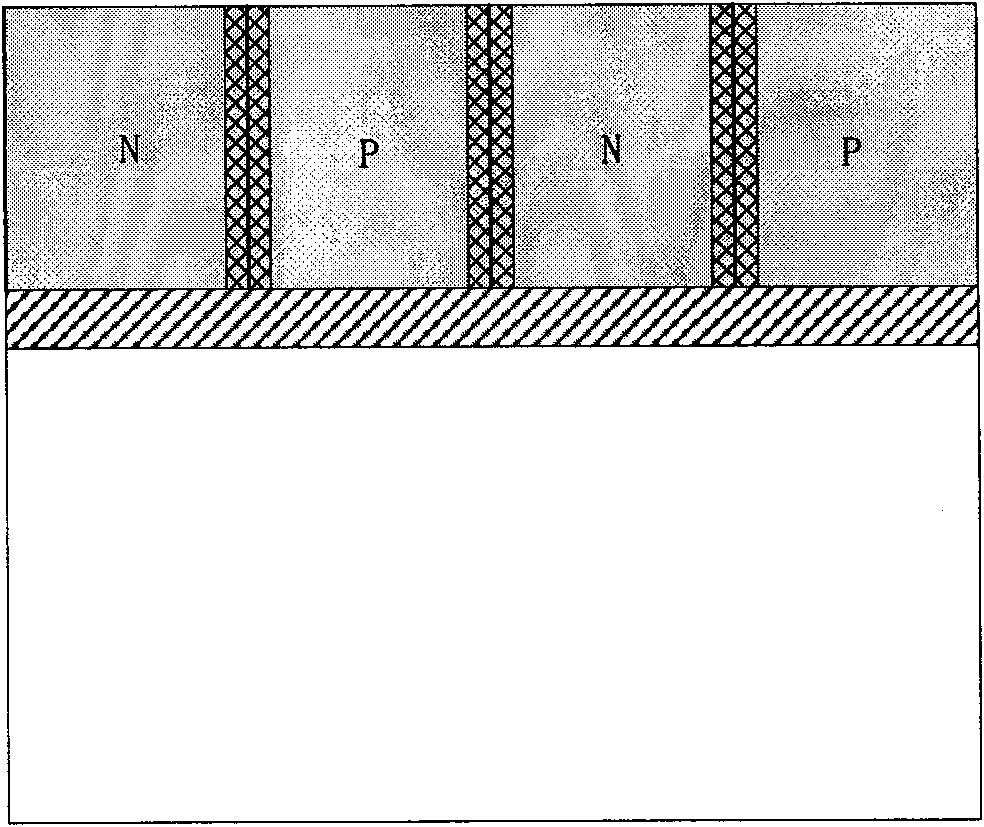

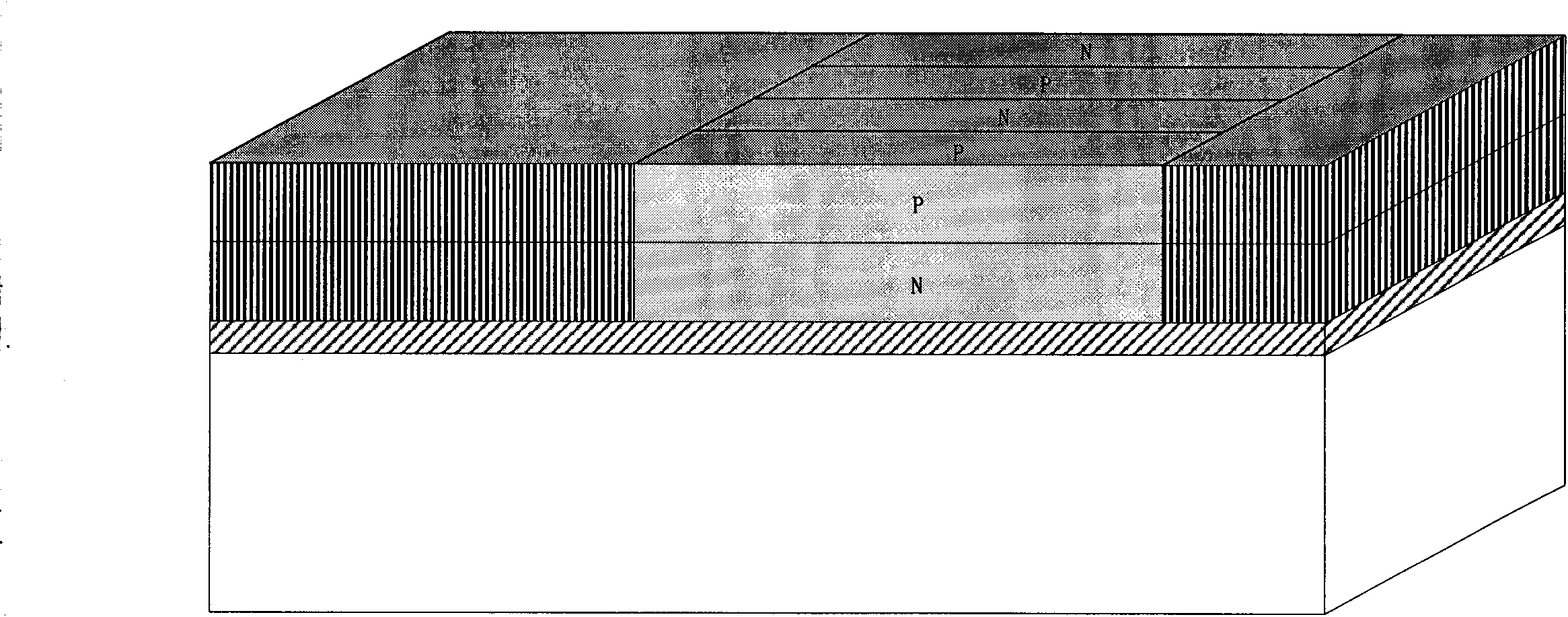

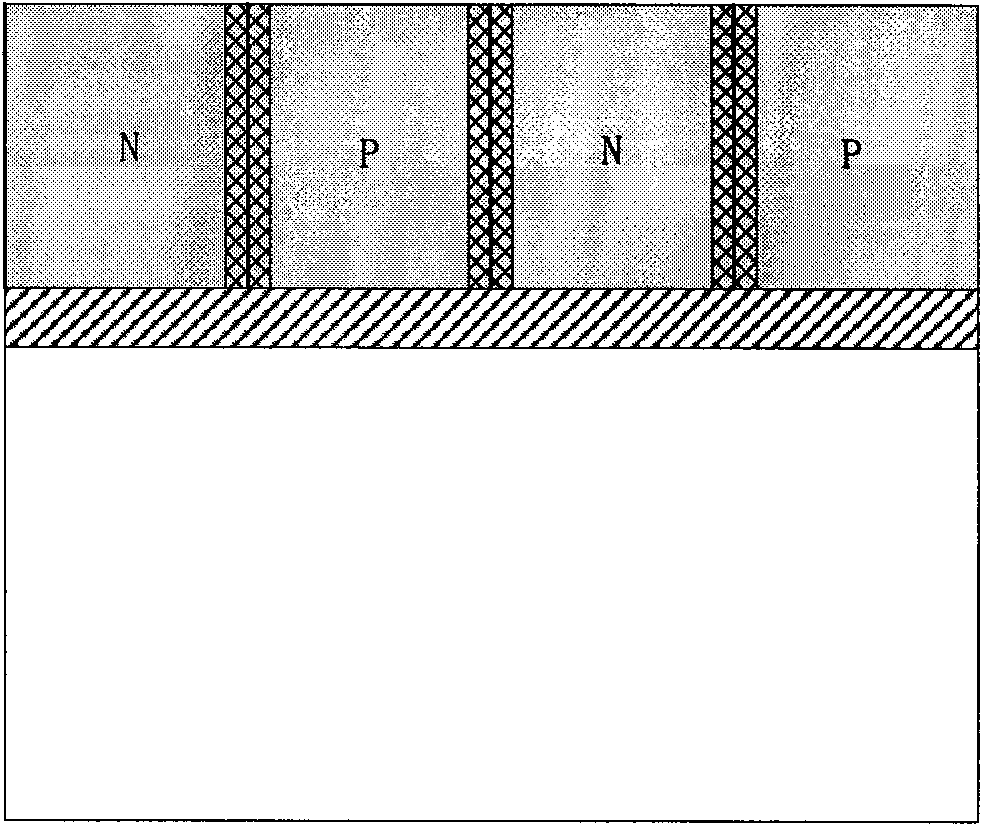

Method for producing SOI (Silicon on Insulator) LDMOS (Laterally Diffused Metal Oxide Semiconductor) device provided with multi-layer super-junction structure

InactiveCN101916729AIncrease contact areaImprove breakdown resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesBody contactSoi substrate

The invention discloses a method for producing an SOI LDMOS device provided with a multi-layer super-junction structure, which comprises the steps of: carrying out ion implantation on top layer silicon by adopting SOI substrate to form a first layer of super-junction structure; then preparing an extensionality layer on the SOI substrate provided with at least one layer of super-junction structure, manufacturing the other layer of super-junction structure by utilizing the same technological conditions for manufacturing the first layer of super-junction structure, and ensuring that the n-type pillar regions and the p-type pillar regions of the upper layer and the lower layer are alternately arranged to form a multi-layer super-junction structure comprising at least two layers of super-junction structure; and manufacturing body regions, grid regions, source regions, drain regions and body contact regions to finish the device. The multi-layer super-junction structure is formed by adopting the extensionality and ion implantation technology, the p-type pillar regions and the n-type pillar regions of the upper and the lower layer super-junction structures are alternately arranged to further increase the contact area among the p-type pillar regions and the n-type pillar regions without bringing remarkable side effects; and the anti-breakdown capacity of the device produced by the invention is higher than that of the traditional super-junction LDMOS.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI +1

Field effect transistor

ActiveUS20090206373A1Improve balanceImprove breakdown resistanceTransistorSemiconductor/solid-state device detailsOptoelectronicsOhmic contact

A field effect transistor includes a GaN epitaxial substrate, a gate electrode formed on an electron channel layer of the substrate, and source and drain electrodes arranged spaced apart by a prescribed distance on opposite sides of the gate electrode. The source and drain electrodes are in ohmic contact with the substrate. At an upper portion of the gate electrode, a field plate is formed protruding like a visor to the side of drain electrode. Between the electron channel layer of the epitaxial substrate and the field plate, a dielectric film is formed. The dielectric film is partially removed at a region immediately below the field plate, to be flush with a terminal end surface of the field plate. The dielectric film extends from a lower end of the removed portion to the drain electrode, to be overlapped on the drain electrode.

Owner:MURATA MFG CO LTD

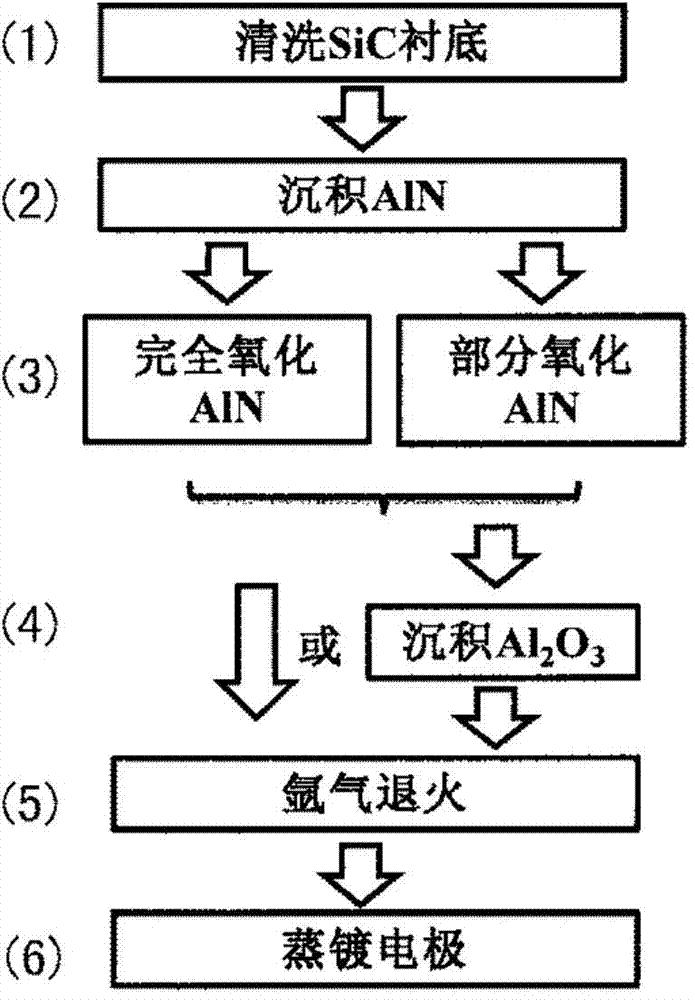

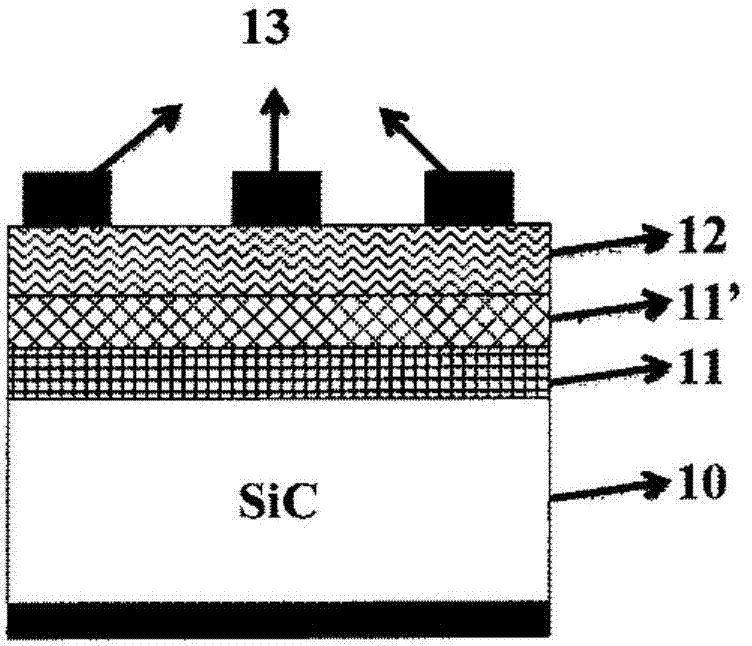

Manufacturing method for SiC-based MOS device gate dielectric thin film

ActiveCN103887163AImprove production efficiencyLow costSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricCharge carrier mobility

A manufacturing method for an SiC-based MOS device gate dielectric thin film comprises the steps that an SiC substrate is cleaned; an AlN thin film is deposited on the cleaned SiC substrate; the AlN thin film is oxidized into an AlxOyNz thin film, through oxidization technology control, the AlN thin film is oxidized into the AlxOyNz thin film completely or partially, and an AlN / AlxOyNz gate dielectric layer is formed; an Al2O3 thin film is deposited onto the AlxOyNz thin film to form an AlxOyNz / Al2O3 stacked gate dielectric layer and an AlN / AlxOyNz / Al2O3 stacked gate dielectric layer; argon annealing is conducted on the three obtained stacked gate dielectric layers; metal electrodes are sputtered or evaporated on the three annealed stacked gate dielectric layers to form an MOS device structure and manufacturing is completed. The gate dielectric thin film manufactured through the method has the advantages of being high in dielectric constant, low in interface state density, high in carrier migration rate and the like.

Owner:厦门肖克利能源技术有限公司

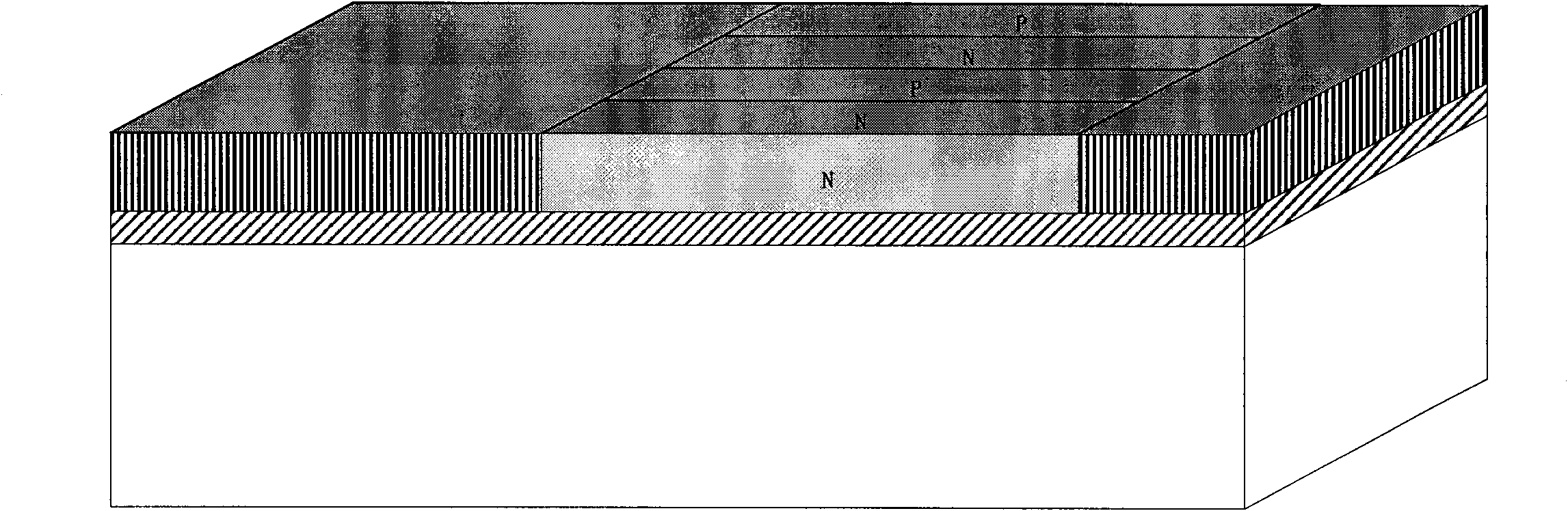

LDMOS device with multilayer super-junction structure

InactiveCN101916780AIncrease contact areaImprove breakdown resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesLDMOSBody region

The invention discloses an LDMOS device with a multilayer super-junction structure. An active region of the device comprises a grid region, a source region and a drain region positioned on two sides of the grid region, a body region positioned under the grid region, and the multilayer super-junction structure positioned between the body region and the drain region, wherein the multilayer super-junction structure comprises at least two layers of super-junction structures arranged from bottom to top in turn; each layer of super-junction structure consists of n-type columnar regions and p-type columnar regions which are transversely and alternately arranged, preferably, the n-type columnar regions and the p-type columnar regions of upper and lower layers of super-junction structures are alternately arranged. The multilayer super-junction structure of the device can further improve the contact area among the n-type columnar regions and the p-type columnar regions, and simultaneously a method for manufacturing the structure cannot bring obvious side effects, so the anti-breakdown capacity of the device can be ensured to be higher than that of the conventional super-junction LDMOS device, and the multilayer super-junction structure also has high expansibility.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI +1

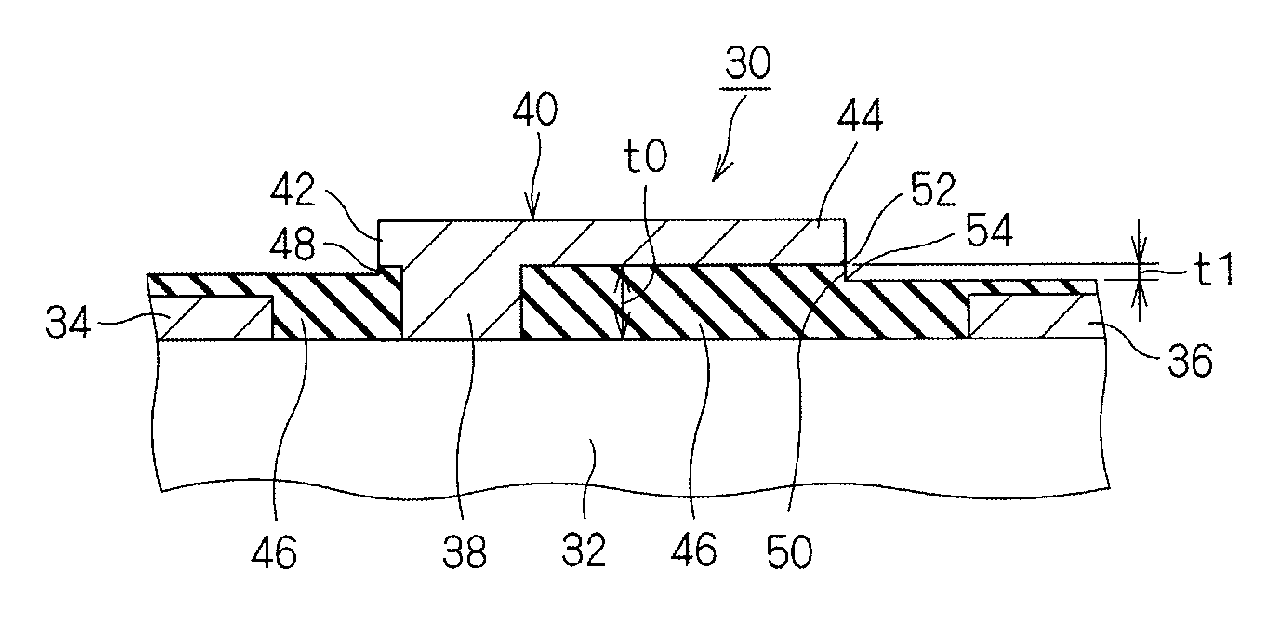

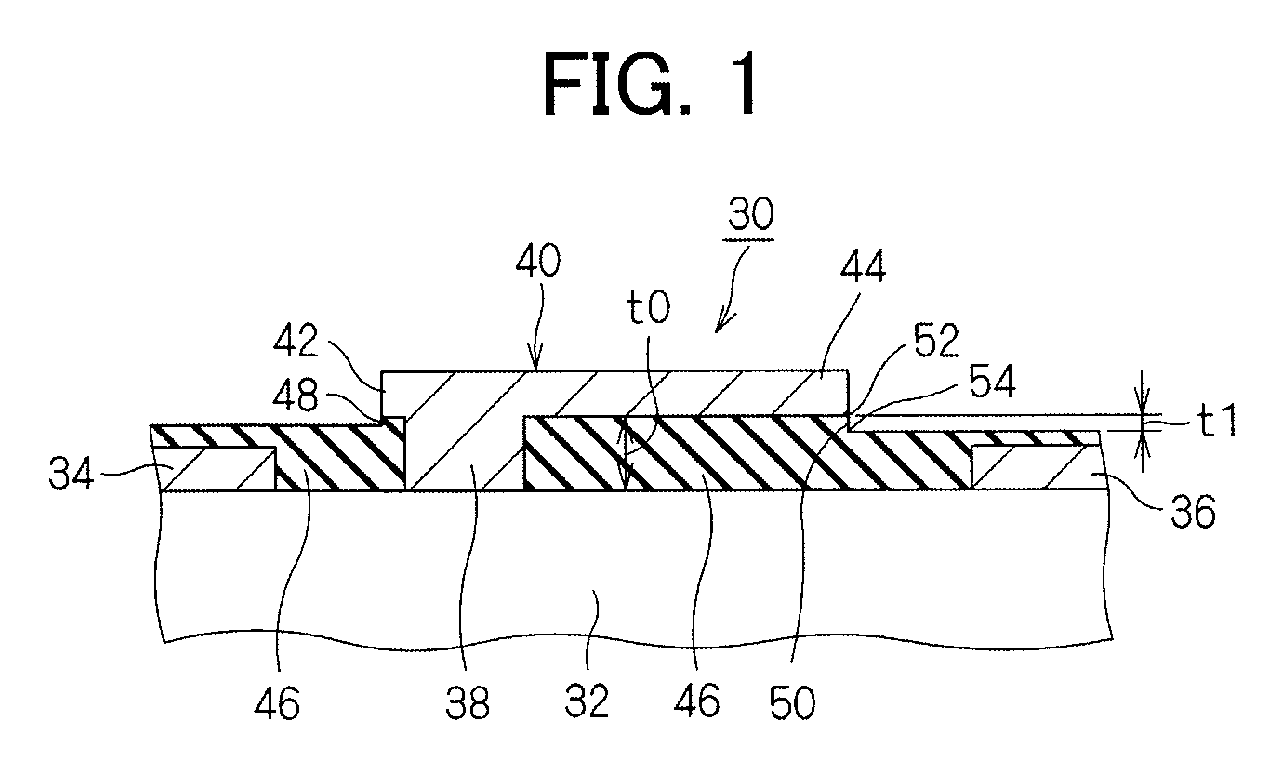

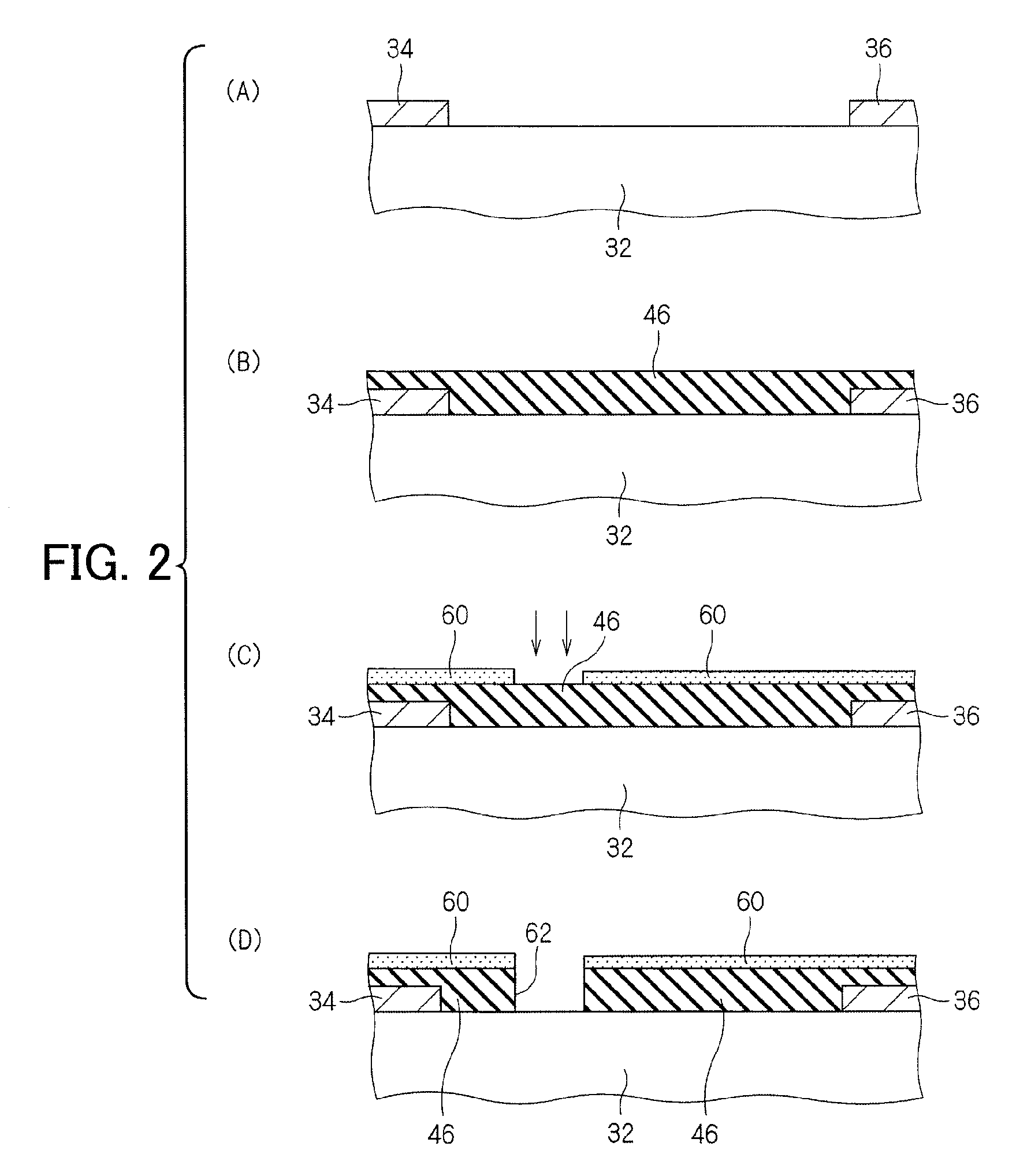

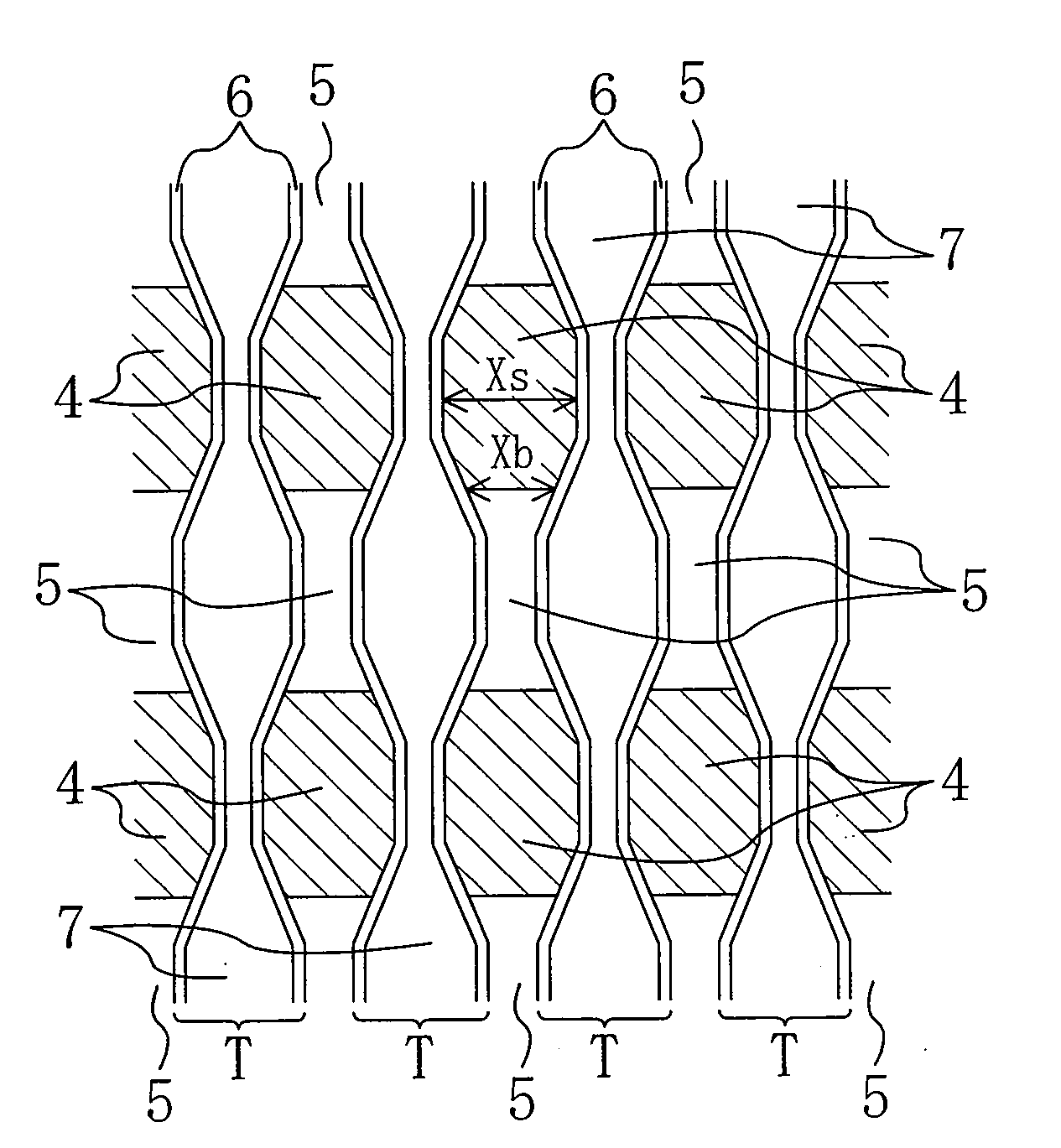

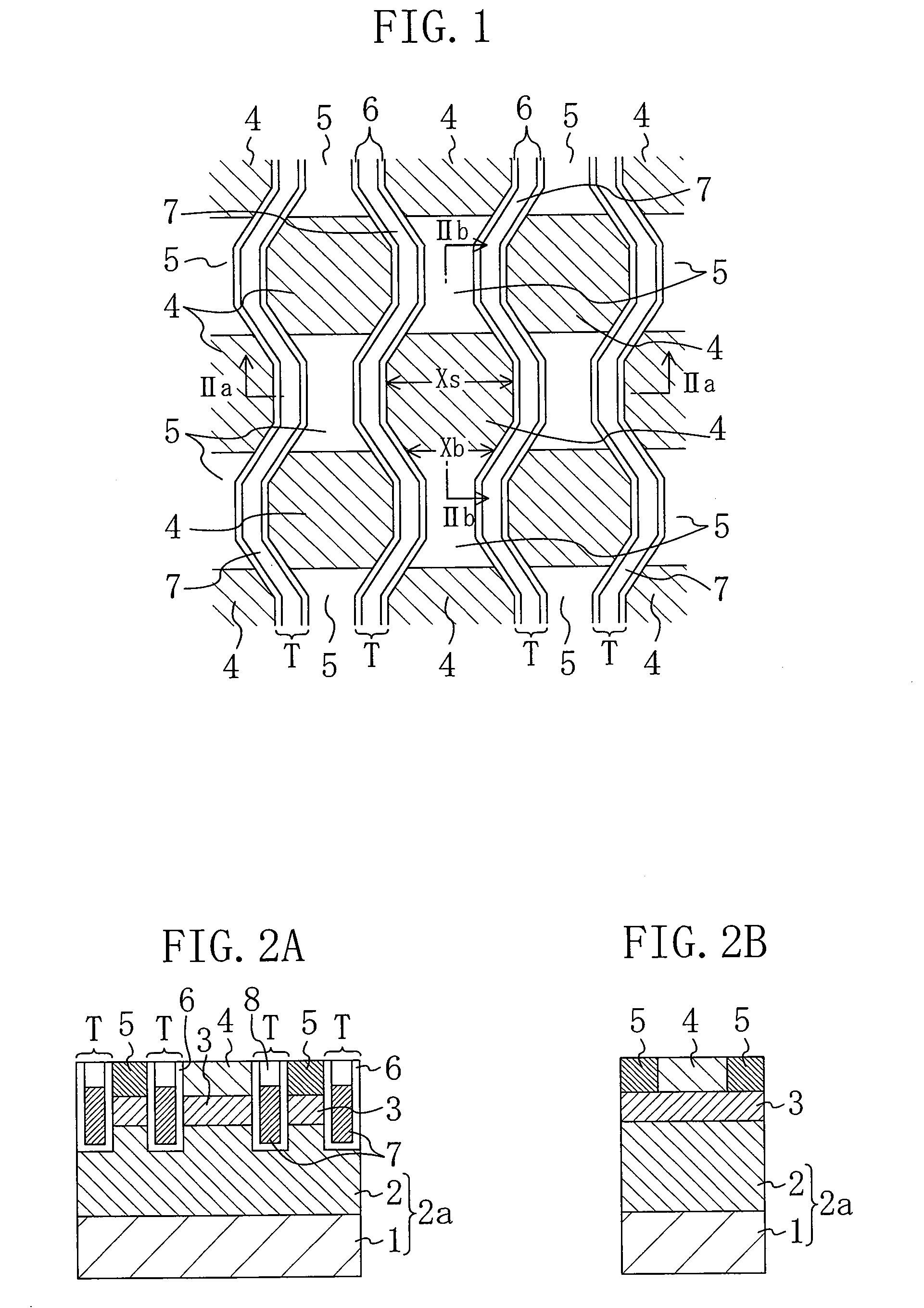

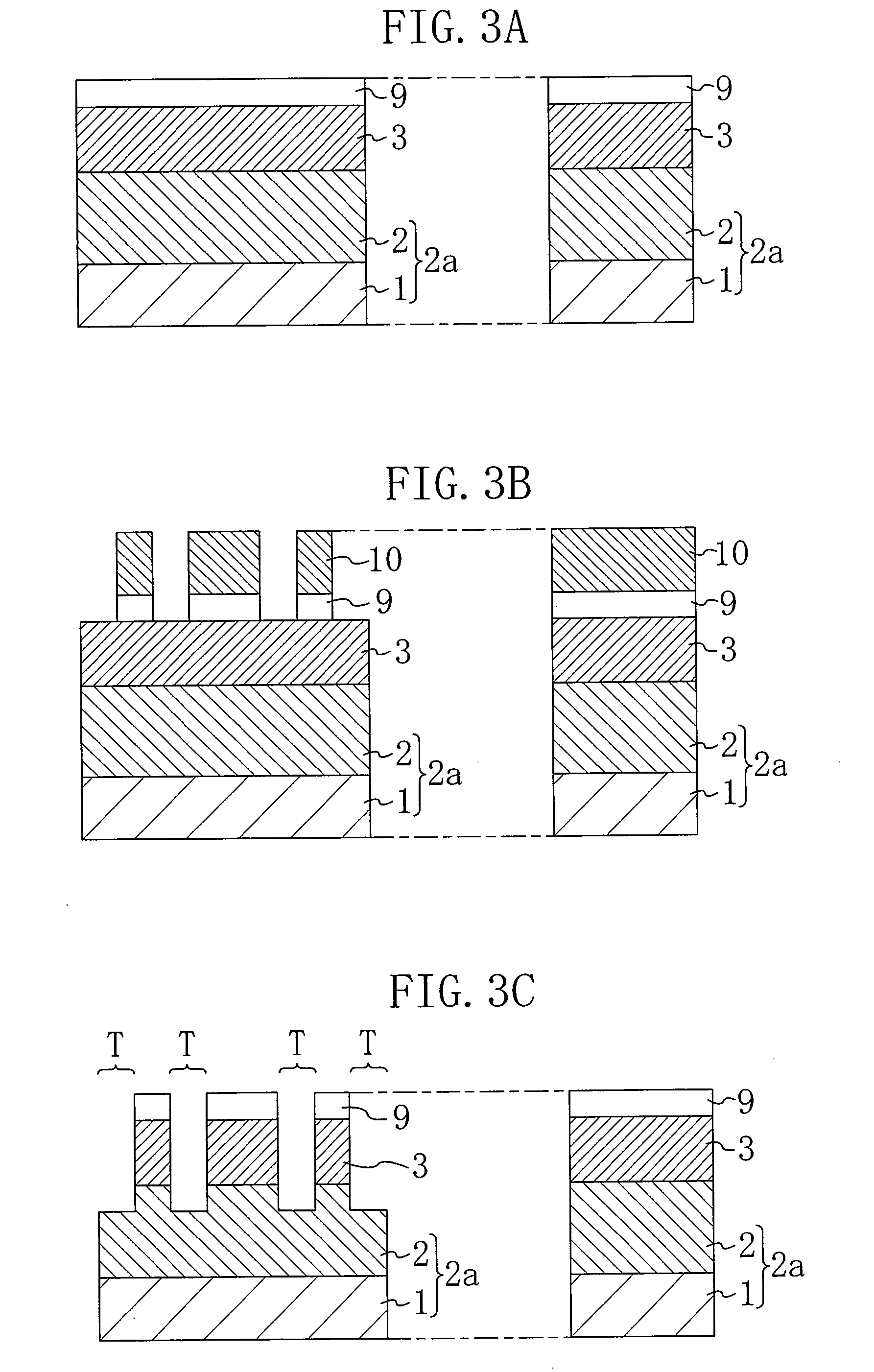

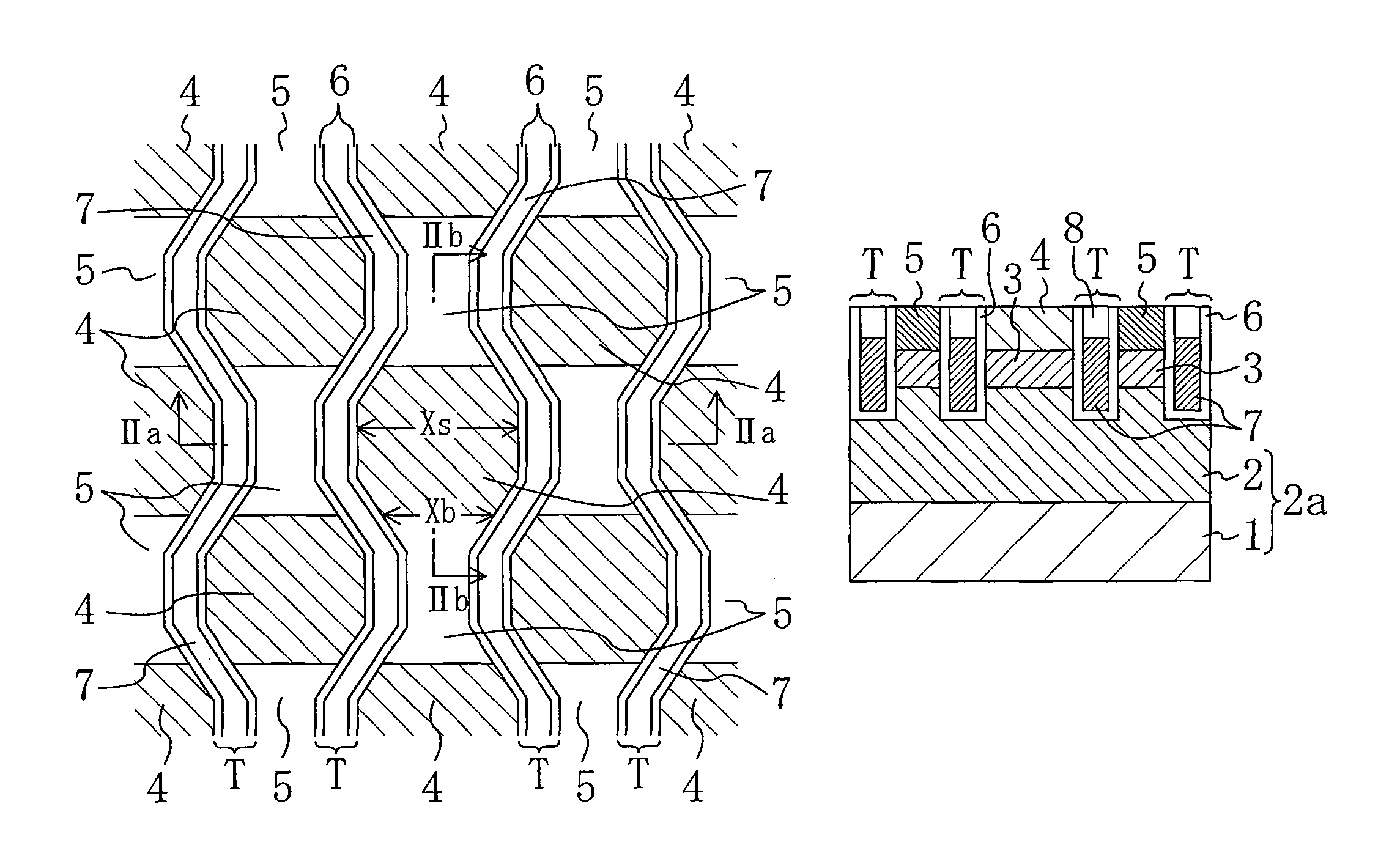

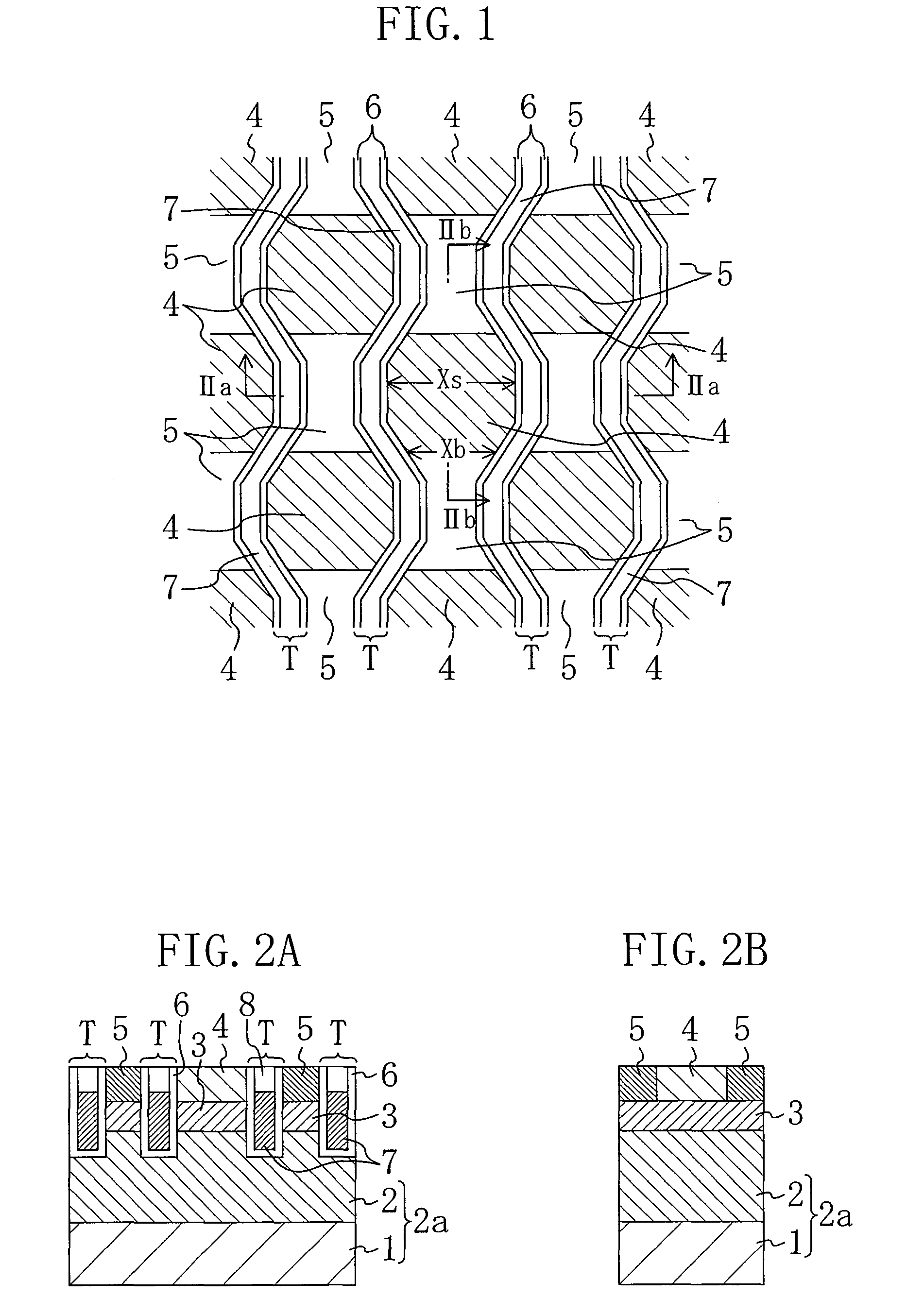

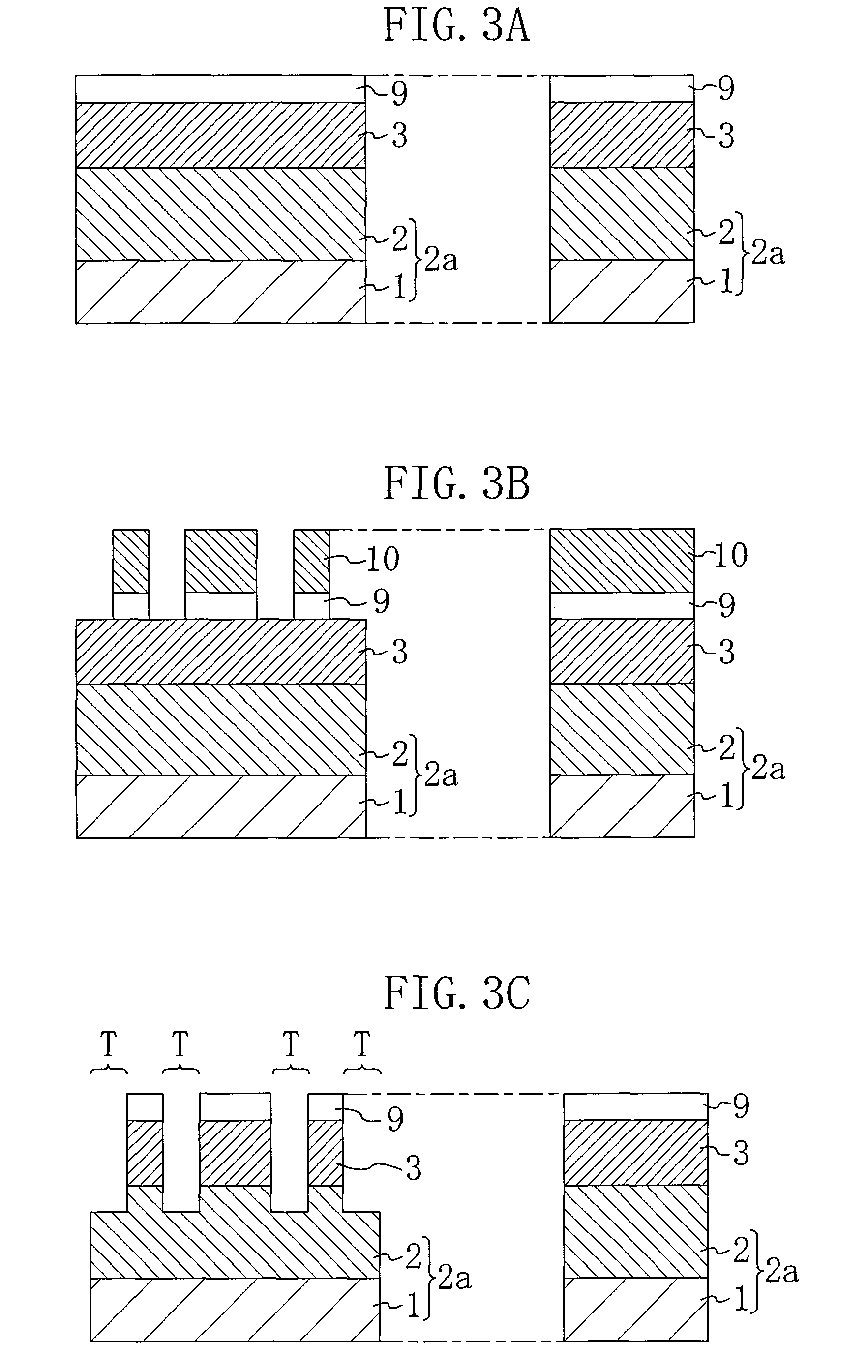

Semiconductor device and method for fabricating the same

InactiveUS20090078994A1Reduce voltageImprove breakdown resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesHigh concentrationEngineering

Disclosed is a semiconductor device having an n-type drain region, a low concentration p-type body region formed on the n-type drain region, an n-type source region formed on the low concentration p-type body region, a high concentration p-type body region formed on the low concentration p-type body region, a gate insulating film, and a gate electrode, wherein a plurality of trenches T which extend in a same direction and each of which forms a continuous concavo-convex shape when viewed from above are formed from top faces of the source region and the high concentration body region and pass through the low concentration body region to reach into the drain region, and wherein the gate electrode is buried in each of the plurality of trenches. A maximum distance between two adjacent trenches T of the n-type source region is greater than a maximum distance between the two adjacent trenches T of the high concentration p-type body region.

Owner:PANASONIC CORP

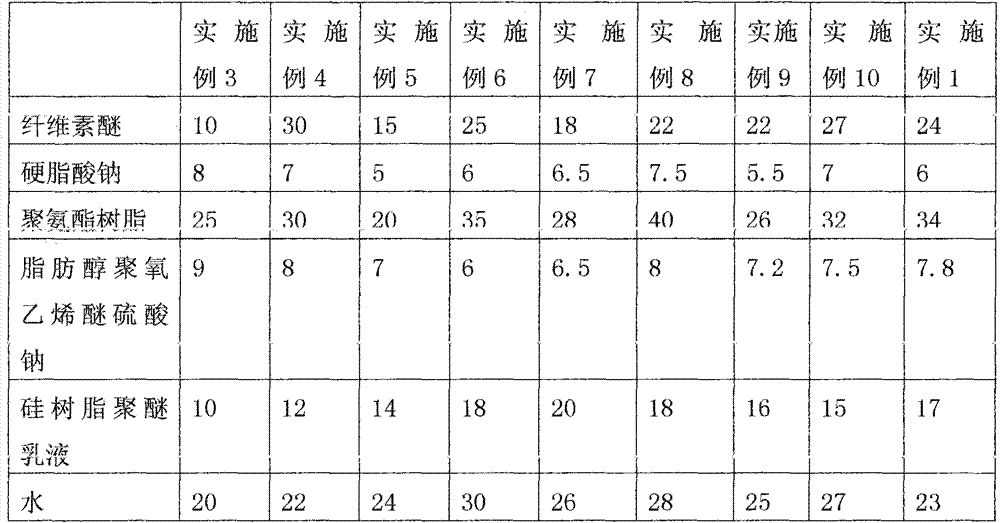

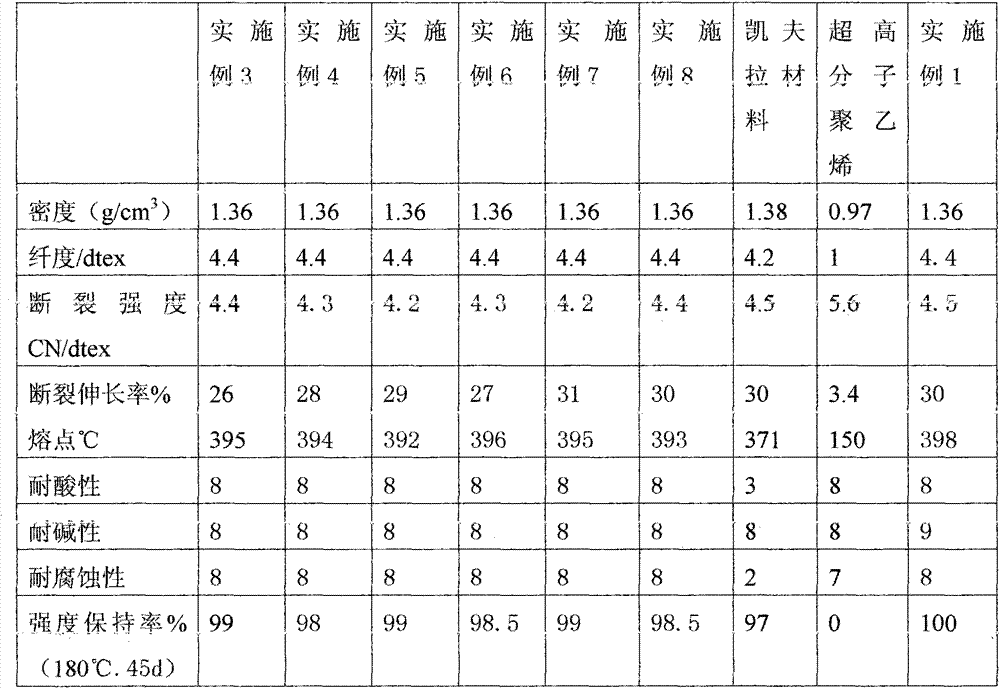

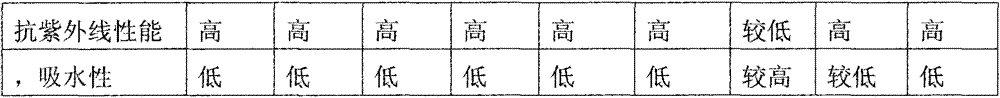

Composite flexible bulletproof material

InactiveCN104748624AGood effectHigh strengthFibre typesHeating/cooling textile fabricsFiberVulcanization

A flexible composite bulletproof material overcomes the defects that an existing bulletproof material is poor in impact force resistance, short in service life and poor in damp-proof performance. The flexible composite bulletproof material is manufactured according to the following processes that A, processed Kevlar fibers and fibers made of ultra-high molecular weight polyethylene are blended and woven into a composite Kevlar fiber layer; B, the woven composite Kevlar fiber layer is heated to 150-200 DEG C through infrared rays in a vacuum environment, and then vulcanization reaction is conducted at the temperature ranging from 200 DEG C to 450 DEG C; C, the reacted composite Kevlar fiber layer is woven, another composite Kevlar fiber layer is crocheted, the step two is repeated, and each composite Kevlar fiber layer and another composite Kevlar fiber layer are staggered by 0.25-0.5 wired tube; D, the step three is repeated many times, and then carbonization treatment is conducted on the lower surface of the multiple layers of woven composite Kevlar fiber layers. The flexible composite bulletproof material is strong in impact force resistance, good in bulletproof effect, long in service life, good in damp-proof performance, and suitable for being popularized and applied.

Owner:杨晓波

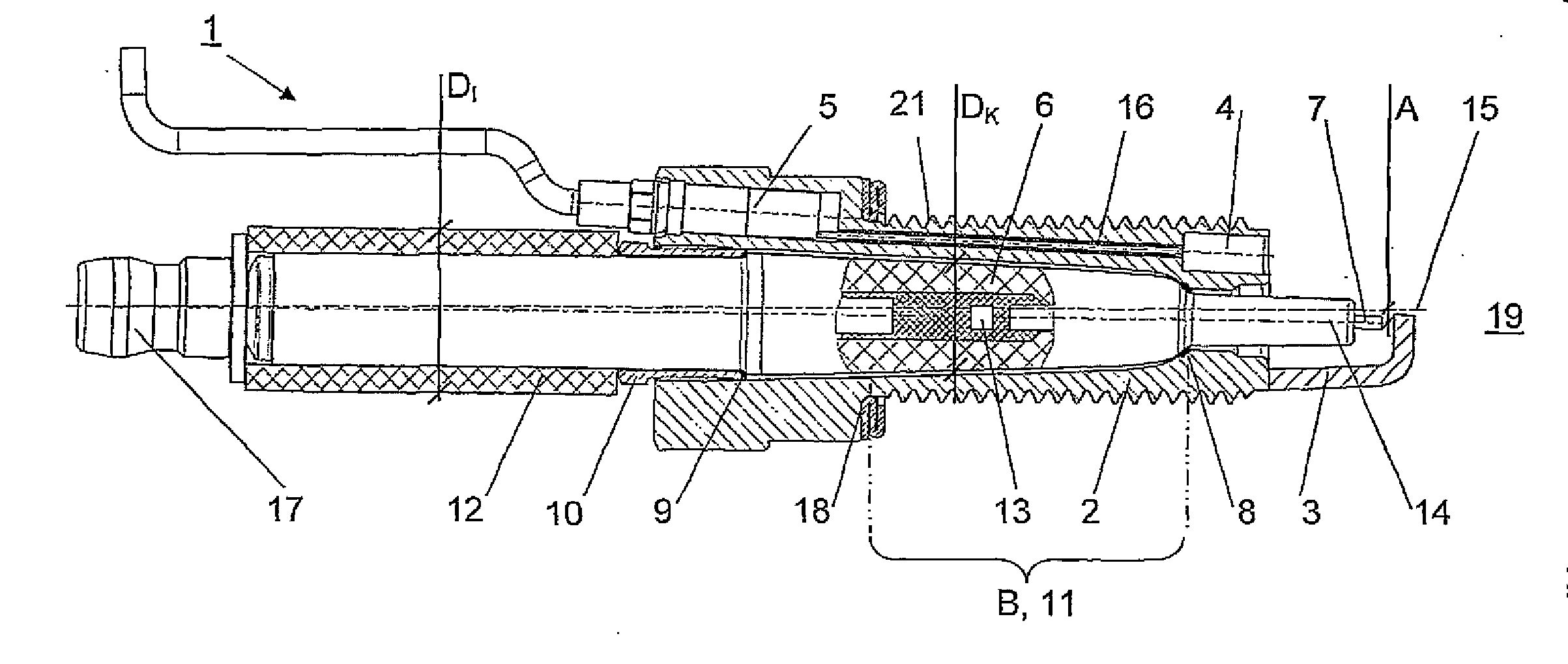

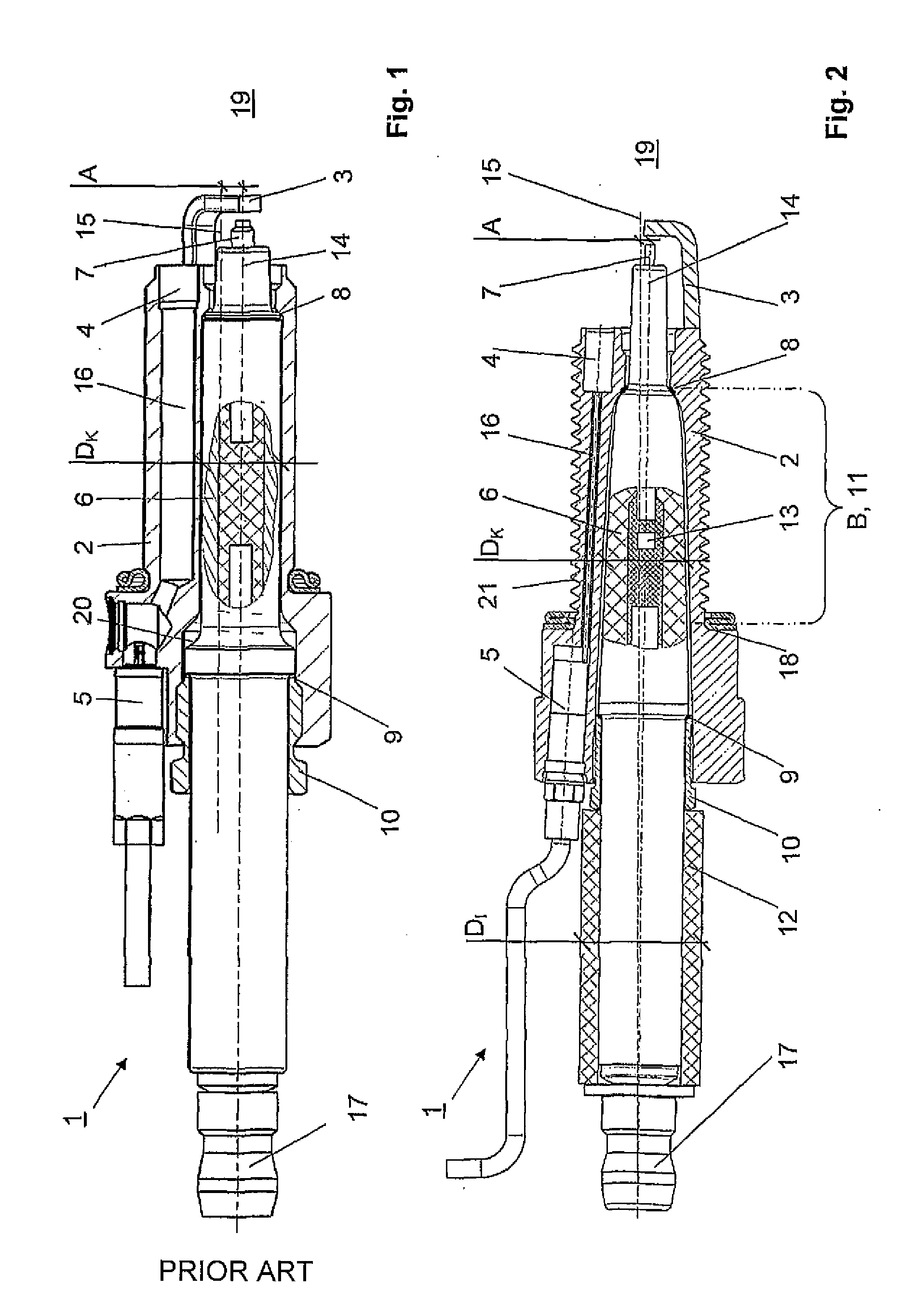

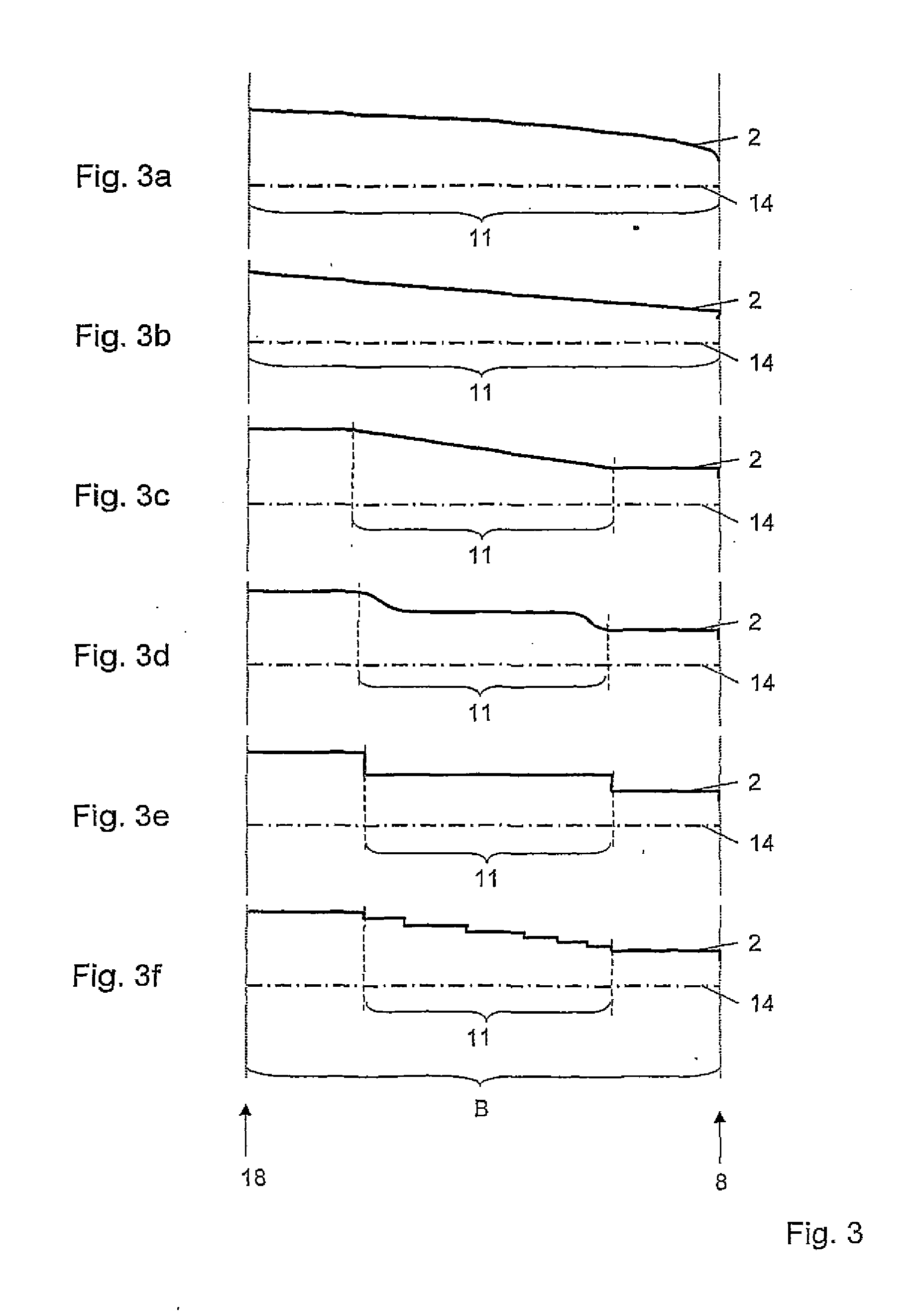

Spark plug having pressure sensor

InactiveUS20110101844A1High mechanical strengthImprove bending strengthInternal-combustion engine testingSparking plugsCombustion chamberEngineering

A spark plug is intended for combustion engines and comprises a metal housing having a ground electrode disposed at the front and a thread having a rear sealing surface for installation in the combustion engine. The spark plug in particular includes a pressure sensor disposed laterally in the housing for determining a combustion chamber pressure and a ceramic body having a center electrode. The ceramic body is disposed in the housing next to the pressure sensor and acting as an electric insulator. As viewed from the combustion chamber, the ceramic body defines a front clamping shoulder and a rear stop for clamping the ceramic body into the housing. The outside diameter of the ceramic body gradually decreases in the region of the thread located between the rear sealing surface and the front clamping shoulder.

Owner:KISTLER HLDG AG

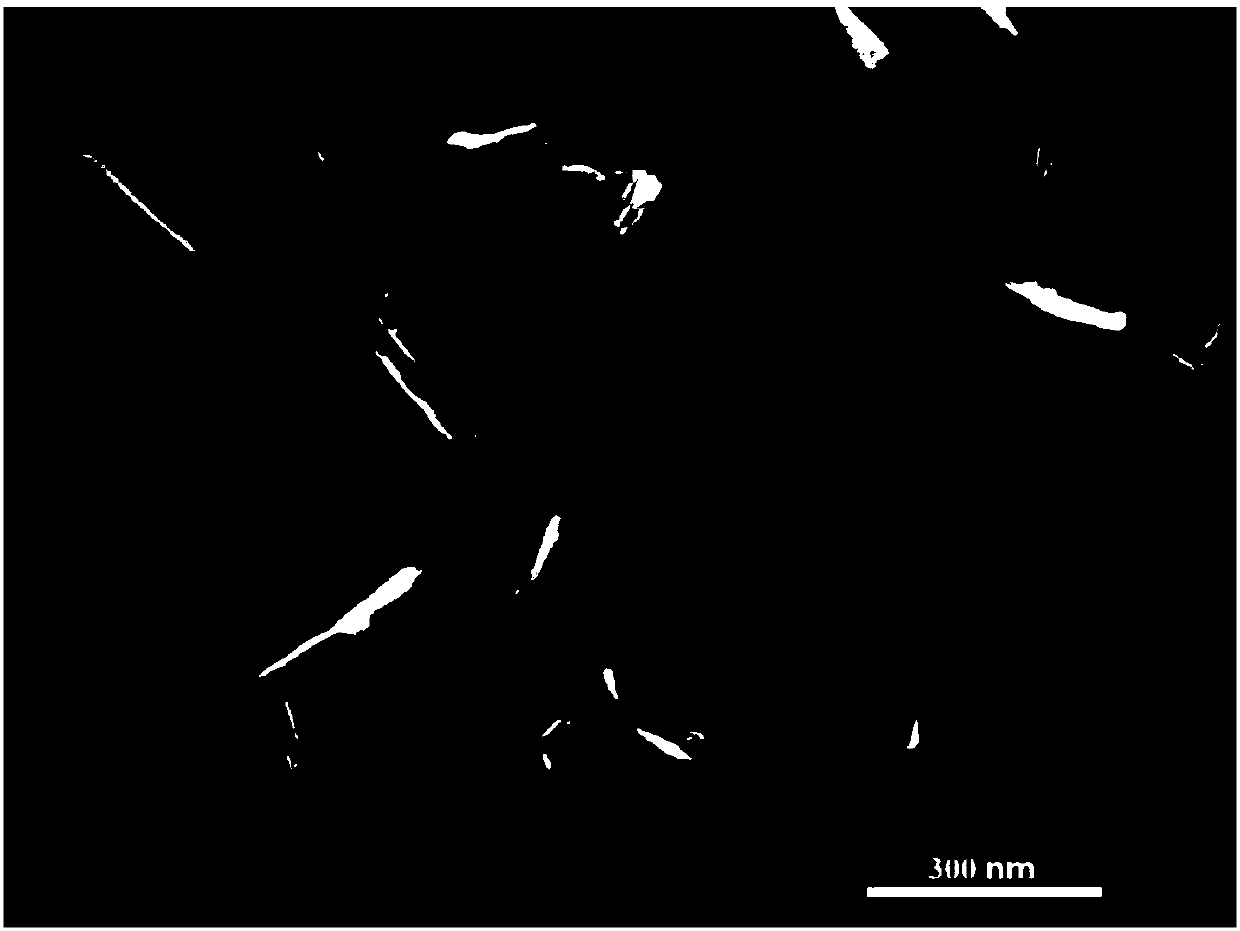

Modified transformer oil, preparation method and application

ActiveCN107739646AImprove breakdown resistancePlay an insulating roleLubricant compositionHeat conductingStructure of the Earth

The invention relates to modified transformer oil. The modified transformer oil consists of base oil and heat-conducting two-dimensional nanosheets dispersed in the base oil; the thickness of the heat-conducting two-dimensional nanosheets is less than 30nm, the sheet diameter is less than 500nm, and the ratio of thickness to radial dimension is less than 1. Since the invention adds the two-dimensional nanosheets in the base oil of the transformer oil, the two-dimensional structures are utilized to form electron traps in the transformer oil, the anisotropy of electron transfer can enhance the distortion of a local electric field in the transformer oil, thus impeding the development of streams and playing an insulating role, and thereby the anti-breakdown property of the transformer oil is effectively increased; the two-dimensional nanosheets added by the invention can form a nanofluid system along with the transformer oil, the heat conductivity coefficient is high, and the heat dispersion of the transformer oil is increased.

Owner:INST OF PROCESS ENG CHINESE ACAD OF SCI

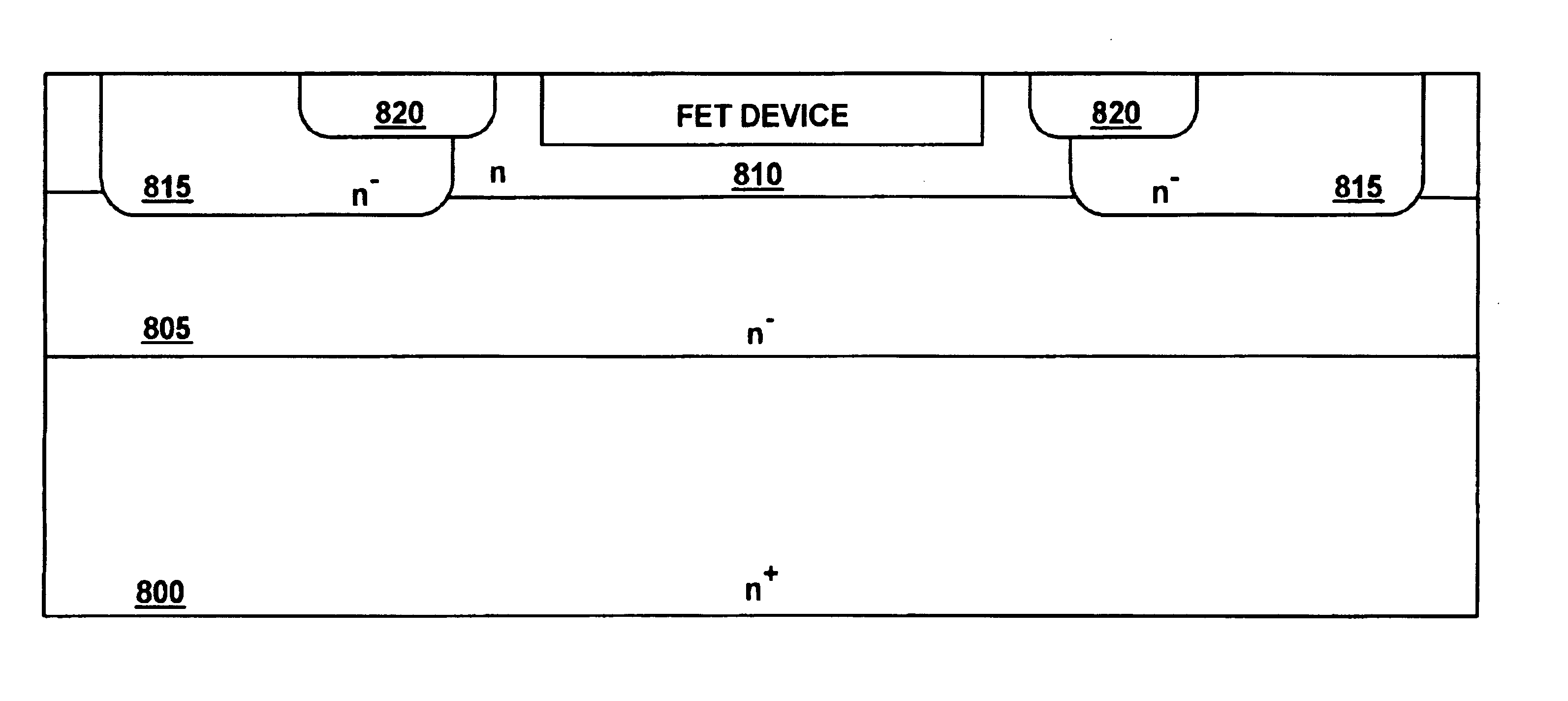

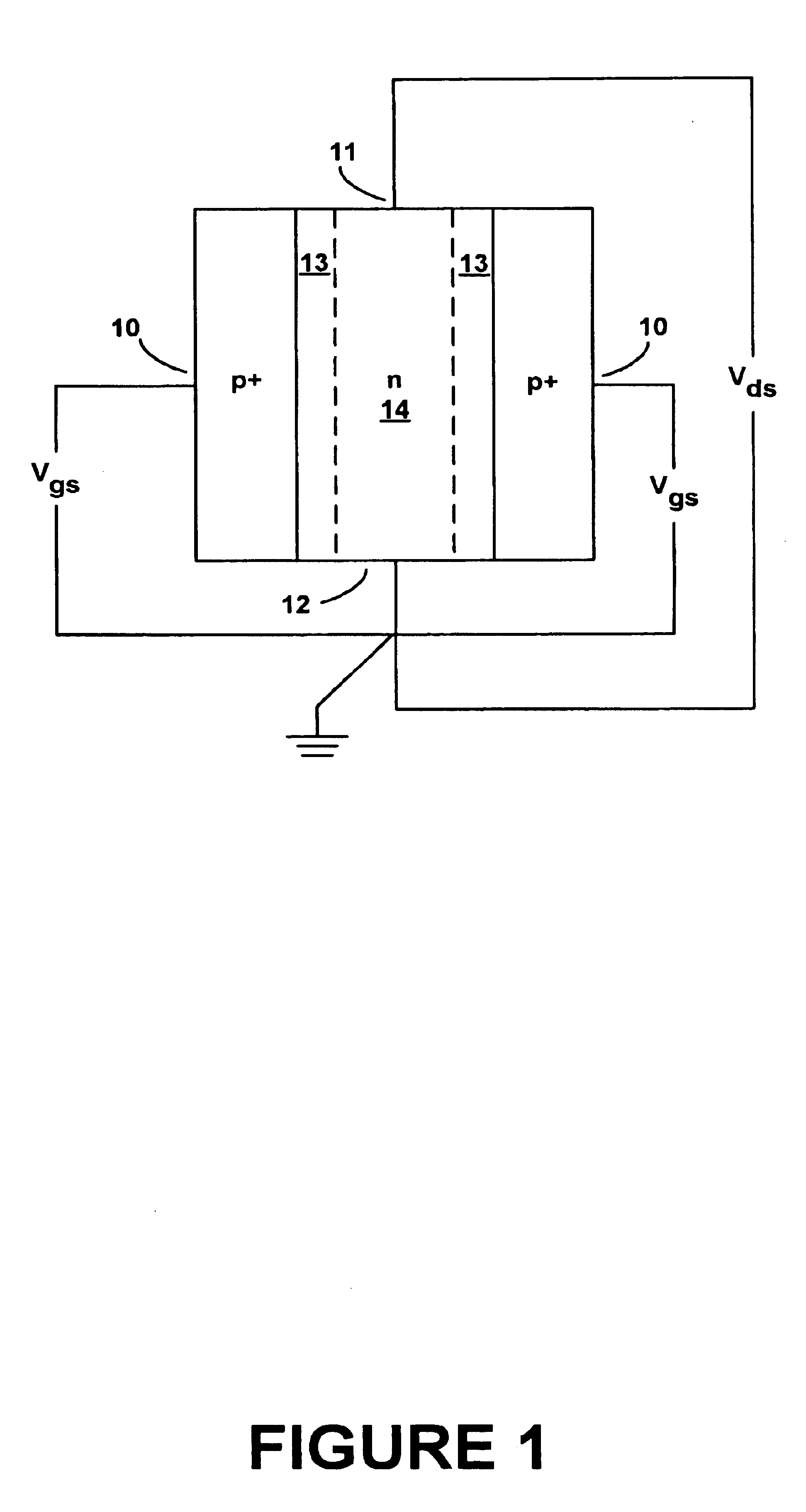

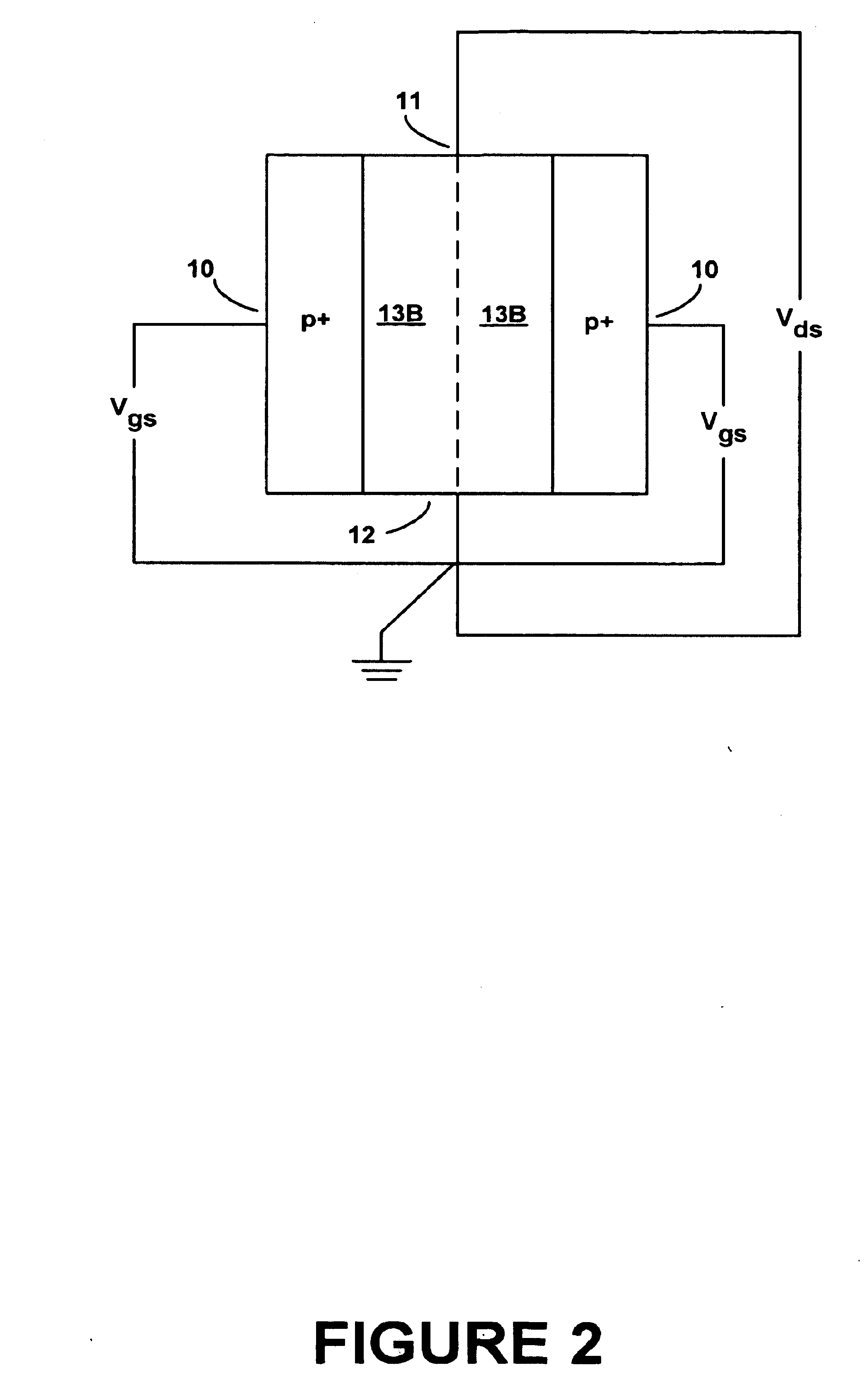

Method and structure for a high voltage junction field effect transistor

InactiveUS6900506B1Guaranteed uptimeImprove breakdown resistanceTransistorSolid-state devicesDopantHigh pressure

A method for fabricating a junction field transistor for high-voltage applications. A lightly doped first epitaxial layer is formed on a highly doped substrate. A second epitaxial layer is deposited with a heavier dopant concentration than the first epitaxial layer. The second layer contains a control structure having a plurality of implanted gate regions and a source. A guard ring is formed to isolate the source and the control structure. The combination of the lightly doped first epitaxial layer and the guard ring enable the JFET to be operated with a breakdown voltage in excess of 100 volts. Multiple guard rings may be used to provide a breakdown voltage in excess of 150 volts.

Owner:POWER INTEGRATIONS INC

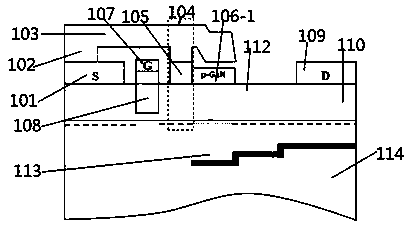

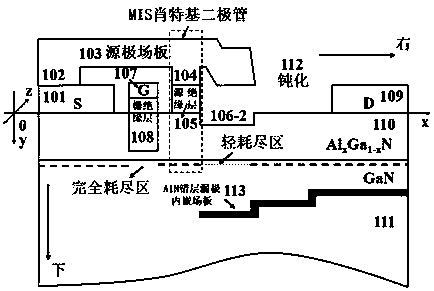

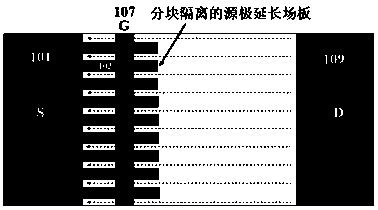

Lateral diffusion eGaN HEMT device integrating reverse diode and embedded drain electrode field plate

ActiveCN110212028AImprove breakdown characteristicsImprove breakdown resistanceSemiconductor devicesLateral diffusionBackward diode

The invention discloses a lateral diffusion eGaN HEMT device integrating a reverse diode and an embedded drain electrode field plate. The device comprises a GaN buffer layer, an AlGaN barrier layer, agate electrode, an under-gate insulating layer, a source electrode, a source electrode extension section, a source electrode field plate, an MIS schottky diode extension section, an MIS schottky diode insulating layer, a p-type GaN or groove, a drain electrode, a passivation layer and an AlN staggered-layer drain electrode embedded field plate, wherein the MIS schottky diode insulating layer is prepared in the middle region, towards the MIS schottky diode extension section and the AlGAN barrier layer surface, of the source electrode field plate; the side, close to the drain electrode, of thediode adopts the p-type GaN or groove, so that the breakdown characteristic of the device is improved; the embedded staggered-layer field plate is adopted below the drain electrode, so that anti-breakdown capability of the drain electrode to the substrate is improved; the design of the staggered layer is suitable for the gradual change distribution of the drain electrode electric field from rightto left, so that the breakdown characteristic of the device is improved; and the source electrode field plate is extended, the gate electrode is wrapped, the MIS schottky diode is formed on the gate drain side, and the diode is made into a block isolation mode, so that the drain electrode current is greatly improved.

Owner:SHANDONG JIANZHU UNIV

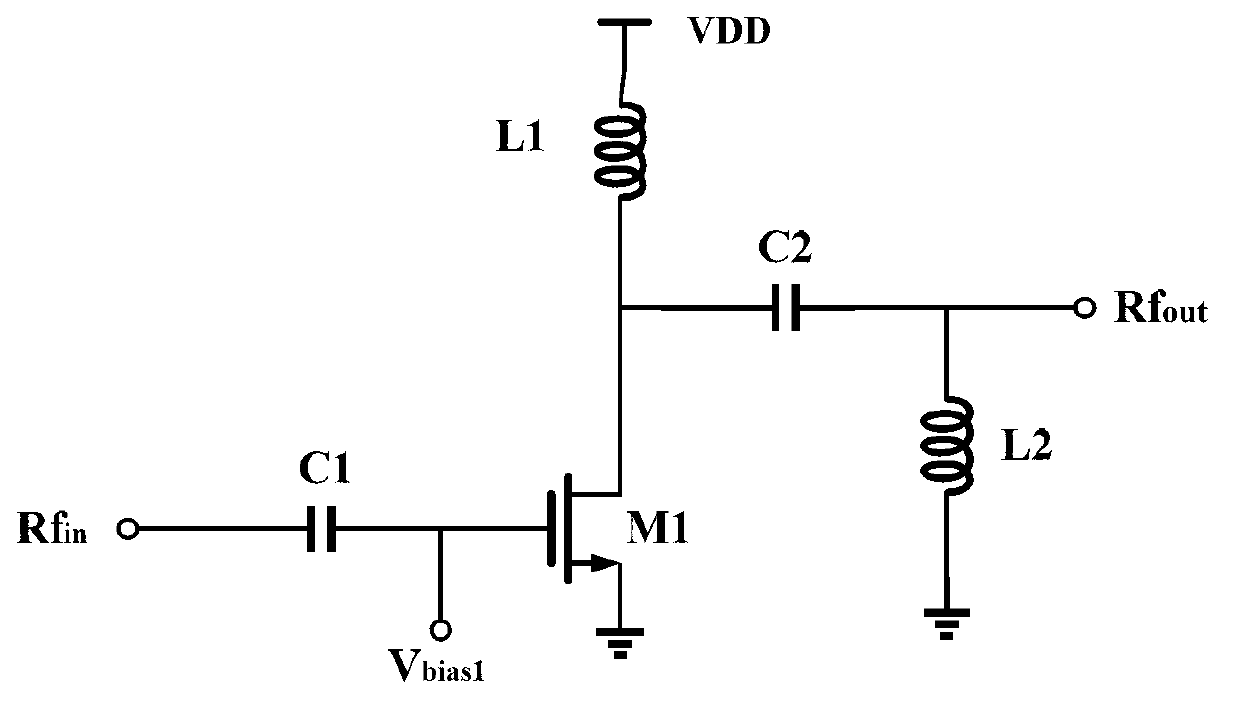

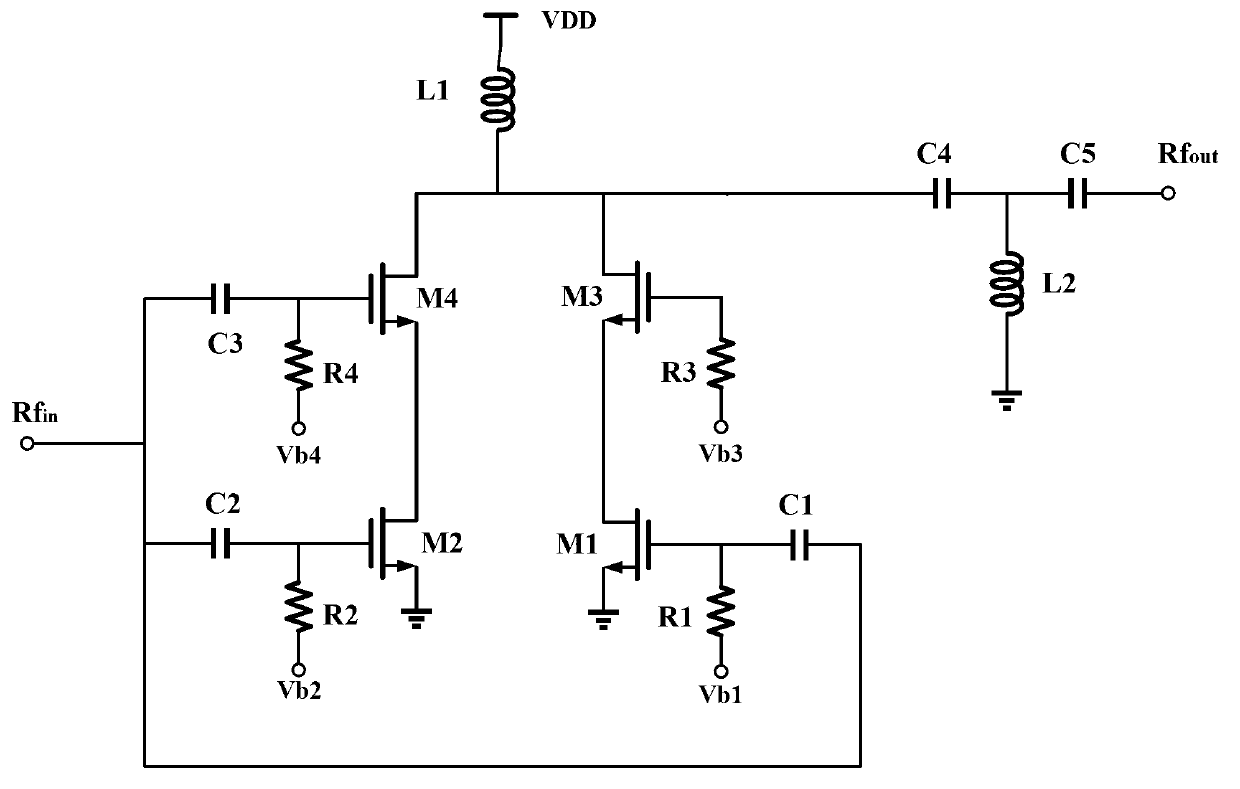

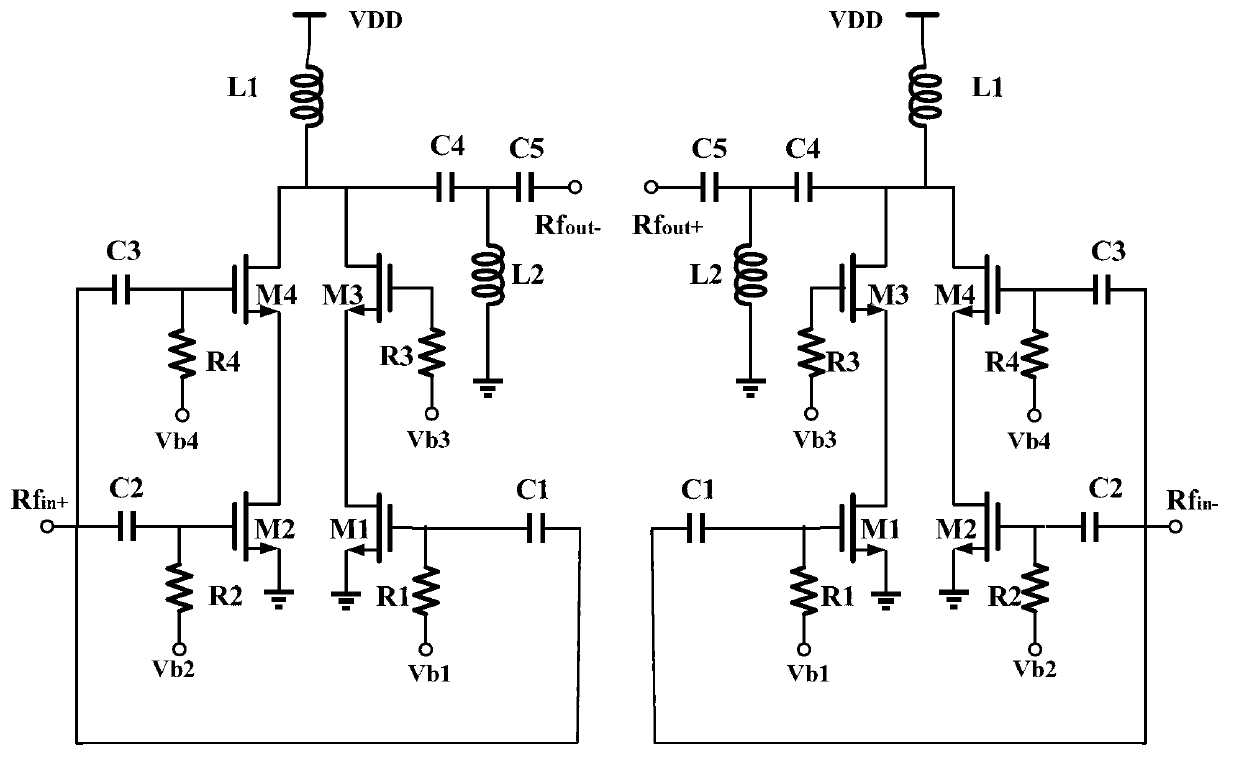

Radio frequency power amplifier with high linearity and high efficiency

ActiveCN103124162AImprove linearityImprove efficiencyHigh frequency amplifiersPower amplifiersAudio power amplifierRadio frequency signal

The invention discloses a radio frequency power amplifier with high linearity and high efficiency. The radio frequency power amplifier with high linearity and high efficiency comprises five capacitors: C1, C2, C3, C4 and C5, four resistances: R1, R2, R3 and R4, four N-channel metal oxide semiconductor (NMOS) pipes: M1, M2, M3 and M4 and two inductances: L1 and L2. Input radio frequency signals (Rfin) are respectively input to grids of the M1, M2 and M4 NMOS pipes through the C1, C2 and C3 capacitors, Vb1, Vb2, Vb3 and Vb4 bias voltages respectively provide direct current to the M1, M2, M3 and M4 NMOS pipes through the R1, R2, R3 and R4 resistances, drain electrode of the M2 NMOS pipe is connected with source electrode of the M4 NMOS pipe, and drain electrode of the M1 NMOS pipe is connected with source electrode of the M3 NMOS pipe. The radio frequency power amplifier with high linearity and high efficiency enhances puncture-resisting performance of a transistor, improves output power, and achieves high linearity and high efficiency of the power amplifier.

Owner:BEIJING MXTRONICS CORP +1

Semiconductor device and method for fabricating the same

InactiveUS7897461B2Reduce voltageImprove breakdown resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesHigh concentrationEngineering

Disclosed is a semiconductor device having an n-type drain region, a low concentration p-type body region formed on the n-type drain region, an n-type source region formed on the low concentration p-type body region, a high concentration p-type body region formed on the low concentration p-type body region, a gate insulating film, and a gate electrode, wherein a plurality of trenches T which extend in a same direction and each of which forms a continuous concavo-convex shape when viewed from above are formed from top faces of the source region and the high concentration body region and pass through the low concentration body region to reach into the drain region, and wherein the gate electrode is buried in each of the plurality of trenches. A maximum distance between two adjacent trenches T of the n-type source region is greater than a maximum distance between the two adjacent trenches T of the high concentration p-type body region.

Owner:PANASONIC CORP

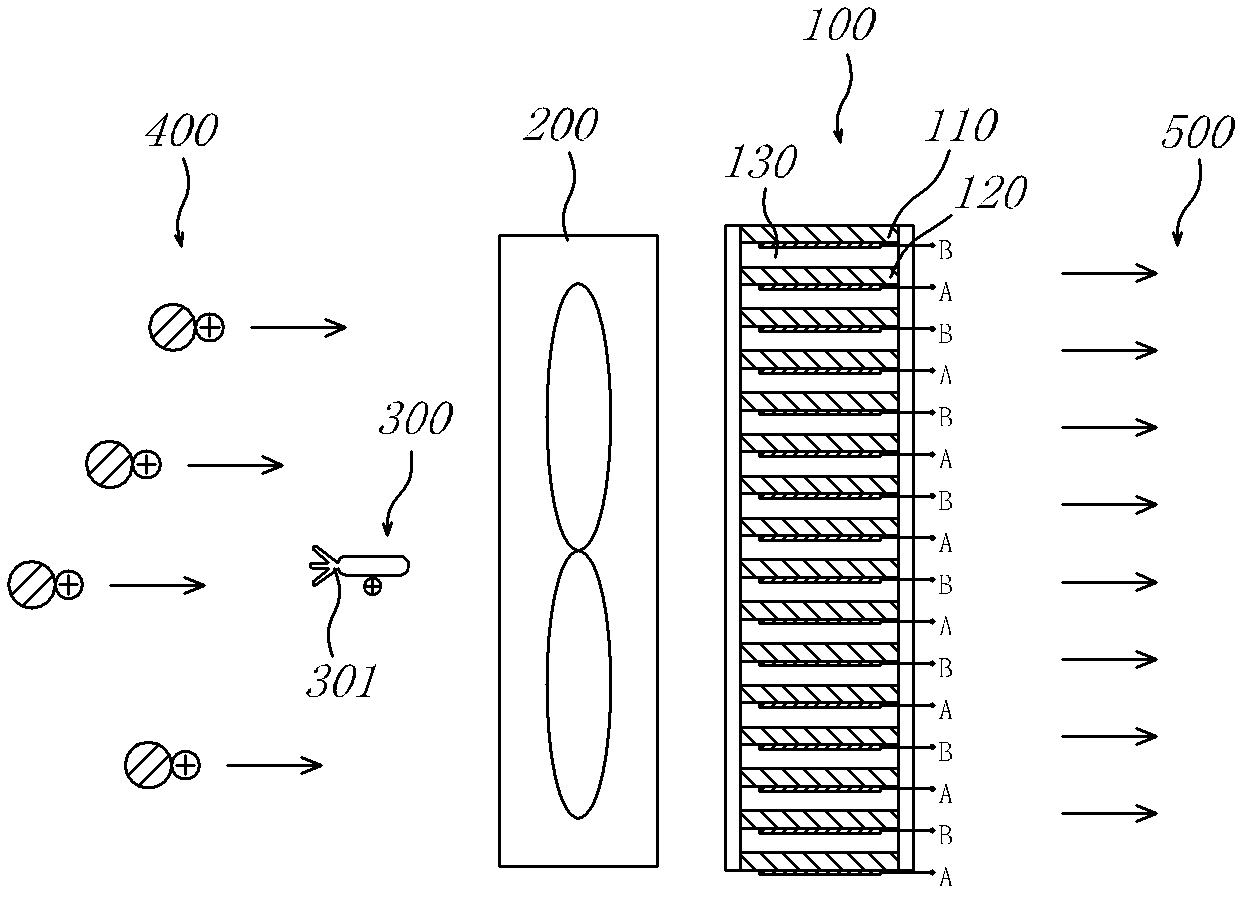

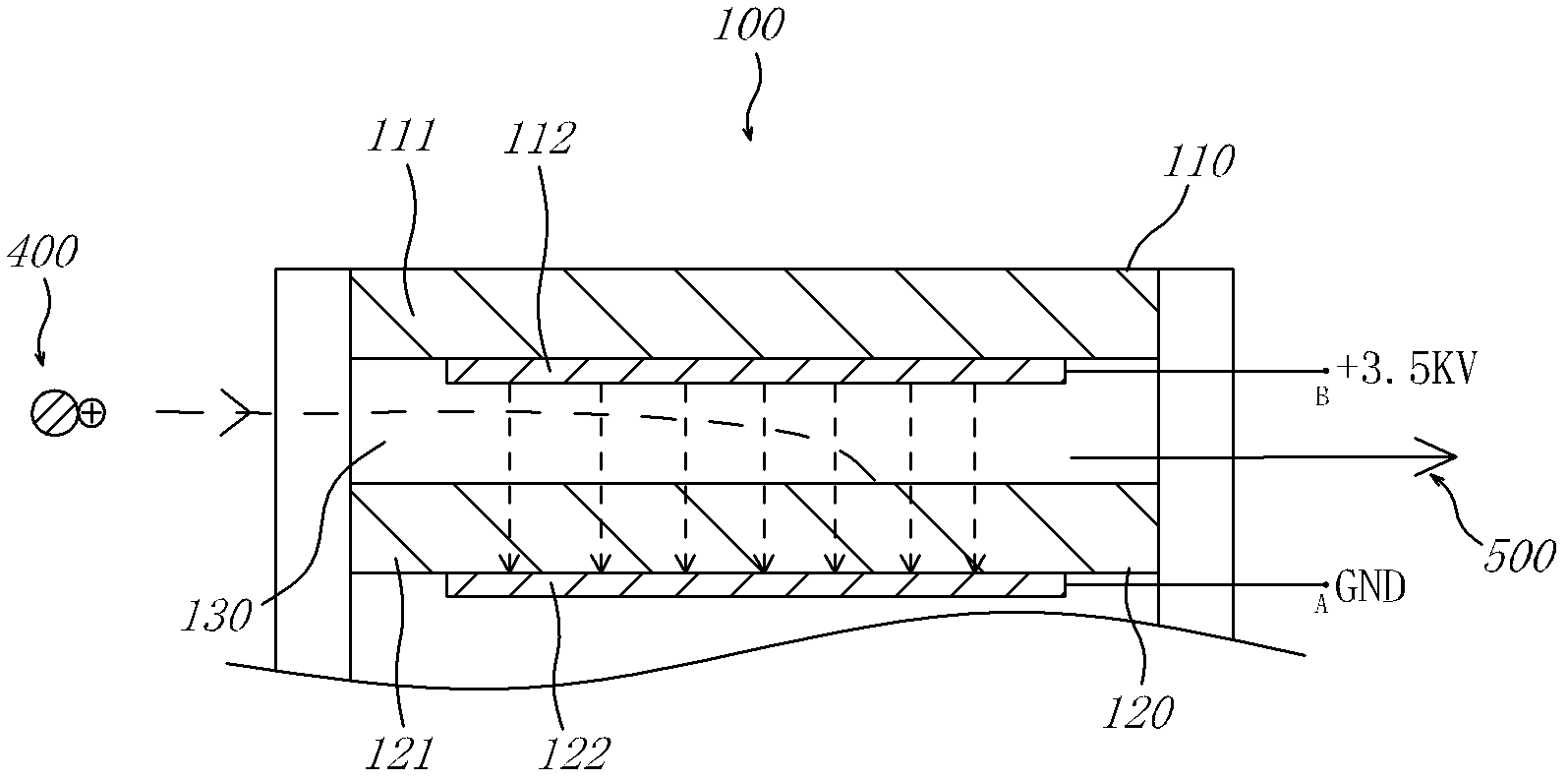

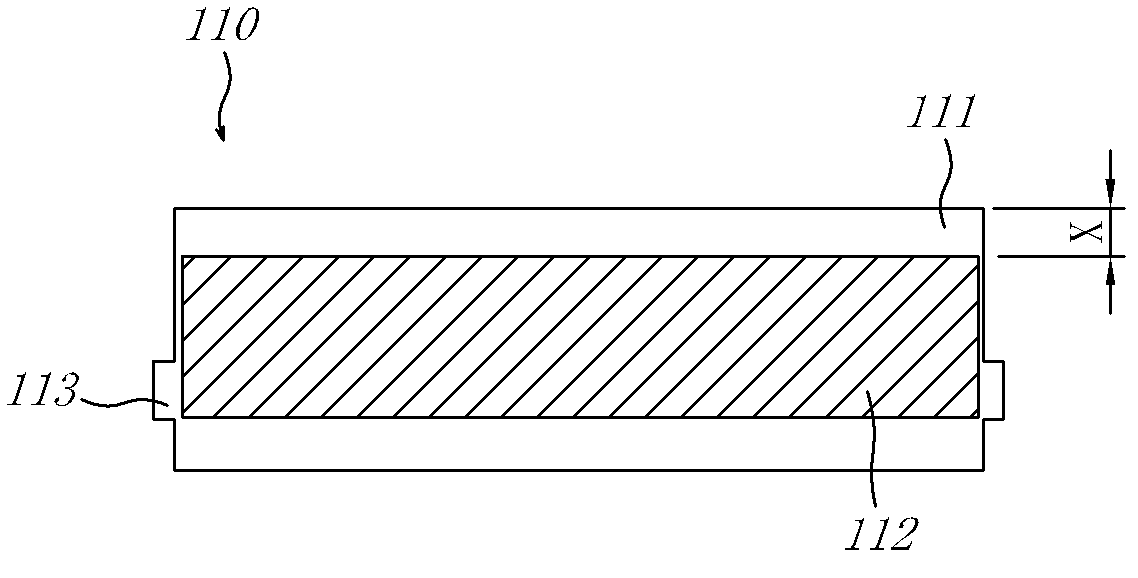

Structure of electrostatic dedusting device

ActiveCN102671762AIncrease resistanceAvoid arcing and sparkingExternal electric electrostatic seperatorElectrode constructionsElectrical resistance and conductanceHigh pressure

The invention discloses a structure of an electrostatic dedusting device. The structure is characterized by comprising a dust collection device, a fan device and a corona device, wherein the dust collection device is provided with dust collection plates which are distributed at intervals in an array mode; a single-way electric field and a dedusting air duct which traverses the electric field arranged between the adjacent dust collection plates; each dust collection plate comprises an insulation substrate and a conducting plate which is in close fit with the surface of the insulation substrate; by the fan device, air to be dedusted forms single-way controllable air flow, and the air flow penetrates through the dedusting air duct; the corona device is provided with a high-pressure emission head for electrifying dust particles in the air flow controlled by the fan device. According to the dedusting device with the structure, the dust collection plates comprise insulation substrates and conducting plates which are in close fit with the surfaces of the insulation substrates, so that the pneumatic design and electric field design of the dust collection device can be separated to avoid mutual influence; and resistance among the conducting plates is improved, and arcing is avoided, so that the optimized dedusting performance and the applicability on different occasions are realized finally.

Owner:ZHANGZHOU WANLIDA ZHONGHUAN TECH INC

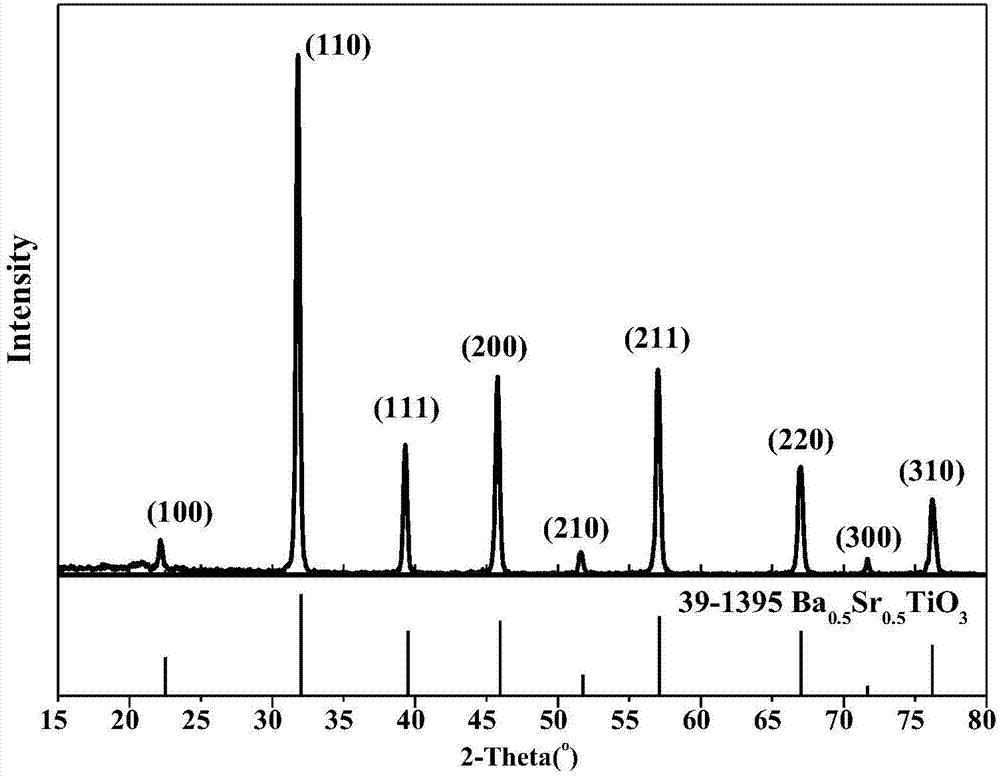

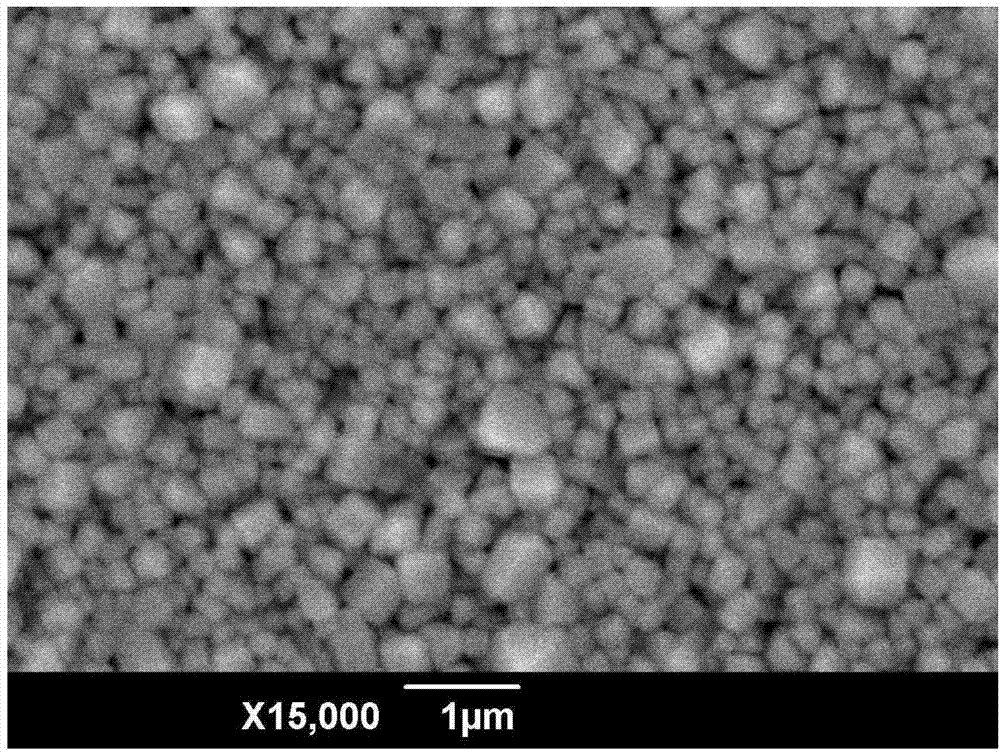

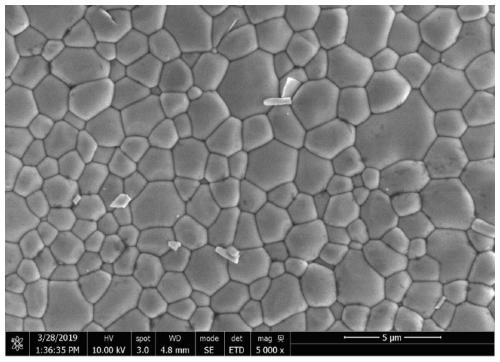

Method for preparing (Ba, Sr) TiO3 nano powder by virtue of Mg<2+> doped hydro-thermal method

ActiveCN104773755AHigh purityGrain refinementMaterial nanotechnologyTitanium compoundsNanoparticleThermal methods

The invention relates to a method for preparing (Ba, Sr) TiO3 nano powder by virtue of a Mg<2+> doped hydrothermal method. The method comprises the following steps: taking BaTiO3 powder and SrTiO3 powder which are synthesized by a hydrothermal method, adding water, mixing fully, then adding MgCl2, and mixing uniformly to obtain a mixed solution; and pouring the mixed solution into a hydrothermal kettle, preserving the heat at 120-180 DEG C for 4-8 hours to perform hydrothermal reaction, and performing centrifugal drying on a generated precipitate to obtain Mg<2+> doped (Ba, Sr) TiO3 nano powder. According to the method provided by the invention, the BaTiO3 powder and SrTiO3 powder which are prepared by the hydrothermal method are adopted as raw materials, then a minute quantity of MgCl2 is doped into the raw materials, and then the Mg<2+> doped (Ba, Sr) TiO3 powder is prepared by using the hydrothermal method under the condition that a mineralizer is not added, so that secondary reaction is effectively avoided, and the prepared powder is high in purity and uniform and meticulous in crystal grain, reaches a nano scale, and can effectively improve the energy storage characteristic and the breakdown resistance of ceramic when used for preparing the ceramic.

Owner:SHAANXI UNIV OF SCI & TECH

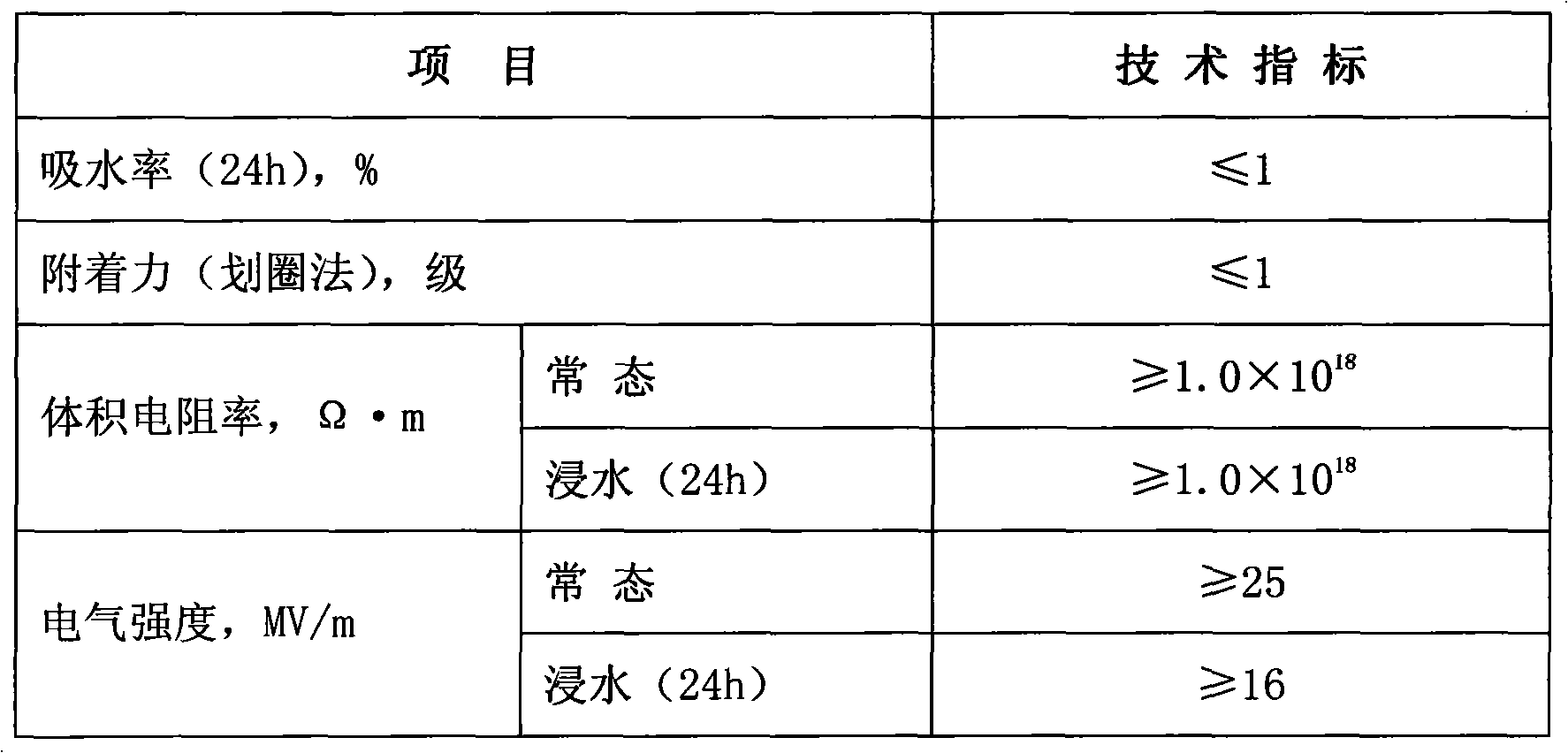

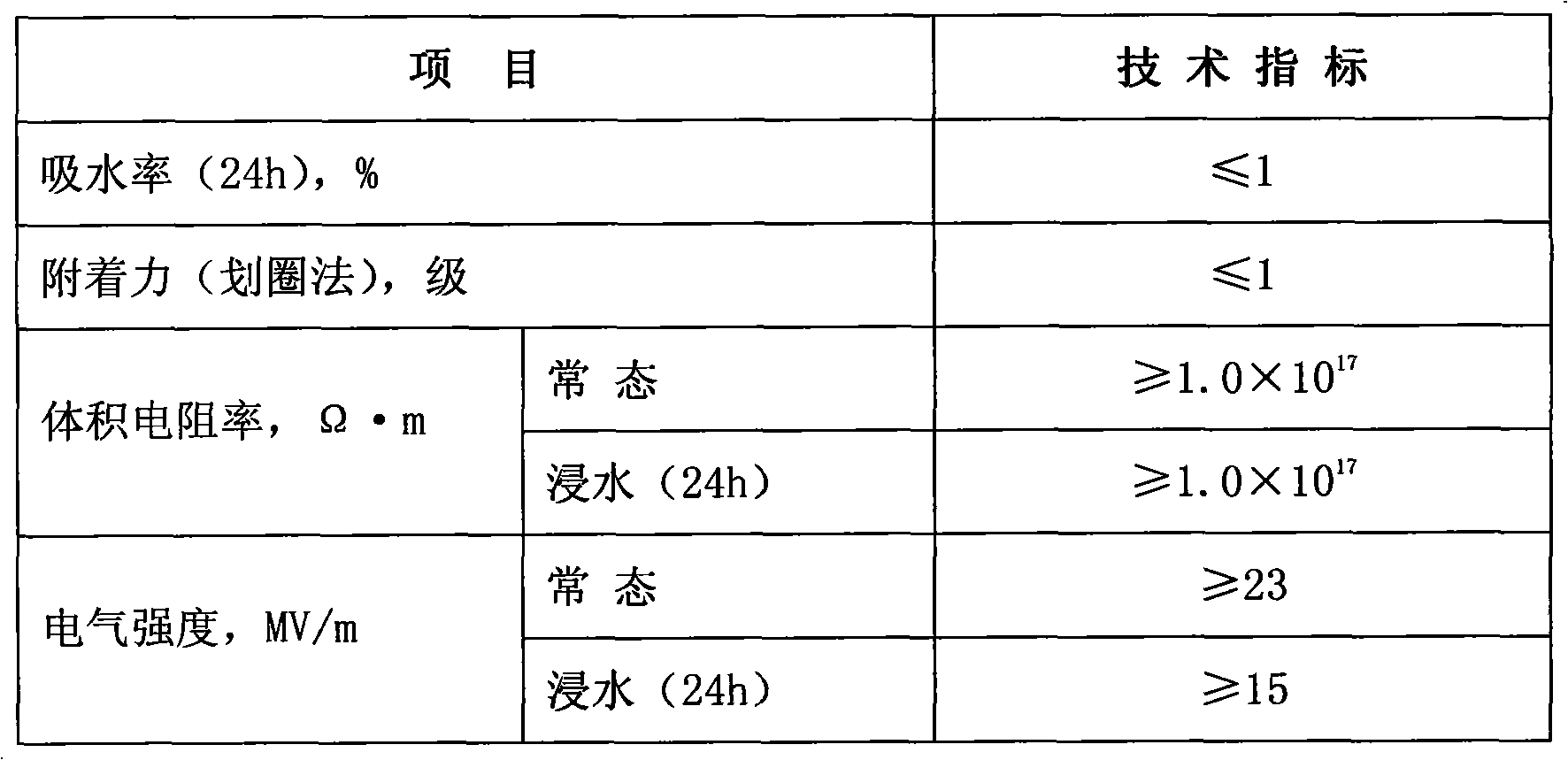

Breakdown-resistant insulating paint

The invention provides breakdown-resistant insulating paint. The breakdown-resistant insulating paint is prepared by mixing emulsion A and emulsion B in a weight ratio of the mixing emulsion A to the emulsion B of 10:1, wherein the emulsion A comprises 30 to 60 parts of organic silicon modified epoxy resin, 50 to 80 parts of filler, 20 to 50 parts of mixed solvent, 5 to 20 parts of inorganic thickening agent, 5 to 10 parts of toughening agent, 5 to 15 parts of flame retardant and 5 to 15 parts of auxiliary flame retardant; and the emulsion B comprises 10 to 30 parts of curing agent and 10 to 30 parts of mixed solvent. One or more of mica powder, ceramic powder, aluminium hydroxide and quartz sand serves as the filler, so the breakdown-resistant insulating paint has excellent breakdown resistance. The breakdown-resistant insulating paint has high adaptability, excellent weather resistance and ageing resistance, excellent adhesion to various metal base materials, high solid content, lowvolume shrinking percentage when being dried and cured and high cracking resistance; and the breakdown-resistant insulating paint can be cured at normal temperature, so the breakdown-resistant insulating paint is simple, convenient, safe and reliable for application.

Owner:QINGDAO AIR NEW MATERIALS

Seabed communication complex cable and preparation method thereof

InactiveCN106229073AGood water resistanceSimple stepsCommunication cablesInsulated cablesRadio frequencyPolyolefin

The invention discloses a seabed communication complex cable and a preparation method thereof. The seabed communication complex cable comprises a cable core, wherein the cable core is sleeved with a polyvinyl chloride water-blocking tape covering, a zinc-coated wire weaved shielding jacket and a cross-linking polyolefin projecting jacket in turn from outer to inner; the silica gel fills the gap between the cable core and the polyvinyl chloride water-blocking tape covering; the silica gel fills the gap between the zinc-coated wire weaved shielding jacket and the cross-linking polyolefin projecting jacket; the cable core comprises a first wire, a single mold optical fiber, a coaxial radio frequency cable and a second wire. The seabed communication complex cable prepared according to the method has excellent water resistance, electrical conductivity and breaking resistance. The preparation method has simple steps and is easy to popularize.

Owner:WUHU HANGTIAN SPECIAL CABLE FACTORY

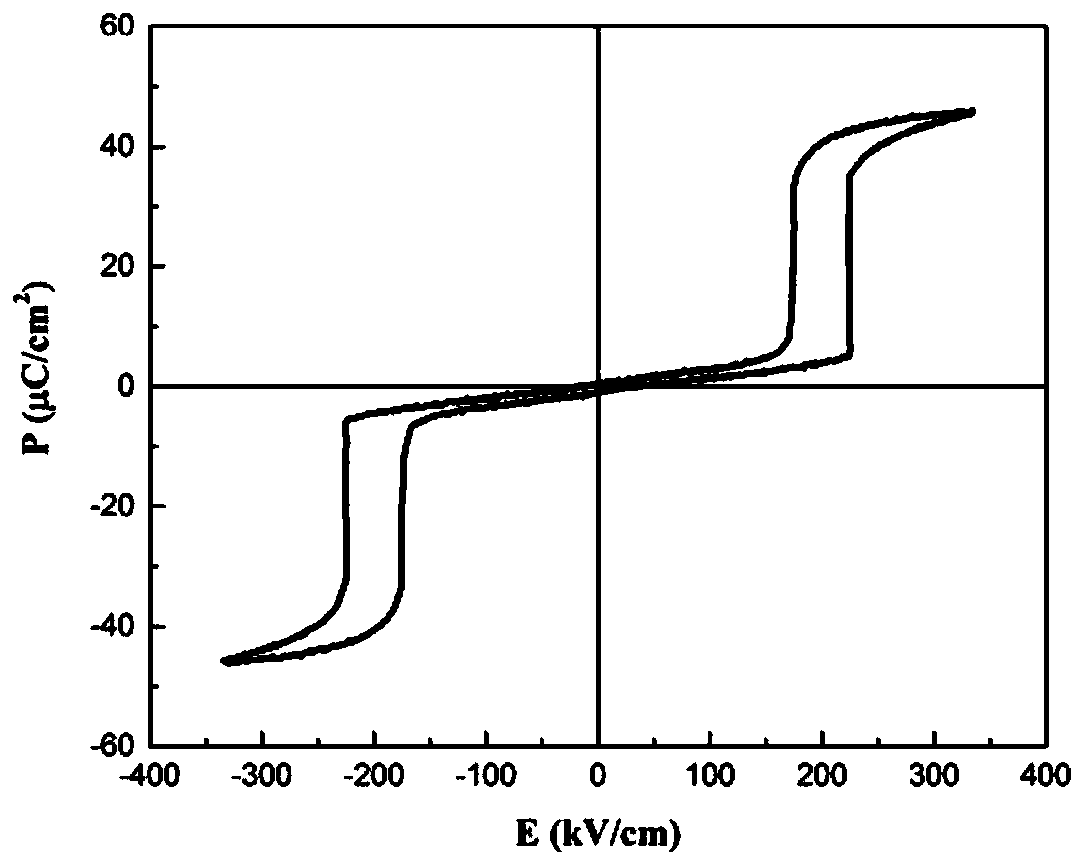

PbHfO3-based anti-ferroelectric material based on film rolling process, preparation method and applications thereof

InactiveCN110467457ASimple manufacturing methodSimple and fast operationFixed capacitor dielectricHigh energyTransducer

The invention relates to a PbHfO3-based anti-ferroelectric material based on a film rolling process, a preparation method and applications thereof, wherein the PbHfO3-based anti-ferroelectric materialhas a chemical general formula of (Pb1-3z / 2Laz)(Hf1-x-ySnxTiy)O3, z is more than 0 and is less than or equal to 0.04, x is more than 0 and is less than or equal to 1.0, and y is more than 0 and is less than 1.0. The preparation method comprises: 1) carrying out mixing grinding on corresponding metal oxides according to the corresponding stoichiometric ratio of (Pb1-3z / 2Laz)(Hf1-x-ySnxTiy)O3; 2) drying, and pre-firing; 3) carrying out secondary grinding, and drying; 4) mixing with a binder, and carrying out rough rolling, finish rolling and cutting; and 5) carrying out binder discharge treatment and sintering treatment to prepare the PbHfO3-based anti-ferroelectric material. According to the present invention, the prepared PbHfO3-based anti-ferroelectric material can be used for preparingpulse power capacitors, energy storage capacitors and transducers; compared with the method in the prior art, the preparation method of the present invention has characteristics of simpleness, easy performing and convenient operation, and is suitable for batch production; and the sample of the present invention has characteristics of adjustable size, wide application range, strong breakdown resistance, high energy storage density and good application value.

Owner:TONGJI UNIV

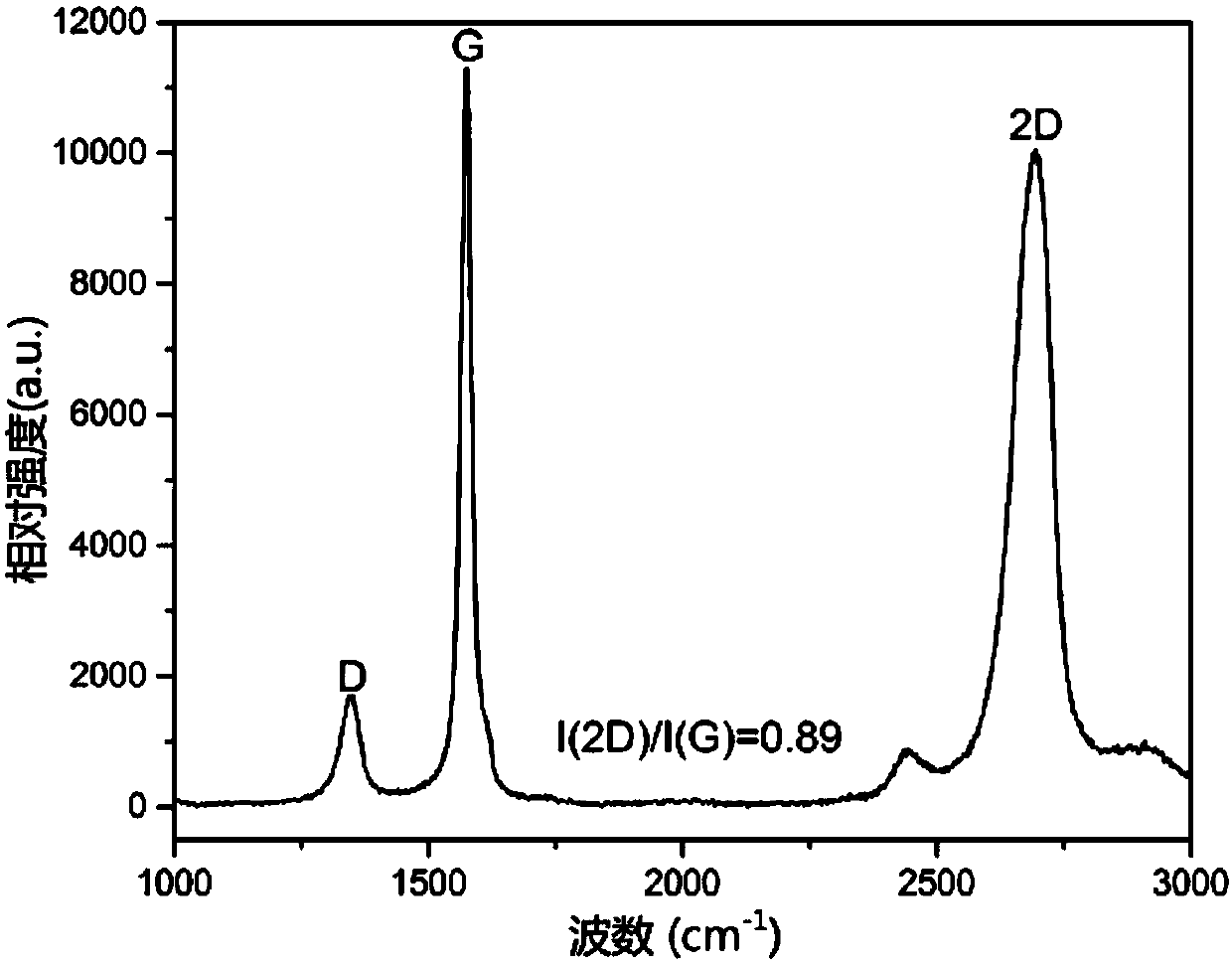

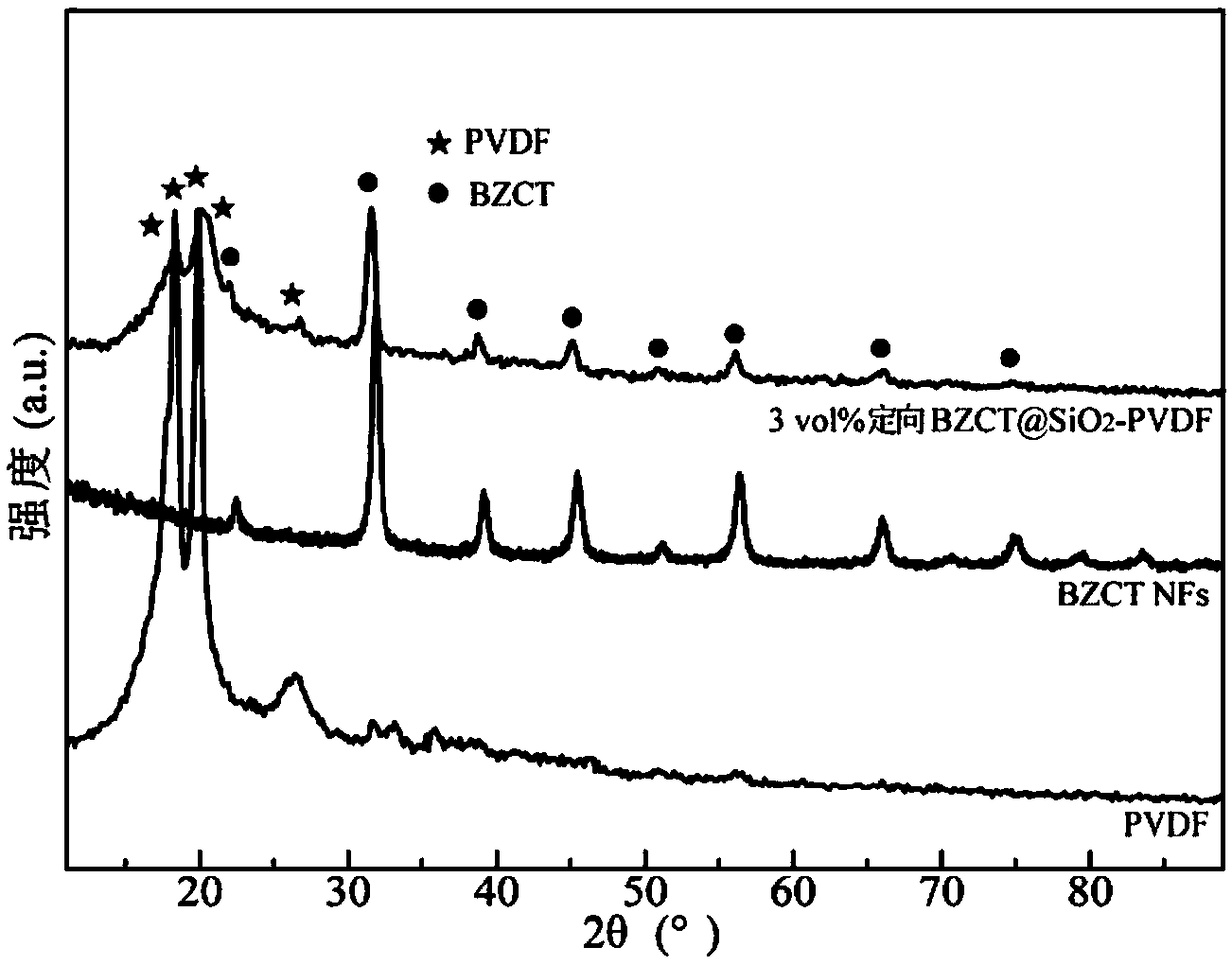

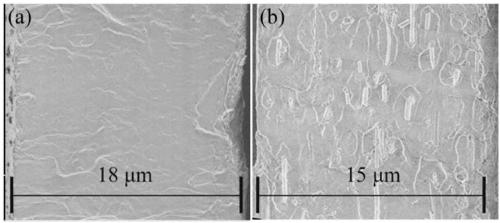

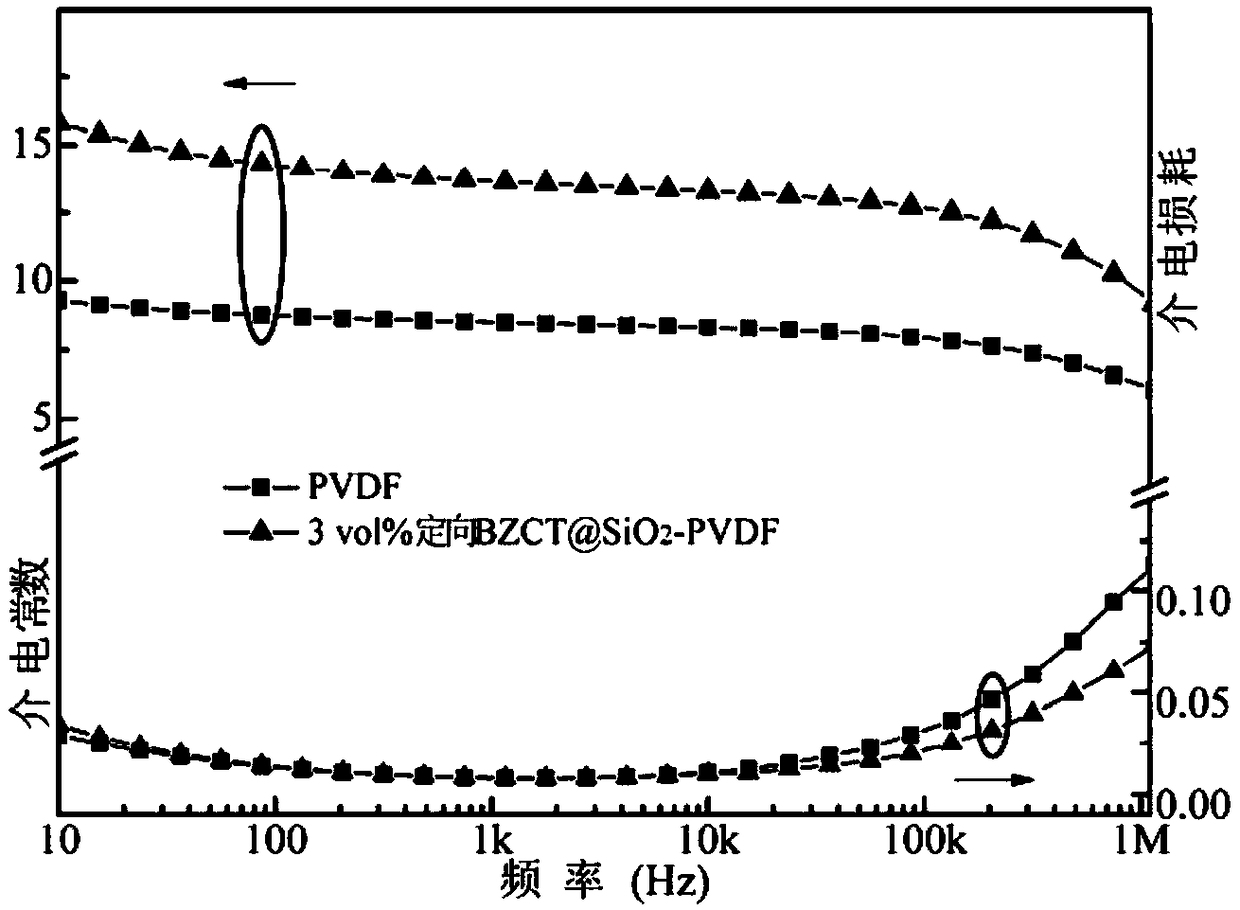

Highly-oriented arrangement core-shell structure fiber polyvinylidene fluoride-based composite medium and preparation method thereof

The invention discloses a highly-oriented arrangement core-shell structure fiber polyvinylidene fluoride-based composite medium and a preparation method thereof, wherein the composite medium is formedby compounding a core-shell structure BZCT@SiO2NFs filling phase and PVDF, the BZCT@SiO2NFs is a core-shell fiber structure, the core layer is barium calcium zirconate titanate, and the shell layer is silicon oxide. According to the present invention, an inorganic fiber filling phase having a large aspect ratio is prepared by using a sol-gel method and an electrospinning technology, the inorganicfiber filling phase is encapsulated with silica, the obtained material and PVDF are compounded, and quenching treatment is performed to obtain the dense highly-oriented one-dimensional core-shell structure inorganic fiber-PVDF-based composite film; and the highly-oriented arrangement one-dimensional core-shell structure inorganic fiber-PVDF-based composite film medium can significantly improve the dielectric property, the breakdown property and the energy storage property so as to maintain the excellent electrical insulation property and the mechanical properties of the polymer.

Owner:HARBIN UNIV OF SCI & TECH