Patents

Literature

59results about How to "Increase parasitic resistance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

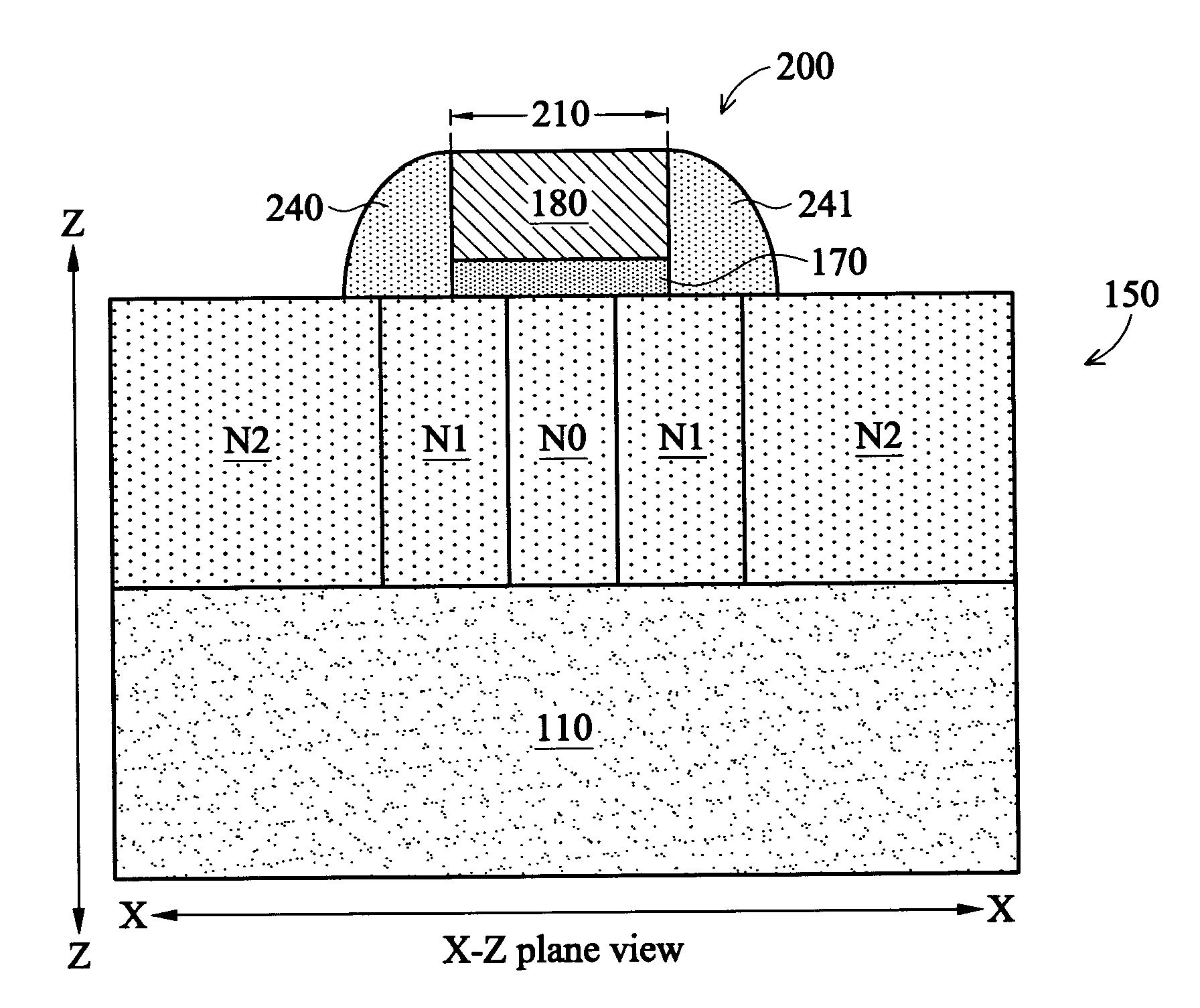

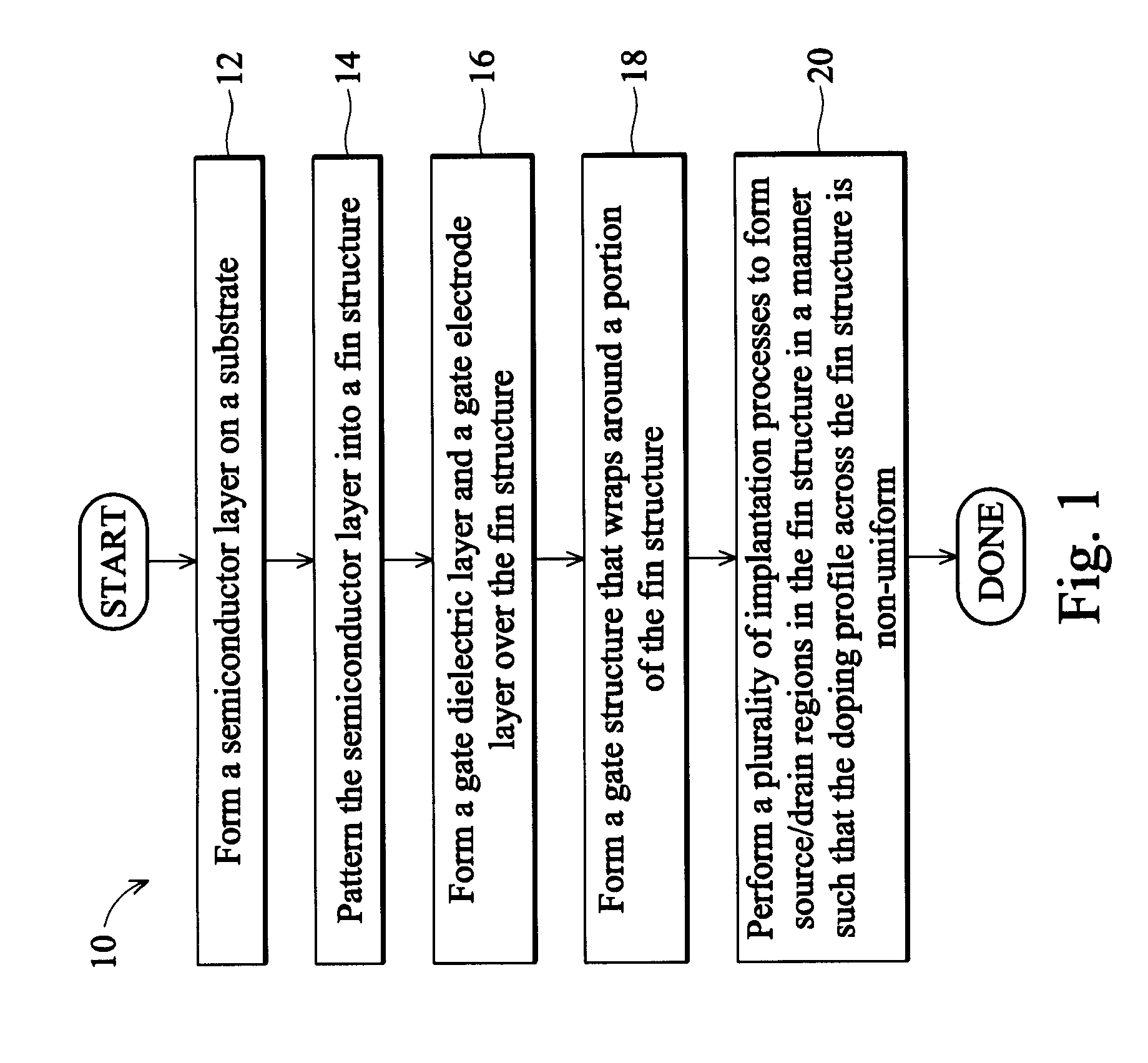

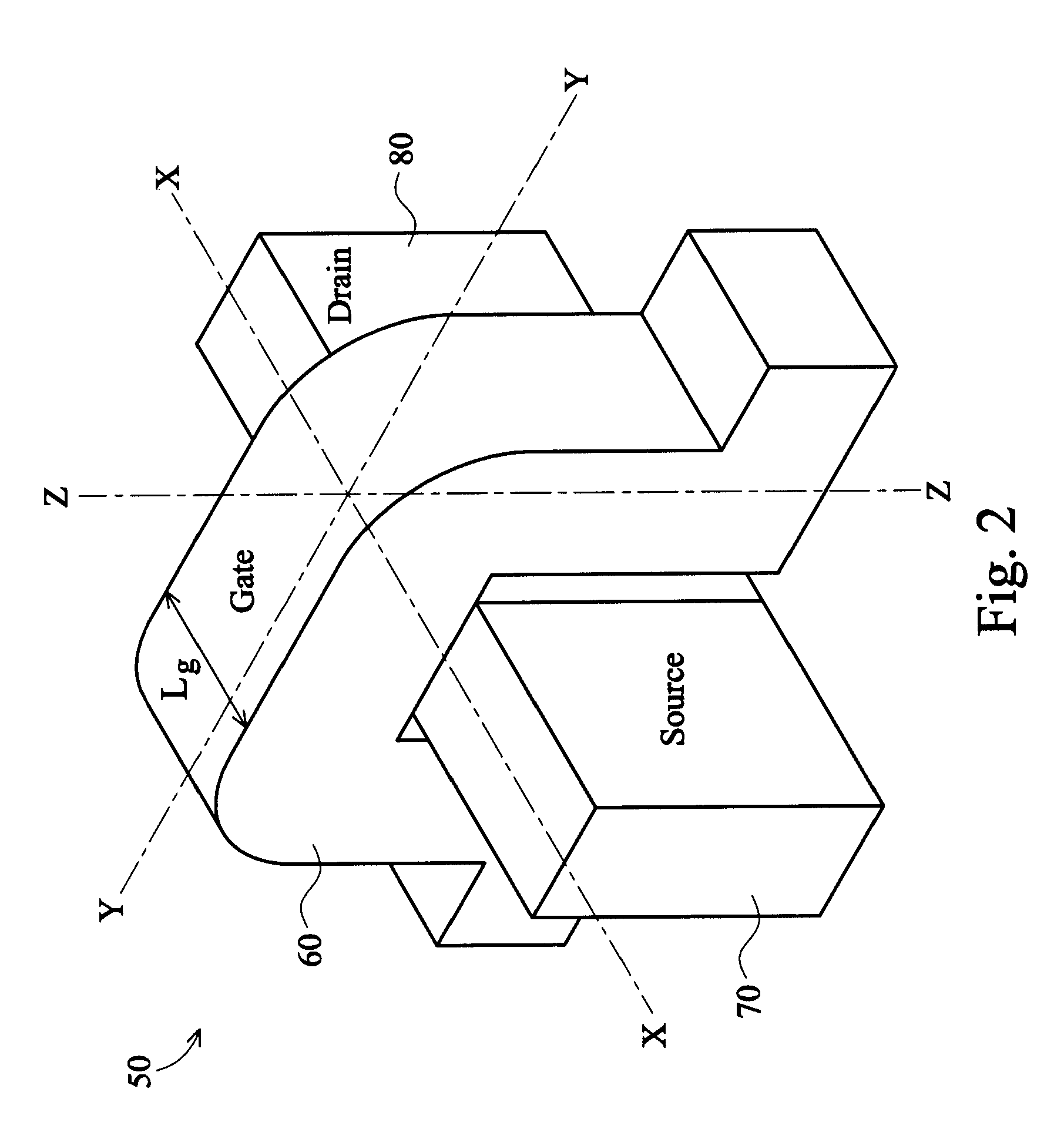

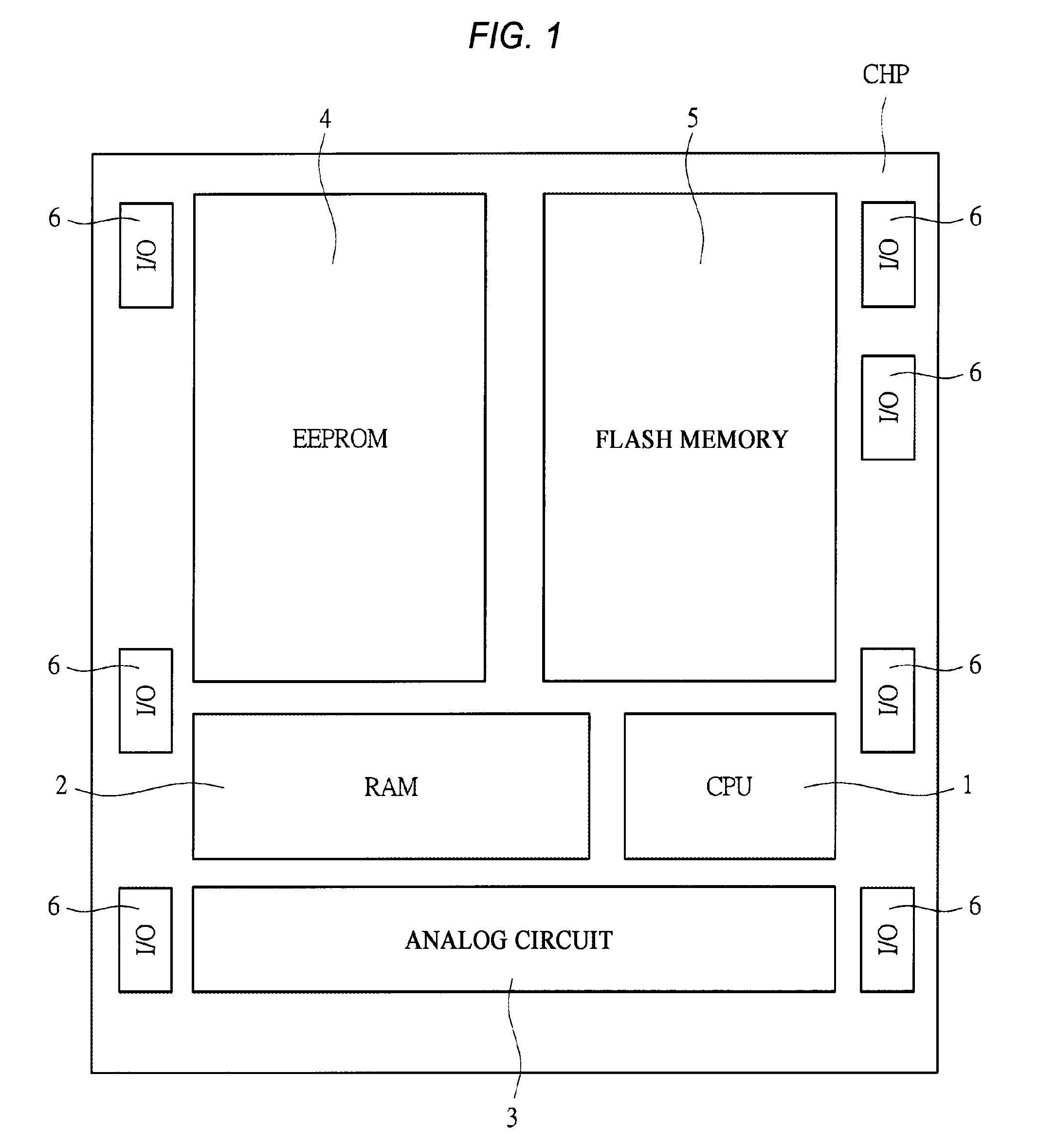

Non-uniform channel junction-less transistor

ActiveUS8487378B2Easy to controlImprove device densitySolid-state devicesSemiconductor/solid-state device manufacturingGate dielectricSemiconductor

Owner:TAIWAN SEMICON MFG CO LTD

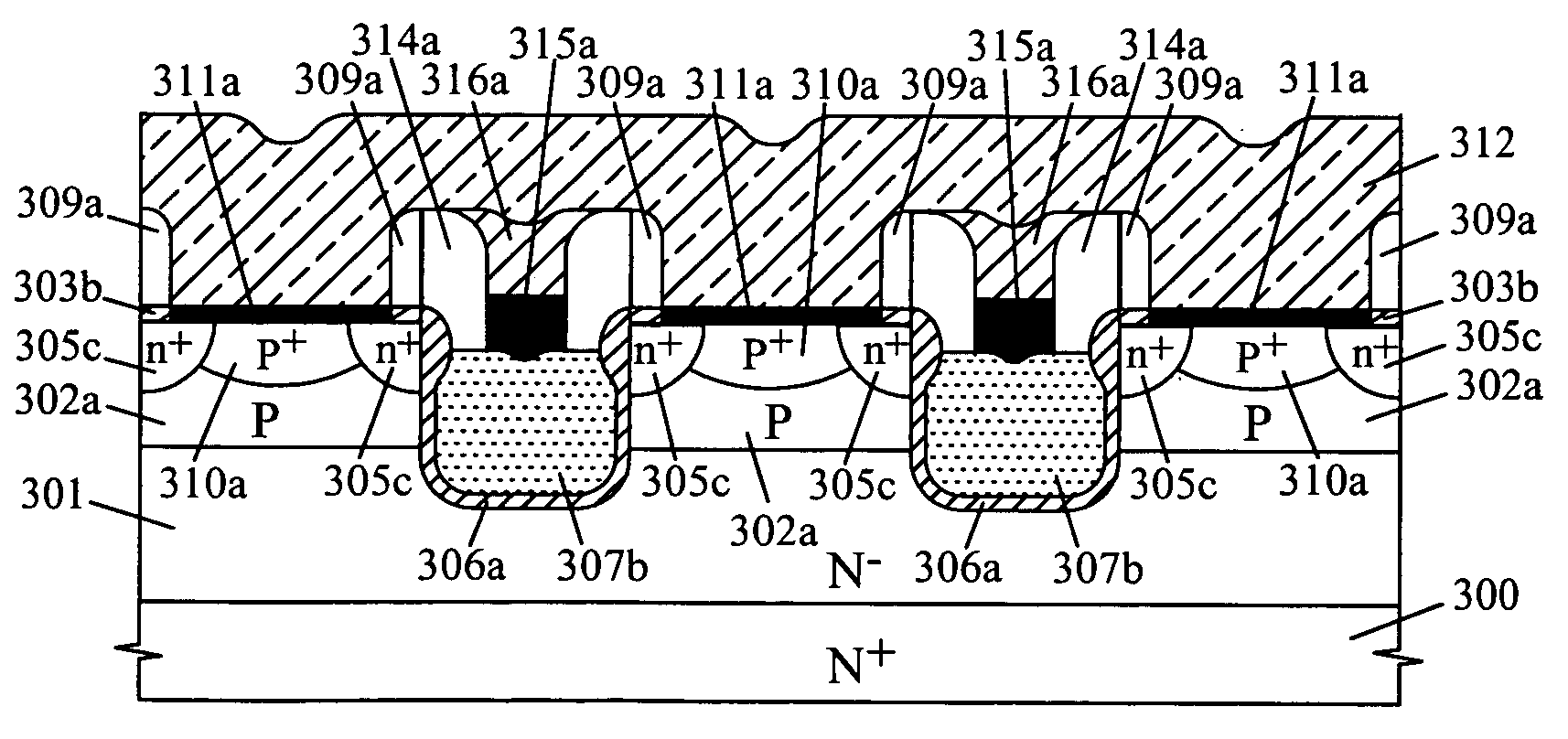

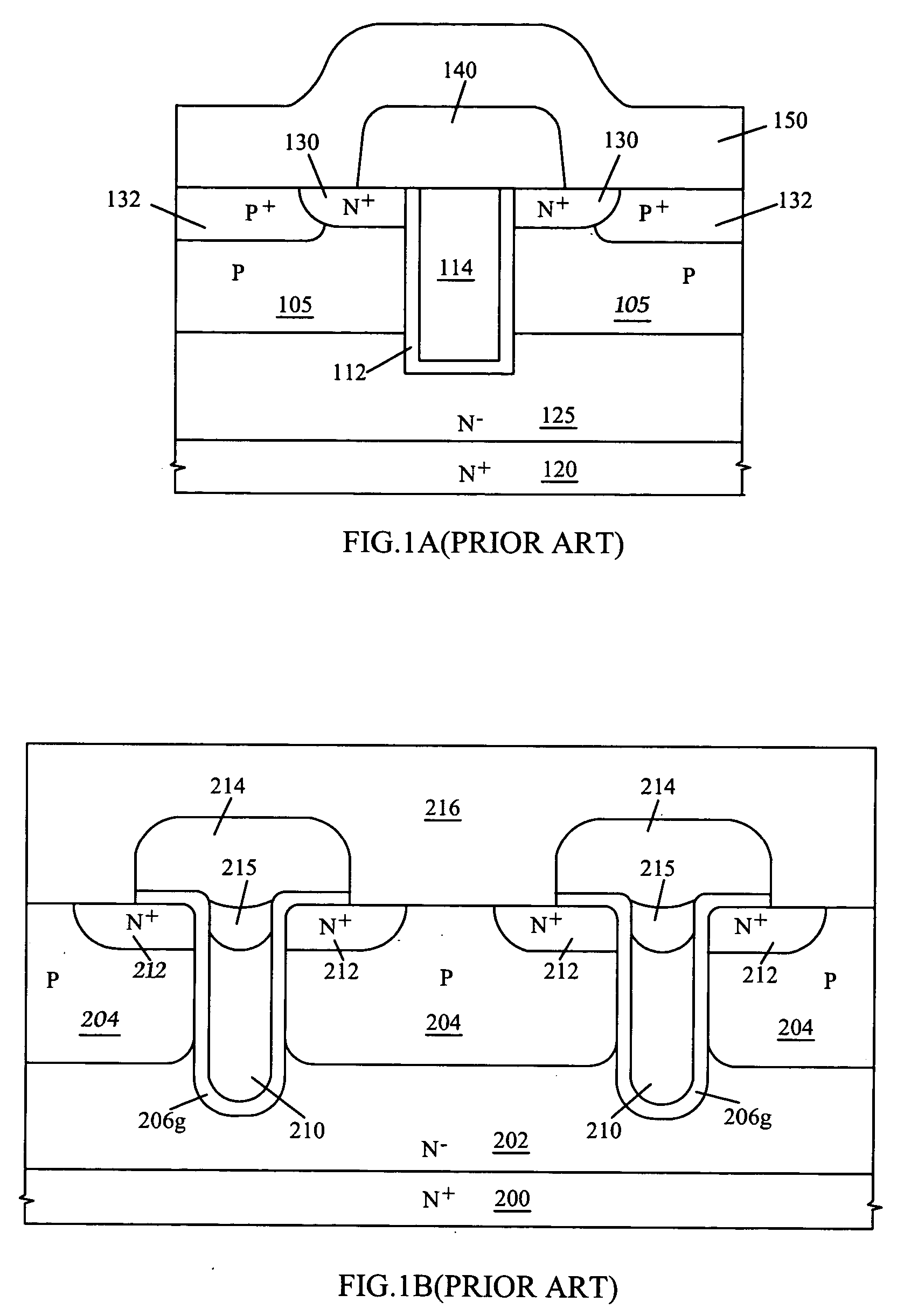

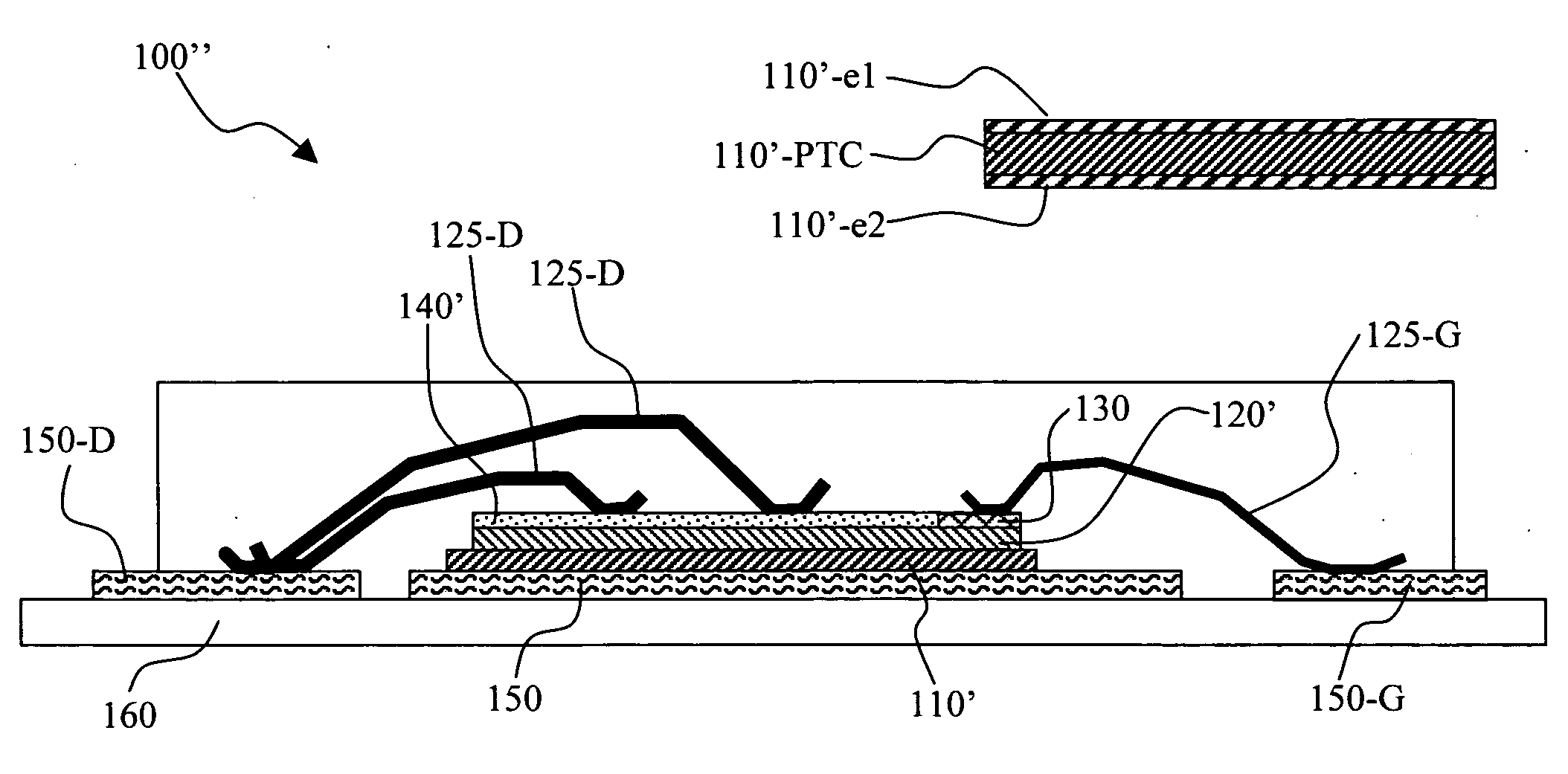

Self-aligned trench-type DMOS transistor structure and its manufacturing methods

InactiveUS20060113588A1Increase resistanceIncreased durabilitySemiconductor devicesDielectricGate dielectric

The self-aligned trench-type DMOS transistor structure comprises a self-aligned source region being surrounded by a trench gate region. The self-aligned source region comprises a moderately-doped p-base diffusion region formed in a lightly-doped epitaxial semiconductor substrate, a self-aligned heavily-doped n+ source diffusion ring formed in a side surface portion of the moderately-doped p-base diffusion region, a heavily-doped p+ contact diffusion region formed in a surface portion of the moderately-doped p-base diffusion region surrounded by the heavily-doped n+ source diffusion ring, and a self-aligned source contact window formed by a semiconductor surface surrounded by a sidewall dielectric spacer. The trench gate region comprises a gate dielectric layer being lined over a trenched semiconductor surface with or without a thicker isolation dielectric layer formed on a bottom trenched semiconductor surface and a self-aligned highly conductive gate layer being formed at least over the gate dielectric layer.

Owner:SILICON BASED TECH

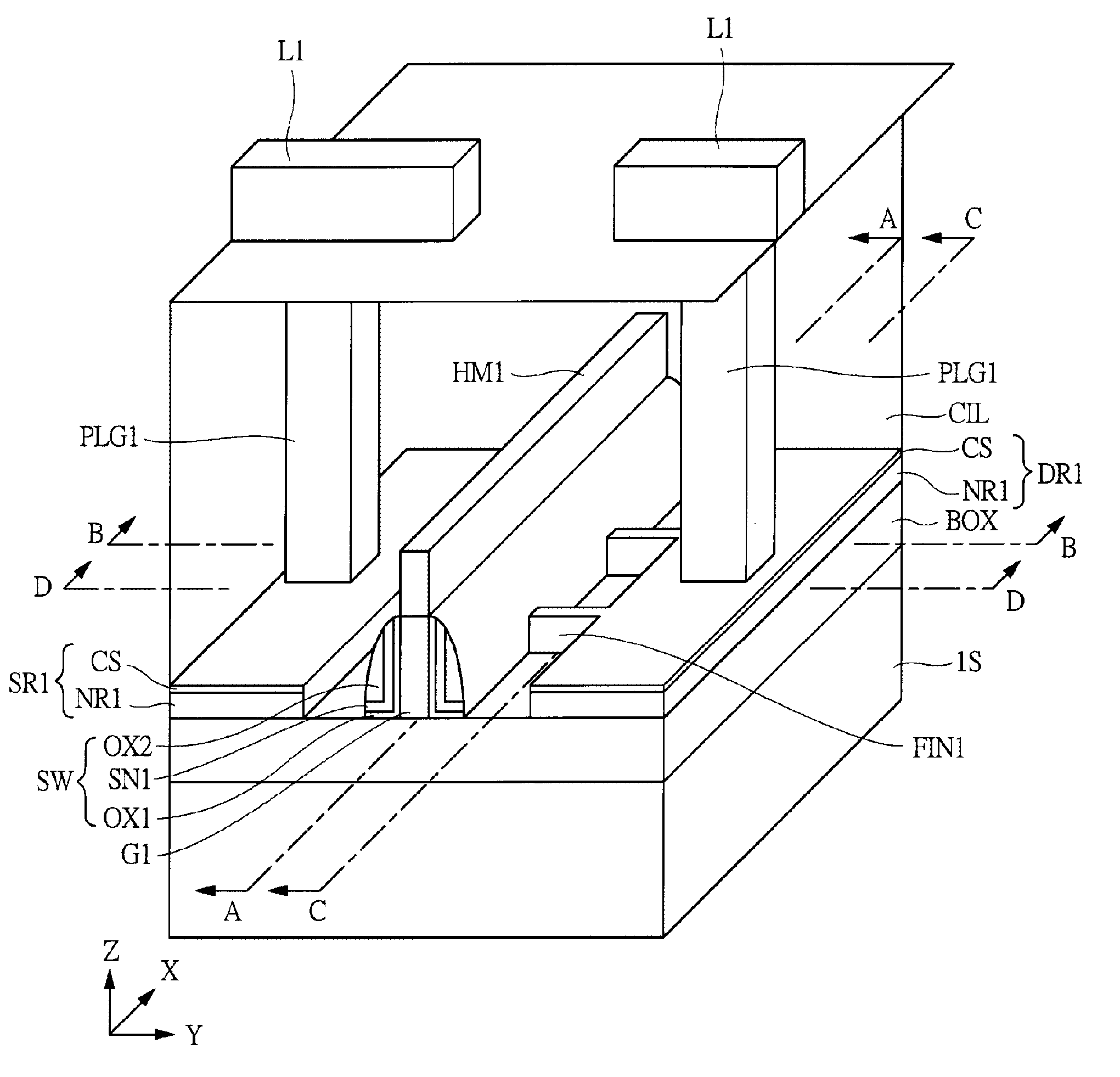

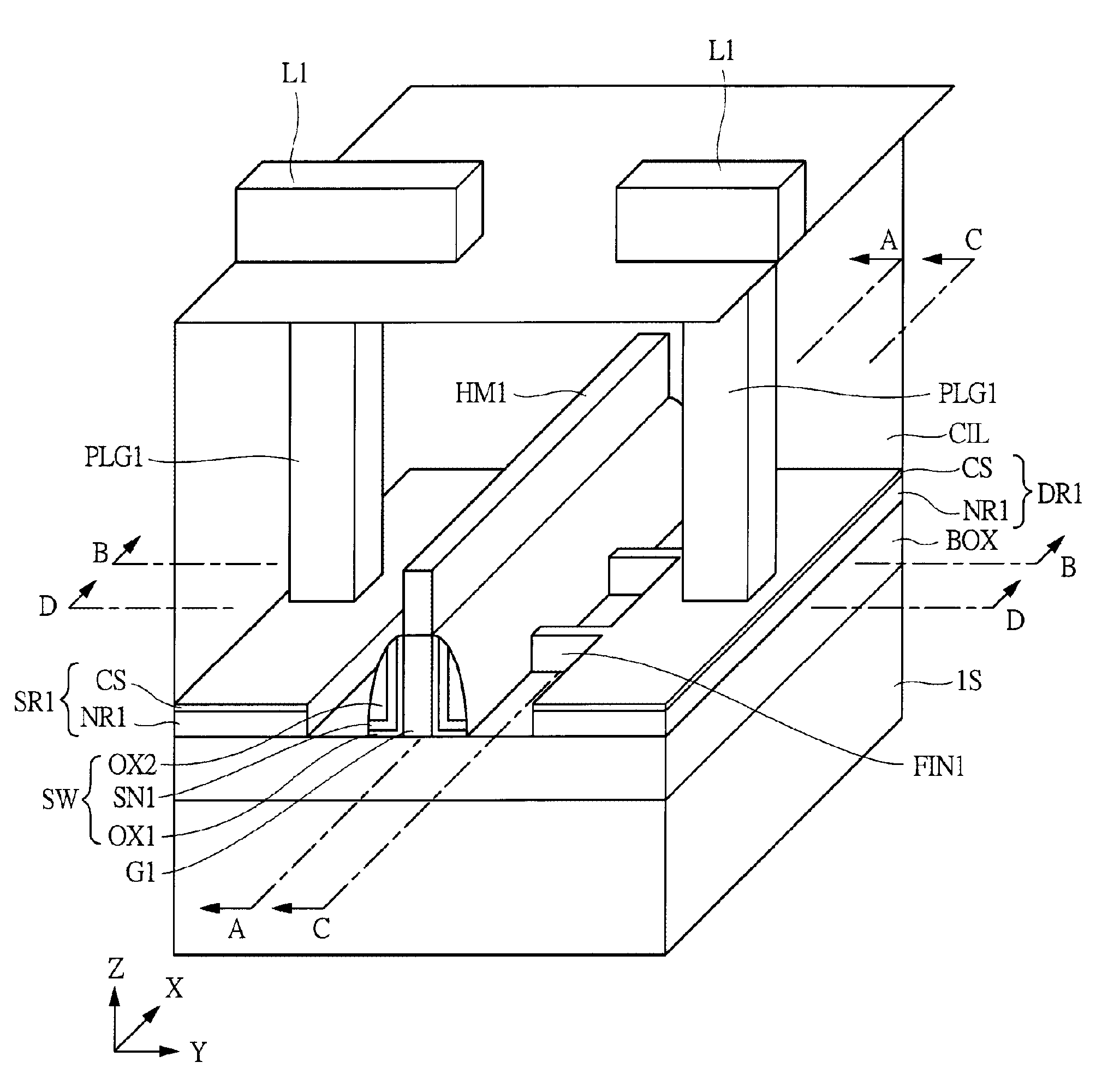

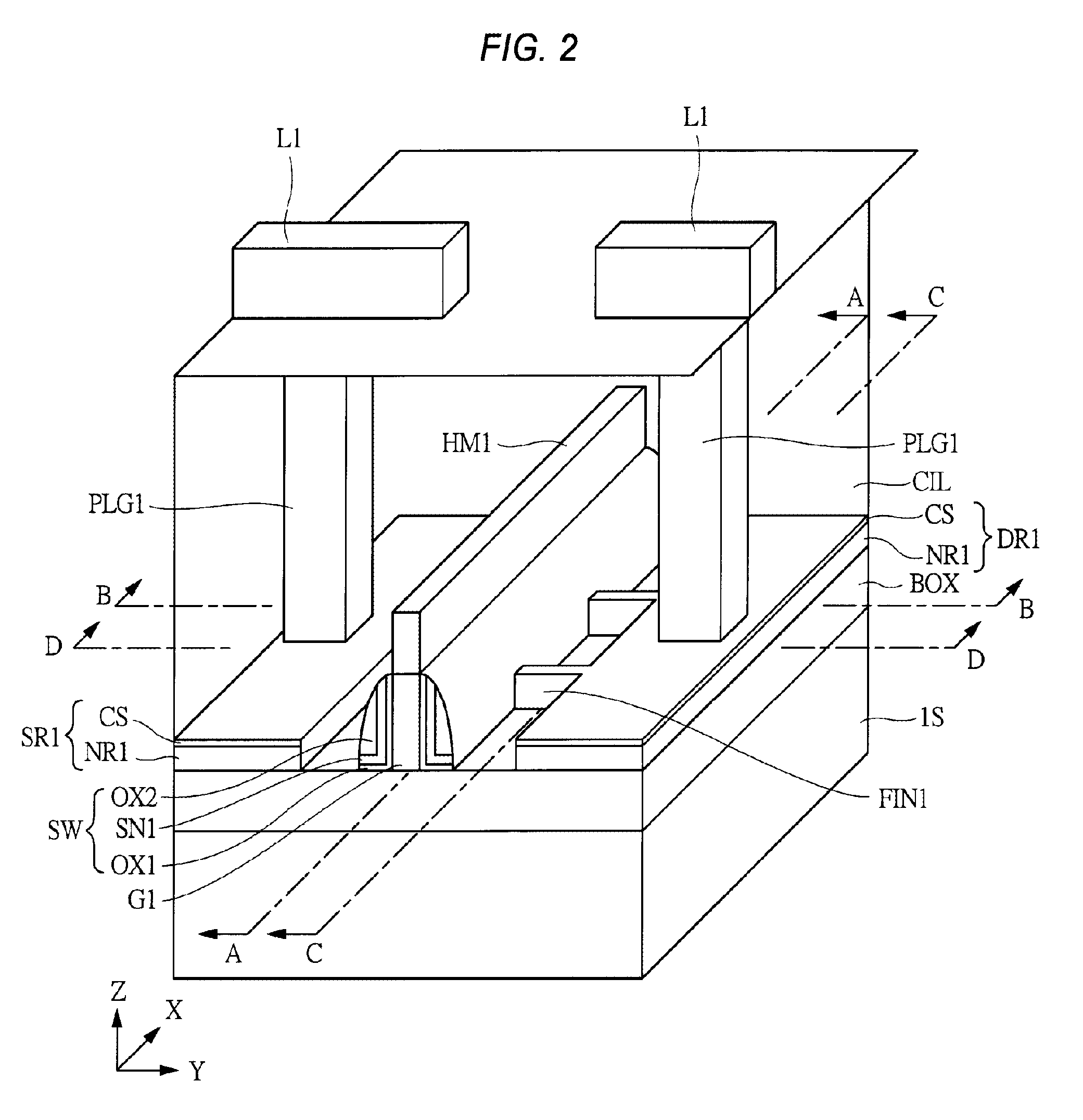

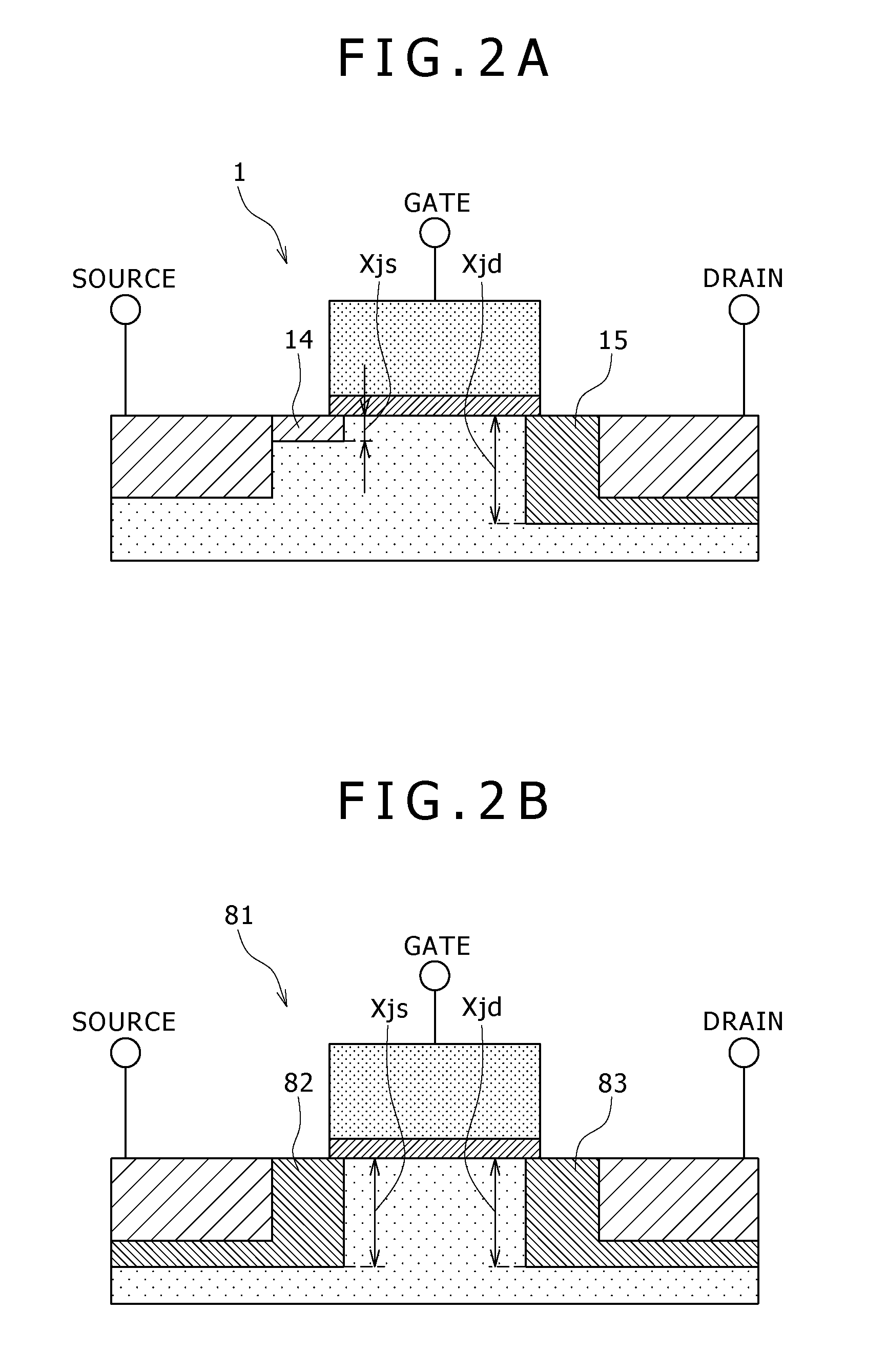

Semiconductor device and method of manufacturing the same

ActiveUS20110049629A1Increase parasitic resistancePotential controllabilityTransistorSolid-state devicesDevice materialSilicon oxide

To provide a technique capable of achieving improvement of the parasitic resistance in FINFETs. In the FINFET in the present invention, a sidewall is formed of a laminated film. Specifically, the sidewall is composed of a first silicon oxide film, a silicon nitride film formed over the first silicon oxide film, and a second silicon oxide film formed over the silicon nitride film. The sidewall is not formed on the side wall of a fin. Thus, in the present invention, the sidewall is formed on the side wall of a gate electrode and the sidewall is not formed on the side wall of the fin.

Owner:RENESAS ELECTRONICS CORP

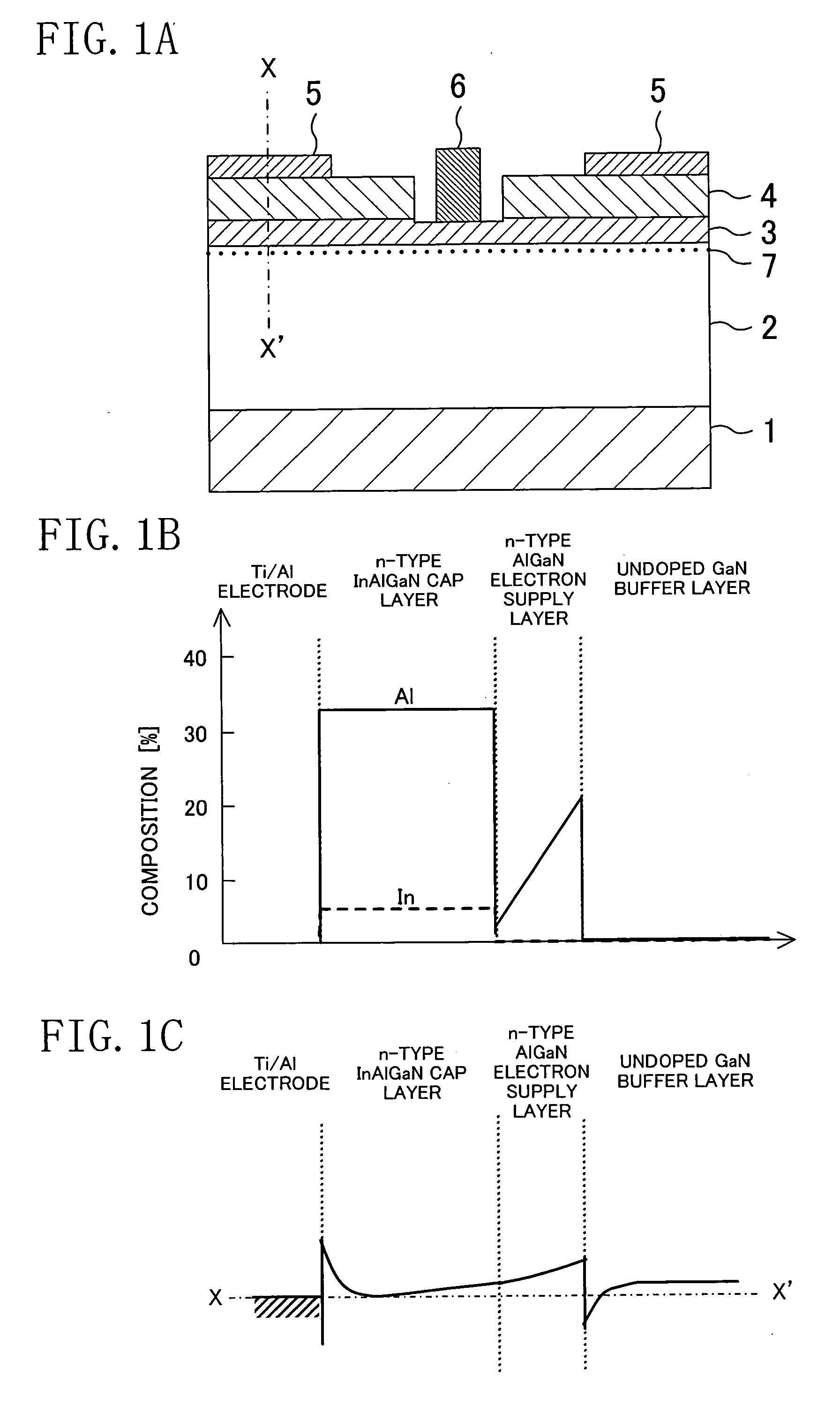

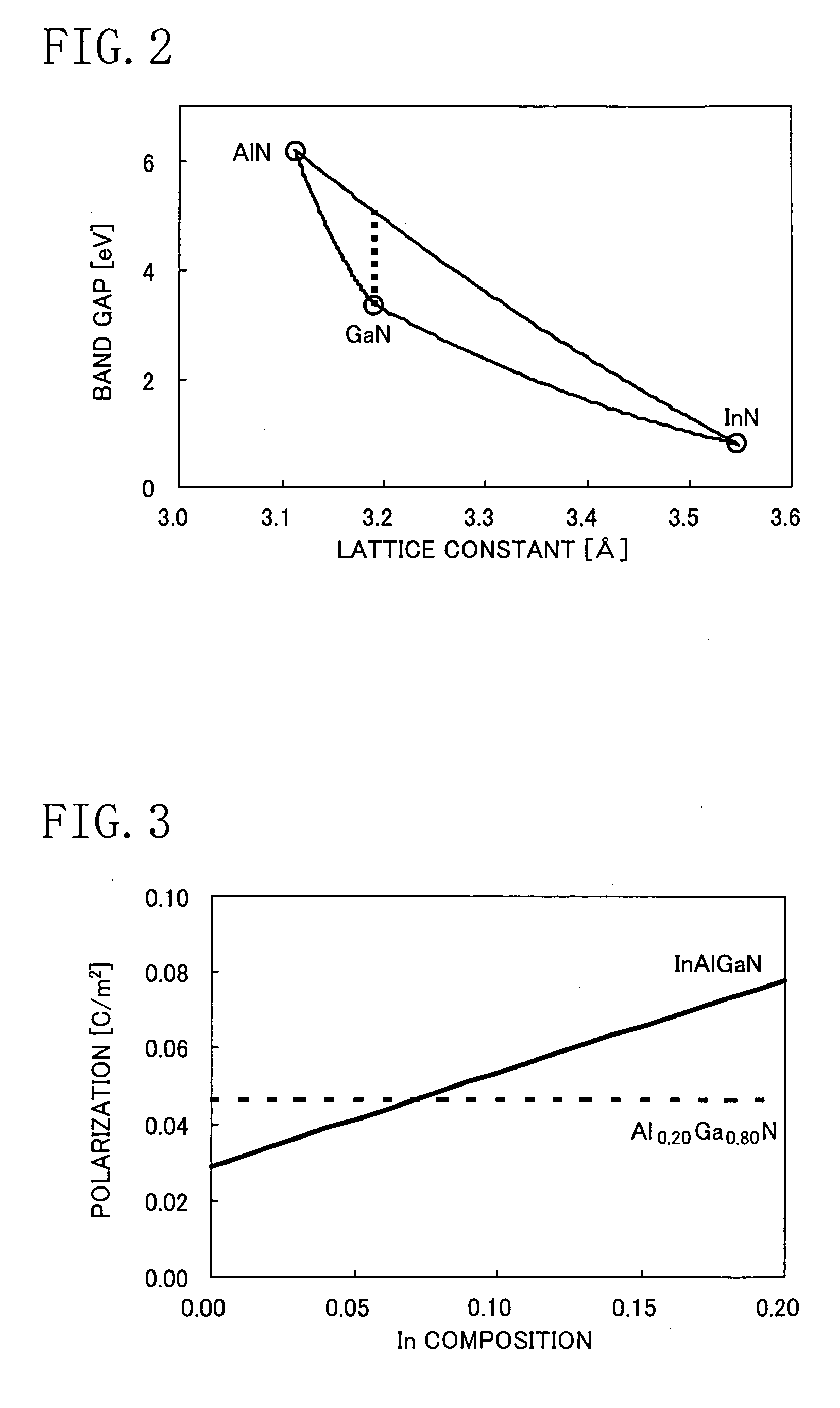

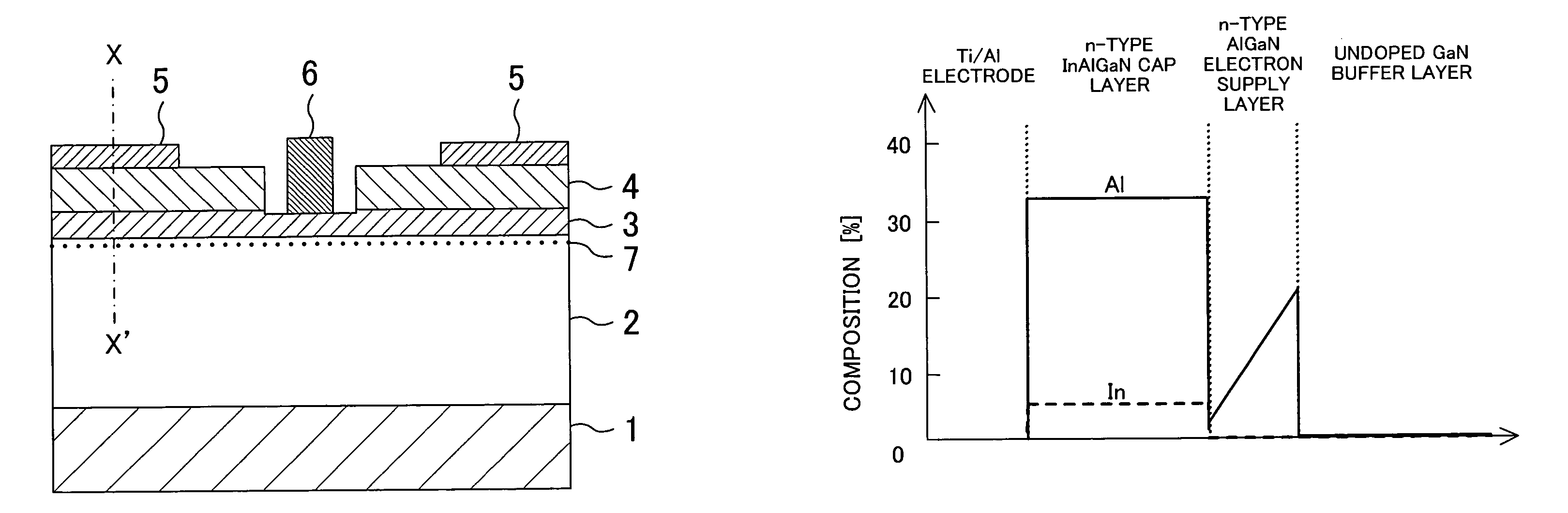

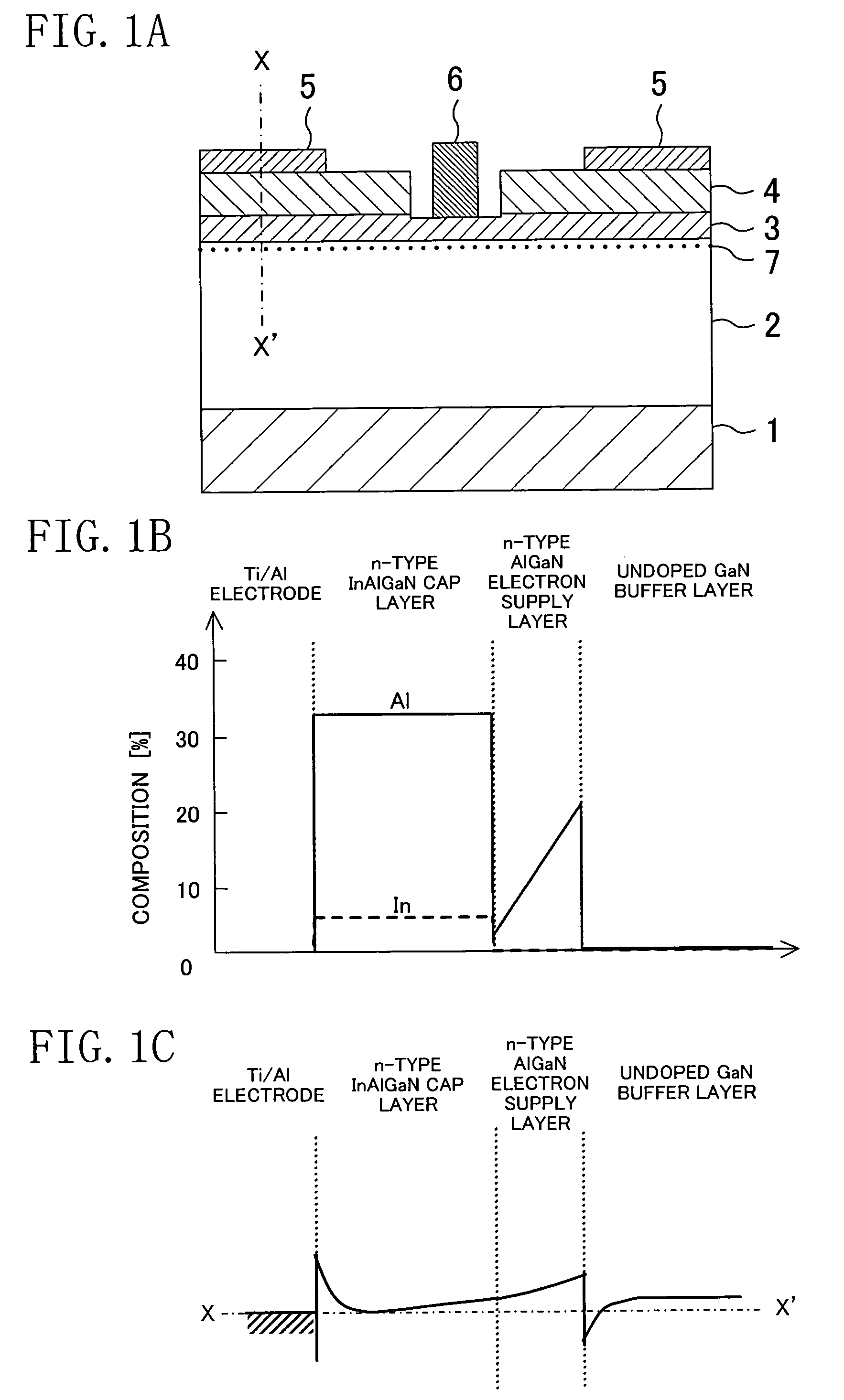

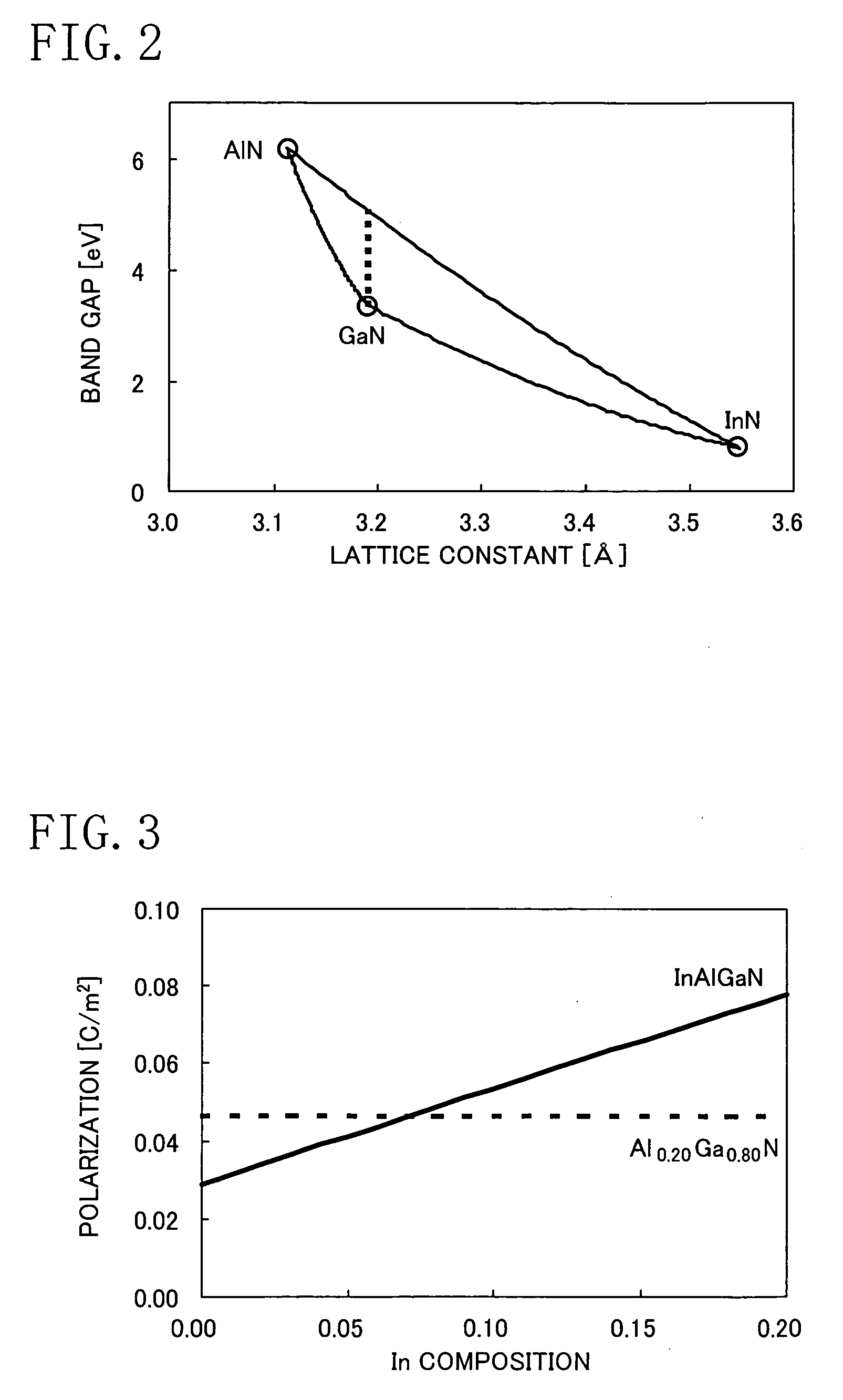

Field effect transistor and method for fabricating the same

ActiveUS20060180831A1High crystallinityIncrease parasitic resistanceSemiconductor devicesConduction bandField-effect transistor

A field effect transistor includes a nitride semiconductor layer; an InxAlyGa1-x-yN layer (wherein 0<x<1, 0<y<1 and 0<x+y<1) formed on the nitride semiconductor layer; and a source electrode and a drain electrode formed on and in contact with the InxAlyGa1-x-yN layer. The lower ends of the conduction bands of the nitride semiconductor layer and the InxAlyGa1-x-yN layer are substantially continuous on the interface therebetween.

Owner:PANASONIC CORP

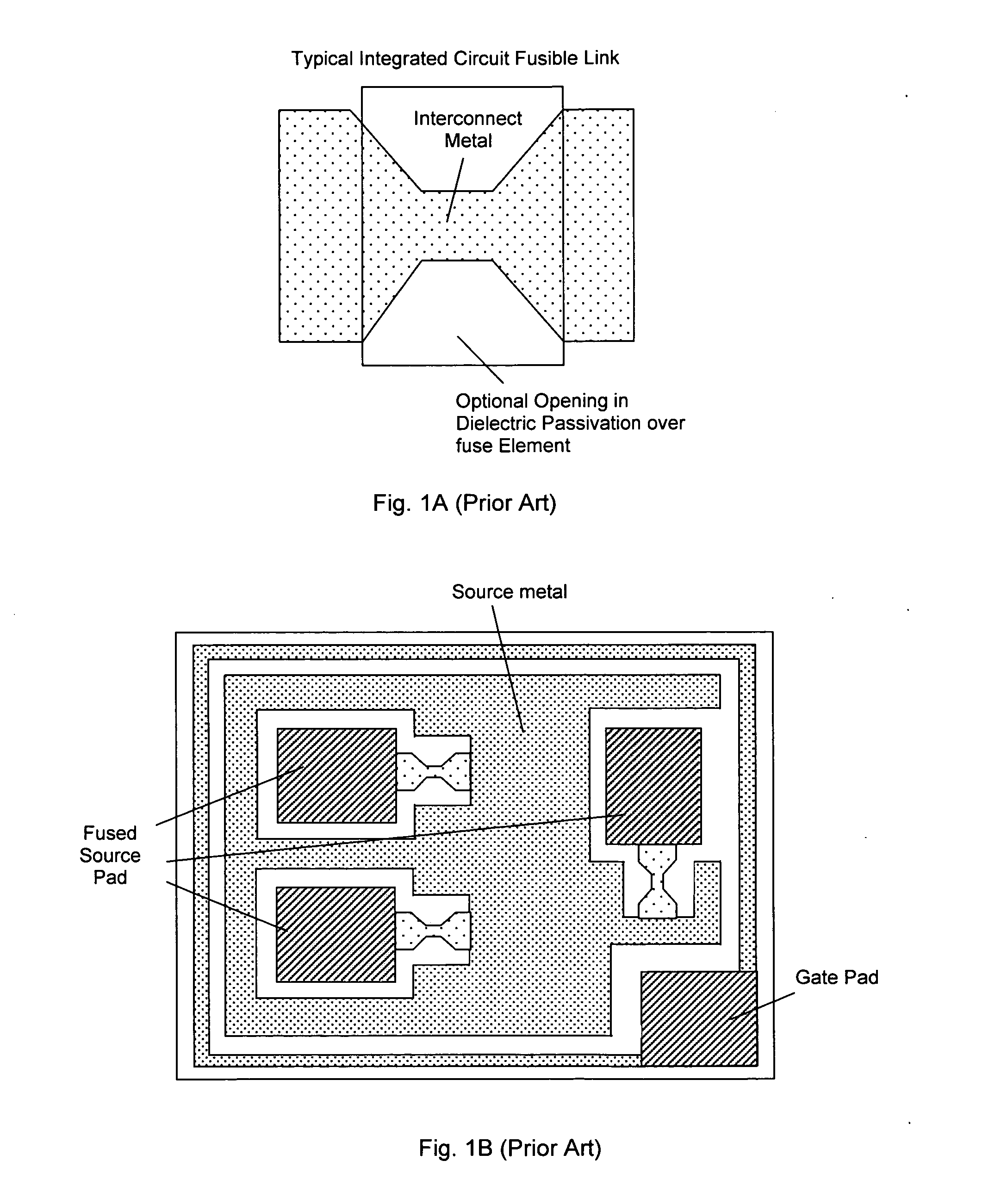

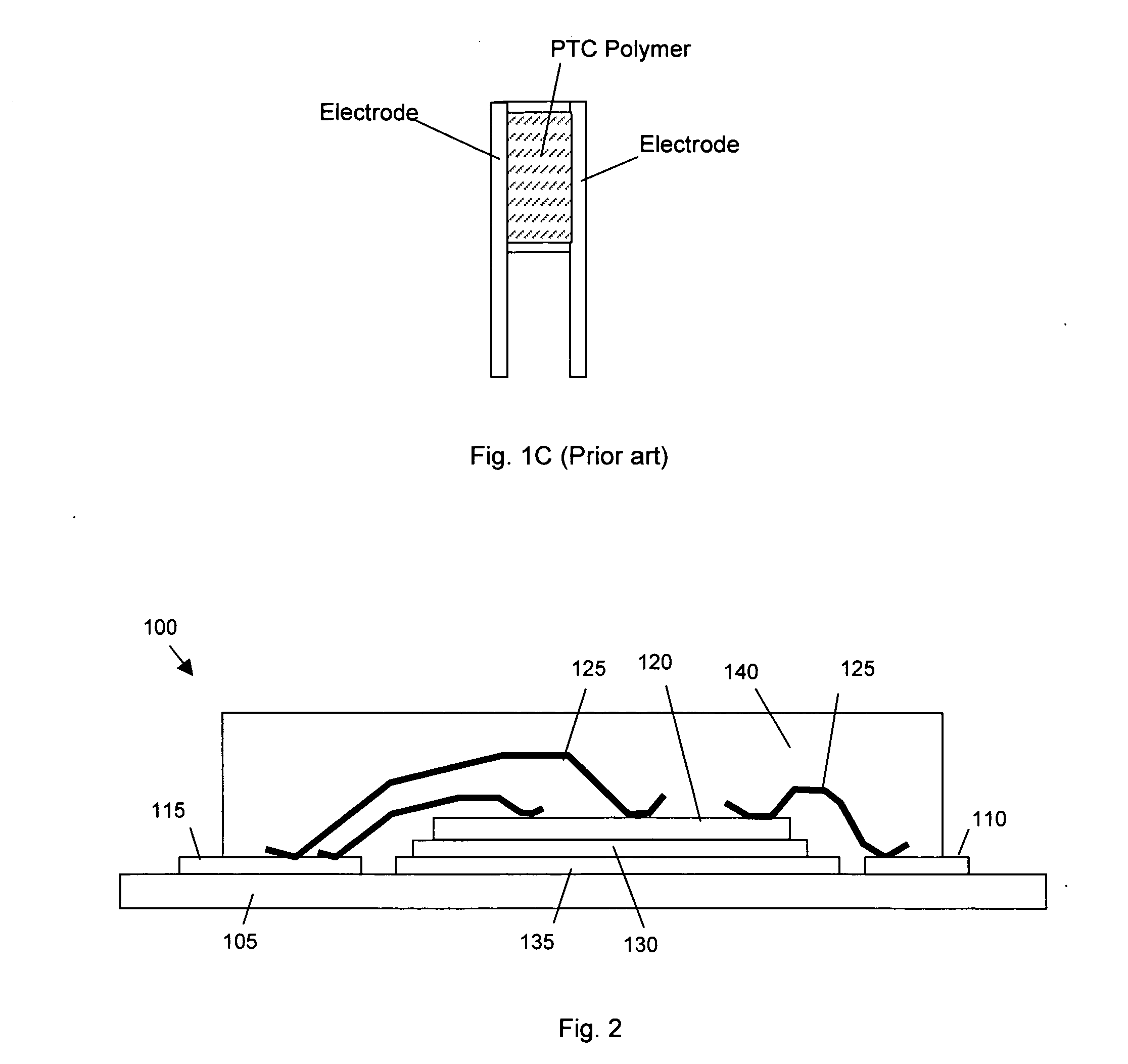

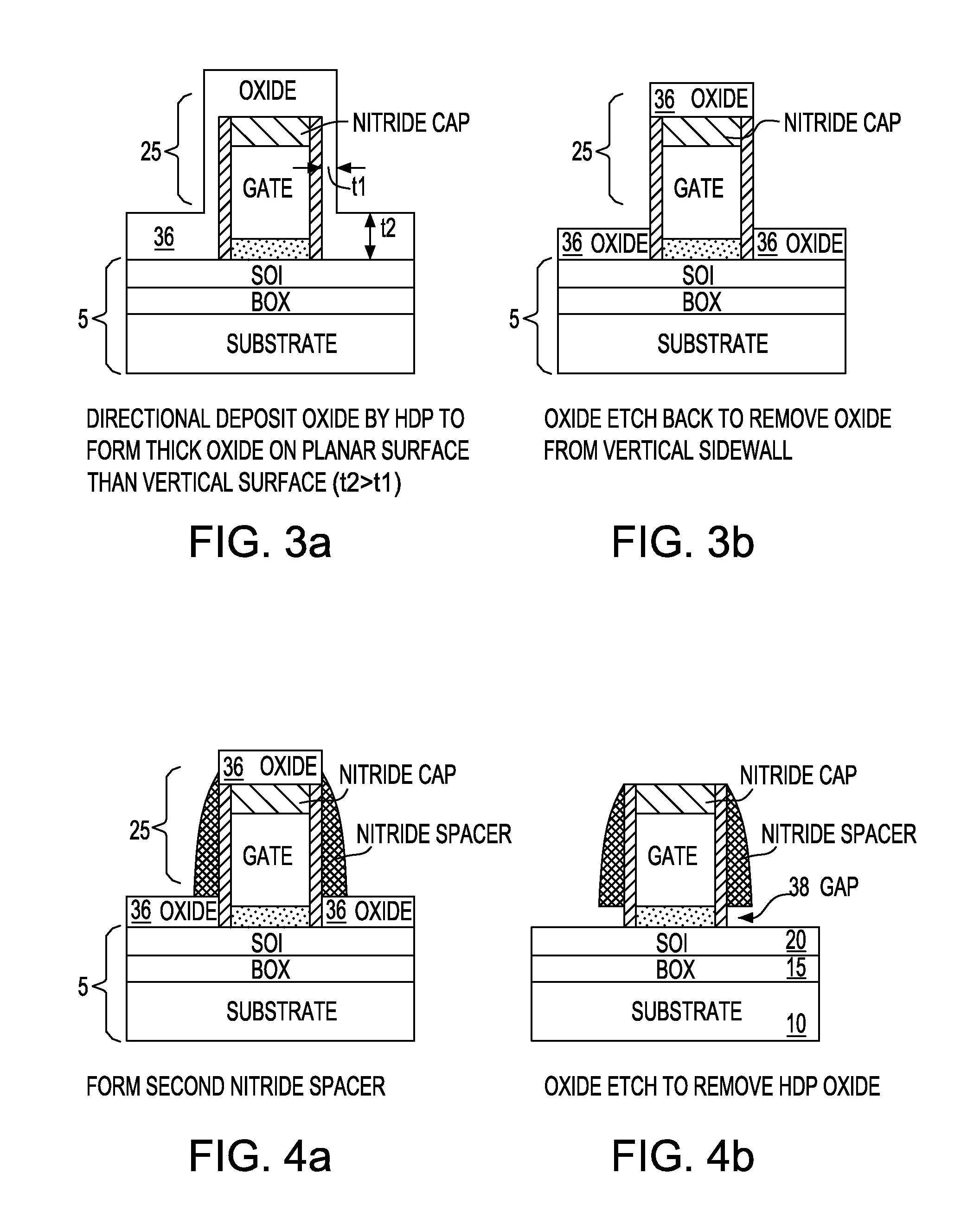

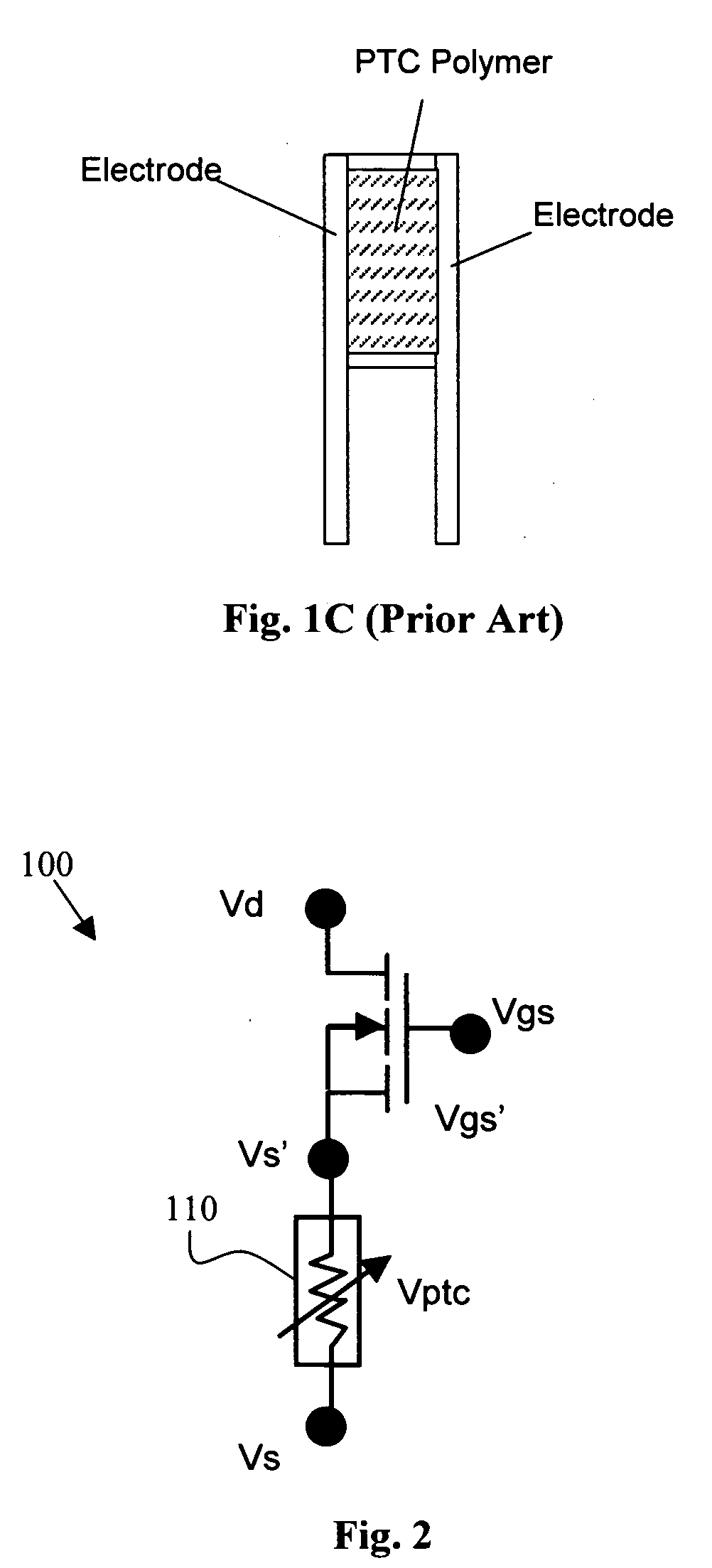

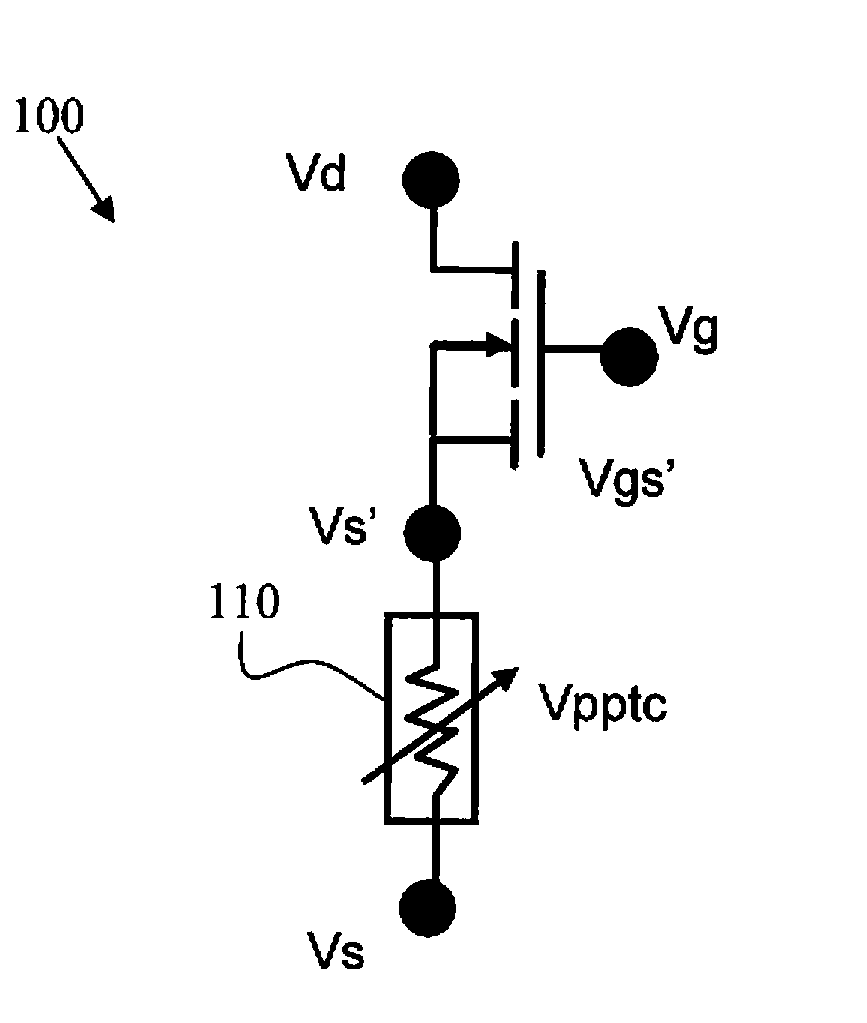

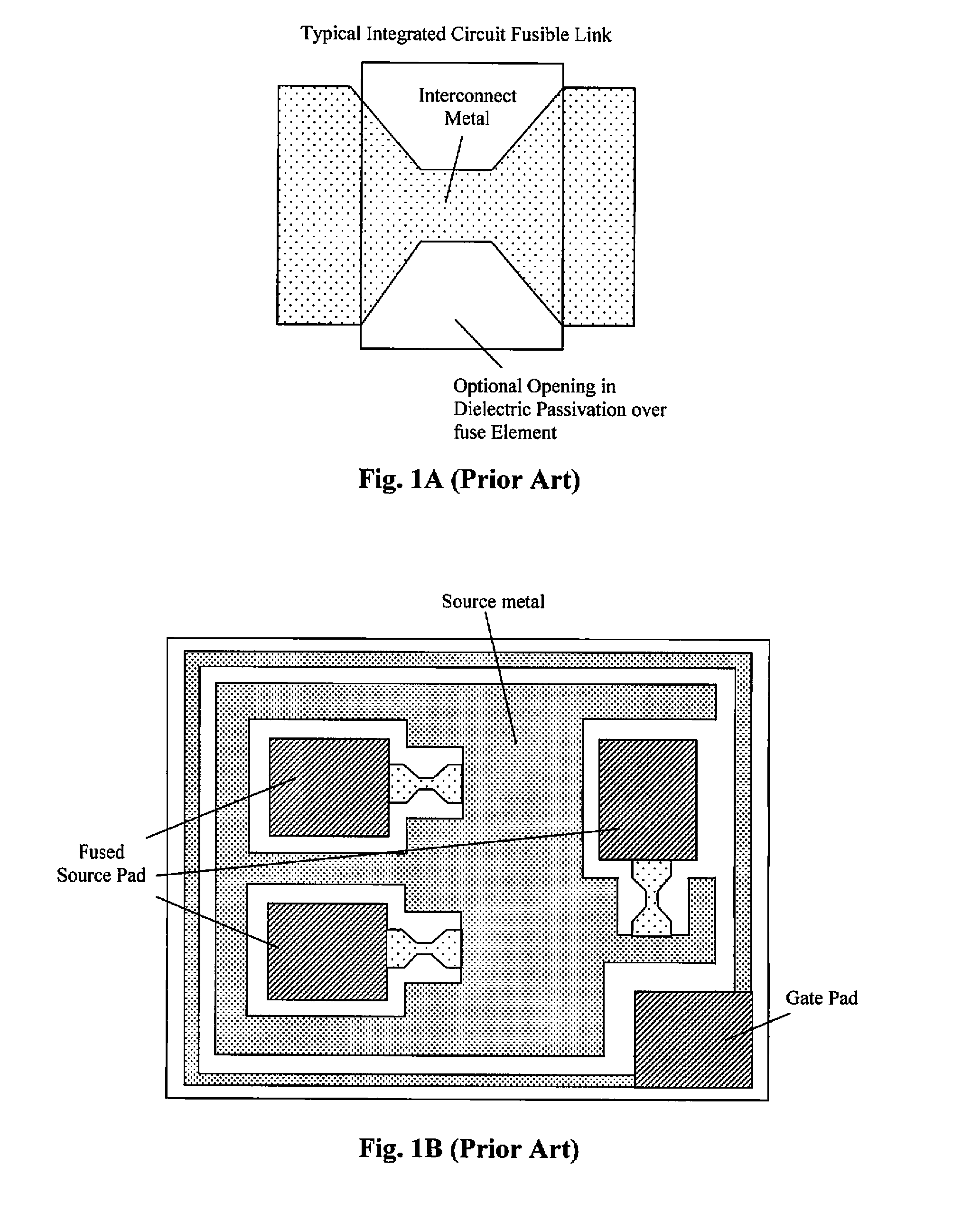

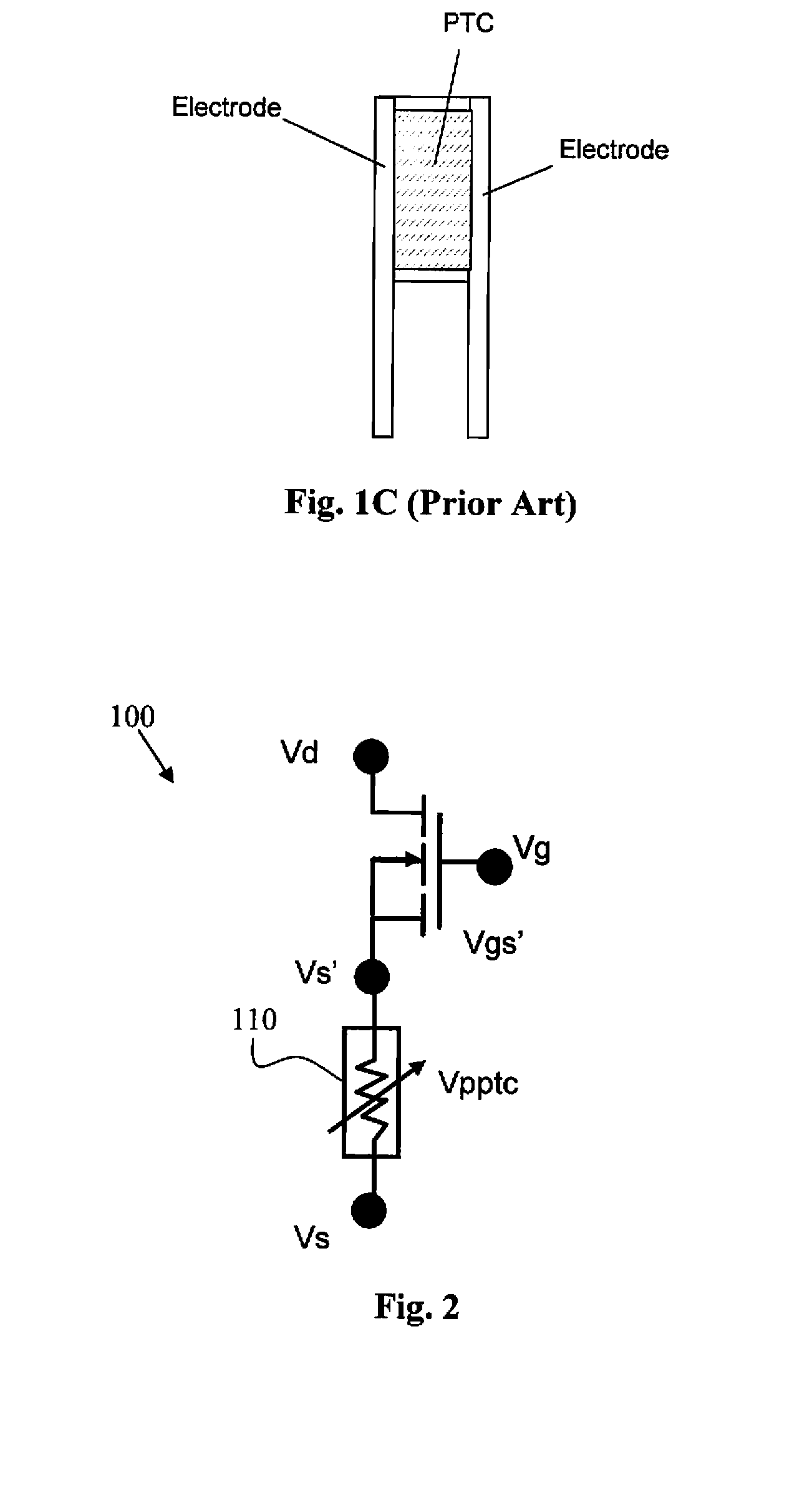

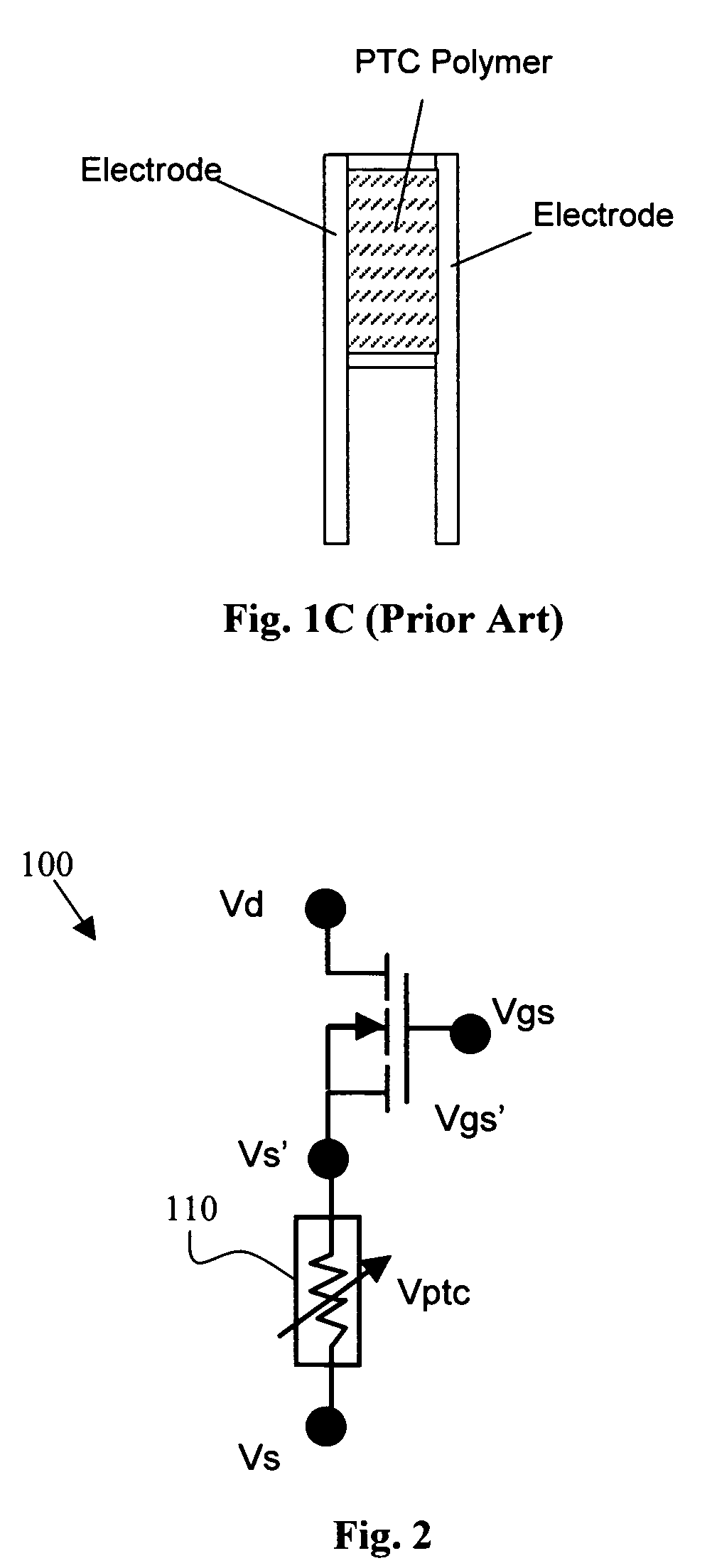

Structure and method for self protection of power device

ActiveUS20080180871A1Increase parasitic resistanceGood thermal couplingSemiconductor/solid-state device detailsSolid-state devicesCurrent limitingSelf protection

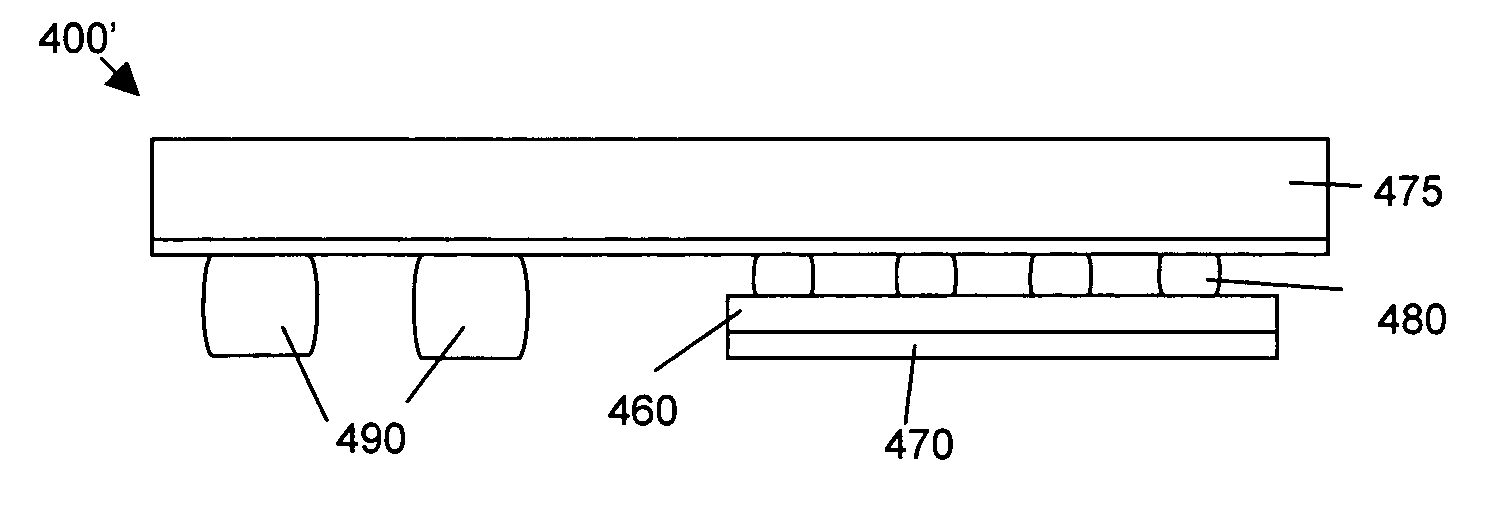

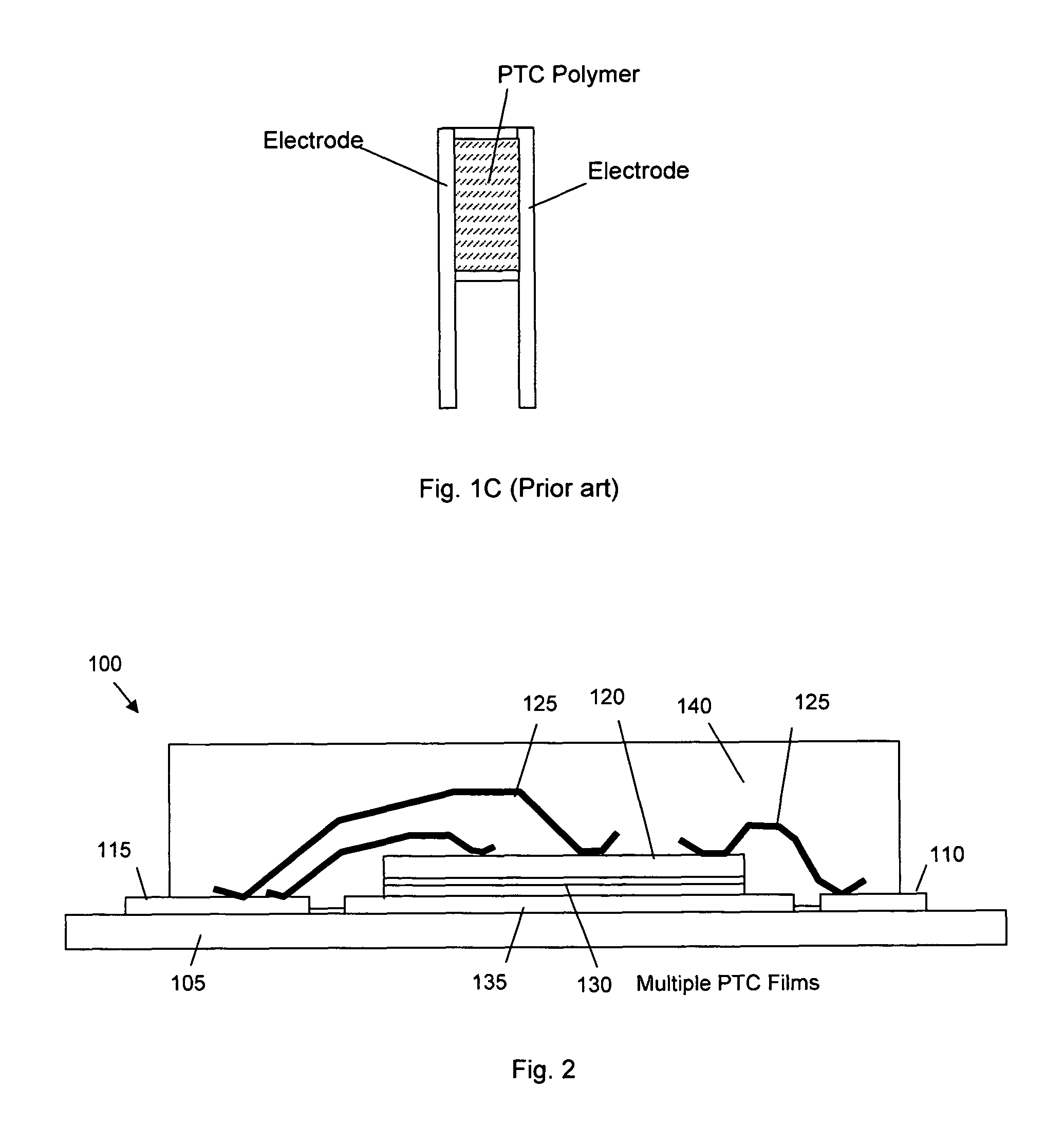

A resetable over-current self-protecting semiconductor power device comprises a vertical power semiconductor chip and an over-current protection layer composed of current limiting material such as a PTC material. The over-current protection layer may be sandwiched between the vertical power semiconductor chip and a conductive plate, which could be a leadframe, a metal plate, a PCB plate or a PCB that the device is mounted on.

Owner:ALPHA & OMEGA SEMICON LTD

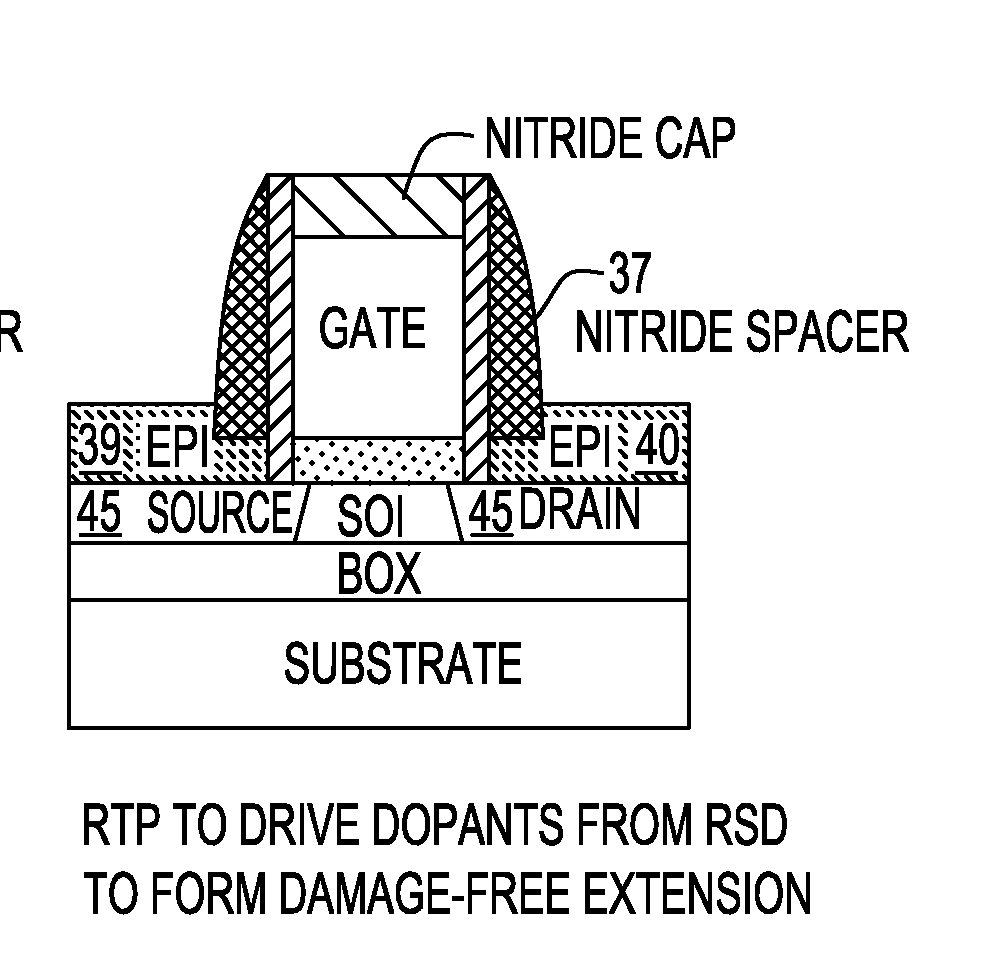

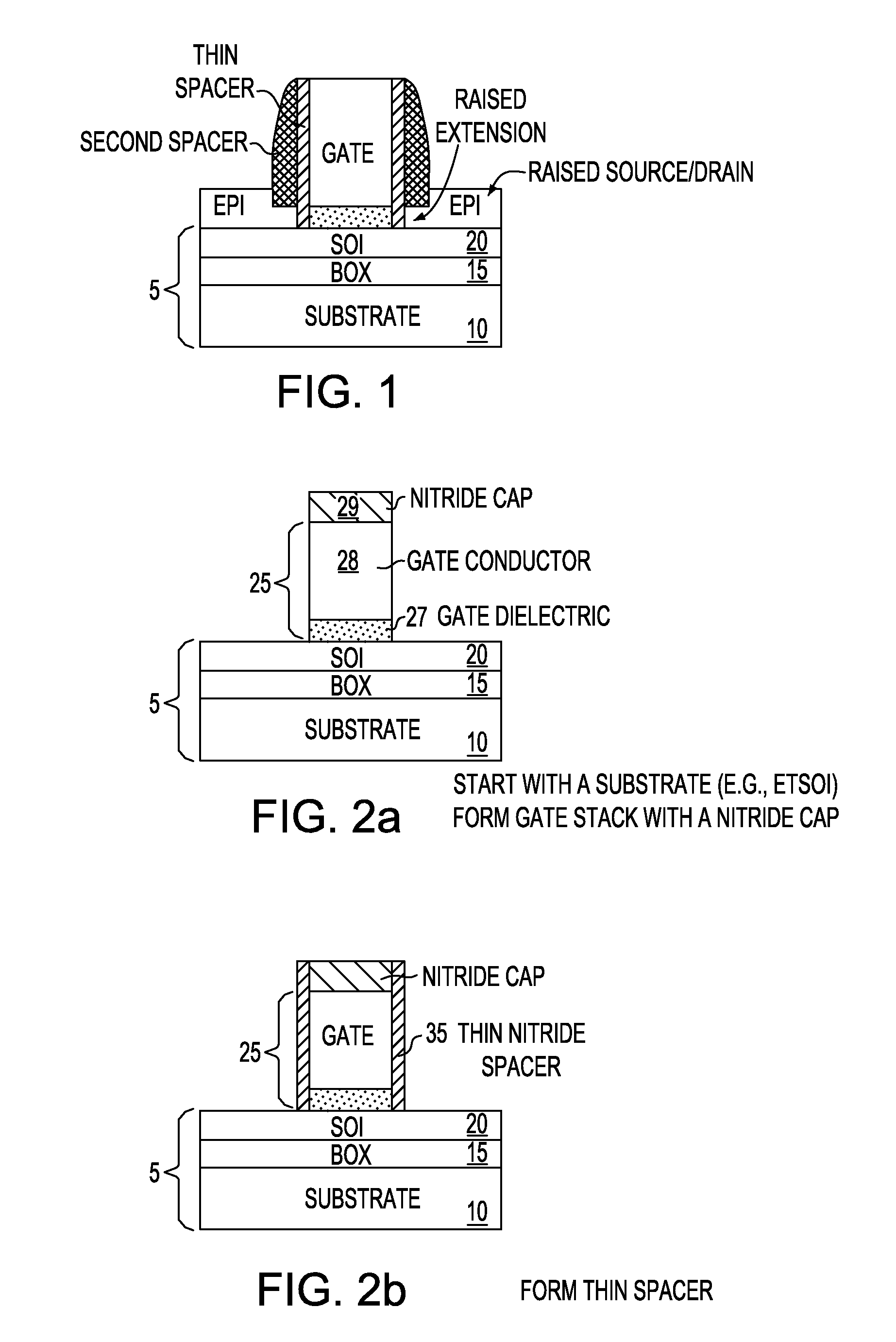

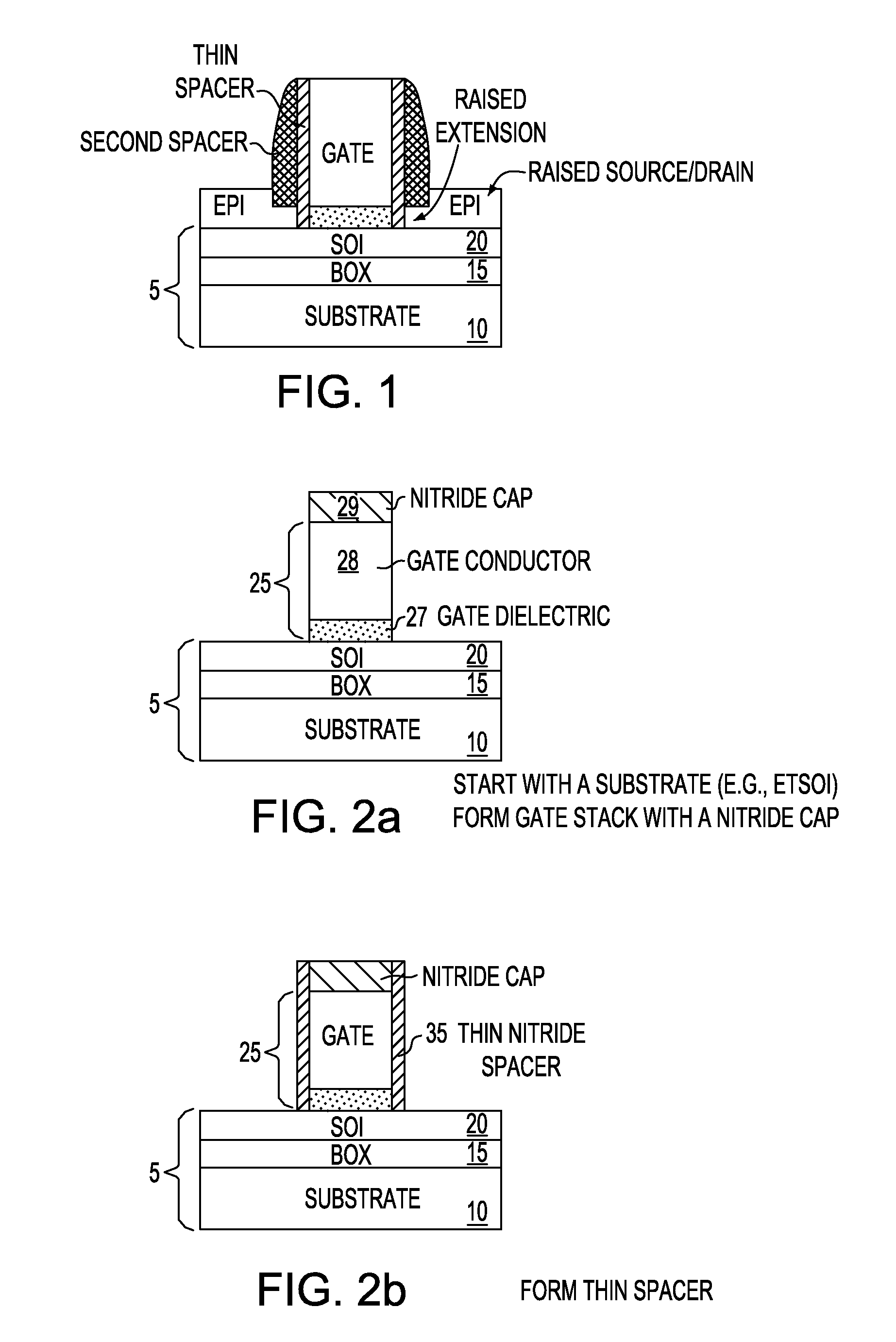

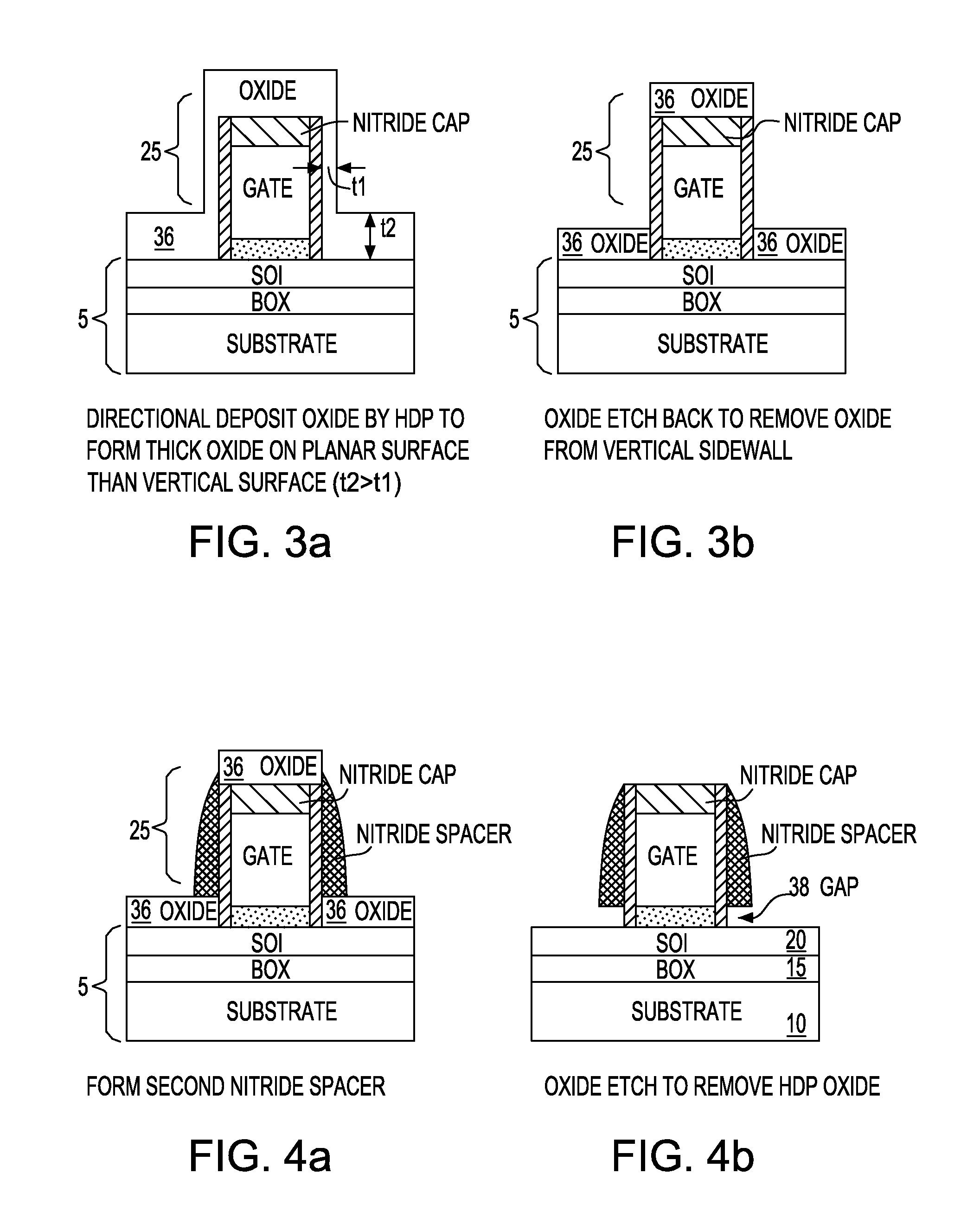

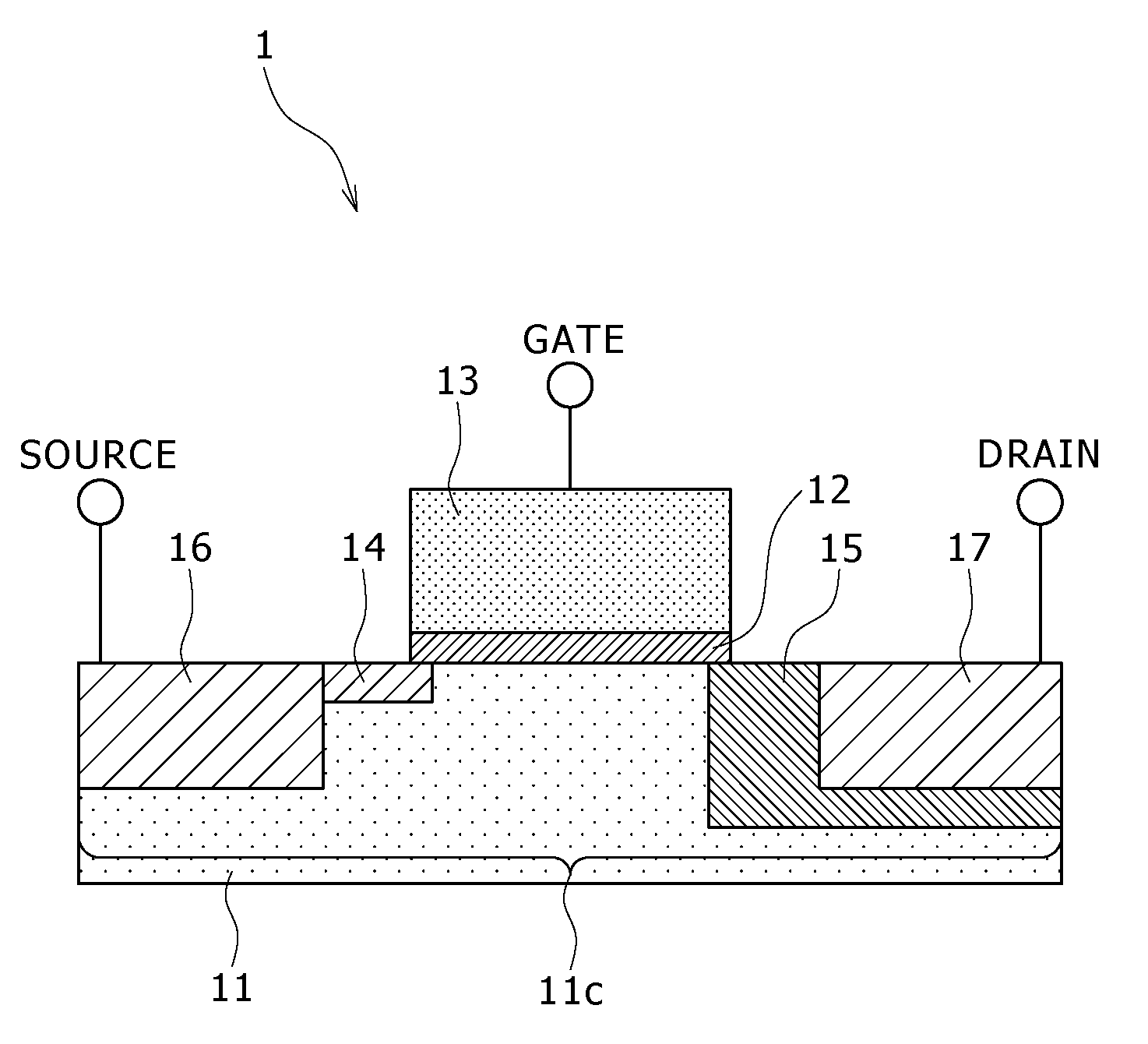

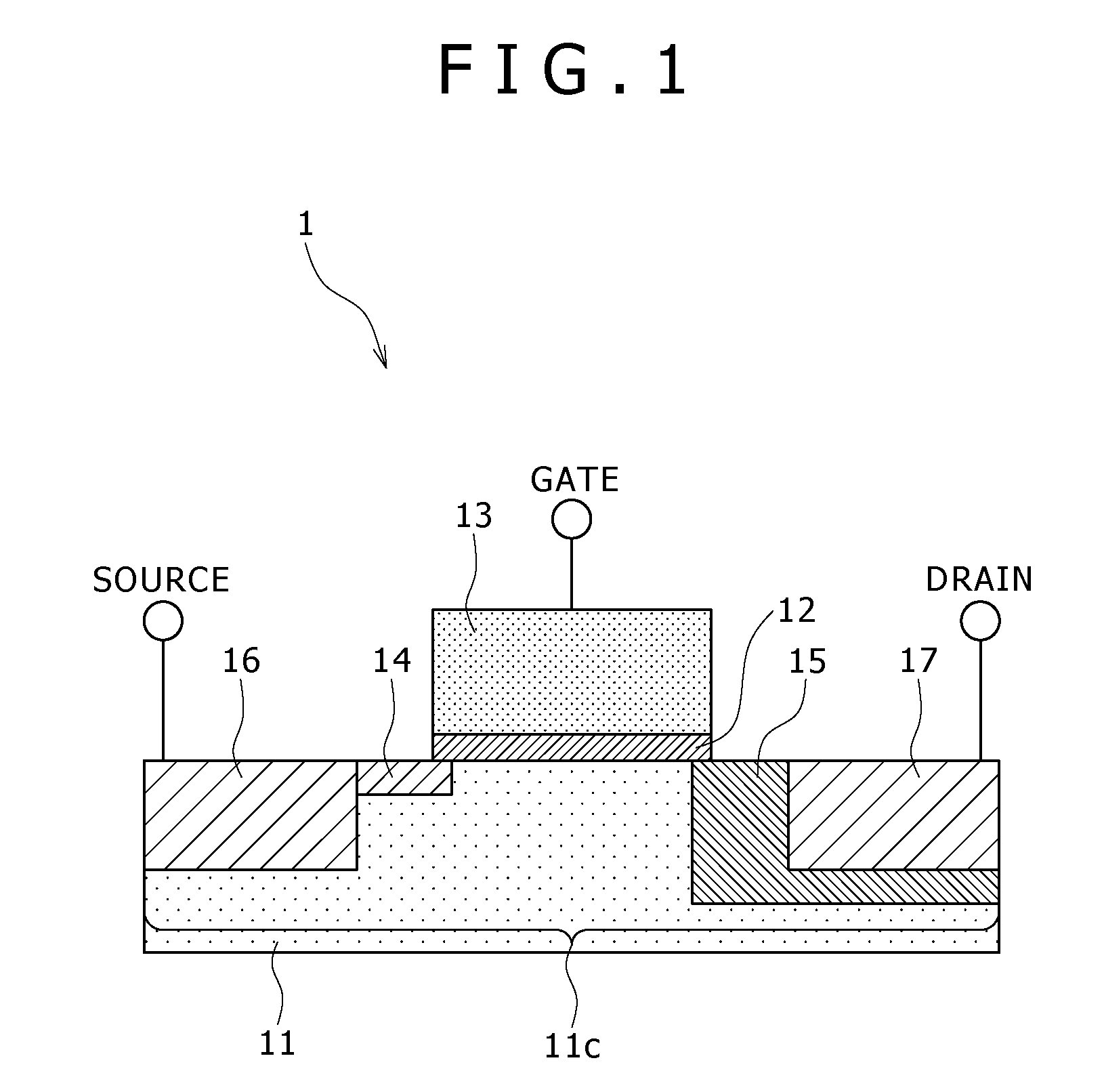

Extremely Thin Semiconductor-on-Insulator (ETSOI) FET Having a Stair-Shape Raised Source/Drain and a Method of Forming the Same

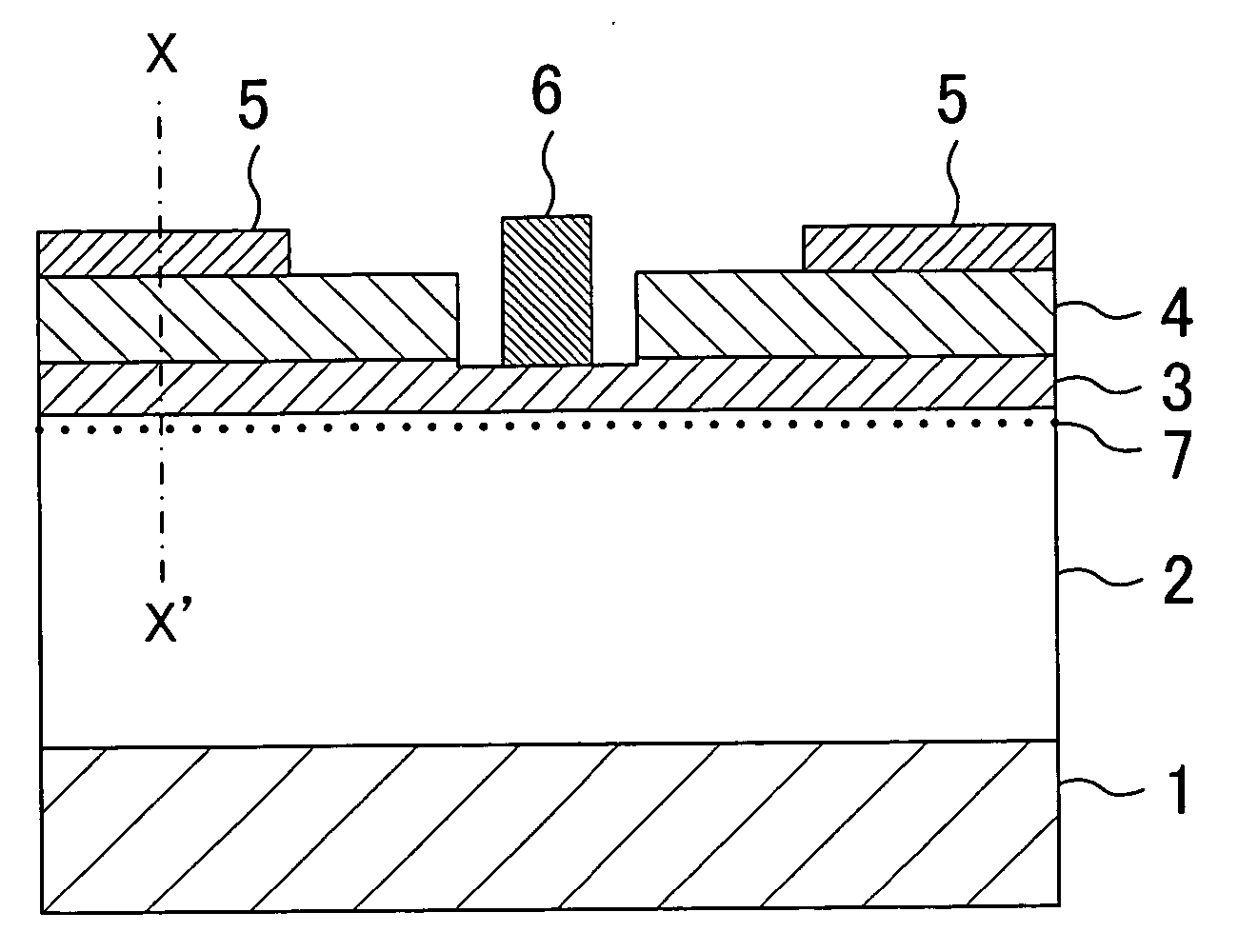

ActiveUS20120061759A1Lower extension resistanceIncrease parasitic resistanceTransistorSolid-state devicesMOSFETSoi substrate

A MOSFET device is formed on top of a semiconductor-on-insulator (SOI) substrate having a semiconductor layer with a thickness ranging from 3 nm to 20 nm. A stair-shape raised extension, a raised source region and a raised drain region (S / D) are formed on top of the SOI substrate. The thinner raised extension region abuts at a thin gate sidewall spacer, lowering the extension resistance without significantly increasing the parasitic resistance. A single epitaxial growth forms the thinner raised extension and the thicker raised S / D preferably simultaneously, reducing the fabrication cost as well as the contact resistance between the raised S / D and the extension. A method of forming the aforementioned MOSFET device is also provided.

Owner:GLOBALFOUNDRIES US INC

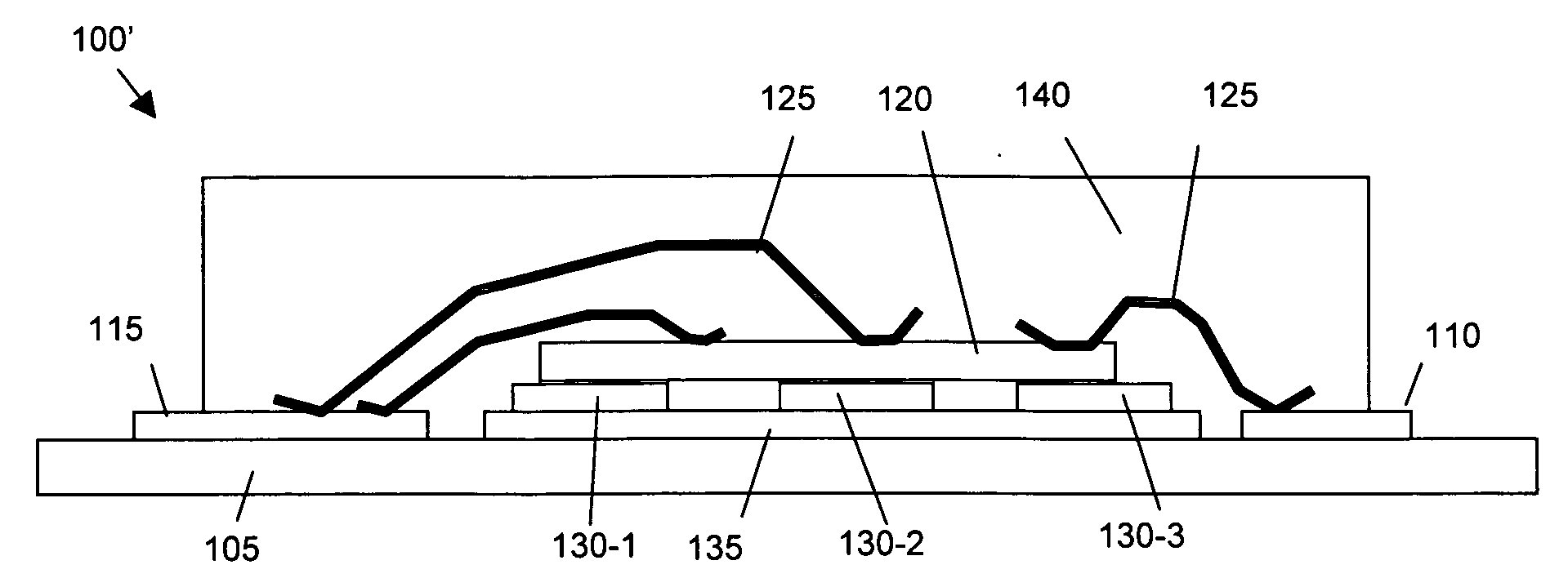

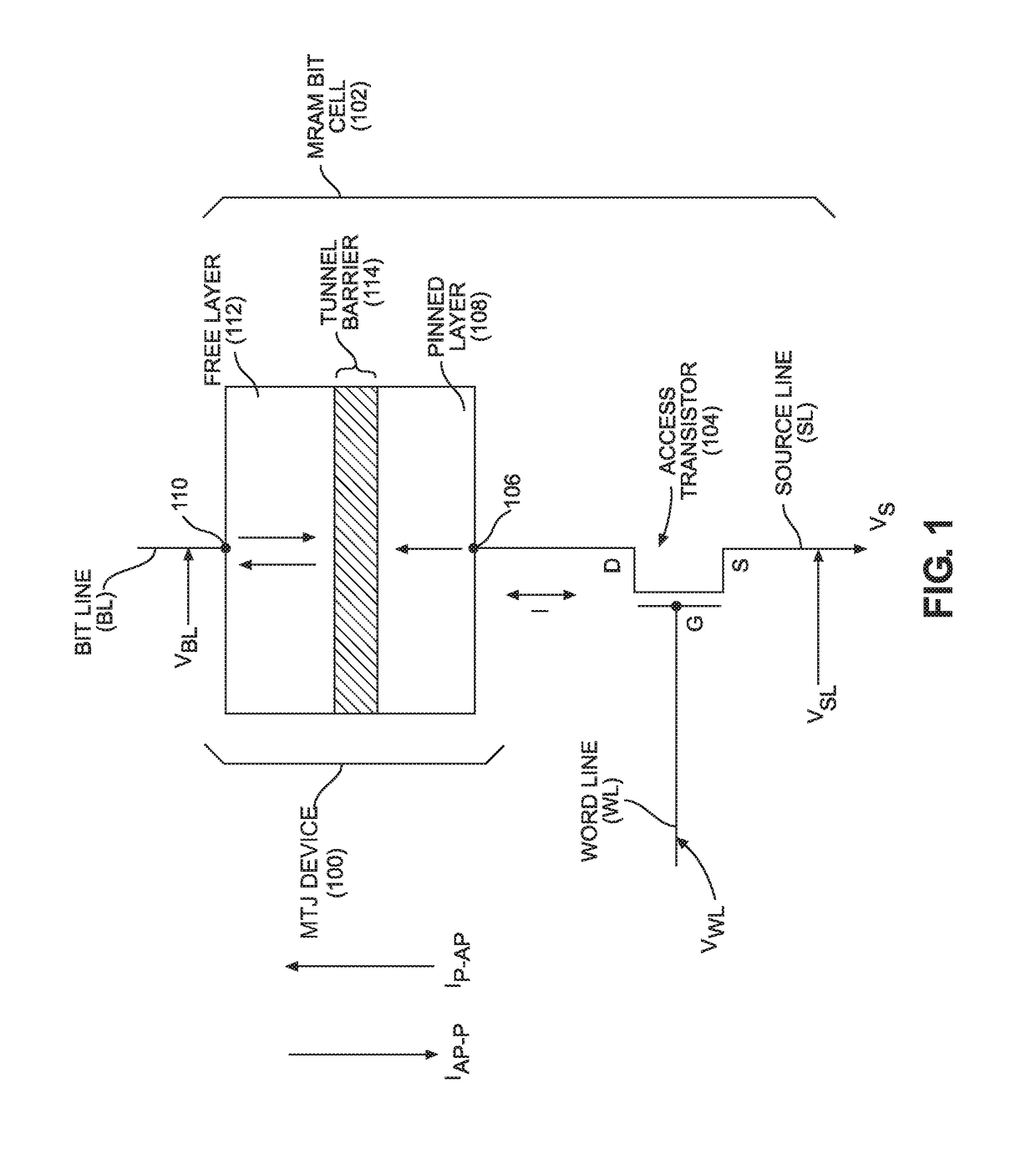

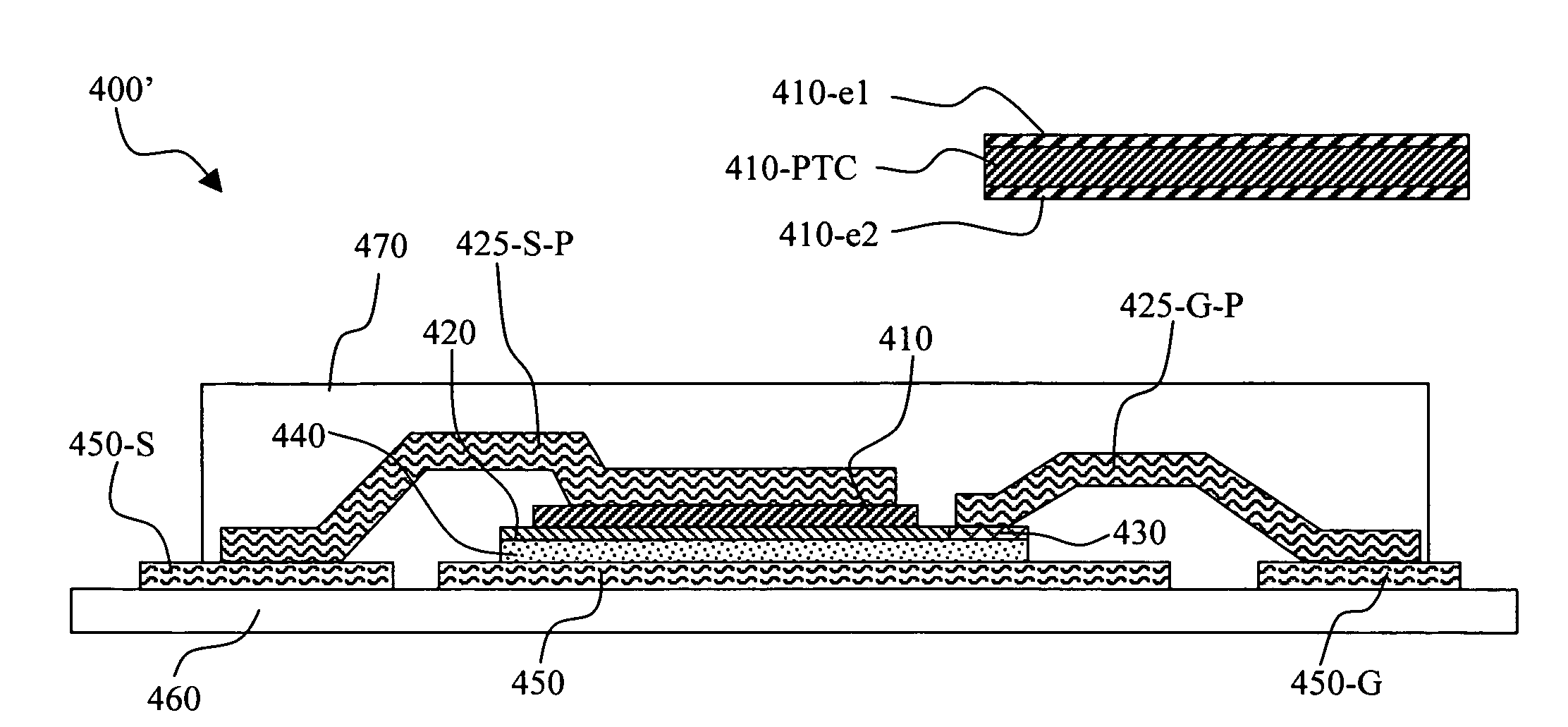

Structure and method for self protection of power device with expanded voltage ranges

InactiveUS20080265326A1Enhanced couplingIncrease parasitic resistanceSemiconductor/solid-state device detailsSolid-state devicesEngineeringVoltage range

A vertical semiconductor power device includes a top surface and a bottom surface of a semiconductor substrate constituting a vertical current path for conducting a current there through. The semiconductor power device further includes an over current protection layer composed of a material having a resistance with a positive temperature coefficient (PTC) and the over current protection layer constituting as a part of the vertical current path connected to a source electrode and providing a feedback voltage a gate electrode of the vertical semiconductor power device for limiting a current passing there through for protecting the semiconductor power device at any voltage.

Owner:ALPHA & OMEGA SEMICON LTD

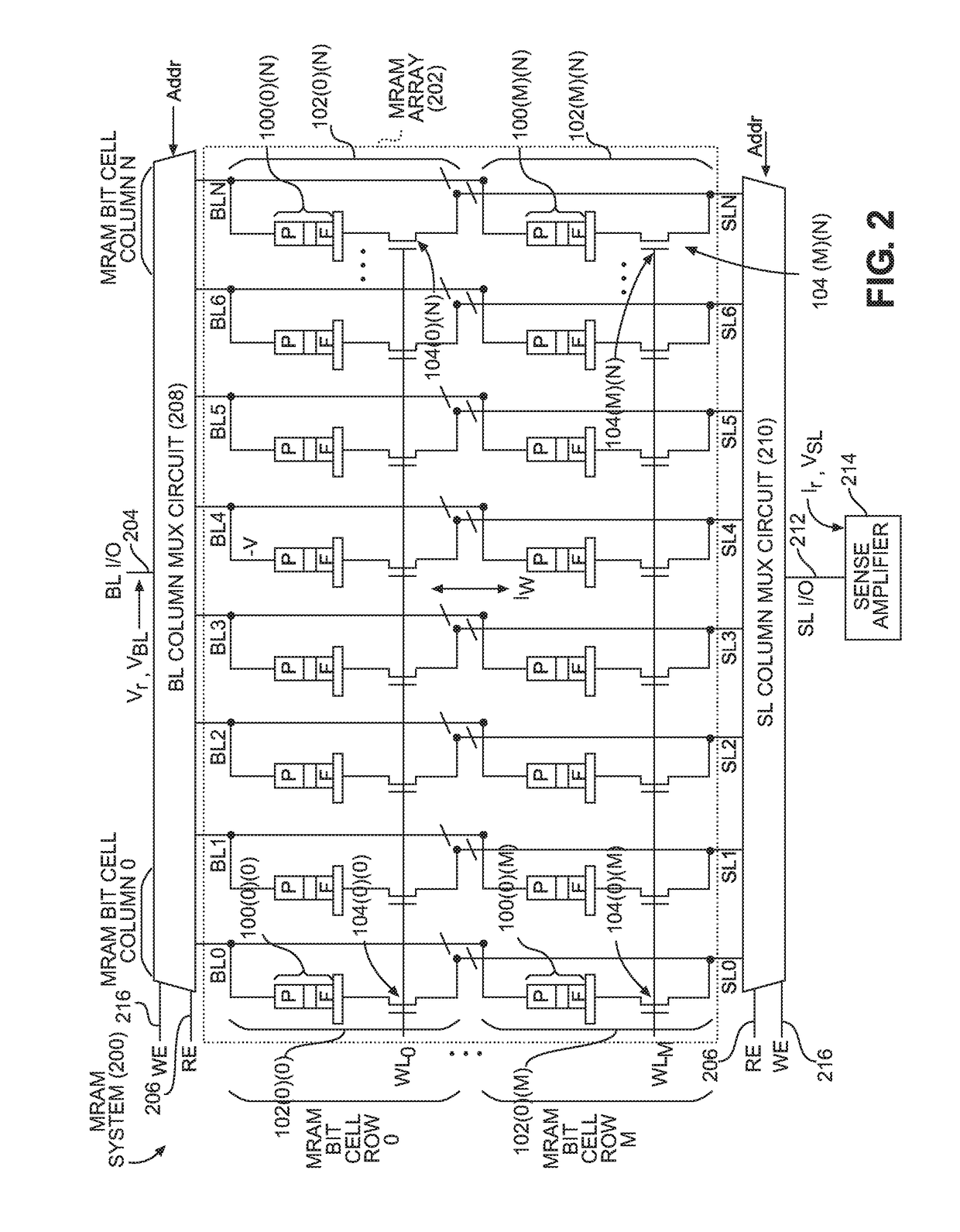

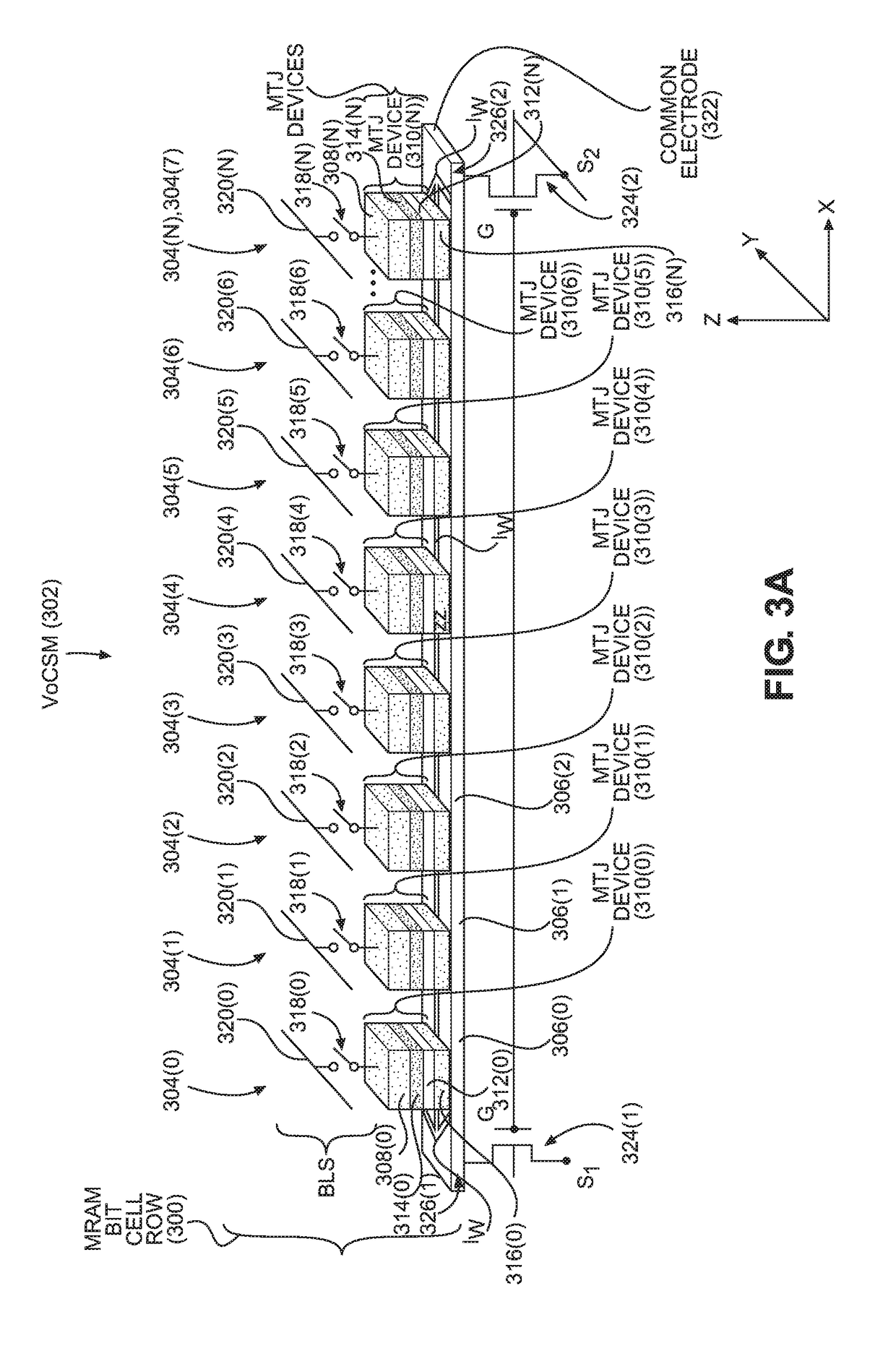

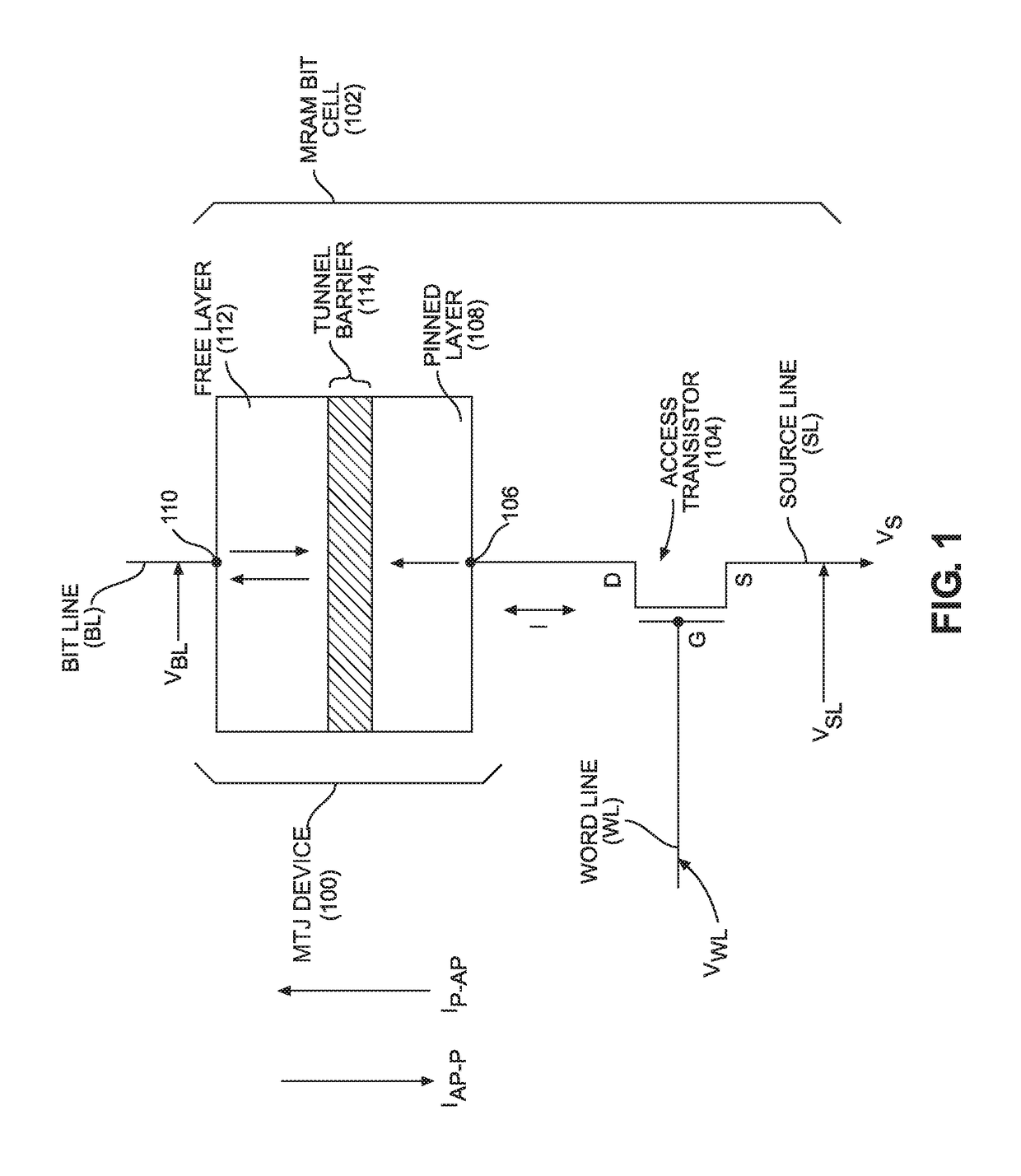

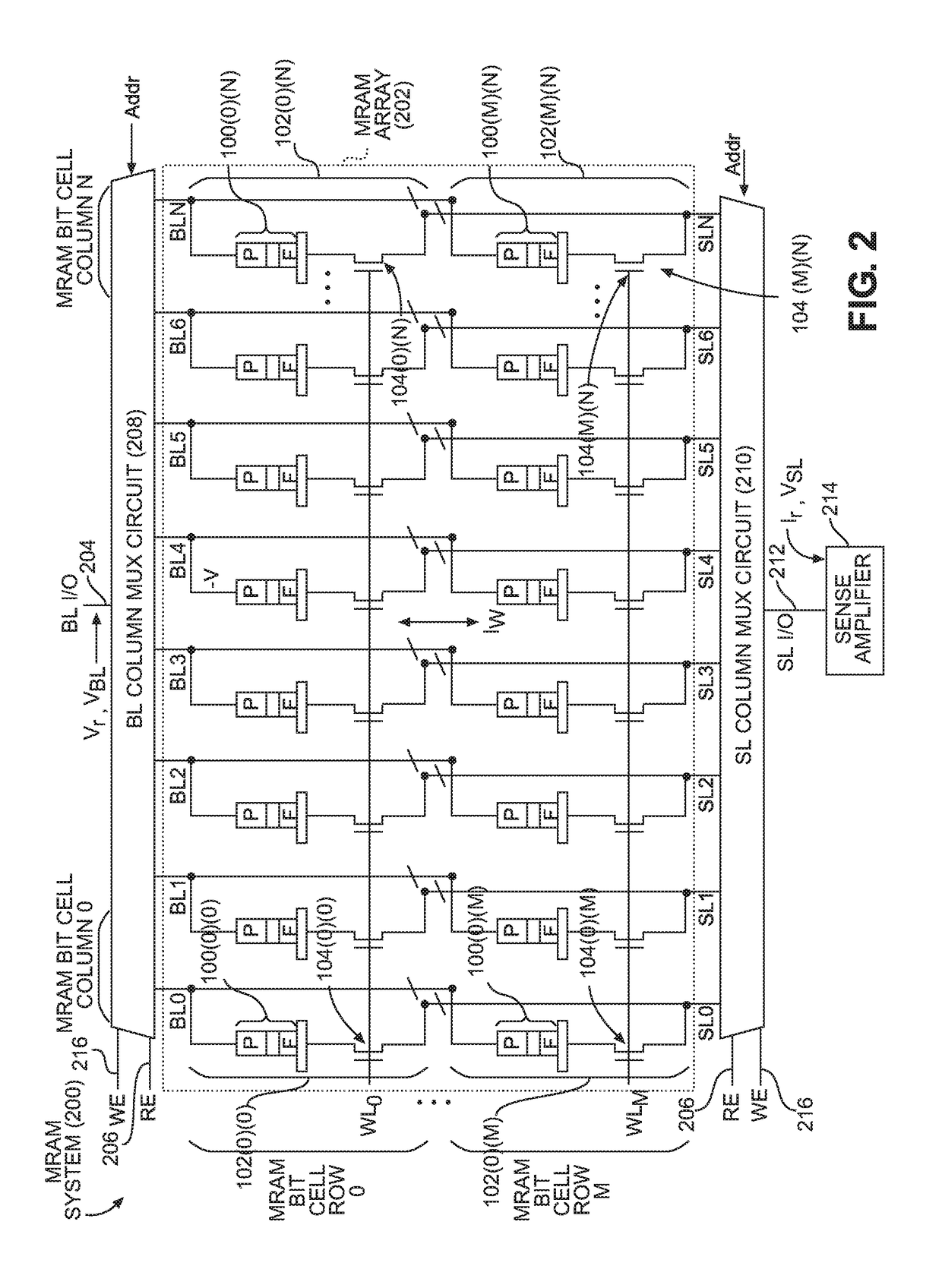

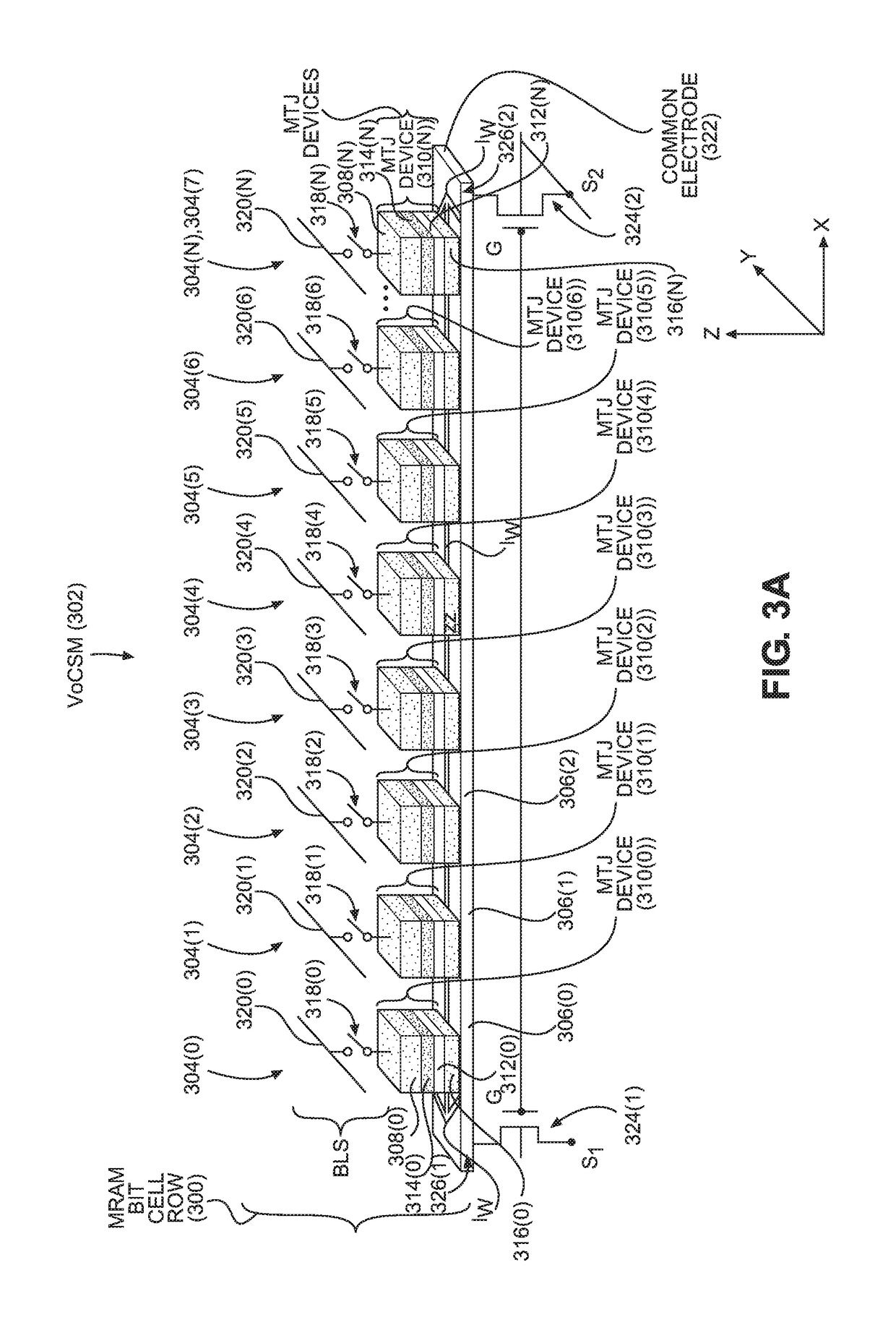

Voltage-switched magneto-resistive random access memory (MRAM) employing separate read operation circuit paths from a shared spin torque write operation circuit path

ActiveUS20190006415A1Reduce energy barrierLess energyMagnetic-field-controlled resistorsSolid-state devicesMagnetoBit cell

Voltage-switched magneto-resistive random access memory (MRAM) employing separate read operation circuit paths from a shared spin torque write operation circuit path is disclosed. The MRAM includes an MRAM array that includes MRAM bit cell rows each including a plurality of MRAM bit cells. MRAM bit cells on an MRAM bit cell row share a common electrode to provide a shared write operation circuit path for write operations. Dedicated read operation circuit paths are also provided for each MRAM bit cell separate from the write operation circuit path. As a result, the read operation circuit paths for the MRAM bit cells do not vary as a result of the different layout locations of the MRAM bit cells with respect to the common electrode. Thus, the read parasitic resistances of the MRAM bit cells do not vary from each other because of their different coupling locations to the common electrode.

Owner:QUALCOMM INC

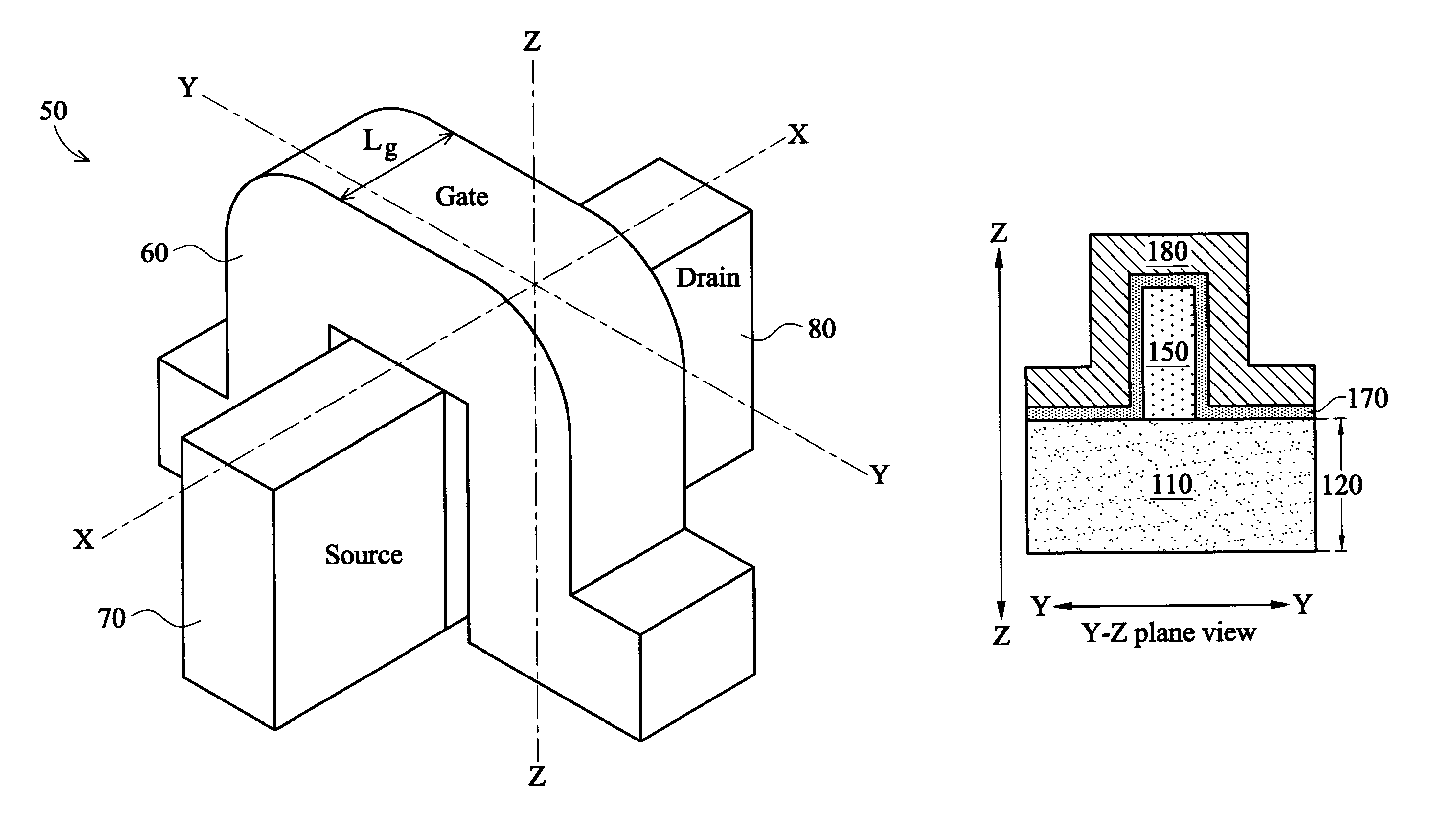

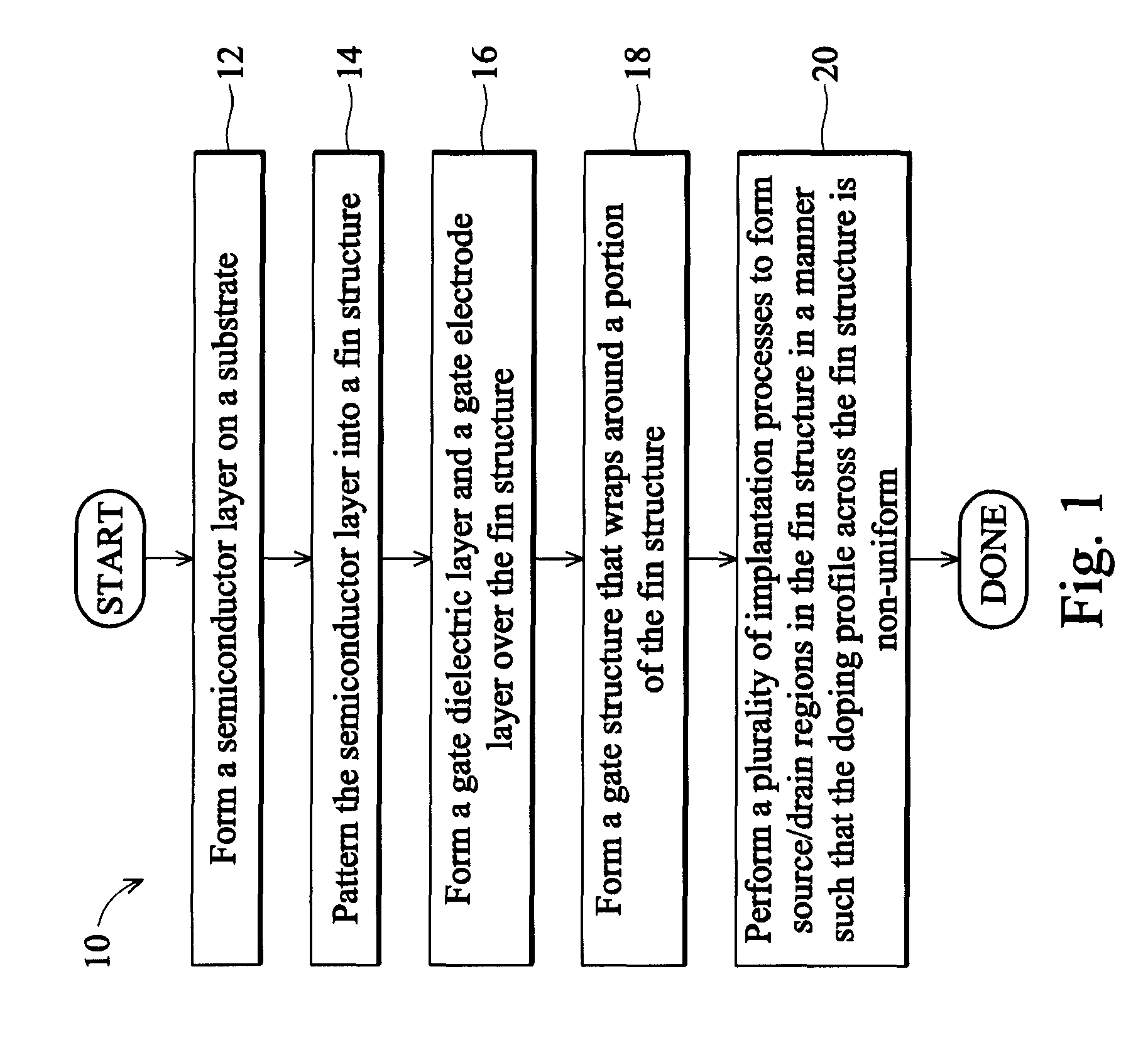

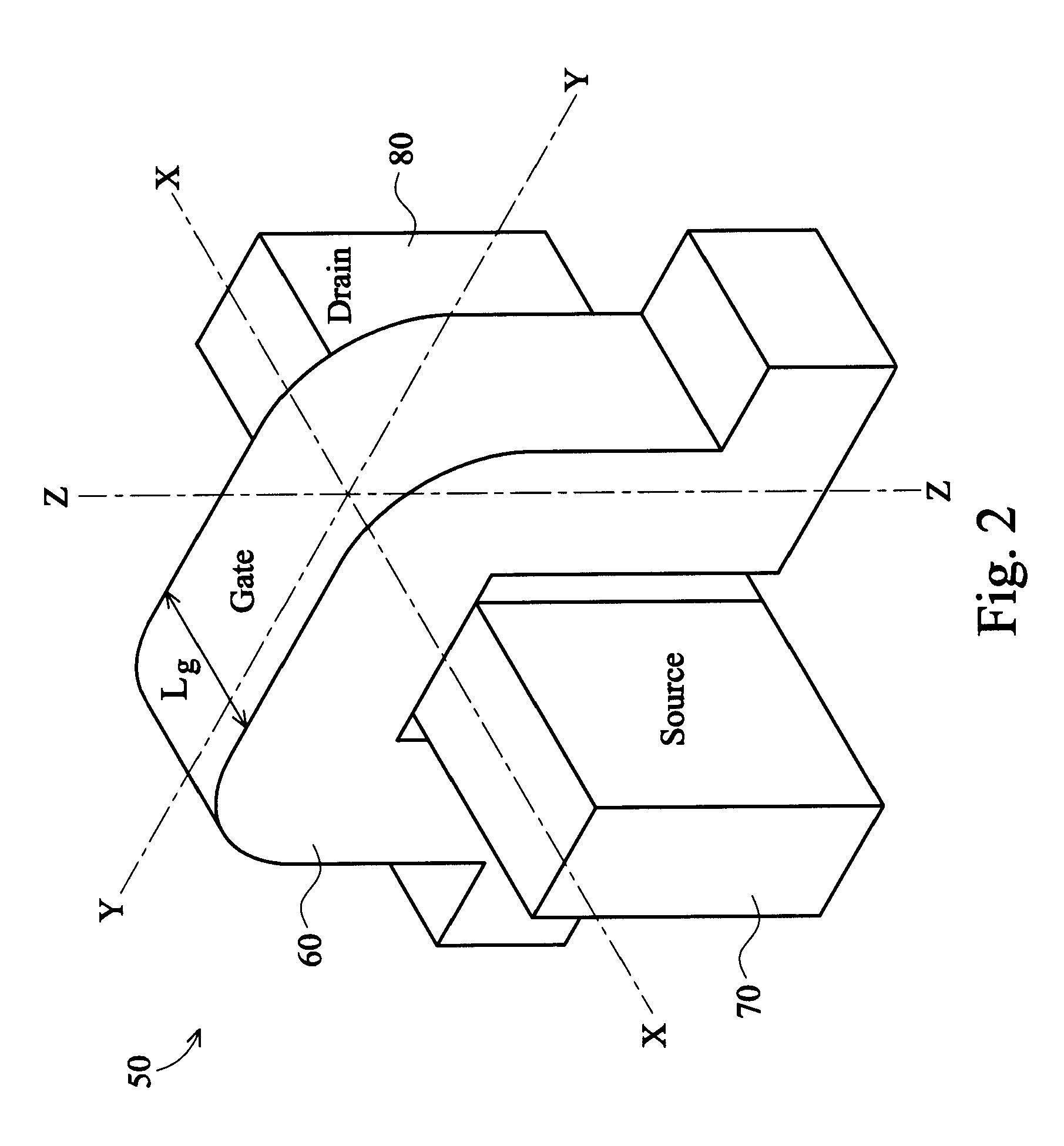

Non-uniform channel junction-less transistor

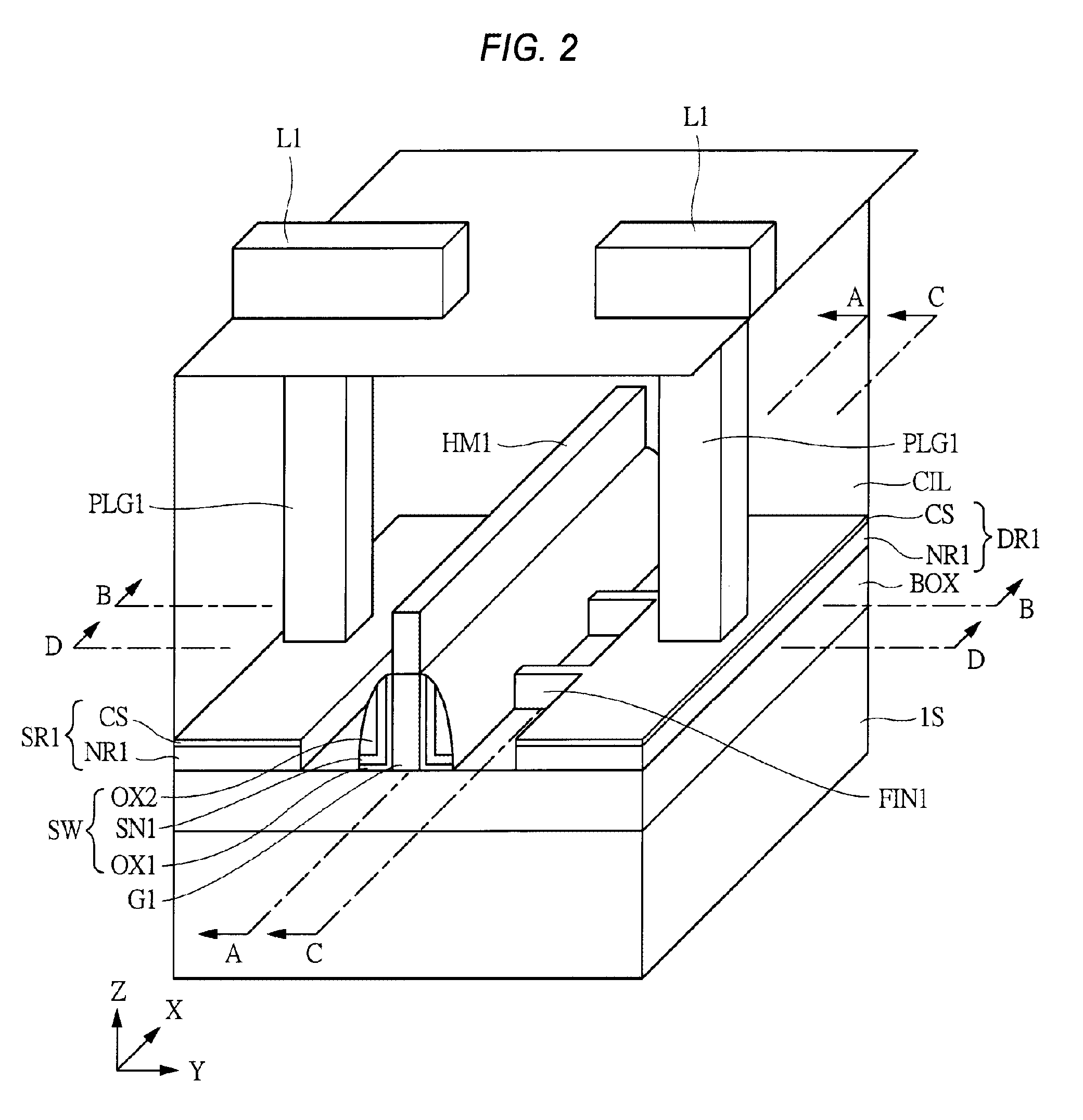

ActiveUS20120187486A1Easy to controlImprove device densitySolid-state devicesSemiconductor/solid-state device manufacturingGate dielectricDielectric layer

The present disclosure discloses a method of forming a semiconductor layer on a substrate. The method includes patterning the semiconductor layer into a fin structure. The method includes forming a gate dielectric layer and a gate electrode layer over the fin structure. The method includes patterning the gate dielectric layer and the gate electrode layer to form a gate structure in a manner so that the gate structure wraps around a portion of the fin structure. The method includes performing a plurality of implantation processes to form source / drain regions in the fin structure. The plurality of implantation processes are carried out in a manner so that a doping profile across the fin structure is non-uniform, and a first region of the portion of the fin structure that is wrapped around by the gate structure has a lower doping concentration level than other regions of the fin structure.

Owner:TAIWAN SEMICON MFG CO LTD

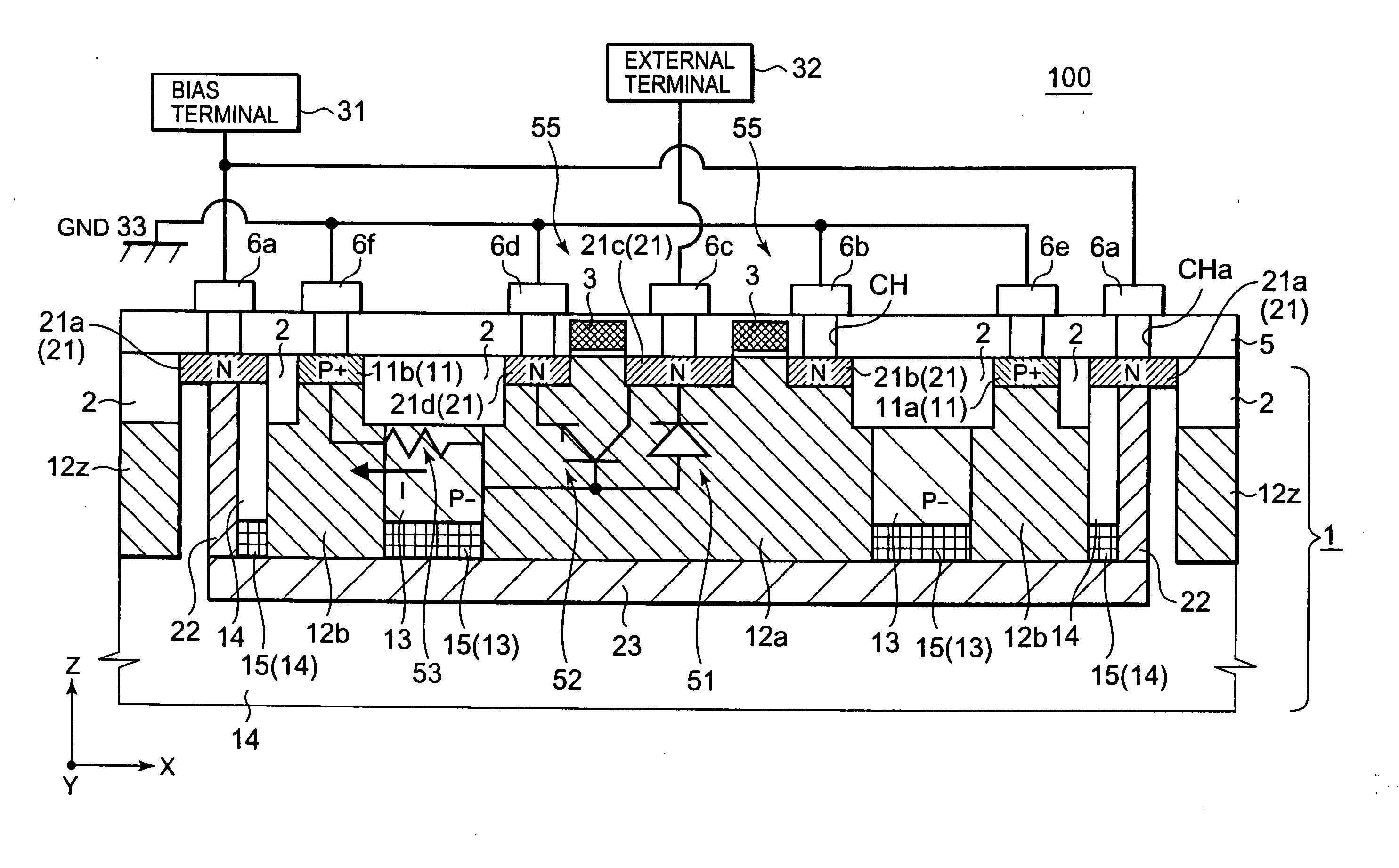

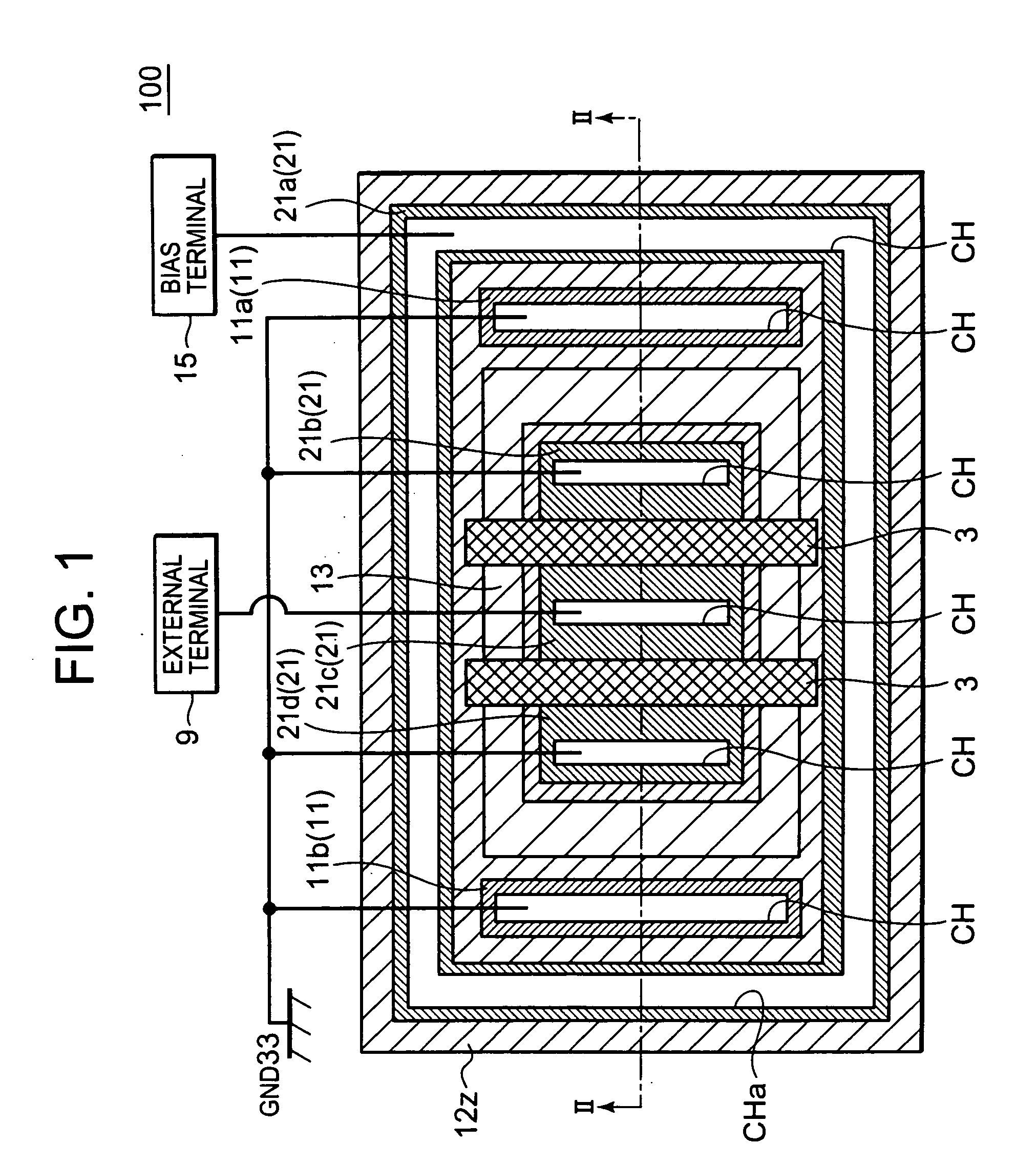

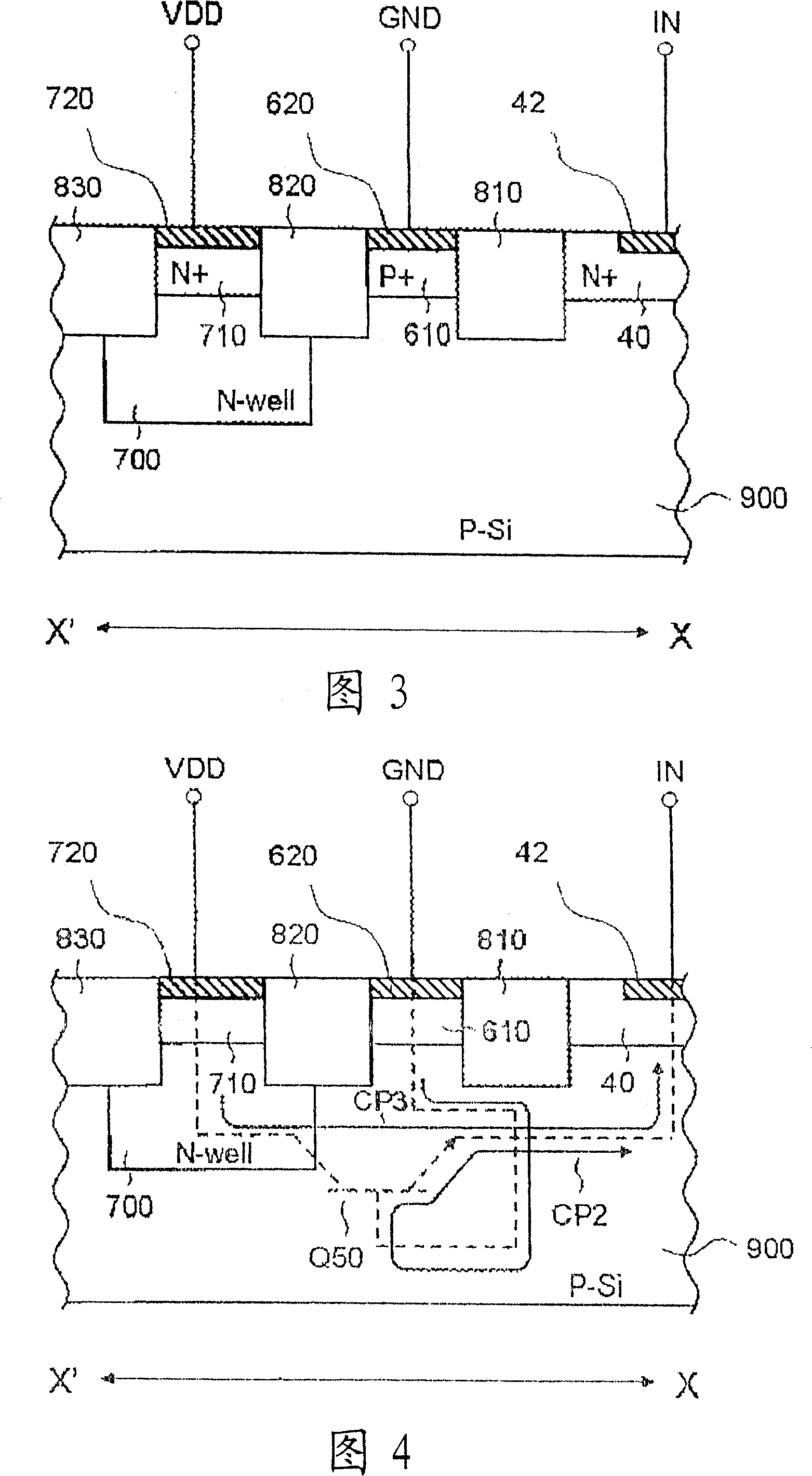

Semiconductor device having electro-static discharge protection element

InactiveUS20100193869A1Increase parasitic resistanceReduce in sizeTransistorSemiconductor/solid-state device detailsElectrostatic discharge protectionEngineering

A semiconductor device includes a semiconductor substrate of a first conductivity-type, a buried diffusion layer of a second conductivity-type formed in the semiconductor substrate, a first well of the second conductivity-type having a bottom portion in contact with a top portion of the buried diffusion layer, the first well having an annular shape in a planar view, and a second well of the first conductivity-type formed to be surrounded by the first well. The semiconductor device further includes a diffusion region formed between a first portion of the second well and a second portion of the second well, the diffusion region having an impurity concentration lower than that of the second well, so that a depletion layer formed in the diffusion region can be provided, a transistor formed on the second well to function as an ESD (electro-static discharge) protection element, and an external terminal connected to a drain of the transistor.

Owner:RENESAS ELECTRONICS CORP

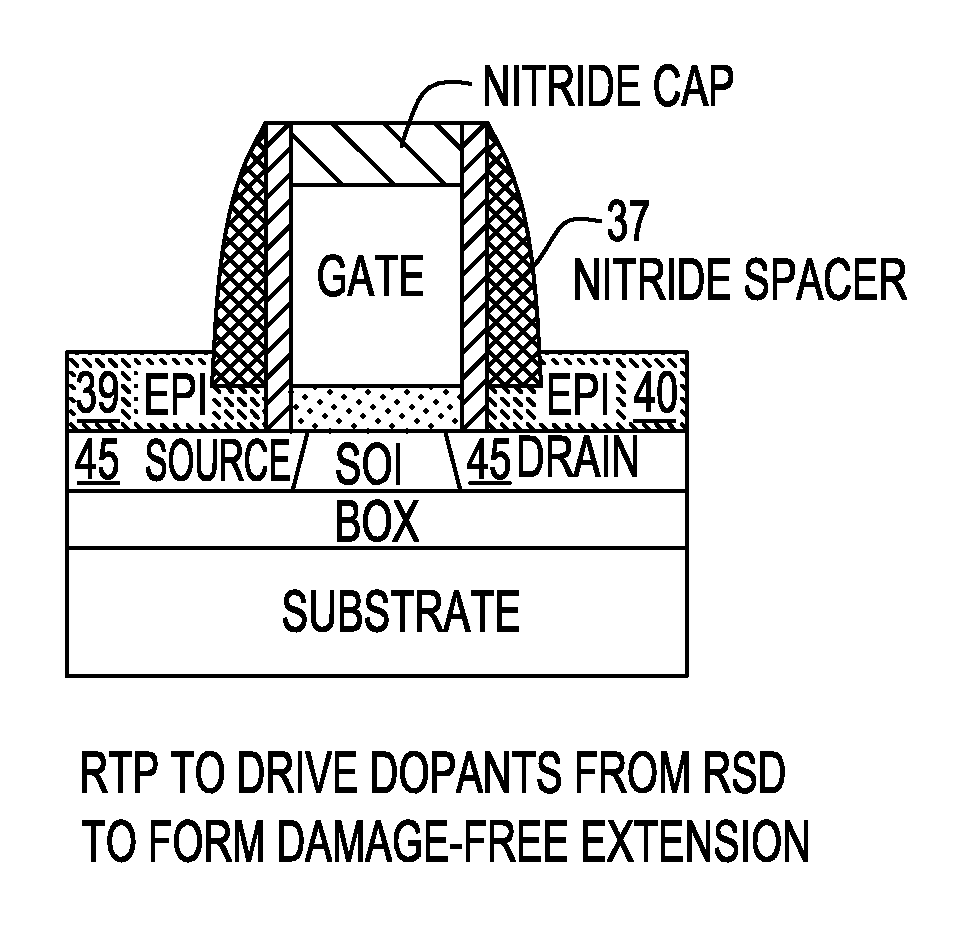

Method of forming an extremely thin semiconductor insulator (ETSOI) FET having a stair-shaped raised source/drain

ActiveUS8574970B2Increase parasitic resistanceReduce resistanceSolid-state devicesSemiconductor/solid-state device manufacturingMOSFETSoi substrate

A MOSFET device is formed on top of a semiconductor-on-insulator (SOI) substrate having a semiconductor layer with a thickness ranging from 3 nm to 20 nm. A stair-shape raised extension, a raised source region and a raised drain region (S / D) are formed on top of the SOI substrate. The thinner raised extension region abuts at a thin gate sidewall spacer, lowering the extension resistance without significantly increasing the parasitic resistance. A single epitaxial growth forms the thinner raised extension and the thicker raised S / D preferably simultaneously, reducing the fabrication cost as well as the contact resistance between the raised S / D and the extension. A method of forming the aforementioned MOSFET device is also provided.

Owner:GLOBALFOUNDRIES US INC

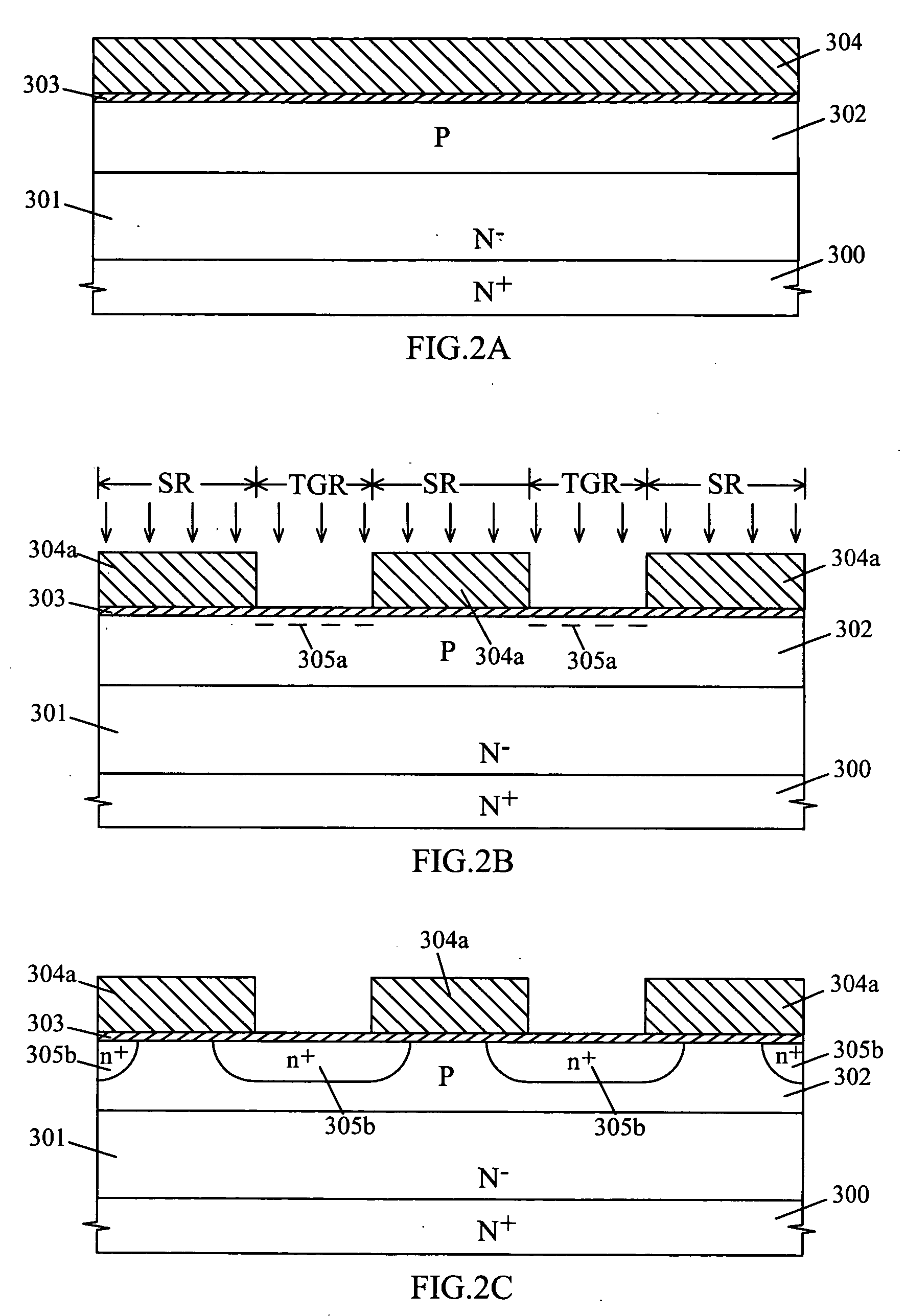

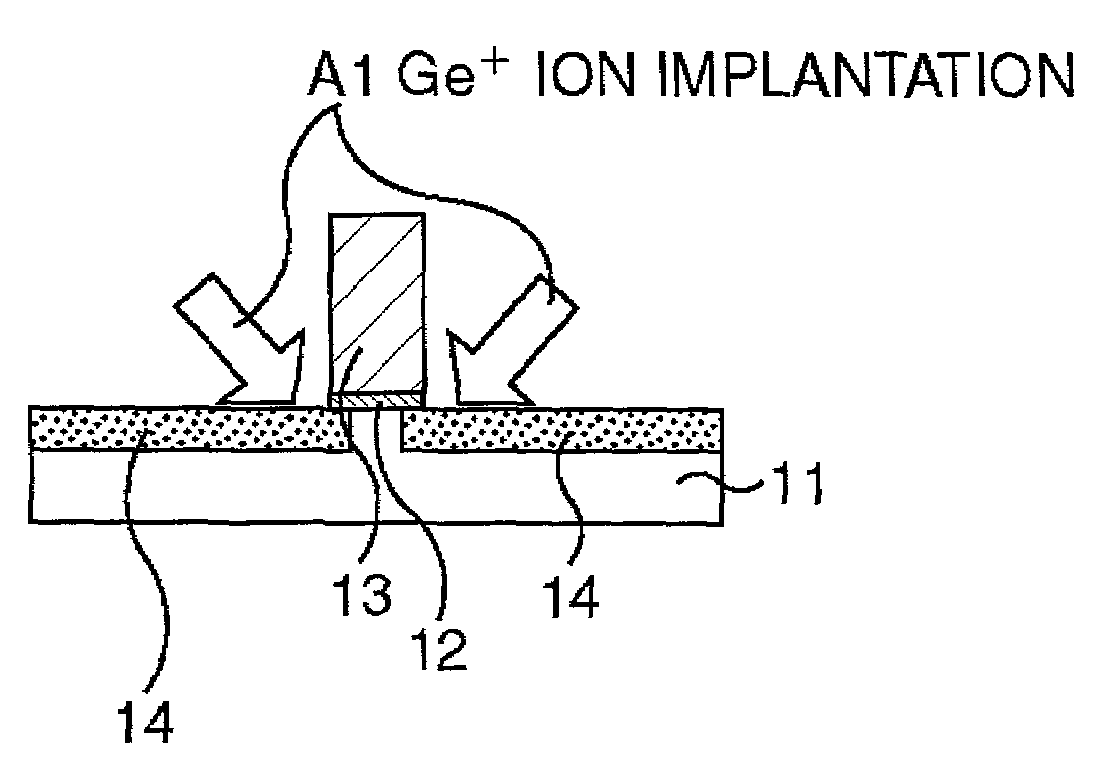

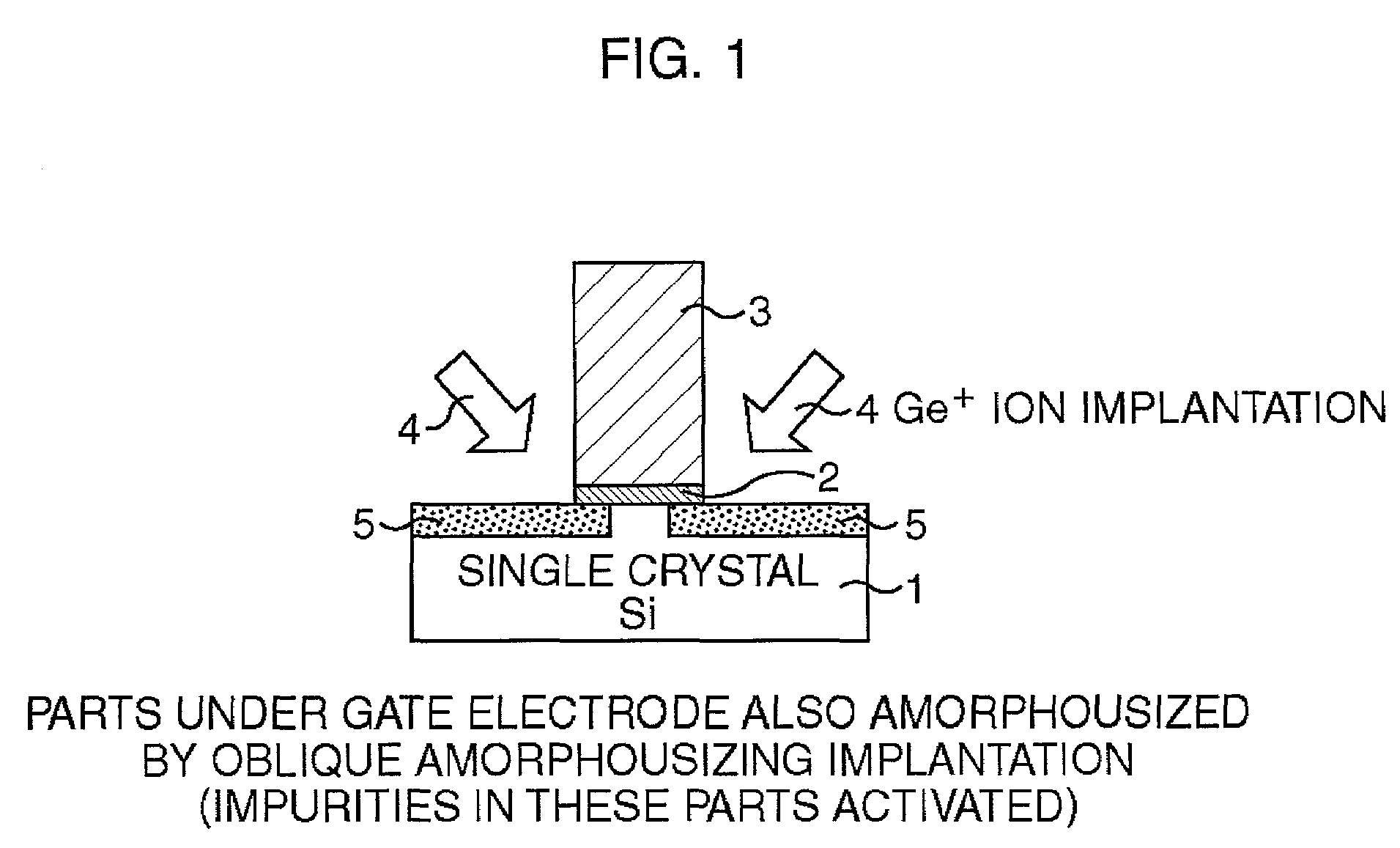

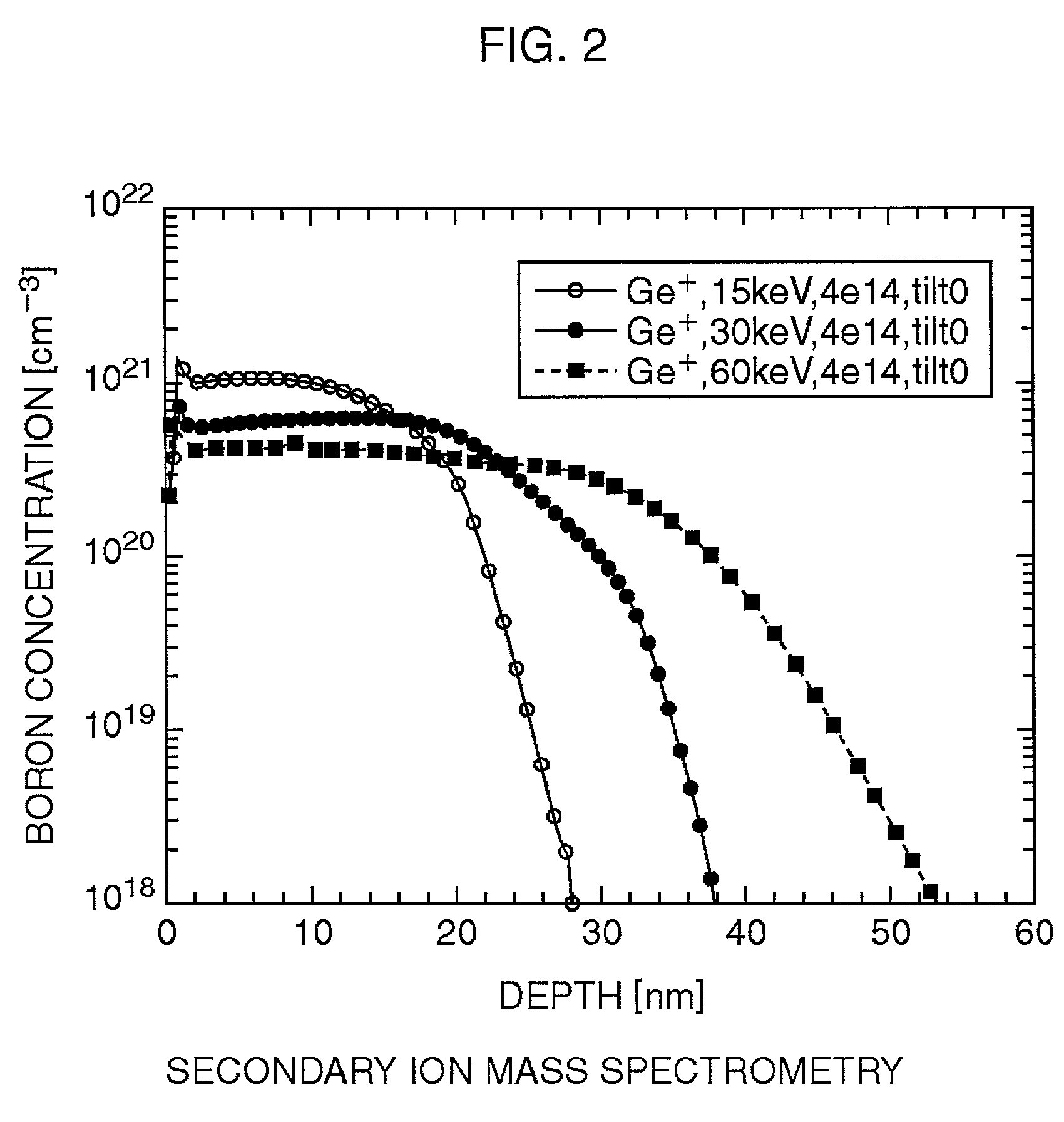

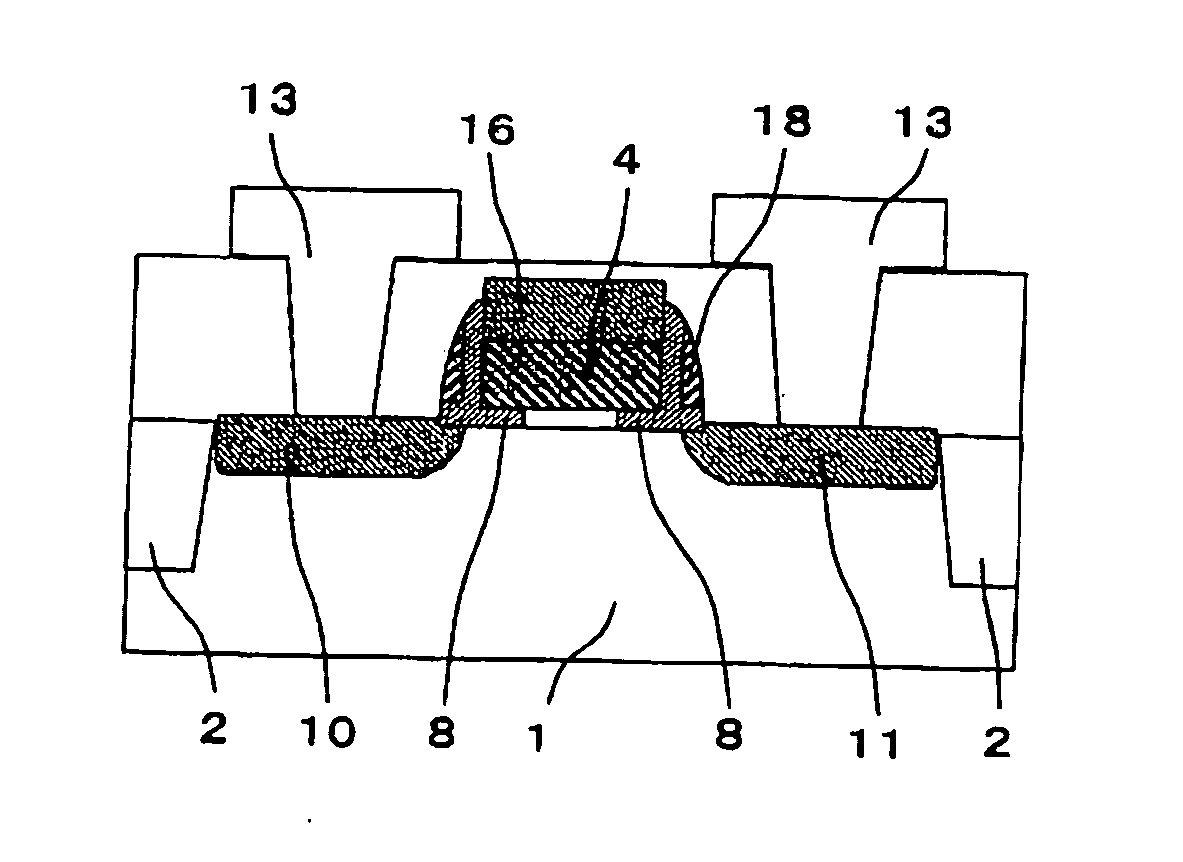

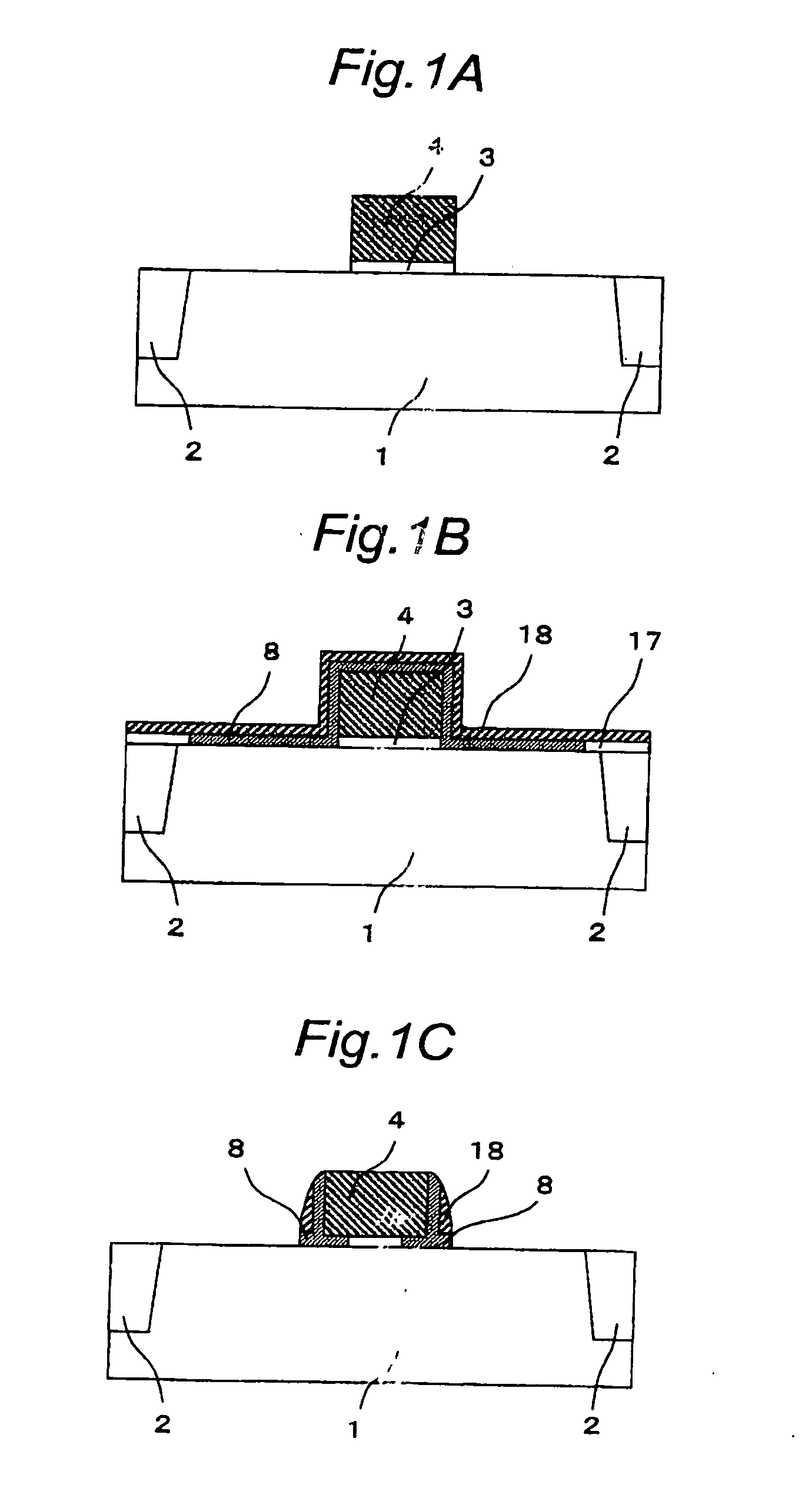

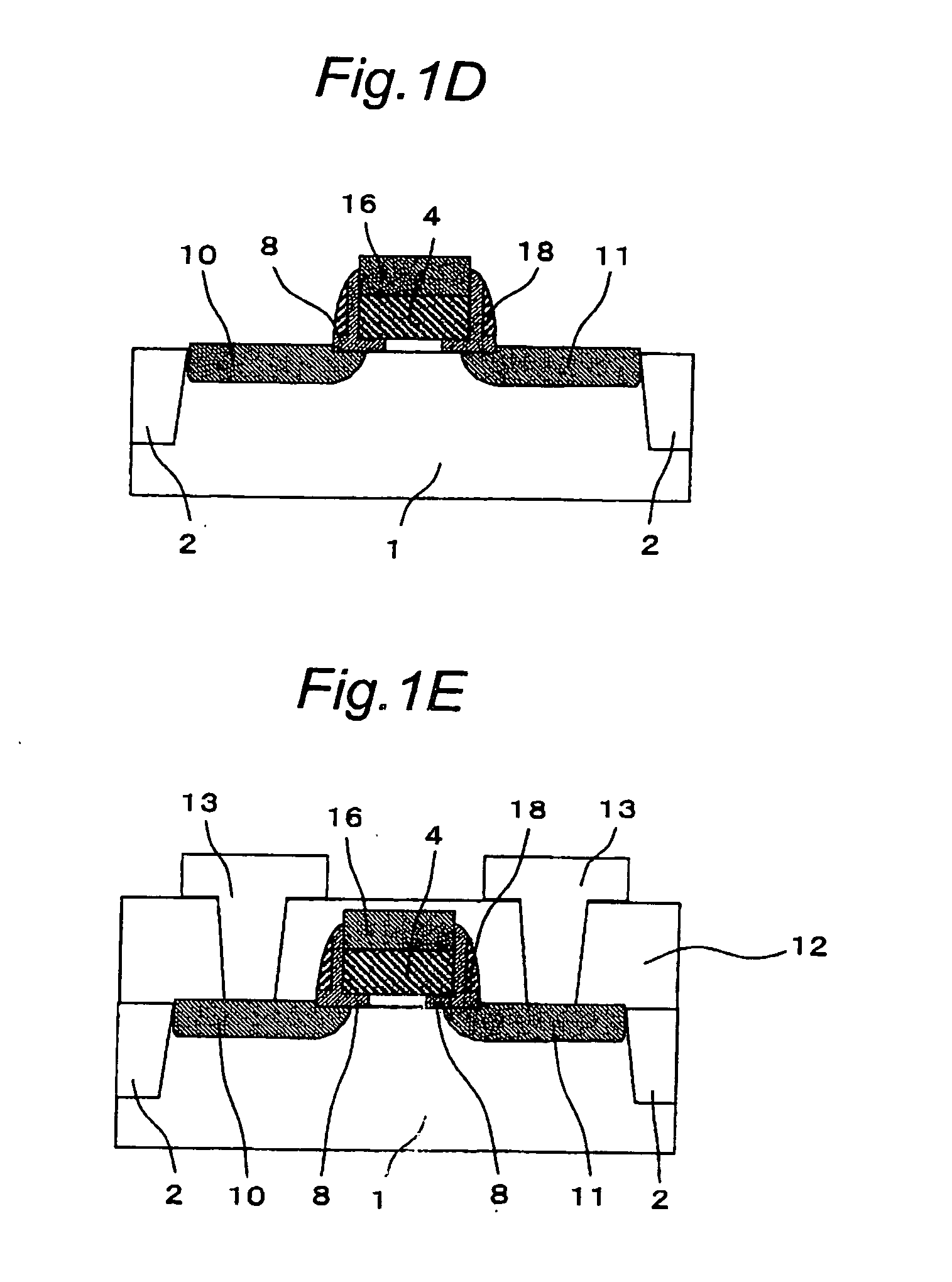

Semiconductor device and manufacturing method thereof

InactiveUS7432146B2Increase parasitic resistanceMore highly integratedTransistorSemiconductor/solid-state device manufacturingSingle crystalIrradiation

Owner:FUJITSU SEMICON LTD

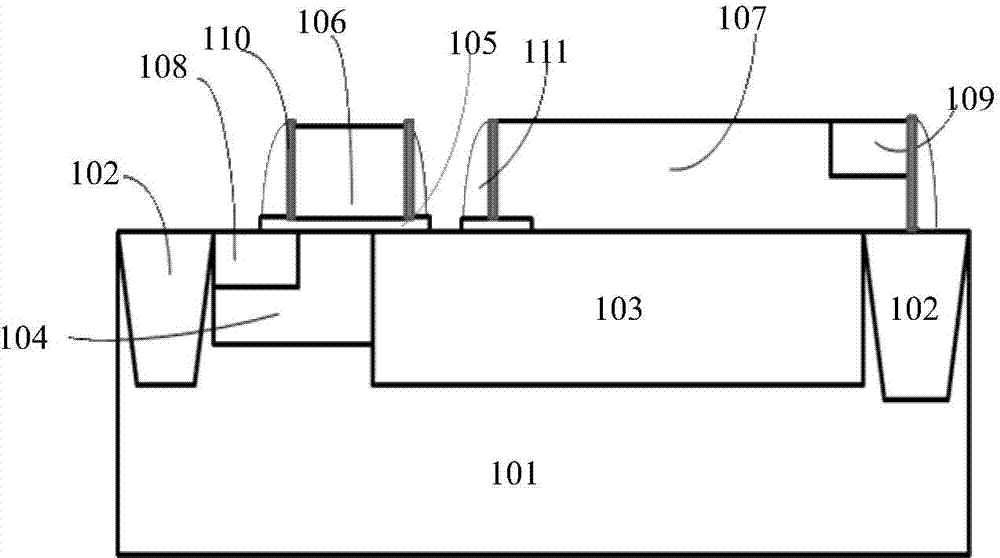

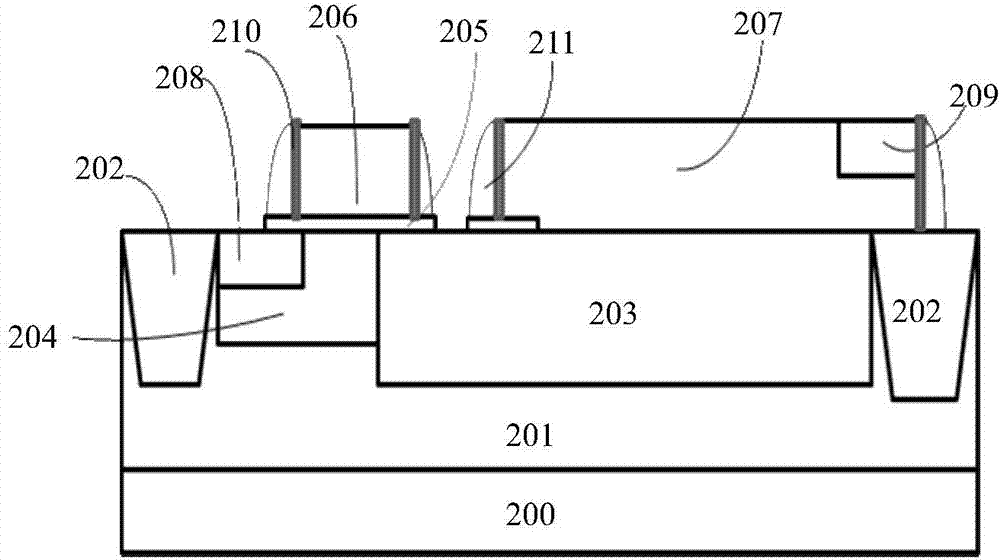

Semiconductor device and method of manufacturing the same

ActiveUS8492230B2Potential controllabilityIncrease resistanceSolid-state devicesSemiconductor/solid-state device manufacturingPower semiconductor deviceSilicon oxide

To provide a technique capable of achieving improvement of the parasitic resistance in FINFETs. In the FINFET in the present invention, a sidewall is formed of a laminated film. Specifically, the sidewall is composed of a first silicon oxide film, a silicon nitride film formed over the first silicon oxide film, and a second silicon oxide film formed over the silicon nitride film. The sidewall is not formed on the side wall of a fin. Thus, in the present invention, the sidewall is formed on the side wall of a gate electrode and the sidewall is not formed on the side wall of the fin.

Owner:RENESAS ELECTRONICS CORP

Semiconductor device and a method of manufacturing the same, and solid-state image pickup device using the same

InactiveUS20100109059A1Improve good performanceAvoid makingTransistorSolid-state devicesHigh concentrationSemiconductor

Disclosed herein is a semiconductor device, including: a gate electrode formed on a semiconductor substrate through a gate insulating film; an extension region formed in the semiconductor substrate on a source side of the gate electrode; a source region formed in the semiconductor substrate on the source side of the gate electrode through the extension region; an LDD region formed in the semiconductor substrate on a drain side of the gate electrode; and a drain region formed in the semiconductor substrate on the drain side of the gate electrode through the LDD region; wherein the extension region is formed at a higher concentration than that of the LDD region so as to be shallower than the LDD region.

Owner:SONY CORP

Semiconductor device and a method of manufacturing the same

InactiveUS20060281285A1Easy to getReduce device areaTransistorSemiconductor/solid-state device detailsDevice materialFixed charge

A semiconductor device has a semiconductor (e.g., a silicon substrate), an electrically conductive region (e.g., a source region and a drain region) which is in contact with the semiconductor to form a Schottky junction, and an insulator. The insulator is in contact with the semiconductor and the electrically conductive region, and has a fixed-charge containing region which contains a fixed charge and extends across a boundary between the semiconductor and the electrically conductive region.

Owner:SHARP KK

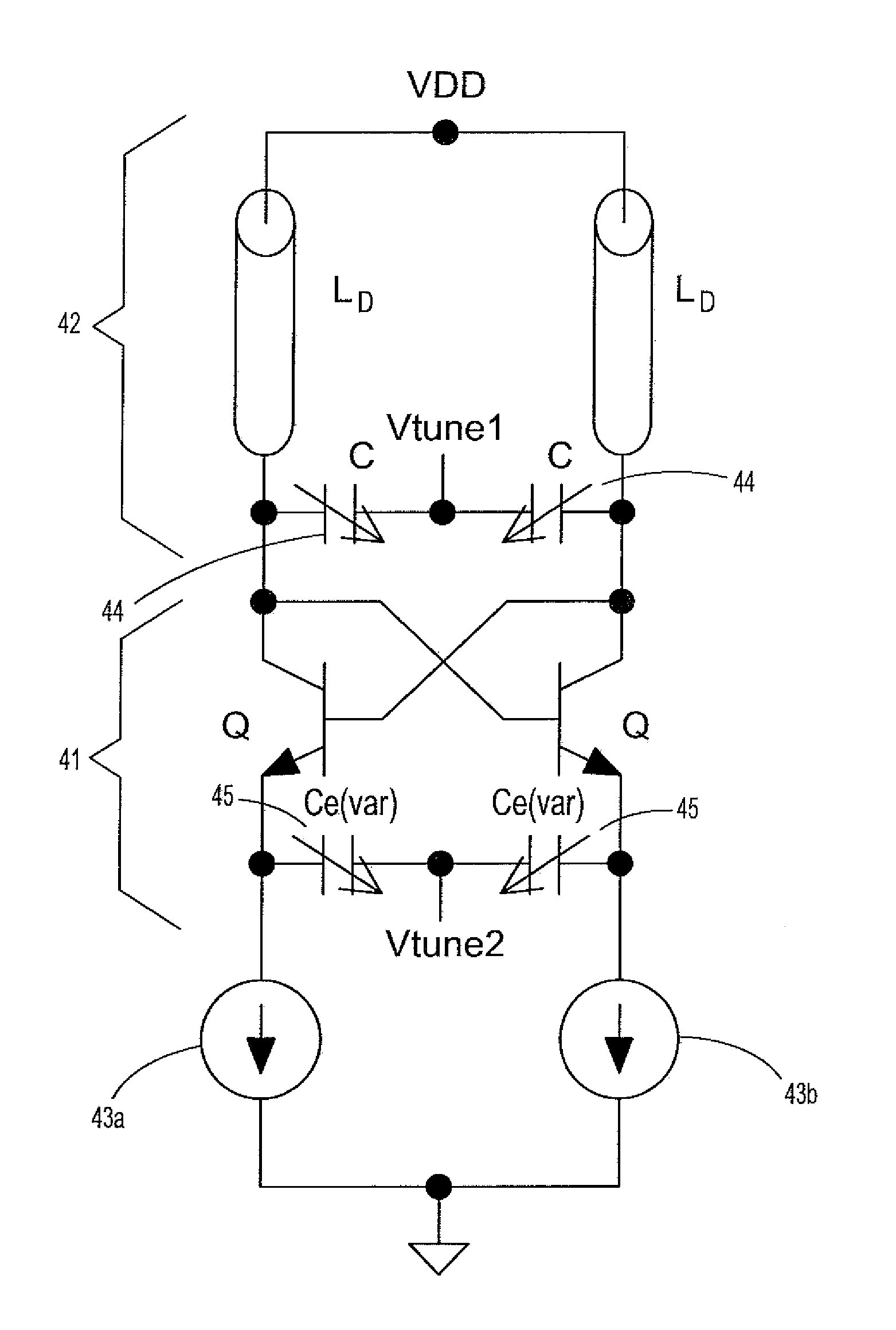

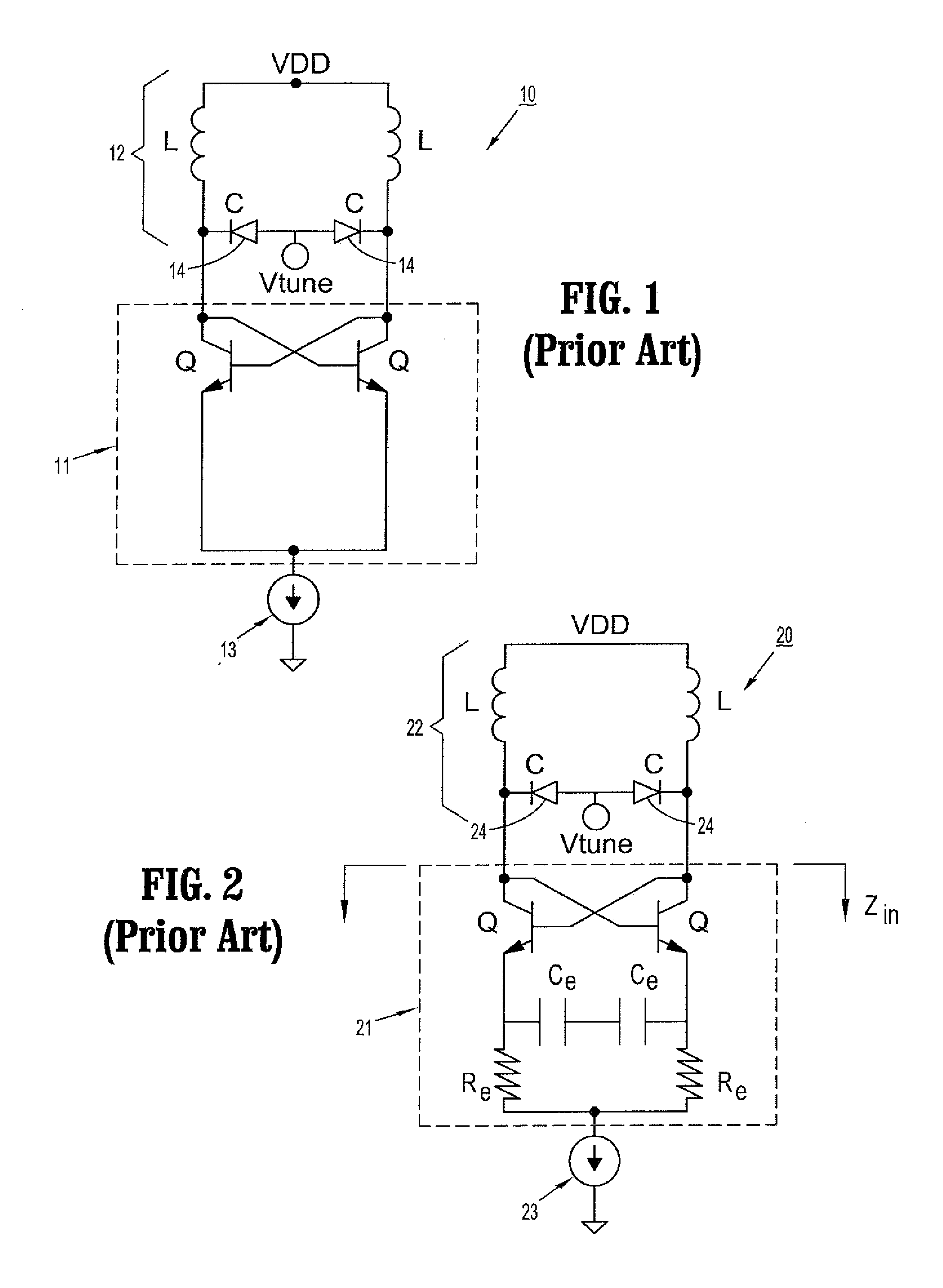

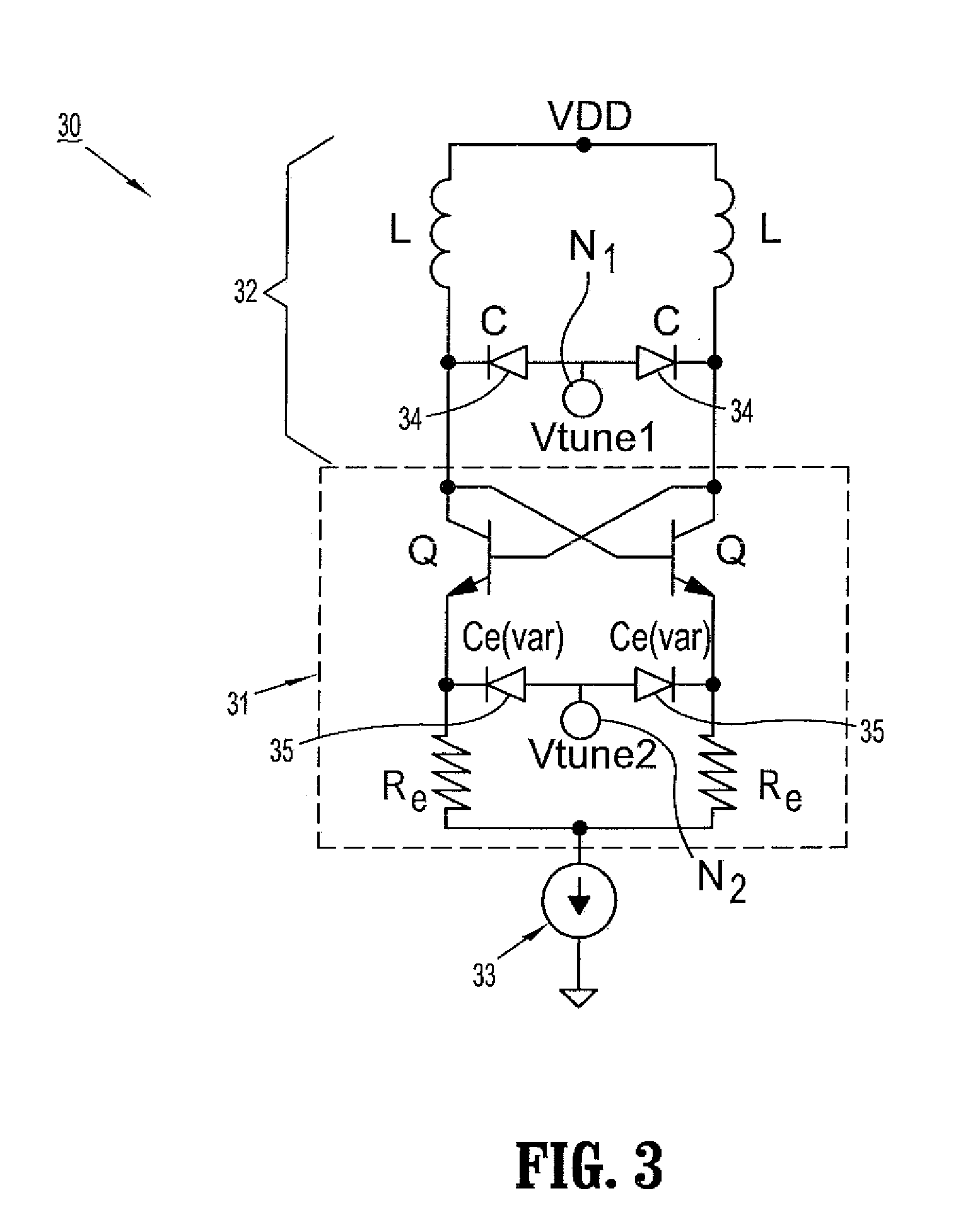

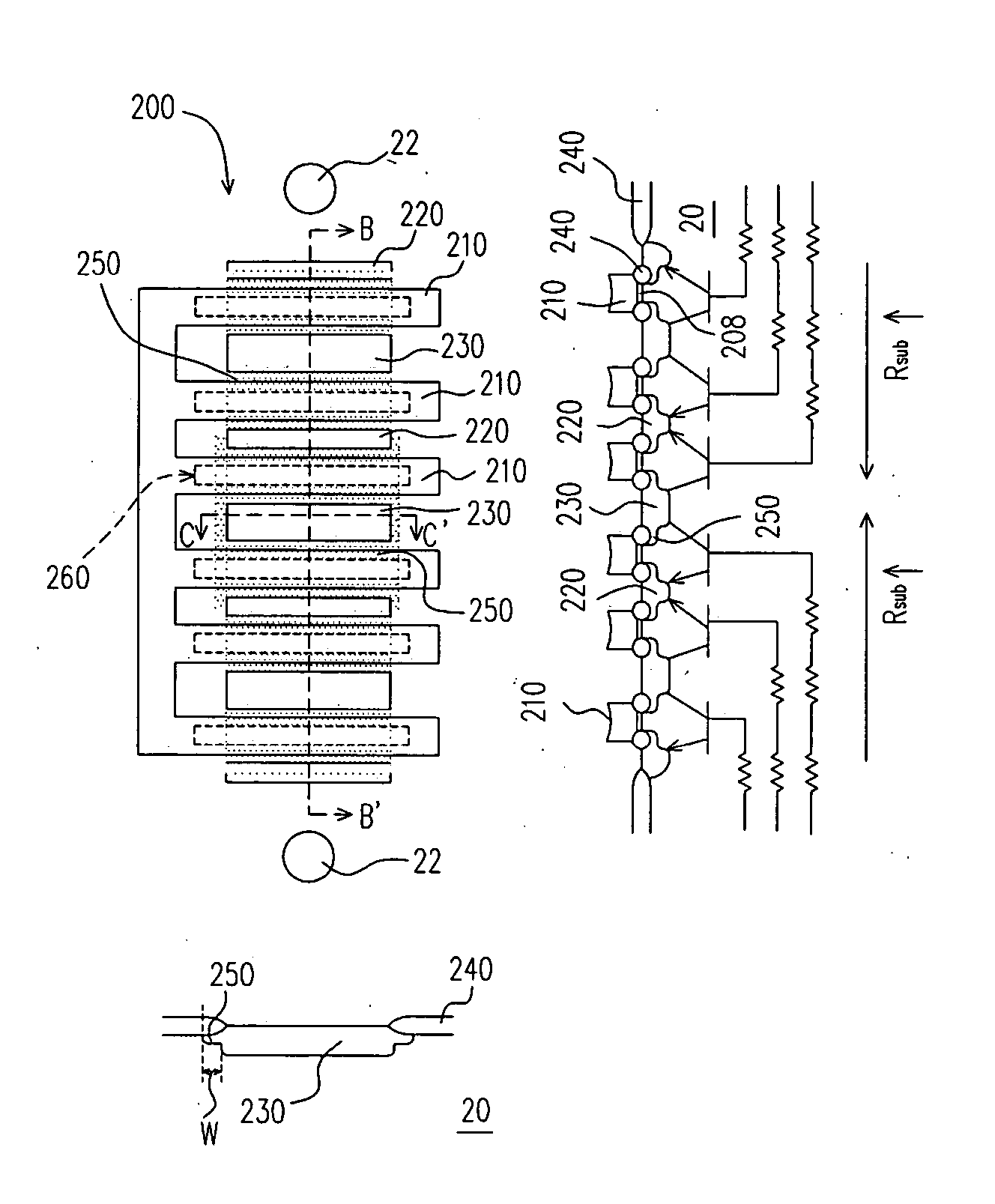

Voltage controlled oscillator circuits and methods using variable capacitance degeneration for increased tuning range

InactiveUS20120235759A1Enhanced oscillationIncrease rangeElectric pulse generatorOscillations generatorsCapacitanceEngineering

Voltage controlled oscillator circuits are provided in which variable capacitance degeneration is employed to provide increased tuning ranges and output amplitudes for VCO circuits for millimeter wave applications.

Owner:IBM CORP

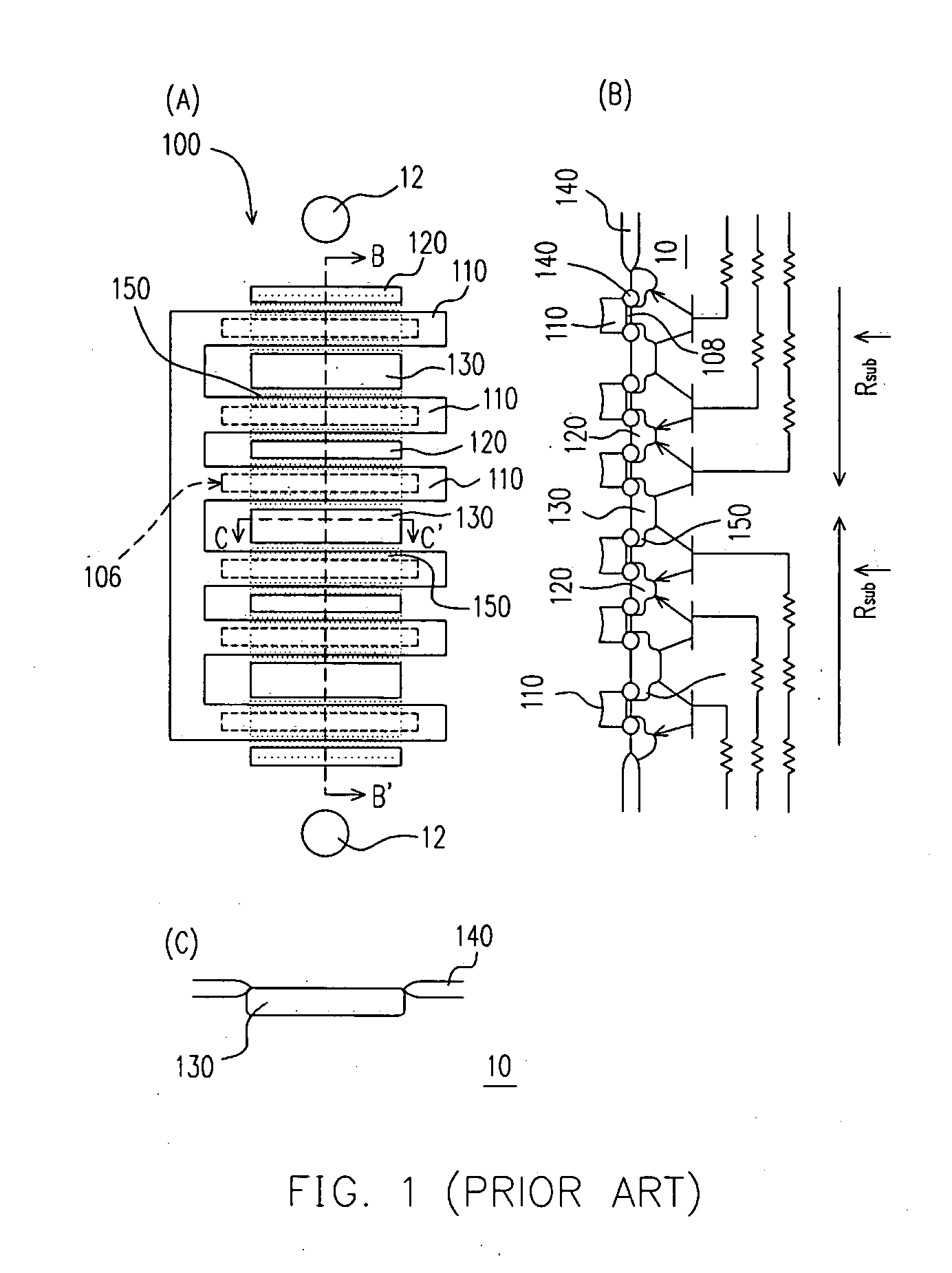

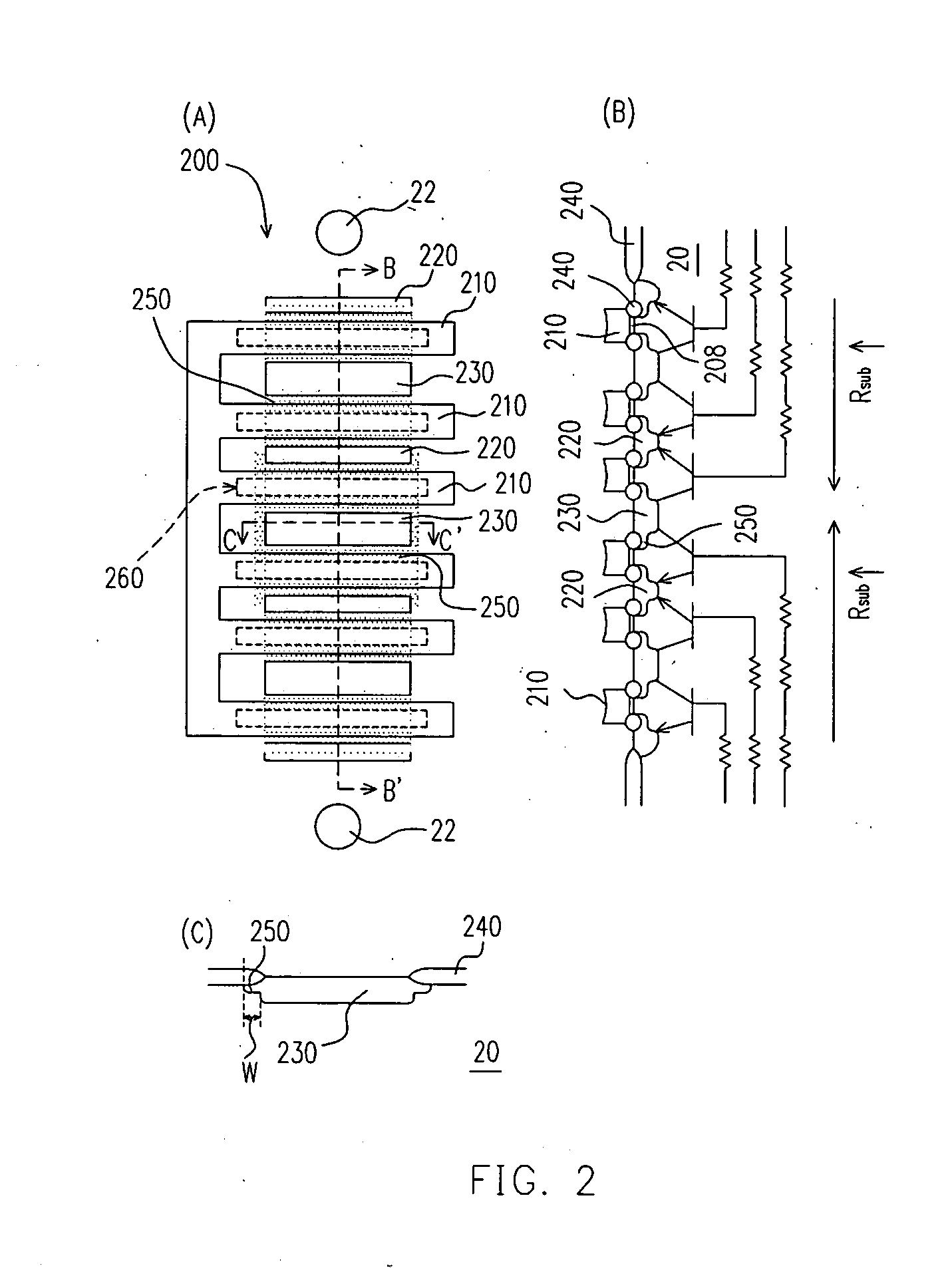

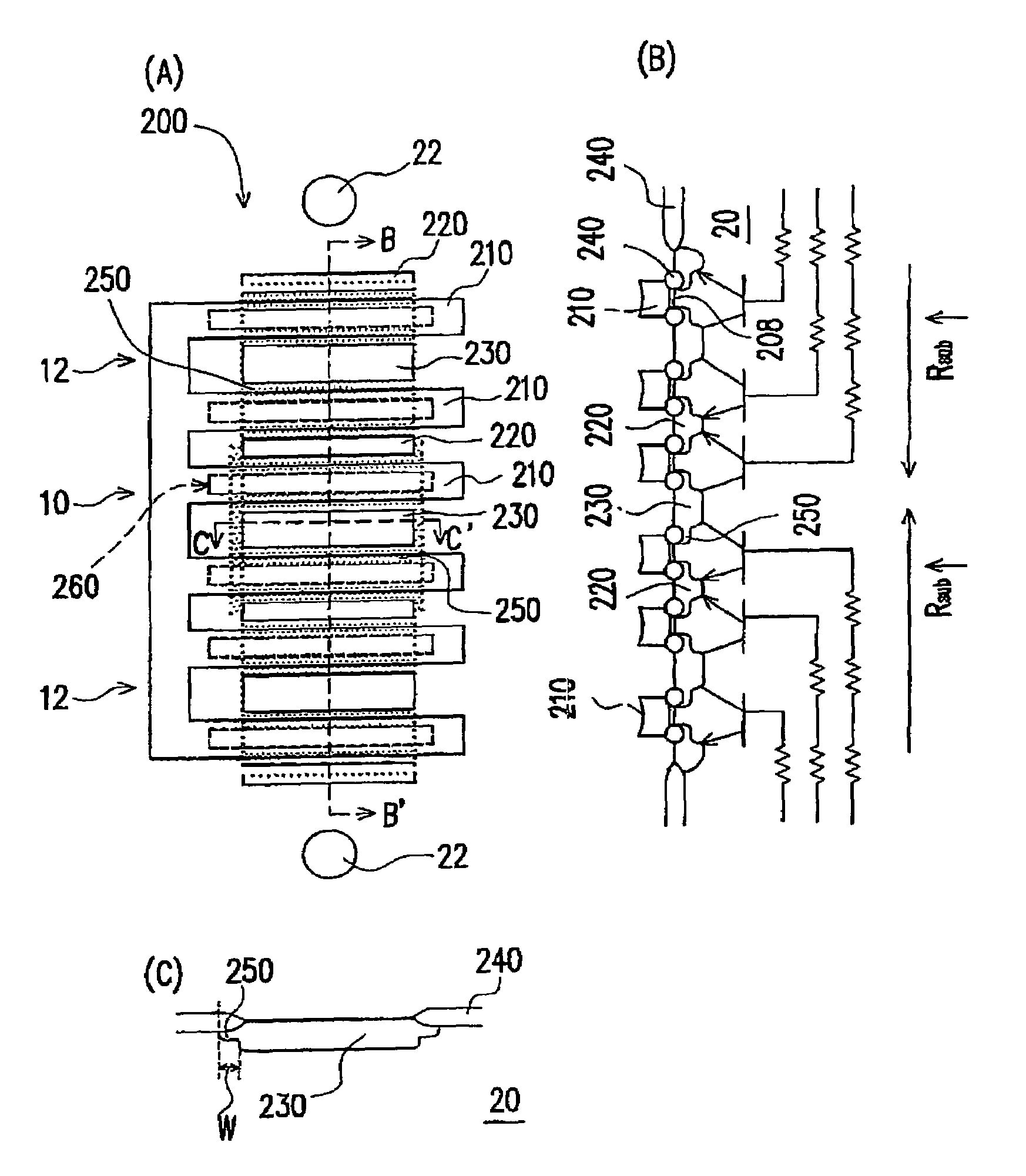

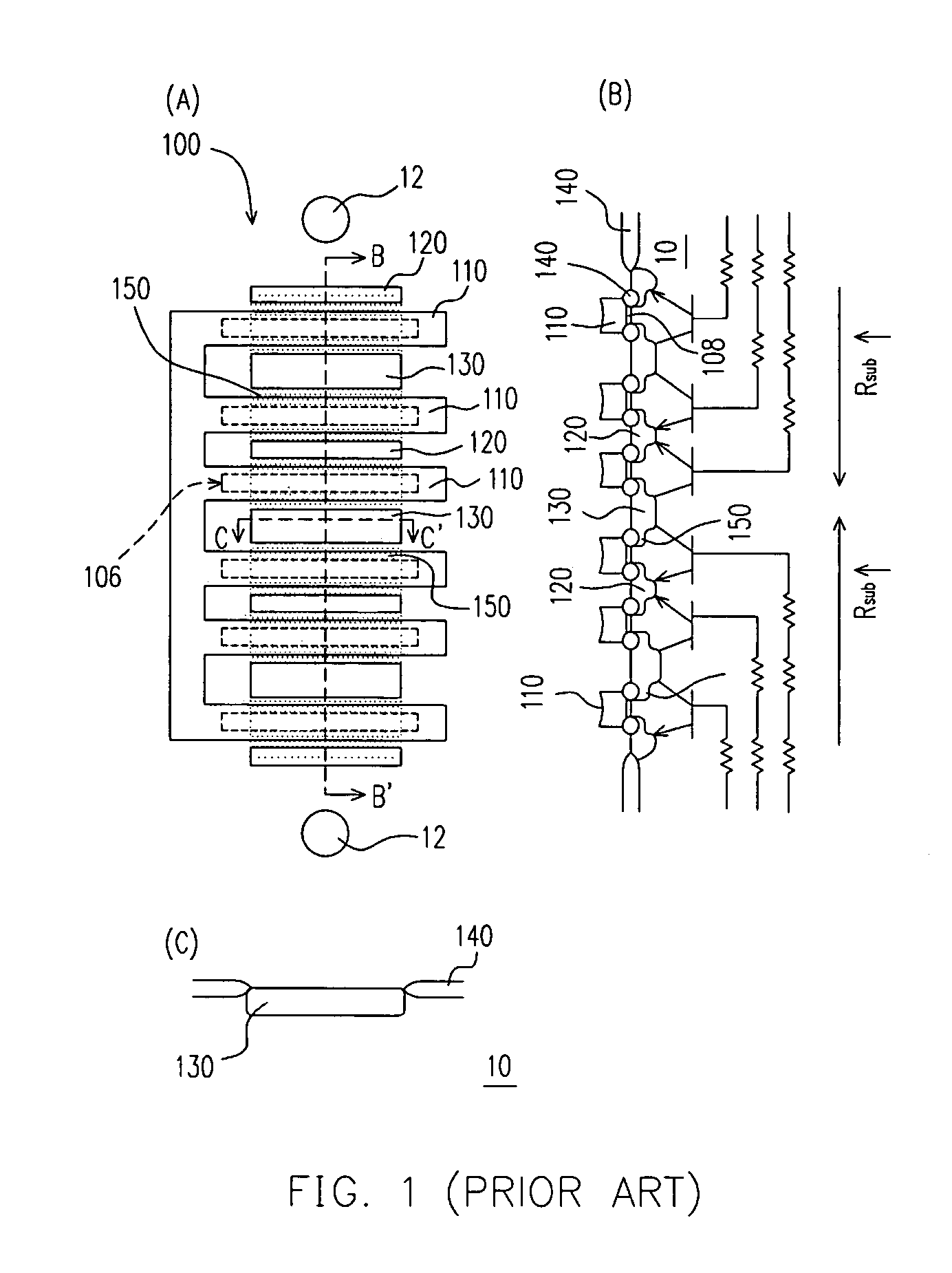

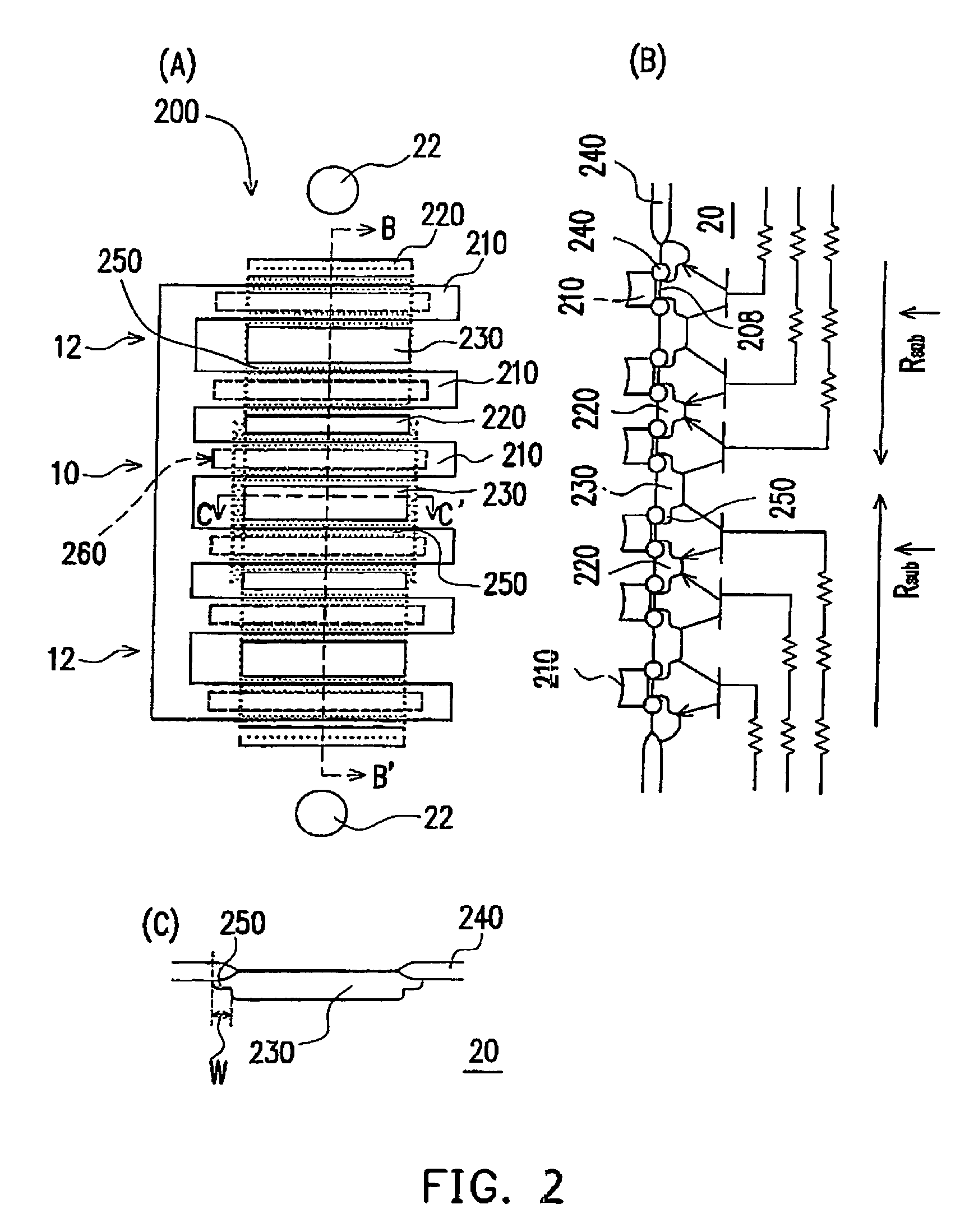

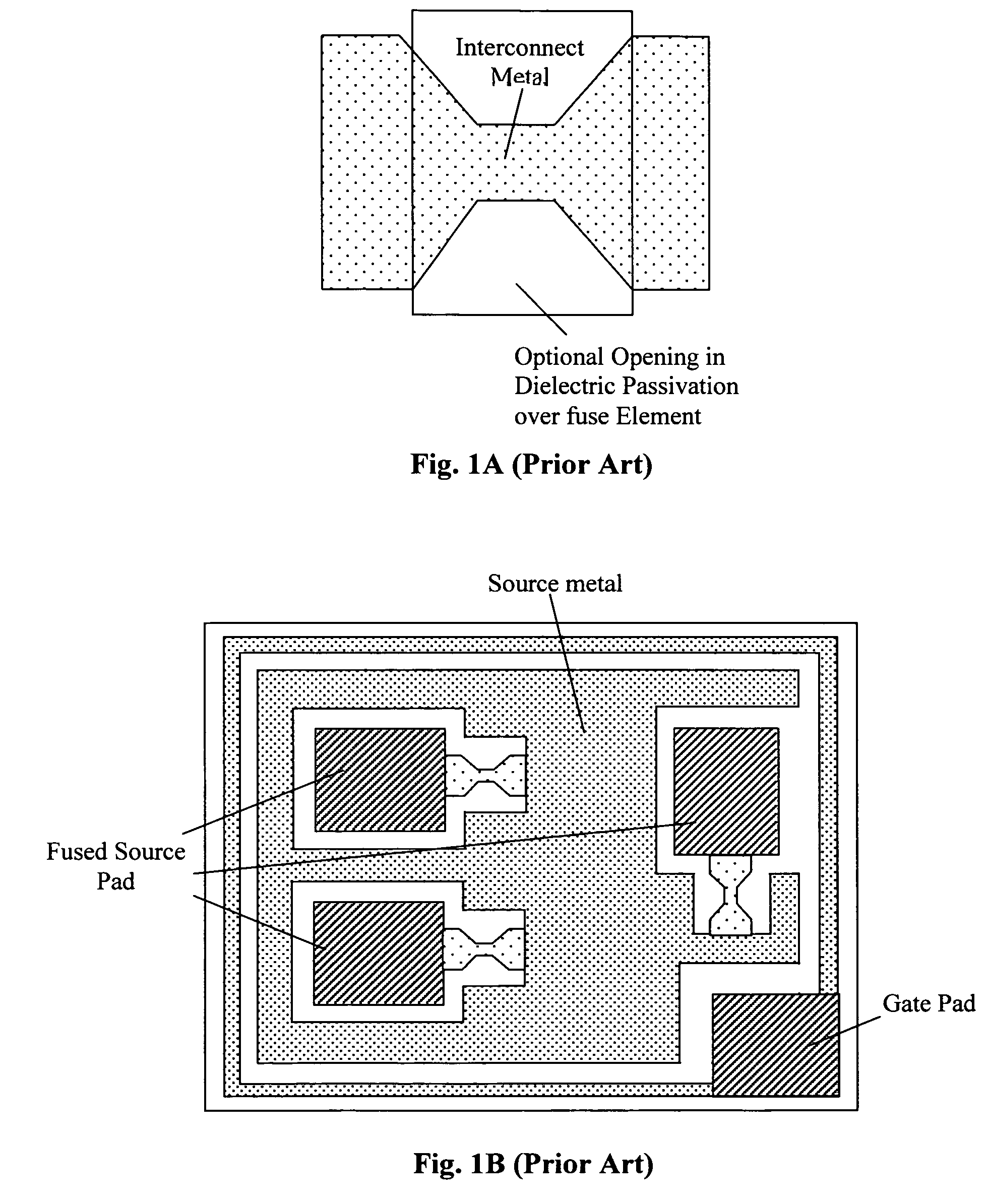

Multi-finger transistor

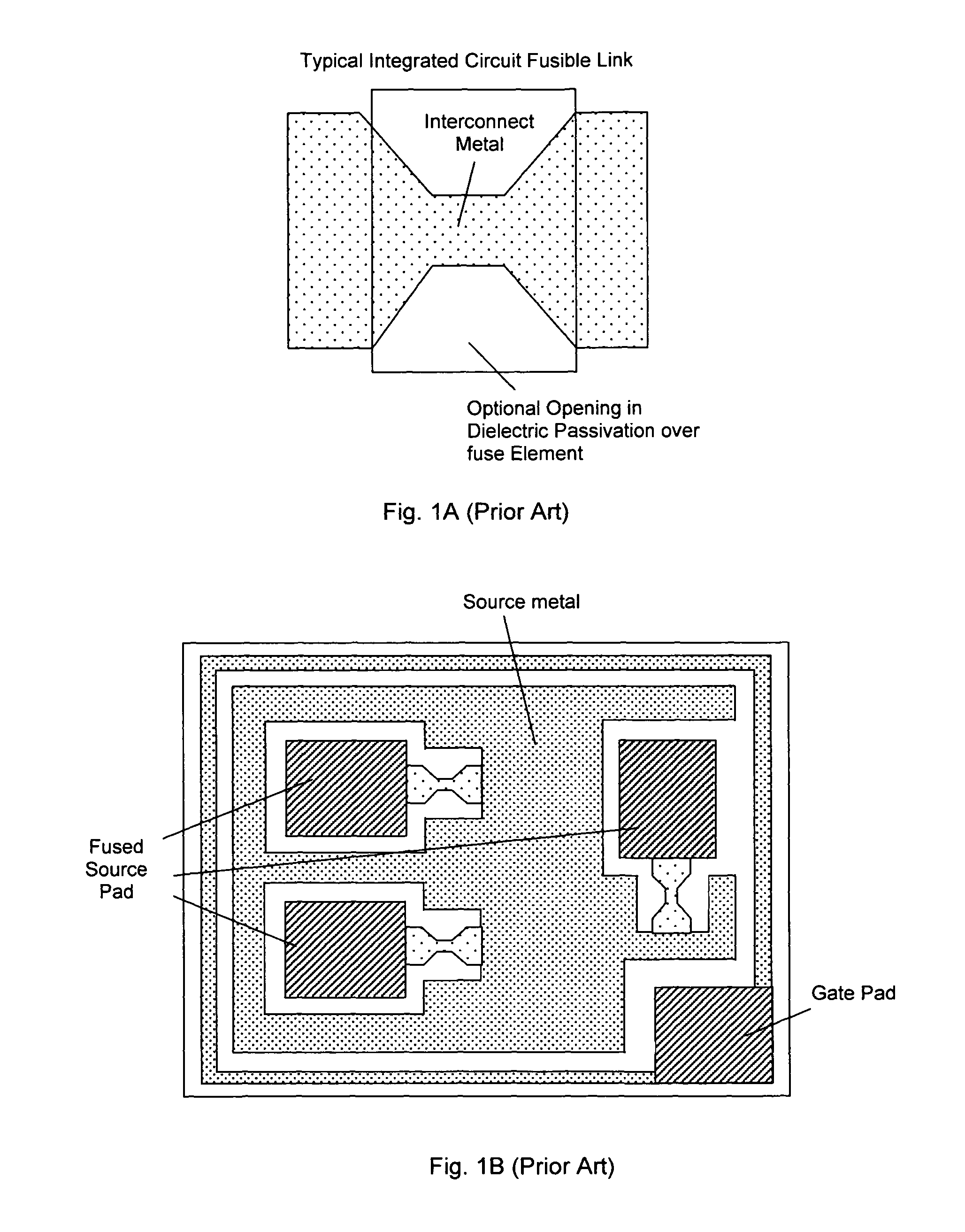

ActiveUS20050082620A1Avoid damageIncrease parasitic resistanceSemiconductor/solid-state device detailsSolid-state devicesGate dielectricPhysics

A multi-finger transistor is described, including multiple parallel transistors. Each transistor includes a gate dielectric layer, a gate, a source / drain region, and a drift region in the peripheral substrate of the source / drain region separating the source / drain region and the channel region under the gate. The width of the drift region extending from the side boundary of the source / drain region increases stepwise from the edge sections of the multi-finger transistor toward the central section of the same.

Owner:UNITED MICROELECTRONICS CORP

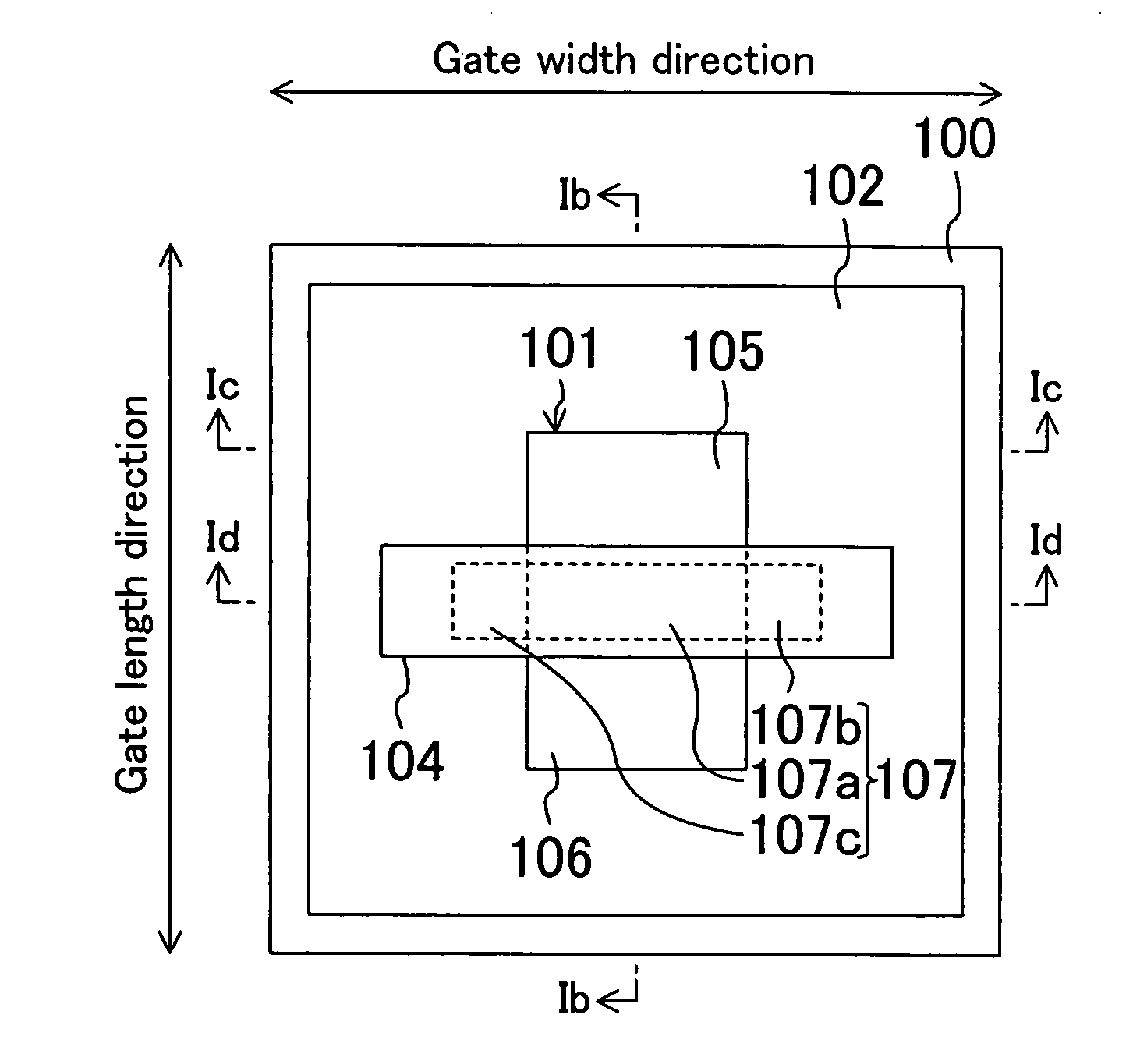

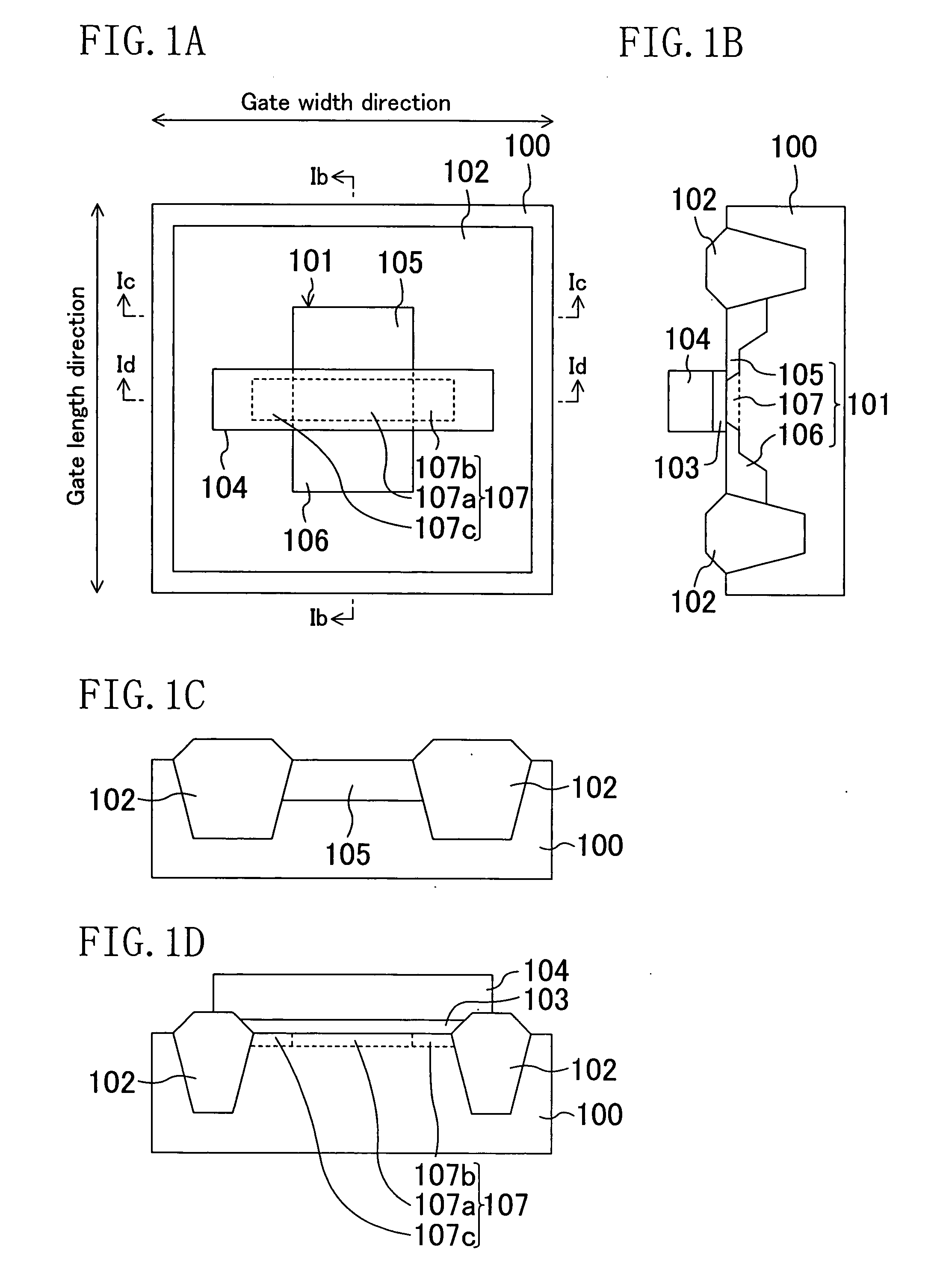

Semiconductor device

InactiveUS20070278613A1Characteristic is suppressedSimple wayTransistorSemiconductor/solid-state device manufacturingEngineeringSemiconductor

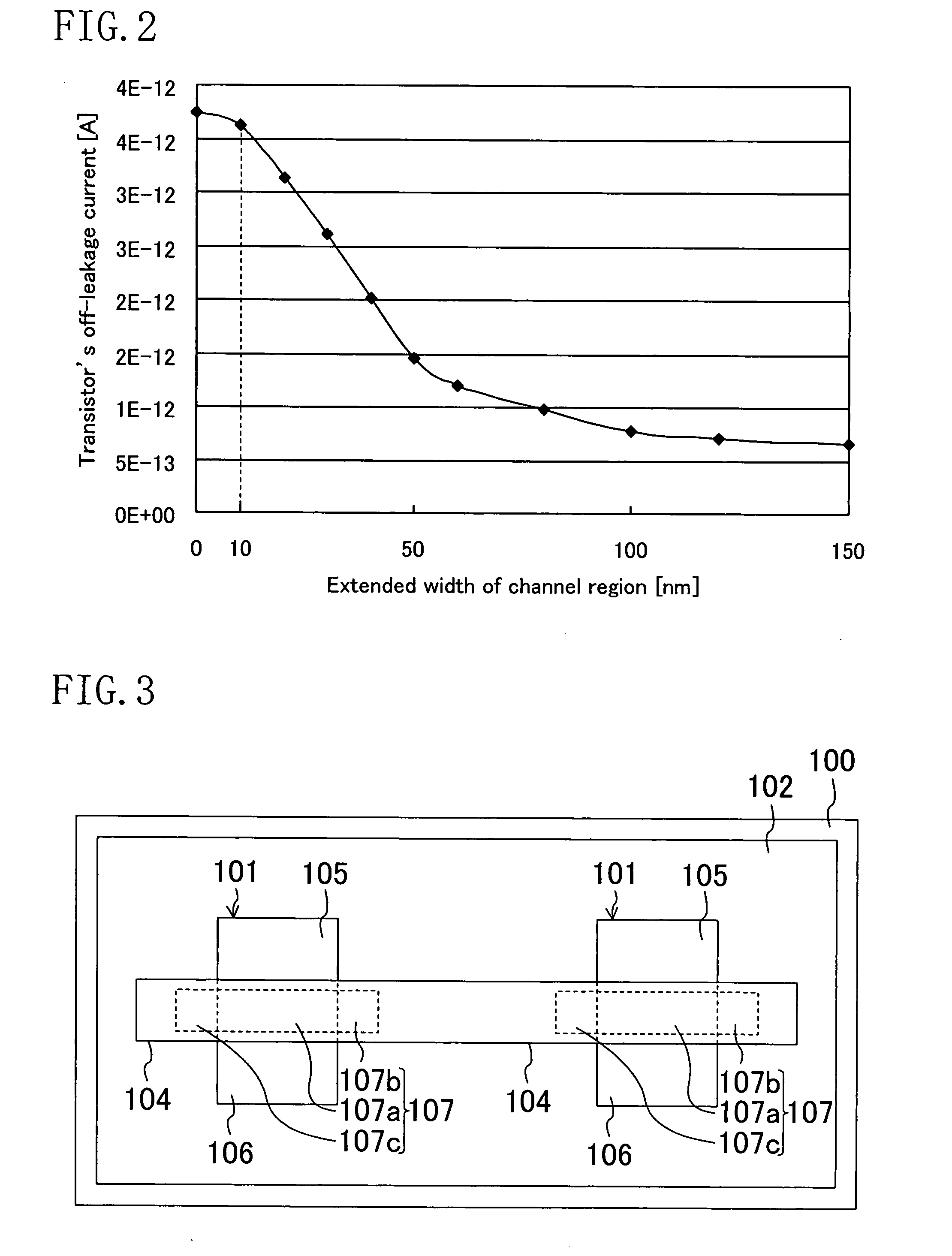

A semiconductor device includes: a semiconductor substrate; a device active portion formed in the semiconductor substrate; a device isolation portion formed in the semiconductor substrate so as to surround the periphery of the device active portion; an insulating film stacked on the device active portion; and a gate electrode stacked on the insulating film. The device active portion includes: a source region and a drain region located opposite each other in a gate length direction, and a channel region interposed between the source region and the drain region. The channel region includes: a central region connecting the source and drain regions and having an approximately rectangular shape, and a protruding region protruding from one side end of the central region in a gate width direction. The channel region is located inwardly of the gate electrode when viewed in the stacking direction.

Owner:PANASONIC CORP

Structure and method for self protection of power device

ActiveUS7999363B2Good thermal couplingIncrease parasitic resistanceSemiconductor/solid-state device detailsSolid-state devicesCurrent limitingSemiconductor chip

A resetable over-current self-protecting semiconductor power device comprises a vertical power semiconductor chip and an over-current protection layer composed of current limiting material such as a PTC material. The over-current protection layer may be sandwiched between the vertical power semiconductor chip and a conductive plate, which could be a leadframe, a metal plate, a PCB plate or a PCB that the device is mounted on.

Owner:ALPHA & OMEGA SEMICON LTD

Structure and method for self protection of power device with expanded voltage ranges

ActiveUS20140334052A1Enhanced couplingIncrease parasitic resistanceSolid-state devicesEmergency protective arrangements for limiting excess voltage/currentElectrical resistance and conductanceEngineering

A vertical semiconductor power device includes a top surface and a bottom surface of a semiconductor substrate constituting a vertical current path for conducting a current there through. The semiconductor power device further includes an over current protection layer composed of a material having a resistance with a positive temperature coefficient (PTC) and the over current protection layer constituting as a part of the vertical current path connected to a source electrode and providing a feedback voltage a gate electrode of the vertical semiconductor power device for limiting a current passing there through for protecting the semiconductor power device at any voltage.

Owner:ALPHA & OMEGA SEMICON INC

Voltage-switched magneto-resistive random access memory (MRAM) employing separate read operation circuit paths from a shared spin torque write operation circuit path

ActiveUS10224368B2Lower energy barrierLess energyMagnetic-field-controlled resistorsSolid-state devicesStatic random-access memoryRandom access memory

Owner:QUALCOMM INC

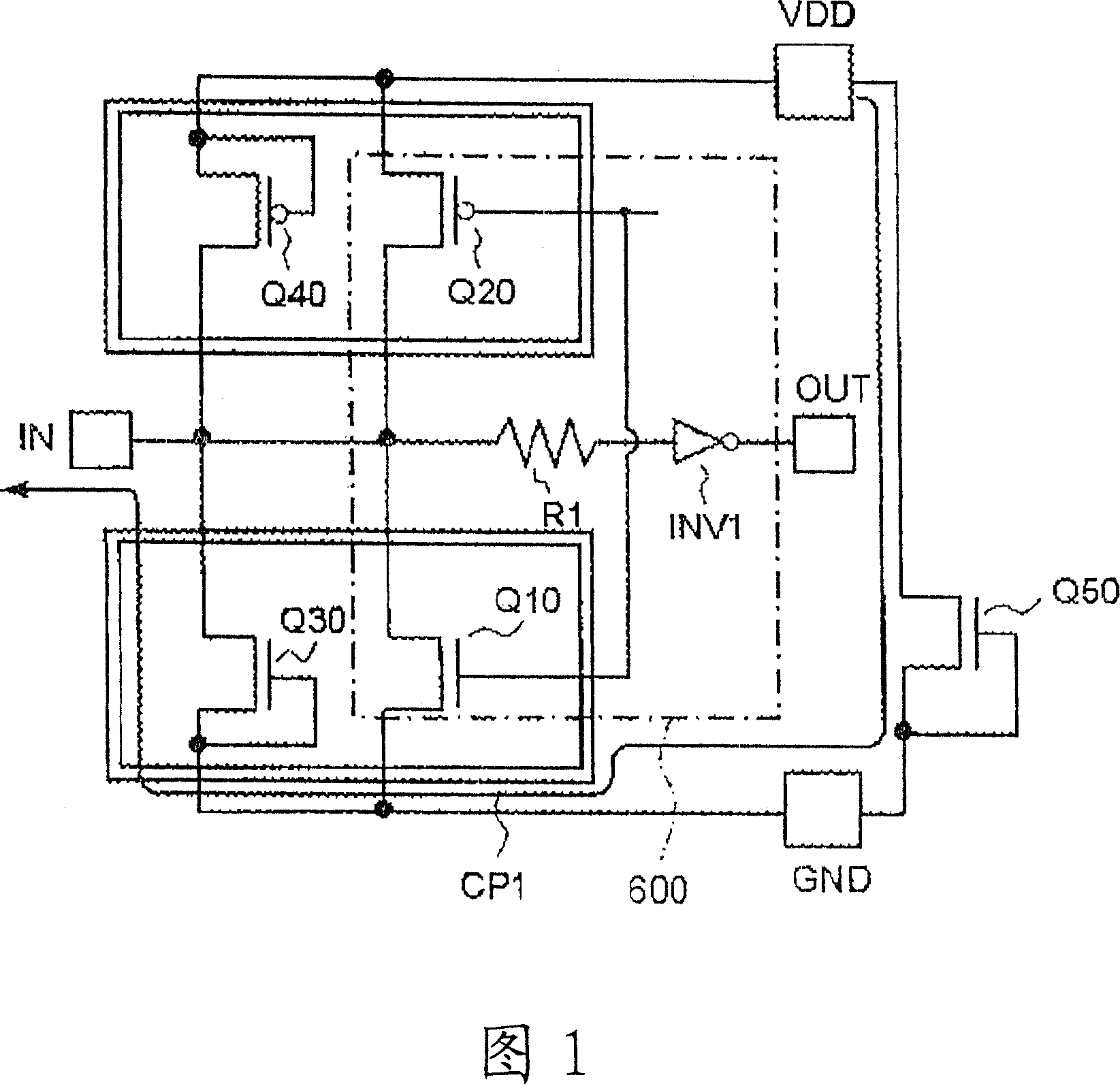

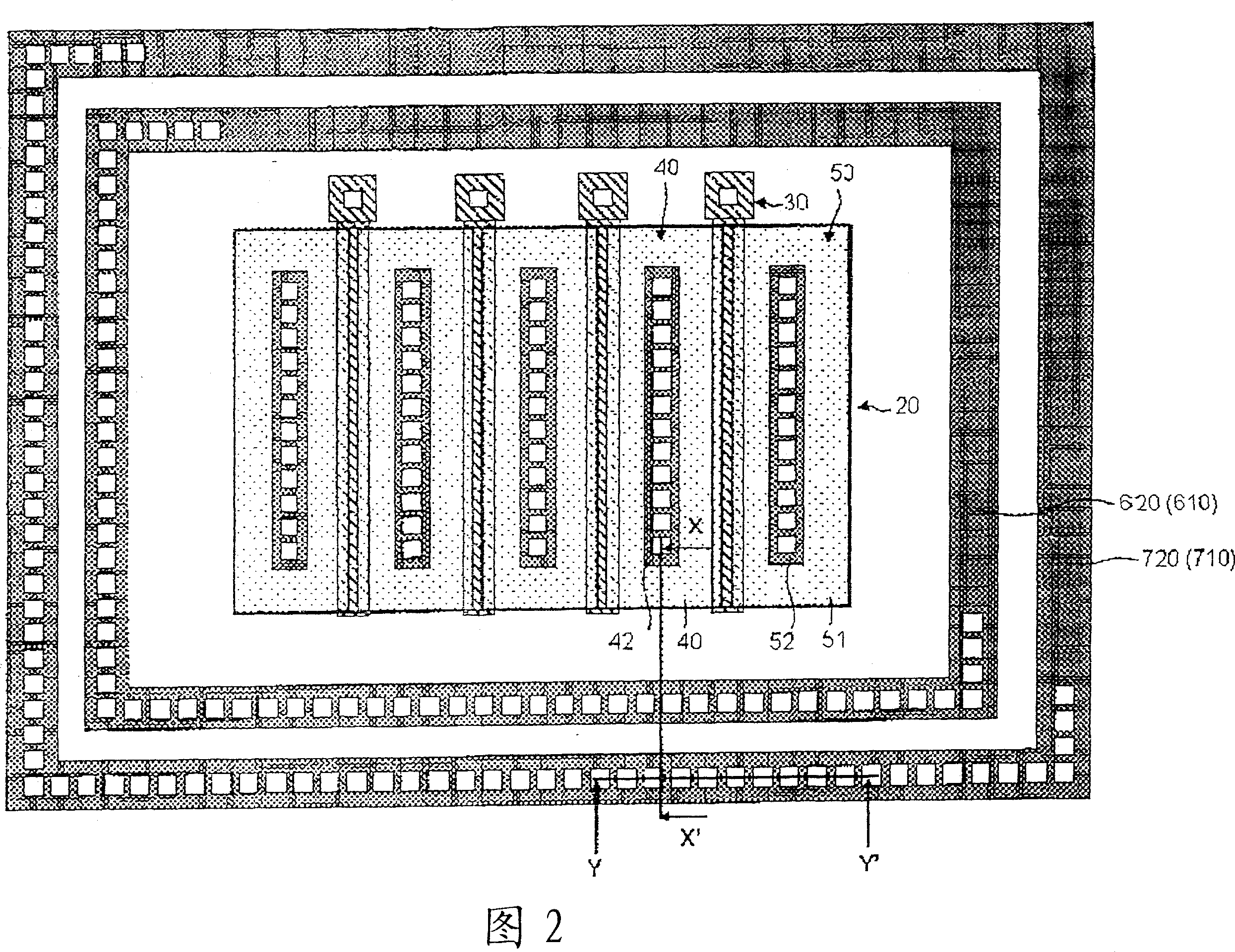

Semiconductor device

InactiveCN101022106AIncrease parasitic resistanceAvoid concentrationTransistorSemiconductor/solid-state device detailsProtection ringEngineering

The invention provides a semiconductor device. The semiconductor device forms a silicide on a protection ring for latch prevention, and avoids the protection ring from being damaged by an ESD surge. As a solving means, the semiconductor device has a structure that, a silicide with a width (W3) is not formed on a surface of a second protection ring for latch prevention, and at a side facing a transistor forming region (20).

Owner:OKI ELECTRIC IND CO LTD

Multi-finger transistor

ActiveUS6972463B2Avoid damageIncrease parasitic resistanceSemiconductor/solid-state device detailsSolid-state devicesGate dielectricPhysics

A multi-finger transistor is described, including multiple parallel transistors. Each transistor includes a gate dielectric layer, a gate, a source / drain region, and a drift region in the peripheral substrate of the source / drain region separating the source / drain region and the channel region under the gate. The width of the drift region extending from the side boundary of the source / drain region increases stepwise from the edge sections of the multi-finger transistor toward the central section of the same.

Owner:UNITED MICROELECTRONICS CORP

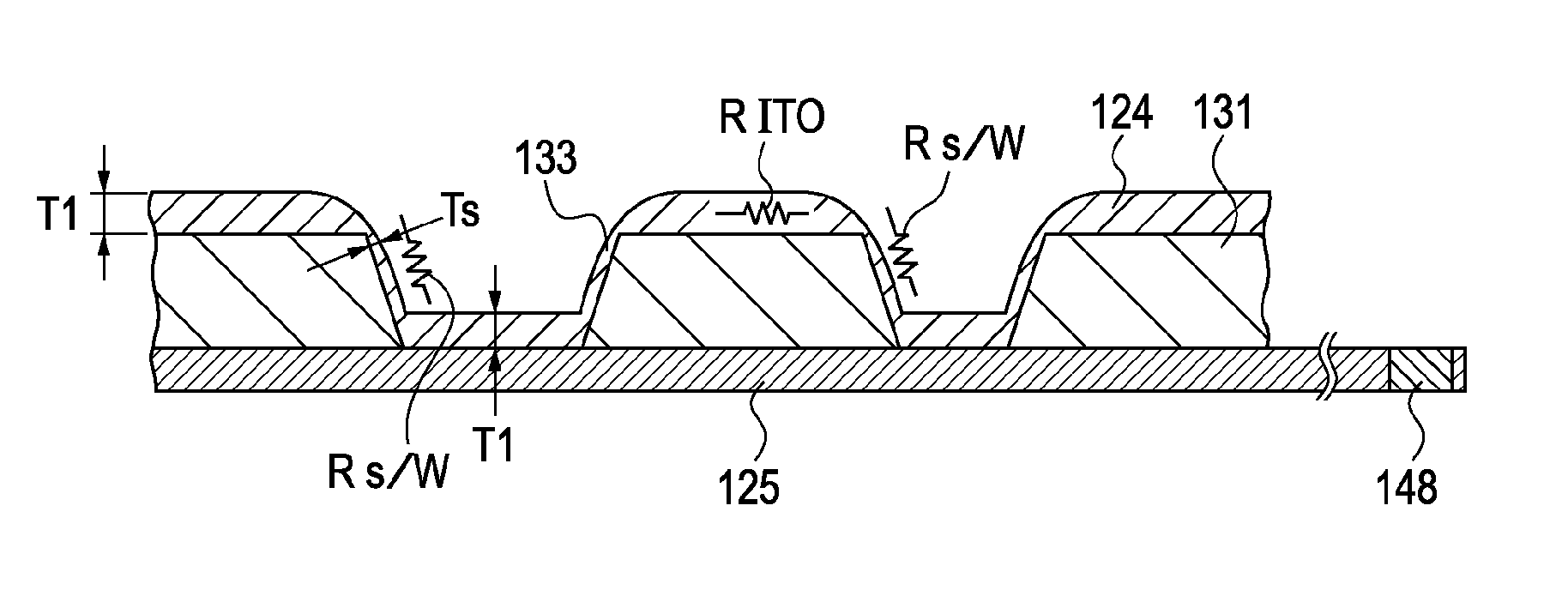

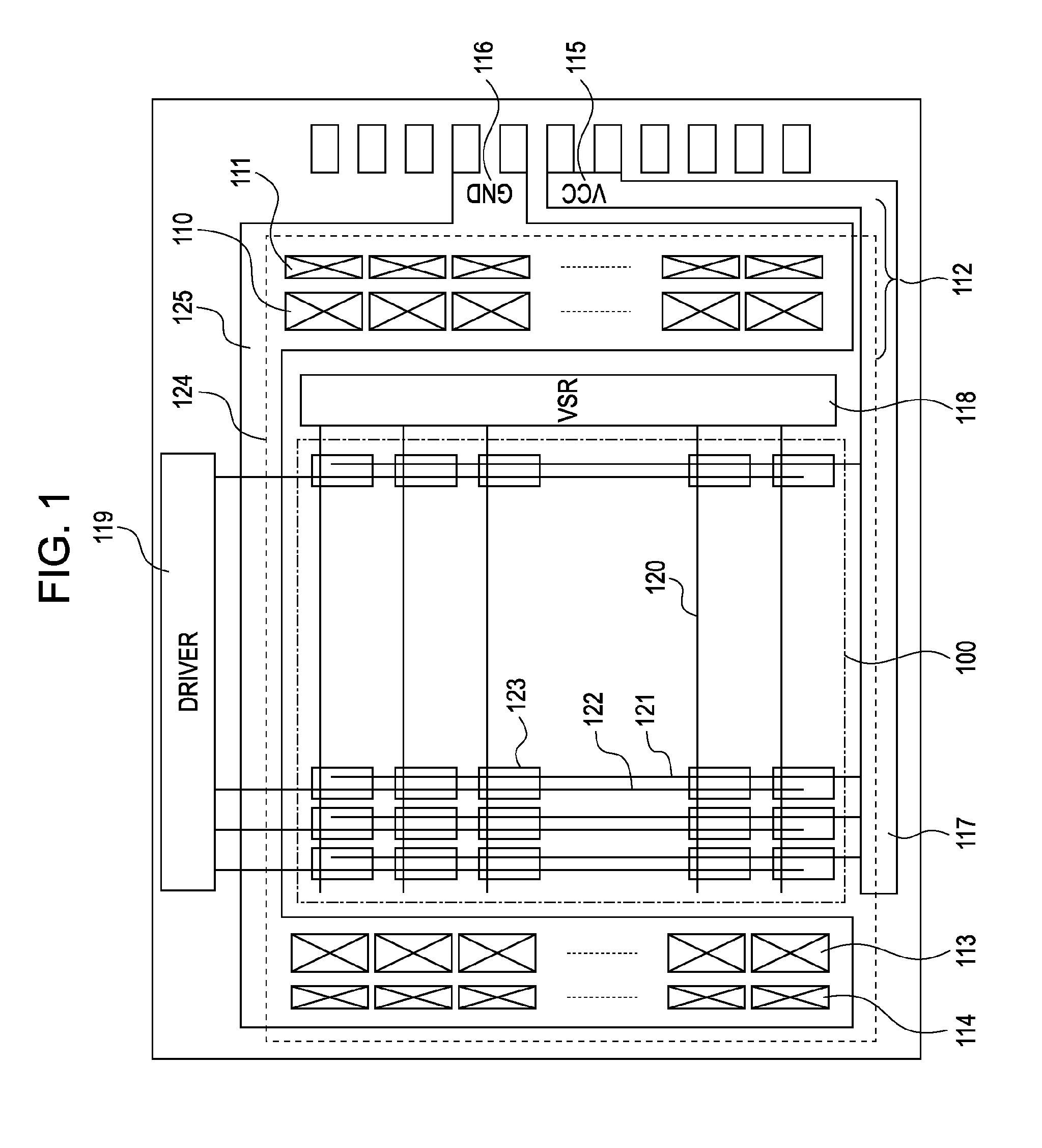

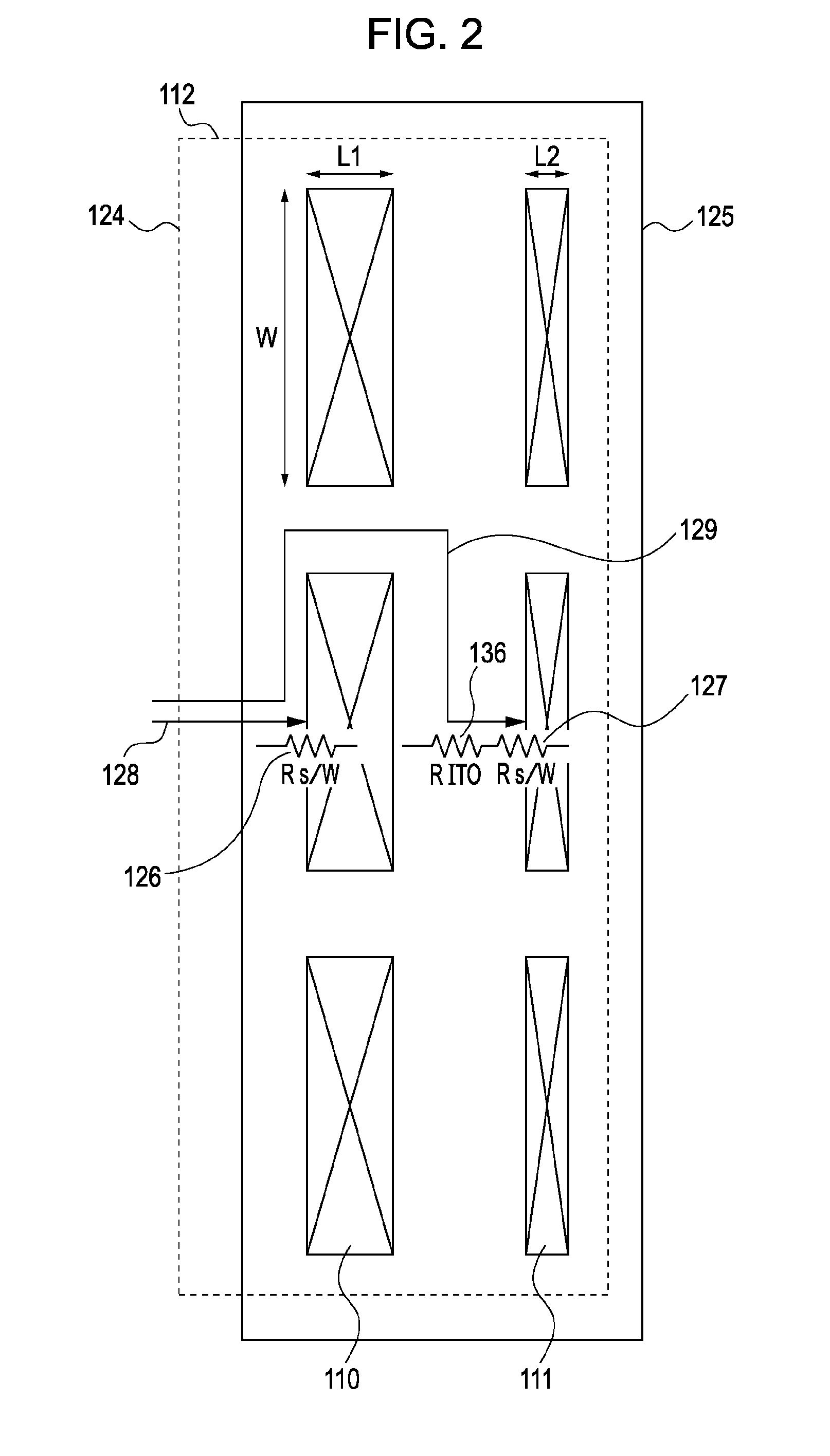

Display apparatus

ActiveUS20100141117A1Increase parasitic resistanceReduce power lossDischarge tube luminescnet screensLamp detailsEngineeringLight emitting device

In a display apparatus, a thin film transistor, a planarization film, and at least two light-emitting devices are provided on a substrate, and the light-emitting device at least includes a light-emitting layer and first and second electrodes. At least two first contact holes and at least two second contact holes are provided in the planarization film at a part outside a display region and connect the first electrode to ground wiring and / or power wiring with a resistance lower than that of the first electrode, the distance between the second contact hole and the display region is longer than that between the first contact hole and the display region, and the opening area of the second contact hole is smaller than that of the first contact hole.

Owner:CANON KK

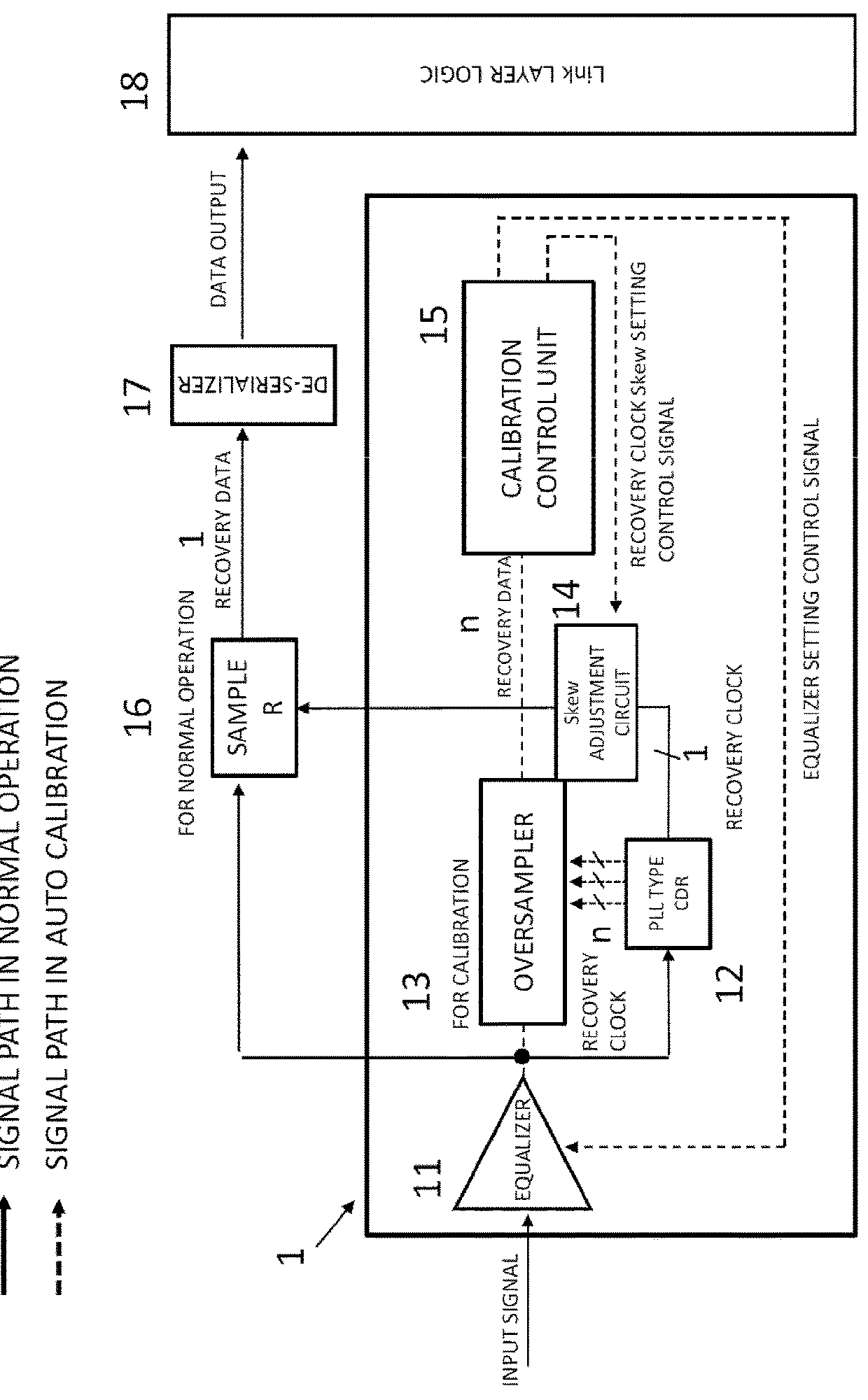

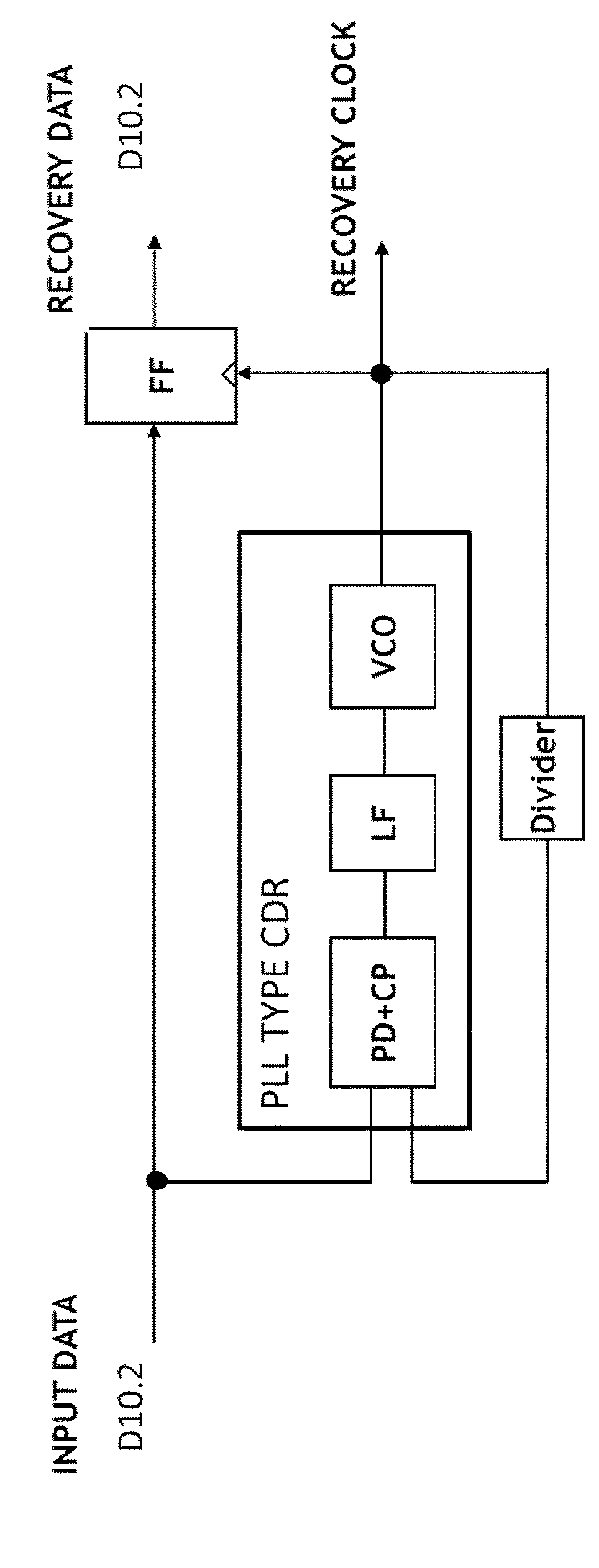

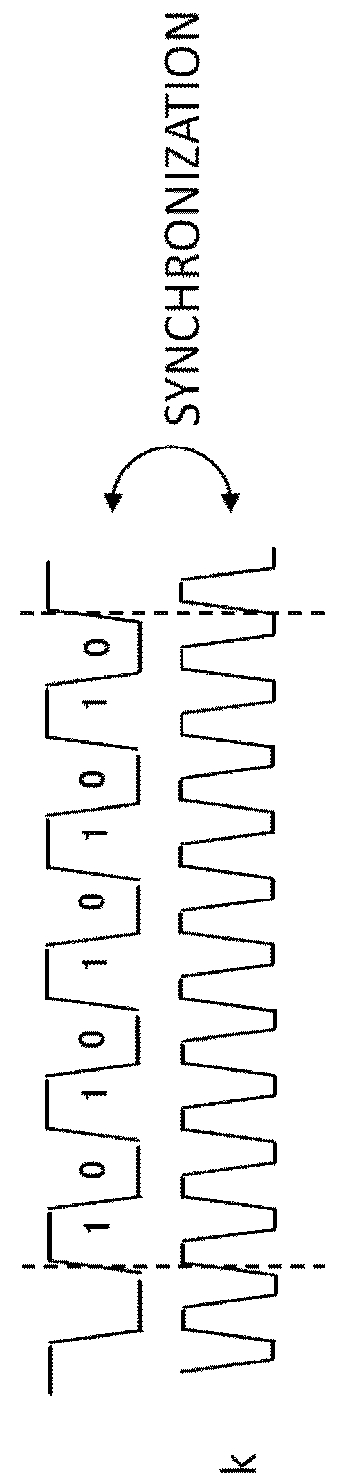

Data reception device

ActiveUS10009199B2Increase parasitic resistanceIncrease working frequencySynchronisation error correctionSynchronisation receiversControl signalWaveform shaping

A data reception device includes: an equalizer circuit that shapes a waveform of an input signal according to a set gain value; a CDR circuit which recovers a plurality of clock signals having different phases in one cycle from the input signal after being subjected to the waveform shaping performed by the equalizer circuit; an oversampler which performs sampling of the waveform-shaped input signal in synchronization with the plurality of clock signals and recovers a plurality of input data from the waveform-shaped input signal; and a calibration control unit which determines whether the oversampler correctly recovers the input data based on a result of the sampling performed by the oversampler, and generates a control signal to set the gain value of the equalizer circuit based on a determination result when it is determined that the input data is not correctly recovered.

Owner:CEREBREX ZHUHAI CO LTD

LDMOS (laterally diffused metal oxide semiconductor) device and manufacturing method thereof

ActiveCN104518027AIncreasing linear currentLower on-resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesOxide semiconductorPolycrystalline silicon

The invention discloses an LDMOS (laterally diffused metal oxide semiconductor) device and a manufacturing method thereof. A drift region of the LDMOS device comprises a first drift region and a second drift region; the first drift region is formed by an ion implantation region formed in a selected area of a silicon substrate; the second drift region is formed by doped polysilicon formed on the surface of the silicon substrate; the second drift region is overlapped on the first drift region, and a drain region is formed in the second drift region. Owing to arrangement of the second drift region, thickness of the whole drift region is increased, and accordingly parasitic resistance of the whole drift region is reduced while effectiveness in increase of linear current of the device and reduction of on resistance of the device can be achieved. In addition, the LDMOS device is capable of keeping high breakdown voltage and is low in process cost.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

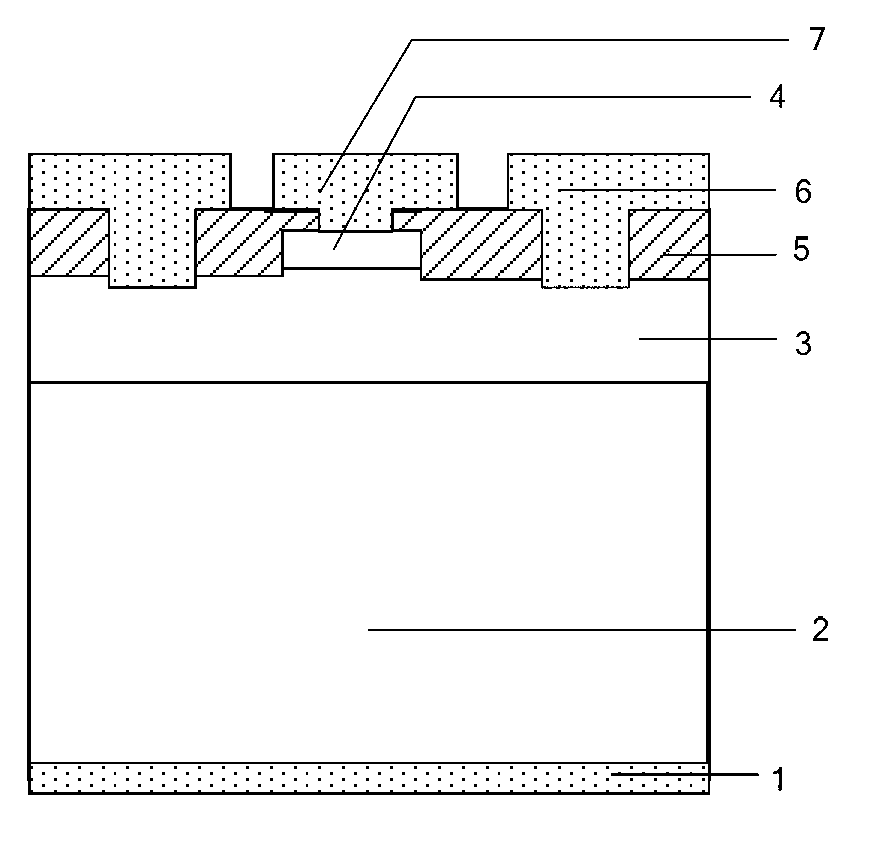

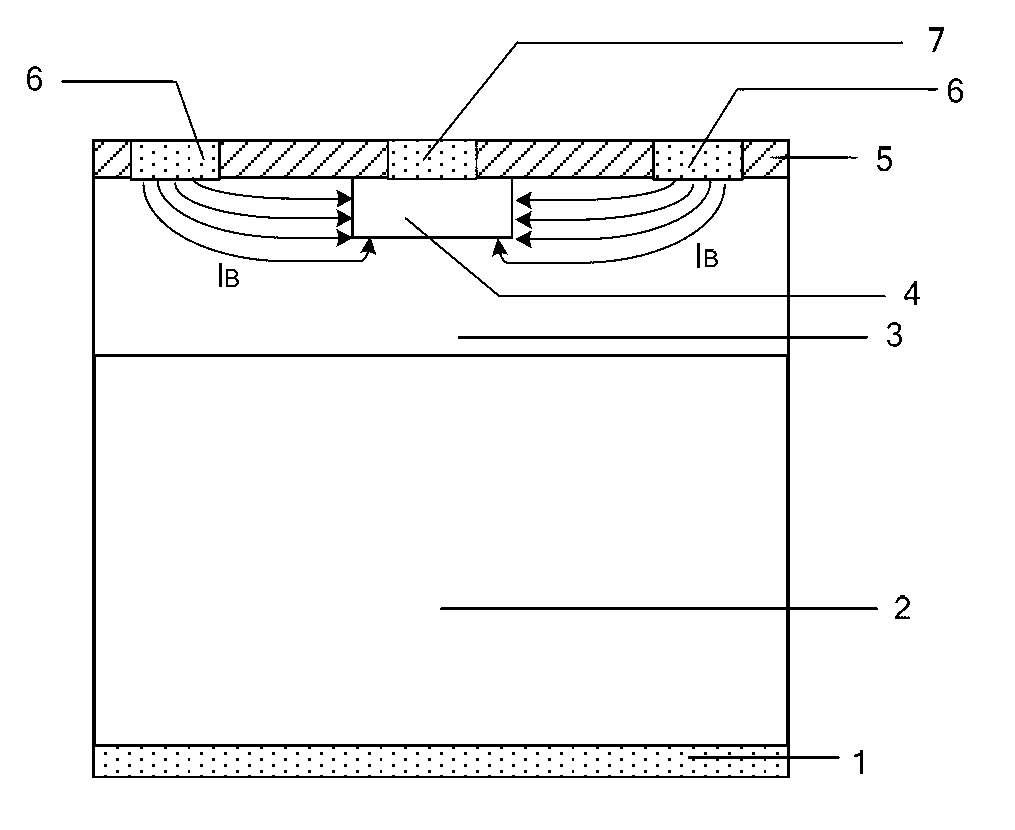

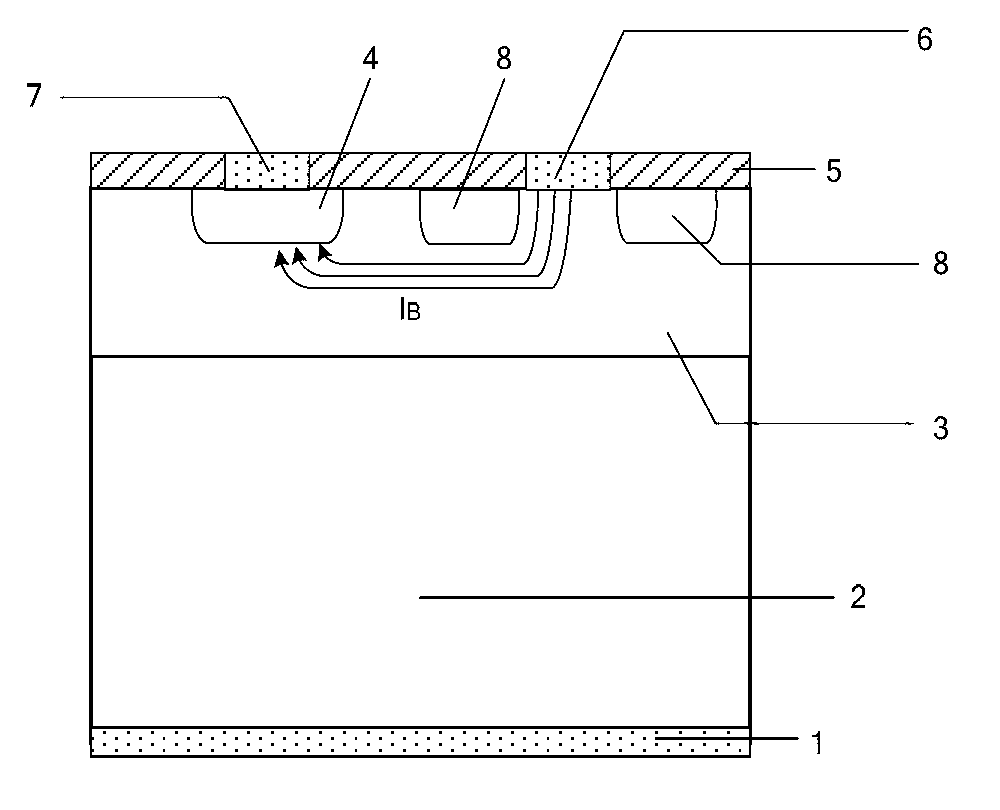

Power bipolar transistor and manufacture method thereof

InactiveCN102856368AIncrease parasitic resistanceOutput power has no effectTransistorSemiconductor/solid-state device manufacturingSemiconductor materialsDevice material

The invention discloses a power bipolar transistor and a manufacture method thereof and belongs to the field of semiconductor devices and technological manufacture. The power bipolar transistor sequentially comprises a collector area metal electrode, a collector area formed by first conduction type semiconductor materials and a base area formed by second conduction type semiconductor materials from bottom to top, wherein a base area metal electrode contacted with the surface of the base area and a transmission area formed by the first conduction type semiconductor materials are arranged above the base area; a transmission area metal electrode contacted with the surface of the transmission area is arranged above the transmission area, and isolation media are filled between the lateral wall of the transmission area and the base area metal electrode and between the base area metal electrode and the transmission area metal electrode. The lateral wall of the transmission area is wrapped by a medium layer, so that current of a base electrode directly flows to the lateral wall of the transmission area by contacting with the base area, and current side concentration effect is remitted. Simultaneously, the base area metal electrode is manufactured on the isolation media by punching holes, parasitic resistance of the base area cannot be added, and no influence can be caused on output power of the power bipolar transistor.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA +1

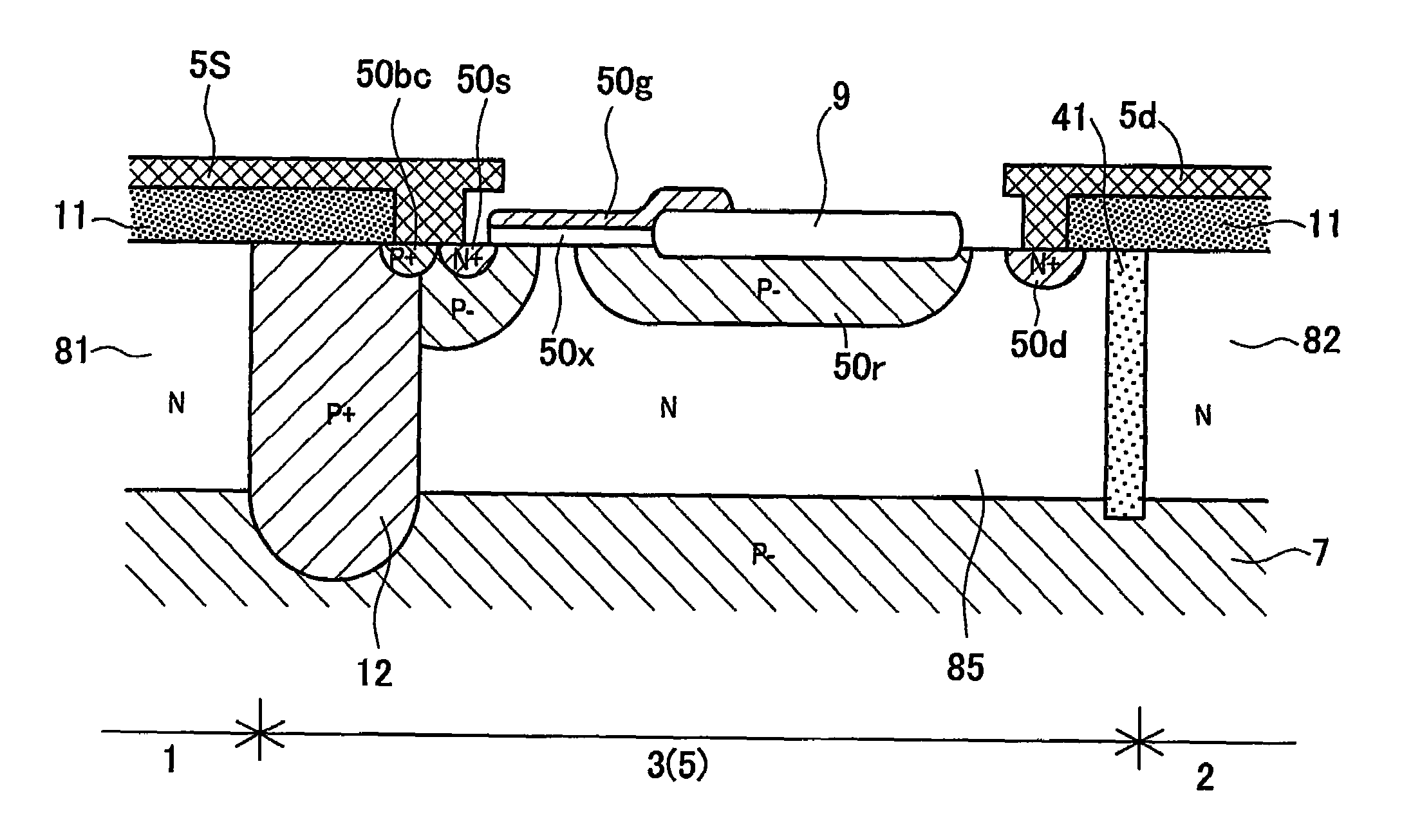

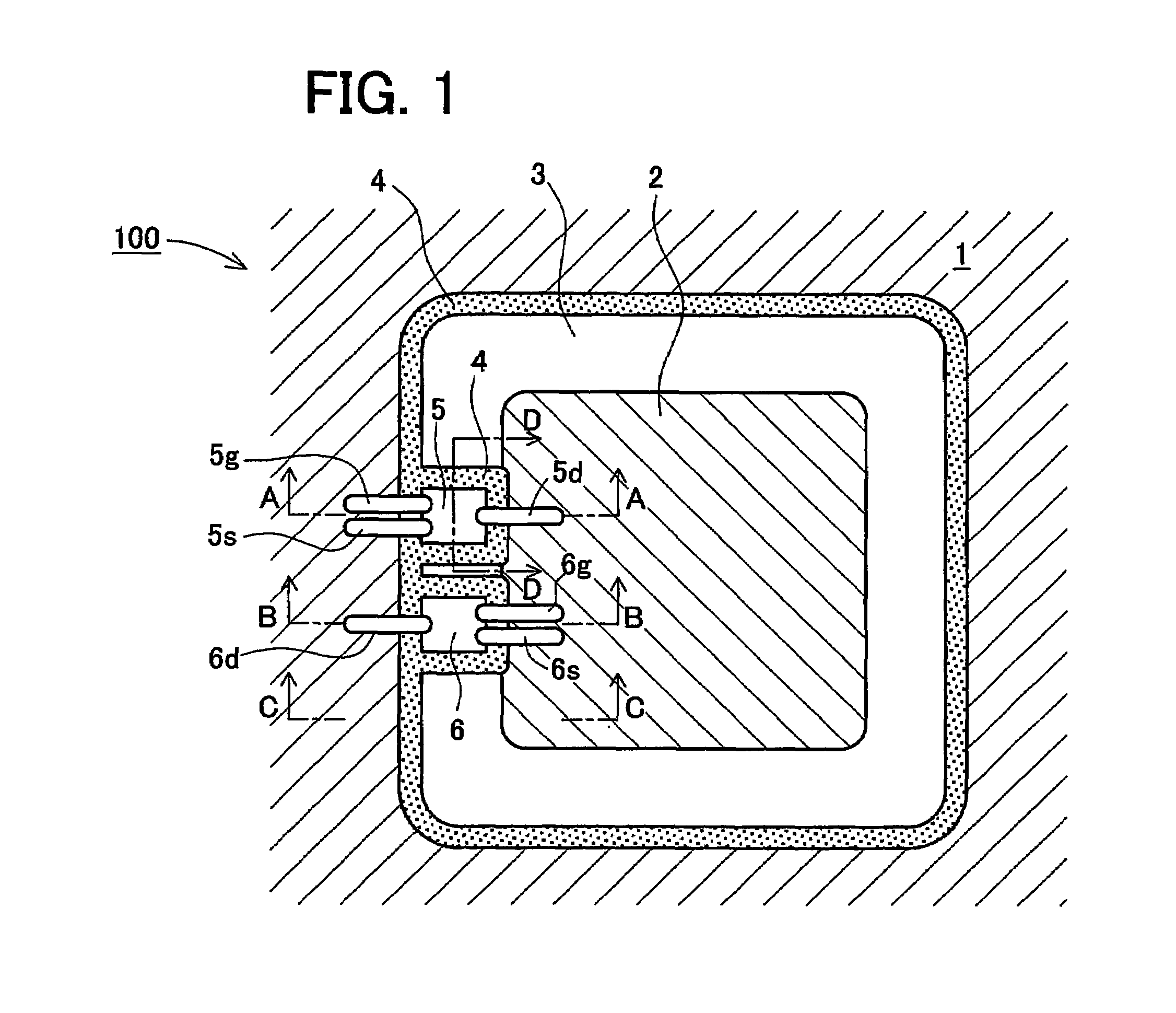

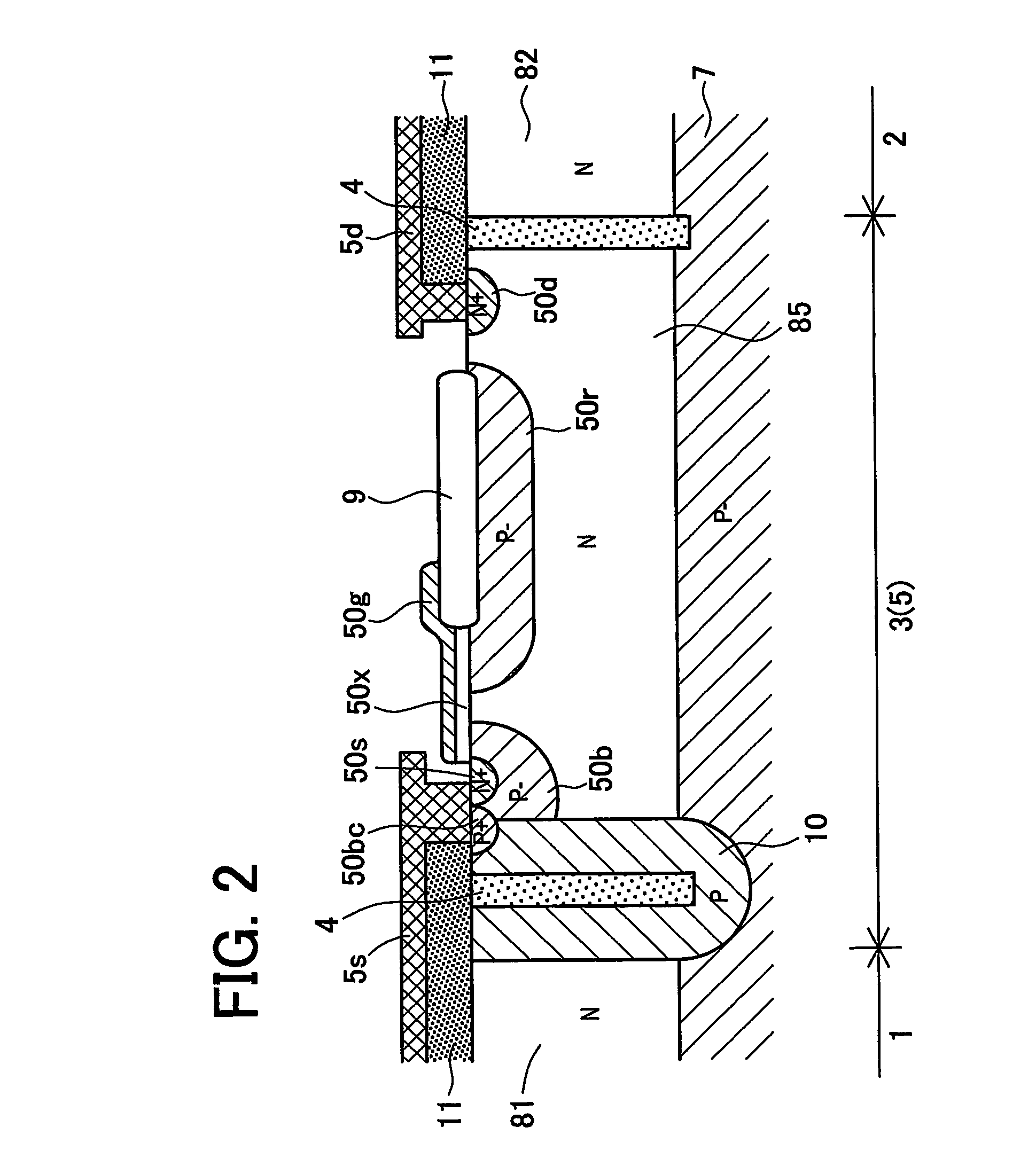

Semiconductor apparatus

ActiveUS7538407B2Simple designPrevent punch-throughTransistorSolid-state devicesEngineeringReference circuit

A semiconductor apparatus (100) comprises a low potential reference circuit region (1) and a high potential reference circuit region (2), and the high potential reference circuit region (2) is surrounded by a high withstand voltage separating region (3). By a trench (4) formed in the outer periphery of the high withstand voltage separating region (3), the low potential reference circuit region (1) and high potential reference circuit region (2) are separated from each other. Further, the trench (4) is filled up with an insulating material, and insulates the low potential reference circuit region (1) and high potential reference circuit region (2). The high withstand voltage separating region (3) is partitioned by the trench (4), high withstand voltage NMOS (5) or high withstand voltage PMOS (6) is provided in the partitioned position.

Owner:TOYOTA JIDOSHA KK

Structure and method for self protection of power device with expanded voltage ranges

InactiveUS8441109B2Enhanced couplingIncrease parasitic resistanceSemiconductor/solid-state device detailsSolid-state devicesElectrical resistance and conductanceEngineering

A vertical semiconductor power device includes a top surface and a bottom surface of a semiconductor substrate constituting a vertical current path for conducting a current there through. The semiconductor power device further includes an over current protection layer composed of a material having a resistance with a positive temperature coefficient (PTC) and the over current protection layer constituting as a part of the vertical current path connected to a source electrode and providing a feedback voltage a gate electrode of the vertical semiconductor power device for limiting a current passing there through for protecting the semiconductor power device at any voltage.

Owner:ALPHA & OMEGA SEMICON LTD

Field effect transistor having nitride semiconductor layer

ActiveUS7714359B2Increase resistanceImprove featuresSemiconductor devicesConduction bandField-effect transistor

A field effect transistor includes a nitride semiconductor layer; an InxAlyGa1-x-yN layer (wherein 0<x<1, 0<y<1 and 0<x+y<1) formed on the nitride semiconductor layer; and a source electrode and a drain electrode formed on and in contact with the InxAlyGa1-x-yN layer. The lower ends of the conduction bands of the nitride semiconductor layer and the InxAlyGa1-x-yN layer are substantially continuous on the interface therebetween.

Owner:PANASONIC CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com