Patents

Literature

74results about How to "Scale down" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

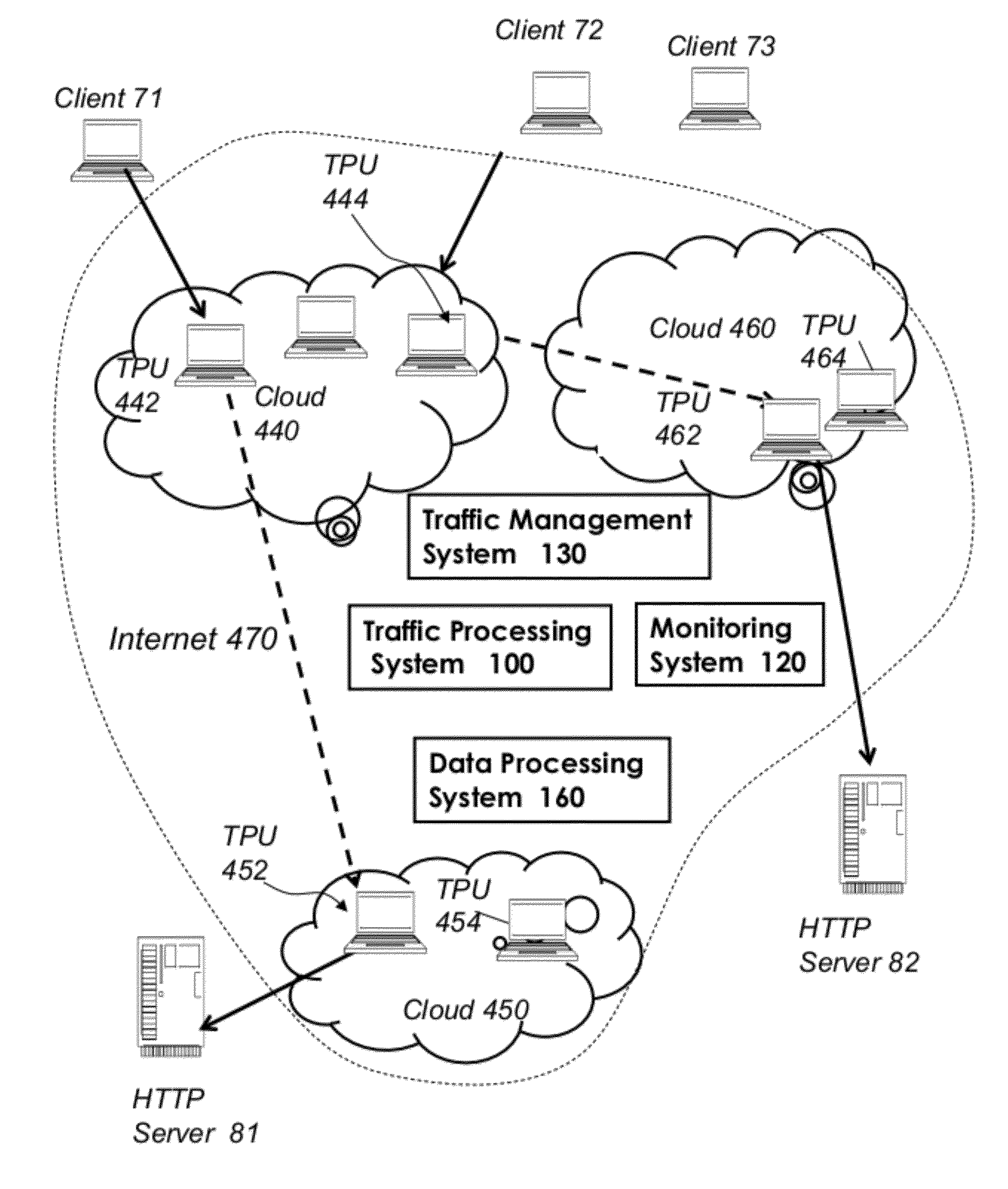

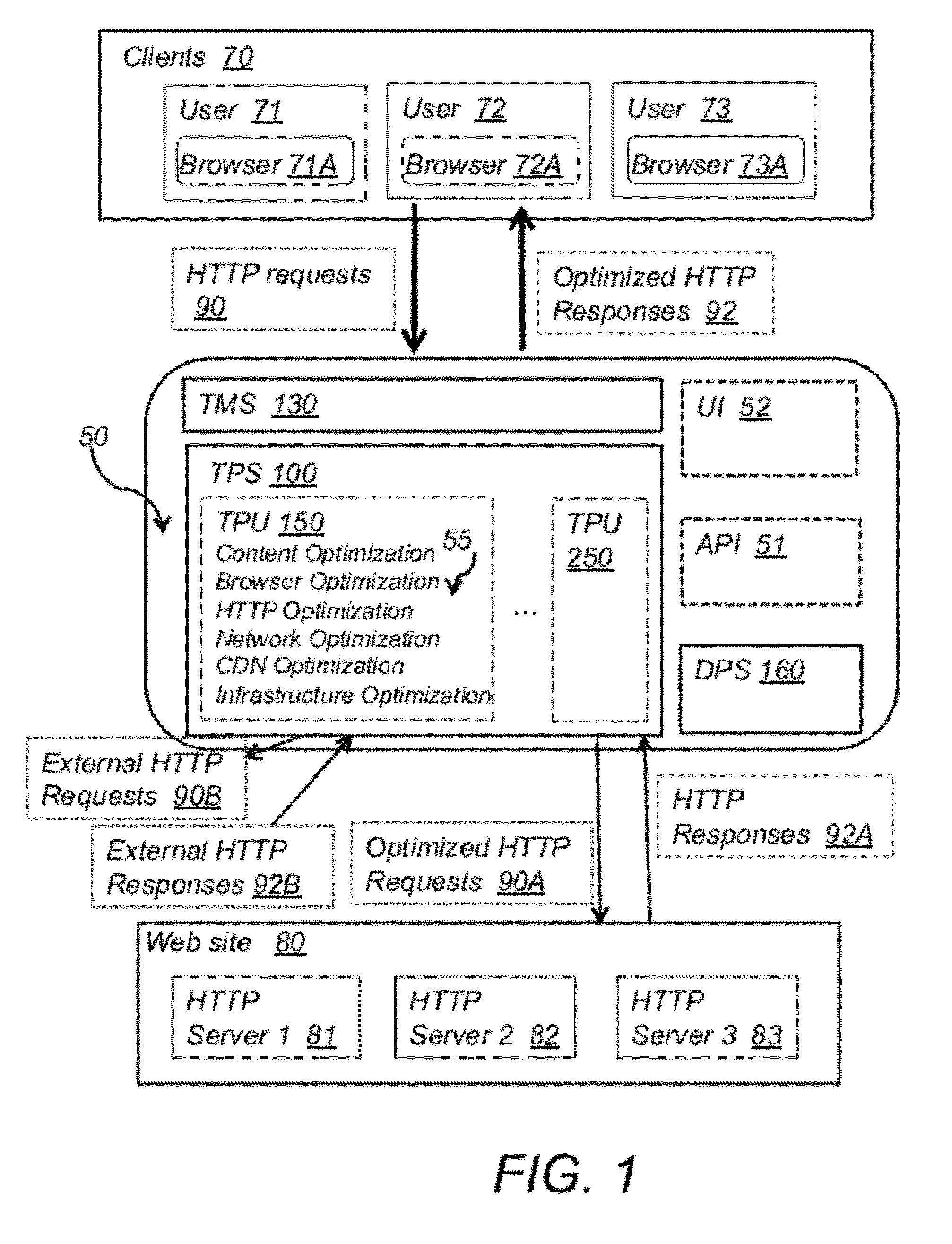

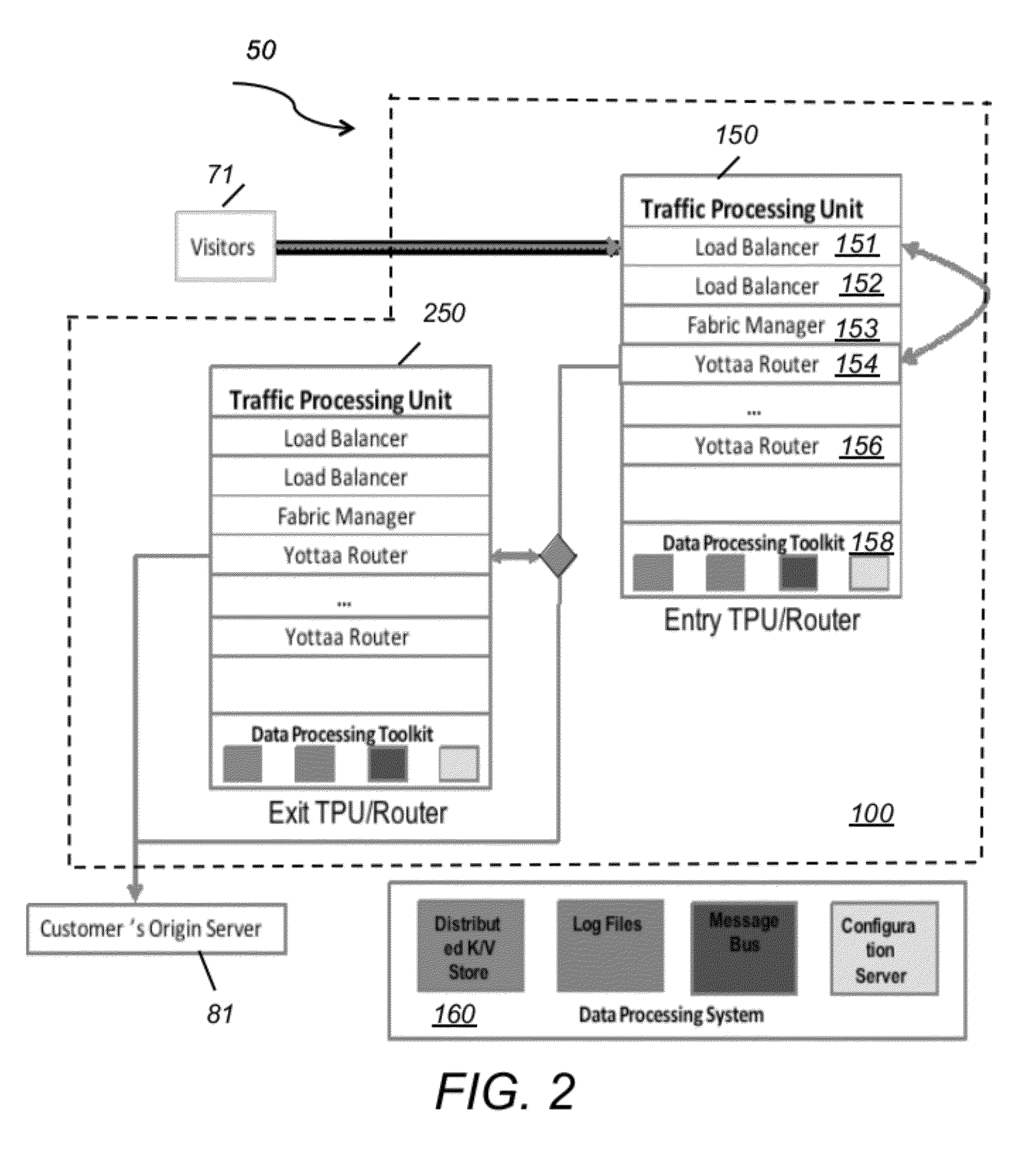

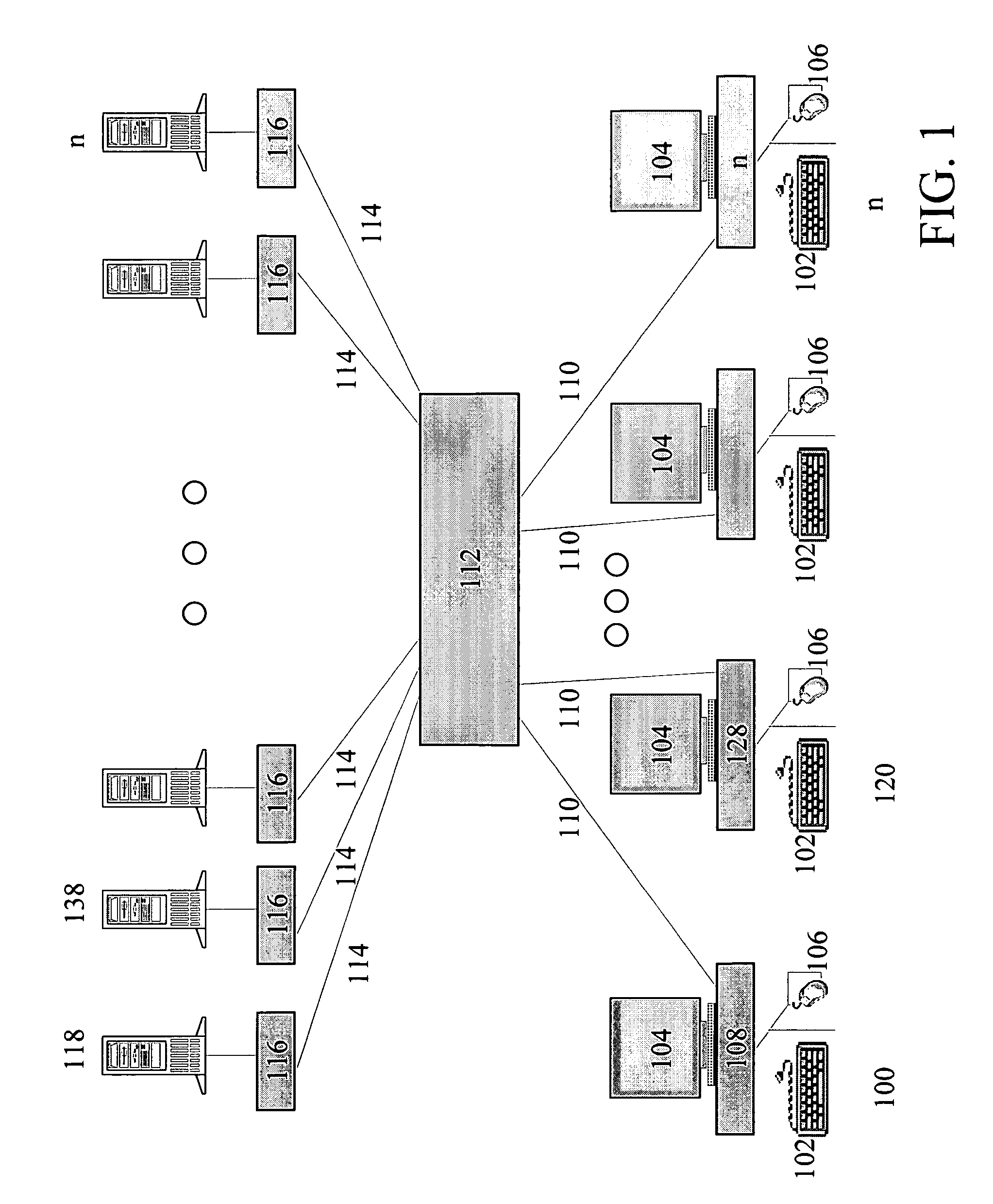

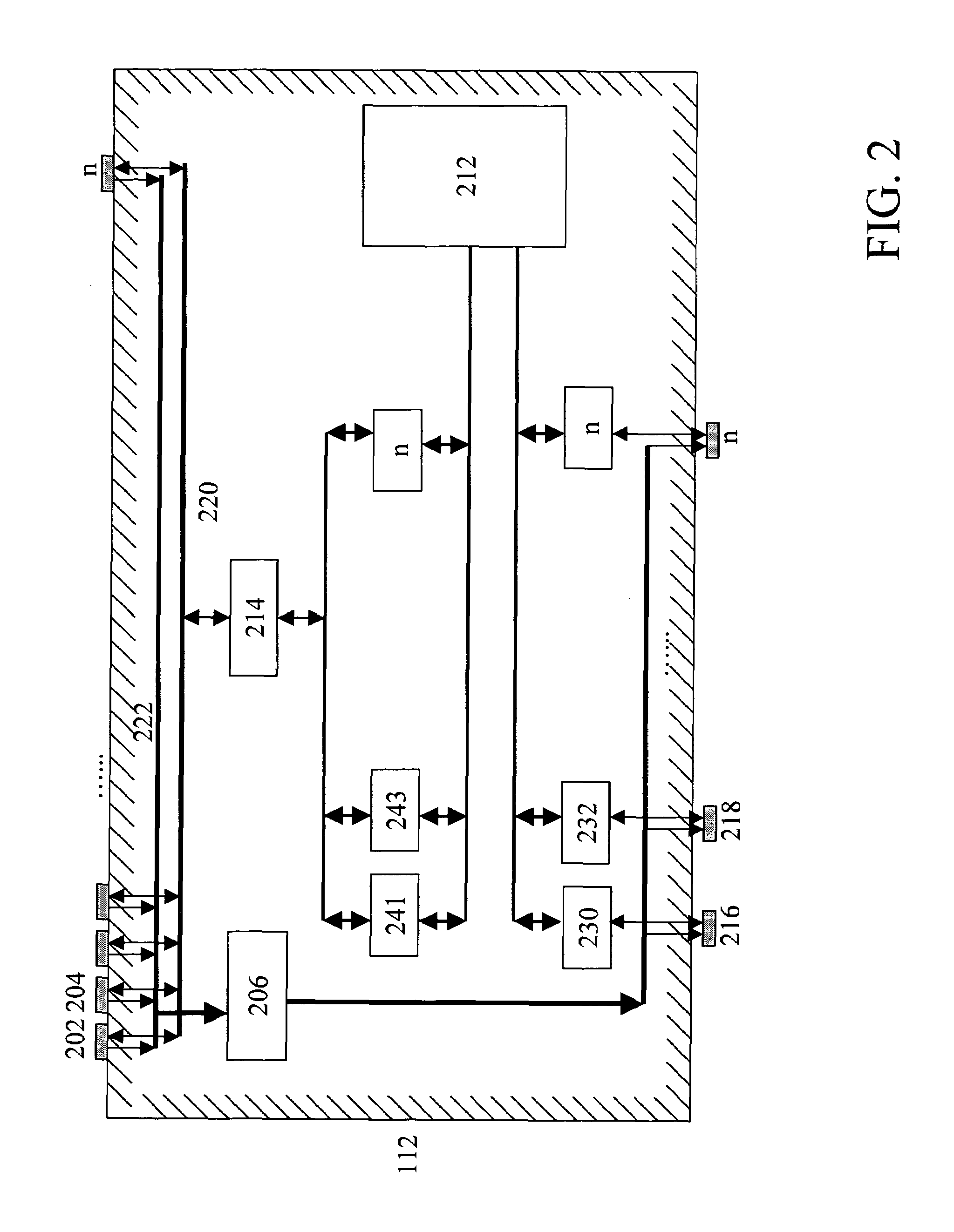

System and method for website performance optimization and internet traffic processing

ActiveUS20110137973A1Addressing slow performanceReduce in quantityMemory loss protectionError detection/correctionTraffic capacityWeb site

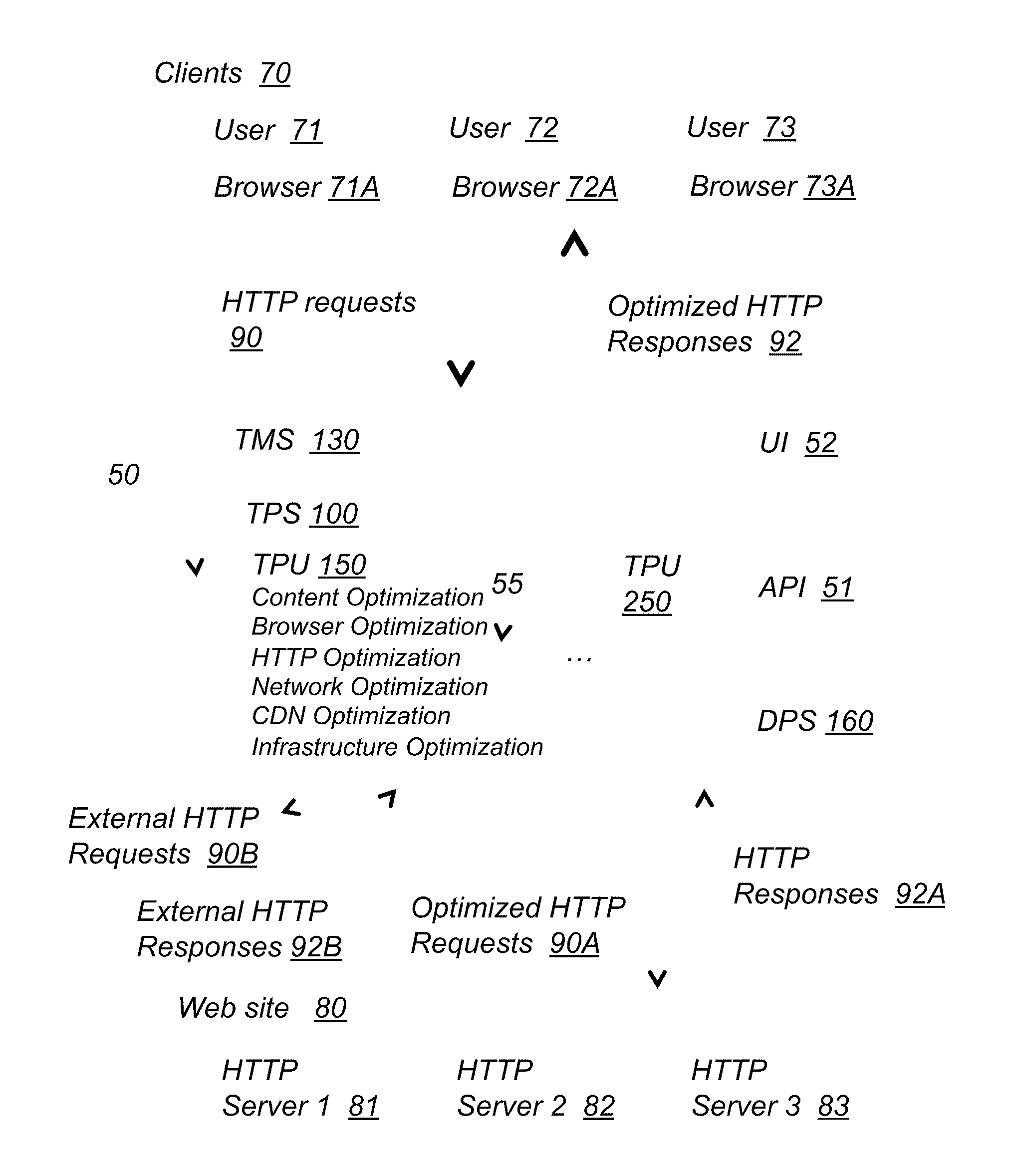

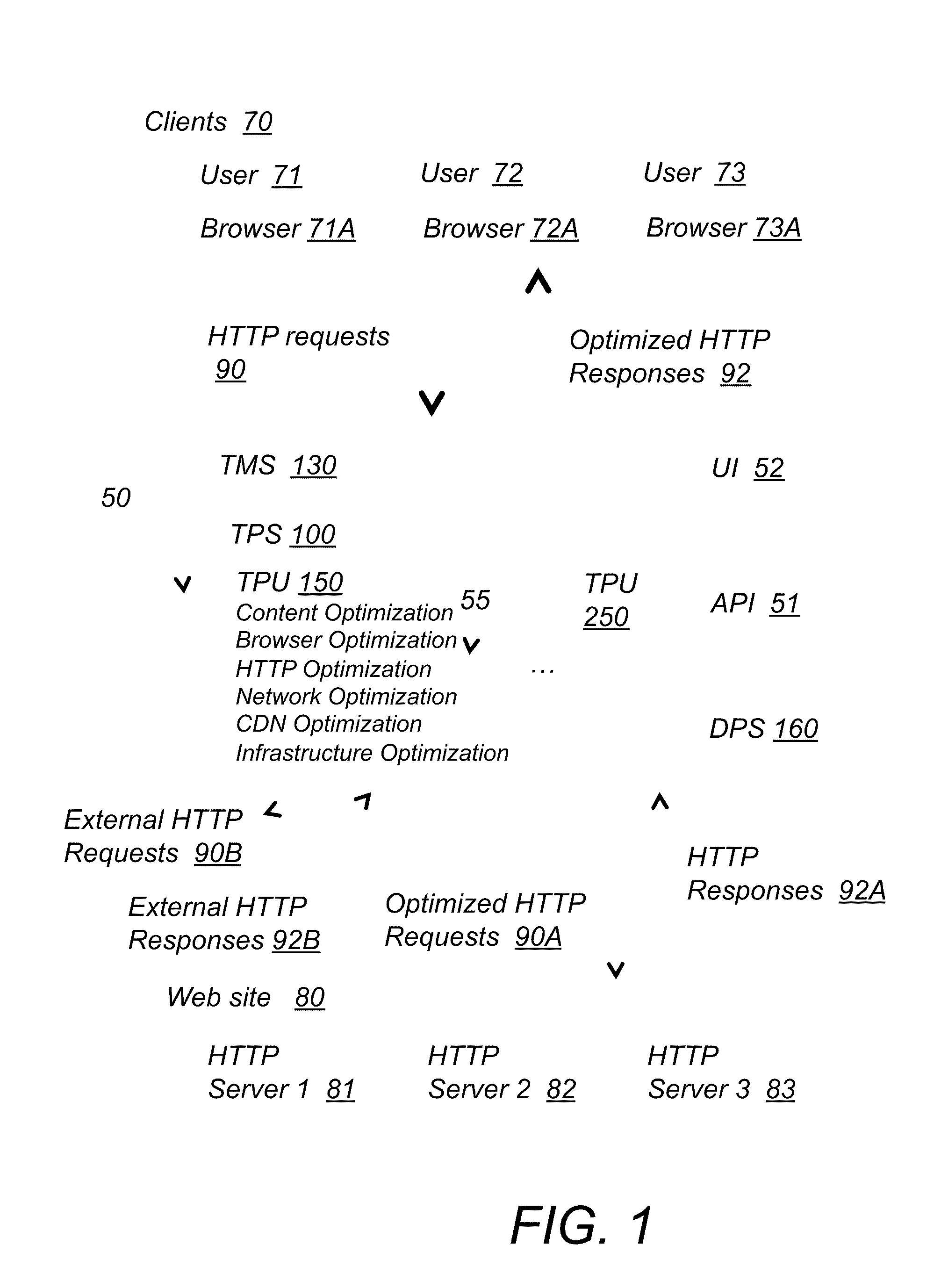

A system for optimizing the performance of a website that runs on one or more HTTP servers and is configured to receive HTTP requests from one or more clients via user agents and provide HTTP responses to the one or more clients includes an intermediary component configured to connect to the clients and the servers via network connections. The intermediary component includes a traffic management system (TMS) that includes means for managing HTTP requests originating from the clients and targeting the servers and HTTP responses originating from the servers and targeting the clients and means for redirecting the HTTP requests to the intermediary component. The intermediary component further includes a traffic processing system that includes means for receiving the redirected HTTP requests and the HTTP responses and means for applying optimization techniques to the redirected HTTP requests and the HTTP responses.

Owner:YOTTAA

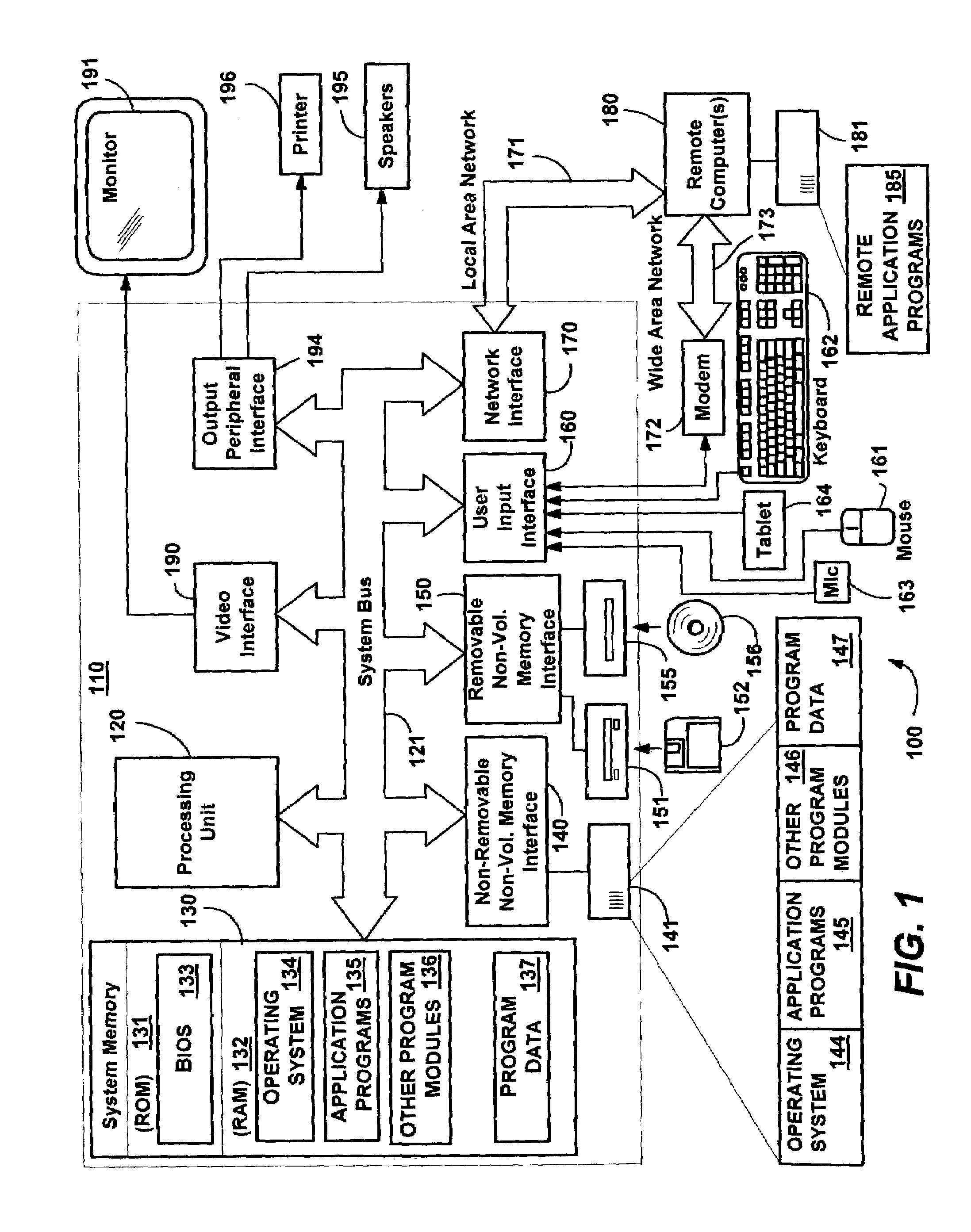

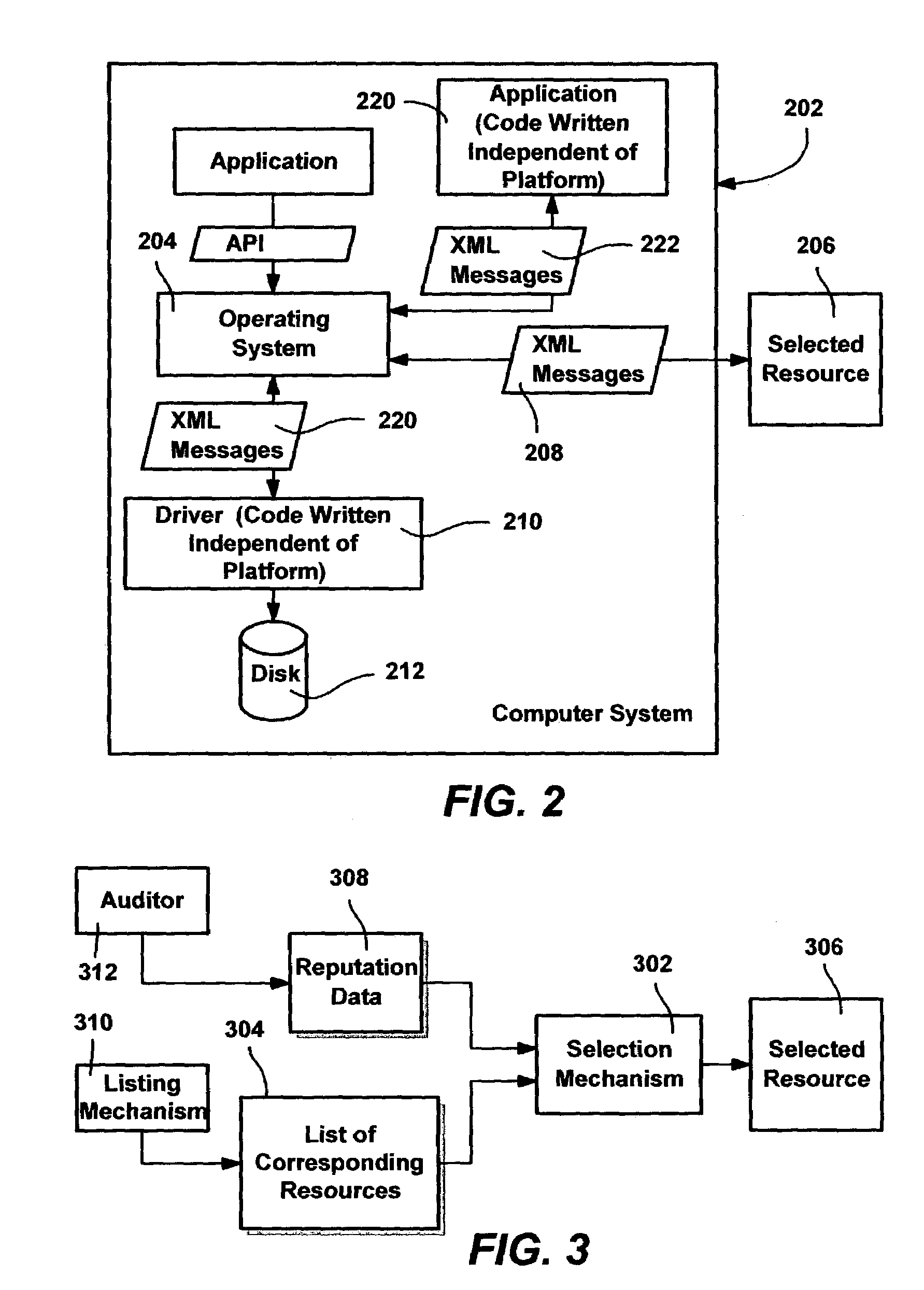

Reputation system for web services

InactiveUS7467206B2Good reputationScale downWeb data indexingNatural language data processingWeb serviceThe Internet

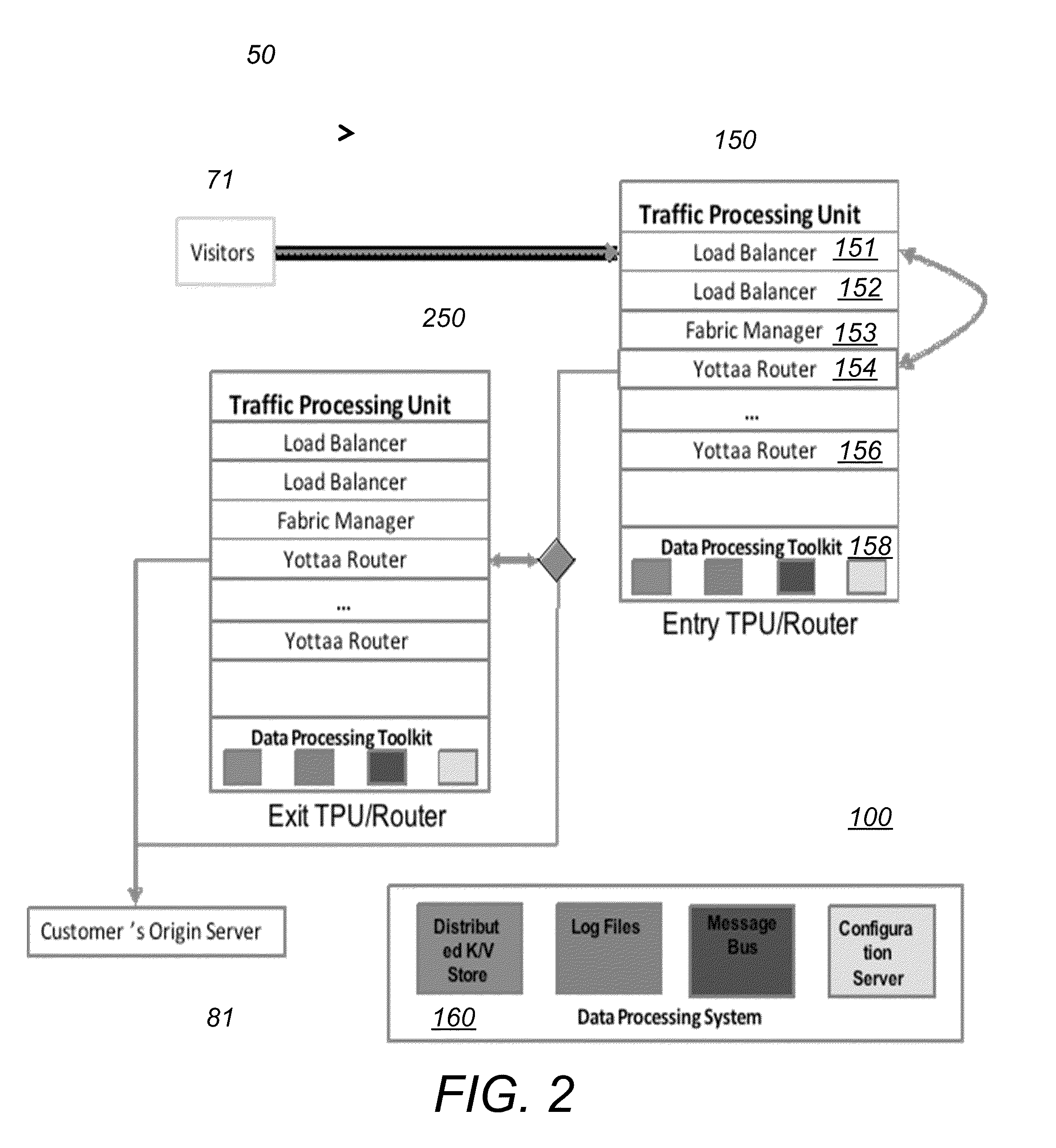

A system and method for automating the web service selection based on reputation information, to help negotiate a contractual web service binding between a client and a server. Reputation information may be schematized into behavioral attributes such as web service responsiveness, web service latency, web service uptime, cost data, business solvency and other trustworthiness and business-related data. Some of the reputation data may be empirically determined, and provided by an independent or other trusted auditor. In one implementation, a client queries a search engine, which returns a ranked list of web services, with the ranking based on reputation scores computed for each web service as collected by an auditor. Clients may provide computational data to weigh the attributes separately. A corporate internet can maintain reputation data for web services to act as an auditor, and a web service server can also execute trusted code to act as an auditor.

Owner:MICROSOFT TECH LICENSING LLC

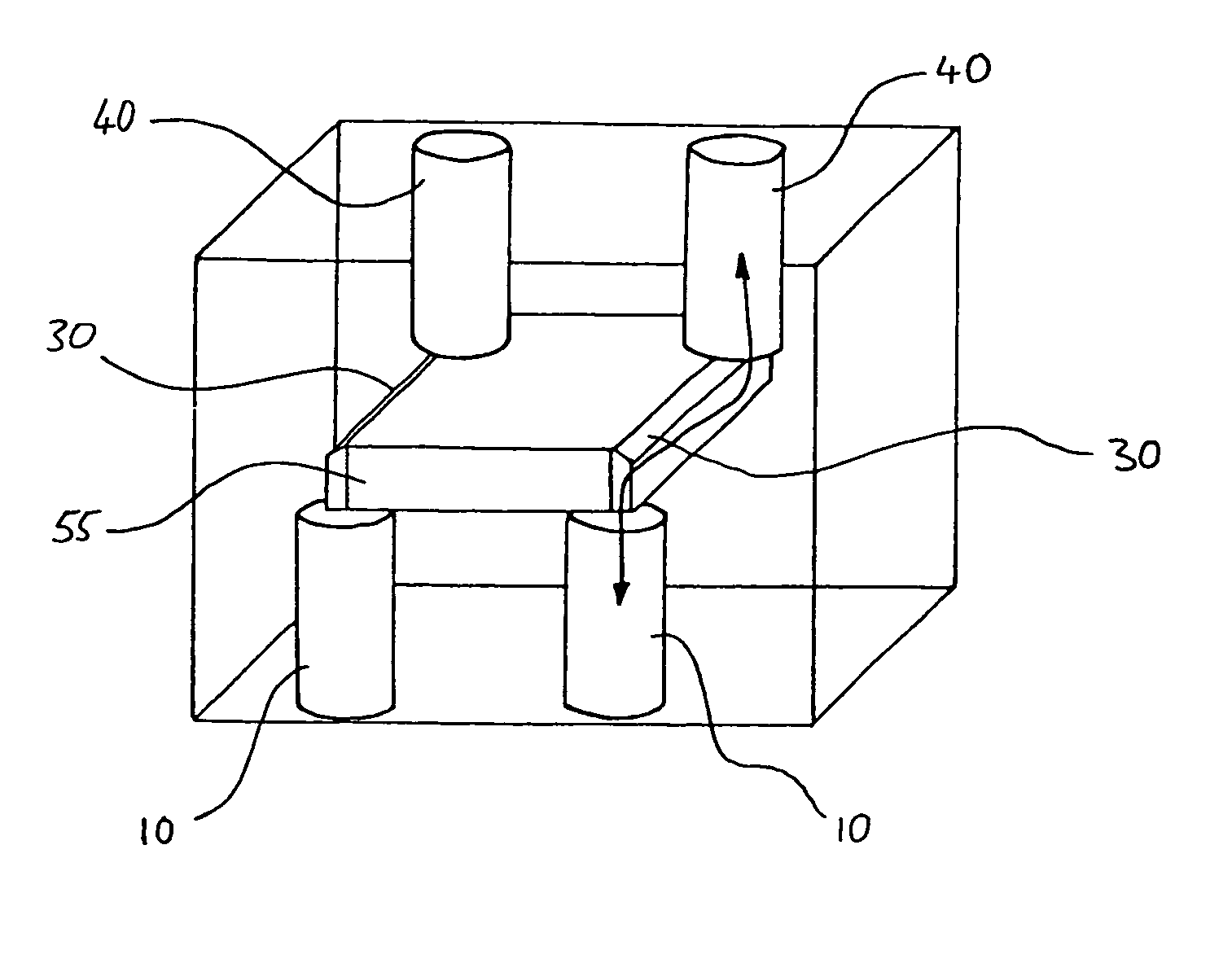

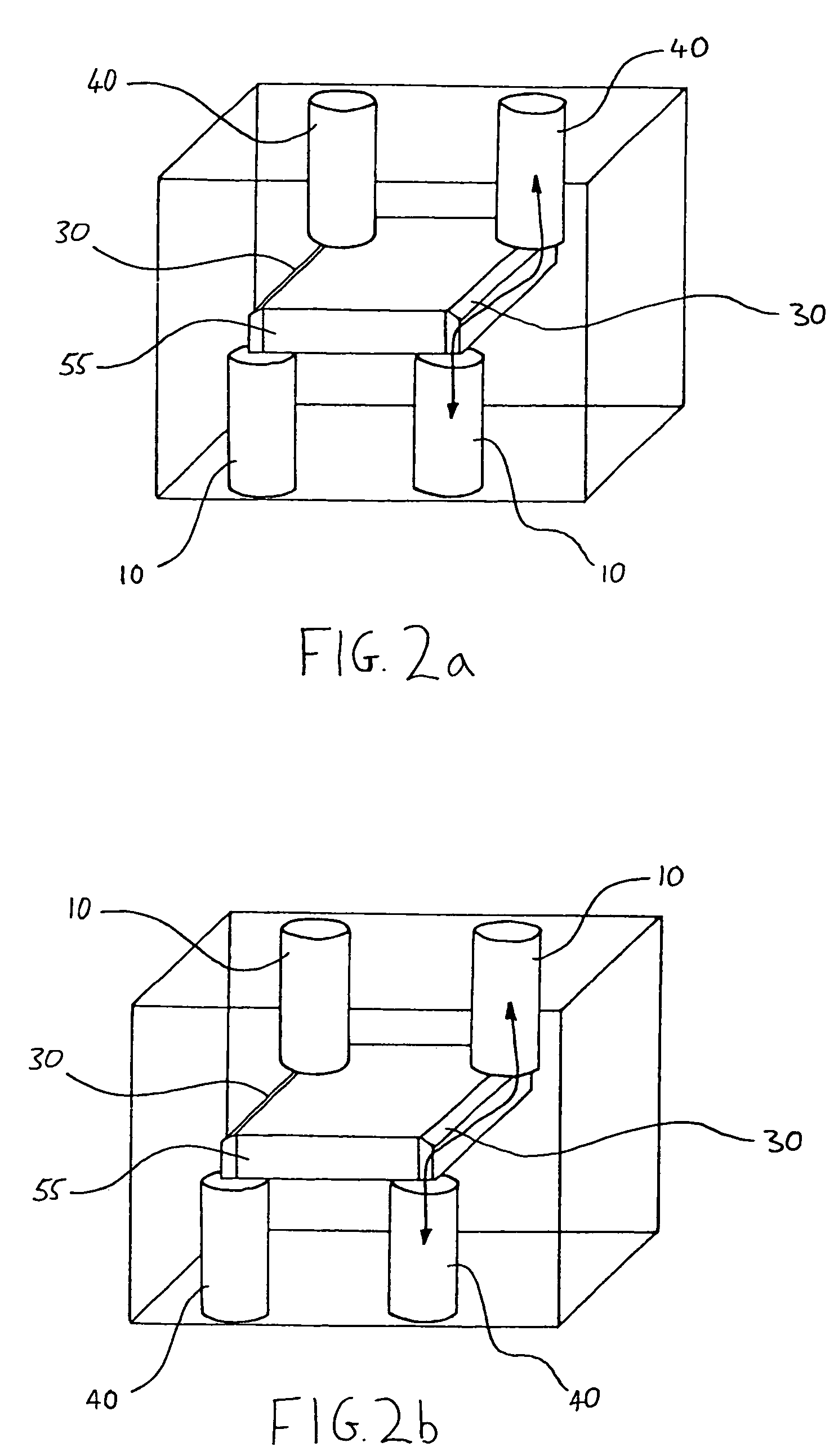

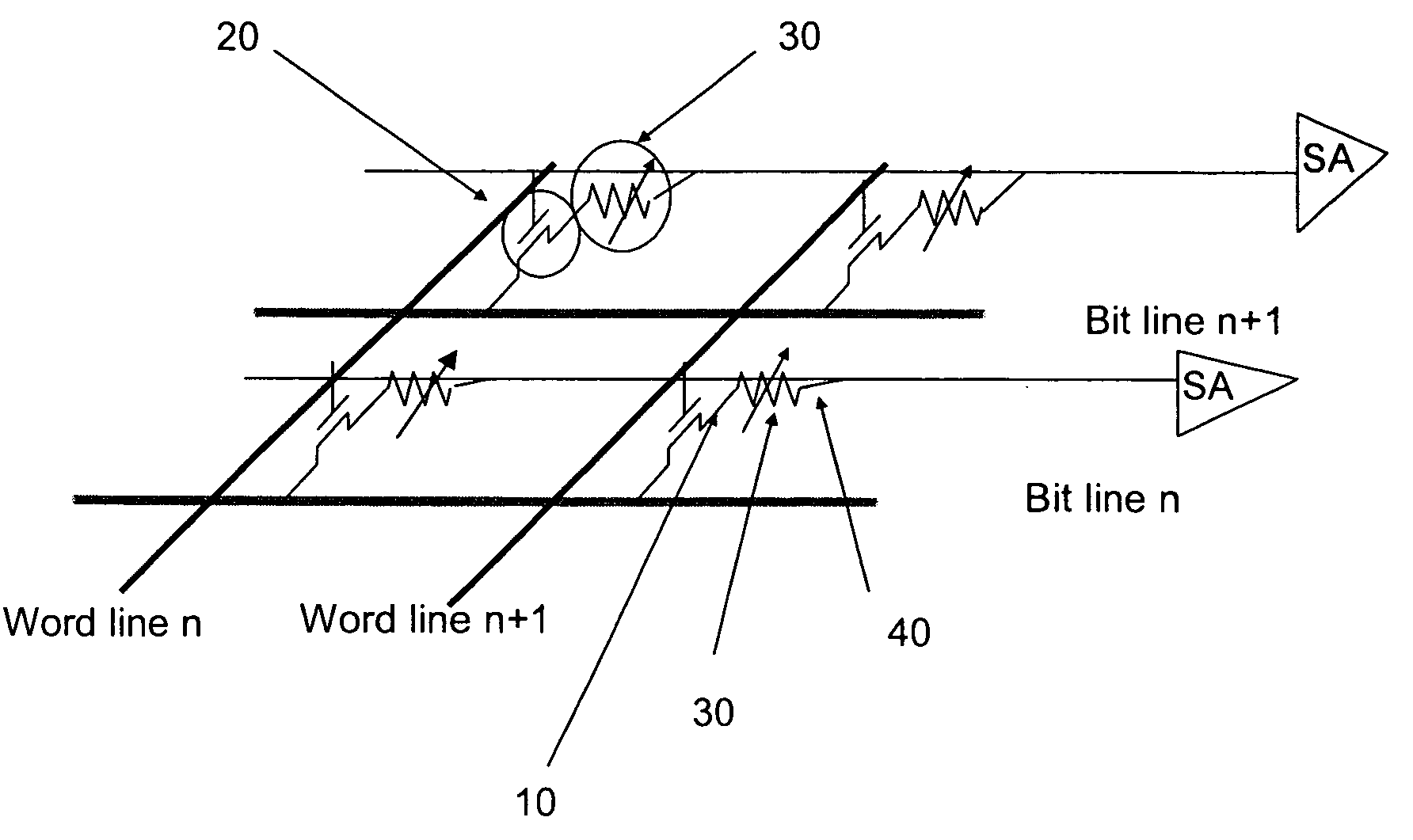

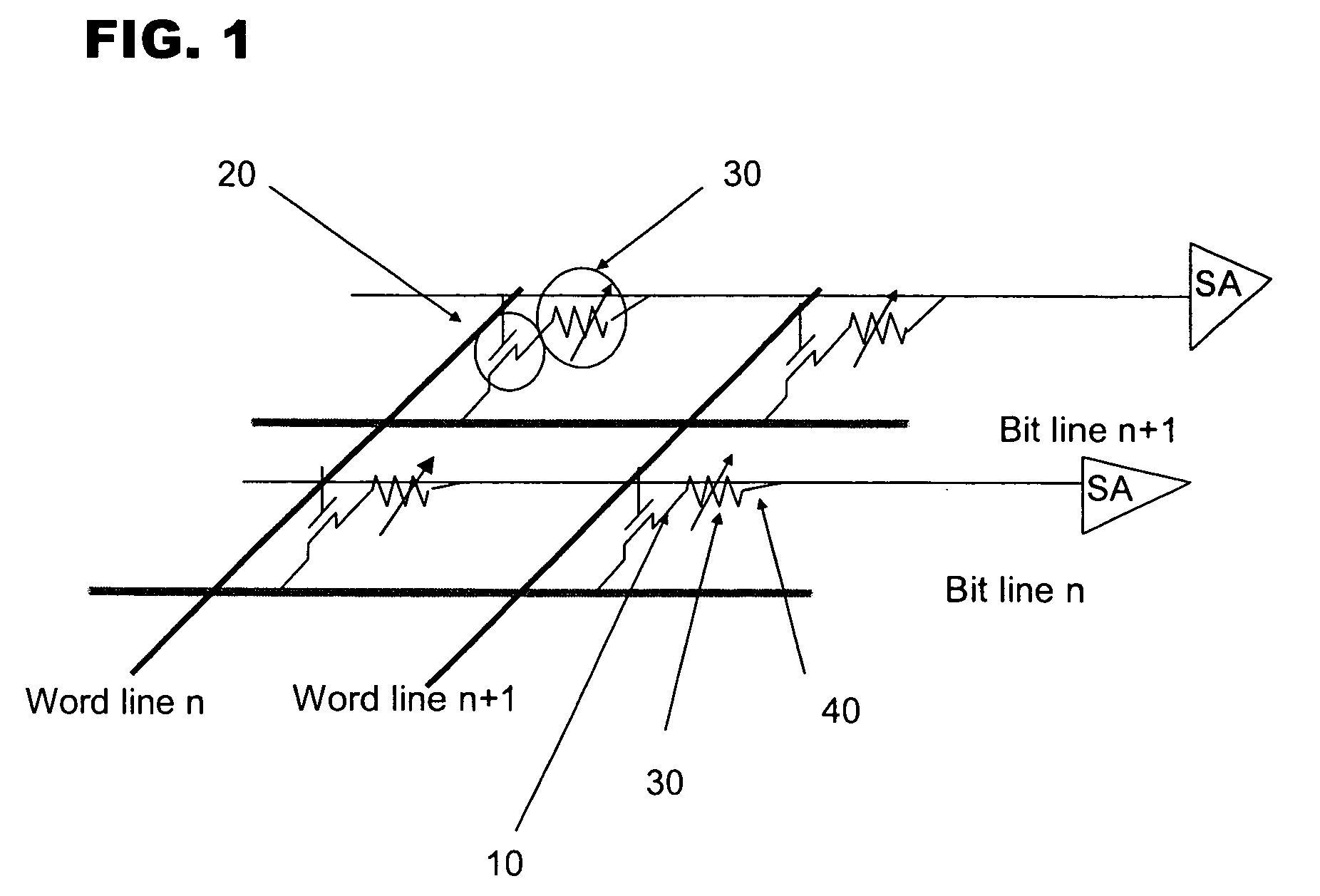

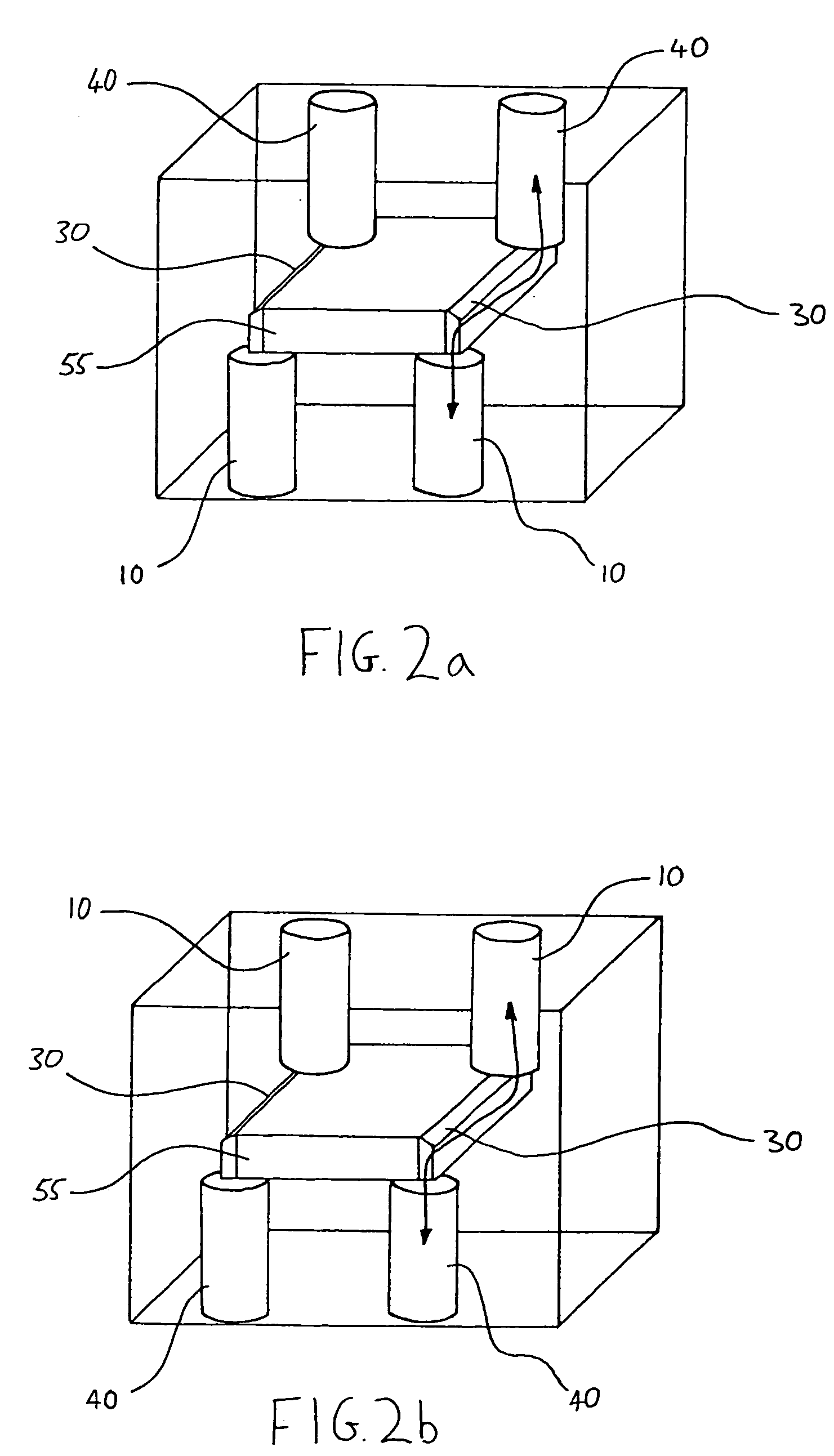

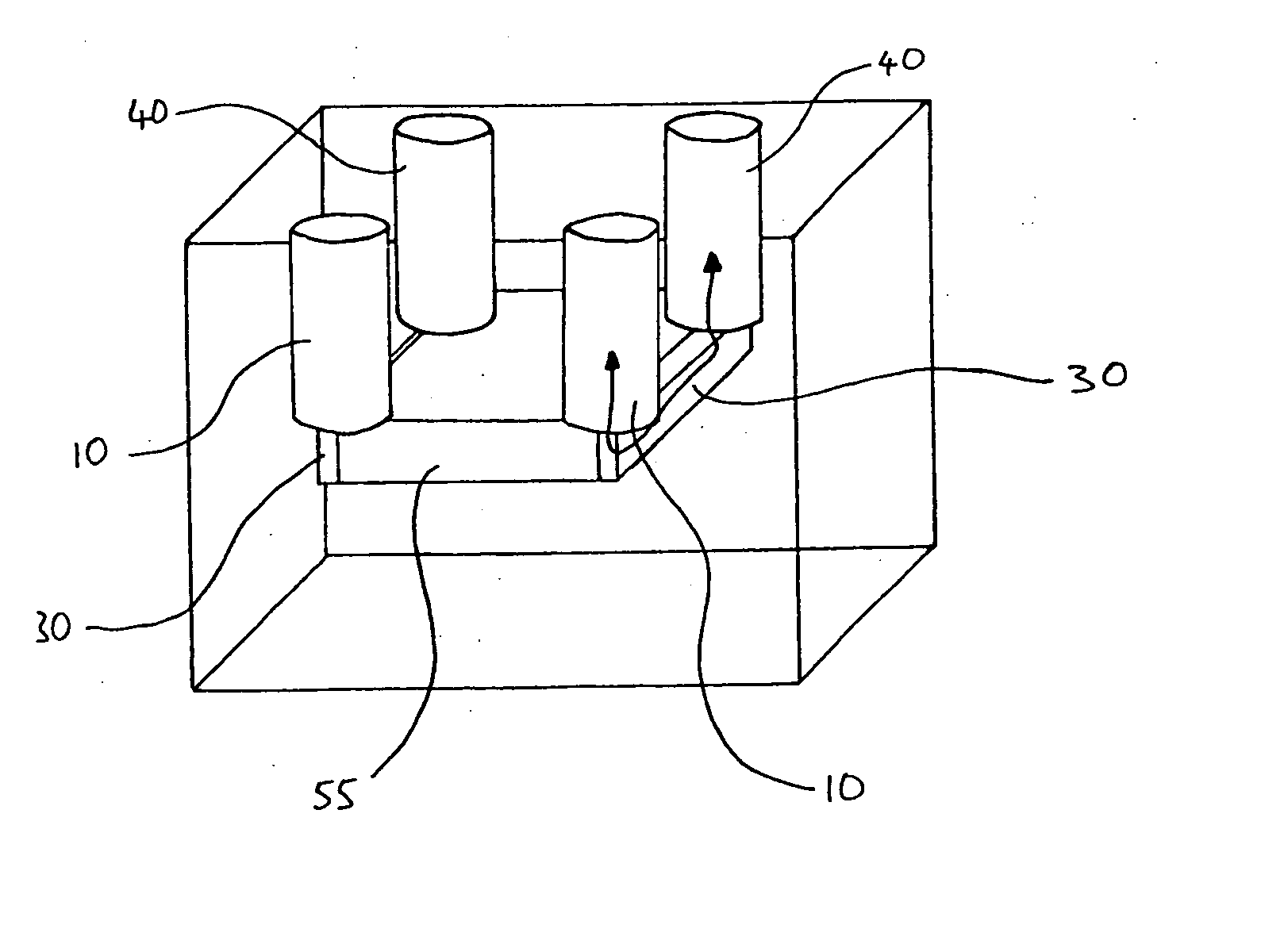

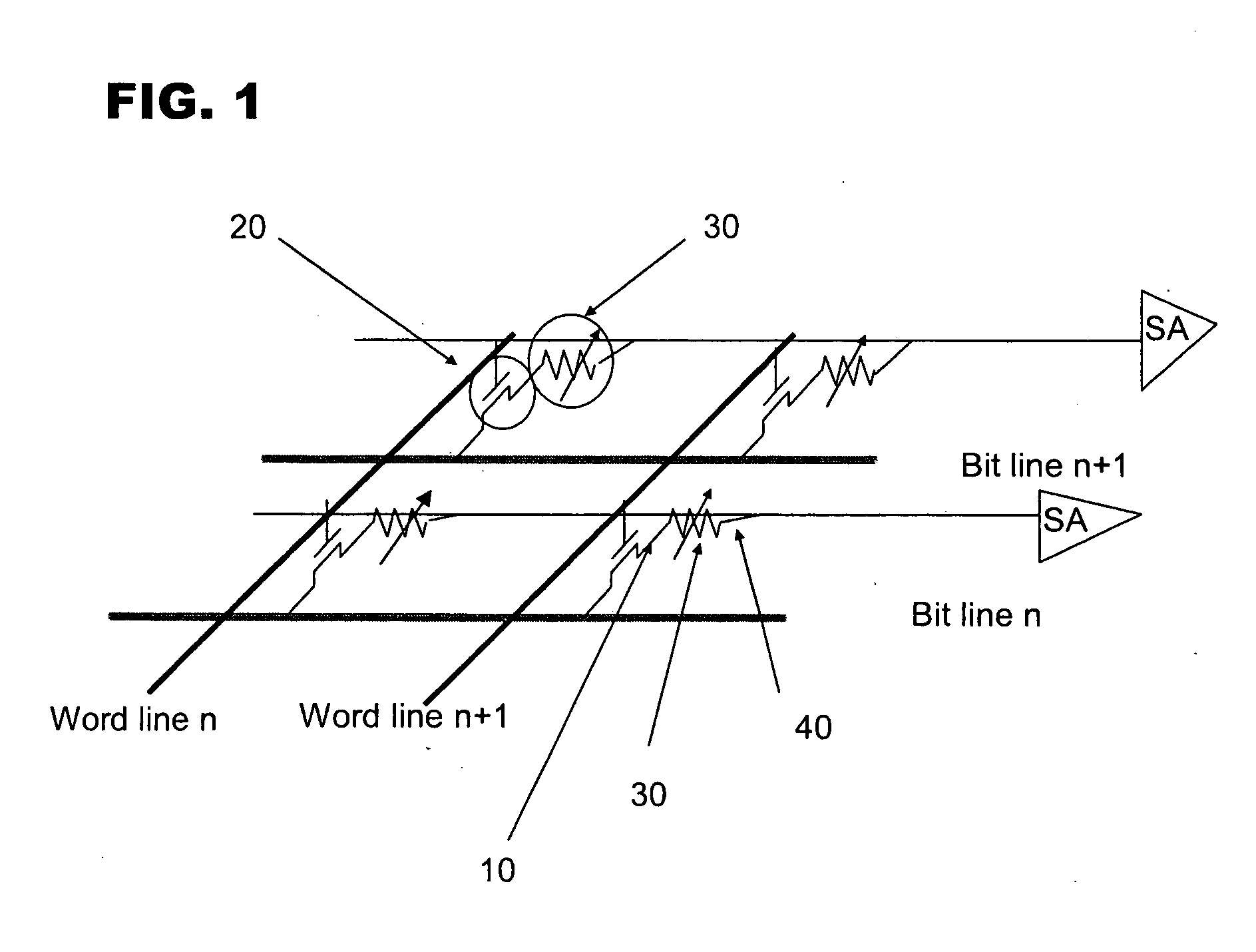

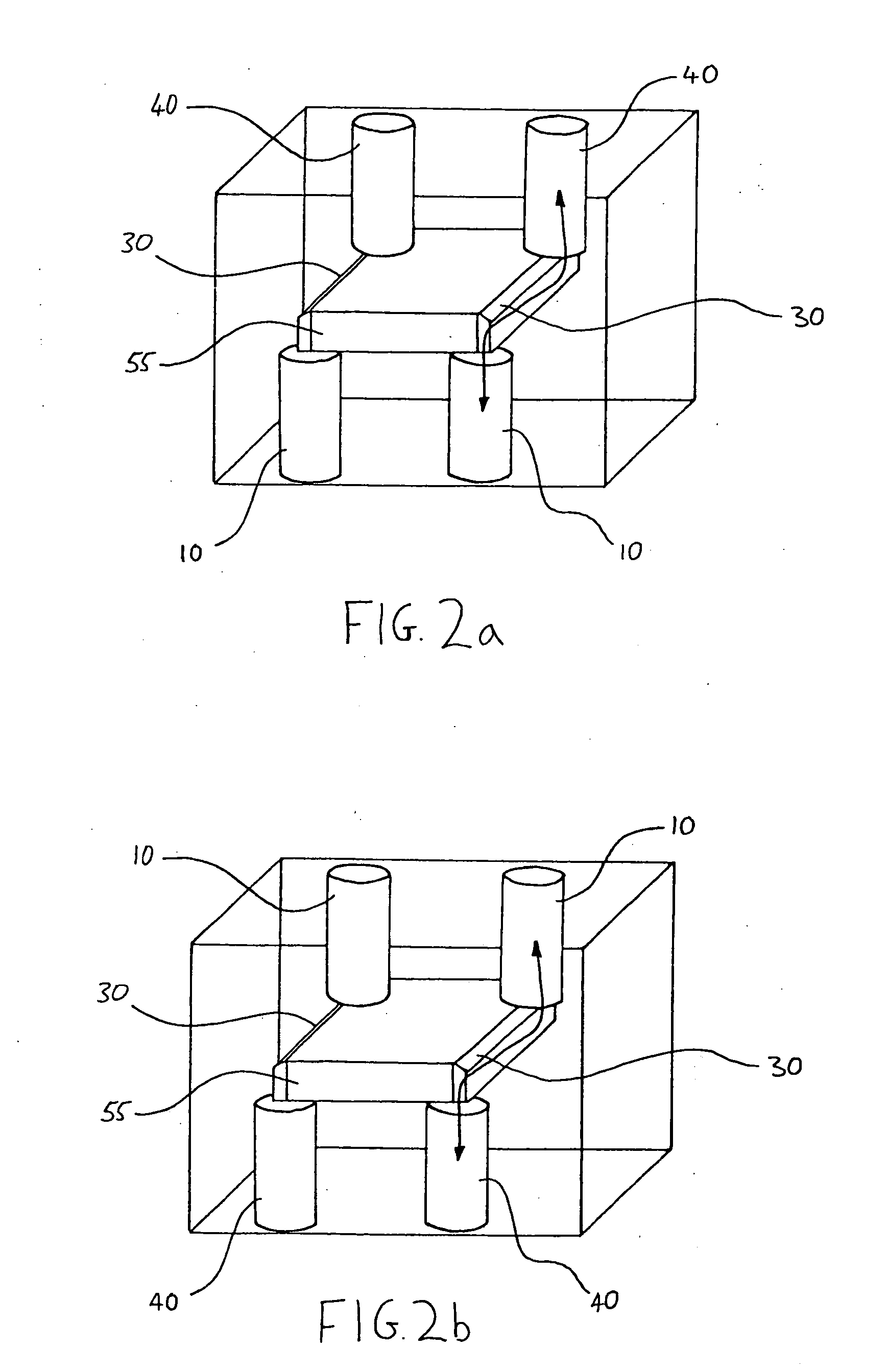

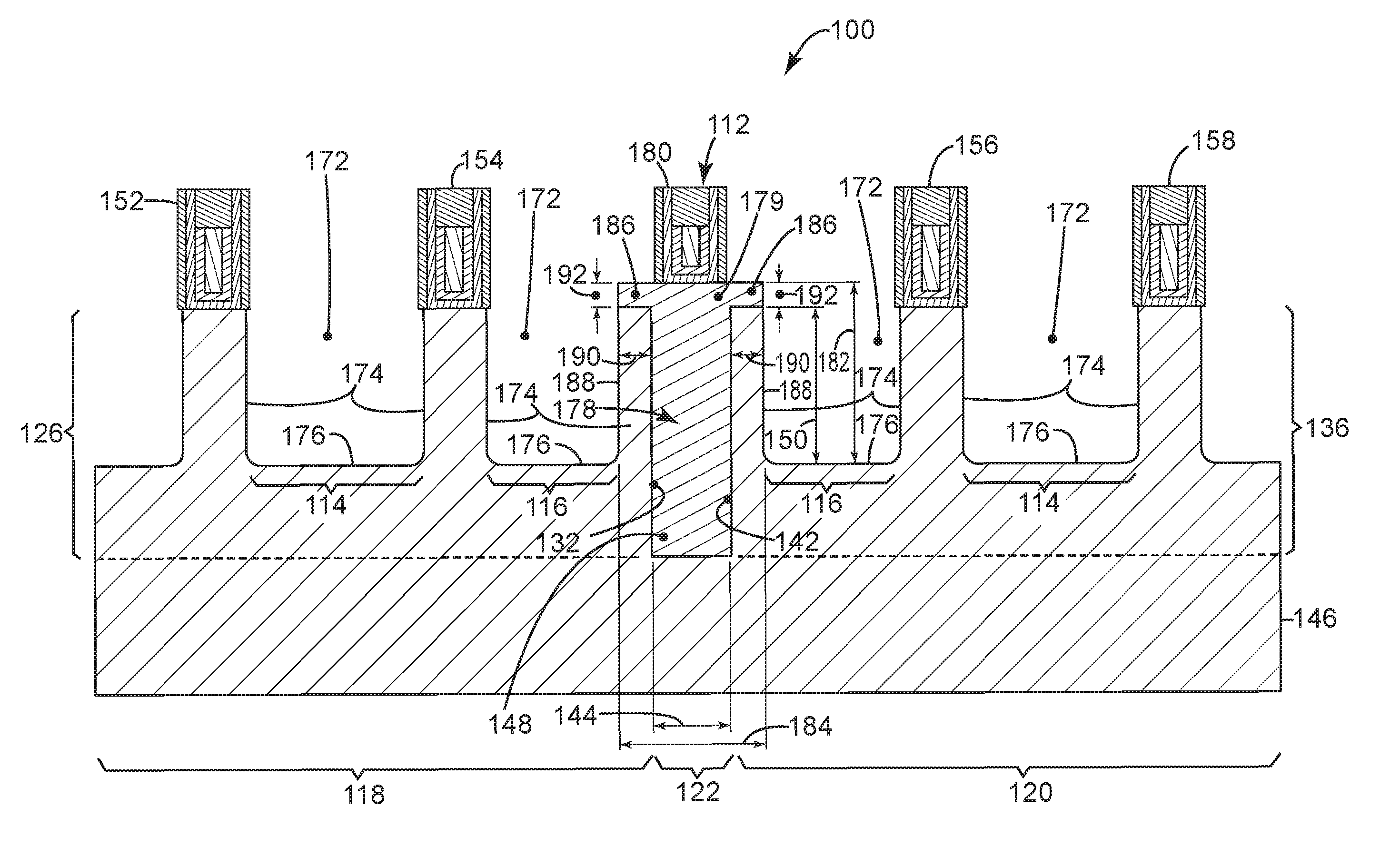

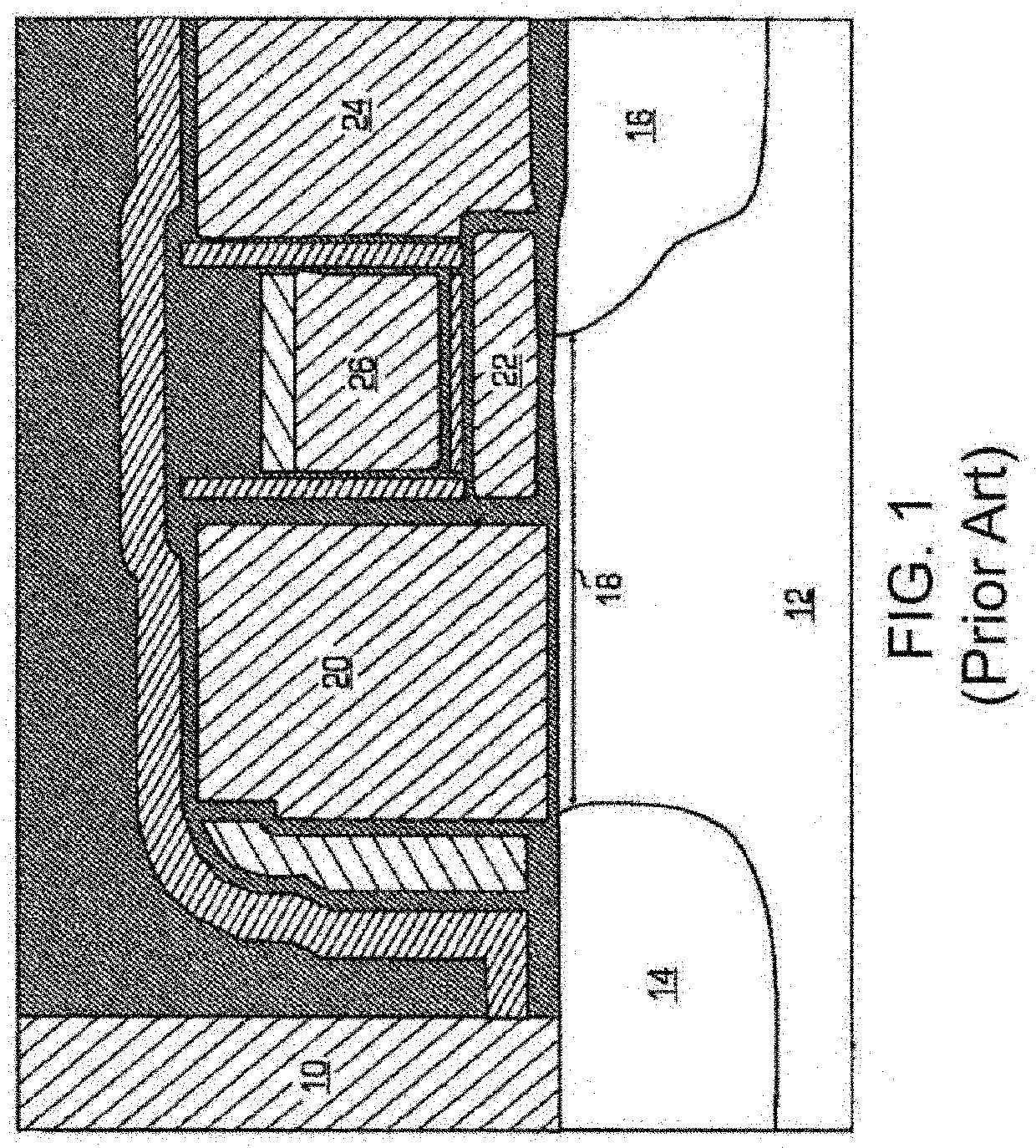

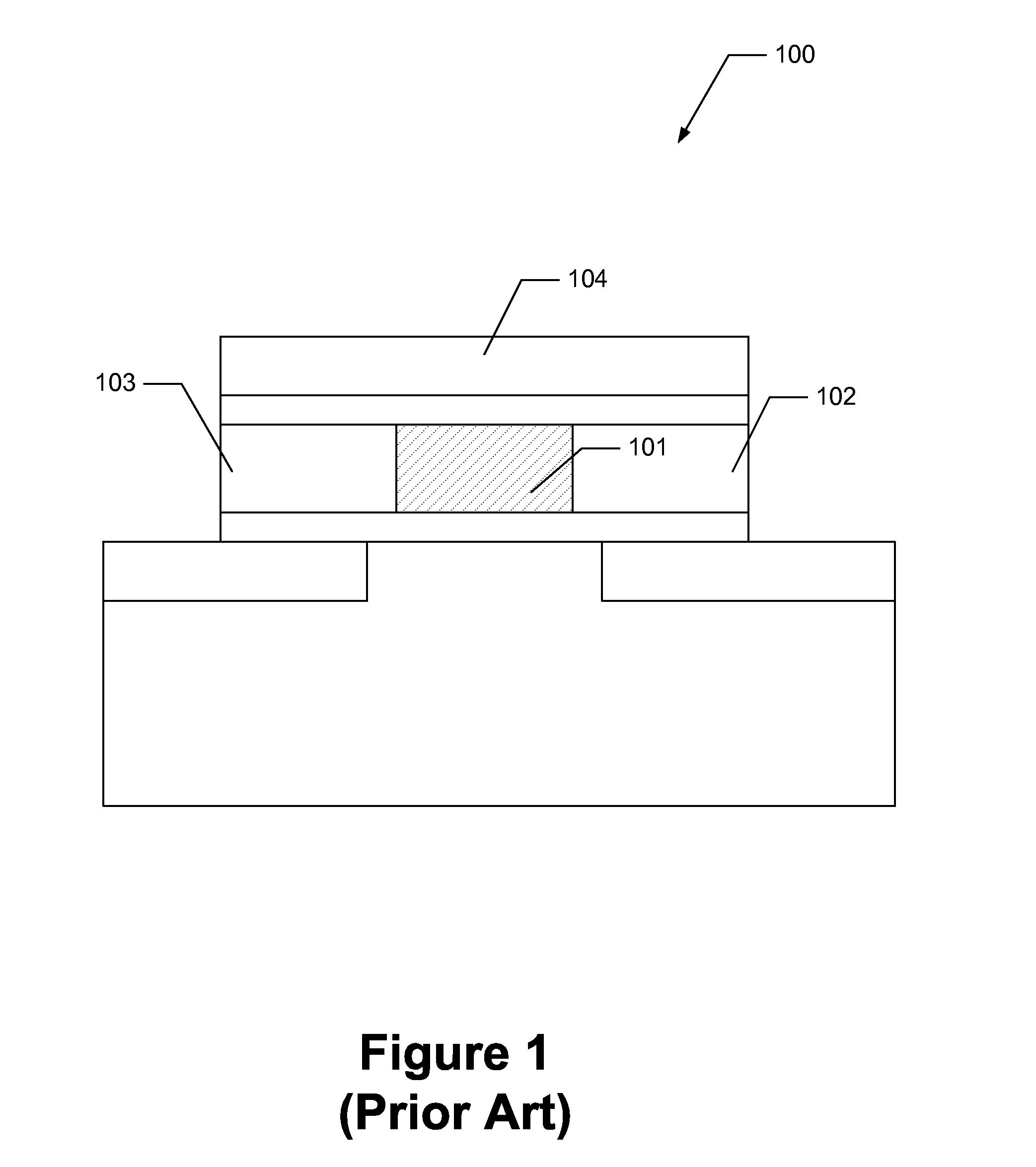

Horizontal chalcogenide element defined by a pad for use in solid-state memories

ActiveUS7038230B2Decreased current/power requirementRemove restrictionsSolid-state devicesRead-only memoriesPhase-change memorySemiconductor

A process for fabricating phase-change elements having ultra small cross-sectional areas for use in phase change memory cells specifically and in semiconductor devices generally in which pads are implemented to create horizontally aligned phase change elements is disclosed. The elements thus defined may be used within chalcogenide memory cells or other semiconductor devices.

Owner:MACRONIX INT CO LTD

System and method for website performance optimization and internet traffic processing

ActiveUS8112471B2Down capacityScale downMemory loss protectionError detection/correctionTraffic capacityNetwork connection

A system for optimizing the performance of a website that runs on one or more HTTP servers and is configured to receive HTTP requests from one or more clients via user agents and provide HTTP responses to the one or more clients includes an intermediary component configured to connect to the clients and the servers via network connections. The intermediary component includes a traffic management system (TMS) that includes means for managing HTTP requests originating from the clients and targeting the servers and HTTP responses originating from the servers and targeting the clients and means for redirecting the HTTP requests to the intermediary component. The intermediary component further includes a traffic processing system that includes means for receiving the redirected HTTP requests and the HTTP responses and means for applying optimization techniques to the redirected HTTP requests and the HTTP responses.

Owner:YOTTAA

Horizontal chalcogenide element defined by a pad for use in solid-state memories

ActiveUS20050145984A1Decreased current/power requirementRemove restrictionsSolid-state devicesRead-only memoriesPhase-change memoryDevice material

A process for fabricating phase-change elements having ultra small cross-sectional areas for use in phase change memory cells specifically and in semiconductor devices generally in which pads are implemented to create horizontally aligned phase change elements is disclosed. The elements thus defined may be used within chalcogenide memory cells or other semiconductor devices.

Owner:MACRONIX INT CO LTD

Horizontal chalcogenide element defined by a pad for use in solid-state memories

InactiveUS20060157681A1Decreased current/power requirementRemove restrictionsSolid-state devicesRead-only memoriesPhase-change memoryDevice material

A process for fabricating phase-change elements having ultra small cross-sectional areas for use in phase change memory cells specifically and in semiconductor devices generally in which pads are implemented to create horizontally aligned phase change elements is disclosed. The elements thus defined may be used within chalcogenide memory cells or other semiconductor devices.

Owner:MACRONIX INT CO LTD

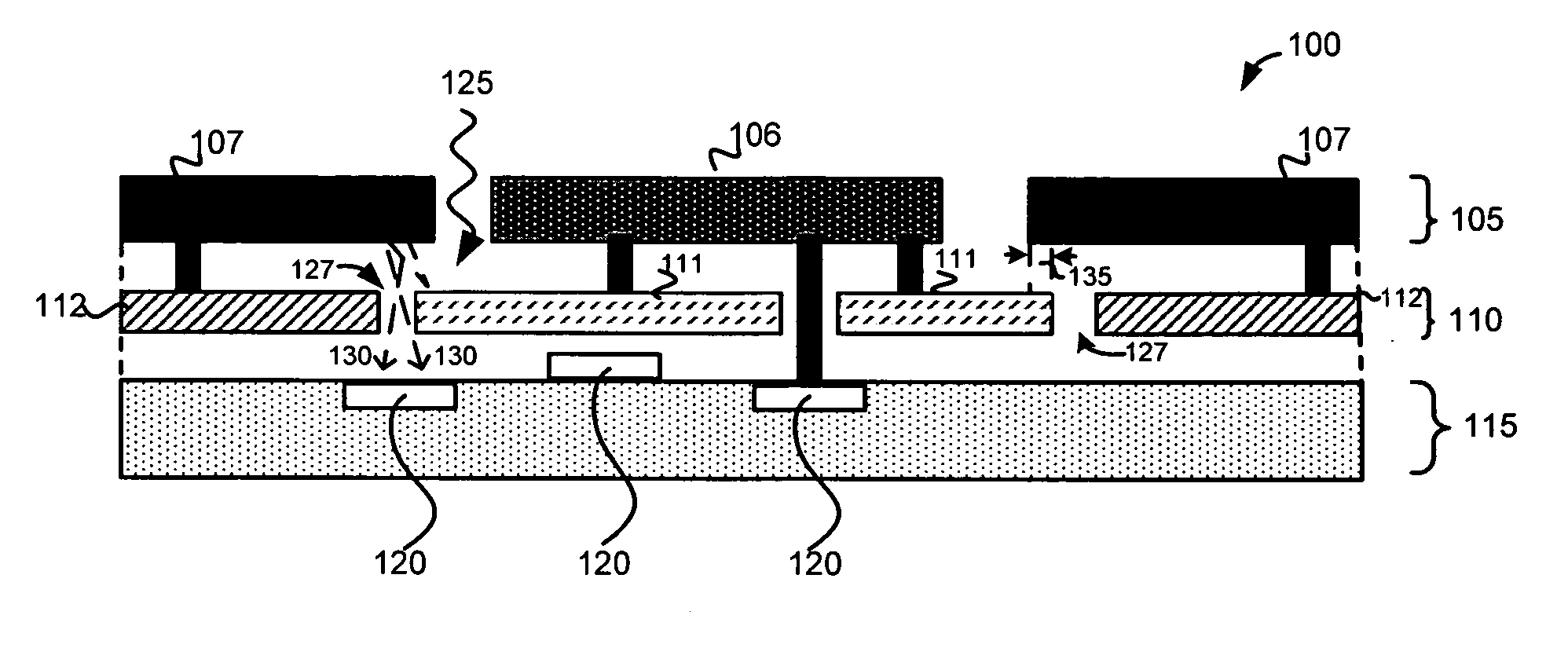

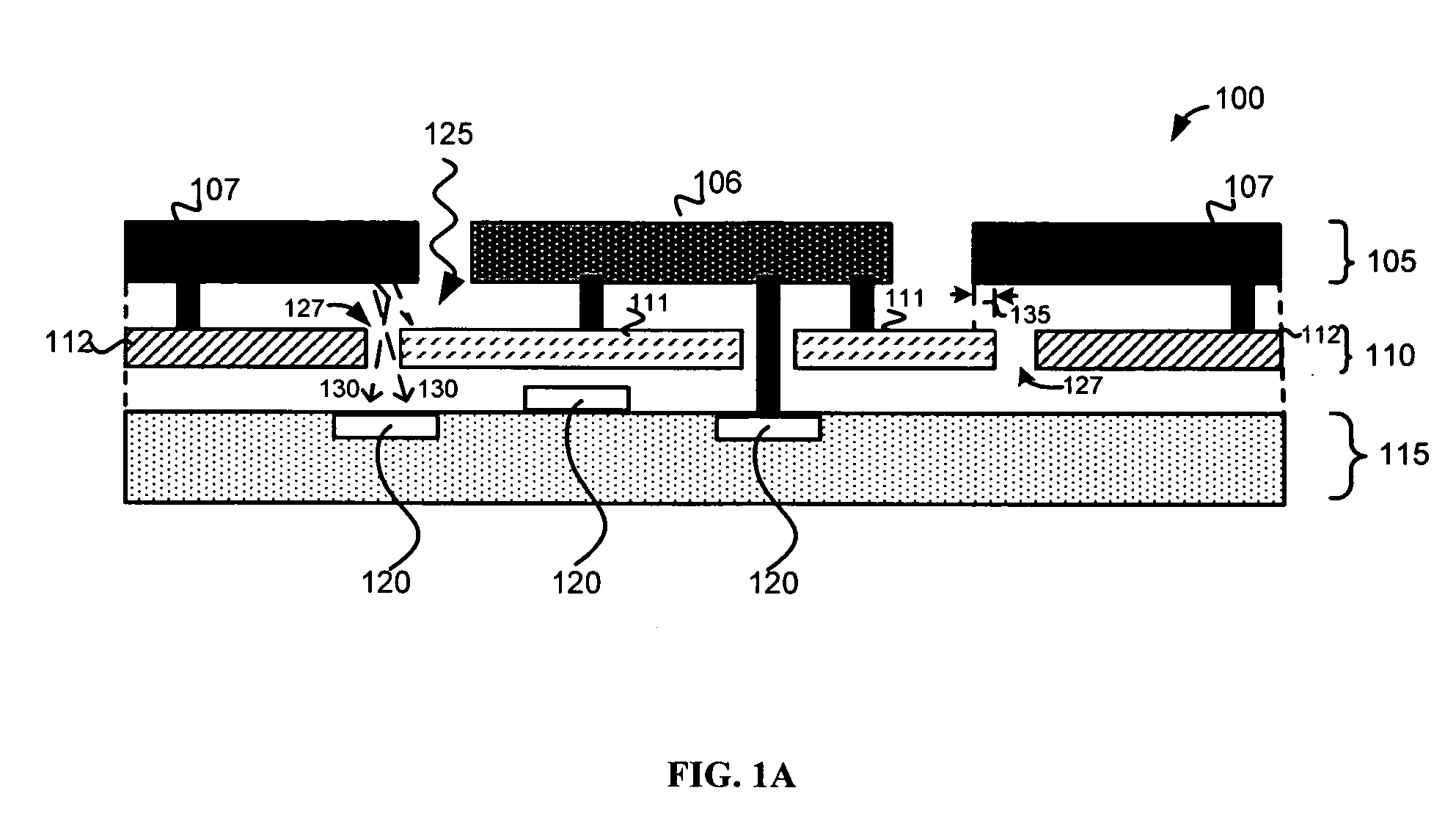

Memory cell dual protection

InactiveUS20050174628A1Reduced stabilityHigh yieldNon-linear opticsMicroelectromechanical systemsElectricitySpatial light modulator

A spatial light modulator for use in projection display applications is provided. The spatial light modulator includes a substrate including a plurality of electrically active circuits and an electrode layer electrically coupled to at least one of the plurality of electrically active circuits. In one embodiment, the electrode layer includes a semi-continuous layer with at least one optical path. The spatial light modulator also includes a shielding layer electrically isolated from the electrode layer and disposed between the substrate and the plurality of electrically active circuits and an electrical connector coupling the shielding layer to a reference potential. In a specific embodiment, the shielding layer of the spatial light modulator converts incident light energy to electrical current and routes the current back to a source. In another specific embodiment, the shielding layer converts electrical field disturbance to electrical current and routes the current back to a source.

Owner:MIRADIA INC

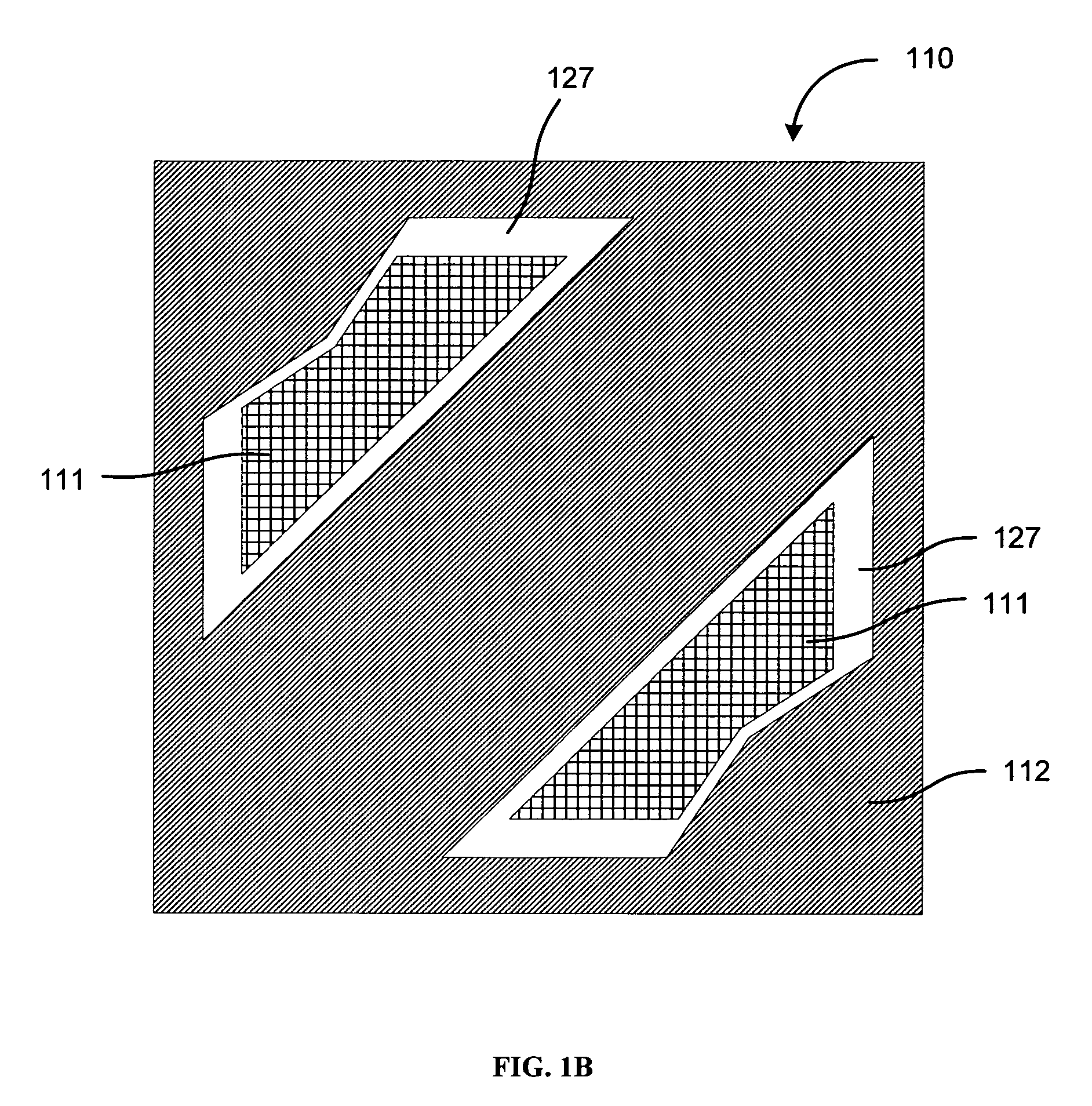

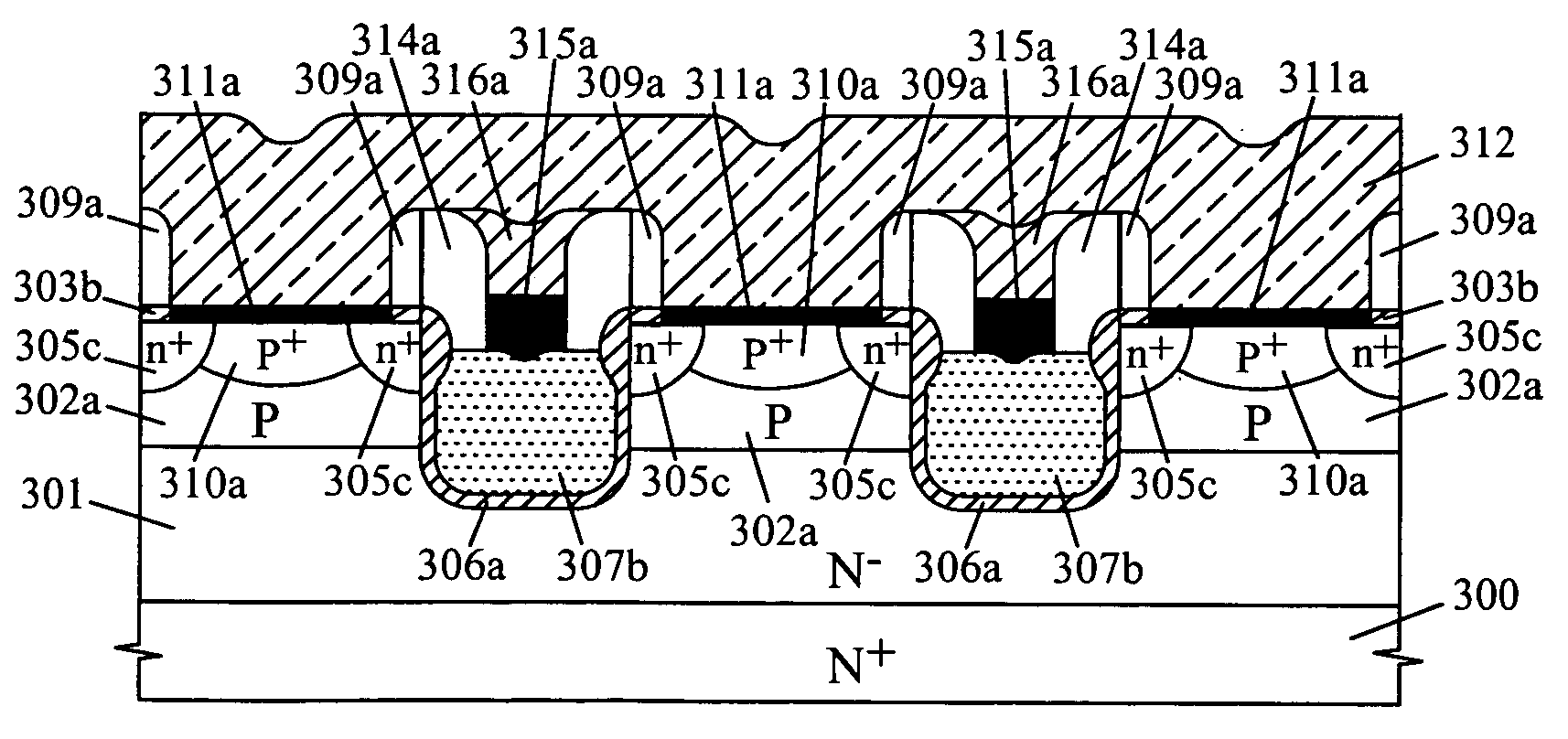

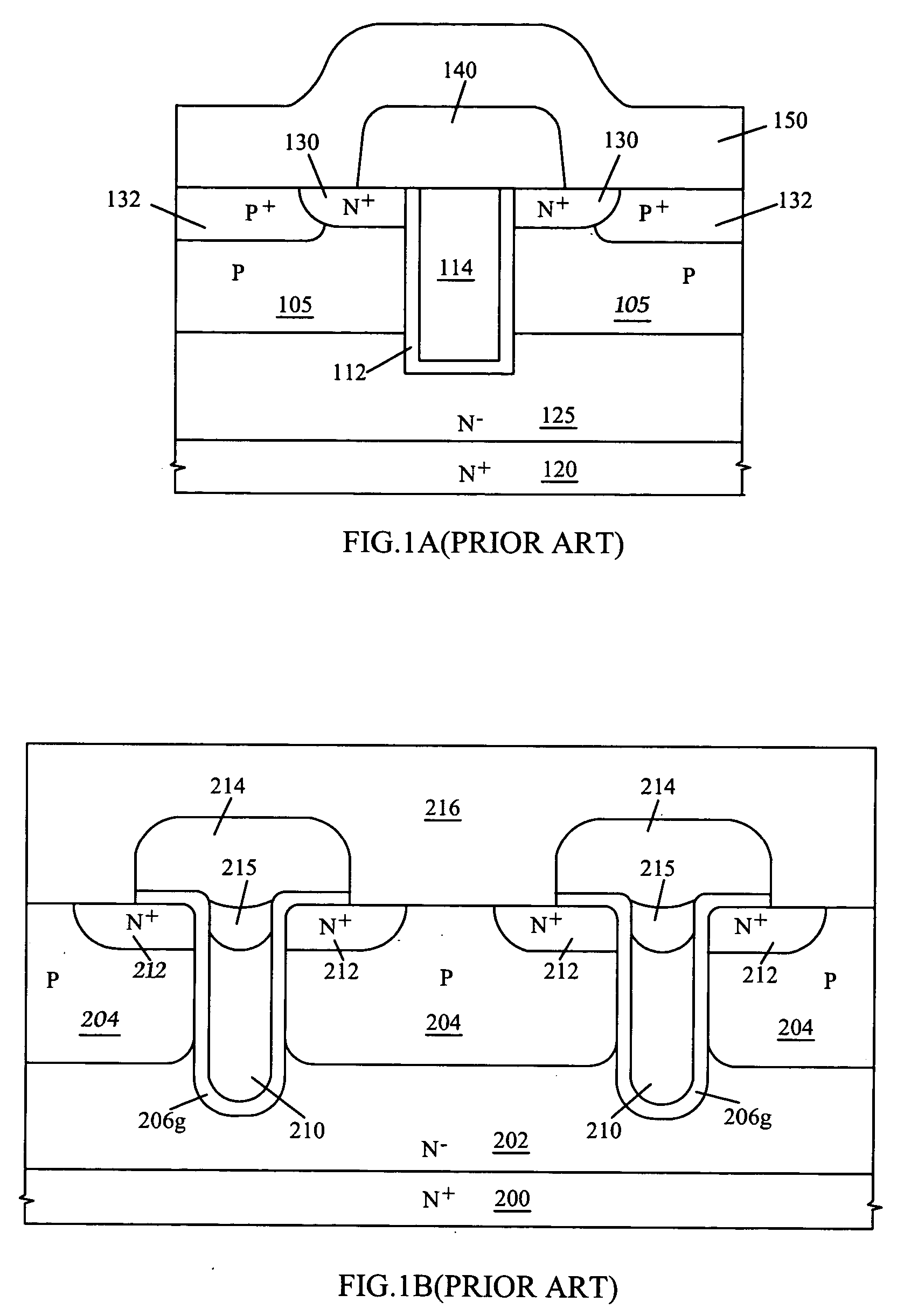

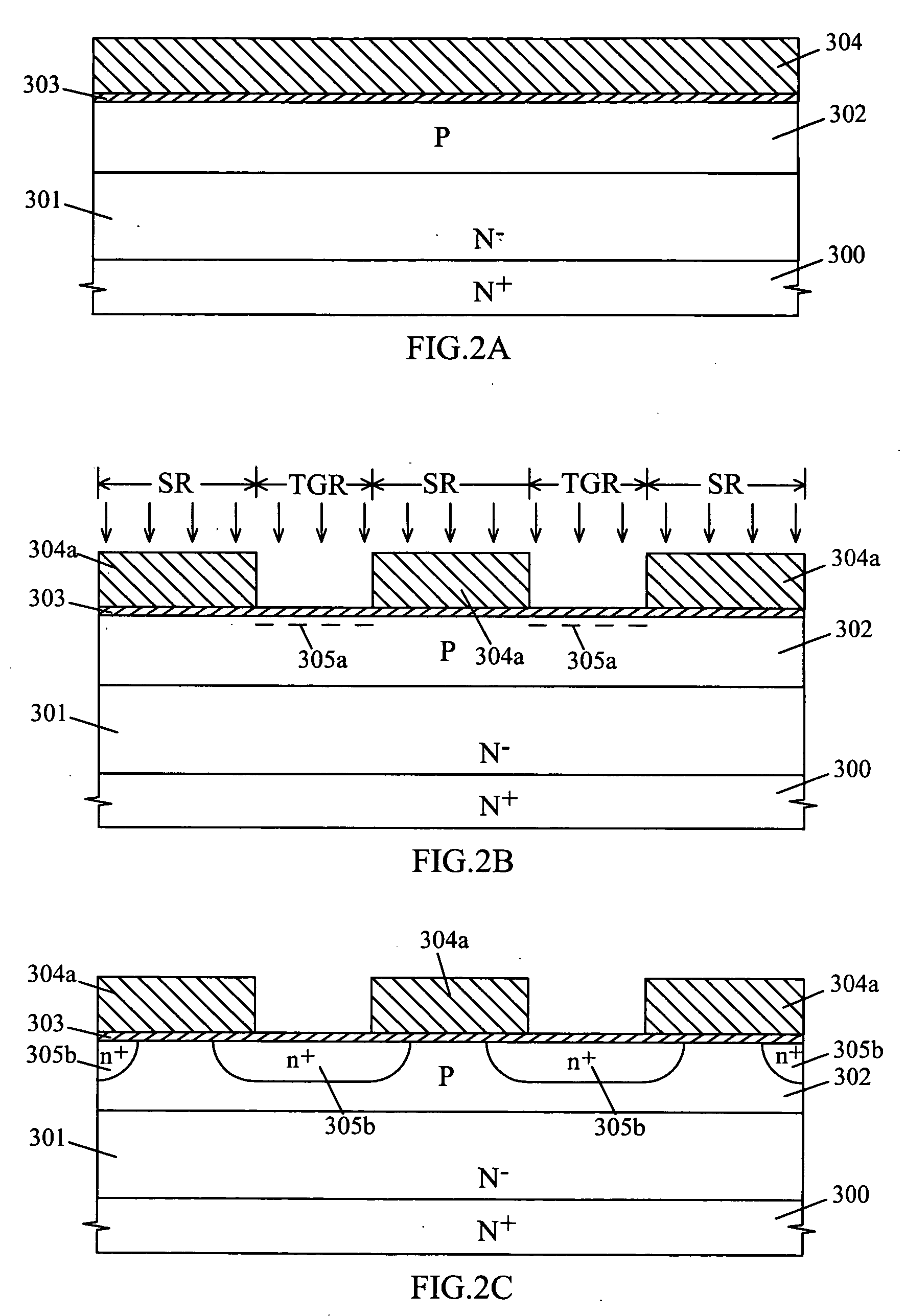

Self-aligned trench-type DMOS transistor structure and its manufacturing methods

InactiveUS20060113588A1Increase resistanceIncreased durabilitySemiconductor devicesDielectricGate dielectric

The self-aligned trench-type DMOS transistor structure comprises a self-aligned source region being surrounded by a trench gate region. The self-aligned source region comprises a moderately-doped p-base diffusion region formed in a lightly-doped epitaxial semiconductor substrate, a self-aligned heavily-doped n+ source diffusion ring formed in a side surface portion of the moderately-doped p-base diffusion region, a heavily-doped p+ contact diffusion region formed in a surface portion of the moderately-doped p-base diffusion region surrounded by the heavily-doped n+ source diffusion ring, and a self-aligned source contact window formed by a semiconductor surface surrounded by a sidewall dielectric spacer. The trench gate region comprises a gate dielectric layer being lined over a trenched semiconductor surface with or without a thicker isolation dielectric layer formed on a bottom trenched semiconductor surface and a self-aligned highly conductive gate layer being formed at least over the gate dielectric layer.

Owner:SILICON BASED TECH

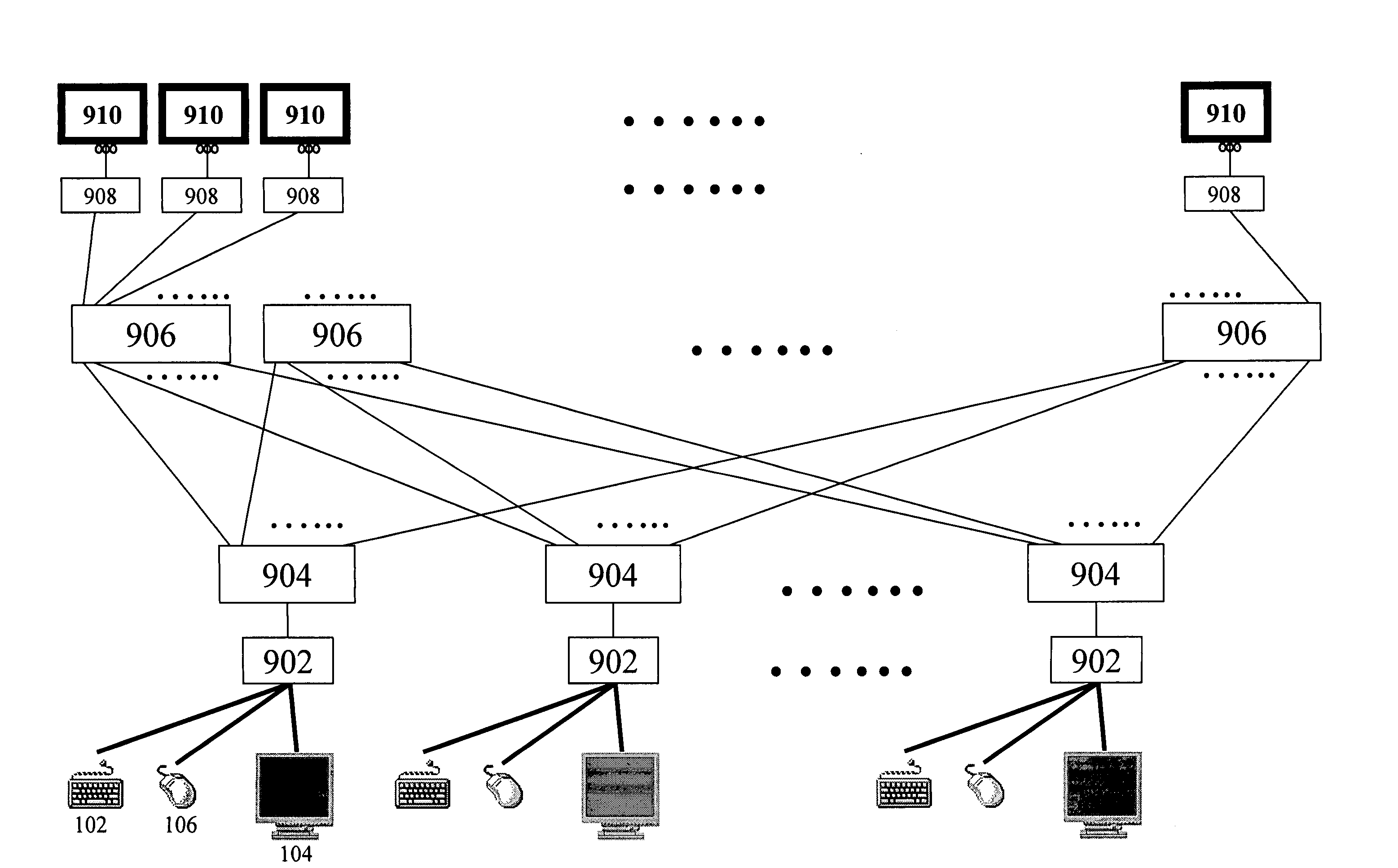

Intelligent modular server management system for selectively operating a plurality of computers

InactiveUS7249167B1Avoid separationLow reliabilityMultiple digital computer combinationsInput/output processes for data processingModularityComputer users

An intelligent, modular server management system for coupling a series of remotely located computers to one or more user stations allowing for selective access of the remotely located computers. A centralized computer matrix switching system is provided to enable a computer user station to access and operate a remotely located computer in a stable environment and transmit analog signals through the switching system over an extended range. The centralized computer matrix switching system receives the input from the computer user station or the remotely located computer, including the keyboard, video monitor and mouse signals, and transmits the signals as though the computer user station was directly coupled to the remotely located computer.

Owner:RARITAN INC +1

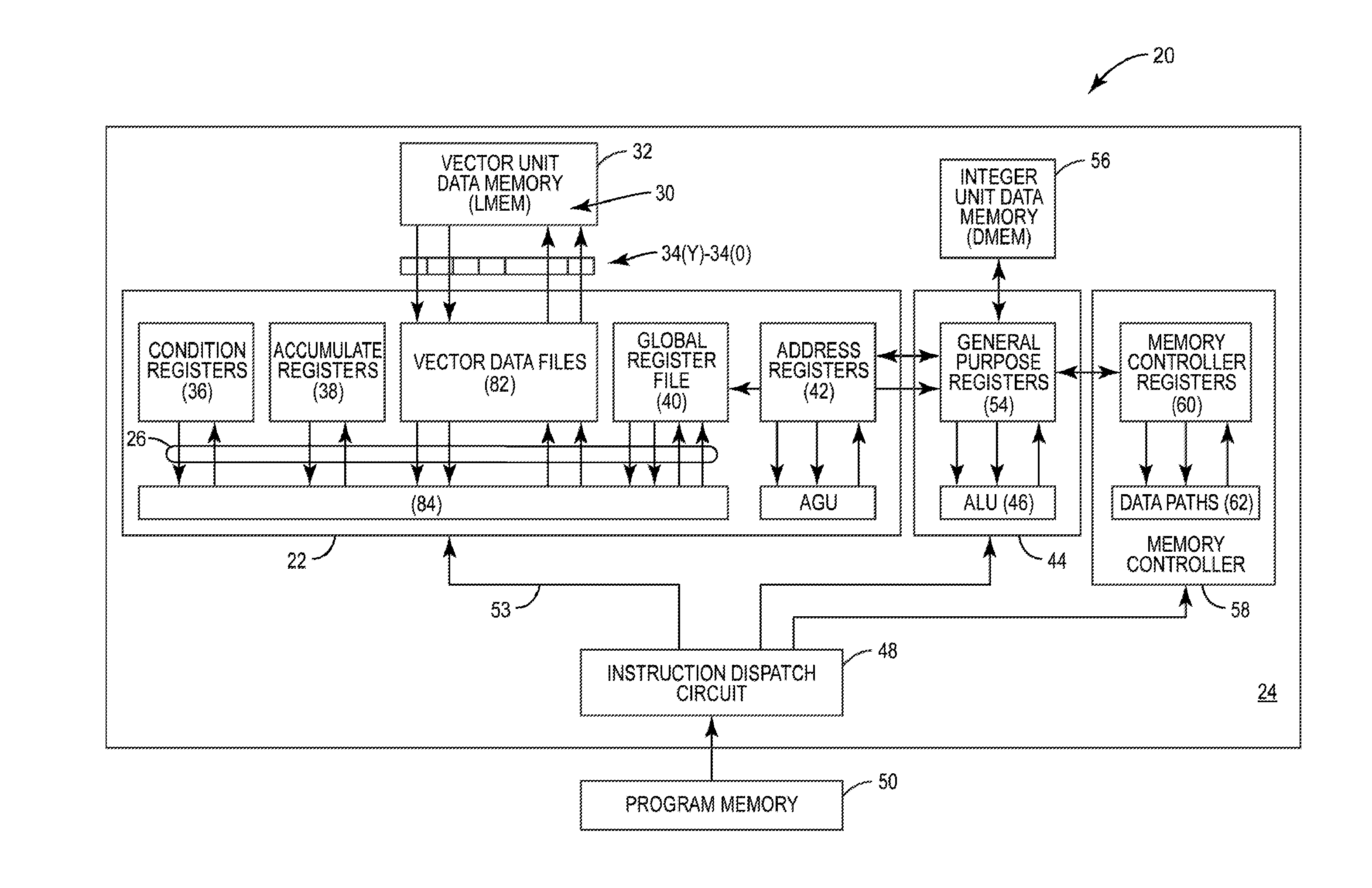

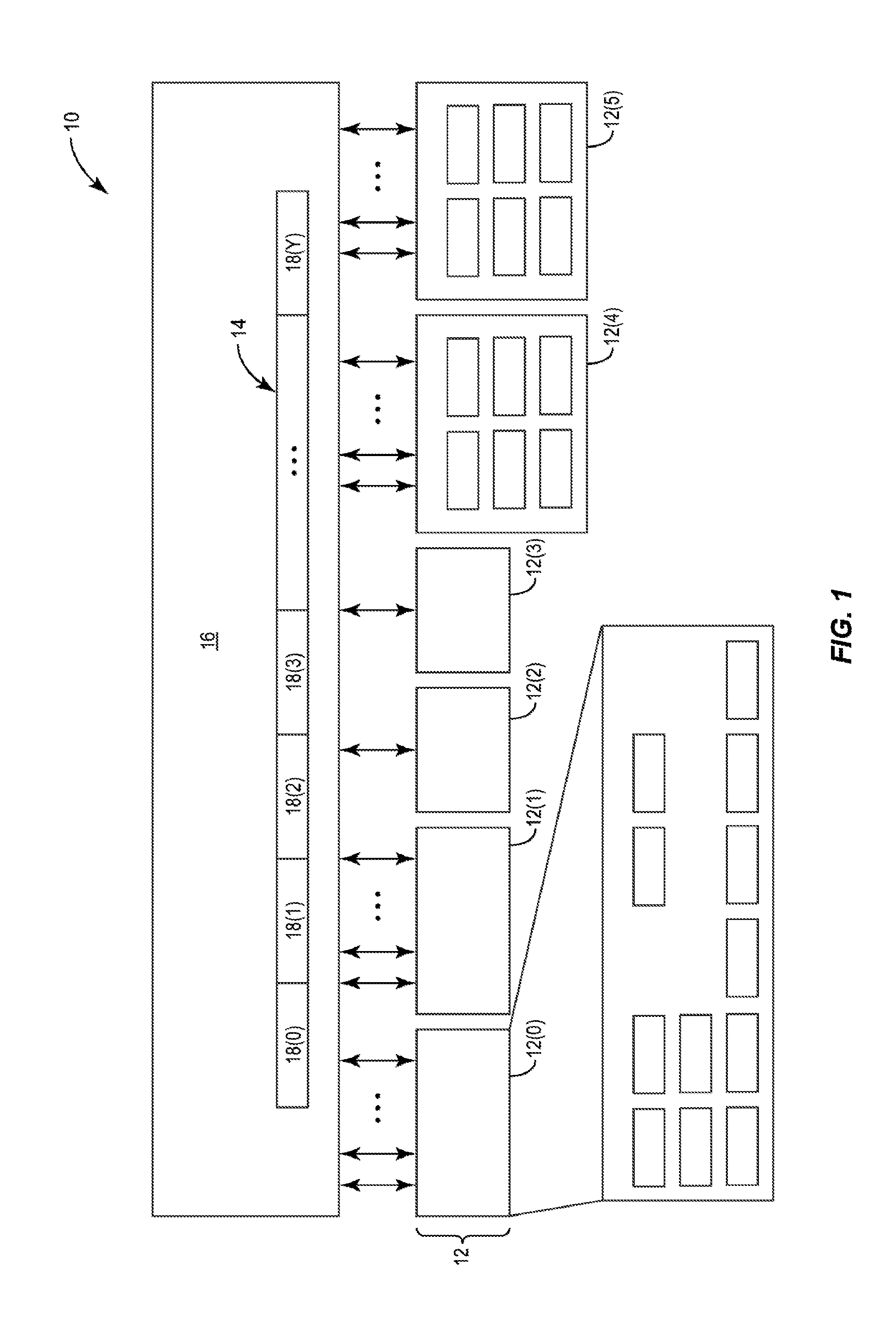

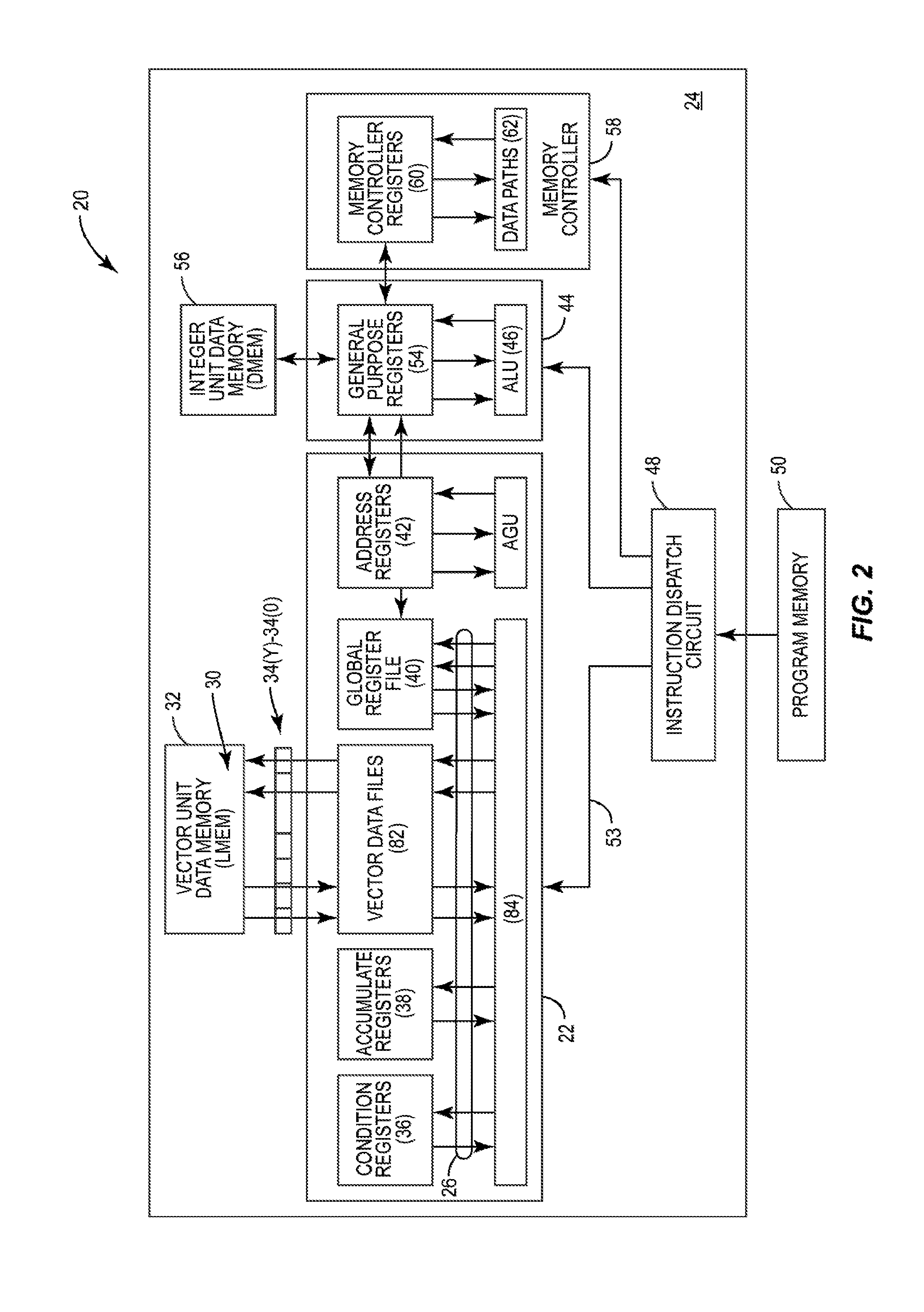

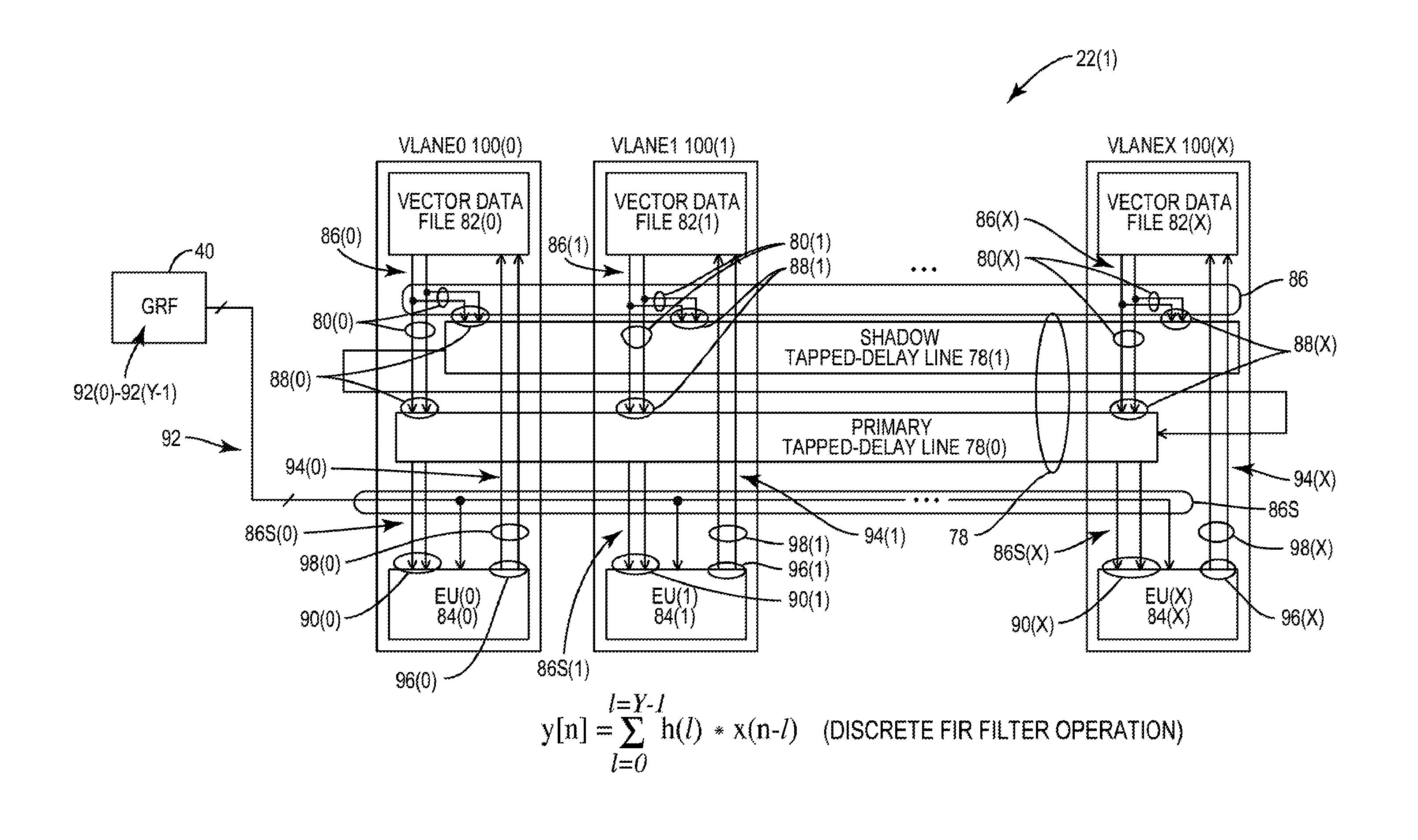

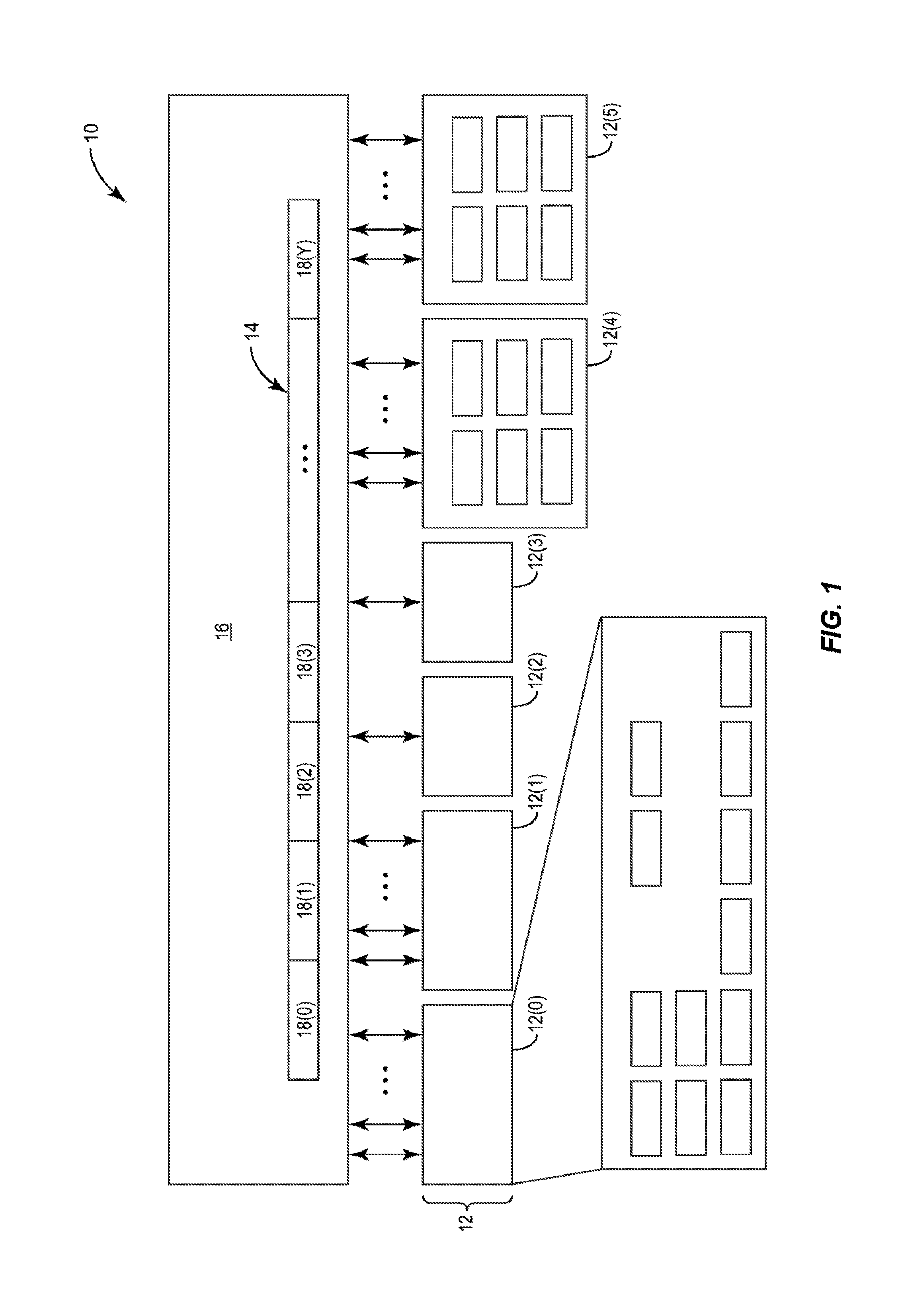

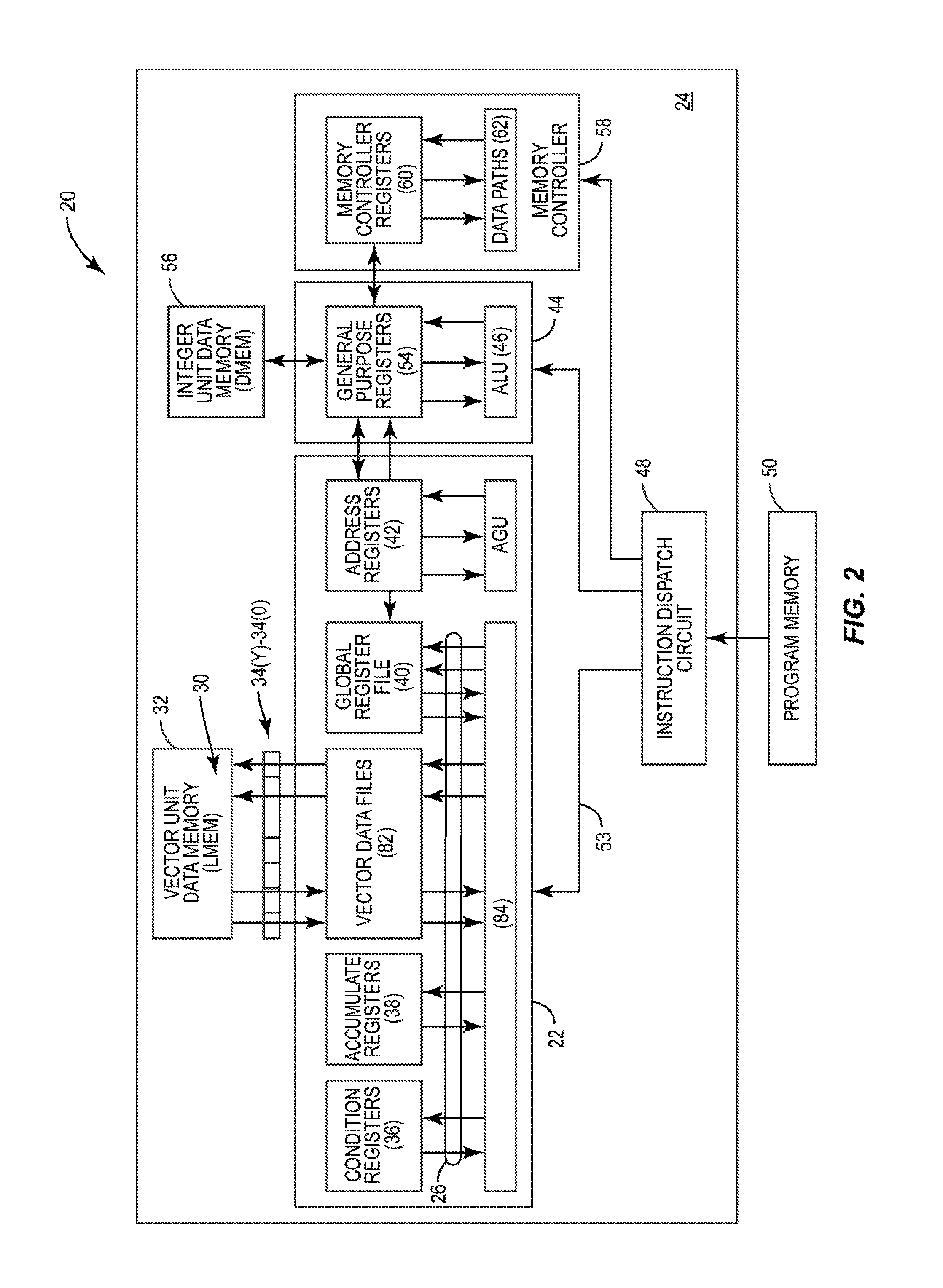

VECTOR PROCESSING ENGINES (VPEs) EMPLOYING A TAPPED-DELAY LINE(S) FOR PROVIDING PRECISION FILTER VECTOR PROCESSING OPERATIONS WITH REDUCED SAMPLE RE-FETCHING AND POWER CONSUMPTION, AND RELATED VECTOR PROCESSOR SYSTEMS AND METHODS

InactiveUS20150143078A1Reduced sample re-fetching and power consumptionMinimize re-fetchingGeneral purpose stored program computerMachine execution arrangementsData fileVector processor

Vector processing engines (VPEs) employing a tapped-delay line(s) for providing precision filter vector processing operations with reduced sample re-fetching and power consumption are disclosed. Related vector processor systems and methods are also disclosed. The VPEs are configured to provide filter vector processing operations. To minimize re-fetching of input vector data samples from memory to reduce power consumption, a tapped-delay line(s) is included in the data flow paths between a vector data file and execution units in the VPE. The tapped-delay line(s) is configured to receive and provide input vector data sample sets to execution units for performing filter vector processing operations. The tapped-delay line(s) is also configured to shift the input vector data sample set for filter delay taps and provide the shifted input vector data sample set to execution units, so the shifted input vector data sample set does not have to be re-fetched during filter vector processing operations.

Owner:QUALCOMM INC

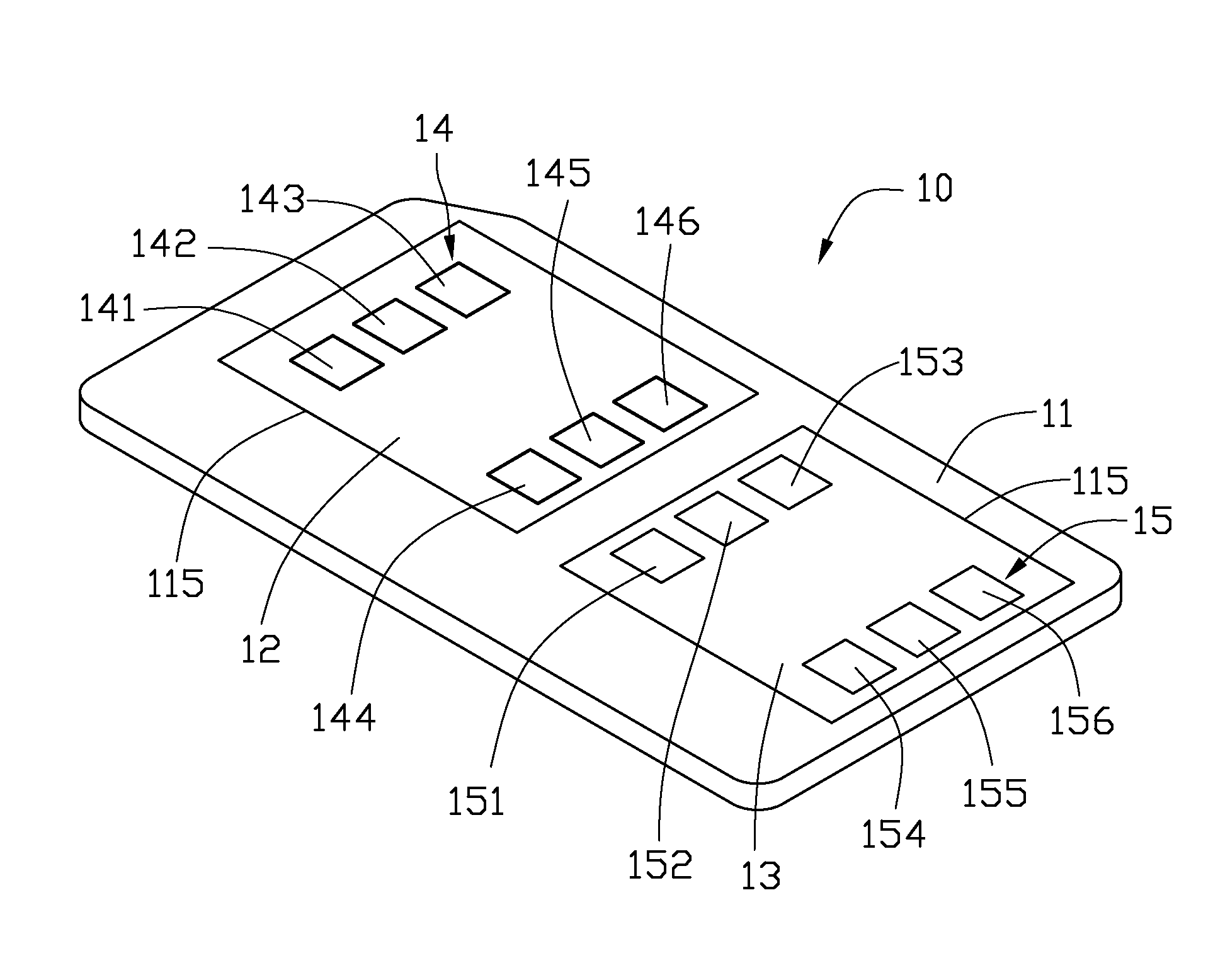

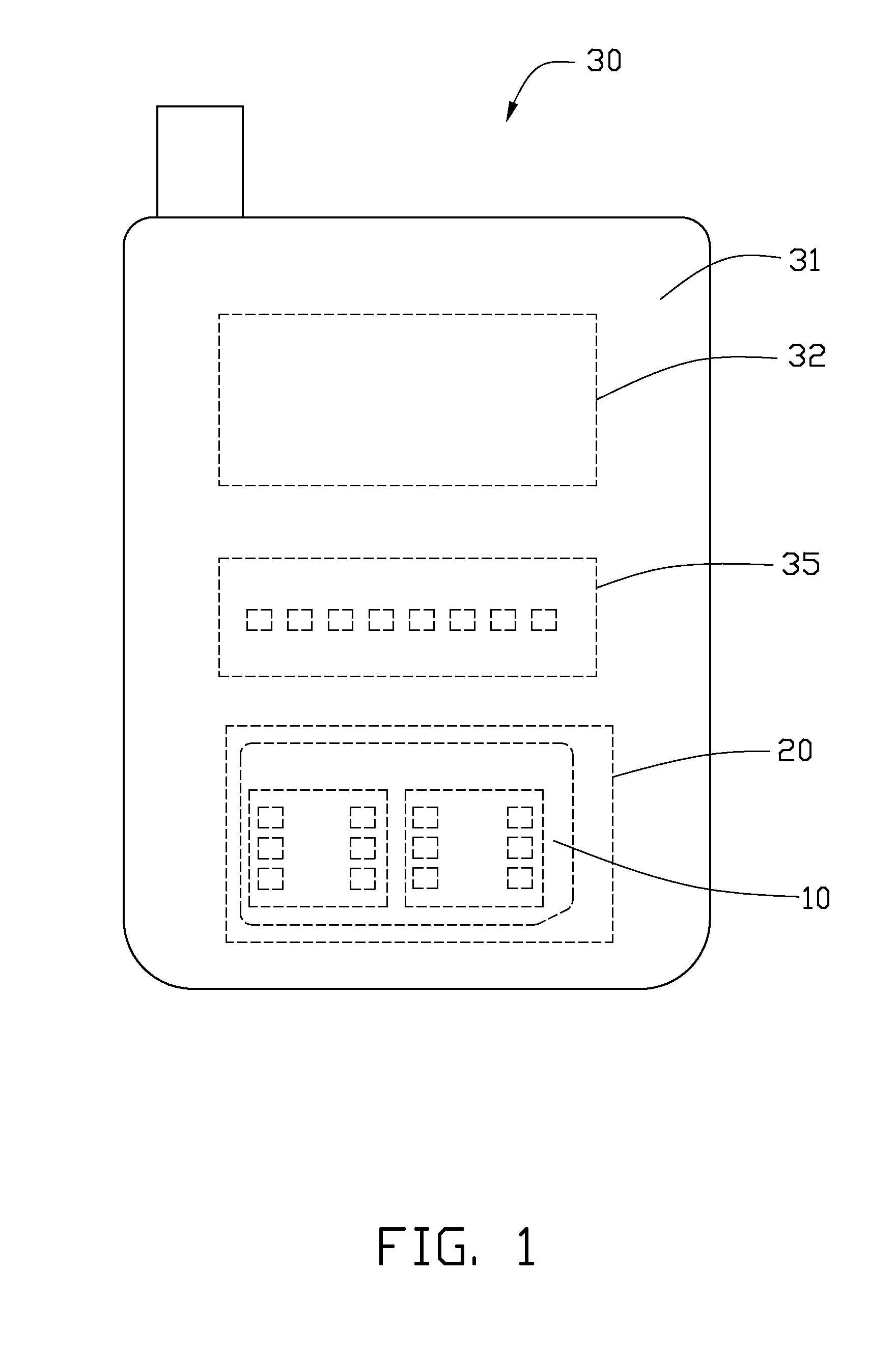

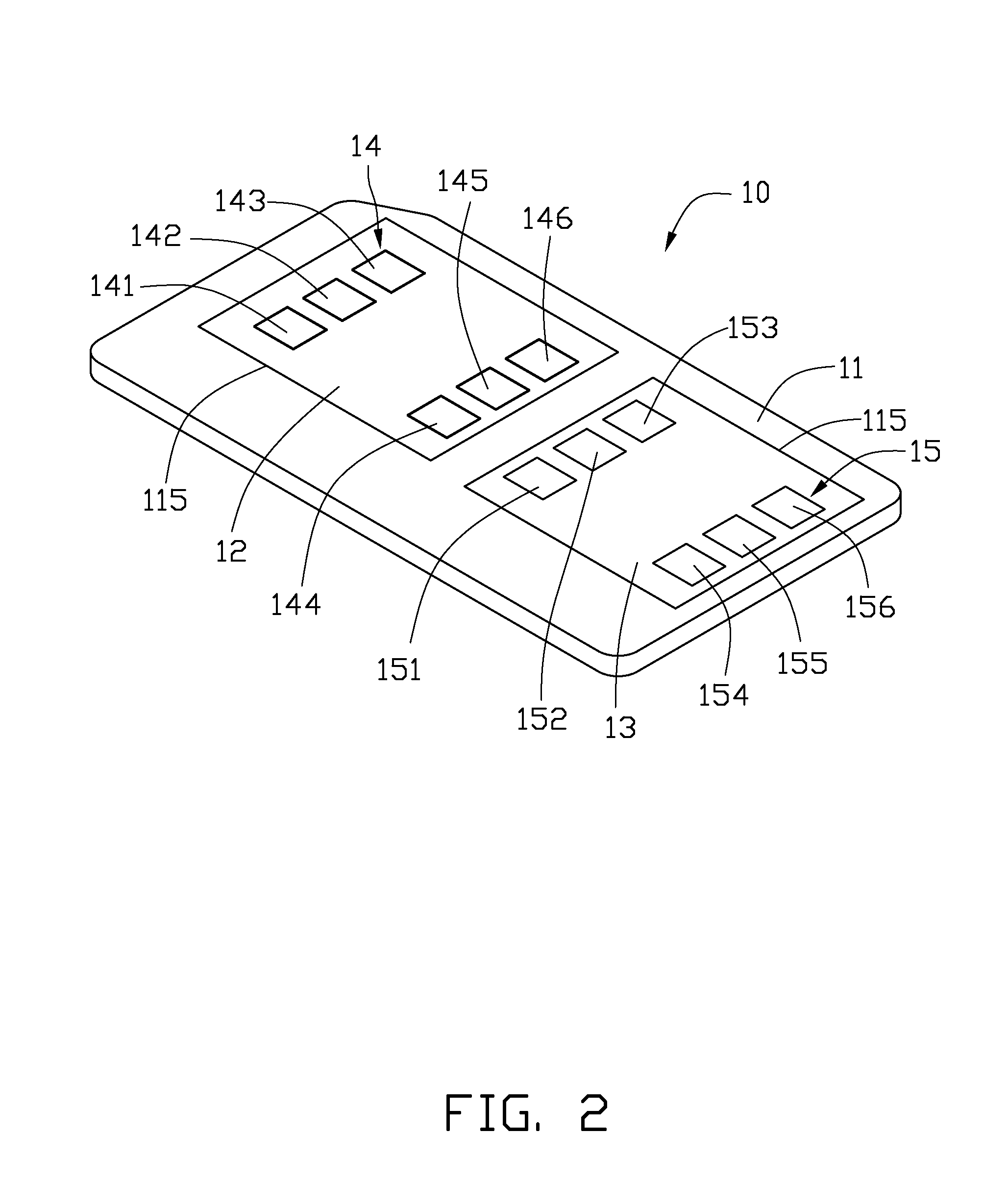

Sim card, sim card holder and electronic device with same

InactiveUS20100165589A1Increase in sizeScale downDevices with card reading facilitySensing record carriersEngineeringElectrical connector

A. SIM card includes a base body, two integrated circuits mounted on the base body, an electrical connector electrically connected to each of the two integrated circuits respectively. A SIM card holder for the SIM card includes a bracket defining a cavity to receive the SIM card, and a terminal connected to each of the electrical connectors respectively. The SIM card and the SIM card holder occupy little space and can be easily assembled and detached.

Owner:SHENZHEN FUTAIHONG PRECISION IND CO LTD +1

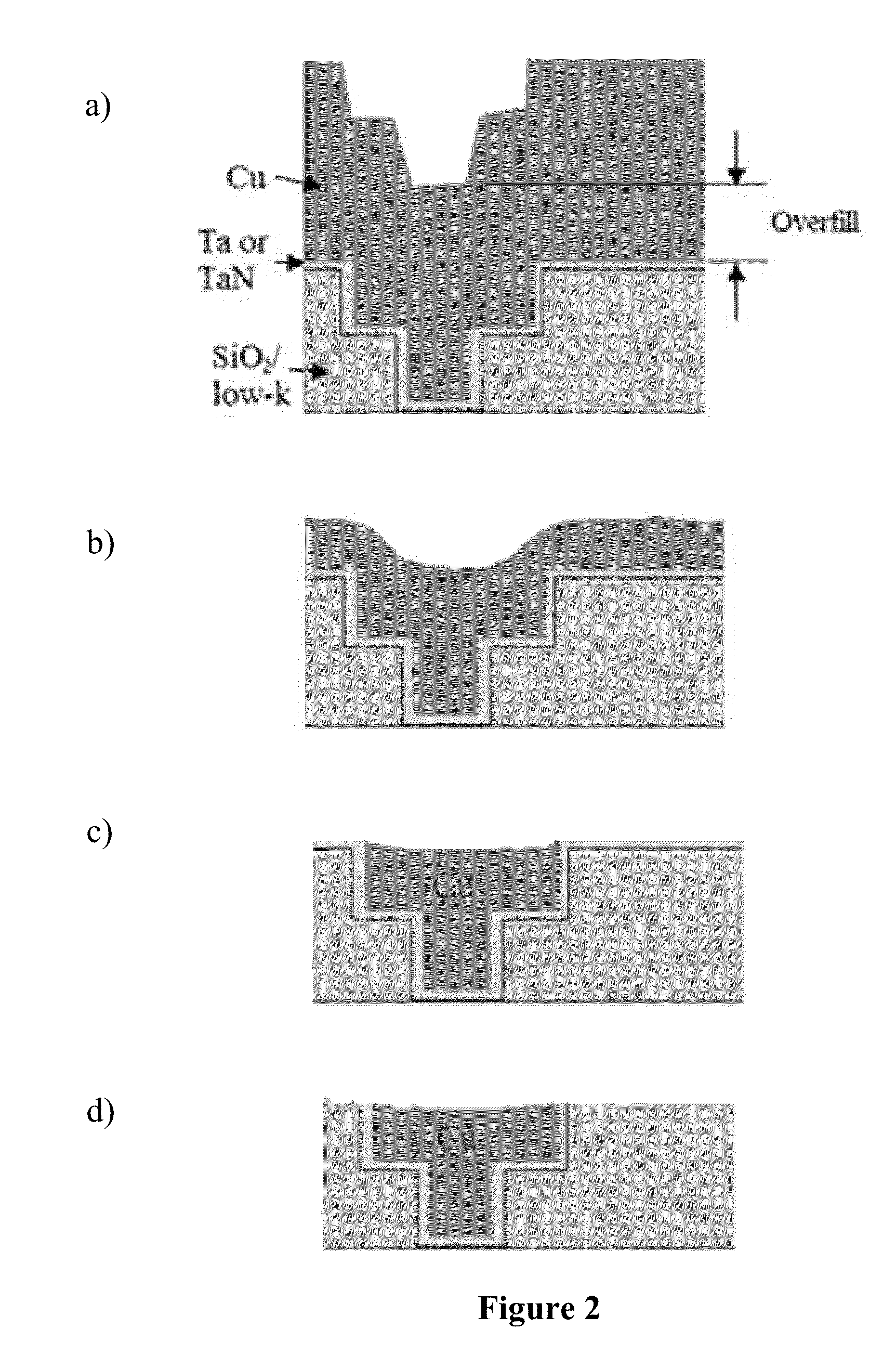

Contact release capsule useful for chemical mechanical planarization slurry

ActiveUS20130280910A1Good dispersionScale downPigmenting treatmentOther chemical processesDispersion stabilitySilica nanoparticles

The invention relates to a contact release capsule comprising a particle, a chemical payload, and a polymer coating, wherein the particle is impregnated with the chemical payload, and the chemical payload is held inside the particle by the polymer coating until the contact release capsule contacts a surface and a shearing force removes the polymer coating allowing the chemical payload to release outside the particle. The contact release capsule is useful in chemical mechanical planarization slurries. Particularly, the contact release capsule may comprise a glycine impregnated silica nanoparticle coated with a polymer, wherein the contact release capsule is dispersed in an aqueous solution and used in the copper chemical mechanical planarization process. Use of the contact release capsule in a slurry for copper chemical mechanical planarization may significantly improve planarization efficiency, decrease unwanted etching and corrosion, and improve dispersion stability.

Owner:GENERAL ENG & RES

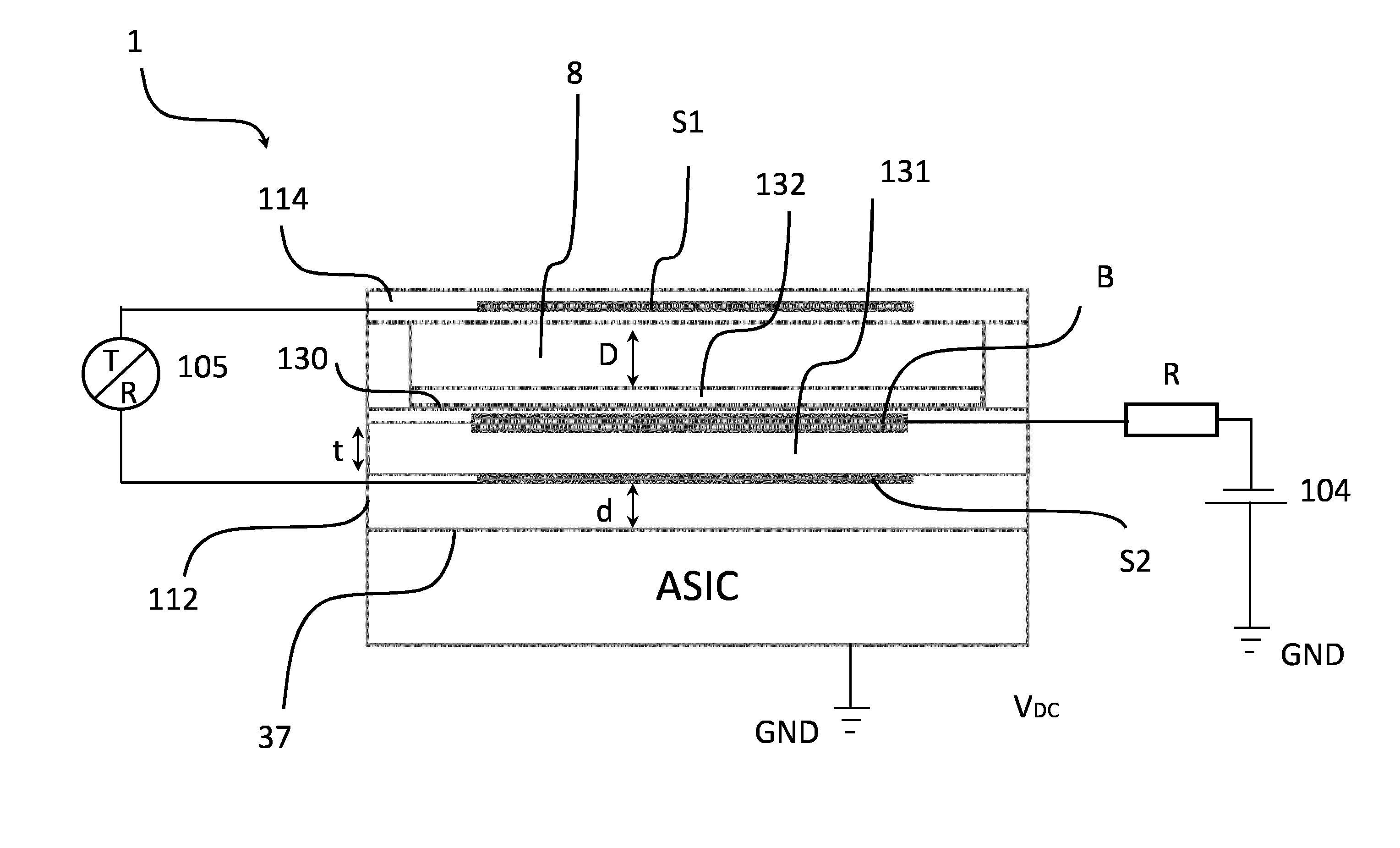

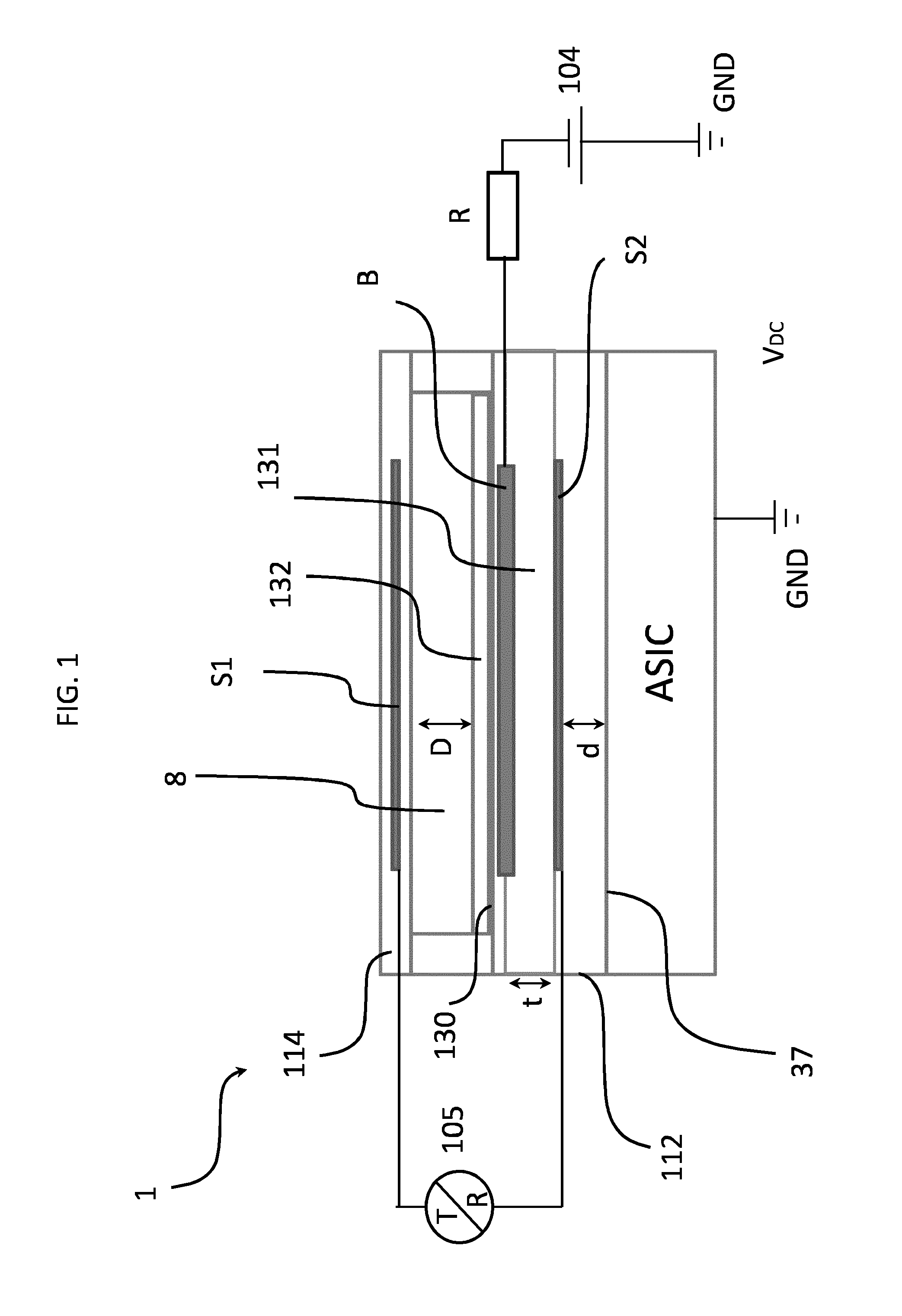

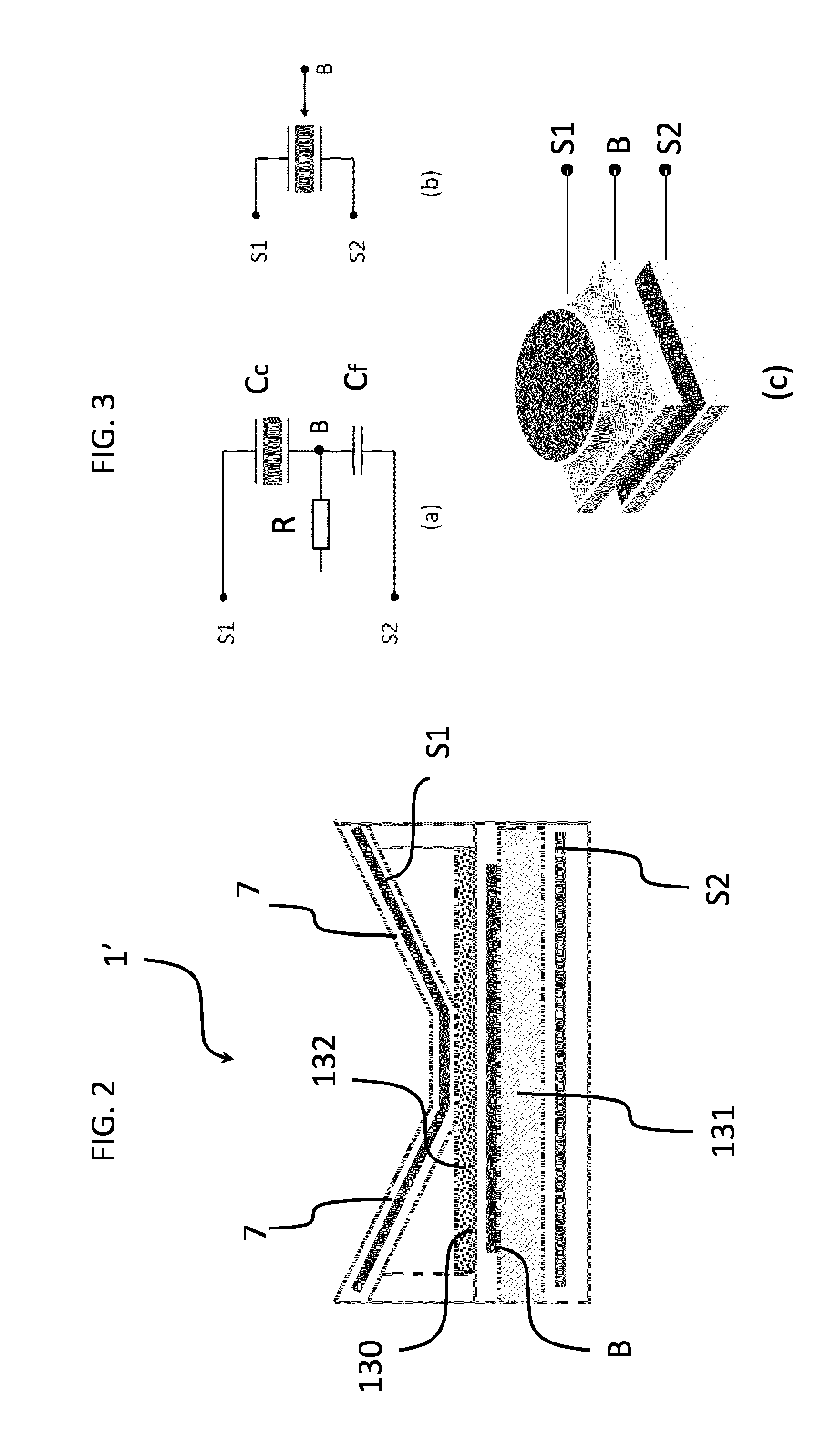

Monolithically integrated three electrode cmut device

ActiveUS20160310992A1Improved and efficient high voltage supplySuitable for miniaturizationUltrasonic/sonic/infrasonic diagnosticsMechanical vibrations separationCapacitive micromachined ultrasonic transducersCell membrane

A capacitive micromachined ultrasonic transducer (CMUT) cell comprising three electrodes: a first electrode coupled to a cell membrane; a second electrode embedded into a cell floor opposing the first electrode and separated therefrom by a gas or vacuum cavity; and a third electrode opposing the second electrode on the cavity side, wherein a dielectric layer is sandwiched between the second electrode and the third electrode to create a capacitive relation between the second electrode and the third electrode. The three electrode CMUT cell provides an ultrasound transducer with two actively driven (controlled) electrodes.

Owner:KONINKLJIJKE PHILIPS NV

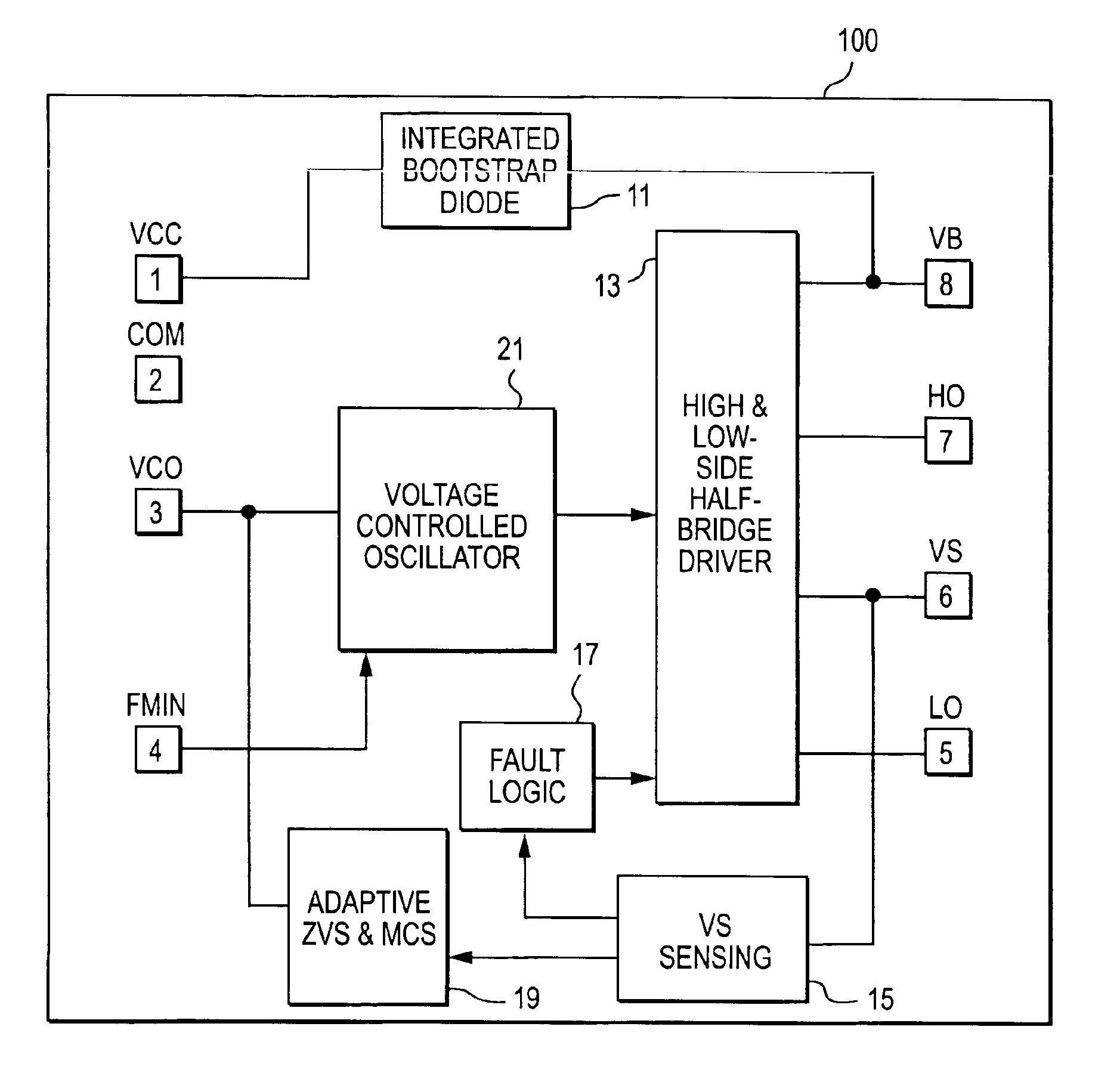

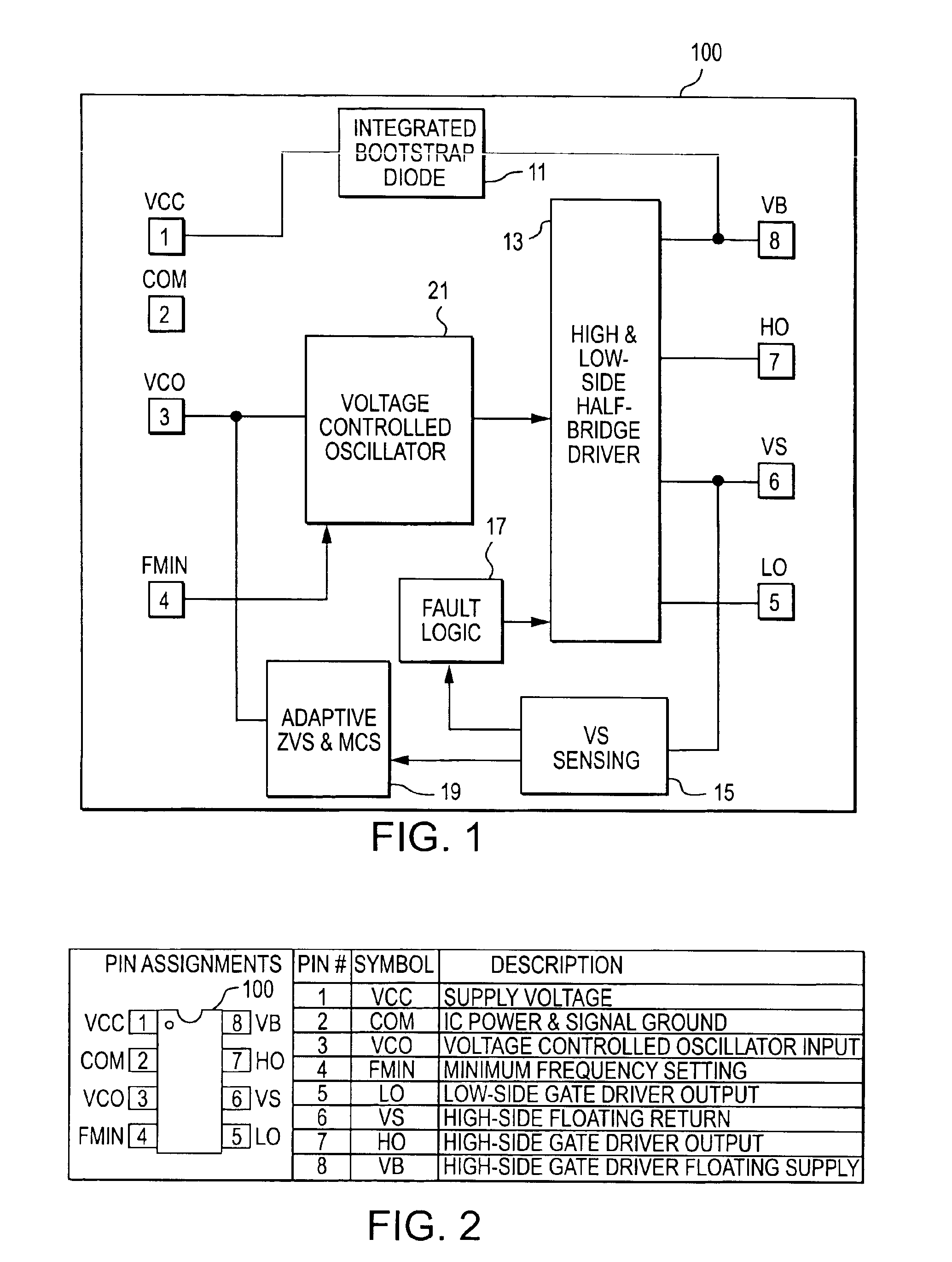

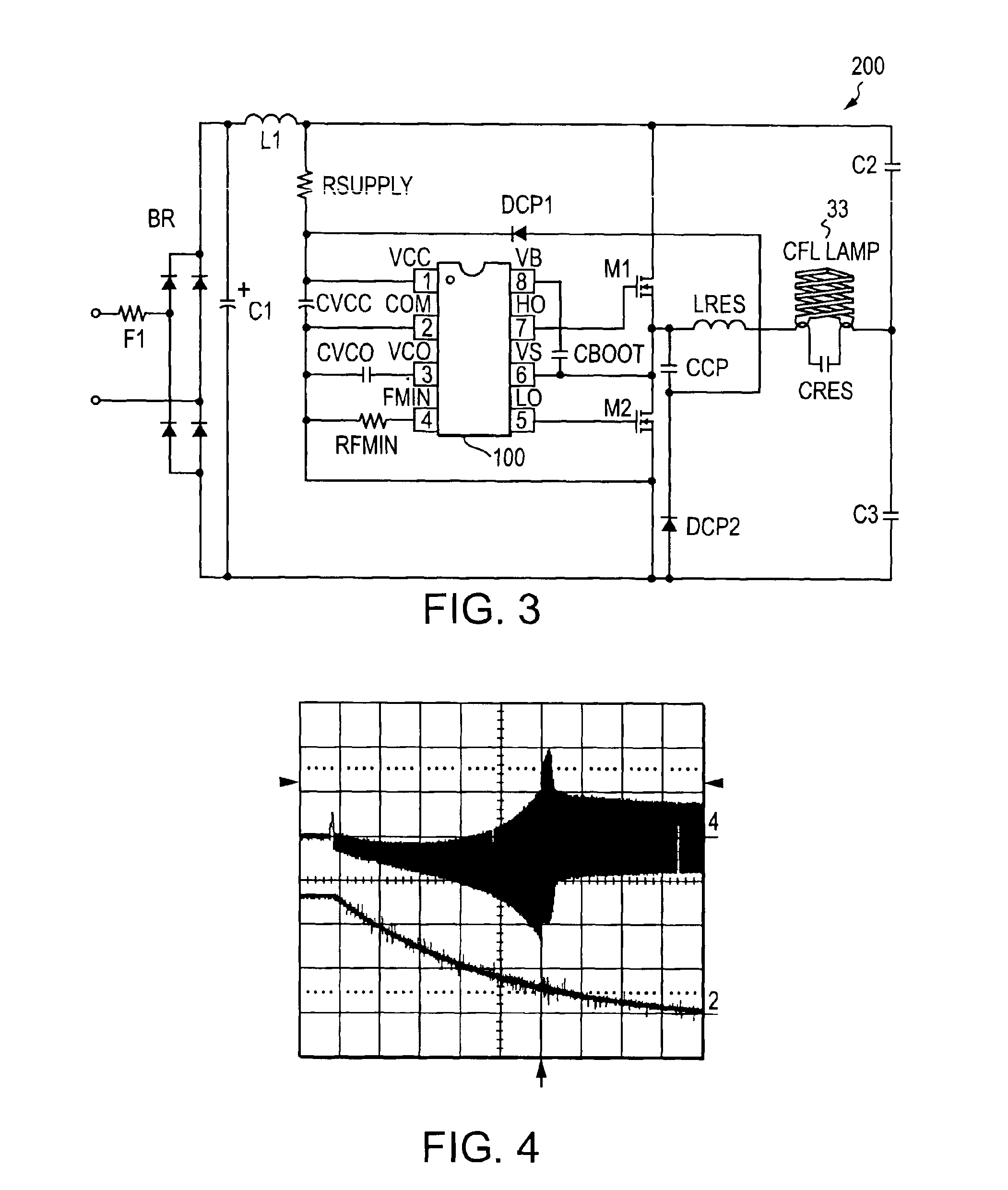

Adaptive ballast control IC

InactiveUS6879115B2Improve performanceScale downElectrical apparatusElectric light circuit arrangementLoad circuitDriver circuit

An integrated circuit for controlling a power supply circuit which delivers power to a load circuit that includes a fluorescent lamp, comprising ballast control and drive circuitry that provides drive signals to the power supply circuit, receives sense signals indicating operating conditions of at least one of the power supply circuit and the load circuit, and responds to the sense signals by modifying the drive signals; and including adaptive zero-voltage-switching and minimum-current-switching (ZVMCS) circuitry, wherein the ZVMCS circuitry senses an output of the power supply circuit, and in response thereto, controls the drive circuitry to maintain the power supply circuit under ZVMCS conditions. The power supply circuit includes a half-bridge circuit with low and high side power devices, the drive signals including low side drive signals to control the low side power device and high side drive signals to control the high side power device; the ballast control and drive circuitry including a low side drive output for providing the low side drive signals to the low side power device and a high side drive output for providing the high side drive signals to the high side power device. The ZVMCS circuit senses an output voltage and / or current at the half-bridge circuit between said high side and low side power devices at a switching time of one of the power devices, and controls the drive signals so as to maintain the output voltage and / or current near or at zero at said switching time.

Owner:INFINEON TECH AMERICAS CORP

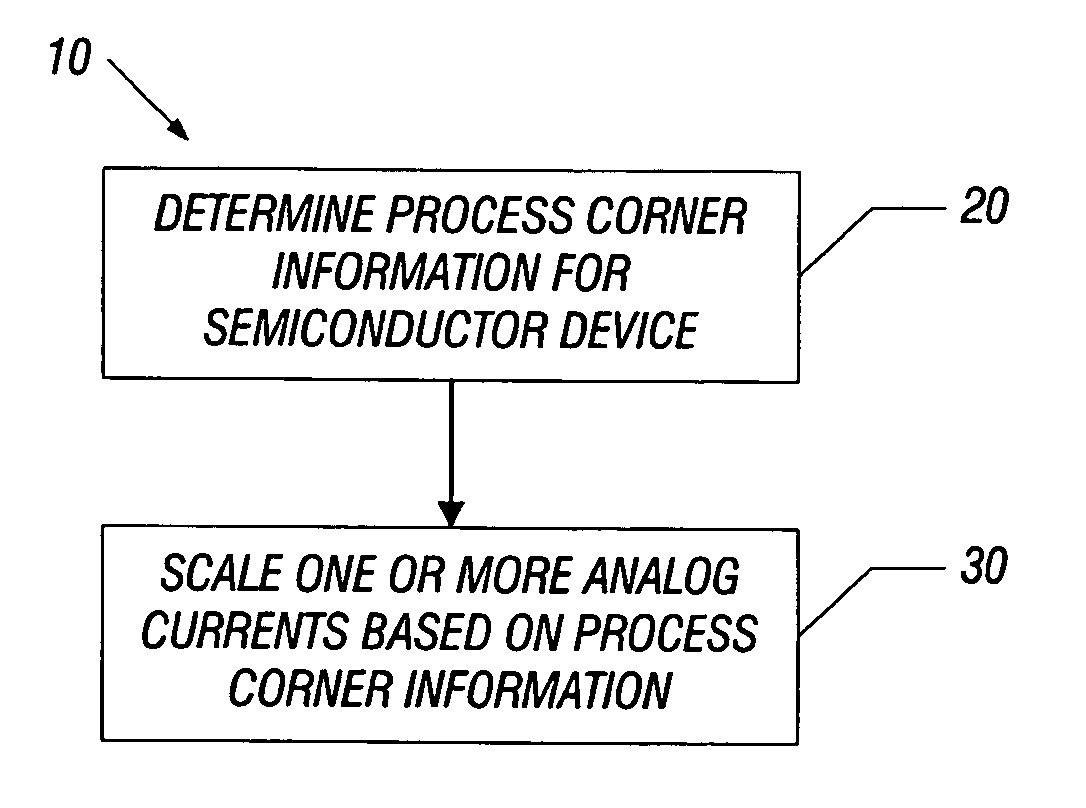

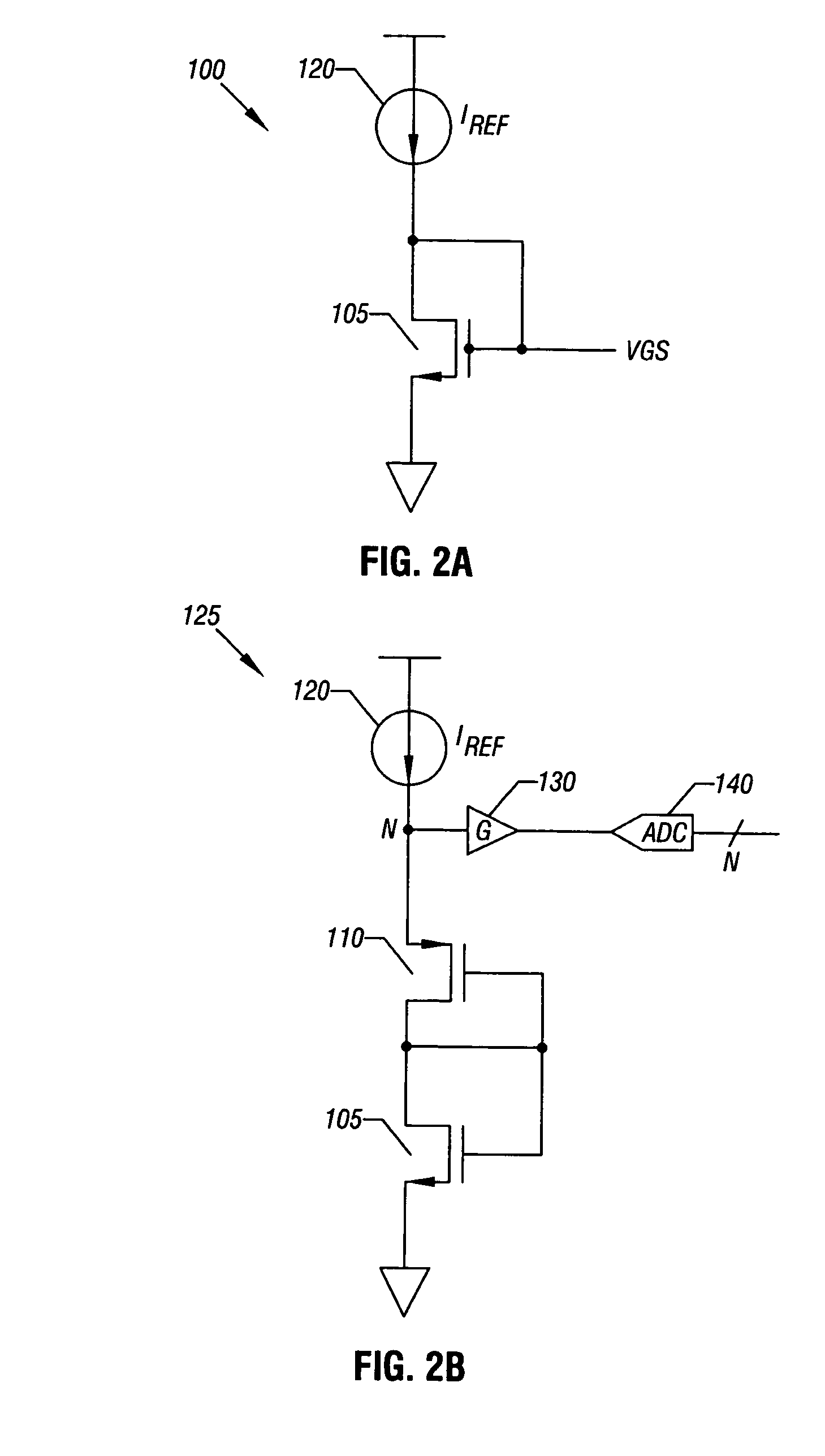

Reducing power dissipation using process corner information

InactiveUS20080076372A1Scale downIncrease currentPower consumption reductionTransmission monitoringCurrent consumptionEngineering

In one embodiment, the present invention includes a method for determining process corner information of an integrated circuit (IC) and controlling at least one analog current for at least one analog circuit of the IC based on the process corner information. More specifically, if the process corner information is indicative of a fast corner IC, the analog current may be scaled down. At the same time that the analog current is scaled down, a current consumption level of digital circuitry of the IC may increase. In this way, overall power consumption of the IC may be reduced to the extent that the analog current(s) are scaled.

Owner:SILICON LAB INC

VECTOR PROCESSING ENGINES (VPEs) EMPLOYING TAPPED-DELAY LINE(S) FOR PROVIDING PRECISION CORRELATION / COVARIANCE VECTOR PROCESSING OPERATIONS WITH REDUCED SAMPLE RE-FETCHING AND POWER CONSUMPTION, AND RELATED VECTOR PROCESSOR SYSTEMS AND METHODS

InactiveUS20150143079A1Minimize re-fetchingReduce power consumptionGeneral purpose stored program computerMachine execution arrangementsData streamCode division multiple access

Vector processing engines (VPEs) employing a tapped-delay line(s) for providing precision correlation / covariance vector processing operations with reduced sample re-fetching and / or power consumption are disclosed. The VPEs disclosed herein are configured to provide correlation / covariance vector processing operations, such as code division multiple access (CDMA) correlation / covariance vector processing operations as a non-limiting example. A tapped-delay line(s) is included in the data flow paths between memory and execution units in the VPE. The tapped-delay line (s) is configured to receive and provide an input vector data sample set to execution units for performing correlation / covariance vector processing operations. The tapped-delay line(s) is also configured to shift the input vector data sample set for each filter delay tap and provide the shifted input vector data sample set to the execution units, so the shifted input vector data sample set need not be re-fetched from the vector data file during the filter vector processing operations.

Owner:UK DO I +1

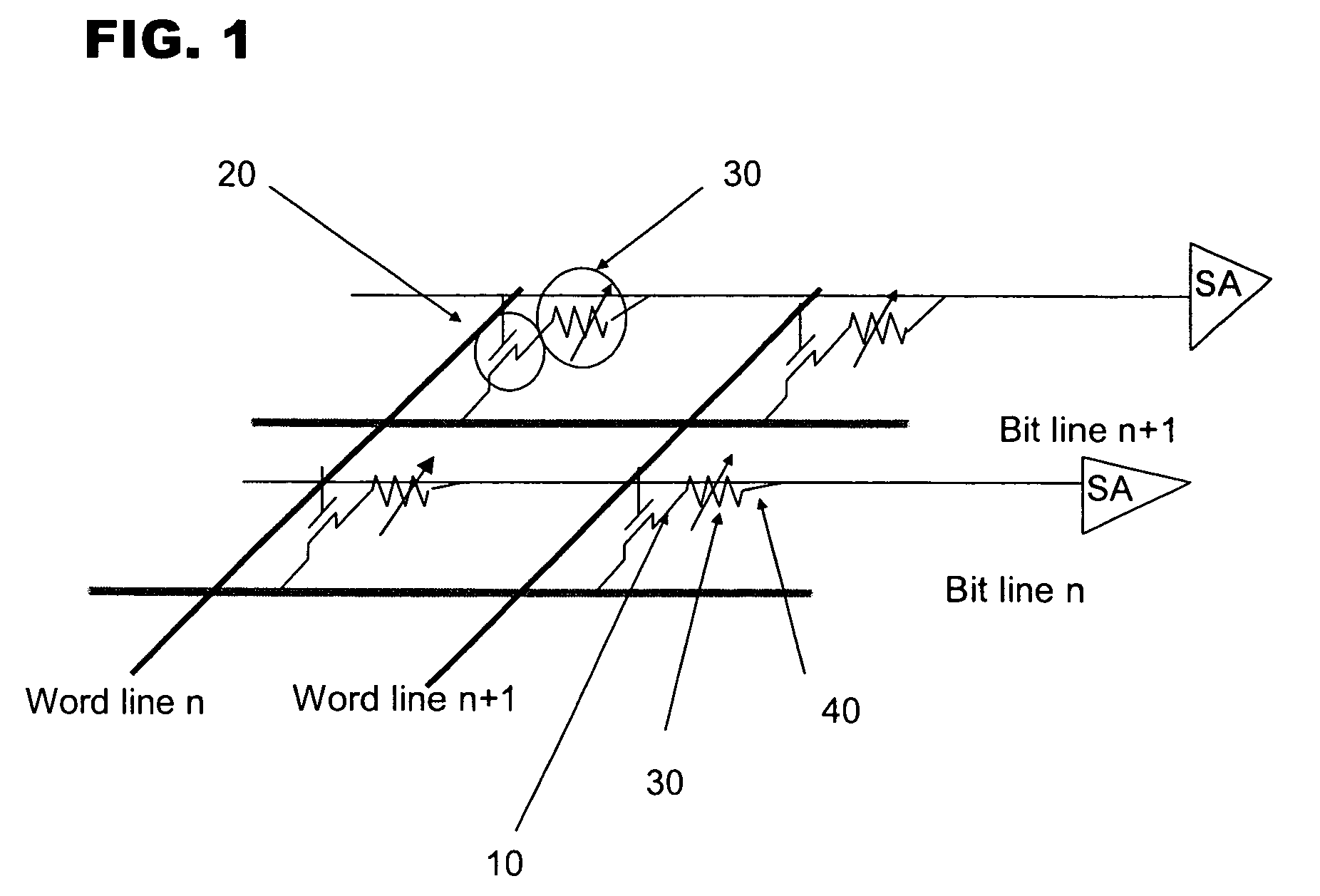

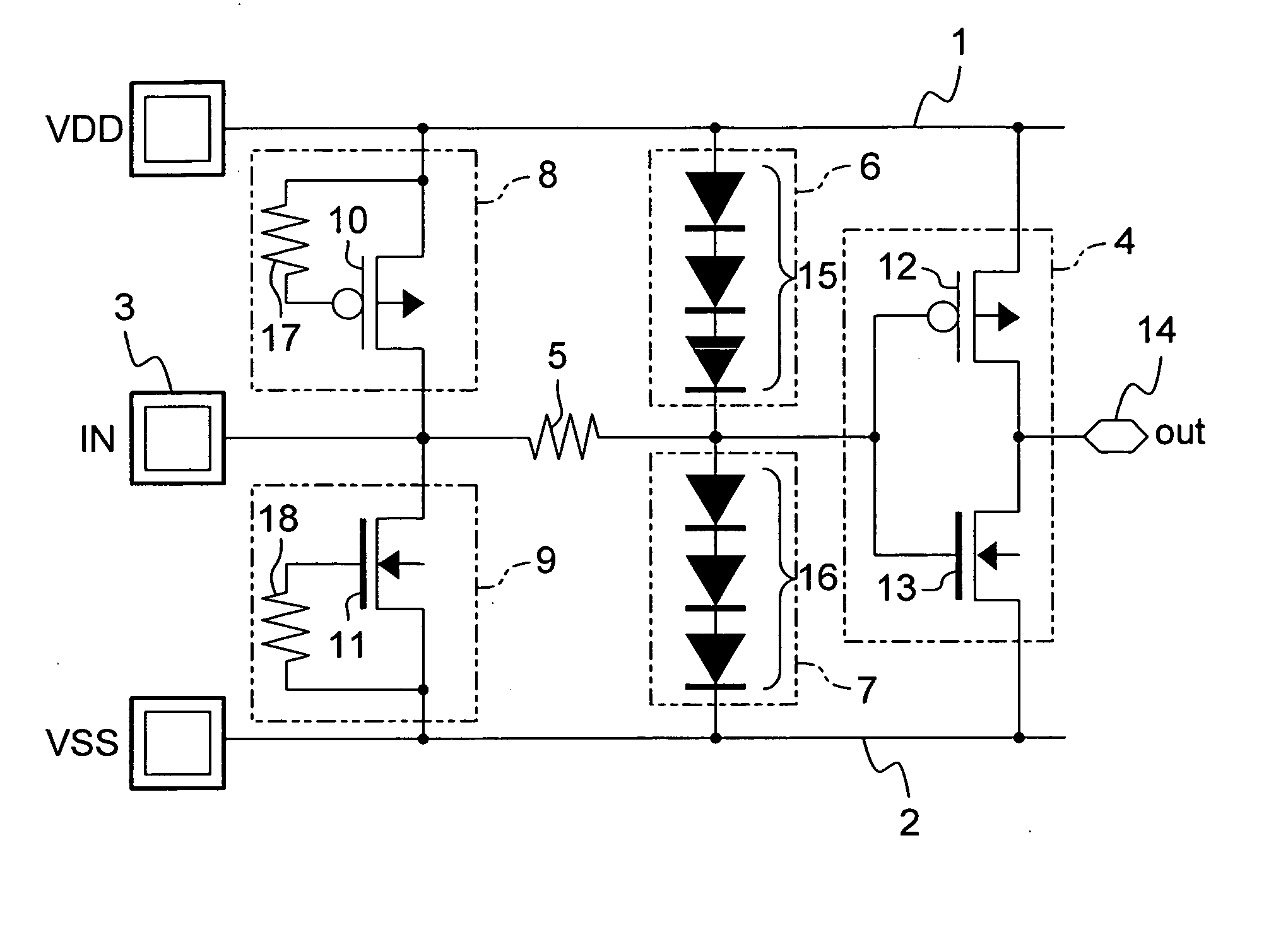

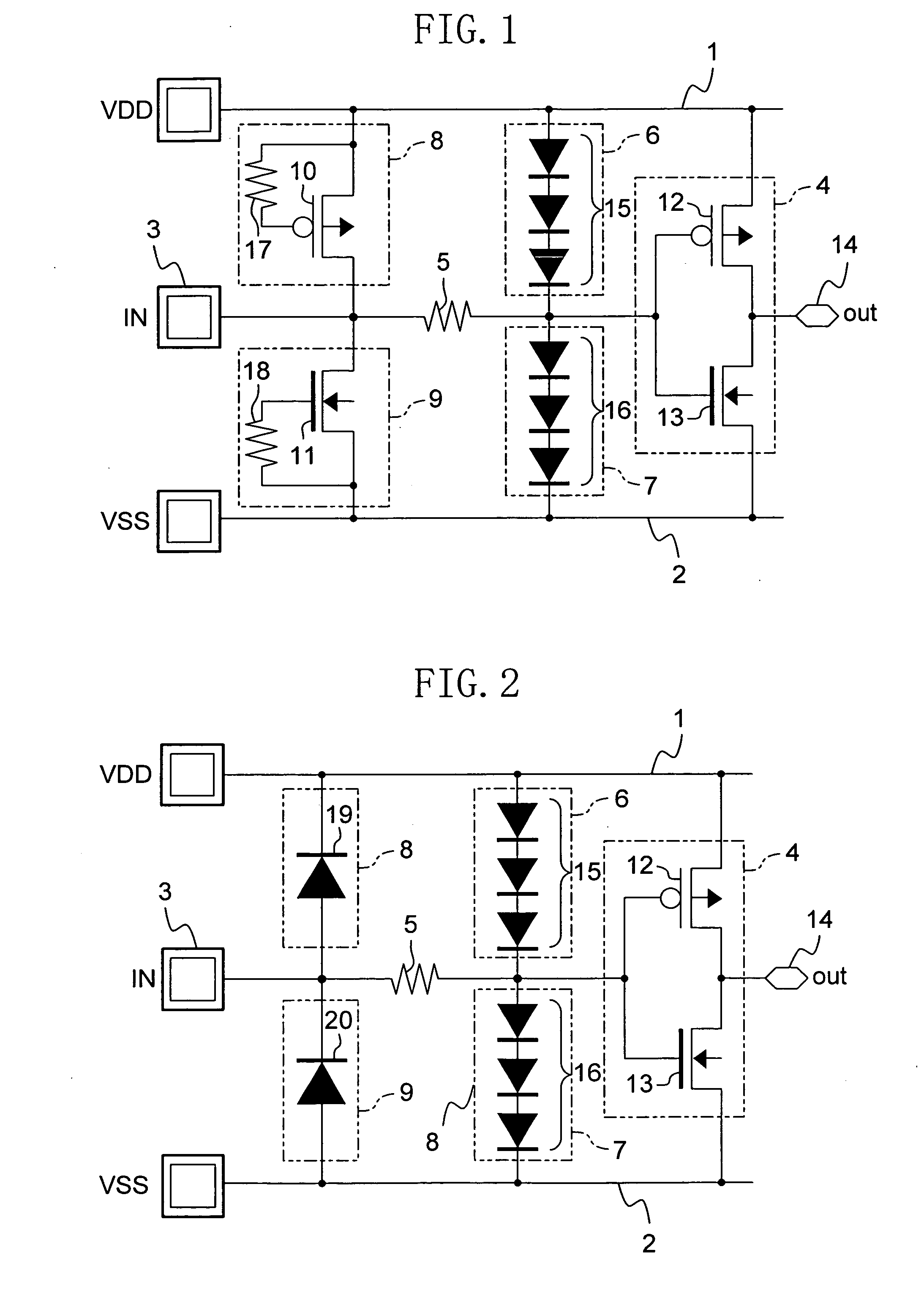

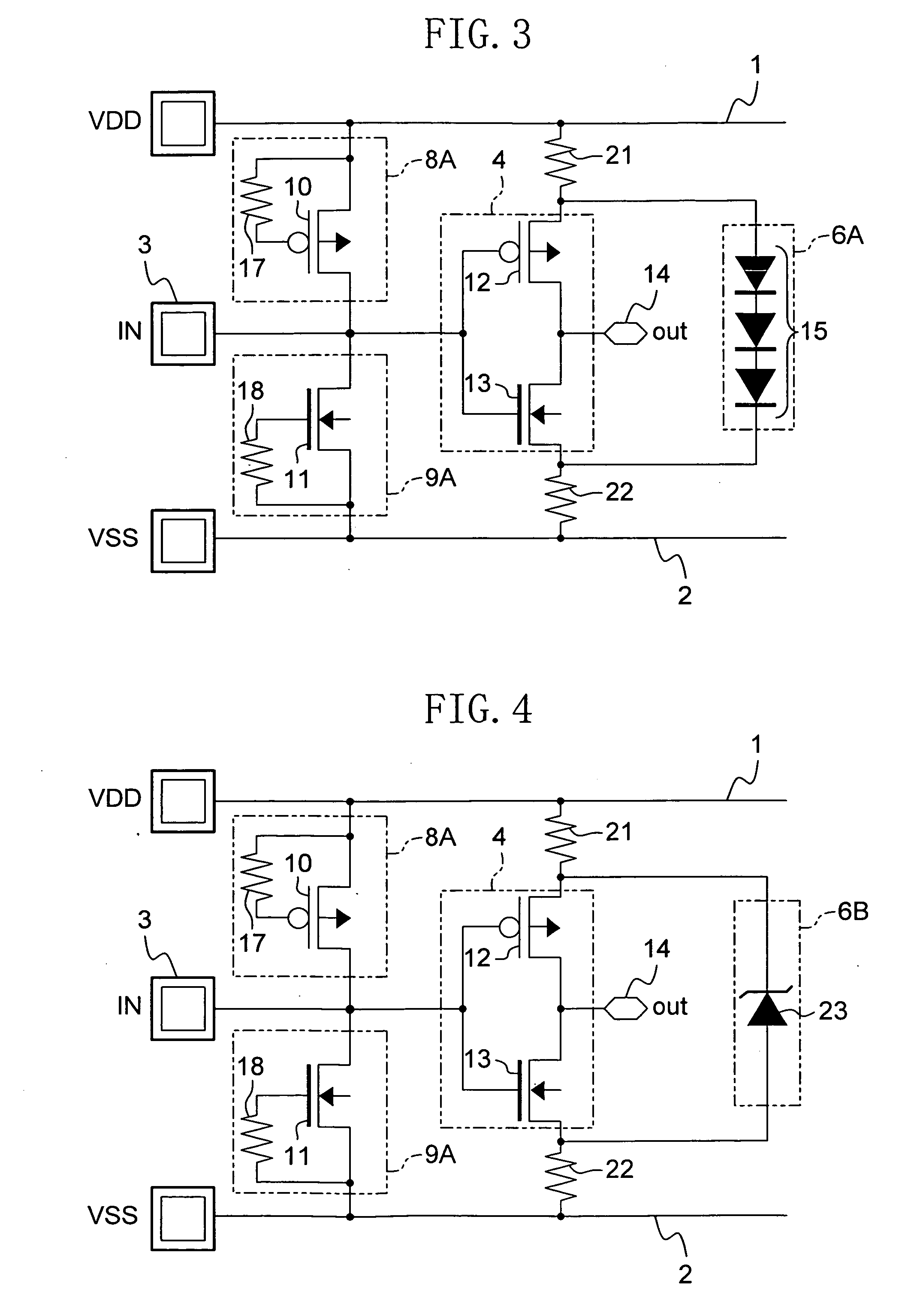

Semiconductor integrated circuit device

InactiveUS20070201175A1Voltage be lowerScale downDiodeEmergency protective arrangements for limiting excess voltage/currentElectrostatic discharge protectionIntegrated circuit

The semiconductor integrated circuit device includes: a circuit to be protected connected between a power supply line and a ground line; a first resistance connected to an external input terminal at one terminal and to an input terminal of the circuit to be protected at the other terminal; a first electrostatic discharge protection circuit including a first voltage drop circuit connected to the power supply line at one terminal and to the input terminal of the circuit to be protected at the other terminal; and a second electrostatic discharge protection circuit including a second voltage drop circuit connected to the input terminal of the circuit to be protected at one terminal and to the ground line at the other terminal.

Owner:PANASONIC CORP

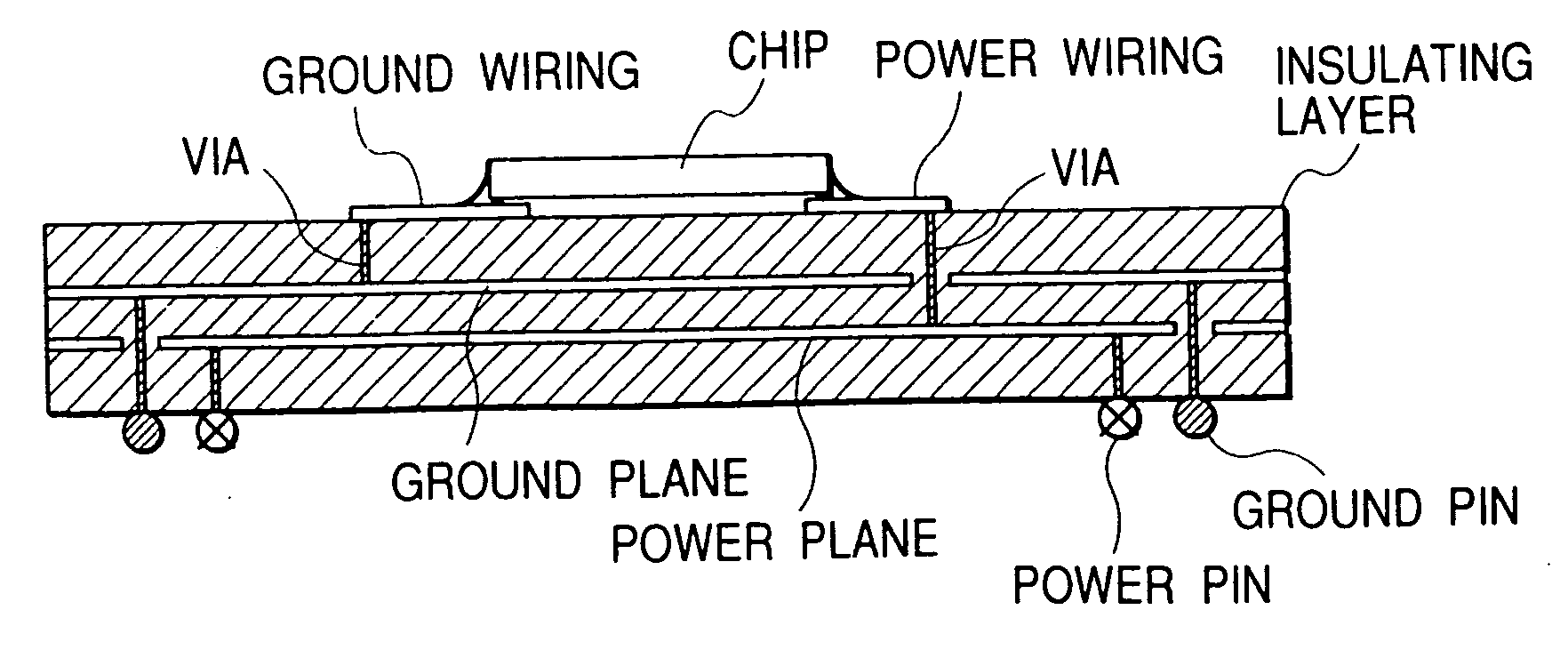

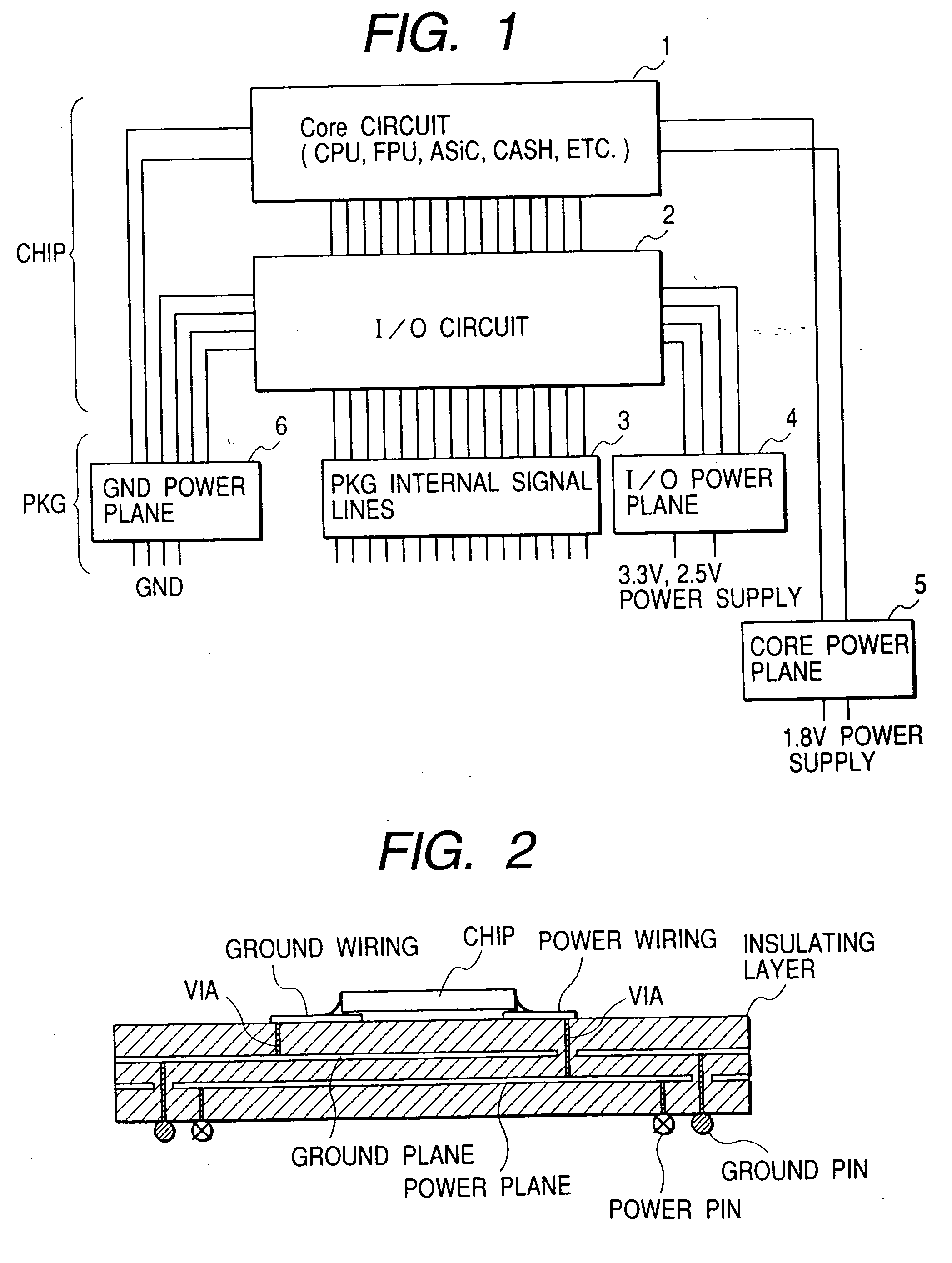

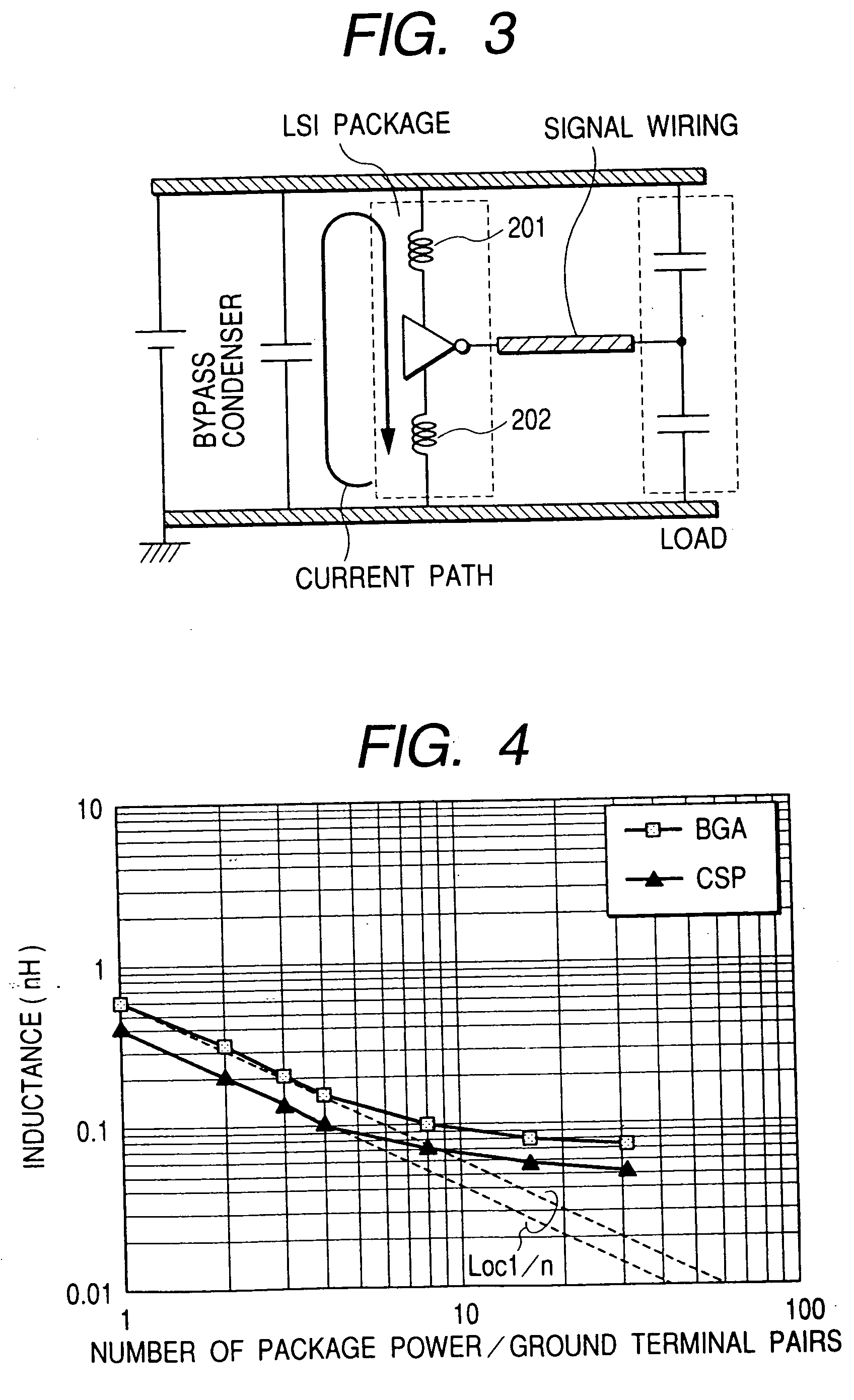

Semiconductor device and an electronic device

InactiveUS20050029648A1Reduce in quantitySuppress power noiseSemiconductor/solid-state device detailsSolid-state devicesDevice materialPower noise

A semiconductor device has a reduced number of external power terminals and is scaled down while suppressing power noise, and an electronic device is efficiently equipped with a bypass condenser. A package substrate has, on its surface, a semiconductor chip having a plurality of output circuits and at least one electrode for supplying a voltage to each of the output circuits, and is provided with external terminals on its back surface and has a plurality of wiring layers.

Owner:RENESAS ELECTRONICS CORP

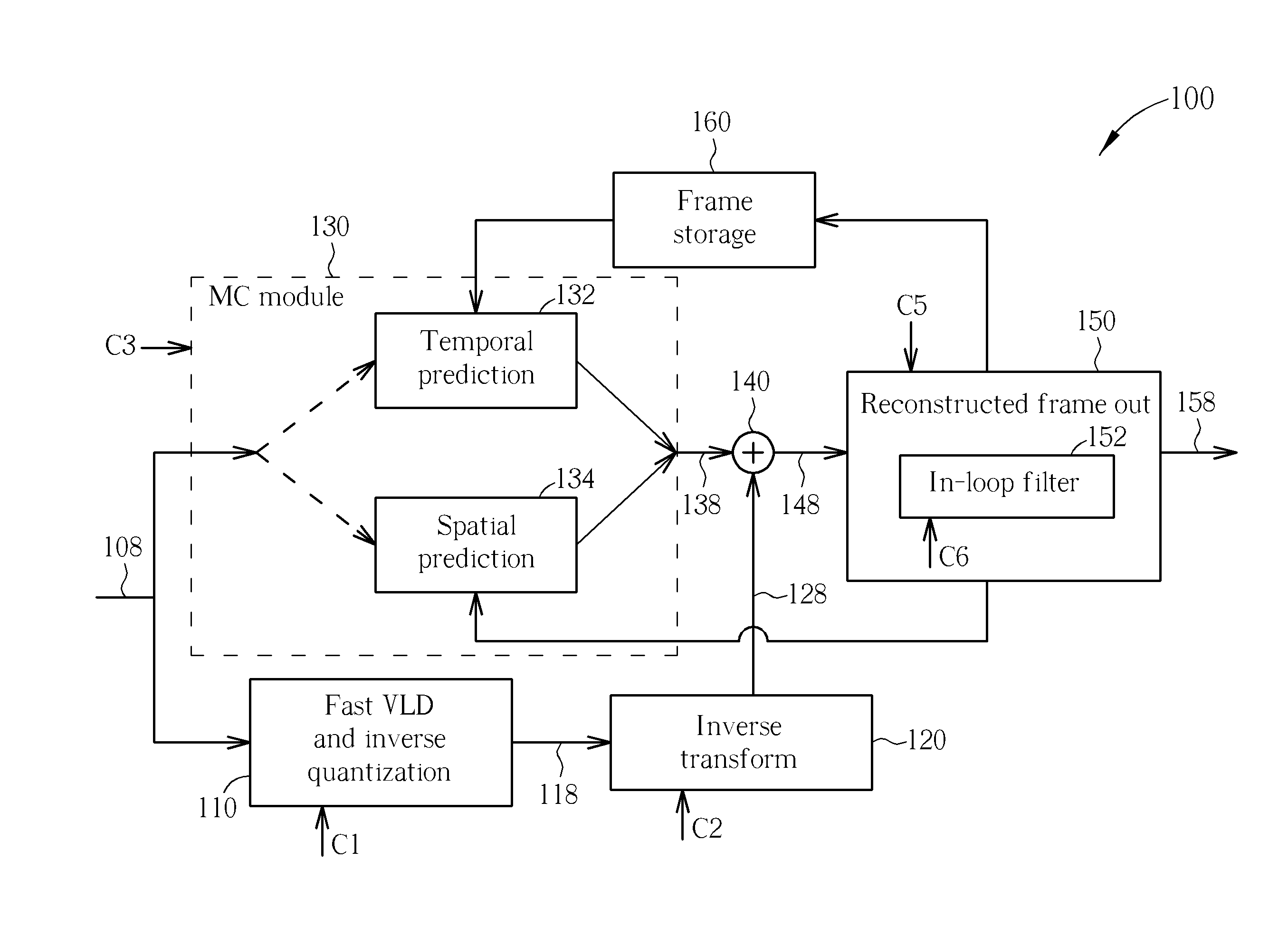

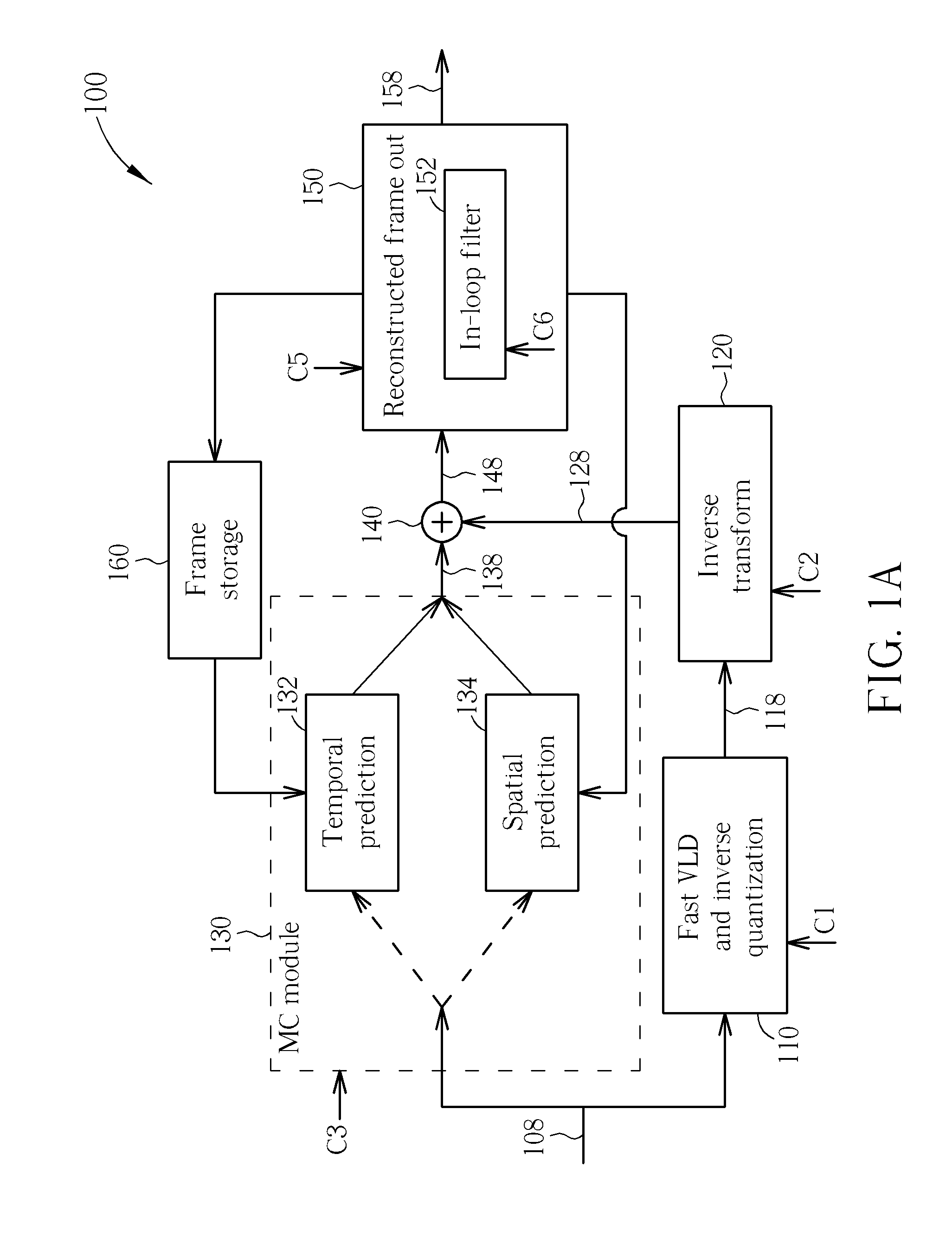

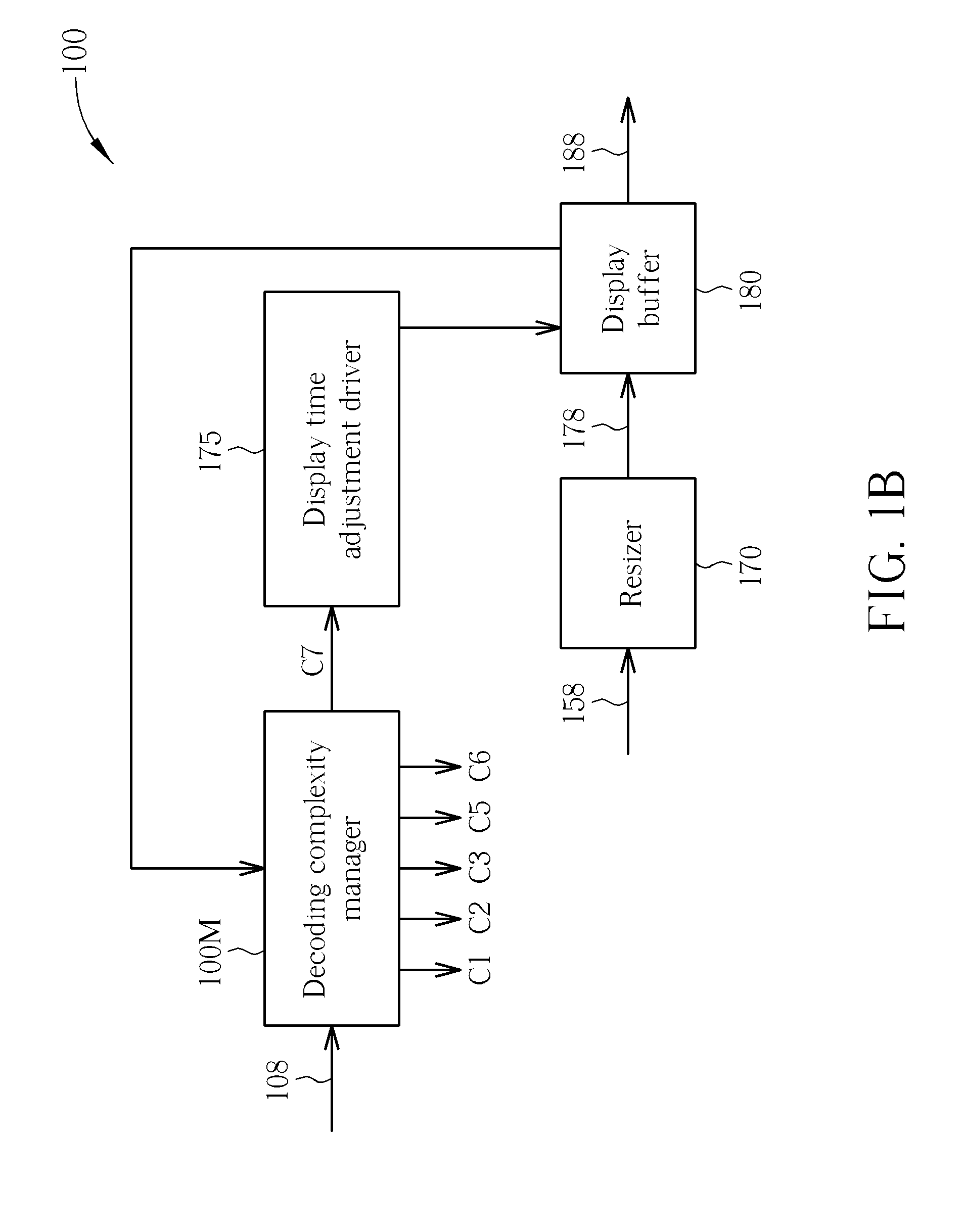

Method for adaptively performing video decoding, and associated adaptive complexity video decoder and adaptive audio/video playback system

ActiveUS20110235713A1Reduce calculation load and power consumptionReduce selection requirementsColor television with pulse code modulationColor television with bandwidth reductionComputer architectureVideo decoder

A method for adaptively performing video decoding includes: performing decoding complexity management based upon bit stream information of an input bit stream, in order to determine whether to reduce decoding complexity of at least one component of a plurality of components within an adaptive complexity video decoder; and selectively reducing decoding complexity of a portion of components within the adaptive complexity video decoder. An associated adaptive complexity video decoder and an associated adaptive audio / video playback system are also provided. In particular, the adaptive complexity video decoder includes a plurality of components and a decoding complexity manager. When needed, the decoding complexity manager delays audio playback of audio information.

Owner:XUESHAN TECH INC

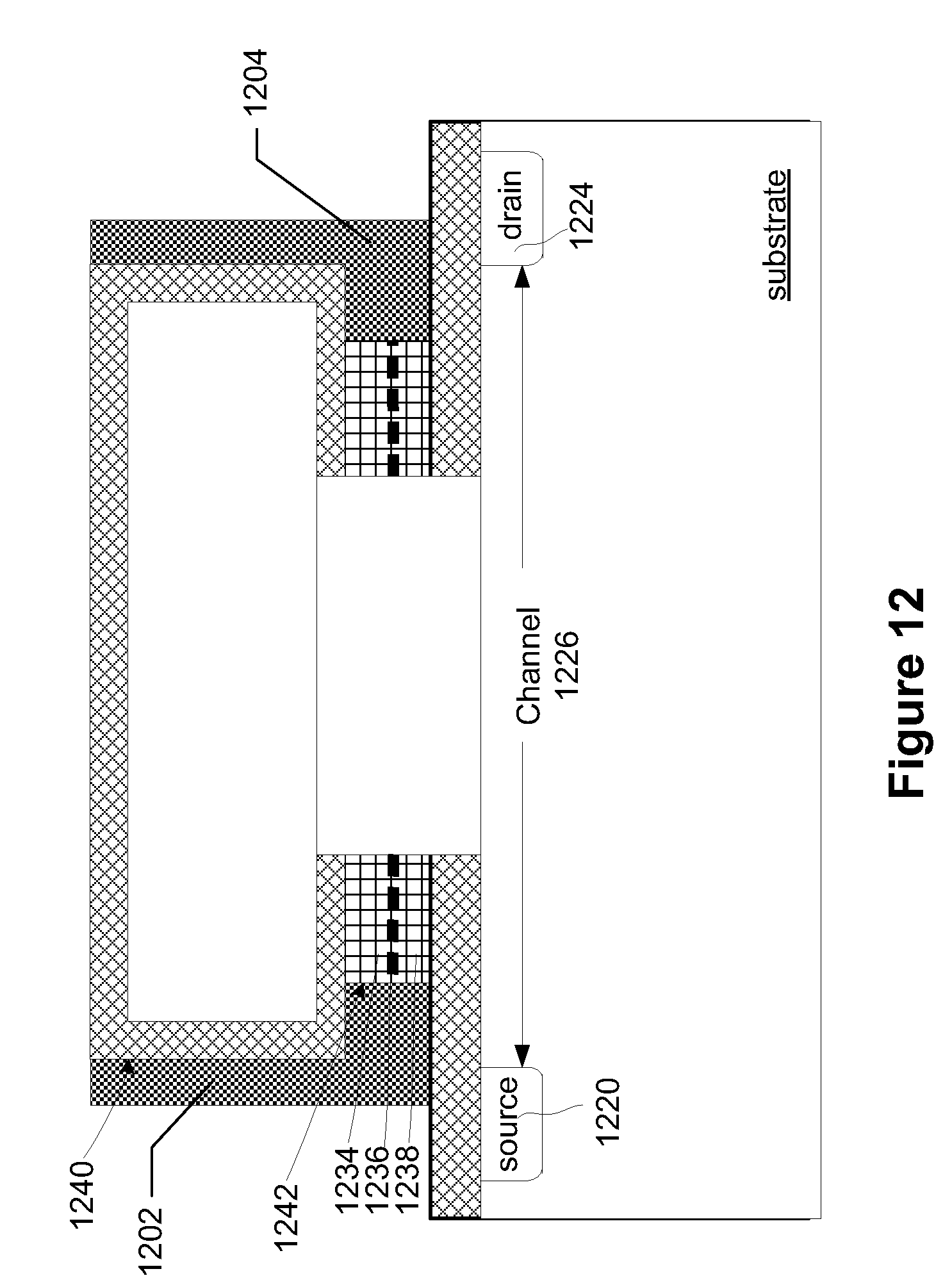

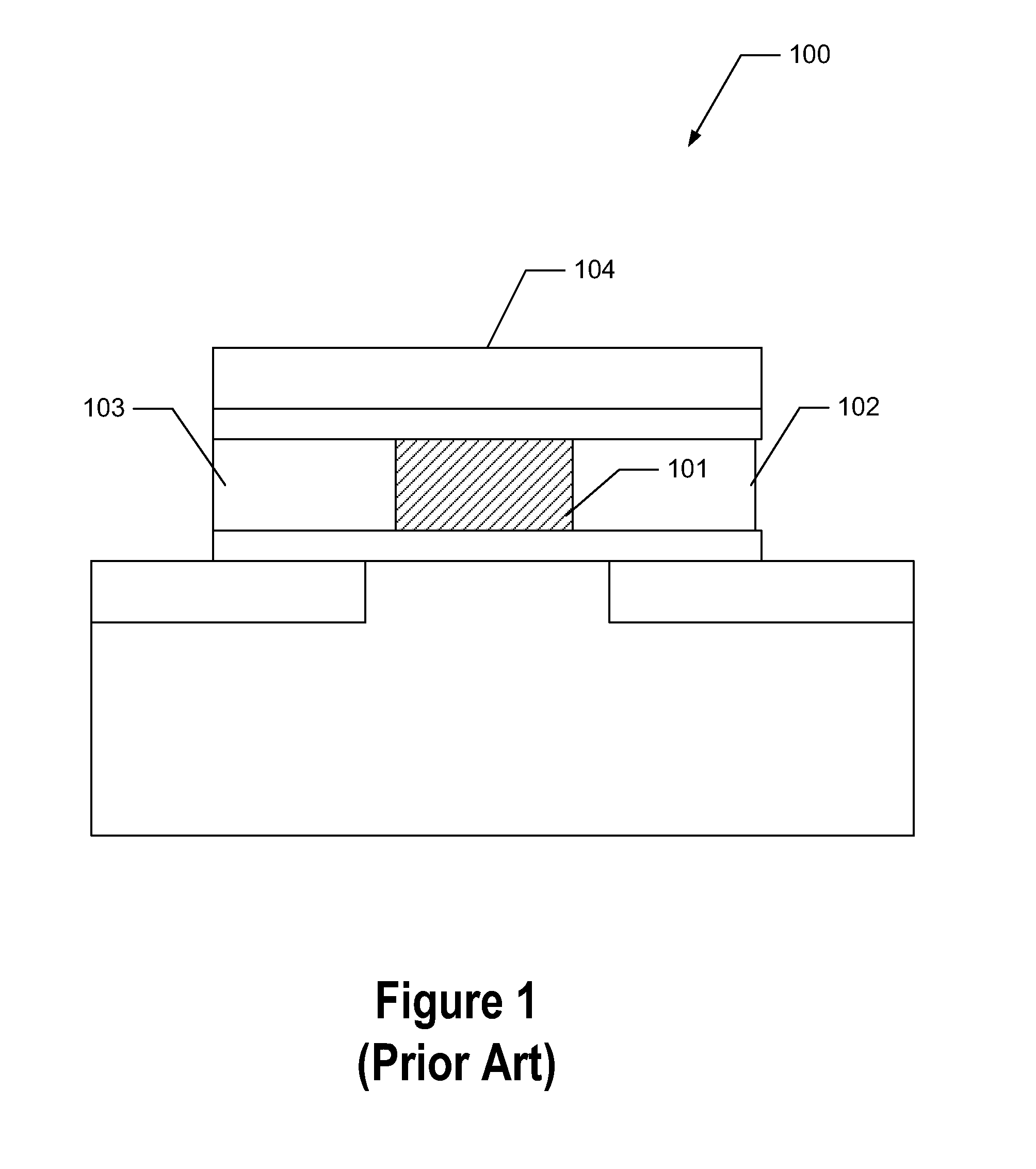

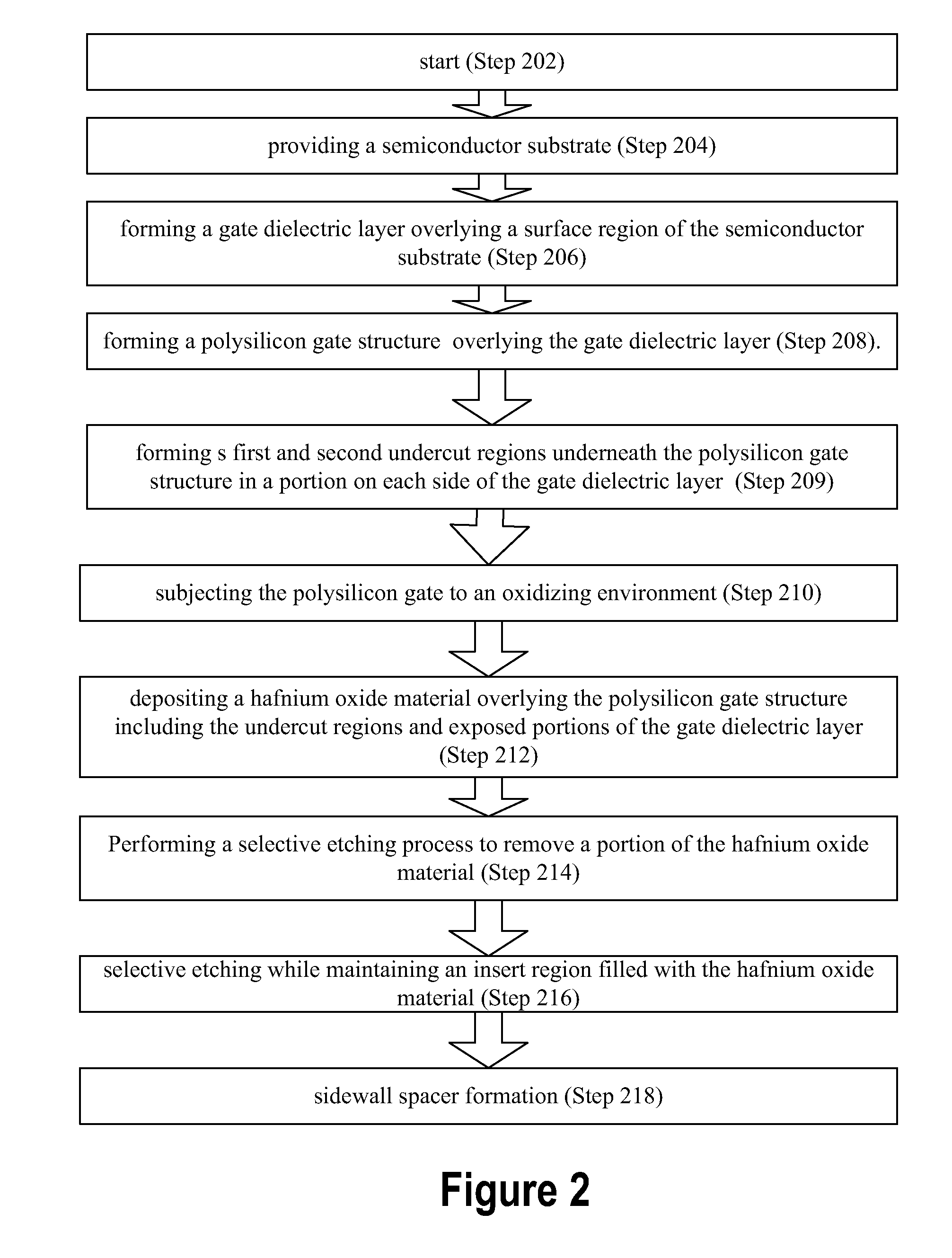

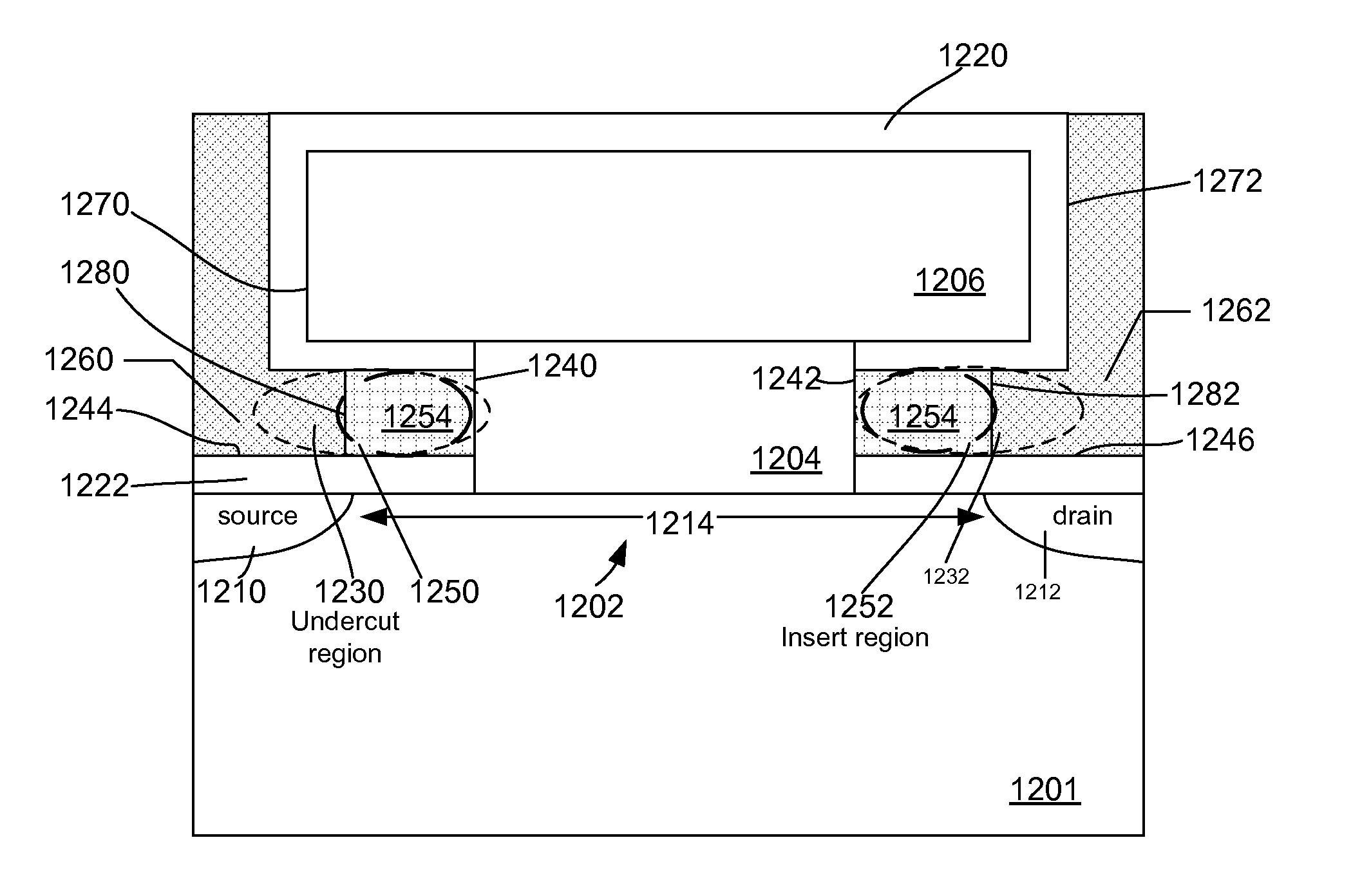

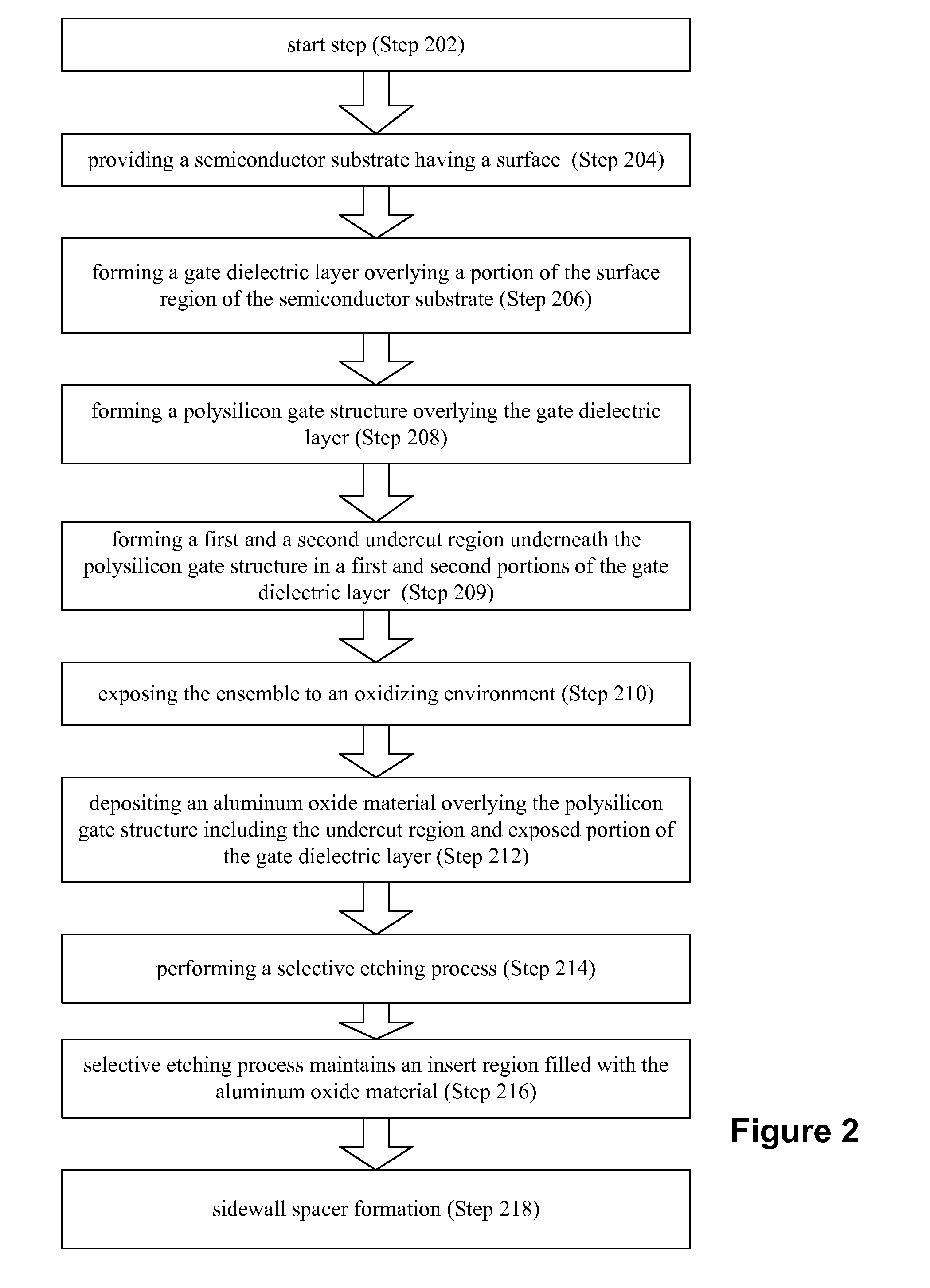

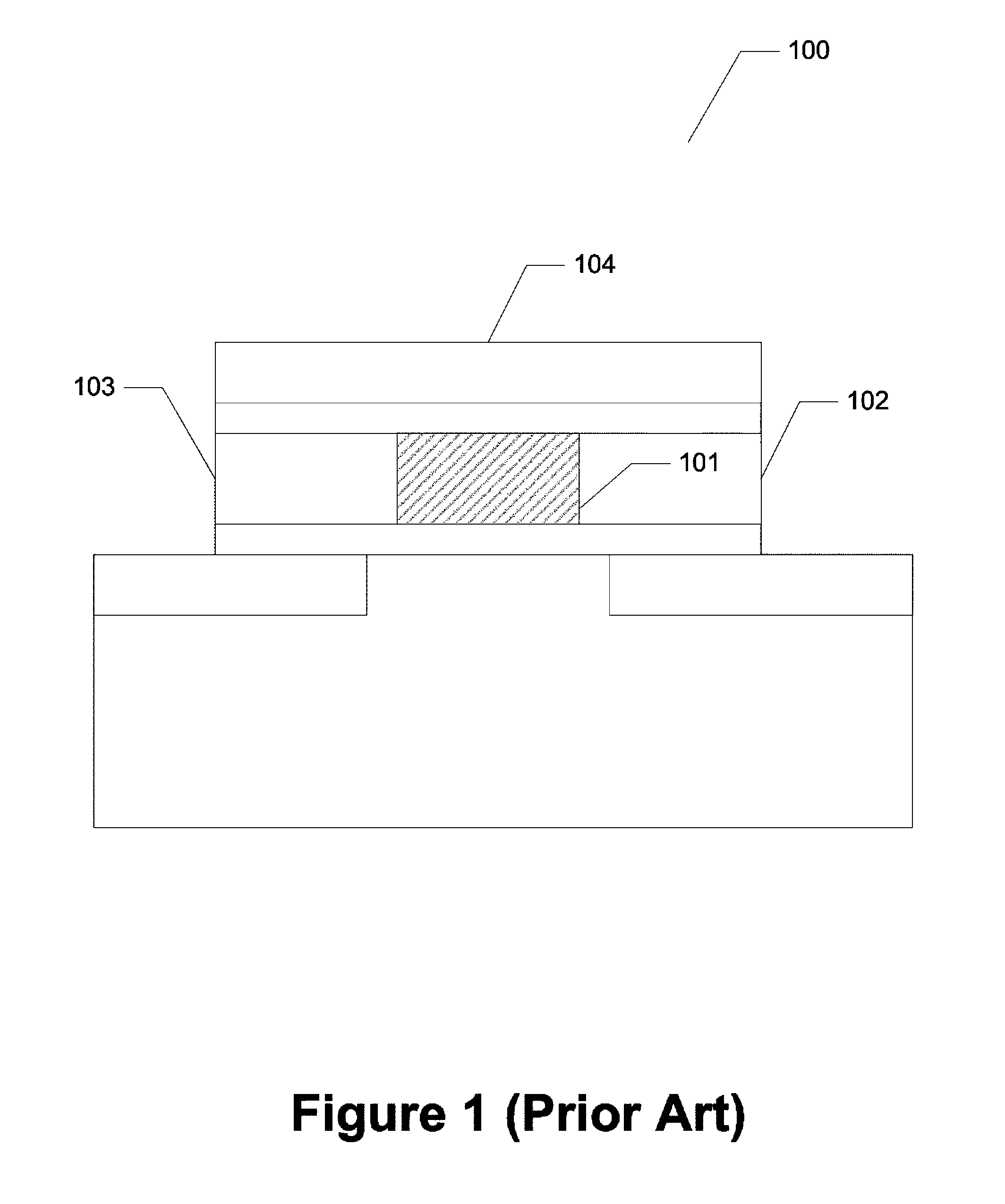

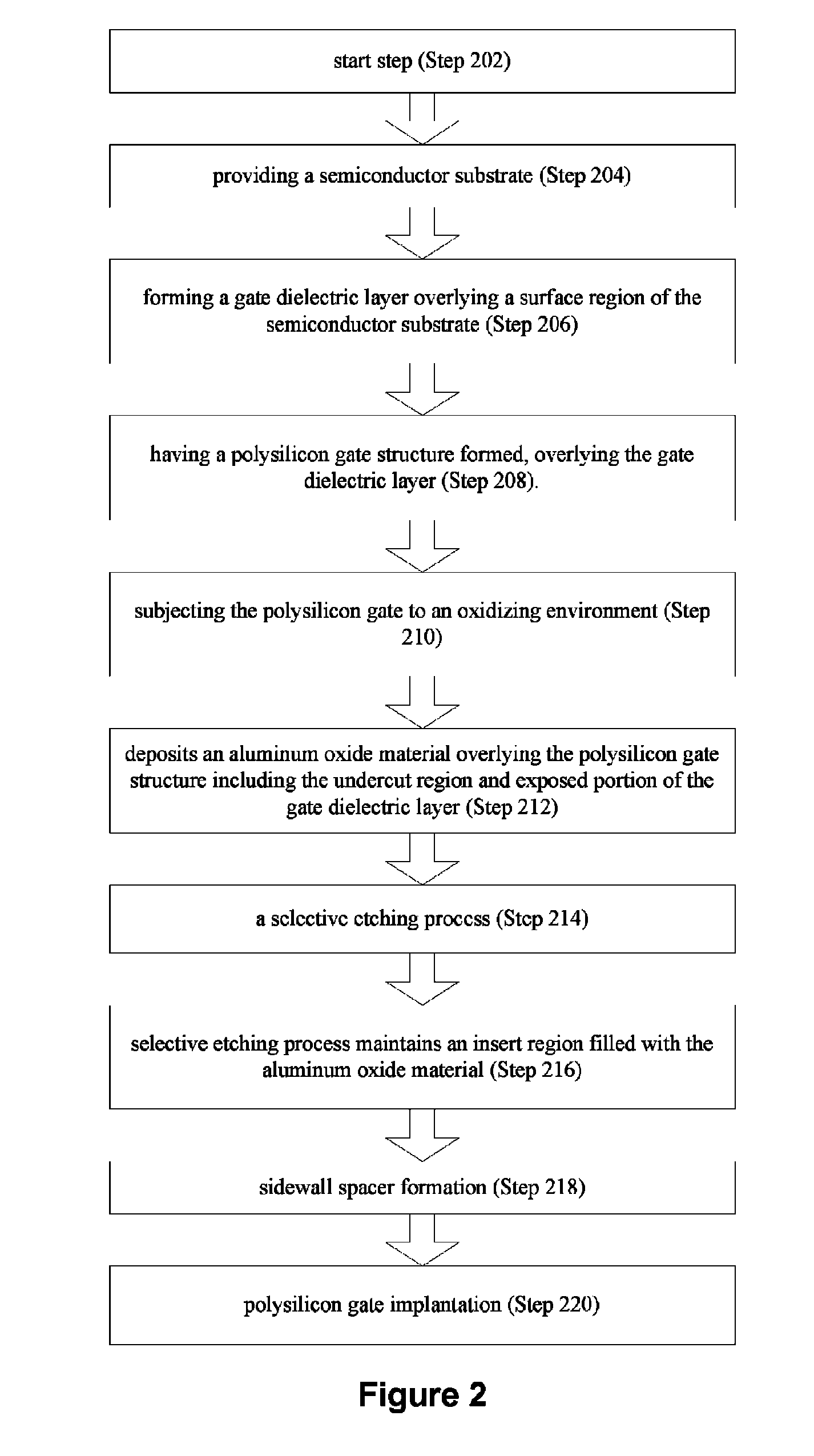

Method for manufacturing twin bit structure cell with hafnium oxide and nano-crystalline silicon layer

InactiveUS20110156129A1Wide rangeImplemented cost-effectivelySemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricNanocrystalline silicon

A method and system for forming a non-volatile memory structure. The method provides a semiconductor substrate and forms a gate dielectric layer overlying a surface region of the semiconductor substrate. A polysilicon gate structure is formed overlying the gate dielectric layer. The method subjects the polysilicon gate structure to an oxidizing environment to cause formation of a first silicon oxide layer overlying the polysilicon gate structure and formation of a second silicon oxide layer overlying a surface region of the substrate. A hafnium oxide material is formed overlying the first and second silicon oxide layers and filling the undercut region. The hafnium oxide material has a nanocrystalline silicon material sandwiched between a first hafnium oxide layer and a second hafnium oxide layer. The hafnium oxide material is selectively etched while a portion of it is maintained in an insert region in a portion of the undercut region.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

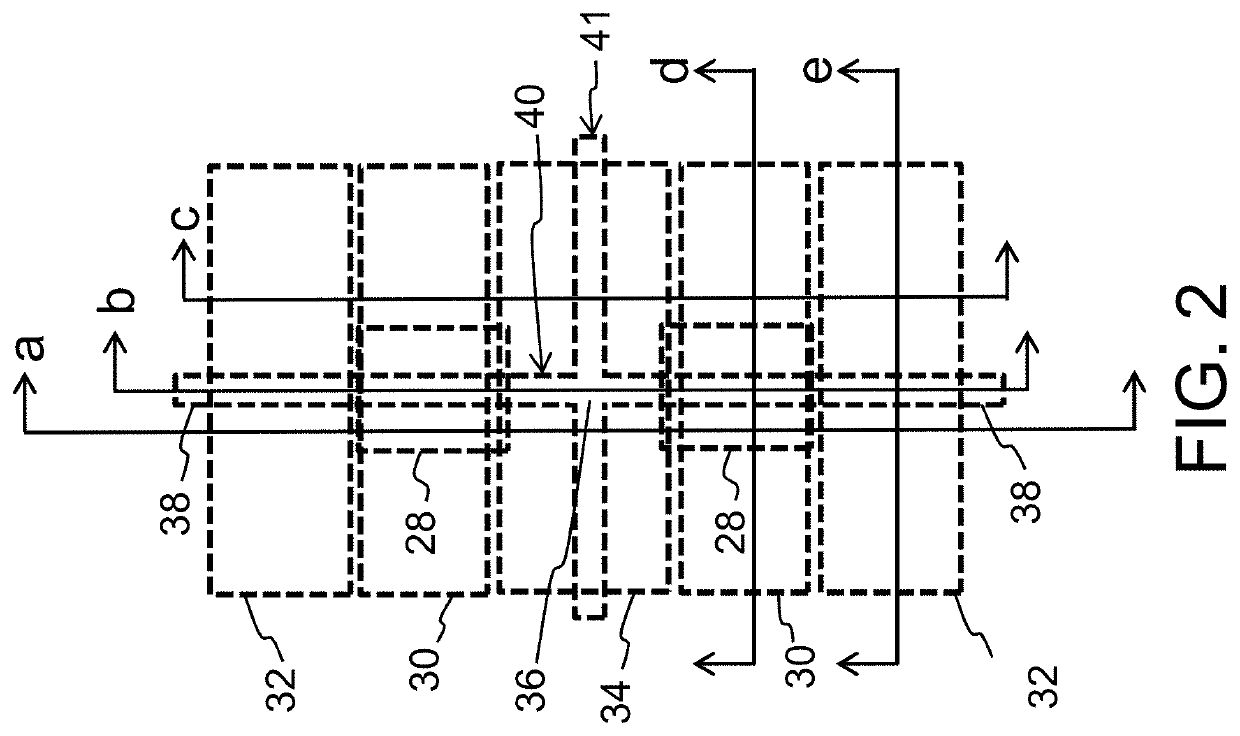

Single diffusion break structure and cuts later method of making

InactiveUS9543298B1Less alignment issueScale downTransistorSolid-state devicesFilling materialsPhotoresist

A method of forming a single diffusion break includes etching rows of fins into a substrate of a structure from a patterned fin hardmask, the remaining fin hardmask being self-aligned with the fins. A first dielectric fill material is disposed and planarized over the structure to expose the fin hardmask. A photoresist layer is disposed over the structure. An isolation region is patterned across the fins to form first and second parallel fin arrays, wherein any remaining photoresist layer has self-aligned edges which are self-aligned with the isolation region. The self-aligned edges are trimmed to expose end portions of the fin hardmask. The exposed end portions are removed. The remaining photoresist layer is removed. A second dielectric fill material is disposed and planarized over the structure to form a base for a single diffusion break (SDB) in the isolation region.

Owner:GLOBALFOUNDRIES INC

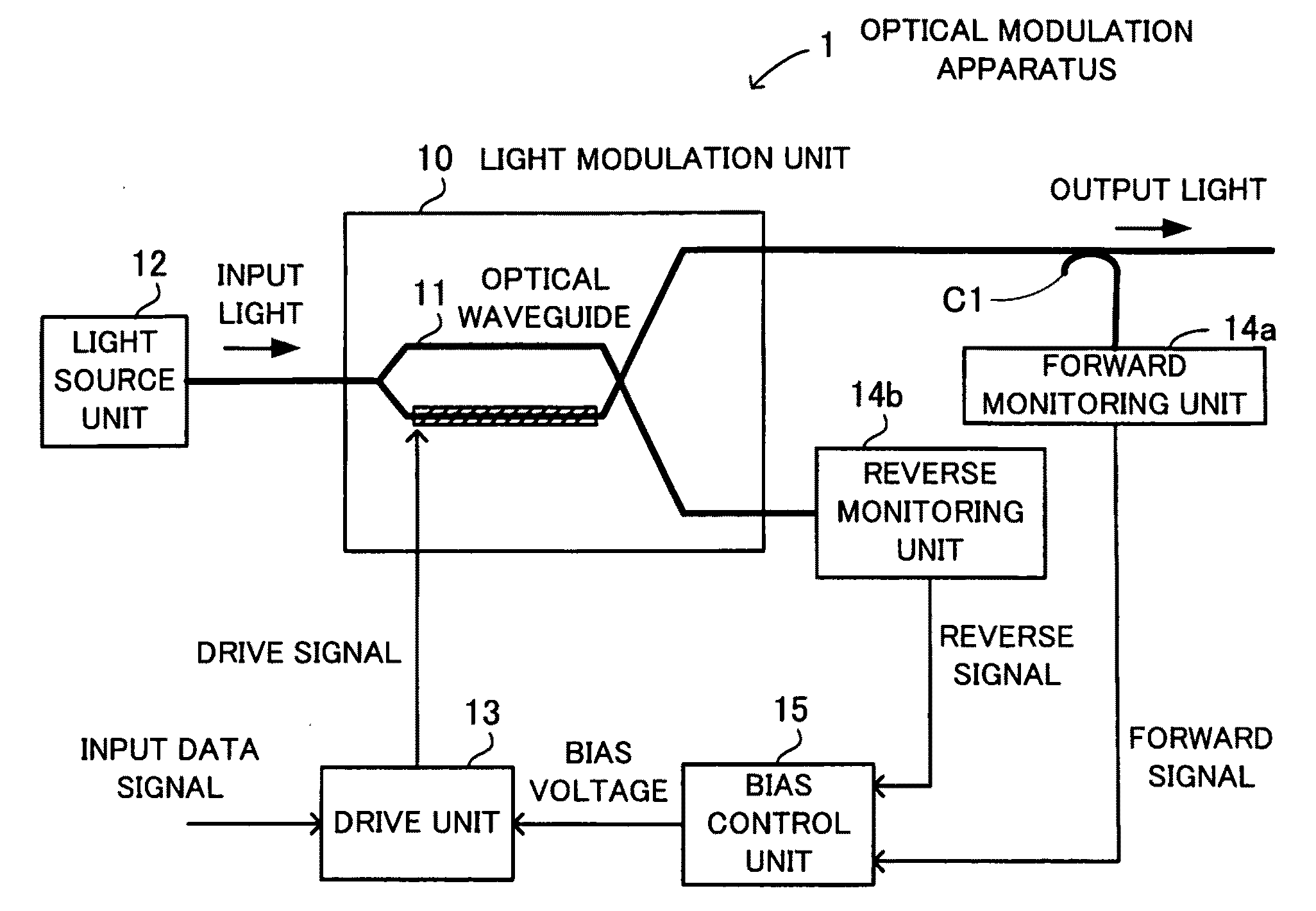

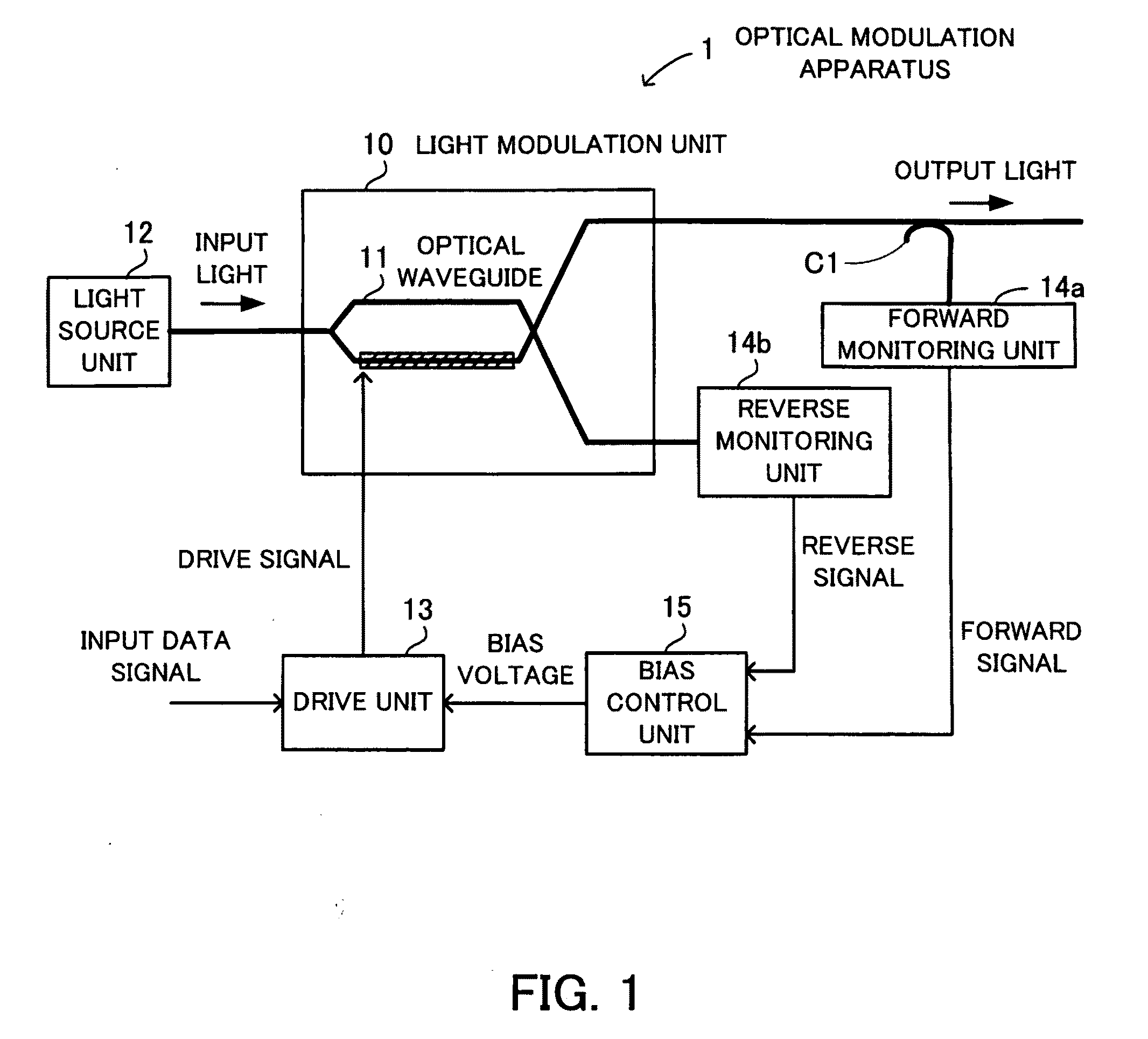

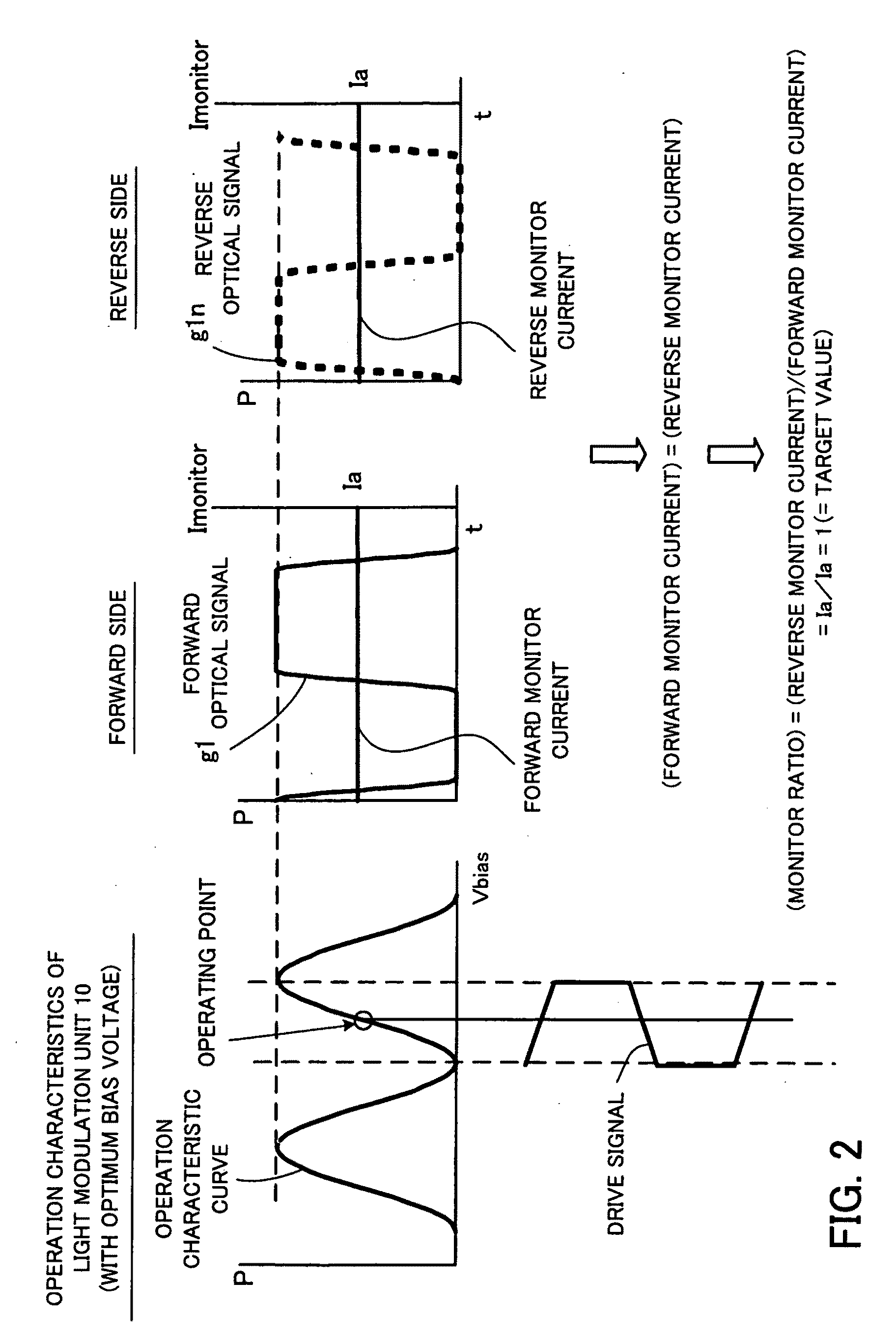

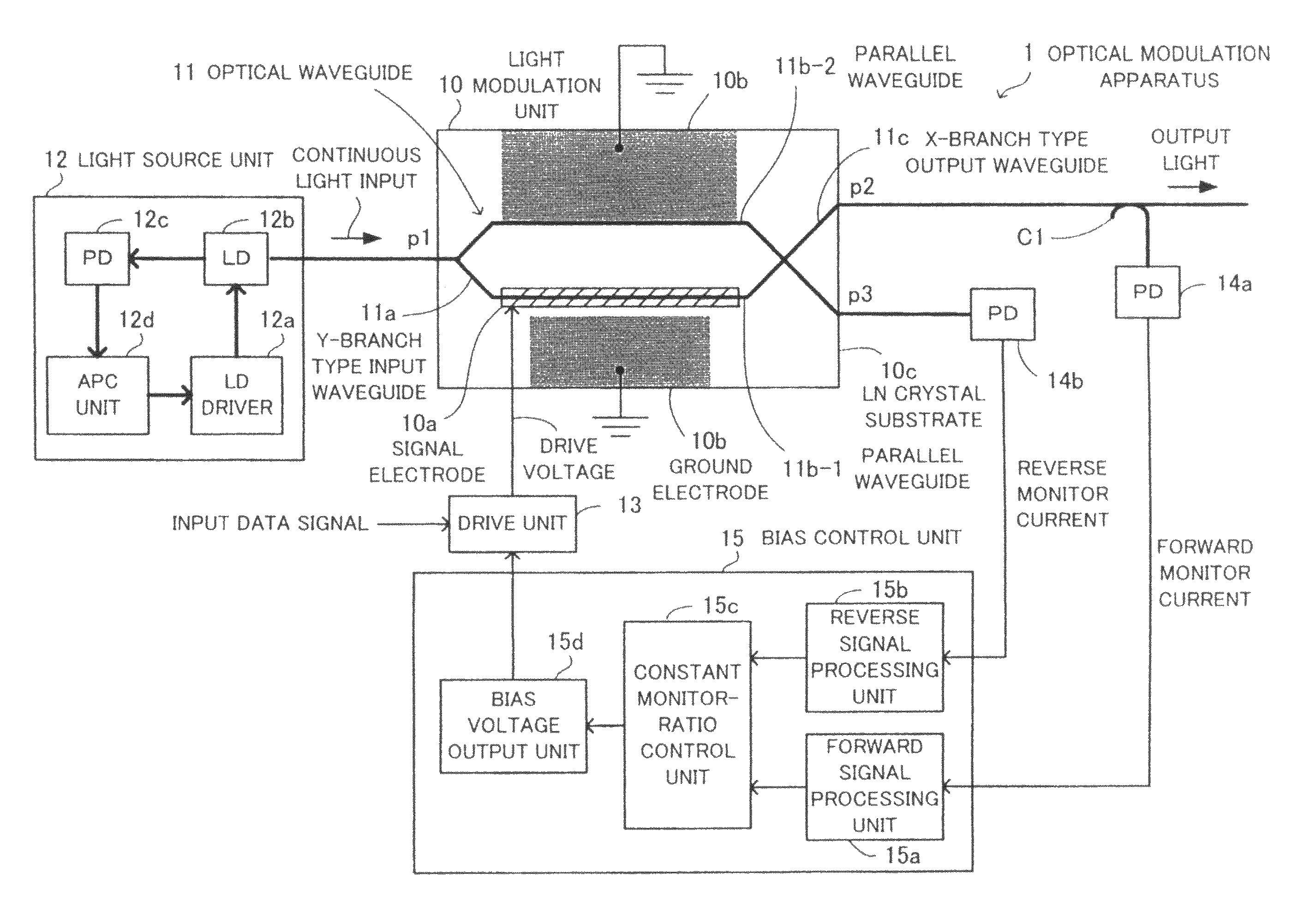

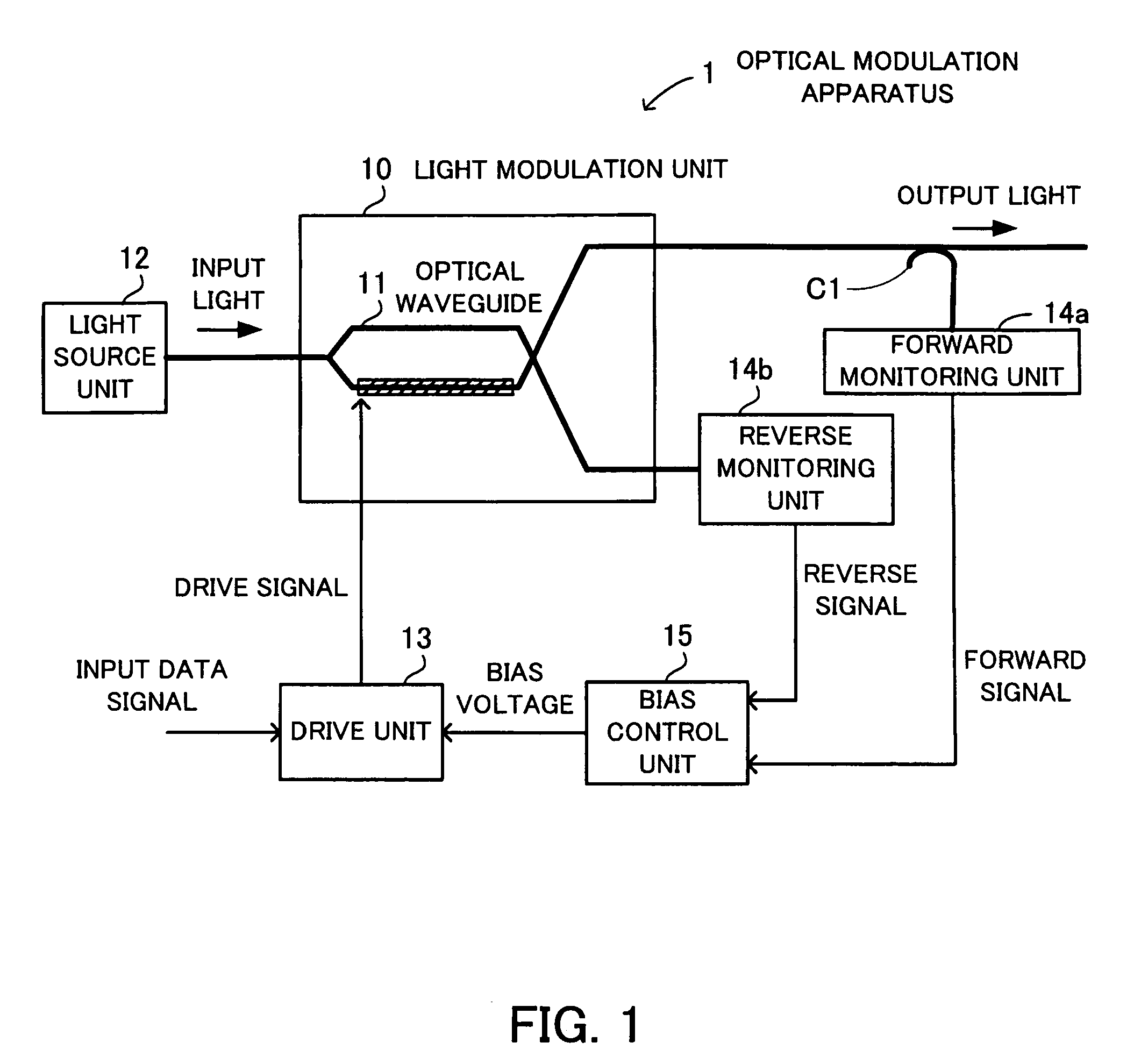

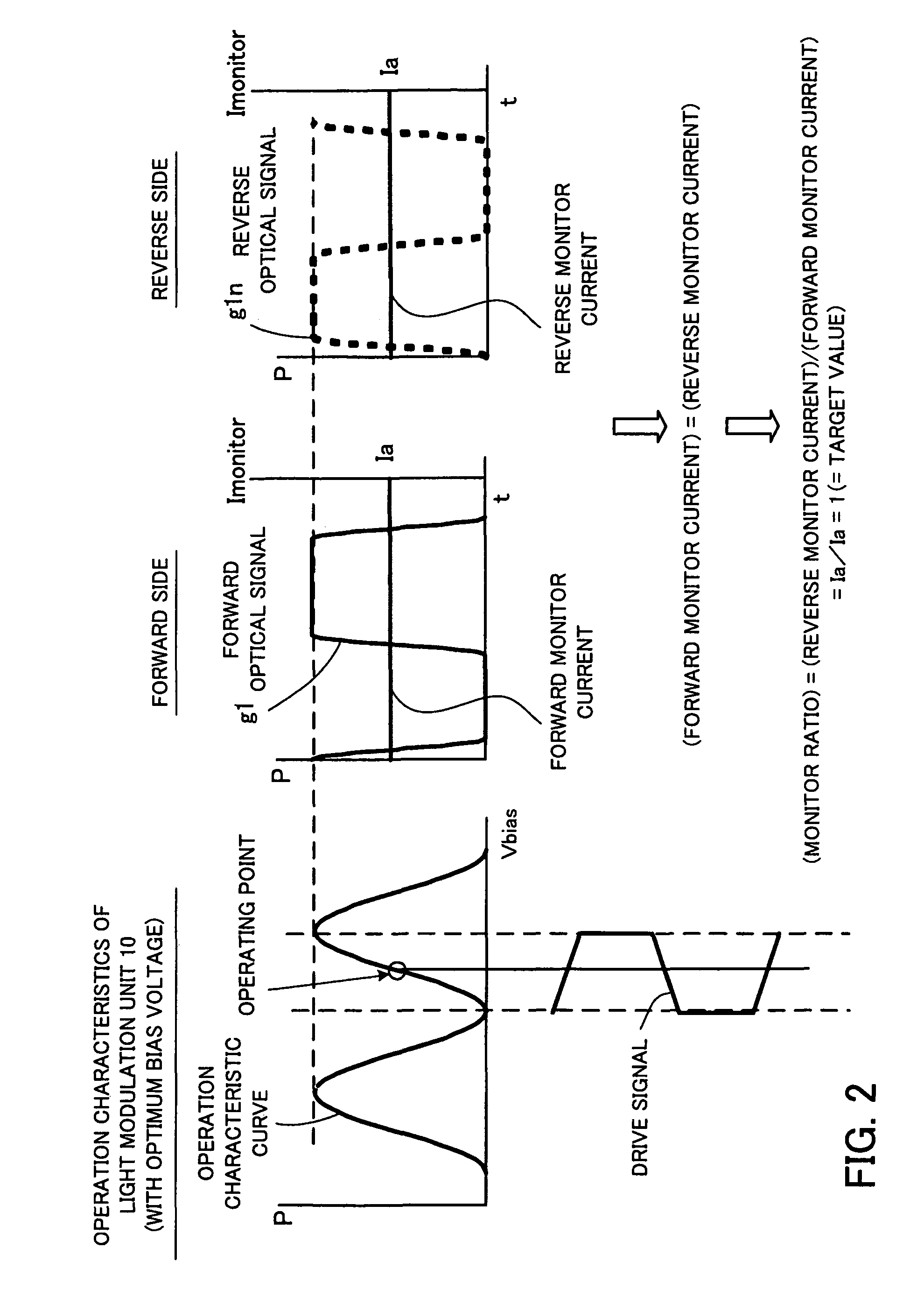

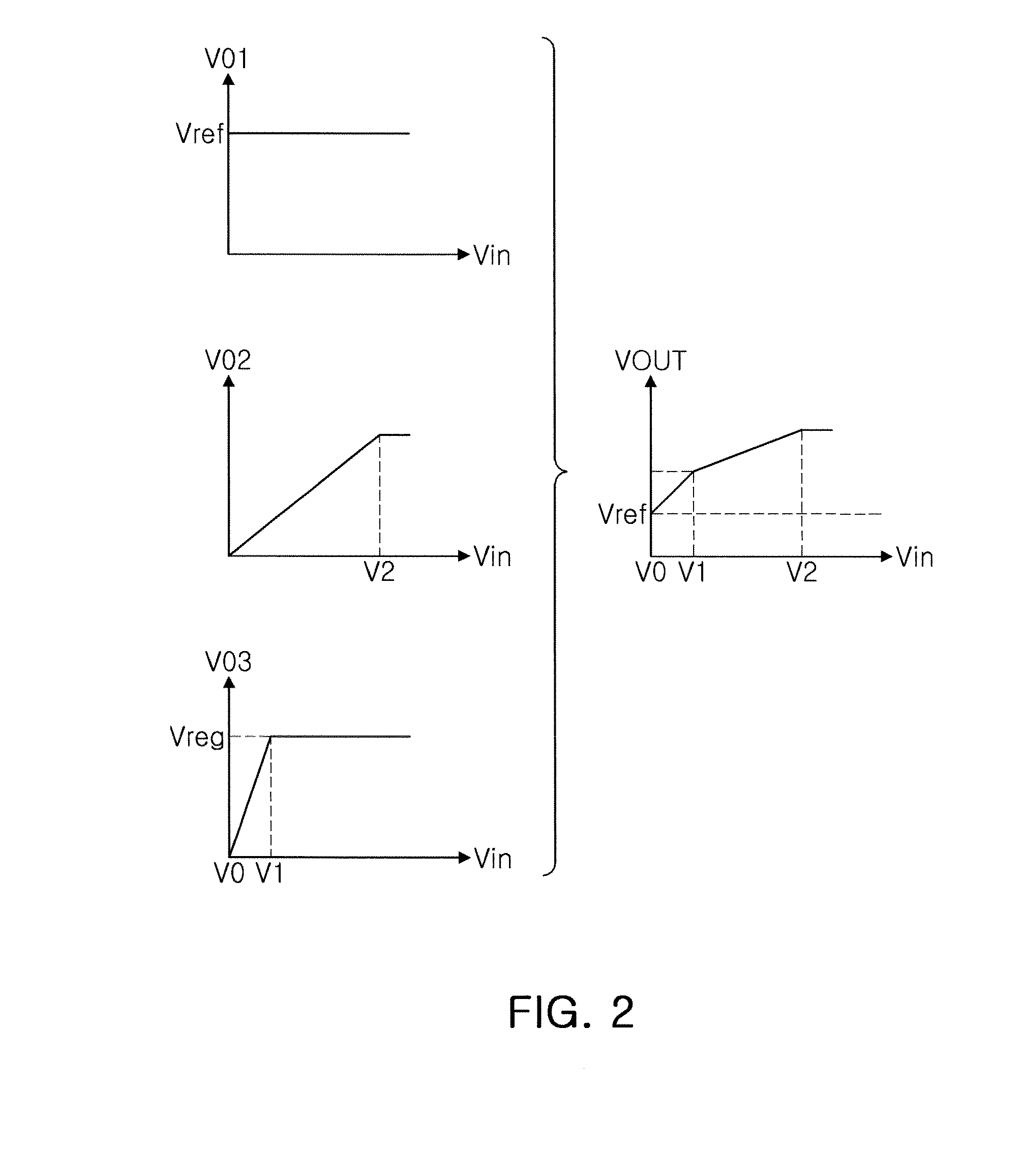

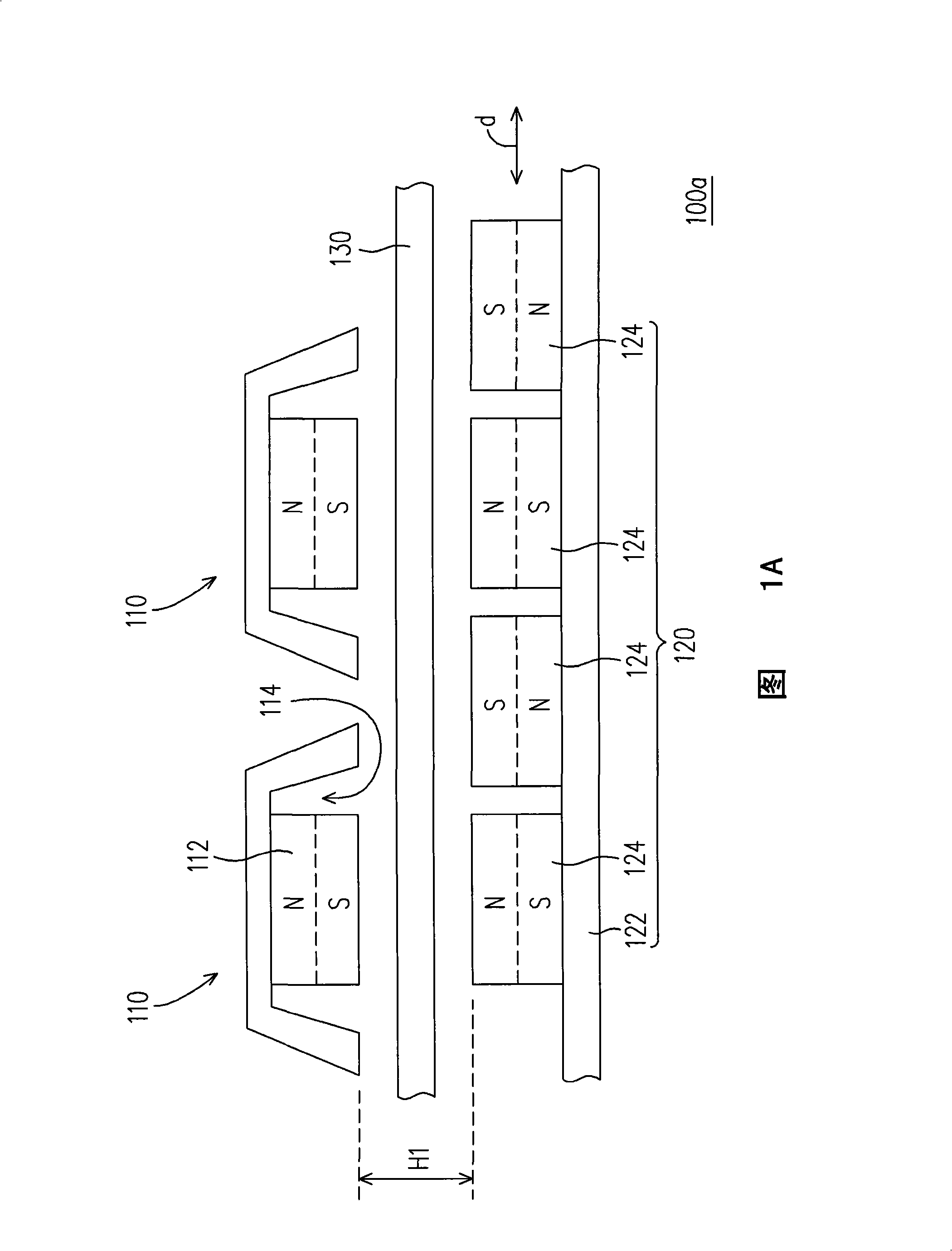

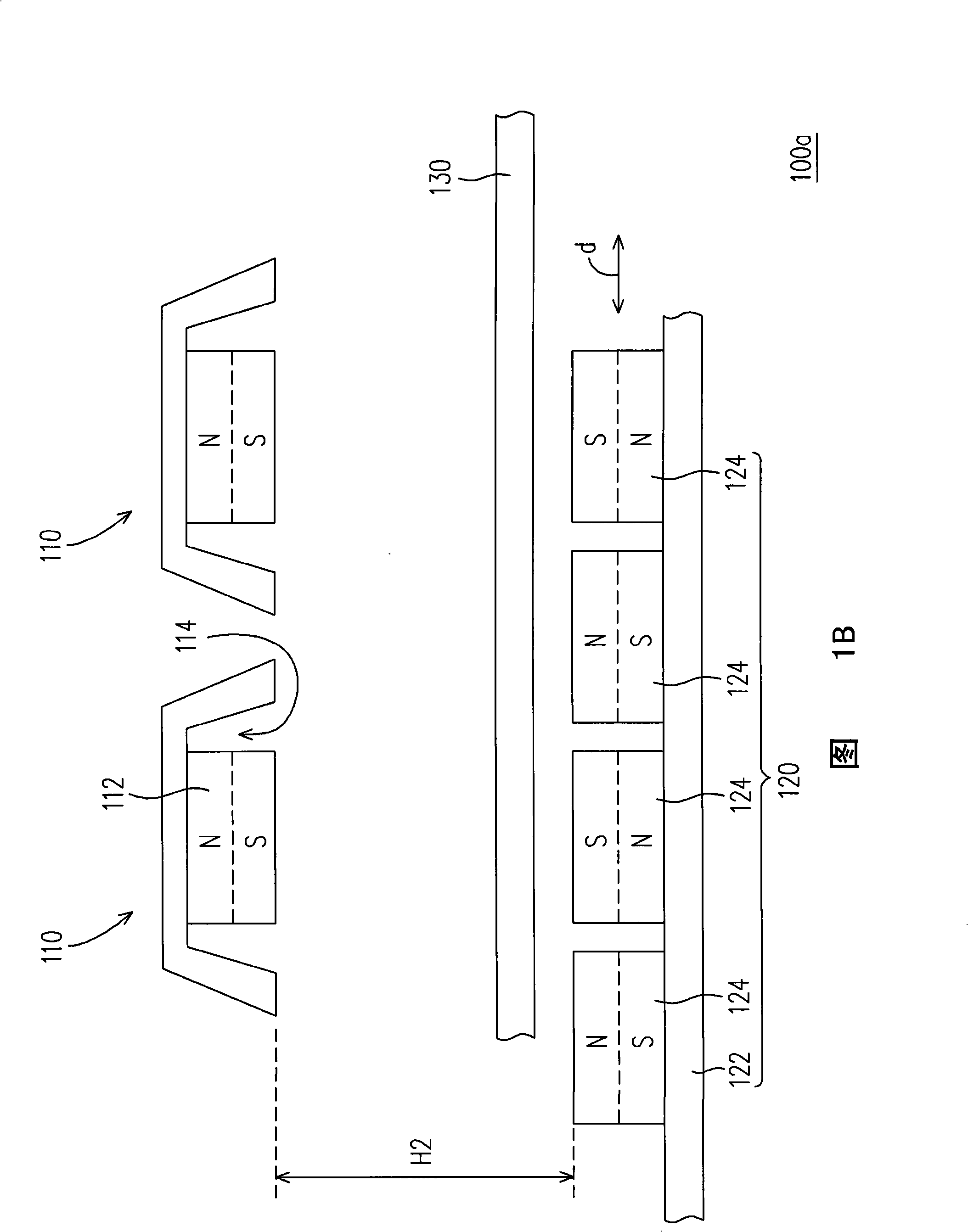

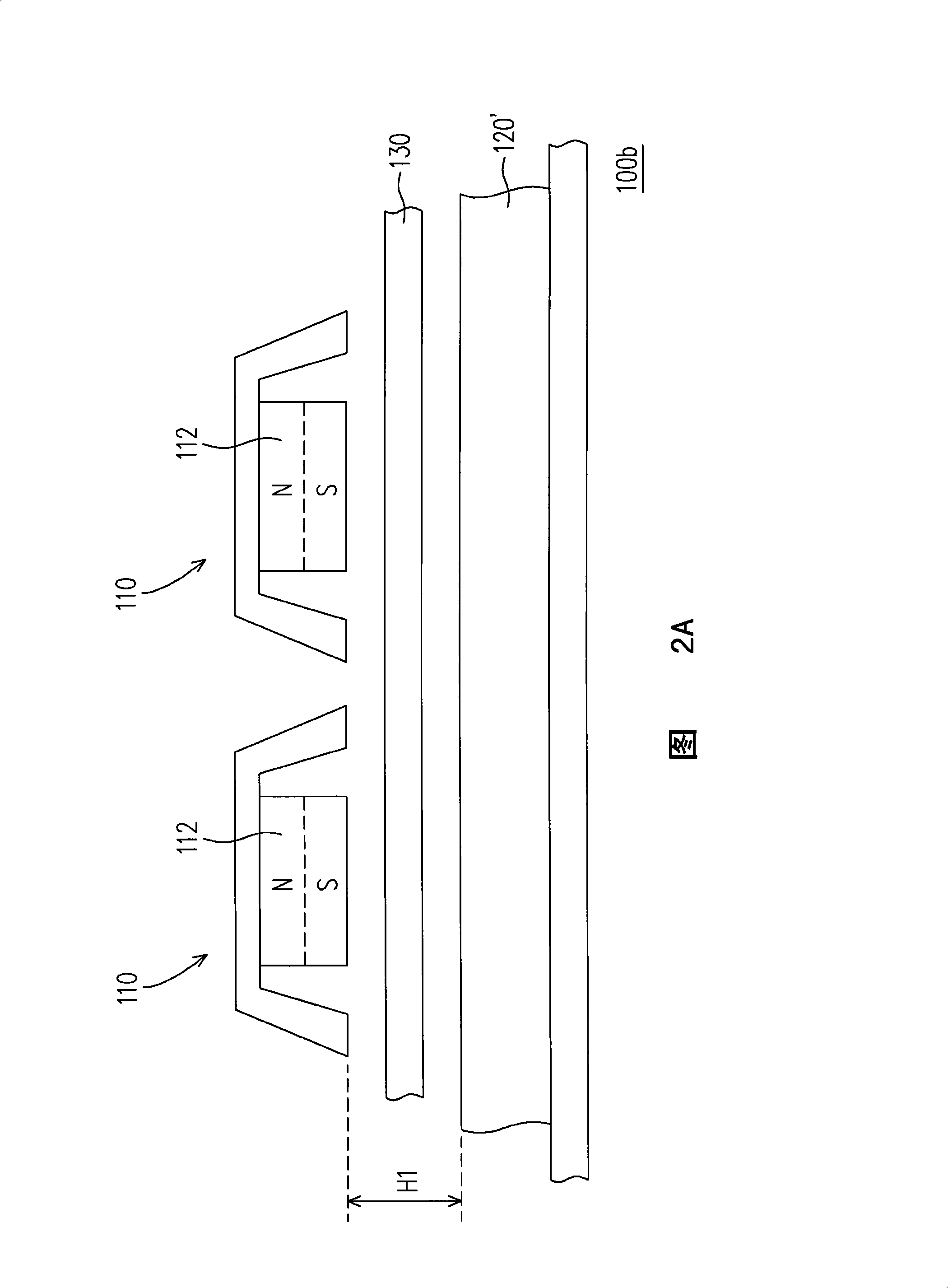

Optical modulation apparatus

InactiveUS20090296192A1Scale down circuitryEasy to controlElectromagnetic transmittersElectromagnetic receiversOperating pointData signal

An optical modulation apparatus that performs optimum bias voltage control for optical modulation without using a pilot tone. A drive unit generates a drive signal by adding a bias voltage to an input data signal. A light modulation unit modulates input light output from a light source unit, in accordance with the drive signal, and outputs the results as optical signals. A forward monitoring unit monitors a forward signal of the light modulation unit and outputs the forward signal. A reverse monitoring unit monitors a reverse signal of the light modulation unit and outputs a reverse signal. A bias control unit controls the bias voltage so that a measured monitor ratio matches a target value of the ratio between the forward signal and the reverse signal, obtained when the operating point of the light modulation unit is in a predetermined position on its operation characteristic curve.

Owner:FUJITSU LTD

Optical modulation apparatus

InactiveUS7826122B2Scale downEasy to controlElectromagnetic transmittersElectromagnetic receiversOperating pointData signal

An optical modulation apparatus that performs optimum bias voltage control for optical modulation without using a pilot tone. A drive unit generates a drive signal by adding a bias voltage to an input data signal. A light modulation unit modulates input light output from a light source unit, in accordance with the drive signal, and outputs the results as optical signals. A forward monitoring unit monitors a forward signal of the light modulation unit and outputs the forward signal. A reverse monitoring unit monitors a reverse signal of the light modulation unit and outputs a reverse signal. A bias control unit controls the bias voltage so that a measured monitor ratio matches a target value of the ratio between the forward signal and the reverse signal, obtained when the operating point of the light modulation unit is in a predetermined position on its operation characteristic curve.

Owner:FUJITSU LTD

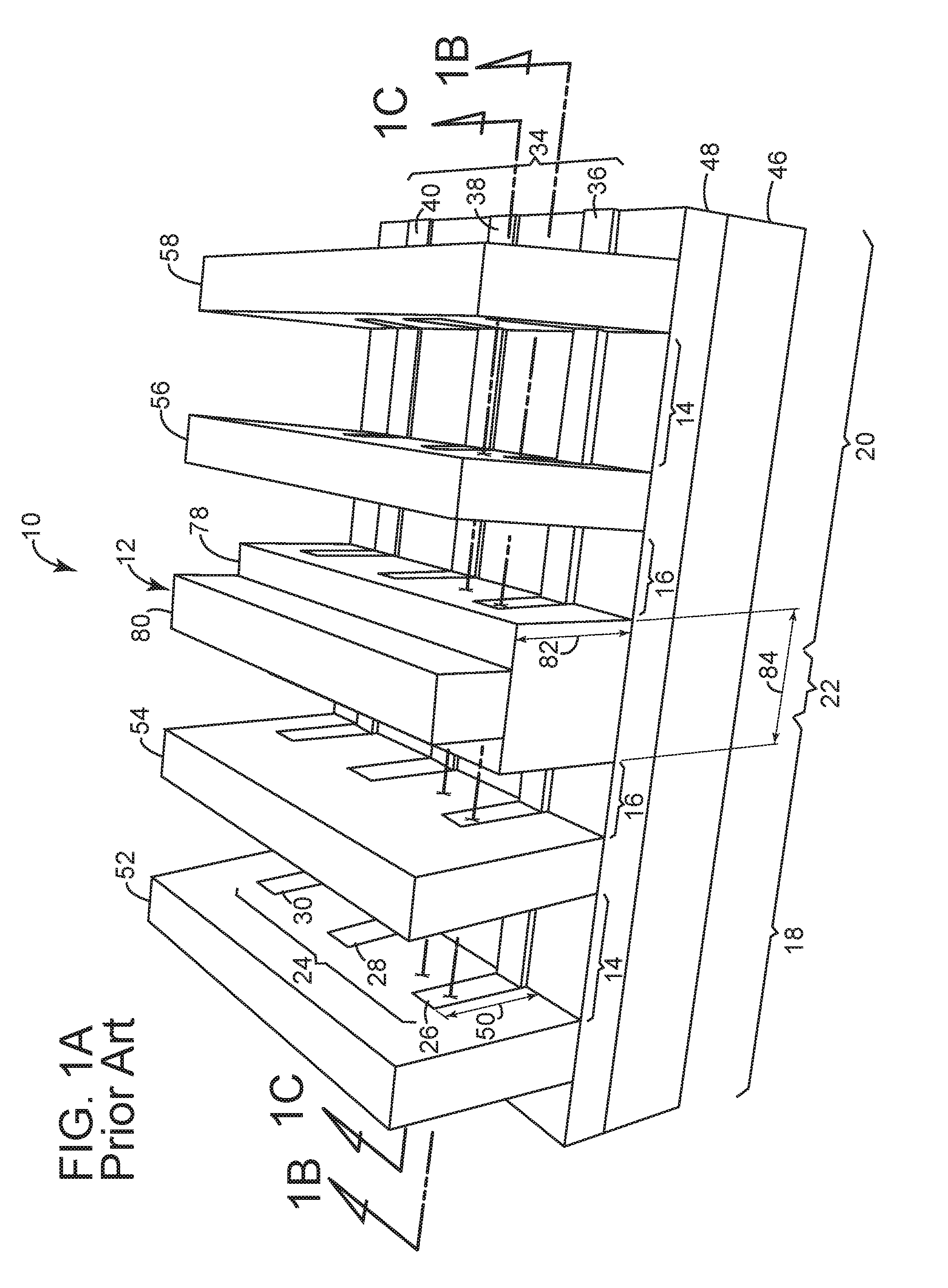

Split Gate Non-volatile Memory Cells With FINFET Structure And HKMG Memory And Logic Gates, And Method Of Making Same

ActiveUS20200176459A1Improve conductivityImprove performanceTransistorSolid-state devicesMemory cellEngineering

A memory device having plurality of upwardly extending semiconductor substrate fins, a memory cell formed on a first fin and a logic device formed on a second fin. The memory cell includes source and drain regions in the first fin with a channel region therebetween, a polysilicon floating gate extending along a first portion of the channel region including the side and top surfaces of the first fin, a metal select gate extending along a second portion of the channel region including the side and top surfaces of the first fin, a polysilicon control gate extending along the floating gate, and a polysilicon erase gate extending along the source region. The logic device includes source and drain regions in the second fin with a second channel region therebetween, and a metal logic gate extending along the second channel region including the side and top surfaces of the second fin.

Owner:SILICON STORAGE TECHNOLOGY

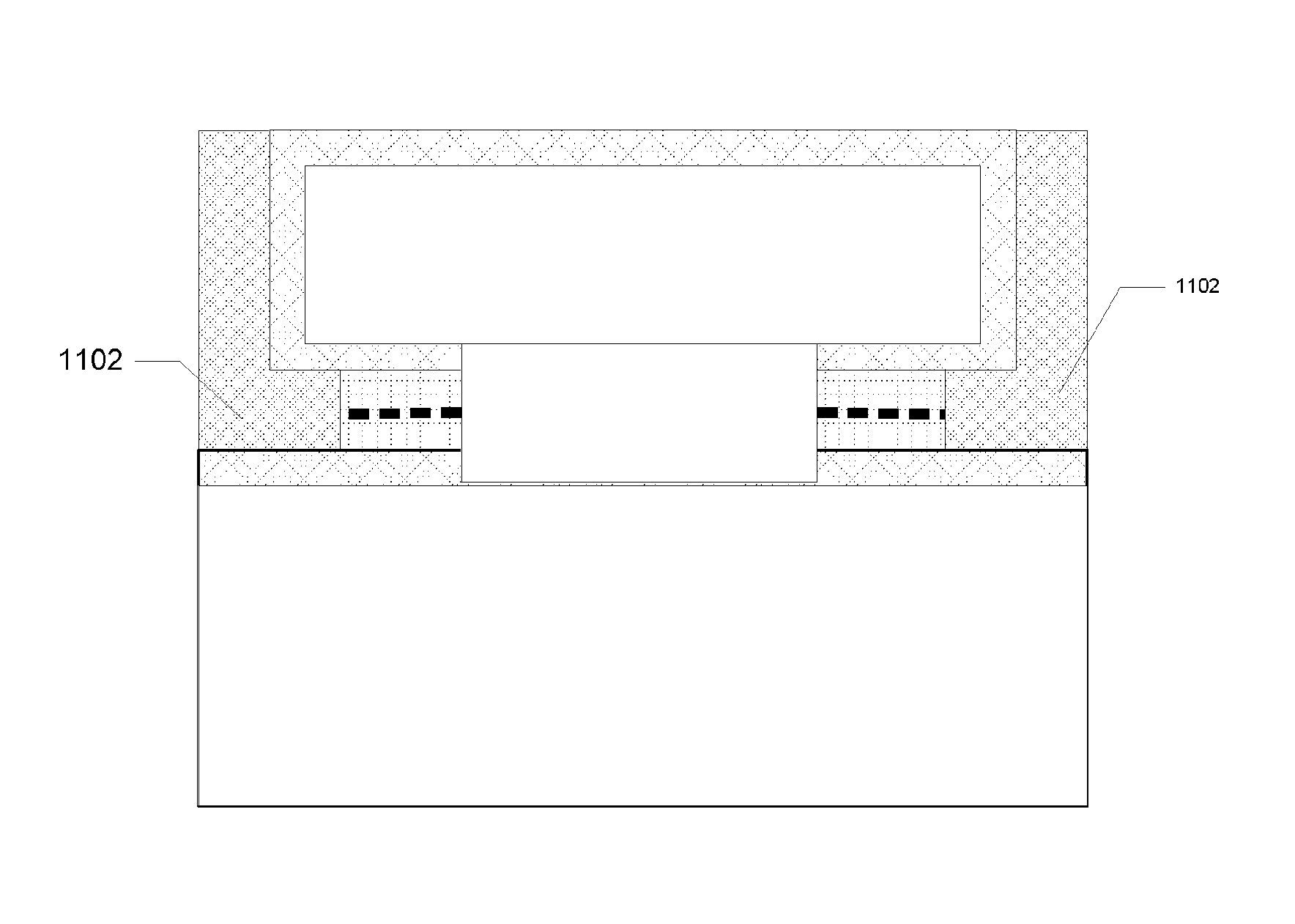

Method for manufacturing twin bit structure cell with aluminum oxide layer

ActiveUS20110140190A1Wide rangeImplemented cost-effectivelySemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricEngineering

A method for manufacturing a twin bit cell structure with an aluminum oxide material includes forming a gate dielectric layer overlying a semiconductor substrate and a polysilicon gate structure overlying the gate dielectric layer. An undercut region is formed in each side of the gate dielectric layer underneath the polysilicon gate structure. Thereafter, an oxidation process is performed to form a first silicon oxide layer on a peripheral surface of the polysilicon gate structure and a second silicon oxide layer on an exposed surface of the semiconductor substrate. Then, an aluminum oxide material is deposited over the first and second silicon oxide layers including the undercut region and the gate dielectric layer. The aluminum oxide material is selectively etched to form an insert region in a portion of the undercut region. A sidewall spacer is formed to isolate and protect the exposed aluminum oxide material and the polysilicon gate structure.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

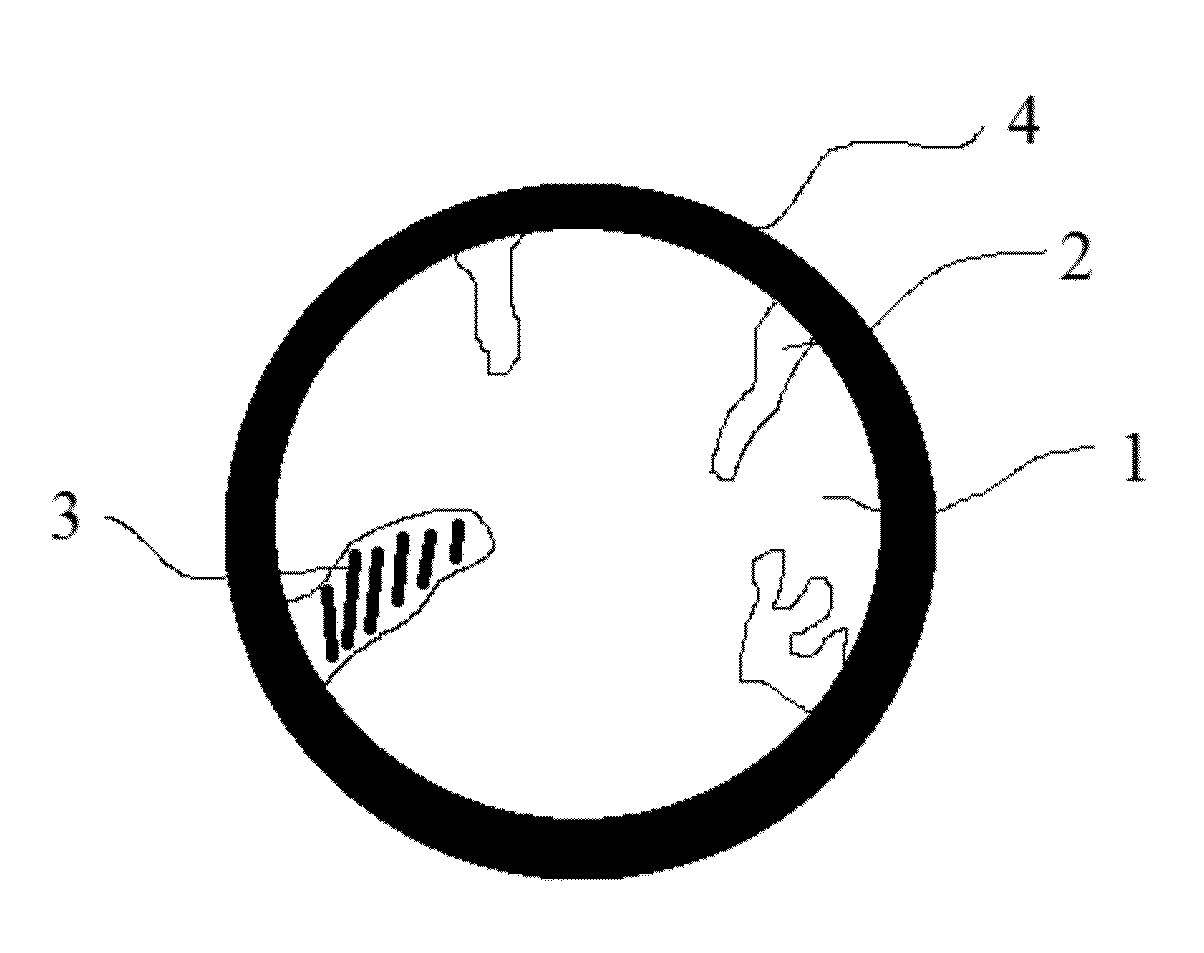

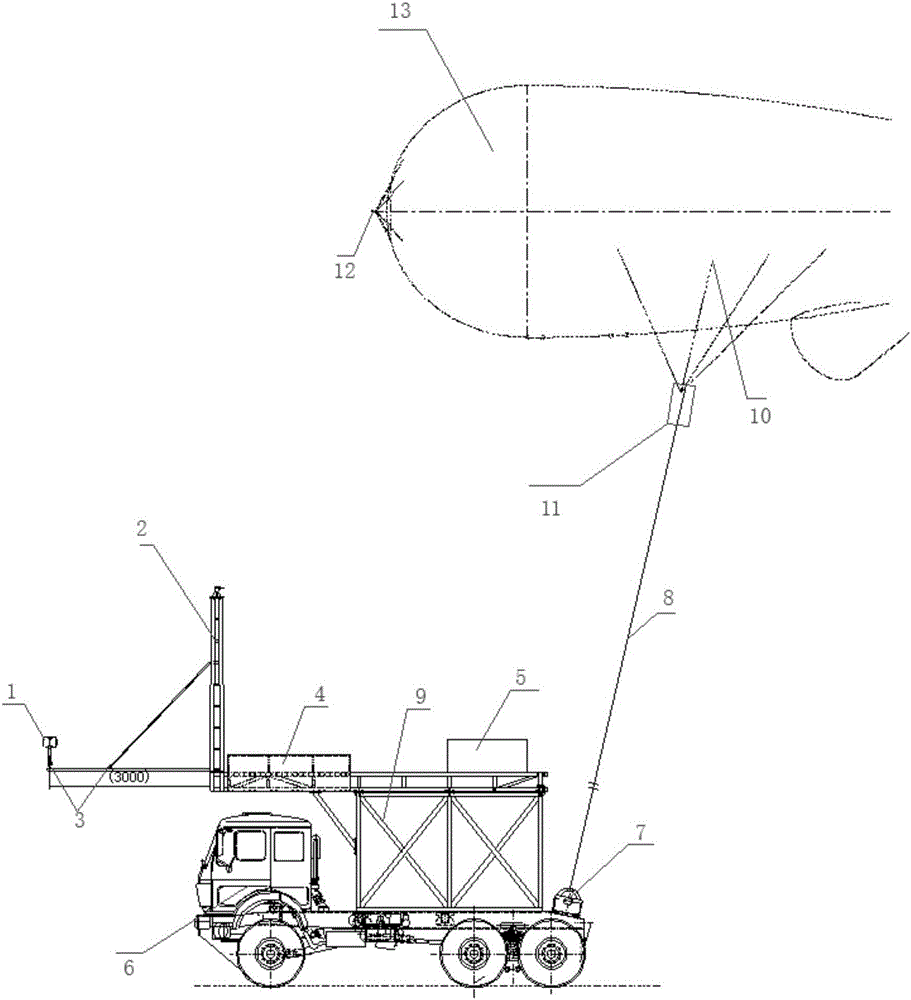

A captive balloon limited wind speed static balance characteristic ground surface drag simulating test apparatus and method

ActiveCN106769138AScale downRaising the bar for security designStructural/machines measurementScale modelSurface drag

The invention brings forward a captive balloon limited wind speed static balance characteristic ground surface drag simulating test apparatus and method. A captive balloon scaled model and a dragging vehicle are comprised. Limited wind speed static balance characteristic analysis of a captive balloon is completed through a ground trailer dragging method. In the design of the test, according to the trailer performance, buoyancy, aerodynamic, gravity and other factors, a certain shrink ratio is set (the shrink ratio is not greater than 5: 1, far less than the wind tunnel test shrink ratio, closer to the real results), and the model after the scaling ensures a same shrink ratio between the outside force applied to the captive balloon and the moment of the captive balloon so as to guarantee that static balance characteristics can reflect the real captive balloon characteristics.

Owner:CHINA SPECIAL TYPE FLIER RES INST

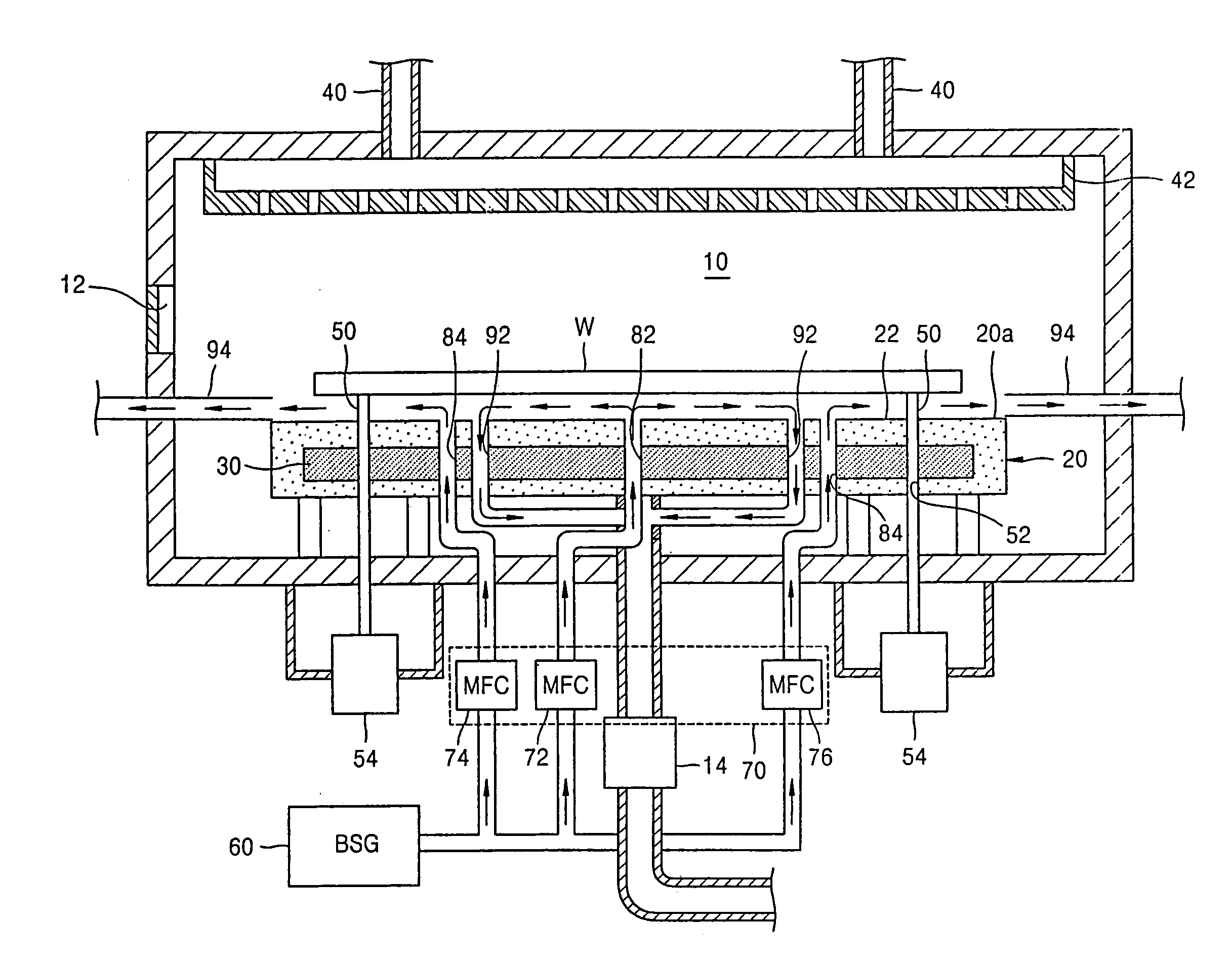

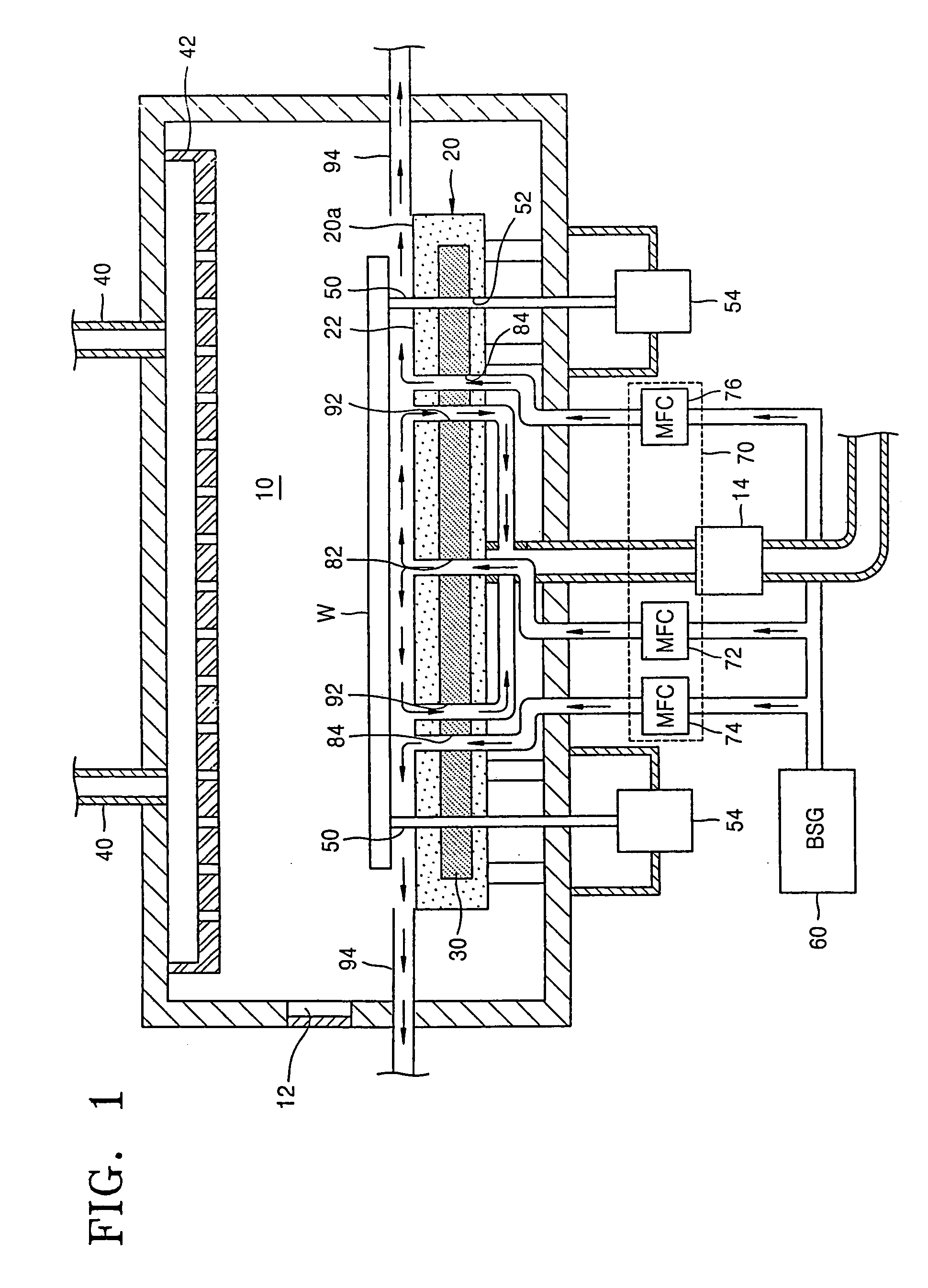

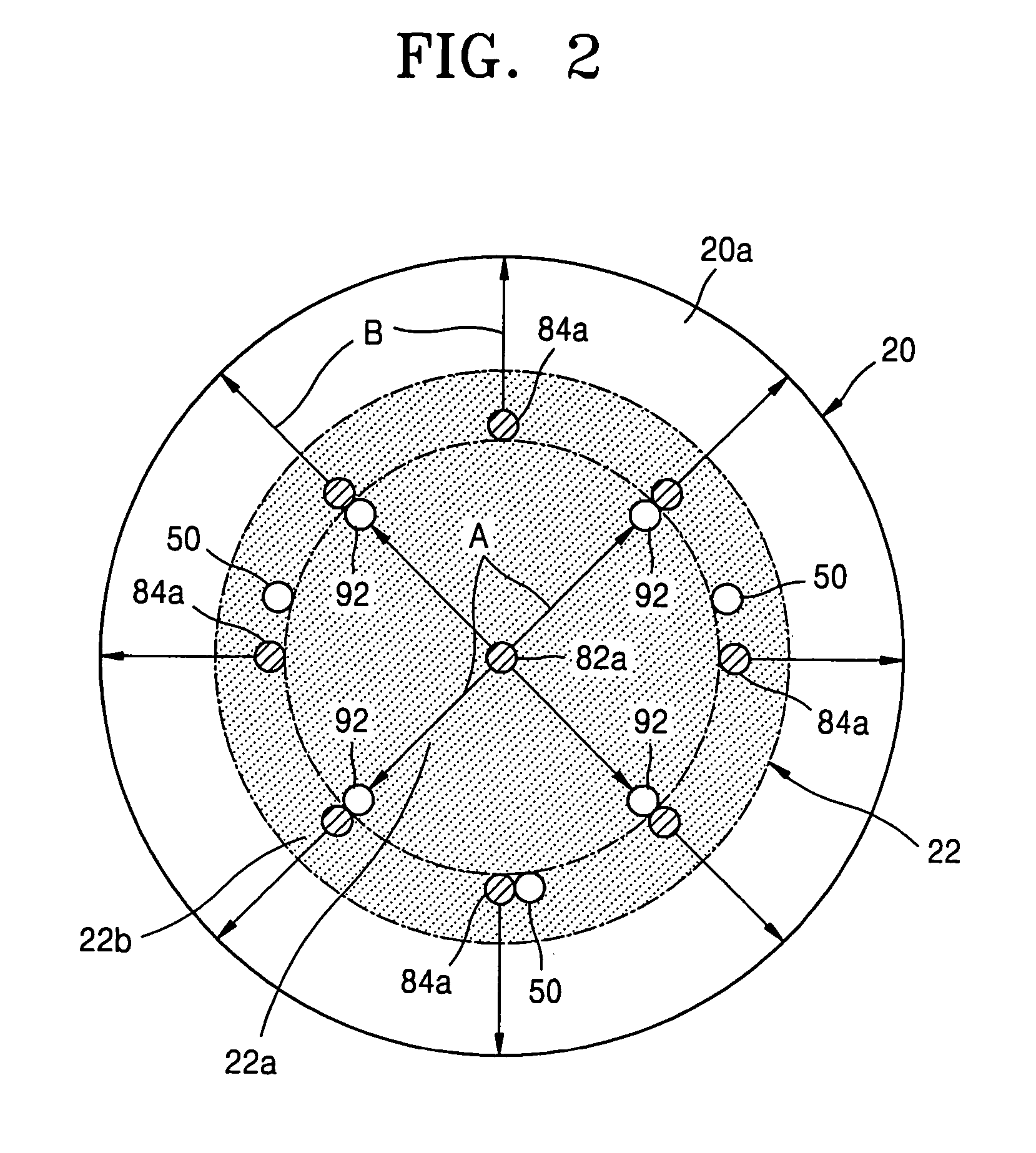

Chemical vapor deposition apparatus and method of forming thin layer using same

InactiveUS20050022741A1Poor thickness distributionScale downSemiconductor/solid-state device manufacturingChemical vapor deposition coatingThin layerEngineering

In one embodiment, a chemical vapor deposition (CVD) apparatus comprising a plurality of backside gas (BSG) passages that pass through a heater table that controls a temperature of a plurality of local areas on a wafer and a method of forming a thin layer using the CVD apparatus are provided. The heater table comprises a wafer supporting area divided into a plurality of local areas that correspond to the local areas of the wafer. Each of the BSG passages has a BSG outlet that supplies the BSG, heated by a heater, to the local areas. Flow controllers control the flow through each of the BSG passages, thereby controlling the temperature of local areas.

Owner:SAMSUNG ELECTRONICS CO LTD

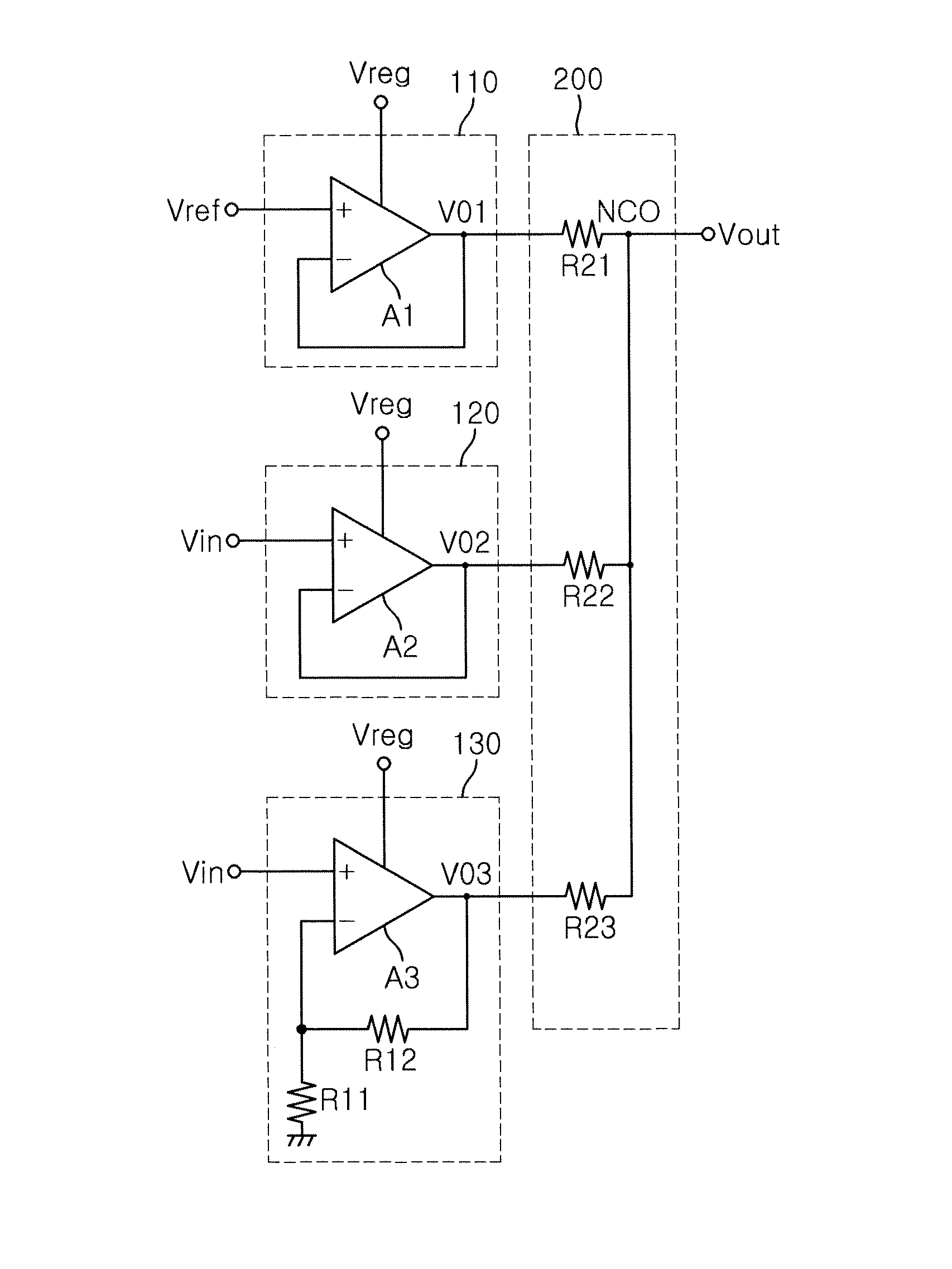

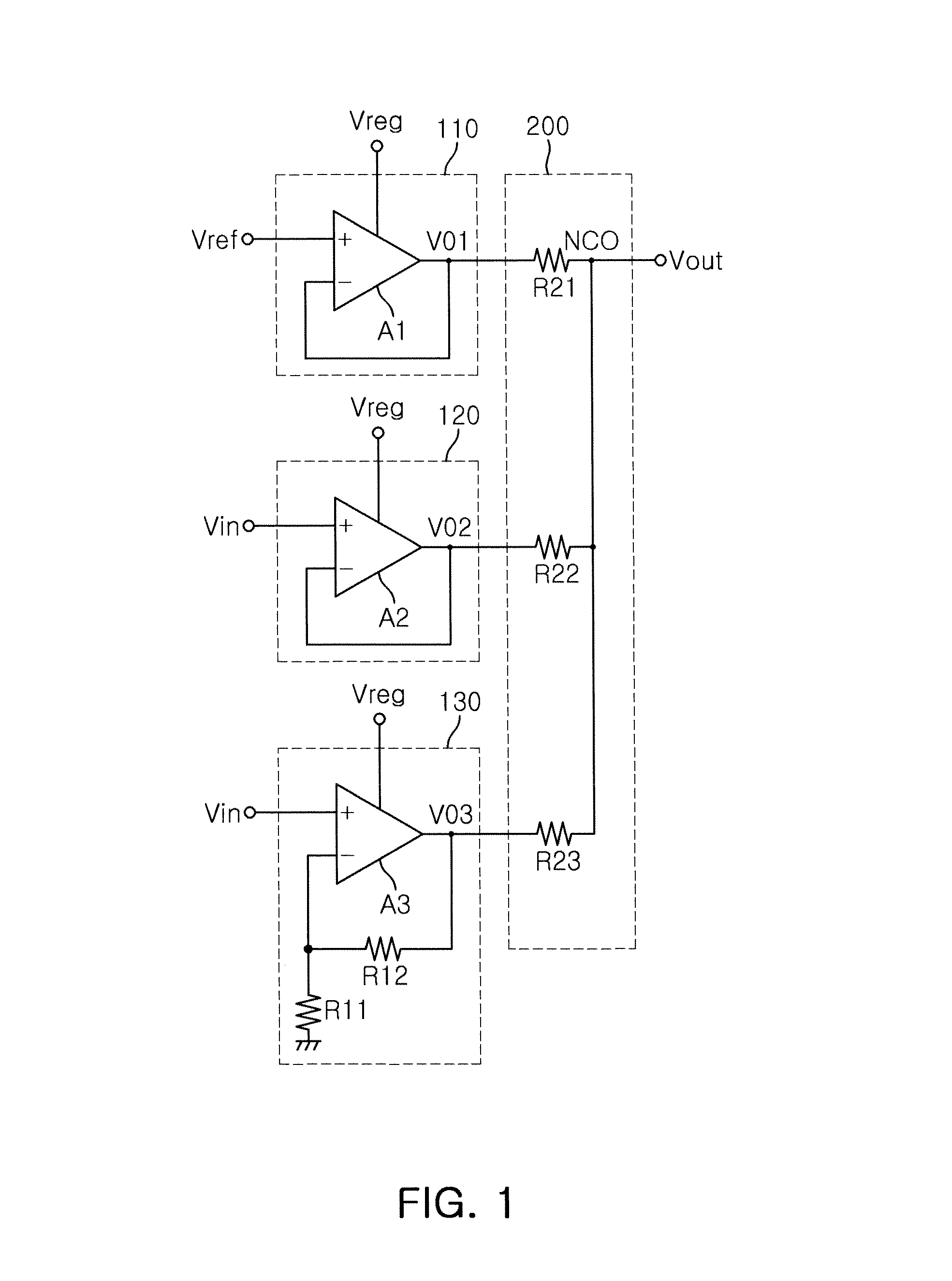

Level shifter

ActiveUS20120049925A1Improve isolationScaling downPulse automatic controlAmplifiersAudio power amplifierEngineering

A level shifter includes: a first buffer amplifier transferring a preset reference voltage to a first output terminal; a second buffer amplifier connected in parallel to the first buffer amplifier and transferring an input voltage to a second output terminal; a positive feedback amplifier connected in parallel to the first buffer amplifier and the second buffer amplifier, and amplifying the input voltage by a preset gain to transfer the amplified input voltage to a third output terminal; and a level regulation unit regulating levels of output signals of the first buffer amplifier, the second buffer amplifier, and the positive feedback amplifier and providing the regulated output signals to a common output node.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

Keyboard

Owner:INVENTEC CORP

Method for manufacturing twin bit structure cell with Al2O3/nano-crystalline Si layer

ActiveUS8114732B2Implemented cost-effectivelyScale downNanoinformaticsSemiconductor/solid-state device manufacturingGate dielectricNanocrystalline silicon

A method and system for forming a non-volatile memory structure. The method includes providing a semiconductor substrate and forming a gate dielectric layer overlying a surface region of the semiconductor substrate. A polysilicon gate structure is formed overlying the gate dielectric layer. The method subjects the polysilicon gate structure to an oxidizing environment to cause formation of a first silicon oxide layer overlying the polysilicon gate structure and formation of an undercut region underneath the polysilicon gate structure. An aluminum oxide material is formed overlying the polysilicon gate structure filling the undercut region. In a specific embodiment, the aluminum oxide material has a nanocrystalline silicon material sandwiched between a first aluminum oxide layer and a second aluminum oxide layer. The aluminum oxide material is subjected to a selective etching process while maintaining the aluminum oxide material in an insert region in a portion of the undercut region. The method forms a sidewall structure overlying a side region of the polysilicon gate structure.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1