Patents

Literature

612results about "Synchronisation error correction" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

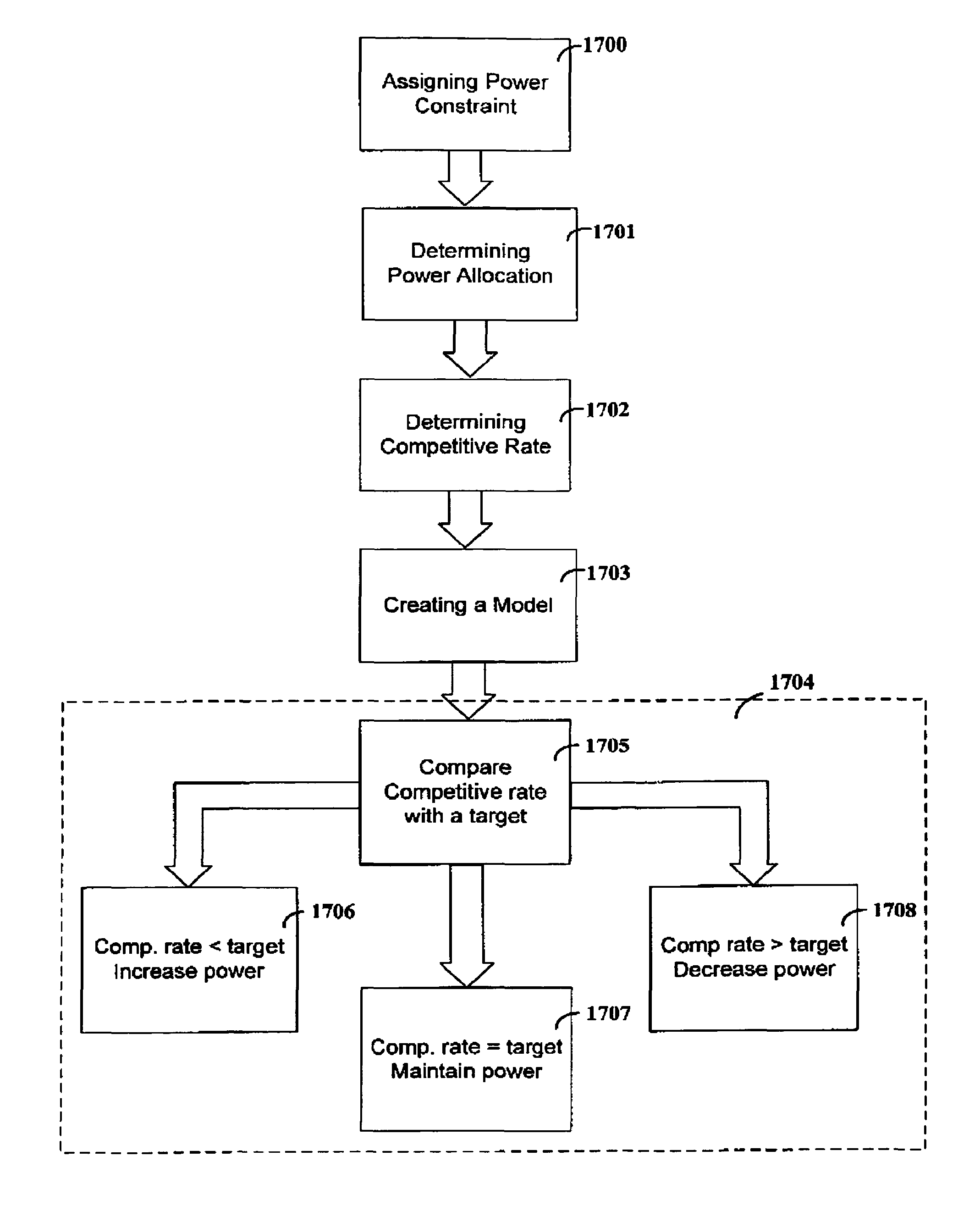

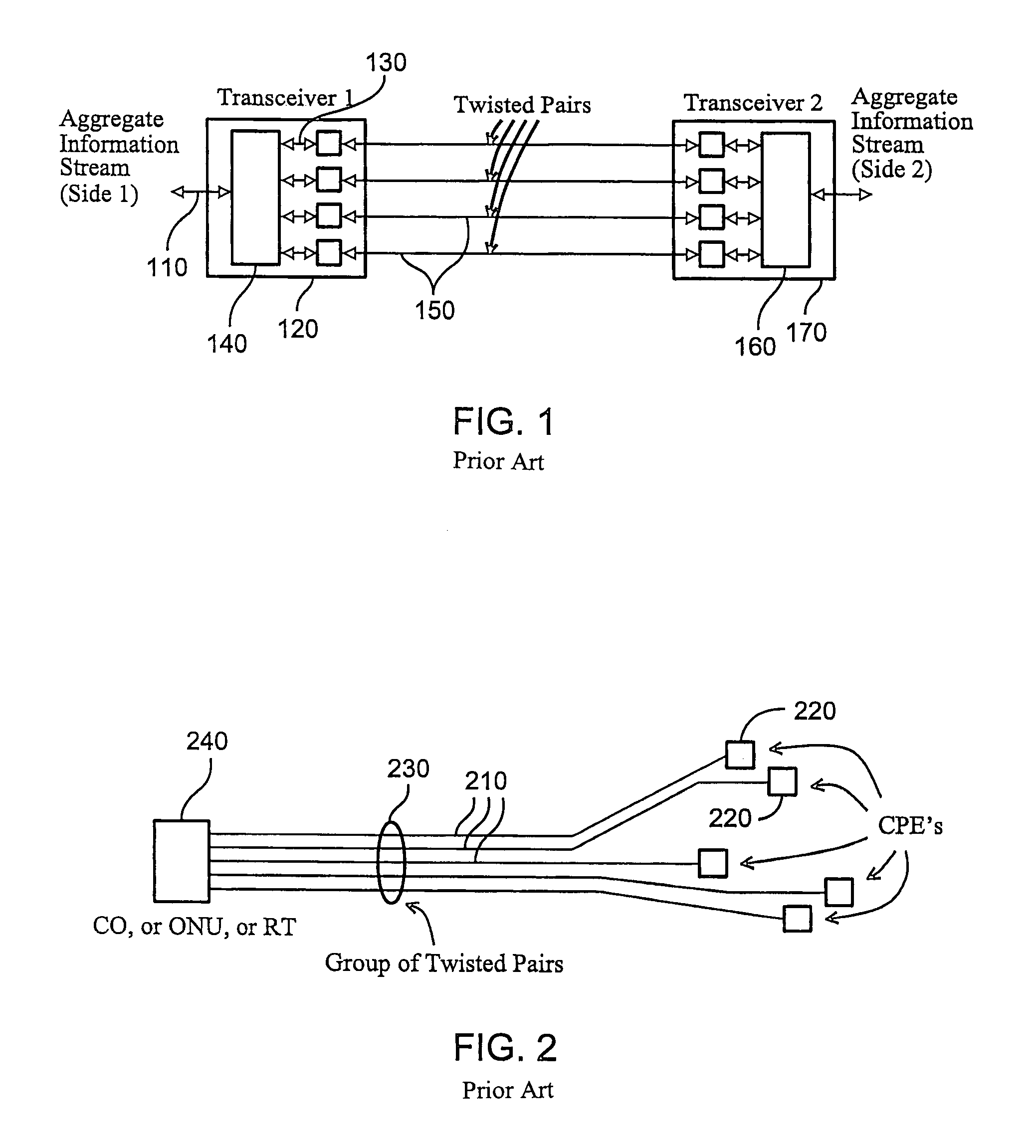

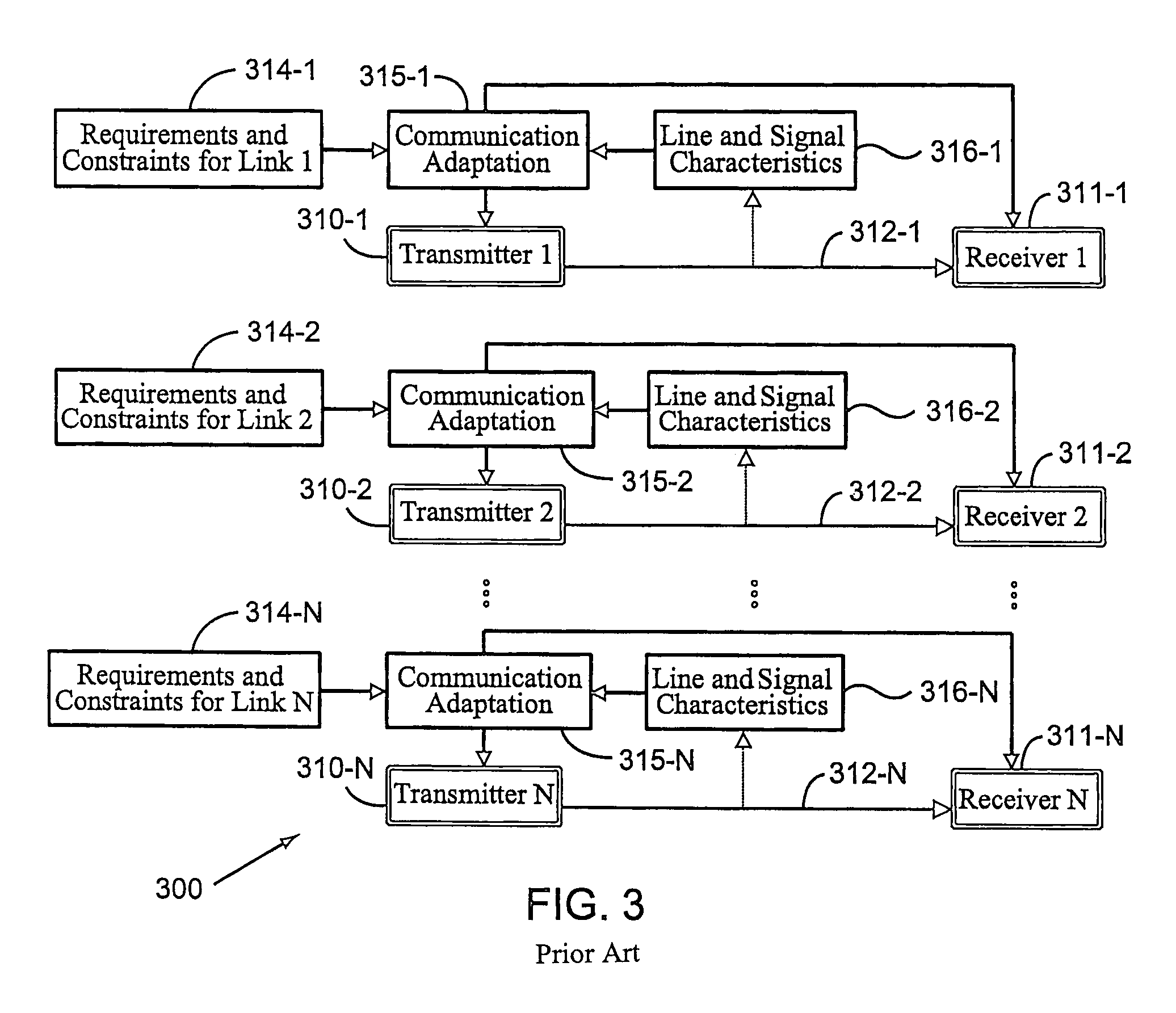

Dynamic digital communication system control

InactiveUS7158563B2Improve performanceMinimize impactError preventionFrequency-division multiplex detailsCommunications systemControl system

Methods, apparatus and systems for dynamically controlling a digital communication system, such as a DSL system, collect information about digital communication lines in the system and adaptively and / or dynamically determine line and signal characteristics of the digital communication lines, including interference effects. Based on the determined characteristics and the desired performance parameters, operation of the digital communication lines is adjusted to improve or otherwise control the performance of the system. The collection and processing of information may be performed by a party that is not a user in the system. This independent party also may control operational characteristics and parameters of the system. The invention can be used to eliminate or reduce signal interference such as crosstalk that can be induced on communication lines in systems such as DSL systems. Specific iterative power allocation and vectored transmission techniques and apparatus are disclosed.

Owner:THE BOARD OF TRUSTEES OF THE LELAND STANFORD JUNIOR UNIV

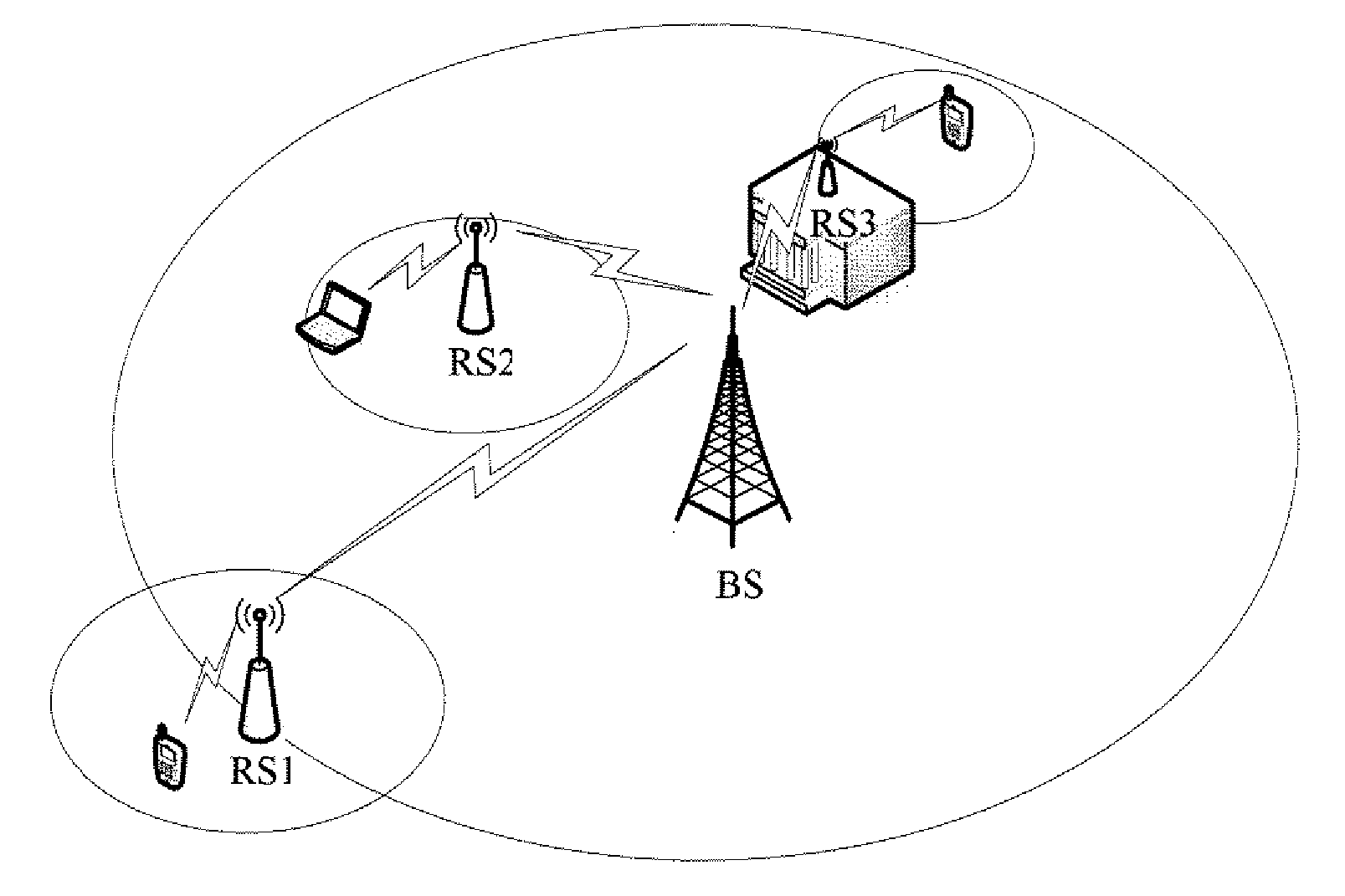

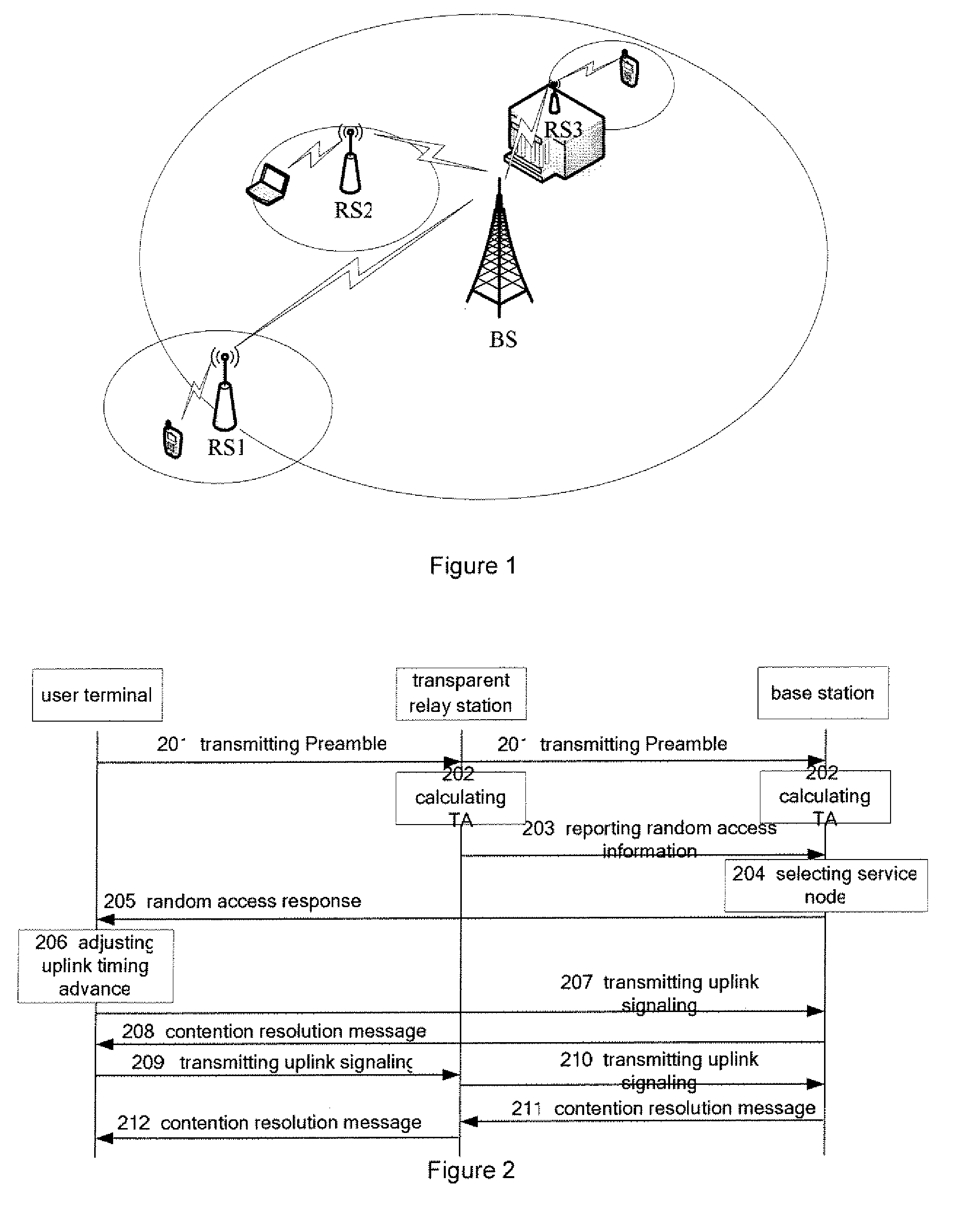

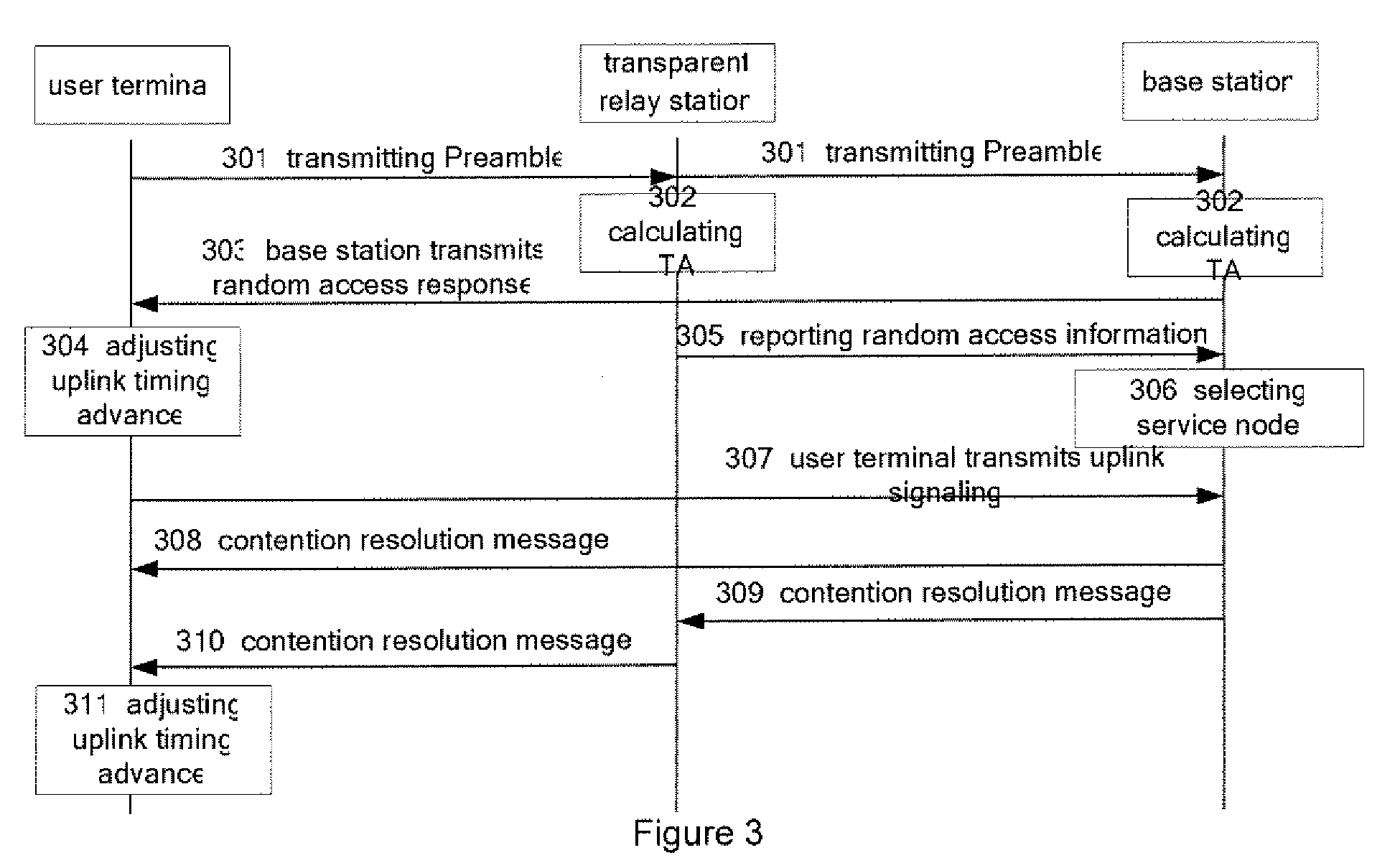

Method of processing in random access procedure, system and apparatus thereof

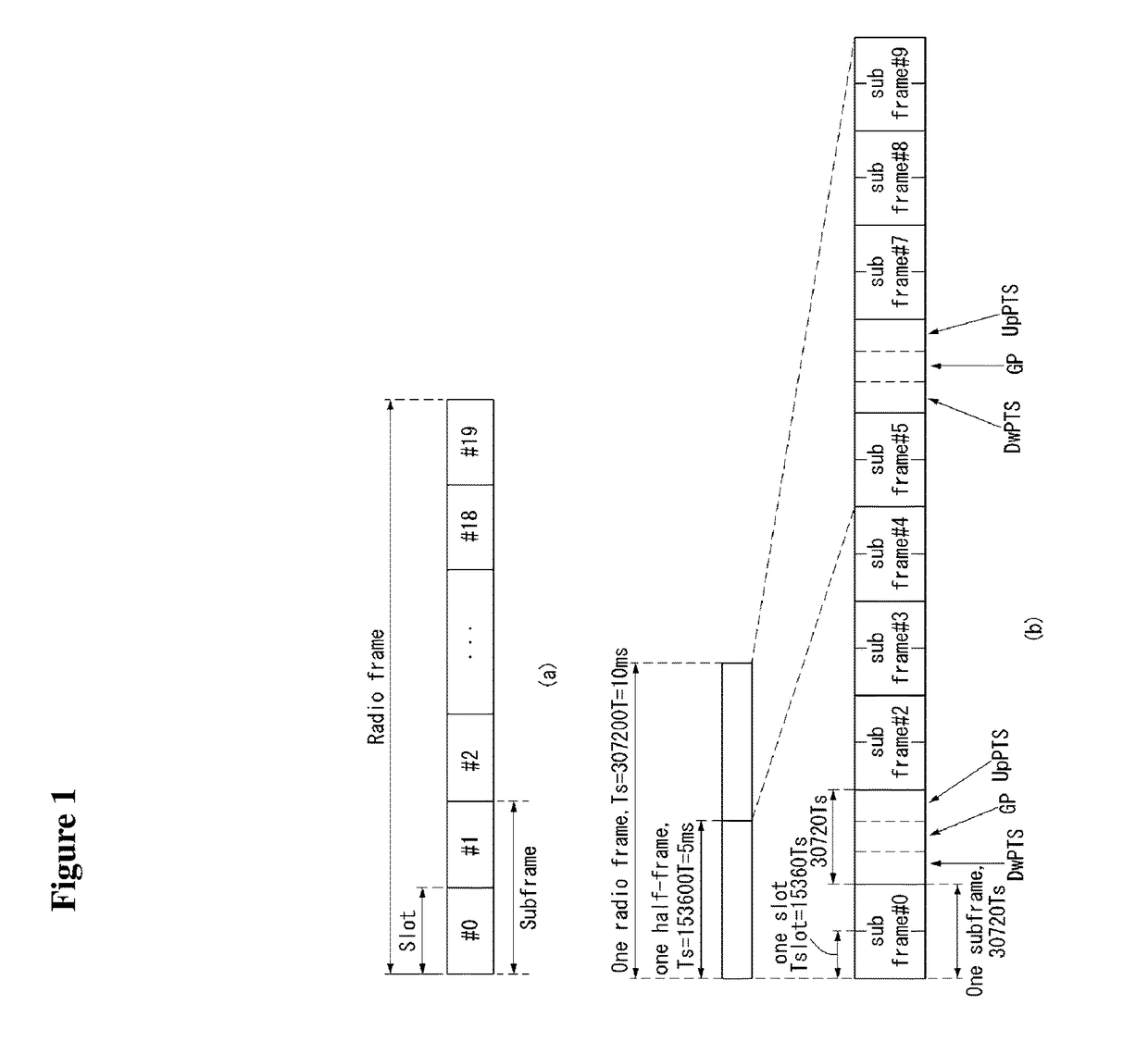

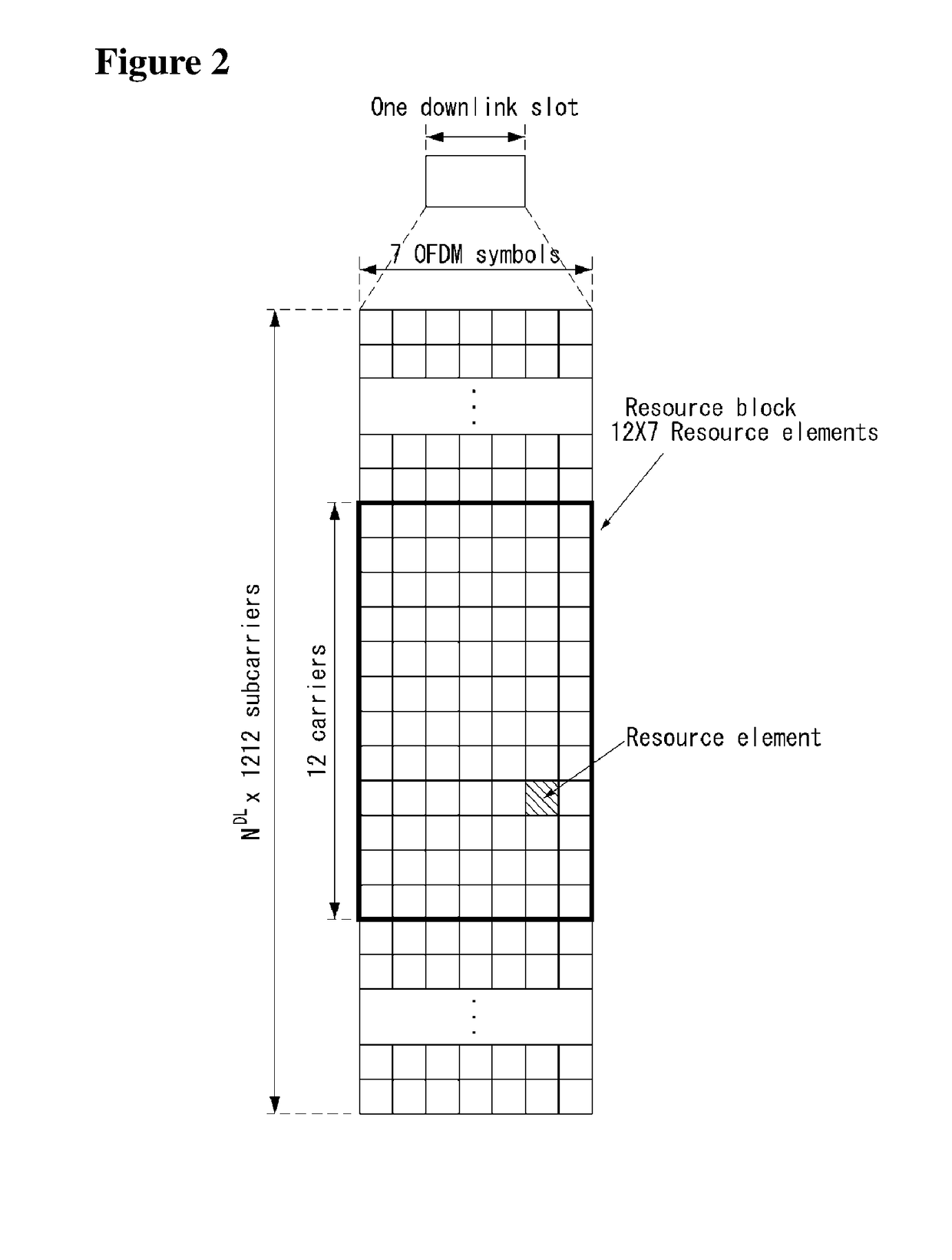

ActiveUS20100302998A1Shorten the construction periodImprove service experienceSynchronisation error correctionFrequency-division multiplex detailsService experienceTiming advance

The present invention proposes a method processing in random access procedure, comprising the following steps: when a Preamble transmitted by a random access node is detected by a base station, the base station calculating TA according to the Preamble detected by itself and transmitting it to the random access node; the base station receiving random access detection information reported from a transparent relay station and selecting a service node for the random access node; the base station receiving an uplink signaling transmitted by the random access node after the random access node adjusted the uplink timing advance according to TA calculated by the base station, and notifying the random access node of the access condition through a contention resolution message according to the selected service node, and the random access node performing an access procedure based on the access condition. According to the present invention, the duration of the random access procedure can be shortened, and the service QOS can be improved, which gives the user better service experience.

Owner:DATANG MOBILE COMM EQUIP CO LTD

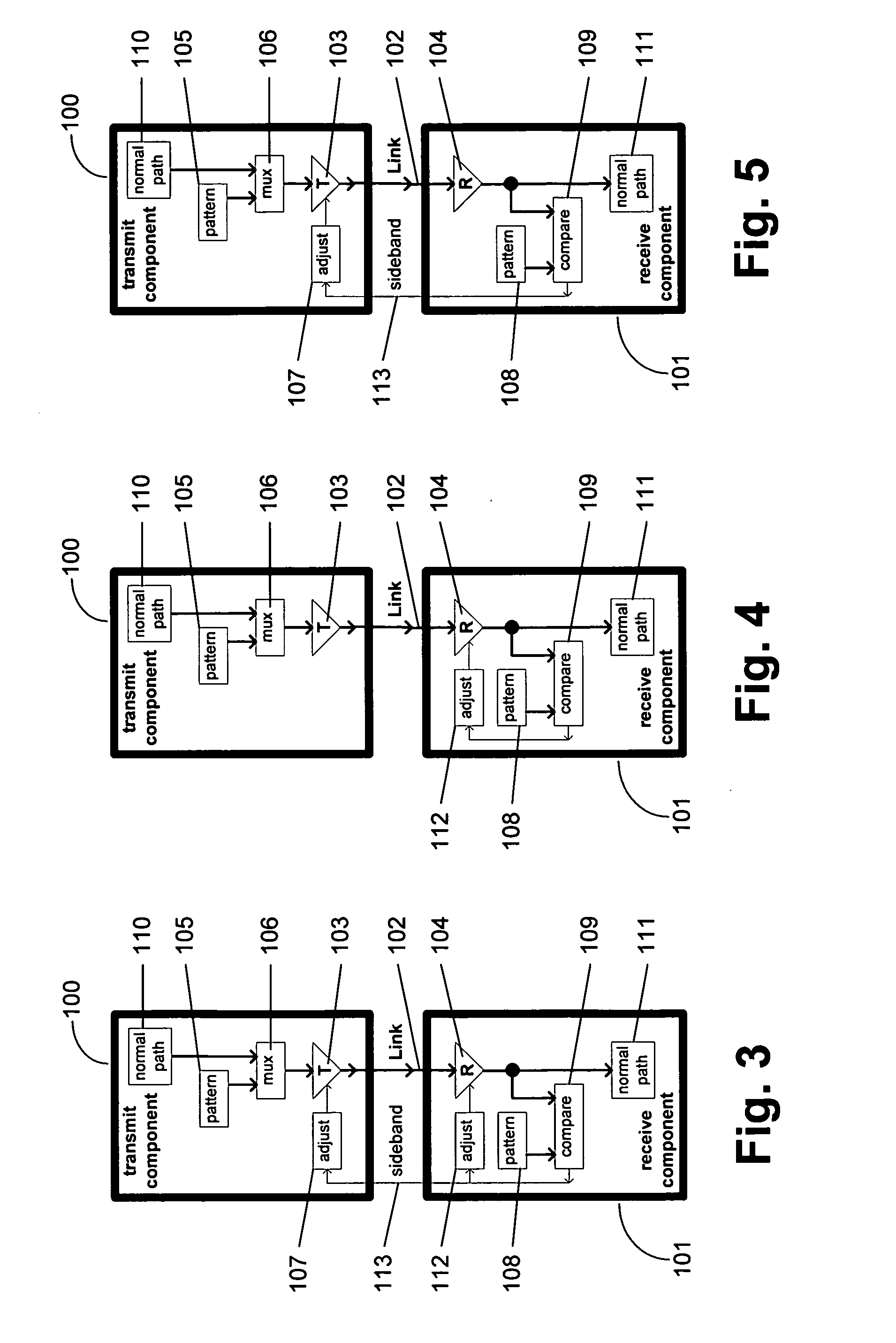

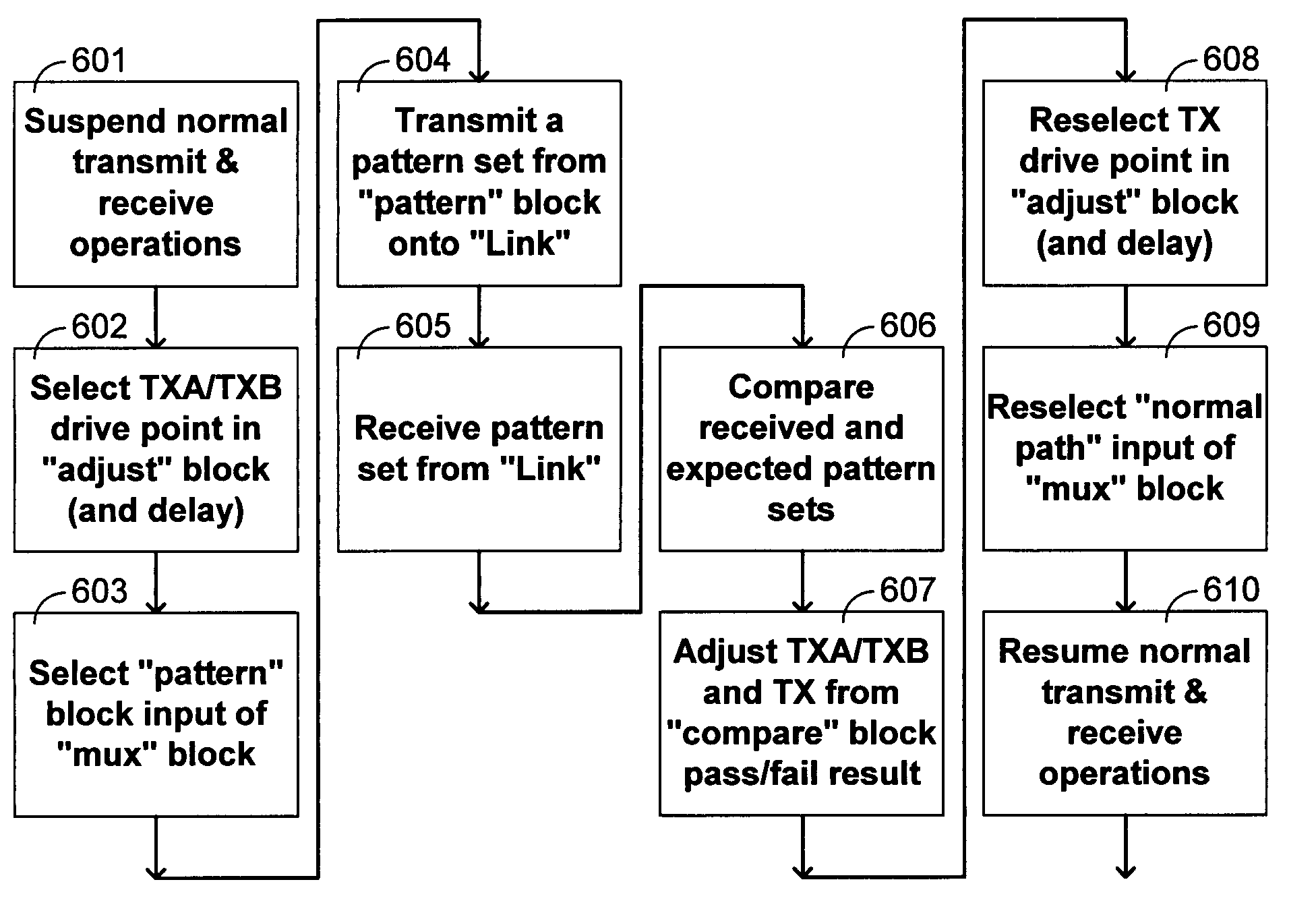

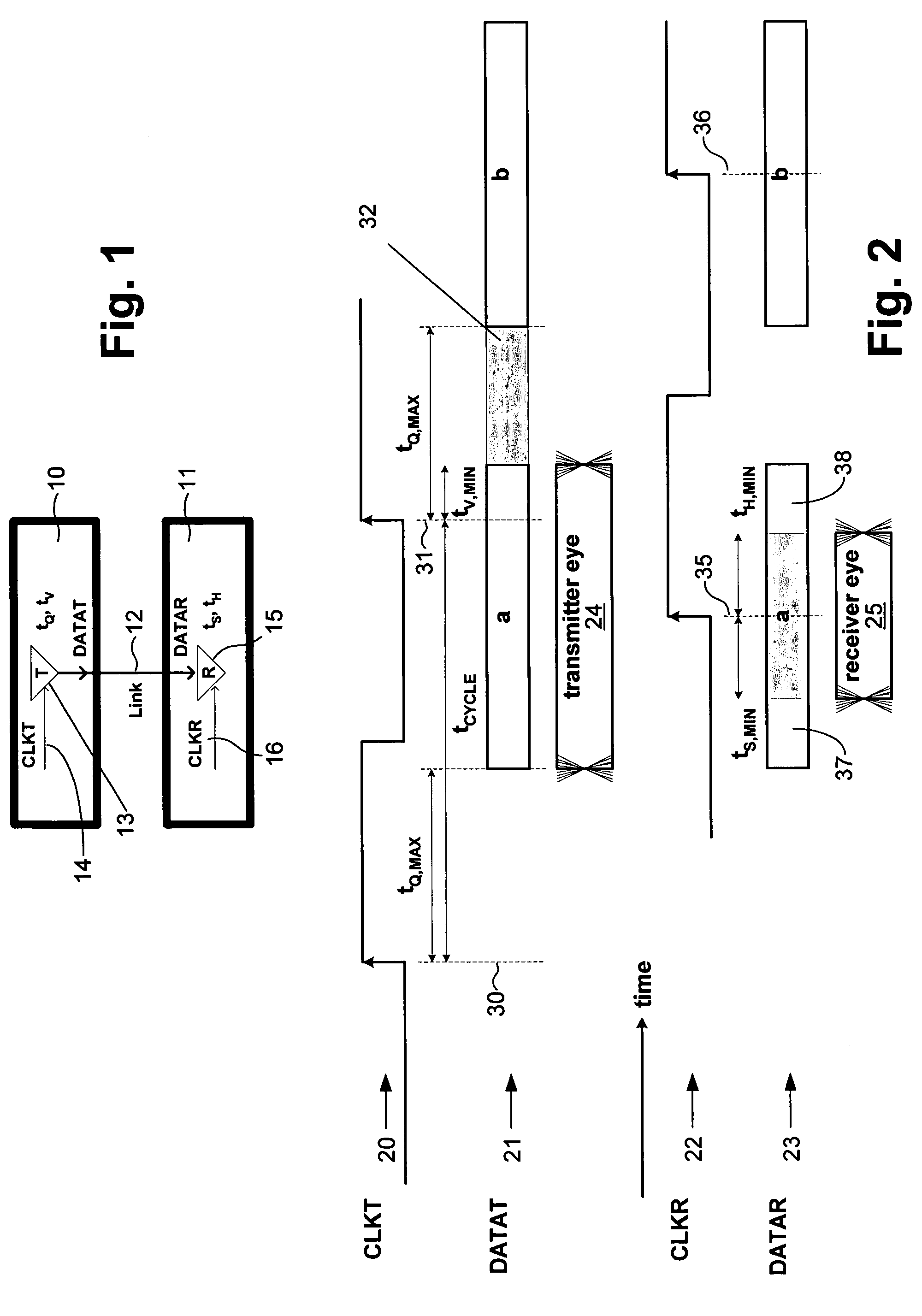

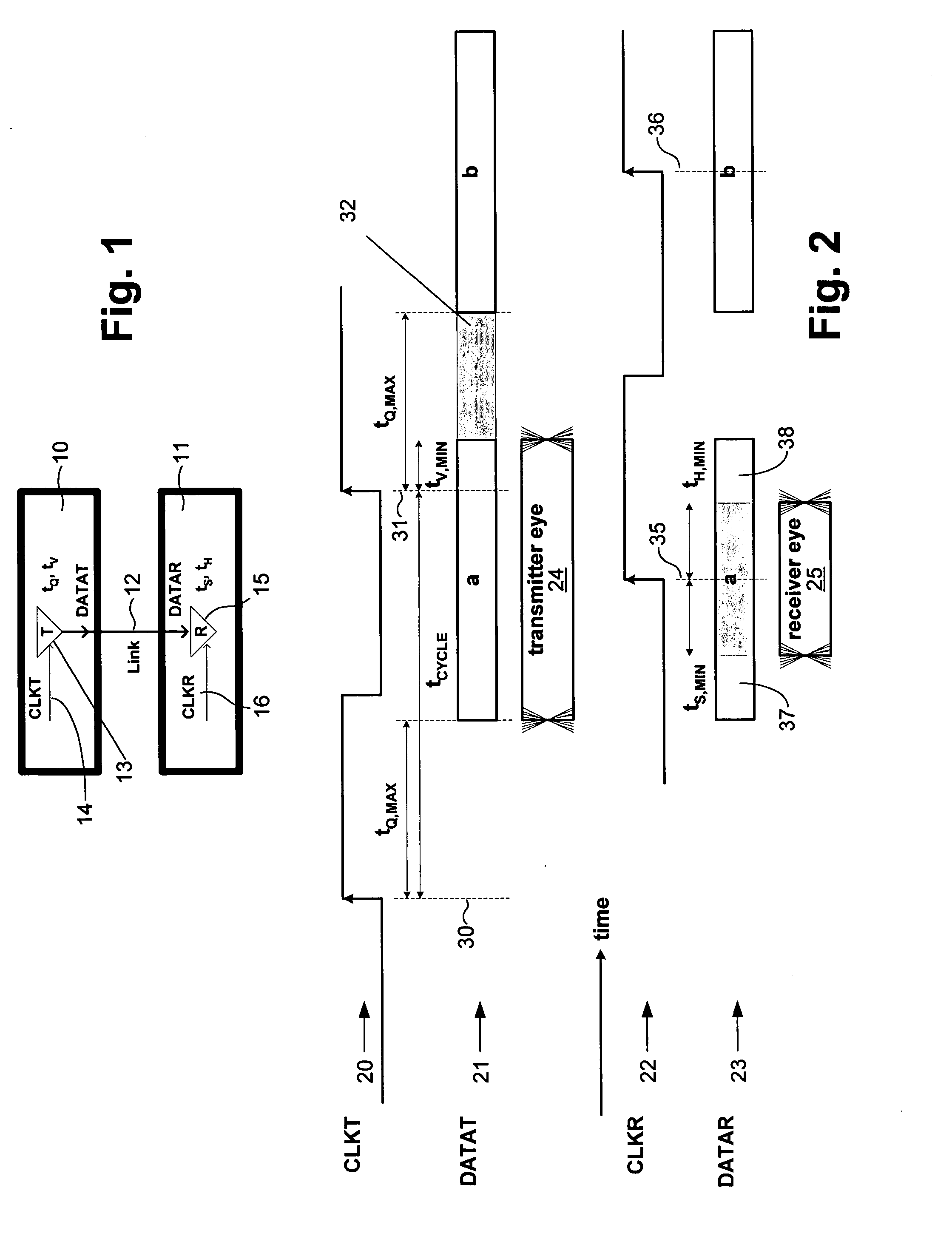

Periodic calibration for communication channels by drift tracking

ActiveUS20050163202A1Simplify sequenceEffectively accountedReceiver initialisationTransmitters monitoringByte

A method and system that provides for execution of a first calibration sequence, such as upon initialization of a system, to establish an operation value, which utilizes an algorithm intended to be exhaustive, and executing a second calibration sequence from time to time, to measure drift in the parameter, and to update the operation value in response to the measured drift. The second calibration sequence utilizes less resources of the communication channel than does the first calibration sequence. In one embodiment, the first calibration sequence for measurement and convergence on the operation value utilizes long calibration patterns, such as codes that are greater than 30 bytes, or pseudorandom bit sequences having lengths of 2N−1 bits, where N is equal to or greater than 7, while the second calibration sequence utilizes short calibration patterns, such as fixed codes less than 16 bytes, and for example as short as 2 bytes long.

Owner:RAMBUS INC

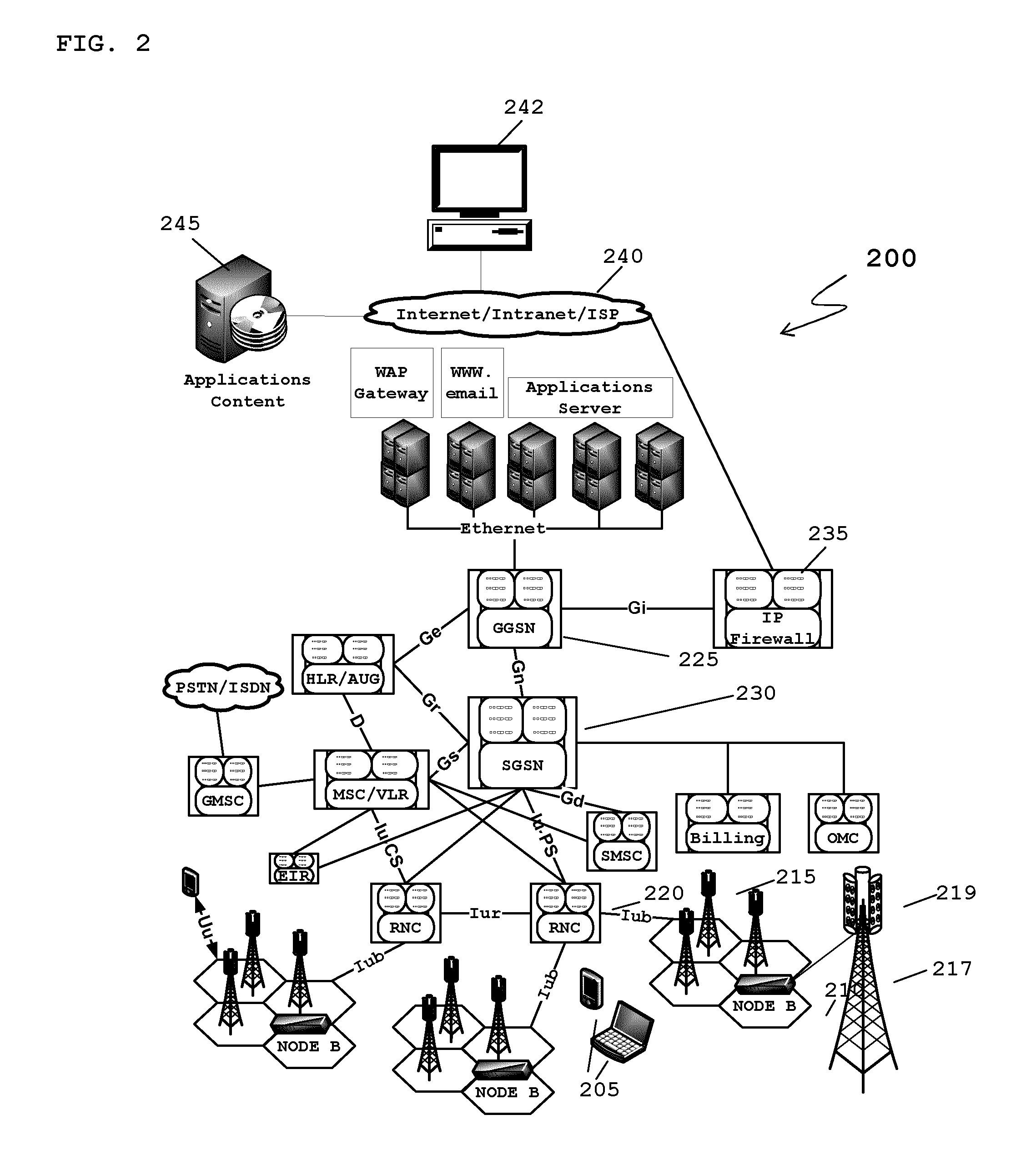

MIMO antenna calibration device, integrated circuit and method for compensating phase mismatch

ActiveUS20130235962A1Mitigate, alleviate or eliminate one orTransmitters monitoringReceivers monitoringMimo antennaEngineering

A multiple input multiple output (MIMO) calibration device (360) for calibrating a phase relationship between at least two signals present on at least two radio frequency (RF) paths coupling a wireless communication unit and the MIMO calibration device (360) is described. The MIMO calibration device (360) is operably coupleable via at least two RF paths between a wireless communication unit and an antenna arrangement (219). The calibration device (360) comprises a processing module (490) configured to: process a coupled amount of at least one first signal from a first path operably coupleable to a first polarisation of the antenna arrangement (219) to determine at least one pilot signal from said at least one first signal; process a coupled amount of at least one second signal from a second path operably coupleable to at least one second polarisation feed of antenna arrangement (219), different to the first polarisation, to determine the at least one pilot signal from said at least one second signal; and determine a first phase relationship of the same pilot signal between the at least two RF paths.

Owner:ANALOG DEVICES INT UNLTD

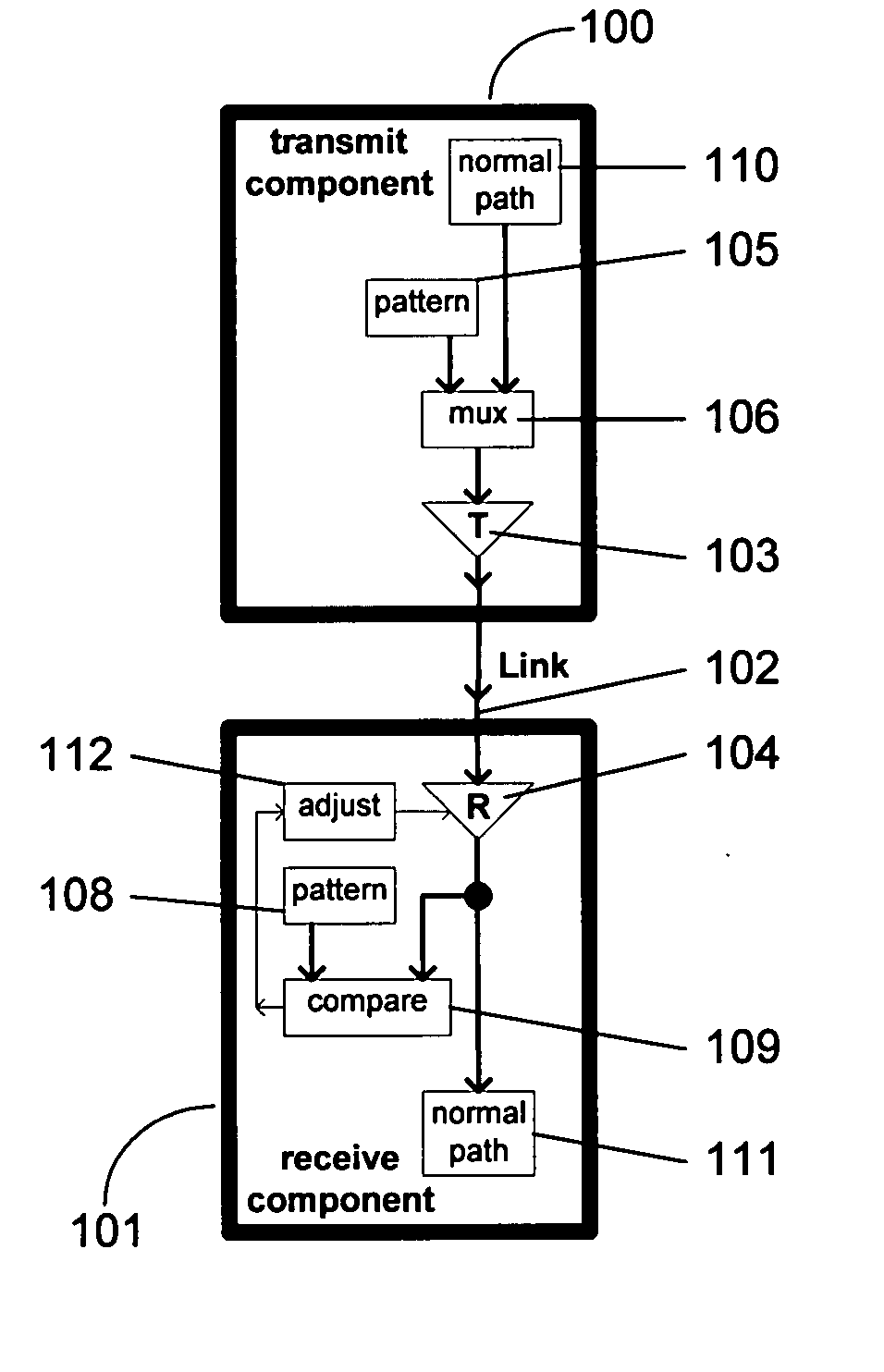

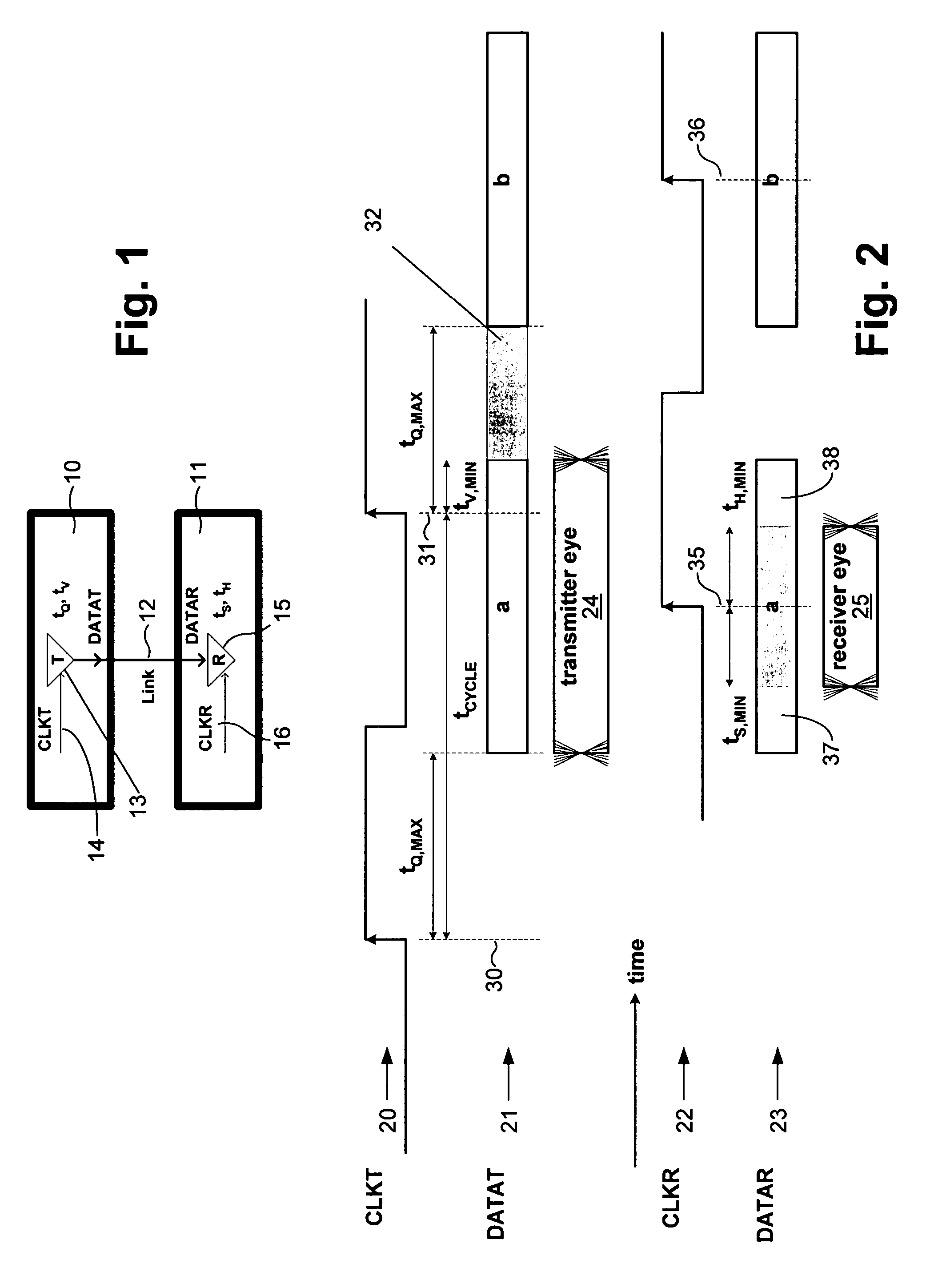

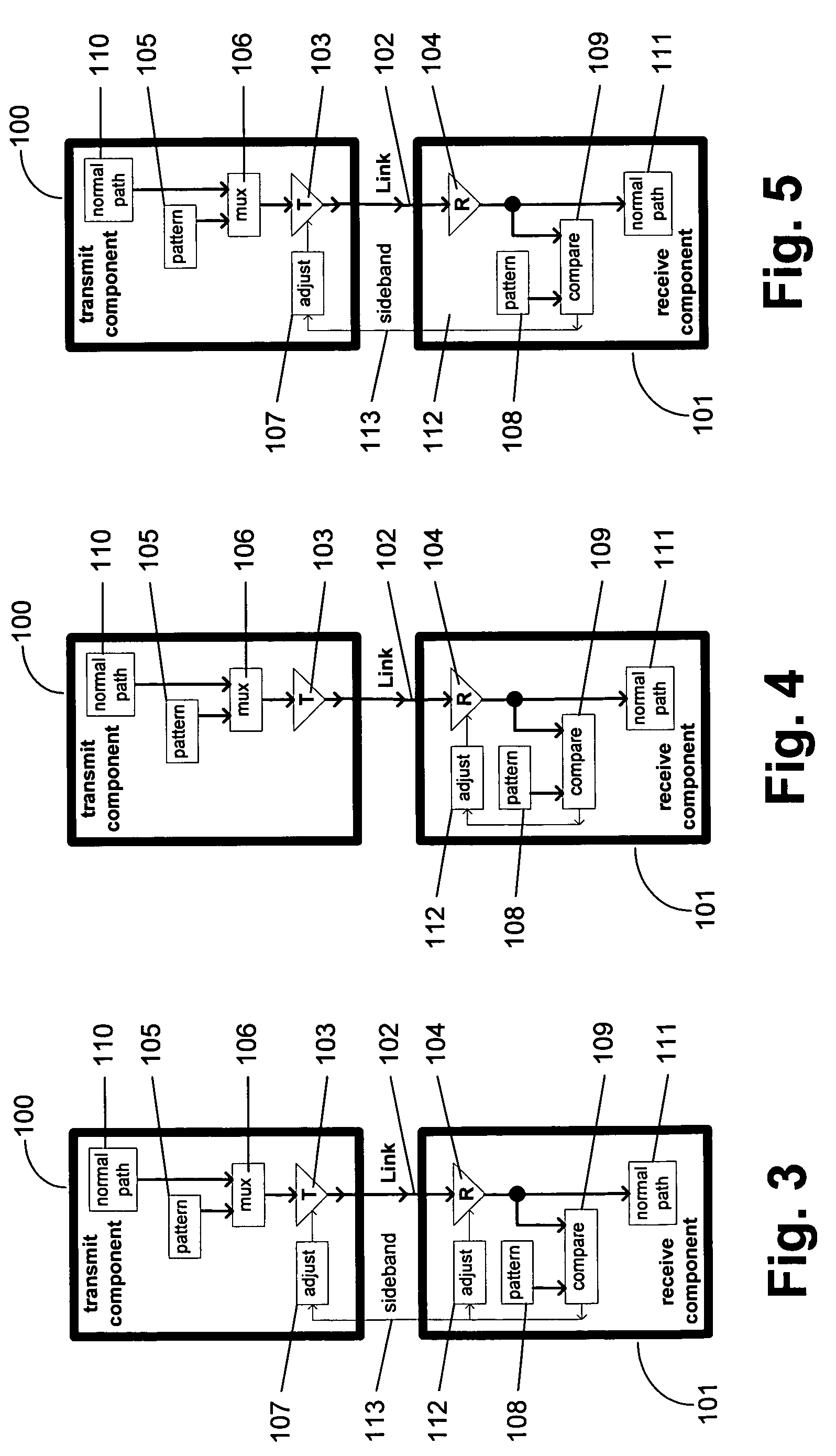

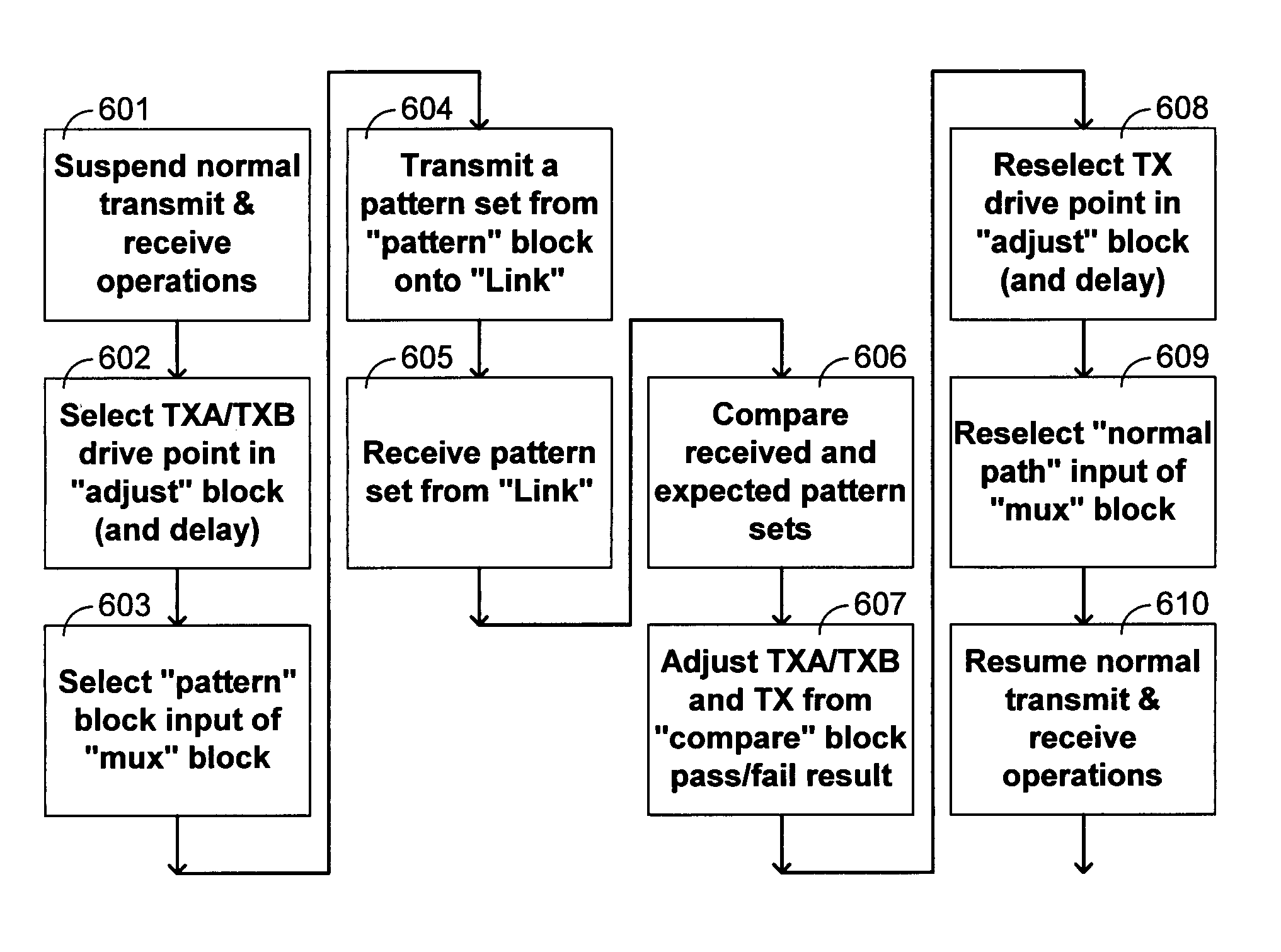

Communication channel calibration for drift conditions

ActiveUS7095789B2Improve memory utilizationIncrease profitLine impedence variation compensationCorrect operation testingTelecommunications linkData source

A method and system provides for execution of calibration cycles from time to time during normal operation of the communication channel. A calibration cycle includes de-coupling the normal data source from the transmitter and supplying a calibration pattern in its place. The calibration pattern is received from the communication link using the receiver on the second component. A calibrated value of a parameter of the communication channel is determined in response to the received calibration pattern. The steps involved in calibration cycles can be reordered to account for utilization patterns of the communication channel. For bidirectional links, calibration cycles are executed which include the step of storing received calibration patterns on the second component, and retransmitting such calibration patterns back to the first component for use in adjusting parameters of the channel at first component.

Owner:K MIZRA LLC

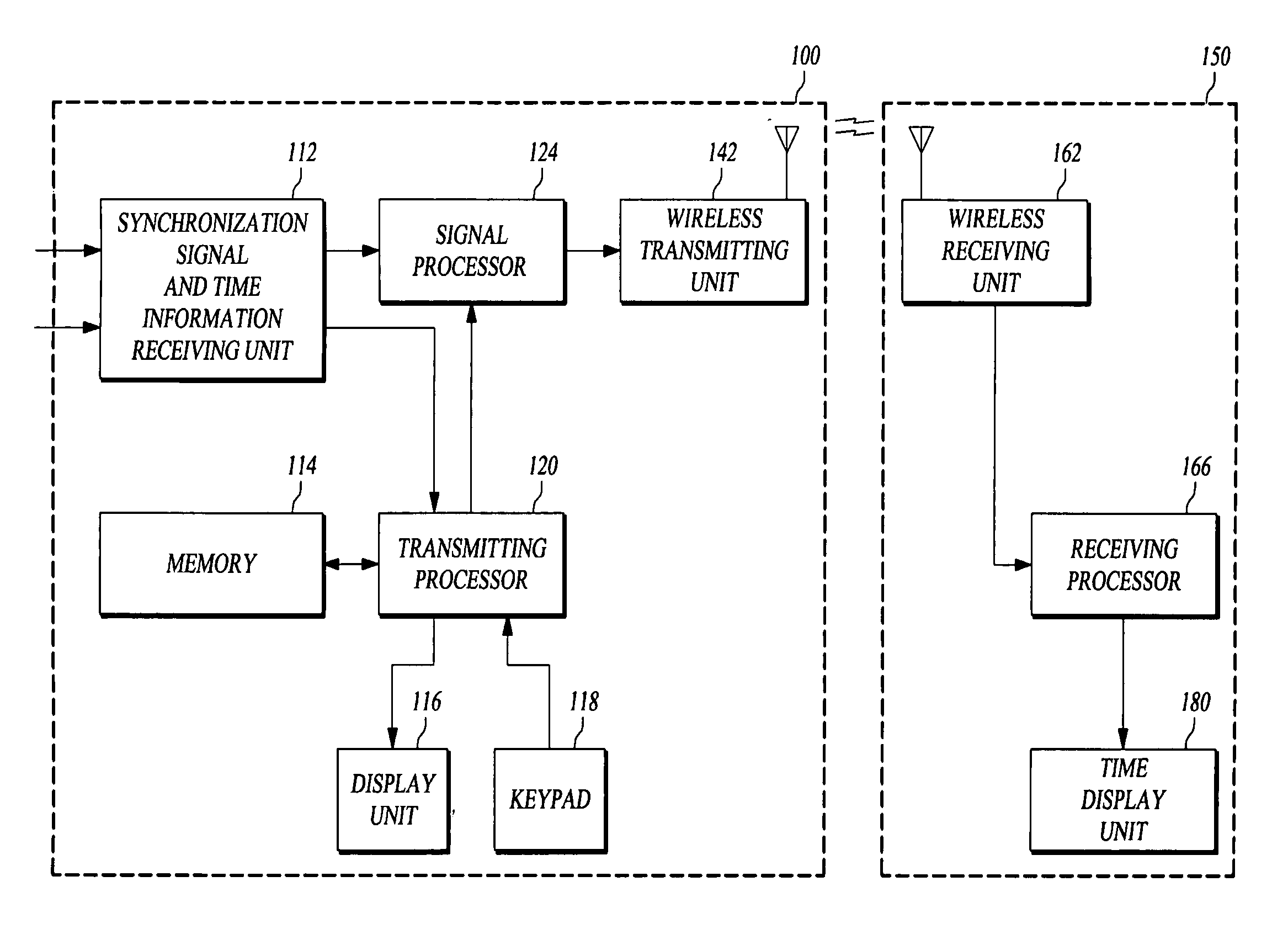

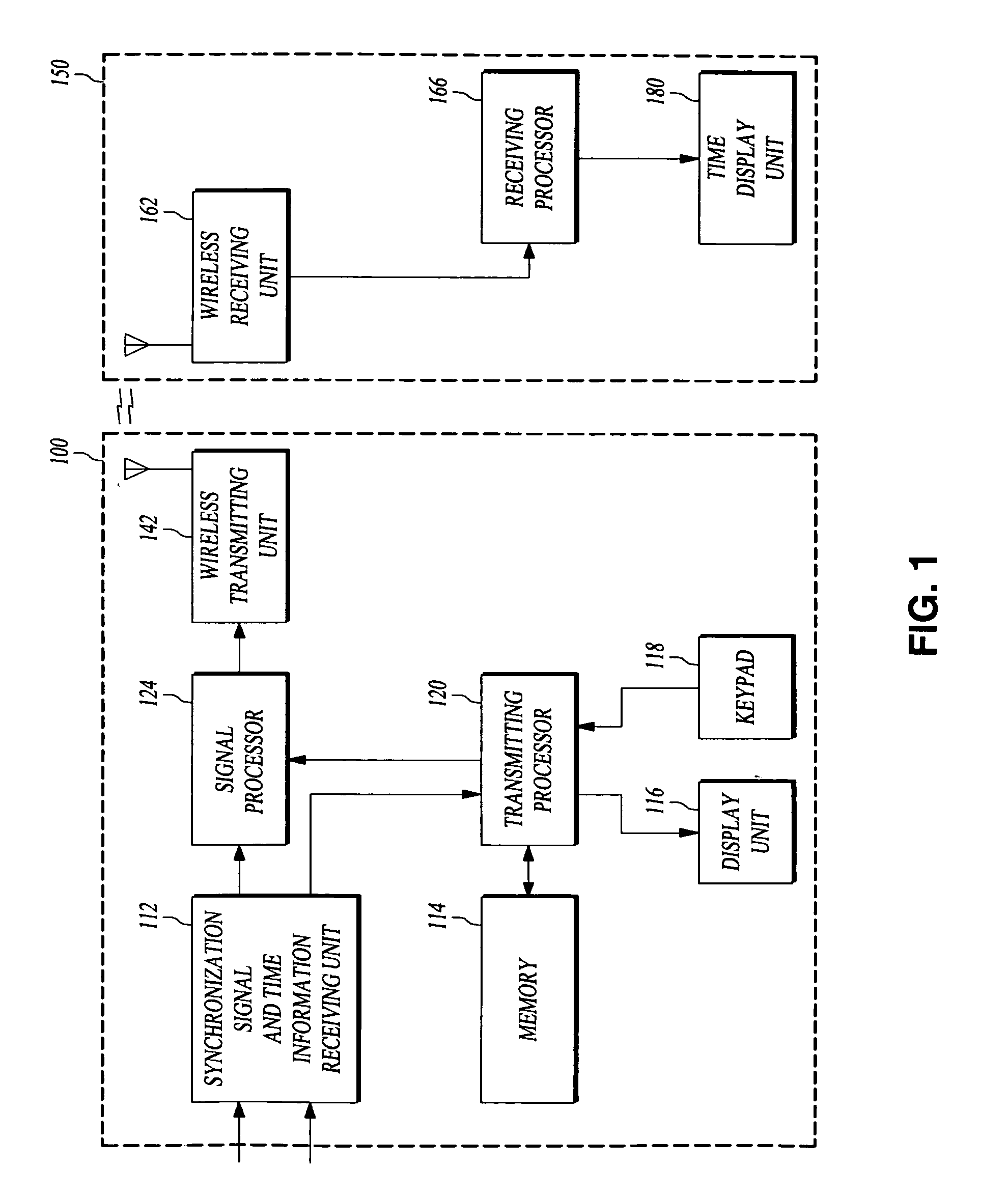

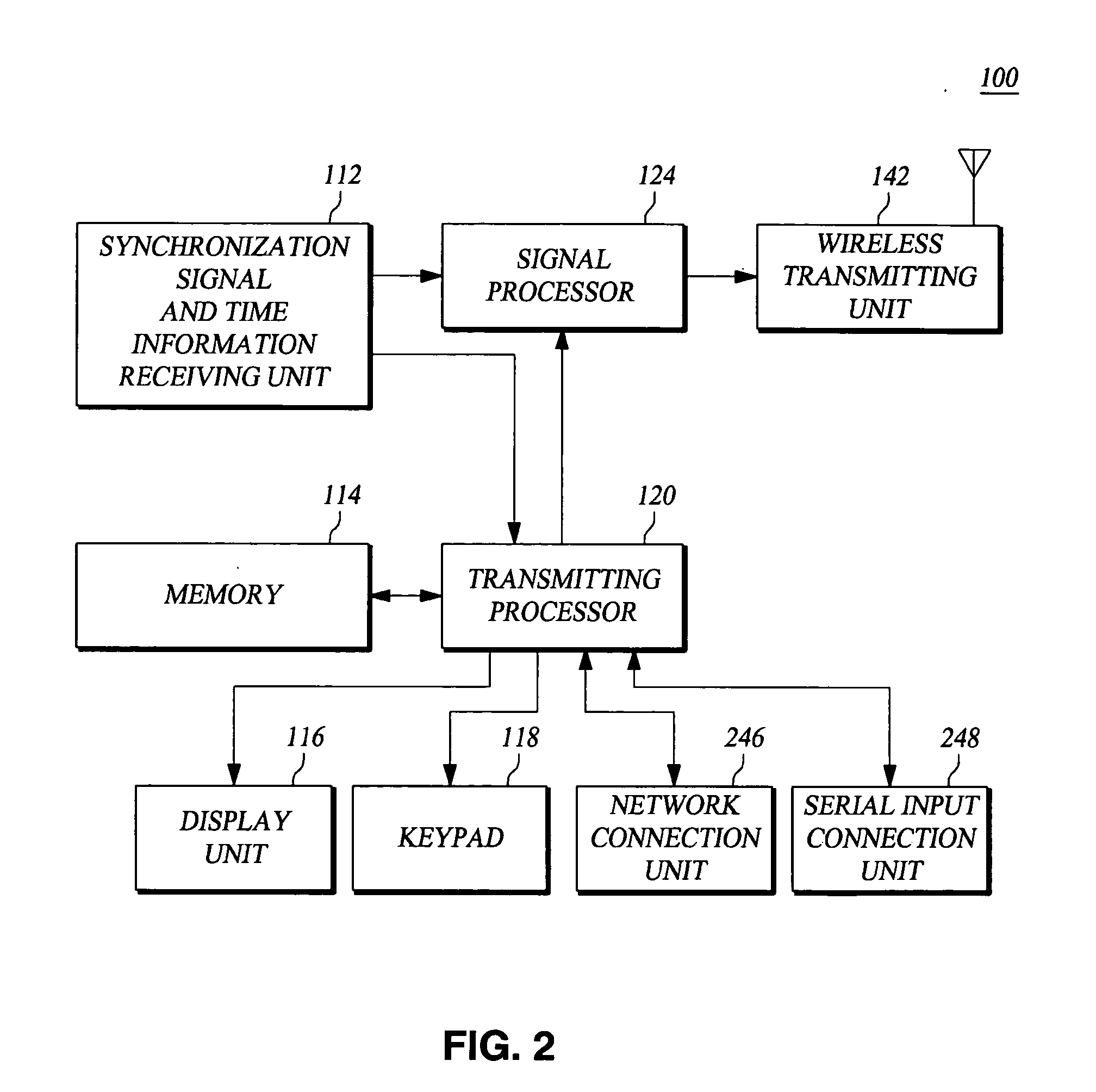

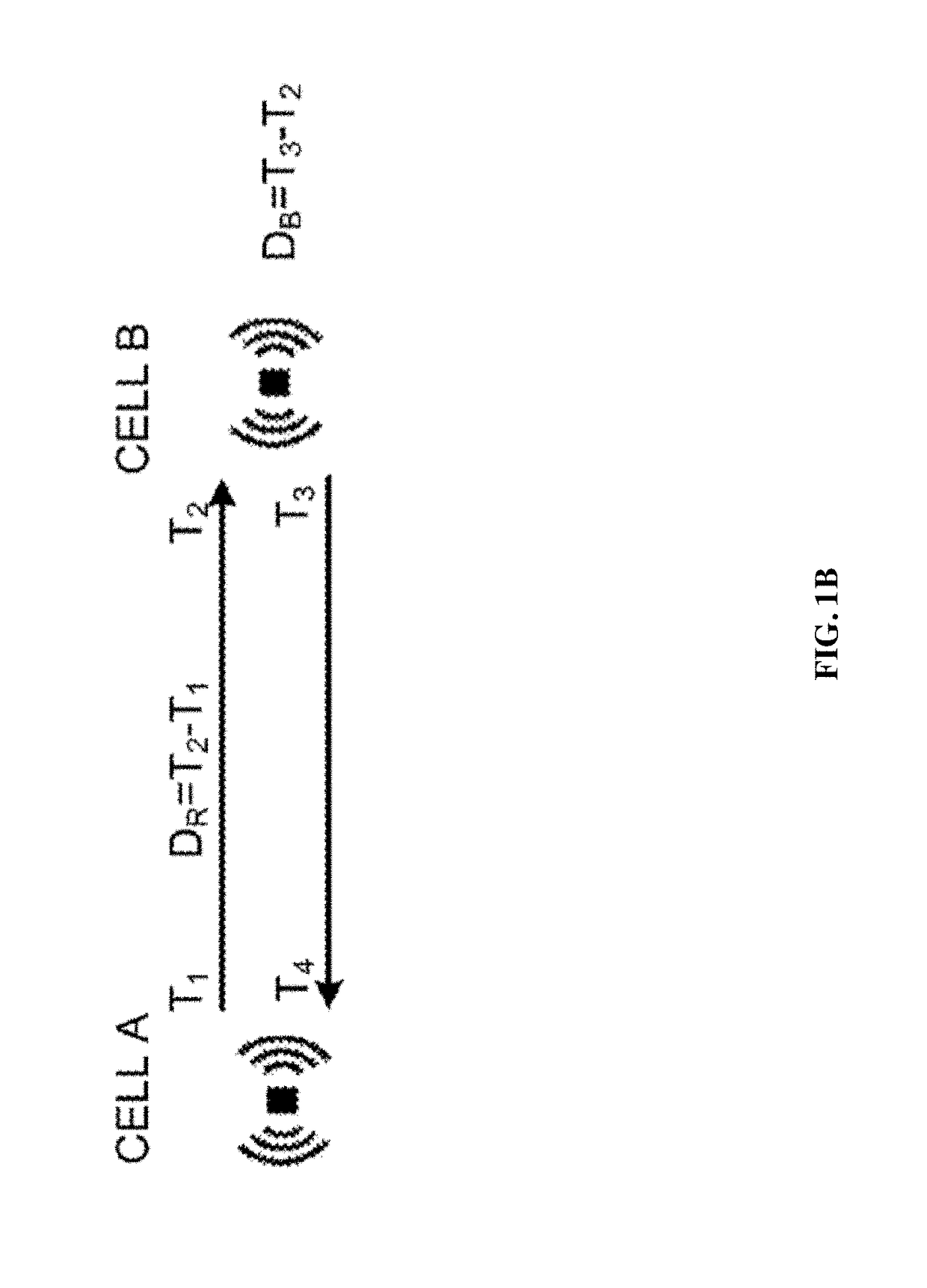

Apparatus for wireless communication and method for synchronizing time thereof

InactiveUS20100034190A1Efficiently and wirelessly transmitting/receiving timeOvercome limitationsSynchronisation arrangementSynchronisation error correctionTelecommunicationsCommunication device

Disclosed are a wireless communication apparatus and a time synchronization method performed thereby.

Owner:HANYANG NAVICOM

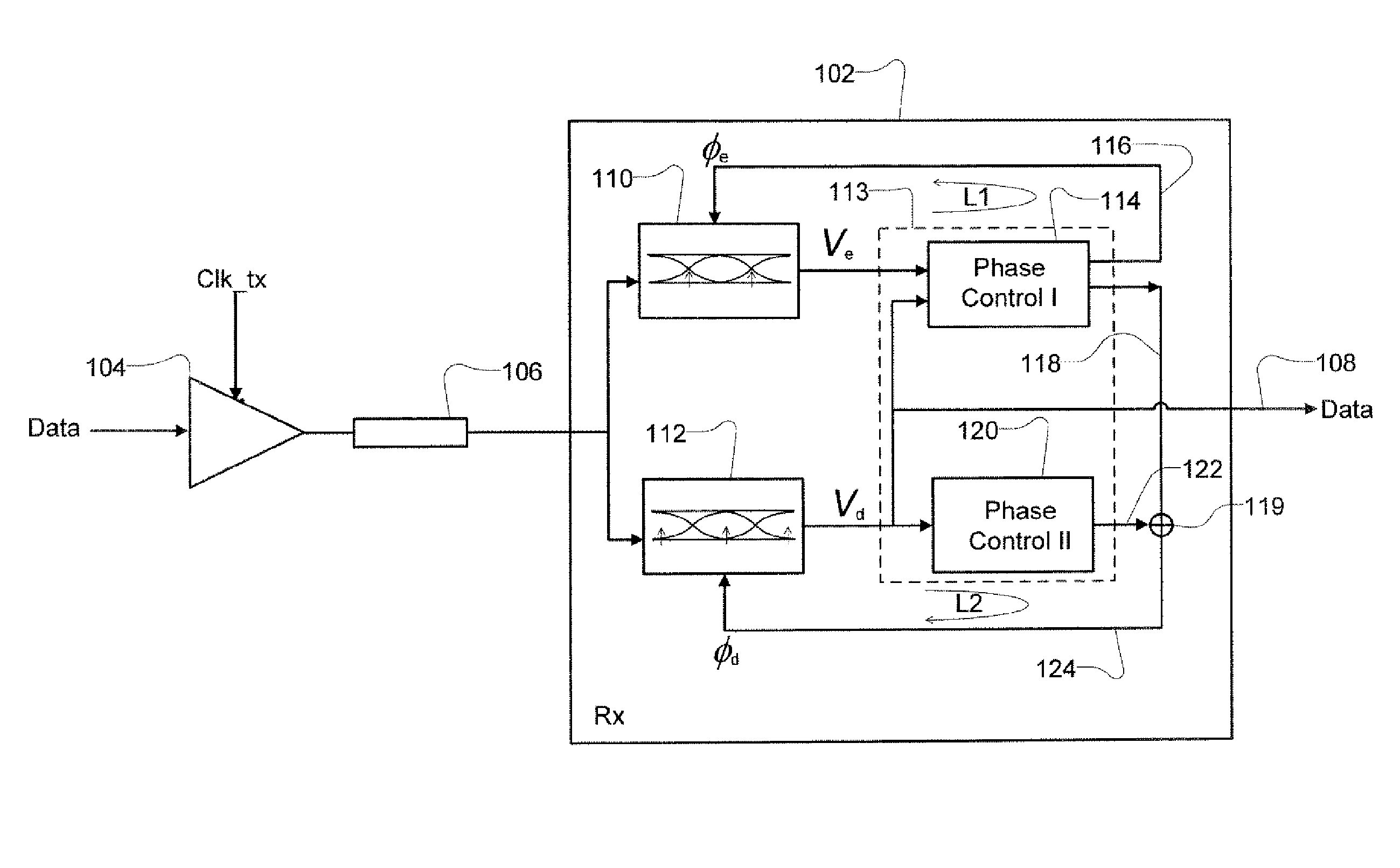

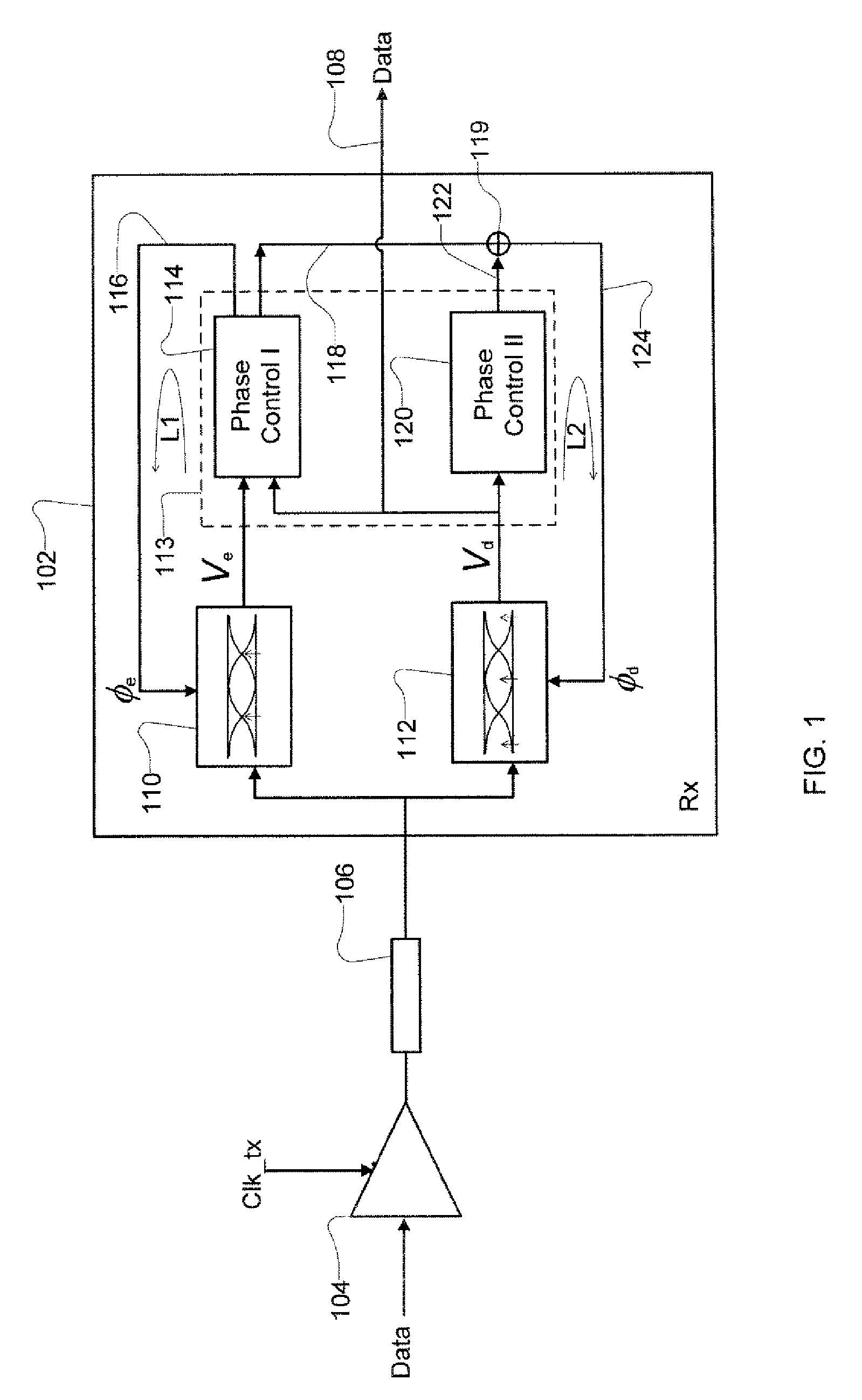

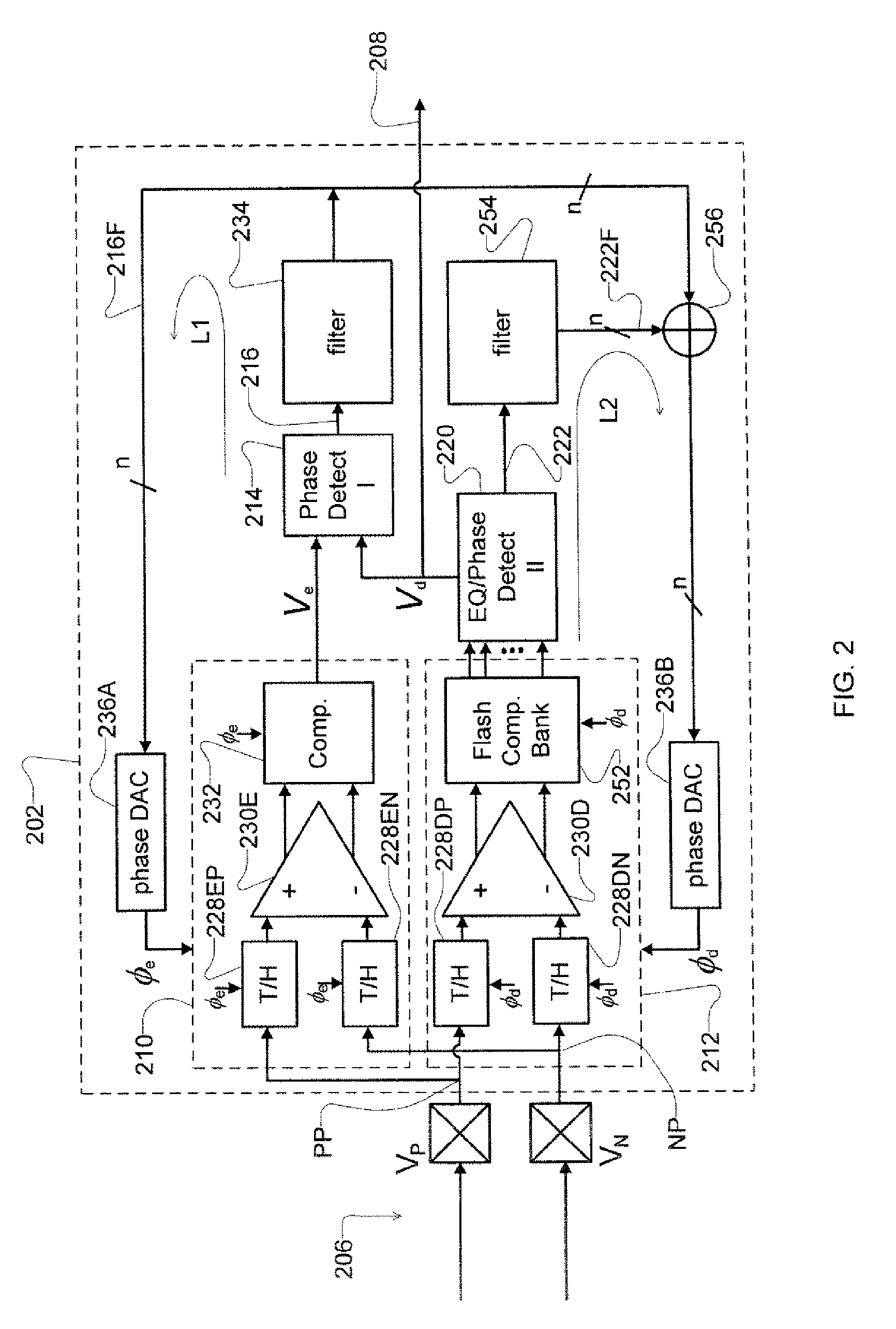

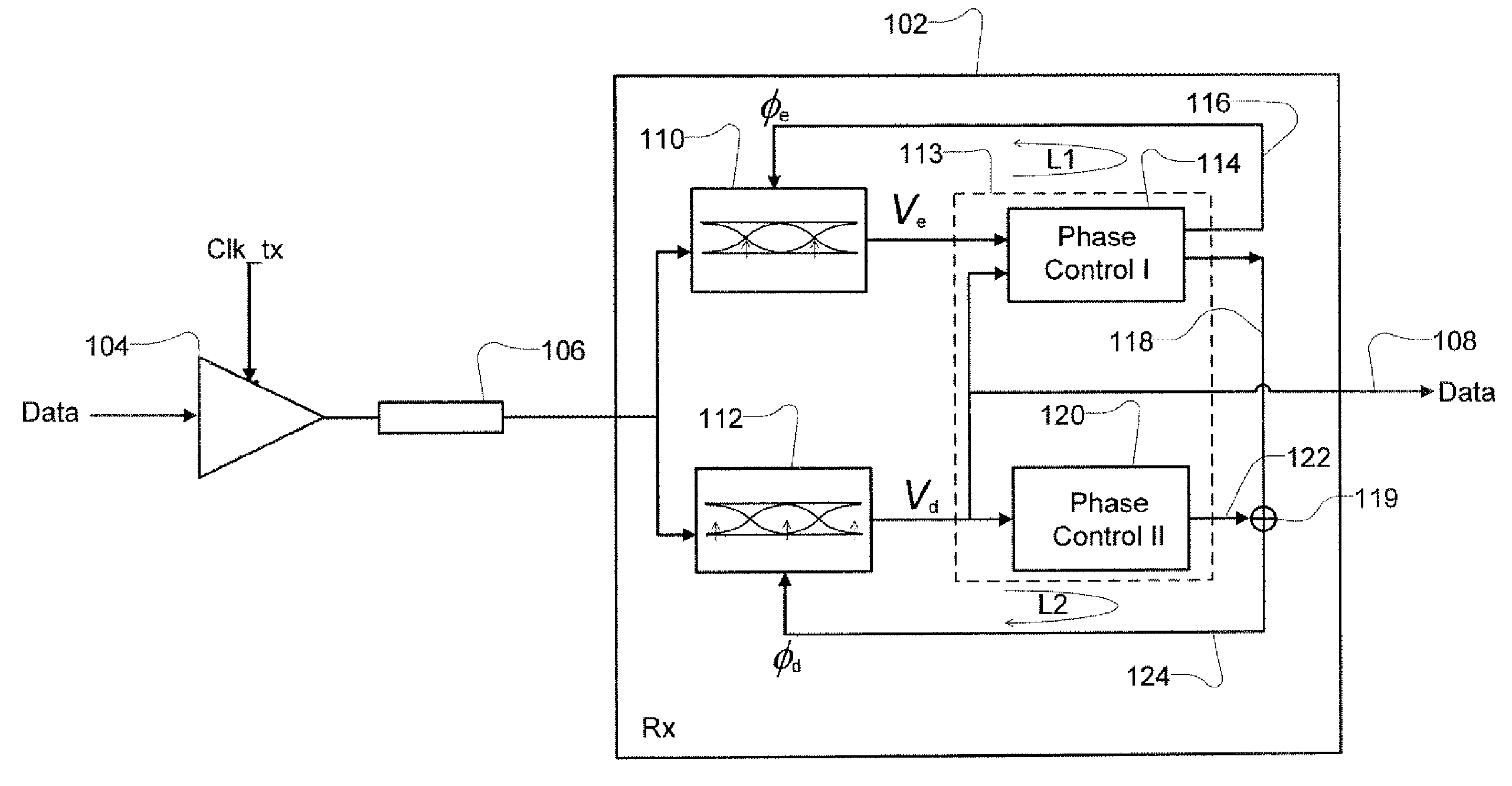

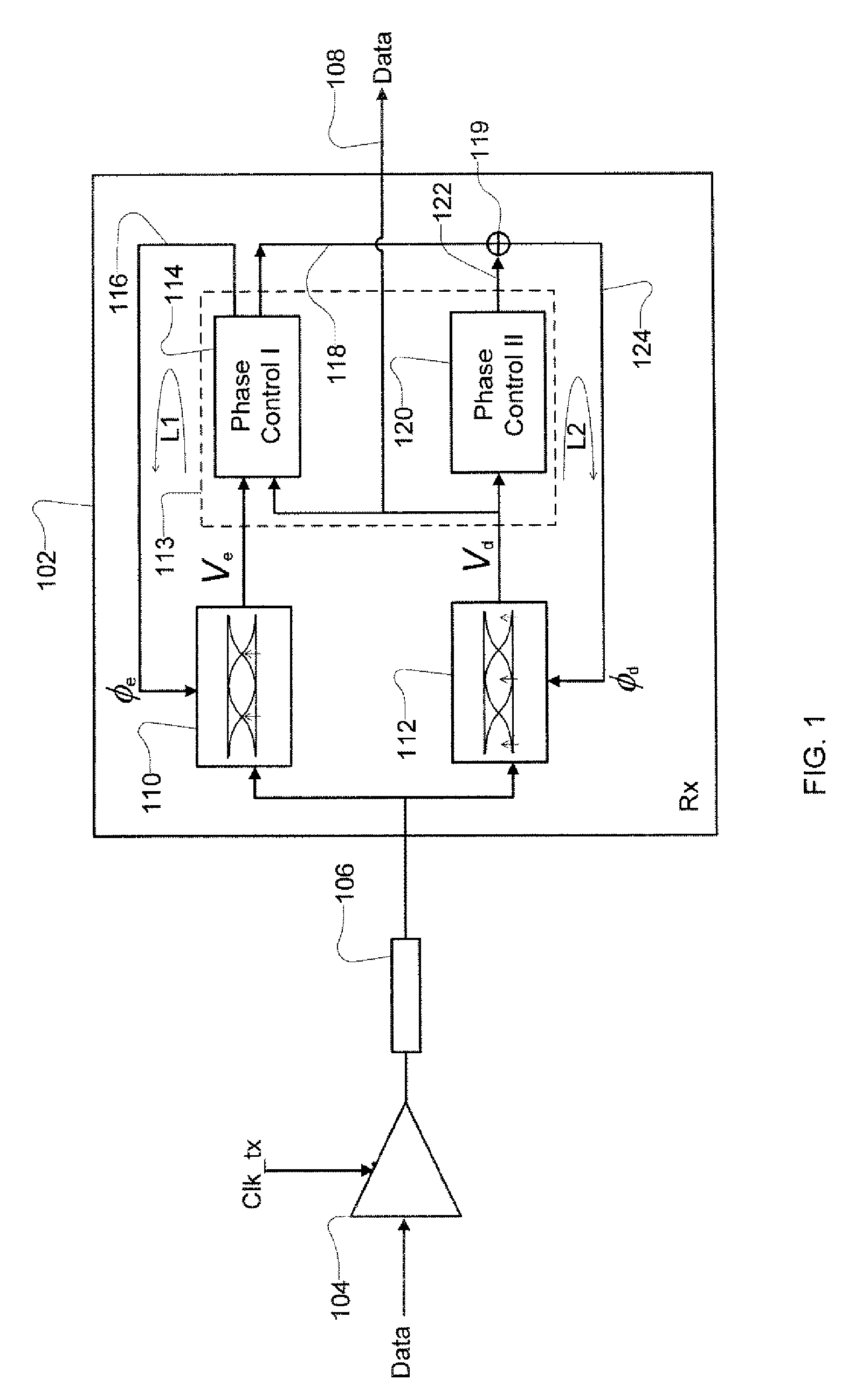

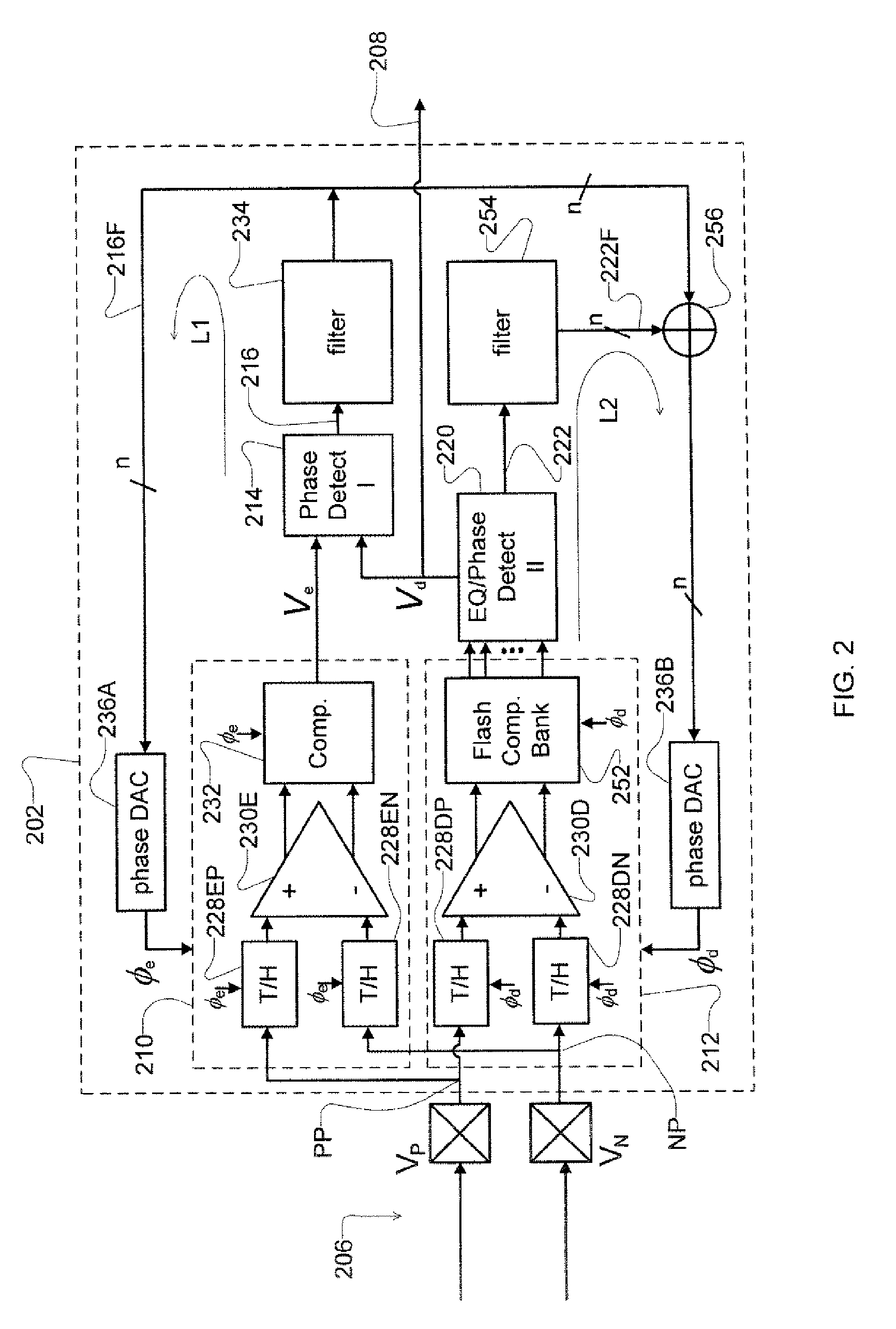

Receiver with enhanced clock and data recovery

ActiveUS8929496B2Receiver initialisationSynchronisation error correctionData transformationBang bang phase detector

A receiver device implements enhanced data reception with edge-based clock and data recovery such as with a flash analog-to-digital converter architecture. In an example embodiment, the device implements a first phase adjustment control loop, with for example, a bang-bang phase detector, that detects data transitions for adjusting sampling at an optimal edge time with an edge sampler by adjusting a phase of an edge clock of the sampler. This loop may further adjust sampling in received data intervals for optimal data reception by adjusting the phase of a data clock of a data sampler such a flash ADC. The device may also implement a second phase adjustment control loop with, for example, a baud-rate phase detector, that detects data intervals for further adjusting sampling at an optimal data time with the data sampler.

Owner:RAMBUS INC

Receiver With Enhanced Clock And Data Recovery

ActiveUS20100289544A1Receiver initialisationSynchronisation error correctionBaudAnalog-to-digital converter

A receiver device implements enhanced data reception with edge-based clock and data recovery such as with a flash analog-to-digital converter architecture. In an example embodiment, the device implements a first phase adjustment control loop, with for example, a bang-bang phase detector, that detects data transitions for adjusting sampling at an optimal edge time with an edge sampler by adjusting a phase of an edge clock of the sampler. This loop may further adjust sampling in received data intervals for optimal data reception by adjusting the phase of a data clock of a data sampler such a flash ADC. The device may also implement a second phase adjustment control loop with, for example, a baud-rate phase detector, that detects data intervals for further adjusting sampling at an optimal data time with the data sampler.

Owner:RAMBUS INC

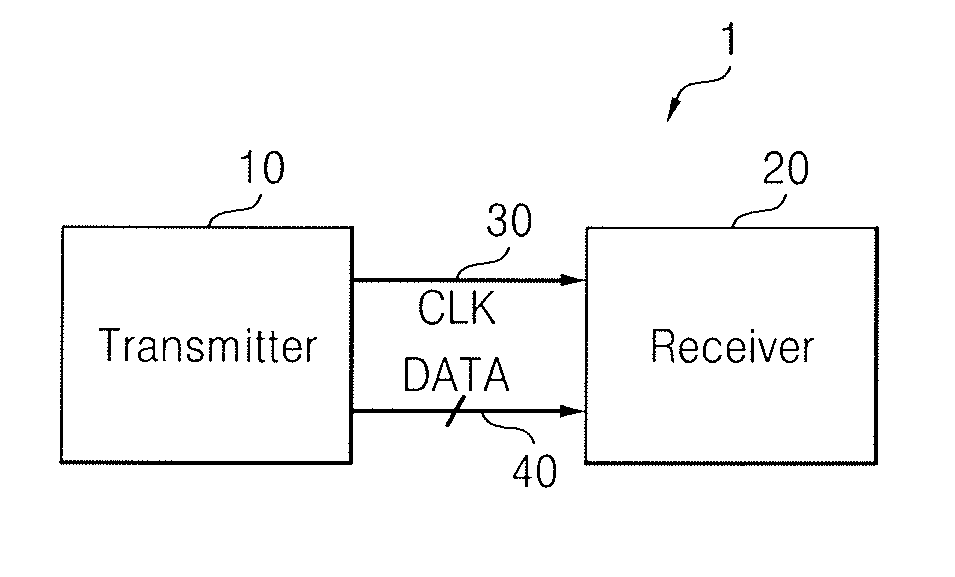

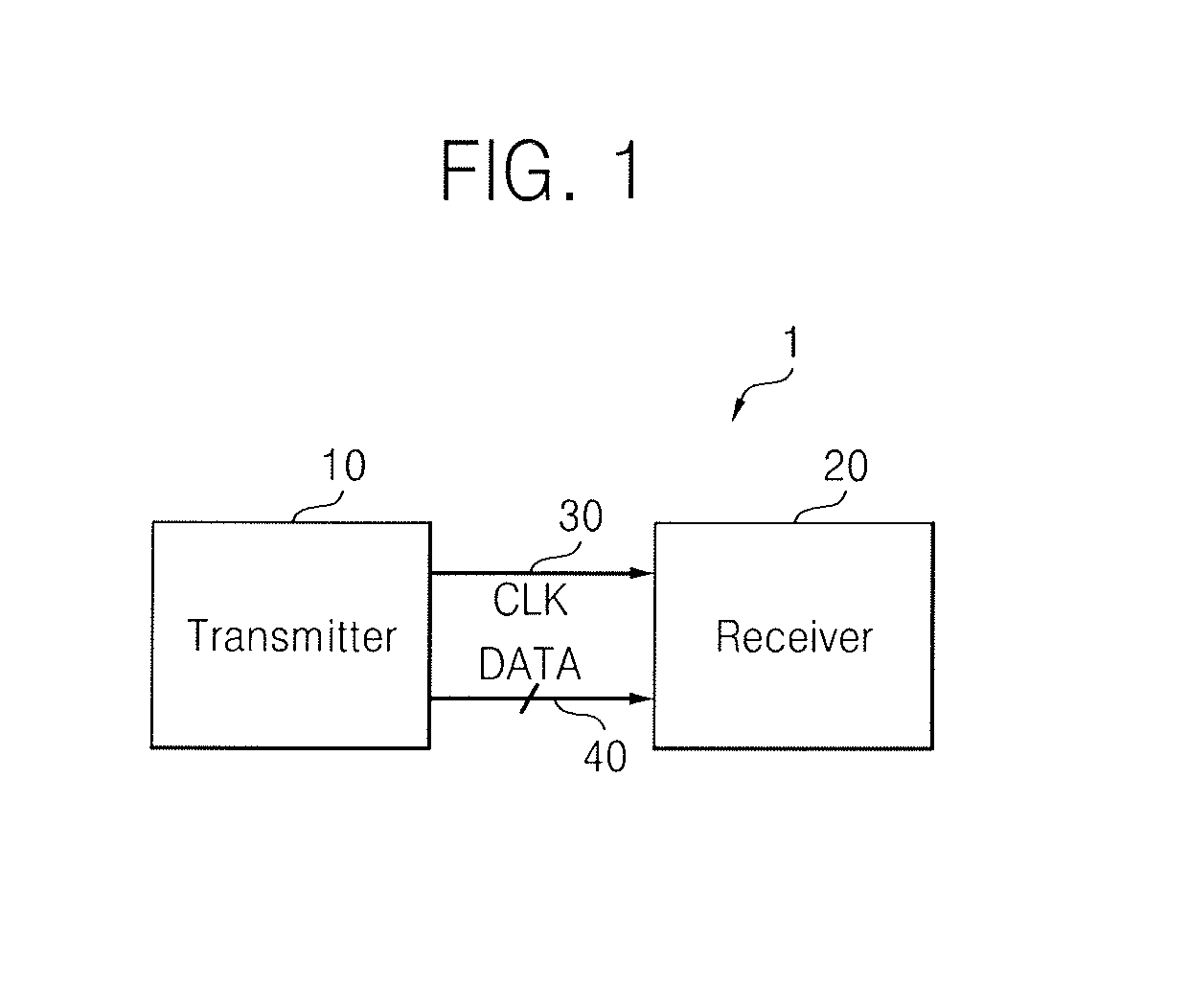

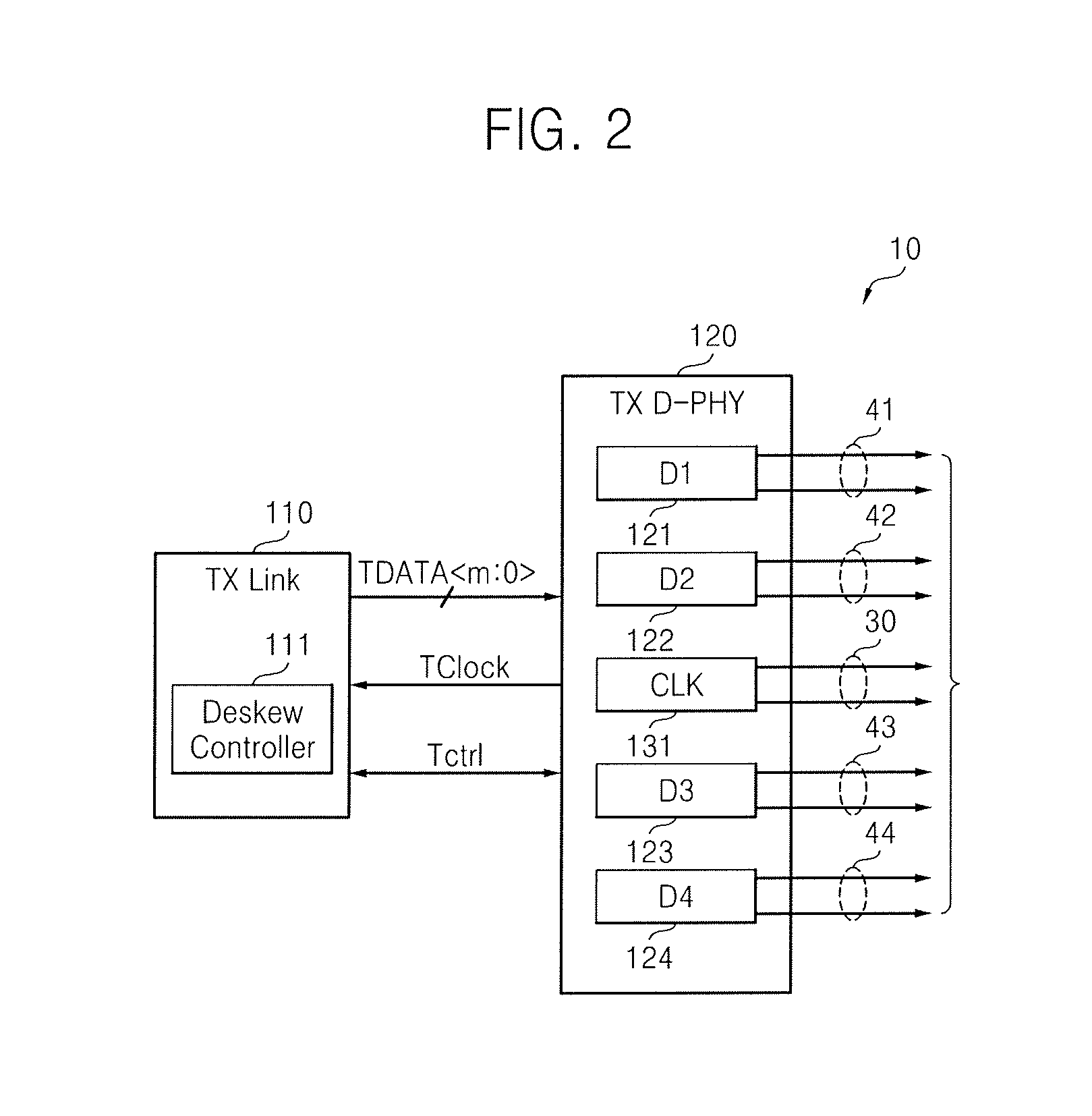

High-speed interface apparatus and deskew method thereof

ActiveUS20150229467A1Channel dividing arrangementsSynchronisation error correctionNormal modeTransmitter

A high-speed interface apparatus and method of correcting skew in the apparatus are provided. A high-speed transmitter includes a transmission D-PHY module that generates and transmits a clock signal through a clock channel, generates a deskew synchronous code and test data in response to a deskew request signal, transmits the deskew synchronous code followed by the test data through a data channel, and transmits a normal synchronous code followed by normal data through the data channel in normal mode.

Owner:SAMSUNG ELECTRONICS CO LTD

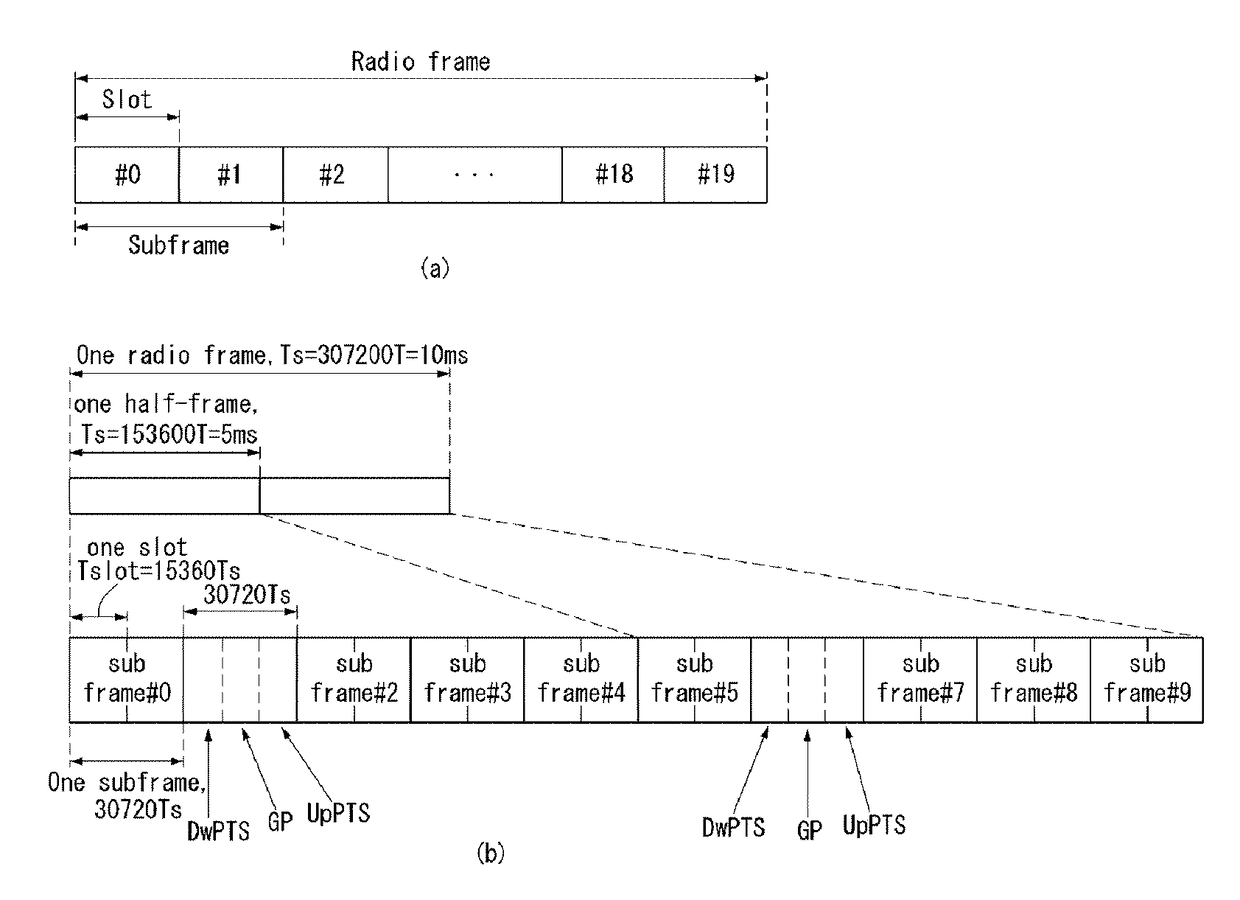

Method and apparatus for synchronizing frequency and time in a wireless communication system

ActiveUS20170223648A1Synchronisation arrangementSynchronisation error correctionCommunications systemFrequency offset

In the present invention, a method for synchronizing frequency and time in a wireless communication system and an apparatus for supporting the same are disclosed. Particularly, a method for synchronizing frequency and time performed by a terminal in a wireless communication system may include receiving a specific signal including a PSS, compensating the specific signal with at least one time offset candidate, generating at least one first differentiation value, generating at least one second differentiation value, calculating a cross correlation value between the at least one first differentiation value and the at least one second differentiation value, and estimating a time offset and a frequency offset of the PSS based on a time offset candidate that corresponds to a greatest cross correlation value among at least one cross correlation value calculated for at least one time offset candidate.

Owner:LG ELECTRONICS INC

Communication channel calibration for drift conditions

ActiveUS20050163203A1Improve memory utilizationIncrease profitLine impedence variation compensationCorrect operation testingTelecommunications linkData source

A method and system provides for execution of calibration cycles from time to time during normal operation of the communication channel. A calibration cycle includes de-coupling the normal data source from the transmitter and supplying a calibration pattern in its place. The calibration pattern is received from the communication link using the receiver on the second component. A calibrated value of a parameter of the communication channel is determined in response to the received calibration pattern. The steps involved in calibration cycles can be reordered to account for utilization patterns of the communication channel. For bidirectional links, calibration cycles are executed which include the step of storing received calibration patterns on the second component, and retransmitting such calibration patterns back to the first component for use in adjusting parameters of the channel at first component.

Owner:RAMBUS INC

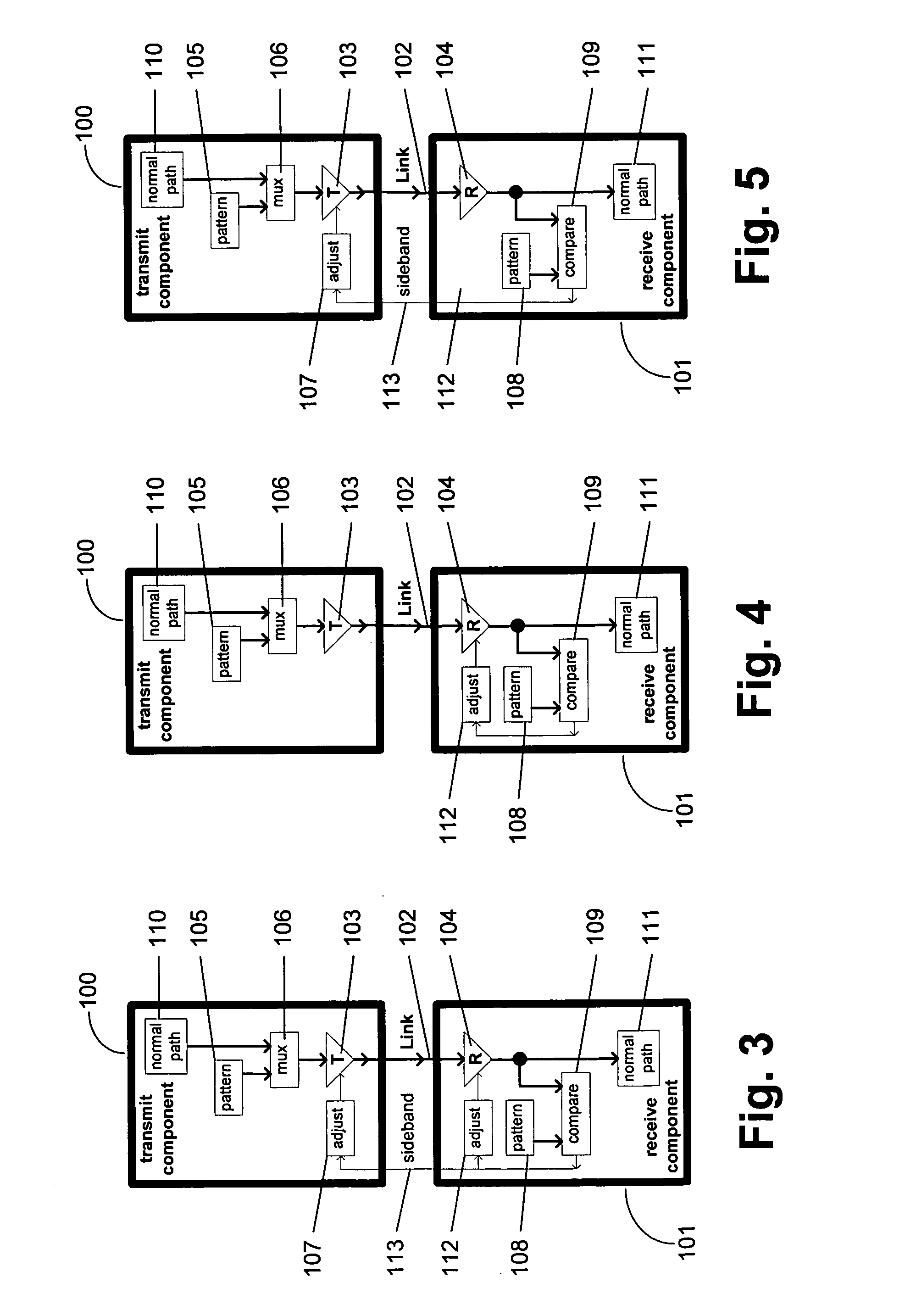

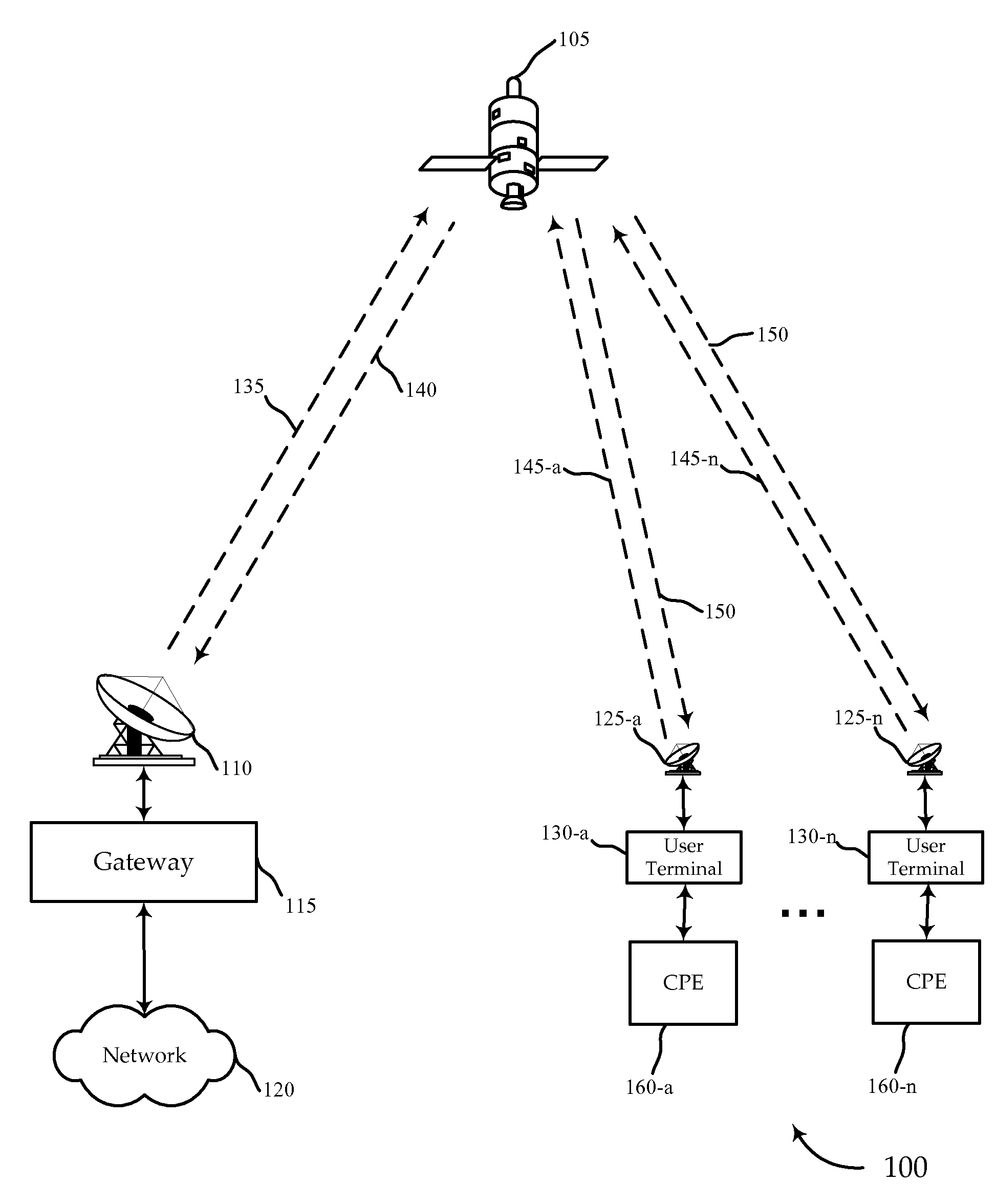

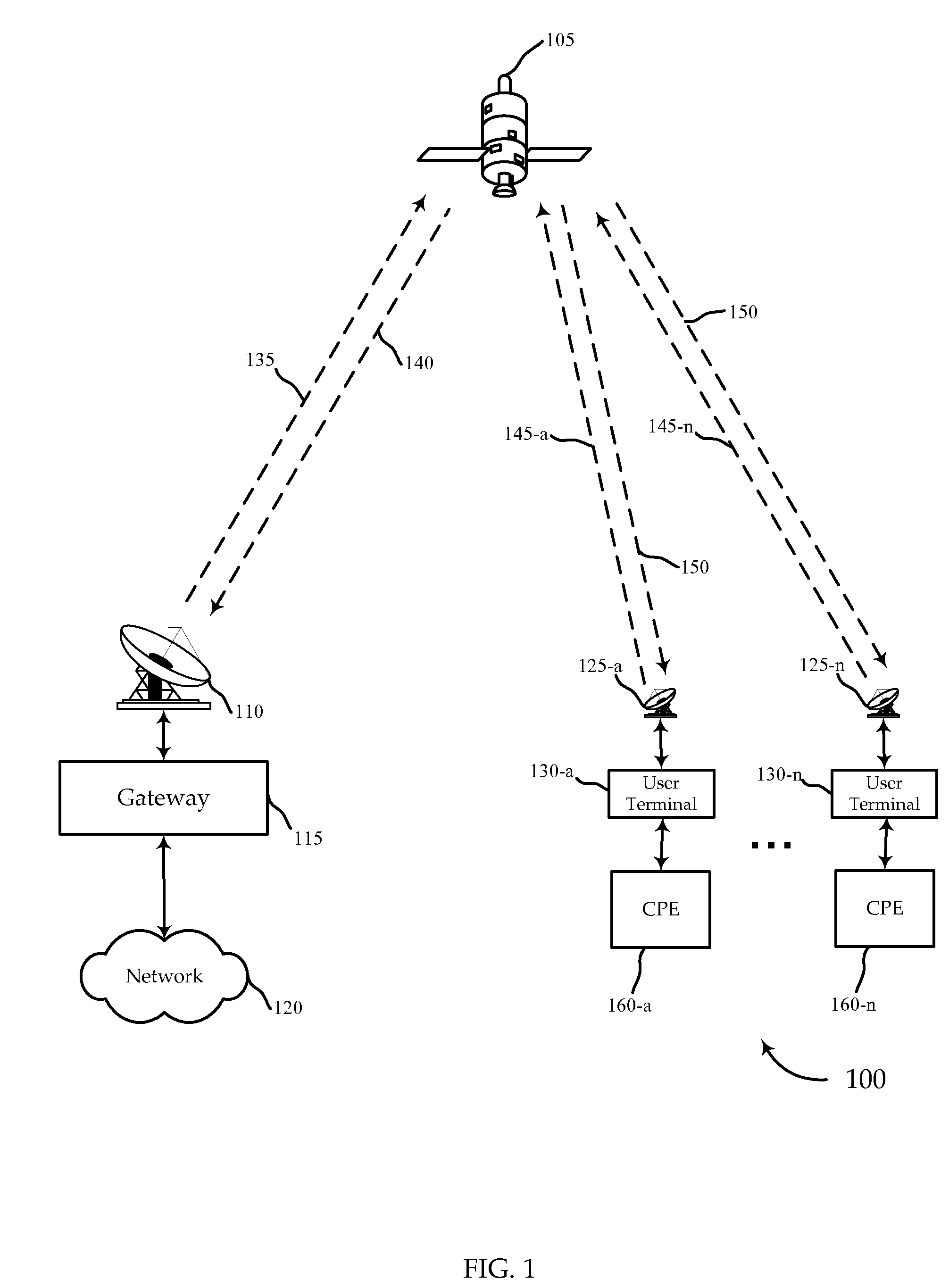

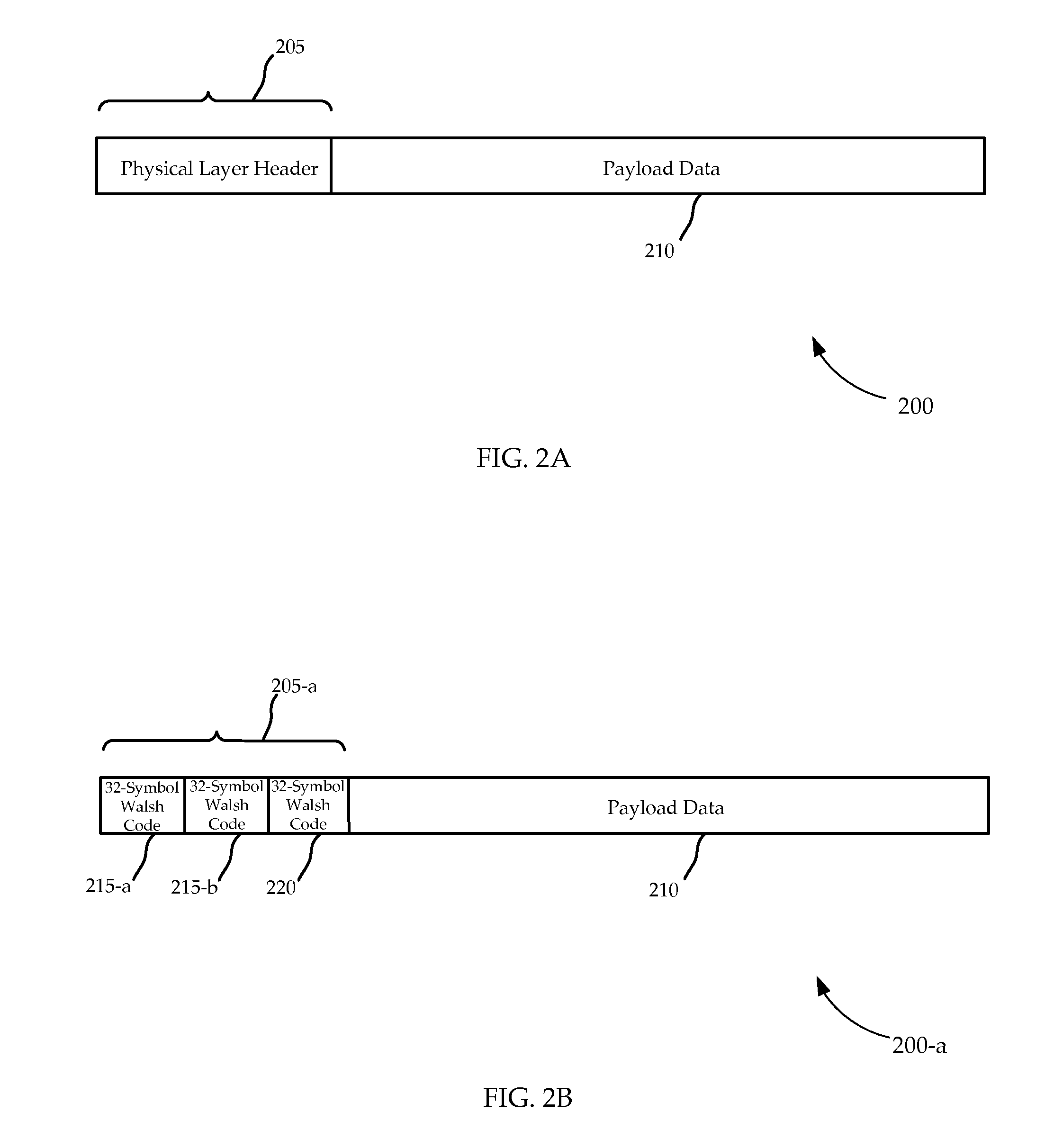

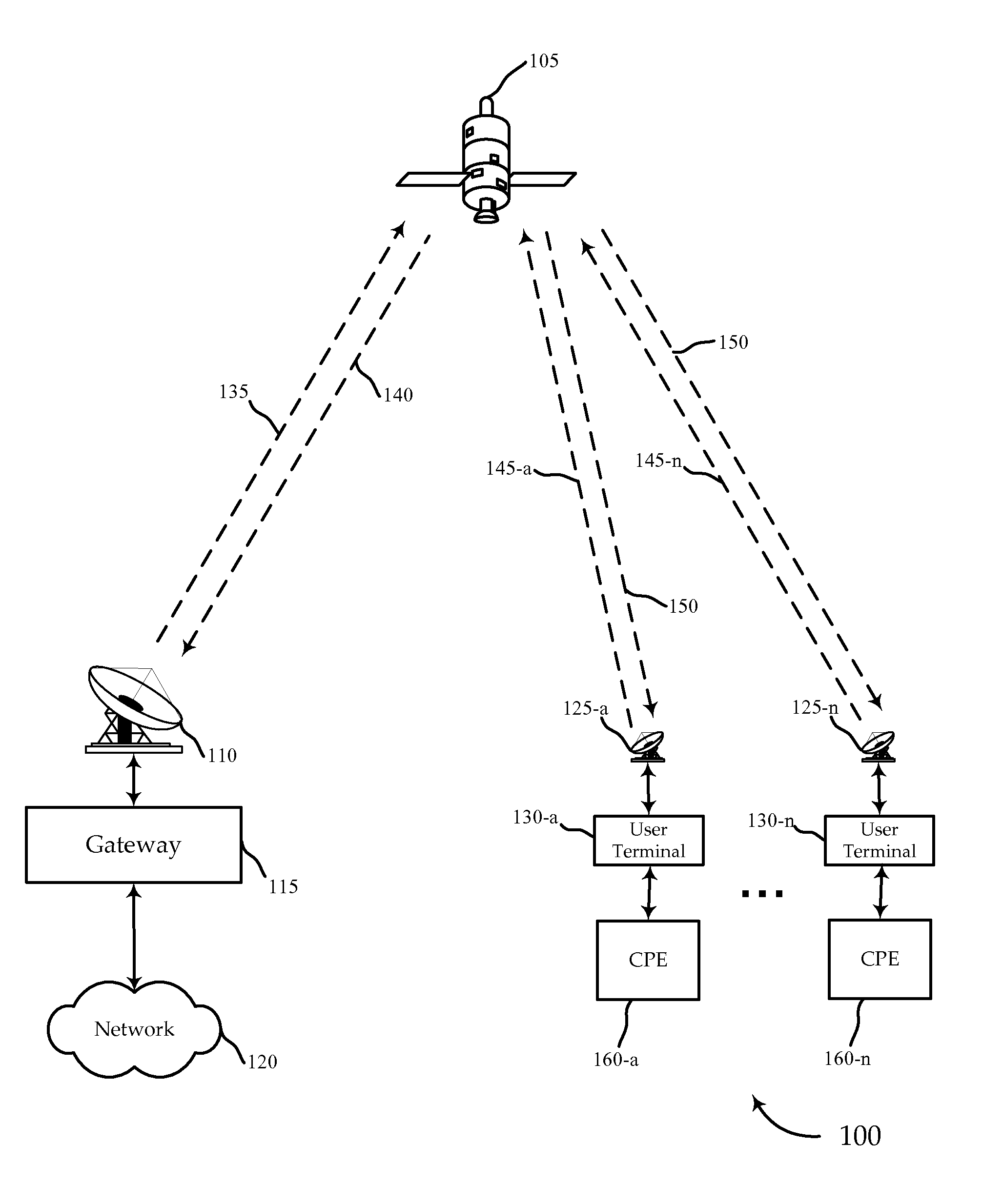

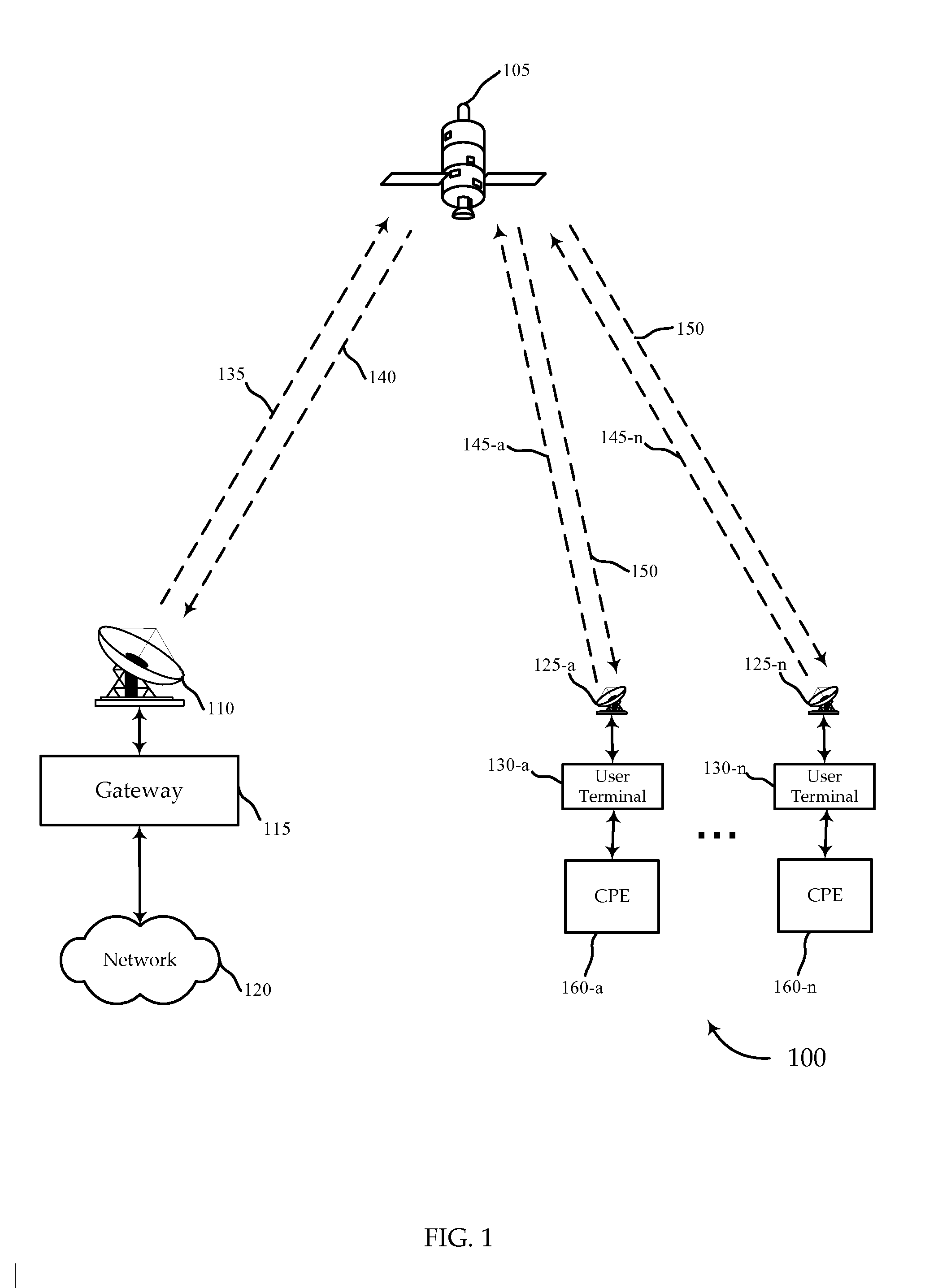

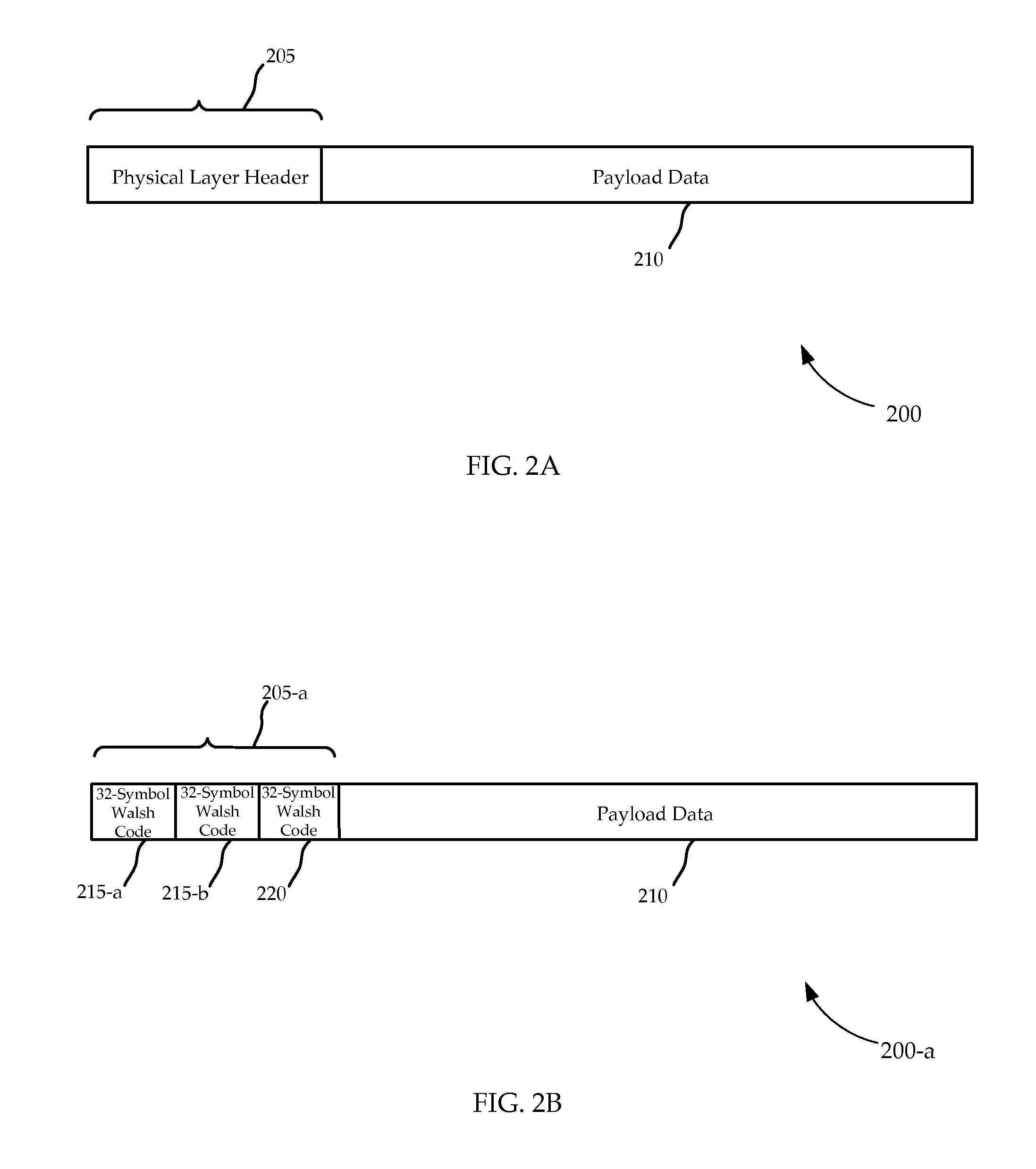

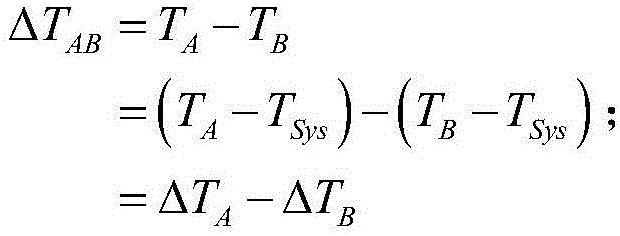

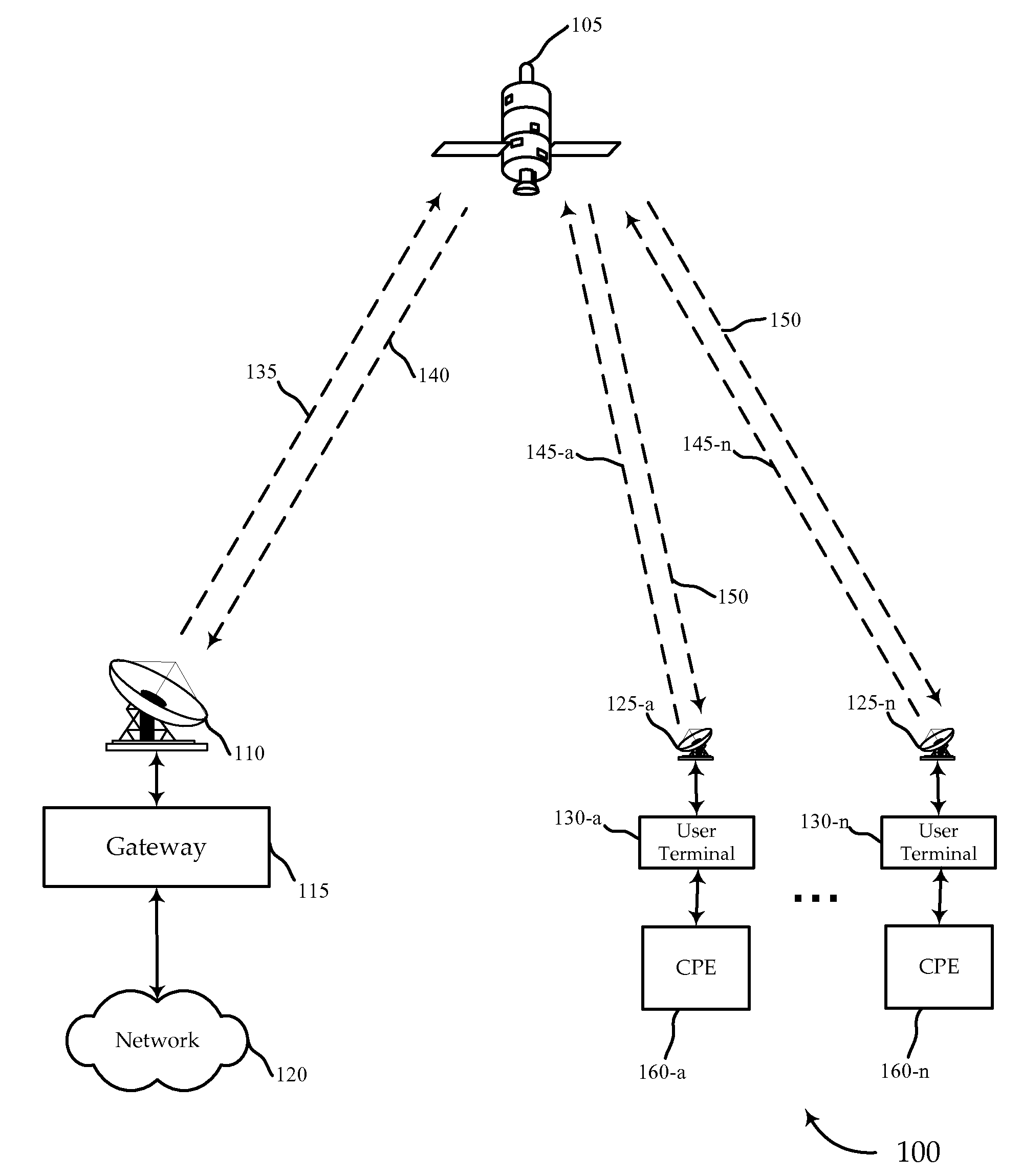

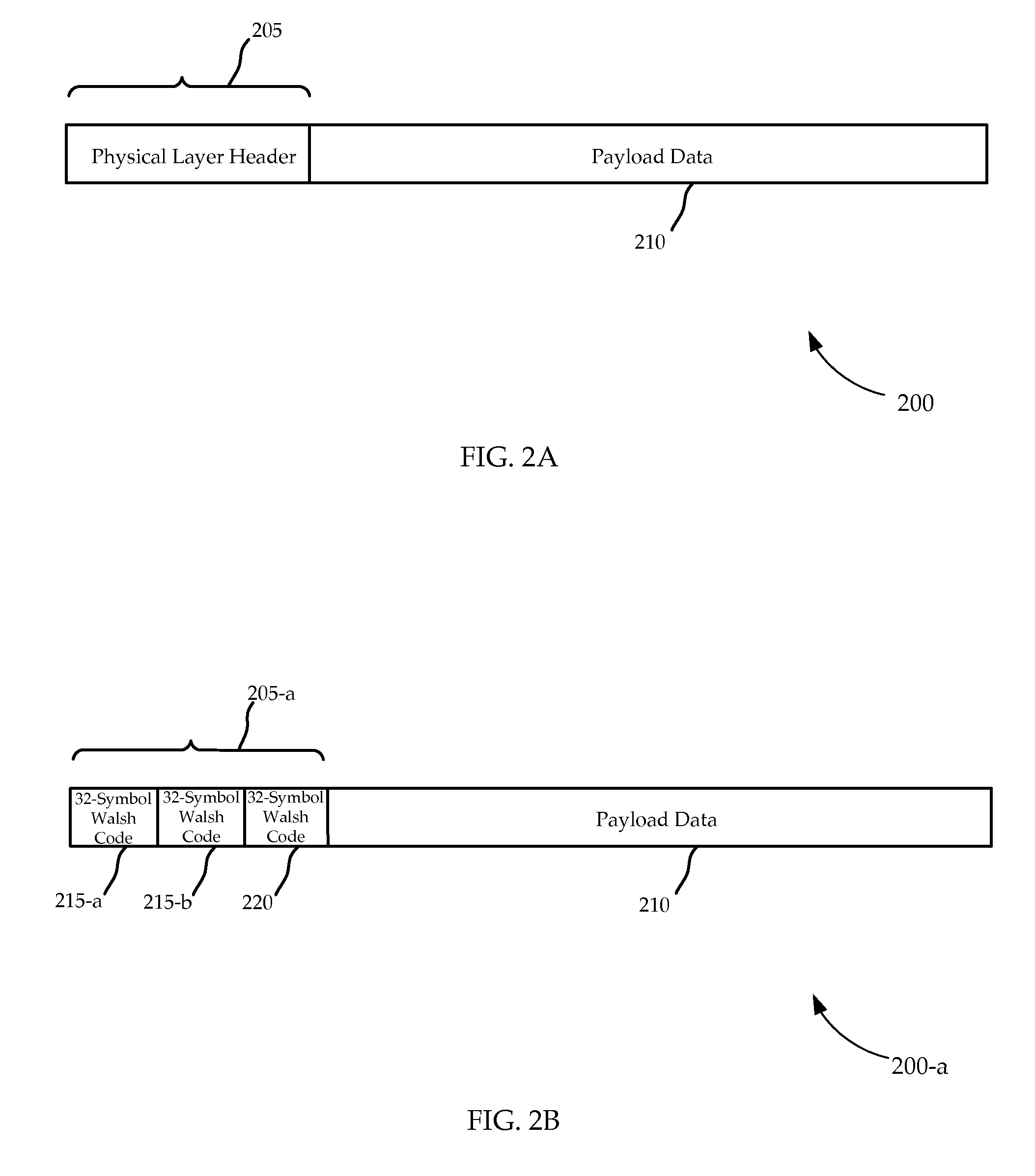

Start of frame correlation for physical layer header synchronization

ActiveUS20100150053A1Synchronisation error correctionTime-division multiplexComputer hardwarePhysical layer

Systems, devices, processors, and methods are described which may be used for the reception of a wireless broadband signal at a user terminal from a gateway via a satellite. A wireless signal may include a series of physical layer frames, each frame including a physical layer header and payload. The received signal is digitized and processed using various novel physical layer headers and related techniques to synchronize the physical layer frames and recover data from physical layer headers for purposes of demodulation and decoding.

Owner:VIASAT INC

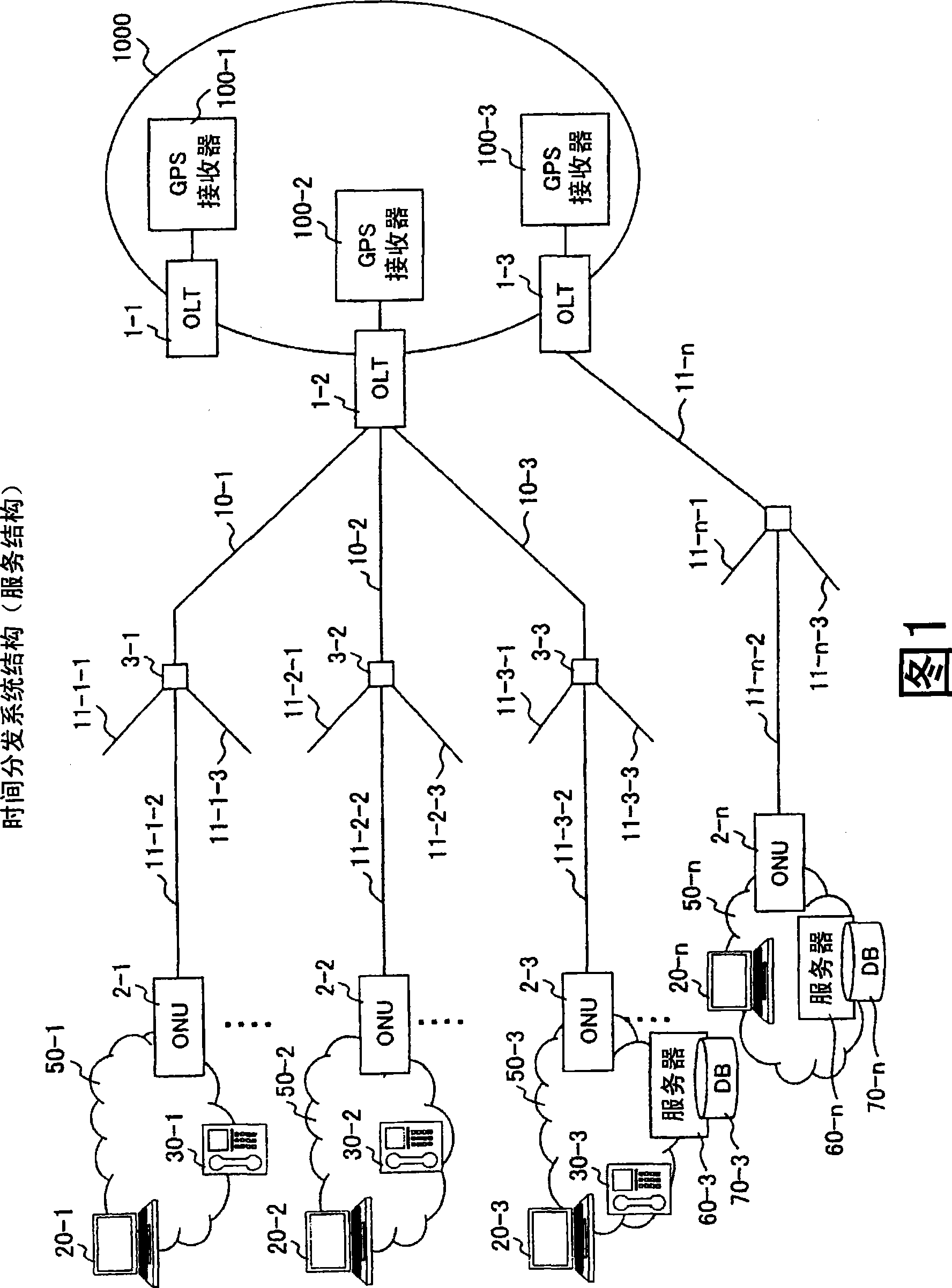

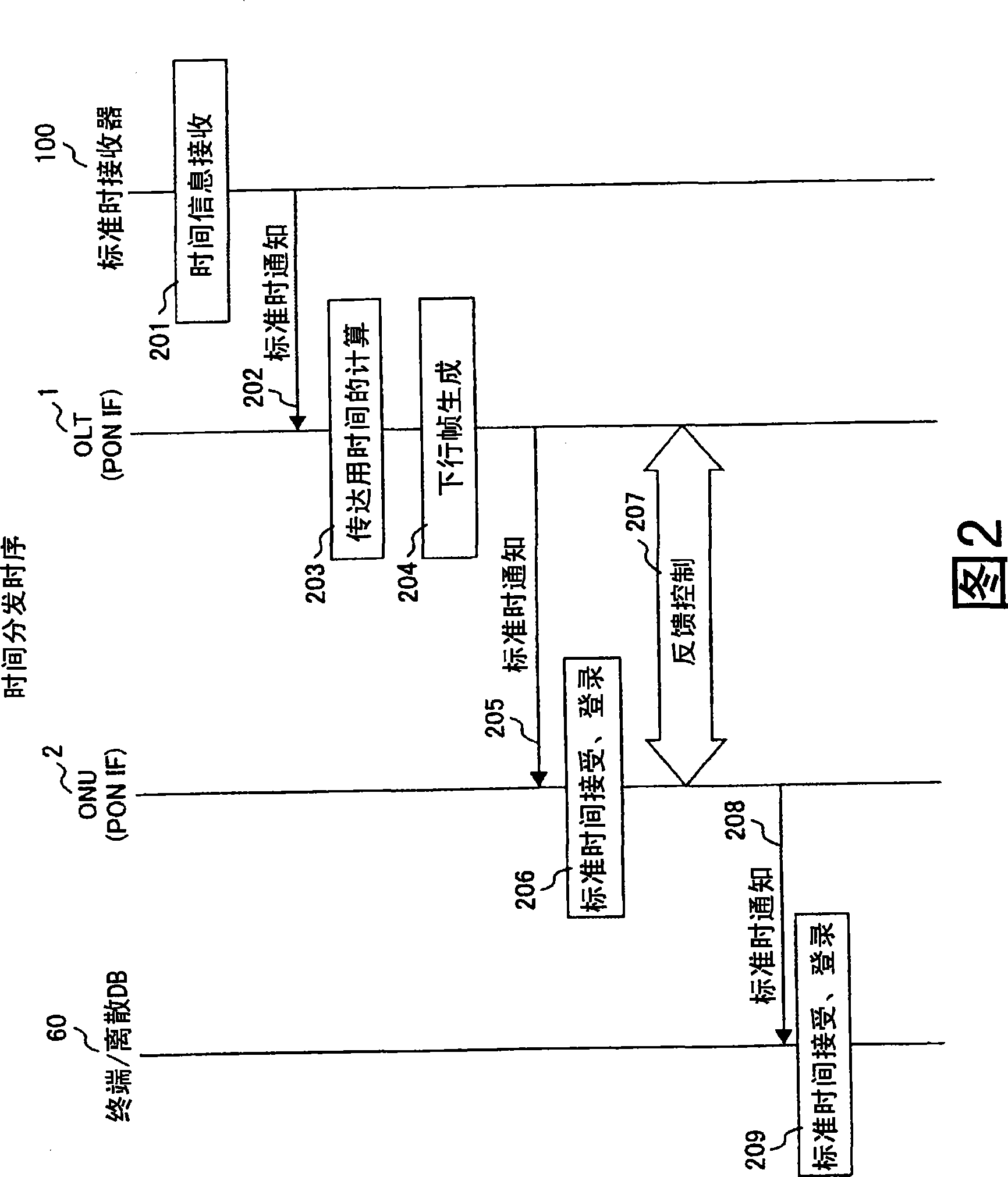

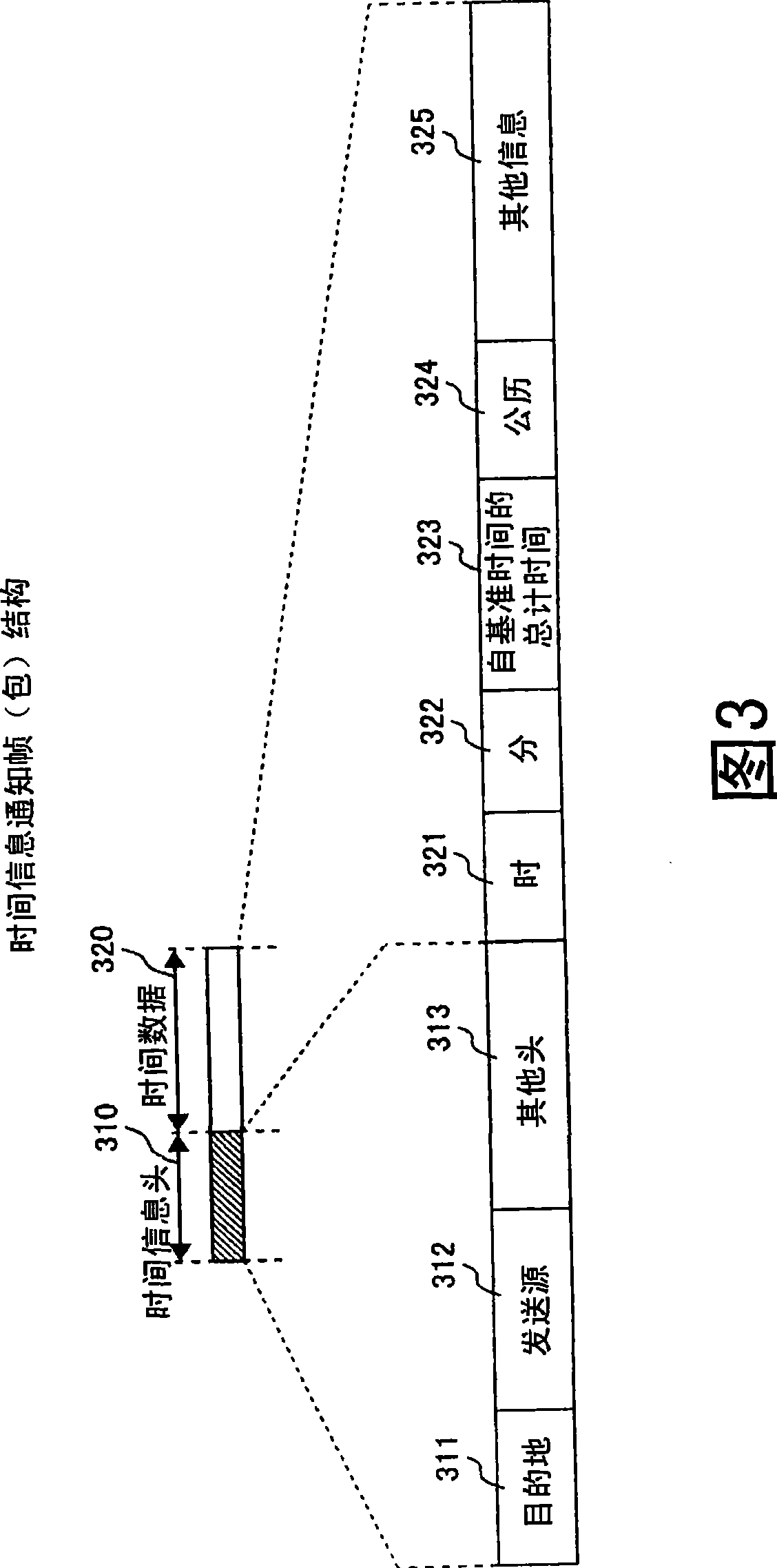

Communication system and its device

InactiveCN101383692ATime synchronizationGuaranteed correctnessMultiplex system selection arrangementsSynchronisation arrangementTime informationCommunications system

The invention provides a communicating system and device thereof, requiring high precision time synchronization of the terminating apparatus. The transmission device uses transmission delay time of reciprocation with the terminal and time information of the transmission device to create a correction value of time information of the terminal and transmits it to the terminal. The terminal includes expected arrival time information based on the time information of the terminal and the correction value received from the transmission device in a frame transmitted to the transmission device. The transmission device compares reception time of the frame with the expected arrival time information in the frame. If they match, the time information of the terminal synchronizes with the time information of the transmission device. If they do not match, the transmission device transmits a new correction value to the terminal. The terminal transmits a frame including expected arrival time information using the new correction value to the transmission device. By repeating such process, the time ofhte terminating apparatus is synchronized with the time of the transmission device.

Owner:HITACHI LTD

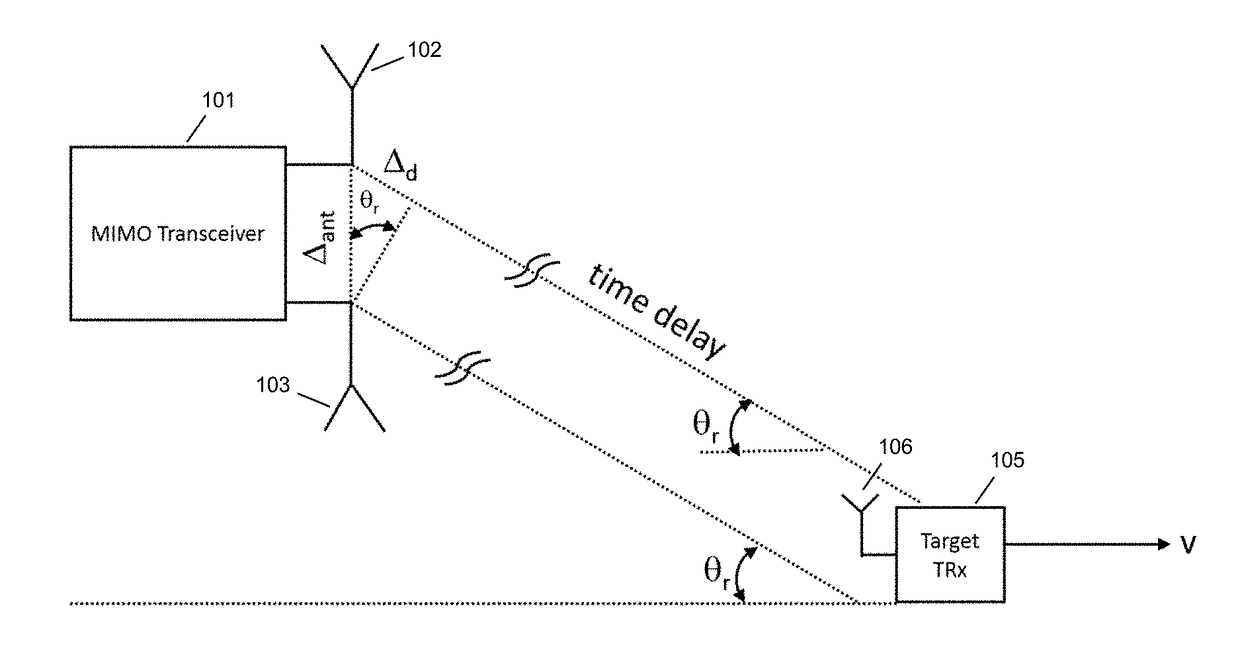

Angle of Arrival Measurements Using RF Carrier Synchronization and Phase Alignment Methods

ActiveUS20170227623A1Synchronisation arrangementRadio wave direction/deviation determination systemsLocal oscillatorQuadrature signal

A method for determining an angle of arrival (AOA) of a received signal is disclosed, comprising: generating a baseband information signal by mixing a received signal with a local oscillator (LO) signal, the received signal being an in-phase signal and quadrature signal uncorrelated with each other and derived from different input data sets; obtaining baseband signal samples of the baseband information signal having an in-phase signal sample and a quadrature signal sample; determining a transmitter phase offset based on an estimated correlation between the in-phase signal samples and the quadrature signal samples; performing a plurality of phase measurements using a plurality of antennas to obtain a plurality of phase measurements; correcting the plurality of phase measurements based on the transmitter phase offset to produce a plurality of corrected phase measurement; and calculating an AOA of the received signal based on the difference between the plurality of corrected phase measurements.

Owner:PHASORLAB

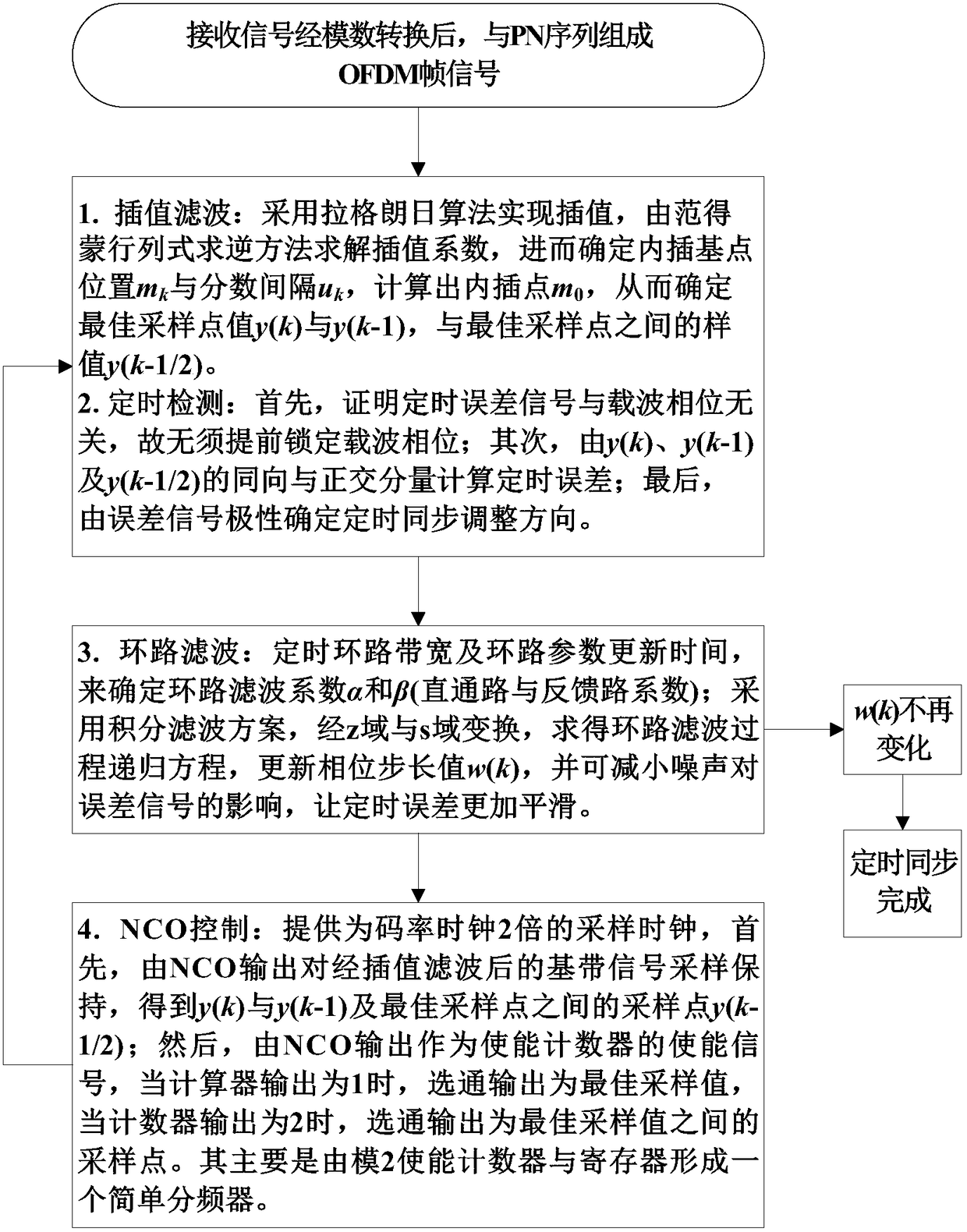

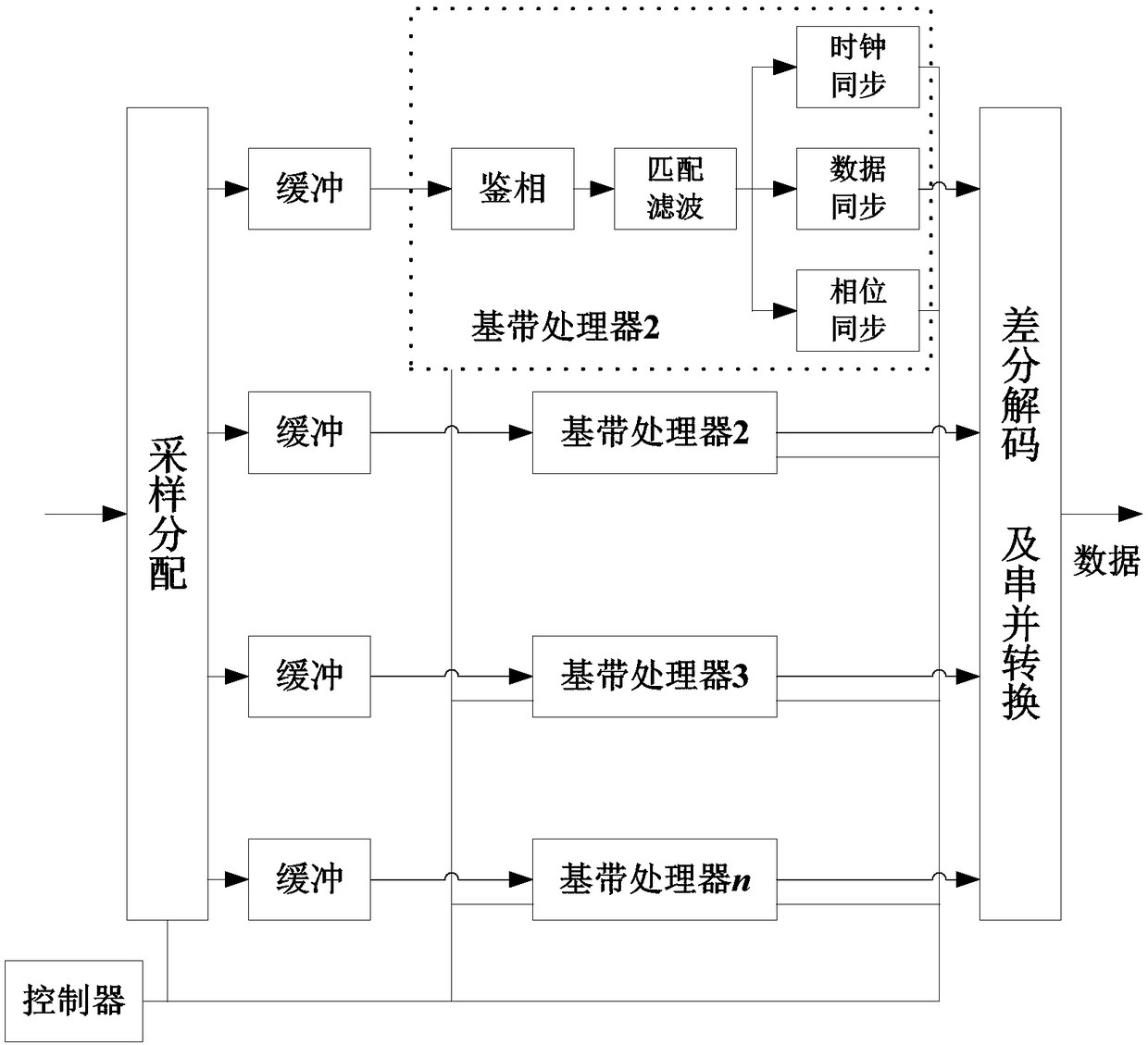

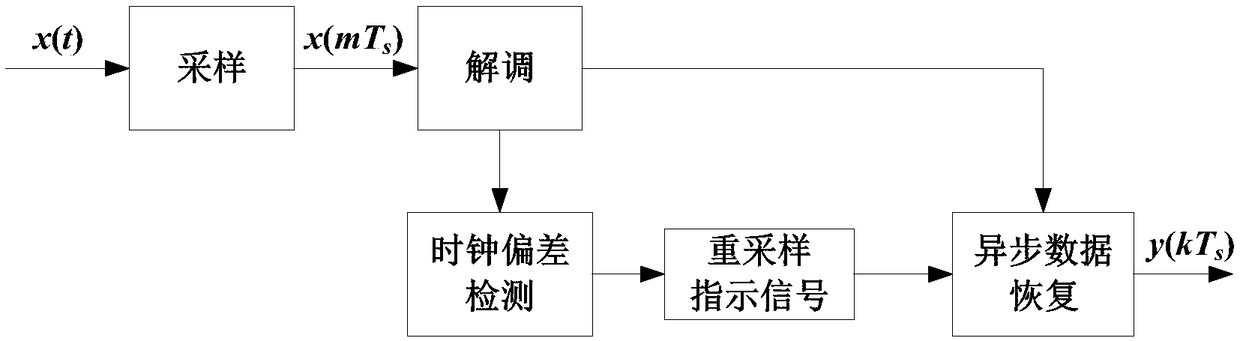

Parallel timing synchronization method based on precise loop filtering

ActiveCN108471347AObvious complicationsSynchronisation error correctionMulti-frequency code systemsLoop filterSignal-to-noise ratio (imaging)

The invention discloses a parallel timing synchronization method based on precise loop filtering. The method is executed according to the following steps: 1, a parallel processing timing synchronization interpolation step; 2, a parallel processing timing error detection step; 3, a parallel processing loop filtering step; and 4, a parallel processing interpolation control step. The scheme of the invention has the advantages of fast synchronization speed and good performance, and is widely applied to the fields of digital communication such as ground wireless emergency communication, satellitesand power line communication suitable for low signal-to-noise-ratio transmission.

Owner:HANGZHOU DIANZI UNIV

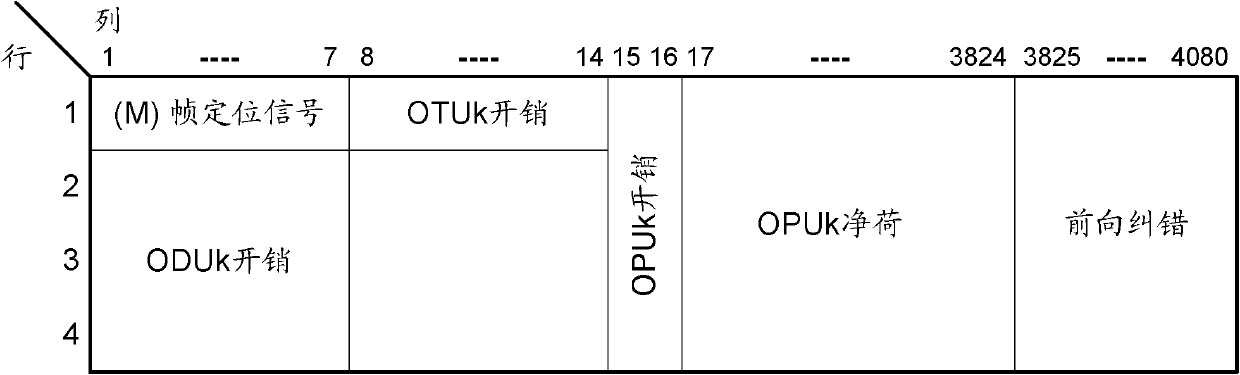

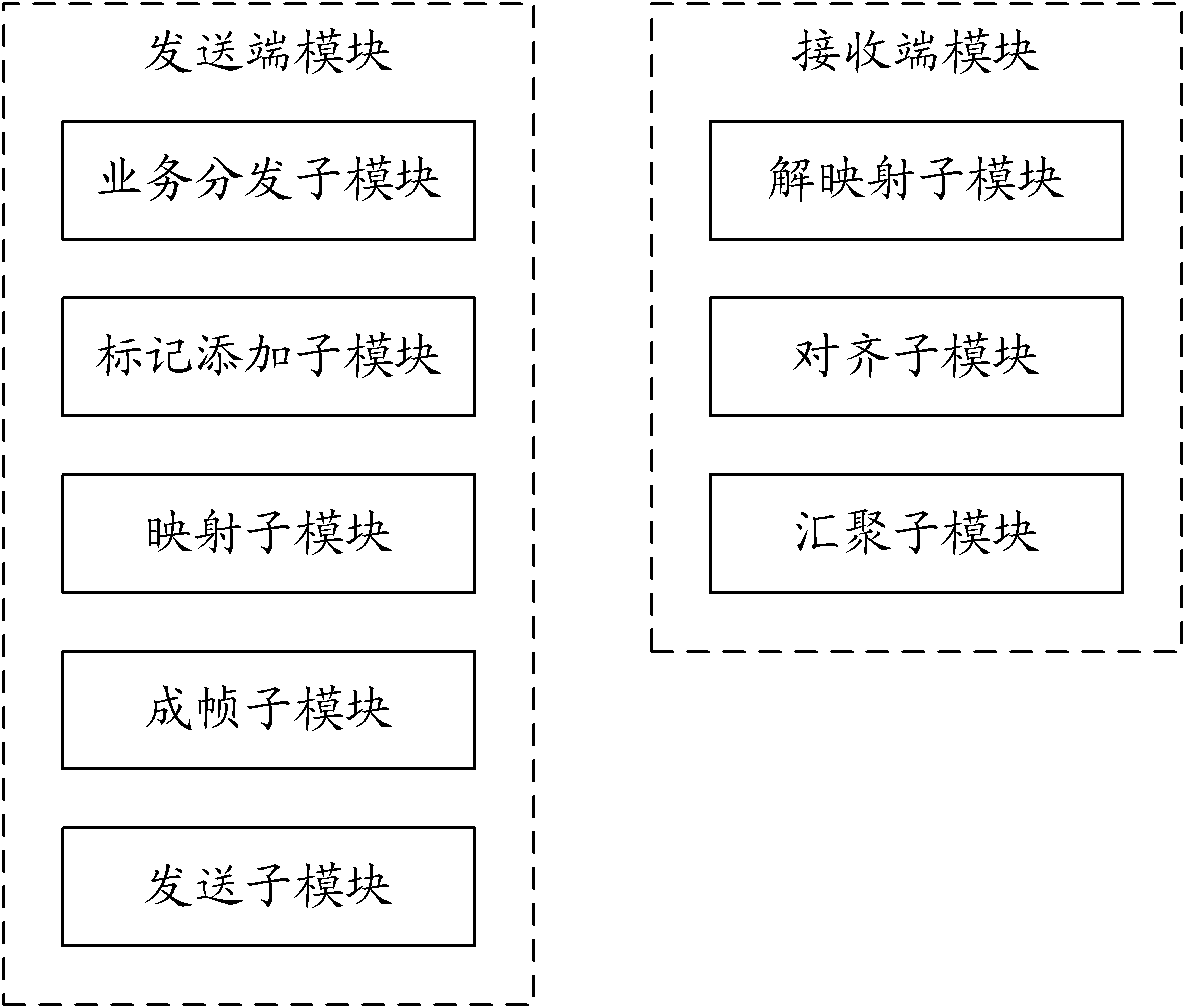

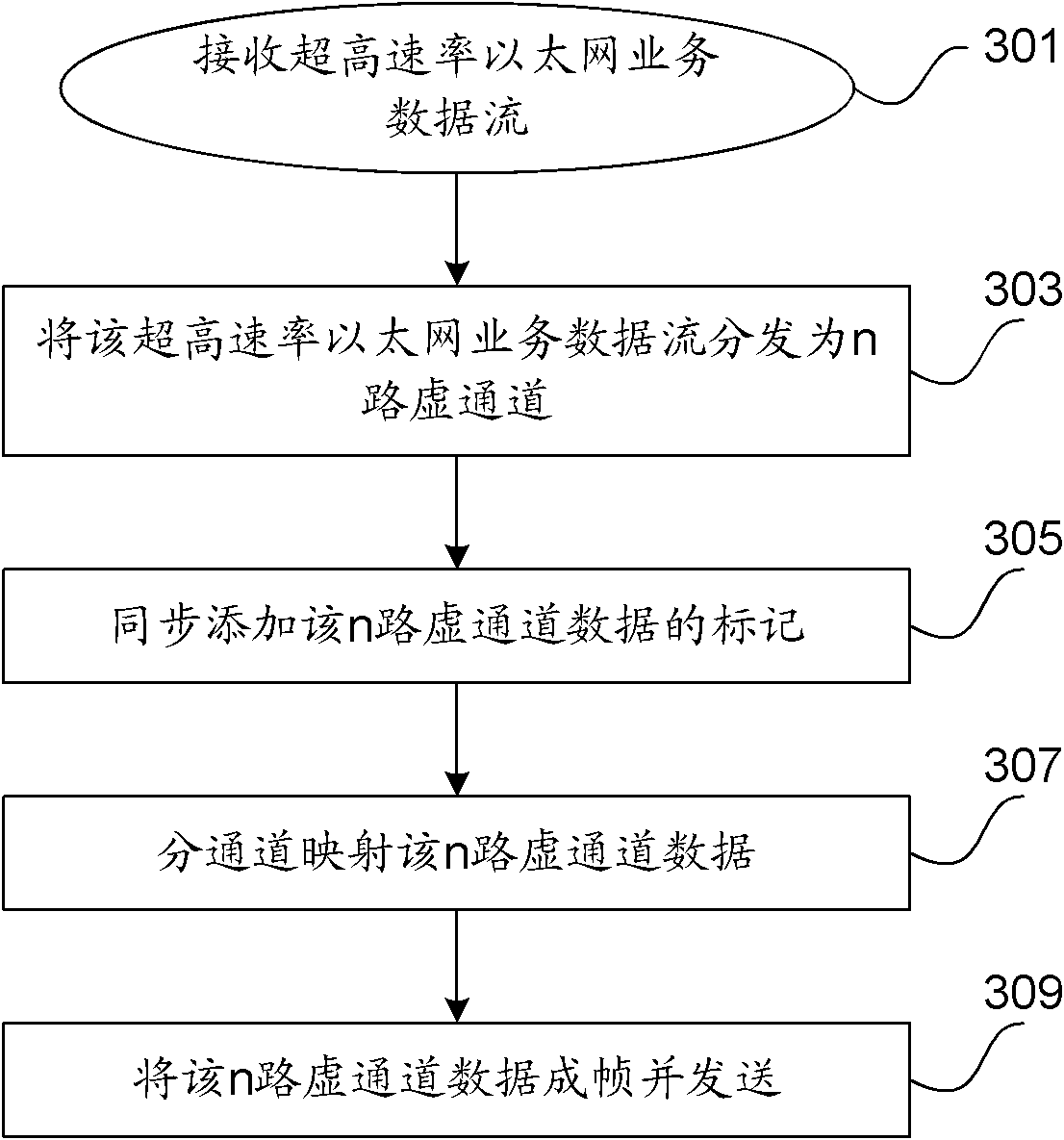

Method and device for transmitting ultra high-speed Ethernet service

ActiveCN102439995AReduce complexityReduce the difficulty of implementationMultiplex system selection arrangementsSynchronisation error correctionUltra high speedData stream

The invention discloses a method and a device for transmitting an ultra high-speed ethernet service. The method comprises the steps of distributing an ultra high-speed ethernet service data stream into a plurality of virtual channels; wherein, the speed of the ultra high-speed ethernet service data stream is greater than 100 GB; synchronously adding the marks of the plurality of virtual channels; branching channels to map the data of the plurality of virtual channels; and combining the data of the plurality of virtual channels and transmitting. The method employs a channeled transmission mode to transmit the ultra high-speed ethernet service transparently, and the ultra high-speed ethernet service is mapped to reduce the complexity of the ultra high-speed ethernet service into a low-speed ethernet service processing level, so that the realization difficulty is reduced.

Owner:HUAWEI TECH CO LTD

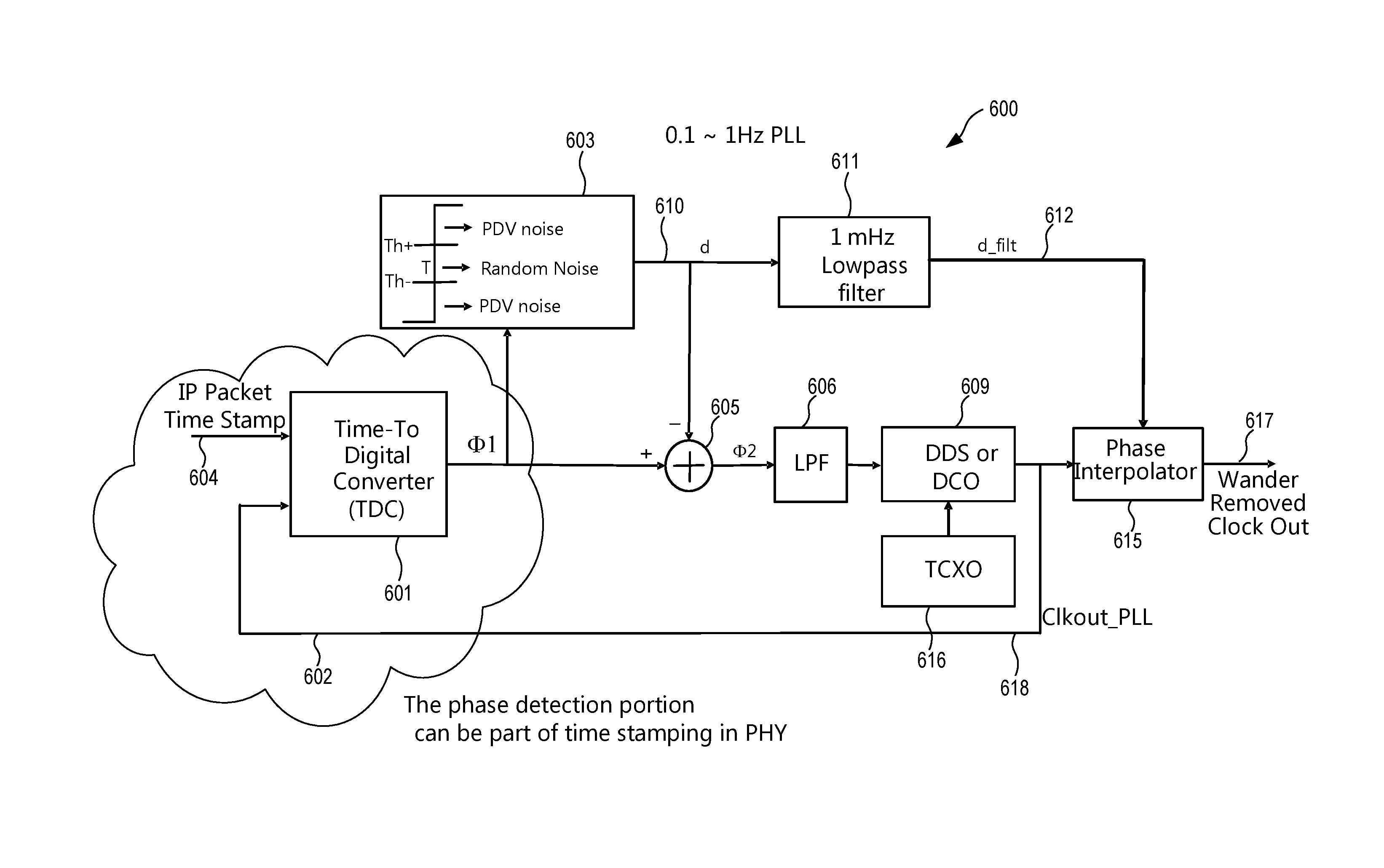

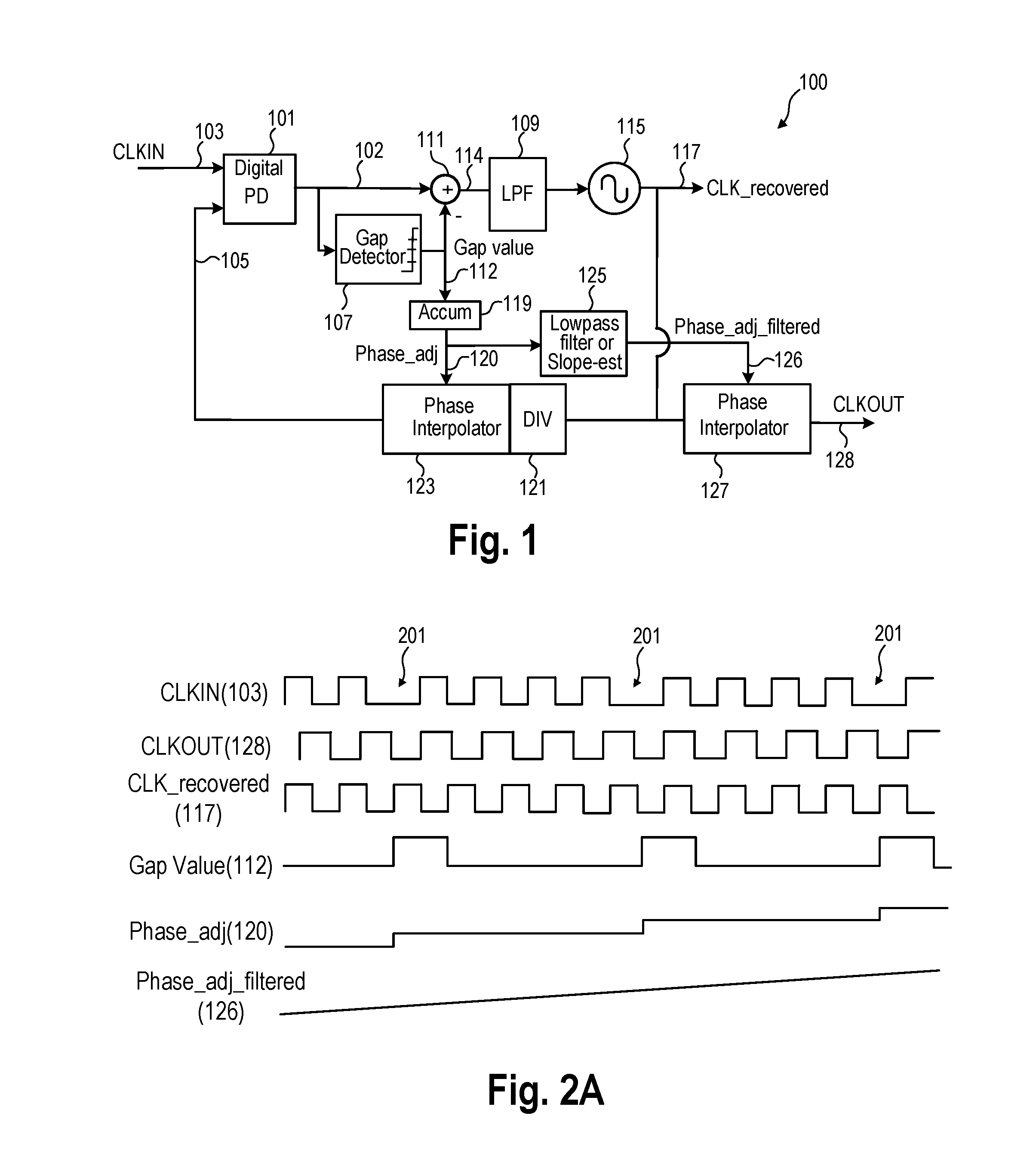

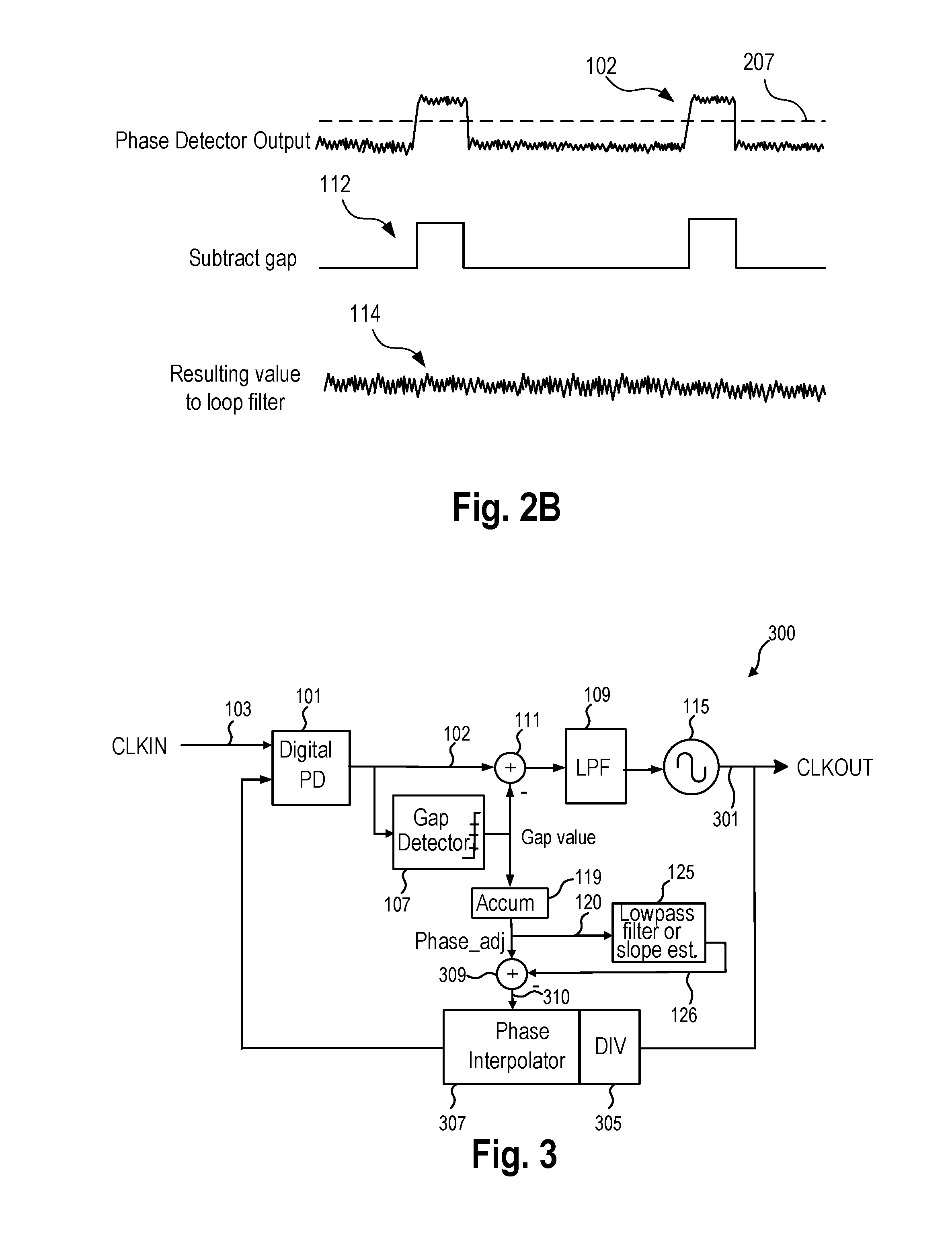

Dual path timing wander removal

ActiveUS20160352506A1Reduce wanderingSynchronisation error correctionModulated-carrier systemsLoop filterLow-pass filter

A more cost effective wander jitter filter utilizes an excursion detector that receives a timing difference between a first signal and a second signal and supplies a first adjustment amount if a magnitude of the timing difference is above a predetermined threshold and otherwise supplies a second adjustment amount of zero. A summing circuit adjusts a magnitude of the timing difference by the first or second adjustment amount. A loop filter receives the summing circuit output and controls an oscillator. The excursion detector output (first adjustment value or zero according to the magnitude of the timing difference) is low pass filtered and the low pass filtered is reintroduced into the oscillator output or the feedback loop. The excursion detector output is accumulated and used to adjust a phase of the feedback signal from the oscillator.

Owner:SKYWORKS SOLUTIONS INC

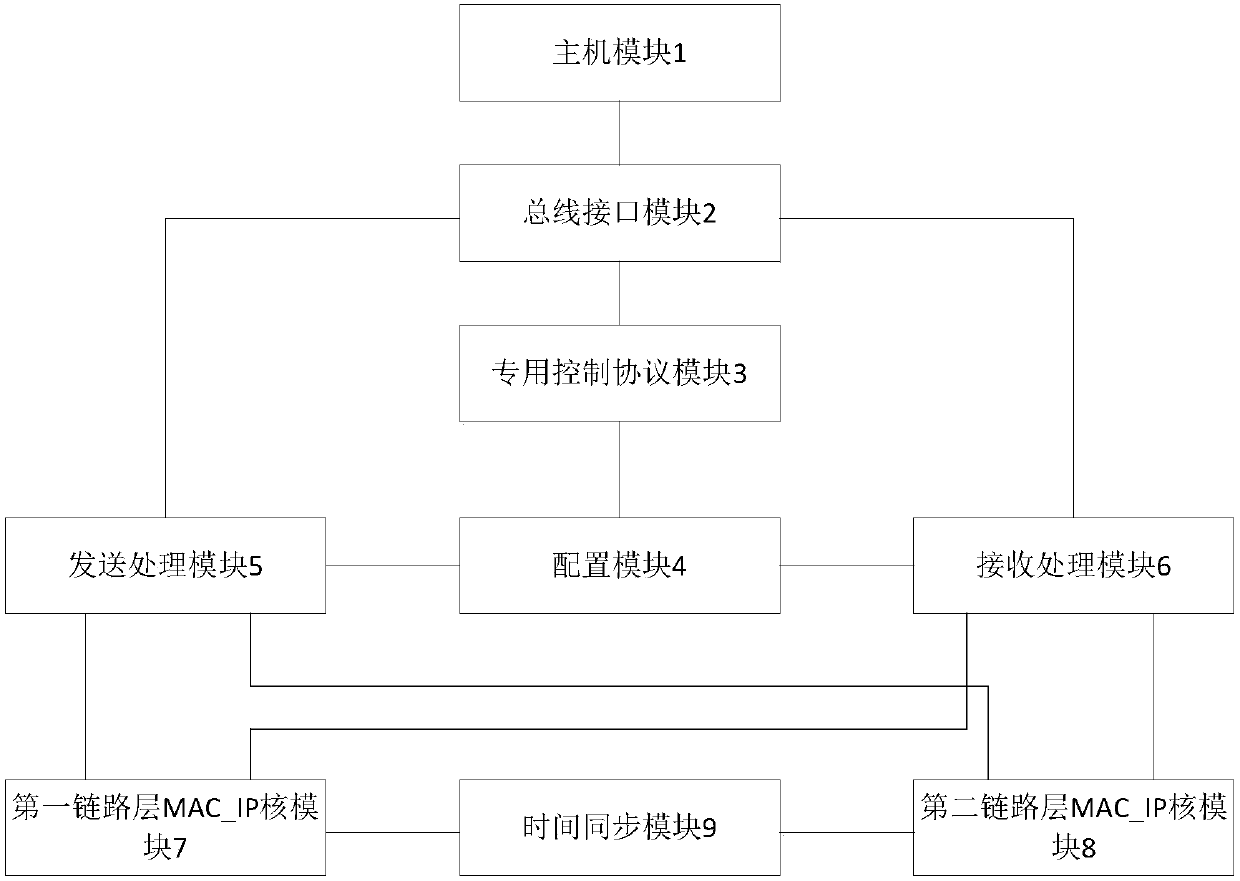

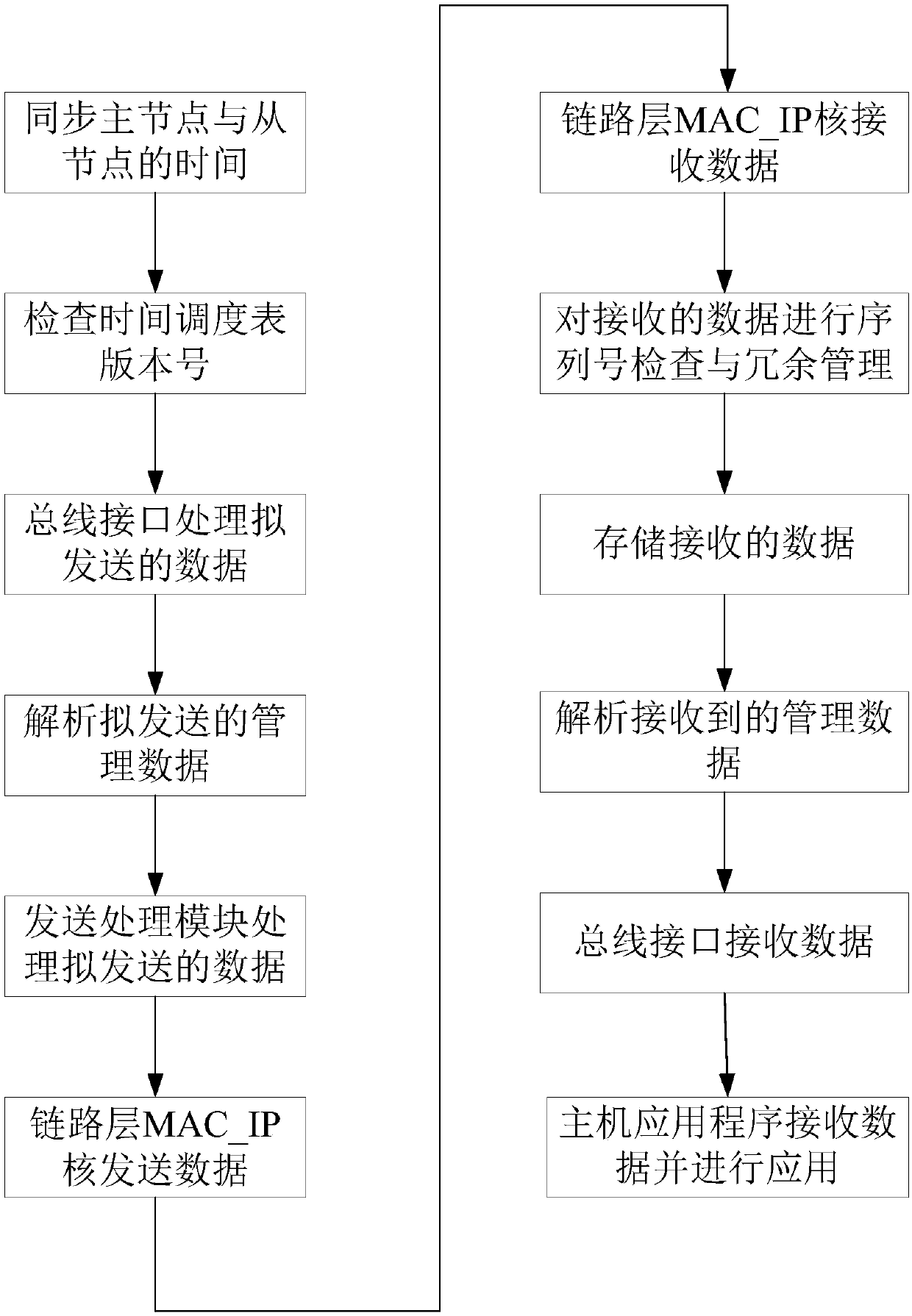

Device and method for implementing time-triggered Ethernet end system

ActiveCN107819539AGuaranteed reliabilityImprove robustnessSynchronisation error correctionTime-division multiplexProtocol processingEnd system

The invention discloses a device and method for implementing a time-triggered Ethernet end system. Based on the Ethernet technology, the time-triggered Ethernet end system capable of transmitting time-triggered data and event-triggered data is implemented by increasing the functions of time synchronization and time trigger. A special protocol processing module of the device can process managementdata more conveniently; and a transmission processing module of the device can guarantee the reliability and the robustness of a network in the data transmission process. By adopting a precise clock synchronization protocol IEEE 1588, the method provided by the invention reduces the difficulty of implementing time synchronization on hardware, and has higher time synchronization stability and synchronization accuracy.

Owner:XIDIAN UNIV

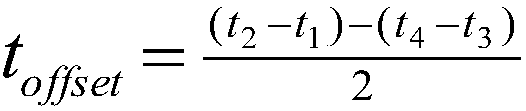

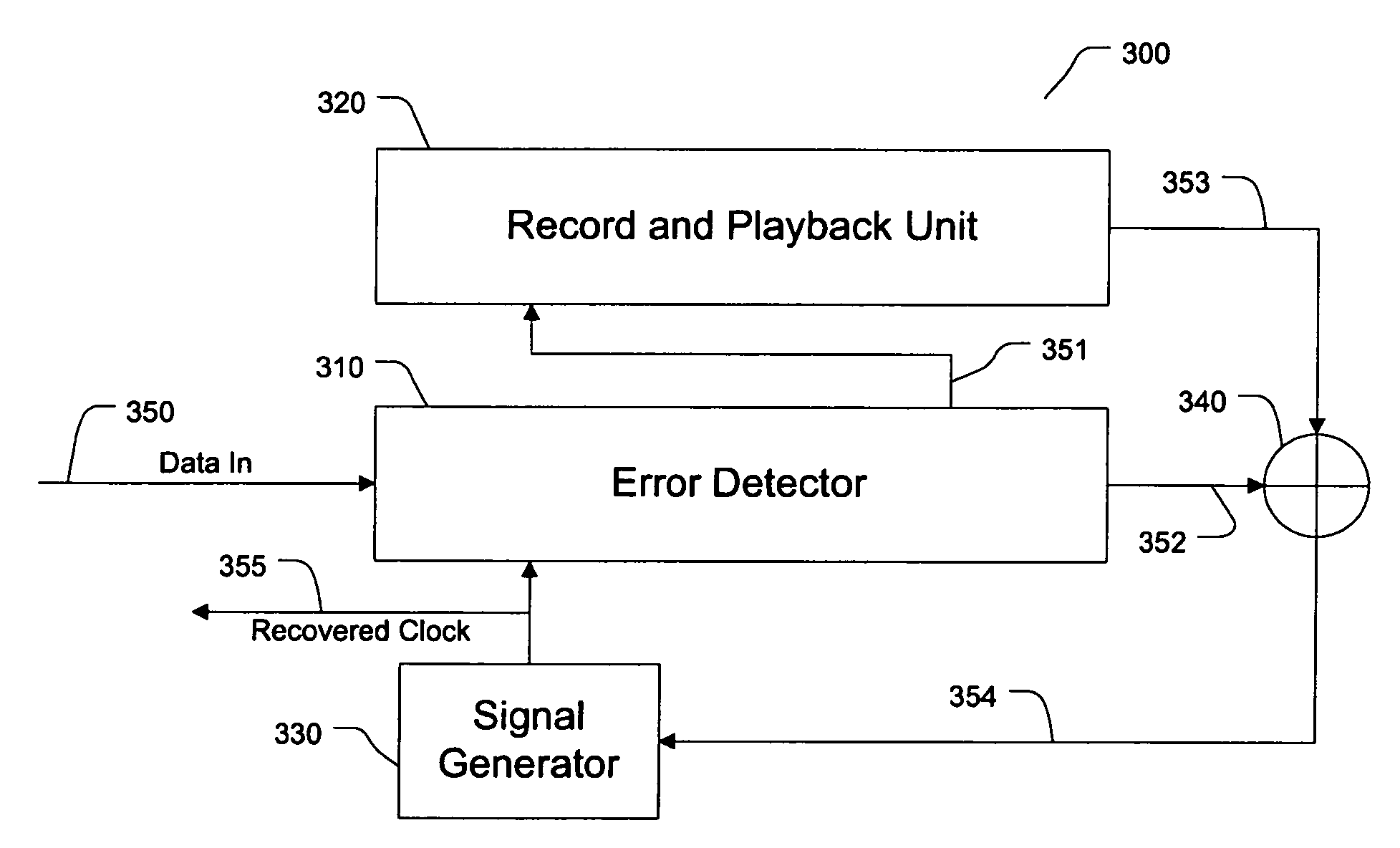

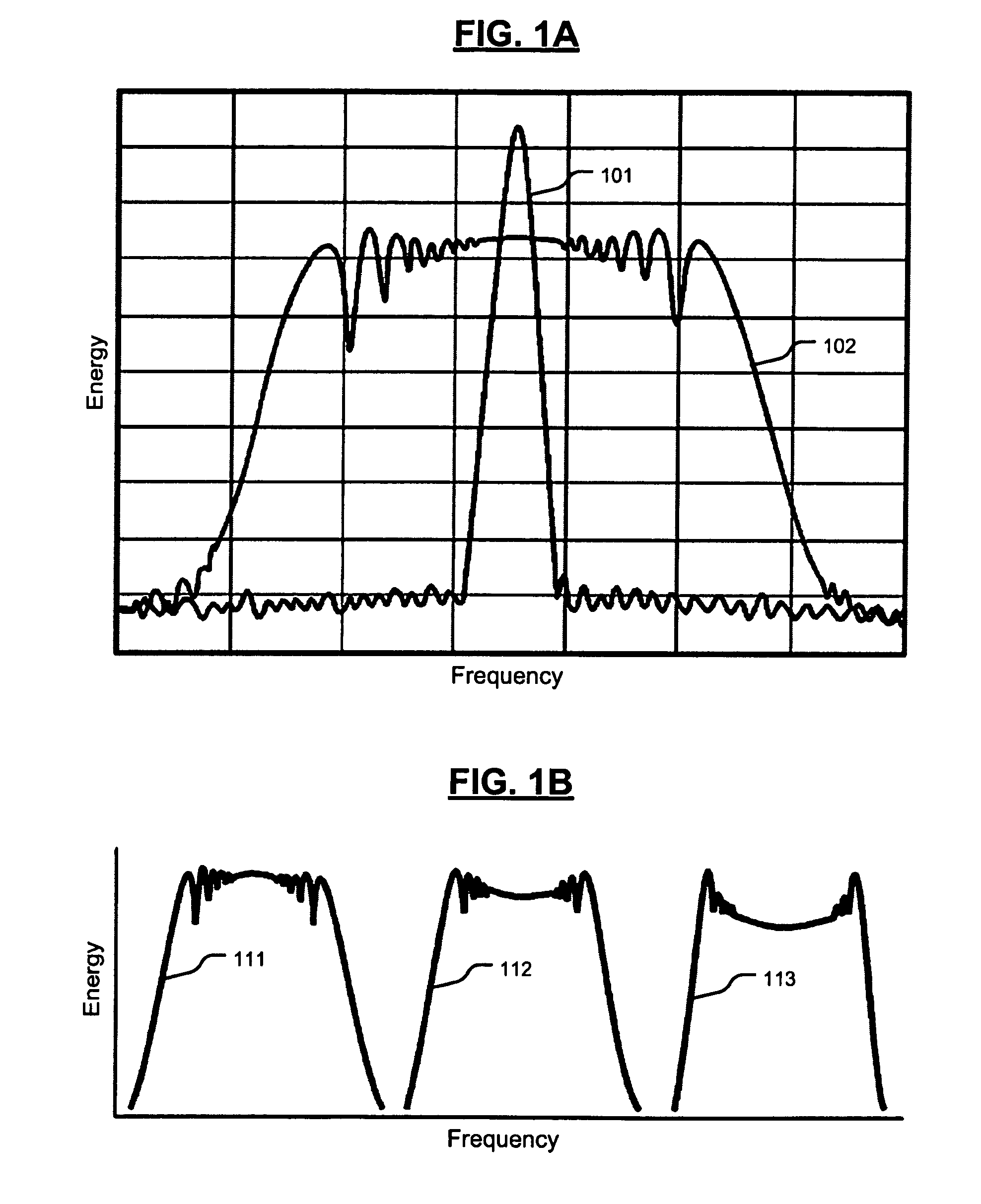

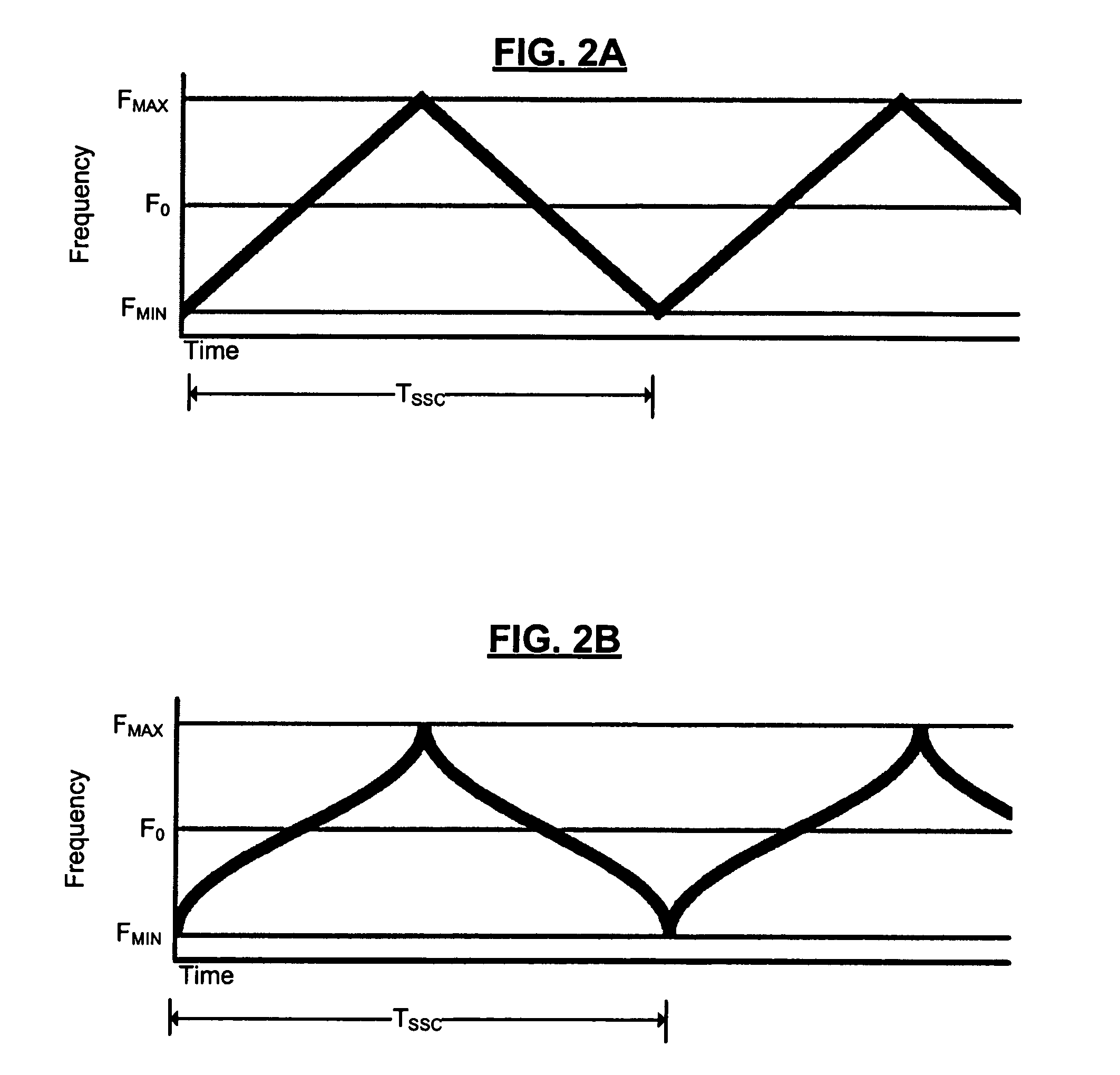

Circuits, methods, apparatus, and systems for recovery of spread spectrum clock

ActiveUS7742556B1Improve noise immunityAccurate trackingSynchronisation error correctionPulse automatic controlDetector circuitsPhase difference

Circuits, methods, apparatus, and systems for recovering a clock from a spread spectrum signal having a periodic modulation profile. The circuits generally include an error detector circuit configured to compare the spread spectrum signal and a recovered clock signal, and to produce a first error signal corresponding to the periodic modulation profile and a second error signal corresponding to phase differences other than the spread spectrum modulation, a record and playback unit configured to record a value to a frequency memory, said value based on the first error signal and produce a third error signal corresponding to a predicted periodic modulation based at least in part on the recorded value, and a signal generator configured to produce the recovered clock signal in response to the second and third error signals.

Owner:MARVELL ASIA PTE LTD

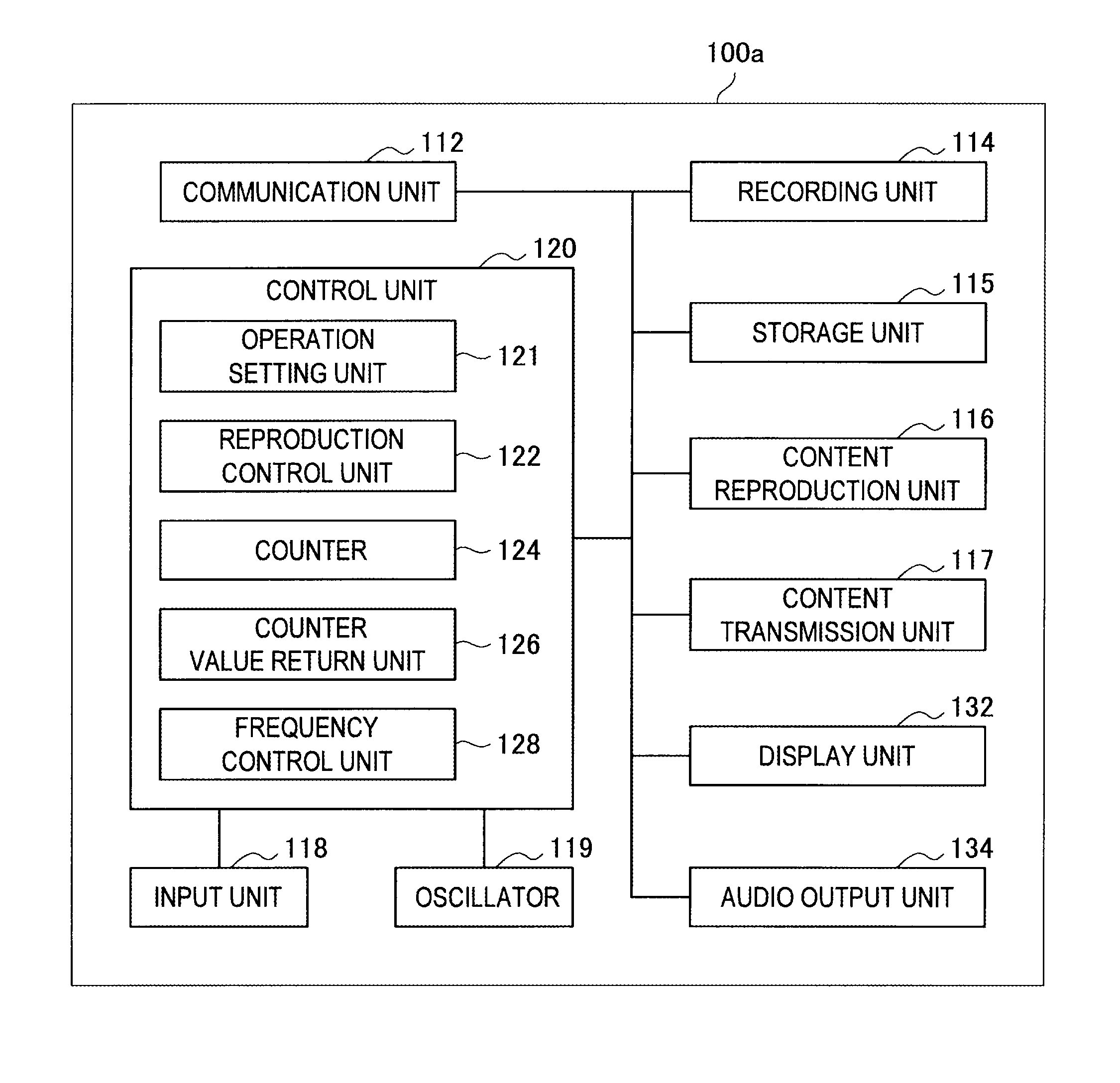

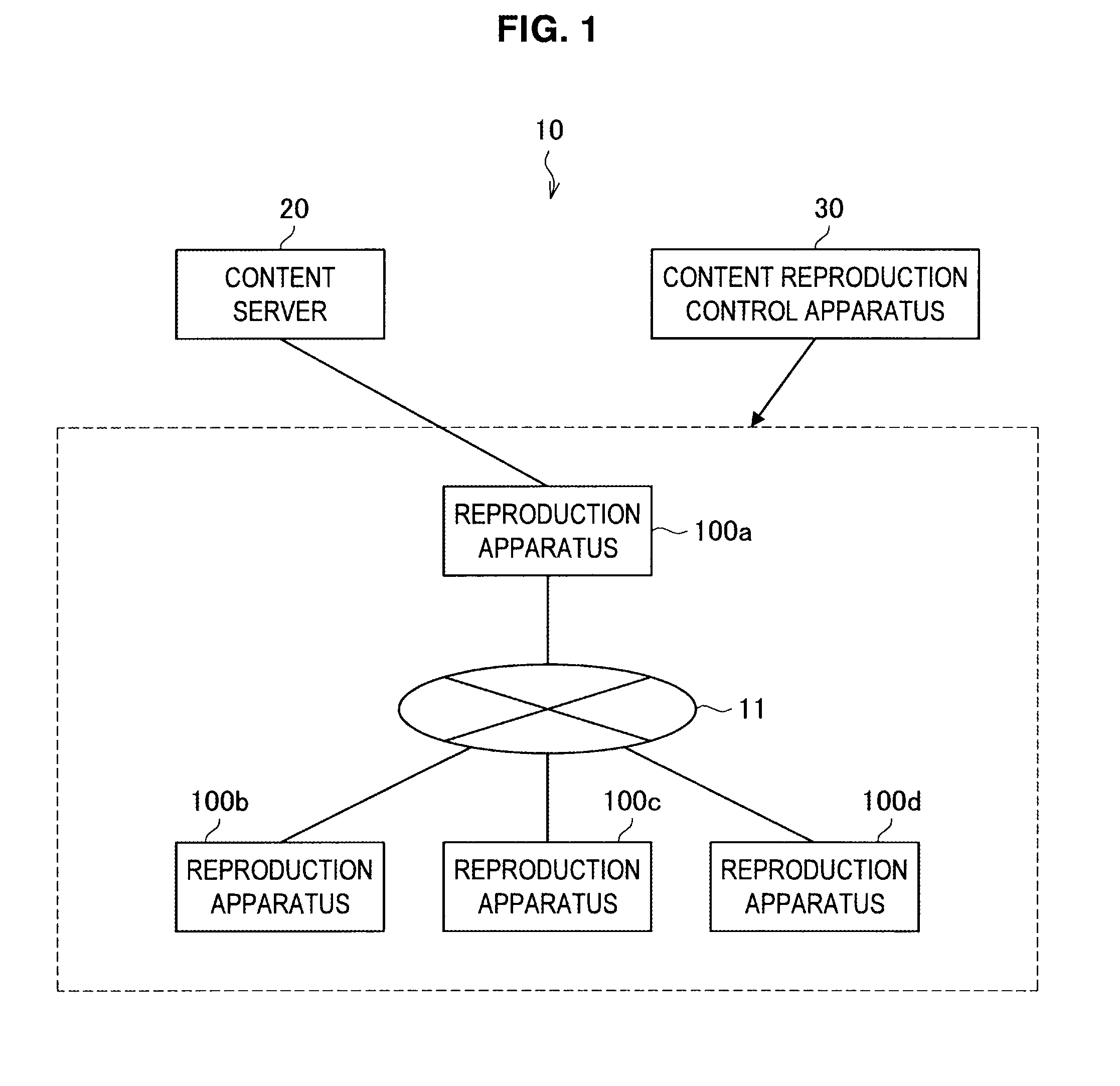

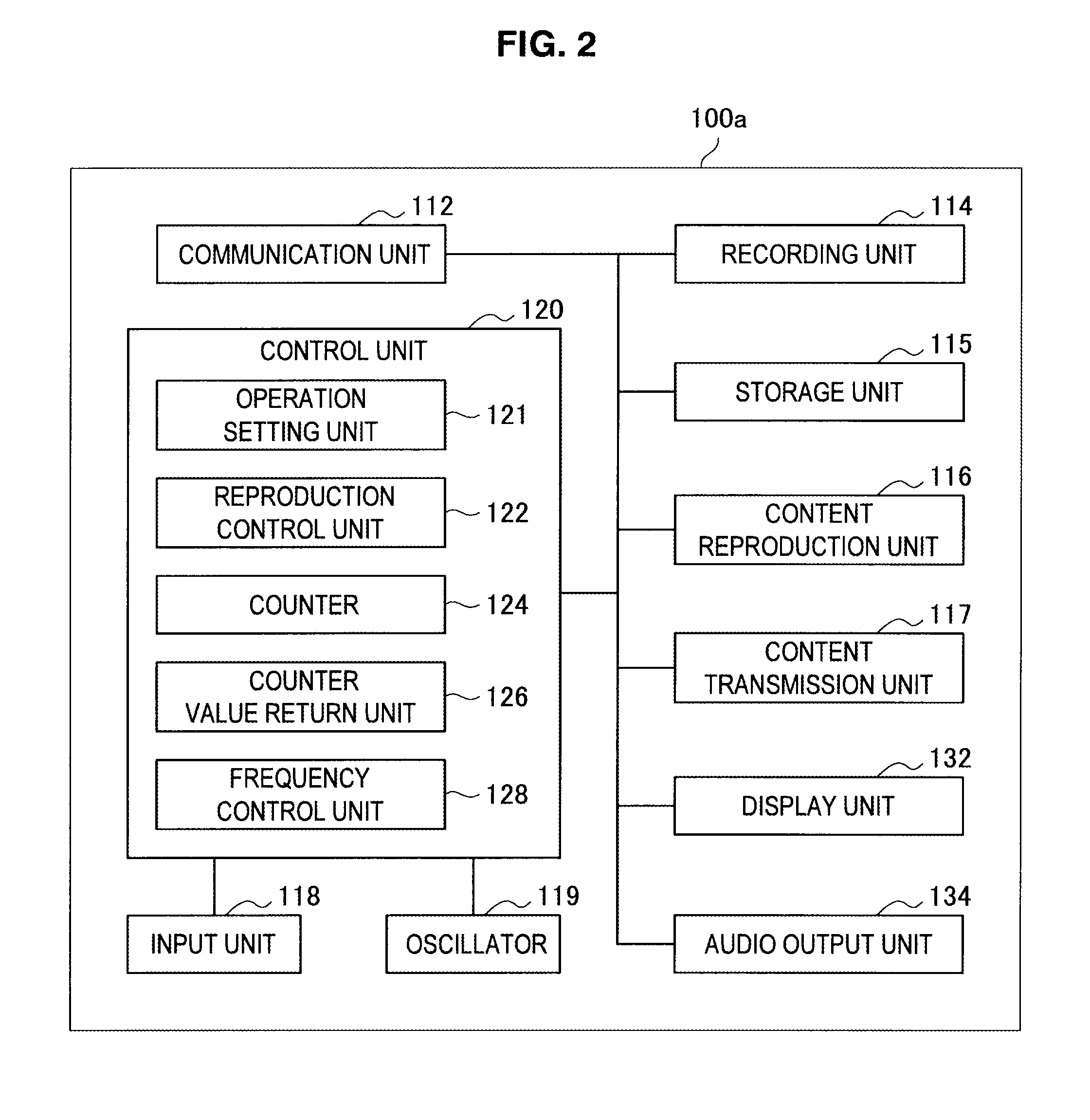

Information processing apparatus, synchronization correction method and computer program

ActiveUS20100318860A1Increase the number ofTelevision system detailsSynchronisation error correctionInformation processingComputer hardware

An information processing apparatus is provided which includes a transmission unit for transmitting a query request for querying another device for a count value held by such other device, a reception unit for receiving a return of the count value from such other device, a correction unit for performing, at a predetermined period, correction processing for synchronizing sampling frequency with such other device based on the received count value, and a reproduction unit for reproducing content in synchronization with such other device based on the sampling frequency. The correction unit corrects by taking into account a Round Trip Time between the transmission of the query request and the reception of the return and residual difference occurred at a previous correction time.

Owner:SONY CORP

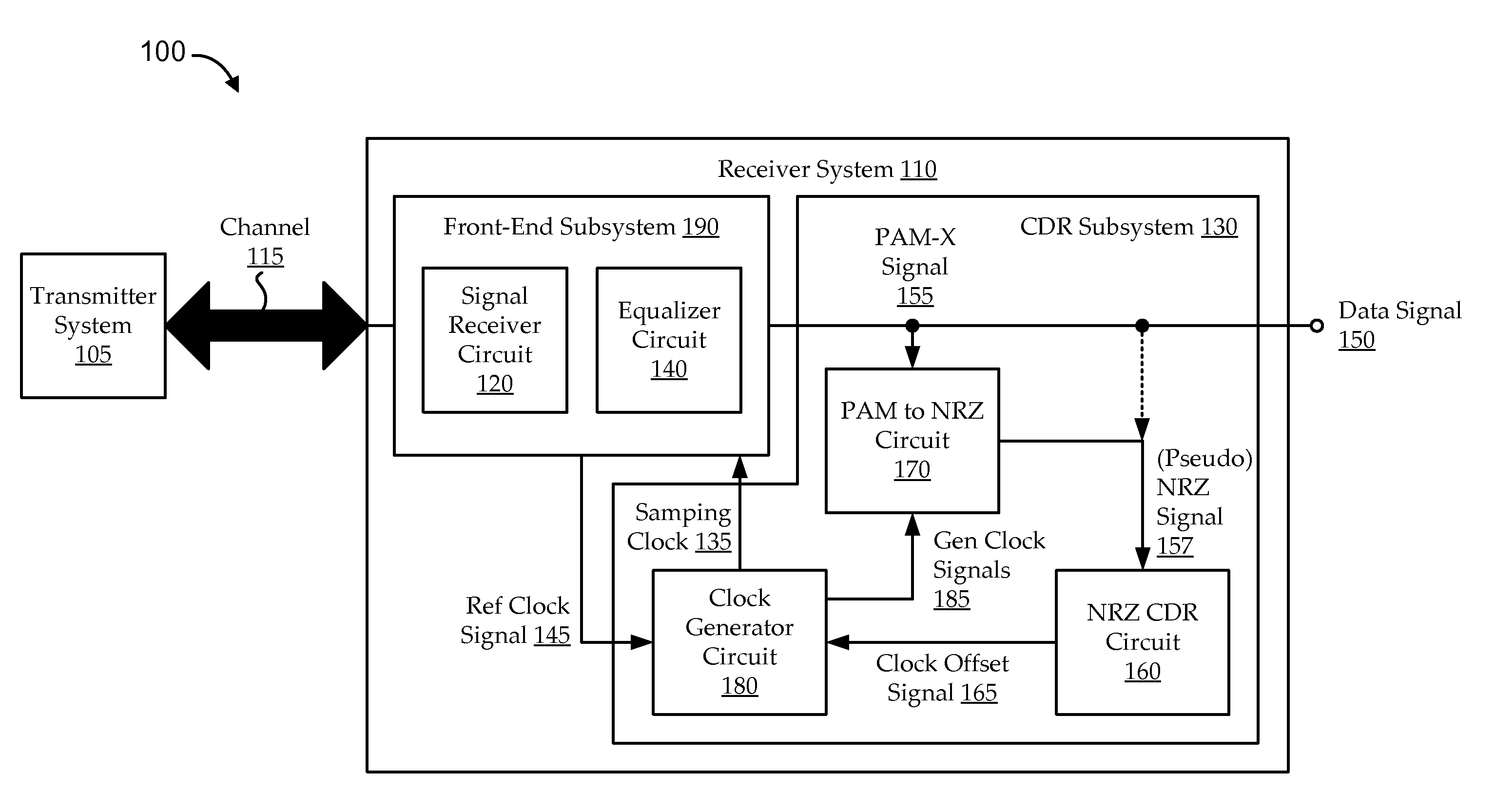

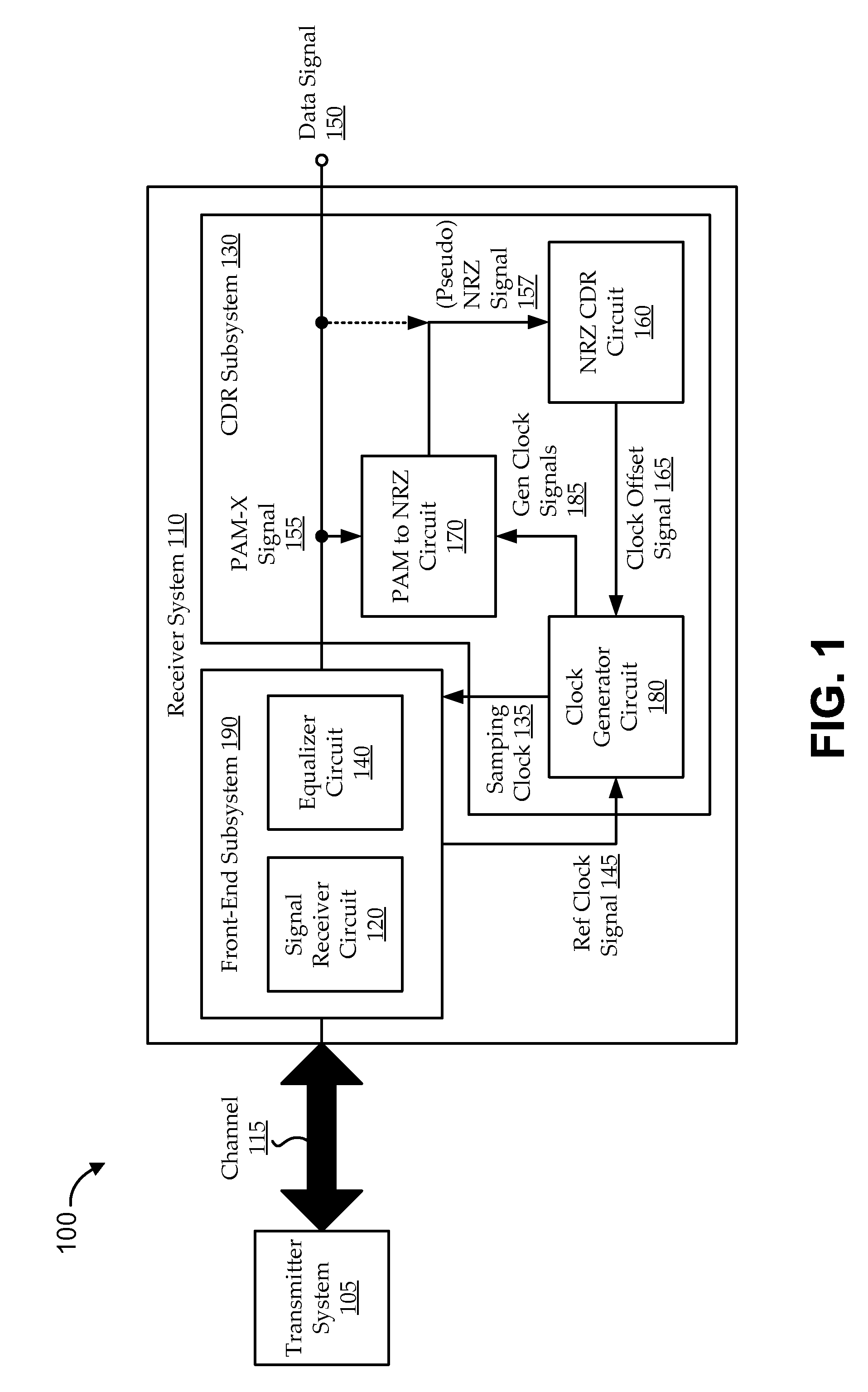

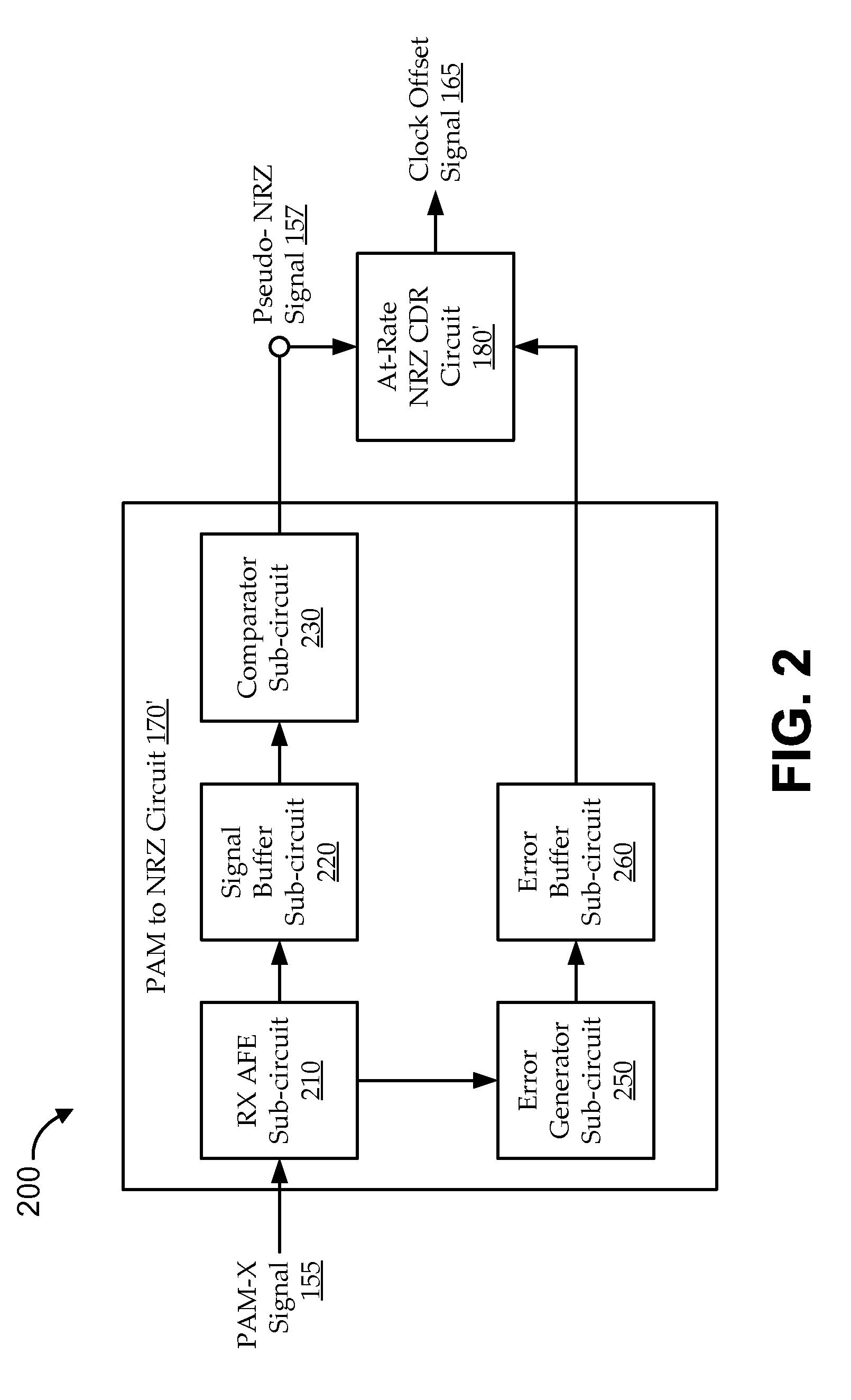

Configurable pulse amplitude modulation clock data recovery

ActiveUS9184906B1Facilitate dual-mode signalingReduce workloadSynchronisation error correctionSynchronisation error detectionReturn-to-zeroDual mode

Embodiments include systems and methods for using generalized pulse amplitude modulation (PAM-X) signaling with an at-rate not-return-to-zero (NRZ) clock data recovery (CDR) system. Some implementations include dual-mode signaling for an at-rate CDR (e.g., using standard NRZ signaling at lower operating frequencies and pseudo-NRZ signaling derived from PAM-X signaling at higher operating frequencies. Embodiments derive an apparent direction of signal transition from PAM-X signaling. The direction can be used to calculate pseudo-NRZ values. For example, when the PAM-X signal transitions in an upward direction, a pseudo-current NRZ value and a pseudo-previous NRZ value of ‘−1’ and ‘+1’ can be generated, respectively. An at-rate NRZ CDR can use the pseudo-NRZ values and a derived error value to make an offset determination. The offset determination can then be used to offset a generated clock signal in the CDR system.

Owner:ORACLE INT CORP

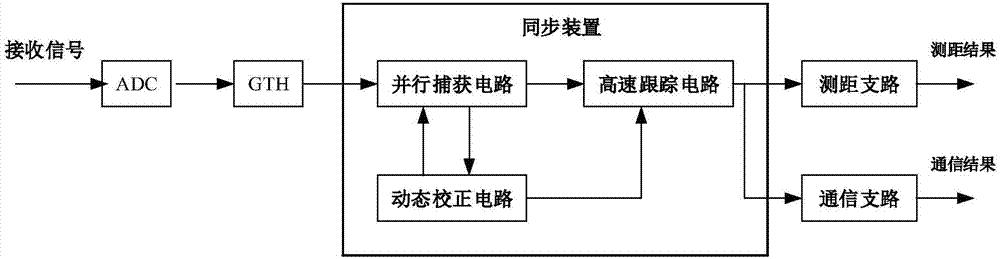

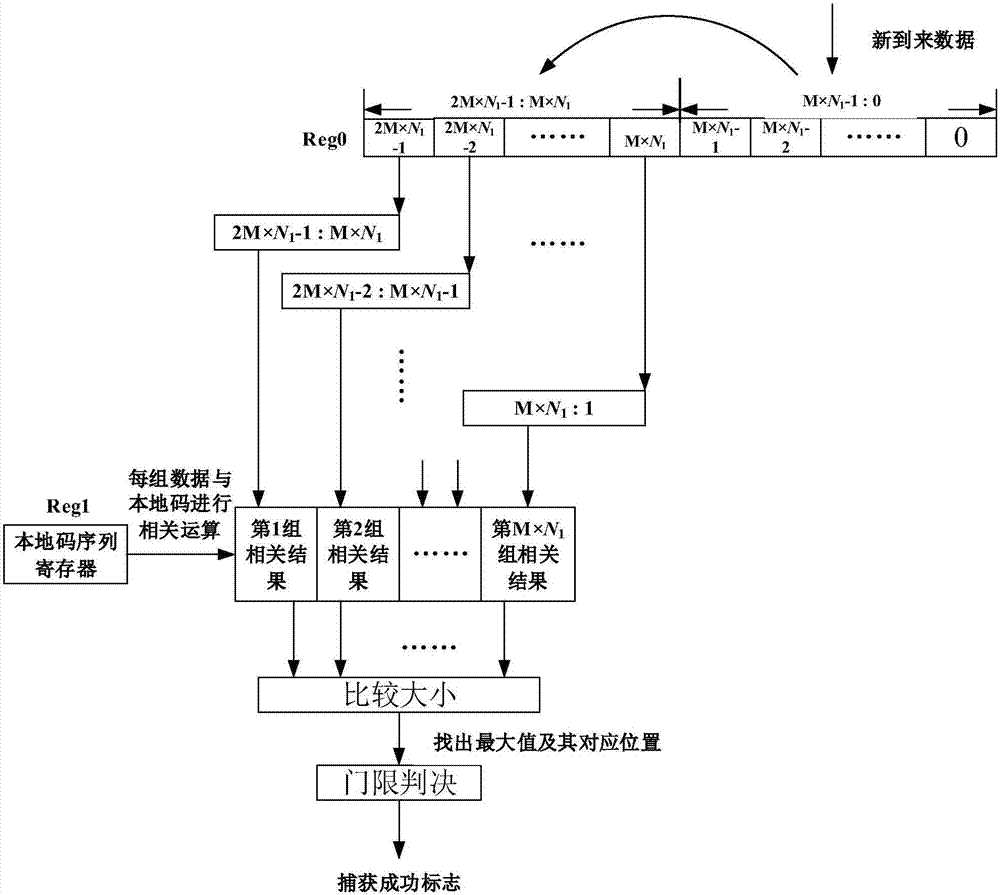

Synchronizer, synchronization method and high-speed receiver by using synchronizer

ActiveCN107425953AReduce processing burdenLow timing requirementsSynchronisation error correctionSynchronisation receiversTransceiverParallel computing

The present invention provides a synchronizer of a laser communication distance measurement integration system, a synchronization method of a laser communication distance measurement integration system and a high-speed receiver by using the synchronizer. The high-speed receiver receives high-speed signals, an analog-digital converter (ADC) is used for sampling of the high-speed signals, the sampling data is sent into a Gigabit transceiver (GTH) to perform serial-parallel conversion, and the high-speed serial data is converted to multi-path parallel data with low rate; the parallel data is sent into the synchronizer for signal synchronization, the parallel data is subjected to steps such as parallel data frame capture, dynamic correction, high-speed phase-locked loop tracking and the like in the synchronizer so as to complete accurate synchronization of the high-speed signals through the receiver; and moreover, on the basis of the accurate synchronization of the signals, and a distance measurement result and communication data can be solved out through the distance measurement branch and the communication branch of the receiver. The clock load is reduced and the complexity of the hardware realization is effectively reduced while ensuring the accurate synchronization of signals and accurate distance measurement and communication result.

Owner:BEIJING INSTITUTE OF TECHNOLOGYGY

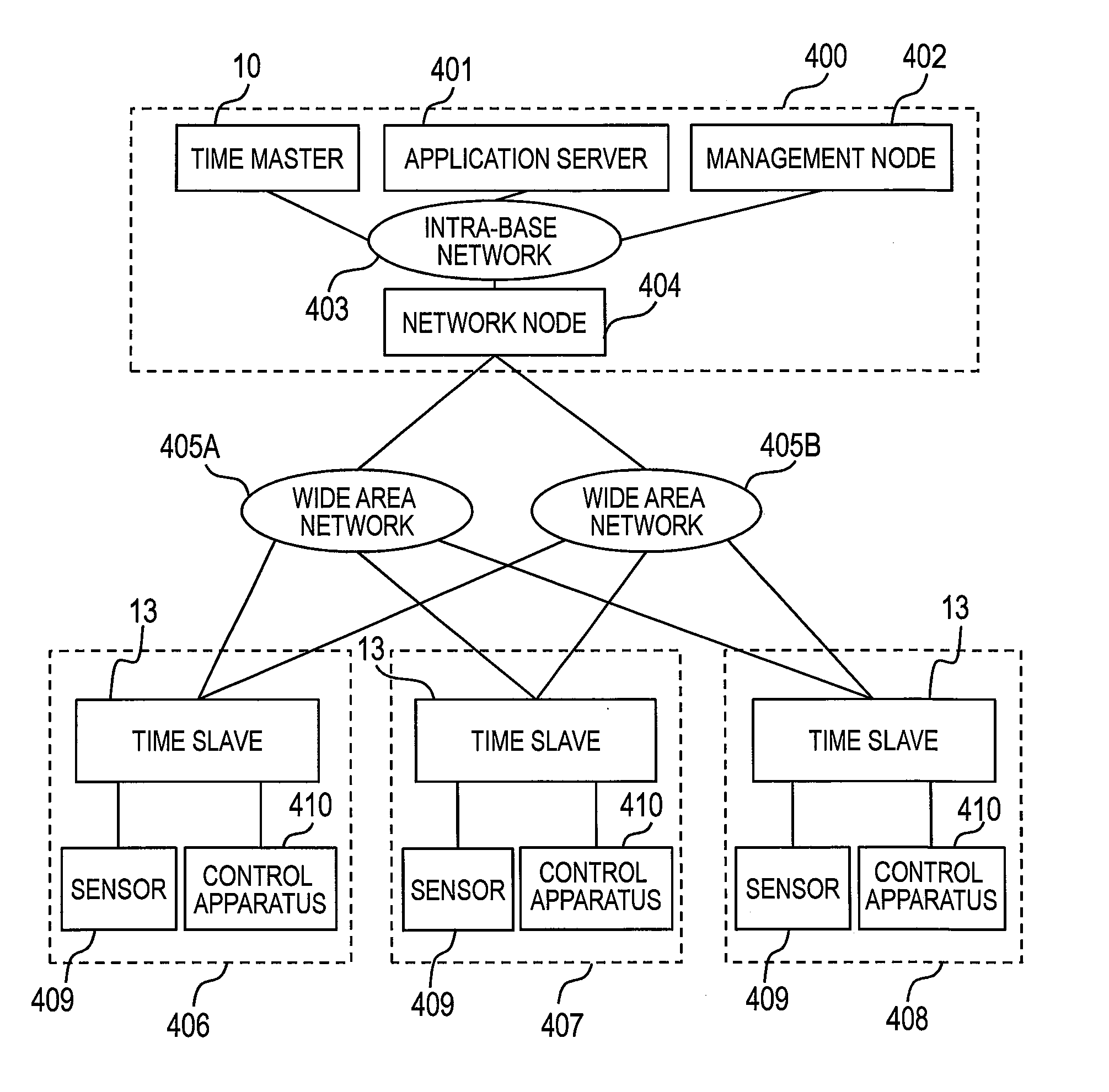

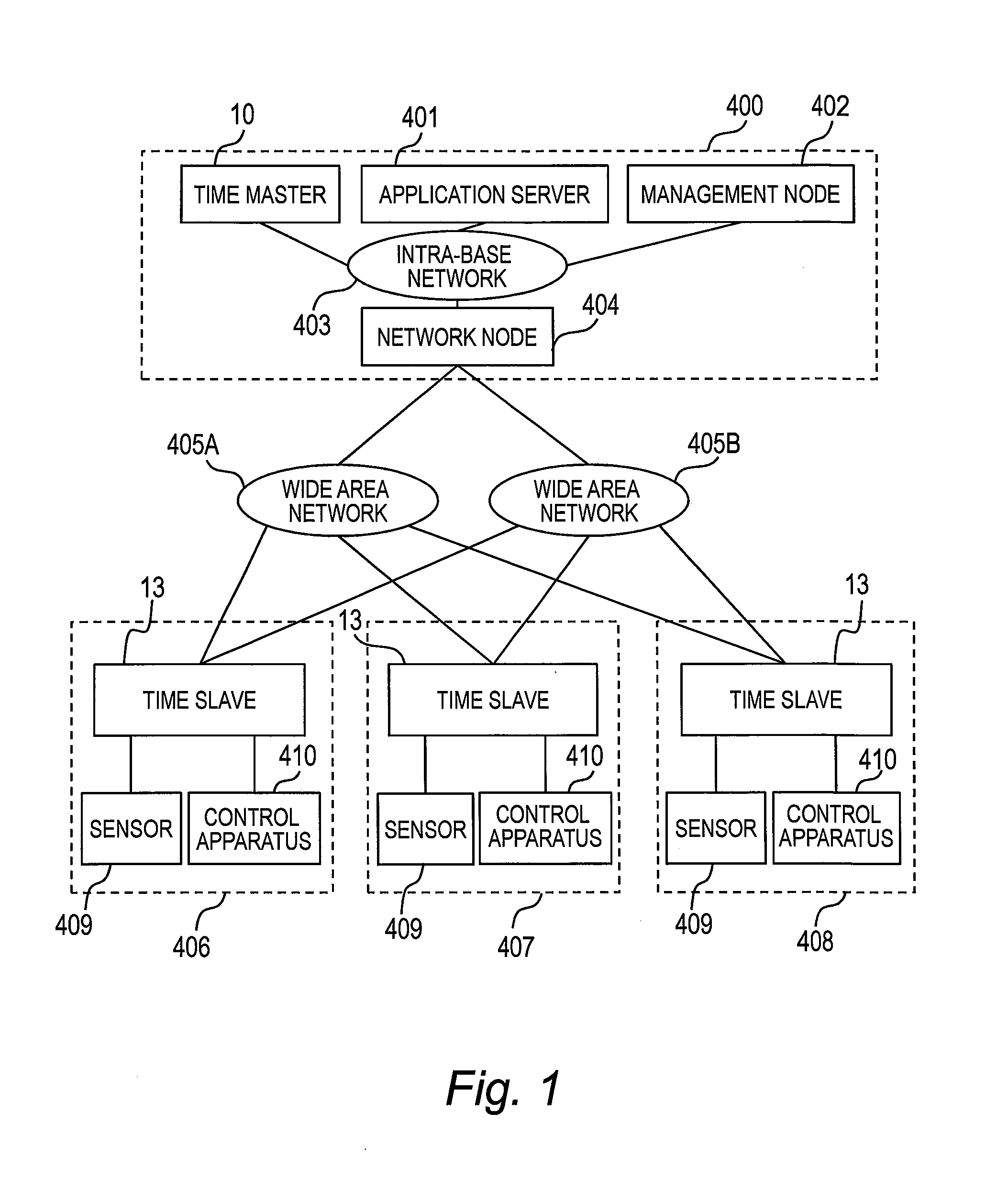

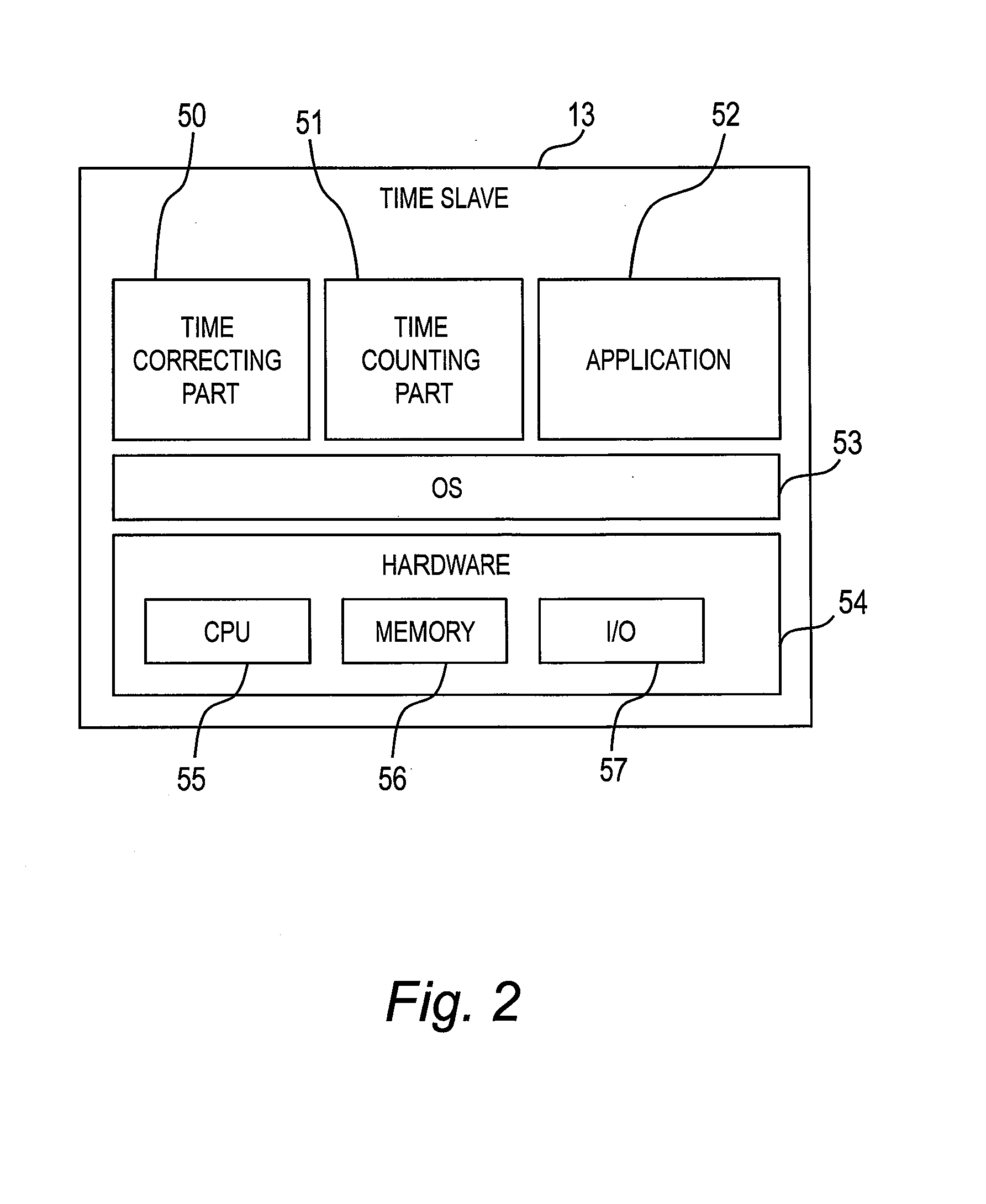

Time synchronization system, management node, and time synchronization method

ActiveUS20140348186A1Time requiredRequires minimizationSynchronisation error correctionTime-division multiplexPrimary stationNetwork switch

A time synchronization system comprises a time master, a time slave, and a management node which are coupled to one another via a plurality of networks. The time master transmits to the time slave a time packet at a given timing through at least one of the plurality of networks. The time slave has a time correcting part for receiving the time packet transmitted from the time master and for correcting time based on the received time packet. The management node has: a network switching determining part for determining whether to switch the network for transmitting a time packet to another of the plurality of networks; and a network switching notifying part for notifying, in a case where it is determined that the network for transmitting the time packet is to be switched, information for identifying the switched-to network to the time slave.

Owner:HITACHI LTD

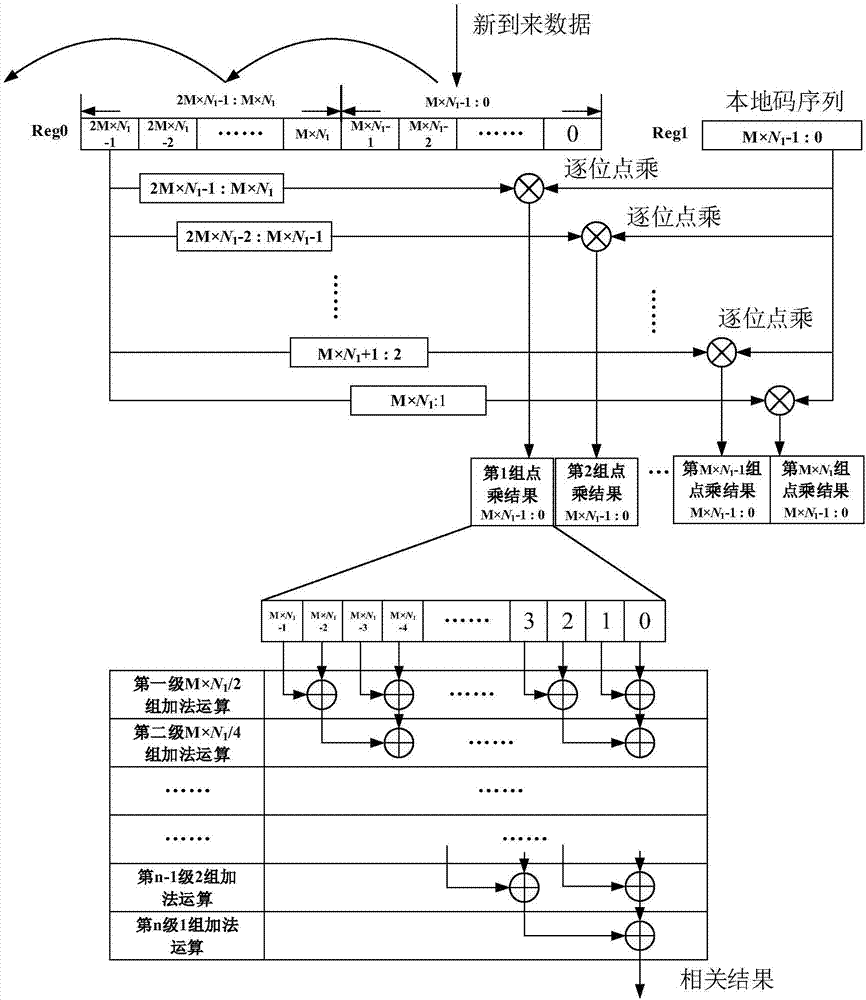

Signal synchronization method, receiving end and system

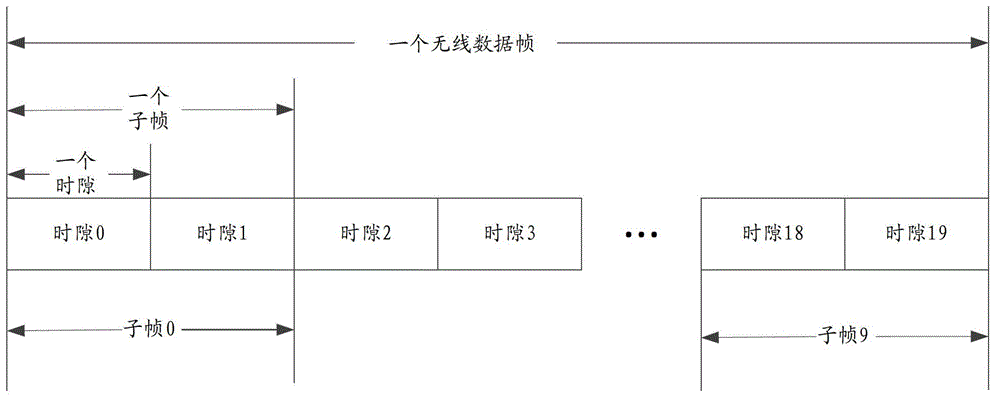

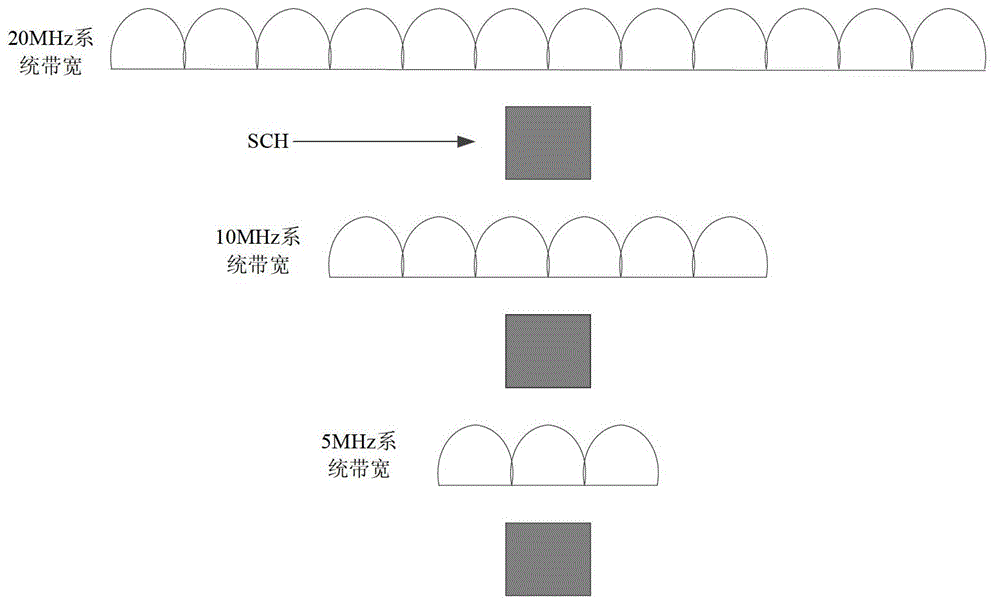

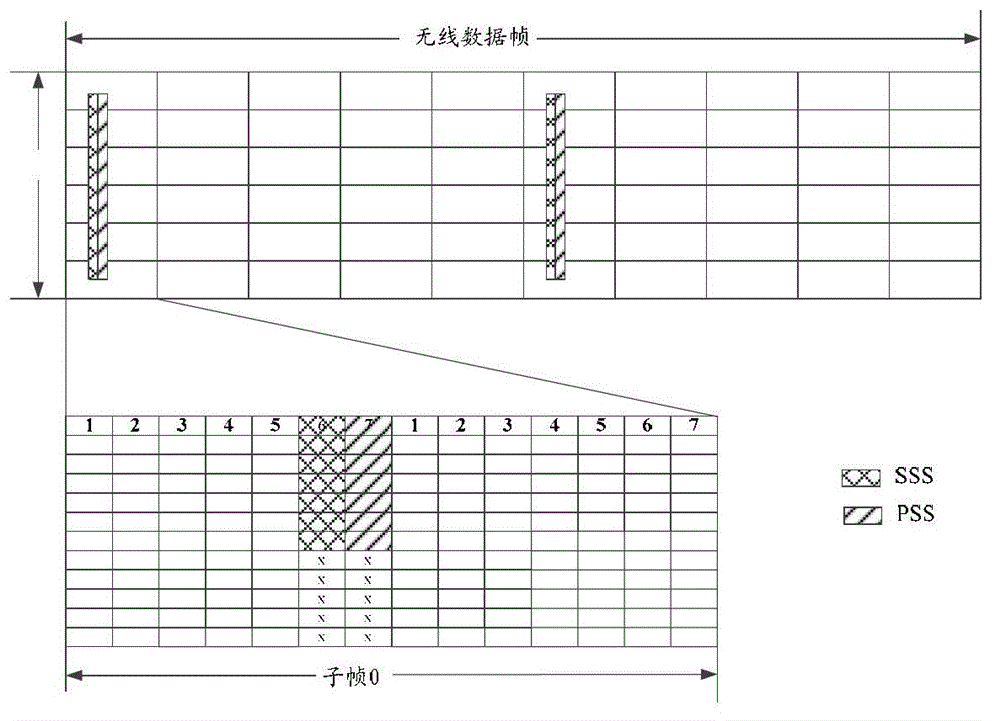

ActiveCN104065604ASolve problems that take a long timeHigh synchronization accuracySynchronisation arrangementSynchronisation error correctionTime domainEstimation methods

The invention discloses a time domain joint synchronization method of downlinks, a receiving end and a system and belongs to the field of communication. The method includes the following steps: obtaining a to-be-analyzed sequence y from a received time domain signal; carrying out timed initial estimation after carrying out Alpha-multiple downsampling on the to-be-analyzed sequence y; carrying out frequency deviation initial estimation after carrying out frequency deviation compensation on the to-be-analyzed sequence y according to an integer-multiple frequency deviation estimation value Epsilon <^> obtained through use the timed initial estimation to obtain a decimal-multiple frequency deviation estimation value Epsilon <^> <f>; after carrying out frequency deviation compensation on the to-be-analyzed sequence y according to the integer-multiple frequency deviation estimation value Epsilon <^> and the decimal-multiple frequency deviation estimation value Epsilon <^> <f>, using a position interval estimated by an initial timing position and a main synchronization sequence to carry out timed reestimation so as to obtain an accurate timing position. The time domain joint synchronization method of the downlinks, the receiving end and the system solve a problem that the prior synchronization and frequency deviation estimation method is low in efficiency and long in consumed time and achieve an effect that the operation complexity is reduced and a timed synchronization result and a frequency deviation estimation result can be mutually combined to realize rapid synchronization is achieved.

Owner:LENOVO (BEIJING) CO LTD

False lock detection for physical layer frame synchronization

ActiveUS20100150054A1Synchronisation error correctionTime-division multiplexComputer hardwarePhysical layer

Systems, devices, processors, and methods are described which may be used for the reception of a wireless broadband signal at a user terminal from a gateway via a satellite. A wireless signal may include a series of physical layer frames, each frame including a physical layer header and payload. The received signal is digitized and processed using various novel physical layer headers and related techniques to synchronize the physical layer frames and recover data from physical layer headers for purposes of demodulation and decoding.

Owner:VIASAT INC

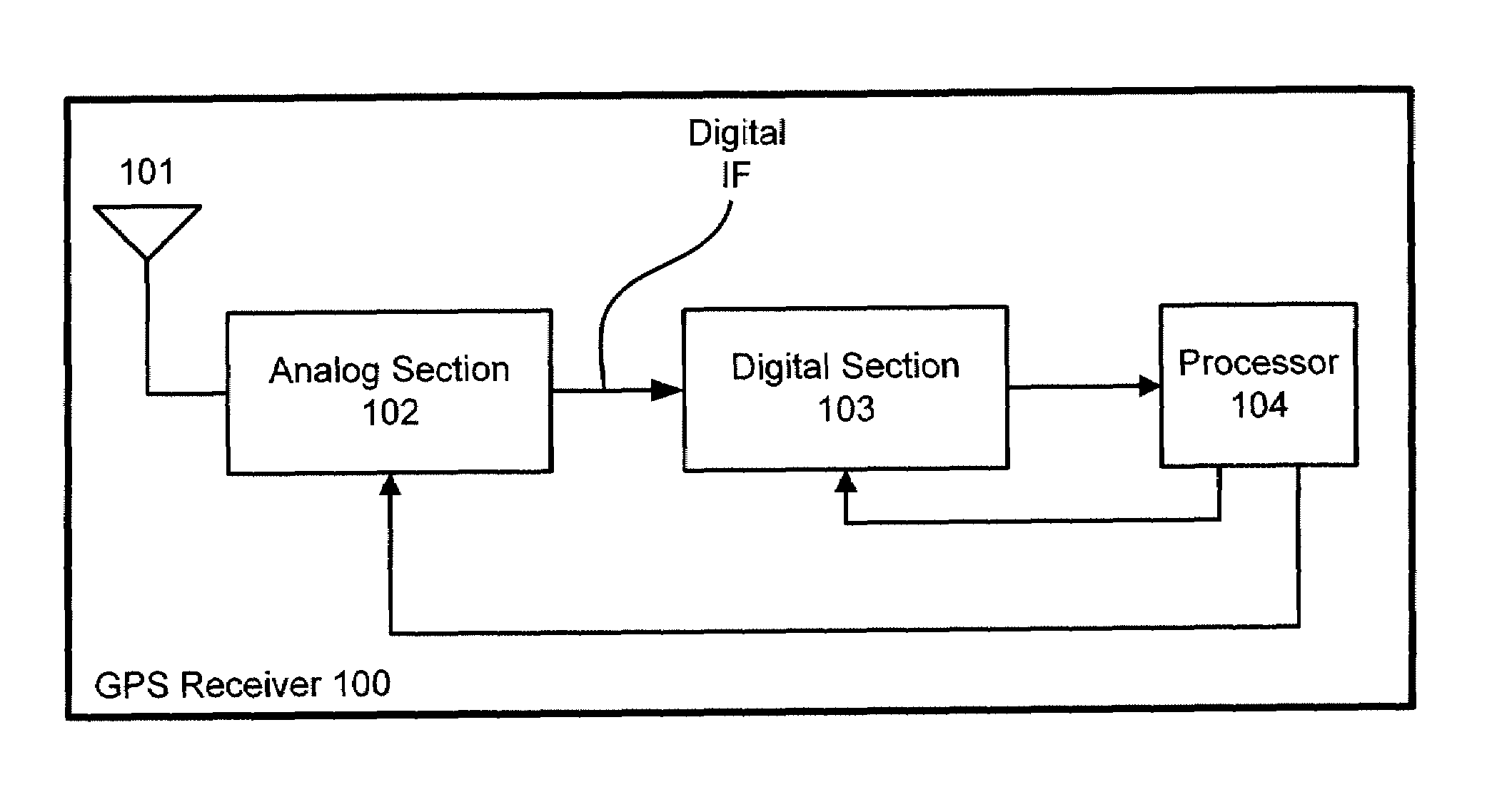

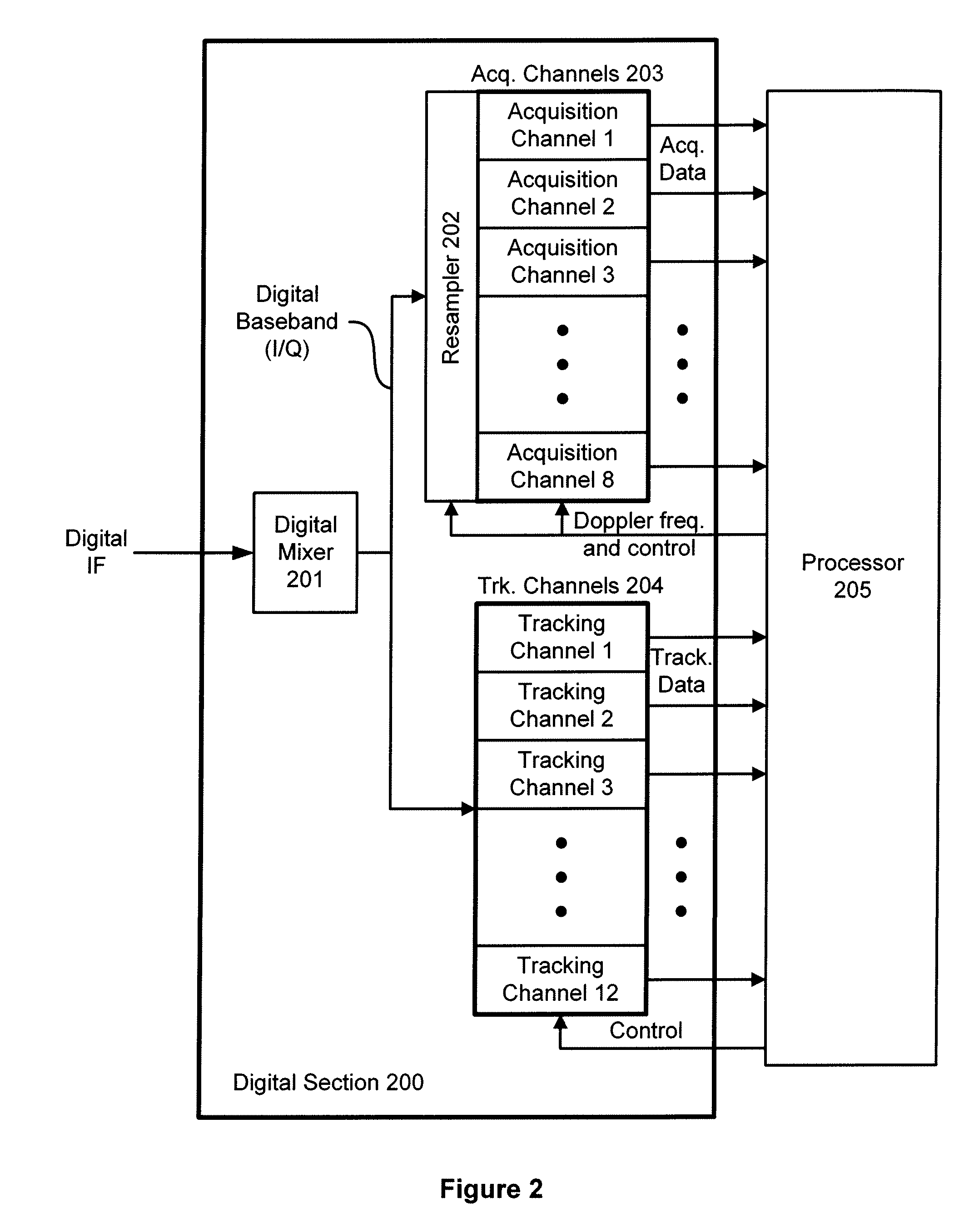

High Sensitivity GPS Receiver

InactiveUS20090079627A1Eliminate the effects ofTelevision system detailsRecord information storageSatellite dataGps receiver

A high sensitivity GPS receiver includes an acquisition engine and a tracking engine. The acquisition engine processes GPS satellite data at data rate that is substantially equal to twice the coarse acquisition (CA) code chip rate. This data rate advantageously enables the acquisition engine to process GPS satellite data with relatively less hardware area than traditional GPS acquisition approaches. In one embodiment, the high efficiency acquisition engine may be over-clocked, thereby allowing different phases of a CA code to be correlated quickly. The tracking engine can advantageously processes GPS satellite data at a data rate that does not have an integer relationship to the CA code chip rate.

Owner:QUALCOMM INC

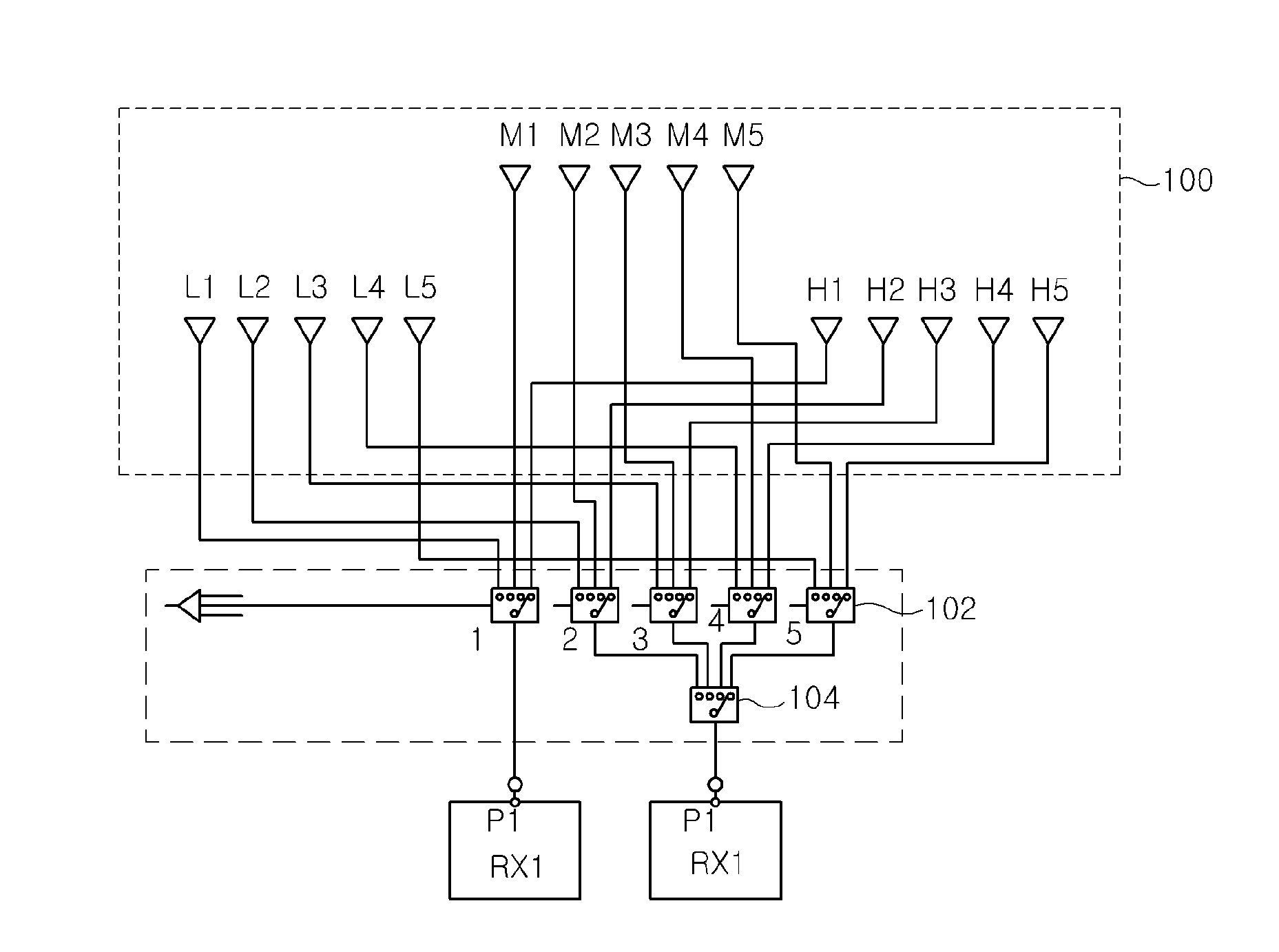

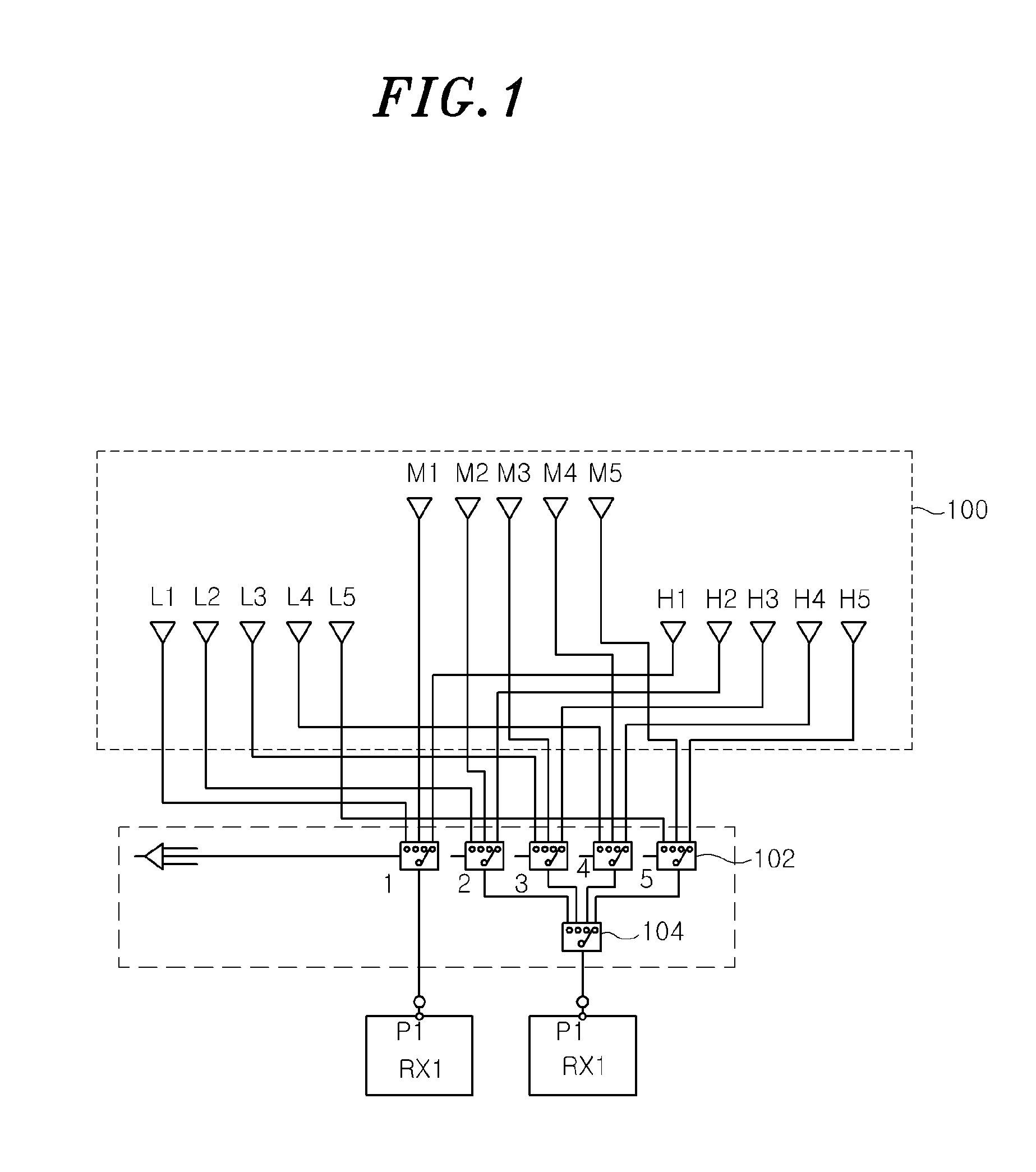

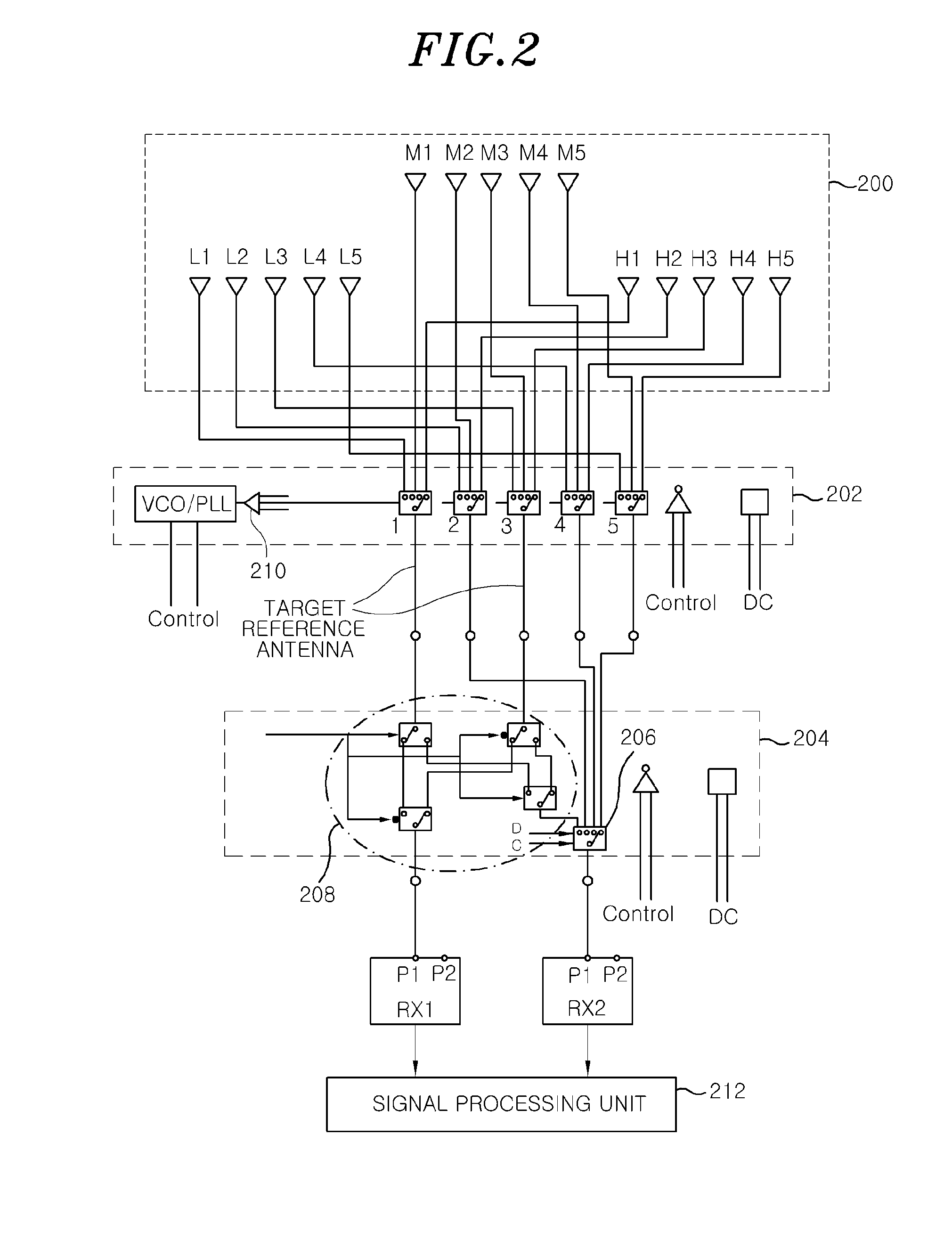

Radio measurement method and radio measurement apparatus using multi-antenna channel multiplex

ActiveUS20150071310A1Reduce the impactReduce noiseRadio wave finder detailsRadio wave direction/deviation determination systemsMultiplexingReference antenna

A radio measurement apparatus comprising: an array antennal selection unit selecting array antennas corresponding to received signals; a reference path selection unit selecting a reference array antenna; a signal processing unit selecting a reference antenna channel through analysis of signal characteristics measured through two reception channels; a sequential channel multiplex unit determining sequentially inputting received signals of remaining array antennas to output the sequentially input signals to a receiver; and a correction signal input unit compensating amplitude and phase characteristics of the respective reception channels.

Owner:ELECTRONICS & TELECOMM RES INST

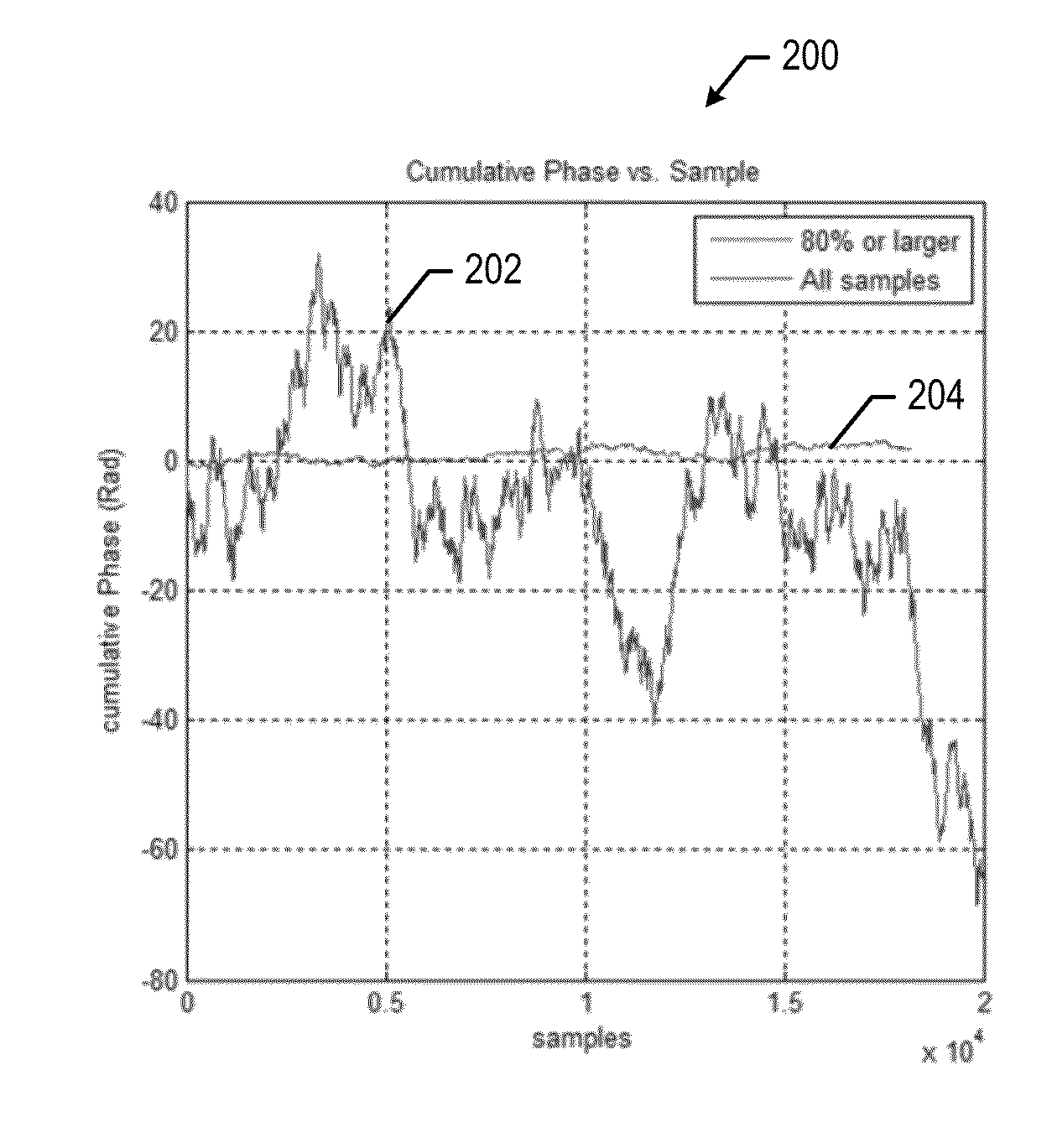

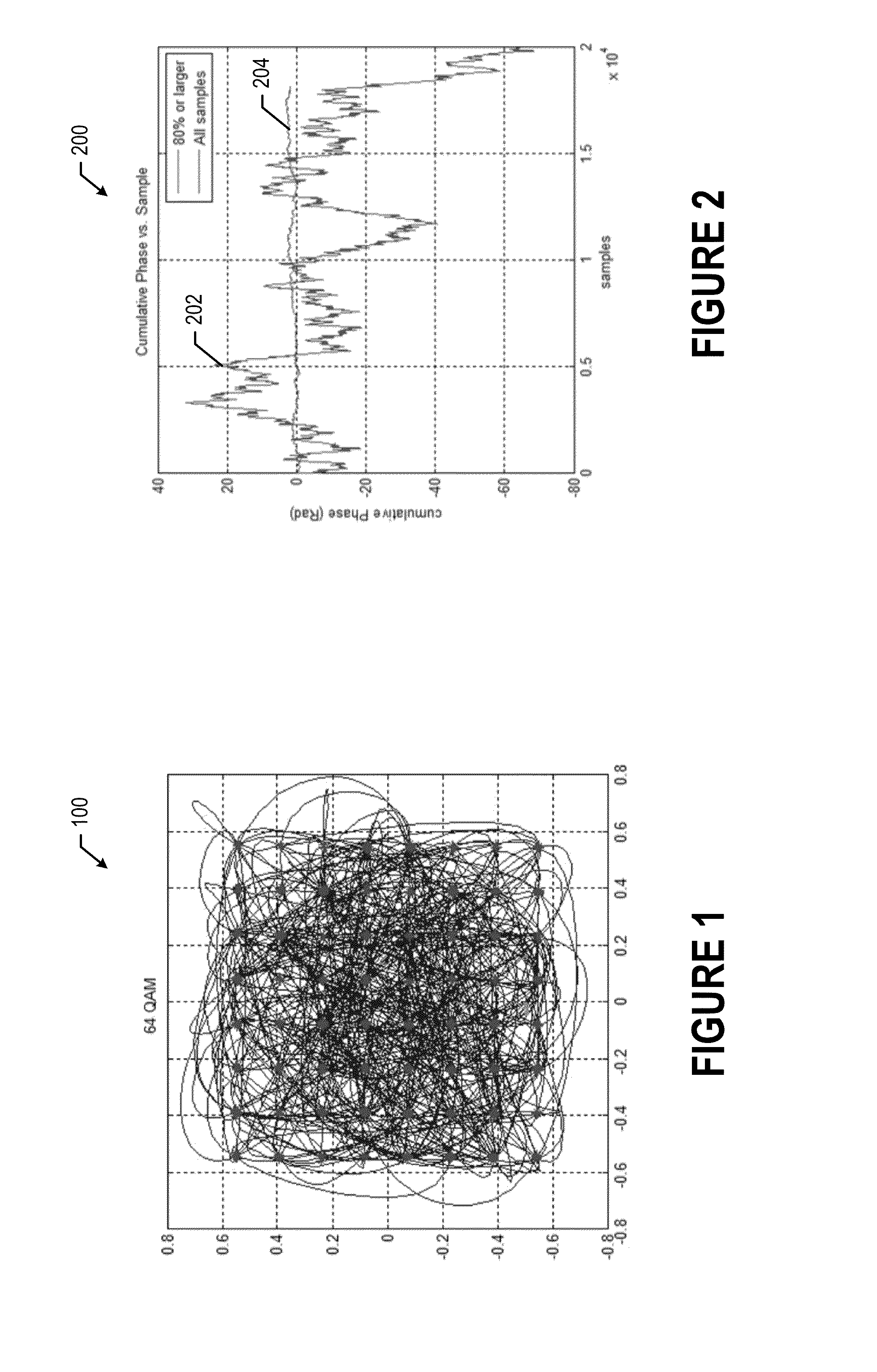

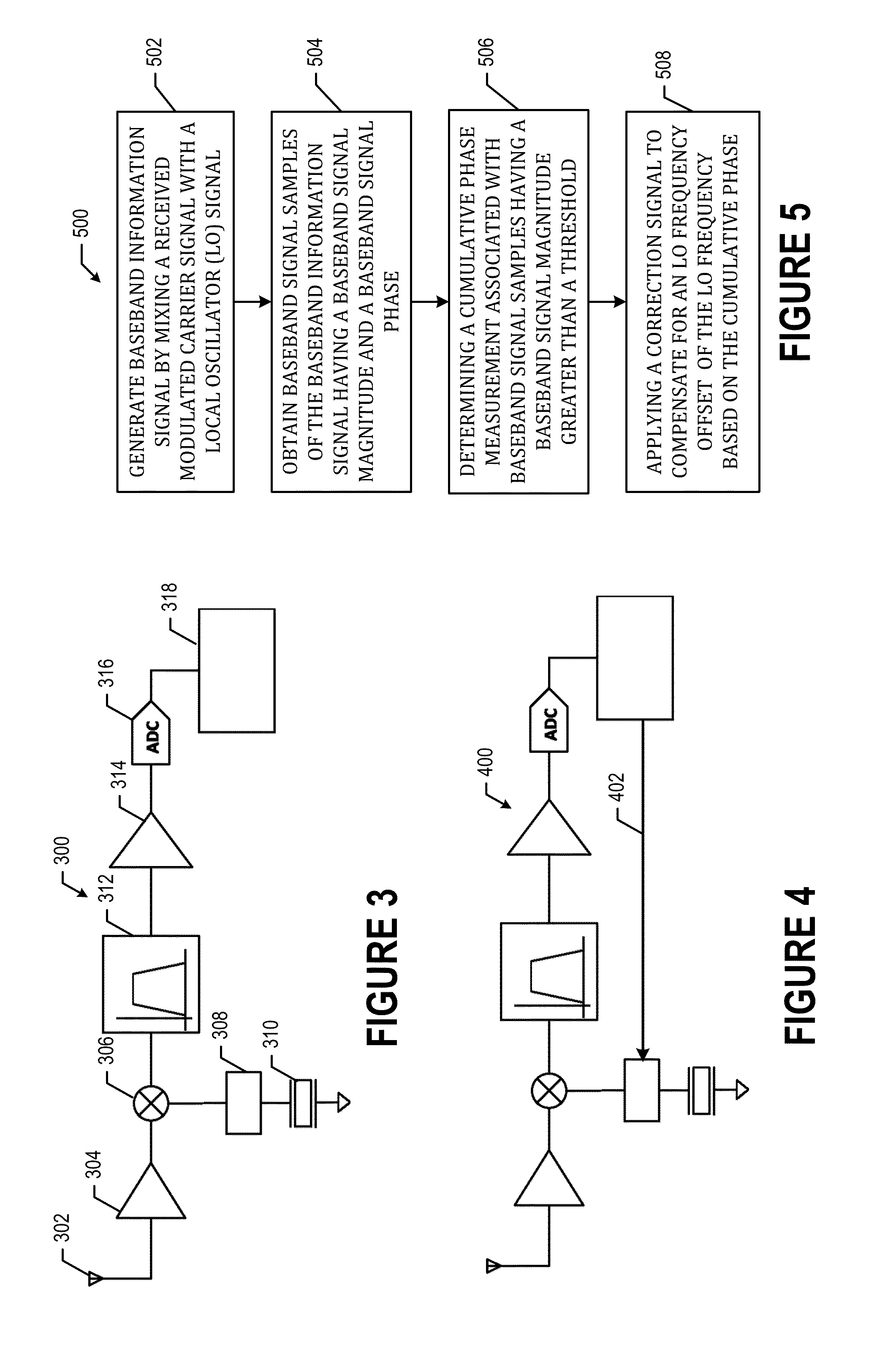

RF Carrier Synchronization and Phase Alignment Methods and Systems

ActiveUS20140093023A1Synchronisation arrangementRadio wave direction/deviation determination systemsLocal oscillatorCarrier signal

A method comprising generating a baseband information signal by mixing a received modulated carrier signal with a local oscillator (LO) signal having an LO frequency; obtaining baseband signal samples of the baseband information signal having a baseband signal magnitude and a baseband signal phase; determining a cumulative phase measurement associated with baseband signal samples having a baseband signal magnitude greater than a threshold; and, applying a correction signal to compensate for an LO frequency offset of the LO frequency based on the cumulative phase.

Owner:PHASORLAB

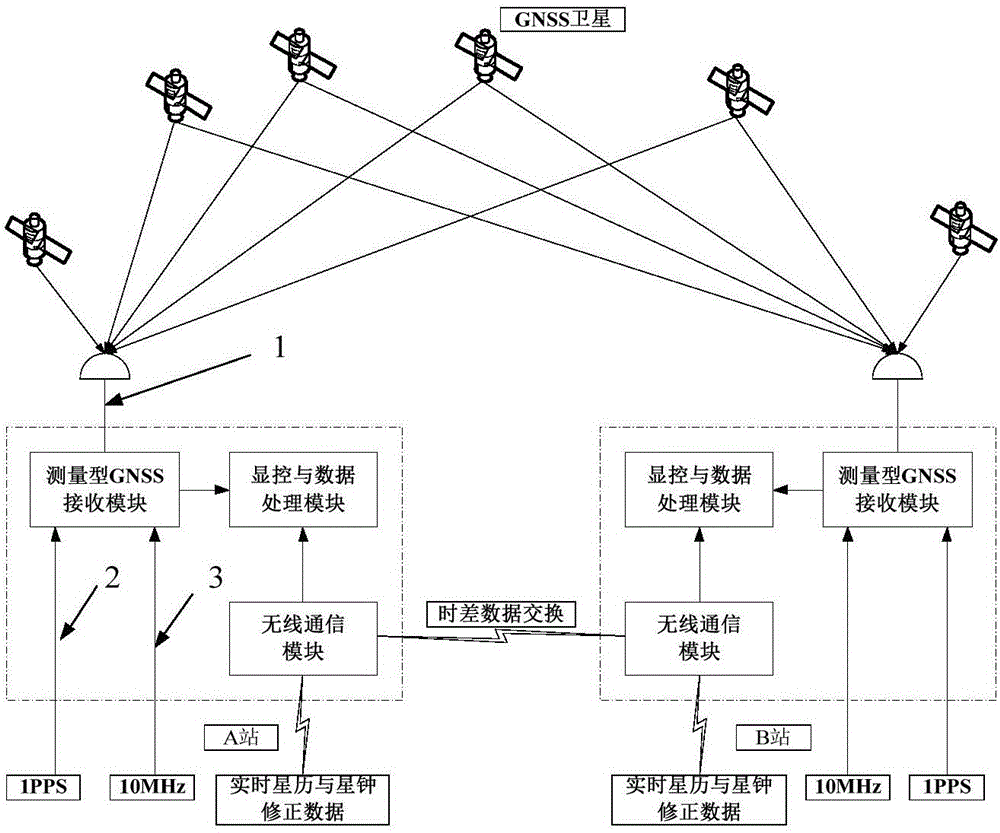

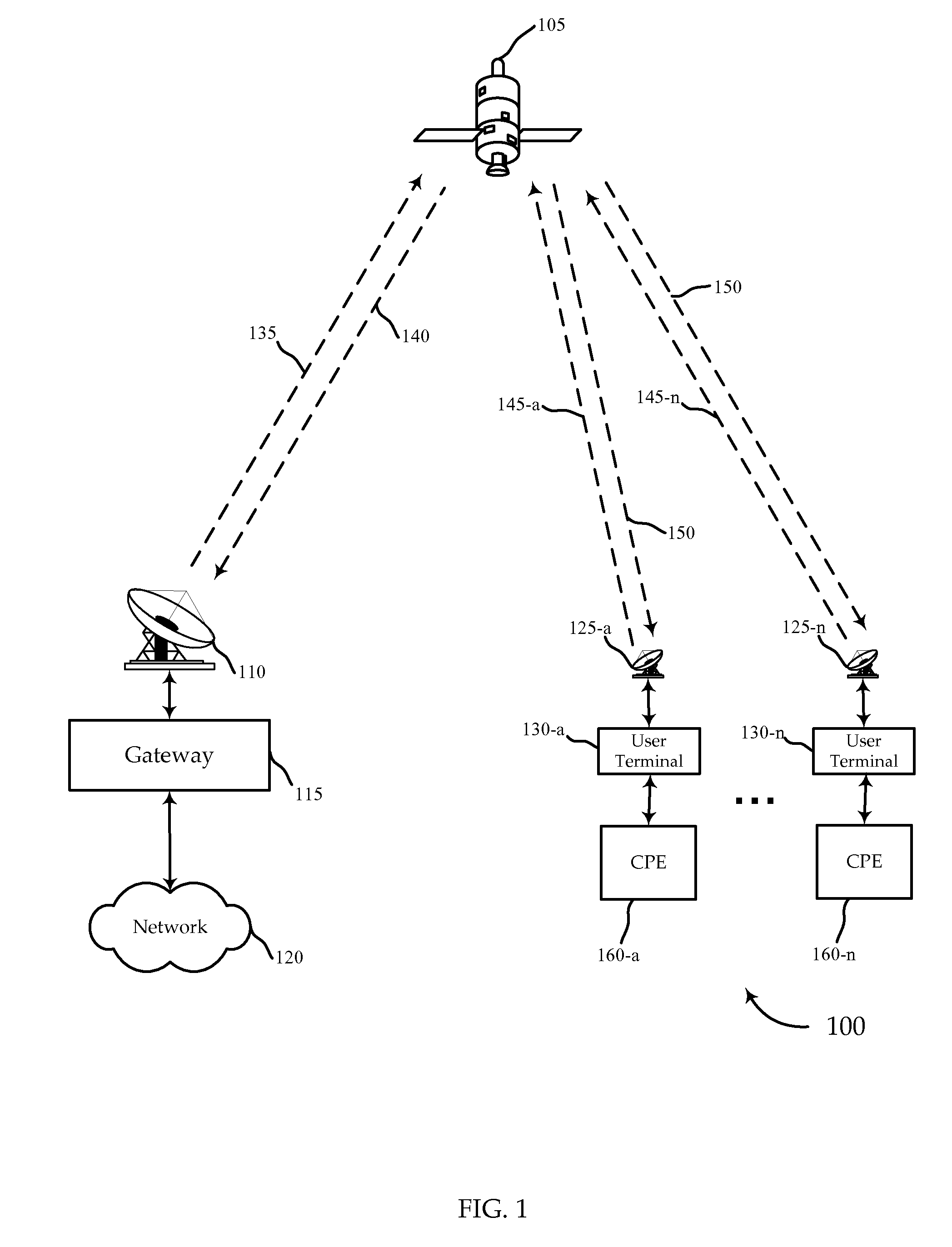

Precise-point-positioning-based real-time time transfer method

InactiveCN106850177AReal-time time transfer implementationSynchronisation error correctionTime-division multiplexData centerOn board

The invention discloses a precise-point-positioning-based real-time time transfer method. According to the method, carrier phase and pseudorange data of a navigation satellite as well as a broadcasting ephemeris and a broadcasting on-board clock are measured and extracted by a measurement receiver; cycle slip detection and non-difference integer ambiguity resolution are carried out on real-time carrier phase data according to real-time ephemeris and on-board clock revised data broadcast by a network server in an IGS data center to obtain time difference between local time and satellite system time; and data exchange is carried out with a communication module after error correction is performed according to a classical precise point positioning model, thereby realizing real-time time transfer between two stations.

Owner:BEIJING INST OF RADIO METROLOGY & MEASUREMENT

Novel physical layer header structure for decoding and synchronization

ActiveUS20100150037A1Synchronisation error correctionData switching by path configurationComputer hardwarePhysical layer

Systems, devices, processors, and methods are described which may be used for the reception of a wireless broadband signal at a user terminal from a gateway via a satellite. A wireless signal may include a series of physical layer frames, each frame including a physical layer header and payload. The received signal is digitized and processed using various novel physical layer headers and related techniques to synchronize the physical layer frames and recover data from physical layer headers for purposes of demodulation and decoding.

Owner:VIASAT INC