Patents

Literature

37results about How to "Low timing requirements" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

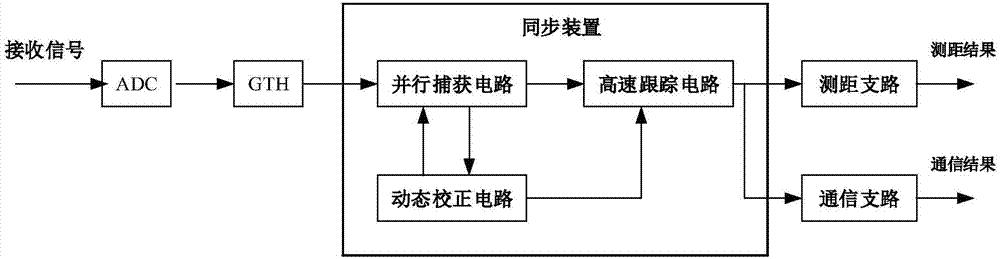

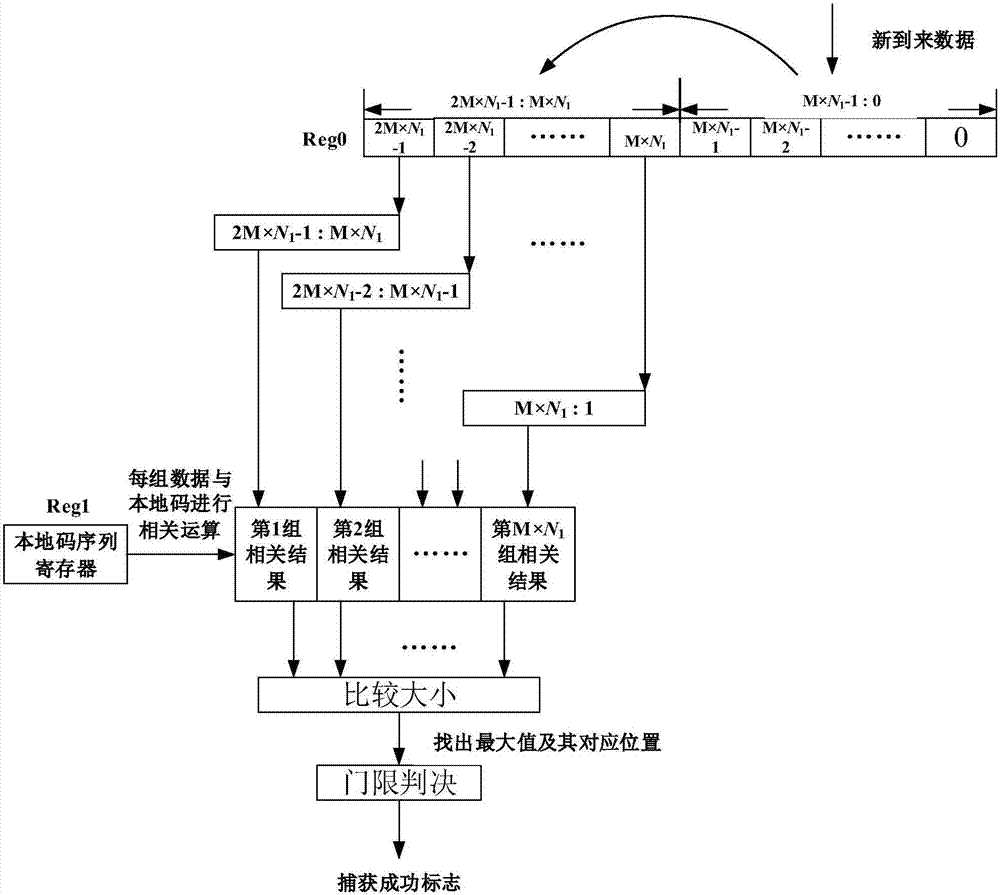

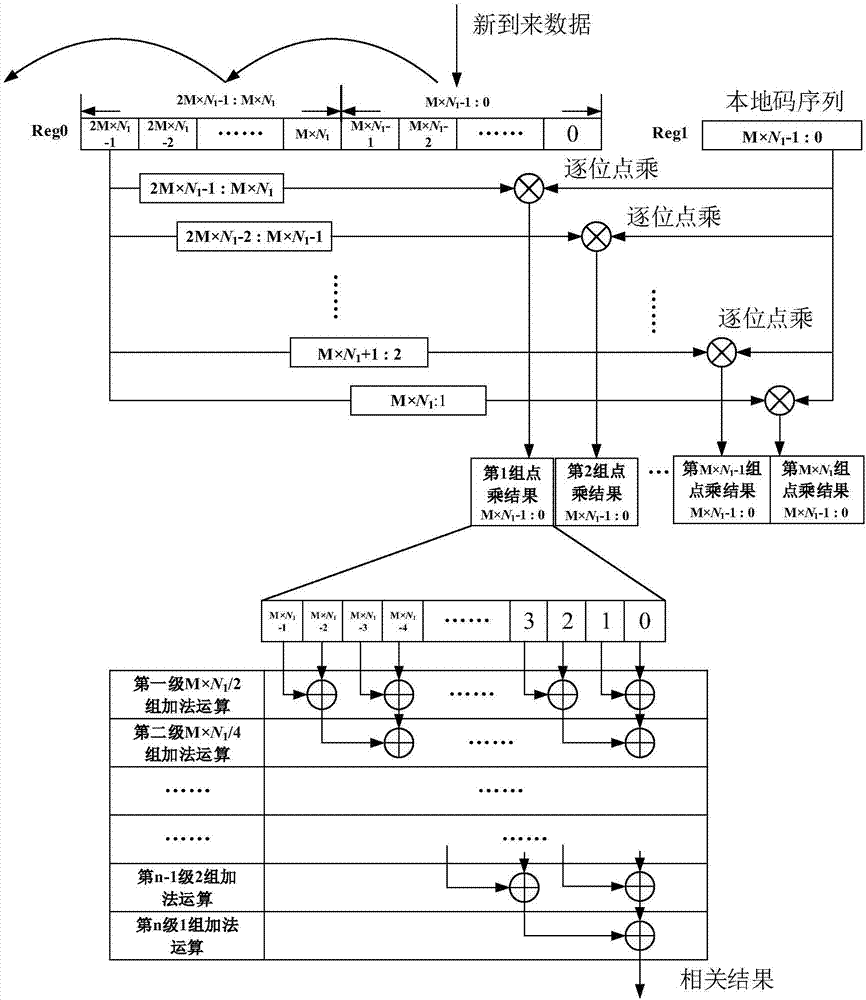

Synchronizer, synchronization method and high-speed receiver by using synchronizer

ActiveCN107425953AReduce processing burdenLow timing requirementsSynchronisation error correctionSynchronisation receiversTransceiverParallel computing

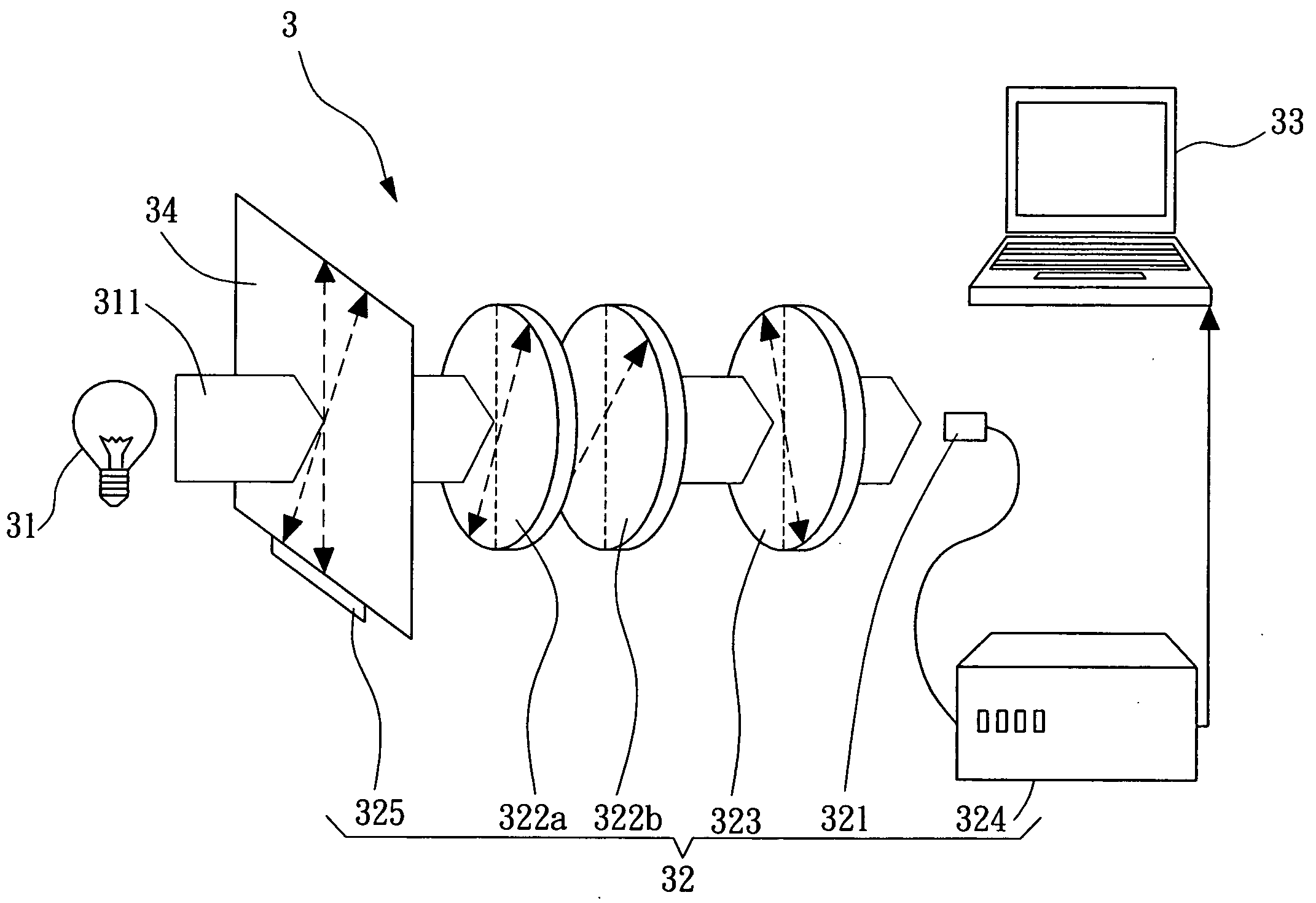

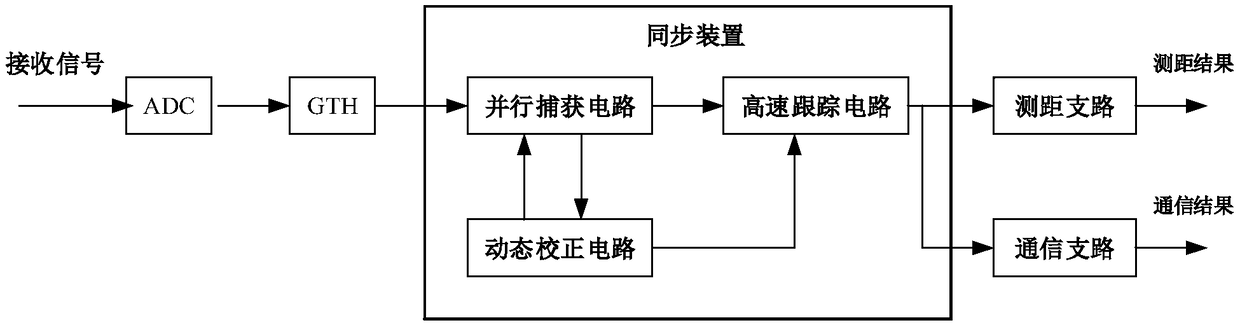

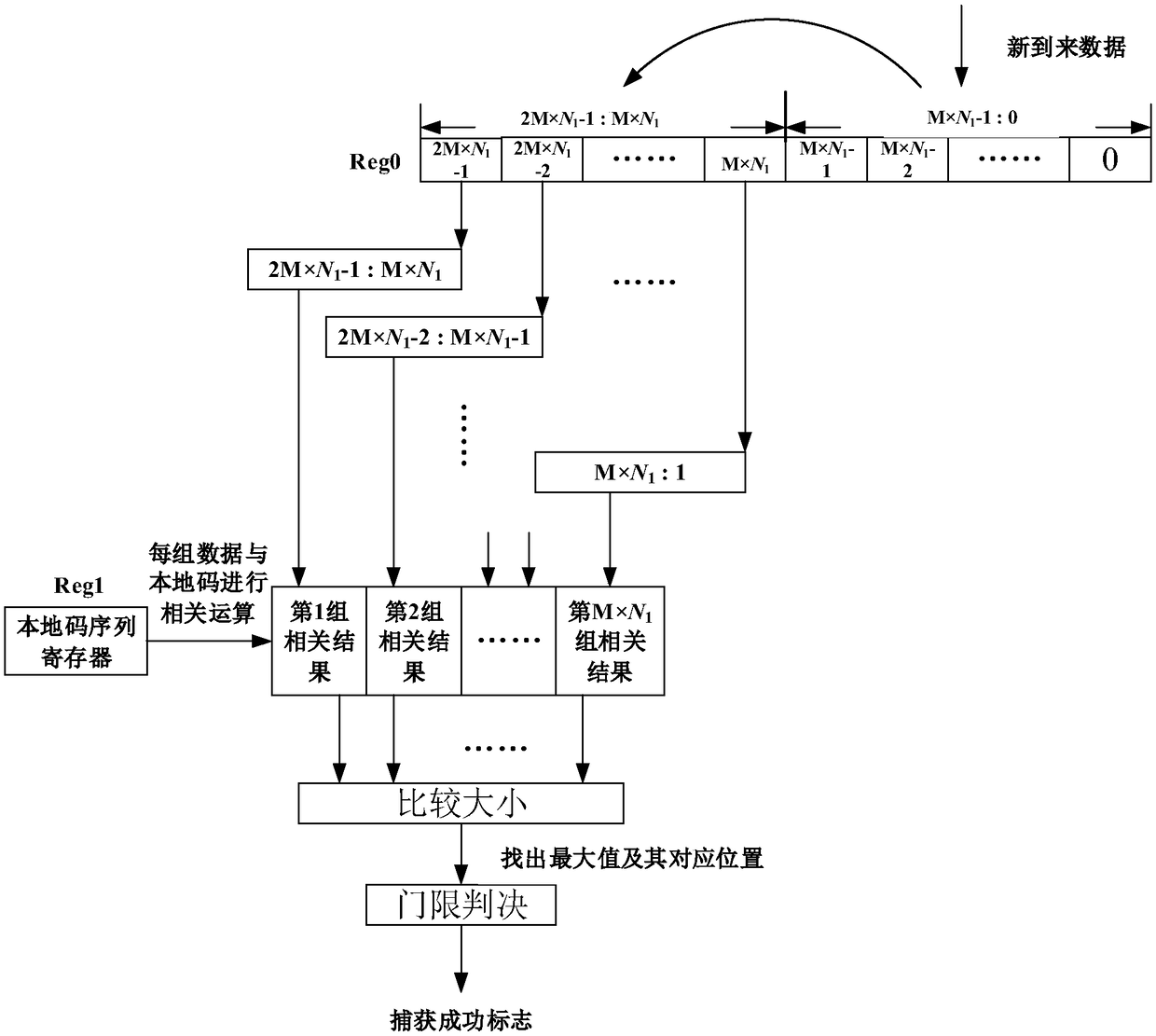

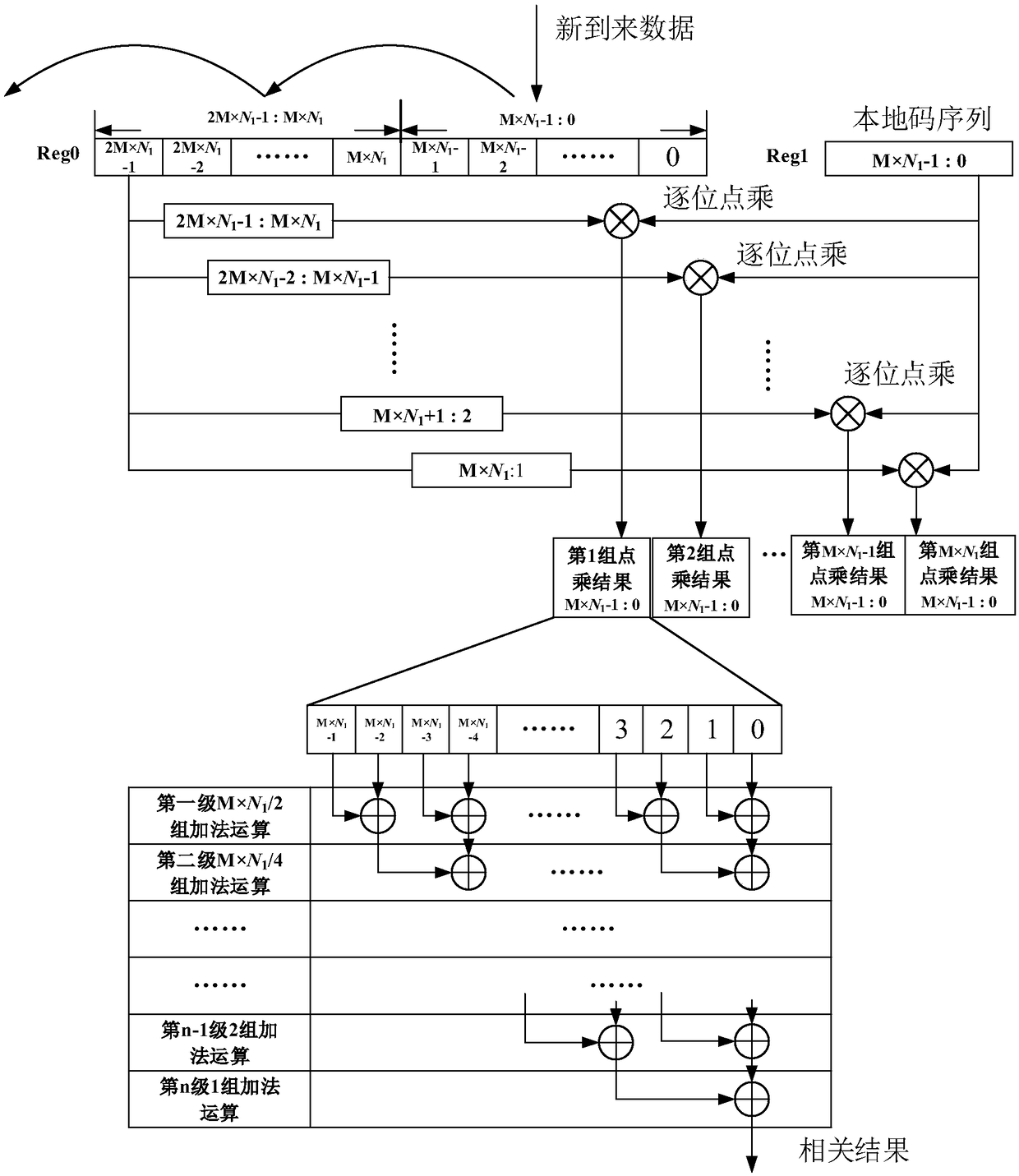

The present invention provides a synchronizer of a laser communication distance measurement integration system, a synchronization method of a laser communication distance measurement integration system and a high-speed receiver by using the synchronizer. The high-speed receiver receives high-speed signals, an analog-digital converter (ADC) is used for sampling of the high-speed signals, the sampling data is sent into a Gigabit transceiver (GTH) to perform serial-parallel conversion, and the high-speed serial data is converted to multi-path parallel data with low rate; the parallel data is sent into the synchronizer for signal synchronization, the parallel data is subjected to steps such as parallel data frame capture, dynamic correction, high-speed phase-locked loop tracking and the like in the synchronizer so as to complete accurate synchronization of the high-speed signals through the receiver; and moreover, on the basis of the accurate synchronization of the signals, and a distance measurement result and communication data can be solved out through the distance measurement branch and the communication branch of the receiver. The clock load is reduced and the complexity of the hardware realization is effectively reduced while ensuring the accurate synchronization of signals and accurate distance measurement and communication result.

Owner:BEIJING INSTITUTE OF TECHNOLOGYGY

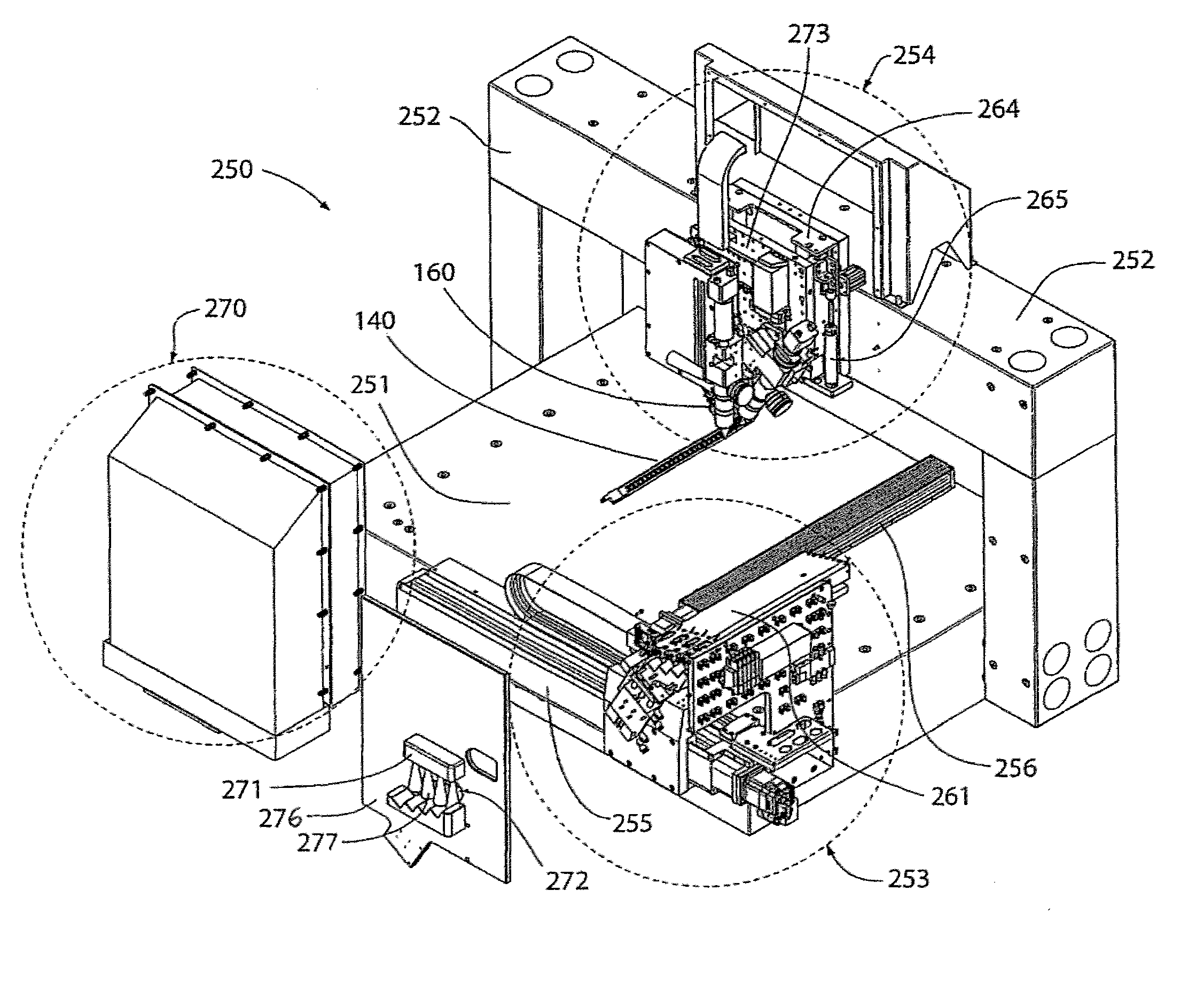

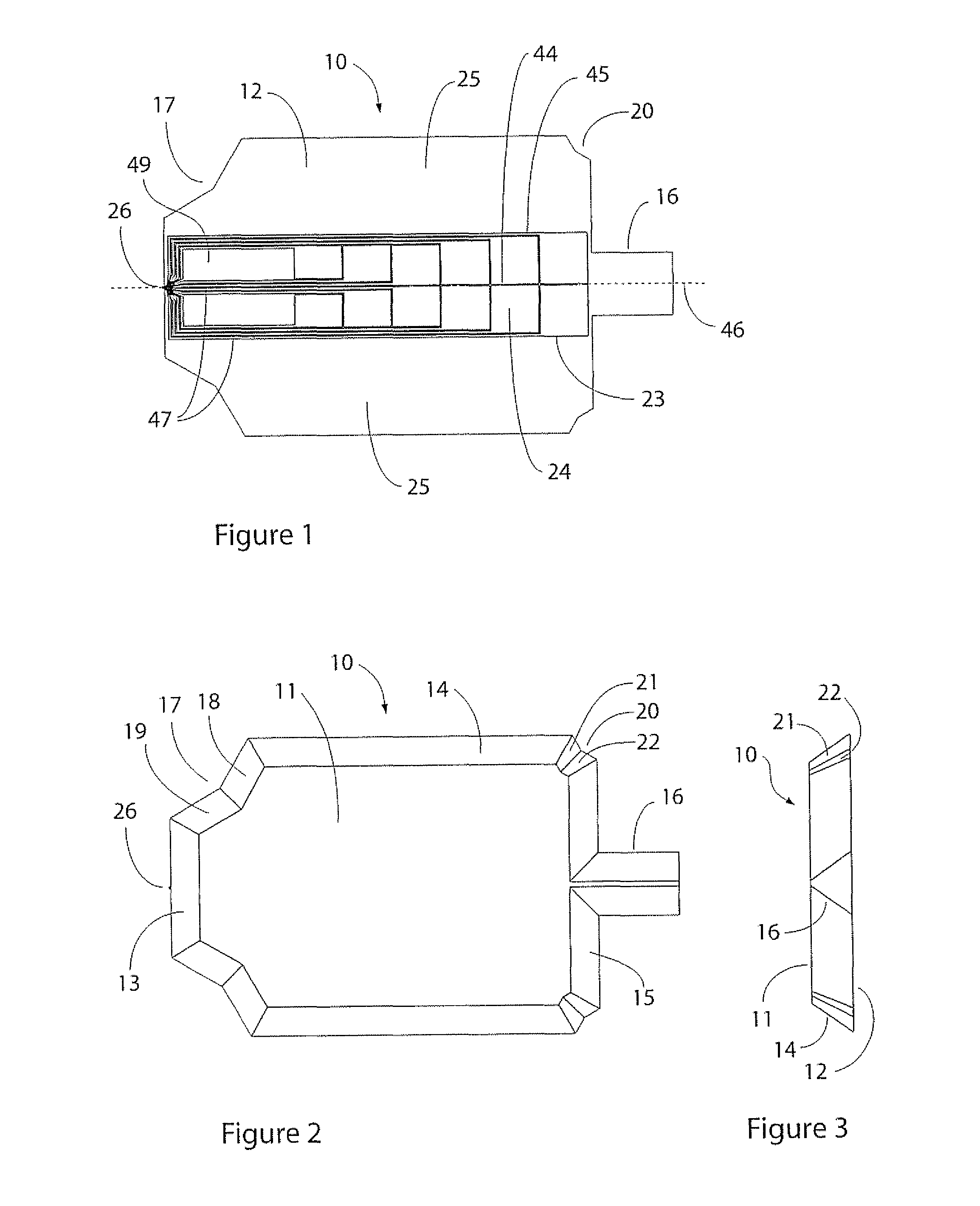

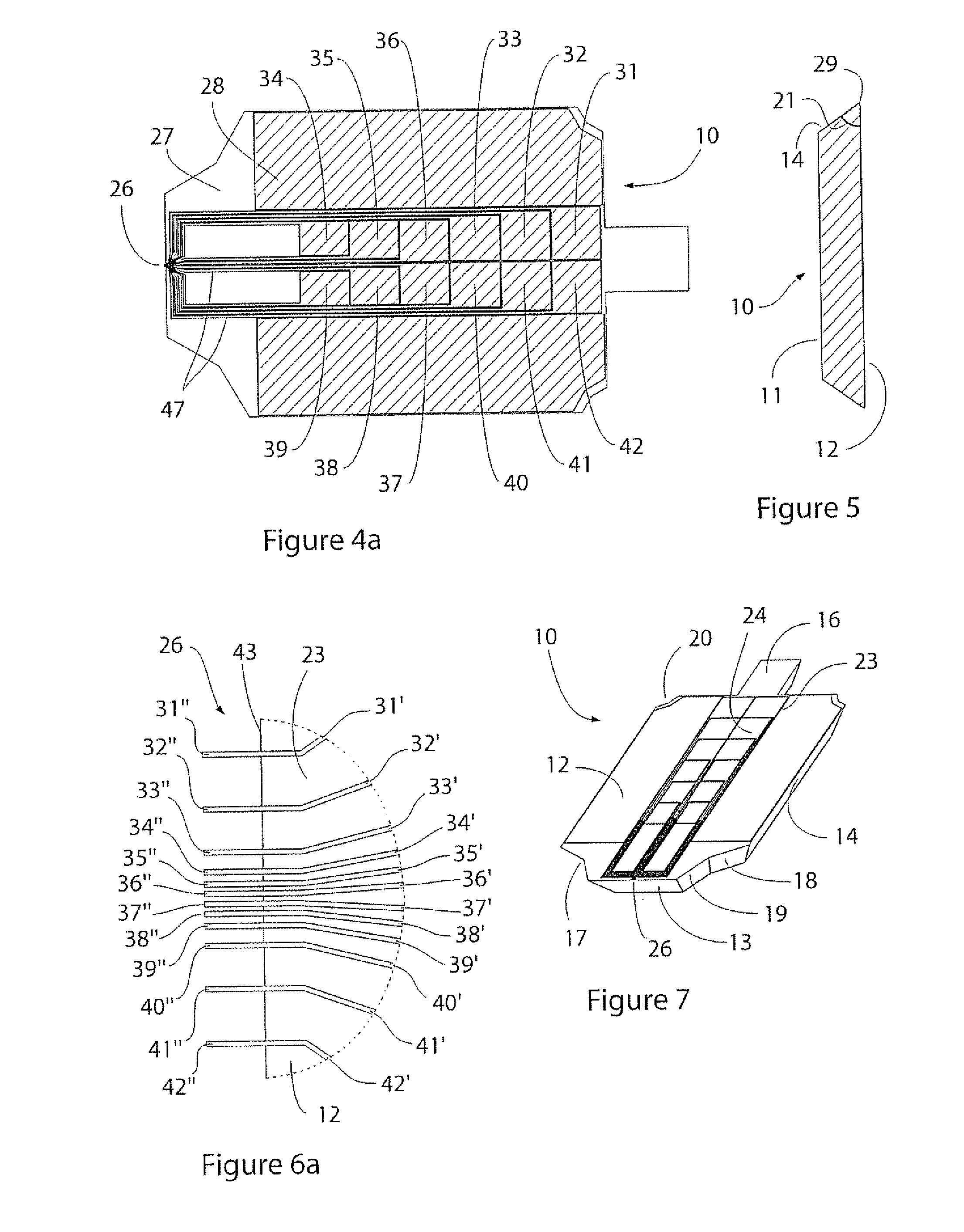

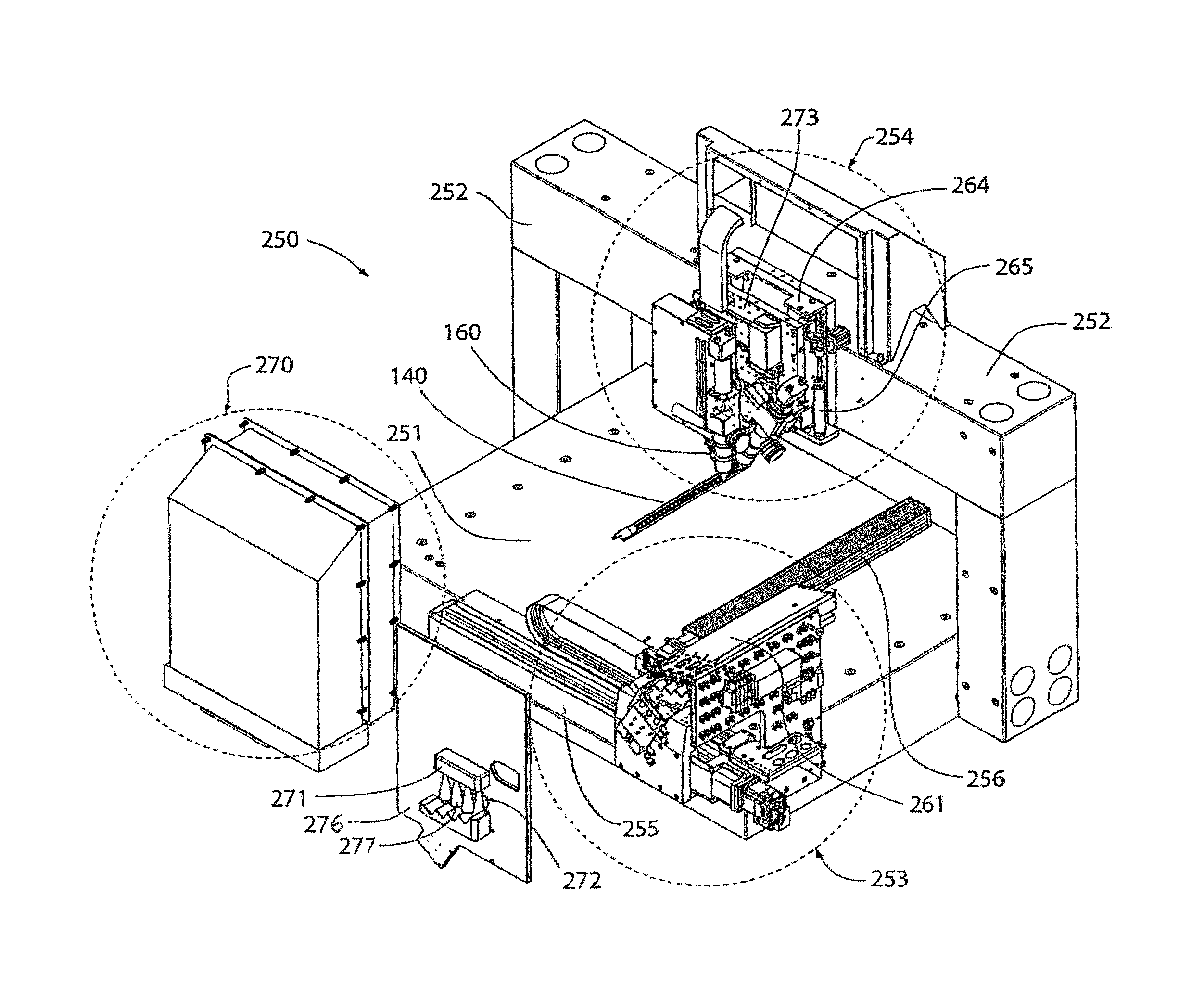

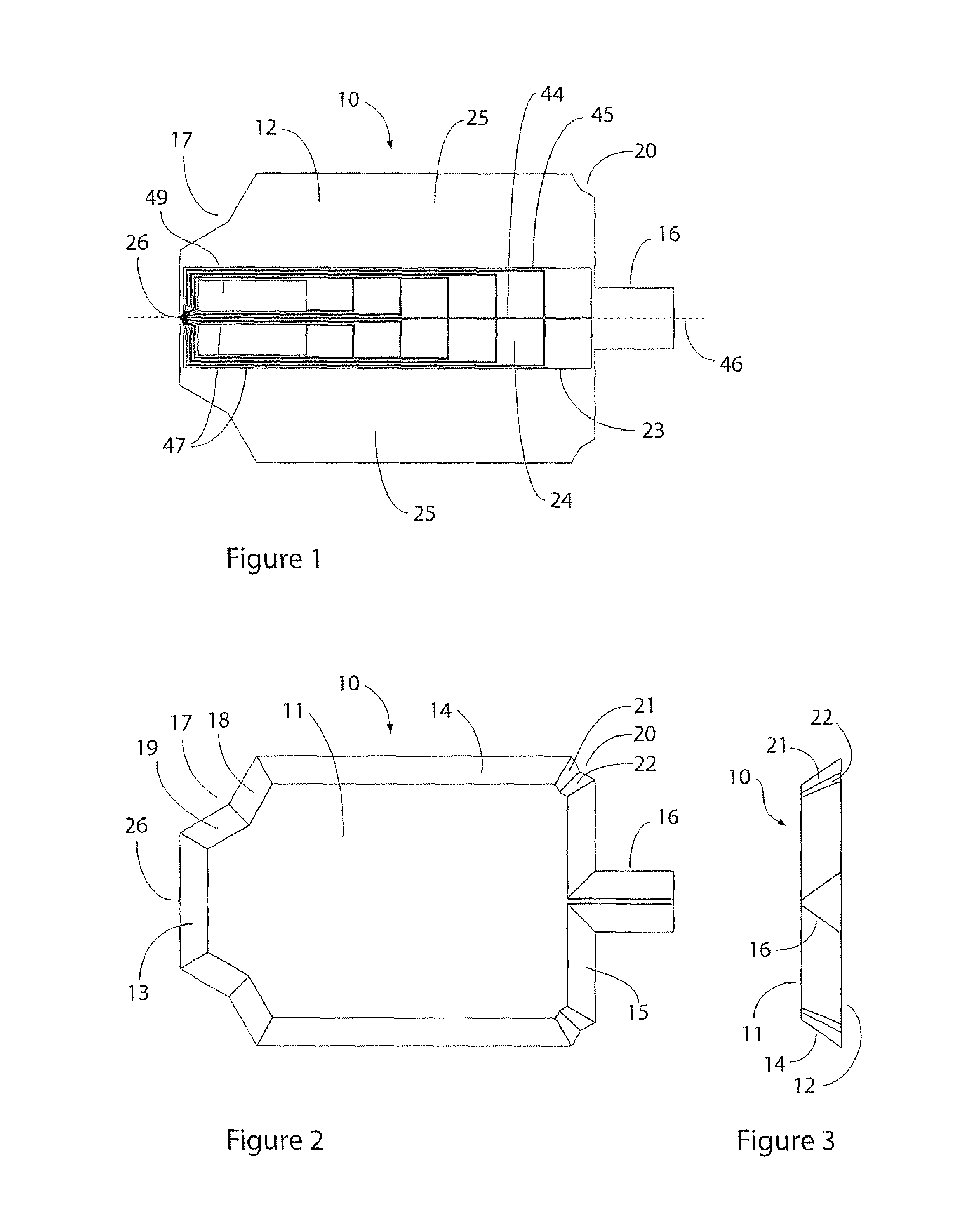

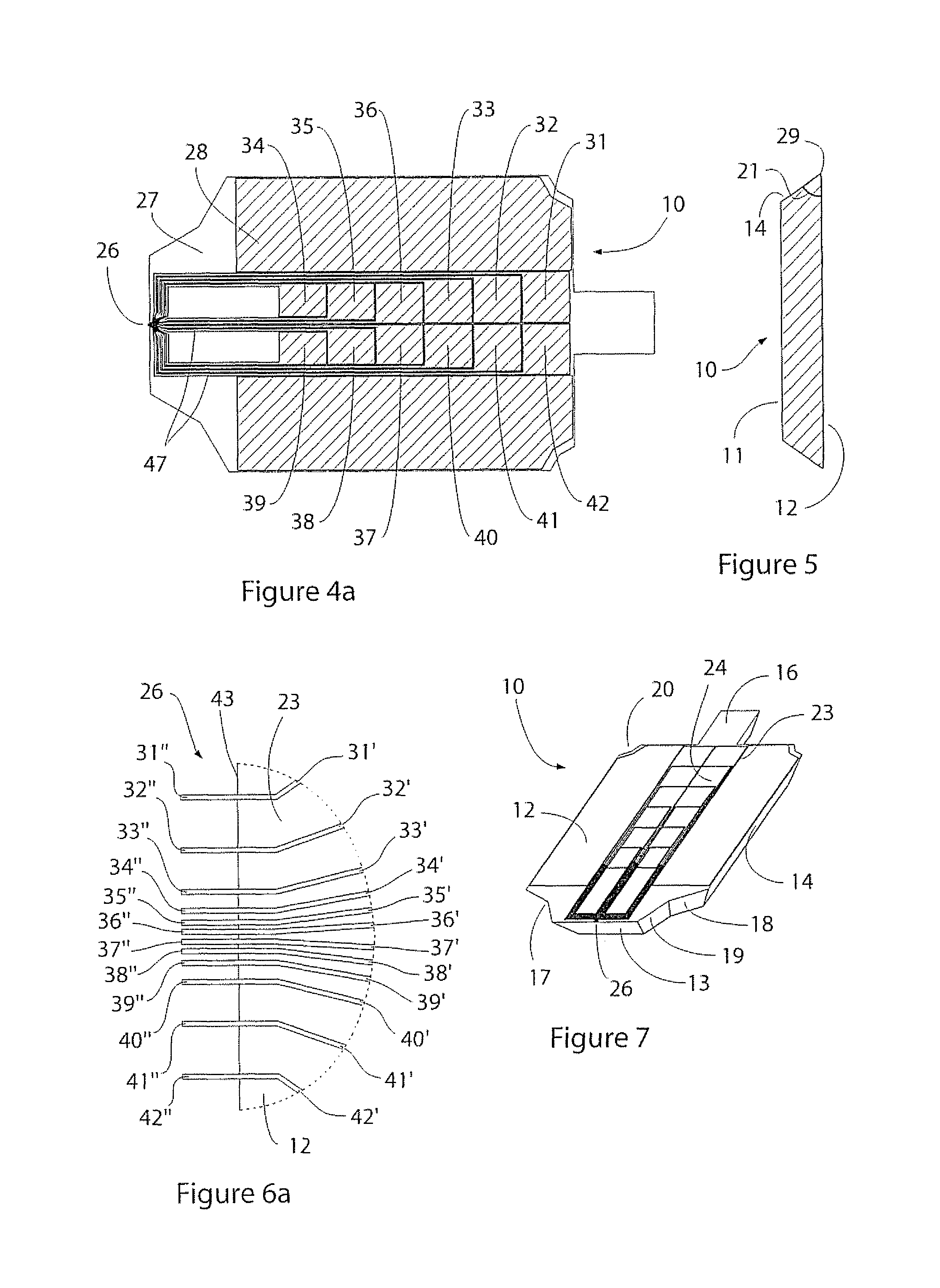

Automated multi-point probe manipulation

ActiveUS20120119770A1Accurately positionImprove accuracyElectrical measurement instrument detailsElectrical testingManipulatorBiomedical engineering

A multi-point probe particularly suitable for automated handling is disclosed. An automated multi-point measuring system including the multi-point probe and a probe manipulator head is also disclosed In addition, an automated multi-point probe gripping system including a probe holder and the probe manipulator head is revealed. Further, a loaded probe loader comprising a probe loader and a probe cassette for handling the multi-point probe is also revealed, where the probe cassette is provided with the probe holder for securing the multi-point probe.

Owner:CAPRES

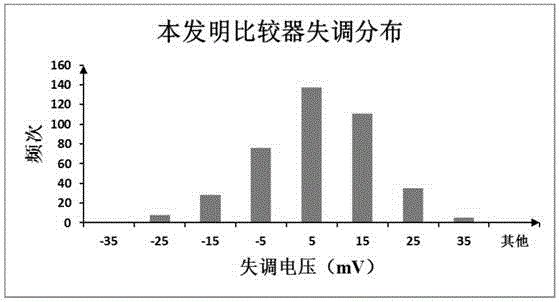

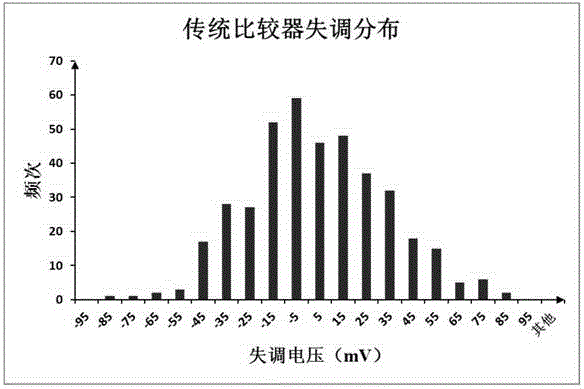

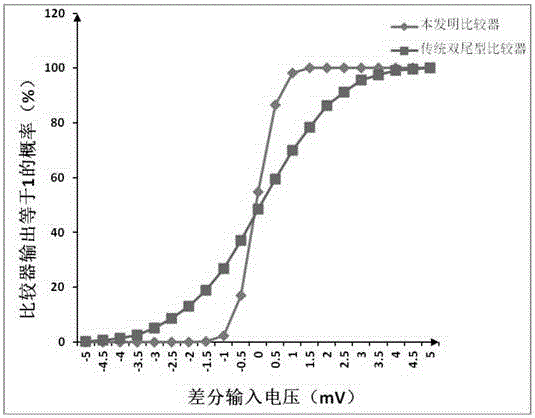

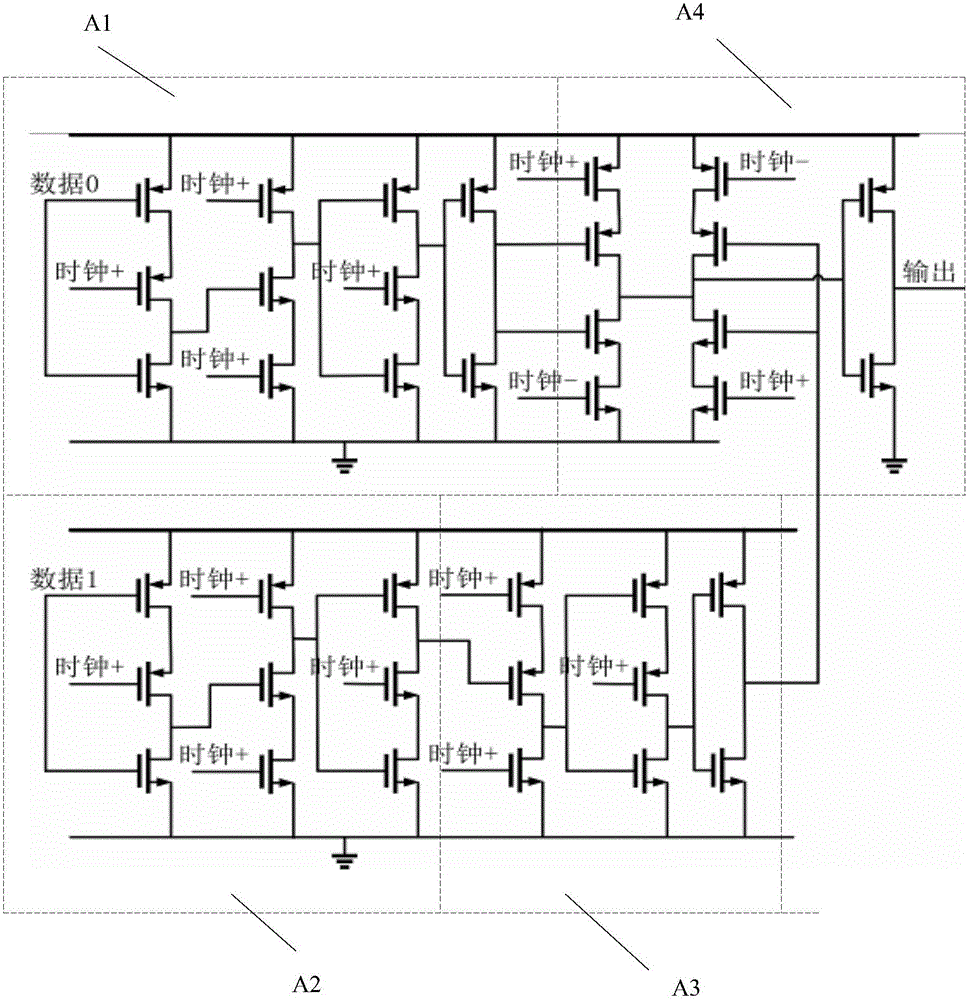

Two-level comparator

InactiveCN106209035AReduce noiseReduce offsetMultiple input and output pulse circuitsCouplingComparators circuits

The present invention relates to a two-level comparator circuit, belonging to the technical field of analog integrated circuits. The two-level comparator circuit comprises an input level and a latch level. The input level comprises a first N-channel metal oxide semiconductor (NMOS) transistor (MN1), a second NMOS transistor (MN2), a third NMOS transistor (MN3), a first p-channel metal oxide semiconductor (PMOS) transistor (MP1), a second PMOS transistor (MP2), a third PMOS transistor (MP3) and a fourth PMOS transistor (MP4). The latch level comprises a fourth NMOS transistor (MN4), a fifth NMOS transistor (MN5), a sixth NMOS transistor (MN6), a seventh NMOS transistor (MN7), an eighth NMOS transistor (MN8), a ninth NMOS transistor (MN9), a fifth PMOS transistor (MP5), a sixth PMOS transistor (MP6), a seventh PMOS transistor (MP7) and an eighth PMOS transistor (MP8). Due to reset of a node X+ and a node X- in a latch level circuit, circuit maladjustment and noise are lowered. A pair of cross-coupling transistors MP1 and MP2 is added in the input level circuit, so that the comparator has the characteristic of working at a high-speed. The two-level comparator is applicable to system circuits of high accuracy.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

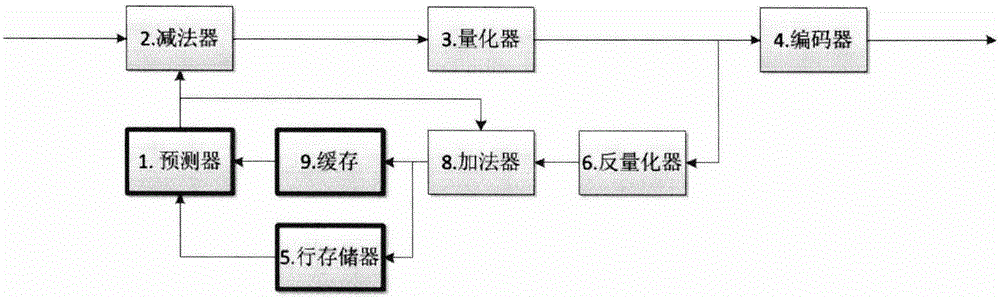

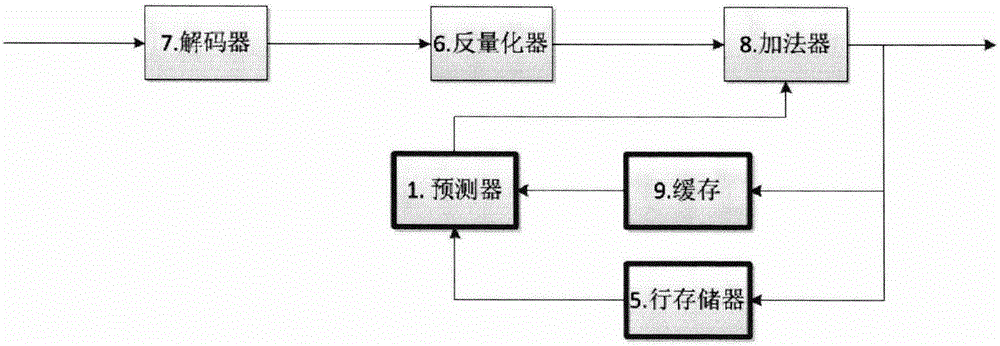

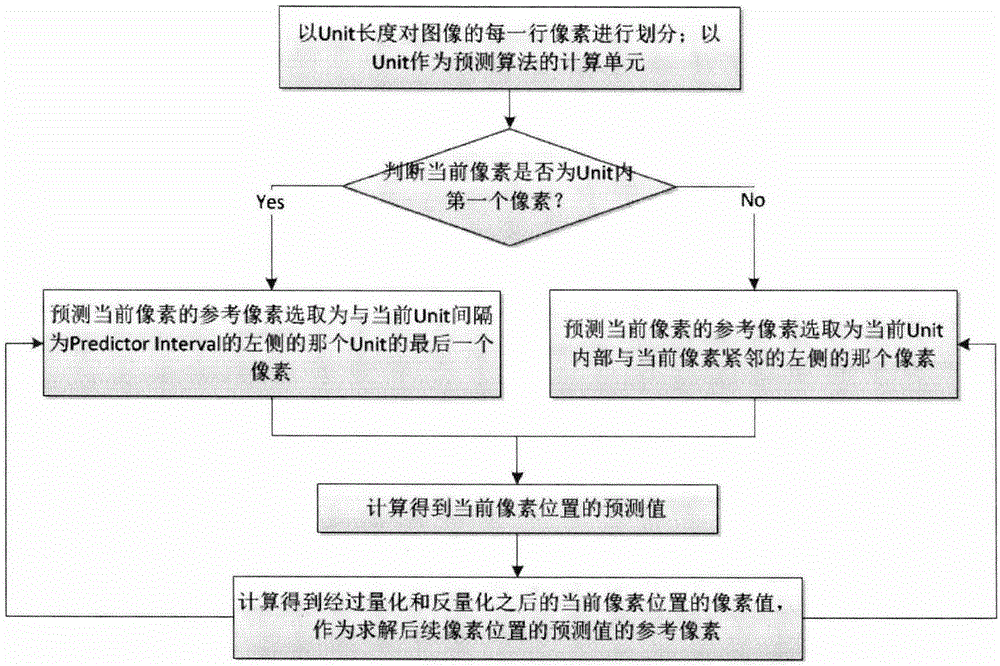

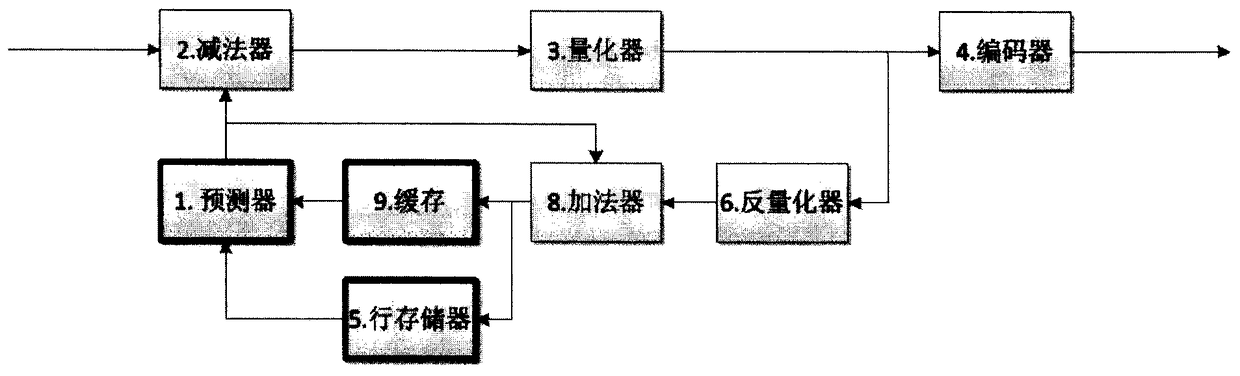

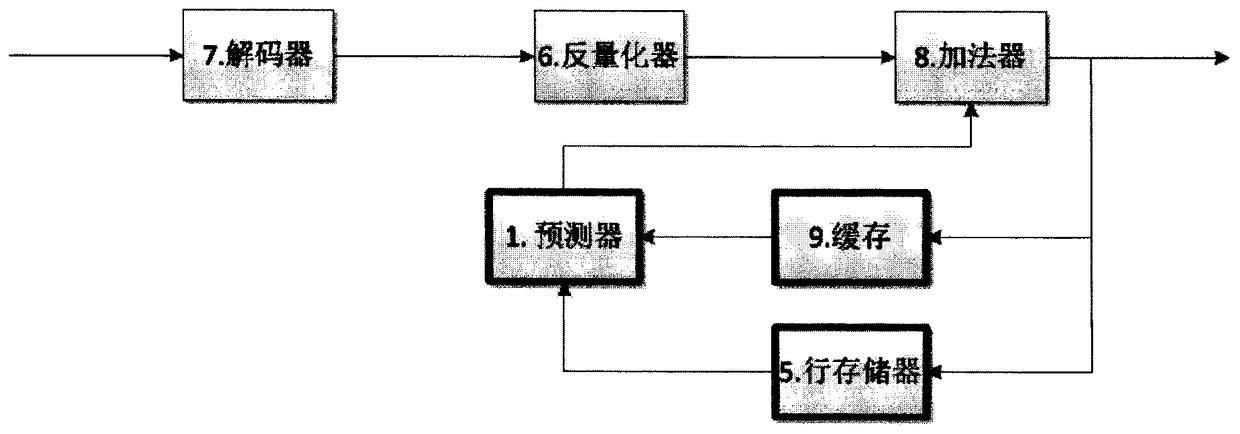

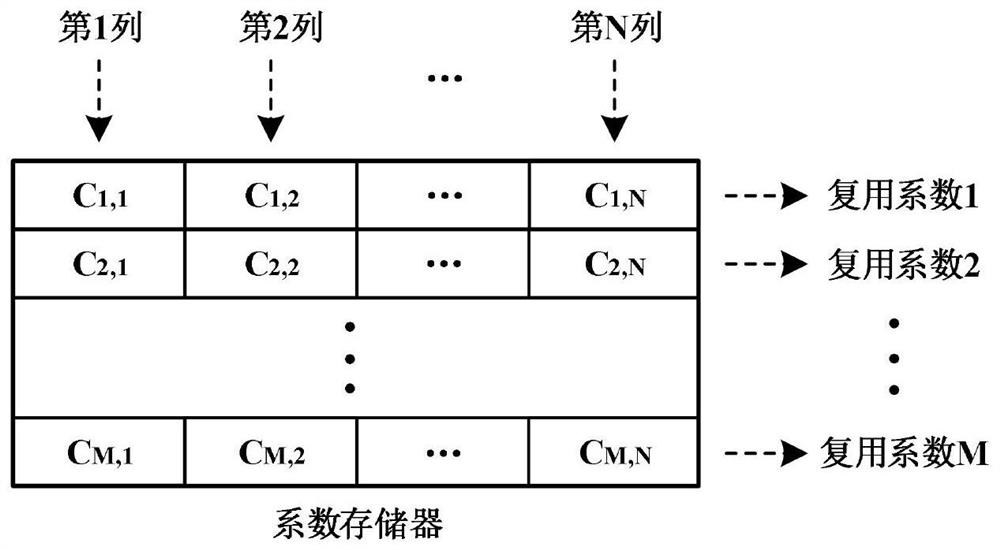

Real-time digital image compression prediction method and system

ActiveCN105208394AMeet Design ComplexityReduce Design ComplexityDigital video signal modificationImage resolutionPrediction interval

The invention discloses a real-time digital image compression prediction method, facilitating realization of a digital circuit and capable of performing time sequence optimization, based on prediction. Based on the prediction method, according to the image resolution, realization difficulty of the digital circuit and trade-off of compression efficiency, numerical values of a group of unit and prediction interval are selected. Higher is the image resolution, higher is the requirement for a time sequence of the digital circuit, at the moment, and the numerical values of the unit and prediction interval can be appropriately increased; according to the values of the selected unit and prediction interval and the position of the unit where a current pixel is located, corresponding reference pixels are selected for calculating the prediction value of the current pixel. By the adoption of the prediction method, the requirement for the time sequence of the digital circuit in a chip can be lowered, high practical value is achieved, and the method is expected to be applied to integrated circuits needing real-time video stream compression and decompression.

Owner:CHIPONE TECH BEIJINGCO LTD

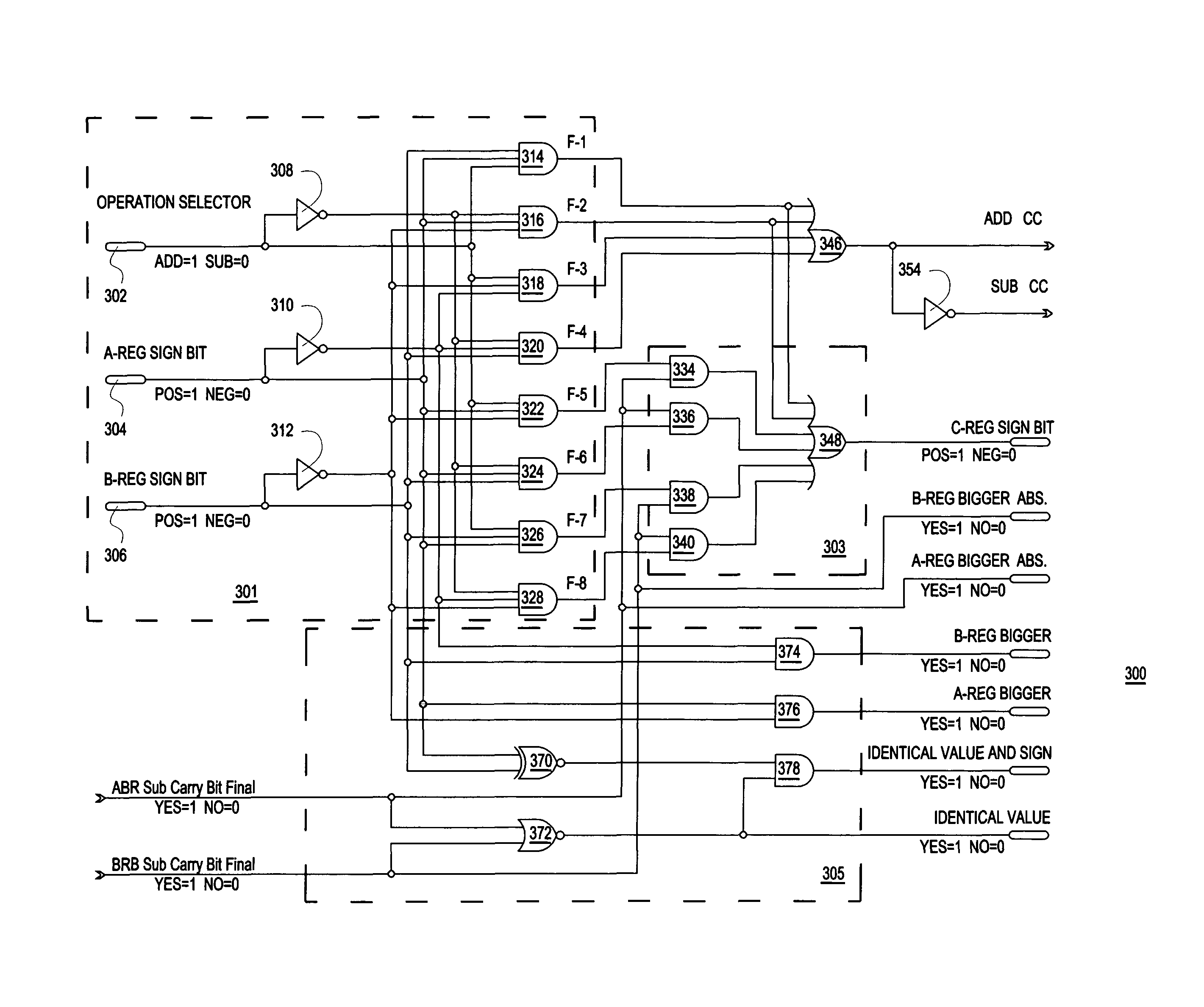

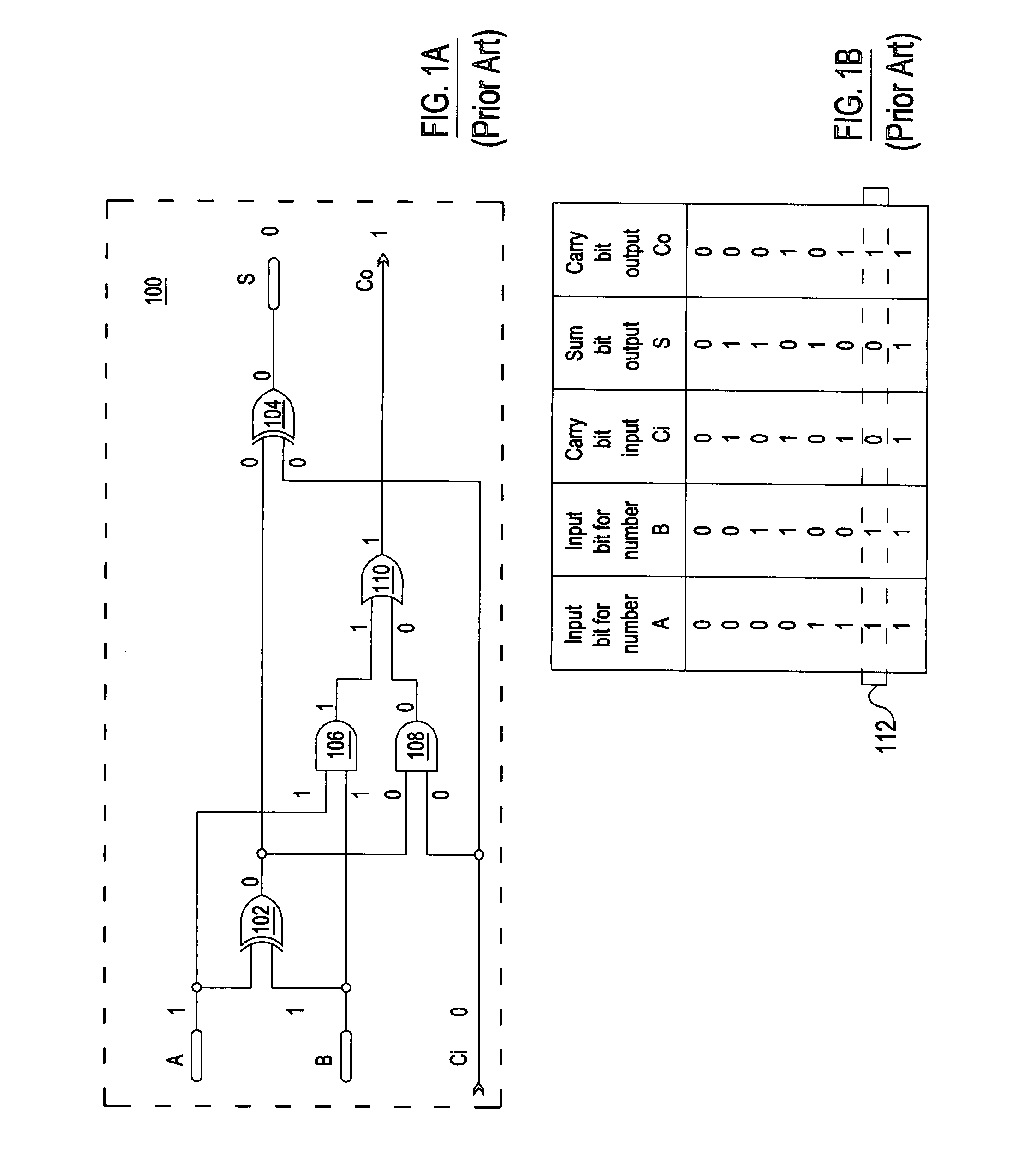

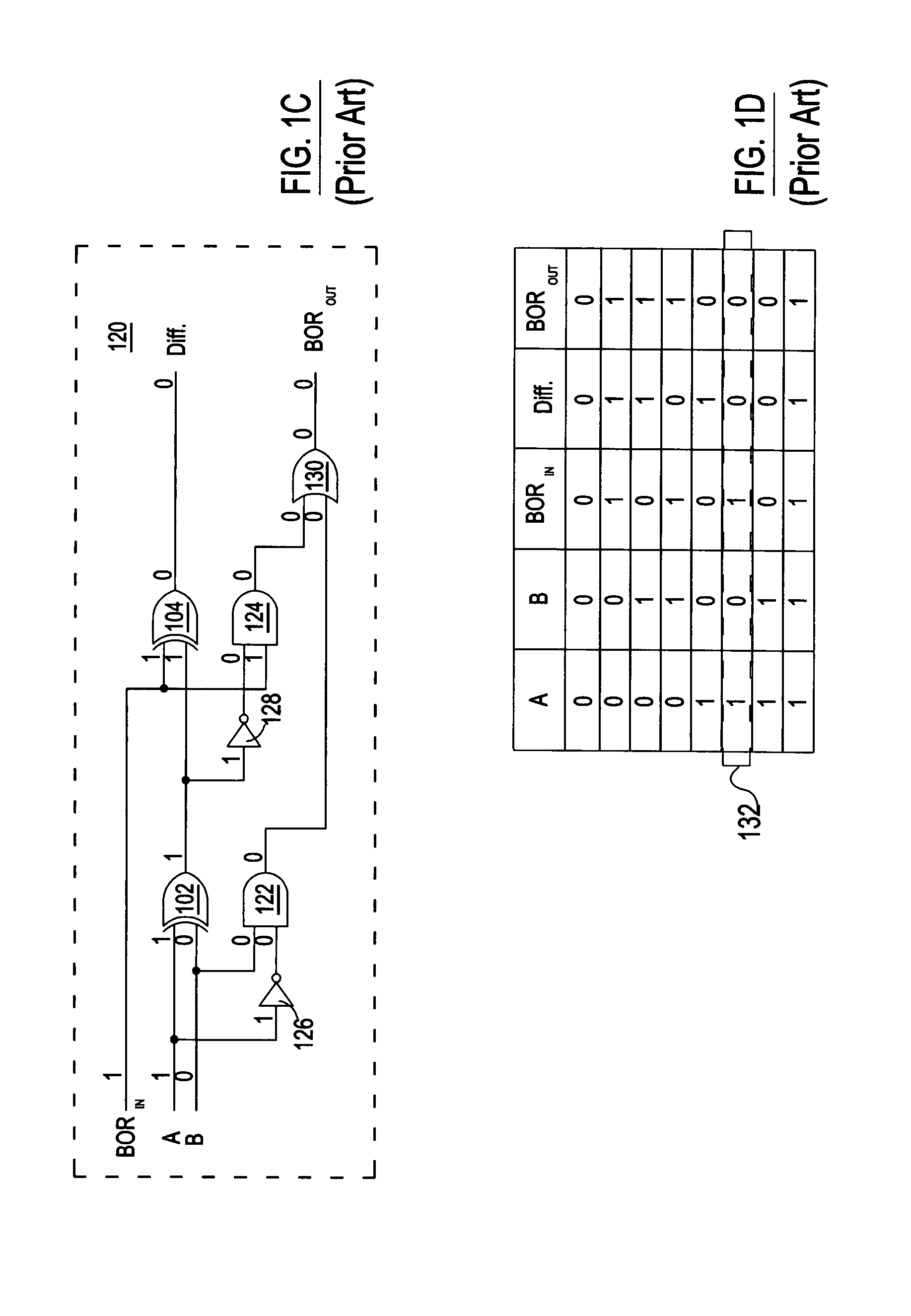

One step binary summarizer

InactiveUS7991820B1Eliminate needEliminate utilizationComputation using non-contact making devicesProcessor registerOperand

The ONE STEP BINARY SUMMARIZER is a digital logic circuit. It is used for summarizing two binary numbers. It contains one Function Generator Module and one or more SUMMARIZER Units. For subtraction it is subtracting Register “A” from Register “B” and Register “B” from Register “A”. The two subtraction and one addition operations are executed simultaneously. The Function Generator Module determines the actual correct operation, (addition or subtraction) and selects the correct results for the resultant operand. The circuit utilizes the subtraction-by-carry method; therefore the subtraction operation does not require any presorting, complementary operations, iterative additions, temporary storage, and multiple instruction sets, etc. The logic-flow is similar, the operational speed is identical for the addition and subtraction operations; and therefore, it is a true Time Symmetrical circuit. It is independent from the initial operation selection, the signs and magnitudes of the input operands.

Owner:SOHAY LESLIE IMRE

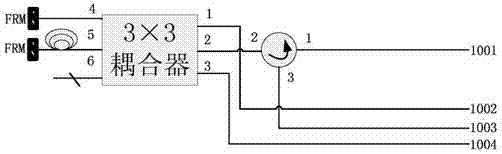

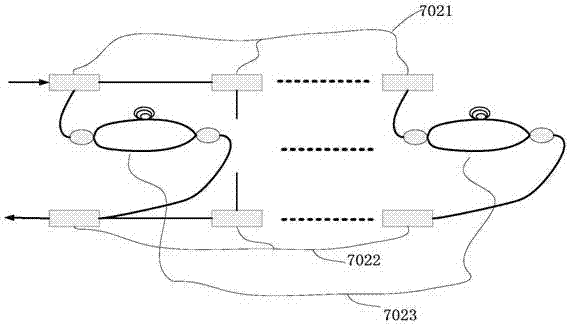

3x3 coupler scheme-based all-fiber interference type circumference security and protection system

InactiveCN107230307AEliminates the effects of changes in light sourcesLower requirementBurglar alarm by disturbance/breaking stretched cords/wiresFiberEngineering

The invention relates to the field of fiber sensing and circumference security and protection, in particular to a 3x3 coupler scheme-based all-fiber interference type circumference security and protection system. The 3x3 coupler scheme-based all-fiber interference type circumference security and protection system is characterized by comprising a multi-wavelength single-frequency laser emission unit (1), a light source protection unit (2), a wavelength multiplexing unit (3), a pulse modulation unit (4), a power amplifier (5), a power distributor (6), a space division sensing array (7), a preamplification unit (8), a wavelength demultiplexing unit (9), an interference matching unit (10), a photoelectric conversion and demodulation unit (11) and a display and control unit (12), wherein the space division sensing array (7) comprises a transmission optical cable (701) and wavelength division sensing arrays (702); each group of wavelength division sensing array (702) comprises multiple groups of wavelength delete multiplexers (7021), wavelength increase multiplexers (7022) and interferometers (7023); each interferometer (7023) corresponds to a single-frequency light source wavelength; the COM (cluster communication) ports of the wavelength delete multiplexers (7021) are input ports.

Owner:WEIHAI BEIYANG PHOTOELECTRIC INFORMATION TECH

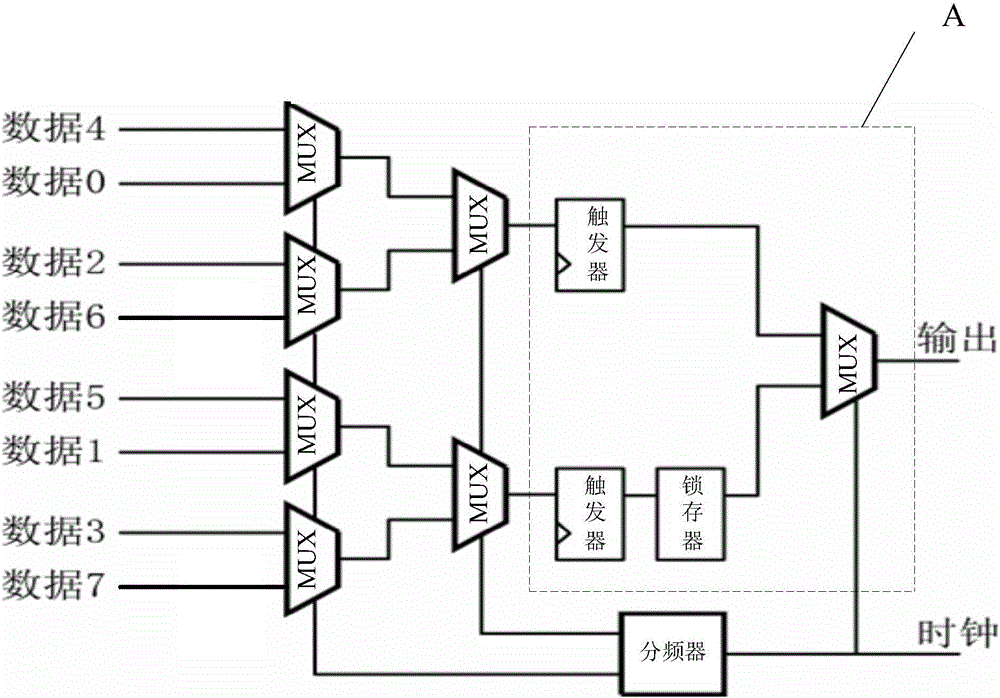

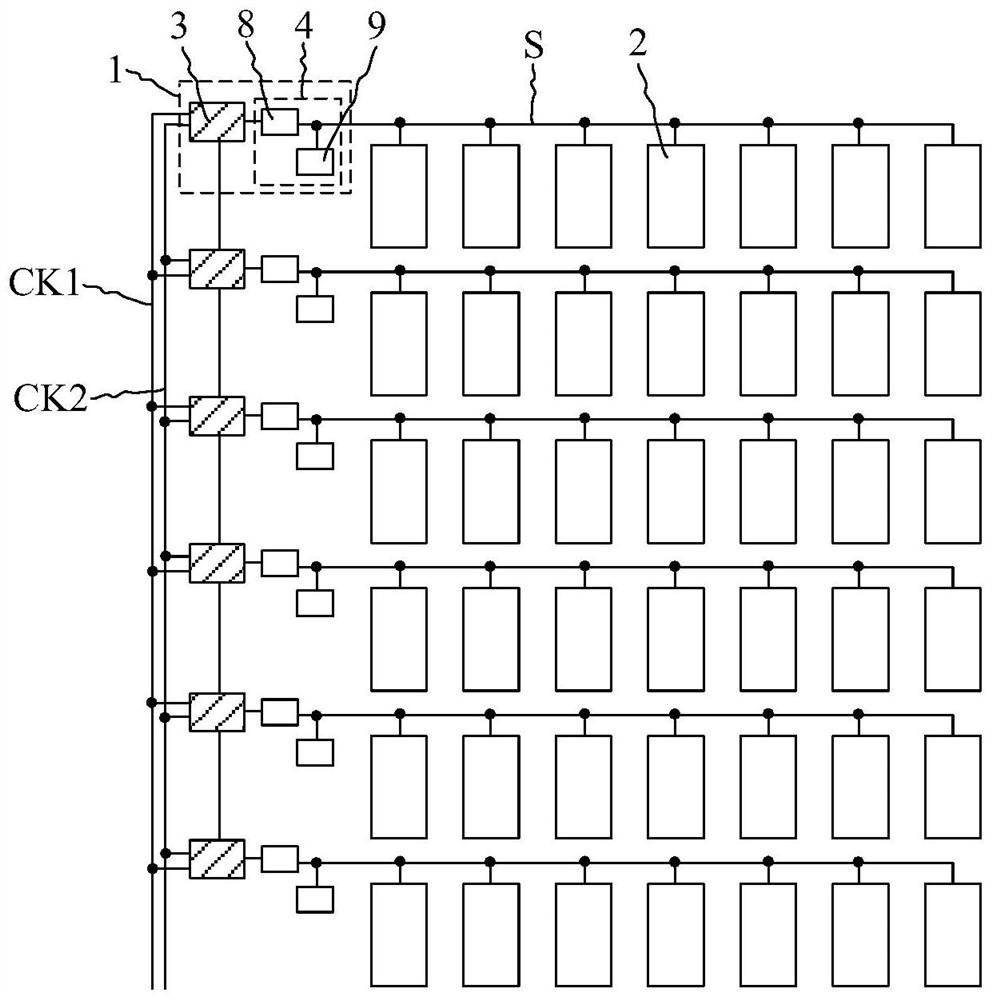

Parallel-serial conversion circuit

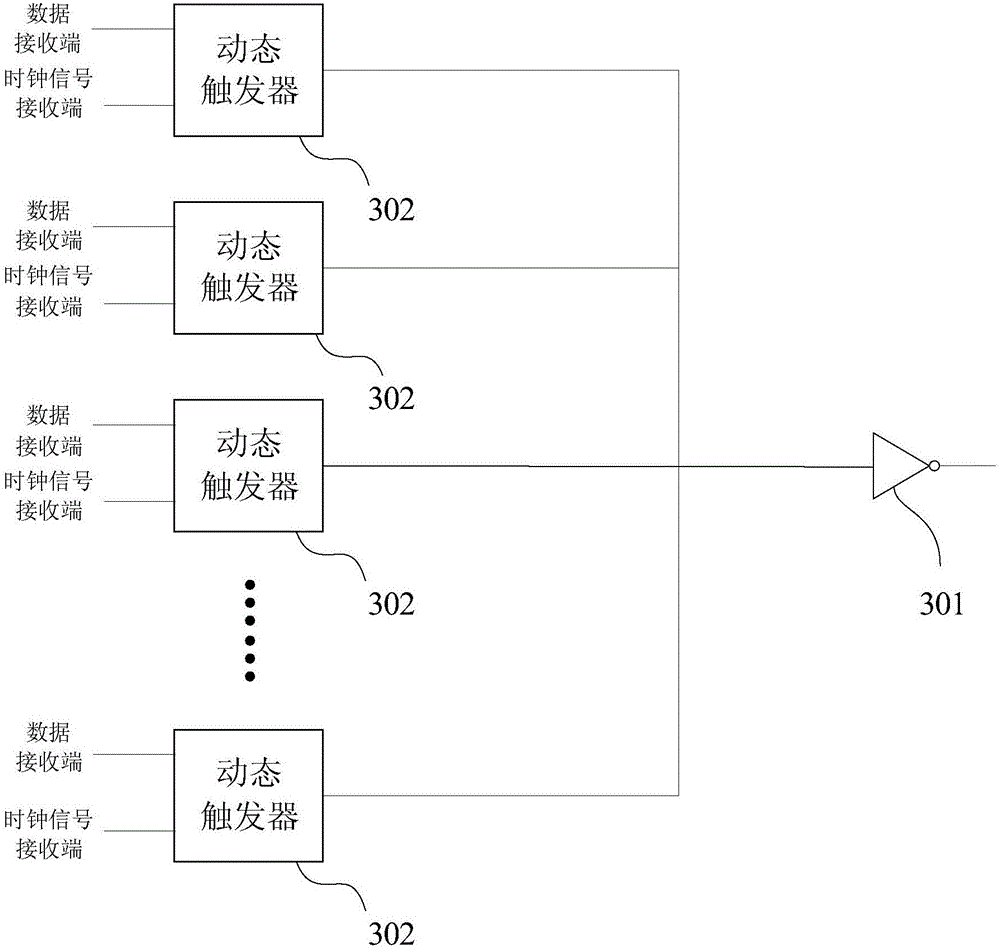

ActiveCN107437945ASimple structureReduce the occupied areaParallel/series conversionTime sequenceClock signal

The present invention provides a parallel-serial conversion circuit. The circuit comprises a phase inverter and N dynamic triggers, wherein N is identical to the number of the bits of received parallel data; the output ends of the N dynamic triggers are connected with the input end of the phase inverter; the data receiving end of the n-th dynamic trigger receives n-th-bit data in the N-bit parallel data; the clock signal receiving end of the n-th dynamic trigger receives n-th clock signals; the clock periods of the clock signals are the same as the update period of the N-bit parallel data; the high eclectic level of the clock signals does not overlap; the circuit structure of each dynamic trigger does not include the phase inverter; and the value of n is a positive integer from 1 to N. The structure of the parallel-serial conversion circuit provided by the invention is simplified, time sequence requirements on paths are lowered, and an area occupied by the circuit is decreased.

Owner:LOONGSON TECH CORP

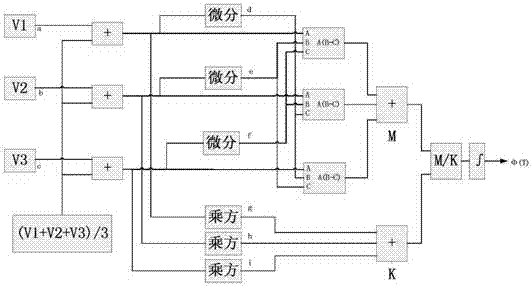

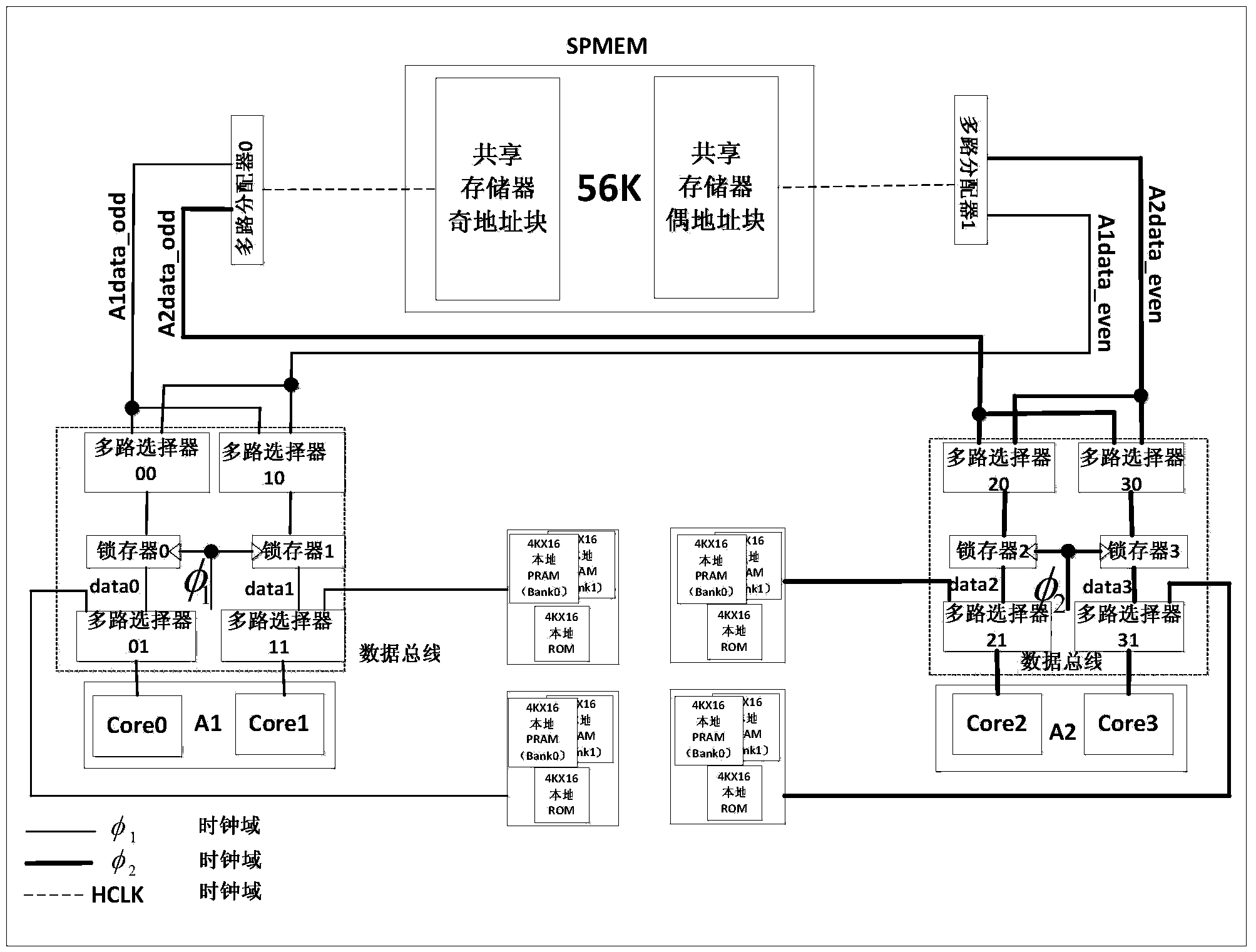

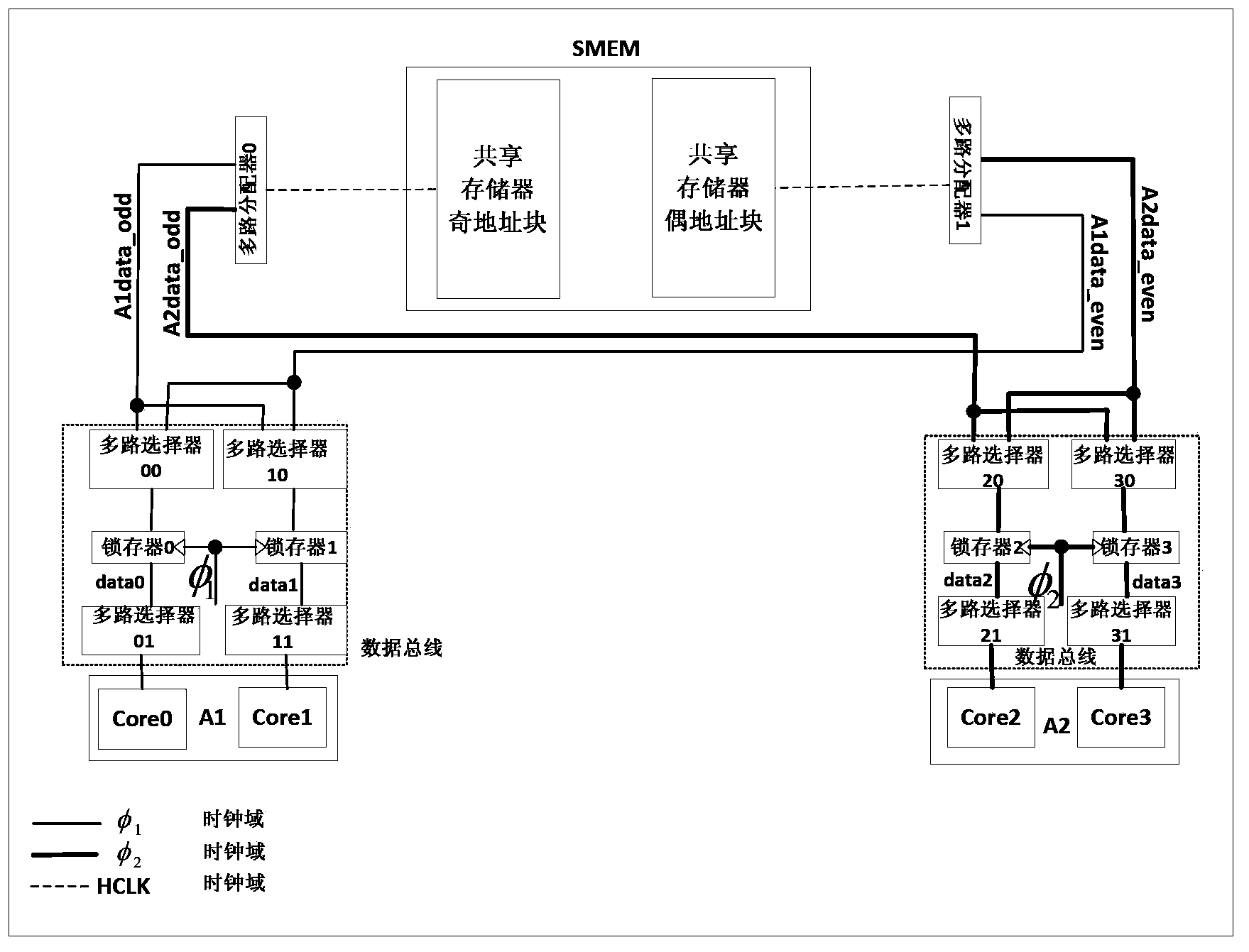

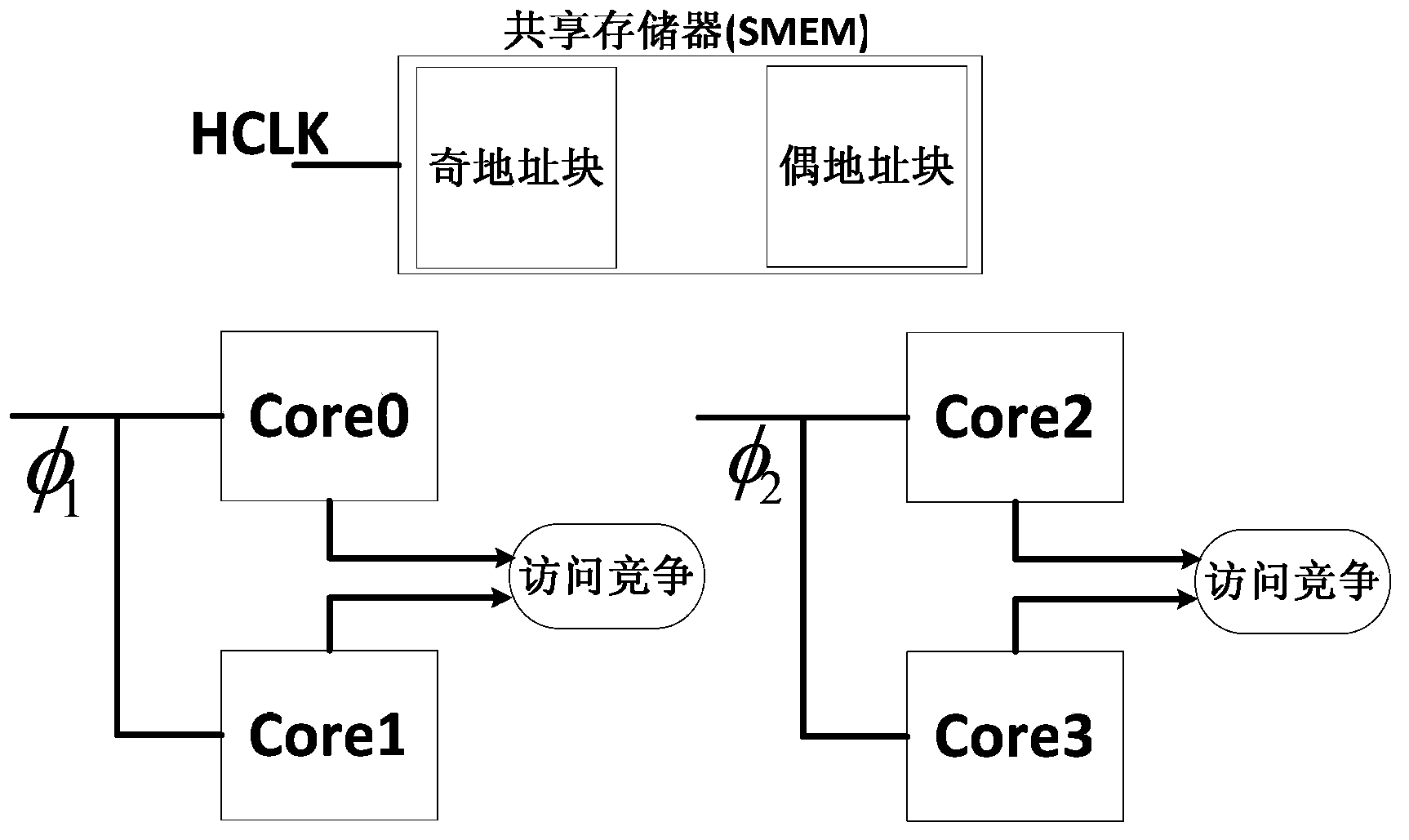

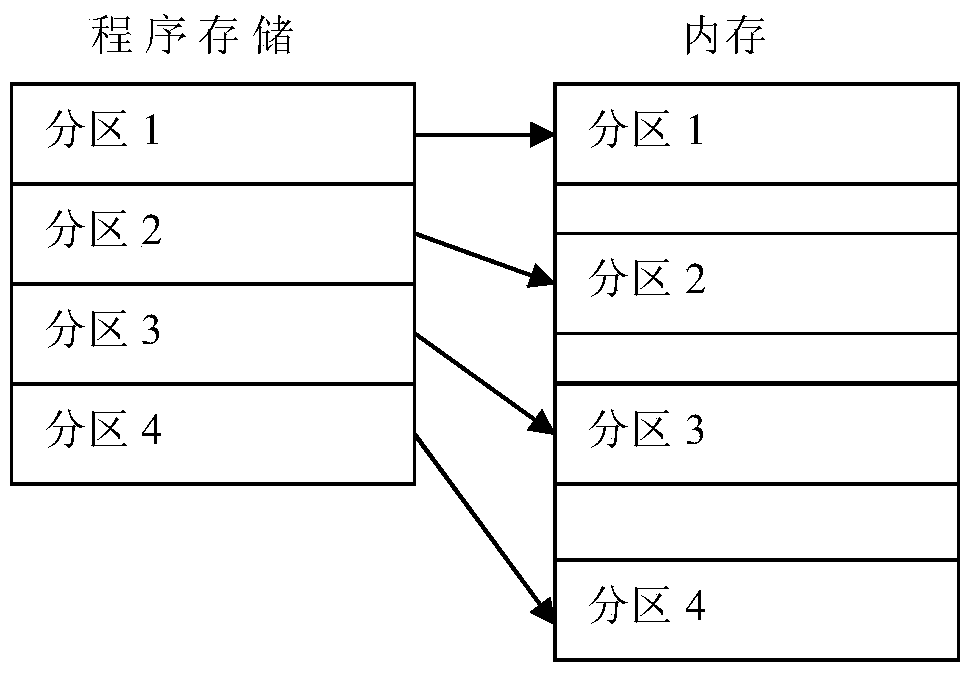

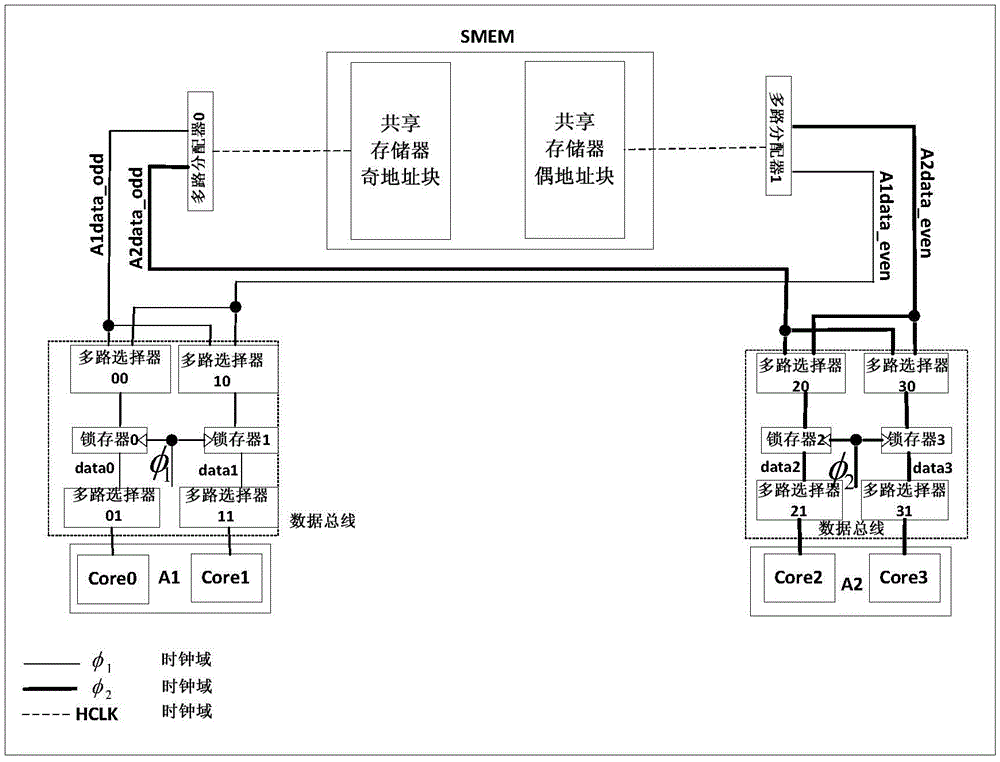

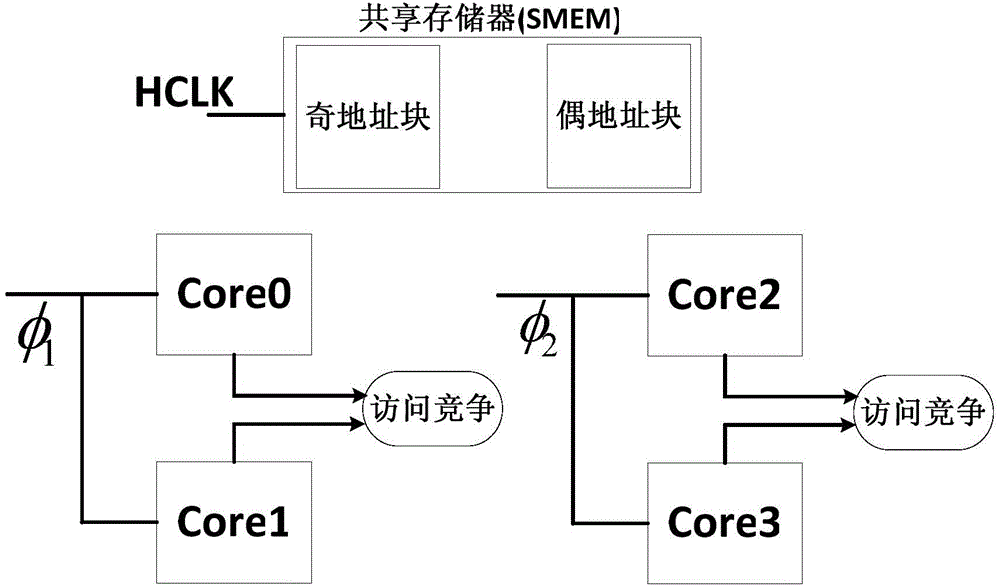

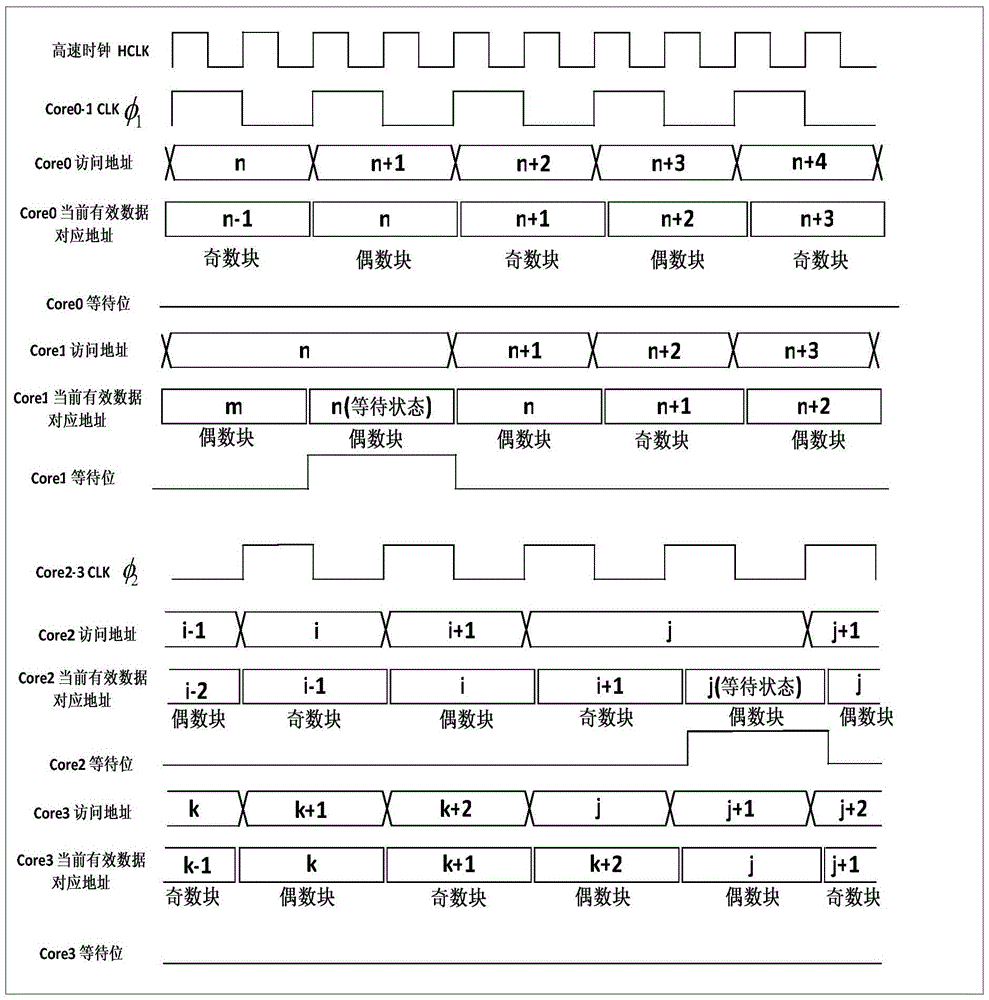

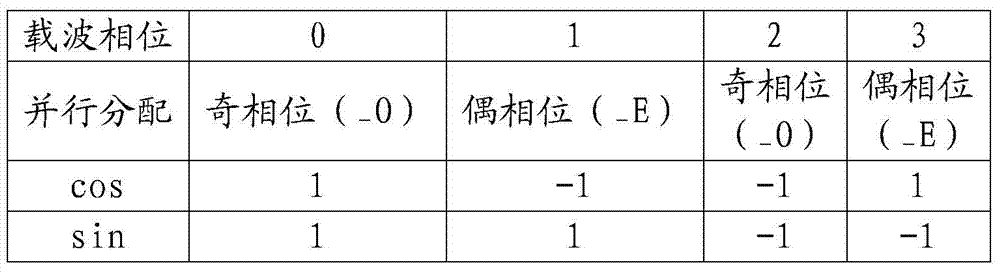

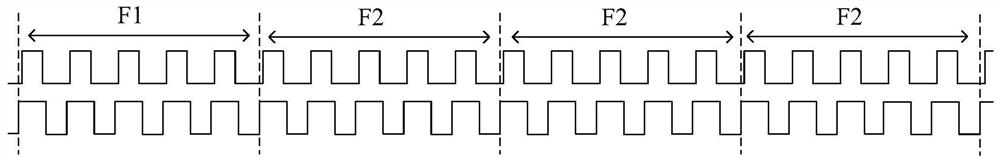

Method for sharing single program memory by four-core processor system

InactiveCN103412848AReduce areaReduce transmission delayDigital computer detailsElectric digital data processingMemory addressAddress bus

The invention discloses a method for sharing a single program memory by a four-core processor system. The method that two-phase clocks are used and the method that memory addresses are separately piled according to odd serial numbers and even serial numbers are combined. Four processors of the four-core processor system are respectively a Core0, a Core1, a Core2 and a Core3, and memory access addresses, corresponding to the four processors, on an address bus are respectively addr0, addr1, addr2 and addr3, wherein the Core0 and the Core1 belong to a set A1 and are driven by the clock phi 1, the Core2 and the Core3 belong to a set A2 and are driven by the clock phi 2, the shared memory SMEM is driven by a clock HCLK, the phase of the clock phi 1 and the phase of the clock phi 2 are opposite, and the frequency of the clock phi 1 and the phase of the clock phi 2 are half the frequency of the clock HCLK. Because the phase of the clock phi 1 and the phase of the clock phi 2 are opposite, the two groups of Cores, namely the A1 and the A2, can independently access the memory without being mutually interrupted or generating accessing competition. The method for sharing the single program memory by the four-core processor system solves the problem of access competition generated when the memory is shared by the four-core processor system.

Owner:UNIV OF SCI & TECH OF CHINA

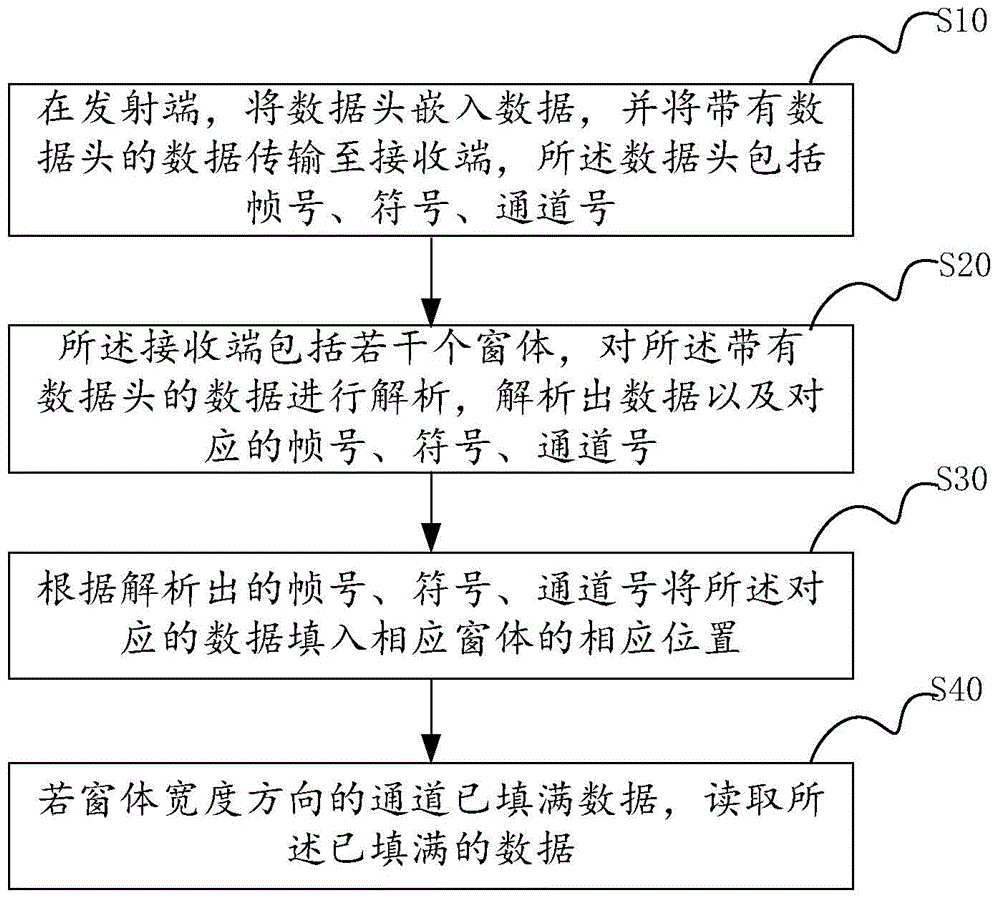

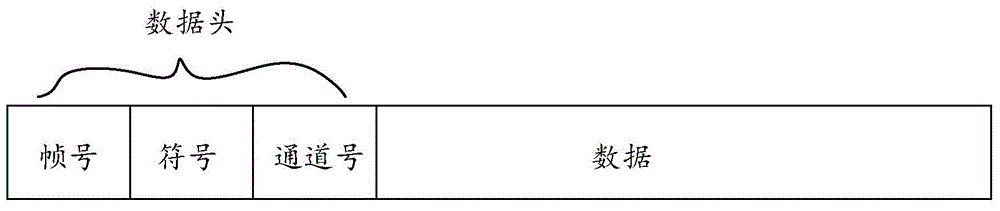

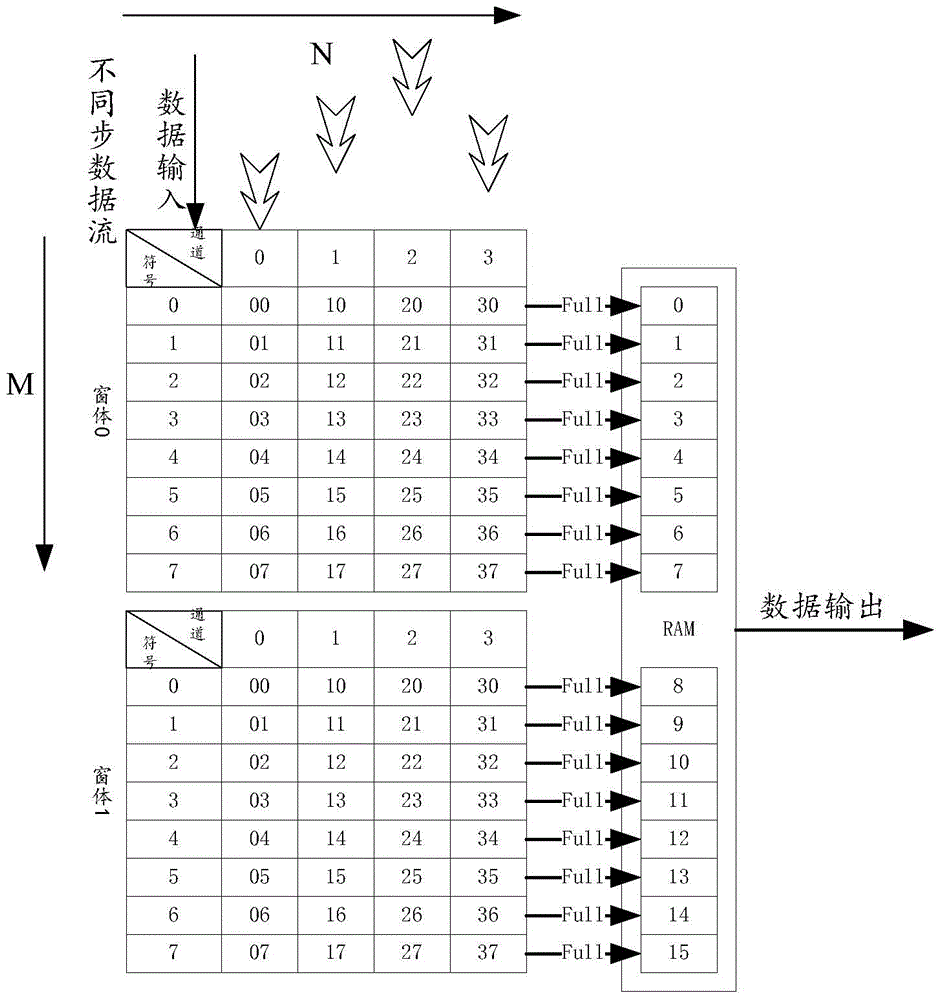

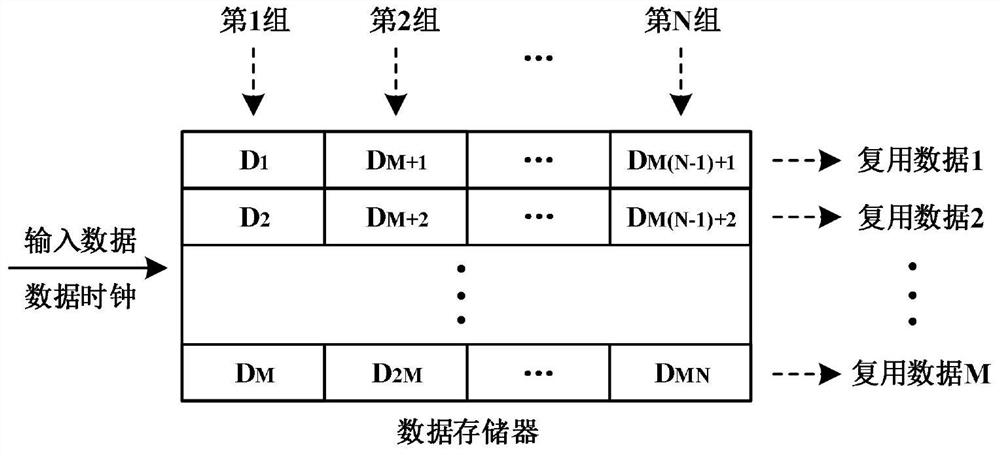

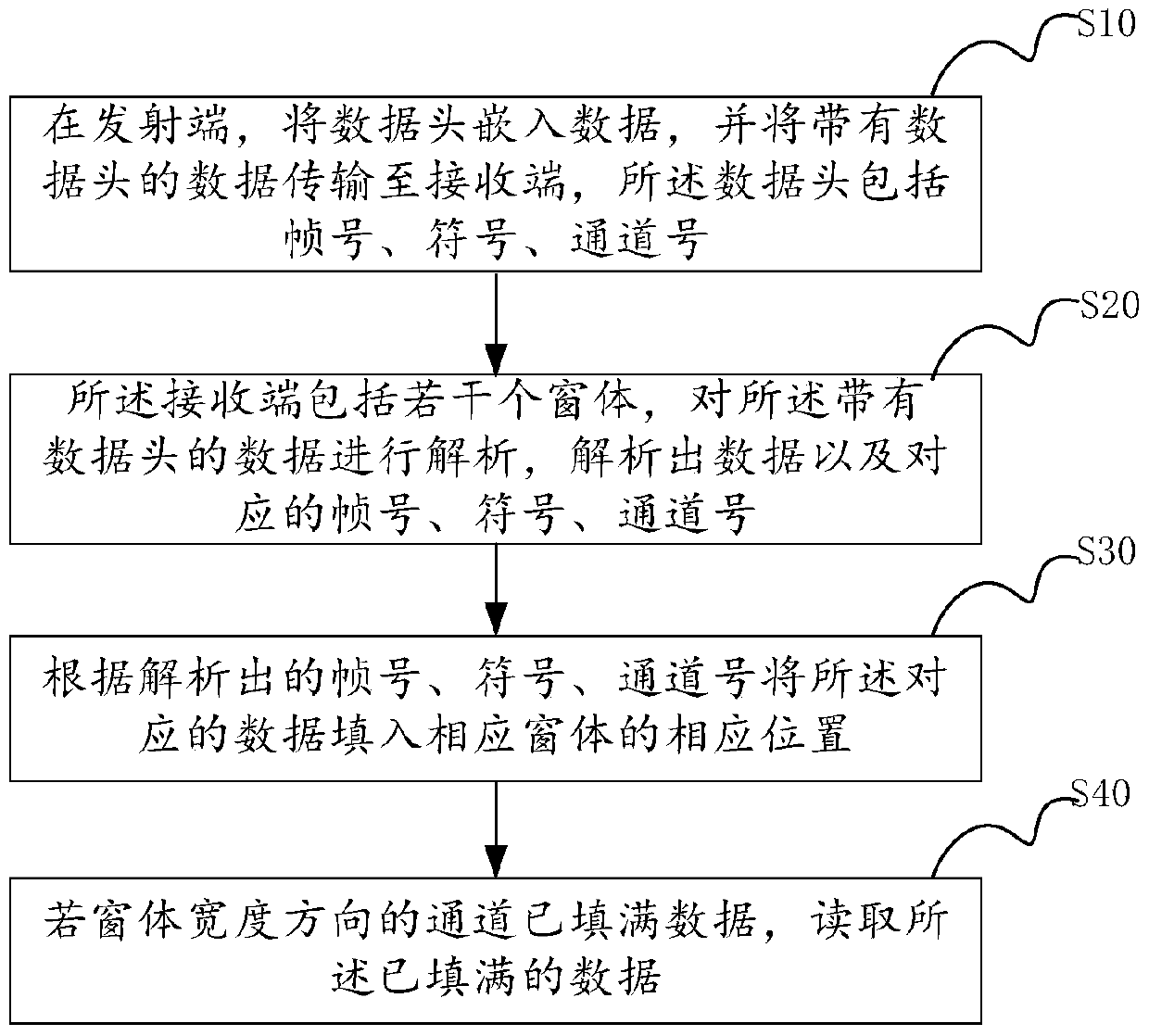

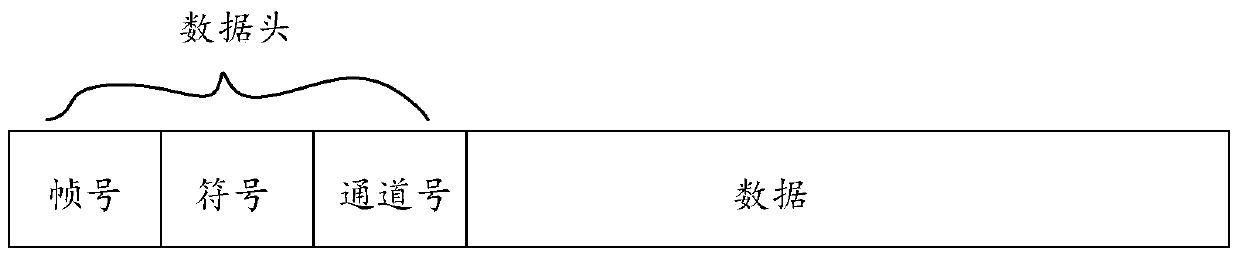

Multichannel data transmission method and system

ActiveCN104954113AImprove transmission efficiencyLow timing requirementsSynchronising arrangementTime delaysEmbedded system

The invention provides a multichannel data transmission method. Data heads are embedded in data at a transmitting end, the data heads include frame numbers, symbols and channel numbers, and the data with the data heads are transmitted to a receiving end; the receiving end comprises multiple window bodies which parse the data heads so that the frame numbers, the symbols and the channel numbers are obtained through parsing; and the data corresponding to the data heads are filled in the corresponding positions of the corresponding window bodies according to the parsed frame numbers, the symbols and the channel numbers. The requirement of synchronous transmission for timing sequence is reduced by the technical scheme, data transmission of different channels does not need to consider time delay difference between channels, the same transmission medium is not needed, multiple channels do not need to be strictly aligned, and even multiple transmitters can be asynchronous so that data transmission efficiency can be enhanced. The invention also provides a multichannel data transmission system.

Owner:SHANGHAI UNITED IMAGING HEALTHCARE

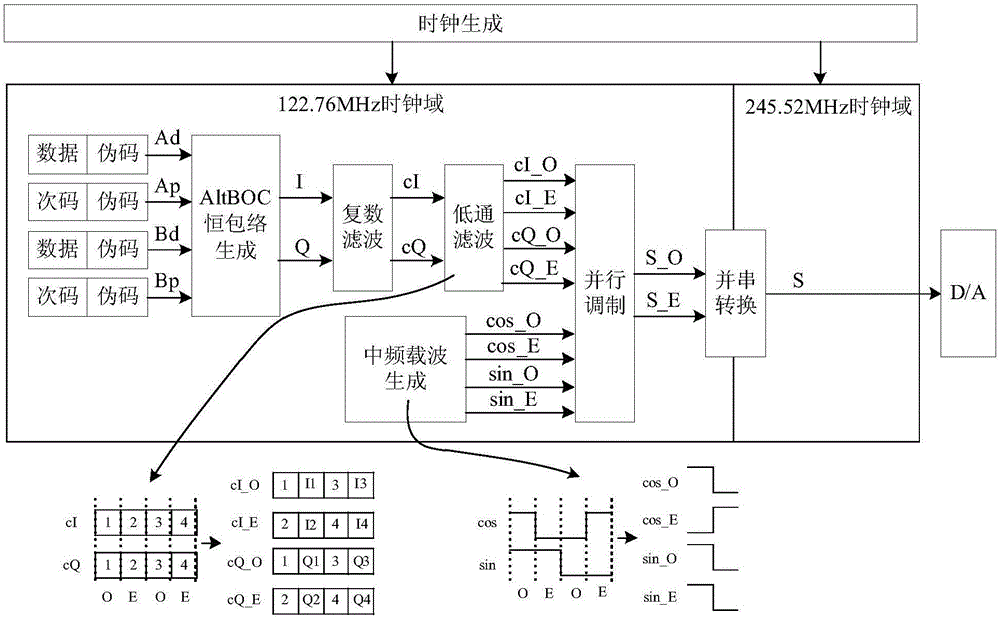

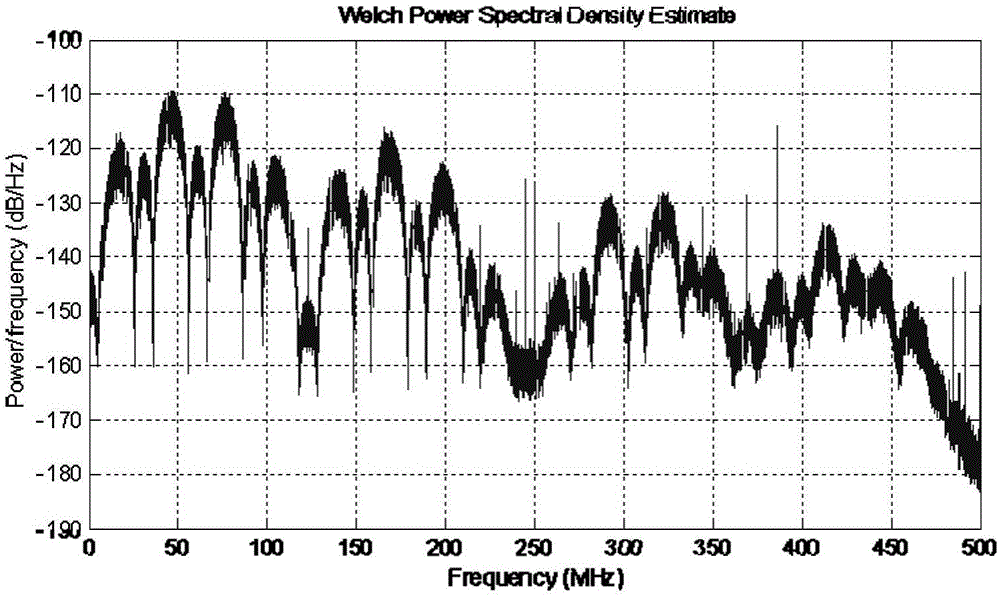

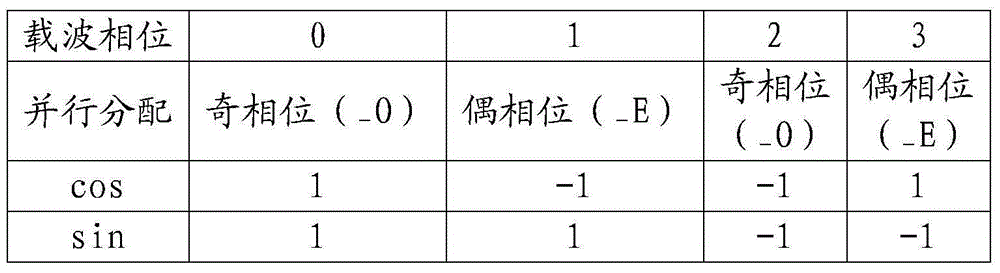

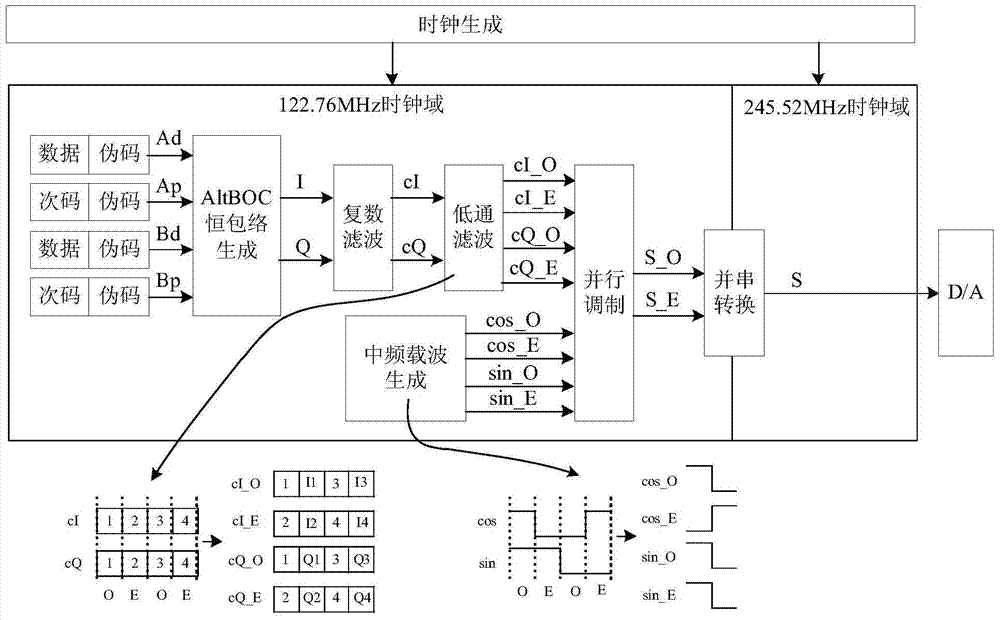

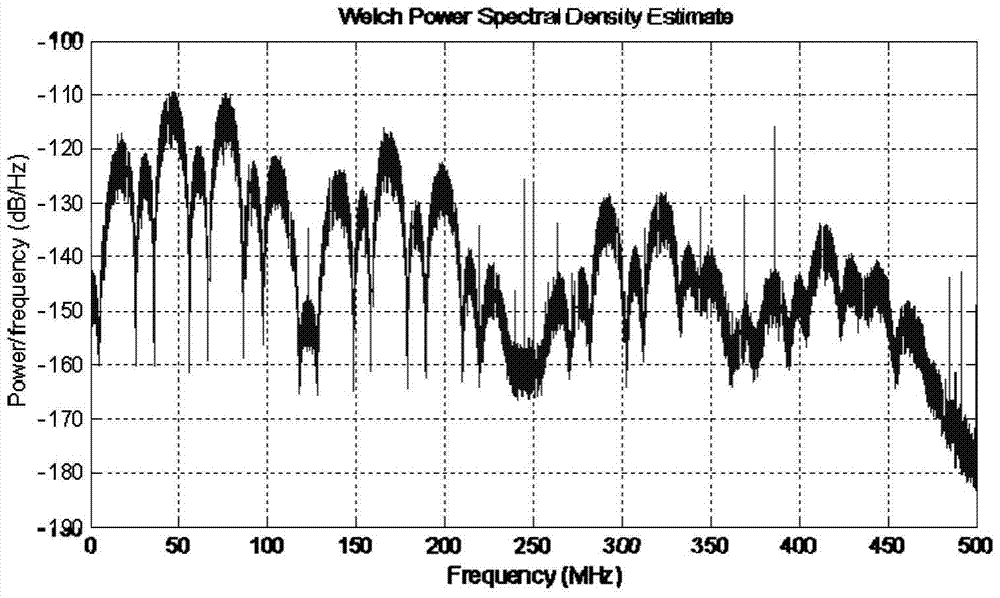

Parallel AltBOC navigation signal intermediate frequency generation method

ActiveCN105116425ALower timing requirementsReduce design costSatellite radio beaconingDistortionCarrier signal

The invention discloses a parallel AltBOC navigation signal intermediate frequency generation method, comprising the steps of: generating I and Q paths of baseband orthogonal signals; utilizing complex filtering to perform amplitude-frequency distortion compensation on I and Q to generate cI and cQ paths of baseband orthogonal signals; performing low pass filtering on generated cI and cQ paths of baseband orthogonal signals; generating intermediate frequency carrier waves; parallelly modulating the intermediate frequency carrier waves and the cI and cQ paths of baseband orthogonal signals; and finally performing parallel-serial conversion to output intermediate frequency signals. The method can generate AltBOC signals with lower frequency, guarantee the channel feature consistency of the I and Q branches, and meanwhile guarantee signal quality.

Owner:XIAN INSTITUE OF SPACE RADIO TECH

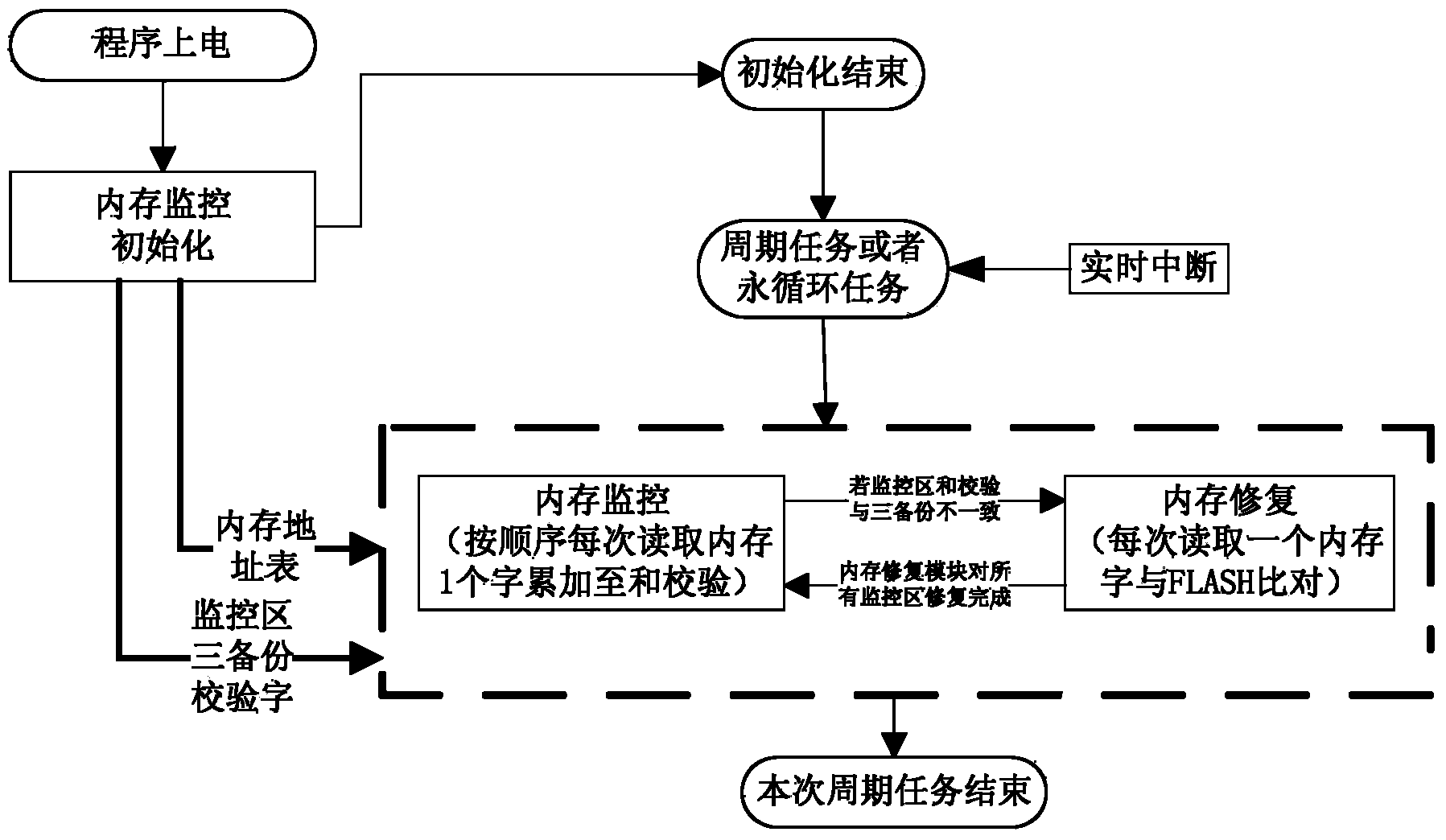

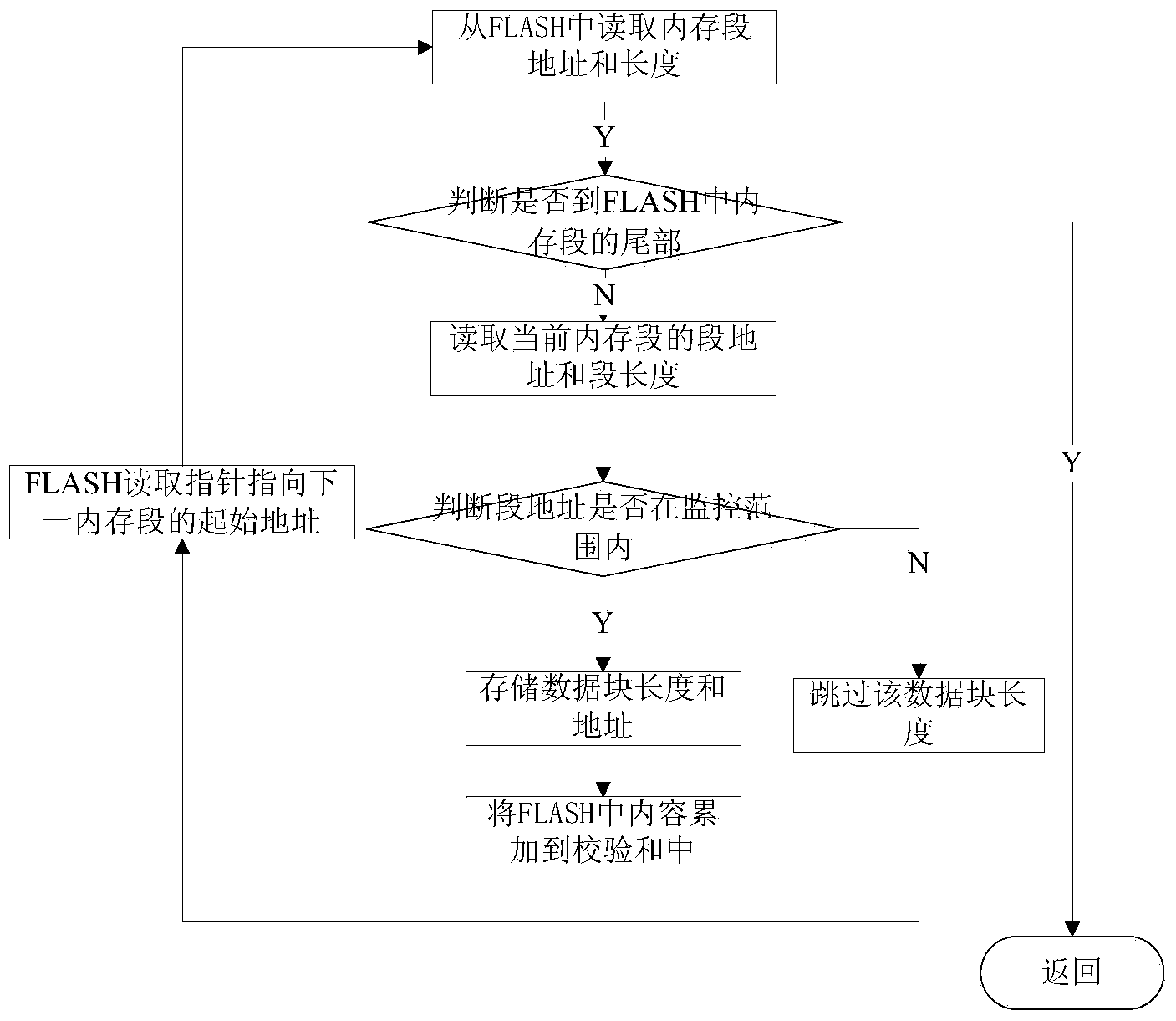

Real-time protection method for single particles of memory of satellite-borne software

InactiveCN103684688AImplement SRAM protectionShort cycle timeError preventionSoftware testing/debuggingIdle timeDependability

The invention discloses a real-time protection method for single particles of a memory of satellite-borne software. The real-time protection method includes judging whether content in the memory is rewritten or not by comparing itself with the corresponding content in a program storage during idle time of operation of the satellite-borne software; if yes, rewriting correct codes into the memory form the program storage. By the real-time protection method, reliability and stability of in-orbit operation of satellite-borne software products are greatly improved, influences of single particle events during in-orbit operation are eliminated, and in-orbit operation requirements of memory operation based satellite-borne software products can be met, so that the real-time protection method has broad engineering application prospect and important engineering application value in the field of satellite-borne real-time embedded systems.

Owner:SPACE STAR TECH CO LTD

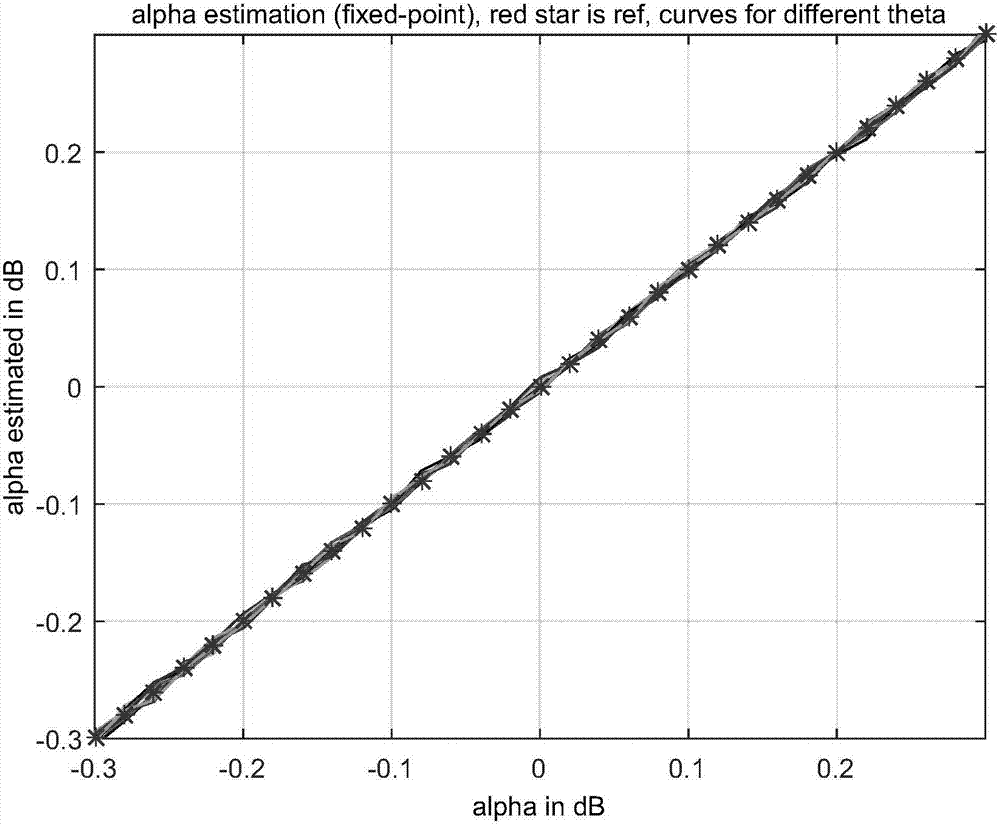

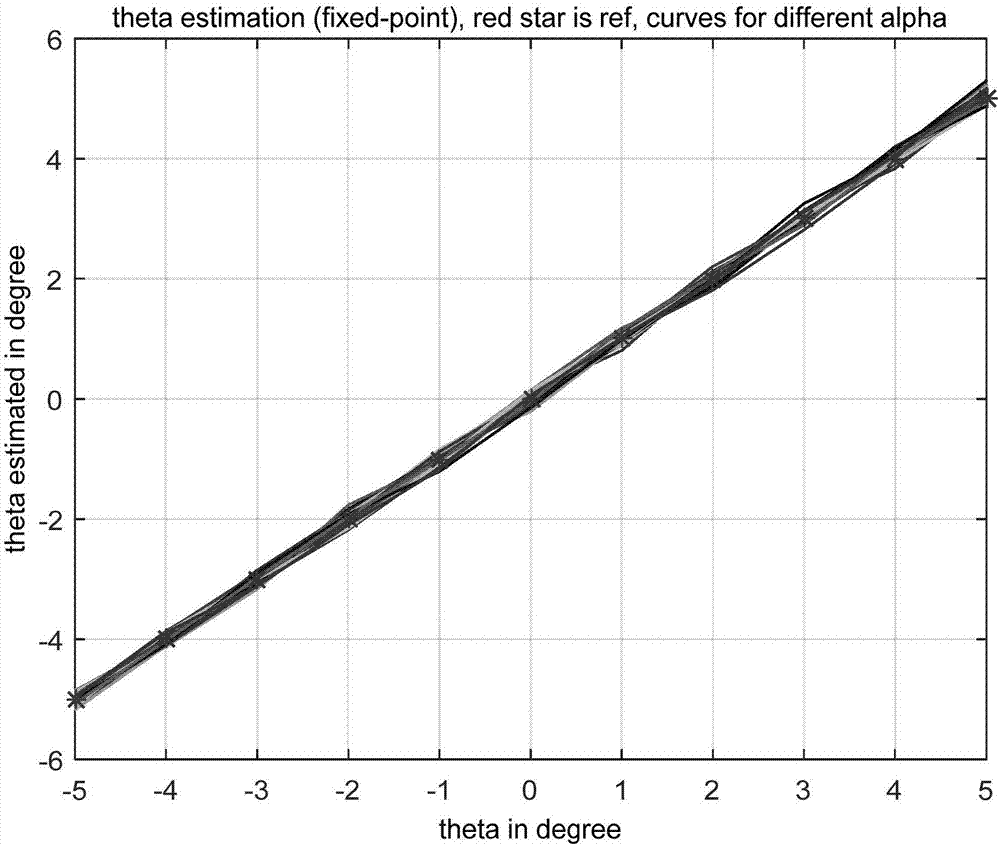

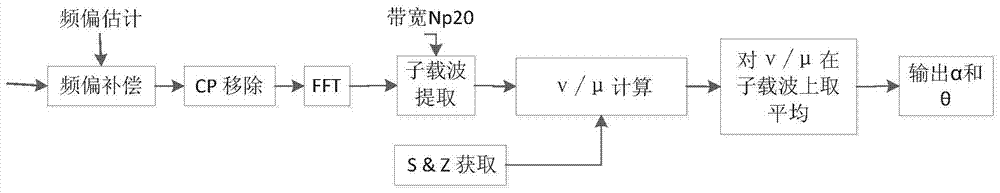

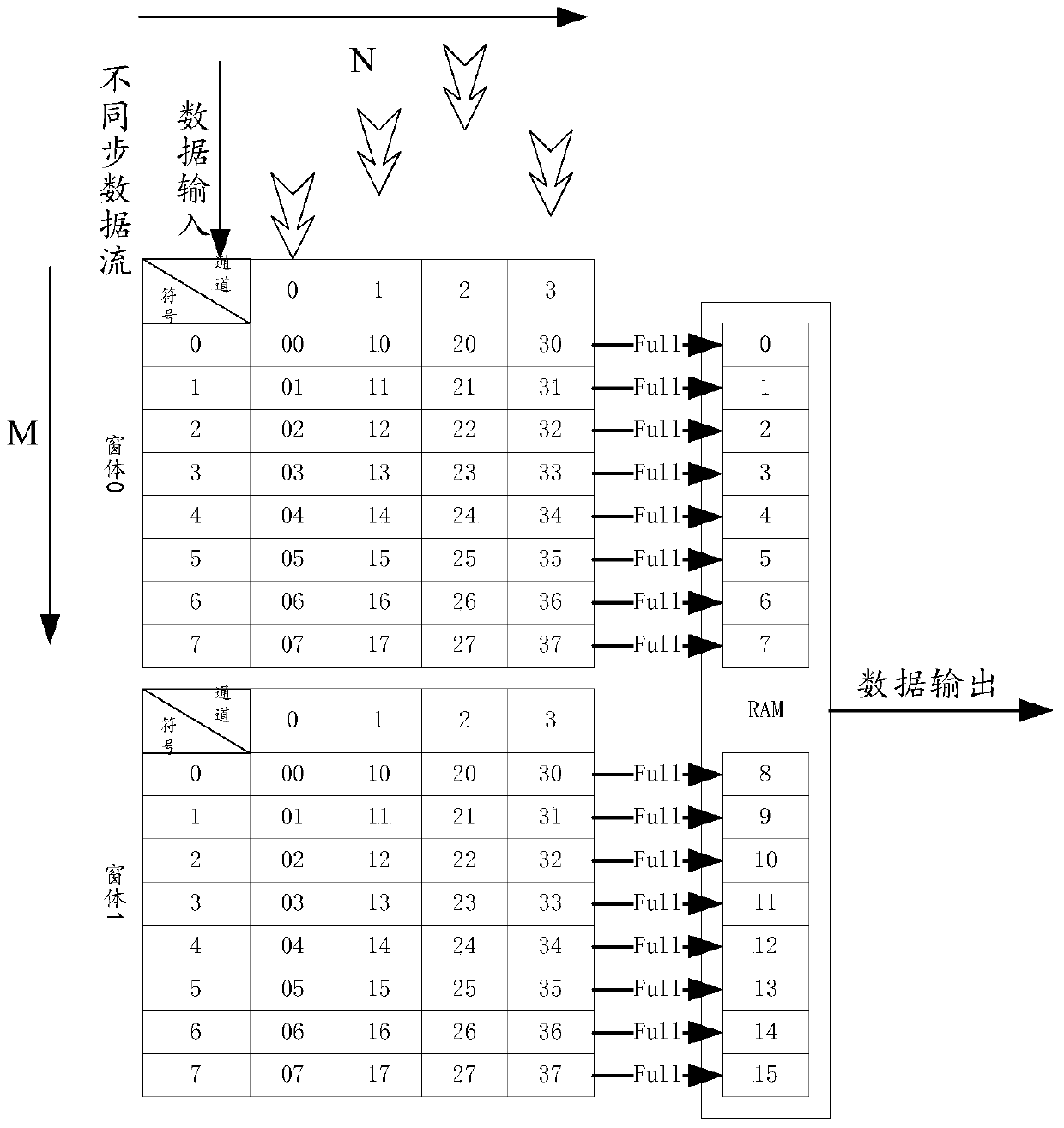

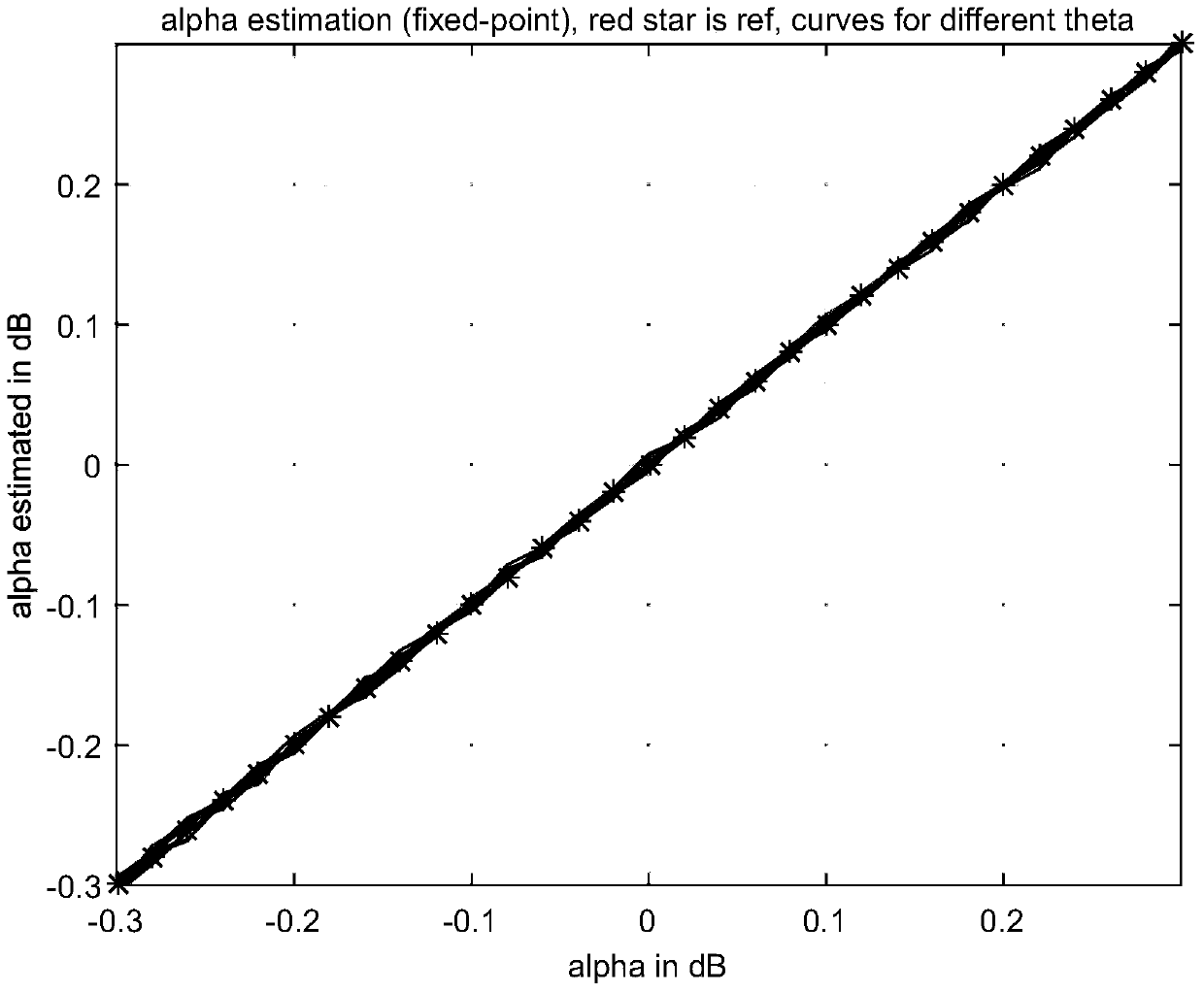

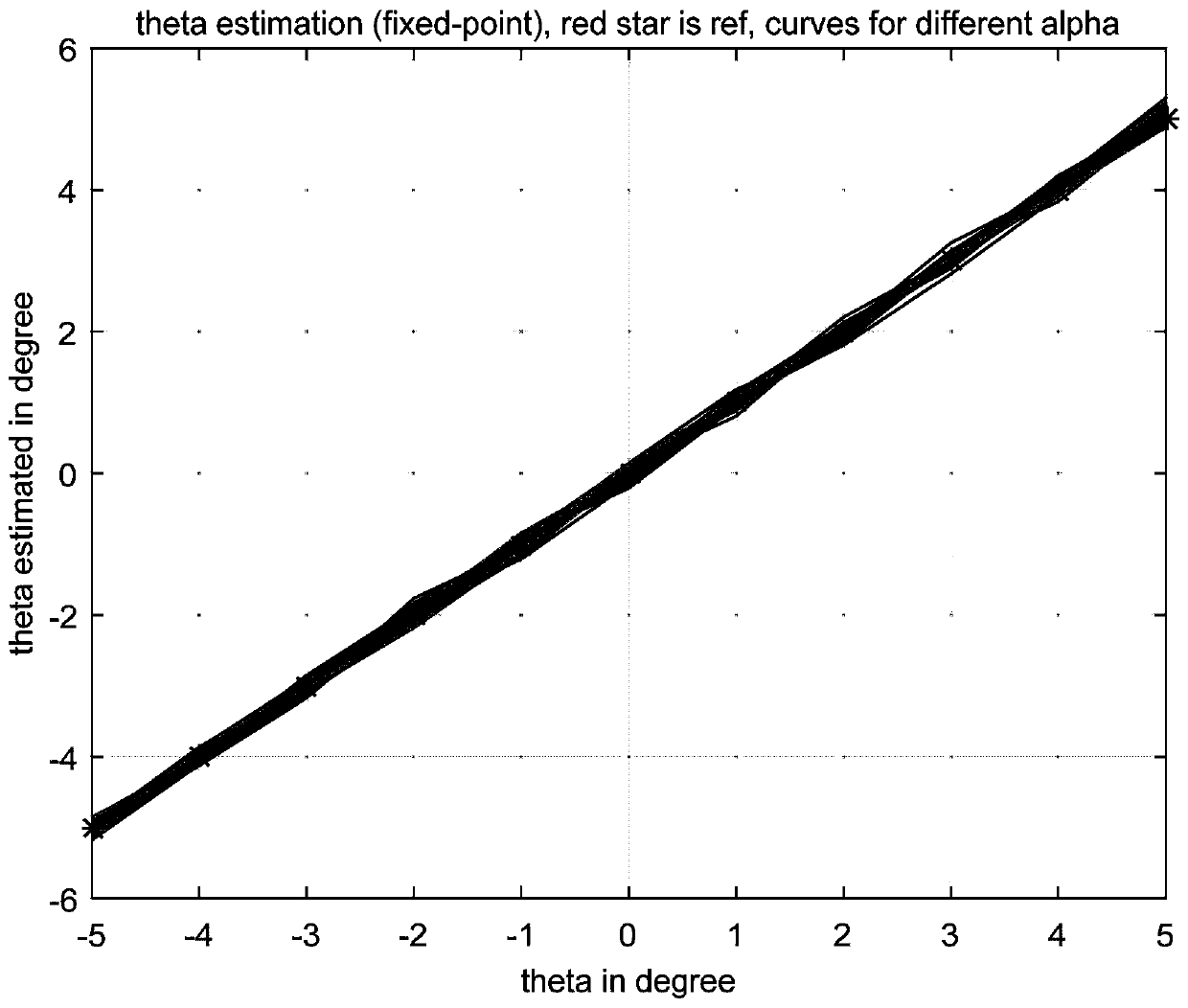

Estimation method and module for in-phase/ quadrature-phase imbalance in OFDM (Orthogonal Frequency Division Multiplexing) system

InactiveCN106911607AAvoid dependenceWide range of applicationsMulti-frequency code systemsMultiple carrier systemsCyclic prefixEngineering

The invention discloses an estimation method and module for in-phase / quadrature-phase (IQ) imbalance in an OFDM (Orthogonal Frequency Division Multiplexing) system. The estimation method comprises the following steps: S1, performing frequency offset compensation on received time domain signals; S2, after removing cyclic prefixes, transforming two different pilot symbols adjacent on time to a frequency domain; S3, extracting subcarriers occupied by the pilot symbols according to the system bandwidth; S4, for the two pilot symbols, obtaining received signals of two pilot signals on each subcarrier; and S5, removing coupling of IQ imbalance parameters and channels, and solving an IQ imbalance estimation value. The method and the module are wide in application and low in requirement for the processing time sequence of a receiver, conform to the demands of most practical application scenes, and are simple in algorithm and small in calculation quantity.

Owner:SHANGHAI RES CENT FOR WIRELESS COMM

A real-time digital image compression prediction method and system

ActiveCN105208394BMeet Design ComplexityReduce Design ComplexityDigital video signal modificationImage resolutionPrediction interval

The invention discloses a real-time digital image compression prediction method, facilitating realization of a digital circuit and capable of performing time sequence optimization, based on prediction. Based on the prediction method, according to the image resolution, realization difficulty of the digital circuit and trade-off of compression efficiency, numerical values of a group of unit and prediction interval are selected. Higher is the image resolution, higher is the requirement for a time sequence of the digital circuit, at the moment, and the numerical values of the unit and prediction interval can be appropriately increased; according to the values of the selected unit and prediction interval and the position of the unit where a current pixel is located, corresponding reference pixels are selected for calculating the prediction value of the current pixel. By the adoption of the prediction method, the requirement for the time sequence of the digital circuit in a chip can be lowered, high practical value is achieved, and the method is expected to be applied to integrated circuits needing real-time video stream compression and decompression.

Owner:CHIPONE TECH BEIJINGCO LTD

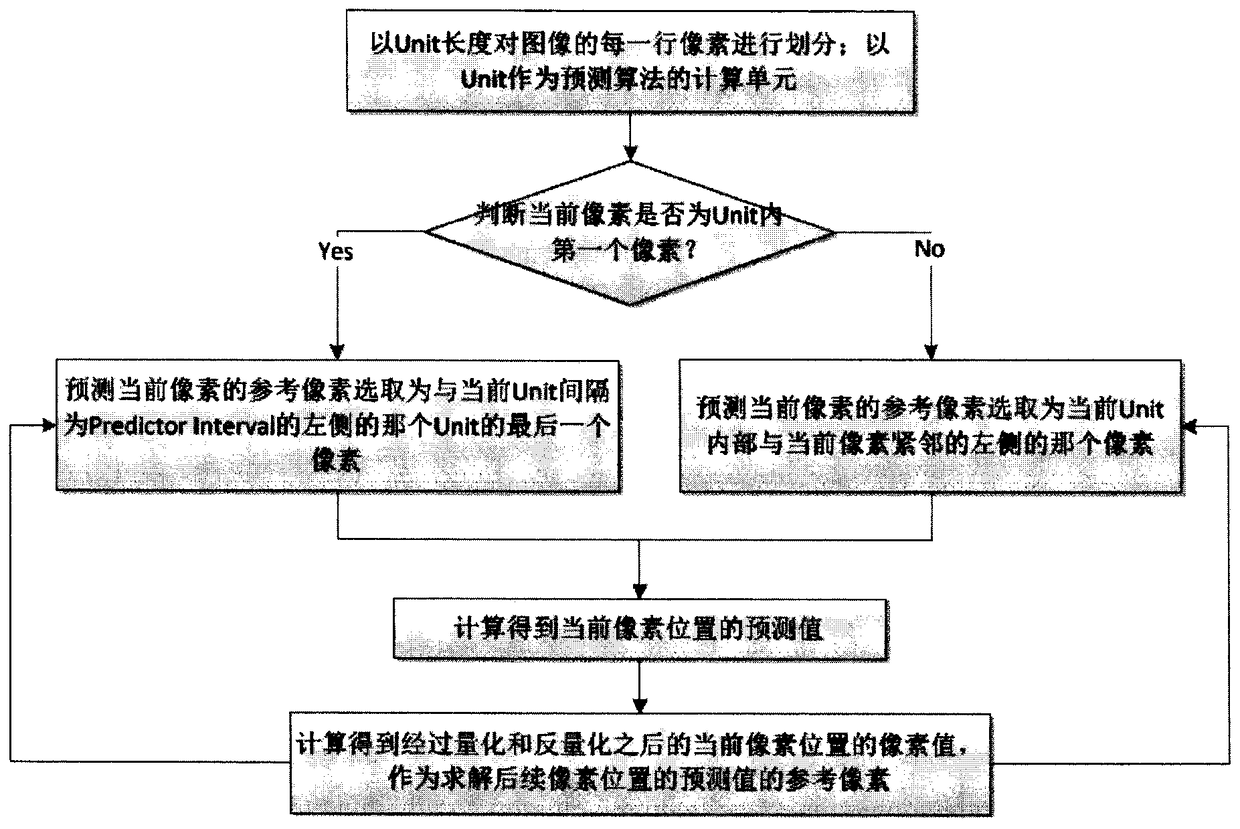

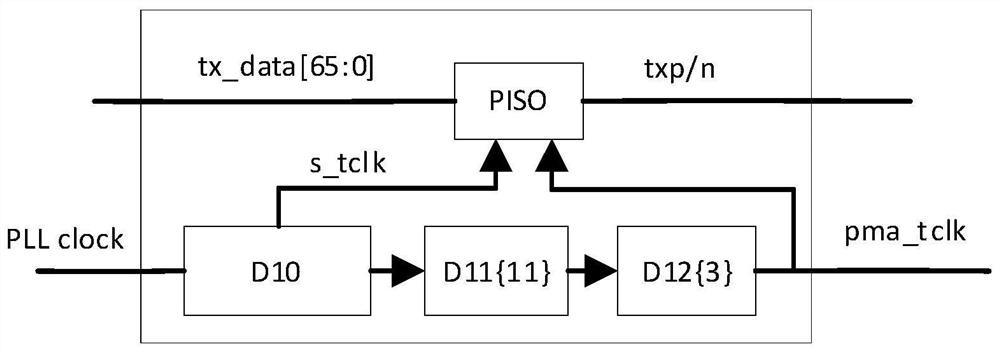

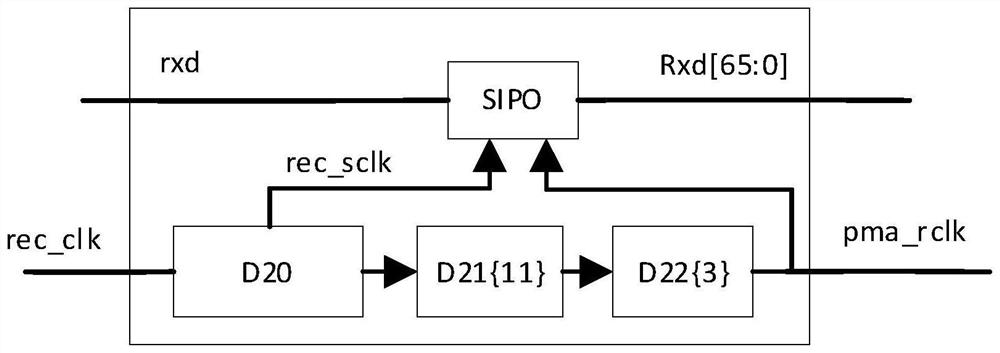

Serdes architecture for 64B/66B conversion

InactiveCN112543158AReduce the number of clocksReduce operating frequencyParallel/series conversionSynchronous/start-stop systemsLogic complexityComputer architecture

The invention provides a serdes architecture for 64B / 66B conversion. The serdes architecture comprises an XLGMII, a PCS layer and a PMA layer; the interface bit width of the PCS layer and the PMA layer is configured to be 66bit. According to the 64B / 6B conversion serdes architecture, the PCS and PMA interface data width is configured to be 66bit, so that the number of clocks in the PCS is reduced,the working frequency and logic complexity in the PCS are effectively reduced, the time sequence requirement of PCS internal digital design is reduced, the chip design cost can be effectively reduced, and the chip performance and reliability are improved.

Owner:SHENZHEN PANGO MICROSYST CO LTD

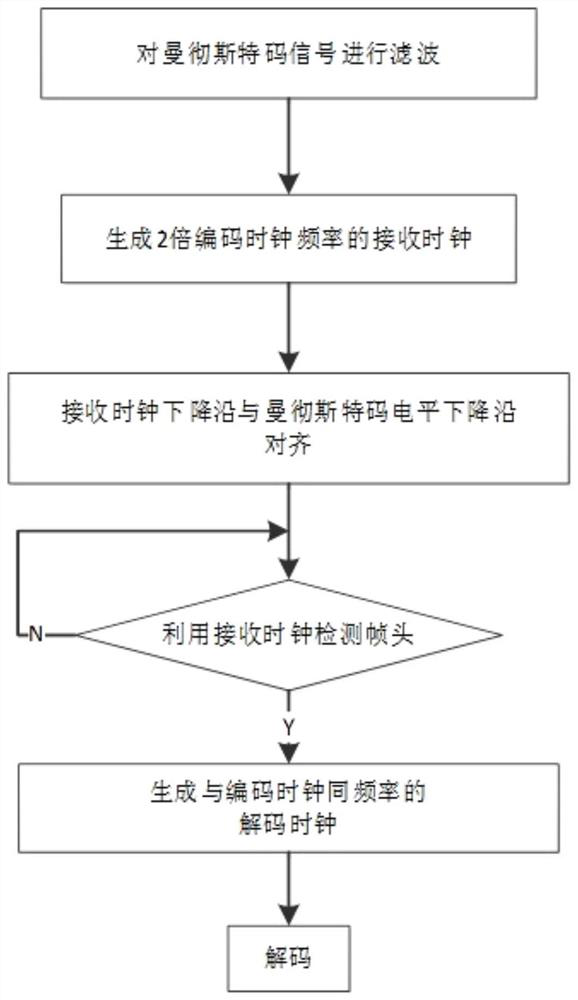

Manchester code decoding method based on FPGA and IEC60044-8 standards

PendingCN111769835ALess writing effortLow timing requirementsIndividual digits conversionComputer architectureManchester code

The invention provides a Manchester code decoding method based on FPGA and IEC60044-8 standards. The Manchester code decoding method comprises the following steps: S1, filtering a Manchester code signal; S2, generating a receiving clock which is used for detecting a level signal in a Manchester code, wherein the frequency of the receiving clock is twice that of an encoding clock; S3, aligning thefalling edge of the receiving clock with the level falling edge of the Manchester code; S4, detecting a frame header by adopting the receiving clock; S5, generating a decoding clock with the same frequency as the encoding clock; S6, decoding, namely sampling the Manchester code detected by the receiving clock by adopting the decoding clock to obtain bit information of the Manchester code. According to the method, the problems that in the prior art, Manchester code decoding is too high in clock requirement and complex in decoding logic are well solved.

Owner:BEIJING ELECTRIC POWER AUTOMATION EQUIP CO LTD

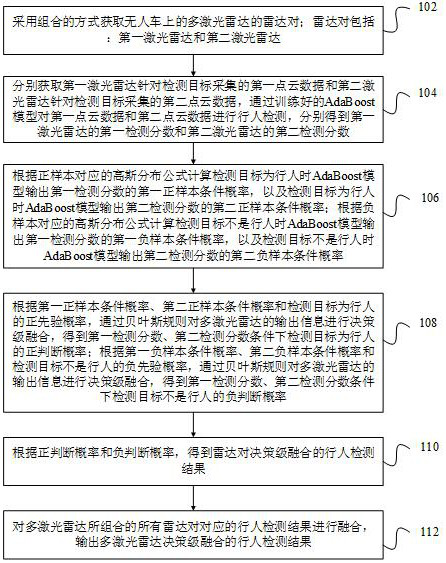

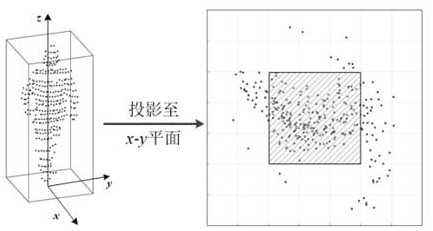

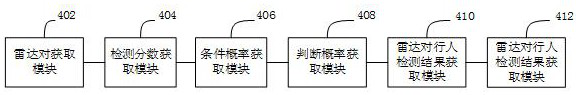

Multi-laser radar decision level fusion method and device for pedestrian detection

ActiveCN112433228AImprove execution efficiencyLow timing requirementsBiometric pattern recognitionElectromagnetic wave reradiationPoint cloudOriginal data

The invention relates to a multi-laser radar decision level fusion method and device for pedestrian detection, computer equipment and a storage medium. The method comprises the following steps of: performing pedestrian detection on point cloud data of a detection target acquired by each laser radar on an unmanned vehicle through a trained AdaBoost algorithm to obtain a pedestrian detection score of a single laser radar; conducting decision level fusion on the detection result of a radar pair formed by combining two laser radars on an unmanned vehicle through a Bayesian rule to obtain a pedestrian detection result of the radar pair, and then acquiring a final pedestrian detection result according to the pedestrian detection results of all the radar pairs in the multiple laser radars. According to the method, the single laser radar can firstly make decisions independently, then the decisions of the multiple laser radars are fused, data level fusion or feature level fusion of the multiplesensors is avoided, and laser radar data collection does not need to be completely synchronized, therefore the method has the advantages of small calculation amount and low requirement for the time sequence of original data of the laser radars.

Owner:NAT UNIV OF DEFENSE TECH

Automated multi-point probe manipulation

ActiveUS8836358B2Reduce riskReduce human contactElectronic circuit testingElectrical measurement instrument detailsEngineeringManipulator

A multi-point probe particularly suitable for automated handling is disclosed. An automated multi-point measuring system including the multi-point probe and a probe manipulator head is also disclosed In addition, an automated multi-point probe gripping system including a probe holder and the probe manipulator head is revealed. Further, a loaded probe loader comprising a probe loader and a probe cassette for handling the multi-point probe is also revealed, where the probe cassette is provided with the probe holder for securing the multi-point probe.

Owner:CAPRES

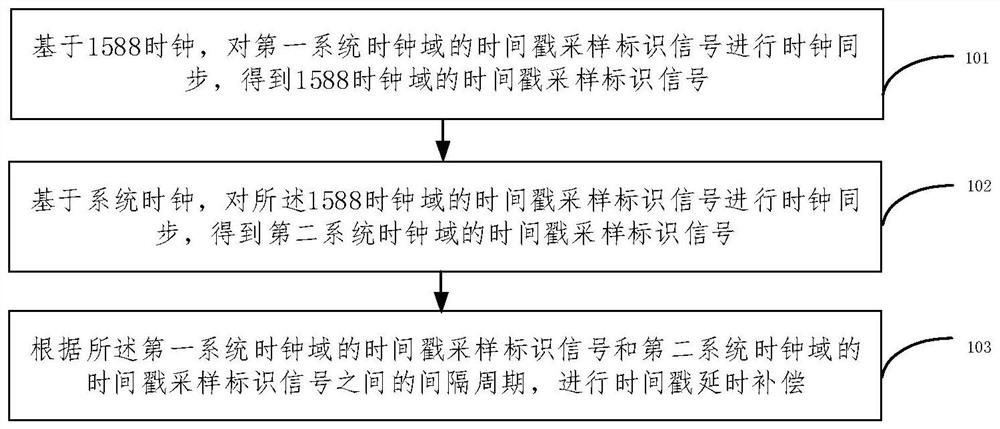

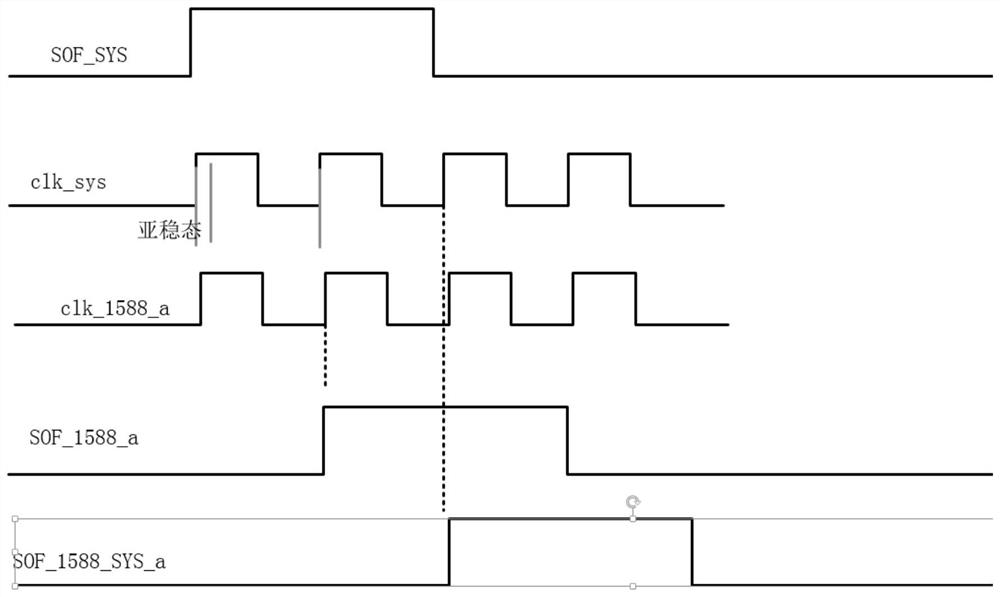

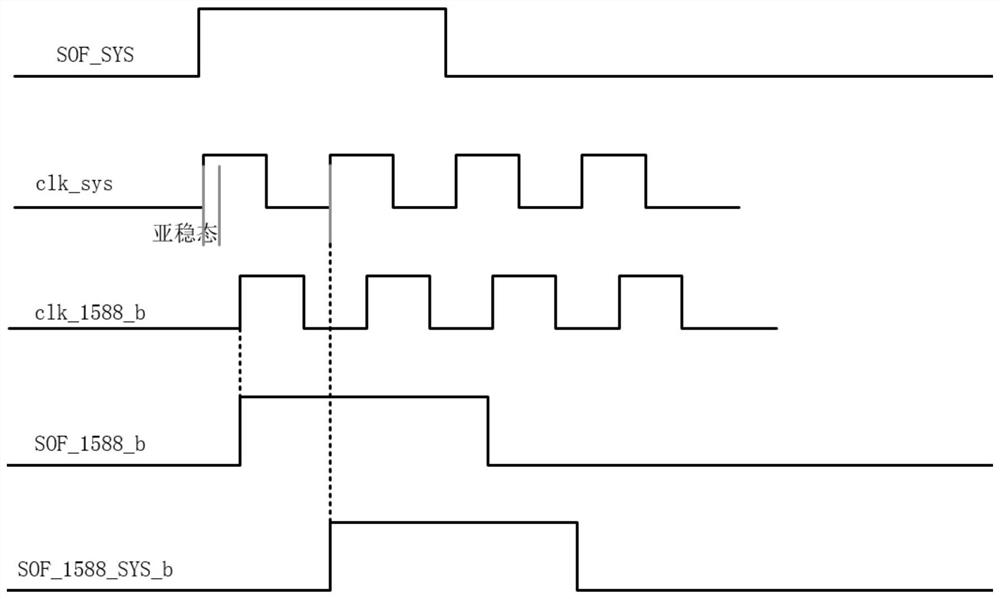

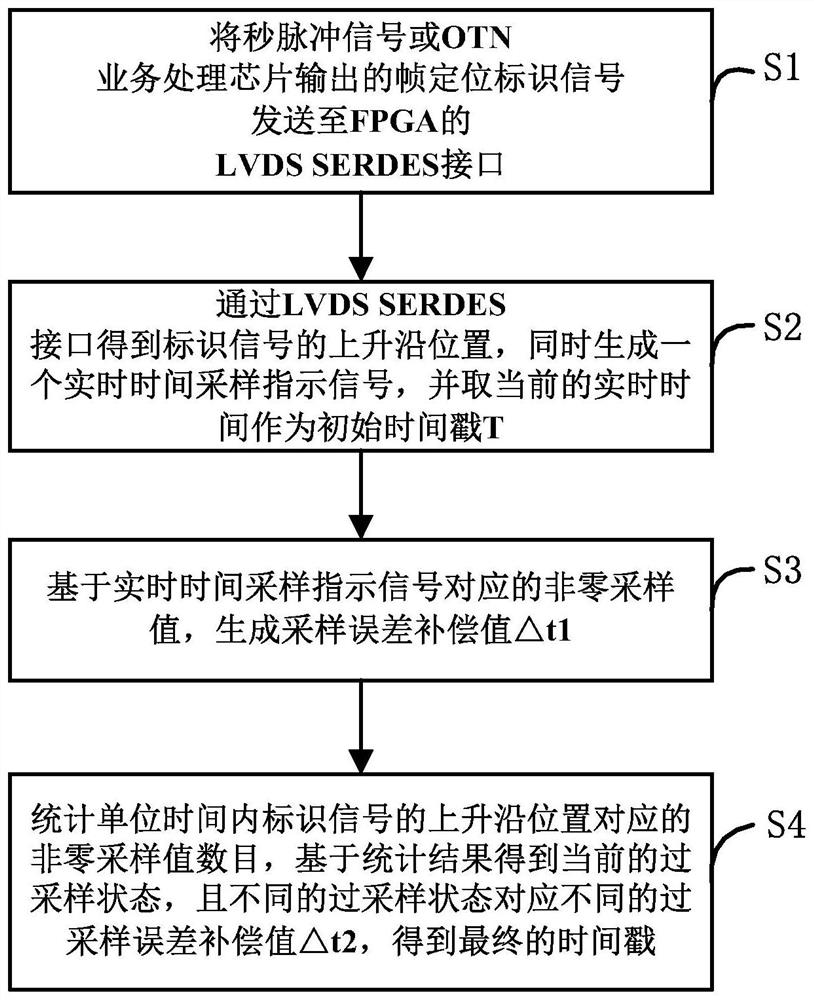

Timestamp jitter compensation method and device

ActiveCN111800212ALow timing requirementsLow costSynchronisation arrangementTime-division multiplexComputer hardwareEngineering

Owner:FENGHUO COMM SCI & TECH CO LTD

A method for sharing a single program memory in a quad-core processor system

InactiveCN103412848BReduce areaReduce transmission delayDigital computer detailsElectric digital data processingMemory addressAddress bus

The invention discloses a method for sharing a single program memory by a four-core processor system. The method that two-phase clocks are used and the method that memory addresses are separately piled according to odd serial numbers and even serial numbers are combined. Four processors of the four-core processor system are respectively a Core0, a Core1, a Core2 and a Core3, and memory access addresses, corresponding to the four processors, on an address bus are respectively addr0, addr1, addr2 and addr3, wherein the Core0 and the Core1 belong to a set A1 and are driven by the clock phi 1, the Core2 and the Core3 belong to a set A2 and are driven by the clock phi 2, the shared memory SMEM is driven by a clock HCLK, the phase of the clock phi 1 and the phase of the clock phi 2 are opposite, and the frequency of the clock phi 1 and the phase of the clock phi 2 are half the frequency of the clock HCLK. Because the phase of the clock phi 1 and the phase of the clock phi 2 are opposite, the two groups of Cores, namely the A1 and the A2, can independently access the memory without being mutually interrupted or generating accessing competition. The method for sharing the single program memory by the four-core processor system solves the problem of access competition generated when the memory is shared by the four-core processor system.

Owner:UNIV OF SCI & TECH OF CHINA

A method for generating intermediate frequency of parallel altboc navigation signal

ActiveCN105116425BLow timing requirementsReduce design costSatellite radio beaconingSignal qualityIntermediate frequency

The invention discloses a parallel AltBOC navigation signal intermediate frequency generation method, comprising the steps of: generating I and Q paths of baseband orthogonal signals; utilizing complex filtering to perform amplitude-frequency distortion compensation on I and Q to generate cI and cQ paths of baseband orthogonal signals; performing low pass filtering on generated cI and cQ paths of baseband orthogonal signals; generating intermediate frequency carrier waves; parallelly modulating the intermediate frequency carrier waves and the cI and cQ paths of baseband orthogonal signals; and finally performing parallel-serial conversion to output intermediate frequency signals. The method can generate AltBOC signals with lower frequency, guarantee the channel feature consistency of the I and Q branches, and meanwhile guarantee signal quality.

Owner:XIAN INSTITUE OF SPACE RADIO TECH

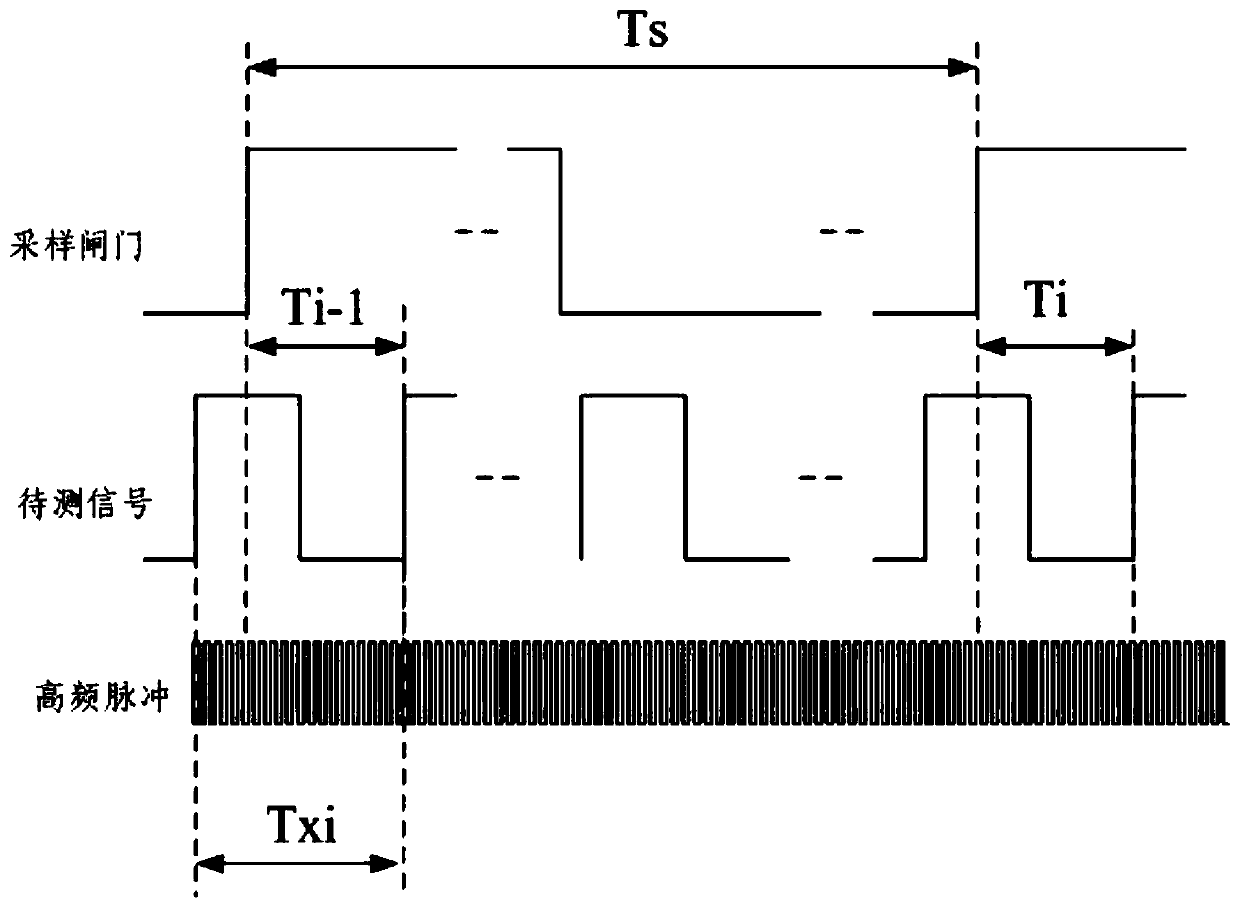

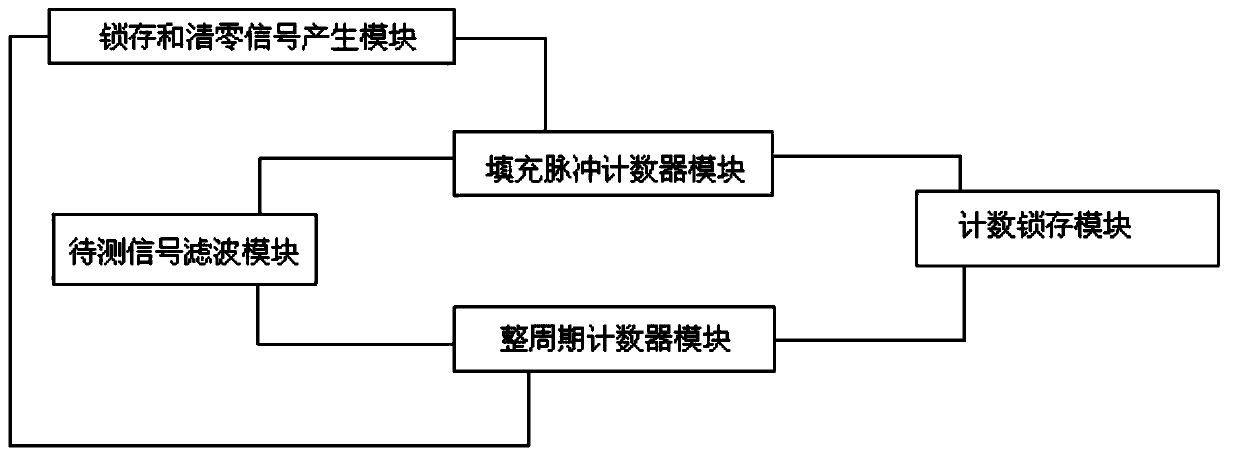

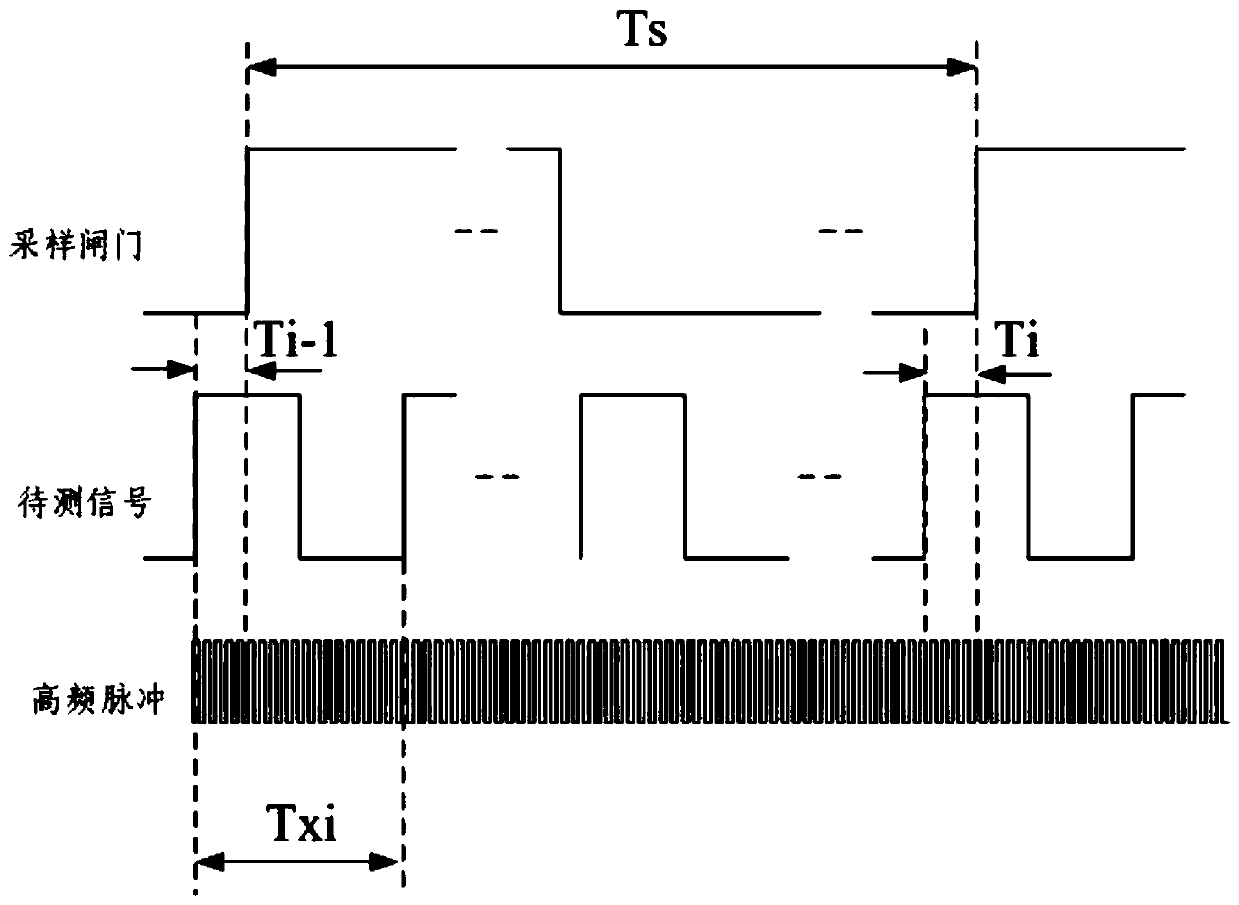

Frequency measurement device applied to inertial navigation system and frequency measurement method thereof

ActiveCN110988468ALow timing requirementsImprove reliabilityNavigation by speed/acceleration measurementsFrequency to pulse train conversionComputer hardwareFrequency measurements

The invention relates to a frequency measurement device applied to an inertial navigation system and a frequency measurement method thereof. The device comprises a to-be-measured signal filtering module, a latch and zero clearing signal generation module, a full-period counter module, a filler pulse counter module and a counting latch module, wherein the to-be-measured signal filtering module performs filtering processing on a to-be-measured signal; the latch and zero clearing signal generation module generates a timing latch signal and a timing zero clearing signal; the full-period counter module counts the pulses of the to-be-measured signal in the whole cycle and sends the obtained value to the counting latch module; the filler pulse counter module is used for counting non-full-period filling high-frequency pulses before a sampling gate period starts and sending an obtained value to the counting latch module; and the counting latch module is used for receiving and storing the counting value sent by the full-period counter module, and is also used for receiving, processing and storing the count value sent by the filler pulse counter module. According to the invention, the problemthat the to-be-measured signal depends on the count value of a gate rear edge is solved, and the time sequence requirement on the gate rear edge is reduced.

Owner:BEIJING AUTOMATION CONTROL EQUIP INST

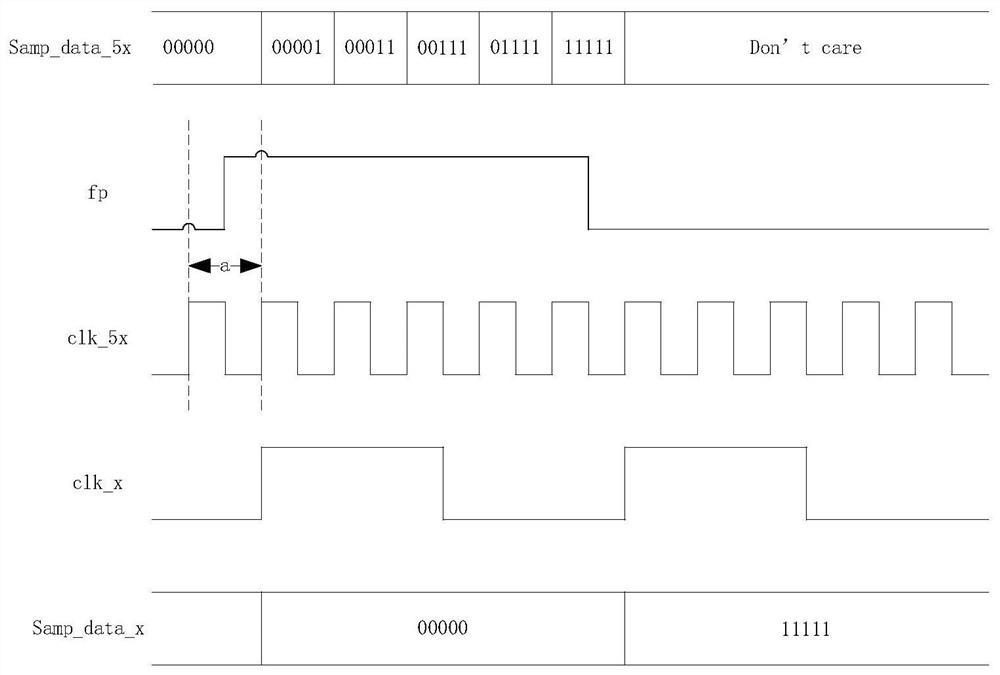

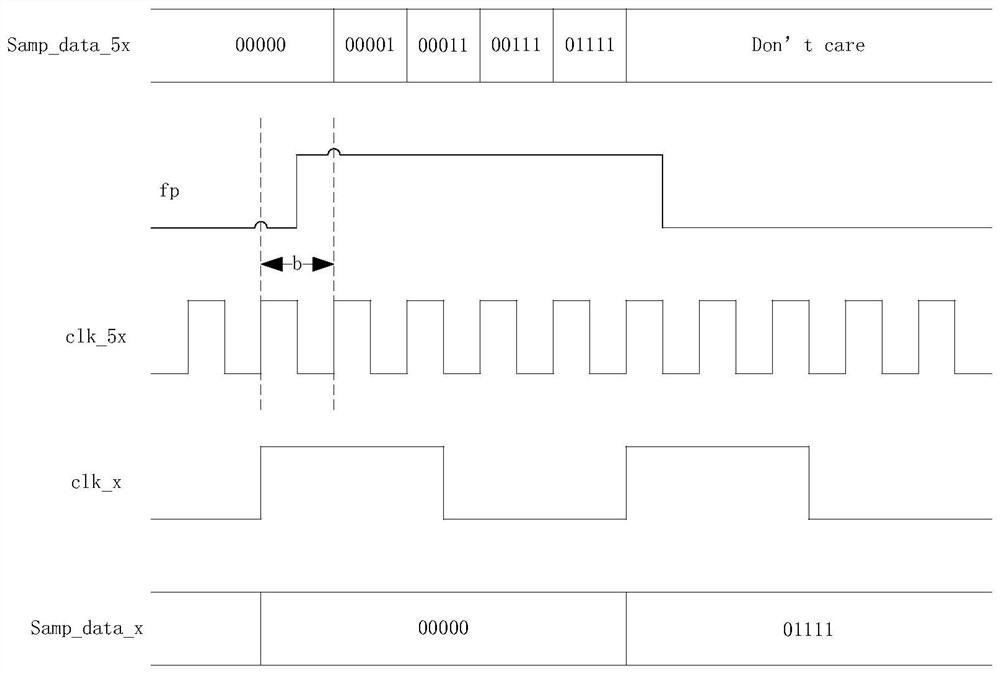

Method and system for improving timestamp precision

ActiveCN112953669ALow timing requirementsHigh precisionTime-division multiplexOversamplingTimestamping

The invention discloses a method and system for improving timestamp precision, and relates to the field of time synchronization, and the method comprises the steps: sending a second pulse signal or a frame positioning identification signal outputted by an OTN business processing chip to an LVDS SERDES interface of an FPGA; obtaining the rising edge position of the frame positioning identification signal through an LVDS SERDES interface, generating a real-time time sampling indication signal at the same time, and taking the current real-time time as an initial timestamp T; generating a sampling error compensation value [delta]t1 based on a non-zero sampling value corresponding to the real-time time sampling indication signal; and obtaining the current oversampling state based on the statistical result, wherein different oversampling states correspond to different oversampling error compensation values [delta]t2, and the final timestamp is equal to the sum of the initial timestamp T, the sampling error compensation value [delta]t1 and the oversampling error compensation value [delta]t2. The method is easy to implement, and the requirement for the time sequence of the FPGA device is low.

Owner:FENGHUO COMM SCI & TECH CO LTD

Method and a device for measuring axial polarizing angle of polarizer

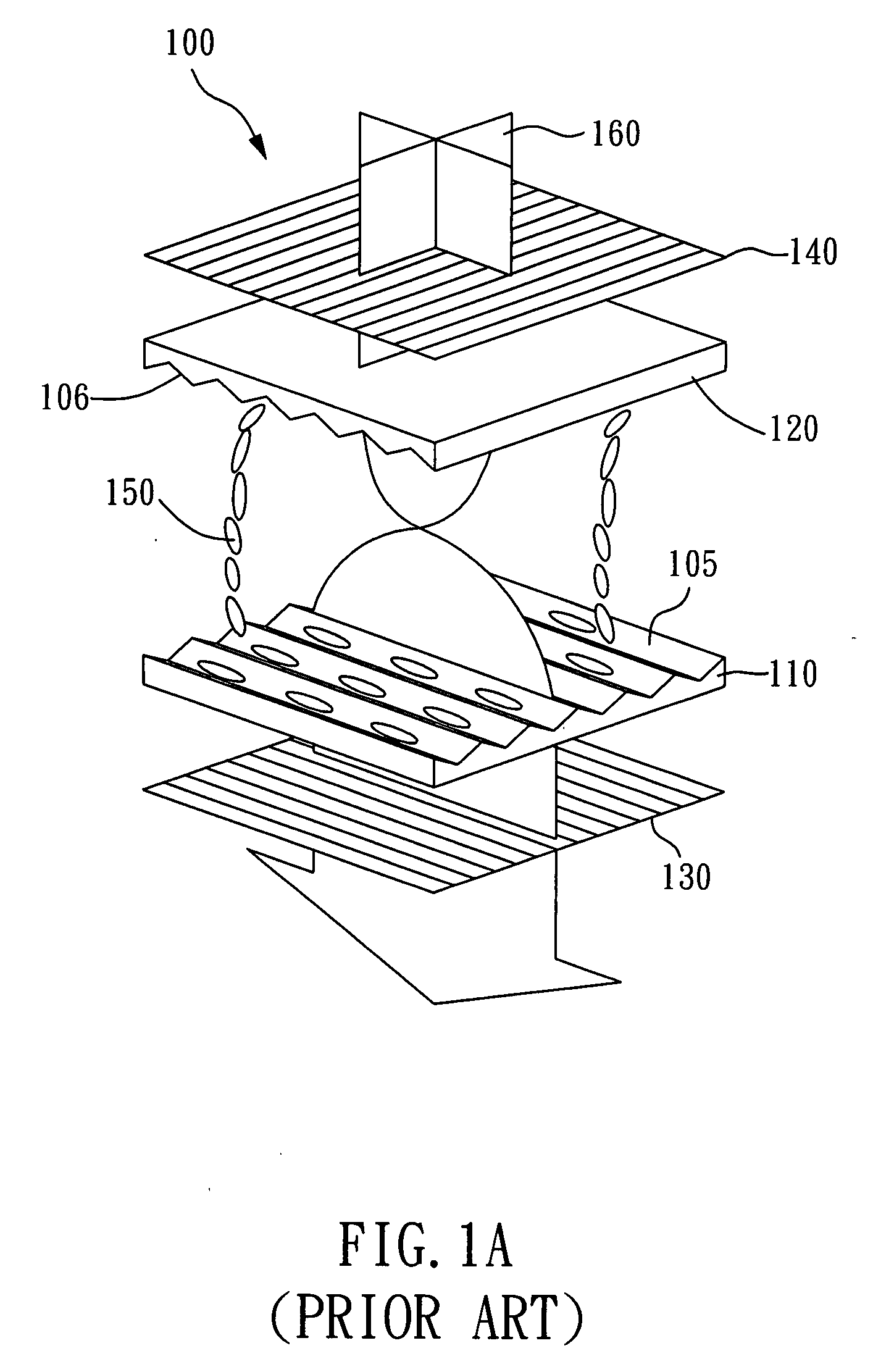

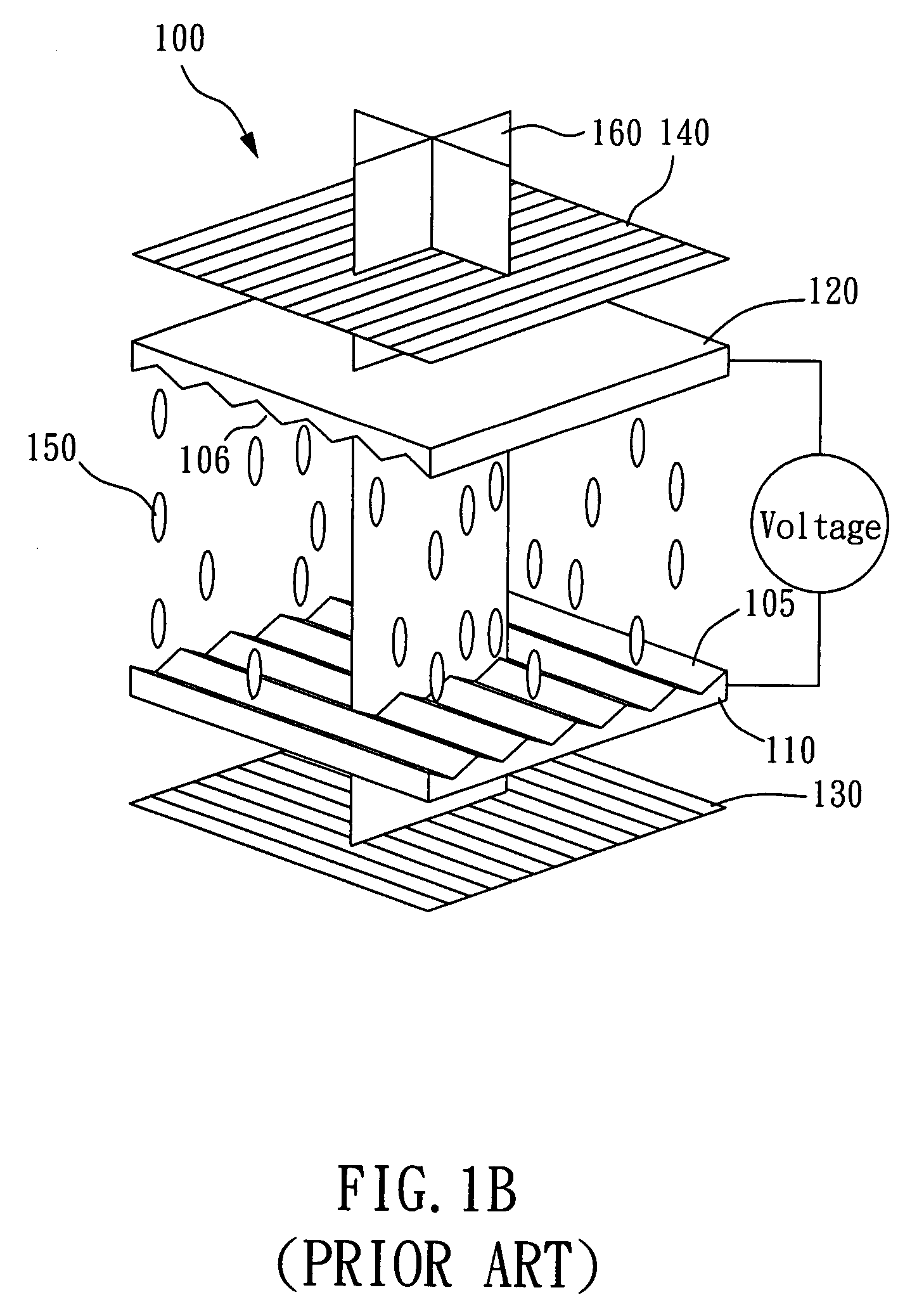

InactiveUS20080129999A1Shorten the timeQuick collectionInvestigating crystalsPolarisation-affecting propertiesElectricityOptoelectronics

The present invention relates to a device and a method for measuring an axial polarizing angle of a polarizer. The apparatus can have a to-be-measured polarizer disposed therein, and comprises a light generating device, a light polarizing device and a measurement comparison device. The light generating device provides a light source. The light polarizing device is disposed corresponding to the light generating device to load the to-be-measured polarizer, and measures a light signal after the light source passes through the to-be-measured polarizer without rotating the to-be-measured polarizer, and transforms it into readable data. The measurement comparison device is electrically connected with the light polarizing device and has at least one preset comparison data to receive the data provided by the light polarizing device and compare it with the comparison data. Thus, after comparing the data provided by the light polarizing device with the comparison data, an axial polarizing angle of the to-be-measured polarizer is quickly and accurately measured and calculated.

Owner:OPTIMAX TECHNOLOGY CORPORATION

Synchronization device, synchronization method and high-speed receiver using the synchronization device

ActiveCN107425953BReduce processing burdenLow timing requirementsSynchronisation error correctionSynchronisation receiversReed receiverTransceiver

The present invention provides a synchronizer of a laser communication distance measurement integration system, a synchronization method of a laser communication distance measurement integration system and a high-speed receiver by using the synchronizer. The high-speed receiver receives high-speed signals, an analog-digital converter (ADC) is used for sampling of the high-speed signals, the sampling data is sent into a Gigabit transceiver (GTH) to perform serial-parallel conversion, and the high-speed serial data is converted to multi-path parallel data with low rate; the parallel data is sent into the synchronizer for signal synchronization, the parallel data is subjected to steps such as parallel data frame capture, dynamic correction, high-speed phase-locked loop tracking and the like in the synchronizer so as to complete accurate synchronization of the high-speed signals through the receiver; and moreover, on the basis of the accurate synchronization of the signals, and a distance measurement result and communication data can be solved out through the distance measurement branch and the communication branch of the receiver. The clock load is reduced and the complexity of the hardware realization is effectively reduced while ensuring the accurate synchronization of signals and accurate distance measurement and communication result.

Owner:BEIJING INSTITUTE OF TECHNOLOGYGY

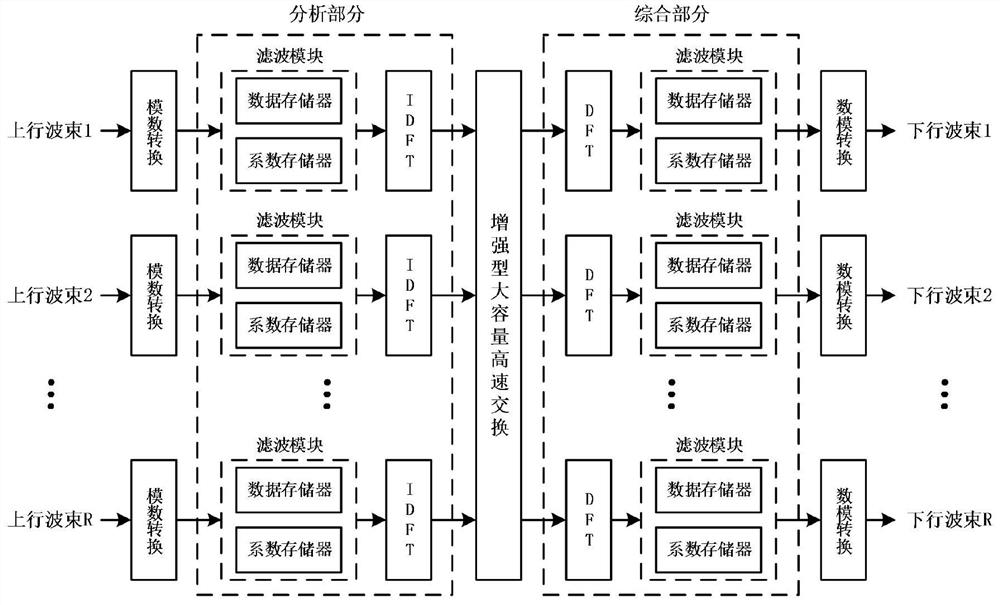

A digital flexible forwarding method and device

ActiveCN113824475BReduce occupancyLow timing requirementsRadio transmissionHigh level techniquesComputer hardwareData set

Owner:NO 54 INST OF CHINA ELECTRONICS SCI & TECH GRP

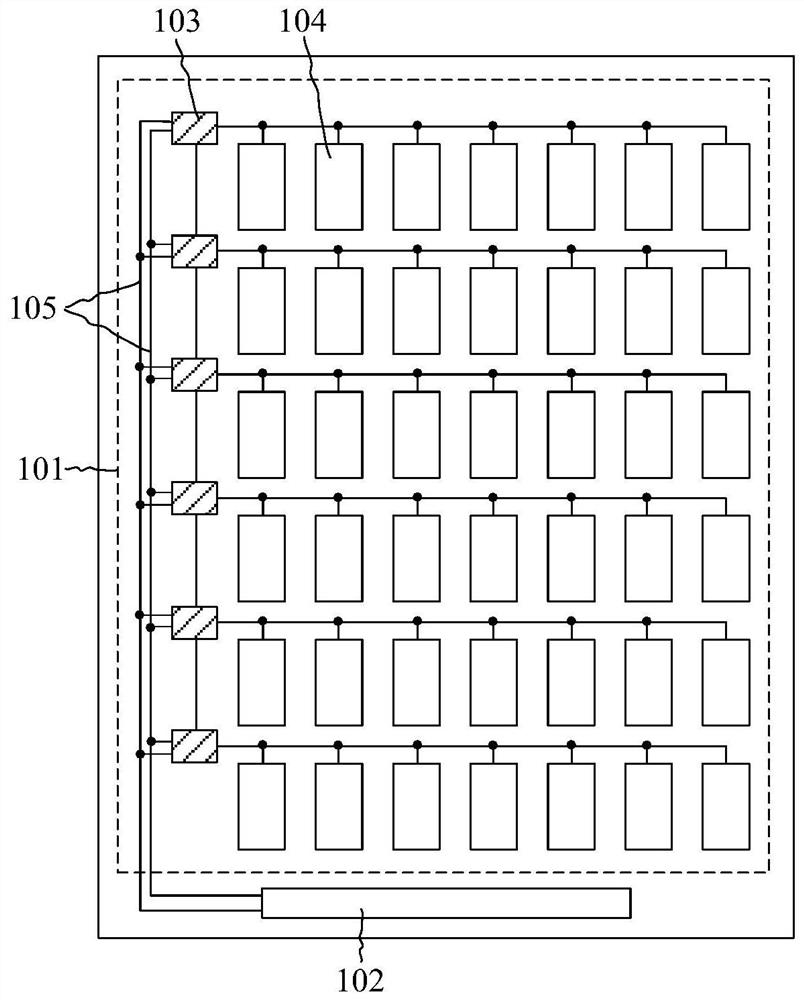

Shift register circuit, driving method thereof and display device

PendingCN114783348ALow timing requirementsReduce power consumptionStatic indicating devicesDigital storageShift registerDisplay device

The embodiment of the invention provides a shift register circuit, a driving method thereof and a display device, relates to the technical field of display, and aims to reduce the power consumption of the display device. The shift register circuit comprises a shift control circuit used for outputting a driving signal; the output control circuit is electrically connected between the shift control circuit and the driving signal line and is used for controlling a signal transmission path between the shift control circuit and the driving signal line to be communicated in a data frame; and in the holding frame, a signal transmission path between the shift control circuit and the driving signal line is controlled to be disconnected, and a disable voltage is output to the driving signal line.

Owner:WUHAN TIANMA MICRO ELECTRONICS CO LTD

Multi-channel data transmission method and system

ActiveCN104954113BImprove transmission efficiencyLow timing requirementsSynchronising arrangementTime delaysEmbedded system

The invention provides a multichannel data transmission method. Data heads are embedded in data at a transmitting end, the data heads include frame numbers, symbols and channel numbers, and the data with the data heads are transmitted to a receiving end; the receiving end comprises multiple window bodies which parse the data heads so that the frame numbers, the symbols and the channel numbers are obtained through parsing; and the data corresponding to the data heads are filled in the corresponding positions of the corresponding window bodies according to the parsed frame numbers, the symbols and the channel numbers. The requirement of synchronous transmission for timing sequence is reduced by the technical scheme, data transmission of different channels does not need to consider time delay difference between channels, the same transmission medium is not needed, multiple channels do not need to be strictly aligned, and even multiple transmitters can be asynchronous so that data transmission efficiency can be enhanced. The invention also provides a multichannel data transmission system.

Owner:SHANGHAI UNITED IMAGING HEALTHCARE

A method for estimating in-phase/quadrature unbalance in ofdm system and its module

InactiveCN106911607BAvoid dependenceLow timing requirementsMulti-frequency code systemsMultiple carrier systemsTime domainEstimation methods

The invention discloses an estimation method and module for in-phase / quadrature-phase (IQ) imbalance in an OFDM (Orthogonal Frequency Division Multiplexing) system. The estimation method comprises the following steps: S1, performing frequency offset compensation on received time domain signals; S2, after removing cyclic prefixes, transforming two different pilot symbols adjacent on time to a frequency domain; S3, extracting subcarriers occupied by the pilot symbols according to the system bandwidth; S4, for the two pilot symbols, obtaining received signals of two pilot signals on each subcarrier; and S5, removing coupling of IQ imbalance parameters and channels, and solving an IQ imbalance estimation value. The method and the module are wide in application and low in requirement for the processing time sequence of a receiver, conform to the demands of most practical application scenes, and are simple in algorithm and small in calculation quantity.

Owner:SHANGHAI RES CENT FOR WIRELESS COMM

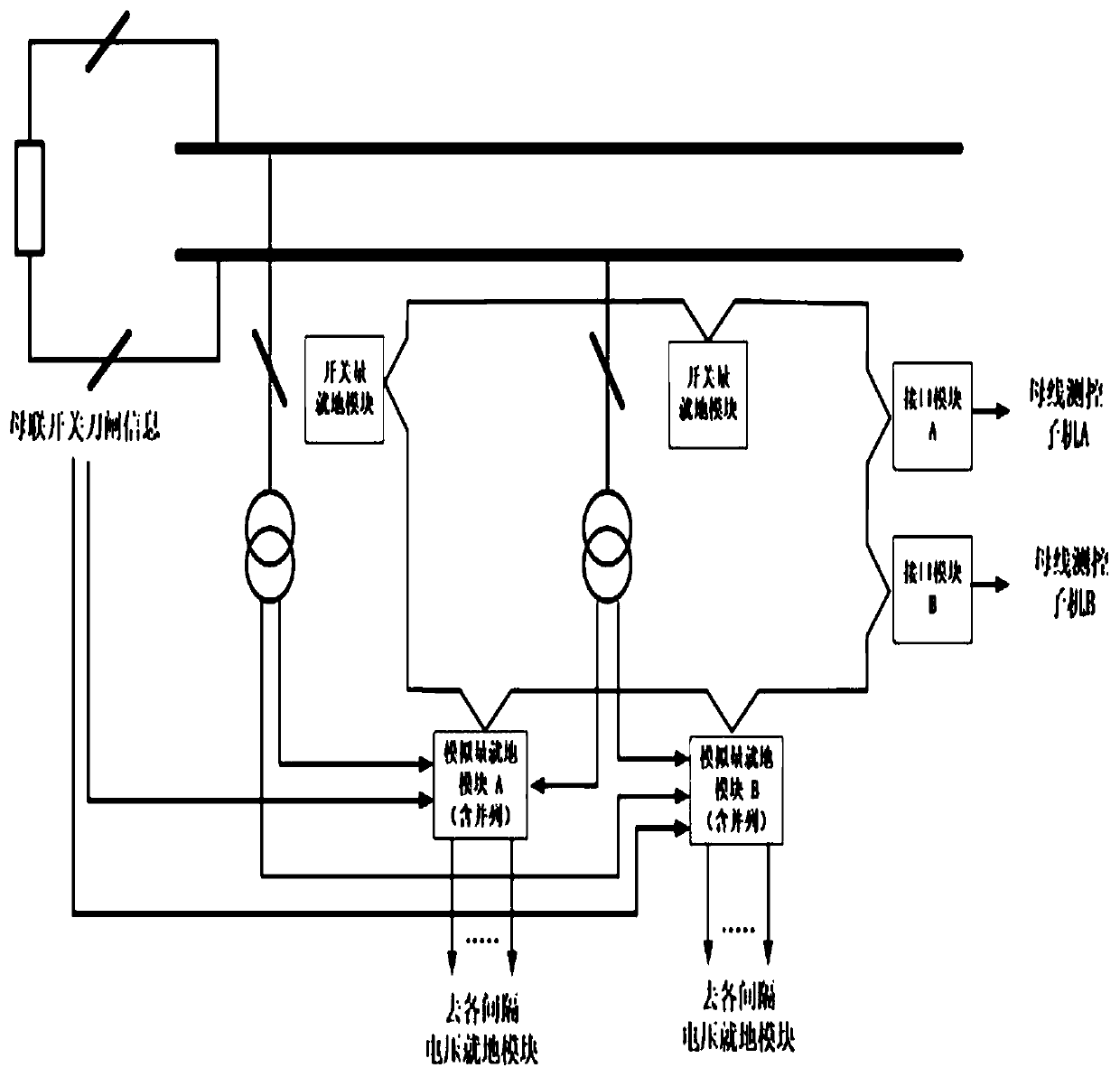

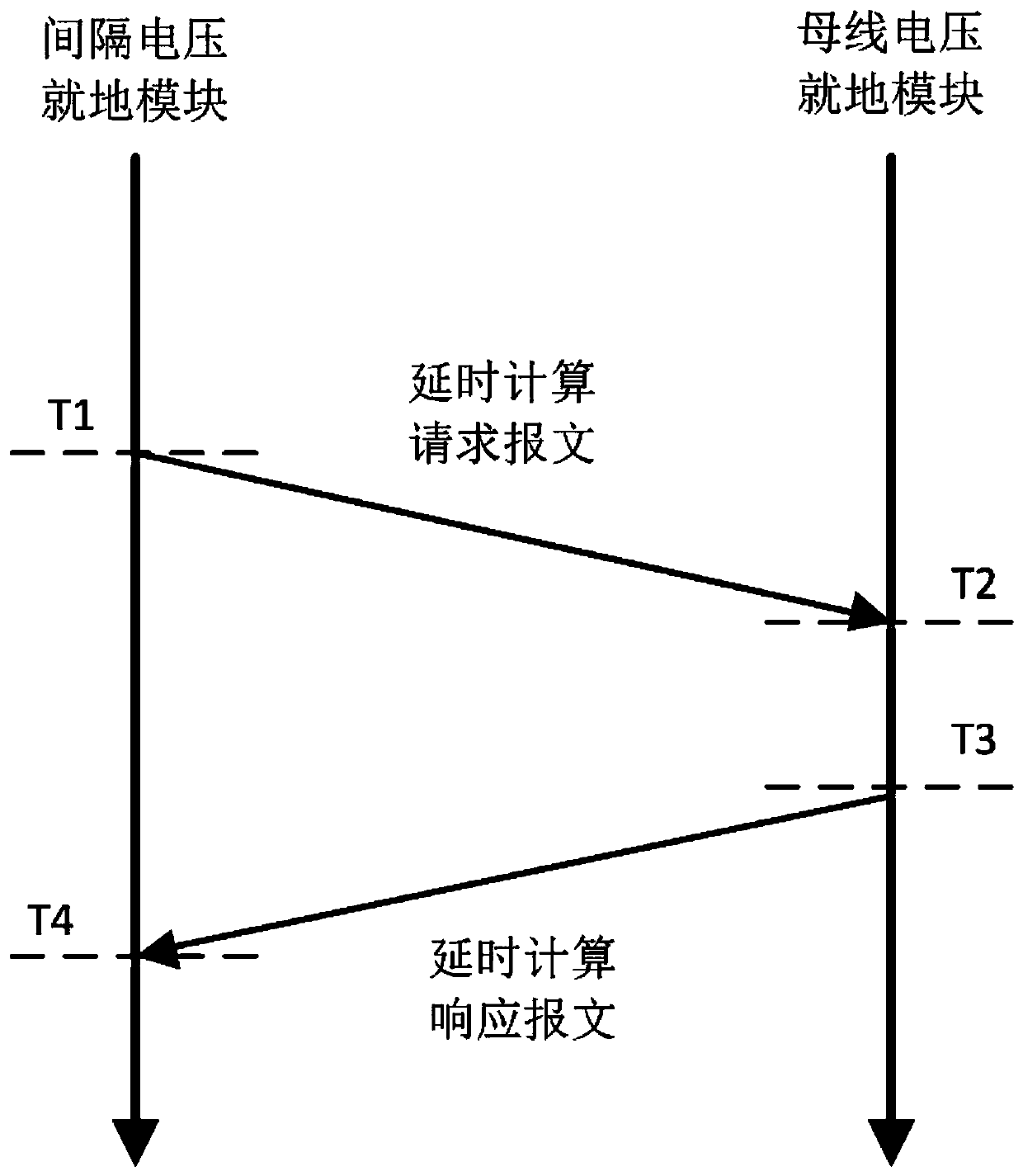

Voltage interactive synchronous sampling method

ActiveCN110954741AFew nodesResolve in-place modulesTime-division multiplexMeasurement using digital techniquesComputer scienceElectric power

The invention discloses a voltage interactive synchronous sampling method, and belongs to the electric power technology field. The method comprises the following step of measuring the channel time delay between a bus voltage local module and an interval voltage local module and the internal sampling time delay of the bus voltage local module, solves the technical problem that the high-voltage sidebus voltage HSR in-loop local module and the spaced HSR in-loop local modules at the middle-voltage side and the low-voltage side need the clock synchronization, and is simple in system architecture,less in HSR in-loop nodes, high in communication efficiency and low in clock synchronization requirement. The synchronization does not depend on an external reference clock source, and the reliability is high.

Owner:SHANGHAI MUNICIPAL ELECTRIC POWER CO

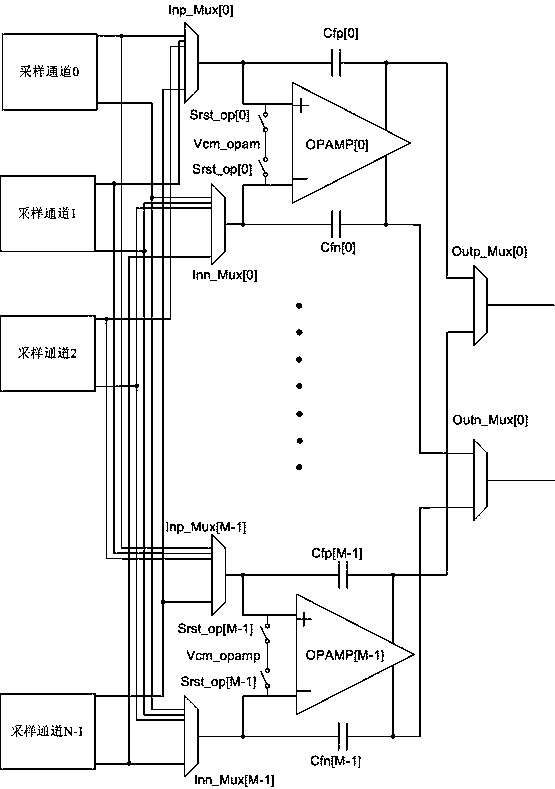

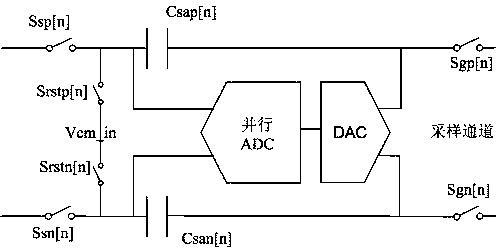

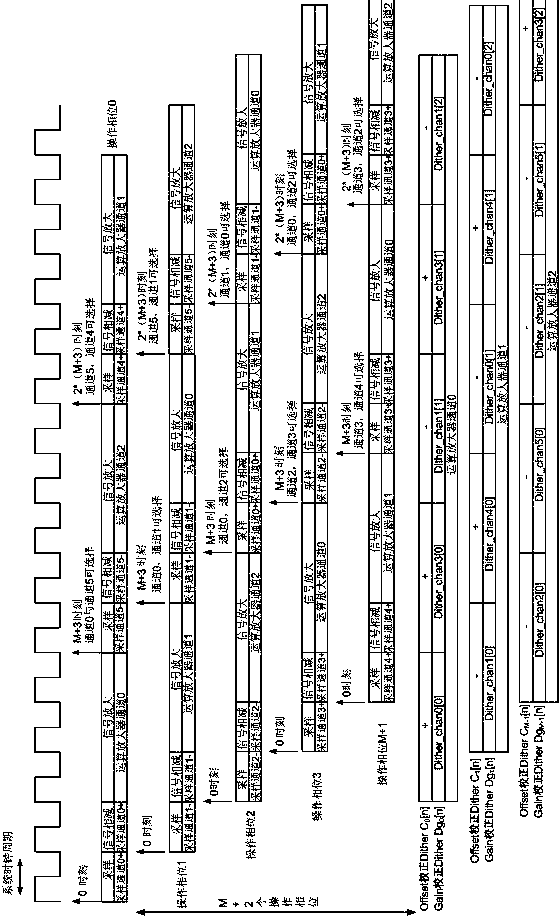

A time-interleaved pipeline ADC system and its timing operation method

ActiveCN105406867BInjection implementationReduce Delay SkewAnalogue-digital convertersCapacitanceAssembly line

The invention discloses a time-interleaved assembly line ADC system and a sequential operation method thereof. The time-interleaved assembly line ADC system comprises a digital-analogue converter structure, a disturbance calibrating signal injection structure and a self-adaptive algorithm principle; under the relatively low system overhead, the digital-analogue converter structure can realize injection of disturbance signals and normalized capacitance parameter correction of various channels; sampling randomization is realized by using a redundancy sampling channel, such that the channel delay deviation is reduced to the noise background; compared with the traditional delay correction method, a lot of power consumption and area overheads can be saved; in combination with randomized sampling channel section, a dynamic reverse circuit in the traditional operational amplifier offset correction circuit is saved by using a non-fixed positive and negative signal polarity channel, such that time sequence requests are reduced; injection of gain correction disturbance signals is separated by using multiple correctable channels; compared with the traditional scheme, a front high-speed sample hold circuit having high power consumption is saved; and the sampling speed of the time-interleaved assembly line ADC system is increased.

Owner:CHENGDU BOSIWEI TECH CO LTD