Method and system for improving timestamp precision

A technology of time stamping and precision, applied in time division multiplexing systems, electrical components, multiplexing communications, etc., can solve problems such as unsatisfactory effects, large errors, and difficult precise control of clock and data routing, etc., to achieve The effect of simple implementation, low timing requirements and high clock frequency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

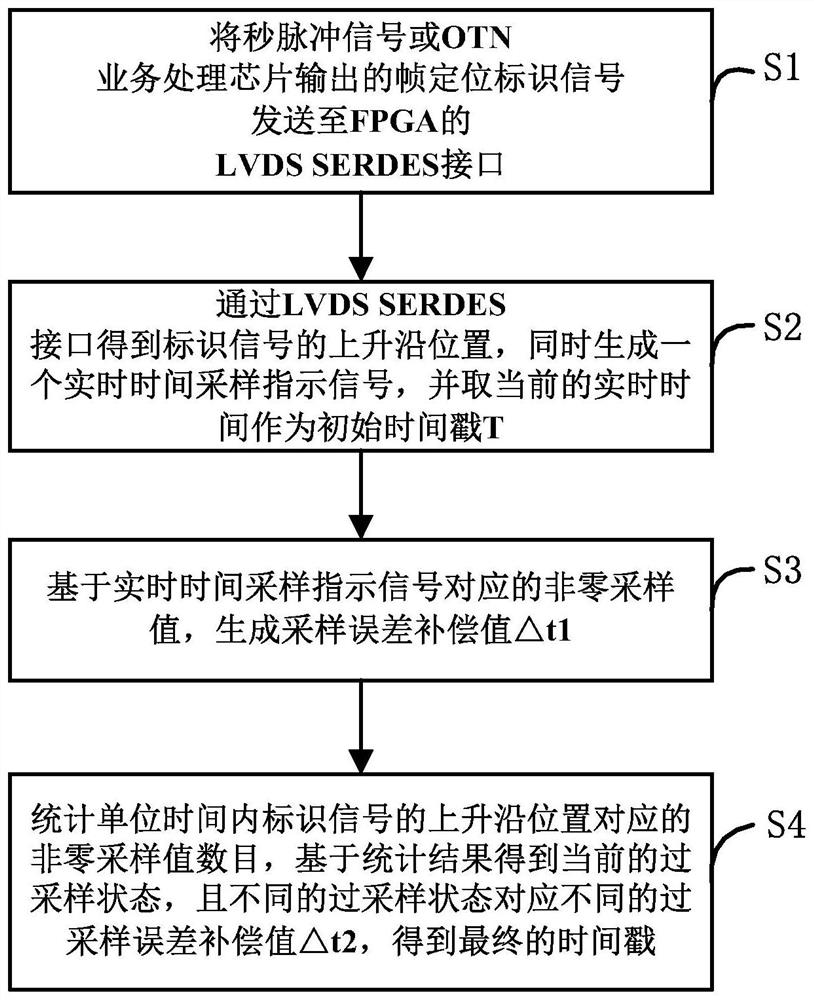

[0053] The embodiment of the present invention provides a method for improving the accuracy of time stamps. The serial-to-parallel conversion function of an LVDS SERDES interface of an FPGA is used to generate an oversampled frame positioning identification signal for the time stamp, and a sampling error compensation value is obtained based on the frame positioning identification signal. Get high-precision timestamps. The embodiments of the present invention also provide a system for improving the accuracy of time stamps accordingly. The scenarios used in the embodiments of the present invention are processing pulse-per-second signals and generating sending and receiving time stamps when an OTN (Optical Transport Network, Optical Transport Network) service card supports the 1588 function through an overhead channel.

[0054] see figure 1 As shown, a method for improving timestamp accuracy provided by an embodiment of the present invention includes:

[0055] S1: Send the puls...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More