Two-level comparator

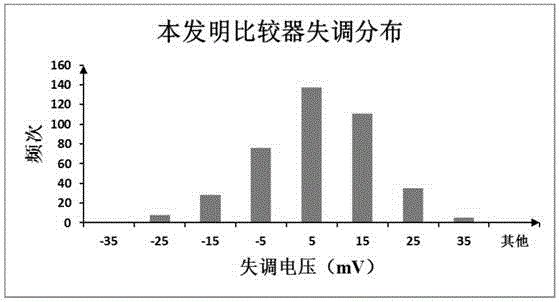

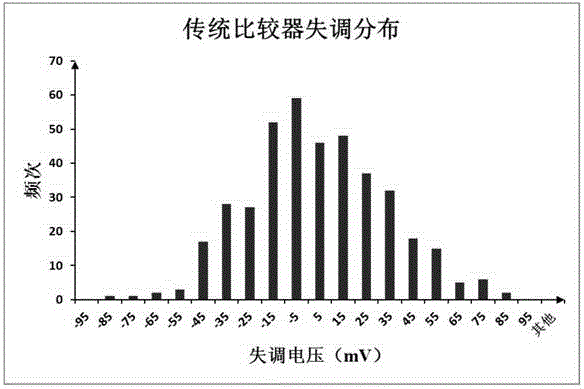

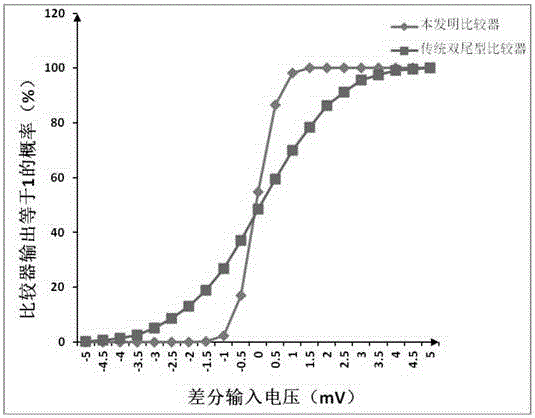

A comparator and input stage technology, applied in the electronic field, can solve the problems of large noise and large offset of the comparator, and achieve the effects of low noise, reduced offset and noise, and low timing requirements

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0016] The present invention will be further described below in conjunction with the accompanying drawings and specific embodiments.

[0017] Aiming at the problems existing in the existing double-tailed comparator circuit, such as very precise timing requirements for the clock signal, relatively large comparator offset, and relatively large noise, the present invention proposes a two-stage comparator circuit. The specific circuit structure is as follows: figure 2 As shown, the two-stage comparator circuit includes an input stage and a latch stage, the input stage is composed of 3 NMOS transistors and 4 PMOS transistors, and the latch stage is composed of 6 NMOS transistors and 4 PMOS transistors; in the input stage The gates of the first NMOS transistor MN1, the third PMOS transistor MP3 and the fourth PMOS transistor MP4 are connected to the clock signal CLK; the drain of the first NMOS transistor MN1 is connected to the source of the second NMOS transistor MN2 and the sourc...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More