Patents

Literature

124 results about "Logic complexity" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Reliable multicast using merged acknowledgements

InactiveUS20060114848A1Reduce trafficSpecial service provision for substationError prevention/detection by using return channelLogic complexityComputer network

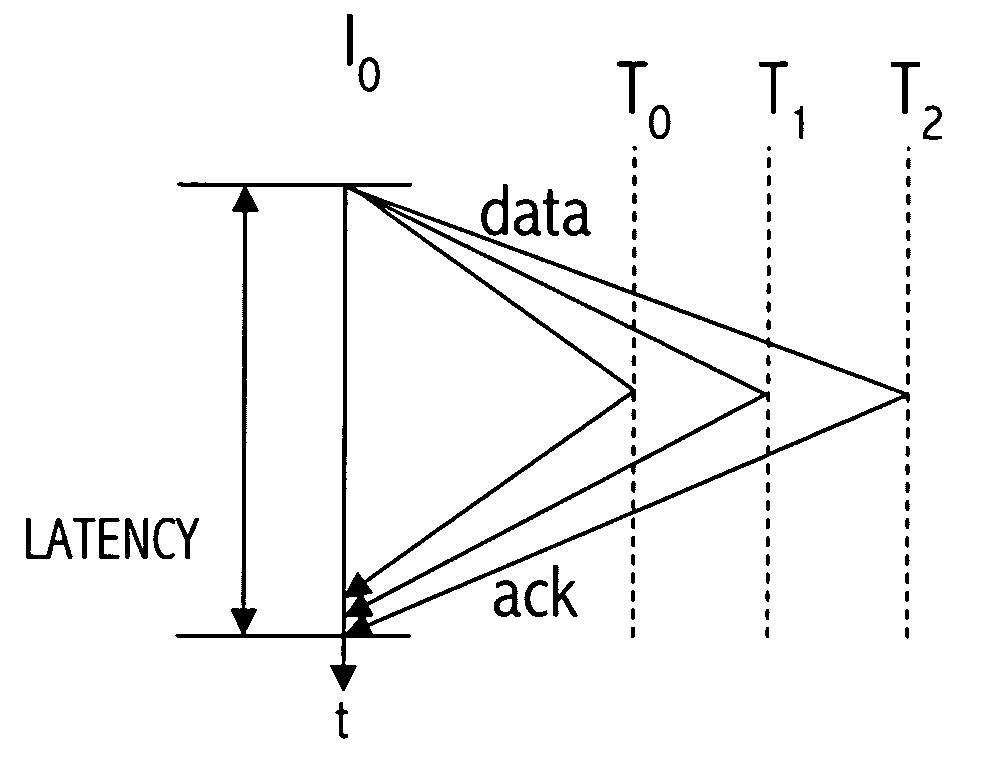

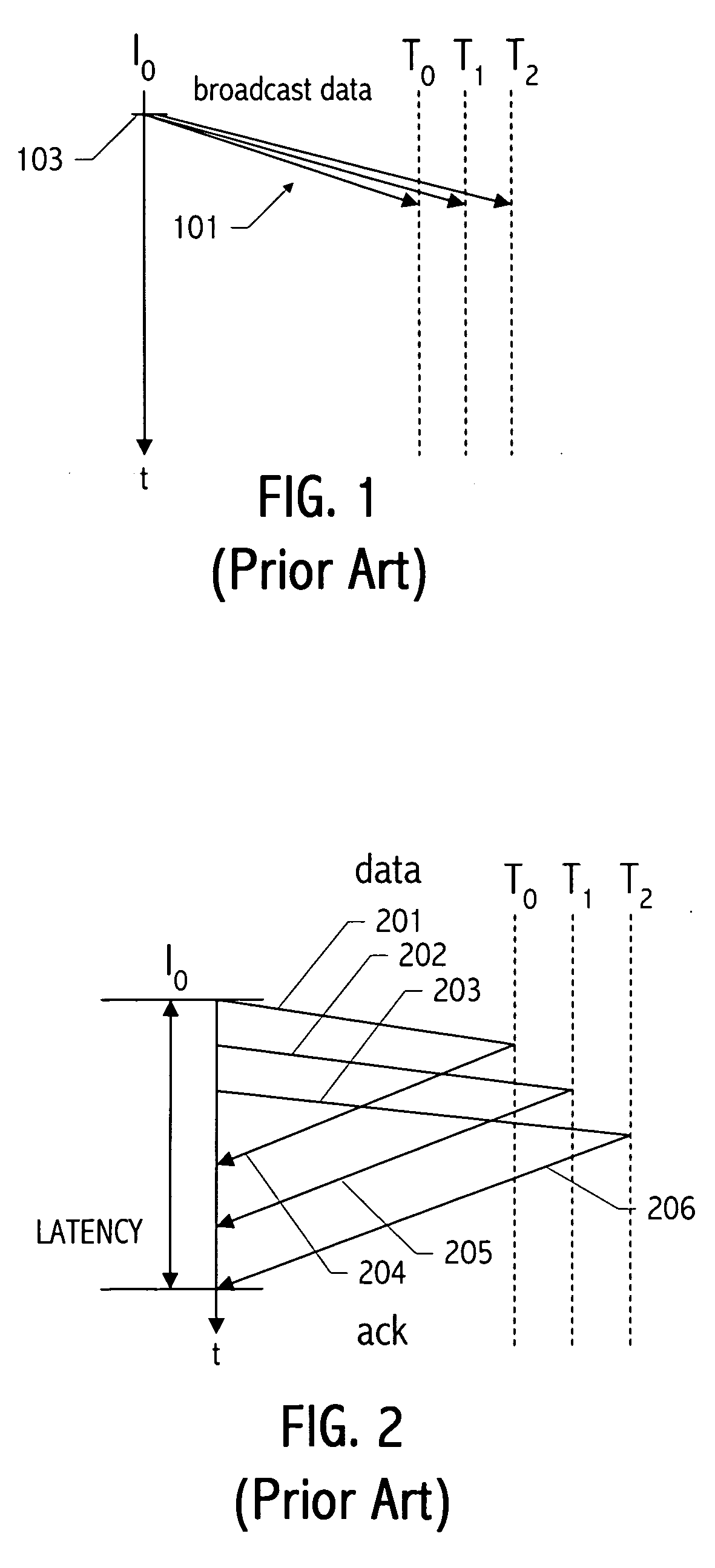

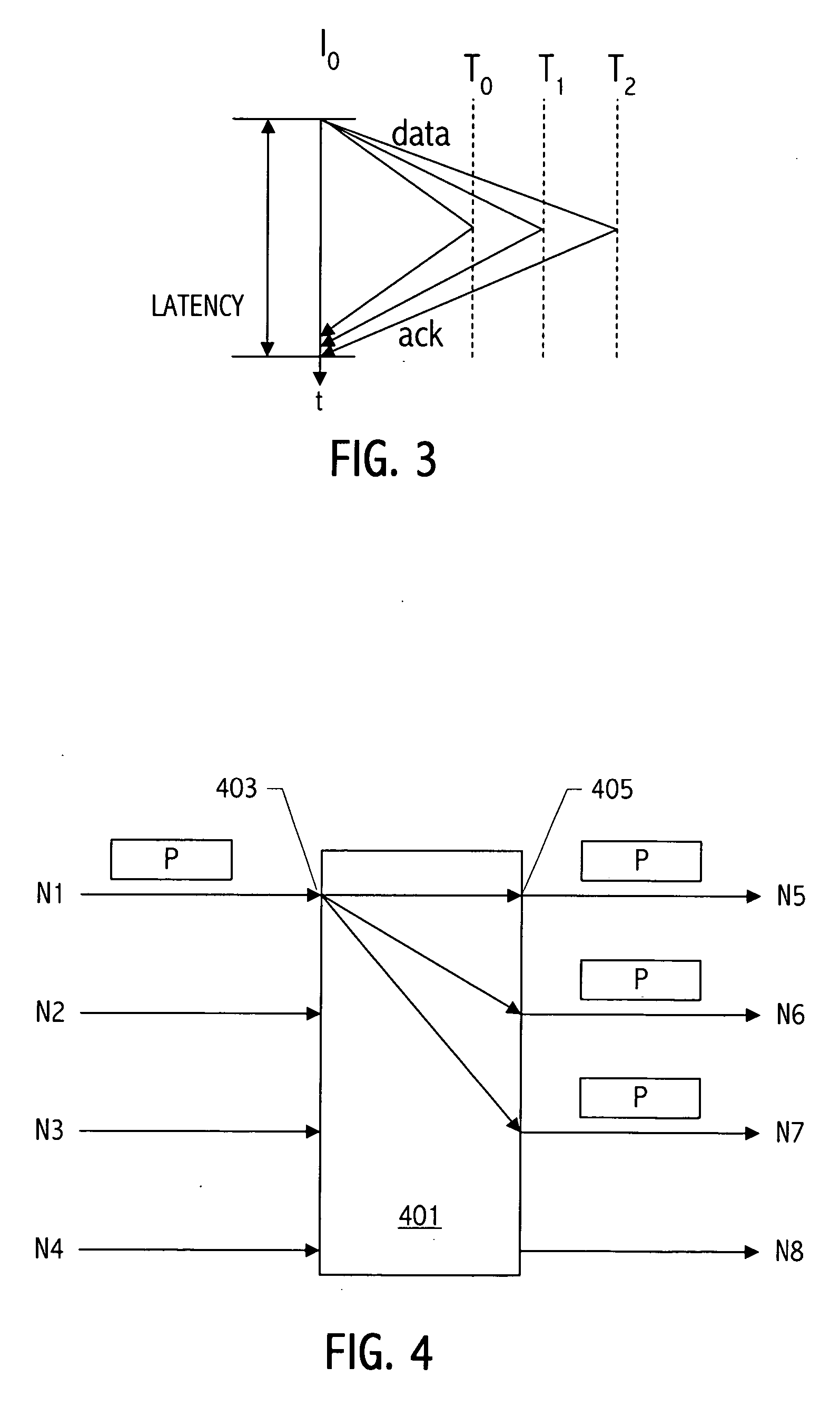

Multiple multicast acknowledgements can be merged into a single multicast acknowledgement, thus reducing traffic and reducing logic complexity. An intermediate node that receives multiple multicast acknowledgements merges the multiple acknowledgements into a single acknowledgement, and then supplies the single merged acknowledgment to the multicast source. Encoding of the single merged acknowledgement conveys to the source which of the multicast targets successfully received (or which failed to receive) the multicast information.

Owner:ORACLE INT CORP

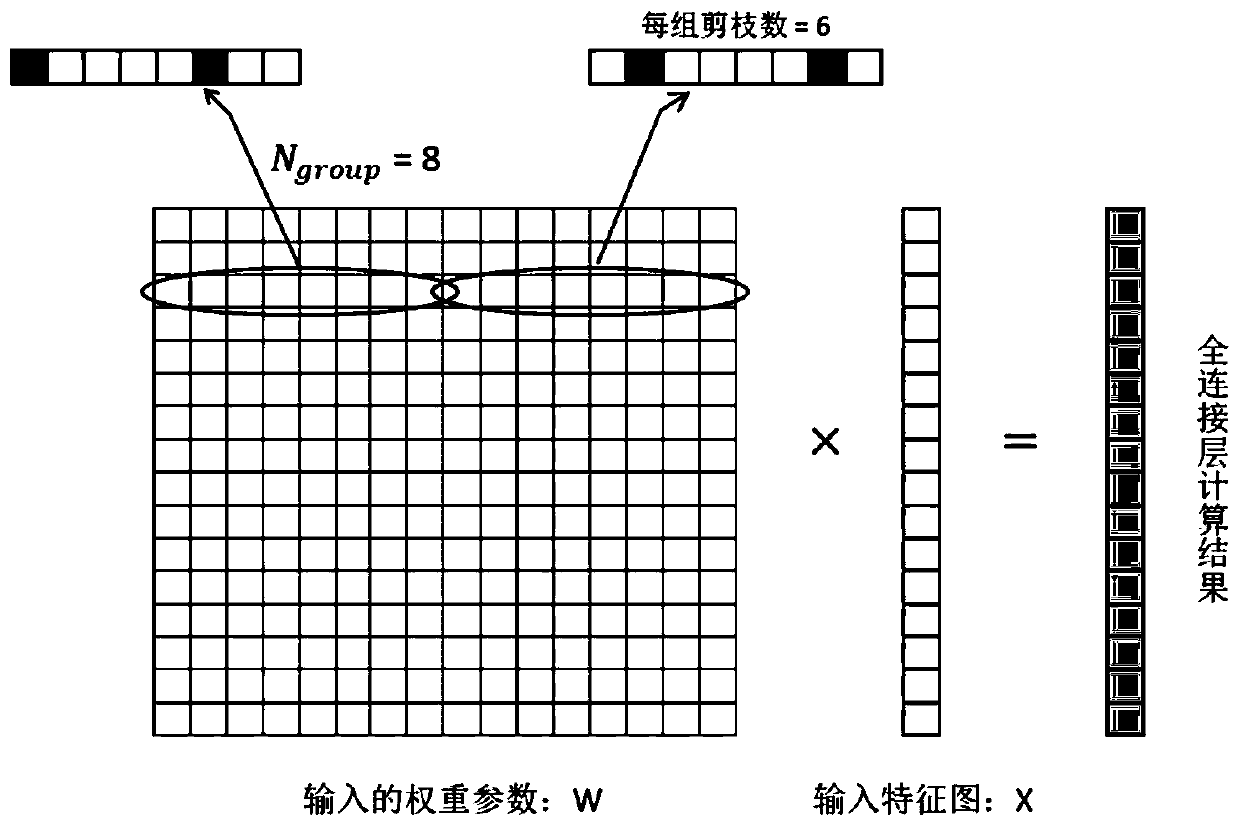

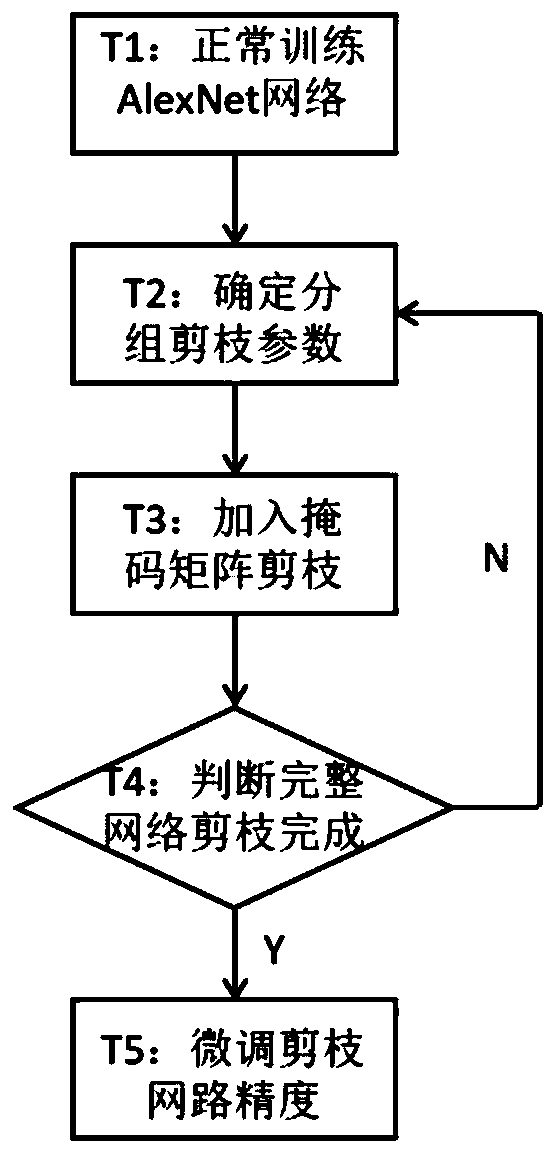

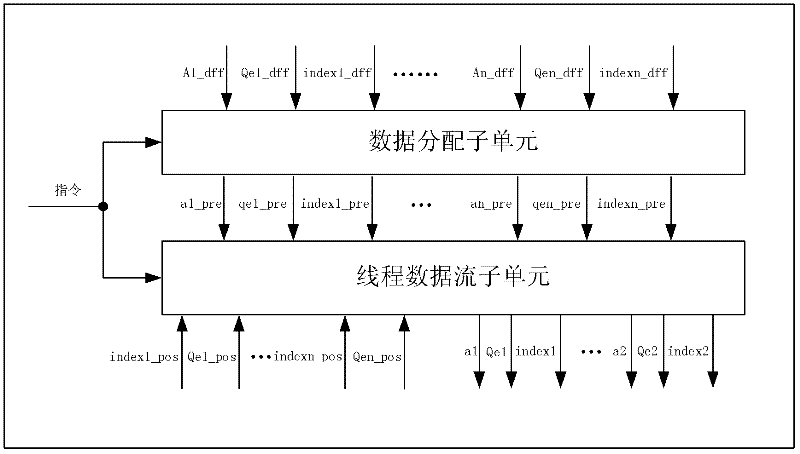

An acceleration method for realizing sparse convolutional neural network inference for hardware

ActiveCN109711532AReduce logic complexityImprove the overall efficiency of forward inferenceNeural architecturesEnergy efficient computingLogic complexityRound complexity

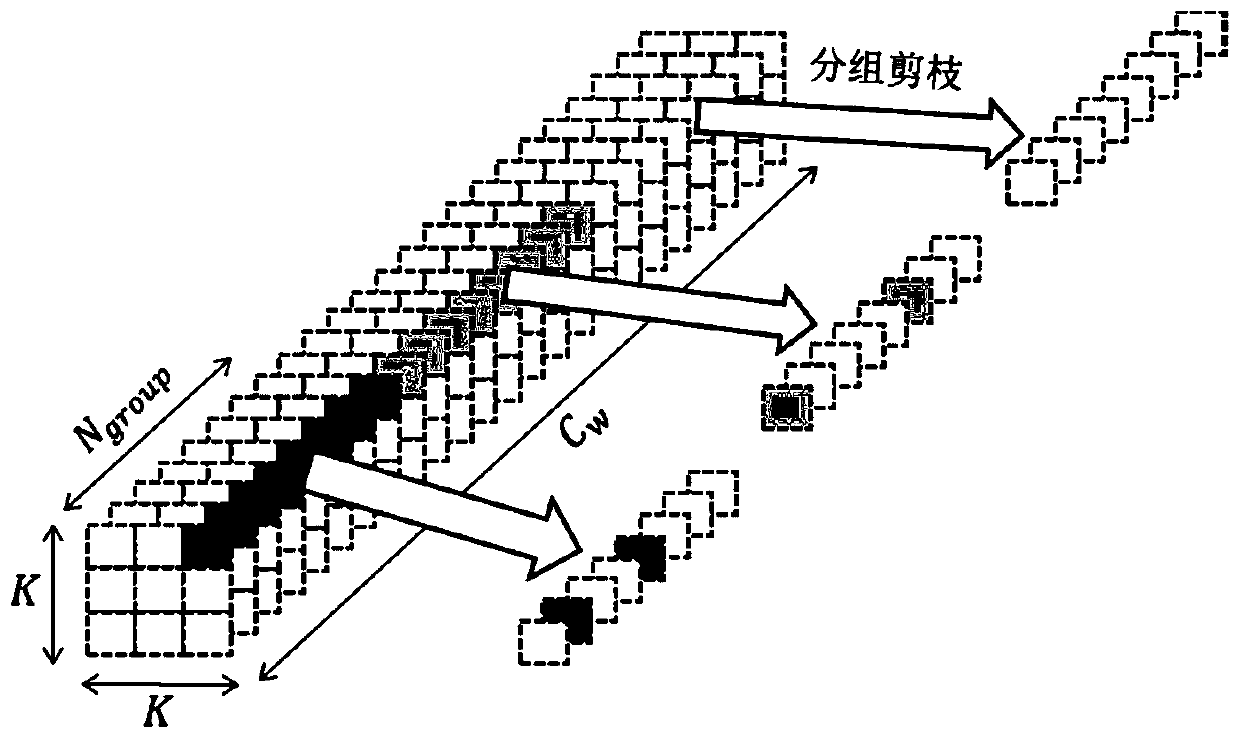

The invention discloses an acceleration method for realizing sparse convolutional neural network inference for hardware. The method comprises a grouping pruning parameter determination method facing asparse hardware acceleration architecture, a grouping pruning training method for sparse hardware acceleration architecture and a deployment method for forward inference of a sparse convolutional neural network. determining the packet length and the pruning rate of packet pruning according to the number of multipliers in the hardware architecture; based on the magnitude cutting mode, cutting weights except the compression rate; The network accuracy and compression rate after pruning are improved through an incremental training mode, the weight and index parameters of a non-pruning position are saved after the pruned network is finely adjusted, the network is sent to a computing unit under a hardware architecture, and the computing unit obtains the activation value of the packet length atthe same time to complete sparse network forward inference. The pruning parameters and the pruning strategy of the algorithm level are set based on the hardware architecture, the logic complexity of the sparse accelerator is reduced, and the overall efficiency of forward inference of the sparse accelerator is improved.

Owner:SOUTHEAST UNIV +2

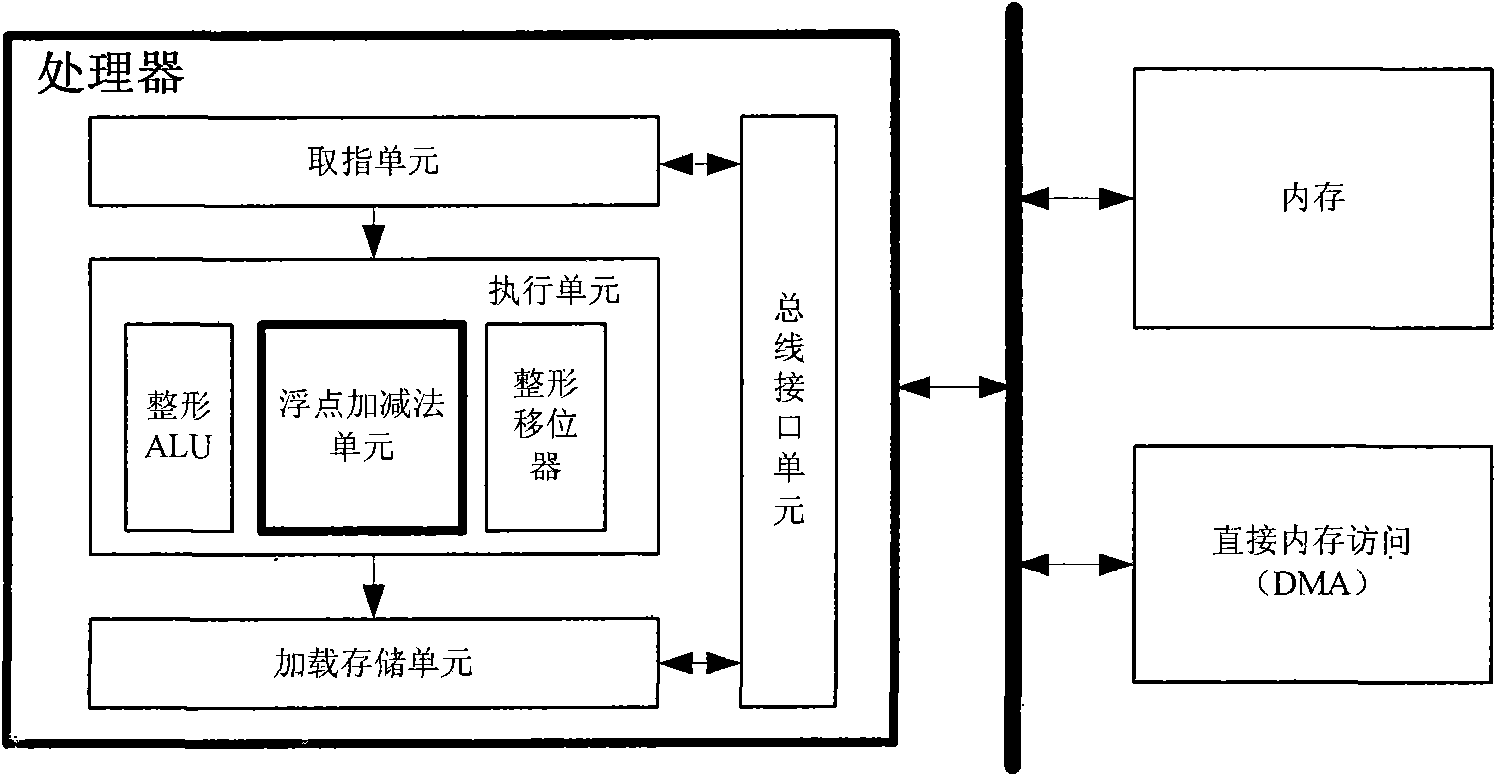

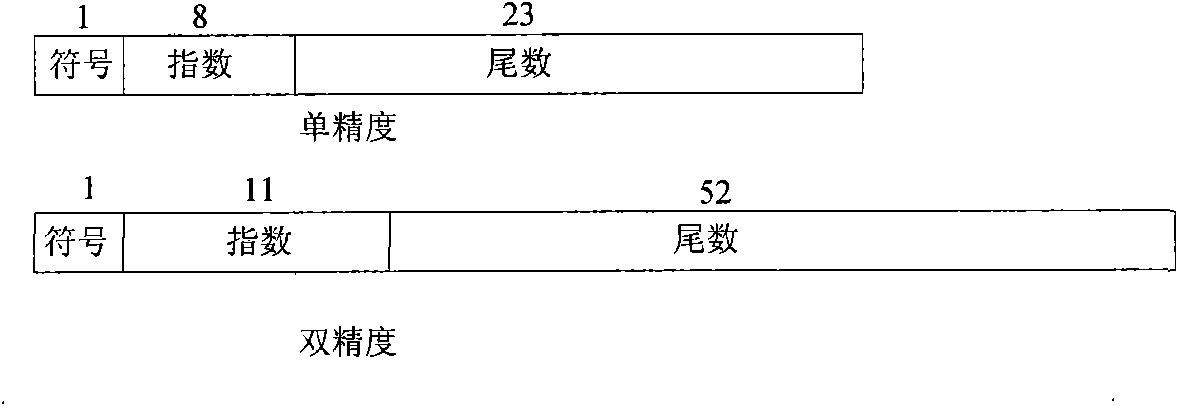

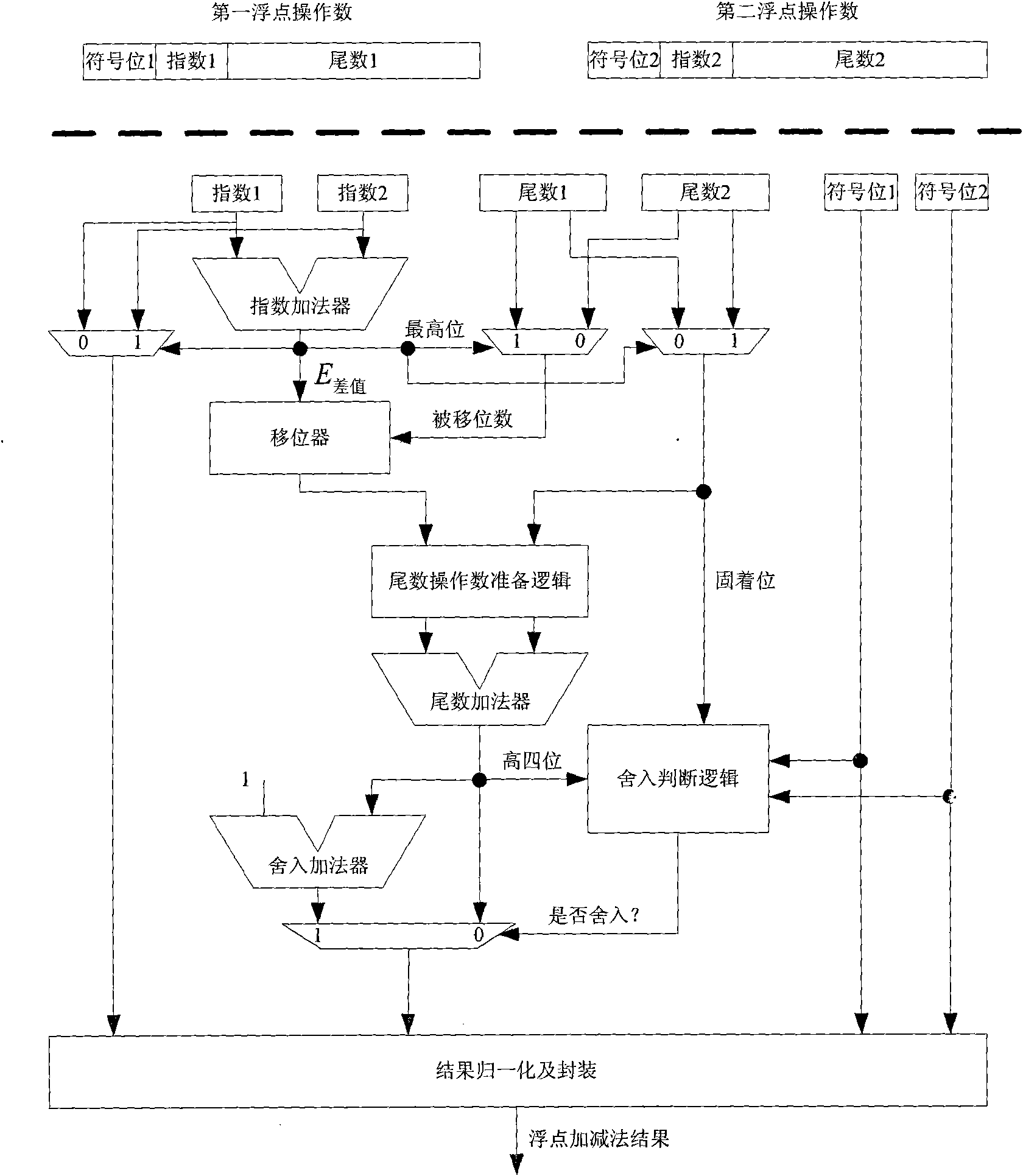

Floating point addition device based on complement rounding

InactiveCN101650642AAvoid preparationAvoid rounding judgment logicComputation using non-contact making devicesLogic complexityRounding

The invention relates to a floating point addition device based on complement rounding, which supports the floating point addition operation and the floating point subtraction operation. The floatingpoint addition device comprises an exponent adder, a mantissa shifter, a mantissa operand preparation logic unit, a mantissa adder, a rounding judgment logic unit and a rounding adder, wherein the mantissa operand preparation logic unit is used for processing the mantissa operand according to sign bits and the exponent difference of the first floating point operand and the second floating point operand, the rounding judgment logic unit is used for executing the uniform rounding judgment on a mantissa addition result, judging the positive and the negative of the mantissa sum according to the highest bit output by the mantissa adder, determining a constant bit for the rounding judgment according to the highest four bits output by the mantissa adder, and unifying original code rounding plus 1judgment logic and complement rounding plus 0 judgment logic; and the rounding adder is used for rounding the mantissa addition result of the floating point and finishing the code extraction and complement operation to the mantissa sum. The invention has the uniform mechanism, avoids the special complex mantissa operand preparation and rounding judgment logic of the floating point addition, and reduces the logic complexity.

Owner:C SKY MICROSYST CO LTD

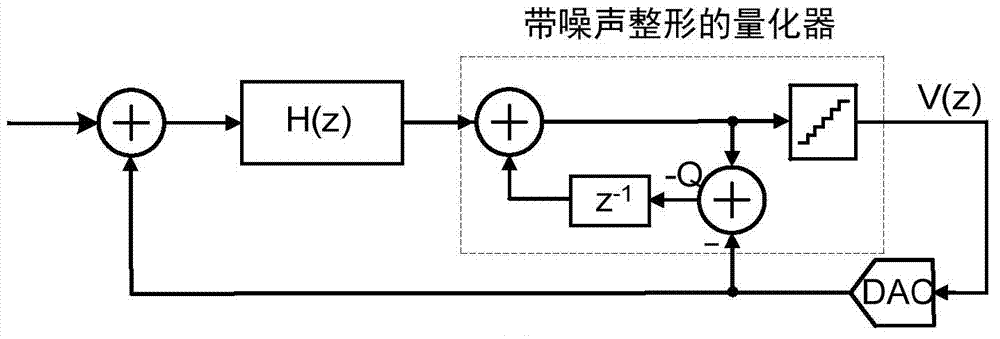

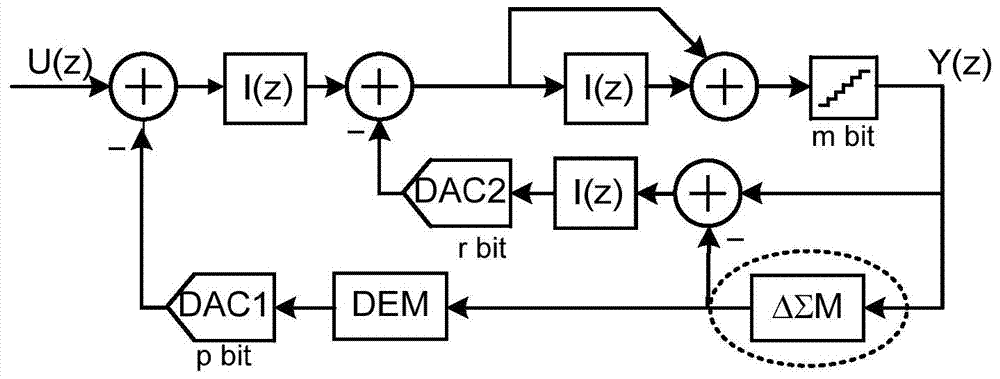

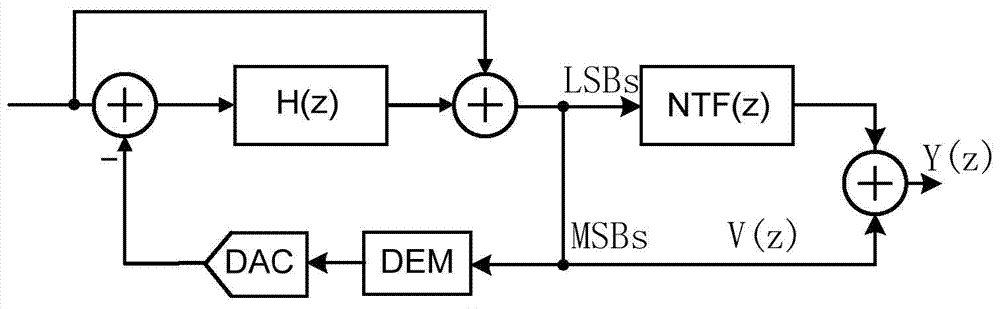

Delta-sigma modulator based on digital-noise coupling technology

ActiveCN103929184ASolve the problem of exponential growth of hardware complexityAvoid Logic Latency IssuesAnalogue conversionLogic complexityEngineering

The invention discloses a delta-sigma modulator based on the digital-noise coupling technology. The structure of a traditional noise coupling delta-sigma modulator is improved, and the output of a quantizer is divided into an MSB part and an LSB part. The MSB part is directly fed back to the input end of the modulator; the LSB part is fed back to the input of the quantizer after digital-to-analogue conversion; then the MSB part and the LSB part are recombined after digital post-processing. The digital-noise coupling technology can fully represent the performance advantage of the high-precision quantizer, the problem of the exponential growth of the matching logic complexity of dynamic components is avoided, the logic time delay of introduction of a digital delta-sigma remodulation scheme provided by formers is also avoided, the quantizing noise leakage caused by mismachining between analog and digital noise transfer functions is further restrained, and therefore the requirement for design of an operational amplifier is lowered, implementation is easy, and the modulator is very suitable for low-power dissipation and broadband application.

Owner:UNIV OF SCI & TECH OF CHINA

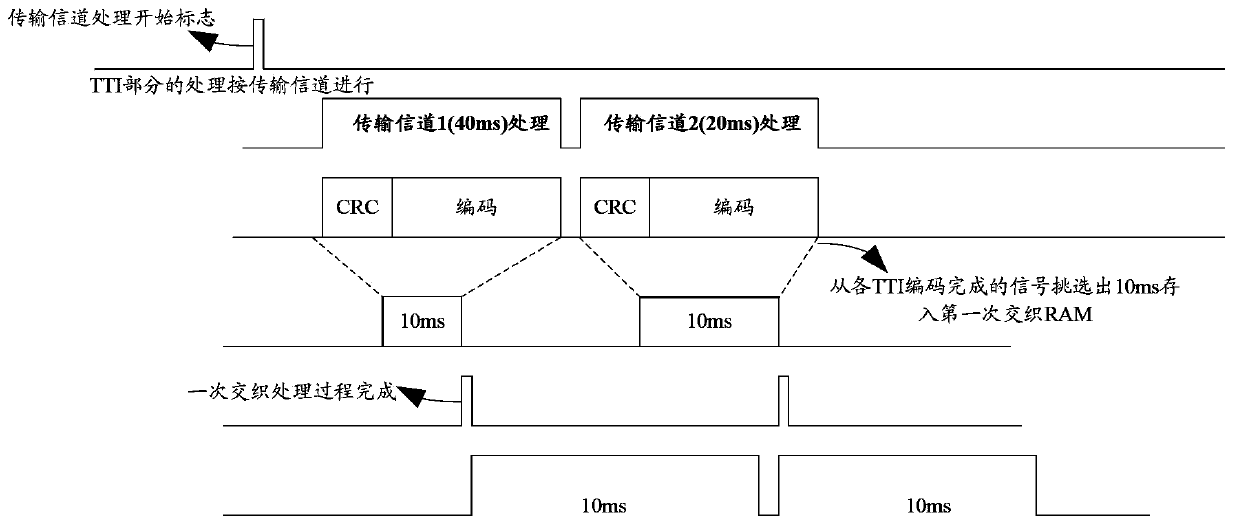

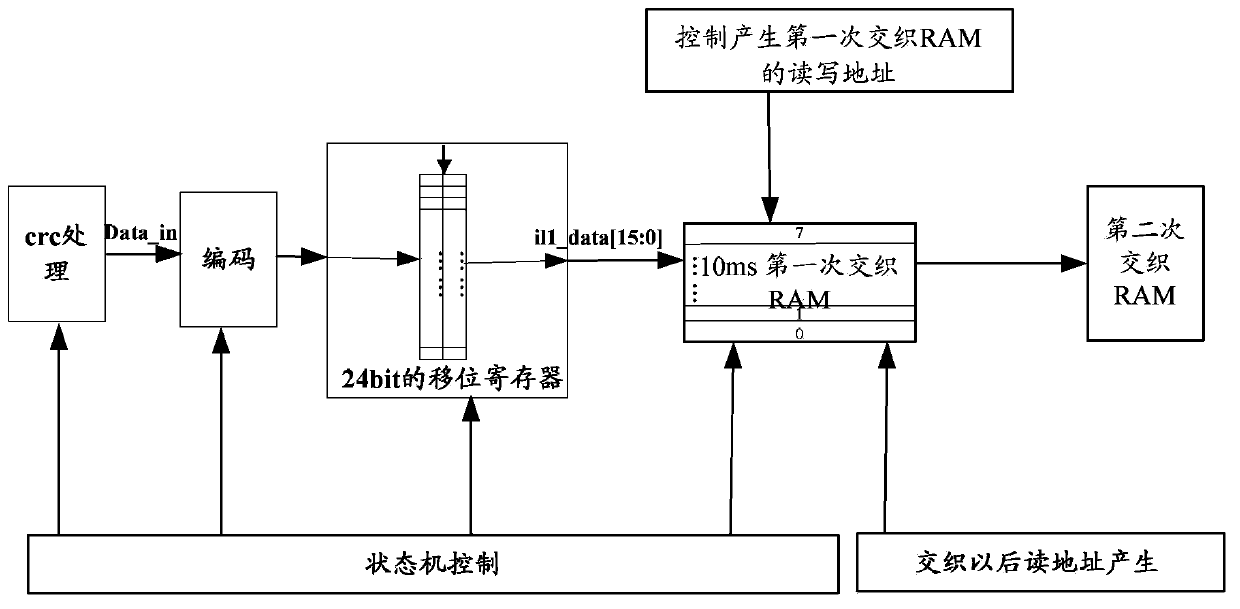

TD-SCDMA uplink transmission channel processing method

ActiveCN103873186AReduce complexityReduce the difficulty of logic processingError preventionTime-division multiplexing usageLogic complexityTD-SCDMA

The invention discloses a TD-SCDMA uplink transmission channel processing method. By the method, the processing of each 10 ms of each transmission channel is successively finished, and ordering processing of the TTIs of eight transmission channels according to size is unnecessary, so that the processing logic complexity is reduced. By using the method, it is unnecessary to store data of all the transmission channels in a large memory to select the 10 ms for processing, instead, data of one 10 ms currently to be processed is directly stored only, and data selection is finished by use of a memory, such that the realization is visual and convenient, the logic processing difficulty in determining a data storage position is reduced, the requirement for interlacing the storage space of the memory at a time is reduced, and the effect of optimizing a whole uplink area is achieved.

Owner:SANECHIPS TECH CO LTD

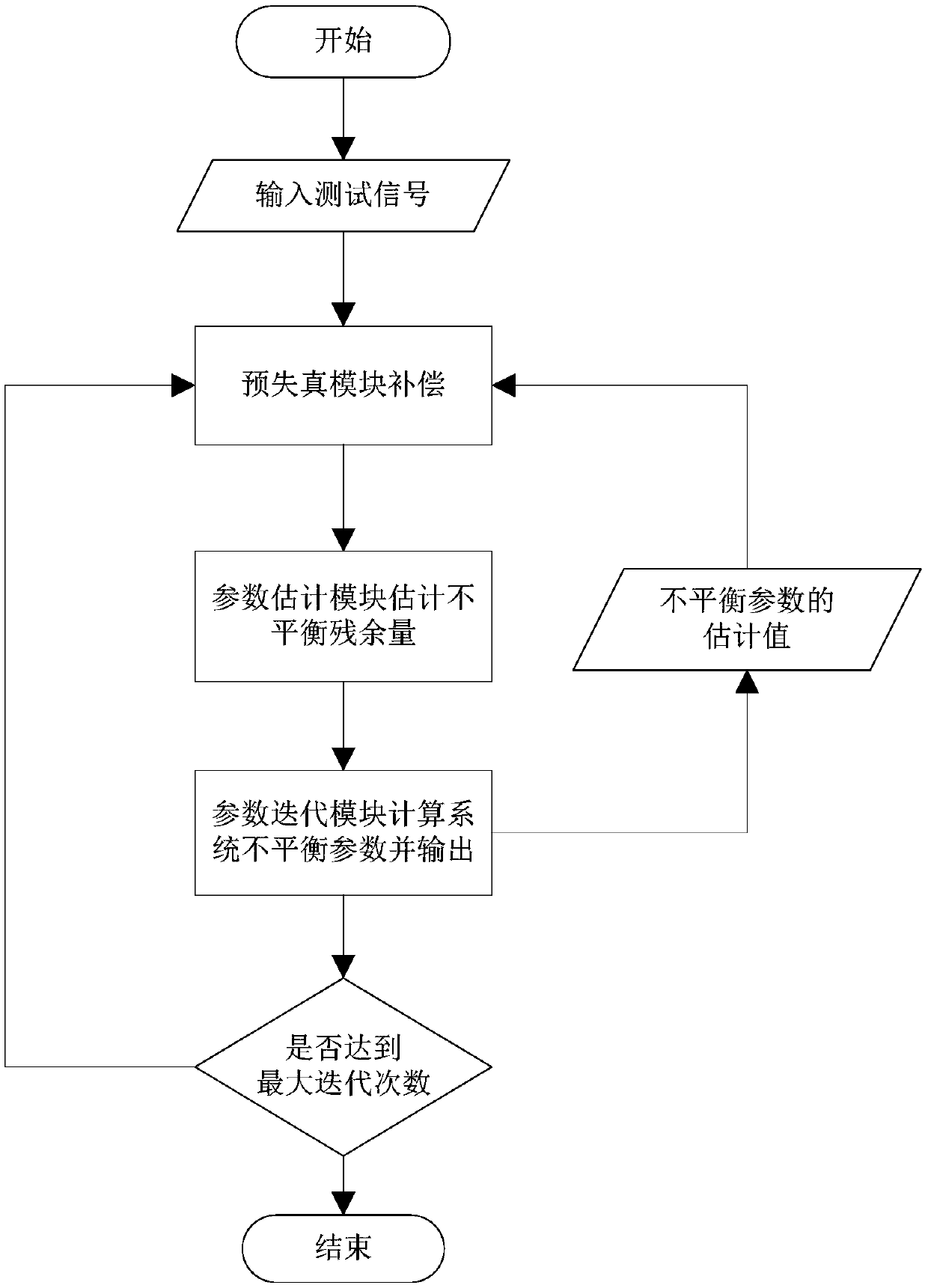

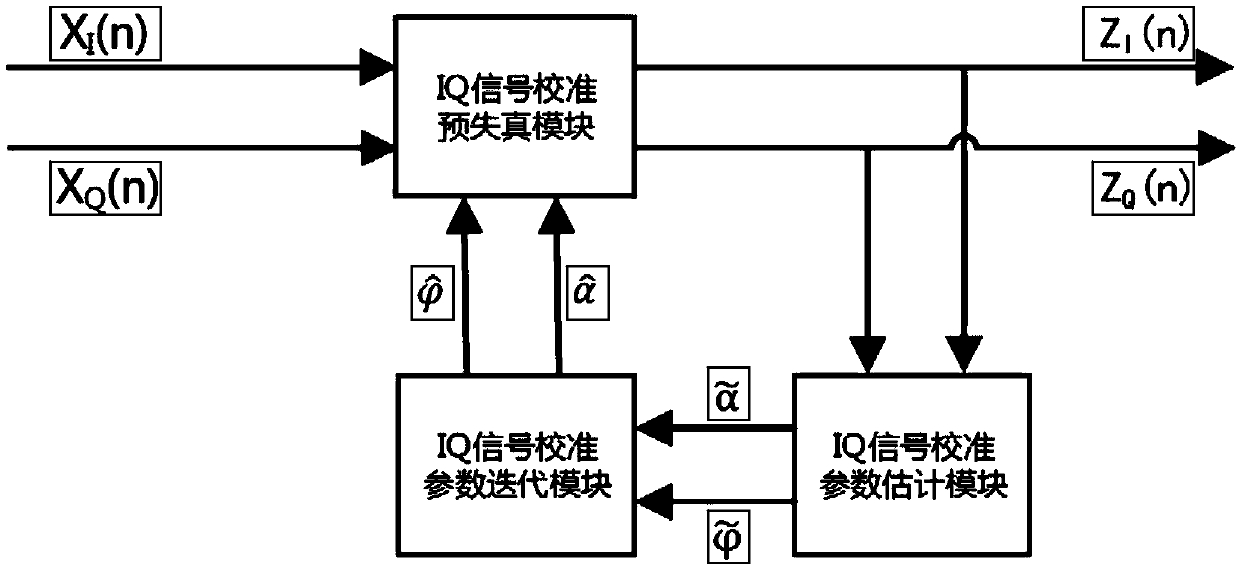

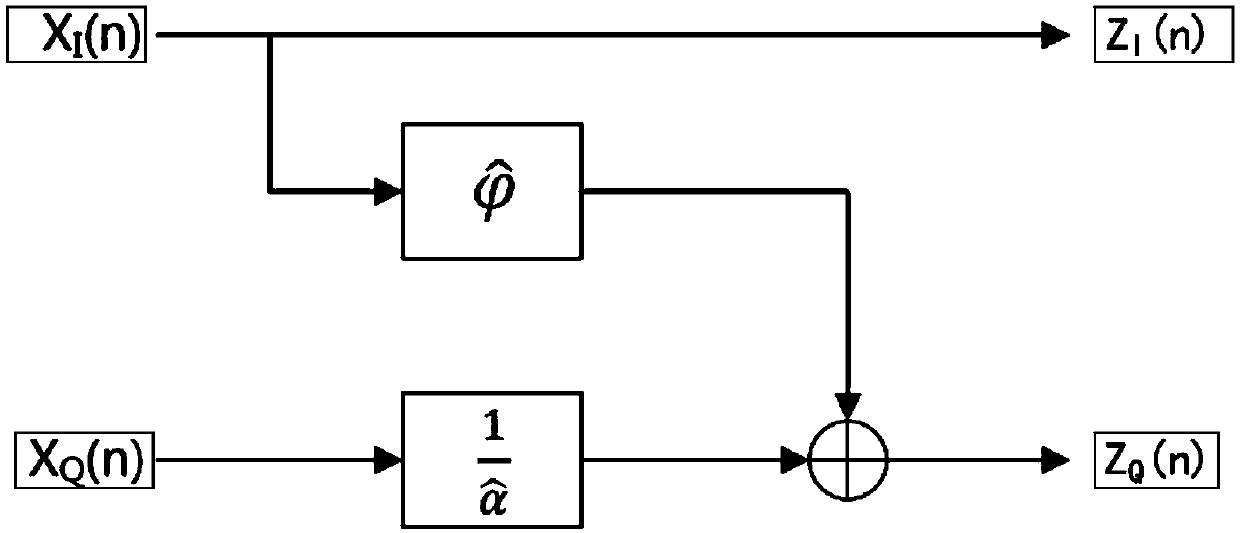

IQ signal calibration compensation method

ActiveCN109617560ASimplify operational complexityReduce logic complexityMultiple carrier systemsLogic complexityClosed loop

The invention discloses an IQ signal calibration compensation method. The method comprises the steps of inputting calibration testing signals into an IQ signal calibration predistortion module; outputting compensated testing signals through compensation computing; inputting the compensated testing signals into an IQ signal calibration parameter estimation module, computing residual volume estimation of imbalance parameters, and outputting the residual volume estimation to an IQ signal calibration parameter iteration module; computing estimated values of iterated imbalance parameters by the IQsignal calibration parameter iteration module; updating the iterated imbalance parameters for compensation, thereby finishing single-time closed loop calibration; and terminating iteration if iteration times reaches the maximum iteration times, thereby finishing compensation. According to the method, closed loop iteration is carried out, complex computing such as extraction of a root and solutionof an inverse trigonometric function is avoided through utilization of an iteration approximation method, computing complexity of blind calibration is simplified, logic complexity of a digital circuitis reduced, under the same circuit area, computing count of the testing signals can be increased, compensation precision is improved, and moreover, through utilization of a closed loop system, stability under an interference condition is improved.

Owner:杭州城芯科技有限公司

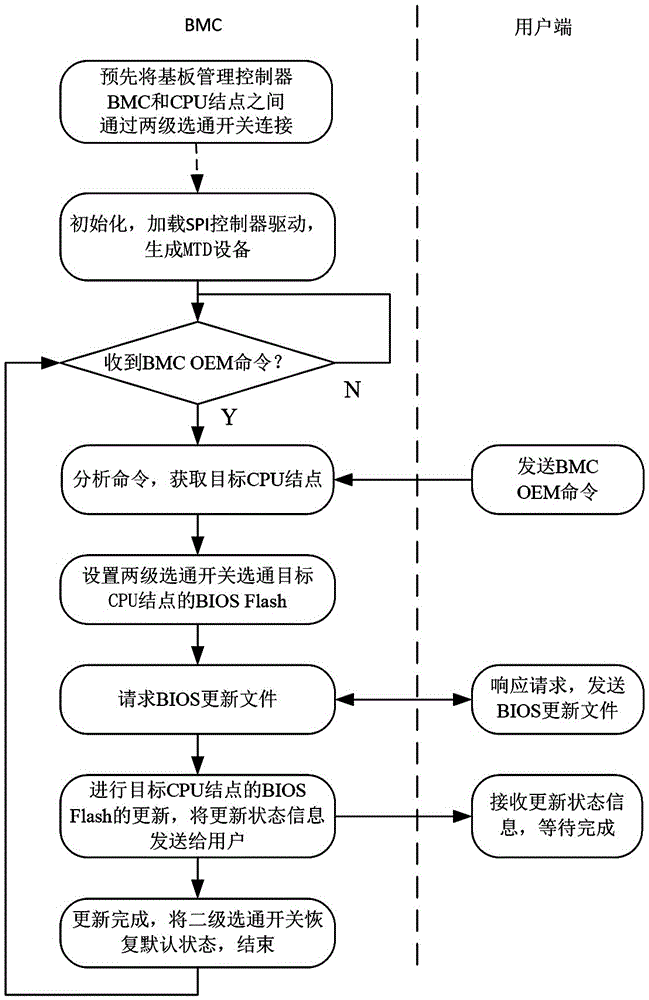

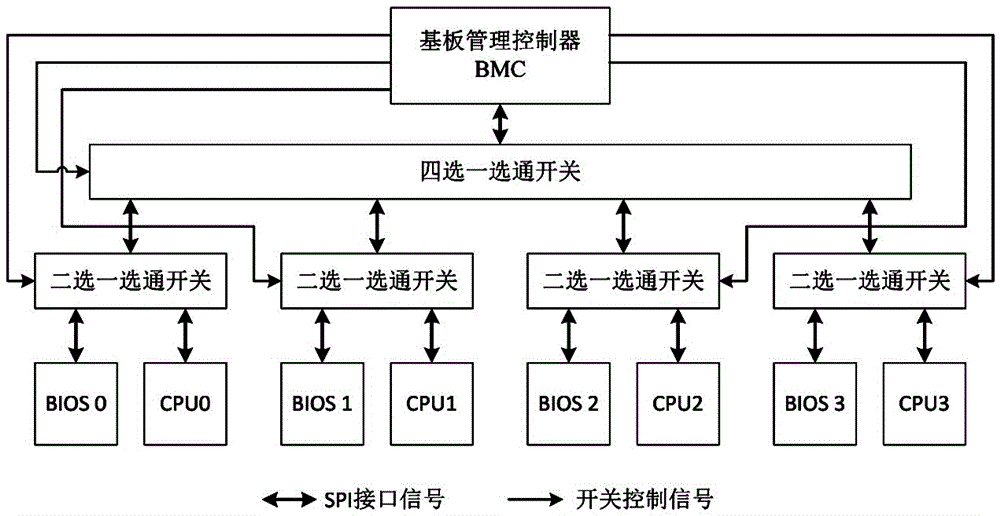

Online BIOS (basic input/output system) refreshing method for multi-node server

InactiveCN105867949ASolve the refresh problemRemote operation is simple and convenientProgram documentationProgram loading/initiatingElectricityLogic complexity

The invention discloses an online BIOS (basic input / output system) refreshing method for a multi-node server. The method comprises steps as follows: a two-stage gating switch circuit comprising a first-stage gating switch and second-stage gating switches is arranged between a BMC (baseboard management controller) and CPU (central processing unit) nodes, after initialization of the BMC is completed, a driver of an SPI (serial peripheral interface) controller is uploaded, an online BIOS refreshing command on a user side is waited, when the online BIOS refreshing command is received, target CPU nodes are determined, the two-stage gating switch circuit is set for gating of BIOS Flash of the target CPU nodes, a BIOS updating file is obtained from the user side, the BIOS updating file is executed for updating, and the state of the two-stage gating switch circuit is restored. With the adoption of the method, the problem about BIOS refreshing of high-density server nodes can be effectively solved, CPUs on a main board can be updated without electrification, the single BMC can manage BIOS refreshing of the multiple CPU nodes, and the method has the advantages that remote operation is realized, the method is simple and convenient, the hardware logic complexity is low, embedded software is simple to realize, the method is convenient to use and the user experience is good.

Owner:NAT UNIV OF DEFENSE TECH

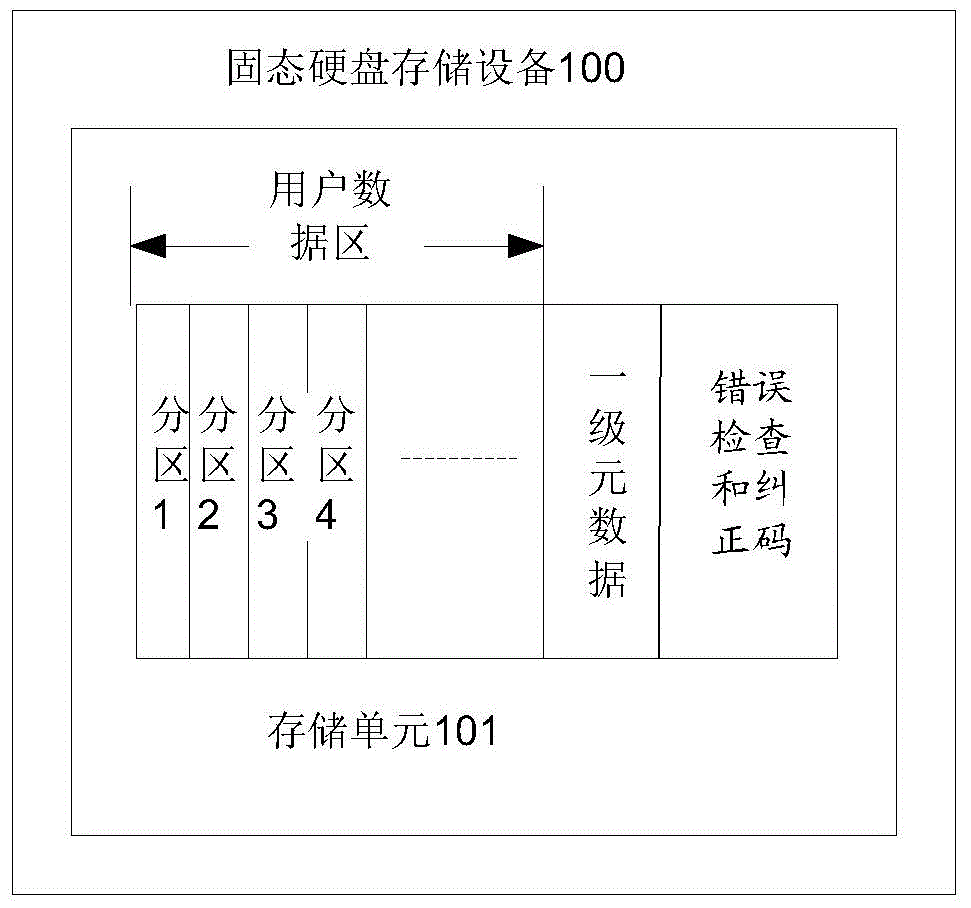

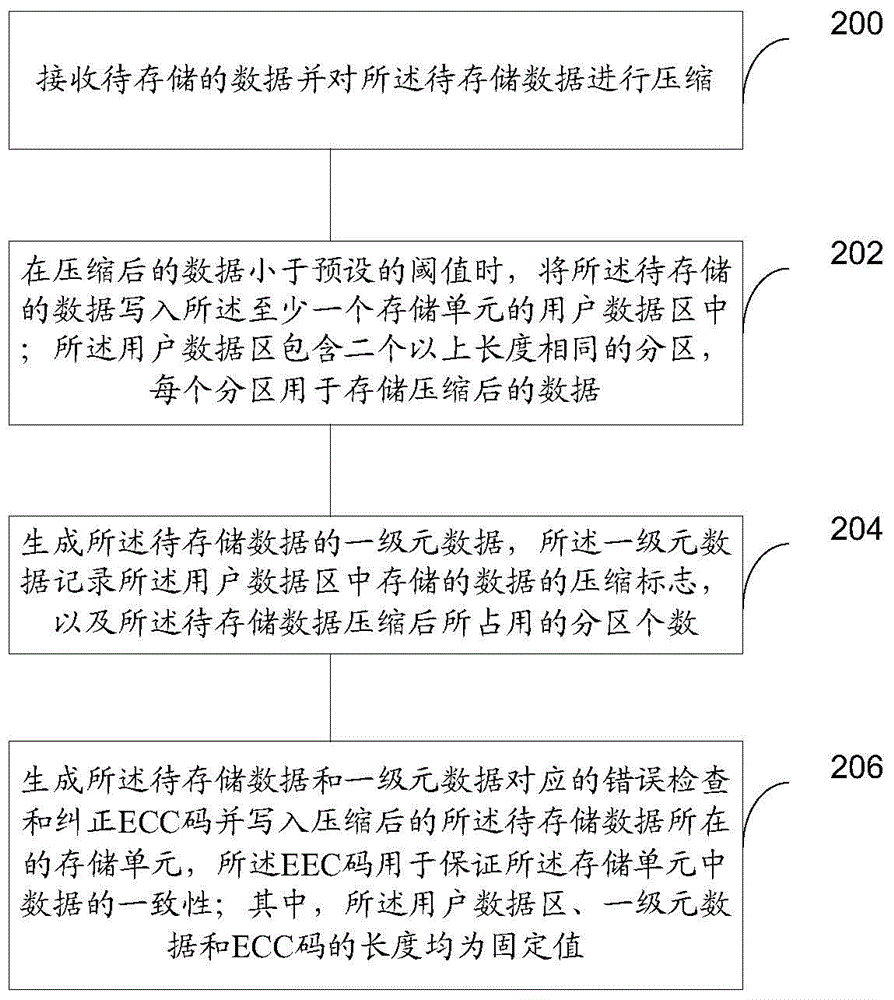

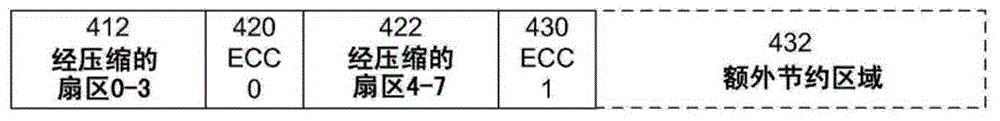

Solid-state disk storage device and data access method of solid-state disk storage device

ActiveCN105808151AGuaranteed lifetime consistencyEnsure consistencyInput/output to record carriersError detection/correctionLogic complexityAccess method

The invention provides a solid-state disk (SSD) storage device and a data access method of the SSD storage device. The problems existing in the prior art that the data management of an SDD is high in complexity, and NandFlash physical pages in a NandFlash physical block are inconsistent in the service life are solved. According to the invention, the user data area, first order metadata and the length of an ECC in each storage cell of the SSD storage device are set to be fixed values, the format of data stored in each storage cell is fixed, the ECC can guarantee the consistency of data in the user data area and the first order metadata according to a fixed code rate, the correctness and integrity of the data in the user data area and the first order metadata are guaranteed, data management is simplified, and the ECC hardware logic complexity is reduced; at the same time, because the ECC code rate is consistent, the consistency of the service life of each storage cell is guaranteed.

Owner:HUAWEI TECH CO LTD

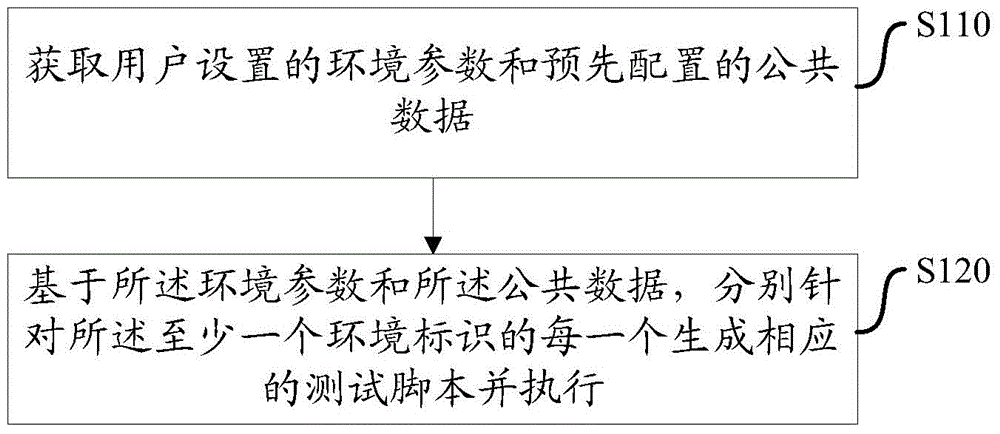

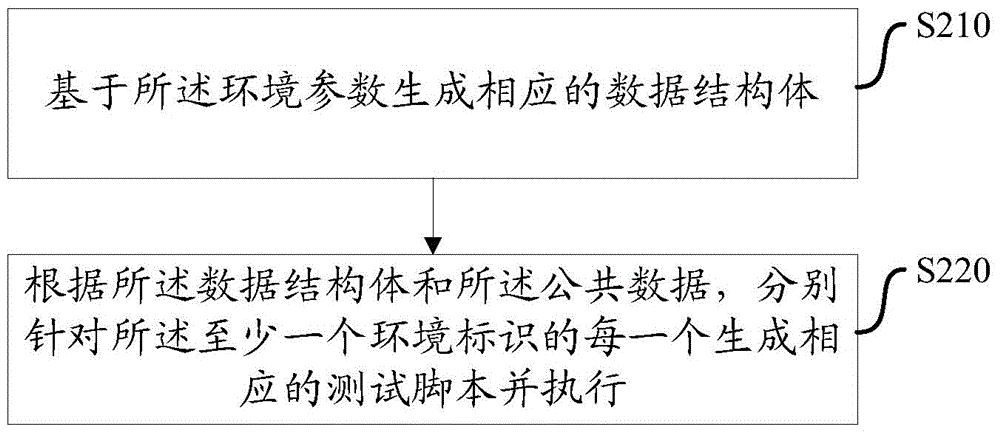

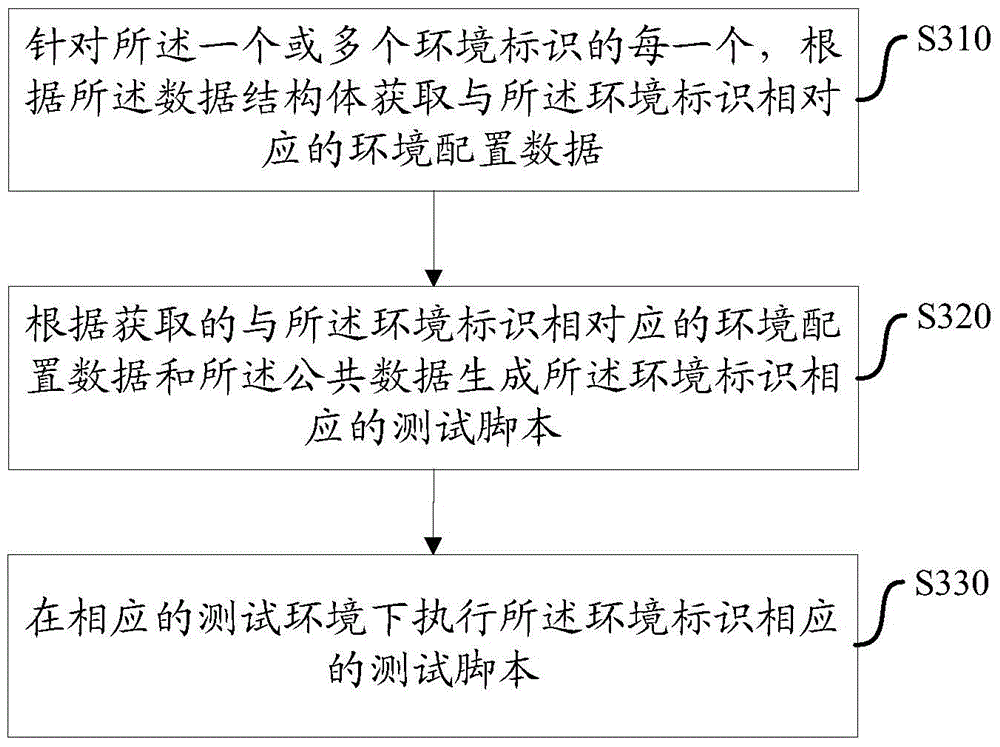

Test method and device under multi-environment

ActiveCN105446865AAvoid mistakesAchieve uniquenessSoftware testing/debuggingSpecific testLogic complexity

The application provides a test method and device under multi-environment; the method comprises the following steps: obtaining user set environment parameters and pre-configured common data, wherein the environment parameters comprise at least one environment label and environment configure data respectively corresponding to the at least one environment label, and the common data refers to the common data in the multi-environment; generating and executing corresponding test scripts respectively aiming at each of the at least one environment label according to the environment parameters and the common data. The method and device can test same test scene under various test environments, thus preventing logic complexity, reducing debug cost, preventing data error in execution, and realizing test script uniqueness under the specific test environment.

Owner:ALIBABA GRP HLDG LTD

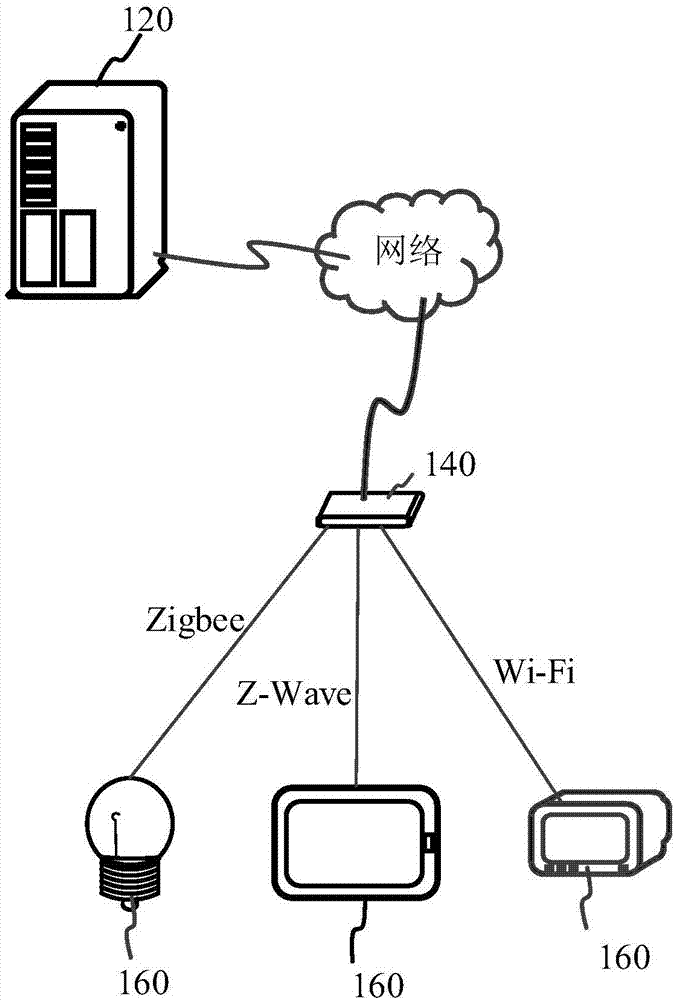

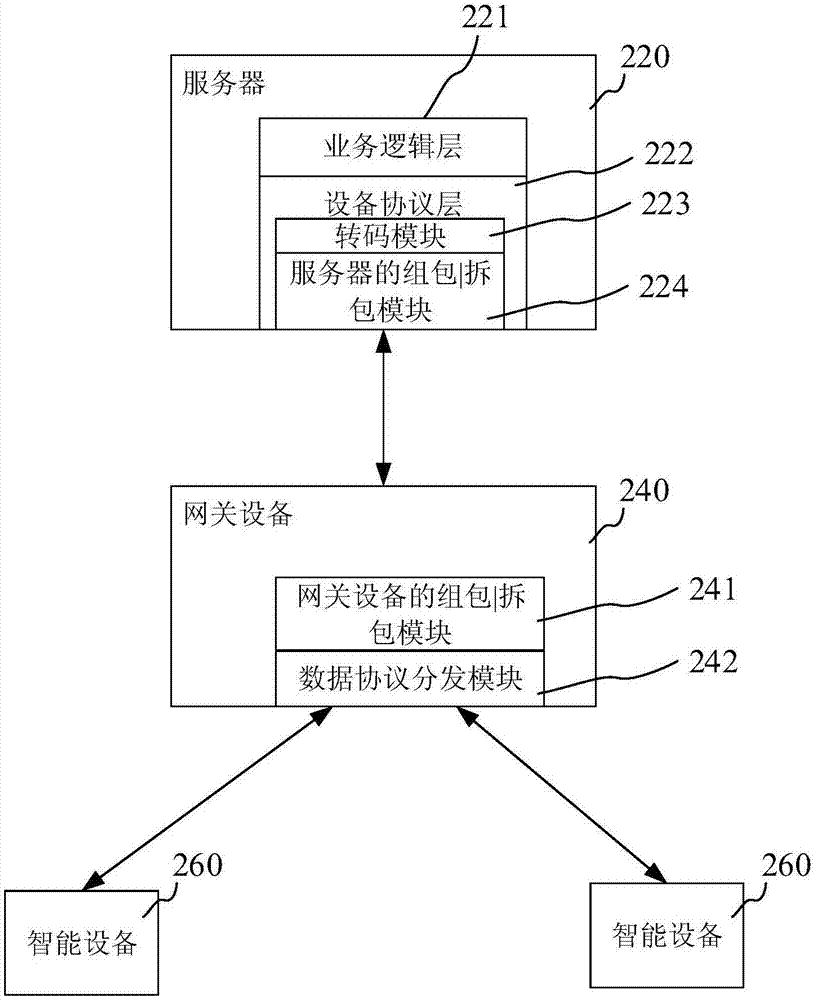

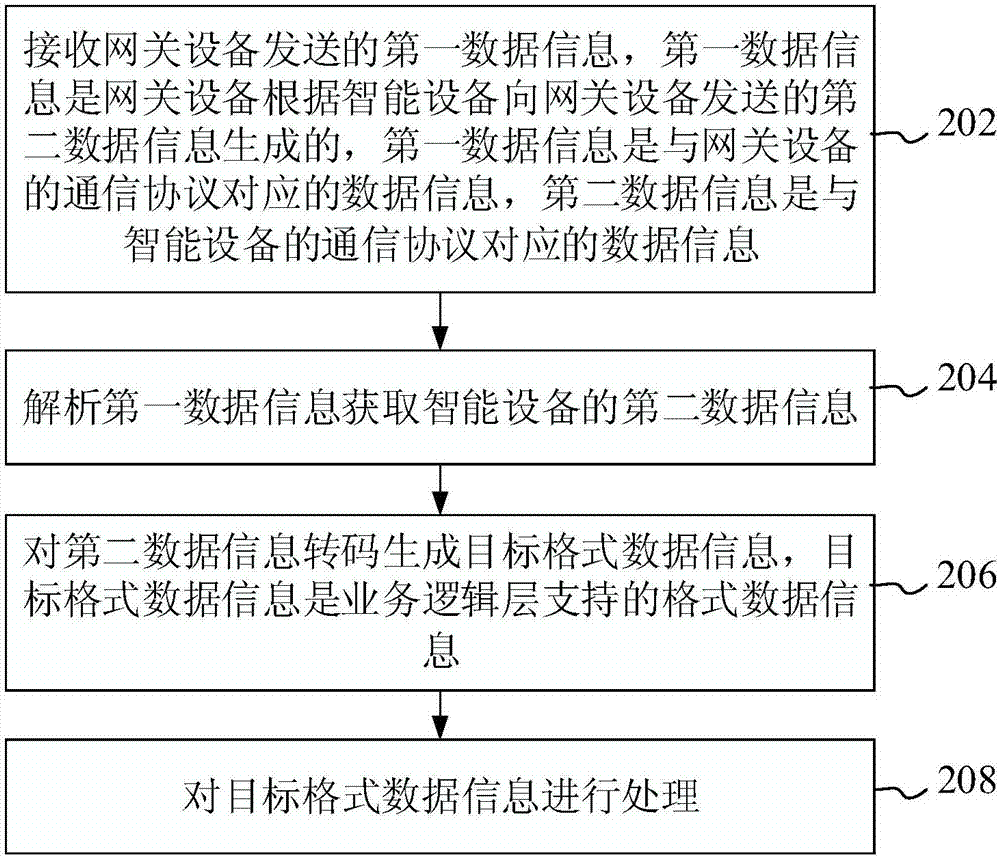

Data processing method, device, server and system

InactiveCN107347025AAvoid unsupportedIncrease hardware costData switching by path configurationNetwork connectionsLogic complexityComputer network

The embodiments of the invention disclose a data processing method, a device, a server and a system, belonging to the field of smart home. The method includes the following steps: a server receives first data information sent by gateway equipment, wherein the server includes an equipment protocol layer and a service logic layer; the server analyzes the first data information to acquire second data information of smart equipment; the server transcodes the second data information to generate target format data information; and the server processes the target format data information. The problem that the software upgrade of the gateway equipment makes gateway logic more complex, puts forward high requirements on the computing capacity of hardware and reduces the maintainability of equipment is solved. A data communication protocol layer is transferred from the gateway equipment to the server. The problem that the gateway equipment fails in support due to access of new equipment or upgrade of old equipment is avoided. The logic complexity of the gateway equipment is reduced. The gateway equipment can support access and functional linkage of more new equipment without software upgrade.

Owner:YUNDING NETWORK TECH BEIJING

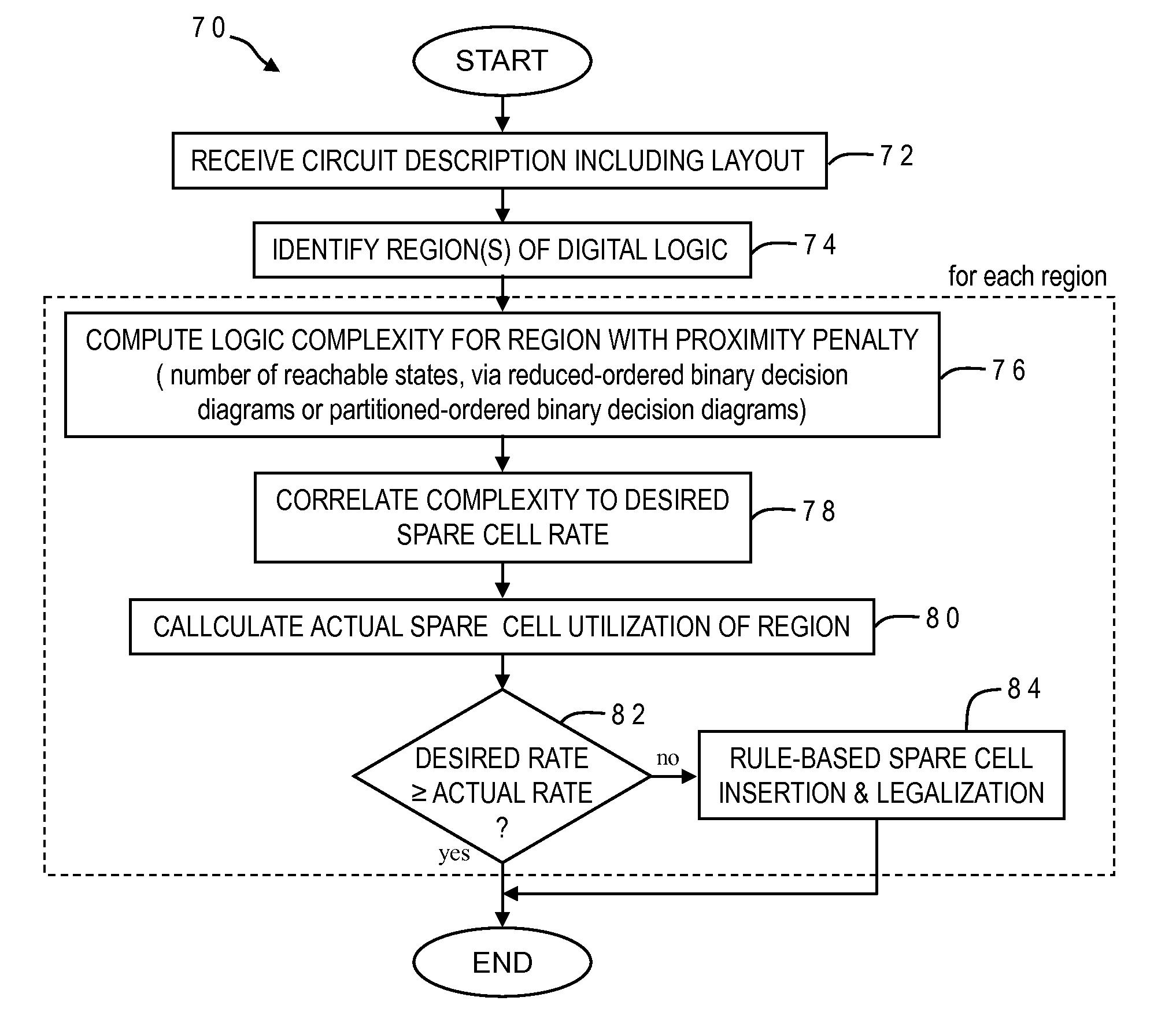

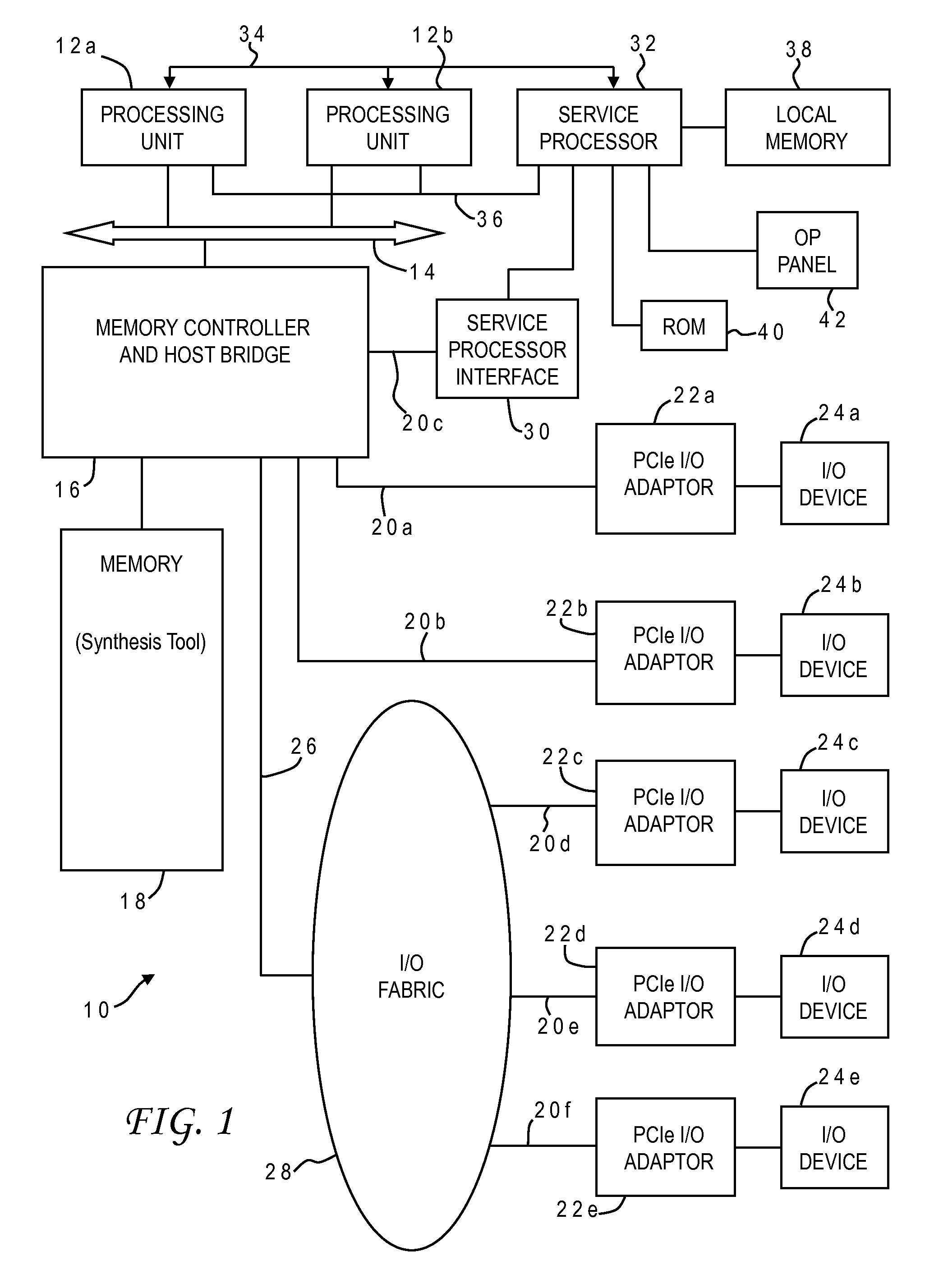

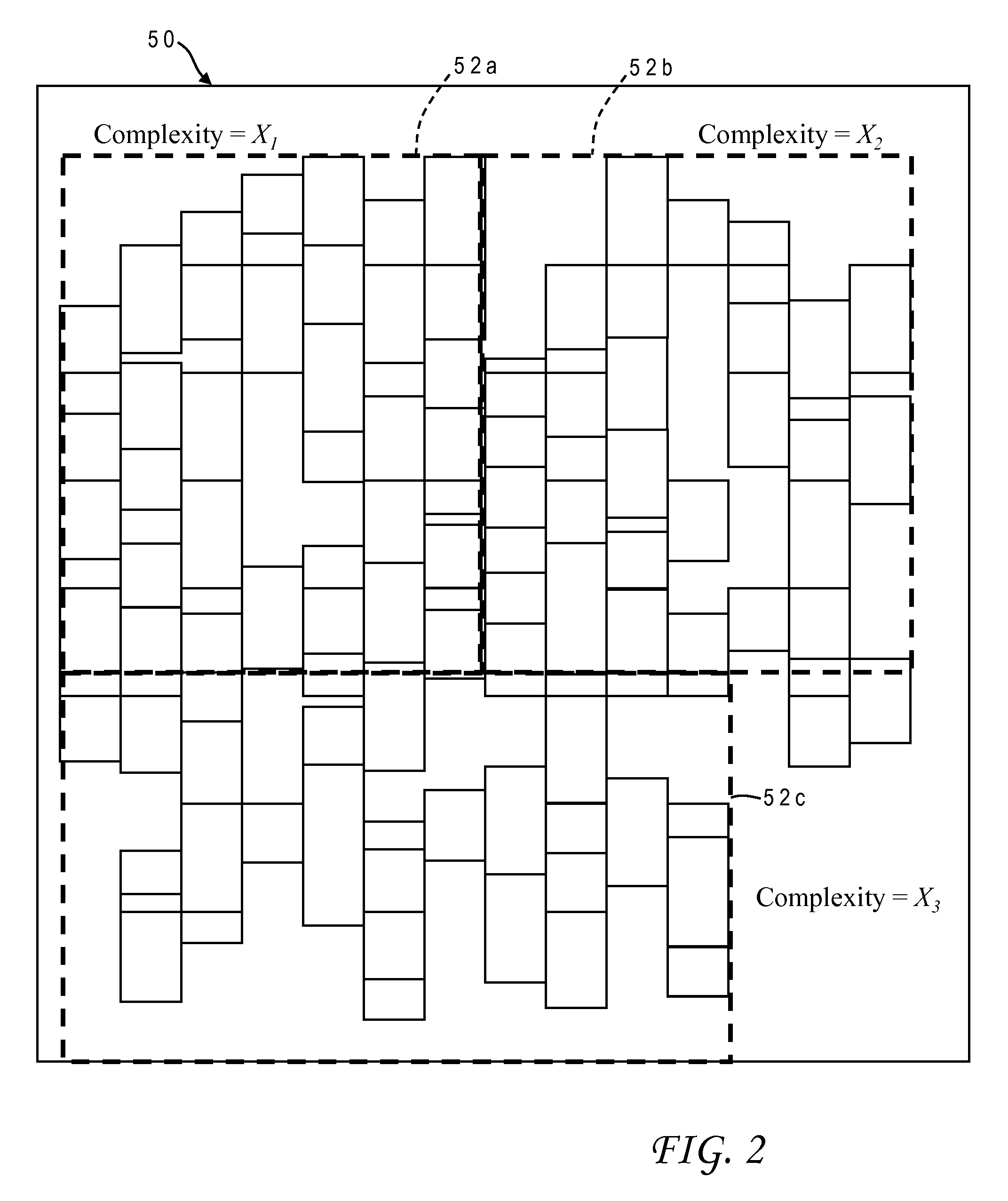

Spare cell insertion based on reachable state analysis

InactiveUS8661391B1CAD circuit designSpecial data processing applicationsLogic complexityEngineering

Spare cells are inserted in a region of an integrated circuit design based on a logic complexity of the region. The logic complexity can be computed based on the number of reachable states of digital logic in the region, and can be correlated to a desired spare cell insertion rate which is then compared to the actual spare cell utilization in the region. The target spare cell rate can further based on logic complexity values for neighboring regions with a proximity penalty.

Owner:GLOBALFOUNDRIES US INC

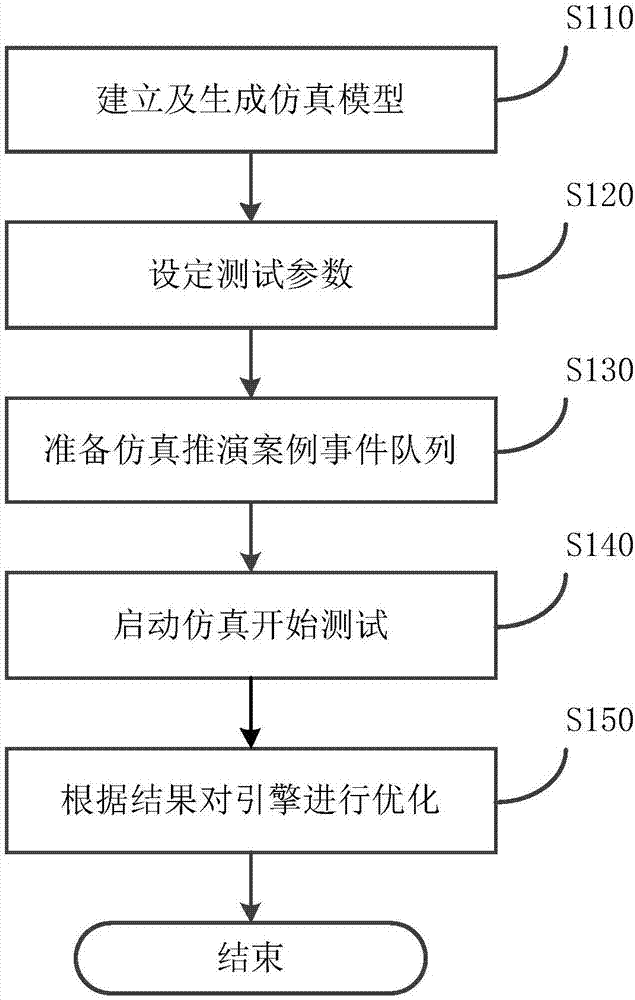

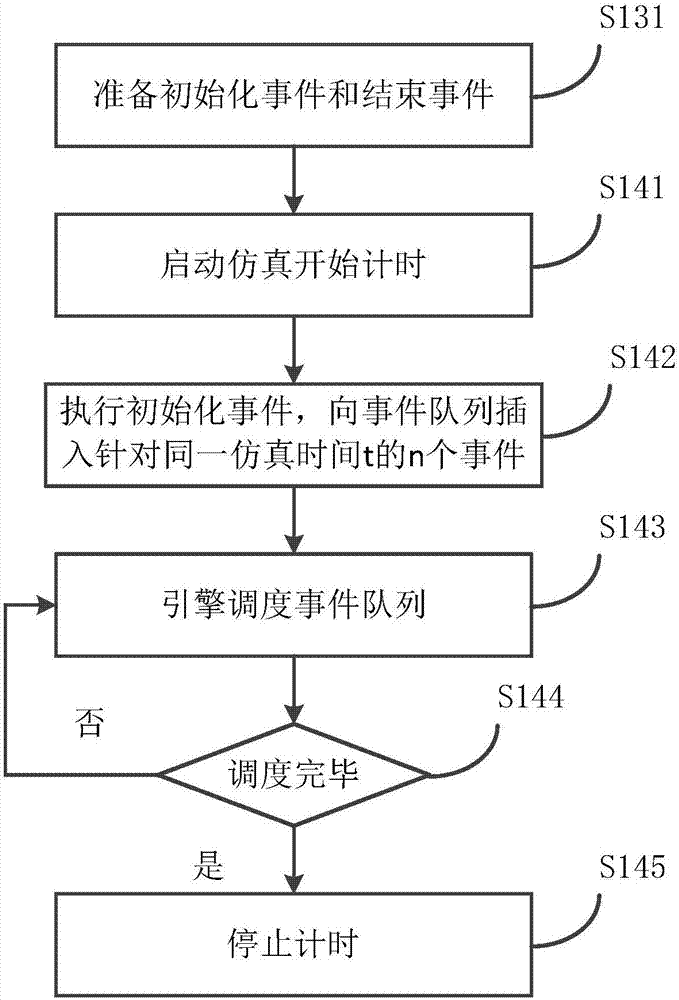

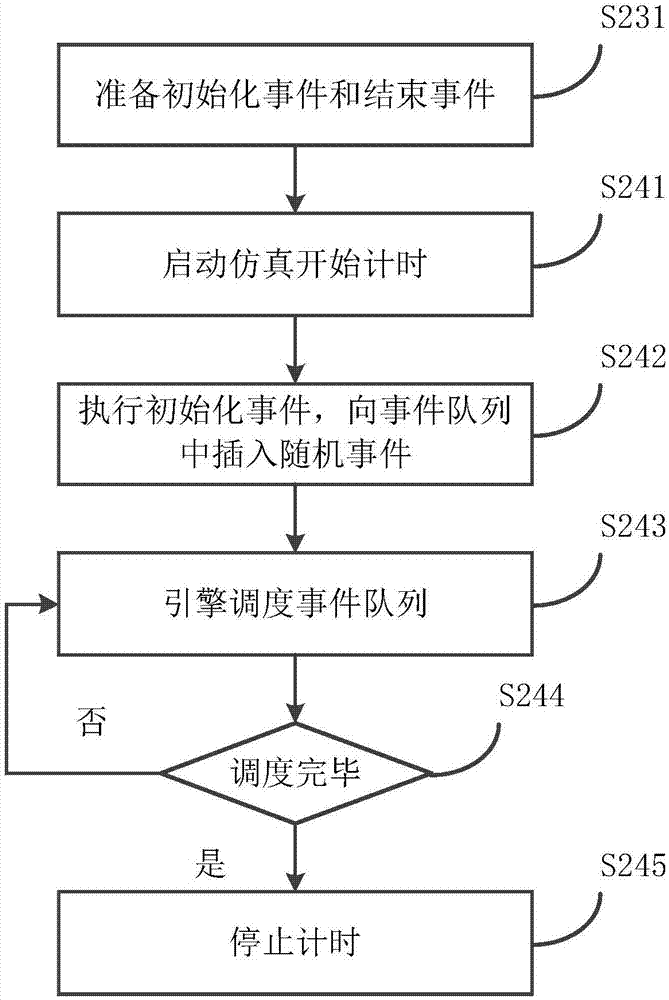

Performance testing method of simulation engine and storage medium

ActiveCN107315889AReduce logic complexityEliminate the effects ofHardware monitoringDesign optimisation/simulationLogic complexityParallel computing

The invention provides a performance testing method of a simulation engine and a storage medium, and is applied to simulation of parallel discrete events. The method performance testing method of the simulation engine includes the steps of establishing and generating a simulation model, using information needed by application managing for configuring the simulation model, using synchronous-event scheduling performance, random-event scheduling performance, event queue managing performance and time marching efficiency to test the simulation model, according to selected performance indexes, preparing simulation event queues separately, and according to the selected performance indexes, starting simulation to start testing till treatment is completed or timing is completed. According to the performance testing method of the simulation engine, a parallel mode and a serial mode are compatible and can be switched; model logic participating in performance testing is extremely low in complexity, and the influence of simulation-model performance on engine performance testing is excluded; testing indexes mainly aims at time coordination of simulation engine event scheduling, can represent basic performance of the engine and has objectivity. An index testing method can be implemented on different simulation engines and has implementation feasibility.

Owner:BEIJING HUARU TECH

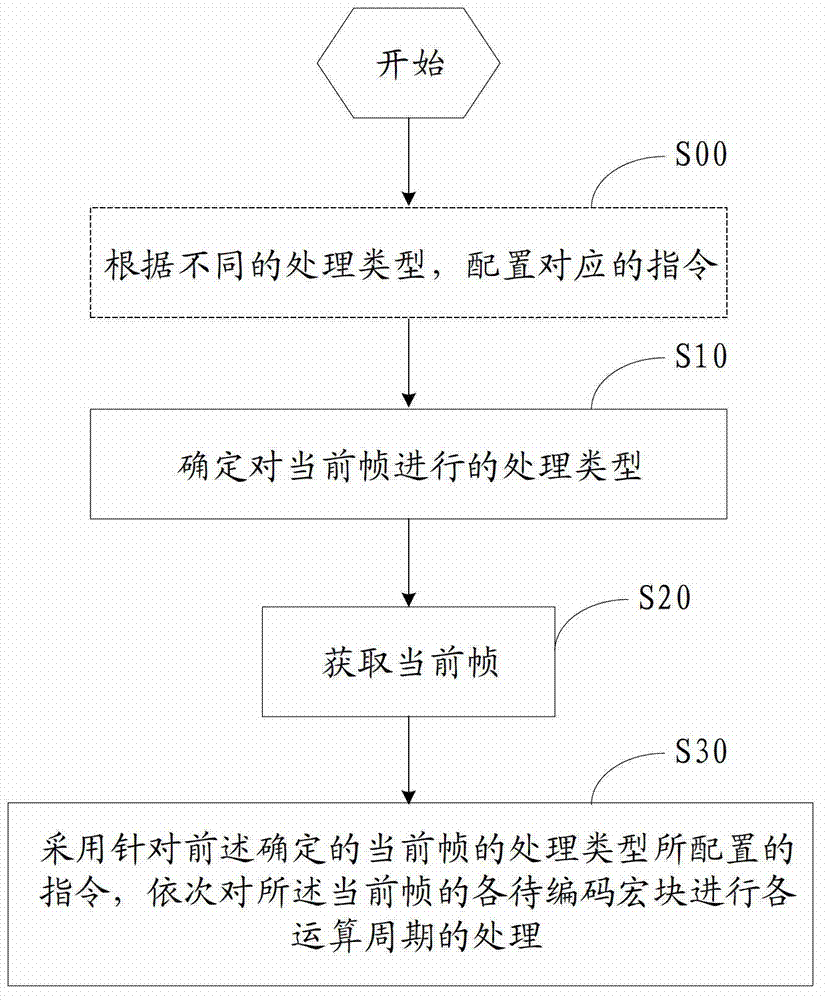

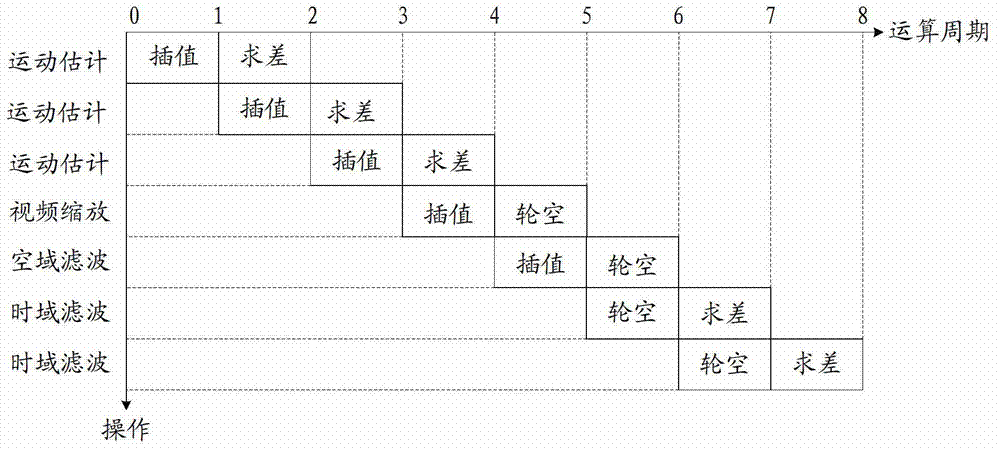

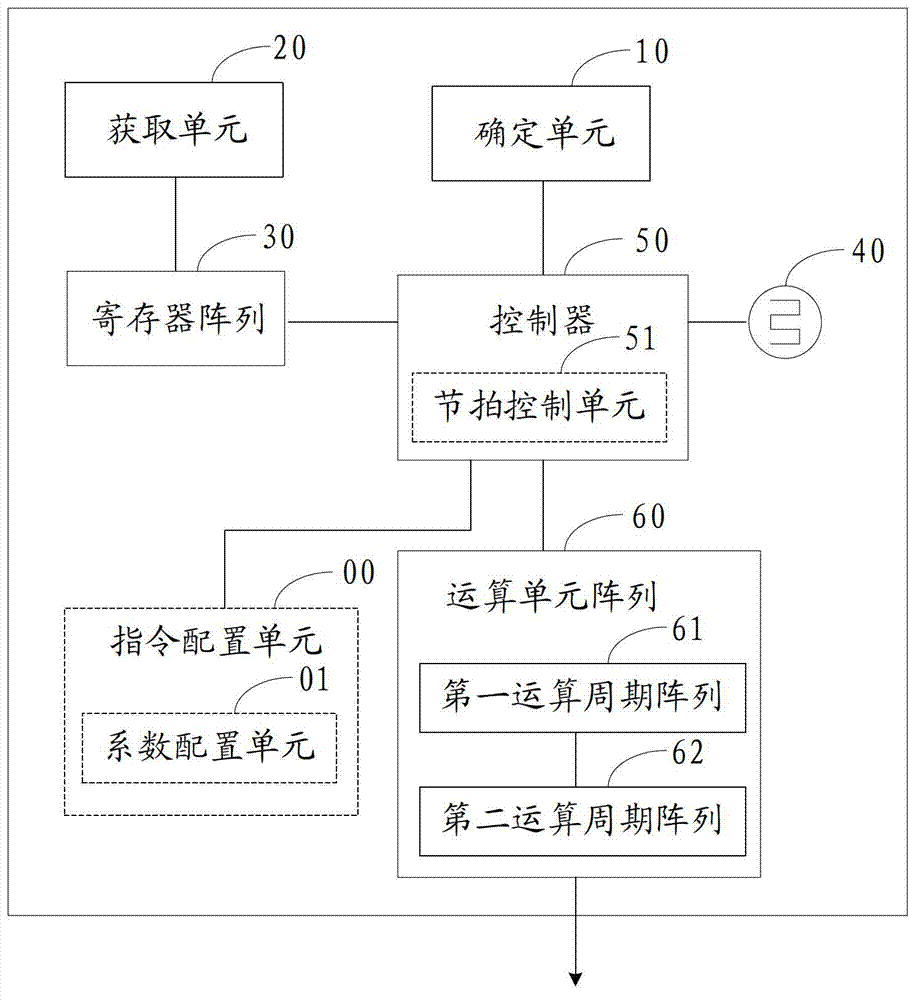

Reusable pixel processing method and reusable video processing chip

ActiveCN102857758AReduce in quantityReduce complexityTelevision systemsDigital video signal modificationLogic complexityProcessing type

The invention discloses a reusable pixel processing method and a reusable video processing chip. According to the method, a same pixel processing device is used for executing at least two types of pixel processing. The method includes: determining processing types for processing a current frame; configuring corresponding commands of the processing types in the pixel processing device; and performing processing of each execution cycle for to-be-coded macro blocks of the current frame sequentially by the aid of the configured commands corresponding to the determined processing types of the current frame. The video processing chip comprises a determining unit, an acquisition unit, a register array, a clock control unit, a controller and an arithmetic unit array. The reusable pixel processing method and the reusable video processing chip have the advantages that by the reusable design technology, registers and arithmetic units are configured by different methods, so that single hardware unit can be reused for multiple operations in a time division manner, computing and storage logic complexity of the chip is lowered, and the area and power consumption of the chip are reduced.

Owner:GALAXYCORE SHANGHAI

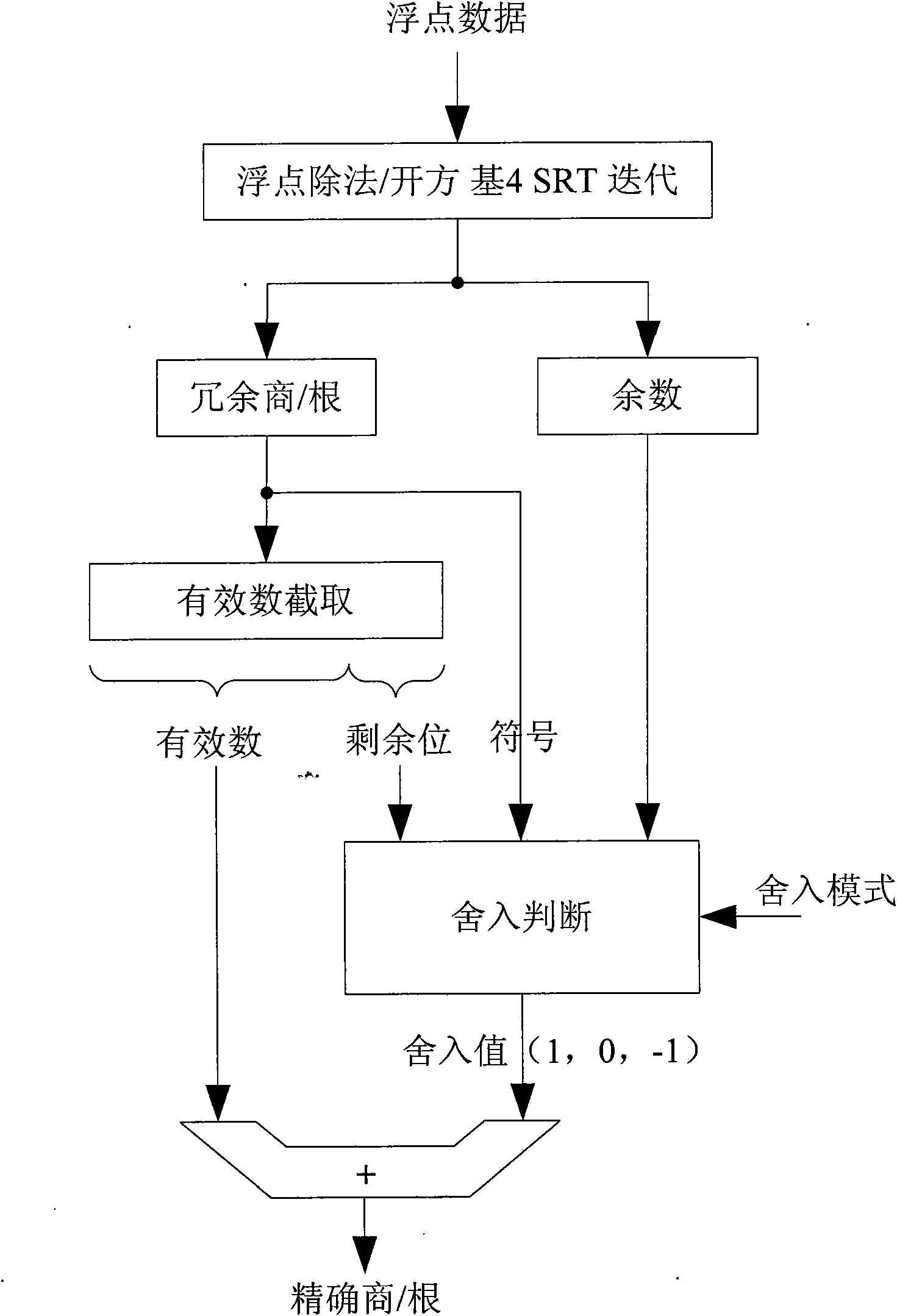

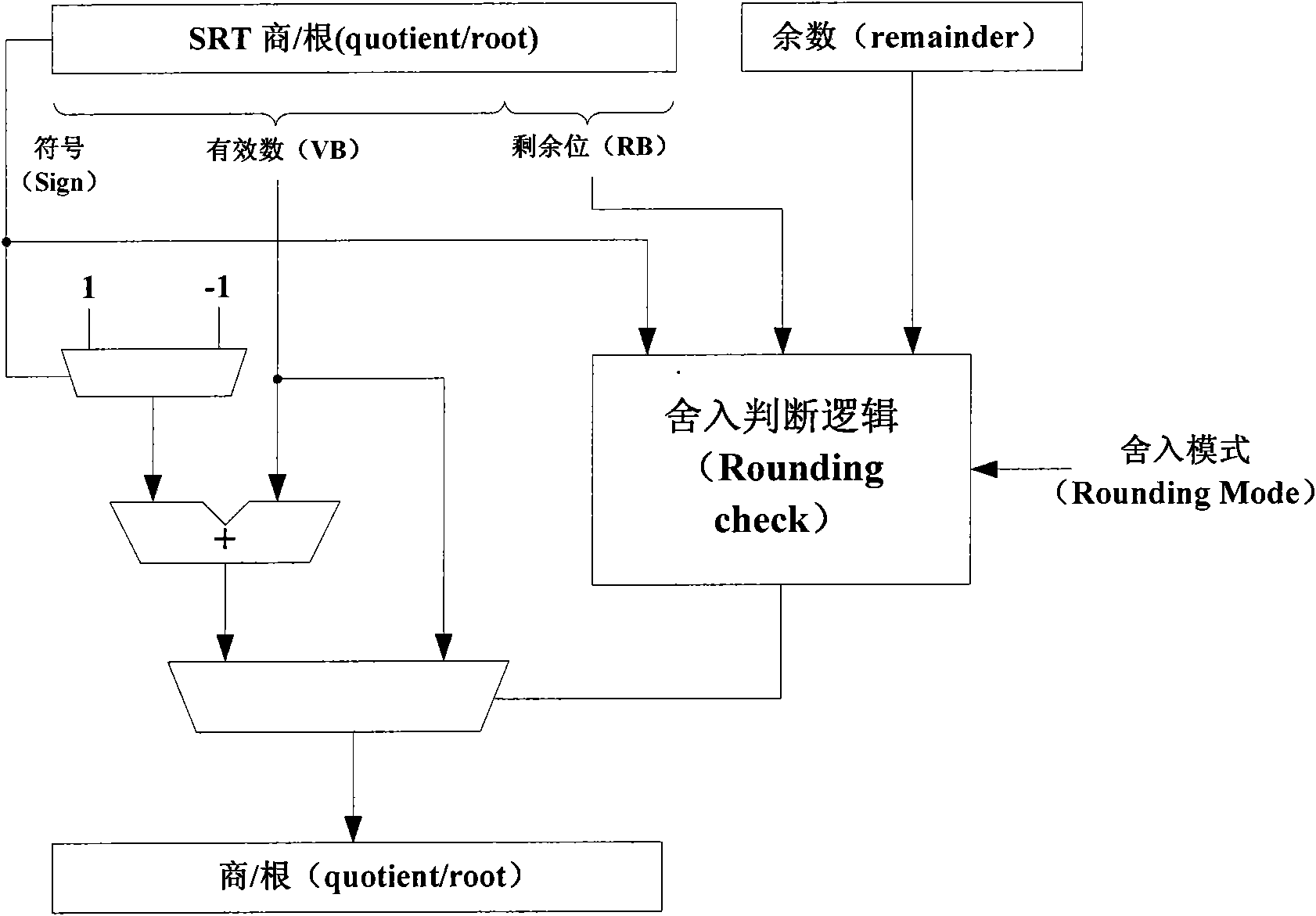

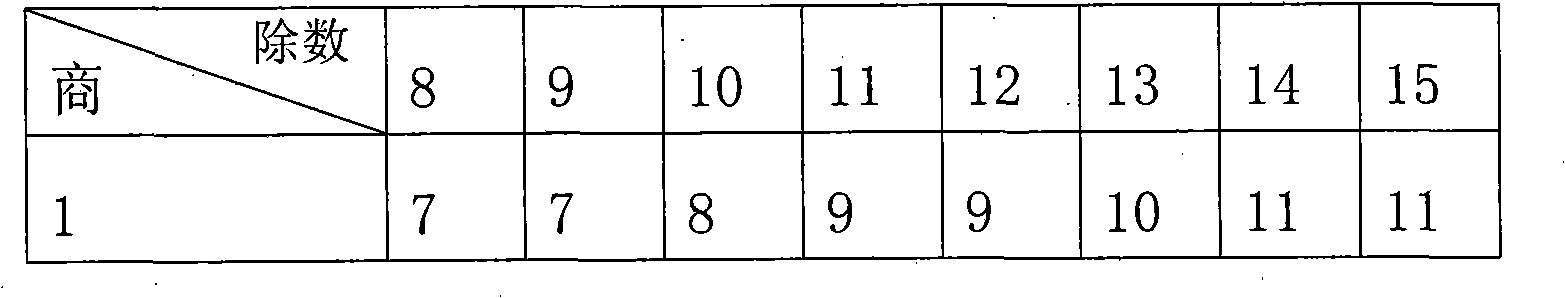

Rounding method for indivisible floating point division radication

ActiveCN101650643AImprove scalabilityEasy to implementDigital data processing detailsLogic complexityRounding

The invention relates to a rounding method for indivisible floating point division radication. The rounding method comprises the following steps: (1) executing an SRT division / radication algorithm toa floating point number input to a floating point coprocessor, and executing a loop operation to the floating point number and then obtaining a quotient / root result; (2) determining the effective number of the floating point number according to the appearance position of the first 1; (3) reducing the effective number result and a remainder obtained by the SRT division / radication algorithm from thequotient / root result of the step (1), and taking the difference as rounding judging information; and executing the left shift operation to the difference obtained by reducing the effective number result of the step (2) from the quotient / root of the step (1), and then taking the obtained number as a residue place; (4)-(7) selecting four kinds of different rounding modes to round; (8) if the rounding operation executed in step (4) to (7) causes the quotient / root result to have a carry bit or a borrow bit, modifying the floating point exponent part, wherein the final rounding result needs to execute the mantissa normalization. The rounding method can reduce the logic complexity, reduce the same hardware cost, and shorten the time sequence.

Owner:C SKY MICROSYST CO LTD

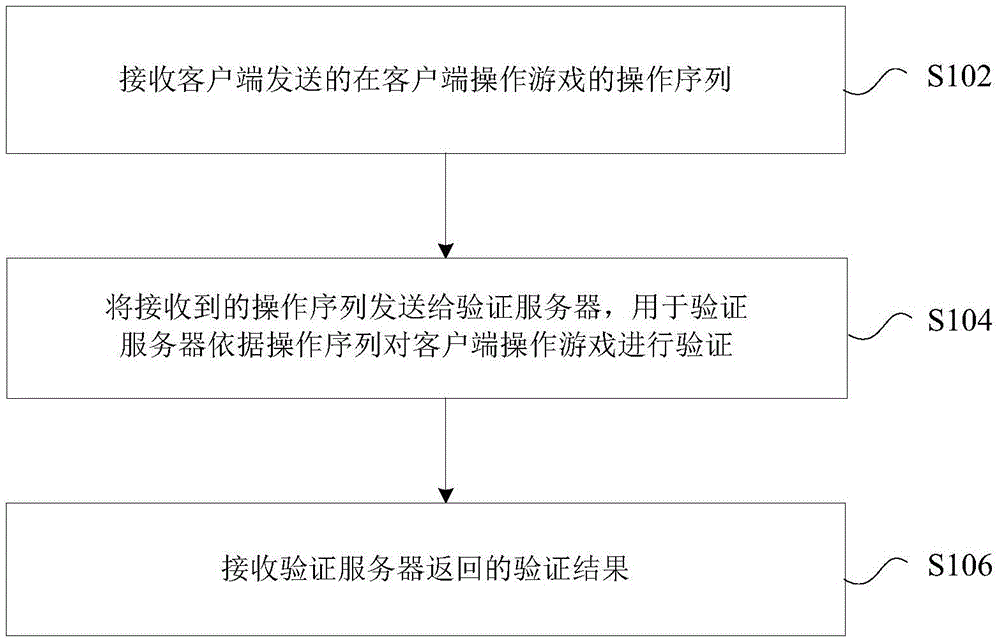

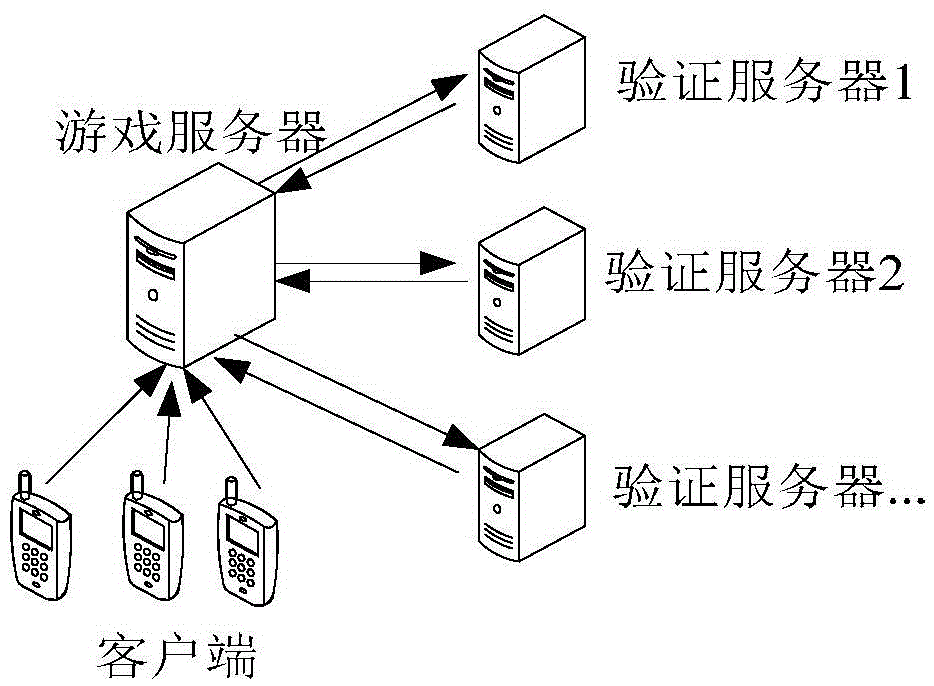

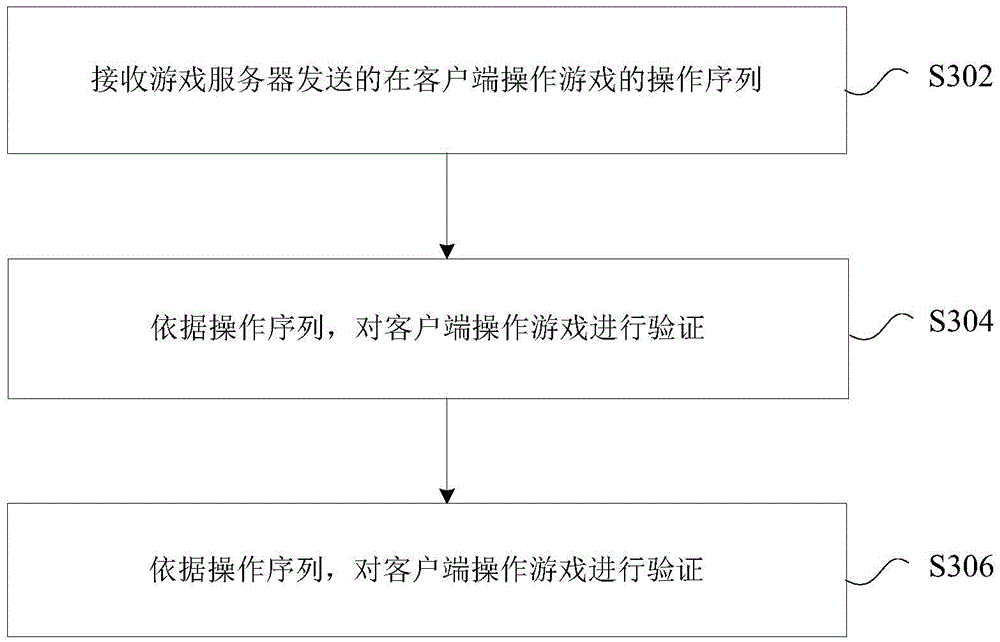

Game verification method and device, game server and verification server

InactiveCN105657067AIncrease computational overheadIncreased computational overhead,Video gamesData switching networksLogic complexityValidation methods

The invention provides a game verification method and device, a game server, a verification server and a game system. The method includes the steps that an operation sequence sent by a client when a game is operated at a client is received; the received operation sequence is sent to the verification server and used for the verification server to verify the game operated by the client according to the operation sequence; a verification result fed back by the verification server is received. By means of the game verification method and device, the game server, the verification server and the game system, the problems that in the prior art, when a game server is used for verifying a game of a client, computation cost of the game server is increased, and logic complexity of the game server is increased are solved, and the effect of greatly reducing loads of the game server is achieved.

Owner:NETEASE (HANGZHOU) NETWORK CO LTD

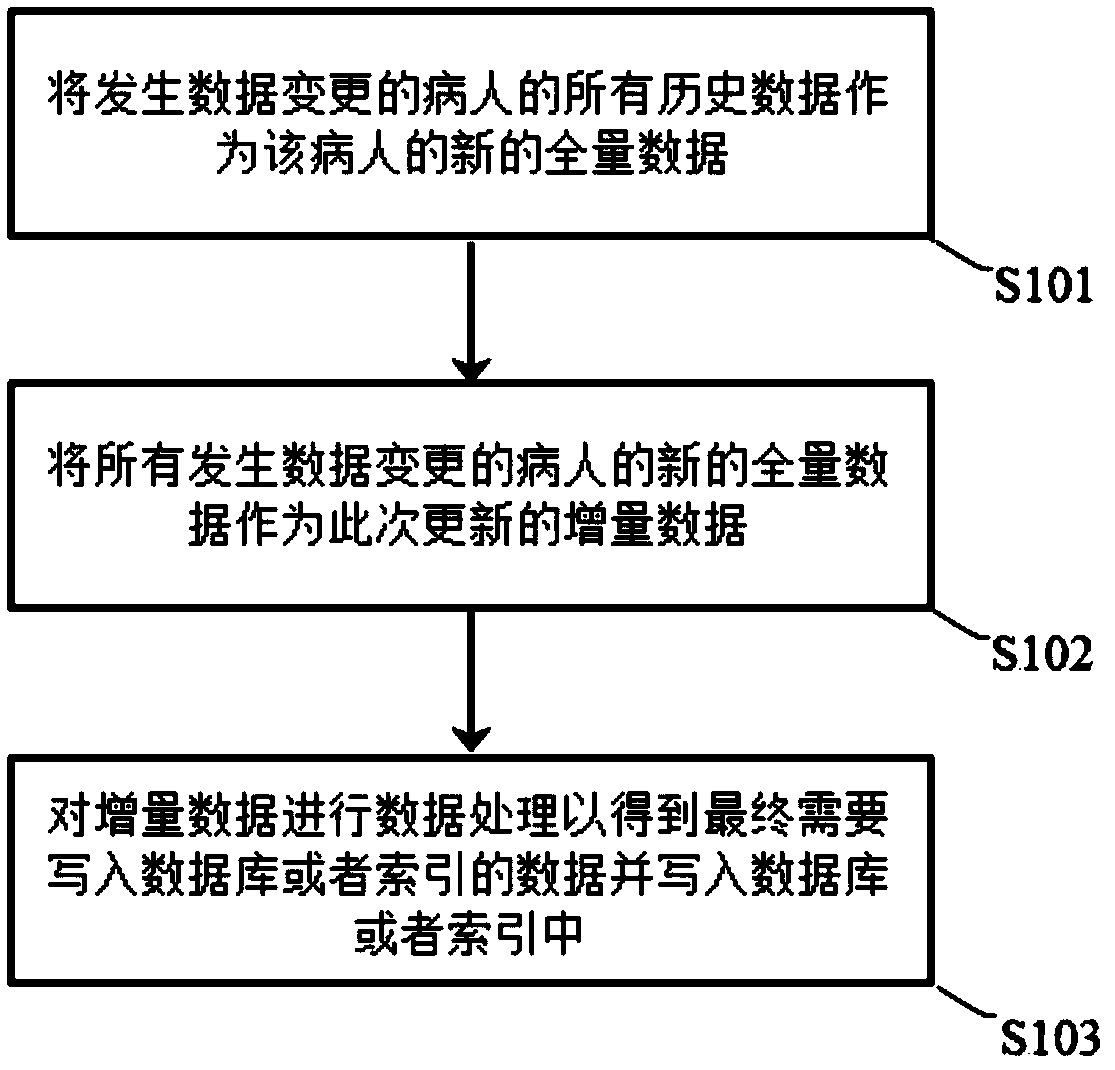

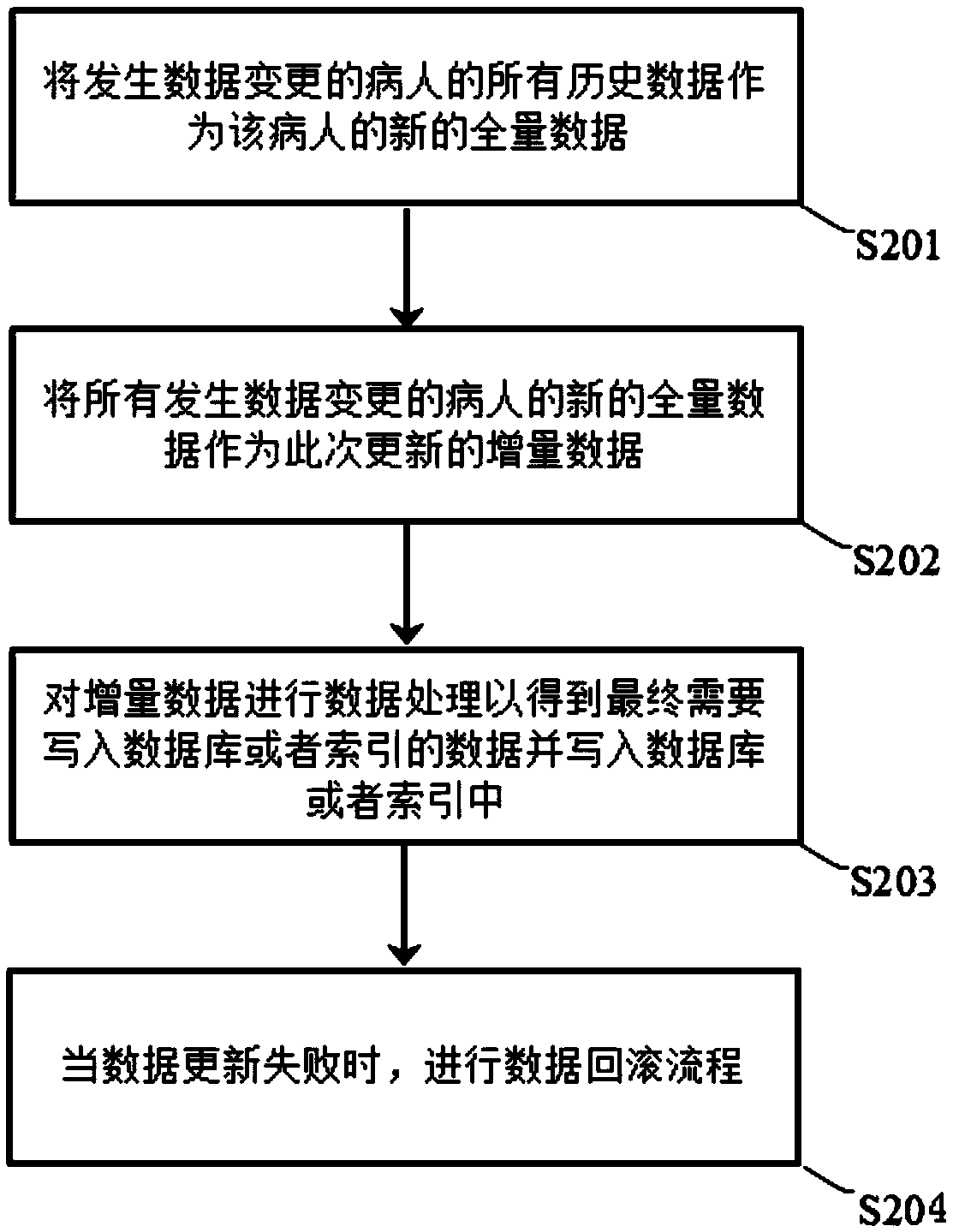

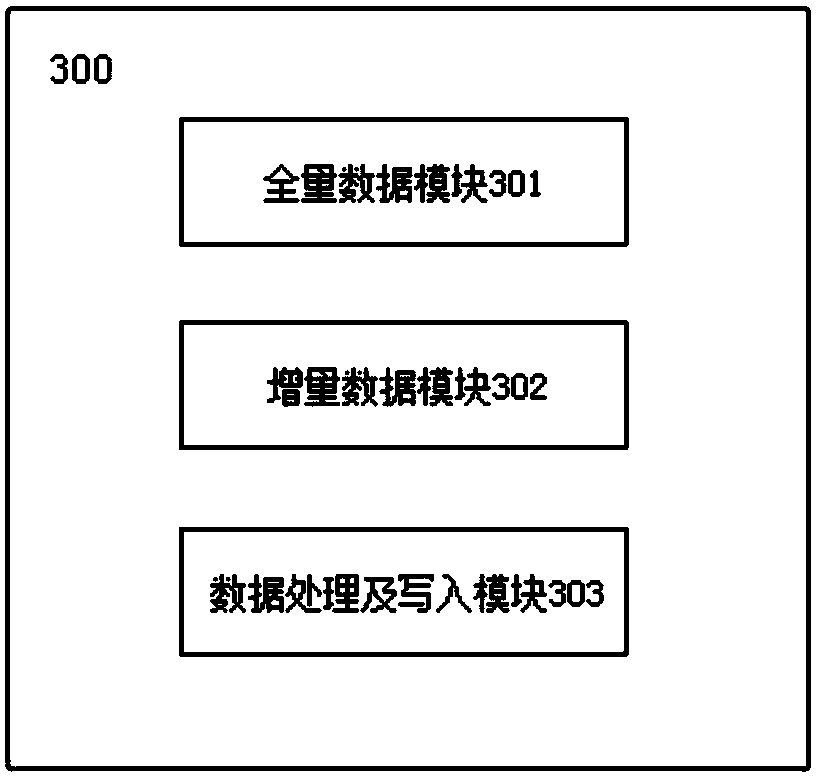

Incremental medical data updating method and system

The invention relates to the technical field of medical data processing, and provides an incremental medical data updating method and a system. The incremental medical data updating method comprises the following steps: all historical data of a patient whose data are changed are taken as new total data of the patient; New full data for all patients whose data have changed as incremental data for this update; And performing data processing on the incremental data to obtain data that ultimately needs to be written into the database or index and written into the database or index. As that total amount in the patient, The incremental data updating is completed under the condition of strictly controlling the time, and under the condition of realizing the data updating of T+1, at the same time,the pressure of the server is reduced to the acceptable range. The incremental data updating can balance the performance and logic complexity of the whole processing flow. In addition, by storing thedata in the key-Value storage system, the speed of data query and concurrent processing ability are greatly improved.

Owner:南京医渡云医学技术有限公司

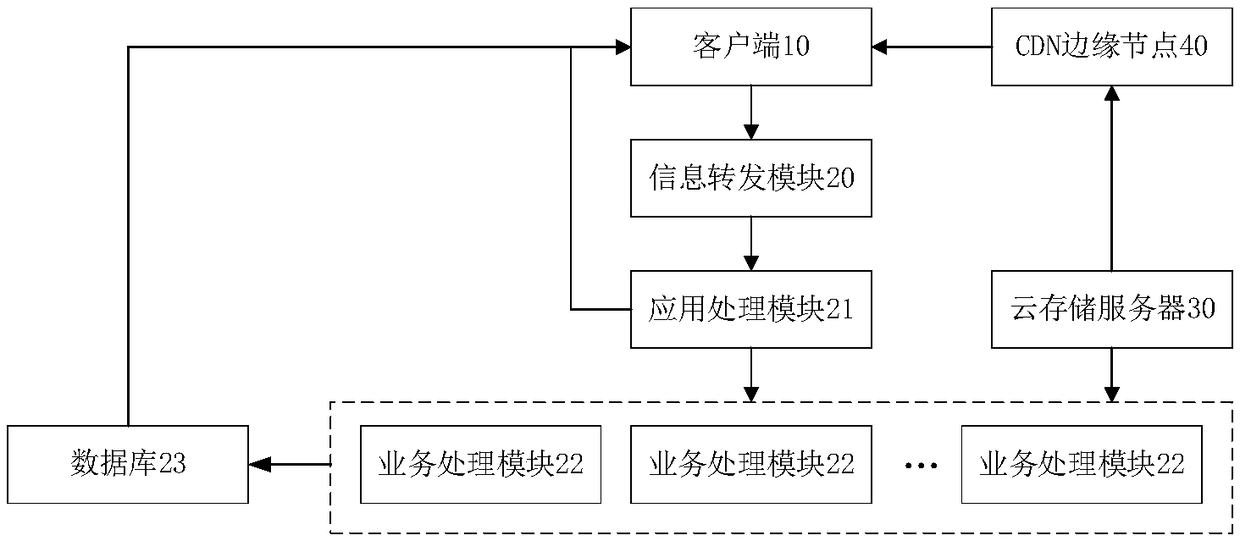

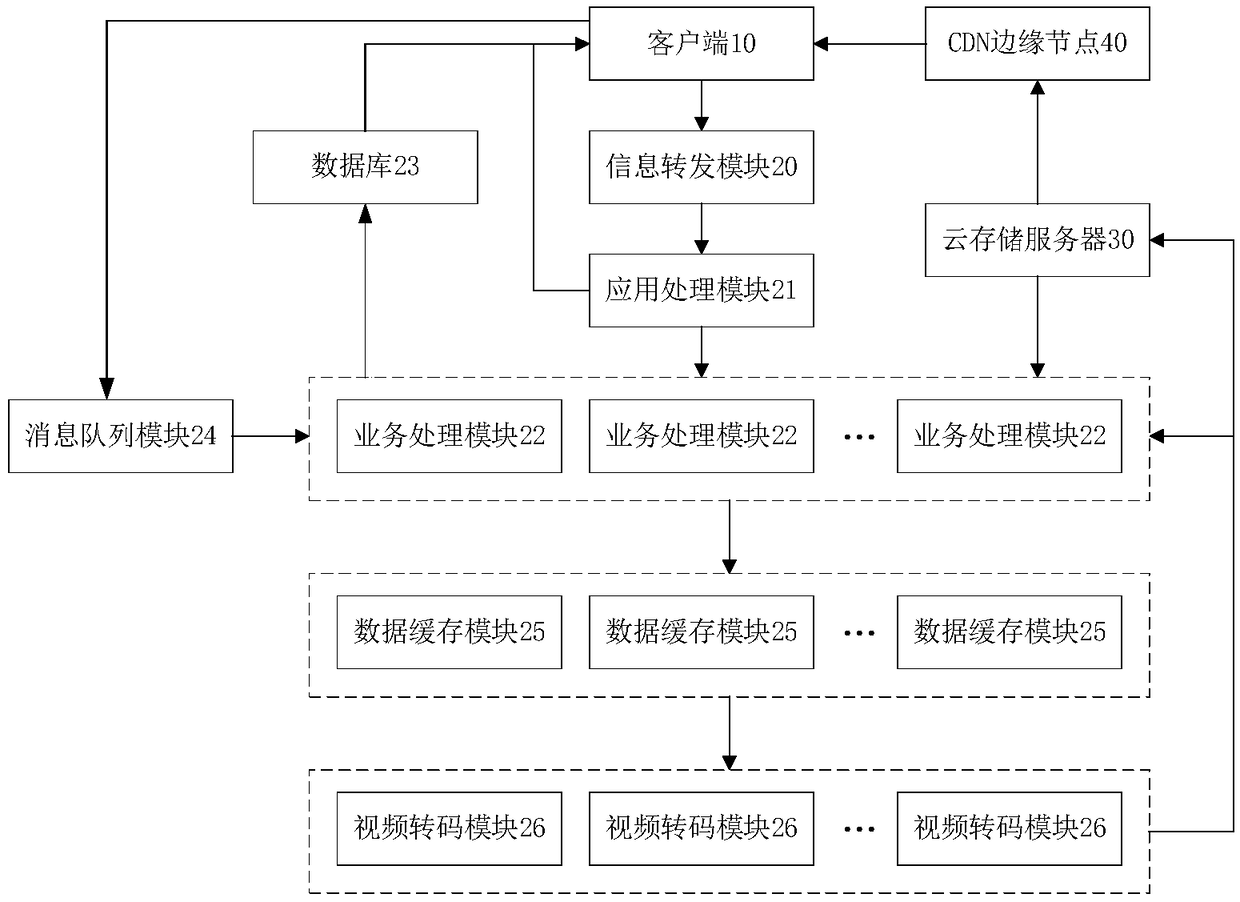

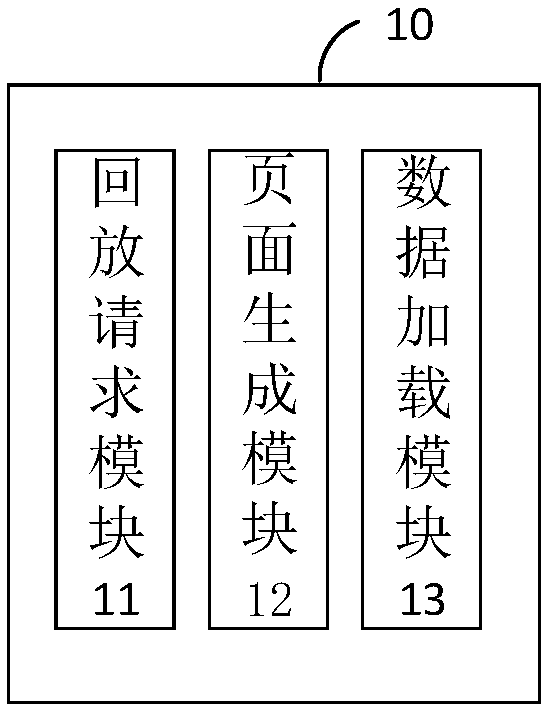

Streaming media playback method, computer equipment and readable medium

The invention discloses a streaming media playback method. The streaming media playback method comprises the steps that an information forwarding module receives a streaming media playback instructionsent by a client; an application processing module receives the streaming media playback instruction, authenticates the legality of the streaming media playback instruction and outputs the legal streaming media playback instruction; and multiple service processing modules receive the legal streaming media playback instruction and look up related information of streaming media files requesting forplayback in a database, return streaming media playback addresses when the related information of the streaming media files exist in the database to enable the client to form a playback page, extracts corresponding storage addresses of the streaming media files from the database and return the storage addresses to the client to enable the client to acquire the streaming media files and load the streaming media files to the playback page. According to the method, the playback logic complexity of multiple streaming media files is reduced, the blocking and error problems of the playback page arereduced, the response speed of the streaming media playback page is increased, and the interaction experience of the streaming media playback page is improved.

Owner:BEIJING DA MI TECH CO LTD

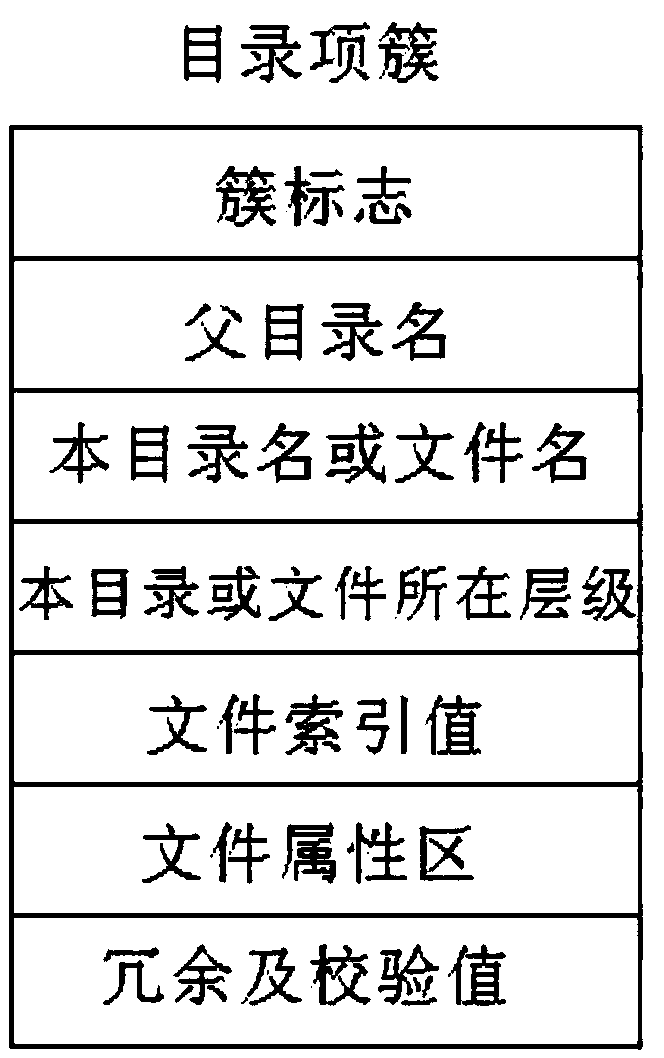

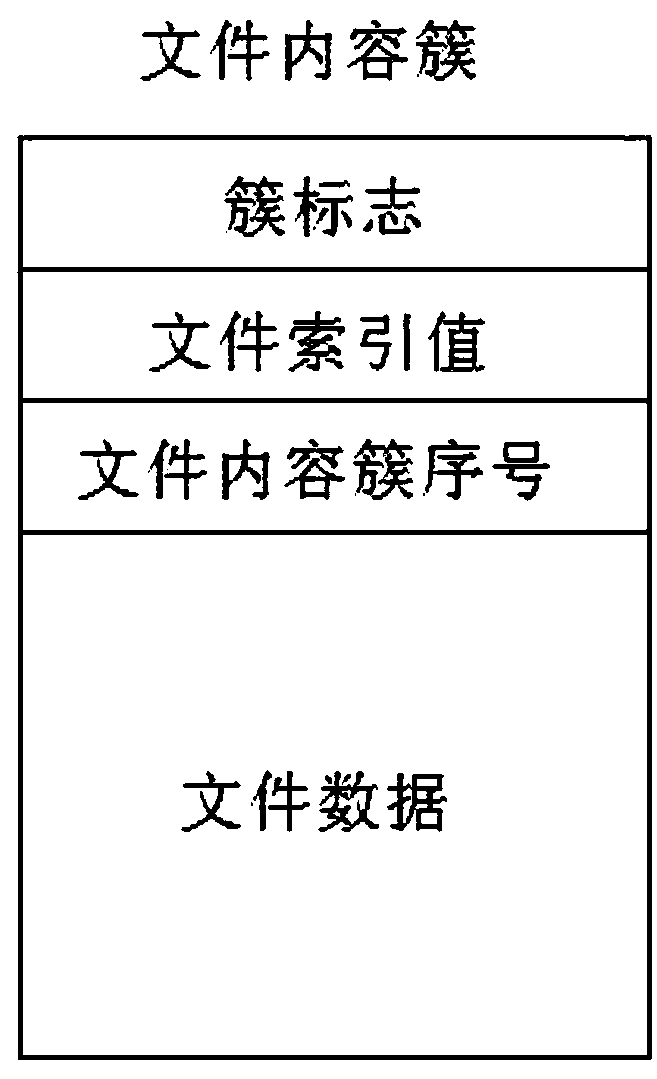

Implementation method of light embedded file system

ActiveCN108021717AImprove access efficiencyReduce capacitySpecial data processing applicationsElectricityLogic complexity

The invention discloses an implementation method of a light embedded file system. The method includes the following steps that memory space of a device is divided into different types of clusters, theclusters include catalog entry clusters and file content clusters, the catalog entry clusters are used for storing index information of files or catalogs, and the file content clusters are used for storing file data. When the system is electrified, a cluster identifier of each cluster is scanned and cached, the types of the clusters are judged by reading the cluster identifiers, whether cluster content is legal or not is judged, and the power-on process is completed. The file system adopts a metadata scattered storage method, the requirement for the RAM capacity of the system is reduced, a file index value scattered storage mode is used for replacing a traditional chain table file maintenance mode, the logic complexity is low and the file access efficiency is high.

Owner:成都三零嘉微电子有限公司

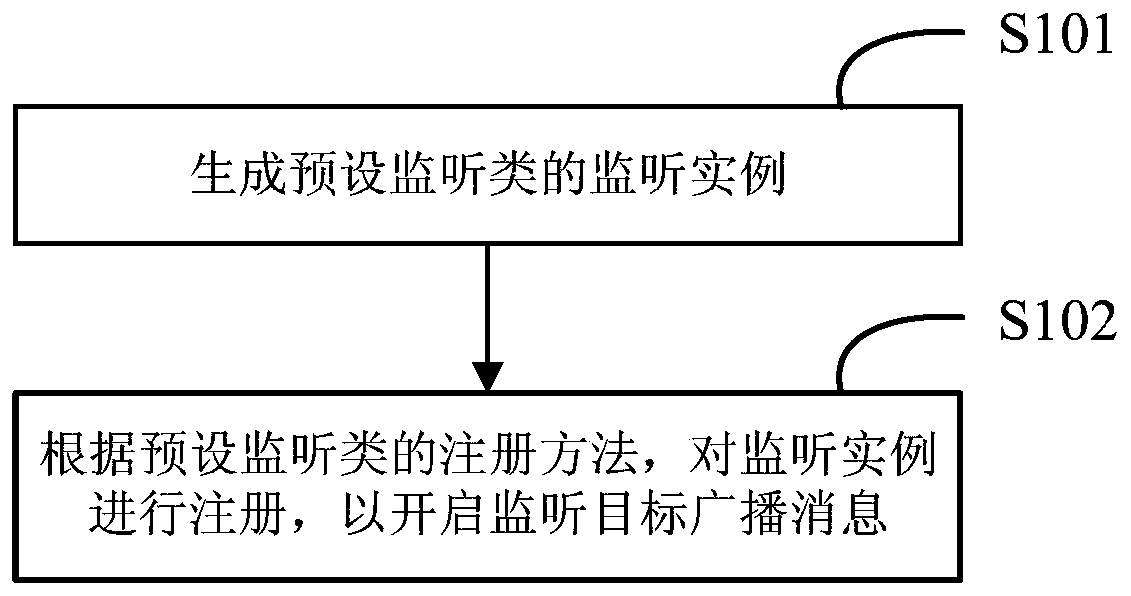

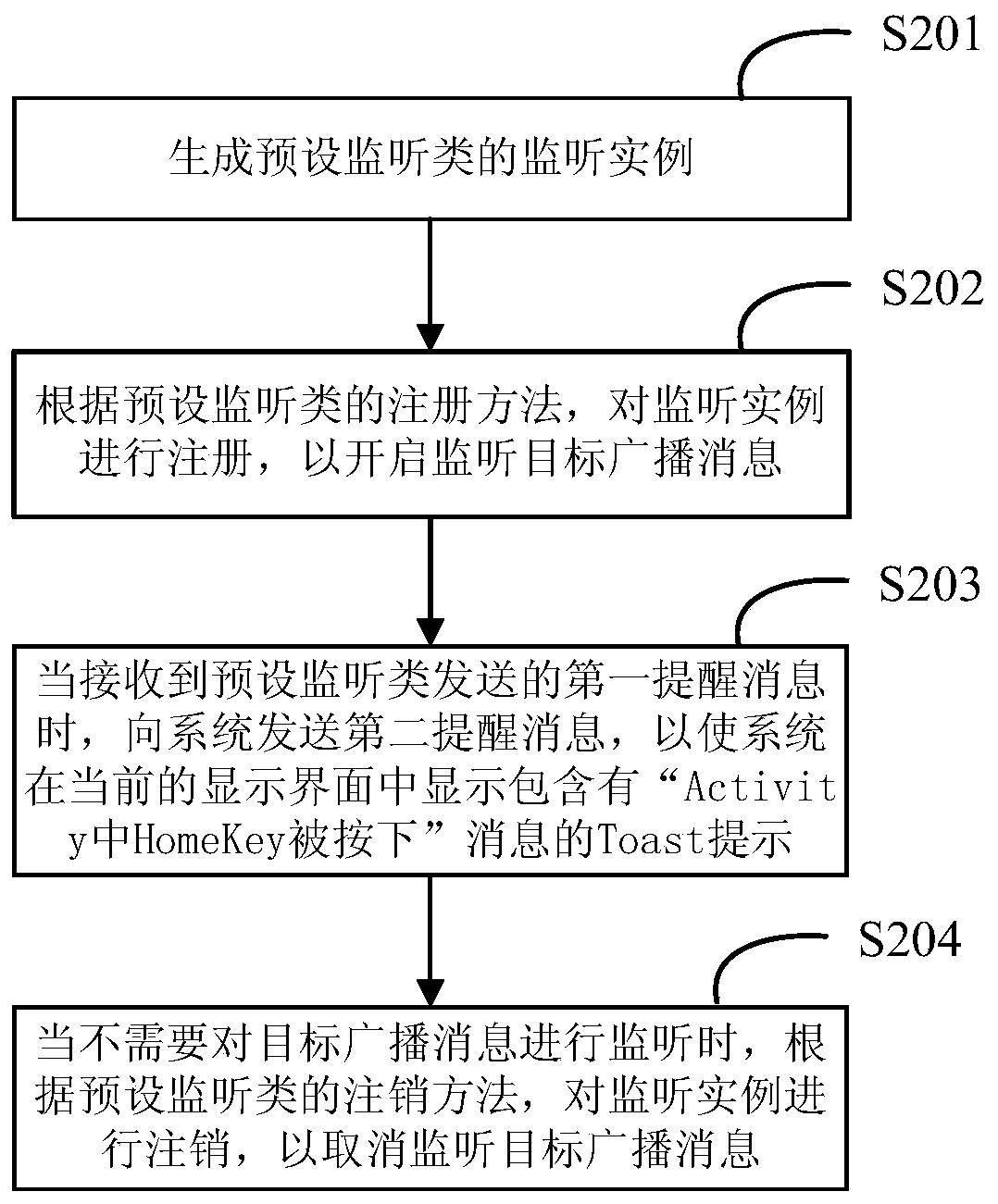

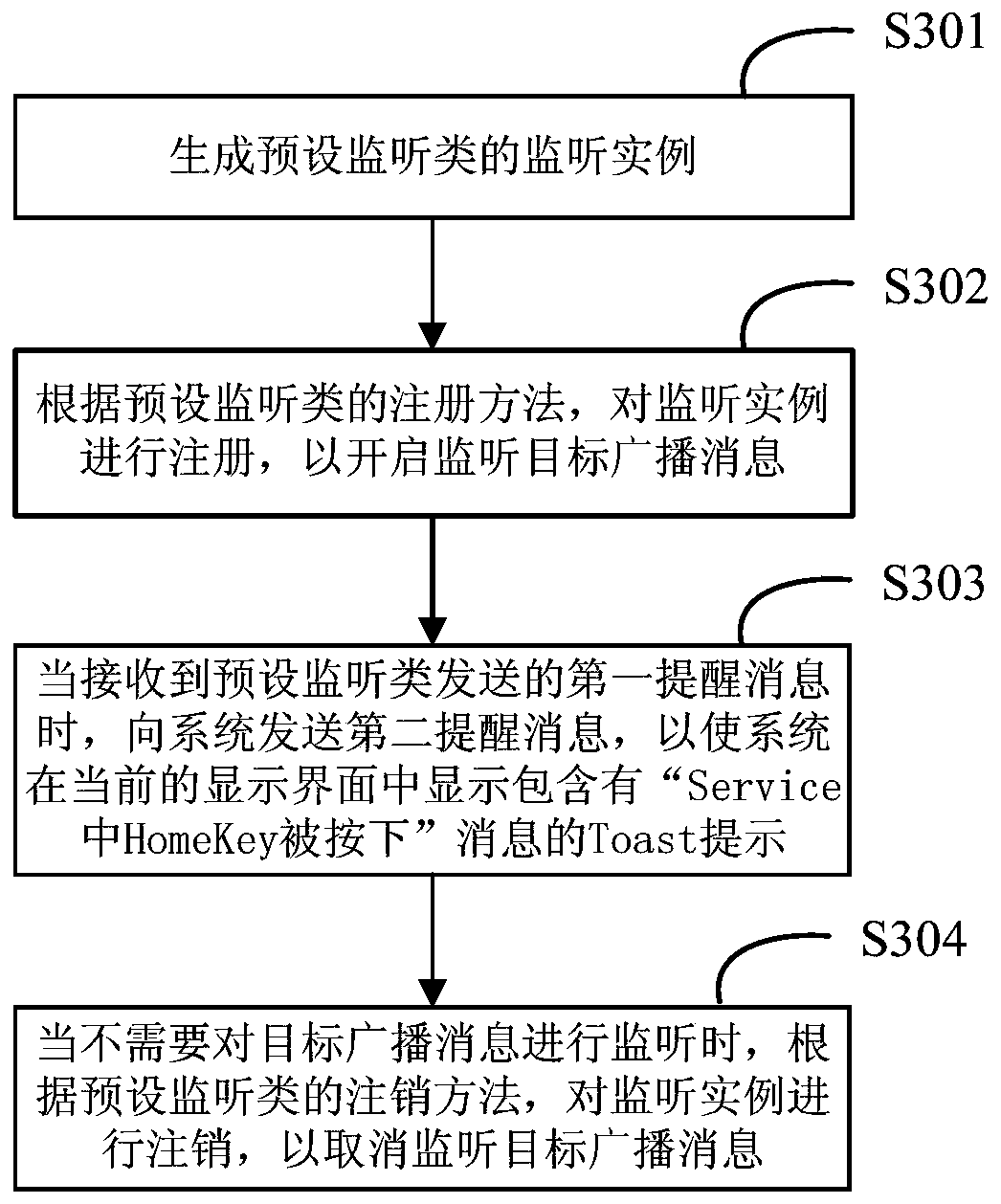

A message monitoring method and device

ActiveCN109710425AReduce complexityReduce couplingInterprogram communicationHardware monitoringLogic complexityCoupling

The embodiment of the invention provides a message monitoring method and device applied to host objects, used for generating a monitoring instance of a preset monitoring class, wherein the preset monitoring class is a subclass of a broadcast receiver class of the system; wherein the preset monitoring class is used for detecting a target broadcast message triggered when the Home key is clicked, thepreset monitoring class realizes reference to a host object through a preset monitoring callback interface, and registration is performed on a monitoring instance according to a registration method of the preset monitoring class so as to start monitoring the target broadcast message. Processing based on the above, the host object can interact with a preset monitoring class through a preset monitoring callback interface; according to the embodiment of the invention, the monitoring of the target broadcast message is realized according to the preset monitoring class, that is, the monitoring processing of the target broadcast message does not need to be completed in the host object, so that the logic complexity and the coupling degree of codes in the host object can be reduced, and the maintenance cost of the system is reduced.

Owner:KINGSOFT

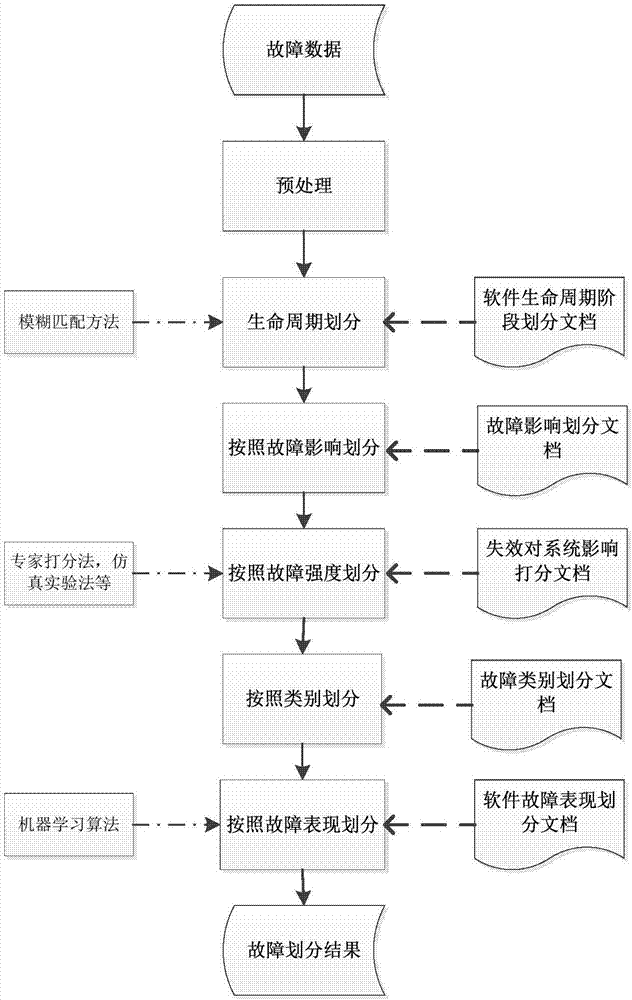

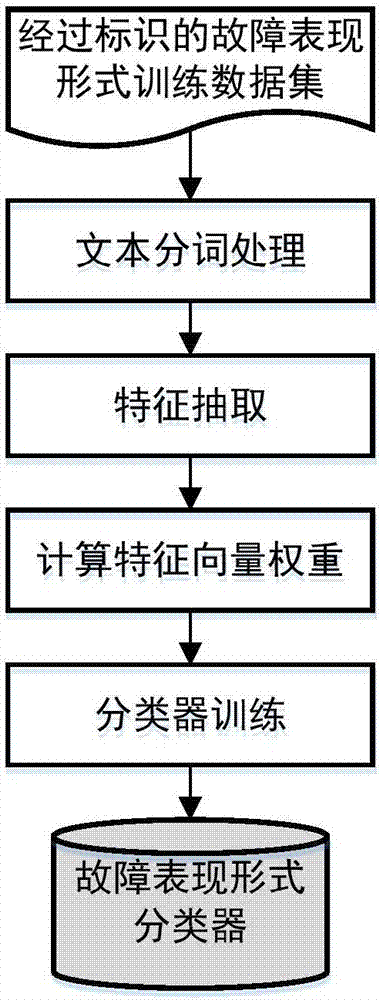

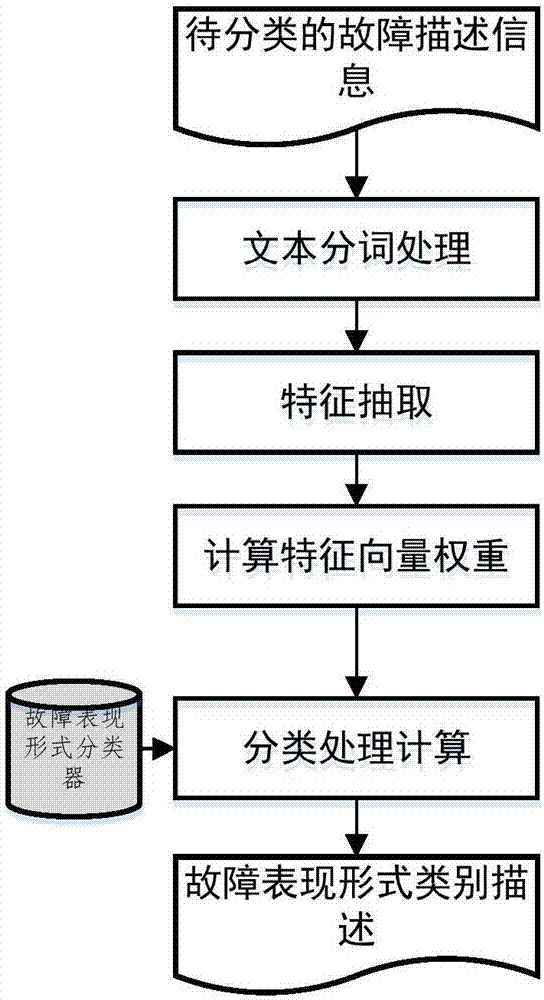

Complex software intensive system oriented fault classification method

InactiveCN107102909AMeticulously dividedHigh precisionFault responseLogic complexityClassification methods

For the problem that the conventional software fault classification methods do not consider new characteristics of a complex software intensive system, the invention provides a complex software intensive system oriented fault classification method which fully considers the new characters such as logic complexity and boundary corrosion of the complex software intensive system, can classify faults according to the life periods and fault classes, and can determine each classification attribute value of fault classification through artificial determination and machine automatic identification. The complex software intensive system oriented fault classification method can improve the accuracy and the precision of fault class division and recognition of the software intensive system, and provides a basis for fault injection research and failure mechanism research of the complex software intensive system.

Owner:BEIHANG UNIV

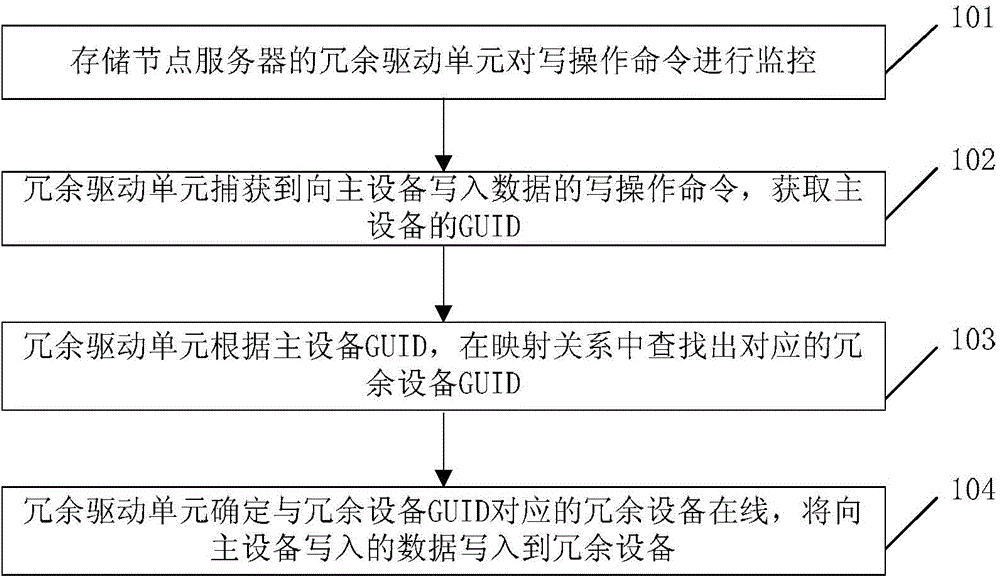

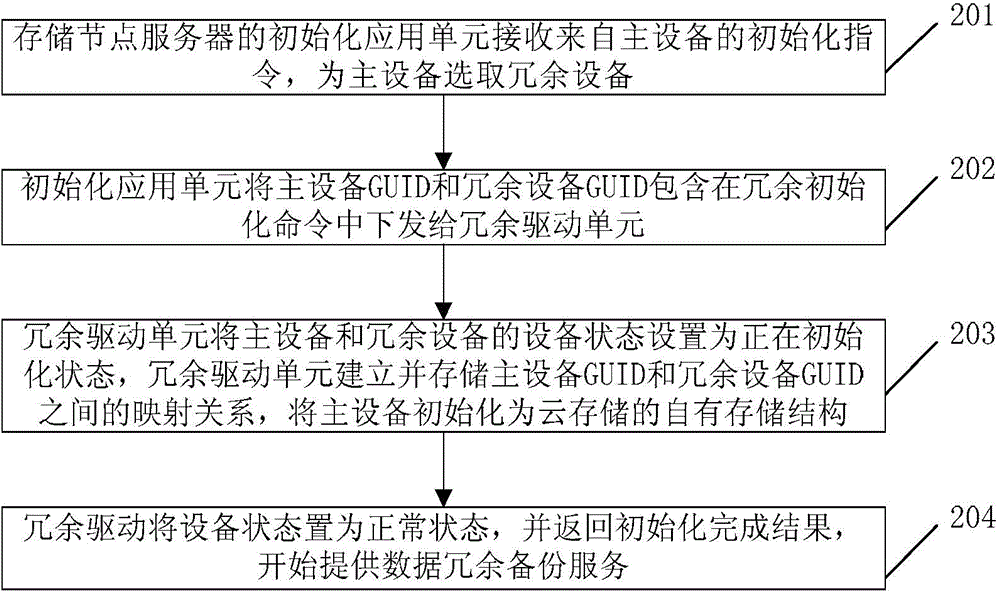

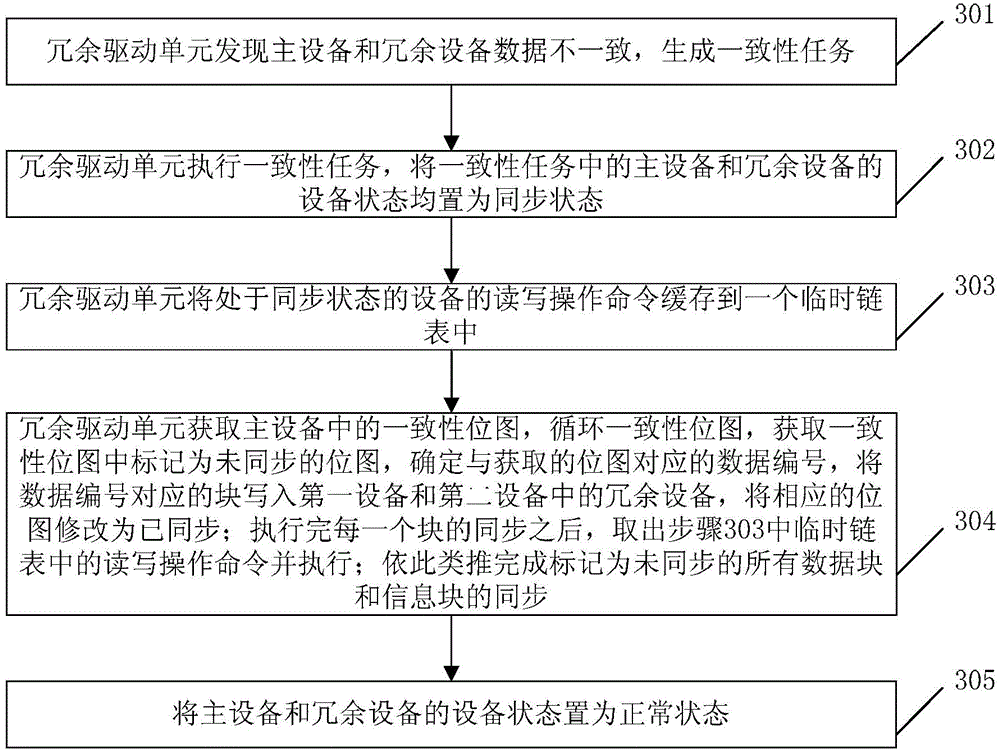

Data redundant backup method, data redundant backup system and storage node server based on cloud storage

ActiveCN104699566AAvoid triggerAvoid logical complexityRedundant operation error correctionLogic complexityCloud storage

The invention discloses a data redundant backup method, a data redundant backup system and a storage node server based on cloud storage. The method comprises the following steps: carrying out monitoring on a write operation command by the redundant driving unit of the storage node server; capturing the write operation command of writing data in main equipment by the redundant driving unit, and obtaining the global unique identification (GUID) of the main equipment; finding out corresponding redundant equipment GUID in the mapping relationship according to the main equipment GUID by the redundant driving unit; determining redundant equipment corresponding to the redundant equipment GUID to be online by the redundant driving unit, and writing data written into the main equipment in the redundant equipment. The scheme can realize real-time and quick redundant backup, and avoids logic complexity in the realization by adopting upper application.

Owner:HANGZHOU HIKVISION DIGITAL TECH

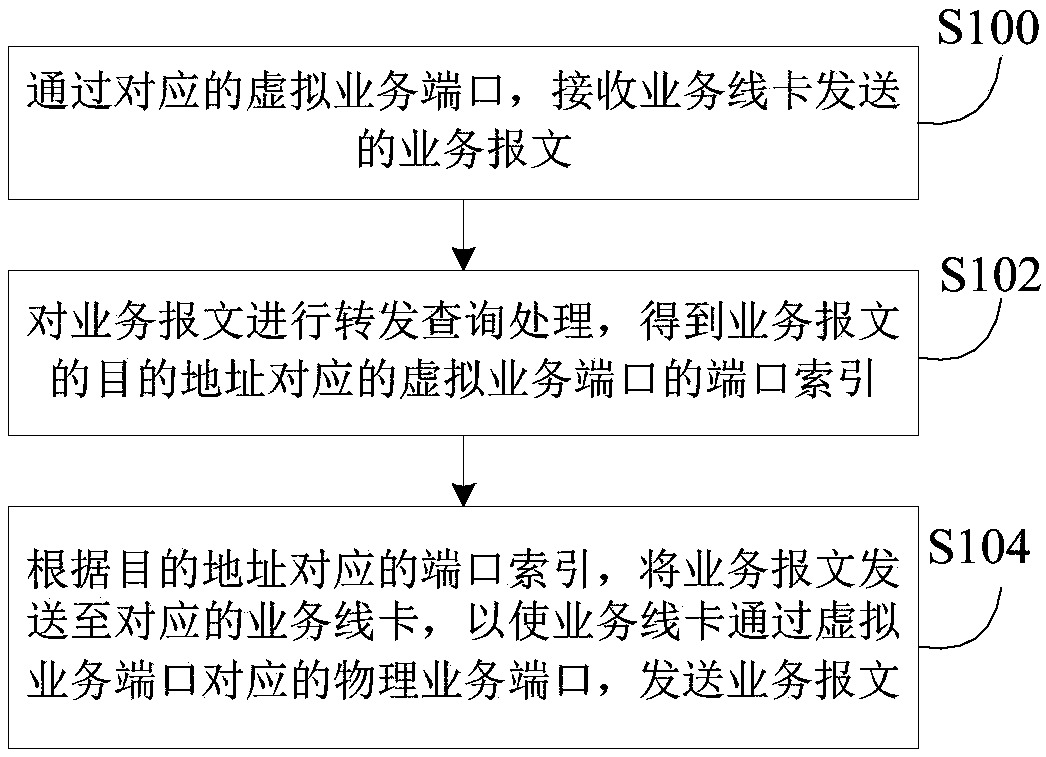

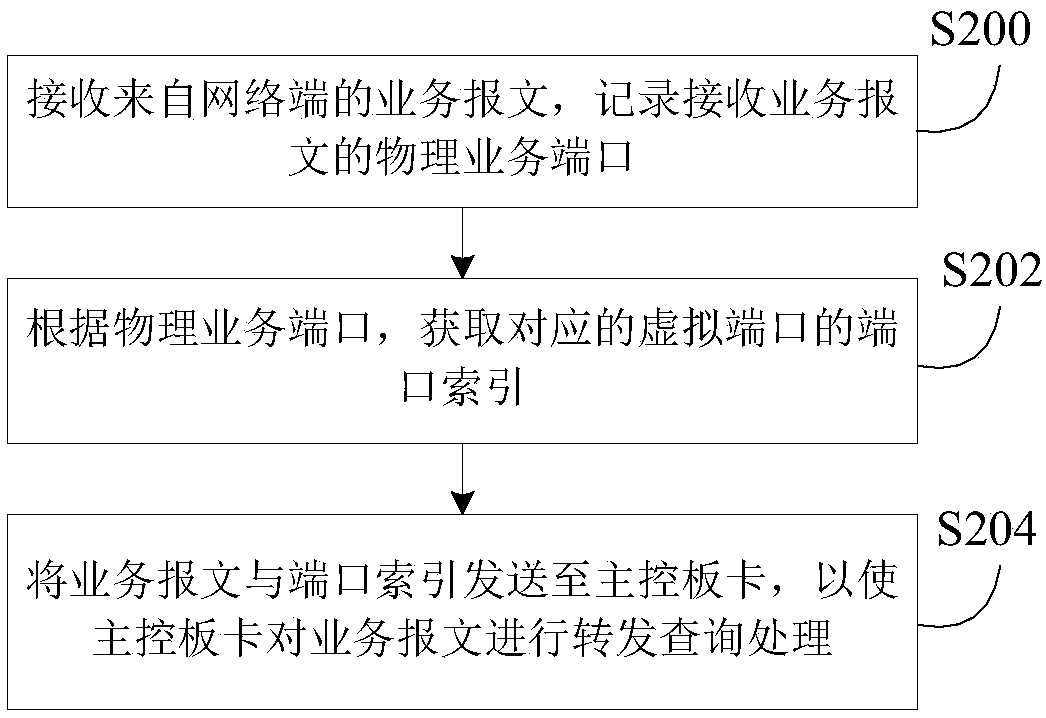

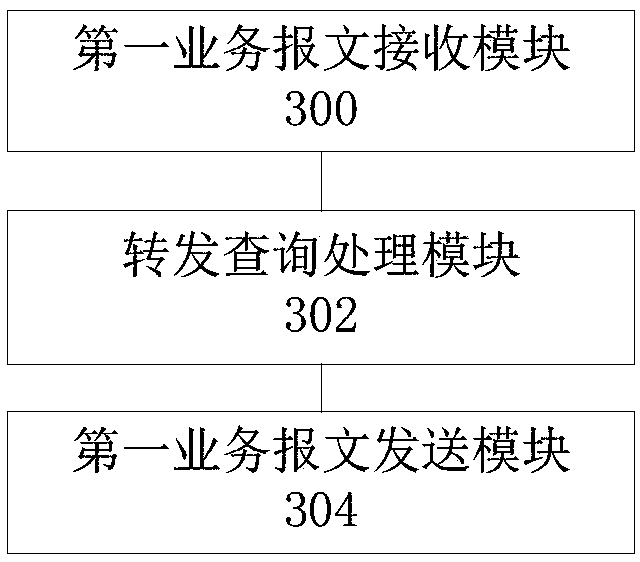

Cross-board processing method, apparatus and system of service messages

ActiveCN108347392AReduce implementation logic complexityReduce couplingData switching networksLogic complexityComputer hardware

The invention provides a cross-board processing method, apparatus and system of service messages. A main control board is connected with one or more service line cards; the main control board is provided with multiple virtual service ports, which are in one-to-one correspondence with the physical service ports of the service line cards and share the same port index; service messages sent by the service line cards are received by corresponding virtual service ports; forwarding query processing is performed on the service messages to obtain the port indexes of the virtual service ports corresponding to the destination addresses of the service messages; and the service messages are sent to the corresponding service line cards according to the port indexes corresponding to the destination addresses, so that the service line cards send the service messages through the physical service ports corresponding to the virtual service ports. By adoption of the cross-board processing method, apparatus and system, the logic complexity of the main control board software module and the coupling of the software modules of the main control board and the service line cards are reduced, and the robustness of the whole system is improved.

Owner:SHENZHEN FORWARD IND CO LTD

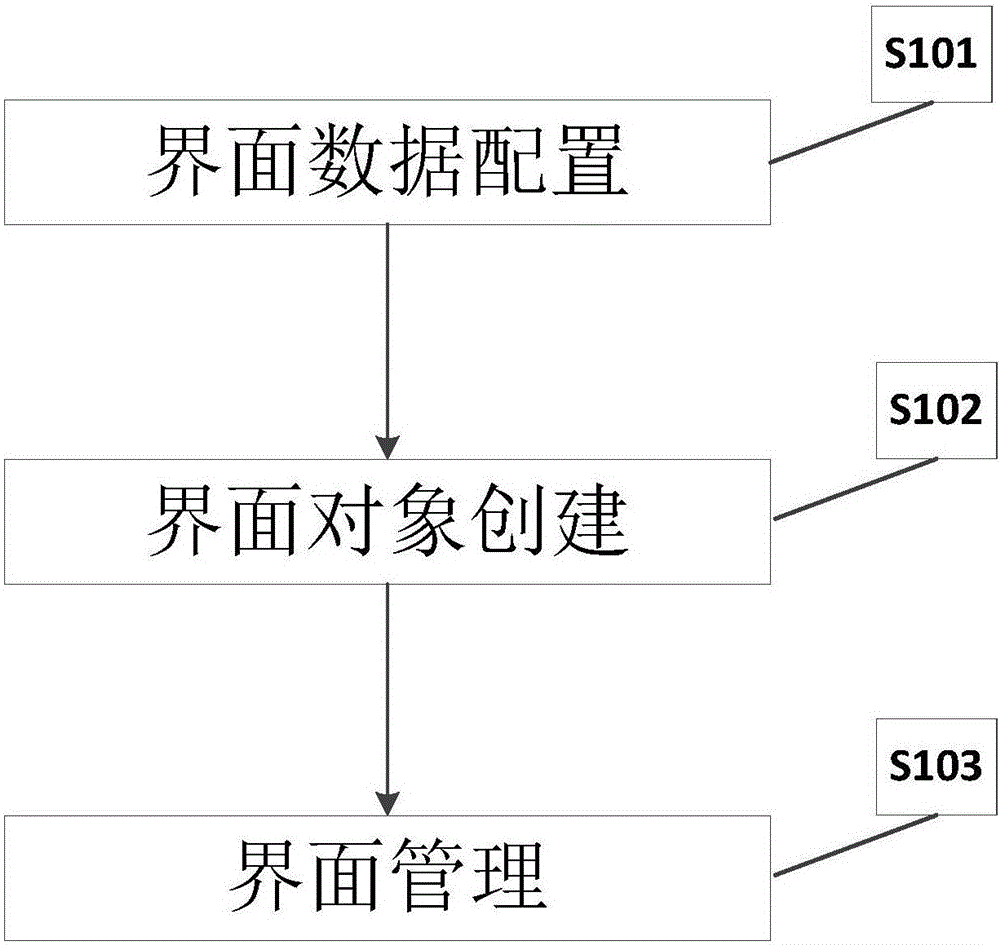

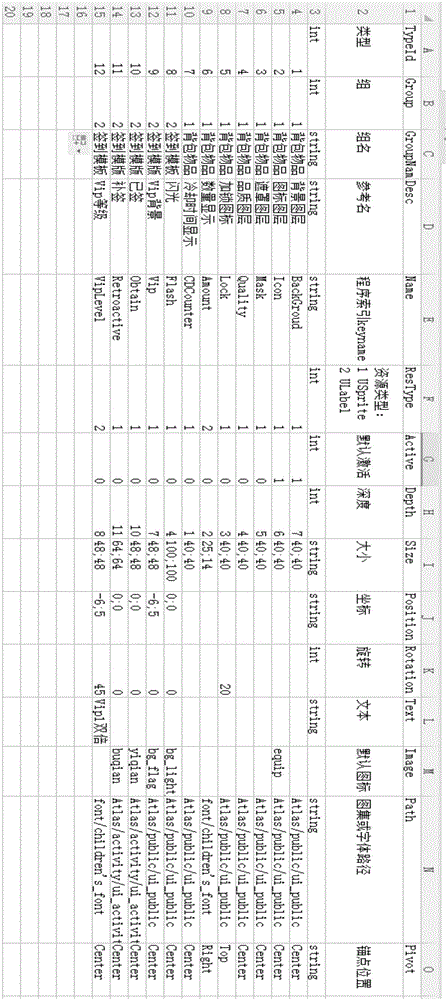

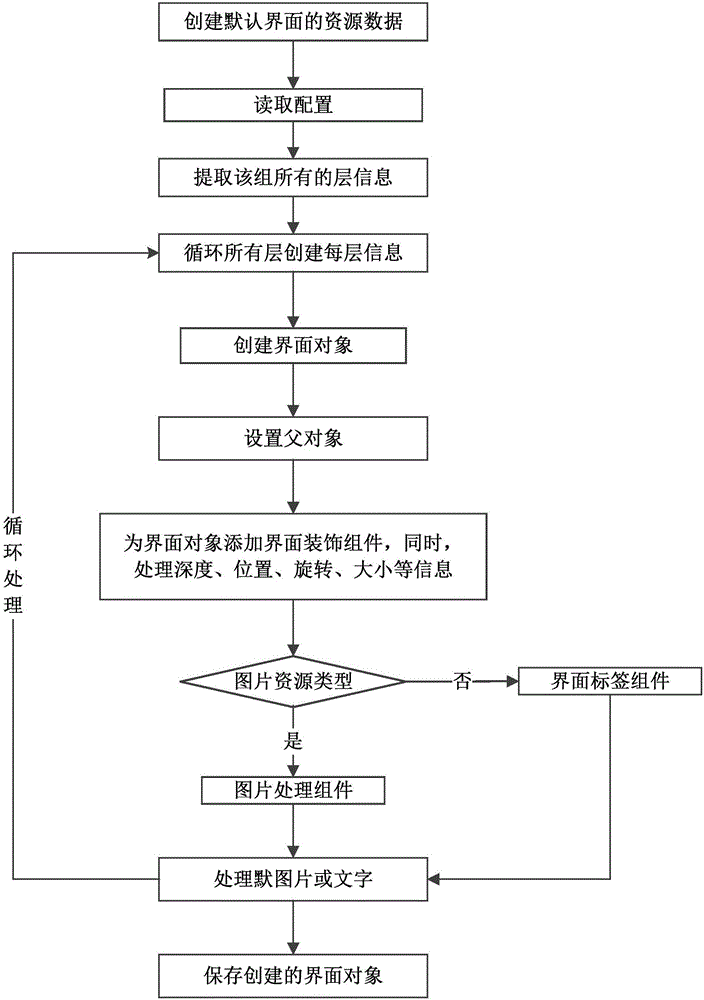

Interface generating system and method

InactiveCN106126257AReduce complexityEasy to adjustVersion controlSpecific program execution arrangementsProgramming languageLogic complexity

The invention discloses an interface generating system according to the technical scheme. The interface generating system comprises an interface configuration module using a data table to store interface resource data, controls and space functions, interface object module for creating an interface object and loading interface resources, an interface management module for obtaining, displaying and editing the interface object. The invention further discloses an interface generating method. The interface generating method comprises the steps of using the data table to store interface resource data and controls, creating the interface object and loading the interface resources, and obtaining, displaying and editing the interface object. The interface generating system has the advantages that the system is easy to understand, maintain and extend structurally; a various-similar-lattice layer-by-layer display function used by an interface can be adjusted and controlled through a configuration table, convenience is brought to adjustment of art workers, and the working efficiency is improved; a general interface is extracted without independent code compiling, the logic complexity is reduced, and the code repeatability is reduced.

Owner:ZHUHAI KINGSOFT ONLINE GAME TECH CO LTD +1

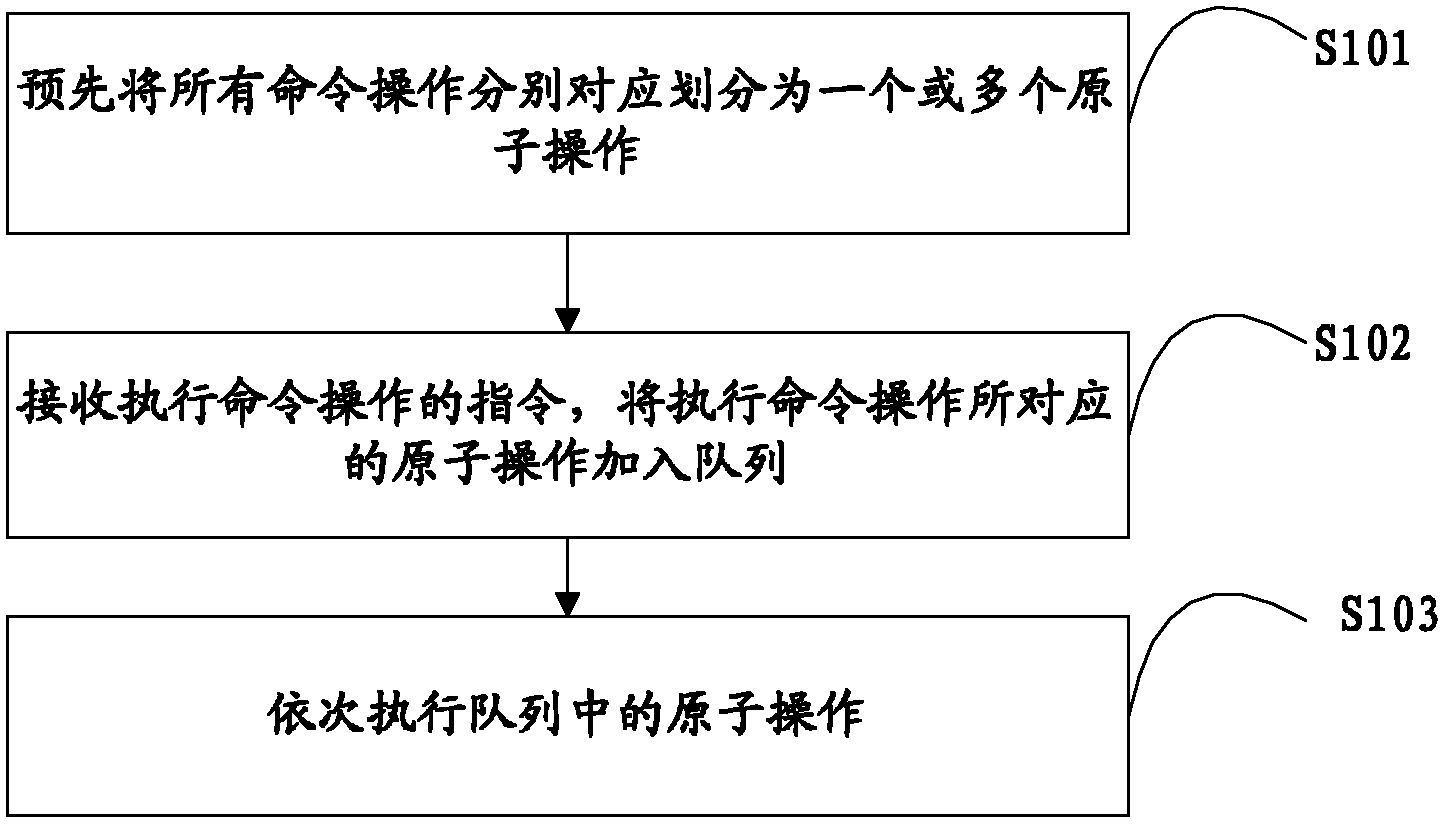

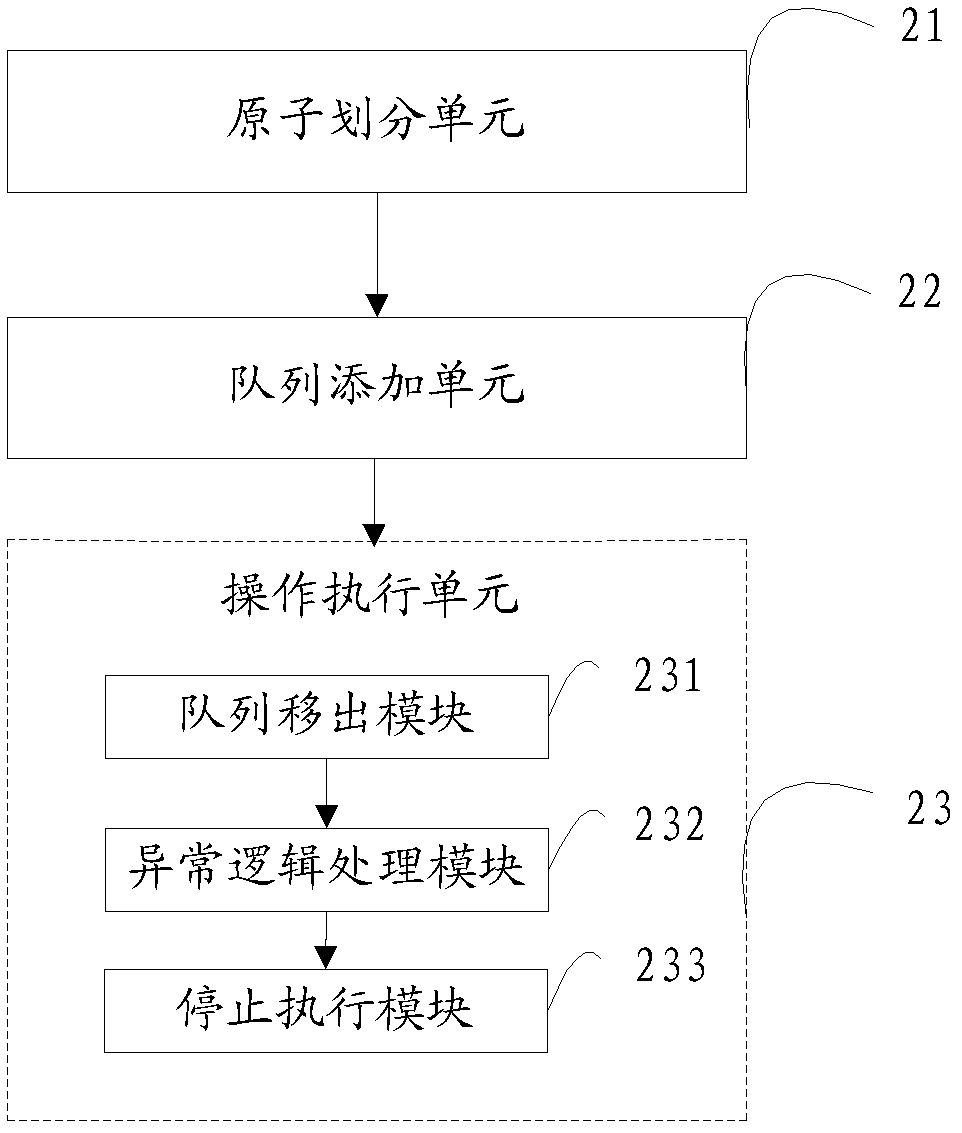

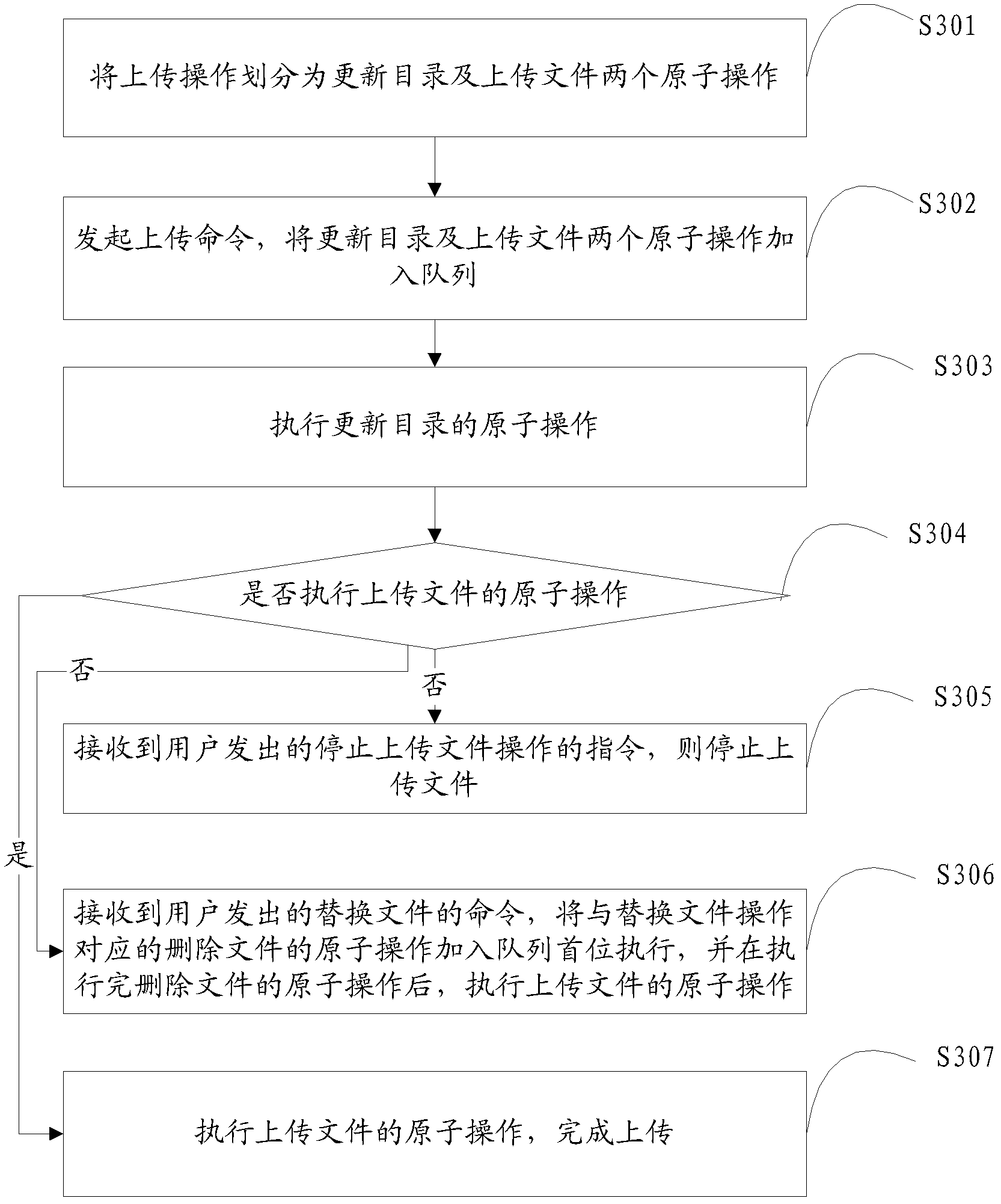

Method and device for complex time sequence processing queue dynamic prediction

InactiveCN103106064ADynamically change the execution logicReduce incidenceMachine execution arrangementsLogic complexityComputer software

The invention belongs to the field of computer software, and provides a method and a device for complex time sequence processing queue dynamic prediction. The method comprises that all order operations are respectively and correspondingly divided into one or a plurality of atomic operations in advance; an order operation executing instruction is received, the corresponding atomic operations executing the order operations are added into a queue; and the atomic operations in the queue are carried out in sequence. According to the method and the device, logic complexity caused when the order operations are carried out is greatly simplified, and generating rate of BUG is reduced.

Owner:TENCENT TECH (SHENZHEN) CO LTD

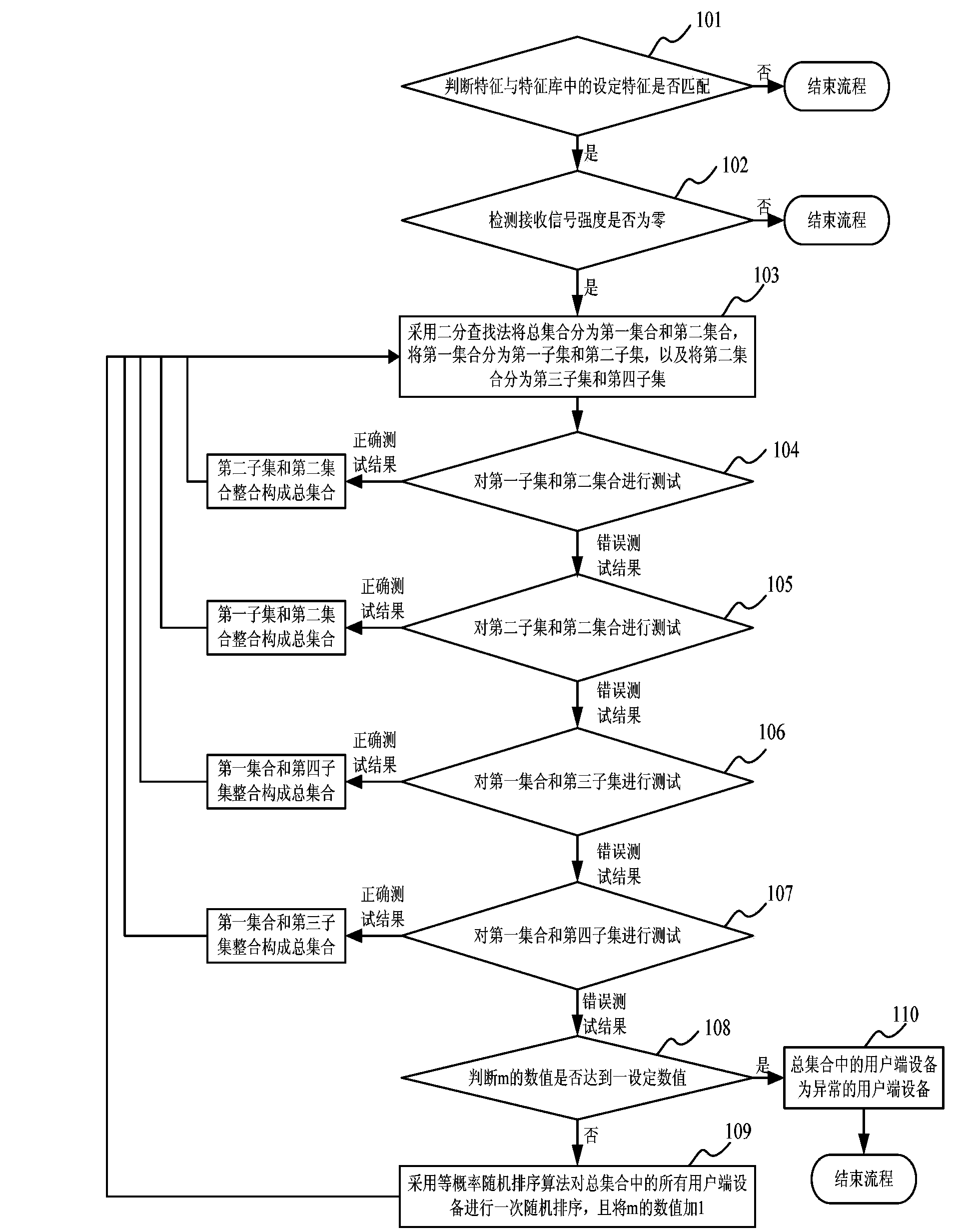

Passive optical network system and detection method for customer premise equipment of passive optical network system

ActiveCN103384353AFind accurate and comprehensiveShort timeMultiplex system selection arrangementsTransmission monitoring/testing/fault-measurement systemsLogic complexityRound complexity

The invention provides a passive optical network system and a detection method for customer premise equipment of the passive optical network system. The detection method includes that when the customer premise equipment is abnormal and signal receiving strength is zero, a dichotomizing searching method is used for performing dichotomization on a total set for three times; a first subset and a second set, a second subset and the second set, a third subset and a first set and a fourth subset and the first set are tested through a burst clock and data recovery method, if test results are right, the subsets corresponding to the right test results are eliminated, the rest subsets and sets form the total set, the dichotomizing searching method is used for performing dichotomization and tests on the total set again, if test results are wrong, random sort is performed on all customer premise equipment in the total set through an equal probability random sort algorithm, and the dichotomizing searching method is used for performing dichotomization and tests again until all abnormal customer premise equipment is detected. According to the passive optical network system and the detection method for the customer premise equipment of the passive optical network system, time consumption is reduced, logical complexity is lowered, and the detection method is flexible.

Owner:PHICOMM (SHANGHAI) CO LTD

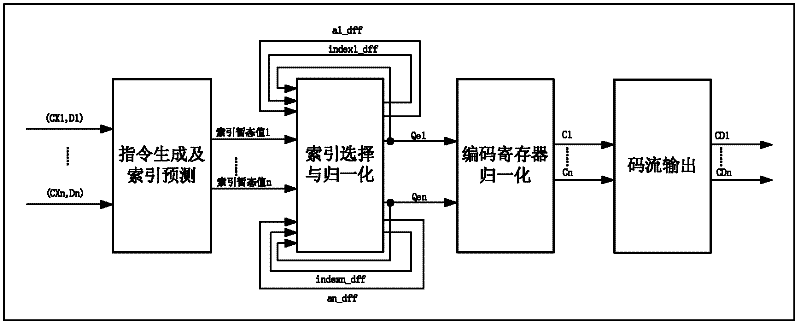

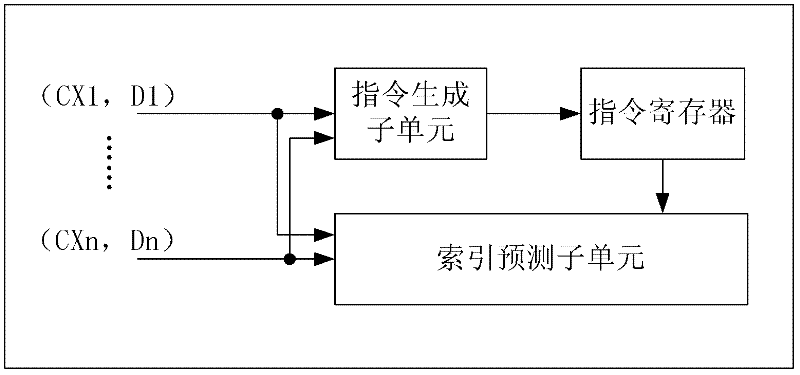

Multi-thread arithmetic coding circuit and method based on standard JPEG 2000

InactiveCN102523455AReduce in quantityReduce areaTelevision systemsDigital video signal modificationLogic complexityRound complexity

The invention discloses a multi-thread arithmetic coding circuit and method based on the standard JPEG 2000 and mainly aims to solve the problem of large area, low encoding efficiency and low throughput of a conventional multi-context arithmetic coder. The coding circuit is characterized in that under the premise of ensuring that the compression result is identical with that of the standard JPEG 2000, a command generating subunit, a command register and a comparator are introduced to a command generating and index forecasting unit' in the arithmetic coder, and the comparator is used for generating a 'command for controlling the thread coding mode; and simultaneously, an interval adjustment selector, a probability estimate selector and an index selector are controlled according to the command value to allocate the last coding result to the current to-be-coded thread, so that the logic complexity is reduced. Besides, according to the invention, LUTs (lookup tables) are split and expanded, wherein the primary LUT stores all possible index values, and the secondary LUT only stores probability estimate value. The simulation result shows that the invention has the characteristics of small area and high throughput and can be applied to high-performance image processing chips.

Owner:XIDIAN UNIV

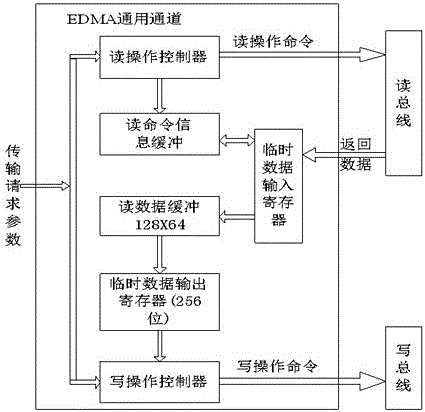

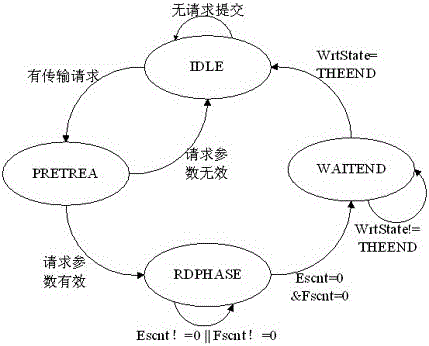

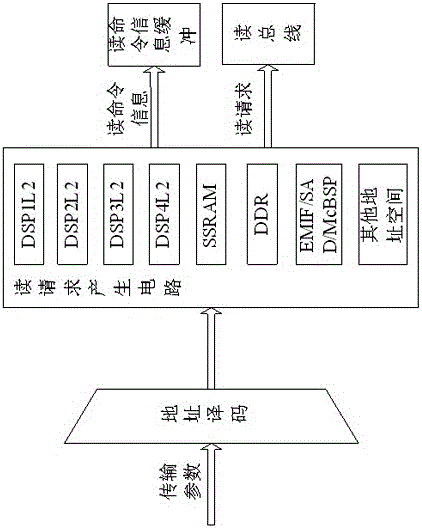

Method for performing communication among EDMA (enhanced direct memory access) different bandwidth devices in multi-core DSP (digital signal processor)

InactiveCN105843771AReduce complexityReduce difficultyDigital computer detailsElectric digital data processingLogic complexityDirect memory access

The invention discloses a method for performing communication among EDMA (enhanced direct memory access) different bandwidth devices in a multi-core DSP (digital signal processor). Each DSP core is provided with an independent processing channel, each channel is independent and can process requests from other DSP cores and other devices, a read operating information cache mechanism and a read operating information return data caching mechanism are realized through synchronous FIFO (first in, first out), accurate matching of return responding and requests is realized, and data communication among different bit width devices is realized. According to the method, read and write operation is controlled by state machines adopting the same working mechanism, and the logic complexity and the design difficulty are effectively reduced.

Owner:LANGCHAO ELECTRONIC INFORMATION IND CO LTD

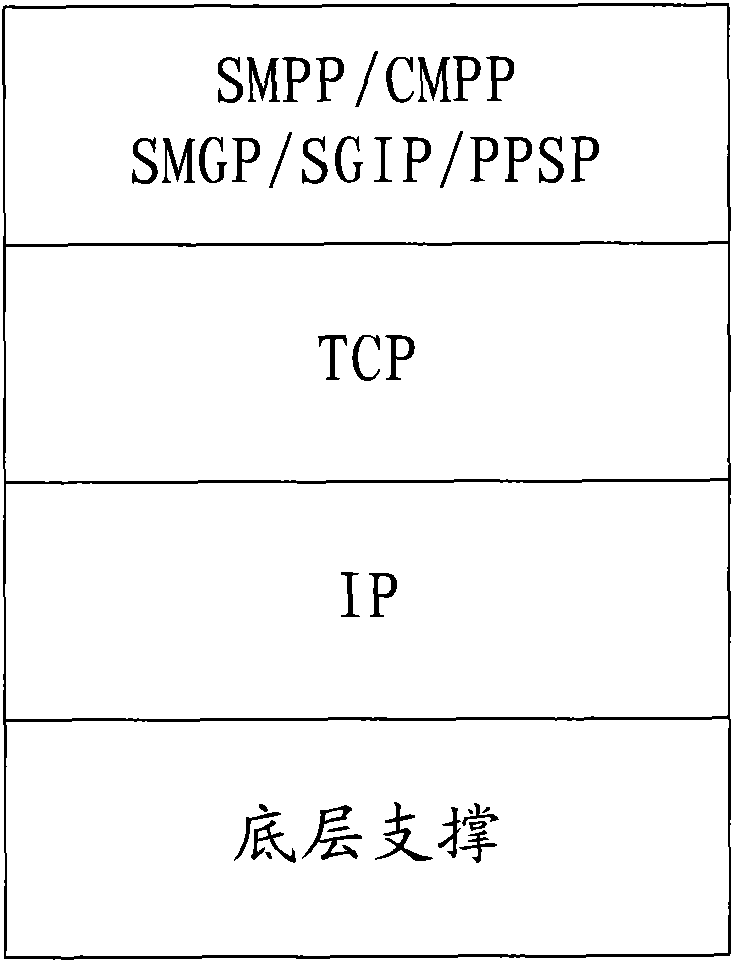

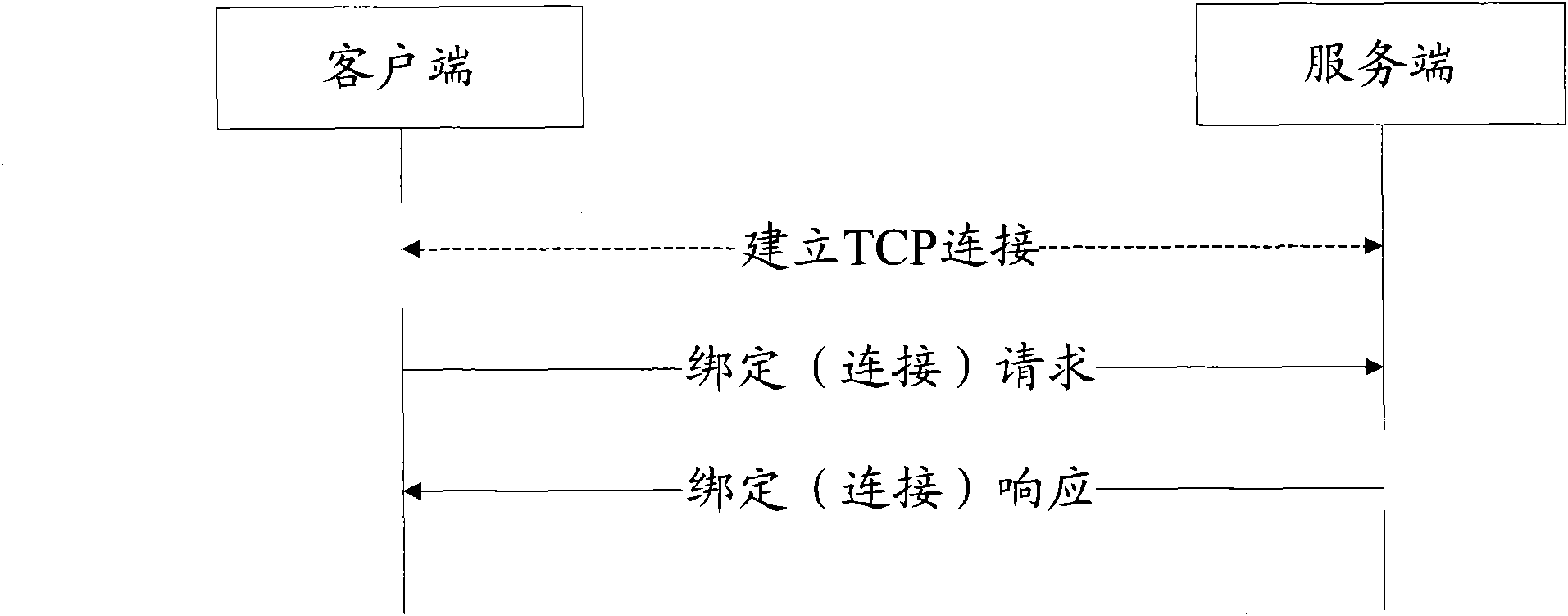

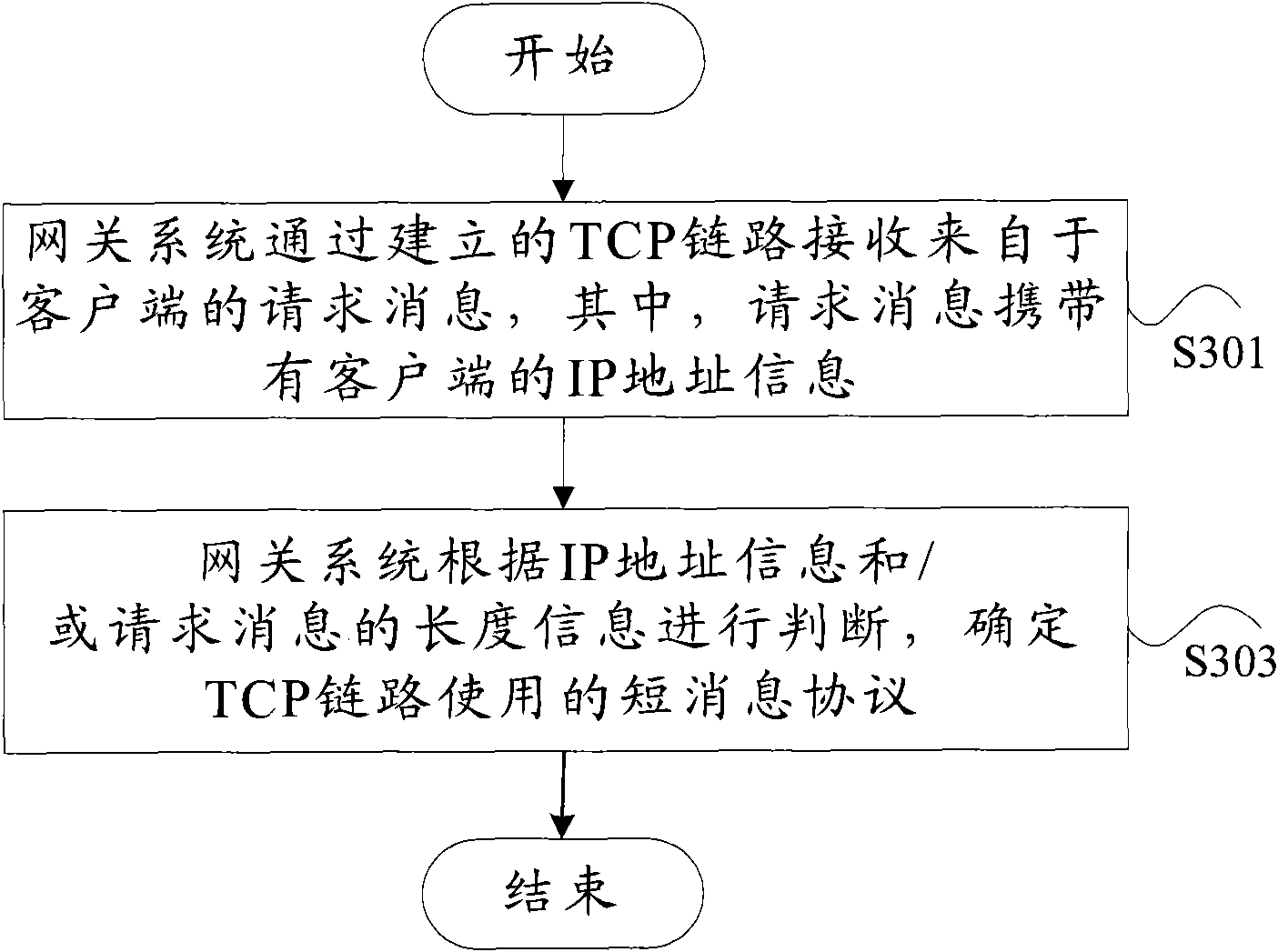

Identification method for short message service (SMS) protocol and gateway system

InactiveCN102045881ASolve problems such as greatly increased logic complexityReduce Logical ComplexityWireless network protocolsMessaging/mailboxes/announcementsLogic complexitySystem configuration

Owner:ZTE CORP

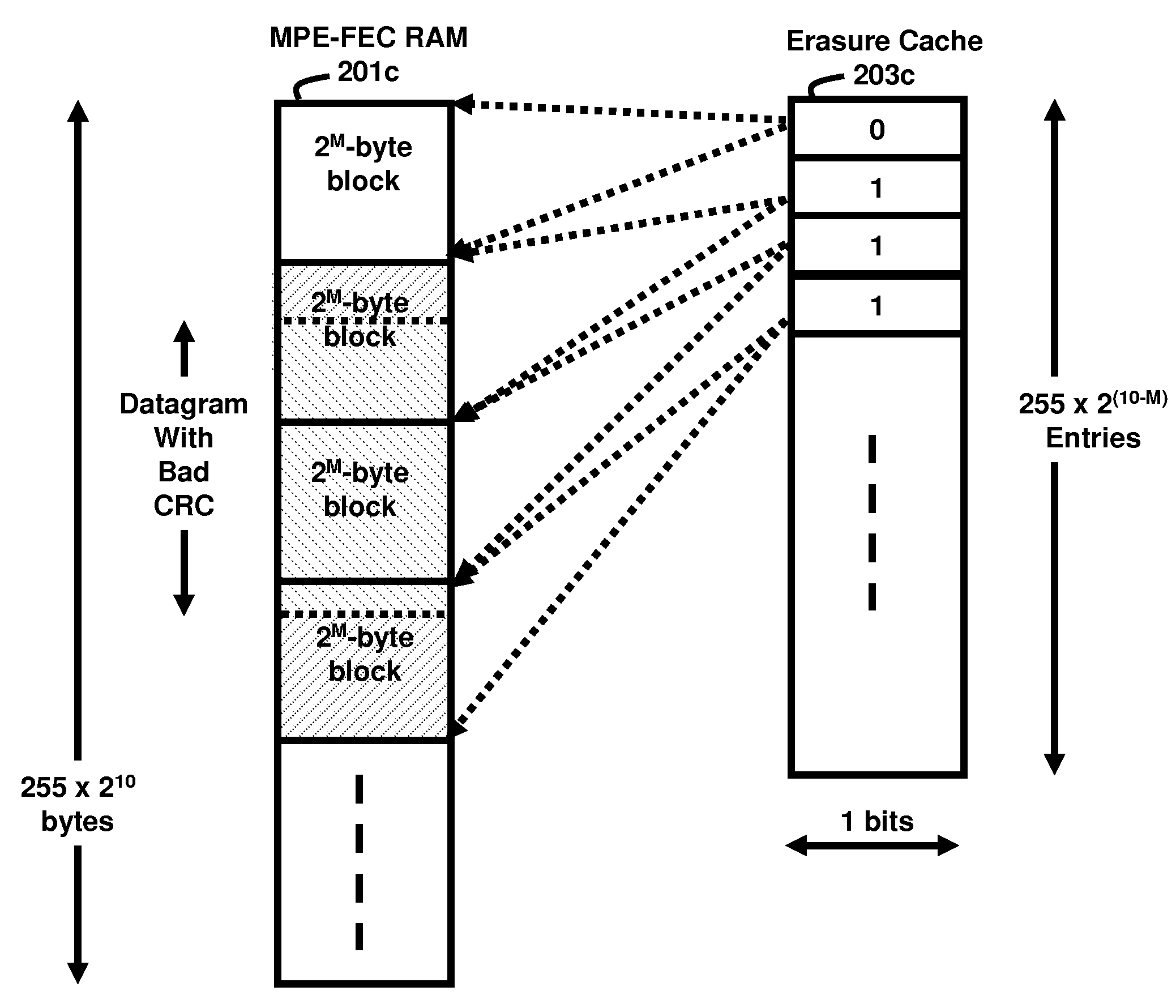

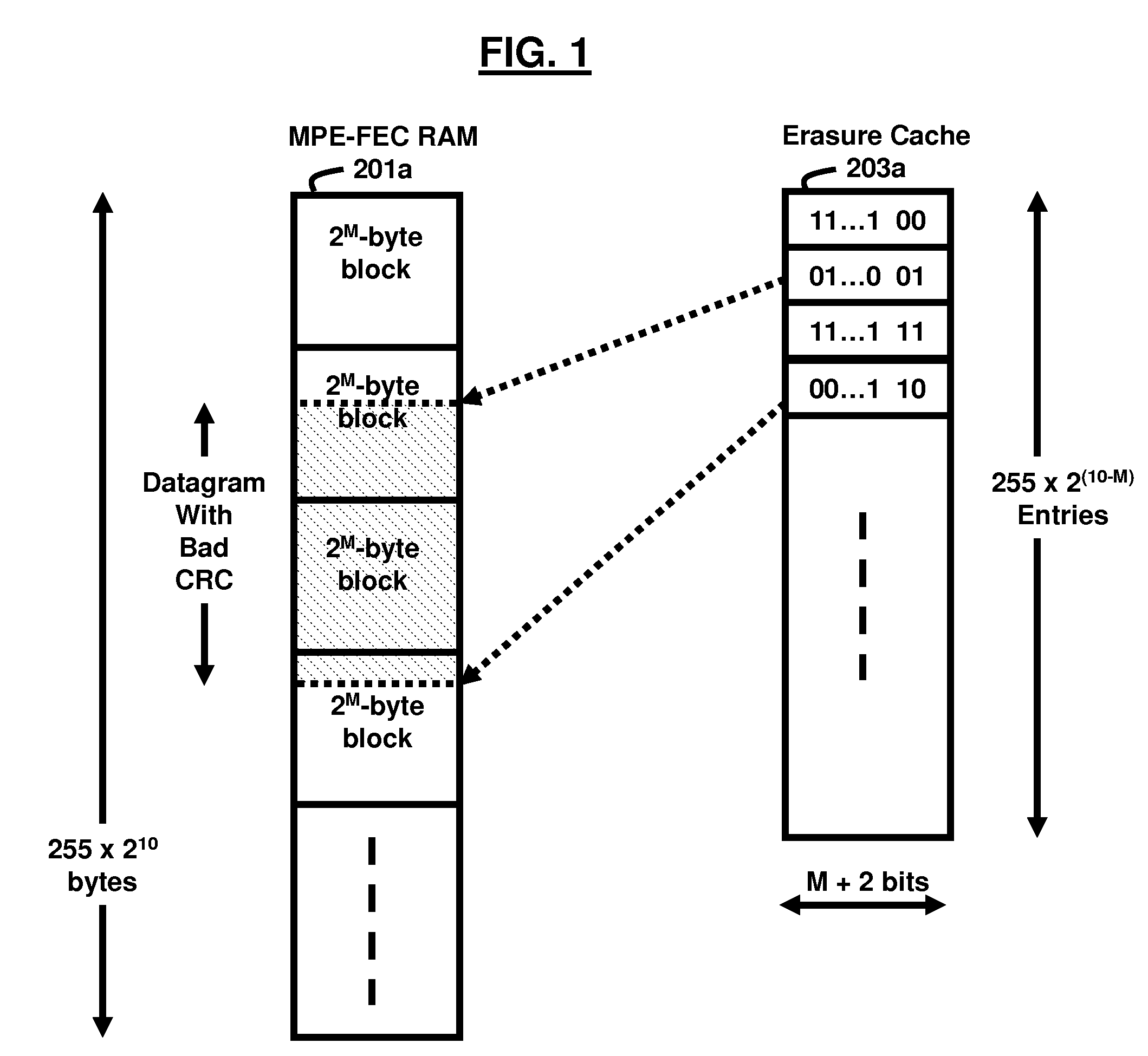

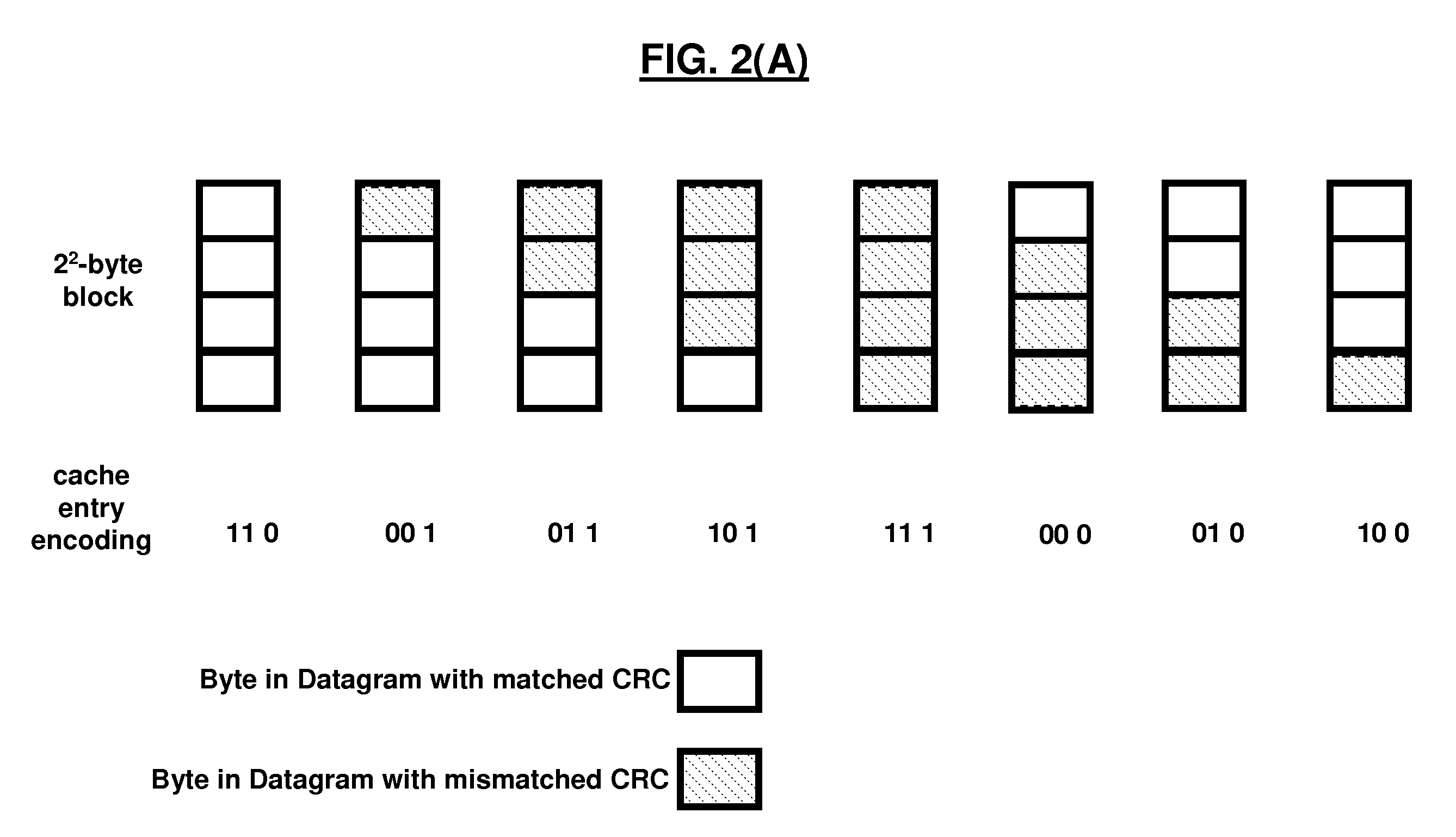

Compact mpe-fec erasure location cache memory for dvb-h receiver

Location cache memory architectures that only require 32 Kbits or less per frame to store erasure information with simple address mapping to the main MPE-FEC RAM for easy column-wise and row-wise access. Alternative architectures are designed to greatly reduce the size and logic complexity of the MPE-FEC erasure cache memory. Two architectures reduce the erasure cache size down to 32 Kbits and 28 Kbits, correspondingly, without introducing additional erasure locations, while another architecture further reduces the required memory size down to 16K, 8K, 4K, or 2K bits with a slight increase in the total erasure locations. All architectures group the data in MPE-FEC frame memory into blocks of 2M consecutive bytes and use one or a few bits to store the erasure status in each block, thereby, greatly reducing the required cache memory size.

Owner:ATMEL CORP

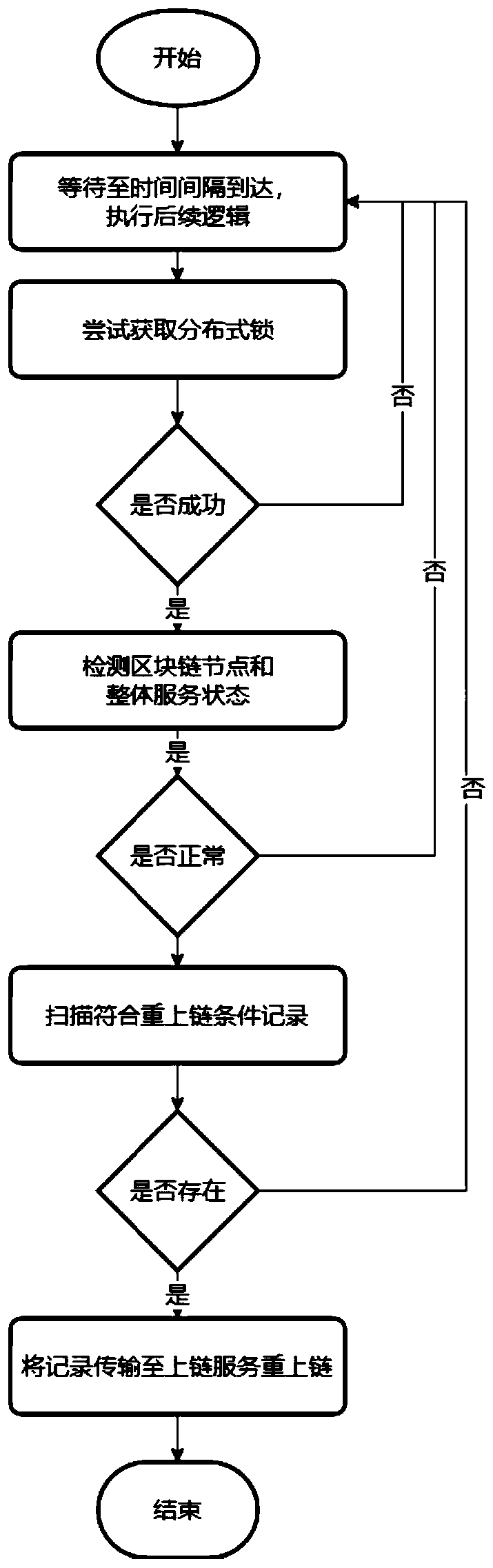

Data linking exception retry method based on block chain

InactiveCN111030846AReduce complexityPrevents interrupts from being lostEnergy efficient computingData switching networksLogic complexityEngineering

The invention discloses a data linking exception retry method based on a block chain. The method employs an independent scanning detection module, reduces the logic complexity and module responsibilities compared with a conventional mode of immediate retry when an exception occurs, and can prevent a part of data linking interruption and loss caused by service downtime in a conventional scheme. Through control via distributed locks, only one service in a plurality of levels of scanning detection services detects and scans records or data with data linking failure to determine whether to re-linkor not. The subsequent linking process is concurrently carried out through the linking service. so that repeated sending behaviors in a distributed lockless environment is avoided, and the overall efficiency and reliability of the linking process are improved.

Owner:HANGZHOU QULIAN TECH CO LTD