Rounding method for indivisible floating point division radication

A rounding and division technology, applied in the direction of instruments, electrical digital data processing, digital data processing components, etc., can solve the problems of low hardware cost, long sequence, high hardware cost, etc., and achieve easy hardware implementation and debugging, algorithm Clear and easy to understand, low hardware cost effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

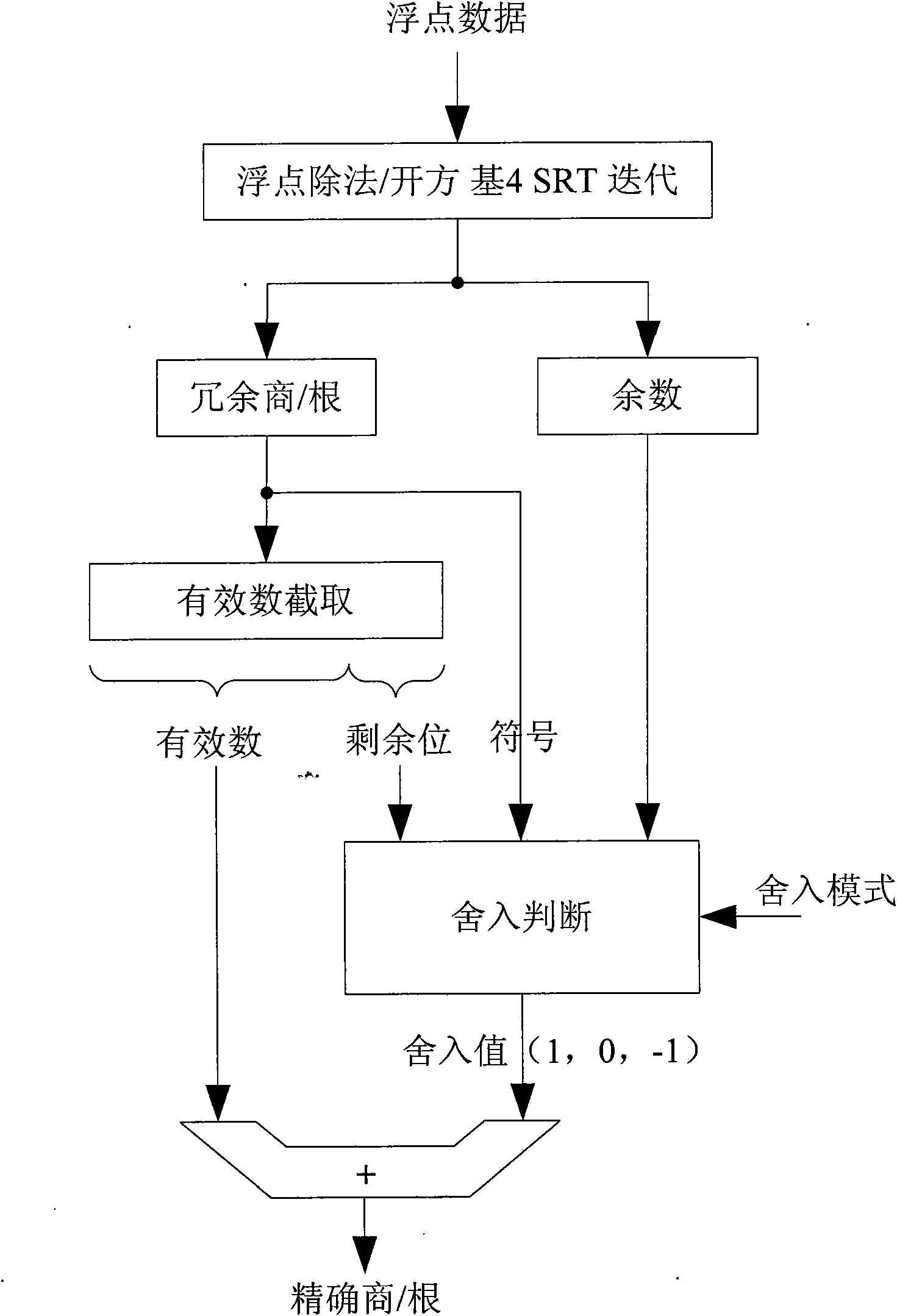

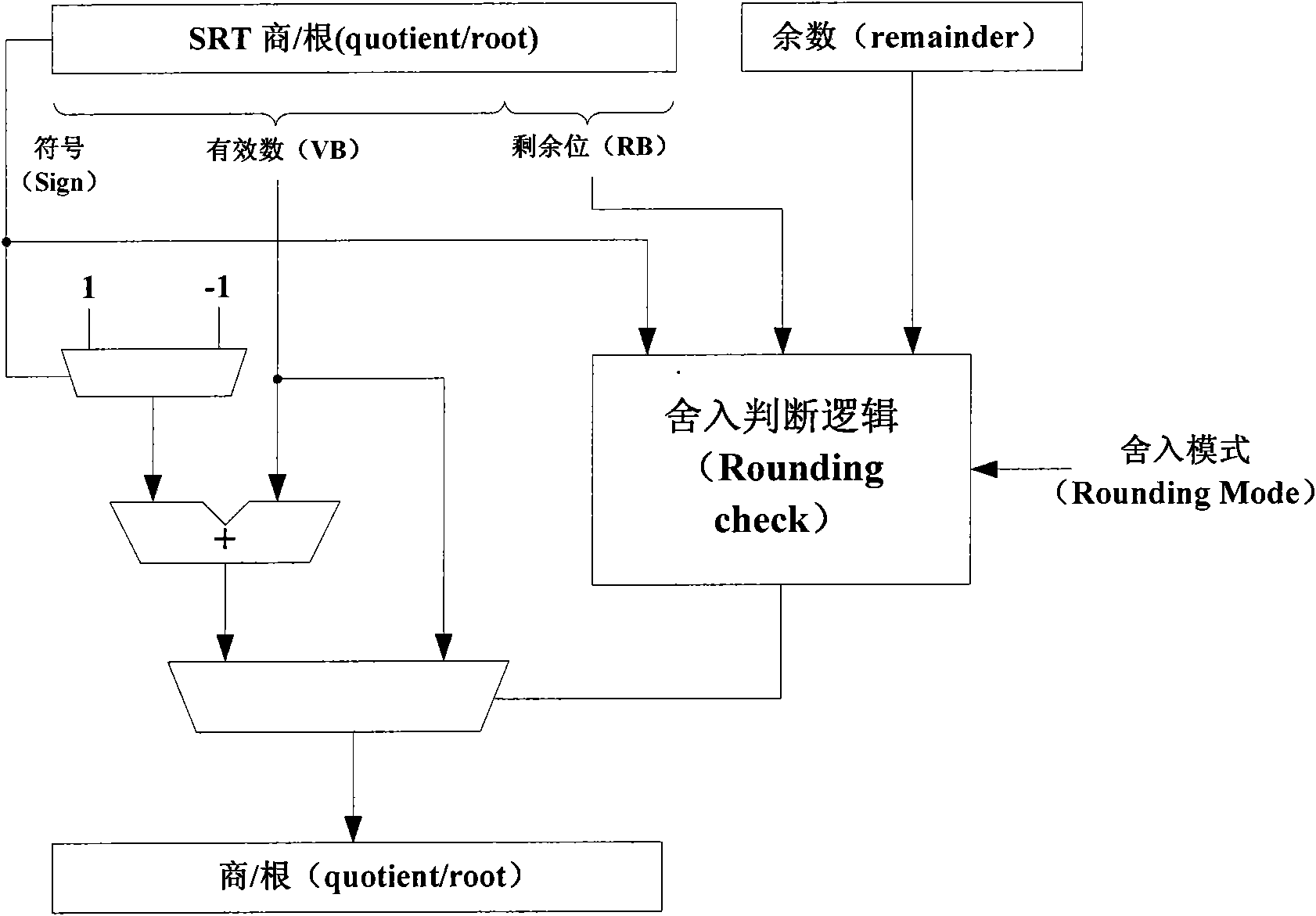

[0036] refer to Figure 1 ~ Figure 2 , a rounding method for the square root of non-divisible floating-point division, comprising the following steps:

[0037] 1) The floating-point number input to the floating-point coprocessor performs SRT division / square root algorithm, and the floating-point number performs a loop operation to obtain the quotient / root result;

[0038] 2) In the quotient / root result obtained in step 1), determine the effective number of the floating-point number according to the position where the first 1 occurs;

[0039] 3) Subtract the result of the quotient / root result in step 1) from the result of the significant number and the remainder obtained by the SRT division / square root algorithm as the rounding judgment information; subtract the quotient / root obtained in step 1) from the result obtained in step 2) The result of significant number is left-shifted, and the number obtained is recorded as the remaining digit, and the position of the decimal point ...

Embodiment 2

[0126] This embodiment is aimed at the floating-point single-precision square root operation.

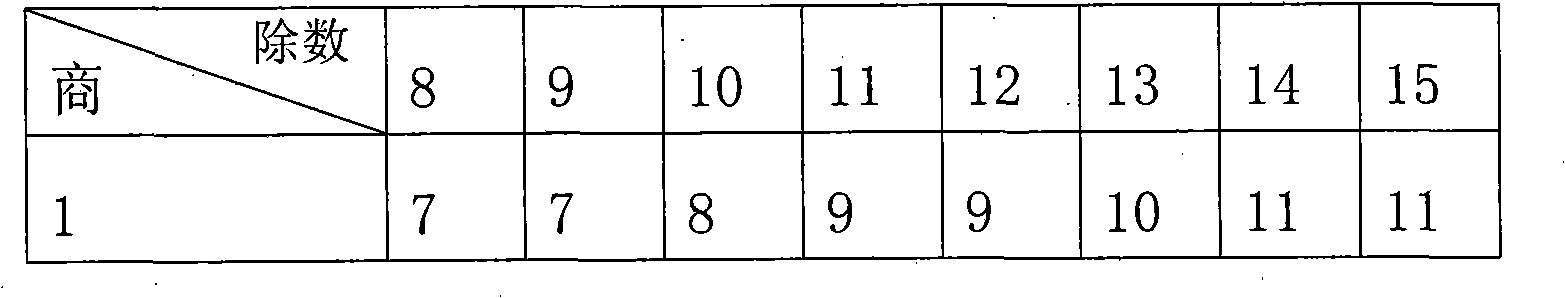

[0127] 1) Perform radix-4SRT division algorithm for two single-precision floating-point numbers input to the floating-point coprocessor, and obtain a 28-bit root result after 14 loop operations: 0.1a 25 a 24 ...a 4 0100 (binary representation), the remainder is greater than 0.

[0128] 2) For the root result obtained in step 1), determine the 24-bit effective number of the single-precision floating-point number according to the position where the first 1 appears: 1a 25 a 24 ...a 4 0 (binary representation). The result of subtracting the effective number from the root in step 1) is: 0.0...00100 (binary representation), this number is used as rounding judgment information.

[0129] 3) The root obtained in step 1) minus the effective number obtained in step 2) is left-shifted, and the position of the decimal point is set after the lowest digit of the effective number indicated in...

Embodiment 3

[0134] The floating-point number of the present embodiment is a double-precision floating-point number, and in the step 1), 28 loop operations are performed to obtain 56 quotient / root results; in step 2), the effective number of the double-precision floating-point number starts from the first 1 A total of 53-bit binary numbers are intercepted, and the intercepted effective number is used as the benchmark number of the rounding operation carried out in step 4) to step 7); in step 3), the double-precision floating-point number is obtained according to the position where the first 1 appears. Two (0.xx) or one (0.x) remaining bits are used for rounding judgment.

[0135] Other steps of this embodiment are the same as in Embodiment 3.

[0136] This embodiment is for floating-point double-precision division operations.

[0137] 1) Perform base 4SRT division algorithm for a double-precision floating-point number input to the floating-point coprocessor, and obtain a 56-bit quotient r...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More