Patents

Literature

46results about How to "Avoid programming" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Non-volatile memory and method with phased program failure handling

InactiveUS20050166087A1Improve efficiencyReduce overheadMemory architecture accessing/allocationMemory adressing/allocation/relocationError processingTime critical

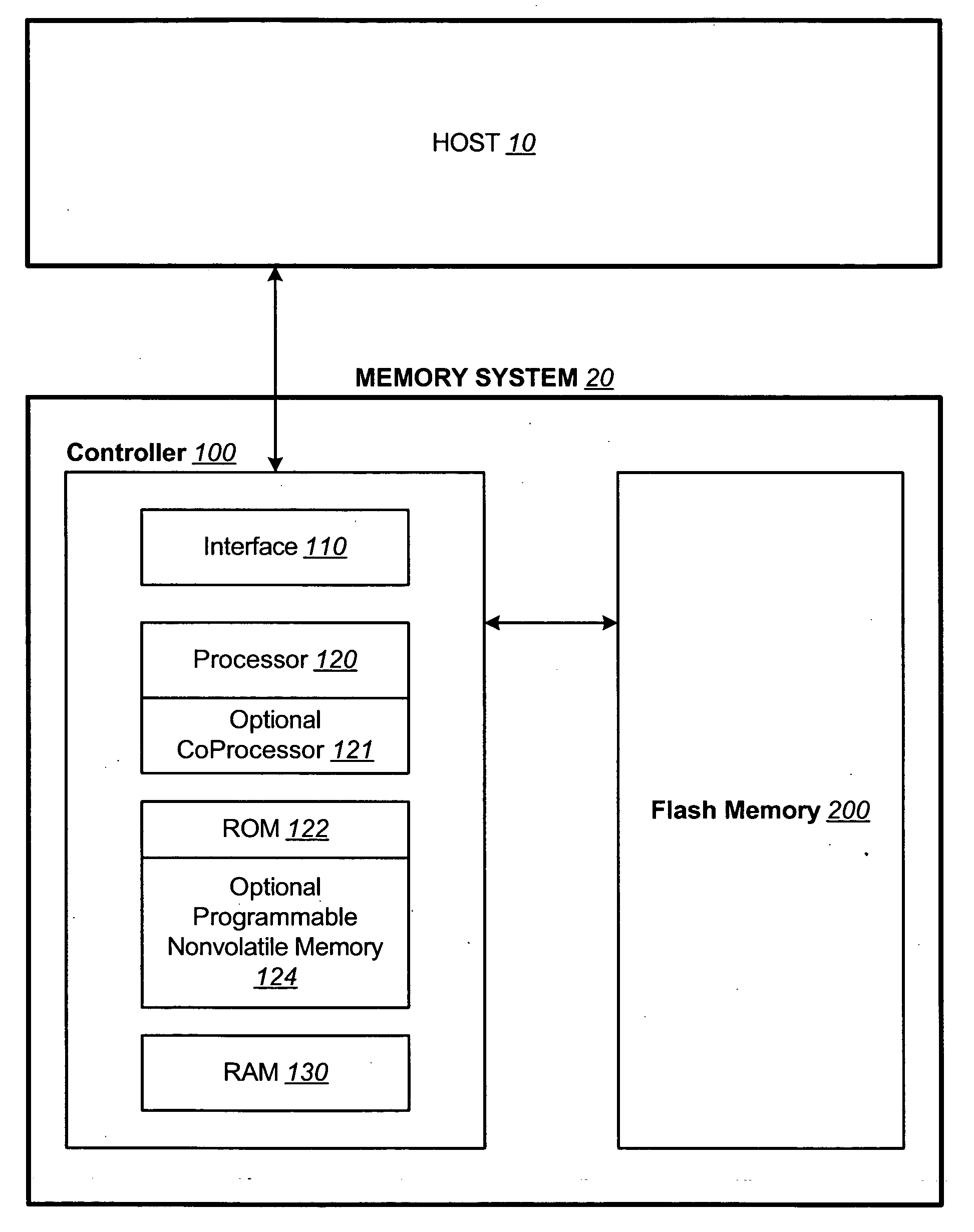

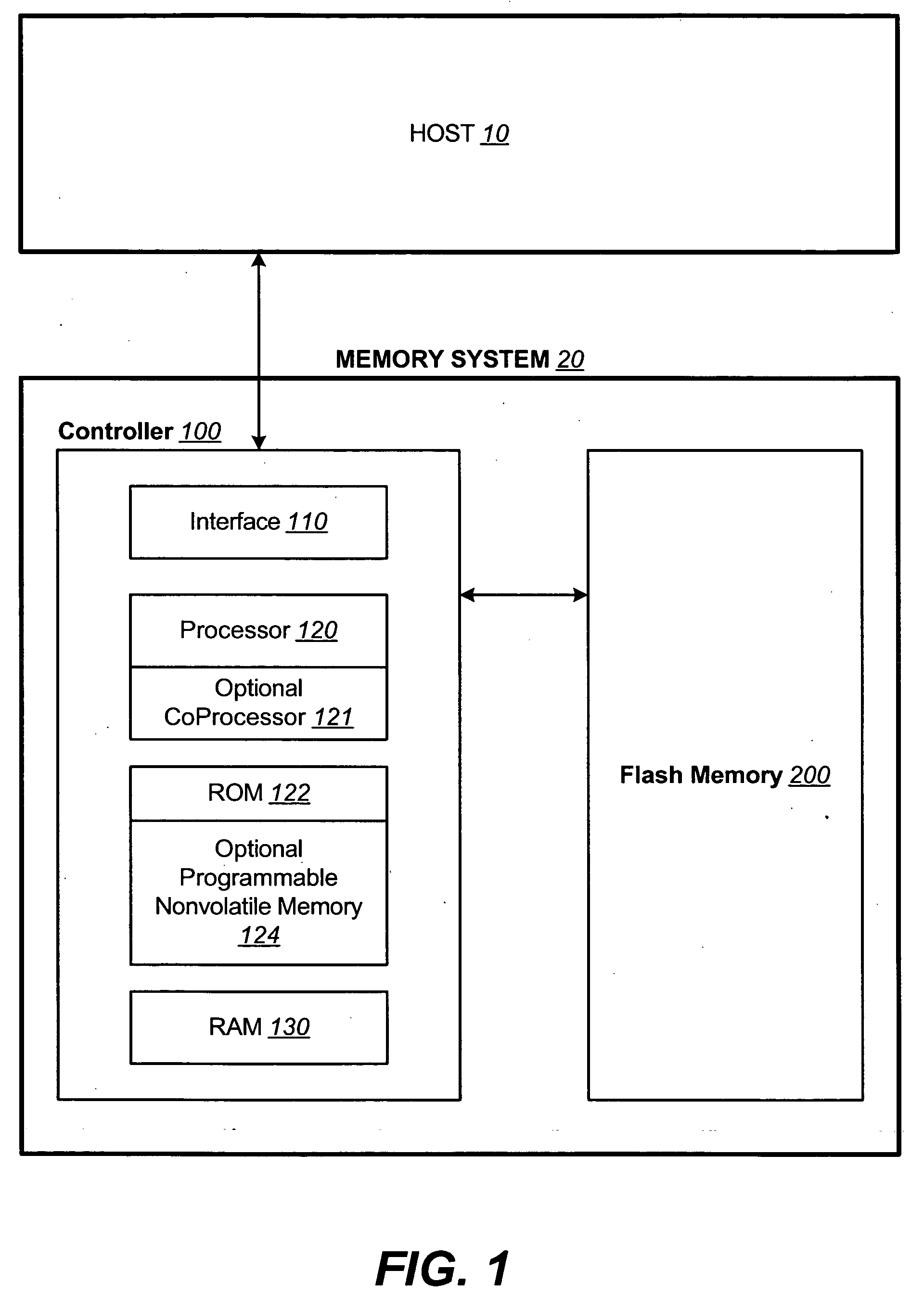

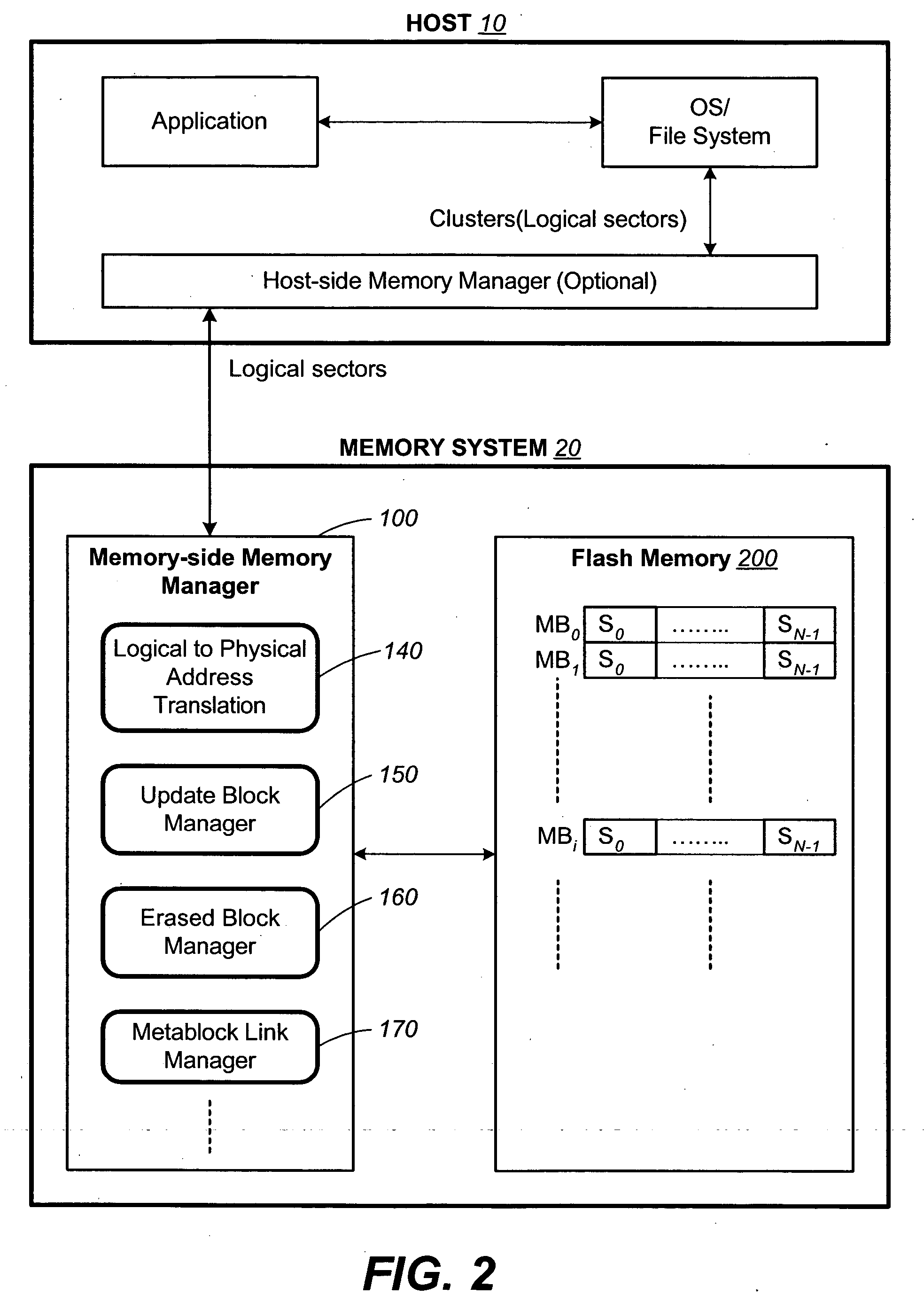

In a memory with block management system, program failure in a block during a time-critical memory operation is handled by continuing the programming operation in a breakout block. Later, at a less critical time, the data recorded in the failed block prior to the interruption is transferred to another block, which could also be the breakout block. The failed block can then be discarded. In this way, when a defective block is encountered during programming, it can be handled without loss of data and without exceeding a specified time limit by having to transfer the stored data in the defective block on the spot. This error handling is especially critical for a garbage collection operation so that the entire operation need not be repeated on a fresh block during a critical time. Subsequently, at an opportune time, the data from the defective block can be salvaged by relocation to another block.

Owner:SANDISK TECH LLC

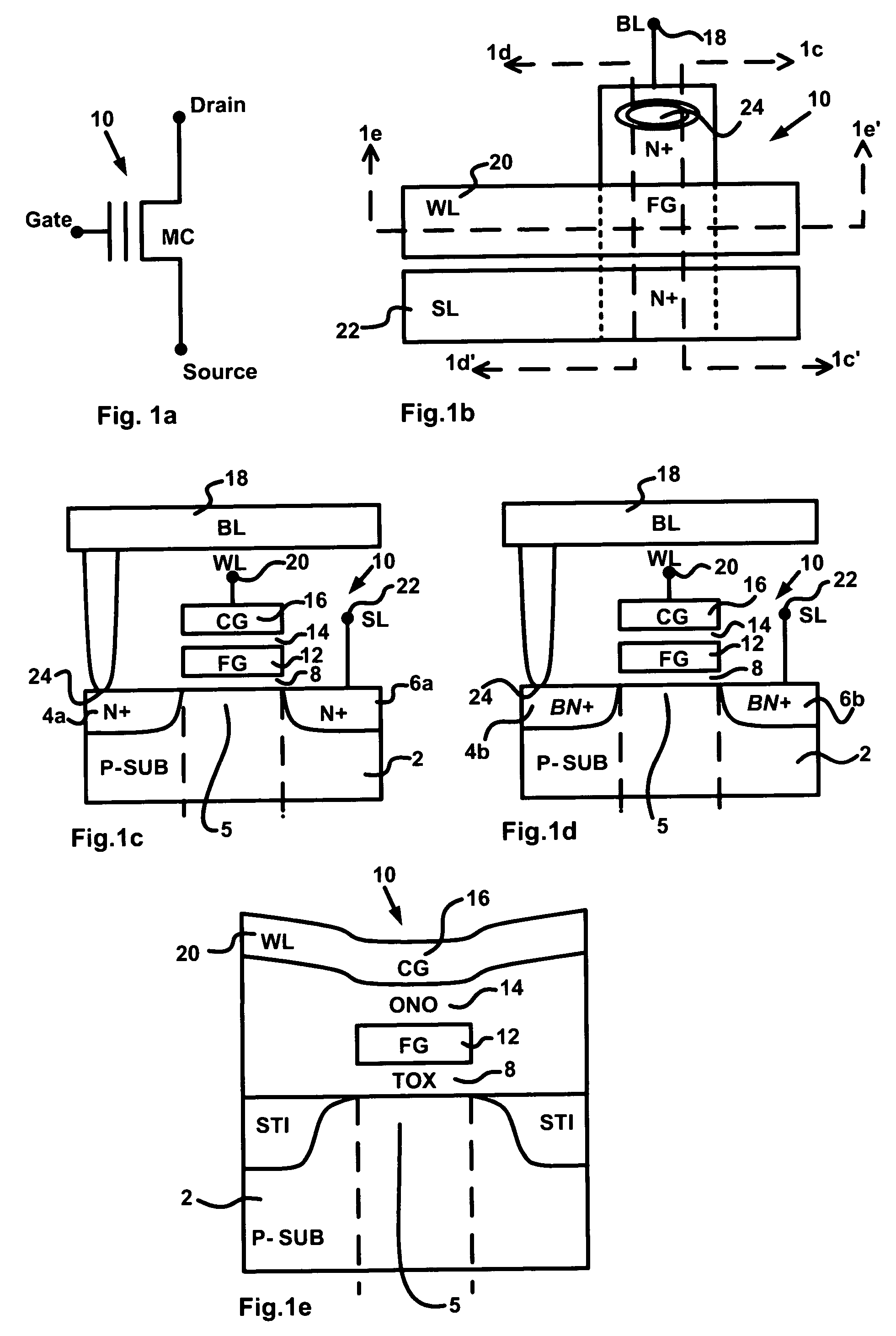

Novel combination nonvolatile integrated memory system using a universal technology most suitable for high-density, high-flexibility and high-security sim-card, smart-card and e-passport applications

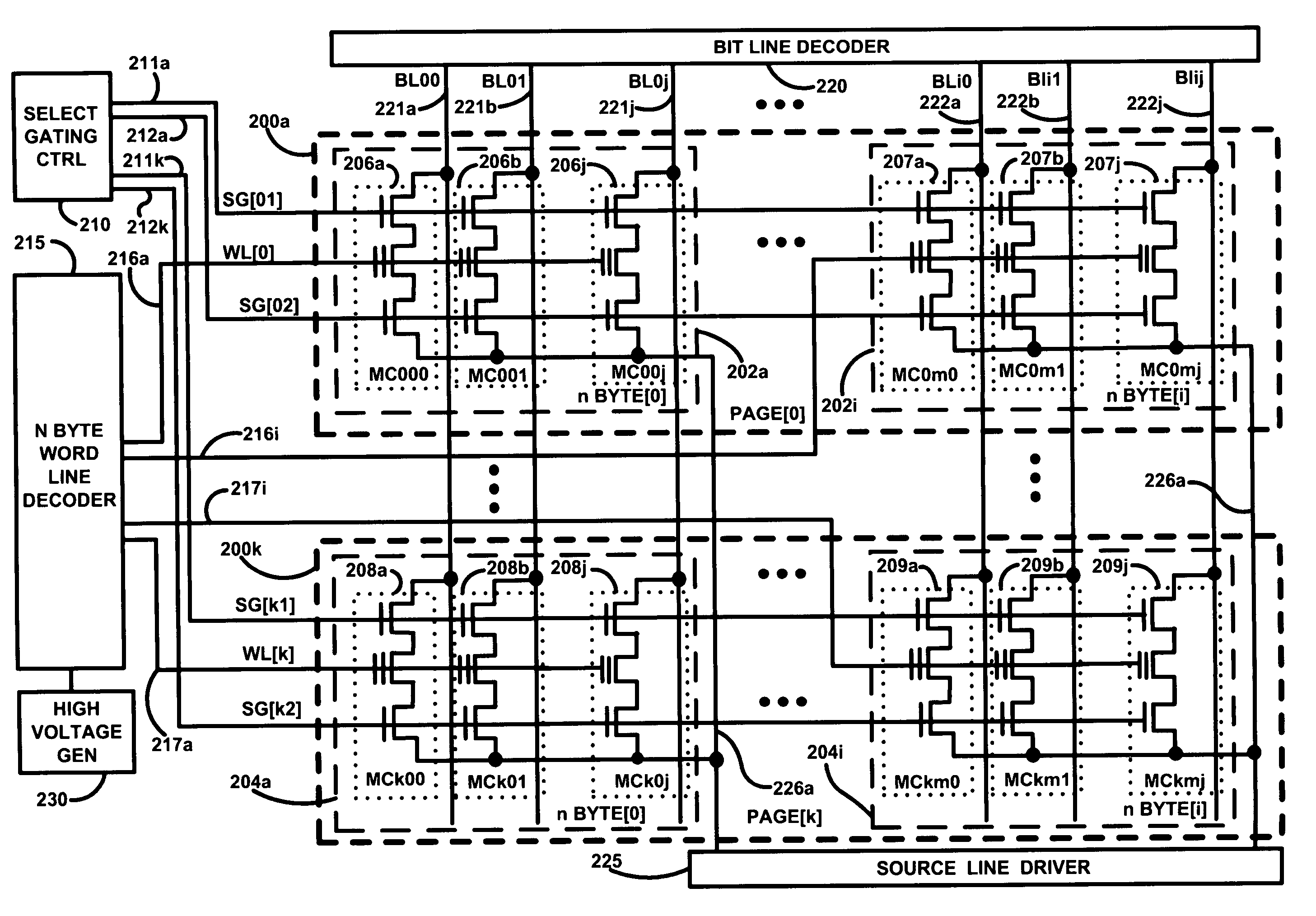

A combination EEPROM, NOR-type Flash and NAND-type Flash nonvolatile memory contains memory cells in which a floating gate transistor forms a NAND-type Flash nonvolatile memory cell, forms a NOR-type Flash nonvolatile memory cells and with one or two select transistors forms a two and three transistor EEPROM cell. The nonvolatile memory cells use a large positive programming voltage (+18V) applied to the word lines or select gating lines for programming the memory cells and a large negative erasing voltage (−18V) applied to the word lines or select gating lines for erasing the memory cells. The NOR-type Flash nonvolatile memory array is used to store code of embedded processor programs or application programs for smart cards. The EEPROM array is preferably used to store byte alterable data and NAND-type Flash nonvolatile memory array is used to store personalized biometric data such as Iris, DNA, facial picture and finger prints.

Owner:CALLAHAN CELLULAR L L C

Programming inhibit for non-volatile memory

ActiveUS7170793B2Reduces or avoids program disturbAvoid programmingRead-only memoriesDigital storageBit lineTheoretical computer science

Owner:SANDISK TECH LLC

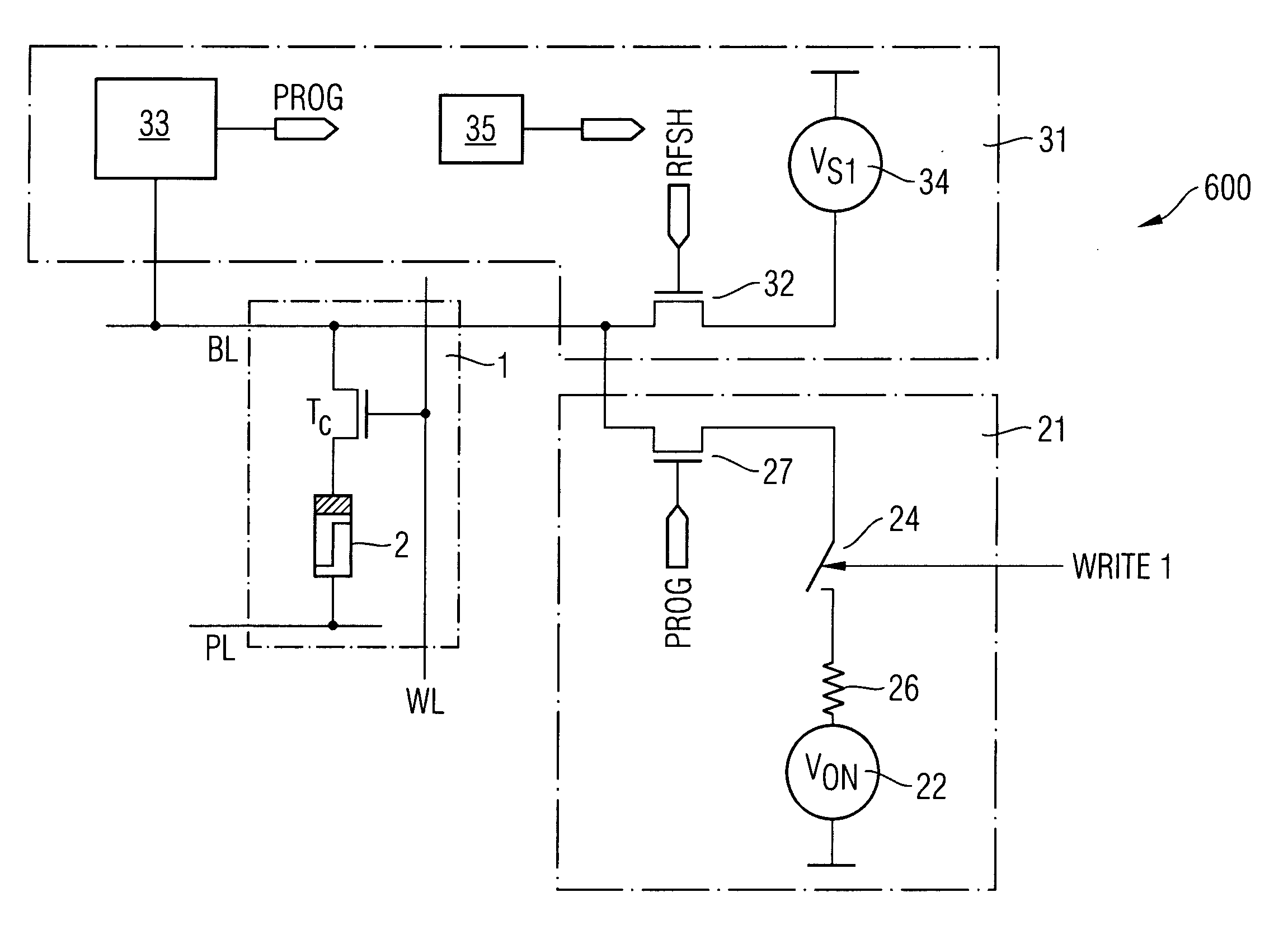

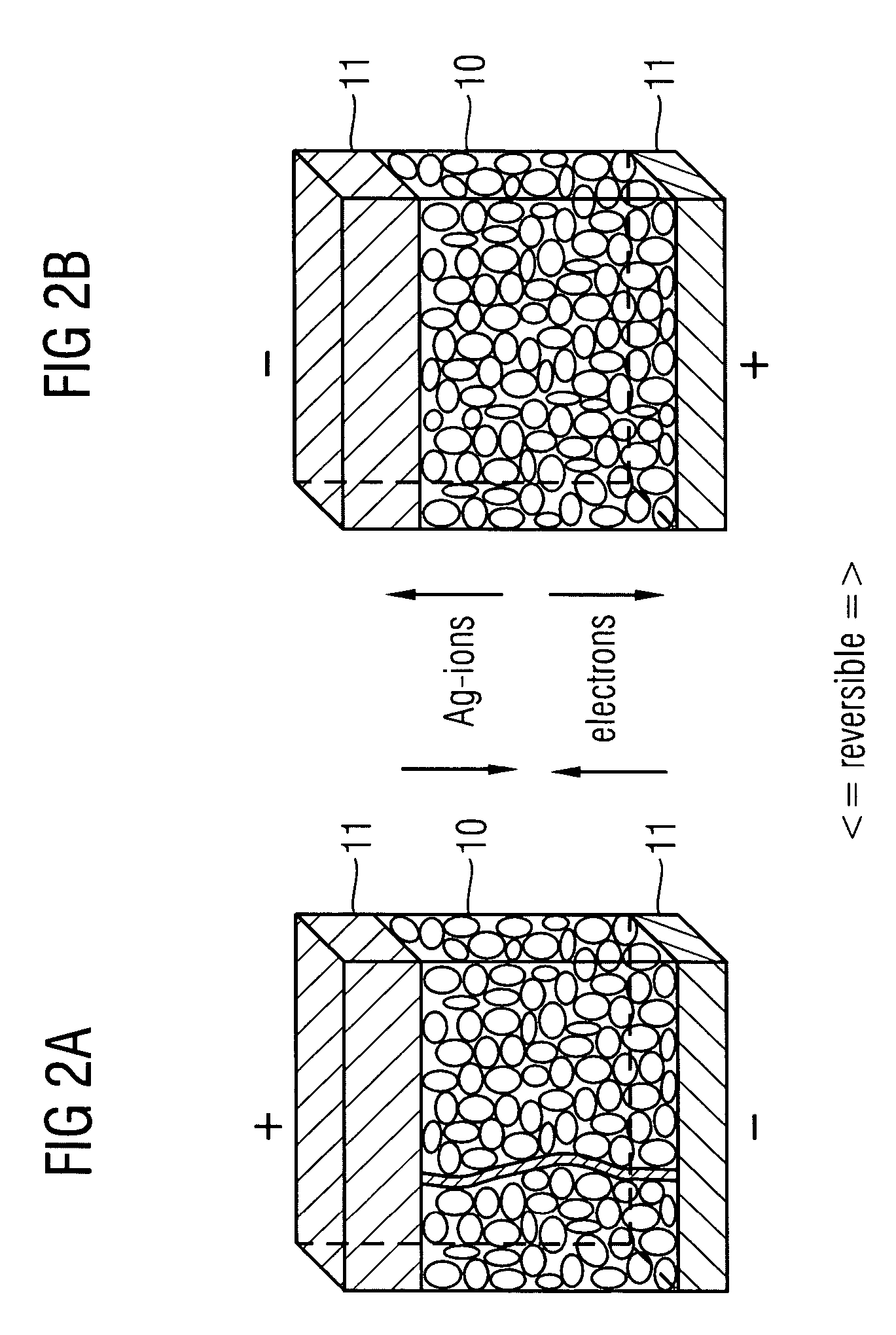

Method for operating a PMC memory cell and CBRAM memory circuit

ActiveUS20060265548A1Avoid programmingReduce developmentRead-only memoriesDigital storageMemory circuitsComputer science

The present invention relates to a method for operating a PMC memory cell for use in a CBRAM memory array, wherein the PMC memory cell includes a solid electrolyte which is adapted to selectively develop and diminish a conductive path depending on an applied electrical field. The PMC memory cell is programmed to change to a programmed state by applying a programming voltage, and the PMC memory cell is erased to change to an erased state by applying an erase voltage. A refresh voltage is applied to the PMC memory cell at a predetermined time to stabilize the programmed state of the PMC memory cell, wherein the refresh voltage is selected such as that, while applying the refresh voltage, a programming of the PMC memory cell in the erased state to a programmed state is prevented, and that, by applying the refresh voltage, a stabilizing of the programmed state of the PMC memory cell is performed.

Owner:ADESTO TECH +1

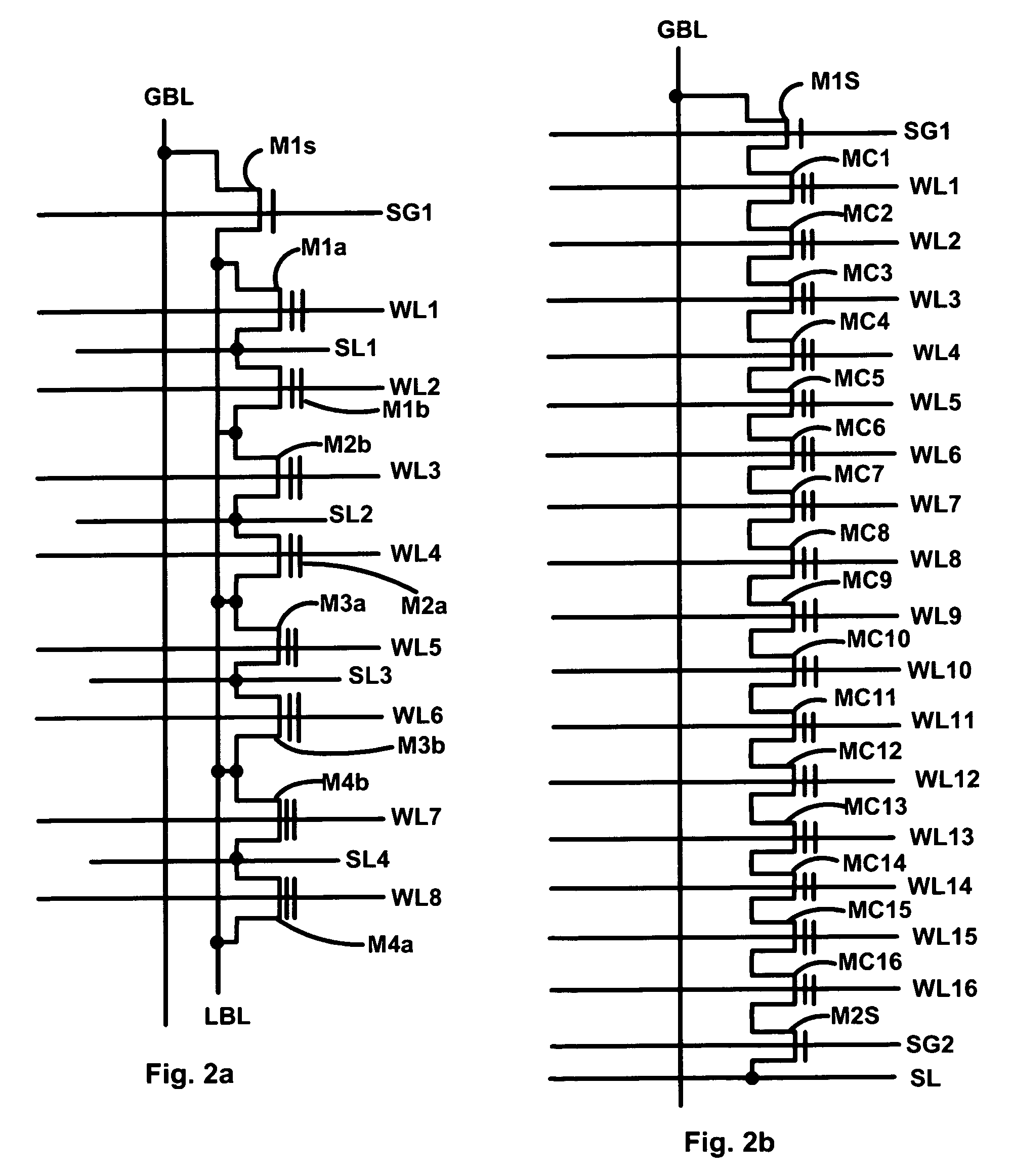

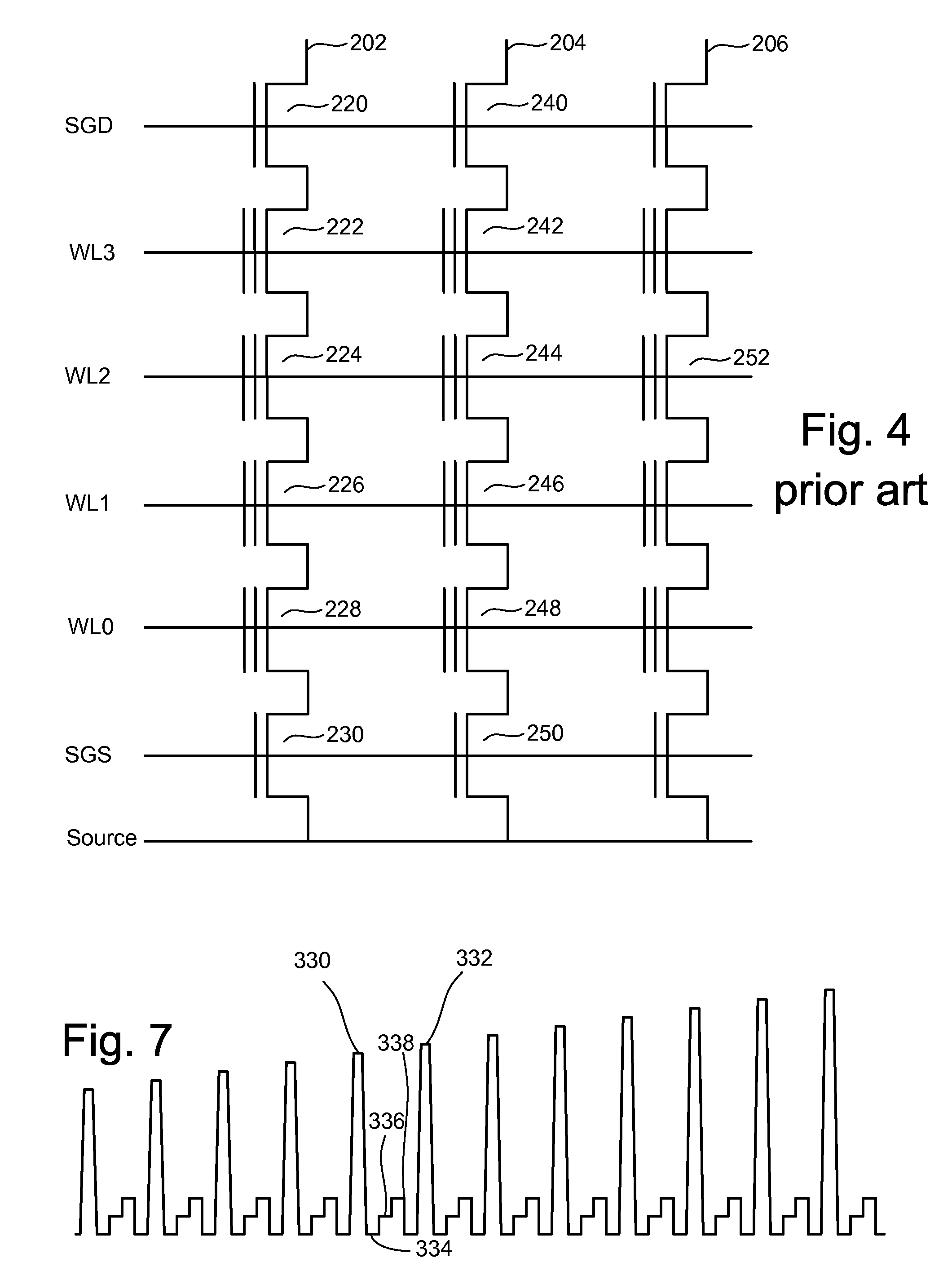

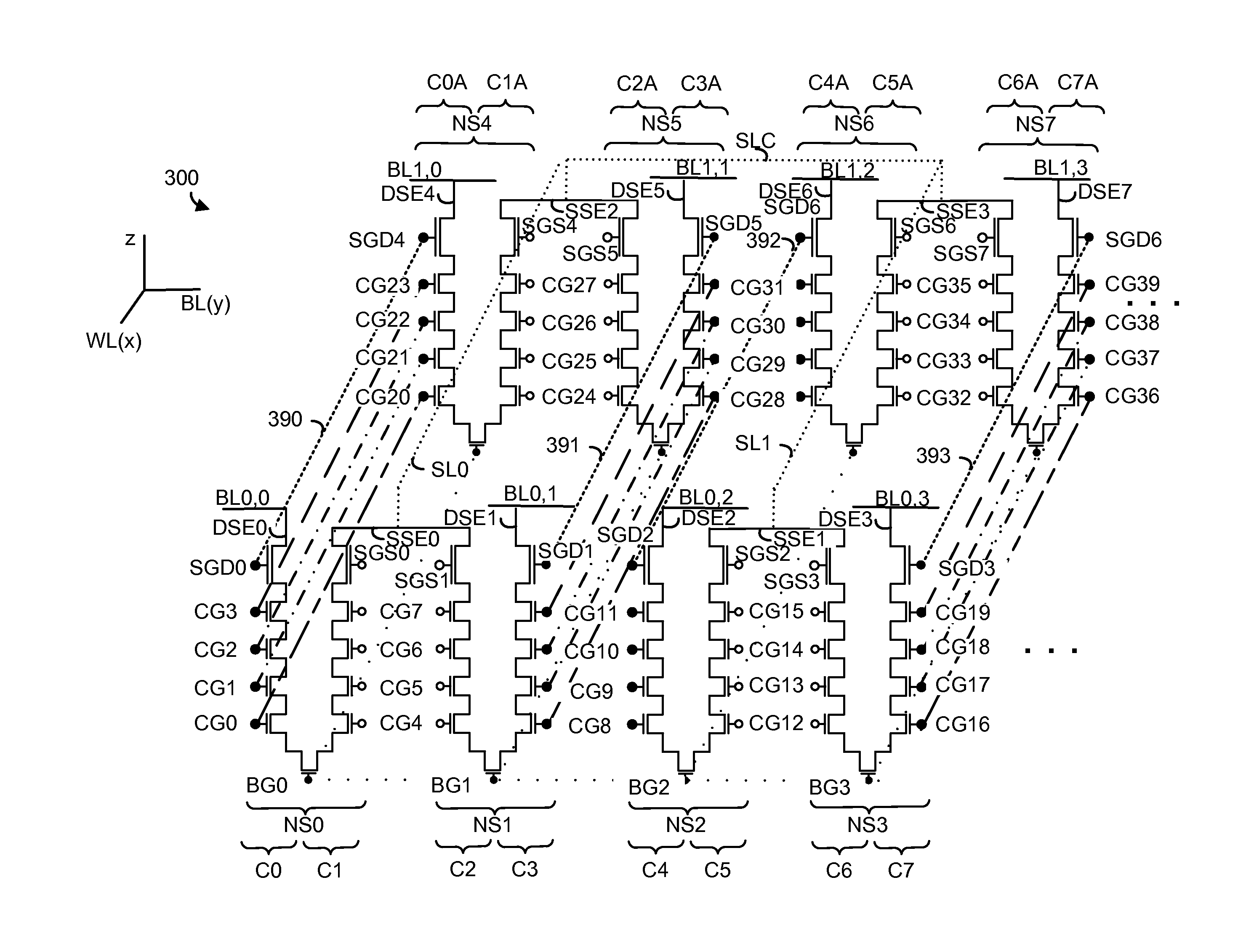

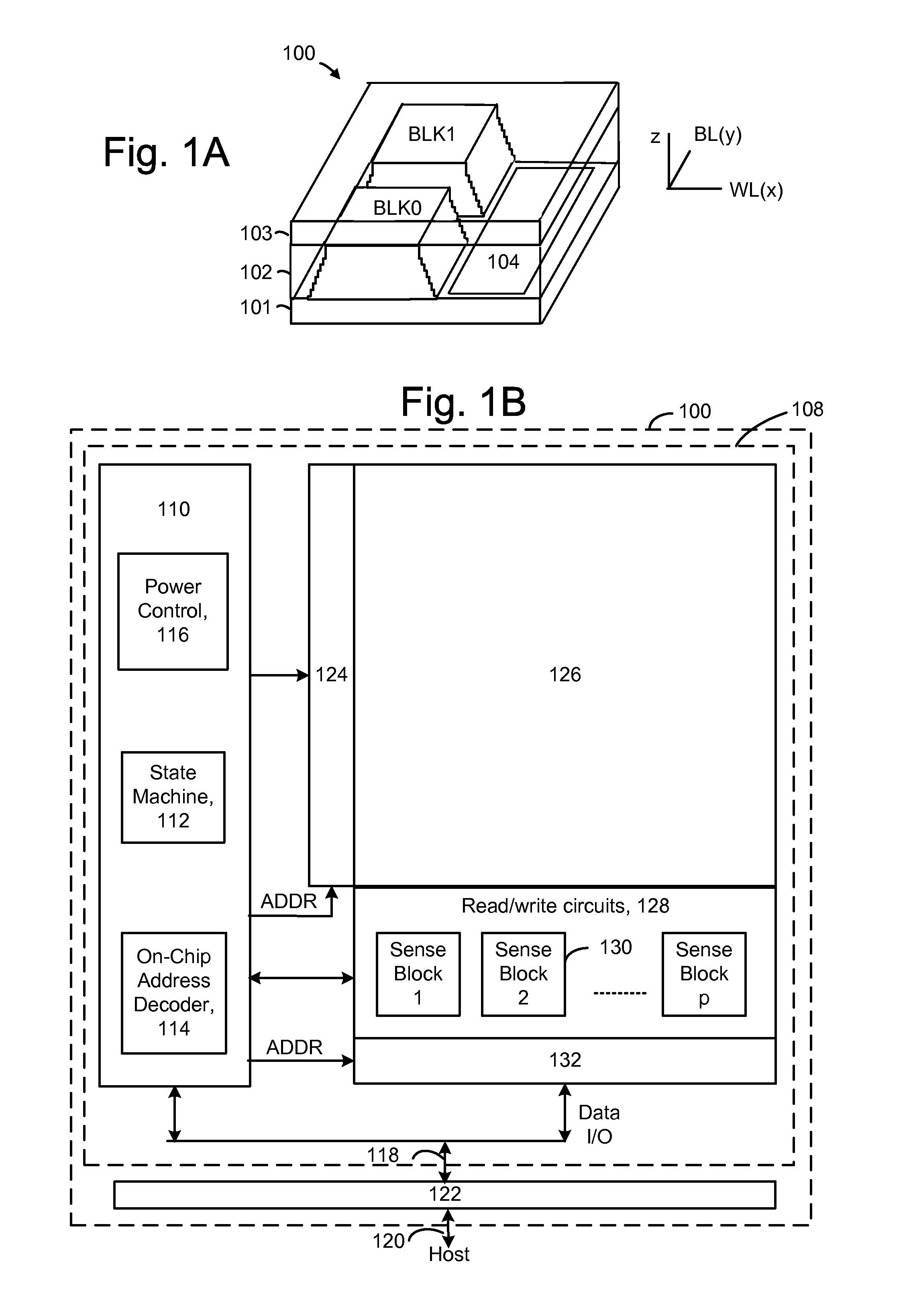

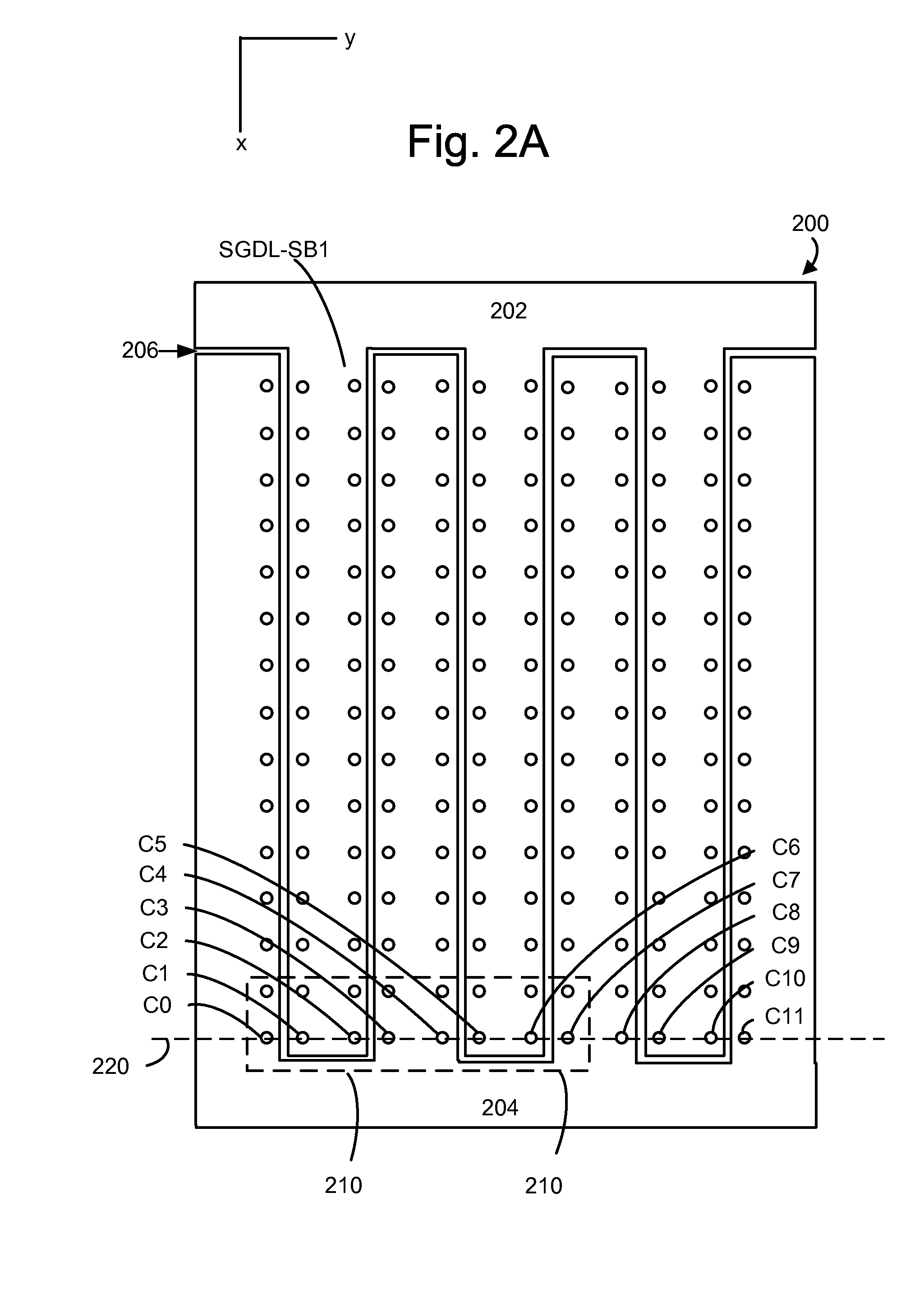

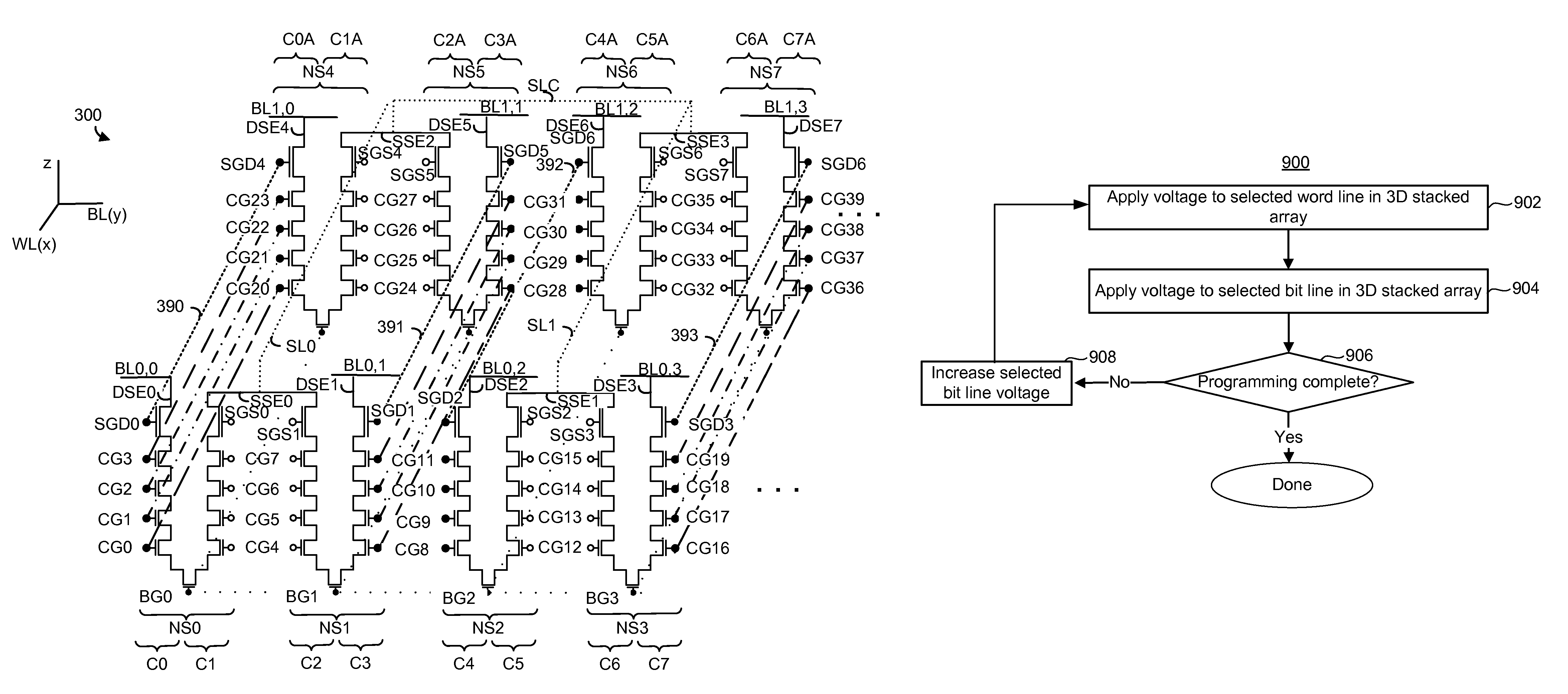

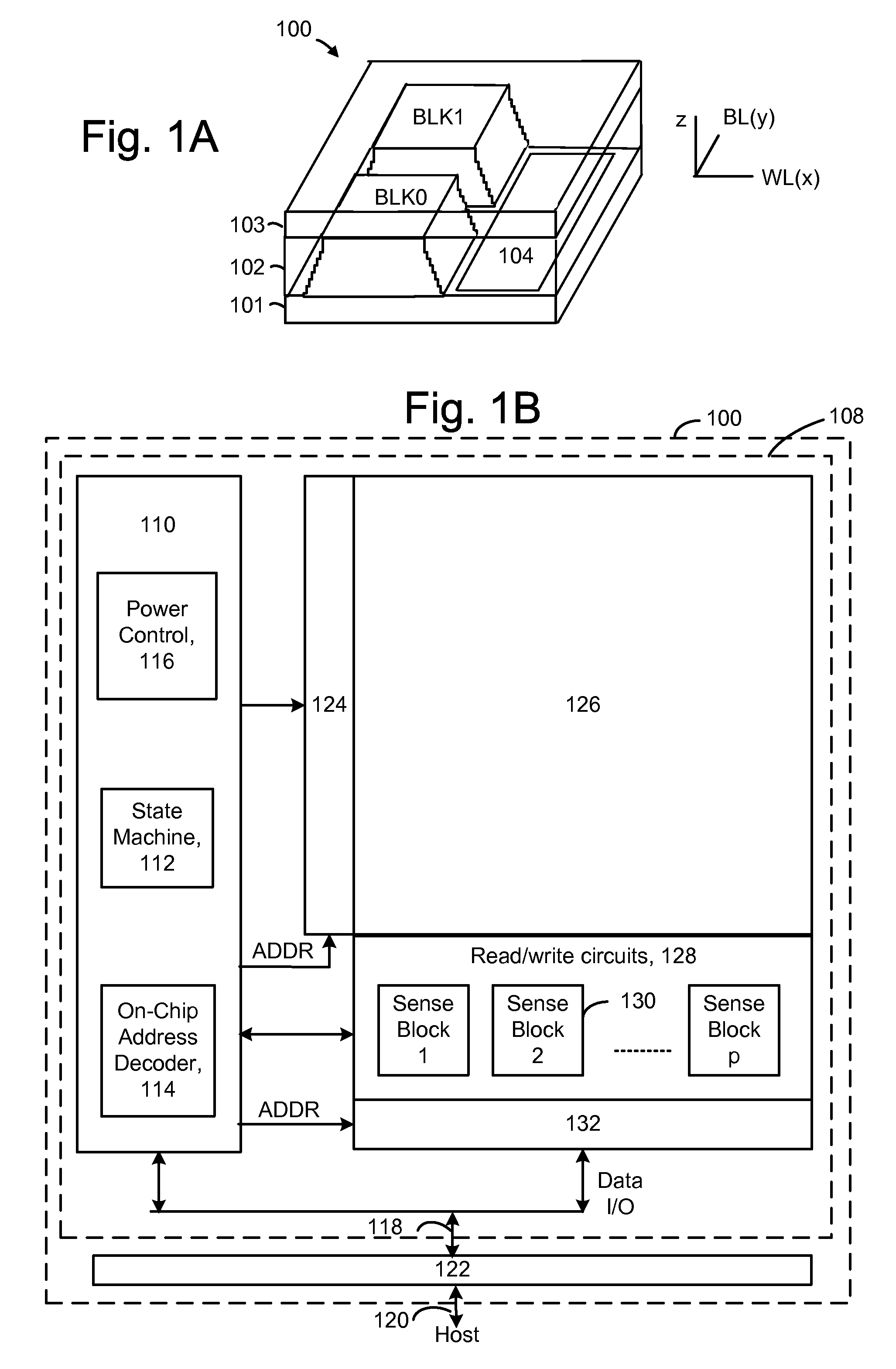

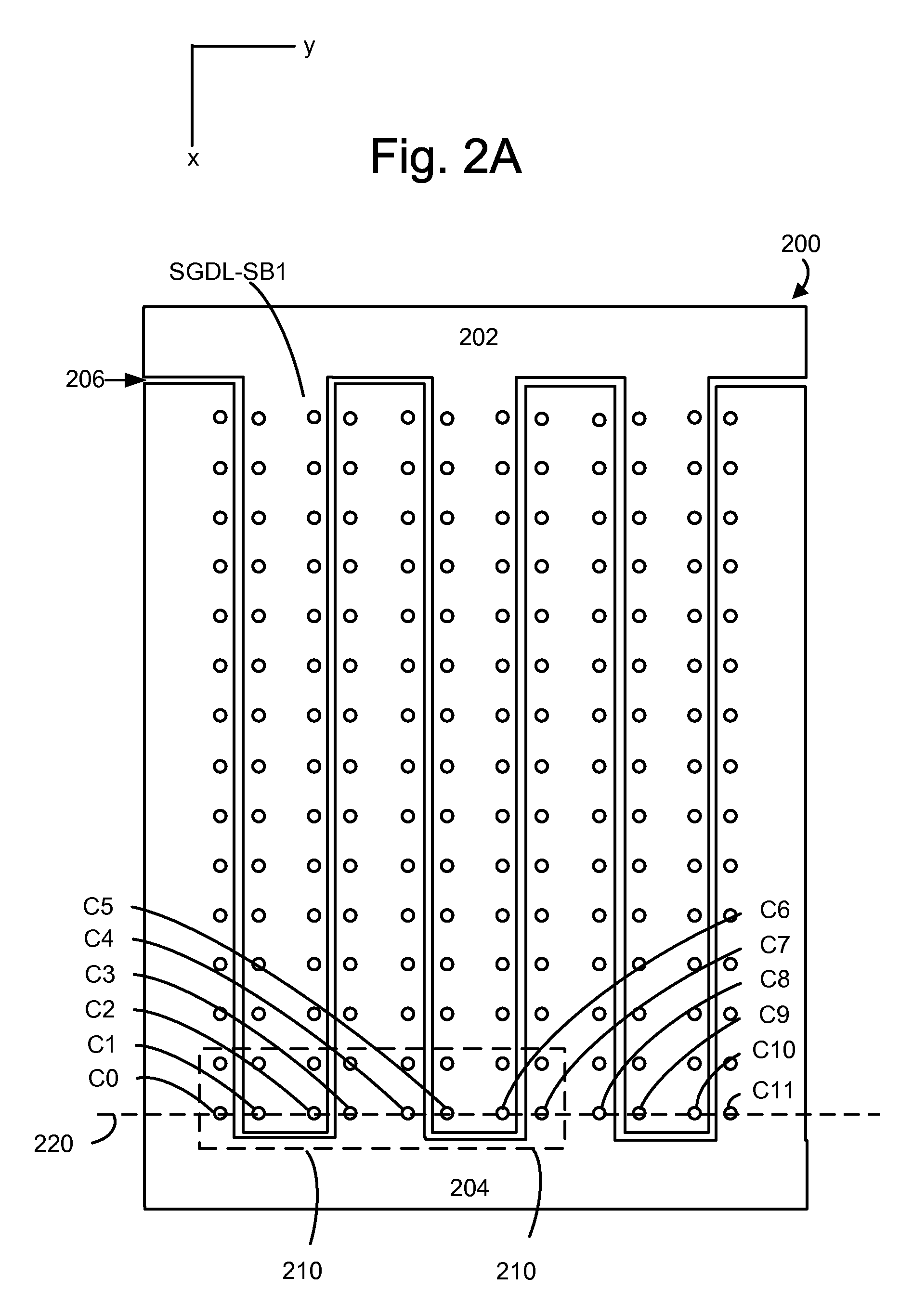

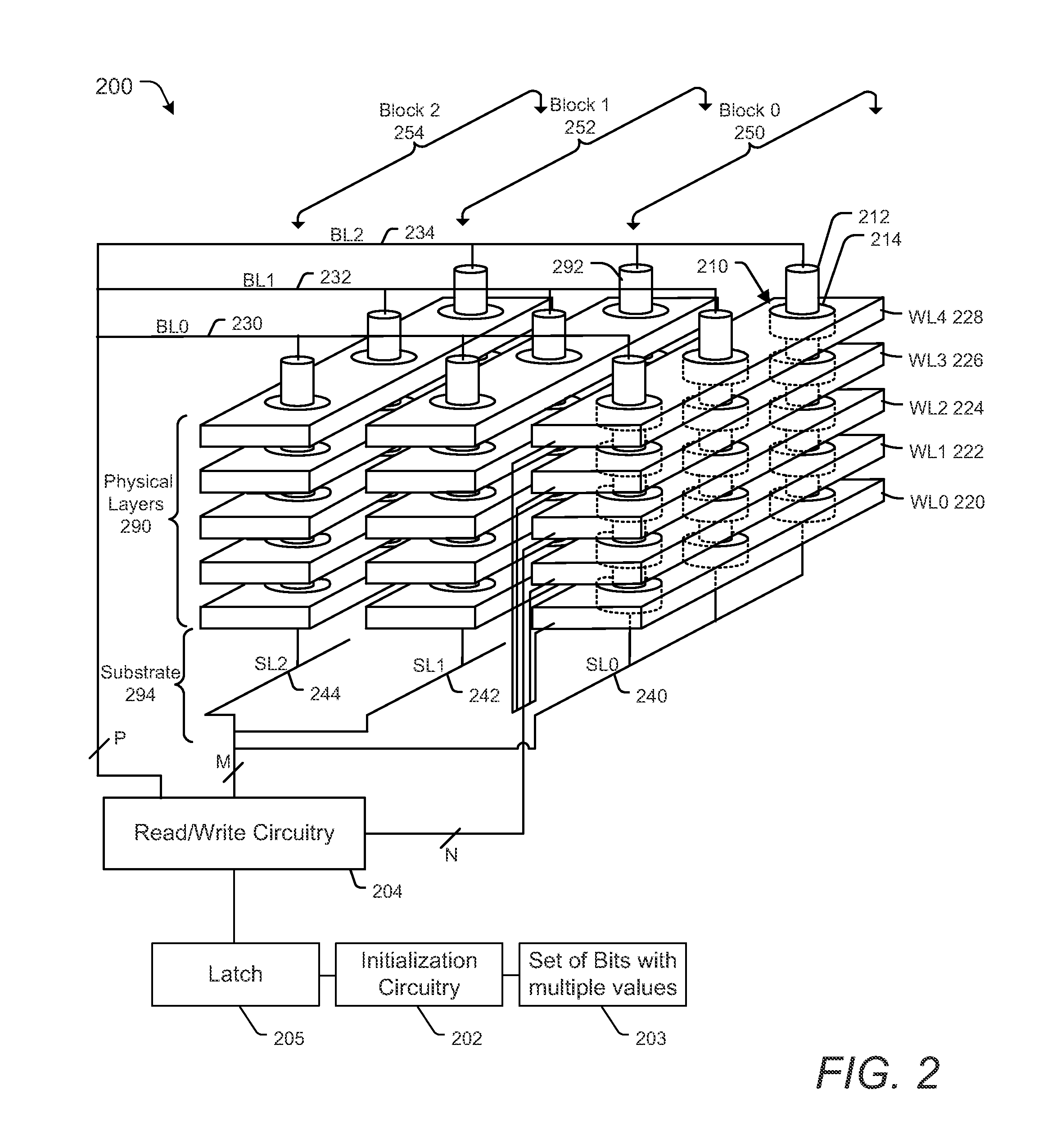

3D stacked non-volatile storage programming to conductive state

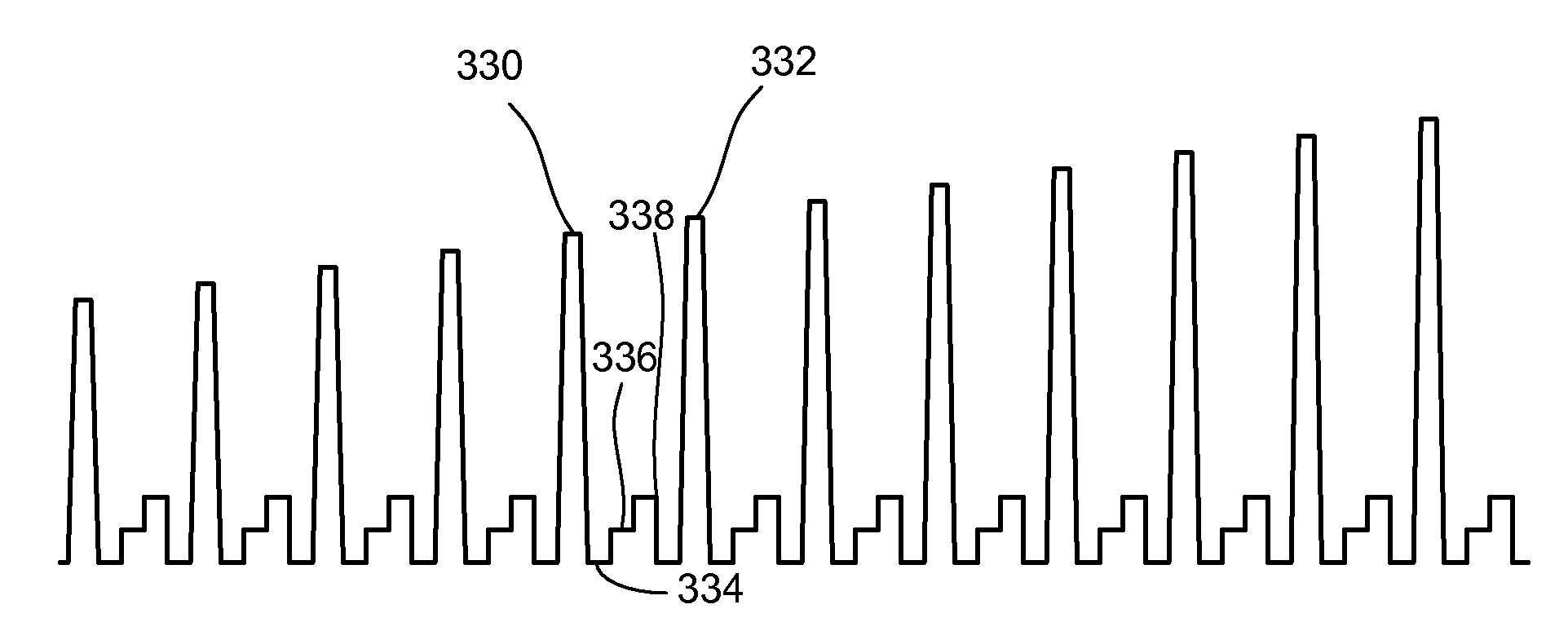

Programming NAND strings in a 3D stacked storage device to a conductive state is disclosed. Storage elements may be erased by raising their Vt and programmed by lowering their Vt. Programming may include applying a series of increasing voltages to selected bit lines until the selected memory cell is programmed. Unselected bit lines may be held at about ground, or close to ground. The selected word line may be grounded, or be held close to ground. Unselected word lines between the selected word line and the bit line may receive about the selected bit line voltage. Unselected word lines between the source line and the selected word line may receive about half the selected bit line voltage. Programming may be achieved without boosting channels of unselected NAND strings to inhibit them from programming. Therefore, program disturb associated with leakage of boosted channel potential may be avoided.

Owner:SANDISK TECH LLC

3D stacked non-volatile storage programming to conductive state

ActiveUS9099202B2Avoid programmingSolid-state devicesRead-only memoriesComputer scienceChannel potential

Programming NAND strings in a 3D stacked storage device to a conductive state. Storage elements may be erased by raising their Vt and programmed by lowering their Vt. Programming may include applying a series of increasing voltages to selected bit lines until the selected memory cell is programmed. Unselected bit lines may be held at about ground, or close to ground. The selected word line may be grounded, or be held close to ground. Unselected word lines between the selected word line and the bit line may receive about the selected bit line voltage. Unselected word lines between the source line and the selected word line may receive about half the selected bit line voltage. Programming may be achieved without boosting channels of unselected NAND strings to inhibit them from programming. Therefore, program disturb associated with leakage of boosted channel potential may be avoided.

Owner:SANDISK TECH LLC

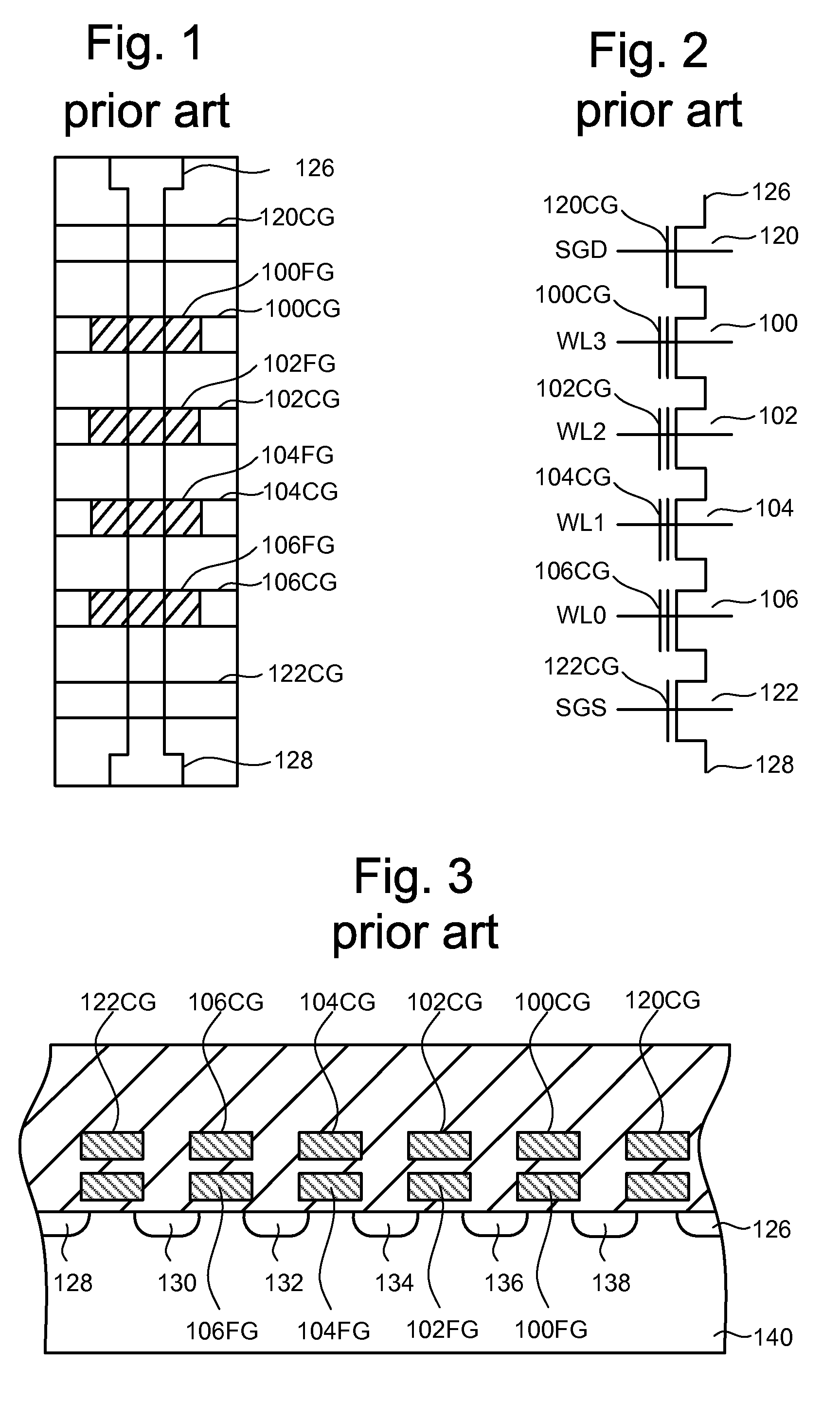

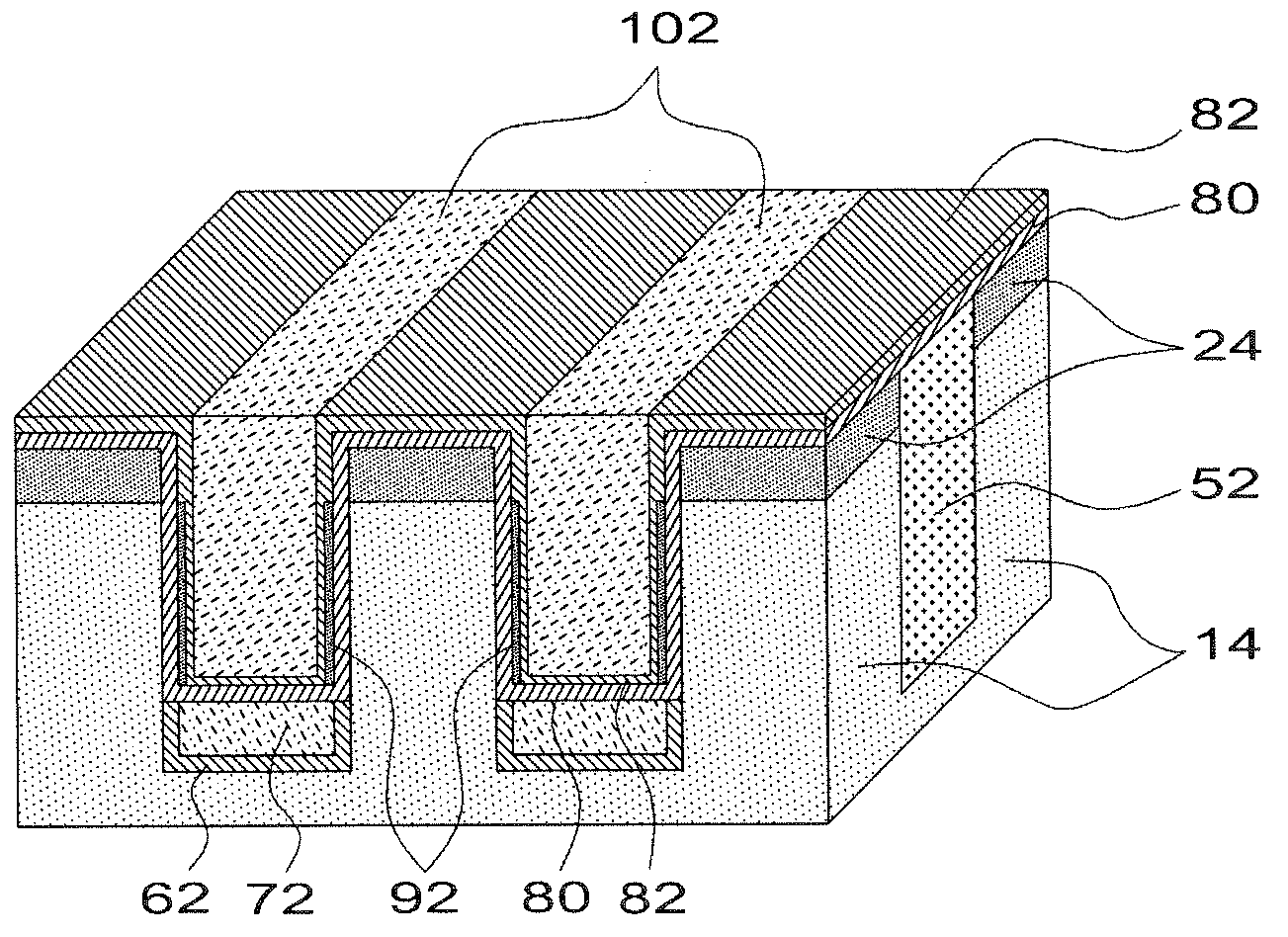

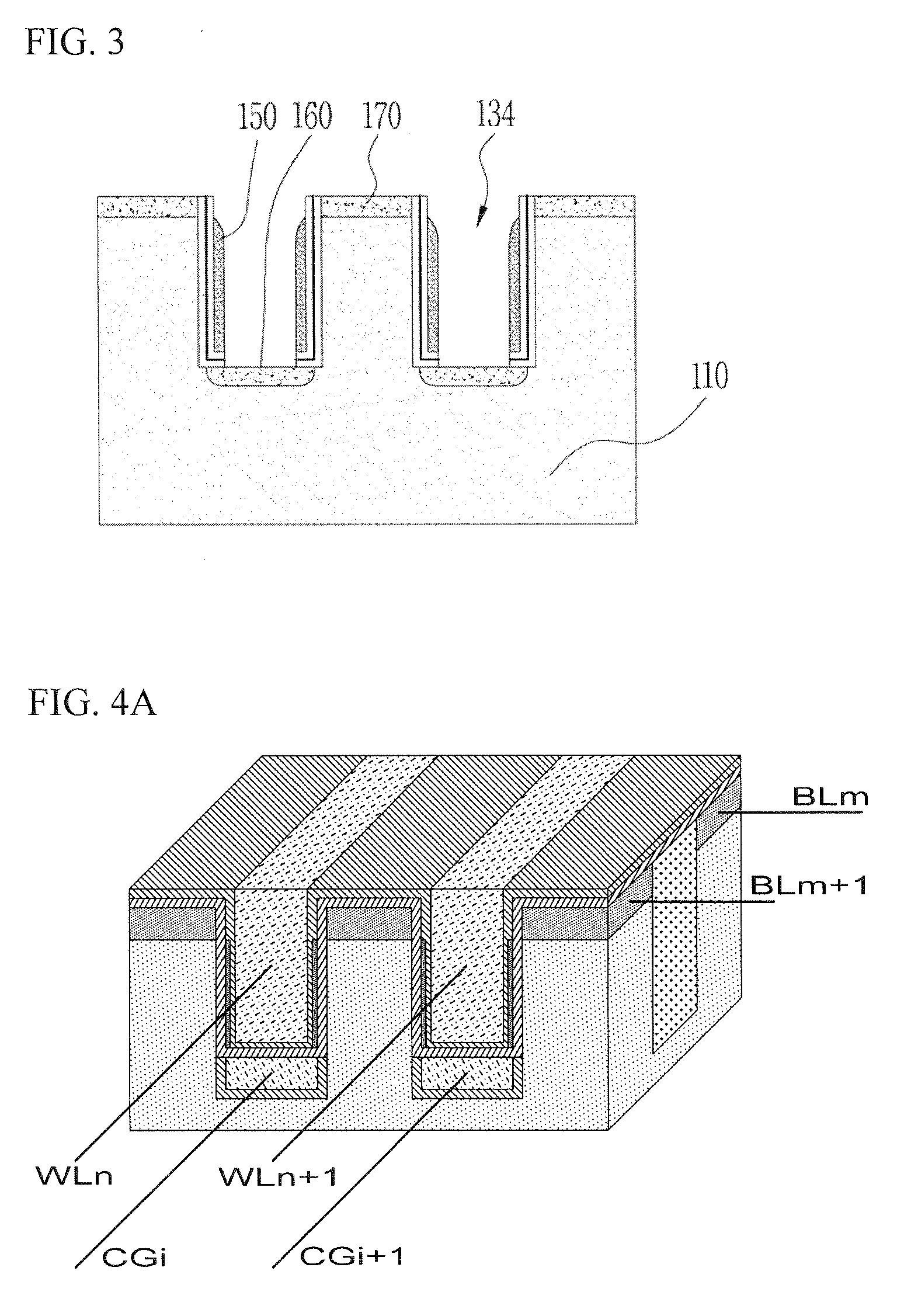

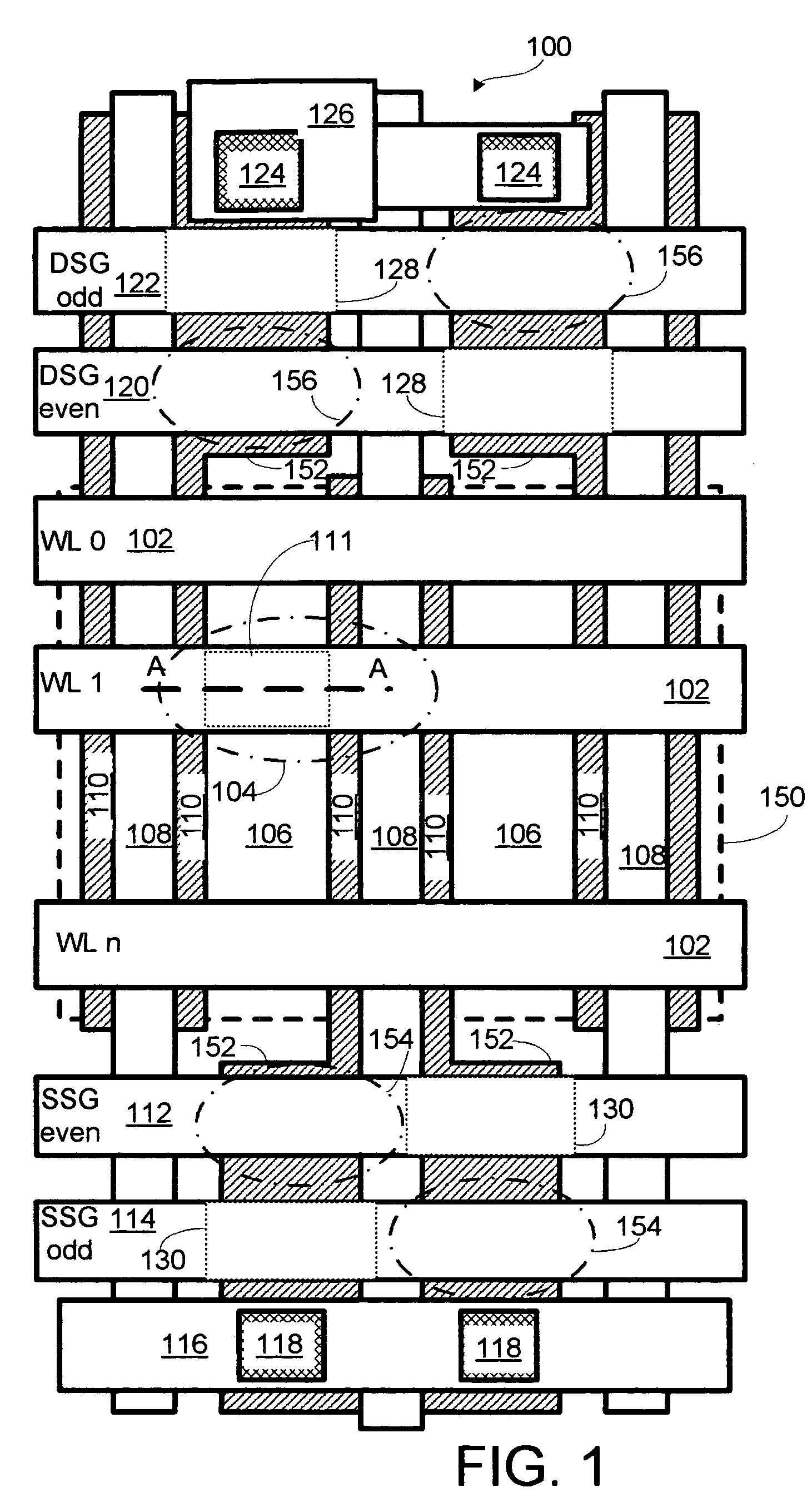

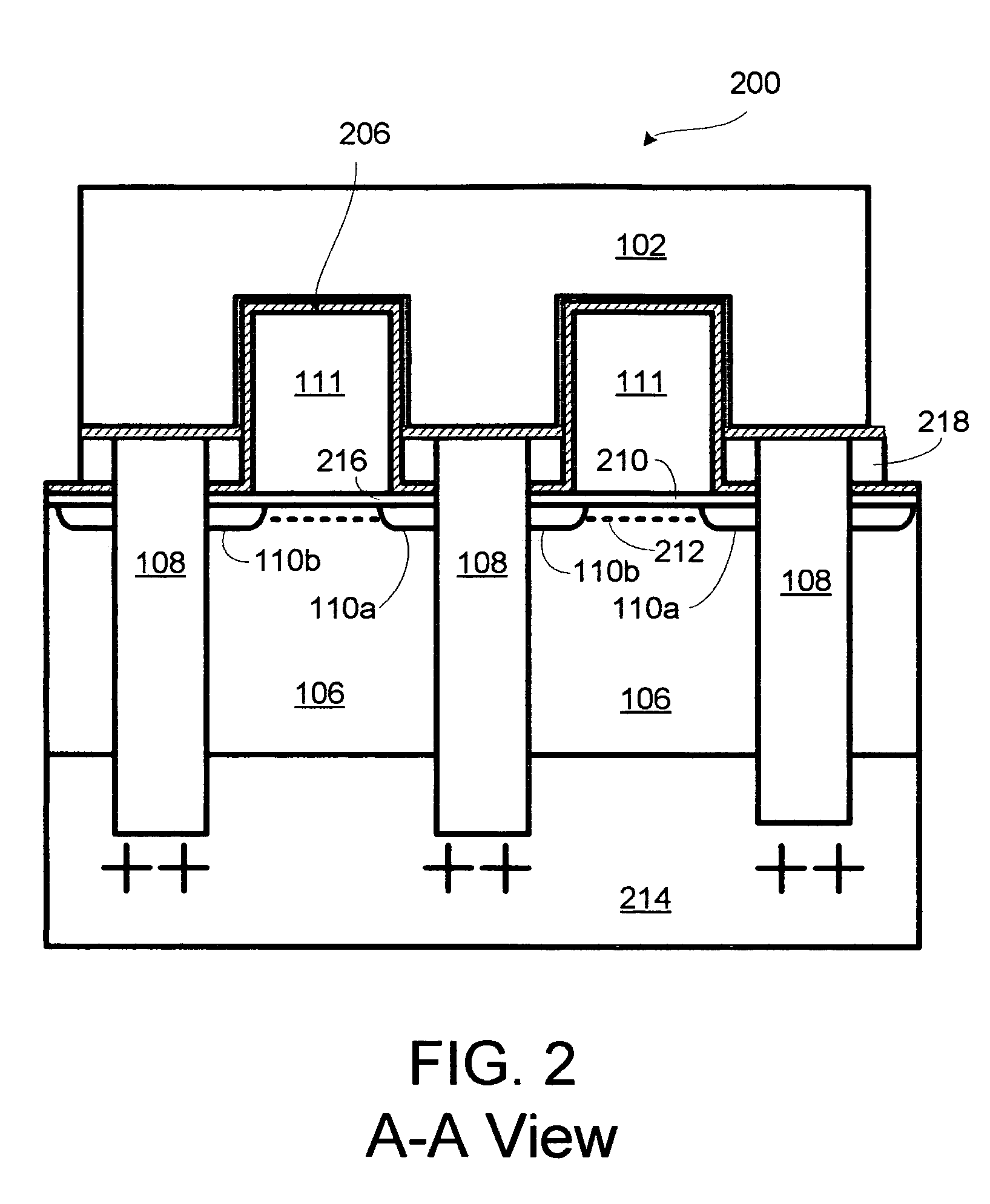

NAND flash memory array with cut-off gate line and methods for operating and fabricating the same

ActiveUS20090207667A1Reduce areaMinimize effect of storage conditionSolid-state devicesRead-only memoriesEngineeringVertical channel

A NAND flash memory array, an operating method and a fabricating method of the same are provided. The NAND flash memory array has a cut-off gate line under a control gate in order to operate two cells having vertical channels independently with one control gate (i.e., a shared word line). The memory cell area is reduced considerably compared to the conventional vertical channel structure, and is better for high integration. A shared cut-off gate turn off is made during a programming operation and prevents programming the opposite cell by a self-boosting effect. It is possible to shield electrically with a shared word line (a control gate) during a reading operation, and minimizes the effect of storage condition of the opposite cell. Also, the NAND flash memory array can be fabricated by using the conventional CMOS process.

Owner:SEOUL NAT UNIV R&DB FOUND

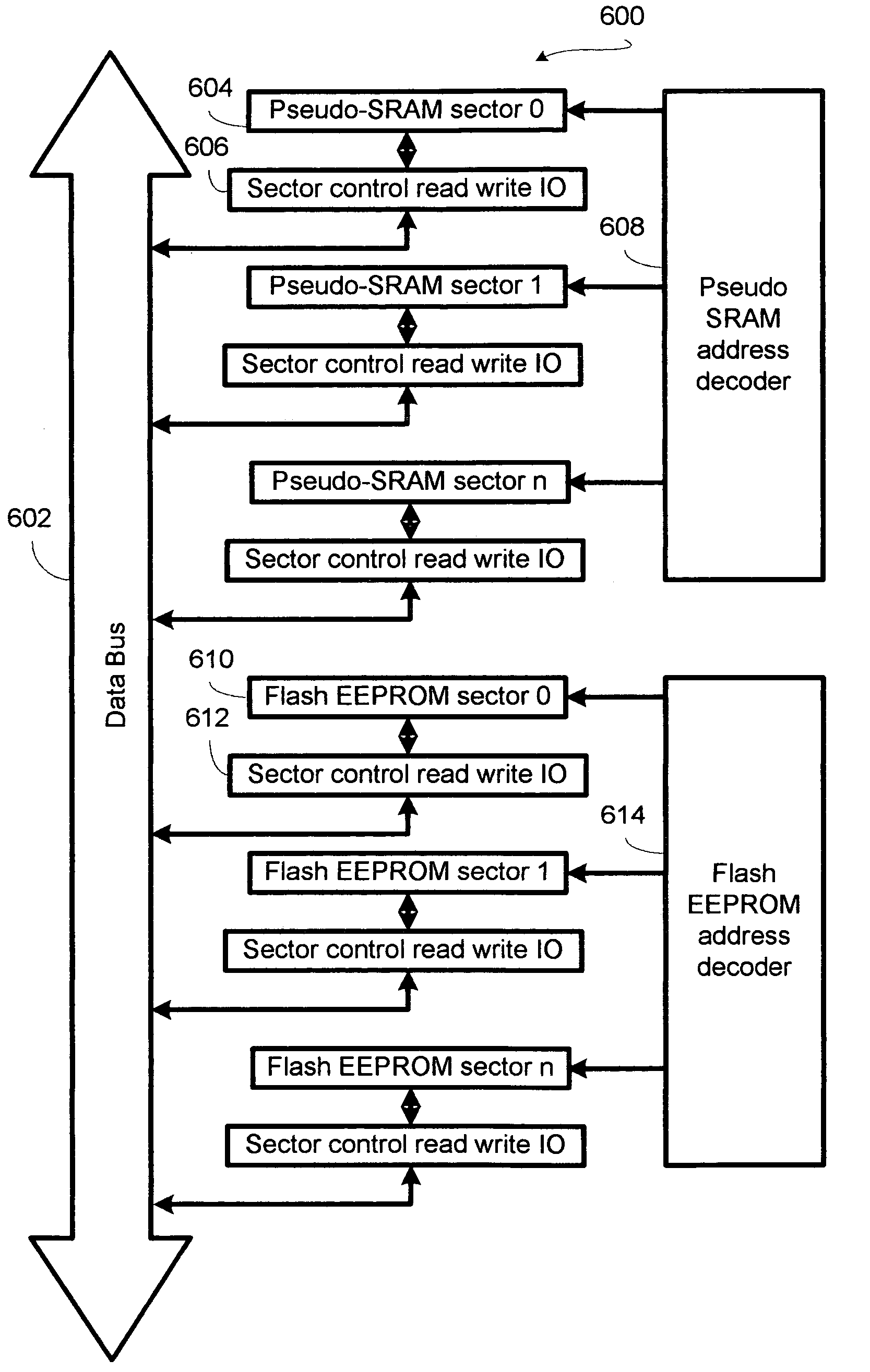

Non-volatile electrically alterable memory cell and use thereof in multi-function memory array

ActiveUS7449744B1Less disturbingAvoid programmingTransistorSemiconductor/solid-state device detailsExternal dataDeep trench

A multi-function memory array that includes a DRAM distributed in several DRAM sectors, a Flash EEPROM distributed in several Flash EEPROM sectors, a data bus interconnecting the DRAM sectors and the Flash EEPROM sectors, and a plurality of memory access control circuitries. Each DRAM sector and Flash EEPROM sector can be accessed independently and data can be transferred between a DRAM sector and a Flash EEPROM sector. External data can also be written into either DRAM or Flash EEPROM. Flash EEPROM in one sector is distributed in rows and columns, and cells in each column are separated from the cells in an adjacent column by deep trench isolation regions.

Owner:SOOCHOW CAPITAL

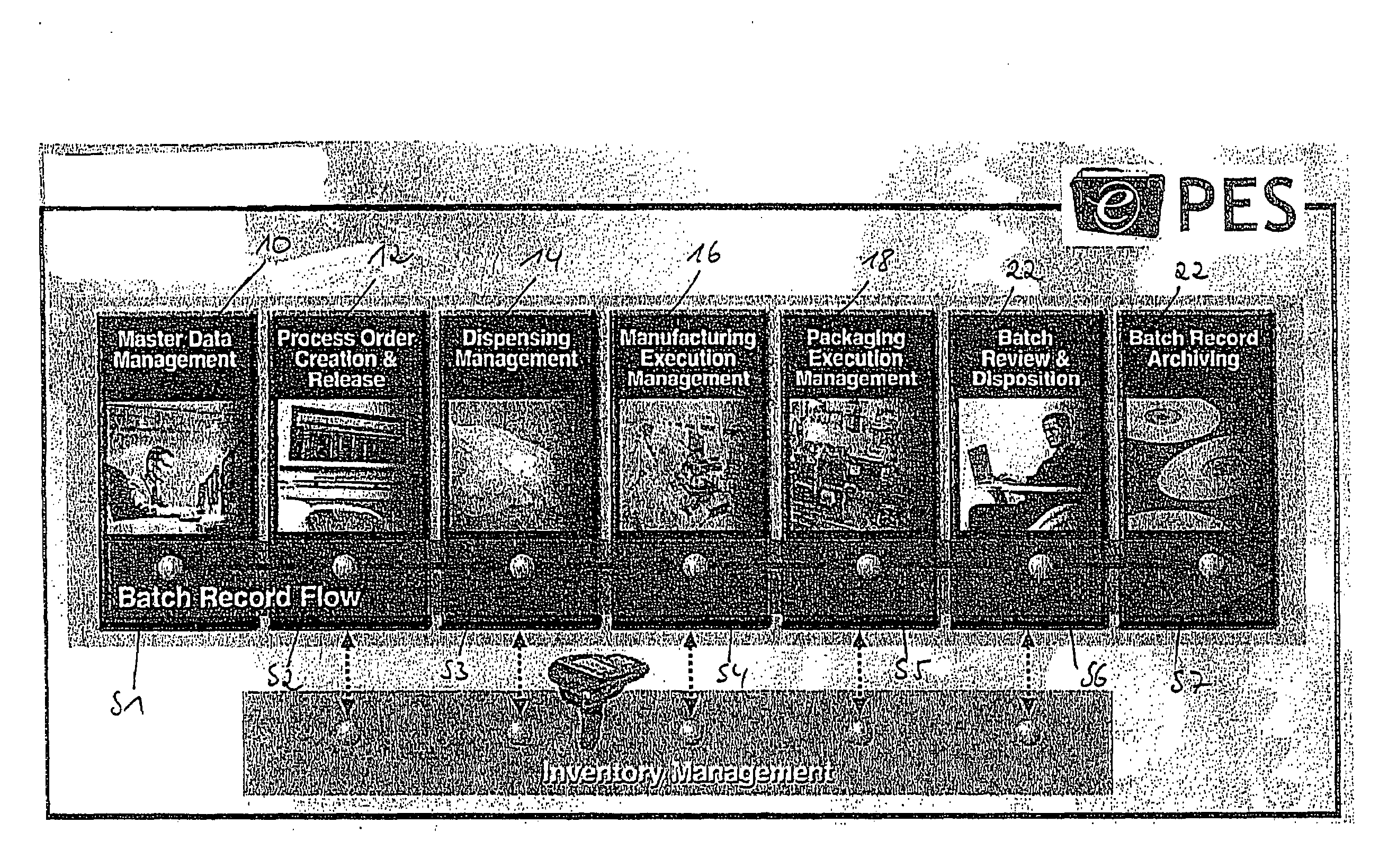

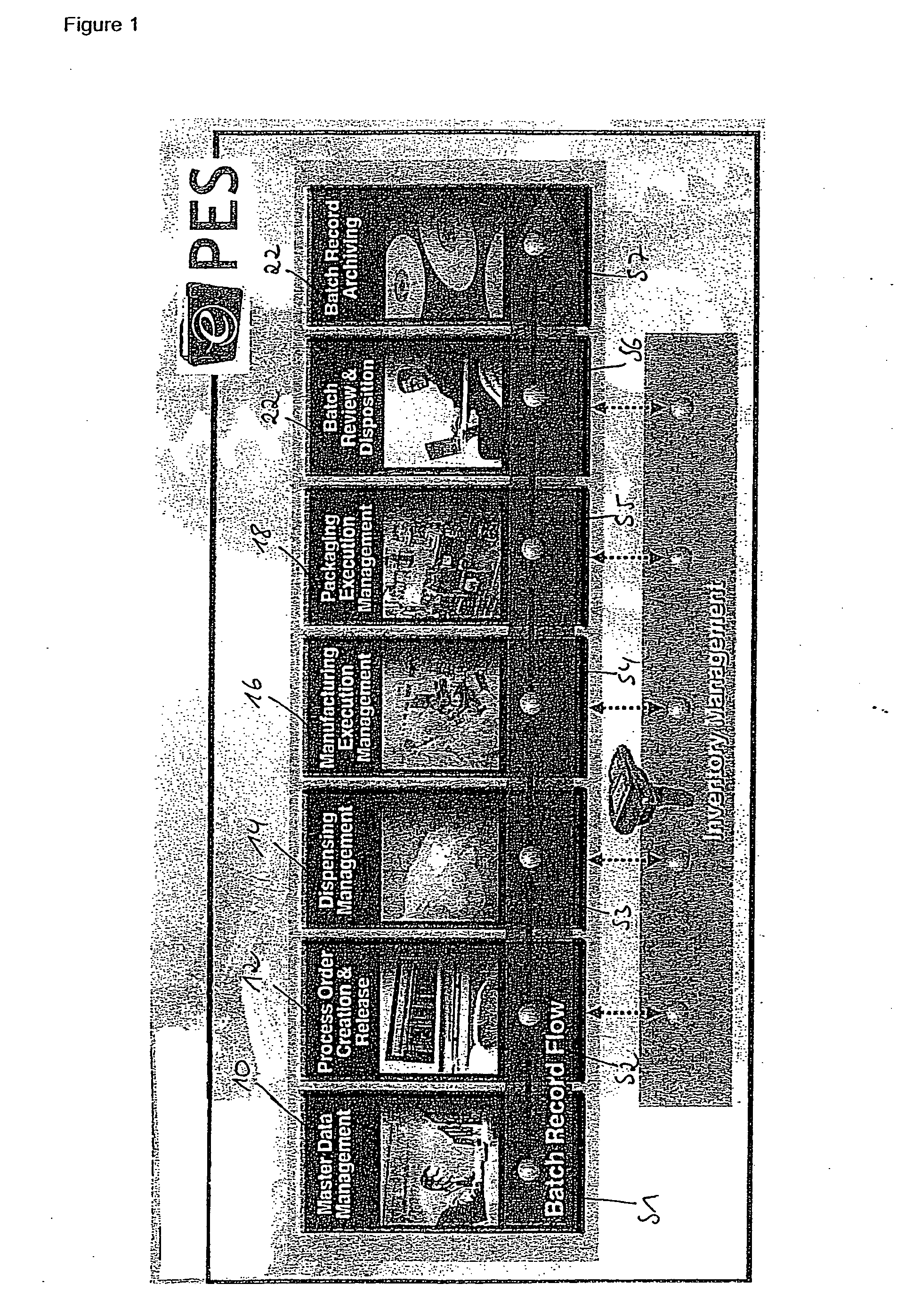

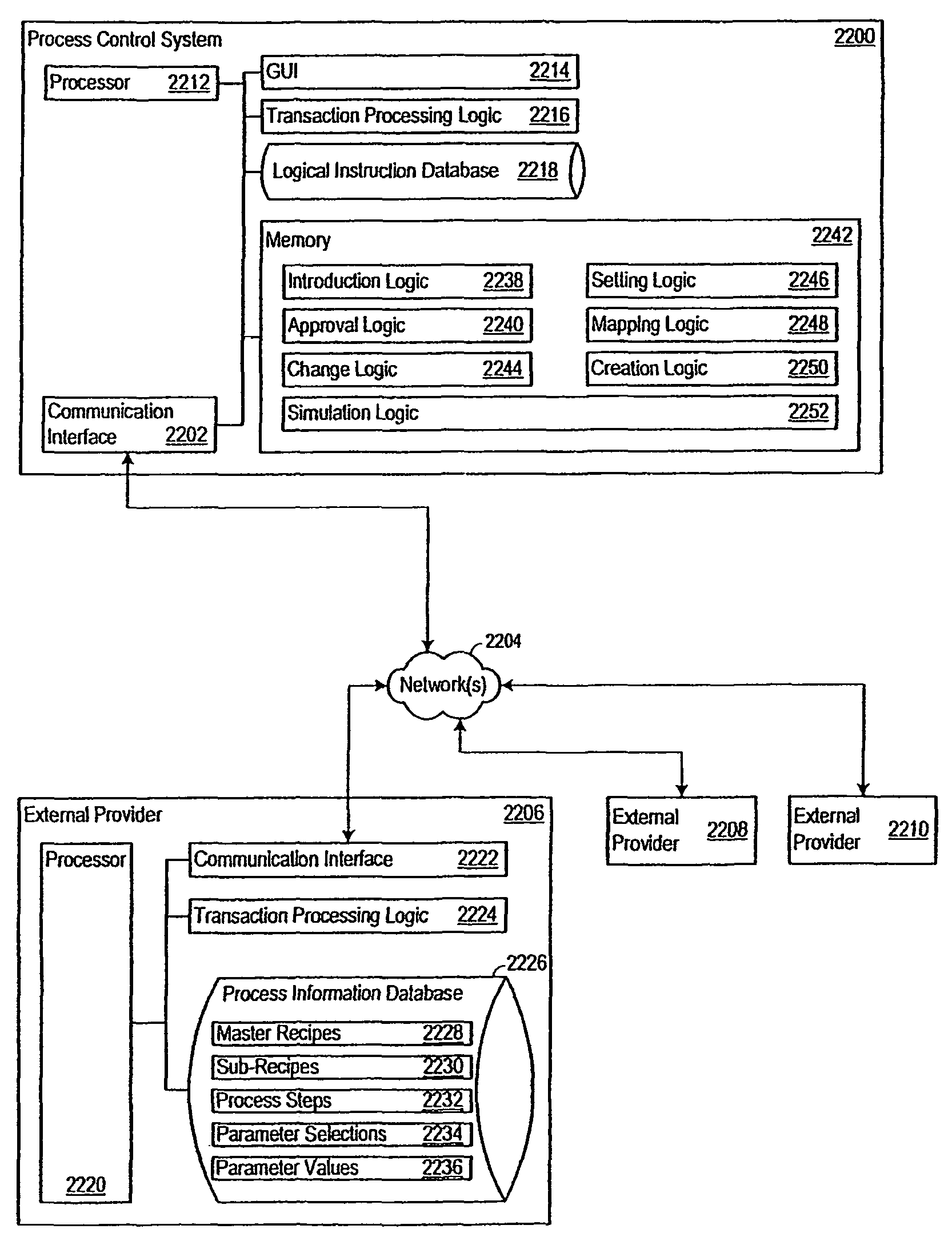

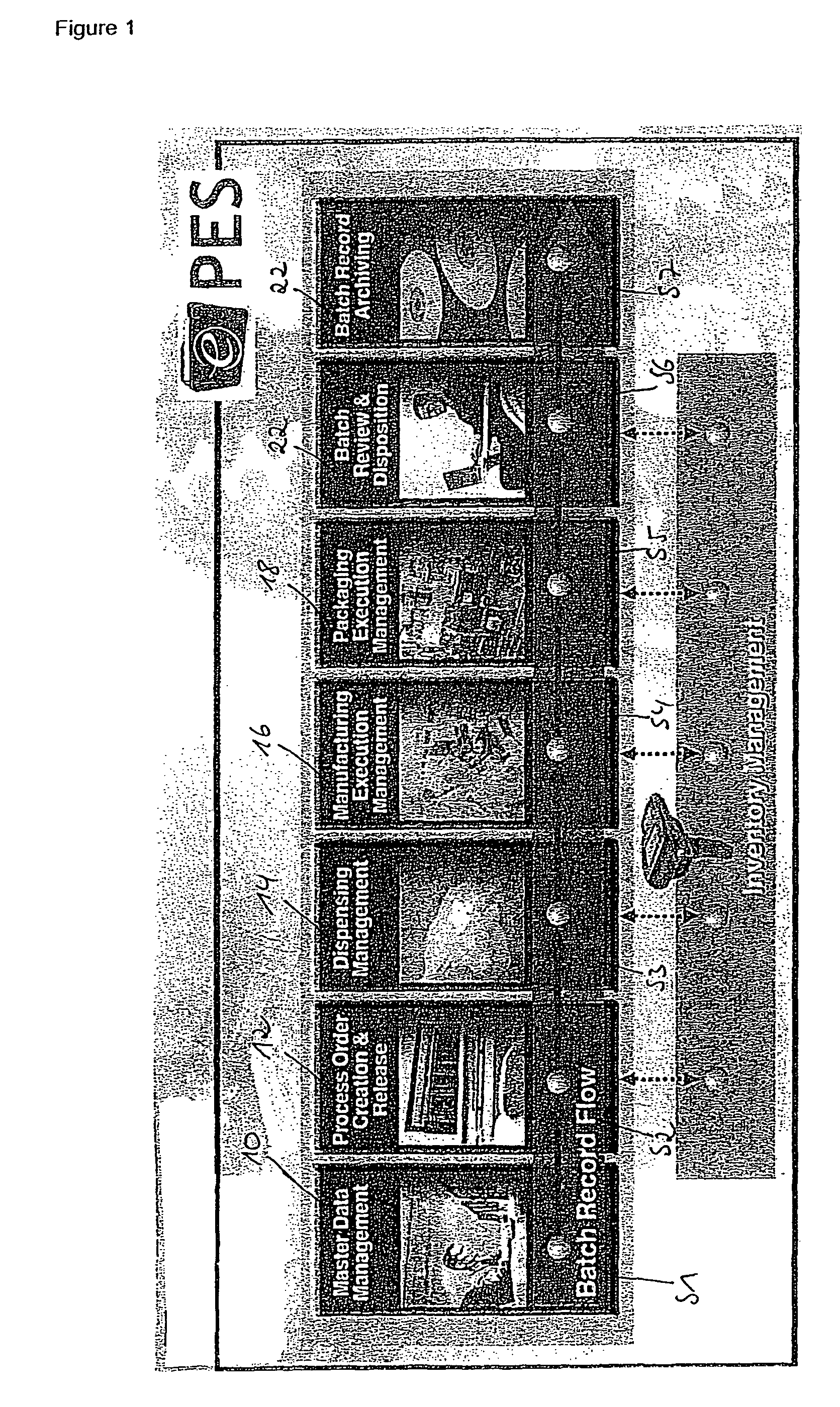

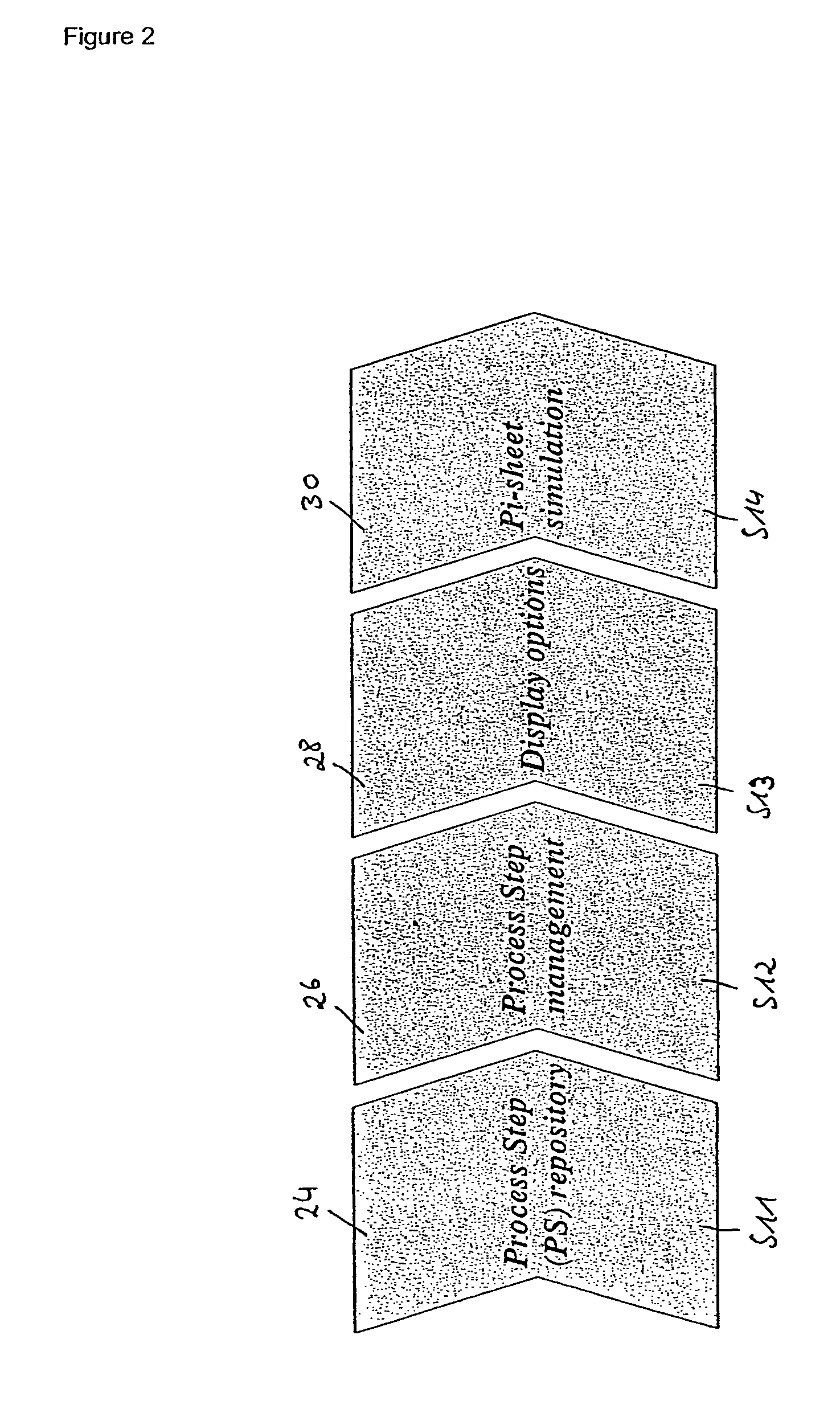

Method for controlling and/or monitoring data processing device and computer program

ActiveUS20080134073A1OptimizationEasy to buildProgramme controlSampled-variable control systemsControlled drugsGraphics

A graphical user interface, implemented in a standard system management environment, accepts selections of logical instruction steps that are external to the standard system management environment. The logical instruction steps may include process steps, specify chemical formulae, or identify other components of master recipes that control drug manufacture or dispensing, as examples. The external logical instruction steps are introduced into the standard system management environment and approved. The standard system management environment subsequently controls the drug manufacturing or dispensing processes according to the external logical instruction steps.

Owner:ACCENTURE GLOBAL SERVICES LTD

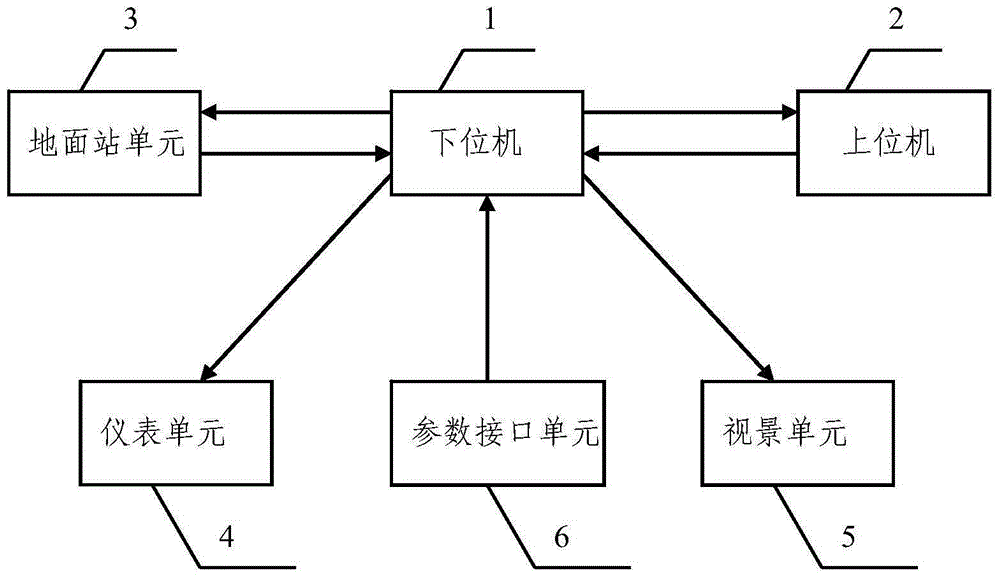

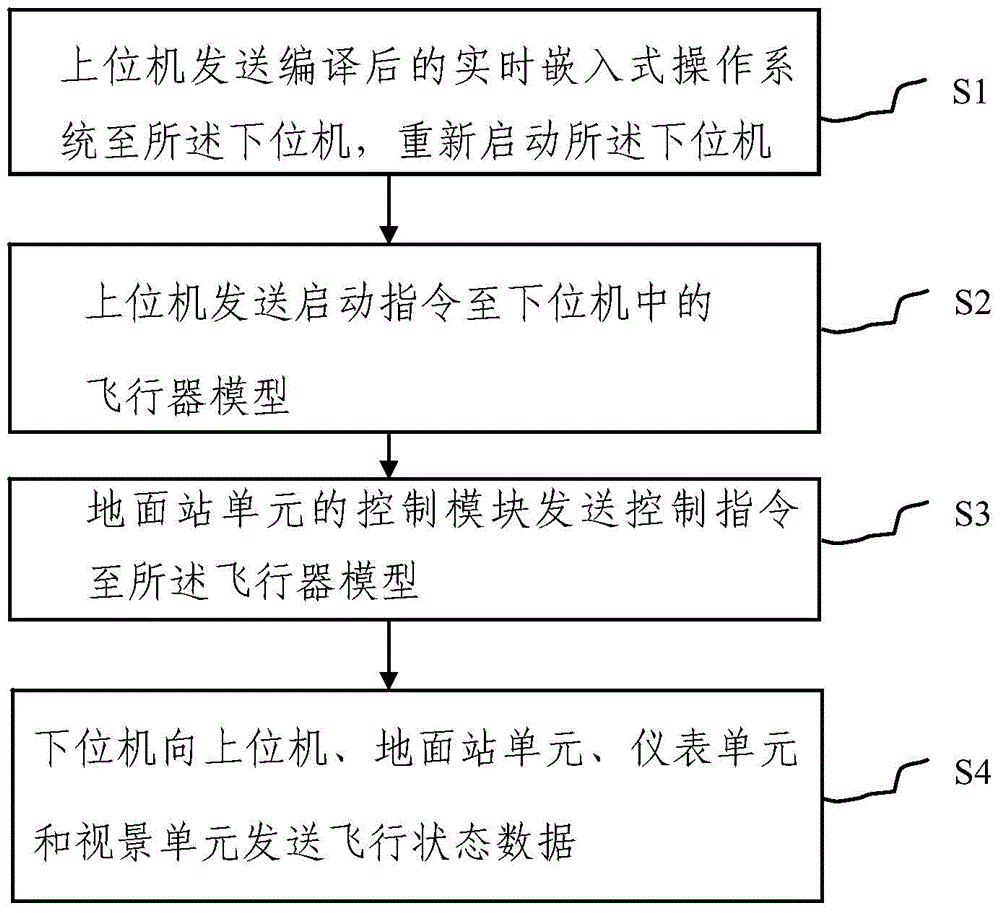

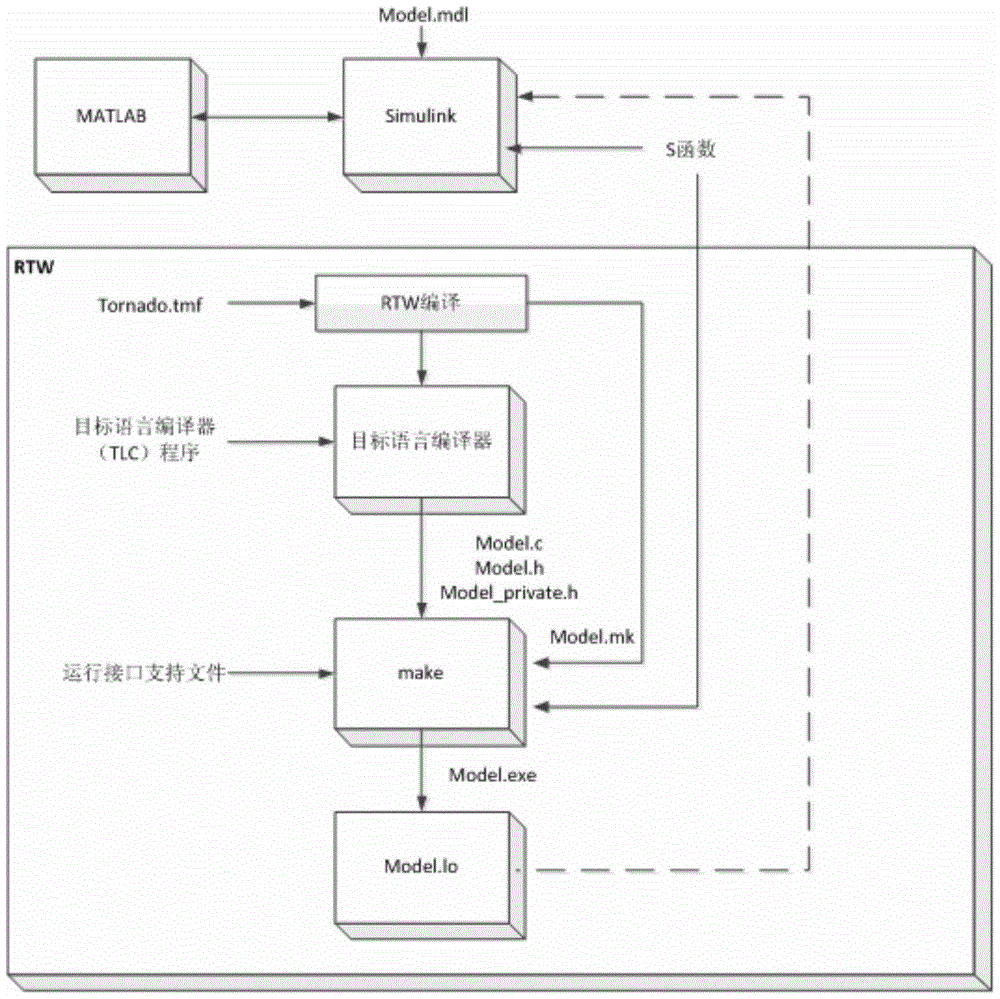

Real-time fixed wing aircraft simulation system and simulation method

InactiveCN105204370AImprove versatilityAvoid programmingSimulator controlReal-time simulationOperational system

The invention relates to a real-time fixed wing aircraft simulation system and a simulation method. The real-time fixed wing aircraft simulation system comprises a lower computer, a host computer, a ground station unit, an instrument unit, a vision unit and a parameter interface unit, wherein the lower computer is used for operating an aircraft model in a real-time embedded system, the host computer is used for compiling an aircraft model application program into the real-time embedded operation system and sending the compiled real-time embedded operation system to the lower computer, PID control parameters of the aircraft model are modified in real time, an operation state of the aircraft model is monitored, and the parameter interface unit is used for sending designated aircraft model parameters to the lower computer to realize real-time simulation of a designated fixed wing aircraft. Through the system and the method, a flight scene is simulated in real time, versatility of the aircraft simulation system is improved, complex programming and debugging are avoided, and simulation cost is reduced.

Owner:成都前沿动力科技有限公司

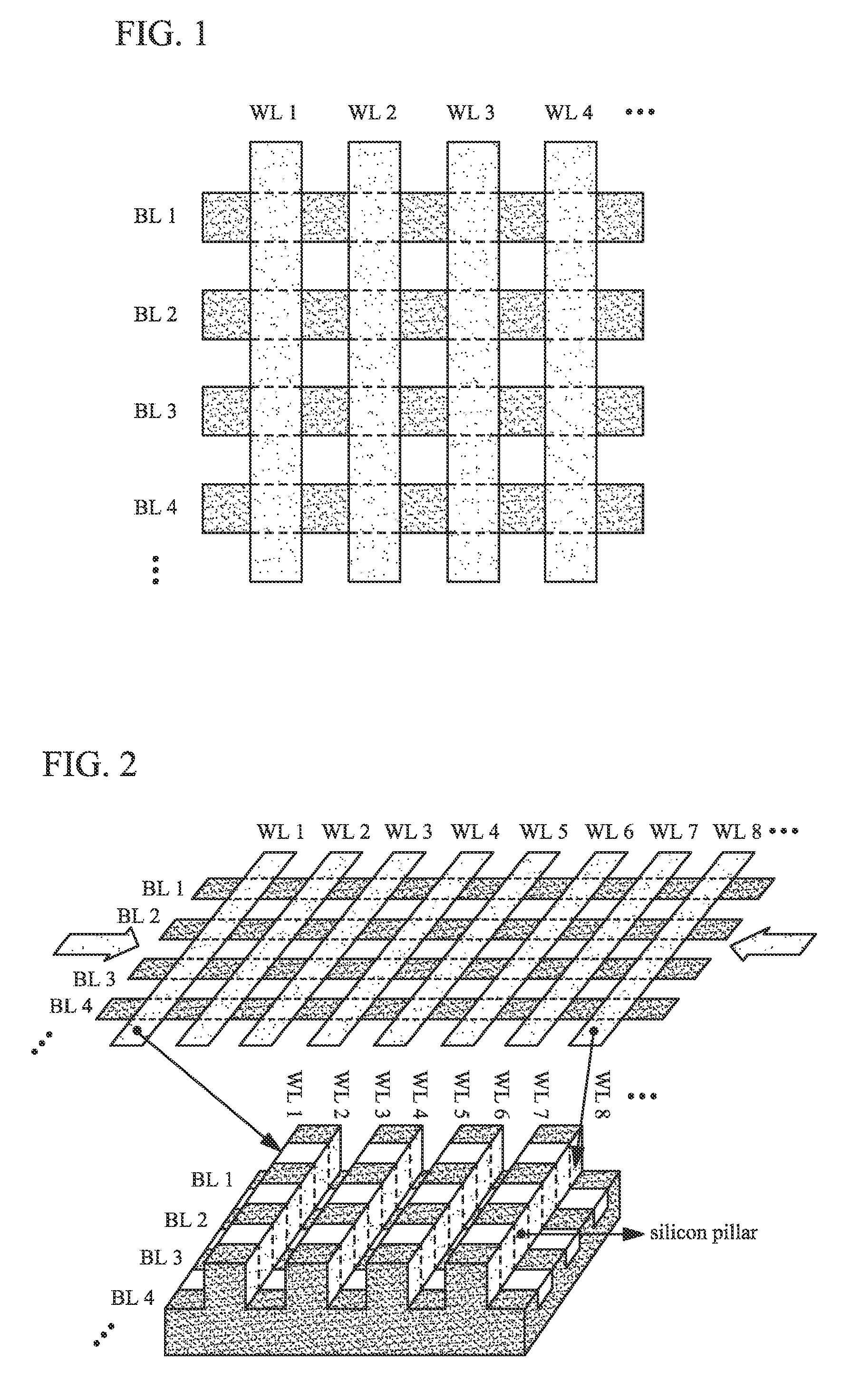

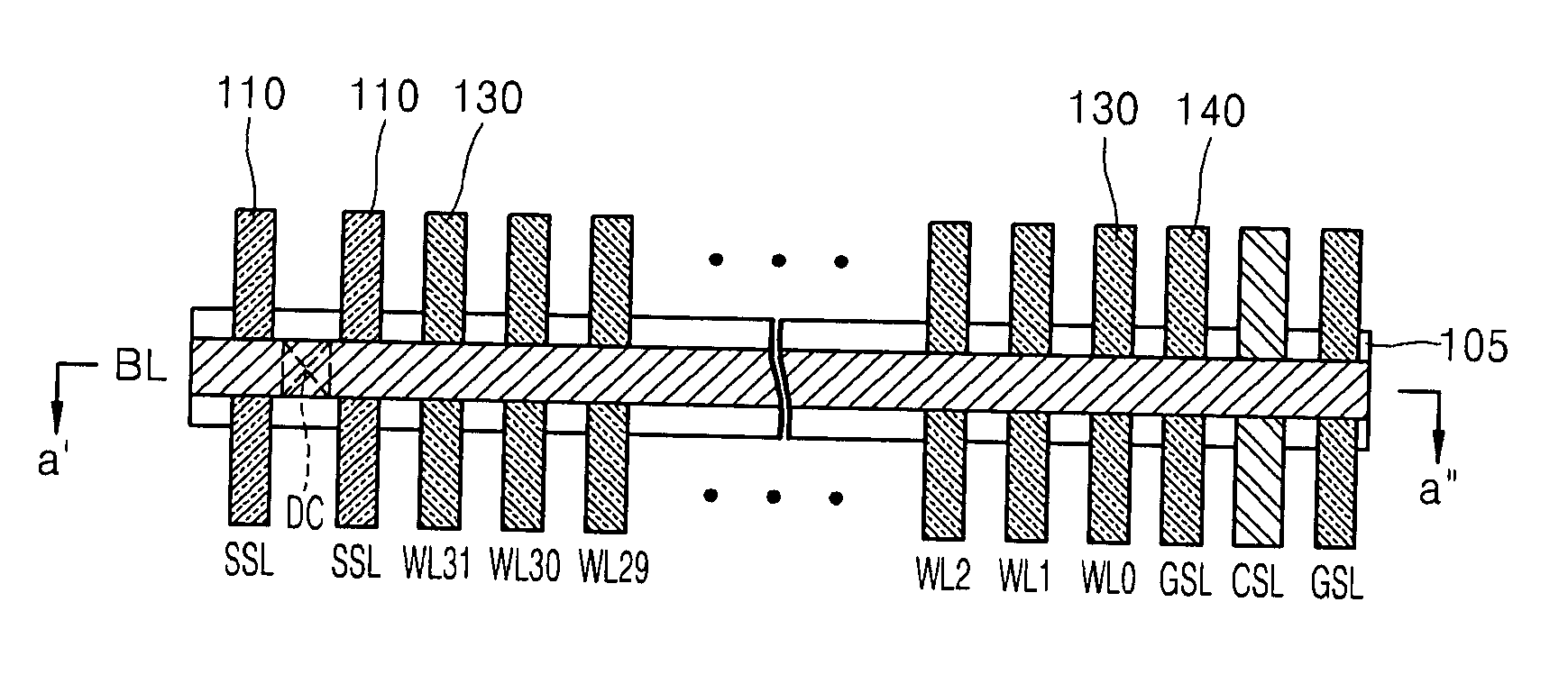

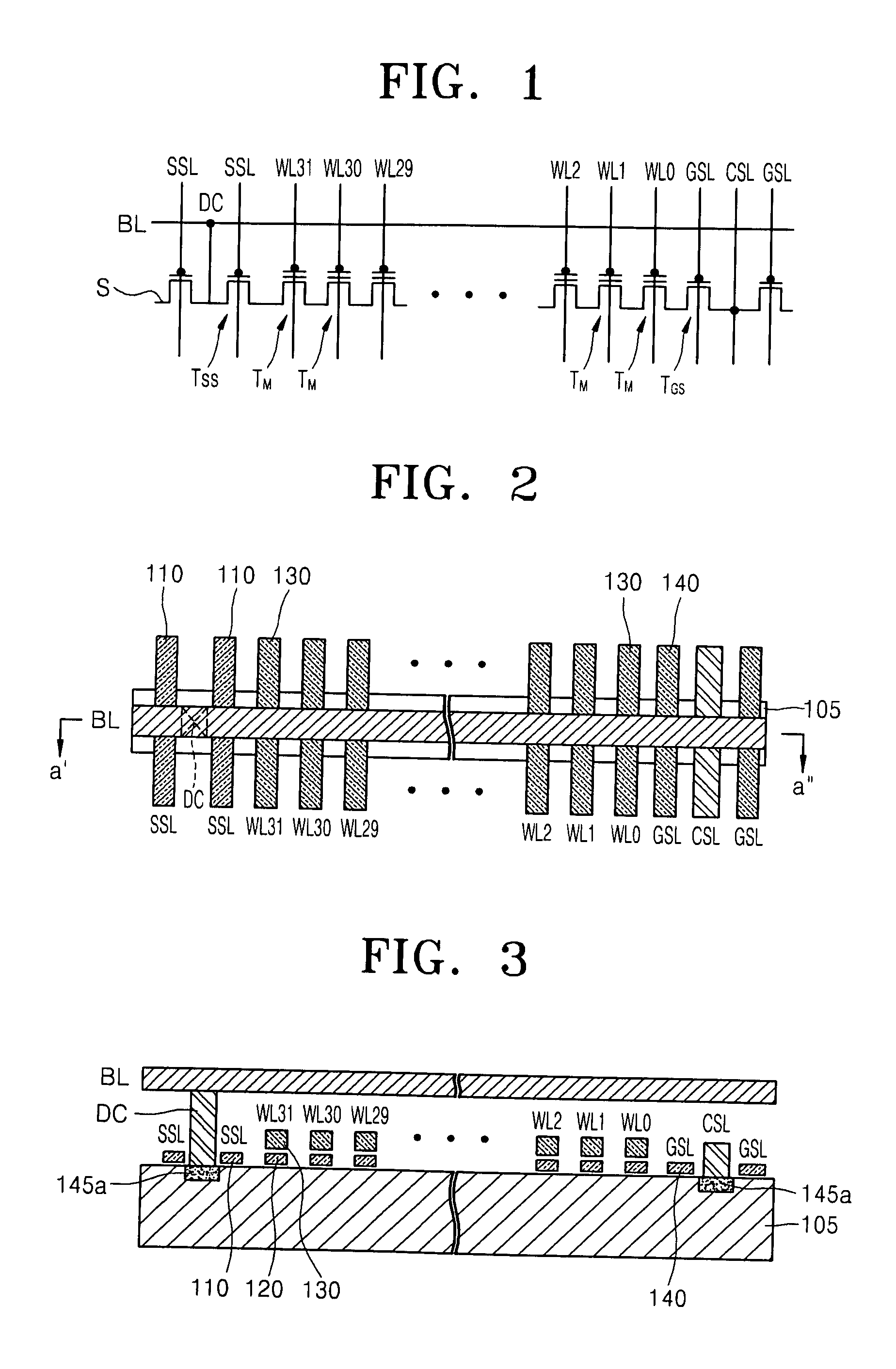

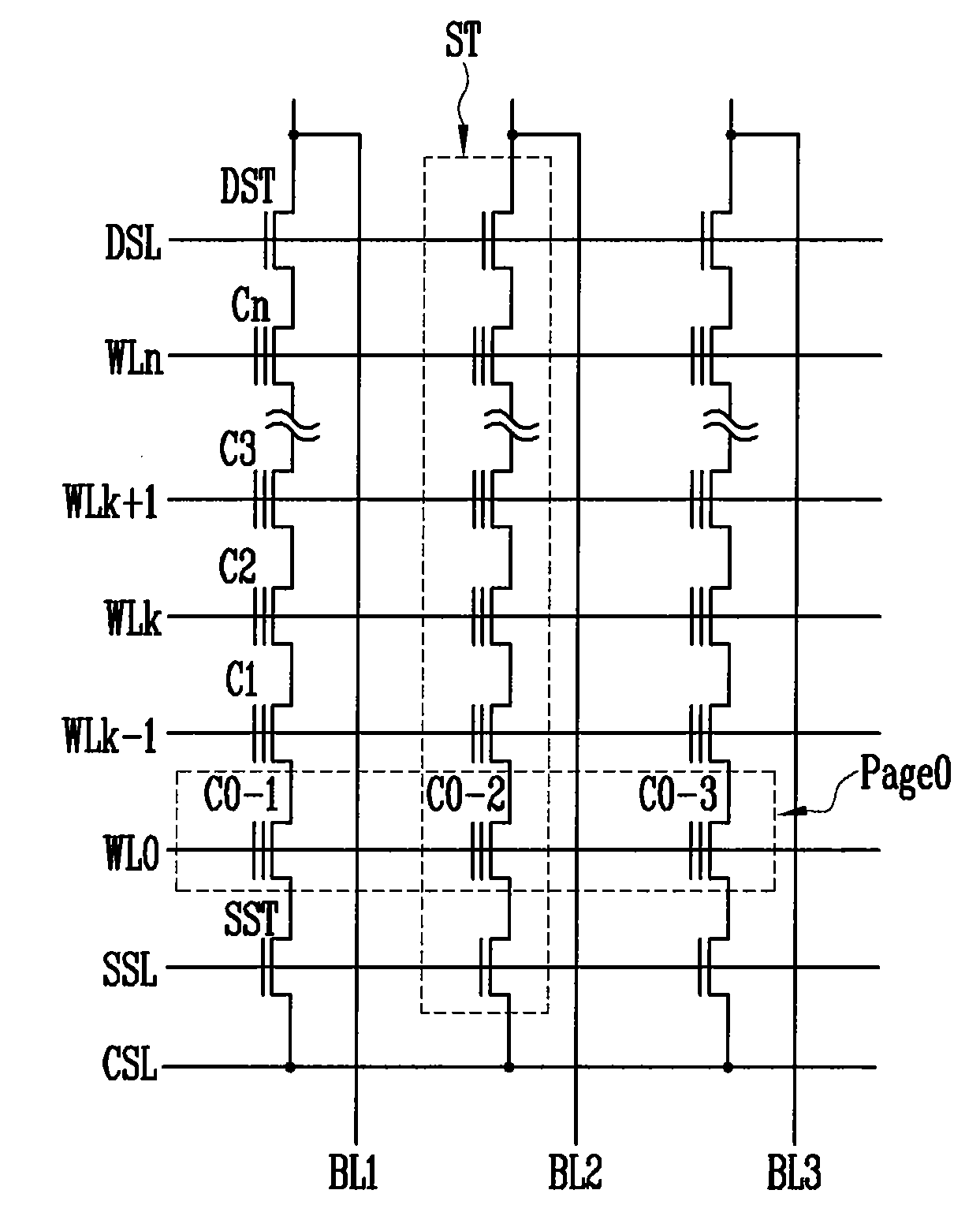

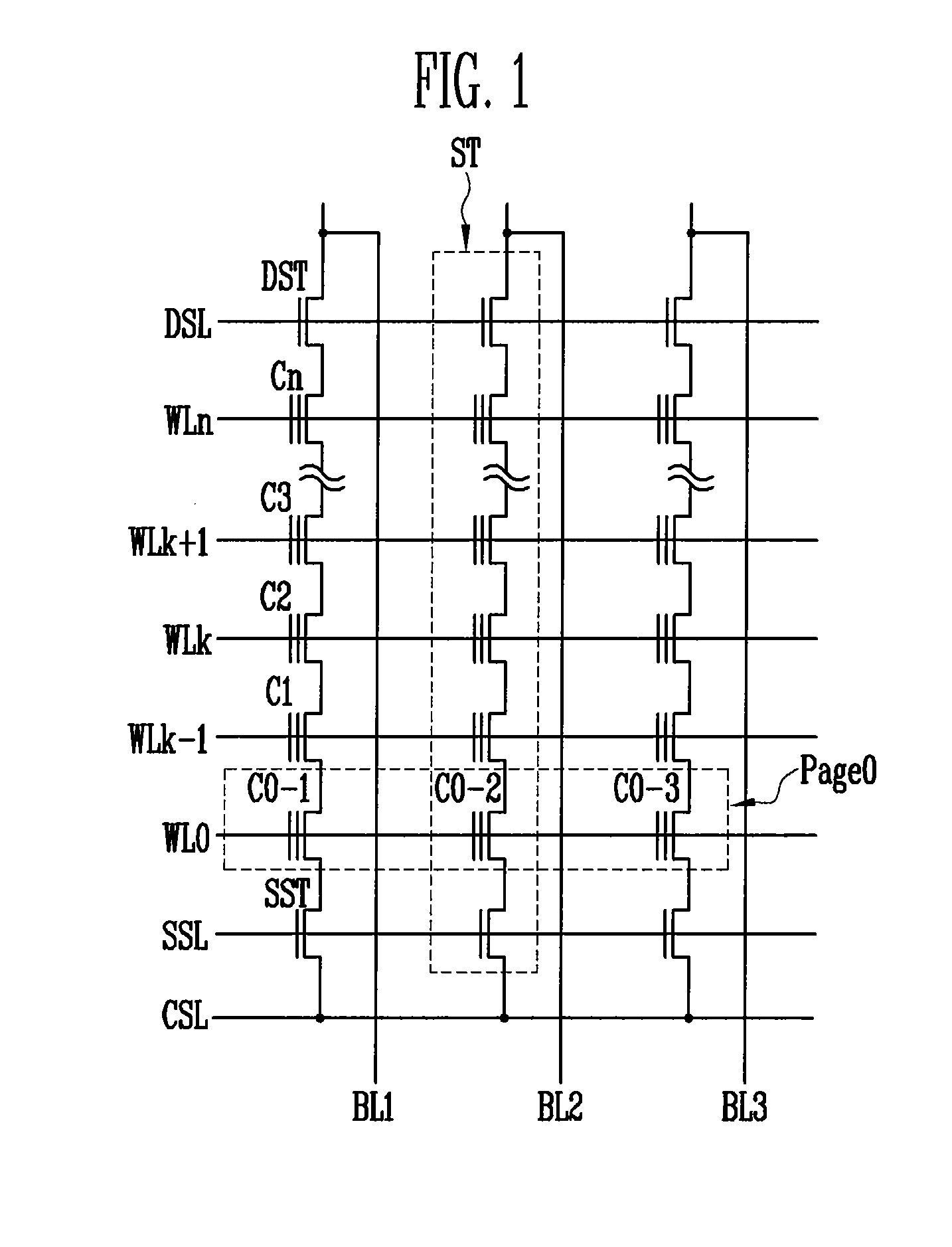

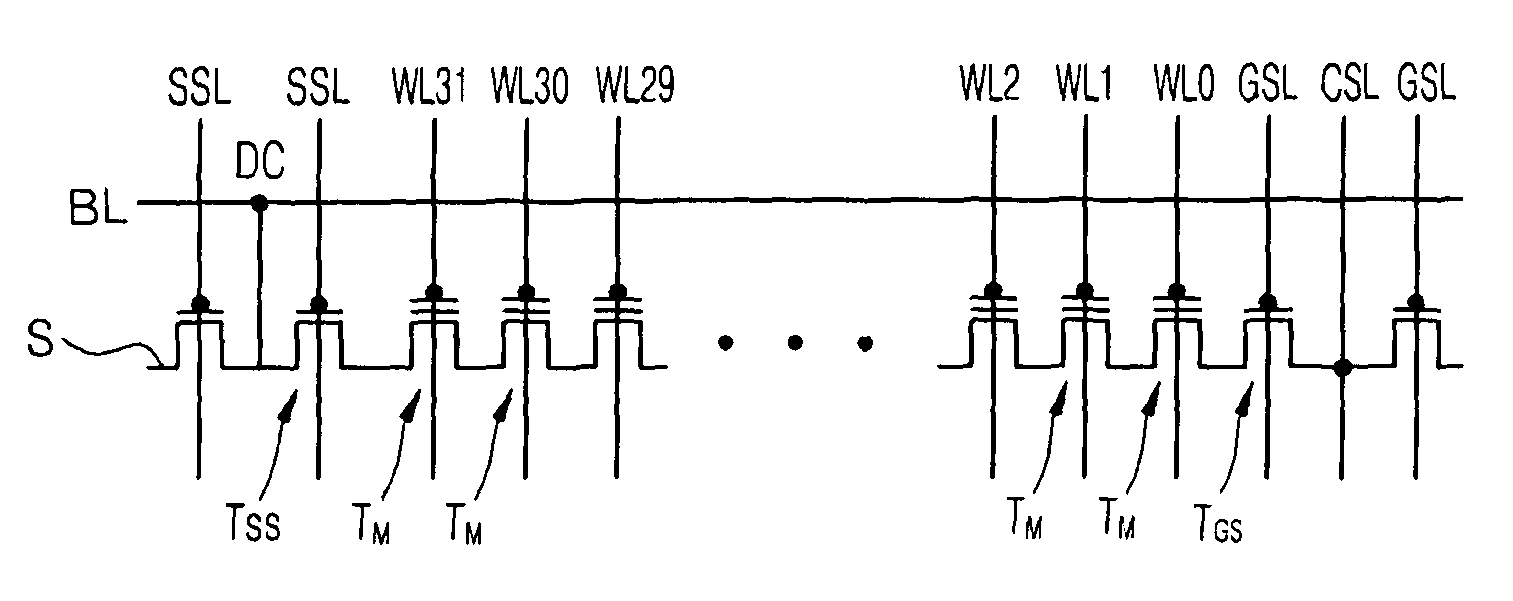

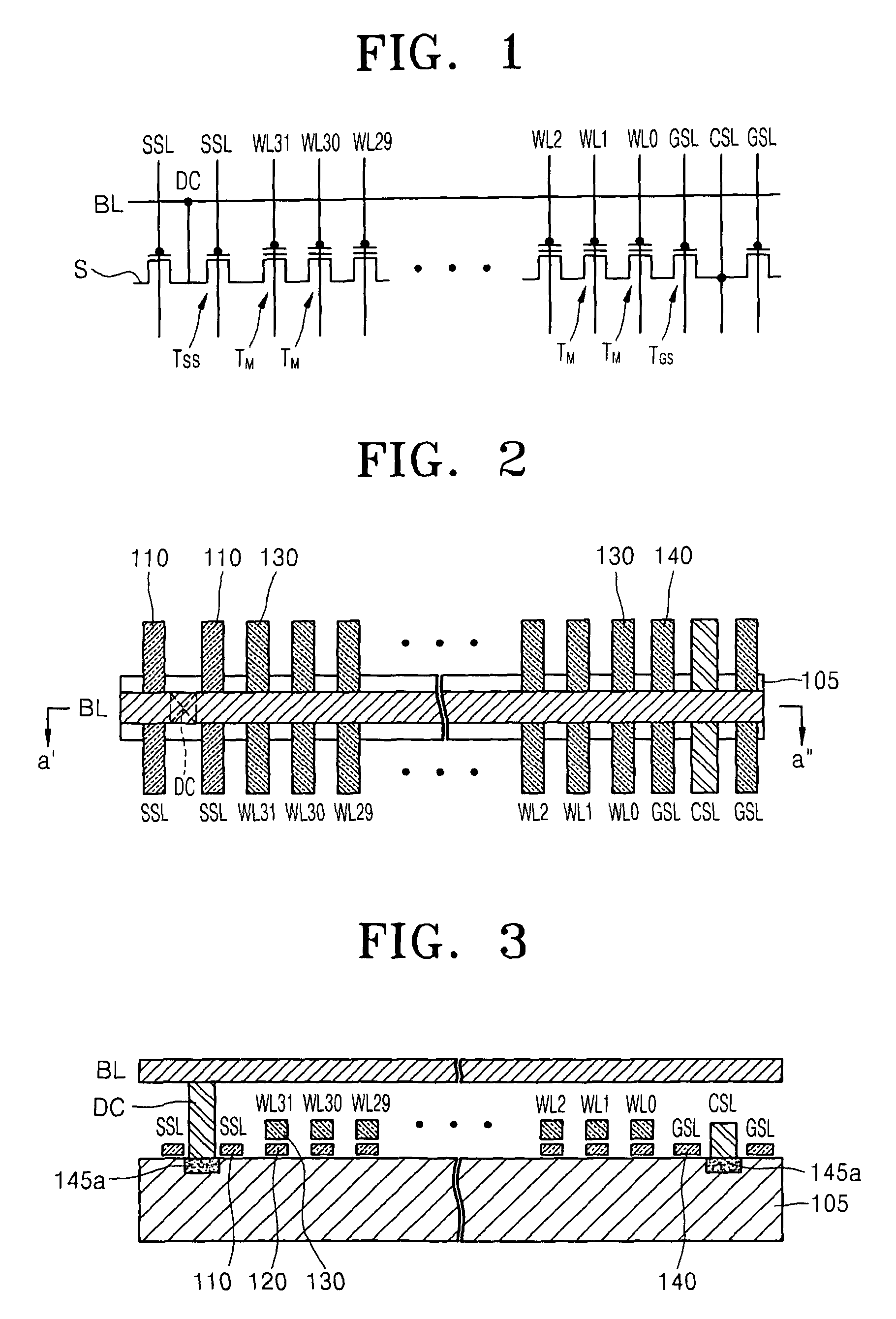

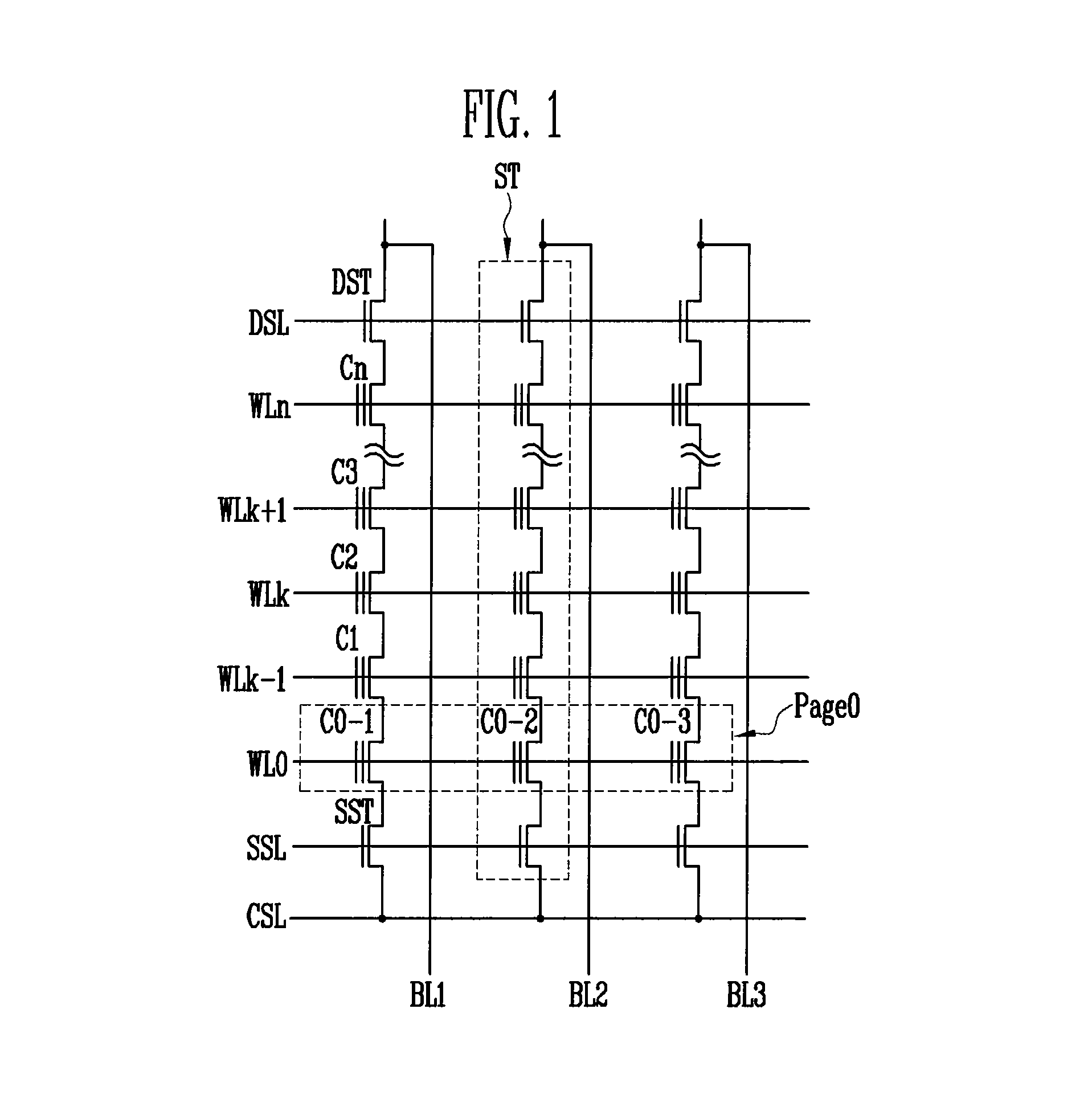

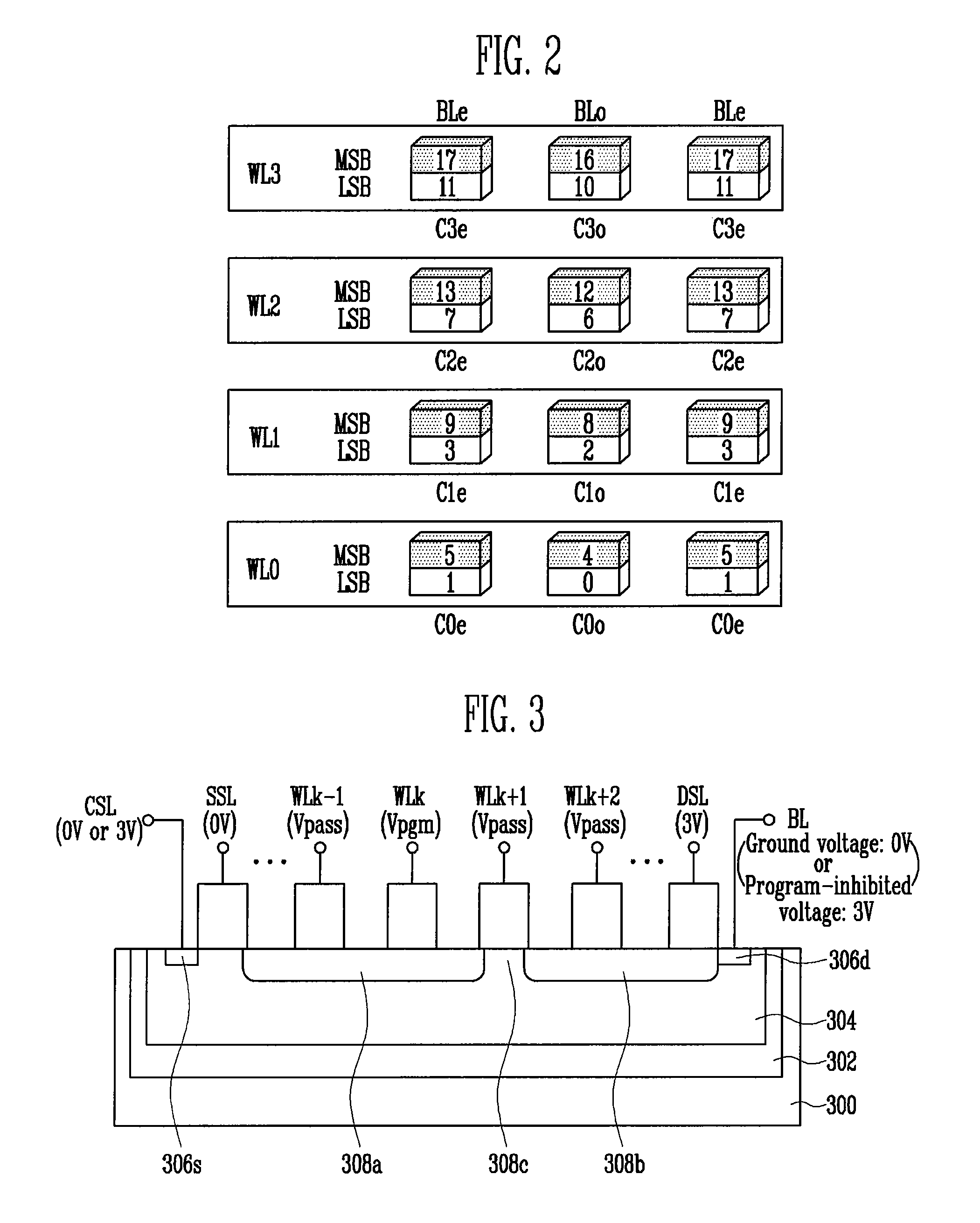

Non-volatile memory devices and methods of operating non-volatile memory devices

A non-volatile memory device, which includes a plurality of memory transistors that are coupled with a plurality of bit lines and a plurality of word lines, and methods of operating a non-volatile memory device are provided. A selected bit line for programming and unselected bit lines for preventing programming are determined from the plurality of bit lines. An inhibiting voltage is applied to at least one inhibiting word line chosen from the plurality of word lines. The at least one inhibiting word line includes a word line positioned closest to a string selection line. A programming voltage is applied to a selected word line chosen from the plurality of word lines. Data is programmed into a memory transistor coupled with the selected word line and the selected bit line while preventing data from being programming into memory transistors coupled with the unselected bit line.

Owner:SAMSUNG ELECTRONICS CO LTD

Method for controlling and/or monitoring data processing device and computer program

ActiveUS7904817B2Easy to buildReduce complexityProgramme controlSampled-variable control systemsGraphicsGraphical user interface

Owner:ACCENTURE GLOBAL SERVICES LTD

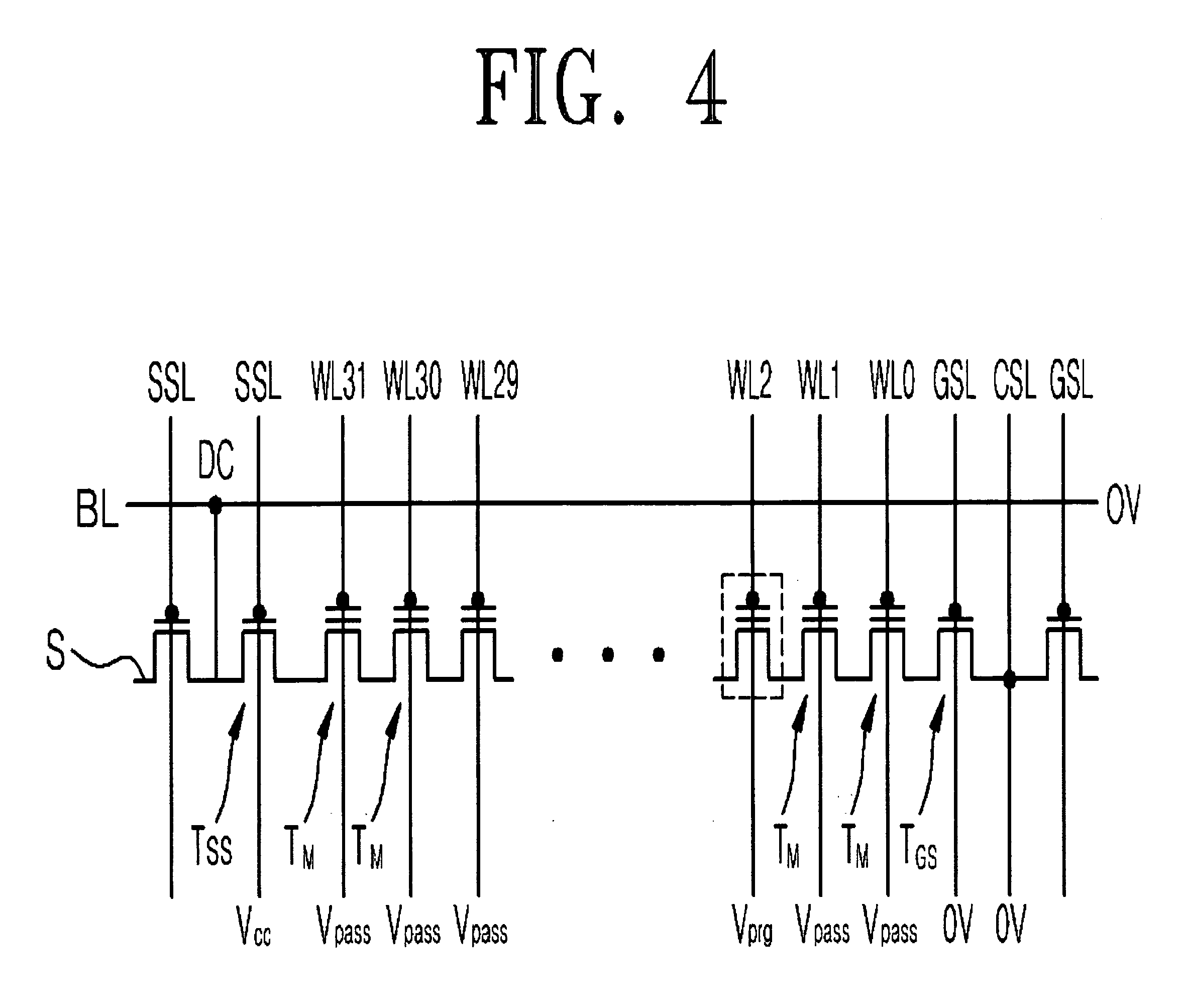

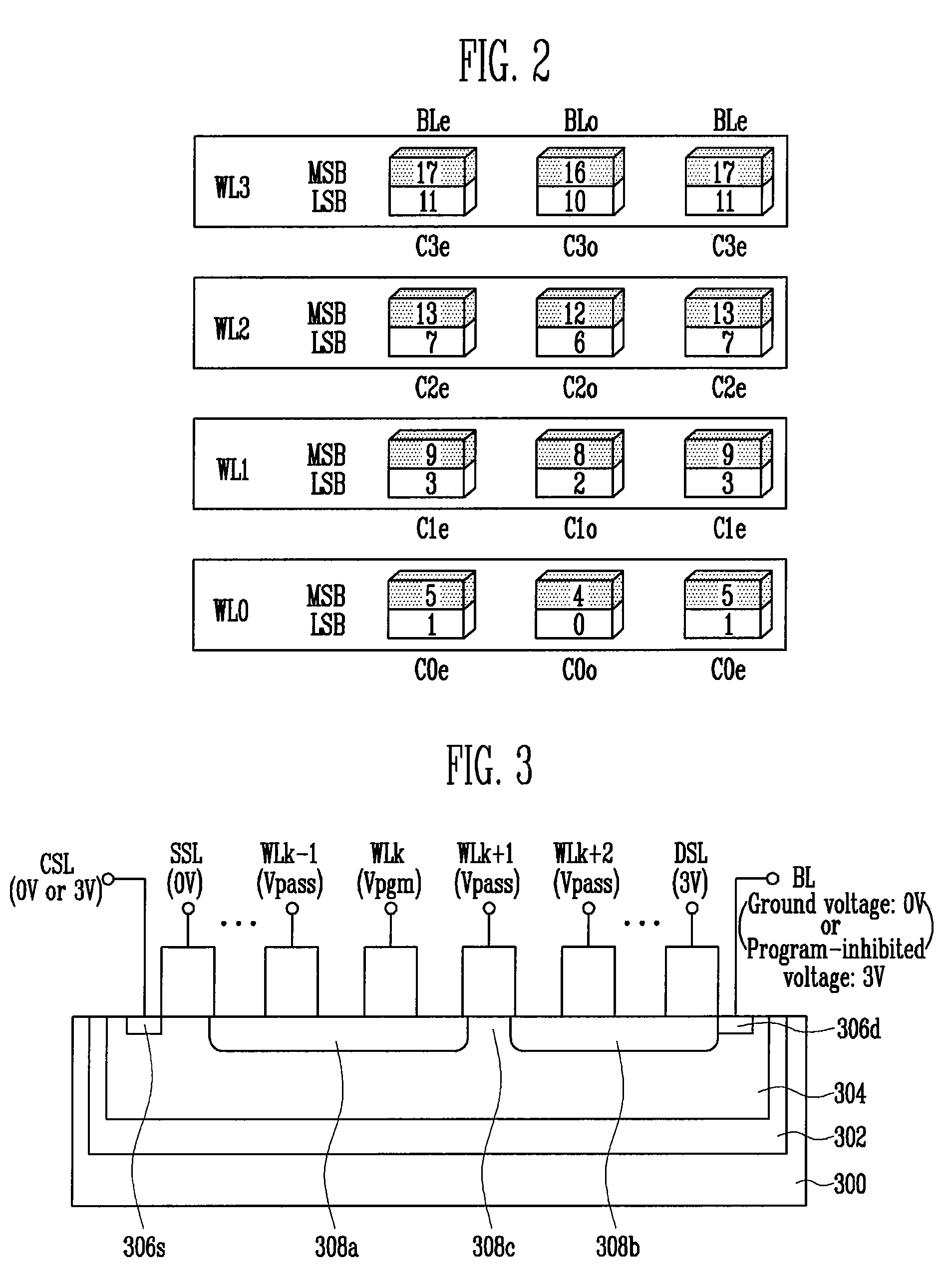

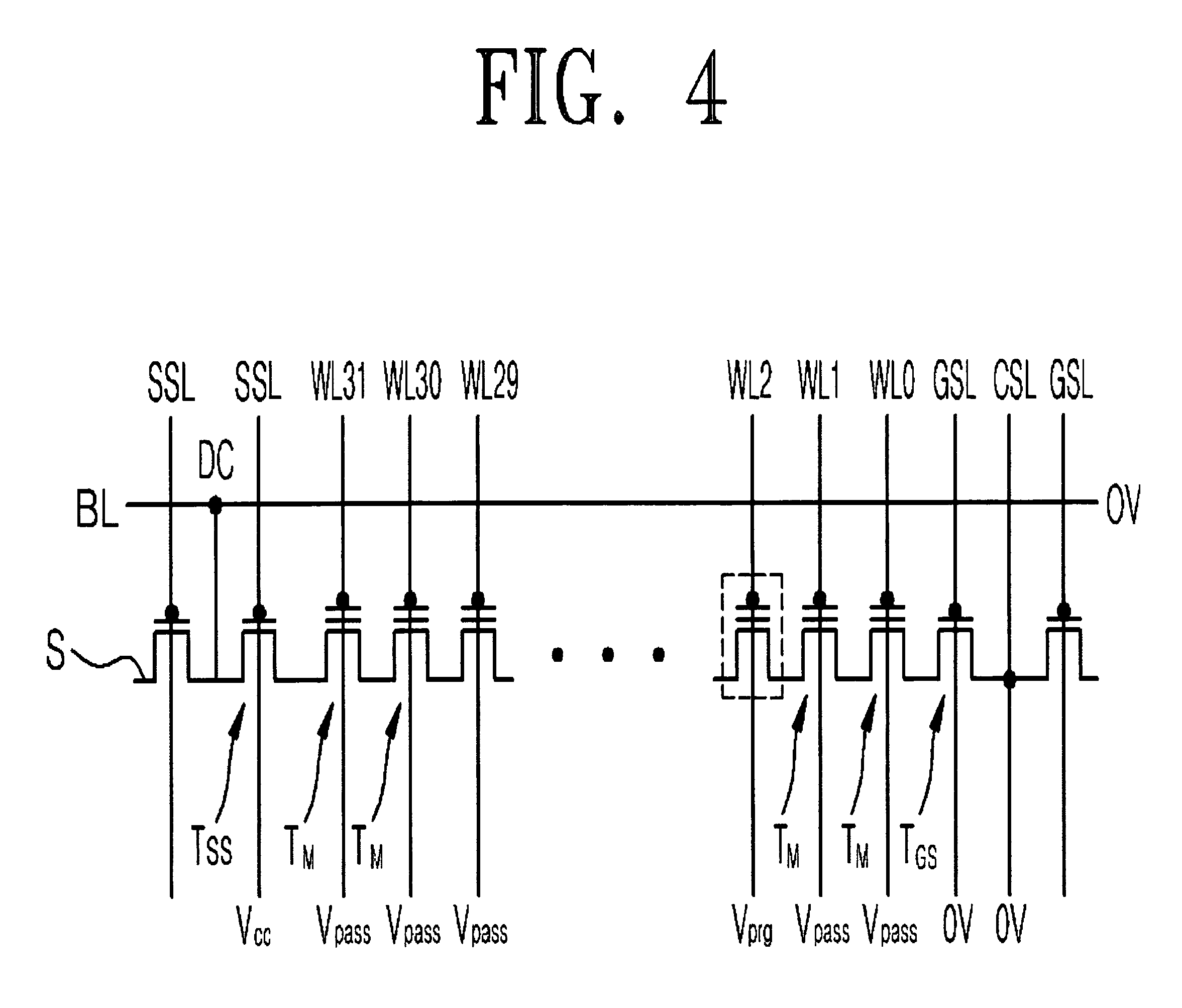

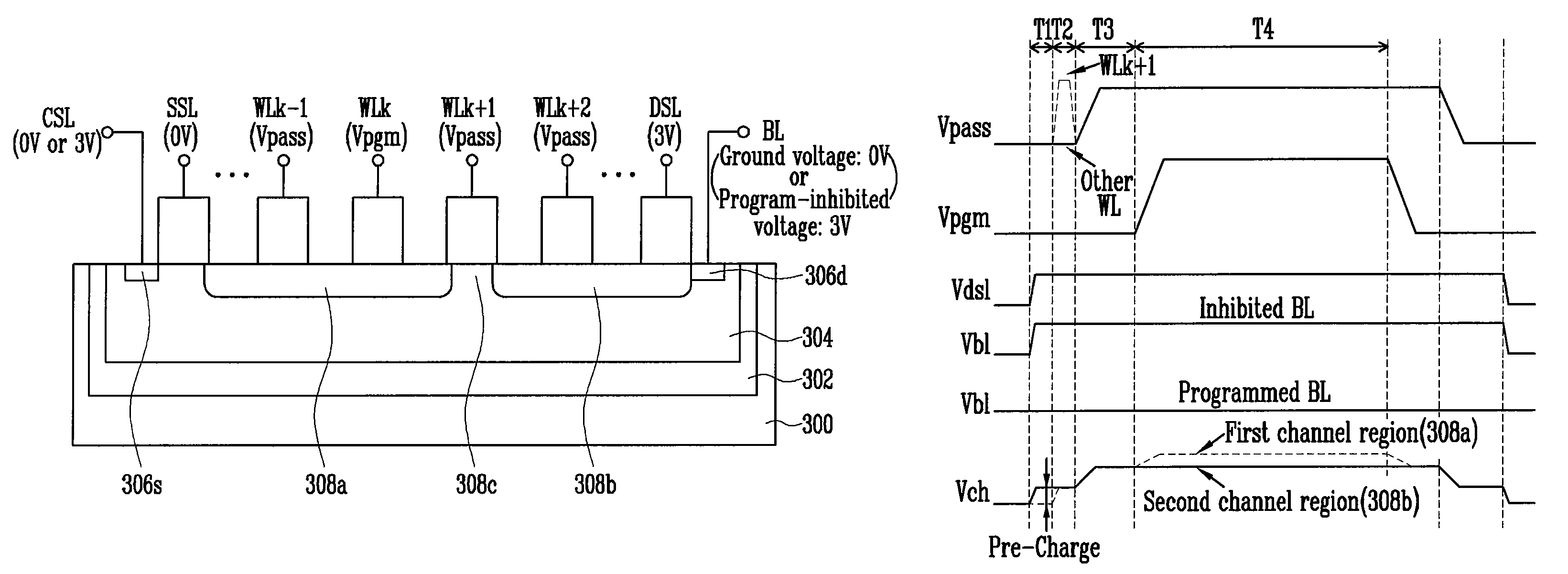

Programming method of flash memory device

ActiveUS20090067242A1Blocking phenomenonAvoid programmingRead-only memoriesDigital storageComputer scienceVoltage

A memory device comprises a drain select line, a source select line, word lines, and a string connected between a bit line and a common source line. A program-inhibited voltage is applied to the bit line and a first voltage of a positive potential is applied to the drain select line. A second voltage for activating a programmed memory cell is applied to a word line to which the programmed memory cell is connected. A programming operation is performed by applying a program voltage to a selected word line and applying a pass voltage to the unselected word lines.

Owner:SK HYNIX INC

Non-volatile memory devices and methods of operating non-volatile memory devices

A non-volatile memory device, which includes a plurality of memory transistors that are coupled with a plurality of bit lines and a plurality of word lines, and methods of operating a non-volatile memory device are provided. A selected bit line for programming and unselected bit lines for preventing programming are determined from the plurality of bit lines. An inhibiting voltage is applied to at least one inhibiting word line chosen from the plurality of word lines. The at least one inhibiting word line includes a word line positioned closest to a string selection line. A programming voltage is applied to a selected word line chosen from the plurality of word lines. Data is programmed into a memory transistor coupled with the selected word line and the selected bit line while preventing data from being programming into memory transistors coupled with the unselected bit line.

Owner:SAMSUNG ELECTRONICS CO LTD

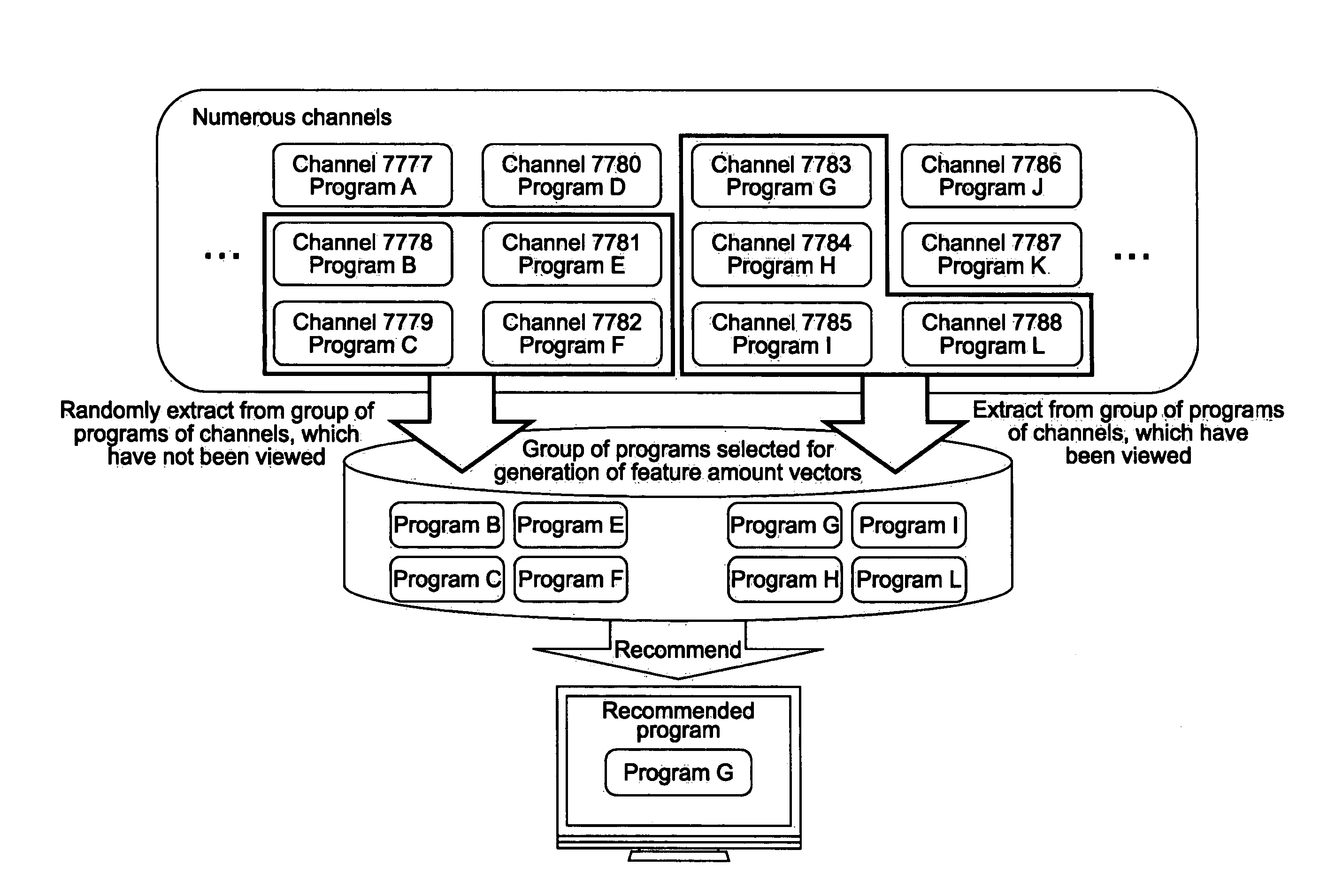

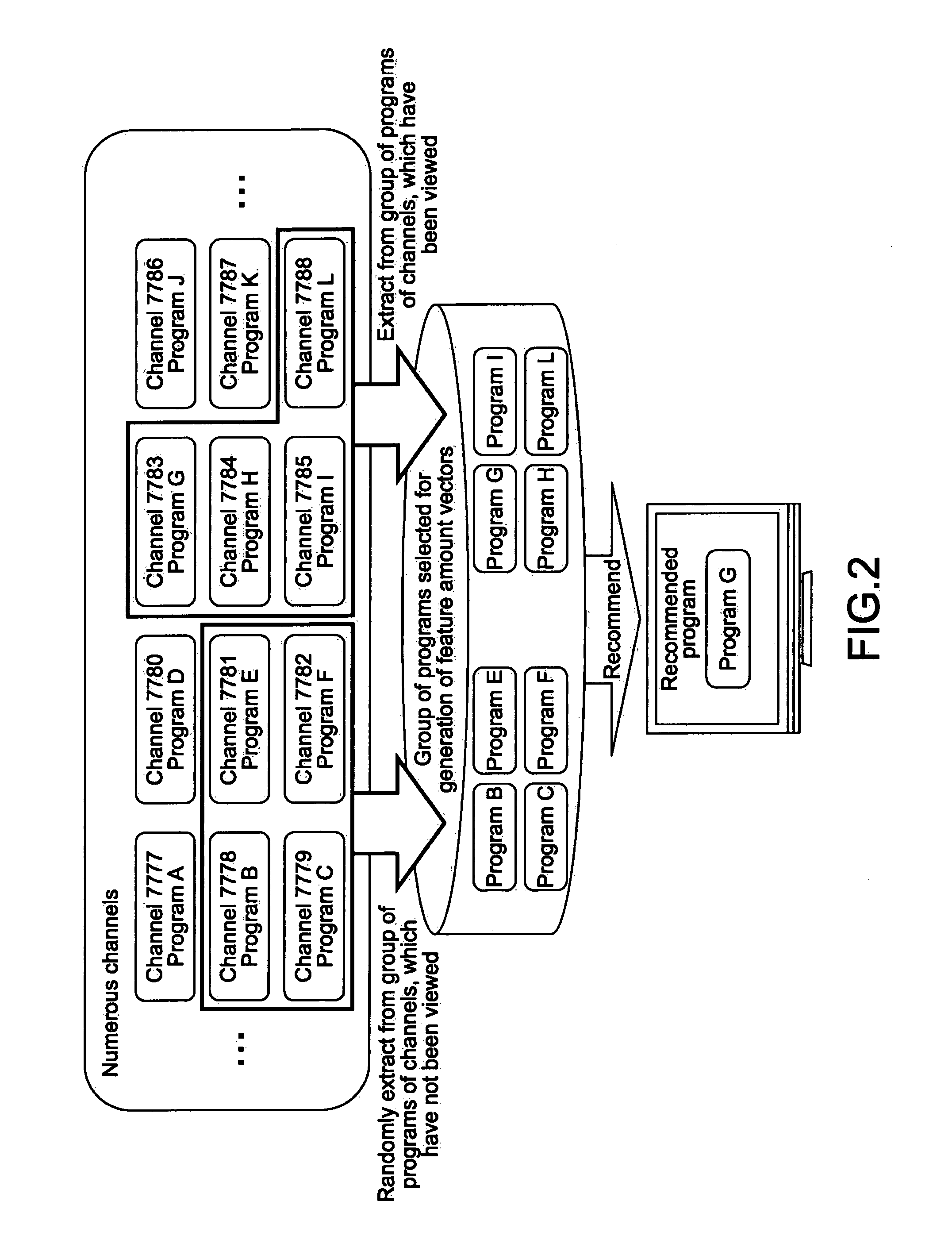

Information processing apparatus, information processing method, and program

InactiveUS20110167454A1Rapid indicationQuick instructionsTelevision system detailsColor television detailsSignal processingInformation processing

Provided is an information processing apparatus including: a broadcast signal processing portion to receive and reproduce a program of a channel chosen by a user; a storage portion to store preference information of the user and to store, as a user viewing history, information of channels viewed by the user; a user preference learning portion to learn the user preference information based on information about the reproduced program, and to record information of the channel of the reproduced program in a viewing history list; a feature information generating portion to select, as first channels, channels among the channels on the air based on the viewing history list, and to generate feature information of a program of the selected first channels; and a recommended program determining portion to determine a recommended program based on the feature information of the program of the channels and on the user preference information.

Owner:SONY CORP

Programming method of flash memory device

Owner:SK HYNIX INC

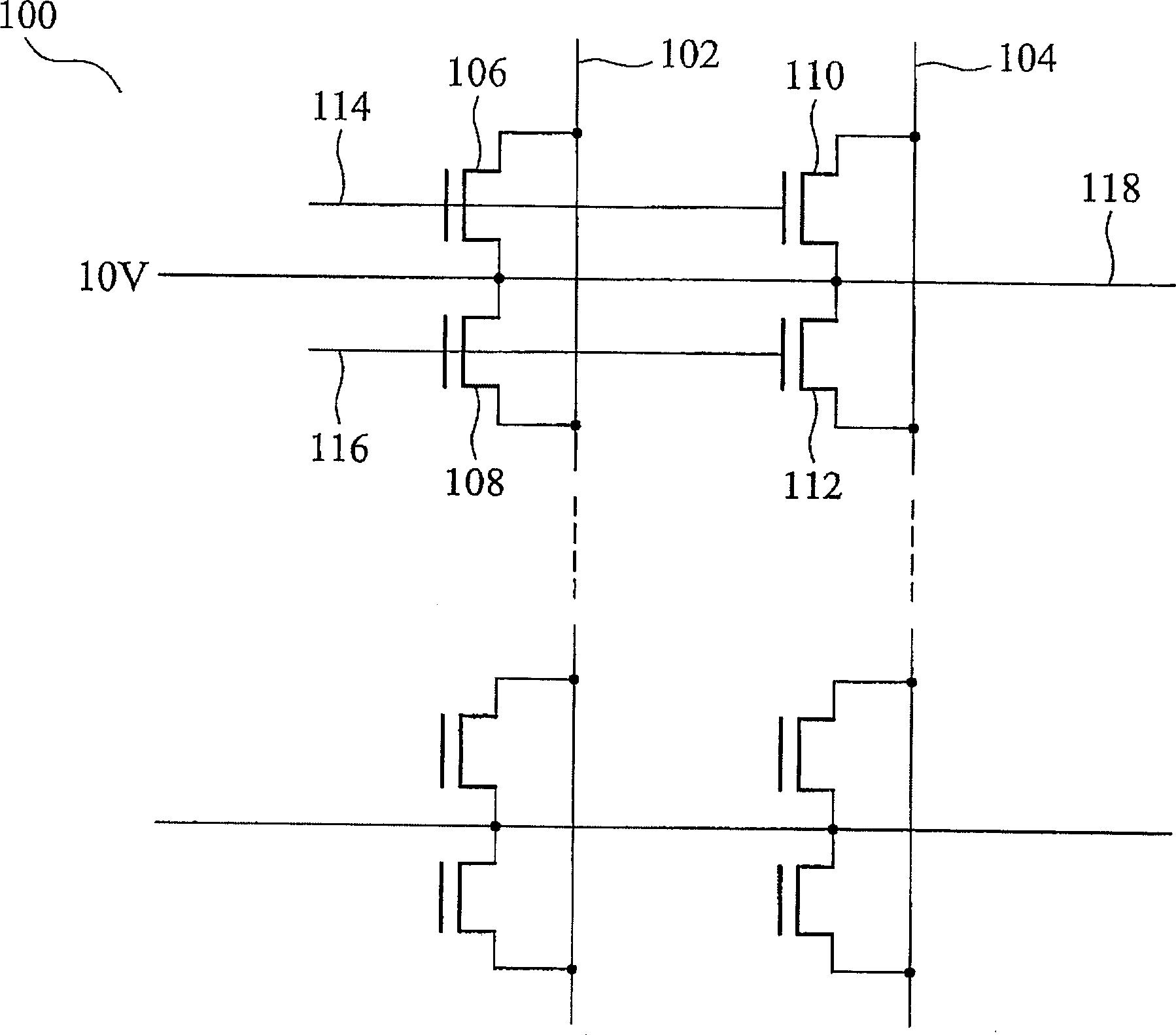

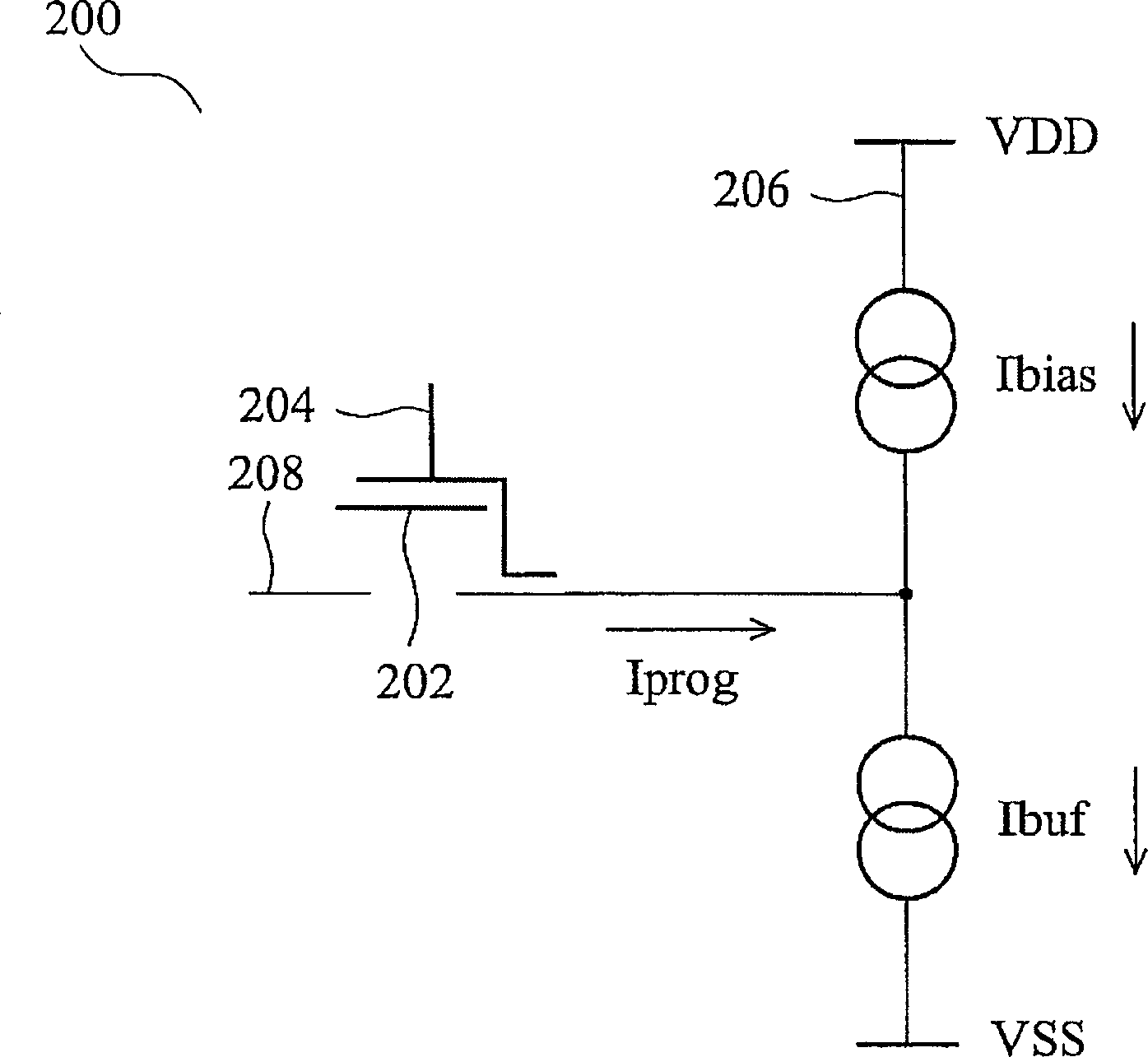

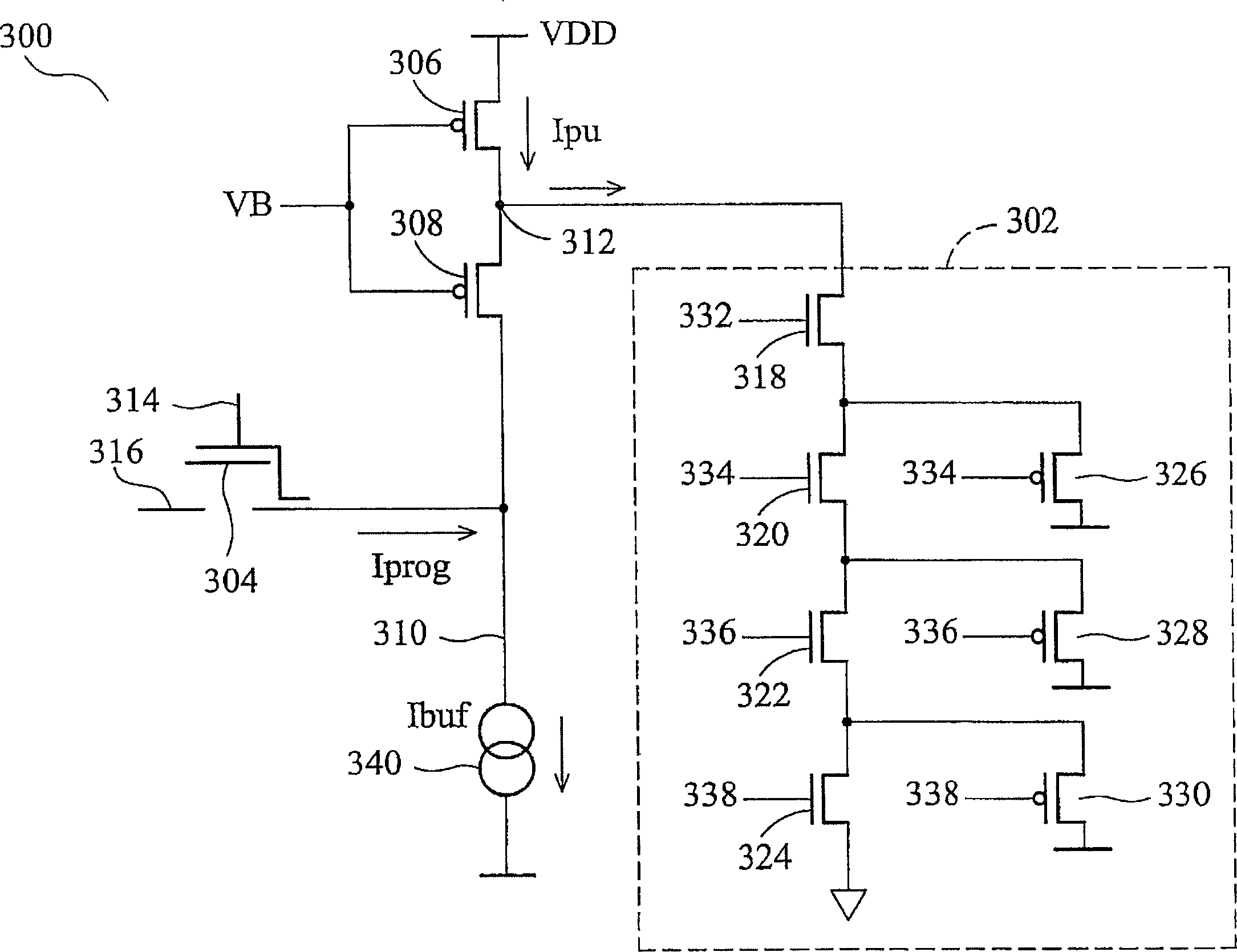

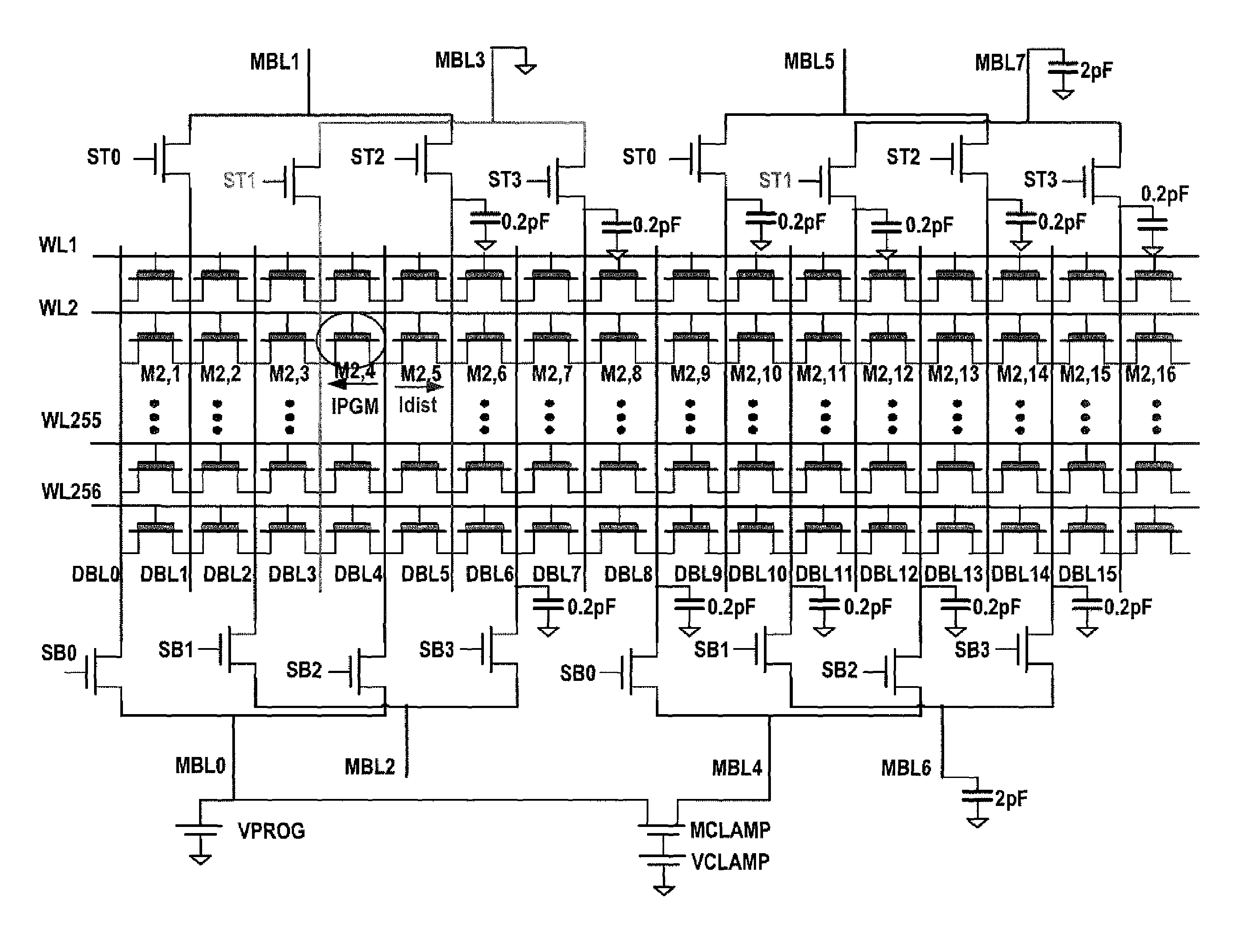

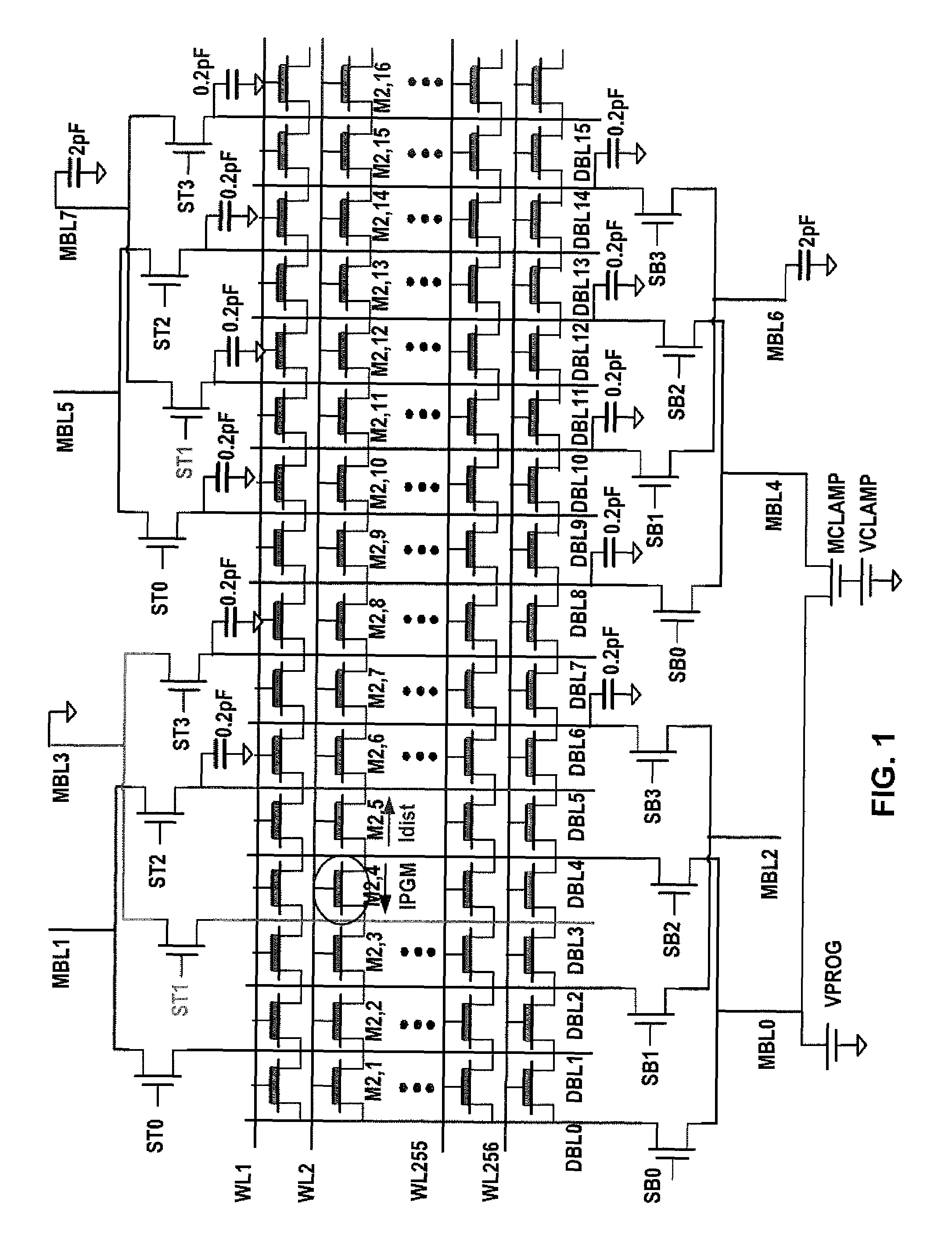

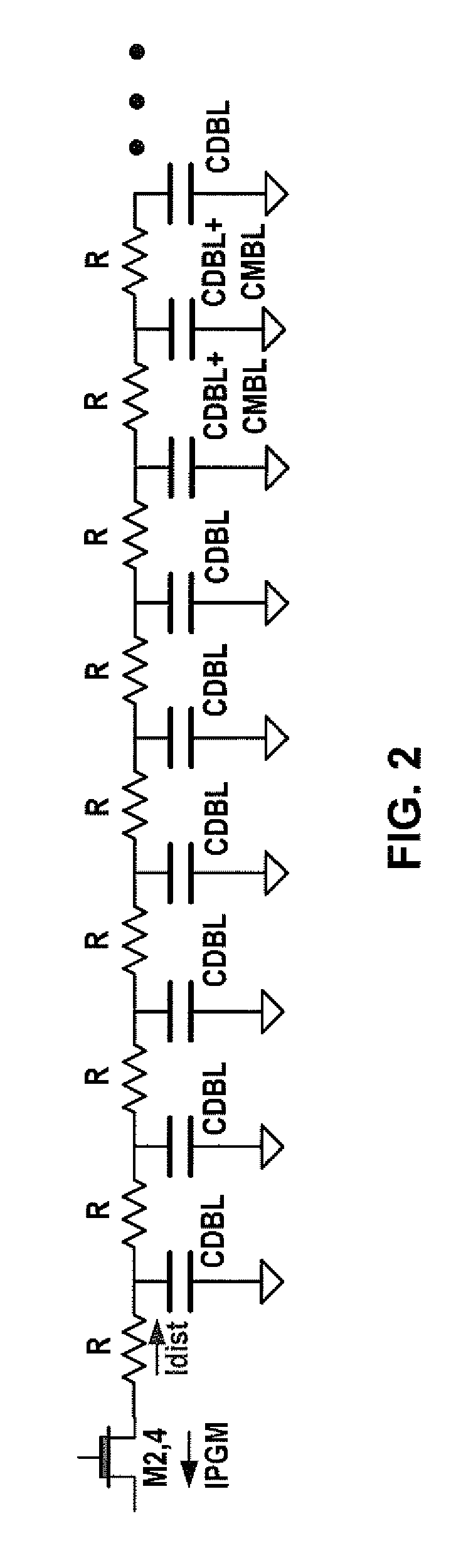

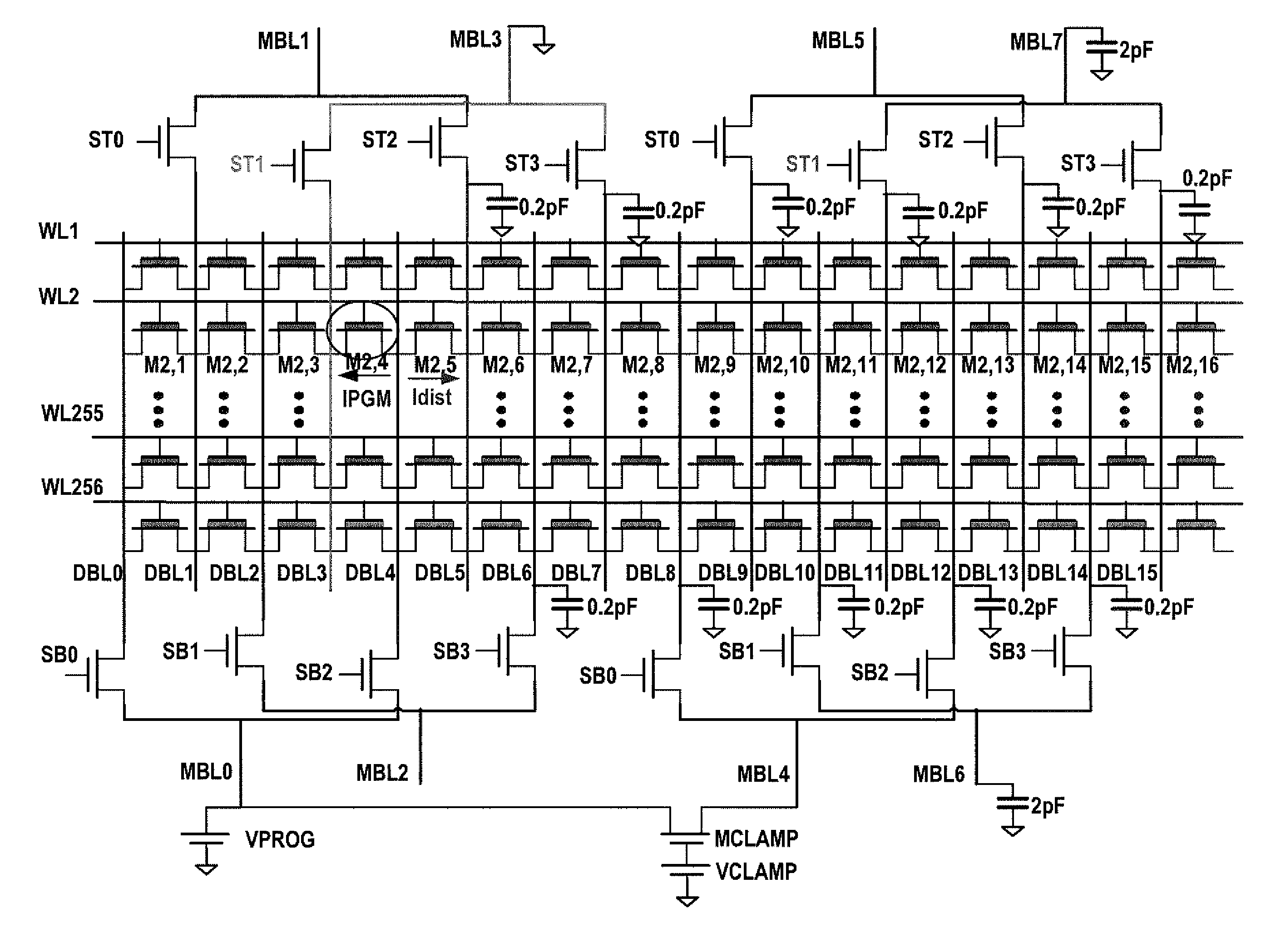

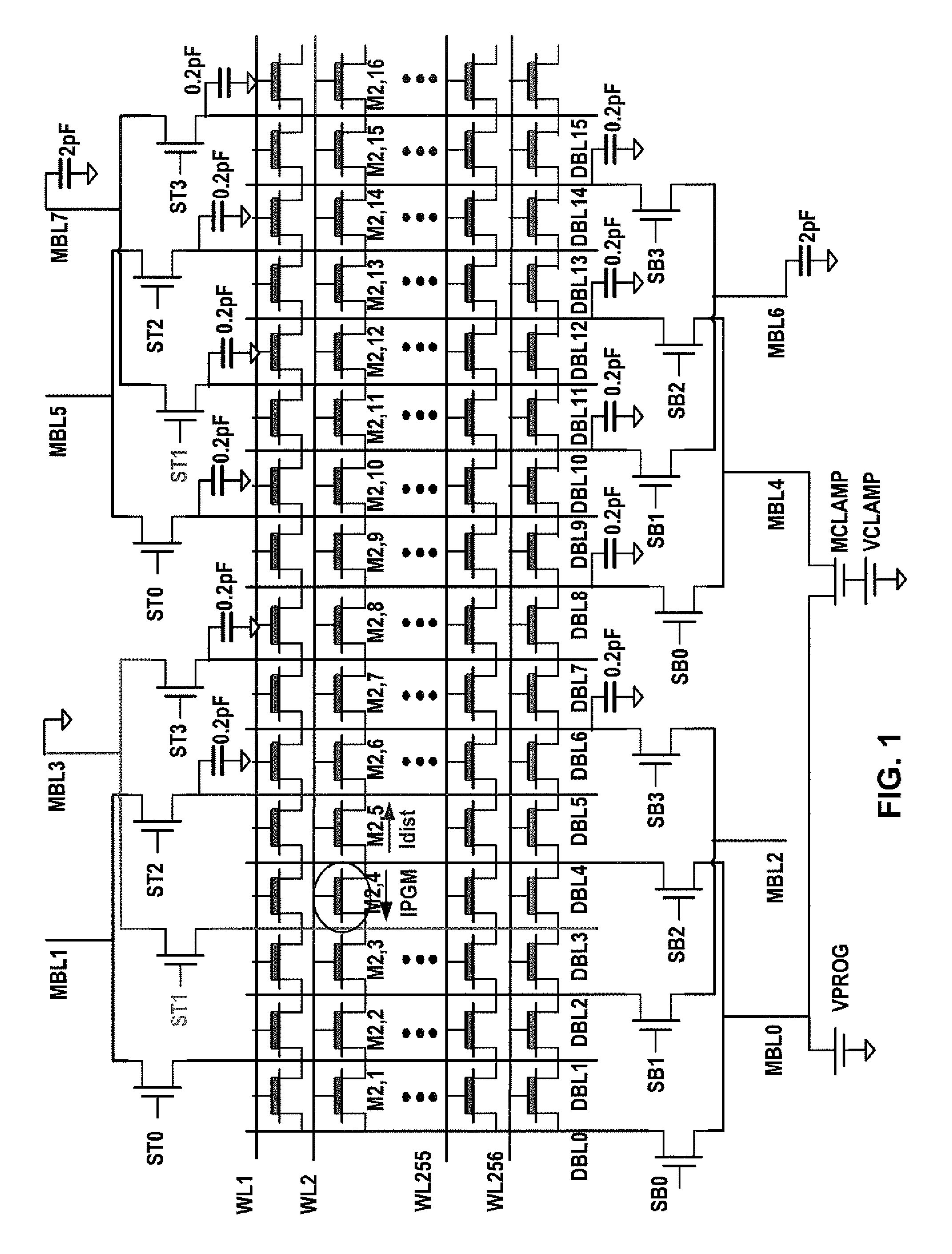

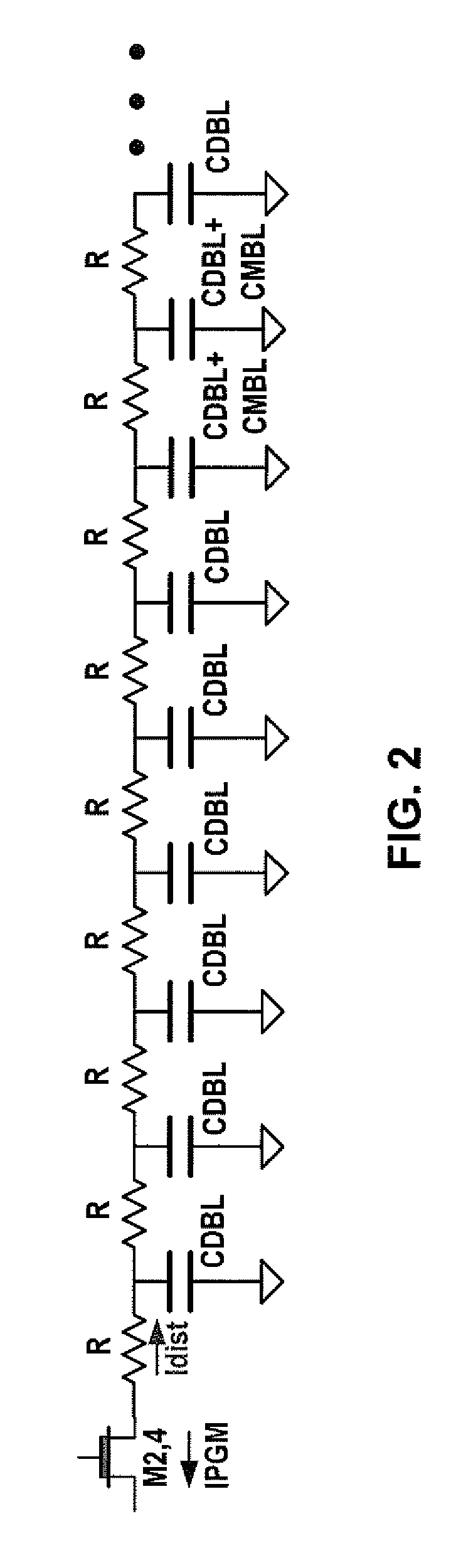

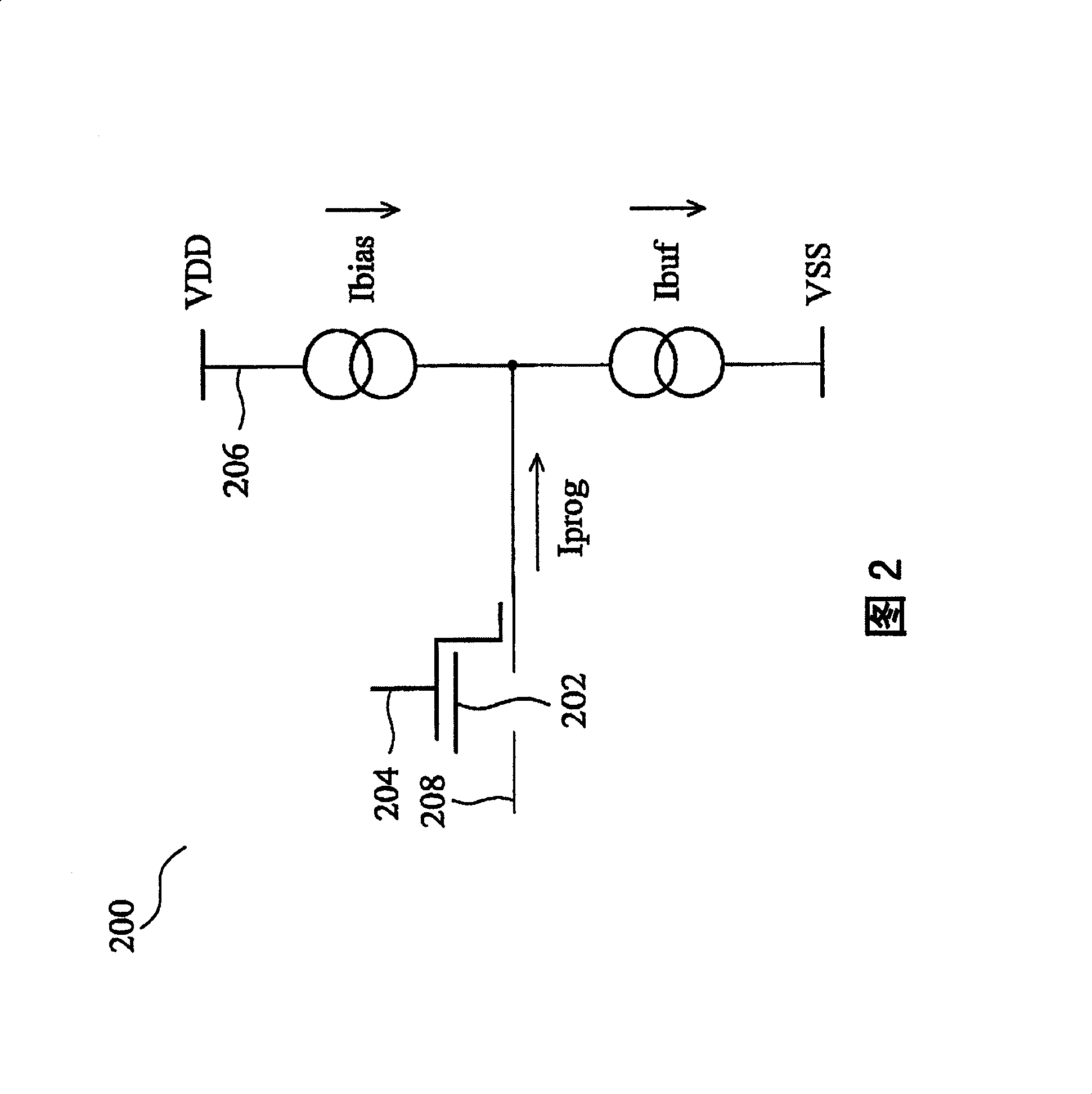

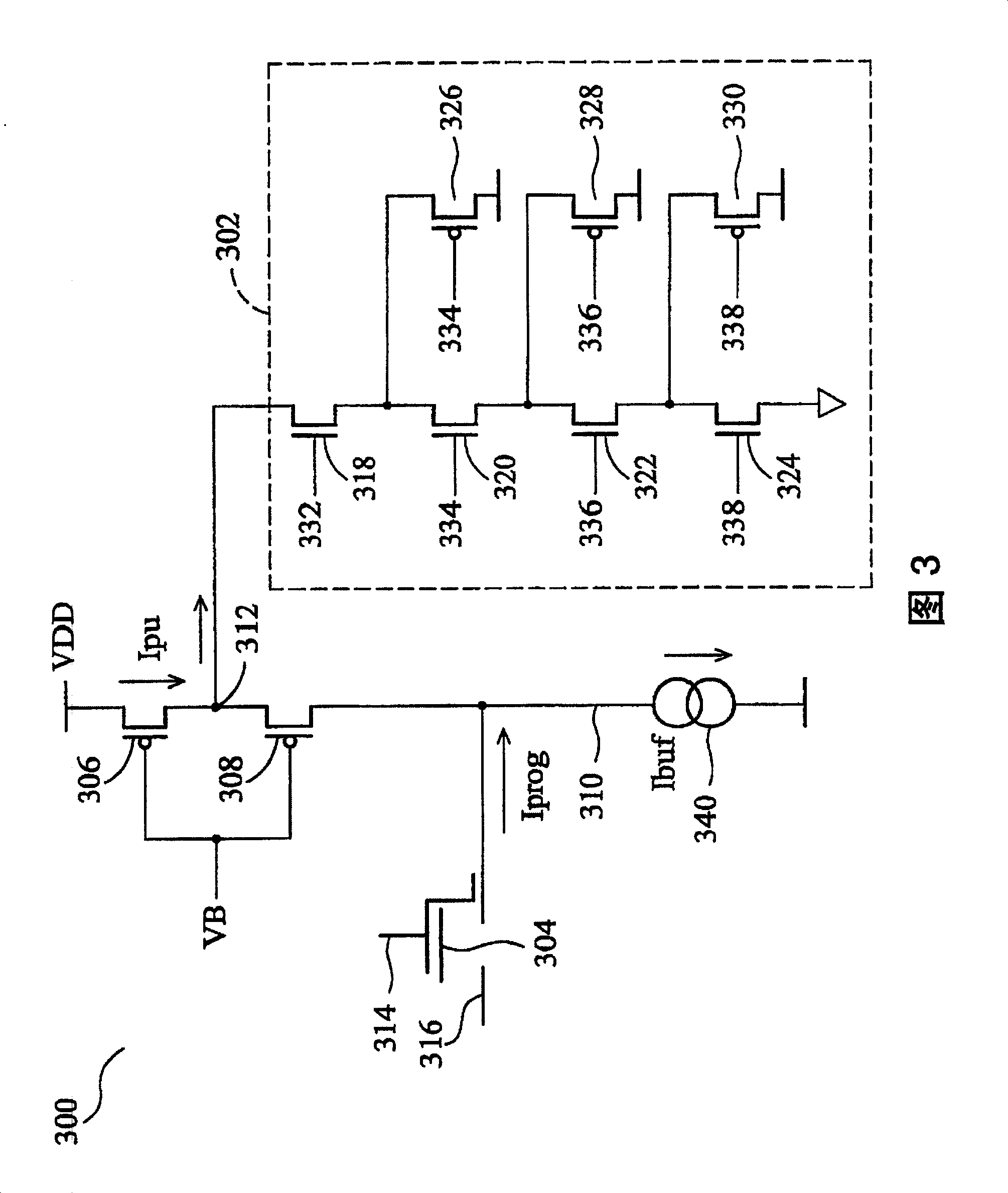

Flash array system and program current stablilization method

A method and system is disclosed for prohibiting program disturbance in a memory array device. The system comprises a bit-line decoder coupled to each bit-line of the memory array for providing a predetermined current diverting path, a biased resistance module placed on the bit-line of the flash memory array through which a pull-up current provided by a predetermined power supply is diverted by the bit-line decoder when a cell of the flash memory array connecting to the bit-line is programmed. The programming current of the cell of the flash memory array is stabilized due to the diverted pull-up current. This invention can reduce variance of programming current by the bit-line decoder diverted pull-up current, so can obtain more exact programming current to get preferable productivity, and this mechanism can be used for upgrading bit-line.

Owner:TAIWAN SEMICON MFG CO LTD

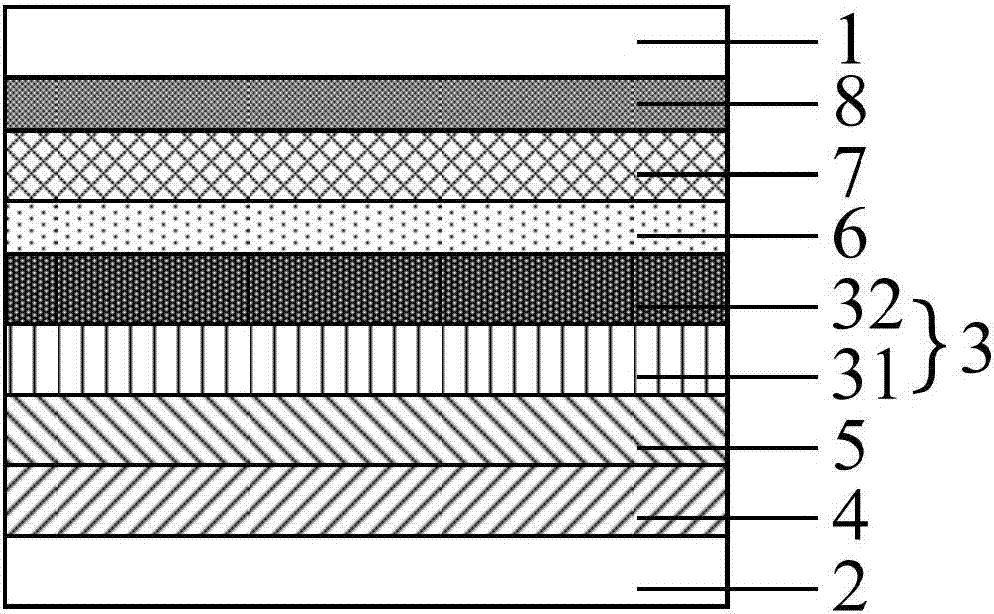

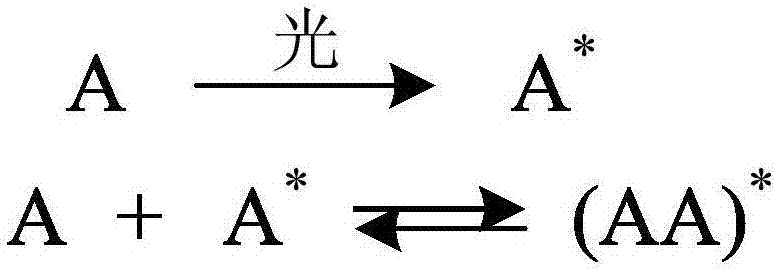

Organic electroluminescent device, OLED substrate, and display device

ActiveCN107154463AImprove coherenceAvoid programmingSolid-state devicesSemiconductor/solid-state device manufacturingDisplay deviceOrganic electroluminescence

The invention provides an organic electroluminescent device, an OLED substrate, and a display device, and belongs to the display technology field. The problems of the conventional organic electroluminescent devices such as low ink-jet printing experiment continuity during the preparation process thereof and requirements on complicated computer programs between different luminescent layers are solved. The organic electroluminescent device comprises a cathode, an anode, and a function layer disposed between the cathode and the anode. The function layer comprises a first luminescent layer and a second luminescent layer, which are sequentially arranged in a direction away from the anode. The first luminescent layer comprises a first blue light luminescent material, and after the cathode and the anode are electrified, the first luminescent layer and the second luminescent layer are used to form a composite product to emit light, the color of which is different from the color of the blue light.

Owner:BOE TECH GRP CO LTD +1

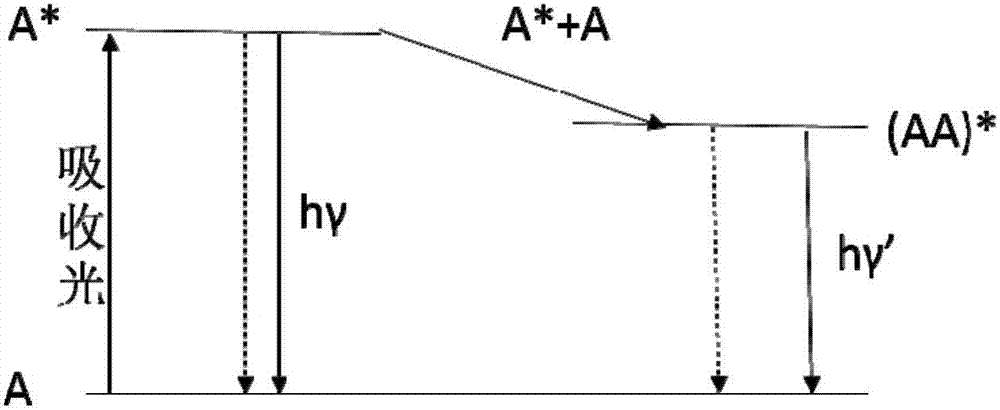

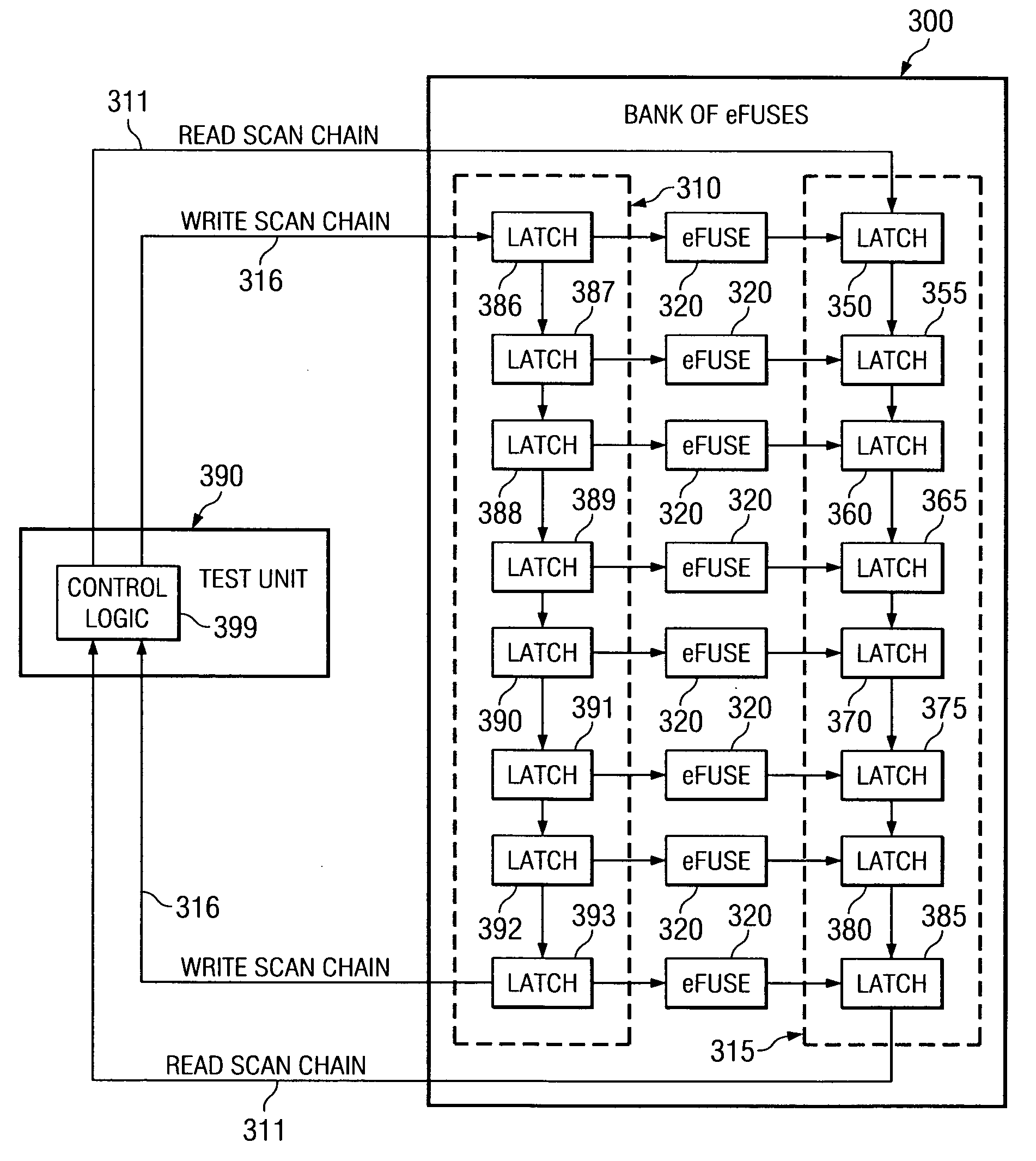

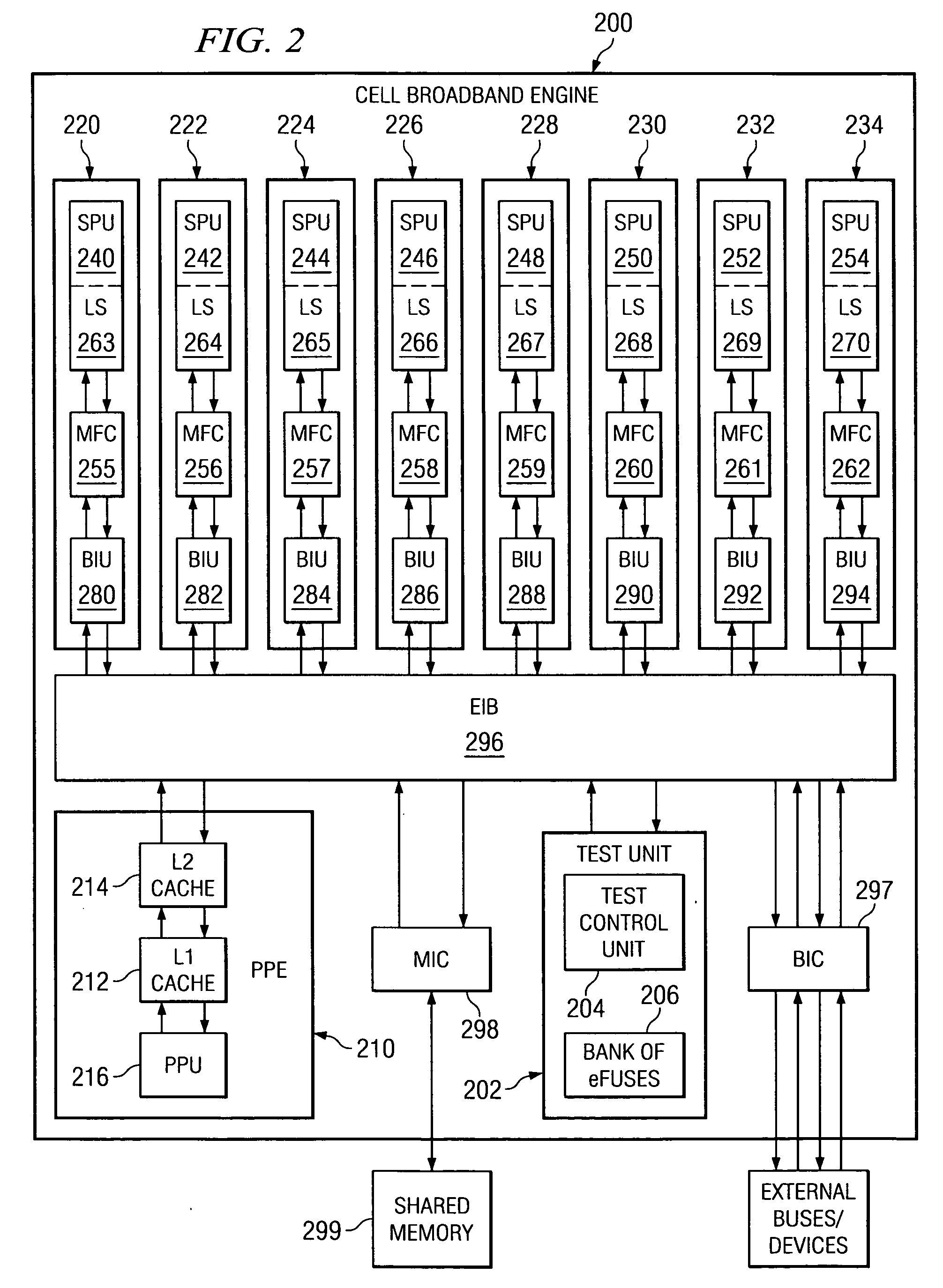

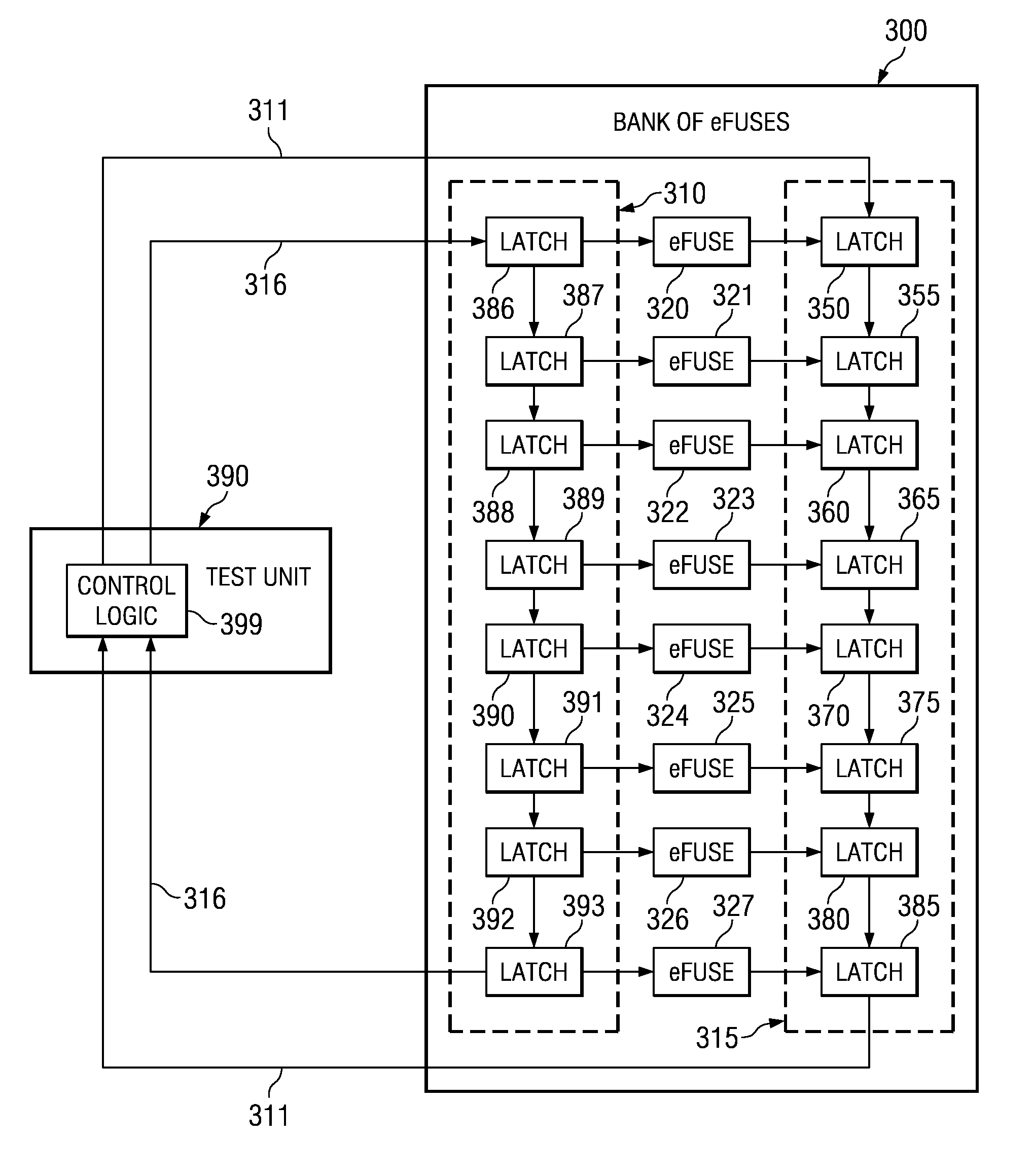

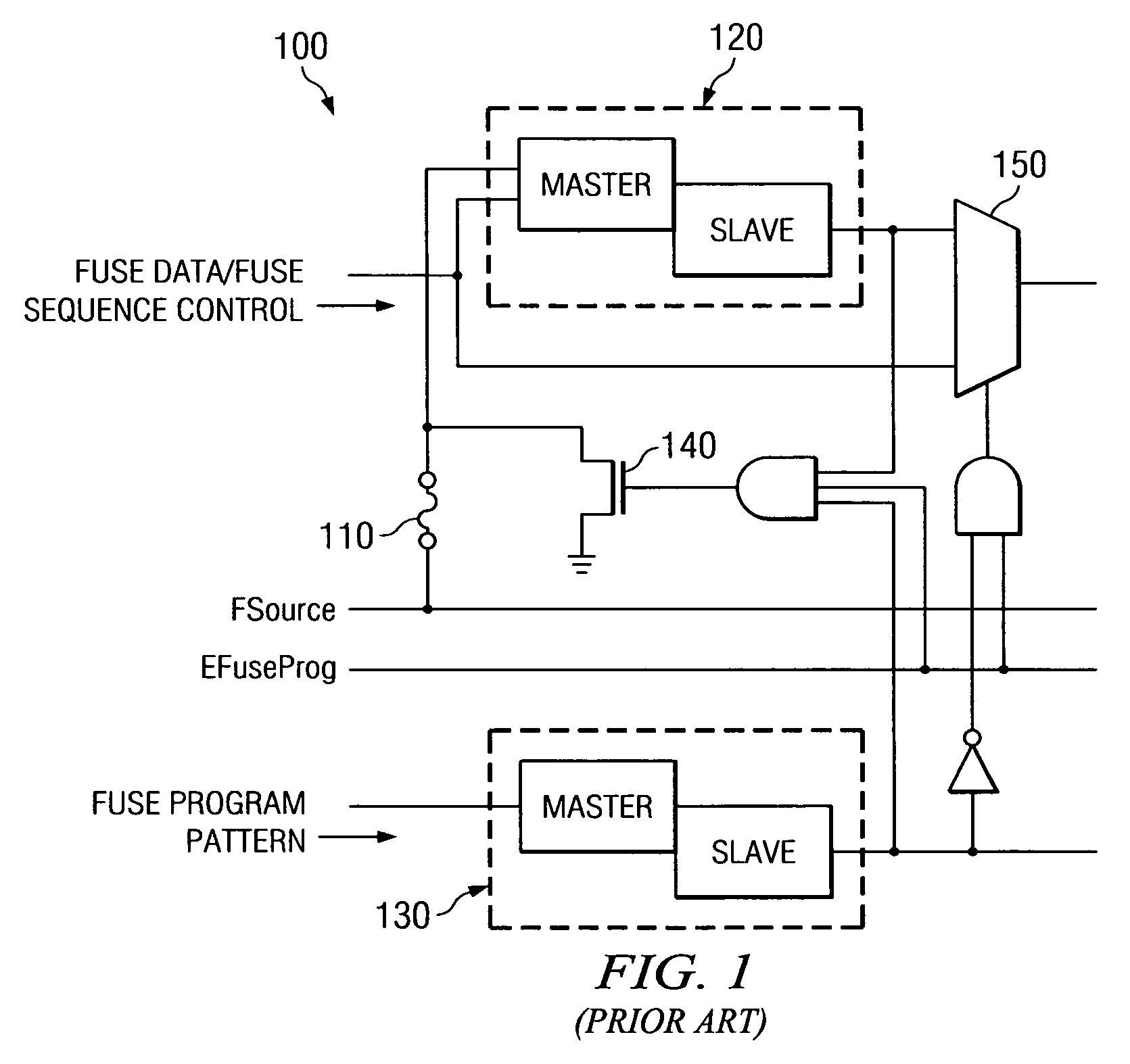

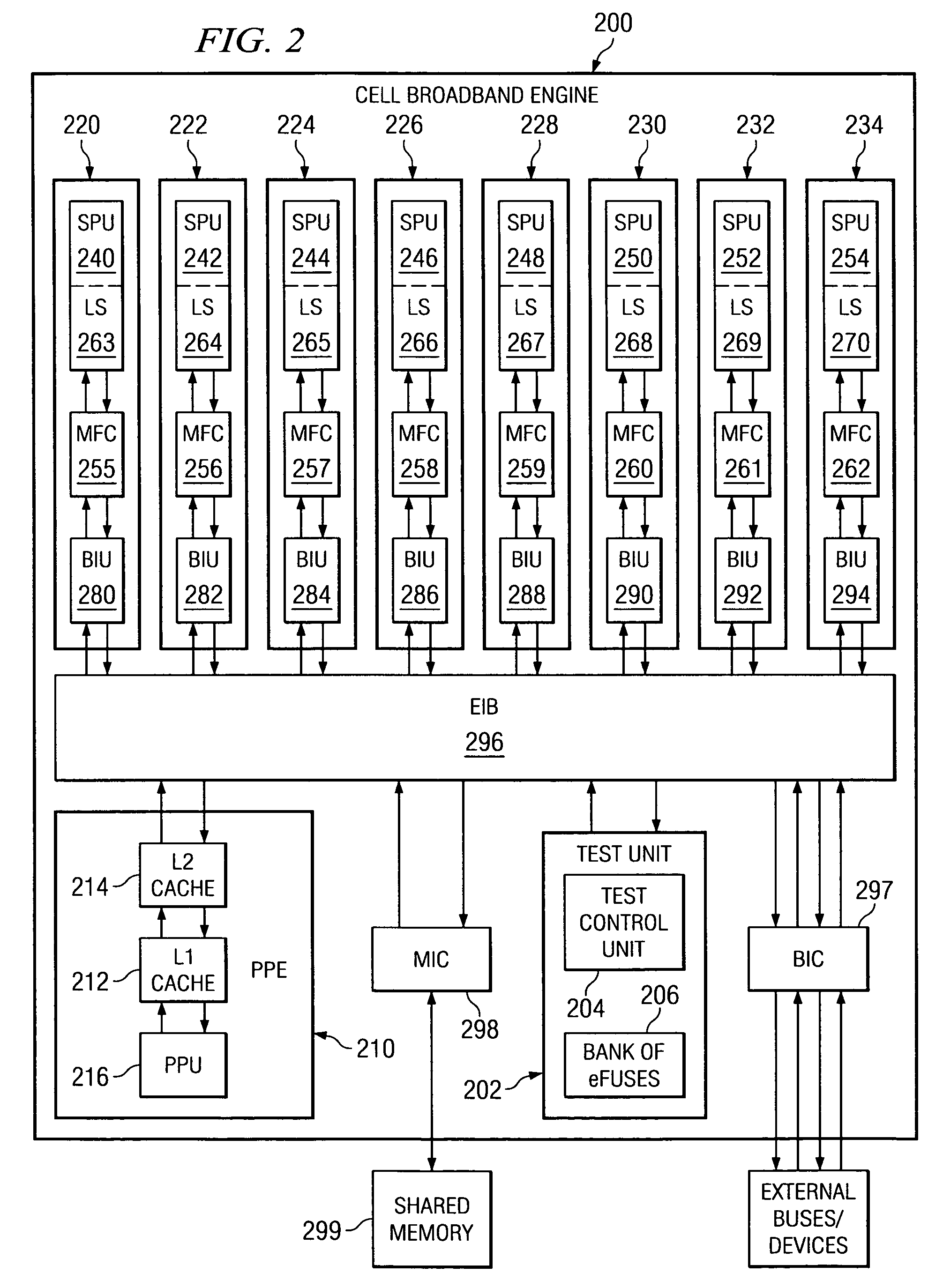

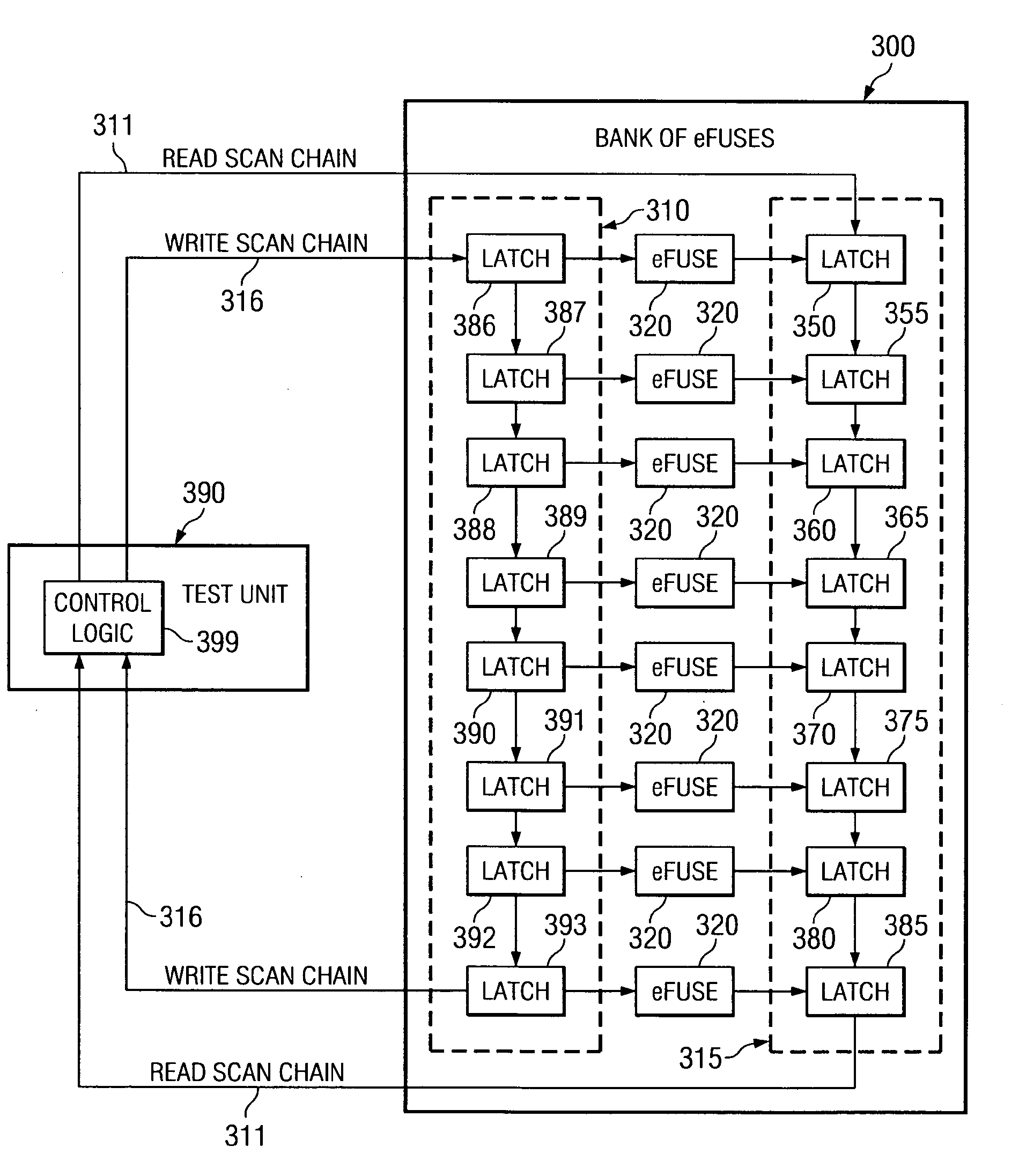

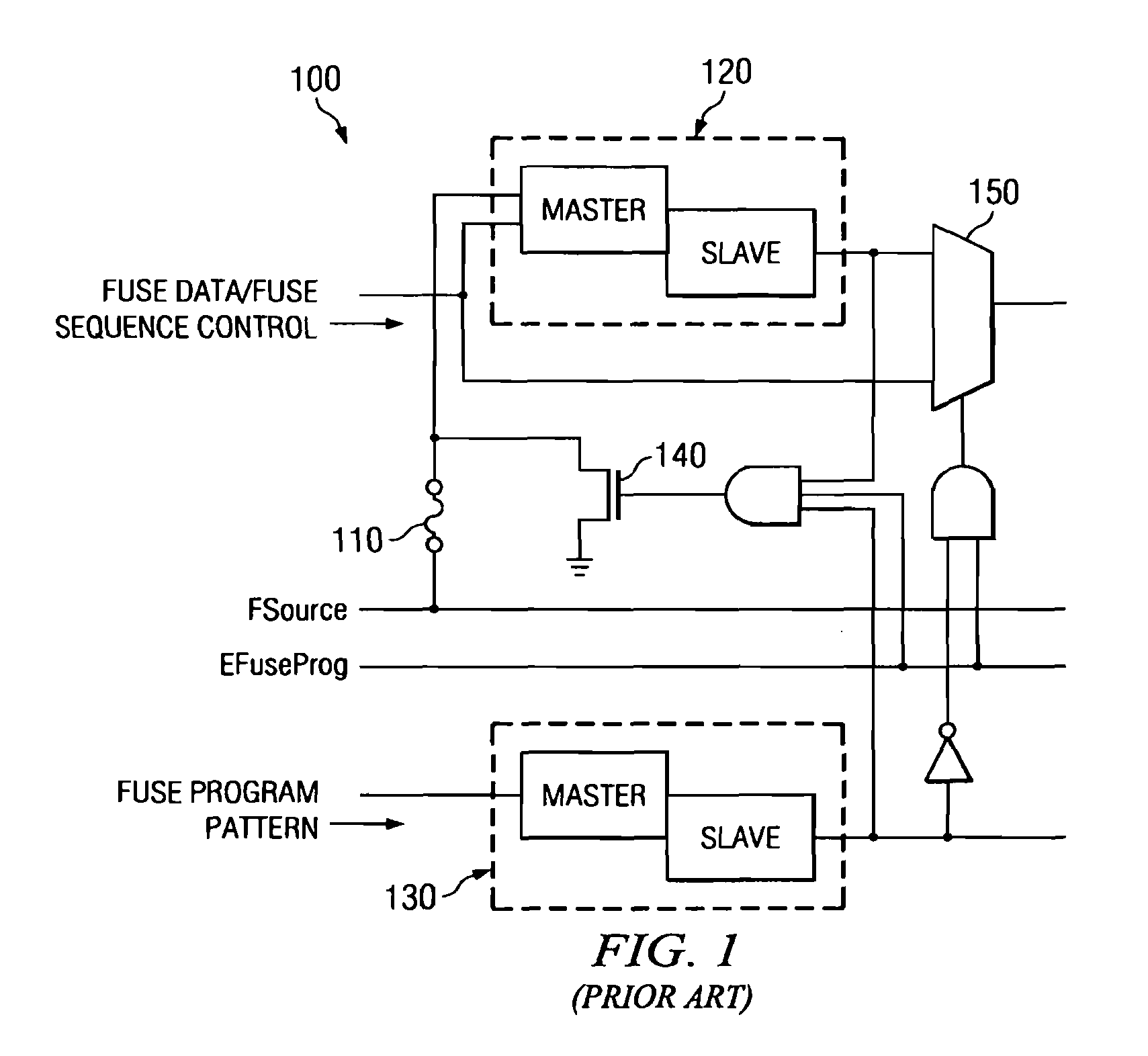

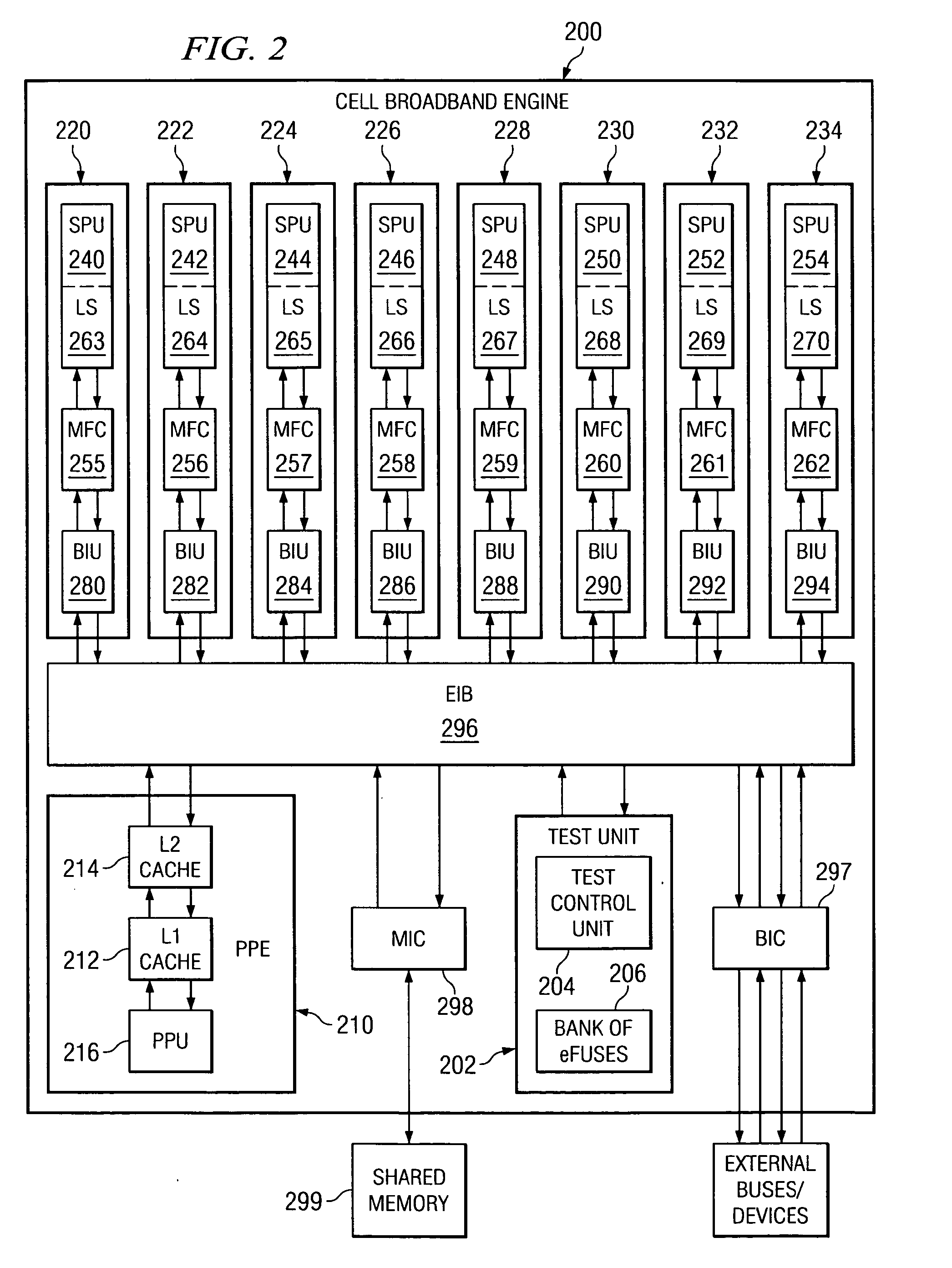

eFuse programming data alignment verification apparatus and method

InactiveUS20070121411A1Avoid programmingElectronic circuit testingRead-only memoriesLogic cellData signal

An eFuse data alignment verification apparatus and method are provided. Alignment latches are provided in a series of latch units of a write scan chain and a logic unit is coupled to the alignment latches. A sequence of data that is scanned-into the series of latch units of the write scan chain preferably includes alignment data values. These alignment data values are placed in positions within the sequence of data that, if the sequence of data is properly scanned-into the series of latch units, cause the data values to be stored in the alignment latches. The logic unit receives data signals from the alignment latches and determines if the proper pattern of data values is stored in the alignment latches. If the proper pattern of data values is present in the alignment latches, then the data is aligned and a program enable signal is sent to the bank of eFuses.

Owner:IBM CORP +1

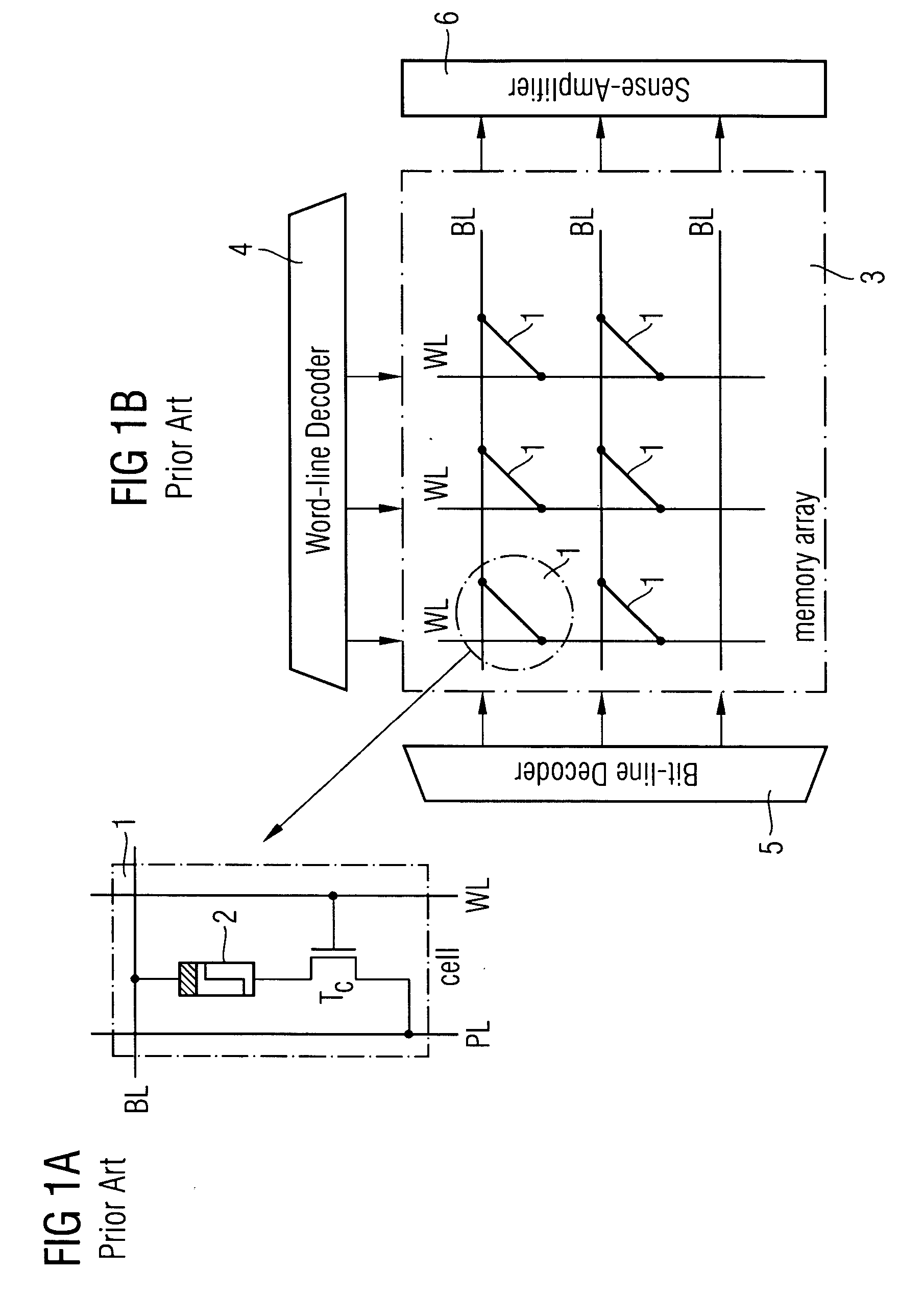

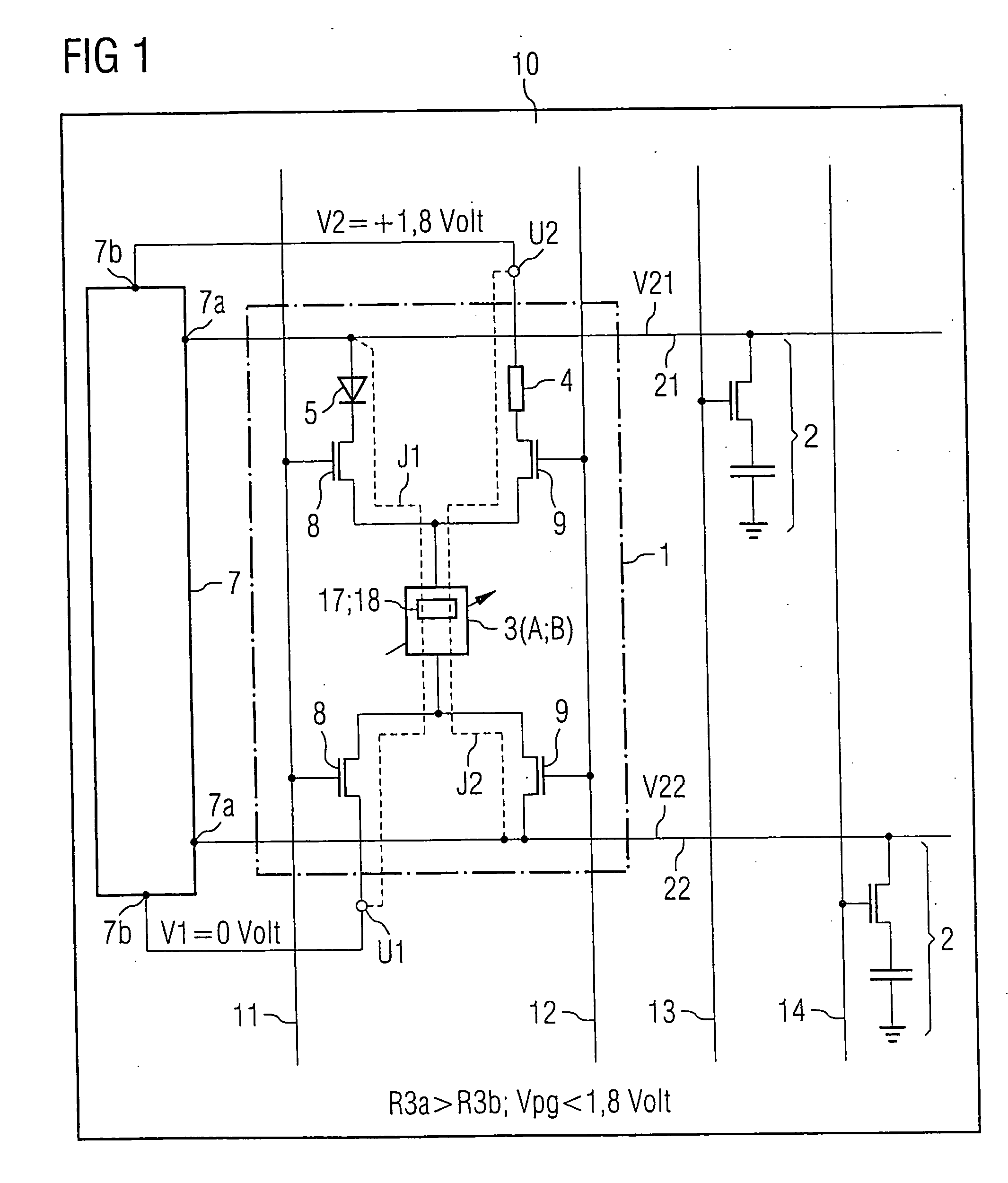

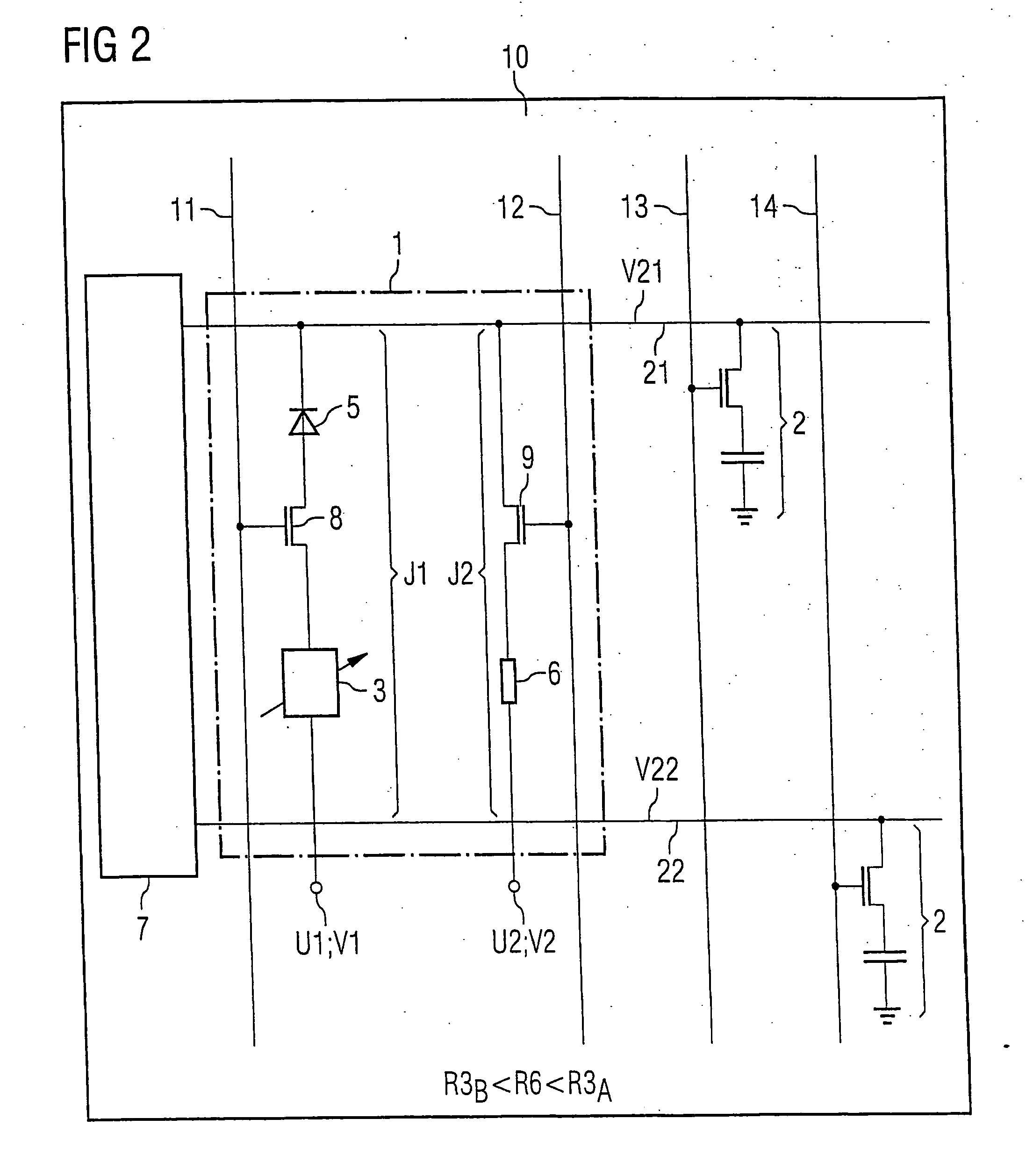

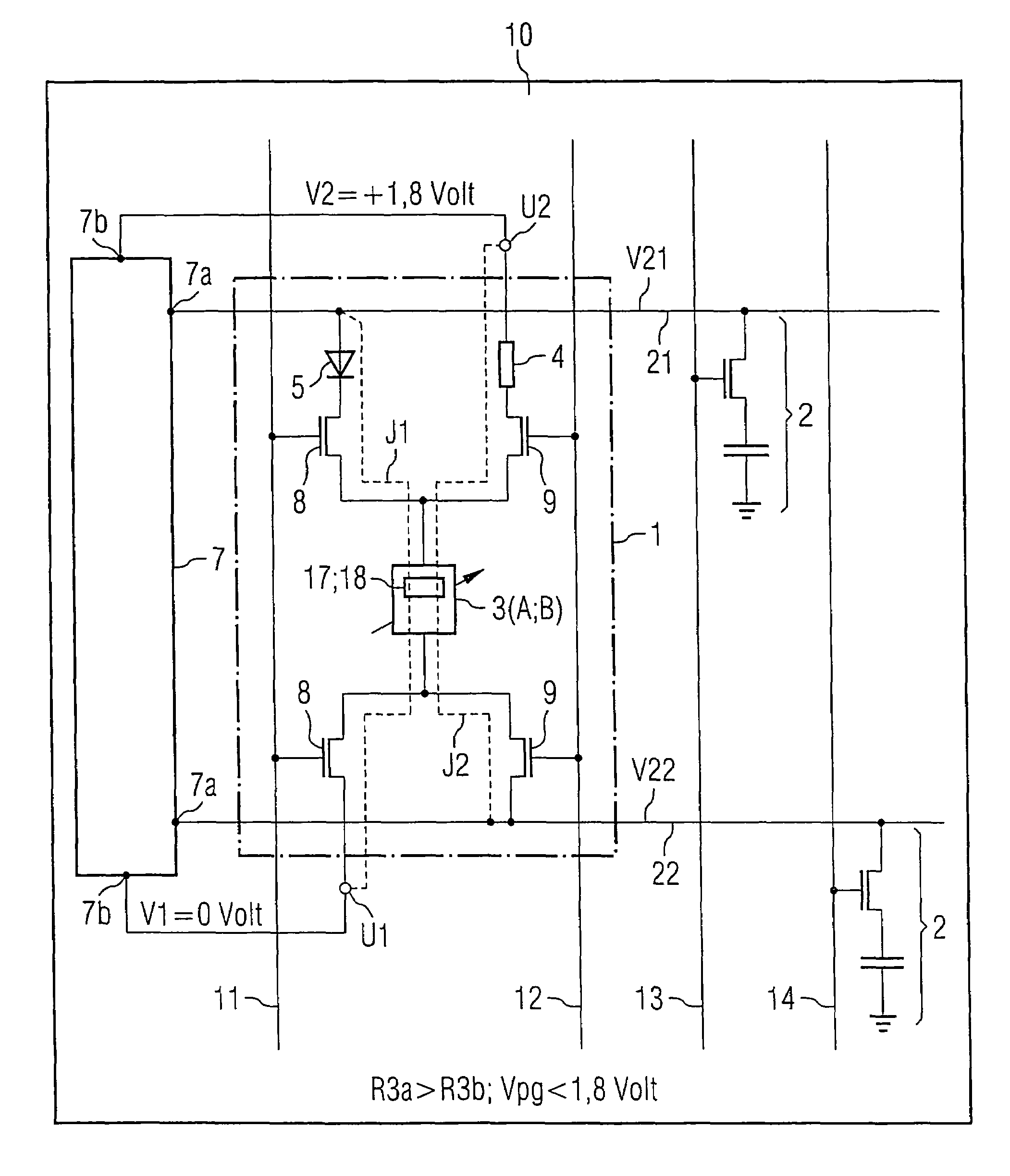

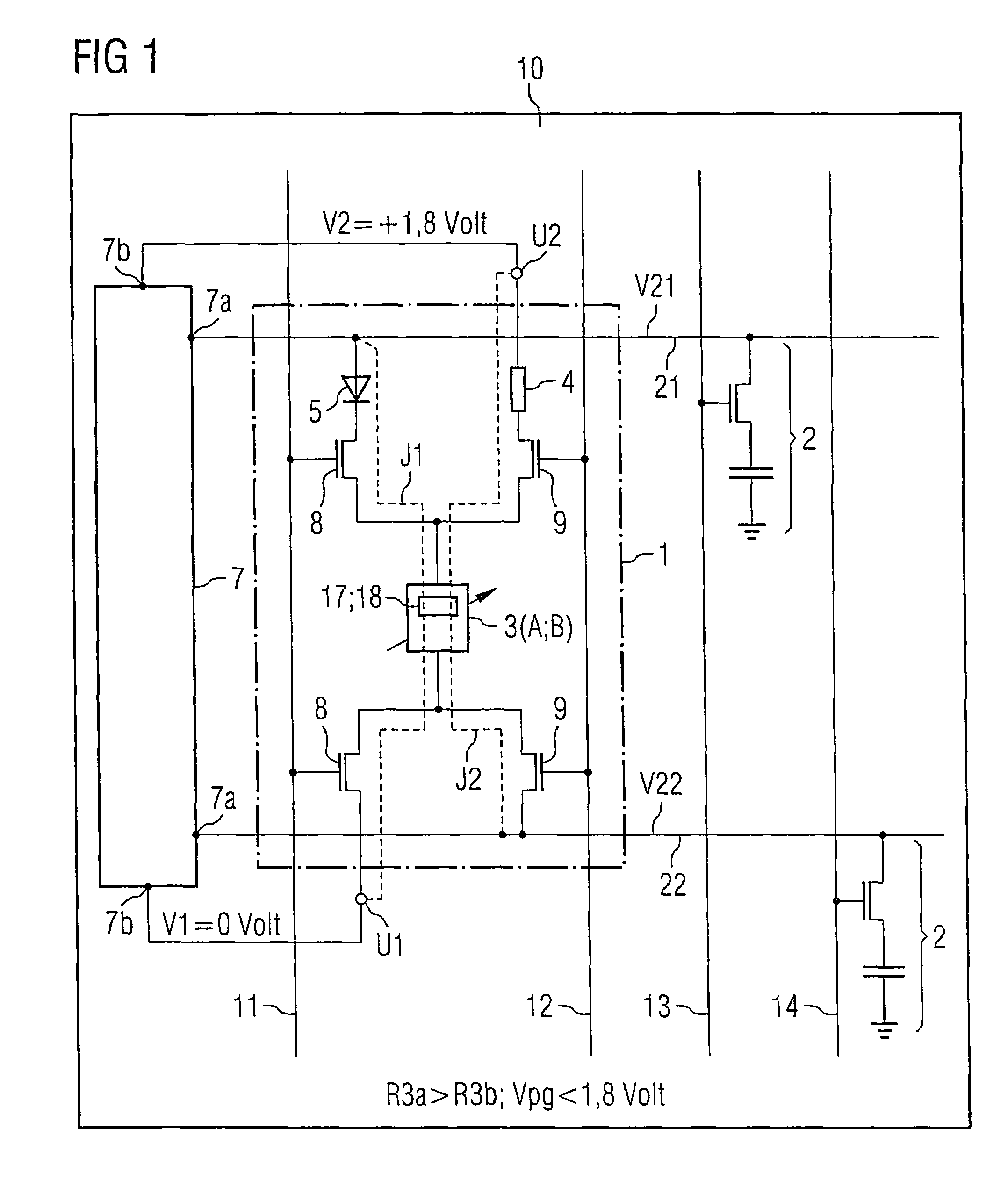

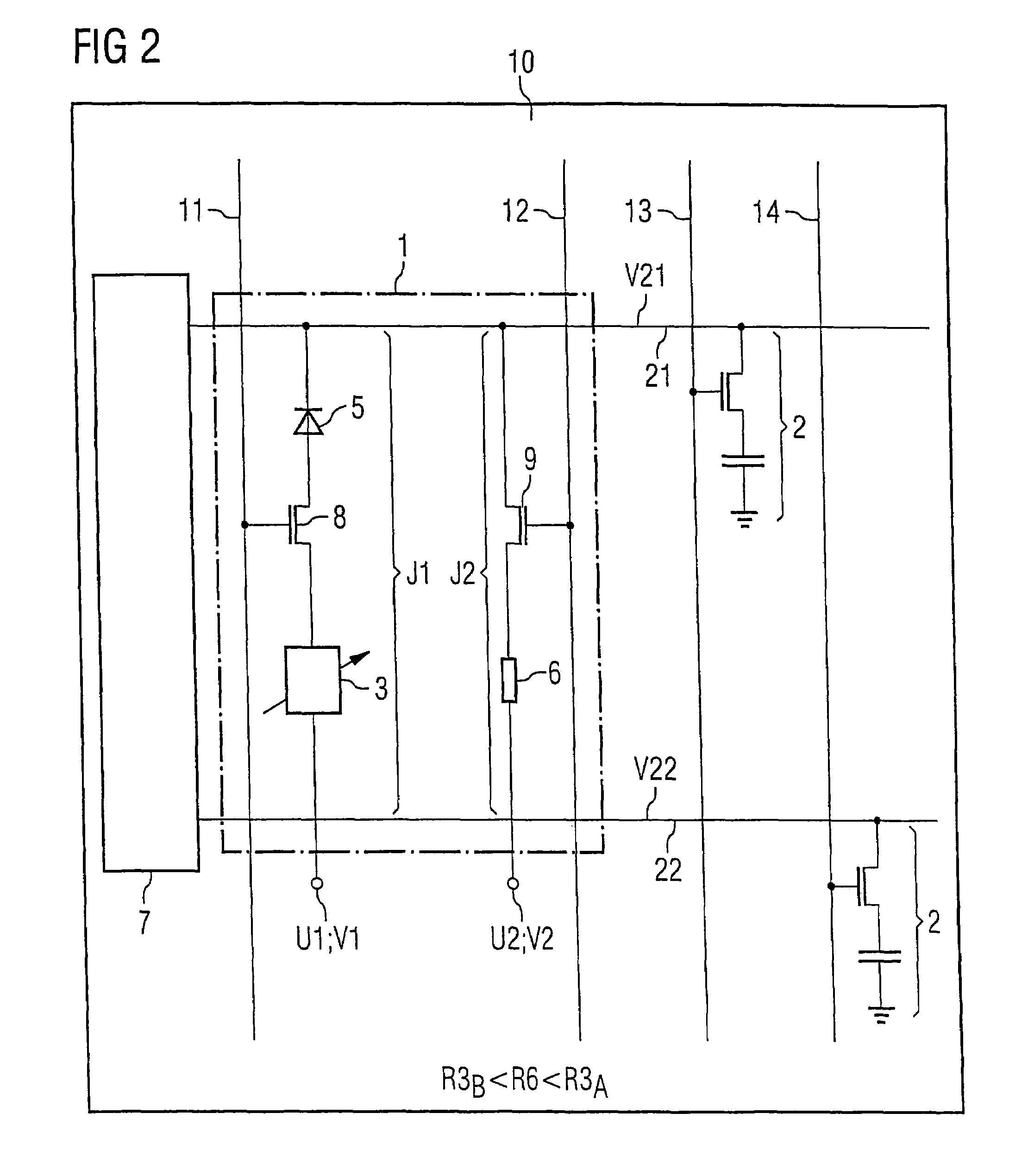

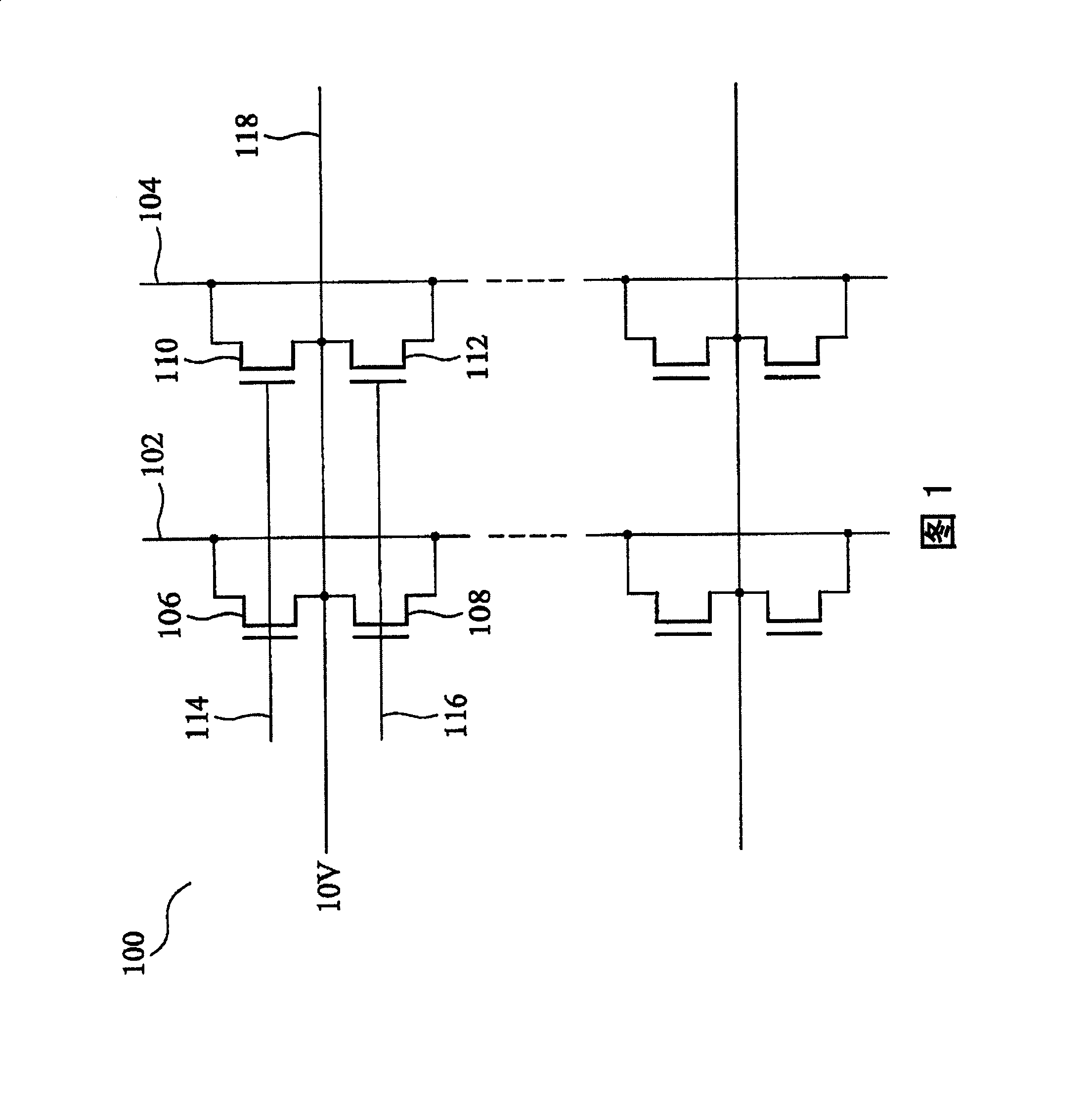

Nonvolatile memory cell and methods for operating a nonvolatile memory cell

A nonvolatile memory cell (1) can be integrated in space-saving fashion into a semiconductor circuit (10) intended for volatile storage with the aid of volatile memory cells (2). The memory cell (1) has a programmable component (3) having an electrical resistance that can be altered by reprogramming, and also first (8) and second switching elements (9), which switch a first current path (J1) or a second current path (J2) in conducting fashion upon activation of optionally a first (11) or a second word line (12). At least one of the two current paths leads via the programmable component (3). Potentials of two bit lines (21, 22) to which the memory cell (1) according to the invention is connected can be altered as a result of the first or the second current path (J1, J2) being activated temporarily. The memory cell (1) permanently stores an item of digital information and can be driven by word lines (11, 12) and bit lines (21, 22) such as are conventionally used in volatile semiconductor memories (10). The invention opens up the possibility of integrating volatile and nonvolatile memory cells into a common memory cell array.

Owner:POLARIS INNOVATIONS LTD

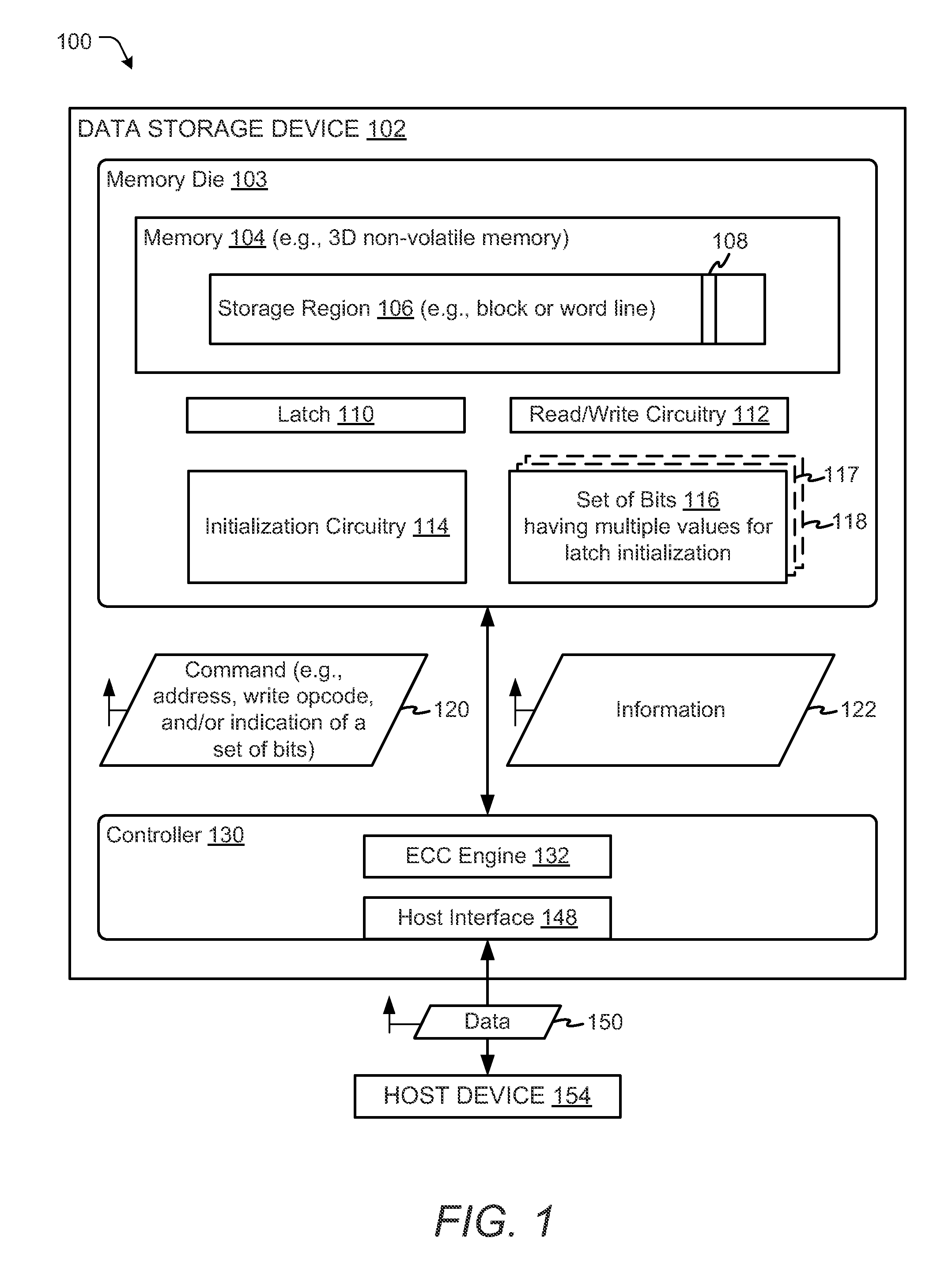

Latch initialization for a data storage device

ActiveUS20160099065A1Total current dropEliminate the effects ofRead-only memoriesDigital storageComputer hardwareComputer architecture

Owner:SANDISK TECH LLC

Method and apparatus for programming nonvolatile memory

InactiveUS7593264B2Weakening rangeAvoid programmingRead-only memoriesDigital storageBit lineComputer science

Embodiments of addressing the programming disturb effect are shown. A medium voltage having a magnitude between the programming voltage and ground is applied to a metal bit line among the cells that are subject to the program disturb effect.

Owner:MACRONIX INT CO LTD

Method and Apparatus for Programming Nonvolatile Memory

InactiveUS20070159887A1Weakening rangeAvoid programmingRead-only memoriesDigital storageVoltageNon-volatile memory

Embodiments of addressing the programming disturb effect are shown. A medium voltage having a magnitude between the programming voltage and ground is applied to a metal bit line among the cells that are subject to the program disturb effect.

Owner:MACRONIX INT CO LTD

eFuse programming data alignment verification apparatus and method

An eFuse data alignment verification apparatus and method are provided. Alignment latches are provided in a series of latch units of a write scan chain and a logic unit is coupled to the alignment latches. A sequence of data that is scanned-into the series of latch units of the write scan chain preferably includes alignment data values. These alignment data values are placed in positions within the sequence of data that, if the sequence of data is properly scanned-into the series of latch units, cause the data values to be stored in the alignment latches. The logic unit receives data signals from the alignment latches and determines if the proper pattern of data values is stored in the alignment latches. If the proper pattern of data values is present in the alignment latches, then the data is aligned and a program enable signal is sent to the bank of eFuses.

Owner:INT BUSINESS MASCH CORP +1

Nonvolatile memory cell and methods for operating a nonvolatile memory cell

A nonvolatile memory cell (1) can be integrated in space-saving fashion into a semiconductor circuit (10) intended for volatile storage with the aid of volatile memory cells (2). The memory cell (1) has a programmable component (3) having an electrical resistance that can be altered by reprogramming, and also first (8) and second switching elements (9), which switch a first current path (J1) or a second current path (J2) in conducting fashion upon activation of optionally a first (11) or a second word line (12). At least one of the two current paths leads via the programmable component (3). Potentials of two bit lines (21, 22) to which the memory cell (1) according to the invention is connected can be altered as a result of the first or the second current path (J1, J2) being activated temporarily. The memory cell (1) permanently stores an item of digital information and can be driven by word lines (11, 12) and bit lines (21, 22) such as are conventionally used in volatile semiconductor memories (10). The invention opens up the possibility of integrating volatile and nonvolatile memory cells into a common memory cell array.

Owner:POLARIS INNOVATIONS LTD

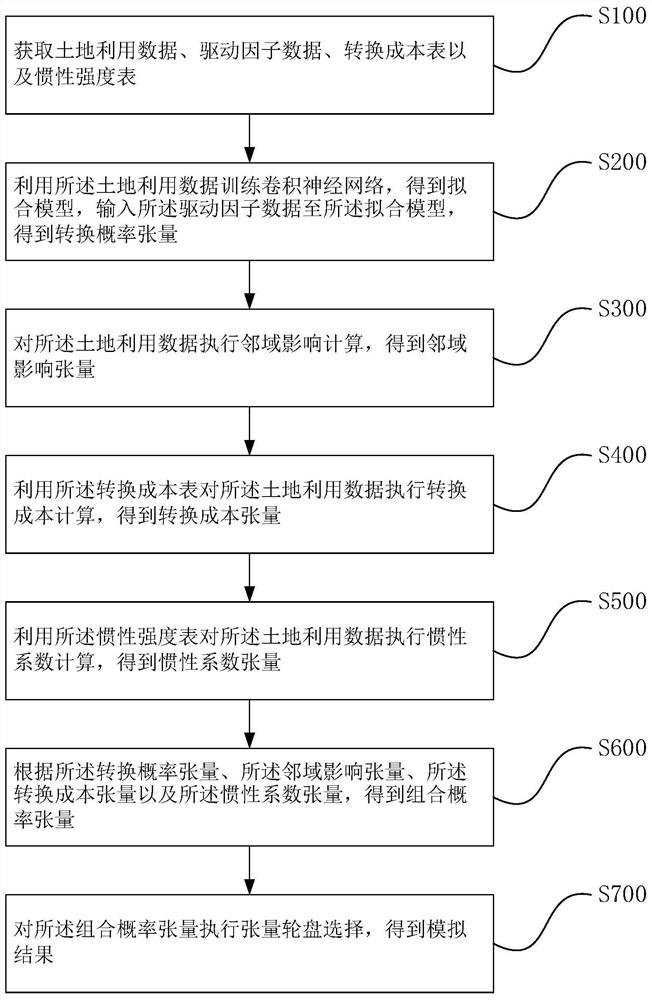

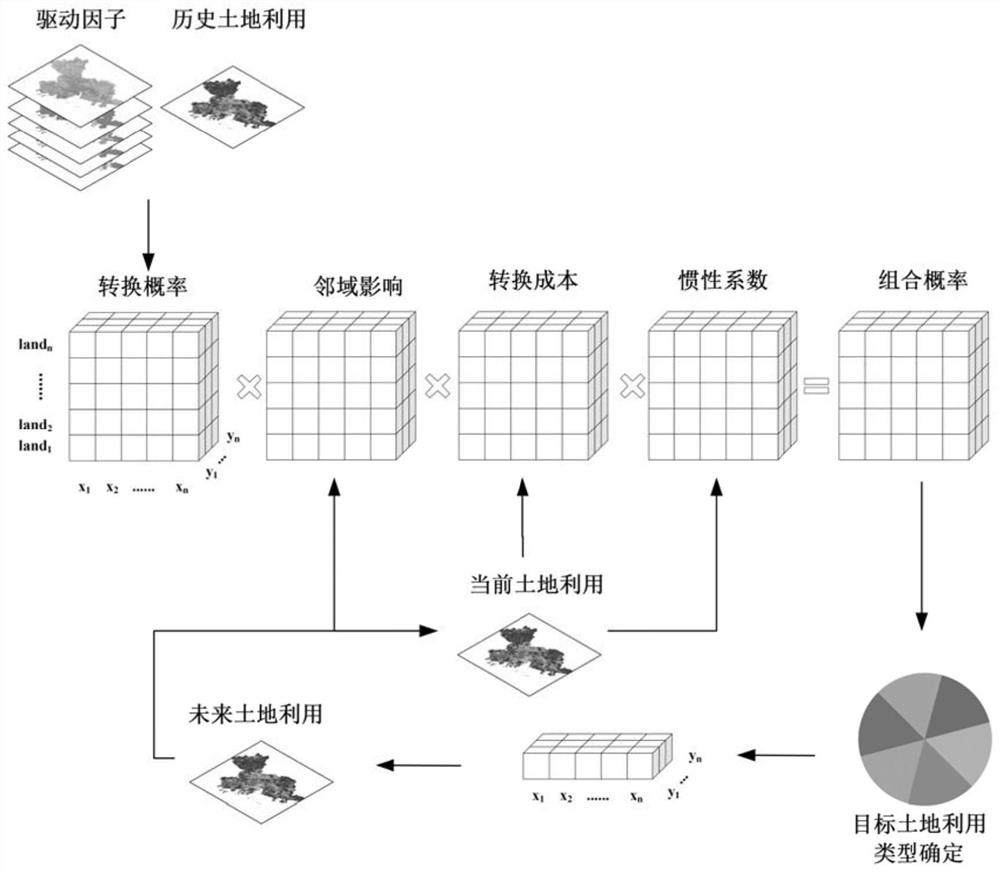

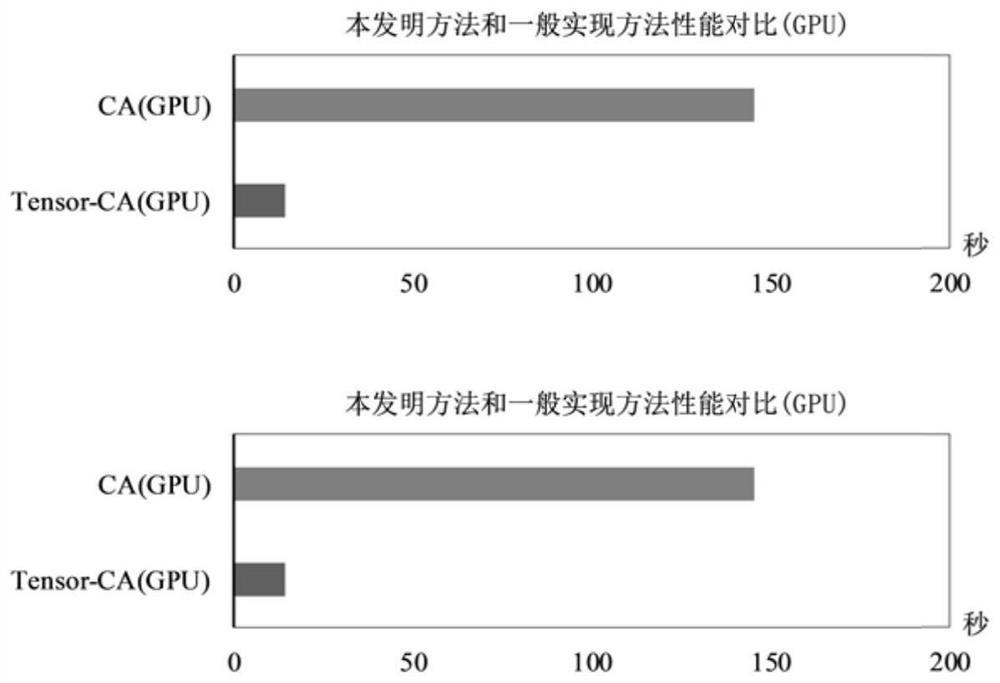

Tensor-based land utilization simulation method, system and device and storage medium

ActiveCN111814368AAvoid designAvoid programmingDesign optimisation/simulationNeural architecturesCellular automationSimulation

The invention discloses a tensor-based land utilization simulation method, system and device and a storage medium. The method comprises the steps of obtaining land utilization data, driving factor data, a conversion cost table and an inertia intensity table; training a convolutional neural network to obtain a fitting model, and further obtaining a conversion probability tensor; executing neighborhood influence calculation to obtain a neighborhood influence tensor; executing conversion cost calculation to obtain a conversion cost tensor; executing inertia coefficient calculation to obtain an inertia coefficient tensor; obtaining a combined probability tensor according to the conversion probability tensor, the neighborhood influence tensor, the conversion cost tensor and the inertia coefficient tensor; and executing tensor wheel disc selection on the combined probability tensor to obtain a simulation result. According to the method, each part in the land utilization simulation process based on the cellular automaton is formalized into the tensor, and the tensor framework is applied to accelerate the operation, so that the efficient land utilization simulation process is realized while the complex parallel algorithm design and CUDA programming are avoided.

Owner:广东国地规划科技股份有限公司 +1

eFuse Programming Data Alignment Verification Apparatus and Method

InactiveUS20080320349A1Avoid programmingElectronic circuit testingRead-only memoriesData signalData value

Owner:INT BUSINESS MASCH CORP

Flash array system and program current stablilization method

Owner:TAIWAN SEMICON MFG CO LTD

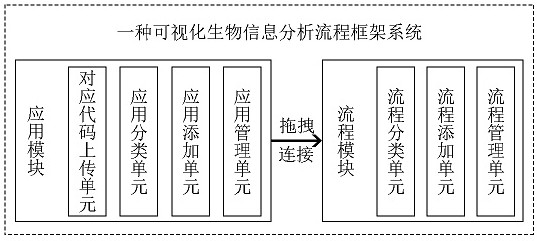

Visual biological information analysis process framework system

InactiveCN112382343AEasy to analyzeReduce the difficulty of analysisData visualisationInstrumentsSimulationSoftware engineering

The invention relates to the field of biological information, and discloses a visual biological information analysis process framework system which comprises an application module and a process module. A plurality of configured biological information applications and software capable of meeting basic conventional analysis requirements of biological information analysis are arranged in the system,direct use of a user is supported, the process is visualized, the user can analyze the biological information more visually, meanwhile, and the system supports custom configuration of the applicationsand the process. A user can configure applications for the first time and then use the applications in multiple processes, the processes can automatically drag the corresponding applications according to requirements, the personalized analysis requirements of the user are met, various biological information analysis scenes can be applied, and the processes are configured in a'drag connection 'mode in the user-defined processes. Operation in the aspect of computer programming is avoided while the process is visualized, the difficulty of biological information analysis is reduced, and the analysis efficiency is improved.

Owner:天津奇云诺德生物医学有限公司

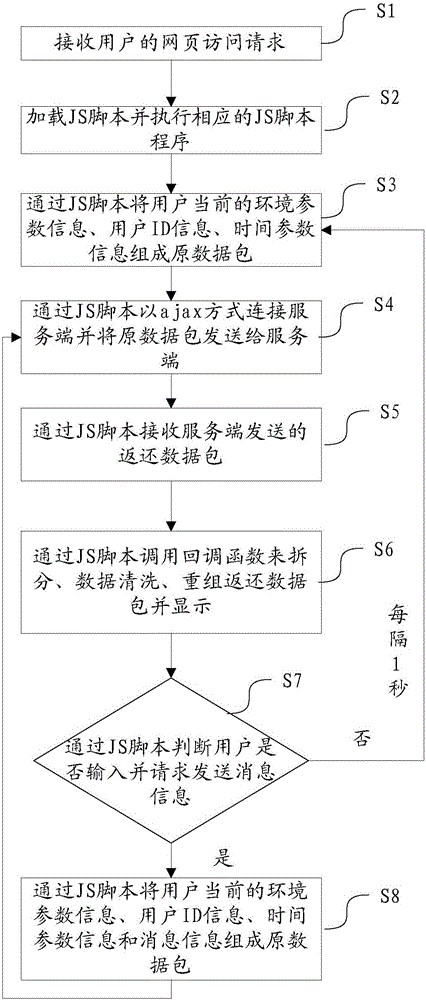

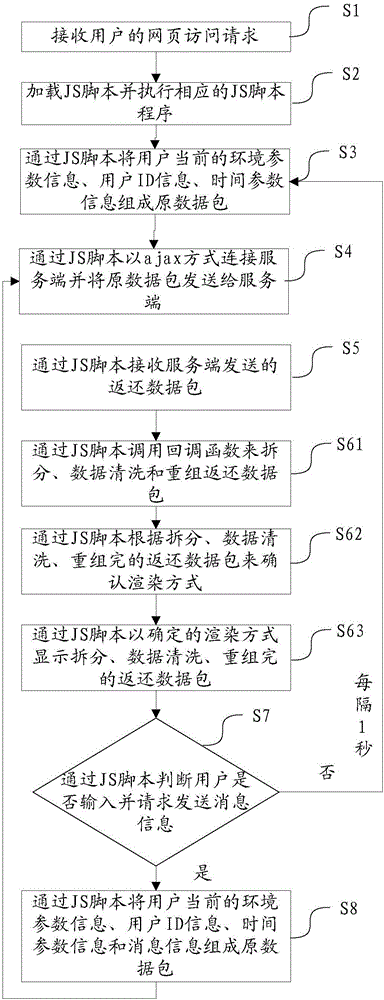

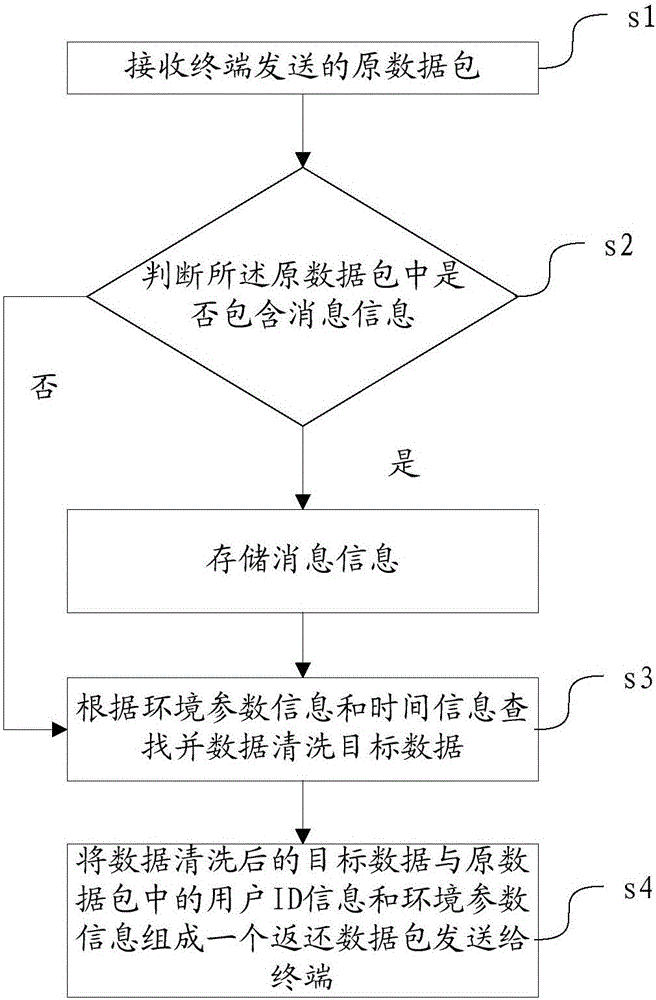

Terminal, server side and instant messaging method and system

PendingCN107528769AImprove mobilityAvoid socket programmingData switching networksData packOriginal data

The application provides a terminal, a server side and an instant messaging method and system. The method comprises the following steps: S1, receiving a webpage access request of a user; S2, loading a JS (JavaScript) script and executing the JS script; S3, constructing current information of the user into an original data packet through the JS script; S4, establishing a connection in an ajax way through the JS script, and transmitting the original data packet to the server side; S5, receiving a returned data packet transmitted by the server side through the JS script; S6, calling a callback function through the JS script in order to process and display the returned data packet; S7, judging whether the user inputs message information and requests transmission of the message information or not through the JS script, if not, executing the steps S3 to S7 repeatedly at an interval of 1 second, and if so, executing a step S8 and then executing the steps S4 to S7; and S8, constructing the current information of the user and the message information through the JS script to obtain the original data packet. The terminal, the server side and the instant messaging method and system are higher in mobility, do not occupy excessive server side resources, and can contribute to lowering of development cost.

Owner:天津转知汇技术成果转化有限公司