Patents

Literature

1110 results about "Error processing" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Definition: A processing error is the error in final survey results arising from the faulty implementation of correctly planned implementation methods.

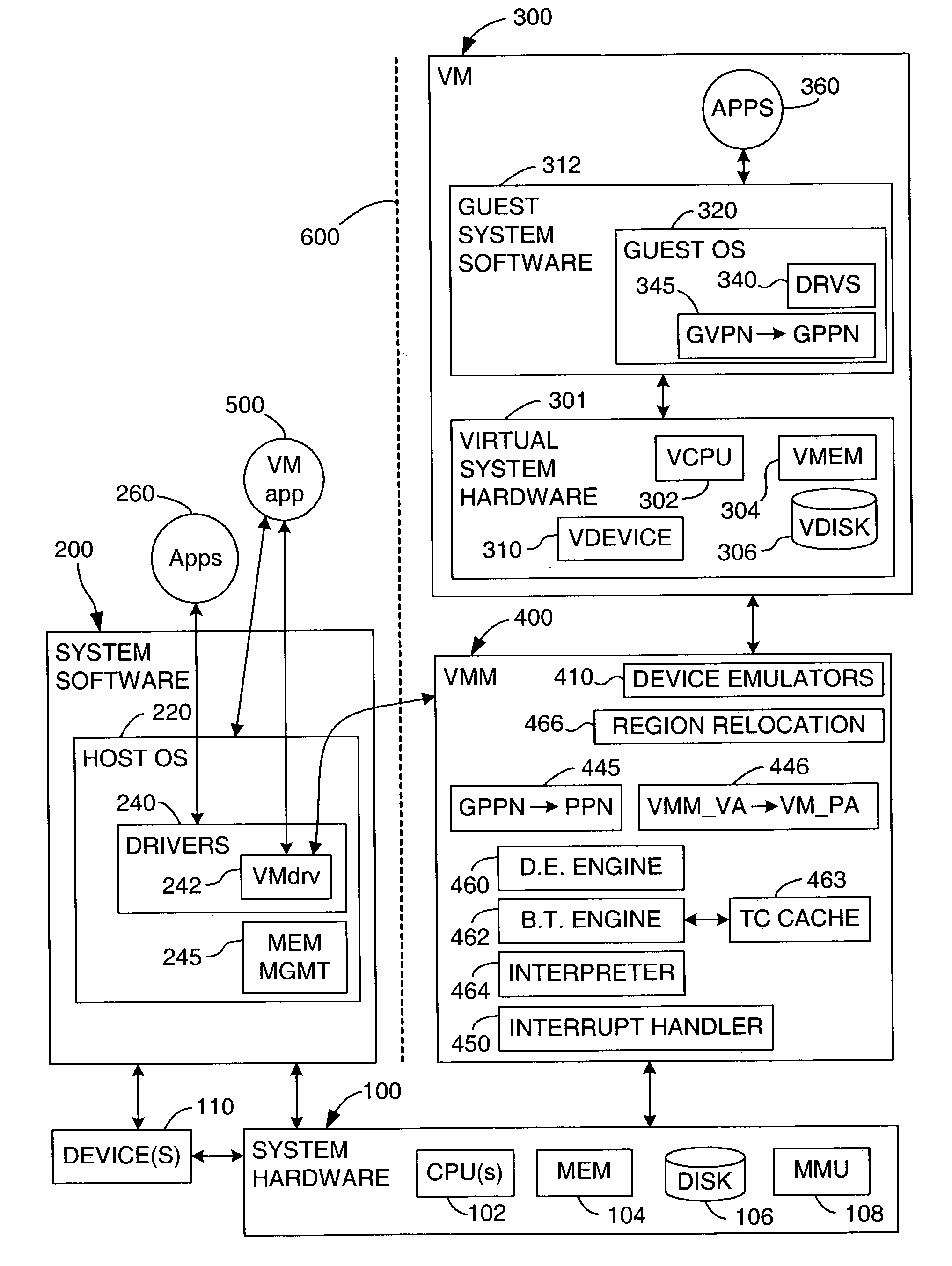

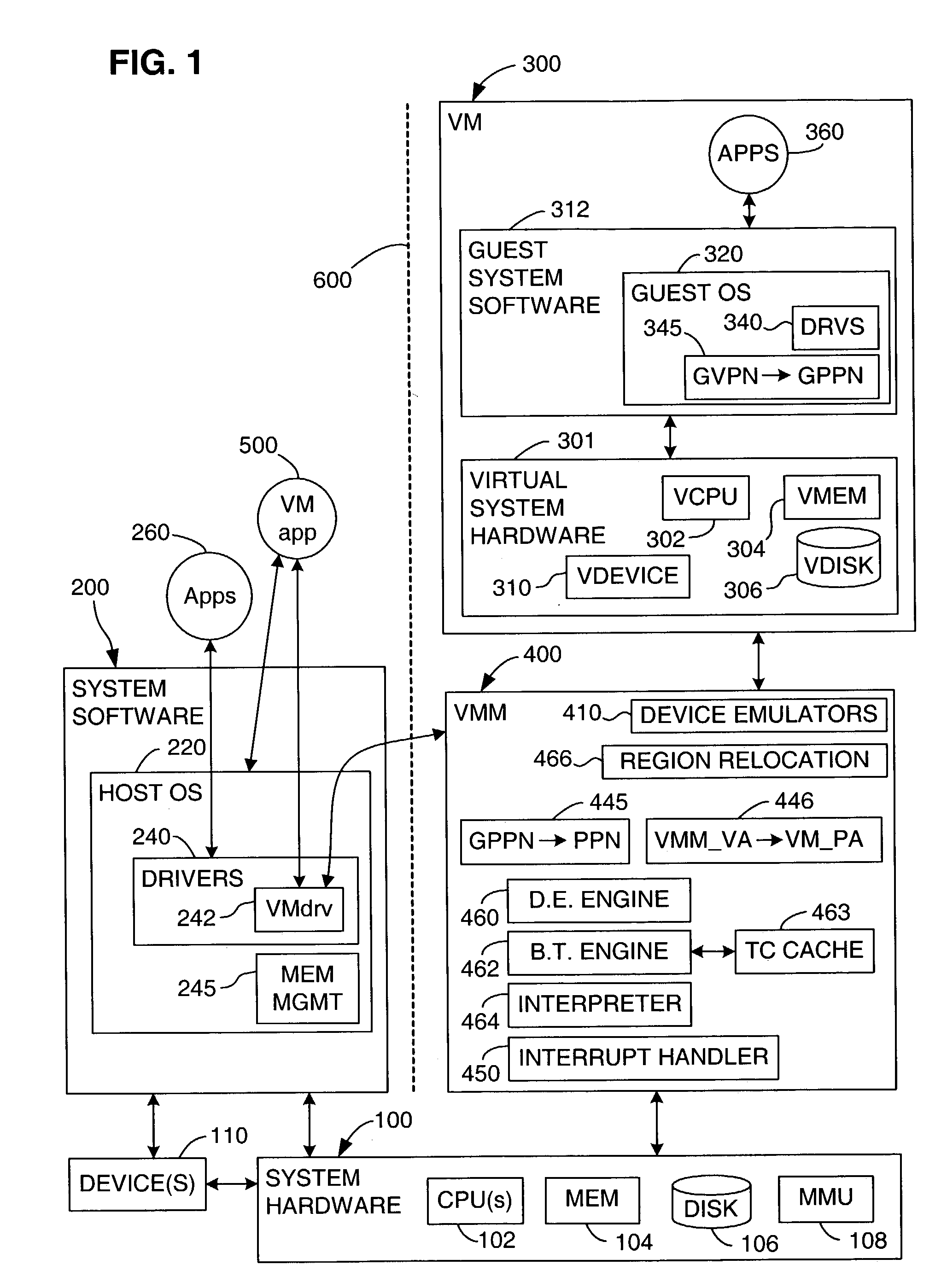

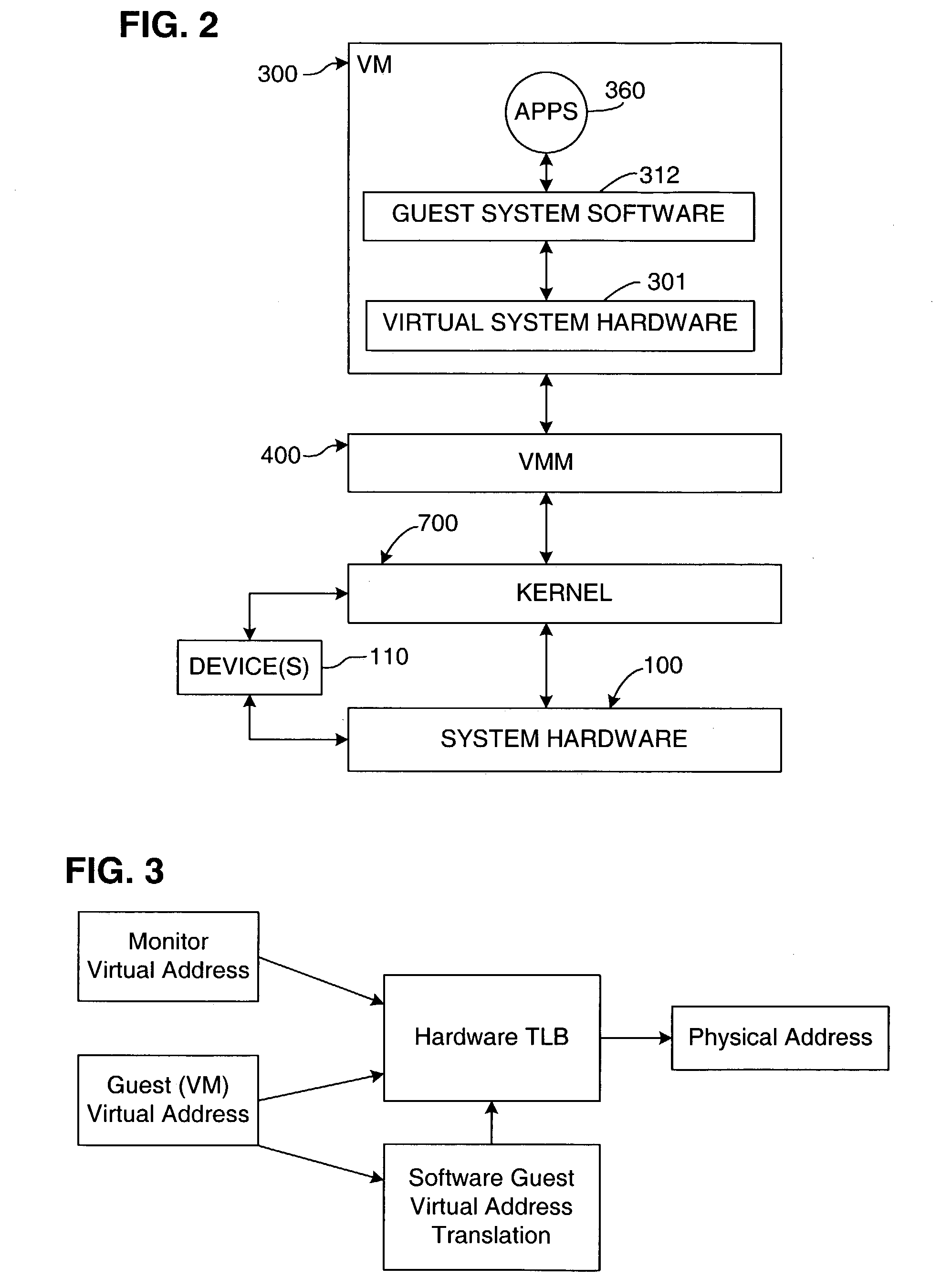

TLB miss fault handler and method for accessing multiple page tables

ActiveUS7111145B1Memory adressing/allocation/relocationComputer security arrangementsVirtual memoryError processing

A virtual memory system implementing the invention provides concurrent access to translations for virtual addresses from multiple address spaces. One embodiment of the invention is implemented in a virtual computer system, in which a virtual machine monitor supports a virtual machine. In this embodiment, the invention provides concurrent access to translations for virtual addresses from the respective address spaces of both the virtual machine monitor and the virtual machine. Multiple page tables contain the translations for the multiple address spaces. Information about an operating state of the computer system, as well as an address space identifier, are used to determine whether, and under what circumstances, an attempted memory access is permissible. If the attempted memory access is permissible, the address space identifier is also used to determine which of the multiple page tables contains the translation for the attempted memory access.

Owner:VMWARE INC

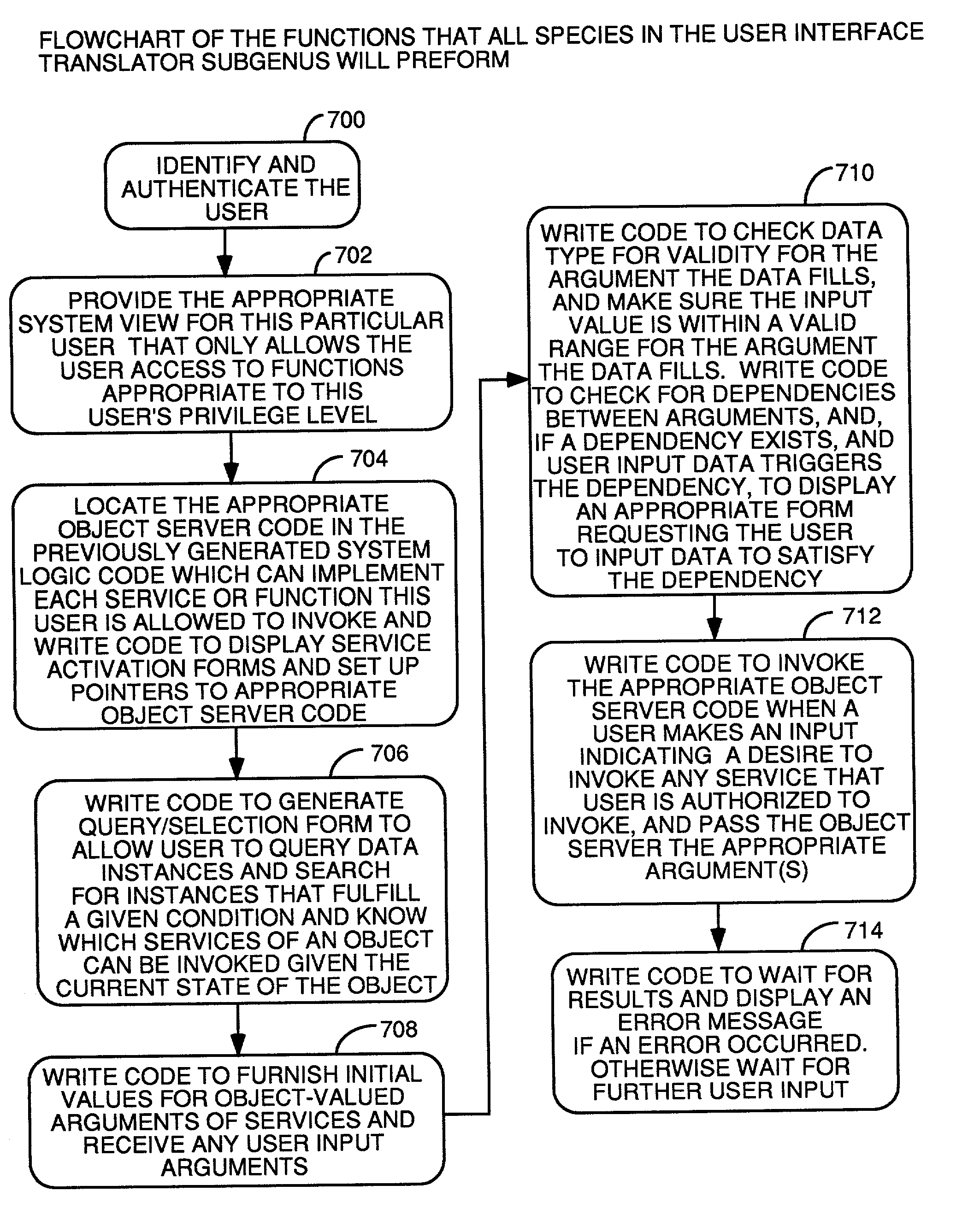

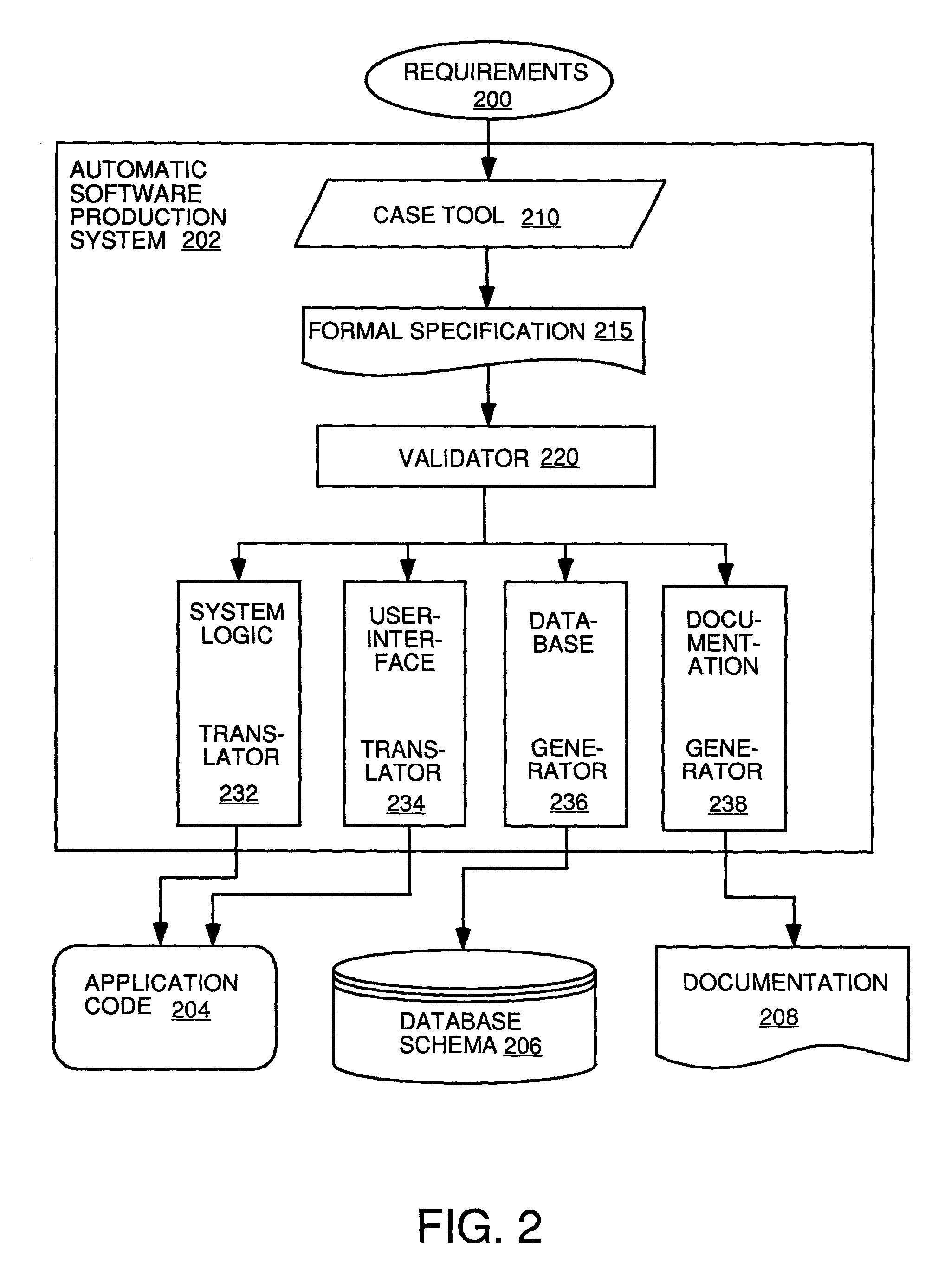

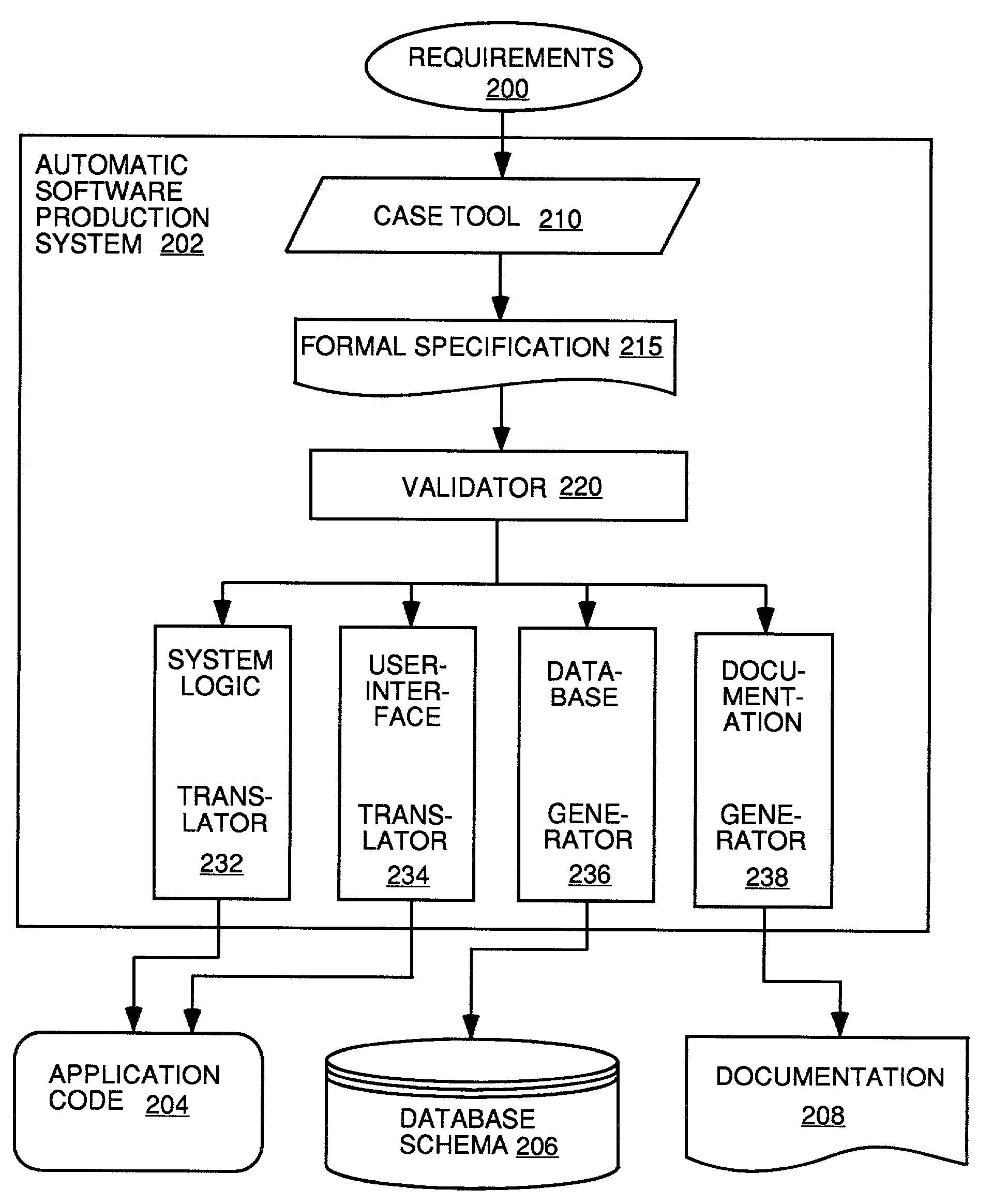

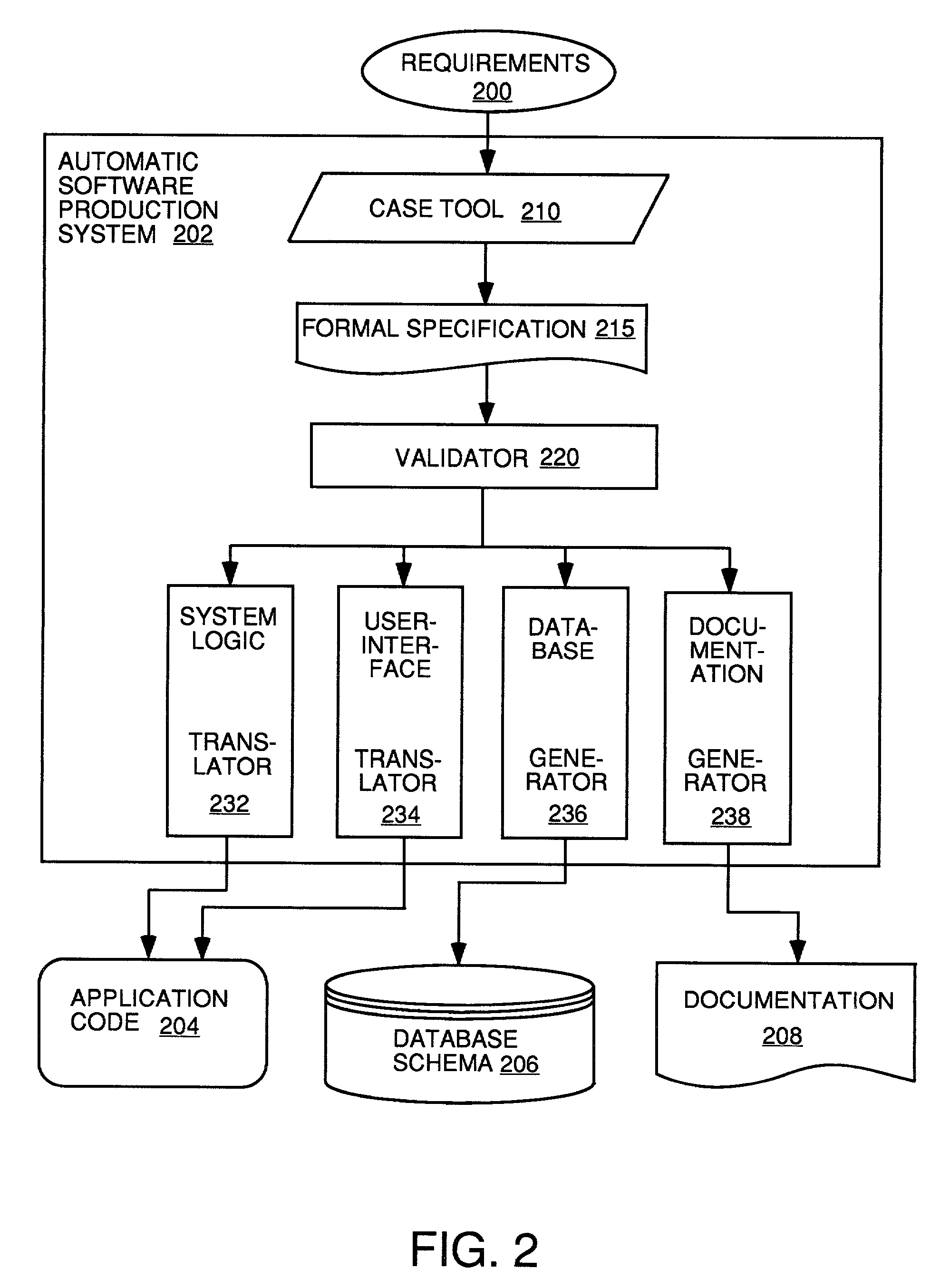

Automatic software production system

InactiveUS7137100B2Shorten the time to marketEasy to useDigital data information retrievalProgram documentationHandling CodeSystem requirements

Owner:SOSY

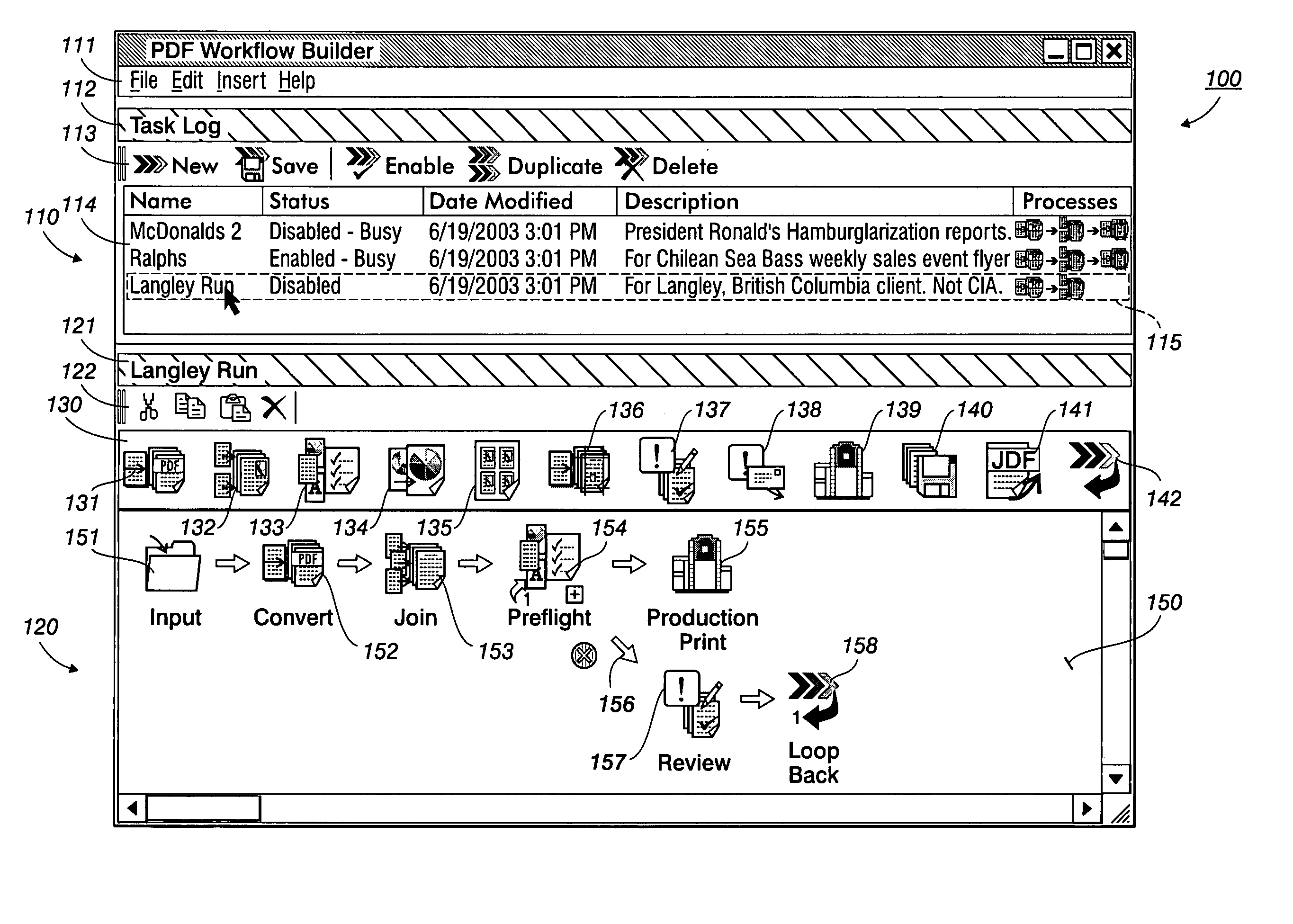

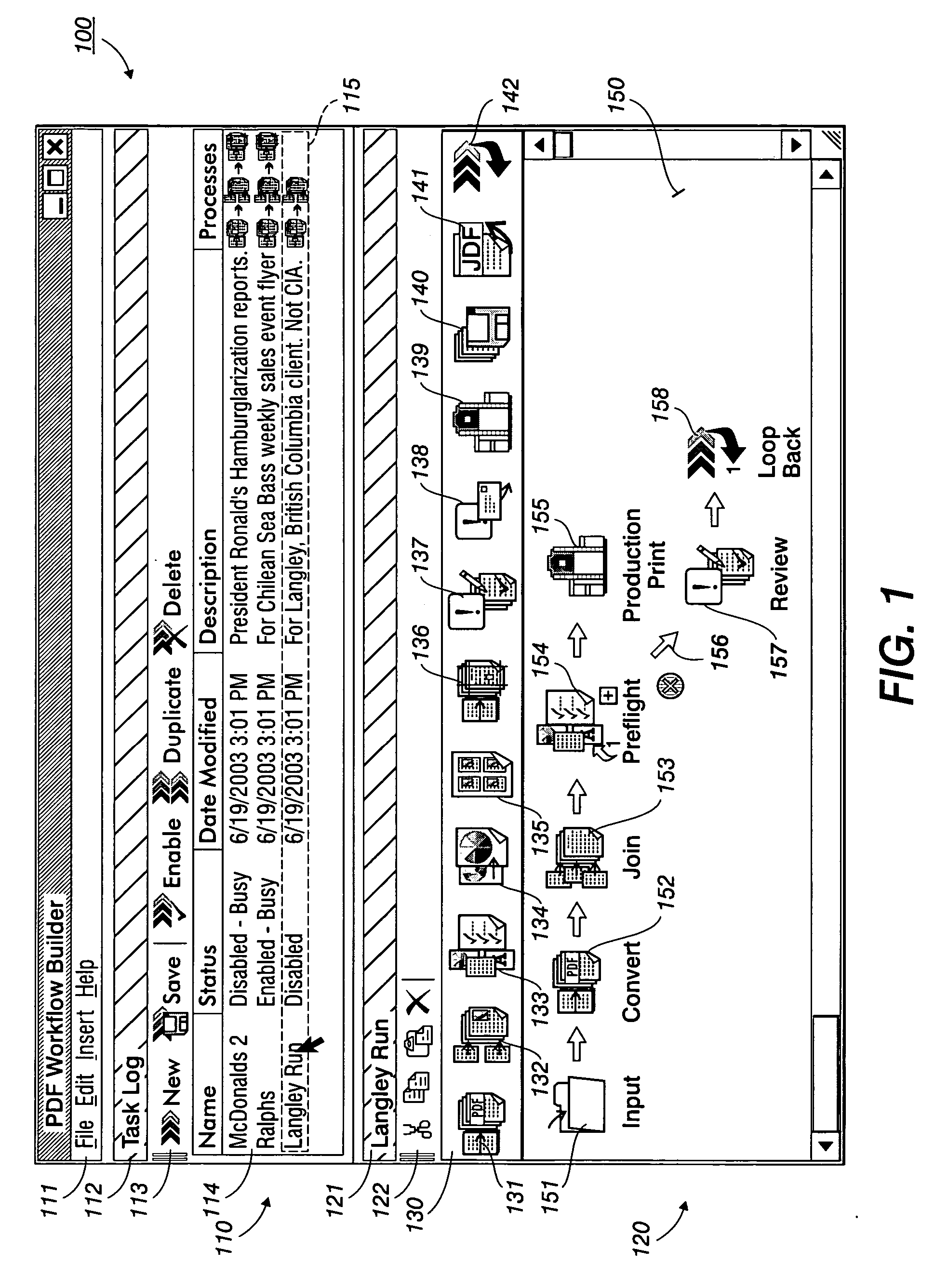

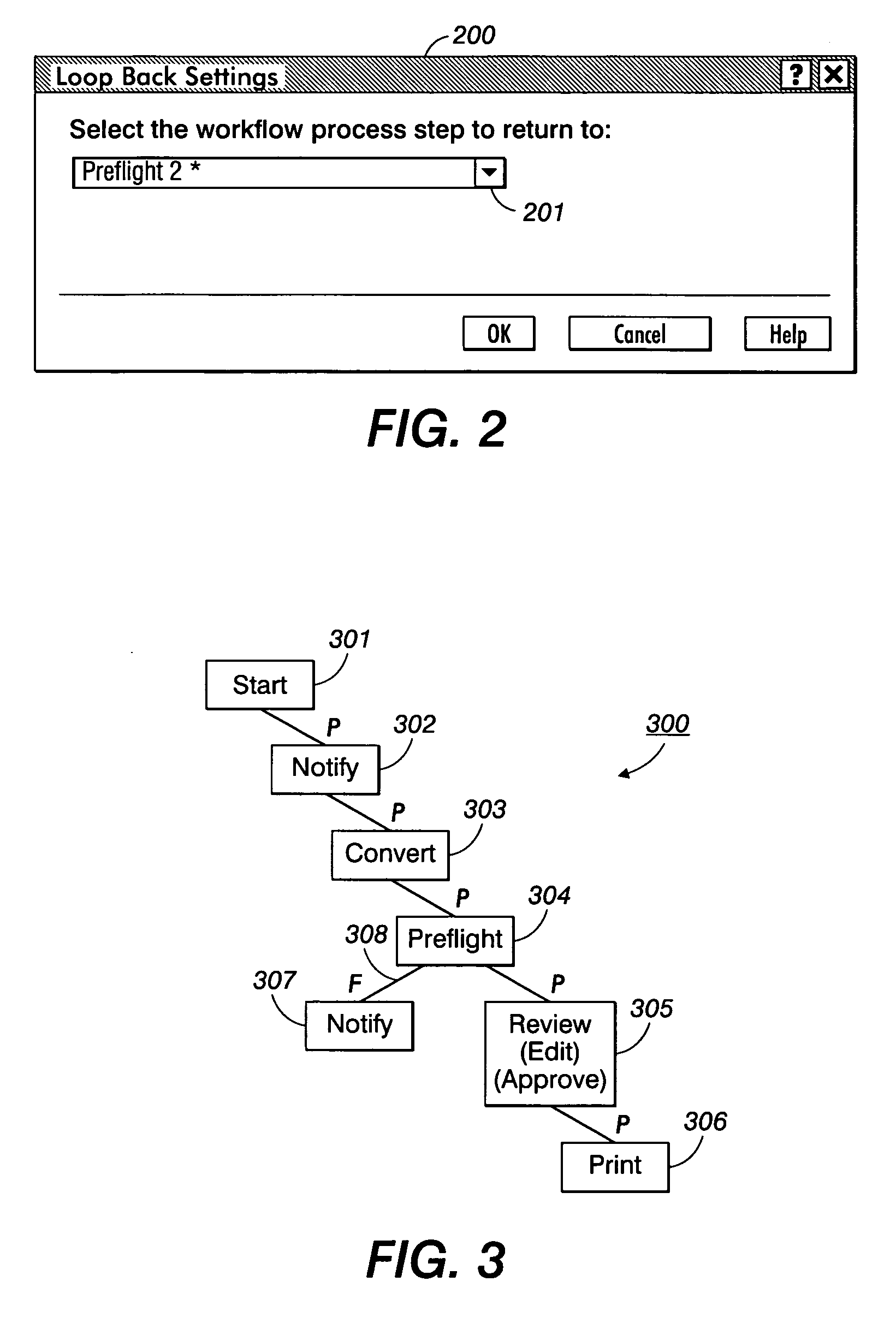

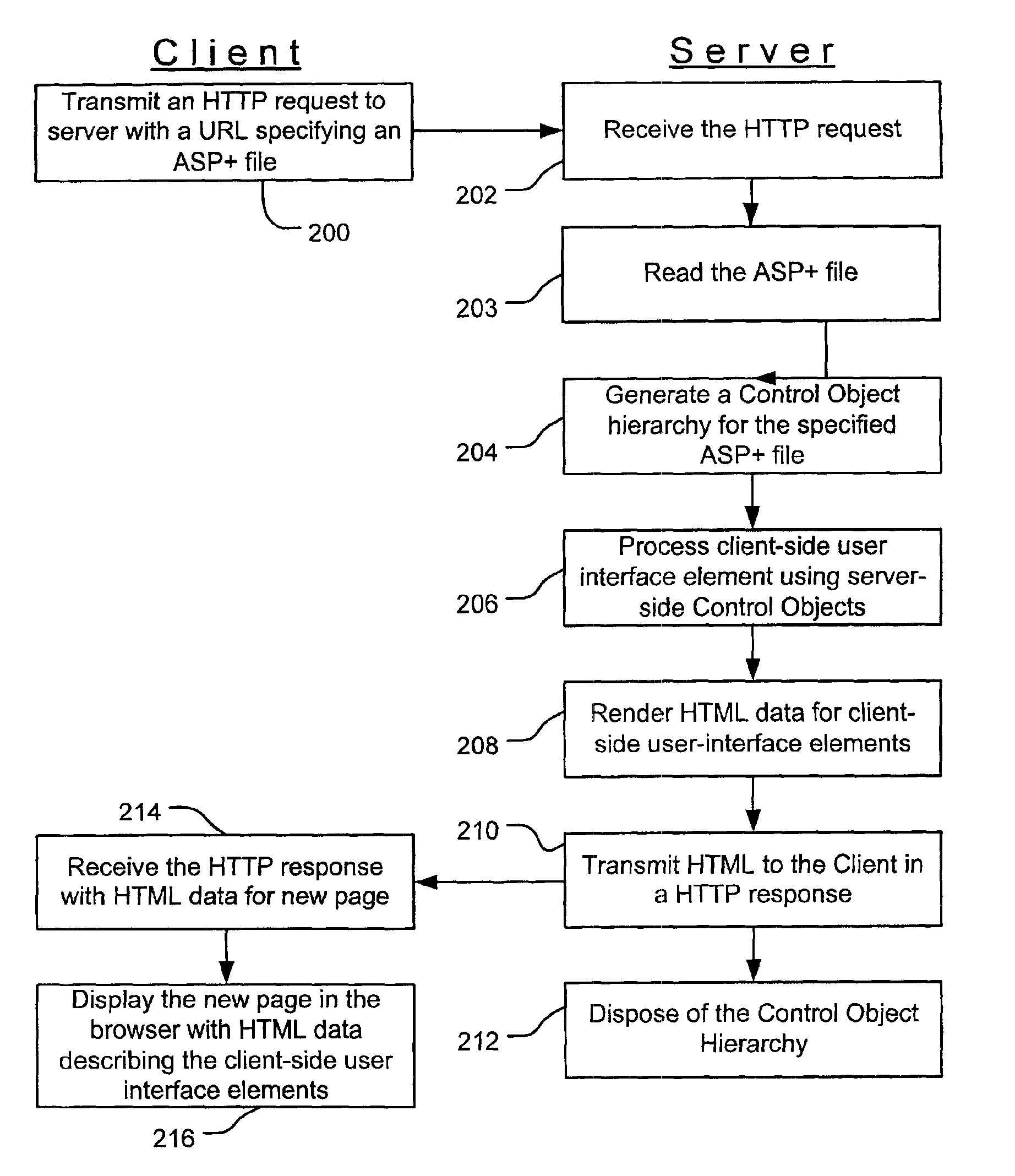

Systems, methods and user interfaces for document workflow construction

InactiveUS20060080616A1Efficient constructionExecution for user interfacesInput/output processes for data processingDrag and dropMain branch

Context sensitive drag-and-drop systems, methods and user interfaces are provided in a Graphical User Interface (GUI) computing environment. Icons representing various tasks may be interactively drag-and-dropped to an adjoining graphically-based workspace in a context-based task-drop location to simply and intuitively construct a graphically-based workflow solution. A collapsible error handling failure branch may be constructed concurrently with the main branch of the workflow process. A loopback path to a higher branch may optionally be constructed for the failure branch. The workflow solution may be applied in a document printing environment for document production, a document copying environment, or an accounting environment, for example, for clear and efficient generation of workflows.

Owner:XEROX CORP

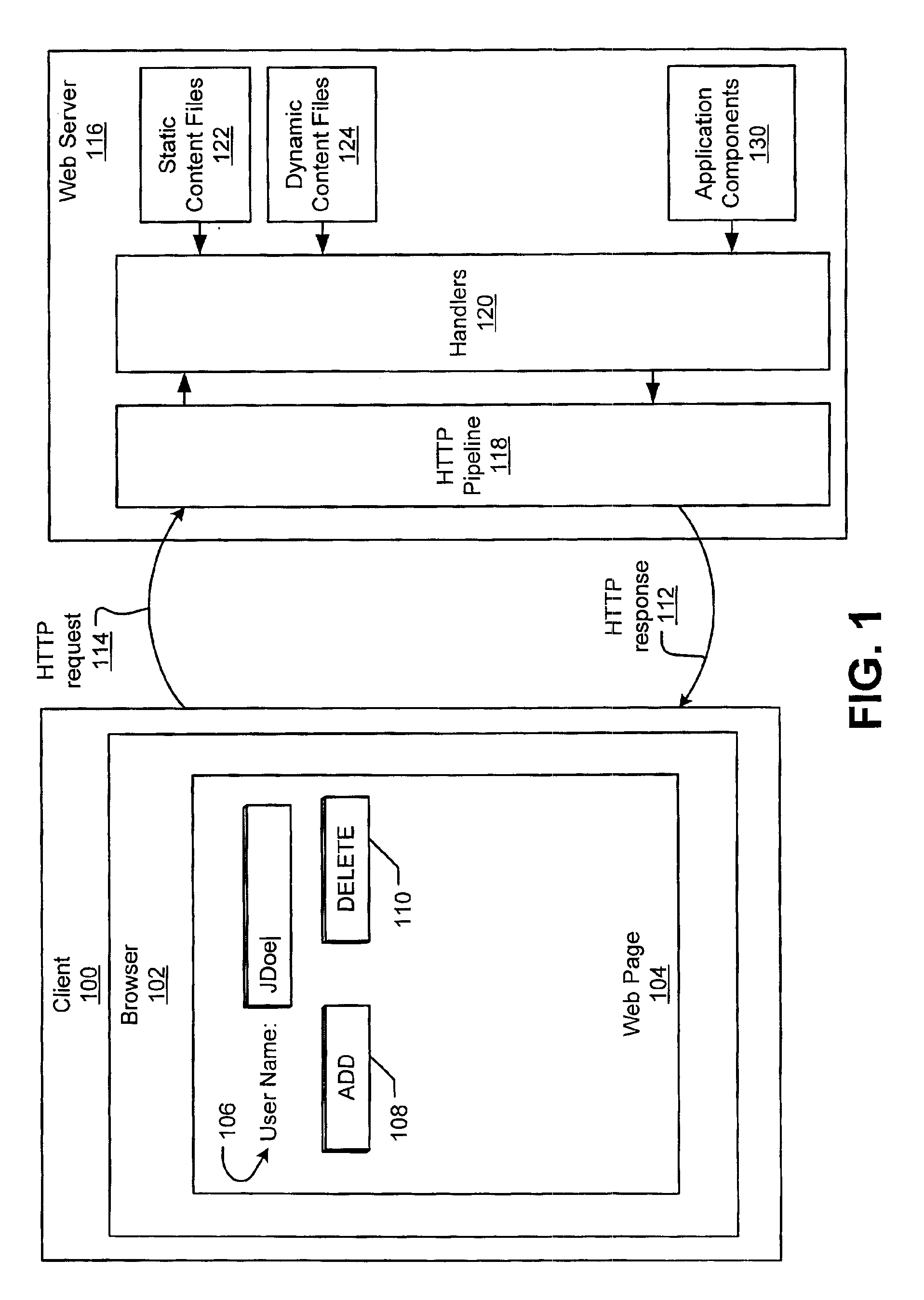

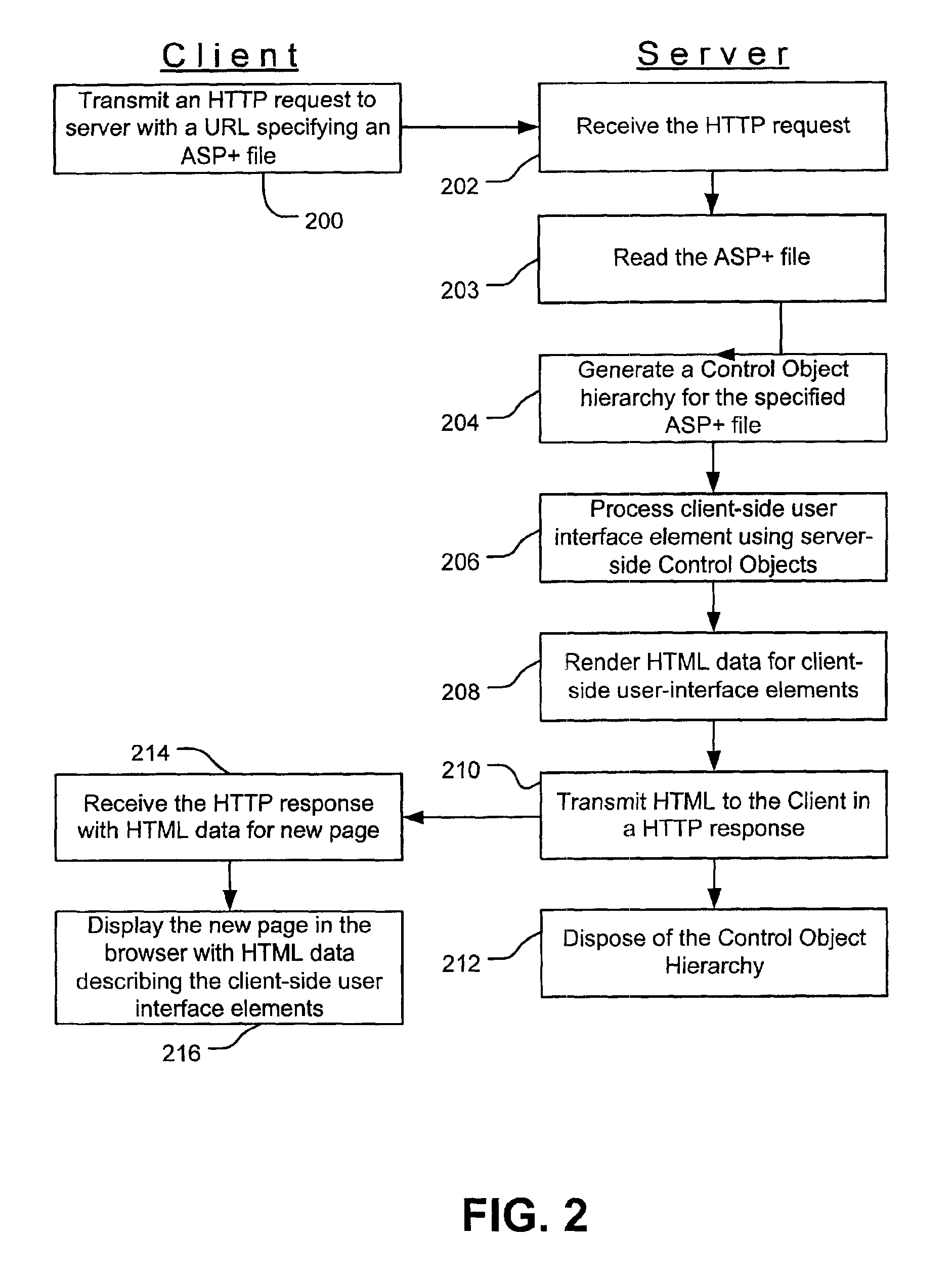

Web controls validation

InactiveUS6915454B1Receipt is inhibitedNon-redundant fault processingSpecific program execution arrangementsError processingFile comparison

Web control validation may be defined using one or more declarations that are included in an ASP+ file by the web page author. The declarations specify server-side objects that validate the input data received in the web page and provide error handling in the event of a validation failure error. Validation declaration parameters specify the validation criteria against which the input data is validated. Example validation operations involve regular expressions, required fields, data comparison, range comparison and custom validation. Validation parameters can also specify- either server-side validation or client-side validation, depending on the client browser's capabilities. In a server-side scenario, a server-side validation object processes the input data received in an HTTP request from the client. In a client-side scenario, a server-side validation object renders the appropriate client-side code to validate the input data without a round trip between the client and the server.

Owner:MICROSOFT TECH LICENSING LLC

Automatic software production system

InactiveUS20030167455A1Shorten the time to marketEasy to useDigital data information retrievalProgram documentationHandling CodeSystem requirements

An automated software production system is provided, in which system requirements are captured, converted into a formal specification, and validated for correctness and completeness. In addition, a translator is provided to automatically generate a complete, robust software application based on the validated formal specification, including user-interface code and error handling code.

Owner:IBORRA JOSE +1

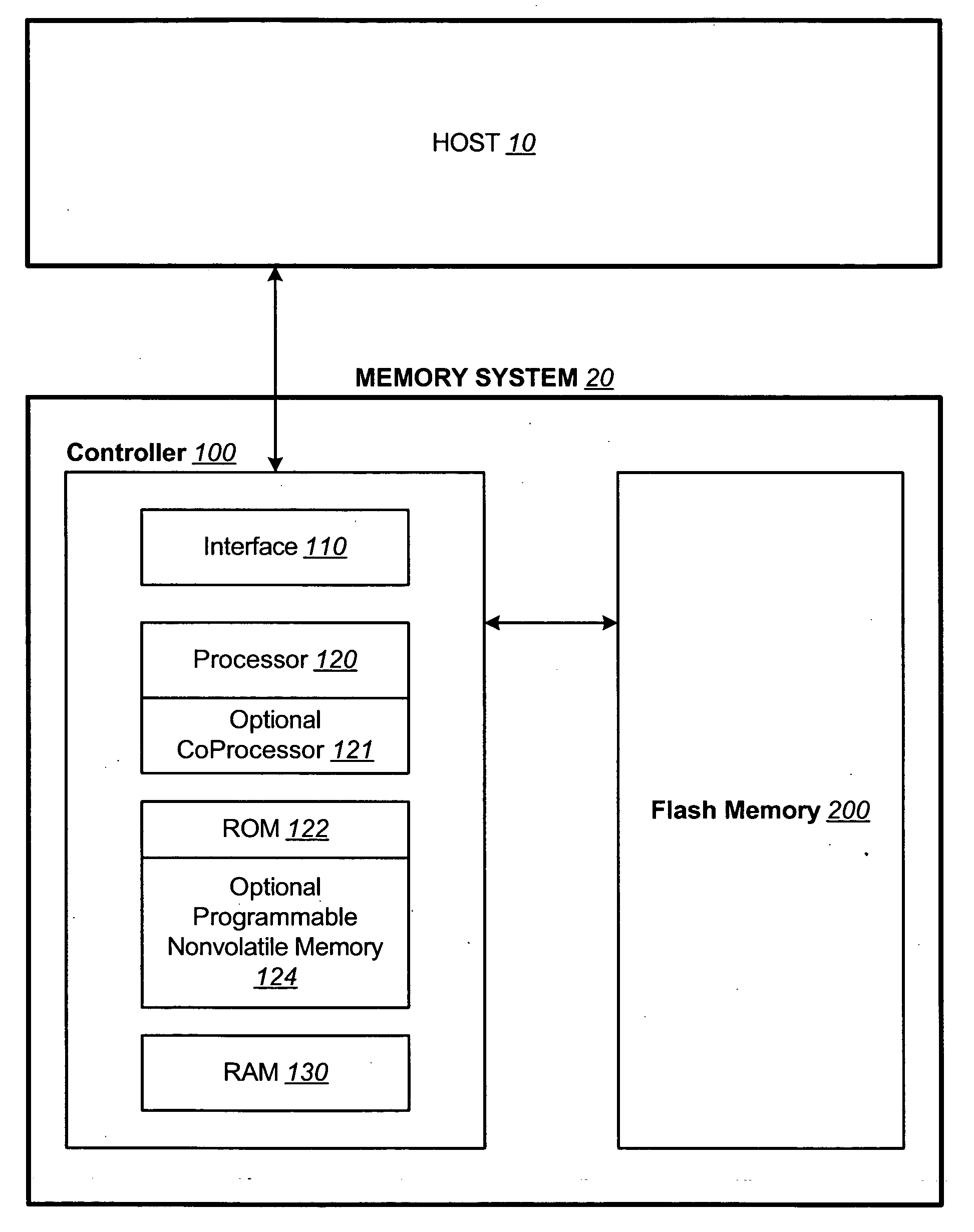

Non-volatile memory and method with phased program failure handling

InactiveUS20050166087A1Improve efficiencyReduce overheadMemory architecture accessing/allocationMemory adressing/allocation/relocationError processingTime critical

In a memory with block management system, program failure in a block during a time-critical memory operation is handled by continuing the programming operation in a breakout block. Later, at a less critical time, the data recorded in the failed block prior to the interruption is transferred to another block, which could also be the breakout block. The failed block can then be discarded. In this way, when a defective block is encountered during programming, it can be handled without loss of data and without exceeding a specified time limit by having to transfer the stored data in the defective block on the spot. This error handling is especially critical for a garbage collection operation so that the entire operation need not be repeated on a fresh block during a critical time. Subsequently, at an opportune time, the data from the defective block can be salvaged by relocation to another block.

Owner:SANDISK TECH LLC

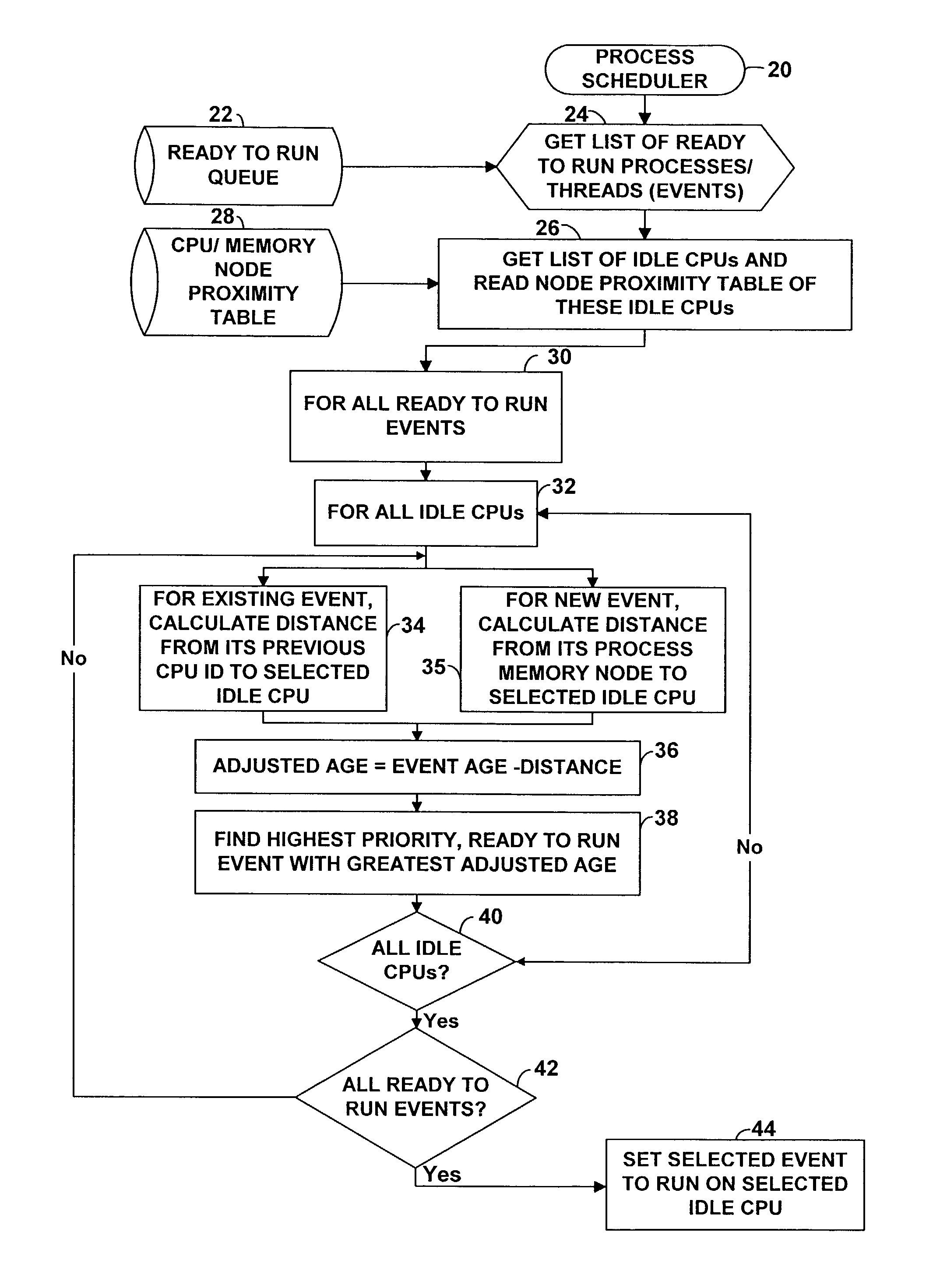

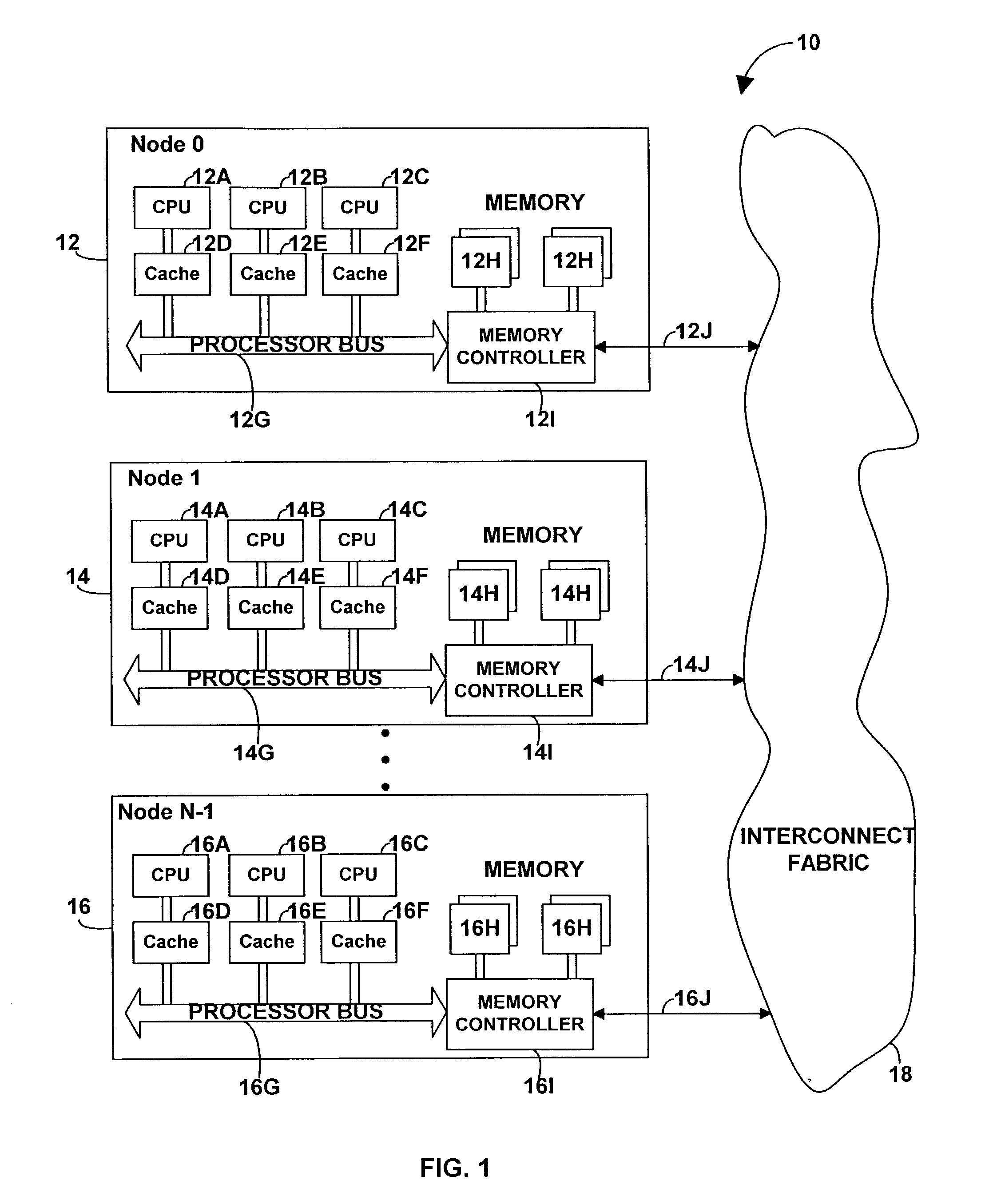

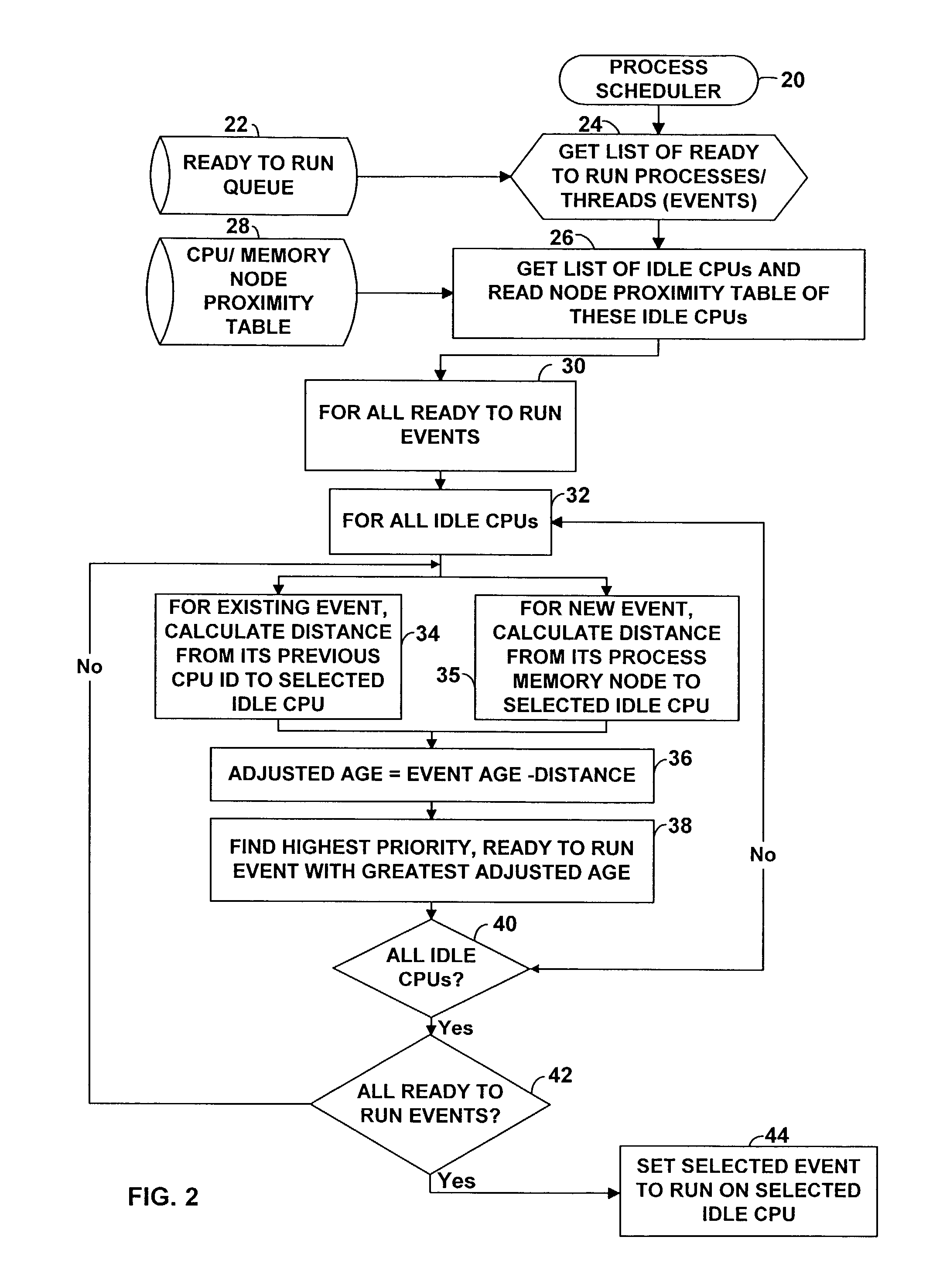

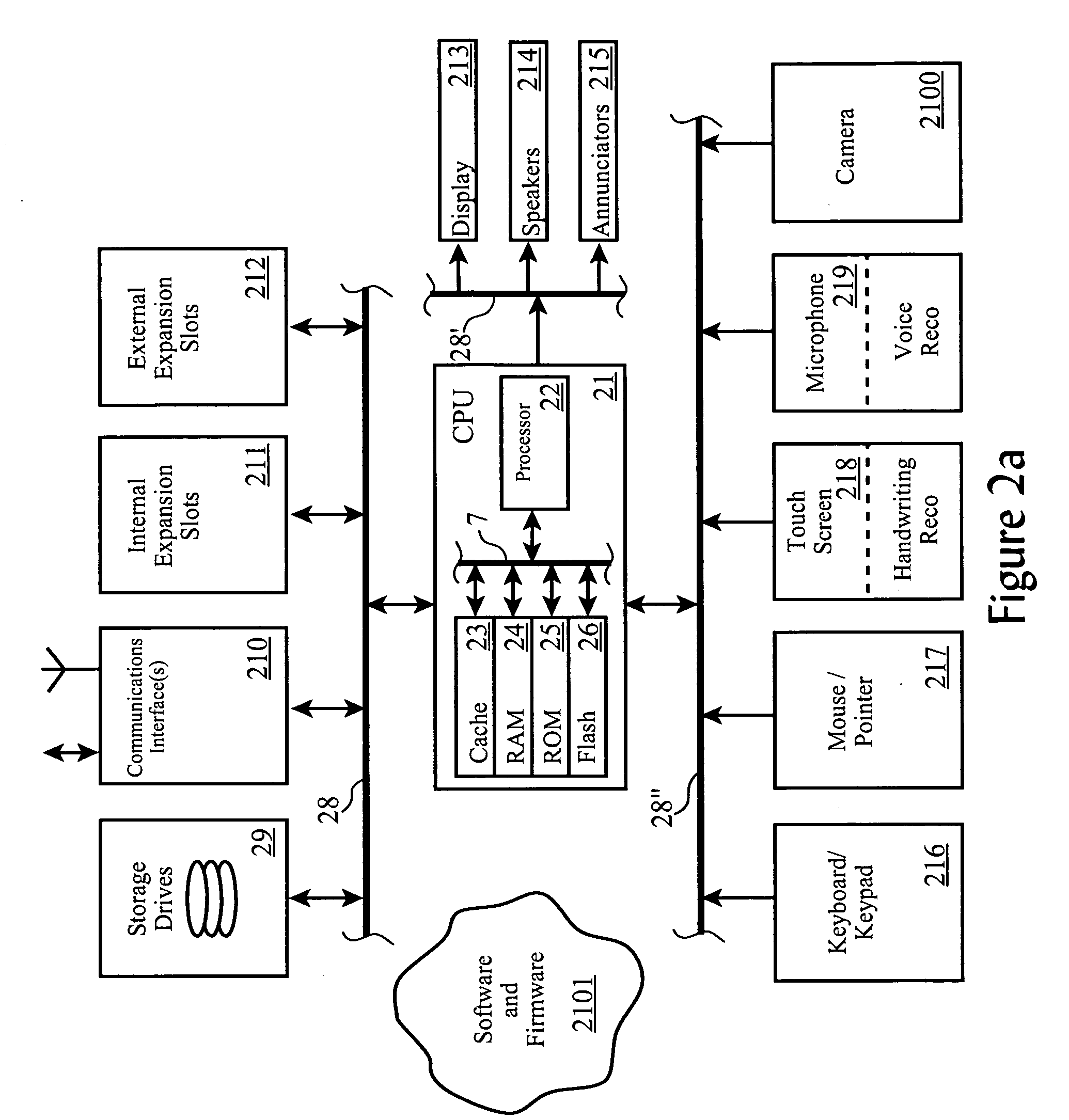

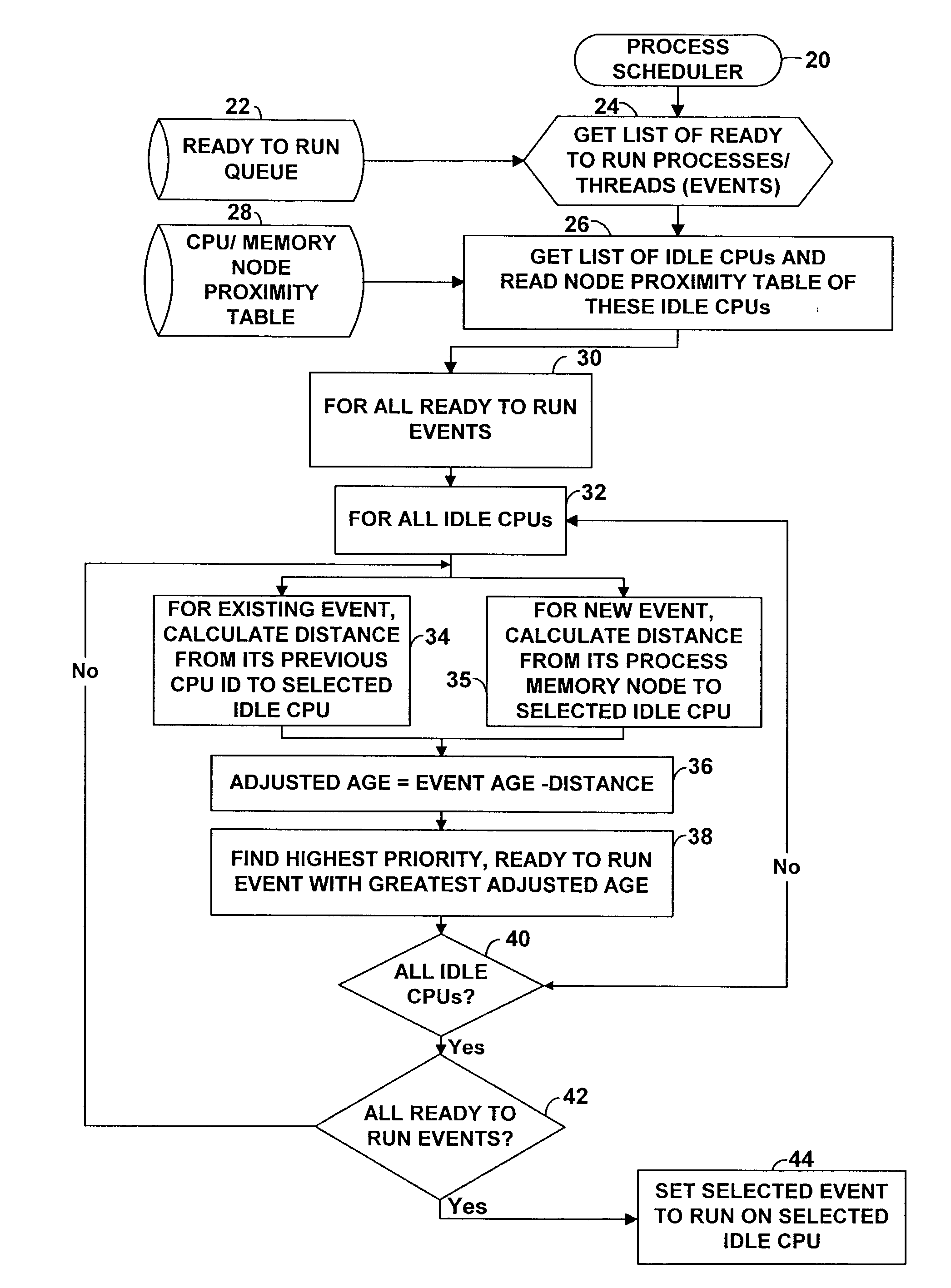

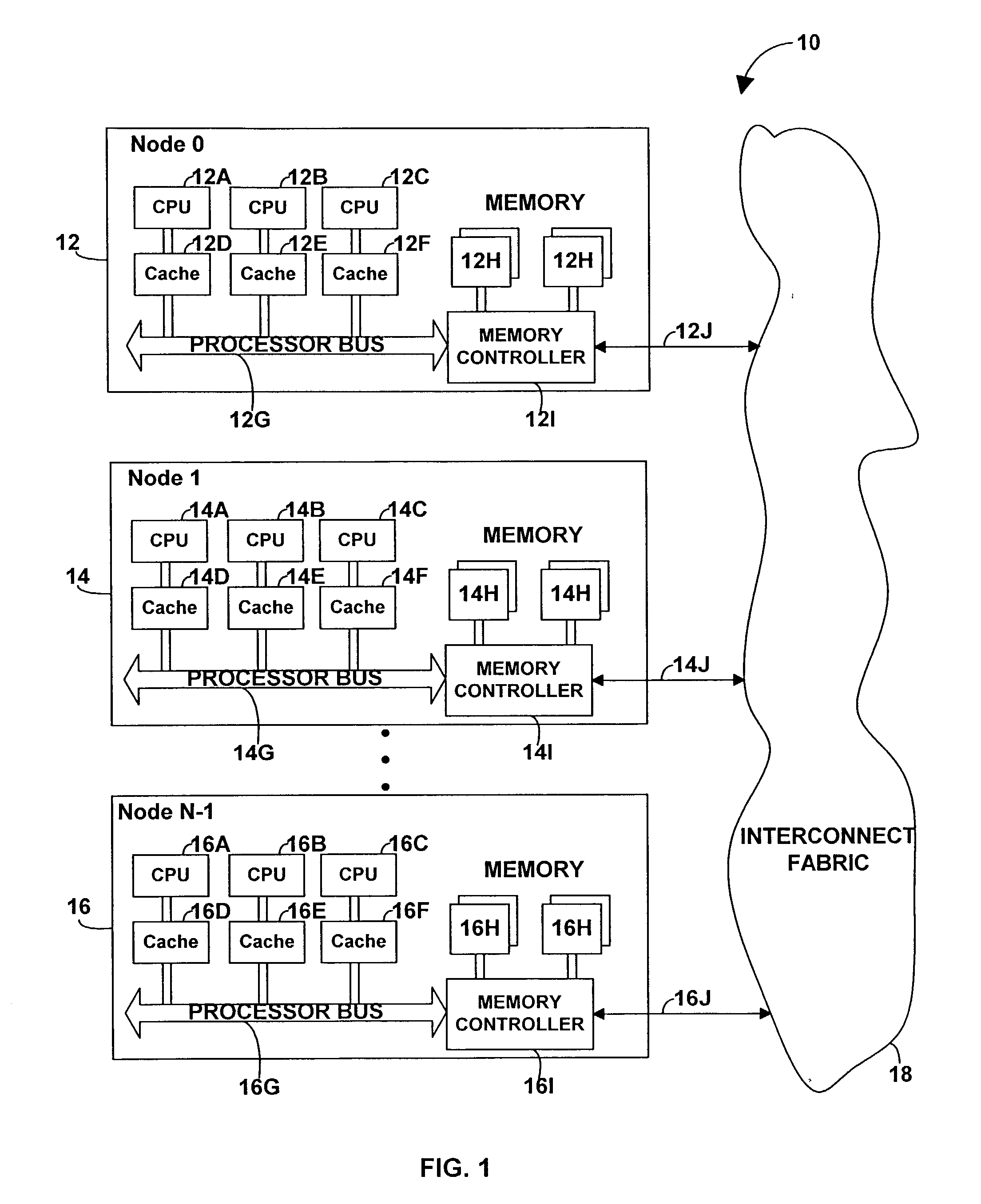

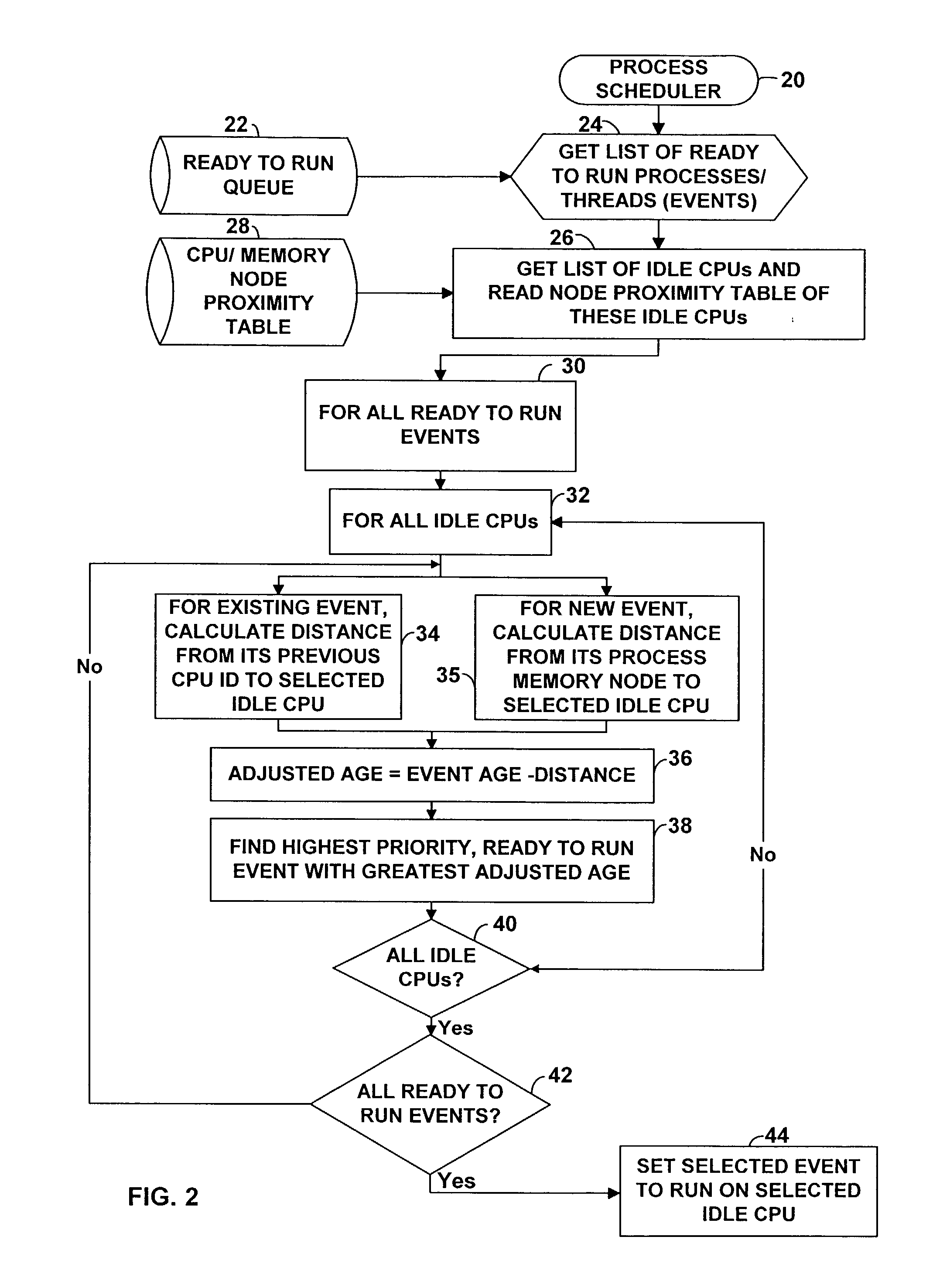

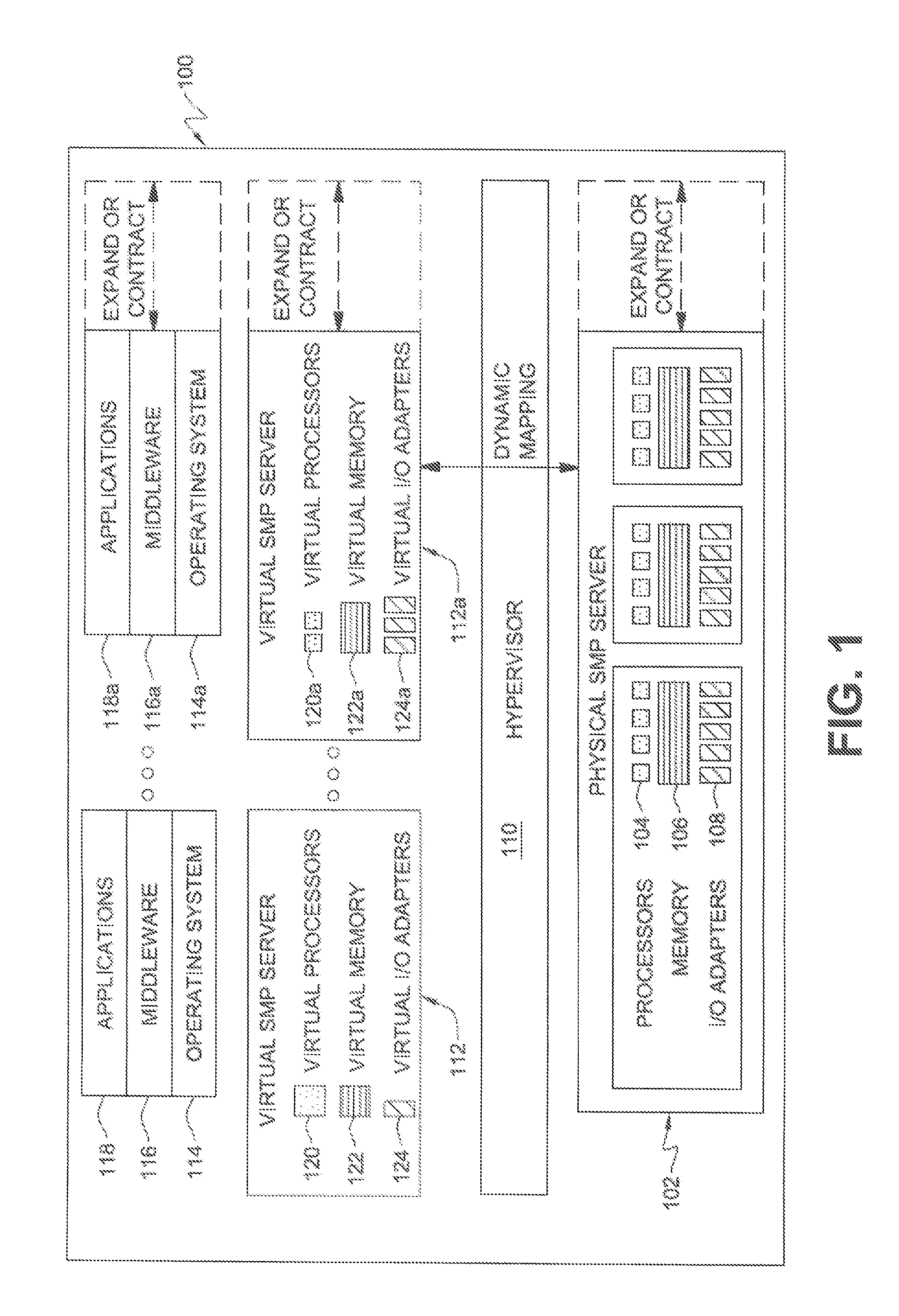

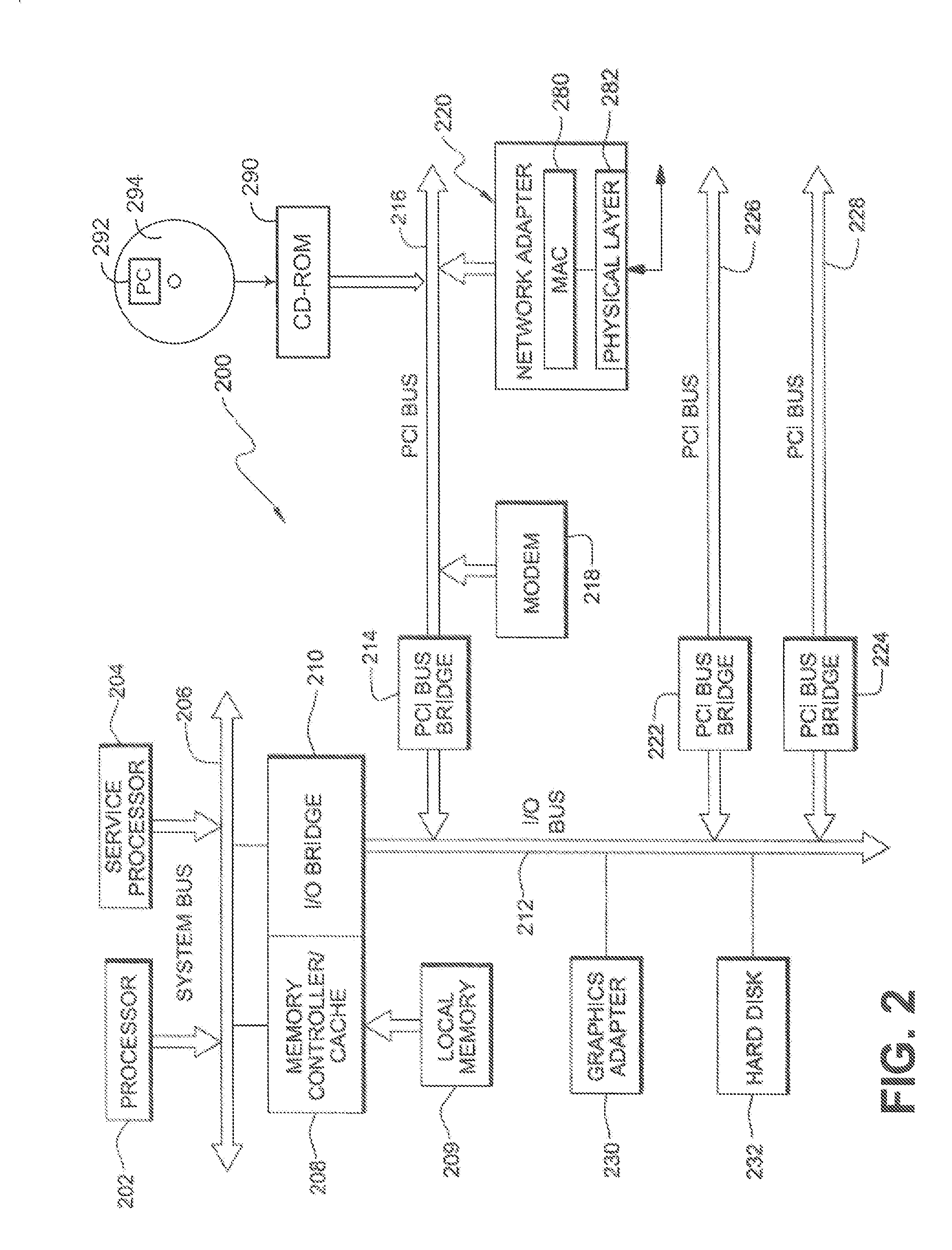

Method and apparatus for optimizing performance in a multi-processing system

InactiveUS7143412B2Interprogram communicationDigital computer detailsError processingThread scheduling

A technique for improving performance in a multi-processor system by reducing access latency by correlating processor, node and memory allocation. Specifically, a Process / Thread Scheduler is modified such that system mapping and node proximity tables may be referenced to help determine processor assignments for ready-to-run processes / threads. Processors are chosen to minimize access latency. Further, the Page Fault Handler is modified such that free memory pages are assigned to a process based partially on the proximity of the memory with respect to the processor requesting memory allocation.

Owner:HEWLETT PACKARD DEV CO LP

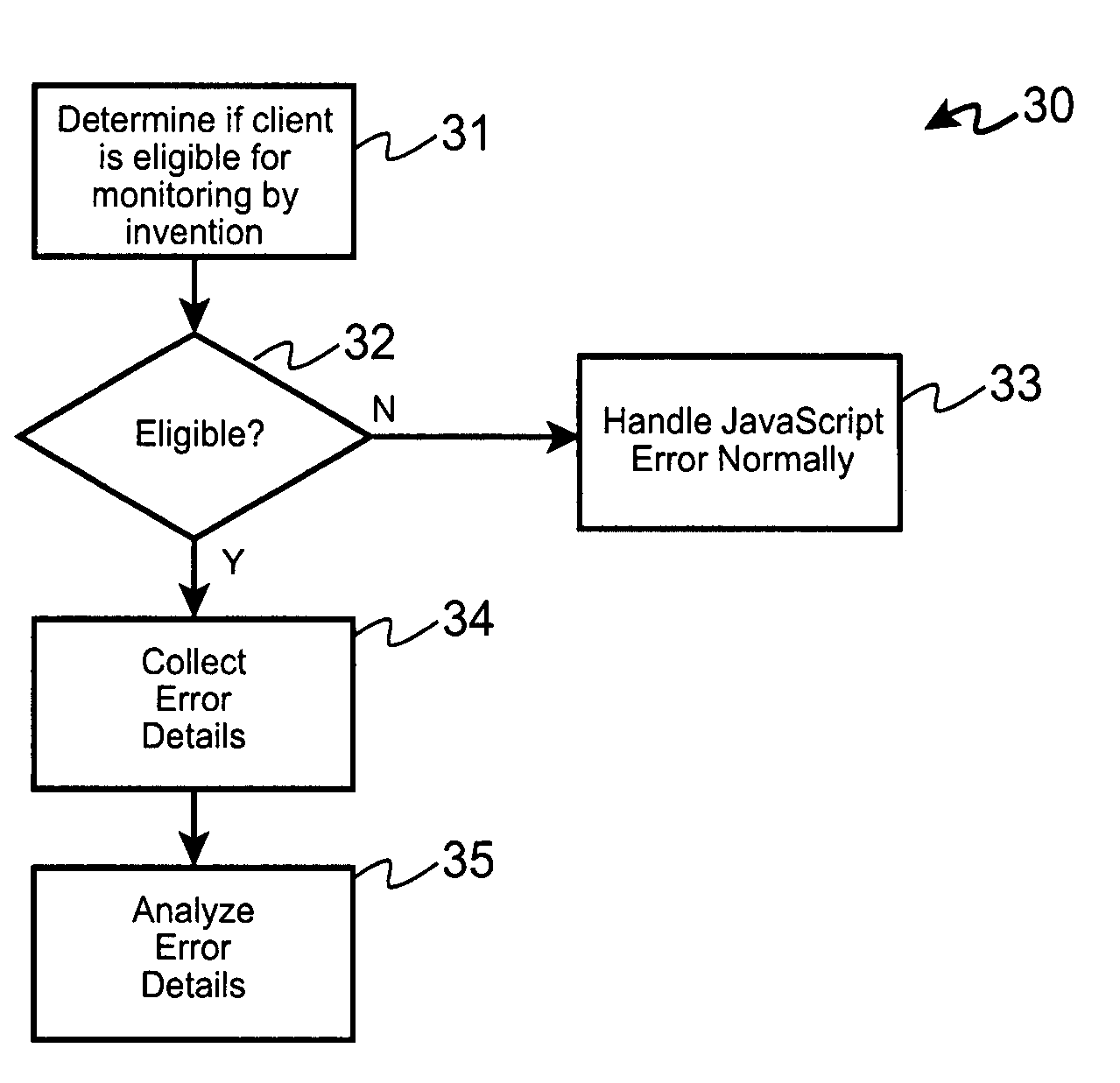

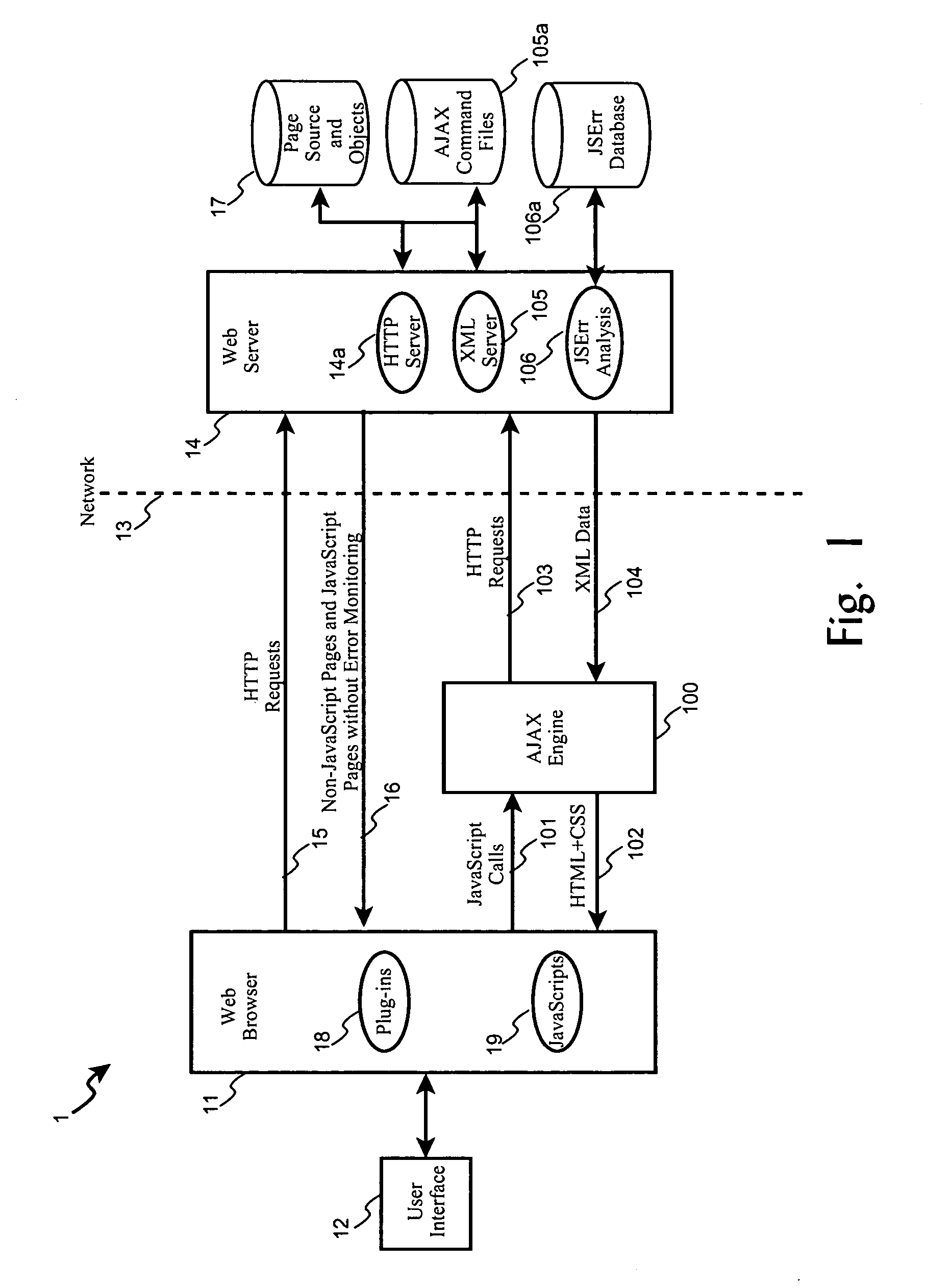

JavaScript error determination and reporting

ActiveUS20070174419A1Multiple digital computer combinationsNon-redundant fault processingWeb browserError processing

A system for unobtrusively monitoring web browser execution of JavaScripts, and reporting errors and / or success of execution of the JavaScripts. Web pages are transmitted from a web page server to a web browser, the pages include at least two JavaScripts and one or more AJAX commands. The web browser executes the JavaScripts, and the AJAX commands using a client-side AJAX engine, including establishing an asynchronous connection between the web browser and an error processing server. When the JavaScript completes successfully or terminates through error, a non-cacheable error details message is sent by the monitoring and collecting JavaScript the error processing server via the asynchronous connection.

Owner:TWITTER INC

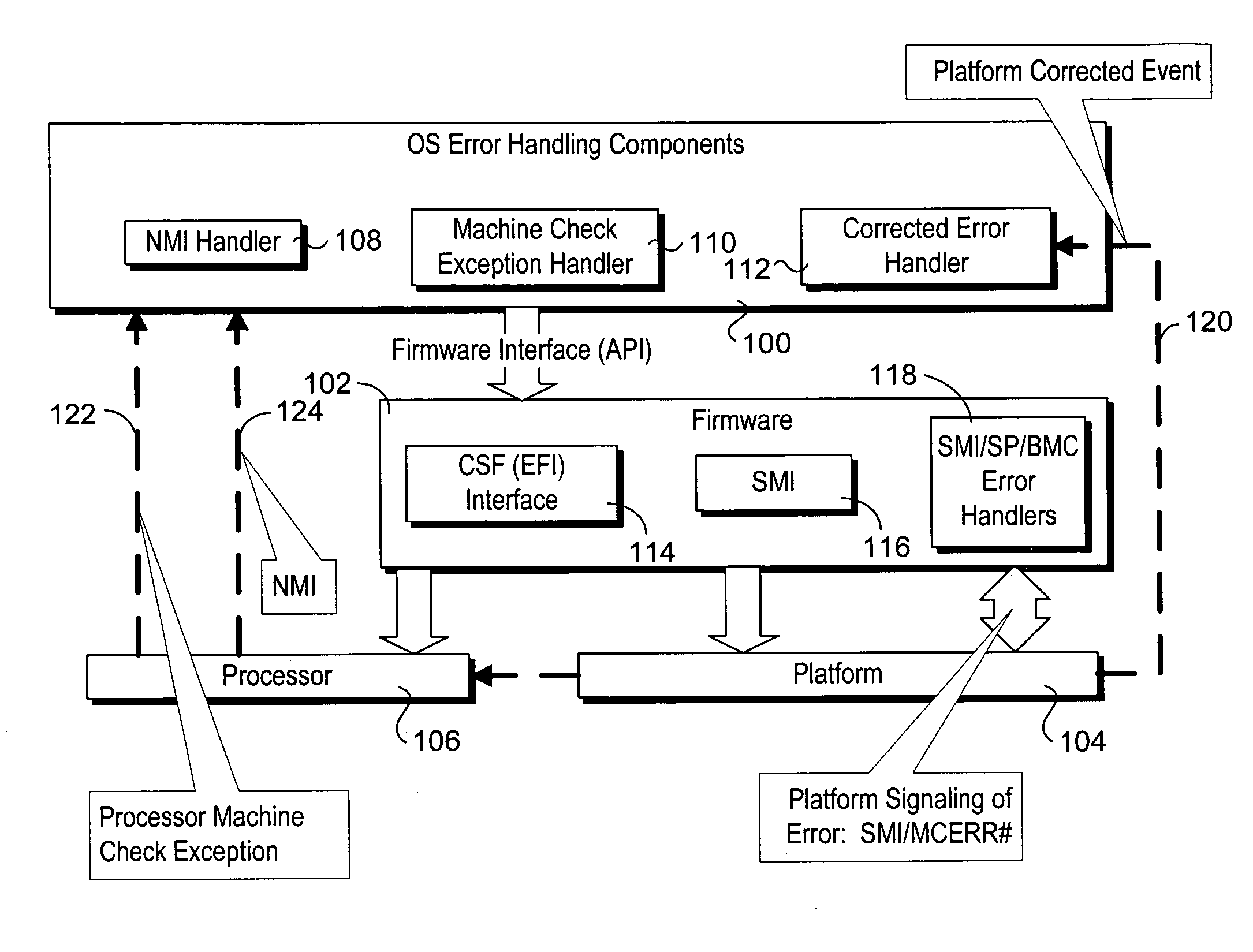

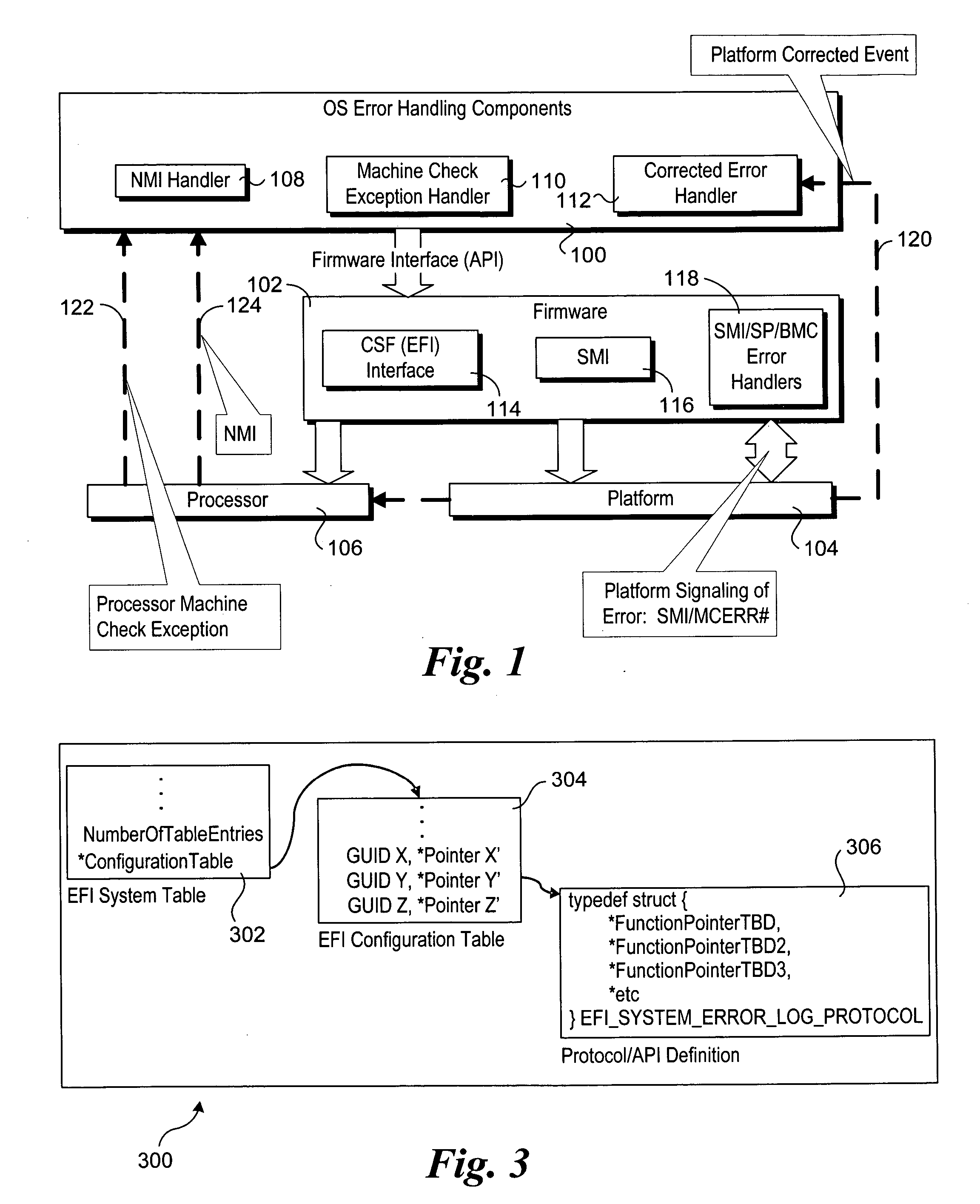

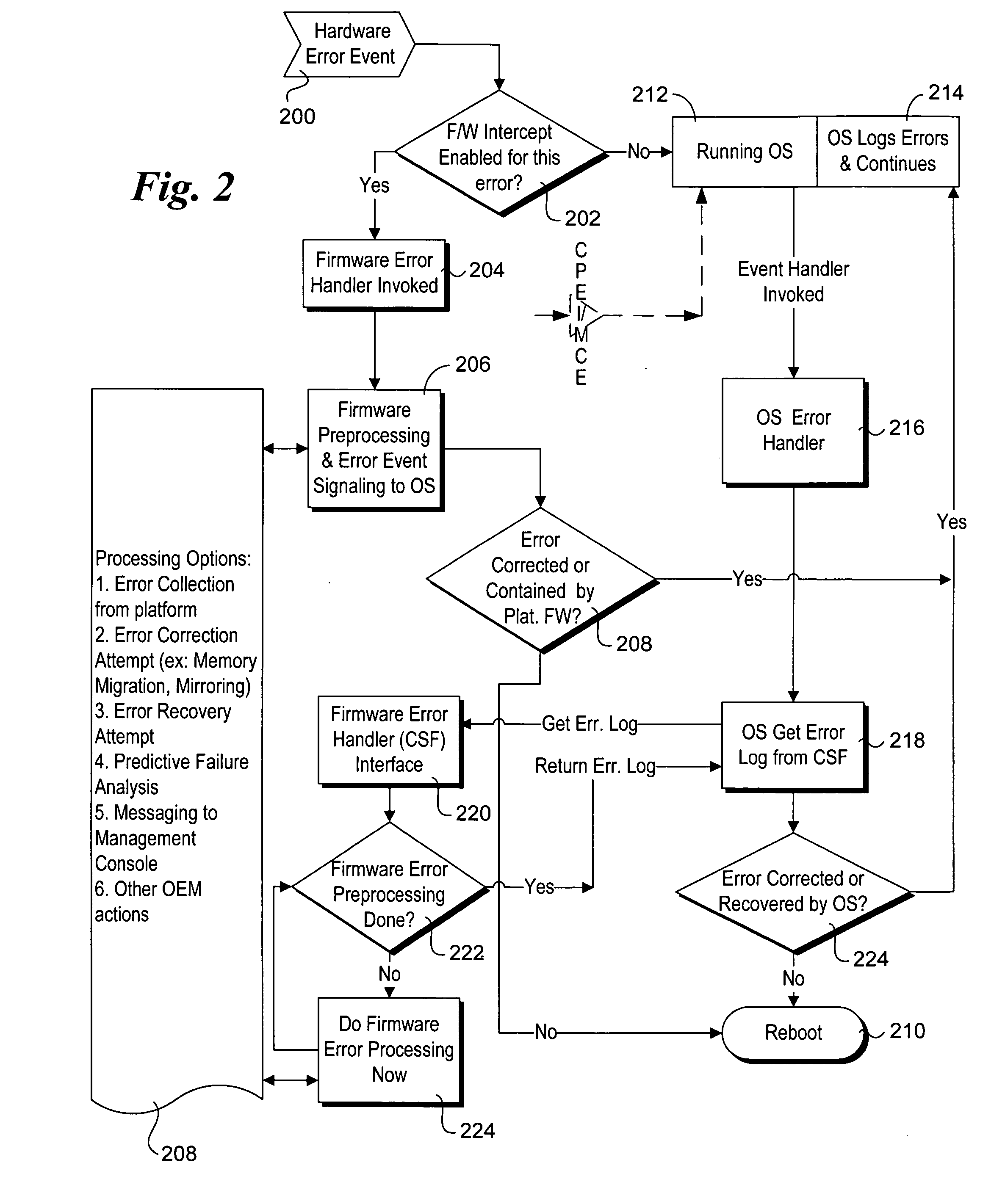

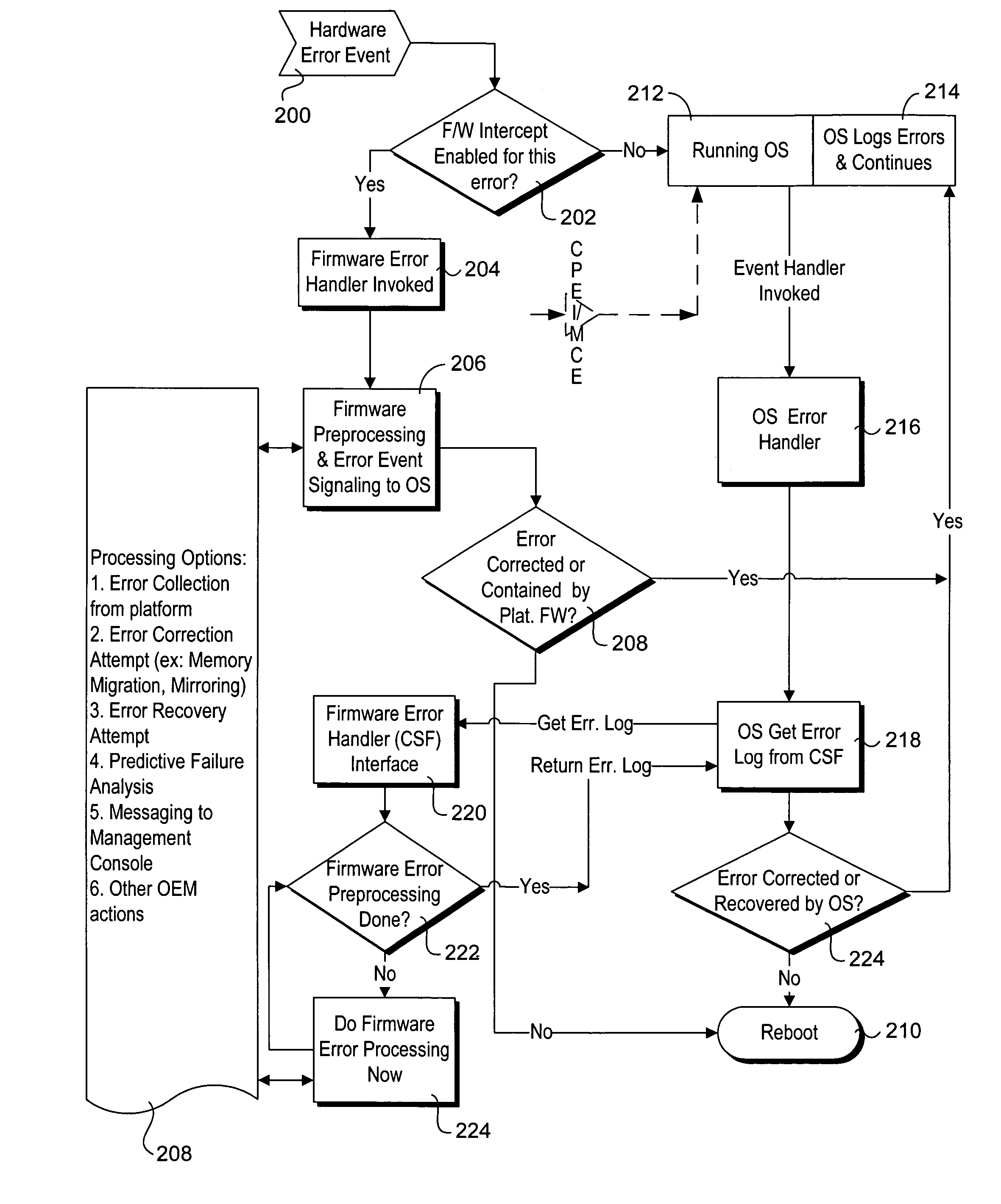

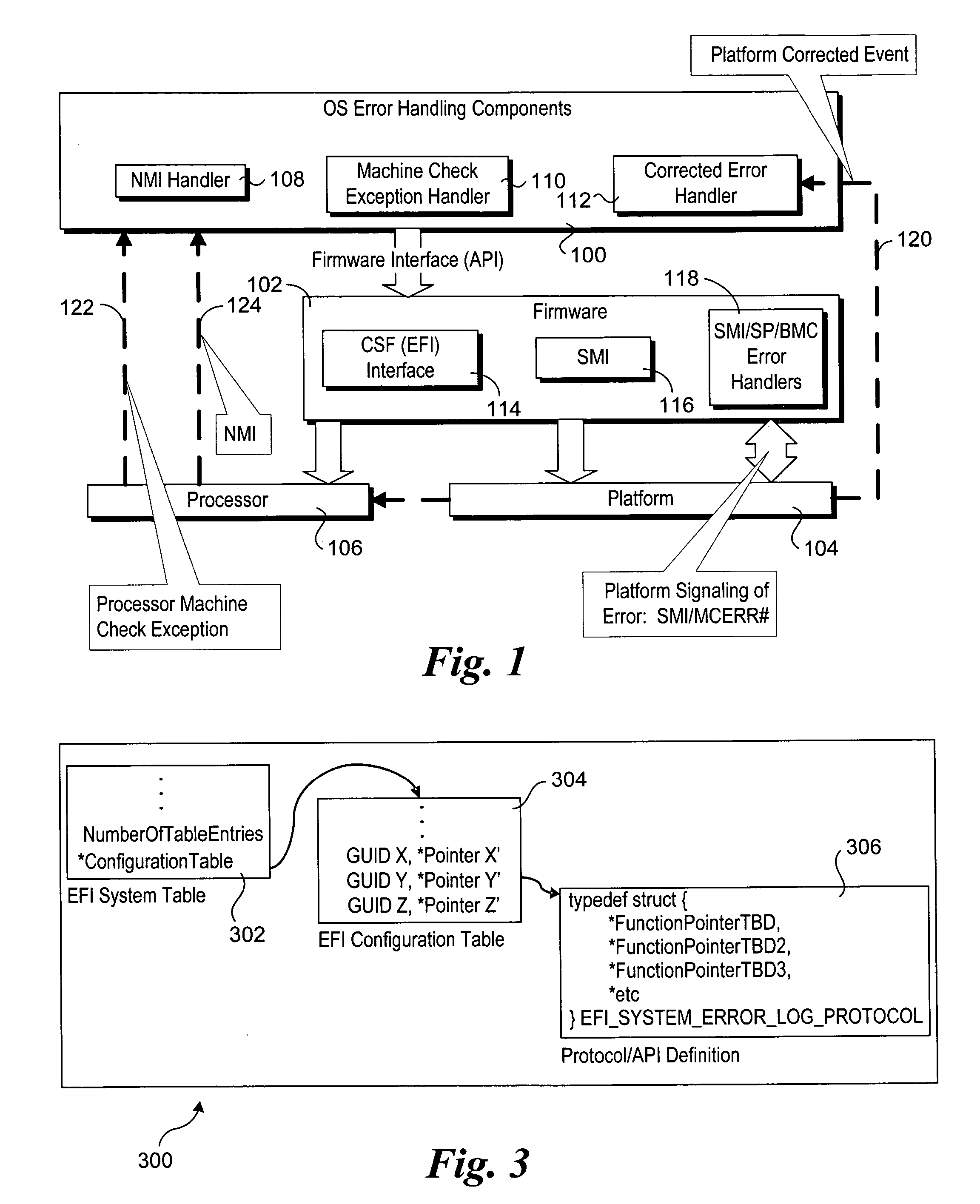

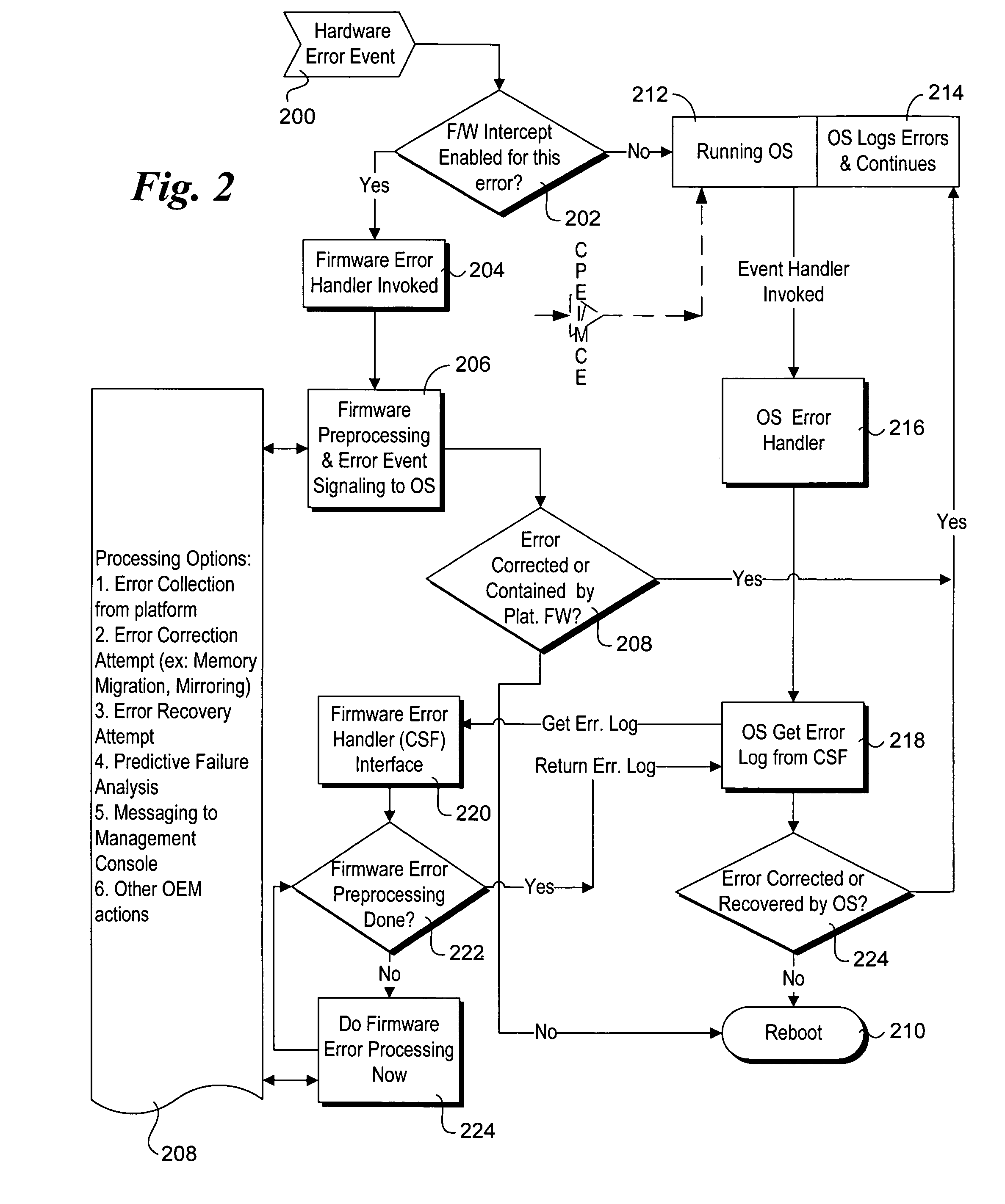

OS and firmware coordinated error handling using transparent firmware intercept and firmware services

Methods and architectures for performing hardware error handling using coordinated operating system (OS) and firmware services. In one aspect, a firmware interface is provided to enable an OS to access firmware error-handling services. Such services enable the OS to access error data concerning platform hardware errors that may not be directed accessed via a platform processor or through other conventional approaches. Techniques are also disclosed for intercepting the processing of hardware error events and directing control to firmware error-handling services prior to attempting to service the error using OS-based services. The firmware services may correct hardware errors and / or log error data that may be later accessed by the OS or provided to a remote management server using an out-of-band communication channel. In accordance with another aspect, the firmware intercept and services may be performed in a manner that is transparent to the OS.

Owner:INTEL CORP

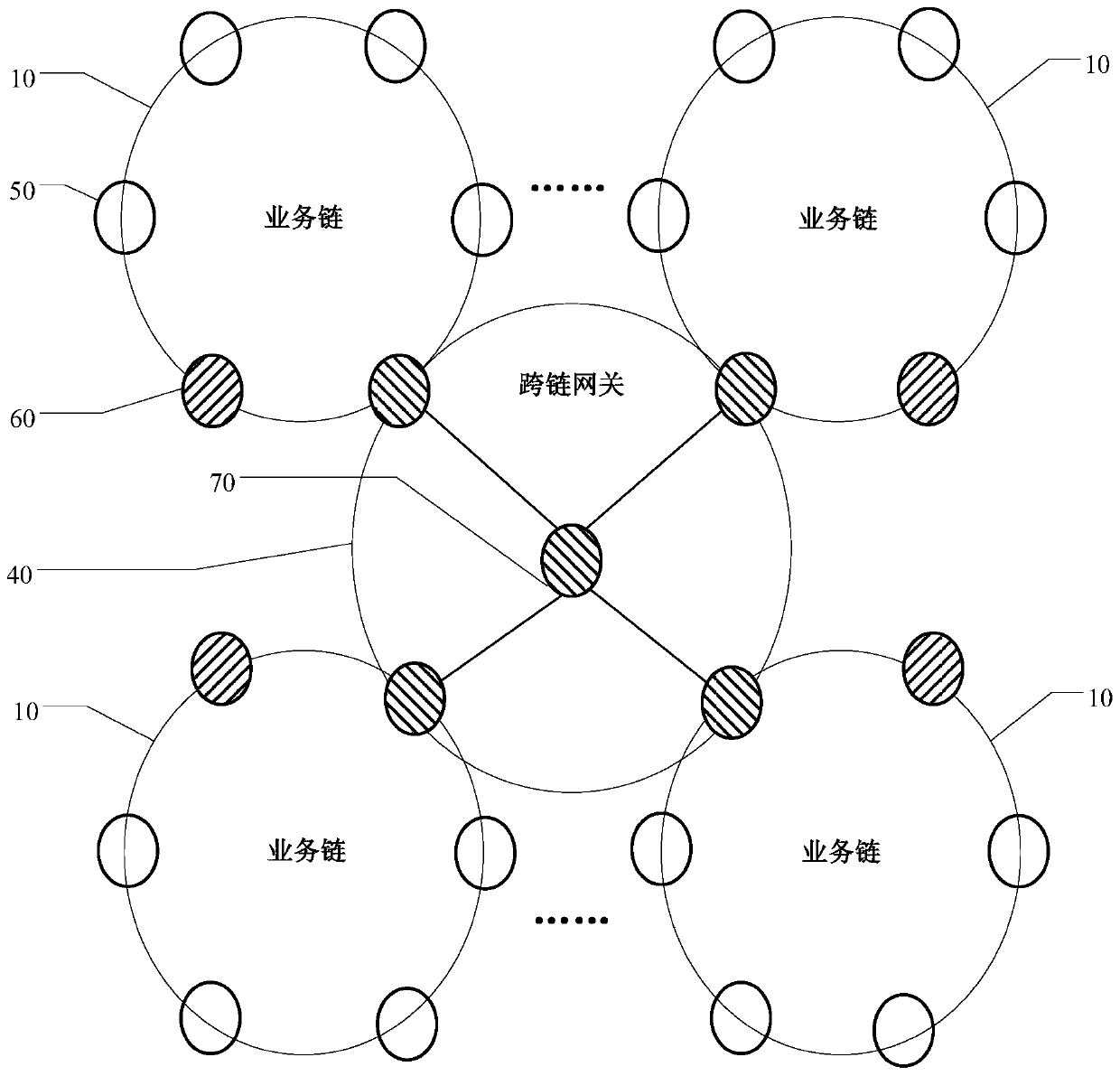

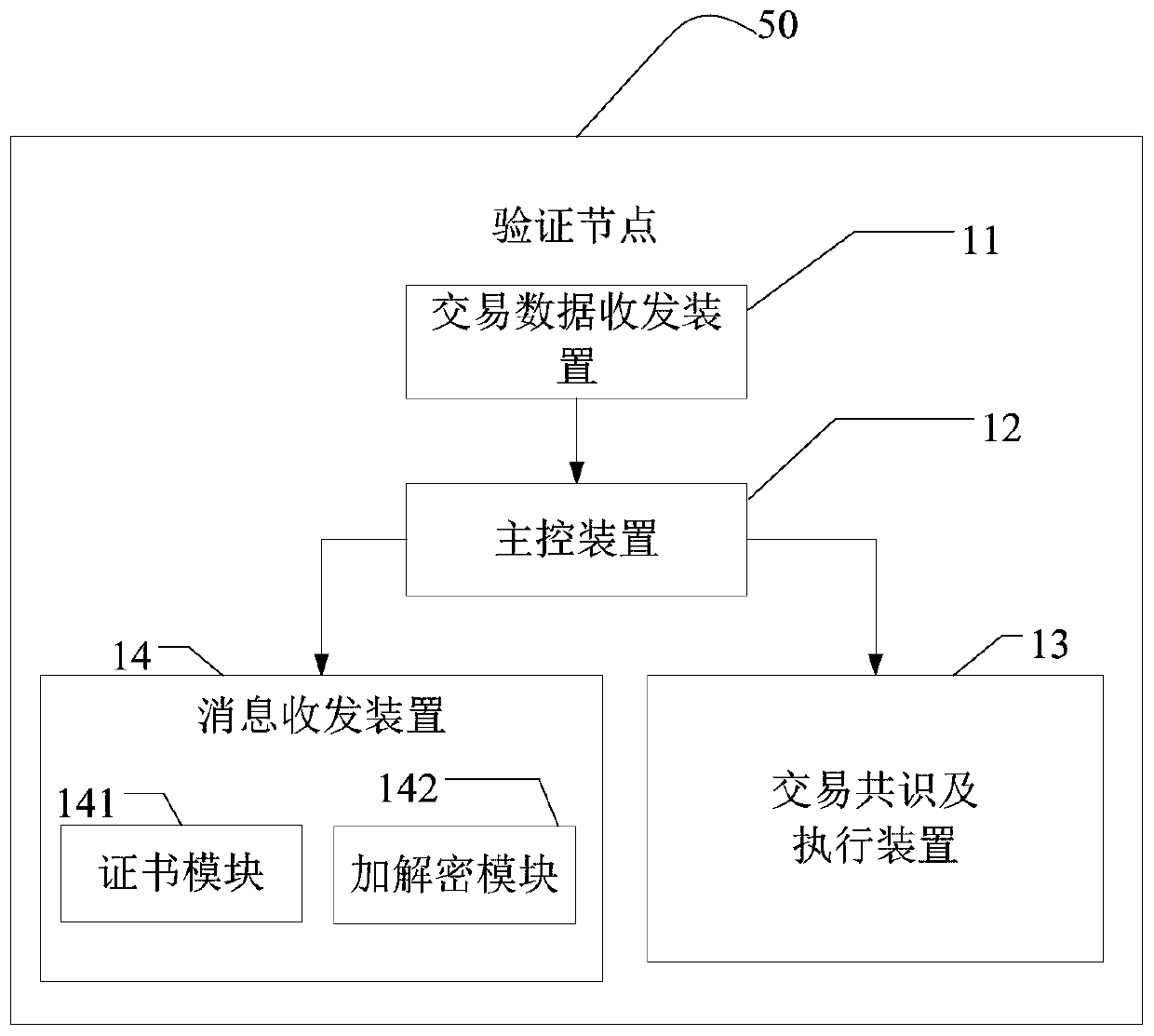

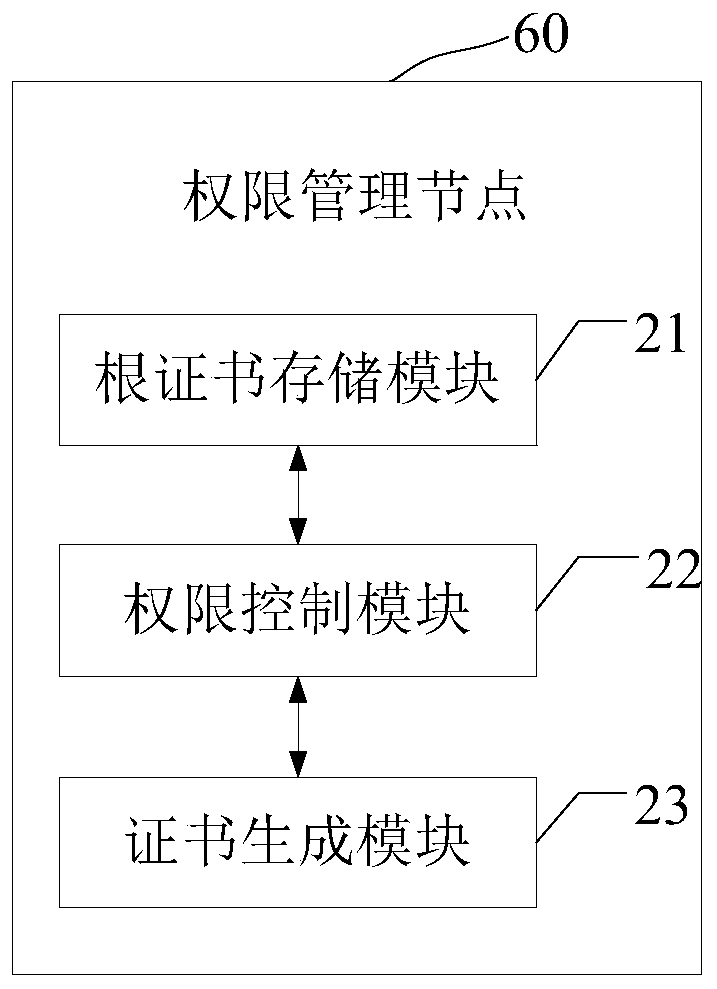

Blockchain-based cross-chain interconnection method, device and system

ActiveCN110266655AReach fusionSolve information silosFinanceUser identity/authority verificationInformation processingError processing

The invention provides a blockchain-based cross-chain interconnection method, a blockchain-based cross-chain interconnection system, computer equipment and a computer readable storage medium, and relates to the technical field of information processing. The system comprises a cross-chain gateway node and a plurality of service chains, each service chain comprises an authority management node, a gateway node and a plurality of verification nodes, and the gateway node in the plurality of service chains and the cross-chain gateway node form a cross-chain gateway; and the cross-chain gateway is used for realizing message format standardization and a cross-chain conversion protocol among the plurality of service chains so as to promote adaptation and forwarding of cross-chain messages, support error processing of request message timeout during cross-chain interconnection and finally realize mutual access and intercommunication of cross-chain data. Mutual access among the alliance chains of a plurality of different block chain technologies is achieved by introducing the bridging gateway chain, the problem of information island among a plurality of block chain systems is solved, and application and popularization of the block chain technology can be accelerated.

Owner:INDUSTRIAL AND COMMERCIAL BANK OF CHINA

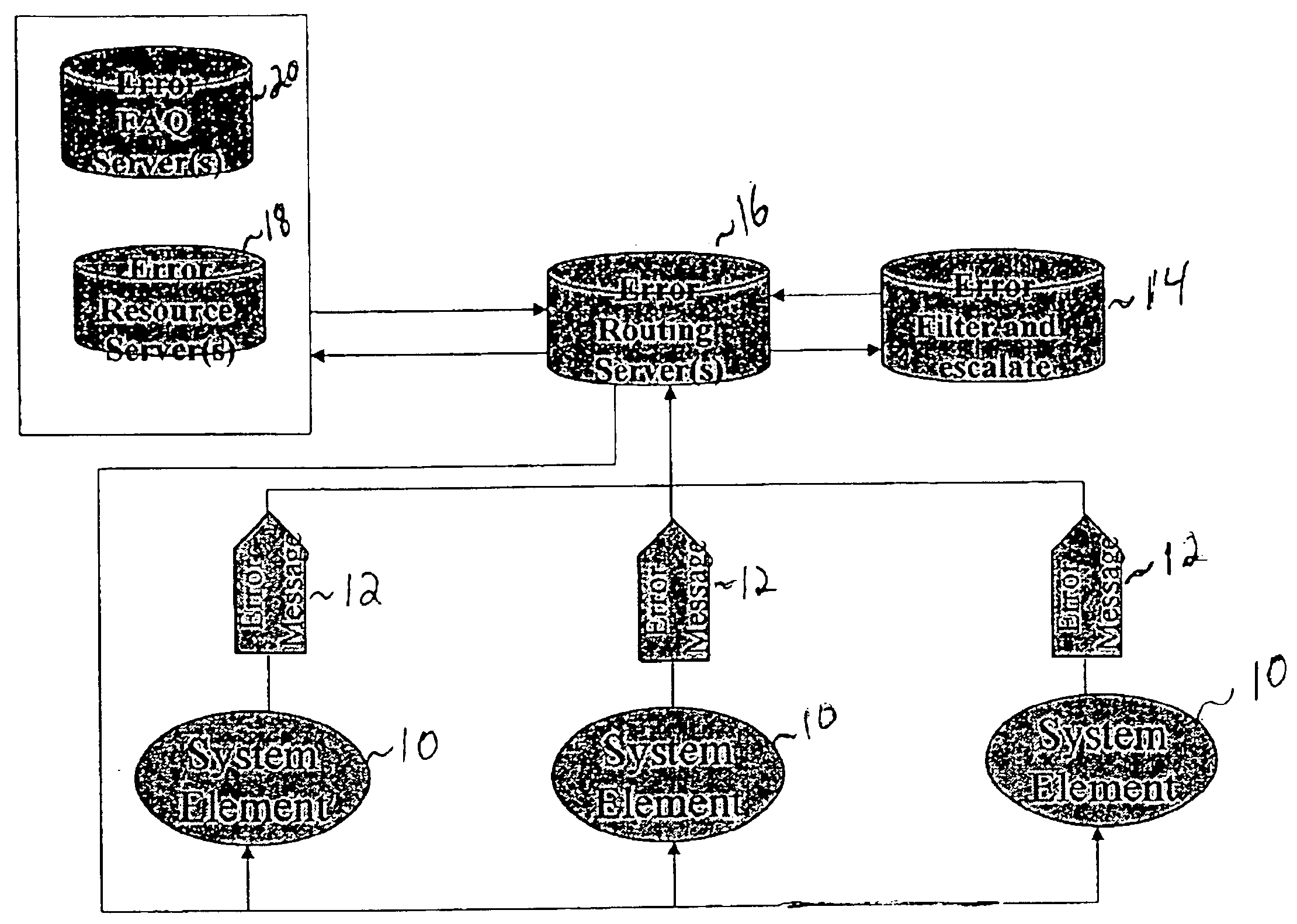

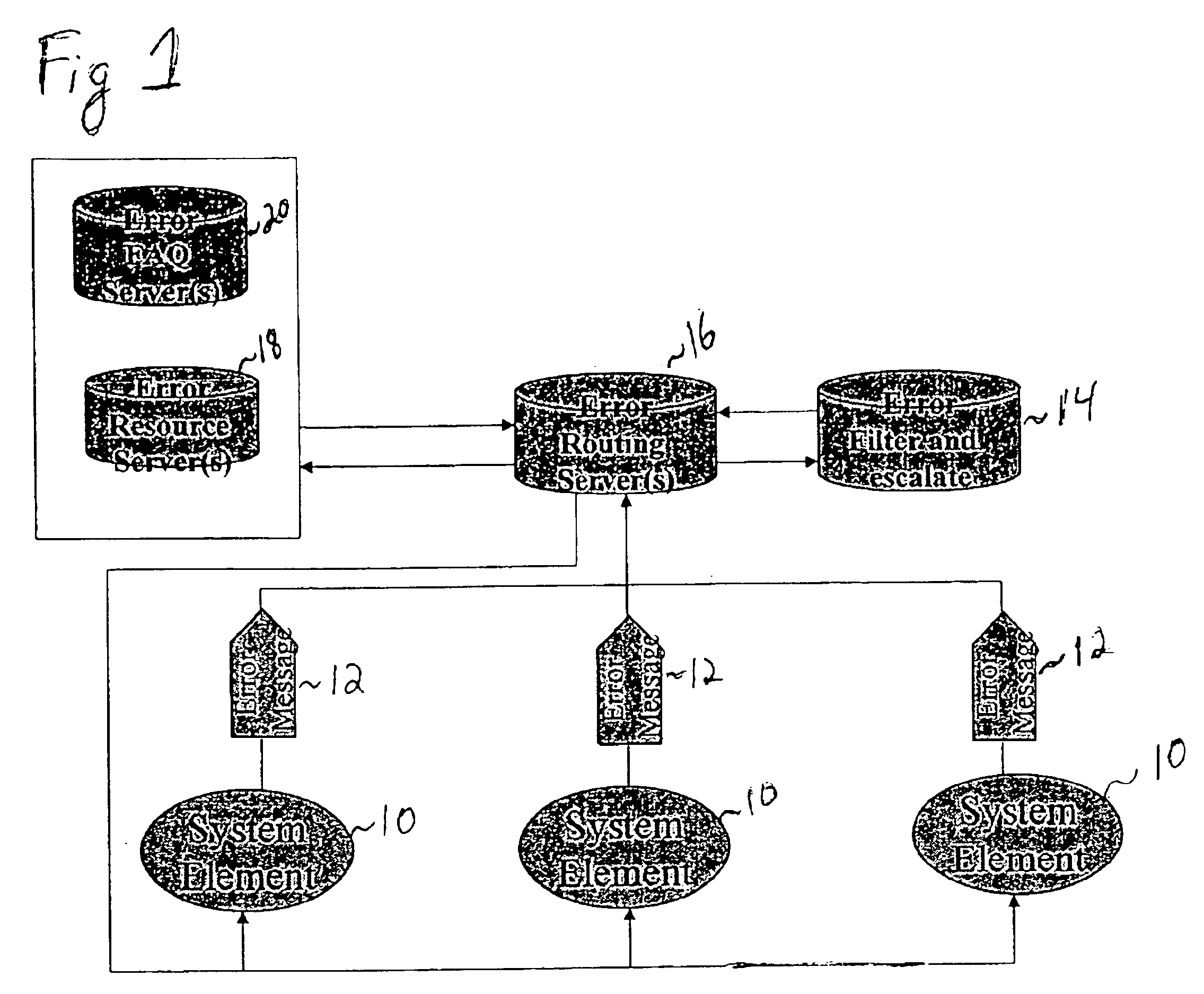

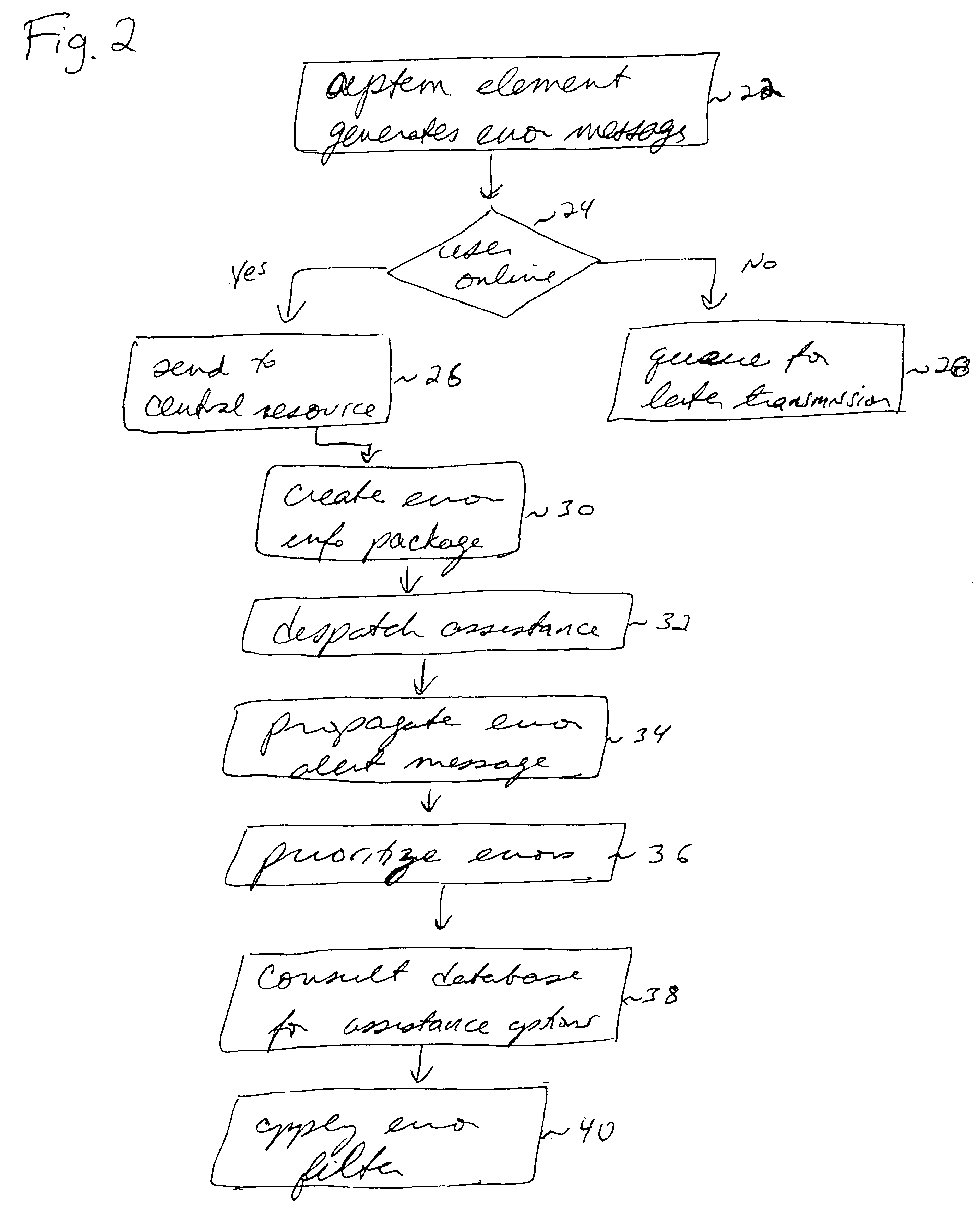

Method and system for handling errors in a distributed computer system

InactiveUS6918059B1Avoid the correction processNon-redundant fault processingData switching networksError processingComputerized system

A method and system for tracking and processing errors in a distributed computer system. As an application encounters an error, a centralized system intercepts and assumes the processing of that error event. The central error processing may be used with a distributed network connecting the applications running on various user computers. Upon receipt of an error message from an application, the system creates an informative error package, propagates appropriate error alert to relevant subsystems, and attempts to resolve the error. The error may be resolved in various ways. For example, the system may select and dispatch appropriate help information to the user; or the system may locate an alternative resource to substitute for the failed resource. The system may prioritize errors when there is more than one error still unresolved at any given time. In addition, the system may filter errors that require different levels of response and the system may direct errors to resources capable of assisting in resolving the error.

Owner:SALESFORCE COM INC

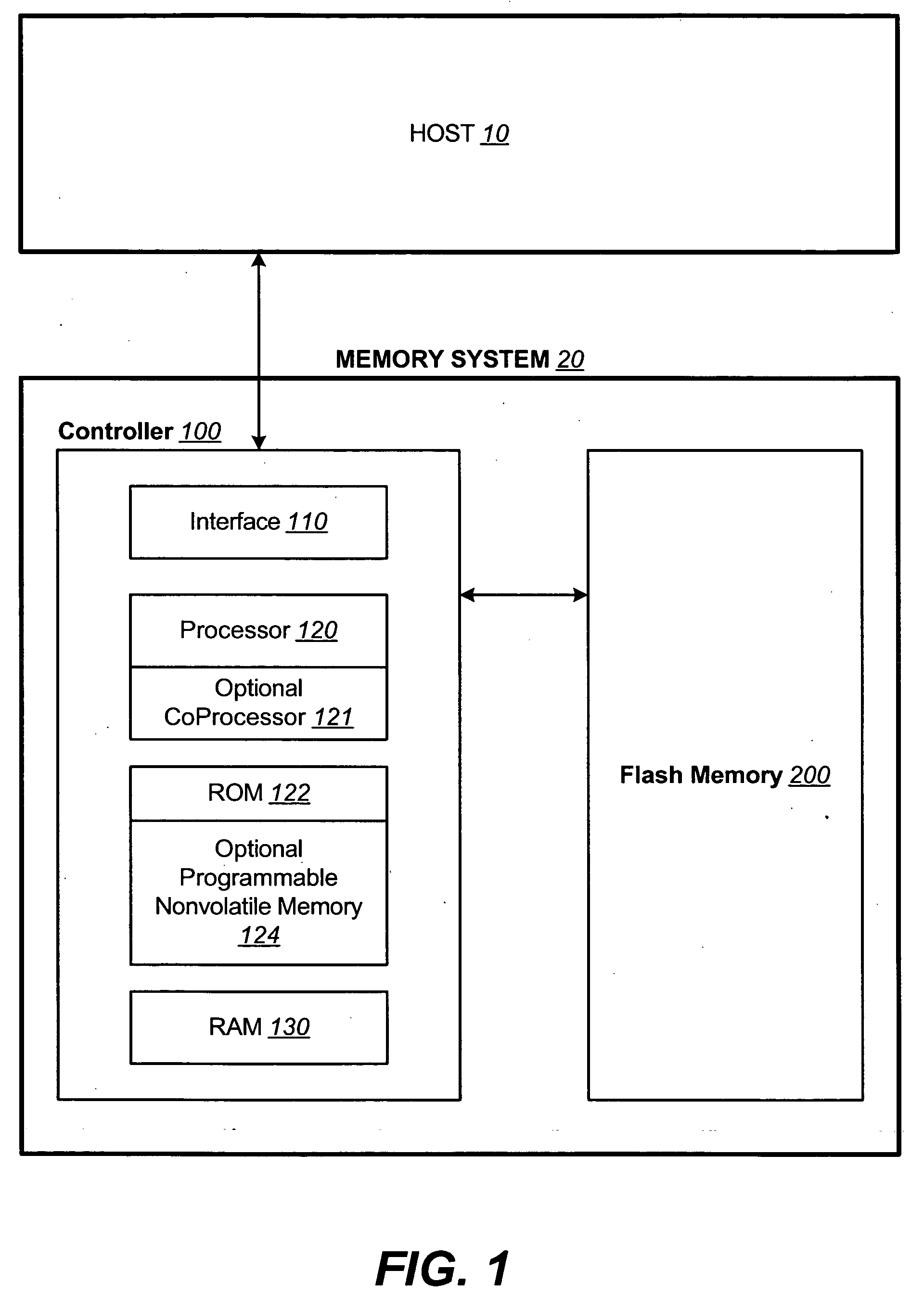

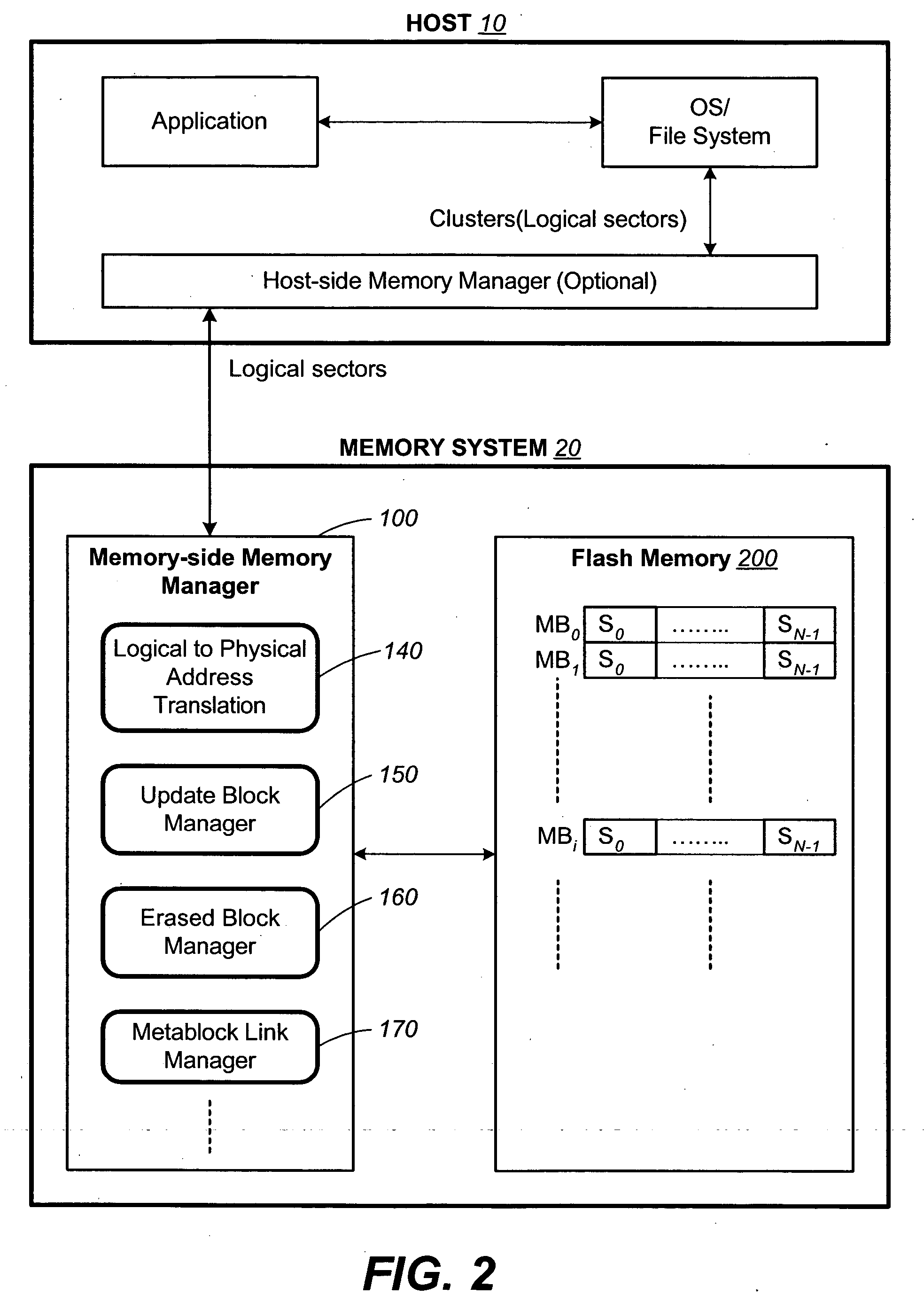

Method and apparatus for optimizing performance in a multi-processing system

InactiveUS20040019891A1Interprogram communicationDigital computer detailsError processingThread scheduling

A technique for improving performance in a multi-processor system by reducing access latency by correlating processor, node and memory allocation. Specifically, a Process / Thread Scheduler is modified such that system mapping and node proximity tables may be referenced to help determine processor assignments for ready-to-run processes / threads. Processors are chosen to minimize access latency. Further, the Page Fault Handler is modified such that free memory pages are assigned to a process based partially on the proximity of the memory with respect to the processor requesting memory allocation.

Owner:HEWLETT PACKARD DEV CO LP

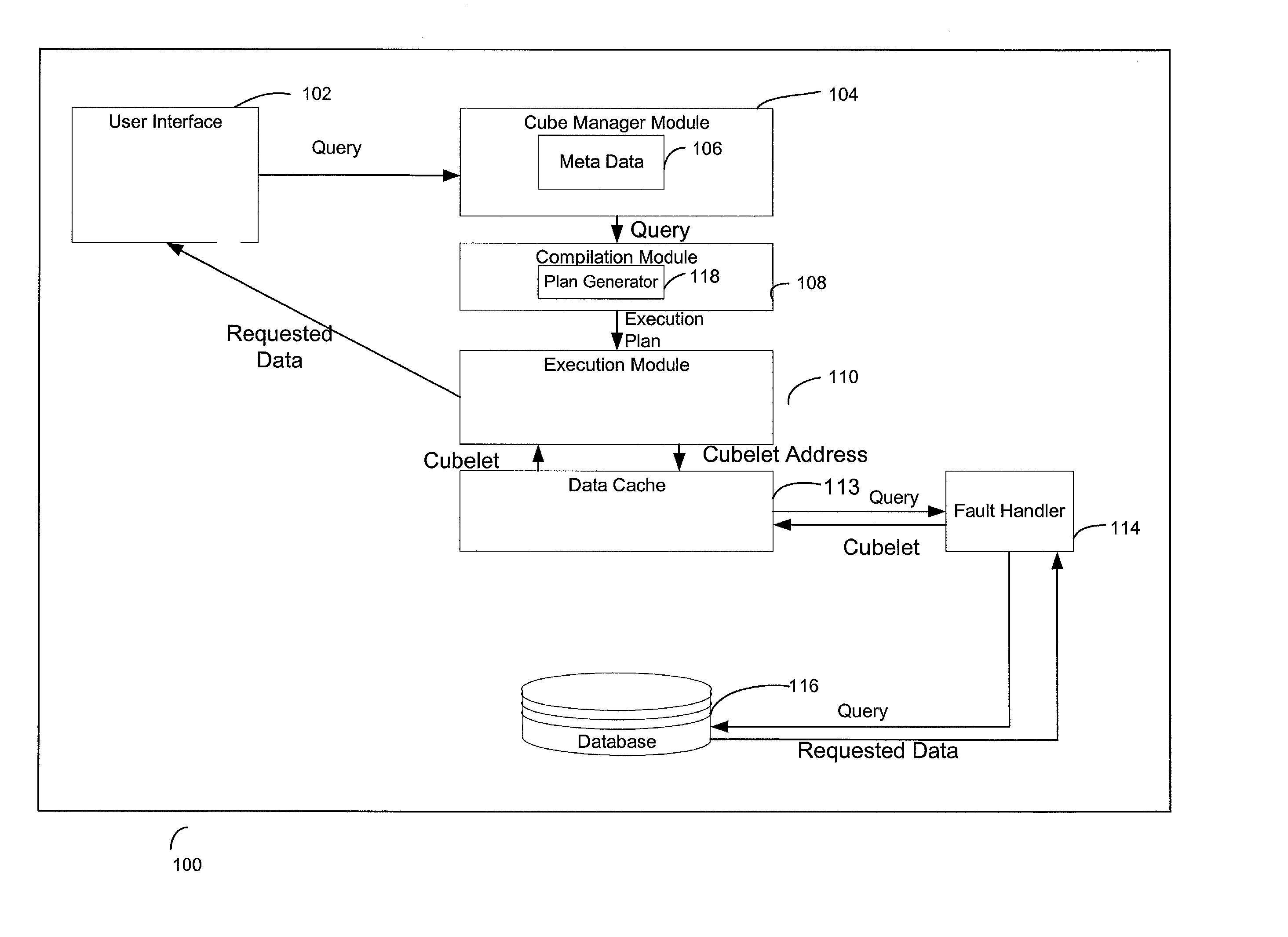

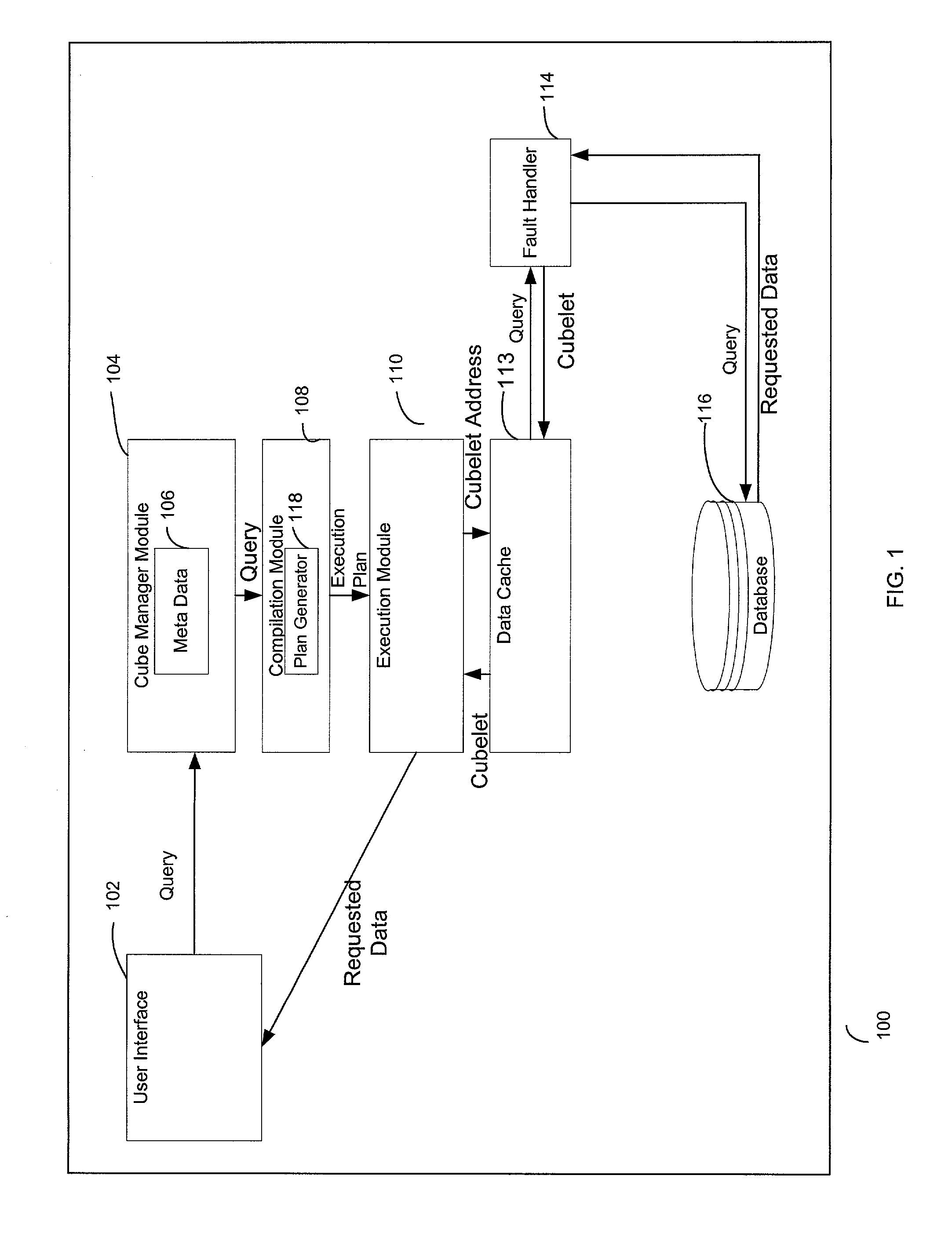

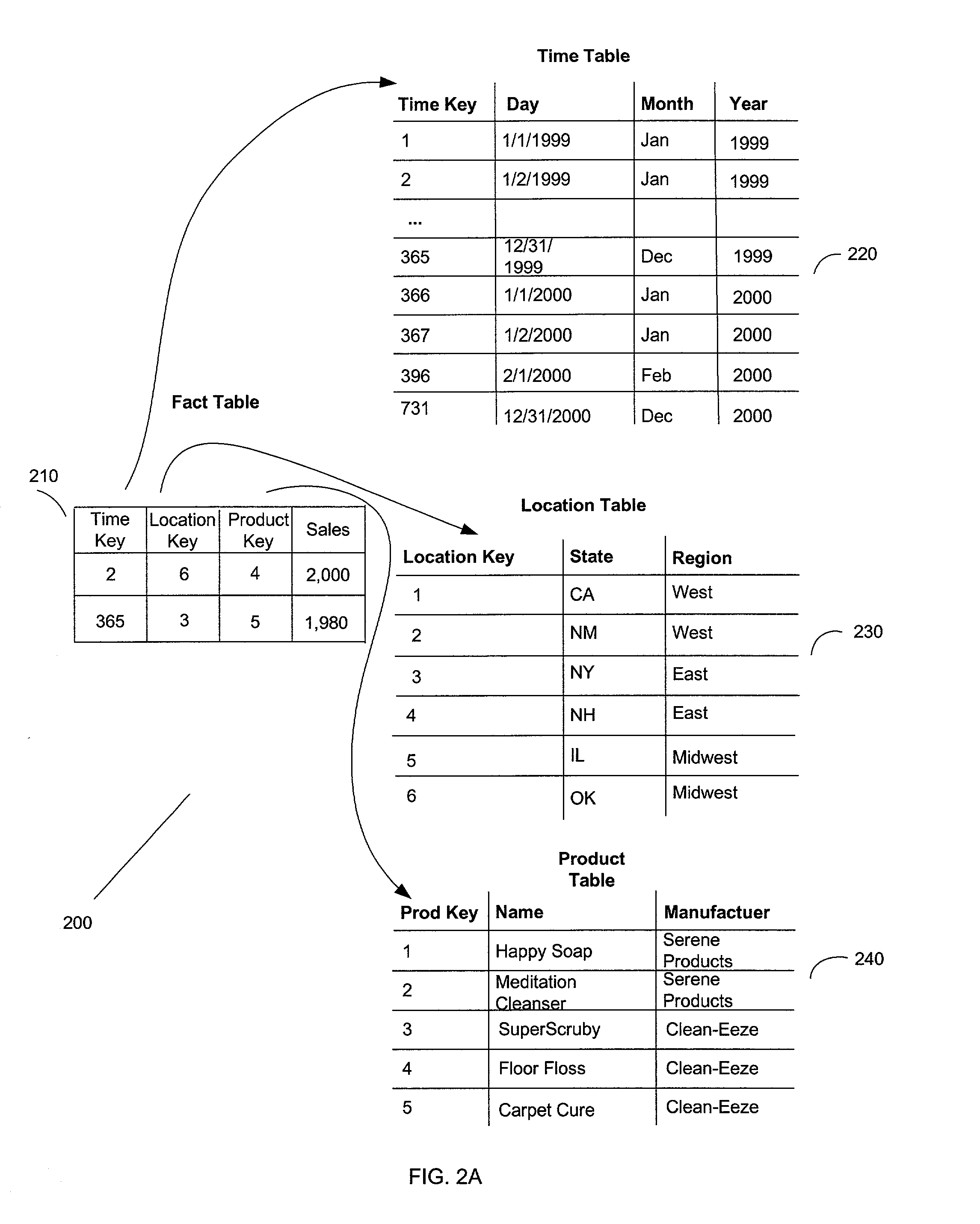

Caching scheme for multi-dimensional data

InactiveUS20020126545A1Data processing applicationsDigital storageLocality of referenceError processing

A system, method, and a computer program product for caching multi-dimensional data based on an assumption of locality of reference. A user sends a query for data. A described compilation module converts the query into a set of cubelet addresses and canonical addresses. In the described embodiment, if the data corresponding to the cubelet address is found in a data cache, the data cache returns the cubelet, which may contain the requested data and data for "nearby" cells. The data corresponding to the canonical addresses is extracted from the returned cubelet. If the data is not found in a data cache, a fault handler queries a back-end database for the cubelet identified by the cubelet address. This cubelet includes the requested data and data for "nearby" cells. The requested data and the data for "nearby cells" are in the form of values of measure attributes and associated canonical addresses. The returned cubelet is then cached and the data corresponding to the canonical addresses is extracted.

Owner:IBM CORP

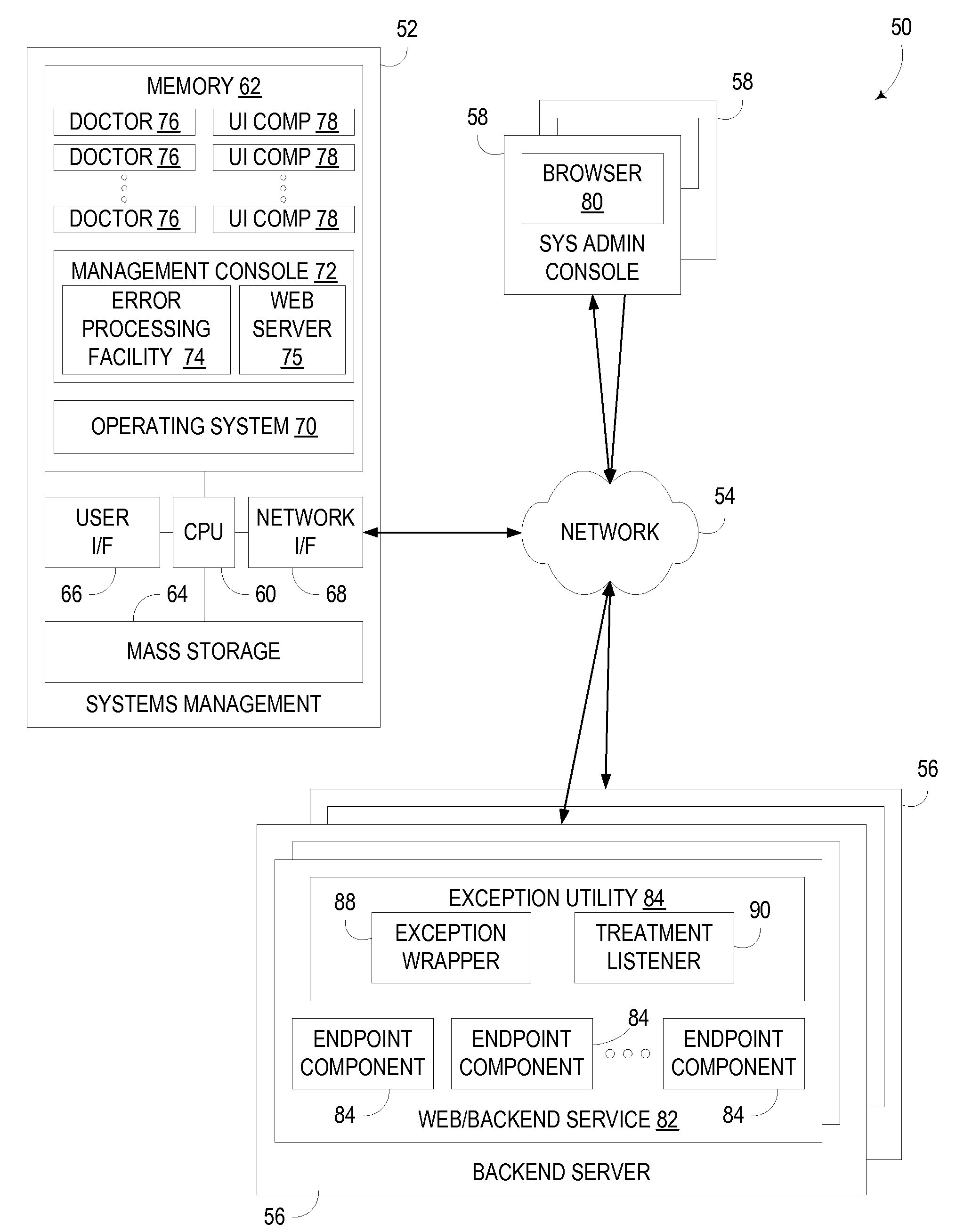

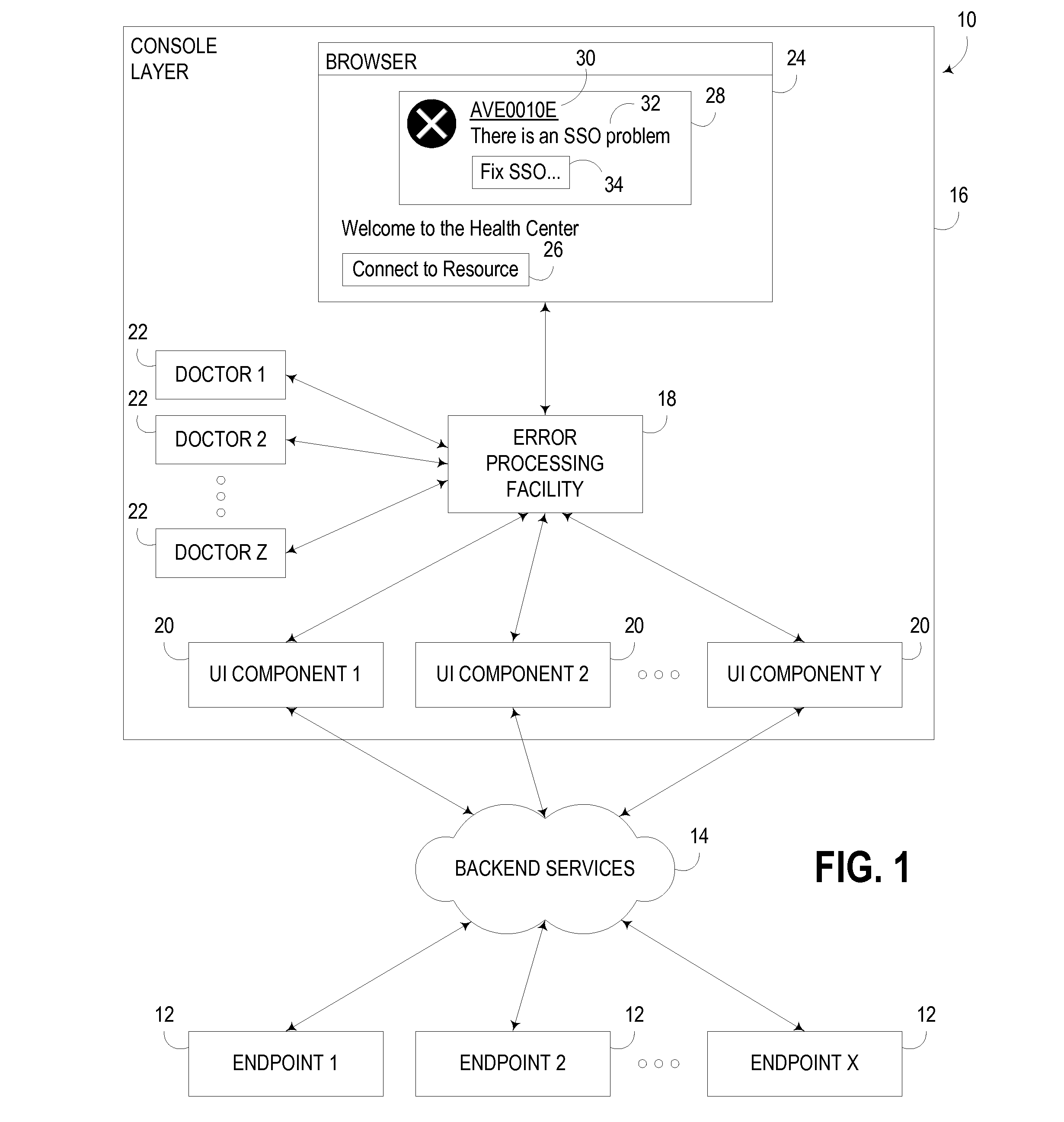

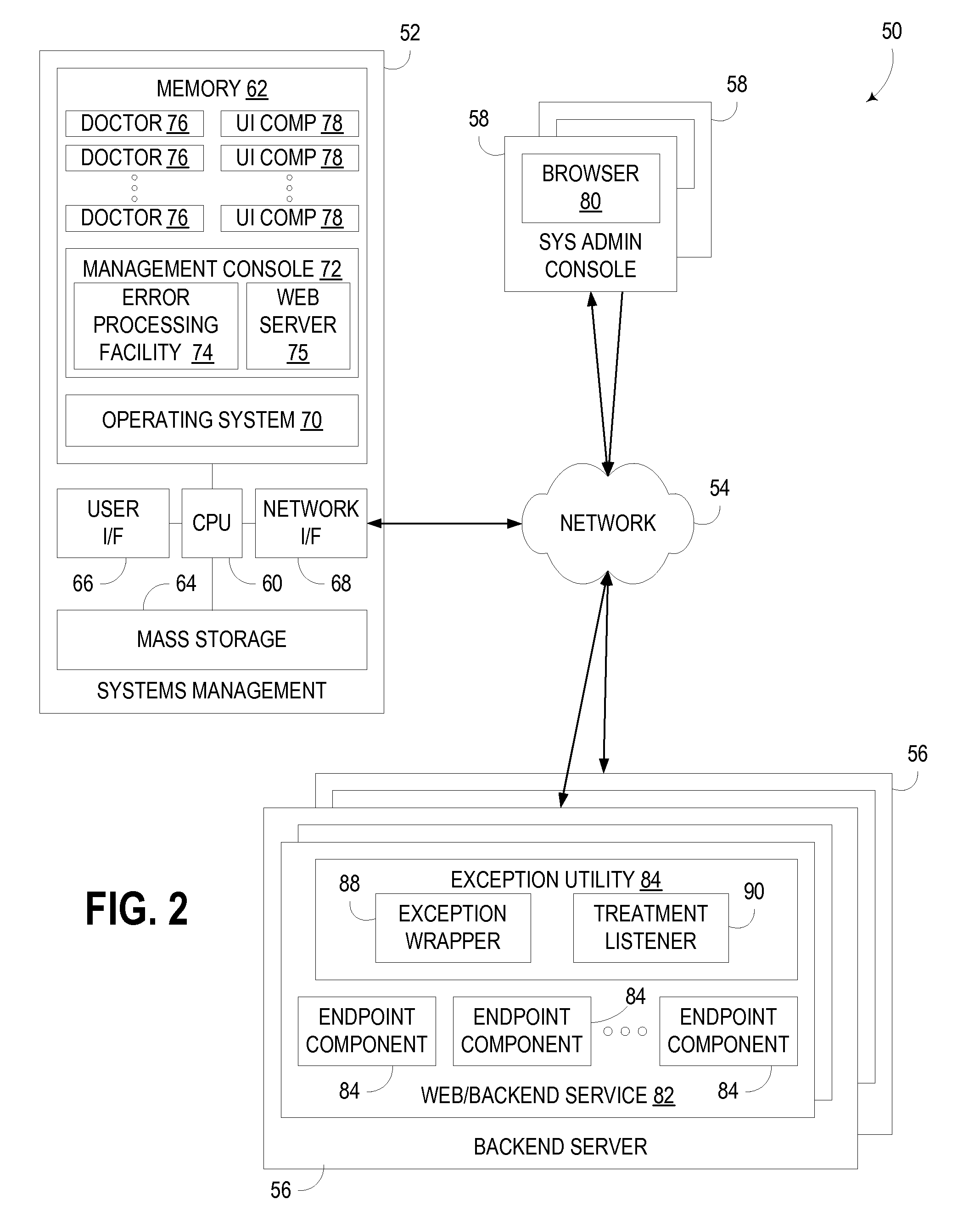

Automated error reporting and diagnosis in distributed computing environment

ActiveUS20080109683A1Increase rangeProvide functionalityNon-redundant fault processingDiagnostic agentError processing

An apparatus, program product and method provide a generic error reporting and diagnosis framework that is readily suited for use in a wide variety of distributed computing environments, and that supports the autonomic reporting, diagnosis, and potentially the remediation of errors. The framework supports the encapsulation of symptomatic data associated with an error in a component of a distributed computing environment such that the encapsulated symptomatic data may be routed to an error processing facility, typically irrespective of the underlying nature of the error and the hardware and / or software platform of the component that generated the error. The error processing facility is in turn capable of routing the encapsulated symptomatic data to one or more diagnostic agents that are capable of processing the symptomatic data to prescribe a treatment for the error.

Owner:SERVICENOW INC

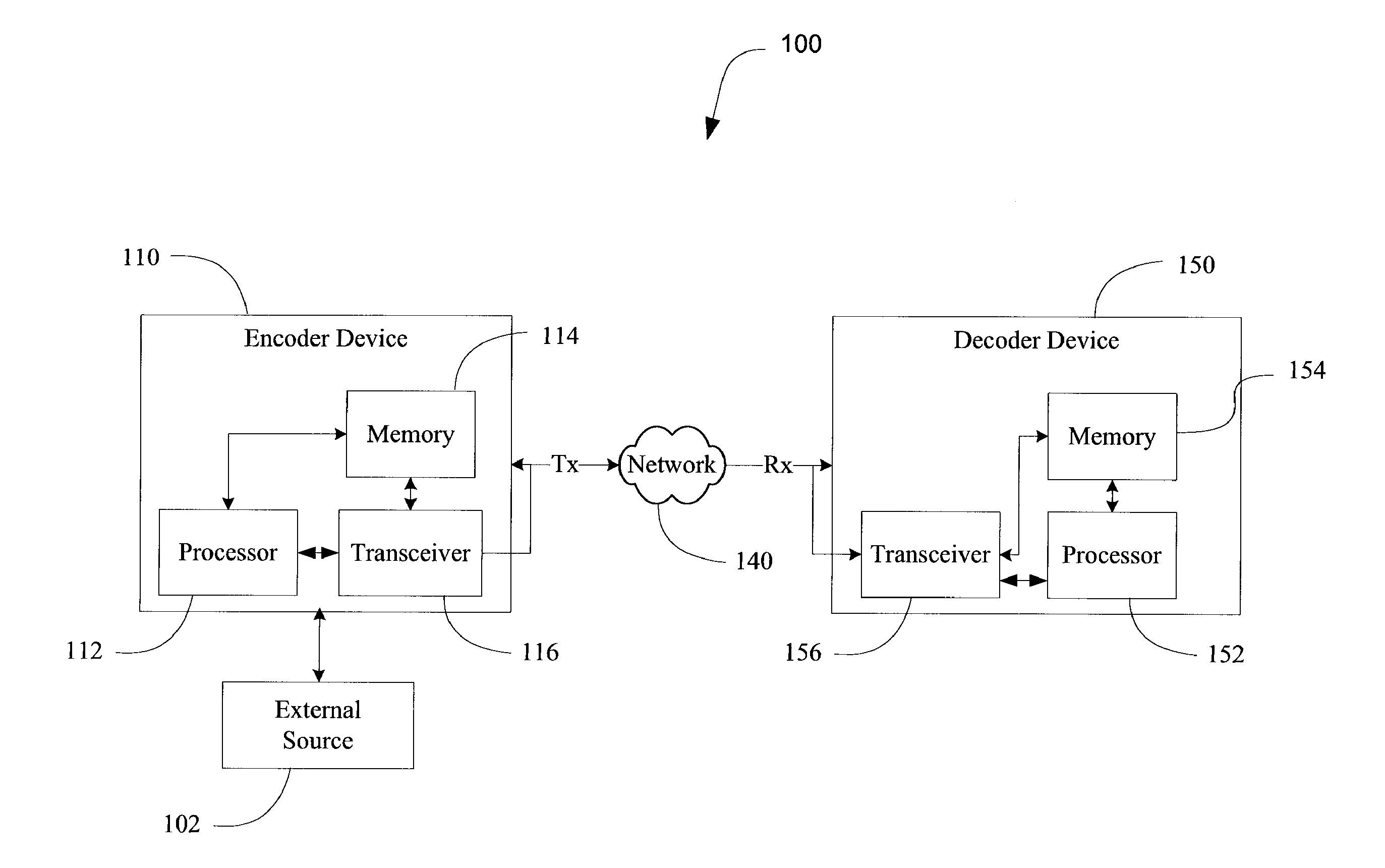

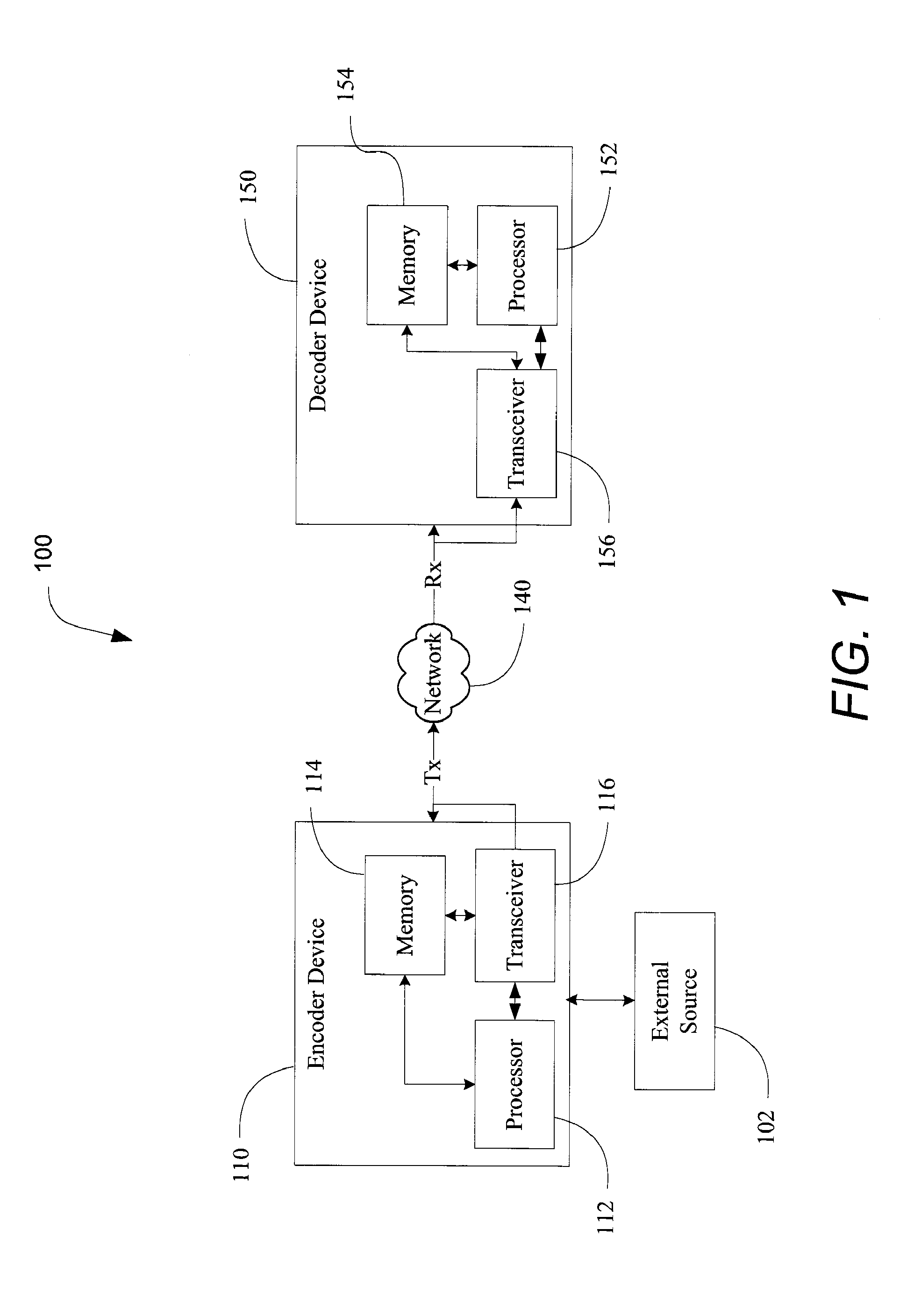

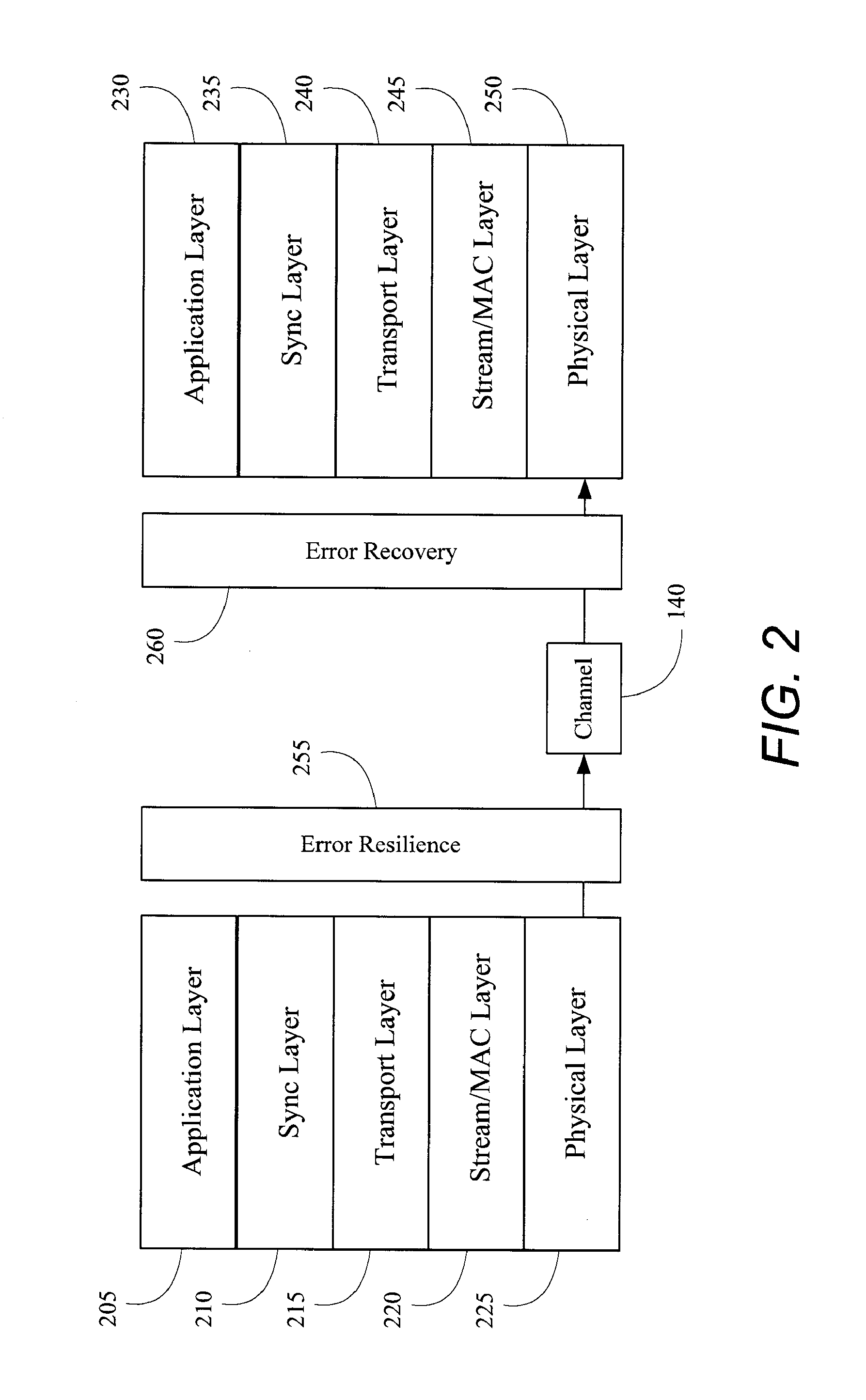

Frame level multimedia decoding with frame information table

ActiveUS20070291836A1Improve errorImprove efficiencyError preventionPicture reproducers using cathode ray tubesScalable compressionEncoder decoder

Apparatus and method to decode video data while maintaining a target video quality using an integrated error control system including error detection, resynchronization and error recovery are described. Robust error control can be provided by a joint encoder-decoder functionality including multiple error resilience designs. In one aspect, error recovery may be an end-to-end integrated multi-layer error detection, resynchronization and recovery mechanism designed to achieve reliable error detection and error localization. The error recovery system may include cross-layer interaction of error detection, resynchronization and error recovery subsystems. In another aspect, error handling of a scalable coded bitstream is coordinated across a base-layer and enhancement layer of scalable compressed video.

Owner:QUALCOMM INC

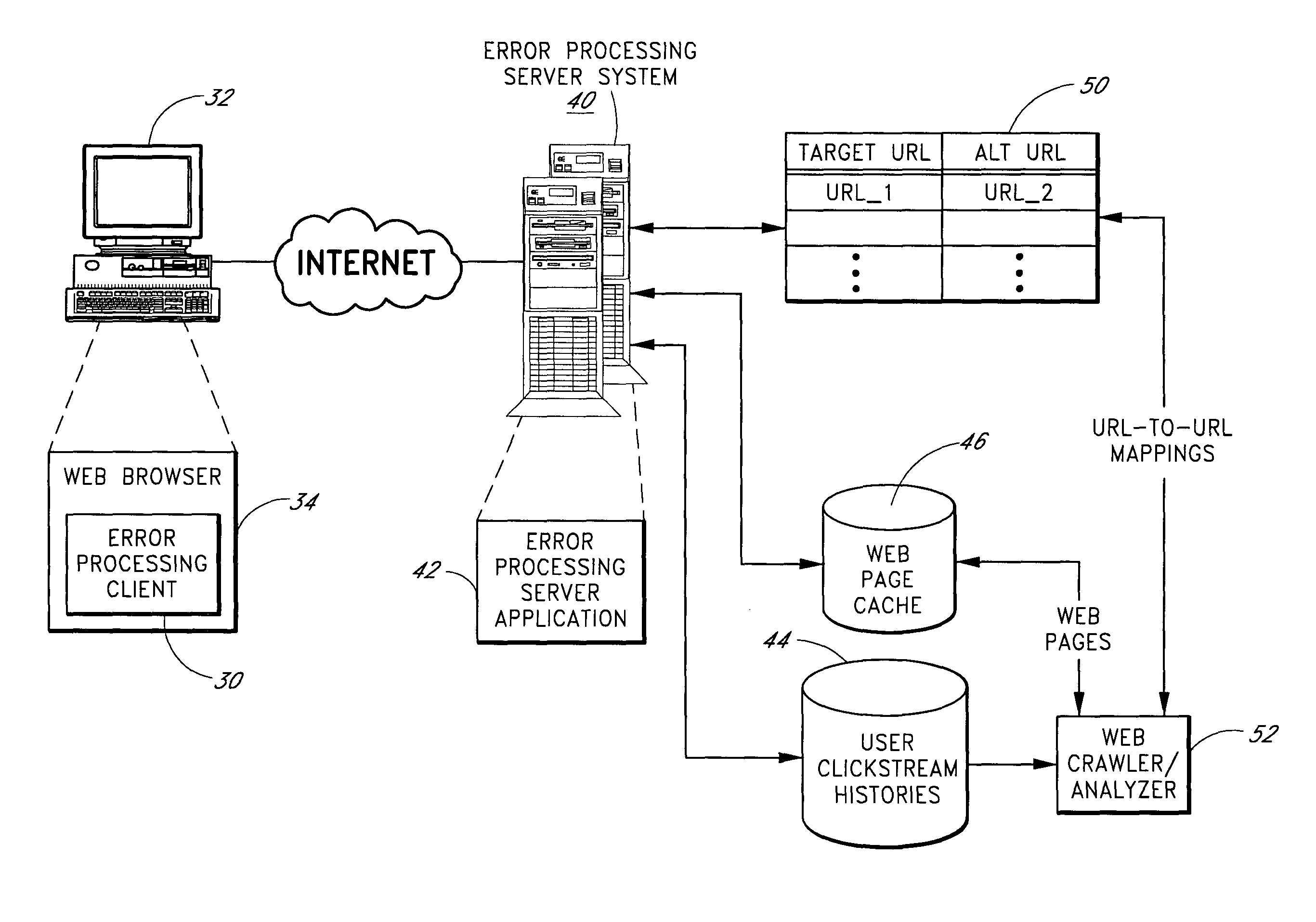

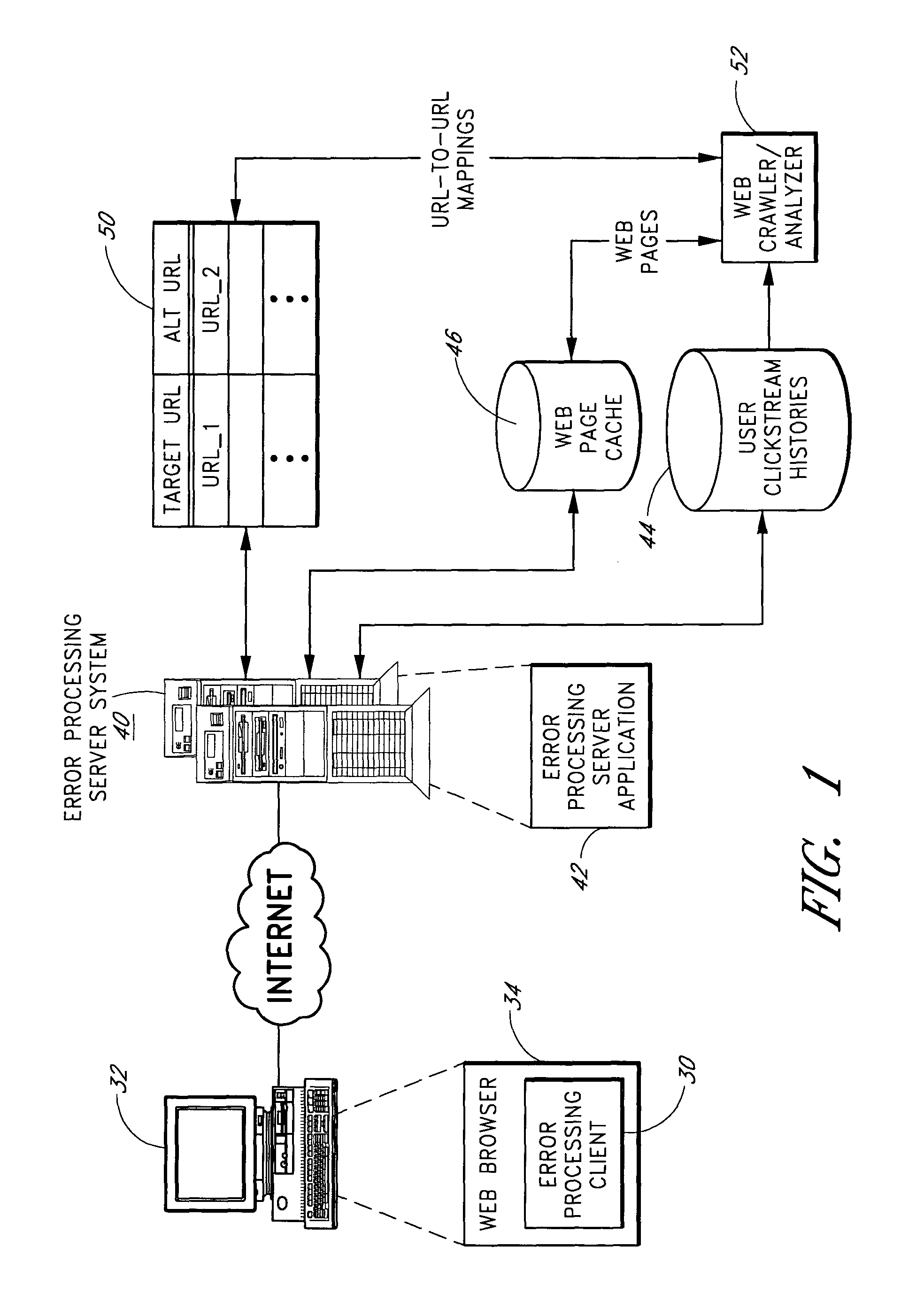

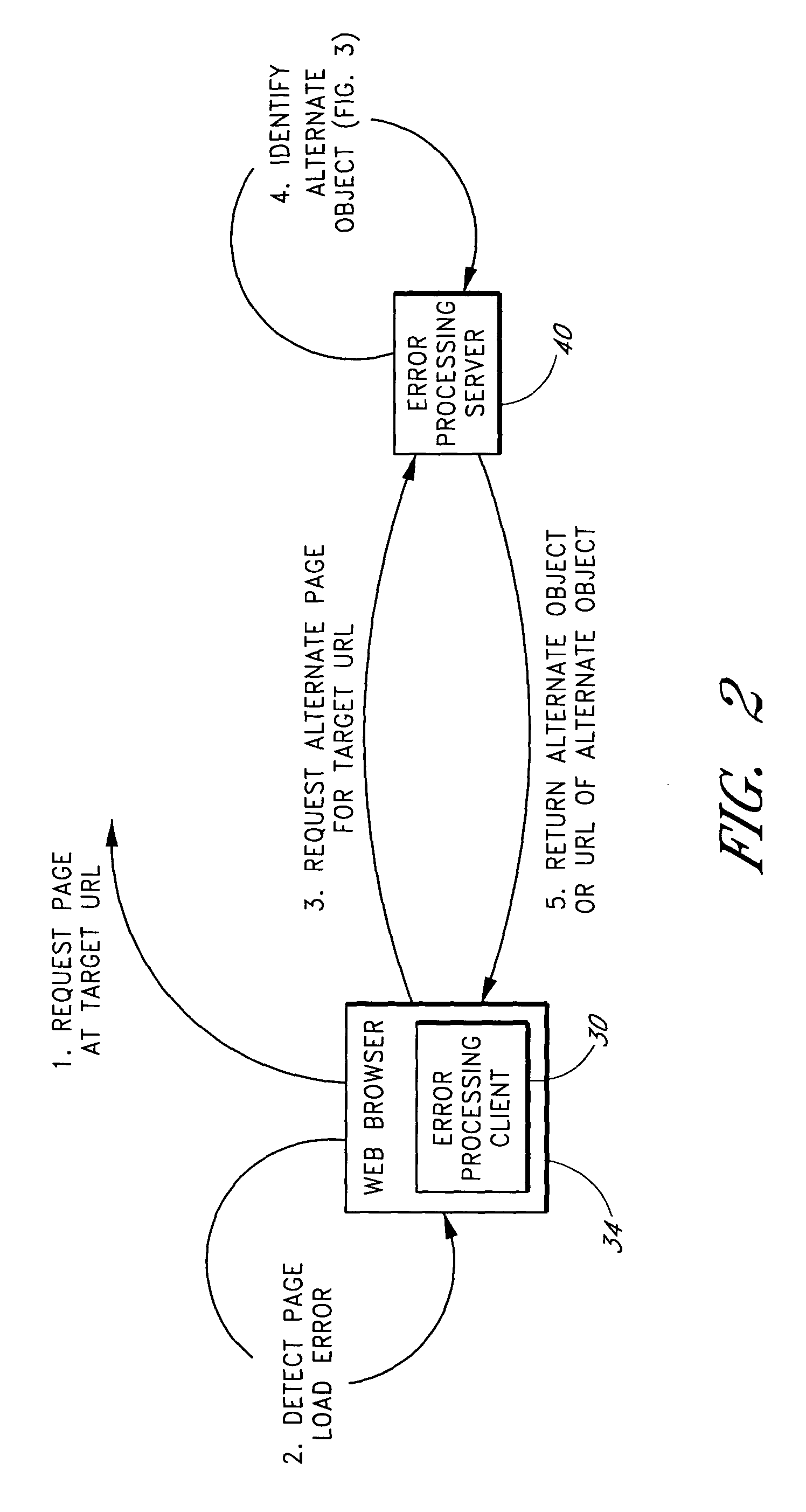

Error processing methods for providing responsive content to a user when a page load error occurs

InactiveUS7325045B1Digital data information retrievalMultiple digital computer combinationsWeb browserError processing

Owner:A9 COM INC

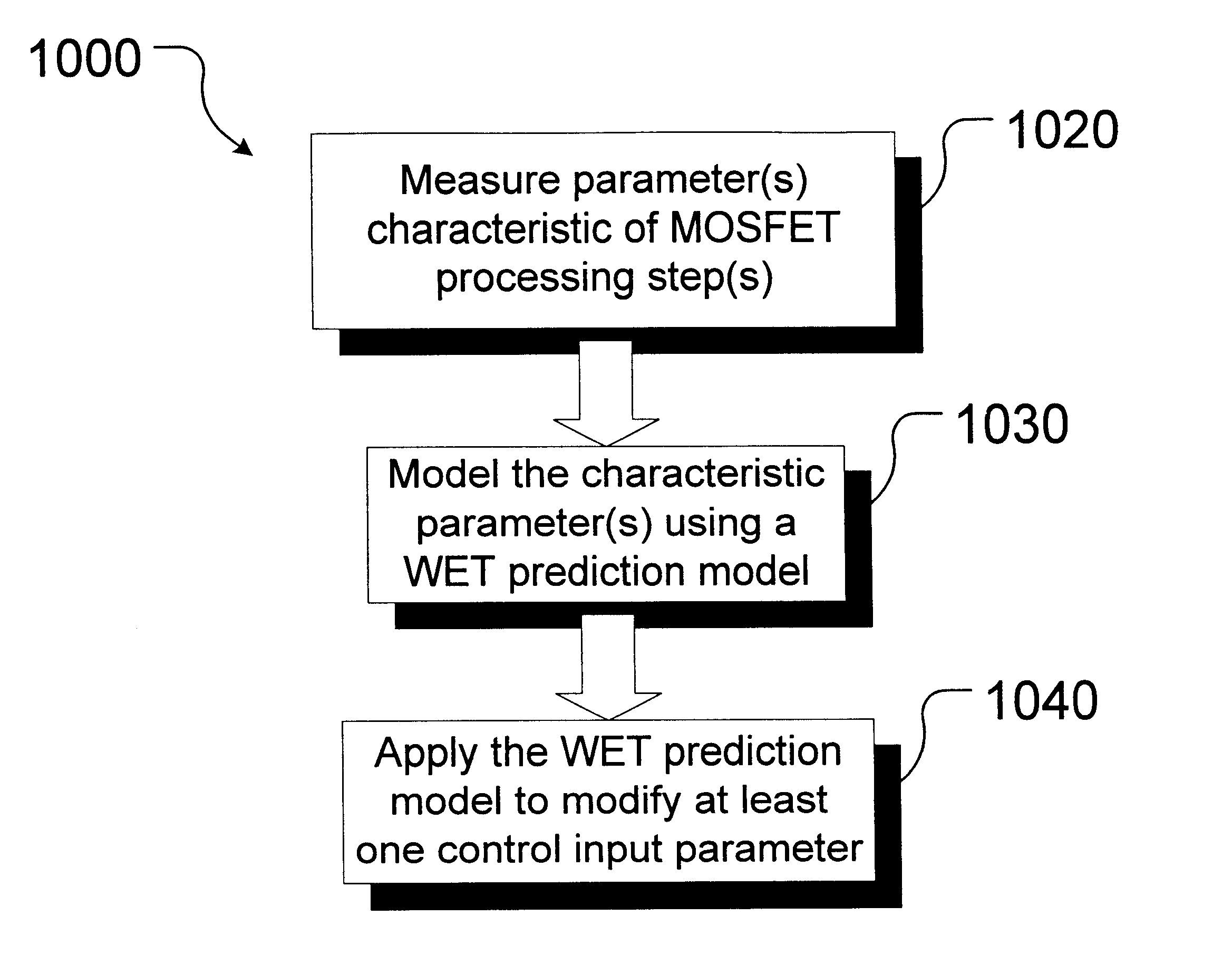

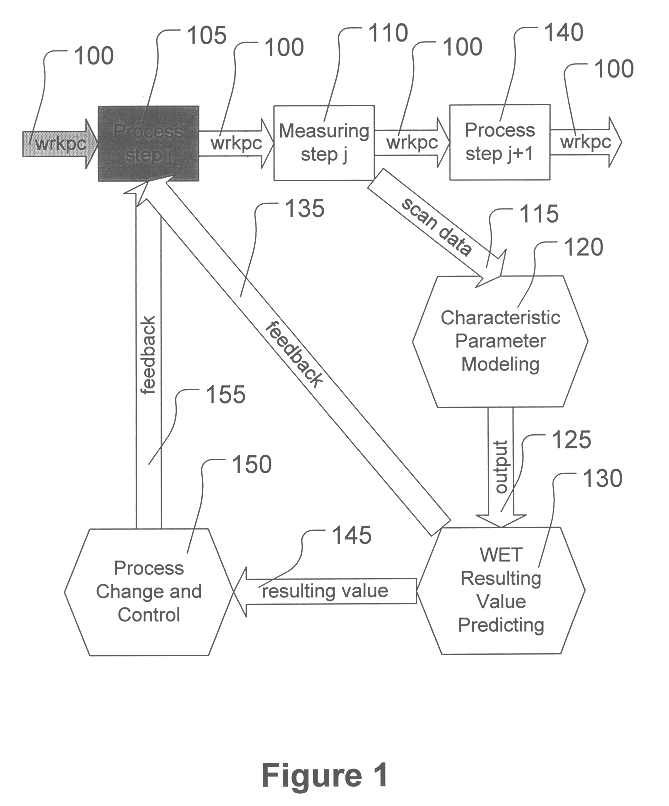

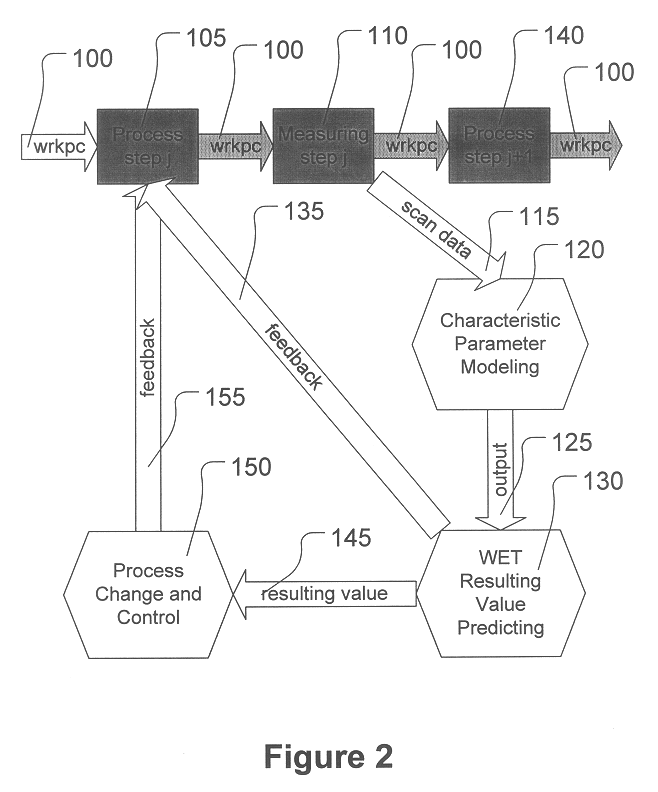

Automated process monitoring and analysis system for semiconductor processing

InactiveUS6622059B1Semiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingError processingFeature parameter

A method is provided for manufacturing, the method comprising processing a workpiece, measuring a parameter characteristic of the processing, and forming an output signal corresponding to the characteristic parameter measured by using the characteristic parameter measured as an input to a transistor model. The method also comprises predicting a wafer electrical test (WET) resulting value based on the output signal, detecting faulty processing based on the predicted WET resulting value, and correcting the faulty processing.

Owner:GLOBALFOUNDRIES INC

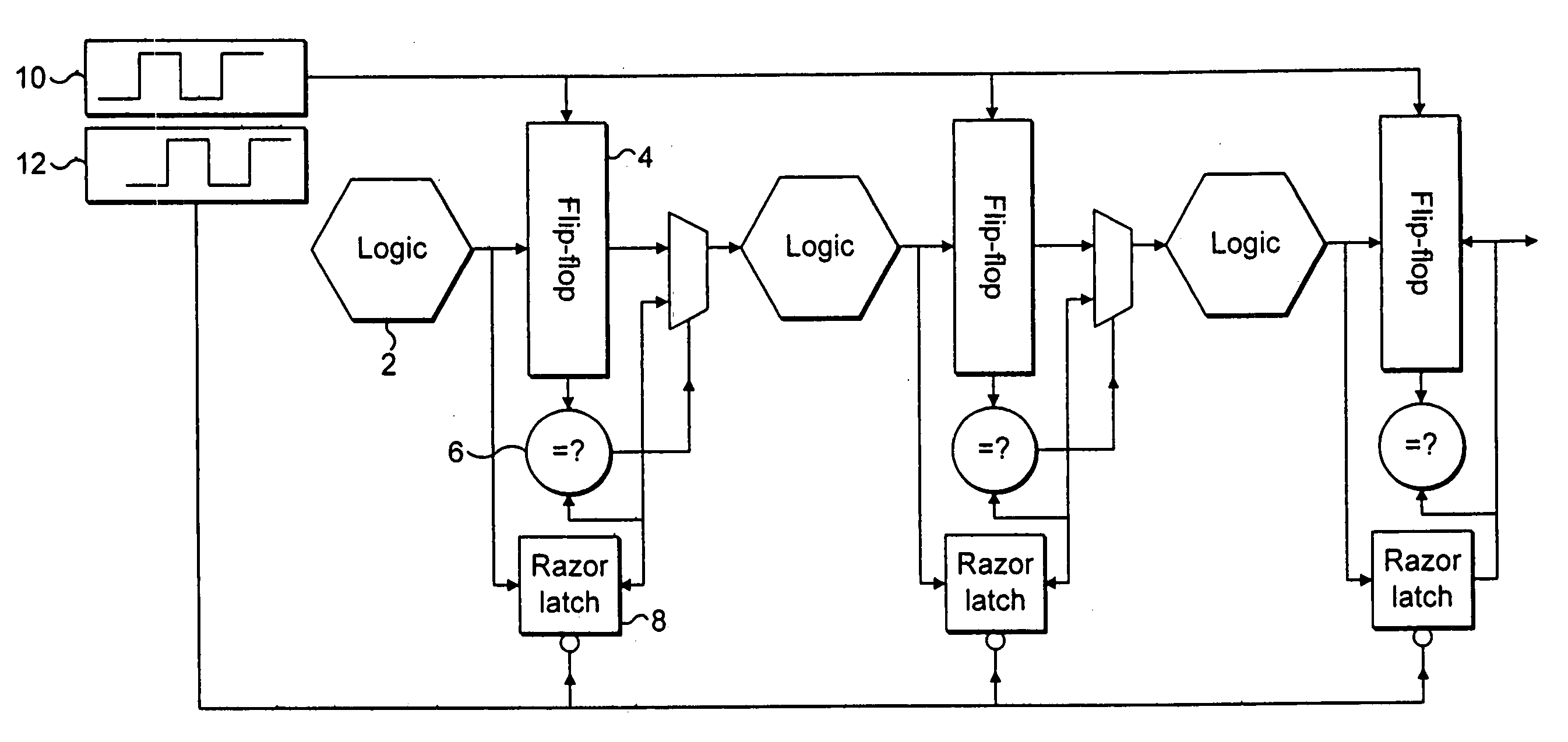

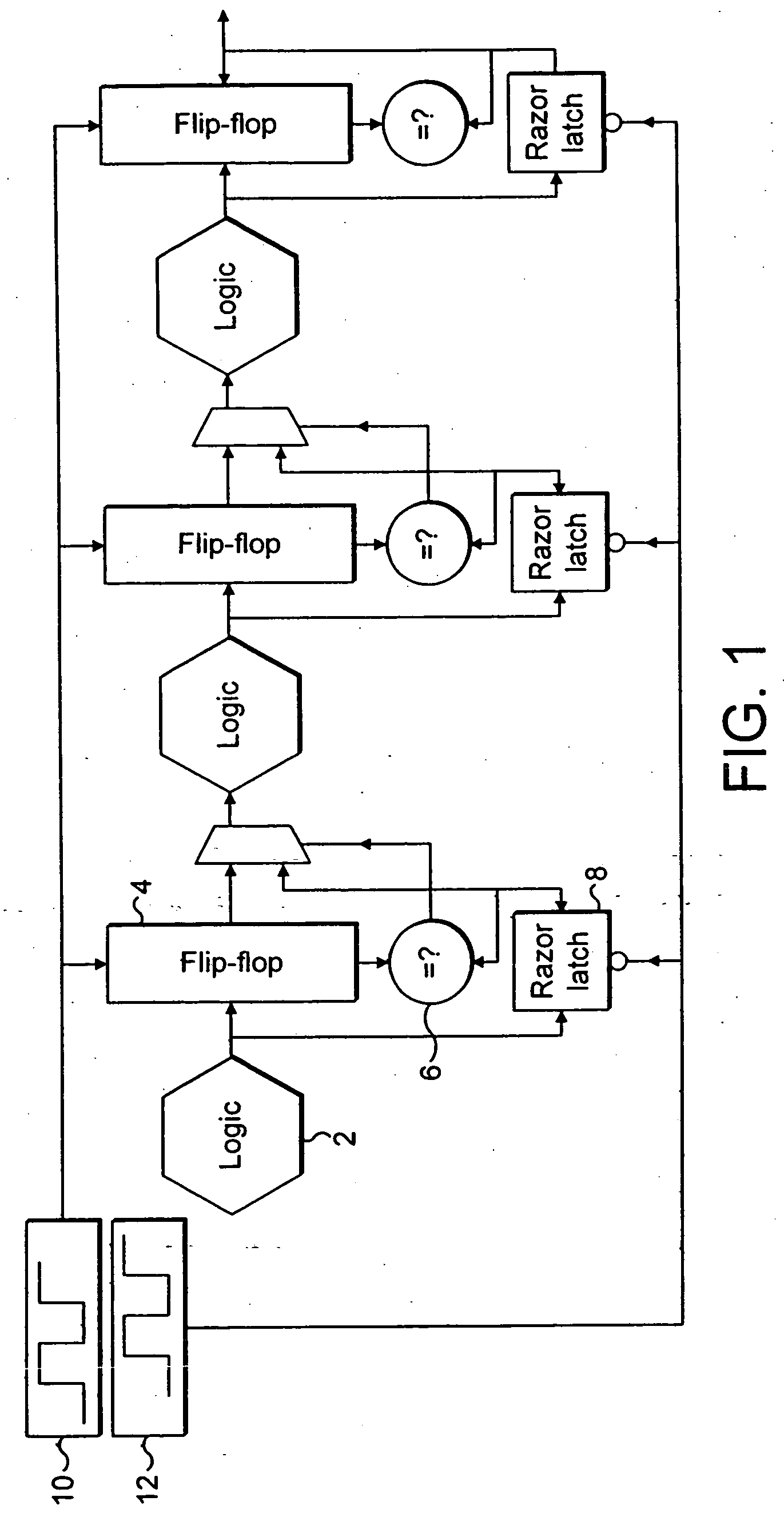

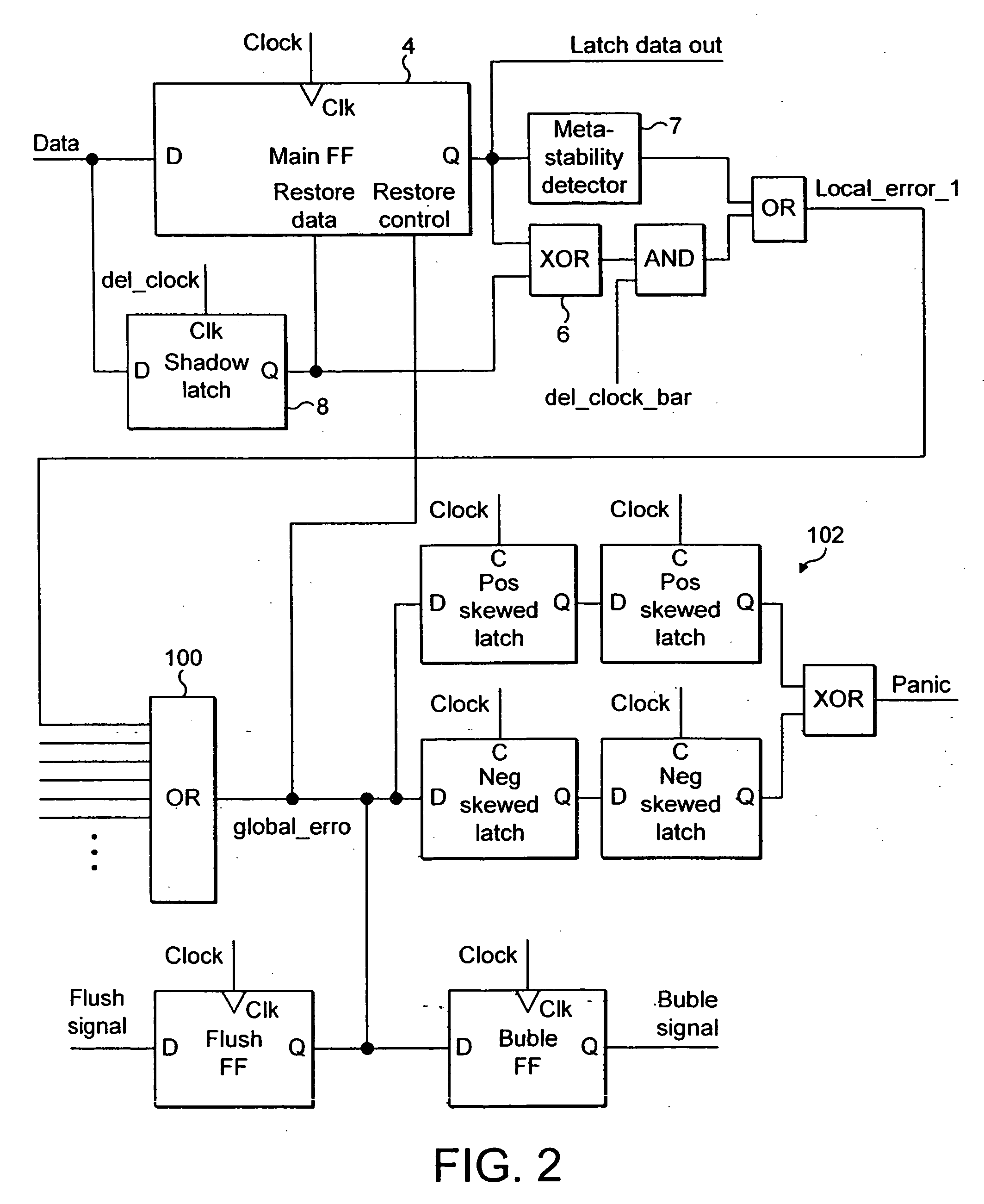

Error recovery within processing stages of an integrated circuit

ActiveUS20050246613A1Easy to modifyReduce the possibilityCode conversionFrequency/rate-modulated pulse demodulationError checkClock rate

An integrated circuit includes a plurality of processing stages each including processing logic 1014, a non-delayed signal-capture element 1016, a delayed signal-capture element 1018 and a comparator 1024. The non-delayed signal-capture element 1016 captures an output from the processing logic 1014 at a non-delayed capture time. At a later delayed capture time, the delayed signal-capture element 1018 also captures a value from the processing logic 1014. An error detection circuit 1026 and error correction circuit 1028 detect and correct random errors in the delayed value and supplies an error-checked delayed value to the comparator 1024. The comparator 1024 compares the error-checked delayed value and the non-delayed value and if they are not equal this indicates that the non-delayed value was captured too soon and should be replaced by the error-checked delayed value. The non-delayed value is passed to the subsequent processing stage immediately following its capture and accordingly error recovery mechanisms are used to suppress the erroneous processing which has occurred by the subsequent processing stages, such as gating the clock and allowing the correct signal values to propagate through the subsequent processing logic before restarting the clock. The operating parameters of the integrated circuit, such as the clock frequency, the operating voltage, the body biased voltage, temperature and the like are adjusted so as to maintain a finite non-zero error rate in a manner that increases overall performance.

Owner:ARM LTD +1

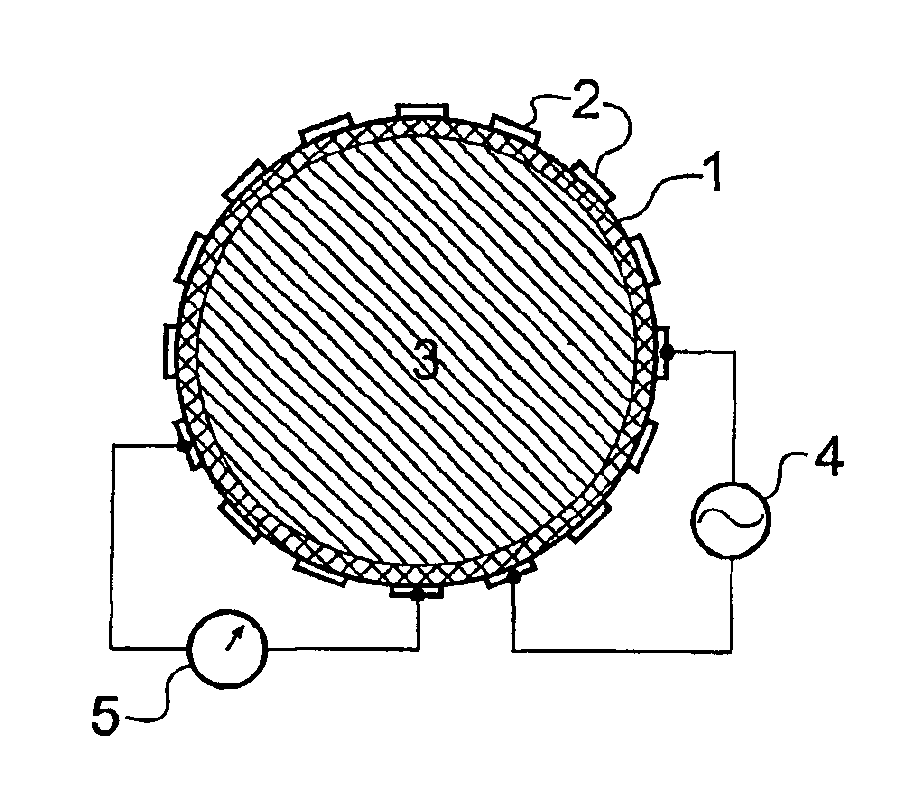

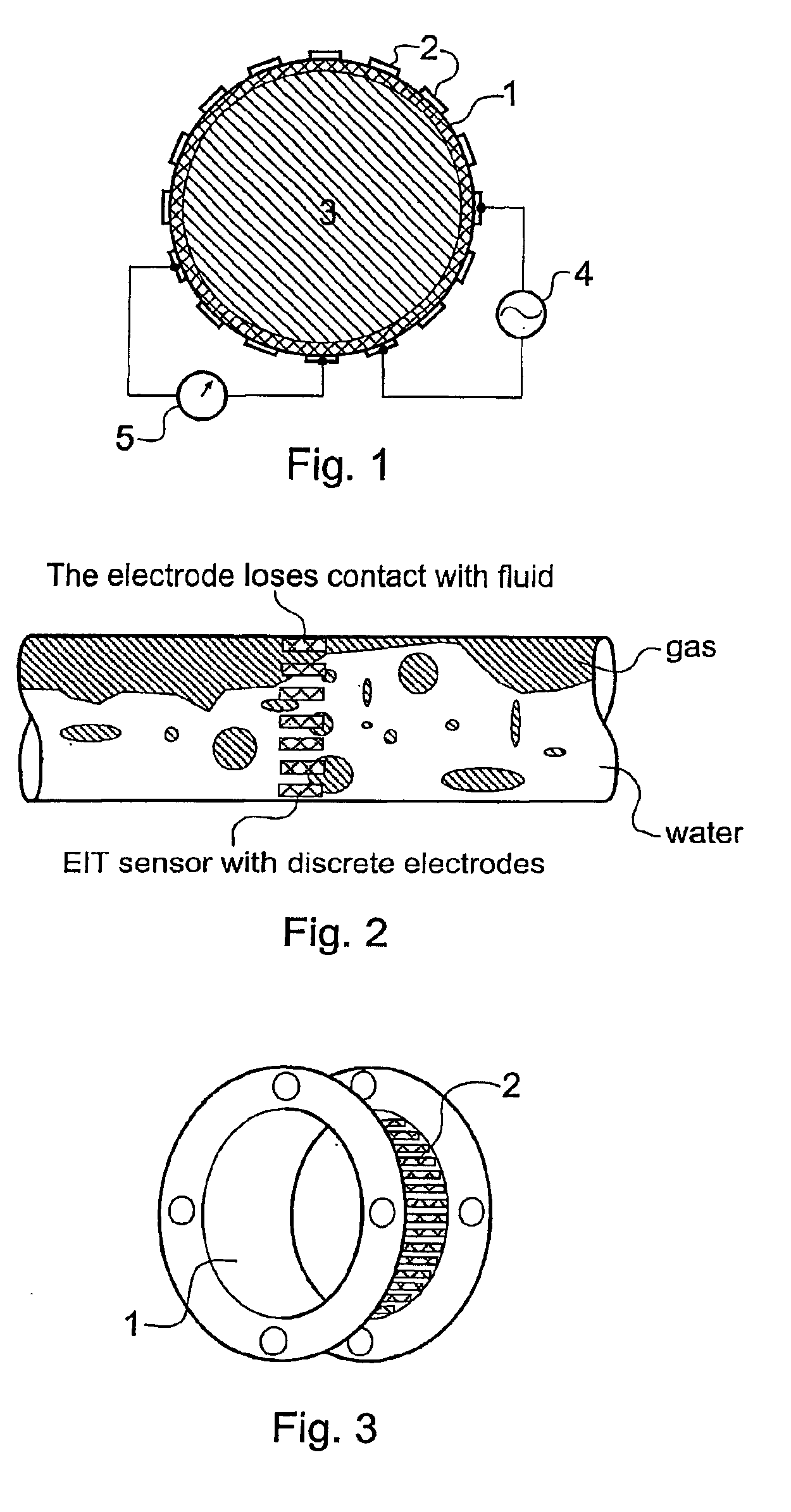

Electrical impedance tomography

InactiveUS6940286B2Improved imaging sensitivity distributionAccurate reconstructionMaterial analysis using wave/particle radiationRadiation/particle handlingElectrical resistance and conductanceElectricity

Methods and apparatus are provided for obtaining a representation of the distribution of electrical impedance within a multiphase flow with an electrically continuous or discontinuous principle flow contained within an electrically conductive solid ring electrode, including providing a plurality of mutually spaced electrical contacts mounted at the outside wall of the ring and electrically contacting with the ring, applying currents or voltages to the ring from the electrical contacts, generating a more homogeneous electric field distribution within the material, measuring voltage or current distribution alone the ring from other electrical contacts, relatively intensifying the imaging sensitivity at the central area of the sensing domain using a π / 2 angle sensing strategy and reconstructing the representation of the impedance distribution using CG method with an error processing strategy.

Owner:LEEDS THE UNIV OF

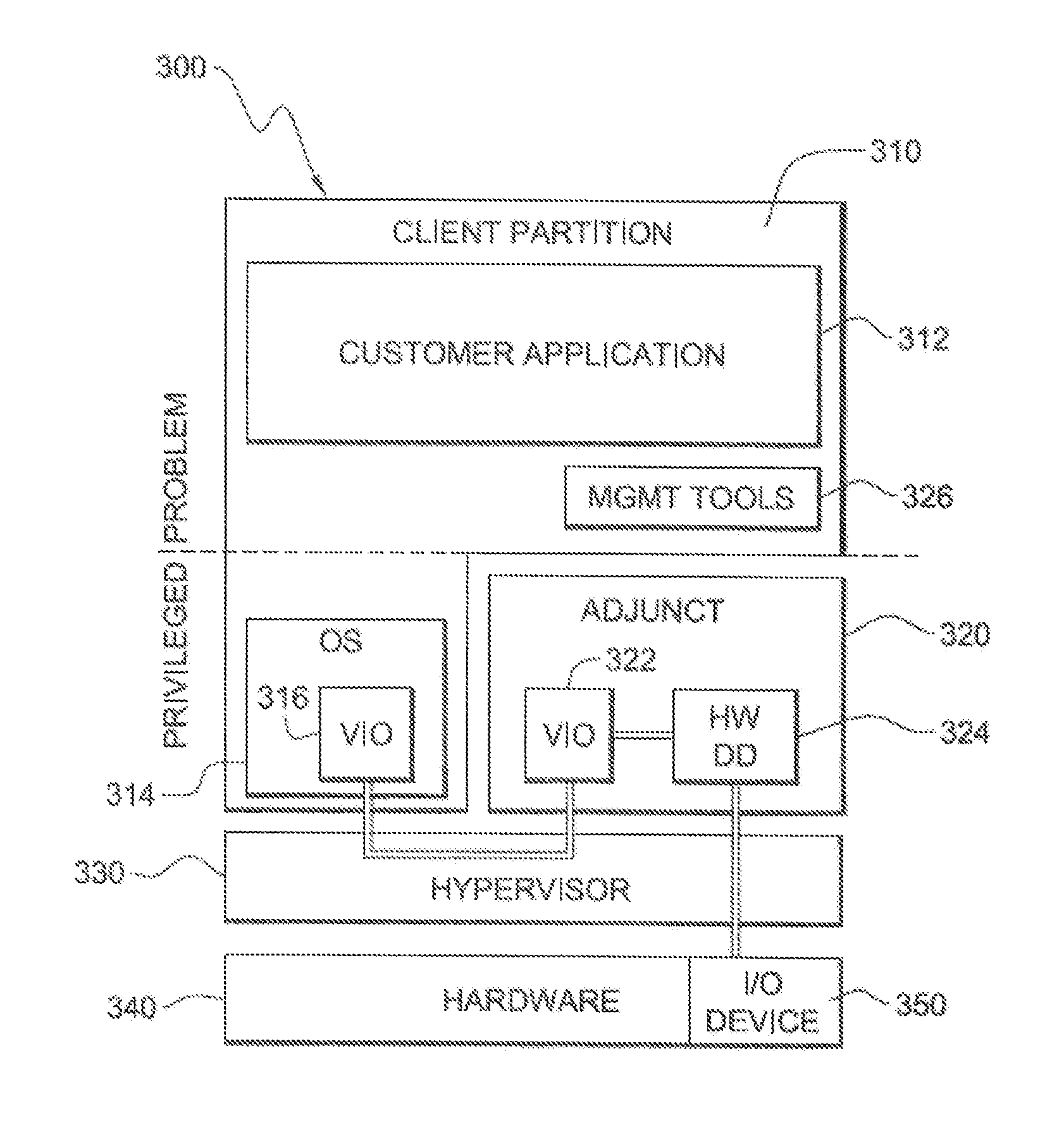

Enhanced error handling for self-virtualizing input/output device in logically-partitioned data processing system

ActiveUS20120159245A1Simplified error handlingAvoid the needNon-redundant fault processingRedundant operation error correctionVirtualizationData processing system

Error handling is simplified for a self-virtualizing IO resource that utilizes a physical function adjunct partition for a physical function in the self-virtualizing IO resource to coordinate error recovery for the self-virtualizing IO resource, by restarting each virtual function adjunct partition associated with that physical function to avoid the need to coordinate error recovery within the logical partitions to which such virtual function adjunct partitions are assigned.

Owner:IBM CORP

OS and firmware coordinated error handling using transparent firmware intercept and firmware services

Methods and architectures for performing hardware error handling using coordinated operating system (OS) and firmware services. In one aspect, a firmware interface is provided to enable an OS to access firmware error-handling services. Such services enable the OS to access error data concerning platform hardware errors that may not be directed accessed via a platform processor or through other conventional approaches. Techniques are also disclosed for intercepting the processing of hardware error events and directing control to firmware error-handling services prior to attempting to service the error using OS-based services. The firmware services may correct hardware errors and / or log error data that may be later accessed by the OS or provided to a remote management server using an out-of-band communication channel. In accordance with another aspect, the firmware intercept and services may be performed in a manner that is transparent to the OS.

Owner:INTEL CORP

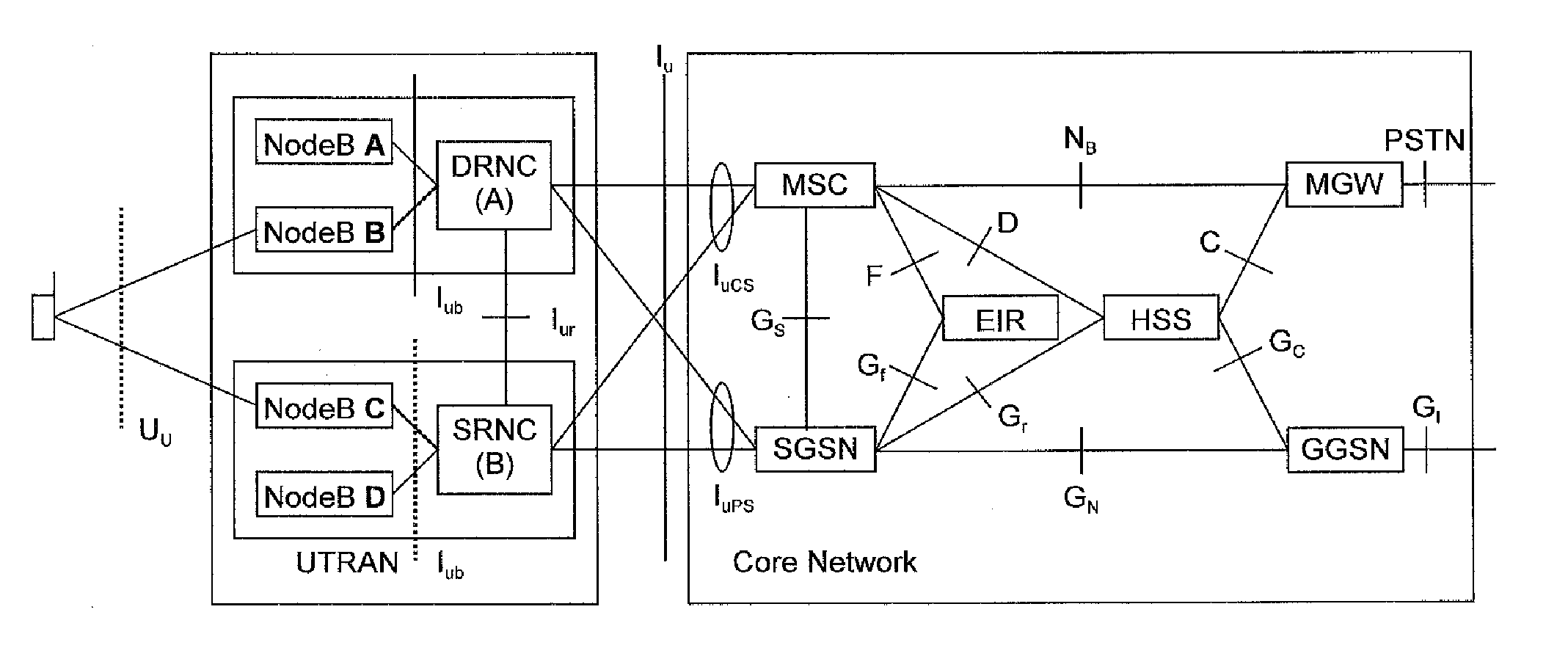

Enhanced Radio Link Control Error Handling

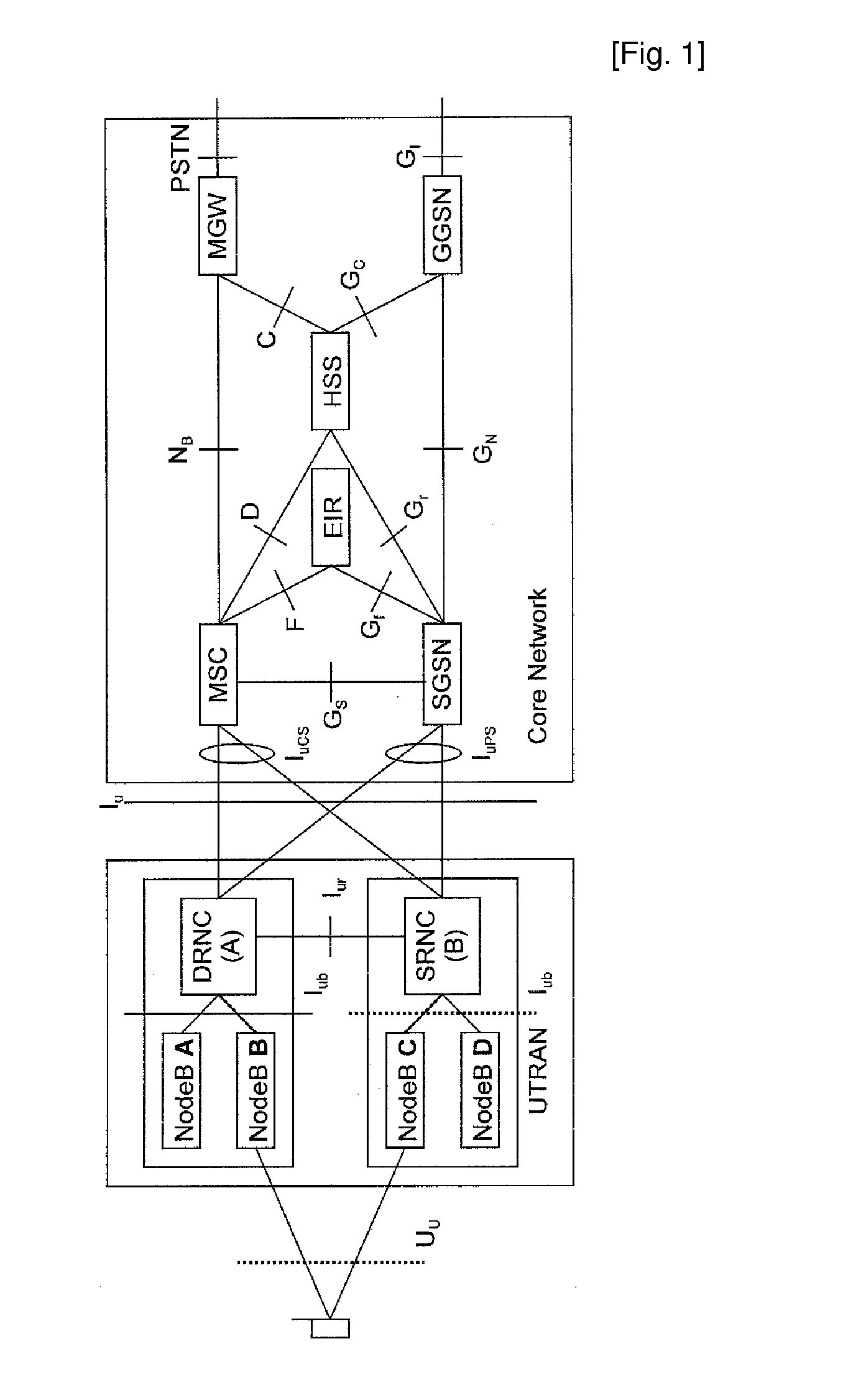

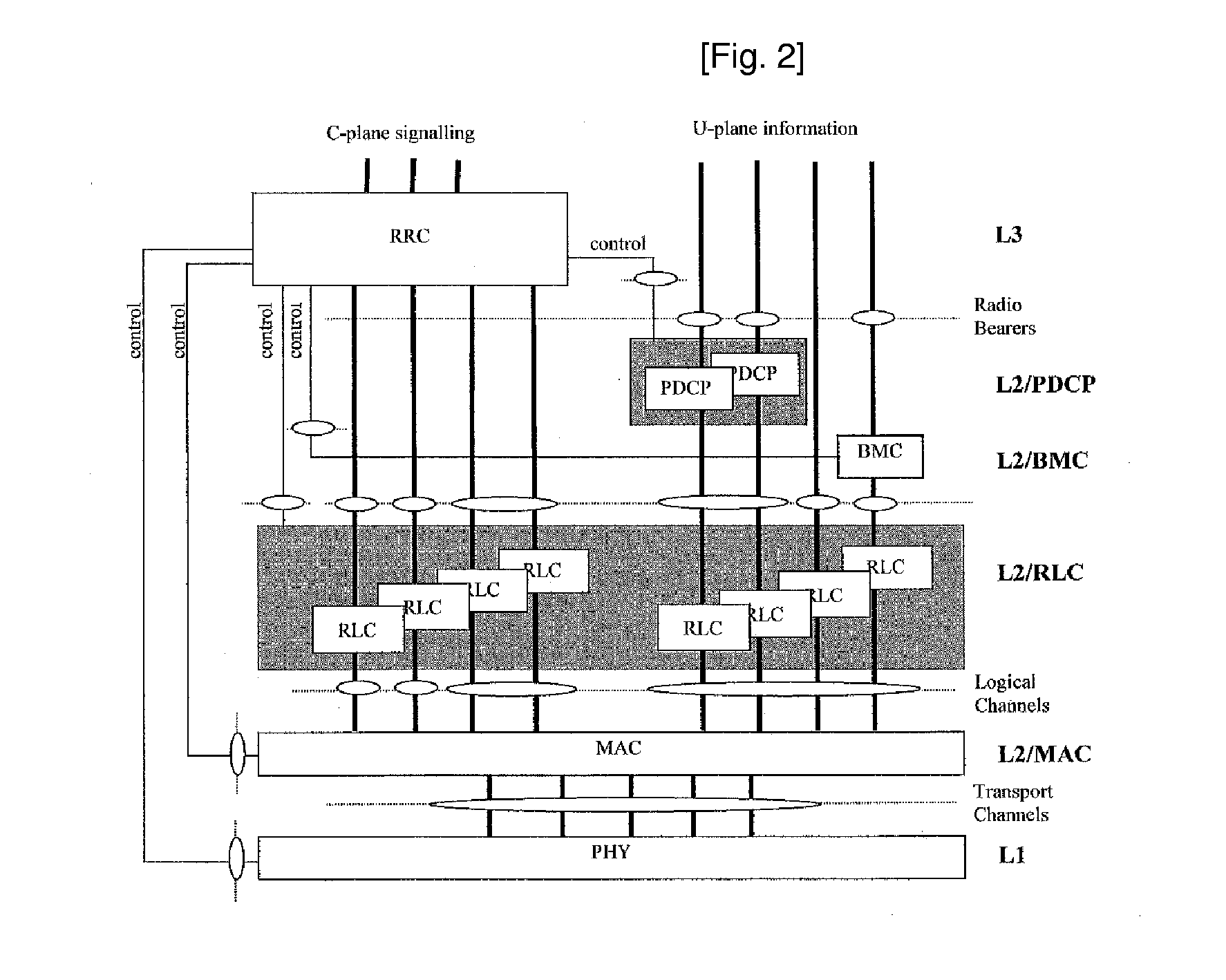

InactiveUS20080064390A1Minimize lost loss of dataNetwork traffic/resource managementNetwork topologiesError processingRadio Link Control

The invention relates to a method for settling an error in a radio link control entity which processes data transmitted by a cellular network to a user equipment, comprising the following steps: the user equipment receives a message from a control entity of the cellular network, said message including data identifying the radio link control entity which is in error, the user equipment re-initializes the radio link control entity according to the data included in the message. Particular application for settling unrecoverable errors affecting a radio link controller of a user equipment in a UMTS network.

Owner:LG ELECTRONICS INC

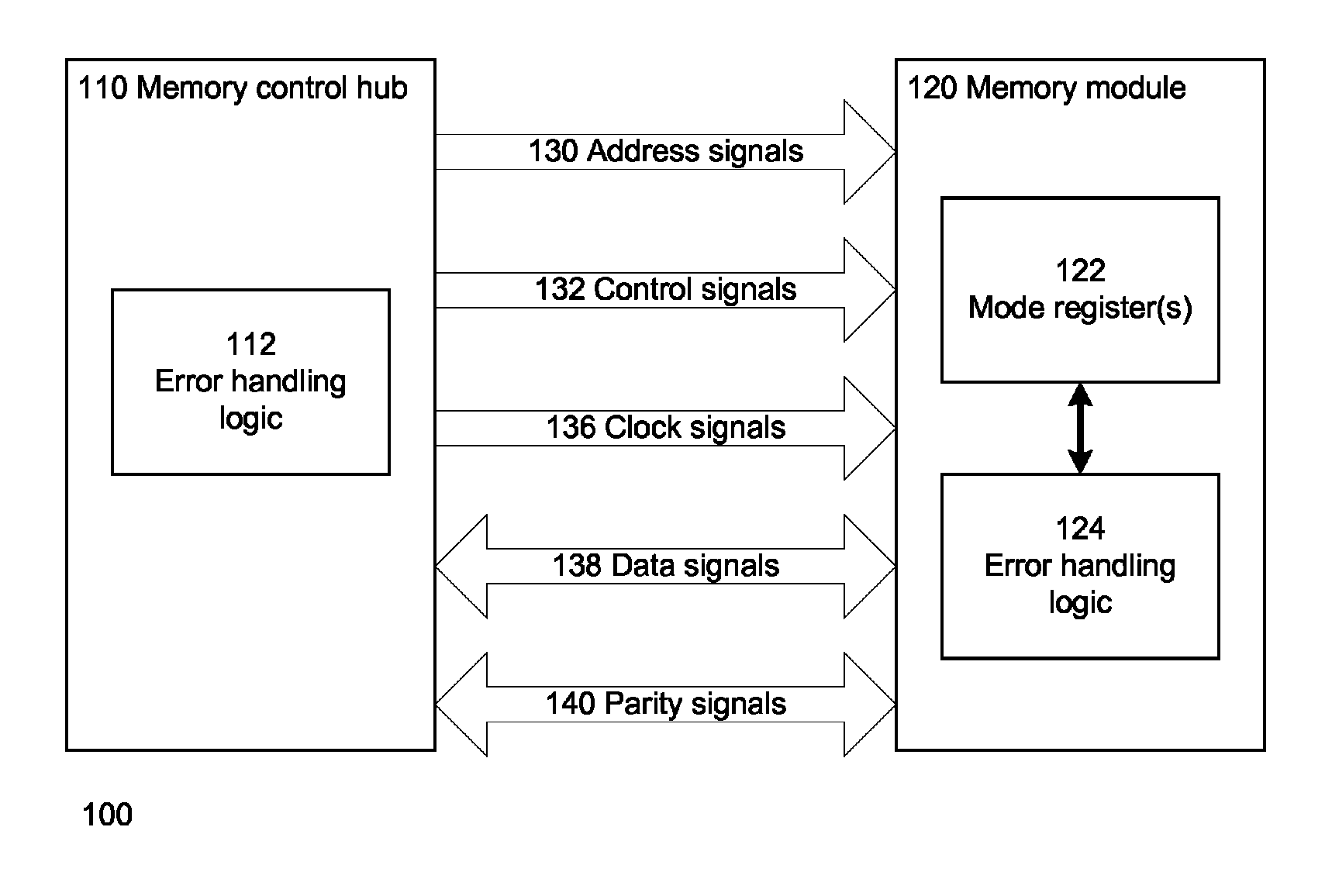

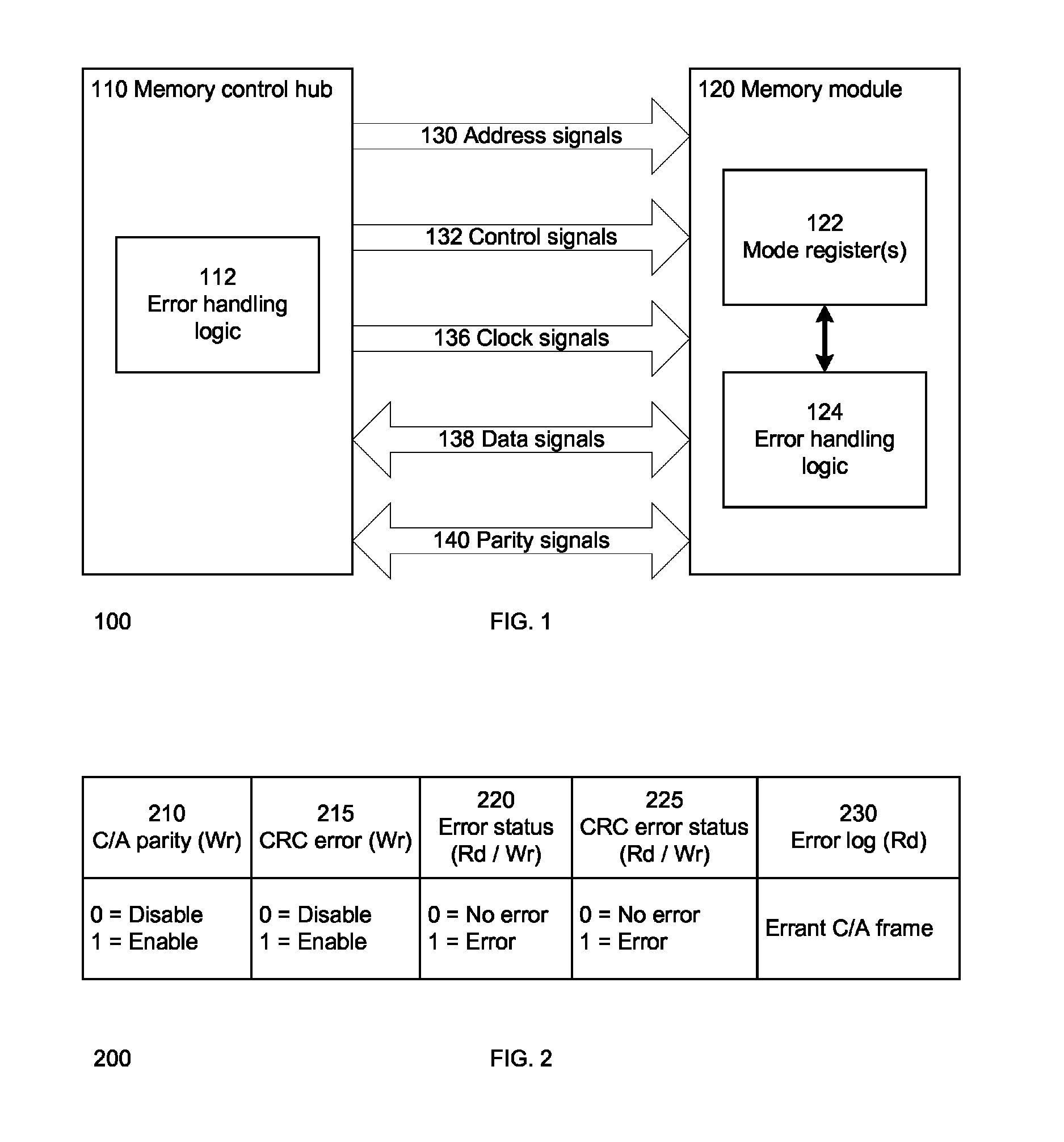

Method and system for error management in a memory device

Owner:SONY CORP

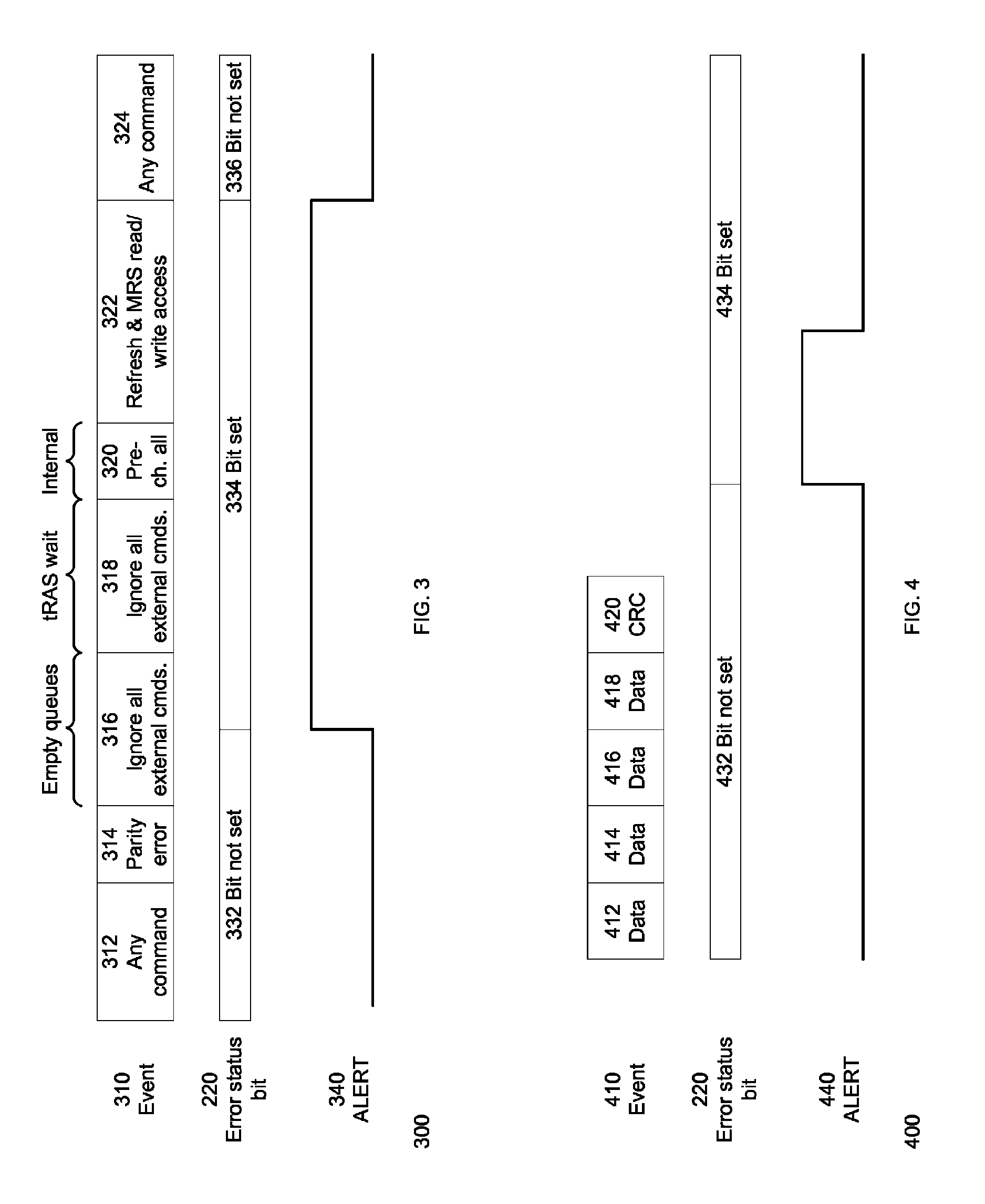

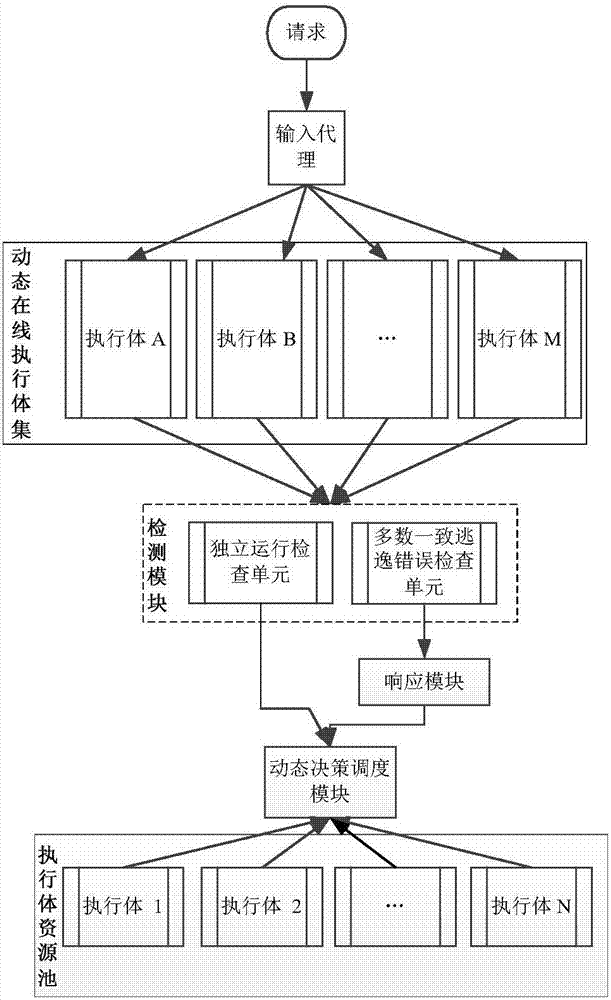

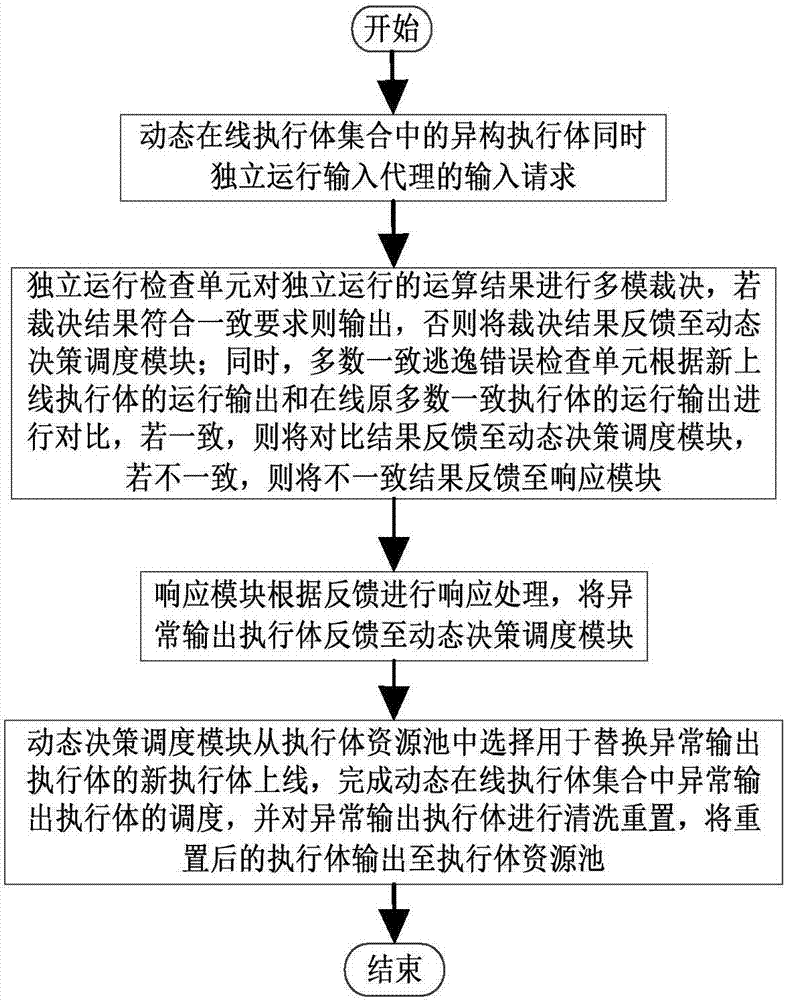

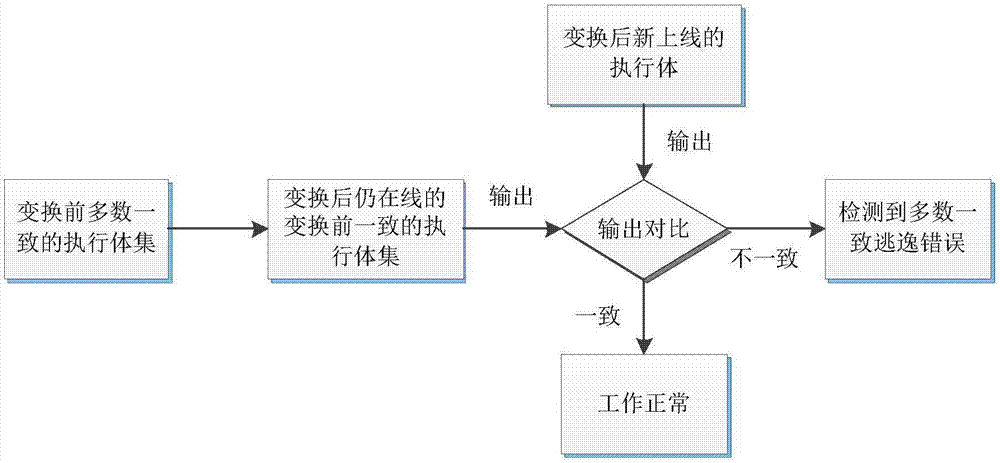

Majority consistent escape error processing device based on mimicry security defense zero-day attack and method thereof

ActiveCN106874755AGuaranteed robustnessGuaranteed survivabilityPlatform integrity maintainanceResource poolError processing

The invention relates to a majority consistent escape error processing device based on mimicry security defense zero-day attack and a method thereof. The method comprises: a heterogeneous executive in a dynamic online executive assembly independently operating an input request; performing multimode adjudication on an operation result, if an adjudication result meets a consistency requirement, outputting the adjudication result, if not, feeding back the adjudication result to a dynamic decision dispatching module; comparing new online executive operation output with online original majority consistent executive operation output, respectively feeding back results to the dynamic decision dispatching module and a responding module; the responding module processing the response according to feedback, and feeding back abnormal output executive to the dynamic decision dispatching module; and the dynamic decision dispatching module selecting new executive to be online from an executive resource pool, and cleaning and resetting offline executives. The method is used to provide means of detection and response when majority of mimicry defense online executives are attacked, and solves security threat a mimicry defense system faces, so as to enhance robustness of the mimicry system.

Owner:THE PLA INFORMATION ENG UNIV

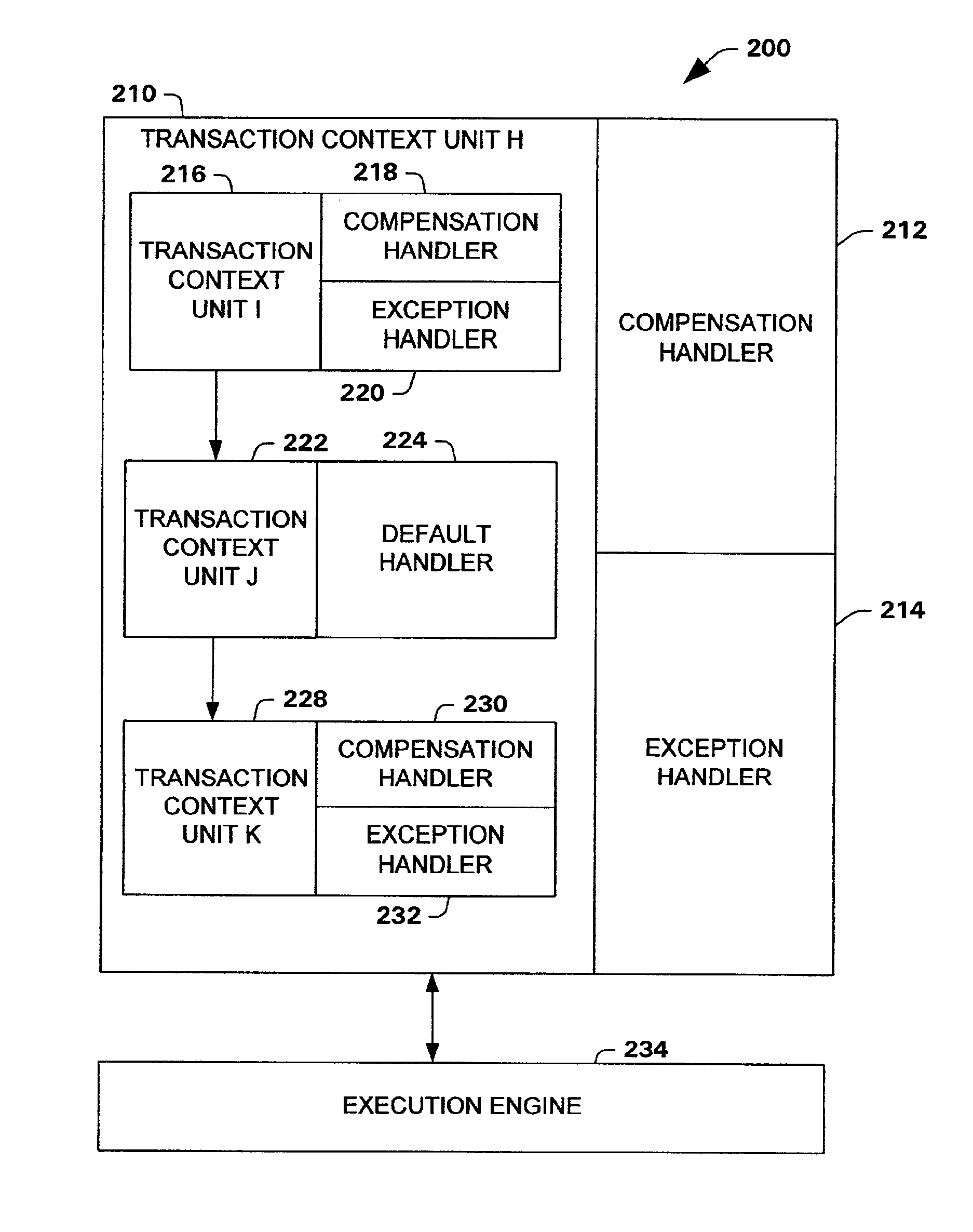

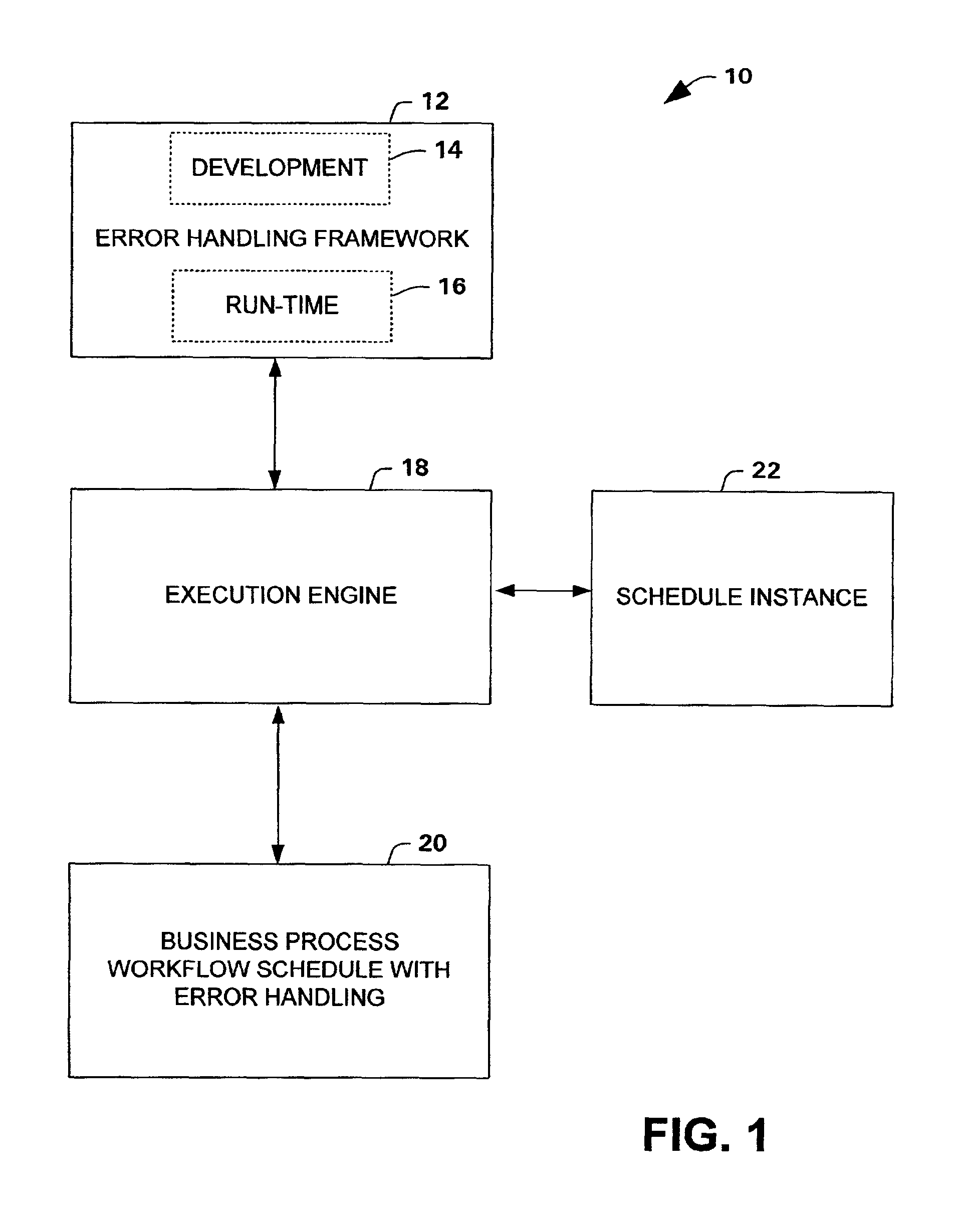

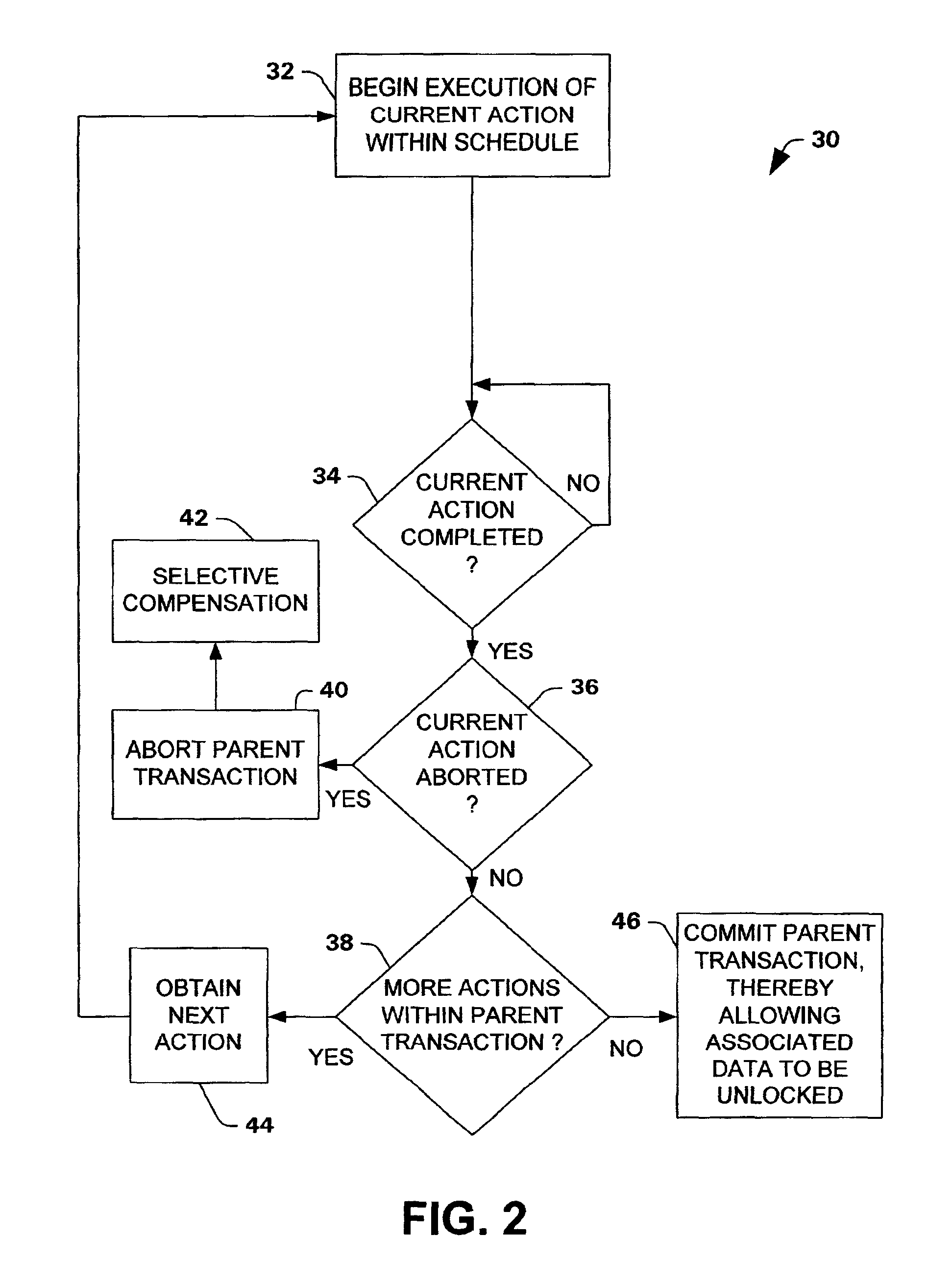

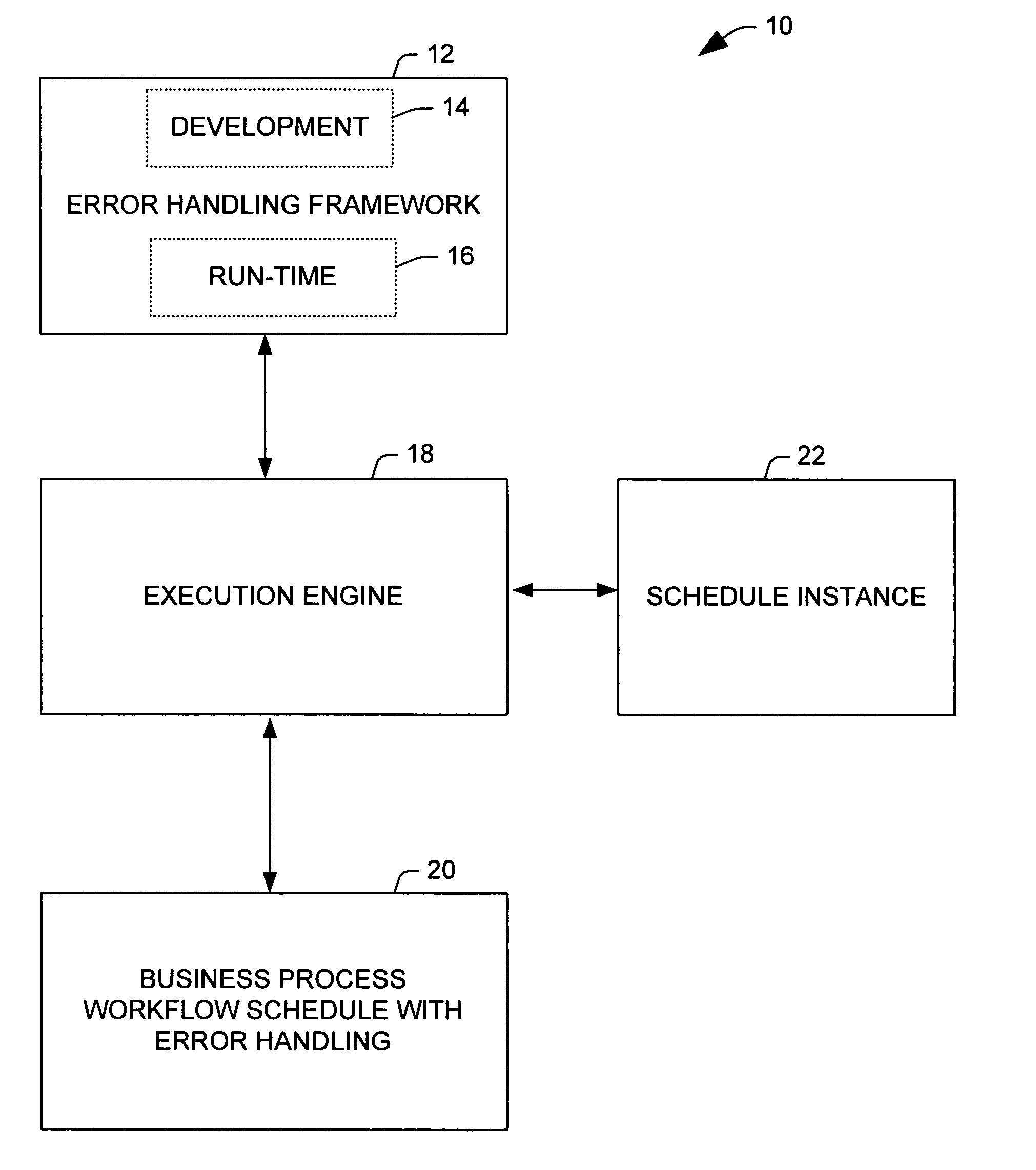

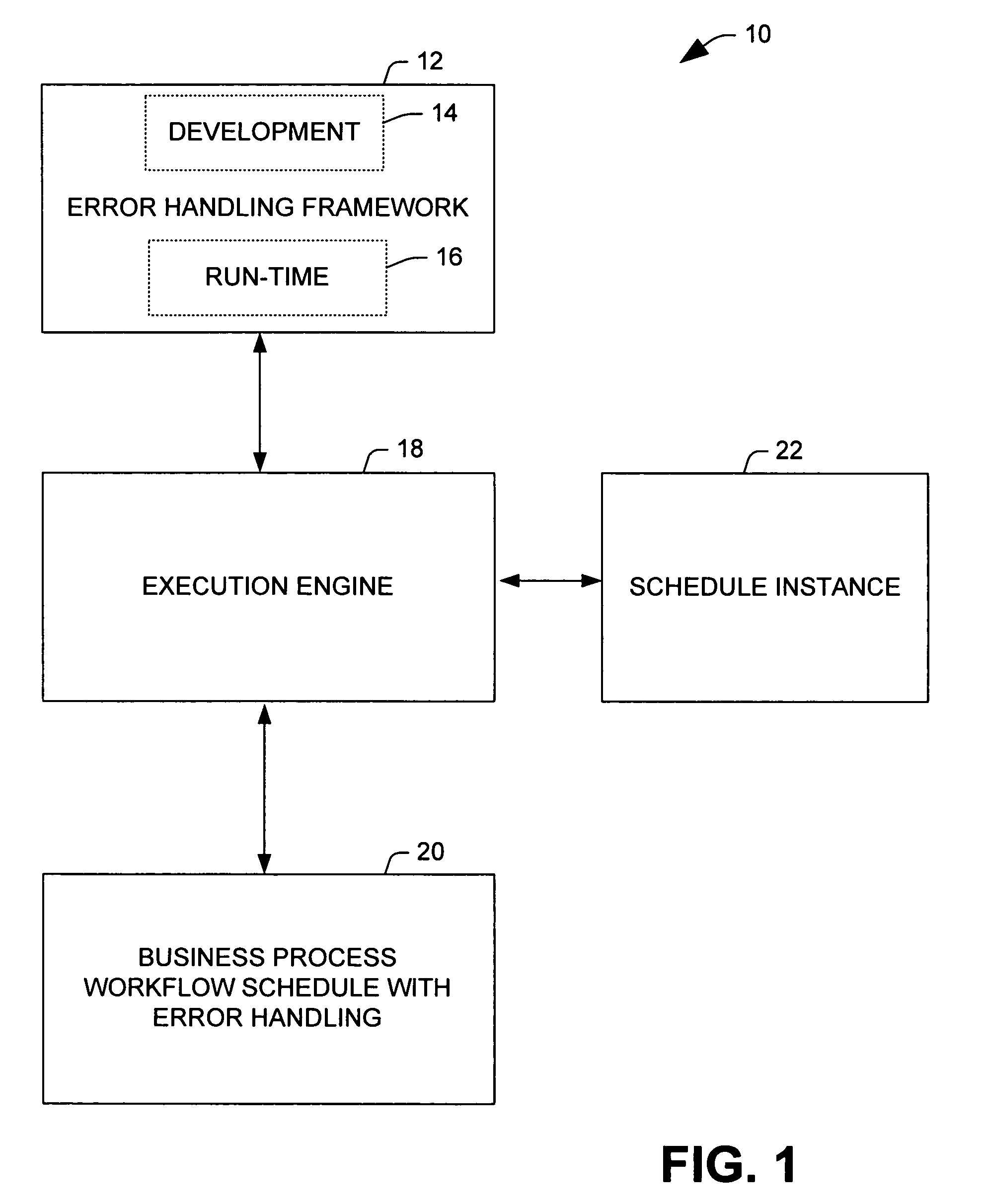

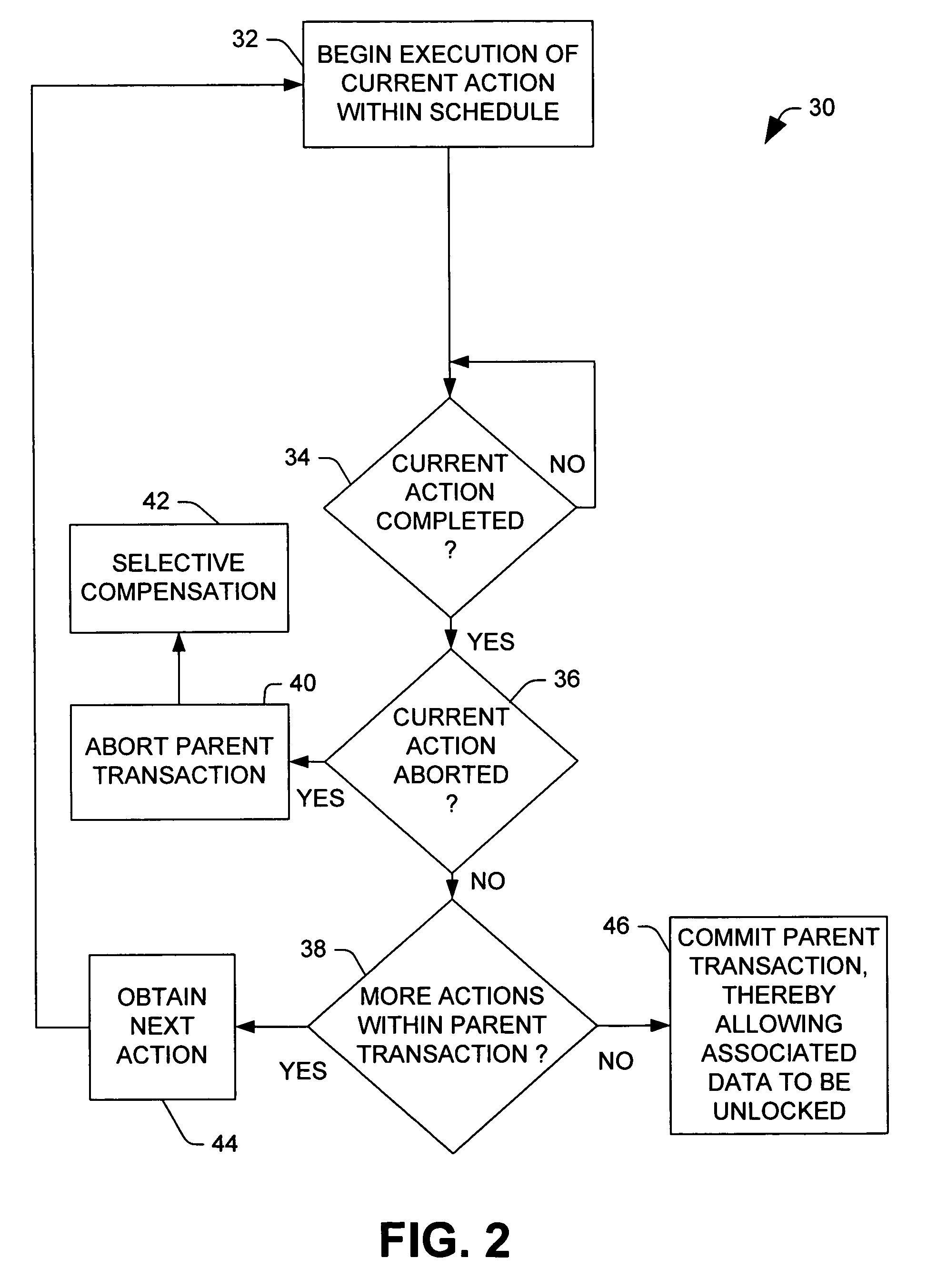

Compensation framework for long running transactions

InactiveUS6918053B1Improve system error recoveryImprove coordinationError detection/correctionOffice automationError processingEngineering

An error-handling framework is provided for business process transactions. The error-handling framework facilitates coordination of the invocation of exception and compensation handlers in response to errors. The error-handling framework includes support for custom ordering of compensation actions, data flow into and out of compensation actions, and management of the process state visible to compensation actions.

Owner:MICROSOFT TECH LICENSING LLC

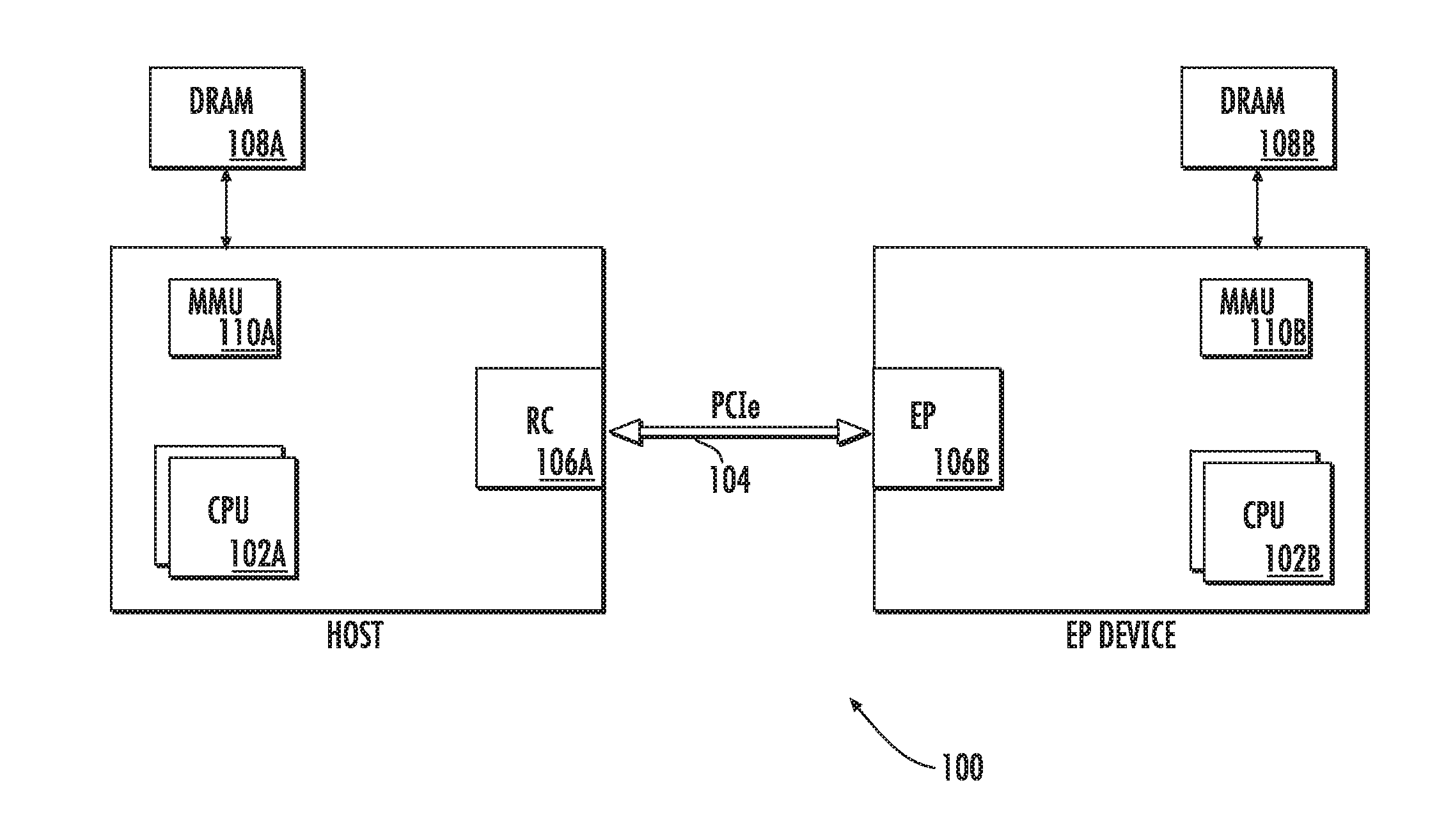

Methods and apparatus for managing power with an inter-processor communication link between independently operable processors

ActiveUS20160103480A1Reduce power consumptionElectric power consumptionError detection/correctionPower supply for data processingError processingMemory interface

Methods and apparatus for an inter-processor communication (IPC) link between two (or more) independently operable processors. In one aspect, the IPC protocol is based on a “shared” memory interface for run-time processing (i.e., the independently operable processors each share (either virtually or physically) a common memory interface). In another aspect, the IPC communication link is configured to support a host driven boot protocol used during a boot sequence to establish a basic communication path between the peripheral and the host processors. Various other embodiments described herein include sleep procedures (as defined separately for the host and peripheral processors), and error handling.

Owner:APPLE INC

Compensation framework for long running transactions

InactiveUS20050193286A1Improve coordinationError recoveryError detection/correctionOffice automationError processingEngineering

An error-handling framework is provided for business process transactions. The error-handling framework facilitates coordination of the invocation of exception and compensation handlers in response to errors. The error-handling framework includes support for custom ordering of compensation actions, data flow into and out of compensation actions, and management of the process state visible to compensation actions.

Owner:MICROSOFT TECH LICENSING LLC

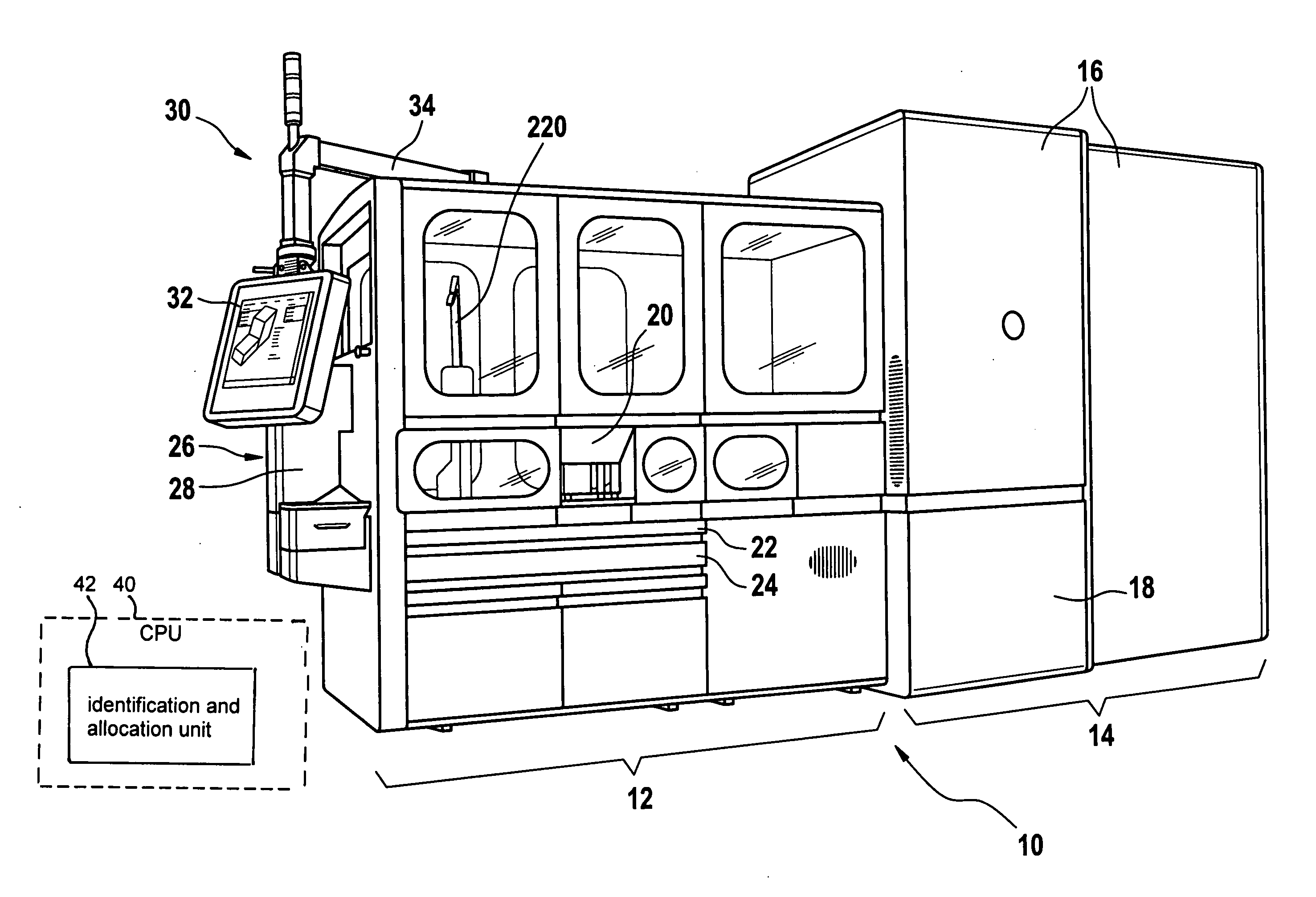

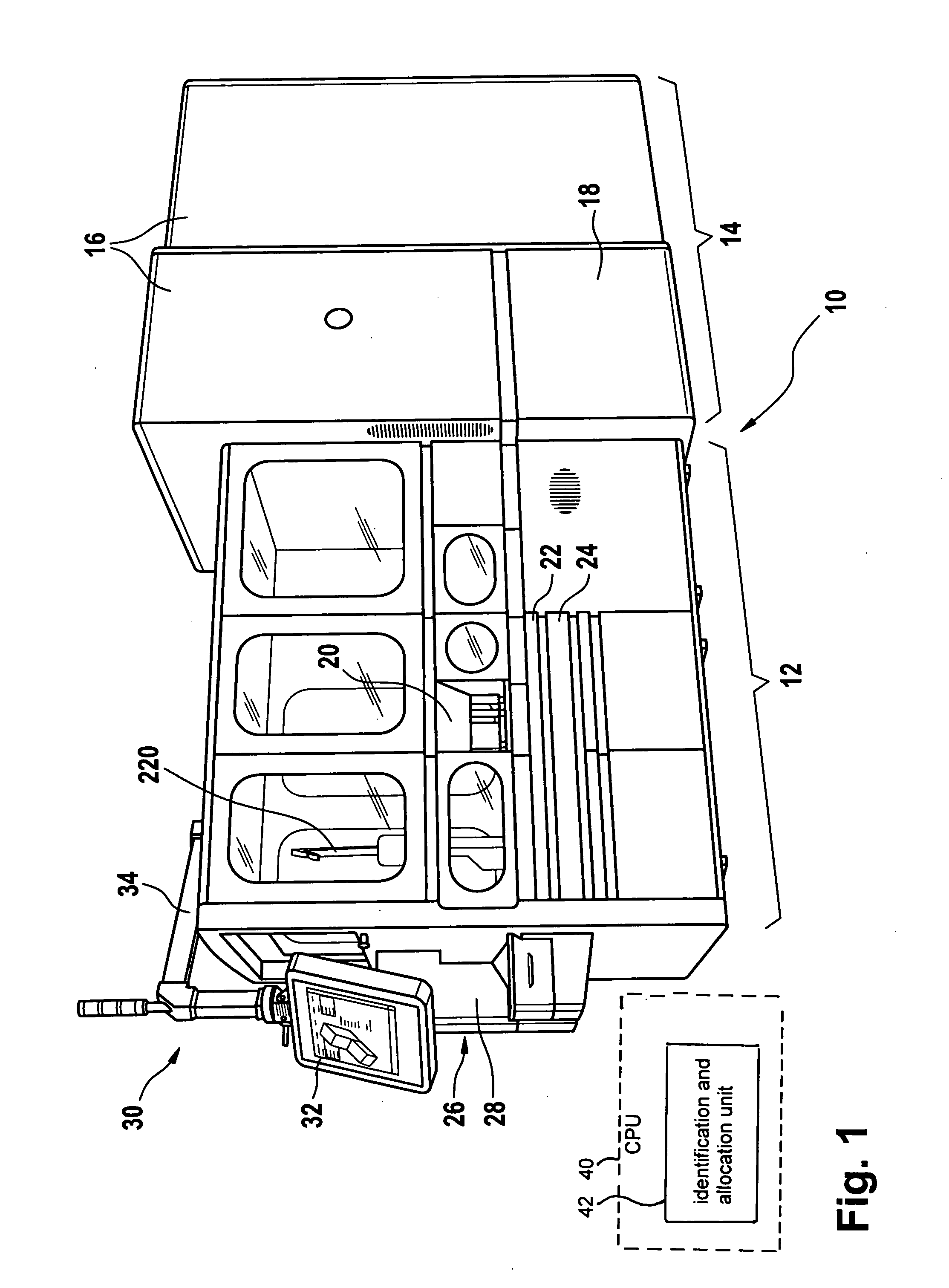

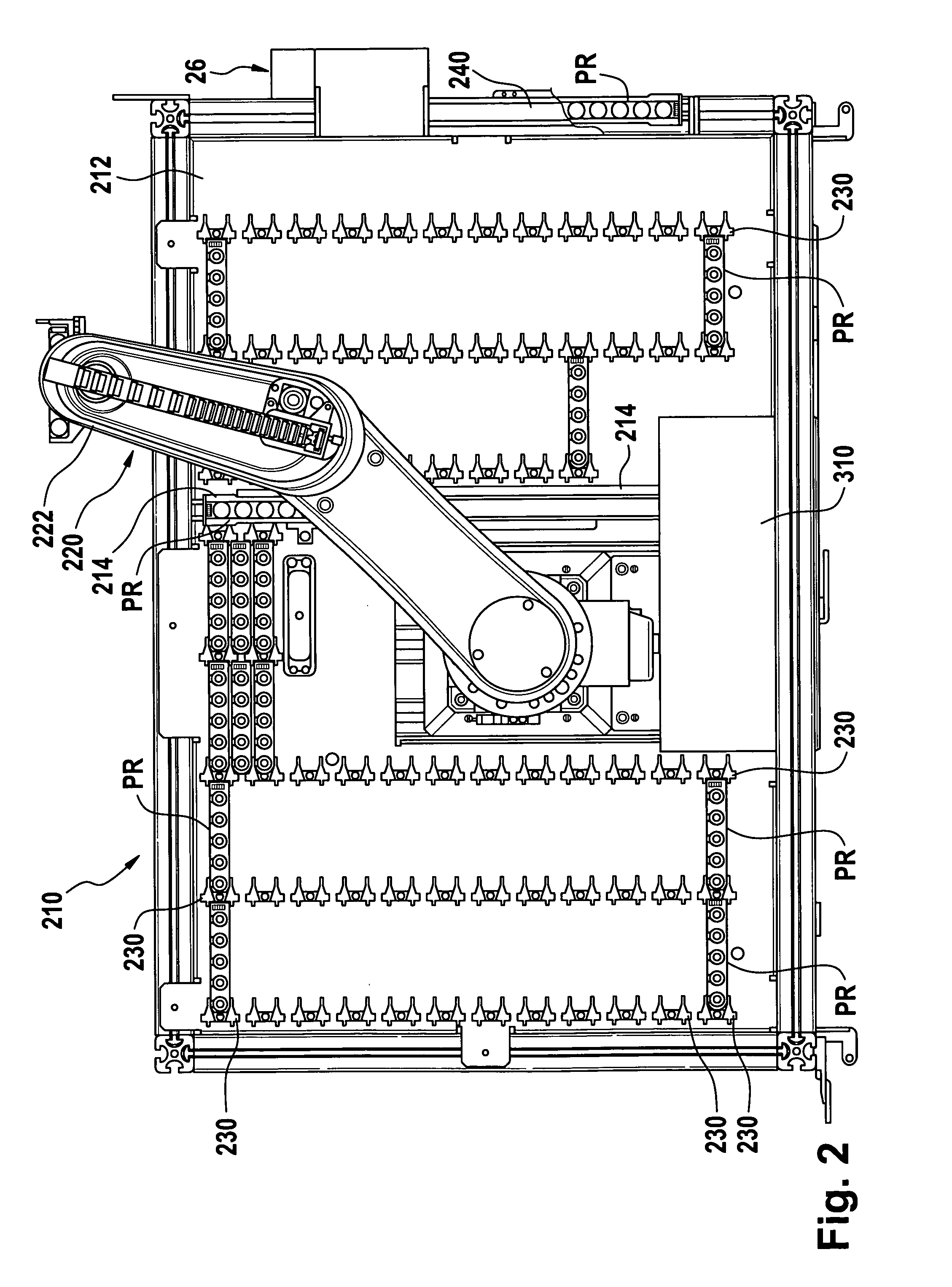

Method and laboratory system for handling sample tubes and an image analyzing unit

ActiveUS20100018330A1Reduce riskReduce breakageSamplingCharacter and pattern recognitionError processingEngineering

A method and laboratory system for handling sample tubes and an image analysing unit are disclosed. The laboratory system comprises a transfer unit for transferring incoming primary racks (PR) containing sample tubes (S), an image analysing unit (310), and an identification and allocation unit. The method to handle laboratory sample tubes includes steps of: transferring an incoming primary rack (PR) containing sample tubes (S) to the image analysing unit (310); determining, in the image analysing unit (310), geometry parameters of at least one sample tube contained in the primary rack by means of image analysing; comparing for each sample tube the determined geometry parameters with predetermined geometry criteria and identifying whether the sample tube's geometry fulfils the predetermined criteria; in case of fulfilment, categorising the sample tube as system conform; otherwise categorising the sample tube as non-system conform. Each sample tube identified as system conform is entered into further processing and each sample tube identified as non-system conform is entered into error processing.

Owner:ROCHE DIAGNOSTICS OPERATIONS INC

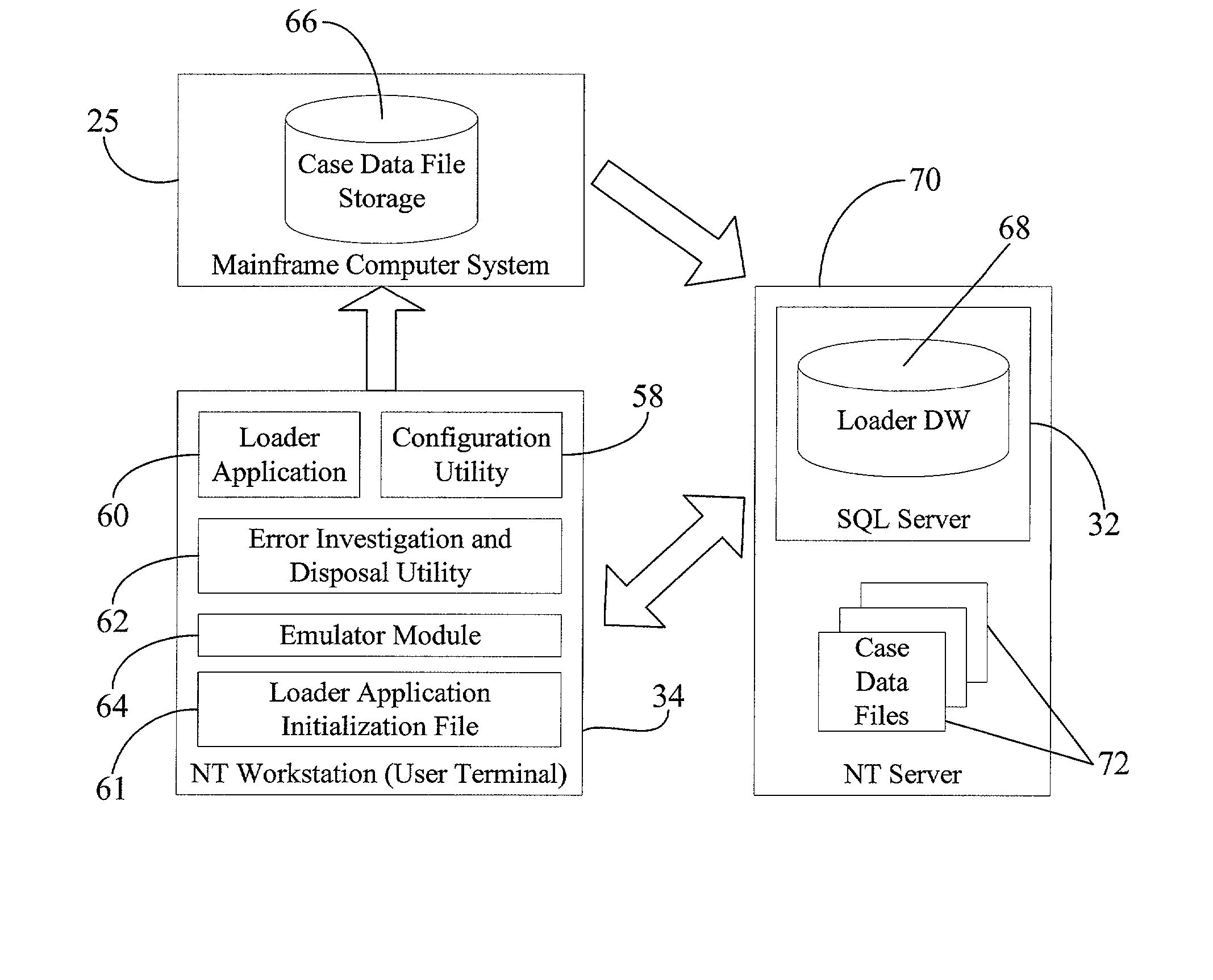

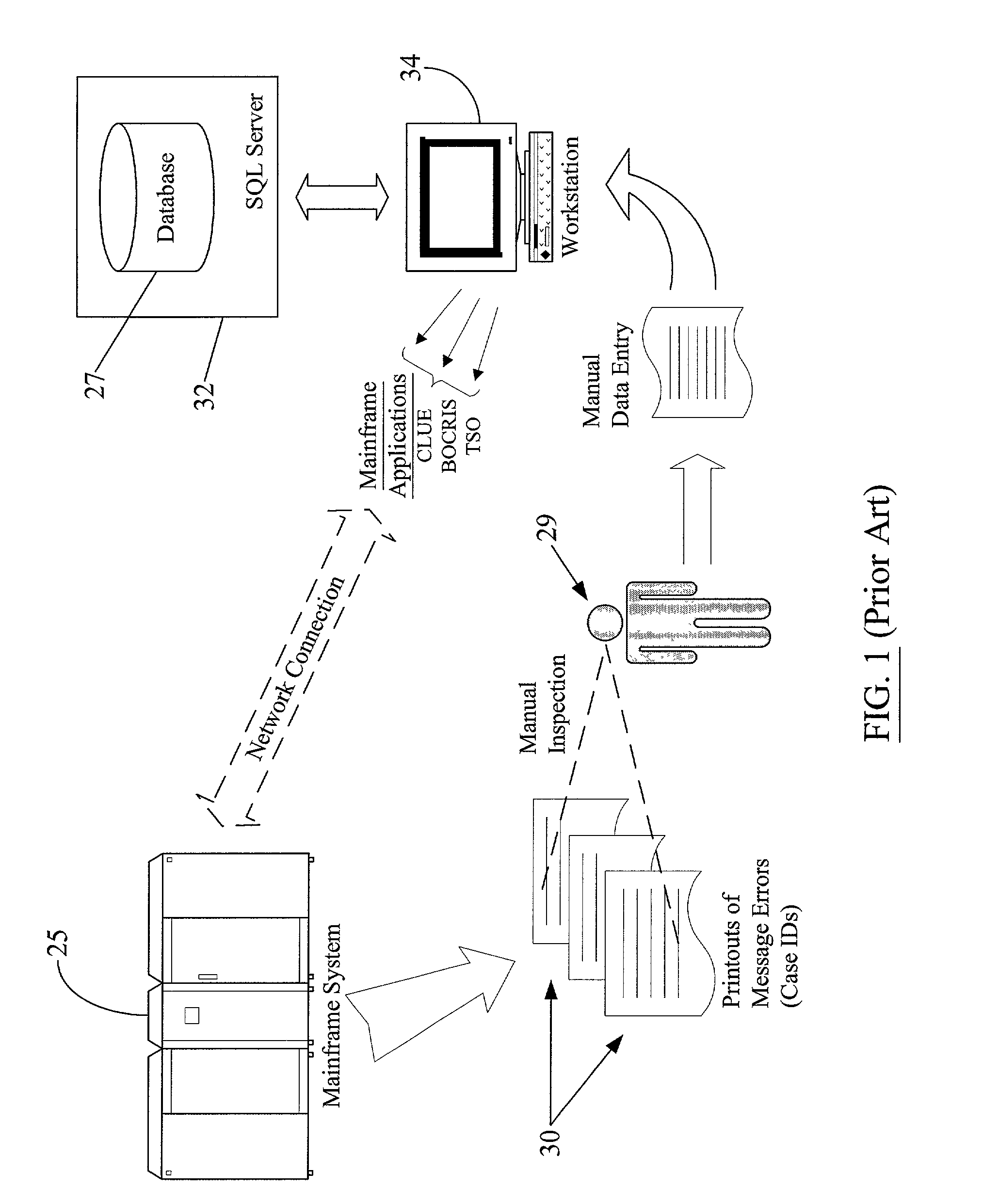

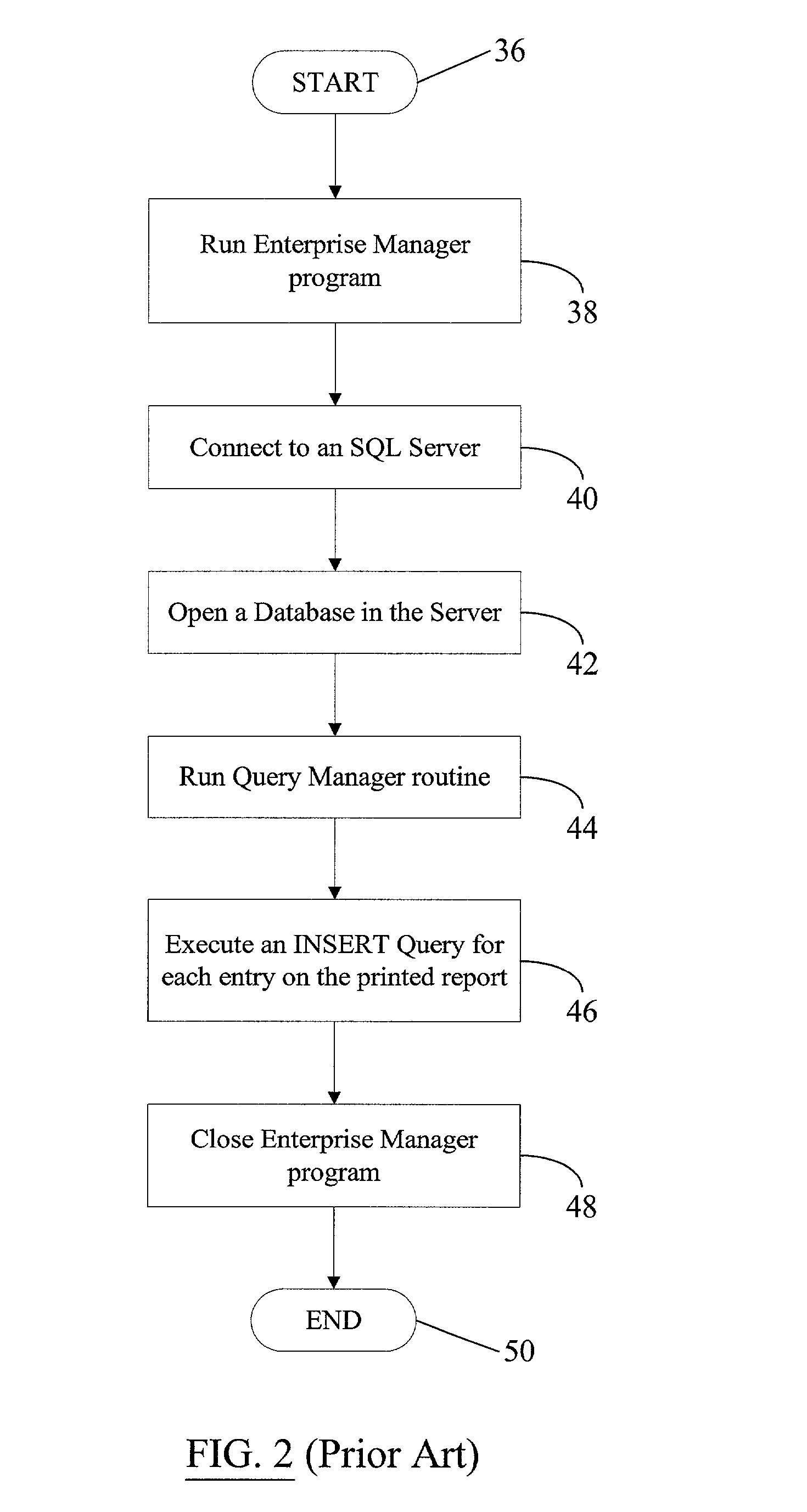

Error usage investigation and disposal system

InactiveUS20020129039A1Reduce errorsFacilitates electronic investigationDatabase management systemsDigital data processing detailsError processingData error

As part of electronically handling a large amount of data (e.g., error messages) generated within, for example, a telephone service provider's billing network, a configuration utility software allows a user to electronically change or update various configuration parameters for another software application, e.g., a loader application, and also to access the performance data generated by the loader application so as to optimize the performance of the loader application in varying data transfer situations. The loader application, in turn, is a computer-based data transfer application that electronically loads a large volume of data, e.g., telecommunication billing data, from one computer into another computer. The loader application thus substantially reduces human involvement during transfers of large amount of data, and thereby also reduces errors typically associated with manual data entries by human data operators. After completion of data transfers, an error handler program facilitates electronic investigation and disposal of errors in the received data, thereby minimizing participation of human operators in the data error rectification process. The reduced reliance on manual identification and correction of data errors thus results in increased accuracy and efficiency in the overall network data management and customer billing operations.

Owner:BELLSOUTH INTPROP COR

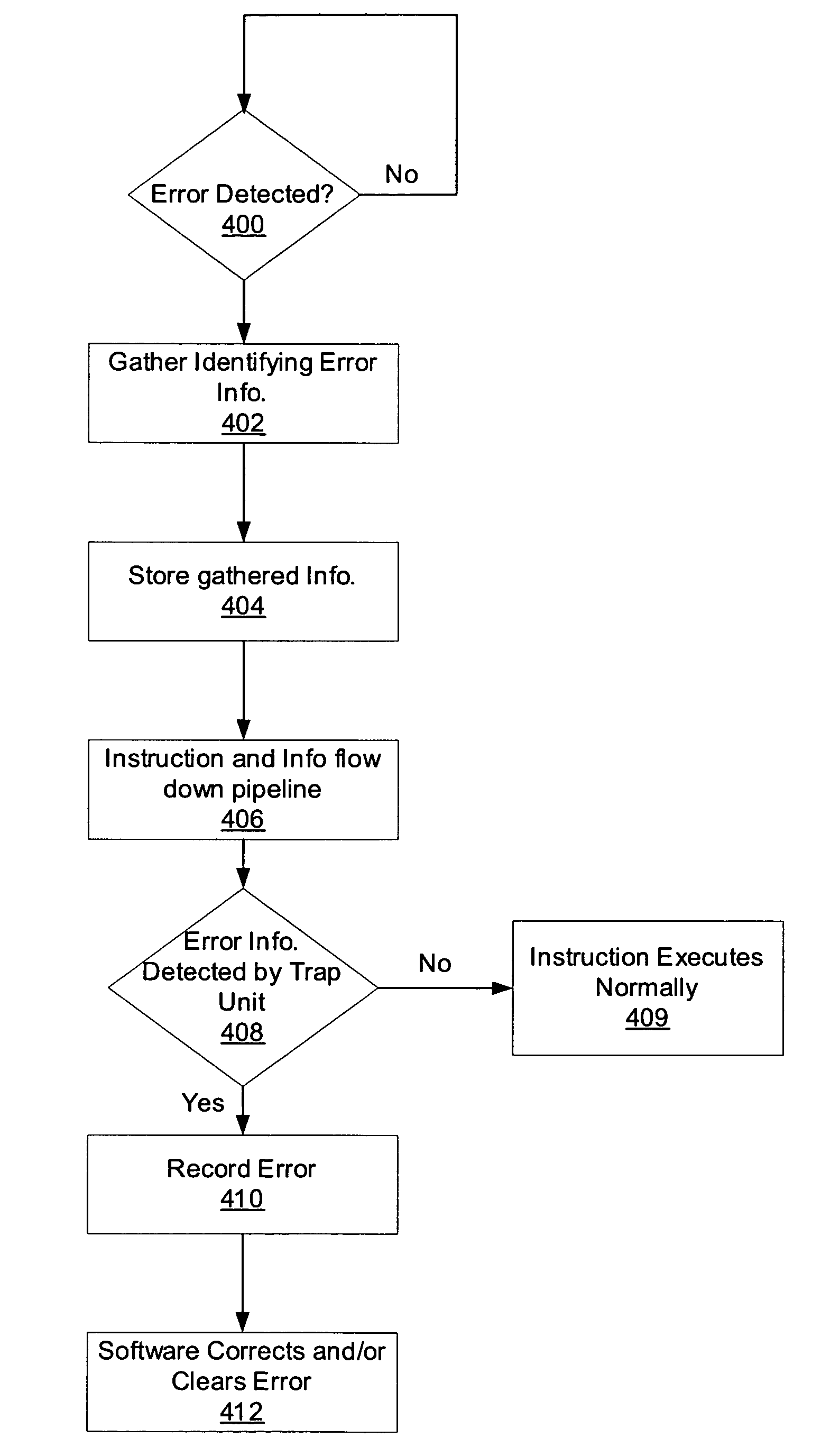

Precise error handling in a fine grain multithreaded multicore processor

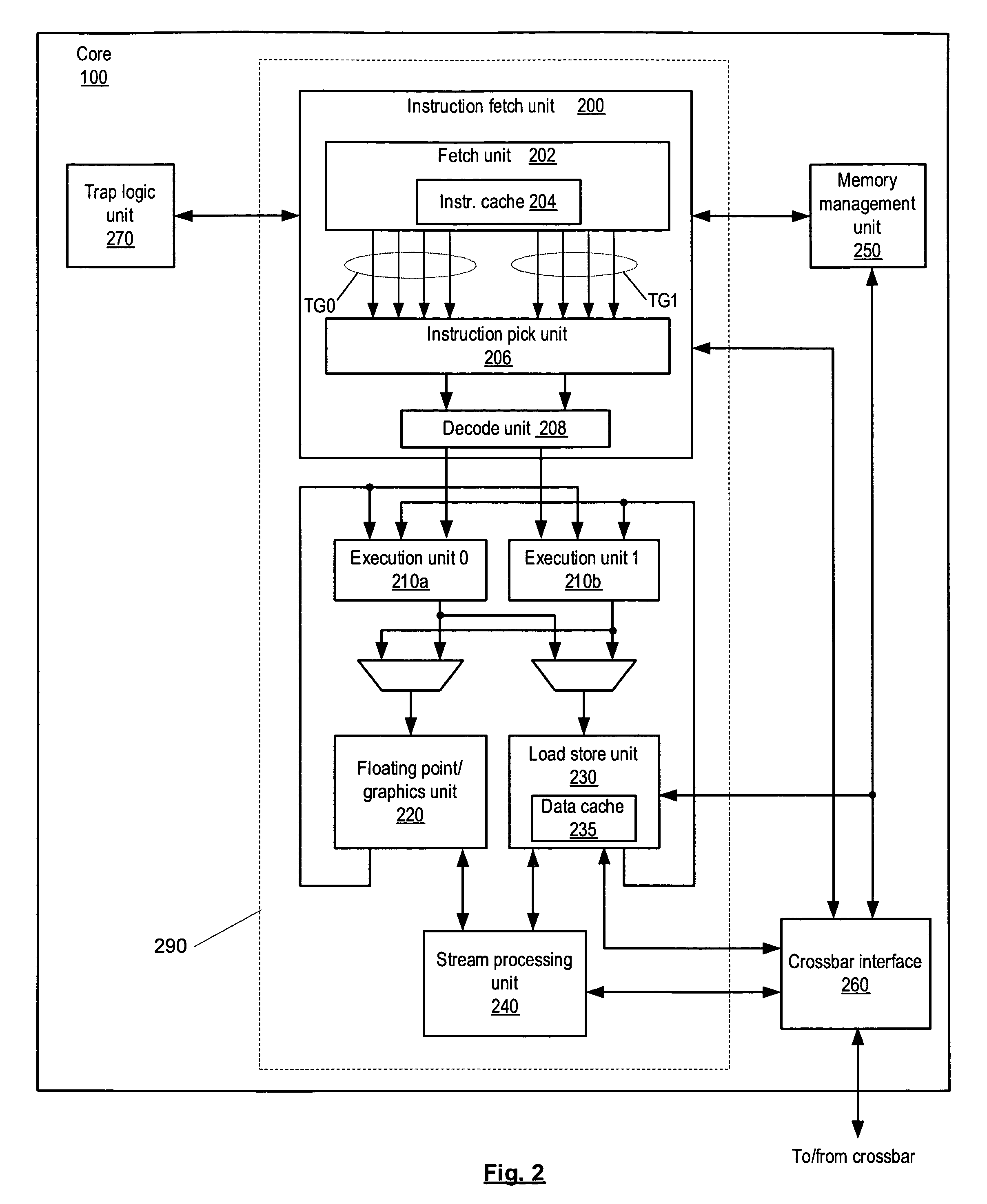

A method and mechanism for error recovery in a processor. A multithreaded processor is configured to utilize software for hardware detected machine errors. Rather than correcting and clearing the detected errors, hardware is configured to report the errors precisely. Both program-related exceptions and hardware errors are detected and, without being corrected by the hardware, flow down the pipeline to a trap unit where they are prioritized and handled via software. The processor assigns each instruction a thread ID and error information as it follows the pipeline. The trap unit records the error by using the thread ID of the instruction and the pipelined error information in order to determine which ESR receives the information and what to store in the ESR. A trap handling routine is then initiated to facilitate error recovery.

Owner:ORACLE INT CORP