Method for performing communication among EDMA (enhanced direct memory access) different bandwidth devices in multi-core DSP (digital signal processor)

A technology of inter-device communication and bandwidth, applied in the field of EDMA communication, can solve the problem of mismatch between requests and responses, and achieve the effect of reducing complexity and difficulty in design and implementation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

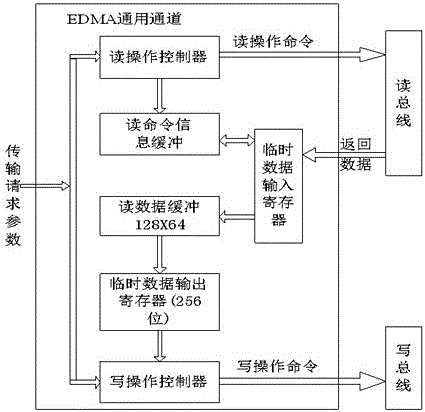

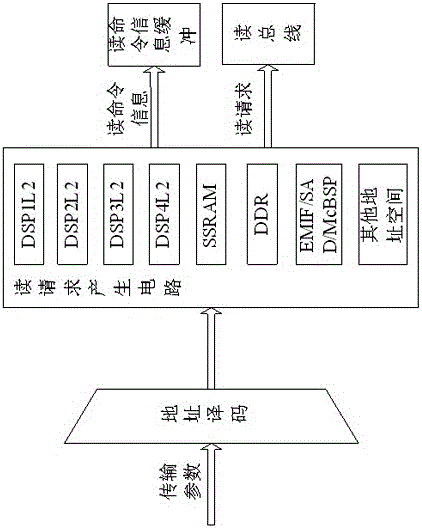

[0052] like figure 1 As shown, a method for communicating between EDMA devices with different bandwidths in a multi-core DSP is characterized in that: each DSP core is allocated an independent processing channel, an EDMA common channel, and each channel can independently process data from other DSP cores and other devices. By adopting synchronous FIFO to realize the read operation information cache mechanism + read operation return data cache processing mechanism, the precise matching between the response return and the request is realized, and data communication between devices with different bit widths is realized.

[0053] In a multi-core DSP, the EDMA controller can access many device spaces, including multiple storage spaces such as memory and peripherals, which involves accurate return of request responses and data interaction between devices with different bit widths;

[0054] The response to the request sent by the bus is returned in the form of broadcast. By adopting ...

Embodiment 2

[0056] On the basis of Embodiment 1, the method described in this embodiment sends a read command through the read operation controller, and updates the relevant parameters of the read operation;

[0057] Every time the read operation controller sends out a read command, the information of the operation is buffered at the same time, including: the data valid bit signal Rd_ValidBytes and the device encoding signal DevNum; the read operation information (read command information buffer) that needs to be buffered is stored in a synchronous FIFO;

[0058] Every time a response is returned, the temporarily stored information is taken out from the FIFO, and the data on the bus is only received when the device information of the returned data is consistent with the temporarily stored device code;

[0059] When the FIFO is read empty, it indicates that the execution of the current read command is completed;

[0060] The data returned by the read command and the buffered read operation i...

Embodiment 3

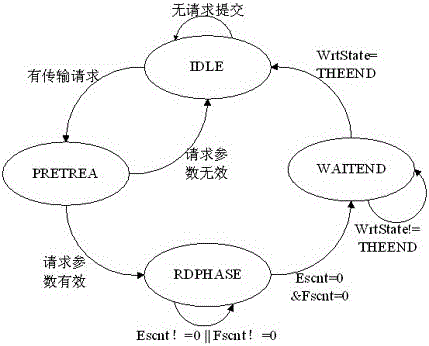

[0066] like figure 2 As shown, on the basis of Embodiment 2, the function of the read operation controller described in this embodiment is realized by the read operation state machine RdState, which contains four states: IDLE, PRETREA, RDPHASE, WAITEND:

[0067] IDLE: idle state;

[0068] PRETREA: Preprocessing state, as long as Escnt is not 0, you can jump to RDPHASE state smoothly. Judging and updating the parameter configuration of the read operation;

[0069] RDPHASE: Generate a read command, and judge the device address space according to the high 16-bit address of SRC Address;

[0070] WAITEND: Wait for the write operation control to complete all write operations; the end condition is defined as only when the read and write state machines enter IDLE at the same time, the current request is completely processed and the next transmission request can be received.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More