Double-inlay structure and its making method

A dual damascene structure and manufacturing method technology, which is applied in semiconductor/solid-state device manufacturing, electrical components, electrical solid-state devices, etc., can solve problems such as inter-metal dielectric layer damage, inter-metal dielectric layer surface damage, and difficulty in cleaning, etc., to achieve increased Large parasitic capacitance, the effect of increasing device reliability and stability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0070] In order to make the above objects, features and advantages of the present invention more comprehensible, specific implementations of the present invention will be described in detail below in conjunction with the accompanying drawings.

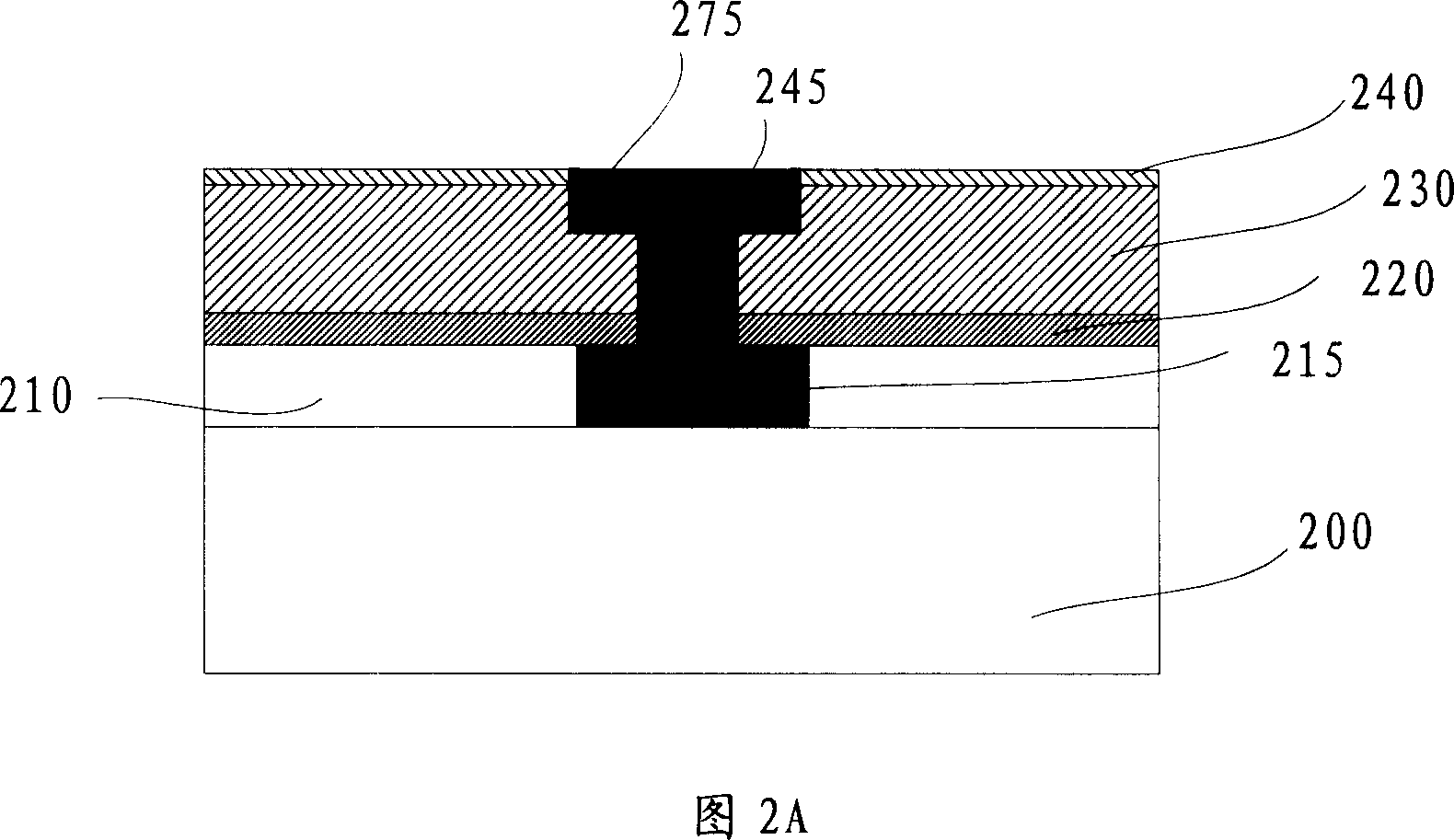

[0071] 2A and 2B are schematic cross-sectional views of the dual damascene structure of the present invention. FIG. 2A shows the first embodiment of the dual damascene structure of the present invention. A dielectric layer 210 is provided on a semiconductor substrate 200 . A metal pattern layer 215 is formed on the dielectric layer 210 through a photolithography process and an etch process, and the metal pattern layer 215 may be aluminum or copper. An etching stop layer 220 is formed on the metal pattern layer 215 and the dielectric layer 210 . The etch stop layer can be one or more layers. The function of the etching stop layer 220 is to prevent the metal of the metal pattern layer 215, such as copper, from diffusing upward; damag...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More